TUSB4020BI

JAJSF53E - JULY 2015 - REVISED JULY 2024

## TUSB4020BI 2 ポートの USB 2.0 ハブ

## 1 特長

• 2ポート USB 2.0 ハブ

INSTRUMENTS

USB 2.0 ハブ機能:

Texas

- マルチ トランザクション トランスレータ (MTT) ハブ: 2 つのトランザクショントランスレータ

- トランザクショントランスレータごとに 4 つの非同期 エンドポイント バッファ

- Type C 互換

- バッテリ充電の規格

- CDP モード (上流ポート接続時)

- DCP モード (上流ポート未接続時)

- DCP モードは中国電気通信業界標準 YD/T 1591-2009 に準拠

- D+/D- デバイダ モード

- ポート単位または一括制御のパワー スイッチングおよ び過電流通知入力

- OTP ROM、シリアル EEPROM、または I<sup>2</sup>C/SMBus ターゲットインターフェイスで次のカスタム構成に対 応:

- VID および PID

- ポートのカスタマイズ

- メーカーおよび製品文字列 (OTP ROM は除く)

- シリアル番号 (OTP ROM は除く)

- 端子選択か、EEPROM または I<sup>2</sup>C/SMBus ターゲット インターフェイスを使用したアプリケーション機能選択

- 128 ビットの UUID (Universally Unique Identifier) を

- USB 2.0 上流ポート経由でオンボードおよびイン シス テムの OTP/EEPROM プログラミングをサポート

- 単一クロック入力、24MHzの水晶振動子または発振

- 特別なドライバ要件なし、USB スタックをサポートする 任意のオペレーティング システムでシームレスに動作

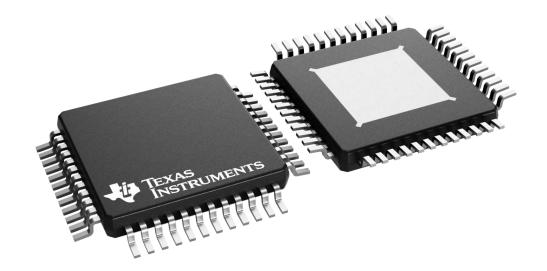

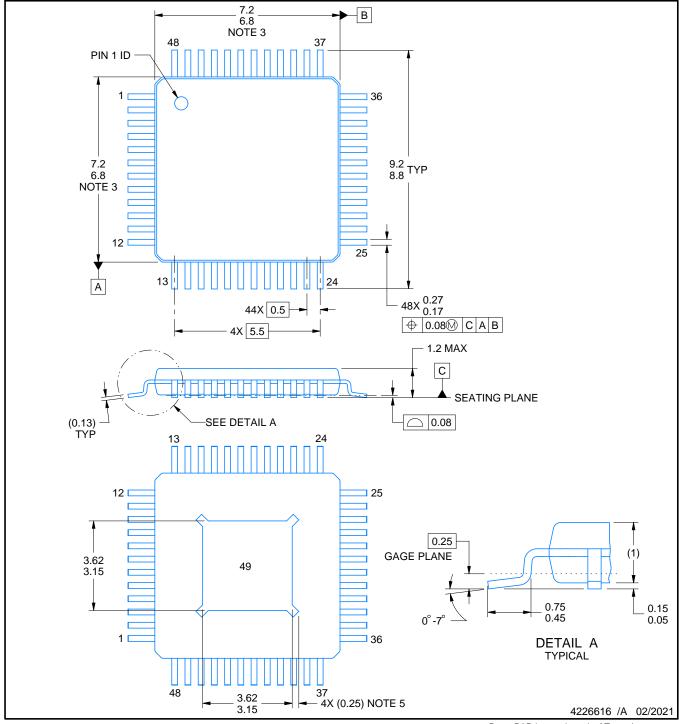

- 48 ピン HTQFP パッケージ (PHP)

# 2 アプリケーション

- コンピュータシステム

- ドッキング・ステーション

- モニタ

- セットトップ ボックス

## 3 概要

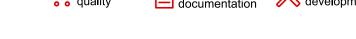

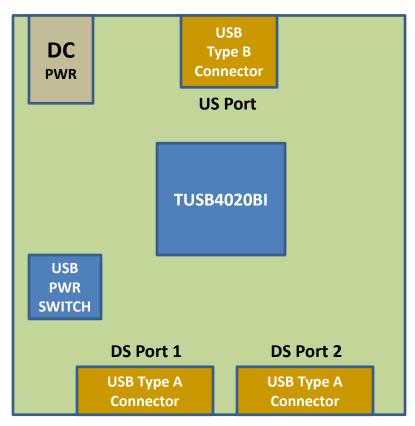

TUSB4020BI は、2 ポートの USB 2.0 ハブです。 上流ポ ートでハイ スピード / フル スピード USB 接続を、2 つの 下流ポートでハイ スピード、フル スピード、ロー スピード USB 接続を提供します。上流のポートが、ハイスピードお よびフル スピード / ロー スピードの接続をサポートする電 気的環境に接続されている場合、下流のポートでハイス ピードおよびフル スピード/ロー スピード USB 接続が有 効になります。上流のポートが、フルスピード/ロースピ ード接続のみをサポートする電気的環境に接続されてい る場合、下流のポートでハイスピード接続が無効になりま す。

TUSB4020BI には、ポートごと、または一括の電力スイッ チングと過電流保護が搭載されています。

ポートパワー個別制御のハブは、各下流ポートへの給電 を USB ホストのリクエストに応じてオン/オフします。また、 ポート パワー個別制御のハブが過電流イベントを検出し た場合には、影響を受ける下流ポートへの電力だけがオ フになります。

一括制御のハブは、いずれかのポートで電力が必要にな ると、すべての下流ポートへの給電をオンにします。下流 ポートへの給電は、すべてのポートが給電を停止できる状 態にならない限り、オフになりません。また、一括制御のハ ブが過電流イベントを検出すると、すべての下流ポートへ の給電がオフになります。

TUSB4020BIの下流ポートは、バッテリ充電用の接続下 流ポート (CDP) ハンドシェイクに対応し、バッテリを充電 するアプリケーションをサポートします。上流ポートが接続 されていないときは、専用充電ポート (DCP) モードもサポ ートします。 DCP モードは、USB バッテリ充電および中国 電気通信業界標準 YD/T 1591-2009 をサポートする USB デバイスに対応します。また、自動モードでは、上流 ポートの未接続時に BC デバイスとデバイダ モード充電ソ リューションをサポートするデバイスが透過的にサポートさ れます。

TUSB4020BI は、バッテリ充電のサポートなどいくつかの機能について端子ストラップ構成を提供しており、OTP ROM、 $I^2C$  EEPROM、または PID、VID、およびカスタム ポートと PHY 構成用の  $I^2C$ /SMBus ターゲット インターフェイスにより、カスタマイズを行えます。また、 $I^2C$  EEPROM または  $I^2C$ /SMBus ターゲット インターフェイスを使用する場合、カスタム ストリングをサポートします。

このデバイスは 48 ピンの HTQFP パッケージで供給され、-40℃~85℃の温度範囲で動作する産業用バージョンです。

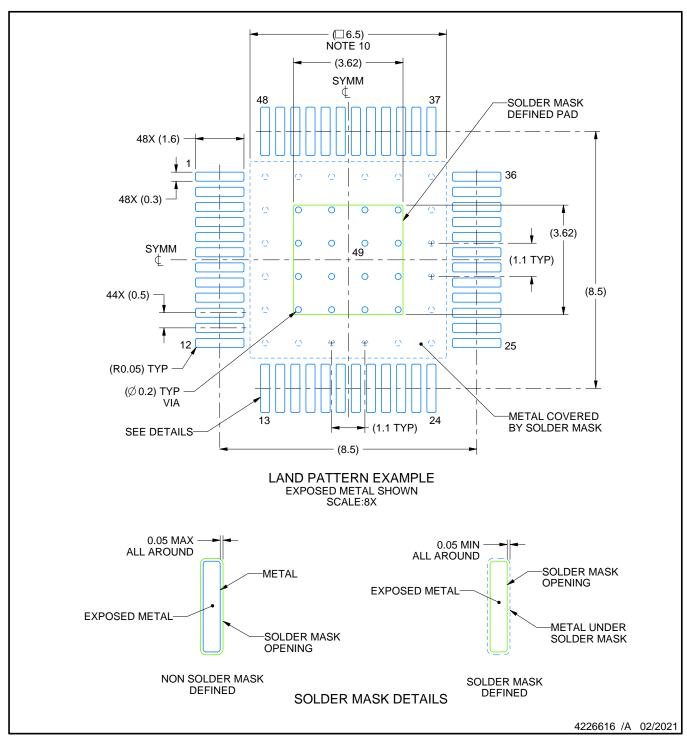

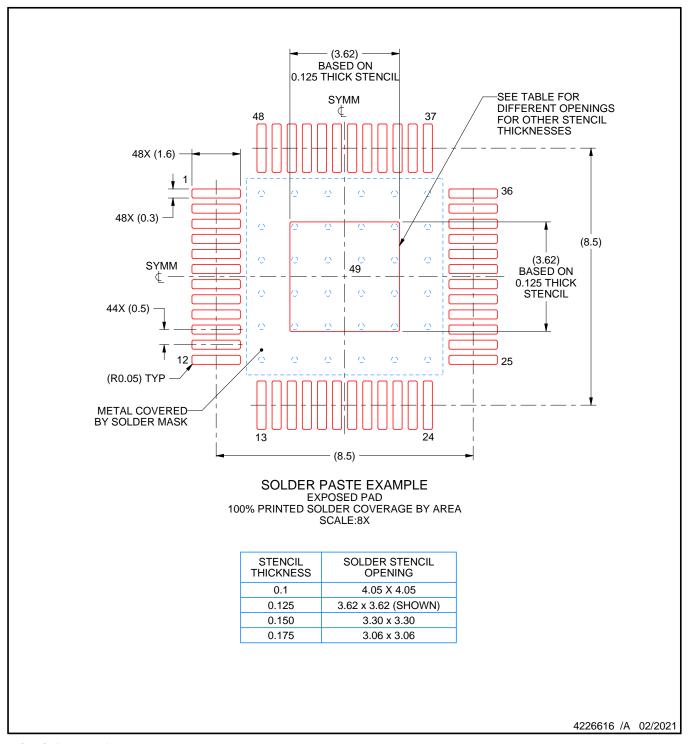

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |  |

|------------|----------------------|--------------------------|--|

| TUSB4020BI | PHP (HTQFP, 48)      | 9mm × 9mm                |  |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

- (2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

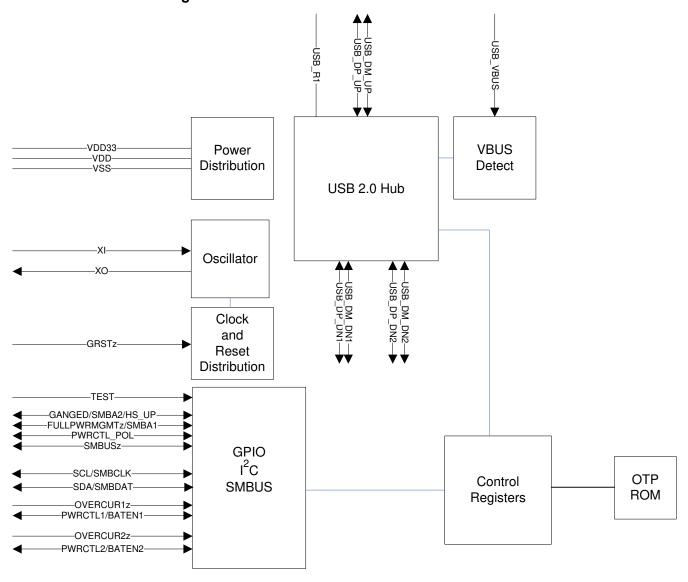

ブロック図

Product Folder Links: TUSB4020BI

## **Table of Contents**

| 1 特長1                                    | 6.5 Programming                         | 13              |

|------------------------------------------|-----------------------------------------|-----------------|

| <b>2</b> アプリケーション1                       | 6.6 Register Maps                       |                 |

| 3 概要1                                    | 7 Application and Implementation        | <mark>26</mark> |

| 4 Pin Configuration and Functions4       | 7.1 Application Information             | 26              |

| 5 Specifications7                        | 7.2 Typical Applications                | <mark>27</mark> |

| 5.1 Absolute Maximum Ratings (1)         | 7.3 Power Supply Recommendations        | 31              |

| 5.2 ESD Ratings7                         | 7.4 Layout                              | 32              |

| 5.3 Recommended Operating Conditions7    | 8 Device and Documentation Support      | 35              |

| 5.4 Thermal Information7                 | 8.1 Documentation Support               | 35              |

| 5.5 3.3V I/O Electrical Characteristics8 | 8.2ドキュメントの更新通知を受け取る方法                   | 35              |

| 5.6 Hub Input Supply Current8            | 8.3 サポート・リソース                           | 35              |

| 5.7 Power-Up Timing Requirements9        | 8.4 Trademarks                          |                 |

| 6 Detailed Description10                 | 8.5 静電気放電に関する注意事項                       | 35              |

| 6.1 Overview                             | 8.6 用語集                                 |                 |

| 6.2 Functional Block Diagram10           | 9 Revision History                      |                 |

| 6.3 Feature Description11                | 10 Mechanical, Packaging, and Orderable |                 |

| 6.4 Device Functional Modes12            | Information                             | 36              |

|                                          |                                         |                 |

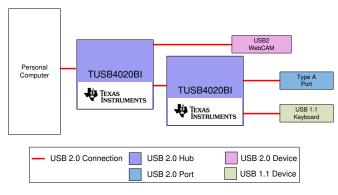

## 4 Pin Configuration and Functions

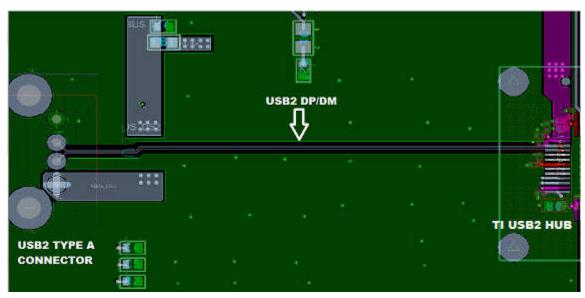

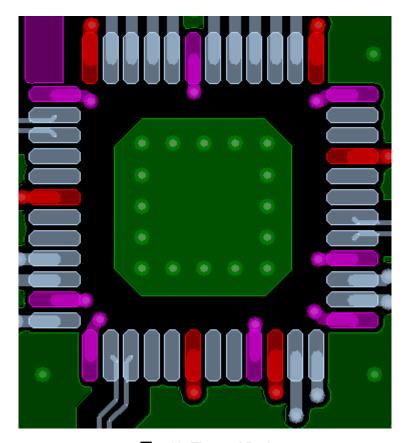

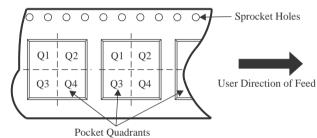

図 4-1. PHP Package, 48-Pin HTQFP (Top View)

表 4-1. Pin Functions

|                    | 2C + 111 III CITOGOTO                                                                                                                         |                     |                                                                                                                                                                           |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN                |                                                                                                                                               | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                               |  |  |  |

| NAME               | NO.                                                                                                                                           | 1166,               | DESCRIFTION                                                                                                                                                               |  |  |  |

| CLOCK AND RESET SI | GNALS                                                                                                                                         |                     |                                                                                                                                                                           |  |  |  |

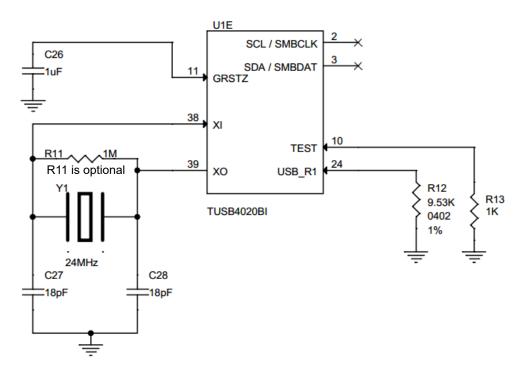

| GRSTz              | 11                                                                                                                                            | I<br>PU             | Global power reset. This reset brings all of the TUSB4020BI internal registers back to the default state. When GRSTz is asserted, the device is completely nonfunctional. |  |  |  |

| XI                 | 38                                                                                                                                            | I                   | Crystal input. This terminal is the crystal input for the internal oscillator. The input can alternately driven by the output of an external oscillator.                  |  |  |  |

| хо                 | Crystal output. This terminal is the crystal output for the internal oscillator. If XI is driver oscillator this pin can be left unconnected. |                     | Crystal output. This terminal is the crystal output for the internal oscillator. If XI is driven by an external oscillator this pin can be left unconnected.              |  |  |  |

| USB UPSTREAM SIGNA | ALS                                                                                                                                           | •                   |                                                                                                                                                                           |  |  |  |

| USB_DP_UP 26 I/O   |                                                                                                                                               | I/O                 | USB high-speed differential transceiver (positive)                                                                                                                        |  |  |  |

| USB_DM_UP          | 27                                                                                                                                            | I/O                 | USB high-speed differential transceiver (negative)                                                                                                                        |  |  |  |

| USB_R1             | 24                                                                                                                                            | I                   | Precision resistor reference. Connect a 9.53kΩ ±1% resistor between USB_R1 and GND.                                                                                       |  |  |  |

Copyright © 2024 Texas Instruments Incorporated

4

Product Folder Links: TUSB4020BI

## 表 4-1. Pin Functions (続き)

| PIN                                                                                        |       |                                                                                                                                                    | 及 4-1. Fill FullCuons (粉起)                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                       | NO.   | TYPE <sup>(1)</sup>                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                          |

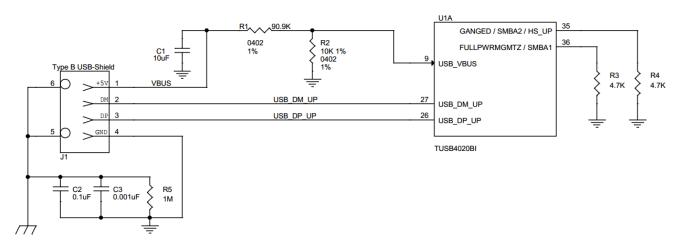

| USB_VBUS                                                                                   | 9     | I                                                                                                                                                  | USB upstream port power monitor. The VBUS detection requires a voltage divider. The signal USB_VBUS must be connected to VBUS through a 90.9k $\Omega$ ±1% resistor and to ground through a 10k $\Omega$ ±1% resistor from the signal to ground.     |

| USB DOWNSTREAM SI                                                                          | GNALS |                                                                                                                                                    |                                                                                                                                                                                                                                                      |

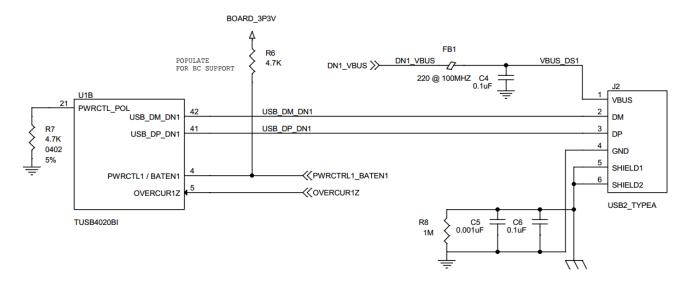

| USB_DP_DN1                                                                                 | 41    | I/O                                                                                                                                                | USB high-speed differential transceiver (positive) downstream port 1.                                                                                                                                                                                |

| USB_DM_DN1                                                                                 | 42    | I/O                                                                                                                                                | USB high-speed differential transceiver (negative) downstream port 1.                                                                                                                                                                                |

|                                                                                            |       |                                                                                                                                                    | USB port 1 power-on control for downstream power or battery charging enable. The terminal is used for control of the downstream power switch for Port 1.                                                                                             |

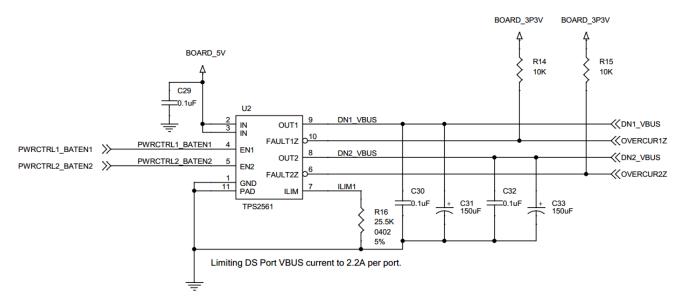

| PWRCTL1/BATEN1                                                                             | 4     | I/O<br>PD                                                                                                                                          | In addition, the value of the terminal is sampled at the deassertion of reset to determine the value of the battery charging support for Port 1 as indicated in the Battery Charging Support register.                                               |

|                                                                                            |       |                                                                                                                                                    | 0 = Battery charging not supported 1 = Battery charging supported                                                                                                                                                                                    |

| the downstream port power switch for port 1.                                               |       | USB DS port 1 overcurrent detection input. This terminal is used to connect the overcurrent output of the downstream port power switch for port 1. |                                                                                                                                                                                                                                                      |

| OVERCUR1z  0 = An overcurrent event has occurred 1 = An overcurrent event has not occurred |       |                                                                                                                                                    |                                                                                                                                                                                                                                                      |

| 0.12.1001.112                                                                              |       |                                                                                                                                                    | If power management is enabled, review the power switch to determine the required external circuitry. In ganged mode, either OVERCUR1z or OVERCUR2z can be used. In ganged mode, the overcurrent is reported as a hub event instead of a port event. |

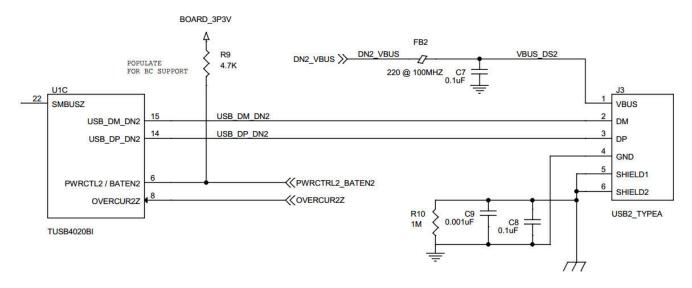

| USB_DP_DN2                                                                                 | 14    | I/O                                                                                                                                                | USB high-speed differential transceiver (positive) downstream port 2.                                                                                                                                                                                |

| USB_DM_DN2                                                                                 | 15    | I/O                                                                                                                                                | USB high-speed differential transceiver (negative) downstream port 2.                                                                                                                                                                                |

|                                                                                            |       |                                                                                                                                                    | Power-on control /battery charging enable for downstream port 2. This terminal is used for control of the downstream power switch for port 2.                                                                                                        |

| PWRCTL2/BATEN2                                                                             | 6     | I/O<br>PD                                                                                                                                          | The value of the terminal is sampled at the deassertion of reset to determine the value of the battery charging support for port 2 as indicated in the Battery Charging Support register.                                                            |

| T WINGTEZ/BATENZ                                                                           |       |                                                                                                                                                    | 0 = Battery charging not supported 1 = Battery charging supported                                                                                                                                                                                    |

|                                                                                            |       |                                                                                                                                                    | Overcurrent detection for downstream port 2. This terminal is used to connect the over current output of the downstream port power switch for port 2.                                                                                                |

| OVERCUR2z                                                                                  | 8     | I<br>PU                                                                                                                                            | 0 = An overcurrent event has occurred 1 = An overcurrent event has not occurred                                                                                                                                                                      |

|                                                                                            |       | . 0                                                                                                                                                | If power management is enabled, review the power switch to determine the required external circuitry. In ganged mode either OVERCUR1z or OVERCUR2z can be used. In ganged mode the overcurrent is reported as a hub event instead of a port event.   |

| I <sup>2</sup> C/SMBUS SIGNALS                                                             |       |                                                                                                                                                    |                                                                                                                                                                                                                                                      |

|                                                                                            |       |                                                                                                                                                    | I <sup>2</sup> C clock/SMBus clock. Function of terminal depends on the setting of the SMBUSz input.                                                                                                                                                 |

|                                                                                            |       |                                                                                                                                                    | When SMBUSz = 1, this terminal acts as the serial clock interface for an I <sup>2</sup> C EEPROM.                                                                                                                                                    |

| SCL/SMBCLK                                                                                 | 2     | I/O<br>PD                                                                                                                                          | When SMBUSz = 0, this terminal acts as the serial clock interface for an SMBus host.                                                                                                                                                                 |

|                                                                                            |       |                                                                                                                                                    | This pin must be pulled up to use the OTP ROM.                                                                                                                                                                                                       |

|                                                                                            |       |                                                                                                                                                    | Can be left unconnected if external interface not implemented.                                                                                                                                                                                       |

|                                                                                            |       |                                                                                                                                                    | I <sup>2</sup> C data/SMBus data. Function of terminal depends on the setting of the SMBUSz input.                                                                                                                                                   |

|                                                                                            |       |                                                                                                                                                    | When SMBUSz = 1, this terminal acts as the serial data interface for an I <sup>2</sup> C EEPROM.                                                                                                                                                     |

| SDA/SMBDAT                                                                                 | 3     | I/O<br>PD                                                                                                                                          | When SMBUSz = 0, this terminal acts as the serial data interface for an SMBus host.                                                                                                                                                                  |

| l                                                                                          |       | . 5                                                                                                                                                | This pin must be pulled up to use the OTP ROM.                                                                                                                                                                                                       |

|                                                                                            |       |                                                                                                                                                    | Can be left unconnected if external interface not implemented.                                                                                                                                                                                       |

## 表 4-1. Pin Functions (続き)

| PIN                                                                                                                     |                                  | TVDE(1) | DESCRIPTION                                                                                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                    | NO.                              | ITPE    | DESCRIPTION                                                                                                                                                                           |  |  |

| TEST AND MISCELLAN                                                                                                      | EOUS SIGNAL                      | s       |                                                                                                                                                                                       |  |  |

|                                                                                                                         |                                  |         | SMBUS mode.                                                                                                                                                                           |  |  |

|                                                                                                                         |                                  |         | The value of the terminal is sampled at the deassertion of reset to enable I <sup>2</sup> C or SMBus mode.                                                                            |  |  |

| SMBUSz                                                                                                                  | 22                               | I<br>PU | 0 = SMBus mode selected<br>1 = I <sup>2</sup> C mode selected                                                                                                                         |  |  |

| SMBUS mode   SMBUS mode   The value of the terminal is sampled at the deassertion of reset to enable I²C or SMBus mode. |                                  |         |                                                                                                                                                                                       |  |  |

|                                                                                                                         |                                  |         | Power control polarity.                                                                                                                                                               |  |  |

|                                                                                                                         |                                  |         | The value of the terminal is sampled at the deassertion of reset to set the polarity of PWRCTL[2:1].                                                                                  |  |  |

| PWRCTL_POL                                                                                                              | 21                               |         |                                                                                                                                                                                       |  |  |

|                                                                                                                         |                                  |         | After reset, this signal is driven low by the TUSB4020BI. Due to this behavior, TI recommends to not tie directly to supply but instead pull up or pull down using external resistor. |  |  |

|                                                                                                                         |                                  |         | Ganged operation enable/SMBus address bit 2/ high-speed status for upstream port                                                                                                      |  |  |

|                                                                                                                         |                                  |         | The value of the terminal is sampled at the deassertion of reset to set the power switch and over current detection mode as follows:                                                  |  |  |

| GANGED/SMBA2/                                                                                                           | 35                               | 1       |                                                                                                                                                                                       |  |  |

| HS_UP                                                                                                                   |                                  | PU      | When SMBus mode is enabled using SMBUSz, this terminal sets the value of the SMBus target address bit 2. SMBus target address bit 3 is always 1 for the TUSB4020BI.                   |  |  |

|                                                                                                                         |                                  |         | After reset, this signal indicates the high-speed USB connection status of the upstream port. A value of 1 indicates the upstream port is connected to a high-speed USB capable port. |  |  |

|                                                                                                                         |                                  |         | Note: individual power control must be enabled for battery charging applications.                                                                                                     |  |  |

|                                                                                                                         |                                  |         | Full power management enable/ SMBus Address bit 1.                                                                                                                                    |  |  |

|                                                                                                                         |                                  |         | The value of the terminal is sampled at the deassertion of reset to set the power switch control follows:                                                                             |  |  |

|                                                                                                                         |                                  |         |                                                                                                                                                                                       |  |  |

| FULLPWRMGMTz/                                                                                                           | 26                               | I DII   | Full power management is the ability to control power to the downstream ports of the TUSB4020BI using PWRCTL[2:1]/BATEN[2:1].                                                         |  |  |

| SMBA1                                                                                                                   | 36                               | 1, PU   | When SMBus mode is enabled using SMBUSz, this terminal sets the value of the SMBus target address bit 1. SMBus target address bit 3 is always 1 for the TUSB4020BI.                   |  |  |

|                                                                                                                         |                                  |         | Can be left unconnected if full power management and SMBus are not implemented.                                                                                                       |  |  |

|                                                                                                                         |                                  |         | After reset, this signal is driven low by the TUSB4020Bl. Due to this behavior, TI recommends to not tie directly to supply but instead pull up or pull down using external resistor. |  |  |

|                                                                                                                         |                                  |         | Note: power switching must be supported for battery charging applications.                                                                                                            |  |  |

| 20.28                                                                                                                   |                                  | I/O     | Reserved. These pins are for internal use only and must be left unconnected on PCB.                                                                                                   |  |  |

| TEST                                                                                                                    | 10                               | I<br>PD | TEST mode enable. When this terminal is asserted high at reset enables test mode. This terminal is reserved for factory use. TI recommends to pull down this terminal to ground.      |  |  |

| POWER AND GROUND                                                                                                        | SIGNALS                          |         |                                                                                                                                                                                       |  |  |

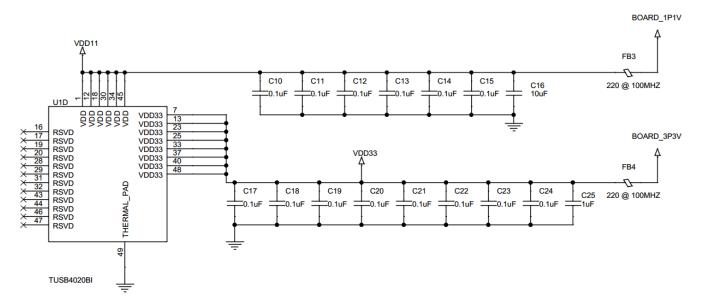

| VDD                                                                                                                     | 1, 12, 18, 30,<br>34, 45         | PWR     | 1.1V power rail                                                                                                                                                                       |  |  |

| VDD33                                                                                                                   | 7, 13, 23, 25,<br>33, 37, 40, 48 | PWR     | 3.3V power rail                                                                                                                                                                       |  |  |

| GND                                                                                                                     | PAD                              | _       | Ground                                                                                                                                                                                |  |  |

<sup>(1)</sup> I = input, O = output, I/O = input/output, PU = internal pullup resistor, PD = internal pulldown resistor, and PWR = power signal

## 5 Specifications

## 5.1 Absolute Maximum Ratings (1)

over operating free-air temperature (unless otherwise noted)

|                  |                                               | MIN  | MAX  | UNIT |

|------------------|-----------------------------------------------|------|------|------|

| Supply Voltage   | V <sub>DD</sub> Steady-state supply voltage   | -0.3 | 1.4  | V    |

|                  | V <sub>DD33</sub> Steady-state supply voltage | -0.3 | 3.8  | V    |

| Voltage          | USB_VBUS pin                                  | -0.3 | 1.4  | V    |

|                  | XI and XO pins                                | -0.4 | 2.45 | V    |

|                  | All other pins                                | -0.3 | 3.8  | V    |

| T <sub>J</sub>   | Operating junction temperature                | -40  | 125  | °C   |

| T <sub>stg</sub> | Storage temperature                           | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 5.2 ESD Ratings

|                    |               |                                                                                 | VALUE | UNIT       |

|--------------------|---------------|---------------------------------------------------------------------------------|-------|------------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±4000 | · · ·      |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±1500 | , <b>v</b> |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                    |                                      | MIN   | NOM | MAX   | UNIT |

|--------------------|--------------------------------------|-------|-----|-------|------|

| VDD <sup>(1)</sup> | 1.1V supply voltage                  | 0.99  | 1.1 | 1.26  | V    |

| VDD33              | 3.3V supply voltage                  | 3     | 3.3 | 3.6   | V    |

| USB_VBUS           | Voltage at USB_VBUS pin              | 0     |     | 1.155 | V    |

| XI, XO             | Voltage at XI and XO pin             | -0.35 |     | 1.98  | V    |

| T <sub>A</sub>     | Operating free-air temperature range | -40   | 25  | 85    | °C   |

| TJ                 | Operating junction temperature range | -40   | 25  | 105   | °C   |

<sup>(1)</sup> A 1.05V, 1.1V, or 1.2V supply can be used as long as minimum and maximum supply conditions are met.

### 5.4 Thermal Information

Copyright © 2024 Texas Instruments Incorporated

|                        |                                              | TUSB4020BI  |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PHP (HTQFP) | UNIT |

|                        |                                              | 48 PINS     |      |

| R <sub>e JA</sub>      | Junction-to-ambient thermal resistance       | 31.8        | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.1        | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 13          | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.9        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.9         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Doods of Folder

## 5.5 3.3V I/O Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                                                               | OPERATION | TEST CONDITIONS             | MIN | TYP MAX         | UNIT |

|------------------|-----------------------------------------------------------------------------------------|-----------|-----------------------------|-----|-----------------|------|

| V <sub>IH</sub>  | High-level input voltage <sup>(1)</sup>                                                 | VDD33     |                             | 2   | VDD33           | V    |

| V <sub>IL</sub>  | Low-level input voltage <sup>(1)</sup>                                                  | VDD33     |                             | 0   | 0.8             | V    |

| VI               | Input voltage                                                                           |           |                             | 0   | VDD33           | V    |

| Vo               | Output voltage <sup>(2)</sup>                                                           |           |                             | 0   | VDD33           | V    |

| t <sub>t</sub>   | Input transition time (t <sub>rise</sub> and t <sub>fall</sub> )                        |           |                             | 0   | 25              | ns   |

| V <sub>hys</sub> | Input hysteresis <sup>(3)</sup>                                                         |           |                             |     | 0.13 ×<br>VDD33 | V    |

| V <sub>OH</sub>  | High-level output voltage                                                               | VDD33     | I <sub>OH</sub> = -4mA      | 2.4 |                 | V    |

| V <sub>OL</sub>  | Low-level output voltage                                                                | VDD33     | I <sub>OL</sub> = 4mA       |     | 0.4             | V    |

| I <sub>OZ</sub>  | High-impedance, output current <sup>(2)</sup>                                           | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±20             | μA   |

| I <sub>OZP</sub> | High-impedance, output current with internal pullup or pulldown resistor <sup>(4)</sup> | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±225            | μΑ   |

| I <sub>I</sub>   | Input current <sup>(5)</sup>                                                            | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±15             | μA   |

- (1) Applies to external inputs and bidirectional buffers

- (2) Applies to external outputs and bidirectional buffers

- (3) Applies to GRSTz

- (4) Applies to pins with internal pullups/pulldowns

- (5) Applies to external input buffers

## 5.6 Hub Input Supply Current

typical values measured at T<sub>A</sub> = 25°C

| PARAMETER                          | VDD33 | VDD11 | UNIT |

|------------------------------------|-------|-------|------|

| PARAMETER                          | 3.3V  | 1.1V  | UNII |

| LOW-POWER MODES                    |       |       |      |

| Power-on (after reset)             | 5     | 39    | mA   |

| Disconnect from host               | 5     | 39    | mA   |

| Suspend                            | 5     | 39    | mA   |

| ACTIVE MODES (US STATE / DS STATE) |       | •     |      |

| 2.0 host / 1 HS device active      | 48    | 71    | mA   |

| 2.0 host / 2 HS devices active     | 60    | 80    | mA   |

| SMBUS Programming current          | 79    | 225   | mA   |

Product Folder Links: TUSB4020BI

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

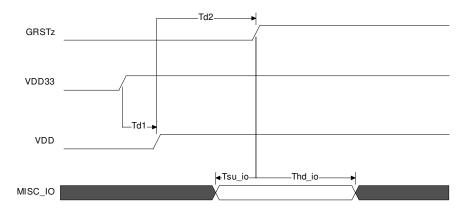

## **5.7 Power-Up Timing Requirements**

|                         |                                                                          | MIN     | NOM | MAX | UNIT |

|-------------------------|--------------------------------------------------------------------------|---------|-----|-----|------|

| t <sub>d1</sub>         | VDD33 stable before VDD stable <sup>(1)</sup>                            | see (2) |     |     | ms   |

| t <sub>d2</sub>         | VDD and VDD33 stable before deassertion of GRSTz                         | 3       |     |     | ms   |

| t <sub>su_io</sub>      | Setup for MISC inputs <sup>(3)</sup> sampled at the deassertion of GRSTz | 0.1     |     |     | μs   |

| t <sub>hd_io</sub>      | Hold for MISC inputs <sup>(3)</sup> sampled at the deassertion of GRSTz. | 0.1     |     |     | μs   |

| t <sub>VDD33_RAMP</sub> | VDD33 supply ramp requirements                                           | 0.2     |     | 100 | ms   |

| t <sub>VDD_RAMP</sub>   | VDD supply ramp requirements                                             | 0.2     |     | 100 | ms   |

- (1) An active reset is required if the VDD33 supply is stable before the VDD11 supply. This active Reset shall meet the 3ms power-up delay counting from both power supplies being stable to the deassertion of GRSTz.

- (2) There is no power-on relationship between VDD33 and VDD unless GRSTz is only connected to a capacitor to GND. Then VDD must be stable minimum of 10 µs before the VDD33.

- (3) MISC pins sampled at deassertion of GRSTz: FULLPWRMGMTz, GANGED, PWRCTL\_POL, SMBUSz, BATEN[4:1], and AUTOENz.

図 5-1. Power-Up Timing Requirements

## **6 Detailed Description**

### 6.1 Overview

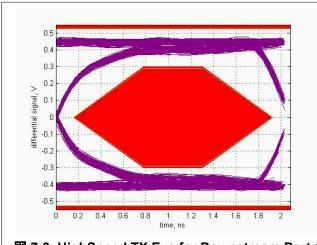

The TUSB4020BI is a two-port USB 2.0 hub, which provides USB high-speed/full-speed connections on the upstream port and USB high-speed, full-speed, or low-speed connections on the downstream ports. When the upstream port is connected to an electrical environment that supports high-speed and full-speed/low-speed connections, USB high-speed and full-speed/low-speed connectivity is enabled on the downstream ports. When the upstream port is connected to an electrical environment that only supports full-speed/low-speed connections, USB high-speed connectivity are disabled on the downstream ports.

## 6.2 Functional Block Diagram

### **6.3 Feature Description**

### 6.3.1 Battery Charging Features

The TUSB4020BI provides support for battery charging. Battery charging support can be enabled on a per port basis through the REG\_6h(batEn[1:0]).

Battery charging support includes both charging downstream port (CDP) and dedicated charging port (DCP) modes. The DCP mode is compliant with the Chinese Telecommunications Industry Standard YD/T 1591-2009.

In addition to standard DCP mode, the TUSB4020BI provides a mode (AUTOMODE) which automatically provides support for DCP devices and devices that support custom charging indication. AUTOMODE is disabled by default. When in AUTOMODE, the port automatically switches between a divider mode and the DCP mode depending on the portable device connected. The divider mode places a fixed DC voltage on the ports DP and DM signals which allows some devices to identify the capabilities of the charger. The default divider mode indicates support for up to 5 W. The divider mode can be configured to report a high-current setting (up to 10 W) through REG\_Ah(HiCurAcpModeEn). When AUTOMODE is enabled through REG\_Ah(autoModeEnz), the CDP mode is not functional. CDP mode can not be used when AUTOMODE is enabled.

The battery charging mode for each port depends on the state of Reg\_6h(batEn[n]), the status of the VBUS input, and the state of REG\_Ah(autoModeEnz) upstream port, as identified in 表 6-1. Battery charging can also be enabled through the PWRCTL1/BATEN1 and PWRCTL2/BATEN2 pins.

|          | 表 6-1. 103B4020Bi Battery Charging Modes |             |                               |  |  |  |  |  |  |  |  |

|----------|------------------------------------------|-------------|-------------------------------|--|--|--|--|--|--|--|--|

| batEn[n] | VBUS                                     | autoModeEnz | BC Mode Port x<br>(x = n + 1) |  |  |  |  |  |  |  |  |

| 0        | Do not care                              | Do not care | Do not care                   |  |  |  |  |  |  |  |  |

|          | <4V                                      | 0           | Automode <sup>(3)</sup> (4)   |  |  |  |  |  |  |  |  |

| 1        | \ \\                                     | 1           | DCP <sup>(1)</sup> (2)        |  |  |  |  |  |  |  |  |

|          | >4\/                                     | 1           | CDP(1)                        |  |  |  |  |  |  |  |  |

表 6-1. TUSB4020BI Battery Charging Modes

- (1) USB device is USB Battery Charging Specification Revision 1.2 Compliant

- (2) USB device is Chinese Telecommunications Industry Standard YD/T 1591-2009

- (3) Auto-mode automatically selects divider-mode or DCP mode.

- (4) Divider mode can be configured for high-current mode through register or OTP settings.

#### 6.3.2 USB Power Management

The TUSB4020BI can be configured for power switched applications using either per-port or ganged powerenable controls and overcurrent status inputs.

Power switch support is enabled by REG\_5h(fullPwrMgmtz) and the per-port or ganged mode is configured by REG\_5h(ganged). The power switch can also be enabled through the FULLPWRMGMTz pin. Also ganged or individual control can be controlled by the GANGED pin.

The TUSB4020BI supports both active-high and active-low power-enable controls. The PWRCTL[2:1] polarity is configured by REG\_Ah(pwrctlPol). The polarity can also be configured by the PWRCTL\_POL pin.

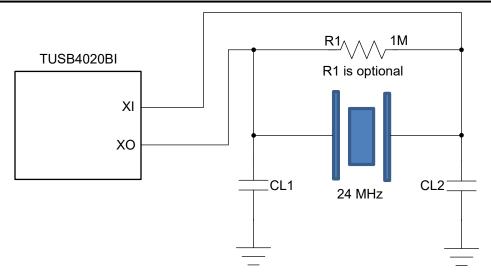

#### 6.3.3 Clock Generation

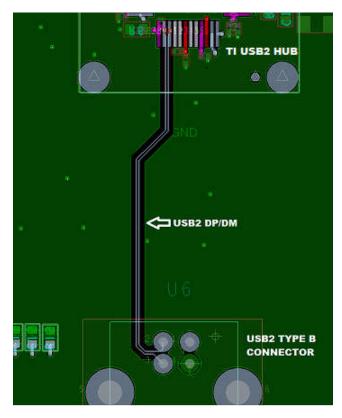

The TUSB4020BI accepts a crystal input to drive an internal oscillator or an external clock source. Keep the XI and XO traces as short as possible and away from any switching leads to minimize noise coupling.

Product Folder Links: TUSB4020BI

図 6-1. TUSB4020BI Clock

#### 6.3.4 Power-Up and Reset

The TUSB4020BI does not have specific power sequencing requirements with respect to the VDD or VDD33 power rails. The VDD or VDD33 power rails can be powered up for an indefinite period of time while the other is not powered up if all of these constraints are met:

- All maximum ratings and recommended operating conditions are observed.

- All warnings about exposure to maximum rated and recommended conditions are observed, particularly junction temperature. These apply to power transitions as well as normal operation.

- Bus contention while VDD33 is powered-up must be limited to 100 hours over the projected lifetime of the device.

- Bus contention while VDD33 is powered-down can violate the absolute maximum ratings.

A supply bus is powered up when the voltage is within the recommended operating range. A supply bus is powered down when the supply is below that range, either stable or in transition.

A minimum reset duration of 3ms is required, which is defined as the time when the power supplies are in the recommended operating range to the deassertion of GRSTz. This can be generated using programmable-delay supervisory device or using an RC circuit.

#### 6.4 Device Functional Modes

#### 6.4.1 External Configuration Interface

The TUSB4020BI supports a serial interface for configuration register access. The device can be configured by an attached I<sup>2</sup>C EEPROM or accessed as a target by a SMBus-capable host controller. The external interface is enabled when both the SCL/SMBCLK and SDA/SMBDAT terminals are pulled up to 3.3V at the deassertion of reset. The mode, I<sup>2</sup>C controller, or SMBus target is determined by the state of SMBUSz terminal at reset.

Product Folder Links: TUSB4020BI

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

### 6.5 Programming

### 6.5.1 One-Time Programmable (OTP) Configuration

The TUSB4020BI allows device configuration through OTP non-volatile memory (OTP). The programming of the OTP is supported using vendor-defined USB device requests. For details using the OTP features, contact a TI representative.

$\pm$  6-2 provides a list features which can be configured using the OTP. The bit field section in  $\pm$  6-2 shows which features can be controlled by OTP ROM. The bits not listed in the table are not accessible by the OTP ROM.

|                               | 3C 0 2. O 11 | Comigurable reactives                                                                                                                      |

|-------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIGURATION REGISTER OFFSET | BIT FIELD    | DESCRIPTION                                                                                                                                |

| REG_01h                       | [7:0]        | Vendor ID LSB                                                                                                                              |

| REG_02h                       | [7:0]        | Vendor ID MSB                                                                                                                              |

| REG_03h                       | [7:0]        | Product ID LSB                                                                                                                             |

| REG_04h                       | [7:0]        | Product ID MSB                                                                                                                             |

| REG_07h                       | [0]          | Port removable configuration for downstream ports 1. OTP configuration is inverse of rmbl[1:0], that is: 1 = Not removable 0 = Removable   |

| REG_07h                       | [1]          | Port removable configuration for downstream ports 2. OTP configuration is inverse of rmbl[1:0], that is:  1 = Not removable  0 = Removable |

| REG_0Ah                       | [1]          | Automode enable                                                                                                                            |

| REG_0Ah                       | [4]          | High-current divider mode enable.                                                                                                          |

| REG_F2h                       | [3:1]        | USB power switch power-on delay.                                                                                                           |

表 6-2. OTP Configurable Features

## 6.5.2 I<sup>2</sup>C EEPROM Operation

The TUSB4020BI supports a single-controller, standard mode (100kbps) connection to a dedicated I<sup>2</sup>C EEPROM when the I<sup>2</sup>C interface mode is enabled. In I<sup>2</sup>C mode, the TUSB4020BI reads the contents of the EEPROM at bus address 1010000b using 7-bit addressing starting at address 0.

If the value of the EEPROM contents at byte 00h equals 55h, the TUSB4020BI loads the configuration registers according to the EEPROM map. If the first byte is not 55h, the TUSB4020BI exits the I<sup>2</sup>C mode and continues execution with the default values in the configuration registers. The hub does not connect on the upstream port until the configuration is completed. If the TUSB4020BI detects an unprogrammed EEPROM (value other than 55h), the device enters programming mode and a programming endpoint within the hub is enabled.

Note, the bytes located above offset Ah are optional. The requirement for data in those addresses depends on the options configured in the Device Configuration, Phy Custom Configuration, and Device Configuration 2 registers.

For details on I<sup>2</sup>C operation, refer to the UM10204 I<sup>2</sup>C-bus Specification and User Manual.

## 6.5.3 SMBus Target Operation

When the SMBus interface mode is enabled, the TUSB4020BI supports read block and write block protocols as a target-only SMBus device.

Product Folder Links: TUSB4020BI

The TUSB4020BI target address is 1000 1xyz, where:

- x is the state of GANGED/SMBA2/HS UP terminal at reset

- y is the state of FULLPWRMGMTz/SMBA1 terminal at reset

- z is the read/write bit; 1 = read access, 0 = write access.

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

13

If the TUSB4020BI is addressed by a host using an unsupported protocol, the device does not respond. The TUSB4020BI waits indefinitely for configuration by the SMBus host and does not connect on the upstream port until the SMBus host indicates configuration is complete by clearing the CFG\_ACTIVE bit.

For details on SMBus requirements, refer to the System Management Bus Specification.

注

During the SMBUS configuration the hub can draw an extra current, this extra current consumption ends as soon as the CFG\_ACTIVE bit is cleared. For more information, see the *Hub Input Supply Current* section in this data sheet.

### 6.6 Register Maps

## 6.6.1 Configuration Registers

The internal configuration registers are accessed on byte boundaries. The configuration register values are loaded with defaults but can be overwritten when the TUSB4020BI is in I<sup>2</sup>C or SMBus mode.

表 6-3. TUSB4020BI Register Map

| BYTE ADDRESS | CONTENTS                                  | EEPROM CONFIGURABLE          |

|--------------|-------------------------------------------|------------------------------|

| 00h          | ROM Signature Register                    | No                           |

| 01h          | Vendor ID LSB                             | Yes                          |

| 02h          | Vendor ID MSB                             | Yes                          |

| 03h          | Product ID LSB                            | Yes                          |

| 04h          | Product ID MSB                            | Yes                          |

| 05h          | Device Configuration Register             | Yes                          |

| 06h          | Battery Charging Support Register         | Yes                          |

| 07h          | Device Removable Configuration Register   | Yes                          |

| 08h          | Port Used Configuration Register          | Yes                          |

| 09h          | Reserved                                  | Yes, program to 00h          |

| 0Ah          | Device Configuration Register 2           | Yes                          |

| 0Bh to 0Fh   | Reserved                                  |                              |

| 10h to 1Fh   | UUID Byte [15:0]                          | No                           |

| 20h to 21h   | LangID Byte [1:0]                         | Yes, if customStrings is set |

| 22h          | Serial Number String Length               | Yes, if customSerNum is set  |

| 23h          | Manufacturer String Length                | Yes, if customStrings is set |

| 24h          | Product String Length                     | Yes, if customStrings is set |

| 25h to 2Fh   | Reserved                                  | Yes                          |

| 30h to 4Fh   | Serial Number String Byte [31:0]          | Yes, if customSerNum is set  |

| 50h to 8Fh   | Manufacturer String Byte [63:0]           | Yes, if customStrings is set |

| 90h to CFh   | Product String Byte [63:0]                | Yes, if customStrings is set |

| D0 to DFh    | Reserved                                  | No                           |

| F0h          | Additional Feature Configuration Register | Yes                          |

| F1h          | Reserved                                  | Yes                          |

| F2h          | Charging Port Control Register            | Yes                          |

| F3 to F7h    | Reserved                                  | No                           |

| F8h          | Device Status and Command Register        | No                           |

| F9 to FFh    | Reserved                                  | No                           |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

14

Product Folder Links: TUSB4020BI

### 6.6.1.1 ROM Signature Register (offset = 0h) [reset = 0h]

## 図 6-2. Register Offset 0h

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 表 6-4. ROM Signature Register

| Bit | Field        | Туре | Reset | Description                                                                                                                                                                                                                                                                                               |

|-----|--------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | romSignature | R/W  | 0h    | ROM Signature Register. This register is used by the TUSB4020BI in I <sup>2</sup> C mode to validate the attached EEPROM has been programmed. The first byte of the EEPROM is compared to the mask 55h and if not a match, the TUSB4020BI aborts the EEPROM load and executes with the register defaults. |

### 6.6.1.2 Vendor ID LSB Register (offset = 1h) [reset = 51h]

### 図 6-3. Register Offset 51h

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 0   | 1   | 0   | 0   | 0   | 1   |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 表 6-5. Vendor ID LSB Register

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | vendorldLsb | R/W  | 51h   | Vendor ID LSB. Least significant byte of the unique vendor ID assigned by the USB-IF; the default value of this register is 51h representing the LSB of the TI Vendor ID 0451h. The value can be overwritten to indicate a customer vendor ID. This field is read/write unless the OTP ROM VID and OTP ROM PID values are non-zero. If both values are non-zero, the value when reading this register shall reflect the OTP ROM value. |

### 6.6.1.3 Vendor ID MSB Register (offset = 2h) [reset = 4h]

## 図 6-4. Register Offset 2h

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Copyright © 2024 Texas Instruments Incorporated

### 表 6-6. Vendor ID MSB Register

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | vendorldMsb | R/W  | 4h    | Vendor ID MSB. Most significant byte of the unique vendor ID assigned by the USB-IF; the default value of this register is 04h representing the MSB of the TI Vendor ID 0451h. The value can be overwritten to indicate a customer vendor ID. This field is read/write unless the OTP ROM VID and OTP ROM PID values are non-zero. If both values are non-zero, the value when reading this register shall reflect the OTP ROM value. |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 6.6.1.4 Product ID LSB Register (offset = 3h) [reset = 25h]

## 図 6-5. Register Offset 3h

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | 0   | 0   | 1   | 0   | 1   |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 表 6-7. Product ID LSB Register

| Bit | Field        | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | productIdLsb | R/W  | 25h   | Product ID LSB. Least significant byte of the product ID assigned by TI. The default value of this register is 25h representing the LSB of the product ID assigned by TI. The value reported in the USB 2.0 device descriptor is the value of this register bit wise XORed with 00000010b. The value can be overwritten to indicate a customer product ID. This field is read/write unless the OTP ROM VID and OTP ROM PID values are non-zero. If both values are non-zero, the value when reading this register shall reflect the OTP ROM value. |

## 6.6.1.5 Product ID MSB Register (offset = 4h) [reset = 80h]

## 図 6-6. Register Offset 4h

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### 表 6-8. Bit Descriptions - Product ID MSB Register

| Bit | Field        | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | productldLsb | R/W  | 80h   | Product ID MSB. Most significant byte of the product ID assigned by TI; the default value of this register is 80h representing the MSB of the product ID assigned by TI. The value can be overwritten to indicate a customer product ID.  This field is read/write unless the OTP ROM VID and OTP ROM PID values are non-zero. If both values are non-zero, the value when reading this register reflects the OTP ROM value. |

Product Folder Links: TUSB4020BI

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

## 6.6.1.6 Device Configuration Register (offset = 5h) [reset = 1Xh]

## 図 6-7. Register Offset 5h

| 7   | 6   | 5   | 4 | 3   | 2   | 1   | 0 |

|-----|-----|-----|---|-----|-----|-----|---|

| 0   | 0   | 0   | 1 | Х   | Х   | 0   | 0 |

| R/W | R/W | R/W | R | R/W | R/W | R/W | R |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 表 6-9. Device Configuration Register

| Bit                                          | Field         | Type | Reset                           | Description Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|---------------|------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                            | customStrings | R/W  | 1Xh                             | Custom strings enable. This bit controls the ability to write to the Manufacturer String Length, Manufacturer String, Product String Length, Product String, and Language ID registers.  0 = The Manufacturer String Length, Manufacturer String, Product String Length, Product String, and Language ID registers are read only.  1 = The Manufacturer String Length, Manufacturer String, Product String Length, Product String, and Language ID registers can be loaded by EEPROM or written by SMBus. The default value of this bit is 0.                   |

| 6                                            | customSernum  | R/W  | 1Xh                             | Custom serial number enable. This bit controls the ability to write to the serial number registers.  0 = The Serial Number String Length and Serial Number String registers are read only.  1 = The Serial Number String Length and Serial Number String registers can be loaded by EEPROM or written by SMBus.  The default value of this bit is 0.                                                                                                                                                                                                            |

| 5 RSVD R/W 1Xh Reserved. This bit is reserve |               | 1Xh  | Reserved. This bit is reserved. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4                                            | RSVD          | R    | 1Xh                             | Reserved. This bit is reserved and returns 1 when read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3                                            | ganged        | R/W  | 1Xh                             | Ganged. This bit is loaded at the deassertion of reset with the value of the GANGED/SMBA2/HS_UP terminal.  0 = When fullPwrMgmtz = 0, each port is individually power switched and enabled by the PWRCTL[2:1]/BATEN[2:1] terminals  1 = When fullPwrMgmtz = 0, the power switch control for all ports is ganged and enabled by the PWRCTL1/BATEN1 terminal When the TUSB4020BI is in I <sup>2</sup> C mode, the TUSB4020BI loads this bit from the contents of the EEPROM. When the TUSB4020BI is in SMBUS mode, the value can be overwritten by an SMBus host. |

| 2                                            | fullPwrMgmtz  | R/W  | 1Xh                             | Full Power Management. This bit is loaded at the deassertion of reset with the value of the FULLPWRMGMTz/SMBA1 terminal.  0 = Port power switching and over-current status reporting is enabled  1 = Port power switching and over-current status reporting is disabled When the TUSB4020BI is in I <sup>2</sup> C mode, the TUSB4020BI loads this bit from the contents of the EEPROM. When the TUSB4020BI is in SMBUS mode, the value can be overwritten by an SMBus host.                                                                                    |

| 1                                            | RSVD          | R/W  | 1Xh                             | Reserved. This bit is reserved and must not be altered from the default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                                            | RSVD          | R    | 1Xh                             | Reserved. This field is reserved and returns 0 when read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Product Folder Links: TUSB4020BI

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック (ご意見やお問い合わせ) を送信

17

### 6.6.1.7 Battery Charging Support Register (offset = 6h) [reset = 0Xh]

## 図 6-8. Register Offset 6h

| 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|

| 0 | 0   | 0   | 0   | 0   | 0   | Х   | X   |

| R | R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 表 6-10. Battery Charging Support Register