# TUSB216-Q1 車載対応 USB 高速シグナル コンディショナ (バッテリ充電コン トローラ付き)

#### 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み - デバイス温度グレード 2:-40℃~105℃

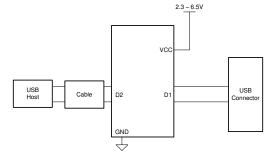

- 広い電源電圧範囲:2.3~6.5V

- USB 切断時およびシャットダウン時の非常に低い消費

- USB 2.0 High Speed 信号のコンディショニングを提

- USB 2.0、OTG 2.0、BC 1.2 に対応

- Low-Speed、Full-Speed、High-Speed 信号処理の サポート

- BC 1.2 CDP バッテリ充電コントローラを内蔵

- 特定のホストやデバイスに非依存

- 最大 5m のケーブルをサポート

- 外付けのプルダウン抵抗により4つの信号ブースト (エッジ・ブーストと DC ブースト) 設定を選択可能

- プルアップまたはプルダウンで選択可能な 3 つの RX 感度設定により、損失が大きいアプリケーション の ISI ジッタを補償

- 2 つの TUSB216-Q1 デバイスを使って最大 10m の ケーブル長に対応

- スケーラブルなソリューション 損失が大きいアプリケ ーションに対応するため、デバイスをデイジー・チェー

- TUSB211A、212、214、217A (3.3V) とピン互換

## 2 アプリケーション

- 車載用インフォテインメントおよびクラスタ

- 車載用ヘッド・ユニット

- アクティブ・ケーブル、延長ケーブル、バックプレーン

#### 3 概要

TUSB216-Q1 は第3世代 USB 2.0 High Speed 信号コ ンディショナーで、伝送チャネルでの AC 損失 (容量性負 荷による) および DC 損失 (抵抗損失による) を補償する ように設計されています。

TUSB216-Q1 には、エッジ・ブースタにより USB 2.0 High Speed 信号の遷移エッジを高速化し、DC ブースト 機能により静的電圧レベルを上げる特許取得済みの設計 が採用されています。

また、TUSB216-Q1 はプリイコライゼーション機能を備え ているため、レシーバ感度を高め、長いケーブルを使用す るアプリケーションで ISI (符号間干渉) ジッタを補償できま す。USB Low Speed および Full Speed 信号特性は、 TUSB216-Q1 による影響を受けません。

TUSB216-Q1 は、パケット・タイミングを変更せず、また、 伝搬遅延やレイテンシを追加せずに、信号品質を向上さ せることができます。

TUSB216-Q1 により、最長 5 メートルのケーブルを使用 したシステムで、USB 2.0 High Speed 近端アイ・コンプラ イアンスに合格することが可能になります。

TUSB216-Q1 は USB On-The-Go (OTG) および Battery Charging (BC 1.2) プロトコルにも対応していま す。 内蔵の BC 1.2 バッテリ充電コントローラは、制御ピン を使って有効化できます。

#### 製品情報

| 部品番号 (1)   | パッケージ <sup>(2)</sup> | 動作温度 (T <sub>A</sub> ) ℃ | パッケージ サイズ <sup>(3)</sup> |

|------------|----------------------|--------------------------|--------------------------|

| TUSB216    |                      | 0~70                     |                          |

| TUSB216I   | RWB (X2QFN, 12)      | -40~85                   | 1.6mm × 1.6mm            |

| TUSB216-Q1 |                      | -40~105                  |                          |

- 製品比較表を参照してください。 (1)

- 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

概略回路図

# **Table of Contents**

| 1 | 特長                                   |   |

|---|--------------------------------------|---|

|   |                                      |   |

| 2 | アプリケーション                             |   |

| 3 | 概要                                   | • |

|   | Device Comparison                    |   |

|   | Pin Configuration and Functions      |   |

| 6 | Specifications                       | ļ |

|   | 6.1 Absolute Maximum Ratings         |   |

|   | 6.2 ESD Ratings                      |   |

|   | 6.3 Recommended Operating Conditions | ļ |

|   | 6.4 Thermal Information              |   |

|   | 6.5 Electrical Characteristics       | ( |

|   | 6.6 Switching Characteristics        |   |

|   | 6.7 Timing Requirements              |   |

|   | Detailed Description                 |   |

|   | 7.1 Overview                         | Ç |

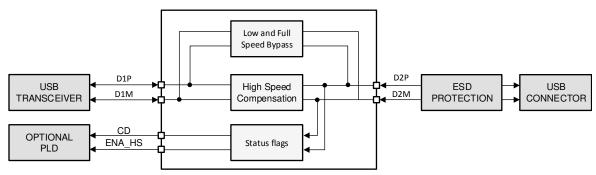

|   | 7.2 Functional Block Diagram         | ( |

|   | 7.3 Feature Description              |   |

| 7.4 Device Functional Modes             |    |

|-----------------------------------------|----|

| 7.5 TUSB216 Registers                   | 10 |

| 8 Application and Implementation        |    |

| 8.1 Application Information             | 14 |

| 8.2 Typical Application                 | 14 |

| 8.3 Power Supply Recommendations        | 22 |

| 8.4 Layout                              | 22 |

| 9 Device and Documentation Support      | 23 |

| 9.1ドキュメントの更新通知を受け取る方法                   | 23 |

| 9.2 サポート・リソース                           | 23 |

| 9.3 Trademarks                          |    |

| 9.4 静電気放電に関する注意事項                       | 23 |

| 9.5 用語集                                 | 23 |

| 10 Revision History                     | 23 |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 23 |

|                                         |    |

# **4 Device Comparison**

|                                                                                                                                                            | TUSB211A                                                         | TUSB212     | TUSB214     | TUSB216                                                          | TUSB217A                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|-------------|------------------------------------------------------------------|------------------------------------------------------------------|

| Industrial Variant Available                                                                                                                               | Υ                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| Automotive Variant Available                                                                                                                               | Υ                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| Supply (V)                                                                                                                                                 | 2.3 to 6.5                                                       | 3.3         | 3.3         | 2.3 to 6.5                                                       | 2.3 to 6.5                                                       |

| DC Boost                                                                                                                                                   | Tandem with AC<br>Boost                                          | 3 levels    | 3 levels    | Tandem with AC<br>Boost                                          | Tandem with AC<br>Boost                                          |

| I2C Control                                                                                                                                                | N                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| RX pre-equalization for ISI compensation                                                                                                                   | N/A                                                              | N/A         | N/A         | 3 levels                                                         | 3 levels                                                         |

| Charging Downstream Port (CDP) controller                                                                                                                  | N/A                                                              | N/A         | Always ON   | Pin Controlled                                                   | Always ON. Dynamically selected by DCP/CDP pin                   |

| Dedicated Charging Port (DCP) controller                                                                                                                   | N/A                                                              | N/A         | N/A         | N/A                                                              | Always ON. Dynamically selected by DCP/CDP pin                   |

| Cable length compensation for near-<br>end high-speed eye mask Compliance<br>(pre-channel before redriver/post-<br>channel after redriver) (meter - gauge) | 6/3 - 28AWG (10 -<br>24AWG with one<br>redriver on each<br>end)  | 4/2 - 28AWG | 4/2 - 28AWG | 6/3 - 28AWG (10 -<br>24AWG with one<br>redriver on each<br>end)  | 6/3 - 28AWG (10 -<br>24AWG with one<br>redriver on each<br>end)  |

| Cable length compensation for far-end high-speed eye mask Compliance (pre-channel before redriver/post-channel after redriver) (meter - gauge)             | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) | 8/6 - 28AWG | 8/6 - 28AWG | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) |

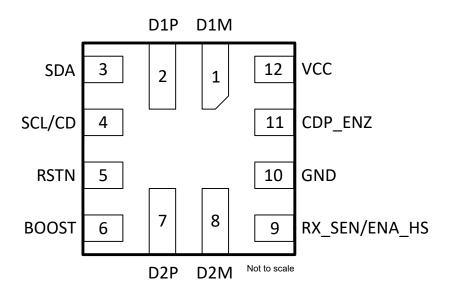

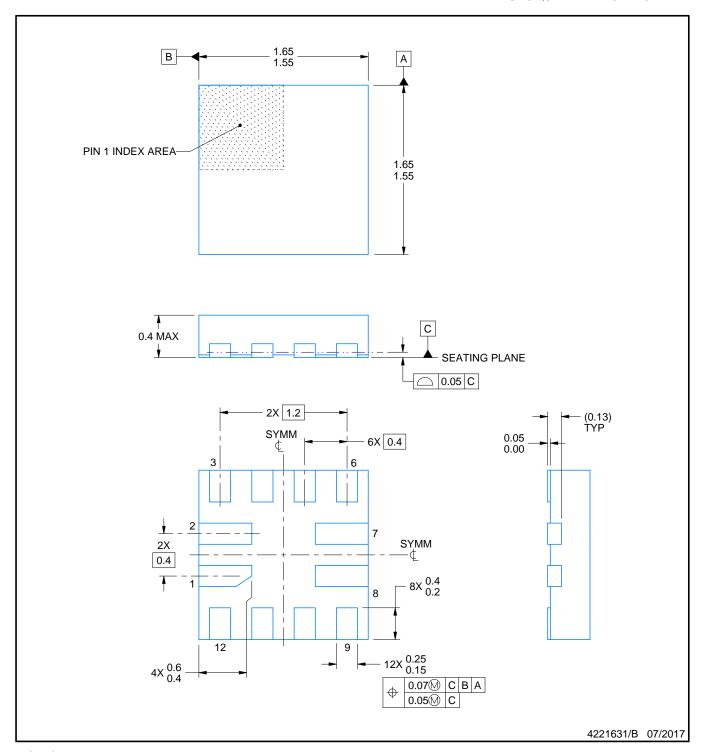

# **5 Pin Configuration and Functions**

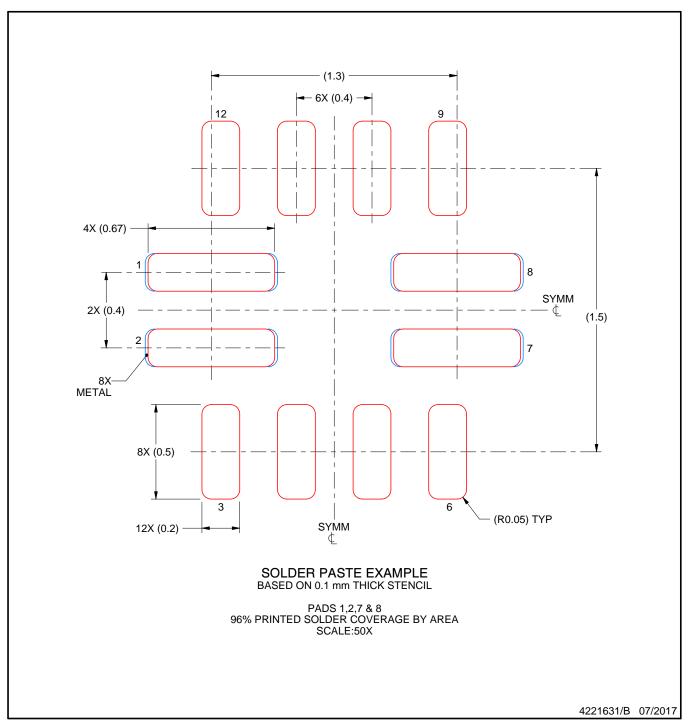

図 5-1. TUSB216-Q1 RWB Package, 12-Pin X2QFN (Top View)

表 5-1. Pin Functions

| PIN                           |     | TYPE(1) INTERNAL |                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------|-----|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                          | NO. | I I PE           | PULLUP/PULLDOWN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| BOOST                         | 6   | I                | N/A             | USB High-speed boost select via external pull down resistor. Both edge boost and DC boost are controlled by a single pin in non-I2C mode. In I2C mode edge boost and DC boost can be individually controlled. Sampled upon power up. Does not recognize real time adjustments. Auto selects BOOST LEVEL = 3 when left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| CDP_ENZ                       | 11  | ļ                | 500 kΩ PU       | Set CDP_ENZ is low to enable BC 1.2 CDP controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RX_SEN <sup>(3)</sup> /ENA_HS | 9   | l/O              | N/A             | In I2C mode: Reserved for TI test purpose. In non-I2C mode: At reset: 3-level input signal RX_SEN. USB High-speed RX Sensitivity Setting to Compensate ISI Jitter H (pin is pulled high) – high RX sensitivity (high loss channel) M (pin is left floating) – medium RX sensitivity (medium loss channel) L (pin is pulled low) – low RX sensitivity (low loss channel) After reset: Output signal ENA_HS. Flag indicating that channel is in High-speed mode. Asserted upon: 1. Detection of USB-IF High-speed test fixture from an unconnected state followed by transmission of USB TEST_PACKET pattern. 2. Squelch detection following USB reset with a successful HS handshake [HS handshake is declared to be successful after single chirp J chirp K pair where each chirp is within 18 µs – 128 µs]. |  |  |

## 表 5-1. Pin Functions (続き)

| PIN                    |     | TYPE <sup>(1)</sup> | INTERNAL                                | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|------------------------|-----|---------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO. | ITPE''              | PULLUP/PULLDOWN                         | DESCRIPTION                                                                                                                                                                                                                                                                                                |

| D2P                    | 7   | I/O                 | N/A                                     | USB High-speed positive port.                                                                                                                                                                                                                                                                              |

| D2M                    | 8   | I/O                 | N/A                                     | USB High-speed negative port.                                                                                                                                                                                                                                                                              |

| GND                    | 10  | Р                   | N/A                                     | Ground                                                                                                                                                                                                                                                                                                     |

| D1M                    | 1   | I/O                 | N/A                                     | USB High-speed negative port                                                                                                                                                                                                                                                                               |

| D1P                    | 2   | I/O                 | N/A                                     | USB High-speed positive port.                                                                                                                                                                                                                                                                              |

| SDA <sup>(2)</sup>     | 3   | I/O                 | 500 kΩ PU<br>1.8 MΩ PD                  | I2C Mode: Bidirectional I2C data pin [7-bit I2C slave address = 0x2C]. In non I2C mode: Reserved for TI test purpose.                                                                                                                                                                                      |

| VCC                    | 12  | Р                   | N/A                                     | Supply power                                                                                                                                                                                                                                                                                               |

| RSTN                   | 5   | I                   | 500 kΩ PU<br>1.8 MΩ PD                  | Device disable/enable.  Low – Device is at reset and in shutdown, and  High - Normal operation.  Recommend 0.1-µF external capacitor to GND to ensure clean power on reset if not driven. If the pin is driven, it must be held low until the supply voltage for the device reaches within specifications. |

| SCL <sup>(2)</sup> /CD | 4   | I/O                 | When RSTN asserted there is a 500 kΩ PD | In I2C mode: I2C clock pin [I2C address = 0x2C]. Non I2C mode: After reset: Output CD. Flag indicating that a USB device is attached (connection detected). Asserted from an unconnected state upon detection of DP or DM pull-up resistor. De-asserted upon detection of disconnect.                      |

- (1) I = input, O = output, P = power

- (2) Pull-up resistors for SDA and SCL pins in I<sup>2</sup>C mode should be R<sub>Pull-up</sub> (depending on I2C bus voltage). If both SDA and SCL are pulled up at power-up the device enters into I<sup>2</sup>C mode.

- (3) Pull-down and pull-up resistors for RX\_SEN pin must follow  $R_{RXSEN1}$  and  $R_{RXSEN2}$  resistor recommendations in non I<sup>2</sup>C mode.

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                 | MIN  | MAX  | UNIT |

|---------------------------------------|---------------------------------|------|------|------|

| Supply voltage range                  | VCC                             | -0.3 | 7    | V    |

| Voltage range USB data                | DxP, DxM                        | -0.3 | 5.5  | V    |

| Voltage range on BOOST pin            | BOOST                           | -0.3 | 1.98 | V    |

| Voltage range other pins              | RX_SEN, CDP_ENZ, SDA, SCL, RSTN | -0.3 | 5.5  | V    |

| Storage temperature, T <sub>stg</sub> |                                 | -65  | 150  | °C   |

| Maximum junction temperature, T       | J (max)                         |      | 125  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |                         |                                                             | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Liectiostatic discharge | Charged-device model (CDM), per AEC Q100-011 <sup>(2)</sup> | ±750  | V    |

- (1) AEC Q100-002 HBM ESD Classification Level 2

- (2) AEC Q100- 011 CDM ESD Classification Level C4A

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                      |                                                    | MIN  | NOM | MAX  | UNIT |

|----------------------|----------------------------------------------------|------|-----|------|------|

| V <sub>CC</sub>      | Supply voltage                                     | 2.3  | 5   | 6.5  | V    |

| T <sub>A</sub>       | Operating free-air temperature (AEC-Q100)          | -40  |     | 105  | °C   |

| T <sub>J</sub>       | Junction temperature (AEC-Q100)                    |      |     | 115  | °C   |

| V <sub>I2C_BUS</sub> | I2C Bus Voltage                                    | 1.62 |     | 3.6  | V    |

| DxP, DxM             | Voltage range USB data                             | 0    |     | 3.6  | V    |

| BOOST                | Voltage range BOOST pin                            | 0    |     | 1.98 | V    |

| DIGITAL              | Voltage range other pins (SCL, SDA, RSTN, CDP_ENZ) | 0    |     | 3.6  | V    |

| RX_SEN               | Voltage range RX_SEN pin                           | 0    |     | 5.0  | V    |

#### 6.4 Thermal Information

|                       | THERMAL METRIC (1)                           | RWB (X2QFN) | UNIT |

|-----------------------|----------------------------------------------|-------------|------|

|                       | I DERWAL METRIC (1)                          | 12 PINS     | UNIT |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 137.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 62          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 67.2        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.9         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 67.3        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

## **6.5 Electrical Characteristics**

Over operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                                                                               | TEST CONDITIONS                                                                          | MIN | TYP (1) | MAX      | UNIT |

|--------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|---------|----------|------|

| POWER                    |                                                                                                         |                                                                                          |     |         |          |      |

| I <sub>ACTIVE_HS</sub>   | High Speed Active Current                                                                               | USB channel = HS mode. 480 Mbps traffic. V <sub>CC</sub> supply stable, with Boost = Max |     | 22      | 36       | mA   |

| I <sub>IDLE_HS</sub>     | High Speed Idle Current                                                                                 | USB channel = HS mode, no traffic.  V <sub>CC</sub> supply stable, Boost = Max           |     | 22      | 36       | mA   |

| I <sub>HS_SUPSPEND</sub> | High Speed Suspend Current                                                                              | USB channel = HS Suspend mode. V <sub>CC</sub> supply stable                             |     | 0.75    | 1.4      | mA   |

| I <sub>FS</sub>          | Full-Speed Current                                                                                      | USB channel = FS mode, 12 Mbps traffic, V <sub>cc</sub> supply stable                    |     | 0.75    | 1.4      | mA   |

| I <sub>DISCONN</sub>     | Disconnect Power                                                                                        | Host side application. No device attachment.                                             |     | 0.80    | 1.4      | mA   |

| I <sub>SHUTDN</sub>      | Shutdown Power                                                                                          | RSTN driven low, V <sub>CC</sub> supply stable                                           |     | 60      | 115      | μA   |

| CONTROL PIN LE           | EAKAGE                                                                                                  |                                                                                          |     |         | <u> </u> |      |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for SDA, RSTN                                                              | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     | 10      | 15       | μA   |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for RX_SEN                                                                 | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     | 6       | 15       | μA   |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for SCL                                                                    | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     |         | 70       | nA   |

| INPUT RSTN               |                                                                                                         | ,                                                                                        | ,   |         |          |      |

| V <sub>IH</sub>          | High level input voltage                                                                                |                                                                                          | 1.5 |         | 3.6      | V    |

| V <sub>IL</sub>          | Low-level input voltage                                                                                 |                                                                                          | 0   |         | 0.5      | V    |

| I <sub>IH</sub>          | High level input current                                                                                | V <sub>IH</sub> = 3.6 V, R <sub>PU</sub> enabled                                         |     |         | ±15      | μA   |

| I <sub>IL</sub>          | Low level input current                                                                                 | V <sub>IL</sub> = 0V, R <sub>PU</sub> enabled                                            |     |         | ±20      | μA   |

| INPUT DIGITAL            |                                                                                                         |                                                                                          |     |         |          |      |

| V <sub>IH</sub>          | High level input voltage (CDP_ENZ)                                                                      |                                                                                          | 1.5 |         | 3.6      | V    |

| V <sub>IL</sub>          | Low-level input voltage (CDP_ENZ)                                                                       |                                                                                          | 0   |         | 0.5      | V    |

| I <sub>IL</sub>          | Low level input current                                                                                 | V <sub>IL</sub> = 0V                                                                     |     |         | ±20      | μA   |

| I <sub>IH</sub>          | High level input current                                                                                | V <sub>IH</sub> = 3.6 V                                                                  |     |         | ±15      | μA   |

| INPUT RX_SEN (           | 3-level input, for mid level leave pin f                                                                | loating)                                                                                 |     |         |          |      |

| V <sub>IH(Max)</sub>     | Maximum High level input voltage                                                                        | VCC = 2.3V to 6.5V                                                                       |     |         | 5.0      | V    |

|                          |                                                                                                         | VCC > 4.5V                                                                               | 3.3 |         |          | V    |

| $V_{IH(Min)}$            | Minimum High level input voltage                                                                        | VCC = 2.3V to 4.5V (% of VCC)                                                            | 75  |         |          | %    |

|                          | 1 1 1                                                                                                   | VCC > 4.5V                                                                               |     |         | 0.75     | V    |

| $V_{IL}$                 | Low level input voltage                                                                                 | VCC = 2.3V to 4.5V (% of VCC)                                                            |     |         | 15       | %    |

| INPUT BOOST              | I                                                                                                       | 1                                                                                        |     |         |          |      |

| R <sub>BOOST_LVL0</sub>  | External pulldown resistor for BOOST Level 0                                                            |                                                                                          |     |         | 160      | Ω    |

| R <sub>BOOST_LVL1</sub>  | External pulldown resistor for BOOST Level 1                                                            |                                                                                          | 1.5 | 1.8     | 2        | kΩ   |

| R <sub>BOOST_LVL2</sub>  | External pulldown resistor for BOOST Level 2                                                            |                                                                                          | 3.4 | 3.6     | 3.96     | kΩ   |

| R <sub>BOOST_LVL3</sub>  | External pulldown resistor for BOOST Level 3 to remove upper limit for resistor value, can be left open |                                                                                          | 7.5 |         |          | kΩ   |

| OUTPUTS CD, EN           | NA_HS                                                                                                   |                                                                                          |     |         |          |      |

| V <sub>OH</sub>          | High level output voltage for CD and ENA_HS                                                             | I <sub>O</sub> = -50 μA, VCC >= 3.0V                                                     | 2.5 |         |          | V    |

| V <sub>OH</sub>          | High level output voltage for CD                                                                        | I <sub>O</sub> = -25 μA, VCC = 2.3V                                                      | 1.7 |         |          | V    |

Copyright © 2023 Texas Instruments Incorporated

۵

Product Folder Links: TUSB216-Q1

## 6.5 Electrical Characteristics (続き)

Over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                             | TEST CONDITIONS                                                           | MIN | TYP (1) | MAX | UNIT |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------|-----|---------|-----|------|

| V <sub>OH</sub>      | High level output voltage for ENA_HS                  | I <sub>O</sub> = -25 μA, VCC = 2.3V                                       | 1.8 |         |     | V    |

| V <sub>OL</sub>      | Low level output voltage for CD and ENA_HS            | Ι <sub>Ο</sub> = 50 μΑ                                                    |     |         | 0.3 | V    |

| I2C                  |                                                       |                                                                           |     |         |     |      |

| C <sub>I2C_BUS</sub> | I <sup>2</sup> C Bus Capacitance                      |                                                                           | 4   |         | 150 | pF   |

| I <sub>OL</sub>      | I <sup>2</sup> C open drain output current            | V <sub>OL</sub> = 0.4V                                                    | 1.5 |         |     | mA   |

| V <sub>IL</sub>      | 2.3V<= VCC<= 4.3V, V <sub>I2C_BUS</sub> = 1.8V +/-10% | $R_{Pull-up}$ =1.6kΩ to 2.5kΩ, % of $V_{I2C\_BUS}$                        |     |         | 25  | %    |

| V <sub>IL</sub>      | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    | $R_{Pull-up}$ =2.8kΩ to 7kΩ, % of $V_{I2C\_BUS}$                          |     |         | 25  | %    |

| V <sub>IH</sub>      | 2.3V<= VCC<= 4.3V, V <sub>I2C_BUS</sub> = 1.8V +/-10% | $R_{Pull-up}$ =1.6kΩ to 2.5kΩ, % of $V_{I2C\_BUS}$                        | 80  |         |     | %    |

| V <sub>IH</sub>      | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    | $R_{Pull-up}$ =2.8kΩ to 7kΩ, % of $V_{I2C\_BUS}$                          | 75  |         |     | %    |

| R <sub>Pull-up</sub> | V <sub>I2C_BUS</sub> = 1.8V +/-10%                    |                                                                           | 1.6 | 2       | 2.5 | kΩ   |

| R <sub>Pull-up</sub> | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    |                                                                           | 2.8 | 4.7     | 7   | kΩ   |

| SCL Frequency        |                                                       |                                                                           |     |         | 400 | kHz  |

| DxP, DxM             |                                                       |                                                                           |     |         | '   |      |

| C <sub>IO_DXX</sub>  | Capacitance to GND                                    | Measured with VNA at 240 MHz, V <sub>CC</sub> supply stable, Redriver off |     | 2.5     |     | pF   |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 5 V, and  $T_A$  = 25°C.

# **6.6 Switching Characteristics**

Over operating free-air temperature range (unless otherwise noted)

| PARAMETER            |                | TEST CONDITIONS                                                        | MIN | TYP (1) MA | X  | UNIT |

|----------------------|----------------|------------------------------------------------------------------------|-----|------------|----|------|

| DxP, DxM US          | B Signals      |                                                                        |     |            |    |      |

| F <sub>BR_DXX</sub>  | I Rif Rafe     | USB channel = HS mode. 480 Mbps traffic. V <sub>CC</sub> supply stable |     | 4          | 30 | Mbps |

| t <sub>R/F_DXX</sub> | Rise/Fall time |                                                                        | 100 |            |    | ps   |

<sup>(1)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ .

English Data Sheet: SLLSF03

## **6.7 Timing Requirements**

|                      |                                                                                                                                 | MIN | NOM MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| POWER UI             | P TIMING                                                                                                                        |     |         |      |

| T <sub>RSTN_PW</sub> | Minimum width to detect a valid RSTN signal assert when the pin is actively driven low                                          | 100 |         | μs   |

| T <sub>STABLE</sub>  | VCC must be stable before RSTN de-assertion                                                                                     | 300 |         | μs   |

| T <sub>READY</sub>   | Maximum time needed for the device to be ready after RSTN is deasserted.                                                        |     | 500     | μs   |

| T <sub>RAMP</sub>    | V <sub>CC</sub> ramp time                                                                                                       |     | 100     | ms   |

| T <sub>RAMP</sub>    | V <sub>CC</sub> ramp time                                                                                                       | 0.2 |         | ms   |

| I2C (STD)            |                                                                                                                                 |     |         |      |

| t <sub>susто</sub>   | Stop setup time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD                            | 4   |         | μs   |

| t <sub>HDSTA</sub>   | Start hold time, SCL (Tr=600ns-1000ns), SDA (Tf=6.5ns-106.5ns), 100kHz STD                                                      | 4   |         | μs   |

| t <sub>SUSTA</sub>   | Start setup time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD                           | 4.7 |         | μs   |

| t <sub>SUDAT</sub>   | Data input or False start/stop, setup time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD | 250 |         | ns   |

| t <sub>HDDAT</sub>   | Data input or False start/stop, hold time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD  | 5   |         | μs   |

| t <sub>BUF</sub>     | Bus free time between START and STOP conditions                                                                                 | 4.7 |         | μs   |

| t <sub>LOW</sub>     | Low period of the I2C clock                                                                                                     | 4.7 |         | μs   |

| t <sub>HIGH</sub>    | High period of the I2C clock                                                                                                    | 4   |         | μs   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals                                                                                           |     | 300     | ns   |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals                                                                                           |     | 1000    | ns   |

| I2C (FM)             |                                                                                                                                 |     |         |      |

| t <sub>susto</sub>   | Stop setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                             | 0.6 |         | μs   |

| t <sub>HDSTA</sub>   | Start hold time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                             | 0.6 |         | μs   |

| t <sub>SUSTA</sub>   | Start setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                            | 0.6 |         | μs   |

| t <sub>SUDAT</sub>   | Data input or False start/stop, setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM  | 100 |         | ns   |

| t <sub>HDDAT</sub>   | Data input or False start/stop, hold time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM   | 0   |         | μs   |

| t <sub>BUF</sub>     | Bus free time between START and STOP conditions                                                                                 | 1.3 |         | μs   |

| t <sub>LOW</sub>     | Low period of the I2C clock                                                                                                     | 1.3 |         | μs   |

| t <sub>HIGH</sub>    | High period of the I2C clock                                                                                                    | 0.6 |         | μs   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals                                                                                           | ,   | 300     | ns   |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals                                                                                           |     | 300     | ns   |

## 7 Detailed Description

#### 7.1 Overview

The TUSB216-Q1 is a USB High-Speed (HS) signal conditioner designed to compensate for ISI signal loss in a transmission channel. TUSB216-Q1 has a patented design for USB Low Speed (LS) and Full Speed (FS) signals. It does not alter the signal characteristics. HS signals are compensated. The design is compatible with USB On-The-Go (OTG) and Battery Charging (BC) specifications.

Programmable signal gain through an external resistor permits fine tuning device performance to optimize signals. This helps pass USB HS electrical compliance tests at the connector. Additional RX sensitivity, tuned by external pull-up resistor and pull-down resistor, allows to overcome attenuation in cables. The TUSB216-Q1 allows application in series to cover longer distances, or high loss transmission paths. A maximum of 4 devices can be daisy-chained.

#### 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

## 7.3 Feature Description

#### 7.3.1 High-Speed Boost

The high-speed booster (combination of edge boost and DC boost) improves the eye width for USB2.0 high-speed signals. It is direction independent and by that is compatible to OTG systems. The BOOST pin is configuring the booster strength with different values of pull down resistors to set 4 levels of boosts, alternatively the boost level can be set through the I2C register according to \$\frac{1}{2}\sumsymbol{2} > 7.4.6\$. Internal circuitry of the signal conditioner reduces possible overshoot.

### 7.3.2 RX Sensitivity

The RX\_SEN pin is a tri-level pin. It is used to set the gain of the device according to system channel loss. RX sensitivity can be increased to recover incoming signals with low vertical eye opening to be able to boost weak signals and helps overcoming high attenuation.

#### 7.4 Device Functional Modes

#### 7.4.1 Low-Speed (LS) Mode

TUSB216-Q1 automatically detects a LS connection and does not enable signal compensation. CD pin is asserted high but ENA\_HS will be low.

#### 7.4.2 Full-Speed (FS) Mode

TUSB216-Q1 automatically detects a FS connection and does not enable signal compensation. CD pin is asserted high but ENA HS will be low

#### 7.4.3 High-Speed (HS) Mode

TUSB216-Q1 automatically detects a HS connection and will enable signal compensation as determined by the configuration of the RX\_SEN pin and the external pull down resistance on its BOOST pin.

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

9

CD pin and ENA HS pin are asserted high when high-speed boost is active.

### 7.4.4 High-Speed Downstream Port Electrical Compliance Test Mode

TUSB216-Q1 will detect HS compliance test fixture and enter downstream port high-speed eye diagram test mode. CD pin will be low and ENA\_HS pin is asserted high when TUSB216-Q1 is in HS eye compliance test mode.

If RSTN pin is asserted low and de-asserted high while TUSB216-Q1 is operating in HS functional mode, TUSB216-Q1 will transition to HS eye compliance test mode and CD asserts low and ENA\_HS remains high. When this occurs signal compensation is enabled.

#### 7.4.5 Shutdown Mode

TUSB216-Q1 can be disabled when its RSTN pin is asserted low. DP, DM traces are continuous through the device in shutdown mode. The USB channel is still fully operational, but there is neither signal compensation, nor any indication from the CD pin as to the status of the channel.

| MODE                                       | CD   | ENA_HS |  |  |  |  |  |

|--------------------------------------------|------|--------|--|--|--|--|--|

| Low-speed                                  | HIGH | LOW    |  |  |  |  |  |

| Full-speed                                 | HIGH | LOW    |  |  |  |  |  |

| High-speed                                 | HIGH | HIGH   |  |  |  |  |  |

| High-speed downstream port electrical test | LOW  | HIGH   |  |  |  |  |  |

| Shutdown                                   | LOW  | LOW    |  |  |  |  |  |

表 7-1. CD and ENA\_HS Pins in Different Modes

#### 7.4.6 I<sup>2</sup>C Mode

TUSB216-Q1 supports 100 and 400 kHz I2C for device configuration, status read back and test purposes. For detail electrical and functional specifications refer to I2C Bus Specification – STANDARD and FAST MODE. This controller is enabled after SCL and SDA pins are sampled high shortly after return from shutdown. In this mode, the CSR can be accessed by I2C read/write transaction to 7-bit slave address 0x2C. It is advised to set CFG\_ACTIVE bit before changing values. This halts the FSM, and reset it after all changes are made. This ensure proper startup into high-speed mode.

#### 7.4.7 BC 1.2 Battery Charging Controller

The TUSB216-Q1 main function is a signal conditioner offering the boost and pre-equalization features to the incoming DP/DM signals. For applications in which USB host or hub does not provide USB BC charging controller functionality, the TUSB216-Q1 can perform this task when CDP\_ENZ is low and BC 1.2 CDP Controller is enabled. When battery charging CDP controller feature is enabled (CDP\_ENZ=low) TUSB216-Q1 supports CDP charging downstream port functionality. CDP\_ENZ has an internal pull up when the pin is left unconnected CDP controller will be disabled.

表 7-2. TUSB216-Q1 Battery Charging Controller Modes

| · · ·            |     |

|------------------|-----|

| Pin 11 (CDP_ENZ) | CDP |

| High             | NO  |

| Low              | YES |

## 7.5 TUSB216 Registers

$\pm$  7-3 lists the memory-mapped registers for the TUSB216 registers. All register offset addresses not listed in  $\pm$  7-3 should be considered as reserved locations and the register contents should not be modified.

表 7-3. TUSB216 Registers

| Offset Acronym |            | Register Name                              | Section |

|----------------|------------|--------------------------------------------|---------|

| 0x1            | EDGE_BOOST | This register is setting EDGE BOOST level. | Go      |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

## 表 7-3. TUSB216 Registers (続き)

| Offset | Acronym       | Register Name                                  | Section |

|--------|---------------|------------------------------------------------|---------|

| 0x3    | CONFIGURATION | This register is selecting device mode.        | Go      |

| 0xE    | DC_BOOST      | This register is setting DC BOOST level.       | Go      |

| 0x25   | RX_SEN        | This register is setting RX Sensitivity level. | Go      |

Complex bit access types are encoded to fit into small table cells.  $\frac{1}{2}$  7-4 shows the codes that are used for access types in this section.

表 7-4. TUSB216 Access Type Codes

| 2                |           |                                        |  |  |  |  |

|------------------|-----------|----------------------------------------|--|--|--|--|

| Access Type      | Code      | Description                            |  |  |  |  |

| Read Type        | Read Type |                                        |  |  |  |  |

| RH               | H<br>R    | Set or cleared by hardware<br>Read     |  |  |  |  |

| Write Type       |           |                                        |  |  |  |  |

| W                | W         | Write                                  |  |  |  |  |

| Reset or Default | Value     |                                        |  |  |  |  |

| -n               |           | Value after reset or the default value |  |  |  |  |

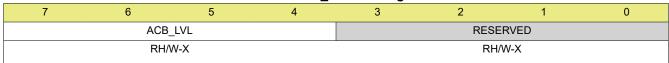

## 7.5.1 EDGE\_BOOST Register (Offset = 0x1) [reset = X]

EDGE\_BOOST is shown in 図 7-1 and described in 表 7-5.

Return to Summary Table.

This register is setting EDGE BOOST level.

## 図 7-1. EDGE\_BOOST Register

## 表 7-5. EDGE\_BOOST Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                         |

|-----|----------|------|-------|---------------------------------------------------------------------|

| 7-4 | ACB_LVL  | RH/W | X     | XXXXb (sampled at startup from BOOST pin)                           |

|     |          |      |       | 0000b to 1111b range                                                |

|     |          |      |       | 0x0 = BOOST PIN LEVEL 0 (lowest edge boost setting)                 |

|     |          |      |       | 0x3 = BOOST PIN LEVEL 1                                             |

|     |          |      |       | 0x6 = BOOST PIN LEVEL 2                                             |

|     |          |      |       | 0xA = BOOST PIN LEVEL 3                                             |

|     |          |      |       | 0xF = (highest edge boost setting)                                  |

| 3-0 | RESERVED | RH/W | Х     | These bits are reserved bits and set by hardware at reset.          |

|     |          |      |       | When this register is modified the software should first read these |

|     |          |      |       | reserved bits and rewrite with the same values                      |

11

Product Folder Links: TUSB216-Q1

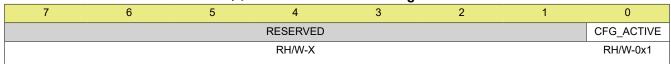

## 7.5.2 CONFIGURATION Register (Offset = 0x3) [reset = X]

CONFIGURATION is shown in  $\boxtimes$  7-2 and described in  $\not\equiv$  7-6.

Return to Summary Table.

This register is selecting device mode.

## 図 7-2. CONFIGURATION Register

#### 表 7-6. CONFIGURATION Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                        |

|-----|------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1 | RESERVED   | RH/W | Х     | These bits are reserved bits and set by hardware at reset.  When this register is modified the software should first read these reserved bits and rewrite with the same values                                     |

| 0   | CFG_ACTIVE | RH/W | 0x1   | Configuration mode After reset, if I2C mode is true (SCL and SDA are both pulled high) set the bit to get into configuration mode and clear to return to normal mode.  0x0 = NORMAL MODE  0x1 = CONFIGURATION MODE |

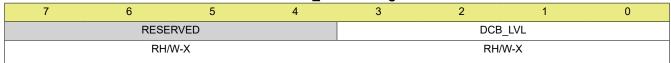

## 7.5.3 DC\_BOOST Register (Offset = 0xE) [reset = X]

DC\_BOOST is shown in  $\boxtimes$  7-3 and described in  $\not\equiv$  7-7.

Return to Summary Table.

This register is setting DC BOOST level.

## 図 7-3. DC\_BOOST Register

#### 表 7-7. DC\_BOOST Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                 |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | RESERVED | RH/W | Х     | These bits are reserved bits and set by hardware at reset.  When this register is modified the software should first read these reserved bits and rewrite with the same values                              |

| 3-0 | DCB_LVL  | RH/W | X     | XXXXb (sampled at startup from BOOST pin) 0000b to 1111b range  0x0 = BOOST PIN LEVEL 0 (lowest dc boost setting)  0x2 = BOOST PIN LEVEL 1 and 2  0x6 = BOOST PIN LEVEL 3  0xF = (highest dc boost setting) |

Copyright © 2023 Texas Instruments Incorporated

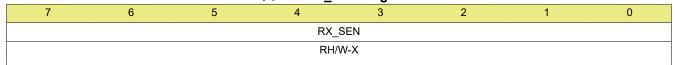

## 7.5.4 RX\_SEN Register (Offset = 0x25) [reset = X]

RX\_SEN is shown in 図 7-4 and described in 表 7-8.

Return to Summary Table.

This register is setting RX Sensitivity level.

## 図 7-4. RX\_SEN Register

## 表 7-8. RX\_SEN Register Field Descriptions

| Bit | Field  | Туре | Reset | Description                                                                                                                                                                  |

|-----|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | RX_SEN | RH/W | X     | XXXXb (sampled at startup from RX_SEN pin) 00000000b to 11111111b range  0x0 = RX_SEN LEVEL LOW  0x33 = RX_SEN LEVEL MID  0x66 = RX_SEN LEVEL HIGH  0xFF = (highest setting) |

13

Product Folder Links: TUSB216-Q1

## 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 Application Information

The purpose of the TUSB216-Q1 is to re-store the signal integrity of a USB High-speed channel up to the USB connector. The loss in signal quality stems from reduced channel bandwidth due to high loss PCB trace and other components that contribute a capacitive load. This can cause the channel to fail the USB near end eye mask. Proper use of the TUSB216-Q1 can help to pass this eye mask.

A secondary purpose is to use the CD pin of the TUSB216-Q1 to control other blocks on the customer platform, if so desired.

#### 8.2 Typical Application

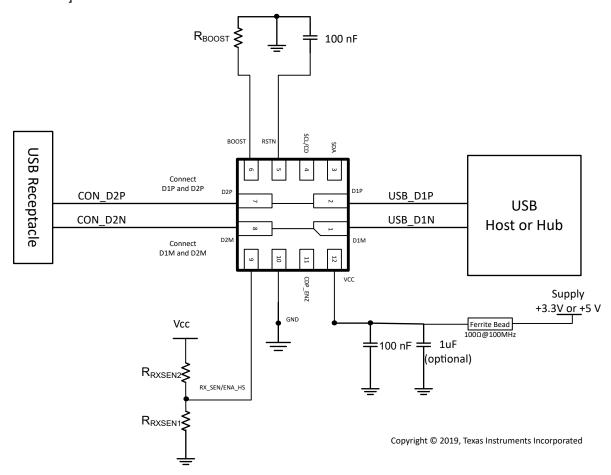

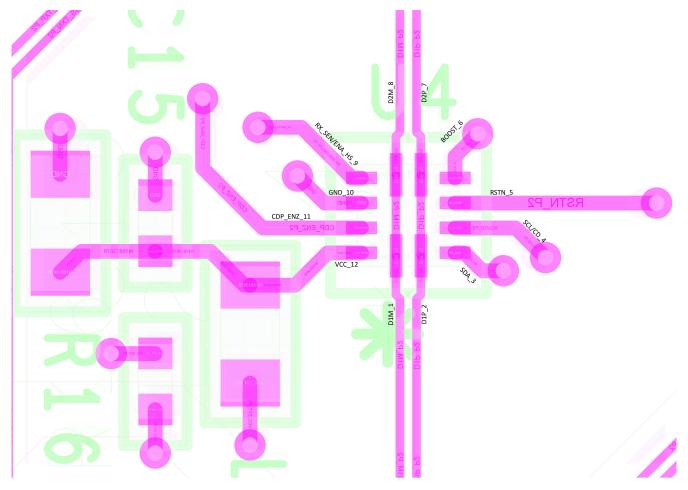

A typical application for TUSB216-Q1 is shown in 🗵 8-1. In this setup, D2P and D2M face the USB connector while D1P and D1M face the USB host. The orientation may be reversed [that is, D2 faces transceiver and D1 faces connector].

図 8-1. TUSB216-Q1 Reference Schematic (Design Example with CDP disabled), CDP\_ENZ Can Be Left Floating but an Option for a Decoupling Capacitor of 0.1 µF is Recommended So the Design is Compatible with Older Devices: TUSB211, TUSB212, TUSB214

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLLSF03

#### 8.2.1 Design Requirements

TUSB216-Q1 requires a valid reset signal as described in the *Power Supply Recommendations* section. The capacitor at RSTN pin is not required if a micro controller drives the RSTN pin according to recommendations.

For this design example, use the parameters shown in 表 8-1, 表 8-2 and 表 8-3.

表 8-1. Design Parameters for 5-V Supply With High Loss System

|                                                      | at o 1. Design i didinet      | ers for 3-v Supply veith in   | ngn Loss Cystem |                                                |  |

|------------------------------------------------------|-------------------------------|-------------------------------|-----------------|------------------------------------------------|--|

|                                                      | VALUE <sup>(1)</sup>          |                               |                 |                                                |  |

| V <sub>CC</sub>                                      | 5 V ±10%                      |                               |                 |                                                |  |

| I <sup>2</sup> C support required in system (Yes/No) |                               |                               |                 |                                                |  |

|                                                      |                               | R <sub>BOOST</sub>            | BOOST Level     |                                                |  |

|                                                      | 0-Ω 0                         |                               | 0               |                                                |  |

| Edge and DC Boost                                    |                               | 1.8 kΩ ±1% 1                  |                 | Boost Level 1:<br>R <sub>BOOST</sub> = 1.8 kΩ  |  |

|                                                      |                               | $3.6 \text{ k}\Omega \pm 1\%$ | 2               |                                                |  |

|                                                      |                               | Do Not Install (DNI)          | 3               |                                                |  |

|                                                      | R <sub>RXSEN1</sub>           | R <sub>RXSEN2</sub>           | RX_SEN Level    | High RX                                        |  |

|                                                      | 22 kΩ - 40 kΩ (27 kΩ typical) | Do Not Install (DNI)          | Low             | Sensitivity Level:  R <sub>RXSEN1</sub> = 37.5 |  |

| RX Sensitivity                                       | Do Not Install (DNI)          | Do Not Install (DNI)          | Medium          | kΩ                                             |  |

|                                                      | 37.5 kΩ <sup>(2)</sup>        | 12.5 kΩ                       | High            | $R_{RXSEN2} = 12.5$ $k\Omega$                  |  |

<sup>(1)</sup> These parameters are starting values for a high loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 5 V supply system could be applicable to 3.3 V supply system as well.

表 8-2. Design Parameters for 3.3-V Supply With Low to Medium Loss System

| PARAMETER                        |                               |                               |              |                                          |  |  |  |

|----------------------------------|-------------------------------|-------------------------------|--------------|------------------------------------------|--|--|--|

| V <sub>CC</sub>                  | 3.3 V ±10%                    |                               |              |                                          |  |  |  |

| I <sup>2</sup> C support require | No                            |                               |              |                                          |  |  |  |

|                                  |                               | R <sub>BOOST</sub>            | BOOST Level  |                                          |  |  |  |

|                                  |                               | 0-Ω 0                         |              | 1                                        |  |  |  |

| Edge and DC Boo                  | st                            | 1.8 kΩ ±1%                    | 1            | Boost Level 0:<br>$R_{BOOST} = 0-\Omega$ |  |  |  |

|                                  |                               | 3.6 kΩ ±1% 2                  |              | 1 10001 0 11                             |  |  |  |

|                                  |                               | Do Not Install (DNI)          | 3            |                                          |  |  |  |

|                                  | R <sub>RXSEN1</sub>           | R <sub>RXSEN2</sub>           | RX_SEN Level | Medium RX                                |  |  |  |

| RX Sensitivity                   | 22 kΩ – 40 kΩ (27 kΩ typical) | Do Not Install (DNI)          | Low          | Sensitivity Level:                       |  |  |  |

|                                  | Do Not Install (DNI)          | Do Not Install (DNI)          | Medium       | R <sub>RXSEN1</sub> = DNI                |  |  |  |

|                                  | Do Not Install (DNI)          | 22 kΩ – 40 kΩ (27 kΩ typical) | High         | R <sub>RXSEN2</sub> = DNI                |  |  |  |

<sup>(1)</sup> These parameters are starting values for a low to medium loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 3.3 V supply system could be applicable to 5 V supply system as well.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

<sup>(2)</sup> This resistor is needed for a 5 V supply to divide the voltage down so the RX\_SEN pin voltage does not exceed 5.0 V.

### 表 8-3. Design Parameters for 2.3-V to 4.3-V VBAT Supply With Low to Medium Loss System

| PARAMETER                                            |                               |                      |              |                                     |  |  |  |

|------------------------------------------------------|-------------------------------|----------------------|--------------|-------------------------------------|--|--|--|

| V <sub>CC</sub>                                      | 2.3 V to 4.3V                 |                      |              |                                     |  |  |  |

| I <sup>2</sup> C support required in system (Yes/No) |                               |                      |              |                                     |  |  |  |

|                                                      |                               | R <sub>BOOST</sub>   | BOOST Level  |                                     |  |  |  |

|                                                      | 0-Ω                           |                      | 0            | 1                                   |  |  |  |

| Edge and DC Boo                                      | st                            | 1.8 kΩ ±1%           | 1            | Boost Level 0:<br>$R_{BOOST} = 0-Ω$ |  |  |  |

|                                                      | 3.6 k                         |                      | 2            | 1180051 0 11                        |  |  |  |

|                                                      |                               | Do Not Install (DNI) | 3            | 7                                   |  |  |  |

|                                                      | R <sub>RXSEN1</sub>           | R <sub>RXSEN2</sub>  | RX_SEN Level | Medium RX                           |  |  |  |

| RX Sensitivity                                       | 22 kΩ – 40 kΩ (27 kΩ typical) | Do Not Install (DNI) | Low          | Sensitivity Level:                  |  |  |  |

|                                                      | Do Not Install (DNI)          | Do Not Install (DNI) | Medium       | R <sub>RXSEN1</sub> = DNI           |  |  |  |

|                                                      | 37.5 kΩ <sup>(2)</sup>        | 12.5 kΩ              | High         | R <sub>RXSEN2</sub> = DNI           |  |  |  |

<sup>(1)</sup> These parameters are starting values for a low to medium loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 2.3 V – 4.3 V supply system could be applicable to 5 V supply system as well.

#### 8.2.2 Detailed Design Procedure

The ideal BOOST setting is dependent upon the signal chain loss characteristics of the target platform. The recommendation is to start with BOOST level 0, and then increment to BOOST level 1, and so on. Same applies to the RX sensitivity setting where it is recommended to plan for the required pads or connections to change boost settings, but to start with RX sensitivity level Low.

In order for the TUSB216-Q1 to recognize any change to the BOOST setting, the RSTN pin must be toggled. This is because the BOOST pin is latched on power up and the pin is ignored thereafter.

注

The TUSB216-Q1 compensates for extra attenuation in the signal path according to the configuration of the RX\_SEN pin. This maximum recommended voltage for this pin is 5 V when selecting the highest RX sensitivity level.

Placement of the device is also dependent on the application goal. 表 8-4 summarizes our recommendations.

#### 表 8-4. Platform Placement Guideline

| PLATFORM GOAL                                              | SUGGESTED TUSB216-Q1 PLACEMENT         |

|------------------------------------------------------------|----------------------------------------|

| Pass USB Near End Mask at the receptacle                   | Close to measurement point (connector) |

| Pass USB Far End Eye Mask at the plug                      | Close to USB PHY                       |

| Cascade multiple TUSB216-Q1s to improve device enumeration | Midway between each USB interconnect   |

Product Folder Links: TUSB216-Q1

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> This resistor is needed for a VBAT supply (2.3 V – 4.3 V) to divide the voltage down so the RX\_SEN pin voltage does not exceed 5.0 V.

## 表 8-5. Table of Recommended Settings

| at our rabio of recommended contingo                             |         |                |  |  |  |  |  |  |

|------------------------------------------------------------------|---------|----------------|--|--|--|--|--|--|

| BOOST and RX_SEN settings (1) for channel loss                   |         |                |  |  |  |  |  |  |

| Pre-channel cable length (Between USB PHY and TUSB216-Q1)        | BOOST   | RX_SEN         |  |  |  |  |  |  |

| 0-3 meter                                                        | Level 0 | Medium or High |  |  |  |  |  |  |

| 2-5 meter                                                        | Level 1 | Medium or High |  |  |  |  |  |  |

| Post-channel cable length (Between TUSB216-Q1 and inter-connect) | BOOST   | RX_SEN         |  |  |  |  |  |  |

| 0-2 meter                                                        | Level 0 | Medium or High |  |  |  |  |  |  |

| 1-4 meter                                                        | Level 1 | Medium or High |  |  |  |  |  |  |

<sup>(1)</sup> These parameters are starting values for different cable lengths. Further tuning might be required based on specific host or device as well as cable length and loss profile.

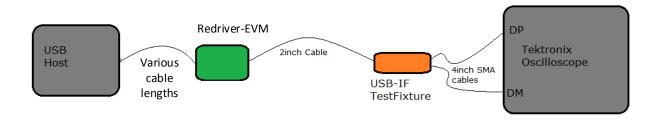

#### 8.2.2.1 Test Procedure to Construct USB High-speed Eye Diagram

注

USB-IF certification tests for High-speed eye masks require the *mandated use* of the USB-IF developed test fixtures. These test fixtures do not require the use of oscilloscope probes. Instead they use SMA cables. More information can be found at the USB-IF Compliance Updates Page. It is located under the *Electrical Specifications* section, ID 86 dated March 2013.

The following procedure must be followed before using any oscilloscope compliance software to construct a USB High-speed Eye Mask:

#### 8.2.2.1.1 For a Host Side Application

- 1. Configure the TUSB216-Q1 to the desired BOOST setting

- 2. Power on (or toggle the RSTN pin if already powered on) the TUSB216-Q1

- 3. Using SMA cables, connect the oscilloscope and the USB-IF host-side test fixture to the TUSB216-Q1

- Enable the host to transmit USB TEST\_PACKET

- 5. Execute the oscilloscope USB compliance software.

- 6. Repeat the above steps in order to re-test TUSB216-Q1 with a different BOOST setting (must reset to change)

#### 8.2.2.1.2 For a Device Side Application

- 1. Configure the TUSB216-Q1 to the desired BOOST setting

- 2. Power on (or toggle the RSTN pin if already powered on) the TUSB216-Q1

- 3. Connect a USB host, the USB-IF device-side test fixture, and USB device to the TUSB216-Q1. Ensure that the USB-IF device test fixture is configured to the 'INIT' position

- 4. Allow the host to enumerate the device

- 5. Enable the device to transmit USB TEST PACKET

- 6. Using SMA cables, connect the oscilloscope to the USB-IF device-side test fixture and ensure that the device-side test fixture is configured to the 'TEST' position.

- 7. Execute the oscilloscope USB compliance software.

- 8. Repeat the above steps in order to re-test TUSB216-Q1 with a different BOOST setting (must reset to change)

Product Folder Links: TUSB216-Q1

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

17

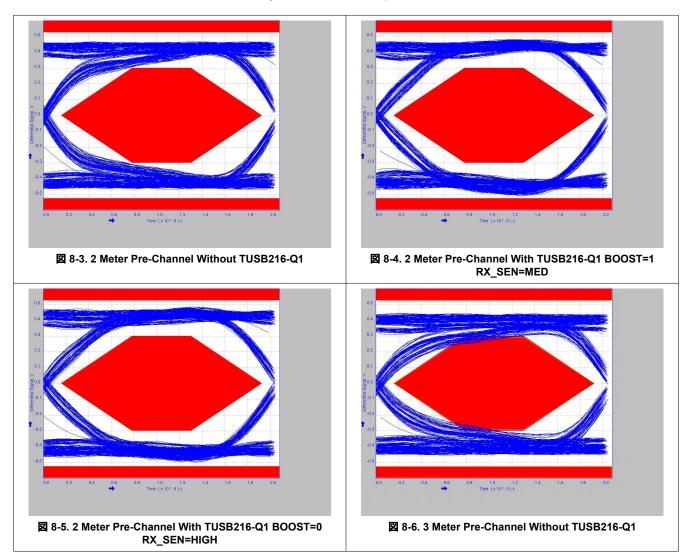

## 8.2.3 Application Curves

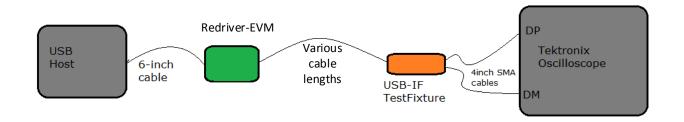

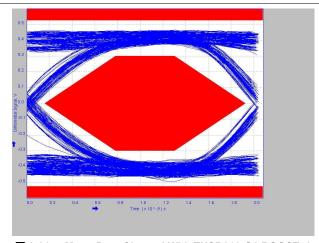

図 8-2. Near End Eye Measurement Set-Up With Pre-Channel Cable

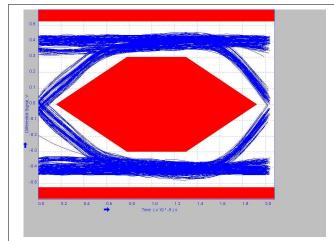

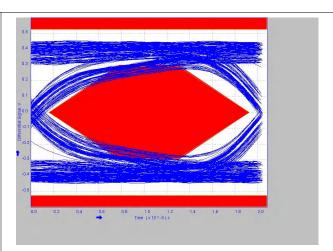

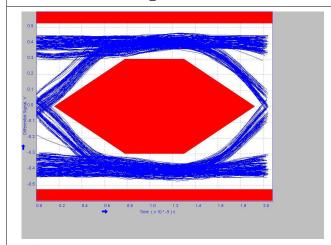

## 8.2.3 Application Curves (continued)

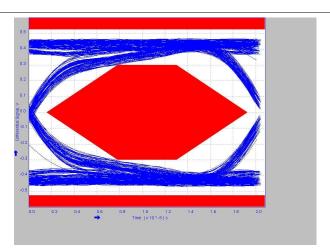

図 8-7. 3 Meter Pre-Channel With TUSB216-Q1 BOOST=0 RX\_SEN=HIGH

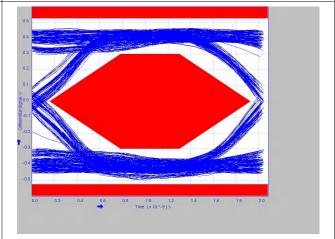

図 8-8. 5 Meter Without TUSB216-Q1

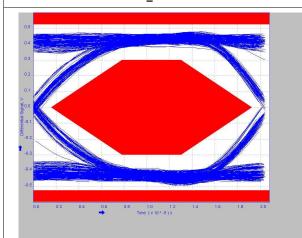

図 8-9. 5 Meter Pre-Channel With TUSB216-Q1 BOOST=1 RX\_SEN=MED

図 8-10. 5 Meter Pre-Channel With TUSB216-Q1 BOOST=2 RX\_SEN=MED

## 8.2.3 Application Curves

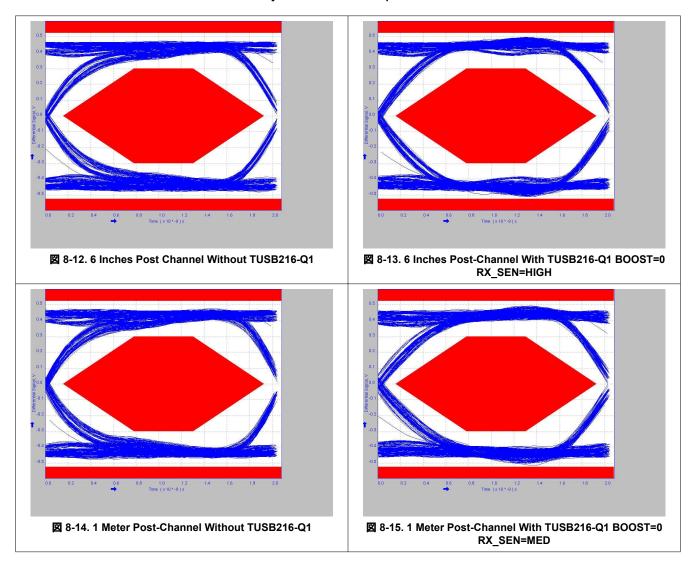

図 8-11. Near End Eye Measurement Set-Up With Post-Channel Cable

## 8.2.3 Application Curves (continued)

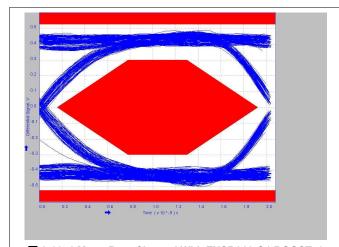

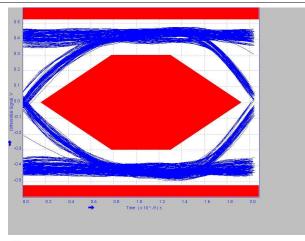

図 8-16. 1 Meter Post-Channel With TUSB216-Q1 BOOST=0 RX\_SEN=HIGH

図 8-17. 2 Meter Post-Channel Without TUSB216-Q1

図 8-18. 2 Meter Post-Channel With TUSB216-Q1 BOOST=1 RX\_SEN=MED

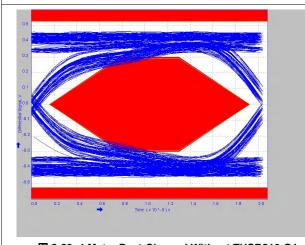

図 8-19. 2 Meter Post-Channel With TUSB216-Q1 BOOST=1 RX\_SEN=HIGH

図 8-20. 4 Meter Post-Channel Without TUSB216-Q1

図 8-21. 4 Meter Post-Channel With TUSB216-Q1 BOOST=2

RX\_SEN=MED

#### 8.3 Power Supply Recommendations

On power up, the interaction of the RSTN pin and power on ramp could result in digital circuits not being set correctly. The device should not be enabled until the power on ramp has settled to minimum recommended supply voltage or higher to ensure a correct power on reset of the digital circuitry. If RSTN cannot be held low by microcontroller or other circuitry until the power on ramp has settled, then an external capacitor from the RSTN pin to GND is required to hold the device in the low power reset state.

The RC time constant should be larger than five times of the power on ramp time (0 to  $V_{CC}$ ). With a typical internal pullup resistance of 500 k $\Omega$ , the recommended minimum external capacitance is calculated as:

[Ramp Time x 5]

$$\div$$

[500 k $\Omega$ ] (1)

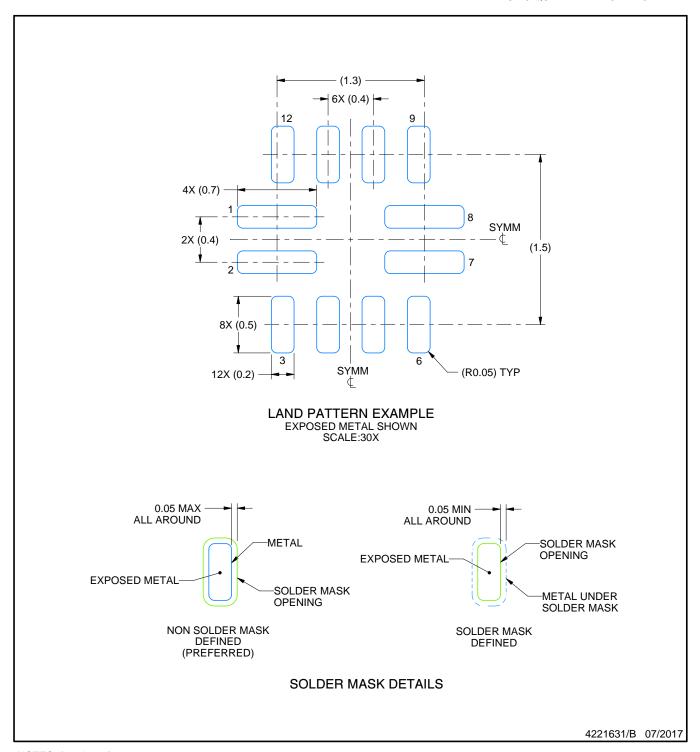

## 8.4 Layout

## 8.4.1 Layout Guidelines

Although the land pattern has matched trace width to pad width, optimal impedance control is based on the user's own PCB stack-up. The recommendation is to maintain  $90 \Omega$  differential routing underneath the device.

## 8.4.2 Layout Example

図 8-22. Layout Example

Copyright © 2023 Texas Instruments Incorporated

## 9 Device and Documentation Support

## 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 9.3 Trademarks

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### 9.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 9.5 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## 10 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (September 2021) to Revision B (December 2023) | Page |

|------------------------------------------------------------------------|------|

| Added more details to Device Comparison section                        | 2    |

| Added 400 kHz I2C support                                              | 6    |

| Added timing table for 400 kHz I2C Fast Mode                           |      |

| Added I2C standard and fast mode support in Detailed Description       |      |

| Changes from Revision * (April 2019) to Revision A (September 2021)    | Page |

| • データシートの最初の公開リリース                                                     | 1    |

|                                                                        |      |

## 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

23

23-May-2025

www.ti.com

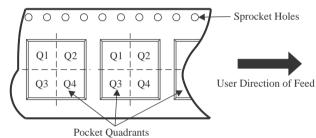

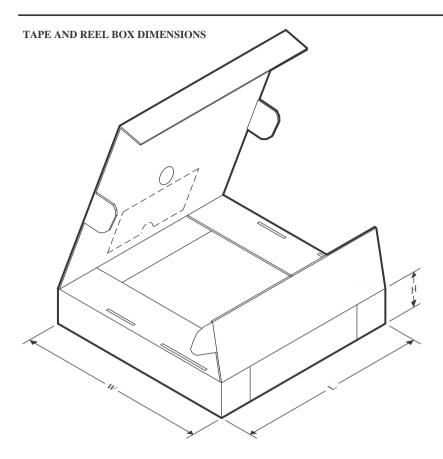

#### PACKAGING INFORMATION

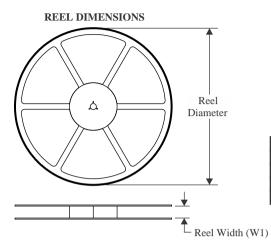

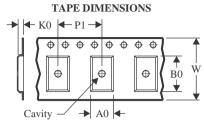

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                  |                       |      | (4)                           | (5)                        |              |                  |

| TUSB216RWBRQ1         | Active | Production    | X2QFN (RWB)   12 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | 26               |

| TUSB216RWBRQ1.A       | Active | Production    | X2QFN (RWB)   12 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | 26               |

| TUSB216RWBTQ1         | Active | Production    | X2QFN (RWB)   12 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | 26               |

| TUSB216RWBTQ1.A       | Active | Production    | X2QFN (RWB)   12 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | 26               |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.