# TSER953 MIPI CSI-2 インターフェイスを搭載した高速、高解像度カメラ、レーダー、その他センサ用の 4.16Gbps V<sup>3</sup>Link シリアライザ

## 1 特長

- 4.16Gbps グレードのシリアルライザにより、フル HD 1080p 2.3MP 60fps および 4MP 30fps イメージャを含む高速センサをサポート

- 低消費電力 (標準値 0.28W)

- IEC 61000-4-2 ESD 準拠

- Power-over-Coax (PoC) 対応トランシーバ

- D-PHY v1.2 および CSI-2 v1.3 準拠のシステムインターフェイス

- 最大 4 つのデータレーン、各レーンは最高 832Mbps

- 最大 4 つの仮想チャネルをサポート

- 高精度なマルチカメラクロッキングおよび同期

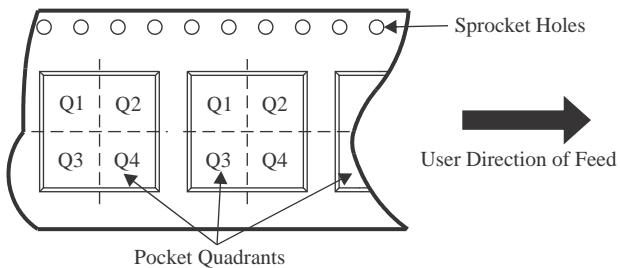

- 柔軟なプログラマブル出力クロックジェネレータ

- CRC データ保護、センサデータ整合性チェック、I<sup>2</sup>C 書き込み保護、電圧および温度測定、プログラマブルアラーム、ライン フォルト検出を含む高度なデータ保護および診断機能

- シングルエンドの同軸またはシールド付きツイストペア(STP)ケーブルに対応

- 超低レイテンシの双方向 I<sup>2</sup>C および GPIO 制御チャネルにより、ECU からの ISP 制御が可能

- 1.8V の単一電源電圧

- TDES954 および TDES960 デシリアルライザと互換

- 幅広い温度範囲:-20°C~85°C

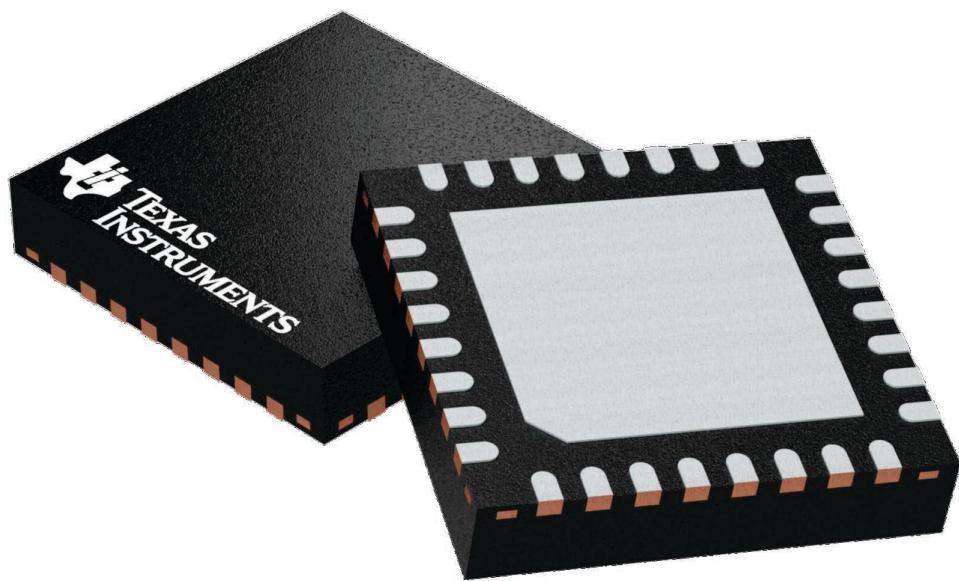

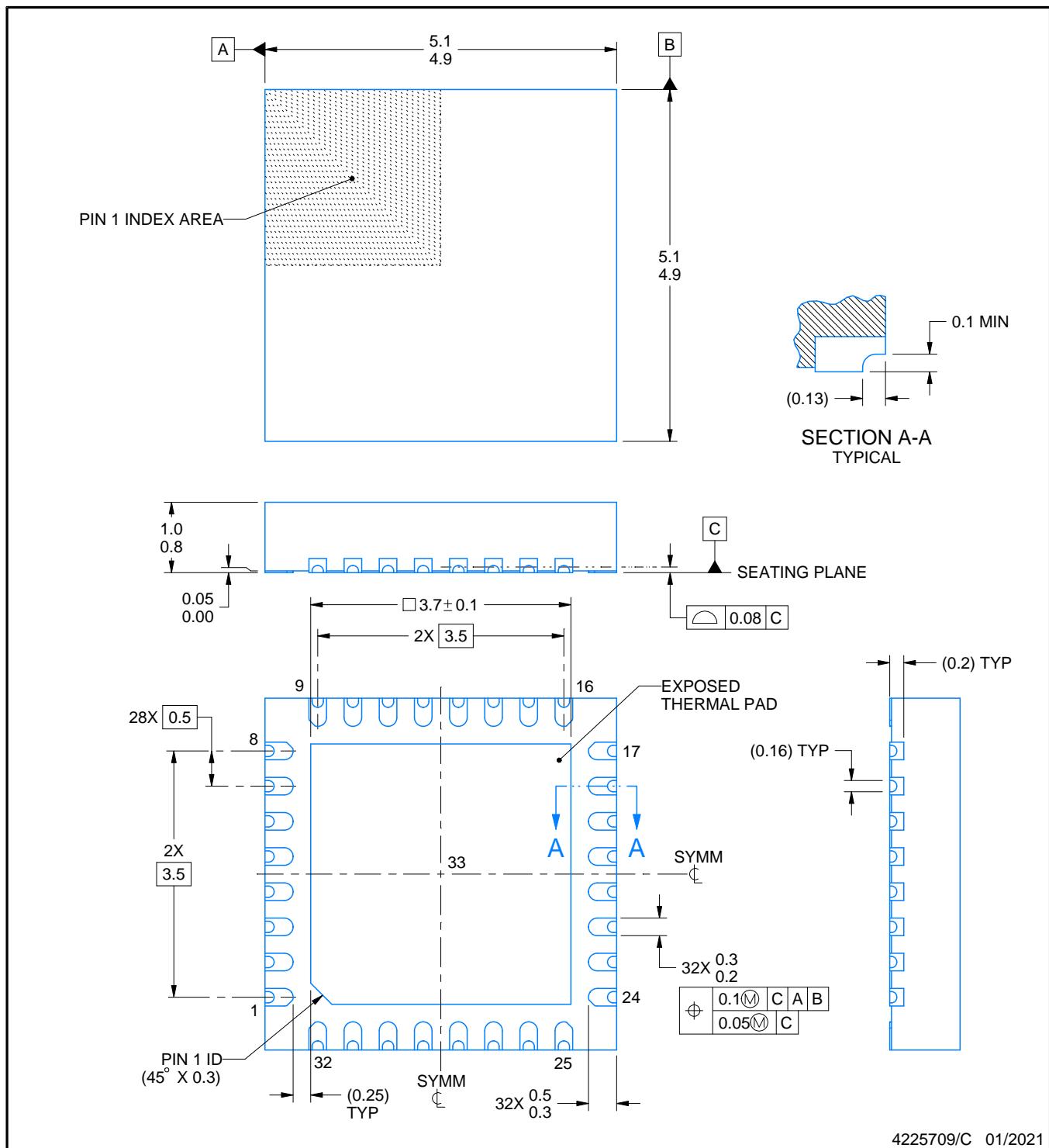

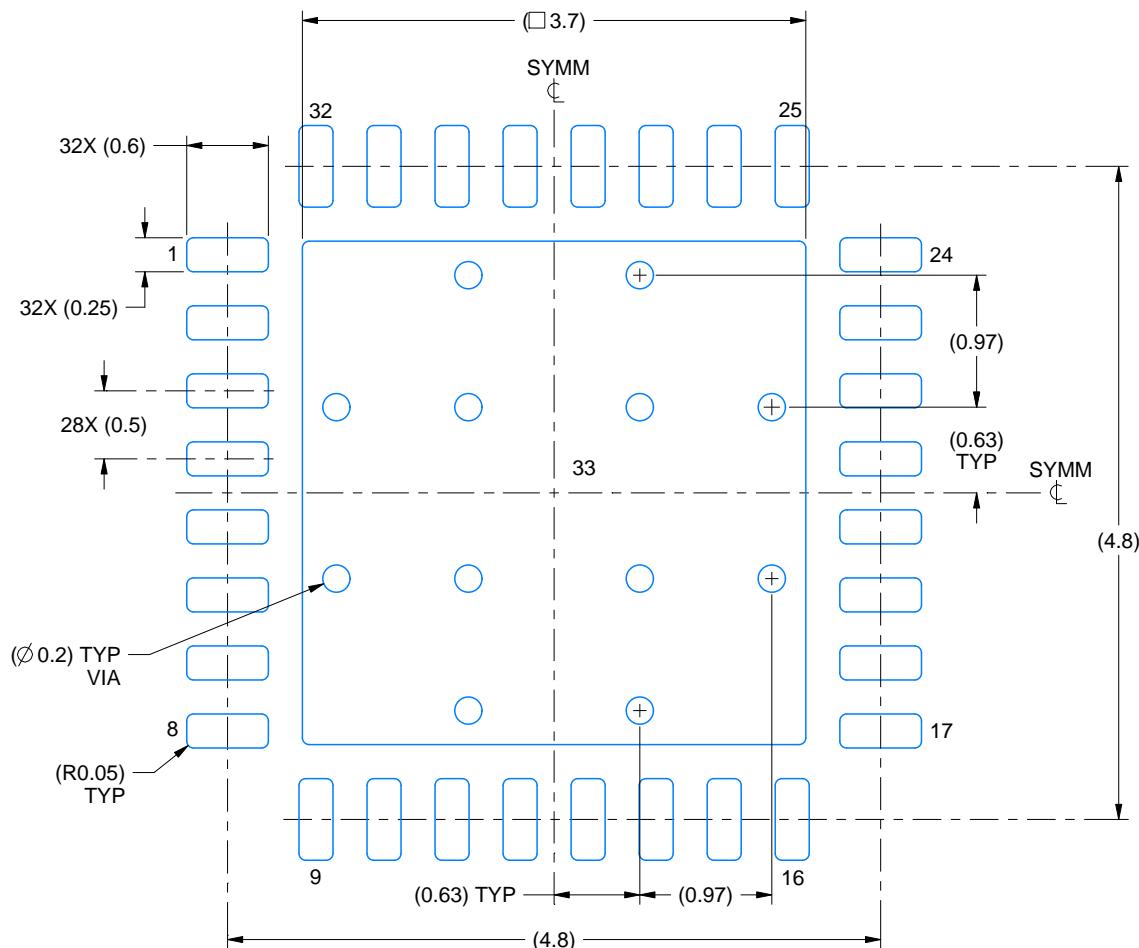

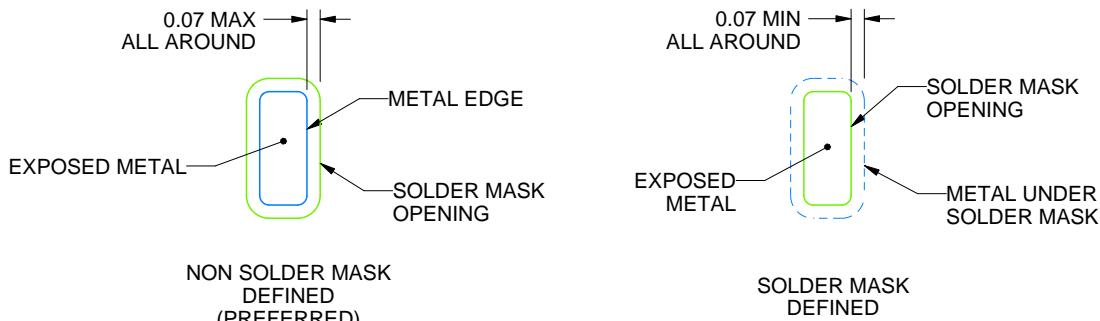

- 小型の 5mm × 5mm VQFN パッケージ、およびコンパクトカメラモジュール設計向けの PoC ソリューションサイズ

## 2 アプリケーション

- 電化製品

- ビデオ監視

- エレベーター / エスカレータ

- 産業用ロボット

- マシンビジョン

- メディカルモニタと診断

- 画像処理

## 3 概要

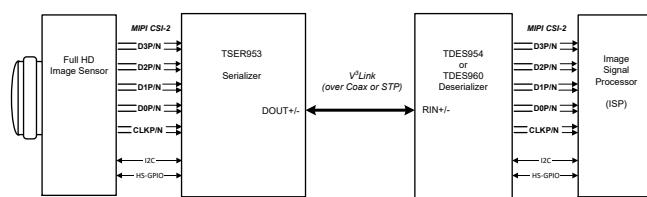

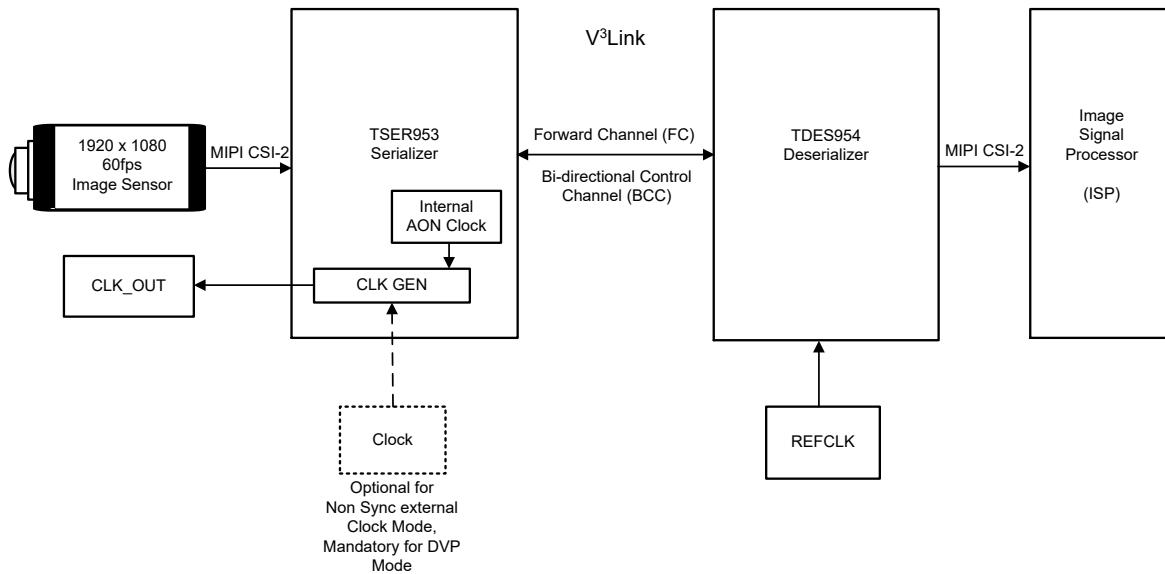

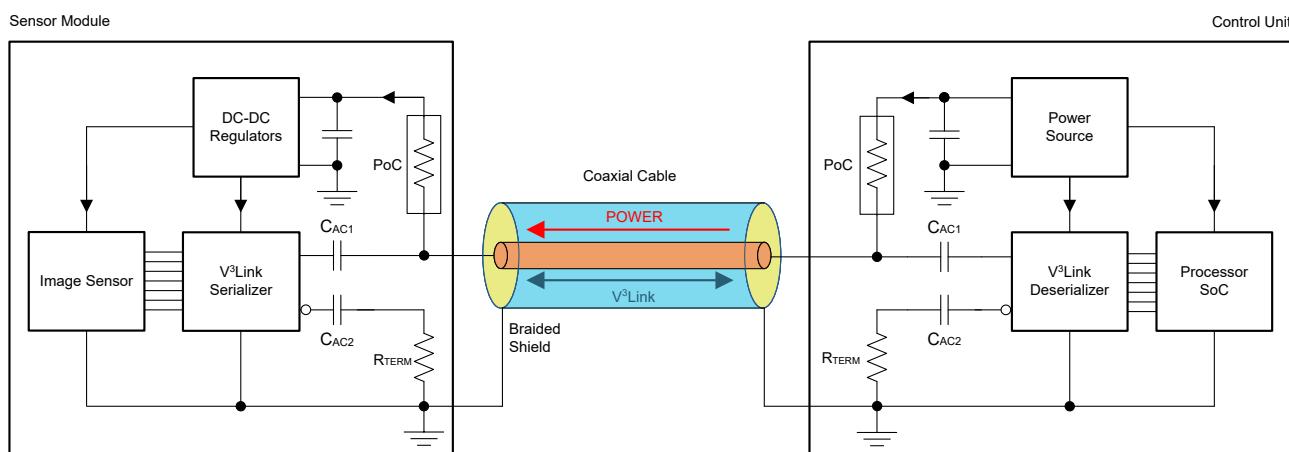

TSER953 シリアルライザは、テキサス・インスツルメンツの V<sup>3</sup>Link デバイス ファミリーの製品で、60fps の 2.3MP イメージャを搭載した高速 RAW データセンサや、4MP/30fps のカメラ、衛星用レーダー、LIDAR、タイム オブ フライト (ToF) センサをサポートするように設計されています。このデバイスは、4.16Gbps の順方向チャネルと超低レイテンシの 50Mbps の双方向制御チャネルを備えており、1 本の同軸ケーブル (PoC) または STP ケーブルによる給電をサポートしています。TSER953 には高度なデータ保護と診断の機能があり、ロボットとオートメーション、医療用画像処理、セキュリティと監視などのさまざまなアプリケーションで高速データ転送をサポートするとともに、産業用や医療用のカメラ アプリケーションの設計を効率化します。TSER953 をデシリアルライザと組み合わせることで、高精度のマルチカメラ センサクロックおよびセンサ同期を行えます。

このシリアルライザは、スペースの制約があるセンサ アプリケーション向けに小型の 5mm × 5mm VQFN パッケージで供給されます。

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ(公称) <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| TSER953 | VQFN (32)            | 5.00mm × 5.00mm          |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ(長さ × 幅)は公称値で、該当する場合はピンも含まれます。

### 代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                      |           |                               |           |

|----------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>          | <b>1</b>  | 6.5 プログラミング                   | <b>27</b> |

| <b>2 アプリケーション</b>    | <b>1</b>  | 6.6 パターン生成                    | <b>30</b> |

| <b>3 概要</b>          | <b>1</b>  | 6.7 レジスタ マップ                  | <b>34</b> |

| <b>4 ピン構成および機能</b>   | <b>3</b>  | <b>7 アプリケーションと実装</b>          | <b>69</b> |

| <b>5 仕様</b>          | <b>6</b>  | 7.1 アプリケーション情報                | <b>69</b> |

| 5.1 絶対最大定格           | 6         | 7.2 代表的なアプリケーション              | <b>72</b> |

| 5.2 ESD 定格           | 6         | 7.3 電源に関する推奨事項                | <b>73</b> |

| 5.3 推奨動作条件           | 7         | 7.4 レイアウト                     | <b>76</b> |

| 5.4 熱に関する情報          | 7         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>80</b> |

| 5.5 電気的特性            | 8         | 8.1 ドキュメントのサポート               | <b>80</b> |

| 5.6 シリアル制御バスの推奨タイミング | 11        | 8.2 ドキュメントの更新通知を受け取る方法        | <b>80</b> |

| 5.7 タイミング図           | 12        | 8.3 サポート・リソース                 | <b>80</b> |

| 5.8 代表的特性            | 13        | 8.4 商標                        | <b>80</b> |

| <b>6 詳細説明</b>        | <b>14</b> | 8.5 静電気放電に関する注意事項             | <b>80</b> |

| 6.1 概要               | 14        | 8.6 用語集                       | <b>80</b> |

| 6.2 機能ブロック図          | 14        | <b>9 改訂履歴</b>                 | <b>80</b> |

| 6.3 機能説明             | 15        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>82</b> |

| 6.4 デバイスの機能モード       | 23        |                               |           |

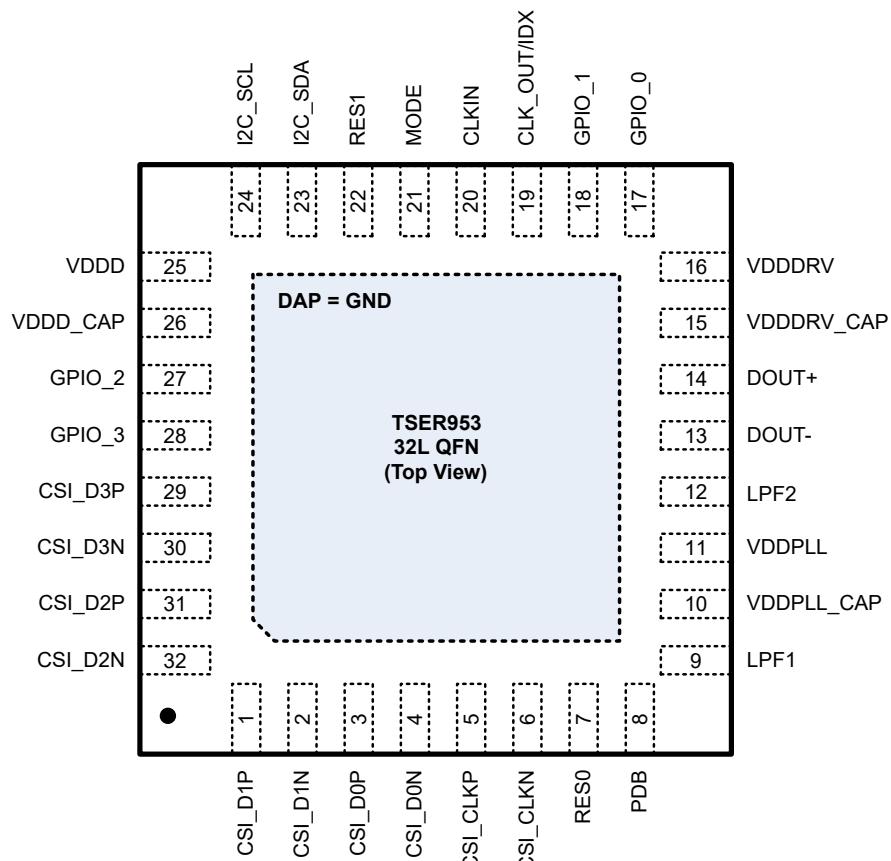

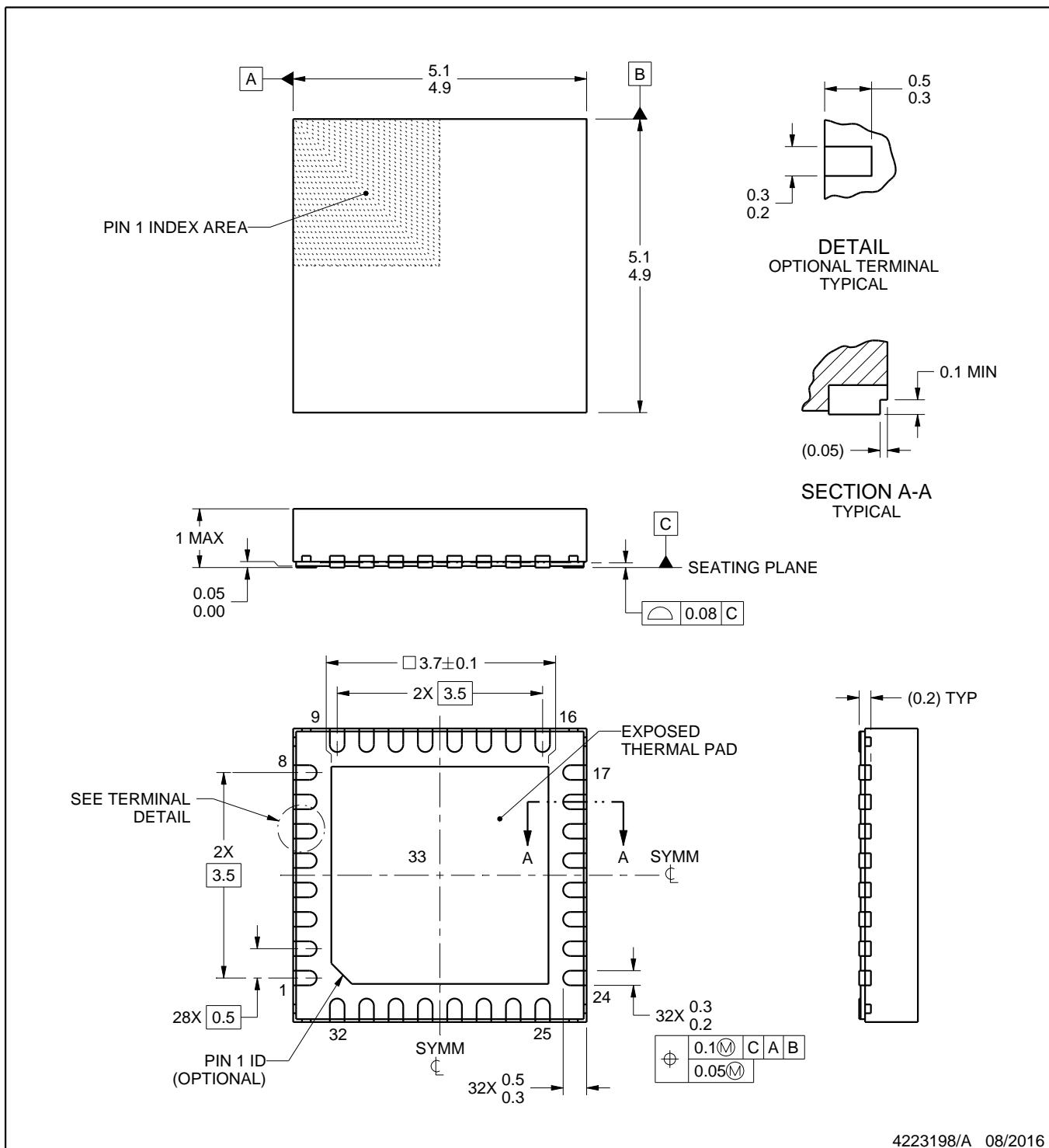

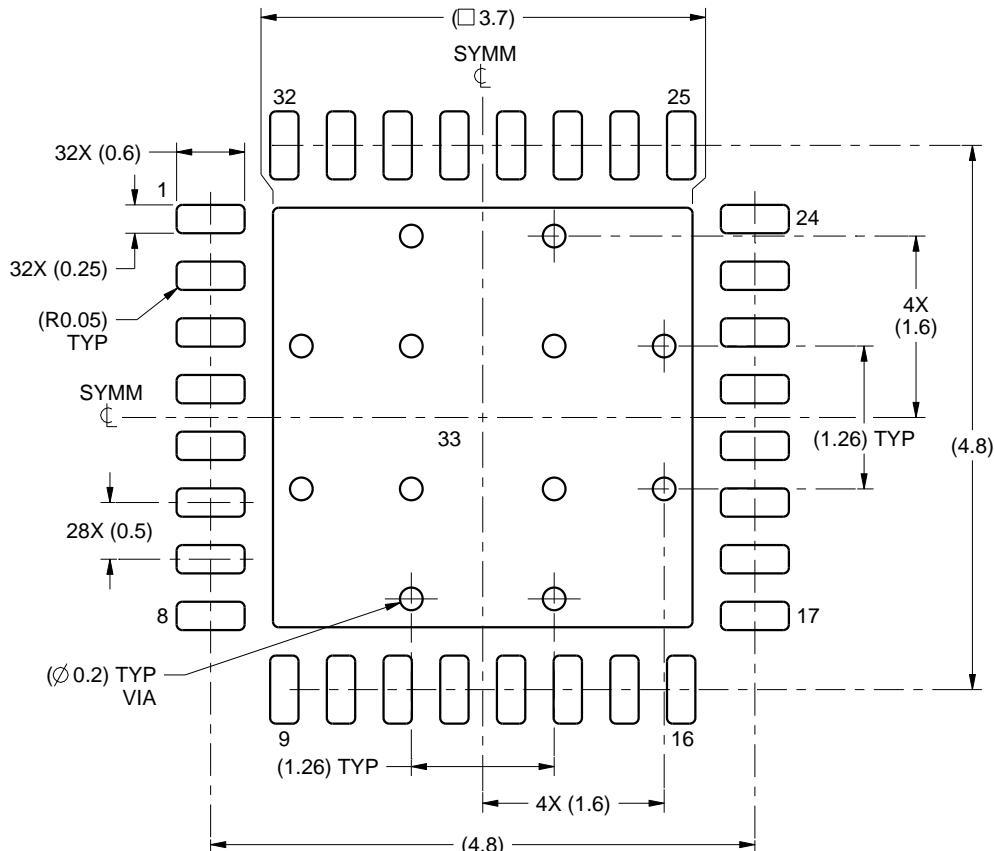

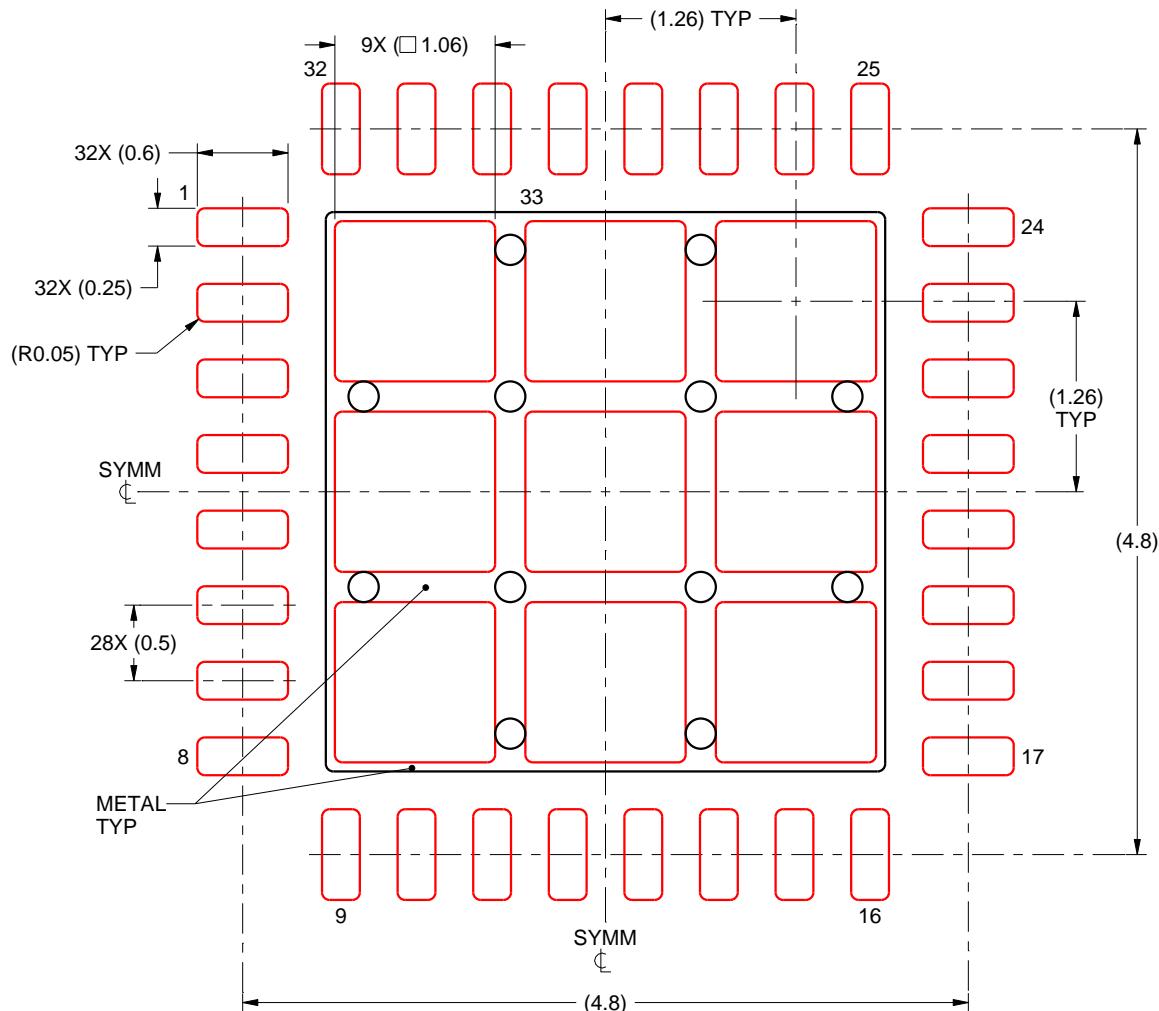

## 4 ピン構成および機能

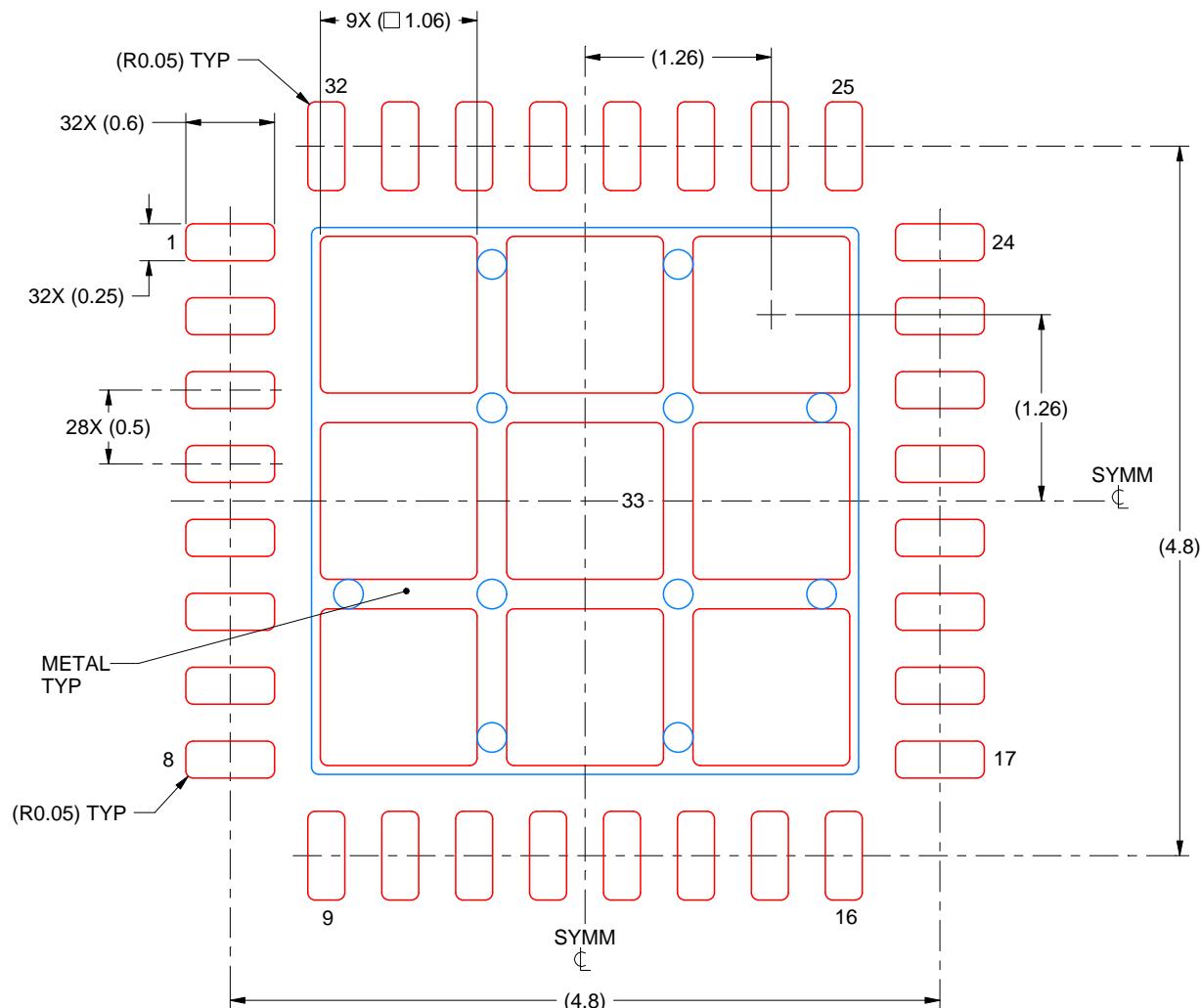

図 4-1. RHB パッケージ

32 ピン VQFN

上面図

表 4-1. ピンの機能

| ピン                    |    | I/O    | 説明                                                                                                        |

|-----------------------|----|--------|-----------------------------------------------------------------------------------------------------------|

| 名称                    | 番号 |        |                                                                                                           |

| <b>CSI インターフェイス</b>   |    |        |                                                                                                           |

| CSI_CLKP              | 5  | I、DPHY | CSI-2 クロック入力ピン。マッチングされた 100Ω (±5%) インピーダンスの相互接続を備えた CSI-2 クロック ソースに接続します。                                 |

| CSI_CLKN              | 6  | I、DPHY |                                                                                                           |

| CSI_D0P               | 3  | I、DPHY |                                                                                                           |

| CSI_D0N               | 4  | I、DPHY |                                                                                                           |

| CSI_D1P               | 1  | I、DPHY |                                                                                                           |

| CSI_D1N               | 2  | I、DPHY | CSI-2 データ入力ピン。マッチングされた 100Ω (±5%) インピーダンスの相互接続を備えた CSI-2 データ ソースに接続します。これらのピンを使用しない場合、フローティングのままでもかまいません。 |

| CSI_D2P               | 31 | I、DPHY |                                                                                                           |

| CSI_D2N               | 32 | I、DPHY |                                                                                                           |

| CSI_D3P               | 29 | I、DPHY |                                                                                                           |

| CSI_D3N               | 30 | I、DPHY |                                                                                                           |

| <b>シリアル制御インターフェイス</b> |    |        |                                                                                                           |

表 4-1. ピンの機能 (続き)

| ピン                           |     | I/O    | 説明                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                           | 番号  |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

| I2C_SDA                      | 23  | OD     | I2C データおよびクロックピン。IDX の設定に応じて、1.8V または 3.3V の電源レールにプルアップします。このデバイスの I2C 実装の詳細については、「 <a href="#">I2C インターフェイスの構成</a> 」を参照してください。I2C プルアップ抵抗の計算に役立つ資料も利用できます ( <a href="#">SLVA689</a> )。                                                                                                                                                                                                                     |

| 構成および制御                      |     |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

| RES0                         | 7   | I      | 予約済みピン – GND に接続                                                                                                                                                                                                                                                                                                                                                                                            |

| RES1                         | 22  | I      | 予約済みピン – 接続しない (フローティングのまま)                                                                                                                                                                                                                                                                                                                                                                                 |

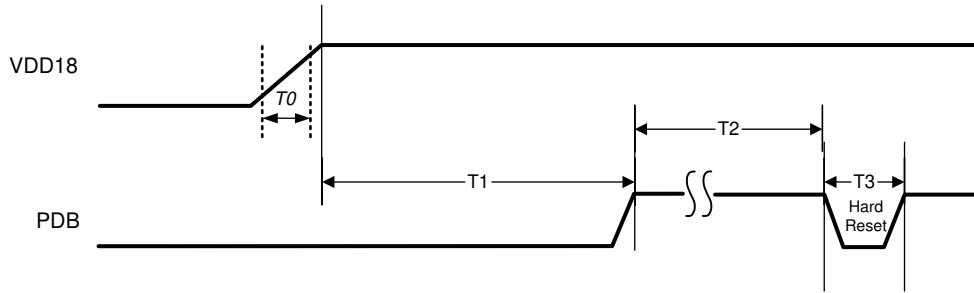

| PDB                          | 8   | I, PD  | パワーダウン反転入力ピン。1MΩ の内部プルダウン。通常、プルダウン付きのプロセッサ GPIO に接続します。PDB 入力を High にすると、本デバイスは有効化され、内部レジスタとステートマシンがデフォルト値にリセットされます。PDB 信号を Low にアサートすると、本デバイスの電源がオフになります。消費電力が最小化されます。このピンのデフォルトの機能は PDB = LOW、パワーダウンです。電源が印加され、必要な最小限のレベルに達するまで、PDB は Low を維持する必要があります。PDB の機能の詳細については、「 <a href="#">パワーダウン (PDB)</a> 」を参照してください。<br><b>PDB 入力は 3.3V 許容ではありません。</b><br>PDB = 1.8V、デバイスを有効化 (通常動作)<br>PDB = 0、デバイスをパワーダウン。 |

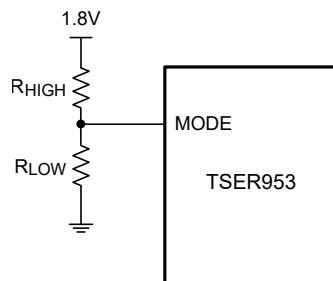

| モード                          | 21  | I, S   | モード選択構成入力。デフォルトの動作モードは、起動時に PDB が Low から High に遷移したときの MODE 入力電圧に基づいてストラップされます。通常、VDD18 への外部プルアップおよび GND への外部プルダウンを介して分圧器に接続して、適切なバイアス電圧を印加します。詳細については、「 <a href="#">モード</a> 」を参照してください。                                                                                                                                                                                                                    |

| CLK_OUT/IDX                  | 19  | I/O, S | IDX ピンは、I2C のプルアップ電圧とデバイス アドレスを設定します。VDD への外部プルアップおよび GND への外部プルダウンを接続して、分圧器を構成します。PDB が Low から High に遷移すると、CLOCK_OUT/IDX ピンでストラップ入力電圧が検出されて機能が判定され、その後 CLK_OUT に転換します。詳細については、「 <a href="#">I2C インターフェイスの構成</a> 」を参照してください。CLK_OUT を使用する場合、このピンの最小抵抗は 35kΩ です。使用しない場合、CLK_OUT/IDX を GND に接続できます。                                                                                                           |

| V <sup>3</sup> Link インターフェイス |     |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

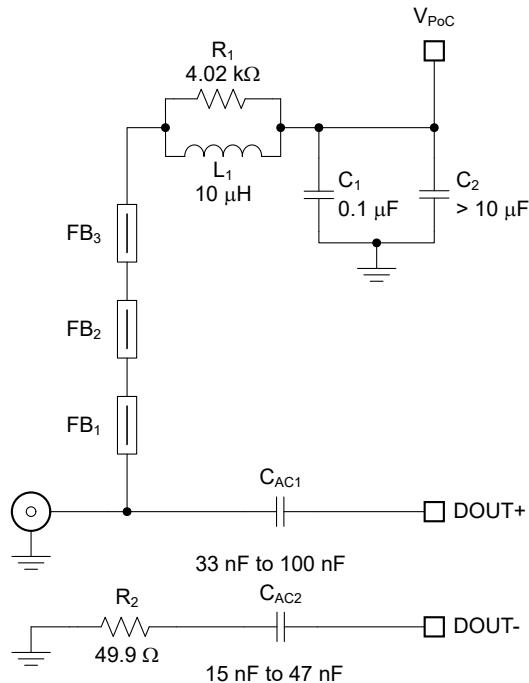

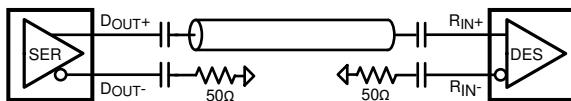

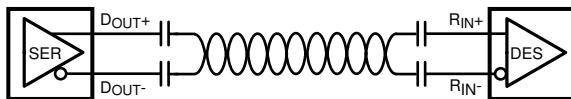

| DOUT-                        | 13  | I/O    | V <sup>3</sup> Link 入力 / 出力ピン。これらのピンは AC 結合する必要があります。標準的な接続図については、 <a href="#">図 7-3</a> および <a href="#">図 7-4</a> 、推奨されるコンデンサの値については、 <a href="#">表 7-3</a> を参照してください。                                                                                                                                                                                                                                     |

| DOUT+                        | 14  | I/O    |                                                                                                                                                                                                                                                                                                                                                                                                             |

| 電源およびグランド                    |     |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDDD_CAP                     | 26  | D, P   | 内部アナログ レギュレータのデカッピング コンデンサの接続。通常、GND との間に 10µF、0.1µF、0.01µF のコンデンサを接続します。外部電源レールには接続しないでください。詳細については「 <a href="#">代表的なアプリケーション</a> 」を参照してください。                                                                                                                                                                                                                                                              |

| VDDDRV_CAP                   | 15  | D, P   | 内部アナログ レギュレータのデカッピング コンデンサの接続。通常、GND との間に 10µF、0.1µF、0.01µF のコンデンサを接続します。外部電源レールには接続しないでください。詳細については「 <a href="#">代表的なアプリケーション</a> 」を参照してください。                                                                                                                                                                                                                                                              |

| VDDPLL_CAP                   | 10  | D, P   | 内部アナログ レギュレータのデカッピング コンデンサの接続。通常、GND との間に 10µF、0.1µF、0.01µF のコンデンサを接続します。外部電源レールには接続しないでください。詳細については「 <a href="#">代表的なアプリケーション</a> 」を参照してください。                                                                                                                                                                                                                                                              |

| VDDD                         | 25  | P      | 1.8V (±5%) 電源ピン。<br>通常、GND との間に 1µF コンデンサと 0.01µF コンデンサを接続します。                                                                                                                                                                                                                                                                                                                                              |

| VDDDRV                       | 16  | P      | 1.8V (±5%) アナログ電源ピン。<br>通常、GND との間に 1µF コンデンサと 0.01µF コンデンサを接続します。                                                                                                                                                                                                                                                                                                                                          |

| VDDPLL                       | 11  | P      | 1.8V (±5%) アナログ電源ピン。<br>通常、GND との間に 1µF コンデンサと 0.01µF コンデンサを接続します。                                                                                                                                                                                                                                                                                                                                          |

| GND                          | DAP | G      | DAP は、VQFN パッケージの裏側の中央にある大きな金属接触部です。グランド ブレーン (GND) に接続します。                                                                                                                                                                                                                                                                                                                                                 |

| ループ フィルタ                     |     |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

| LPF1                         | 9   | P      | ループ フィルタ 1: <a href="#">セクション 7.2.2.4</a> の説明に従って接続します。                                                                                                                                                                                                                                                                                                                                                     |

| LPF2                         | 12  | P      | ループ フィルタ 2: <a href="#">セクション 7.2.2.4</a> の説明に従って接続します。                                                                                                                                                                                                                                                                                                                                                     |

| クロック インターフェイスおよび GPIO        |     |        |                                                                                                                                                                                                                                                                                                                                                                                                             |

**表 4-1. ピンの機能 (続き)**

| ピン     |    | I/O     | 説明                                                                                                                                                                                                                                                                                                      |

|--------|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |         |                                                                                                                                                                                                                                                                                                         |

| GPIO_0 | 17 | I/O, PD | 汎用入出力ピン。これらのピンは、入力の電圧を検出するように構成することもできます。「 <a href="#">電圧および温度の検出</a> 」参照。電源オン時、これらの GPIO ピンは、デフォルトで $300\text{k}\Omega$ (標準値) の内部プルダウン抵抗を備えた入力に設定されます。これらのピンを使用しない場合は、フローティングのままにできますが、 <code>GPIOx_INPUT_EN</code> を 0 に設定してピンをディセーブルにすることを推奨します。プログラム機能については、 <a href="#">セクション 6.3.6</a> を参照してください。 |

| GPIO_1 | 18 | I/O, PD |                                                                                                                                                                                                                                                                                                         |

| GPIO_2 | 27 | I/O, PD |                                                                                                                                                                                                                                                                                                         |

| GPIO_3 | 28 | I/O, PD |                                                                                                                                                                                                                                                                                                         |

| CLKIN  | 20 | I       | 基準クロック入力ピン。非同期外部クロック モードで動作する場合、このピンをローカル クロック ソースに接続します。他のクロック モードと同様に、このピンを使わない場合はオープンのままにできます。クロック モードの詳細については、 <a href="#">表 6-8</a> を参照してください。                                                                                                                                                     |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                          | ピンまたは周波数                                                                                                    | 最小値  | 最大値                   | 単位 |

|--------------------------|-------------------------------------------------------------------------------------------------------------|------|-----------------------|----|

| 電源電圧、VDD                 | VDDD、<br>VDDDRV、<br>VDDPLL                                                                                  | -0.3 | 2.16                  | V  |

| 入力電圧                     | GPIO[3:0]、<br>PDB、CLKIN、<br>IDX、MODE、<br>CSI_CLKP/N、<br>CSI_D0P/N、<br>CSI_D1P/N、<br>CSI_D2P/N、<br>CSI_D3P/N | -0.3 | V <sub>DD</sub> + 0.3 | V  |

| V <sup>3</sup> Link 出力電圧 | DOUT+、<br>DOUT-                                                                                             | -0.3 | 1.21                  | V  |

| オープンドレイン電圧               | I <sub>2</sub> C_SDA、<br>I <sub>2</sub> C_SCL                                                               | -0.3 | 3.96                  | V  |

| 接合部温度、T <sub>J</sub>     |                                                                                                             |      | 150                   | °C |

| 保管温度、T <sub>stg</sub>    |                                                                                                             | -65  | 150                   | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

|                    |      |                                                                                                                              |                           | 値      | 単位 |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ESD 分類レベル<br>3A <sup>(1)</sup>                                                                                   | メディア依存インターフェイスピンを除くすべてのピン | ±4000  | V  |

|                    |      |                                                                                                                              | メディア依存インターフェイスピン          |        |    |

|                    |      | デバイス帯電モデル (CDM) ESD 分類レベル C6                                                                                                 |                           | ±1500  | V  |

|                    |      | IEC 61000-4-2<br>R <sub>D</sub> = 330Ω、C <sub>S</sub> = 150pF                                                                | 接触放電<br>(DOUT+ および DOUT-) | ±8000  | V  |

|                    |      |                                                                                                                              | 気中放電<br>(DOUT+ および DOUT-) | ±18000 | V  |

|                    |      | ISO 10605<br>R <sub>D</sub> = 330Ω、C <sub>S</sub> = 150pF および 330pF<br>R <sub>D</sub> = 2kΩ、C <sub>S</sub> = 150pF および 330pF | 接触放電<br>(DOUT+ および DOUT-) | ±8000  | V  |

|                    |      |                                                                                                                              | 気中放電<br>(DOUT+ および DOUT-) | ±18000 | V  |

- ANSI/ESDA/JEDEC JS-001 仕様に従って HBM ストレス試験を実施しています。

### 5.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|                                                          |                                                                           | 最小値  | 公称値                | 最大値                      | 単位 |

|----------------------------------------------------------|---------------------------------------------------------------------------|------|--------------------|--------------------------|----|

| 電源電圧                                                     | VDD (VDDD、VDDDRV、VDDPLL)                                                  | 1.71 | 1.8                | 1.89                     | V  |

| オープンドレイン電圧                                               | I <sub>2</sub> C_SDA、I <sub>2</sub> C_SCL = V <sub>(I<sub>2</sub>C)</sub> | 1.71 |                    | 3.6                      | V  |

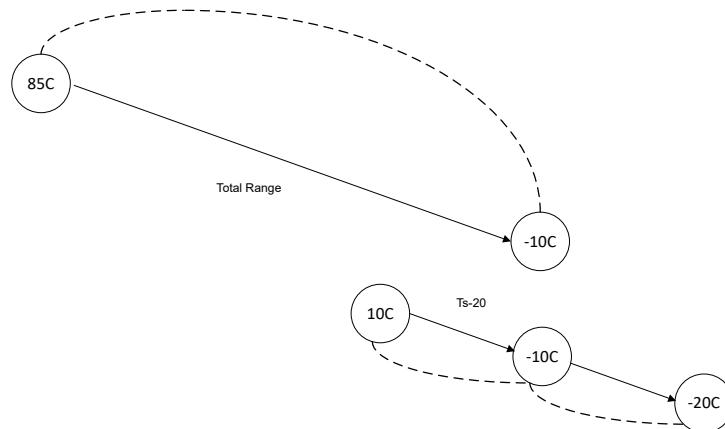

| 自由気流での動作温度 (T <sub>A</sub> )                             |                                                                           | -20  | 25                 | 85                       | °C |

| 温度低下終了温度 (T <sub>s</sub> = 開始温度) <sup>(3)</sup>          | 10°C < T <sub>s</sub> ≤ 85°C                                              |      | -10                |                          | °C |

| 温度低下終了温度 (T <sub>s</sub> = 開始温度) <sup>(3)</sup>          | T <sub>s</sub> ≤ 10°C                                                     |      | T <sub>s</sub> -20 |                          | °C |

| MIPi データレート (CSI-2 レーンごと)                                |                                                                           | 80   | 832                | Bps                      |    |

| 基準クロック周波数                                                |                                                                           | 25   | 104                | MHz                      |    |

| ローカル I <sub>2</sub> C 周波数 (f <sub>I<sub>2</sub>C</sub> ) |                                                                           |      | 1                  | MHz                      |    |

| 電源ノイズ <sup>(4)</sup>                                     | VDD (VDDD、VDDDRV、VDDPLL)                                                  |      | 25                 | mV <sub>p-p</sub>        |    |

| DOUT+ と DOUT- (PSR) 間の差動電源ノイズ                            | f = 10kHz～50MHz<br>(同軸モードのみ)                                              |      | 25                 | mV <sub>p-p</sub>        |    |

|                                                          | f = 30Hz、10～90% の立ち上がり / 立ち下がり時間 > 100μs<br>(同軸モードのみ)                     |      | 25                 | mV <sub>p-p</sub>        |    |

| 非同期モードの入力クロック ジッタ (t <sub>JIT</sub> )                    | CLKIN                                                                     |      | 0.05               | UI_CLK_IN <sup>(2)</sup> |    |

| バックチャネル入力ジッタ (t <sub>JIT-BC</sub> )                      | DOUT+、DOUT-                                                               |      | 0.4                | UI_BC <sup>(1)</sup>     |    |

- (1) バックチャネルユニット間隔 (UI\_BC) は 1/(BC ラインレート) です。たとえば、標準的な UI\_BC は 1/100MHz = 10ns です。ジッタ許容値が 0.4UI の場合、次の式を使用して UI のジッタを秒に変換します。10ns × 0.4UI = 4ns

- (2) 非同期モード - 特定のクロックについて、UI は 1/clock\_freq として定義されます。たとえば、クロック = 50MHz の場合、標準的な UI\_CLK\_IN は 1/50MHz = 20ns です。

- (3) ソフトウェア構成を使用した、連続的な PLL ロックのための温度低下終了温度。デバイスの構成については、[セクション 9.1.1 「システムの初期化」](#)を参照してください。

- (4) DC - 50MHz

### 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | TSER953    | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | RHB (VQFN) |      |

|                       |                   | 32 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 31.5       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 10.9       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 20         | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 1          | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.2        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 10.9       | °C/W |

- (1) 従来および最新の熱測定基準の詳細については、アプリケーションレポート『半導体および IC パッケージの熱評価基準』、SPRA953 を参照してください。

## 5.5 電気的特性

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。

| パラメータ                                        | テスト条件                                                 | ピンまたは周波数                                           | 最小値                     | 標準値                     | 最大値                     | 単位            |

|----------------------------------------------|-------------------------------------------------------|----------------------------------------------------|-------------------------|-------------------------|-------------------------|---------------|

| <b>消費電力</b>                                  |                                                       |                                                    |                         |                         |                         |               |

| $I_{DD\_TOTAL}$                              | 電源電流<br><br>416MHz CSI 入力クロック、4 レーン モード、チエッカーボード パターン | VDDPLL、<br>VDDD、<br>VDDDRV                         | 160                     | 225                     |                         | mA            |

| $I_{DDPLL}$                                  |                                                       | VDDPLL                                             | 55                      | 80                      |                         |               |

| $I_{DDD}$                                    |                                                       | VDDD                                               | 45                      | 70                      |                         |               |

| $I_{DDDRV}$                                  |                                                       | VDDDRV                                             | 60                      | 75                      |                         |               |

| <b>1.8V LVC MOS I/O (VDD) = 1.71V~1.89V)</b> |                                                       |                                                    |                         |                         |                         |               |

| $V_{OH}$                                     | High レベル出力電圧                                          | $I_{OH} = -4\text{mA}$                             | GPIO[3:0]、<br>CLK_OUT   | $V_{(VDD)} - 0.45$      | $V_{(VDD)}$             | V             |

| $V_{OL}$                                     | Low レベル出力電圧                                           | $I_{OL} = +4\text{mA}$                             | GPIO[3:0]、<br>CLK_OUT   | GND                     | 0.45                    | V             |

| $V_{IH}$                                     | High レベル入力電圧                                          |                                                    | GPIO[3:0]、<br>PDB、CLKIN | $V_{(VDD)} \times 0.65$ | $V_{(VDD)}$             | V             |

| $V_{IL}$                                     | Low レベル入力電圧                                           |                                                    | GPIO[3:0]、<br>PDB、CLKIN | GND                     | $V_{(VDD)} \times 0.35$ | V             |

| $I_{IH}$                                     | 入力 HIGH 電流                                            | $V_{IN} = V_{(VDD)}$                               | GPIO[3:0]、<br>PDB、CLKIN |                         | 20                      | $\mu\text{A}$ |

| $I_{IL}$                                     | 入力 LOW 電流                                             | $V_{IN} = \text{GND}$                              | GPIO[3:0]、<br>PDB、CLKIN | -20                     |                         | $\mu\text{A}$ |

| $I_{os}$                                     | 出力短絡電流                                                | $V_{OUT} = 0\text{V}$                              |                         |                         | -36                     | mA            |

| $I_{oz}$                                     | トライステート出力電流                                           | $V_{OUT} = V_{(VDD)}$ 、 $V_{OUT} = \text{GND}$     | GPIO[3:0]、<br>CLK_OUT   |                         | $\pm 20$                | $\mu\text{A}$ |

| $C_{IN}$                                     | 入力容量                                                  |                                                    |                         |                         | 5                       | pF            |

| <b>V<sup>3</sup>リンク入力 / 出力</b>               |                                                       |                                                    |                         |                         |                         |               |

| $V_{IN-BC}$                                  | シングルエンド入力電圧                                           | 同軸構成、 $50\Omega$ 、最大ケーブル長                          | DOUT+、<br>DOUT-         | 120                     |                         | mV            |

| $V_{ID-BC}$                                  | 差動入力電圧                                                | STP 構成、 $100\Omega$ 、最大ケーブル長                       | DOUT+、<br>DOUT-         | 240                     |                         |               |

| $E_{H-FC}$                                   | フォワード チャネル アイの高さ                                      | 同軸構成、V <sup>3</sup> Link フォワード チャネル = 4.16Gbps     | DOUT+、<br>DOUT-         | 425                     |                         | mVp-p         |

|                                              |                                                       | STP 構成、V <sup>3</sup> Link フォワード チャネル = 4.16Gbps   | DOUT+、<br>DOUT-         | 850                     |                         |               |

| $t_{TR-FC}$                                  | フォワード チャネル出力遷移時間                                      | V <sup>3</sup> Link フォワード チャネル = 4.16Gbps、20% ~80% | DOUT+、<br>DOUT-         | 65                      |                         | ps            |

| $t_{JIT-FC}$                                 | フォワード チャネル出力のジッタ                                      | 同期モード、f/15 -3dB CDR ループ BW で測定                     | DOUT+、<br>DOUT-         | 0.21                    |                         | UI            |

|                                              |                                                       | 非同期モード、f/15 –3dB CDR ループ BW で測定                    | DOUT+、<br>DOUT-         | 0.22                    |                         |               |

| $f_{REF}$                                    | 内部基準周波数                                               | 非同期内部クロック モード                                      |                         | 24.2                    | 25.5                    | MHz           |

| <b>V<sup>3</sup>Link ドライバ仕様 (差動)</b>         |                                                       |                                                    |                         |                         |                         |               |

| $V_{ODp-p}$                                  | 出力差動電圧                                                | $R_L = 100\Omega$                                  | DOUT+、<br>DOUT-         | 1040                    | 1150                    | 1340          |

| $\Delta V_{OD}$                              | 出力電圧不平衡                                               |                                                    | DOUT+、<br>DOUT-         | 5                       | 24                      | mV            |

## 5.5 電気的特性 (続き)

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。

| パラメータ                                     |                     | テスト条件                | ピンまたは周波数        | 最小値                                                                | 標準値  | 最大値 | 単位                |   |

|-------------------------------------------|---------------------|----------------------|-----------------|--------------------------------------------------------------------|------|-----|-------------------|---|

| V <sub>os</sub>                           | 出力差動オフセット電圧         |                      |                 | DOUT+、<br>DOUT-                                                    | 575  |     | mV                |   |

| ΔV <sub>os</sub>                          | オフセット電圧不balance     |                      |                 | DOUT+、<br>DOUT-                                                    | 2    |     | mV                |   |

| I <sub>os</sub>                           | 出力短絡電流              | DOUT = 0V            | DOUT+、<br>DOUT- | -22                                                                |      | mA  |                   |   |

| R <sub>T</sub>                            | 内部終端抵抗              | DOUT+ と DOUT- の間     | DOUT+、<br>DOUT- | 80                                                                 | 100  | 120 | Ω                 |   |

| <b>V<sup>3</sup>Link ドライバ仕様 (シングルエンド)</b> |                     |                      |                 |                                                                    |      |     |                   |   |

| V <sub>OUT</sub>                          | シングルエンド出力電圧         | R <sub>L</sub> = 50Ω | DOUT+、<br>DOUT- | 520                                                                | 575  | 670 | mV <sub>p-p</sub> |   |

| I <sub>os</sub>                           | 出力短絡電流              | DOUT = 0V            | DOUT+、<br>DOUT- | -22                                                                |      | mA  |                   |   |

| R <sub>T</sub>                            | シングルエンド終端抵抗         |                      |                 | DOUT+、<br>DOUT-                                                    | 40   | 50  | 60                | Ω |

| <b>電圧と温度の検出</b>                           |                     |                      |                 |                                                                    |      |     |                   |   |

| V <sub>ACC</sub>                          | 電圧精度                | 「電圧と温度の検出」を参照        |                 | GPIO[1:0]                                                          | ±1   |     | LSB               |   |

| T <sub>ACC</sub>                          | 温度精度                | 「電圧と温度の検出」を参照        |                 | ±1                                                                 |      | LSB |                   |   |

| <b>CSI-2 HS インターフェイス DC 仕様</b>            |                     |                      |                 |                                                                    |      |     |                   |   |

| V <sub>CMRX(DC)</sub>                     | 同相電圧、HS 受信モード       |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 70   | 330 | mV                |   |

| V <sub>IDTH</sub>                         | 差動入力 High スレッショルド   |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 70   |     | mV                |   |

| V <sub>IDTL</sub>                         | 差動入力 Low スレッショルド    |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | -70  |     | mV                |   |

| Z <sub>ID</sub>                           | 差動入力インピーダンス         |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 80   | 100 | 125               | Ω |

| <b>CSI-2 HS インターフェイス AC 仕様</b>            |                     |                      |                 |                                                                    |      |     |                   |   |

| t <sub>HOLD</sub>                         | データ - クロック セットアップ時間 |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 0.15 |     | UI                |   |

| t <sub>SETUP</sub>                        | データ - クロック ホールド時間   |                      |                 | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 0.15 |     | UI                |   |

## 5.5 電気的特性 (続き)

特記のない限り、推奨動作条件での電源電圧および温度範囲に適用。

| パラメータ                          | テスト条件                                                         | ピンまたは周波数                                                           | 最小値                                           | 標準値                  | 最大値                  | 単位 |

|--------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|----------------------|----------------------|----|

| <b>CSI-2 LP インターフェイス DC 仕様</b> |                                                               |                                                                    |                                               |                      |                      |    |

| V <sub>IH</sub>                | ロジック High の入力電圧                                               | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 880                                           | 790                  |                      | mV |

| V <sub>IL</sub>                | ロジック Low の入力電圧                                                | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N |                                               | 710                  | 550                  | mV |

| V <sub>HYST</sub>              | 入力ヒステリシス                                                      | CSI_D3P/N、<br>CSI_D2P/N、<br>CSI_D1P/N、<br>CSI_D0P/N、<br>CSI_CLKP/N | 25                                            | 75                   |                      | mV |

| <b>LVC MOS I/O</b>             |                                                               |                                                                    |                                               |                      |                      |    |

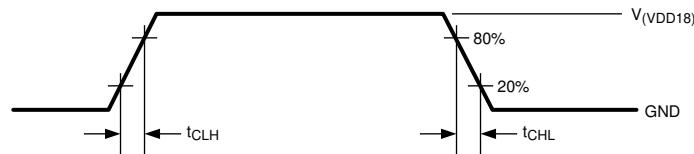

| t <sub>CLH</sub>               | LVC MOS の Low から High への遷移時間<br>$V_{(VDD)} = 1.71 \sim 1.89V$ | GPIO[3:0]                                                          |                                               | 2                    |                      | ns |

| t <sub>CHL</sub>               | LVC MOS の High から Low への遷移時間<br>$V_{(VDD)} = 1.71 \sim 1.89V$ | GPIO[3:0]                                                          |                                               | 2                    |                      | ns |

| t <sub>PDB</sub>               | PDB リセット パルス幅                                                 | PDB                                                                | 3                                             |                      |                      | ms |

| <b>シリアル制御バス</b>                |                                                               |                                                                    |                                               |                      |                      |    |

| V <sub>IH</sub>                | 入力 HIGH レベル                                                   | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA                      | 0.7 ×<br>$V_{(I2C)}$                          |                      |                      | mV |

| V <sub>IL</sub>                | 入力 LOW レベル                                                    | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA                      | GND                                           | 0.3 ×<br>$V_{(I2C)}$ |                      | mV |

| V <sub>HY</sub>                | 入力ヒステリシス                                                      | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA                      |                                               | >50                  |                      | mV |

| V <sub>OL</sub>                | 出力 Low レベル                                                    | $V_{(I2C)} < 2V$ 、 $I_{OL} = 3mA$ 、標準モード / ファースト モード               | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | 0                    | 0.2 ×<br>$V_{(I2C)}$ | V  |

|                                |                                                               | $V_{(I2C)} < 2V$ 、 $I_{OL} = 20mA$ 、ファースト モード プラス                  | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | 0                    | 0.2 ×<br>$V_{(I2C)}$ | V  |

|                                |                                                               | $V_{(I2C)} > 2V$ 、 $I_{OL} = 3mA$ 、標準モード / ファースト モード               | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | 0                    | 0.4                  | V  |

|                                |                                                               | $V_{(I2C)} > 2V$ 、 $I_{OL} = 20mA$ 、ファースト モード プラス                  | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | 0                    | 0.4                  | V  |

| I <sub>IH</sub>                | 入力 HIGH 電流                                                    | $V_{IN} = V_{(I2C)}$                                               | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | -10                  | 10                   | μA |

| I <sub>IL</sub>                | 入力 LOW 電流                                                     | $V_{IN} = 0V$                                                      | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | -10                  | 10                   | μA |

| C <sub>IN</sub>                | 入力容量                                                          |                                                                    | I <sub>2C</sub> _SCL、<br>I <sub>2C</sub> _SDA | 5                    |                      | pf |

## 5.6 シリアル制御バスの推奨タイミング

I<sup>2</sup>C の電源および温度範囲内 (特に記述のない限り)

|              |                                    |               | 最小値  | 標準値  | 最大値     | 単位 |

|--------------|------------------------------------|---------------|------|------|---------|----|

| $f_{SCL}$    | SCL クロック周波数                        | スタンダード モード    | >0   | 100  | kHz     |    |

|              |                                    | ファースト モード     | >0   | 400  | kHz     |    |

|              |                                    | ファースト モード プラス | >0   | 1    | MHz     |    |

| $t_{LOW}$    | SCL Low 期間                         | スタンダード モード    | 4.7  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 1.3  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.5  |      | $\mu$ s |    |

| $t_{HIGH}$   | SCL High 期間                        | スタンダード モード    | 4.0  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 0.6  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.26 |      | $\mu$ s |    |

| $t_{HD:STA}$ | START または REPEAT-START 条件のホールド時間   | スタンダード モード    | 4.0  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 0.6  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.26 |      | $\mu$ s |    |

| $t_{SU:STA}$ | START または REPEAT-START 条件のセットアップ時間 | スタンダード モード    | 4.7  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 0.6  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.26 |      | $\mu$ s |    |

| $t_{HD:DAT}$ | データ ホールド時間                         | スタンダード モード    | 0    |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 0    |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0    |      | $\mu$ s |    |

| $t_{SU:DAT}$ | データ セットアップ時間                       | スタンダード モード    | 250  |      | ns      |    |

|              |                                    | ファースト モード     | 100  |      | ns      |    |

|              |                                    | ファースト モード プラス | 50   |      | ns      |    |

| $t_{SU:STO}$ | STOP 条件のセットアップ時間                   | スタンダード モード    | 4.0  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 0.6  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.26 |      | $\mu$ s |    |

| $t_{BUF}$    | STOP と START 間のバス解放時間              | スタンダード モード    | 4.7  |      | $\mu$ s |    |

|              |                                    | ファースト モード     | 1.3  |      | $\mu$ s |    |

|              |                                    | ファースト モード プラス | 0.5  |      | $\mu$ s |    |

| $t_r$        | SCL および SDA 立ち上がり時間                | スタンダード モード    |      | 1000 | ns      |    |

|              |                                    | ファースト モード     |      | 300  | ns      |    |

|              |                                    | ファースト モード プラス |      | 120  | ns      |    |

| $t_f$        | SCL および SDA 立ち下がり時間                | スタンダード モード    |      | 300  | ns      |    |

|              |                                    | ファースト モード     |      | 300  | ns      |    |

|              |                                    | ファースト モード プラス |      | 120  | ns      |    |

| $C_b$        | 各バス ラインの容量性負荷                      | スタンダード モード    |      | 400  | pF      |    |

|              |                                    | ファースト モード     |      | 400  | pF      |    |

|              |                                    | ファースト モード プラス |      | 550  | pF      |    |

| $t_{VD:DAT}$ | データ有効時間                            | スタンダード モード    |      | 3.45 | $\mu$ s |    |

|              |                                    | ファースト モード     |      | 0.9  | $\mu$ s |    |

|              |                                    | ファースト モード プラス |      | 0.45 | $\mu$ s |    |

## 5.6 シリアル制御バスの推奨タイミング (続き)

I<sup>2</sup>C の電源および温度範囲内 (特に記述のない限り)

|                     |               |               | 最小値 | 標準値 | 最大値  | 単位 |

|---------------------|---------------|---------------|-----|-----|------|----|

| t <sub>VD;ACK</sub> | データ有効アクノリッジ時間 | スタンダード モード    |     |     | 3.45 | μs |

|                     |               | ファースト モード     |     |     | 0.9  | μs |

|                     |               | ファースト モード プラス |     |     | 0.45 | μs |

| t <sub>SP</sub>     | 入力フィルタ        | ファースト モード     |     |     | 50   | ns |

|                     |               | ファースト モード プラス |     |     | 50   | ns |

図 5-1. LVC MOS 遷移時間

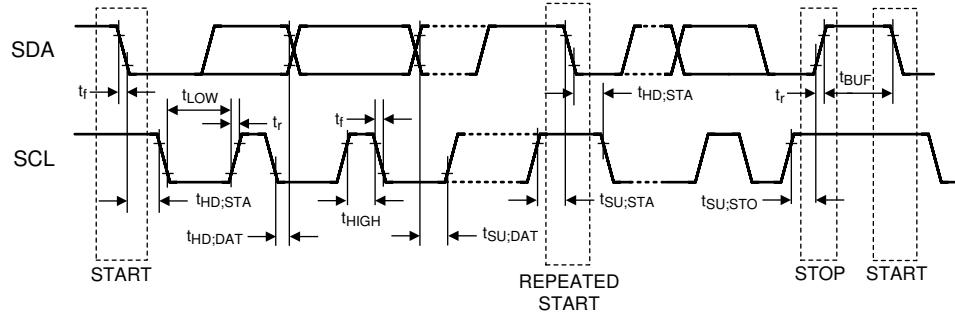

図 5-2. I<sup>2</sup>C シリアル 制御バスのタイミング

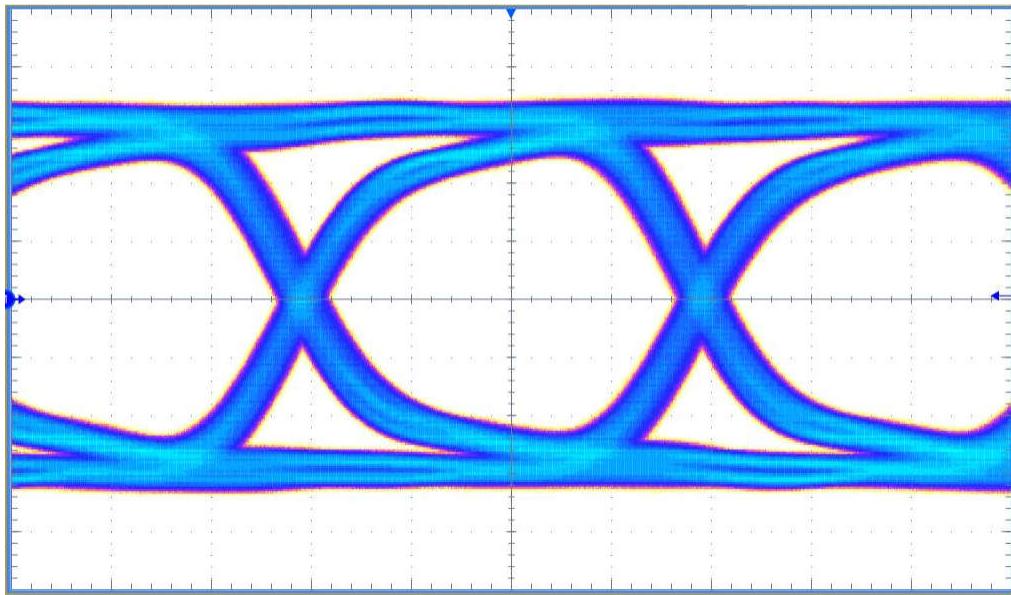

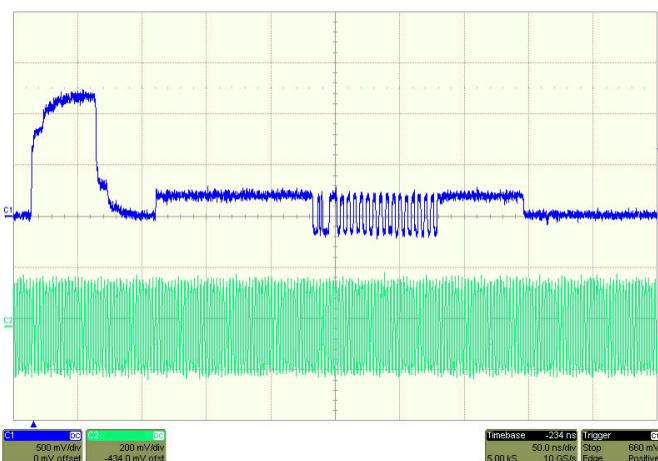

## 5.8 代表的特性

縦軸: 100mV/div

横軸: 62.5ps/div

図 5-3. シリアライザ出力から 4Gb/s V<sup>3</sup>Link フォワード チャネル レートでのアイ ダイアグラム

## 6 詳細説明

### 6.1 概要

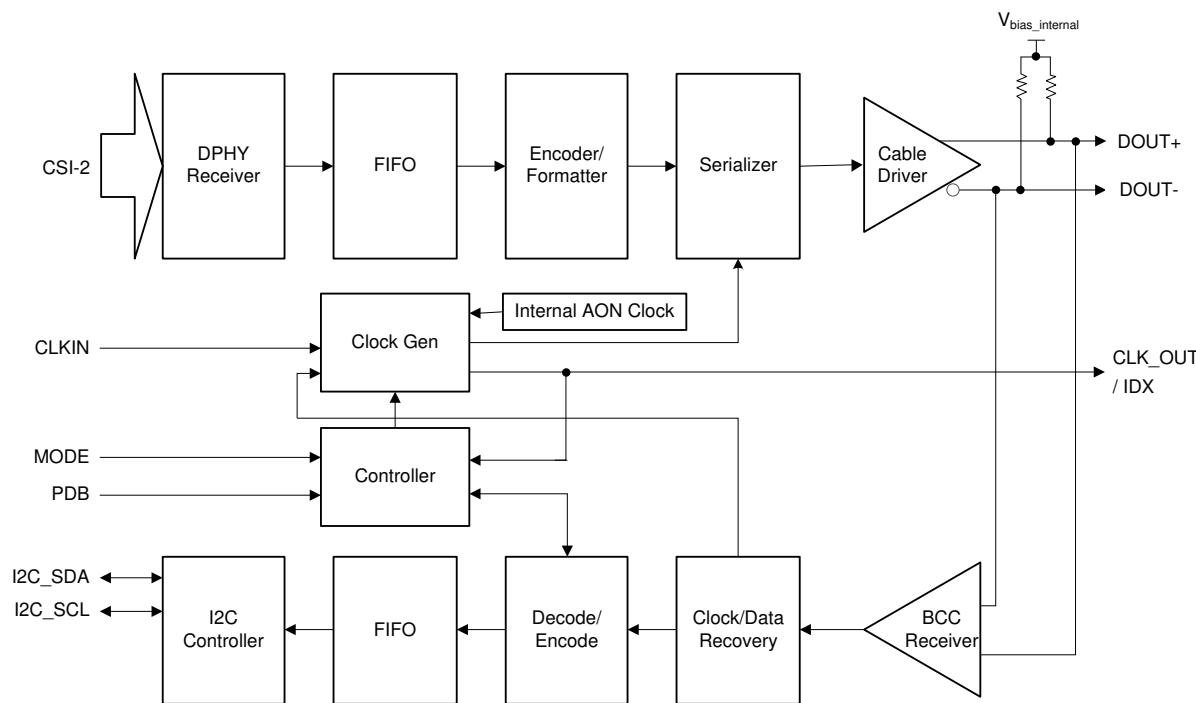

TSE953 は、MIPI CSI-2 インターフェイスを使用する、高解像度イメージ センサまたはその他のセンサからのデータをシリアル化します。このシリアルライザは、TDES954 デシリアルライザ（デュアル ハブ）、TDES960 デシリアルライザ（クワッド ハブ）、さらには他の将来出現する V<sup>3</sup>Link デシリアルライザと、インターフェイスできるように最適化されています。シリアルライザとデシリアルライザの間の相互接続は、同軸ケーブルまたはシールド付きツイストペア (STP) ケーブルのいずれかになります。TSE953 はサラウンド ビューなどのマルチセンサ システムをサポートするように設計されており、TDES954 および TDES960 ハブを経由してセンサを同期できます。

TSE953 シリアルライザおよび対応するデシリアルライザは、I<sup>2</sup>C 互換インターフェイスを備えています。I<sup>2</sup>C 互換インターフェイスにより、ローカル ホストコントローラからシリアルライザまたはデシリアルライザ デバイスをプログラムできます。さらに、このデバイスには双方向制御チャネル (BCC) が組み込まれており、シリアルライザとデシリアルライザ間、およびリモート I<sup>2</sup>C ターゲットデバイス間の通信が可能です。

双方向制御チャネル (BCC) は、高速フォワード チャネル（シリアルライザからデシリアルライザへ）の組み込み信号伝達と、バック チャネル（デシリアルライザからシリアルライザへ）の低速信号伝達を組み合わせて実装されています。このインターフェイスを介して、BCC はシリアル リンクを経由して 1 つの I<sup>2</sup>C バスから別のバスへ I<sup>2</sup>C トランザクションをブリッジするメカニズムを提供します。

### 6.2 機能ブロック図

## 6.3 機能説明

TSER953 は、V<sup>3</sup>Link シリアライザであり、60fps の 2-MP イメージャ、4-MP/30fps のカメラ、衛星用レーダー、LIDAR、タイムオブフライト (ToF) カメラをサポートするように設計されています。このチップは、最大 4.16Gbps で動作するフォワードチャネルに加えて、超低レイテンシの 50Mbps 双方向制御チャネルを備えています。フォワードチャネル、双方向制御チャネル、および電力の伝送は、同軸ケーブル (Power-over-Coax) または STP ケーブルでサポートされています。TSER953 には高度なデータ保護と診断の機能があり、ロボットとオートメーション、医療用画像処理、セキュリティと監視などのさまざまなアプリケーションで高速データ転送をサポートするとともに、産業用や医療用のカメラ アプリケーションの設計を効率化します。TSER953 をデシリアライザと組み合わせることで、高精度のマルチカメラ センサ クロックおよびセンサ同期を行えます。

### 6.3.1 CSI-2 レシーバ

TSER953 は、センサから CSI-2 ビデオ データを受信します。CSI-2 動作中、D-PHY は 1 つのクロック レーンと 1 つ以上のデータ レーンで構成されます。TSER953 は、ターゲット デバイスであり、順方向の単方向 レーンのみをサポートしています。低消費電力エスケープ モードはサポートされていません。

#### 6.3.1.1 CSI-2 レシーバの動作モード

通常動作中、データ レーンは、制御 モードまたは高速 モードになります。高速 モードでは、データはバースト転送され、停止状態 (LP-11) で開始および終了します。D-PHY を通常 モードから低消費電力 モードに移行させるための遷移状態が存在します。

高速 モードに移行するシーケンスは、LP-11、LP-01、LP-00: このシーケンスに入ると、停止状態 (LP-11) が受信されるまでデータ レーンは高速 モードに維持されます。

#### 6.3.1.2 CSI-2 レシーバの高速 モード

高速データ伝送中、アナログ D-PHY の HS RX が適切に終了できるようにデジタル D-PHY は終了信号を生成し、LP RX は LP-00 状態を維持する必要があります。CSI-2 のデータ レーンとクロック レーンはどちらも同じ方法で動作します。TSER953 は、CSI-2 の連続クロック レーン モードと非連続クロック レーン モードの両方をサポートしています。このモードはレジスタ 0x02[6] を使用して設定する必要があります、イメージ センサのクロック モードに追従する必要があります。連続クロック レーン モードでは、クロック レーンは高速 モードのままでです。

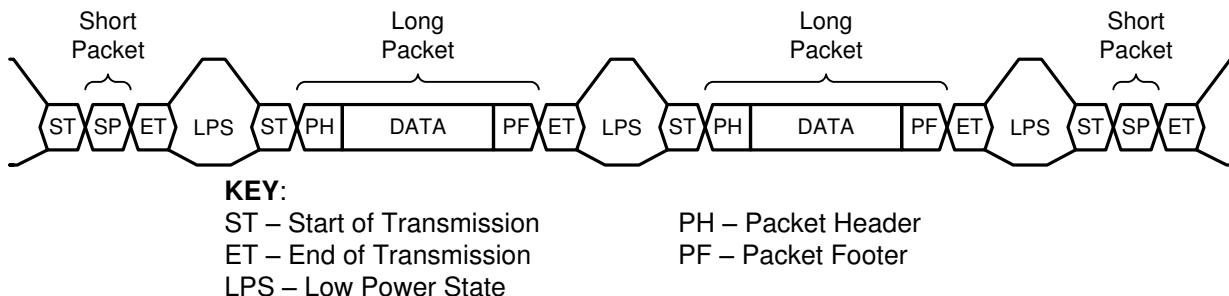

#### 6.3.1.3 CSI-2 プロトコル層

CSI-2 パケットには、ショート パケットとロング パケットの 2 種類があります。ショート パケットにはフレーム開始 / ライン開始などの情報が含まれます。ロング パケットでは、フレーム開始をアサートした後にデータが伝送されます。**図 6-1** に、ショート パケットとロング パケットによる CSI-2 プロトコル層の構造を示します。TSER953 は、1、2、4 レーン構成をサポートしています。

##### DATA:

図 6-1. ショート パケットとロング パケットによる CSI-2 プロトコル層

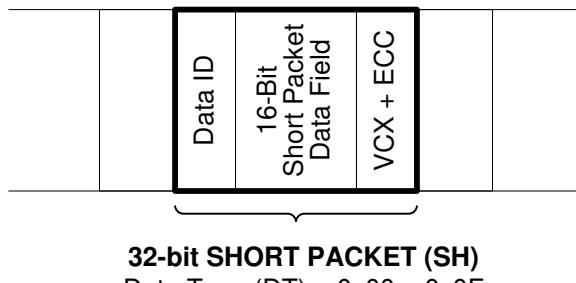

### 6.3.1.4 CSI-2 ショート パケット

このショートパケットは、フレームまたはラインの同期を実現します。図 6-2 に、ショート パケットの構造を示します。ショート パケットは、データタイプ 0x00~0x0F によって識別されます。

図 6-2. CSI-2 ショート パケット

### 6.3.1.5 CSI-2 ロング パケット

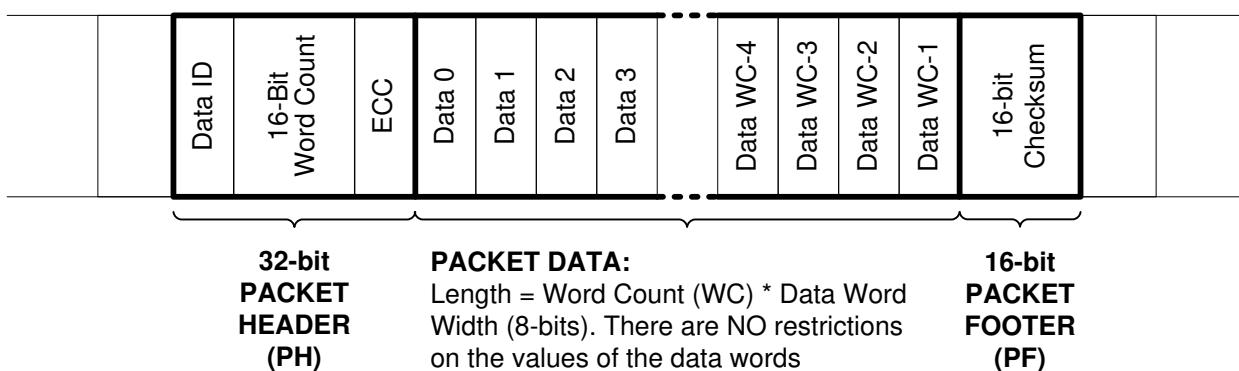

ロング パケットは、32 ビットのパケット ヘッダー (PH)、ワード数可変 (8 ビットデータ ワード) のアプリケーション固有のデータペイロード、16 ビットのパケット フッター (PF) という 3 つの要素で構成されています。パケット ヘッダはさらに、8 ビットのデータ識別子、16 ビットのワード数フィールド、8 ビットの ECC の 3 つの要素で構成されています。パケット フッターは、16 ビットチェックサムという 1 つの要素だけです。図 6-3 に、ロング パケットの構造を示します。

図 6-3. CSI-2 ロング パケットの構造

表 6-1. CSI-2 ロング パケット構造の説明

| パケット部品 | フィールド名      | サイズ(ビット) | 説明                                                    |

|--------|-------------|----------|-------------------------------------------------------|

| ヘッダー   | VC / データ ID | 8        | 仮想チャネル識別子およびデータタイプ情報が含まれます。                           |

|        | ワード数        | 16       | パケット データ内のデータ ワード数。ワードは 8 ビットです。                      |

|        | ECC         | 8        | データ ID および WC フィールドの ECC。1 ビットの誤り訂正と 2 ビットの誤り検出が可能です。 |

| データ    | データ         | WC × 8   | アプリケーション固有のペイロード (8 ビットで WC 個のワード)。                   |

| フッター   | チェックサム      | 16       | パケット データの 16 ビット CRC (巡回冗長検査)。                        |

### 6.3.1.6 CSI-2 のエラーと検出

#### 6.3.1.6.1 CSI-2 の ECC 検出および訂正

CSI-2 パケット ヘッダーには 6 ビットの誤り訂正符号 (ECC) が含まれています。32 ビット長のパケット ヘッダー内の ECC は、1 ビットの誤りが発生した場合に訂正でき、2 ビットの誤りが発生した場合に検出できます。この機能は、CSI-2 入力を監視して ECC 1 ビットの誤り訂正を行うため追加されました。ECC エラーが検出されると、ECC エラー検出レジス

タがセットされ、ECC エラーが検出されたことを示すアラーム通知ビットがデシリアルライザに送信されます。レジスタ制御を使用して、アラームをイネーブルまたはディセーブルできます。

#### 6.3.1.6.2 CSI-2 のチェックサム検出

CSI-2 のロング パケット ヘッダーには、送信終了前に、16 ビットのチェックサムが含まれています。TSER953 は、受信した CSI-2 データのチェックサムを計算します。チェックサム エラーが検出された場合、チェックサム エラー ステータスは CSI\_ERR\_STATUS レジスタ (0x5D) に保存され、双方向制御チャネルを経由してデシリアルライザに転送されます。

#### 6.3.1.6.3 D-PHY のエラー検出

TSER953 は、SoT および SoT 同期エラーを検出して報告します。

#### 6.3.1.6.4 CSI-2 レシーバのステータス

受信ポートについては、レジスタ アクセスにより、いくつかのステータス機能を追跡および監視できます。このステータス表示は、エラー条件の場合と、ライン長測定値の変化の場合に使用できます。これらは、CSI\_ERR\_CNT (0x5C)、CSI\_ERR\_STATUS (0x5D)、CSI\_ERR\_DLANE01 (0x5E)、CSI\_ERR\_DLANGE23 (0x5F)、CSI\_ERR\_CLK\_LANE (0x60) レジスタで使用できます。

### 6.3.2 V<sup>3</sup>Link フォワード チャネル トランスマッタ

TSER953 は、最大 4.16Gbps の速度で信号を駆動できる高速信号トランスマッタを備えています。

#### 6.3.2.1 フレーム フォーマット

TSER953 は、データを 40 ビット長フレームにフォーマットします。各フレームは、DC 平衡を保ち、十分なデータライン遷移を確保するようにエンコードされます。各フレームには、ビデオ ペイロード データ、I<sup>2</sup>C フォワード チャネル データ、CRC 情報、フレーミング情報、CSI-2 インターフェイスの状態に関する情報が含まれています。

#### 6.3.3 V<sup>3</sup>Link バック チャネル レシーバ

V<sup>3</sup>Link バック チャネルは、V<sup>3</sup>Link インターフェイス経由で、エンコードされたバック チャネル信号を受信します。バック チャネル フレームは、30 ビットのフレームで、I<sup>2</sup>C コマンドおよび GPIO データが含まれています。バック チャネル フレームは、エンコードされたクロックとデータをデシリアルライザから受信するので、データ ビットレートは、受信される最高周波数の半分の周波数です。

バック チャネル周波数は、対応するデシリアルライザと組み合わせて動作するようにプログラム可能です。デフォルト設定は、MODE ストラップ ピンにより決定されます。TDES954 または TDES960 と組み合わせて動作させるには、バック チャネルを TSER953 の同期モードで 50Mbps 動作に、非同期モードで 10Mbps 動作にプログラムする必要があります。

### 6.3.4 シリアライザのステータスと監視

TSER953 は、拡張された V<sup>3</sup>Link 診断、システム監視、内蔵セルフ テスト機能を備えています。このデバイスは、フォワード チャネルとバックワード チャネルのデータにエラーがないか監視し、ステータスレジスタで通知します。また、このデバイスは、システム レベルの診断のために、電圧および温度の測定もサポートしています。内蔵セルフ テスト機能により、外部データ接続なしで、フォワード チャネルとバック チャネルのデータ送信をテストできます。

TSER953 は、フォワード チャネル経由でアラームおよびセンサ ステータス データを送信して、CSI-2 インターフェイス、双方向制御チャネル (BCC)、GPIO 電圧センサ、内部温度センサを監視できます。そのデータは、リンクされた対応するデシリアライザの SENSOR\_STS\_x レジスタ (0x51~0x54) でアクセスできます。ステータス ビットは常に送信されます。アラーム ビットの送信は、シリアルライザのレジスタ 0x1C~0x1E で、イネーブルにしておく必要があります。

**表 6-2. デシリアライザのアラーム ステータス割り込み**

| ビット | SENSOR_STS_0 | SENSOR_STS_1 | SENSOR_STS_2 | SENSOR_STS_3      |

|-----|--------------|--------------|--------------|-------------------|

| 7   | 0            | 0            | 0            | 0                 |

| 6   | 0            | 電圧 1 検出レベル   | 0            | 0                 |

| 5   | CSI アラーム     | 電圧 1 検出レベル   | 0            | 0                 |

| 4   | BCC アラーム     | 電圧 1 検出レベル   | 0            | CSI 2 ビット ECC エラー |

| 3   | BC リンク検出     | 0            | 0            | CSI チェックサム エラー    |

| 2   | 温度検出アラーム     | 電圧 0 検出レベル   | 温度検出レベル      | D-PHY SOT エラー     |

| 1   | 電圧 1 検出アラーム  | 電圧 0 検出レベル   | 温度検出レベル      | D-PHY 同期エラー       |

| 0   | 電圧 0 検出アラーム  | 電圧 0 検出レベル   | 温度検出レベル      | D-PHY 制御エラー       |

デシリアライザ SENSOR\_STS の CSI-2 エラー ステータスおよびアラームは次のとおりです。CSI-2 アラーム、CSI-2 制御エラー、CSI-2 同期エラー、CSI-2 転送開始エラー、CSI-2 チェックサム エラー、CSI-2 ECC 2 ビット エラー。これらのビットのステータスは、シリアルライザのレジスタ 0x5D~0x60 で読み取ることもできます。BCC エラー アラームは、BCC リンク検出および CRC エラーでトリガれます。これらの状態は、レジスタ 0x52 から読み出すことができます。

電圧検出レベルおよび電圧検出アラームは、Sensor\_V0 (0x58) および Sensor\_V1 (0x59) に対応しています。また、温度検出レベルとアラームは、Sensor\_T (0x5A) で見ることができます。

#### 6.3.4.1 フォワード チャネルの診断

TSER953 は、フォワード チャネル リンクのステータスを監視します。フォワード チャネル高速 PLL ロックのステータスは、HS\_PLL\_LOCK ビット (レジスタ 0x52[2]) で通知されます。TDES954 と組み合わせて使用すると、V<sup>3</sup>Link デシリアライザのロック ステータスも RX\_LOCK\_DETECT ビット (レジスタ 0x52[6]) で通知されます。

#### 6.3.4.2 バック チャネルの診断

TSER953 は、バック チャネル リンクのステータスを監視します。バック チャネル CRC エラーは、CRC\_ERR ビット (レジスタ 0x52[1]) で通知されます。CRC エラーの数は CRC エラー カウンタに保存され、CRC\_ERR\_CNT1 (レジスタ 0x55) および CRC\_ERR\_CNT2 (レジスタ 0x56) レジスタに通知されます。CRC エラー カウンタは、CRC\_ERR\_CLR (レジスタ 0x49[3]) を 1 に設定することでリセットされます。

BIST 機能を実行しているとき、TSER953 は、BIST\_CRC\_ERR ビット (レジスタ 0x52[3]) に BIST CRC エラーが検出されたかどうかを通知します。BIST エラーの数は BIST\_ERR\_CNT フィールド (レジスタ 0x54) で通知されます。BIST\_CRC エラー カウンタは、BIST\_CRC\_ERR\_CLR (レジスタ 0x49[5]) を 1 に設定することでリセットされます。

#### 6.3.4.3 電圧と温度の検出

TSER953 は、電圧測定および温度測定をサポートしています。温度センサと電圧センサはどちらも 3 ビット ADC を搭載しています。これらのセンサを構成して、信号を監視し、信号が設定制限値を超えたときにフラグを立てることができます。

たとえば、電圧センサを使用して 1.8V のラインを監視し、電圧が 1.85V を上回るか 1.75V を下回った場合にフラグを立てることができます。その後、このフラグをデシリアルライザに転送し、リンクのデシリアルライザ側で割り込みをセットできます。同様に、TSER953 の内部温度が範囲外になると、温度センサはアラームビットをトリガします。

GPIO0 と GPIO1 はどちらも、入力に印加される電圧を検出するように構成できます。このセクションに関連するレジスタについては [表 6-32～表 6-37](#) を参照してください。

与えられた電圧または温度に対して、測定精度は  $\pm 1\text{ LSB}$  です。これは、[表 6-3](#) および [表 6-4](#) に示す最も近い値に対応する入力電圧または温度に対して、結果として得られる ADC 出力コードは、最も近い  $\pm 1$  コード分の精度であることを意味します。

**表 6-3. ADC コードと入力電圧との関係**

| GPIO VIN (V)        | コード |

|---------------------|-----|

| $VIN < 0.85$        | 000 |

| $0.85 < VIN < 0.90$ | 001 |

| $0.90 < VIN < 0.95$ | 010 |

| $0.95 < VIN < 1.00$ | 011 |

| $1.00 < VIN < 1.05$ | 100 |

| $1.05 < VIN < 1.10$ | 101 |

| $1.10 < VIN < 1.15$ | 110 |

| $1.15 < VIN$        | 111 |

**表 6-4. ADC コードと温度との関係**

| 温度 (°C)         | コード |

|-----------------|-----|

| $-20 < T < -10$ | 001 |

| $-10 < T < 15$  | 010 |

| $15 < T < 35$   | 011 |

| $35 < T < 55$   | 100 |

| $55 < T < 75$   | 101 |

| $75 < T < 85$   | 110 |

#### 6.3.4.3.1 プログラミング例

このセクションでは、TSER953 および TDES954 の設定例を示します。ここでは、TSER953 の GPIO1 の電圧を監視して、アラームをセットし、さらに TDES954 の INT ピンをアサートします。

```

# TSER953 Settings

WriteI2C(0x17,0x3E) # Enable Sensor, Select GPIO1 to sense

WriteI2C(0x18,0x80) # Enable Sensor Gain Setting (Use Default)

WriteI2C(0x1A,0x62) # Set Sensor Upper and Lower Limits (Use Default)

WriteI2C(0x1D,0x3F) # Enable Sensor Alarms

WriteI2C(0x1E,0x7F) # Enable Sending Alarms over BCC

# Register 0x57 readout (bits 2 and 3), indicates if the voltage on the GPIO1 is below or above the

thresholds set in the register 0x1A.

# TDES954 Settings

WriteI2C(0x23,0x81) # Enable Interrupts, Enable Interrupts for the camera attached to RX0

WriteI2C(0x4C,0x01) # Enable Writes to RX0 registers

WriteI2C(0xD8,0x08) # Interrupt on change in Sensor Status

# Register 0x51 and 0x52 readouts indicate Sensor data. Register 0x24[7] bit readout indicates the

Alarm bit. The alarm bit can be routed to GPIO3/INT through GPIO_PIN_CTL and GPIO_OUT_SRC registers.

```

#### 6.3.4.4 組み込み自己テスト

オプションの実速度での内蔵セルフ テスト (BIST) 機能を使うと、外部データ接続を使わずに高速シリアル リンクとバックチャネルをテストできます。この機能は、試作段階、デバイスの量産時、インシステム テスト、システムの診断に役立ちます。

BIST モードは、デシリアルライザの **BIST 構成レジスタ 0xB3[0]** によってイネーブルされ、必ず同期モードで実行する必要があります。デシリアルライザで BIST が開始されると、BIST イネーブル信号がバックチャネル経由でシリアルライザに送信されます。シリアルライザは、疑似ランダムシーケンスの連続ストリームを出力し、リンクを実速度で駆動します。デシリアルライザは、テストパターンを検出し、そのパターンのエラーを監視します。シリアルライザは、各バックチャネルフレームの CRC フィールドによって示されたエラーも追跡します。適切なデータ受信の開始を識別するためにはロック通知が必要ですが、リンク障害やデータ破損をよく示すものは、デシリアルライザ側の各 RX ポートについて、**BIST\_ERR\_COUNT** レジスタ 0x57 のエラーカウンタの内容です。BIST モードは、試作段階、デバイスの量産時、インシステム テスト、システムの診断に役立ちます。

### 6.3.5 フレーム同期の動作

対応するデシリアルライザと組み合わせると、TSE953 のいずれかの GPIO ピンをフレーム同期に使用できます。この機能は、複数のセンサを 1 つのデシリアルライザ ハブに接続する場合に役立ちます。フレーム同期信号 (FrameSync) は、バックチャネルのいずれかの GPIO を使用してバックチャネル経由で送信できます。FrameSync 信号は、有限のスキーでシリアルライザに到着します。

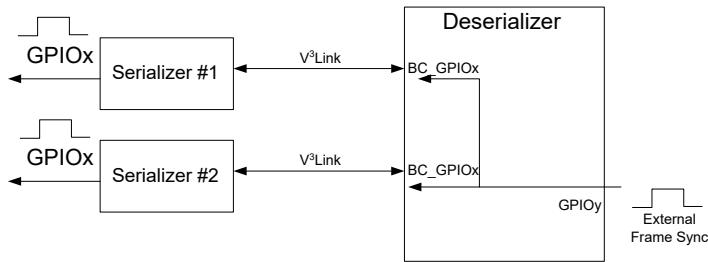

#### 6.3.5.1 外部フレーム同期

外部フレーム同期モードでは、デバイスの GPIO ピンの 1 つを経由してデシリアルライザに外部信号が入力されます。外部フレーム同期信号は、バックチャネルの GPIO 信号を介して、接続されている 1 つまたは複数の V<sup>3</sup>Link シリアルライザに伝搬できます。外部フレーム同期モードで想定されるスキータイミングは、1 バックチャネルフレーム周期のオーダーであり、50Mbps で動作している場合は 600ns です。

図 6-4. 外部フレーム同期

外部フレーム同期モードの有効化は、デシリアルライザ側で実行します。詳細については、デシリアルライザのデータシートを参照してください。

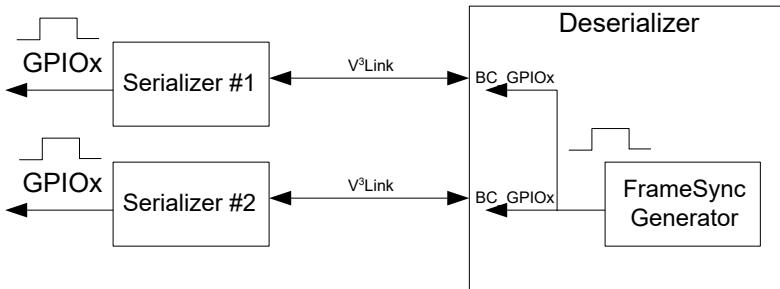

#### 6.3.5.2 フレーム同期の内部生成

内部フレーム同期モードでは、内部で生成されたフレーム同期信号が、バックチャネルの GPIO 信号を通して接続されている 1 つまたは複数の V<sup>3</sup>Link シリアルライザに送信されます。

図 6-5. 内部フレーム同期

フレーム同期の動作は、デシリアルライザ レジスタによって制御されます。詳細については、デシリアルライザのデータシートを参照してください。

### 6.3.6 GPIO サポート

TSER953 は、GPIO0～GPIO3 の 4 つのピンをサポートしており、I<sup>2</sup>C バス経由でレジスタ 0x0D、0x0E、0x53 を使って監視、構成、制御できます。これらの GPIO は、さまざまな状況で使用するようにプログラム可能です。GPIO0 および GPIO1 には追加の診断機能があり、外部電圧レベルを検出するようにプログラムできます。

#### 6.3.6.1 GPIO のステータス

GPIO ピン 0～3 それぞれのステータス HIGH または LOW は、GPIO\_PIN\_STS レジスタ 0x53 から読み出すことができます。レジスタ (0x0E) の対応する GPIOx\_INPUT\_EN ビットを設定すると、このレジスタ読み取り動作は、入力として構成されているときの GPIO ピンのステータスを提供します。GPIO が output として使用されているときに GPIO のステータスを読み取るには、レジスタ (0x0E) の GPIOx\_INPUT\_EN ビットおよび GPIOx\_OUT\_EN ビットの両方をセットする必要があります。

**表 6-5. GPIO の構成**

| 構成             | 有効             | 有効               | 有効             | 無効             |

|----------------|----------------|------------------|----------------|----------------|

| 目的             | 出力として GPIO を使用 | 出力として GPIO を使用   | 入力として GPIO を使用 | 入力として GPIO を使用 |

| GPIOx_INPUT_EN | 0              | 1                | 1              | 1              |

| GPIOx_OUT_EN   | 1              | 1 <sup>(1)</sup> | 0              | 1              |

| GPIO_STS       | 機能しない          | 機能               | 機能             | 該当なし           |

**注**

(1) GPIOx\_INPUT\_EN がセットされている場合、内部プルダウンが GPIO 出力に接続されているため、ユーザーはそのプルダウン抵抗がアプリケーション固有の使用に干渉しないことを確認する必要があります。

#### 6.3.6.2 GPIO の入力制御

初期化時、デフォルトでは GPIO0～GPIO3 は入力としてイネーブルになります。GPIO\_INPUT\_CTRL (0x0E) レジスタ (ビット 3:0) を使って入力イネーブルを制御できます。GPIO\_INPUT\_CTRL[3:0] ビットが 1 に設定されている場合、対応する GPIO\_INPUT\_CTRL[7:4] ビットを 0 に設定する必要があります。GPIO の数は、レジスタ (0x33) の FC\_GPIO\_EN を使用して設定およびイネーブルする必要があります。

#### 6.3.6.3 GPIO の出力制御

個々の GPIO 出力制御は、表 6-27 の GPIO\_INPUT\_CTRL (0x0E) レジスタ (ビット 7:4) によりプログラムできます。GPIO を出力ピンとして使用するためには、GPIO\_INPUT\_CTRL[7:4] ビットを 1 に設定する必要があります。

#### 6.3.6.4 フォワード チャネル GPIO

TSER953 の GPIO ピンの入力は、V<sup>3</sup>Link インターフェイスを介して、対応するデシリアルライザに転送できます。順方向で最大 4 つの GPIO をサポートしています。

フォワード チャネル GPIO のタイミングは、シリアルライザで割り当てられた GPIO の数に依存します。TSER953 シリアルライザからの単一の GPIO 入力が、対応するデシリアルライザの GPIO 出力にリンクされている場合、その値はすべてのフォワード チャネル送信フレームでサンプリングされます。2 つの GPIO がリンクされている場合は、2 つのフォワード チャネルフレームごとにサンプリングされ、3 つまたは 4 つの GPIO がリンクされている場合は、5 フレームごとにサンプリングされます。GPIO の標準的なレイテンシは約 225ns ですが、ケーブルの長さによって異なります。情報が複数のフレームに分散されるため、通常、ジッタはサンプリング期間のオーダー (フォワード チャネルフレームの数) に基づいて増加します。リンクされた GPIO のスループットに対して、4 倍のオーバーサンプリング レートを維持することを推奨します。たとえば、REFCLK = 25MHz の 4Gbps 同期モードで動作している場合、フォワード チャネル経由でリンクされる GPIO の数に基づく最大推奨 GPIO 入力周波数を 表 6-6 に示します。

**表 6-6. フォワードチャネル GPIO の標準的タイミング**

| リンクされたフォワードチャネル GPIO の数 (FC_GPIO_EN) | V <sup>3</sup> Link ラインレート = 4Gbps でのサンプリング周波数 (MHz) | 推奨されるフォワードチャネル GPIO 最大周波数 (MHz) | レイテンシの標準値 (ns) | ジッタの標準値 (ns) |

|--------------------------------------|------------------------------------------------------|---------------------------------|----------------|--------------|

| 1                                    | 100                                                  | 25                              | 225            | 12           |

| 2                                    | 50                                                   | 12.5                            | 225            | 24           |

| 4                                    | 20                                                   | 5                               | 225            | 60           |

**6.3.6.5 バックチャネル GPIO**

出力としてイネーブルになっているとき、TSER953 の GPIO ピンを、LOCAL\_GPIO\_DATA レジスタ (0x0D) を使用してプログラムすると、対応するデシリアライザからのリモートデータを出力するようにできます。V<sup>3</sup>Link バックチャネルで受信できる最大信号周波数は、表 6-7 に示すように、TSER953 のクロックモードに依存します。

**表 6-7. バックチャネル GPIO の標準タイミング**

| TSER953 クロックモード | バックチャネルレート (Mbps) | サンプリング周波数 (kHz) | バックチャネル GPIO の最大推奨周波数 (kHz) | レイテンシの標準値 (μs) | ジッタの標準値 (μs) |

|-----------------|-------------------|-----------------|-----------------------------|----------------|--------------|

| 同期モード           | 50                | 1670            | 416                         | 1.5            | 0.7          |

| 非同期モード          | 10                | 334             | 83.5                        | 3.2            | 3            |

| DVP モード         | 2.5               | 83.5            | 20                          | 12.2           | 12           |

## 6.4 デバイスの機能モード

### 6.4.1 クロッキング モード

TSER953 は複数のクロック供給方式をサポートしており、MODE ピンで選択します。TSER953 では、フォワード チャネルは、転送されるビデオ データで設定される要件よりも高い帯域幅で動作し、フォワード チャネルのデータレートは、基準クロックにより設定されます。クロックモードでは、デバイスが何を基準クロックとして使用するかが決定されます。最も一般的な構成は、ローカル基準発振器が不要な同期モードです。詳細については、[表 6-8 を参照してください。](#)

TSER953 のデフォルト モードは、電源投入時に MODE ピンにバイアスを印加することで設定されます。動作モード設定の詳細については、[セクション 6.4.2 を参照してください。](#)

**表 6-8. クロッキング モード**

| モード                                | 分周               | 基準ソース                   | 基準周波数 (f)<br>(MHz) | FC データレート | CSI 帯域幅 ≤ | CLK_OUT <sup>(3)</sup>       |

|------------------------------------|------------------|-------------------------|--------------------|-----------|-----------|------------------------------|

| 同期                                 | 該当なし             | バック チャネル <sup>(1)</sup> | 23~26              | f × 160   | f × 128   | f × 160 / HS_CLK_DIV × (M/N) |

| 同期 (ハーフ レート)                       | 該当なし             | バック チャネル <sup>(1)</sup> | 11.5~13            | f × 160   | f × 128   | f × 160 / HS_CLK_DIV × (M/N) |

| 非同期外部クロック                          | CLKIN_DIV = b000 | 外部クロック <sup>(2)</sup>   | 25~52              | f × 80    | f × 64    | f × 80 / HS_CLK_DIV × (M/N)  |

|                                    | CLKIN_DIV = b001 | 外部クロック <sup>(2)</sup>   | 50~104             | f × 40    | f × 32    | f × 40 / HS_CLK_DIV × (M/N)  |

| 非同期内部クロック                          | OSCCLK_SEL = 1   | 内部クロック                  | 48.4~51            | f × 80    | f × 64    | 該当なし                         |

| 非同期内部クロック (ハーフレート)                 | OSCCLK_SEL = 0   | 内部クロック                  | 24.2~25.5          | f × 80    | f × 64    | 該当なし                         |

| DVP 外部クロック<br>デシリアライザ モード:RAW10    | 該当なし             | 外部クロック                  | 25~66.5            | f × 28    | f × 20    | f × 28 / HS_CLK_DIV × (M/N)  |

| DVP 外部クロック<br>デシリアライザ モード:RAW12 HF | 該当なし             | 外部クロック                  | 25~70              | f × 28    | f × 18    | f × 28 / HS_CLK_DIV × (M/N)  |

(1) バック チャネルは V<sup>3</sup>Link 双方向制御チャネルから回復されます。ローカル基準クロック ソースは必要ありません。バック チャネルの周波数設定については、デシリアライザのデータシートを参照してください。

(2) ローカル基準クロック ソースが必要です。CLKIN ピンにクロック ソースを供給します。

(3) HS\_CLK\_DIV を 16、8、4 のいずれかに設定します (デフォルト)。

図 6-6. クロック供給システムの図

#### 6.4.1.1 同期モード

同期モードで動作すると、レシーバおよびマルチ センサ システム内のすべてのセンサが、同じクロック ドメイン内の共通クロックにロックされるという利点が得られ、データ バッファリングや再同期の必要性が低減または排除されます。同期クロック モードでは、センサ モジュール内の基準発振器のコスト、スペース、潜在的な故障ポイントも削減できます。

このモードでは、V<sup>3</sup>Link バック チャネルを経由してデシリアルライザからシリアルライザにクロックが渡され、シリアルライザは、このクロックを、接続されているイメージ センサの基準クロック、および、デシリアルライザに戻るリンクの基準クロックとして使用できます (V<sup>3</sup>Link フォワード チャネル)。このモードで動作するためには、TSER953 は、TDES954 または TDES960 など、この機能をサポートするデシリアルライザとペアで使用する必要があります。

#### 6.4.1.2 非同期クロック モード

非同期クロック モードでは、外部基準クロックがシリアルライザに供給されます。シリアルライザは、このクロックを使用して V<sup>3</sup>Link フォワード チャネルと、取り付けられているイメージ センサのための外部基準クロックを生成します。CSI-2 モードの場合、CSI-2 インターフェイスはこのクロックと同期できます。CSI-2 のレートはライン レートよりも低くする必要があります。たとえば、50MHz のクロックの場合、V<sup>3</sup>Link のフォワード チャネル レートは 4Gbps であり、CSI-2 のスループットは ≤ 3.32Gbps である必要があります (表 6-8 を参照)。

#### 6.4.1.3 非同期内部モード

非同期内部クロック モードでは、シリアルライザは、内部の常時オン クロック (AON) をフォワード チャネルの基準クロックとして使用します。内部クロック モードを使用する場合、OSCCLK\_SEL で最大データ レート選択を設定 (0x05[3] = 1) するとともに、CLK\_OUT 機能をディセーブルする必要があります。イメージ センサまたは ISP には、別個のリファレンスが提供されます。CSI-2 モードの場合、CSI-2 インターフェイスはこのクロックと同期できます。CSI-2 のレートはライン レートよりも低くする必要があります。たとえば、24.2MHz の内部クロックの場合、V<sup>3</sup>Link のフォワード チャネル レートは 3.872Gbps、CSI-2 のスループットは ≤ 3.1Gbps である必要があります (表 6-8 を参照)。

#### 6.4.1.4 DVP 互換モード

TSER953 を DVP モードに設定して、DVP モードのデシリアルライザとペアにできます。このモードは、TSER953 の MODE ピンを使って構成する必要がありますが、レジスタ MODE\_SEL 0x03[2:0] を使って、現在のモードを確認したりオーバライドしたりできます。このフィールドは常に、デバイスのモード設定を示しています。このレジスタのビット 4 が 0 の場合、このフィールドは読み取り専用で、モード設定を示します。PDB が Low から High に遷移するとき、MODE はスト

ラップ値からラッチされます。抵抗ストラップが DVP 外部クロック モードに正しく設定されている場合、その値は 101 (0x5) と読み出されます。または、このレジスタのビット 4 が 1 に設定されている場合、MODE フィールドは読み出し / 書き込み可能になり、101 にプログラムして、正しい DVP 互換モードを割り当てることもできます。これは、[表 6-16](#) に示すとおりです。

TSER953 に供給される CSI-2 入力データは、DVP 外部クロック モードを使用する場合、CLKIN に印加される入力周波数に同期させる必要があります。DVP 外部クロック モードの場合、DVP モード デシリアルライザから出力される PCLK 周波数は CLKIN に関連付けることもできます。詳細については、『[パラレル出力デシリアルライザで動作するための下位互換モード](#)』(SNLA270) を参照してください。

**表 6-9. DVP 構成に使用されるレジスタのリスト**

| レジスタ | レジスタ名            | レジスタの説明                                                                   |

|------|------------------|---------------------------------------------------------------------------|

| 0X03 | MODE_SEL         | 必要に応じてストラップ値をオーバーライドおよび確認し、また、外部クロックで DVP を構成するために使用します。                  |

| 0X04 | BC_MODE_SELE_CTR | DVP モードを RAW 10 または RAW 12 に上書きできます。                                      |

| 0X10 | DVP_CFG          | DVP モードでデータを構成できます。これには、ロング、YUV、および指定された型などのデータ型が含まれます。                   |

| 0X11 | DVP_DT           | DVP_DT_MATCH_EN がアサートされている場合、RAW 10 または 12 モードに関係なく、特定のデータタイプのパケットを許可します。 |

#### 6.4.1.5 CLK\_OUT の構成

TSER953 を同期または非同期の外部クロック モードで使用する場合、CLK\_OUT はイメージ センサの基準クロックとして使用されます。非同期内部クロック モードで動作している場合、CLK\_OUT 機能はディセーブルになります。外部 CLK\_OUT の周波数は次のように設定されます (式 1 および 式 2 を参照)。

$$\text{CLK\_OUT} = \text{FC} \times \frac{\text{M}}{\text{HS\_CLK\_DIV} \times \text{N}} \quad (1)$$

ここで、

- FC はフォワード チャネルのデータ レートであり、M、HS\_CLK\_DIV、N はレジスタ 0x06 および 0x07 で設定されるパラメータです。

$$\frac{\text{FC}}{\text{HS\_CLK\_DIV}} < 1.05 \text{ GHz} \quad (2)$$

CLK\_OUT を生成する PLL はデジタル PLL であるため、N/M の比が整数の場合、ジッタは非常に小さくなります。N/M が整数でない場合、信号のジッタは HS\_CLK\_DIV/FC とほぼ等しくなります。したがって、N/M を整数比にできない場合は、HS\_CLK\_DIV として小さい値を選択することが最適です。

システムで特定の CLK\_OUT 周波数 (たとえば 37.125MHz) が必要な場合、設計者は M = 9、N = 0xF2、HS\_CLK\_DIV = 4 の値を選択すれば、37.190MHz の出力周波数、0.175% の周波数誤差、これに伴うジッタを約 1ns することができます。または、M = 1、N = 0x1B、HS\_CLK\_DIV = 4 とすれば、CLK\_OUT = 37.037MHz となり、0.24% の周波数誤差で、ジッタをさらに低減できます。3 番目の方法は、M = 1、N = 0x1B、HS\_CLK\_DIV = 4 を使用することですが、同期モードのデシリアライザに 25.000MHz 基準クロック周波数 (REFCLK) を使用する代わりに、25.059MHz の周波数を使用します。そして 2x リファレンスをデシリアライザのバック チャネルから TSER953 に供給することにより、低ジッタと低周波数誤差を備えた CLK\_OUT = 37.124MHz を生成できます。

#### 6.4.2 モード

TSER953 は、4 種類のモードのいずれかで動作できます。電源投入時に MODE ピンにバイアス電圧を印加して、デフォルト モードで動作させることができます。この電圧を設定するには、VDDPLL と GND の間の分圧器を使用して適切なバイアスを印加します。この分圧器は、VDDD ピンの電位を基準にする必要があります。電源投入後、レジスタアクセスにより、モードを読み出したり変更したりできます。

図 6-7. MODE の構成

表 6-10. ストラップ構成モードの選択

| モード選択            |           | $V_{TARGET}$ 電圧範囲        |                          |                          | $V_{TARGET}$ ストラップ電圧 | ストラップ抵抗の推奨値(許容誤差 1%) |                     | 説明                                                                      |

|------------------|-----------|--------------------------|--------------------------|--------------------------|----------------------|----------------------|---------------------|-------------------------------------------------------------------------|

| モード              | 名称        | 比の最小値                    | 比の標準値                    | 比の最大値                    | $V_{(VDD)} = 1.8V$   | $R_{HIGH} (k\Omega)$ | $R_{LOW} (k\Omega)$ |                                                                         |

| 0                | 同期        | 0                        | 0                        | $0.133 \times V_{(VDD)}$ | 0                    | オープン                 | 10                  | CSI-2 同期モード – デシリアルライザから生成された V <sup>3</sup> Link クロック基準。               |

| 2                | 非同期外部クロック | $0.288 \times V_{(VDD)}$ | $0.325 \times V_{(VDD)}$ | $0.367 \times V_{(VDD)}$ | 0.586                | 75                   | 35.7                | CSI-2 非同期クロック – CCLKIN ピンの外部クロック基準入力から生成された V <sup>3</sup> Link クロック基準。 |

| 3                | 非同期内部クロック | $0.412 \times V_{(VDD)}$ | $0.443 \times V_{(VDD)}$ | $0.474 \times V_{(VDD)}$ | 0.792                | 71.5                 | 56.2                | CSI-2 非同期 – 内部 AON クロックから生成された V <sup>3</sup> Link クロック基準。              |

| 5 <sup>(1)</sup> | DVP モード   | $0.642 \times V_{(VDD)}$ | $0.673 \times V_{(VDD)}$ | $0.704 \times V_{(VDD)}$ | 1.202                | 39.2                 | 78.7                | 外部クロックの DVP。                                                            |

(1) DVP デシリアルライザにも MODE ピン (21) があります。ただし、デシリアルライザの MODE ピンによって、データ形式が決まります。RAW10、RAW12 LF、または RAW12 HF。TSER953 は、RAW12 LF をサポートしていないことに注意してください。

## 6.5 プログラミング

### 6.5.1 I<sup>2</sup>C インターフェイス構成

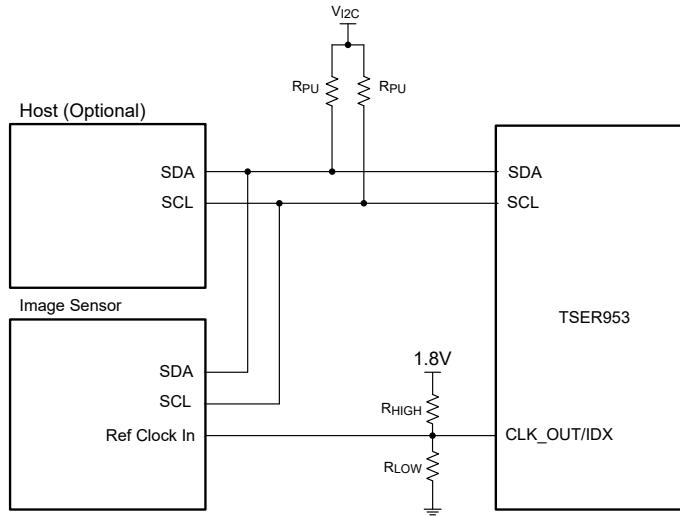

このシリアルライザは、I<sup>2</sup>C 互換シリアル制御バスを使って設定できます。複数のデバイスがシリアル制御バスを共有できます（最大 2 つのデバイス アドレスをサポート）。デバイス アドレスは、IDX ピンに接続された抵抗分圧器 ( $R_{HIGH}$  および  $R_{LOW}$  – 図 6-8 を参照）によって設定されます。

#### 6.5.1.1 CLK\_OUT/IDX

CLK\_OUT/IDX ピンは 2 つの機能を果たします。電源オン時に、IDX ピンの電圧が VDD と比較され、この比率によって TSER953 の構成用の各種パラメータが設定されます。TSER953 を構成した後、CLK\_OUT/IDX ピンは、イメージ センサに基準クロックを提供するためのクロック ソースに切り替わります。CLK\_OUT 機能を使用する場合、CLK\_OUT/IDX ピンにおいて 35kΩ の最小負荷インピーダンスが必要です。

##### 6.5.1.1.1 IDX

IDX ピンは、制御インターフェイスを 2 つの可能なデバイス アドレスのいずれか 1 つ、すなわち 1.8V または 3.3V 基準 I<sup>2</sup>C アドレスに設定します。プルアップ抵抗とプルダウン抵抗を使って、適切な IDX 入力ピン電圧を設定する必要があります（表 6-11 参照）。IDX 分圧抵抗は、ピン #25 (TSER953 のピン側のフェライト フィルタの後) を基準とする必要があります。

表 6-11. IDX の設定

| IDX | $V_{TARGET}$ 電圧範囲          |                            |                            | $V_{IDX}$ の目標電圧  | ストラップ抵抗の推奨値(許容誤差 1%) |                     | $I^{2}C$ 8 ビットアドレス | $I^{2}C$ 7 ビットアドレス | $V_{(I^{2}C)}$ ( $I^{2}C$ I/O 電圧) |

|-----|----------------------------|----------------------------|----------------------------|------------------|----------------------|---------------------|--------------------|--------------------|-----------------------------------|

|     | 比の最小値                      | 比の標準値                      | 比の最大値                      | $V_{VDD} = 1.8V$ | $R_{HIGH} (k\Omega)$ | $R_{LOW} (k\Omega)$ |                    |                    |                                   |

| 1   | 0                          | 0                          | $0.131 \times V_{(VDD18)}$ | 0                | オープン                 | 40.2                | 0x30               | 0x18               | 1.8 V                             |

| 2   | $0.178 \times V_{(VDD18)}$ | $0.214 \times V_{(VDD18)}$ | $0.256 \times V_{(VDD18)}$ | 0.385            | 180                  | 47.5                | 0x32               | 0x19               | 1.8 V                             |

| 3   | $0.537 \times V_{(VDD18)}$ | $0.564 \times V_{(VDD18)}$ | $0.591 \times V_{(VDD18)}$ | 1.015            | 82.5                 | 102                 | 0x30               | 0x18               | 3.3 V                             |

| 4   | $0.652 \times V_{(VDD18)}$ | $0.679 \times V_{(VDD18)}$ | $0.706 \times V_{(VDD18)}$ | 1.223            | 68.1                 | 137                 | 0x32               | 0x19               | 3.3 V                             |

図 6-8. IDX ピンのバイアス回路

### 6.5.2 I<sup>2</sup>C インターフェイス動作

シリアル制御バスは、SCL と SDA という 2 つの信号で構成されます。SCL はシリアルバスクロック入出力信号で、SDA はシリアルバスデータ入出力信号です。SCL 信号と SDA 信号はどちらも、1.8V または 3.3V のどちらかに選択される  $V_{I2C}$  への外付けプルアップ抵抗を必要とします。

標準モードおよびファースト I<sup>2</sup>C モードでは、 $R_{PU} = 4.7k\Omega$  のプルアップ抵抗を推奨します。ファーストプラスモードでは、 $R_{PU} = 470\Omega$  のプルアップ抵抗を推奨します。しかしこのプルアップ抵抗値は、容量性負荷およびデータレートの要件に応じて、さらに調整できます。これらの信号は、High に引き上げられるか、Low に駆動されます。IDX ピンは、制御インターフェイスを 2 つの可能なデバイスアドレスのどちらかに設定します。プルアップ抵抗 ( $R_{HIGH}$ ) およびプルダウン抵抗 ( $R_{LOW}$ ) を使って、適切な IDX 入力ピン電圧を設定します。

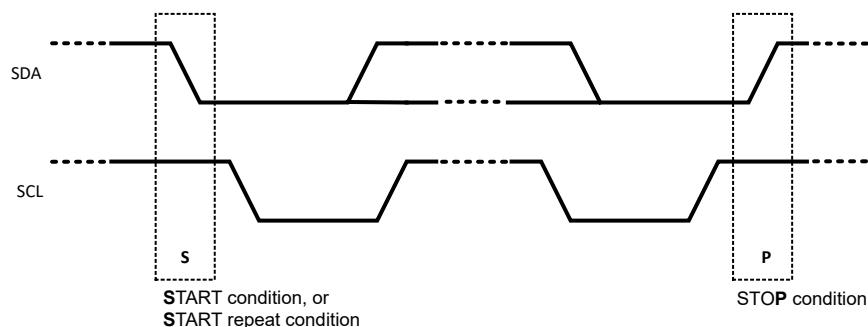

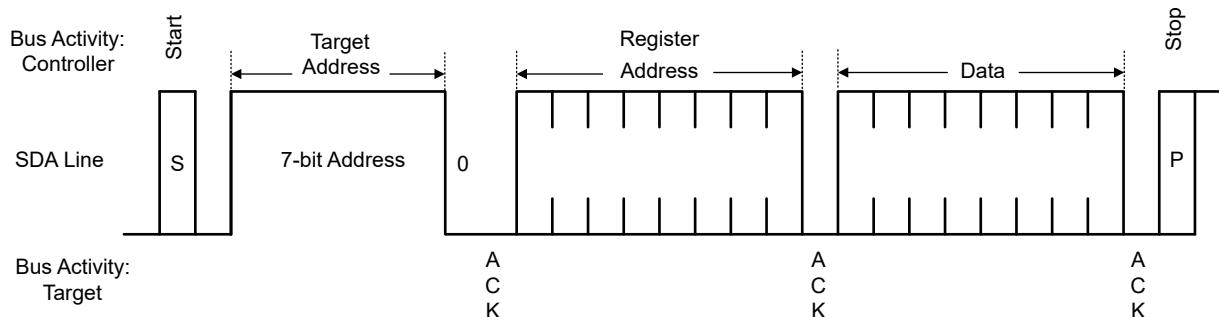

シリアルバスプロトコルは、START、REPEAT-START、STOP によって制御されます。START は、SDA が High である間に SCL が Low に遷移したときに発生します。STOP は、SDA が High に遷移したときに SCL も High である場合に発生します。図 6-9 を参照してください。

図 6-9. START 条件と STOP 条件

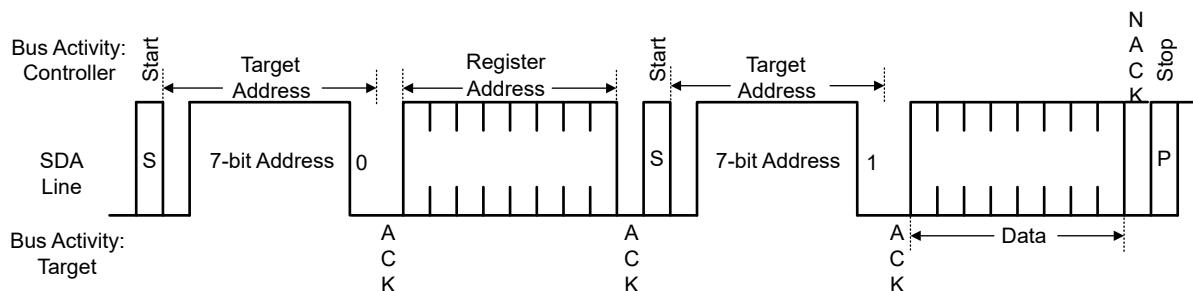

I<sup>2</sup>C ターゲットと通信するには、ホストコントローラ（コントローラ）はターゲットアドレスにデータを送信し、応答を待ちます。この応答は、アクノリッジ (ACK) ビットと呼ばれます。バス上のターゲットにアドレスが正しく設定されている場合、ターゲットは、SDA バスを Low に駆動することによって、コントローラへアクノリッジ (ACK) を返します。アドレスがデバイスのターゲットアドレスと一致しない場合、ターゲットは、SDA を High に引き上げることによって、コントローラへノットアクノリッジ (NACK) を返します。ACK は、データの送信中にもバス上で発生します。コントローラがデータを書き込んでいると

き、ターゲットは、データ バイトを正常に受信する毎に ACK を返します。コントローラがデータを読み出しているとき、コントローラは、データ バイトを受信する毎に ACK を返すことによって、次のデータ バイト要求をターゲットに通知します。コントローラが読み出しを停止する場合、コントローラは、最後のデータ バイトの読み出し後に NACK を送信し、バス上に STOP 条件を生成します。バス上のすべての通信は、START 条件または 繰り返し START 条件によって開始されます。バス上のすべての通信は、STOP 条件によって終了します。[図 6-10](#) に読み出しを示し、[図 6-11](#) に書き込みを示します。

図 6-10. I<sup>2</sup>C バスの読み出し

図 6-11. I<sup>2</sup>C バスの書き込み

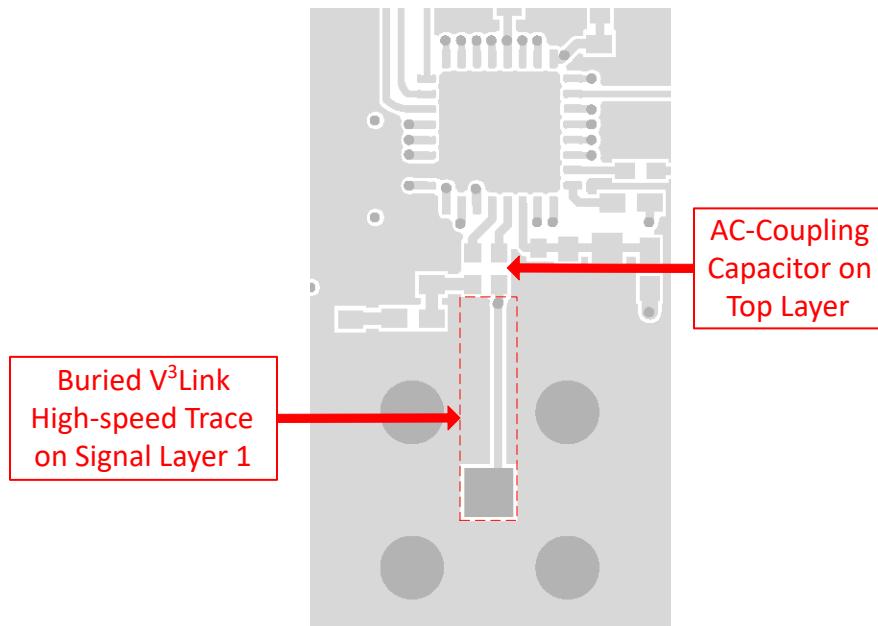

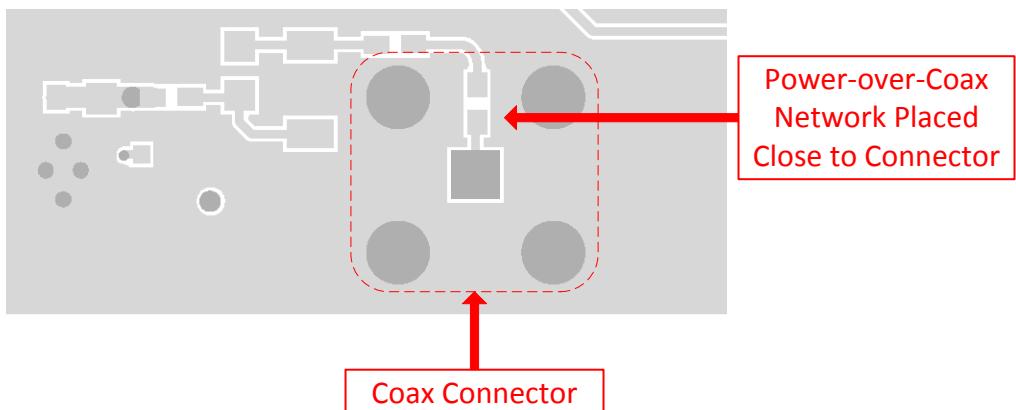

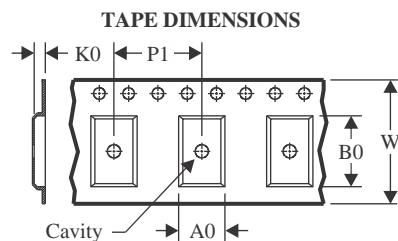

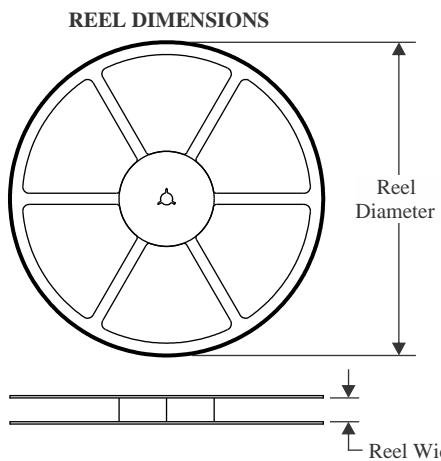

シリアルインターフェイスに配置されたすべての I<sup>2</sup>C コントローラは、I<sup>2</sup>C クロック ストレッチングをサポートする必要があります。I<sup>2</sup>C インターフェイスの要件およびスループットに関する考慮事項の詳細については、『双方向制御チャネルによる FPD-Link III 上の I<sup>2</sup>C 通信』アプリケーション ノート (SNLA131) を参照してください。