# TRF1305A2 15dB ゲイン、デュアルチャネル、DC から 5.8GHz BW 超、RF 完全差動アンプ

## 1 特長

- 性能が最適化された 3 つのパワー ゲインのバリエーション:

- 15dB (TRF1305A2)

- 10dB (TRF1305B2)

- 5dB (TRF1305C2)

- 固定ゲインは外付け抵抗で低減可能

- 幅広い大信号 RF 帯域幅:

- D2D: 5.8GHz (3dB)、5.2GHz (1dB)

- S2D: 6.1GHz (3dB)、5.2GHz (1dB)

- OP1dB (差動 100Ω 負荷):

- D2D: 15dBm (2GHz)、11.6dBm (4GHz)

- S2D: 15.2dBm (2GHz)、11.8dBm (4GHz)

- OIP3 ( $P_O = 1\text{dBm}$ トーン):

- D2D: 32.5dBm (2GHz)、21dBm (4GHz)

- S2D: 33dBm (2GHz)、22dBm (4GHz)

- ノイズ フィギュア:

- D2D: 9.2dB (2GHz)、11.7dB (4GHz)

- S2D: 9.6dB (2GHz)、11.4dB (4GHz)

- スルーレート: 25kV/μs

- 広い入力 ( $\pm 1\text{V}$ ) および出力 ( $\pm 0.5\text{V}$ ) の同相電圧範囲

- 柔軟な構成とモード:

- シングルエンド入力、差動出力 (S2D)

- 差動入力、差動出力 (D2D)

- AC 結合または DC 結合の入出力

- 調整可能な出力同相電圧

- 同相入力範囲拡張モード

- 5V、單一または分割電源をサポート

- アクティブな消費電力: チャネルあたり 503mW

- 各チャネルのパワーダウン

## 2 アプリケーション

- RF サンプリングまたは GSPS ADC ドライバ

- 試験および測定機器

- ワイヤレス通信テスト

- RF デジタイザ

- オシロスコープ (DSO)

- 高速デジタイザ

- スペクトル アナライザ

- ベクトル信号トランシーバ (VST)

- 質量分析システム

- 同相モード レベル シフト

- IQ ミキサ インターフェイス

## 3 説明

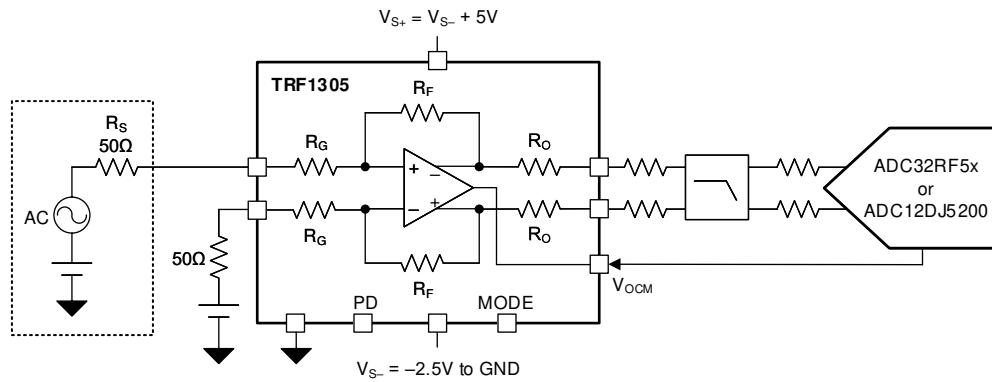

TRF1305A2 は、非常に高性能な閉ループのデュアル チャネル RF アンプで、真の DC から 5.8GHz を超える動作 帯域幅を持ちます。このデバイスは、ADC12DJ5200RF や ADC32RF5x などの高速で高性能な ADC を、DC 結合または AC 結合のインターフェイスで駆動する優れた性能を備えています。このアンプは、RF、ゼロ IF、複素 IF、および高速の時間領域アプリケーションでの使用に最適化されています。このデバイスは、固定ゲイン構成での性能に最適化されています。より低いゲインが必要な場合は、外付け抵抗を使用します。

TRF1305A2 は、異なる出力同相電圧と入力同相電圧を設定できる VOCM ピンを備えています (たとえば、レベルシフトや、異なる DC 同相電圧を持つほとんどの IQ 降圧コンバータの ADC インターフェイス アプリケーション用)。TRF1305A2 は、フローティング 2 レールの分割電源または單一電源のオプション、および入力同相範囲をより電源に近い範囲へと拡張できる MODE ピンを備えています。このデバイスはまた、各チャネルを個別にオフにするパワーダウン機能も備えています。

このデバイスは、テキサス インスツルメンツ独自の高度な BiCMOS プロセスで製造されており、省スペースの 2.5mm × 3mm、16 ピンの WQFN-FCRLF パッケージとして供給されます。

## 製品情報

| 部品番号 (1)  | パワー ゲイン | パッケージ (2)        |

|-----------|---------|------------------|

| TRF1305A2 | 15dB    | RYP              |

| TRF1305B2 | 10dB    | (WQFN-FCRLF, 16) |

| TRF1305C2 | 5dB     |                  |

(1) セクション 4 を参照してください。

(2) 詳細については、セクション 11 を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

S2D 構成で高速 ADC を駆動する TRF1305A2

## 目次

|                            |    |                        |    |

|----------------------------|----|------------------------|----|

| 1 特長                       | 1  | 7.2 機能ブロック図            | 39 |

| 2 アプリケーション                 | 1  | 7.3 機能説明               | 40 |

| 3 説明                       | 1  | 7.4 デバイスの機能モード         | 41 |

| 4 デバイス比較表                  | 4  | 8 アプリケーションと実装          | 43 |

| 5 ピン構成および機能                | 5  | 8.1 アプリケーション情報         | 43 |

| 6 仕様                       | 6  | 8.2 代表的なアプリケーション       | 47 |

| 6.1 絶対最大定格                 | 6  | 8.3 電源に関する推奨事項         | 49 |

| 6.2 ESD 定格                 | 6  | 8.4 レイアウト              | 49 |

| 6.3 推奨動作条件                 | 6  | 9 デバイスおよびドキュメントのサポート   | 51 |

| 6.4 熱に関する情報                | 6  | 9.1 ドキュメントのサポート        | 51 |

| 6.5 電気的特性 - D2D 構成での AC 仕様 | 8  | 9.2 ドキュメントの更新通知を受け取る方法 | 51 |

| 6.6 電気的特性 - S2D 構成での AC 仕様 | 10 | 9.3 サポート・リソース          | 51 |

| 6.7 電気的特性 - DC およびタイミング仕様  | 12 | 9.4 商標                 | 51 |

| 6.8 代表的特性:D2D 構成           | 13 | 9.5 静電気放電に関する注意事項      | 51 |

| 6.9 代表的特性:S2D 構成           | 28 | 9.6 用語集                | 51 |

| 7 詳細説明                     | 39 | 10 改訂履歴                | 51 |

| 7.1 概要                     | 39 | 11 メカニカル、パッケージ、および注文情報 | 51 |

## 4 デバイス比較表

| デバイス      | ゲイン  | チャネル数 |

|-----------|------|-------|

| TRF1305A1 | 15dB | 1     |

| TRF1305B1 | 10dB |       |

| TRF1305C1 | 5dB  |       |

| TRF1305A2 | 15dB | 2     |

| TRF1305B2 | 10dB |       |

| TRF1305C2 | 5dB  |       |

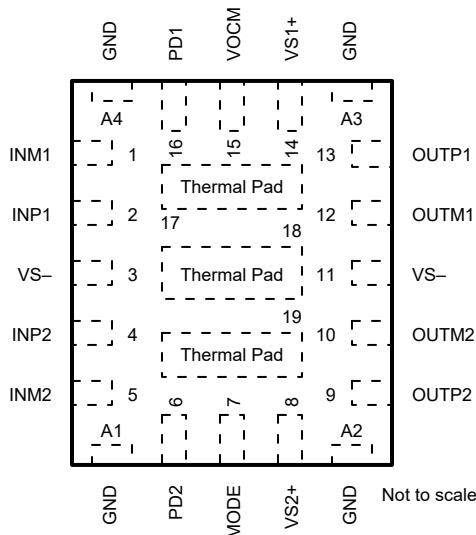

## 5 ピン構成および機能

図 5-1. RYP パッケージ (デュアル チャネル)、16 ピン WQFN-FCRLF (上面図)

表 5-1. ピンの機能

| ピン       |                | タイプ | 説明                                                                                                                |

|----------|----------------|-----|-------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号             |     |                                                                                                                   |

| GND      | A1, A2, A3, A4 | —   | グラウンド。基板上のグラウンド プレーンに接続します。サーマル パッドと内部で短絡。                                                                        |

| INM1     | 1              | 入力  | チャネル 1(Ch1)の差動入力信号の負側。                                                                                            |

| INM2     | 5              | 入力  | チャネル 2(Ch2)の差動入力信号の負側。                                                                                            |

| INP1     | 2              | 入力  | チャネル 1(Ch1)の差動入力信号の正側。                                                                                            |

| INP2     | 4              | 入力  | チャネル 2(Ch2)の差動入力信号の正側。                                                                                            |

| モード      | 7              | 入力  | モードの選択ピン。詳細については、 <a href="#">Mode ピン</a> のセクションを参照してください。                                                        |

| OUTM1    | 12             | 出力  | Ch1 向け差動出力信号の負側                                                                                                   |

| OUTM2    | 10             | 出力  | Ch2 向け差動出力信号の負側                                                                                                   |

| OUTP1    | 13             | 出力  | Ch1 向け差動出力信号の正側                                                                                                   |

| OUTP2    | 9              | 出力  | Ch2 向け差動出力信号の正側                                                                                                   |

| PD1      | 16             | 入力  | Ch1 向けパワーダウン信号、GND を基準とします。1.8V と 3.3V の両方のロジックをサポートしています。<br>ロジック 0 またはオープン = チャネル有効化済みです。ロジック 1 = チャネルはパワー ダウン。 |

| PD2      | 6              | 入力  | Ch2 向けパワーダウン信号、GND を基準とします。1.8V と 3.3V の両方のロジックをサポートしています。<br>ロジック 0 またはオープン = チャネル有効化済みです。ロジック 1 = チャネルはパワー ダウン。 |

| VOCM     | 15             | 入力  | 出力同相電圧入力ピン。両方のチャネルに共通です。このピンをフローティングにすると、出力同相電圧が $V_{S-} + 2.5V$ に設定されます。                                         |

| VS-      | 3, 11          | 電源  | 負電源ピンです。両方のチャネルに共通です。                                                                                             |

| VS1+     | 14             | 電源  | Ch1 向け正電源ピン。 $V_{S1+} = V_{S2+}$ であるように維持します。                                                                     |

| VS2+     | 8              | 電源  | Ch2 向け正電源ピン。 $V_{S1+} = V_{S2+}$ であるように維持します。                                                                     |

| サーマル パッド | 17, 18, 19     | —   | サーマル パッド。基板上の放熱グラウンド プレーンに接続します。内部的に GND に短絡。                                                                     |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|            |                                      |                    | 最小値            | 最大値            | 単位  |

|------------|--------------------------------------|--------------------|----------------|----------------|-----|

| $V_{S-}$   | 負電源電圧、GND 基準                         |                    | -3             | 0.3            | V   |

| $V_{S+}$   | 正電源電圧、 $V_{S1+} = V_{S2+}$ になるようにします |                    | -0.3           | $V_{S-} + 5.5$ | V   |

| $V_S$      | 合計電源電圧、 $V_S = V_{S+} - V_{S-}$      |                    | -0.3           | 5.5            | V   |

| $P_{IN}$   | 入力 RF 電力 <sup>(2)</sup>              |                    |                | 20             | dBm |

| $V_{PD}$   | PD ピンの電圧、GND 基準                      | $V_{S+} \geq 3.3V$ | -0.3           | 3.6            | V   |

|            |                                      | $V_{S+} < 3.3V$    | -0.3           | $V_{S+} + 0.3$ | V   |

| $V_{OCM}$  | VOCM ピン電圧                            |                    | $V_{S-} + 1$   | $V_{S-} + 4$   | V   |

| $V_{MODE}$ | MODE ピン電圧                            |                    | $V_{S-} - 0.3$ | $V_{S-} + 3.3$ | V   |

| $T_J$      | 接合部温度                                |                    | -40            | 150            | °C  |

| $T_{stg}$  | 保存温度                                 |                    | -40            | 150            | °C  |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) デバイス電源が供給されているときは、デバイスのピンのスイングを  $V_{S-} \pm 0.3V$  に制限します。

### 6.2 ESD 定格

|             |      |                                                                   | 値     | 単位 |

|-------------|------|-------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>      | ±1000 | V  |

|             |      | 荷電デバイス モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|          |                                 | 最小値  | 公称値 | 最大値  | 単位 |

|----------|---------------------------------|------|-----|------|----|

| $V_{S-}$ | 負電源電圧                           | -2.5 | 0   | 0    | V  |

| $V_S$    | 合計電源電圧、 $V_S = V_{S+} - V_{S-}$ | 4.75 | 5   | 5.25 | V  |

| $T_J$    | 接合部温度                           | -40  |     | 125  | °C |

### 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | TRF1305A2        | 単位   |

|----------------------|---------------------|------------------|------|

|                      |                     | RYP (WQFN-FCRLF) |      |

|                      |                     | 16 ピン            |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 51.8             | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 24.5             | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 14.5             | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 1.4              | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 14.3             | °C/W |

| 熱評価基準 <sup>(1)</sup>  |                   | TRF1305A2        | 単位   |

|-----------------------|-------------------|------------------|------|

|                       |                   | RYP (WQFN-FCRLF) |      |

|                       |                   | 16 ピン            |      |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 10.7             | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 6.5 電気的特性 - D2D 構成での AC 仕様

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM}$  = 中間電源、D2D ac 結合入出力差動ソース インピーダンス ( $Z_S$ ) =  $100\Omega$ 、差動出力負荷 ( $Z_L$ ) =  $100\Omega$ 、外部入力抵抗ネットワーク (図 8-6 を参照)、入力が  $R_{IN\_SH}$  までデエンベデッドされ、デバイスピンまで出力 (特に記述のない限り)

| パラメータ        |                     | テスト条件                                                                | 最小値                 | 標準値 | 最大値 | 単位  |

|--------------|---------------------|----------------------------------------------------------------------|---------------------|-----|-----|-----|

| <b>AC 特性</b> |                     |                                                                      |                     |     |     |     |

| SSBW         | 小信号帯域幅 (3dB)        | $P_{IN} = -20\text{dBm}$ (各入力)                                       | 5.8                 | GHz |     |     |

|              | 小信号帯域幅 (1dB)        | $P_{IN} = -20\text{dBm}$ (各入力)                                       | 5.2                 |     |     |     |

| LSBW         | 大信号帯域幅 (3dB)        | 差動 $P_{IN} = -8\text{dBm}$                                           | 5.8                 | GHz |     |     |

|              | 大信号帯域幅 (1dB)        | 差動 $P_{IN} = -8\text{dBm}$                                           | 5.2                 |     |     |     |

| Sdd21        | パワー ゲイン             | $f = 500\text{MHz}$                                                  | 14.4                | dB  |     |     |

|              |                     | $f = 4\text{GHz}$                                                    | 15.9                |     |     |     |

|              | 温度範囲全体でのゲイン変動       | $f = 4\text{GHz}$ 、 $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | 1.3                 |     |     | dB  |

| Sdd11        | 入力リターン ロス           | $f = 10\text{MHz} \sim 5\text{GHz}$                                  | -11                 |     |     | dB  |

| Sdd12        | 逆アイソレーション           | $f < 5\text{GHz}$ (デバイスは有効)                                          | -25                 |     |     | dB  |

|              | チャネル間のゲインの不整合       | $f = 10\text{MHz} \sim 5\text{GHz}$                                  | $\pm 0.1$           |     |     | dB  |

|              | チャネル間の位相の不整合        | $f = 10\text{MHz} \sim 5\text{GHz}$                                  | $\pm 0.5$           |     |     | °   |

|              | チャネル間のクロストーク        | $f = 1\text{GHz}$                                                    | -62                 |     |     | dBc |

| OP1dB        | 出力 1dB の圧縮ポイント      | $f = 500\text{MHz}$                                                  | 15.5                | dBm |     |     |

|              |                     | $f = 1\text{GHz}$                                                    | 15.4                |     |     |     |

|              |                     | $f = 2\text{GHz}$                                                    | 15                  |     |     |     |

|              |                     | $f = 3\text{GHz}$                                                    | 13.7                |     |     |     |

|              |                     | $f = 4\text{GHz}$                                                    | 11.6                |     |     |     |

|              |                     | $f = 5\text{GHz}$                                                    | 9.1                 |     |     |     |

| HD2          | 2 次高調波歪             | $V_O = 2V_{PP}$ ( $P_O = 7\text{dBm}$ )                              | $f = 500\text{MHz}$ | dBc |     |     |

|              |                     |                                                                      | $f = 1\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 2\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 3\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 4\text{GHz}$   |     |     |     |

| HD3          | 3 次高調波歪             | $V_O = 2V_{PP}$ ( $P_O = 7\text{dBm}$ )                              | $f = 500\text{MHz}$ | dBc |     |     |

|              |                     |                                                                      | $f = 1\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 2\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 3\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 4\text{GHz}$   |     |     |     |

| OIP2         | 出力の 2 次インターフェト ポイント | $P_O = 1\text{dBm/トーン}$ 、<br>2MHz 間隔                                 | $f = 500\text{MHz}$ | dBm |     |     |

|              |                     |                                                                      | $f = 1\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 2\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 3\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 4\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 5\text{GHz}$   |     |     |     |

| OIP3         | 出力の 3 次インターフェト ポイント | $P_O = 1\text{dBm/トーン}$ 、<br>2MHz 間隔                                 | $f = 500\text{MHz}$ | dBm |     |     |

|              |                     |                                                                      | $f = 1\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 2\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 3\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 4\text{GHz}$   |     |     |     |

|              |                     |                                                                      | $f = 5\text{GHz}$   |     |     |     |

## 6.5 電気的特性 - D2D 構成での AC 仕様 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM}$  = 中間電源、D2D ac 結合入出力差動ソースインピーダンス ( $Z_S$ ) =  $100\Omega$ 、差動出力負荷 ( $Z_L$ ) =  $100\Omega$ 、外部入力抵抗ネットワーク (図 8-6 を参照)、入力が  $R_{IN\_SH}$  までデエンベデッドされ、デバイスピンまで出力 (特に記述のない限り)

| パラメータ |               | テスト条件               | 最小値 | 標準値    | 最大値 | 単位     |

|-------|---------------|---------------------|-----|--------|-----|--------|

| NF    | ノイズ指数         | $f = 500\text{MHz}$ |     | 7.3    |     | dB     |

|       |               | $f = 1\text{GHz}$   |     | 7.8    |     |        |

|       |               | $f = 2\text{GHz}$   |     | 9.2    |     |        |

|       |               | $f = 3\text{GHz}$   |     | 10.8   |     |        |

|       |               | $f = 4\text{GHz}$   |     | 11.7   |     |        |

|       |               | $f = 5\text{GHz}$   |     | 12.1   |     |        |

| NSD   | 出力ノイズ スペクトル密度 | $f = 500\text{MHz}$ |     | -152   |     | dBm/Hz |

|       |               | $f = 1\text{GHz}$   |     | -151.5 |     |        |

|       |               | $f = 2\text{GHz}$   |     | -149.8 |     |        |

|       |               | $f = 3\text{GHz}$   |     | -147.2 |     |        |

|       |               | $f = 4\text{GHz}$   |     | -146.2 |     |        |

|       |               | $f = 5\text{GHz}$   |     | -147.9 |     |        |

## 6.6 電気的特性 - S2D 構成での AC 仕様

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。特に断りがない限り、入力および出力はデバイスのピンまでデエンベッドされています

| パラメータ                    |                      | テスト条件                                                                | 最小値       | 標準値 | 最大値 | 単位  |

|--------------------------|----------------------|----------------------------------------------------------------------|-----------|-----|-----|-----|

| <b>AC 特性</b>             |                      |                                                                      |           |     |     |     |

| SSBW                     | 小信号帯域幅 (3dB)         | $P_{\text{IN}} = -20\text{dBm}$ (各入力)                                | 6.1       | GHz |     |     |

|                          | 小信号帯域幅 (1dB)         | $P_{\text{IN}} = -20\text{dBm}$ (各入力)                                | 5.2       |     |     |     |

| LSBW                     | 大信号帯域幅 (3dB)         | シングル エンド $P_{\text{IN}} = -8\text{dBm}$                              | 6.1       | GHz |     |     |

|                          | 大信号帯域幅 (1dB)         | シングル エンド $P_{\text{IN}} = -8\text{dBm}$                              | 5.2       |     |     |     |

| Sds21                    | パワー ゲイン              | $f = 500\text{MHz}$                                                  | 14.8      | dB  |     |     |

|                          |                      | $f = 4\text{GHz}$                                                    | 15        |     |     |     |

|                          | 温度範囲全体でのゲイン変動        | $f = 4\text{GHz}$ , $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | 1.5       |     |     | dB  |

| Sss11                    | 入力リターン ロス            | $f = 10\text{MHz} \sim 3\text{GHz}$ <sup>(1)</sup>                   | -11       | dB  |     |     |

| Sss11                    | 入力リターン ロス            | $f = 4\text{GHz}$ <sup>(1)</sup>                                     | -10       |     |     |     |

| Sss11                    | 入力リターン ロス            | $f = 5\text{GHz}$ <sup>(1)</sup>                                     | -8        |     |     |     |

| Ssd12                    | 逆アイソレーション            | $f < 5\text{GHz}$ (デバイスは有効)                                          | -25       |     |     | dB  |

|                          | チャネル間のゲインの不整合        | $f = 10\text{MHz} \sim 5\text{GHz}$                                  | $\pm 0.1$ |     |     | dB  |

|                          | チャネル間の位相の不整合         | $f = 10\text{MHz} \sim 5\text{GHz}$                                  | $\pm 1$   |     |     | °   |

|                          | チャネル間のクロストーク         | $f = 1\text{GHz}$                                                    | -48       |     |     | dBc |

| $G_{\text{IMB}}$         | 差動出力ゲイン不均衡           | $f < 5\text{GHz}$ , $P_{\text{IN}} = -20\text{dBm}$ , $50\Omega Z_S$ | $\pm 0.1$ |     |     | dB  |

| $\text{PH}_{\text{IMB}}$ | 差動出力位相の不均衡           | $f < 5\text{GHz}$ , $P_{\text{IN}} = -20\text{dBm}$ , $50\Omega Z_S$ | $\pm 1.2$ |     |     | °   |

| OP1dB                    | 出力 1dB の圧縮ポイント       | $f = 500\text{MHz}$                                                  | 15.4      | dBm |     |     |

|                          |                      | $f = 1\text{GHz}$                                                    | 15.7      |     |     |     |

|                          |                      | $f = 2\text{GHz}$                                                    | 15.2      |     |     |     |

|                          |                      | $f = 3\text{GHz}$                                                    | 13.8      |     |     |     |

|                          |                      | $f = 4\text{GHz}$                                                    | 11.8      |     |     |     |

|                          |                      | $f = 5\text{GHz}$                                                    | 10        |     |     |     |

| HD2                      | 2 次高調波歪              | $f = 500\text{MHz}$                                                  | -60       | dBc |     |     |

|                          |                      | $f = 1\text{GHz}$                                                    | -58       |     |     |     |

|                          |                      | $f = 2\text{GHz}$                                                    | -48       |     |     |     |

|                          |                      | $f = 3\text{GHz}$                                                    | -50       |     |     |     |

|                          |                      | $f = 4\text{GHz}$                                                    | -46       |     |     |     |

|                          |                      | $f = 500\text{MHz}$                                                  | -69       |     |     |     |

| HD3                      | 3 次高調波歪              | $f = 1\text{GHz}$                                                    | -59       | dBc |     |     |

|                          |                      | $f = 2\text{GHz}$                                                    | -54       |     |     |     |

|                          |                      | $f = 3\text{GHz}$                                                    | -58       |     |     |     |

|                          |                      | $f = 4\text{GHz}$                                                    | -48       |     |     |     |

|                          |                      | $f = 500\text{MHz}$                                                  | 70        | dBm |     |     |

|                          |                      | $f = 1\text{GHz}$                                                    | 61        |     |     |     |

| OIP2                     | 出力の 2 次インターフェース ポイント | $f = 2\text{GHz}$                                                    | 50        |     |     |     |

|                          |                      | $f = 3\text{GHz}$                                                    | 51        |     |     |     |

|                          |                      | $f = 4\text{GHz}$                                                    | 51        |     |     |     |

|                          |                      | $f = 5\text{GHz}$                                                    | 51        |     |     |     |

|                          |                      | $f = 500\text{MHz}$                                                  |           |     |     |     |

|                          |                      | $f = 1\text{GHz}$                                                    |           |     |     |     |

## 6.6 電気的特性 - S2D 構成での AC 仕様 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。特に断りがない限り、入力および出力はデバイスのピンまでデエンベッドされています

| パラメータ |                     | テスト条件                                | 最小値                 | 標準値    | 最大値 | 単位     |

|-------|---------------------|--------------------------------------|---------------------|--------|-----|--------|

| OIP3  | 出力の 3 次インターセプト ポイント | $P_O = 1\text{dBm/トーン}$ 、<br>2MHz 間隔 | $f = 500\text{MHz}$ | 44     |     | dBm    |

|       |                     |                                      | $f = 1\text{GHz}$   | 39     |     |        |

|       |                     |                                      | $f = 2\text{GHz}$   | 33     |     |        |

|       |                     |                                      | $f = 3\text{GHz}$   | 28     |     |        |

|       |                     |                                      | $f = 4\text{GHz}$   | 22     |     |        |

|       |                     |                                      | $f = 5\text{GHz}$   | 19     |     |        |

| NF    | ノイズ指數               |                                      | $f = 500\text{MHz}$ | 7.8    |     | dB     |

|       |                     |                                      | $f = 1\text{GHz}$   | 8      |     |        |

|       |                     |                                      | $f = 2\text{GHz}$   | 9.6    |     |        |

|       |                     |                                      | $f = 3\text{GHz}$   | 10.5   |     |        |

|       |                     |                                      | $f = 4\text{GHz}$   | 11.4   |     |        |

|       |                     |                                      | $f = 5\text{GHz}$   | 12     |     |        |

| NSD   | 出力ノイズ スペクトル密度       |                                      | $f = 500\text{MHz}$ | -151.3 |     | dBm/Hz |

|       |                     |                                      | $f = 1\text{GHz}$   | -151.2 |     |        |

|       |                     |                                      | $f = 2\text{GHz}$   | -149.6 |     |        |

|       |                     |                                      | $f = 3\text{GHz}$   | -148.5 |     |        |

|       |                     |                                      | $f = 4\text{GHz}$   | -147   |     |        |

|       |                     |                                      | $f = 5\text{GHz}$   | -147.6 |     |        |

(1) 入力リターン ロスを改善する方法については、[セクション 8.1.1.1](#) を参照してください。

## 6.7 電気的特性 - DC およびタイミング仕様

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング  $\text{VOCM}$ 、 $\text{PD}$ 、および  $\text{MODE}$  ピン、 $\text{V}_{\text{ICM}} = \text{中間供給}$ 、 $Z_L = 100\Omega$  で、仕様は S2D および D2D 構成の両方に適用されます (特に記述のない限り)。

| パラメータ                 |                                   | テスト条件                                                                                                                          | 最小値            | 標準値            | 最大値 | 単位                      |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----|-------------------------|

| <b>DC 特性</b>          |                                   |                                                                                                                                |                |                |     |                         |

| $V_{\text{OD-MAX}}$   | 最大差動出力電圧                          | $f = 1\text{GHz}$                                                                                                              | 4              |                |     | $V_{\text{PP}}$         |

|                       | スルーレート                            | 2V $V_O$ ステップ、DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$                                                          | 25             |                |     | $\text{kV}/\mu\text{s}$ |

|                       | 出力差動オフセット電圧                       |                                                                                                                                | $\pm 3$        |                |     | $\text{mV}$             |

|                       | オーバードライブの復帰時間                     | DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、各 SE 出力の 2 倍のオーバードライブから各出力電圧セッティングまでの範囲で、 $\pm 50\text{mV}$ 未満にセッティング | 6              |                |     | $\text{ns}$             |

| <b>同相</b>             |                                   |                                                                                                                                |                |                |     |                         |

| $V_{\text{ICM}}$      | 入力同相電圧                            | デフォルトの範囲 <sup>(1)</sup>                                                                                                        | $V_{S-} + 1.5$ | $V_{S-} + 3.5$ |     | $\text{V}$              |

| $V_{\text{OCM}}$      | 出力同相電圧                            |                                                                                                                                | $V_{S-} + 2$   | $V_{S-} + 3$   |     | $\text{V}$              |

|                       | $V_{\text{OCM}}$ 電圧からの出力同相オフセット電圧 |                                                                                                                                | -20            | 20             |     | $\text{mV}$             |

| <b>インピーダンス</b>        |                                   |                                                                                                                                |                |                |     |                         |

| $Z_{\text{IN-SE}}$    | シングルエンド入力インピーダンス                  | S2D、 $\text{INP}$ ピンで $\text{INM}$ ピンに $50\Omega$ 終端                                                                           | 45.8           |                |     | $\Omega$                |

| $Z_{\text{IN-DIFF}}$  | 差動入力インピーダンス                       | D2D、デバイス ピンで                                                                                                                   | 13.5           |                |     | $\Omega$                |

| $Z_{\text{O-DIFF}}$   |                                   | D2D、 $R_{\text{IN\_SH}}$ については、図 8-6 を参照してください                                                                                 | 59.7           |                |     |                         |

|                       | 差動出力インピーダンス                       | $f = \text{dc}$ 付近                                                                                                             | 8              |                |     | $\Omega$                |

| <b>電源</b>             |                                   |                                                                                                                                |                |                |     |                         |

| $I_{\text{QA}}$       | アクティブ時の静止電流                       | 両方のチャネルがアクティブ                                                                                                                  | 201            |                |     | $\text{mA}$             |

|                       |                                   | 一方のチャネルがアクティブ、もう一方のチャネルはパワーダウンします                                                                                              | 112            |                |     |                         |

| $I_{\text{QPD}}$      | パワーダウン静止時電流                       | すべてのチャネルがパワーダウンします                                                                                                             | 23             |                |     | $\text{mA}$             |

| <b>パワーダウン</b>         |                                   |                                                                                                                                |                |                |     |                         |

| $V_{\text{PD\_Hi}}$   | PD ピンはロジック high                   | GND 基準。セクション 6.1 を参照してください                                                                                                     | 1.35           |                |     | $\text{V}$              |

| $V_{\text{PD\_Lo}}$   | PD ピンはロジック low                    | GND 基準。セクション 6.1 を参照してください                                                                                                     |                | 0.3            |     | $\text{V}$              |

| $I_{\text{PD\_Bias}}$ | PD バイアス電流 (PD ピンの電流)              | PD = high (1.8V ロジック)                                                                                                          | 10.5           | 15             |     | $\mu\text{A}$           |

|                       |                                   | PD = high (3.3V ロジック)                                                                                                          | 19             | 30             |     |                         |

| $t_{\text{ON}}$       | ターンオン時間                           | S2D、dc 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、50% $V_{\text{PD}}$ から 90% RF OUT に遷移                             | 25             |                |     | $\text{ns}$             |

| $t_{\text{OFF}}$      | ターンオフ時間                           | S2D、dc 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、50% $V_{\text{PD}}$ から 10% RF OUT に遷移                             | 20             |                |     | $\text{ns}$             |

(1) D2D 構成では、 $V_{\text{ICM}}$  範囲は  $V_{S+}$  または  $V_{S-}$  に近く拡張できます。セクション 7.4.1 も参照してください。

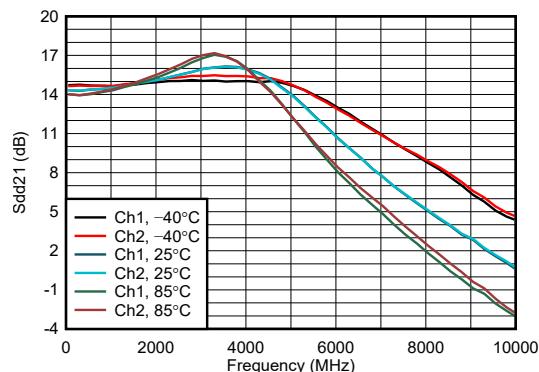

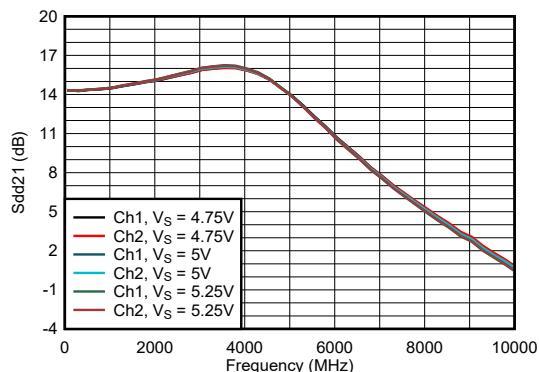

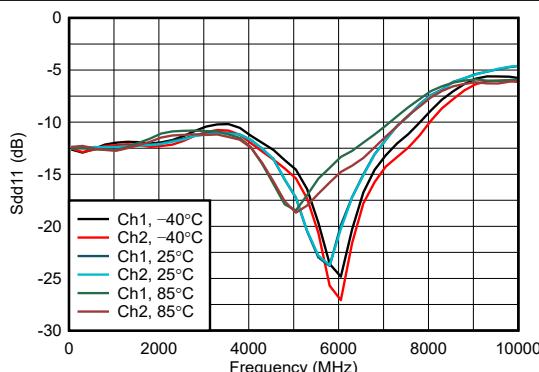

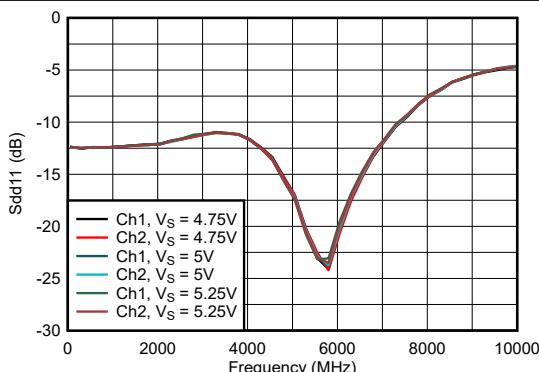

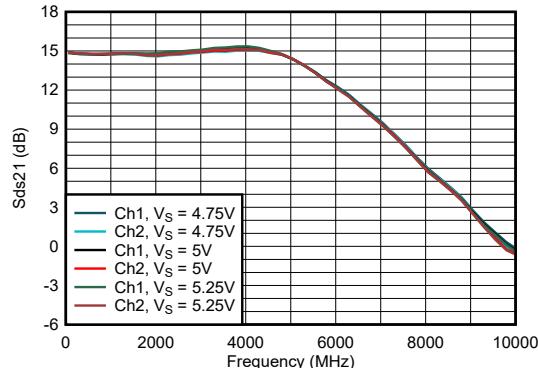

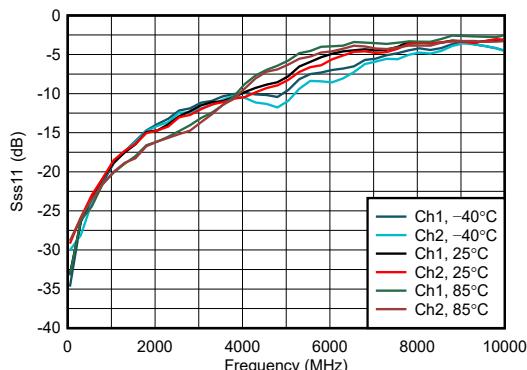

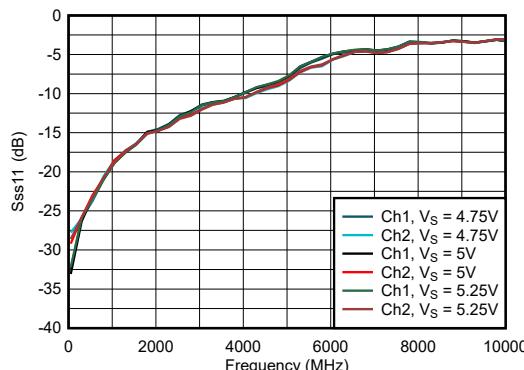

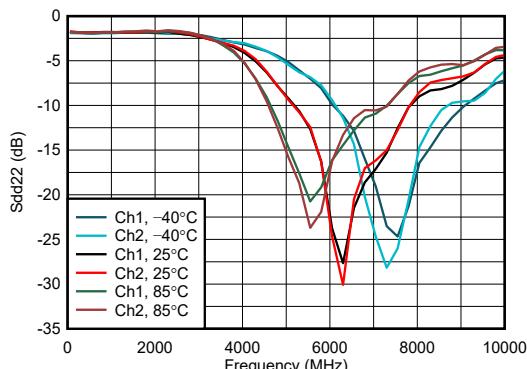

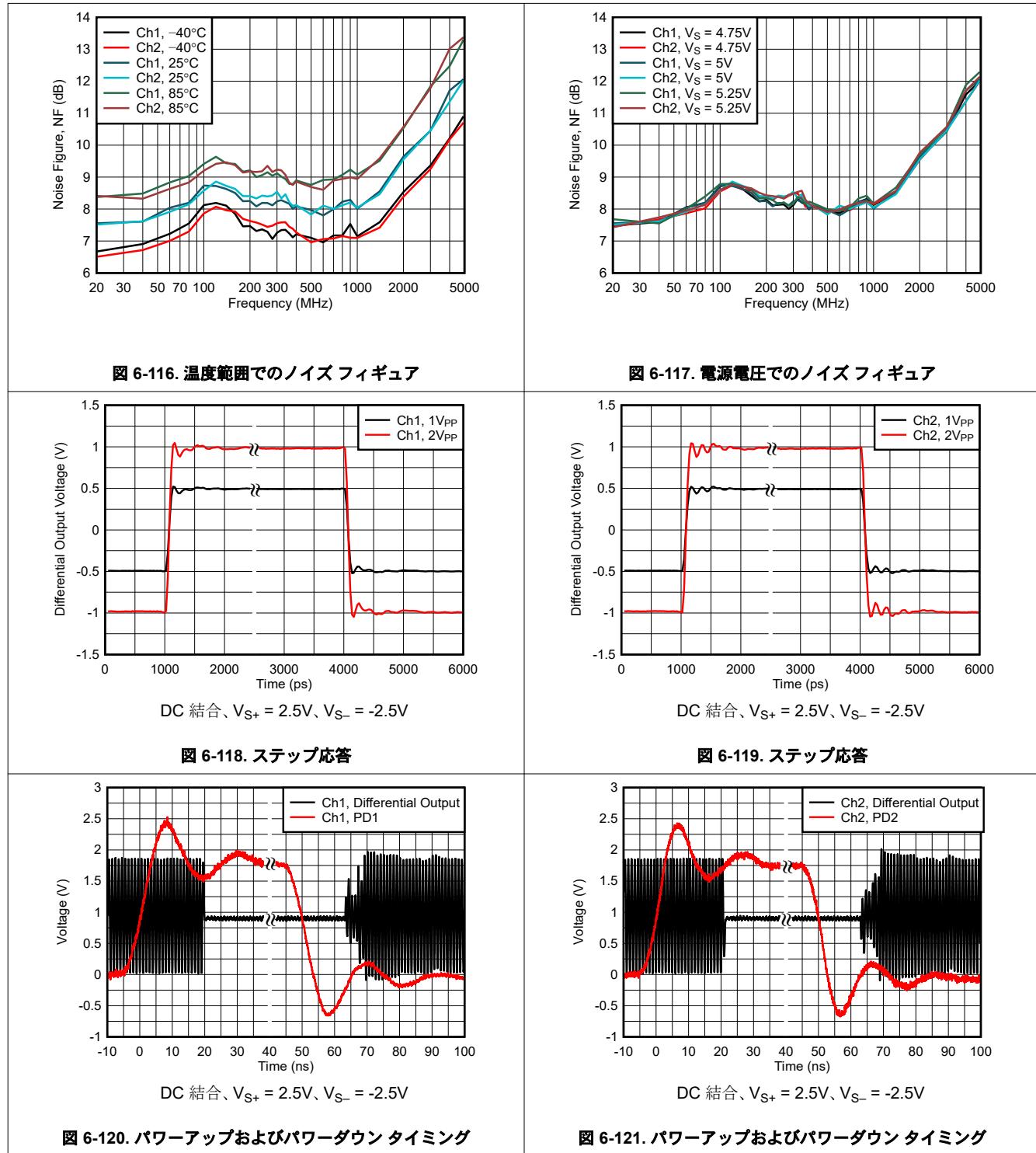

## 6.8 代表的特性 : D2D 構成

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM}$  = 中間電圧、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{IN\_SH}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-1. 動作温度範囲における電力ゲイン (Sdd21)

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-2. 電源電圧におけるパワーゲイン (Sdd21)

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-3. 温度範囲全体にわたる入力リターンロス (Sdd11)

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-4. 電源電圧にわたる入力リターンロス (Sdd11)

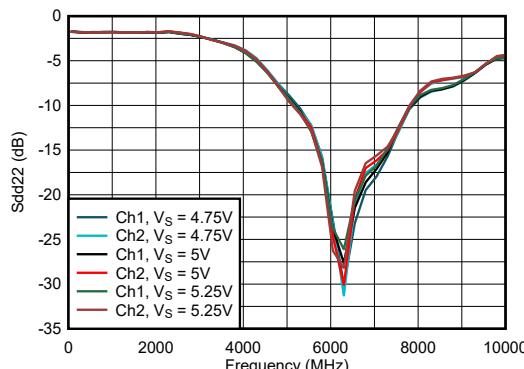

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-5. 温度範囲全体での出力リターンロス (Sdd22)

$P_{IN} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-6. 電源電圧範囲全体にわたる出力リターンロス (Sdd22)

## 6.8 代表的特性 : D2D 構成 (続き)

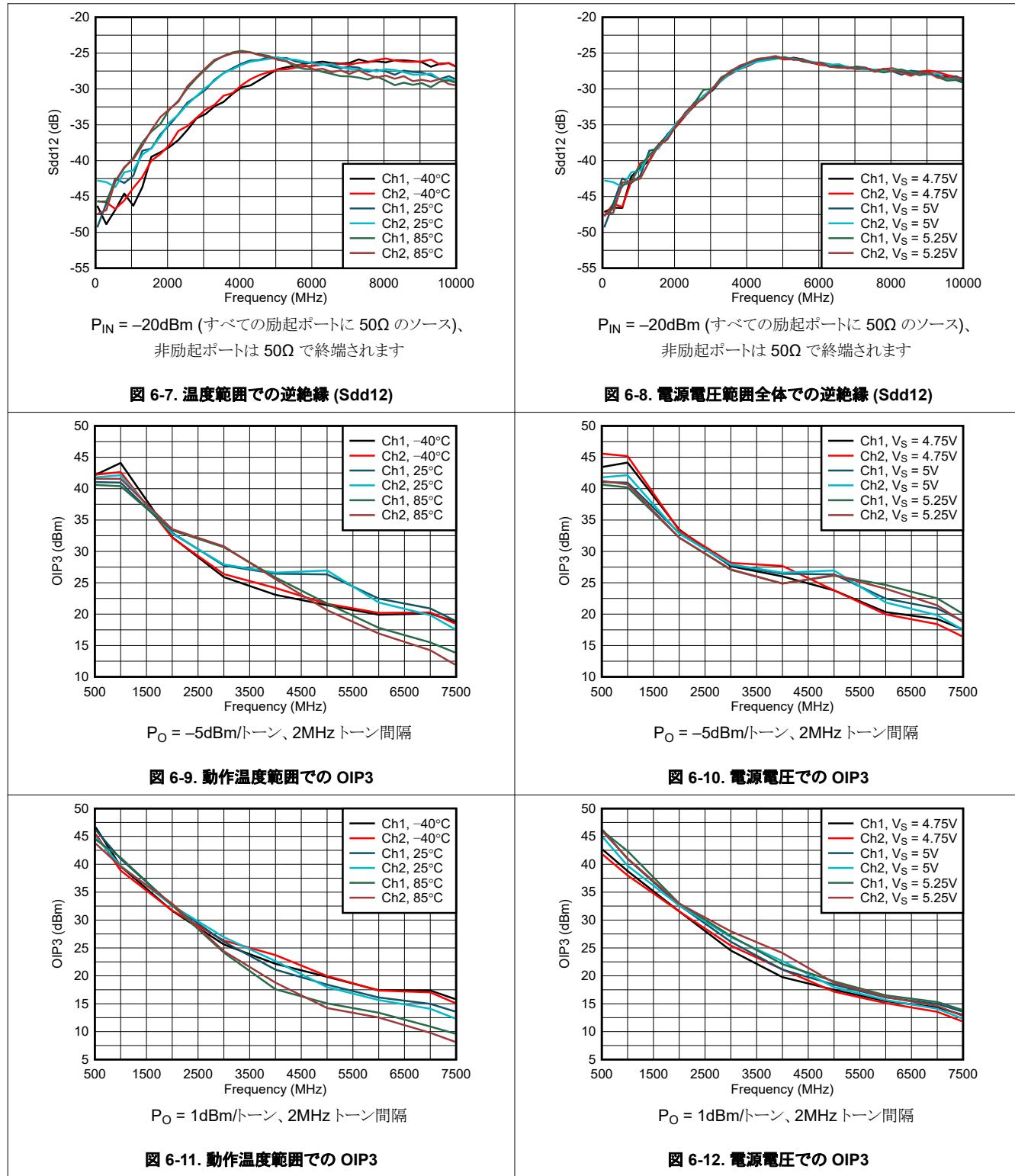

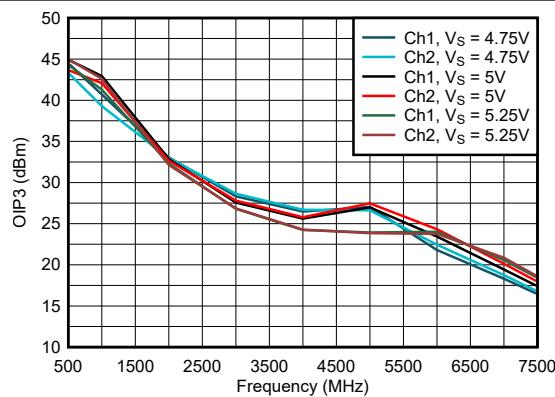

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

## 6.8 代表的特性 : D2D 構成 (続き)

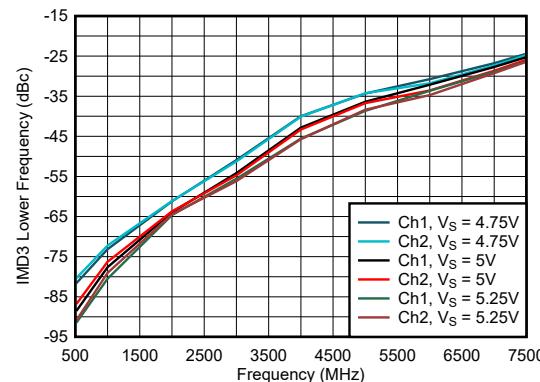

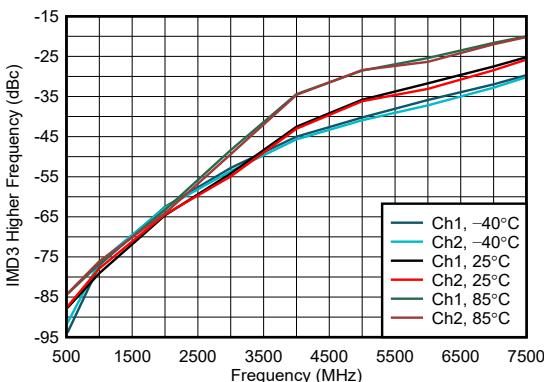

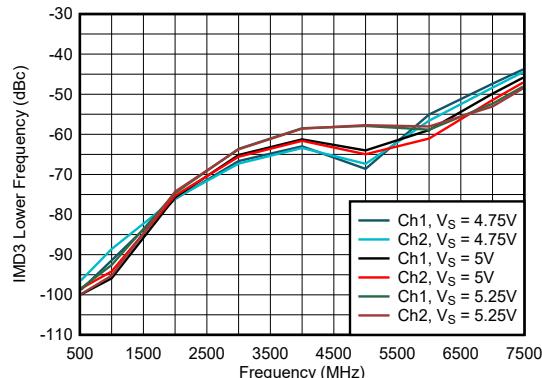

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}}$  = 中間電圧、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

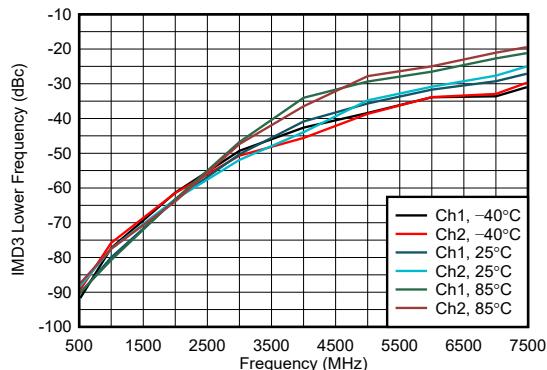

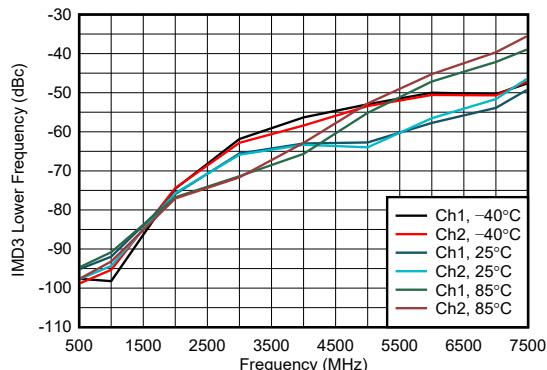

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-13. 全温度範囲で IMD3 低い

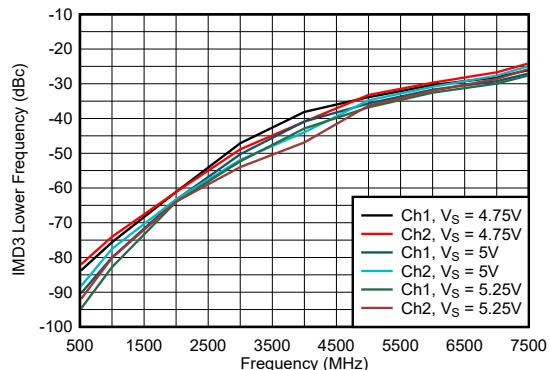

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-14. 電源電圧全体で IMD3 低い

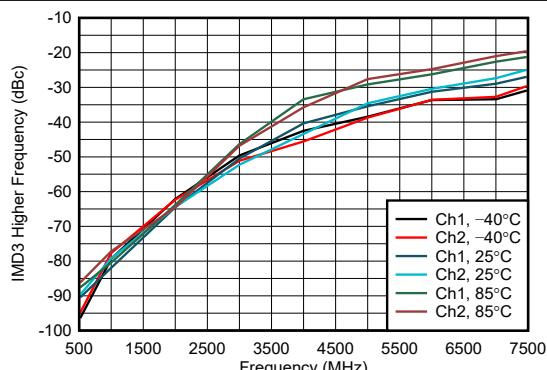

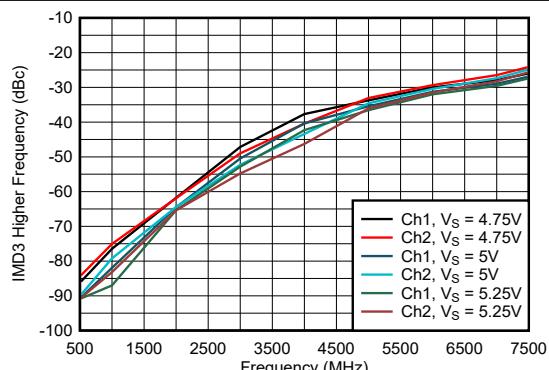

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-15. 全温度範囲で IMD3 高い

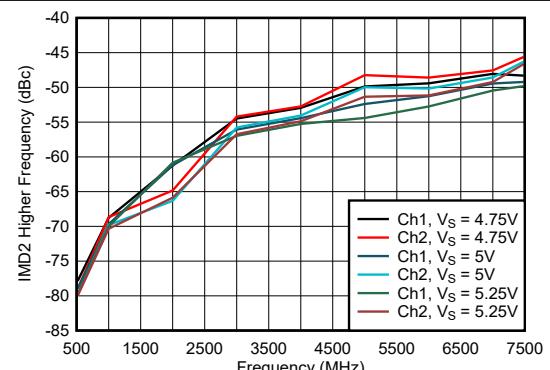

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-16. 電源電圧全体で IMD3 高い

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-17. 全温度範囲で IMD3 低い

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-18. 電源電圧全体で IMD3 低い

## 6.8 代表的特性 : D2D 構成 (続き)

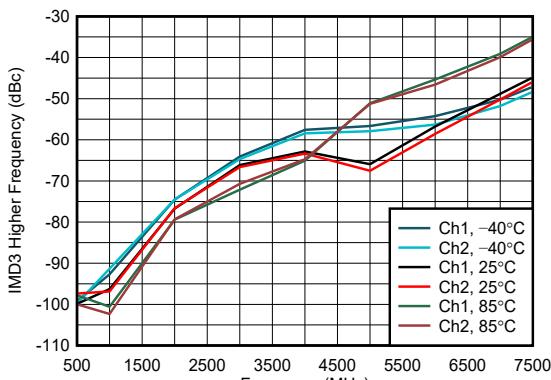

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-19. 全温度範囲で IMD3 高い

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-20. 電源電圧全体で IMD3 高い

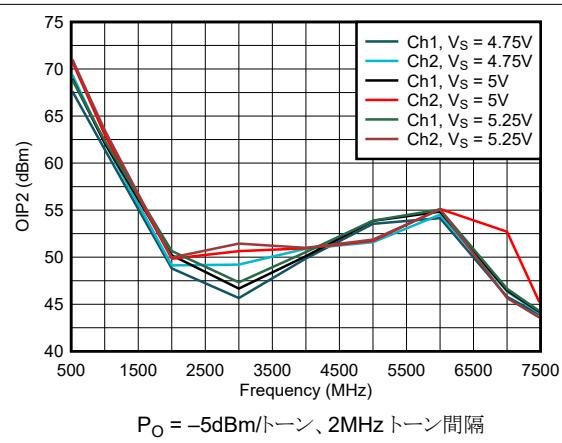

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-21. 動作温度範囲での OIP2

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-22. 電源電圧での OIP2

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-23. 動作温度範囲での OIP2

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-24. 電源電圧での OIP2

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}}$  = 中間電圧、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

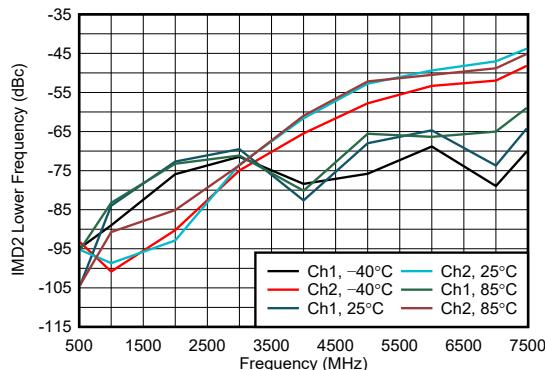

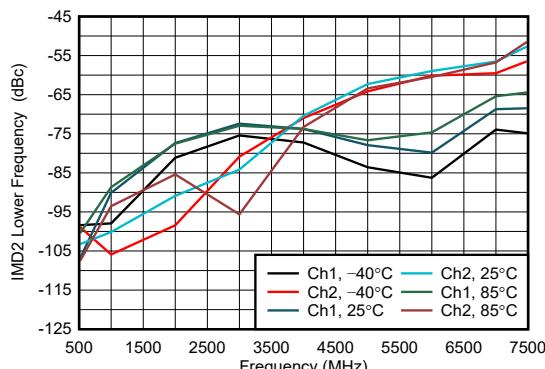

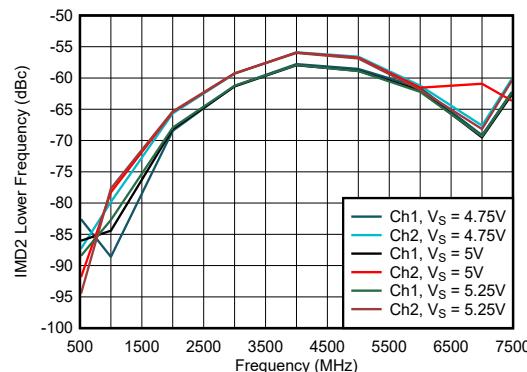

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-25. 全温度範囲で IMD2 低い

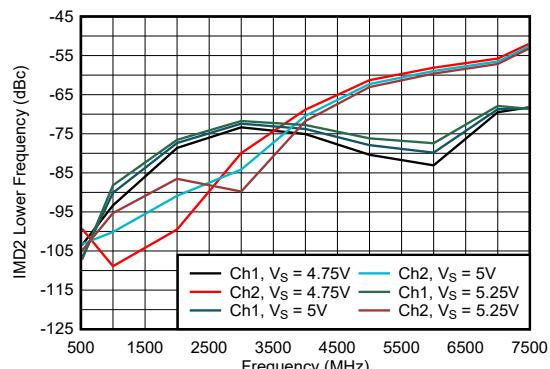

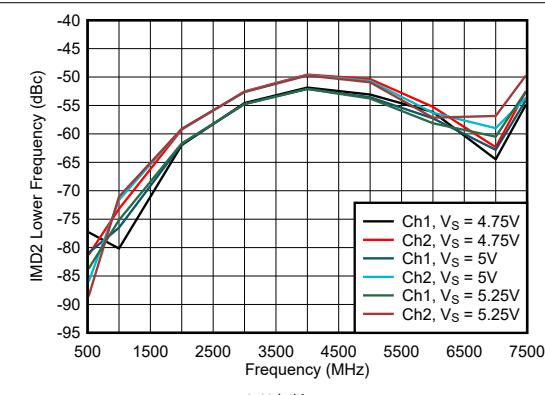

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-26. 電源電圧全体で IMD2 低い

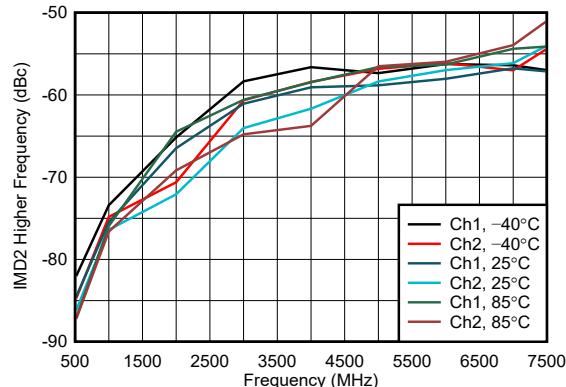

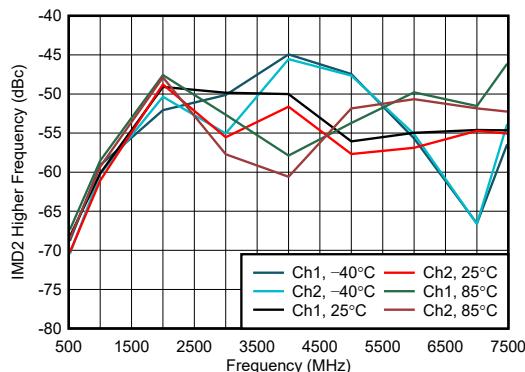

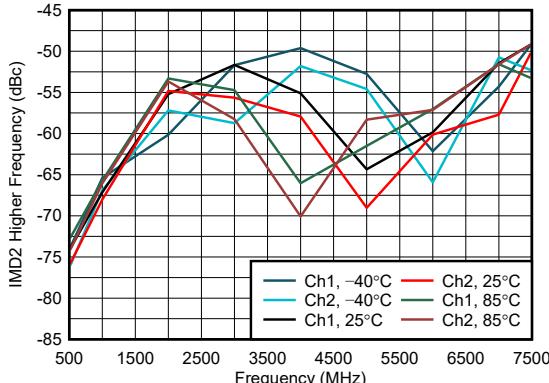

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-27. 全温度範囲で IMD2 高い

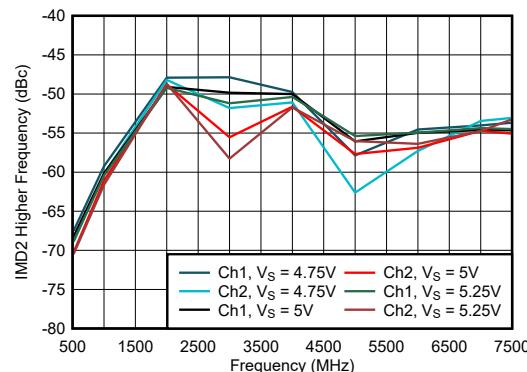

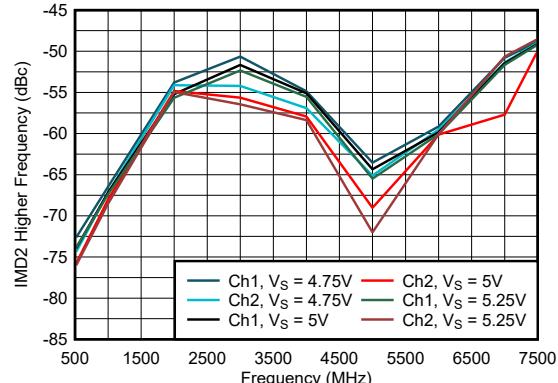

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-28. 電源電圧全体で IMD2 高い

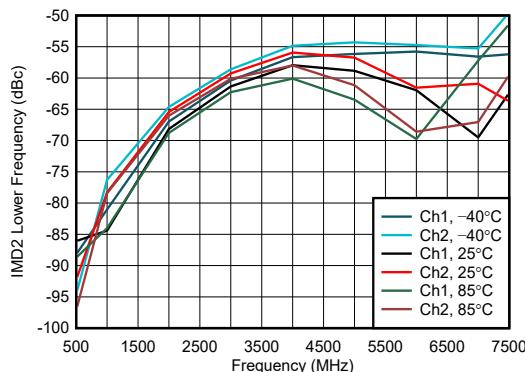

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-29. 全温度範囲で IMD2 低い

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}、2\text{MHz} \text{ トーン間隔}$

図 6-30. 電源電圧全体で IMD2 低い

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-31. 全温度範囲で IMD2 高い

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-32. 電源電圧全体で IMD2 高い

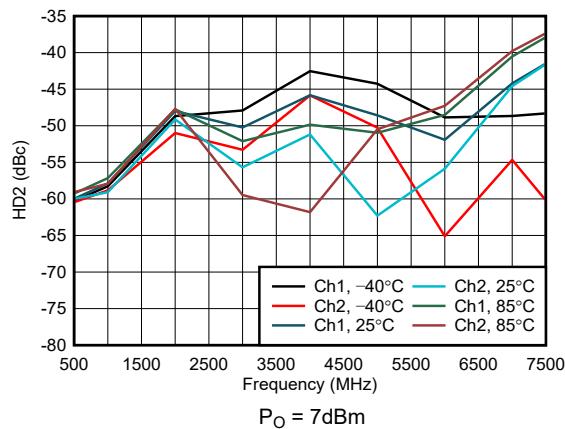

$P_O = 7\text{dBm}$

図 6-33. 動作温度範囲での HD2

$P_O = 7\text{dBm}$

図 6-34. 電源電圧での HD2

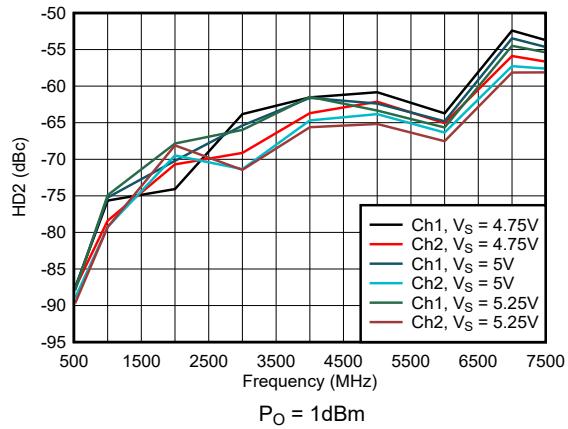

$P_O = 1\text{dBm}$

図 6-35. 動作温度範囲での HD2

$P_O = 1\text{dBm}$

図 6-36. 電源電圧での HD2

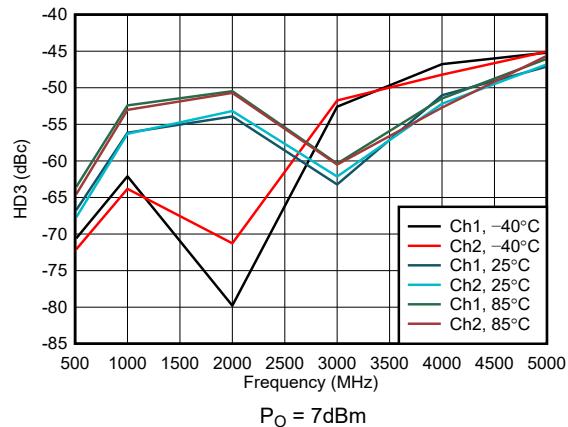

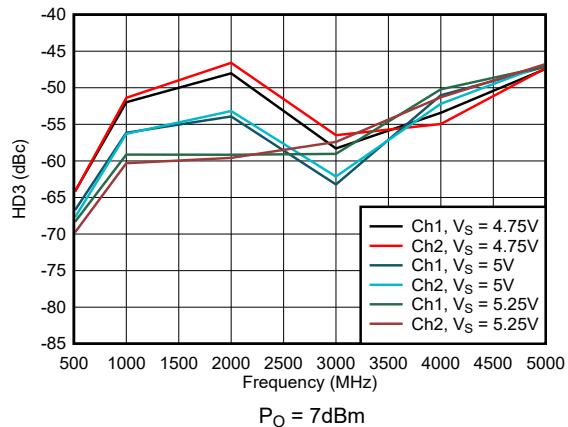

## 6.8 代表的特性 : D2D 構成 (続き)

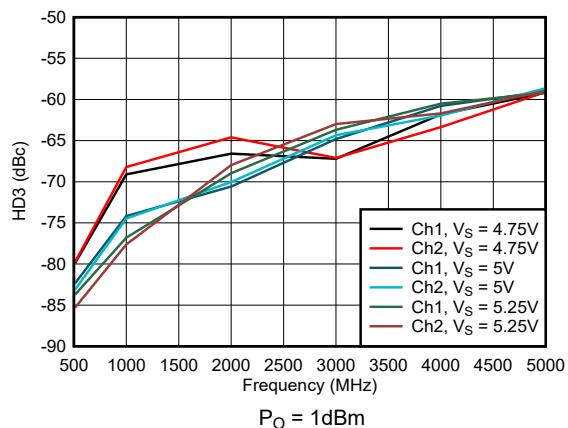

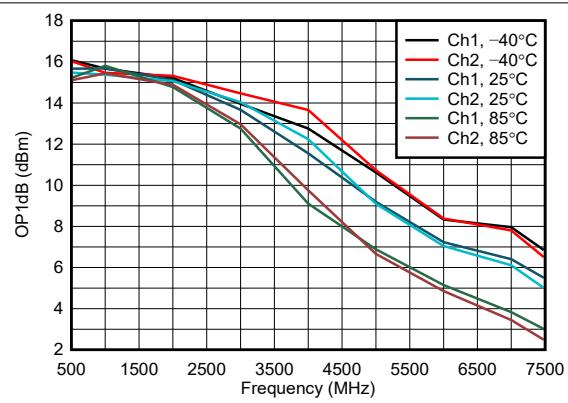

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

図 6-37. 動作温度範囲での HD3

図 6-38. 電源電圧での HD3

図 6-39. 動作温度範囲での HD3

図 6-40. 電源電圧での HD3

図 6-41. 動作温度範囲での OP1dB

図 6-42. 電源電圧での OP1dB

## 6.8 代表的特性 : D2D 構成 (続き)

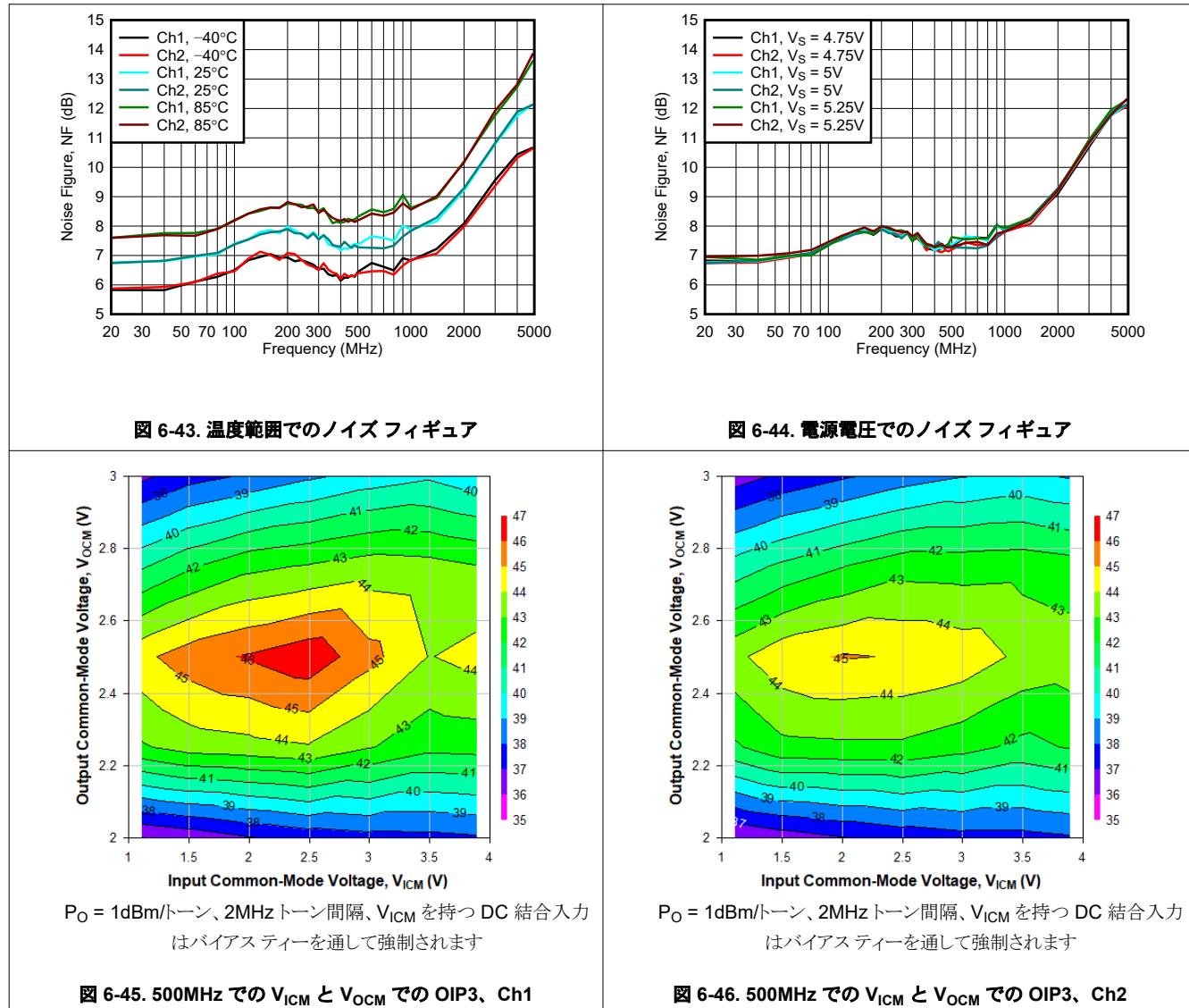

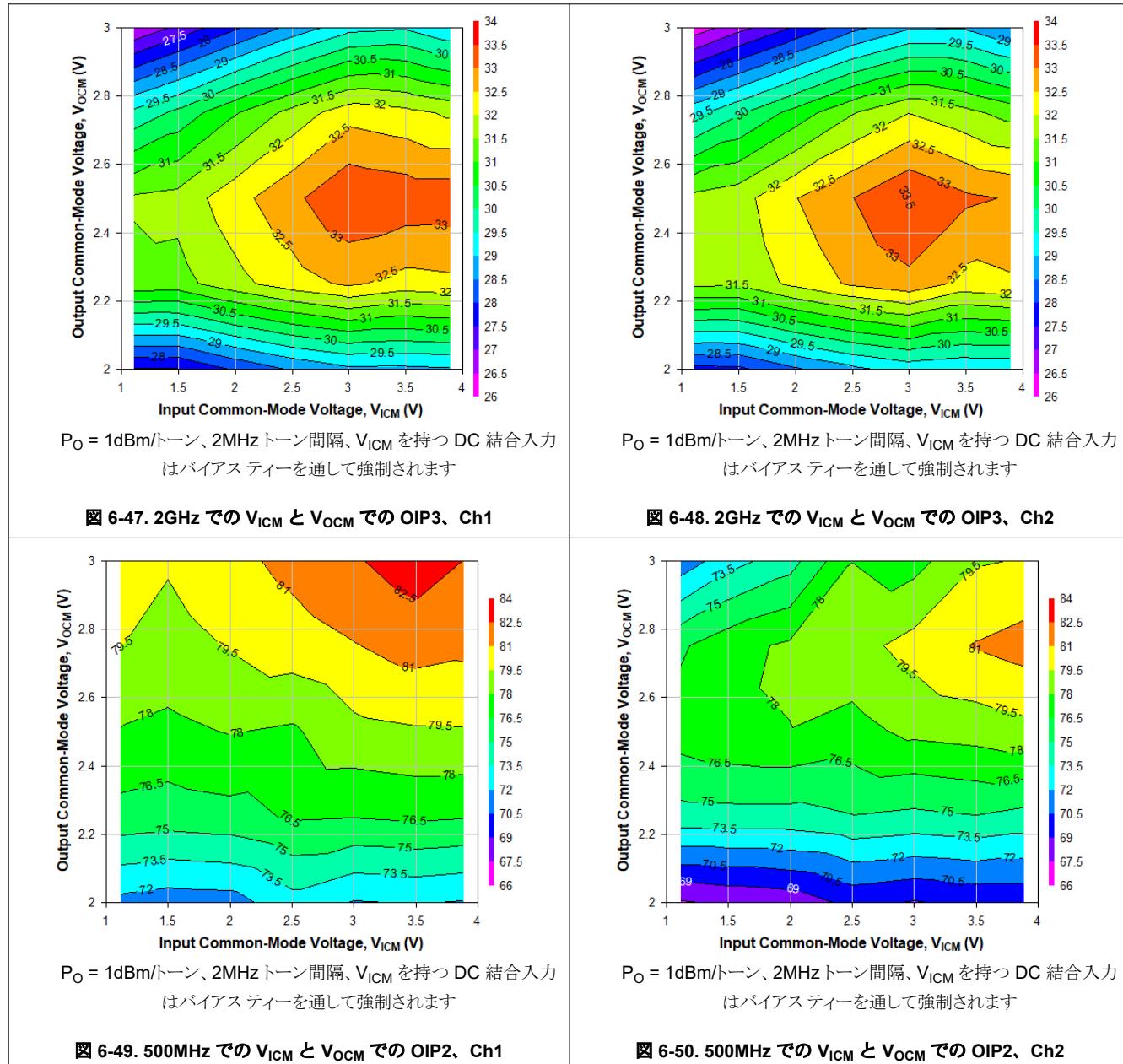

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}}$  = 中間電圧、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{\text{ICM}} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{\text{IN\_SH}}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

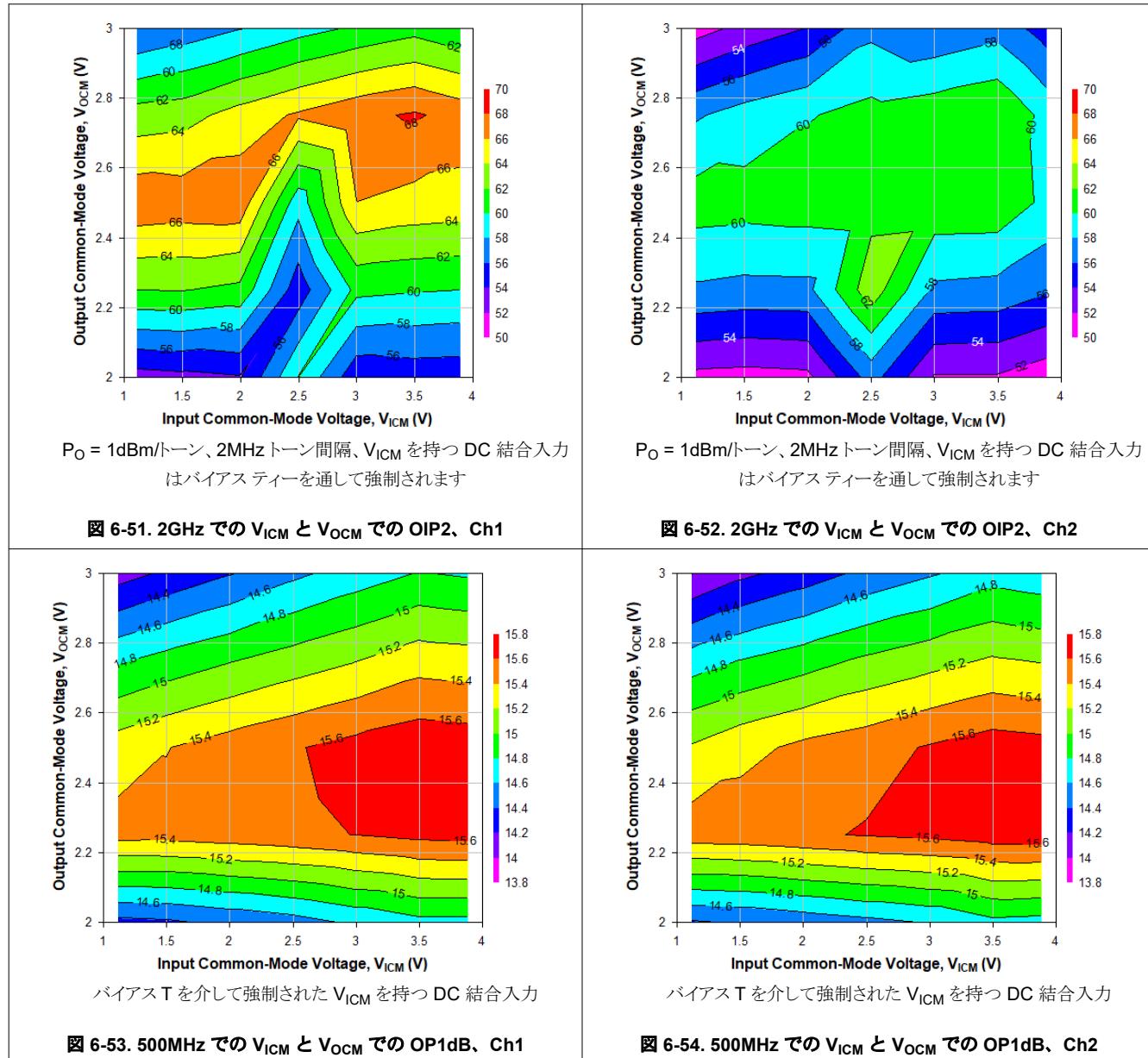

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{IN\_SH}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

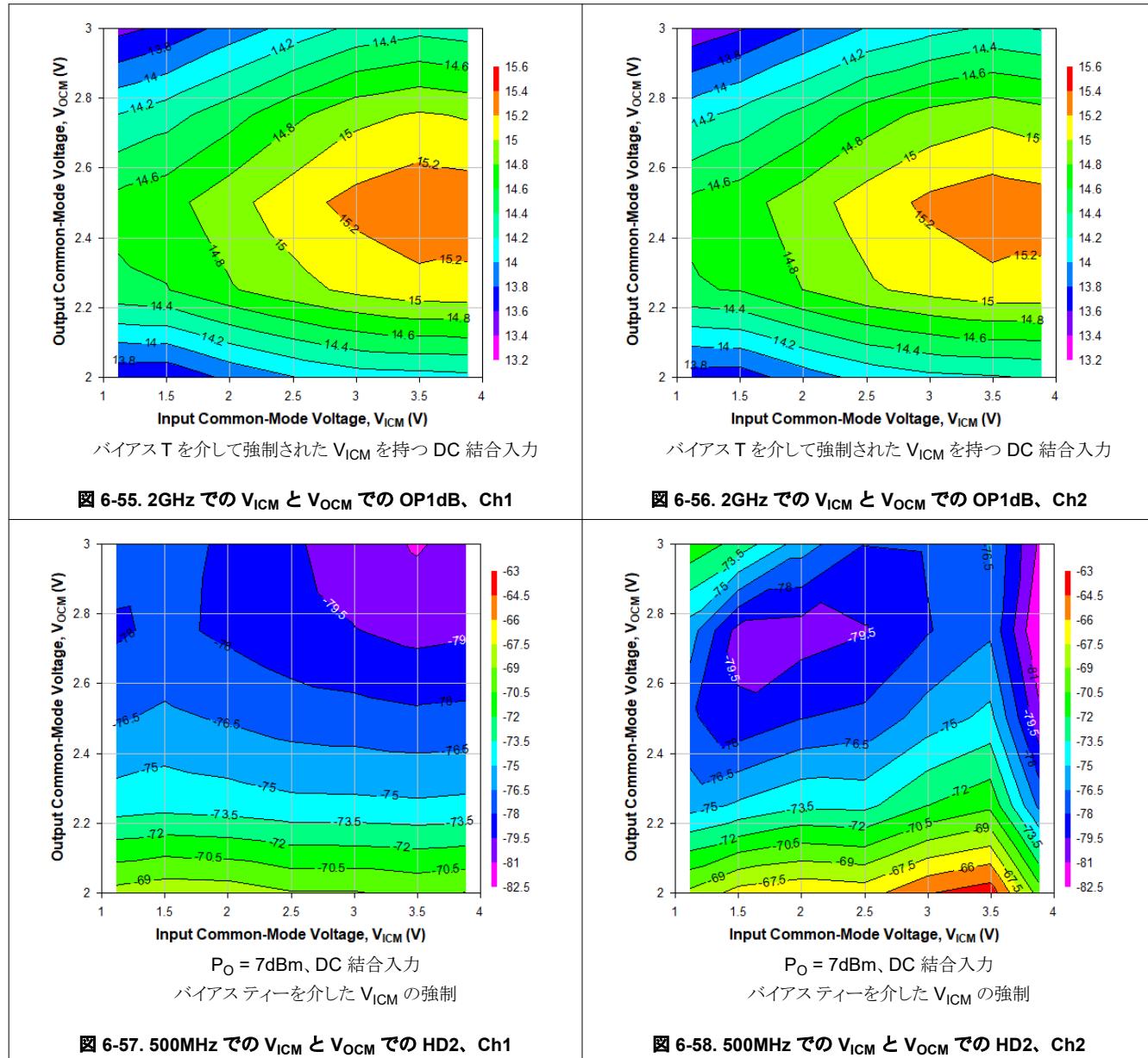

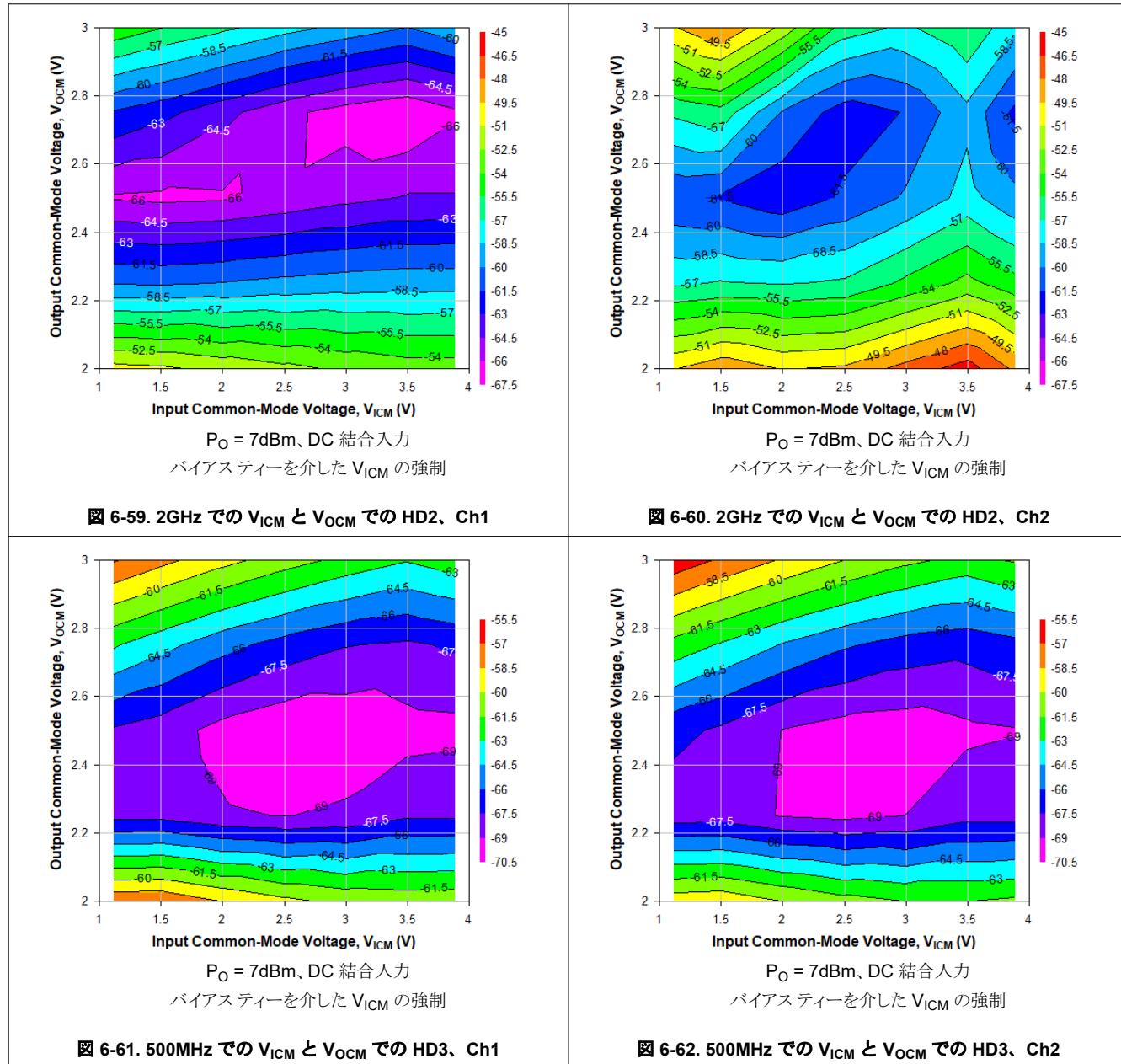

## 6.8 代表的特性 : D2D 構成 (続き)

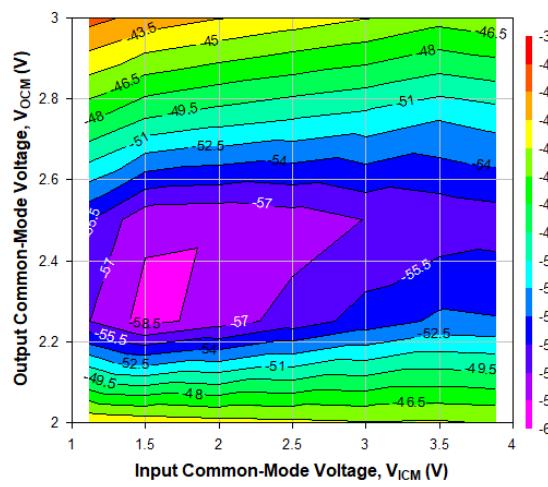

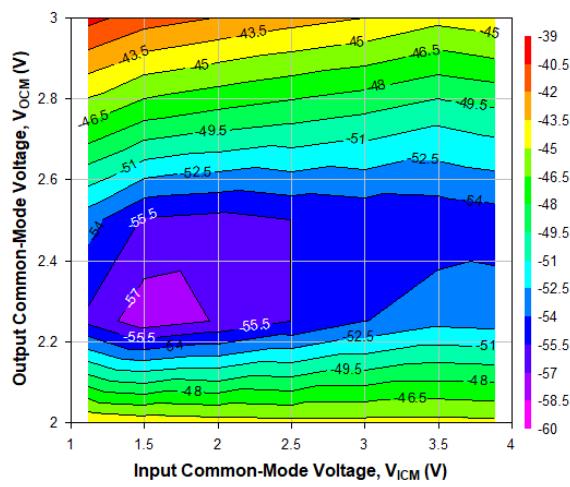

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{IN\_SH}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

図 6-63. 2GHz での  $V_{ICM}$  と  $V_{OCM}$  での HD3、Ch1

$P_O = 7\text{dBm}$ 、DC 結合入力

バイアス ティーを介した  $V_{ICM}$  の強制

図 6-64. 2GHz での  $V_{ICM}$  と  $V_{OCM}$  での HD3、Ch2

$P_O = 7\text{dBm}$ 、DC 結合入力

バイアス ティーを介した  $V_{ICM}$  の強制

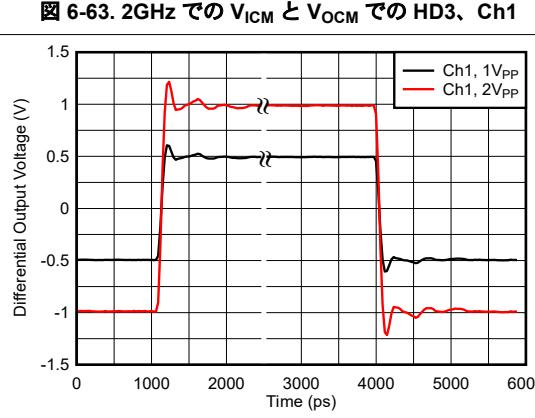

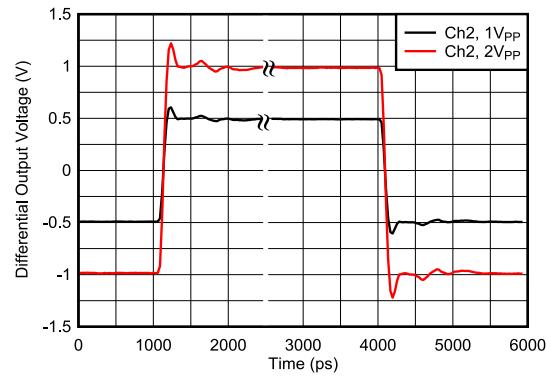

図 6-65. ステップ応答

図 6-66. ステップ応答

## 6.8 代表的特性 : D2D 構成 (続き)

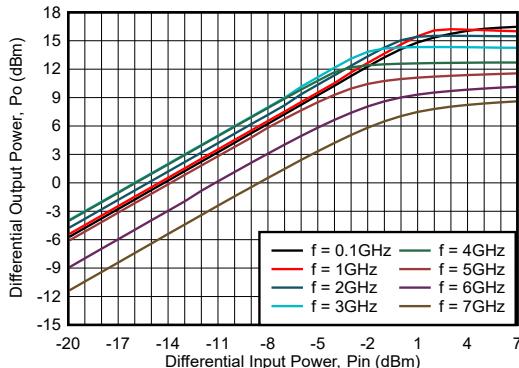

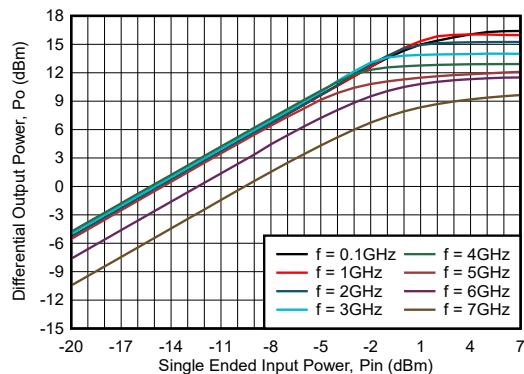

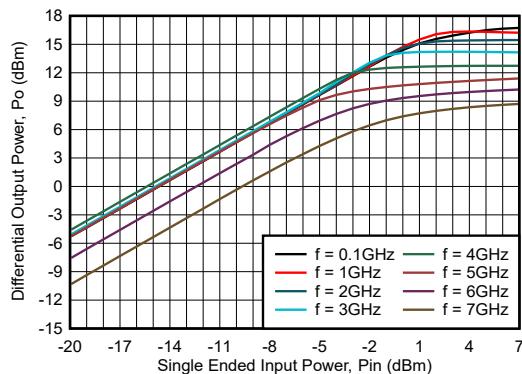

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM}$  = 中間電圧、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{IN\_SH}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

図 6-67. 差動入力電力に対する差動出力電力、Ch1

図 6-68. 差動入力電力に対する差動出力電力、Ch2

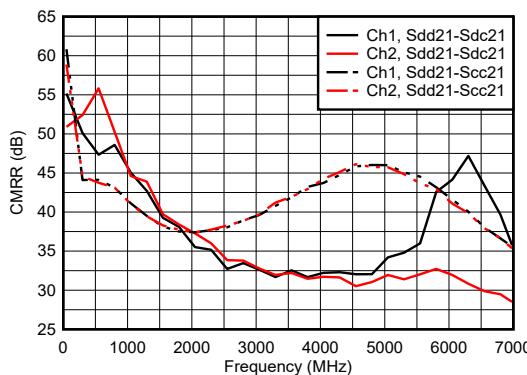

Sdc21 および Scc21 に  $50\Omega$  ソース  $c$  を備えた各駆動入力ピンでの  $P_{IN} = -20\text{dBm}$  はコモンモード用です

図 6-69. 同相信号除去比 (CMRR)

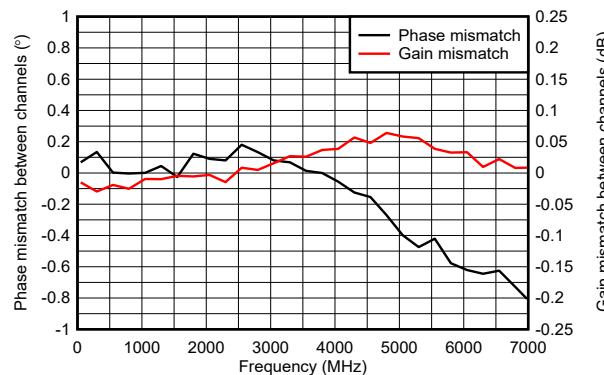

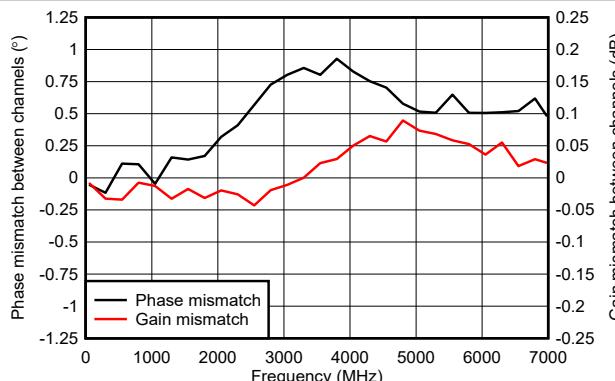

$P_{IN} = -20\text{dBm}$  ( $50\Omega$  ソース、各駆動入力ピン)

図 6-70. チャネル間のゲインと位相の不整合

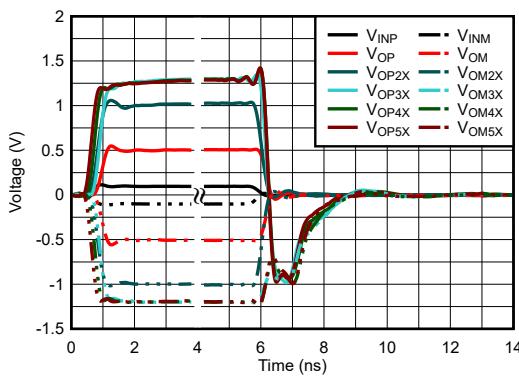

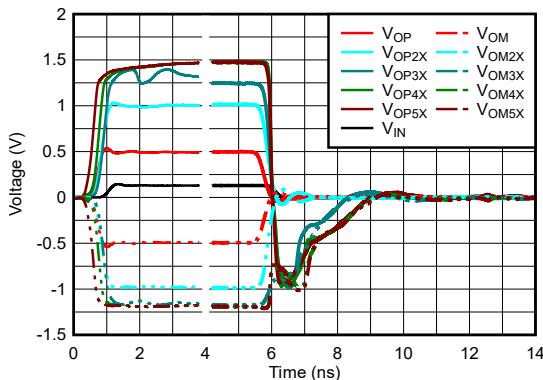

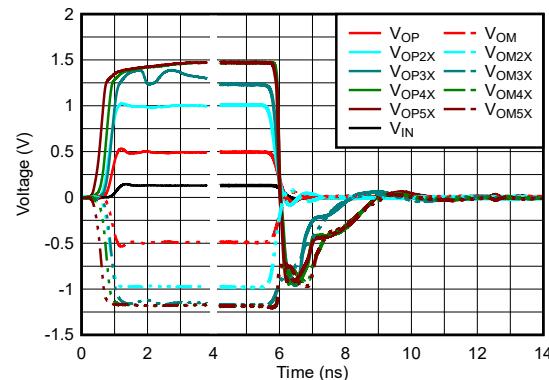

DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、出力電圧 2 ~ 5 倍は、それぞれに示すように、入力電圧が  $VIN$  の 2 ~ 5 倍のときです

図 6-71. オーバードライブ復帰応答、Ch1

DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、出力電圧 2 ~ 5 倍は、それぞれに示すように、入力電圧が  $VIN$  の 2 ~ 5 倍のときです

図 6-72. オーバードライブ復帰応答、Ch2

## 6.8 代表的特性 : D2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、フローティング VOCM、PD、および MODE ピン、 $V_{ICM} = \text{中間電圧}$ 、 $Z_S = 100\Omega$ 、 $Z_L = 100\Omega$  の D2D ac 結合入出力構成、外部入力抵抗ネットワーク (図 8-6 を参照)、 $R_{IN\_SH}$  までの入力デエンベデッド、デバイスピンまでの出力、図に示す周囲温度、および DUT 特性の一部として含まれる抵抗ネットワーク (特に記載のない限り)

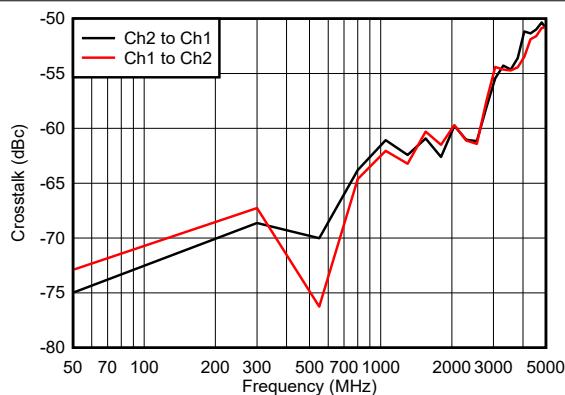

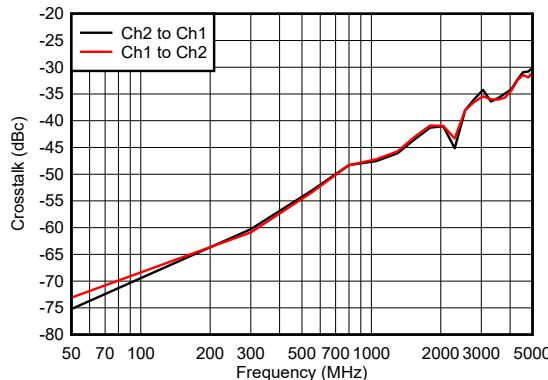

$P_{IN} = -20\text{dBm}$  (50 $\Omega$  ソース、各駆動入力ピン)

図 6-73. クロストーク

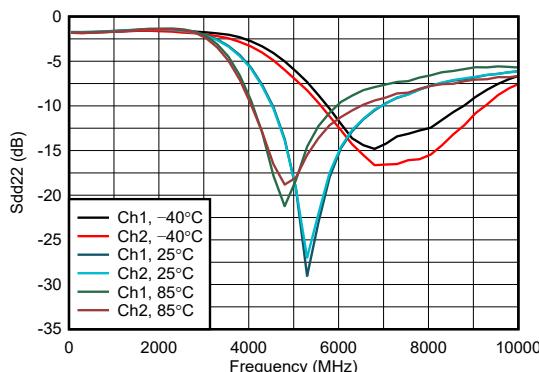

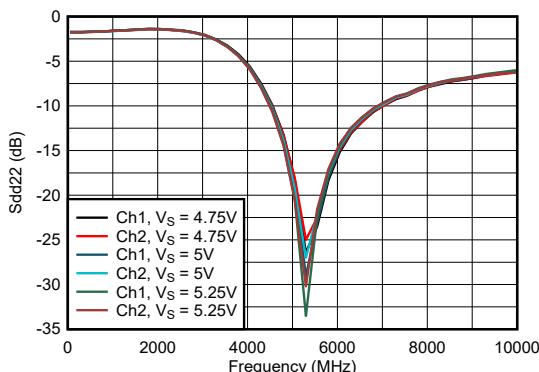

## 6.9 代表的特性 : S2D 構成

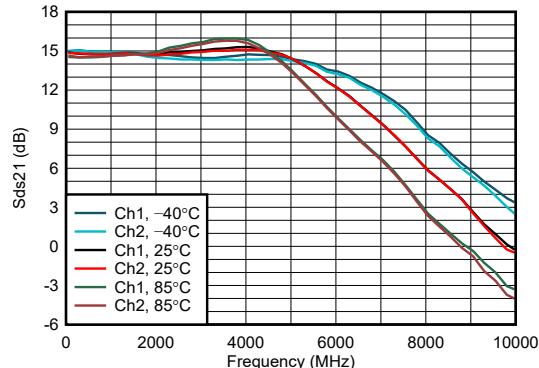

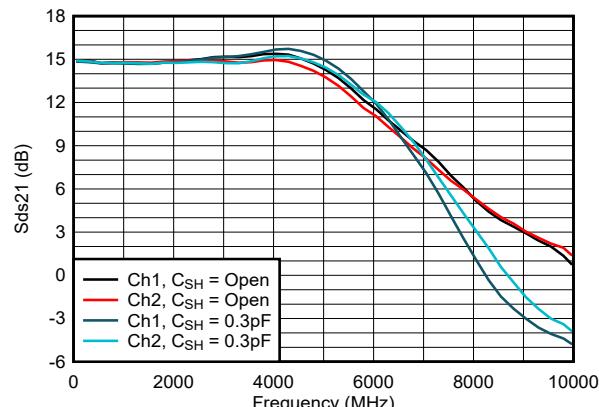

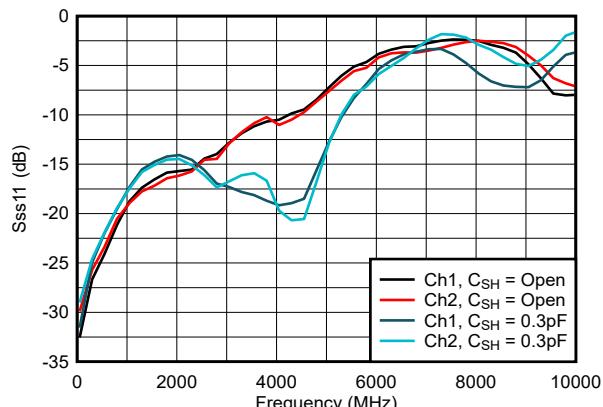

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、PD および MODE ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-74. 動作温度範囲における電力ゲイン (Sds21)

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-75. 電源電圧におけるパワーゲイン (Sds21)

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-76. 温度範囲全体にわたる入力リターンロス (Sss11)

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-77. 電源電圧にわたる入力リターンロス (Sss11)

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-78. 温度範囲全体での出力リターンロス (Sdd22)

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-79. 電源電圧範囲全体にわたる出力リターンロス (Sdd22)

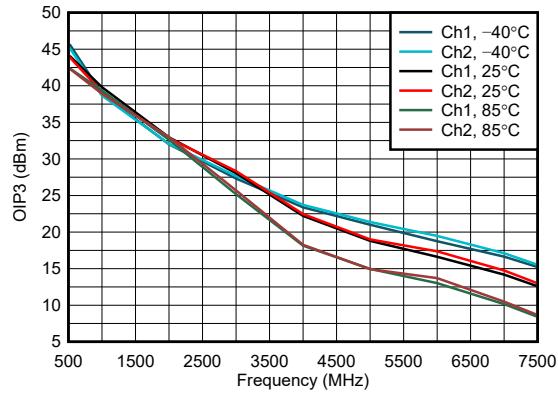

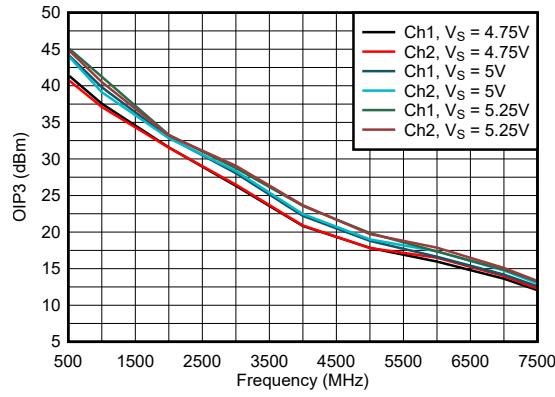

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

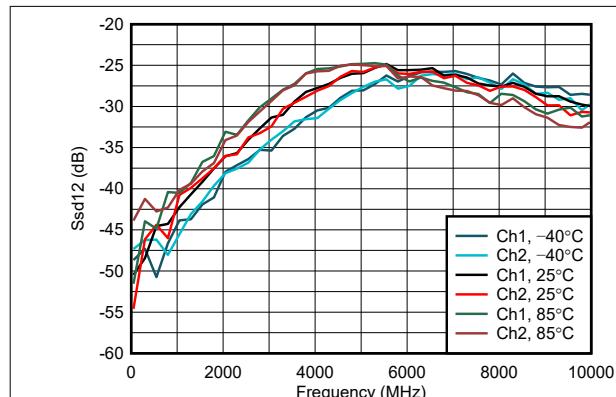

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-80. 溫度範囲での逆絶縁 (Ssd12)

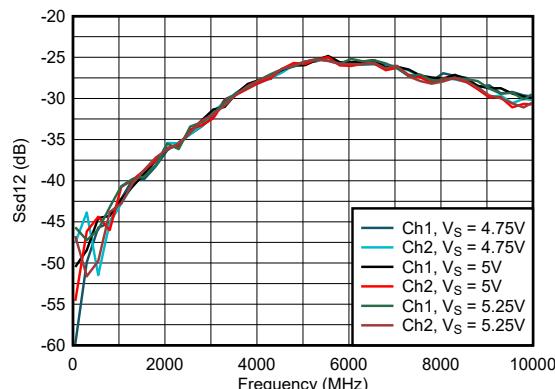

$P_{\text{IN}} = -20\text{dBm}$  (すべての励起ポートに  $50\Omega$  のソース)、

非励起ポートは  $50\Omega$  で終端されます

図 6-81. 電源電圧範囲全体での逆絶縁 (Ssd12)

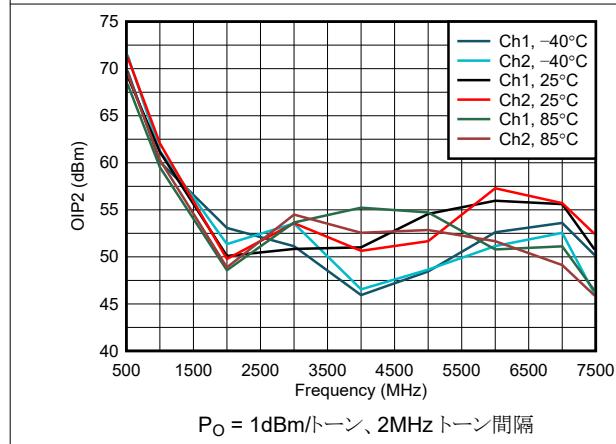

$P_O = -5\text{dBm}/\text{トーン}, 2\text{MHz} \text{ トーン間隔}$

図 6-82. 動作温度範囲での OIP3

$P_O = -5\text{dBm}/\text{トーン}, 2\text{MHz} \text{ トーン間隔}$

図 6-83. 電源電圧での OIP3

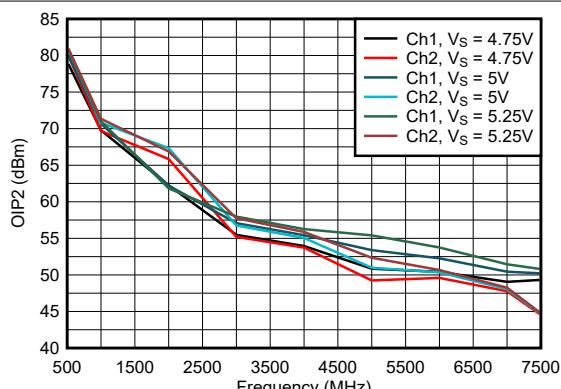

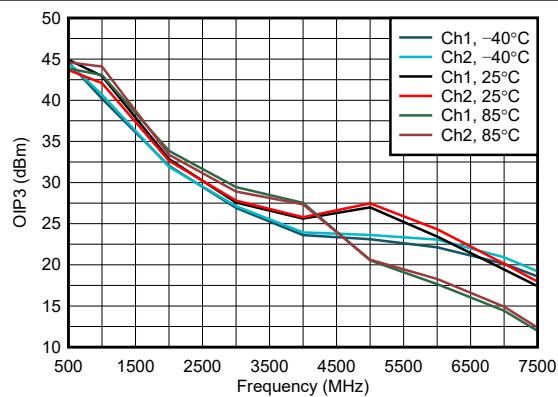

$P_O = 1\text{dBm}/\text{トーン}, 2\text{MHz} \text{ トーン間隔}$

図 6-84. 動作温度範囲での OIP3

$P_O = 1\text{dBm}/\text{トーン}, 2\text{MHz} \text{ トーン間隔}$

図 6-85. 電源電圧での OIP3

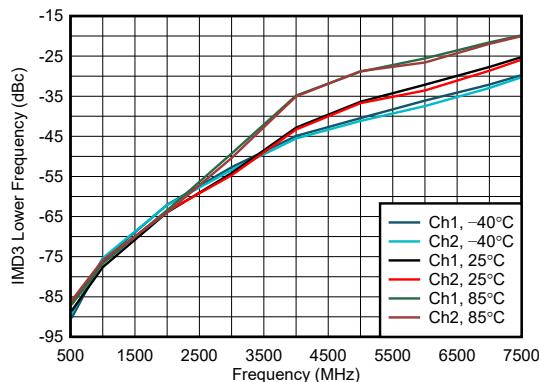

## 6.9 代表的特性 : S2D 構成 (続き)

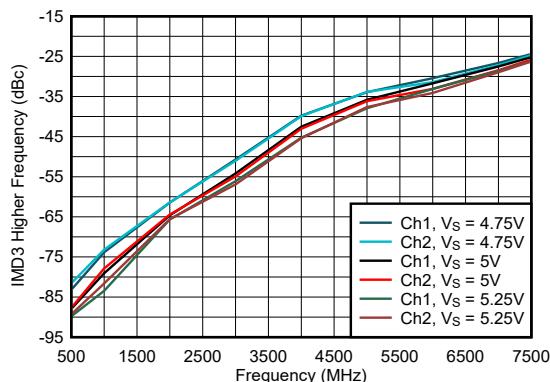

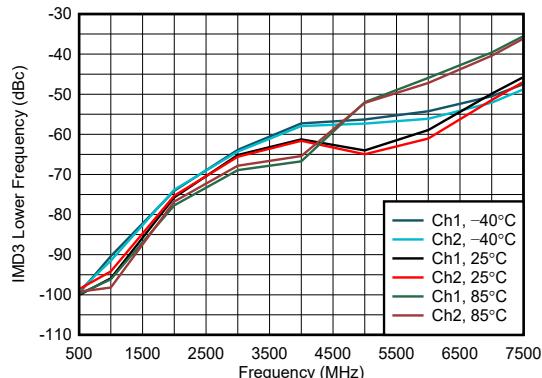

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

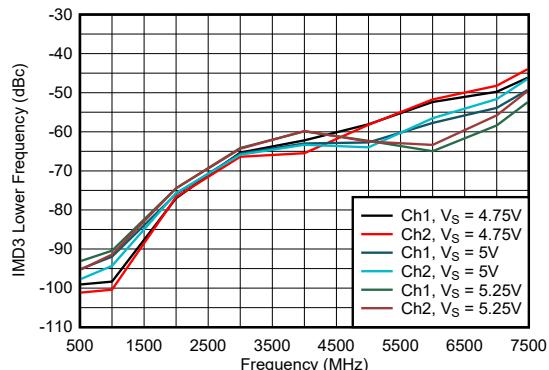

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-86. 全温度範囲で IMD3 低い

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-87. 電源電圧全体で IMD3 低い

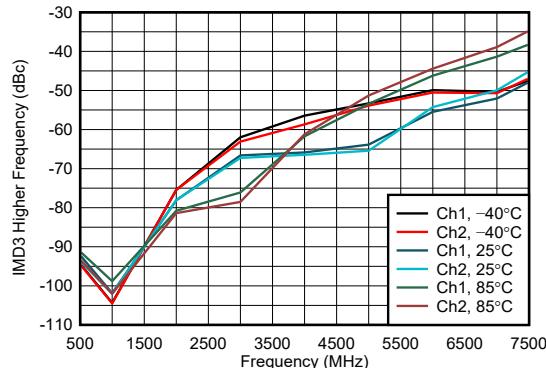

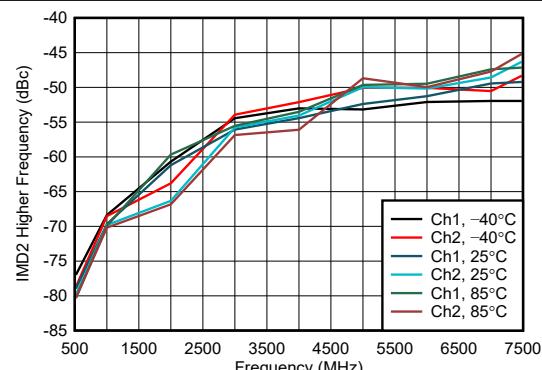

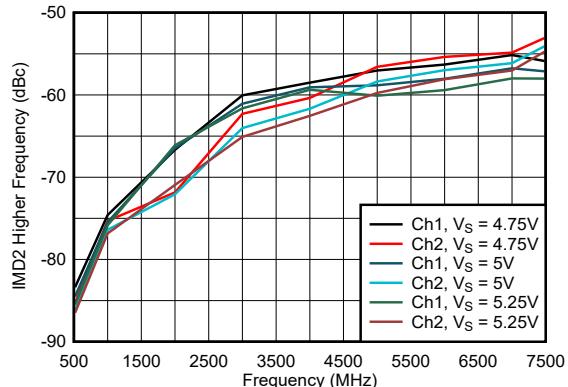

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-88. 全温度範囲で IMD3 高い

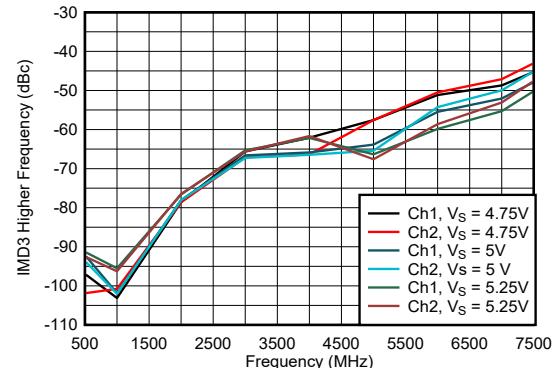

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-89. 電源電圧全体で IMD3 高い

## 6.9 代表的特性 : S2D 構成 (続き)

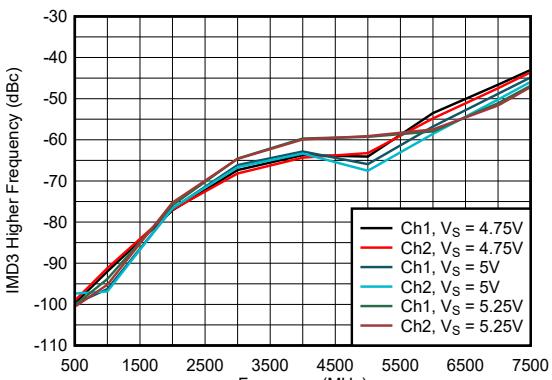

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-90. 全温度範囲で IMD3 低い

$(2f_1 - f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-91. 電源電圧全体で IMD3 低い

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-92. 全温度範囲で IMD3 高い

$(2f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-93. 電源電圧全体で IMD3 高い

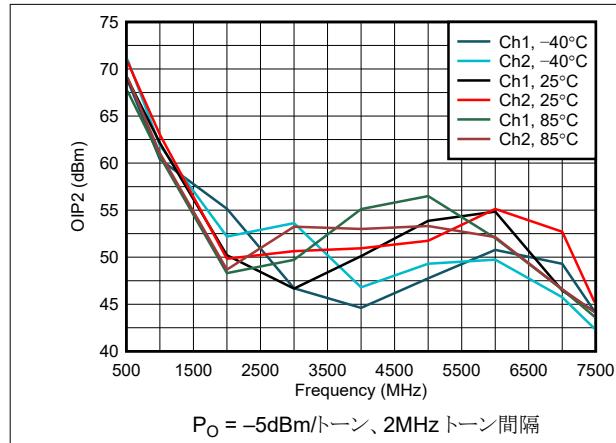

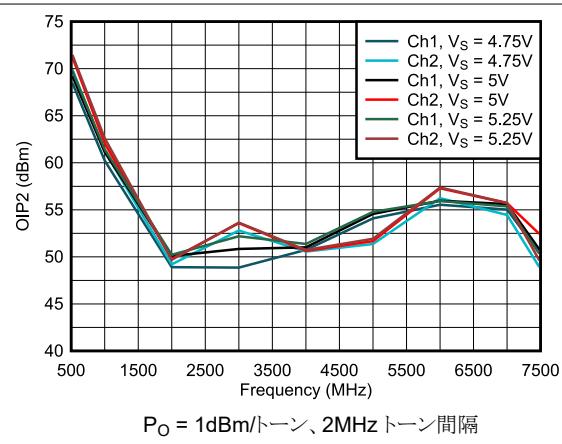

## 6.9 代表的特性 : S2D 構成 (続き)

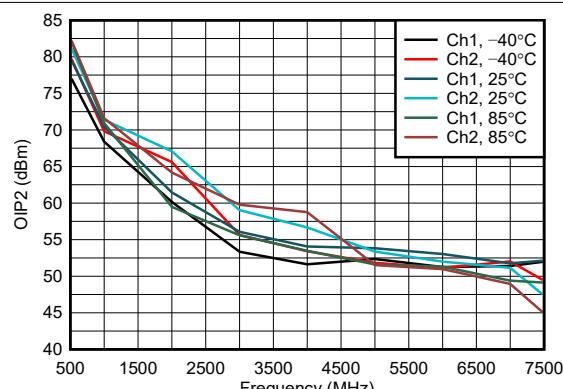

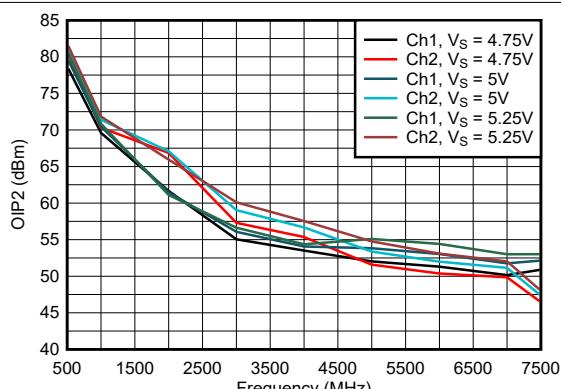

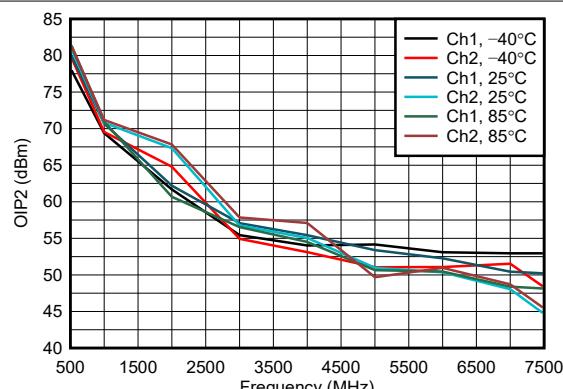

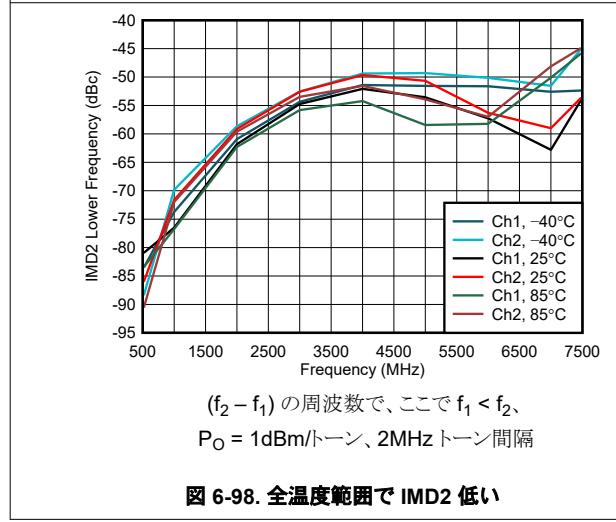

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、PD および MODE ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

図 6-94. 動作温度範囲での OIP2

図 6-95. 電源電圧での OIP2

図 6-96. 動作温度範囲での OIP2

図 6-97. 電源電圧での OIP2

図 6-98. 全温度範囲で IMD2 低い

図 6-99. 電源電圧全体で IMD2 低い

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-100. 全温度範囲で IMD2 高い

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = 1\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-101. 電源電圧全体で IMD2 高い

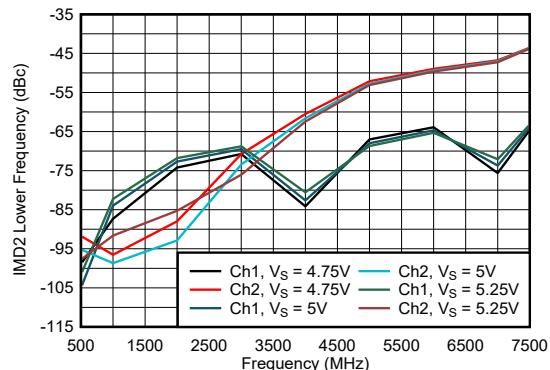

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-102. 全温度範囲で IMD2 低い

$(f_2 - f_1)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-103. 電源電圧全体で IMD2 低い

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、PD および MODE ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-104. 全温度範囲で IMD2 高い

$(f_1 + f_2)$  の周波数で、ここで  $f_1 < f_2$ 、

$P_O = -5\text{dBm}/\text{トーン}$ 、2MHz トーン間隔

図 6-105. 電源電圧全体で IMD2 高い

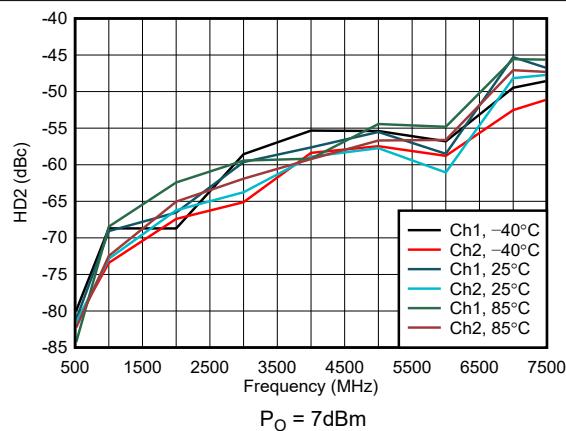

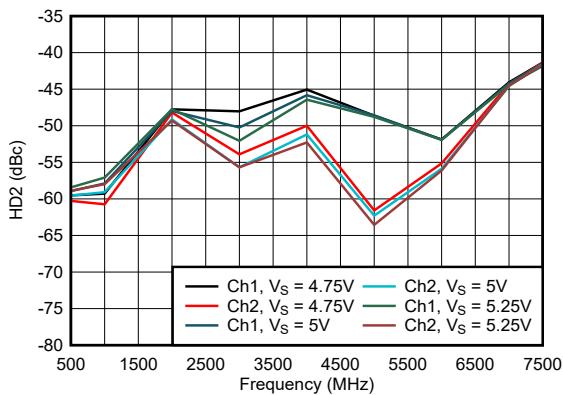

$P_O = 7\text{dBm}$

図 6-106. 動作温度範囲での HD2

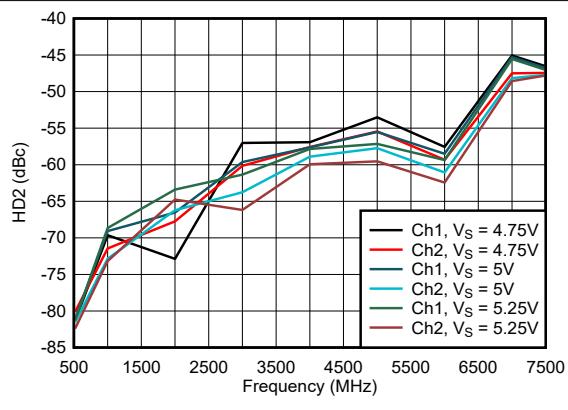

$P_O = 7\text{dBm}$

図 6-107. 電源電圧での HD2

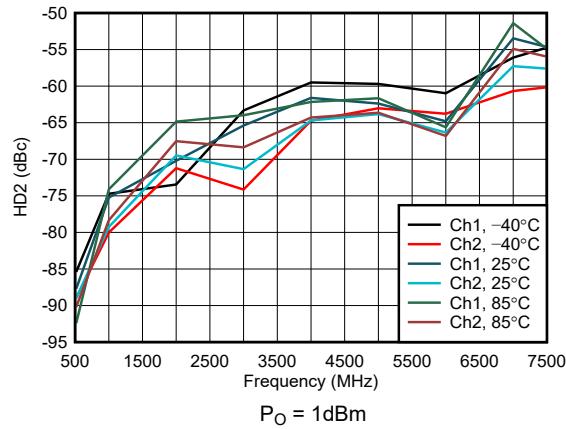

$P_O = 1\text{dBm}$

図 6-108. 動作温度範囲での HD2

$P_O = 1\text{dBm}$

図 6-109. 電源電圧での HD2

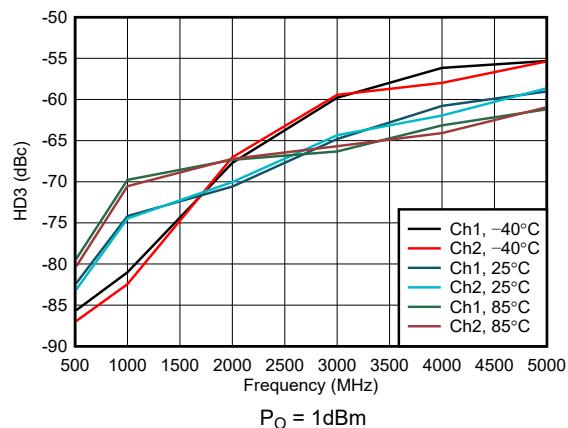

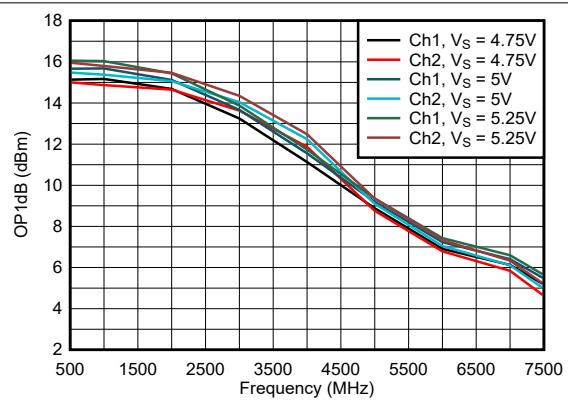

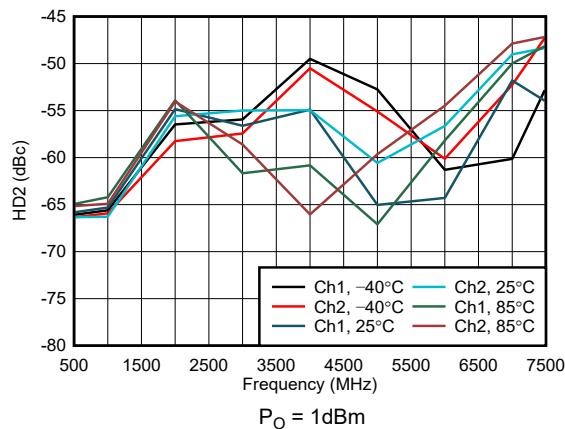

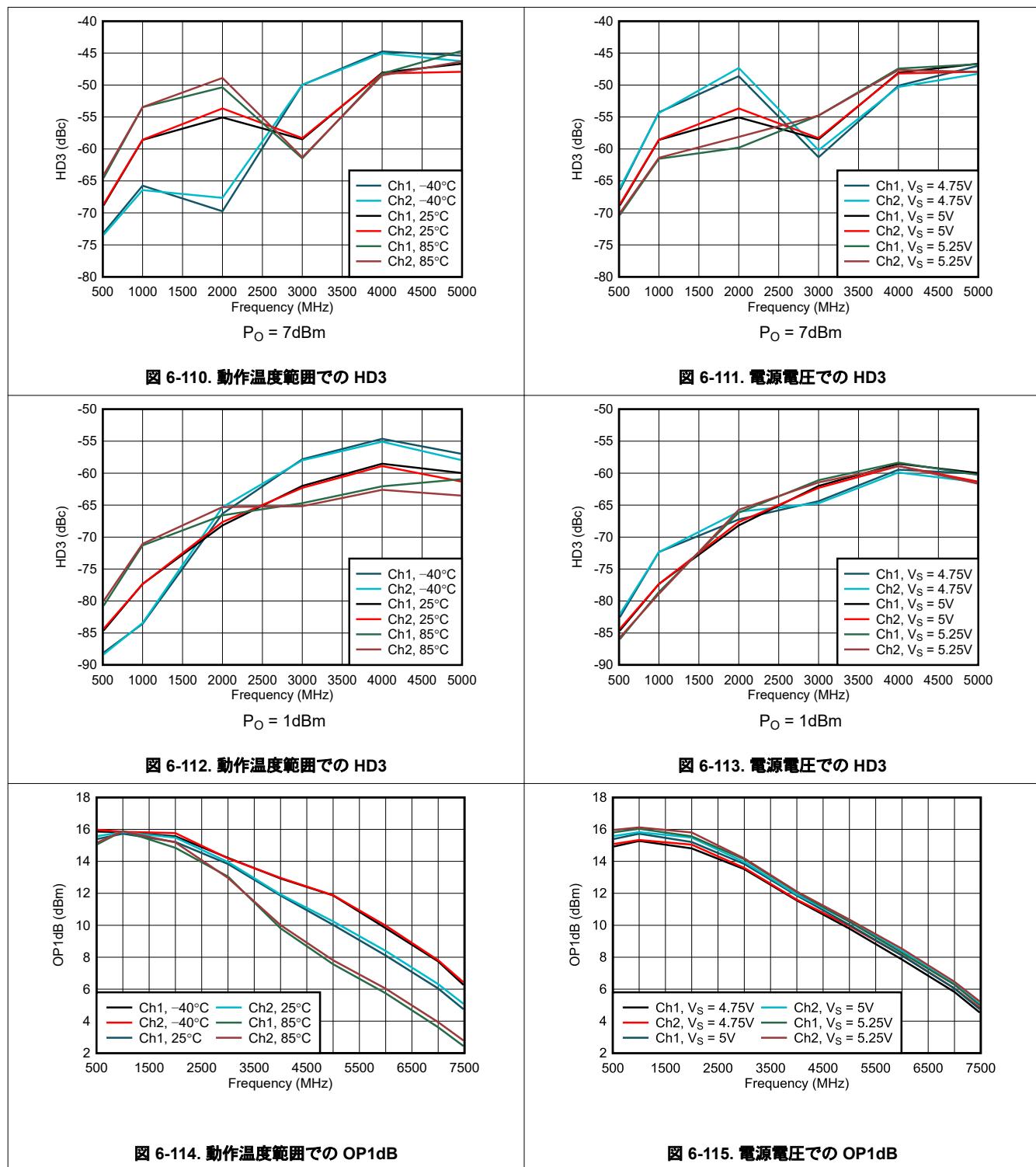

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

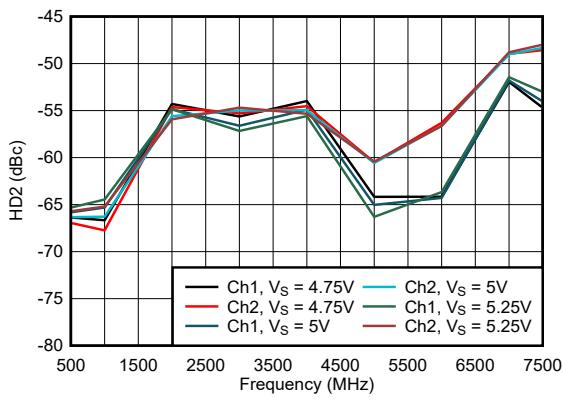

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、PD および MODE ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

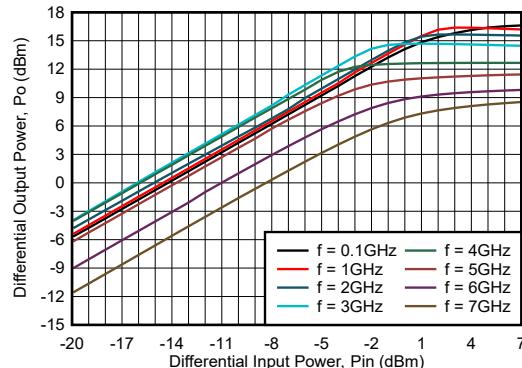

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、 $\text{PD}$  および  $\text{MODE}$  ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

図 6-122. シングルエンド入力電力における差動出力電力、Ch1

図 6-123. シングルエンド入力電力における差動出力電力、Ch2

$P_{\text{IN}} = -20\text{dBm}$  (50Ω ソース、各駆動入力ピン)

図 6-124. 同相信号除去比 (CMRR)

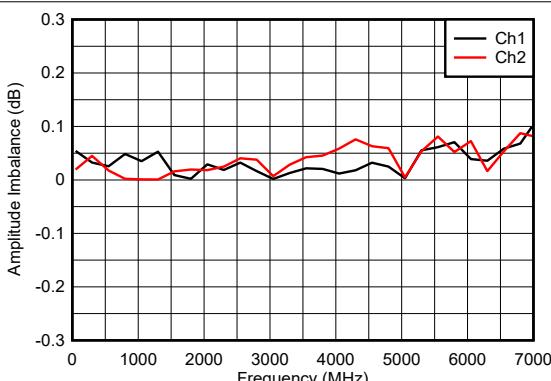

$P_{\text{IN}} = -20\text{dBm}$  (50Ω ソース、各駆動入力ピン)

図 6-125. チャネル間のゲインと位相の不整合

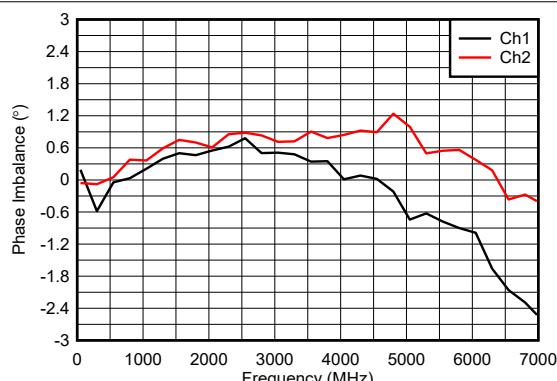

$P_{\text{IN}} = -20\text{dBm}$  (50Ω ソース、各駆動入力ピン)

図 6-126. 振幅不均衡

$P_{\text{IN}} = -20\text{dBm}$  (50Ω ソース、各駆動入力ピン)

図 6-127. 位相不均衡

## 6.9 代表的特性 : S2D 構成 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$ 、 $\text{VOCM}$  はフローティング、PD および MODE ピンは開放、 $V_{\text{ICM}}$  は電源電圧の中点に設定されます。 $C_{\text{SH}} = \text{Open}$ 、 $R_{\text{TERM}} = 50\Omega$ 、 $Z_S = 50\Omega$ 、 $Z_L = 100\Omega$  の S2D ac 結合入出力構成 (図 8-4 を参照)。入力および出力はデバイスのピンまでデエンベッドされており、特に断りがない限り、示されている周囲温度条件下で測定されています

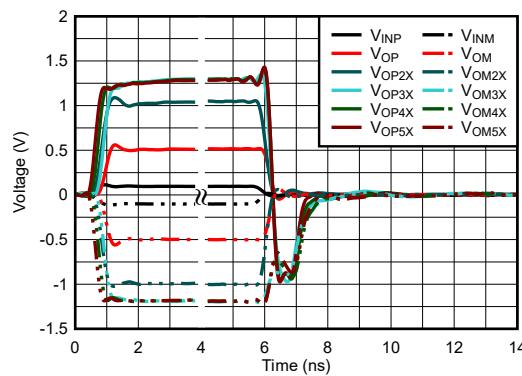

DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、出力電圧 2 ~ 5 倍は、それぞれに示すように、入力電圧が  $V_{\text{IN}}$  の 2 ~ 5 倍のときです

図 6-128. オーバー ドライブ復帰応答、Ch1

DC 結合、 $V_{S+} = 2.5\text{V}$ 、 $V_{S-} = -2.5\text{V}$ 、出力電圧 2 ~ 5 倍は、それぞれに示すように、入力電圧が  $V_{\text{IN}}$  の 2 ~ 5 倍のときです

図 6-129. オーバー ドライブ復帰応答、Ch2

$P_{\text{IN}} = -20\text{dBm}$  (50 $\Omega$  ソース、各駆動入力ピン)

図 6-130. クロストーク

## 7 詳細説明

### 7.1 概要

TRF1305A2、TRF1305B2、および TRF1305C2 (TRF1305x2) デバイスは、非常に広帯域の信号用に最適化されたデュアル チャネルの高性能完全差動 RF アンプです。このデバイス ファミリは主に、差動入力 (ADC) および出力 (DAC) 信号伝達を必要とする高速および RF データコンバータと接続するよう設計されています。TRF1305x2 は、DC または AC 結合に対応し、シングルエンド入力および差動出力 (S2D)、または差動入出力 (D2D) として構成することができます。このデバイスには、出力コモン モードピン (VOCM) があり、目的の同相出力電圧を柔軟に設定できます。VOCM ピンにより、両方の共有チャネルに同じ出力同相電圧を設定できます。このアンプを使用すると、直接変換システムで使用する場合、データコンバータを DC 結合 IQ 復調器または変調器と接続できます。TRF1305x2 ファミリには、3 つの固定電力ゲイン派生値 (15dB、10dB、5dB) があり、クローズ ドループ帰還型アンプアーキテクチャを採用しています。

これらのデバイスは、正と負電源間の差動電圧が 5V (標準値) の 2 レール電源から電力を供給され、分割電源または単一電源構成に使用できます。パワー ダウン機能も利用でき、各アンプ チャネルを個別にパワー ダウンできます。

アンプの出力は低インピーダンスです。任意のインピーダンスに一致させるには、適切な外部直列終端または抵抗パッドを使用します。

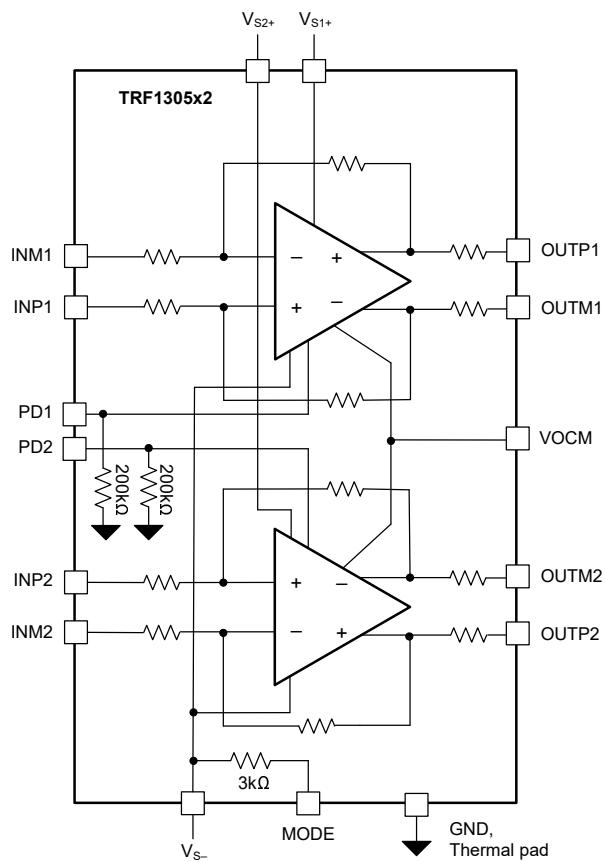

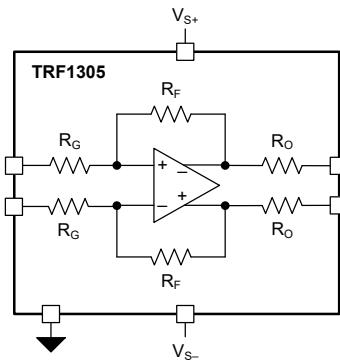

### 7.2 機能ブロック図

このセクションでは、デュアル チャネル TRF1305x2 の機能ブロック図を示します。出力同相モード制御ピンは、両チャネル共通です。

VS1+ と VS2+ の両方から給電される特定の共通内部回路があります。そのため、基板の VS1+ と VS2+ の両方を短絡し、1 つのチャネルのみを使用しても両方に電圧を供給します。負の電源 VS- は、両方のチャネルで共有されています。

## 7.3 機能説明

TRF1305x2 には、以下の主要なコンテンツが含まれています。

- 電源に依存しないサーマル パッドを備えた 2 レールのフローティング電源

- サーマル パッドを GND に接続します。

- RF 信号および PD<sub>x</sub> ピンは GND を基準とします

- 単一電源または分割電源動作

- シングルエンド入力または差動入力構成をサポート

- 性能が最適化された、プリセット固定ゲイン バリアントです

- 出力同相モード制御

- MODE ピン:  $V_{ICM}$  範囲が  $V_{S+}$  または  $V_{S-}$  モードの近くに拡張されます

- デジタル ロジック制御可能なパワーダウン オプション

### 7.3.1 完全差動 RF アンプ

TRF1305x2 は、広帯域幅を持つ電圧帰還型完全差動アンプ (FDA) です。これらのアンプは、バリエーションのデバイスに応じて、15dB、10dB、5dB の差動パワーゲインになるよう設計されています。これらのアンプは時間領域特性が優れており、高いスルーレート、高い入力および出力同相範囲、高速な過渡セトリング タイムを実現しています。

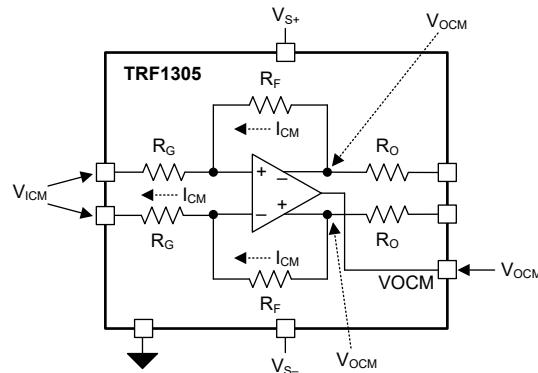

FDA デバイスの出力平均電圧 (同相モード) は、別々の同相ループによって制御されます。目標出力同相電圧は、V<sub>O</sub>CM 入力ピンによって設定されます。

### 7.3.2 出力同相モード制御

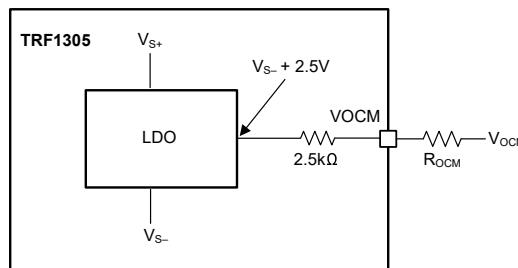

図 7-1 に、出力同相モード制御の機能図を示します。内部的には、V<sub>O</sub>CM ピンの電位は LDO 出力電圧によって設定されます。これは、2.5k $\Omega$  抵抗経由で接続された  $V_{S+} + 2.5V$  と等しい値です。

V<sub>O</sub>CM ピンをフローティングにすることもできます。出力ピンの出力同相電圧 (OUTPx および OUTMx) は、V<sub>O</sub>CM ピンがオープンのとき、デフォルトで LDO 出力電圧  $V_{S+} + 2.5V$  になります。V<sub>O</sub>CM ピンをフローティングにすると、V<sub>O</sub>CM 電圧は  $V_S = 5V$  の場合、中間電源と等しくなります。V<sub>O</sub>CM ピンが駆動されている場合は、低インピーダンスのソースからピンを駆動します。デバイス出力で強制 V<sub>O</sub>CM 電圧を正確に反映するため、R<sub>O</sub>CM の値は 25 $\Omega$  未満に制限します。

図 7-1. 出力同相モード制御

### 7.3.3 内部抵抗構成

TRF1305x2 の内部レジスタの構成を、図 7-2 に示します。表 7-1 さまざまなゲイン バリエーションについて、これらの抵抗の値を示します。

図 7-2. TRF1305x2 の内部抵抗構成

表 7-1. 抵抗値

| 型番        | ゲイン (dB) | R <sub>G</sub> (Ω) | R <sub>F</sub> (Ω) | R <sub>O</sub> (Ω) |

|-----------|----------|--------------------|--------------------|--------------------|

| TRF1305A2 | 15       | 6.25               | 258                | 4                  |

| TRF1305B2 | 10       | 12.5               | 161                | 4                  |

| TRF1305C2 | 5        | 17                 | 97                 | 4                  |

## 7.4 デバイスの機能モード

### 7.4.1 MODE ピン

TRF1305x2 には、MODE ピンを使用して構成可能な追加の有用な機能があります。デバイス モードを選択するには、MODE ピンと VS2+ の間に最大許容誤差  $\pm 2\%$  のプルアップ抵抗を接続するか、MODE ピンに強制的に電圧を印加します。内部的に、MODE ピンは  $3\text{k}\Omega$  抵抗を介して  $V_{S-}$  を基準にします(セクション 7.2 を参照)。この選択されたモードは両方のチャネルに適用されます。

表 7-2 に、各モードのプルアップ抵抗の値、プルアップ抵抗が使用されているときの MODE ピンで予想される電圧 ( $V_{MODE}$ )、またはデバイスマードとモード構成の設定に必要な  $V_{MODE}$  電圧を示します。 $V_{MODE}$  電圧スレッショルドは、隣接モードの標準  $V_{MODE}$  電圧とのほぼ中間です。MODE 機能を使用する場合は、MODE ピンにデカッピング コンデンサを使用します。

表 7-2. MODE ピン構成

| モード番号 | VS2+ へのプルアップ抵抗<br>(最大許容誤差 $\pm 2\%$ )                                                     | MODE ピン電圧、 $V_{MODE}$<br>(V) | $V_{ICM}$ 範囲拡張 <sup>(1)</sup>            |

|-------|-------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|

| 0     | オープン                                                                                      | $V_{S-}$                     | デフォルトの $V_{ICM}$ 範囲                      |

| 1     | $25.6\text{k}\Omega$                                                                      | $V_{S-} + 0.52\text{V}$      | ローサイド、 $V_{ICM}$ 範囲を $V_{S-}$ に近づけて拡張します |

| 2     | $12.8\text{k}\Omega$                                                                      | $V_{S-} + 0.94\text{V}$      | ハイサイド、 $V_{ICM}$ 範囲を $V_{S+}$ に近づけて拡張します |

| 該当なし  | プルアップ抵抗 $< 10\text{k}\Omega$ は使用できません。 $V_{MODE} > V_{S-} + 1.15\text{V}$ の設定には使用しないでください |                              |                                          |

(1) D2D 構成でのみ使用できます。

電源をオフにせずにモードを切り替えるには、プルアップ抵抗オプションと VS2+ の間に接続したスイッチまたはマルチプレクサを使用するか、またはモードに適切な  $V_{MODE}$  電圧を強制的に設定します。ただし、ベスト プラクティスは、モード変更の間にパワーダウン機能を使用してデバイスをパワーダウンすることです。セクション 7.4.2 も参照してください。ローサイド  $V_{ICM}$  範囲拡張モードでは、電流がソースされ、ハイサイド シンク電流が供給されます。次の「入力コモンモード拡張」セクションも参照してください。デバイスを電源オフ状態からアクティブ モードにする前に、外部回路がこれらの電流をシンクまたはソースする準備ができた状態を維持します。

#### 7.4.1.1 入力同相拡張

いずれかの  $V_{ICM}$  拡張モードで構成されている場合、TRF1305A2 は、「電気的特性」で規定されているデフォルトの入力同相範囲ではなく、 $V_{S+}$  または  $V_{S-}$  のうちのいずれかに近い  $V_{ICM}$  電圧をサポートします。 $V_{ICM}$  拡張モードは、D2D 構成でのみ機能します。

ローサイド  $V_{ICM}$  拡張モードで構成されている場合、TRF1305A2 はデフォルトのオプションよりも 350mV 低い入力同相電圧をサポートします。たとえば、TRF1305A2 バリアントでは、 $V_{ICM}$  電圧範囲の下限がデフォルト値の  $V_{S-} + 1.5V$  から  $V_{S-} + 1.15V$  まで拡大され、高い方の値は  $V_{S-} + 3.5V$  から  $V_{S-} + 3.15V$  にシフトします。 $V_{ICM}$  電圧が最低である場合、INPx と INMx ピンに接続された外部回路によって、約 15mA の電流をシンクします。

ハイサイド  $V_{ICM}$  拡張モードで構成されている場合、TRF1305A2 はデフォルトのオプションよりも 350mV 高い入力同相電圧をサポートします。たとえば、TRF1305A2 バリアントでは、 $V_{ICM}$  電圧範囲の上限がデフォルトの  $V_{S-} + 3.5V$  から  $V_{S-} + 3.85V$  まで拡大され、低い方の値は  $V_{S-} + 1.5V$  から  $V_{S-} + 1.85V$  にシフトします。 $V_{ICM}$  電圧が最高の場合、INPx と INMx ピンに接続されている外部回路から約 15mA の電流をソースします。

ローサイド  $V_{ICM}$  拡張モードで INPx と INMx ピンから流れ出る電流をシンクするため、もしくはハイサイド  $V_{ICM}$  拡張モードで INPx と INMx ピンに流れ込む電流をソースするため、電源に接続されている抵抗を使ってください。

#### 7.4.2 パワーダウン モード

TRF1305x2 には、アクティブとパワーダウンの 2 つのバイアス モードがあり、PD ピンの電圧で制御されます。PD ピンは、200k $\Omega$  抵抗を通して GND を基準としています。セクション 7.2 も参照してください。 $V_{S+} \geq 3.3V$  構成を使用する場合は、高 PD 電圧が  $V_{S+}$  から導出される場合には、PD 電圧が絶対最大定格を超えないようにしてください。

PD1 と PD2 で各チャネルを独立に制御し、各チャネルを個別にパワーダウンします。パワーダウン制御用に、1.8V と 3.3V の両方のデジタル ロジックがサポートされています。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

#### 8.1.1 入出力インターフェイスに関する検討事項

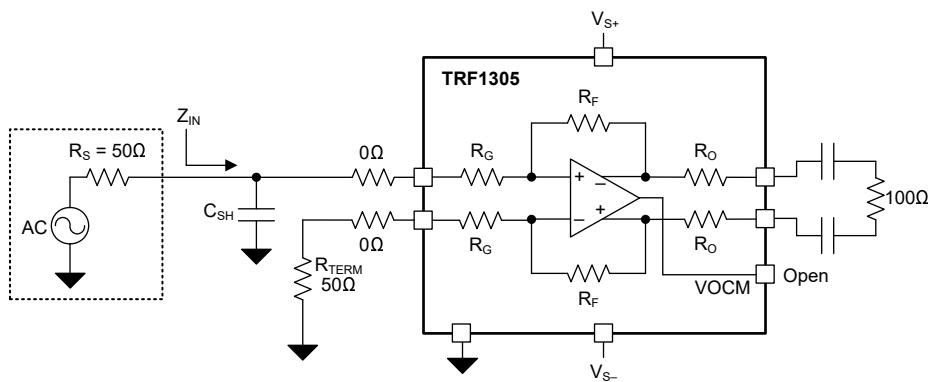

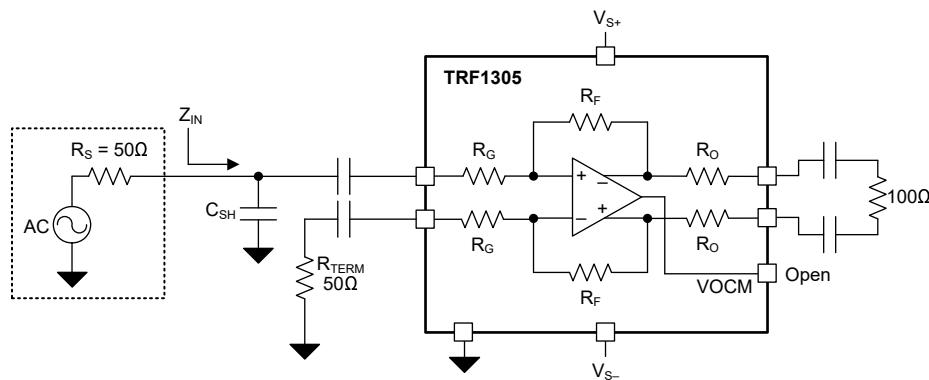

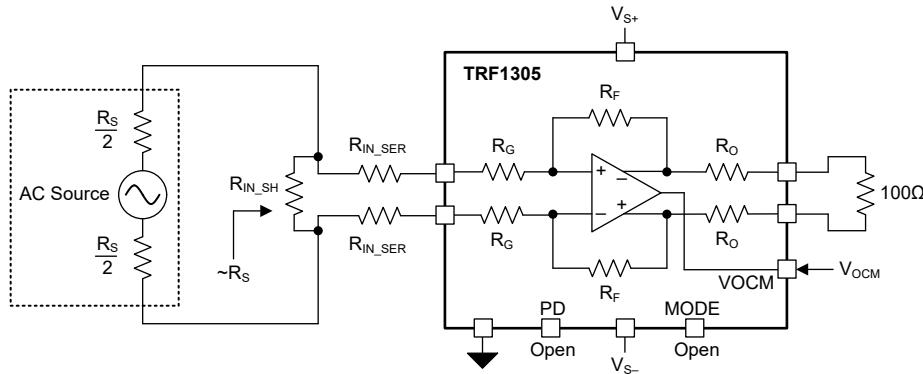

##### 8.1.1.1 シングルエンド入力

シングルエンド入力構成では、アンプの入力ピンの 1 つがソースから駆動され、もう 1 つの入力は外付け抵抗で終端されます。図 8-1 に、dc 結合、シングルエンド入力構成を  $50\Omega$  ソースから駆動し、マッチングします。図 8-1 に、INP ピンで同じ  $50\Omega$  のインピーダンスを持つソースにマッチングするために、非駆動 INM ピンを外付け抵抗で終端する方法を示します。

図 8-1 の  $C_{SH}$  は通常オープンです。セクション 6.9 に示す性能曲線は、デバイスの入力ピンまで入力をディエンベデッドし、デバイスの出力ピンまで出力をデエンベデッドするというものです。したがって、セクション 6.9 に示す  $S_{ss11}$  はアンプの入力リターン損失を表しています。 $C_{SH}$  に  $0.3\text{pF}$  のコンデンサを取り付けることで、 $C_{SH}$  における入力リターン ロス ( $S_{ss11}$ ) が改善されます。図 8-3 はこの改善を示しており、図 8-2 に示すアンプ帯域内の周波数フラットネスには影響を与えません。 $C_{SH}$  を使用すると、ノイズ指數や直線性に影響しません。

図 8-1. DC 結合、シングルエンド入力、 $50\Omega$  ソースにマッチング

$T_A = 25^\circ\text{C}, V_S = 5\text{V}$  で、入力は  $C_{\text{SH}}$  までデエンベデッドされます

図 8-2.  $C_{\text{SH}}$  に対するパワー ゲイン (Sds21)

$T_A = 25^\circ\text{C}, V_S = 5\text{V}$  で、入力は  $C_{\text{SH}}$  までデエンベデッドされます

図 8-3.  $C_{\text{SH}}$  に対する入力リターン ロス (Sss11)

図 8-4 に、入力と出力に AC 結合コンデンサを直列に追加することで、図 8-1 のデザインをシングルエンド AC 結合入力用に構成する方法を示します。

図 8-4. AC 結合、シングルエンド入力、 $50\Omega$  ソースにマッチング

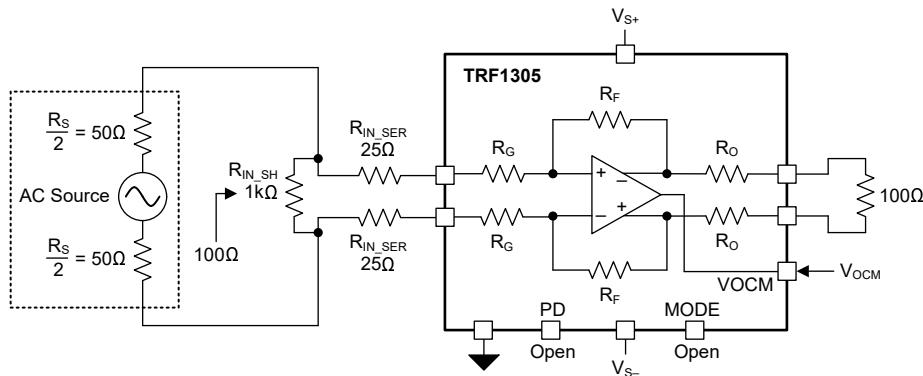

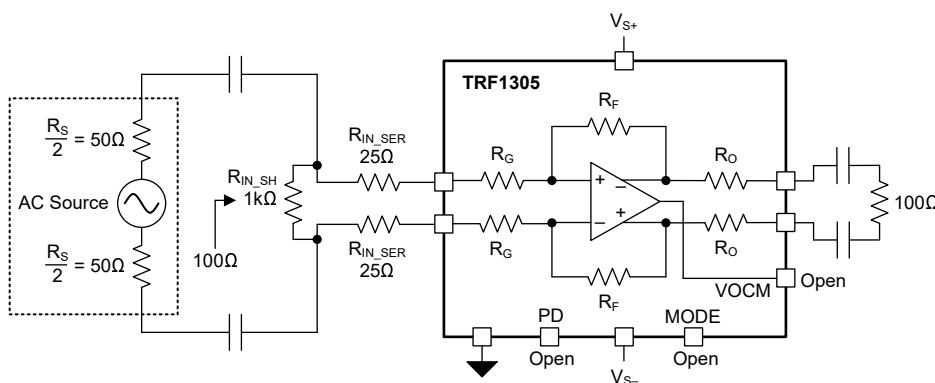

### 8.1.1.2 差動入力

図 8-5 に、3 つの抵抗で構成される簡単なネットワークを使用して、 $100\Omega$  の差動ソースに差動入力をマッチングする方法を示します。 $1\text{k}\Omega$  シヤント抵抗  $R_{\text{IN\_SH}}$  は DC から低周波数までは影響を与えませんが、TRF1305x2 の完全な広帯域性能を実現するには、この抵抗が必要です。図 8-6 に、AC 結合差動入力設計の構成を示します。 $100\Omega$  の入力を想定した TRF1305x2 のすべてのゲインバージョンで、 $100\Omega$  の差動ソースとマッチングする抵抗値は、図 8-6 と図 8-5 で動作します。

高周波 (RF) マッチングを実現するには、高周波 (RF) 抵抗 (0201 を推奨) を使用してください。

図 8-5. DC 結合差動入力、100Ω の差動信号源にマッチング

図 8-6. AC 結合差動入力、100Ω の差動信号源にマッチング

#### 8.1.1.3 DC 結合に関する検討事項

TRF1305x2 は、広い範囲の入力 DC 同相 (CM) 電圧に対応しています。TRF1305x2 が入力に DC 結合されているとき、ソースの DC 電流負荷を考慮します。図 8-7 は、入力 CM 電圧  $V_{ICM}$  が出力 CM 電圧  $V_{OCM}$  と異なる場合、ソースとの間に正味の DC 電流が発生することを示しています。式 1 に、ソース電流またはシンク電流  $I_{CM}$  と入力および出力 CM 電圧との関係を示します。

$$I_{CM} = \frac{(V_{OCM} - V_{ICM})}{(R_F + R_G)} \quad (1)$$

図 8-7. 入力同相電圧と出力同相電圧が等しくない場合の正味 DC 電流フロー

### 8.1.2 差動入力構成での外付け抵抗によるゲイン調整

TRF1305x2 では、差動入力構成の一部である入力外部抵抗回路を構成することで、ゲインを多少調整できます。図 8-8 に、シャント抵抗  $R_{IN\_SH}$  と、アンプの入力ピンに接続された 2 つの直列入力抵抗  $R_{IN\_SER}$  で構成される外部入力ネットワークを示します。

図 8-8. 外部抵抗ネットワークによるゲイン調整

表 8-1 に、100Ω の差動ソース インピーダンス用の抵抗構成を示します。

表 8-1.  $R_S = 100\Omega$  の抵抗表

| TRF1305A2  |                  |                   |

|------------|------------------|-------------------|

| 電力ゲイン (dB) | $R_{IN\_SH}$ (Ω) | $R_{IN\_SER}$ (Ω) |

| 15         | 1000             | 25                |

| 14         | 365              | 29                |

| 13         | 233              | 33                |

| 12         | 176              | 38                |

| 11         | 145              | 43                |

| 10         | 125              | 49                |

抵抗アッテネータでは dB 対 dB のノイズ指数の劣化が発生するため、外付けの抵抗減衰ネットワークは小さなゲイン調整のためにのみ使用してください。全体のゲインを達成するため、減衰を最小限に抑える必要があるアンプ バージョンを使用します。

## 8.2 代表的なアプリケーション

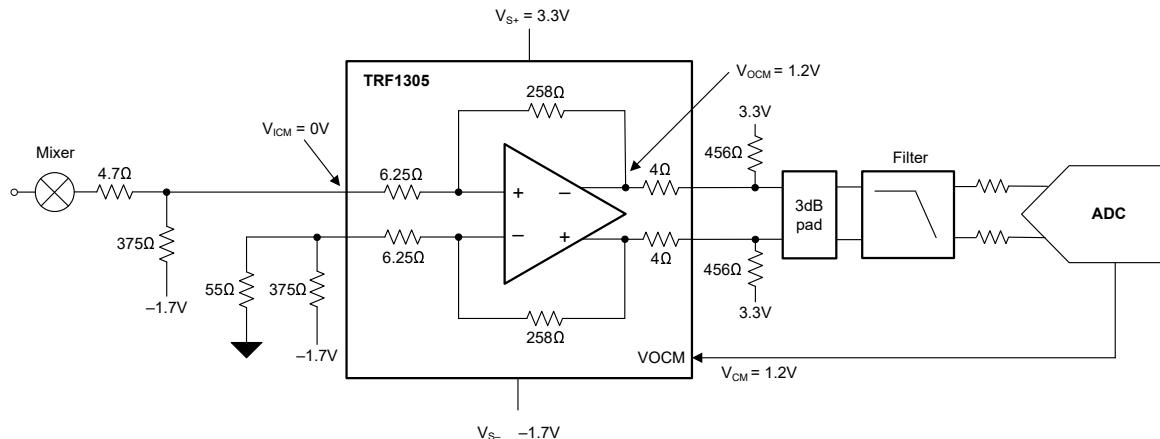

### 8.2.1 ゼロ IF レシーバの ADC ドライバとしての TRF1305A2

図 8-9. ゼロ IF レシーバの ADC ドライバとしての TRF1305A2

IQ 復調器を 1 対の ADC と接続するゼロ IF (ダイレクト ダウン コンバージョン) アプリケーションを考えます。この場合、TRF1305A2 を復調器と ADC 間のインターフェイス アンプとして使用します。復調器出力の DC 同相モードと ADC 入力は異なります。TRF1305A2 DC は、信号チェーンのシグナル インテグリティを低下させることなく、復調器を ADC に結合します。

#### 8.2.1.1 設計要件

IQ 復調器アプリケーションの主な設計要件は、パッシブミキサと RF ADC を接続することです。このミキサの同相電圧は 0V です。ADC には、1.2V の入力同相電圧が必要で、フルスケール スイングは  $1.35V_{PP}$  です。電源を選択し、ADC ドライバ アンプとして TRF1305A2 の入出力回路を設計して、DC レベル シフトおよび増幅機能を実行します。

#### 8.2.1.2 詳細な設計手順

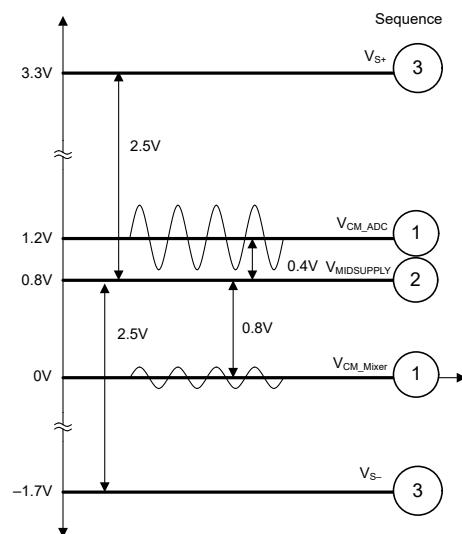

最初の手順は、TRF1305A2 電源を選択することです。中電源電圧  $V_{MIDSUPPLY}$  が、ADC 同相 (CM) 電圧とミキサ CM 電圧の間にあることを維持します。アンプの出力 CM 範囲が入力 CM 範囲よりも小さいため、 $V_{MIDSUPPLY}$  は通常、ADC CM に近く配置されます。アンプの入力と出力の信号の DC が、有効な動作同相電圧範囲内であるように維持します。入力 CM の拡張範囲が必要な場合は、MODE ピンを使用してください。

図 8-10. 特定の同相電圧を使用した電源電圧の選択

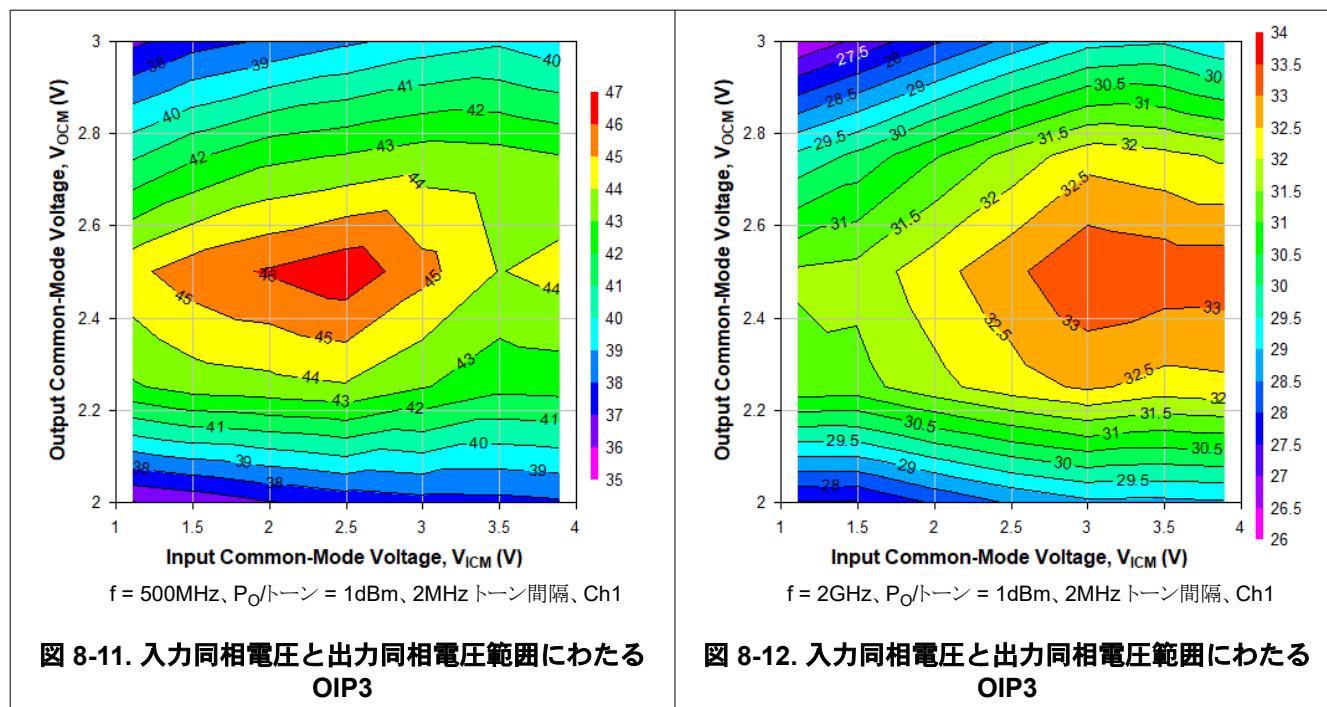

図 8-10 に、 $V_{MIDSUPPLY}$  を 0.8V と選択する方法を示します。これにより、アンプの入力では  $V_{MIDSUPPLY} = 0.8V$  の CM オフセットが発生し、出力では  $V_{MIDSUPPLY}$  による 0.4V (1.2V ~ 0.8V) の CM オフセットが発生します。CM のオフセットはアンプの有効な同相範囲内であるため、TRF1305A2 の電源としては  $V_{S+} = 3.3V$  (0.8V + 2.5V) および  $V_{S-} = -1.7V$  (0.8V ~ 2.5V) を選択します。最高の OIP3 性能を得るために入力および出力 CM 電圧を選択することにより、電源をさらに最適化できます。セクション 8.2.1.3 に、入力同相電圧と出力同相電圧それぞれに対応した OIP3 を示す輪郭グラフを示します。

出力 CM は入力 CM よりも大きいため、dc 電流の正味 4.54mA ( $(1.2V - 0V)/(258\Omega + 6.25\Omega)$ ) は内部帰還抵抗を経由して出力から入力へ流れます。パッシブ ミキサーの選択に応じて、ミキサーのバイアス条件が妨げられないように、この電流をミキサーの外部にシンクする必要があります。INP ピンと -1.7V の電源に接続された  $375\Omega$  のプルダウン抵抗が適切です。4.54mA の DC 電流がアンプから完全に供給されている場合は、出力ヘッドルームに影響を与える可能性があります。したがって、アンプ出力に接続された 1 対のプルアップ抵抗を使用して、電源から外部から電流を供給します。OUTP および OUTM から 3.3V への  $456\Omega$  のプルアップ抵抗が十分です。

| チャネルミキサ出力は  $50\Omega$  ポートを持ち、小さな ( $4.7\Omega$ ) 直列抵抗を介してアンプ INP ピンに接続されます。INM ピンは、 $55\Omega$  の抵抗を介してグランドに、 $375\Omega$  の抵抗を介して -1.7V に終端されています。この構成により、アンプの INP および INM の各入力ピンで同じ入力インピーダンスを持つことができます。ミキサのインピーダンスは  $43\Omega$  に近く、(理論的には) -20dB 以上の反射損失を実現します。これらの抵抗ネットワークが原因で、ゲインが多少低下することに注意してください。図 8-9 で選択した抵抗の値を出発点として適切です。実際には、DC 条件と RF 性能を同時に満たすために、しばしば何らかの調整が必要になります。

アンプ出力では、 $100\Omega$  の差動インピーダンスを持つ  $3dB$  パッドを使用して、 $100\Omega$  の差動入力インピーダンスを持つアンチエイリアシング フィルタとマッチングします。フィルタ出力は、適切なマッチングを行うように ADC に接続されます。図 8-9 は | チャネルのみを示します。Q チャネルの構成は同一です。

### 8.2.1.3 アプリケーション曲線

## 8.3 電源に関する推奨事項

### 8.3.1 電源電圧

TRF1305x2 の場合は、VS1+ と VS2+ の両方の電源ピンを互いに同じ電圧に短絡し、デバイスが適切に動作するようにします。VS+ と VS- の間の標準差動電源は 5V です。VS+ および VS- 電源ピンは、「絶対最大定格」および「推奨動作条件」に記載されている規定範囲内で、サーマル パッドに対してフローティングにできます。

### 8.3.2 単電源動作

VS- ピンは、単一電源構成ではグランドに接続されます。単一電源動作は、入力のソースの DC 同相電圧と出力の駆動回路が本質的にデカッピングされているため、AC 結合構成では最も便利です。

### 8.3.3 単一電源動作

分割電源構成では、「絶対最大定格」および「推奨動作条件」に規定されている範囲内に VS+ および VS- 電圧を選択します。TRF1305x2 では、VS- 電源の負電圧を選択できるため、入力ネットワークと出力ネットワークの要件に応じて、入力および出力の同相電圧を柔軟に選択できます。

### 8.3.4 電源のデカッピング

VS+ と VS- の電源ピンは、外付けコンデンサを使用して個別にグランドに分離されています。TRF1305x2 では、基板レイアウトを容易にするため、VS+ デカッピングを VS1+ と GND、VS2+ と GND に個別に分割できます。デカッピング コンデンサはデバイスの電源ピンに近付けて配置します。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

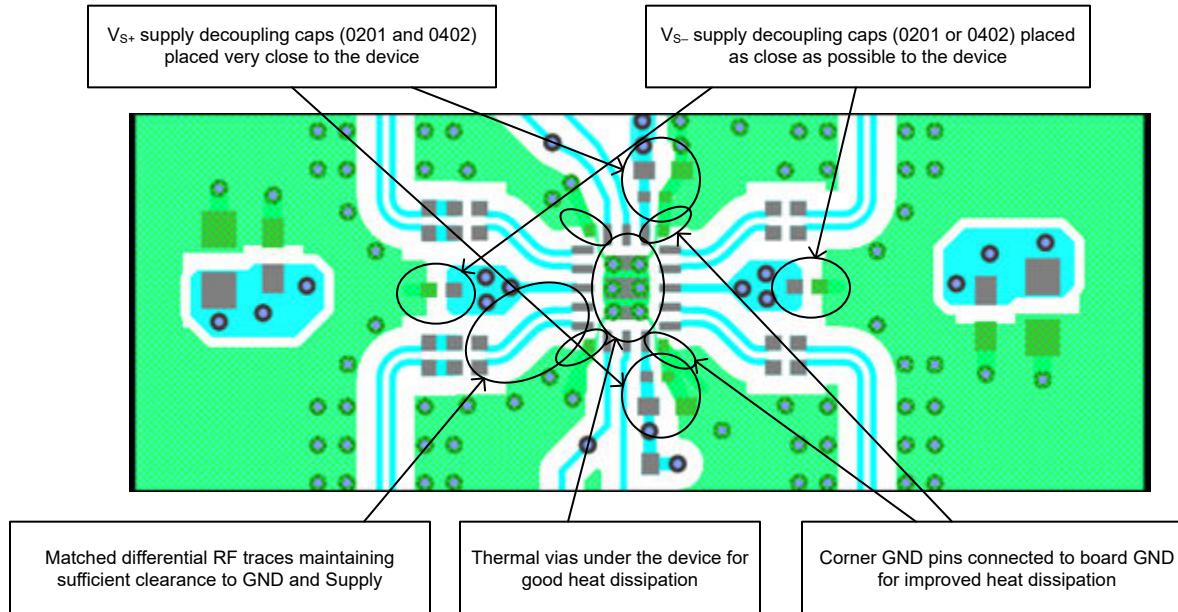

TRF1305x2 デバイスは、広帯域、閉ループ帰還アンプです。ゲインの大きい広帯域 RF アンプを設計する場合は、安定性と最適化された性能を維持するために、基板レイアウトに関する特定の注意事項を考慮してください。マルチレイヤ基板を使用して、シグナル インテグリティ、パワー インテグリティ、熱性能を維持します。

RF 入力および出力ラインを接地された同一平面導波管 (GCPW) ラインとして配線します。グランド ピンは RF 信号の基準となります。PCB の第 2 層には、アンプの近くにグランド カットアウトがないことを維持します。位相不均衡を最小限に抑えるために、両方のチャネルの出力差動ラインの長さを一致させます。入力配線の長さを一致させることも重要です。特に入力構成が差動の場合は重要です。可能な場合は、小型フットプリントの受動部品を使用します。

放熱特性を改善するため、デバイスの下のサーマル ビアを使ってデバイスのサーマル パッドを基板のグランド プレーンに接続します。放熱性能を高めるため、本デバイスのサーマル パッドを基板の上層グランド プレーンに接続します。

#### 8.4.1.1 熱に関する注意事項

TRF1305x2 は、熱特性が優れた WQFN-FCRLF パッケージで供給されます。デバイス下のサーマル パッドを基板上の放熱性グランド プレーンに接続します。優れた熱設計を行うには、サーマル ビアを使って PCB 最上層のサーマル パッド プレーンを内層のグランド プレーンに接続します。

#### 8.4.2 レイアウト例

図 8-13 に、差動入力構成を使用した TRF1305x2 のレイアウト例を示します。主要な領域が図で強調表示されています。

図 8-13. レイアウト例 : TRF1305x2、差動入力

TRF1305A2 は、[TRF1305A2 プロダクト フォルダ](#)から注文できる EVM ボードを使用して評価できます。評価ボードの構成とテスト構成の詳細については、[『TRF1305x2 EVM ユーザー ガイド』](#)を参照してください。

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

関連資料については、以下を参照してください。

- ・ テキサス インスツルメンツ、[『TRF1305x2-D2D EVM ユーザー ガイド』](#)

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付           | 改訂 | 注      |

|--------------|----|--------|

| October 2025 | *  | 初版リリース |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TRF1305A2RYPR         | Active        | Production           | VQFN-FCRLF<br>(RYP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | 1305A2              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

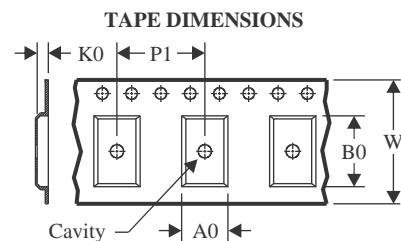

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

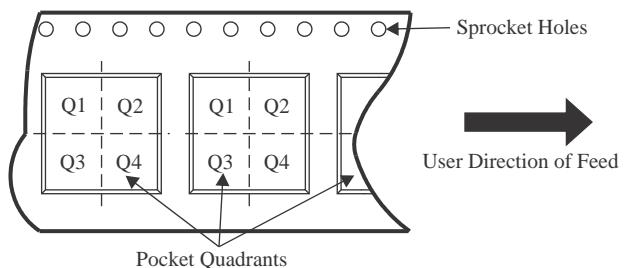

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

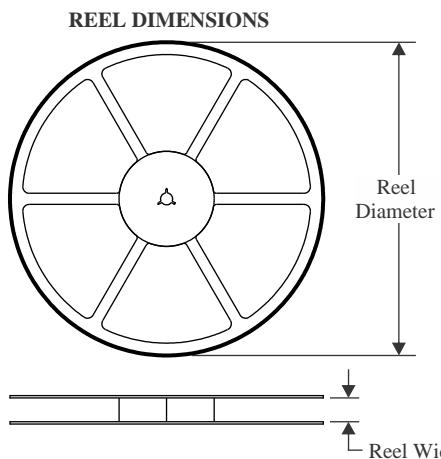

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TRF1305A2RYPR | VQFN-FCRLF   | RYP             | 16   | 2000 | 330.0              | 12.4               | 2.8     | 3.3     | 1.2     | 4.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TRF1305A2RYPR | VQFN-FCRLF   | RYP             | 16   | 2000 | 338.0       | 355.0      | 50.0        |

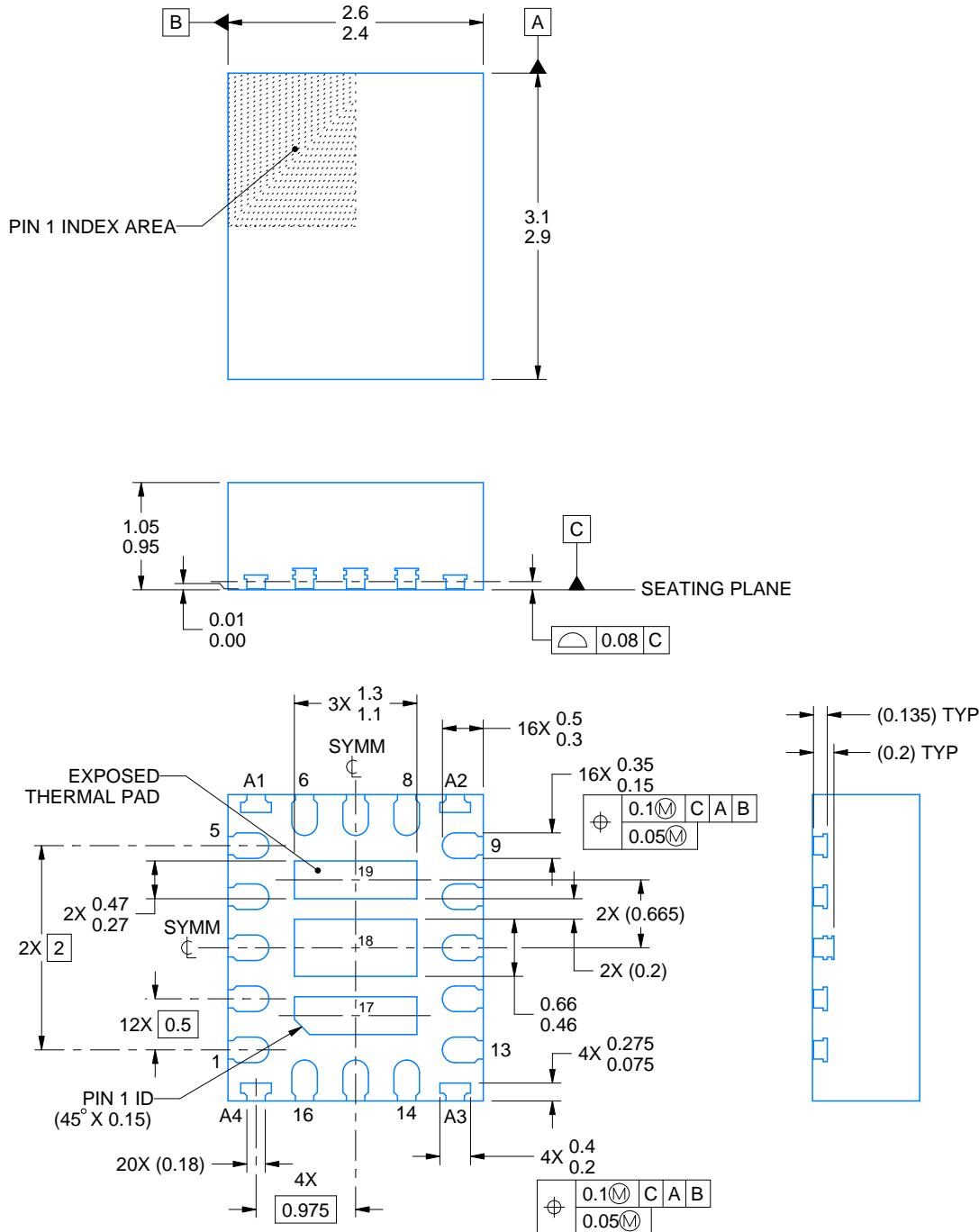

## PACKAGE OUTLINE

**RYP0016A**

## **VQFN-FCRLF - 1.05 mm max height**

## PLASTIC QUAD FLATPACK - NO LEAD

4226528/D 04/2024

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

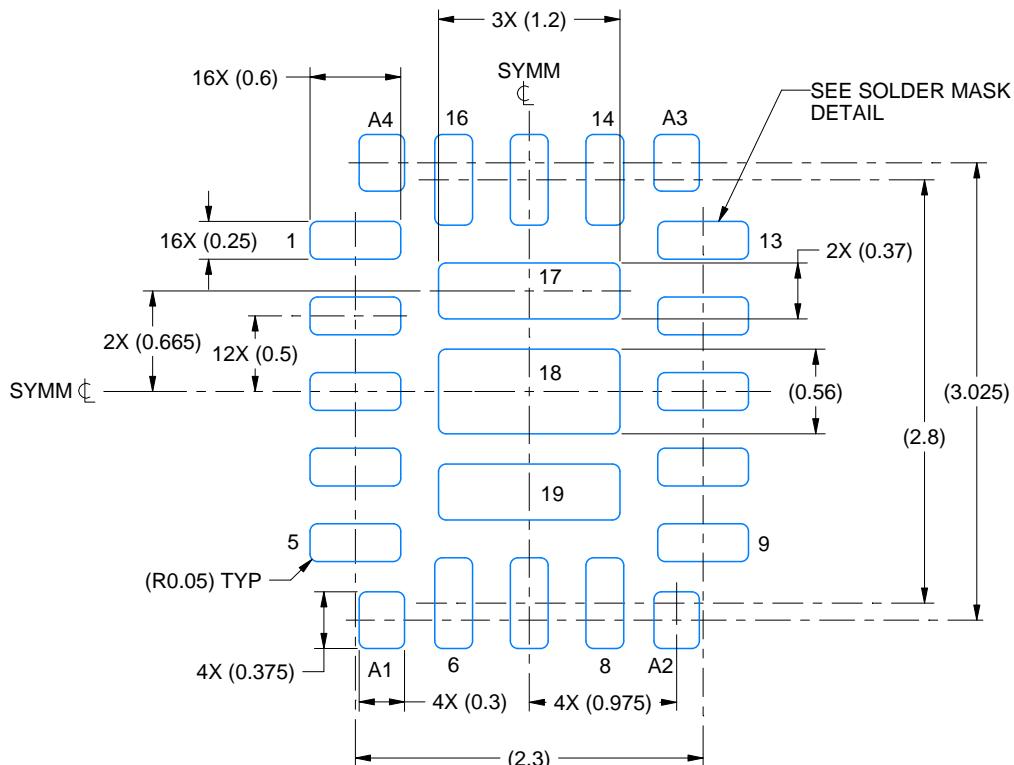

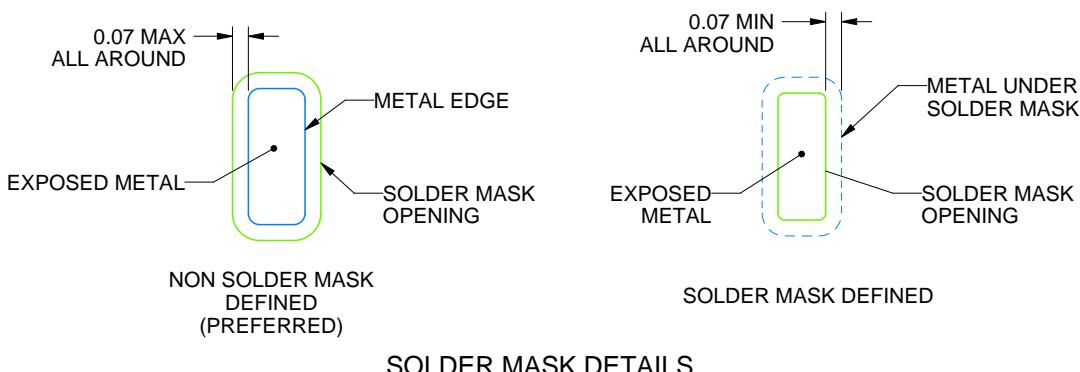

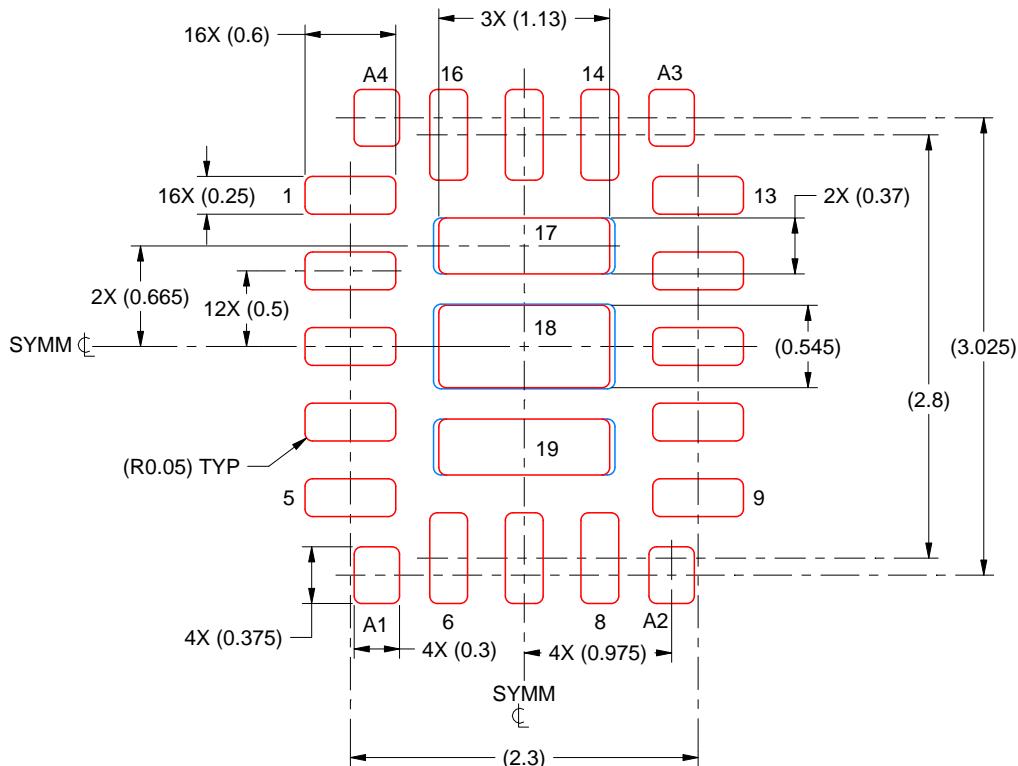

# EXAMPLE BOARD LAYOUT

RYP0016A

VQFN-FCRLF - 1.05 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

4226528/D 04/2024

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

**RYP0016A**

**VQFN-FCRLF - 1.05 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

**SOLDER PASTE EXAMPLE**

BASED ON 0.125 MM THICK STENCIL

SCALE: 20X

**PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE**

PADS 17 & 19: 94%

PAD 18: 92%

4226528/D 04/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月