# TPSM8D6C24 2.95V ~ 16V、デュアル 35A またはシングル 70A、最大 4 相スタッカブル、PMBus® 降圧パワー モジュール

## 1 特長

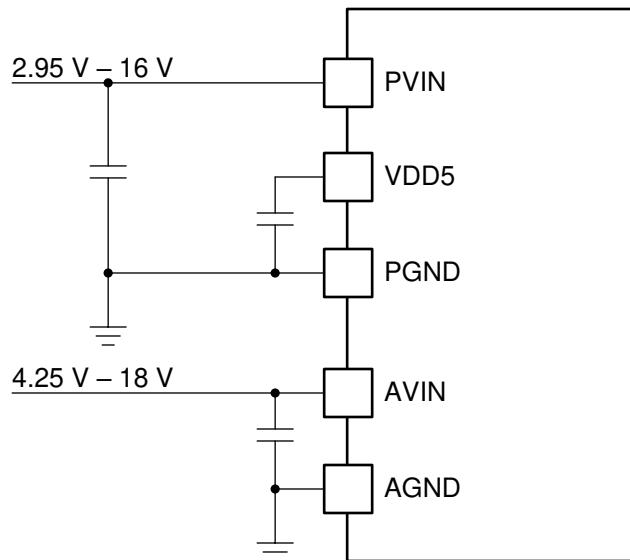

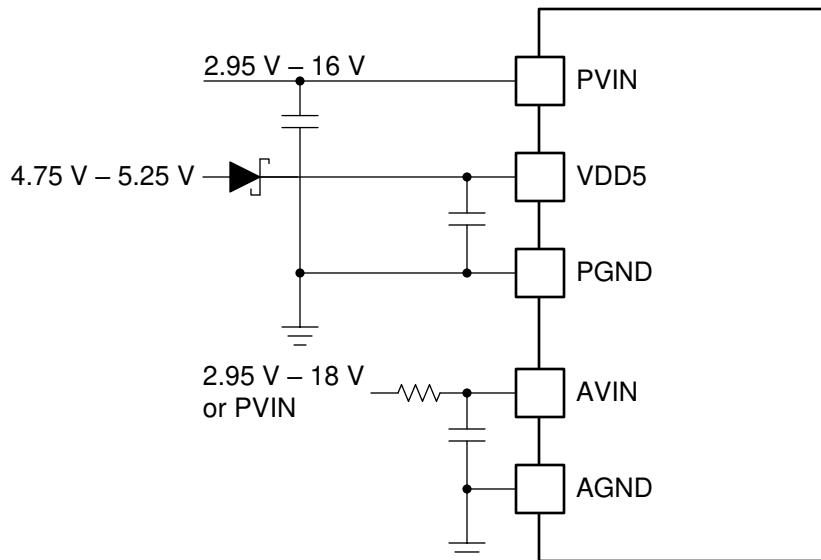

- 4.25V~16V (PVIN を AVIN に接続、内部 LDO)

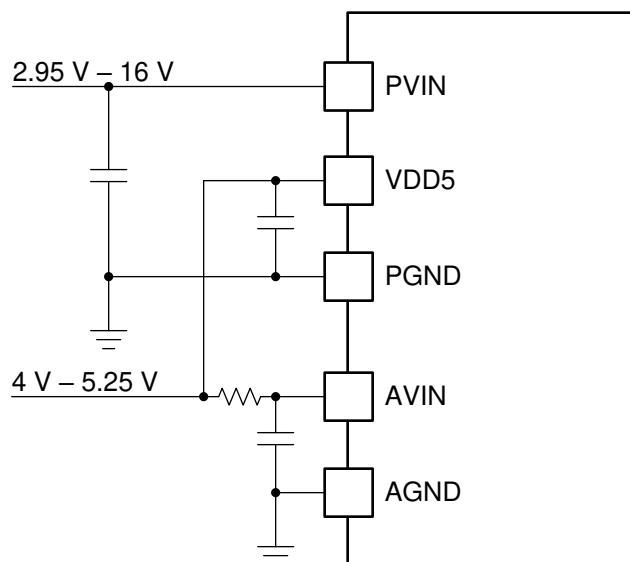

- 2.95V~16V (PVIN および AVIN 分割レール、または VDD5 に外部バイアスを印加)

- MOSFET、インダクタ、基本的なパッシブ部品を内蔵

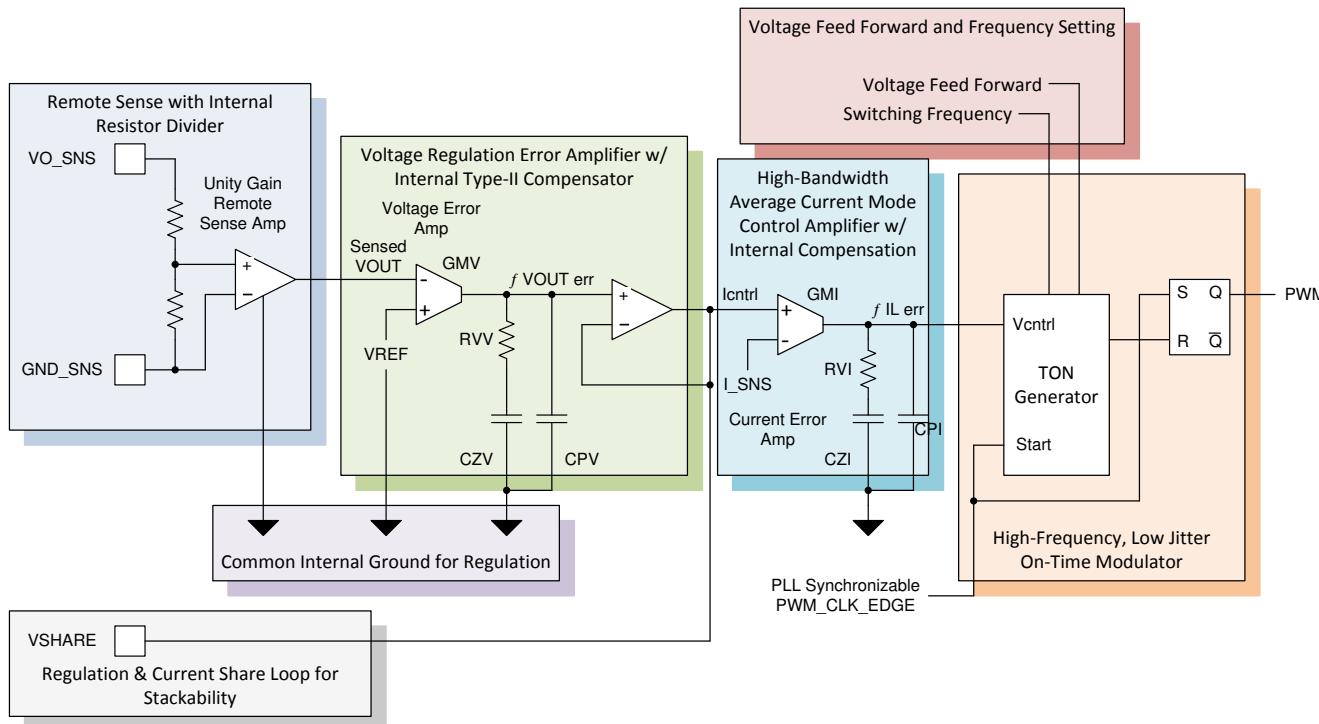

- 選択可能な内部補償を備えた平均電流モード制御

- ピンストラップで設定可能な 0.5V~3.6V の出力電圧範囲

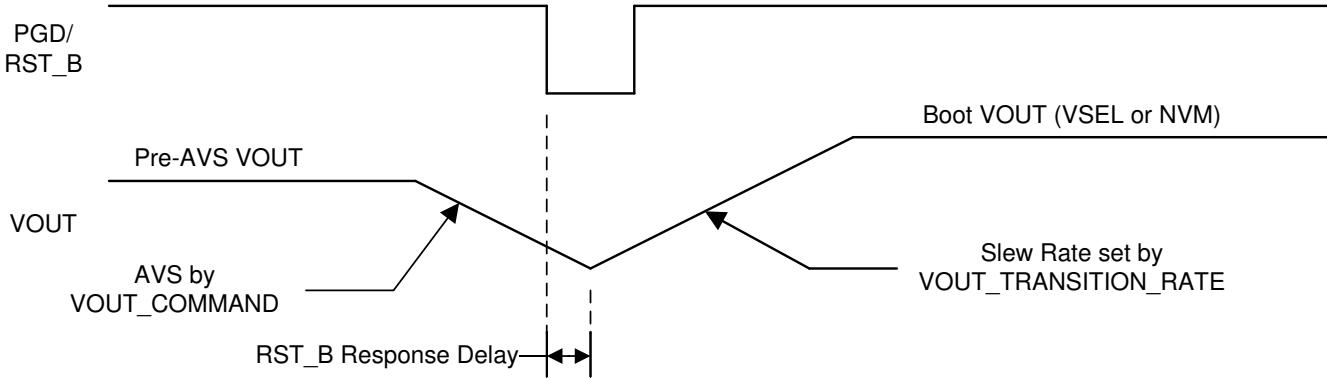

- 0.25V ~ 3.6V の PMBus® VOUT\_COMMAND 範囲

- 豊富な PMBus コマンドセット、V<sub>OUT</sub>、I<sub>OUT</sub>、ダイ温度のテレメトリを含む

- 内部 FB デバイダ (分圧抵抗) を使った差動リモートセンシングにより、V<sub>OUT</sub> 誤差を 1% 未満に低減

- 接合部温度範囲: -40°C ~ +125°C

- PMBus による AVS およびマージニング機能

- マルチファンクション選択 (MSEL) ピンによる PMBus デフォルト値のピンストラップ設定

- 275kHz~1.1MHz で 9 つのスイッチング周波数を選択可能

- 周波数同期入力 / 同期出力

- プリバイアス出力をサポート

- 16mm × 20mm × 4.3mm、59 ピン MOW パッケージ

- [WEBENCH® Power Designer](#) により、TPSM8D6C24 を使用するカスタム設計を作成

## 2 アプリケーション

- データ・センター・スイッチ、ラック・サーバー

- アクティブ・アンテナ・システム、リモート無線 / ベースバンド・ユニット

- 自動試験装置、CT、PET、MRI

- ASIC、SoC、FPGA、DSP コア、I/O 電圧

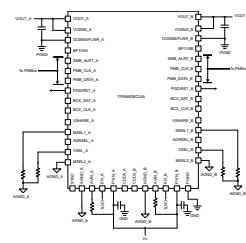

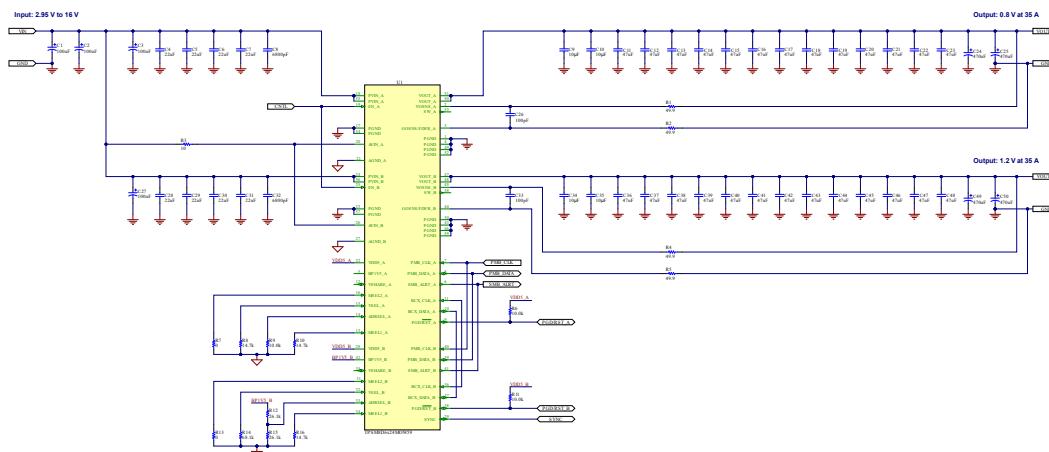

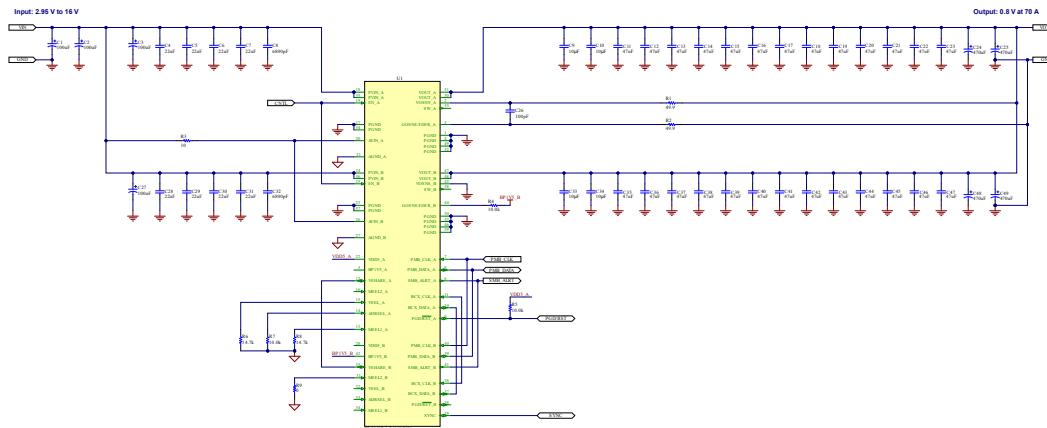

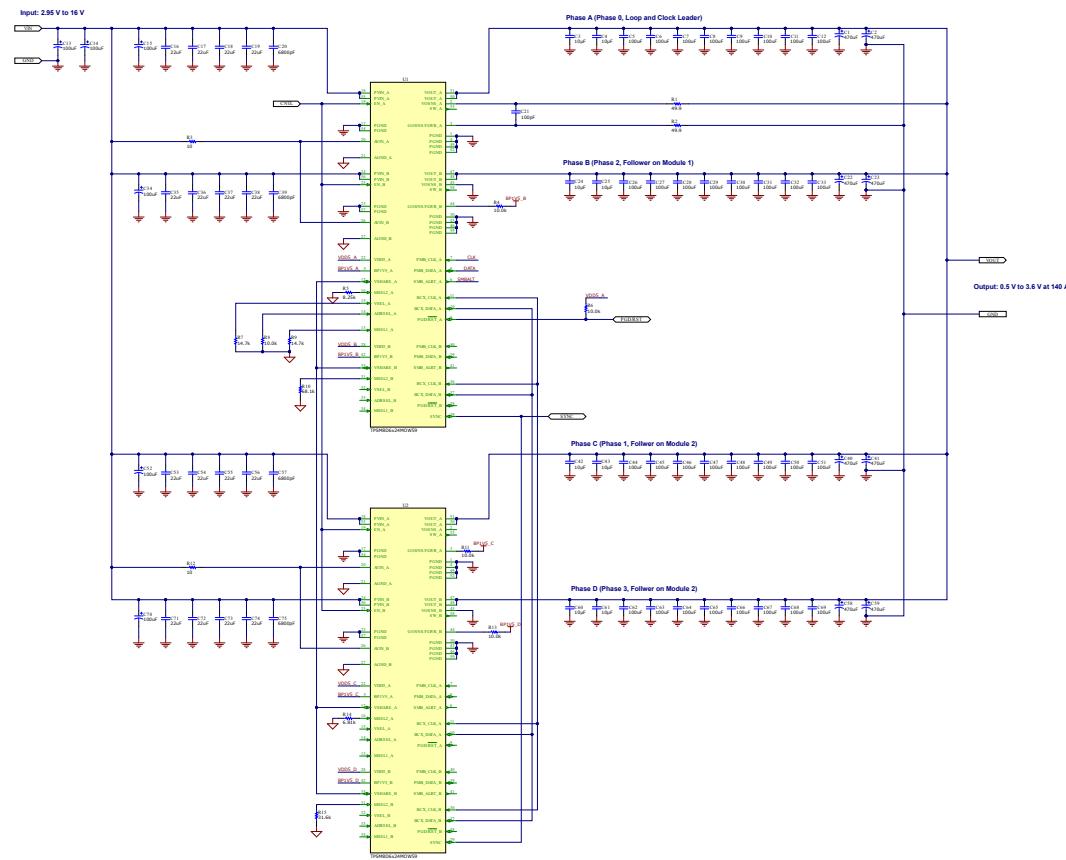

アプリケーション概略図

## 3 説明

TPSM8D6C24 は使いやすい高集積非絶縁型 DC/DC 降圧パワー モジュールです。TPSM8D6C24 を使うと、2 つの独立した 35A 出力、または 1 つのスタッカブル 2 相 70A 出力を得ることができます。2 つのモジュールをスタッカブル接続することで、1 つの 4 相 140A 出力を得ることもできます。本デバイスには、内部 5V LDO を外部 5V 電源でオーバードライブし、入力電圧を最低 2.95V まで低下させ、コンバータの効率を向上させるオプションがあります。

TPSM8D6C24 パワー モジュールは入力フィードフォワードによる独自の固定周波数電流モード制御を採用しており、内部補償部品を選択可能であるため、サイズを最小化し、幅広い出力容量で安定性を確保できます。

1MHz クロックをサポートする PMBus インターフェイスは、出力電圧、出力電流、内部ダイ温度などの主要パラメータを監視するためだけではなく、コンバータを設定するための便利な標準化されたデジタル インターフェイスを提供します。デフォルト条件への応答は、システム要件に応じて、再起動、ラッチ オフ、無視のいずれかに設定できます。スタッカブル デバイス間のバックチャネル通信により、1 つの出力レールに電力を供給するすべての TPSM8D6C24 コンバータが 1 つのアドレスを共有できるため、システムソフトウェア、ファームウェア設計を簡素化できます。出力電圧、スイッチング周波数、ソフトスタート時間、過電流プロテクションなどの主要なパラメータは、プログラムなしでのパワーオンをサポートするため、PMBus 通信を使わずに BOM 選定を通して設定することもできます。

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| TPSM8D6C24 | MOW (QFM、59)         | 16.00mm × 20.00mm        |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はビンも含まれます

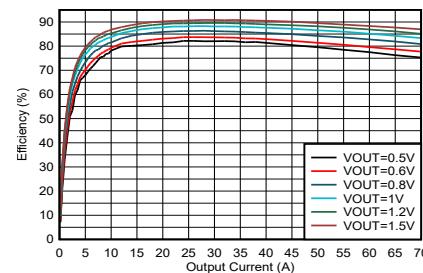

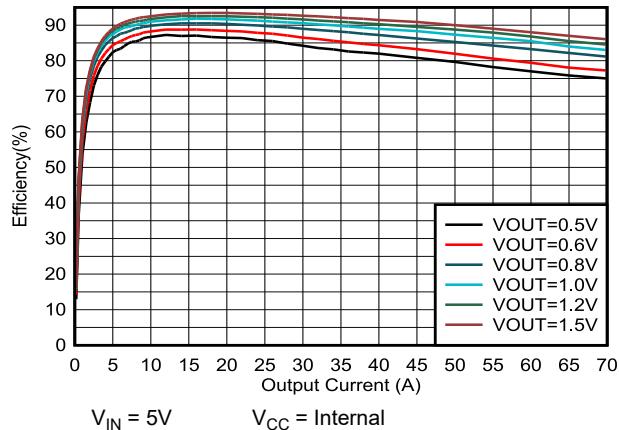

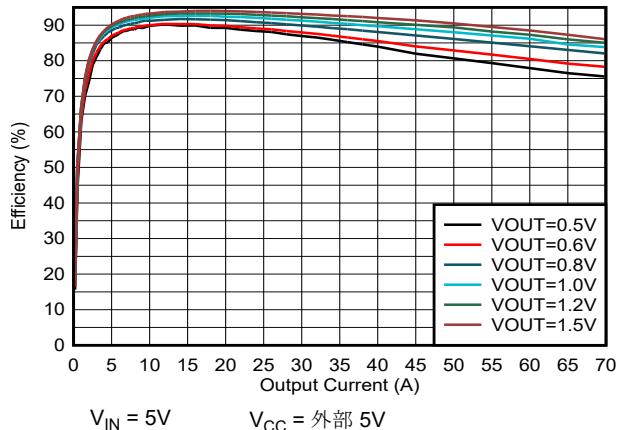

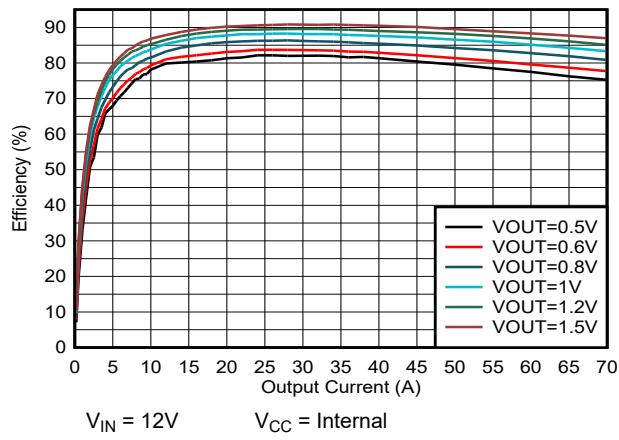

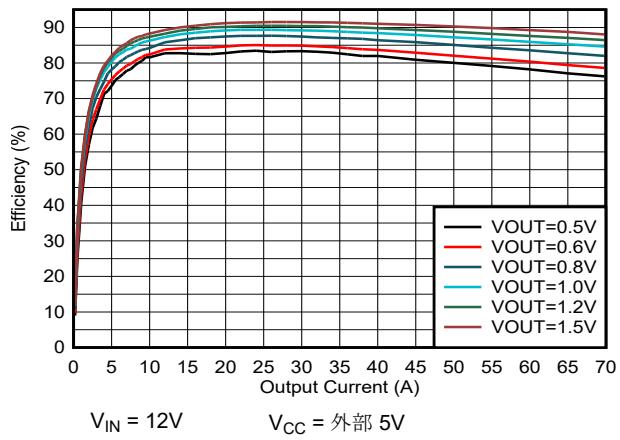

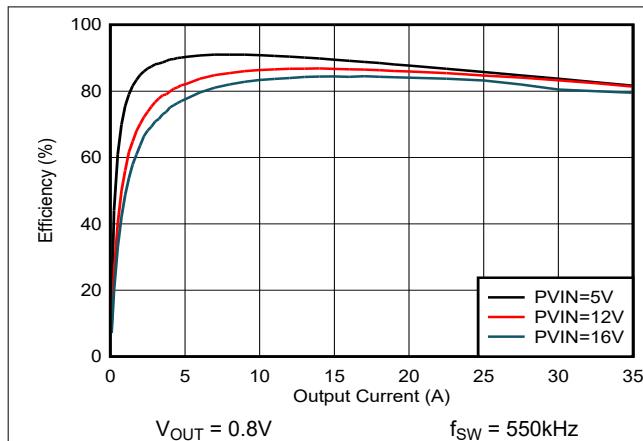

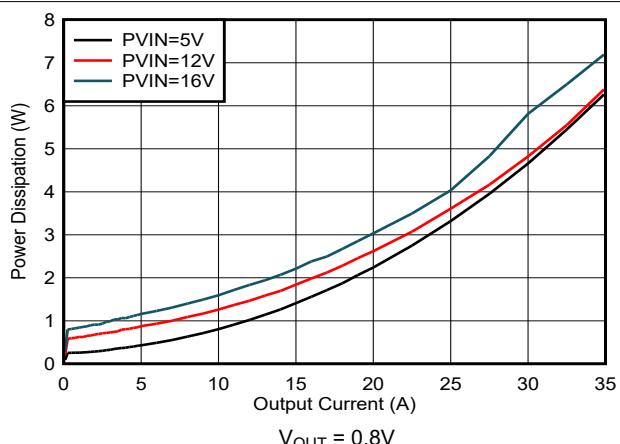

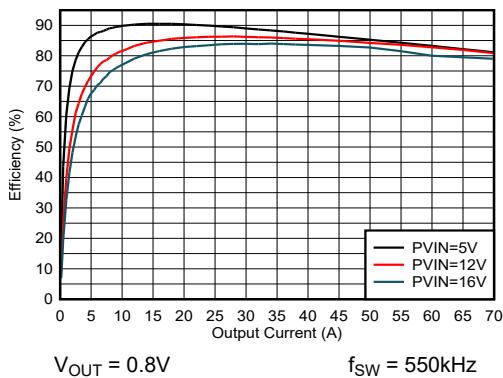

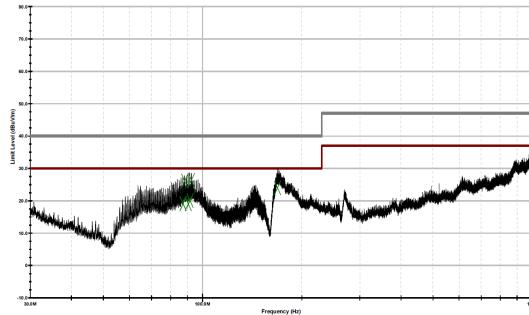

効率、12Vin、内部バイアス、Fsw = 550kHz

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLUSEJ1](#)

## 目次

|                                      |    |                                                     |     |

|--------------------------------------|----|-----------------------------------------------------|-----|

| 1 特長                                 | 1  | 7.39 (46h) IOUT_OC_FAULT_LIMIT                      | 92  |

| 2 アプリケーション                           | 1  | 7.40 (47h) IOUT_OC_FAULT_RESPONSE                   | 94  |

| 3 説明                                 | 1  | 7.41 (4Ah) IOUT_OC_WARN_LIMIT                       | 95  |

| 4 ピン構成および機能                          | 4  | 7.42 (4Fh) OT_FAULT_LIMIT                           | 96  |

| 5 仕様                                 | 6  | 7.43 (50h) OT_FAULT_RESPONSE                        | 97  |

| 5.1 絶対最大定格                           | 6  | 7.44 (51h) OT_WARN_LIMIT                            | 99  |

| 5.2 ESD 定格                           | 6  | 7.45 (55h) VIN_OV_FAULT_LIMIT                       | 100 |

| 5.3 推奨動作条件                           | 6  | 7.46 (56h) VIN_OV_FAULT_RESPONSE                    | 101 |

| 5.4 熱に関する情報                          | 7  | 7.47 (58h) VIN_UV_WARN_LIMIT                        | 103 |

| 5.5 電気的特性                            | 7  | 7.48 (60h) TON_DELAY                                | 104 |

| 5.6 代表的特性                            | 15 | 7.49 (61h) TON_RISE                                 | 105 |

| 6 詳細説明                               | 18 | 7.50 (62h) TON_MAX_FAULT_LIMIT                      | 106 |

| 6.1 概要                               | 18 | 7.51 (63h) TON_MAX_FAULT_RESPONSE                   | 107 |

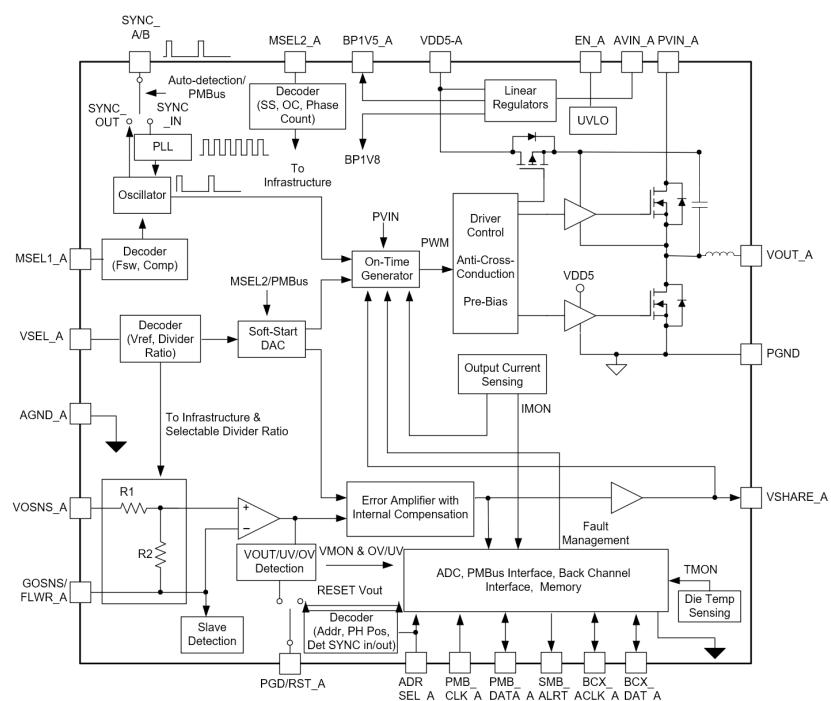

| 6.2 機能ブロック図                          | 18 | 7.52 (64h) TOFF_DELAY                               | 108 |

| 6.3 機能説明                             | 19 | 7.53 (65h) TOFF_FALL                                | 109 |

| 6.4 デバイスの機能モード                       | 34 | 7.54 (78h) STATUS_BYTE                              | 110 |

| 6.5 プログラミング                          | 35 | 7.55 (79h) STATUS_WORD                              | 111 |

| 7 レジスタ マップ                           | 48 | 7.56 (7Ah) STATUS_VOUT                              | 113 |

| 7.1 ブロック コマンドの文書化規則                  | 48 | 7.57 (7Bh) STATUS_IOUT                              | 114 |

| 7.2 (01h) OPERATION                  | 49 | 7.58 (7Ch) STATUS_INPUT                             | 115 |

| 7.3 (02h) ON_OFF_CONFIG              | 51 | 7.59 (7Dh) STATUS_TEMPERATURE                       | 116 |

| 7.4 (03h) CLEAR_FAULTS               | 52 | 7.60 (7Eh) STATUS_CML                               | 117 |

| 7.5 (04h) PHASE                      | 53 | 7.61 (7Fh) STATUS_OTHER                             | 118 |

| 7.6 (10h) WRITE_PROTECT              | 54 | 7.62 (80h) STATUS_MFR_SPECIFIC                      | 119 |

| 7.7 (15h) STORE_USER_ALL             | 55 | 7.63 (88h) READ_VIN                                 | 120 |

| 7.8 (16h) RESTORE_USER_ALL           | 56 | 7.64 (8Bh) READ_VOUT                                | 121 |

| 7.9 (19h) CAPABILITY                 | 57 | 7.65 (8Ch) READ_IOUT                                | 122 |

| 7.10 (1Bh) SMBALERT_MASK             | 58 | 7.66 (8Dh) READ_TEMPERATURE_1                       | 123 |

| 7.11 (1Bh) SMBALERT_MASK_VOUT        | 59 | 7.67 (98h) PMBUS_REVISION                           | 124 |

| 7.12 (1Bh) SMBALERT_MASK_IOUT        | 60 | 7.68 (99h) MFR_ID                                   | 125 |

| 7.13 (1Bh) SMBALERT_MASK_INPUT       | 61 | 7.69 (9Ah) MFR_MODEL                                | 126 |

| 7.14 (1Bh) SMBALERT_MASK_TEMPERATURE | 62 | 7.70 (9Bh) MFR_REVISION                             | 127 |

| 7.15 (1Bh) SMBALERT_MASK_CML         | 63 | 7.71 (9Eh) MFR_SERIAL                               | 128 |

| 7.16 (1Bh) SMBALERT_MASK_OTHER       | 64 | 7.72 (ADh) IC_DEVICE_ID                             | 129 |

| 7.17 (1Bh) SMBALERT_MASK_MFR         | 65 | 7.73 (AEh) IC_DEVICE_REV                            | 130 |

| 7.18 (20h) VOUT_MODE                 | 66 | 7.74 (B1h) USER_DATA_01<br>(COMPENSATION_CONFIG)    | 131 |

| 7.19 (21h) VOUT_COMMAND              | 67 | 7.75 (B5h) USER_DATA_05<br>(POWER_STAGE_CONFIG)     | 133 |

| 7.20 (22h) VOUT_TRIM                 | 69 | 7.76 (D0h) MFR_SPECIFIC_00<br>(TELEMETRY_CONFIG)    | 134 |

| 7.21 (24h) VOUT_MAX                  | 71 | 7.77 (DAh) MFR_SPECIFIC_10 (READ_ALL)               | 136 |

| 7.22 (25h) VOUT_MARGIN_HIGH          | 72 | 7.78 (DBh) MFR_SPECIFIC_11 (STATUS_ALL)             | 138 |

| 7.23 (26h) VOUT_MARGIN_LOW           | 73 | 7.79 (DCh) MFR_SPECIFIC_12 (STATUS_PHASE)           | 140 |

| 7.24 (27h) VOUT_TRANSITION_RATE      | 74 | 7.80 (E4h) MFR_SPECIFIC_20 (SYNC_CONFIG)            | 141 |

| 7.25 (29h) VOUT_SCALE_LOOP           | 75 | 7.81 (ECh) MFR_SPECIFIC_28 (STACK_CONFIG)           | 142 |

| 7.26 (2Bh) VOUT_MIN                  | 77 | 7.82 (EDh) MFR_SPECIFIC_29 (MISC_OPTIONS)           | 143 |

| 7.27 (33h) FREQUENCY_SWITCH          | 78 | 7.83 (EEh) MFR_SPECIFIC_30<br>(PIN_DETECT_OVERRIDE) | 144 |

| 7.28 (35h) VIN_ON                    | 80 | 7.84 (EFh) MFR_SPECIFIC_31<br>(DEVICE_ADDRESS)      | 146 |

| 7.29 (36h) VIN_OFF                   | 81 | 7.85 (F0h) MFR_SPECIFIC_32 (NVM_CHECKSUM)           | 147 |

| 7.30 (37h) INTERLEAVE                | 82 | 7.86 (F1h) MFR_SPECIFIC_33 (SIMULATE_FAULT)         | 148 |

| 7.31 (38h) IOUT_CAL_GAIN             | 84 | 7.87 (FCh) MFR_SPECIFIC_44 (FUSION_ID0)             | 150 |

| 7.32 (39h) IOUT_CAL_OFFSET           | 85 | 7.88 (FDh) MFR_SPECIFIC_45 (FUSION_ID1)             | 151 |

| 7.33 (40h) VOUT_OV_FAULT_LIMIT       | 86 | 8 アプリケーションと実装                                       | 152 |

| 7.34 (41h) VOUT_OV_FAULT_RESPONSE    | 87 | 8.1 アプリケーション情報                                      | 152 |

| 7.35 (42h) VOUT_OV_WARN_LIMIT        | 88 |                                                     |     |

| 7.36 (43h) VOUT_UV_WARN_LIMIT        | 89 |                                                     |     |

| 7.37 (44h) VOUT_UV_FAULT_LIMIT       | 90 |                                                     |     |

| 7.38 (45h) VOUT_UV_FAULT_RESPONSE    | 91 |                                                     |     |

---

|                                   |            |                              |            |

|-----------------------------------|------------|------------------------------|------------|

| 8.2 代表的なアプリケーション .....            | 152        | 9.2 ドキュメントの更新通知を受け取る方法 ..... | 171        |

| 8.3 2 相アプリケーション .....             | 160        | 9.3 サポート・リソース .....          | 171        |

| 8.4 4 相アプリケーション .....             | 165        | 9.4 商標 .....                 | 171        |

| 8.5 電源に関する推奨事項 .....              | 167        | 9.5 静電気放電に関する注意事項 .....      | 172        |

| 8.6 レイアウト .....                   | 167        | 9.6 用語集 .....                | 172        |

| <b>9 デバイスおよびドキュメントのサポート .....</b> | <b>171</b> | <b>10 改訂履歴 .....</b>         | <b>172</b> |

| 9.1 デバイス サポート .....               | 171        | 11 メカニカル、パッケージ、および注文情報 ..... | 173        |

---

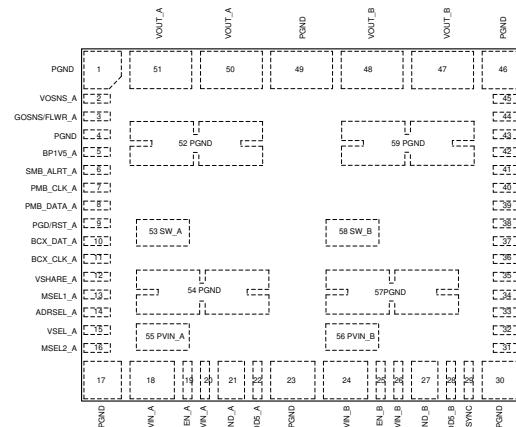

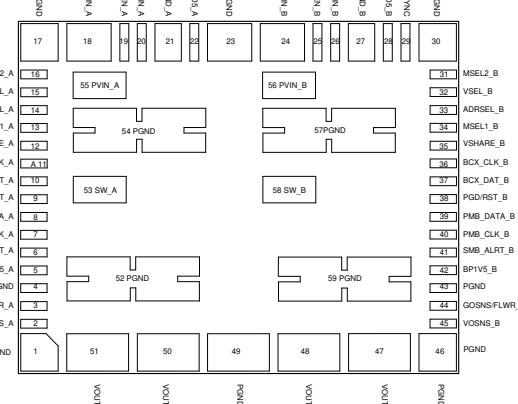

## 4 ピン構成および機能

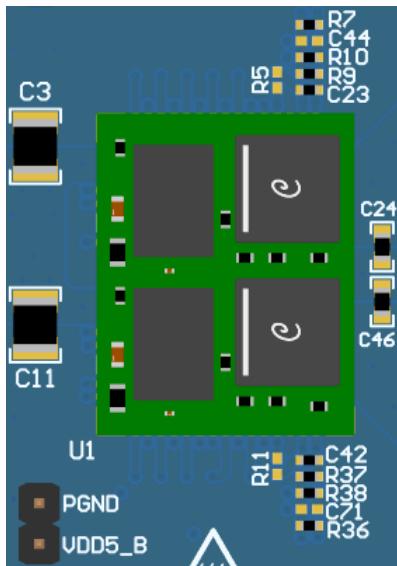

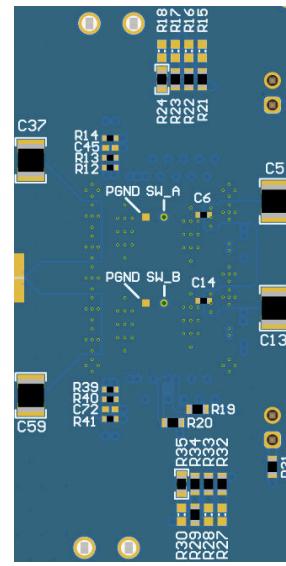

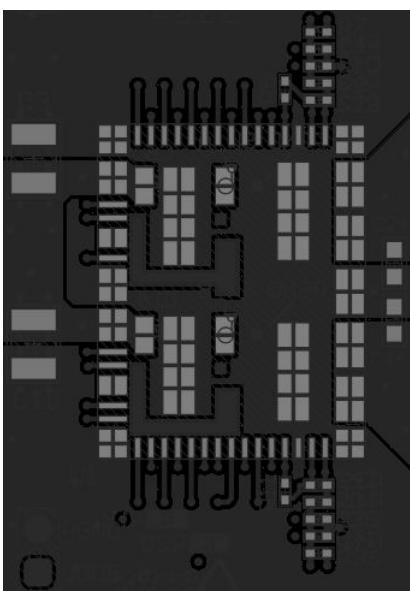

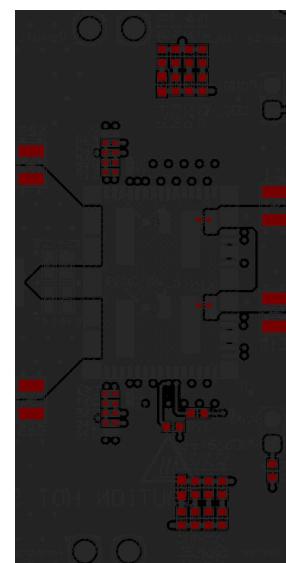

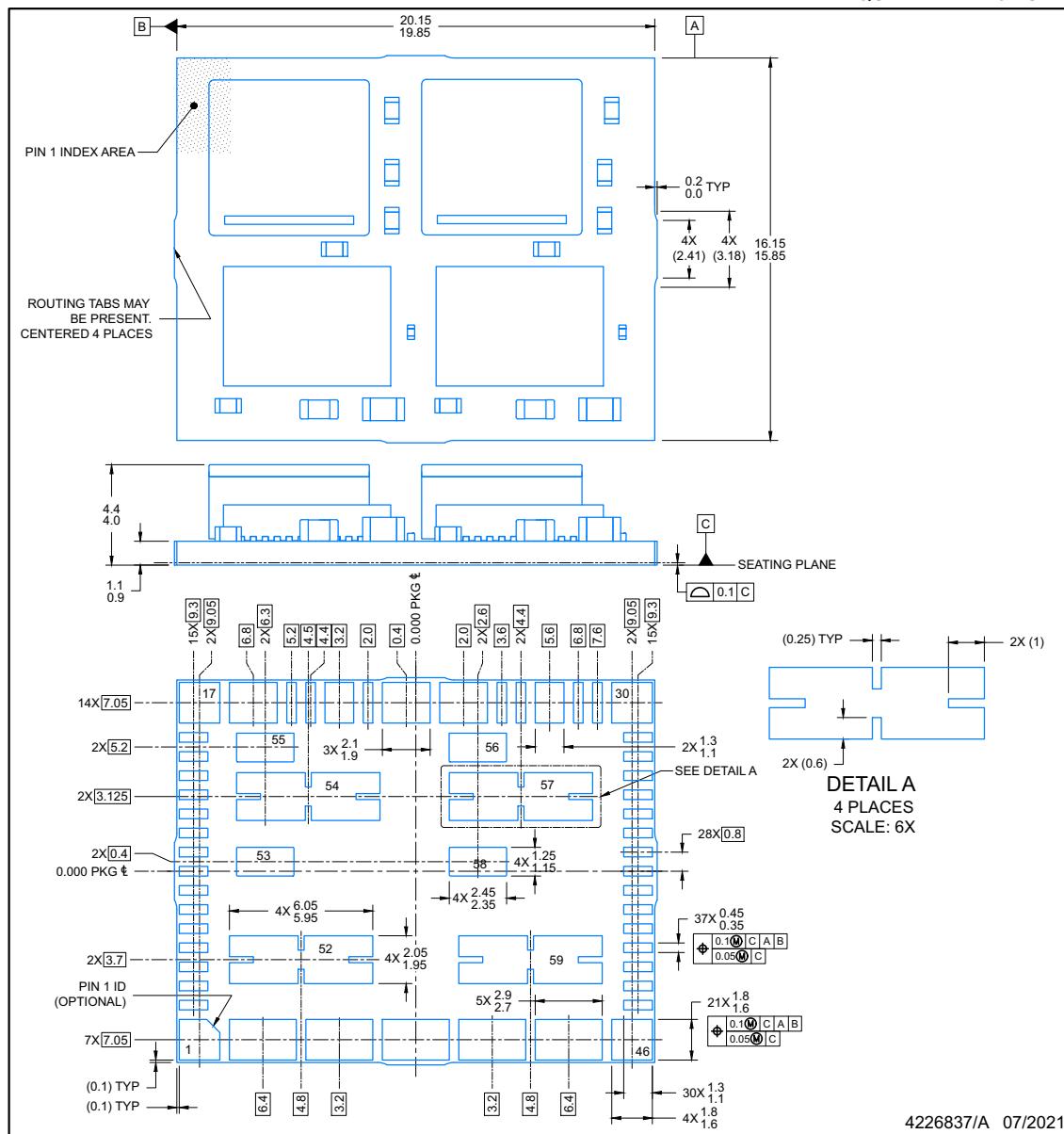

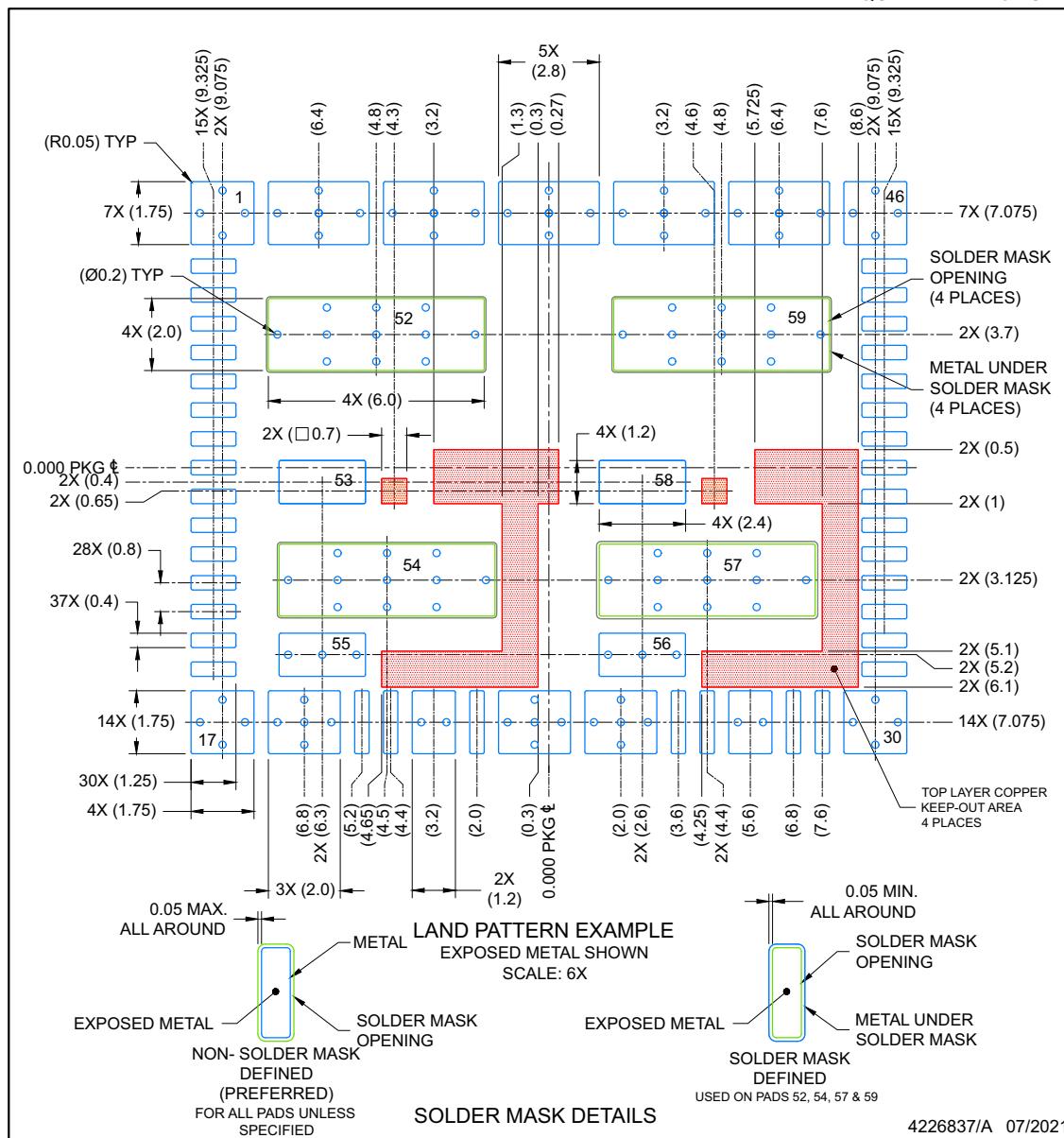

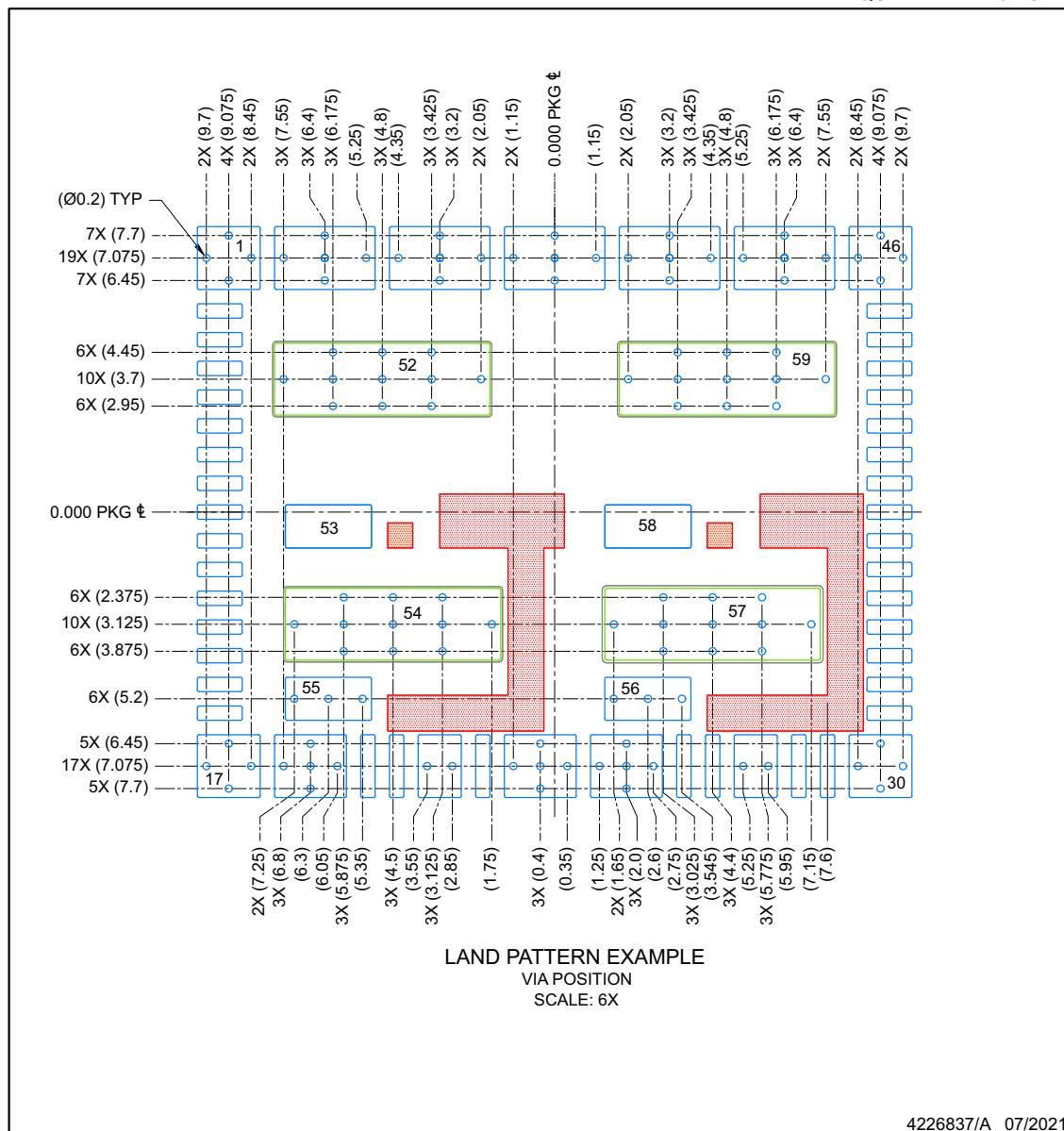

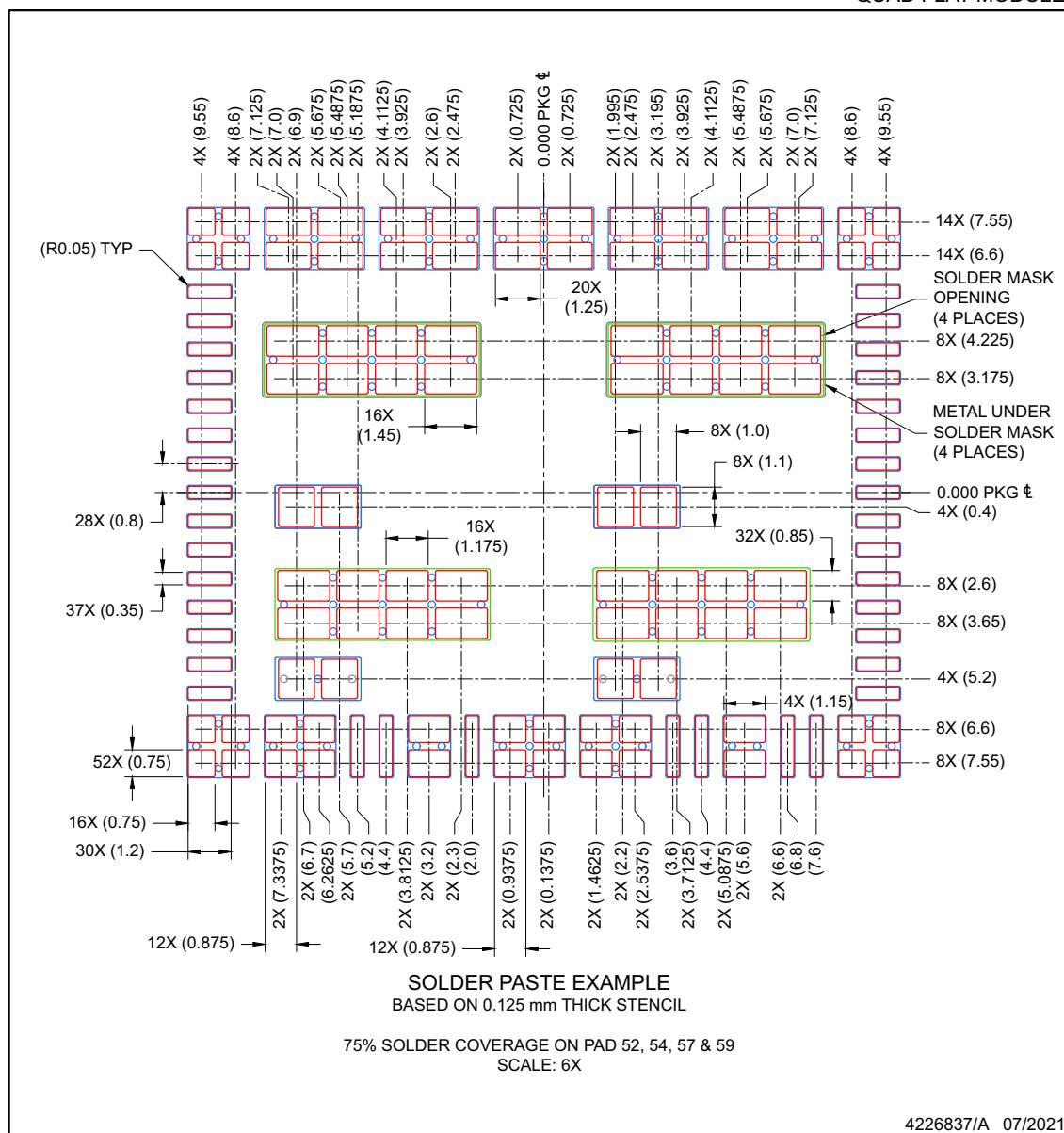

図 4-1. 59 ピン QFM-MOW パッケージ (上面図)

図 4-2. 59 ピン QFM-MOW パッケージ (底面図)

表 4-1. ピンの機能

| ピン           |                                              | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                       |

|--------------|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| PGND         | 1, 4, 17, 23, 30, 43, 46, 49, 52, 54, 57, 59 | —                 | 電力段のグランド帰路。ピン 52, 54, 57, 59 は、デバイスのサーマル パッドとしても機能します。                                                                                                                                                                                                                                                                   |

| VOSNS_A      | 2                                            | I                 | リモートセンスアンプの正の入力。スタンダードアロン デバイスまたは多相構成のループ コントローラ デバイスの場合、VOSNS ピンを負荷側の出力電圧に接続します。多相構成のループ フォロワー デバイスの場合、出力電圧検出やレギュレーションにリモート センスアンプは必要なく、このピンをフローティングのままにできます。位相的な <b>READ_VOUT</b> コマンドで別の電圧を監視する場合は、GOSNS への内部抵抗が BP1V5 に接続されているため、VOSNS を $1\text{k}\Omega$ 未満の抵抗デバイスで $0\text{V} \sim 0.75\text{V}$ の範囲に維持する必要があります。 |

| VOSNS_B      | 45                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| GOSNS/FLWR_A | 3                                            | I                 | ループ コントローラ デバイスのリモート センスアンプの負入力、または High にプルアップしてループ フォロワーを示します。スタンダードアロン デバイスまたは多相構成のループ コントローラ デバイスの場合、GOSNS ピンを負荷側のグランドに接続します。多相構成のループ フォロワー デバイスの場合、デバイスがループ フォロワーであることを示すために、GOSNS ピンを BP1V5 にプルアップする必要があります。                                                                                                       |

| GOSNS/FLWR_B | 44                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| BP1V5_A      | 5                                            | O                 | MSEL, VSEL, ADRSEL ピン用の $1.5\text{V}$ 内部レギュレータの出力。外部バイパス処理不要。他の回路への電力供給を目的として設計されています。                                                                                                                                                                                                                                   |

| BP1V5_B      | 42                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| SMB_ALRT_A   | 6                                            | O                 | SMBus のアラート ピン。SMBus 仕様を参照してください。                                                                                                                                                                                                                                                                                        |

| SMB_ALRT_B   | 41                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| PMB_CLK_A    | 7                                            | I                 | PMBus CLK ピン。最新の <b>PMBus 仕様</b> を参照してください。                                                                                                                                                                                                                                                                              |

| PMB_CLK_B    | 40                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| PMB_DATA_A   | 8                                            | I/O               | PMBus DATA ピン。最新の <b>PMBus 仕様</b> を参照してください。                                                                                                                                                                                                                                                                             |

| PMB_DATA_B   | 39                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| PGD/RST_A    | 9                                            | I/O               | オーブンドレインのパワー グッドまたは(21h) <b>VOUT_COMMAND RESET#</b> (EDh) <b>MFR_SPECIFIC_29 (MISC_OPTIONS)</b> のユーザープログラマブル RESET# ビットによって決定されます。デフォルトのピンの機能は、オーブンドレインのパワーグッド インジケータです。RESET# として構成した場合、(EDh) <b>MFR_SPECIFIC_29 (MISC_OPTIONS)</b> の PULLUP# ビットによって内部プルアップをイネーブルまたはディスエーブルにできます。                                      |

| PGD/RST_B    | 38                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| BCX_DATA_A   | 10                                           | I/O               | スタックされたデバイス間のバックチャネル通信に使用するデータ                                                                                                                                                                                                                                                                                           |

| BCX_DATA_B   | 37                                           |                   |                                                                                                                                                                                                                                                                                                                          |

| BCX_CLK_A    | 11                                           | I/O               | スタックされたデバイス間のバックチャネル通信用のクロック                                                                                                                                                                                                                                                                                             |

| BCX_CLK_B    | 36                                           |                   |                                                                                                                                                                                                                                                                                                                          |

表 4-1. ピンの機能 (続き)

| ピン        |                | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                          |

|-----------|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号             |                   |                                                                                                                                                                                                                                             |

| VSHARE_A  | 12             | I/O               | 多段階動作のための電圧共有信号。スタンドアロン デバイスの場合、VSHARE ピンをフローティングのままにする必要があります。VSHARE は、最大 50 pF の容量で AGND にバイパスできます。                                                                                                                                       |

| VSHARE_B  | 35             |                   |                                                                                                                                                                                                                                             |

| MSEL1_A   | 13             | I                 | スイッチング周波数と内部補償パラメータの各種オプションについては、このピンを BP1V5 と AGND との間の抵抗デバイダに接続します。MSEL1 のプログラミング セクションを参照してください。                                                                                                                                         |

| MSEL1_B   | 34             |                   |                                                                                                                                                                                                                                             |

| ADRSEL_A  | 14             | I                 | PMBus アドレスと周波数同期の各種オプション (SYNCIN または SYNCOUT 機能として SYNC ピンを決定することを含む) については、BP1V5 と AGND との間の抵抗デバイダにこのピンを接続します。ADRSEL のプログラミング セクションを参照してください。                                                                                              |

| ADRSEL_B  | 33             |                   |                                                                                                                                                                                                                                             |

| VSEL_A    | 15             | I                 | 内部電圧帰還分圧器の各種オプションとデフォルトの出力電圧については、このピンを BP1V5 と AGND との間の抵抗デバイダに接続します。VSEL のプログラミング を参照してください。                                                                                                                                              |

| VSEL_B    | 32             |                   |                                                                                                                                                                                                                                             |

| MSEL2_A   | 16             | I                 | ソフトスタート時間、過電流フルトリミット、マルチフェーズ情報の各種オプションについては、このピンを BP1V5 と AGND との間の抵抗デバイダに接続します。GOSNS が BP1V5 に接続されている場合、ループ フォロワー デバイス (BP1V5 に接続されている GOSNS) については、MSEL2 のループ フォロワー デバイス用 プログラミング (GOSNS を BP1V5 に接続) または MSEL2 のプログラミング のセクションを参照してください。 |

| MSEL2_B   | 31             |                   |                                                                                                                                                                                                                                             |

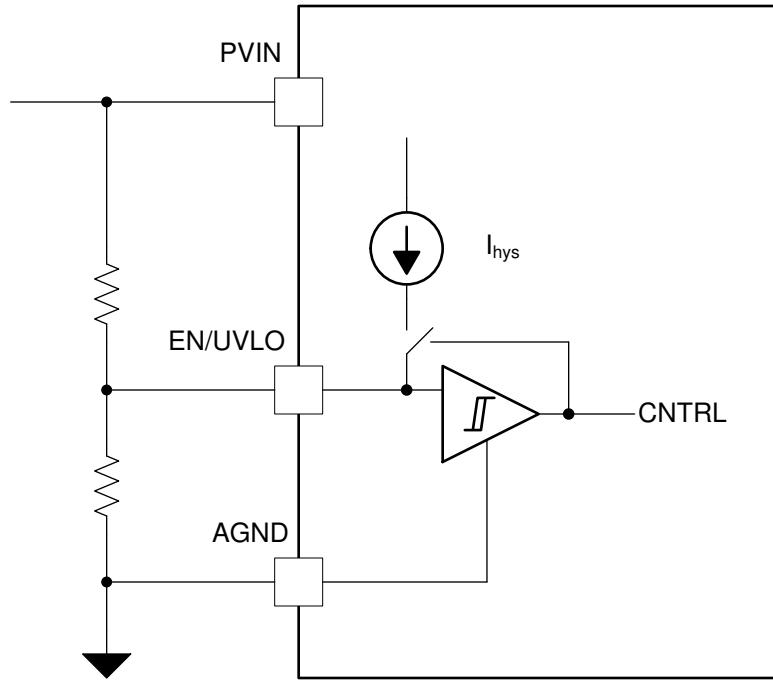

| EN/UVLO_A | 19             | I                 | PMBus CONTROL ピンとしてスイッチングを有効にします。EN/UVLO を抵抗デバイダに接続して、入力電圧 UVLO をプログラムすることもできます。                                                                                                                                                            |

| EN/UVLO_B | 25             |                   |                                                                                                                                                                                                                                             |

| PVIN_A    | 18, 55         | I                 | 電力段への入力電力。これらのピンから PGND への低インピーダンスのバイパスが重要です。PVIN から PGND へは、X5R 以上の定格を持つ最大 PVIN 電圧の 1.5 倍以上のセラミック コンデンサを使用してバイパスする必要があります。                                                                                                                 |

| PVIN_B    | 24, 56         |                   |                                                                                                                                                                                                                                             |

| AVIN_A    | 20             | I                 | コントローラへの入力電源                                                                                                                                                                                                                                |

| AVIN_B    | 26             |                   |                                                                                                                                                                                                                                             |

| AGND_A    | 21             | —                 | コントローラ用のアナログ グランド帰路。AGND ピンを PCB 基板のサーマル パッドに直接接続します。                                                                                                                                                                                       |

| AGND_B    | 27             |                   |                                                                                                                                                                                                                                             |

| VDD5_A    | 22             | O                 | 5V 内部レギュレータの出力。バイパス コンデンサは内蔵されているため、外部バイパスは不要です。                                                                                                                                                                                            |

| VDD5_B    | 28             |                   |                                                                                                                                                                                                                                             |

| SYNC      | 29             | I/O               | 周波数同期のため、ADRSEL ピンまたは (E4h) MFR_SPECIFIC_20 (SYNC_CONFIG) PMBus コマンドを使用して、このピンを SYNC IN または SYNC OUT ピンとしてプログラムできます。位相 A と位相 B では、SYNC は内部で互いに接続されます。SYNC ピンは、単相構成でモジュールを使用する場合、フローティングのままできます。                                             |

| VOUT_A    | 50, 51         | O                 | 各チャネルの出力。出力バイパス コンデンサをこのピンに接続します。                                                                                                                                                                                                           |

| VOUT_B    | 47, 48         |                   |                                                                                                                                                                                                                                             |

| サーマル パッド  | 52, 54, 57, 59 | —                 | サーマル パッドは、PCB への熱伝導率を向上させるために広い面積の銅で作られた PGND ピンです。最高の放熱特性を得るには、サーマル パッドに十分な半田領域が必要です。                                                                                                                                                      |

| SW_A      | 53             | I/O               | デバイスのスイッチ電源出力。必要に応じて、出力平均化フィルタとブートストラップを、このピン ループに接続します。                                                                                                                                                                                    |

| SW_B      | 58             |                   |                                                                                                                                                                                                                                             |

(1) I = 入力、O = 出力

## 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                |                                                  | 最小値  | 最大値  | 単位 |

|----------------|--------------------------------------------------|------|------|----|

| 入力電圧           | AVIN                                             | -0.3 | 18   | V  |

|                | PVIN                                             | -0.3 | 16   |    |

|                | PVIN_A, PVIN_B, < 2ms 過渡                         | -0.3 | 19   |    |

|                | EN/UVLO, VOSNS, SYNC, VSEL, MSEL1, MSEL2, ADRSEL | -0.3 | 5.5  |    |

|                | VSHARE, GOSNS/LOOP FLWR                          | -0.3 | 1.98 |    |

|                | PMB_CLK, PMB_DATA, BCX_CLK, BCX_DAT              | -0.3 | 5.5  |    |

| VDD5 外部バイアス範囲  |                                                  | 4.25 | 5.25 |    |

| 出力電圧           | VOUT                                             | 0.5  | 3.6  | V  |

|                | VDD5, SMB_ALRT, PGD/RST                          | -0.3 | 5.5  |    |

|                | BP1V5                                            | -0.3 | 1.65 |    |

| $T_J$ 接合部動作温度  |                                                  | -40  | 150  | °C |

| $T_{stg}$ 保管温度 |                                                  | -55  | 150  | °C |

(1) 「絶対最大定格」外での動作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                           | 値     | 単位 |

|-------------|------|-----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | ±2000 | V  |

|             |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±1500 |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                        |                                  | 最小値  | 公称値 | 最大値 | 単位 |

|------------------------|----------------------------------|------|-----|-----|----|

| $V_{AVIN}$             | 内部 LDO によるコントローラ入力電圧             | 4.25 | 12  | 18  | V  |

| $V_{AVIN}$             | $VDD5$ に有効な外部バイアスを印加するコントローラ入力電圧 | 2.95 | 12  | 18  | V  |

| $V_{PVIN}$             | 内部 LDO による電力段入力電圧                | 4.25 | 12  | 16  | V  |

| $V_{PVIN}$             | $VDD5$ に有効な外部バイアスを印加する電力段入力電圧    | 2.95 | 12  | 16  | V  |

| $V_{OUT}$              | 出力電圧範囲                           | 0.5  |     | 3.6 | V  |

| $IOUT_{MAX(1\ phase)}$ | 各相の最大連続出力電流                      |      |     | 35  | A  |

| $IOUT_{MAX(Total)}$    | モジュールごとの最大合計連続出力電流               |      |     | 70  | A  |

| 位相                     | スタッカブル可能な相の最大数                   |      |     | 4   |    |

| $T_J$                  | 接合部温度                            | -40  |     | 125 | °C |

| $T_A$                  | 周囲温度                             | -40  |     | 105 | °C |

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                  | QFM (MOW) | 単位   |

|----------------------|------------------|-----------|------|

|                      |                  | 59 ピン     |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗     | 12.6      | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ | 0.78      | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ | 9.8       | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびIC パッケージの热評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ ,  $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ ,  $f_{\text{SW}} = 550\text{kHz}$ , ゼロ消費電力 (特に注記がない限り)

| パラメータ                          | テスト条件                                | 最小値                                             | 標準値                                      | 最大値        | 単位            |

|--------------------------------|--------------------------------------|-------------------------------------------------|------------------------------------------|------------|---------------|

| <b>入力電源電圧</b>                  |                                      |                                                 |                                          |            |               |

| $V_{\text{AVIN}}$              | 入力電源電圧範囲                             | 内部 LDO によるコントローラ入力電圧                            | 4.25                                     | 18         | V             |

| $V_{\text{AVIN}}$              | 入力電源電圧範囲                             | 有効な外部バイアスを印加するコントローラ入力電圧                        | 2.95                                     | 18         |               |

| $V_{\text{PVIN}}$              | 電力段電圧範囲                              | 内部 LDO による電力段入力電圧                               | 4.25                                     | 16         |               |

| $V_{\text{PVIN}}$              | 電力段電圧範囲                              | 有効な外部バイアスを印加する電力段入力電圧                           | 2.95                                     | 16         |               |

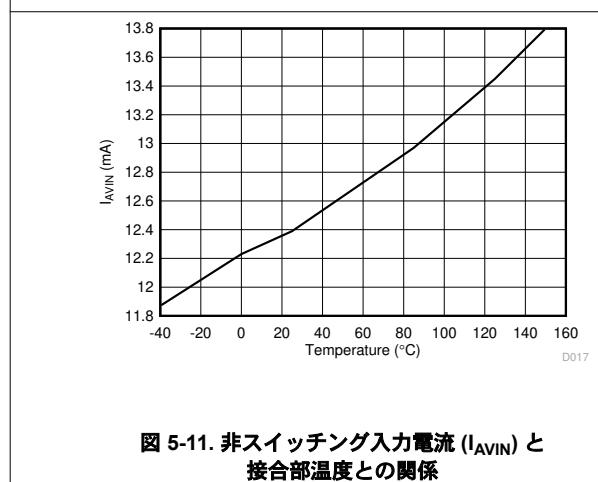

| $I_{\text{AVIN}}$              | 入力動作電流                               | コンバータのスイッチングなし、各位相                              | 12.5                                     | 17         | mA            |

| <b>AVIN UVLO</b>               |                                      |                                                 |                                          |            |               |

| $V_{\text{AVIN_Uvlo}}$         | パワー オン リセット用アナログ入力電圧 UVLO (PMBus 通信) | イネーブル スレッショルド                                   | 2.5                                      | 2.7        | V             |

|                                | 無効化用アナログ入力電圧 UVLO                    |                                                 | 2.09                                     | 2.3        | V             |

|                                | アナログ入力電圧 UVLO のヒステリシス                |                                                 | 250                                      |            | mV            |

| $t_{\text{delay(uvlo_PMBus)}}$ | AVIN UVLO から PMBus の準備完了までの遅延        | $AVIN = 3\text{V}$                              | 8                                        |            | ms            |

| <b>PVIN UVLO</b>               |                                      |                                                 |                                          |            |               |

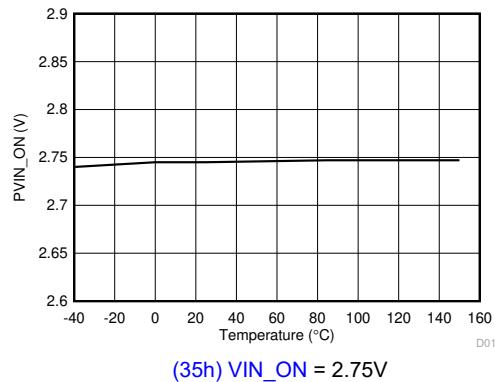

| $V_{\text{IN\_ON}}$            | 電源入力ターンオン電圧                          | 工場出荷時のデフォルト設定                                   | 2.75                                     |            | V             |

|                                |                                      | プログラマブルな範囲                                      | 2.75                                     | 15.75      |               |

|                                |                                      | 分解能                                             | 0.25                                     |            |               |

|                                |                                      | 精度                                              | -5%                                      | 5%         |               |

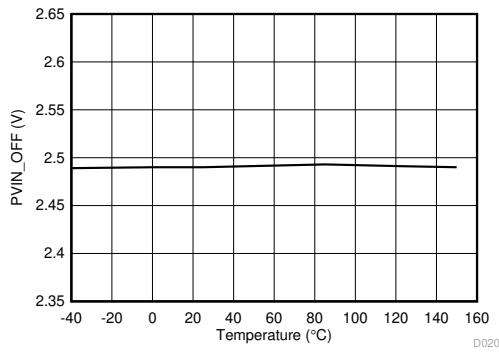

| $V_{\text{IN\_OFF}}$           | 電力入力ターンオフ電圧                          | 工場出荷時のデフォルト設定                                   | 2.5                                      |            | V             |

|                                |                                      | プログラマブルな範囲                                      | 2.5                                      | 15.5       |               |

|                                |                                      | 分解能                                             | 0.25                                     |            |               |

|                                |                                      | 精度                                              | -5%                                      | 5%         |               |

| <b>イネーブルおよび UVLO</b>           |                                      |                                                 |                                          |            |               |

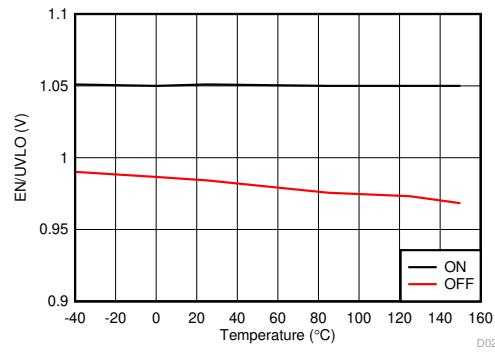

| $V_{\text{EN_Uvlo}}$           | EN/UVLO 電圧立ち上がりスレッショルド               |                                                 | 1.05                                     | 1.1        | V             |

|                                | EN/UVLO 電圧立ち下がりスレッショルド               |                                                 | 0.9                                      |            |               |

| $V_{\text{EN_hys}}$            | EN/UVLO 電圧ヒステリシス                     | EN/UVLO に外部抵抗なし                                 | 70                                       |            | mV            |

| $I_{\text{EN_hys}}$            | EN/UVLO ヒステリシス電流                     | $V_{\text{EN/UVLO}} = 1.1\text{V}$              | 4.5                                      | 5.5        | $\mu\text{A}$ |

|                                | EN/UVLO ヒステリシス電流                     | $V_{\text{EN/UVLO}} = 0.9\text{V}$              | -100                                     | -5         | nA            |

| <b>リモート センス アンプ</b>            |                                      |                                                 |                                          |            |               |

| $Z_{\text{RSA}}$               | リモート センス入力インピーダンス                    | $V_{\text{OSNS}} - G_{\text{OSNS}} = 1\text{V}$ | $V_{\text{OSNS}}$ から $G_{\text{OSNS}}$ へ | 85 130 165 | k $\Omega$    |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ 、 $f_{\text{SW}} = 550\text{kHz}$ 、ゼロ消費電力 (特に注記がない限り)

| パラメータ                    |                                          | テスト条件                                                                           | 最小値                                                                                       | 標準値   | 最大値    | 単位               |  |

|--------------------------|------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|--------|------------------|--|

| $V_{\text{IRNG(GOSNS)}}$ | レギュレーション精度のための GOSNS 入力範囲 <sup>(1)</sup> |                                                                                 | $V_{\text{OSNS}} - V_{\text{GOSNS}} = 1\text{V}$ 、 $V_{\text{OUT\_SCALE\_LOOP}} \leq 0.5$ |       | -0.05  | 0.05             |  |

| $V_{\text{IRNG(VOSNS)}}$ | レギュレーション精度のための VOSNS 入力範囲 <sup>(1)</sup> |                                                                                 | $V_{\text{GOSNS}} = \text{AGND}$ 、 $V_{\text{OUT\_SCALE\_LOOP}} \leq 0.5$                 |       | -0.1   | 5.5              |  |

| リファレンス電圧とエラー アンプ         |                                          |                                                                                 |                                                                                           |       |        |                  |  |

| $V_{\text{REF}}$         | 基準電圧 <sup>(1)</sup>                      | デフォルト設定                                                                         | 0.4                                                                                       |       | V      |                  |  |

|                          |                                          | リファレンス電圧の範囲 <sup>(1)</sup>                                                      | 0.25                                                                                      |       | 0.75   | V                |  |

|                          |                                          | リファレンス電圧分解能 <sup>(1)</sup>                                                      | $2^{-12}$                                                                                 |       | V      |                  |  |

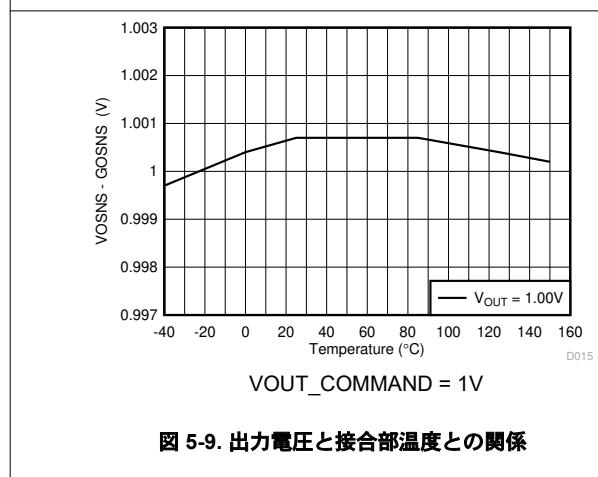

| $V_{\text{OUT(ACC)}}$    | 出力電圧精度                                   | $V_{\text{OUT}} = 1000\text{mV}$                                                | $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$ <sup>(2)</sup>                        | 0.992 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 500\text{mV}$                                                 |                                                                                           | 0.492 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 1500\text{mV}$                                                |                                                                                           | 1.490 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 1000\text{mV}$                                                | $0^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ <sup>(2)</sup>                          | 0.994 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 500\text{mV}$                                                 |                                                                                           | 0.494 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 1500\text{mV}$                                                |                                                                                           | 1.492 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 1000\text{mV}$                                                | $0^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ <sup>(2)</sup>                           | 0.995 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 500\text{mV}$                                                 |                                                                                           | 0.495 |        | V                |  |

|                          |                                          | $V_{\text{OUT}} = 1500\text{mV}$                                                |                                                                                           | 1.493 |        | V                |  |

| $G_{\text{mEA}}$         | プログラム可能なエラー アンプの相互コンダクタンス                |                                                                                 | 25                                                                                        |       | 200    | $\mu\text{s}$    |  |

|                          | 分解能 <sup>(1)</sup>                       | 4 つの設定: $25\mu\text{s}$ 、 $50\mu\text{s}$ 、 $100\mu\text{s}$ 、 $200\mu\text{s}$ | 25                                                                                        |       |        |                  |  |

|                          | 無負荷帯域幅 <sup>(1)</sup>                    | 8                                                                               |                                                                                           | MHz   |        |                  |  |

| $R_{\text{pEA}}$         | プログラム可能な並列抵抗の範囲                          |                                                                                 | 5                                                                                         |       | 315    | $\text{k}\Omega$ |  |

|                          | 分解能 <sup>(1)</sup>                       | 5                                                                               |                                                                                           |       |        |                  |  |

| $C_{\text{intEA}}$       | プログラム可能な積分器コンデンサの範囲                      |                                                                                 | 1.25                                                                                      |       | 18.75  | pF               |  |

|                          | 分解能 <sup>(1)</sup>                       | 1.25                                                                            |                                                                                           | pF    |        |                  |  |

| $C_{\text{pEA}}$         | プログラム可能な並列コンデンサの範囲                       |                                                                                 | 6.25                                                                                      |       | 193.75 | $\text{pF}$      |  |

|                          | 分解能 <sup>(1)</sup>                       | 6.25                                                                            |                                                                                           |       |        |                  |  |

| 電流 GM アンプ                |                                          |                                                                                 |                                                                                           |       |        |                  |  |

| $G_{\text{mBUF}}$        | プログラム可能な電流エラー アンプの相互コンダクタンス              |                                                                                 | 25                                                                                        |       | 200    | $\mu\text{s}$    |  |

|                          | 分解能 <sup>(1)</sup>                       | 4 つの設定: $25\mu\text{s}$ 、 $50\mu\text{s}$ 、 $100\mu\text{s}$ 、 $200\mu\text{s}$ | 25                                                                                        |       |        |                  |  |

|                          | 無負荷帯域幅 <sup>(1)</sup>                    | 17                                                                              |                                                                                           | MHz   |        |                  |  |

| $R_{\text{pBUF}}$        | プログラム可能な並列抵抗の範囲                          |                                                                                 | 5                                                                                         |       | 315    | $\text{k}\Omega$ |  |

|                          | 分解能 <sup>(1)</sup>                       | 5                                                                               |                                                                                           |       |        |                  |  |

| $R_{\text{intBUF}}$      | プログラム可能な積分抵抗の範囲 <sup>(1)</sup>           |                                                                                 | 800                                                                                       |       | 1600   | $\text{k}\Omega$ |  |

|                          | 分解能 <sup>(1)</sup>                       | 800                                                                             |                                                                                           |       |        |                  |  |

| $C_{\text{intBUF}}$      | プログラム可能な積分器コンデンサの範囲                      |                                                                                 | 0.3125                                                                                    |       | 4.6875 | $\text{pF}$      |  |

|                          | 分解能 <sup>(1)</sup>                       | 0.3125                                                                          |                                                                                           |       |        |                  |  |

| $C_{\text{pBUF}}$        | プログラム可能な並列コンデンサの範囲                       |                                                                                 | 3.125                                                                                     |       | 96.875 | $\text{pF}$      |  |

|                          | 分解能 <sup>(1)</sup>                       | 3.125                                                                           |                                                                                           |       |        |                  |  |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ ,  $f_{\text{SW}} = 550\text{kHz}$ , ゼロ消費電力 (特に注記がない限り)

| パラメータ                      |                                                     | テスト条件                                                                                             | 最小値          | 標準値        | 最大値  | 単位            |

|----------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------|------------|------|---------------|

| <b>発振器</b>                 |                                                     |                                                                                                   |              |            |      |               |

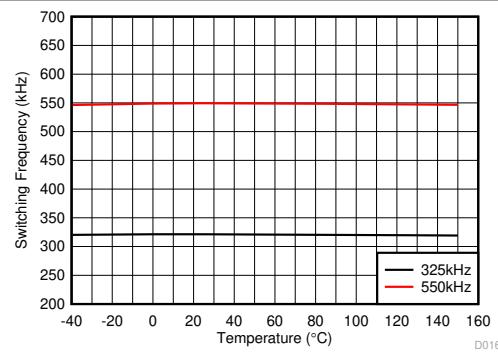

| $f_{\text{SW}}$            | 調整範囲 <sup>(2)</sup>                                 |                                                                                                   | 275          | 1100       |      | kHz           |

|                            | スイッチング周波数 <sup>(2)</sup>                            |                                                                                                   | 500          | 550        | 600  |               |

| <b>同期</b>                  |                                                     |                                                                                                   |              |            |      |               |

| $V_{\text{IH(sync)}}$      | High レベル入力電圧                                        |                                                                                                   | 1.35         |            |      | V             |

| $V_{\text{IL(sync)}}$      | Low レベル入力電圧                                         |                                                                                                   |              |            | 0.8  |               |

| $t_{\text{pw(sync)}}$      | 同期入力の最小パルス幅                                         |                                                                                                   |              | 200        |      | ns            |

| $\Delta f_{\text{SYNC}}$   | FREQUENCY_SWITCH 周波数からの SYNC ピン周波数範囲 <sup>(1)</sup> |                                                                                                   | -20%         | 20%        |      |               |

| $V_{\text{OH(sync)}}$      | 同期高出力電圧                                             | 負荷 100 $\mu\text{A}$                                                                              | VDD5 – 0.85V | VDD5       |      | V             |

| $V_{\text{OL(sync)}}$      | 同期低出力電圧                                             | 負荷 2.4mA                                                                                          |              | 0.4        |      | V             |

| $t_{\text{PLL}}$           | PLL ロック時間                                           | $f_{\text{sw}} = 550\text{kHz}$ , SYNC クロック周波数 495kHz ~ 605kHz <sup>(1)</sup>                     |              | 65         |      | $\mu\text{s}$ |

| PhaseErr                   | 位相インターリーブ エラー <sup>(5)</sup>                        | $f_{\text{sw}} < 1.1\text{MHz}$                                                                   |              | 9          | 度    |               |

|                            |                                                     | $f_{\text{sw}} \geq 1.1\text{MHz}$                                                                |              | 23         | ns   |               |

| <b>リセット</b>                |                                                     |                                                                                                   |              |            |      |               |

| $V_{\text{IH(reset)}}$     | High レベル入力電圧 <sup>(1)</sup>                         |                                                                                                   | 1.35         |            |      | V             |

| $V_{\text{IL(reset)}}$     | Low レベル入力電圧                                         |                                                                                                   |              | 0.8        |      |               |

| $t_{\text{pw(reset)}}$     | 最小 RESET_B パルス幅                                     |                                                                                                   |              | 200        |      | ns            |

| $R_{\text{pullup(reset)}}$ | 内部プルアップ抵抗                                           | $V_{\text{RESET}} = 0.8\text{V}$                                                                  | RESET# = 1   | 25         | 34   | 55            |

| $V_{\text{pullup(reset)}}$ | 内部プルアップ電圧                                           | $I_{\text{RESET}} = 10\mu\text{A}$                                                                | RESET# = 1   | VDD5 - 0.5 |      | V             |

| <b>VDD5 レギュレータ</b>         |                                                     |                                                                                                   |              |            |      |               |

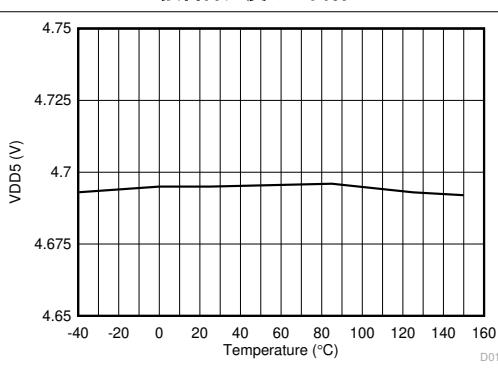

| $V_{\text{VDD5}}$          | レギュレータ出力電圧                                          | デフォルト、 $I_{\text{VDD5}} = 10\text{mA}$                                                            | 4.5          | 4.7        | 4.9  | V             |

|                            | プログラマブルな範囲 <sup>(1)</sup>                           |                                                                                                   | 3.9          | 5.3        |      | V             |

|                            | 分解能                                                 |                                                                                                   | 200          |            |      | mV            |

| $V_{\text{VDD5(do)}}$      | レギュレータドロップアウト電圧                                     | $V_{\text{AVIN}} - V_{\text{VDD5}}, V_{\text{AVIN}} = 4.5\text{V}, I_{\text{VDD5}} = 25\text{mA}$ | 130          | 285        |      | mV            |

| $I_{\text{VDD5SC}}$        | レギュレータ短絡電流 <sup>(1)</sup>                           | $V_{\text{AVIN}} = 4.5\text{V}$                                                                   | 100          |            |      | mA            |

| $V_{\text{VDD5ON(IF)}}$    | ピンストラップ用の VDD5 有効電圧                                 |                                                                                                   |              | 2.62       | 2.85 | V             |

| $V_{\text{VDD5OFF(IF)}}$   | ピンストラップ用の VDD5 無効電圧                                 |                                                                                                   | 2.25         | 2.48       |      | V             |

| $V_{\text{VDD5ON(SW)}}$    | VDD5 のスイッチング有効電圧                                    |                                                                                                   |              | 4.05       |      | V             |

| $V_{\text{VDD5OFF(SW)}}$   | VDD5 のスイッチング無効電圧                                    |                                                                                                   | 3.10         |            |      | V             |

| $V_{\text{VDD5UV(hyst)}}$  | レギュレータ UVLO 電圧ヒステリシス                                |                                                                                                   | 400          |            |      | mV            |

| $V_{\text{BOOT(drop)}}$    | ブートストラップ電圧降下                                        | $I_{\text{BOOT}} = 20\text{mA}, V_{\text{DD5}} = 4.5\text{V}$                                     |              | 225        |      | mV            |

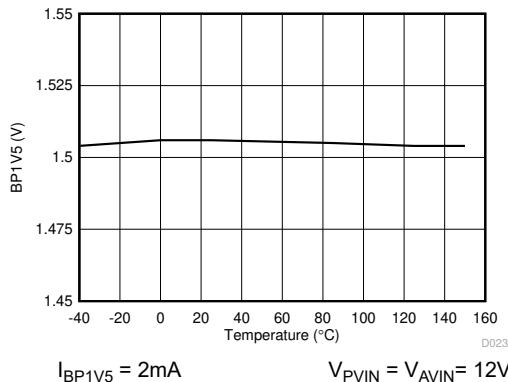

| <b>BP1V5 レギュレータ</b>        |                                                     |                                                                                                   |              |            |      |               |

| $V_{\text{BP1V5}}$         | 1.5V レギュレータ出力電圧                                     | $V_{\text{AVIN}} \geq 4.5\text{V}, I_{\text{BP1V5}} = 5\text{mA}$                                 | 1.42         | 1.5        | 1.58 | V             |

| $I_{\text{BP1V5SC}}$       | 1.5V レギュレータ短絡電流 <sup>(1)</sup>                      |                                                                                                   | 30           |            |      | mA            |

| <b>PWM</b>                 |                                                     |                                                                                                   |              |            |      |               |

| $t_{\text{ON(min)}}$       | コントロール可能な最小パルス幅 <sup>(1)</sup>                      |                                                                                                   |              | 20         |      | ns            |

| $t_{\text{OFF(min)}}$      | PWM 最小オフ時間 <sup>(1)</sup>                           |                                                                                                   | 400          | 500        |      | ns            |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ ,  $f_{\text{SW}} = 550\text{kHz}$ , ゼロ消費電力 (特に注記がない限り)

| パラメータ                         | テスト条件                                | 最小値                                                                        | 標準値  | 最大値   | 単位               |

|-------------------------------|--------------------------------------|----------------------------------------------------------------------------|------|-------|------------------|

| <b>ソフトスタート</b>                |                                      |                                                                            |      |       |                  |

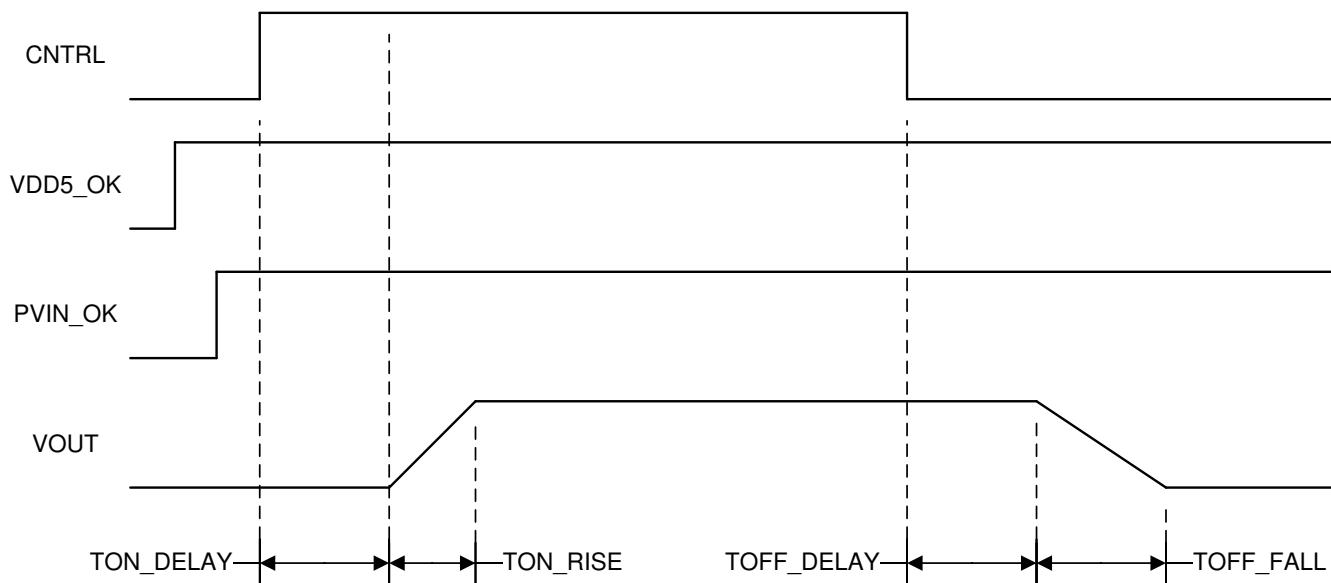

| $t_{\text{ON\_RISE}}$         | ソフトスタート時間                            | 工場出荷時のデフォルト設定                                                              | 3    |       | ms               |

|                               |                                      | プログラマブルな範囲 <sup>(1) (3)</sup>                                              | 0    | 31.75 |                  |

|                               |                                      | 分解能                                                                        | 0.25 |       |                  |

|                               |                                      | 精度、 $\text{TON\_RISE} = 3\text{ms}$                                        | -10% | 15%   |                  |

| $t_{\text{ON\_MAX\_FLT\_LT}}$ | 出力パワー アップまでの時間の上限                    | 工場出荷時のデフォルト設定 <sup>(4)</sup>                                               | 0    |       | ms               |

|                               |                                      | プログラマブルな範囲 <sup>(1) (4)</sup>                                              | 0    | 127.5 |                  |

|                               |                                      | 分解能                                                                        | 0.5  |       |                  |

|                               |                                      | 精度 <sup>(1)</sup>                                                          | -10% | 15%   |                  |

| $t_{\text{ON\_DELAY}}$        | ターンオン遅延                              | 工場出荷時のデフォルト設定                                                              | 0    |       | ms               |

|                               |                                      | プログラマブルな範囲 <sup>(1)</sup>                                                  | 0    | 127.5 |                  |

|                               |                                      | 分解能                                                                        | 0.5  |       |                  |

|                               |                                      | 精度 <sup>(1)</sup>                                                          | -10% | 15%   |                  |

| <b>ソフトストップ</b>                |                                      |                                                                            |      |       |                  |

| $t_{\text{OFF\_FALL}}$        | ソフトストップ時間                            | 工場出荷時のデフォルト設定 <sup>(3)</sup>                                               | 0.5  |       | ms               |

|                               |                                      | プログラマブルな範囲 <sup>(1) (3)</sup>                                              | 0    | 31.75 |                  |

|                               |                                      | 分解能                                                                        | 0.25 |       |                  |

|                               |                                      | 精度、 $t_{\text{OFF\_FALL}} = 1\text{ms}$                                    | -10% | 15%   |                  |

| $t_{\text{OFF\_DELAY}}$       | ターンオフ遅延時間                            | 工場出荷時のデフォルト設定                                                              | 0    |       | ms               |

|                               |                                      | プログラマブルな範囲 <sup>(1)</sup>                                                  | 0    | 127.5 |                  |

|                               |                                      | 分解能                                                                        | 0.5  |       |                  |

|                               |                                      | 精度 <sup>(1)</sup>                                                          | -10% | 15%   |                  |

| <b>電源入力過電圧 / 低電圧</b>          |                                      |                                                                            |      |       |                  |

| $V_{\text{PVINOVF}}$          | 電源入力過電圧フォルト制限                        | 工場出荷時のデフォルト設定                                                              | 20   |       | V                |

|                               |                                      | プログラマブルな範囲                                                                 | 6    | 20    |                  |

|                               |                                      | 分解能                                                                        | 1    |       |                  |

| $V_{\text{PVINUW}}$           | 電源入力低電圧警告制限                          | 工場出荷時のデフォルト設定                                                              | 2.5  |       | V                |

|                               |                                      | プログラマブルな範囲                                                                 | 2.5  | 15.75 |                  |

|                               |                                      | 分解能                                                                        | 0.25 |       |                  |

| <b>電力段</b>                    |                                      |                                                                            |      |       |                  |

| $R_{\text{HS}}$               | ハイサイド電力供給デバイス オン抵抗                   | $V_{\text{BOOT}} - V_{\text{SW}} = 4.5\text{V}$ , $T_J = 25^\circ\text{C}$ | 4.5  |       | $\text{m}\Omega$ |

| $R_{\text{LS}}$               | ローサイド電力供給デバイス オン抵抗                   | $V_{\text{VDD5}} = 4.5\text{V}$ , $T_J = 25^\circ\text{C}$                 | 0.9  |       | $\text{m}\Omega$ |

| $R_{\text{swpd}}$             | SW 内部プルダウン抵抗                         |                                                                            | 3    | 30    | 35               |

| $V_{\text{wkdr(on)}}$         | PVIN 立ち上がり時の、弱いハイサイド ゲート駆動トリガスレッショルド |                                                                            |      | 14.75 | V                |

| $V_{\text{wkdr(off)}}$        | PVIN 立ち下がり時の、弱いハイサイド ゲート駆動回復スレッショルド  |                                                                            |      | 14.35 | V                |

| $t_{\text{DEAD(LtoH)}}$       | ローサイド オフからハイサイド オンまでの電力段ドライバのデッドタイム  | $V_{\text{VDD5}} = 4.5\text{V}$ , $T_J = 25^\circ\text{C}$ <sup>(1)</sup>  | 6    |       | ns               |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ ,  $f_{\text{SW}} = 550\text{kHz}$ , ゼロ消費電力 (特に注記がない限り)

| パラメータ                                           |                                                            | テスト条件                                                                     | 最小値                            | 標準値 | 最大値                   | 単位       |  |  |

|-------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------|-----|-----------------------|----------|--|--|

| $t_{\text{DEAD(Ht0L)}}$                         | ハイサイド オフからローサイド オンまでの電力段ドライバのデッドタイム                        | $V_{\text{VDD5}} = 4.5\text{V}$ , $T_J = 25^\circ\text{C}$ <sup>(1)</sup> | 6                              |     | ns                    |          |  |  |

| <b>電流共有</b>                                     |                                                            |                                                                           |                                |     |                       |          |  |  |

| $I_{\text{SHARE(acc)}}$                         | 2つのデバイスの出力電流共有精度は、2つのデバイス間の電流差を2つのデバイスの合計電流で割った比率として定義されます | デバイスあたり $I_{\text{OUT}} \geq 20\text{A}$ <sup>(5)</sup>                   | -10%                           |     | 10%                   |          |  |  |

|                                                 | 2つのデバイスの出力電流共有精度は、各デバイス間の電流差と全デバイスの平均値として定義されます            | デバイスあたり $I_{\text{OUT}} < 20\text{A}$ <sup>(5)</sup>                      | -2                             |     | 2                     |          |  |  |

| 2つのデバイスの出力電流共有精度は、各デバイス間の電流差と全デバイスの平均値として定義されます | デバイスあたり $I_{\text{OUT}} < 10\text{A}$ <sup>(5)</sup>       | -1                                                                        |                                | 1   | A                     |          |  |  |

| $V_{\text{VSHARE}}$                             | $V_{\text{SHARE}}$ 故障トリップ スレッショルド                          |                                                                           |                                |     | 0.1                   |          |  |  |

|                                                 | $V_{\text{SHARE}}$ 故障リリース スレッショルド                          |                                                                           |                                |     | 0.2                   |          |  |  |

| <b>ローサイド電流制限保護</b>                              |                                                            |                                                                           |                                |     |                       |          |  |  |

| $t_{\text{OFF(OC)}}$                            | 再起動試行間隔のオフ時間 <sup>(1)</sup>                                | 工場出荷時のデフォルト設定                                                             | $7 \times t_{\text{ON\_RISE}}$ |     | $t_{\text{ON\_RISE}}$ |          |  |  |

|                                                 | 範囲                                                         |                                                                           |                                |     |                       |          |  |  |

| $IO_{\text{OC\_FLT\_LMT}}$                      | 出力電流過電流の故障スレッショルド                                          | 工場出荷時のデフォルト設定                                                             | 52                             |     | $t_{\text{ON\_RISE}}$ |          |  |  |

|                                                 |                                                            | プログラマブルな範囲                                                                | 8                              |     |                       |          |  |  |

|                                                 |                                                            | 分解能                                                                       | 2                              |     |                       |          |  |  |

| $I_{\text{NEGOC}}$                              | 負の出力電流過電流の保護スレッショルド                                        |                                                                           |                                |     | -20                   |          |  |  |

| $IO_{\text{OC\_WRN\_LMT}}$                      | 出力電流過電流警告スレッショルド                                           | 工場出荷時のデフォルト設定                                                             | 40                             |     | $t_{\text{ON\_RISE}}$ |          |  |  |

|                                                 |                                                            | プログラマブルな範囲                                                                | 8                              |     |                       |          |  |  |

|                                                 |                                                            | 分解能                                                                       | 2                              |     |                       |          |  |  |

| $I_{\text{OC(acc)}}$                            | 出力電流過電流の故障エラー                                              | $I_{\text{OUT}} = 20\text{A}$                                             | -2                             |     | 4                     |          |  |  |

|                                                 |                                                            | $I_{\text{OUT}} = 35\text{A}$ <sup>(5)</sup>                              | -4                             |     |                       |          |  |  |

| $I_{\text{HSOC}}$                               | 出力電流過電流の故障精度                                               | $I_{\text{OUT}} = 10\text{A}$                                             | -1                             |     | 2                     |          |  |  |

|                                                 |                                                            | $I_{\text{OUT}} = 20\text{A}$ <sup>(5)</sup>                              | -2                             |     |                       |          |  |  |

| <b>ハイサイド短絡保護</b>                                |                                                            |                                                                           |                                |     |                       |          |  |  |

| $I_{\text{HSOC}}$                               | ローサイド過電流制限に対するハイサイド短絡保護の故障スレッショルドの比率                       | $T_J = 25^\circ\text{C}$ <sup>(5)</sup>                                   | 105%                           |     | 150%                  |          |  |  |

|                                                 | ハイサイド電流センスのブランギング時間                                        |                                                                           |                                |     | 100                   |          |  |  |

| <b>パワー グッド (PGOOD) と過電圧 / 低電圧警告</b>             |                                                            |                                                                           |                                |     |                       |          |  |  |

| $R_{\text{PGD}}$                                | PGD ブルダウン抵抗                                                | $I_{\text{PGD}} = 5\text{mA}$                                             | 30                             |     | 50                    | $\Omega$ |  |  |

| $I_{\text{PGD(OH)}}$                            | PGD ピンへの出力 High オープンドレイン リーク電流                             | $V_{\text{PGD}} = 5\text{V}$                                              | 15                             |     | $\mu\text{A}$         |          |  |  |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ 、 $f_{\text{SW}} = 550\text{kHz}$ 、ゼロ消費電力 (特に注記がない限り)

| パラメータ                    |                                                     | テスト条件                                                                | 最小値  | 標準値  | 最大値  | 単位  |     |

|--------------------------|-----------------------------------------------------|----------------------------------------------------------------------|------|------|------|-----|-----|

| $V_{\text{PGD(OI)}}$     | PGD ピン出力 Low レベル電圧、電源電圧なし                           | $V_{\text{AVIN}} = 0$ 、 $I_{\text{PGD}} = 80\mu\text{A}$             |      | 0.8  |      | V   |     |

| $V_{\text{OVW}}$         | 過電圧警告スレッショルド (VOSNS 立ち上がり時の PGD スレッショルド)            | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 106% | 110% | 114% | VOC |     |

|                          | 範囲                                                  |                                                                      | 103% |      | 116% |     |     |

|                          | 分解能                                                 |                                                                      |      |      | 1%   |     |     |

| $V_{\text{UVW}}$         | 低電圧警告スレッショルド (VOSNS 立ち下がり時の PGD スレッショルド)            | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 86%  | 90%  | 94%  | VOC |     |

|                          | 範囲                                                  |                                                                      | 84%  |      | 97%  |     |     |

|                          | 分解能                                                 |                                                                      |      |      | 1%   |     |     |

| $V_{\text{PGD(rise)}}$   | VOSNS 立ち上がり時の PGD リリース スレッショルドおよび低電圧警告デアサーとのスレッショルド | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ |      | 95%  |      |     |     |

| $V_{\text{PGD(fall)}}$   | VOSNS 立ち下がり時の PGD スレッショルドおよび過電圧警告デアサーとのスレッショルド      | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ |      | 105% |      |     |     |

| 出力過電圧および低電圧の故障保護         |                                                     |                                                                      |      |      |      |     |     |

| $V_{\text{OVF}}$         | 過電圧の故障スレッショルド                                       | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 111% | 115% | 119% | VOC |     |

|                          | 範囲                                                  | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 105% |      | 140% |     |     |

|                          | 分解能                                                 | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ |      |      | 2.5% |     |     |

| $V_{\text{UVF}}$         | 低電圧の故障スレッショルド                                       | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 81%  | 85%  | 89%  | VOC |     |

|                          | 範囲                                                  | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} = 1.00\text{V}$              | 60%  |      | 95%  |     |     |

|                          | 分解能                                                 | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} = 1.00\text{V}$              |      |      | 2.5% |     |     |

| $V_{\text{UVF(max)}}$    | 低電圧の故障スレッショルドの最大設定                                  |                                                                      |      | 91%  | 95%  | 99% | VOC |

| $V_{\text{OVF(fix)OFF}}$ | 固定過電圧の故障スレッショルド                                     | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} (V_{\text{OC}}) = 1\text{V}$ | 1.15 | 1.2  | 1.25 | V   |     |

|                          | 復帰スレッショルド <sup>(1)</sup>                            | 工場出荷時のデフォルト設定、 $V_{\text{OUT\_COMMAND}} = 1.00\text{V}$              |      |      | 0.4  |     |     |

| 出力電圧トリミング                |                                                     |                                                                      |      |      |      |     |     |

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{\text{PVIN}} = V_{\text{AVIN}} = 12\text{V}$ ,  $f_{\text{SW}} = 550\text{kHz}$ , ゼロ消費電力 (特に注記がない限り)

| パラメータ                      |                               | テスト条件                                                                                 |                                                      | 最小値       | 標準値   | 最大値                     | 単位                      |  |

|----------------------------|-------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|-----------|-------|-------------------------|-------------------------|--|

| $V_{\text{OUTRES}}$        |                               | $V_{\text{OUT\_COMMAND}}$ のデフォルト分解能、トリミングおよびマージン、 $V_{\text{OUT\_SCALE\_LOOP}} = 0.5$ |                                                      | 1.90      | 1.95  | 2.00                    | mV                      |  |

|                            |                               | プログラマブルな範囲 <sup>(1)</sup>                                                             |                                                      | $2^{-12}$ |       | $2^{-5}$                | V                       |  |

| $V_{\text{OUT\_TRAN\_RT}}$ | 出力電圧遷移レート                     | 工場出荷時のデフォルト設定                                                                         |                                                      | 1         |       | $\text{mV}/\mu\text{s}$ |                         |  |