**TPSM82916**

# TPSM82916 3V~17V、6A、低ノイズ、低リップルの降圧モジュール、フェラ イト ビーズ フィルタ補償機能内蔵

## 1 特長

- 小さい出力 1/f ノイズ:20µV<sub>RMS</sub> 未満 (100Hz~ 100kHz)

- 小さい出力電圧リップル:10µV<sub>RMS</sub> 未満 (フェライトビ ーズの後)

- 優れた PSRR:65dB 超 (最大 100kHz)

- 2.2MHz、1.4MHz、または 1.0MHz の固定周波数ピ ーク電流モード制御

- 外部クロックと同期可能

- 2 段目 L-C フィルタとしてフェライト ビーズを使用でき る内蔵ループ補償機能 (30dB 減衰)

- スペクトラム拡散変調

- 入力電圧範囲:3.0V~17V

- 出力電圧範囲:0.8V~5.5V

- 25m $\Omega/7$ m $\Omega$   $\oslash$  R<sub>DSon</sub>

- ±1% の出力電圧精度 (全温度範囲)

- 高精度のイネーブル入力により以下を実現

- ユーザー定義の低電圧誤動作防止機能

- 正確なシーケンシング

- 可変ソフトスタート

- パワー グッド出力

- 出力放電 (オプション)

- -40°C~125°Cの接合部温度範囲

- 4.0mm × 4.7mm × 3.0mm QFN

- WEBENCH® Power Designer により、TPSM82916 を使用するカスタム設計を作成

## 2 アプリケーション

- 通信インフラ

- 試験および測定機器

- 航空宇宙および防衛 (レーダー、航空電子機器)

- 医療用

## 3 説明

TPSM82916 デバイスは、高効率、低ノイズ、低リップルの 電流モード同期整流降圧 モジュールです。このデバイス は、通常はポストレギュレーションに LDO を使用するよう な、ノイズの影響を受けやすいアプリケーション (たとえ ば、高速 ADC、クロックおよびジッタ クリーナ、シリアライ ザ、デシリアライザ、レーダー)向けに設計されています。

出力電圧リップルを低減するため、本デバイスのループ補 償は、オプションの 2 段目フェライト ビーズ L-C フィルタ を使用して動作するように設計されています。 NR/SS ピン に接続されたコンデンサで内部基準電圧をフィルタ処理 することで、低ノイズ LDO と同様の低い周波数ノイズ レベ ルをさらに達成しています。これらの機能を組み合わせる ことで、出力電圧リップルを 10µV<sub>RMS</sub> 未満に抑えることが できます。

本デバイスは 2.2MHz、1.4MHz または 1MHz の固定ス イッチング周波数で動作し、外部クロックにも同期できま す。オプションのスペクトラム拡散変調方式を使用すると、 DC/DC スイッチング周波数をより広い範囲にわたって拡 散できるため、ミキシングスプリアスを低減できます。

#### パッケージ情報

| 型番        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| TPSM82916 | VCE (QFN-FCMOD, 16)  | 4.7mm × 4.0mm            |

- 詳細については、セクション 10 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンを含みます。

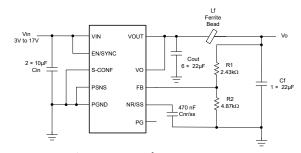

代表的なアプリケーション

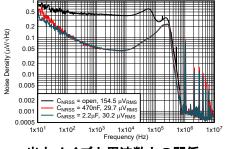

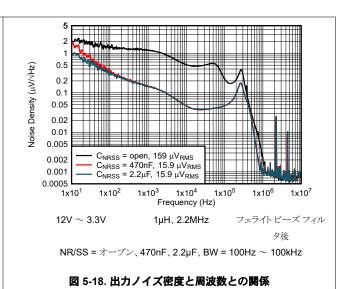

出力ノイズと周波数との関係

# 目次

| 1 特長           | 1  |

|----------------|----|

| 2 アプリケーション     | 1  |

| 3 説明           |    |

| 4 ピン構成および機能    |    |

| 5 仕様           | 5  |

| 5.1 絶対最大定格     |    |

| 5.2 ESD 定格     | 5  |

| 5.3 推奨動作条件     | 5  |

| 5.4 熱に関する情報    | 6  |

| 5.5 電気的特性      | 6  |

| 5.6 代表的特性      |    |

| 6 詳細説明         | 12 |

| 6.1 概要         | 12 |

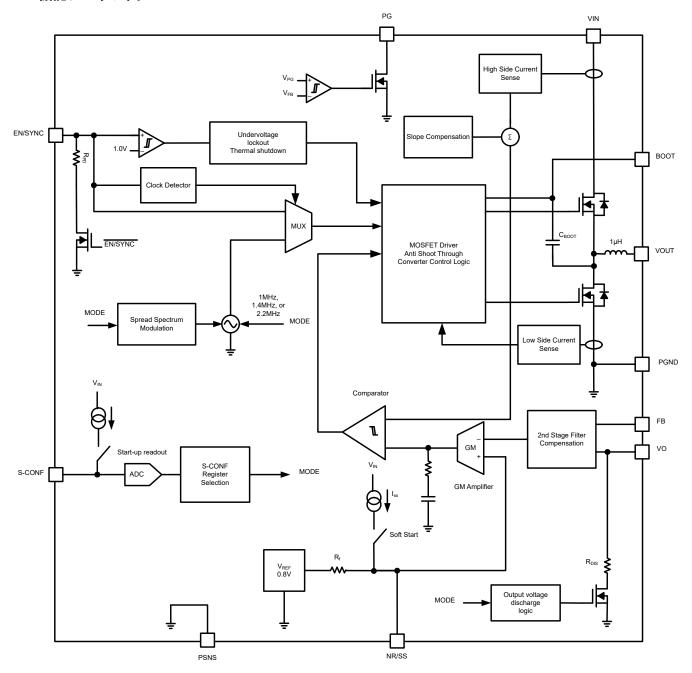

| 6.2 機能ブロック図    |    |

| 6.3 機能説明       | 14 |

| 6.4 デバイスの機能モード |    |

| 7 | アフリケーションと美装           | .19 |

|---|-----------------------|-----|

|   | 7.1 アプリケーション情報        | 19  |

|   | 7.2 代表的なアプリケーション      | 19  |

|   | 7.3 電源に関する推奨事項        | 26  |

|   | 7.4 レイアウト             | 27  |

| 8 | デバイスおよびドキュメントのサポート    | 29  |

|   | 8.1 デバイス サポート         | 29  |

|   | 8.2ドキュメントのサポート        | 29  |

|   | 8.3ドキュメントの更新通知を受け取る方法 | 29  |

|   | 8.4 サポート・リソース         | 29  |

|   | 8.5 商標                | 30  |

|   | 8.6 静電気放電に関する注意事項     |     |

|   | 8.7 用語集               |     |

| 9 | 改訂履歴                  |     |

| 1 | 0 メカニカル、パッケージ、および注文情報 | 31  |

|   |                       |     |

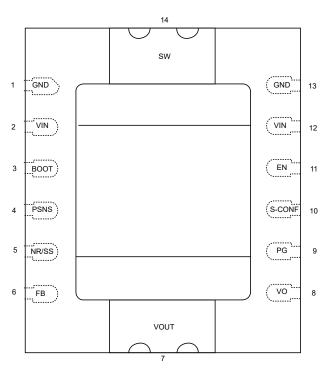

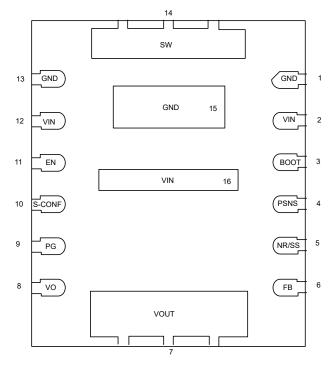

# 4 ピン構成および機能

図 4-1. 16 ピン VCE QFN-FCMOD パッケージ (上面図)

図 4-2. 16 ピン VCE QFN-FCMOD パッケージ (底面図)

3

Product Folder Links: TPSM82916

## 表 4-1. ピンの機能

| ピン          |                                                              | 種類(1)   | 3X BB                                                                                                                                                                              |

|-------------|--------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号          | 名称                                                           | 1里沒(*** | 説明                                                                                                                                                                                 |

| 1、13、<br>15 | PGND                                                         | _       | 電源グランド接続                                                                                                                                                                           |

| 2、12、<br>16 | VIN                                                          | I       | 電源入力電圧ピン                                                                                                                                                                           |

| 3           | BOOT<br>(NC)                                                 | I       | 内蔵のハイサイド MOSFET ゲートドライバ用電源。このピンは内部でコンデンサに接続されています。このピンに何も接続しないでください。                                                                                                               |

| 4           | PSNS                                                         | _       | 電力センスグランド、GND プレーンに直接接続                                                                                                                                                            |

| 5           | NR/SS                                                        | 0       | このピンに接続するコンデンサによって、デバイスのソフトスタート時間および低周波数ノイズレベルが設定されます。                                                                                                                             |

| 6           | FB                                                           | 0       | デバイスのフィードバックピン                                                                                                                                                                     |

| 7           | VOUT                                                         | 0       | VOUT ピン。 推奨出力キャパシタンスに接続します。                                                                                                                                                        |

| 8           | VO                                                           | I       | 出力電圧検出ピン。このピンは、1番目のインダクタの後段に直接接続する必要があります。                                                                                                                                         |

| 9           |                                                              |         | オープンドレインのパワー グッド出力。 V <sub>OUT</sub> がパワーグッド スレッショルド未満の場合、このピンは GND にプルされます。 ロジック High を出力するには、プルアップ抵抗が必要です。 このピンはオープンのままにできます。 使用しない場合は GND に接続できます。                              |

| 10          | S-CONF                                                       | 0       | スマート構成ピン。このレジスタは、デバイスの動作モードを設定します。セクション 6.3.1 を参照してください。                                                                                                                           |

| 11          | 11 FN/SYNC 本デバイスは無効化されます。High にプルすると、本デバイスは有効化されます。本デバイスが無効化 |         | イネーブル / ディスエーブル ピン。スレッショルド コンパレータが内蔵されています。ロジック Low に接続すると、本デバイスは無効化されます。High にプルすると、本デバイスは有効化されます。本デバイスが無効化された場合、このピンでは、500kΩ (標準値) の内部プルダウン抵抗が作用します。このピンにクロックを印加すると、本デバイスを同期できます |

| 14          | SW(NC)                                                       | 0       | 電力段のスイッチ ピン。このピンは、コンバータの SW およびインダクタに内部接続されています。これらのパッドはデバイスの下に配置しできる限り小さくしてください。必要な場合にテストノードを接続する以外、パッドには何も接続しないでください。                                                            |

(1) I = 入力、O = 出力

Copyright © 2025 Texas Instruments Incorporated

4

Product Folder Links: TPSM82916

## 5 仕様

## 5.1 絶対最大定格

接合部動作温度範囲内 (特に記述のない限り)(1)

|                  |                                | 最小値  | 最大値                   | 単位 |

|------------------|--------------------------------|------|-----------------------|----|

|                  | VIN, EN/SYNC, PG, S-CONF       | -0.3 | 18                    | V  |

|                  | SW (DC)                        | -0.3 | V <sub>IN</sub> + 0.3 | V  |

|                  | SW (AC、10ns 未満) <sup>(3)</sup> | -2.5 | 21                    | V  |

| 電圧 (2)           | BOOT                           | -0.3 | V <sub>IN</sub> + 6   |    |

|                  | BOOT から SW へ                   | -0.3 | 6                     |    |

|                  | VO、FB、NR/SS                    | -0.3 | 6                     | V  |

|                  | VSNS-                          | -0.3 | 0.3                   | V  |

| シンク電流            | PG                             |      | 10                    | mA |

| T <sub>stg</sub> | 保存温度                           | -65  | 150                   | °C |

| TJ               | 接合部温度                          | -40  | 150                   | °C |

<sup>(1) 「</sup>絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

## 5.2 ESD 定格

|                    |      |                                                                      | 値     | 単位 |

|--------------------|------|----------------------------------------------------------------------|-------|----|

| V                  | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>         | ±2000 | V  |

| V <sub>(ESD)</sub> |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に<br>準拠、すべてのピン <sup>(2)</sup> | ±500  | V  |

<sup>(1)</sup> JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

接合部動作温度範囲内 (特に記述のない限り)

|                                   |                                     | 最小値 | 公称值 | 最大値 | 単位 |

|-----------------------------------|-------------------------------------|-----|-----|-----|----|

| V <sub>IN</sub>                   | 入力電圧                                | 3.0 |     | 17  | V  |

| V <sub>OUT</sub>                  | 出力電圧                                | 0.8 |     | 5.5 | V  |

| C <sub>IN</sub>                   | 実効入力容量                              | 5   | 10  |     | μF |

| C <sub>OUT</sub>                  | 実効出力キャパシタンス                         | 80  | 120 | 200 | μF |

| L <sub>f</sub>                    | 実効フィルタ インダクタンス                      | 0   | 10  | 50  | nΗ |

| C <sub>f</sub>                    | 実効フィルタ容量                            | 20  | 40  | 160 | μF |

| C <sub>OUT</sub> + C <sub>f</sub> | 1 段目と2 段目の L-C フィルタを含む、実効総出力キャパシタンス | 80  |     | 400 | μF |

| I <sub>OUT</sub>                  | TPSM82916 の出力電流                     | 0   |     | 6   | Α  |

| T <sub>J</sub> <sup>(1)</sup>     | 接合部温度                               | -40 |     | 125 | °C |

(1) 接合部温度が 125℃ を超えると、動作寿命が短くなります。

<sup>(2)</sup> すべての電圧値は、回路のグランド端子 GND を基準としたものです。

<sup>(3)</sup> スイッチング動作時。

<sup>(2)</sup> JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.4 熱に関する情報

| <b>熱評価基準</b> <sup>(1)</sup> |                     | TPSM8291x<br>VCE (QFN-FCMOD) | 単位   |

|-----------------------------|---------------------|------------------------------|------|

|                             |                     | TPSM8291xEVM                 |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 25.7                         | °C/W |

| R <sub>0JC(top)</sub>       | 接合部からケース (上面) への熱抵抗 | n/a <sup>(2)</sup>           | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | n/a <sup>(2)</sup>           | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

- (2) EVM には適用されません。

## 5.5 電気的特性

推奨する入力電圧範囲全域において、 $T_J$ =  $-40^{\circ}$ C  $\sim 125^{\circ}$ C。標準値は、Vin = 12V および  $T_J$  =  $25^{\circ}$ C での値 (特に記述のない限り)。

|                       | パラメータ                                | テスト条件                                                                | 最小値  | 標準値  | 最大値  | 単位 |

|-----------------------|--------------------------------------|----------------------------------------------------------------------|------|------|------|----|

| 電源                    |                                      |                                                                      |      |      |      |    |

| IQ                    | 静止時電流                                | EN = High、無負荷、デバイスがスイッチン<br>グ、fsw = 1MHz                             |      | 5    |      | mA |

| I <sub>SD</sub>       | シャットダウン電流                            | EN = GND, $T_J$ = $-40^{\circ}$ C $\sim 125^{\circ}$ C               |      | 0.5  | 70   | μΑ |

| V <sub>UVLO</sub>     | 低電圧誤動作防止                             | V <sub>IN</sub> 立ち上がり、T <sub>J</sub> = -40°C ~ 125°C                 | 2.85 | 2.92 | 3.0  | V  |

| V <sub>HYS</sub>      | 低電圧ロックアウトヒステリシス                      |                                                                      |      | 200  |      | mV |

| <b>-</b>              | サーマル シャットダウンのスレッショルド                 | T」立ち上がり                                                              |      | 170  |      | °C |

| $T_{JSD}$             | サーマル シャットダウン ヒステリシス                  | T <sub>J</sub> 立ち下がり                                                 |      | 20   |      | °C |

| 制御とイン                 | ターフェイス                               |                                                                      |      |      | 1    |    |

| V <sub>H_EN</sub>     | EN/SYNC の High レベル入力 — スレッショルド電圧     |                                                                      | 0.97 | 1.01 | 1.04 | V  |

| V <sub>L_EN</sub>     | EN/SYNC の Low レベル入力スレッショルド<br>電圧     |                                                                      | 0.87 | 0.9  | 0.93 | V  |

| V <sub>H_SYNC</sub>   | EN/SYNC の High レベル入力スレッショルド クロック信号   | EN/SYNC = クロック                                                       | 1.1  |      |      | V  |

| V <sub>L_SYNC</sub>   | EN/SYNC の Low レベル入力スレッショルド<br>クロック信号 | EN/SYNC = クロック                                                       |      |      | 0.4  | V  |

| I <sub>EN, LKG</sub>  | EN/SYNC への入力リーク電流                    | EN/SYNC = GND または VIN、-40℃ ≤<br>T <sub>J</sub> ≤ 125℃                |      | 5    | 160  | nA |

| R <sub>PD</sub>       | EN/SYNC のプルダウン抵抗                     | EN/SYNC = Low                                                        | 330  | 500  |      | kΩ |

| t <sub>delay</sub>    | イネーブル遅延時間                            | EN/SYNC High からデバイスがスイッチング を開始するまでの時間、 $R_{S-CONF}$ = 80.6k $\Omega$ |      | 1    |      | ms |

| I <sub>NR/SS</sub>    | NR/SS ソース電流                          |                                                                      | 67.5 | 75   | 82.5 | μA |

| R <sub>S-CONF</sub>   | S-CONF 抵抗のステップ範囲精度                   | S-CONF 表 に従った、すべての設定に対する Rs-conf の許容誤差                               | -4   |      | +4   | %  |

| $V_{PG}$              | パワー グッド スレッショルド                      | V <sub>FB</sub> の立ち上がり。公称 V <sub>FB</sub> を基準とします。                   | 93   | 95   | 98   | %  |

| $V_{PG}$              | パワー グッド スレッショルド                      | V <sub>FB</sub> の立ち下がり。公称 V <sub>FB</sub> を基準とします。                   | 88   | 90   | 93   | %  |

| V <sub>PG</sub> , OL  | PGピンの Low レベル出力電圧                    | I <sub>SINK</sub> = 1mA                                              |      |      | 0.4  | V  |

| I <sub>PG</sub> , LKG | PG ピンへの入力リーク電流                       | V <sub>PG</sub> = 5V, -40°C ≤ T <sub>J</sub> ≤ 125°C                 |      | 5    | 500  | nA |

| t <sub>PG、DLY</sub>   | パワーグッド遅延時間                           | V <sub>FB</sub> 立ち下がり                                                |      | 8    |      | μs |

| <br>出力                | 1                                    |                                                                      |      |      |      |    |

Product Folder Links: TPSM82916

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

# 5.5 電気的特性 (続き)

推奨する入力電圧範囲全域において、 $T_J$ = -40°C  $\sim$  125°C。標準値は、Vin = 12V および  $T_J$  = 25°C での値 (特に記述のない限り)。

|                        | パラメータ                      | テスト条件                                                                                                                                                                                               | 最小値   | 標準値  | 最大値   | 単位                |

|------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------------------|

| t <sub>on</sub>        | 最小オン時間                     | V <sub>IN</sub> ≥ 5V, I <sub>out</sub> = 1A                                                                                                                                                         |       | 35   |       | ns                |

| t <sub>off</sub>       | 最小オフ時間                     | V <sub>IN</sub> ≥ 5V, I <sub>out</sub> = 1A                                                                                                                                                         |       | 50   |       | ns                |

| V <sub>FB</sub>        | フィードバック レギュレーション精度         | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                                                                                                      | 0.792 | 0.8  | 0.808 | V                 |

| I <sub>FB、LKG</sub>    | FB への入力リーク電流               | V <sub>FB</sub> = 0.8V <sub>\</sub> -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                                                                  |       | 1    | 70    | nA                |

| I <sub>VO,LKG</sub>    | VO への入力リーク電流               | V <sub>VO</sub> = 1.2V <sub>×</sub> –40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                                                                  |       | 0.01 | 30    | μA                |

| PSRR                   | 電源除去比                      | $V_{\text{IN}}$ = 12V、1.2 $V_{\text{OUT}}$ 、1A、 $C_{\text{NR/SS}}$ = 470nF、 $f_{\text{sw}}$ = 1MHz、 $C_{\text{FF}}$ = オープン、 $C_{\text{OUT}}$ = 4 × 22 $\mu$ F、f ≤ 100 $k$ Hz                        |       | 65   |       | dB                |

| PSRR                   | 電源除去比                      | $V_{\text{IN}}$ = 5V、1.2 $V_{\text{OUT}}$ 、1A、 $C_{\text{NR/SS}}$ = 470nF、 $f_{\text{sw}}$ = 2.2MHz、 $C_{\text{FF}}$ = オープン、 $C_{\text{OUT}}$ = 4 × 22 $\mu$ F、f ≤ 100kHz                           |       | 70   |       | dB                |

| V <sub>NRMS</sub>      | 出力電圧 RMS ノイズ               | $V_{\text{IN}}$ = 12V、BW = 100Hz $\sim$ 100kHz、 $C_{\text{NR}/}$ $_{\text{SS}}$ = 470nF、 $f_{\text{SW}}$ = 1MHz、 $V_{\text{OUT}}$ = 1.2V、 $C_{\text{FF}}$ = オープン、 $C_{\text{OUT}}$ = 4 × 22 $\mu$ F |       | 24.4 |       | μV <sub>RMS</sub> |

| V <sub>NRMS</sub>      | 出力電圧 RMS ノイズ               | $V_{\text{IN}}$ = 5V、BW = 100Hz $\sim$ 100kHz、 $C_{\text{NR}/\text{SS}}$ = 470nF、 $f_{\text{SW}}$ = 2.2MHz、 $V_{\text{OUT}}$ = 1.2V、 $C_{\text{FF}}$ = オープン、 $C_{\text{OUT}}$ = 4 × 22 $\mu$ F      |       | 16.5 |       | μV <sub>RMS</sub> |

| V <sub>opp</sub>       | f <sub>SW</sub> での出力リップル電圧 | $V_{IN} = 12V$ , $f_{SW} = 1MHz$ , $V_{OUT} = 1.2V$ , $C_{OUT} = 4 \times 22\mu F$ , $L_f = 10nH$ , $C_f = 22\mu F$                                                                                 |       | 36   |       | μV <sub>RMS</sub> |

| R <sub>DIS</sub>       | 出力放電抵抗                     | EN/SYNC = GND, V <sub>OUT</sub> = 1.2V, V <sub>IN</sub> ≥ 5V <sub>o</sub>                                                                                                                           |       | 3.5  |       | Ω                 |

| R <sub>DIS</sub>       | 出力放電抵抗                     | EN/SYNC = GND, V <sub>OUT</sub> = 5V, V <sub>IN</sub> ≥ 5V <sub>°</sub>                                                                                                                             |       | 16   |       | Ω                 |

| f <sub>SW</sub>        | スイッチング周波数                  | 2.2MHz 設定                                                                                                                                                                                           | 1.98  | 2.2  | 2.42  | MHz               |

| f <sub>SW</sub>        | スイッチング周波数                  | 1.4MHz 設定                                                                                                                                                                                           | 1.26  | 1.4  | 1.54  | MHz               |

| f <sub>SW</sub>        | スイッチング周波数                  | 1MHz 設定                                                                                                                                                                                             | 0.9   | 1    | 1.18  | MHz               |

| D <sub>SYNC</sub>      | 同期デューティサイクル                |                                                                                                                                                                                                     | 45    |      | 55    | %                 |

| t <sub>sync_elay</sub> | 同期位相遅延                     | EN/SYNC の立ち上がりエッジから SW の立ち上がりエッジまでの位相遅延                                                                                                                                                             |       | 90   |       | ns                |

| I <sub>SWpeak</sub>    | ピークスイッチの電流制限               | TPSM82916                                                                                                                                                                                           | 7.9   | 8.5  | 9.1   | Α                 |

| I <sub>SWvalley</sub>  | バレー スイッチの電流制限              | TPSM82916                                                                                                                                                                                           |       | 7.8  |       | Α                 |

| Ineg <sub>valley</sub> | 負のバレー電流制限                  |                                                                                                                                                                                                     |       | -2.9 | -2    | Α                 |

| P                      | ハイサイド FET オン抵抗             | V <sub>IN</sub> ≧ 5V                                                                                                                                                                                |       | 25   |       | mΩ                |

| R <sub>DS(ON)</sub>    | ローサイド FET オン抵抗             | V <sub>IN</sub> ≧ 5V                                                                                                                                                                                |       | 7.5  |       | mΩ                |

Product Folder Links: TPSM82916

#### 5.6 代表的特性

V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 1.2V、T<sub>A</sub> = 25℃、BOM = 表 7-1、(特に記述のない限り)

## 5.6 代表的特性 (続き)

V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 1.2V、T<sub>A</sub> = 25℃、BOM = 表 7-1、(特に記述のない限り)

English Data Sheet: SLVSH49

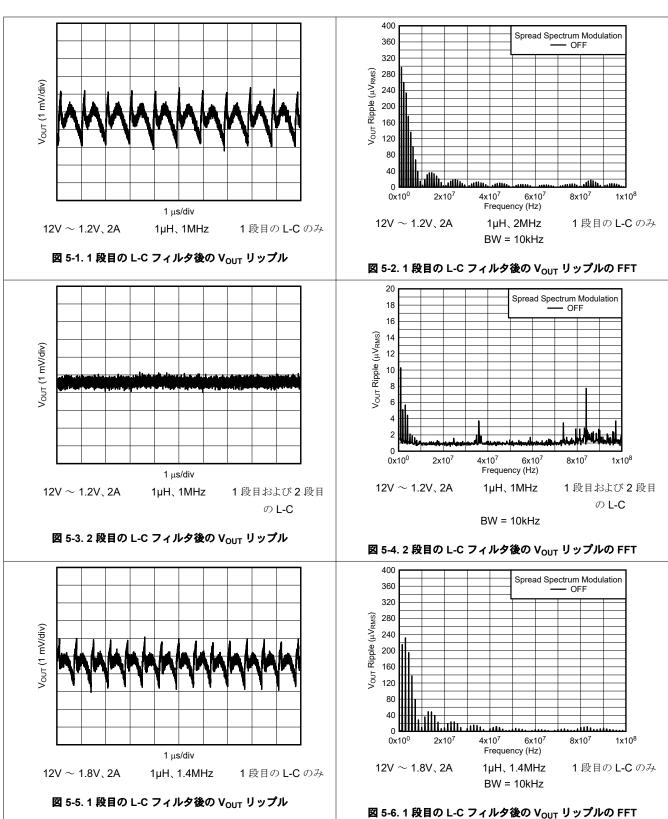

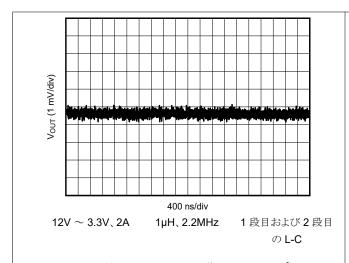

## 5.6 代表的特性 (続き)

V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 1.2V、T<sub>A</sub> = 25℃、BOM = 表 7-1、(特に記述のない限り)

図 5-11. 2 段目の L-C フィルタ後の V<sub>OUT</sub> リップル

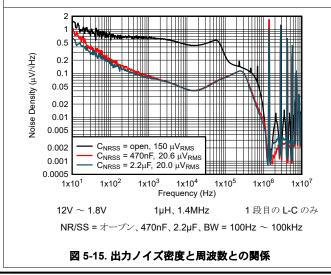

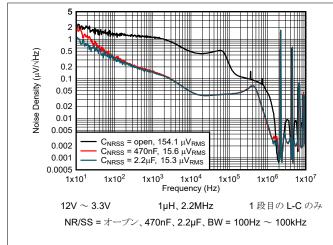

図 5-13. 出力ノイズ密度と周波数との関係

20 Spread Spectrum Modulation 18 16 Vout Ripple (µVRMS) 14 12 10 8 6 2x10 4x10<sup>7</sup> 8x107 1x10<sup>8</sup> 0x10 6x10 Frequency (Hz)  $12V \sim 3.3V, 2A$ 1µH, 2.2MHz 1段目および2段目 の L-C BW = 10kHz

#### 図 5-12. 2 段目の L-C フィルタ後の V<sub>OUT</sub> リップルの FFT

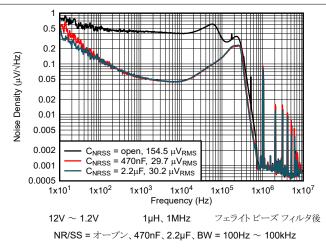

図 5-14. 出力ノイズ密度と周波数との関係

Copyright © 2025 Texas Instruments Incorporated

## 5.6 代表的特性 (続き)

V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 1.2V、T<sub>A</sub> = 25℃、BOM = 表 7-1、(特に記述のない限り)

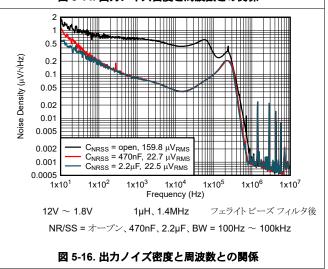

図 5-17. 出力ノイズ密度と周波数との関係

English Data Sheet: SLVSH49

## 6 詳細説明

#### 6.1 概要

TPSM82916 低ノイズ、低リップル同期整流降圧 モジュール は、固定周波数の電流モード モジュール です。この モジュール は、フィルタリングされた内部リファレンスを備えており、低ノイズ LDO と同様の低ノイズ出力を実現します。この モジュール は、2.2MHz、1.4MHz、1MHz のいずれかのスイッチング周波数、および大きなインダクタンスを使用することによって、出力電圧リップルの低減を実現します。小型の 2 段目 L-C フィルタを出力に追加すると、出力電圧リップルをさらに低減できます。この追加は、フェライト ビーズまたは小型インダクタを使用し、その後段に出力コンデンサを接続することによって可能です。内部補償は、最大 50nH の外付けフィルタ インダクタで安定性を維持します。この 2 段目のフィルタ両端での電圧降下を防止するため、本デバイスはフィルタの後段で出力電圧を安定化します。 TPSM82916 は、オプションのスペクトラム拡散変調をサポートしています。たとえば、ADC に電力を供給する場合、スペクトラム拡散変調はミキシング スプリアスを低減します。スイッチング周波数、スペクトラム拡散変調、出力放電は、S-CONF ピンを使用して設定します。

English Data Sheet: SLVSH49

# 6.2 機能ブロック図

#### 6.3 機能説明

## 6.3.1 スマート構成 (S-CONF)

この S-CONF ピンは、抵抗値に基づいてデバイスを構成します。このピンは、EN/SYNC が High になった後に読み取られます。このデバイス構成は、動作中には変更できません。EN が 200mV 未満にプルされた場合、または VIN が UVLO を下回った場合、S-CONF の値は再度読み取られます。表 6-1 に、スイッチング周波数、スペクトラム拡散変調、出力放電、同期の構成オプションを示します。

内部回路が抵抗値を正しく検出できるようにするため、抵抗と S-CONF ピンの間の距離をできるだけ短くし、S-CONF ピンにはコンデンサを配置しないでください。

表 6-1. S-CONF デバイス構成モード

| S-CONF | スイッチング周波数 | スペクトラム拡散 | 出力放電 | SYNC                                     |

|--------|-----------|----------|------|------------------------------------------|

| VIN    | 2.2MHz    | OFF      | OFF  | なし                                       |

| GND    | 1MHz      | OFF      | OFF  | なし                                       |

| 4.87kΩ | 1.4MHz    | OFF      | OFF  | なし                                       |

| 6.04kΩ | 1.4MHz    | OFF      | OFF  | $1.2 \mathrm{MHz} \sim 1.6 \mathrm{MHz}$ |

| 7.5kΩ  | 2.2MHz    | OFF      | OFF  | 1.9MHz ∼ 2.42MHz                         |

| 9.31kΩ | 1MHz      | OFF      | OFF  | $0.9 \mathrm{MHz} \sim 1.2 \mathrm{MHz}$ |

| 11.5kΩ | 1MHz      | ランダム     | OFF  | なし                                       |

| 14.3kΩ | 1.4MHz    | ランダム     | OFF  | なし                                       |

| 18.2kΩ | 2.2MHz    | ランダム     | OFF  | なし                                       |

| 22.1kΩ | 1MHz      | OFF      | オン   | なし                                       |

| 27.4kΩ | 1.4MHz    | OFF      | オン   | なし                                       |

| 34kΩ   | 2.2MHz    | OFF      | オン   | なし                                       |

| 42.2kΩ | 1MHz      | OFF      | オン   | $0.9 \mathrm{MHz} \sim 1.2 \mathrm{MHz}$ |

| 52.3kΩ | 1.4MHz    | OFF      | オン   | $1.2 \mathrm{MHz} \sim 1.6 \mathrm{MHz}$ |

| 64.9kΩ | 2.2MHz    | OFF      | オン   | 1.9MHz ∼ 2.42MHz                         |

| 80.6kΩ | 1MHz      | ランダム     | オン   | なし                                       |

| 100kΩ  | 1.4MHz    | ランダム     | オン   | なし                                       |

| 124kΩ  | 2.2MHz    | ランダム     | オン   | なし                                       |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

Product Folder Links: TPSM82916

#### 6.3.2 デバイス イネーブル (EN/SYNC)

このデバイスは、EN/SYNC ピンを High レベルにすることによってイネーブルになり、正確な立ち上がりスレッショルド電圧は標準で 1.01V です。デバイスがイネーブルされた後、動作モードは S-CONF ピンの設定によって設定されます。この動作は、本デバイスのスタートアップ遅延時間  $t_{delay}$  の間に発生します。 $t_{delay}$  が経過すると、内部ソフトスタート回路は、コンデンサ  $C_{NR/SS}$  によって設定されるソフトスタート時間にわたって出力電圧を上昇させます。スタートアップ遅延時間  $t_{delay}$  は、選択した S-CONF の値によって異なります。S-CONF 抵抗を小さくすると、スタートアップ遅延時間が最短になります。

EN/SYNC ピンには、アクティブ プルダウン抵抗 R<sub>PD</sub> があります。この抵抗により、EN/SYNC ピンを Low レベルに駆動 できない場合に、本デバイスが制御されていない状態でスタートアップすることを防止できます。 プルダウン抵抗は、スタートアップ後に切り離されます。 EN を Low レベルに設定すると、本デバイスはシャットダウン状態に移行し、プルダウン抵抗が再度有効化されます。

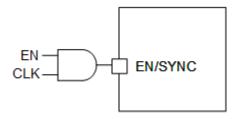

### 6.3.3 デバイス同期 (EN/SYNC)

EN/SYNC ピンは、デバイスを同期するためにも使用されます。このピンにクロック信号が印加されると、デバイスがイネーブルになり、S-CONF ピンの構成を読み取ります。外部クロック周波数は、S-CONF ピンによって設定されたクロック同期周波数範囲内にする必要があります。クロック信号がクロックから静的な High に変わると、デバイスは外部クロックから内部クロックに切り替わります。外部クロックを使用してデバイスをシャットダウンするには、EN/SYNC を少なくとも 10µs の間 Low にする必要があります。

クロック信号は、電気的特性表に規定されているロジックレベルに対応したロジック信号であり、EN/SYNC ピンに直接印加できます。図 6-1 に示すように、AND ゲートなどの外部ロジックを使用して、個別のイネーブル入力とクロック入力を組み合わせることができます。

図 6-1. 個別のイネーブル信号による同期 (オプション)

#### 6.3.4 スペクトラム拡散変調

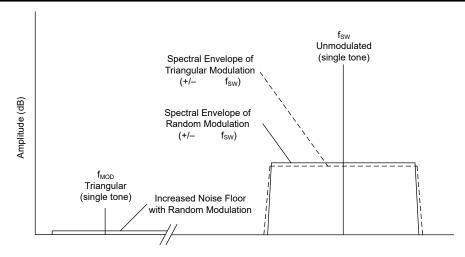

S-CONF ピンを使用して、スペクトラム拡散変調をイネーブルまたはディスエーブルできます。 DC/DC モジュール は、使用するスイッチング周波数と同じ周波数で出力電圧リップルを生じます。 ADC またはアナログ フロント エンド (AFE) に電力を供給する場合、スイッチング周波数により、出力周波数スペクトルに高周波ミキシング スプリアスおよび低周波数スプリアスが発生します。 オプションの 2 段目 L-C フィルタを使用すると モジュール のリップルおよびスプリアスを最大 30dB 低減できます。

このデバイスには、表 6-1 に従って S-CONF ピンに接続された抵抗で選択される、ランダム スペクトラム拡散変調 (SSM) 方式が内蔵されています。ランダム変調を選択してスイッチング周波数をより広い周波数範囲に拡散することが可能です。変調の拡散幅は、デバイスのスイッチング周波数の ±10% です。この SSM は、レシーバの帯域幅が変調周波数以下の場合に、高い減衰を実現します。これは、一般に、高速 ADC アプリケーションのように、高速フーリエ変換 (FFT) の後処理を使用するシステムに当てはまります。変調周波数でノイズの影響を受けやすいアプリケーションでは、ランダム SSM を使用します。図 5-2 に示すように、ランダム スペクトラム拡散変調を使用すると、出力スペクトラムのスプリアスも低減できます。ランダム化された変調では、疑似ランダム生成期間中にすべてのトーンが 1 回生成されるように、フィボナッチリニアフィードバック シフト レジスタ (LFSR) を使用します。周波数の拡散を 図 6-2

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

図 6-2. スペクトラム拡散変調

## 6.3.5 出力放電

出力放電は、S-CONF の設定に応じてイネーブルまたはディスエーブルされます。出力放電がイネーブルの場合、放電抵抗  $R_{DIS}$  (標準値  $7\Omega$ ) により、出力電圧が "Low" にプルダウンされます。出力放電機能は、サーマルシャットダウン中、UVLO 中、または EN/SYNC が "Low" になったときに有効にされます。

#### 6.3.6 低電圧誤動作防止 (UVLO)

低い入力電圧でデバイスが誤動作するのを防止するため、デバイスがイネーブルされるのは、入力電圧が低電圧誤動作防止スレッショルドを上回った後です。入力電圧が低電圧スレッショルドを下回ると、デバイスはディスエーブルになります。

#### 6.3.7 パワー グッド出力

本デバイスには、パワー グッド出力があります。FB ピンの電圧が公称電圧の 95% を超えると PG ピンはハイインピーダンスになり、公称電圧の 90% (標準値) を下回ると Low に駆動されます。表 6-2 に、PG ピンの代表的なロジックを示します。PG ピンはオープンドレイン出力であり、最大 10mA までシンクできるよう指定されています。パワーグッド出力には、18V 未満の任意の電圧レールに接続されたプルアップ抵抗が必要です。PG 信号を他の モジュール の EN ピンに接続することによって、PG 信号を複数のレールのシーケンシングに使用できます。使用しない場合は、PG ピンをフロートのままにするか GND に接続します。PG には、Low になる前に通常 8µs のグリッチ除去時間があります。

|                         | ニックラの仏術                                              | PG のロジック | ステータス |

|-------------------------|------------------------------------------------------|----------|-------|

| デバイスの状態                 |                                                      | 高インピーダンス | Low   |

| 有効 (EN/SYNC = High)     | $V_{FB} \ge V_{PG}$                                  | ✓        |       |

|                         | t <sub>PG</sub> 後に、V <sub>FB</sub> < V <sub>PG</sub> |          | ✓     |

| シャットダウン (EN/SYNC = Low) |                                                      |          | ✓     |

| UVLO                    | $0.7V < V_{IN} < V_{UVLO}$                           |          | ✓     |

| サーマル シャットダウン            | $T_{J} > T_{JSD}$                                    |          | ✓     |

| 電源の取り外し                 | V <sub>IN</sub> < 0.7V                               | ✓        |       |

表 6-2. パワー グッド ピンのロジック

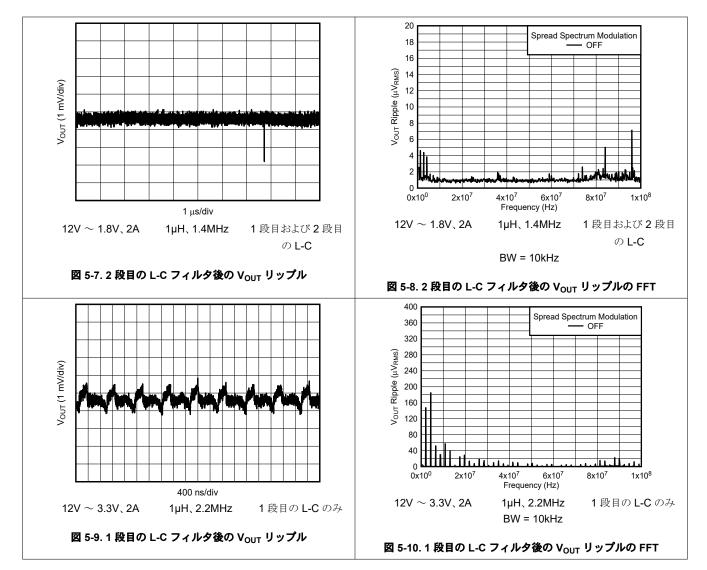

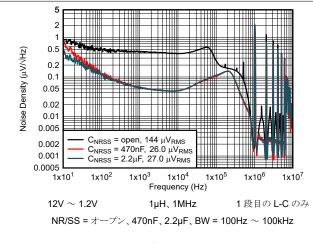

#### 6.3.8 ノイズ リダクションおよびソフトスタート コンデンサ (NR/SS)

このピンに接続するコンデンサにより、モジュールの低周波数ノイズが低減され、ソフトスタート時間が設定されます。コンデンサが大きいほど、ノイズは減少し、モジュールのスタートアップ時間は長くなります。通常、470nFのコンデンサをこのピンに接続してスタートアップ時間を5msにしますが、これより長いスタートアップ時間や短いスタートアップ時間も使用

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

できます。軽負荷でのソフトスタート時には、出力電圧を放電しないようにするため、必要に応じてスイッチング パルスをスキップします。デバイスはプリバイアス出力電圧への起動ができます。

このデバイスは、*セクション* 6.2 に示すように、リファレンス電圧に R-C フィルタを追加することによって、低ノイズを実現します。スタートアップ時、NR/SS コンデンサは 75µA (標準値) の定電流で 0.8V まで充電されます。より大きな NR/SS コンデンサを使用すると低周波数ノイズが低くなります。スタートアップ時間が 35ms のときの NR/SS キャップの最大値は 3.3µF です。最小スタートアップ時間は内部で 0.7ms に設定され、これは NR/SS コンデンサが小さい場合や、NR/SS コンデンサがない場合に発生します。

#### 6.3.9 電流制限と短絡保護

このデバイスは、短絡および過電流から保護されています。スイッチ電流制限により、デバイスを大きなインダクタ電流から保護して、入力電圧レールから過剰な電流が流れるのを防ぎます。インダクタの短絡や飽和、または重い負荷、または出力回路の短絡状態が原因で、過剰な電流が発生する可能性があります。インダクタ電流がスレッショルド I<sub>SWpeak</sub> に達すると、ハイサイド MOSFET がオフになり、ローサイド MOSFET がオンになって、インダクタ電流を減少させます。ローサイド電流がローサイド ソース電流制限値 I<sub>SWvalley</sub> を下回ると、ハイサイド MOSFET が再度オンになります。

内部の伝搬遅延のため、特に、入力電圧が高く、かつ使用しているインダクタンスが非常に小さい場合、実際の電流は静 的制限値を上回ることがあります。動的な電流制限値は、次の式 1 に従って計算できます:

$$I_{PEAK(typ)} = I_{SWpeak} + \left(\frac{V_L}{L}\right) \times t_{PD} \tag{1}$$

ここで、

- I<sub>SWpeak</sub> は、**電気的特性**で規定されている静的電流制限値。

- L はインダクタンス であり、内部で 1μH。

- V<sub>I</sub> は、インダクタの両端の電圧 (VIN VOUT)。

- t<sub>PD</sub> は、50ns (標準値)の内部伝搬遅延。

ローサイド MOSFET には負の電流制限機能もあり、インダクタを通って入力に過剰な電流が流れ込むのを防止します。 ローサイド シンク電流が制限を超えた場合、ローサイド MOSFET はオフになります。このシナリオでは、次のサイクルの 開始まで両方の MOSFET がオフとなります。

#### 6.3.10 サーマル シャットダウン

接合部温度が 170℃ (標準値、20℃ のヒステリシスあり) を超えると、デバイスはサーマル シャットダウンに移行します。

#### 6.4 デバイスの機能モード

## 6.4.1 固定周波数のパルス幅変調

出力電圧リップルを最小限に抑えるため、本デバイスは無負荷まで固定周波数 PWM で動作します。1MHz、1.4MHz、2.2MHz のスイッチング周波数は、S-CONF ピンを使用して選択します。

#### 6.4.2 低デューティ サイクルでの動作

入力電圧が高い場合または出力電圧が低い場合、70ns の最小オン時間により、入力と出力の間の最大電圧差と、選択したスイッチング周波数が制限されます。最小オン時間に達すると、出力電圧はレギュレーション ポイントを上回ります。詳細な設計推奨事項については、表 7-2 を参照してください。

#### 6.4.3 高デューティ サイクル動作 (100% デューティ サイクル)

このデバイスは、100%のデューティサイクルモードに移行することによって、入力と出力の間の電圧差を低く抑えます。このモードでは、ハイサイド MOSFET スイッチが継続的にオンになります。出力電圧レギュレーションを維持するための入力電圧の最小値は、負荷電流と出力電圧レベルに応じて、次のように計算できます:

$$V_{IN\ (min)} = V_{OUT\ (min)} + I_{OUT} \times \left(R_{DS\ (ON)} + R_L\right)$$

(2)

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

17

Product Folder Links: TPSM82916

- V<sub>OUT(min)</sub> は 負荷が許容できる最小出力電圧。

- l<sub>out</sub> は出力電流。

- R<sub>DS(ON)</sub> はハイサイド MOSFET の R<sub>DS(ON)</sub>。

- R<sub>L</sub> は、使用しているインダクタの DC 抵抗。

固定周波数スイッチングを維持するために必要な最小オフ時間は、50ns (標準値)、60ns (最大値)です。スイッチングパ ルス中にこの制限に達した場合、デバイスは出力電圧レギュレーションを維持するため、スイッチング パルスをスキップし ます。入力電圧がさらに低下すると、本デバイスは 100% モードに移行します。

## 6.4.4 2 段目の L-C フィルタ補償 (オプション)

低ノイズ、低リップルの大半のアプリケーションでは、負荷の前にフェライト ビーズとバイパス コンデンサを使用します。2 段目の L-C フィルタの使用は、ADC、DAC、ジッタ クリーナなどの負荷電流が一定の低ノイズかつ低リップルのアプリケ ーションに特に便利です。2 段目の L-C フィルタはオプションであり、このフィルタを用いずにデバイスを使用できます。フ ィルタを使用しない場合、本デバイスは、 図 5-10 に示すように、280μV<sub>RMS</sub> の出力電圧リップルがある場合に、 16.9μV<sub>RMS</sub> の低出力電圧ノイズを示します。 図 5-12 に示すように、2 段目の L-C フィルタは出力電圧リップルをさらに 約 30dB 減衰させます。 ロード レギュレーションを改善するため、本デバイスは 2 段目の L-C フィルタの後段の出力電圧 をリモート検出でき、L-C フィルタによって生成される追加の二重極に対して内部的に補償されます。

2 段目の L-C フィルタをできるだけ小さくするため、10nH ~ 50nH のインダクタンス用に最適化された内部補償がありま す。 小型フェライト ビーズ、あるいは PCB のトレースでさえも、出力電圧リップルをフィルタリングするために十分なインダ クタンスを実現します。詳細については、セクション 7.2.2.2.3 を参照してください。

Copyright © 2025 Texas Instruments Incorporated

Product Folder Links: TPSM82916

## 7アプリケーションと実装

#### 注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 7.1 アプリケーション情報

この TPSM82916 ファミリのデバイスは、低ノイズおよび低出力電圧リップルを実現するよう設計されています。

## 7.2 代表的なアプリケーション

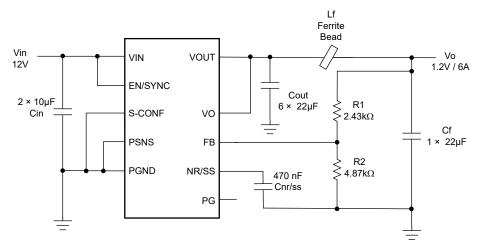

図 7-1. 代表的な回路図

次の表に、ほとんどのアプリケーションに対して推奨される部品のリストを示します。

#### 表 7-1. 部品のリスト

| リファレンス                               | 部品番号                | 説明                                                                      | 製造元           |

|--------------------------------------|---------------------|-------------------------------------------------------------------------|---------------|

| TPS8291x                             | TPS8291x            | 低ノイズかつ低リップルの降圧モジュー<br>ル                                                 | テキサス・インスツルメンツ |

| C <sub>IN</sub>                      | C2012X7S1E106K125AC | セラミック コンデンサ:2 × 10μF ±10%<br>25V セラミック コンデンサ X7S 0805                   | TDK           |

| C <sub>OUT</sub>                     | C2012X7S1A226M125AC | セラミック コンデンサ:6 × 22µF、10V、<br>±20%、X7S、0805                              | TDK           |

| L <sub>f</sub>                       | BLE32SN120SN1L      | フェライト ビーズ                                                               | MuRata        |

| C <sub>f</sub>                       | C2012X7S1A226M125AC | セラミック コンデンサ:1 × 22µF、10V、<br>±20%、X7S、0805 × 22µF、10V、<br>±20%、X7S、0805 | TDK           |

| C <sub>NR/SS</sub> , C <sub>FF</sub> |                     | セラミック コンデンサ                                                             | 標準            |

| R1、R2、R3、R4                          |                     | 抵抗                                                                      | 標準            |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

English Data Sheet: SLVSH49

#### 7.2.1 設計要件

外付け部品は、アプリケーションのニーズだけでなく、デバイスの制御ループの安定性基準も満たしている必要があります。本デバイスは外付け部品の一定の範囲内で動作するよう設計されており、また、効率、出力リップル、部品数、最小1/fノイズについて最適化できます。

入力電圧が 6V 以下の標準的なアプリケーションでは、2.2MHz のスイッチング周波数で使用します。入力電圧が 6V を超えるアプリケーションでは、出力電圧に応じて、1MHz または 1.4MHz のスイッチング周波数で使用して、効率を最適化できます。

次の表に記載されていないアプリケーション事例では、TPSM82916 回路を設計する方法が 2 つあります。 *セクション* 7.2.2.1 では、回路を自動的に設計する WEBENCH を使用します。 あるいは、これに代わって、 *セクション* 7.2.2.2 の計算を使用できます。

|      |                    |                                | _               |       |                        |  |

|------|--------------------|--------------------------------|-----------------|-------|------------------------|--|

| 設計目標 | V <sub>IN</sub>    | V <sub>OUT</sub>               | F <sub>SW</sub> | インダクタ | 出力コンデンサ <sup>(2)</sup> |  |

| 標準値  | 12V <sup>(1)</sup> | ≤ 1.4V <sup>(1)</sup>          | 1MHz            |       | 6 × 22µF、10V、0805      |  |

| 標準値  | 12V                | 1.4V < V <sub>OUT</sub> ≤ 2.2V | 1.4MHz          | 1µH   | 6 × 22μF、10V、0805      |  |

| 標準値  | 12V                | > 2.2V                         | 2.2MHz          | 1µH   | 8 × 22µF、10V、0805      |  |

| 標準値  | 5V                 | ≤ 3.3V                         | 2.2MHz          | 1µH   | 6 × 22μF、10V、0805      |  |

| 標準値  | 5V                 | > 3.3V                         | 2.2MHz          | 1µH   | 8 × 22µF、10V、0805      |  |

表 7-2. 標準的なシングル L-C フィルタ設計における推奨事項

- (1) 入力と出力の間の最大電圧差は、デバイスの最大の最小オン時間である 70ns によって制限されます。入力電圧が 12V を超える場合、または 出力電圧が 1V 未満の場合には、この制限が特に重要になります。セクション 7.2.2.2.1 を参照してください。

- (2) 出力コンデンサの型番については、表 7-4 を参照してください。

2 段目の L-C フィルタはオプションです。このフィルタを用いずにデバイスを使用して、20μV<sub>RMS</sub> (標準値) 未満のノイズを実現できるためです。出力リップル電圧をさらに減衰させるには、2 段目のフィルタを追加します。FB 抵抗を 2 段目のL-C フィルタ コンデンサに接続することによって、出力電圧を 2 段目の L-C フィルタの後に検出できます。この動作によりリモート センスが実現でき、フェライト ビーズによる出力電圧降下を最小化できます。出力電圧に基づく 2 段目 L-C フィルタの推奨事項については、以下の表を参照してください。

表 7-3. 2 段目 L-C (フェライト ビーズ) フィルタの設計に関する推奨事項

| VOUT (V) | フェライト ビーズのインピーダンス (100MHz 時) <sup>(2)</sup> | 出力コンデンサ (1)       |

|----------|---------------------------------------------|-------------------|

| ≤ 2.2V   | $8\sim 20\Omega$                            | 1 × 22μF、10V、0805 |

| > 2.2V   | $8\sim 20\Omega$                            | 2 × 22µF、10V、0805 |

- (1) 出力コンデンサの型番については、表 7-4 を参照してください。

- (2) 2 段目の L-C フィルタの型番については、表 7-5 を参照してください。

#### 7.2.2 詳細な設計手順

特定の設計が表 7-2 に見つからない場合は、設計を生成するために WEBENCH を使用することをお勧めします。または、セクション 7.2.2.2 の手動設計手順に従ってください。

#### 7.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリック すると、WEBENCH Power Designer により、TPSM82916 デバイスを使用するカスタム設計を作成できます。

- 1. 最初に、入力電圧 (V<sub>IN</sub>)、出力電圧 (V<sub>OUT</sub>)、出力電流 (I<sub>OUT</sub>) の要件を入力します。

- 効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 3. 出力電圧リップルを最適化するための「advanced」(詳細) タブを開きます。

- 4. TPSM82916 の設計では、左側のドロップダウンで、2 段目 L-C フィルタを有効にし、また、その他の設定を変更できます。

のせ) を送信 Copyright © 2025 Texas Instruments Incorporated Product Folder Links: *TPSM82916*

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、www.ti.com/ja-jp/WEBENCH でご覧になれます。

#### 7.2.2.2 外付け部品の選択

#### 7.2.2.2.1 スイッチング周波数の選択

スイッチング周波数は、効率 (周波数を下げる)またはリップル ノイズ (周波数を上げる)を最適化するように選択できます。より高い 1.4MHz または 2.2MHz の設定を使用すると、帰還ループのゲインが大きくなり、出力ノイズが低くなる可能性があります。ただし、最小オン時間およびデューティサイクルに関する追加の検討事項も考慮する必要があります。最初に、式 3 を使用してデューティサイクルを計算します。効率が高くなるとオン時間が短くなるため、より安全なアプローチはアプリケーションで予測される効率よりも高い効率を使うことです。

$$D = \frac{V_{OUT}}{V_{IN} \times \eta} \tag{3}$$

ここで

η = 推定効率 (効率曲線から数値を使用するか、安全を期した仮定として 0.9 を使用)

次に、式4を使用して、1MHz、1.4MHz、2.2MHzを使用したオン時間の計算を行います。オン時間は、常に最小オン時間の70nsを上回っている必要があります。最大入力電圧と最大効率を使用して、最小デューティサイクル D<sub>min</sub>を決定します。f<sub>sw</sub>には最大スイッチング周波数を使用します。

$$T_{ON} = \frac{D_{min}}{f_{SW\ min}} \tag{4}$$

したがって、

- t<sub>ON min</sub> の最小値 < 70ns が 2.2MHz に対して成立する場合、1.4MHz を使用します。

- t<sub>ON min</sub> の最小値 < 70ns が 1.4MHz に対して成立する場合、1MHz を使用します

- ton min の最小値 < 70ns が 1MHz に対して成立する場合、最大入力電圧を減少させます。

- toN\_min の最小値 ≥ 70ns の場合は、最高の効率を得るにはより低い周波数を使用し、ノイズとリップルを最小限にするには最大の周波数を使用します。

#### 7.2.2.2.2 出力コンデンサの選択

実効出力キャパシタンスの取り得る範囲は、シングル L-C システム設計の場合、 $80\mu F$  (最小値)  $\sim 400\mu F$  (最大値) です。2 段目の L-C フィルタを使用する場合、1 段目の L-C フィルタは  $80\mu F$   $\sim 160\mu F$  の出力キャパシタンスを持ち、2 段目の L-C フィルタ (使用する場合) は  $20\mu F$  以上の容量を持ち、両方の L-C フィルタの合計容量は  $400\mu F$  未満である必要があります。負荷過渡テストとボード線図の測定は、安定性を検証するための適切な方法です。

注

低温 (−10°C 未満) の動作を必要とする設計では、シングル L-C システム設計では 120µF の最小実効出力 キャパシタンスで使用し、2 段目 L-C フィルタ設計を使用する場合は 1 段目の L-C フィルタ内の最小実効容量を 120µF で使用することを推奨します。

セラミック コンデンサ (X5R または X7R) を用いることを推奨します。 高容量のセラミック コンデンサには DC バイアス効果による容量の減少が発生し、最終的な実効容量に大きな影響を与えます。 パッケージサイズと電圧定格を考慮しながら、 適切なコンデンサを慎重に選択してください。 出力コンデンサの ESR および ESL も、 低ノイズ アプリケーション用の

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

21

出力コンデンサの選択において重要な検討事項となります。パッケージ サイズが小さいほど、通常は ESL および ESR は小さくなります。安定動作のために必要な容量と電圧定格を満たす限り、0805 以下のパッケージを推奨します。表 7-4 に、推奨コンデンサの一覧を示します。

表 7-4. 推奨出力コンデンサ

| コンデンサ タイプ | コンデンサ値   | 製造元                       | 電圧 (V) | パッケージ |

|-----------|----------|---------------------------|--------|-------|

| バルクキャパシタ  | 22μF、X7S | TDK C2012X7S1A226M125AC   | 10     | 0805  |

| バルクキャパシタ  | 47µF、X7R | Murata GRM32ER71A476ME15L | 10     | 1210  |

#### 7.2.2.2.3 2 段目の L-C フィルタのフェライト ビーズの選定

2 段目 L-C フィルタにフェライト ビーズを使用すると、外部部品点数を最小限に抑えることができます。 ノイズに敏感な回路のほとんどは、 高周波減衰用の RF ビーズを入力のデフォルト部品として使用しているためです。

モジュール の効率を可能な限り高く保持するために、全負荷時のインダクタンスが十分に大きく、DC 抵抗が低い (10mΩ 未満) フェライトビーズを選択するよう徹底してください。 負荷電流が増加すると、フェライト ビーズのインダクタンスは減少します。 したがって、フェライト ビーズの電流定格は、目的の負荷電流よりもはるかに大きくなくてはなりません。

**100MHz** で  $8\Omega \sim 20\Omega$  のインピーダンスのフェライト ビーズを選択することを推奨します。 大電流が必要な場合は、フェライト ビーズを並列に使用できますが、この使用により、インダクタンスとフィルタリングが半分になる可能性があります。 使用可能なフェライト ビーズについては、表 7-5 を参照してください。

| 表 7-5. | 推奨フ | 'ェライ | <b> </b> | ビー | -ズ |

|--------|-----|------|----------|----|----|

|        |     |      |          |    |    |

| 部品番号           | 製造元              | サイズ  | 100MHz 時のイン<br>ピーダンス | 100MHz 時のインダク<br>タンス (計算値) | DC 抵抗  | 電流定格  |

|----------------|------------------|------|----------------------|----------------------------|--------|-------|

| BLE18PS080SN1  | MuRata           | 0603 | 8.5 Ω                | 13.5nH                     | 4mΩ    | 5A    |

| BLE32SN120SN1L | MuRata           | 1210 | 12 Ω                 | 18nH                       | 0.78mΩ | 20A   |

| 74279221100    | Wurth Elektronik | 1206 | 10 Ω                 | 15.9nH                     | 3mΩ    | 10.5A |

| 7427922808     | Wurth Electronik | 0603 | 8 Ω                  | 12.7nH                     | 5mΩ    | 9.5A  |

内部補償は、2 段目のフィルタで最大 50nH のインダクタンスで安定するように設計されています。低リップルを実現するため、2 段目の L-C フィルタに必要なインダクタンスはわずか 5nH ~ 10nH です。インダクタンスは、選択した モジュール のスイッチング周波数 (1MHz、1.4MHz、2.2MHz) においてインダクタンスが類似していると仮定して、100MHz のフェライト ビーズ インピーダンスの仕様から推定でき、これは、一部のメーカーの Web サイトで利用可能なツールで検証できます。フェライト ビーズのインダクタンスを計算するには、式 5 を使用します:

$$L = \frac{Z}{2\pi \times f} \tag{5}$$

ここで、

- $\mathbf{Z}$  は、指定した周波数 (通常は 100MHz) におけるフェライト ビーズのインピーダンスです。 単位は  $\Omega$  です。

- f は指定周波数 (通常は 100MHz) です。

#### 7.2.2.2.4 入力コンデンサの選択

最高の出力および入力電圧フィルタリングを実現するために、X5R または X7R セラミック コンデンサを推奨します。入力コンデンサは、入力電圧リップルを最小化し、入力電圧スパイクを抑制し、このデバイスに安定したシステム レールを実現します。10µF 以上のコンデンサを推奨します。2 個を並列接続すると、入力電圧リップル フィルタリングが向上し、隣接回路へのノイズ結合が最小限に抑えられます。コンデンサの電圧定格も考慮に入れる必要があり、DC バイアスのディレーティング後に必要な 5µF の最小実効容量を備えている必要があります。

バルク入力コンデンサに加えて、VIN ピンと PGND ピンの間に小さなコンデンサを直接配置して、入力ループの寄生インダクタンスを最小限に抑え、デバイスの高周波ノイズを最小限に抑える必要があります。入力コンデンサの配置は出力ノイ

Copyright © 2025 Texas Instruments Incorporated

ズに影響するため、*セクション* 7.4.2 に示すように、バルク コンデンサとバイパス コンデンサの両方を配置するときは注意する必要があります。表 7-6 に、推奨入力コンデンサの一覧を示します。

表 7-6. 推奨入力コンデンサ

| 入力コンデンサのタイプ | コンデンサ値    | 製造元                          | 定格電圧(V) | パッケージ サイズ |

|-------------|-----------|------------------------------|---------|-----------|

| バルクコンデンサ    | 10μF、X7S  | TDK<br>C2012X7S1E106K125AC   | 25      | 0805      |

| バイパスコンデンサ   | 2.2nF、X7R | Murata<br>GRM155R71E222KA01D | 25      | 0402      |

#### 7.2.2.2.5 出力電圧の設定

出力電圧を式 6 に従って、 $0.8V \sim 5.5V$  の範囲内に設定するように、R1 および R2 の抵抗を選択します。帰還回路の ノイズに対する堅牢性を保ち、抵抗の自己発生ノイズを低減するには、R2 を  $5k\Omega$  以下に設定します。『DC/DC コンバータの抵抗性帰還分圧器の設計上の検討事項』Analog Design Journal で説明されているように、FB 抵抗の値を小さくすると、ノイズ耐性が向上しますが、軽負荷効率は低下します。

$$R_1 = R_2 \times \left(\frac{V_{OUT}}{V_{FR}} - 1\right) = R_2 \times \left(\frac{V_{OUT}}{0.8 V} - 1\right) \tag{6}$$

| VOUT (V) | R1     | R2     |

|----------|--------|--------|

| 0.9      | 604 Ω  | 4.87kΩ |

| 1.0      | 1.21kΩ | 4.87kΩ |

| 1.2      | 2.43kΩ | 4.87kΩ |

| 1.8      | 6.04kΩ | 4.87kΩ |

| 2.5      | 10.4kΩ | 4.87kΩ |

| 3.3      | 15.2kΩ | 4.87kΩ |

| 5        | 25.5kΩ | 4.87kΩ |

フィードフォワード コンデンサ (CFF) は適切な動作のために必要ではありませんが、出力ノイズをさらに改善できる場合があります。ただし、パワー グッド (PG) 機能はスタートアップ時に CFF が大きい場合は有効ではなく、大きな負荷過渡時にPG ピンが誤トリガされる可能性があるため、CFF を選択する際には注意が必要です。フィードフォワード コンデンサを使用することの長所と短所の説明については、『*低ドロップアウト レギュレータでフィードフォワード コンデンサを使用することの長所と短所*』アプリケーション ノートも参照してください。

#### 7.2.2.2.6 NR/SS コンデンサの選定

*セクション* 6.3.8 で説明したように、NR/SS コンデンサは合計ノイズとソフトスタート時間の両方に影響を及ぼします。5ms のソフトスタート時間と優れたノイズ性能を実現するための推奨値は 470nF です。スタートアップ時間が 35ms のときの NR/SS キャップの最大値は 3.3μF です。1μF を上回る値を使用すると、ノイズ特性の改善は最小限です。以下の式を使用して、目的のソフトスタート時間または選択したコンデンサ値に基づいてソフトスタート時間を計算します。

$$t_{SS}\left(s\right) = \frac{C_{NRSS} \times 0.8 \,V}{I_{NRSS}} \tag{7}$$

$$C_{NRSS}\left(F\right) = \frac{I_{NRSS} \times t_{SS}}{0.8 \, V} \tag{8}$$

Product Folder Links: TPSM82916

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

23

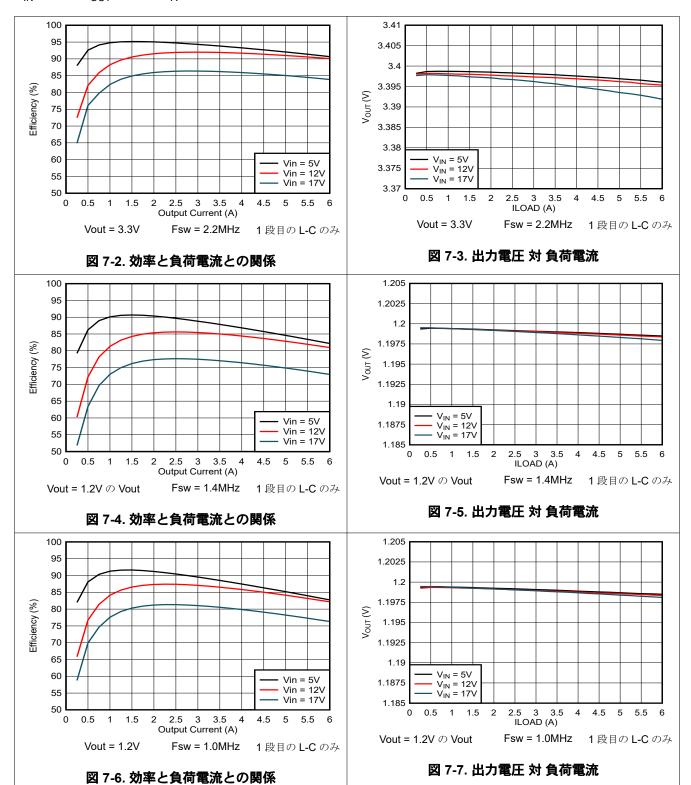

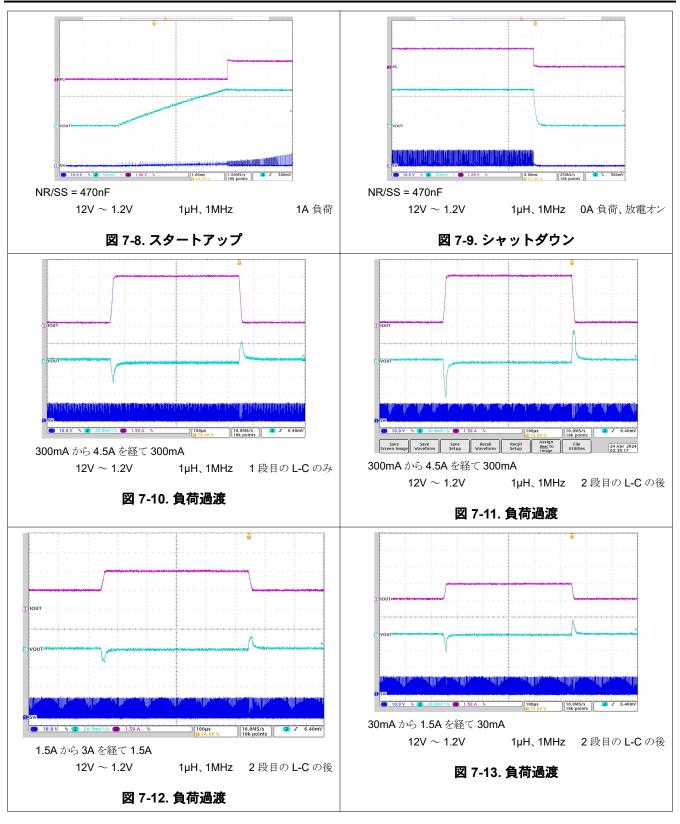

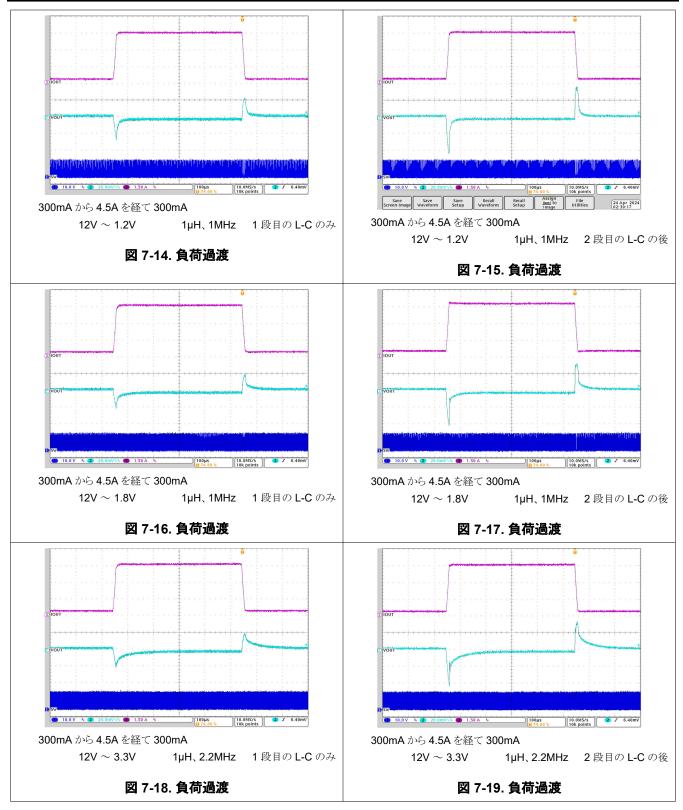

### 7.2.3 アプリケーション曲線

V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 1.2V、T<sub>A</sub> = 25℃、BOM = 表 7-1

English Data Sheet: SLVSH49

## 7.3 電源に関する推奨事項

TPSM82916 の電源は、TPSM82916 の電源電圧、出力電圧、出力電流に応じた電流定格でなくてはなりません。

## 7.4 レイアウト

## 7.4.1 レイアウトのガイドライン

特に高いスイッチング周波数の場合、スイッチ モード電源を動作させるために、適切なレイアウトが非常に重要です。 TPSM82916 デバイスの PCB レイアウトでは、最高の性能を得るために細心の注意が必要です。レイアウトが不適切な場合、ラインと負荷のレギュレーションの不良、不安定、EMI 放射の増加、ノイズの増加などの問題につながる可能性があります。一般的なベストプラクティスの詳細な説明については、『*降圧コンバータの優れた PCB レイアウトを行うための 5 つのステップ*』Analog Design Journal を参照してください。デバイスに固有の推奨事項を以下に示します。

- 入力コンデンサは、デバイスの VIN ピンと PGND ピンにできる限り近づけて配置してください。この配置は、最も重要な部品配置です。入力コンデンサは ビアを避けて VIN ピンと PGND ピンに直接配線します。

- 出力コンデンサのグランドを PGND ピンの近くに配置し、ビアを避けて直接配線します。インダクタから出力コンデンサへの接続長を最小限に抑えます。

- VOピンを出力コンデンサ Cour に直接接続します。

- NR/SS、VO、FB の各ピンへの接続などの敏感なパターンは、短いパターンで接続し、SW ピンなどのノイズ源から離して配線します。

- ビアを介して PSNS ピンをシステムの GND プレーンに直接接続します。

- 2 段目 L-C フィルタ  $L_f$  および  $C_f$  は、2 段目 L-C フィルタの周囲の放射結合を低減するため、負荷の近くに配置します

- 図 7-21 に示すように、キープ アウト領域にはフェライト ビーズを配置しないでください

- FB 抵抗 R1 および R2 は FB ピンの近くに配置し、VOUT 接続を R1 から負荷にリモート センス パターンとして配線します。2 段目 L-C フィルタを使用する場合は、Lf の後段にこの接続を行う必要があります。

- 図 7-21 のほか、評価基板に実装されている推奨レイアウトおよび EVM ユーザー ガイド『『『TPSM82916 降圧コンバータ評価基板』EVM ユーザー ガイド に記載されている推奨レイアウトを参照してください。

#### 7.4.2 レイアウト例

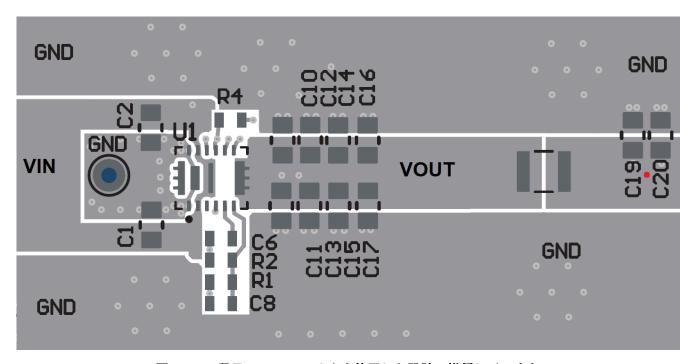

図 7-20. シングル L-C フィルタの推奨レイアウト

資料に関するフィードバック(ご意見やお問い合わせ)を送信

27

#### 注

赤点は、最善の DC レギュレーションを実現するために帰還センスを配置する必要のある場所を示しています。 シングル L-C 構成の場合、帰還センスは VOUT コンデンサの近くに配置されます。 2 段目の L-C フィルタ設計の場合、帰還センスは VOUT\_FILT コンデンサの後の負荷の近くに配置されます。

図 7-21. 2 段目の L-C フィルタを使用した設計の推奨レイアウト

#### 注

インダクタと出力コンデンサの間にフェライトビーズが配置されて いない 限り、フェライトビーズをデバイスに近づけて配置できます。フェライトビーズをさらに離して配置すると、フェライトビーズの出力に対する容量性結合や電磁結合を防止できます。フェライトビーズをキープ アウト領域に配置すると、フェライトビーズのフィルタリング効果は大幅に低減されます。フェライトビーズをビアを経由して基板の裏面に配線する場合は、フェライトビーズがこの領域にある場合は、層の間に十分なグランドプレーンを確保してください。

Product Folder Links: TPSM82916

Copyright © 2025 Texas Instruments Incorporated

## 8 デバイスおよびドキュメントのサポート

## 8.1 デバイス サポート

## 8.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 8.1.2 開発サポート

#### 8.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリック すると、WEBENCH Power Designer により、TPSM82916 デバイスを使用するカスタム設計を作成できます。

- 1. 最初に、入力電圧 (V<sub>IN</sub>)、出力電圧 (V<sub>OUT</sub>)、出力電流 (I<sub>OUT</sub>) の要件を入力します。

- 2. 効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 3. 出力電圧リップルを最適化するための「advanced」(詳細) タブを開きます。

- 4. TPSM82916 の設計では、左側のドロップダウンで、2 段目 L-C フィルタを有効にし、また、その他の設定を変更できます。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、www.ti.com/ja-jp/WEBENCH でご覧になれます。

## 8.2 ドキュメントのサポート

#### 8.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス インスツルメンツ、『*低ドロップアウト レギュレータでフィードフォワード コンデンサを使用することの長所と短 所*』アプリケーション ノート

- テキサス インスツルメンツ、『『『*TPSM82916 降圧コンバータ評価基板*』EVM ユーザー ガイド

- テキサス インスツルメンツ、『*降圧コンバータの優れた PCB レイアウトを実現する 5 つのステップ*』Analog Design Journal

- テキサス インスツルメンツ、『*DC/DC コンバータにおける抵抗性帰還デバイダの設計上の検討事項*』Analog Design Journal

#### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

29

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 8.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 8.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Changes from Revision \* (October 2024) to Revision A (June 2025)

**Page**

• ドキュメントのステータスを「事前情報」から「量産データ」に変更......1

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

31

Product Folder Links: TPSM82916

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

www.ti.com 6-Nov-2025

#### PACKAGING INFORMATION

| Ord | lerable part number | Status | Material type | Package   Pins          | Package qty   Carrier | RoHS    | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----|---------------------|--------|---------------|-------------------------|-----------------------|---------|-------------------------------|----------------------------|--------------|------------------|

| Т   | TPSM82916VCER       | Active | Production    | QFN-FCMOD<br>(VCE)   16 | 3000   LARGE T&R      | In-Work | Call TI                       | Level-2-250C-1 YEAR        | -40 to 125   | TM82916          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-Jul-2025

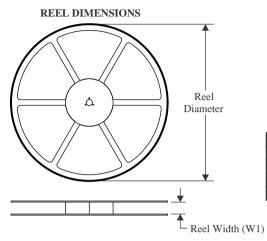

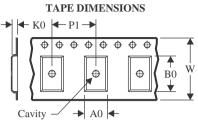

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

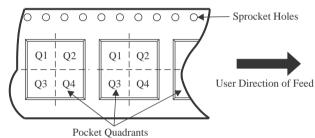

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPSM82916VCER | QFN-<br>FCMOD   | VCE                | 16 | 3000 | 330.0                    | 12.4                     | 4.3        | 5.0        | 3.3        | 8.0        | 12.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-Jul-2025

## \*All dimensions are nominal

| Ì | Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | TPSM82916VCER | QFN-FCMOD    | VCE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |  |

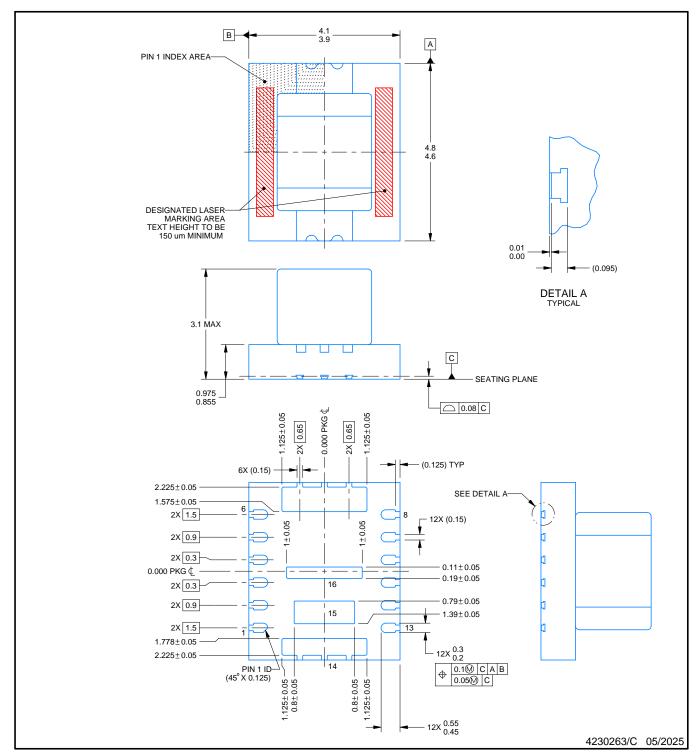

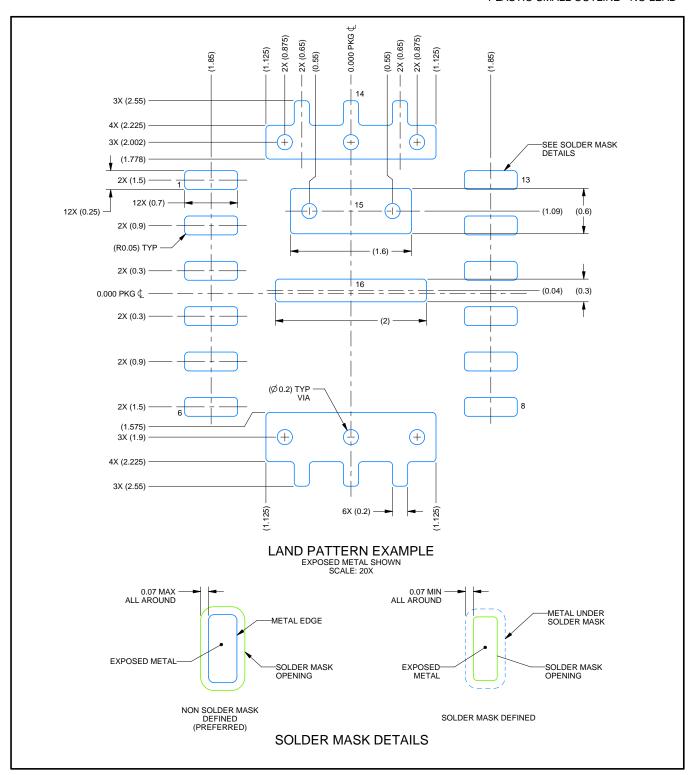

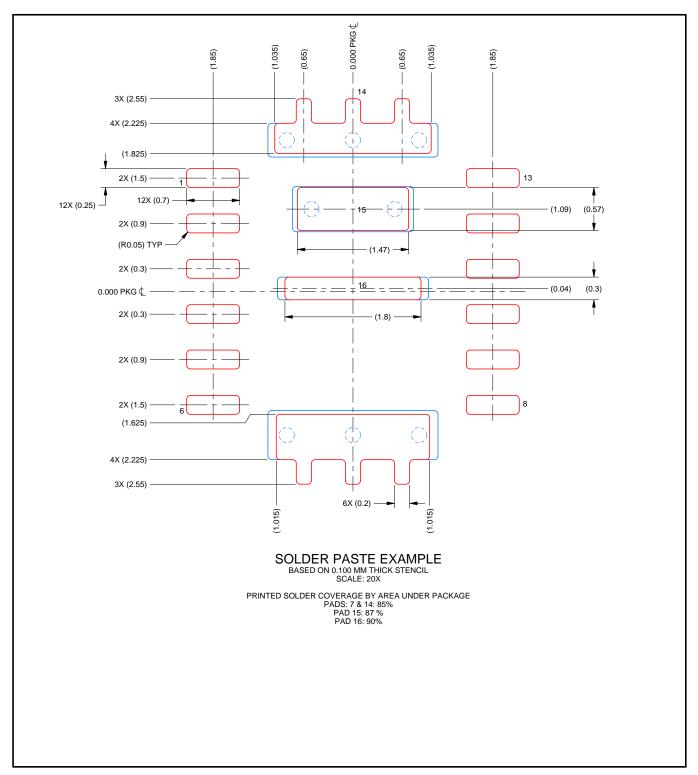

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月