# TPSM82830x、低 EMI、2.25V~5.5V 入力、1A、2A、3A 降圧パワー モジュール、インダクタ内蔵、QFN および MagPack™ パッケージ

## 1 特長

- EMI 性能の最適化

- CISPR 11/32 準拠が容易

- MagPack テクノロジーはインダクタと IC をシールド

- オンチップのノイズ フィルタリング コンデンサを内蔵

- 調整可能な出力電圧: 0.5V~4.5V

- 1% の FB 電圧精度 (-40°C~125°C  $T_J$ )

- 55mΩ ドロップアウト抵抗

- 入力電圧範囲: 2.25V~5.5V

- 2.0MHz のスイッチング周波数

- 7µA の動作時静止電流

- DCS-Control トポロジ

- 優れた過度応答

- MODE ピンで FPWM または PSM を選択可能

- 1.2V GPIO をサポート

- 100% デューティ サイクル動作による最小のドロップアウト電圧

- アクティブ出力放電

- パワー グッド出力

- サーマル シャットダウン保護機能

- ヒップまたはラッチオフ OCP/OVP

- ボンド ワイヤなしのパッケージ オプション

- 標準 QFN、高さ 1.95mm

- シールド付き MagPack パッケージ、高さ 1.95mm

- WEBENCH® Power Designer により、TPSM828303 を使用するカスタム設計を作成

## 2 アプリケーション

- 産業用 PC

- LPDDR5 0.5V VDDQ 電源

- ASIC、SoC、MCU の電源

- ファクトリ オートメーション / 制御

- 医療用患者モニタ

- 一般的なポイント オブ ロード (POL)

## 3 説明

TPSM82830x は、インダクタと EMI 低減技術を備えた 1A、2A、3A、ピン互換の使いやすい同期整流式降圧 DC/DC モジュール ファミリです。これらのデバイスは、小さな出力容量で高速過渡応答を実現するために DCS-Control トポロジを使用します。出力電圧は最小 0.5V に設定でき、動作時の接合部温度範囲全体にわたって 1% の高い帰還電圧精度を維持します。MODE ピンにより、省電力モードと強制 PWM モードを選択できます。パワー セーブ モードはバッテリの寿命の延長を目的とするもので、強制 PWM モードは準固定スイッチング周波数で、インダクタの連続導通によってリップルを低減します。内部ソフトスタート回路によって突入電流が低減し、パワーグッド信号によって正しい出力電圧が示されます。ヒップ短絡保護機能と、サーマル シャットダウンの組み合わせにより、デバイスおよびアプリケーションを保護します。このファミリは、3.0mm × 3.0mm の QFN パッケージと 2.5mm × 2.6mm の MagPack パッケージで供給されます。

### 製品情報

| 部品番号 <sup>(2)</sup>       | 出力電流 | パッケージ <sup>(3)</sup> | パッケージ サイズ <sup>(1)</sup> |

|---------------------------|------|----------------------|--------------------------|

| TPSM828301                | 1A   |                      |                          |

| TPSM828302                | 2A   | RDS (QFN-FCMOD, 9)   | 3.0mm × 3.0mm            |

| TPSM828303                | 3A   |                      |                          |

| TPSM828301 <sup>(4)</sup> | 1A   |                      |                          |

| TPSM828302 <sup>(4)</sup> | 2A   | VCB (QFN-FCMOD, 10)  | 2.6mm × 2.5mm            |

| TPSM828303                | 3A   |                      |                          |

(1) 「デバイスのオプション」の表を参照してください。

(2) 詳細については、セクション 11 を参照してください。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はビンも含まれます。

(4) 開発中製品情報 (量産データではありません)。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

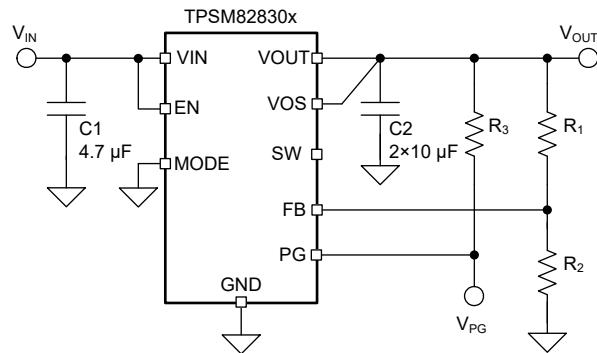

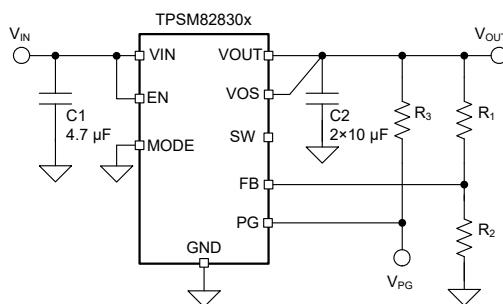

代表的なアプリケーション回路図

## 目次

|                         |    |                        |    |

|-------------------------|----|------------------------|----|

| 1 特長                    | 1  | 7.4 デバイスの機能モード         | 15 |

| 2 アプリケーション              | 1  | 8 アプリケーションと実装          | 17 |

| 3 説明                    | 1  | 8.1 アプリケーション情報         | 17 |

| 4 デバイスのオプション            | 4  | 8.2 代表的なアプリケーション       | 17 |

| 5 ピン構成および機能             | 4  | 8.3 電源に関する推奨事項         | 30 |

| 6 仕様                    | 6  | 8.4 レイアウト              | 30 |

| 6.1 絶対最大定格              | 6  | 9 デバイスおよびドキュメントのサポート   | 32 |

| 6.2 ESD 定格              | 6  | 9.1 デバイス サポート          | 32 |

| 6.3 推奨動作条件              | 6  | 9.2 ドキュメントのサポート        | 32 |

| 6.4 熱に関する情報 (RDS パッケージ) | 7  | 9.3 サポート・リソース          | 32 |

| 6.5 熱に関する情報 (VCB パッケージ) | 7  | 9.4 商標                 | 32 |

| 6.6 電気的特性               | 7  | 9.5 静電気放電に関する注意事項      | 33 |

| 6.7 代表的特性               | 9  | 9.6 用語集                | 33 |

| 7 詳細説明                  | 10 | 10 改訂履歴                | 33 |

| 7.1 概要                  | 10 | 11 メカニカル、パッケージ、および注文情報 | 34 |

| 7.2 機能ブロック図             | 11 | 11.1 テープおよびリール情報       | 35 |

| 7.3 機能説明                | 11 |                        |    |

## 4 デバイスのオプション

| 部品番号                            | 出力電流 | ソフトスタート、<br>tSS | OCP モード | パッケージ   | 出力電圧  |

|---------------------------------|------|-----------------|---------|---------|-------|

| TPSM828301ARDSDR                | 1A   | 300μs           | ヒップ(2)  | QFN RDS | 可変(1) |

| TPSM828302ARDSDR                | 2A   | 300μs           | ヒップ(2)  | QFN RDS |       |

| TPSM828303ARDSDR                | 3A   | 300μs           | ヒップ(2)  | QFN RDS |       |

| TPSM828303KPVCBR <sup>(3)</sup> | 1A   | 880μs           | ヒップ(2)  | QFN VCB |       |

| TPSM828301APVCBR <sup>(3)</sup> | 1A   | 300μs           | ヒップ(2)  | QFN VCB |       |

| TPSM828302APVCBR <sup>(3)</sup> | 2A   | 300μs           | ヒップ(2)  | QFN VCB |       |

| TPSM828303APVCBR                | 3A   | 300μs           | ヒップ(2)  | QFN VCB |       |

- (1) 固定出力電圧バージョンについては、マーケティング部門に供給状況をお問い合わせください。

(2) OCP/OVP ラッチオフのバージョンについては、マーケティング部門に供給状況をお問い合わせください。

(3) 開発中製品情報（量産データではありません）。

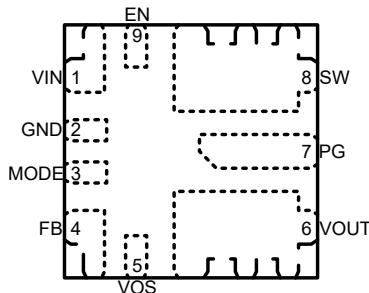

## 5 ピン構成および機能

図 5-1. RDS パッケージ、9 ピン QFN-FCMOD 上面図

表 5-1. ピンの機能：RDS パッケージ

| ピン   |    | 種類 <sup>(1)</sup> | 説明                                                                                                                  |

|------|----|-------------------|---------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |                   |                                                                                                                     |

| VIN  | 1  | PWR               | 入力電圧ピン入力コンデンサを $V_{IN}$ と GND の間に、できるだけ近づけて接続します。                                                                   |

| GND  | 2  | PWR               | グランドピン                                                                                                              |

| モード  | 3  | I                 | このピンが Low にプルされると、デバイスは PSM/PWM モードで動作し、High になると強制 PWM モードで動作します。これは、デバイスが動作中のときにも実行できます。このピンをフローティングのままにしないでください。 |

| FB   | 4  | I                 | フィードバックピン。抵抗分圧器の出力をこのピンに接続します。                                                                                      |

| VOS  | 5  | I                 | 出力電圧検出ピン。このピンはインダクタの後に接続してください。                                                                                     |

| VOUT | 6  | PWR               | 出力電圧ピン                                                                                                              |

| PG   | 7  | O                 | パワーグッドオープンドレイン出力ピン。プルアップ抵抗は最大 5.5V の電圧に接続できます。このピンを使用しない場合は、フローティングのままにします。                                         |

| SW   | 8  | PWR               | コンバータのスイッチピン。内部でインダクタに接続されています。EMI を最小限に抑えるため、このピンを未接続のままにするか、またはこのピンを小さなパッドに半田付けて、熱性能を向上させます。                      |

| EN   | 9  | I                 | デバイスイネーブルピン。デバイスをイネーブルにするには、このピンを High にします。このピンを Low にすると、デバイスはディスエーブルになります。このピンを未接続のままにしないでください。                  |

(1) I = 入力、O = 出力、PWR = パワー

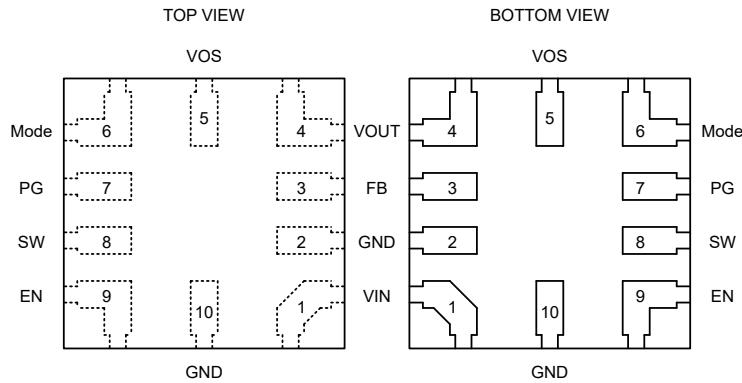

図 5-2. VCB パッケージ、10 ピン QFN-FCMOD

表 5-2. ピンの機能 : VCB パッケージ

| ピン   |       | 種類 <sup>(1)</sup> | 説明                                                                                                                   |

|------|-------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号    |                   |                                                                                                                      |

| VIN  | 1     | PWR               | 入力電圧ピン入力コンデンサを $V_{IN}$ と GND の間に、できるだけ近づけて接続します。                                                                    |

| GND  | 2, 10 | PWR               | グランド ピン                                                                                                              |

| FB   | 3     | I                 | フィードバック ピン。抵抗分圧器の出力をこのピンに接続します。                                                                                      |

| VOUT | 4     | PWR               | 出力電圧ピン                                                                                                               |

| VOS  | 5     | I                 | 出力電圧検出ピン。このピンはインダクタの後に接続してください。                                                                                      |

| モード  | 6     | I                 | このピンが Low にプルされると、デバイスは PSM/PWM モードで動作し、High になると強制 PWM モードで動作します。これは、デバイスが動作中のときにも実行できます。このピンをフローティング のままにしないでください。 |

| PG   | 7     | O                 | パワー グッド オープンドレイン出力ピン。プルアップ抵抗は最大 5.5V の電圧に接続できます。このピンを使用しない場合は、フローティングのままにします。                                        |

| SW   | 8     | PWR               | コンバータのスイッチ ピン。内部でインダクタに接続されています。EMI を最小限に抑えるため、このピンを未接続のままにするか、またはこのピンを小さなパッドに半田付けして、熱性能を向上させます。                     |

| EN   | 9     | I                 | デバイス イネーブル ピン。デバイスをイネーブルにするには、このピンを High にします。このピンを Low にすると、デバイスはディスエーブルになります。このピンを未接続のままにしないでください。                 |

(1) I = 入力、O = 出力、PWR = パワー

## 6 仕様

### 6.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                   |                                 | 最小値  | 最大値            | 単位 |

|-------------------|---------------------------------|------|----------------|----|

| 電圧 <sup>(2)</sup> | VIN, EN, MODE, FB, PG           | -0.3 | 6              | V  |

|                   | SW (DC), VOS, VOUT              | -0.3 | $V_{IN} + 0.3$ | V  |

|                   | SW (AC, 10ns 未満) <sup>(3)</sup> | -2.5 | 10             | V  |

| 動作時接合部温度          | $T_J$                           | -40  | 125            | °C |

| 保存温度              | $T_{stg}$                       | -55  | 125            | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、回路のグランド端子 GND を基準としたものです。

- (3) スイッチング動作時

### 6.2 ESD 定格

|             |      |                                                           | 値          | 単位 |

|-------------|------|-----------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM), ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM), ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 500$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|           |                                  | 最小値  | 公称値 | 最大値 | 単位 |

|-----------|----------------------------------|------|-----|-----|----|

| $V_{IN}$  | 入力電圧範囲                           | 2.25 | 5.5 | 5.5 | V  |

| $V_{OUT}$ | 出力電圧範囲                           | 0.5  | 4.5 | 4.5 | V  |

| $C_{IN}$  | 実効入力キャパシタンス <sup>(1)</sup>       | 3    |     |     | μF |

| $C_{OUT}$ | 実効出力キャパシタンス <sup>(1)</sup>       | 12   | 200 | 200 | μF |

| $I_{OUT}$ | 出力電流範囲、TPSM828301                |      | 1   | 1   | A  |

| $I_{OUT}$ | 出力電流範囲、TPSM828302                |      | 2   | 2   | A  |

| $I_{OUT}$ | 出力電流範囲、TPSM828303 <sup>(2)</sup> |      | 3   | 3   | A  |

| $I_{PG}$  | パワーグッド入力電流能力                     |      | 1   | 1   | mA |

| $T_J$     | 動作時接合部温度 <sup>(2)</sup>          | -40  | 125 | 125 | °C |

- (1) 表のすべてのコンデンサに記載されている値は実効容量で、DC バイアス効果も含まれています。セラミック コンデンサの DC バイアス効果により、電圧を印加したときの実効容量は公称値より小さくなります。実効静電容量と印加される DC 電圧との関係については、メーカーの DC バイアス曲線を確認してください。

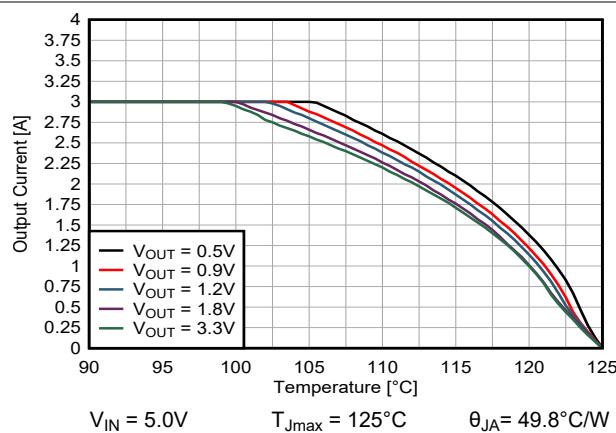

- (2) 消費電力が大きく、周囲温度が高いアプリケーションでは、モジュールを動作温度範囲内で動作させるには、最大出力電流をディレーティングする必要があります。

## 6.4 热に関する情報 (RDS パッケージ)

| 热評価基準 <sup>(1)</sup>  |                     | TPSM82830xARDSR  |                     | 単位   |  |

|-----------------------|---------------------|------------------|---------------------|------|--|

|                       |                     | RDS (QFN-FCMOD)  |                     |      |  |

|                       |                     | 9 ピン (JEDEC ボード) | 9 ピン (EVM ボード)      |      |  |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 59.4             | 49.8                | °C/W |  |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 66.5             | 該当なし <sup>(2)</sup> | °C/W |  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 16.8             | 該当なし <sup>(2)</sup> | °C/W |  |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3              | 0.5                 | °C/W |  |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 16.7             | 23.2                | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』注記を参照してください。

(2) EVM には適用されません。

## 6.5 热に関する情報 (VCB パッケージ)

| 热評価基準 <sup>(1)</sup>  |                     | TPSM828303PVCBR       |                       | 単位   |  |

|-----------------------|---------------------|-----------------------|-----------------------|------|--|

|                       |                     | VCB (QFN-FCMOD)       |                       |      |  |

|                       |                     | 10 ピン (JEDEC ボード)     | 10 ピン (EVM ボード)       |      |  |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 83.1                  | 66.5                  | °C/W |  |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 37.1                  | 該当なし <sup>(2)</sup>   | °C/W |  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 27.4                  | 該当なし <sup>(2)</sup>   | °C/W |  |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | (-1.7) <sup>(3)</sup> | (-1.6) <sup>(3)</sup> | °C/W |  |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 27.2                  | 35.3                  | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』注記を参照してください。

(2) EVM には適用されません。

(3) インダクタの消費電力は、接合部から上面への負の特性パラメータにつながるため、ケースの上面温度はアクティブ回路の温度よりも高くなる可能性があります。

## 6.6 電気的特性

T<sub>J</sub> = -40°C to +125°C、V<sub>IN</sub> = 2.25V ~ 5.5V。標準値は、T<sub>J</sub> = 25°C および V<sub>IN</sub> = 5V での値 (特に記述のない限り)

| パラメータ                  | テスト条件                                                                                                       | 最小値  | 標準値  | 最大値  | 単位 |

|------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|----|

| <b>電源</b>              |                                                                                                             |      |      |      |    |

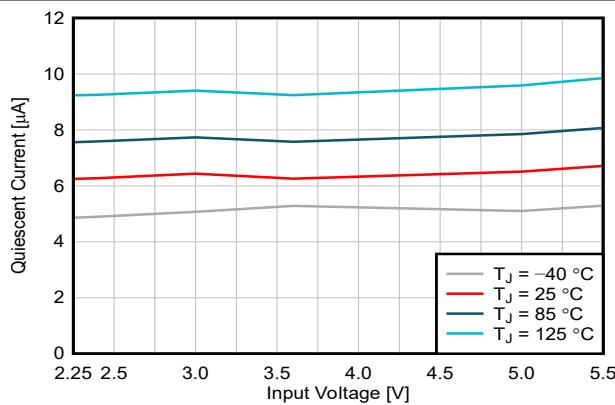

| I <sub>Q</sub>         | 動作時静止電流<br>EN = V <sub>IN</sub> , I <sub>OUT</sub> = 0 mA, V <sub>OUT</sub> = 1.8V, モード = GND、デバイスのスイッチングあり | 7    | 17   |      | μA |

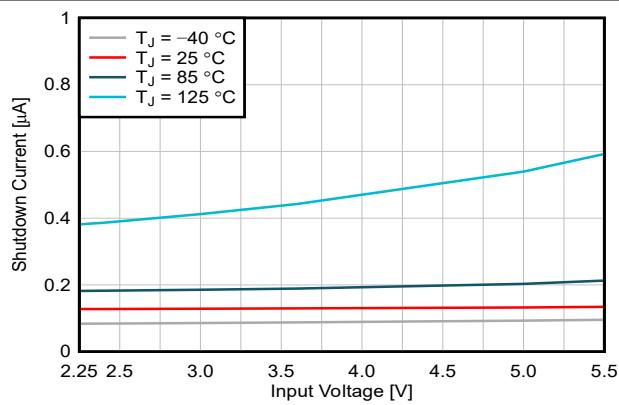

| I <sub>SD</sub>        | V <sub>IN</sub> のシャットダウン時の電源電流<br>EN = low, T <sub>J</sub> = -40°C ~ 85°C                                   | 100  | 700  |      | nA |

| V <sub>UVLO(+)</sub>   | 立ち上がり UVLO スレッショルド電圧 (V <sub>IN</sub> )                                                                     | 2.05 | 2.15 | 2.25 | V  |

| V <sub>UVLO(hys)</sub> | UVLO ヒステリシス (V <sub>IN</sub> )                                                                              | 90   | 120  |      | mV |

| <b>サーマル シャットダウン</b>    |                                                                                                             |      |      |      |    |

| T <sub>J(SD)</sub>     | サーマル シャットダウンのスレッショルド<br>T <sub>J</sub> 立ち上がり                                                                | 150  |      |      | °C |

| T <sub>J(HYS)</sub>    | サーマル シャットダウンヒステリシス                                                                                          | 20   |      |      | °C |

| <b>ロジック ピン</b>         |                                                                                                             |      |      |      |    |

| V <sub>EN(+)</sub>     | High レベル入力電圧 (EN)                                                                                           | 0.8  |      |      | V  |

| V <sub>EN(-)</sub>     | Low レベル入力電圧 (EN)                                                                                            |      | 0.35 |      | V  |

| V <sub>MODE(+)</sub>   | High レベル入力電圧 (MODE)                                                                                         | 0.8  |      |      | V  |

| V <sub>MODE(-)</sub>   | Low レベル入力電圧 (MODE)                                                                                          |      | 0.35 |      | V  |

| I <sub>EN(LKG)</sub>   | EN の入力リーコンデンサ電流<br>V <sub>EN</sub> = HIGH                                                                   | 10   | 100  |      | nA |

| I <sub>MODE(LKG)</sub> | MODE の入力リーコンデンサ電流<br>V <sub>MODE</sub> = HIGH                                                               | 10   | 100  |      | nA |

| <b>スタートアップ</b>         |                                                                                                             |      |      |      |    |

| t <sub>ss</sub>        | 内部固定ソフトスタート時間<br>V <sub>OUT</sub> = 0 ~ V <sub>OUT</sub> = 95%                                              | 180  | 300  | 440  | μs |

## 6.6 電気的特性 (続き)

$T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ 、 $V_{IN} = 2.25\text{V} \sim 5.5\text{V}$ 。標準値は、 $T_J = 25^{\circ}\text{C}$  および  $V_{IN} = 5\text{V}$  での値 (特に記述のない限り)

| パラメータ          |                                | テスト条件                                                                                | 最小値   | 標準値  | 最大値  | 単位               |

|----------------|--------------------------------|--------------------------------------------------------------------------------------|-------|------|------|------------------|

| $t_{SS}$       | 内部固定ソフトスタート時間                  | $V_{OUT} = 0 \sim V_{OUT} = 95\%$ 、TPSM82830xK バージョンのみ                               | 530   | 880  | 1300 | $\mu\text{s}$    |

| $t_{d(EN)}$    | イネーブル遅延時間                      | EN が HIGH になってからデバイスのスイッチング開始まで                                                      |       | 120  | 220  | $\mu\text{s}$    |

| <b>基準電圧</b>    |                                |                                                                                      |       |      |      |                  |

| $V_{FB}$       | 帰還電圧精度                         | PWM モード <sup>(1)</sup>                                                               | 495   | 500  | 505  | $\text{mV}$      |

| $V_{FB}$       | 帰還電圧精度                         | PWM モード <sup>(1)</sup>                                                               | -1    | +1   |      | %                |

| $V_{FB}$       | 帰還電圧精度                         | PFM モード、 $C_{OUT,eff} \geq 15\mu\text{F}$                                            | -1    | +2   |      | %                |

| $I_{FB(LKG)}$  | FB 入力リーク電流、可変バージョン             | $V_{FB} = 0.5\text{V}$                                                               |       | 10   | 70   | $\text{nA}$      |

| $I_{VOS(LKG)}$ | VOS の入力リーク電流                   | $V_{EN} = \text{low}$                                                                |       | 100  | 500  | $\text{nA}$      |

| <b>パワーグッド</b>  |                                |                                                                                      |       |      |      |                  |

| $V_{PG,UV(+)}$ | 立ち上がりパワーグッド レッショルド電圧 (出力低電圧)   | PG ピン Low、 $V_{FB}$ 立ち上がり                                                            | 94    | 96   | 98   | %                |

| $V_{PG,UV(-)}$ | 立ち下がりパワーグッド レッショルド電圧 (出力低電圧)   | PG ピン High、 $V_{FB}$ 立ち下がり                                                           | 90    | 92   | 94   | %                |

| $V_{PG,OV(+)}$ | 立ち上がりパワーグッド レッショルド電圧 (出力過電圧)   | PG ピン High、 $V_{FB}$ 立ち上がり                                                           | 108   | 110  | 112  | %                |

| $V_{PG,OV(-)}$ | 立ち下がりパワーグッド レッショルド電圧 (出力過電圧)   | PG ピン Low、 $V_{FB}$ 立ち下がり                                                            | 102.5 | 105  | 107  | %                |

| $t_{d(PG)}$    | スタートアップ時のパワーグッド遅延              | スタートアップ時の PG ピンの Low から High への遷移                                                    |       | 128  |      | $\mu\text{s}$    |

| $t_{d(PGO)}$   | 動作中のパワーグッドのグリッチ除去遅延            | PG ピンの High から Low、または Low から High への遷移                                              | 30    | 45   | 60   | $\mu\text{s}$    |

| $I_{PG(LKG)}$  | オーブンドレイン出力が High の PG ピンのリーク電流 | $V_{PG} = 5.0\text{V}$                                                               |       | 10   | 100  | $\text{nA}$      |

| $V_{PG,OL}$    | PG ピンの Low レベル出力電圧             | $I_{PG} = 1\text{mA}$                                                                |       |      | 0.4  | V                |

| <b>電力段</b>     |                                |                                                                                      |       |      |      |                  |

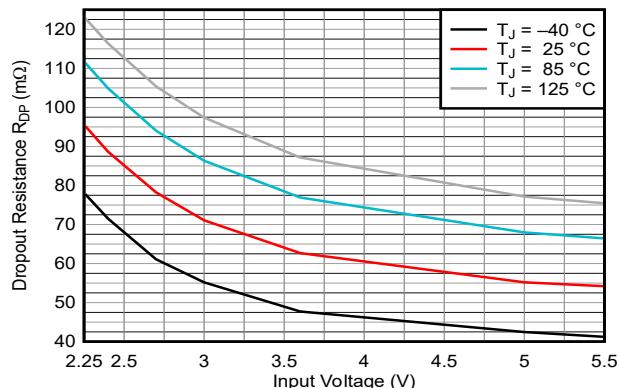

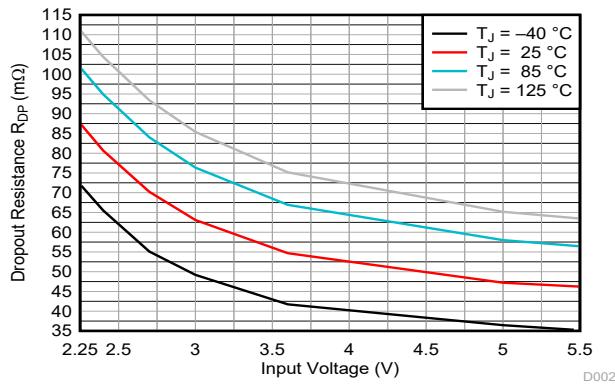

| $R_{DP}$       | ドロップアウト抵抗                      | TPSM82830x、 $V_{IN} \geq 5\text{V}$ 、100% モード、 $T_J = 25^{\circ}\text{C}$ 、VCB パッケージ |       | 55   |      | $\text{m}\Omega$ |

| $R_{DP}$       | ドロップアウト抵抗                      | TPSM82830x、 $V_{IN} \geq 5\text{V}$ 、100% モード、 $T_J = 25^{\circ}\text{C}$ 、RDS パッケージ |       | 61   |      | $\text{m}\Omega$ |

| $R_{DP}$       | ドロップアウト抵抗                      | TPSM82830x、 $V_{IN} = 2.7\text{V}$ 、100% モード、 $T_J = 25^{\circ}\text{C}$             |       | 78   | 105  | $\text{m}\Omega$ |

| $f_{SW}$       | スイッチング周波数、PWM モード              | $I_{OUT} = 1\text{A}$ 、 $V_{OUT} = 1.8\text{V}$                                      |       | 2.0  |      | MHz              |

| <b>過電流保護</b>   |                                |                                                                                      |       |      |      |                  |

| $I_{HS(OC)}$   | ハイサイド ピーク電流制限                  | TPSM828301                                                                           | 1.8   | 2.1  | 2.6  | A                |

| $I_{HS(OC)}$   | ハイサイド ピーク電流制限                  | TPSM828302                                                                           | 2.7   | 3.3  | 3.9  | A                |

| $I_{HS(OC)}$   | ハイサイド ピーク電流制限                  | TPSM828303                                                                           | 4.0   | 4.6  | 5.4  | A                |

| $I_{LS(NOC)}$  | 上限側負の電流制限                      | LS FET のシンク電流制限                                                                      |       | -1.8 |      | A                |

| <b>出力放電</b>    |                                |                                                                                      |       |      |      |                  |

| $I_{DIS}$      | SW ピンの出力放電電流                   | $V_{IN} > 2\text{V}$ 、 $V_{SW} = 0.4\text{V}$ 、 $EN = \text{LOW}$                    | 75    | 400  |      | $\text{mA}$      |

(1) 出力電圧精度は、静的パラメータとして指定されます。ダイナミック挙動については、データシートの対応するセクションを参照してください。

## 6.7 代表的特性

図 6-1. TPSM82830x ドロップアウト抵抗 RDS パッケージ

図 6-2. TPSM82830x ドロップアウト抵抗 VCB パッケージ

図 6-3. シャットダウン電流

図 6-4. 静止電流

## 7 詳細説明

### 7.1 概要

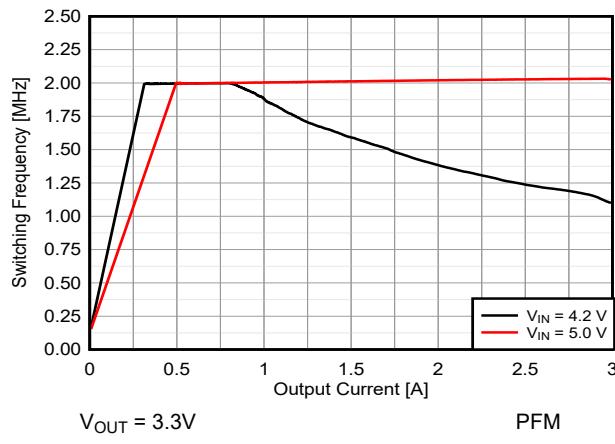

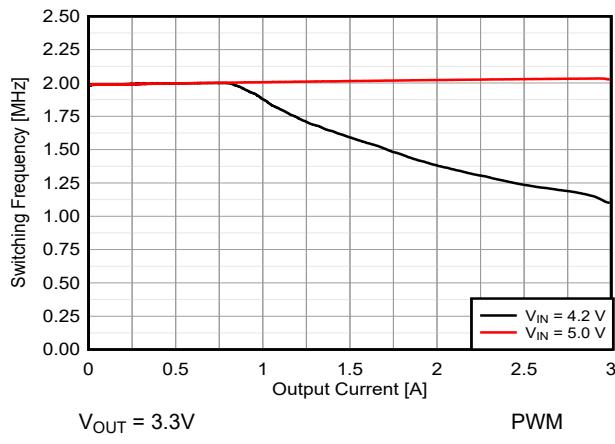

TPSM82830x は、1A、2A、3A バージョンの低電圧降圧 モジュール ファミリです。これらのデバイスは、中出力電流および大出力電流時のパルス幅変調 (PWM) から、低出力電流時にパルス周波数変調 (PFM) ヘシームレスに遷移する DCS-Control 方式を使用しています。PWM 動作中、デバイスは 2MHz でスイッチングします。PFM 動作中は、スイッチング周波数は負荷電流に応じて変化し、負荷電流が減少すると減少します。可能な限り低い出力電圧リップル、または一定のスイッチング周波数を必要とするアプリケーションでは、MODE ピンに High ロジック レベルを印加すると、あらゆる負荷条件において PWM が使用されます (低出力電流時の効率が低下します)。外部抵抗デバイダを使用して、出力電圧を 0.5V ~ 4.5V の範囲で設定し、公称スイッチング周波数は入力電圧範囲全体にわたって制御された変動を持つ 2MHz です。

ヒカップ保護とラッチオフ保護の両方の動作をサポートするデバイス バリアントがあります。

TPSM82830x デバイスには、このシリーズの従来のデバイスに比べて 2 つの大きな利点があります。PFM および PWM モードの両方で高速コンパレータを使用することで過渡性能が大幅に向上し、最適化されたゲート ドライバとオンチップ デカップリング コンデンサによって EMI が低減されます。

VCB パッケージ バージョンは MagPack 技術を使用し、最高性能のパワー モジュール設計を実現します。テキサス インスツルメンツ独自の磁気統合 MagPack パッケージング技術を活用したこれらのパワーモジュールは、業界をリードする電力密度、高効率、優れた熱性能、使いやすさ、および EMI エミッションの低減を実現します。

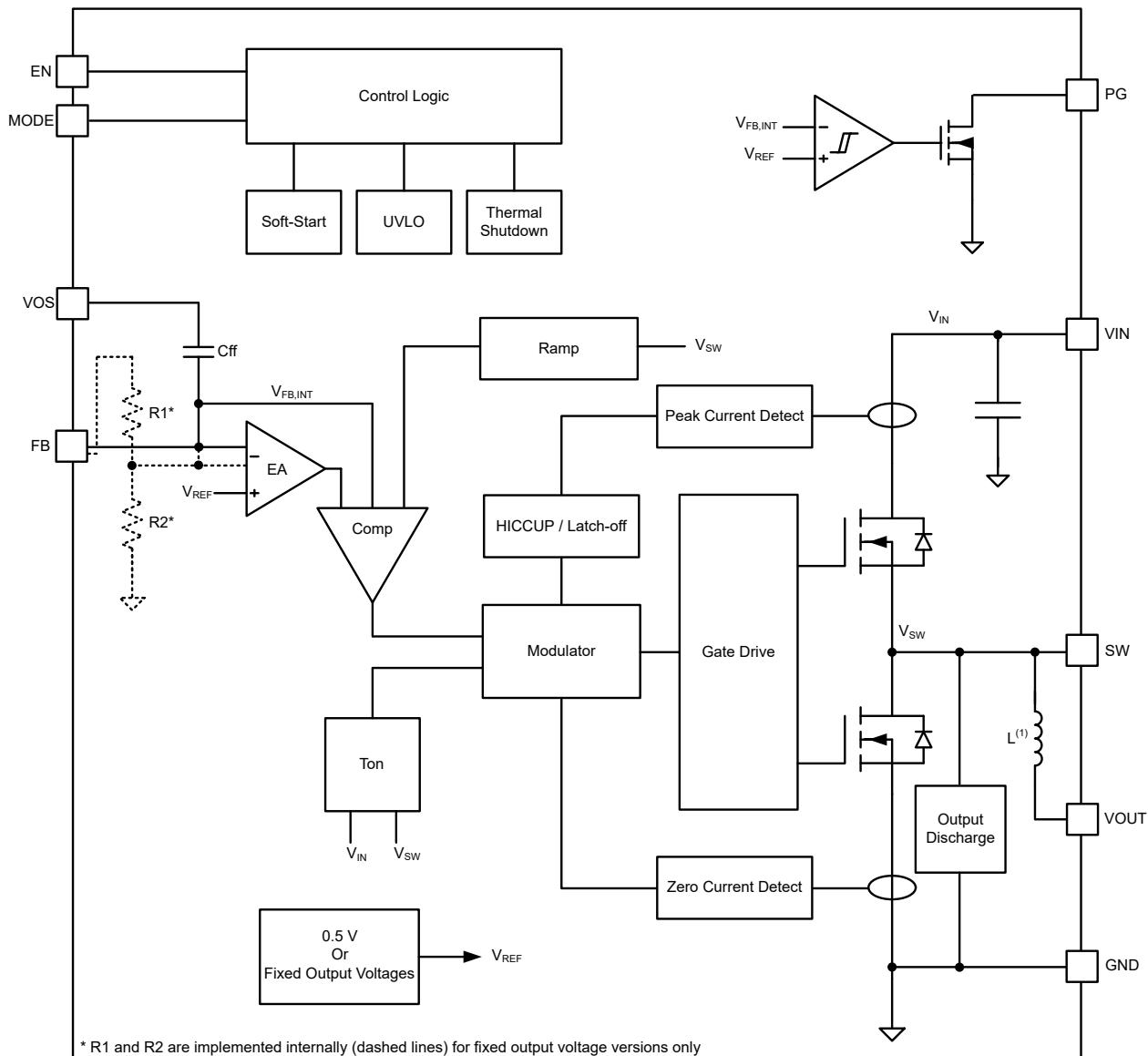

## 7.2 機能ブロック図

A. インダクタンス値は RDS パッケージで 470nH、VCB パッケージで 400nH。

## 7.3 機能説明

### 7.3.1 パルス幅変調 (PWM) 動作

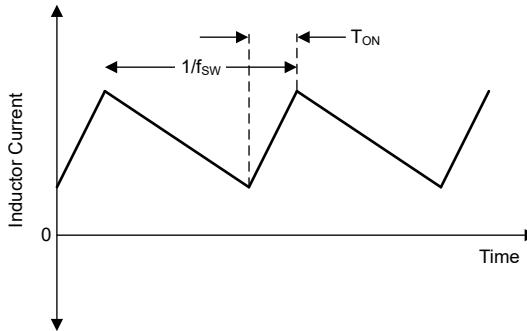

図 7-1 に示されているように、MODE ピンが低く、負荷電流がインダクタ リップル電流の 1/2 より大きい場合、デバイスは連続導通モード (CCM) のパルス幅変調で動作します。PWM 動作は、スイッチング周波数が安定した適応型一定オンタイム制御がベースとなっています。定常状態で安定したスイッチング周波数を達成するため、オン時間は次のように計算されます。

$$T_{ON} = \frac{V_{OUT}}{V_{IN}} \times 500\text{ns} \quad (1)$$

MODE ピンが HIGH のとき、コンバータはすべての負荷電流に対して強制 PWM 動作を維持します。

図 7-1. 連続導通モード (PWM-CCM) 電流波形

### 7.3.2 パワー セーブ モード (PSM) 動作

軽負荷時に高い効率を維持するため、本デバイスは不連続導通モード (DCM) との境界でパワー セーブ モード (PSM) に移行します。このイベントは、出力電流がインダクタ リップル電流の  $1/2$  より小さくなった場合に発生します。図 7-2 に示されているように、デバイスは固定オン時間で動作し、スイッチング周波数は負荷電流に比例して低下します。次のように計算します。

$$f_{PSM} = \frac{2 \times I_{OUT}}{T_{ON}^2 \times \frac{V_{IN}}{V_{OUT}} \left[ \frac{V_{IN} - V_{OUT}}{L} \right]} \quad (2)$$

RDS パッケージの場合は  $L=470\text{nH}$ 、VCB パッケージの場合は  $L=400\text{nH}$  を使用します。

図 7-2. 不連続導通モード (PSM/DCM) 電流波形

PSM では、出力電圧が公称目標値よりわずかに高くなります。これは、より大きな出力容量を使用することで最小化できます。デューティ サイクルが  $90\%$  を超えると、デバイスは PSM に移行せず、PWM モードで出力レギュレーションを維持します。

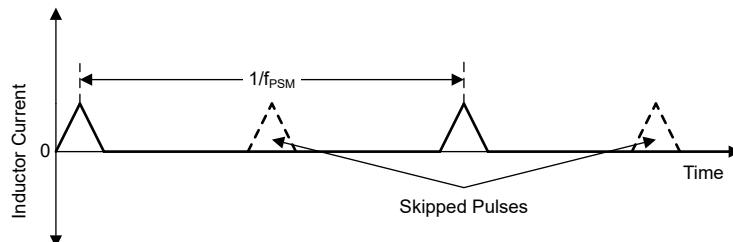

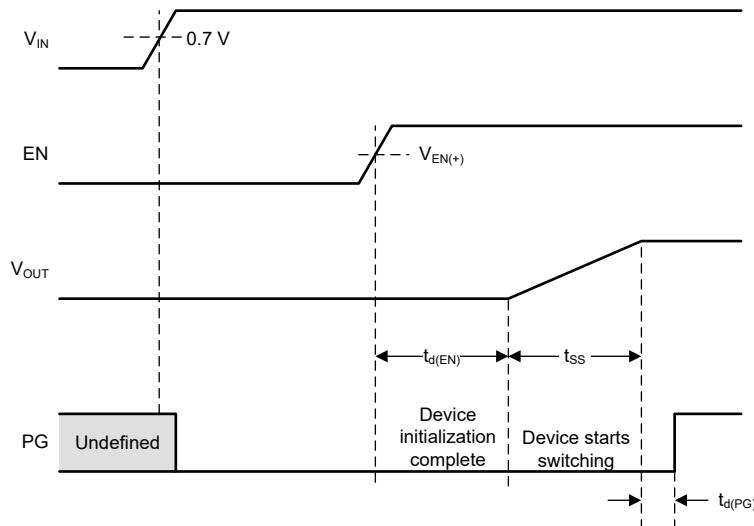

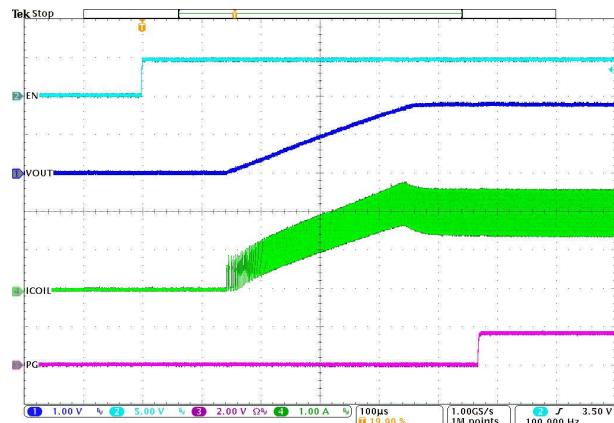

### 7.3.3 スタートアップおよびソフトスタート

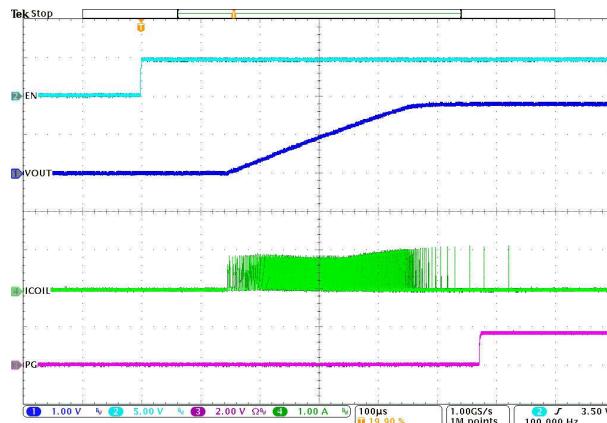

EN 電圧が High になると、デバイスはデフォルト値のデバイス レジスタへのロードを開始します。この動作は、 $t_{d(EN)}$  内で実行されます。その後、内蔵ソフトスタート回路は、スタートアップ時の出力電圧を制御します。この制御により、過剰な突入電流が回避され、出力電圧の上昇が制御されます。この制御により、インピーダンスが高い電源またはバッテリによる望ましくない電圧低下も防止できます。最後に、PG 信号にスタートアップ時の遅延  $t_{d(PG)}$  があります。図 7-3 に、EN ピンが VIN にプルアップされる場合のスタートアップ シーケンスを示します。

図 7-3. EN が VIN にプルアップされるときのスタートアップタイミング

図 7-4 に、外部信号が EN ピンに接続されている場合のスタートアップシーケンスを示します。ソフトスタート機能には、もう 1 つの目的があります。スタートアップ中に出力コンデンサを充電する必要があります。より高い出力電圧と大きな出力容量の組み合わせにより、過電流事象が発生し、デバイスが正常にスタートアップすることを防止します。回路設計者は、目標出力電圧およびスタートアップ時間に応じて、最大出力容量を選択する必要があります。TPSM82830xK バージョンは、より長いスタートアップ時間で、ピーク出力電流を低減できます。

図 7-4. 外部信号が EN ピンに接続されている場合のスタートアップタイミング

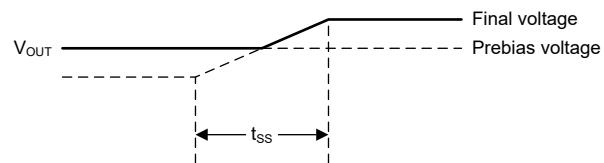

TPSM82830x は、初めてイネーブルになると、プリバイアスされた出力から起動する可能性があります。新しいプリバイアス動作では、アクティブ出力放電を無効化するために、パワー サイクルを行う必要があります。図 7-5 に、プリバイアスされた出力電圧へのスタートアップを示します。

図 7-5. プリバイアス出力の起動

### 7.3.4 サイクル単位の電流制限の切り替え

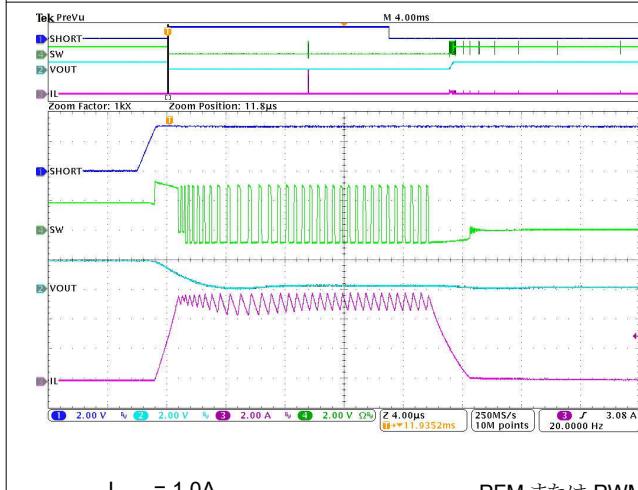

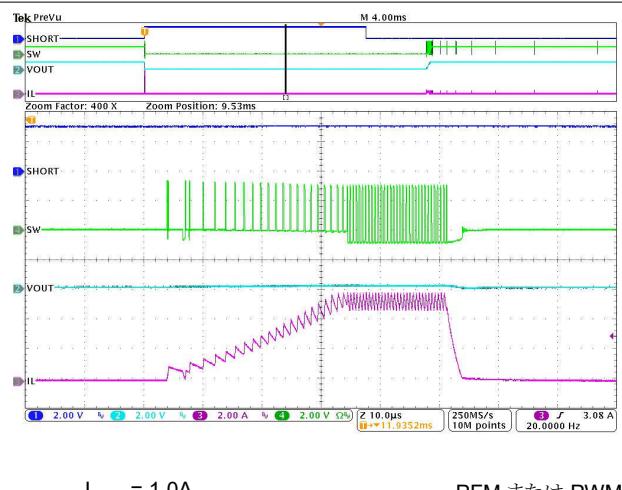

ファミリの全デバイスには、サイクル単位の電流制限機能があります。重負荷または短絡状態のいずれかが原因で、ハイサイド FET の電流がハイサイド電流制限を超えていることを検出すると、デバイスは直ちにハイサイド FET をオフにし、ローサイド FET をオンにします。次のスイッチングサイクルの開始時に、ハイサイド FET が再度オンになります。電流制限コンパレータの伝搬遅延 (通常 60ns) により、デバイスが電流制限条件を検出したときにハイサイド FET に流れる電流は、デバイスの「電気的特性」に指定されている電流制限よりもわずかに高くなる可能性があることに注意してください。

### 7.3.5 低電圧誤動作防止

低電圧誤動作防止 (UVLO) 機能は、入力電圧が UVLO スレッショルドよりも低下した場合にデバイスの誤動作を防止します。

### 7.3.6 サーマル シャットダウン

本デバイスの接合部温度  $T_J$  は内蔵の温度センサによって監視されています。 $T_J$  が 150°C (標準値) を超えると、デバイスはサーマル シャットダウンに移行し、ヒステリシスは通常 20°C です。 $T_J$  が十分に低下すると、デバイスは通常動作に復帰します。

### 7.3.7 EMI 性能の最適化

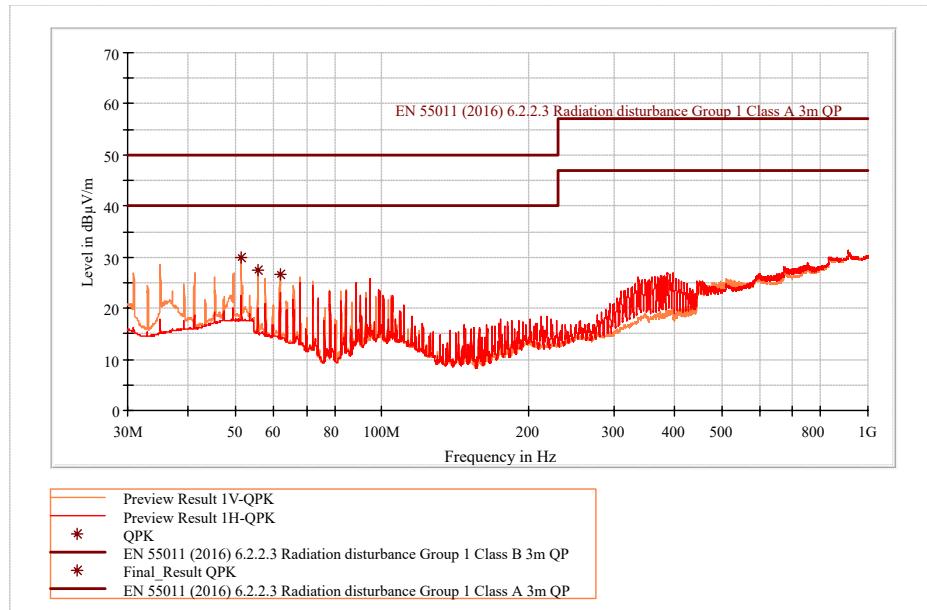

TPSM82830x デバイスは、電磁干渉 (EMI) を最小化するための高度な手法を採用しており、厳格な EMI 規格にシンプルに準拠できます。コンデンサをシリコンに直接統合することで、寄生容量が低減し、ループ面積が最小化されるので、主に 450MHz より高い周波数でのノイズ放射を効果的に低減できます。オンチップ コンデンサにより、高周波の AC スイッチング電流とダンピング電圧リンクに対する低インダクタンスのパスが確保されます。

また、オンチップ コンデンサに加えて、高度なスルーレート制御メカニズムを搭載し、電源電圧を平滑化することで、ゲートドライバを改善しています。スイッチ ノードの電圧は、鋭いエッジを減らし、電圧オーバーシュートを最小限に抑えるように制御されるため、その結果、EMI が減少します。

上記のプロットは、TPSM828303ARDSSR と標準的な BOM を使用した評価基板で測定しています。

$I_{OUT} = 3A$

$V_{IN} = 5.5V$

$V_{OUT} = 1.8V$

図 7-6. 放射 EMI 性能 (クラス A およびクラス B 制限での CISPR 11 放射型電磁波テスト)

### 7.3.8 VOUT の精度

表 7-1 に一覧されているように、TPSM82830x の出力電圧精度はさまざまな要因に左右されます。アプリケーションに関する適切な設計手段の選択に役立つように、軽減の可能性と責任を一覧しています。

**表 7-1. 出力電圧精度**

| 要因               | 軽減                                                          | 責任                |

|------------------|-------------------------------------------------------------|-------------------|

| フィードバック デバイダ     | フィードバック デバイダの抵抗精度の向上                                        | 回路設計              |

| エラー アンプ          | デバイス キャリブレーション                                              | デバイス メーカー         |

| 基準電圧             | デバイス キャリブレーション                                              | デバイス メーカー         |

| 入力電圧および入力電圧の過渡現象 | 低インピーダンス電源、入力コンデンサを負荷ステップに適応                                | 回路設計              |

| 負荷電流および負荷電流過渡現象  | 負荷ステップに出力コンデンサを適応                                           | 回路設計              |

| ノイズ              | 入力フィルタ、ダイフィルタ、ピン配置、レイアウト                                    | 回路設計者およびデバイス メーカー |

| 基板レイアウト          | ノイズに敏感な信号からノイズの多い信号を分離し、ノイズに敏感な信号に近接した場所にあるデジタル信号でスルーレートを制御 | 回路設計者およびデバイス メーカー |

出力過渡は、VOUT の精度に大きな影響を及ぼす可能性があります。遅い変更は規制ループによって補償され、処置は不要です。システム オンチップやマイクロプロセッサのような高速過渡応答は、レギュレーション ループの速度を超えることがあります。一時的なエネルギー リザーバとして出力容量を必要とすることがあります。DCS トポロジにより、複数のスイッチング サイクルで発生する変化に対して出力容量を低減できます。負荷ステップが瞬間的な場合、つまり 1 クロック サイクル以内に負荷ステップ全体が完了する場合は、十分な出力容量が必要です。このニーズは、出力静電容量の許容範囲が大きい TPSM82830x によりサポートされます。

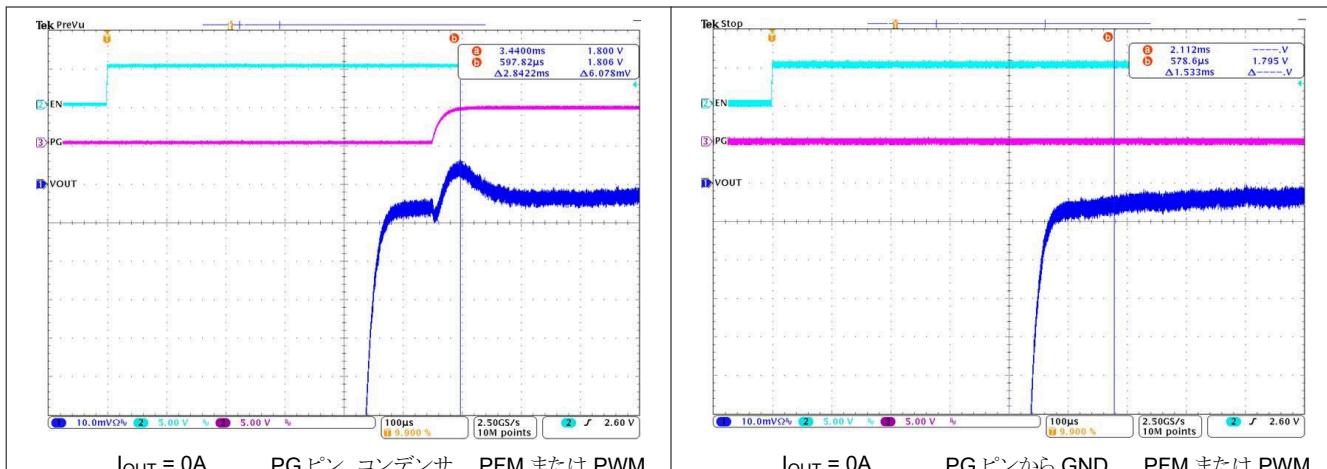

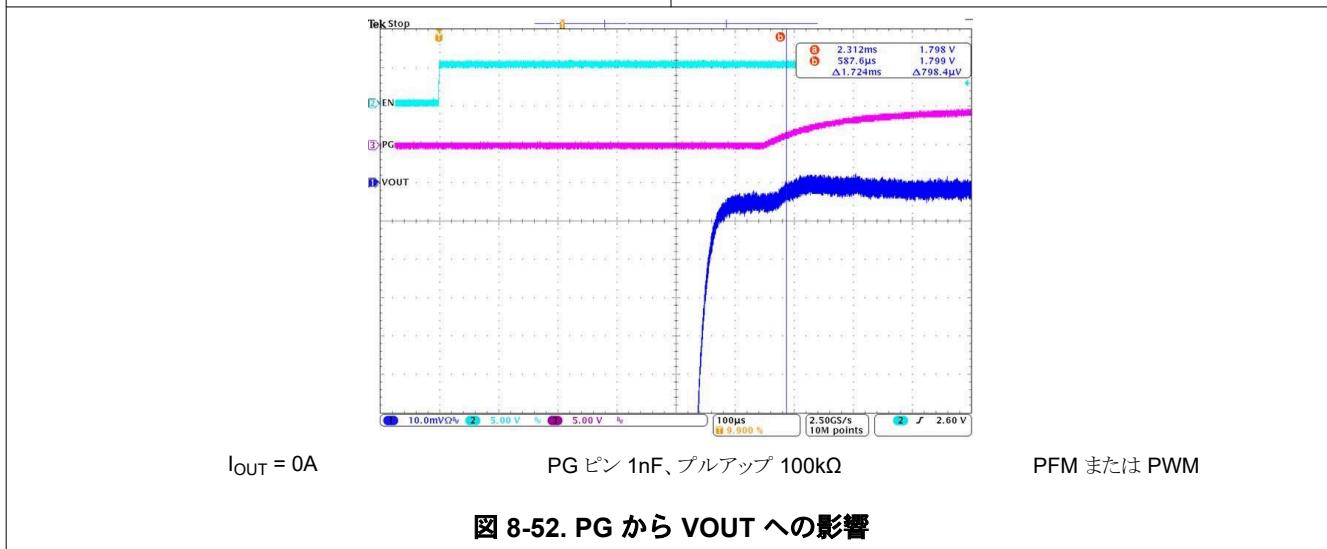

TPSM82830x の PG ピンは、敏感な VOS ピンの近くに配置されています。このため、PG が出力電圧にトグルすることによる影響が見られます (PG から VOUT への影響を参照)。レイアウトの VOS と FB を PG からできるだけ離すことで、この影響を最小限に抑えることができます。レイアウトの密度が非常に高い場合、最大 33nF のコンデンサを PG ピンに追加することで、影響を最小化できます。対策として、回路設計者は、レイアウト内の PG に接続するオプションのコンデンサとして、フットプリントを追加することができます。

## 7.4 デバイスの機能モード

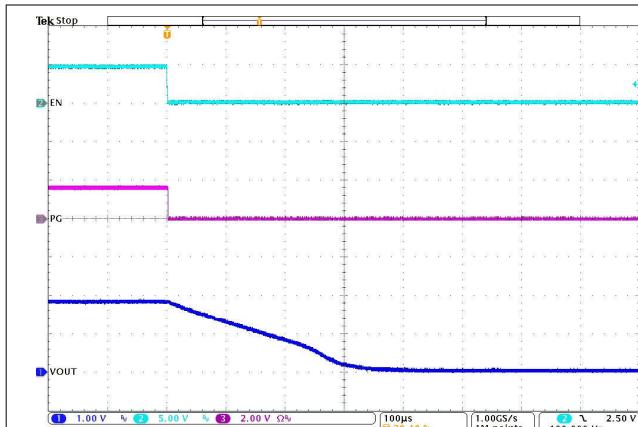

### 7.4.1 イネーブル、ディスエーブル、出力放電

イネーブル (EN) が High に設定されると、デバイスは動作を開始します。入力スレッショルド レベルは、通常、立ち上がり信号で 0.8V、立ち下がり信号で 0.35V です。EN をフローティングのままにしないでください。EN が Low になると、標準値 100nA のシャットダウン電流が強制的にシャットダウンされます。シャットダウン中、内部パワー MOSFET および制御回路全体がオフになり、出力電圧は電流シンクによって SW ピンを通してアクティブに放電されます。したがって、放電が機能するには VIN が印加されたままである必要があります。

### 7.4.2 最小デューティ サイクルおよび 100% モード動作

非常に低いデューティ サイクルでも、適切な調整を常に確保するためにスイッチング周波数が必要に応じて低減されるため、小さなデューティ サイクルに制限はありません。

出力電圧 (VOUT) が入力電圧 (VIN) に近いと、デバイスは 100% モードに移行します。ハイサイド スイッチが継続的にオンになっている間、ローサイド スイッチはオフになります。これは、バッテリ駆動のアプリケーションにおいて、バッテリ電圧の範囲全体を最大限に活用して最長の動作時間を実現するために特に有用です。VIN および VOUT の差は、ハイサイド FET の両端間の電圧降下とインダクタの DC 抵抗によって決まります。特定の VOUT 値を維持するために必要な最小 VIN は、次のように推定されます。

$$V_{IN,min} = V_{OUT} + I_{OUT,MAX} \times R_{DP} \quad (3)$$

ここで、

- $V_{IN,min}$  = 出力電圧を維持するための最小入力電圧

- $I_{OUT,MAX}$  = 最大出力電流

- $R_{DP} = V_{IN}$  から  $V_{OUT}$  への抵抗 (これには、ハイサイド MOSFET オン抵抗とインダクタ DC 抵抗が含まれる)

### 7.4.3 パワーグッド

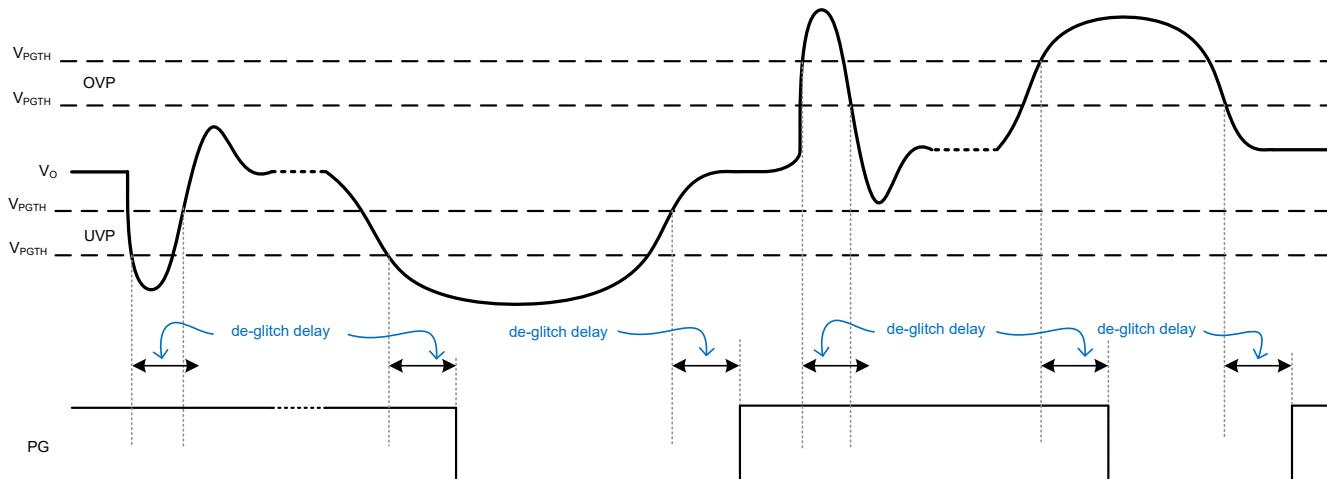

には、パワーグッド (PG) 機能が内蔵されています。出力電圧が公称値に達すると、PG ピンはハイ インピーダンスになります。それ以外の場合は、ディスエーブルのとき、UVLO、サーマル シャットダウンのとき、PG は Low です (表 7-2 を参照)。PG は、上限および下限電圧スレッショルドを持つウインドウ コンバレータによって構成されています。PG ピンはオープンドレイン出力であり、最大 1mA までシンクできるよう指定されています。パワーグッド出力には、5.5V 未満の任意の電圧レールに接続されたプルアップ抵抗が必要です。

表 7-2. PG ピン ロジック

| デバイス条件       | ロジック ステータス                      |     |

|--------------|---------------------------------|-----|

|              | HIGH Z                          | Low |

| イネーブル        | EN = High, $V_{FB} \geq 0.48V$  | ✓   |

|              | EN = High, $V_{FB} \leq 0.56V$  | ✓   |

|              | EN = High, $V_{FB} \leq 0.525V$ | ✓   |

|              | EN = High, $V_{FB} \geq 0.55V$  | ✓   |

| シャットダウン      | EN = Low                        | ✓   |

| サーマル シャットダウン | $T_J > T_{JSD}$                 | ✓   |

| UVLO         | $0.7V < V_{IN} < V_{UVLO}$      | ✓   |

| 電源の取り外し      | $V_{IN} < 0.7V$                 | ✓   |

PG 信号を他のコンバータの EN ピンに接続することで、PG 信号を複数のレールのシーケンシングに使用できます。PG ピンを使用しない場合は、未接続のままにしてください。図 7-7 に示されているように、PG の立ち上がりエッジと立ち下がりエッジには  $t_{d(PGO)}$  ブランкиング時間があります。スタートアップ時、ソフトスタートの終了後の PG 信号の遅延は  $t_{d(PG)}$  となります。

図 7-7. パワーグッド動作

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

以下のセクションでは、代表的なアプリケーションに基づいて、いくつかの入力および出力電圧の選択肢について、電源設計を完成させるための外部部品の設計について説明します。

TPSM82830x は、必要なパワー インダクタがパッケージに内蔵されている同期整流降圧コンバータ パワー モジュールです。インダクタンス値は、RDS パッケージの場合は 470nH (許容誤差  $\pm 20\%$ )、VCB パッケージの場合は 400nH (許容誤差  $\pm 20\%$ ) です。パッケージ カテゴリのファミリ製品は、相互にピン間の互換性および BOM 間の互換性があります。

### 8.2 代表的なアプリケーション

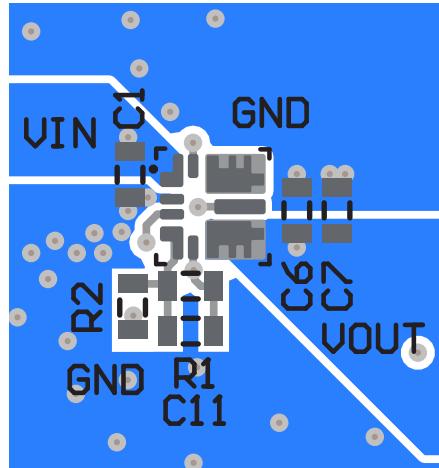

図 8-1. TPSM82830x の代表的なアプリケーション

#### 8.2.1 設計要件

この設計例では、表 8-1 に記載されているパラメータを入力パラメータとして使用します。

表 8-1. 設計パラメータ

| 設計パラメータ  | 数値の例         |

|----------|--------------|

| 入力電圧     | 2.25V ~ 5.5V |

| 出力電圧     | 1.8V         |

| 出力リップル電圧 | < 15mV       |

この例で使用する部品のリストを 表 8-2 に示します。

表 8-2. 部品のリスト

| リファレンス | 説明                                                      | 製造元            |

|--------|---------------------------------------------------------|----------------|

| C1     | 4.7μF、セラミックコンデンサ、6.3V、X7R、サイズ 0603、JMK107BB7475KA-T     | Taiyo Yuden    |

| C2     | 2 × 10μF、セラミックコンデンサ、10V、X7R、サイズ 0603、GRM188Z71A106KA73D | Murata (村田製作所) |

| R1     | 出力電圧に応じて、523kΩ 1/16W、1%、サイズ 0402 (1.8V の場合)             | 標準             |

| R2     | 200kΩ、チップ抵抗、1/16 W、1%、サイズ 0402                          | 標準             |

| R3     | 100kΩ、チップ抵抗、1/16 W、1%、サイズ 0402                          | 標準             |

## 8.2.2 詳細な設計手順

### 8.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPSM82830x デバイスを使用するカスタム設計を作成できます。

- 好みの部品がある場合は型番フィールドに型番を入力し、部品リストが表示されるまで待ちます。好みがない場合は、このフィールドを空白のままにします。

- 次のセクション（型番を入力して開始した場合は自動入力されます）で、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- 「設計上の検討事項」セクションで、設計の優先順位を選択します。

- 設計提案を参照し、生成された設計を、テキサス インスツルメンツが提供している他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

これらで、WEBENCH ツールの詳細をご覧ください：[設計ツールとシミュレーションツール](#)。

### 8.2.2.2 出力電圧の設定

出力電圧は、[式 4](#) に応じて、外部抵抗デバイスによって設定されます。

$$R1 = R2 \times \left( \frac{V_{OUT}}{V_{FB}} - 1 \right) = R2 \times \left( \frac{V_{OUT}}{0.5V} - 1 \right) \quad (4)$$

$R2$  は  $200\text{k}\Omega \sim 600\text{k}\Omega$  の任意の値に設定でき、許容できるノイズ耐性を備えながら軽負荷時に高い効率を実現します。

### 8.2.2.3 入力コンデンサの選択

入力コンデンサは、コンバータの低インピーダンス エネルギー源であり、安定した動作に役立ちます。降圧コンバータの入力電流は脈動しているので、最良の入力電圧フィルタリングによって入力電圧スパイクを最小限に抑えるために、低 ESR のセラミック入力コンデンサを使用する必要があります。VIN ピンと GND ピンの間に、これらのピンにできる限り近づけて配置します。

ほとんどのアプリケーションでは、より大きい値を使うと入力電流リップルが低減されるため、 $3\mu\text{F}$  の最小実効入力容量で十分です。高インピーダンス ソースで動作する場合は、スタートアップ時および負荷過渡時の電圧降下を回避するため、TI は  $\geq 10\mu\text{F}$  の大きな入力バッファ コンデンサを推奨しています。さらに、デバイスで入力にノイズが発生する場合は、小さなデカップリング コンデンサを使用することもできます。入力電圧フィルタリング改善のためには、入力コンデンサをいくらでも大きくすることができます。

[表 8-3](#) に、推奨コンデンサー一覧を示します。

**表 8-3. 推奨コンデンサー一覧**

| 静電容量 (公称値) [ $\mu\text{F}$ ] | 定格電圧 [V] | 寸法 [mm]                       | MFR 型番 <sup>(1)</sup>     |

|------------------------------|----------|-------------------------------|---------------------------|

| 4.7                          | 6.3      | $1.6 \times 0.8 \times 0.8$   | MSASJ168BB7475MTNA01、太陽誘電 |

| 4.7                          | 10       | $2.0 \times 1.25 \times 1.25$ | C2012X7R1A475K125AC、TDK   |

| 10                           | 10       | $1.6 \times 0.8 \times 0.8$   | GRM188Z71A106KA73#、村田製作所  |

(1) 「[サードパーティ製品に関する免責事項](#)」を参照してください。

#### 8.2.2.4 出力コンデンサの選択

TPSM82830x の DCS-Control 方式では、小さいセラミック コンデンサを使用できます。出力電圧リップルが最も少ないで、ESR 値の低いセラミック コンデンサが推奨されます。高い周波数まで低抵抗を維持し、温度による静電容量の変動を小さくするために、TI は X7R または X5R 誘電体を使うことを推奨しています。軽負荷電流時には、コンバータはパワー セーブモードで動作し、出力電圧リップルは出力コンデンサの値に依存します。大きい出力コンデンサを使用すれば、出力電圧リップルを低減できます。DC バイアスで容量がディレーティングされることを考慮して、場合に推奨される最小小実効出力容量は  $12\mu\text{F}$  です。推奨される標準的な出力コンデンサ値は、X5R または X7R 誘電体を使用した  $2 \times 10\mu\text{F}$  または  $1 \times 22\mu\text{F}$  です。[表 8-4](#)

**表 8-4. 推奨コンデンサー一覧**

| 静電容量 (公称値) [ $\mu\text{F}$ ] | 定格電圧 [V] | 寸法 [mm]                       | MFR 型番 <sup>(1)</sup>     |

|------------------------------|----------|-------------------------------|---------------------------|

| 10                           | 6.3      | $2.0 \times 1.5 \times 1.25$  | MSASJ21GAB7106MTNA01、太陽誘電 |

| 10                           | 10       | $2.0 \times 1.25 \times 1.25$ | C2012X7R1A106K125AC、TDK   |

| 10                           | 10       | $1.6 \times 0.8 \times 0.8$   | GRM188Z71A106KA73#、村田製作所  |

| 10                           | 10       | $1.6 \times 0.8 \times 0.8$   | C1608X5R1A106K080AC、TDK   |

| 22                           | 10       | $2.0 \times 1.25 \times 1.25$ | GRM21BZ71A226ME15#、村田製作所  |

| 22                           | 10       | $1.6 \times 0.8 \times 0.8$   | C1608X5R1A226M080AC、TDK   |

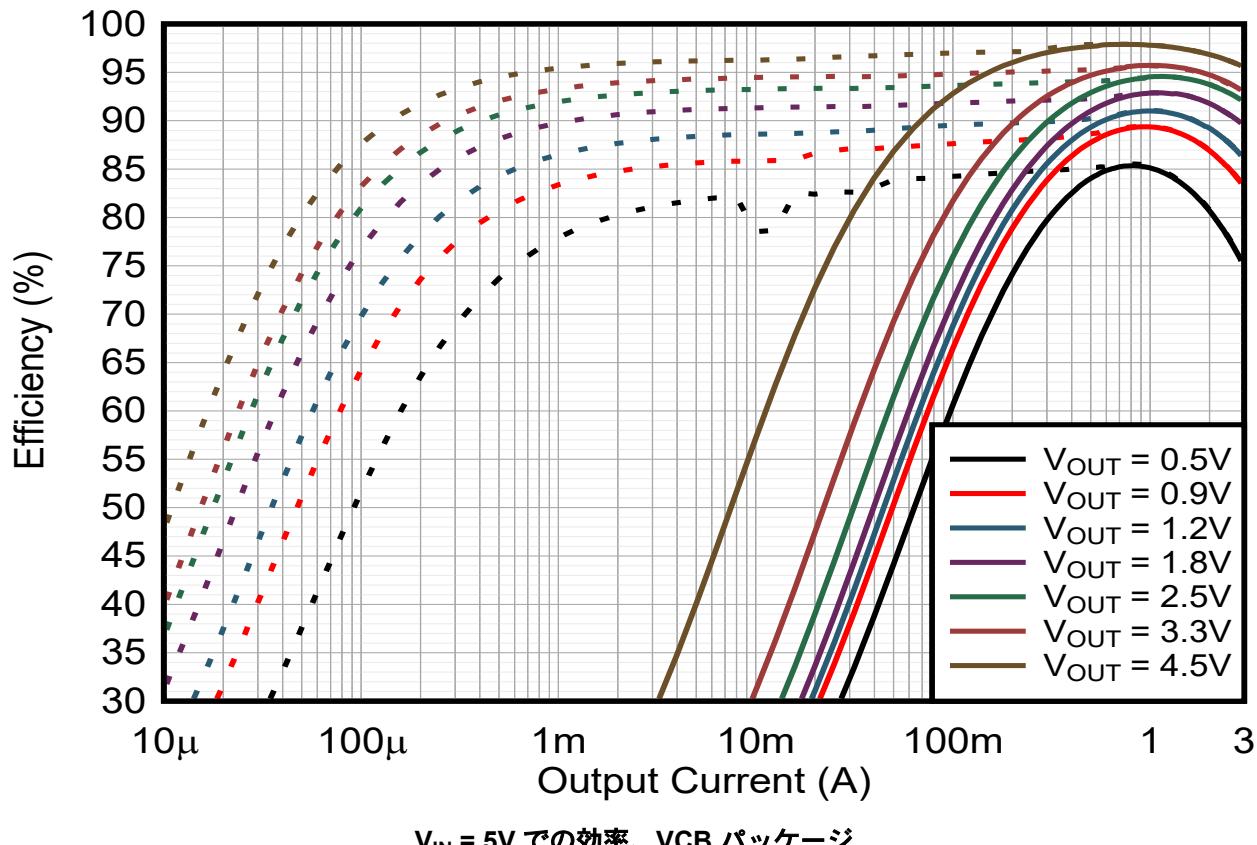

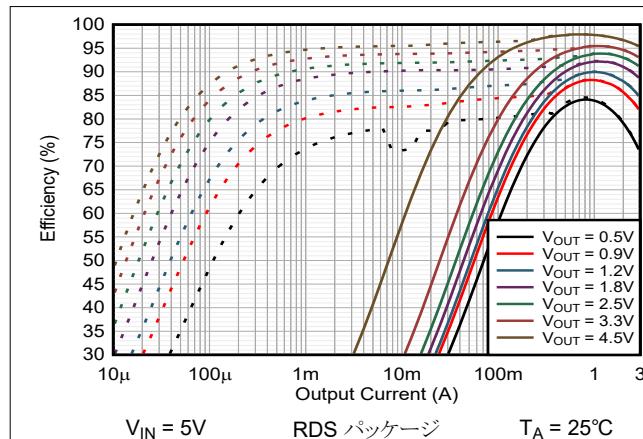

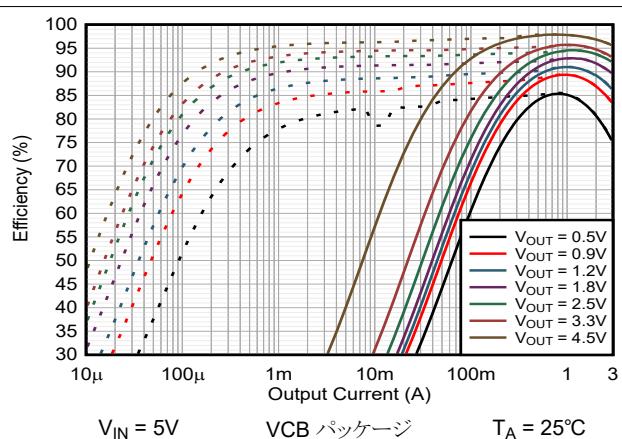

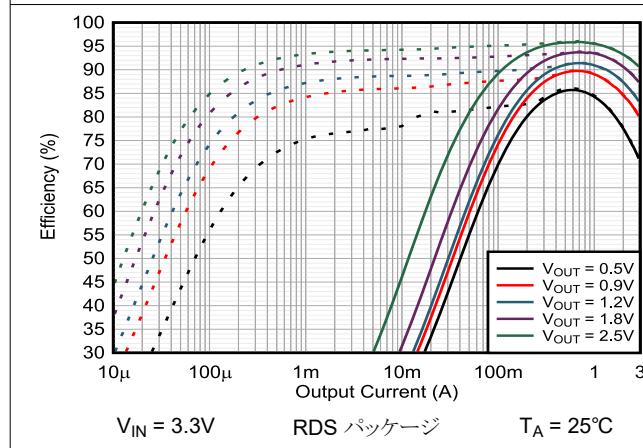

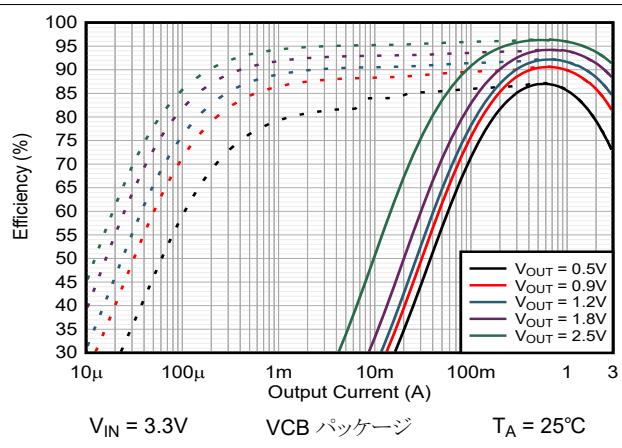

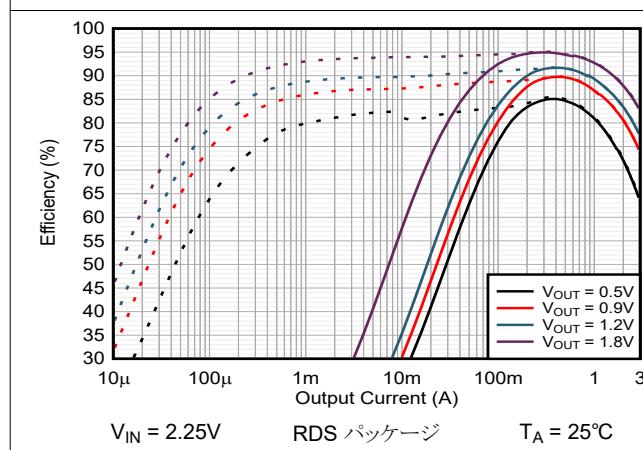

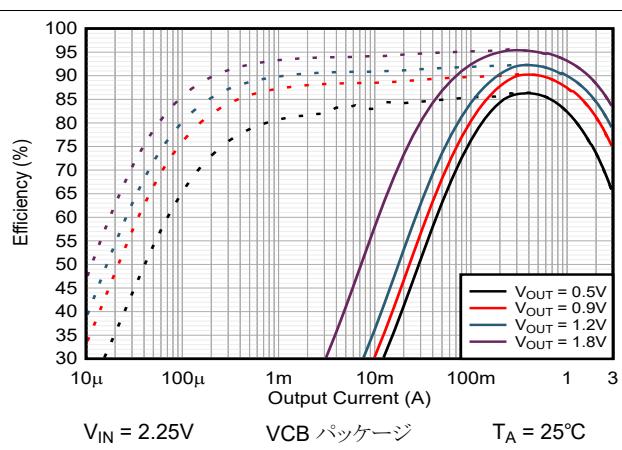

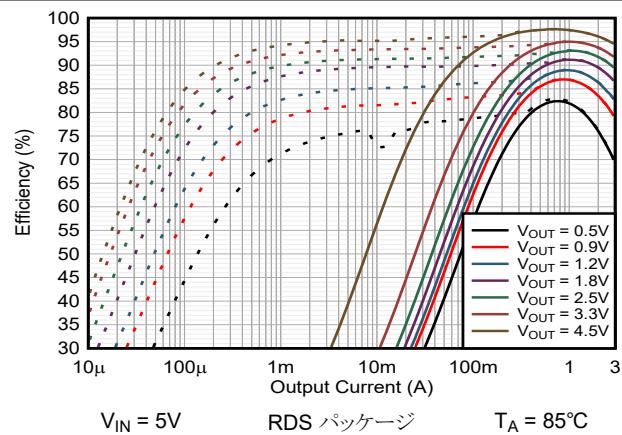

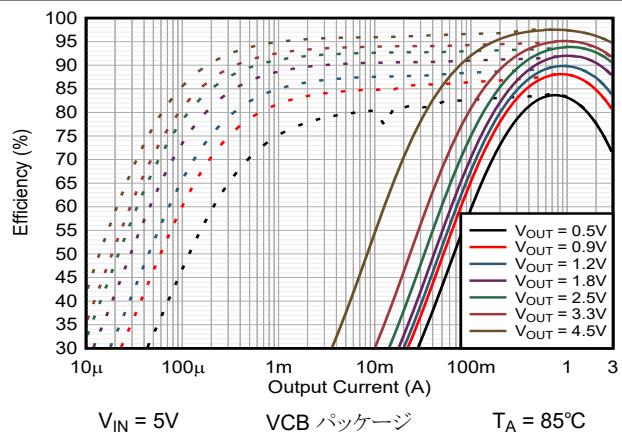

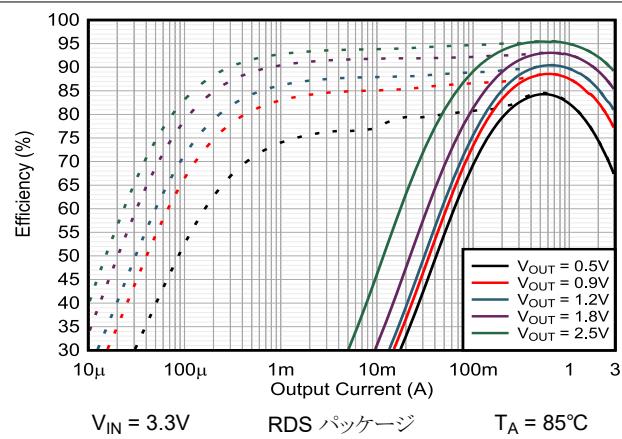

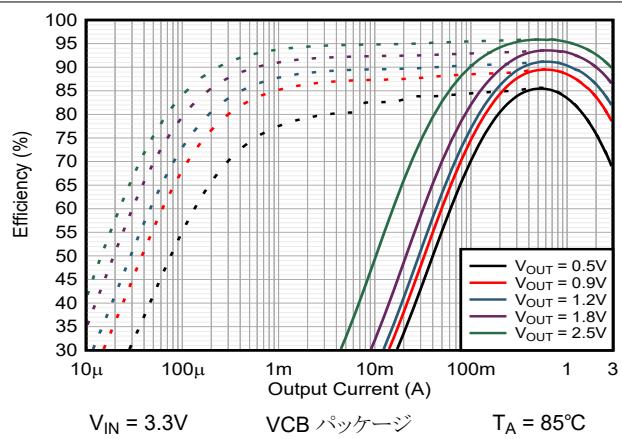

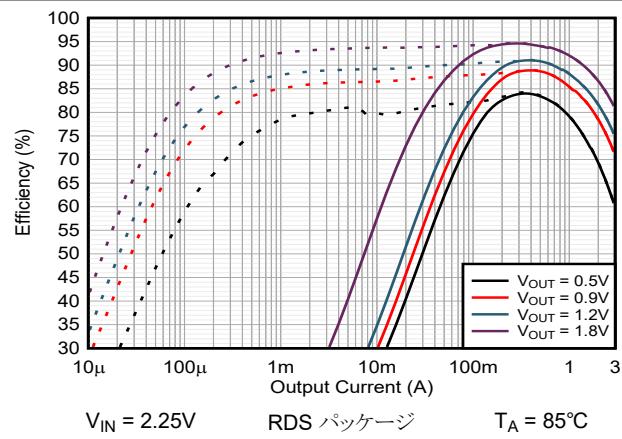

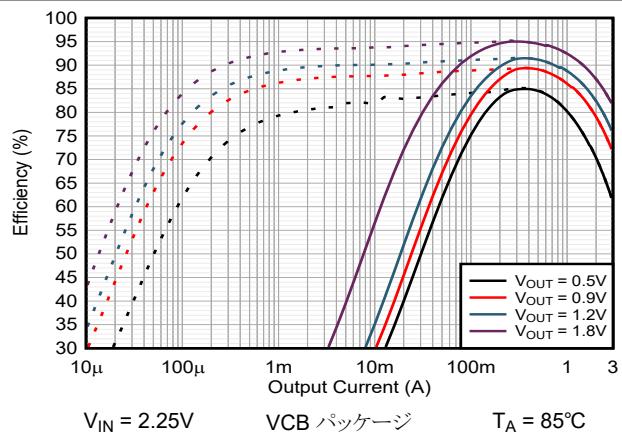

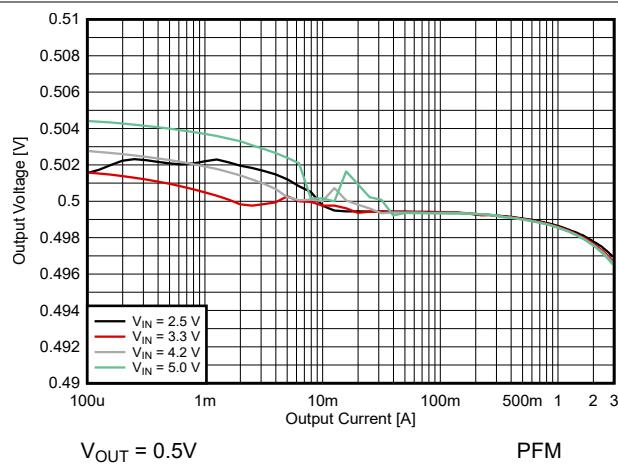

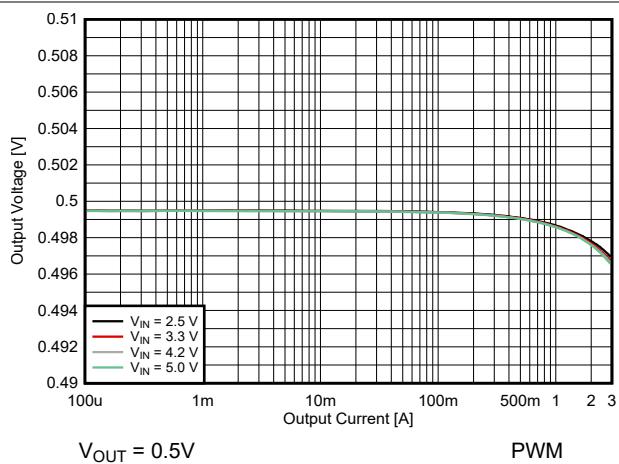

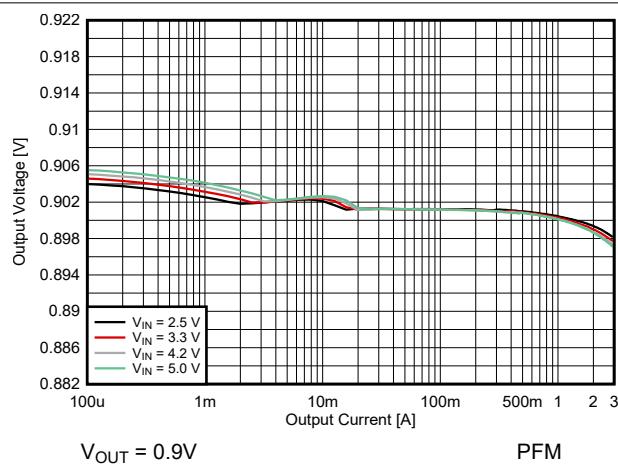

### 8.2.3 アプリケーション曲線

$T_A = 25^\circ\text{C}$ ,  $V_{IN} = 5\text{V}$ ,  $V_{OUT} = 1.8\text{V}$ , BOM = 表 8-2 特に記述のない限り

図 8-2. 効率と出力電流との関係

図 8-3. 効率と出力電流との関係

図 8-4. 効率と出力電流との関係

図 8-5. 効率と出力電流との関係

図 8-6. 効率と出力電流との関係

図 8-7. 効率と出力電流との関係

図 8-8. 効率と出力電流との関係

図 8-9. 効率と出力電流との関係

図 8-10. 効率と出力電流との関係

図 8-11. 効率と出力電流との関係

図 8-12. 効率と出力電流との関係

図 8-13. 効率と出力電流との関係

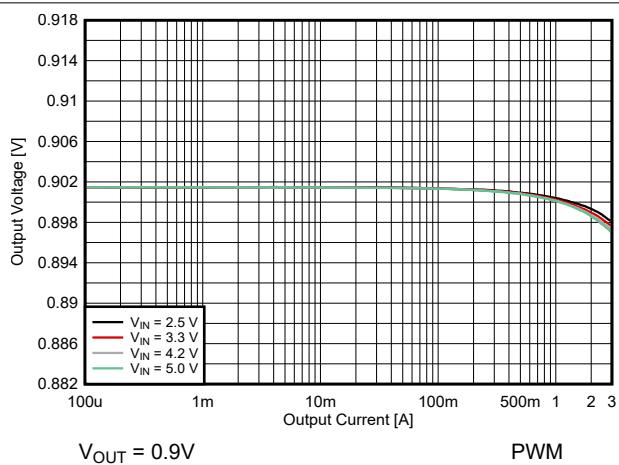

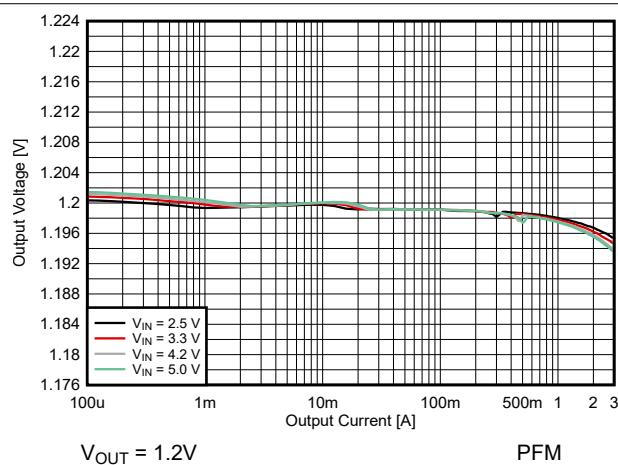

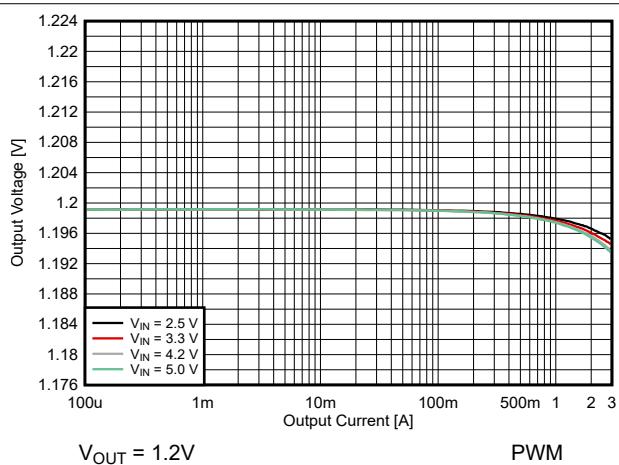

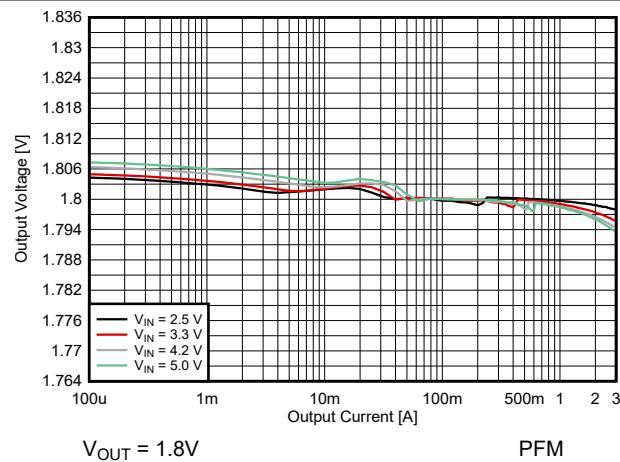

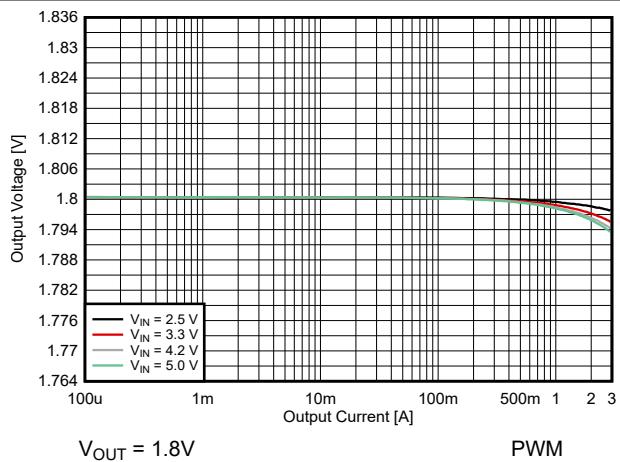

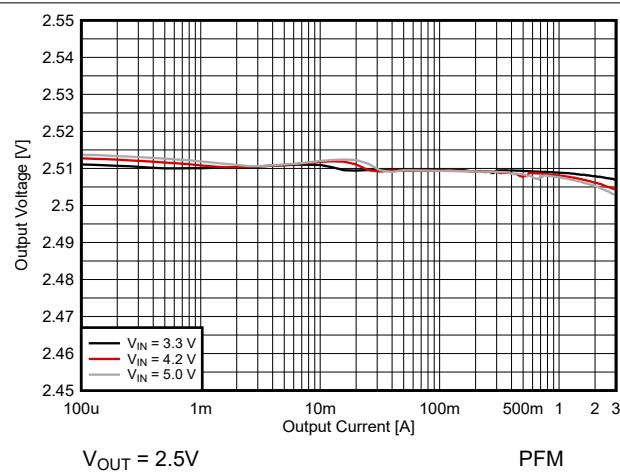

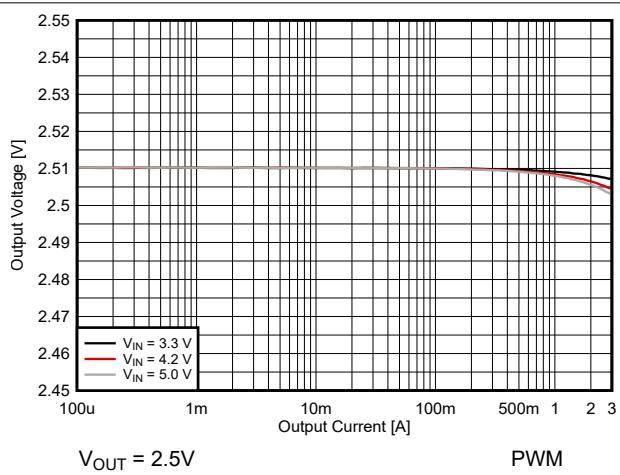

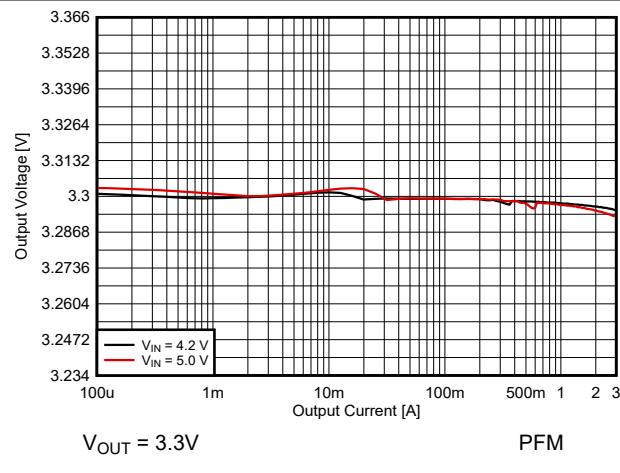

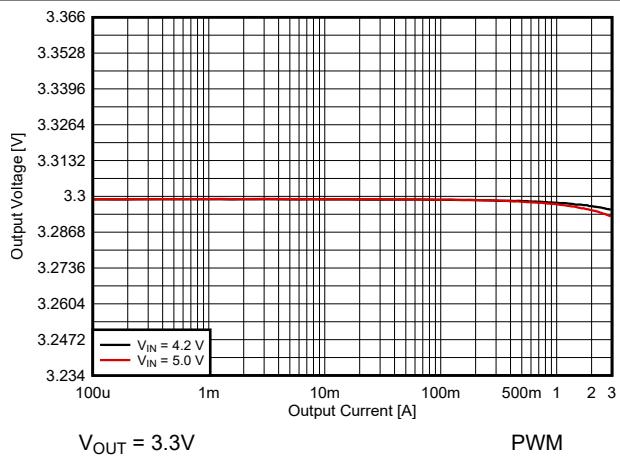

図 8-14. 出力電圧と出力電流との関係

図 8-15. 出力電圧と出力電流との関係

図 8-16. 出力電圧と出力電流との関係

図 8-17. 出力電圧と出力電流との関係

図 8-18. 出力電圧と出力電流との関係

図 8-19. 出力電圧と出力電流との関係

図 8-20. 出力電圧と出力電流との関係

図 8-21. 出力電圧と出力電流との関係

図 8-22. 出力電圧と出力電流との関係

図 8-23. 出力電圧と出力電流との関係

図 8-24. 出力電圧と出力電流との関係

図 8-25. 出力電圧と出力電流との関係

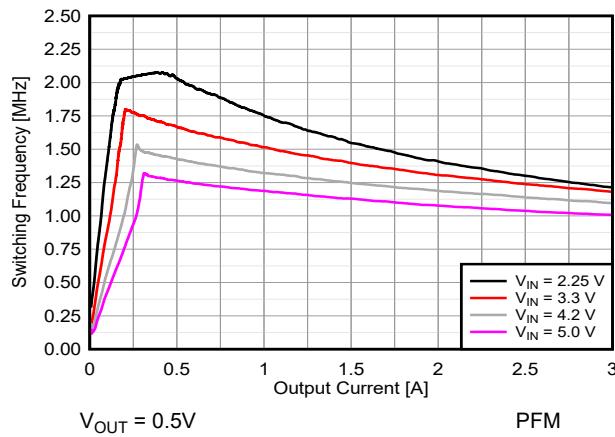

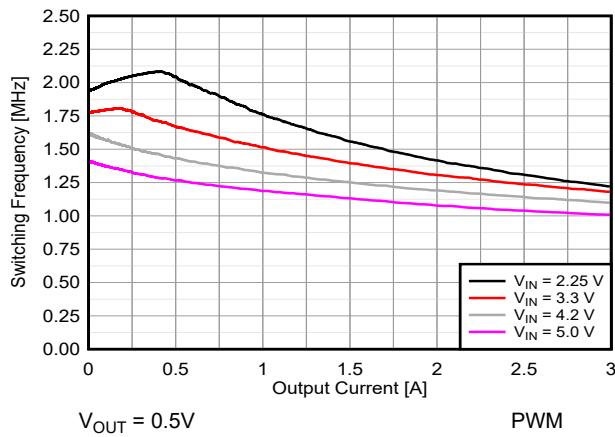

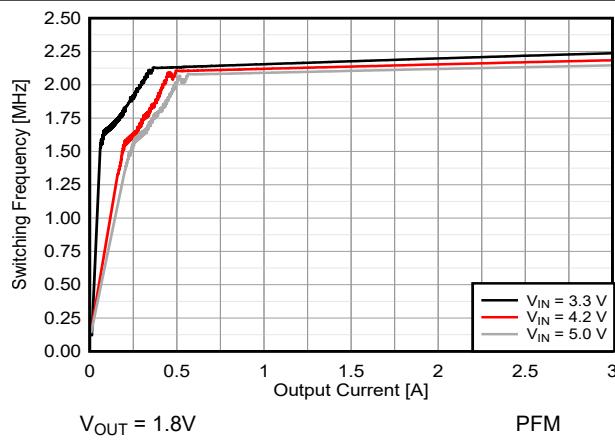

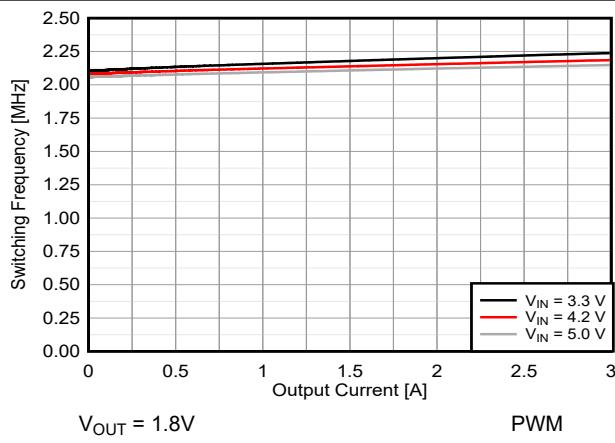

図 8-26. スイッチング周波数と出力電流との関係

図 8-27. スイッチング周波数と出力電流との関係

図 8-28. スイッチング周波数と出力電流との関係

図 8-29. スイッチング周波数と出力電流との関係

図 8-30. スイッチング周波数と出力電流との関係

図 8-31. スイッチング周波数と出力電流との関係

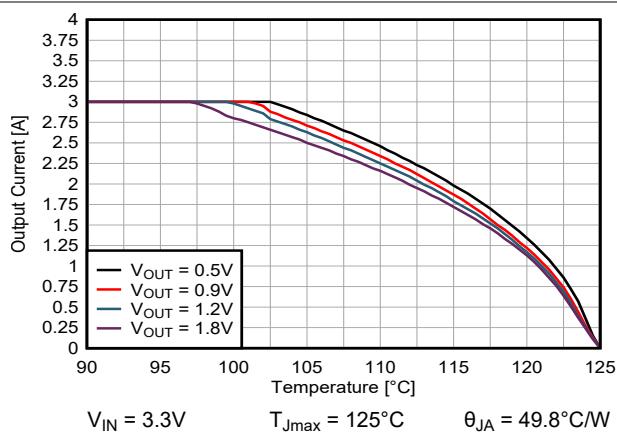

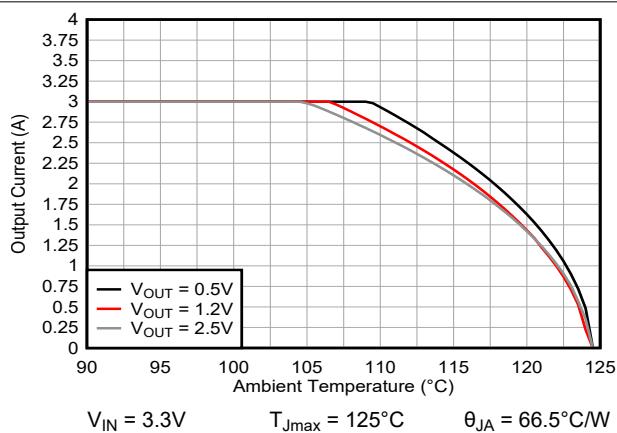

図 8-32. 热ディレーティング (安全動作領域) RDS パッケージ

図 8-33. 热ディレーティング (安全動作領域) RDS パッケージ

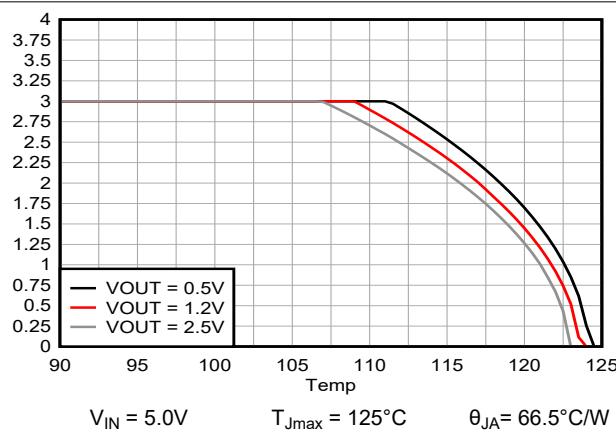

図 8-34. 热ディレーティング (安全動作領域) VCB パッケージ

図 8-35. 热ディレーティング (安全動作領域) VCB パッケージ

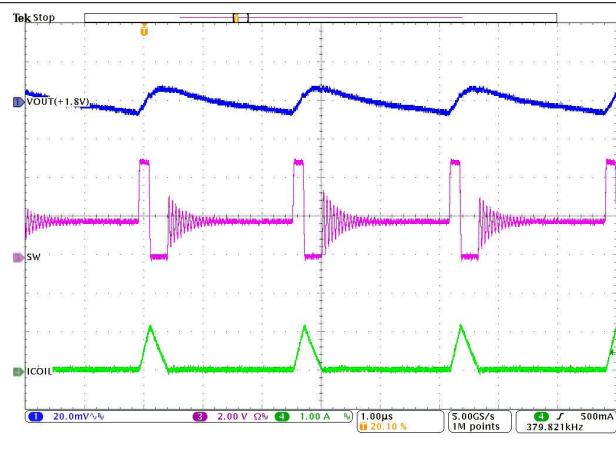

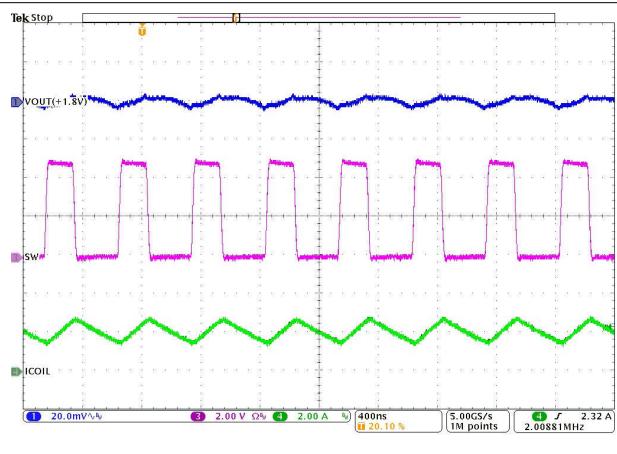

図 8-36. 出力電圧リップル

図 8-37. 出力電圧リップル

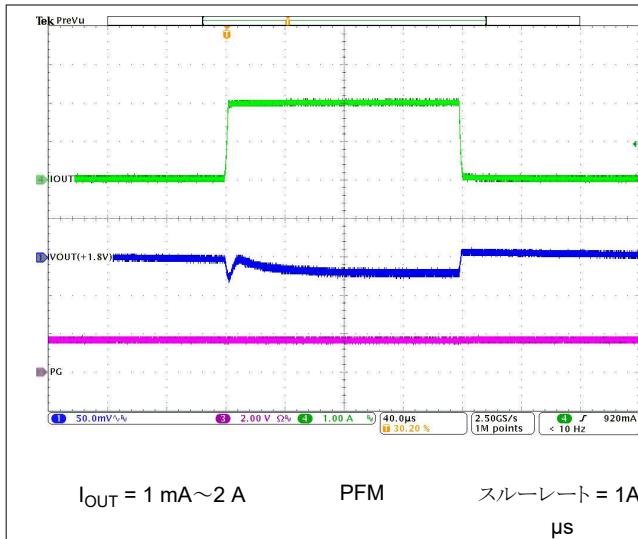

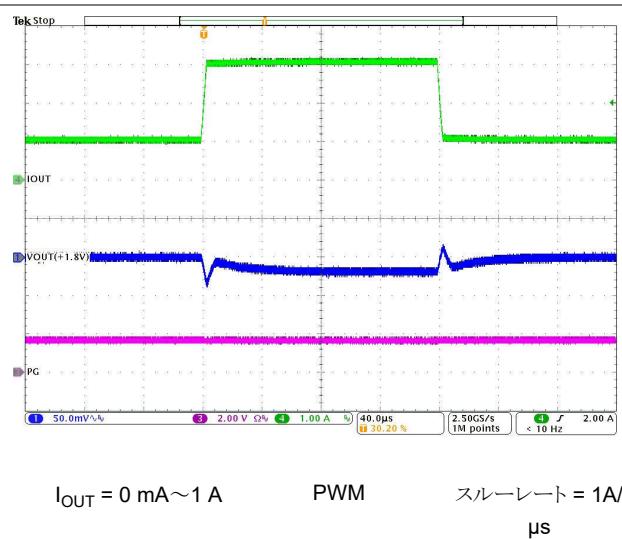

図 8-38. 負荷過渡

図 8-39. 負荷過渡

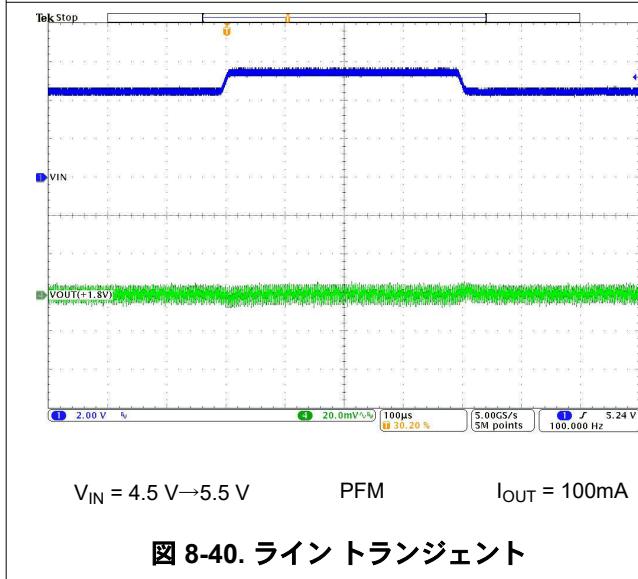

図 8-40. ライントランジエント

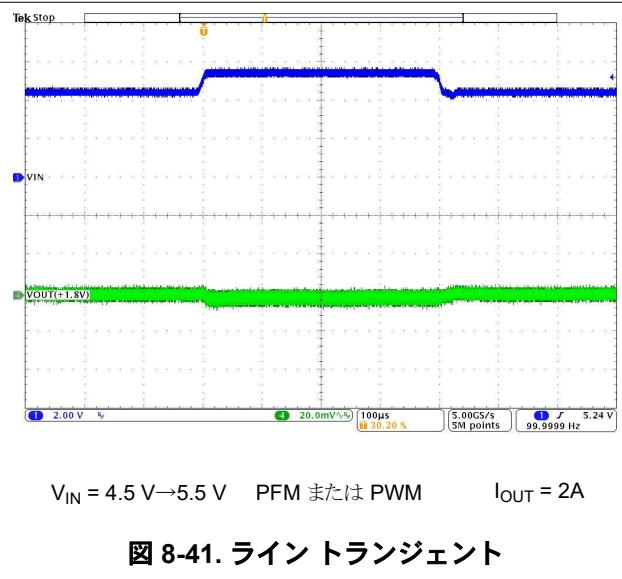

図 8-41. ライントランジエント

$V_{IN} = 3.0 \text{ V} \rightarrow 3.6 \text{ V}$  PFM  $I_{OUT} = 100\text{mA}$

$V_{OUT} = 1.8\text{V}$

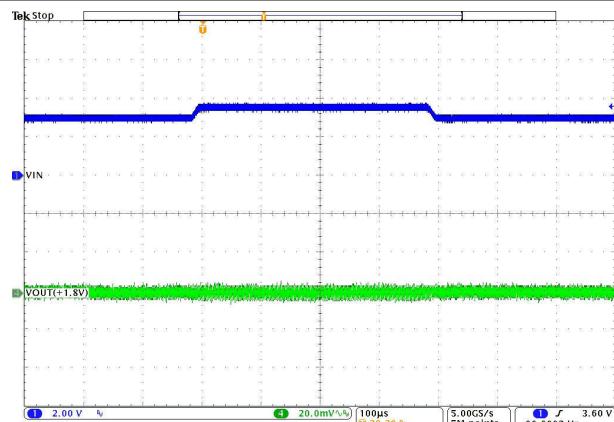

図 8-42. ライントランジエント

$V_{IN} = 3.0 \text{ V} \rightarrow 3.6 \text{ V}$  PFM または PWM  $I_{OUT} = 2\text{A}$

$V_{OUT} = 1.8\text{V}$

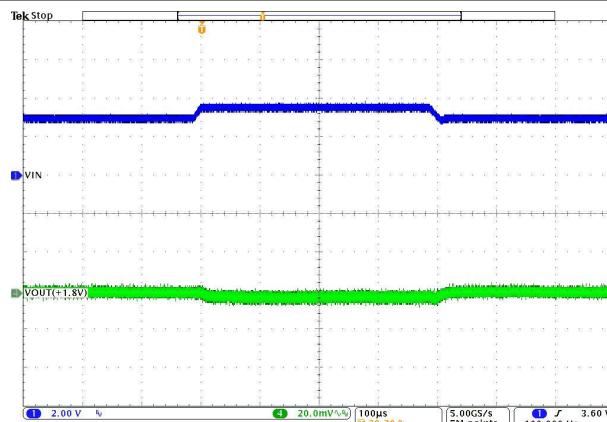

図 8-43. ライントランジエント

$I_{OUT} = 2\text{A}$  PFM または PWM

図 8-44. 負荷ありの起動

$I_{OUT} = 0\text{mA}$  PFM

図 8-45. 無負荷時の起動

$I_{OUT} = 0\text{mA}$

PFM

図 8-46. ディスエーブル、無負荷時のアクティブ出力放電

$I_{OUT} = 1\text{A}$

PFM または PWM

図 8-47. HICCUP 短絡保護機能

$I_{OUT} = 1.0\text{A}$

PFM または PWM

図 8-48. ヒカップ短絡保護機能 (拡大表示)

$I_{OUT} = 1.0\text{A}$

PFM または PWM

図 8-49. ヒカップ短絡保護機能 (拡大表示 - 2 番目のヒカップ)

図 8-50. PG から VOUT への影響

図 8-51. PG から VOUT への影響

図 8-52. PG から VOUT への影響

## 8.3 電源に関する推奨事項

TPSM82830x ファミリには、入力電源に関する特別な要件はありません。これは、2.25V ~ 5.5V の入力電源電圧範囲で動作するように設計されています。入力電源の出力電流は、デバイスの電源電圧、出力電圧、および出力電流に応じて定格を設定する必要があります。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

PCB (プリント基板) レイアウトは、デバイスの高性能を維持するための重要なステップです。推奨される低 EMI PCB レイアウトについては、「[レイアウト例](#)」を参照してください。

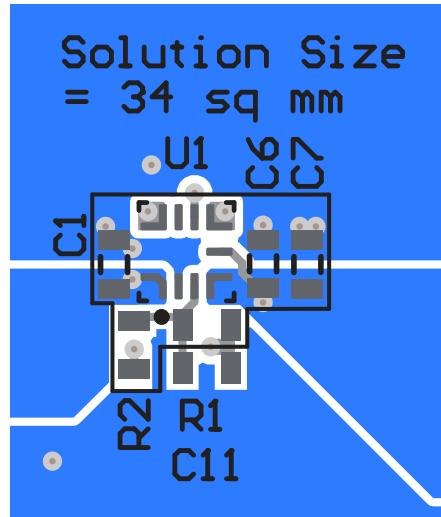

- 入力コンデンサ、出力コンデンサ、インダクタは、IC にできる限り近づけて配置します。これにより、電源トレースが短くなります。これらの電源トレースを直接かつ広く配線することで、トレース抵抗と寄生インダクタンスを低く抑えることができます。

- グランドの電位シフトを避けるため、入力コンデンサおよび出力コンデンサのローサイドは GND ピンに正しく接続します。

- ノイズが誘発されないように特に注意してください。FB に接続されているセンストレースは信号トレースです。これらの配線は SW ノードから離して配置します。FB 抵抗の出力電圧トレースは、出力コンデンサに接続する必要があります。

- 優れた EMI 性能を持つ部品の配置、配線、熱設計の例については、「[レイアウト例](#)」を参照してください。

### 8.4.2 レイアウト例

図 8-53. PCB レイアウトに関する推奨事項 (RDS パッケージ)

図 8-54. PCB レイアウトに関する推奨事項 (VCB パッケージ)

#### 8.4.2.1 熱に関する注意事項

一般に、低背でファインピッチの表面実装パッケージに IC を実装する場合は、消費電力に特別な注意が必要です。熱結合、エアフロー、追加ヒートシンク、対流面、他の発熱部品の存在など、システムに依存する多くの問題により、所定の部品の消費電力の限界が左右されます。

熱性能を向上させるための 2 つの基本的なアプローチは次の通りです。

- PCB 設計による消費電力性能の改善

- システムへのエアフローの導入

「熱に関する情報モジュール」の「熱データ」セクションには、実際のアプリケーションの PCB 設計を考慮に入れた EVM のデバイスの熱評価基準が記載されています。PCB 上の IC のパッドに接続する大きな銅プレーンにより、デバイスの放熱性能が向上します。熱パラメータの使用方法の詳細については、『熱特性』アプリケーション ノート、『JEDEC PCB 設計を使用したリニアパッケージとロジックパッケージの熱特性』、『半導体および IC パッケージの熱指標』を参照してください。

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 9.1.2 開発サポート

##### 9.1.2.1 WEBENCH® ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer により、TPSM82830x デバイスを使用するカスタム設計を作成できます。

- 好みの部品がある場合は型番フィールドに型番を入力し、部品リストが表示されるまで待ちます。好みがない場合は、このフィールドを空白のままにします。

- 次のセクション(型番を入力して開始した場合は自動入力されます)で、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- 「設計上の検討事項」セクションで、設計の優先順位を選択します。

- 設計提案を参照し、生成された設計を、テキサス・インスツルメンツが提供している他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

これらで、WEBENCH ツールの詳細をご覧ください:[設計ツールとシミュレーションツール](#)。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『[JEDEC PCB 設計を使用するリニアおよびロジック パッケージの熱特性](#)』アプリケーションノート

- テキサス・インスツルメンツ、『[半導体およびIC パッケージの熱評価基準](#)』アプリケーションノート

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.4 商標

MagPack™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (June 2024) to Revision C (April 2025)</b>                                                                                                                          | <b>Page</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 「MagPack 技術はインダクタと IC をシールド」の箇条書き項目を追加.....                                                                                                                                                    | 1           |

| 「CISPR に準拠した測定値を使用可能」の箇条書き項目を追加.....                                                                                                                                                           | 1           |

| 「PSpice と SIMPLIS のモデルを使用可能」の箇条書き項目を追加.....                                                                                                                                                    | 1           |

| パッケージ オプションを更新して、パッケージの高さと「ボンド ワイヤなし」の箇条書きを追加.....                                                                                                                                             | 1           |

| 「デバイス情報」の表から「TPSM828303PVCBR (事前情報)」を削除。.....                                                                                                                                                  | 1           |

| 「デバイス情報」の表から「パッケージの高さ」を削除.....                                                                                                                                                                 | 1           |

| 「デバイス情報」の表に「TPSM828301 (VCB)」と「TPSM828302 (VCB) (開発中製品の情報)」を追加.....                                                                                                                            | 1           |

| 「説明」に「1A、2A、3A のピン互換ファミリー」を追加.....                                                                                                                                                             | 1           |

| 「説明」の「デバイスは DCS-Control トポロジをベースとしており、出力容量が小さく、高速過渡応答を実現します」を「小さな出力容量で高速過渡応答を実現するために、デバイスは DCS-Control トポロジを使用します」に変更.....                                                                     | 1           |

| 「説明」の「パワー セーブ モードは低出力電流でバッテリ寿命を延ばし、強制 PWM モードはインダクタの連続導通を維持し、一定のスイッチング周波数でリップルを低減します」を「パワー セーブ モードはバッテリ寿命の延長を目的とするもので、強制 PWM モードは準固定スイッチング周波数で、インダクタの連続導通によってリップルを低減します」に変更.....               | 1           |

| 「説明」の「内部のソフトスタート回路によって電圧が上昇し、厳密に制御されてパワーグッド信号によって正しい出力電圧が示されます」を「内部ソフトスタート回路によって突入電流が低減し、パワーグッド信号によって正しい出力電圧が示されます」に変更.....                                                                    | 1           |

| 「説明」から「このデバイスは 100% モードをサポートします」を削除.....                                                                                                                                                       | 1           |

| 「説明」の「3.0mm × 3.0mm × 1.95mm の QFN パッケージおよび 2.5mm × 2.6mm × 1.95mm」を「3.0mm × 3.0mm の QFN パッケージおよび 2.5mm × 2.6mm」に変更.....                                                                       | 1           |

| 「デバイスのオプション」の表の TPSM828303PVCBR から「事前情報 (生産データではありません)」の注記を削除..                                                                                                                                | 4           |

| 「デバイスのオプション」の表の TPSM828303KPVCBR, TPSM828301APVCBR, TPSM828302APVCBR に「事前情報 (生産データではありません)」の注記を追加.....                                                                                         | 4           |

| 「デバイスのオプション」の表の TPSM828303PVCBR の「事前情報」を TPSM828303APVCBR の「生産での使用許可発行」に変更.....                                                                                                                | 4           |

| 「デバイスのオプション」の表に、ソフトスタート時間情報の列を追加.....                                                                                                                                                          | 4           |

| 両方の「ピン機能」の表のピン 8 の説明を「内部パワー MOSFET とインダクタに接続されている」から変更 EMI が増加する可能性があるため、このピンを大きなトレースに接続しないでください。このピンは未接続のままにしておくことも、半田付けしてインダクタに内部接続することもできます。EMI を最小限に抑えるため、このピンを未接続のままにするか、または半田付けします。..... | 4           |

| 「絶対最大定格」の 1 行目から「VOUT」を削除.....                                                                                                                                                                 | 6           |

| 「絶対最大定格」の電圧に 2 行追加 (1 つはピン SW (DC)、VOS、VOUT の場合、もう 1 つは SW (AC, < 10ns) の場合)、表注記「スイッチング中」を追加.....                                                                                              | 6           |

| デバイスバージョン TPSM828303xK のスタートアップ セクションの「電気的特性」の表にパラメータ tSS を追加....                                                                                                                              | 6           |

| 動作中のグリッチ除去遅延のパワーグッド セクションのパラメータ名「td(PG)」を「(PGO)」に変更.....                                                                                                                                       | 6           |

|                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • リファレンス電圧セクションのパラメータ VFB に、パラメータが DC パラメータであることを示す表注記を追加.....                                                                                                                                                                                                                                                                                                                                                 | 6  |

| • 段落「VCB パッケージバージョンは、EMI をさらに低減するために、MagPack 技術を使用しています。」を変更<br>MagPack は、テキサス インスツルメンツ独自の磁気統合パッケージング技術であり、最高性能のパワー モジュール<br>設計を実現します。EMI の低減に加えて、MagPack はパワー モジュールの効率と放熱特性を向上します。この機能<br>により、VCB パッケージバージョンは最高性能のパワー モジュール設計を実現するために MagPack 技術を採用し<br>ており、業界をリードする電力密度を実現できます。テキサス インスツルメンツ独自の磁気統合 MagPack パッケージ<br>ング技術を活用したこれらのパワー モジュールは、業界をリードする電力密度、高効率、優れた熱性能、使いやすさ、<br>および EMI エミッションの低減を実現します。..... | 10 |

| • 内蔵インダクタのインダクタンスに関する表注記を追加.....                                                                                                                                                                                                                                                                                                                                                                               | 11 |

| • VCB パッケージのバージョンの内蔵インダクタのインダクタンスを「340nH」から「400nH」に変更。.....                                                                                                                                                                                                                                                                                                                                                    | 12 |

| • スタートアップ時間の値をテキストの「固定値」から「仕様表への参照」に変更.....                                                                                                                                                                                                                                                                                                                                                                    | 12 |

| • より低速なスタートアップのためのバージョン TPSM82830xK を参照して、出力コンデンサの選択とスタートアップ時<br>間の関係に関する説明を追加.....                                                                                                                                                                                                                                                                                                                            | 12 |

| • 「VOUT の精度」セクションを追加.....                                                                                                                                                                                                                                                                                                                                                                                      | 15 |

| • PG 信号遅延時間の値をテキストの「固定値」から「仕様表への参照」に変更.....                                                                                                                                                                                                                                                                                                                                                                    | 16 |

| • VCB パッケージバージョンのインダクタンスを「340nH」から「400nH」に変更。.....                                                                                                                                                                                                                                                                                                                                                             | 17 |

| • VIN と VOUT および抵抗の固定値を、設計パラメーターテーブルと BOM テーブルへの参照に図を変更.....                                                                                                                                                                                                                                                                                                                                                   | 17 |

| • 「部品のリスト」の表に「1.8V VOUT の抵抗値」を追加.....                                                                                                                                                                                                                                                                                                                                                                          | 17 |

| • WEBENCH ツールの使用に関する古い手順を最新の説明に変更.....                                                                                                                                                                                                                                                                                                                                                                         | 18 |

| • タイトル「PG から VOUT への影響」の 3 つの図を追加.....                                                                                                                                                                                                                                                                                                                                                                         | 20 |

| • WEBENCH ツールの使用に関する古い手順を最新の説明に変更.....                                                                                                                                                                                                                                                                                                                                                                         | 32 |

**Changes from Revision A (December 2023) to Revision B (June 2024)**

**Page**

|                                   |   |

|-----------------------------------|---|

| • TPSM828303PVCBR (事前情報) を追加..... | 1 |

|-----------------------------------|---|

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

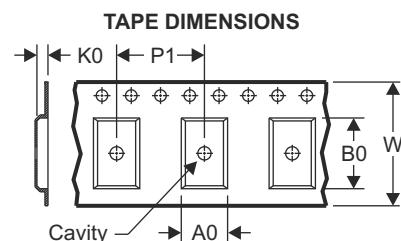

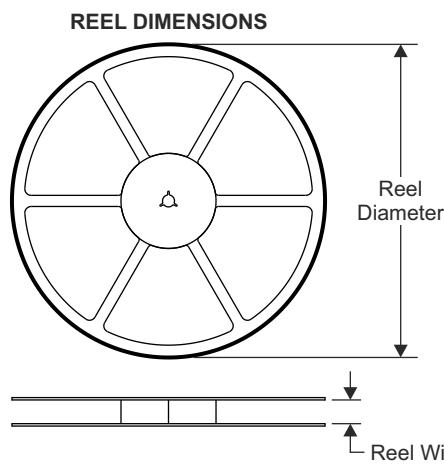

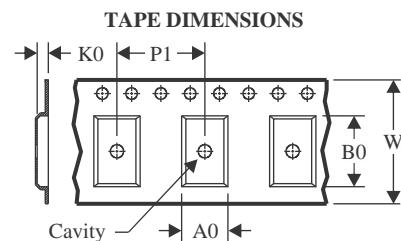

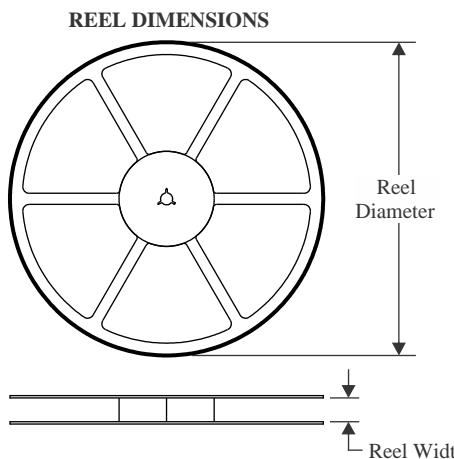

## 11.1 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

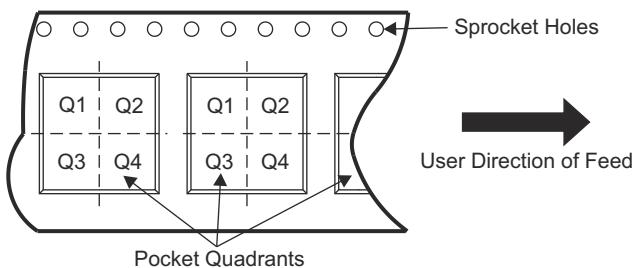

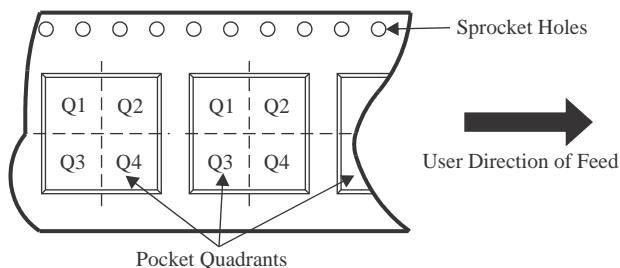

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス            | パッケージ<br>タイプ  | パッケージ<br>図 | ピン | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|-----------------|---------------|------------|----|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| TPSM828303PVCBR | QFN-<br>FCMOD | RDS        | 9  | 3000 | 180            | 8.4              | 0.77       | 1.65       | 0.5        | 8.0        | 12.0      | Q1           |

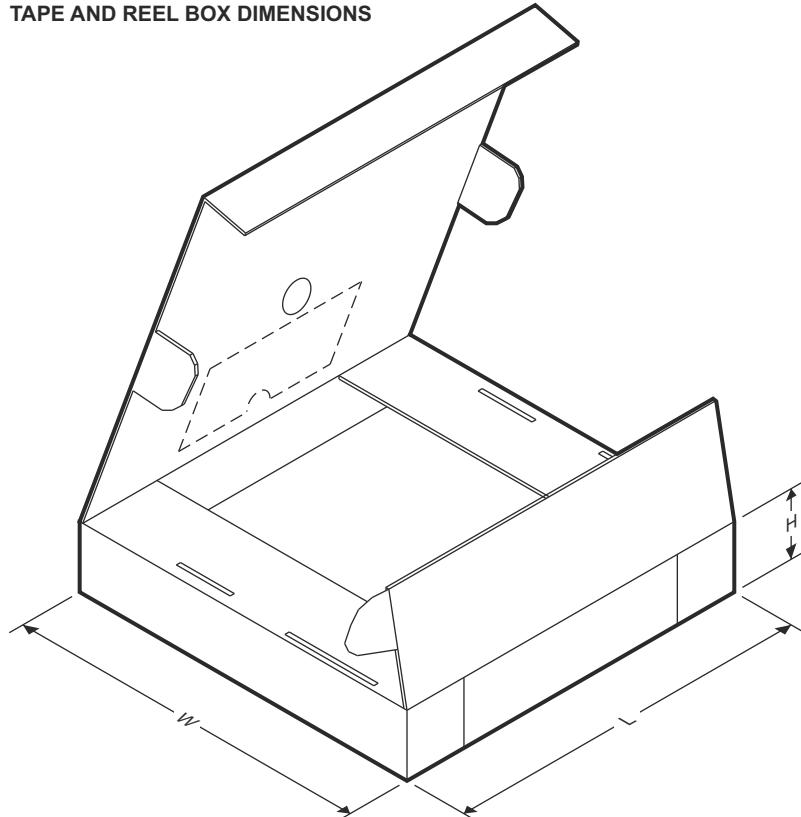

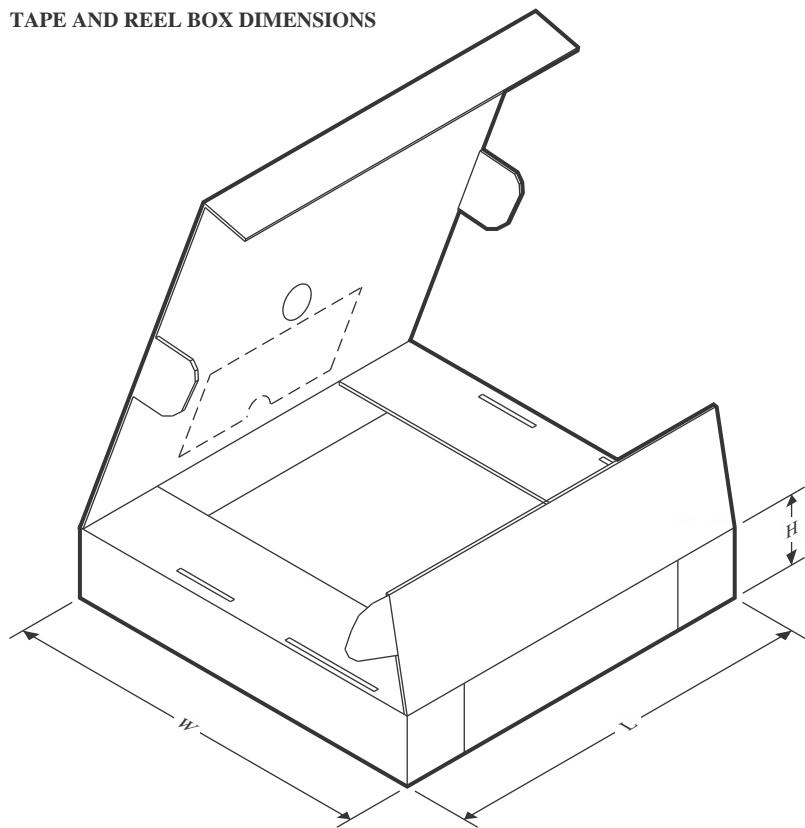

## TAPE AND REEL BOX DIMENSIONS

| デバイス            | パッケージタイプ  | パッケージ図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|-----------------|-----------|--------|----|------|---------|--------|---------|

| TPSM828303PVCBR | QFN-FCMOD | RDS    | 9  | 3000 | 182     | 182    | 20      |

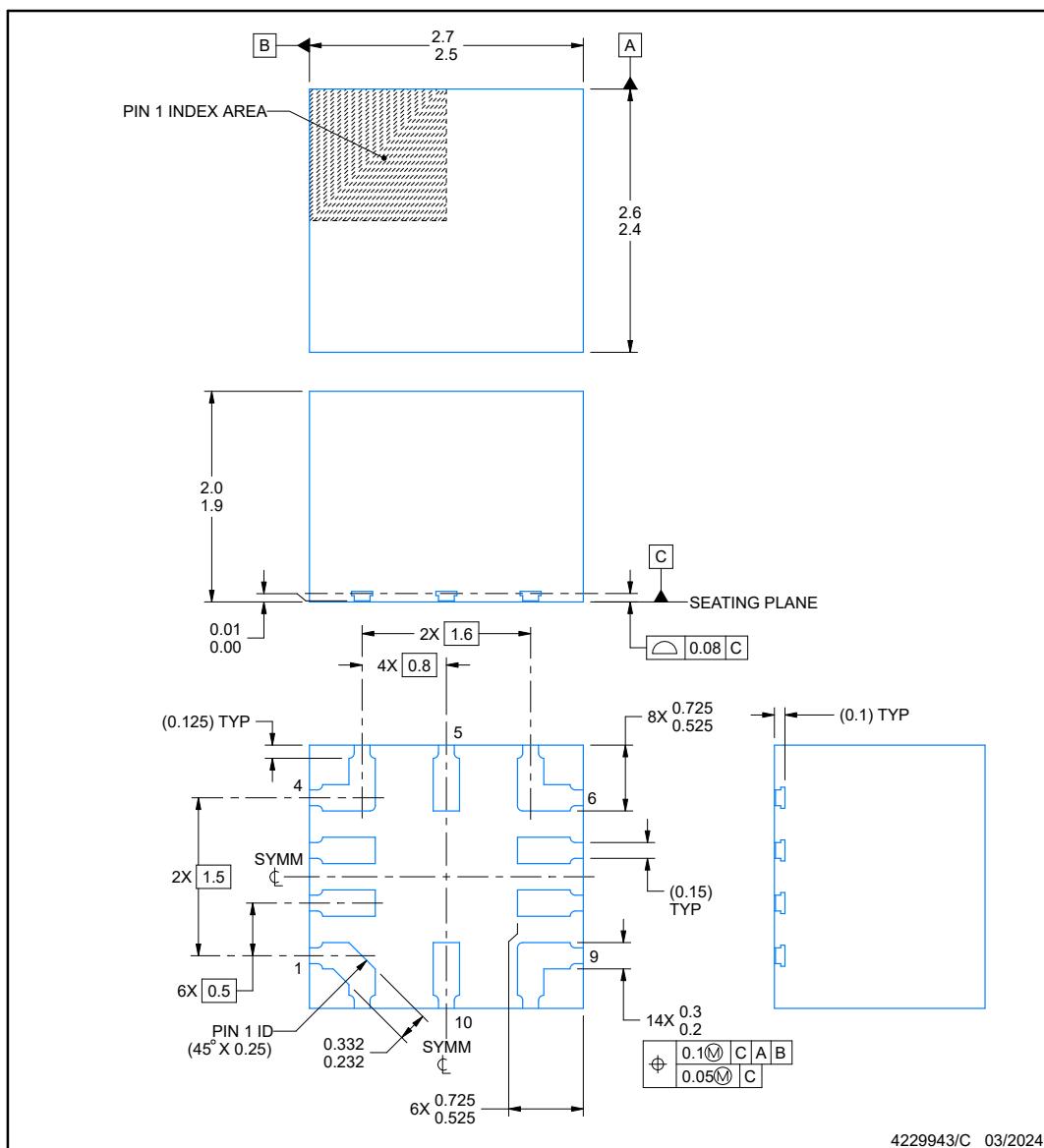

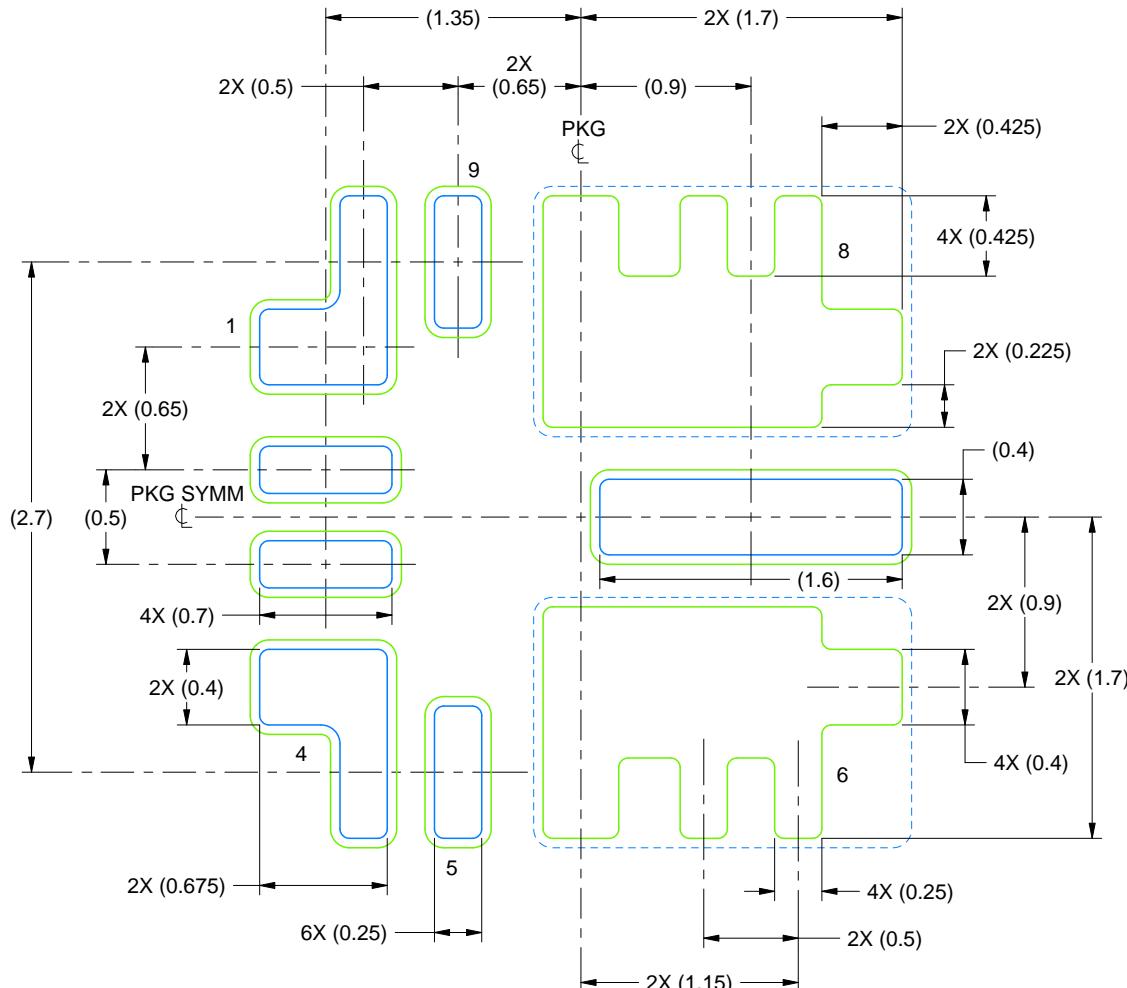

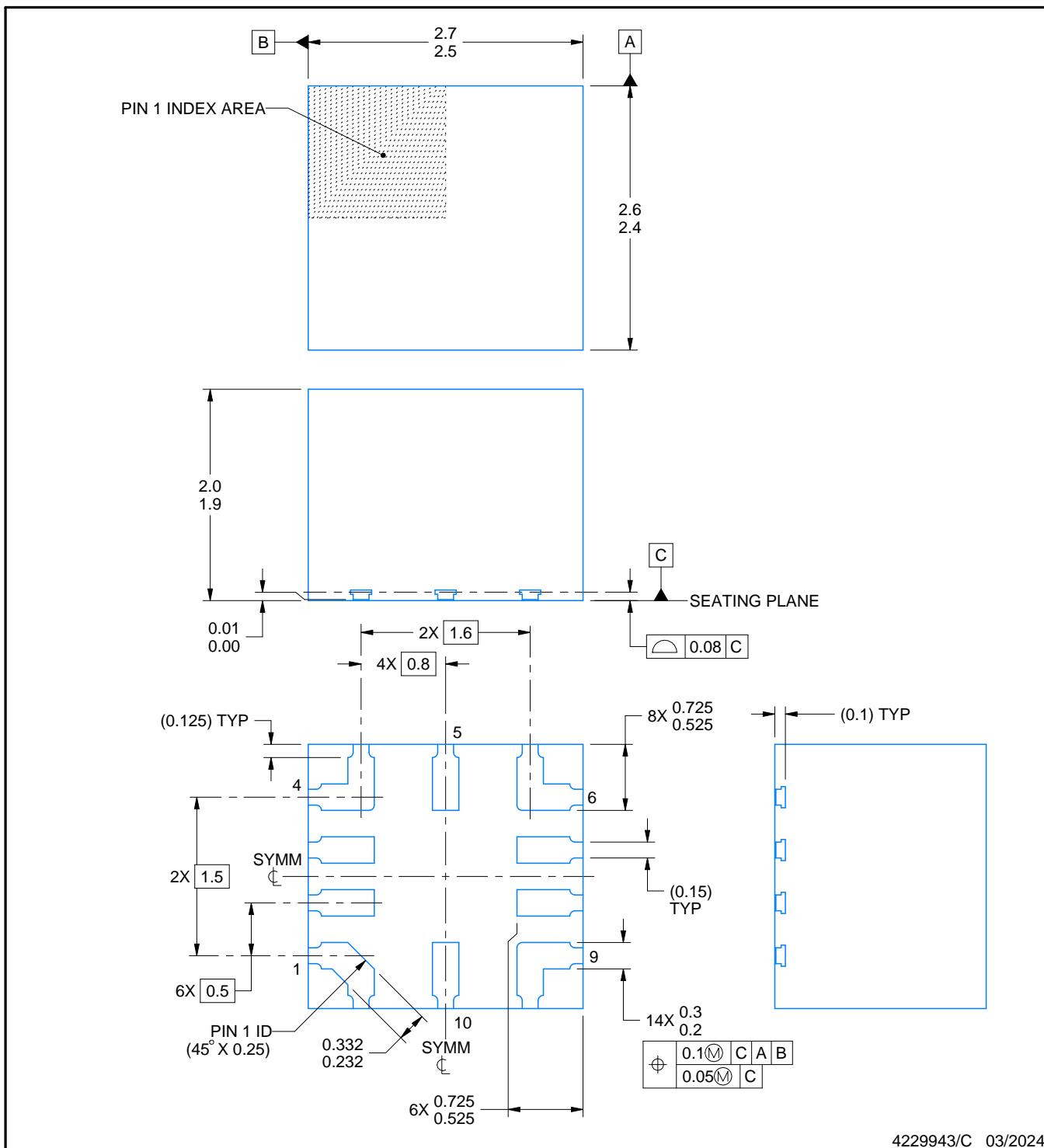

**VCB0010A**

**PACKAGE OUTLINE**

**QFN-FCMOD - 2 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

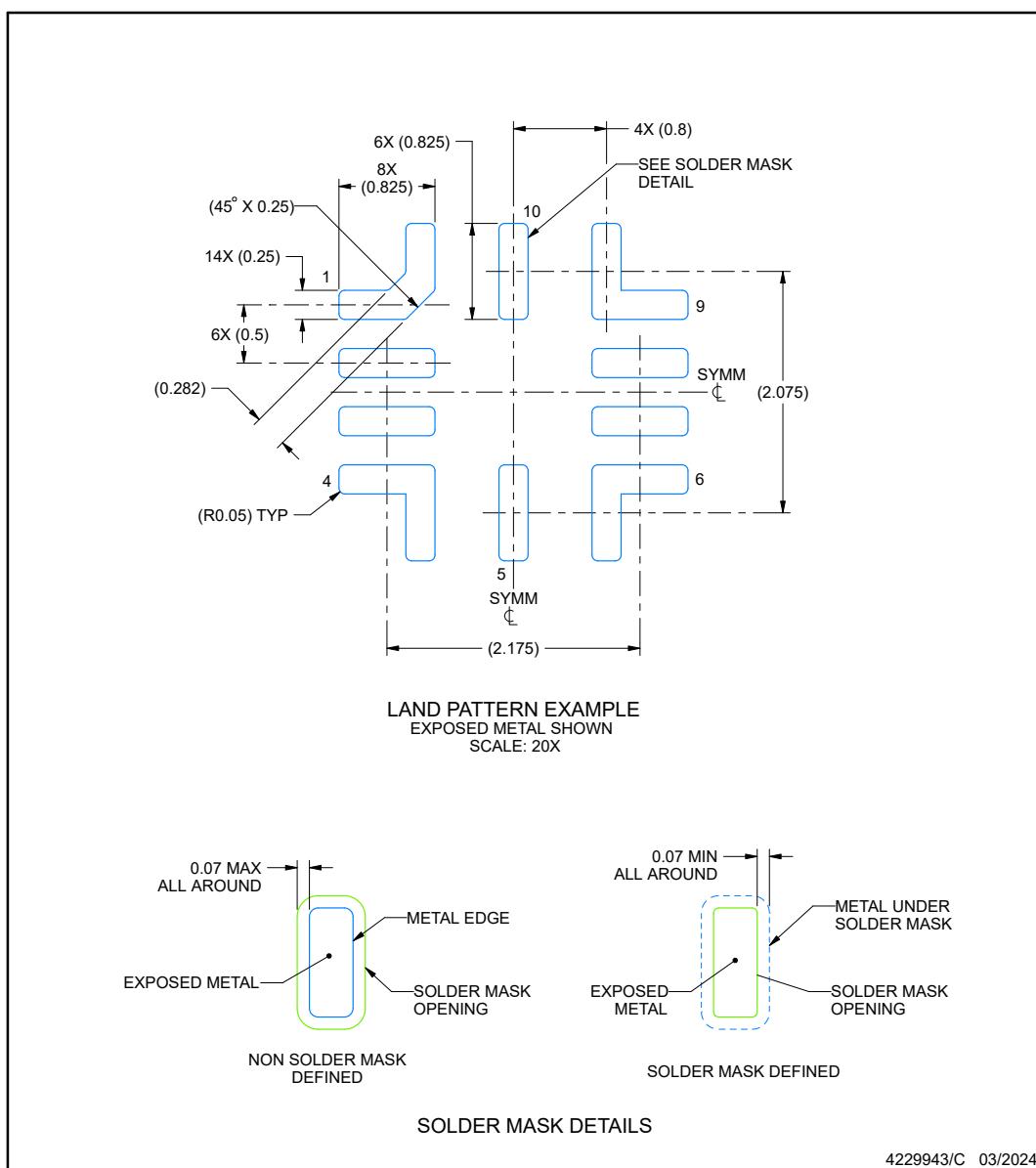

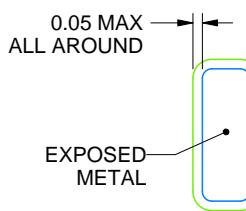

**EXAMPLE BOARD LAYOUT**

**VCB0010A**

**QFN-FCMOD - 2 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

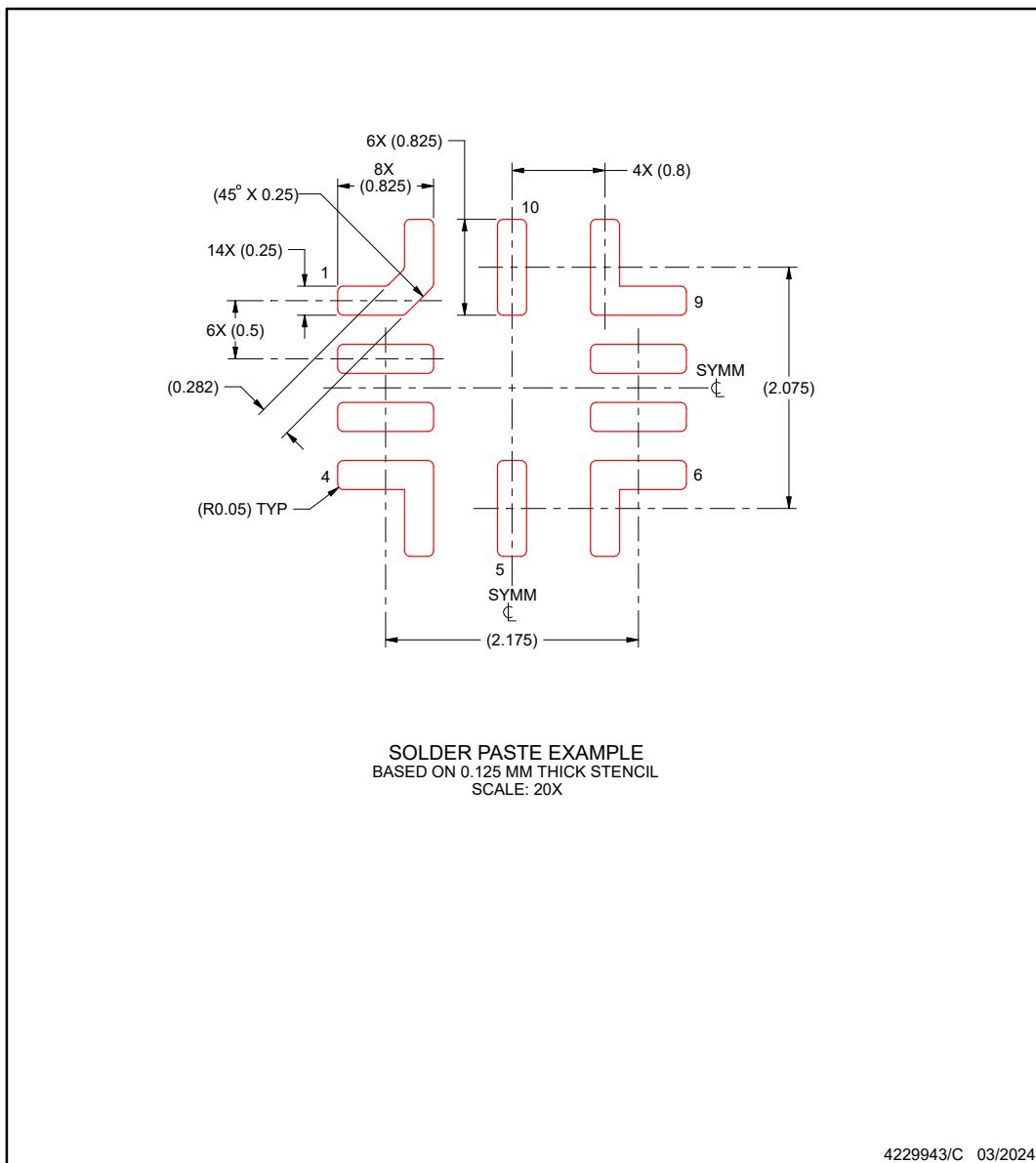

## EXAMPLE STENCIL DESIGN

**VCB0010A**

**QFN-FCMOD - 2 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number            | Status<br>(1) | Material type<br>(2) | Package   Pins       | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------------|---------------|----------------------|----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPSM828301ARDSR</a>  | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8301              |

| TPSM828301ARDSR.A                | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8301              |

| <a href="#">TPSM828302ARDSR</a>  | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8302              |

| TPSM828302ARDSR.A                | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8302              |

| TPSM828302ARDSR.B                | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| <a href="#">TPSM828303APVCBR</a> | Active        | Production           | QFN-FCMOD (VCB)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 3QPI                |

| TPSM828303APVCBR.A               | Active        | Production           | QFN-FCMOD (VCB)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 3QPI                |

| <a href="#">TPSM828303ARDSR</a>  | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8303              |

| TPSM828303ARDSR.A                | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 125   | TM8303              |

| TPSM828303ARDSR.B                | Active        | Production           | QFN-FCMOD (RDS)   9  | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| <a href="#">XPSM828303PVCBR</a>  | Active        | Preproduction        | QFN-FCMOD (VCB)   10 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| XPSM828303PVCBR.A                | Active        | Preproduction        | QFN-FCMOD (VCB)   10 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

---

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPSM828301ARDSSR | QFN-FCMOD    | RDS             | 9    | 3000 | 330.0              | 17.6               | 3.3     | 3.3     | 2.25    | 8.0     | 12.0   | Q2            |

| TPSM828302ARDSSR | QFN-FCMOD    | RDS             | 9    | 3000 | 330.0              | 17.6               | 3.3     | 3.3     | 2.25    | 8.0     | 12.0   | Q2            |

| TPSM828303APVCBR | QFN-FCMOD    | VCB             | 10   | 2500 | 330.0              | 12.4               | 2.9     | 2.8     | 2.2     | 8.0     | 12.0   | Q2            |

| TPSM828303ARDSSR | QFN-FCMOD    | RDS             | 9    | 3000 | 330.0              | 17.6               | 3.3     | 3.3     | 2.25    | 8.0     | 12.0   | Q2            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPSM828301ARDSR  | QFN-FCMOD    | RDS             | 9    | 3000 | 336.0       | 336.0      | 48.0        |

| TPSM828302ARDSR  | QFN-FCMOD    | RDS             | 9    | 3000 | 336.0       | 336.0      | 48.0        |

| TPSM828303APVCBR | QFN-FCMOD    | VCB             | 10   | 2500 | 367.0       | 367.0      | 35.0        |

| TPSM828303ARDSR  | QFN-FCMOD    | RDS             | 9    | 3000 | 336.0       | 336.0      | 48.0        |

## PACKAGE OUTLINE

**RDS0009A**

## **QFN-FCMOD - 2.05 mm max height**

## QUAD FLATPACK - NO LEAD

4228326/D 11/2025

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

## EXAMPLE BOARD LAYOUT

**RDS0009A**

## **QFN-FCMOD - 2.05 mm max height**

## QUAD FLATPACK - NO LEAD

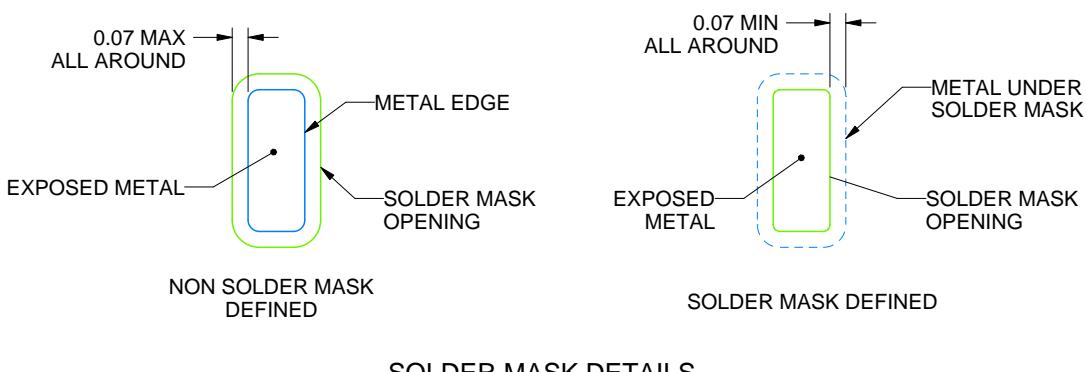

## LAND PATTERN EXAMPLE

NON SOLDER MASK

DEFINED

PADS 1-5, 7 & 9

## SOLDER MASK DETAILS

4228326/D 11/2025

#### NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

RDS0009A

QFN-FCMOD - 2.05 mm max height

QUAD FLATPACK - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 25X

PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

PADS 1, 4 & 7: 88%

PADS 6 & 8: 76%

4228326/D 11/2025

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# PACKAGE OUTLINE

VCB0010A

QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4229943/C 03/2024

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

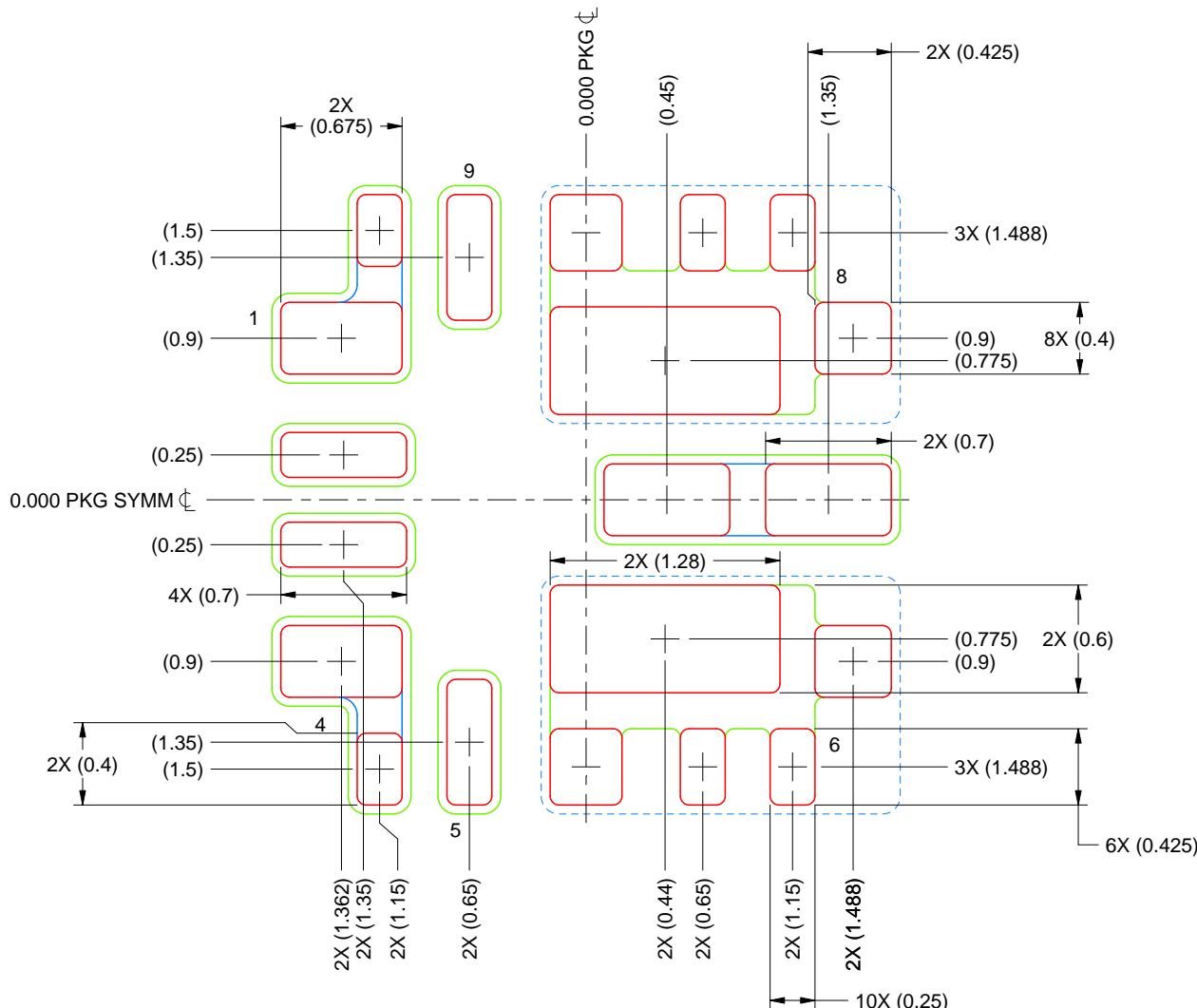

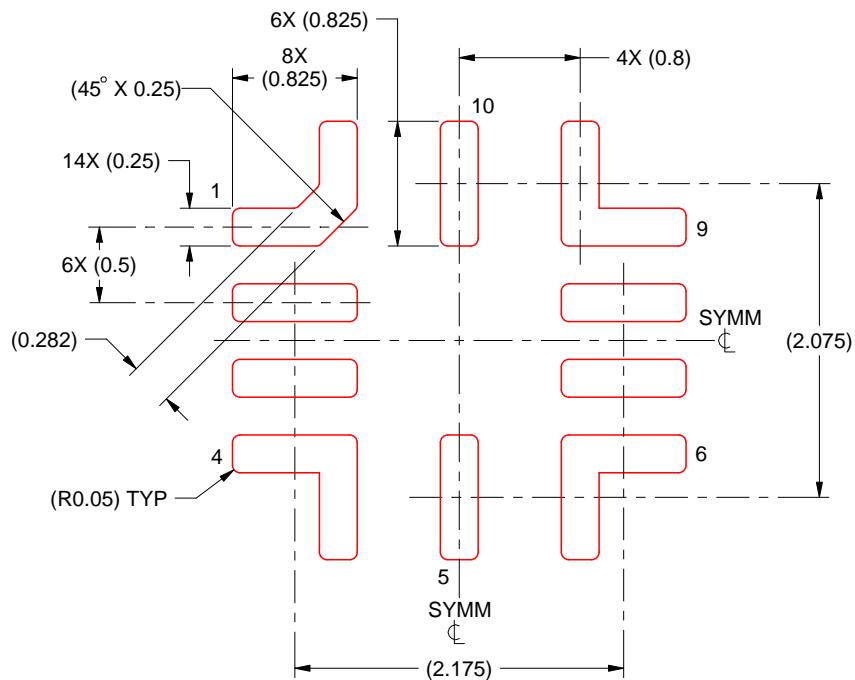

# EXAMPLE BOARD LAYOUT

VCB0010A

QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

SOLDER MASK DETAILS

4229943/C 03/2024

NOTES: (continued)

3. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

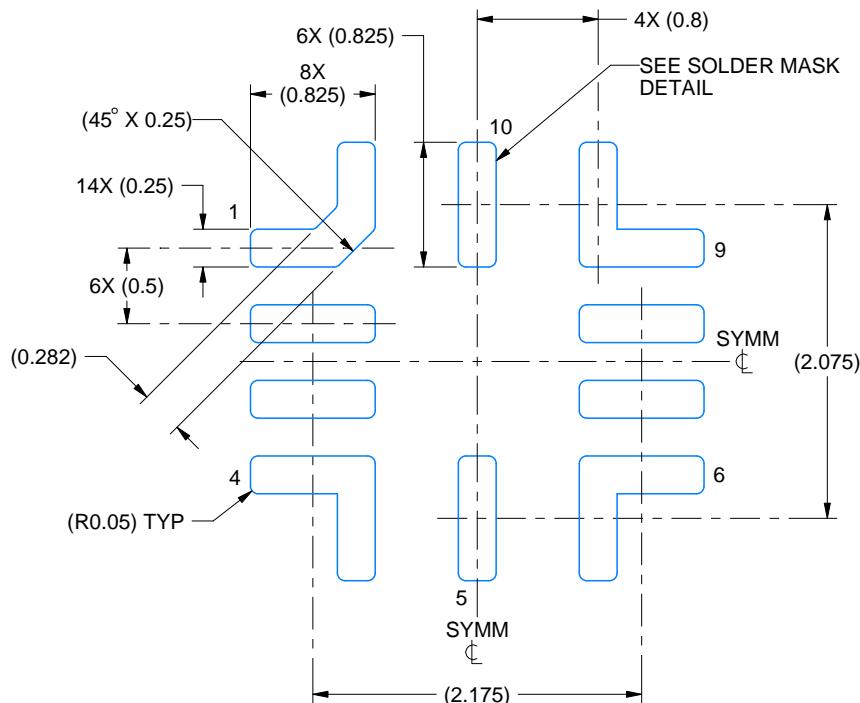

# EXAMPLE STENCIL DESIGN

VCB0010A

QFN-FCMOD - 2 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 MM THICK STENCIL

SCALE: 20X

4229943/C 03/2024

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月