**TPSM63610E** JAJSPV0A – FEBRUARY 2023 – REVISED NOVEMBER 2023

# TPSM63610E 高密度、3V~36V 入力、1V~20V 出力 8A (10A ピーク)、拡張温度範 囲および Enhanced HotRod™ QFN パッケージ採用降圧電源モジュール

# 1 特長

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- 用途の広い 36V<sub>IN</sub>、8A<sub>OUT</sub> 同期整流式降圧モジュ

- MOSFET、インダクタ、コントローラを内蔵

- 出力電圧を調整可能、1V~20V

- 6.5mm×7.5mm×4mmのオーバーモールド・ パッケージ

- -55℃~125℃の接合部温度範囲

- 200kHz~2.2MHz の範囲で周波数を調整可能

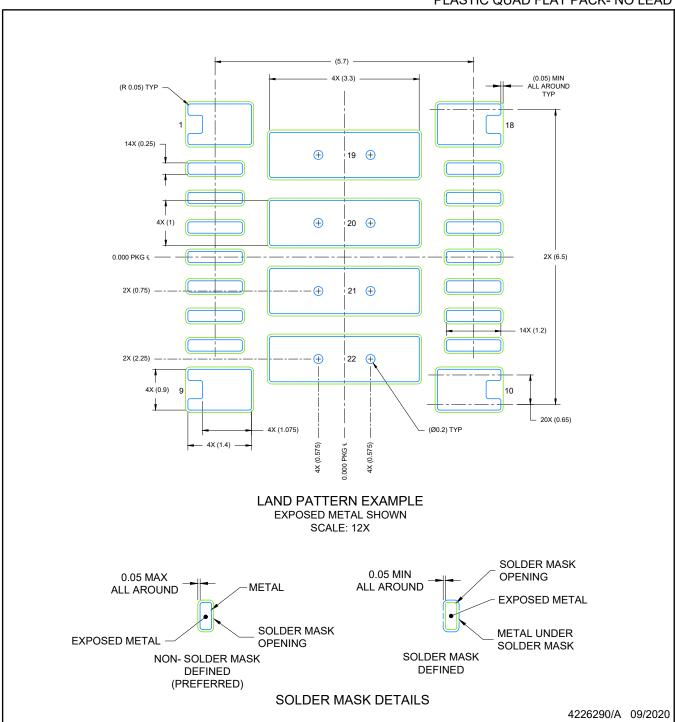

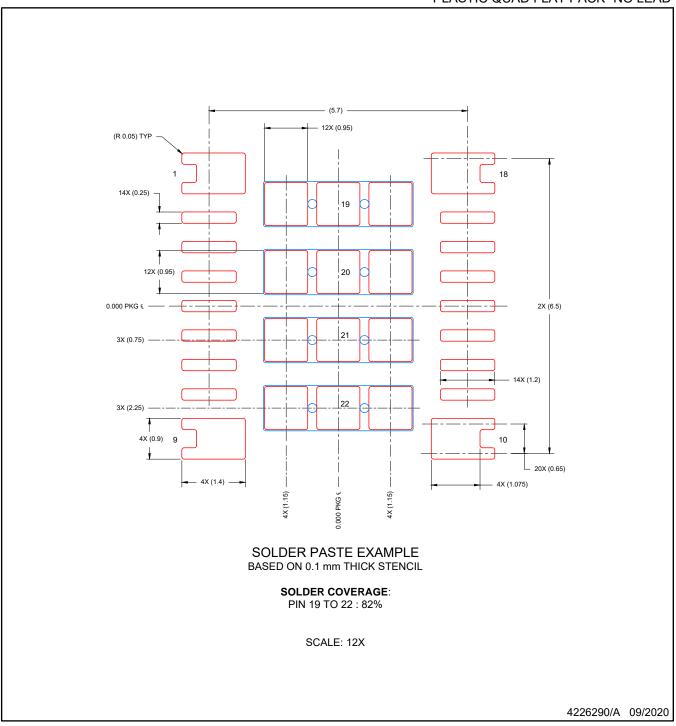

- 負電圧出力に対応可能

- 全負荷範囲にわたって極めて高い効率を実現

- 95% 以上のピーク効率

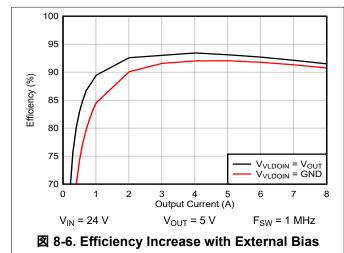

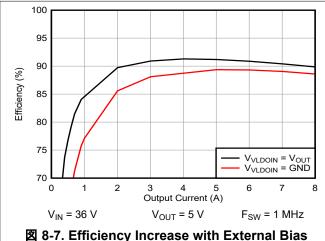

- 外部バイアス・オプションによる効率向上

- 放熱パッドによる熱インピーダンスの低減。 EVM  $\theta_{JA} = 18.2$ °C/W

- シャットダウン時静止電流:0.6μA (標準値)

- 非常に小さい伝導および放射 EMI シグネチャ

- デュアル入力パスと内蔵コンデンサを備えた低 ノイズ・パッケージにより、スイッチのリンギ ングが減少

- 抵抗により調整可能なスイッチ・ノードのスル ーレート

- CISPR 11 および 32 Class B の放射規格に準拠

- スケーラブルな電源に対応した設計

- TPSM63608 (36V、6A) とピン互換

- 堅牢な設計のための本質的な保護機能

- 高精度のイネーブル入力とオープン・ドレイン の PGOOD インジケータによるシーケンシン グ、制御、V<sub>IN</sub> UVLO

- 過電流およびサーマル・シャットダウン保護機

- WEBENCH® Power Designer により、 TPSM63610E を使用するカスタム設計を作成

# 2 アプリケーション

- 試験および測定、航空宇宙および防衛

- ファクトリ・オートメーション / 制御

- 降圧および反転型の昇降圧電源

# 3 概要

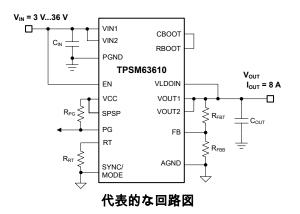

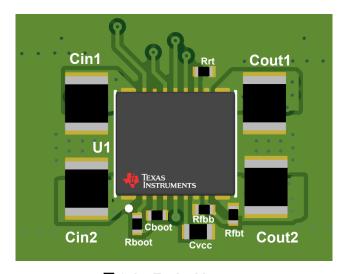

同期整流式降圧モジュール・ファミリから派生した TPSM63610E は、パワー MOSFET、シールド付きイ ンダクタ、受動部品を Enhanced HotRod™ QFN パッ ケージに実装した高集積 36V、8A DC/DC ソリューシ ョンです。このモジュールは、VIN および VOUT ピ ンをパッケージの角に配置し、入力および出力コンデ ンサの配置を最適化しています。モジュールの下面に は大きな 4 つのサーマル・パッドがあるため、単純 なレイアウトが可能で、製造時の扱いも容易です。

出力電圧が 1V~20V の TPSM63610E は、小さな PCB フットプリントで低 EMI の設計を迅速かつ容易 に実装できるよう設計されています。このトータル・ ソリューションを使用すると、外付け部品はわずか 4 個で済み、設計プロセスで磁気および補償のための部 品選択も不要です。

TPSM63610E モジュールはスペースに制約のある アプリケーション向けに小型でシンプルな設計となっ ていますが、調整可能な入力電圧 UVLO 用のヒ ステリシス付き高精度イネーブル、抵抗によりプログ ラム可能なスイッチ・ノードのスルーレート、EMI 改善のためのスペクトラム拡散機能など、堅牢な性能 を実現するための多くの機能を備えています。また、 VCC、ブートストラップ、入力コンデンサを内蔵し ているため、信頼性と密度が向上します。このモジュ ールは、全負荷電流範囲 (FPWM) にわたって一定の スイッチング周波数に設定することも、可変周波数 (PFM) に設定して軽負荷時の効率を高めることもで きます。シーケンシング、フォルト保護、出力電圧監 視用の PGOOD インジケータも内蔵しています。

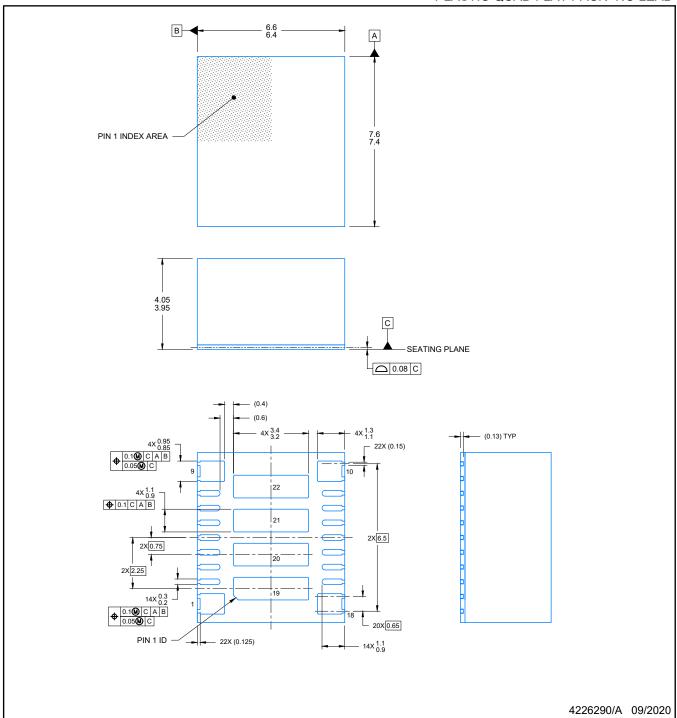

# パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ・サイズ<br>(2) |

|------------|----------------------|------------------|

| TPSM63610E | RDF (B3QFN、22)       | 7.50mm × 6.50mm  |

- (1) 供給されているすべてのパッケージについては、セクション 11 を参照してください。

- パッケージ・サイズ (長さ×幅) は公称値であり、該当する場 合はピンも含まれます。

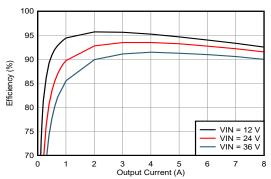

代表的な効率、V<sub>OUT</sub> = 5V、F<sub>SW</sub> = 1MHz

# **Table of Contents**

| 1 特長                                 | 1  | 8.3 Feature Description                 | 14 |

|--------------------------------------|----|-----------------------------------------|----|

| 2 アプリケーション                           |    | 8.4 Device Functional Modes             |    |

| 3 概要                                 |    | 9 Applications and Implementation       |    |

| 4 Revision History                   |    | 9.1 Application Information             |    |

| 5 Device Comparison Table            |    | 9.2 Typical Applications                |    |

| 6 Pin Configuration and Functions    | .4 | 9.3 Power Supply Recommendations        |    |

| 7 Specifications                     |    | 9.4 Layout                              | 31 |

| 7.1 Absolute Maximum Ratings         |    | 10 Device and Documentation Support     |    |

| 7.2 ESD Ratings                      |    | 10.1 Device Support                     |    |

| 7.3 Recommended Operating Conditions | .6 | 10.2 Documentation Support              | 35 |

| 7.4 Thermal Information              | .7 | 10.3 ドキュメントの更新通知を受け取る方法                 |    |

| 7.5 Electrical Characteristics       | .7 | 10.4 サポート・リソース                          | 35 |

| 7.6 System Characteristics           | 10 | 10.5 Trademarks                         | 35 |

| 7.7 Typical Characteristics          |    | 10.6 静電気放電に関する注意事項                      | 35 |

| 8 Detailed Description               |    | 10.7 用語集                                | 35 |

| 8.1 Overview                         |    | 11 Mechanical, Packaging, and Orderable |    |

| 8.2 Functional Block Diagram         |    | Information                             | 36 |

| -                                    |    |                                         |    |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision * (February 2023) to Revision A (November 2023)          | Page |

|---|-------------------------------------------------------------------------------|------|

| • | Added junction temperature range in the Absolute Maximum Ratings table        | 6    |

| • | Added ambient temperature range in the Recommended Operating Conditions table | 6    |

# **5 Device Comparison Table**

| DEVICE     | ORDERABLE PART<br>NUMBER | RATED OUTPUT CURRENT CURRENT (TRANSIENT CONDITIONS) |      | JUNCTION TEMPERATURE RANGE |  |  |

|------------|--------------------------|-----------------------------------------------------|------|----------------------------|--|--|

| TPSM63610  | TPSM63610RDFR            | 8 A                                                 | 10 A | –40°C to 125°C             |  |  |

| TPSM63610E | TPSM63610EXTRDFR         | 8 A                                                 | 10 A | –55°C to 125°C             |  |  |

| TPSM63608  | TPSM63608RDFR            | 6 A                                                 | 8 A  | –40°C to 125°C             |  |  |

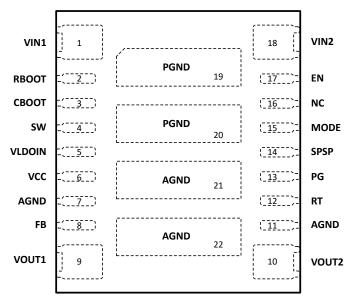

# **6 Pin Configuration and Functions**

図 6-1. 22-Pin B3QFN RDF Package (Top View)

表 6-1. Pin Functions

|       | PIN TYPE(1 |      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | NAME       | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1, 18 | VIN1, VIN2 | Р    | Input supply voltage. Connect the input supply to these pins. Connect input capacitors between these pins and PGND in close proximity to the device.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2     | RBOOT      | I    | External bootstrap resistor connection. RBOOT is brought out to use in conjunction with CBOOT to effectively lower the value of the internal series bootstrap resistance to adjust the switch-node slew rate, if necessary. A resistance from 0 to 500 $\Omega$ can be connected between RBOOT and CBOOT. A resistance of 0 $\Omega$ has the fastest slew rate and highest efficiency. A value of 100 $\Omega$ creates a nice balance between efficiency and EMI. Leaving open sets the slew rate to 20 ns and TI does not recommend due to increased self heating. |

| 3     | СВООТ      | 0    | Bootstrap pin for the internal high-side gate driver. A 100-nF bootstrap capacitor is internally connected from this pin to SW within the module to provide the bootstrap voltage. CBOOT is brought out to use in conjunction with RBOOT to effectively lower the value of the internal series bootstrap resistance to adjust the switch-node slew rate, if necessary.                                                                                                                                                                                              |

| 4     |            |      | Switch node. Do not place any external component on this pin or connect to any signal. The amount of copper placed on this pin must be kept to a minimum to prevent issues with noise and EMI.                                                                                                                                                                                                                                                                                                                                                                      |

| 5     | VLDOIN     | Р    | Input bias voltage. Input to the internal LDO that supplies the internal control circuits. Connect to an output voltage point to improve efficiency. Connect an optional high-quality 0.1-µF to 1-µF capacitor from this pin to ground for improved noise immunity. If the output voltage is above 12 V, connect this pin to ground.                                                                                                                                                                                                                                |

| 6     | VCC        | Р    | Internal LDO output. Used as a supply to the internal control circuits. Do not connect to any external loads. A 1-μF capacitor internally connects from VCC to AGND.                                                                                                                                                                                                                                                                                                                                                                                                |

# 表 6-1. Pin Functions (続き)

| 1                | PIN             | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.              | NAME            | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7, 11, 21,<br>22 | AGND            | G       | Analog ground. Zero-voltage reference for internal references and logic. All electrical parameters are measured with respect to this pin. <i>These pins must be connected to PGND</i> . See <i>Layout Example</i> for a recommended layout.                                                                                                                                                                                                                                                                                                                                                                             |

| 8                | FB              | I       | Feedback input. Connect the midpoint of the feedback resistor divider to this pin. Connect the upper resistor ( $R_{FBT}$ ) of the feedback divider to $V_{OUT}$ at the desired point of regulation. Connect the lower resistor ( $R_{FBB}$ ) of the feedback divider to AGND. Do not leave open or connect to ground.                                                                                                                                                                                                                                                                                                  |

| 9, 10            | VOUT1,<br>VOUT2 | Р       | Output voltage. These pins are connected to the internal buck inductor. Connect these pins to the output load and connect external output capacitors between these pins and PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12               | RT              | ı       | Frequency setting pin used to set the switching frequency between 200 kHz and 2.2 MHz by placing an external resistor from RT to AGND. Connect to VCC for 400 kHz. Connect to ground for 2.2 MHz. Do not leave open.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13               | PG              | 0       | Open-drain power-good monitor output that asserts low if the FB voltage is not within the specified window thresholds. A $10$ -k $\Omega$ to $100$ -k $\Omega$ pullup resistor to a suitable voltage is required . If not used, PG can be left open or connected to GND.                                                                                                                                                                                                                                                                                                                                                |

| 14               | SPSP            | ı       | Connect to VCC or through a resistor to ground to enable spread spectrum. Connect to GND to disable spread spectrum. If using spread spectrum, a VCC connection turns off the spread spectrum tone correction while a resistor to ground (10-30 k $\Omega$ ) adjusts the tone correction to lower the output voltage ripple. Do not float this pin.                                                                                                                                                                                                                                                                     |

| 15               | SYNC/<br>MODE   | I       | This pin controls the mode of operation of the device. Modes include Auto mode (automatic PFM/PWM operation), forced pulse width modulation (FPWM), and synchronized to an external clock. The clock triggers on the rising edge of an applied external clock. Pull low to enable PFM operation, pull high to enable FPWM, or connect to a clock to synchronize to an external frequency in FPWM mode. Do not float this pin. When synchronized to an external clock, use the RT pin to set the internal frequency close to the synchronized frequency to avoid disturbances if the external clock is turned on and off |

| 16               | NC              | _       | No connection. Tie to GND or leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17               | EN              | ı       | Precision enable input to regulator. High = on, low = off. Can be connected to VIN. Precision enable allows the pin to be used as an adjustable UVLO. Do not float                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19, 20           | PGND            | G       | Power ground. This is the return current path for the power stage of the device. Connect these pads to the input supply return, the load return, and the capacitors associated with the VIN and VOUT pins. See <i>Layout Example</i> for a recommended layout.                                                                                                                                                                                                                                                                                                                                                          |

(1) P = Power, G = Ground, I = Input, O = Output

資料に関するフィードバック(ご意見やお問い合わせ)を送信

English Data Sheet: SLVSH65

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range<sup>(1)</sup>

|                                         | PARAMETER                                               | MIN  | MAX                   | UNIT |

|-----------------------------------------|---------------------------------------------------------|------|-----------------------|------|

| Voltages                                | Transient VIN to AGND, PGND <sup>(2)</sup>              | -0.3 | 42                    | V    |

| Voltages                                | Continuous VIN to AGND, PGND <sup>(2)</sup>             | -0.3 | 36                    | V    |

| Voltages                                | SW to AGND, PGND                                        | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| Voltages                                | RBOOT, CBOOT to SW                                      | -0.3 | 5.5                   | V    |

| Voltages                                | Transient EN or SYNC/MODE to AGND, PGND <sup>(2)</sup>  | -0.3 | 42                    | V    |

| Voltages                                | Continuous EN or SYNC/MODE to AGND, PGND <sup>(2)</sup> | -0.3 | 36                    | V    |

| Voltages                                | BIAS to AGND, PGND                                      | -0.3 | 16                    | V    |

| Voltages                                | FB to AGND, PGND: Adjustable Versions                   | -0.3 | 5.5                   | V    |

| Voltages                                | RESET to AGND, PGND                                     | 0    | 20                    | V    |

| Current                                 | RESET sink current <sup>(4)</sup>                       | 0    | 10                    | mA   |

| Voltages                                | RT to AGND, PGND                                        | -0.3 | 5.5                   | V    |

| Voltages                                | VCC to AGND, PGND                                       | -0.3 | 5.5                   | V    |

| Voltages                                | PGND to AGND <sup>(3)</sup>                             | -1   | 2                     | V    |

| Peak reflow case temperature            |                                                         |      | 250                   | °C   |

| Maximum<br>number of<br>reflows allowed |                                                         |      | 3                     |      |

| Mechanical vibration                    | MIL-STD-883D, Method 2007.2, 20 Hz to 2 kHz             |      | 20                    | G    |

| Mechanical<br>shock                     | MIL-STD-883D, Method 2002.3, 1 ms, 1/2 sine, mounted    |      | 1500                  | G    |

| TJ                                      | Junction temperature                                    | -55  | 150                   | °C   |

| T <sub>stg</sub>                        | Storage temperature                                     | -65  | 150                   | °C   |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) A maximum of 42 V can be sustained at this pin for duration of ≤ 100 ms at a duty cycle of ≤ 0.01%. 36 V can be sustained for the life of this device.

- (3) This specification applies to voltage durations of 100 ns or less. The maximum D.C. voltage must not exceed +/- 0.3 V.

- (4) Do not exceed the pin voltage rating.

# 7.2 ESD Ratings

|                    |                         |                                                                           | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Lieurostatic disoriarge | Charged-device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002 <sup>(2)</sup> | ±750  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -55°C to 125°C (unless otherwise noted) (1)

|               |                                   |     |  | MIN | MAX | UNIT |

|---------------|-----------------------------------|-----|--|-----|-----|------|

| Input voltage | Input Voltage Range <sup>(1</sup> | l . |  | 3   | 36  | V    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLVSH65

Over the recommended operating junction temperature range of -55°C to 125°C (unless otherwise noted) (1)

|                   |                                                            | MIN         | MAX  | UNIT |

|-------------------|------------------------------------------------------------|-------------|------|------|

| Output voltage    | Output Adjustment Range for adjustable output versions (2) | 1           | 20   | V    |

| Frequency         | Frequency adjustment range                                 | 200         | 2200 | kHz  |

| Sync<br>Frequency | Synchronization frequency range                            | 200         | 2200 | kHz  |

| Output current    | Гоит                                                       | 0           | 8    | Α    |

| Temperature       | Operating ambient temperature, T <sub>A</sub>              | -55         | 105  | °C   |

| Temperature       | Operating junction temperature, T <sub>J</sub>             | <b>–</b> 55 | 125  | °C   |

<sup>(1) 3.7</sup> V is required at VIN for start-up, an extended input voltage range down to 3.0 V is possible after start-up; See Minimum input voltage for start-up conditions.

#### 7.4 Thermal Information

|                       |                                                           | TPSM636XX |      |

|-----------------------|-----------------------------------------------------------|-----------|------|

|                       | THERMAL METRIC (1)                                        | RDF       | UNIT |

|                       |                                                           | 22 PINS   | _    |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance (TPSM63610EVM) (3) | 18        | °C/W |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance (JESD 51-7) (2)    | 25        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                 | 12.8      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                      | 7.4       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                | 0.7       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter              | 7.2       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance              | 3.6       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report

# 7.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature range of -55°C to +125°C, unless otherwise noted. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN}$  = 12. VIN1 shorted to VIN2 =  $V_{IN}$ .  $V_{OUT}$  is output set point.

| PARAMETER            |                                                                 | TEST CONDITIONS                                                      | MIN | TYP   | MAX   | UNIT |

|----------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|-----|-------|-------|------|

| SUPPLY VC            | DLTAGE (VIN PIN)                                                |                                                                      |     |       |       |      |

| V                    | Minimum operating input voltage                                 | Needed to start up                                                   |     |       | 3.7   | V    |

| $V_{IN}$             | wii iii ii ii operating input voitage                           | Once Operating                                                       |     |       | 3     | V    |

| V <sub>IN_OP_H</sub> | Minimum voltage hysteresis                                      |                                                                      |     | 1     |       | V    |

| IQ                   | Non-switching input current; measured at VIN pin <sup>(3)</sup> | V <sub>FB</sub> = +5%, V <sub>BIAS</sub> = 5 V                       |     | 0.5   | 10    | μA   |

| I <sub>SD</sub>      | Shutdown quiescent current; measured at VIN pin                 | V <sub>EN</sub> = 0 V, V <sub>IN</sub> = 12 V                        |     | 0.57  | 7.5   | μA   |

| I <sub>B</sub>       | Current into BIAS pin (not switching)                           | V <sub>FB</sub> = +5%, V <sub>BIAS</sub> = 5 V, Auto Mode<br>Enabled |     | 18.5  | 26    | μA   |

| ENABLE (E            | N PIN)                                                          |                                                                      |     |       | '     |      |

| V <sub>EN</sub>      | Enable input-threshold voltage - rising                         | V <sub>EN</sub> rising                                               | 1.0 | 1.263 | 1.365 | V    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

<sup>(2)</sup> Under no conditions can the output voltage be allowed to fall below zero volts.

<sup>(2)</sup> The value of R<sub>OJA</sub> given in this table is only valid for comparison with other packages and can not be used for design purposes. These values were calculated in accordance with JESD 51-7, and simulated on a 4-layer JEDEC board. They do not represent the performance obtained in an actual application. For example, the EVM R<sub>OJA</sub> = 21.6 °C/W. For design information please see the thermal design and layout section.

<sup>(3)</sup> Refer to the EVM User's Guide for board layout and additional information. For thermal design information please see the thermal design and layout section.

Limits apply over the recommended operating junction temperature range of -55°C to +125°C, unless otherwise noted. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25$ °C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 12$ . VIN1 shorted to VIN2 =  $V_{IN}$ .  $V_{OUT}$  is output set point.

|                           | oly: $V_{IN} = 12$ . VIN1 shorted to VIN2 = $V_{IN}$                                                                                                                   | TEST CONDITIONS                                                                                       | MIN   | TYP  | MAX   | UNIT |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>EN_HYST</sub>      | Enable threshold hysteresis                                                                                                                                            |                                                                                                       | 0.1   | 0.35 | 0.5   | V    |

| V <sub>EN_WAKE</sub>      | Enable Wake-up threshold                                                                                                                                               |                                                                                                       | 0.4   |      |       | V    |

| l <sub>EN</sub>           | Enable pin input current                                                                                                                                               | V <sub>IN</sub> = V <sub>EN</sub> = 12 V                                                              |       | 1.5  | 50    | nA   |

| INTERNAL LD               | O (VCC PIN)                                                                                                                                                            |                                                                                                       |       |      |       |      |

| \ /                       | Internal VCC valtage                                                                                                                                                   | V <sub>BIAS</sub> = 0V                                                                                |       | 3.4  |       | V    |

| V <sub>CC</sub>           | Internal VCC voltage  V <sub>BIAS</sub> = 3.3 V, 20 mA                                                                                                                 |                                                                                                       |       | 3.2  |       | V    |

| V <sub>CC_UVLO</sub>      | V <sub>IN</sub> voltage at which Internal VCC under voltage lock-out is released                                                                                       | I <sub>VCC</sub> = 0A                                                                                 |       |      | 3.75  | V    |

| V <sub>CC_UVLO_HYST</sub> | Internal VCC under voltage lock-out hysteresis below V <sub>CC_UVLO</sub>                                                                                              |                                                                                                       |       | 1.2  |       | V    |

| VOLTAGE REF               | ERENCE (FB PIN)                                                                                                                                                        |                                                                                                       |       |      |       |      |

| V <sub>FB</sub>           | Initial reference voltage accuracy for adjustable (1 V FB) versions                                                                                                    | V <sub>IN</sub> = 3.0 V to 36 V, FPWM Mode                                                            | 0.985 | 1    | 1.015 | V    |

| I <sub>FB</sub>           | Input current from FB to AGND                                                                                                                                          | Adjustable versions only, V <sub>FB</sub> = 1 V                                                       |       |      | 50    | nA   |

| CURRENT LIM               | ITS                                                                                                                                                                    |                                                                                                       |       |      |       |      |

| I <sub>SC_8</sub>         | Short circuit high-side current Limit                                                                                                                                  |                                                                                                       | 11.5  | 13.8 | 15.7  | Α    |

| I <sub>LS-LIMIT_8</sub>   | Low-side current limit                                                                                                                                                 |                                                                                                       |       | 9.2  | 10.5  | Α    |

| PEAK-MIN_8                | Minimum Peak Inductor Current                                                                                                                                          | 8 A Variant, Duty cycle approaches 0%                                                                 |       | 1.9  |       | Α    |

| L-NEG_8                   | Negative current limit                                                                                                                                                 |                                                                                                       | -6.4  | -5.3 | -3.9  | Α    |

| I <sub>L-ZC</sub>         | Zero-cross current limit. Positive current direction is out of SW pin.                                                                                                 | Auto Mode, static measurement                                                                         |       | 70   |       | mA   |

| V <sub>HICCUP</sub>       | Hiccup threshold on FB pin                                                                                                                                             |                                                                                                       | 0.36  | 0.4  | 0.44  | V    |

| POWER GOOD                | (/RESET PIN)                                                                                                                                                           |                                                                                                       |       |      |       |      |

| V RESET-OV                | RESET upper threshold - Rising                                                                                                                                         | % of FB voltage                                                                                       | 109.5 | 112  | 114.5 | %    |

| V RESET-UV                | RESET lower threshold - Falling                                                                                                                                        | % of FB voltage                                                                                       | 93    | 95   | 97.5  | %    |

| V RESET_GUARD             | RESET UV threshold as percentage of steady state output voltage with output voltage and UV threshold, falling, read at the same T <sub>J</sub> , and V <sub>IN</sub> . | Falling                                                                                               |       |      | 97    | %    |

| V RESET-HYS-<br>FALLING   | RESET fallling threshold hysteresis                                                                                                                                    | % of FB voltage                                                                                       |       | 1.3  |       | %    |

| V RESET-HYS-<br>RISING    | RESET rising threshold hysteresis                                                                                                                                      | % of FB voltage                                                                                       |       | 1.3  |       | %    |

| V RESET_VALID             | Minimum input voltage for proper RESET function                                                                                                                        | Measured when V <sub>RESET</sub> < 0.4 V with 10 kOhm pullup to external 5 V                          |       |      | 1.2   | V    |

|                           |                                                                                                                                                                        | 46.0 μA pull up to $\overline{\text{RESET}}$ pin, $V_{\text{IN}}$ = 1.0 $V$ , $V_{\text{EN}}$ = 0 $V$ |       |      | 0.4   |      |

| $V_{OL}$                  | RESET Low-level function output voltage                                                                                                                                | 1 mA pull up to $\overline{RESET}$ pin, $V_{IN}$ = 12 V, $V_{EN}$ = 0 V                               |       |      | 0.4   | V    |

|                           |                                                                                                                                                                        | 2 mA pull up to $\overline{\text{RESET}}$ pin, $V_{\text{IN}}$ = 12 V, $V_{\text{EN}}$ = 3.3 V        |       |      | 0.4   |      |

| RESET                     | RESET ON resistance,                                                                                                                                                   | V <sub>EN</sub> = 5 V, 1mA pull up current                                                            |       | 44   | 125   | Ω    |

| RESET                     | RESET ON resistance,                                                                                                                                                   | V <sub>EN</sub> = 0 V, 1mA pull up current                                                            |       | 18   | 40    | Ω    |

| RESET_FILTER              | RESET edge deglitch delay                                                                                                                                              |                                                                                                       | 10    | 26   | 45    | μs   |

|                           | RESET active time                                                                                                                                                      | Time FB must be valid before RESET is                                                                 | 1.2   | 2.1  | 3.75  | ms   |

www.ti.com/ja-jp

Limits apply over the recommended operating junction temperature range of -55°C to +125°C, unless otherwise noted. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 12$ . VIN1 shorted to VIN2 =  $V_{IN}$ .  $V_{OLIT}$  is output set point.

| Conditions app            | oly: V <sub>IN</sub> = 12. VIN1 shorted to VIN2 = V                                     | TEST CONDITIONS                                                                                              | MIN   | TYP  | MAX  | UNIT |

|---------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| f                         |                                                                                         |                                                                                                              |       |      |      |      |

| fosc                      | Internal oscillator frequency                                                           | RT = GND                                                                                                     | 1.90  | 2.2  | 2.42 | MHz  |

| f <sub>OSC</sub>          | Internal oscillator frequency                                                           | RT = VCC                                                                                                     | 320   | 400  | 450  | kHz  |

| f <sub>FIXED_2.2MHz</sub> | Oscillator frequency measured using maximum value of RT resistor to select 2.2 MHz      | RT = 6.81 kΩ                                                                                                 | 1.95  | 2.2  | 2.42 | MHz  |

| f <sub>FIXED_0.4MHz</sub> | Oscillator frequency measured using minimum value of RT resistor to select 0.4 MHz      | RT = 40.2 kΩ                                                                                                 | 352   | 400  | 448  | kHz  |

| f <sub>ADJ</sub>          | Center Trim oscillator frequency                                                        | RT = 22.6 kΩ                                                                                                 | 630   | 700  | 770  | kHz  |

| V <sub>SYNCDL</sub>       | SYNC/MODE input voltage low                                                             |                                                                                                              | 0.4   |      |      | V    |

| V <sub>SYNCDH</sub>       | SYNC/MODE input voltage high                                                            |                                                                                                              |       |      | 1.7  | V    |

| V <sub>SYNCD_HYST</sub>   | SYNC/MODE input voltage hysteresis                                                      |                                                                                                              | 0.185 |      | 1    | V    |

| R <sub>SYNC</sub>         | Internal pulldown resistor to ensure SYNC/MODE doesn't float                            |                                                                                                              |       | 100  |      | kΩ   |

| tsync_edge                | High and Loww duration needed for synchronizing clock to be recognized on SYNC/MODE pin |                                                                                                              | 100   |      |      | ns   |

| t <sub>MSYNC</sub>        | Time at one level needed to indicate FPWM or Auto Mode                                  |                                                                                                              | 7     |      | 20   | μs   |

| t <sub>LOCK</sub>         | Time needed for clock to lock to a valid synchronization signal                         | RT = 39.2 kΩ                                                                                                 |       | 4.3  |      | ms   |

| SPREAD SPE                | CTRUM                                                                                   |                                                                                                              |       |      | '    |      |

| ΔFc+                      | Frequency increase of internal oscillator from spread spectrum                          |                                                                                                              | 1     | 4    | 7.5  | %    |

| ΔFc-                      | Frequency decrease of internal oscillator from spread spectrum                          |                                                                                                              | -8    | -4   | -1   | %    |

| HIGH SIDE DR              | RIVE (CBOOT PIN)                                                                        |                                                                                                              |       |      |      |      |

| V <sub>CBOOT_UVLO</sub>   | Voltage on CBOOT pin compared to SW which will turnoff high-side switch                 |                                                                                                              |       | 1.9  |      | V    |

| MOSFETS                   |                                                                                         |                                                                                                              |       |      |      |      |

| R <sub>DS-ON-HS</sub>     | High-side MOSFET on-resistance                                                          | Load = 1 A, C <sub>BOOT-SW</sub> = 3.2 V                                                                     |       | 21   | 39   | mΩ   |

| R <sub>DS-ON-LS</sub>     | Low-side MOSFET on-resistance                                                           | Load = 1 A, C <sub>BOOT-SW</sub> = 3.2 V                                                                     |       | 13   | 25   | mΩ   |

| PWM LIMITS (              | SW PIN)                                                                                 |                                                                                                              |       |      |      |      |

| t <sub>ON-MIN</sub>       | Minimum HS switch on-time                                                               | $V_{IN}$ =18 V, $V_{SYNC/MODE}$ = 5 V, $I_{OUT}$ = 2A, $R_{BOOT}$ = 0 $\Omega$                               |       | 62   | 81   | ns   |

| t <sub>OFF-MIN</sub>      | Minimum HS switch off-time                                                              | V <sub>IN</sub> = 5 V                                                                                        |       | 70   | 103  | ns   |

| t <sub>ON-MAX</sub>       | Maximum switch on-time                                                                  | HS timeout in dropout                                                                                        | 6.9   | 8.9  | 11   | μs   |

|                           |                                                                                         | While in frequency fold-back                                                                                 | 98    |      |      |      |

| $D_{MAX}$                 | Maximum switch duty cycle                                                               | fsw =1.85 MHz                                                                                                |       | 87   |      | %    |

| START UP                  |                                                                                         |                                                                                                              |       |      |      |      |

| t <sub>EN</sub>           | Turn-on delay                                                                           | V <sub>IN</sub> = 12 V, C <sub>VCC</sub> = 1 μF, time from EN high to first SW pulse if output starts at 0 V |       | 0.82 | 1.2  | ms   |

| t <sub>SS</sub>           | Time from first SW pulse to V <sub>REF</sub> at 90%, of set point.                      |                                                                                                              | 1.6   | 2.2  | 2.7  | ms   |

| t <sub>W</sub>            | Short circuit wait time ("hiccup" time)                                                 |                                                                                                              |       | 40   |      | ms   |

# 7.6 System Characteristics

The following specifications apply only to the typical applications circuit, with nominal component values. Specifications in the typical (TYP) column apply to  $T_J = 25^{\circ}$ C only. These specifications are not ensured by production testing.

|                    | PARAMETER                                                                                                                                                                                  | TEST CONDITIONS                                                                                                             | MIN | TYP  | MAX | UNIT |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| SUPPLY             |                                                                                                                                                                                            |                                                                                                                             |     |      |     |      |

| I <sub>IN</sub>    | Input supply current when in regulation $V_{IN} = V_{EN/SYNC} = 24 \text{ V}, V_{OUT} = V_{VLDOIN} = 3.3 \text{ V}, V_{MODE} = 0 \text{ V}, F_{SW} = 1 \text{ MHz}, I_{OUT} = 0 \text{ A}$ |                                                                                                                             |     | 8    |     | μΑ   |

| OUTPUT             | VOLTAGE                                                                                                                                                                                    |                                                                                                                             |     |      | •   |      |

| ΔV <sub>OUT1</sub> | Load regulation                                                                                                                                                                            | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 0.1 A to 8 A                                           |     | 4    |     | mV   |

| $\Delta V_{OUT2}$  | Line regulation                                                                                                                                                                            | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 4 V to 36 V, I <sub>OUT</sub> = 8 A                                             |     | 1    |     | mV   |

| ΔV <sub>OUT3</sub> | Load transient                                                                                                                                                                             | V <sub>OUT</sub> = 5 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 0 A to 4 A at 1 A/μs, C <sub>OUT(derated)</sub> = 100 μF |     | 150  |     | mV   |

| EFFICIEN           | ICY                                                                                                                                                                                        |                                                                                                                             |     |      |     |      |

| η                  | Efficiency                                                                                                                                                                                 | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = V <sub>VLDOIN</sub> = 3.3 V, I <sub>OUT</sub> = 4 A, F <sub>SW</sub> = 1 MHz     |     | 92.1 |     | %    |

| η                  | Efficiency                                                                                                                                                                                 | V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = V <sub>VLDOIN</sub> = 3.3 V, I <sub>OUT</sub> = 4 A, F <sub>SW</sub> = 1 MHz     |     | 91   |     | %    |

| η                  | Efficiency                                                                                                                                                                                 | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = V <sub>VLDOIN</sub> = 5 V, I <sub>OUT</sub> = 4 A, F <sub>SW</sub> = 1 MHz       |     | 94.3 |     | %    |

| η                  | Efficiency                                                                                                                                                                                 | V <sub>IN</sub> = 24 V, V <sub>OUT</sub> = V <sub>VLDOIN</sub> = 5 V, I <sub>OUT</sub> = 4 A, F <sub>SW</sub> = 1 MHz       |     | 93   |     | %    |

10

Product Folder Links: TPSM63610E

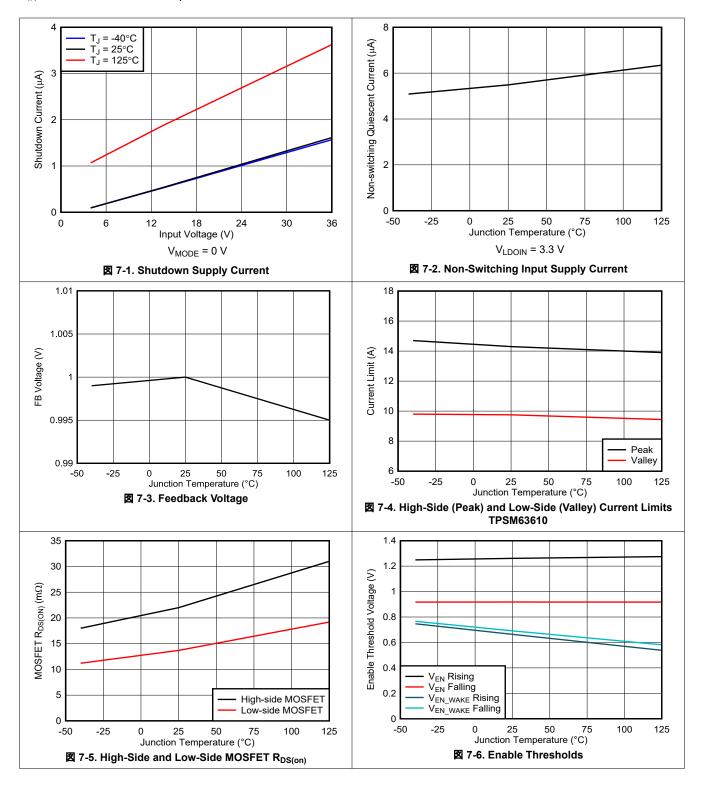

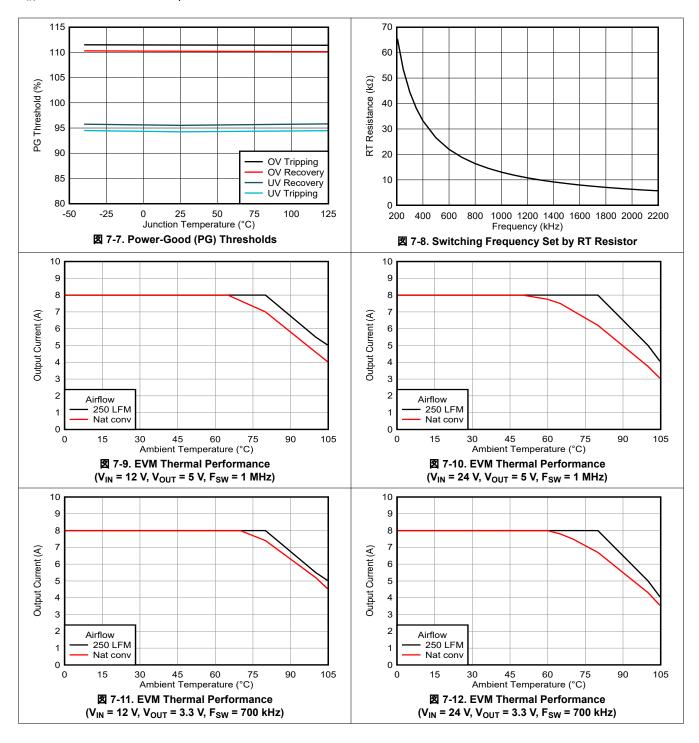

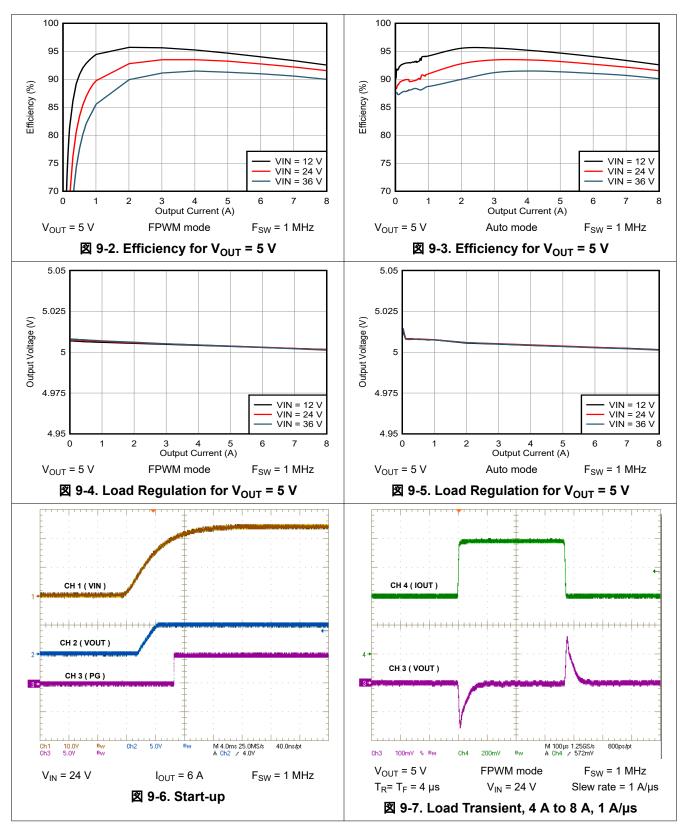

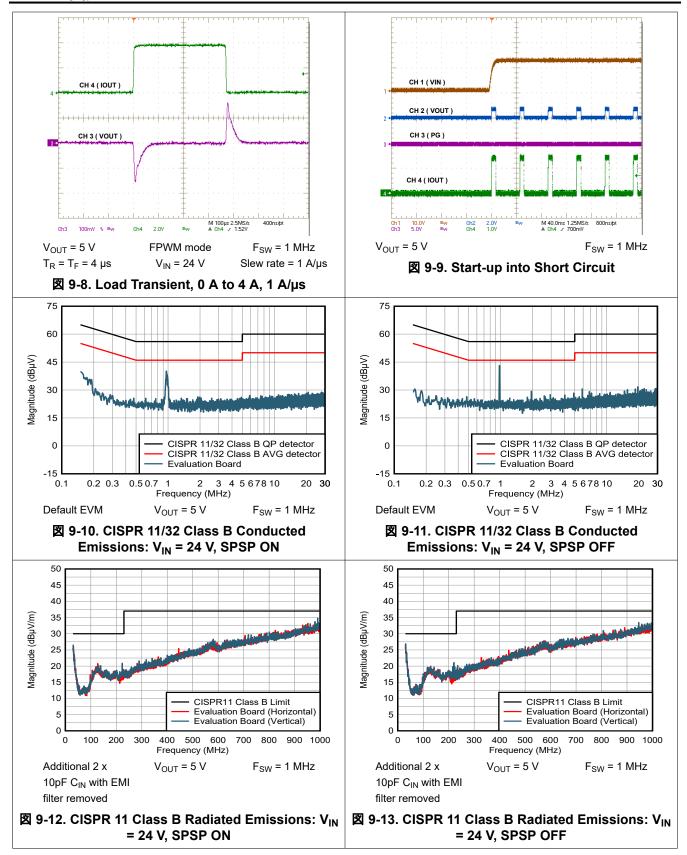

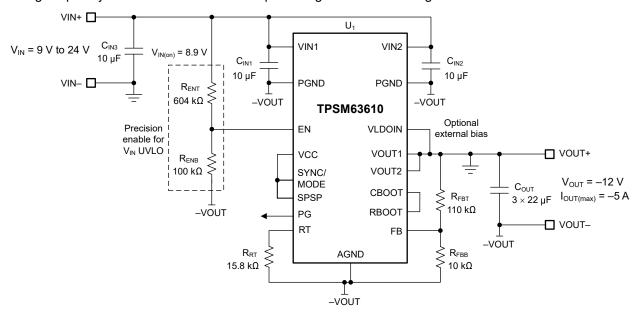

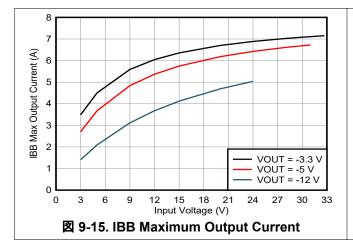

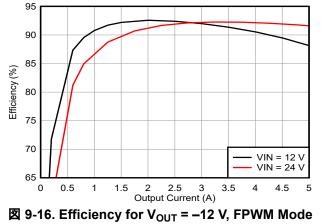

# 7.7 Typical Characteristics

V<sub>IN</sub> = 12 V, unless otherwise specified.

# 7.7 Typical Characteristics (continued)

V<sub>IN</sub> = 12 V, unless otherwise specified.

# 8 Detailed Description

### 8.1 Overview

The TPSM63610E is an easy-to-use, synchronous buck DC/DC power module designed for a wide variety of applications where reliability, small solution size, and low EMI signature are of paramount importance. With integrated power MOSFETs, a buck inductor, and PWM controller, the TPSM63610E operates over an input voltage range of 3 V to 36 V with transients as high as 42 V. The module delivers up to 8-A (10-A peak) DC load current with high conversion efficiency and ultra-low input quiescent current in a very small solution footprint. Control loop compensation is not required, reducing design time and external component count.

With a programmable switching frequency from 200 kHz to 2.2 MHz using its RT pin or an external clock signal, the TPSM63610E incorporates specific features to improve EMI performance in noise-sensitive applications:

- · An optimized package and pinout design enables a shielded switch-node layout that mitigates radiated EMI

- Parallel input and output paths with symmetrical capacitor layouts minimize parasitic inductance, switch-voltage ringing, and radiated field coupling

- · Dual-random spread spectrum (DRSS) modulation reduces peak emissions

- · Resistor-programmable switch-node slew rate

- · Clock synchronization and FPWM mode enable constant switching frequency across the load current range

- · Integrated power MOSFETs with enhanced gate drive control enable low-noise PWM switching

Together, these features significantly reduce EMI filtering requirements, while helping to meet CISPR 11 and CISPR 32 Class B EMI limits for conducted and radiated emissions.

The TPSM63610E module also includes inherent protection features for robust system requirements:

- An open-drain PGOOD indicator for power-rail sequencing and fault reporting

- · Precision enable input with hysteresis, providing

- Programmable line undervoltage lockout (UVLO)

- Remote ON and OFF capability

- · Internally fixed output-voltage soft start with monotonic start-up into prebiased loads

- Hiccup-mode overcurrent protection with cycle-by-cycle peak and valley current limits

- Thermal shutdown with automatic recovery.

Leveraging a pin arrangement designed for simple layout that requires only a few external components, the TPSM63610E is specified to maximum junction temperatures of 125°C. See typical performance curves to estimate suitability in a given ambient environment.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

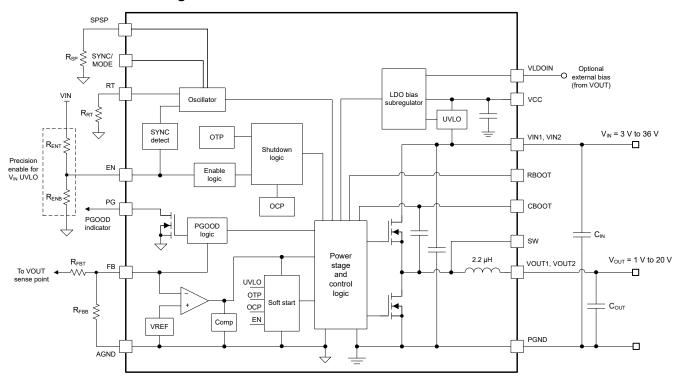

### 8.2 Functional Block Diagram

# 8.3 Feature Description

# 8.3.1 Input Voltage Range (VIN1, VIN2)

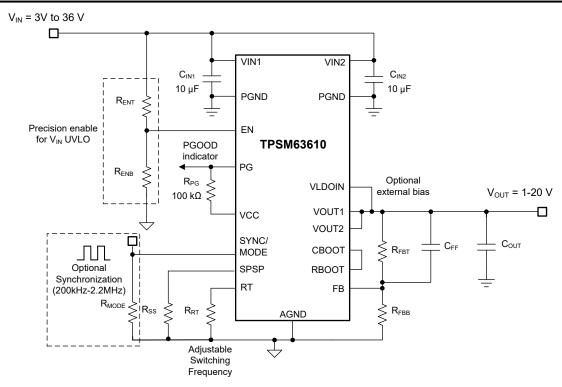

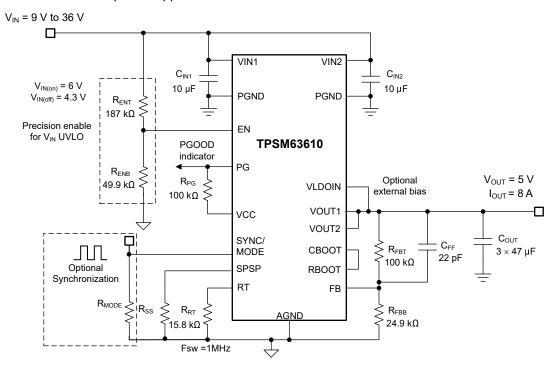

With a steady-state input voltage range from 3 V to 36 V, the TPSM63610E module is intended for step-down conversions from typical 12-V, 24-V, and 28-V input supply rails. The schematic circuit in 🗵 8-1 shows all the necessary components to implement a TPSM63610E-based buck regulator using a single input supply.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

図 8-1. TPSM63610E Schematic Diagram with Input Voltage Operating Range of 3 V to 36 V

The minimum input voltage required for start-up is 3.7 V. Take extra care to make sure that the voltage at the VIN pins of the module (VIN1 and VIN2) does not exceed the absolute maximum voltage rating of 42 V during line or load transient events. Voltage ringing at the VIN pins that exceeds the *Absolute Maximum Ratings* can damage the IC.

#### 8.3.2 Adjustable Output Voltage (FB)

The TPSM63610E has an adjustable output voltage range from 1 V up to a maximum of 20 V or slightly less than  $V_{IN}$ , whichever is lower. Setting the output voltage requires two feedback resistors, designated as  $R_{FBT}$  and  $R_{FBB}$  in  $\boxtimes$  8-1. The reference voltage at the FB pin is set at 1 V with a feedback system accuracy over the full junction temperature range of ±1%. The junction temperature range for the device is –55°C to 125°C.

Calculate the value for  $R_{FBB}$  using  $\pm$  1 below based on a recommended value for  $R_{FBT}$  of 100 k $\Omega$ .

$$R_{\text{FBB}}(k\Omega) = \frac{R_{\text{FBT}}(k\Omega)}{\frac{V_{\text{OUT}}}{1} - 1} \tag{1}$$

表 8-1 lists the standard resistor values for several output voltages and the recommended switching frequency range to maintain reasonable peak-to-peak inductor ripple current. This table also includes the minimum required output capacitance for each output voltage setting to maintain stability. The capacitances as listed represent *effective* values for ceramic capacitors derated for DC bias voltage and temperature. Furthermore, place a feedforward capacitor, C<sub>FF</sub>, in parallel with R<sub>FBT</sub> to increase the phase margin when the output capacitance is close to the minimum recommended value.

| V <sub>OUT</sub> (V) | R <sub>FBB</sub> (kΩ) | SUGGESTED<br>F <sub>SW</sub> RANGE<br>(kHz) | C <sub>OUT(min)</sub> (μF)<br>(EFFECTIVE) | BOM <sup>(2)</sup>    | C <sub>FF</sub> (pF) | V <sub>OUT</sub> (V) | R <sub>FBB</sub> (kΩ) | SUGGESTED<br>F <sub>SW</sub> RANGE<br>(MHz) | C <sub>OUT(min)</sub> (μF)<br>(EFFECTIVE) | BOM <sup>(2)</sup>  | C <sub>FF</sub> (pF) |

|----------------------|-----------------------|---------------------------------------------|-------------------------------------------|-----------------------|----------------------|----------------------|-----------------------|---------------------------------------------|-------------------------------------------|---------------------|----------------------|

| 1                    | Open                  | 200 to 750                                  | 400                                       | 4 × 100<br>µF (6.3 V) | _                    | 9                    | 12.5                  | 0.75 to 1.5                                 | 66                                        | 4 × 47 μF<br>(16 V) | _                    |

| 1.8                  | 125                   | 300 to 900                                  | 350                                       | 4 × 100<br>μF (6.3 V) | 100                  | 12                   | 9.09                  | 1 to 1.7                                    | 30                                        | 3 × 22 μF<br>(25 V) | _                    |

| 3.3                  | 43.4                  | 400 to 1100                                 | 100                                       | 4 × 47 μF<br>(10 V)   | 47                   | 15                   | 7.14                  | 1 to 1.9                                    | 20                                        | 3 × 22 μF<br>(25 V) | _                    |

| 5                    | 25                    | 500 to 1400                                 | 75                                        | 3 × 47 μF<br>(10 V)   | 22                   | 20                   | 5.26                  | 1.2 to 2.2                                  | 15                                        | 3 × 22 μF<br>(25 V) | _                    |

- (1)  $R_{FBT} = 100 \text{ k}\Omega$ .

- (2) Refer to 表 8-3 for the output capacitor list.

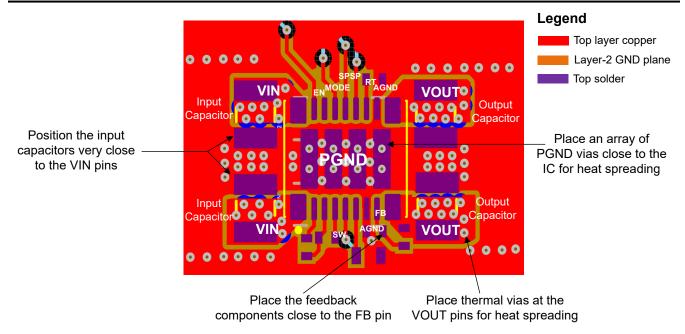

Note that higher feedback resistances consume less DC current. However, an upper  $R_{FBT}$  resistor value higher than 1 M $\Omega$  renders the feedback path more susceptible to noise. Higher feedback resistances generally require more careful layout of the feedback path. Make sure to locate the feedback resistors close to the FB and AGND pins, keeping the feedback trace as short as possible (and away from noisy areas of the PCB). See *Layout Example* guidelines for more detail.

#### 8.3.3 Input Capacitors

Input capacitors are necessary to limit the input ripple voltage to the module due to switching-frequency AC currents. TI recommends using ceramic capacitors to provide low impedance and high RMS current rating over a wide temperature range.  $\pm$  2 gives the input capacitor RMS current. The highest input capacitor RMS current occurs at D = 0.5, at which point the RMS current rating of the capacitors must be greater than half the output current.

$$I_{\text{CIN, rms}} = \sqrt{D \times \left(I_{\text{OUT}}^2 \times (1 - D) + \frac{\Delta i_L^2}{12}\right)}$$

(2)

where

D = V<sub>OUT</sub> / V<sub>IN</sub> is the module duty cycle.

Ideally, the DC and AC components of input current to the buck stage are provided by the input voltage source and the input capacitors, respectively. Neglecting inductor ripple current, the input capacitors source current of amplitude ( $I_{OUT}-I_{IN}$ ) during the D interval and sink  $I_{IN}$  during the 1 – D interval. Thus, the input capacitors conduct a square-wave current of peak-to-peak amplitude equal to the output current. The resultant capacitive component of AC ripple voltage is a triangular waveform. Together with the ESR-related ripple component,  $\vec{\pm}$  3 gives the peak-to-peak ripple voltage amplitude:

$$\Delta V_{\rm IN} = \left(\frac{I_{\rm OUT} \times D \times (1 - D)}{F_{SW} \times C_{IN}} + I_{\rm OUT} \times R_{\rm ESR}\right)$$

(3)

式 4 gives the input capacitance required for a particular load current:

$$C_{\text{IN}} \ge \left(\frac{I_{\text{OUT}} \times D \times (1 - D)}{F_{\text{SW}} \times (\Delta V_{\text{IN}} - I_{\text{OUT}} \times R_{\text{ESP}})}\right) \tag{4}$$

where

ΔV<sub>IN</sub> is the input voltage ripple specification.

The TPSM63610E requires a minimum of two 10-µF ceramic input capacitors, preferably with X7R or X7S dielectric and in 1206 or 1210 footprint. Additional capacitance can be required for applications to meet conducted EMI specifications, such as CISPR 11 or CISPR 32.

表 8-2 includes a preferred list of capacitors by vendor. To minimize the parasitic inductance in the switching loops, position the ceramic input capacitors in a symmetrical layout close to the VIN1 and VIN2 pins and connect the capacitor return terminals to the PGND pins using a copper ground plane under the module.

| 表 8-2. Recommended Ceram | ic Input Ca | apacitors |

|--------------------------|-------------|-----------|

|--------------------------|-------------|-----------|

| VENDOR <sup>(1)</sup> | DIELECTRIC | PART NUMBER         | CASE SIZE | CAPACITANCE (μF) <sup>(2)</sup> | RATED VOLTAGE (V) |

|-----------------------|------------|---------------------|-----------|---------------------------------|-------------------|

| TDK                   | X7R        | C3216X7R1H106K160AC | 1206      | 10                              | 50                |

| Murata                | X7S        | GCM32EC71H106KA03K  | 1210      | 10                              | 50                |

| AVX                   | X7R        | 12105C106MAT2A      | 1210      | 10                              | 50                |

| Murata                | X7R        | GRM32ER71H106KA12L  | 1210      | 10                              | 50                |

<sup>(1)</sup> Consult capacitor suppliers regarding availability, material composition, RoHS and lead-free status, and manufacturing process requirements for any capacitors identified in this table. See the *Third-Party Products Disclaimer*.

As discussed in *Power Supply Recommendations*, an electrolytic bulk capacitance (68  $\mu$ F to 100  $\mu$ F) provides low-frequency filtering and parallel damping to mitigate the effects of input parasitic inductance resonating with the low-ESR, high-Q ceramic input capacitors.

### 8.3.4 Output Capacitors

表 8-1 lists the TPSM63610E minimum amount of required output capacitance. The effects of DC bias and temperature variation must be considered when using ceramic capacitance. For ceramic capacitors in particular, the package size, voltage rating, and dielectric material contribute to differences between the standard rated value and the actual effective value of the capacitance.

When including additional capacitance above  $C_{OUT(min)}$ , the capacitance can be ceramic type, low-ESR polymer type, or a combination of the two. See  $\frac{1}{8}$  8-3 for a preferred list of output capacitors by vendor.

VENDOR(1) DIELECTRIC CASE SIZE CAPACITANCE (µF)(2) VOLTAGE (V) PART NUMBER GRM31CZ71C226ME15L Murata TDK X7R C3225X7R1C226M250AC 1210 22 16 Murata X7R GRM32ER71C226KEA8K 1210 22 16 TDK X65 C3216X6S1E226M160AC 1206 22 25 AVX X7R 12103C226KAT4A 1210 25 22 Murata X7R GRM32ER71E226ME15L 1210 25 AVX 1210ZC476MAT2A 10 X7R 1210 47 Murata X7R GRM32ER71A476ME15L 1210 47 10 Murata X6S GRM32FC81C476MF15L 1210 47 16 TDK C3216X6S0G107M160AC 1206 4 X65 100 X6T GRM31CD80J107MEA8L 1206 Murata 100 6.3 Murata X7S GRM32EC70J107ME15L 1210

表 8-3. Recommended Ceramic Output Capacitors

# 8.3.5 Switching Frequency (RT)

Connect a resistor, designated as  $R_{RT}$  in  $\boxtimes$  8-1, between RT and AGND to set the switching frequency within the range of 200 kHz to 2.2 MHz. Refer to  $\rightrightarrows$  5 to calculate  $R_{RT}$  for a desired frequency.

$$R_{RT}(k\Omega) = \frac{16.4}{F_{SW}[MHz]} - 0.633$$

(5)

資料に関するフィードバック(ご意見やお問い合わせ)を送信

<sup>(2)</sup> Nameplate capacitance values (the effective values are lower based on the applied DC voltage and temperature).

<sup>(1)</sup> Consult capacitor suppliers regarding availability, material composition, RoHS and lead-free status, and manufacturing process requirements for any capacitors identified in the table. See the *Third-Party Products Disclaimer*.

<sup>(2)</sup> Nameplate capacitance values (the effective values are lower based on the applied DC voltage and temperature).

Refer to 表 8-1 or use the simplified expression in 式 5 to find a switching frequency that sets an inductor ripple current of 25% to 40% of the 8-A module current rating at nominal input voltage: Refer to *Frequency Synchronization (SYNC/MODE)* if clock synchronization is required.

# 8.3.6 Precision Enable and Input Voltage UVLO (EN)

The EN pin provides precision ON and OFF control for the TPSM63610E. After the EN pin voltage exceeds the rising threshold and  $V_{IN}$  is above its minimum turn-on threshold, the device starts operation. The simplest way to enable the TPSM63610E is to connect EN directly to VIN. This action allows the TPSM63610E to start up when  $V_{IN}$  is within its valid operating range. However, many applications benefit from the use of an enable divider network as shown in  $\boxtimes$  8-1, which establishes a precision input undervoltage lockout (UVLO). This can be used for sequencing, to prevent re-triggering the device when used with long input cables, or to reduce the occurrence of deep discharge of a battery power source. An external logic signal can also be used to drive the enable input to toggle the output on and off and for system sequencing or protection.

Calculate R<sub>ENB</sub> using 式 6:

$$R_{ENB}[k\Omega] = R_{ENT}[k\Omega] \times \left(\frac{V_{EN\_RISE}[V]}{V_{IN(on)}[V] - V_{EN\_RISE}[V]}\right)$$

(6)

#### where

- A typical value for  $R_{ENT}$  is 100  $k\Omega$ .

- V<sub>EN RISE</sub> is enable rising threshold voltage of 1.263 V (typical).

- V<sub>IN(on)</sub> is the desired start-up input voltage.

### 8.3.7 Frequency Synchronization (SYNC/MODE)

Synchronize the internal oscillator of the TPSM63610E with a positive clock edge to SYNC/MODE, as shown in 8-1. The synchronization frequency range is 200 kHz to 2.2 MHz.

TI recommends to tie a resistor from SYNC/MODE to either VCC or ground to keep the pin from floating if the sync signal is lost or off at start-up. A value in the 100-k $\Omega$  range. After a valid synchronization signal is applied for 2048 cycles, the clock frequency changes to that of the applied signal.

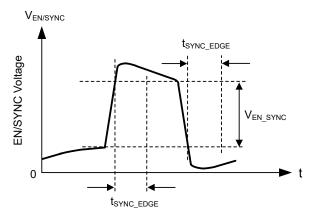

Referring to 🗵 8-2, the voltage edge at the SYNC/MODE pin must exceed the SYNC amplitude threshold, V<sub>SYNCDH</sub>, of 1.8 V to trip the internal synchronization pulse detector. In addition, the minimum SYNC/MODE rising and falling pulse durations must be longer than the SYNC signal hold time, t<sub>SYNC EDGE</sub>, of 100 ns.

図 8-2. Typical SYNC Waveform

## 8.3.8 Spread Spectrum

Spread spectrum is configurable using the SPSP pin. Spread spectrum eliminates peak emissions at specific frequencies by spreading these peaks across a wider range of frequencies than a part with fixed-frequency

資料に関するフィードバック(ご意見やお問い合わせ)を送信

operation. The TPSM63610E implements a modulation pattern designed to reduce low frequency-conducted emissions from the first few harmonics of the switching frequency. The pattern can also help reduce the higher harmonics that are more difficult to filter, which can fall in the FM band. These harmonics often couple to the environment through electric fields around the switch node and inductor. The TPSM63610E uses a ±4% (typical) spread of frequencies which can spread energy smoothly across the FM and TV bands. The device implements Dual Random Spread Spectrum (DRSS). DRSS is a combination of a triangular frequency spreading pattern and pseudorandom frequency hopping. The combination allows the spread spectrum to be very effective at spreading the energy at the following:

- Fundamental switching harmonic with slow triangular pattern

- High frequency harmonics with additional psuedorandom jumps at the switching frequency

The advantage of DRSS is its equivalent harmonic attenuation in the upper frequencies with a smaller fundamental frequency deviation. This reduces the amount of input current and output voltage ripple that is introduced at the modulating frequency. Additionally, the TPSM63610E also allows further reduction of the output voltage ripple caused by the spread spectrum modulating pattern. With the SPSP pin grounded, the spread spectrum is disabled. With the SPSP pin tied to VCC, the spread spectrum is on. With the SPSP pin tied through a resistor to ground, the spread spectrum is on. Also, a modulating tone correction is applied to the switcher to reduce the output voltage ripple caused by the frequency modulation. The resistor is usually around 20 kΩ, and can be more precisely calculated using  $\vec{x}$  7. Where  $I_{RATED}$  = 8 A for TPSM63610E, L = 2.2 $\mu$ H.

$$R_{SPSP}[k\Omega] = \frac{14.17 \times \frac{V_{IN}}{V_{OUT}}}{\frac{V_{IN} - V_{OUT}}{I_{RATED} \times L \times F_{SW}} + 1.22} \tag{7}$$

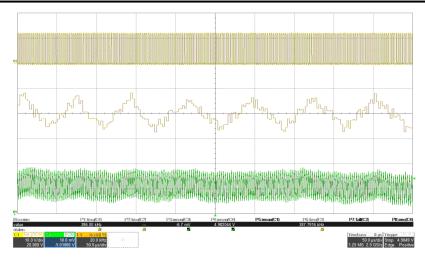

図 8-3. Output Ripple Without Ripple Cancellation Showing V<sub>SW</sub> (Top), F<sub>SW</sub> (Middle), V<sub>OUT</sub> (Bottom)

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

图 8-4. Output Ripple with Ripple Cancellation Showing V<sub>SW</sub> (Top), F<sub>SW</sub> (Middle), V<sub>OUT</sub> (Bottom)

The spread spectrum is only available while the clock of the TPSM63610E are free running at their natural frequency. Any of the following conditions overrides spread spectrum, turning it off:

- The clock is slowed due to operation at low input voltage. This is operation in dropout.

- The clock is slowed under light load in auto mode. This is normally not seen above 750-mA load. Note that if the device is operating in FPWM mode, spread spectrum is active, even if there is no load.

- The clock is slowed due to high input-to-output voltage ratio. This mode of operation is expected if on-time reaches minimum on time.

### 8.3.9 Power-Good Monitor (PG)

The TPSM63610E provides a power-good status signal to indicate when the output voltage is within a regulation window of 94% to 112%. The PG voltage goes low when the feedback (FB) voltage is outside of the specified PGOOD thresholds (see  $\boxed{2}$  7-7). This action can occur during current limit and thermal shutdown, as well as when disabled and during start-up.

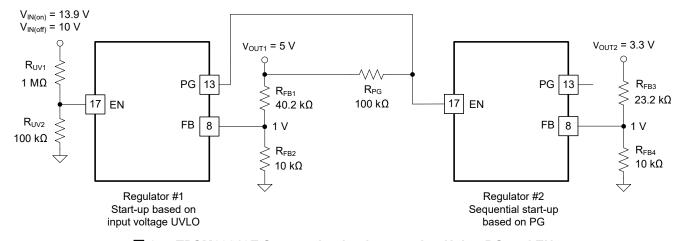

PG is an open-drain output, requiring an external pullup resistor to a DC supply, such as VCC or  $V_{OUT}$ . To limit current supplied by VCC, the recommended range of pullup resistance is 20 k $\Omega$  to 100 k $\Omega$ . A 26- $\mu$ s deglitch filter prevents false flag operation for short excursions of the output voltage, such as during line and load transients. When EN is pulled low, PG is forced low and remains remains valid as long as the input voltage is above 1 V (typical). Use the PG signal for start-up sequencing of downstream regulators, as shown in  $\boxtimes$  8-5, or for fault protection and output monitoring.

図 8-5. TPSM63610E Sequencing Implementation Using PG and EN

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 8.3.10 Adjustable Switch-Node Slew Rate (RBOOT, CBOOT)

Adjust the switch-node slew rate of the TPSM63610E to slow the switch-node voltage rise time and improve EMI performance at high frequencies. However, slowing the rise time decreases efficiency. Care must be taken to balance the improved EMI versus the decreased efficiency.

Place a resistor from RBOOT and CBOOT to allow adjustment of the internal resistance to balance EMI and efficiency performance. If improved EMI is not required, connect RBOOT to CBOOT to short the internal resistor, thus resulting in highest efficiency. If lower EMI is required, connect a resistor from 100  $\Omega$  – 500  $\Omega$  to. Floating the R<sub>BOOT</sub> pin results in 20-ns rise time and TI does not recommend due to increased power loss for higher load currents.

### 8.3.11 Bias Supply Regulator (VCC, VLDOIN)

VCC is the output of the internal LDO subregulator used to supply the control circuits of the TPSM63610E. The nominal VCC voltage is 3.3 V. The VLDOIN pin is the input to the internal LDO. Connect this input to V<sub>OUT</sub> to provide the lowest possible input supply current. If the VLDOIN voltage is less than 3.1 V, VIN1 and VIN2 directly power the internal LDO.

To prevent unsafe operation, VCC has UVLO protection that prevents switching if the internal voltage is too low. See V<sub>CC UVLO</sub> and V<sub>CC UVLO HYS</sub> in the *Electrical Characteristics*.