# TPS92691/-Q1マルチトポロジLEDドライバ、レール・ツー・レール電流センス・アンプ付き

## 1 特長

- 広範囲な入力電圧：4.5V～65V

- 広範囲な出力電圧：2V～65V

- 低入力オフセットのレール・ツー・レール電流センス・アンプ

- 25°C～140°Cの接合部温度範囲にわたって±3%以内のLED電流精度

- ハイサイドおよびローサイドの電流センス実装に対応

- 高インピーダンスのアナログLED電流調整入力(IADJ)、コントラスト比15:1以上

- 内蔵の直列Nチャネル調光ドライバ・インターフェイスによって1000:1以上の直列FET PWM調光比を実現

- システム障害検出および診断用の連続LED電流モニタ出力

- プログラミング可能なスイッチング周波数、外部クロック同期にも対応

- プログラミング可能なソフト・スタートおよびスロープ補償

- 包括的な障害保護回路：VCC低電圧誤動作防止(UVLO)、出力過電圧保護(OVP)、サイクルバイ-サイクルの電流制限、過熱保護

- TPS92691-Q1：車載対応Q100グレード1認定済み

## 2 アプリケーション

- TPS92691-Q1：自動車外装照明アプリケーション

- 建築用および一般用照明アプリケーション

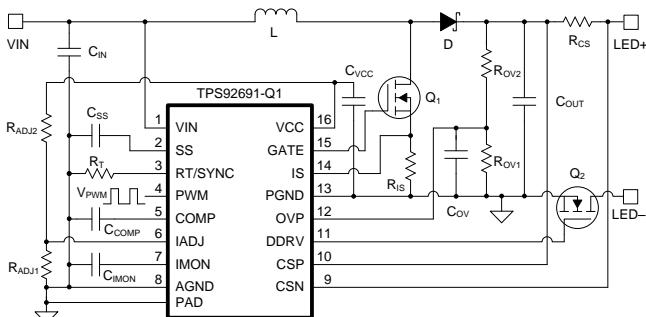

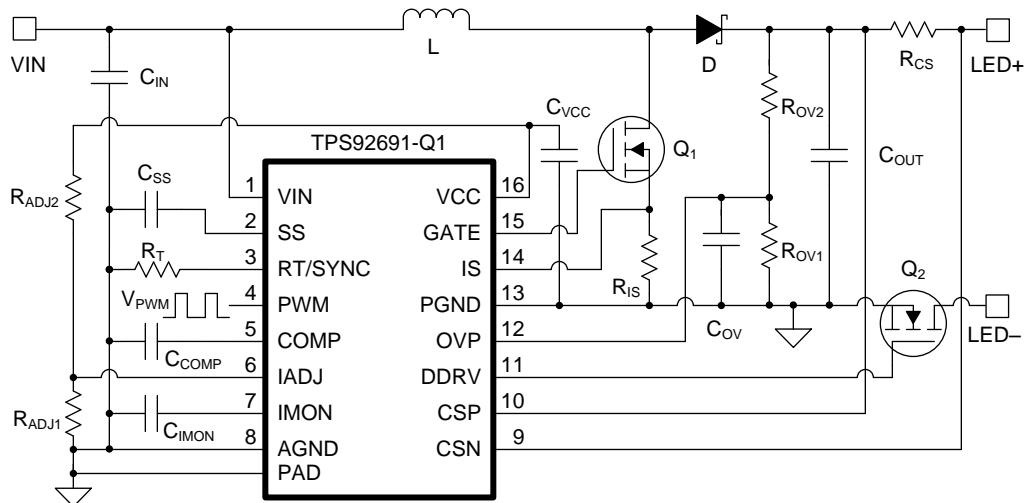

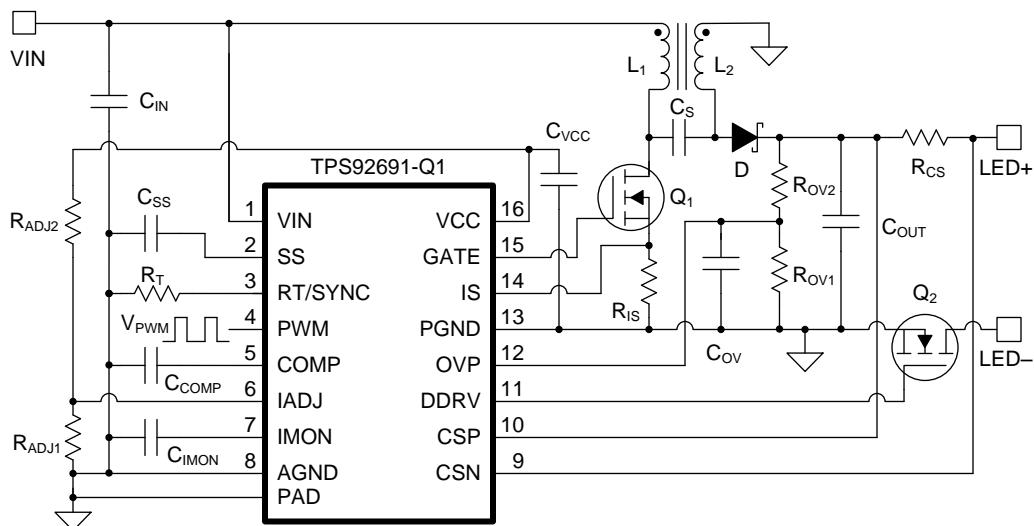

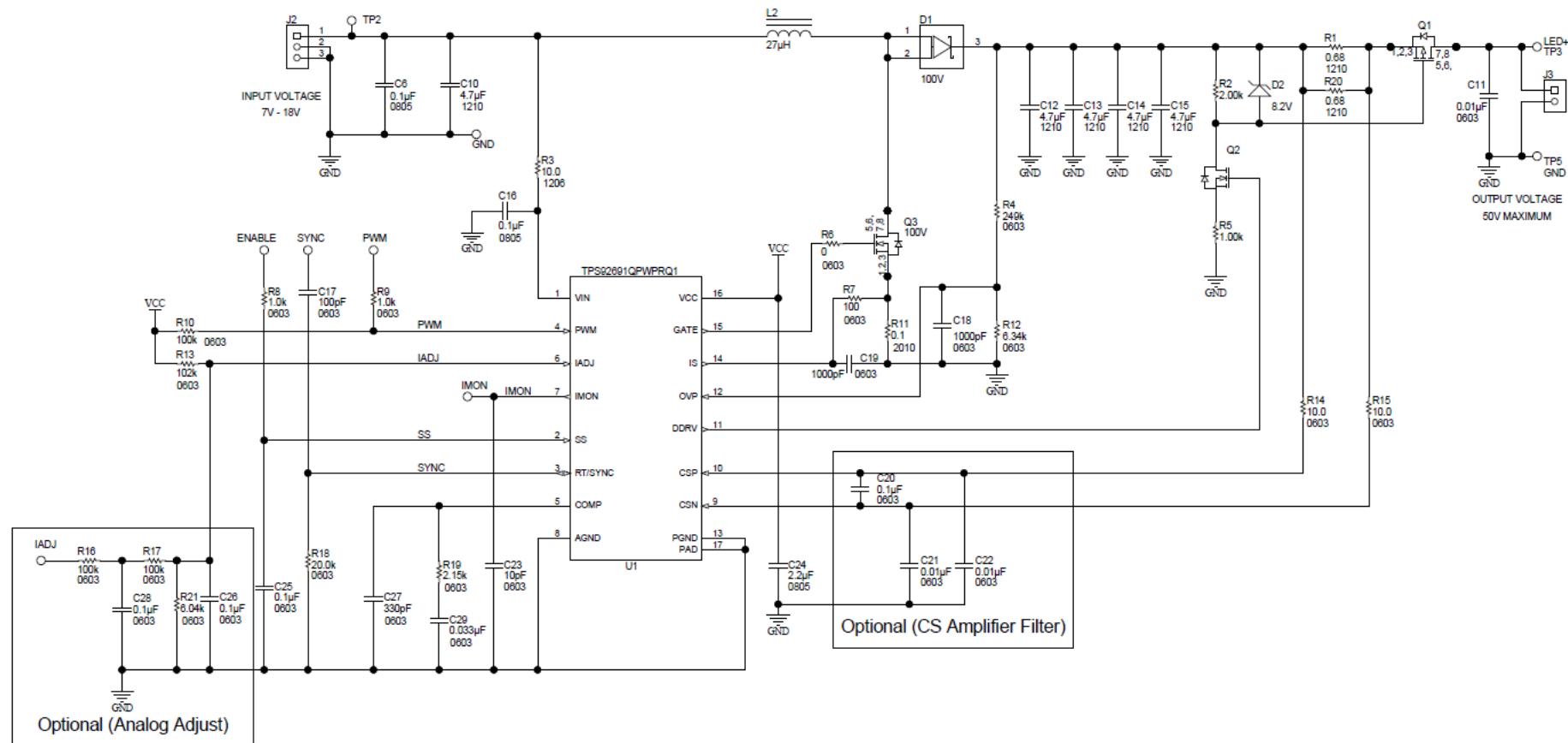

### 昇圧LEDドライバ・アプリケーションの標準回路図

## 3 概要

TPS92691/-Q1は、幅広い範囲の昇圧または降圧ドライバ・トポロジをサポートできる汎用性の高いLEDコントローラです。固定周波数のピーク電流モード制御手法を実装し、プログラミング可能なスイッチング周波数、スロープ補償、およびソフト・スタート・タイミング機能を備えています。高電圧(65V)のレール・ツー・レール電流センス・アンプを内蔵し、ハイサイドまたはローサイドの直列センス抵抗を使用してLED電流を直接測定することができます。アンプは入力オフセット電圧が低くなるよう設計され、25°C～140°Cの接合部温度範囲および0～60Vのコモン・モード電圧範囲にわたって±3%以内のLED電流精度が得られます。

LED電流は、アナログまたはPWM調光手法により独立して変調できます。高インピーダンスのアナログ調整(IADJ)入力で電圧を140mVから2.25Vまで変化させることにより、15:1の範囲でリニアなアナログ調光応答が得られます。PWM入力ピンを希望的なデューティ・サイクルおよび周波数で変調することによって、LED電流のPWM調光が可能です。オプションのDDRVゲート・ドライバ出力を使用して、直列FET調光機能をイネーブルにすると、1000:1のコントラスト比を実現できます。

TPS92691/-Q1は、電流モニタ(IMON)出力を通して、連続LEDステータス・チェックをサポートします。これにより、LEDの短絡や開放の検出および保護が可能です。さらに障害保護機能として、VCC UVLO、出力OVP、サイクルバイ-サイクルの電流制限、および過熱保護機能を備えています。

### 製品情報<sup>(1)</sup>

| 型番          | パッケージ       | 本体サイズ(公称)     |

|-------------|-------------|---------------|

| TPS92691-Q1 | HTSSOP (16) | 5.10mm×6.60mm |

| TPS92691    |             |               |

(1) 提供されているすべてのパッケージについては、卷末の注文情報を参照してください。

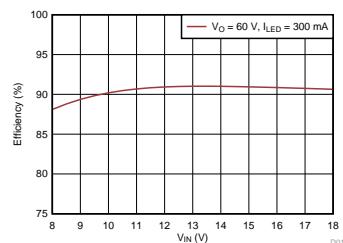

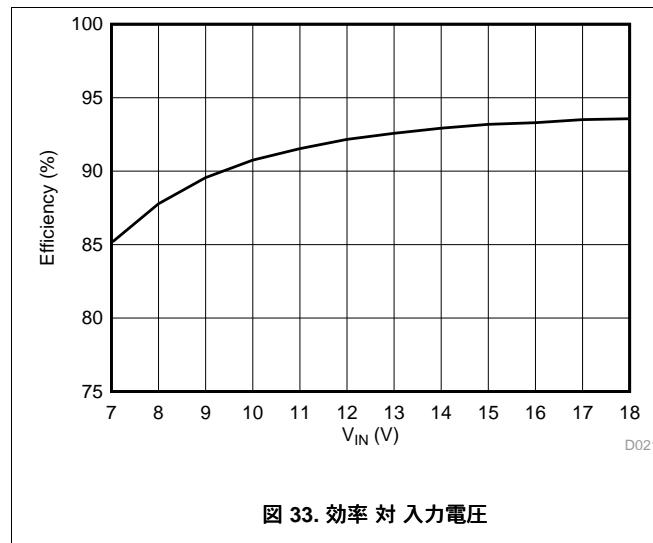

### 効率 対 出力電圧

## 目次

|          |                 |    |           |                           |    |

|----------|-----------------|----|-----------|---------------------------|----|

| <b>1</b> | 特長 .....        | 1  | 7.4       | デバイスの機能モード .....          | 17 |

| <b>2</b> | アプリケーション .....  | 1  | <b>8</b>  | アプリケーションと実装 .....         | 18 |

| <b>3</b> | 概要 .....        | 1  | 8.1       | アプリケーション情報 .....          | 18 |

| <b>4</b> | 改訂履歴 .....      | 2  | 8.2       | 代表的なアプリケーション .....        | 28 |

| <b>5</b> | ピン構成および機能 ..... | 3  | <b>9</b>  | 電源に関する推奨事項 .....          | 39 |

| <b>6</b> | 仕様 .....        | 4  | <b>10</b> | レイアウト .....               | 39 |

| 6.1      | 絶対最大定格 .....    | 4  | 10.1      | レイアウトのガイドライン .....        | 39 |

| 6.2      | ESD定格 .....     | 4  | 10.2      | レイアウト例 .....              | 40 |

| 6.3      | 推奨動作条件 .....    | 4  | <b>11</b> | デバイスおよびドキュメントのサポート .....  | 41 |

| 6.4      | 熱特性について .....   | 5  | 11.1      | 関連リンク .....               | 41 |

| 6.5      | 電気的特性 .....     | 5  | 11.2      | コミュニティ・リソース .....         | 41 |

| 6.6      | 代表的特性 .....     | 7  | 11.3      | 商標 .....                  | 41 |

| <b>7</b> | 詳細説明 .....      | 11 | 11.4      | 静電気放電に関する注意事項 .....       | 41 |

| 7.1      | 概要 .....        | 11 | 11.5      | 用語集 .....                 | 41 |

| 7.2      | 機能ブロック図 .....   | 12 | <b>12</b> | メカニカル、パッケージ、および注文情報 ..... | 41 |

| 7.3      | 機能説明 .....      | 12 |           |                           |    |

## 4 改訂履歴

| 日付       | 改訂内容 | 注  |

|----------|------|----|

| 2015年12月 | *    | 初版 |

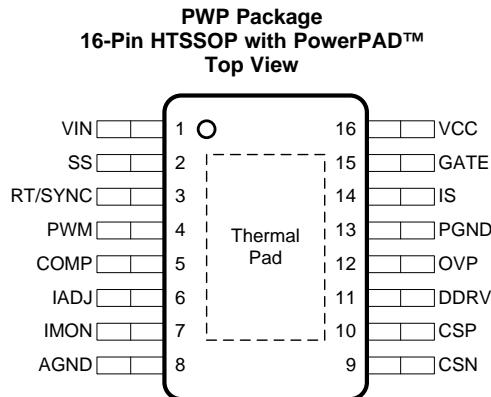

## 5 ピン構成および機能

ピン機能

| 番号       | ピン      | I/O | 説明                                                                                                                                                           |

|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | VIN     | —   | 内部VCCレギュレータの入力電源。GNDとの間に100nFのバイパス・コンデンサをコントローラに近づけて配置します。                                                                                                   |

| 2        | SS      | I/O | ソフト・スタート・プログラミング・ピン。AGNDとの間にコンデンサを接続することで、スタートアップ時間を延長できます。このピンをGNDに短絡するとスイッチングをディスエーブルにできます。                                                                |

| 3        | RT/SYNC | I/O | 発振周波数プログラミング・ピン。AGNDとの間に抵抗を接続することで、発振周波数が設定されます。100nFの直列コンデンサを通して外部クロック・パルスを入力し、内部発振器を同期させることもできます。                                                          |

| 4        | PWM     | I   | PWM調光入力。このピンの電圧を2.3V(標準)未満にすると、スイッチングがオフになり、発振器はアイドル状態となり、COMPピンは切断され、DDRV出力はグランドに設定されます。入力信号のデューティ・サイクルに基づき、PWM調光動作で平均LED電流を制御します。PWM調光に使用しない場合は、VCCに接続します。 |

| 5        | COMP    | I/O | トランスコンダクタンス誤差増幅器の出力。目的の閉ループ応答を得るために補償回路を接続します。                                                                                                               |

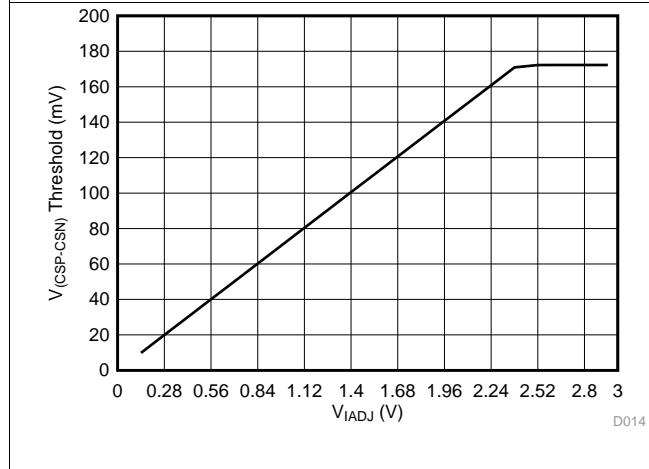

| 6        | IADJ    | I   | LED電流リファレンス入力。100kΩの直列抵抗を通してVCCに接続することにより、内部リファレンス電圧が2.42Vに設定され、電流センス・スレッショルドV(CSP-CSN)が172mVに設定されます。このピンを0V~2.25Vの外部電圧源で変調することにより、アナログ調光を実装できます。            |

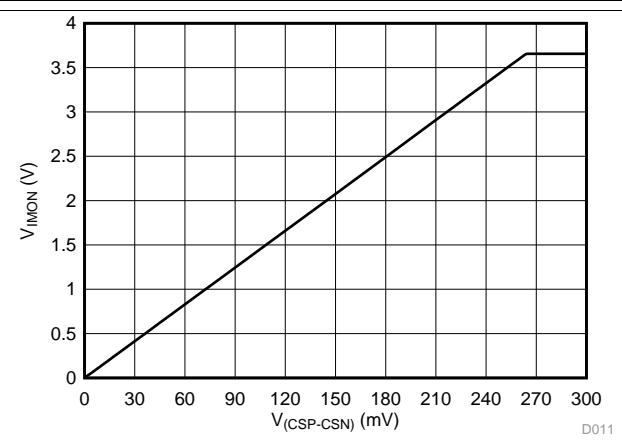

| 7        | IMON    | O   | LED電流通知ピン。CSP/CSN入力によってセンスされたLED電流が、 $V_{IMON} = 14 \times I_{LED} \times R_{cs}$ として通知されます。AGNDとの間に1nFのセラミック・コンデンサを使用してバイパスします。                             |

| 8        | AGND    | —   | アナログ・グランド。内部電圧リファレンスおよびアナログ回路のリターンです。回路のグランドであるGNDに接続することで、リターン・バスを形成します。                                                                                    |

| 9        | CSN     | I   | 電流センス・アンプの負入力(−)。LED電流センス抵抗 $R_{CS}$ の負ノードに直接接続します。                                                                                                          |

| 10       | CSP     | I   | 電流センス・アンプの正入力(+)。LED電流センス抵抗 $R_{CS}$ の正ノードに直接接続します。                                                                                                          |

| 11       | DDRV    | O   | 直列調光FETゲート・ドライバ出力。外部NチャネルMOSFETのゲートに接続するか、またはPチャネルMOSFETを使用したレベルシフト回路に接続することで、直列FET PWM調光を実装します。                                                             |

| 12       | OVP     | I   | ヒステリシス付き過電圧保護入力。出力電圧との間に分圧抵抗を接続することで、OVPスレッショルドおよびヒステリシスを設定します。                                                                                              |

| 13       | PGND    | —   | 内部NチャネルMOSFETゲート・ドライバのパワー・グランド接続ピン。回路のグランドであるGNDに接続することで、リターン・バスを形成します。                                                                                      |

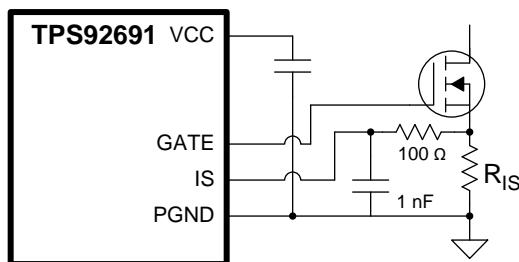

| 14       | IS      | I   | スイッチ電流センス入力。NチャネルMOSFETのソースのスイッチ電流センス抵抗 $R_{IS}$ に接続します。                                                                                                     |

| 15       | GATE    | O   | NチャネルMOSFETのゲート・ドライバ出力。外部スイッチングNチャネルMOSFETのゲートに接続します。                                                                                                        |

| 16       | VCC     | —   | VCCバイアス電源ピン。2.2μF~4.7μFのセラミック・コンデンサをコントローラに近づけて配置し、PGNDとの間でローカルにデカッピングします。                                                                                   |

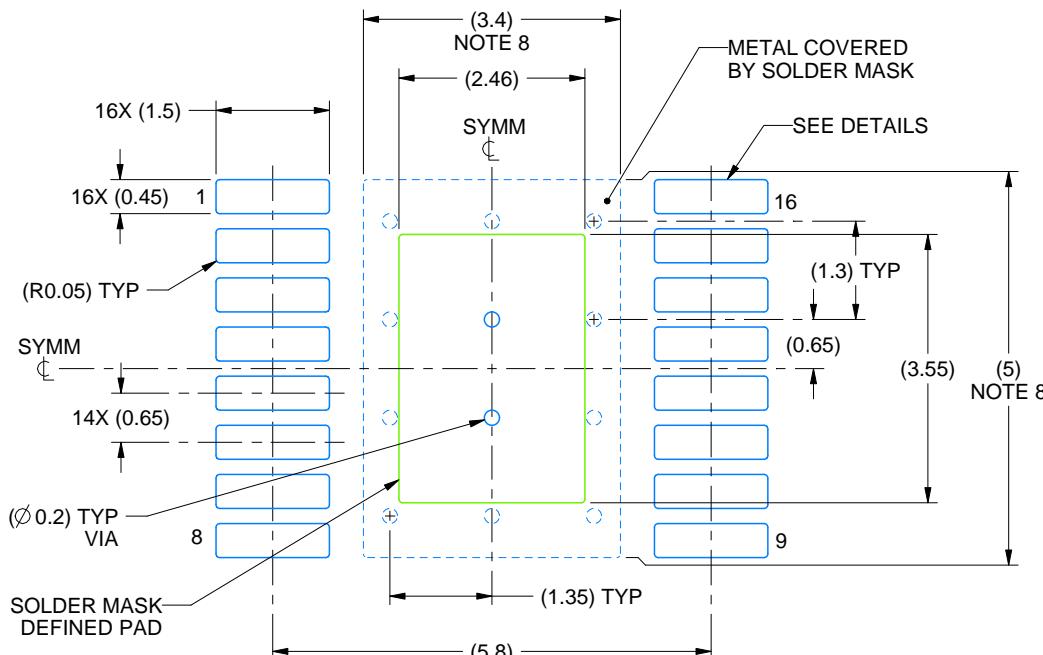

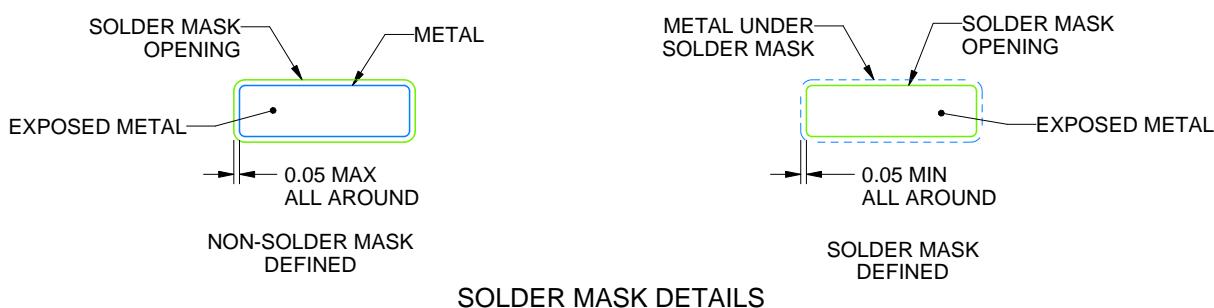

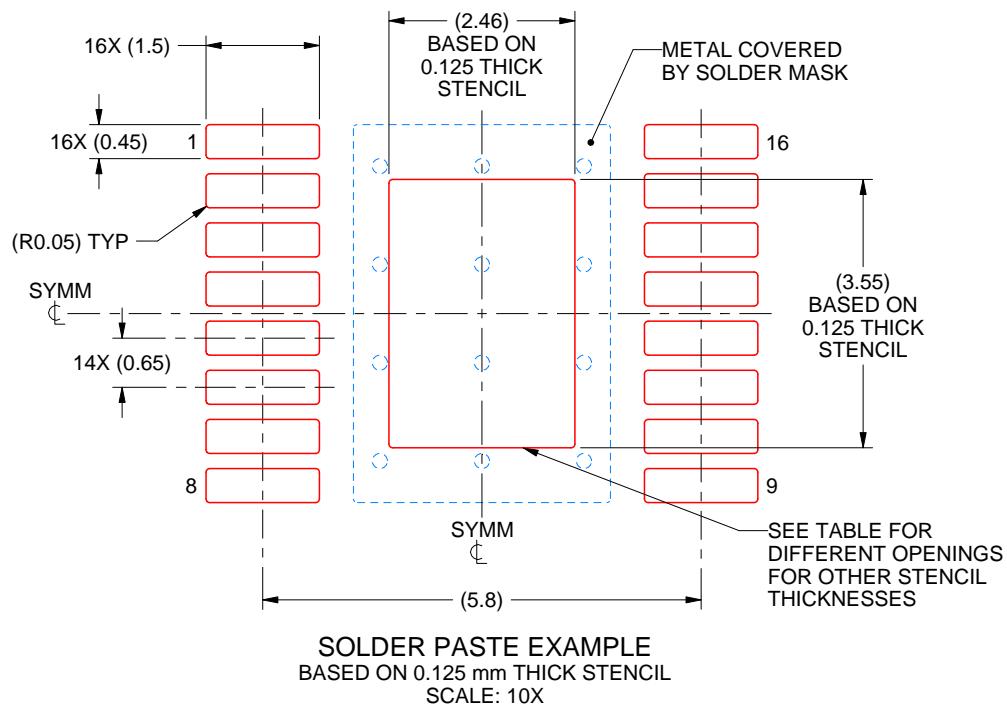

| PowerPAD |         | —   | 適切な動作のためには、露出したPowerPADにAGNDおよびPGNDピンを接続する必要があります。このPowerPADは、複数のビアを使用してPCBグランド・プレーンに接続することで、優れた熱特性が得られます。                                                   |

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)(2)</sup>

|                                                |                                  | <b>MIN</b> | <b>MAX</b> | <b>UNIT</b> |

|------------------------------------------------|----------------------------------|------------|------------|-------------|

| Input voltage                                  | VIN, CSP, CSN                    | -0.3       | 65         | V           |

|                                                | IADJ, IS, PWM, RT/SYNC           | -0.3       | 8.8        | V           |

|                                                | OVP, SS                          | -0.3       | 5.5        | V           |

|                                                | CSP to CSN <sup>(3)</sup> , PGND | -0.3       | 0.3        | V           |

| Output voltage <sup>(4)</sup>                  | VCC, GATE, DDRV                  | -0.3       | 8.8        | V           |

|                                                | COMP                             | -0.3       | 5.0        | V           |

| Source current                                 | IMON                             | —          | 100        | μA          |

|                                                | GATE, DDRV (Pulsed <20 ns)       | —          | 500        | mA          |

| Sink current                                   | GATE, DDRV (Pulsed <20 ns)       | —          | 500        | mA          |

| Operating junction temperature, T <sub>J</sub> |                                  | -40        | 140        | °C          |

| Storage temperature, T <sub>stg</sub>          |                                  |            | 150        | °C          |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) 特に指定のない限り、すべての電圧値はAGNDを基準にしています。

- (3) 連続持続電圧

- (4) すべての出力ピンに対して外部電圧の印加の仕様は規定されていません。

### 6.2 ESD定格

|                                            |                         |                                                                                          | <b>VALUE</b>                            | <b>UNIT</b> |

|--------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|-----------------------------------------|-------------|

| <b>TPS92691-Q1 IN PWP (HTSSOP) PACKAGE</b> |                         |                                                                                          |                                         |             |

| V <sub>(ESD)</sub>                         | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002, all pins <sup>(1)</sup>                        | ±2000                                   | V           |

|                                            |                         | Charged-device model (CDM), per AEC Q100-011                                             | All pins except 1, 8, 9, and 16<br>±500 |             |

|                                            |                         | Pins 1, 8, 9, and 16                                                                     | ±750                                    |             |

| <b>TPS92691 IN PWP (HTSSOP) PACKAGE</b>    |                         |                                                                                          |                                         |             |

| V <sub>(ESD)</sub>                         | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(2)</sup>              | ±2000                                   | V           |

|                                            |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(3)</sup> | ±500                                    |             |

- (1) AEC Q100-002では、HBMストレス試験をANSI/ESDA/JEDEC JS-001仕様に従って実施することを示しています。

- (2) JEDECのドキュメントJEP155に、500V HBMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

- (3) JEDECのドキュメントJEP157に、250V CDMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                                     |                                     | <b>MIN</b>            | <b>NOM</b> | <b>MAX</b>               | <b>UNIT</b> |

|-------------------------------------|-------------------------------------|-----------------------|------------|--------------------------|-------------|

| V <sub>IN</sub>                     | Supply input voltage                | 6.5                   | 14         | 65                       | V           |

| V <sub>IN</sub> , crank             | Supply input, battery crank voltage | 4.5                   |            |                          | V           |

| V <sub>CSP</sub> , V <sub>CSN</sub> | Current sense common mode           | 0                     |            | 60                       | V           |

| f <sub>SW</sub>                     | Switching frequency                 | 80                    |            | 700                      | kHz         |

| f <sub>SYNC</sub>                   | SYNC frequency                      | 0.8 × f <sub>SW</sub> |            | 1.2 × f <sub>SW</sub>    | kHz         |

| V <sub>IADJ</sub>                   | Current reference voltage           | 0.14                  |            | V <sub>IADJ(CLAMP)</sub> | V           |

| T <sub>A</sub>                      | Operating ambient temperature       | -40                   |            | 125                      | °C          |

## 6.4 热特性について

| THERMAL METRIC <sup>(1)</sup> |                                              | TPS92691/-Q1 | UNIT |

|-------------------------------|----------------------------------------------|--------------|------|

|                               |                                              | PWP (HTSSOP) |      |

|                               |                                              | 16 PINS      |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 40.8         | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 26.1         | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 22.2         | °C/W |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 0.8          | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 22.0         | °C/W |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 2.3          | °C/W |

(1) 従来および新しい熱測定値の詳細については、半導体およびICパッケージの熱測定値のアプリケーション・レポートSPRA953を参照してください。

## 6.5 電気的特性

T<sub>J</sub> = -40°C～140°C、V<sub>IN</sub> = 14V、V<sub>IADJ</sub> = 2.2V、C<sub>VCC</sub> = 1μF、C<sub>COMP</sub> = 2.2nF、R<sub>CS</sub> = 100mΩ、R<sub>T</sub> = 20kΩ、V<sub>PWM</sub> = 5V、GATEおよびDDRVは無負荷(特に記述のない限り)<sup>(1)</sup>

| PARAMETER                                    |                                  | TEST CONDITIONS                                    | MIN   | TYP | MAX   | UNIT |

|----------------------------------------------|----------------------------------|----------------------------------------------------|-------|-----|-------|------|

| <b>INPUT VOLTAGE (VIN)</b>                   |                                  |                                                    |       |     |       |      |

| V <sub>DO</sub>                              | LDO dropout voltage              | I <sub>CC</sub> = 20 mA, V <sub>IN</sub> = 5 V     |       | 300 |       | mV   |

| <b>BIAS SUPPLY (VCC)</b>                     |                                  |                                                    |       |     |       |      |

| V <sub>CC(REG)</sub>                         | Regulation voltage               | No load                                            | 7.0   | 7.5 | 8.0   | V    |

| V <sub>CC(UVLO)</sub>                        | Supply undervoltage protection   | VCC rising threshold, V <sub>IN</sub> = 8 V        |       | 4.1 | 4.35  | V    |

|                                              |                                  | VCC falling threshold, V <sub>IN</sub> = 8 V       | 3.75  | 4.0 |       | V    |

|                                              |                                  | Hysteresis                                         |       | 100 |       | mV   |

| I <sub>CC(LIMIT)</sub>                       | Supply current limit             | V <sub>CC</sub> = 0V                               | 26    | 38  | 46    | mA   |

| I <sub>CC(STBY)</sub>                        | Supply stand-by current          | V <sub>PWM</sub> = 0 V                             |       | 1.8 | 2.1   | mA   |

| I <sub>CC(SW)</sub>                          | Supply switching current         | V <sub>CC</sub> = 7.5 V, C <sub>GATE</sub> = 1 nF  |       | 5.1 | 6.6   | mA   |

| <b>OSCILLATOR (RT/SYNC)</b>                  |                                  |                                                    |       |     |       |      |

| f <sub>SW</sub>                              | Switching frequency              | R <sub>T</sub> = 40 kΩ                             | 165   | 200 | 230   | kHz  |

|                                              |                                  | R <sub>T</sub> = 20 kΩ                             | 327   | 390 | 448   | kHz  |

| V <sub>RT</sub>                              | RT output voltage                |                                                    |       | 1   |       | V    |

| V <sub>SYNC</sub>                            | SYNC rising threshold            | V <sub>RT/SYNC</sub> rising                        |       | 2.7 | 3.1   | V    |

|                                              | SYNC falling threshold           | V <sub>RT/SYNC</sub> falling                       | 1.8   | 2   |       | V    |

| t <sub>SYNC(MIN)</sub>                       | Minimum SYNC clock pulse width   |                                                    |       | 100 |       | ns   |

| <b>GATE DRIVER (GATE)</b>                    |                                  |                                                    |       |     |       |      |

| R <sub>GH</sub>                              | Gate driver high side resistance | I <sub>GATE</sub> = -10 mA                         |       | 5.4 | 11.2  | Ω    |

| R <sub>GL</sub>                              | Gate driver low side resistance  | I <sub>GATE</sub> = 10 mA                          |       | 4.3 | 10.5  | Ω    |

| <b>CURRENT SENSE (IS)</b>                    |                                  |                                                    |       |     |       |      |

| V <sub>IS(LIMIT)</sub>                       | Current limit threshold          |                                                    | 497   | 525 | 550   | mV   |

| t <sub>IS(BLANK)</sub>                       | Leading edge blanking time       |                                                    | 103   | 150 | 188   | ns   |

| t <sub>IS(FAULT)</sub>                       | Current limit fault time         |                                                    |       | 35  |       | μs   |

| t <sub>ILMT(DLY)</sub>                       | IS to GATE propagation delay     | V <sub>IS</sub> pulsed from 0 to 1 V               |       | 100 |       | ns   |

| <b>PWM COMPARATOR AND SLOPE COMPENSATION</b> |                                  |                                                    |       |     |       |      |

| D <sub>MAX</sub>                             | Maximum duty cycle               |                                                    | 90.4% | 93% | 94.7% |      |

| V <sub>LV</sub>                              | IS to COMP level shift voltage   | No slope compensation added                        | 1.17  | 1.5 | 1.8   | V    |

| V <sub>SL</sub>                              | Slope compensation               | D = D <sub>MAX</sub> (with max slope compensation) |       | 200 |       | mV   |

| I <sub>LV</sub>                              | IS level shift bias current      | No slope compensation added                        |       | 25  |       | μA   |

| I <sub>LV</sub> + I <sub>SL</sub>            | IS level shift source current    | D = D <sub>MAX</sub> (with max slope compensation) |       | 115 |       | μA   |

(1) 特に指定のない限り、すべての電圧値はAGNDを基準にしています。

## 電気的特性 (continued)

$T_J = -40^\circ\text{C} \sim 140^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)<sup>(1)</sup>

| PARAMETER                                 | TEST CONDITIONS                                                                                                           | MIN                                                      | TYP   | MAX  | UNIT             |                  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|------|------------------|------------------|

| <b>CURRENT SENSE AMPLIFIER (CSP, CSN)</b> |                                                                                                                           |                                                          |       |      |                  |                  |

| $V_{CS(offset)}$                          | Cumulative offset voltage at $V_{CSP} = 60\text{V}$ and $V_{(CSP-CSN)} = 150\text{ mV}$ , referred to current sense input | $-40^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$      | -5.2  | 5.9  | mV               |                  |

|                                           |                                                                                                                           | $25^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$       | -4.4  | 4.6  | mV               |                  |

|                                           | Cumulative offset voltage at $V_{CSP} = 60\text{V}$ and $V_{(CSP-CSN)} = 10\text{ mV}$ , referred to current sense input  | $-40^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$      | -3.5  | 5.0  | mV               |                  |

|                                           |                                                                                                                           | $25^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$       | -2.8  | 4.0  | mV               |                  |

|                                           | Cumulative offset voltage at $V_{CSN} = 0\text{V}$ and $V_{(CSP-CSN)} = 150\text{ mV}$ , referred to current sense input  | $-40^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$      | -5.9  | 6.7  | mV               |                  |

|                                           |                                                                                                                           | $25^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$       | -4.7  | 5.0  | mV               |                  |

| $CS_{(BW)}$                               | Cumulative offset voltage at $V_{CSN} = 0\text{V}$ and $V_{(CSP-CSN)} = 10\text{ mV}$ , referred to current sense input   | $-40^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$      | -2.3  | 3.2  | mV               |                  |

|                                           |                                                                                                                           | $25^\circ\text{C} \leq T_J \leq 140^\circ\text{C}$       | -1.7  | 2.6  | mV               |                  |

| $CS_{(BW)}$                               | Current sense unity gain bandwidth                                                                                        |                                                          | 500   |      | kHz              |                  |

| $I_{CS(BIAS)}$                            | CSP, CSN bias current                                                                                                     | $V_{CSP, CSN} = 60\text{ V}$                             |       | 4    | $\mu\text{A}$    |                  |

| <b>CURRENT MONITOR (IMON)</b>             |                                                                                                                           |                                                          |       |      |                  |                  |

| $V_{IMON(CL)}$                            | IMON output voltage clamp                                                                                                 |                                                          | 3.2   | 3.7  | 4.2              | V                |

| $V_{IMON(OS)}$                            | IMON buffer offset voltage                                                                                                |                                                          | -11.4 | -1.6 | 7.3              | mV               |

| <b>ANALOG ADJUST (IADJ)</b>               |                                                                                                                           |                                                          |       |      |                  |                  |

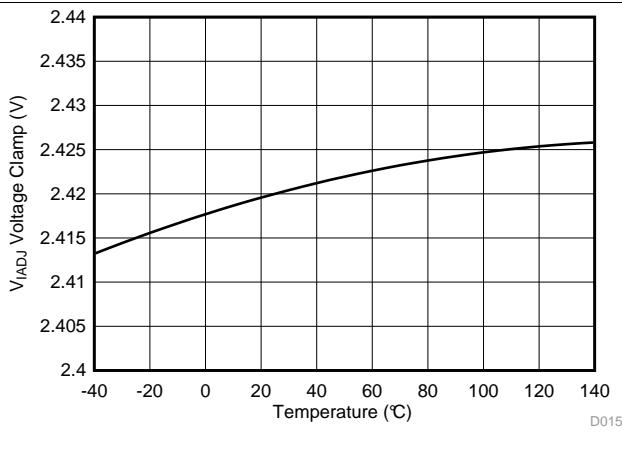

| $V_{IADJ(CL)}$                            | IADJ internal clamp voltage                                                                                               | $I_{IADJ} = 1\text{ }\mu\text{A}$                        | 2.27  | 2.42 | 2.55             | V                |

| $I_{IADJ(BIAS)}$                          | IADJ input bias current                                                                                                   | $V_{IADJ} < 2.2\text{ V}$                                |       | 90   | nA               |                  |

| $R_{IADJ(LMT)}$                           | IADJ current limiting series resistor                                                                                     | $V_{IADJ} > 2.6\text{ V}$                                |       | 12   | $\text{k}\Omega$ |                  |

| <b>ERROR AMPLIFIER (COMP)</b>             |                                                                                                                           |                                                          |       |      |                  |                  |

| $g_m$                                     | Transconductance                                                                                                          |                                                          | 121   |      | $\mu\text{A/V}$  |                  |

| $I_{COMP(SRC)}$                           | COMP current source capacity                                                                                              | $V_{IADJ} = 1.4\text{ V}$ , $V_{(CSP-CSN)} = 0\text{ V}$ | 130   |      | $\mu\text{A}$    |                  |

| $I_{COMP(SINK)}$                          | COMP current sink capacity                                                                                                | $V_{IADJ} = 0\text{ V}$ , $V_{(CSP-CSN)} = 0.1\text{ V}$ | 130   |      | $\mu\text{A}$    |                  |

| $EA_{(BW)}$                               | Error amplifier bandwidth                                                                                                 | -3 dB                                                    |       | 5    | MHz              |                  |

| $V_{COMP(RST)}$                           | COMP pin reset voltage                                                                                                    |                                                          | 100   |      | mV               |                  |

| $R_{COMP(DCH)}$                           | COMP discharge FET resistance                                                                                             |                                                          | 246   |      | $\Omega$         |                  |

| <b>SOFT-START (SS)</b>                    |                                                                                                                           |                                                          |       |      |                  |                  |

| $I_{SS}$                                  | Soft-start source current                                                                                                 |                                                          | 7     | 10   | 12.8             | $\mu\text{A}$    |

| $V_{SS(RST)}$                             | Soft-start pin reset voltage                                                                                              |                                                          |       | 25   |                  | mV               |

| $R_{SS(DCH)}$                             | SS discharge FET resistance                                                                                               |                                                          | 260   |      | $\Omega$         |                  |

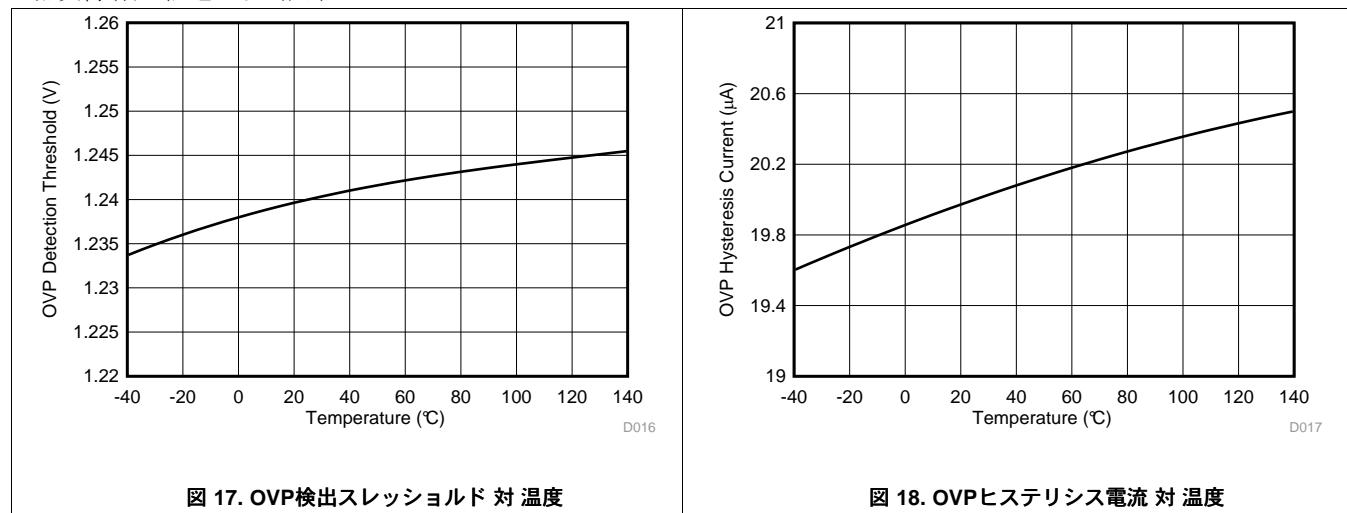

| <b>OVERVOLTAGE PROTECTION (OVP)</b>       |                                                                                                                           |                                                          |       |      |                  |                  |

| $V_{OVP(THR)}$                            | OVP detection threshold                                                                                                   |                                                          | 1.18  | 1.24 | 1.31             | V                |

| $I_{OVP(HYS)}$                            | OVP hysteresis current                                                                                                    |                                                          | 12    | 20   | 27.5             | $\mu\text{A}$    |

| <b>PWM INPUT (PWM)</b>                    |                                                                                                                           |                                                          |       |      |                  |                  |

| $V_{PWM(HIGH)}$                           | Schmitt trigger logic level (high threshold)                                                                              |                                                          |       | 2.5  | 2.7              | V                |

| $V_{PWM(LOW)}$                            | Schmitt trigger logic level (low threshold)                                                                               |                                                          | 2.0   | 2.3  |                  | V                |

| $R_{PWM(PD)}$                             | PWM pulldown resistance                                                                                                   |                                                          |       | 1    |                  | $\text{M}\Omega$ |

| $t_{DLY(RISE)}$                           | PWM to DDRV rising delay                                                                                                  |                                                          |       | 54   |                  | ns               |

| $t_{DLY(FALL)}$                           | PWM to DDRV falling delay                                                                                                 |                                                          |       | 72   |                  | ns               |

| <b>PWM GATE DRIVE OUTPUT (DDRV)</b>       |                                                                                                                           |                                                          |       |      |                  |                  |

| $R_{DH}$                                  | DDRV high-side resistance                                                                                                 |                                                          | 6.1   | 12.8 |                  | $\Omega$         |

| $R_{DL}$                                  | DDRV low-side resistance                                                                                                  |                                                          | 5.2   | 11.4 |                  | $\Omega$         |

## 電気的特性 (continued)

$T_J = -40^\circ\text{C} \sim 140^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)<sup>(1)</sup>

| PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------|-----------------|-----|-----|-----|------|

| <b>THERMAL SHUTDOWN</b>      |                 |     |     |     |      |

| Thermal shutdown temperature |                 |     | 175 |     | °C   |

| Thermal shutdown hysteresis  |                 |     | 25  |     | °C   |

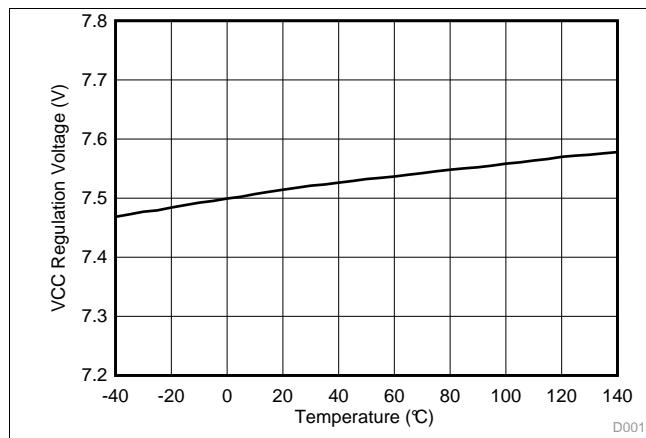

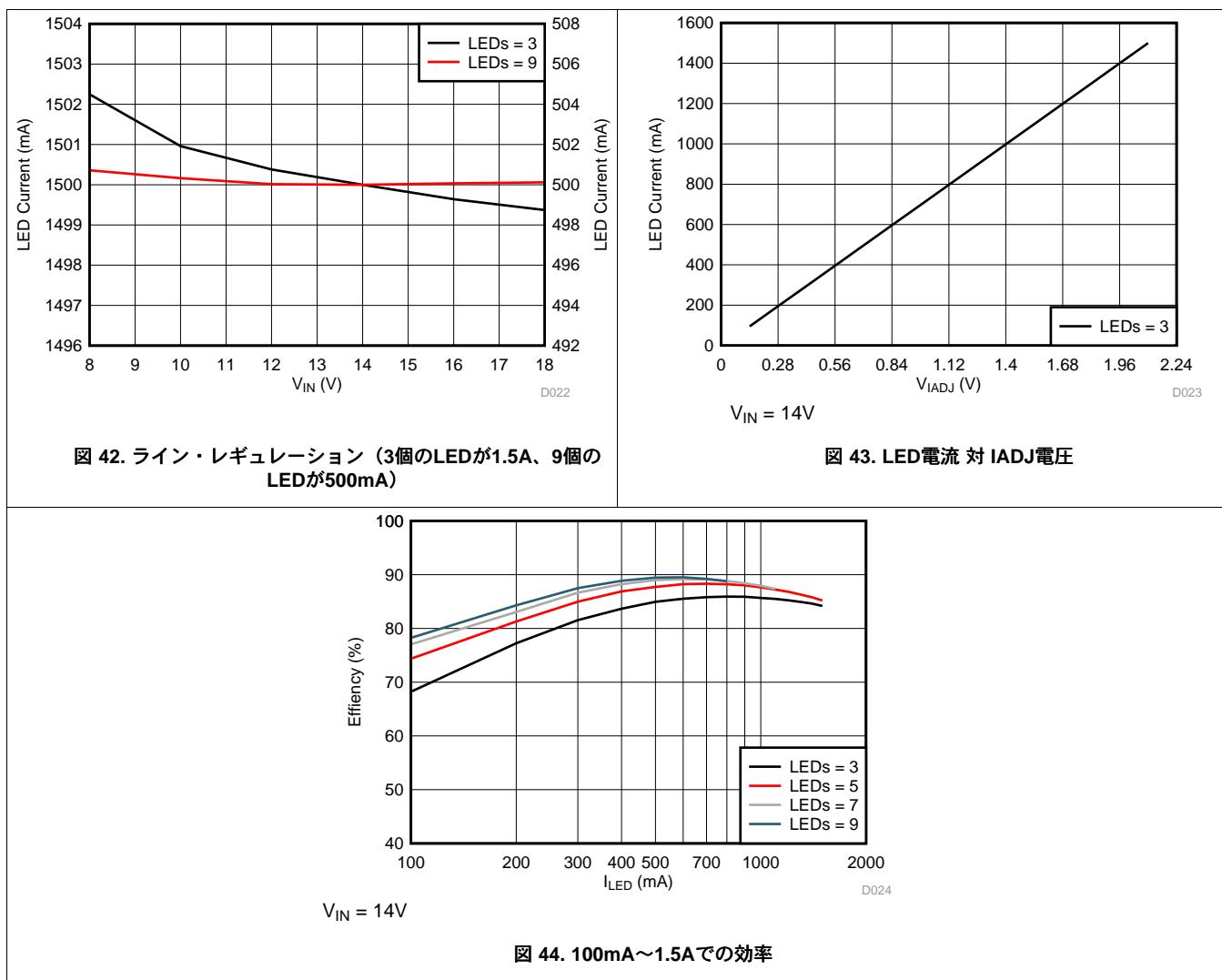

### 6.6 代表的特性

$T_A = 25^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)

図 1. VCCレギュレーション電圧 対 温度

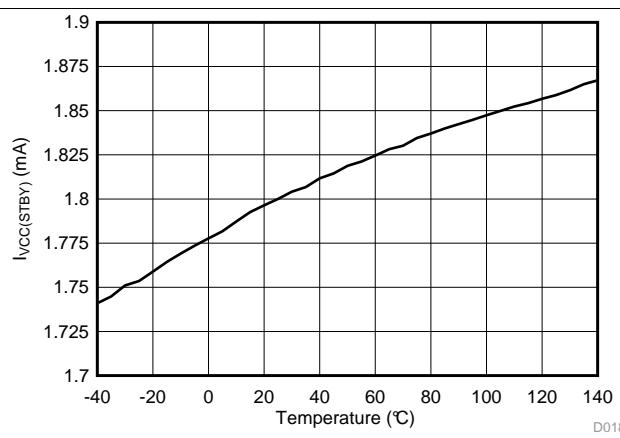

図 2. スタンバイ電流 対 温度

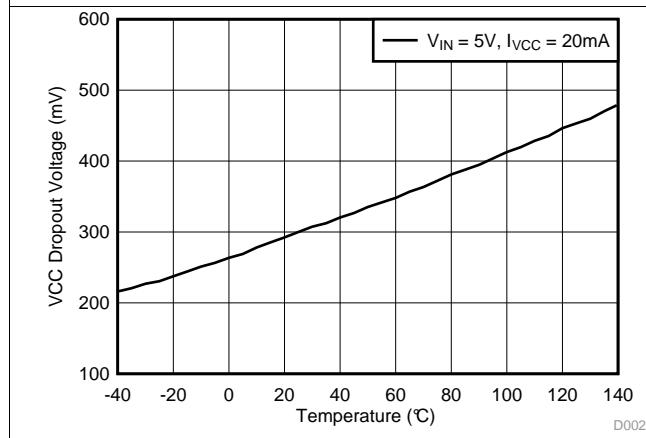

図 3. VCCドロップアウト電圧 対 温度

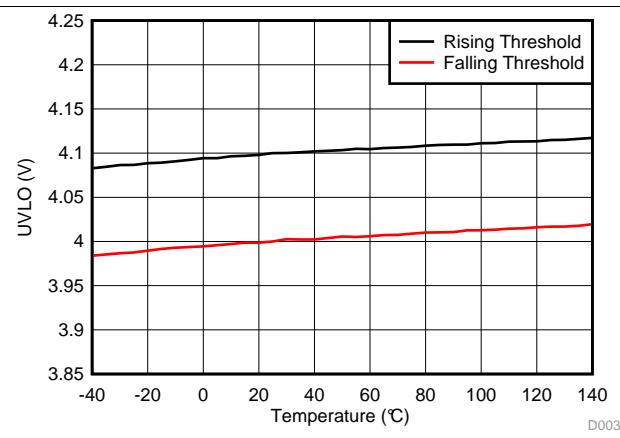

図 4. UVLOスレッショルド 対 温度

## 代表的特性 (continued)

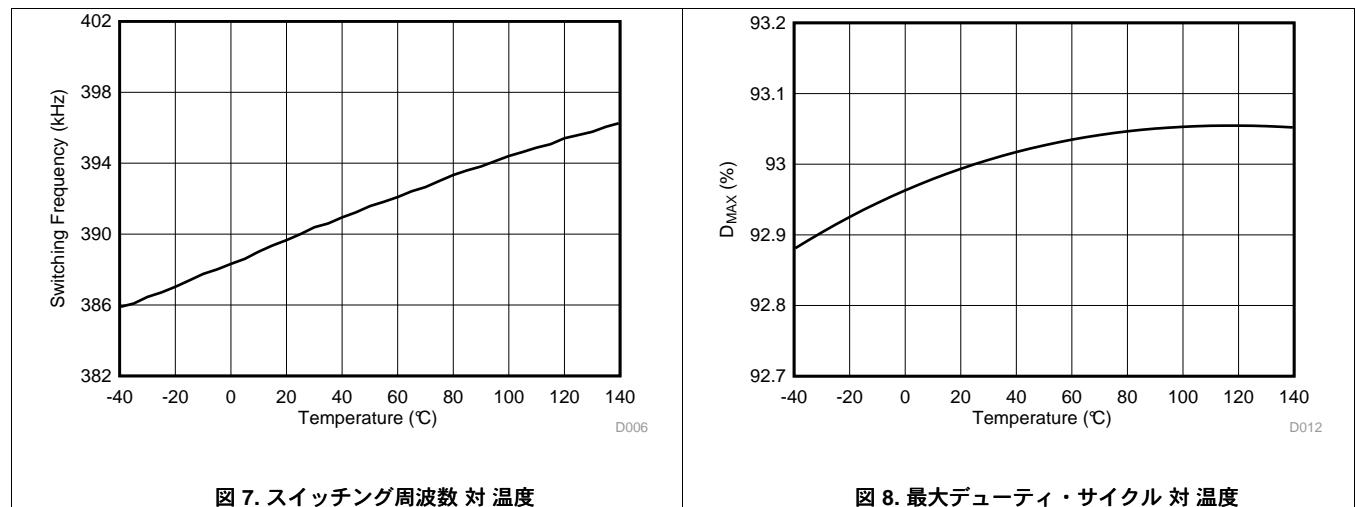

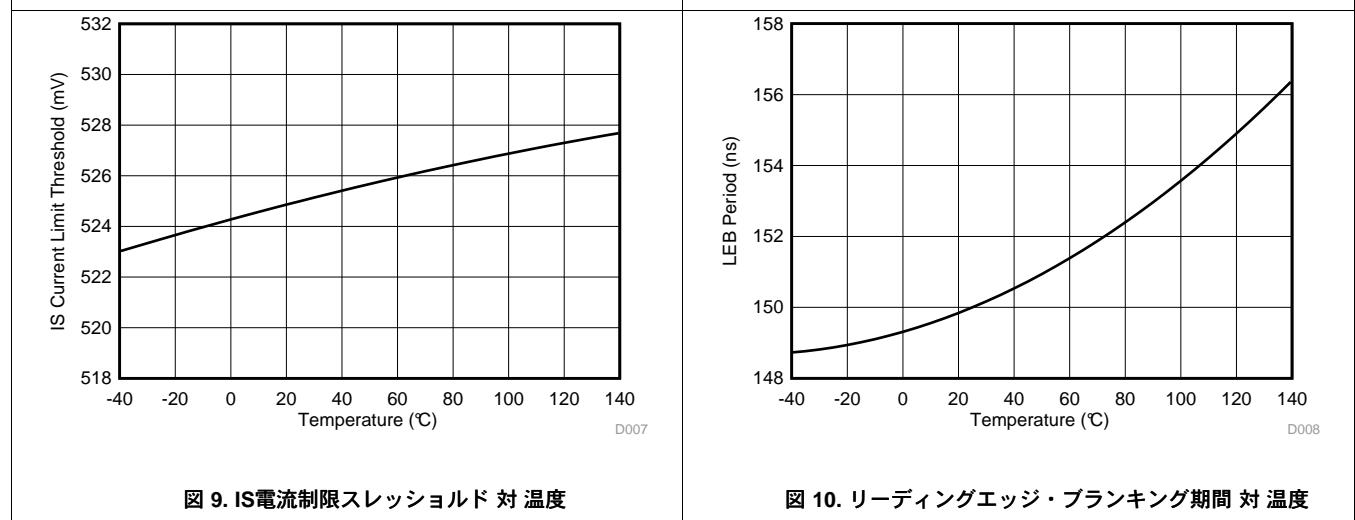

$T_A = 25^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)

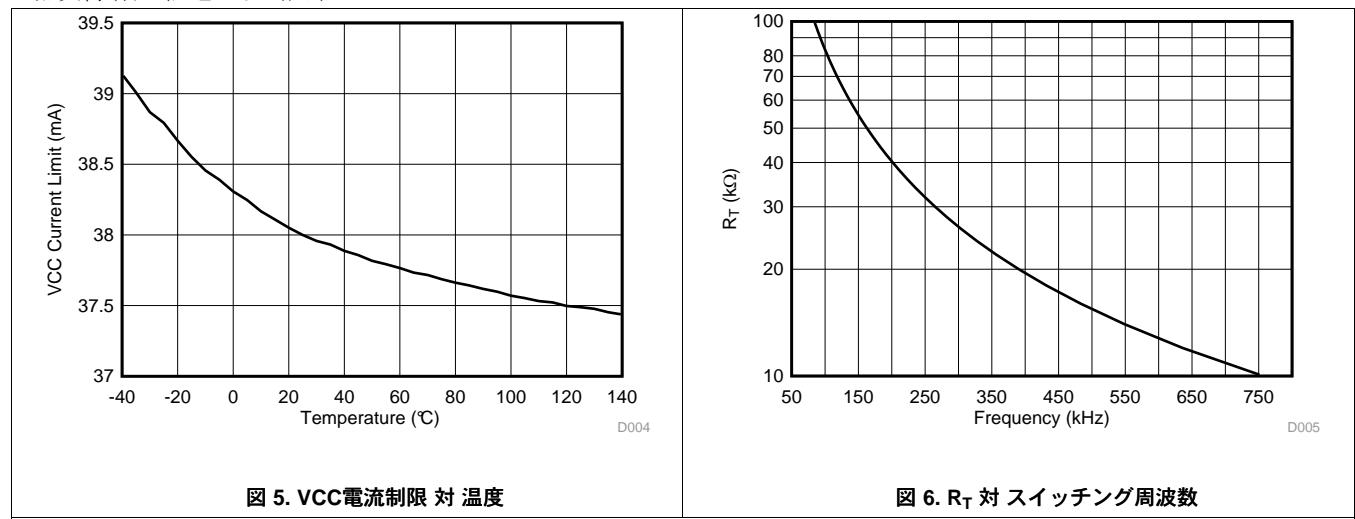

図 5. VCC電流制限 対 温度

図 6.  $R_T$  対 スイッチング周波数

図 7. スイッチング周波数 対 温度

図 8. 最大デューティ・サイクル 対 温度

図 9. IS電流制限スレッショルド 対 温度

図 10. リーディングエッジ・プランギング期間 対 温度

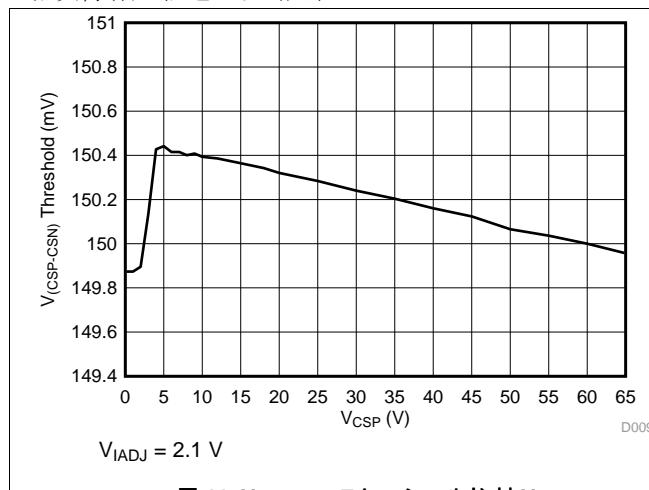

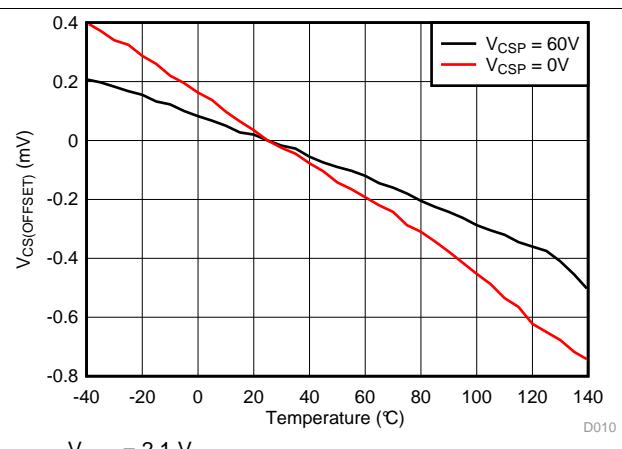

## 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)

図 11.  $V_{(CSP-CSN)}$ スレッショルド 対  $V_{CSP}$

図 12. 電流センス・アンプ・オフセット 対 温度

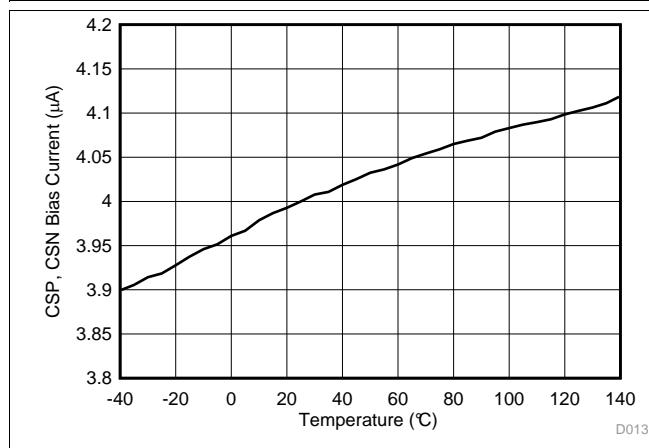

図 13. CSP/CSN入力バイアス電流 対 温度

図 14.  $V_{IMON}$  対  $V_{(CSP-CSN)}$

図 15.  $V_{(CSP-CSN)}$ スレッショルド 対  $V_{IADJ}$

図 16.  $V_{IADJ}$ 電圧クランプ 対 温度

## 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_{IN} = 14\text{V}$ 、 $V_{IADJ} = 2.2\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、 $C_{COMP} = 2.2\text{nF}$ 、 $R_{CS} = 100\text{m}\Omega$ 、 $R_T = 20\text{k}\Omega$ 、 $V_{PWM} = 5\text{V}$ 、GATEおよびDDRVは無負荷(特に記述のない限り)

図 17. OVP検出スレッショルド 対 温度

図 18. OVPヒステリシス電流 対 温度

## 7 詳細説明

### 7.1 概要

TPS92691-Q1は、入力電圧範囲の広い(4.5V~65V)コントローラであり、昇圧または降圧コンバータ・トポロジに基づく高効率でコンパクトなLEDドライバを実装するために、必要なすべての機能を備えています。固定周波数のピーク電流モード制御手法によって定電流出力を実現し、直列接続LEDの单一ストリングを駆動するのに理想的です。低入力オフセットのレール・ツー・レール電流センス・アンプを内蔵することで、幅広い範囲の出力電圧(0V~65V)をサポートし、1個~20個以上の白色LEDからなるLEDストリングに電力を供給できます。このコントローラは、LED構成およびドライバ・トポロジに基づいて、ハイサイドまたはローサイドの電流シャント・センス手法に対応します。アナログ調整入力IADJで設定されるLED電流センス・スレッショルドにより、電圧 $V_{IADJ}$ を140mVから2.25Vまで変化させて、15:1のリニア範囲にわたるアナログ(振幅)調光を実現できます。IADJ入力によってLED電流を外部からプログラミングでき、LEDの校正、輝度補正、熱管理などが容易です。PWM入力に基づいてLED電流のデューティ・サイクルを変化させることにより、高い分解能とリニアな調光応答が得られます。このPWM入力はGATEおよびDDRV駆動出力を直接制御し、内部発振器も制御します。また、LED負荷と直列に配置した外部MOSFETを使用することで、コントラスト比1000:1以上の高速PWM調光を実現できます。電流モニタ出力IMONにより、レール・ツー・レール電流センス・アンプで測定されたLED電流の瞬時ステータスを通知します。この機能は、LEDの短絡および開放障害を示すために搭載され、LEDドライバ・トポロジに依存しないケーブル・ハーネスの障害検出も可能になります。その他の障害保護機能として、サイクル-バイ-サイクル電流制限、ヒステリシスに基づく過電圧保護、VCC低電圧保護、過熱シャットダウン、およびSSピンのプルダウンによるリモート・シャットダウン機能を備えています。

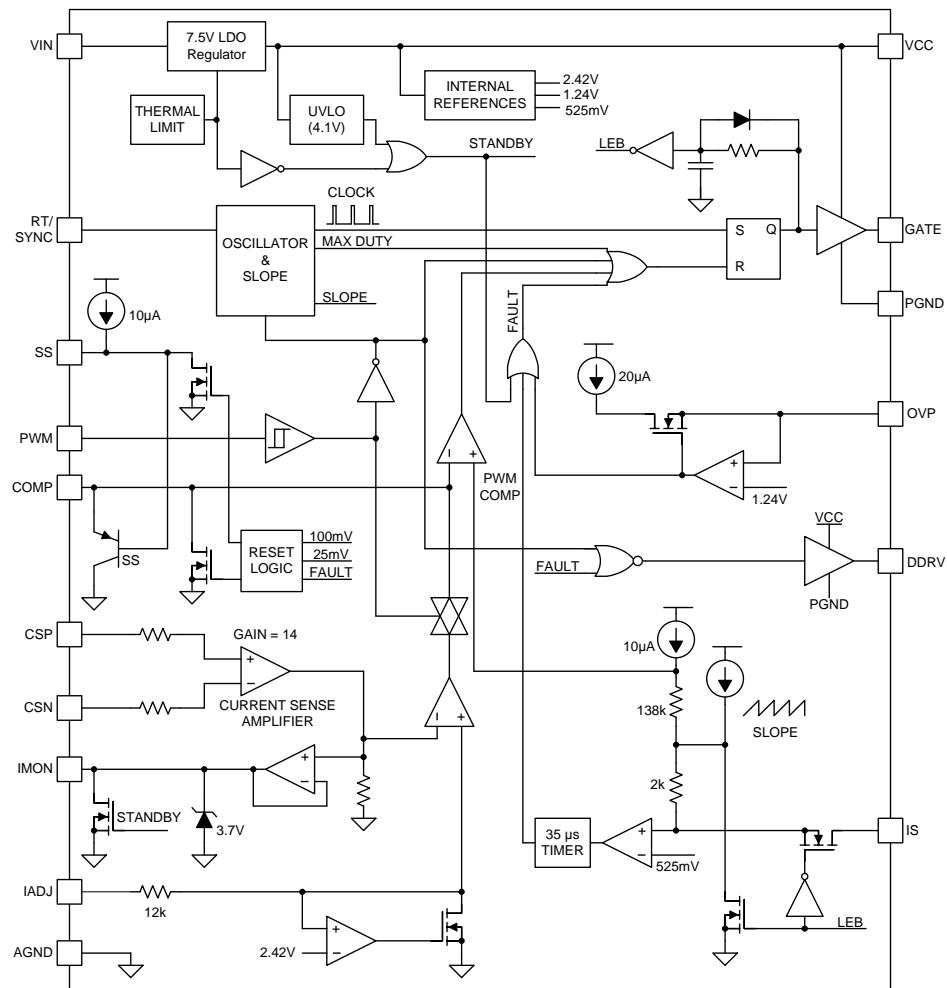

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 内部レギュレータおよび低電圧誤動作防止 (UVLO)

このICは、入力 $V_{IN}$ 定格65Vのリニア・レギュレータを内蔵し、それによって7.5V(標準)の $V_{CC}$ バイアス電源および他の内部リファレンス電圧を生成します。 $V_{CC}$ 出力を監視することで、UVLO保護を実装しています。デバイスは $V_{CC}$ が4.1V(標準)のスレッショルドを上回るとイネーブルになり、 $V_{CC}$ が4.0V(標準)のスレッショルドを下回るとディスエーブルになります。遷移中のチャッタリングを避けるために、UVLOコンパレータによって0.1Vのヒステリシスを実現しています。UVLOスレッショルドは内部で固定され、調整はできません。電源電流 $I_{CC}$ は26mA(最小)に制限され、 $V_{CC}$ ピンの短絡状況時にデバイスを保護しています。 $V_{CC}$ 電源は、内部回路とNチャネル・ゲート・ドライバ出力(GATEおよびDDRV)に電力を供給します。適切な動作を確保するためには、 $V_{CC}$ 出力とPGNDの間に $2.2\mu F$ ~ $4.7\mu F$ のバイパス・コンデンサを接続する必要があります。入力電圧 $V_{IN}$ が7.5Vを下回ると、レギュレータはドロップアウト状態で動作し、20mAの電源電流に対して $V_{CC}$ が $V_{IN}$ よりも300mV低く設定されます。 $V_{CC}$ は内部レギュレータのレギュレーション済み出力であり、外部電源によって駆動することは推奨しません。

### 7.3.2 発振器

TPS92691/-Q1のスイッチング周波数は、RT/SYNCピンとAGNDピンの間に接続した1個の外付け抵抗によってプログラミングできます。目的の周波数 $f_{SW}$ (Hz)を設定するための抵抗値は、式 1 で計算できます。

## 機能説明 (continued)

$$R_T = \frac{1.432 \times 10^{10}}{(f_{SW})^{1.047}} \quad (\Omega) \quad (1)$$

図 6に、スイッチング周波数と抵抗 $R_T$ の関係をグラフで示しています。入力および出力電圧の動作範囲全体にわたって最適な性能を実現し、効率を最大限に高めるには、80kHz～700kHzのスイッチング周波数設定を推奨します。それより高いスイッチング周波数で動作する場合は、NチャネルMOSFETの特性を慎重に選択し、追加のスイッチング損失および接合部温度の上昇を考慮に入れる必要があります。

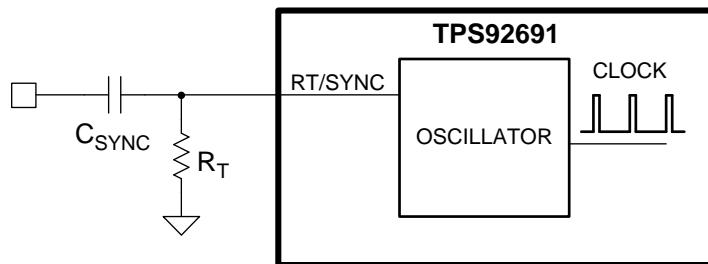

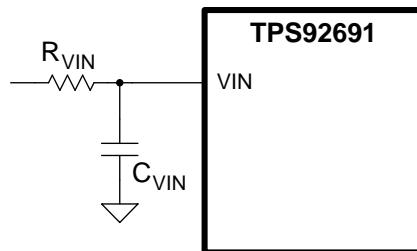

**図 19. AC結合による発振器の同期**

内部発振器は、RT/SYNCピンに外部クロック・パルスをAC結合して、同期させることができます(図 19を参照)。内部の同期パルス検出器で認識されるためには、RTピンに入力される同期クロックの立ち上がりエッジがRT同期スレッショルドを超える必要があります。外部同期パルスの周波数は、 $R_T$ 抵抗でプログラミングされる内部発振周波数の±20%以内とすることを推奨します。また、適切な同期のために、100nFの最小結合コンデンサおよび100nsの標準パルス幅を推奨します。外部同期クロックが失われた場合には、内部発振器が $R_T$ 抵抗に基づいてスイッチング・レートを制御することにより、出力電流のレギュレーションを維持します。 $R_T$ 抵抗は、発振器が単独で動作しているか外部クロックと同期しているかに関係なく、常に必要です。

### 7.3.3 ゲート・ドライバ

TPS92691-Q1は、出力 $V_{GATE}$ を $V_{CC}$ とPGNDの間でスイッチングするNチャネル・ゲート・ドライバを内蔵しています。500mAのピーク・ソース電流およびシンク電流により、MOSFETのゲートとドレインのノード電圧のスルーレートを制御し、スイッチングによって生じる伝導および放射EMIを制限します。ゲート・ドライバの電源電流 $I_{CC(GATE)}$ は、MOSFETの合計ゲート駆動電荷( $Q_G$ )およびコンバータの動作周波数 $f_{SW}$ に依存します( $I_{CC(GATE)} = Q_G \times f_{SW}$ )。接合部温度の上昇およびスイッチの遷移損失を制限するために、ゲート電荷仕様の低いMOSFETを推奨します。

NチャネルMOSFETデバイスを選択する際には、 $V_{IN}$ が $V_{CC}$ レギュレーション・レベルを下回るドロップアウト領域で動作する場合のスレッショルド電圧を考慮してください。7V未満の入力電圧でデバイスを動作させる必要がある場合には、スレッショルド電圧が5V未満の論理レベル・デバイスを推奨します。

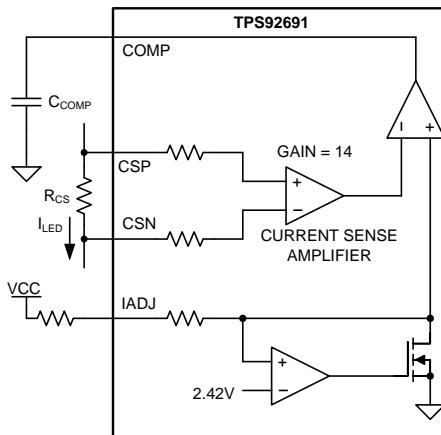

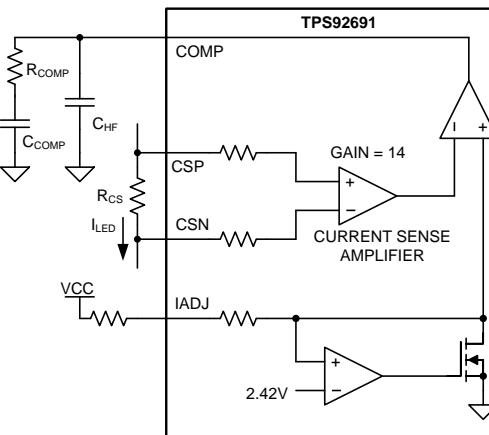

### 7.3.4 レール・ツー・レール電流センス・アンプ

内部のレール・ツー・レール電流センス・アンプは、0V～65Vのコモン・モード範囲にわたり、CSP入力とCSN入力の間の差動電圧降下に基づいて平均LED電流を測定します。差動電圧 $V_{(CSP-CSN)}$ は、電圧ゲイン係数である14倍に増幅され、トランスクンダクタンス誤差増幅器の負入力に接続されます。推奨コモン・モード電圧範囲および温度範囲にわたって、累積入力オフセット電圧(電圧ゲイン誤差、固有電流センス・オフセット電圧、およびトランスクンダクタンス誤差増幅器のオフセット電圧の和)を5mV未満に制限することにより、正確なLED電流帰還が得られます。

## 機能説明 (continued)

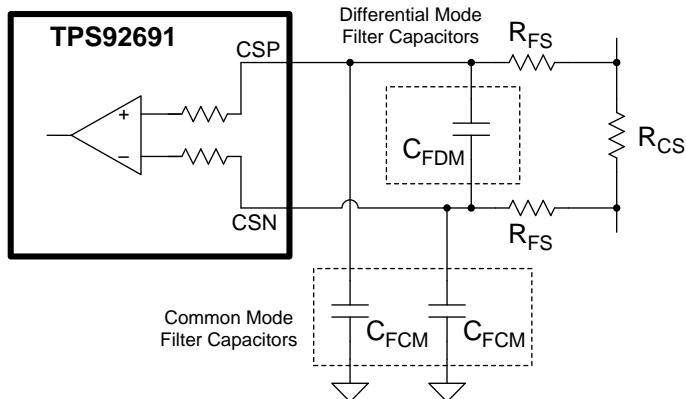

**図 20. 電流センス・アンプの入力フィルタ・オプション**

図 20に示すように、コモン・モードまたは差動モードのローパス・フィルタをオプションで実装することにより、ダイオードの逆方向回復に起因する大きな出力電圧リップルやスイッチング電流スパイクの影響を平滑化できます。アンプのバイアス電流による追加のオフセットを制限し、最高の精度とライン・レギュレーションを実現するために、 $10\Omega$ ～ $100\Omega$ の範囲のフィルタ抵抗を推奨します。

### 7.3.5 トランスコンダクタンス誤差増幅器

内部のトランスコンダクタンス誤差増幅器は、LED電流センス帰還電圧と外部のIADJ入力電圧との差に比例した誤差信号を生成します。誤差増幅器の出力に補償回路を接続することで、閉ループ・レギュレーションが実現されます。ほとんどのLEDドライバ・アプリケーションでは、COMP出力とグランドの間にコンデンサを接続して単純な積分補償回路を実装することにより、安定した応答を実現できます。適切な開始点として、 $10nF$ ～ $100nF$ のコンデンサを推奨します。COMP出力とグランドの間に、直列抵抗とコンデンサから構成される比例積分補償回路を実装すると、より高い閉ループ帯域幅を実現できます。コンバータのトポロジに基づき、補償回路は最小 $60^\circ$ の位相余裕と $10dB$ のゲイン余裕が得られるよう調整する必要があります。「[アプリケーションと実装](#)」のセクションに詳細な式を示しています。

### 7.3.6 スイッチ電流センスおよび内部スロープ補償

メインMOSFETの電流をIS入力ピンで監視することにより、ピーク電流モード制御を実装しています。GATE出力のデューティ・サイクルは、 $R_{IS}$ 抵抗で測定されるピーク・スイッチ電流を内部のCOMP電圧スレッショルドと比較することで得られます。デューティ・サイクルが50%を超える場合の低調波発振を防ぐため、測定されたセンス電圧 $V_{IS}$ に内部スロープ信号が加算されます。内部発振器の周波数に同期された $100\mu A$ のノコギリ波ランプ電流から、固定された振幅(200mV)を持つリニアなスロープ電圧 $V_{SL}$ が得られます。内部のブランкиング回路を使用し、新しいスイッチング周期の開始後にIS入力を150nsにわたって内部でシャントすることにより、MOSFETのスイッチング電流スパイクの伝播およびデューティ・サイクルの早期終了を防いでいます。ドロップアウト領域( $V_{IN} < 7V$ )での動作中に追加のノイズを抑制するために、 $100\Omega$ ～ $500\Omega$ の抵抗値を持つ外部ローパスRCフィルタの使用を推奨します。

内部の冗長コンバレータによってサイクル-バイ-サイクル電流制限が実現され、IS入力電圧 $V_{IS}$ が $525mV$ (標準)のスレッショルドを超えると、GATE出力は直ちに停止されます。電流制限動作が発生すると、SSピンとCOMPピンが内部でグランドに接続され、コントローラの状態をリセットします。35μsの内部障害タイマが満了した後、GATE出力がイネーブルになり、SSピンを通して新しいスタートアップ・シーケンスが開始されます。

## 機能説明 (continued)

### 7.3.7 アナログ調整入力

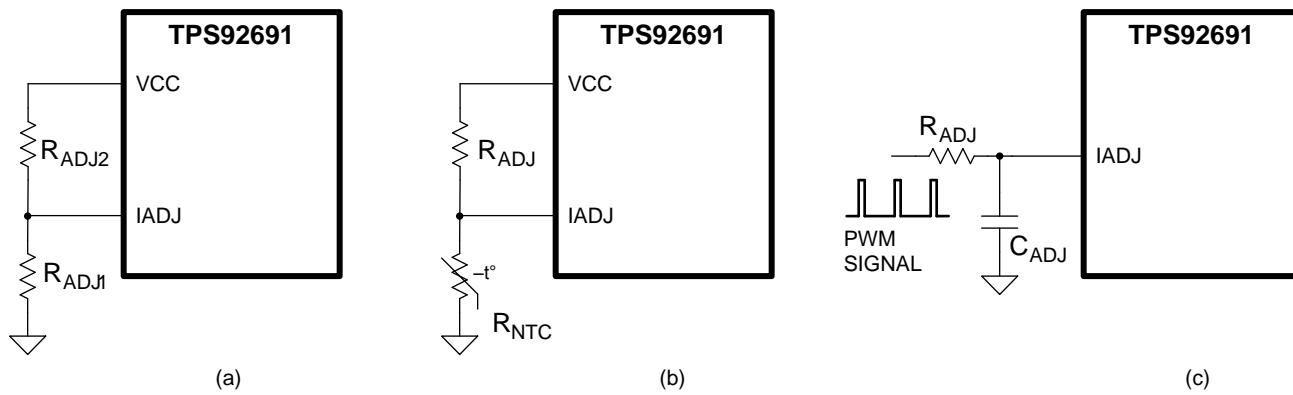

LED電流センス抵抗にかかる電圧 $V_{(CSP-CSN)}$ は、電流センス・アンプ電圧のゲインである14が乗算されたアナログ調整入力電圧 $V_{IADJ}$ にレギュレーションされます。 $V_{CC}$ からの分圧抵抗または外部の電圧源を使用して $IADJ$ の電圧を140mV～2.25Vの範囲で変化させることにより、LED電流を直線的に調整できます。外付け抵抗を通して $IADJ$ ピンを $V_{CC}$ に接続すると、2.42Vの内部リファレンス電圧に基づいてLED電流を設定できます。図21に、 $IADJ$ 電圧を設定する各種の方法を示します。 $IADJ$ 入力をNTC抵抗とともに使用することで、図21(b)に示すような温度フォールドバック保護を実装できます。PWM信号を1次または2次ローパス・フィルタとともに使用すると、図21(c)に示すように $IADJ$ 電圧をプログラミングできます。

- a. VCCからの分圧抵抗による静的なリファレンス設定

- b. 外付けNTC抵抗を使用した温度フォールドバック回路

- c. 外部PWM信号のローパス・フィルタリングによるアナログ調光

図 21. アナログ調整入力電圧の設定

### 7.3.8 PWM入力および直列調光FETゲート・ドライバ出力

TPS92691/-Q1は、出力LED電流のパルス幅変調用に調光入力(PWM)を内蔵しています。PWM入力ピンに接続されたパルス電圧源のデューティ・サイクルを変調することで、LEDの輝度を直線的に変化させることができます。PWM入力を2.3V(標準)未満にすると、スイッチングがオフになり、発振器が一時停止し、COMPピンが切断されます。DDRV出力はGNDに設定され、補償回路および出力コンデンサの電荷が保持されます。PWM入力電圧の立ち上がりエッジ( $V_{PWM} > 2.5V$ )で、GATEおよびDDRV出力がイネーブルになり、インダクタ電流が以前の定常状態値まで増加します。COMPピンが接続されて誤差增幅器および発振器がイネーブルになるのは、スイッチ電流センス電圧 $V_{IS}$ がCOMP電圧 $V_{COMP}$ を上回ったときのみです。このときコンバータは直ちに、最小のLED電流オーバーシュートで強制的に定常状態動作を開始します。調光が不要である場合は、PWMピンを $V_{CC}$ に接続してください。ピンが未接続またはフローティングのときは、内部のプルダウン抵抗によって入力がLowに設定され、デバイスはディスエーブルになります。

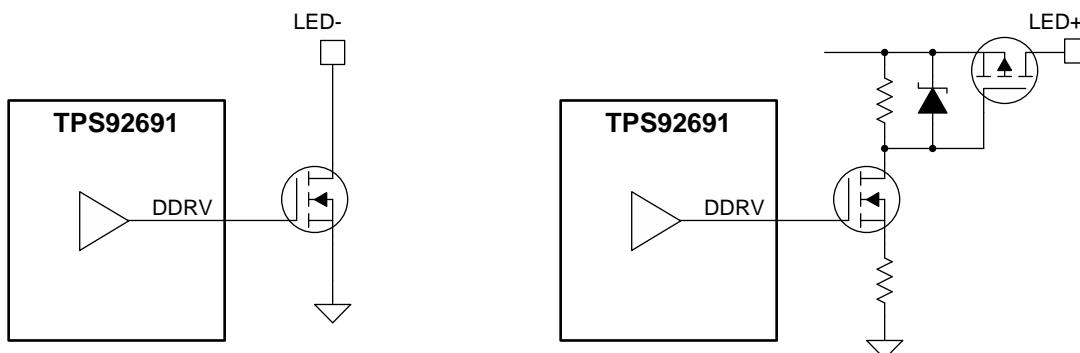

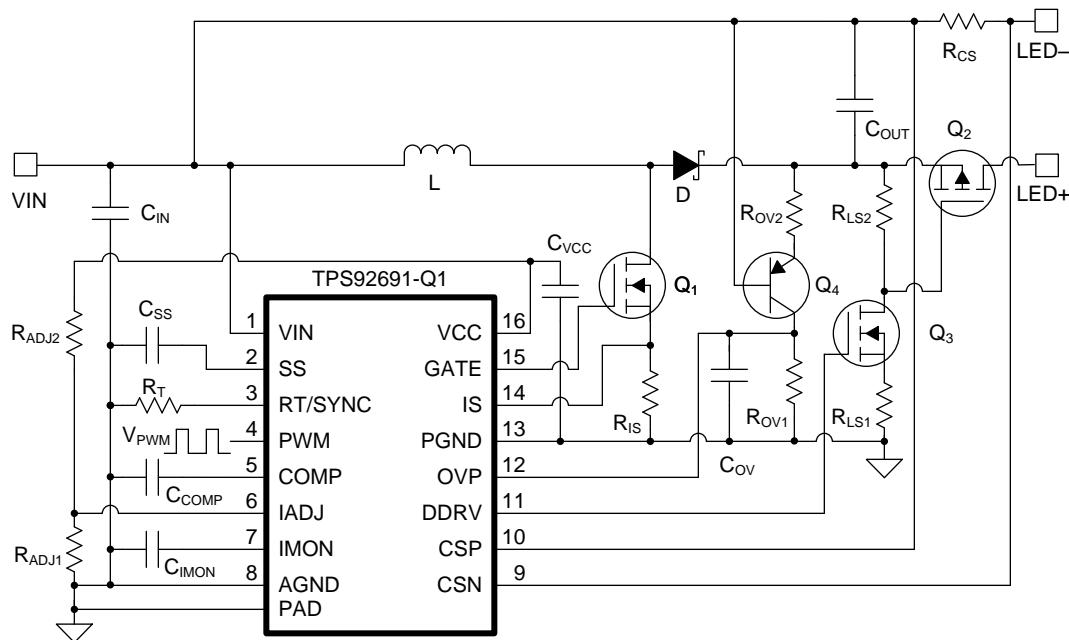

図 22. 直列調光FETの接続

## 機能説明 (continued)

DDRV出力は、PWM入力信号に追従します。また、ローサイドの直列接続Nチャネル調光FETを制御するために、最大500mAのピーク電流をシンクおよびソースできます。または、DDRV出力を外部のレベルシフト回路で変換することにより、ハイサイドの直列Pチャネル調光FETを駆動することもできます(図 22を参照)。直列調光FETは、PWM入力に対してLED電流の立ち上がりおよび立ち下がり時間を高速化することで、高いコントラスト比を実現します。調光FETを使用しないと、立ち上がりおよび立ち下がり時間がインダクタのスルーレートおよびシステムの閉ループ帯域幅によって制限されます。

DDRVピンを使用しない場合は、未接続のままにしてください。

### 7.3.9 ソフト・スタート

ソフト・スタート機能は、レギュレータを定常状態動作点へと徐々に到達させることで、スタートアップ時のストレスやサージを低減します。TPS92691/-Q1は、LED電流がレギュレーション・スレッショルドに近づくまでの間、COMPピンの電圧をSSピンの電圧(ダイオードで分離)へとクランプします。 $10\mu A$ の内部ソフト・スタート電流源によって、SSピンに接続された外付けソフト・スタート・コンデンサ $C_{SS}$ の電圧が徐々に上昇します。その結果、COMP電圧はGNDからゆっくりと上昇します。

内部の $10\mu A$ 電流源は、VCCがUVLOスレッショルドを超えたときにオンになります。ソフト・スタート・シーケンスの開始時には、SSプルダウン・スイッチがアクティブになります。電圧 $V_{SS}$ が $25mV$ を下回ると解除されます。また、SSピンを外部スイッチでプルダウンしてスイッチングを停止させることもできます。SSピンを外部で駆動してスイッチングをイネーブルにする場合は、スタートアップ時に大きな過渡電圧が生じないように補償コンデンサを選択することで、COMPピンのスルーレートを制御する必要があります。 $C_{SS}$ の値は、ソフト・スタートの遷移期間中に出力コンデンサを充電できるよう十分な大きさである必要があります。

### 7.3.10 電流モニタ出力

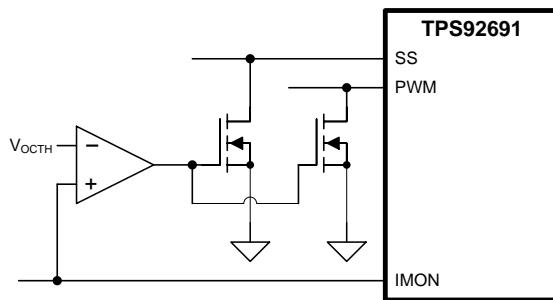

IMONピンの電圧は、レール・ツー・レール電流センス・アンプによって外付けの電流シャント抵抗で測定されたLED電流を示しています。IMON電圧とLED電流の間には、アンプのゲイン係数である14を乗数とした直線的な関係があります(図 14を参照)。IMON出力を外部のマイコンやコンパレータに接続することで、プログラミング可能なスレッショルド $V_{OCTH}$ に基づき、LEDの開放、短絡、またはケーブル・ハーネス障害の検出と緩和が容易になります。IMON電圧は、内部で $3.7V$ にクランプされています。

図 23. IMON出力を使用したLED過電流保護

### 7.3.11 過電圧保護

TPS92691/-Q1デバイスは専用のOVPピンを搭載し、入力または出力の過電圧保護に使用できます。このピンには、 $20\mu A$ (標準)のヒステリシス電流を持つ $1.24V$ (標準)の高精度スレッショルドがあります。過電圧スレッショルド制限は、入力または出力端子とGNDとの間の分圧抵抗回路によって設定されます。OVPピンの電圧がリファレンス・スレッショルドを超えると、GATEおよびDDRVピンが直ちにLowになり、SSおよびCOMPコンデンサが放電されます。電圧が低下し、 $20\mu A$ のソース電流と外付け分圧抵抗によって設定されるヒステリシス・スレッショルドを下回ると、GATEがイネーブルになり、新しいスタートアップ・シーケンスが開始されます。

## 機能説明 (continued)

### 7.3.12 過熱保護

最大接合部温度を超えた場合にコントローラを保護する目的で、内部に過熱シャットダウン回路が実装されています。この回路がアクティブになると(標準で $175^{\circ}\text{C}$ )、コントローラは強制的にシャットダウン・モードになり、内部レギュレータがディスエーブルになります。この機能は、デバイスの過熱や損傷を防ぐことを意図して設計されています。

## 7.4 デバイスの機能モード

このデバイスには、追加の機能モードはありません。

## 8 アプリケーションと実装

注: 以降のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPS92691/-Q1コントローラは、昇圧、降圧、昇降圧、SEPIC、Cuk、フライバックなどのLEDドライバ・トポロジの実装に適しています。TPS92691/-Q1デバイスに対して部品値を選択するための設計手順を以下に示します。ここでは、昇圧、降圧、および昇降圧コンバータに対する設計プロセスの概要を示しています。昇降圧コンバータに対して導出された式は、変更を加えることで、1:1の結合インダクタSEPICコンバータに対する部品選択にも使用できます。この設計手順は、フライバックおよびCukコンバータ・トポロジにも簡単に適応可能です。

図 24. 昇圧LEDドライバ

図 25. SEPIC LED ドライバ

## アプリケーション情報 (continued)

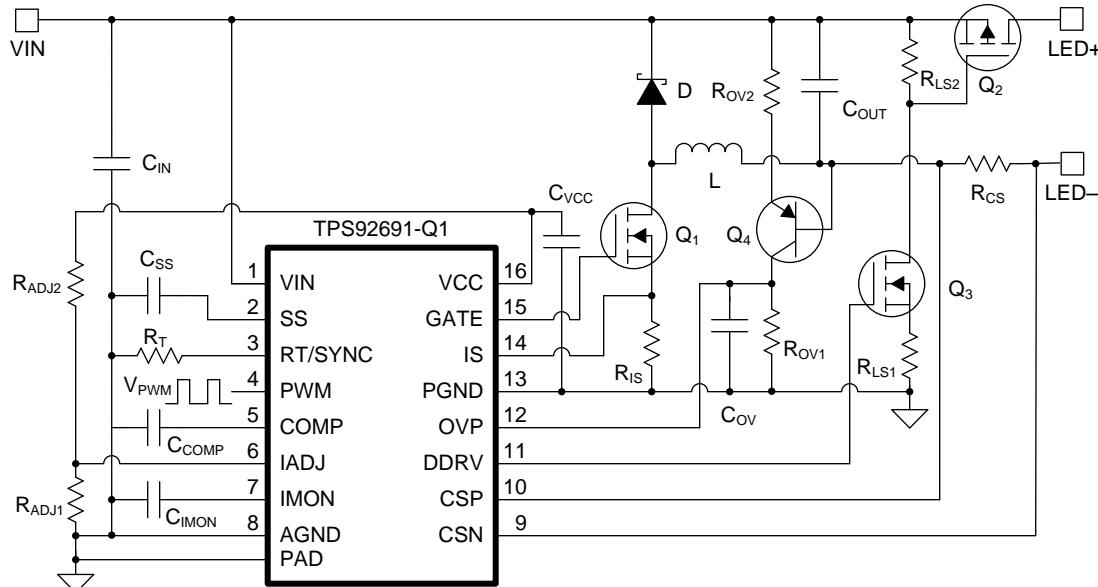

図 26. 昇降圧LED ドライバ

図 27. 降圧LED ドライバ

## アプリケーション情報 (continued)

### 8.1.1 デューティ・サイクルに関する考慮事項

スイッチのデューティ・サイクルDは、コンバータの動作を定義するものであり、入力電圧および出力電圧の関数となっています。定常状態では、デューティ・サイクルは次の式で求められます。

降圧:

$$D = \frac{V_O}{V_{IN}} \quad (2)$$

昇圧:

$$D = \frac{V_O - V_{IN}}{V_O} \quad (3)$$

昇降圧:

$$D = \frac{V_O}{V_{IN} + V_O} \quad (4)$$

最小デューティ・サイクル $D_{MIN}$ と最大デューティ・サイクル $D_{MAX}$ は、上記の式にそれぞれ最大入力電圧 $V_{IN(MAX)}$ と最小入力電圧 $V_{IN(MIN)}$ を代入することによって計算できます。デバイスで実現可能な最小デューティ・サイクルは、リーディングエッジ・ブランкиング期間およびスイッチング周波数によって決定されます。最大デューティ・サイクルは、最小のオフ時間可能にするために、内部発振器によって93%（標準）に制限されます。仕様で規定された入力および出力電圧範囲にわたって閉ループLED電流レギュレーションを維持するために、動作時のデューティ・サイクルはデバイスの動作制限範囲内に保つ必要があります。

### 8.1.2 インダクタの選択

インダクタのピーク・ツー・ピーク・リップル電流 $\Delta i_{L(PP)}$ は、インダクタのコア損失と銅損との間のバランスを考慮して、一般に最大インダクタ電流 $I_L$ の10%～80%に設定されます。インダクタのリップル電流が大きいほど、インダクタのサイズを小さくできますが、LED電流リップルを平滑化するための出力コンデンサの負担が大きくなります。目的のリップル比RR、スイッチング周波数 $f_{SW}$ 、最大デューティ・サイクル $D_{MAX}$ 、および標準LED電流 $I_{LED}$ が与えられたとき、インダクタ値は次のように計算できます。

降圧:

$$\Delta i_{L(PP)} = RR \cdot I_L = RR \cdot I_{LED} \quad (5)$$

$$I_L = \frac{(V_{IN(MIN)} - V_O) \times D_{MAX}}{\Delta i_{L(PP)} \times f_{SW}} \quad (6)$$

昇圧および昇降圧:

$$\Delta i_{L(PP)} = RR \cdot I_L = RR \cdot \frac{I_{LED}}{1 - D_{MAX}} \quad (7)$$

$$I_L = \frac{V_{IN(MIN)} \times D_{MAX}}{\Delta i_{L(PP)} \times f_{SW}} \quad (8)$$

別の方法として、出力電力 $P_{O(BDRY)}$ に基づいて規定されるCCM-DCM境界条件からインダクタを選択することもできます。インダクタの選択は、バッテリ駆動のLEDドライバ・アプリケーションがCCMでの動作の保証が必要です。そうしますと、幅広い範囲のプログラミング可能なLED電流設定点を持つ、さまざまなLEDストリング構成をサポートできます。出力電力は、最小LED電流と、特定のアプリケーションに対する最小出力電圧要件に基づいて計算する必要があります。

$$P_{O(BDRY)} \leq I_{LED(MIN)} \times V_{O(MIN)} \quad (9)$$

## アプリケーション情報 (continued)

降圧:

$$L = \frac{V_{O(MAX)}^2}{2 \times P_{O(BDRY)} \times f_{SW}} \times \left( 1 - \frac{V_{O(MAX)}}{V_{IN}} \right) \quad (10)$$

昇圧:

$$L = \frac{V_{IN}^2}{2 \times P_{O(BDRY)} \times f_{SW}} \times \left( 1 - \frac{V_{IN}}{V_{O(MAX)}} \right) \quad (11)$$

昇降圧:

$$L = \frac{1}{2 \times P_{O(BDRY)} \times f_{SW} \times \left( \frac{1}{V_{O(MAX)}} + \frac{1}{V_{IN}} \right)^2} \quad (12)$$

インダクタの飽和電流定格は、最大動作温度時のピーク・インダクタ電流  $I_{L(PK)}$  を上回っている必要があります。

$$I_{L(PK)} = I_L + \frac{V_{IN(MIN)} \times D_{MAX}}{2 \times L \times f_{SW}} \quad (13)$$

### 8.1.3 出力コンデンサの選択

出力コンデンサは、スイッチングによって生じる不連続または大きなリップル電流を減衰させ、目的のピーク・ツー・ピーク LED電流リップル  $\Delta i_{LED(PP)}$  を実現するために必要となります。コンデンサの値は、LEDストリングの合計直列抵抗  $r_D$ 、スイッチング周波数  $f_{SW}$ 、およびコンバータのトポロジ（昇圧または降圧）に依存します。降圧およびCukトポロジの場合、インダクタがLED負荷と直列であるため、昇圧、昇降圧、SEPICトポロジと比較して、同じLEDリップル電流を実現するために必要なコンデンサは小さくなります。目標のLEDリップル電流に対して必要となる容量は、以下の式に基づいて計算できます。

降圧:

$$C_{OUT} = \frac{\Delta i_{L(PP)}}{8 \times f_{SW} \times r_D \times \Delta i_{LED(PP)}} \quad (14)$$

昇圧および昇降圧:

$$C_{OUT} = \frac{I_{LED} \times D_{MAX}}{f_{SW} \times r_D \times \Delta i_{LED(PP)}} \quad (15)$$

出力コンデンサを選択する際には、ESRおよびESL特性を考慮することが重要です。これらはLEDの電流リップルに直接影響するためです。セラミック・コンデンサは、低いESR、高いリップル電流定格、長い寿命、良好な温度特性といった特長により、最適な選択肢となります。セラミック・コンデンサを選択する場合には、高い温度およびDCバイアス動作条件に関連したディレーティング要素を考慮することが重要です。TIでは、最大LEDスタック電圧よりも大きな電圧定格を持つX7Rコンデンサを推奨します。セラミック・コンデンサと並列にアルミ電解コンデンサを使用することで、大容量を提供できます。このアルミ電解コンデンサは、長い動作寿命を確保するために必要なRMS電流定格および温度定格を備えている必要があります。許容される最小のRMS出力コンデンサ電流定格  $I_{COUT(RMS)}$  は、以下の式で近似できます。

降圧:

$$I_{COUT(RMS)} = \frac{\Delta i_{LED(PP)}}{\sqrt{12}} \quad (16)$$

昇圧および昇降圧:

## アプリケーション情報 (continued)

$$I_{COUT(RMS)} = I_{LED} \times \sqrt{\frac{D_{MAX}}{1-D_{MAX}}} \quad (17)$$

これらの式(式 14~式 17)は、固定されたLED負荷を既知の出力電圧とLED電流で駆動する設計に最も適しています。幅広い範囲のプログラミング可能なLED電流設定点を持つさまざまなLEDストリング構成をサポートする必要があるアプリケーションでは、最大出力電力  $P_{O(MAX)}$ に基づく出力容量を反映するように上記の式を調整することで、動作範囲全体にわたってLED電流リップル仕様を満たす必要があります。「[代表的な昇降圧LEDドライバ](#)」に、昇降圧LEDドライバに対する詳細を示しています。

### 8.1.4 入力コンデンサの選択

入力コンデンサ  $C_{IN}$  は、入力電圧リップルを平滑化し、入力電圧やPWM調光電圧の過渡事象中に入力電流を供給するためのエネルギーを蓄積します。昇圧、SEPIC、およびCukトポロジの直列インダクタは、連続的な入力電流を提供するため、目的の入力リップル電圧  $\Delta V_{IN(PP)}$  を実現するために必要な入力コンデンサは小さくて済みます。降圧および昇降圧トポロジでは、入力電流が不連続であるため、同じ入力電圧リップルを得るために必要なコンデンサは大きくなります。スイッチング周波数  $f_{SW}$  および最大デューティ・サイクル  $D_{MAX}$  に基づき、入力コンデンサ値は次のように計算できます。

降圧:

$$C_{IN} = \frac{I_{LED} \times D_{MAX} \times (1-D_{MAX})}{f_{SW} \times \Delta V_{IN(PP)}} \quad (18)$$

昇圧:

$$C_{IN} = \frac{\Delta i_{L(PP)}}{8 \times f_{SW} \times \Delta V_{IN(PP)}} \quad (19)$$

昇降圧:

$$C_{IN} = \frac{I_{LED} \times D_{MAX}}{f_{SW} \times \Delta V_{IN(PP)}} \quad (20)$$

X7R誘電体を使用したセラミック・コンデンサは、低いESR、高いリップル電流定格、良好な温度特性といった特長により、最適な選択肢となります。PWM調光を使用するアプリケーションに対しては、セラミック・コンデンサとともにアルミ電解コンデンサを使用することを推奨します。それにより、LED電流の立ち上がりおよび立ち下がりエッジで生じる大きな入力過渡電流による電圧変動を最小限に抑えることができます。

図 28. VIN フィルタ

ほとんどのアプリケーションに対して、デバイスにできる限り近づけて配置した  $0.1\mu F$  のセラミック・コンデンサによって VIN ピンをバイパスすること、また、 $10\Omega$  の直列抵抗を追加して  $150\text{kHz}$  のローパス・フィルタを作成し、不要な高周波ノイズを除去することを強く推奨します。

## アプリケーション情報 (continued)

### 8.1.5 メインのパワーMOSFETの選択

パワーMOSFETは、最大スイッチ・ノード電圧 $V_{SW}$ に耐え、コンバータのトポロジに基づくRMS電流をスイッチングできる必要があります。動作の安全性を確保するために、最大スイッチ・ノード電圧よりも20%以上大きなドレイン電圧 $V_{DS}$ 定格を持つMOSFETを推奨します。MOSFETのドレイン-ソース間降伏電圧 $V_{DS}$ およびRMS電流の定格は、以下の式で計算します。

降圧:

$$V_{DS} = V_{IN(MAX)} \times 1.2 \quad (21)$$

$$I_{Q(RMS)} = I_{LED} \times \sqrt{D_{MAX}} \quad (22)$$

昇圧:

$$V_{DS} = V_{O(OV)} \times 1.2 \quad (23)$$

$$I_{Q(RMS)} = I_{LED} \times \frac{\sqrt{D_{MAX}}}{1 - D_{MAX}} \quad (24)$$

昇降圧:

$$V_{DS} = (V_{IN(MAX)} + V_{O(OV)}) \times 1.2 \quad (25)$$

$$I_{Q(RMS)} = I_{LED} \times \frac{\sqrt{D_{MAX}}}{1 - D_{MAX}} \quad (26)$$

ここで、電圧 $V_{O(OV)}$ は過電圧保護スレッショルドであり、障害状況でのワーストケースの出力電圧です。

ゲート駆動損失およびスイッチング損失を最小限に抑えるために、合計ゲート電荷 $Q_g$ の低いMOSFETを選択します。

MOSFETの $R_{DS}$ 抵抗は通常、それほど重要なパラメータではありません。これは、高い動作周波数では、スイッチの導通損失がコンバータの合計損失中でわずかな割合しか占めないためです。スイッチング損失と導通損失は、次のように計算します。

$$P_{COND} = R_{DS} \times I_{Q(RMS)}^2 \quad (27)$$

$$P_{SW} = \frac{I_L \times V_{SW}^2 \times C_{RSS} \times f_{SW}}{I_{GATE}} \quad (28)$$

$C_{RSS}$ は、MOSFETの逆方向伝達容量です。 $I_L$ は、平均インダクタ電流です。 $I_{GATE}$ は、ゲート駆動出力電流であり、標準で500mAです。MOSFETの電力定格およびパッケージは、合計損失の計算値、動作周囲温度、および許容される最大温度上昇に基づいて選択する必要があります。

### 8.1.6 整流ダイオードの選択

ショットキー・ダイオード(整流器として使用する場合)は、順方向電圧降下が小さく、逆方向回復時間がゼロに近いため、最大の効率が得られます。信頼性の高い動作のために、逆方向降伏電圧 $V_{D(BR)}$ がMOSFETのドレイン-ソース間電圧 $V_{DS}$ 以上であるダイオードを推奨します。ショットキー・ダイオードのリーク電流特性について理解しておくことが重要です。これは、特に動作温度が高い場合に、コンバータの全体的な動作や効率への影響が大きいためです。

ダイオードを流れる電流 $I_D$ は、次の式で与えられます。

$$I_D = I_L \times (1 - D_{MAX}) \quad (29)$$

このダイオードは電流定格を上回るように選択し、パッケージは最大許容温度を超えて電力を消費できる特性を持つ必要があります。

## アプリケーション情報 (continued)

### 8.1.7 LED電流のプログラミング

LED電流は、外付けの電流センス抵抗 $R_{CS}$ およびアナログ調整電圧 $V_{IADJ}$ によって設定されます。電流センス抵抗はLED負荷と直列に接続し、ハイサイド(出力 $V_O$ に接続)とローサイド(グラウンドGNDに接続)のいずれかに配置できます。内部レール・ツー・レール電流センス・アンプのCSPおよびCSN入力を $R_{CS}$ 抵抗に接続することで、閉ループ・レギュレーションを実現します。 $V_{IADJ} > 2.5$  Vのとき、内部の2.42Vリファレンスによって $V_{(CSP-CSN)}$ スレッショルドが172mVに設定され、LED電流は次の値に制御されます。

$$I_{LED} = \frac{0.172}{R_{CS}} \quad (30)$$

LED電流は、 $V_{IADJ}$ を140mV～2.25Vの範囲で変化させることによりプログラミングできます。LED電流は次の式で計算します。

$$I_{LED} = \frac{V_{IADJ}}{14 \times R_{CS}} \quad (31)$$

最高の性能を得るには、出力電圧リップルを50mVに制限する必要があります。LED電流の精度に対する電圧リップルやノイズの影響を最小限に抑えるために、CSPおよびCSN入力と直列に10Ωの抵抗、およびグラウンドとの間に0.01μFのコンデンサを接続して、ローパス・コモン・モード・フィルタを構成することを推奨します(図 20を参照)。また、CSPとCSNの間に0.1μFのコンデンサを接続して、高周波差動ノイズをフィルタリングします。

### 8.1.8 スイッチ電流センス抵抗およびスロープ補償

スイッチ電流センス抵抗 $R_{IS}$ は、ピーク電流モード制御の実装、およびピーク・スイッチ電流制限の設定に使用されます。スイッチ電流センス抵抗 $R_{IS}$ の値は、スロープ補償ランプの大きさ( $V_{SL}$ )に基づいて安定した内部電流ループ動作を実現できるように選択します。また、障害状況時にメイン・スイッチングMOSFETを保護できる必要があります。 $R_{IS}$ には、以下の2つの式で計算した値のうち小さい方の値を選択します。

$$R_{IS} = \frac{2 \times V_{SL} \times L \times f_{SW}}{V_{O(MAX)}} \quad (32)$$

$$R_{IS} = \frac{V_{IS(LIMIT)} - V_{SL} \times D_{MAX}}{I_{L(PK)}} \quad (33)$$

内部スロープ補償電圧 $V_{SL}$ は、200mV(標準)に固定されています。必要に応じて、ISピンと直列に抵抗を配置することで、スロープ補償を大きくすることができます。ピーク・スイッチ電流制限は、525mV(標準)の内部電流制限スレッショルドに基づいて設定されます。また、PWM調光中の動作の信頼性を確保するために、スロープ補償に基づいて調整されます。

図 29. IS入力フィルタ

1nFおよび100Ωによるローパス・フィルタの使用はオプションです。使用する場合は、内部スロープ補償信号への影響を制限するために、抵抗値を500Ω未満にする必要があります。

## アプリケーション情報 (continued)

### 8.1.9 帰還補償

開ループ応答は、変調器の伝達関数(式 34)と帰還伝達関数の積です。1次近似を使用し、変調器の伝達関数は、出力コンデンサによって生成される单一の極、および昇圧/昇降圧トポロジでは、インダクタによって生成される右半平面のゼロとしてモデル化できます。これらはいずれも、LEDストリングの動的抵抗 $r_D$ に依存します。TIではセラミック・コンデンサを推奨しているため、分析では出力コンデンサのESRを無視しています。また、小信号変調器モデルにはDCゲイン係数も含まれ、これはデューティ・サイクル、出力電圧、およびLED電流に依存します。

$$\frac{\hat{V}_{\text{COMP}}}{\hat{I}_{\text{LED}}} = G_0 \frac{\left(1 - \frac{s}{\omega_Z}\right)}{\left(1 + \frac{s}{\omega_P}\right)} \quad (34)$$

表 1 に、小信号モデルのパラメータの式をまとめています。

帰還伝達関数には、電流センス抵抗と、トランスコンダクタンス誤差増幅器のループ補償が含まれています。誤差増幅器の出力に接続された補償回路を使用して、ループのゲインおよび位相特性を設定します。COMPとGNDAの間の単純なコンデンサ $C_{\text{COMP}}$ (図 30を参照)により、積分補償が実現され、原点に極が生成されます。または、 $R_{\text{COMP}}$ 、 $C_{\text{COMP}}$ 、 $C_{\text{HF}}$ によって構成される回路(図 31を参照)を使用して、比例積分(PI)補償を実装し、原点の極、低周波数のゼロ、および高周波数の極を生成できます。

**表 1. 小信号モデルのパラメータ**

|     | DCゲイン( $G_0$ )                                                                               | 極周波数( $\omega_P$ )                                                                        | ゼロ周波数( $\omega_Z$ )                                           |

|-----|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 降圧  | 1                                                                                            | $\frac{1}{r_D \times C_{\text{OUT}}}$                                                     | —                                                             |

| 昇圧  | $\frac{(1-D) \times V_O}{R_{\text{IS}} \times (V_O + (r_D \times I_{\text{LED}}))}$          | $\frac{V_O + (r_D \times I_{\text{LED}})}{V_O \times r_D \times C_{\text{OUT}}}$          | $\frac{V_O \times (1-D)^2}{L \times I_{\text{LED}}}$          |

| 昇降圧 | $\frac{(1-D) \times V_O}{R_{\text{IS}} \times (V_O + (D \times r_D \times I_{\text{LED}}))}$ | $\frac{V_O + (D \times r_D \times I_{\text{LED}})}{V_O \times r_D \times C_{\text{OUT}}}$ | $\frac{V_O \times (1-D)^2}{D \times L \times I_{\text{LED}}}$ |

帰還伝達関数は、以下のように定義されます。

積分補償による帰還伝達関数:

$$-\frac{\hat{V}_{\text{COMP}}}{\hat{I}_{\text{LED}}} = \frac{14 \times g_M \times R_{\text{CS}}}{s \times C_{\text{COMP}}} \quad (35)$$

比例積分補償による帰還伝達関数:

$$-\frac{\hat{V}_{\text{COMP}}}{\hat{I}_{\text{LED}}} = \frac{14 \times g_M \times R_{\text{CS}}}{s \times (C_{\text{COMP}} + C_{\text{HF}})} \frac{(1 + s \times R_{\text{COMP}} \times C_{\text{COMP}})}{\left(1 + s \times R_{\text{COMP}} \times \left(\frac{C_{\text{COMP}} \times C_{\text{HF}}}{C_{\text{COMP}} + C_{\text{HF}}}\right)\right)} \quad (36)$$

原点の極は、出力の定常状態誤差を最小化します。PI補償では、低周波数のゼロをクロスオーバー周波数よりも1桁低く配置することにより、高い帯域幅が得られます。補償回路の計算には、以下の式を使用します。

図 30. 積分補償

図 31. 比例積分補償

降圧での積分補償:

$$C_{COMP} = \frac{8.75 \times 10^{-3} \times R_{CS}}{\omega_P} \quad (37)$$

昇圧および昇降圧での比例積分補償:

$$C_{COMP} = 8.75 \times 10^{-3} \times \left( \frac{R_{CS} \times G_0}{\omega_Z} \right) \quad (38)$$

$$C_{HF} = \frac{C_{COMP}}{100} \quad (39)$$

$$R_{COMP} = \frac{1}{\omega_P \times C_{COMP}} \quad (40)$$

ループ応答は、ステップ入力過渡電圧を印加することによって確認します。目標は、LED電流のオーバーシュートとアンダーシュートを最小限に抑え、抑制された応答を得ることです。PWM調光性能を最適化するには、補償回路の追加調整が必要になる場合があります。

### 8.1.10 ソフト・スタート

ソフト・スタート時間( $t_{SS}$ )は、LED電流が目標設定点に達するまでに必要な時間です。必要なソフト・スタート時間 $t_{SS}$ は、SSピンとGNDとの間のコンデンサ $C_{SS}$ を使用してプログラミングされ、LED電流、出力コンデンサ、および出力電圧に基づいています。

$$C_{SS} = 12.5 \times 10^{-6} \left( t_{SS} - \frac{C_{OUT} \times V_{OUT}}{I_{LED}} \right) \quad (41)$$

### 8.1.11 過電圧保護

過電圧スレッショルドは、昇圧およびSEPICトポジの場合、出力電圧 $V_O$ とグランドとの間に接続した分圧抵抗 $R_{OV2}$ および $R_{OV1}$ を使用してプログラミングします(図 24および図 25を参照)。昇降圧または降圧構成のように、LEDがグランド以外の電位を基準としている場合は、PNPトランジスタとレベルシフト抵抗を使用して出力電圧をセンスし、グランドに変換します(図 27および図 26を参照)。過電圧ターンオフ・スレッショルド $V_{O(OV)}$ は、次のようにになります。

昇圧:

$$V_{O(OV)} = V_{OVP(THR)} \times \left( \frac{R_{OV1} + R_{OV2}}{R_{OV1}} \right) \quad (42)$$

降圧および昇降圧:

$$V_{O(OV)} = V_{OVP(THR)} \times \frac{R_{OV2}}{R_{OV1}} + 0.7 \quad (43)$$

過電圧ヒステリシス $V_{OV(HYS)}$ は、次のようにになります。

$$V_{OV(HYS)} = I_{OVP(HYS)} \times R_{OV2} \quad (44)$$

### 8.1.12 PWM調光に関する考慮事項

PWM調光を行う場合、TPS92691-Q1では、LED負荷と直列に追加のMOSFETが必要になります。このMOSFETは、出力電圧 $V_O$ よりも大きな電圧定格と、公称LED電流 $I_{LED}$ よりも10%以上大きな電流定格を持つ必要があります。

PWMの立ち上がりエッジ遷移に対して、抑制されたLED電流応答を実現するためには、外部FETのスルーレートを制御することが重要です。ローサイドのNチャネル調光FETに対しては、GATEピンと直列に抵抗を配置することでスルーレートを制御します。立ち上がりおよび立ち下がり時間は、この抵抗の値およびMOSFETのゲート-ソース間容量に依存します。直列抵抗をダイオードでバイパスすることにより、立ち上がり時間を速く、立ち下がり時間を遅くして、100:1以上のコントラスト比を得ることができます。ハイサイドのPチャネル調光FETを使用する場合は、レベルシフト回路に適切な抵抗( $R_{LS1}$ および $R_{LS2}$ )を選択することで、立ち上がりおよび立ち下がり時間を制御できます(図 26を参照)。

## 8.2 代表的なアプリケーション

### 8.2.1 代表的な昇圧LEDドライバ

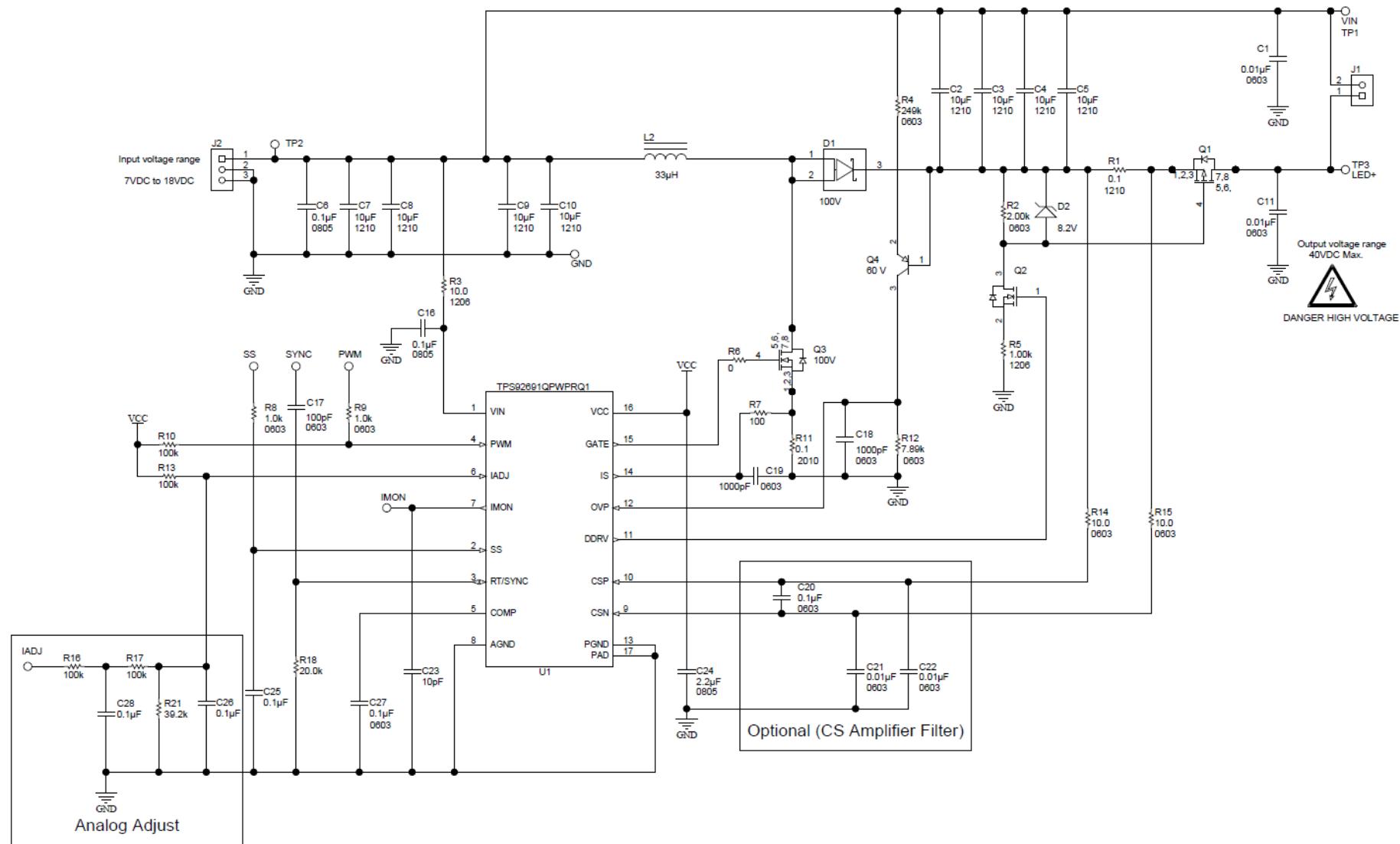

図 32. ハイサイド電流センスによる昇圧LEDドライバ

### 8.2.1.1 設計要件

表 2 に、昇圧LEDドライバ・アプリケーションの設計パラメータを示します。

**表 2. 設計パラメータ**

| パラメータ               | 測定条件             | 最小   | 標準   | 最大 | 単位       |

|---------------------|------------------|------|------|----|----------|

| <b>入力特性</b>         |                  |      |      |    |          |

| 入力電圧範囲              |                  | 7    | 14   | 18 | V        |

| 入力UVLO設定            |                  | 4.5  |      |    | V        |

| <b>出力特性</b>         |                  |      |      |    |          |

| LED順方向電圧            |                  | 3.2  |      |    | V        |

| 直列LED数              |                  | 12   |      |    |          |

| $V_O$               | 出力電圧 LED+ ~ LED- | 38.4 |      |    | V        |

| $I_{LED}$           | 出力電流             | 500  |      |    | mA       |

| $RR$                | LED電流リップル比       | 5%   |      |    |          |

| $r_D$               | LEDストリング抵抗       | 4    |      |    | $\Omega$ |

| 最大出力電力              |                  | 20   | 25   |    | W        |

| PWM調光範囲             | 240HzのPWM周波数     | 4%   | 100% |    |          |

| <b>システム特性</b>       |                  |      |      |    |          |

| $\Delta i_L(PP)$    | インダクタ電流リップル      | 20%  |      |    |          |

| $\Delta V_{IN(PP)}$ | 入力電圧リップル         | 70   |      |    | mV       |

| $V_{O(OV)}$         | 出力過電圧保護スレッショルド   | 50   |      |    | V        |

| $V_{OV(HYS)}$       | 出力過電圧保護ヒステリシス    | 5    |      |    | V        |

| $t_{ss}$            | ソフト・スタート時間       | 8    |      |    | ms       |

| スイッチング周波数           |                  | 390  |      |    | kHz      |

### 8.2.1.2 詳細な設計手順

この手順は、昇圧LEDドライバ・アプリケーションに対するものです。

#### 8.2.1.2.1 デューティ・サイクルの計算

D、 $D_{MAX}$ 、および $D_{MIN}$ を求めます。

$$D = \frac{V_O - V_{IN}}{V_O} = \frac{38.4 - 14}{38.4} = 0.6354 \quad (45)$$

$$D_{MAX} = \frac{V_O - V_{IN(MIN)}}{V_O} = \frac{38.4 - 7}{38.4} = 0.8177 \quad (46)$$

$$D_{MIN} = \frac{V_O - V_{IN(MAX)}}{V_O} = \frac{38.4 - 18}{38.4} = 0.5312 \quad (47)$$

#### 8.2.1.2.2 スイッチング周波数の設定

$R_T$ を求めます。

$$R_T = \frac{1.432 \times 10^{10}}{(f_{SW})^{1.047}} = \frac{1.432 \times 10^{10}}{(390 \times 10^3)^{1.047}} = 20.05 \times 10^3 \quad (48)$$

最も近い標準値である20k $\Omega$ を選択します。

#### 8.2.1.2.3 インダクタの選択

インダクタの値は、連続導通モード(CCM)の動作を確保し、目的のリップル仕様 $\Delta i_L(PP)$ が得られるように選択する必要があります。

$$\Delta i_{L(PP)} = RR \times \frac{I_{LED}}{1 - D_{MAX}} = 0.2 \times \frac{0.5}{1 - 0.8177} = 0.5485 \quad (49)$$

インダクタの値を求めます。

$$L = \frac{V_{IN(MIN)} \times D_{MAX}}{\Delta i_{L(PP)} \times f_{SW}} = \frac{7 \times 0.8177}{0.5485 \times 390 \times 10^3} = 26.76 \times 10^{-6} \quad (50)$$

最も近い標準インダクタは27μFです。選択したインダクタに基づくインダクタ・リップルの期待値は次のようにになります。

$$\Delta i_{L(PP)} = \frac{V_{IN(MIN)} \times D_{MAX}}{L \times f_{SW}} = \frac{7 \times 0.8177}{27 \times 10^{-6} \times 390 \times 10^3} = 0.5436 \quad (51)$$

インダクタの飽和電流定格は、ピーク・インダクタ電流*I<sub>L(PK)</sub>*よりも大きい必要があります。

$$I_{L(PK)} = \frac{I_{LED}}{1 - D_{MAX}} + \frac{V_{IN(MIN)} \times D_{MAX}}{2 \times L \times f_{SW}} = \frac{0.5}{1 - 0.8177} + \frac{7 \times 0.8177}{2 \times 27 \times 10^{-6} \times 390 \times 10^3} = 3.01 \quad (52)$$

#### 8.2.1.2.4 出力コンデンサの選択

仕様で規定されるピーク・ツー・ピークLED電流リップルΔ*i<sub>LED(PP)</sub>*は、次のとおりです。

$$\Delta i_{LED(PP)} = 0.05 \times I_{LED} = 25 \times 10^{-3} \quad (53)$$

目標のLED電流リップルを実現するために必要な出力容量は、次のようにになります。

$$C_{OUT} = \frac{I_{LED} \times D_{MAX}}{f_{SW} \times r_D \times \Delta i_{LED(PP)}} = \frac{0.5 \times 0.8177}{390 \times 10^3 \times 4 \times 25 \times 10^{-3}} = 10.48 \times 10^{-6} \quad (54)$$

DCバイアス動作で40%のディレーティング係数を考慮し、4.7μFの100V定格X7Rセラミック・コンデンサを4個並列に使用することで、18.8μFの結合出力容量が得られます。

#### 8.2.1.2.5 入力コンデンサの選択

入力コンデンサは、入力配線を通して伝達されるスイッチング・ノイズを低減し、LEDドライバの入力インピーダンスを小さくするために必要です。ピーク・ツー・ピーク入力リップル電圧Δ*V<sub>IN(PP)</sub>*を70mVに制限するためには必要なコンデンサは、次の式で与えられます。

$$C_{IN} = \frac{\Delta i_{L(PP)}}{8 \times f_{SW} \times \Delta V_{IN(PP)}} = \frac{0.5436}{8 \times 390 \times 10^3 \times 70 \times 10^{-3}} = 2.49 \times 10^{-6} \quad (55)$$

4.7μF/50VのX7Rセラミック・コンデンサを選択します。

#### 8.2.1.2.6 メインNチャネルMOSFETの選択

MOSFETの定格は、以下で与えられる最大出力電圧およびRMSスイッチ電流を上回っている必要があります。

$$V_{DS} = V_{O(OV)} \times 1.2 = 50 \times 1.2 = 60 \quad (56)$$

$$I_{Q(RMS)} = I_{LED} \times \frac{\sqrt{D_{MAX}}}{1 - D_{MAX}} = 0.5 \times \frac{\sqrt{0.8177}}{1 - 0.8177} = 2.48 \quad (57)$$

この設計に対しては、電流定格が3Aを超える60Vまたは100VのNチャネルMOSFETが必要となります。

#### 8.2.1.2.7 整流ダイオードの選択

ダイオードは、以下の電圧および電流定格に基づいて選択する必要があります。

$$V_{D(BR)} = V_{O(OV)} \times 1.2 = 50 \times 1.2 = 60 \quad (58)$$

$$I_D = I_L \times (1 - D_{MAX}) = I_{LED} = 0.5 \quad (59)$$

この設計に対しては、逆方向リーケ電流が低い60Vまたは100Vのショットキー・ダイオードが適しています。パッケージは、0.5Aの連続順方向電流 $I_D$ によって生じる消費電力を処理できる必要があります。

### 8.2.1.2.8 LED電流のプログラミング

LED電流は、電流シャント抵抗 $R_{CS}$ と、IADJピンの電圧 $V_{IADJ}$ によって設定される $V_{(CSP-CSN)}$ スレッショルドに基づいています。デフォルトで、IADJは外付け抵抗を通してVCCに接続されます。それによって、2.42Vの内部リファレンス電圧がインバブルになり、 $V_{(CSP-CSN)}$ スレッショルドは172mVに設定されます。電流シャント抵抗の値は次の式で計算されます。

$$R_{CS} = \frac{0.172}{I_{LED}} = \frac{0.172}{0.5} = 0.344 \quad (60)$$

0.68Ωの抵抗を2個並列に接続して、0.34Ωの $R_{CS}$ を実現します。

### 8.2.1.2.9 スイッチ電流制限およびスロープ補償の設定

スイッチ電流センス抵抗 $R_{IS}$ は、以下の式を計算し、最小の値を選択することによって決定します。

$$R_{IS} = \frac{2 \times V_{SL} \times L \times f_{SW}}{V_{O(MAX)}} = \frac{2 \times 0.2 \times 27 \times 10^{-6} \times 390 \times 10^3}{38.4} = 0.11 \quad (61)$$

$$R_{IS} = \frac{V_{IS(LIMIT)} - V_{SL} \times D_{MAX}}{I_{L(PK)}} = \frac{0.525 - 0.2 \times 0.8177}{3.01} = 0.12 \quad (62)$$

標準値である0.1Ωを選択します。

### 8.2.1.2.10 補償パラメータの導出

昇圧コンバータの変調器伝達関数は、公称 $V_{IN}$ 電圧および対応するデューティ・サイクルDに対して導出され、次の式で与えられます。(詳細については、表 1 を参照してください。)

$$\frac{\hat{v}_{LED}}{\hat{v}_{COMP}} = G_0 \frac{\left(1 - \frac{s}{\omega_Z}\right)}{\left(1 + \frac{s}{\omega_P}\right)} = 3.466 \frac{\left(1 - \frac{s}{378.12 \times 10^3}\right)}{\left(1 + \frac{s}{14 \times 10^3}\right)} \quad (63)$$

比例積分補償部品である $C_{COMP}$ および $R_{COMP}$ は、以下の式によって求められます。

$$C_{COMP} = 8.75 \times 10^{-3} \times \left( \frac{R_{CS} \times G_0}{\omega_Z} \right) = 8.75 \times 10^{-3} \times \left( \frac{0.34 \times 3.466}{378.12 \times 10^3} \right) = 27.27 \times 10^{-9} \quad (64)$$

$$R_{COMP} = \frac{1}{\omega_P \times C_{COMP}} = \frac{1}{14 \times 10^3 \times 33 \times 10^{-9}} = 2.165 \times 10^3 \quad (65)$$

最も近い標準値として33nFのコンデンサと2.15kΩの抵抗を選択します。高周波極の位置は、100pFの $C_{HF}$ コンデンサによって設定されます。

### 8.2.1.2.11 スタートアップ時間の設定

8msでのスタートアップを実現するために必要なソフト・スタート・コンデンサは、次の式で与えられます。

$$C_{SS} = 12.5 \times 10^{-6} \left( t_{SS} - \frac{C_{OUT} \times V_{OUT}}{I_{LED}} \right) = 12.5 \times 10^{-6} \left( 8 \times 10^{-3} - \frac{18.8 \times 10^{-6} \times 38.4}{0.5} \right) = 81.9 \times 10^{-9} \quad (66)$$

最も近い標準コンデンサである100nFを選択します。

### 8.2.1.2.12 過電圧保護スレッショルドの設定

50Vの過電圧保護スレッショルドと5Vのヒステリシスは、分圧抵抗 $R_{OV1}$ および $R_{OV2}$ によって設定されます。

$$R_{OV2} = \frac{V_{OV(HYS)}}{20 \times 10^{-6}} = \frac{5}{20 \times 10^{-6}} = 250 \times 10^3 \quad (67)$$

$$R_{OV1} = \left( \frac{1.24}{V_{O(OV)} - 1.24} \right) R_{OV2} = \left( \frac{1.24}{50 - 1.24} \right) 250 \times 10^3 = 6.36 \times 10^3 \quad (68)$$

標準抵抗値である249kΩおよび6.34kΩを選択します。

#### 8.2.1.2.13 PWM調光に関する考慮事項

直列調光FETは、100%～4%のデューティ・サイクルというPWM調光仕様を満たす必要があります。このアプリケーションには、60V、2AのNチャネルFETが適しています。

または、60V、2AのPチャネルFETを使用してPWM調光を実現することもできます。Pチャネル調光FETのゲートへのDDRV信号の変換には、外部にレベルシフト回路が必要です。1kΩおよび2kΩのレベル・トランジスタ抵抗と小信号NチャネルMOSFETによって、5mAの駆動能力と15Vのゲート-ソース間電圧が設定されます。このNチャネルMOSFETのゲートはDDRVに接続します。

デフォルトでは、PWMピンが100kΩの抵抗を通してVCCに接続され、スタートアップ時にデバイスがイネーブルになります。

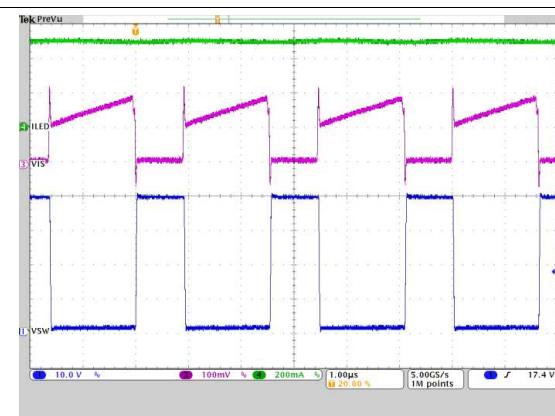

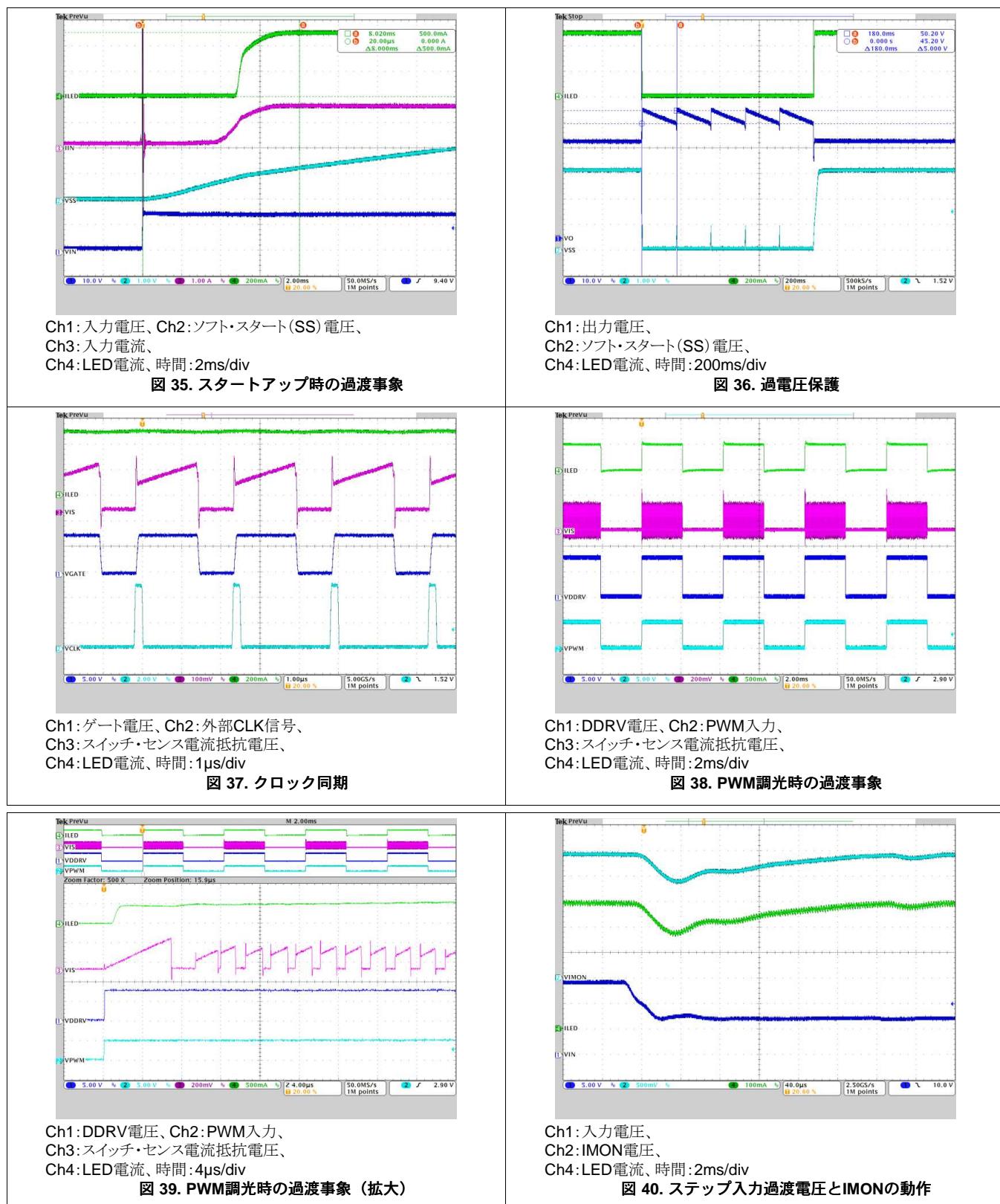

#### 8.2.1.3 アプリケーション曲線

これらの曲線は、昇圧LEDドライバに対するものです。

## 8.2.2 代表的な昇降圧LEDドライバ

図 41. 昇降圧LEDドライバ

### 8.2.2.1 設計要件

昇降圧LEDドライバは、複数のLED負荷構成をサポートするアプリケーションに必要な柔軟性を提供します。そのようなアプリケーションに対しては、より広い範囲の出力電圧およびLED電流仕様に対応できるように、「[アプリケーション情報](#)」で示した設計手順を変更する必要があります。この設計は、照明アプリケーション用のルーメン出力仕様によって設定される、最大出力電力  $P_{O(MAX)}$ に基づいています。ここでは、3~9個のLEDを直列に接続した、最大出力電力15Wのバッテリ駆動アプリケーションに対する設計手順の概要を示します。

固定された数のLEDを使用し、(輝度補正用に)狭いLED電流範囲を持つアプリケーションの場合は、より低いBOMコストで最適化された回路を開発するために、「[アプリケーション情報](#)」で示された設計式とともに、「[代表的な昇圧LEDドライバ](#)」で昇圧LEDドライバに対して示されたような単純化された設計手順を使用することを推奨します。

**表 3. 設計パラメータ**

| パラメータ                | 測定条件              | 最小  | 標準   | 最大   | 単位       |

|----------------------|-------------------|-----|------|------|----------|

| <b>入力特性</b>          |                   |     |      |      |          |

| 入力電圧範囲               |                   | 7   | 14   | 18   | V        |

| 入力UVLO設定             |                   | 4.5 |      |      | V        |

| <b>出力特性</b>          |                   |     |      |      |          |

| LED順方向電圧             |                   | 3.2 |      |      | V        |

| 直列LED数               |                   | 3   | 6    | 9    |          |

| $V_O$                | 出力電圧              | 9.6 | 19.2 | 28.8 | V        |

| $I_{LED}$            | 出力電流              | 500 | 750  | 1500 | mA       |

| $\Delta i_{LED(PP)}$ | LED電流リップル         | 5%  |      |      |          |

| $r_D$                | LEDストリング抵抗        | 1   | 2    | 3    | $\Omega$ |

| $P_{O(MAX)}$         | 最大出力電力            |     |      | 15   | W        |

| PWM調光範囲              | 240HzのPWM周波数      | 4%  |      | 100% |          |

| <b>システム特性</b>        |                   |     |      |      |          |

| $P_{O(BDRY)}$        | CCM-DCM境界条件での出力電力 | 5   |      |      | W        |

| $\Delta V_{IN(PP)}$  | 入力電圧リップル          | 70  |      |      | mV       |

| $V_{O(OV)}$          | 出力過電圧保護スレッショルド    | 40  |      |      | V        |

| $V_{OV(HYS)}$        | 出力過電圧保護ヒステリシス     | 5   |      |      | V        |

| $t_{ss}$             | ソフト・スタート時間        | 8   |      |      | ms       |

| スイッチング周波数            |                   | 390 |      |      | kHz      |

### 8.2.2.2 詳細な設計手順

#### 8.2.2.2.1 デューティ・サイクルの計算

D、 $D_{MAX}$ 、および $D_{MIN}$ を求めます。

$$D = \frac{V_O}{V_O + V_{IN}} = \frac{19.2}{19.2 + 14} = 0.5783 \quad (69)$$

$$D_{MAX} = \frac{V_{O(MAX)}}{V_{O(MAX)} + V_{IN(MIN)}} = \frac{28.8}{28.8 + 7} = 0.8045 \quad (70)$$

$$D_{MIN} = \frac{V_{O(MIN)}}{V_{O(MIN)} + V_{IN(MAX)}} = \frac{9.6}{9.6 + 18} = 0.3478 \quad (71)$$

#### 8.2.2.2.2 スイッチング周波数の設定

抵抗  $R_T$ を求めます。

$$R_T = \frac{1.432 \times 10^{10}}{(f_{SW})^{1.047}} = \frac{1.432 \times 10^{10}}{(390 \times 10^3)^{1.047}} = 20.05 \times 10^3 \quad (72)$$

### 8.2.2.2.3 インダクタの選択

インダクタは、CCM-DCM境界電力要件である  $P_{O(BDRY)}$  を満たすように選択します。一般に、この境界条件は、最小のLED順方向電圧降下とLED電流に基づき、可能な最小の動作電力でCCM動作がイネーブルになるよう設定されます。ほとんどのアプリケーションでは、 $P_{O(BDRY)}$  は最大出力電力  $P_{O(MAX)}$  の  $1/3$  に設定されます。インダクタの値は、最大入力電圧  $V_{IN(MAX)}$  および最大出力電圧  $V_{O(MAX)}$  に対して計算します。

$$L = \frac{1}{2 \times P_{O(BDRY)} \times f_{SW} \times \left( \frac{1}{V_{O(MAX)}} + \frac{1}{V_{IN(MAX)}} \right)^2} = \frac{1}{2 \times 5 \times 390 \times 10^3 \times \left( \frac{1}{28.8} + \frac{1}{18} \right)^2} = 31.46 \times 10^{-6} \quad (73)$$

最も近い標準値である  $33\mu H$  を選択します。インダクタのリップル電流は、次の式で与えられます。

$$\Delta i_L(PP) = \frac{V_{IN(MIN)} \times D_{MAX}}{L \times f_{SW}} = \frac{7 \times 0.8045}{33 \times 10^{-6} \times 390 \times 10^3} = 0.4376 \quad (74)$$

インダクタの飽和定格は、最大出力電力に基づいて次の式で計算されるピーク電流値を上回る必要があります。

$$I_{L(PK)} = P_{O(MAX)} \times \left( \frac{1}{V_{O(MIN)}} + \frac{1}{V_{IN(MIN)}} \right) + \frac{V_{O(MIN)} \times V_{IN(MIN)}}{2 \times L \times f_{SW} \times (V_{O(MIN)} + V_{IN(MIN)})} \quad (75)$$

$$I_{L(PK)} = 15 \times \left( \frac{1}{9.6} + \frac{1}{7} \right) + \frac{9.6 \times 7}{2 \times 33 \times 10^{-6} \times 390 \times 10^3 \times (9.6 + 7)} = 3.863$$

### 8.2.2.2.4 出力コンデンサの選択

出力コンデンサは、5%のピーク・ツー・ピークLED電流リップル仕様を達成するように選択する必要があります。最大電力に基づき、コンデンサは次の式で計算されます。

$$C_{OUT} = \frac{P_{O(MAX)}}{f_{SW} \times r_{D(MIN)} \times \Delta i_{LED(PP)} \times (V_{O(MIN)} + V_{IN(MIN)})} \quad (76)$$

$$C_{OUT} = \frac{15}{390 \times 10^3 \times 1 \times 0.075 \times (9.6 + 7)} = 30.9 \times 10^{-6}$$

出力電力の範囲全体にわたってLED電流リップル仕様を満たすために、最小で4個の  $10\mu F/50V X7R$  セラミック・コンデンサを並列で使用する必要があります。DCバイアス動作でのディレーティング係数に基づいて、追加の容量が必要となる場合もあります。

### 8.2.2.2.5 入力コンデンサの選択

入力コンデンサは、ピーク・ツー・ピーク入力リップル仕様  $\Delta V_{IN(PP)}$  に基づいて計算します。動作範囲全体にわたってリップルを  $70mV$  に制限するために必要なコンデンサは、次のように求められます。

$$C_{IN} = \frac{P_{O(MAX)}}{f_{SW} \times \Delta V_{IN(PP)} \times (V_{O(MIN)} + V_{IN(MIN)})} = \frac{15}{390 \times 10^3 \times 0.07 \times (9.6 + 7)} = 33.1 \times 10^{-6} \quad (77)$$

$10\mu F/50V$  の  $X7R$  セラミック・コンデンサを4個並列に使用することで、 $40\mu F$  の結合容量が得られます。DCバイアス動作でのディレーティング係数に基づいて、追加の容量が必要となる場合もあります。

### 8.2.2.2.6 メインNチャネルMOSFETの選択

トランジスタの最小電圧定格および電流定格を計算します。

$$V_{DS} = 1.2 \times (V_{O(OV)} + V_{IN(MAX)}) = 1.2 \times (40 + 18) = 69.6 \quad (78)$$

$$I_{Q(RMS)} = \frac{P_{O(MAX)}}{V_{IN(MIN)}} \sqrt{1 + \frac{V_{IN(MIN)}}{V_{O(MIN)}}} = \frac{15}{7} \sqrt{1 + \frac{7}{9.6}} = 2.82 \quad (79)$$

このアプリケーションでは、電流定格が3Aを超える60Vまたは100VのNチャネルMOSFETが必要となります。

### 8.2.2.2.7 整流ダイオードの選択

ショットキー・ダイオードの最小電圧定格および電流定格を計算します。

$$V_{D(BR)} = 1.2 \times (V_{O(OV)} + V_{IN(MAX)}) = 1.2 \times (40 + 18) = 69.6 \quad (80)$$

$$I_D = I_{LED(MAX)} = 1.5 \quad (81)$$

このアプリケーションでは、電流定格が1.5Aを超える60Vまたは100Vのショットキー・ダイオードが必要となります。温度範囲全体にわたって信頼性の高い動作を確保するために、複数の低電流定格ダイオードを並列に使用する代わりに、1個の高電流ダイオードを使用することを推奨します。

### 8.2.2.2.8 スイッチ電流制限およびスロープ補償の設定

$R_{IS}$ を求めます。

$$R_{IS} = \frac{2 \times V_{SL} \times L \times f_{SW}}{V_{O(MAX)}} = \frac{2 \times 0.2 \times 33 \times 10^{-6} \times 390 \times 10^3}{28.8} = 0.179 \quad (82)$$

$$R_{IS} = \frac{V_{IS(LIMIT)} - V_{SL} \times D_{MAX}}{I_{L(PK)}} = \frac{0.525 - 0.2 \times 0.8045}{3.863} = 0.094 \quad (83)$$

2つの計算値のうち小さい方の値に基づき、 $0.1\Omega$ の標準抵抗を選択します。この抵抗により、入力および出力電圧範囲全体にわたって、低調波発振のない安定した電流ループ動作が実現されます。

### 8.2.2.2.9 LED電流のプログラミング

LED電流は、LEDストリング構成と一致するようにプログラミングできます。これは、図 21に示されるように、与えられたセンス抵抗 $R_{CS}$ に対して、 $V_{CC}$ とGNDの間に分圧抵抗 $R_{ADJ1}$ および $R_{ADJ2}$ を接続することにより行います。精度を最大限に高めるために、仕様のLED電流1.5Aに対して、IADJピンの電圧は2.1Vに設定します。それにより、電流センス抵抗 $R_{CS}$ は次のように求められます。

$$R_{CS} = \frac{V_{IADJ}}{14 \times I_{LED(MAX)}} = \frac{2.1}{14 \times 1.5} = 0.1 \quad (84)$$

標準抵抗である $0.1\Omega$ を選択します。表 4に、各種の電流設定に対するIADJピンの電圧と $R_{ADJ1}$ および $R_{ADJ2}$ 抵抗の選択肢をまとめます。

表 4. 設計要件

| LED電流 | IADJ電圧( $V_{IADJ}$ ) | $R_{ADJ1}$ | $R_{ADJ2}$ |

|-------|----------------------|------------|------------|

| 500mA | 700mV                | 10.2kΩ     | 100kΩ      |

| 750mA | 1.05V                | 16.2kΩ     | 100kΩ      |

| 1.5A  | 2.1V                 | 39.2kΩ     | 100kΩ      |

### 8.2.2.2.10 補償パラメータの導出

単純な積分補償器を使用することにより、幅広い動作範囲の全体にわたって安定した動作を実現するための適切な開始点が得られます。最小の周波数極位置を持つ変調器の伝達関数は、最大出力電圧 $V_{O(MAX)}$ 、デューティ・サイクル $D_{MAX}$ 、LEDの動的抵抗 $r_{D(MAX)}$ 、および最小LEDストリング電流 $I_{LED(MIN)}$ に基づいて計算されます。(詳細については、表1を参照してください。)

$$\frac{\hat{I}_{LED}}{\hat{V}_{COMP}} = G_0 \frac{\left(1 - \frac{s}{\omega_Z}\right)}{\left(1 + \frac{s}{\omega_P}\right)} = 1.876 \frac{\left(1 - \frac{s}{82.92 \times 10^3}\right)}{\left(1 + \frac{s}{8.68 \times 10^3}\right)} \quad (85)$$

安定した動作を実現するために必要な補償用コンデンサは、次のようにになります。

$$C_{COMP} = \frac{8.75 \times 10^{-3} \times R_{CS}}{\omega_P} = \frac{8.75 \times 10^{-3} \times 0.1}{8.68 \times 10^3} = 100.8 \times 10^{-9} \quad (86)$$

100nFのコンデンサを選択します。

より高い帯域幅と優れた過渡性能を実現するために、比例積分補償器を使用することもできます。ただし、安定した動作を確保するには、動作範囲全体にわたって補償器のパラメータを実験的に調整する必要があります。

### 8.2.2.2.11 スタートアップ時間の設定

8msのスタートアップ時間に基づき、ソフト・スタート・コンデンサ $C_{SS}$ の値を求めます。

$$C_{SS} = 12.5 \times 10^{-6} \left( t_{SS} - \frac{C_{OUT} \times V_{OUT(MAX)}}{I_{LED(MIN)}} \right) = 12.5 \times 10^{-6} \left( 8 \times 10^{-3} - \frac{40 \times 10^{-6} \times 28.8}{0.5} \right) = 71.2 \times 10^{-9} \quad (87)$$

100nFのソフト・スタート・コンデンサを選択します。

### 8.2.2.2.12 過電圧保護スレッショルドの設定

抵抗 $R_{OV1}$ および $R_{OV2}$ の値を求めます。

$$R_{OV2} = \frac{V_{OV(HYS)}}{20 \times 10^{-6}} = \frac{5}{20 \times 10^{-6}} = 250 \times 10^3 \quad (88)$$

$$R_{OV1} = \frac{1.24 \times R_{OV2}}{V_{O(OV)} - 0.7} = \frac{1.24 \times 250 \times 10^3}{40 - 0.7} = 7.89 \times 10^3 \quad (89)$$

最も近い標準値である249kΩと7.87kΩ、および60VのPNPトランジスタを使用して、OVPスレッショルドを40V(ヒステリシス5V)に設定します。

### 8.2.2.2.13 PWM調光に関する考慮事項

60V、2AのPチャネルFETを外部のレベルシフト回路とともに使用して、PWM調光を実現します。1kΩおよび2kΩのレベル・トランスレータ抵抗と小信号NチャネルMOSFETによって、5mAの駆動能力と15Vのゲート-ソース間電圧が設定されます。このNチャネルMOSFETのゲートはDDRVに接続します。

### 8.2.2.3 アプリケーション曲線

これらの曲線は、昇降圧LEDドライバに対するものです。

## 9 電源に関する推奨事項

このデバイスは、4.5V～65Vの入力電源電圧範囲で動作するよう設計されています。入力には車載バッテリまたは他のレギュレーション済み電源を使用できます。入力電源がTPS92691/-Q1デバイスから数インチ以上離れている場合は、ノイズやEMIの問題に対処するために、セラミック・バイパス・コンデンサに加えて追加のバルク容量または入力フィルタが必要となることがあります。

## 10 レイアウト

### 10.1 レイアウトのガイドライン

- スイッチング・レギュレータの性能は、部品の選択だけでなくPCBのレイアウトにも依存します。いくつかの単純なガイドラインに従うことで、ノイズをできる限り除去し、回路内でのEMIの発生を最小限に抑えることができます。

- 最もEMIが発生しやすいのは不連続電流です。したがって、これらの経路の配線には注意してください。TPS92691/-Q1降圧レギュレータ内の不連続電流の主要な経路には、入力コンデンサC<sub>IN</sub>、再循環ダイオードD、NチャネルMOSFET Q1、および直列抵抗R<sub>S</sub>が含まれます。TPS92691/-Q1昇圧レギュレータでは、不連続電流は出力コンデンサC<sub>OUT</sub>、ダイオードD、NチャネルMOSFET Q1、および電流センス抵抗R<sub>IS</sub>を通って流れます。昇降圧レギュレータの場合は、両方のループが不連続であるため、注意深くレイアウトを行う必要があります。寄生インダクタンスを最小限に抑えるために、これらのループはできる限り小さくし、すべてのコンポーネント間を太く短いパターンで接続する必要があります。特に、(L、D、Q1が接続される)スイッチ・ノードは、コンポーネントの接続に必要な最小限の大きさにします。

## レイアウトのガイドライン (continued)

スイッチ・ノードの短い電流経路に隣接させて大きな銅箔を配置することにより、過度の発熱を最小限に抑えることができます。

- CSPおよびCSNのパターンは、ケルビン接続を使用して一緒に電流センス抵抗へと配線し、接続はできる限り短くします。必要に応じて、コモン・モードおよび差動モードのノイズ・フィルタを使用してスイッチング・ノイズやダイオードの逆方向回復ノイズを減衰させ、内部の電流センス・アンプに影響を与えないようにします。

- COMP, IS, OVP, PWM, IADJの各ピンはすべて高インピーダンス入力であり、外部からのノイズが結合しやすいため、これらのノードを含むループは、可能な限り小さくする必要があります。

- アプリケーションによっては、LEDまたはLEDアレイをTPS92691/-Q1から遠く離して配置するか、またはワイヤリング・ハーネスで接続された別のPCB上に配置できます。出力コンデンサを使用していて、LEDアレイが大きいかまたはレギュレータの他の部分から分離されている場合には、コンデンサのACインピーダンスに対する寄生インダクタンスの影響を低減するために、出力コンデンサをLEDの近くに配置する必要があります。

- TPS92691/-Q1には、電力消費を助けるために露出したサーマル・パッドが備えられています。露出したパッドの下にいくつかのビアを追加すると、デバイスからの放熱性能が向上します。接合部-周囲間の熱抵抗はアプリケーションによって異なります。最も重要な変数は、PCB内の銅の面積と、露出したパッドの下のビアの数です。デバイスの露出したパッドをPCBに接続する際の半田付けの完全性は非常に重要です。過度のボイドが存在すると、放熱能力が低下します。

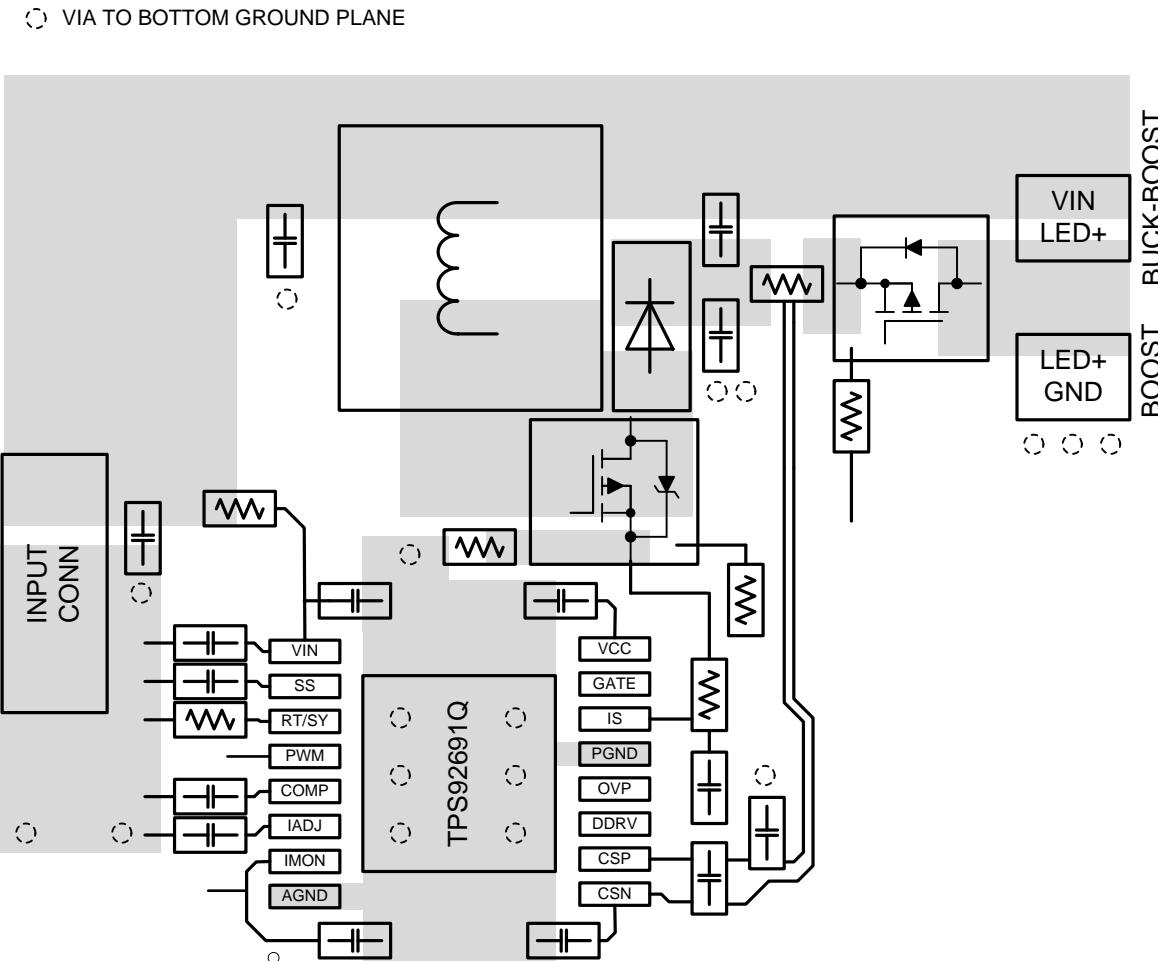

## 10.2 レイアウト例

図 45. レイアウトに関する推奨事項

## 11 デバイスおよびドキュメントのサポート

### 11.1 関連リンク

次の表に、クリック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクリック・アクセスが含まれます。

**表 5. 関連リンク**

| 製品          | プロダクト・フォルダ                    | サンプルとご購入                      | 技術資料                          | ツールとソフトウェア                    | サポートとコミュニティ                   |

|-------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| TPS92691    | <a href="#">ここをクリックしてください</a> |

| TPS92691-Q1 | <a href="#">ここをクリックしてください</a> |

### 11.2 コミュニティ・リソース

以下のリンクから、TIのコミュニティ・リソースにアクセスできます。リンクされているコンテンツは、投稿者のコンテンツがそのまま掲載されたものです。TIがこの内容を保証するものではなく、また必ずしもTIの見解が反映されたものではありません。TIの[使用条件](#)を参照してください。

"**TI E2E™オンライン・コミュニティ**" — **TIのE2E (Engineer-to-Engineer)** コミュニティ。エンジニア間の情報共有をサポートする目的で作成されたものです。[e2e.ti.com](http://e2e.ti.com)で質問し、知識を共有し、アイディアを検討するなど、技術的な問題を解決するためのコミュニティ・サイトです。

"**設計サポート**" — **TIの設計サポート** 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

### 11.3 商標

PowerPAD, E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.4 静電気放電に関する注意事項

これらのデバイスは、限定期的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 11.5 用語集

**SLYZ022 — TI用語集**.

この用語集には、用語や略語の一覧および定義が記載されています。

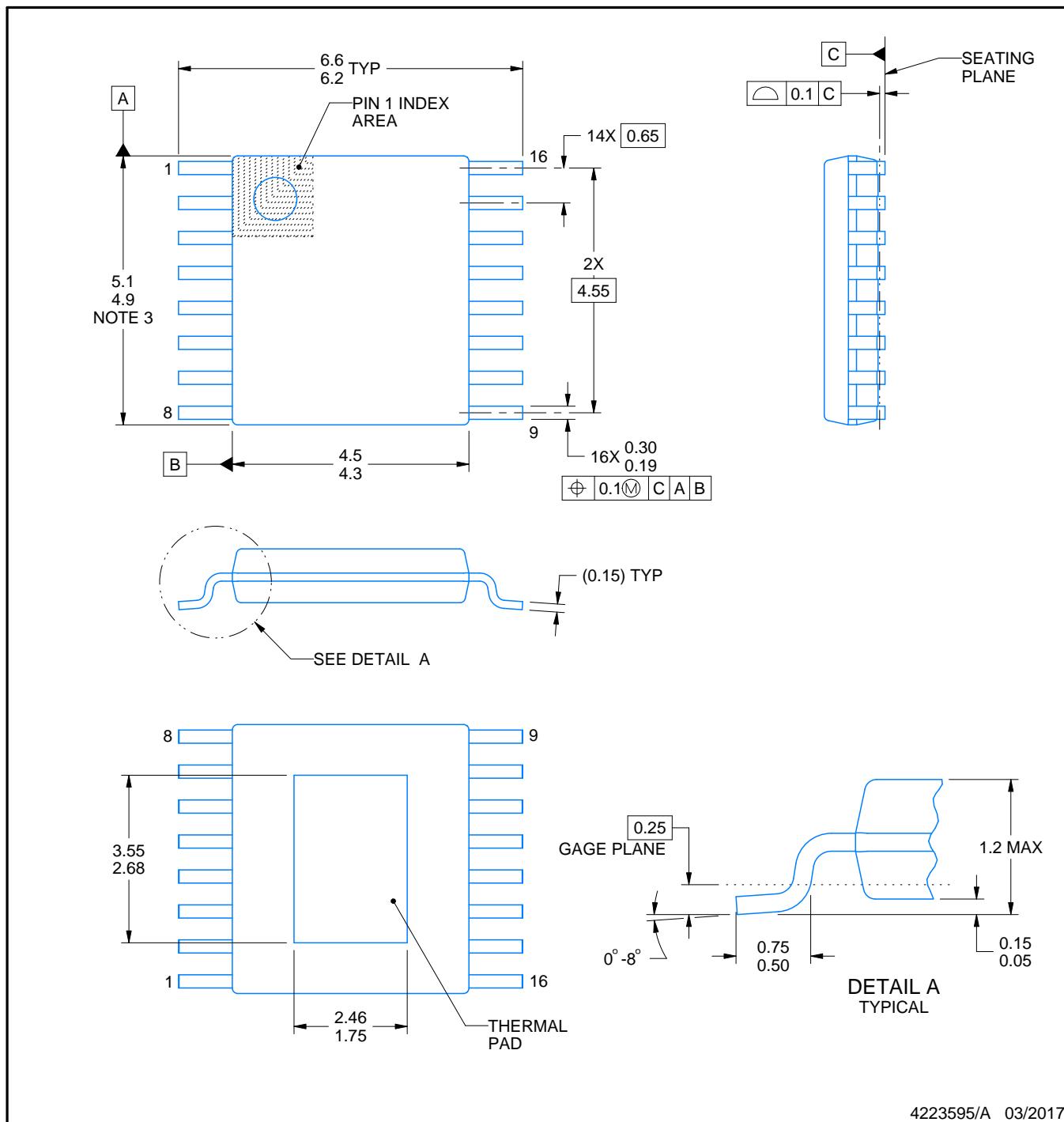

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number           | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|---------------------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS92691PWP</a>     | Active        | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691               |

| TPS92691PWP.A                   | Active        | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691               |

| <a href="#">TPS92691PWPR</a>    | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691               |

| TPS92691PWPR.A                  | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691               |

| <a href="#">TPS92691QPWPQ1</a>  | Active        | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691Q              |

| TPS92691QPWPQ1.A                | Active        | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691Q              |

| <a href="#">TPS92691QPWPRQ1</a> | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691Q              |

| TPS92691QPWPRQ1.A               | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691Q              |

| <a href="#">TPS92691QPWPTQ1</a> | Active        | Production           | HTSSOP (PWP)   16 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 92691Q              |