**TPS81256**

JAJSEO3D – JUNE 2012 – REVISED FEBRUARY 2018

# TPS81256 3W、高効率、 MicroSiP™パッケージの昇圧コンバータ

## 1 特長

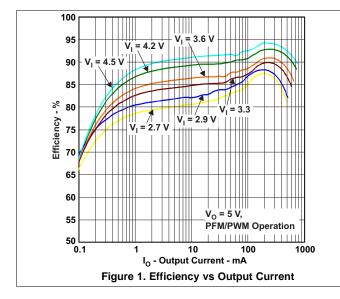

4MHz動作時に91%の効率

Instruments

- 2.5V~5.5Vの広いV<sub>IN</sub>範囲

- $V_{OUT} = 5.0V$ ,  $V_{IN} \ge 3.3V$   $CI_{OUT} \ge 550$  mA

- 固定出力電圧: 5.0V

- 合計DC電圧精度: ±2%

- 消費電流: 43uA

- クラス最高のラインおよび負荷過渡

- V<sub>IN</sub> ≥ V<sub>OUT</sub>の動作をサポート

- 低リップルの軽負荷PFMモード

- シャットダウン時に負荷を完全に切断

- サーマル・シャットダウンおよび過負荷保護機能

- 1mm未満の薄型のソリューション

- 合計ソリューション・サイズ < 9mm<sup>2</sup>

- 9ピンのMicroSiPパッケージ

## 2 アプリケーション

- 携帯電話、スマートフォン、タブレットPC

- モノラルおよびステレオAPAアプリケーション

- USB-OTG、HDMIアプリケーション

- USB充電ポート(5V)

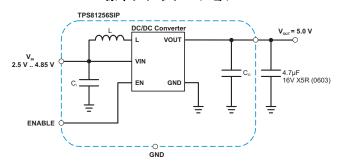

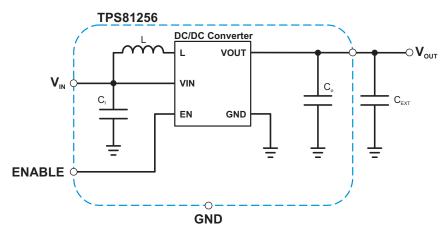

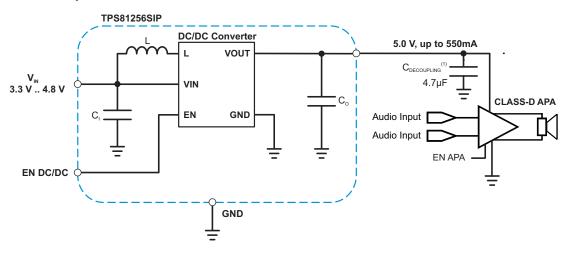

#### 標準アプリケーション

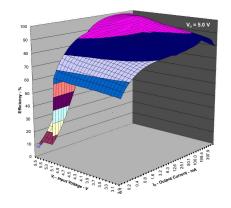

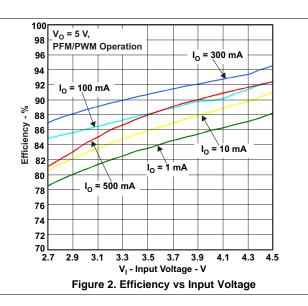

## 効率と負荷電流との関係

## 3 概要

TPS81256デバイスは完全なMicroSiP DC/DC昇圧電源 ソリューションで、バッテリ駆動の携帯アプリケーションを対 象としています。スイッチング・レギュレータ、インダクタ、入 出力コンデンサがパッケージに内蔵されています。小さな 出力コンデンサを追加するだけで、設計が完了します。

TPS81256は、バッテリ駆動の携帯アプリケーション用に 最適化された、高周波数の同期整流昇圧DC/DCコン バータを基礎としています。

このDC/DCコンバータはレギュレートされた4MHzのスイッチング周波数で動作し、負荷電流が小さいときはパワーセービング・モードの動作に移行して、負荷電流の全範囲にわたって高効率を維持します。

PFMモードでは、軽負荷動作時の静止電流が43µA (標準値)に低下し、バッテリ駆動時間が延長されます。 TPS81256は低消費電力のアプリケーションを意図しており、リチウムイオン・バッテリの電圧範囲の全体にわたって3Wを超える出力電力を供給できます。シャットダウン・モードでの入力電流は1µA未満(標準値)なので、バッテリ駆動時間を最大化できます。

TPS81256は外付け部品の数が最小限なので、9mm<sup>2</sup> 未満の非常に小型のソリューションを実現できます。このソリューションは小型(2.6mm×2.9mm)、薄型(1.0mm)の BGAパッケージに封入されており、標準的な表面実装機器による自動組み立てに適しています。

#### 製品情報®

| 型番       | パッケージ    | 本体サイズ(公称)       |

|----------|----------|-----------------|

| TPS81256 | μSIP (9) | 2.925mm×2.575mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

| _ |     |

|---|-----|

|   | ·77 |

|   |     |

|      | No. E                                                                         | 4       | ^                   | Application and Implementation           | 40   |

|------|-------------------------------------------------------------------------------|---------|---------------------|------------------------------------------|------|

| 1    | 特長アプリケーション                                                                    |         | 9                   | Application and Implementation           |      |

| 2    |                                                                               |         |                     | 9.1 Application Information              |      |

| 3    | 概要                                                                            |         |                     | 9.3 System Examples                      |      |

| 4    | 改訂履歴                                                                          |         | 10                  |                                          |      |

| 5    | Device Options                                                                |         |                     | Power Supply Recommendations             |      |

| 6    | Pin Configuration and Functions                                               |         | 11                  | <b>,</b>                                 |      |

| 7    | Specifications                                                                | 4       |                     | 11.1 Layout Guidelines                   |      |

|      | 7.1 Absolute Maximum Ratings                                                  | 4       |                     | 11.2 Layout Example                      |      |

|      | 7.2 ESD Ratings                                                               | 4       |                     | 11.3 Surface Mount Information           |      |

|      | 7.3 Recommended Operating Conditions                                          | 4       | 40                  | 11.4 Thermal and Reliability Information |      |

|      | 7.4 Thermal Information                                                       | 5       | 12                  | デバイスおよびドキュメントのサポート                       |      |

|      | 7.5 Electrical Characteristics                                                | 5       |                     | 12.1 デバイス・サポート                           |      |

|      | 7.6 Typical Characteristics                                                   | 6       |                     | 12.2 コミュニティ・リソース                         |      |

| 8    | Detailed Description                                                          | 9       |                     | 12.3 商標                                  |      |

|      | 8.1 Overview                                                                  | 9       |                     | 12.4 静電気放電に関する注意事項                       |      |

|      | 8.2 Functional Block Diagram                                                  | 9       |                     | 12.5 Glossary                            |      |

|      | 8.3 Feature Description                                                       | 9       | 13                  | メカニカル、パッケージ、および注文情報                      | 21   |

|      | 8.4 Device Functional Modes                                                   | 11      |                     |                                          |      |

|      | 番号末尾の英字は改訂を表しています。その改訂)<br>sion C (February 2016) から Revision D に変            |         |                     |                                          | Page |

| • /  | ペッケージの図面を更新                                                                   |         |                     |                                          | 22   |

| Revi | sion B (February 2015) から Revision C に変                                       | 更       |                     |                                          | Page |

| • *  | カニカル・データ図面と一致するよう、DとEの寸法                                                      | を入れ替え   | 説明で[8               | 3バンプ」を「9バンプ」に変更                          | 21   |

|      | 量加「コミュニティ・リソース」セクション                                                          |         |                     |                                          |      |

|      | 三加「コミューティ・リケーへ」 ピクション                                                         |         |                     |                                          | 21   |

| Revi | sion A (August 2013) から Revision B に変更                                        |         |                     |                                          | Page |

| ٢    | 製品情報」表、「ESD定格」表、「機能説明」セクション、「システム例」セクション、「電源に関する推奨事場が、、パッケージ、および注文情報」セクションを追り | 項」セクション | 、「デバイ               | <i>、スおよびドキュメントのサポート」セクション、「メカ</i>        | 7=   |

|      | Changed the pinout drawing to match the device                                |         |                     |                                          |      |

|      | E更 SIPパッケージの「上面図」画像の方向を、「YI                                                   |         |                     | _                                        |      |

|      | で、 ○ ・ ・                                                                      |         | , , , , , , , , , , | 1.7 CILO ( M ) 05/10 III                 |      |

| 2012 | 年6月発行のものから更新                                                                  |         |                     |                                          | Page |

# 5 Device Options

| PART NUMBER | OUTPUT VOLTAGE | PACKAGE MARKING<br>CHIP CODE |

|-------------|----------------|------------------------------|

| TPS81256    | 5.0V           | TT                           |

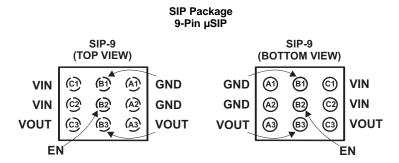

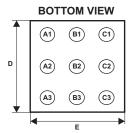

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN  |            | 1/0 | DESCRIPTION                                                                                                                                                                                                    |  |

|------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO.        | 1/0 | DESCRIPTION                                                                                                                                                                                                    |  |

| EN   | B2         | I   | This is the enable pin of the device. Connecting this pin to ground forces the device into shutdown mode. Pulling this pin high enables the device. This pin must not be left floating and must be terminated. |  |

| GND  | A1, A2, B1 |     | Ground pin.                                                                                                                                                                                                    |  |

| VIN  | C1, C2     | I   | Power supply input.                                                                                                                                                                                            |  |

| VOUT | A3, B3, C3 | 0   | Boost converter output.                                                                                                                                                                                        |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                         |                                                                         | MIN  | MAX                | UNIT |

|-----------------------------------------|-------------------------------------------------------------------------|------|--------------------|------|

| Input voltage                           | Voltage at VIN <sup>(2)</sup> , VOUT <sup>(2)</sup> , EN <sup>(2)</sup> | -0.3 | 6                  | V    |

| I and a sum of                          | Continuous average current into VIN (3)                                 |      | 1.05               | Α    |

| Input current                           | Pulsed current into VIN (4)                                             |      | 1.3                | Α    |

| Power dissipation                       |                                                                         |      | Internally limited |      |

| Operating temperature, T <sub>A</sub> ( | 3)(4)(5)                                                                | -40  | 85                 | °C   |

| Operating virtual junction te           | mperature, T <sub>J</sub>                                               | -40  | 150                | °C   |

| Storage temperature, T <sub>stg</sub>   |                                                                         | -55  | 125                | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2) All voltages are with respect to network ground terminal.

- (3) Limit the junction and the (top side) inductor case temperature to 110°C, limit the (top side) capacitor case temperature to 85°C for 2000h operation at maximum output power. Contact TI for more details on lifetime estimation.

- (4) Limit the (top side) inductor case temperature to 140°C and the (top side) capacitor temperature to 115°C for 100h operation. Contact TI for more details on lifetime estimation.

- (5) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A(max)</sub>) is dependent on the maximum operating junction temperature (T<sub>J(max)</sub>), the maximum power dissipation of the device in the application (P<sub>D(max)</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A(max)</sub> = T<sub>J(max)</sub> (θ<sub>JA</sub> X P<sub>D(max)</sub>). To achieve optimum performance, it is recommended to operate the device with a maximum junction temperature of 125°C, a maximum inductor case temperature of 125°C and a maximum capacitor case temperature of 85°C.

## 7.2 ESD Ratings

|                    | _                       |                                                                               |       |      |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         |                                                                               | VALUE | UNIT |

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1000 | V    |

|                    |                         | Machine Model - (MM)                                                          | ±200  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                                             | MIN | NOM MA | X UNIT |

|-----------------------|-------------------------------------------------------------|-----|--------|--------|

| V <sub>I</sub>        | Input voltage range                                         | 2.5 | 5      | 5 V    |

| $R_L$                 | Minimum resistive load for start-up (V <sub>I</sub> ≤ 4.8V) | 65  |        | Ω      |

| C <sub>EXT</sub>      | Output capacitance                                          | 2   | 3      | 60 μF  |

| T <sub>A</sub>        | Ambient temperature                                         | -40 | 3      | 5 °C   |

| TJ                    | Operating junction temperature                              | -40 | 12     | .5 °C  |

| T <sub>CASE_IND</sub> | Operating inductor case temperature                         |     | 12     | .5 °C  |

| T <sub>CASE_CAP</sub> | Operating capacitor case temperature                        |     | 3      | 5 °C   |

#### 7.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>                | TPS81256            | UNIT |

|-----------------|----------------------------------------------|---------------------|------|

|                 | I THERMAL METRIC                             | μSIP (SIP) – 9 PINS | UNIT |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 62                  |      |

| ΨЈВ             | Junction-to-board characterization parameter | 31                  | °C/W |

| ΨЈТ             | Junction-to-case (top) thermal resistance    | -                   |      |

<sup>(1)</sup> Thermal data have been simulated with high-K board (per JEDEC standard).

## 7.5 Electrical Characteristics

Minimum and maximum values are at  $V_{IN}$  = 2.5V to 5.5V,  $V_{OUT}$  = 5.0V (or  $V_{IN}$ , whichever is higher), EN = 1.8V,  $T_A$  = -40°C to 85°C; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are at  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 5.0V, EN = 1.8V,  $T_A$  = 25°C (unless otherwise noted).

|                     | PARAMETER                                                        | TEST CONDITIONS                                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY              | CURRENT                                                          |                                                                                                                                        |      |      |      |      |

|                     | Operating quiescent current into V <sub>IN</sub> <sup>(1)</sup>  | I <sub>OUT</sub> = 0mA, V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 3.6V                                                                |      | 30   | 50   | μA   |

| IQ                  | Operating quiescent current into V <sub>OUT</sub> <sup>(1)</sup> | EN = V <sub>IN</sub> Device not switching                                                                                              |      | 7    | 20   | μΑ   |

| I <sub>SD</sub>     | Shutdown current <sup>(1)</sup>                                  | EN = GND                                                                                                                               |      | 0.85 | 5.0  | μΑ   |

|                     |                                                                  | Falling                                                                                                                                |      | 2.0  | 2.1  | V    |

| $V_{UVLO}$          | Under-voltage lockout threshold                                  | Hysteresis                                                                                                                             |      | 0.1  |      | V    |

| ENABLE              | Ξ                                                                |                                                                                                                                        |      |      |      |      |

| V <sub>IL</sub>     | Low-level input voltage                                          |                                                                                                                                        |      |      | 0.4  | V    |

| V <sub>IH</sub>     | High-level input voltage                                         |                                                                                                                                        | 1.0  |      |      | V    |

| I <sub>lkg</sub>    | Input leakage current                                            | Input connected to GND or V <sub>IN</sub>                                                                                              |      |      | 0.5  | μA   |

| OUTPUT              | Т                                                                |                                                                                                                                        |      |      |      |      |

|                     |                                                                  | 2.5V ≤ V <sub>IN</sub> ≤ 4.85V, I <sub>OUT</sub> = 0mA<br>PWM operation. Open Loop                                                     | 4.92 | 5    | 5.08 | V    |

| $V_{\text{OUT}}$    | Regulated DC output voltage                                      | $3.3\text{V} \le \text{V}_{\text{IN}} \le 4.85\text{V}$ , $0\text{mA} \le \text{I}_{\text{OUT}} \le 550\text{mA}$<br>PFM/PWM operation | 4.85 | 5    | 5.2  | V    |

|                     |                                                                  | $2.9V \le V_{IN} \le 4.85V$ , $0mA \le I_{OUT} \le 450mA$<br>PFM/PWM operation                                                         | 4.85 | 5    | 5.2  | V    |

|                     | Power-save mode output ripple voltage                            | PFM operation, I <sub>OUT</sub> = 1mA                                                                                                  |      | 35   |      | mVpk |

| $\Delta V_{OUT}$    | PWM mode output ripple voltage                                   | PWM operation, I <sub>OUT</sub> = 200mA                                                                                                |      | 8    |      | mVpk |

| POWER               | SWITCH                                                           |                                                                                                                                        |      |      |      |      |

| r <sub>DS(on)</sub> | Input-to-output On-resistance                                    | V <sub>I</sub> = 5.25 V. Device not switching                                                                                          |      | 320  |      | mΩ   |

| I <sub>lkg</sub>    | Reverse leakage current into VOUT <sup>(1)</sup>                 | EN = GND                                                                                                                               |      |      | 5    | μA   |

| I <sub>LIM</sub>    | Average input current limit                                      | $EN = V_{IN}. V_{IN} = 3.3V$                                                                                                           |      | 1180 |      | mA   |

|                     | Overtemperature protection                                       |                                                                                                                                        |      | 140  |      | °C   |

|                     | Overtemperature hysteresis                                       |                                                                                                                                        |      | 20   |      | °C   |

| OSCILL              | ATOR                                                             | ,                                                                                                                                      | 1    |      | -    |      |

| fosc                | Oscillator frequency                                             | $V_{IN} = 3.6V, V_{OUT} = 5.0V, I_{OUT} = 500mA$                                                                                       |      | 4    |      | MHz  |

| TIMING              |                                                                  |                                                                                                                                        | 1    |      | -    |      |

|                     | 0                                                                | I <sub>OUT</sub> = 0mA Time from active EN to start switching                                                                          |      | 70   |      | μs   |

|                     | Start-up time                                                    | I <sub>OUT</sub> = 0mA<br>Time from active EN to V <sub>OUT</sub>                                                                      |      | 400  |      | μs   |

<sup>(1)</sup> Maximum values can vary over lifetime due to intrinsic capacitor ageing effects. For more details, refer to *Thermal and Reliability Information* section.

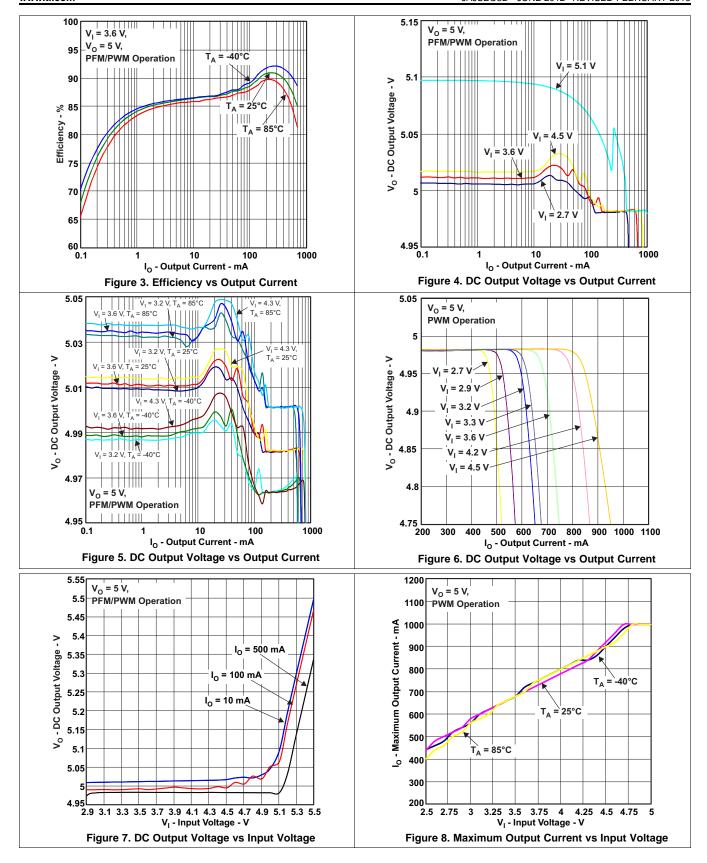

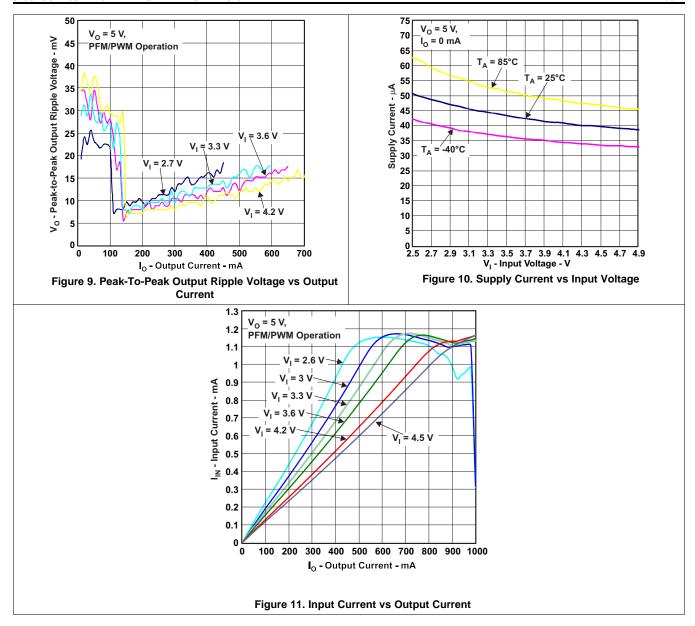

# 7.6 Typical Characteristics

## **Table 1. Table of Graphs**

|                  |                                    |                   | FIGURE                          |

|------------------|------------------------------------|-------------------|---------------------------------|

|                  | <b>F</b> #:=:                      | vs Output current | Figure 1, Figure 3              |

| η                | Efficiency                         | vs Input voltage  | Figure 2                        |

| Vo               | DC output voltage                  | vs Output current | Figure 4, Figure 5,<br>Figure 6 |

|                  |                                    | vs Input voltage  | Figure 7                        |

| Io               | Maximum output current             | vs Input voltage  | Figure 8                        |

| $\Delta V_{O}$   | Peak-to-peak output ripple voltage | vs Output current | Figure 8                        |

| I <sub>CC</sub>  | Supply current                     | vs Input voltage  | Figure 10                       |

| I <sub>LIM</sub> | Input current                      | vs Output current | Figure 11                       |

**Table 2. Table of Animated Performance Characteristics**

|                                             |                                                 | VIDEO    |

|---------------------------------------------|-------------------------------------------------|----------|

| AC Load Response                            | vs. Input Voltage                               | Video 1  |

| Load Transient Response (10mA to 400mA)     | vs. Input Voltage                               | Video 2  |

|                                             | vs. Base Load Current (2.9V <sub>IN</sub> )     | Video 3  |

| Load Transient Response (to 400mA)          | vs. Base Load Current (3.6V <sub>IN</sub> )     | Video 4  |

|                                             | vs. Base Load Current (4.2 <sub>VIN</sub> )     | Video 5  |

|                                             | vs. Delay to Load Current (2.9V <sub>IN</sub> ) | Video 6  |

| Start-Up Response                           | vs. Delay to Load Current (3.6V <sub>IN</sub> ) | Video 7  |

|                                             | vs. Delay to Load Current (4.2V <sub>IN</sub> ) | Video 8  |

| Start-Up Response (200mA I <sub>OUT</sub> ) | vs. Input Voltage                               | Video 9  |

| Overload Response                           | vs. Input Voltage                               | Video 10 |

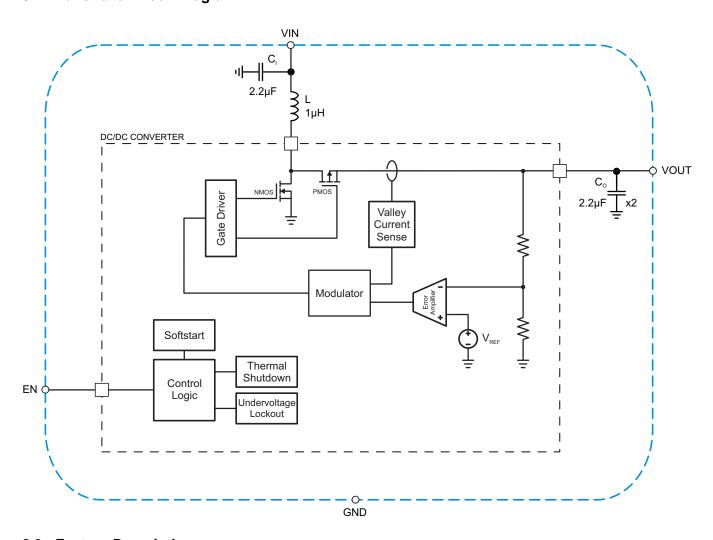

## 8 Detailed Description

#### 8.1 Overview

The TPS81256 is a stand-alone, synchronous, step-up converter module. The converter operates at a quasi-constant 4-MHz frequency pulse width modulation (PWM) at moderate to heavy load currents. At light load currents, the TPS81256 converter operates in power-save mode with pulse frequency modulation (PFM).

#### 8.2 Functional Block Diagram

## 8.3 Feature Description

#### 8.3.1 Operation

During PWM operation, the converter uses a novel quasi-constant on-time valley current mode control scheme to achieve excellent line/load regulation and allows the use of a small ceramic inductor and capacitors. Based on the  $V_{\text{IN}}/V_{\text{OUT}}$  ratio, a simple circuit predicts the required on-time.

At the beginning of the switching cycle, the low-side N-MOS switch is turned-on and the inductor current ramps up to a peak current that is defined by the on-time and the inductance. In the second phase, once the on-timer has expired, the rectifier is turned-on and the inductor current decays to a preset valley current threshold. Finally, the switching cycle repeats by setting the on timer again and activating the low-side N-MOS switch.

#### **Feature Description (continued)**

In general, a dc/dc step-up converter can only operate in "true" boost mode, i.e. the output "boosted" by a certain amount above the input voltage. The TPS81256 device operates differently as it can smoothly transition in and out of zero duty cycle operation. Therefore the output can be kept as close as possible to its regulation limits even though the converter is subject to an input voltage that tends to be excessive. In this operation mode, the output current capability of the regulator is limited to ca. 150mA. Refer to the typical characteristics section (DC Output Voltage vs. Input Voltage) for further details.

The current mode architecture with adaptive slope compensation provides excellent transient load response while requiring only one external tiny capacitor for output filtering and loop stability purposes. Internal soft-start and loop compensation simplifies the application design process.

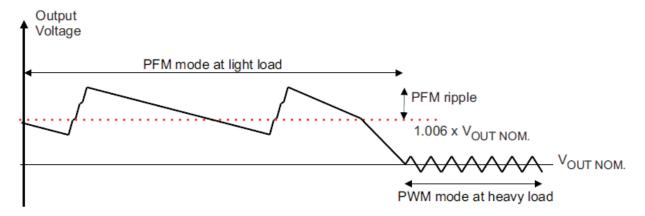

#### 8.3.2 Power-Save Mode

The TPS81256 integrates a power-save mode to improve efficiency at light load. In power-save mode the converter only operates when the output voltage trips below a set threshold voltage.

It ramps up the output voltage with several pulses and goes into power save mode when the output voltage exceeds the set threshold voltage.

PFM mode is exited and the PWM mode entered in case the output current can no longer be supported in PFM mode.

Figure 12. Power-Save Example

#### 8.3.3 Current Limit Operation, Maximum Output Current

The TPS81256 directly and accurately controls the average input current through intelligent adjustment of the valley current limit. The current limit circuit employs a valley current sensing scheme. Current limit detection occurs during the off-time by sensing of the voltage drop across the synchronous rectifier.

The output voltage is reduced as the power stage of the device operates in a constant current mode. The maximum continuous output current  $(I_{OUT(CL)})$ , before entering current limit (CL) operation, can be defined by Equation 1.

$$I_{OUT(DC)} = I_{IN(CL)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \eta$$

(1)

The output current,  $I_{OUT(DC)}$ , is the average of the rectifier ripple current waveform. When the load current is increased such that the lower peak is above the current limit threshold, the off-time is increased to allow the current to decrease to this threshold before the next on-time begins (so called frequency fold-back mechanism). When the current limit is reached the output voltage decreases during further load increase.

#### 8.4 Device Functional Modes

#### 8.4.1 Softstart, Enable

The TPS81256 device starts operation when EN is set high and starts up with the soft-start sequence. For proper operation, the EN pin must be terminated and must not be left floating.

The TPS81256 device has an internal softstart circuit that limits the inrush current during start-up. The first step in the start-up cycle is the pre-charge phase. During pre-charge, the rectifying switch is turned on until the output capacitor is charged to a value close to the input voltage. The rectifying switch is current limited (approx. 200mA) during this phase. This mechanism is used to limit the output current under short-circuit condition.

Once the output capacitor has been biased to the input voltage, the converter starts switching. The soft-start system progressively increases the on-time as a function of the input-to-output voltage ratio. As soon as the output voltage is reached, the regulation loop takes control and full current operation is permitted.

Pulling the EN pin low forces the device in shutdown, with a shutdown current of typically  $1\mu A$ . In this mode, true load disconnect between the battery and load prevents current flow from  $V_{IN}$  to  $V_{OUT}$ , as well as reverse flow from  $V_{OUT}$  to  $V_{IN}$ .

#### 8.4.2 Load Disconnect and Reverse Current Protection

Regular boost converters do not disconnect the load from the input supply and therefore a connected battery will be discharge during shutdown. The advantage of TPS81256 is that this converter is disconnecting the output from the input of the power supply when it is disabled (so called true shutdown mode). In case of a connected battery it prevents it from being discharge during shutdown of the converter.

#### 8.4.3 Undervoltage Lockout

The under voltage lockout circuit prevents the device from malfunctioning at low input voltages and the battery from excessive discharge. It disables the output stage of the converter once the falling  $V_{IN}$  trips the under-voltage lockout threshold  $V_{UVLO}$  which is typically 2.0V. The device starts operation once the rising  $V_{IN}$  trips  $V_{UVLO}$  threshold plus its hysteresis of 100 mV at typically 2.1V.

## 8.4.4 Thermal Regulation

The TPS81256 device contains a thermal regulation loop that monitors the die temperature during the pre-charge phase. If the die temperature rises to high values of about 110°C, the device automatically reduces the current to prevent the die temperature from increasing further. Once the die temperature drops about 10°C below the threshold, the device will automatically increase the current to the target value. This function also reduces the current during a short-circuit condition.

#### 8.4.5 Thermal Shutdown

As soon as the junction temperature,  $T_J$ , exceeds 140°C (typically) the device goes into thermal shutdown. In this mode, the high-side and low-side MOSFETs are turned-off. When the junction temperature falls below the thermal shutdown minus its hysteresis, the device continuous the operation.

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The TPS81256 device is a complete MicroSiP™ DC/DC step-up power solution intended for battery-powered portable applications.

## 9.2 Typical Application

Figure 13. 5-V Power Supply

#### 9.2.1 Design Requirements

The following design guidelines provide a component selection process for the typical application circuit shown to operate the device within the *Recommended Operating Conditions*.

## 9.2.2 Detailed Design Procedure

## 9.2.2.1 Output Capacitor Selection $C_{EXT}$

Because of the pulsating output current nature of the boost converter, a low ESR output capacitor is required to maintain control loop stability, to enhance the converter's transient response and to reduce the output voltage ripple. For the output capacitor, it is recommended to use small ceramic capacitors placed as close as possible to the VOUT and GND pins of the IC. The minimum capacitance is  $2\mu F$ .

To get an estimate of the steady ripple due to charging and discharging the output capacitance, Equation 2 can be used.

$$\Delta V = \frac{I_{OUT} \cdot (V_{OUT} - V_{IN})}{C \cdot V_{OUT} \cdot f}$$

(2)

Where f is the switching frequency which is 4MHz (typically.) and C is the effective output capacitance. Notice the TPS81256 device already incorporates ca.  $1.2\mu$ F effective output capacitance.

In practice, the total ripple is larger due to the ESR of the output capacitor. This additional component of the ripple can be calculated using Equation 3:

$$V_{ESR} = I_{OUT} \bullet R_{ESR}$$

(3)

## **Typical Application (continued)**

An MLCC capacitor with twice the value of the calculated minimum should be used due to DC bias effects. The output capacitor requires either an X7R or X5R dielectric. Y5V and Z5U dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies. There are no additional requirements regarding minimum ESR. Larger capacitors cause lower output voltage ripple as well as lower output voltage drop during load transients but the total output capacitance value should not exceed ca. 30µF.

DC bias effect: high cap. ceramic capacitors exhibit DC bias effects, which have a strong influence on the device's effective capacitance. Therefore the right capacitor value has to be chosen very carefully. Package size and voltage rating in combination with material are responsible for differences between the rated capacitor value and it's effective capacitance. For instance, a  $4.7\mu F$  X5R 16V 0603 MLCC capacitor would typically show an effective capacitance of less than  $2.5\mu F$  (under 5V bias condition, high temperature and ageing effects).

Because the damping factor in the output path is directly related to several resistive parameters (e.g. inductor DCR, power-stage  $r_{DS(on)}$ , PWB DC resistance, load switches  $r_{DS(on)}$  ...) that are temperature dependant, the converter small and large signal behavior must be checked over the input voltage range, load current range and temperature range.

The easiest sanity test is to evaluate, directly at the converter's output, the following aspects:

- PFM/PWM efficiency

- PFM/PWM and PWM load transient response

During the recovery time from a load transient, the output voltage can be monitored for settling time, overshoot or ringing that helps judge the converter's stability. Without any ringing, the loop has usually more than 45° of phase margin.

Table 3. Recommended Capacitor C<sub>FXT</sub>

| REFERENCE | DESCRIPTION                   | PART NUMBER, MANUFACTURER <sup>(1)</sup> |

|-----------|-------------------------------|------------------------------------------|

| $C_{EXT}$ | 4.7μF, 16V, 0603, X5R ceramic | GRM188R61C475KAAJ, muRata                |

(1) See Third-Party Products Disclaimer

## 9.2.2.2 Input Capacitor Selection

In a dc/dc boost converter, since the input current is continuous, only minimum input capacitance is required. The TPS81256 device integrates a low ESR decoupling capacitor to prevent large voltage transients that can cause misbehavior of the device or interference in other circuits in the system.

For most applications, the input capacitor that is integrated into the TPS81256 should be sufficient. If the application exhibits a noisy or erratic switching frequency, experiment with additional input capacitance to find a remedy. Multilayer ceramic capacitors are an excellent choice for input decoupling of the step-up converter as they have extremely low ESR and are available in small footprints. Additional input capacitors should be located as close as possible to the device.

The TPS81256 uses a tiny ceramic input capacitor. When a ceramic capacitor is combined with trace or cable inductance, such as from a wall adapter, a load step at the output can induce ringing at the VIN pin. This ringing can couple to the output and be mistaken as loop instability or can even damage the part. In this circumstance, additional "bulk" capacitance, such as electrolytic or tantalum, should be placed between the input of the converter and the power source lead to reduce ringing that can occur between the inductance of the power source leads and C<sub>1</sub>.

# TEXAS INSTRUMENTS

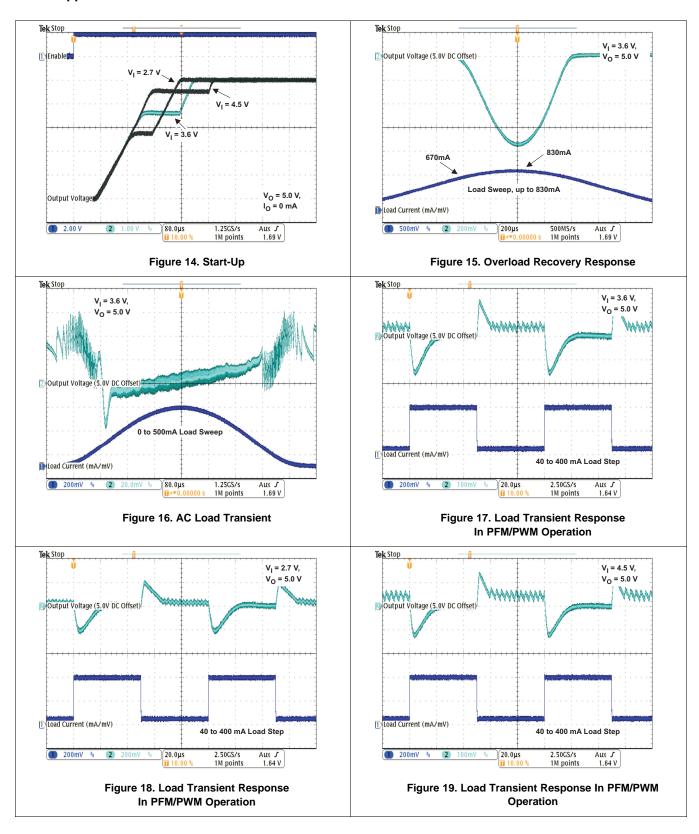

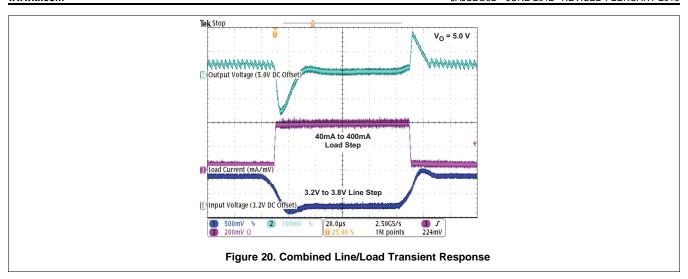

#### 9.2.3 Application Curves

## 9.3 System Examples

<sup>(9)</sup> The capacitor is not only required to decouple the audio power amplifier, but is also required to stable operation of the SMPS converter.

The SMPS converter should be located in the close vicinity of the audio power amplifier.

Figure 21. "Boosted" Audio Power Supply

# **System Examples (continued)**

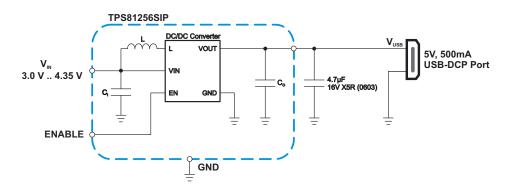

Figure 22. Battery Powered USB-DCP Power Supply

## 10 Power Supply Recommendations

The TPS81256 has no special requirements for its input power supply. The input power supply's output current needs to be rated according to the supply voltage, output voltage and output current of the TPS81256

## 11 Layout

## 11.1 Layout Guidelines

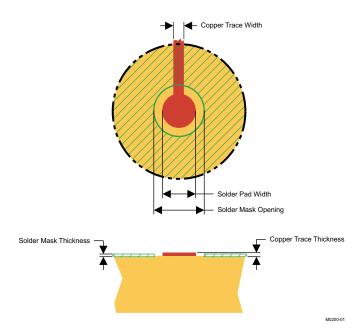

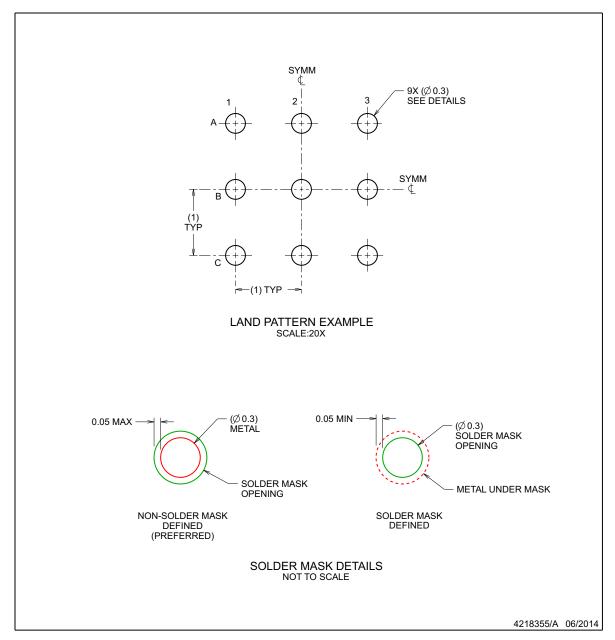

In making the pad size for the  $\mu SiP$  LGA balls, it is recommended that the layout use non-solder-mask defined (NSMD) land. With this method, the solder mask opening is made larger than the desired land area, and the opening size is defined by the copper pad width. Figure 23 shows the appropriate diameters for a MicroSiP layout.

#### 11.2 Layout Example

Figure 23. Recommended Land Pattern Image and Dimensions

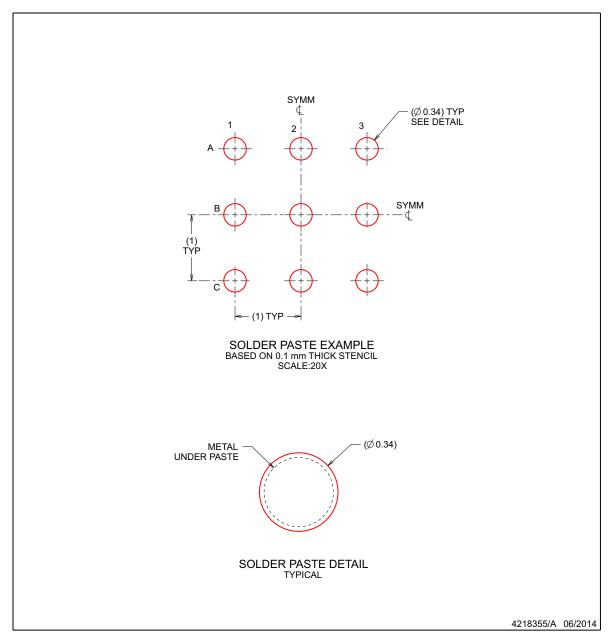

| SOLDER PAD<br>DEFINITIONS <sup>(1)(2)(3)(4)</sup> | COPPER PAD | SOLDER MASK <sup>(5)</sup><br>OPENING | COPPER<br>THICKNESS | STENCIL (6)<br>OPENING | STENCIL THICKNESS |

|---------------------------------------------------|------------|---------------------------------------|---------------------|------------------------|-------------------|

| Non-solder-mask defined (NSMD)                    | 0.30mm     | 0.360mm                               | 1oz max (0.032mm)   | 0.34mm diameter        | 0.1mm thick       |

- Circuit traces from non-solder-mask defined PWB lands should be 75μm to 100μm wide in the exposed area inside the solder mask opening. Wider trace widths reduce device stand off and affect reliability.

- (2) Best reliability results are achieved when the PWB laminate glass transition temperature is above the operating the range of the intended application.

- (3) Recommend solder paste is Type 3 or Type 4.

- (4) For a PWB using a Ni/Au surface finish, the gold thickness should be less than 0.5mm to avoid a reduction in thermal fatigue performance.

- (5) Solder mask thickness should be less than 20 μm on top of the copper circuit pattern.

- (6) For best solder stencil performance use laser cut stencils with electro polishing. Chemically etched stencils give inferior solder paste volume control.

#### 11.3 Surface Mount Information

The TPS81256 MicroSiP DC/DC converter uses an open frame construction that is designed for a fully automated assembly process and that features a large surface area for pick and place operations. See the "Pick Area" in the package drawings.

Package height and weight have been kept to a minimum thereby to allow the MicroSiP device to be handled similarly to a 0805 component.

See JEDEC/IPC standard J-STD-20b for reflow recommendations.

## 11.4 Thermal and Reliability Information

The TPS81256 output current may need to be de-rated if it is required to operate in a high ambient temperature or deliver a large amount of continuous power. The amount of current de-rating is dependent upon the input voltage, output power and environmental thermal conditions. Care should especially be taken in applications where the localized PWB temperature exceeds 65°C.

The TPS81256 die and inductor temperature should be kept lower than the maximum rating of 125°C, so care should be taken in the circuit layout to ensure good heat sinking. Sufficient cooling should be provided to ensure reliable operation.

To estimate the junction temperature, approximate the power dissipation within the TPS81256 by applying the typical efficiency stated in this datasheet to the desired output power; or, by taking a power measurement if you have an actual TPS81256 device or a TPS81256EVM evaluation module. Then calculate the internal temperature rise of the TPS81256 above the surface of the printed circuit board by multiplying the TPS81256 power dissipation by the thermal resistance.

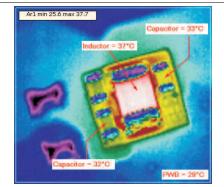

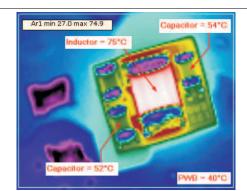

The thermal resistance numbers listed in the Thermal Information table are based on modeling the MicroSiP package mounted on a high-K test board specified per JEDEC standard. For increased accuracy and fidelity to the actual application, it is recommended to run a thermal image analysis of the actual system. Figure 24 and Figure 25 are thermal images of Tl's evaluation board with readings of the temperatures at specific locations on the device.

Figure 24. V<sub>IN</sub>=3.6v, V<sub>OUT</sub>=5v, I<sub>OUT</sub>=300ma 150mw Power Dissipation At Room Temperature

Figure 25. V<sub>IN</sub>=3.6v, V<sub>OUT</sub>=5v, I<sub>OUT</sub>=600ma 600mw Power Dissipation At Room Temperature

The TPS81256 is equipped with a thermal shutdown that will inhibit power switching at high junction temperatures. The activation threshold of this function, however, is above 125°C to avoid interfering with normal operation. Thus, it follows that prolonged or repetitive operation under a condition in which the thermal shutdown activates necessarily means that the components internal to the MicroSiP™ package are subjected to high temperatures for prolonged or repetitive intervals, which may damage or impair the reliability of the device.

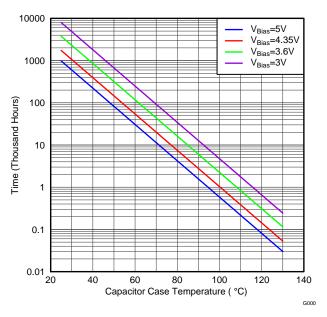

MLCC capacitor reliability/lifetime is dependant on temperature and applied voltage conditions. At higher temperatures, MLCC capacitors are subject to stronger stress. On the basis of frequently evaluated failure rates determined at standardized test conditions, the reliability of all MLCC capacitors can be calculated for their actual operating temperature and voltage.

## Thermal and Reliability Information (continued)

Figure 26. Capacitor Lifetime vs Capacitor Case Temperature

Failures caused by systematic degradation can be described by the Arrhenius model. The most critical parameter (IR) is the Insulation Resistance (i.e. leakage current). The drop of IR below a lower limit (e.g. 1  $M\Omega$ ) is used as the failure criterion, see Figure 26. It should be noted that the wear-out mechanisms occurring in the MLCC capacitors are not reversible but cumulative over time.

## 12 デバイスおよびドキュメントのサポート

#### 12.1 デバイス・サポート

#### 12.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供される場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワークの製品またはサービスの是認の表明を意味するものではありません。

## 12.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

#### 12.3 商標

MicroSiP, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 12.4 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## MicroSiP DC/DCモジュールのパッケージ・サイズ

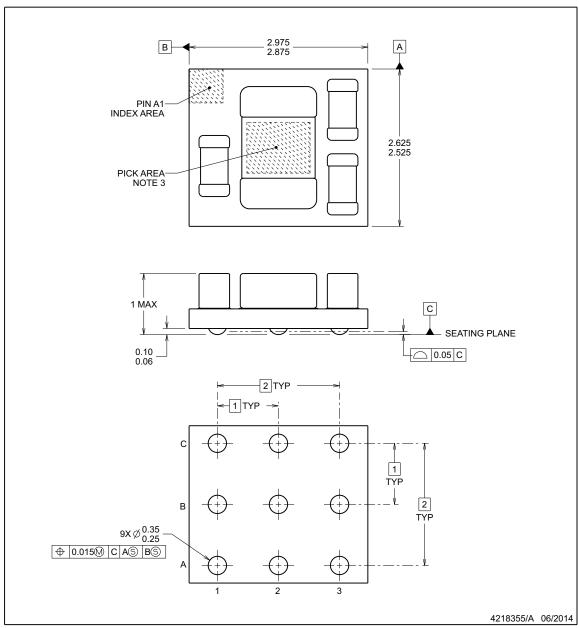

TPS81256デバイスは、9バンプのボール・グリッド・アレイ(BGA)パッケージで供給されます。パッケージの寸法は次のとおりです。

- $D = 2.925 \pm 0.05$ mm

- $E = 2.575 \pm 0.05$ mm

#### コード

- CC パッケージのマーキングのチップ・コード(詳細は「パッケージ・オプション」の付録を参照)

- YML Y: 年、M: 月、L: ロットのトレース・コード

- LSB L: ロットのトレース・コード、S: サイトのコード、B: ボード・ロケータ

図 27. µSIP 9ピンの寸法とマーキング

**SIP0009A**

## **PACKAGE OUTLINE**

## MicroSiP<sup>™</sup>- 1 mm max height

MICRO SYSTEM IN PACKAGE

#### MicroSiP is a trademark of Texas Instruments.

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

For pick and place nozzle recommendation, see product datasheet.

Location, size and quantity of each component are for reference only and may vary.

23

## **EXAMPLE BOARD LAYOUT**

## **SIP0009A**

## MicroSiP<sup>™</sup> - 1 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

5. For more information, see Texas Instruments literature number SBVA017 (www.ti.com/lit/sbva017).

## **EXAMPLE STENCIL DESIGN**

# **SIP0009A**

## MicroSiP™- 1 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

www.ti.com 5-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status           | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |                  |               |                |                       |      | (4)                           | (5)                        |              |                  |

| TPS81256SIPR          | Last<br>Time Buy | Production    | uSiP (SIP)   9 | 3000   LARGE T&R      | Yes  | OSP                           | Level-2-260C-1 YEAR        | -40 to 125   | ТТ               |

| TPS81256SIPT          | Last<br>Time Buy | Production    | uSiP (SIP)   9 | 250   SMALL T&R       | Yes  | OSP                           | Level-2-260C-1 YEAR        | -40 to 125   | TT               |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Mar-2023

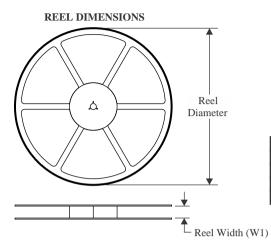

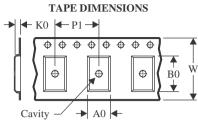

## TAPE AND REEL INFORMATION

|    | -                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

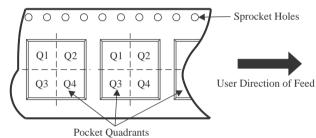

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | _    | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS81256SIPR | uSiP | SIP                | 9 | 3000 | 178.0                    | 9.0                      | 2.83       | 3.18       | 1.2        | 4.0        | 8.0       | Q2               |

| TPS81256SIPT | uSiP | SIP                | 9 | 250  | 178.0                    | 9.0                      | 2.83       | 3.18       | 1.2        | 4.0        | 8.0       | Q2               |

www.ti.com 17-Mar-2023

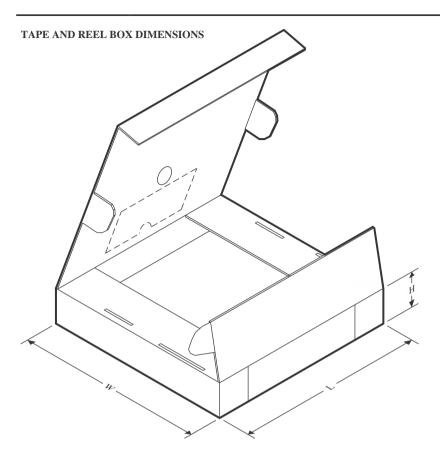

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS81256SIPR | uSiP         | SIP             | 9    | 3000 | 223.0       | 194.0      | 35.0        |

| TPS81256SIPT | uSiP         | SIP             | 9    | 250  | 223.0       | 194.0      | 35.0        |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated