# TPS7H502x-SP および TPS7H502x-SEP 放射線耐性 1MHz 電流モード PWM コントローラ（統合ゲートドライバ付き）

## 1 特長

- 耐放射線性能:

- 吸収線量 (TID) 100krad(Si)までの放射線耐性保証 (RHA)

- シングルイベントランチアップ (SEL)、シングルイベントバーンアウト (SEB)、シングルイベントゲートラップチャージ (SEGR) 耐性: LET = 75MeV-cm<sup>2</sup>/mg

- LET = 75MeV-cm<sup>2</sup>/mg まで、SET (シングルイベント過渡) および SEFI (シングルイベント機能割り込み) 特性を評価済み

- コントローラ段とドライバ段の両方で 4.5V ~ 14V の入力電圧範囲

- 専用ゲートドライバ電圧入力ピン (PVIN) により、シリコンと GaN 両方のデバイスを駆動

- 12V における 1.2A のピークソースおよびシンク能力

- VLDO リニアレギュレータ出力を GaN の駆動用に PVIN へ接続するオプション

- 4.5V~5.5V のプログラマブルリニアレギュレータ (VLDO)

- 温度、放射線、ラインおよび負荷レギュレーションの全範囲で 0.6V ±1% の電圧リファレンス

- スイッチング周波数: 100kHz~1MHz

- 外部クロック同期機能

- 調整可能なスロープ補償とソフトスタート機能

- ASTM E595 に準拠したガス排出試験済みのプラスチックパッケージ

## 2 アプリケーション

- 人工衛星の電源

- 通信ペイロード

- レーダー画像処理ペイロード

- 衛星用電源システム (EPS)

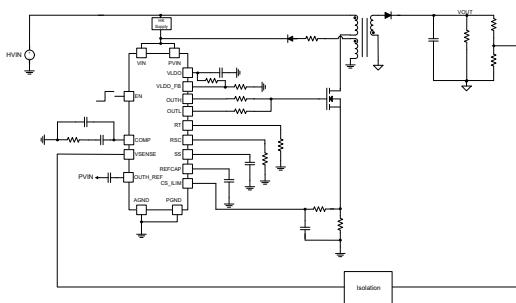

代表的なアプリケーション回路

## 3 説明

TPS7H502x は放射線耐性を持つ、電流モード単端 PWM コントローラで、ゲートドライバを内蔵しており、シリコンおよび窒化ガリウム (GaN) パワー半導体を用いたコンバータ設計の両方に使用できます。TPS7H502x は、ソフトスタート、イネーブル、調整可能なスロープ補償などのいくつかの主要な機能を統合しながら、コンパクトなパッケージ サイズを維持しています。このコントローラは、0.6V ±1% の電圧リファレンス公差を備えており、高精度なパワー コンバータ設計をサポートします。

TPS7H502x は、SYNC ピンを通じて外部クロックを使用して動作させることも、RT ピンを使用して内部オシレータをユーザーが決定した周波数で設定して動作させることができます。このデバイスは、最大 1MHz の周波数でスイッチングできます。コントローラのドライバ段は、4.5V から 14V の広い入力電圧範囲を持ち、ピークソースおよびシンク電流は最大 1.2A をサポートします。プログラム可能なレギュレータ VLDO は、GaN FET と連携して動作するために、ドライバステージ (PVIN) の入力に直接接続して、適切に制御されたゲート電圧を供給することもできます。プログラム可能なレギュレータは、4.5V から 5.5V の電圧範囲を持っています。TPS7H5020 デバイスの最大デューティサイクルは 100% で、TPS7H5021 の最大デューティサイクルは 50% です。このコントローラは、フライバック、フォワード、昇圧など、多くの電力コンバータトポジをサポートしています。

## 製品情報

| 部品番号 (1)                         | グレード     | 本体サイズ (2)                    |

|----------------------------------|----------|------------------------------|

| 5962R2420101PYE                  | QMLP-RHA | 24 ピンのプラスチック 4.40mm × 7.80mm |

| 5962R2420102PYE <sup>(3)</sup>   |          | 質量 = 100.6mg                 |

| TPS7H5020MPWPTSEP                | SEP      |                              |

| TPS7H5021MPWPTSEP <sup>(3)</sup> |          |                              |

(1) 詳細は、[デバイス比較表](#)をご覧ください。

(2) 質量は公称値であり、本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

(3) 製品プレビュー。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 7.3 機能説明               | 28 |

| 2 アプリケーション  | 1  | 7.4 デバイスの機能モード         | 44 |

| 3 説明        | 1  | 8 アプリケーションと実装          | 45 |

| 4 デバイス比較表   | 3  | 8.1 アプリケーション情報         | 45 |

| 5 ピン構成および機能 | 4  | 8.2 代表的なアプリケーション       | 45 |

| 6 仕様        | 6  | 8.3 電源に関する推奨事項         | 54 |

| 6.1 絶対最大定格  | 6  | 8.4 レイアウト              | 55 |

| 6.2 ESD 定格  | 6  | 9 デバイスおよびドキュメントのサポート   | 58 |

| 6.3 推奨動作条件  | 7  | 9.1 ドキュメントのサポート        | 58 |

| 6.4 熱に関する情報 | 7  | 9.2 ドキュメントの更新通知を受け取る方法 | 58 |

| 6.5 電気的特性   | 8  | 9.3 サポート・リソース          | 58 |

| 6.6 品質適合検査  | 11 | 9.4 商標                 | 58 |

| 6.7 代表的特性   | 13 | 9.5 静電気放電に関する注意事項      | 58 |

| 7 詳細説明      | 26 | 9.6 用語集                | 58 |

| 7.1 概要      | 26 | 10 改訂履歴                | 58 |

| 7.2 機能ブロック図 | 27 | 11 メカニカル、パッケージ、および注文情報 | 59 |

## 4 デバイス比較表

| ジェネリック型番      | 放射線定格                                                                        | グレード <sup>(1)</sup> | パッケージ            | 発注用製品型番                           | デューティサイクル制限(公称値) |

|---------------|------------------------------------------------------------------------------|---------------------|------------------|-----------------------------------|------------------|

| TPS7H5020-SP  | 最大 100krad (Si) RLAT の TID および DSEE フリー (LET = 75MeV-cm <sup>2</sup> /mg まで) | QMLP-RHA            | 24 ピン HTSSOP PWP | 5962R2420101PYE                   | 100%             |

| TPS7H5020-SEP | 最大 50krad (Si) RLAT の TID および DSEE フリー (LET = 43MeV-cm <sup>2</sup> /mg まで)  | 宇宙向けに強化されたプラスチック    | 24 ピン HTSSOP PWP | TPS7H5020MPWPTS EP                | 100%             |

| TPS7H5021-SP  | 最大 100krad (Si) RLAT の TID および DSEE フリー (LET = 75MeV-cm <sup>2</sup> /mg まで) | QMLP-RHA            | 24 ピン HTSSOP PWP | 5962R2420102PYE <sup>(2)</sup>    | 50%              |

| TPS7H5021-SEP | 最大 50krad (Si) RLAT の TID および DSEE フリー (LET = 43MeV-cm <sup>2</sup> /mg まで)  | 宇宙向けに強化されたプラスチック    | 24 ピン HTSSOP PWP | TPS7H5021MPWPTS EP <sup>(2)</sup> | 50%              |

(1) 部品のグレードについての詳細は、[部品のグレード](#)をご覧下さい。

(2) 製品レビュー。

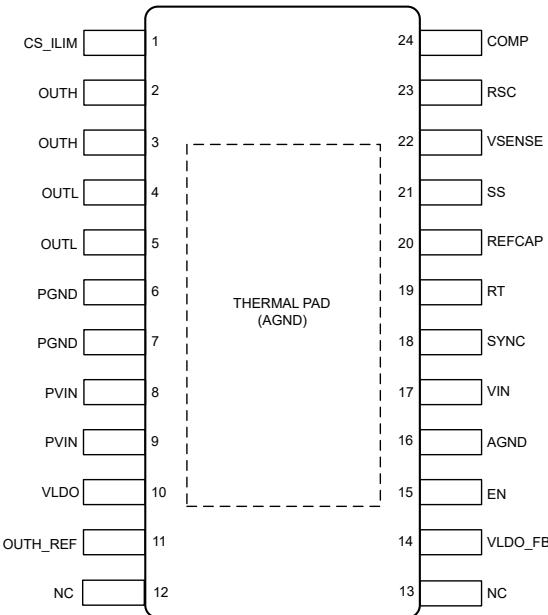

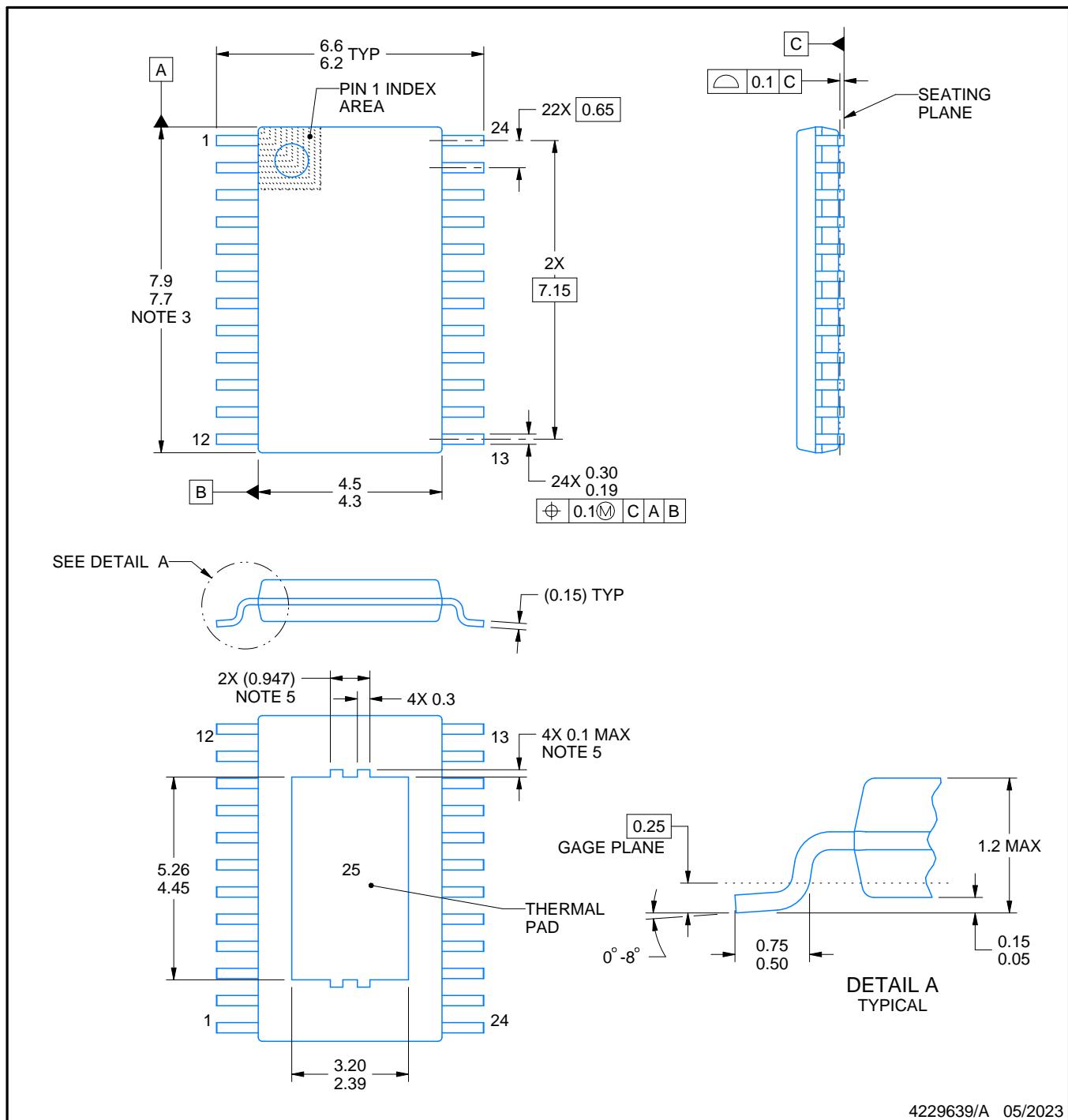

## 5 ピン構成および機能

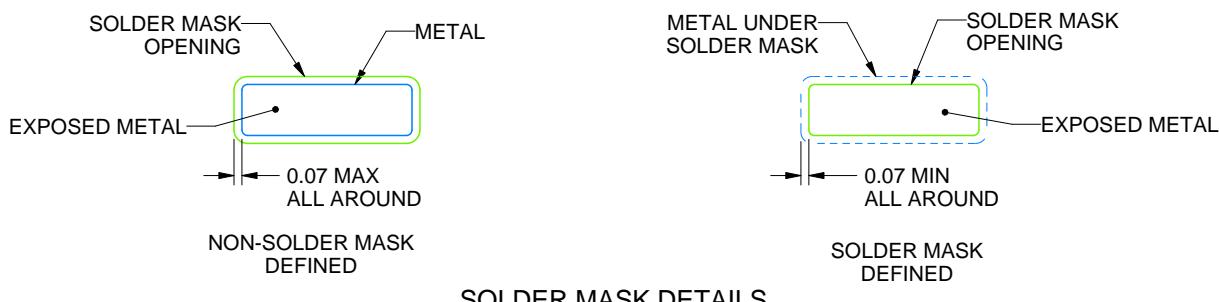

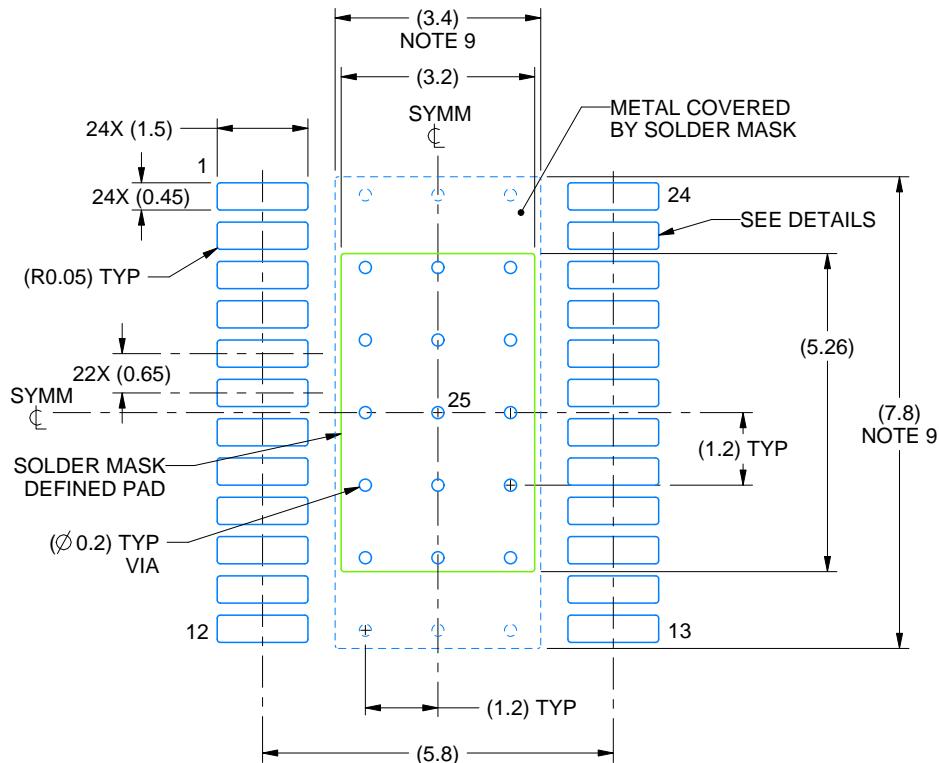

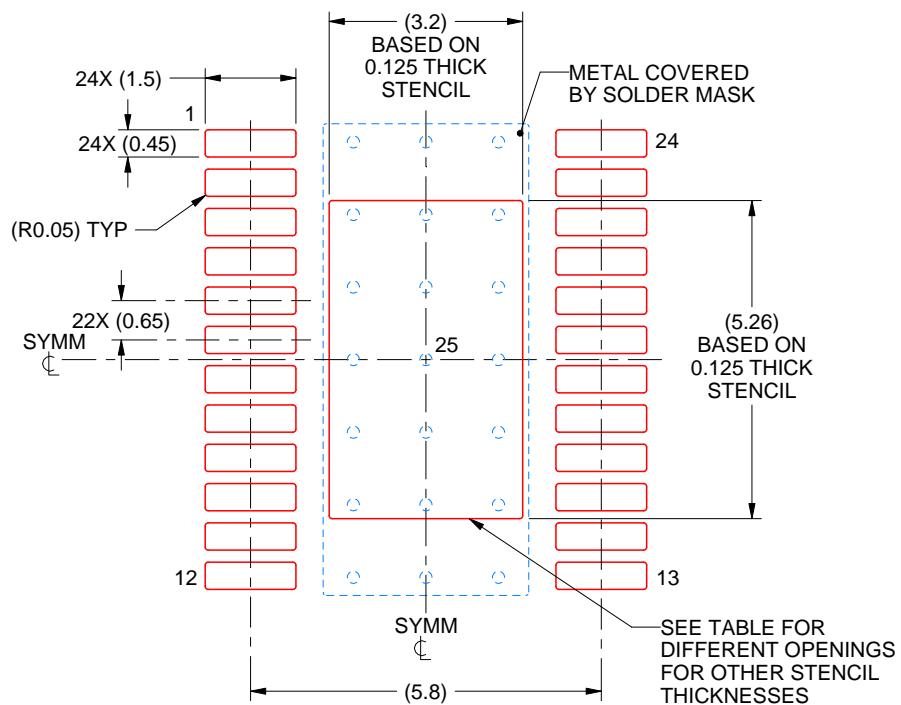

**図 5-1. PWP パッケージ

24 ピン HTSSOP (サーマル パッド付き)

(上面図)**

**表 5-1. ピンの機能**

| ピン      |        | I/O | 説明                                                                                                                                                                                                                    |

|---------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | HTSSOP |     |                                                                                                                                                                                                                       |

| CS_ILIM | 1      | I   | PWM 制御およびサイクルごとの過電流保護のための電流検出 CS_ILIM 端子の電圧が 1V を超えると、PWM コントローラで過電流がトリガーされます。CS_ILIM で検出される波形は、PWM コンパレータの入力にある COMP/CCSR 電圧と比較して 150mV のオフセットを含んでいます。                                                               |

| OUTH    | 2, 3   | O   | ドライバ段のソース電流出力。電力トランジスタのゲートには、短く低インダクタンスの経路で接続します。OUTH と GaN FET のゲートの間に抵抗を使用して、ターンオン速度を調整できます。                                                                                                                        |

| OUTL    | 4, 5   | O   | ドライバ段のシンク電流出力。電力トランジスタのゲートには、短く低インダクタンスの経路で接続します。OUTL ピンとトランジスタのゲート端子の間に抵抗を挿入することで、ターンオフ時の動作速度を調整できます。                                                                                                                |

| PGND    | 6, 7   | —   | ドライバ段の電源グランド。電力トランジスタのソースに接続します。プリント基板レベルで AGND に接続します。                                                                                                                                                               |

| PVIN    | 8, 9   | I   | ドライバ段電圧入力。PVIN の電圧範囲は 4.5V から 14V です。電力トランジスタのゲートに供給される電圧は、PVIN の入力電圧とほぼ等しくなります。単一電源動作の場合、このピンを VIN に接続できます。また、VLDO に接続することで、4.5V ~ 5.5V の範囲で安定化されたゲート駆動電圧を電力トランジスタのゲートに供給することもできます。                                  |

| VLDO    | 10     | O   | 内部レギュレータのプログラマブル出力。規定された GaN 対応ドライバ電圧を得るために、PVIN に接続できます。4.5V から 5.5V の範囲で、VLDO から VLDO_FB への抵抗と VLDO_FB から AGND への別の抵抗で構成される抵抗分圧回路を使用して電圧を設定できます。正常に動作させるためには、これらの抵抗を常に実装する必要があります。AGND との間に少なくとも 1μF の外部コンデンサが必要です。 |

**表 5-1. ピンの機能 (続き)**

| ピン       |        | I/O | 説明                                                                                                                                                                                                                                        |

|----------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | HTSSOP |     |                                                                                                                                                                                                                                           |

| OUTH_REF | 11     | O   | OUTH ドライバステージのリターン OUTH_REF の電圧は、通常、PVIN に印加されている電圧より 6V 低くなっています。PVIN の電圧が 6V 以上の場合、OUTH_REF と PVIN の間に 220nF のコンデンサを接続します。これにより、過渡応答が改善され、放射線による单一事象過渡障害 (SET) の可能性を最小限に抑えることができます。PVIN 電圧が 6V 未満の場合、プリント基板レベルで OUTH_REF を PGND に接続します。 |

| VLDO_FB  | 14     | I   | VLDO フィードバックピン。VLDO 出力電圧の設定に使用します。VLDO と AGND の間に分圧抵抗を使用して、公称 1.2V に設定します。適切な動作のためには、抵抗デバイダに常に実装する必要があります。                                                                                                                                |

| EN       | 15     | I   | イネーブル。EN ピンに 0.6V を超える電圧を接続すると、デバイスが有効になります。さらに、入力低電圧誤動作防止 (UVLO) 機能は、VIN と GND の間に接続した抵抗デバイダを使用して調整できます。                                                                                                                                 |

| AGND     | 16     | —   | グランド。コントローラ回路のリターンです。プリント基板レベルで PGND に接続します。                                                                                                                                                                                              |

| VIN      | 17     | I   | コントローラ入力電圧。VIN の電圧範囲は 4.5V から 14V です。内部制御回路に電力を供給します。単一電源動作では PVIN に接続できます。                                                                                                                                                               |

| SYNC     | 18     | I   | 外部クロック入力。SYNC は 100kHz から 1MHz の外部クロックを受け付けます。外部クロックには、40%~60% のデューティサイクルを使用します。コントローラ出力のスイッチング周波数は、外部クロックの周波数と同じです。RT は、抵抗で設定される周波数が外部クロック周波数と一致するように実装する必要があります。外部同期を使用する予定がない場合、SYNC は VLDO に直接接続するか、10kΩ 抵抗を介して GND に接続できます。          |

| RT       | 19     | I/O | コントローラのスイッチング周波数プログラミング。コントローラのスイッチング周波数を設定するために、RT から GND に抵抗を接続します。外部クロック入力を使用する場合でも、抵抗は引き続き接続する必要があり、外部クロックの周波数に合わせて適切な値を選定する必要があります。                                                                                                  |

| REFCAP   | 20     | O   | 1.2V 内部レギュレータ出力。AGND との間に 470nF の外付けコンデンサが必要です。外部回路によって負荷を接続しないでください。                                                                                                                                                                     |

| SS       | 21     | I/O | ソフトスタート。このピンに接続された外部コンデンサによって、内部電圧リフレンスの立ち上がり時間が設定されます。トラッキングとシーケンシングに使用できます。                                                                                                                                                             |

| VSENSE   | 22     | I   | エラー アンプの反転入力。コンバータの出力からの抵抗デバイダによって、通常 0.6V に設定されるフィードバックピンです。                                                                                                                                                                             |

| RSC      | 23     | I/O | コントローラのスロープ補償設定。RSC から AGND に接続された抵抗によって、目的的スロープ補償が設定されます。                                                                                                                                                                                |

| COMP     | 24     | I/O | エラー アンプ出力。出力は CCSR の係数で分圧され、このスケーリングされた電圧が PWM コンバレータへの入力となります。このピンに周波数補償を接続します。                                                                                                                                                          |

| NC       | 12, 13 | —   | 接続なし。このピンは内部接続されていません。これらのピンは、電荷の蓄積を防ぐために GND に接続できます。                                                                                                                                                                                    |

| サーマル パッド | —      | —   | サーマル パッド。AGND に内部接続します。放熱性を向上させるために、プリント基板上の 1 つ以上のグランド プレーンに接続します。                                                                                                                                                                       |

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内(特に記載がない限り)(1)

|                       | 最小値  | 最大値      | 単位 |

|-----------------------|------|----------|----|

| VIN                   | -0.3 | 16       | V  |

| PVIN                  | -0.3 | 16       | V  |

| SYNC                  | -0.3 | 7.5      | V  |

| EN                    | -0.3 | 7.5      | V  |

| RT                    | -0.3 | 3.6      | V  |

| VSENSE                | -0.3 | 3.6      | V  |

| SS                    | -0.3 | 3.3      | V  |

| RSC                   | -0.3 | 3.6      | V  |

| COMP <sup>(2)</sup>   | -0.3 | 6.0      | V  |

|                       | -0.3 | VLDO+0.3 |    |

| CS_ILIM               | -0.3 | 7.5      | V  |

| OUTL                  | -0.3 | 16       | V  |

| OUTH_REF              | -0.3 | 10       | V  |

| VLDO <sup>(2)</sup>   | -0.3 | 7.5      | V  |

|                       | -0.3 | VIN+0.3  |    |

| VLDO_FB               | -0.3 | 1.9      | V  |

| REFCAP <sup>(2)</sup> | -0.3 | 1.9      | V  |

|                       | -0.3 | VLDO+0.3 |    |

| 動作時接合部温度              | -55  | 150      | °C |

| 保存温度                  | -65  | 150      | °C |

- (1) 絶対最大定格外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) ピンの絶対最大電圧は、提示された 2 つの条件のうち低い方に従うべきです。

### 6.2 ESD 定格

|             |      |                                                                  | 値          | 単位 |

|-------------|------|------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | $\pm 1000$ | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 250$  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                     | 最小値 | 公称値 | 最大値  | 単位   |

|---------------------|-----|-----|------|------|

| VIN                 | 4.5 |     | 14   | V    |

| PVIN                | 4.5 |     | 14   | V    |

| SYNC                | 0   |     | 7    | V    |

| EN                  | 0   |     | 7    | V    |

| COMP <sup>(1)</sup> | 0   |     | 2.3  | V    |

| VSENSE              | 0   | 0.6 | 1    | V    |

| VLDO_FBF            | 0   | 1.2 | 1.3  | V    |

| SS                  | 0   |     | 1.5  | V    |

| CS_ILIM             | 0   |     | 1.5  | V    |

| OUTH、OUTL           | 0   |     | 14   | V    |

| 入力電圧スルーレート(VIN)     |     |     | 0.03 | V/μs |

| 入力電圧スルーレート(PVIN)    |     |     | 0.03 | V/μs |

| 動作時接合部温度            | -55 |     | 125  | °C   |

(1) 詳細については、『[電流検出と PWM 生成](#)』を参照してください。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TP7H502x | 単位   |

|-----------------------|-------------------|----------|------|

|                       |                   | HTSSOP   |      |

|                       |                   | 24 ピン    |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 26.6     | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 0.9      | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 7.7      | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 18.0     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.2      | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 7.7      | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『[半導体および IC パッケージの熱評価基準](#)』アプリケーション レポートを参照してください。

## 6.5 電気的特性

$T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $\text{PVIN} = \text{VIN} = 4.5\text{V} \sim 14\text{V}$ 、 $\text{VLDO} = 5\text{V}$ 、 $\text{OUT}$  は無負荷(特に記述のない限り)

| パラメータ                   | テスト条件             |                                                                                                                   | サブグループ <sup>(1)</sup>                                                                                                     | 最小値     | 標準値               | 最大値  | 単位   |               |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|-------------------|------|------|---------------|

| <b>電源電圧および電流</b>        |                   |                                                                                                                   |                                                                                                                           |         |                   |      |      |               |

| IDD                     | 動作電源電流            | OUT は無負荷、 $\text{PVIN} = \text{VIN}$                                                                              | $f_{\text{SW}} = 100\text{kHz}$                                                                                           | 1, 2, 3 | 6.8               | 11   | mA   |               |

|                         |                   |                                                                                                                   | $f_{\text{SW}} = 500\text{kHz}$                                                                                           | 1, 2, 3 | 8.5               | 17   |      |               |

| IDD                     | 動作電源電流            | OUT は無負荷、 $\text{PVIN} = \text{VIN}$                                                                              | $f_{\text{SW}} = 1\text{MHz}$                                                                                             | 1, 2, 3 | 10.3              | 25   | mA   |               |

| IDD                     | 動作電源電流            | OUT の $C_{\text{LOAD}} = 1000\text{pF}$ 、 $\text{PVIN} = \text{VIN}$                                              | $f_{\text{SW}} = 100\text{kHz}$                                                                                           | 1, 2, 3 | 8.5               | 12   | mA   |               |

| IDD                     | 動作電源電流            | OUT の $C_{\text{LOAD}} = 1000\text{pF}$ 、 $\text{PVIN} = \text{VIN}$                                              | $f_{\text{SW}} = 500\text{kHz}$                                                                                           | 1, 2, 3 | 14.5              | 22   |      |               |

| IDD                     | 動作電源電流            | OUT の $C_{\text{LOAD}} = 1000\text{pF}$ 、 $\text{PVIN} = \text{VIN}$                                              | $f_{\text{SW}} = 1\text{MHz}$                                                                                             | 1, 2, 3 | 22.5              | 28   | mA   |               |

| IDD                     | 動作電源電流            | $C_{\text{LOAD}} = 1000\text{pF}$ ( $\text{OUT}, \text{VIN}=12\text{V}$ 、 $\text{PVIN}=\text{VLDO} = 5\text{V}$ ) | $f_{\text{SW}} = 100\text{kHz}$                                                                                           | 1, 2, 3 | 7                 | 10   | mA   |               |

|                         |                   |                                                                                                                   | $f_{\text{SW}} = 500\text{kHz}$                                                                                           | 1, 2, 3 | 10                | 13   |      |               |

|                         |                   |                                                                                                                   | $f_{\text{SW}} = 1\text{MHz}$                                                                                             | 1, 2, 3 | 13.5              | 20   |      |               |

| $I_{\text{start}}$      | スタートアップ電流         | $\text{VIN} = 3.5\text{V}$                                                                                        |                                                                                                                           | 1, 2, 3 | 3.8               | 5    | mA   |               |

| $I_{\text{DD(dis)}}$    | スタンバイ電流           | $\text{EN} = 0\text{V}$                                                                                           |                                                                                                                           | 1, 2, 3 |                   | 8    | mA   |               |

| VLDO                    | 内部リニア レギュレータ出力電圧  | $C_{\text{VLDO}} = 1\mu\text{F}$                                                                                  | $5\text{V} \leq \text{VIN} \leq 14\text{V}$ ,<br>$\text{RVT} = 10\text{k}\Omega$ ,<br>$\text{RVB} = 3.74\text{k}\Omega$   | 1, 2, 3 | 4.36              | 4.49 | 4.62 |               |

|                         |                   |                                                                                                                   | $5.5\text{V} \leq \text{VIN} \leq 14\text{V}$ ,<br>$\text{RVT} = 10\text{k}\Omega$ ,<br>$\text{RVB} = 3.24\text{k}\Omega$ | 1, 2, 3 | 4.84              | 4.99 | 5.14 |               |

|                         |                   |                                                                                                                   | $6\text{V} \leq \text{VIN} \leq 14\text{V}$ ,<br>$\text{RVT} = 10\text{k}\Omega$ ,<br>$\text{RVB} = 2.87\text{k}\Omega$   | 1, 2, 3 | 5.31              | 5.48 | 5.65 |               |

| VLDO_DO                 | 内部リニア ドロップアウト電圧   | $I_{\text{VLDO}} = 25\text{mA}$ , $C_{\text{VLDO}} = 1\mu\text{F}$                                                |                                                                                                                           | 1, 2, 3 |                   | 0.4  | V    |               |

| I_VLDO                  | 最大 VLDO 出力電流      | $\text{VLDO}$ は、無負荷時の $\text{VLDO}$ の 96% 以上であること。 $C_{\text{VLDO}} = 1\mu\text{F}$                               | $\text{VIN} = \text{VLDO} + 0.5\text{V}$                                                                                  | 1, 2, 3 | 25 <sup>(4)</sup> |      | mA   |               |

|                         |                   |                                                                                                                   | $\text{VIN} = \text{VLDO} + 1\text{V}$                                                                                    | 1, 2, 3 | 55 <sup>(4)</sup> |      |      |               |

|                         |                   |                                                                                                                   | $\text{VIN} \geq 7\text{V}$                                                                                               | 1, 2, 3 | 90 <sup>(4)</sup> |      |      |               |

| <b>イネーブルおよび低電圧誤動作防止</b> |                   |                                                                                                                   |                                                                                                                           |         |                   |      |      |               |

| $V_{\text{ENR}}$        | イネーブル立ち上がりスレッショルド |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 0.57              | 0.63 | 0.66 | V             |

| $V_{\text{ENF}}$        | イネーブル立ち下がりスレッショルド |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 0.48              | 0.52 | 0.55 | V             |

| I_EN                    | イネーブル入力リーク電流      | $\text{VIN} = 14\text{V}$                                                                                         | $\text{EN} = 1\text{V}$                                                                                                   | 1, 2, 3 | 1                 | 100  | nA   |               |

|                         |                   |                                                                                                                   | $\text{EN} = 7\text{V}$                                                                                                   | 1, 2, 3 | 30                | 700  | nA   |               |

| PVIN_UVLOR              | PVIN UVLO 立ち上がり   |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.65              | 3.76 | 3.95 | V             |

| PVIN_UVLOF              | PVIN UVLO 立ち下がり   |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.45              | 3.56 | 3.75 | V             |

| VIN_UVLOR               | VIN UVLO 立ち上がり    |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.85              | 3.96 | 4.15 | V             |

| VIN_UVLOF               | VIN UVLO 立ち下がり    |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.65              | 3.76 | 3.95 | V             |

| VLDO_UVLOR              | VLDO UVLO の立ち上がり  |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.65              | 3.77 | 3.95 | V             |

| VLDO_UVLOF              | VLDO UVLO の立ち下がり  |                                                                                                                   |                                                                                                                           | 1, 2, 3 | 3.45              | 3.59 | 3.75 | V             |

| <b>ソフトスタート</b>          |                   |                                                                                                                   |                                                                                                                           |         |                   |      |      |               |

| $I_{\text{SS}}$         | ソフトスタート電流         | $\text{SS} = 0.3\text{V}$                                                                                         |                                                                                                                           | 1, 2, 3 | 2.0               | 2.8  | 3.4  | $\mu\text{A}$ |

## 6.5 電気的特性 (続き)

$T_A = -55^\circ\text{C} \sim 125^\circ\text{C}$ ,  $\text{PVIN} = \text{VIN} = 4.5\text{V} \sim 14\text{V}$ ,  $\text{VLDO} = 5\text{V}$ ,  $\text{OUT}$  は無負荷(特に記述のない限り)

| パラメータ                     |                                          | テスト条件                                                                                | サブグループ <sup>(1)</sup>          | 最小値       | 標準値   | 最大値   | 単位                            |

|---------------------------|------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|-----------|-------|-------|-------------------------------|

| <b>エラー アンプ</b>            |                                          |                                                                                      |                                |           |       |       |                               |

| $\text{EA}_{\text{gm}}$   | エラー アンプの相互コンダクタンス                        | $-10\mu\text{A} < I_{\text{COMP}} < 10\mu\text{A}$ , $V_{(\text{COMP})} = 1\text{V}$ | 1, 2, 3                        | 1100      | 1750  | 2700  | $\mu\text{A}/\text{V}$        |

| $\text{EA}_{\text{DC}}$   | DC ゲイン                                   | $V_{\text{SENSE}} = 0.6\text{V}$                                                     |                                |           | 13000 |       | $\text{V}/\text{V}$           |

| $\text{EA}_{\text{ISRC}}$ | エラー アンプのソースおよび電流                         | $V_{(\text{COMP})} = 1\text{V}, 100\text{mV}$ 入力オーバードライブ                             | 1, 2, 3                        | 95        | 210   |       | $\mu\text{A}$                 |

| $\text{EA}_{\text{ISNK}}$ | エラー アンプのシンク電流                            | $V_{(\text{COMP})} = 1\text{V}, 100\text{mV}$ 入力オーバードライブ                             | 1, 2, 3                        | 95        | 210   |       | $\mu\text{A}$                 |

| $\text{EA}_{\text{ro}}$   | エラー アンプ出力抵抗                              |                                                                                      |                                |           | 8     |       | $\text{M}\Omega$              |

| $\text{EA}_{\text{os}}$   | エラー アンプ入力オフセット電圧                         |                                                                                      | 1, 2, 3                        | -5        | 6     |       | $\text{mV}$                   |

| $\text{EA}_{\text{IB}}$   | 誤差アンプ入力バイアス電流                            |                                                                                      | 1, 2, 3                        |           |       | 25    | $\text{nA}$                   |

| $\text{EA}_{\text{BW}}$   | 帯域幅                                      |                                                                                      | 1, 2, 3                        |           | 7.5   |       | $\text{MHz}$                  |

| <b>発振器</b>                |                                          |                                                                                      |                                |           |       |       |                               |

| $\text{SYNC}_{\text{IL}}$ | SYNC 入力 Low レベル                          | VLDO = 4.5V                                                                          | $V_{\text{IN}} < 5\text{V}$    | 1, 2, 3   |       | 0.8   | V                             |

|                           |                                          |                                                                                      | $V_{\text{IN}} \geq 5\text{V}$ | 1, 2, 3   |       | 0.8   |                               |

|                           |                                          | VLDO = 5.5V                                                                          | $V_{\text{IN}} < 6\text{V}$    | 1, 2, 3   |       | 0.8   |                               |

|                           |                                          |                                                                                      | $V_{\text{IN}} \geq 6\text{V}$ | 1, 2, 3   |       | 0.8   |                               |

| $\text{SYNC}_{\text{IH}}$ | High レベルでの同期                             | VLDO = 4.5V                                                                          | $V_{\text{IN}} < 5\text{V}$    | 1, 2, 3   | 3.5   |       | V                             |

|                           |                                          |                                                                                      | $V_{\text{IN}} \geq 5\text{V}$ | 1, 2, 3   | 3.5   |       |                               |

|                           |                                          | VLDO = 5.5V                                                                          | $V_{\text{IN}} < 6\text{V}$    | 1, 2, 3   | 3.5   |       |                               |

|                           |                                          |                                                                                      | $V_{\text{IN}} \geq 6\text{V}$ | 1, 2, 3   | 3.5   |       |                               |

| $f_{\text{SYNC}}$         | 周波数範囲内での同期                               |                                                                                      |                                | 4, 5, 6   | 100   | 1000  | $\text{kHz}$                  |

| $D_{\text{SYNC}}$         | デューティサイクルでの同期 (TPS7H5020)                | 外部クロックのデューティサイクル                                                                     |                                | 4, 5, 6   | 40%   | 60%   |                               |

| $D_{\text{SYNC}}$         | デューティサイクルでの同期 (TPS7H5021) <sup>(5)</sup> | 外部クロックのデューティサイクル、 $f \geq 200\text{kHz}$                                             |                                | 4, 5, 6   | 48%   | 52%   |                               |

| $D_{\text{SYNC}}$         | デューティサイクルでの同期 (TPS7H5021) <sup>(5)</sup> | 外部クロックのデューティサイクル、 $100\text{kHz} \leq f < 200\text{kHz}$                             |                                | 4, 5, 6   | 49%   | 51%   |                               |

| $DT_{\text{INT}}$         | 外部クロックから内部クロックまでの検出時間                    | RT が実装済み                                                                             |                                | 9, 10, 11 | 2     | 5     | $(1/f_{\text{sw}}) \text{ s}$ |

| $DT_{\text{EXT}}$         | 内部クロックから外部クロックへの検出時間                     | RT が実装済み                                                                             |                                | 9, 10, 11 | 2     | 5     | $(1/f_{\text{sw}}) \text{ s}$ |

| $f_{\text{sw}}$           | RT にプログラムされたスイッチング周波数                    | RT = $1.18\text{M}\Omega$ $1.07\text{M}\Omega$                                       |                                | 4, 5, 6   | 80    | 95    | 110                           |

|                           |                                          | RT = $560\text{k}\Omega$ $511\text{k}\Omega$                                         |                                | 4, 5, 6   | 175   | 195   | 220                           |

|                           |                                          | RT = $210\text{k}\Omega$ $205\text{k}\Omega$                                         |                                | 4, 5, 6   | 450   | 500   | 550                           |

| $f_{\text{sw}}$           | RT にプログラムされたスイッチング周波数                    | RT = $100\text{k}\Omega$ $90.9\text{k}\Omega$                                        |                                | 4, 5, 6   | 925   | 1000  | 1100                          |

| <b>電圧リファレンス</b>           |                                          |                                                                                      |                                |           |       |       |                               |

| $V_{\text{REF}}$          | 内部基準電圧 <sup>(2)</sup>                    | COMP, COMP = VSENSE で測定                                                              | $T_A = 25^\circ\text{C}$       | 1         | 0.597 | 0.600 | 0.603                         |

|                           |                                          |                                                                                      | $T_A = -55^\circ\text{C}$      | 3         | 0.594 | 0.598 | 0.602                         |

|                           |                                          |                                                                                      | $T_A = 125^\circ\text{C}$      | 2         | 0.597 | 0.601 | 0.604                         |

| REFCAP                    | REFCAP 電圧                                | C <sub>REFCAP</sub> = $470\text{nF}$                                                 |                                | 1, 2, 3   | 1.208 | 1.223 | 1.235                         |

|                           |                                          |                                                                                      |                                |           |       |       |                               |

## 6.5 電気的特性 (続き)

$T_A = -55^\circ\text{C} \sim 125^\circ\text{C}$ ,  $\text{PVIN} = \text{VIN} = 4.5\text{V} \sim 14\text{V}$ ,  $\text{VLDO} = 5\text{V}$ ,  $\text{OUT}$  は無負荷(特に記述のない限り)

| パラメータ                  |                      | テスト条件                                                                       | サブグループ <sup>(1)</sup>  | 最小値       | 標準値  | 最大値  | 単位   |

|------------------------|----------------------|-----------------------------------------------------------------------------|------------------------|-----------|------|------|------|

| <b>電流検出</b>            |                      |                                                                             |                        |           |      |      |      |

| CCSR                   | COMP と CS_ILIM の比    | RSC = オープン                                                                  | 1, 2, 3                | 1.94      | 2.0  | 2.06 |      |

| V <sub>CS_ILIM</sub>   | 電流制限(過電流)スレッショルド     |                                                                             | 1, 2, 3                | 0.96      | 1.0  | 1.04 | V    |

|                        | CS_ILIM から OUT までの遅延 | CS_ILIM = 1V から OUT 立ち下がりの 90% まで                                           | 9, 10, 11              | 65        | 115  | ns   |      |

| <b>スロープ補償</b>          |                      |                                                                             |                        |           |      |      |      |

| SC                     | スロープ補償               | f <sub>SW</sub> = 100kHz, RSC = 1.18MΩ                                      |                        | 0.029     |      |      | V/μs |

|                        |                      | f <sub>SW</sub> = 200kHz, RSC = 562kΩ                                       |                        | 0.072     |      |      |      |

|                        |                      | f <sub>SW</sub> = 500kHz, RSC = 100kΩ                                       |                        | 0.306     |      |      |      |

| SC                     | スロープ補償               | f <sub>SW</sub> = 1000kHz, RSC = 49.9kΩ                                     |                        | 0.605     |      |      | V/μs |

| <b>サーマル シャットダウン</b>    |                      |                                                                             |                        |           |      |      |      |

| T <sub>SD</sub>        | サーマル シャットダウン エントリ    |                                                                             |                        | 185       |      |      | °C   |

| T <sub>SD_HYS</sub>    | サーマル シャットダウン ヒステリシス  |                                                                             |                        | 15        |      |      | °C   |

| <b>ゲートドライバ</b>         |                      |                                                                             |                        |           |      |      |      |

| V <sub>OL</sub>        | Low レベル電圧            | I <sub>OL</sub> = 50mA                                                      | 1, 2, 3                | 0.08      | 0.15 |      | V    |

| PVIN - V <sub>OH</sub> | High レベル出力電圧         | I <sub>OH</sub> = 50mA                                                      | 1, 2, 3                | 0.13      | 0.25 |      | V    |

| t <sub>R_OUT</sub>     | 出力立ち上がり時間            | C <sub>LOAD</sub> = 1000pF、10% ~ 90%                                        | VIN = PVIN = 4.5V      | 9, 10, 11 | 7    | 14   | ns   |

|                        |                      |                                                                             | VIN = PVIN = 5V        | 9, 10, 11 | 7    | 14   |      |

| t <sub>R_OUT</sub>     | OUT の立ち上がり時間         | C <sub>LOAD</sub> = 1000pF、10% ~ 90%                                        | VIN = PVIN = 12V       | 9, 10, 11 | 9.5  | 18   | ns   |

|                        |                      |                                                                             | VIN = PVIN = 14V       | 9, 10, 11 | 11.5 | 20   |      |

| t <sub>R_OUT</sub>     | 出力立ち上がり時間            | C <sub>LOAD</sub> = 1000pF、10% ~ 90%<br>C <sub>LOAD</sub> = 220pF、10% ~ 90% | VIN = 12V, PVIN = VLDO | 9, 10, 11 | 8.5  | 16   | ns   |

|                        |                      |                                                                             |                        | 9, 10, 11 | 4.5  | 12   |      |

| t <sub>F_OUT</sub>     | 出力立ち下がり時間            | C <sub>LOAD</sub> = 1000pF、90% ~ 10%                                        | VIN = PVIN = 4.5V      | 9, 10, 11 | 6.5  | 14   | ns   |

|                        |                      |                                                                             | VIN = PVIN = 5V        | 9, 10, 11 | 6.5  | 14   |      |

| t <sub>F_OUT</sub>     | OUT の立ち下がり時間         | C <sub>LOAD</sub> = 1000pF、90% ~ 10%                                        | VIN = PVIN = 12V       | 9, 10, 11 | 9.5  | 18   | ns   |

|                        |                      |                                                                             | VIN = PVIN = 14V       | 9, 10, 11 | 11   | 18   |      |

| t <sub>F_OUT</sub>     | 出力立ち下がり時間            | C <sub>LOAD</sub> = 1000pF、90% ~ 10%<br>C <sub>LOAD</sub> = 220pF、90% ~ 10% | VIN = 12V, PVIN = VLDO | 9, 10, 11 | 6.5  | 14   | ns   |

|                        |                      |                                                                             |                        | 9, 10, 11 | 3.5  | 10   |      |

| I <sub>OH</sub>        | ピークソース電流             | PVIN = 4.5V                                                                 | 1, 2, 3                | 0.55      |      |      | A    |

|                        |                      | PVIN = 5V                                                                   | 1, 2, 3                | 0.7       |      |      |      |

| I <sub>OH</sub>        | ピークソース電流             | PVIN = 12V                                                                  | 1, 2, 3                | 1.2       |      |      | A    |

|                        |                      | PVIN = 14V                                                                  | 1, 2, 3                | 1.2       |      |      |      |

## 6.5 電気的特性 (続き)

T<sub>A</sub> = -55°C~125°C、PVIN = VIN = 4.5V~14V、VLDO = 5V、OUT は無負荷(特に記述のない限り)

| パラメータ               |                 | テスト条件                          |                | サブグループ <sup>(1)</sup> | 最小値 | 標準値  | 最大値 | 単位 |

|---------------------|-----------------|--------------------------------|----------------|-----------------------|-----|------|-----|----|

| I <sub>OH</sub>     | ピークソース電流        | VIN = 12V, PVIN = VLDO         | VLDO = 4.5V    | 1, 2, 3               |     | 0.55 |     | A  |

|                     |                 |                                | VLDO = 5V      | 1, 2, 3               |     | 0.7  |     |    |

|                     |                 |                                | VLDO = 5.5V    | 1, 2, 3               |     | 0.85 |     |    |

| I <sub>OL</sub>     | ピークシンキング電流      | PVIN = 4.5V                    |                | 1, 2, 3               |     | 0.7  |     | A  |

|                     |                 | PVIN = 5V                      |                | 1, 2, 3               |     | 0.8  |     |    |

| I <sub>OL</sub>     | ピークシンク電流        | PVIN = 12V                     |                | 1, 2, 3               |     | 1.3  |     | A  |

|                     |                 | PVIN = 14V                     |                | 1, 2, 3               |     | 1.3  |     |    |

| I <sub>OL</sub>     | ピークシンキング電流      | VIN = 12V, PVIN = VLDO         | VLDO = 4.5V    | 1, 2, 3               |     | 1.05 |     | A  |

|                     |                 |                                | VLDO = 5V      | 1, 2, 3               |     | 1.3  |     |    |

|                     |                 |                                | VLDO = 5.5V    | 1, 2, 3               |     | 1.55 |     |    |

| R <sub>OH</sub>     | プルアップ抵抗         | OUT から 100mA                   |                | 1, 2, 3               |     | 2.6  | 4.7 | Ω  |

| R <sub>OL</sub>     | プルダウン抵抗         | OUT に 100mA を印可                |                | 1, 2, 3               |     | 1.6  | 2.8 | Ω  |

| V <sub>UCLAMP</sub> | 電源なし OUT クランプ電圧 | スイッチングが無効化、、OUT に 1mA プルアップを印加 | PVIN = 0V      | 1, 2, 3               |     | 0.7  | 1   | V  |

|                     |                 |                                | 0V < PVIN < 5V | 1, 2, 3               |     | 1.8  | 2.5 |    |

### PWM デューティサイクル

|                      |                                        |                                                          |           |     |     |     |

|----------------------|----------------------------------------|----------------------------------------------------------|-----------|-----|-----|-----|

| T <sub>LEB</sub>     | リーディングエッジのブランディング時間                    | VIN が 5V 以上 14V 以下の範囲で、OUT が立ち上がりの 10% に達してからブランディング終了まで | 9, 10, 11 | 30  | 80  | ns  |

| t <sub>on_min</sub>  | 最小オン時間 <sup>(3)</sup>                  |                                                          | 9, 10, 11 | 135 | 165 | ns  |

| t <sub>off_min</sub> | 最小オフ時間 (TPS7H5020) <sup>(3)</sup>      |                                                          | 9, 10, 11 | 55  | 70  | ns  |

| D <sub>MAX</sub>     | 最大デューティサイクル (TPS7H5021) <sup>(5)</sup> |                                                          | 9, 10, 11 | 42% | 46% | 50% |

(1) サブグループは QML 部品に適用されます。サブグループの定義については、セクション 6.6 を参照してください。

(2) 誤差アンプのオフセットを含めるように、COMP ピンで測定されます。

(3) 詳細については、「[最小オン時間およびオフ時間](#)」を参照してください。

(4) VLDO は、少なくとも指定されたテスト条件で、この電流をサポートできます。ただし、PVIN を VLDO に接続してコントローラを動作させる場合は、最も安定した動作を確保するために、VLDO から取り出す外部電流をこの値より低く抑えることを推奨します。

(5) TPS7H5021 は製品レビュー デバイスです。この仕様は、情報提供のみを目的として提供されています。

## 6.6 品質適合検査

MIL-STD-883、方法 5005 - グループ A

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 1      | 静的テスト      | 25      |

| 2      | 静的テスト      | 125     |

| 3      | 静的テスト      | -55     |

| 4      | 動的テスト      | 25      |

| 5      | 動的テスト      | 125     |

| 6      | 動的テスト      | -55     |

| 7      | 機能テスト      | 25      |

| 8A     | 機能テスト      | 125     |

| 8B     | 機能テスト      | -55     |

| 9      | スイッチング テスト | 25      |

| 10     | スイッチング テスト | 125     |

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 11     | スイッチング テスト | -55     |

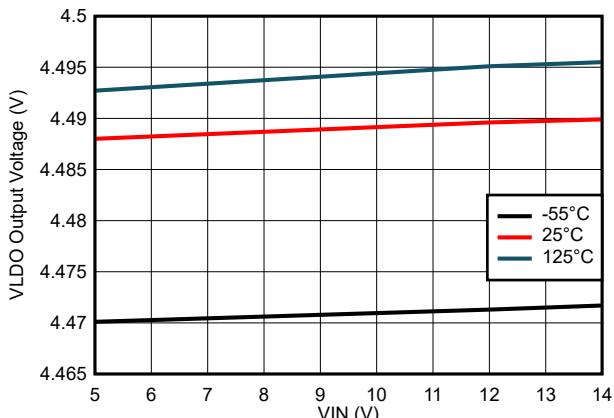

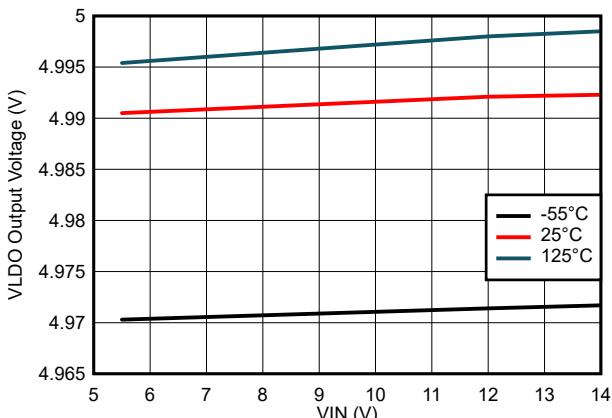

## 6.7 代表的特性

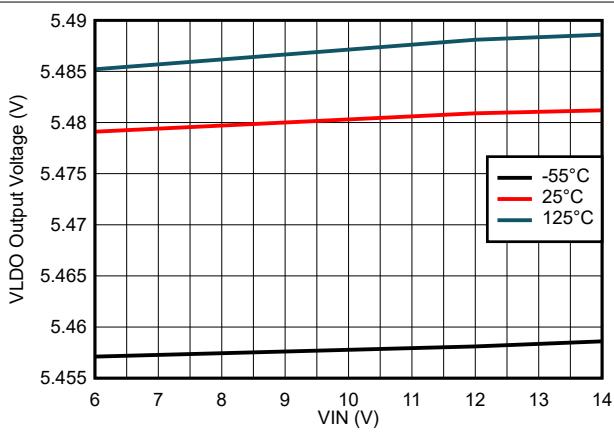

典型的な特性は、 $P_{VIN}=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

$R_{VT} = 10\text{k}\Omega, R_{VB} = 3.74\text{k}\Omega$

図 6-1. 内部リニア レギュレータの出力電圧と入力電圧との関係

$R_{VT} = 10\text{k}\Omega, R_{VB} = 3.24\text{k}\Omega$

図 6-2. 内部リニア レギュレータの出力電圧と入力電圧との関係

$R_{VT} = 10\text{k}\Omega, R_{VB} = 2.87\text{k}\Omega$

図 6-3. 内部リニア レギュレータの出力電圧と入力電圧との関係

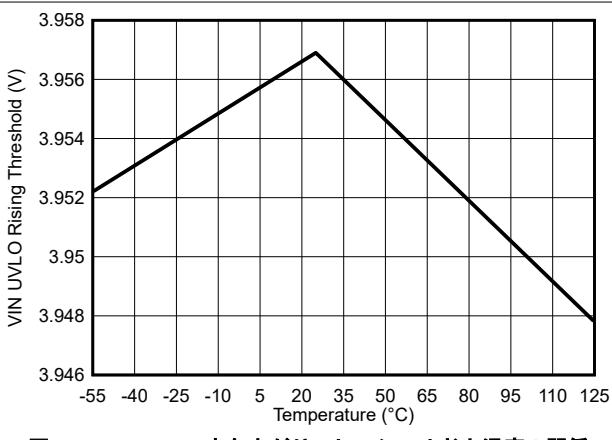

図 6-4. VIN UVLO 立ち上がりリスレッショルドと温度の関係

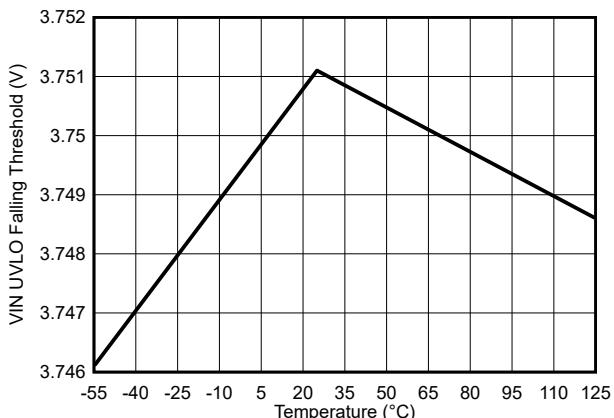

図 6-5. VIN UVLO 立ち下がりリスレッショルドと温度の関係

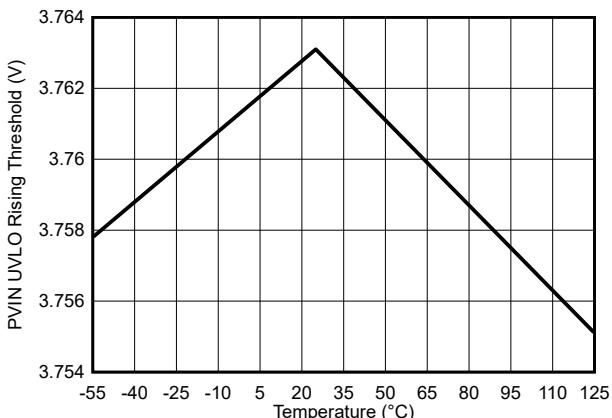

図 6-6. PVIN UVLO 立ち上がりリスレッショルドと温度の関係

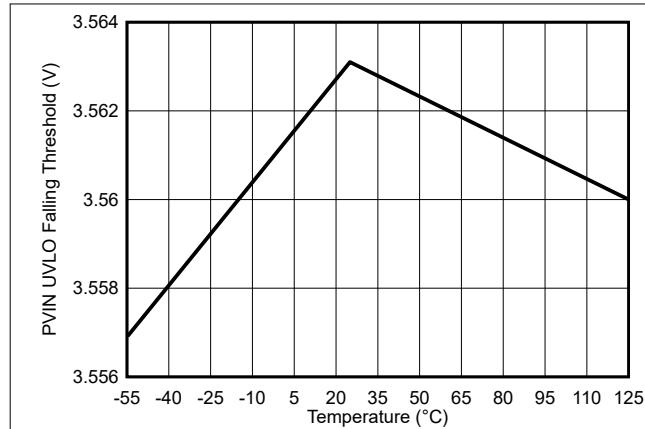

## 6.7 代表的特性 (続き)

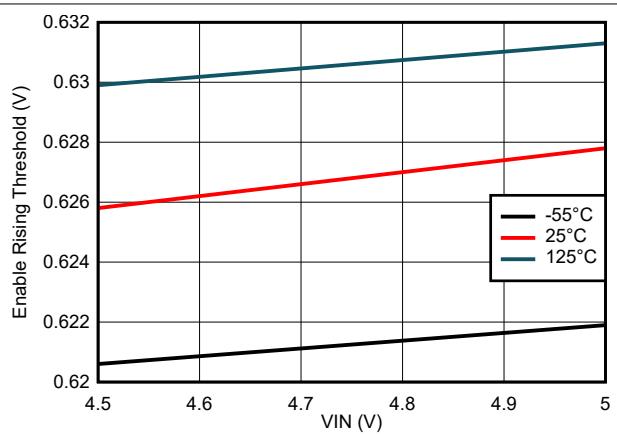

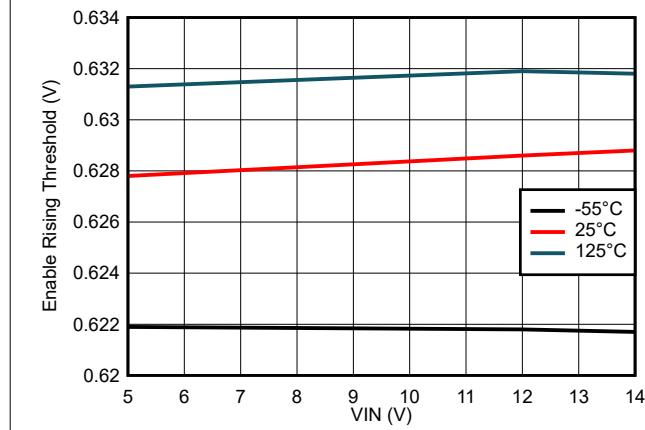

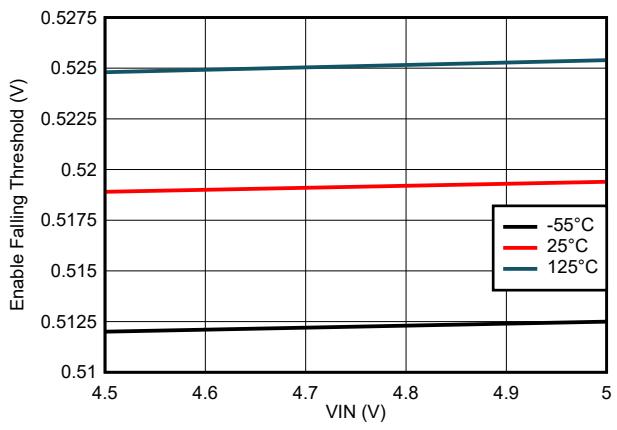

典型的な特性は、 $PVIN=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^{\circ}\text{C}, 25^{\circ}\text{C}, 125^{\circ}\text{C}$  の場合で示されています(特に記載がない限り)。

図 6-7. PVIN UVLO 立ち下がりスレッショルドと温度の関係

図 6-8. イネーブル立ち上がりスレッショルドと入力電圧との関係

VIN = 5V~14V

図 6-9. イネーブル立ち上がりスレッショルドと入力電圧との関係

VIN = 4.5V~5V

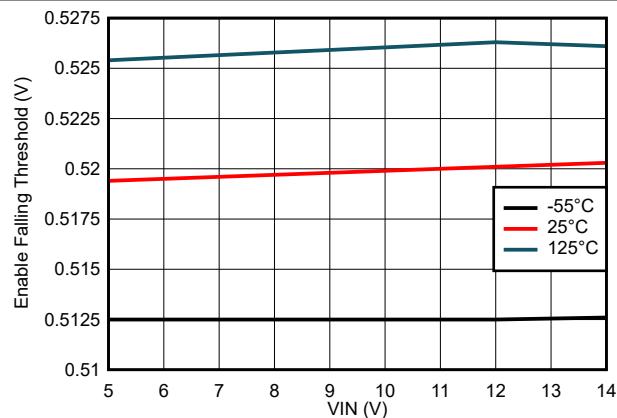

図 6-10. イネーブル立ち下がりスレッショルドと入力電圧との関係

## 6.7 代表的特性 (続き)

典型的な特性は、PVIN=VIN が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^{\circ}\text{C}, 25^{\circ}\text{C}, 125^{\circ}\text{C}$  の場合で示されています(特に記載がない限り)。

VIN = 5V ~ 14V

図 6-11. イネーブル立ち下がりスレッショルドと入力電圧との関係

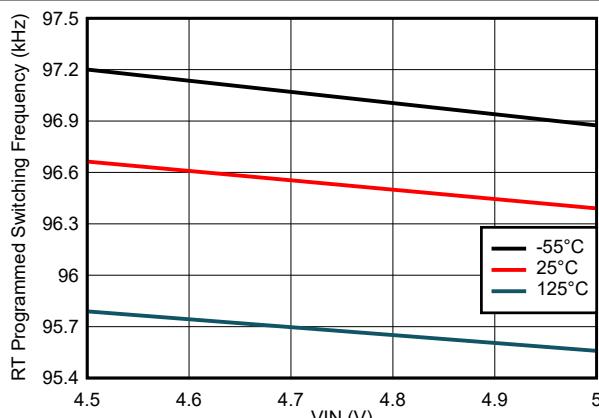

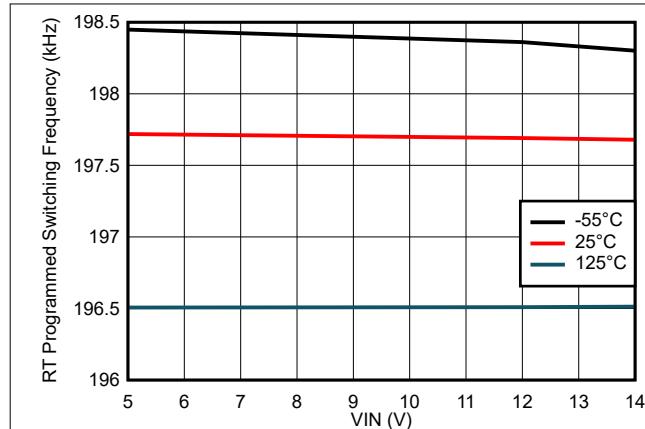

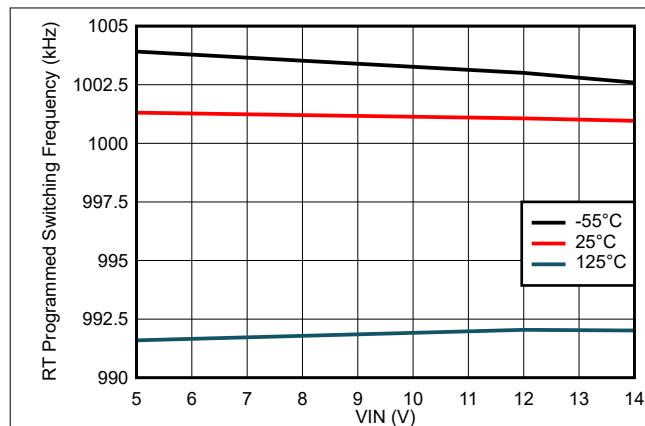

VIN = 4.5V ~ 5V, RT = 1.18MΩ

図 6-12. スイッチング周波数と入力電圧との関係

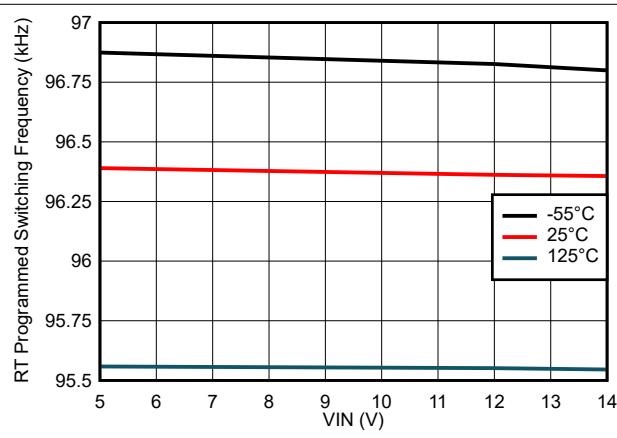

VIN = 5V ~ 14V, RT = 1.18MΩ

図 6-13. スイッチング周波数と入力電圧との関係

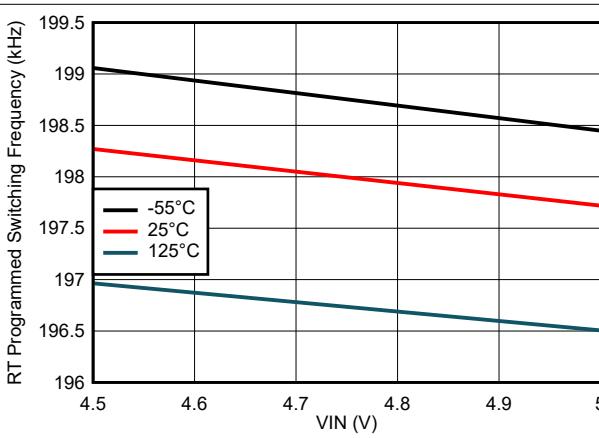

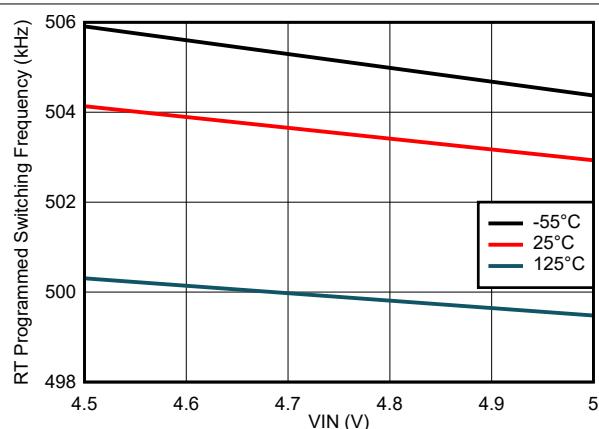

VIN = 4.5V ~ 5V, RT = 560kΩ

図 6-14. スイッチング周波数と入力電圧との関係

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^{\circ}\text{C}, 25^{\circ}\text{C}, 125^{\circ}\text{C}$  の場合で示されています(特に記載がない限り)。

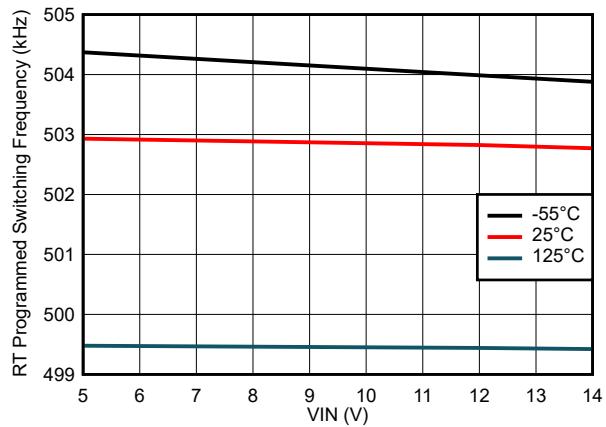

VIN = 5V ~ 14V, RT = 560kΩ

図 6-15. スイッチング周波数と入力電圧との関係

VIN = 4.5V ~ 5V, RT = 210kΩ

図 6-16. スイッチング周波数と入力電圧との関係

VIN = 5V ~ 14V, RT = 210kΩ

図 6-17. スイッチング周波数と入力電圧との関係

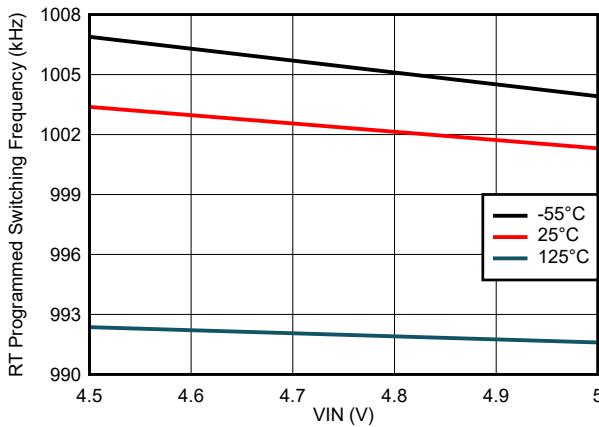

VIN = 4.5V ~ 5V, RT = 100kΩ

図 6-18. スイッチング周波数と入力電圧との関係

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

VIN = 5V ~ 14V, RT = 100kΩ

図 6-19. スイッチング周波数と入力電圧との関係

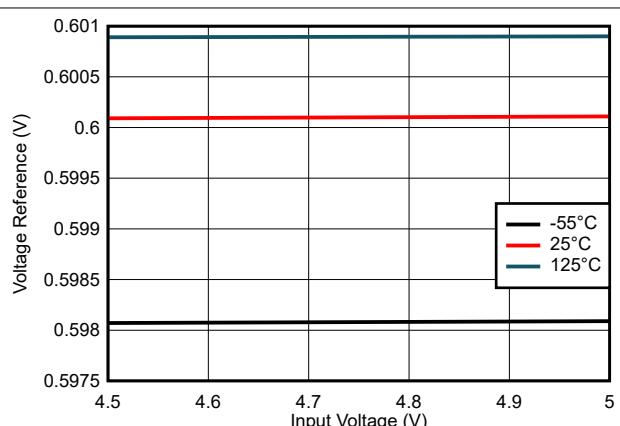

VIN = 4.5V~5V

図 6-20. リファレンス電圧と入力電圧との関係

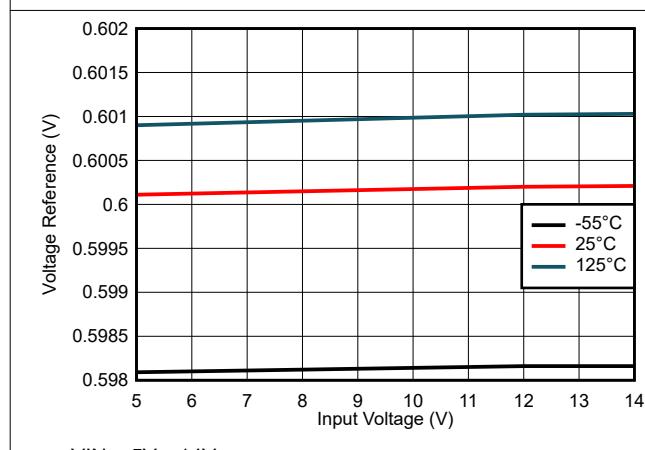

VIN = 5V~14V

図 6-21. リファレンス電圧と入力電圧との関係

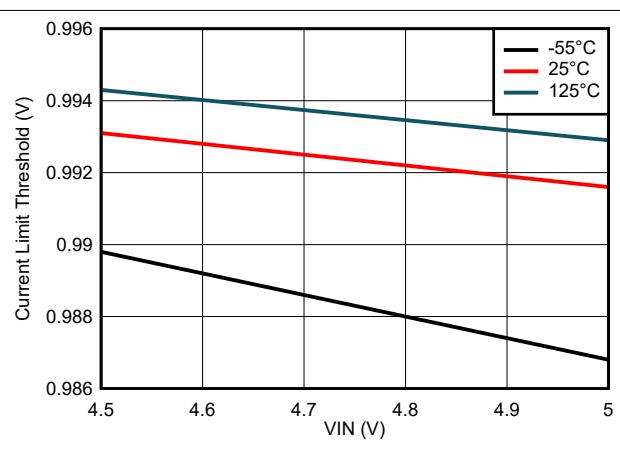

VIN = 4.5V~5V

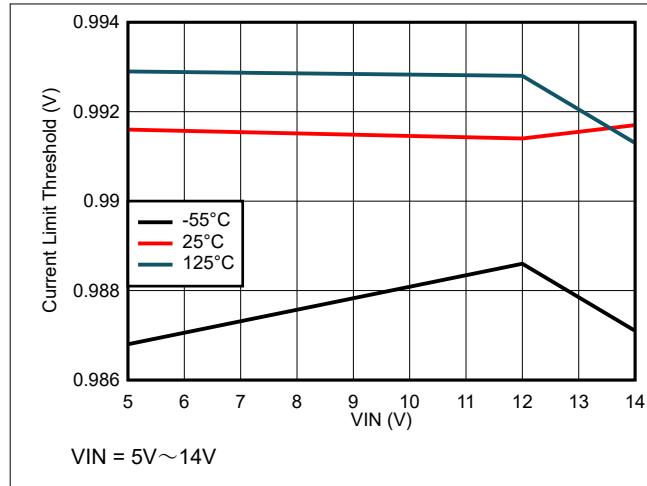

図 6-22. 電流制限スレッショルドと入力電圧との関係

## 6.7 代表的特性 (続き)

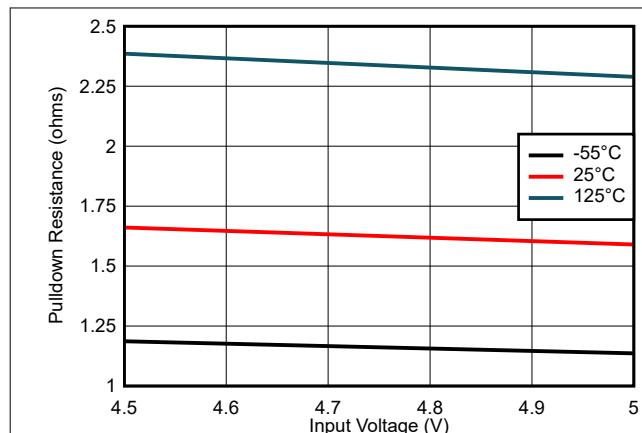

典型的な特性は、 $P_{VIN}=V_{IN}$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^{\circ}\text{C}, 25^{\circ}\text{C}, 125^{\circ}\text{C}$  の場合で示されています(特に記載がない限り)。

図 6-23. 電流制限スレッショルドと入力電圧との関係

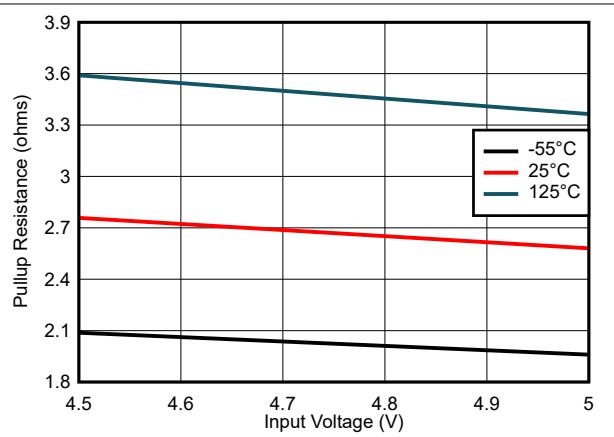

図 6-24. プルアップ抵抗と入力電圧との関係

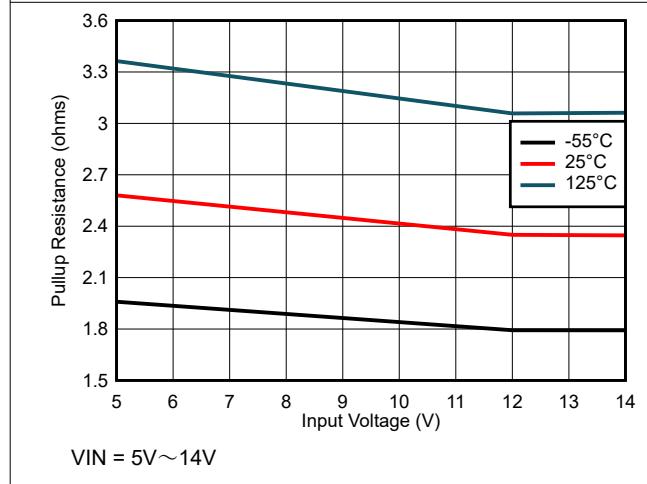

図 6-25. プルアップ抵抗と入力電圧との関係

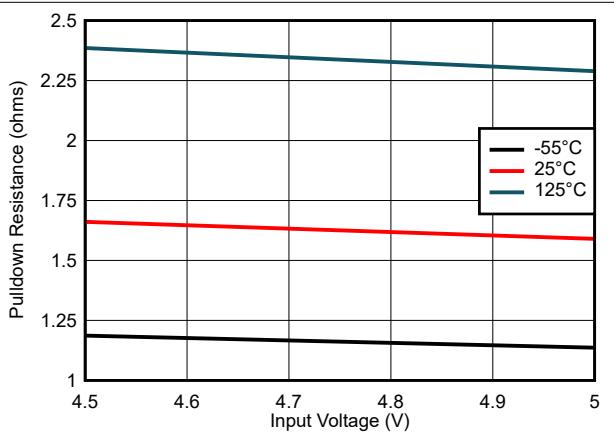

図 6-26. プルダウン抵抗と入力電圧との関係

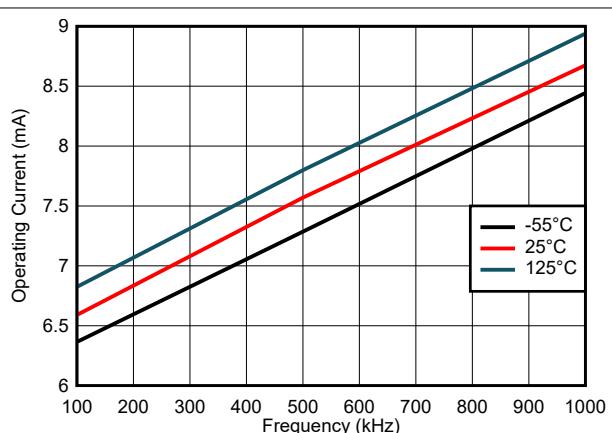

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=V_{IN}$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

VIN = 5V~14V

図 6-27. プルダウン抵抗と入力電圧との関係

VIN = 5V, C<sub>LOAD</sub> なし

図 6-28. 動作供給電流と周波数との関係

VIN = 12V, C<sub>LOAD</sub> なし

図 6-29. 動作供給電流と周波数との関係

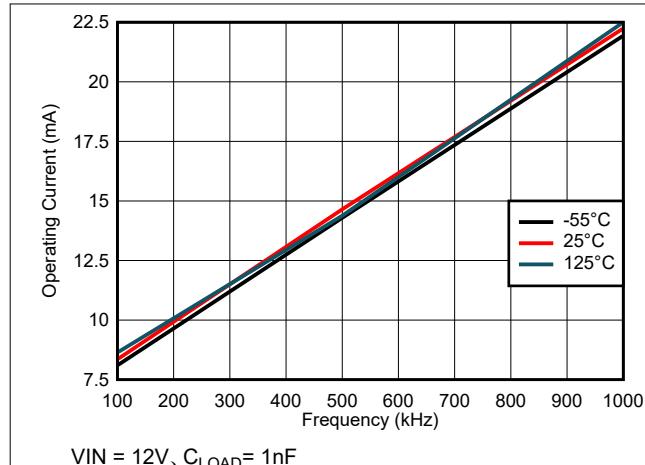

VIN = 5V, C<sub>LOAD</sub> = 1nF

図 6-30. 動作供給電流と周波数との関係

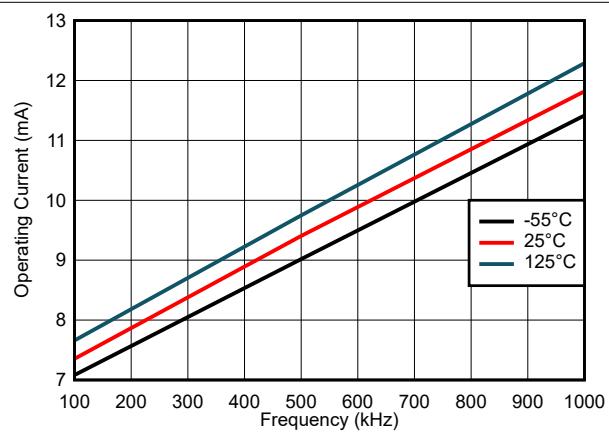

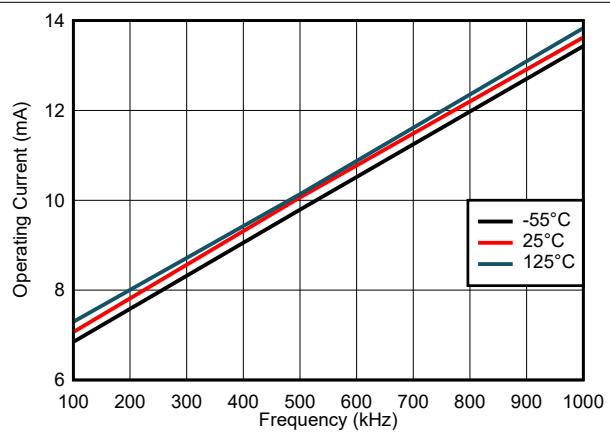

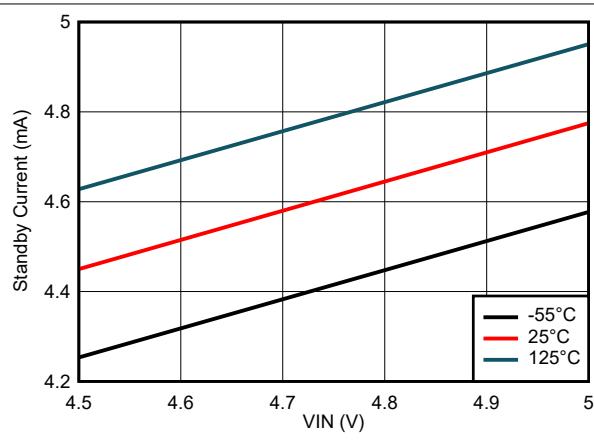

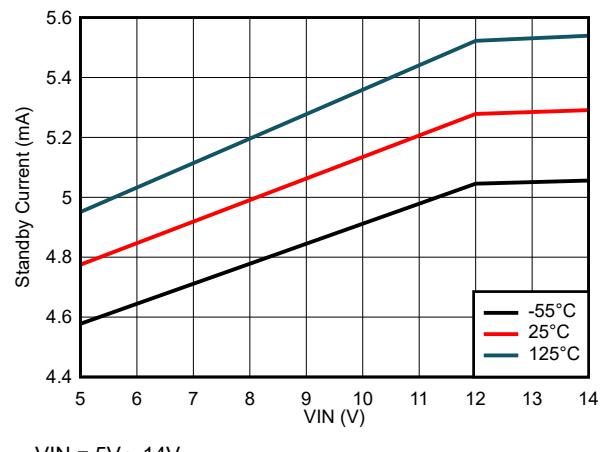

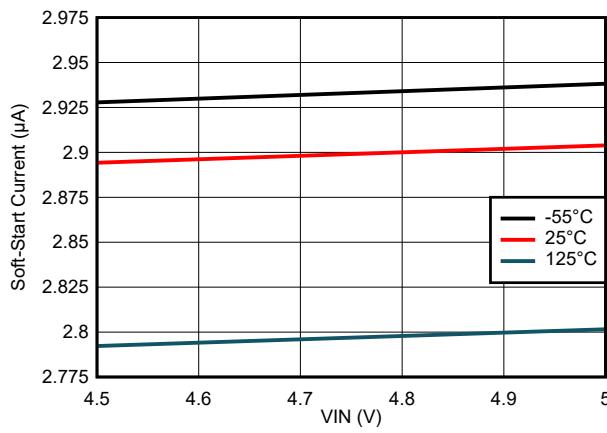

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=V_{IN}$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

図 6-31. 動作供給電流と周波数との関係

図 6-32. スタンバイ電流と入力電圧との関係

図 6-33. スタンバイ電流と入力電圧との関係

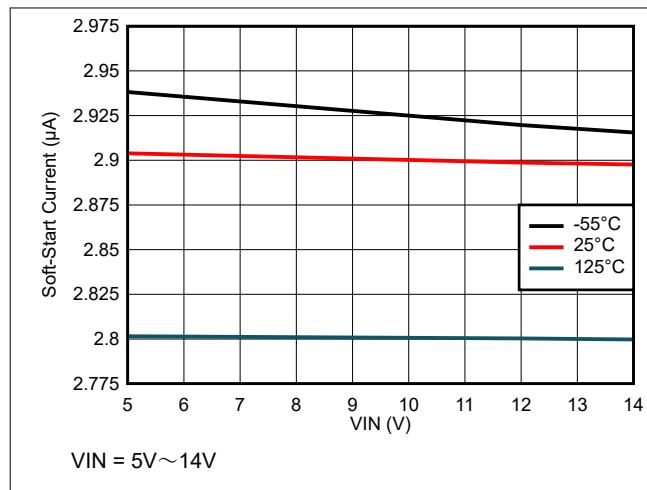

図 6-34. ソフトスタート電流と入力電圧との関係

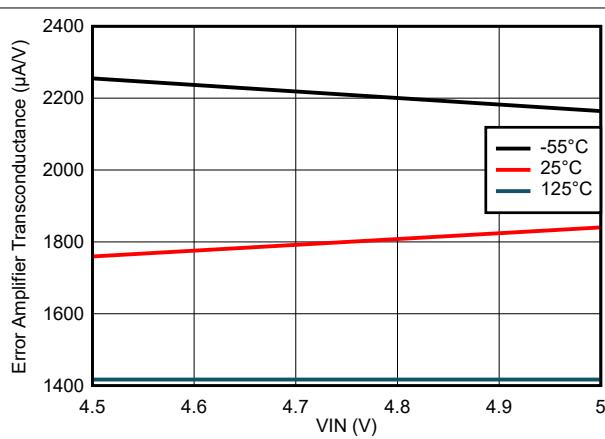

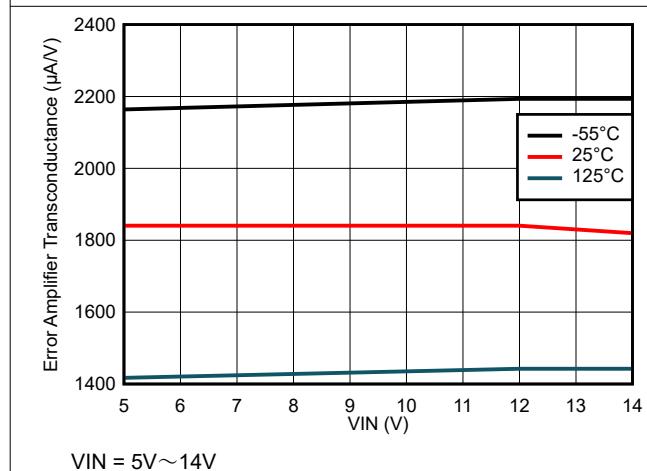

## 6.7 代表的特性 (続き)

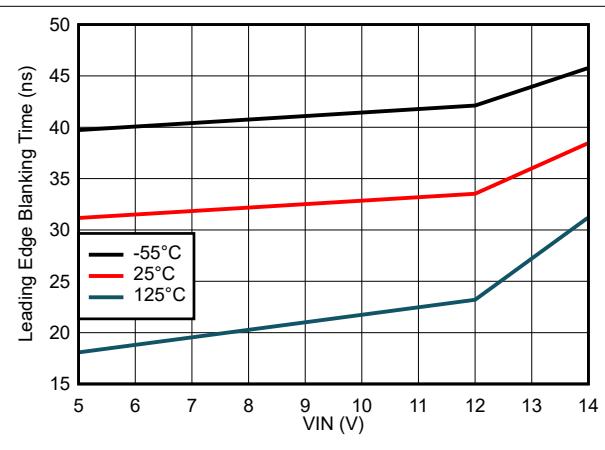

典型的な特性は、 $P_{VIN}=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

図 6-35. ソフトスタート電流と入力電圧との関係

図 6-36. エラー アンプの相互コンダクタンスと入力電圧との関係

図 6-37. エラー アンプの相互コンダクタンスと入力電圧との関係

図 6-38. リーディング エッジ ブランкиング時間と入力電圧との関係

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

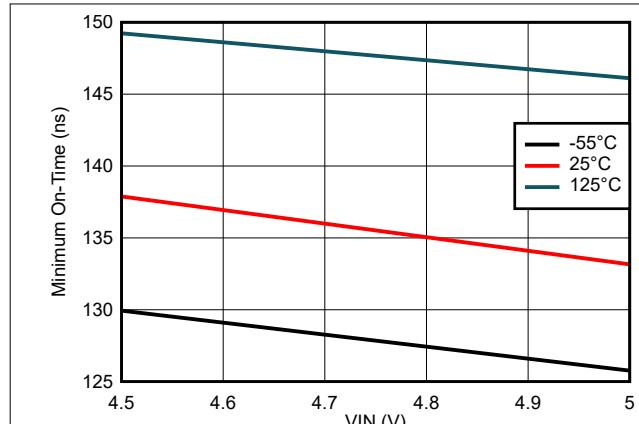

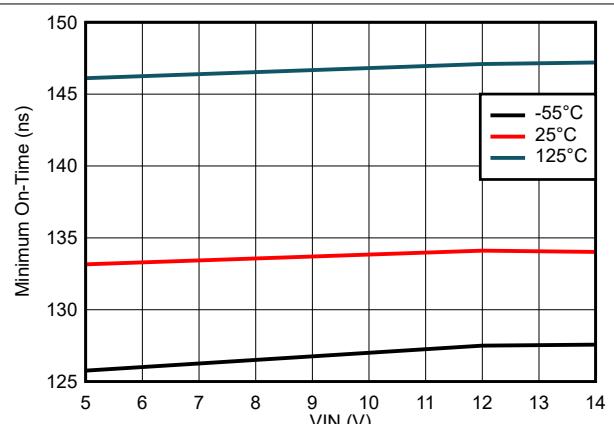

VIN = 4.5V~5V

図 6-39. 最小オン時間と入力電圧との関係

VIN = 5V~14V

図 6-40. 最小オン時間と入力電圧との関係

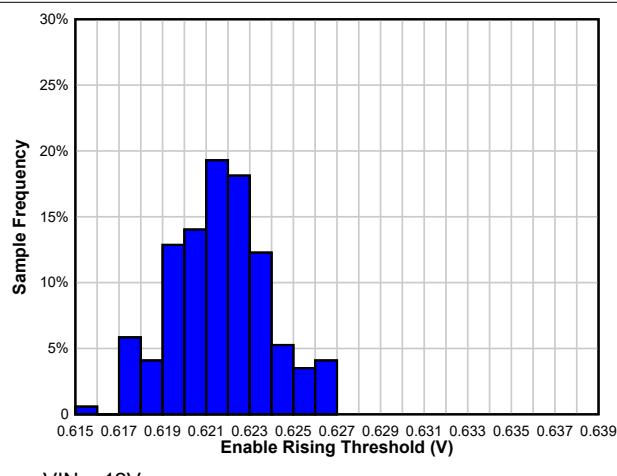

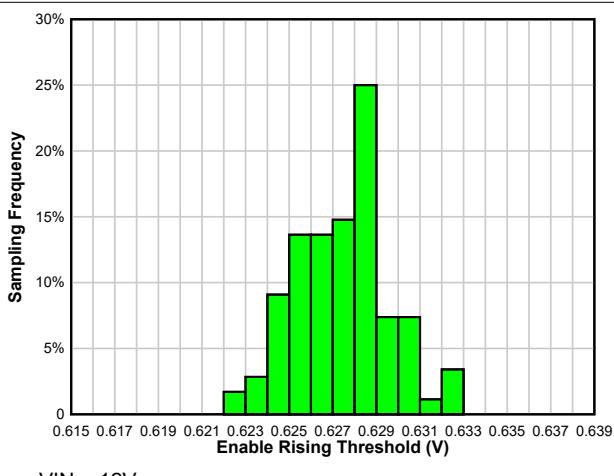

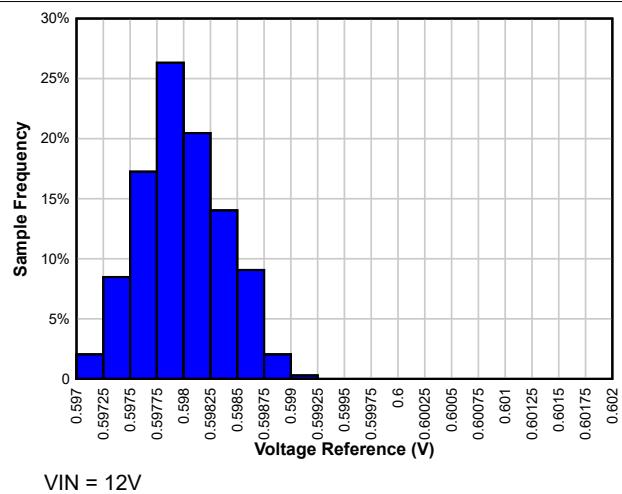

VIN = 12V

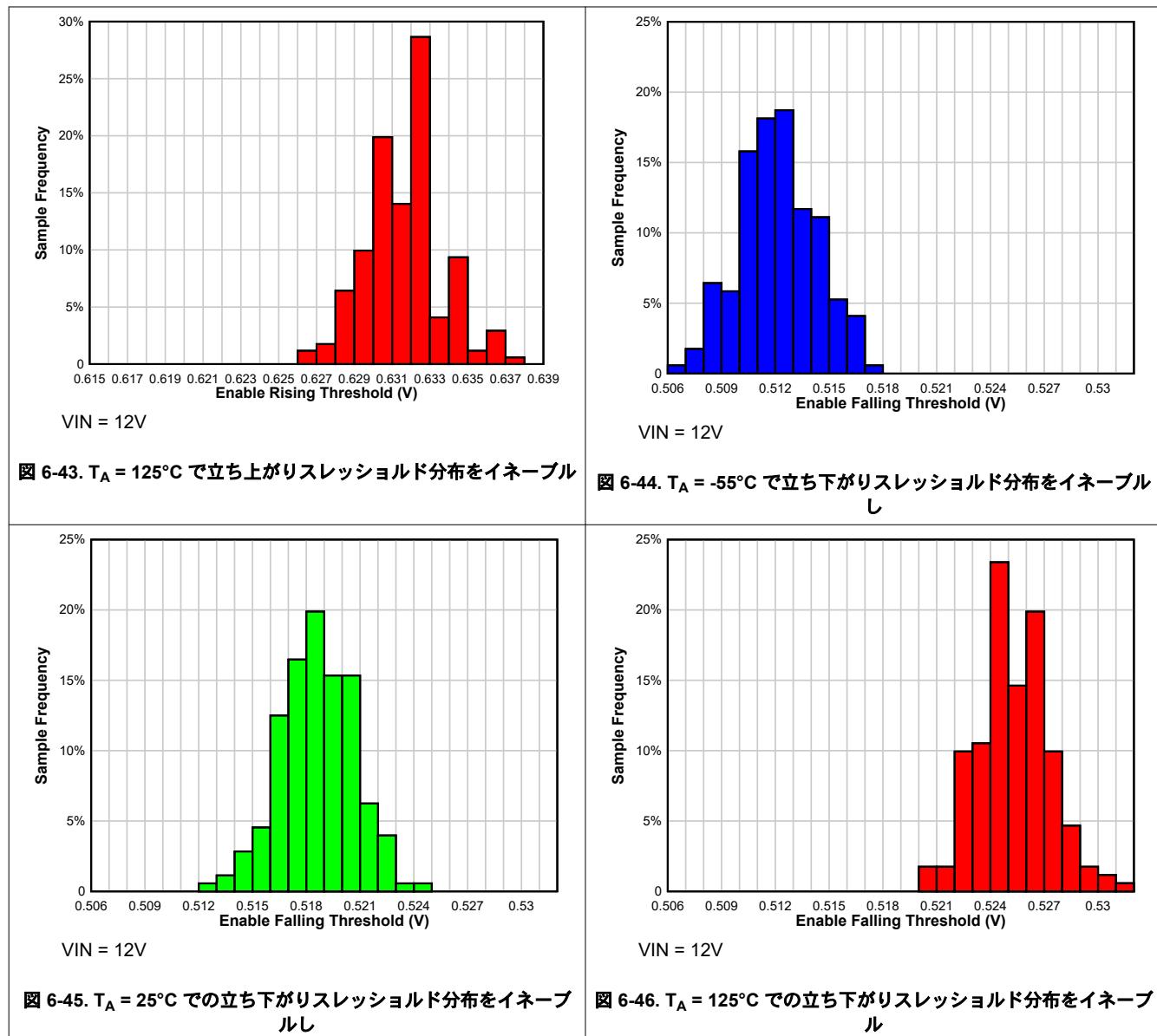

図 6-41.  $T_A = -55^\circ\text{C}$  で立ち上がりレスレッショルド分布をイネーブル

VIN = 12V

図 6-42.  $T_A = 25^\circ\text{C}$  で立ち上がりレスレッショルド分布をイネーブル

## 6.7 代表的特性 (続き)

典型的な特性は、 $PVIN=VIN$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=V_{IN}$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

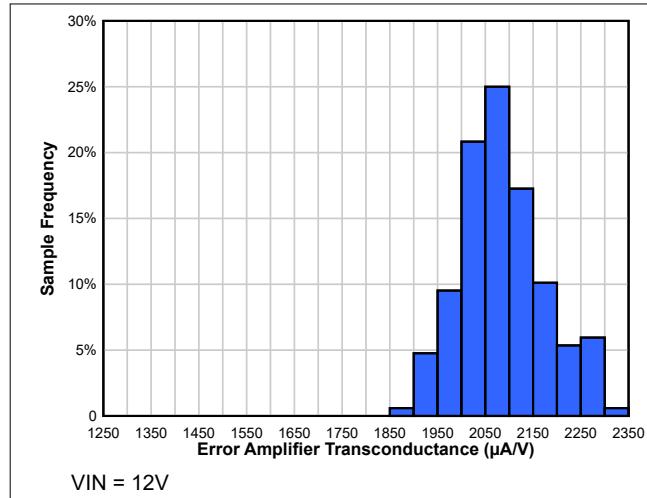

図 6-47.  $T_A = -55^\circ\text{C}$  でのエラー アンプの相互コンダクタンス分布

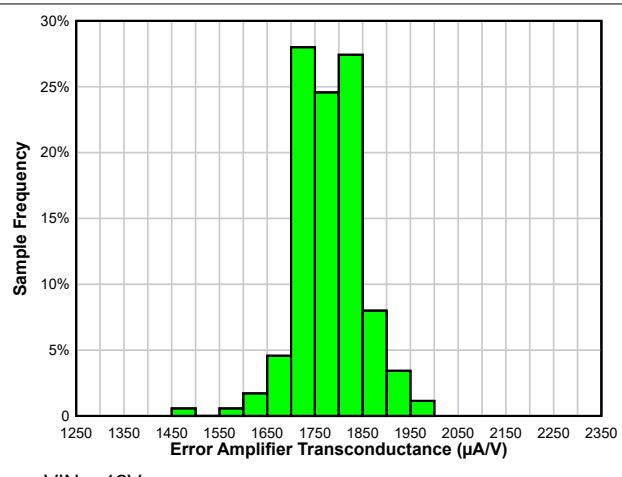

図 6-48.  $T_A = 25^\circ\text{C}$  でのエラー アンプの相互コンダクタンス分布

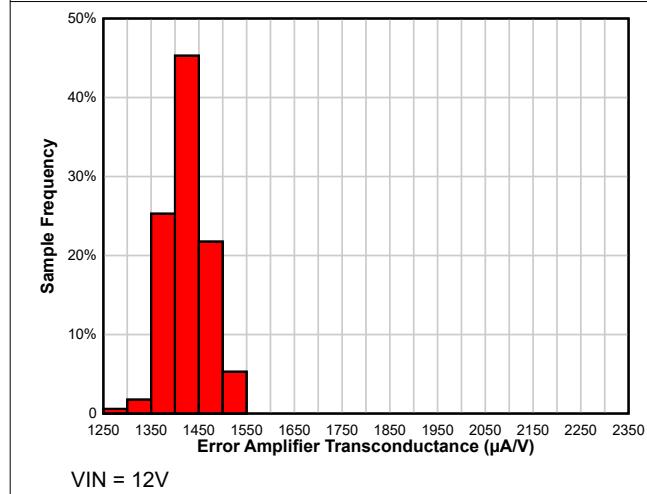

図 6-49.  $T_A = 125^\circ\text{C}$  でのエラー アンプの相互コンダクタンス分布

図 6-50.  $T_A = -55^\circ\text{C}$  での出力電圧の精度分布

## 6.7 代表的特性 (続き)

典型的な特性は、 $P_{VIN}=V_{IN}$  が 4.5V から 14V の範囲で、スイッチング周波数が 500kHz、温度が  $T_A = -55^\circ\text{C}, 25^\circ\text{C}, 125^\circ\text{C}$  の場合で示されています(特に記載がない限り)。

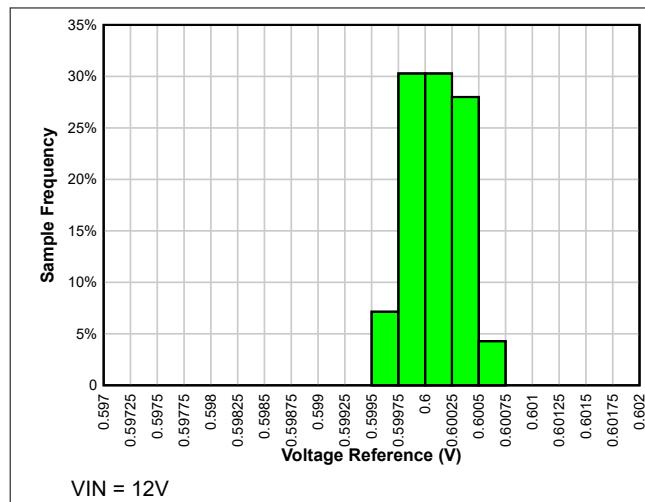

VIN = 12V

図 6-51.  $T_A = 25^\circ\text{C}$  での出力電圧の精度分布

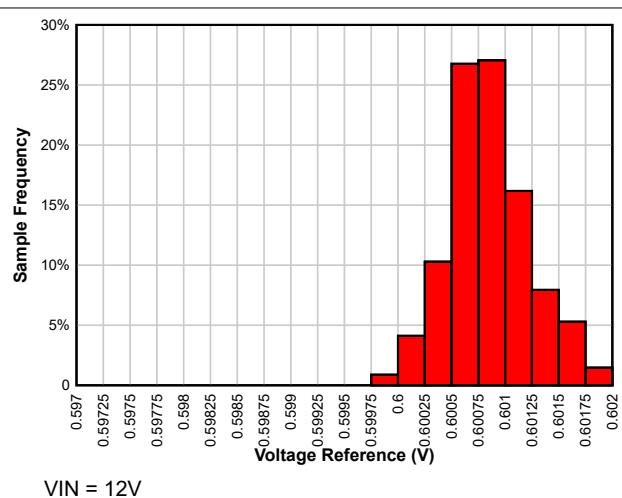

VIN = 12V

図 6-52.  $T_A = 125^\circ\text{C}$  での出力電圧の精度分布

## 7 詳細説明

### 7.1 概要

TPS7H502x は、放射線耐性が強化された電流モードのシングルエンド PWM コントローラで、統合されたゲートドライバを内蔵しています。このデバイスは、すべての動作モードで最大 1MHz の動作が可能です。このコントローラは、宇宙用パワー コントローラの設計に使用することを目的としており、フライバック、フォワード、ブーストなどのトポロジに対応できます。TPS7H5020 の公称最大デューティサイクルは 100% であり、TPS7H5021 の公称 50% のデューティサイクル制限があります。

このコントローラは、0.6V ±1% の電圧リファレンスを搭載しており、高精度なコンバータ設計を可能にします。ソフトスタート、イネーブル、調整可能なスロープ補償などの機能がコントローラに組み込まれており、全体的なコンバータ設計を簡素化し、外部コンポーネントの必要数を最小限に抑えます。このコンバータは、SYNC ピンを通じて外部クロックと同期させることもできます。外部クロックの同期範囲は 100kHz から 1MHz であり、これは内部発信器モードでの周波数範囲と同じです。

コントローラは、VIN ピンと PVIN ピンを通じて、それぞれコントローラ電圧とドライバ段用の別々の電圧入力を提供します。これらの入力の電圧範囲は 4.5V から 14V であり、ユーザーに大きな柔軟性を提供します。統合されたドライバは、シリコン FET(典型的な 12V のゲート電圧)および GaN パワー半導体デバイス(典型的な 5V のゲート電圧)の両方で使用できます。GaN デバイスを駆動する場合、VLDO レギュレータ出力は PVIN に直接接続することができ、ユーザーが希望する場合は、PVIN に別の電源を使用することもできます。VLDO は 4.5V~5.5V の範囲でプログラム可能です。

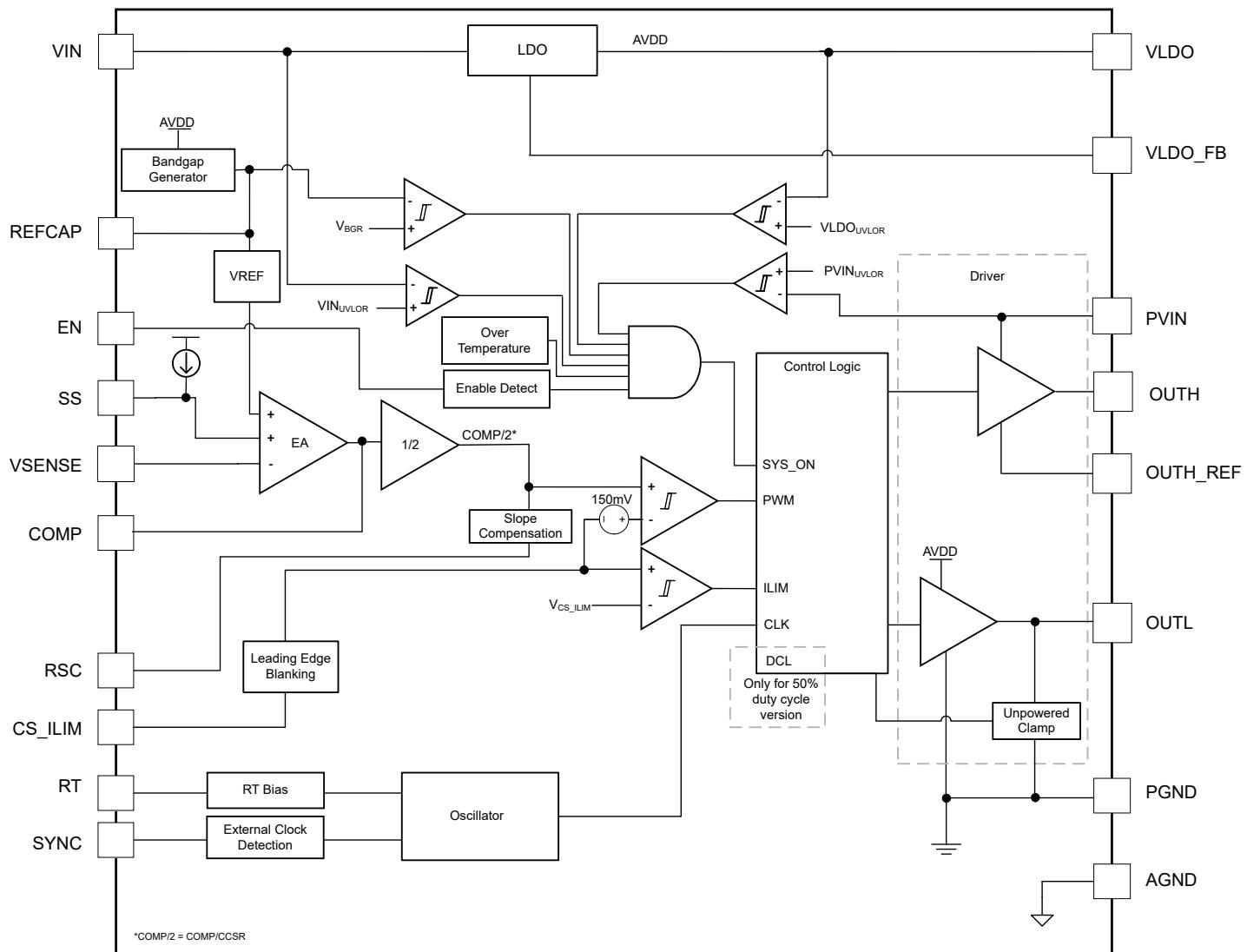

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電圧 (VIN) および VLDO

定常状態動作中は、TPS7H502x の入力電圧は 4.5V ~ 14V の間にする必要があります。VIN と AGND の間には、少なくとも  $0.1\mu\text{F}$  のバイパス キャパシタンスが必要です。入力バイパス コンデンサは、コントローラにできるだけ近くに配置する必要があります。VIN、EN、および GND の間に接続された抵抗分圧回路を使用して、入力電圧の UVLO を調整できます。

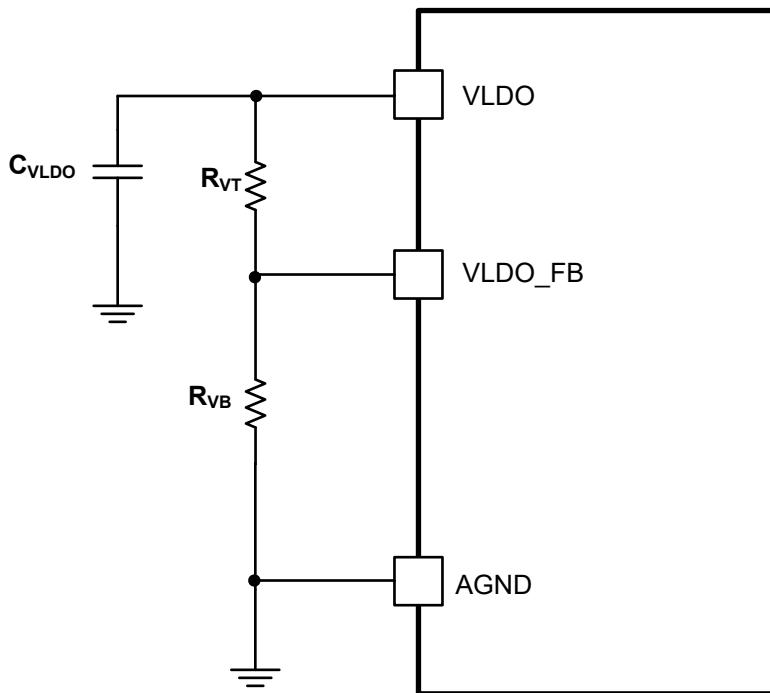

VIN に印加される電圧は、VLDO の電圧を生成する内部レギュレータの入力として機能します。VLDO の出力は、4.5V から 5.5V の範囲でプログラム可能です。これにより、VLDO を PVIN に接続し、コントローラを使用して GaN パワー半導体デバイスを駆動できます。VLDO をプログラムする際、抵抗分圧回路は 2 つの抵抗で構成されます：VLDO と VLDO\_FB の間の  $R_{VT}$  と、VLDO\_FB と AGND の間の  $R_{VB}$ 。[式 1](#) を使用して、適切な  $R_{VB}$  抵抗を選択できます。

$$R_{VB} = \frac{V_{REFCAP}}{V_{LDO} - V_{REFCAP}} \times R_{VT} \quad (1)$$

ここで

- $V_{REFCAP} = 1.223\text{V}$  (標準値)

- VLDO は、内部レギュレータの希望する出力電圧で、4.5V から 5.5V の範囲内です。

- $R_{VT}$  は、VLDO と VLDO\_FB の間に配置され、ユーザーによって選択された上側の抵抗値(例:  $10\text{k}\Omega$ )です。

図 7-1. VLDO 出力電圧をプログラミングする構成

VLDO がドライバ段への入力として使用されないアプリケーションでは、VLDO を 5V に設定するための抵抗を選択することが推奨されます。抵抗  $R_{VT}$  および  $R_{VB}$  は、常に実装する必要があります。VLDO レギュレータの最大ドロップアウト電圧は 0.4V です。VLDO レギュレータのヘッドルーム電圧が増加すると、その出力電流容量も増加しますが、入力電圧が 7V に達するまで続きます。これで、VLDO レギュレータの最大電流能力を実現できます。詳細については、「電気的特性」をご覧ください。これは、VLDO が GaN FET を駆動するために PVIN に規定された入力電圧を供給するアプリケーションにおいて重要になります。FET に要求されるゲート電流は、次のように決まります：

$$I_g = Q_g \times f_{sw} \quad (2)$$

ここで

- $I_g$  は GaN FET のゲート電流

- $Q_{Qg}$  は GaN FET の総ゲート電荷量(メーカーのデータシートに掲載)

- $f_{sw}$  は、電源コンバータのスイッチング周波数

このシナリオでは、VLDO が FET に供給する外部電流は、レギュレータの能力を超えてはなりません。VLDO に接続することの推奨容量は  $1\mu\text{F}$  です。デバイスの EN ピンは VLDO にも接続できます。

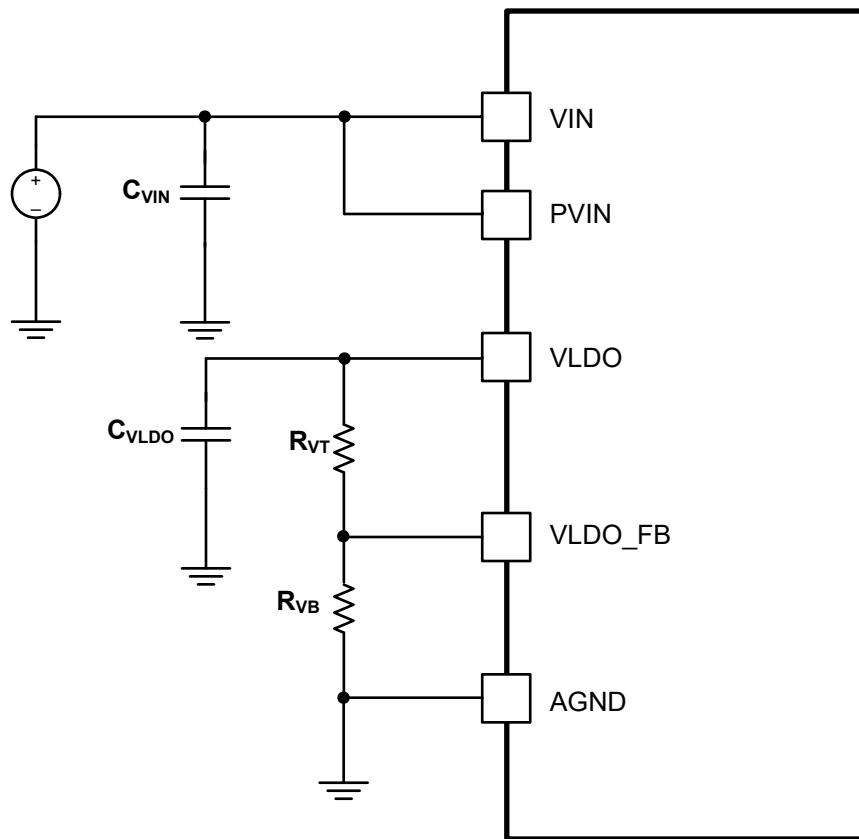

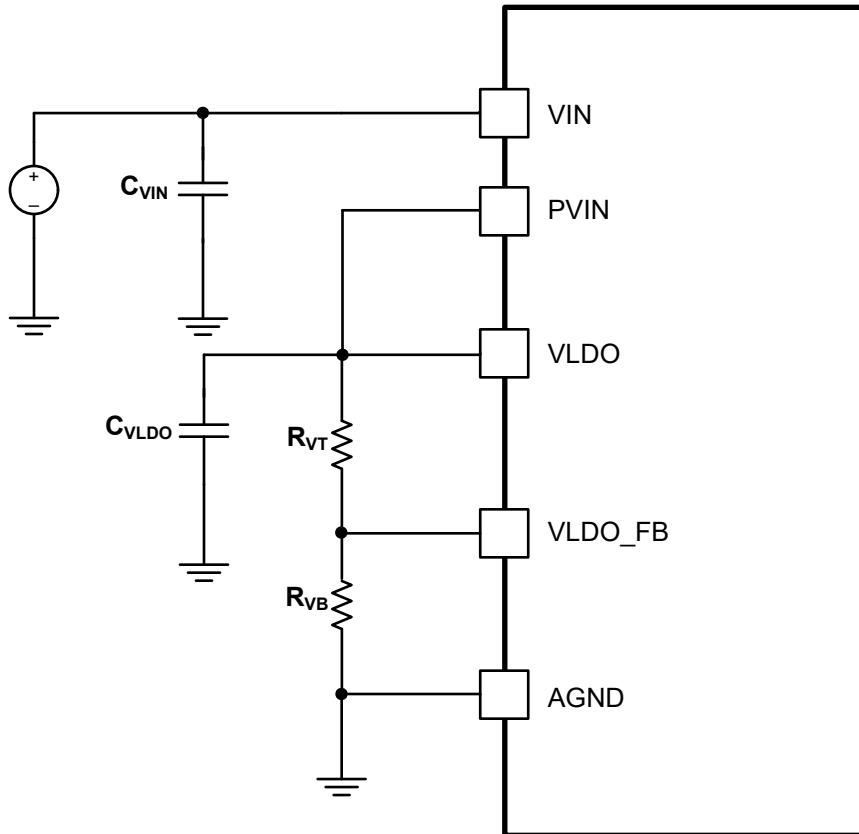

### 7.3.2 ドライバの入力電圧(PVIN)

TPS7H502x のドライバ段の入力電圧範囲は  $4.5\text{V} \sim 14\text{V}$  です。デバイスの OUT ピンに供給される電圧は、PVIN に供給される電圧とほぼ等しくなります。そのため、コントローラはシリコン MOSFET および GaN FET ベースのパワーコンバータ設計の両方に適切なゲート電圧を供給するために使用できます。シリコン MOSFET の場合、標準ゲート電圧は  $10\text{V} \sim 12\text{V}$  です。GaN パワー半導体デバイスは通常、 $4.5\text{V}$  から  $6\text{V}$  のゲート電圧を必要とします。必要なゲート電圧は選択されたスイッチング デバイスに依存するため、コントローラはユーザーが特定のアプリケーションに適した電圧をドライバステージに供給できる機能を提供します。PVIN は、単一電源動作のために VIN に直接接続できます。この構成は、シリコン MOSFET または GaN FET のいずれかを駆動するために使用できます。この構成では、VLDO が内部回路に  $5\text{V}$  を供給するように  $R_{VT}$  と  $R_{VB}$  を選択することを推奨します。VLDO 出力のプログラムの詳細については、「[入力電圧\(VIN\)およびVLDO](#)」を参照してください。

図 7-2. PVIN と VIN の間の接続の構成

VLDO は、 $4.5\text{V}$  から  $5.5\text{V}$  の規定されたゲートドライブ電圧を得るために、PVIN に接続することもできます。PVIN と PGND の間には、 $1\mu\text{F}$  の最小容量を推奨します。PVIN が VLDO に接続されると、これには VLDO で必要な  $1\mu\text{F}$  のキャパシタンスが含まれる場合があります。追加の容量も使用できますが、VLDO レギュレータの適切な安定性を維持するため、合計容量が  $4.7\mu\text{F}$  を超えないようにする必要があります。

図 7-3. PVIN と VLDO の接続構成

### 7.3.3 スタートアップ

コントローラの出力がスイッチングを開始する前に、以下の条件を満たす必要があります：

- VLDO は、立ち上がり UVLO スレッショルドを超えます

- VIN は、立ち上がり UVLO スレッショルドを超えます

- PVIN は、立ち上がり UVLO スレッショルドを超えます

- 内部 1.2V バンドギャップ電圧を利用できます

- イネーブル信号 EN は立ち上がり電圧スレッショルドを上回っています

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドより低くなっている

前述のすべての条件が満たされると、ソフトスタート プロセスが開始されます。

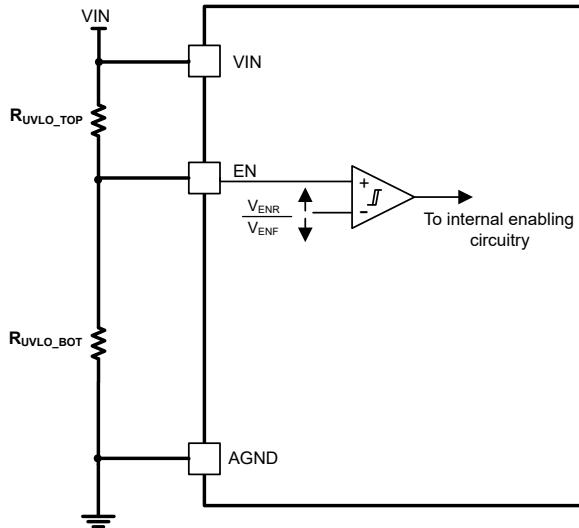

### 7.3.4 イネーブルおよび低電圧誤動作防止 (UVLO)

TPS7H502x を EN ピンで有効化するためのいくつかの方法があります。このピンは VLDO に直接接続することができ、VLDO の電圧が EN ピンの立ち上がり電圧スレッショルドを超えると、デバイスが有効化されることになります。このピンは、シーケンシングが必要な場合に外部で生成された信号や互換性のある PGOOD 信号で駆動することもできます。最後に、図 7-4 に示すように、2 つの抵抗を使用して、VIN がユーザーが設定した閾値を超えたときにコントローラを有効化するようにプログラムできます。2 つの抵抗は分圧回路として構成され、1 つは VIN と EN の間に、もう 1 つは EN と AGND の間に配置されます。

図 7-4. 2 つの外部抵抗を使用したピン構成の有効化

式 3 を使って、ユーザーはデバイスの希望する最大起動電圧に基づいて、選択した  $R_{UVLO\_BOT}$  の値に対する  $R_{UVLO\_TOP}$  の値を計算できます。これらの選択された抵抗を使用して、式 4 を使って最小スタートアップ電圧を決定できます。

$$R_{UVLO\_TOP} = R_{UVLO\_BOT} \times \left( \frac{V_{START\_MAX}}{V_{ENR\_MAX}} - 1 \right) \quad (3)$$

$$V_{START\_MIN} = V_{ENR\_MIN} \times \left( \frac{R_{UVLO\_TOP}}{R_{UVLO\_BOT}} + 1 \right) \quad (4)$$

図 7-4 の 2 つの抵抗構成では、入力電圧が特定のスレッショルドを下回ると、コントローラは過電圧ロックアウトによりシャットダウンします。これは、EN ピンのヒステリシスによるものです。シャットダウンが予想される電圧を決定するには、式 5 および式 6 を使用します。

$$V_{STOP\_MAX} = V_{ENF\_MAX} \times \left( \frac{R_{UVLO\_TOP}}{R_{UVLO\_BOT}} + 1 \right) \quad (5)$$

$$V_{STOP\_MIN} = V_{ENF\_MIN} \times \left( \frac{R_{UVLO\_TOP}}{R_{UVLO\_BOT}} + 1 \right) \quad (6)$$

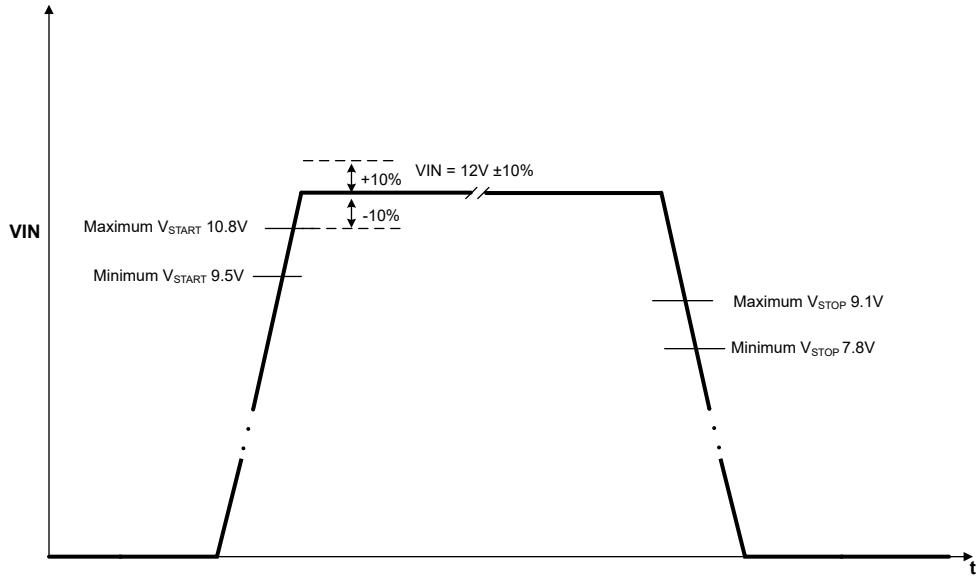

$R_{UVLO\_TOP}$  と  $R_{UVLO\_BOT}$  の値を選択するときは、ユーザーが注意する必要があることに注意してください。適切な動作を確保するために、これらの抵抗の選定を最適化することが推奨されます。UVLO 値は、すべての状況でデバイスが期待通りにオンになることを確実にするために、入力電圧の 75% 以下である必要があります。UVLO をこれより高く設定すると、デバイスのターンオンで問題が発生する可能性があります。図 7-5 は、12V レール上での期待される起動電圧と UVLO 電圧を示しており、最大起動電圧は公称入力電圧の 90% です。この場合、入力電圧が公称値の 75% から 65% の間に低下すると、ターンオフが発生します。

図 7-5. VIN = 12V の 2 つの抵抗構成における起動電圧と UVLO 電圧

### 7.3.5 電圧リファレンス

コントローラは、内部で 1.2V のバンドギヤップ リファレンスを生成し、これがさまざまな制御ロジック ブロックで使用されます。これは、定常状態動作時に REFCAP ピンに印加される電圧です。この電圧は 0.6V に分圧され、エラー アンプのリファレンスを生成します。エラー アンプのリファレンス電圧は、エラー アンプのオフセットを考慮して COMP ピンで測定し、「仕様」に示すようにレギュレーションを  $\pm 1\%$  以内に維持します。この基準電圧の許容公差が小さいため、高精度のパワー コンバータを設計できます。適切な電気的動作を確保し、デバイスの堅牢な单一事象トランジェント (SET) 性能を保証するために、REFCAP ピンには 470nF のコンデンサをグランドに接続する必要があります。

### 7.3.6 エラー アンプ

TPS7H502x コントローラは、相互コンダクタンスの誤差増幅器を使用しています。エラー アンプは、VSENSE ピンの電圧を SS ピンの電圧または内部の 0.6V 電圧リファレンスの低い方と比較します。エラー アンプの相互コンダクタンスは、通常動作時で 1500 $\mu$ A/V です。周波数補償ネットワークは、COMP ピンと AGND の間に接続されます。誤差増幅器の DC ゲインは通常 14,500V/V です。

### 7.3.7 出力電圧プログラミング

電力コンバータの V<sub>OUT</sub> から VSENSE ピンへの抵抗分圧回路を使用して設定されます。出力電圧は、公称基準電圧 0.6V に分割する必要があります。R<sub>BOTTOM</sub> の選択には、式 7 を使用できます。

$$R_{\text{BOTTOM}} = \frac{V_{\text{REF}}}{V_{\text{OUT}} - V_{\text{REF}}} \times R_{\text{TOP}} \quad (7)$$

ここで

- $V_{\text{REF}} = 0.6\text{V}$  (標準値)

- $V_{\text{OUT}}$  は希望する出力電圧

- $R_{\text{TOP}}$  はユーザーが選択する上側抵抗の値(例: 10k $\Omega$ )

R<sub>BOTTOM</sub> および R<sub>TOP</sub> に許容誤差の小さい抵抗(1% 以下)を使用して、出力電圧設定ポイントの精度を向上させることを推奨します。

### 7.3.8 ソフトスタート(SS)

ソフトスタート回路は、定常状態プログラム済み出力に達するまで、コンバータの出力電圧を徐々に上昇させます。ソフト・スタート中、エラー アンプは SS ピンの電圧が  $V_{REF}$  より高くなるまでの間、ソフトスタート ピンの電圧を基準として使用します。 $SS$  ピンの電圧が  $V_{REF}$  を上回ると、ソフトスタート期間が終了します。

$SS$  ピンと AGND の間に接続されたコンデンサが、PWM コントローラのソフトスタート時間制御します。次の式を使って、目的のソフトスタート時間のコンデンサを選択できます。

$$t_{SS} = \frac{C_{SS} \times V_{REF}}{I_{SS}} \quad (8)$$

ここで

- $t_{SS}$  は、必要なソフトスタート時間です

- $V_{REF}$  は 0.6V(標準値)の電圧リファレンス

- $I_{SS}$  は、2.8 $\mu$ A のソフト・スタート充電電流(標準値)

### 7.3.9 スイッチング周波数および外部同期

TPS7H502x コントローラには、デバイスのスイッチング周波数を設定するための 2 つのモードがあります：内部オシレータモードと外部同期モードです。デバイスは、RT ピンと SYNC ピンの状態に基づいて、これらのモードのいずれかに設定されます。SYNC ピンでクロック入力が検出されると、デバイスは外部同期モードで動作します。それ以外の場合、デバイスは内部発振器で動作し、RT から AGND への抵抗によって決定された周波数で動作します。RT は両方の動作モードに設定する必要があります。

**表 7-1. 発振器のモードと構成**

| モード   | RT                                                                    | SYNC                      | スイッチング周波数                                          |

|-------|-----------------------------------------------------------------------|---------------------------|----------------------------------------------------|

| 内部発振器 | AGND との間に抵抗を実装しました。                                                   | フローティング                   | RT 値に応じて 100kHz ~ 1MHz の範囲で構成できます。                 |

| 外部同期  | AGND との間に抵抗を実装しました。SYNC の入力クロック周波数と一致するように選択する必要があります。 <sup>(1)</sup> | 100kHz ~ 1MHz の外部クロックの入力。 | 同期入力クロックに同期しました。スイッチングは、外部クロックと 1:1 の周波数と位相が一致します。 |

(1) 50% のデューティサイクル制限 (TPS7H5021) のデバイスを使用する場合の外部同期モードで RT 抵抗を選択する具体的なガイダンスについては、[TPS7H5021 との外部同期](#)を参照してください。

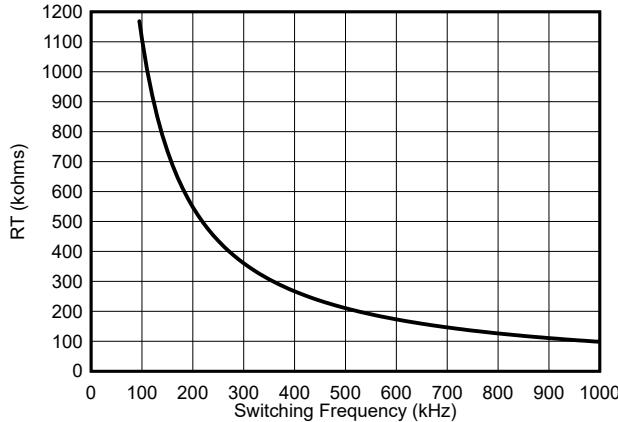

#### 7.3.9.1 内部発振器モード

RT ピンから AGND への抵抗が、デバイスのスイッチング周波数を設定します。TPS7H502x コントローラは、名目上のスイッチング周波数範囲が 100kHz から 1MHz です。内部発振器モードでは、RT ピンに実装する必要があります。[式 9](#) に、目的のスイッチング周波数に基づいた RT 値の計算を示します。[図 7-6](#) の曲線は、TPS7H502x で指定されたスイッチング周波数に対応する RT 値を示しています。

$$RT = \frac{112390}{f_{SW}} - 14.2 \quad (9)$$

ここで

- RT は k $\Omega$  単位です

- f<sub>sw</sub> は kHz 単位です

図 7-6. RT とスイッチング周波数

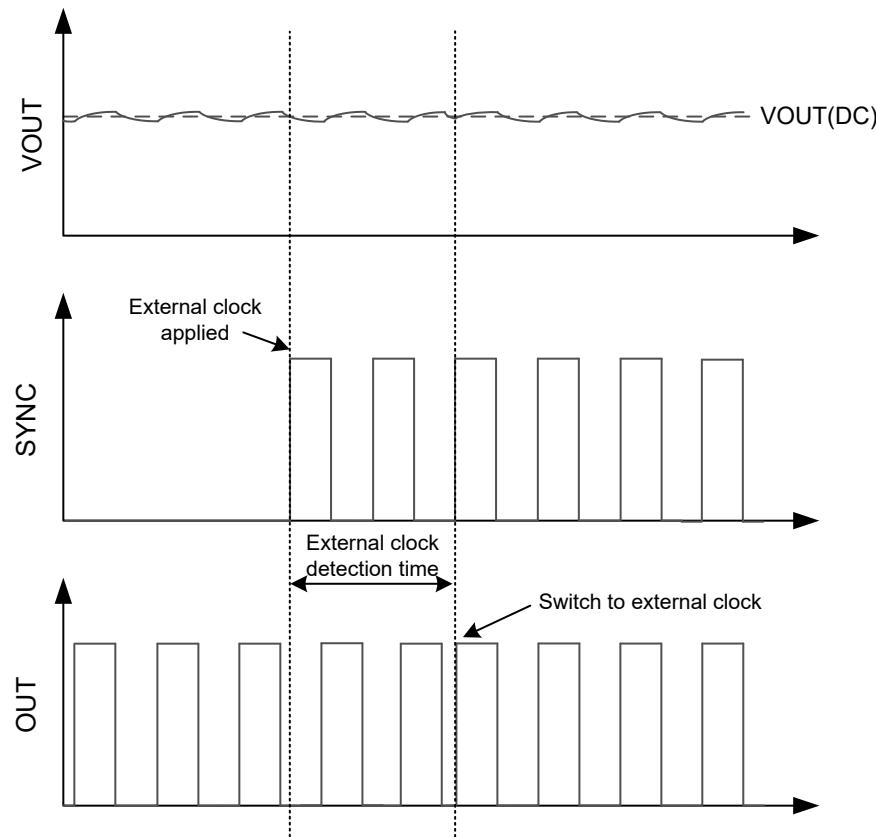

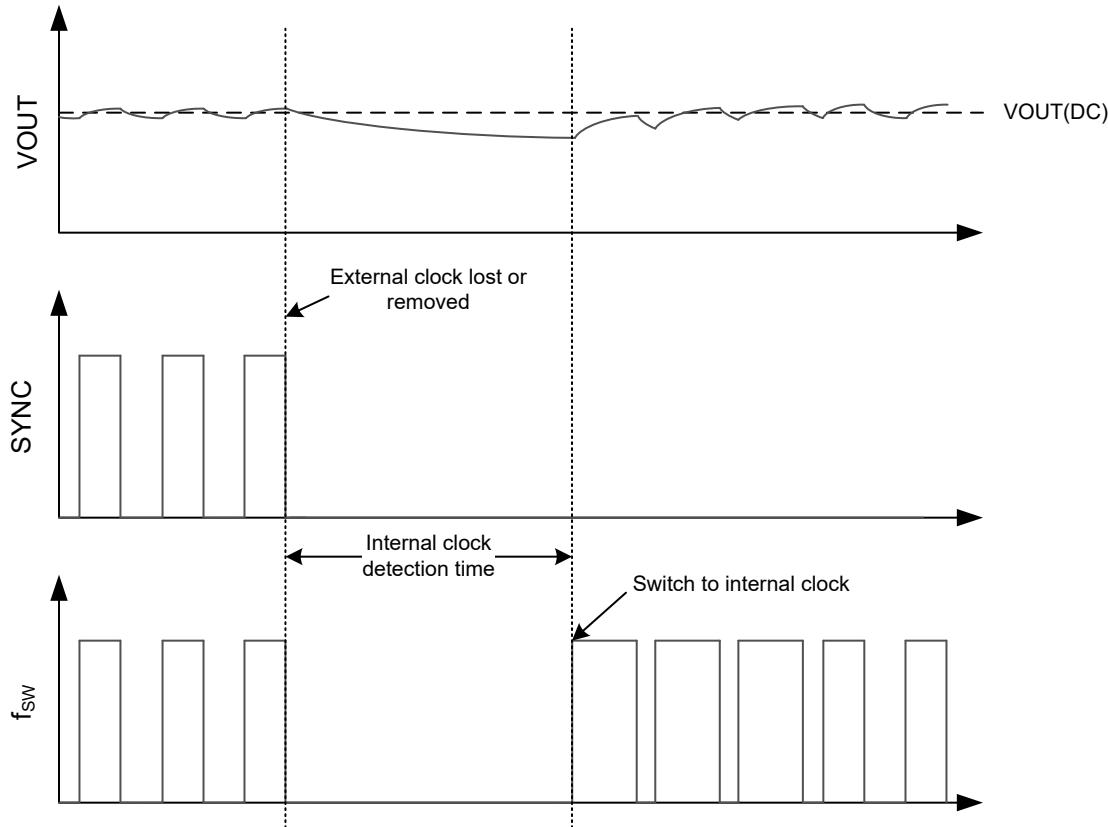

### 7.3.9.2 外部同期モード

コントローラは、SYNC ピンにクロックを入力することで外部同期モードで使用できます。印加する外部クロックは、目的のスイッチング周波数に設定する必要があります。外部クロックは、100kHz から 1MHz の範囲で、デューティサイクルが 50% である必要があります。50% のデューティサイクルを持つ外部クロックを使用することが推奨されます。このモードでは、コントローラは SYNC ピンに入力されたクロック信号と位相を合わせてスイッチングします。SYNC ピンはコントローラの入力としてのみ機能することに注意してください。

外部同期モードで動作する場合、RT ピンには AGND への抵抗を接続する必要があります。RT 抵抗で設定されたスイッチング周波数は、外部クロック周波数の  $\pm 10\%$  の範囲内である必要があります。スイッチング周波数は外部クロック周波数と 1:1 の関係にあります。コントローラが SYNC ピンにクロックが適用される前に内部発信器モードで動作している場合、クロックが適用されてから検出と切り替えが行われるまでに約 2~5 サイクルかかります。外部同期モードで動作していてクロックが失われた場合、検出が行われるまでに約 2~5 サイクルかかり、その後内部発信器への切り替えが行われます。

図 7-7. 内部クロックから外部クロックへの遷移

図 7-8. 外部から内部へのクロック遷移

#### 7.3.9.2.1 TPS7H5021 との外部同期

TPS7H5021 を外部同期モードで使用する場合、50% のデューティサイクル制限 (DCL) の最大値を維持するために実装すべき、いくつかの重要な動作上の違いがあります。外部同期モードに示すように、すべてのアプリケーションで最高の性能を得るには、外部クロックに 50% のデューティサイクルが必要です。しかし、TPS7H5021 におけるこのデューティサイクルの許容誤差は  $\pm 10\%$  ですが、このクロックのデューティサイクルは TPS7H5021 でより厳密に制御する必要があります。特に、TPS7H5021 を 100kHz ~ 200kHz で使用する場合、最大 50% の DCL を維持するために、外部クロックのデューティサイクルを 49% ~ 51% の範囲で維持する必要があります。200kHz を超えると、デューティサイクルの範囲は 48% ~ 52% の範囲で変化する場合があります。

さらに、すべての外部同期の使用ケースにおいて、RT ピンには必ず抵抗を接続して AGND に落とす必要があります。これにより、コンバータは、クロックが印加される前、またはクロックが喪失した場合にスイッチングを維持できます。ただし、200kHz を超えるスイッチング周波数を計画している場合、内部発振器モードで説明されているように、RT 抵抗の値は、標準的な RT 抵抗の選択肢と比較してわずかに変化します。ユーザーは式 9 を使用して得られる抵抗よりも約 30% 高い抵抗を選択する必要があります。

$$RT \approx 1.3 \times \left( \frac{112390}{f_{SW}} - 14.2 \right) \quad (10)$$

以下に、各種の外部同期周波数に対する RT 選択の値の例を示します。

表 7-2. TPS7H5021 外部同期モードの推奨 RT 値

| 外部同期周波数 | 推奨 RT 値                |

|---------|------------------------|

| 100kHz  | 1.18MΩ - TPS7H5020 と同じ |

| 200kHz  | 732kΩ                  |

| 500kHz  | 274kΩ                  |

**表 7-2. TPS7H5021 外部同期モードの推奨 RT 値 (続き)**

| 外部同期周波数 | 推奨 RT 値 |

|---------|---------|

| 1MHz    | 130kΩ   |

更新された抵抗値の選択による主な影響として、クロックが入力されていない場合、コントローラはこの新しい RT 値によって決まる低い周波数でスイッチングすることに注意してください。外部クロックが適用されない状態で長時間動作する場合は、この低いスイッチング周波数がシステム全体の設計に及ぼす影響を評価する必要があります。[表 7-3](#) に、TPS7H5021 で外部同期を使用するための要件の概要を示します。

**表 7-3. TPS7H5021 の外部同期のガイドライン**

| 目標周波数     | 許容クロックデューティサイクル範囲 | RT 抵抗の選択                               |

|-----------|-------------------|----------------------------------------|

| < 200kHz  | 49%~51%           | <a href="#">式 9 参照 - TPS7H5020 と同じ</a> |

| 200kHz 以上 | 48%~52%           | <a href="#">式 10 参照</a>                |

### 7.3.10 デューティ サイクルの制約

TPS7H5020 コントローラの最大デューティ サイクルは公称 100% です。このコントローラでは、出力は 100% デューティ サイクルに対応できますが、「[最小オン時間とオフ時間](#)」に記載されているように、コントローラの最小オフ時間に基づいて最大デューティ サイクルを設定することをユーザーにお勧めします。

TPS7H5021 コントローラの最大デューティ サイクルは公称 50% です。このデューティ サイクル制限に関連する仕様については「[仕様](#)」を参照してください。このデバイスで外部同期オシレータ モードを使用する場合、デバイス仕様を満たすために、ユーザーは正確に 50% のデューティ サイクルを持つ外部クロックを供給することが推奨されます。推奨範囲を超えるデューティ サイクルの外部クロックを使用すると、最大デューティ サイクル制限が十分に機能せず、性能が低下する可能性があります。詳細については、[TPS7H5021 との外部同期](#)を参照してください。

**表 7-4. TPS7H502x 最大デューティ サイクル**

| デバイス      | 最大デューティ サイクル (公称) |

|-----------|-------------------|

| TPS7H5020 | 100%              |

| TPS7H5021 | 50%               |

### 7.3.11 最小オン時間、最小オフ時間

TPS7H502x の出力には、最小オン時間としておおよそ 135ns (標準値) があります。最小オン時間は、出力がオン状態を維持する最小の時間です。そのため、最小オン時間は、電源コンバータ設計の入力から出力への変換比に制約を課す可能性があります。最小オン時間の制限を克服するためには、コンバータのスイッチング周波数およびトランジスタの巻数比 (該当する場合) の慎重な選定が必要です。単一スイッチの順方向、フライバック、およびブーストコンバータで連続導通モードを使用する場合、以下の式を使用して、主電源スイッチのオン時間が設計に適切であることを確認できます。

フォワードの場合:

$$t_{on\_min} < \frac{V_{OUT} + V_D}{(V_{IN} \times N_{SP}) \times f_{SW}} \quad (11)$$

ここで

- $t_{on\_min}$  はコントローラの最小オン時間です

- $V_{OUT}$  は、コンバータの希望する出力電圧です

- $V_{IN}$  はコンバータの入力電圧です

- $V_F$  は整流ダイオードの順方向電圧です

- $N_{PS}$  は、トランジスタの一次側と二次側の巻数比です

- $N_{SP}$  は、トランジスタの 2 次 / 1 次巻線比です ( $N_{PS}$  の逆数)

- $f_{SW}$  はコンバータのスイッチング周波数です

プライバックの場合：

$$t_{on\_min} < \frac{(V_{OUT} + V_D) \times N_{PS}}{(V_{IN} + (V_{OUT} + V_D) \times N_{PS}) \times f_{SW}} \quad (12)$$

昇圧の場合：

$$t_{on\_min} < \frac{V_{OUT} + V_D - V_{IN}}{(V_{OUT} + V_D) \times f_{SW}} \quad (13)$$

同様に、最小オフ時間もコンバータの動作に制限を加えます。最小オフ時間は、次回のオン動作前に出力がオフの状態で維持される最小の時間です。出力が通常の PWM 動作によりスイッチングサイクル中にオフになった場合、出力は少なくとも 40ns(標準値)の間、オフ状態を維持します。ほとんどのアプリケーションでは、コンバータの定常状態でのデューティサイクルは 100% よりはるかに低く、出力はこの期間よりもずっと長くオフの状態を維持することができます。TPS7H5021 では、デューティサイクルが 50% の標準最大値に制限されているため、コントローラの最小オフ時間は問題にはなりません。

パワー・コンバータ設計で TPS7H5020 を使用する場合、最小オフ時間を考慮する必要がある状況があります。具体的には、このようなケースはデューティサイクルが 100% に近く、次のスイッチングサイクルの開始時にターンオフが発生する場合に発生します。これらのアプリケーションでは、コンバータのフィードバックループによって決定される意図されたオフ時間が、コントローラの最小オフ時間よりも短くなります。そのため、コントローラの最小オフ時間が次のスイッチングサイクルでの出力オン動作を遅延させます。これはすべての動作周波数で考慮する必要がありますが、最小オフ時間がスイッチング周期の中でより大きな割合を占める高周波数では、効果がより顕著になります。例えば、1MHz のスイッチング周波数では、デューティサイクルが 96% (標準値)を超えると、次のサイクルのオン動作が遅延します。定常状態でコンバータの期待される動作を維持するために、式 14 に示すように、ユーザーはコンバータ設計に最大デューティサイクルを設定できます。

$$D_{MAX} < 1 - (t_{off\_min} \times f_{SW}) \quad (14)$$

ここで

- $D_{MAX}$  は、次のサイクルでのオン動作遅延を避けるために推奨される最大コンバータデューティサイクルです

- $t_{off\_min}$  は、コントローラの最小オフ時間です

- $f_{SW}$  は、電源コンバータのスイッチング周波数

### 7.3.12 パルススキップ

TPS7H502x コントローラには、スタートアップ時や過渡期間、特に高周波動作時におけるコントローラの最小オンタイムに関連するコンバータの動作問題を防ぐために、パルススキップモードが実装されています。このモード中、出力は定期的にスイッチングを停止します。高周波動作時に最小オンタイムが長すぎると、ソフトスタート期間中に電流の暴走などの問題を引き起こす可能性があります。パルススキップは、スタートアップ期間中のピーク電流を低減することによって、この問題を解決できます。高周波コンバータ設計では、コンバータの  $V_{IN}$  と  $V_{OUT}$  の比率が最小オンタイムよりも小さい必要なデューティサイクルを引き起こす場合、コントローラの出力は要求される出力電圧を維持するためにパルスをスキップします。パルススキップは、以下の両方の条件が存在する場合に発生します：

- COMP ピンの電圧は、システムクロックの立ち上がりエッジで 0.3V 未満です

- 前のデューティサイクルは 50% 未満でした

TPS7H5021 の場合、デューティサイクルは常に 50% 未満であるため、パルススキップを開始するためには最初の条件のみが必要です。

### 7.3.13 リーディングエッジのブランкиング時間

OUT が高くなると、リーディングエッジブランкиング時間が実装され、一次電源スイッチの最初のターンオン後に、検出された電流波形における過渡現象やノイズが電流検出ループに検出されないようにします。リーディングエッジブランкиング時間は 30ns(標準値)に固定されています。CS\_ILIM ピンに RC フィルタを使用して、コンバータのスイッチング周波

数よりもカットオフ周波数が十分に大きい場合、ノイズをさらに除去することもできます。一般的な目安は、目標カットオフをスイッチング周波数の 10 倍とすることです。

### 7.3.14 電流センスと PWM 生成 (CS\_ILIM)

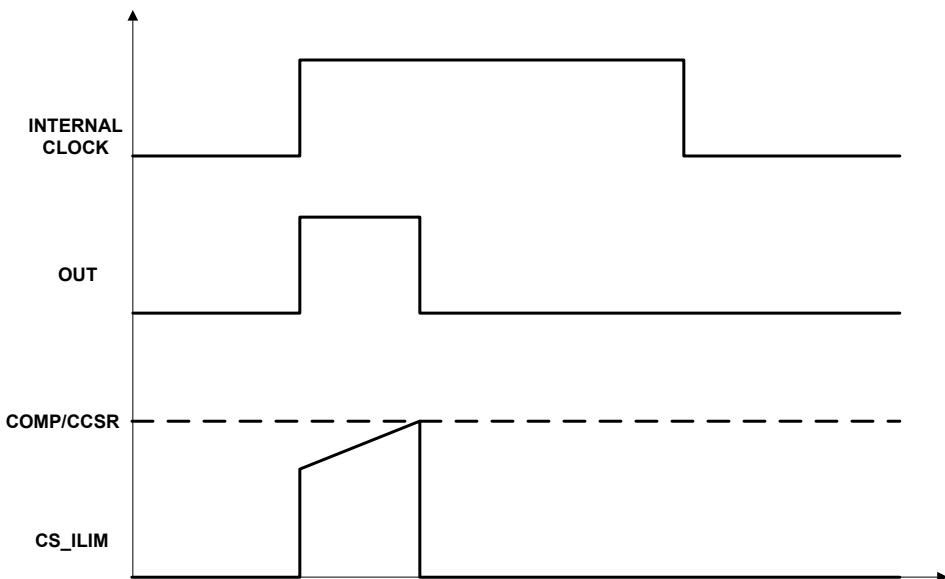

CS\_ILIM ピンは、パワー コンバータのメイン スイッチ電流を反映した信号によって駆動されます。電流信号は、COMP ピンの入力範囲と互換性がある必要があります。図 7-9 に示すように、COMP ピンの電圧はピーク電流のリファレンスとして使用されます。コントローラの出力である OUT は、内部クロック信号によってオンになり、検出された電流信号のピークが COMP/CCSR ピンの電圧（おおよそ COMP/2）に達するとオフになります。このピーク電流検出信号は、PWM コンパレータで COMP/CCSR と比較される際に、150mV のオフセット電圧が含まれていることに注意してください。CS\_ILIM ピンは、コントローラの電流制限の設定にも使用されます。スロープ補償が RSC ピンを使用して実装されている場合、スロープ補償ランプは COMP/CCSR 信号から減算され、スロープ補償された COMP/CCSR 電圧とピーク電流検出信号が交差した時点で OUT がオフになります。ユーザーが内部エラー アンプをバイパスして COMP ピンを外部から駆動する場合、このピンで使用可能な電圧範囲は最大でおおよそ 2.3V です。CS\_ILIM の電流制限をアクティブにするスレッショルドは 1V であり、COMP は CCSR によってスケールダウンされるため、COMP に印加される外部電圧が 2.3V を超えると、PWM コンパレータおよびフィードバック ループはそれに応答しなくなります。

図 7-9. ピーク電流モード制御と PWM 生成

CS\_ILIM から AGND に接続された抵抗は、PWM の適切な動作と過電流保護の両方のために電流を検出するために使用されます。電気的仕様では、電流制限のスレッショルド  $V_{CS\_ILIM}$  が 1V(標準値)に設定されています。これは、このピンの電圧がしきい値に達すると、デバイスが電流制限モードに入り、出力 (OUT) がオフになることを示しています。式 15 は、選択した電流制限値に対するセンス抵抗の値を決定するための計算式を示しています。

$$R_{CS} = \frac{V_{CS\_ILIM}}{I_{LIM}} \quad (15)$$

$I_{LIM}$  の値は、電流をどこで、どのように検出するかを考慮する必要があることに注意してください。ソース側のプライマリ FET から AGND 間に検出抵抗を設けた、1 次側制御の絶縁型コンバータの場合、負荷電流に基づいて  $I_{LIM}$  を適切に計算する必要があります。トポロジにかかわらず、 $R_{CS}$  の値を決定する際は、通常動作時のピーク電流と過電流トリップ ポイントとの間に十分なマージンがあることを確認する必要があります。

### 7.3.15 ゲート ドライバの出力

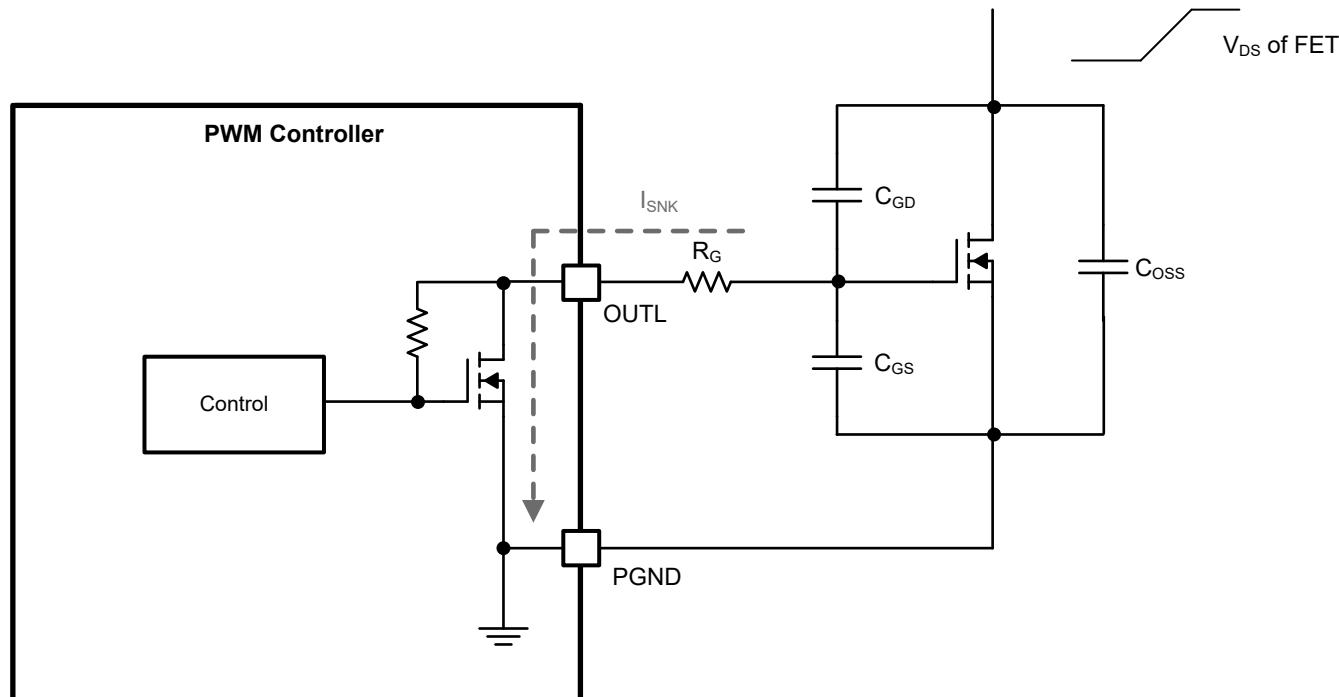

TPS7H502x は、4.5V から 14V のゲート電圧を必要とするパワー半導体デバイスを駆動するために使用できるため、シリコン MOSFET と GaN FET ベースのパワー コンバータの両方に適したコントローラです。ゲートドライバ段は分割出力

を備えています。これらの出力は OUTH と OUTL で、順にソーシング出力とシンク出力です。これらの分割出力は、駆動されている電源デバイスのターンオンまたはターンオフ経路に追加の抵抗を配置することで、ターンオンおよびターンオフ速度を独立して調整する柔軟性を提供します。これらの出力は、PVIN の 12V 入力で 1.2A(標準)をソーシングおよびシンクすることができます。

### 7.3.16 電源なしの電圧クランプ

TPS7H502x には、ゲートドライバ出力に電圧クランプが含まれています。このクランプは、VIN が約 2V 未満の場合のみ動作します。VIN の電圧が低い場合、内部の OUTL ドライバは十分に電力が供給されず、そのためドライバ出力を積極的に低く引き下げることができません。これにより、ドライバ出力が高インピーダンス状態になる可能性があり、電源なしの電圧クランプが追加されてこの問題を軽減しました。この電源なしクランプは、コントローラが無効になっている間のみ動作します。

コンバータのバス電圧 **V<sub>BUS</sub>** は、コントローラの入力 **V<sub>IN</sub>** が低い状態で上昇し始めることができます。OUTL と PGND の間に十分に低いインピーダンスがない場合、バス電圧のスルーレート ( $dV/dt$ ) により、ゲート-ドレイン容量 **C<sub>GD</sub>** を通じて FET が意図せずオンになる可能性があります。**C<sub>GD</sub>** を流れる誘導電流は、ゲート-ソース間容量 **C<sub>GS</sub>** を FET のゲート-ソース閾値を超えるまで充電し、これにより **V<sub>BUS</sub>** から PGND への不正な電流が流れることができます。電力が供給されていない電圧クランプは、ドライバに十分な電圧が供給され、コントローラが有効化されるまで、FET のゲート電圧を制限します。電圧クランプの値は、「仕様」表に表示されます。コントローラが有効化されると、電圧クランプは無効化され、コントローラとドライバの正常な動作には干渉しません。クランプを非アクティブにする条件は、「スタートアップ」に示すように、デバイスの起動に必要な条件と同じであることに注意してください。外部プルダウン抵抗を OUT と PGND の間に接続することで、電力供給されていない電圧クランプを補完し、意図しないターンオンに関連する問題をさらに軽減することができます。使用する場合は、10kΩ から 50kΩ までの範囲のプルダウン抵抗を推奨します。外部抵抗を追加すると、デバイスの静止電流および動作電流がわずかに増加することに注意してください。小さい抵抗を使用すると、これらの電流の増加が大きくなります。

図 7-10. 電源なしの電圧クランプ

### 7.3.17 ソース ドライバのリターン (OUTH REF)

ドライバのソース・ドライバ(OUTH)ステージのリターンは OUTH\_REF ピンに出力されており、特定の動作条件下で 220nF の外部コンデンサを接続できます。OUTH\_REF の電圧は、PVIN の電圧よりおよそ 6V 低くなります。このピン

と PVIN の間に外部コンデンサを接続することにより、ドライバの過渡性能が改善されるだけでなく、放射線誘発单一事象トランジエント(SET)に対する抑制効果も得られます。OUTH\_REF コンデンサは、PVIN に外部電圧が 6V 以上適用される場合にのみ必要であることに注意してください。PVIN が 6V 未満の場合、OUTH\_REF は PGND に直接接続できます。

**表 7-5. OUTH\_REF の接続**

| ドライバの入力電圧 | 構成                                     |

|-----------|----------------------------------------|

| PVIN < 6V | OUTH_REF を PGND に接続します。                |

| PVIN ≥ 6V | OUTH_REF と PVIN の間に 220nF のコンデンサを接続します |

### 7.3.18 勾配補償 (RSC)

スイッチング電源コンバータ設計でピーク電流モード制御を使用する場合、主電源スイッチのデューティサイクルが 50% を超えると、コンバータが不安定な状態に入る可能性があります。基本的に、コンバータは、ピーク電流と平均電流の誤差が次のスイッチングサイクルごとに増加する状態になります。この不安定性は、サブハーモニック振動として知られ、スロープ補償を加えることで緩和できます。TPS7H502x では、スロープ補償は電圧ランプの形で行われ、エラー アンプ出力を CCSR(COMP と CS\_ILIM の比)で割った値から差し引かれます。全デューティサイクル範囲での安定性を確保するための最小スロープ補償は  $0.5 \times m$  に等しく、ここで  $m$  はインダクタの降下電流スロープです。推奨されるスロープ補償は  $1 \times m$  で、この値を超える増加は安定性の改善にはつながりません。

フォワード コンバータおよびブースト コンバータでは、スロープ補償を出力インダクタ電流の降下スロープに等しく設定できます。フライバック コンバータでは、スロープ補償はフライバックトランジスの電流の降下スロープを使用して計算されます。絶縁型トポロジでは、検出された電流波形がトランジスの巻数比も考慮する必要があることに注意してください。

フォワードの場合:

$$SC = \frac{V_{OUT} \times R_{CS} \times A_{CS}}{L_{OUT} \times N_{PS}} \quad (16)$$

フライバックの場合:

$$SC = \frac{V_{OUT} \times R_{CS} \times A_{CS}}{L_{PRI} \times N_{PS}} \quad (17)$$

昇圧の場合:

$$SC = \frac{(V_{OUT} - V_{IN}) \times R_{CS} \times A_{CS}}{L} \quad (18)$$

ここで

- SC はスロープ補償値で、V/ $\mu$ s 単位です

- $L_{OUT}$  出力インダクタの値( $\mu$ H 単位)(フォワード)

- $L_{PRI}$  は 1 次側インダクタンス値( $\mu$ H 単位)(フライバック)

- L は、 $\mu$ H 単位のインダクタ値(昇圧)

- $N_{PS}$  はトランジスの巻数比

- $R_{CS}$  は、電流検出トランジスの 2 次巻線の巻数

- $A_{CS}$  は電流センス段に関連するゲインであり、使用する場合は電流検出アンプとトランジスも含まれます

- $V_{OUT}$  はレギュレートされた出力電圧

- $V_{IN}$  は最大入力電圧

TPS7H502x コントローラでは、RSC ピンから AGND への抵抗を使用して、希望するスロープ補償を設定できます。式 19 は、RSC の適切な抵抗値を決定するための計算を示しています。

$$RSC = \frac{29.5}{SC \cdot 1.07} \quad (19)$$

ここで

- SC は、希望するスロープ補償の値(V/μs 単位)です

- RSC は kΩ 単位です

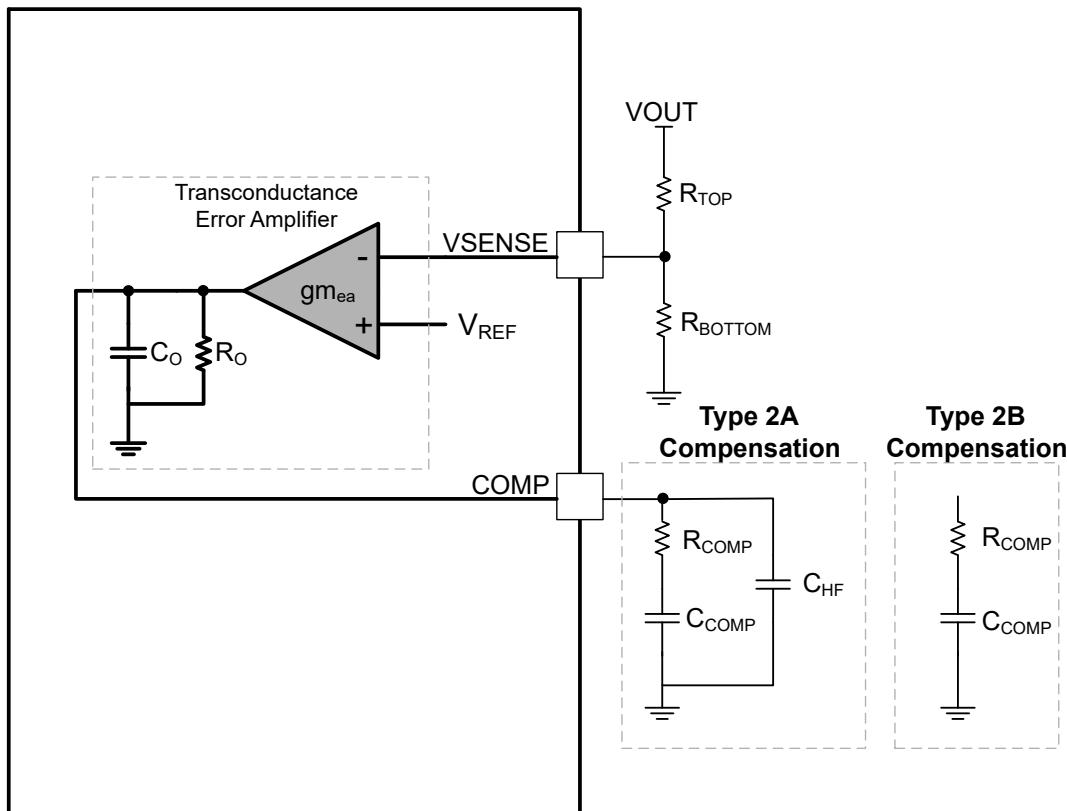

### 7.3.19 周波数補償

TPS7H502x は相互コンダクタンス型エラー アンプ(OTA)を使用しているため、Type 2A または Type 2B の周波数補償を適用できます。2 種類の補償方式の主な違いは、Type 2A が高周波ノイズの減衰を目的として、 $R_{COMP}$  および  $C_{COMP}$  と並列にコンデンサ  $C_{HF}$  を追加していることです。これらの部品は、コントローラの COMP ピン(OTA の出力)と AGND の間に接続されます。

図 7-11. TPS7H502x 周波数補償オプション

TPS7H502x がサポートするトポロジに対しては、以下の手順と式を使用して補償部品を選定できます。特に記載がない限り、式中のすべてのパラメータは標準単位(つまり、H はインダクタンス、F は静電容量、Hz は周波数など)で表されています。

- コンバータの目的のクロスオーバ周波数( $f_c$ )を選択します。ブーストコンバータおよびフライバックコンバータには、右半平面(RHP)ゼロが存在し、これがコンバータの目標クロスオーバ周波数を制限することに注意してください。これらのトポロジでは、クロスオーバ周波数は RHP ゼロ周波数の 1/4 ~ 1/10 の範囲に設定することを推奨します。フォワードコンバータでは、クロスオーバ周波数はスイッチング周波数の 1/10 以下に設定することを推奨します。

- パワーステージの相互コンダクタンス  $G_M$  を計算します。

- フォワードコンバータの場合:

$$G_M = \frac{N_{PS}}{A_{CS} \times R_{CS}} \quad (20)$$

- フライバックコンバータの場合:

$$G_M = \frac{(1 - D_{MAX}) \times N_{PS}}{A_{CS} \times R_{CS}} \quad (21)$$

- 昇圧コンバータの場合:

$$G_M = \frac{(1 - D_{MAX})}{A_{CS} \times R_{CS}} \quad (22)$$

ここで

- $N_{PS}$  は、トランスの一次側と二次側の巻数比です。

- $A_{CS}$  は、電流センスステージに関するゲインです。

- $R_{CS}$  は電流検出抵抗の値で、単位は  $\Omega$  です。

- $D_{MAX}$  は、アプリケーションの最大デューティサイクルです。

3. 目標クロスオーバ周波数を達成するために、エラー アンプ ネットワークのゲイン  $A_{VM}$  を計算します。

$$A_{VM} = \frac{2\pi \times f_C \times C_{OUT}}{G_M} \quad (23)$$

ここで

- $f_C$  は選択されたクロスオーバー周波数です

- $C_{OUT \min}$  は最小出力キャパシタンスです

- $G_M$  は、パワーステージの相互コンダクタンスです。

4. 必要なゲイン  $A_{VM}$ 、エラー アンプの相互コンダクタンス  $g_{MEA}$ 、およびフィードバック抵抗値に基づいて、 $R_{COMP}$  を計算します。

$$R_{COMP} = \frac{A_{VM}}{g_{MEA} \times K_{FB}} \quad (24)$$

ここで

$$K_{FB} = \frac{R_{BOTTOM}}{R_{BOTTOM} + R_{TOP}} \quad (25)$$

5. エラー アンプ ネットワークのゼロを、目標クロスオーバ周波数のおおよそ  $1/10$  に設定することを推奨します。

$$f_{ZEA} = \frac{1}{2\pi \times R_{COMP} \times C_{COMP}} = \frac{f_C}{10} \quad (26)$$

したがって、次のようにになります。

$$C_{COMP} = \frac{1}{2\pi \times (0.1 \times f_C) \times R_{COMP}} \quad (27)$$

6. 補償回路の高周波のポールを設定します。フォワード コンバータでは、これをコンバータの ESR ゼロの周波数と同じに設定できます。昇圧コンバータおよびフライバック コンバータの場合は、ESR ゼロと RHP ゼロのうち、低い方に設定します。

$$f_{HF} = \frac{1}{2\pi \times R_{COMP} \times C_{HF}} = f_{Z\_ESR} \text{ or } f_{RHPZ} \quad (28)$$

したがって、次のようにになります。

$$C_{HF} = \frac{1}{2\pi \times f_{Z\_ESR} \times R_{COMP}} \quad (29)$$

または

$$C_{HF} = \frac{1}{2\pi \times f_{RHPZ} \times R_{COMP}} \quad (30)$$

ここで説明した手順は、部品選定のための出発点として意図されていることに注意してください。周波数補償は反復的なプロセスとなることが多く、最適な値は通常、コンバータのハードウェア テストによって得られます。

### 7.3.20 サーマル シャットダウン

接合部温度が標準 185°C を超えると内部のサーマル シャットダウン回路がデバイスのスイッチングを強制停止します。接合部温度が標準 170°C を下回ると、デバイスはパワーアップ シーケンスを再び開始します。

## 7.4 デバイスの機能モード

TPS7H502x シリーズは、固定周波数のピーク電流モード制御を使用しています。コントローラは、コンバータのピーク電流とデューティ サイクルを調整します。内部発振器は電源スイッチのゲート ドライバ出力のターンオンを開始します。外部電源スイッチの電流は外部抵抗を通じて検出され、内部コンパレータを介して比較されます。COMP ピンで生成された電圧は、内部の抵抗を通じて降圧されます。検出された電流が降圧された COMP 電圧に達すると、電力スイッチがオフになります。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPS7H502x は、ゲートドライバを内蔵した放射線耐性 PWM コントローラです。このドライバは、入力電圧範囲が 4.5V から 14V で、最大 1MHz のプログラム可能なスイッチング周波数を提供します。さらに、統合されたドライバは、コントローラのプログラム可能な LDO を活用し、その出力から PVIN への接続を行うことで、GaN FET と連携して動作するように構成できます。シリコン MOSFET と組み合わせてドライバを使用するために、PVIN には最大 14V の高い入力電圧を使用できます。コントローラは、フライバック、フォワード、昇圧など、さまざまな電源トポロジをサポートできますが、これらに限定されません。

### 8.2 代表的なアプリケーション

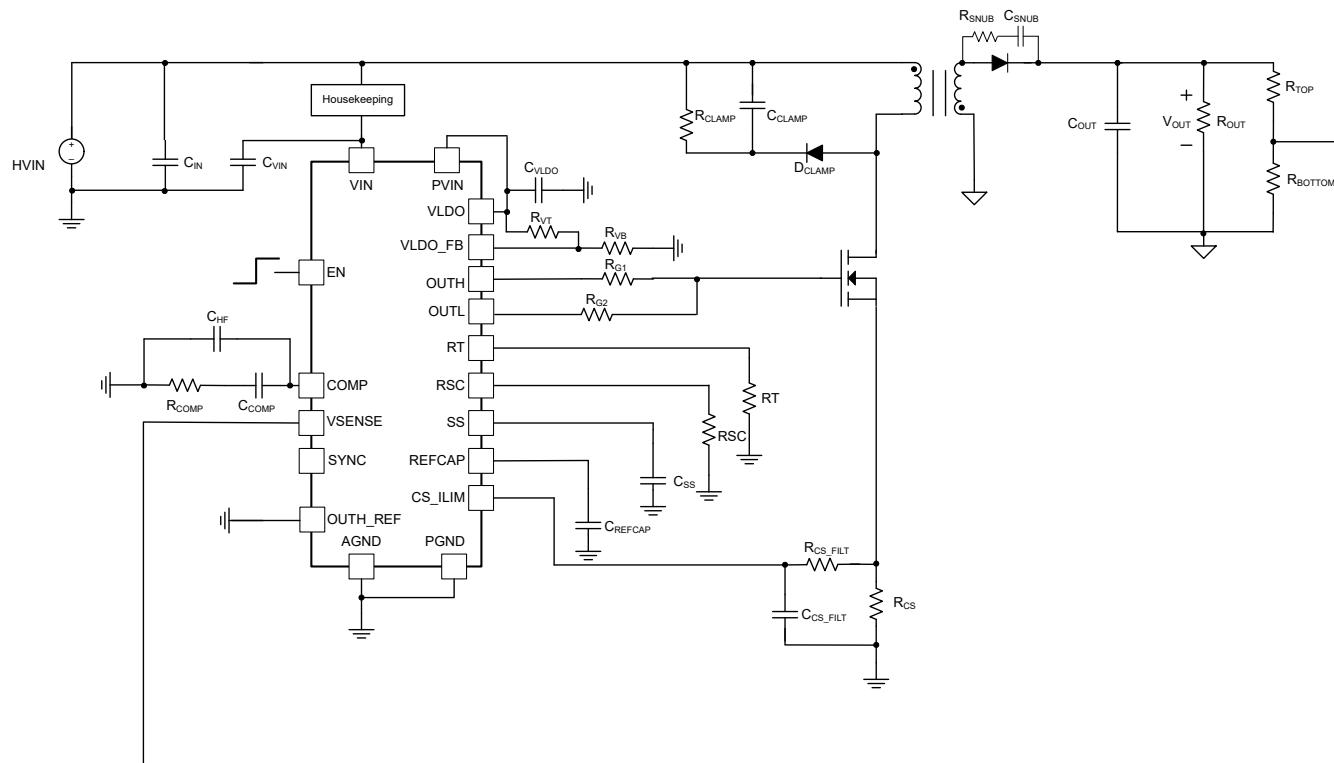

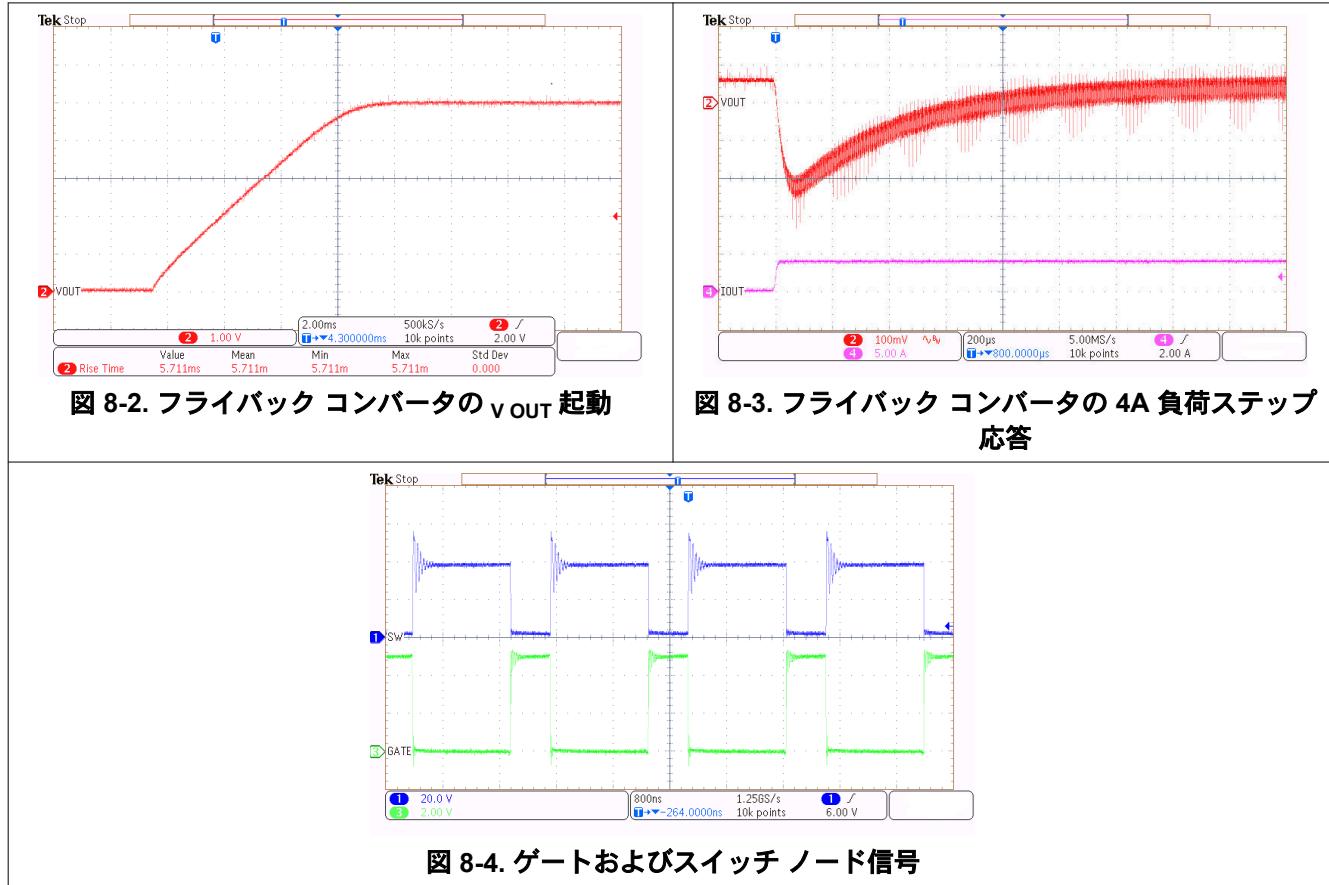

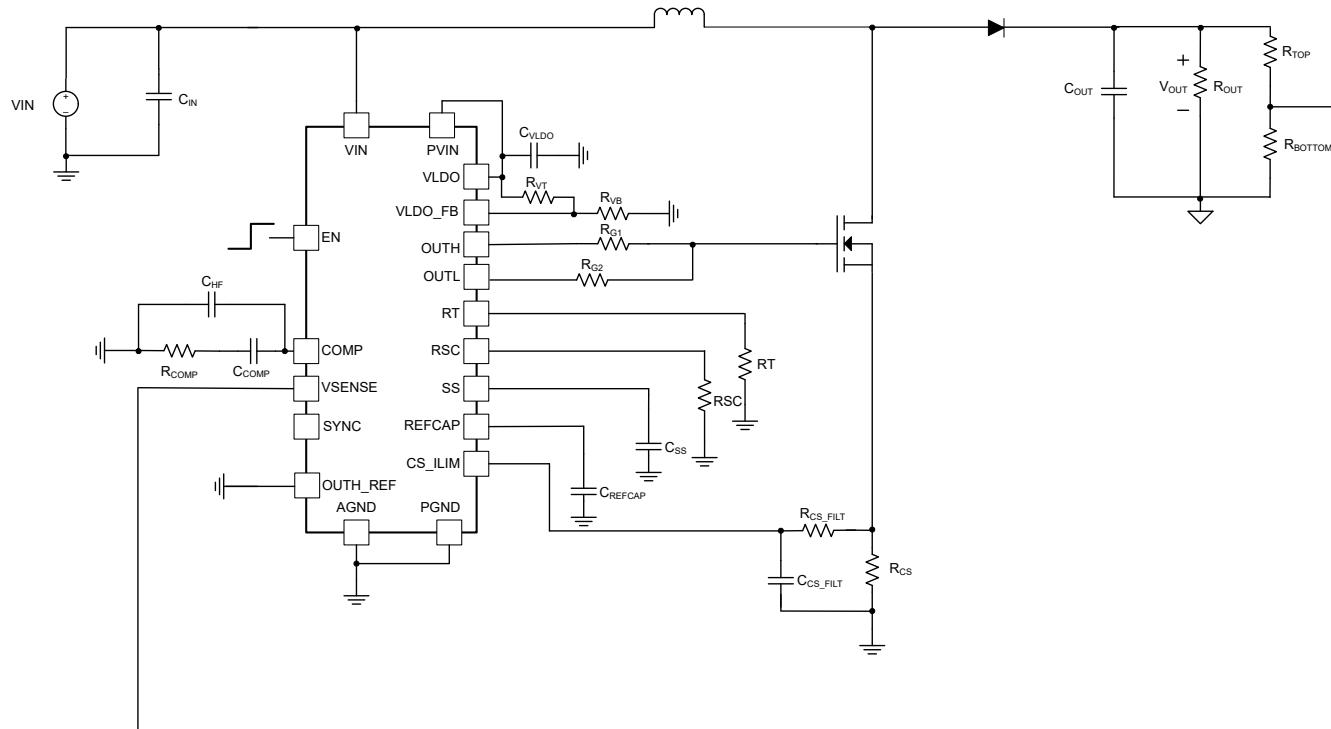

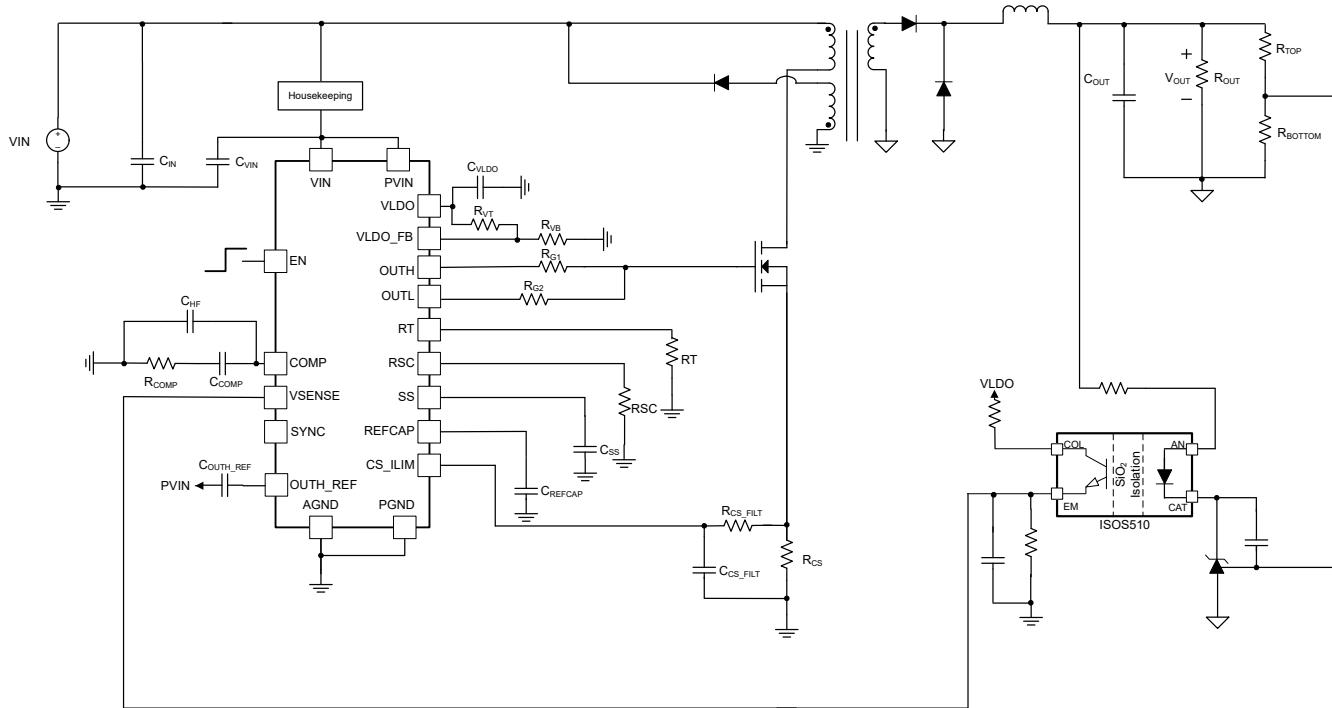

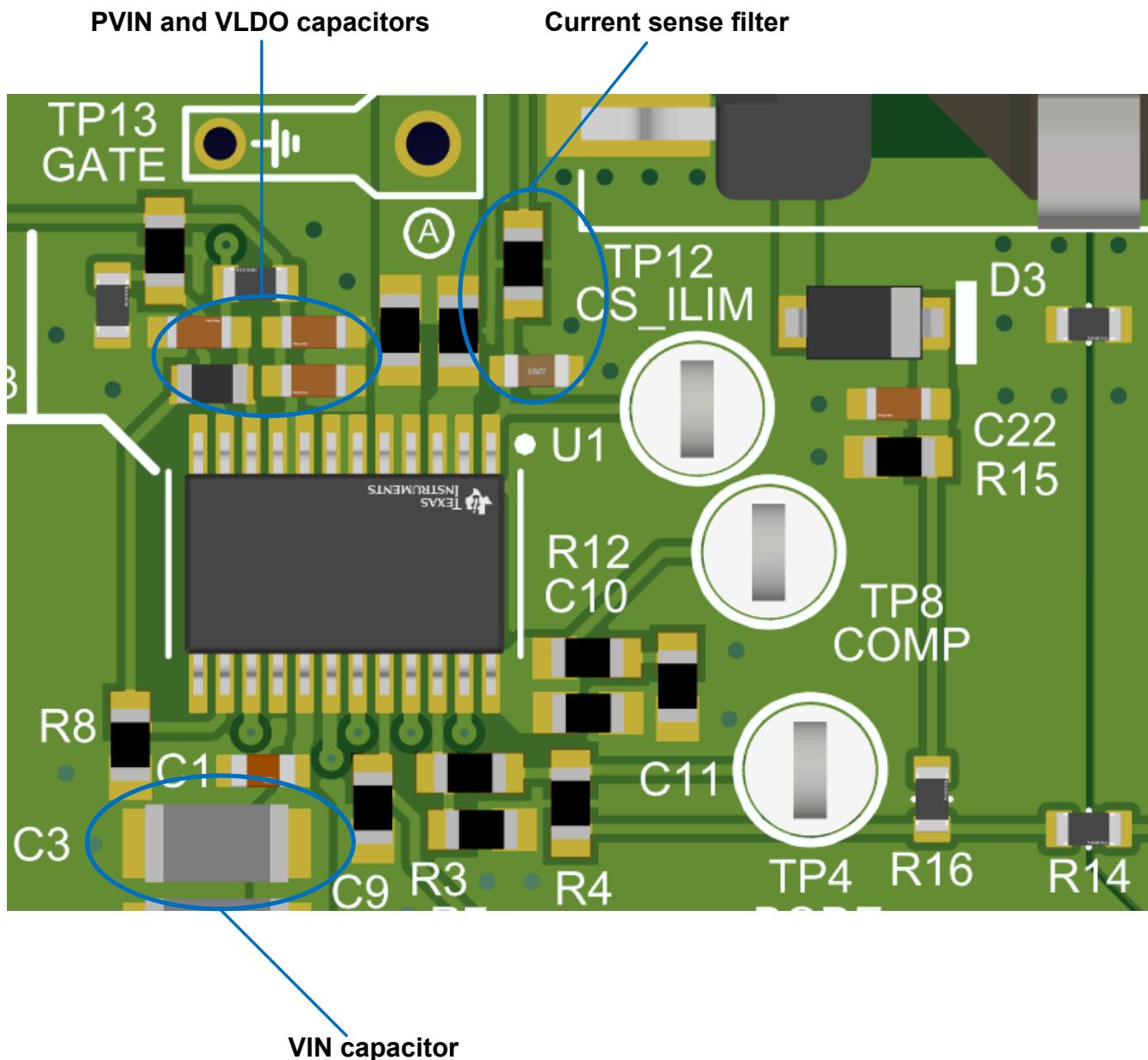

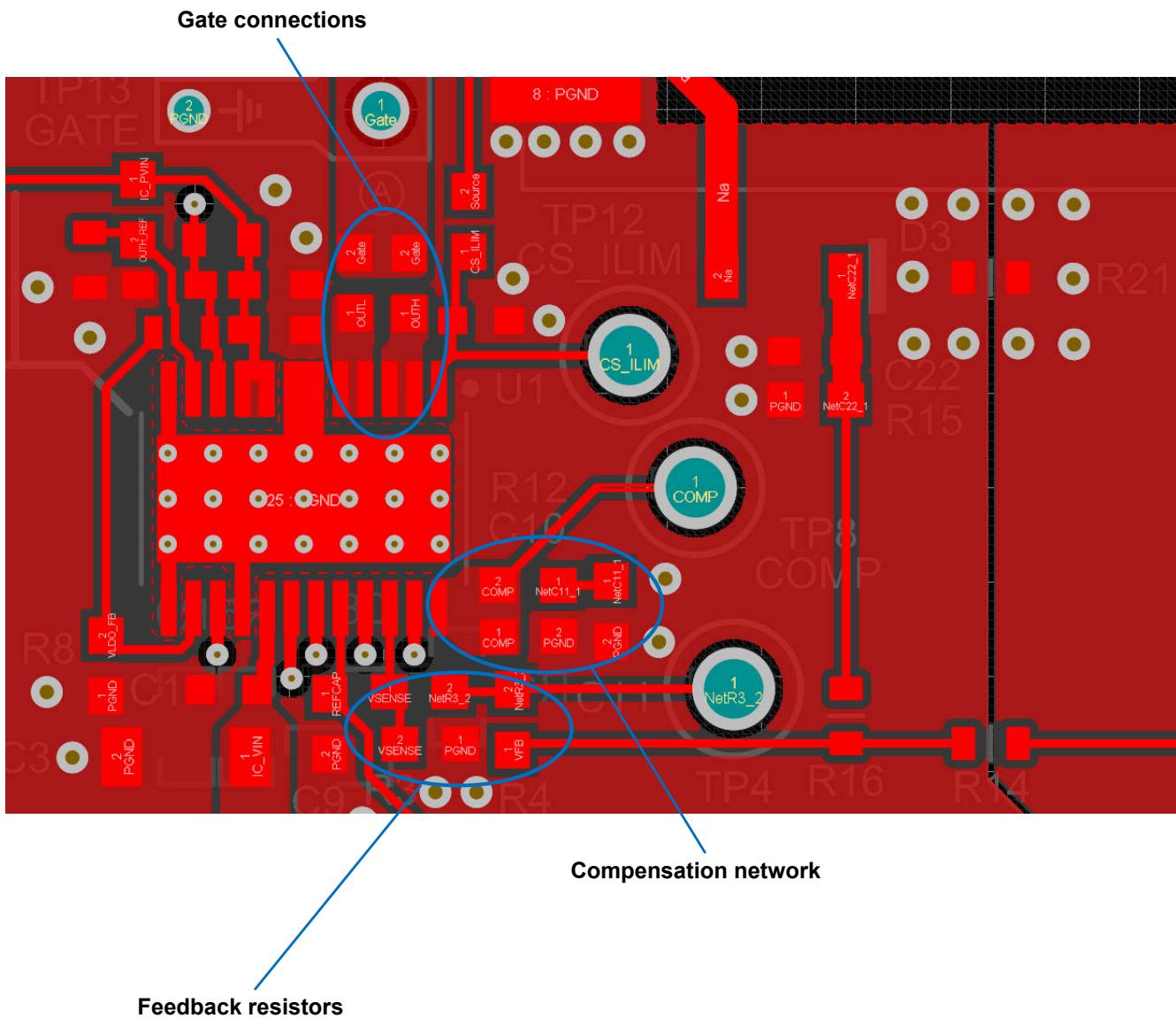

図 8-1. 代表的なアプリケーション回路図

#### 8.2.1 設計要件

提供された例では、GaN パワー半導体デバイスを一次スイッチング FET として使用したフライバックコンバータの設計が詳述されています。目的は、TPS7H5020 のコンポーネント選定方法と、コンバータのパワーステージにおける主要なコンポーネントの選定方法を示すことです。

**表 8-1. 設計パラメータ**

| 設計パラメータ         | 値                |

|-----------------|------------------|

| 入力電圧範囲          | 22V ~ 36V、公称 28V |

| 出力電圧            | 5V ±10%          |

| 最大出力電流          | 4A               |

| スイッチング周波数       | 500kHz           |

| ターゲット帯域幅        | ≈4kHz            |

| 全負荷ステップ(4A)過渡応答 | ≤ 375mV          |

## 8.2.2 詳細な設計手順

### 8.2.2.1 スイッチング周波数

フライバックコンバータは、500kHz のスイッチング周波数で動作するように設計されました。宇宙規格のコンバータ設計では、このスイッチング周波数において GaN パワーデバイスがシリコン製の対抗デバイスに対して優れた利点を持つことが明確に示されています。式 31 を使用すると、目的の周波数に必要な RT 抵抗を決定できます。 $f_{SW}$  の値は kHz 単位、RT は kΩ 単位であることに注意します。

$$RT = \frac{112390}{f_{SW}} - 14.2 \quad (31)$$

$$RT = \frac{112390}{500} - 14.2 = 210.5\text{k}\Omega \quad (32)$$

設計には、標準的な抵抗値として 210kΩ が理想的です。利用可能性のため、205kΩ の値はわずかに小さくなりました。

### 8.2.2.2 出力電圧設定用抵抗の選定

このコンバータの出力電圧は 5V です。VSENSE に接続された帰還分圧抵抗は、目的の  $V_{OUT}$  に対応するよう選択します。R<sub>TOP</sub> に 10kΩ の抵抗が選定された場合、分圧器の下側抵抗の値を計算できます。

$$R_{BOTTOM} = \frac{V_{REF}}{V_{OUT} - V_{REF}} \times R_{TOP} \quad (33)$$

$$R_{BOTTOM} = \frac{0.6V}{5V - 0.6V} \times 10\text{k}\Omega = 1.36\text{k}\Omega \quad (34)$$

必要な R<sub>TOP</sub> と R<sub>BOTTOM</sub> の値は、それぞれ 10kΩ と 1.37kΩ です。

### 8.2.2.3 ドライバ PVIN 構成

この設計例では、意図されたパワー半導体デバイスは GaN FET です。このため、VLDO はドライバの PVIN に接続されます。VLDO は 4.5V から 5.5V に設定可能であり、この例では名目上の駆動電圧として 5V が選定されています。VLDO を 5V 動作に設定するために、VLDO\_FB と GND の間に適切な抵抗を選定するために式 35 が使用されます。

$$R_{VB} = \frac{V_{REFCAP}}{V_{LDO} - V_{REFCAP}} \times R_{VT} \quad (35)$$

$$R_{VB} = \frac{1.225V}{5V - 1.225V} \times 10\text{k}\Omega = 3245\Omega \quad (36)$$

$R_{VB}$  の値は 3.24kΩ に選定されます。PVIN が VLDO に接続され、6V 未満の場合、OUTH\_REF は 表 7-5 に従って直接 GND に接続する必要があります。

### 8.2.2.4 ソフトスタート コンデンサの選択

この設計では、ソフトスタート時間は、突入電流を制限するのに十分な時間があるよう選択されています。選定されたソフトスタート用コンデンサの値は  $33\text{nF}$  です。この値に基づいて、ソフトスタート時間を計算できます。

$$t_{SS} = \frac{C_{SS} \times V_{REF}}{I_{SS}} \quad (37)$$

$$t_{SS} = \frac{33\text{nF} \times 0.6V}{2.8\mu\text{A}} = 7.07\text{ms} \quad (38)$$

ソフトスタート時間は、設計の場合約  $7.1\text{ms}$  です。

### 8.2.2.5 トランスの設計

トランスの巻線比と 1 次側インダクタンスは、コンバータの目標仕様に基づいて決定されます。巻線比は、最大デューティサイクル 35% に基づいて計算されます。

$$N_{PS\_MAX} = \frac{V_{IN\_MIN} \times D_{MAX}}{(V_{OUT} + V_D) \times (1 - D_{MAX})} \quad (39)$$

$$N_{PS\_MAX} = \frac{22V \times 0.35}{(5V + 0.7V) \times (1 - 0.35)} = 2.08 \quad (40)$$

設計には巻線比 2 が選定されました。実際の巻線比に基づいて、最小および最大デューティサイクルを計算できます。

$$D_{MIN} = \frac{(V_{OUT} + V_D) \times N_{PS}}{(V_{OUT} + V_D) \times N_{PS} + V_{IN\_MAX}} \quad (41)$$

$$D_{MIN} = \frac{(5V + 0.7V) \times 2}{(5V + 0.7V) \times 2 + 22V} = 0.241 \quad (42)$$

$$D_{MAX} = \frac{(V_{OUT} + V_D) \times N_{PS}}{(V_{OUT} + V_D) \times N_{PS} + V_{IN\_MIN}} \quad (43)$$

$$D_{MAX} = \frac{(5V + 0.7V) \times 2}{(5V + 0.7V) \times 2 + 22V} = 0.341 \quad (44)$$

1 次側インダクタンスは、20% の電流リップルに基づいて計算しました。

$$L_P = \frac{V_{IN\_MAX}^2 \times D_{MIN}^2}{V_{OUT} \times I_{OUT} \times f_{SW} \times \%RIPPLE} \quad (45)$$

$$L_P = \frac{36V^2 \times 0.24^2}{5V \times 4A \times 500\text{kHz} \times 0.2} = 37.3\mu\text{H} \quad (46)$$

実際の設計で選定された一次インダクタンスは  $30\mu\text{H}$  で、これにより実際のリップルはおよそ 25% となります。以下の方程式は、トランスの適切な設計に必要な一次および二次電流を計算する方法を詳述しています。これらの式は、トランスの物理構造を定義するのに役立ちます。

$$I_{RIPPLE} = \frac{V_{OUT} \times I_{OUT} \times \%RIPPLE}{V_{IN\_MAX} \times D_{MIN}} \quad (47)$$