# TPS7H500x-SP 放射線耐性保証 (RHA)、2MHz、電流モード PWM コントローラ

### 1 特長

- 耐放射線性能:

- 放射線耐性保証 (RHA): TID 100krad(Si) (最大值)

- SEL、SEB、SEGR 耐性: LET = 75MeV-cm<sup>2</sup>/mg (最大値)

- SET および SEFI 特性: LET = 75MeV-cm<sup>2</sup>/mg (最大値)

- SET 特性評価時にコントローラ出力のクロス導通イ ベント発生なし

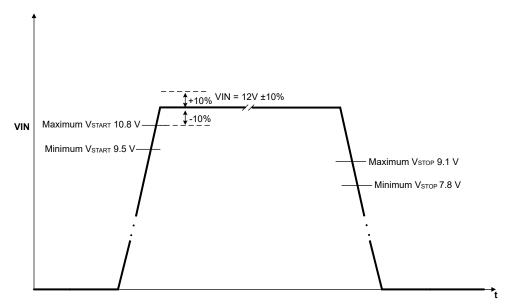

- 入力電圧:4V~14V

- 温度、放射線、ラインおよび負荷レギュレーションの全 範囲で 0.613V +0.7%/-1% の電圧リファレンス

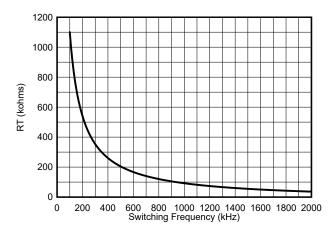

- スイッチング周波数:100kHz~2MHz

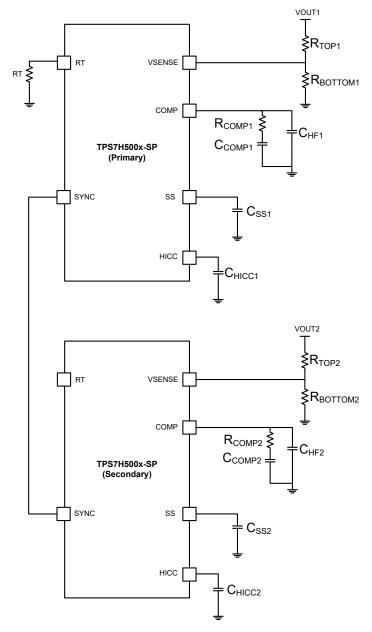

- 外部クロック同期機能

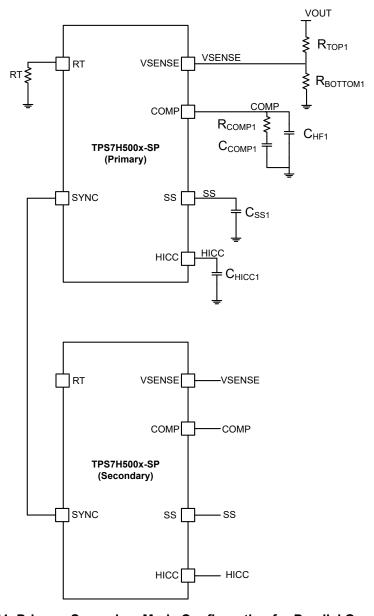

- 複数の同期整流出力

- TPS7H5001-SP、TPS7H5002-SP、 TPS7H5003-SP

- 調整可能なデッドタイム

- TPS7H5001-SP、TPS7H5002-SP

- 調整可能な立ち上がりエッジブランク時間

- TPS7H5001-SP、TPS7H5002-SP、 TPS7H5004-SP

- 構成可能なデューティサイクル制限

- TPS7H5001-SP、TPS7H5002-SP、 TPS7H5003-SP

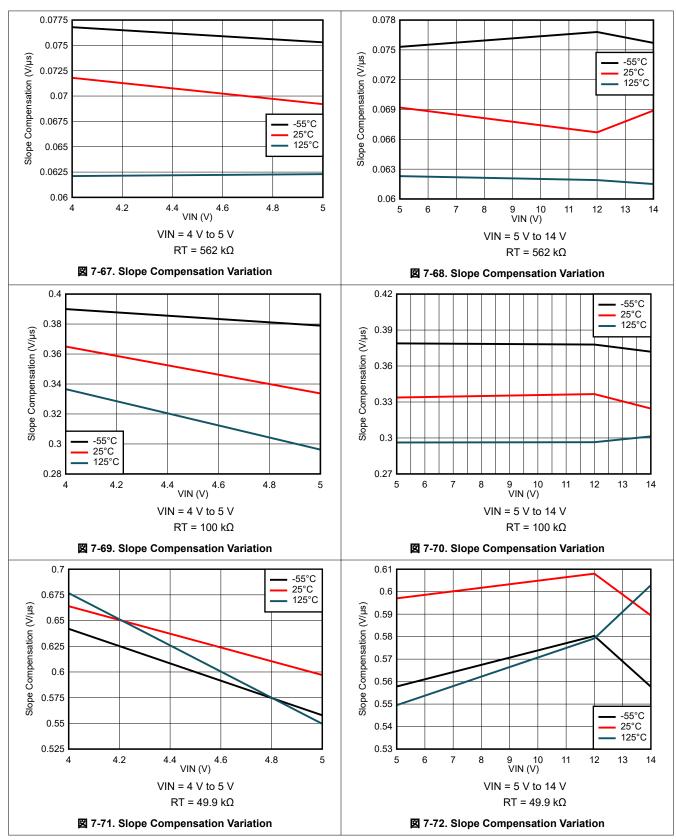

- 調整可能なスロープ補償とソフトスタート機能

- パッケージとして CFP と TSSOP を選択可能

# 2 アプリケーション

- 人工衛星のポイント・オブ・ロード電源:FPGA、マイクロ コントローラ、データ・コンバータ、ASIC 向け

- 通信ペイロード

- コマンドおよびデータの処理

- 衛星用電源システム (EPS)

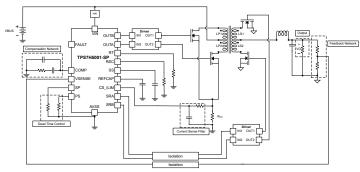

TPS7H5001-SP の代表的なアプリケーション

### 3 概要

TPS7H500x-SP ファミリの高速放射線耐性保証 PWM コ ントローラ。本コントローラは、宇宙用途を対象とした DC/DC コンバータトポロジの設計に役立つ多くの機能を 備えています。このコントローラは 0.613V +0.7%/-1% の 精度を持つ内部リファレンスを備えており、最大 2MHz の スイッチング周波数を構成できます。各デバイスは、プログ ラム可能なスロープ補償およびソフトスタート機能を備え ています。

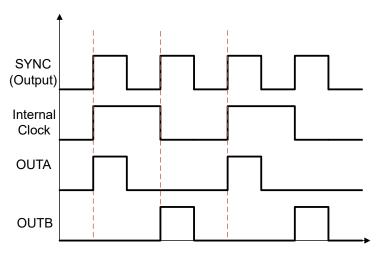

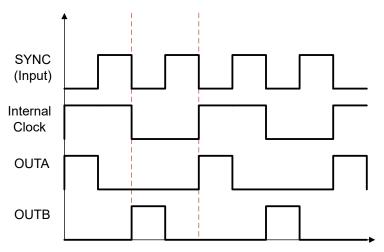

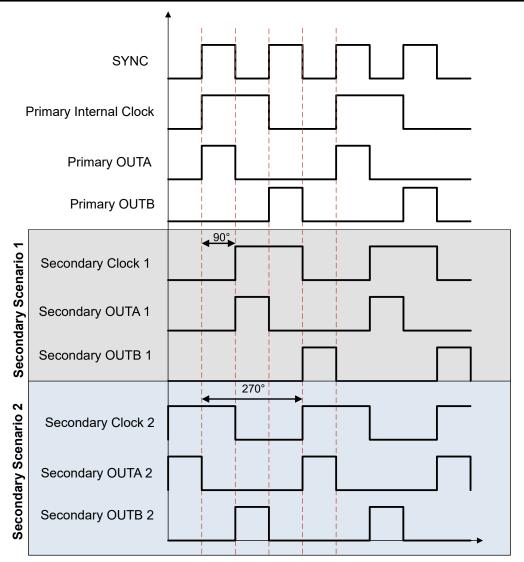

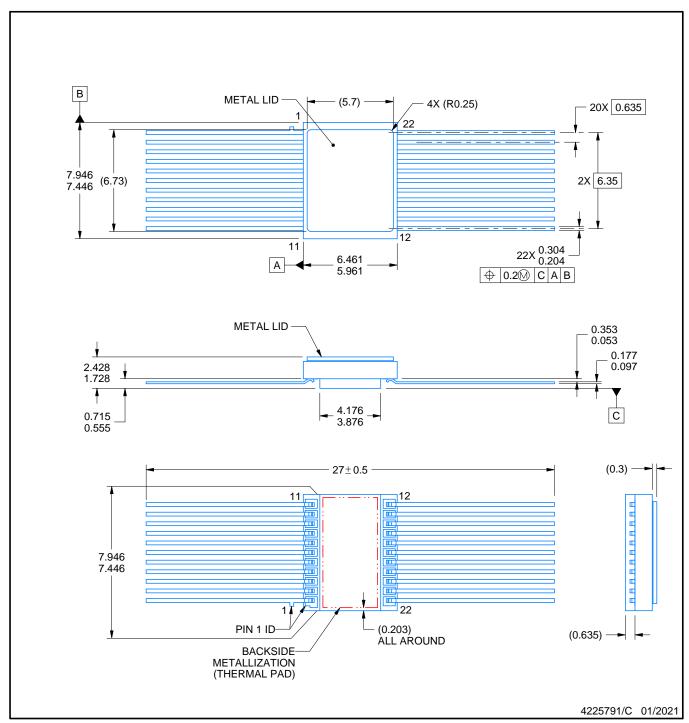

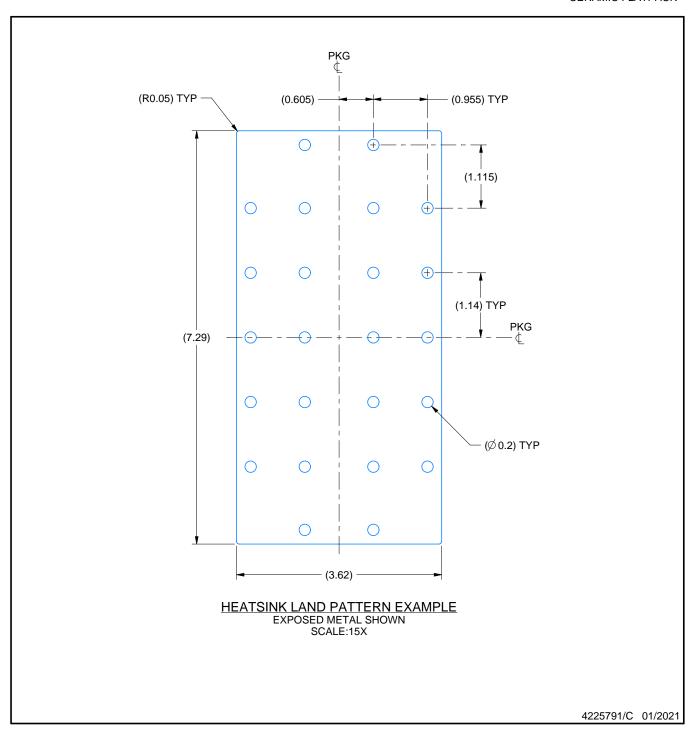

TPS7H500x-SP シリーズは、SYNC ピン経由で外部クロ ックを使用して、またはユーザーがプログラムした周波数 で内部クロックを使用して駆動できます。 本コントローラ フ ァミリでは、スイッチング出力、同期整流機能、デッド タイ ム (固定または設定可能)、立ち上がりエッジ ブランク時間 (固定または設定可能)、デューティ サイクル制限値をユー ザーが選択できます。TPS7H500x-SP シリーズの各デバ イスは、22 ピン CFP セラミック パッケージと 24 ピン TSSOP プラスチック パッケージの両方で供給されます。

#### 製品情報

| 部品 <del>番号 <sup>(1)</sup></del> | グレード            | 本体サイズ                           |

|---------------------------------|-----------------|---------------------------------|

| 5962R1822201VXC                 |                 |                                 |

| 5962R1822202VXC                 | OMLV-RHA        |                                 |

| 5962R1822203VXC                 | QIVILV-IXI IA   |                                 |

| 5962R1822204VXC                 |                 | 22 ピンのセラミック<br>6.21mm × 7.69mm  |

| TPS7H5001HFT/EM                 |                 | 質量=415.6mg <sup>(2)</sup>       |

| TPS7H5002HFT/EM                 | エンジニアリング サ      |                                 |

| TPS7H5003HFT/EM                 | ンプル             |                                 |

| TPS7H5004HFT/EM                 |                 |                                 |

| 5962R1822201PYE                 |                 |                                 |

| 5962R1822202PYE                 | OMLP-RHA        | 24 ピンのプラスチック<br>4.40mm × 7.80mm |

| 5962R1822203PYE                 | QWEI -KIIA      | 質量=102.3mg <sup>(2)</sup>       |

| 5962R1822204PYE                 |                 |                                 |

| 5962R1822201V9A                 |                 |                                 |

| 5962R1822202V9A                 | OMLV-RHA KGD    |                                 |

| 5962R1822203V9A                 | QWEV TO WITHOUT |                                 |

| 5962R1822204V9A                 |                 | ダイ                              |

| TPS7H5001Y/EM                   |                 | 2 1                             |

| TPS7H5002Y/EM                   | エンジニアリング サ      |                                 |

| TPS7H5003Y/EM                   | ンプル             |                                 |

| TPS7H5004Y/EM                   |                 |                                 |

- 詳細は、デバイスオプション表をご覧ください。

- 質量の精度は ±10% です。

# **Table of Contents**

| 1 特長                                         |    |

|----------------------------------------------|----|

|                                              |    |

| 2 アプリケーション                                   | 1  |

| 3 概要                                         | 1  |

| 4 Device Comparison Table                    | 3  |

| 5 Device Options                             |    |

| 6 Pin Configuration and Functions            | 5  |

| 7 Specifications                             | 14 |

| 7.1 Absolute Maximum Ratings                 | 14 |

| 7.2 ESD Ratings                              | 14 |

| 7.3 Recommended Operating Conditions         | 14 |

| 7.4 Thermal Information                      | 14 |

| 7.5 Electrical Characteristics: All Devices  | 15 |

| 7.6 Electrical Characteristics: TPS7H5001-SP | 17 |

| 7.7 Electrical Characteristics: TPS7H5002-SP | 18 |

| 7.8 Electrical Characteristics: TPS7H5003-SP | 18 |

| 7.9 Electrical Characteristics: TPS7H5004-SP |    |

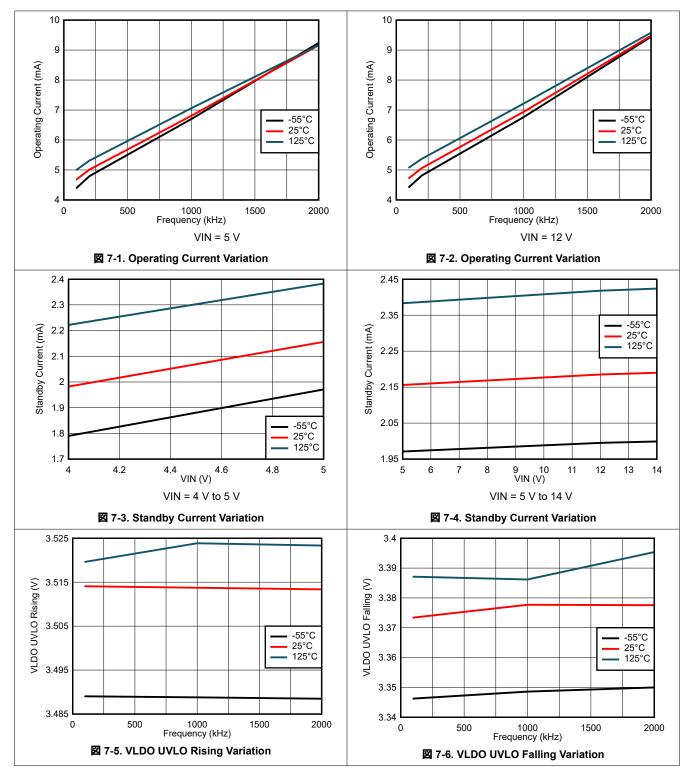

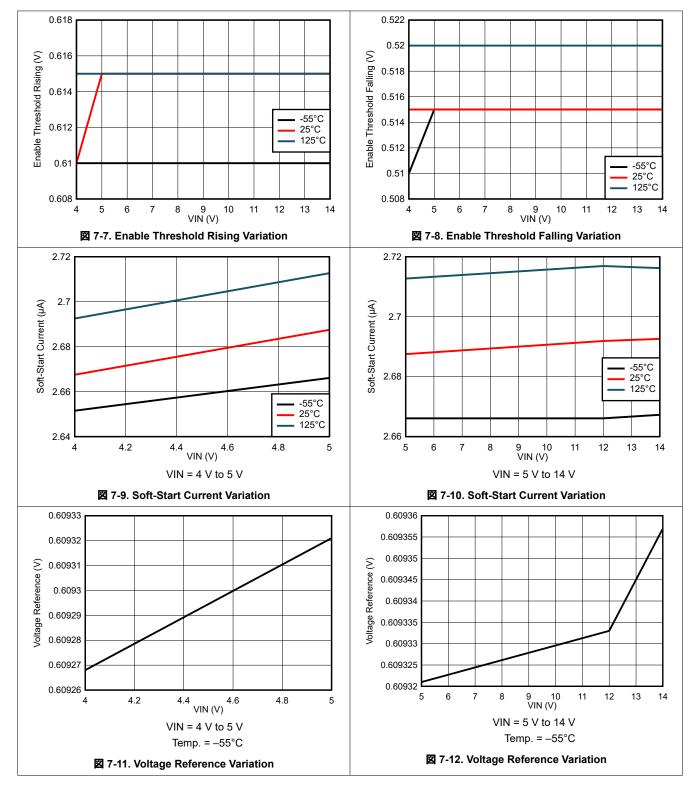

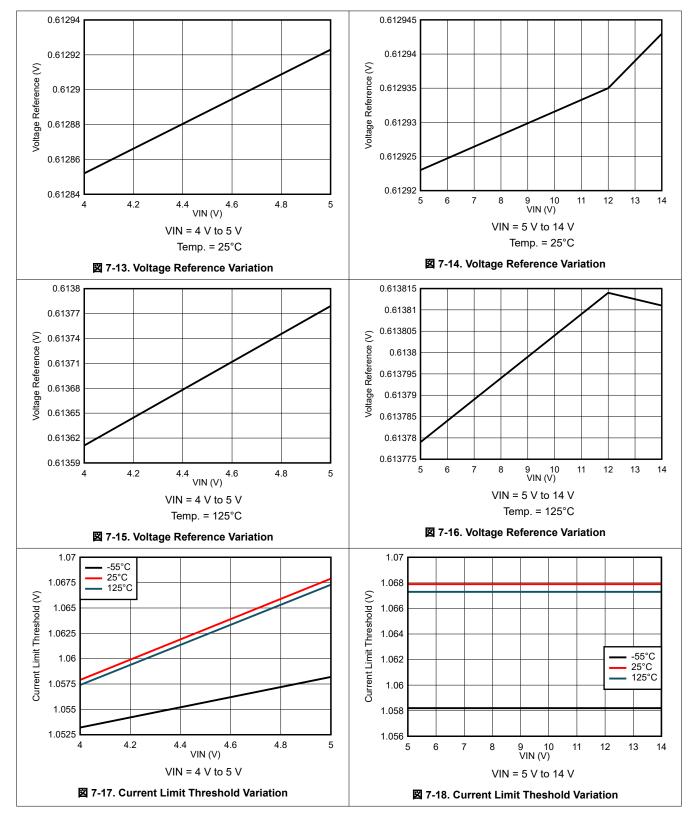

| 7.10 Typical Characteristics                 | 20 |

| 8 Detailed Description                       | 32 |

| 8.1 Overview                                 | 32 |

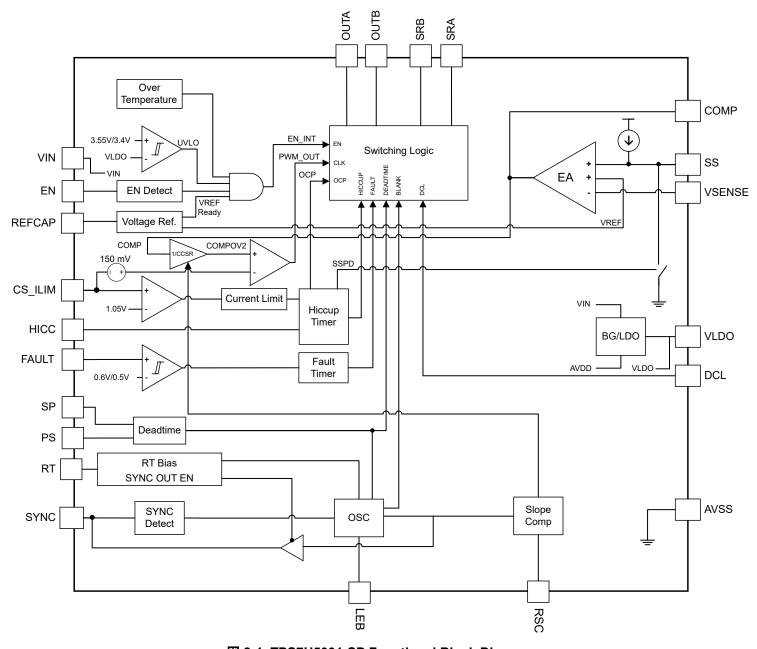

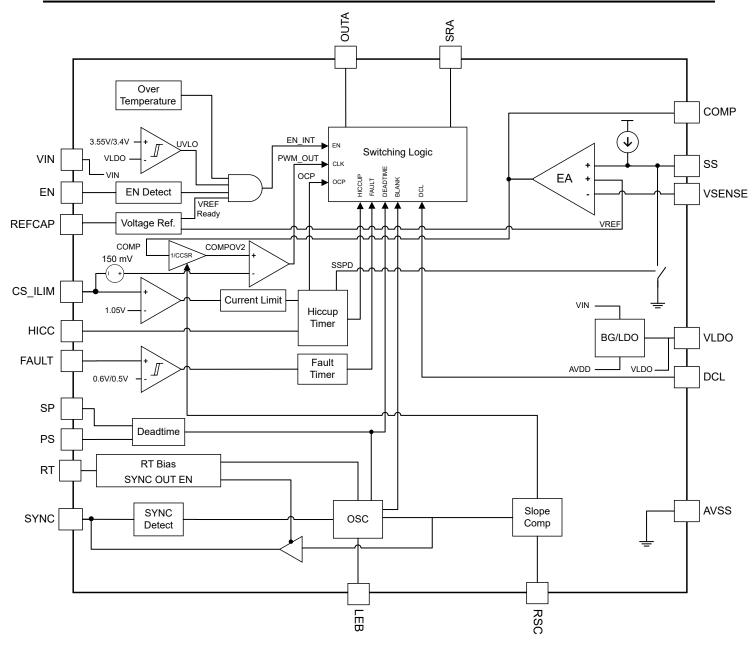

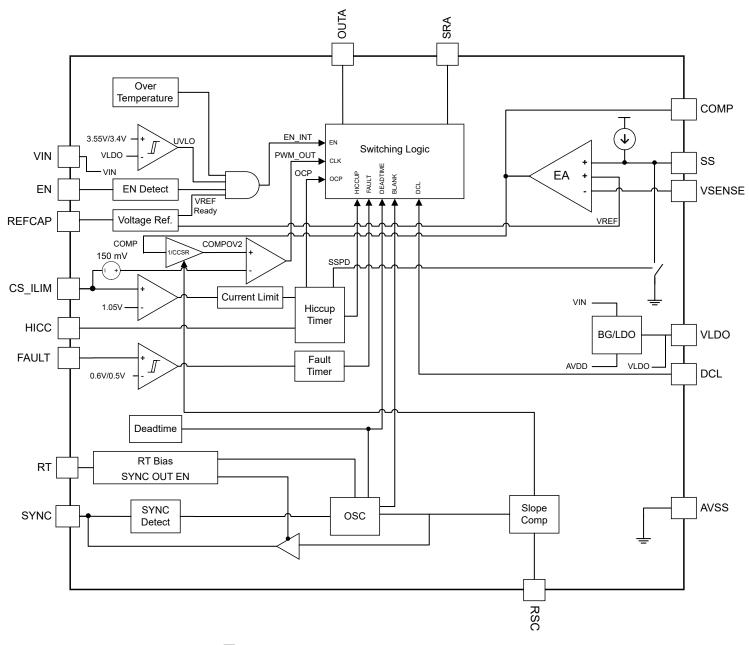

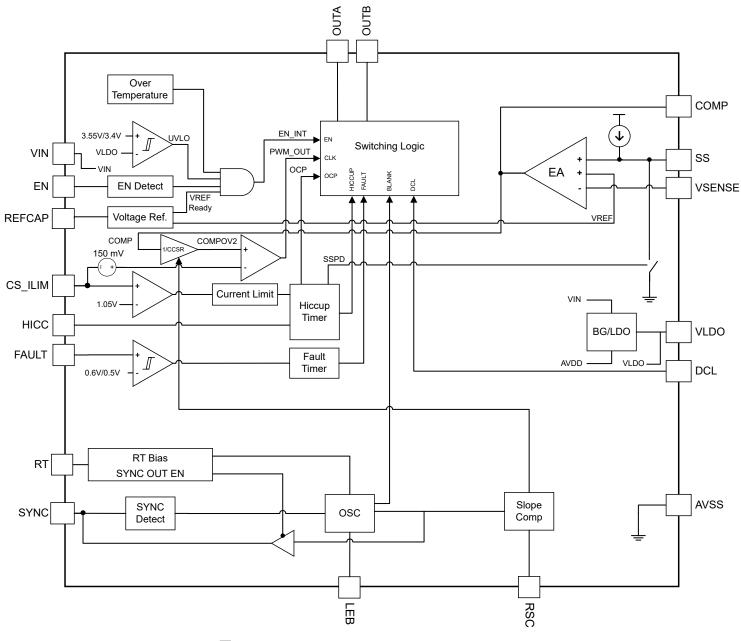

| 8.2 Functional Block Diagram            | 33              |

|-----------------------------------------|-----------------|

| 8.3 Feature Description                 | <mark>37</mark> |

| 8.4 Device Functional Modes             |                 |

| 9 Application and Implementation        | 56              |

| 9.1 Application Information             | <u>56</u>       |

| 9.2 Typical Application                 | 56              |

| 9.3 Power Supply Recommendations        |                 |

| 9.4 Layout                              | 66              |

| 10 Device and Documentation Support     |                 |

| 10.1 Documentation Support              | 70              |

| 10.2ドキュメントの更新通知を受け取る方法                  | 70              |

| 10.3 サポート・リソース                          | 70              |

| 10.4 Trademarks                         | 70              |

| 10.5 静電気放電に関する注意事項                      | 70              |

| 10.6 用語集                                | 70              |

| 11 Revision History                     | <del>7</del> 0  |

| 12 Mechanical, Packaging, and Orderable |                 |

| Information                             | 72              |

|                                         |                 |

# **4 Device Comparison Table**

| DEVICE       | PRIMARY OUTPUTS | SYNCHRONOUS<br>RECTIFIER<br>OUTPUTS | DEAD-TIME<br>SETTING     | LEADING EDGE<br>BLANK TIME<br>SETTING | DUTY CYCLE LIMIT<br>OPTIONS |

|--------------|-----------------|-------------------------------------|--------------------------|---------------------------------------|-----------------------------|

| TPS7H5001-SP | 2               | 2                                   | Resistor programmable    | Resistor<br>programmable              | 50%, 75%, 100%              |

| TPS7H5002-SP | 1               | 1                                   | Resistor<br>programmable | Resistor<br>programmable              | 75%, 100%                   |

| TPS7H5003-SP | 1               | 1                                   | Fixed (50-ns typical)    | Fixed (50-ns typical)                 | 75%, 100%                   |

| TPS7H5004-SP | 2               | 0                                   | Not applicable           | Resistor<br>programmable              | 50%                         |

# **5 Device Options**

| GENERIC PART<br>NUMBER | RADIATION RATING <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GRADE <sup>(2)</sup>                | PACKAGE         | ORDERABLE PART<br>NUMBER <sup>(3)</sup> |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----------------------------------------|

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QMLV-RHA                            | 22-pin CFP HFT  | 5962R1822201VXC                         |

|                        | TID of 100 krad(Si) RLAT,<br>DSEE free to LET = 75 MeV-cm <sup>2</sup> /mg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KGD (QMLV-RHA)                      | Die             | 5962R1822201V9A                         |

| TPS7H5001-SP           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QMLP-RHA                            | 24-pin TSSOP PW | 5962R1822201PYE                         |

|                        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Engineering sample <sup>(4)</sup>   | 22-pin CFP HFT  | TPS7H5001HFT/EM                         |

|                        | Notic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Engineering sample                  | Die             | TPS7H5001Y/EM                           |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QMLV-RHA                            | 22-pin CFP HFT  | 5962R1822202VXC                         |

|                        | TID of 100 krad(Si) RLAT,<br>DSEE free to LET = 75 MeV-cm <sup>2</sup> /mg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KGD (QMLV-RHA)                      | Die             | 5962R1822202V9A                         |

| TPS7H5002-SP           | Journal of the second of the s | QMLP-RHA                            | 24-pin TSSOP PW | 5962R1822202PYE                         |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     | 22-pin CFP HFT  | TPS7H5002HFT/EM                         |

|                        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Engineering sample <sup>(4)</sup>   | Die             | TPS7H5002Y/EM                           |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QMLV-RHA                            | 22-pin CFP HFT  | 5962R1822203VXC                         |

|                        | TID of 100 krad(Si) RLAT,<br>DSEE free to LET = 75 MeV-cm <sup>2</sup> /mg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KGD (QMLV-RHA)                      | Die             | 5962R1822203V9A                         |

| TPS7H5003-SP           | Journal of the second of the s | QMLP-RHA                            | 24-pin TSSOP PW | 5962R1822203PYE                         |

|                        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Engineering sample <sup>(4)</sup>   | 22-pin CFP HFT  | TPS7H5003HFT/EM                         |

|                        | Notie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Engineering sample                  | Die             | TPS7H5003Y/EM                           |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QMLV-RHA                            | 22-pin CFP HFT  | 5962R1822204VXC                         |

|                        | TID of 100 krad(Si) RLAT,<br>DSEE free to LET = 75 MeV-cm <sup>2</sup> /mg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KGD (QMLV-RHA)                      | Die             | 5962R1822204V9A                         |

| TPS7H5004-SP           | Joe not to be not surface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | QMLP-RHA                            | 24-pin TSSOP PW | 5962R1822204PYE                         |

|                        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Engineering sample <sup>(4)</sup>   | 22-pin CFP HFT  | TPS7H5004HFT/EM                         |

|                        | Notic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Engineering sample(*)               | Die             | TPS7H5004Y/EM                           |

| SN0022HFT              | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mechanical "dummy" package (no die) | 22-pin CFP HFT  | SN0022HFT                               |

<sup>(1)</sup> TID is total ionizing dose and DSEE is destructive single event effects. Additional information is available in the associated TID reports and SEE reports for each product.

<sup>(2)</sup> For additional information about part grade, view SLYB235.

<sup>(3)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

<sup>(4)</sup> These units are intended for engineering evaluation only. They are processed to a noncompliant flow. These units are not suitable for qualification, production, radiation testing or flight use. Parts are not warranted for performance over the full MIL specified temperature range of –55°C to 125°C or operating life.

# **6 Pin Configuration and Functions**

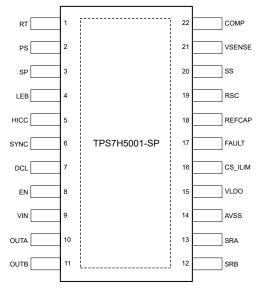

図 6-1. TPS7H5001-SP HFT Package 22-Pin CFP With Thermal Pad (Top View)

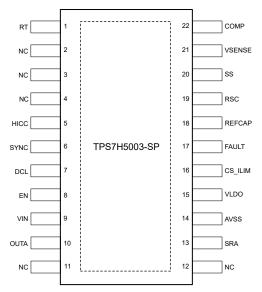

図 6-3. TPS7H5003-SP HFT Package 22-Pin CFP With Thermal Pad (Top View)

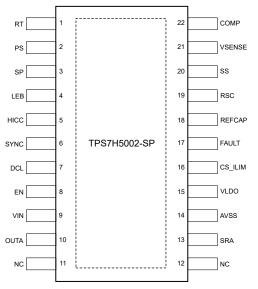

図 6-2. TPS7H5002-SP HFT Package 22-Pin CFP With Thermal Pad (Top View)

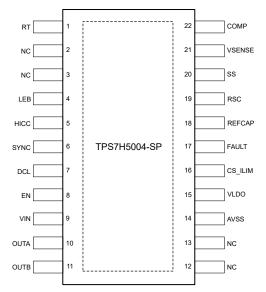

図 6-4. TPS7H5004-SP HFT Package 22-Pin CFP With Thermal Pad (Top View)

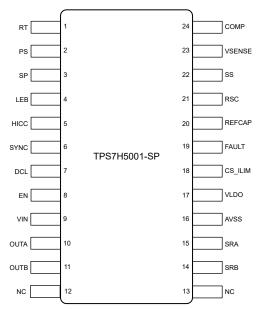

図 6-5. TPS7H5001-SP PW Package 24-Pin TSSOP (Top View)

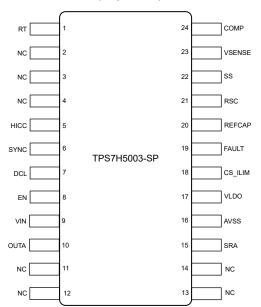

図 6-7. TPS7H5003-SP PW Package 24-Pin TSSOP (Top View)

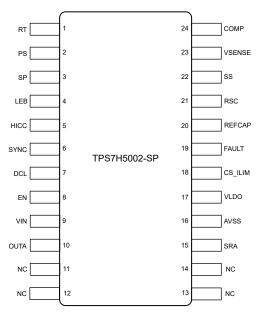

図 6-6. TPS7H5002-SP PW Package 24-Pin TSSOP (Top View)

図 6-8. TPS7H5004-SP PW Package 24-Pin TSSOP (Top View)

### 表 6-1. Pin Functions

|      |       |         |       | PIN     | ±X 0-1. F1 |        |       |         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------|---------|-------|---------|------------|--------|-------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | TPS7H | 5001-SP | TPS7H | 5002-SP | TPS7H50    | 003-SP | TPS7H | 5004-SP | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NAME | CFP   | TSSOP   | CFP   | TSSOP   | CFP        | TSSOP  | CFP   | TSSOP   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RT   | 1     | 1       | 1     | 1       | 1          | 1      | 1     | 1       | I/O | In internal oscillation mode, the RT pin must be populated with a resistor to AVSS. When the RT pin is floating, a 200-kHz to 4-MHz external clock is required at the SYNC pin. The frequency of the external clock must be twice the desired switching frequency.                                                                                                                                                             |

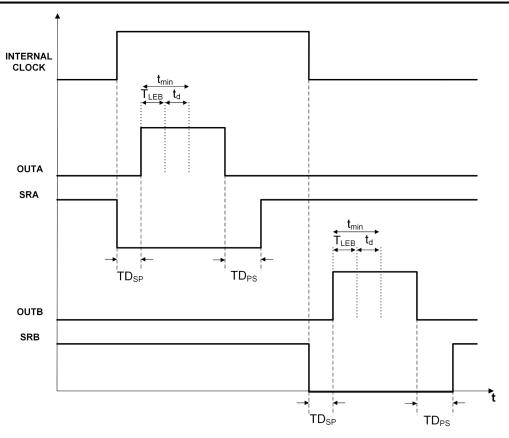

| PS   | 2     | 2       | 2     | 2       | _          | _      | _     | _       | I/O | Primary off to synchronous rectifier on dead-time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                      |

| SP   | 3     | 3       | 3     | 3       | -          | _      | _     | _       | I/O | Synchronous rectifier off to primary on dead-time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                      |

| LEB  | 4     | 4       | 4     | 4       | _          | _      | 4     | 4       | I/O | Leading edge blank time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                                                |

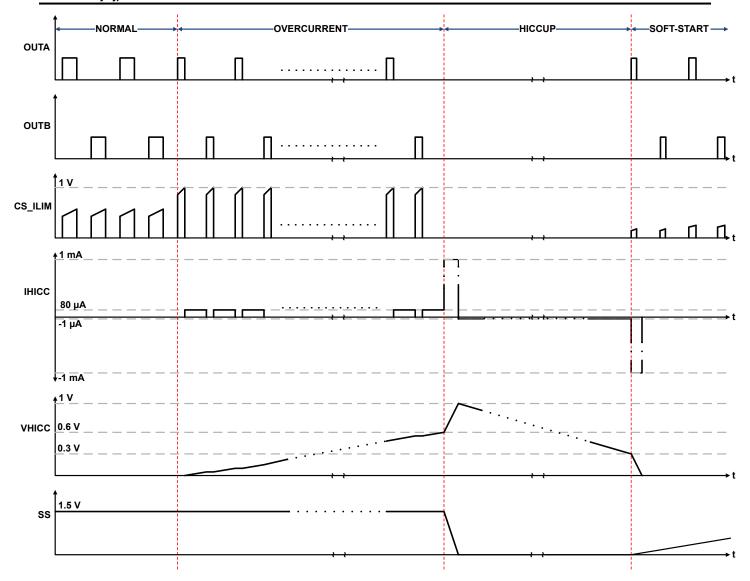

| HICC | 5     | 5       | 5     | 5       | 5          | 5      | 5     | 5       | I/O | Cycle-by-cycle current limit time delay and hiccup time setting. Delay time and hiccup time determined by capacitor from HICC to AVSS. Connecting this pin to AVSS disables hiccup mode.                                                                                                                                                                                                                                       |

| SYNC | 6     | 6       | 6     | 6       | 6          | 6      | 6     | 6       | I/O | When the RT pin is floating, SYNC is configured as an input for a 200-kHz to 4-MHz external clock. In this case, the external clock input gets inverted and the system clock will run at half the frequency of the external clock input. When the RT pin is populated with a resistor to AVSS, SYNC outputs a 200-kHz to 4-MHz clock signal at twice the device switching frequency in phase with the switching of the device. |

# 表 6-1. Pin Functions (続き)

| タ G-1. First unctions (病にと) |       |         |       |         |        |        |       |         |     |                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|-------|---------|-------|---------|--------|--------|-------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                        | TPS7H | 5001-SP | TPS7H | 5002-SP | TPS7H5 | 003-SP | TPS7H | 5004-SP | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

| INAIVIE                     | CFP   | TSSOP   | CFP   | TSSOP   | CFP    | TSSOP  | CFP   | TSSOP   |     |                                                                                                                                                                                                                                                                                                                                                                                             |

| DCL                         | 7     | 7       | 7     | 7       | 7      | 7      | 7     | 7       | I/O | Duty cycle limit configurability. For TPS7H5001-SP, connect to AVSS for 50% duty cycle limit, floating for 75%, and VLDO for 100%. For TPS7H5002-SP and TPS7H5003-SP, the DCL pin can be left floating or connected to VLDO to set the maximum duty cycle to 75% or 100%, respectively. For TPS7H5004-SP, this pin must be connected to AVSS in order to obtain the 50% maximum duty cycle. |

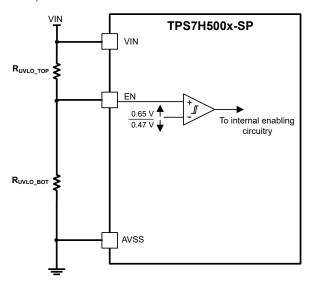

| EN                          | 8     | 8       | 8     | 8       | 8      | 8      | 8     | 8       | I   | Connecting the EN pin to the VLDO pin or external source greater than 0.6 V enables the device. In addition, input undervoltage lockout (UVLO) can be adjusted with two resistors.                                                                                                                                                                                                          |

| VIN                         | 9     | 9       | 9     | 9       | 9      | 9      | 9     | 9       | I   | Input supply to the device.<br>Input voltage range is from 4<br>V to 14 V.                                                                                                                                                                                                                                                                                                                  |

| OUTA                        | 10    | 10      | 10    | 10      | 10     | 10     | 10    | 10      | 0   | Primary switching output A.                                                                                                                                                                                                                                                                                                                                                                 |

| OUTB                        | 11    | 11      | _     | _       | _      | _      | 11    | 11      | 0   | Primary switching output B.<br>Active only when DCL =<br>AVSS.                                                                                                                                                                                                                                                                                                                              |

| SRB                         | 12    | 14      | _     | _       | _      | _      | _     | _       | 0   | Synchronous rectifier output B. Active only when DCL = AVSS.                                                                                                                                                                                                                                                                                                                                |

| SRA                         | 13    | 15      | 13    | 15      | 13     | 15     | _     | _       | 0   | Synchronous rectifier output A.                                                                                                                                                                                                                                                                                                                                                             |

| AVSS                        | 14    | 16      | 14    | 16      | 14     | 16     | 14    | 16      | _   | Ground of the device. The thermal pad, lid, and seal ring of the device are internally connected to ground for the ceramic package (CFP).                                                                                                                                                                                                                                                   |

| VLDO                        | 15    | 17      | 15    | 17      | 15     | 17     | 15    | 17      | 0   | Output of internal regulator.<br>Requires at least 1-µF<br>external capacitor to AVSS.                                                                                                                                                                                                                                                                                                      |

| CS_ILIM                     | 16    | 18      | 16    | 18      | 16     | 18     | 16    | 18      | I/O | Current sense for PWM control and cycle-by-cycle overcurrent protection. An input voltage over 1.05 V on CS_ILIM will trigger an overcurrent in the PWM controller. The sensed waveform on CS_ILIM contains a 150-mV offset when compared to the COMP/2 voltage at the input of the PWM comparator.                                                                                         |

# 表 6-1. Pin Functions (続き)

|        | PIN   |         |        |                   |                    |                               |                 |                           |     |                                                                                                                                                                                                                                                                    |

|--------|-------|---------|--------|-------------------|--------------------|-------------------------------|-----------------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | TPS7H | 5001-SP | TPS7H  | 5002-SP           | TPS7H50            | 003-SP                        | TPS7H           | 5004-SP                   | I/O | DESCRIPTION                                                                                                                                                                                                                                                        |

| NAME   | CFP   | TSSOP   | CFP    | TSSOP             | CFP                | TSSOP                         | CFP             | TSSOP                     |     |                                                                                                                                                                                                                                                                    |

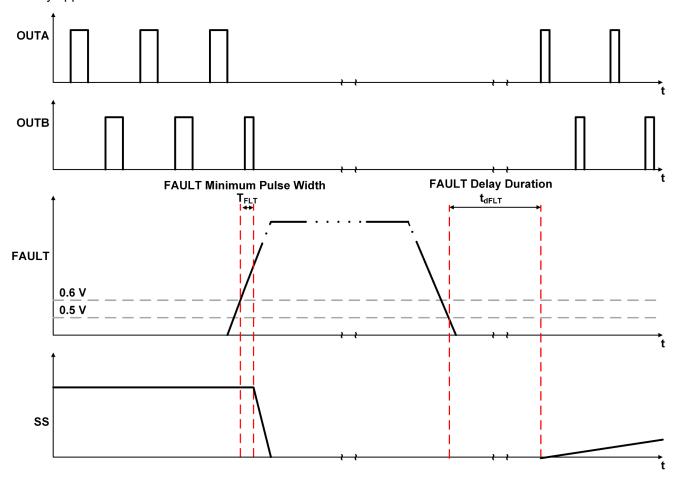

| FAULT  | 17    | 19      | 17     | 19                | 17                 | 19                            | 17              | 19                        | I   | Fault protection pin. When the rising threshold of the FAULT pin is exceeded, the outputs will stop switching. After the external voltage drops below the falling threshold, the device will restart after a set delay. Connect this pin to AVSS to disable FAULT. |

| REFCAP | 18    | 20      | 18     | 20                | 18                 | 20                            | 18              | 20                        | 0   | 1.2-V internal reference.<br>Requires a 470-nF external<br>capacitor to AVSS.                                                                                                                                                                                      |

| RSC    | 19    | 21      | 19     | 21                | 19                 | 21                            | 19              | 21                        | I/O | A resistor from RSC to<br>AVSS sets the desired slope<br>compensation.                                                                                                                                                                                             |

| SS     | 20    | 22      | 20     | 22                | 20                 | 22                            | 20              | 22                        | I/O | Soft start. An external capacitor connected to this pin sets the internal voltage reference rise time. The voltage on this pin overrides the internal reference. It can be used for tracking and sequencing.                                                       |

| VSENSE | 21    | 23      | 21     | 23                | 21                 | 23                            | 21              | 23                        | I   | Inverting input of the error amplifier.                                                                                                                                                                                                                            |

| COMP   | 22    | 24      | 22     | 24                | 22                 | 24                            | 22              | 24                        | I/O | Error amplifier output. Connect frequency compensation to this pin.                                                                                                                                                                                                |

| NC     | N/A   | 12, 13  | 11, 12 | 11, 12,<br>13, 14 | 2, 3, 4, 11,<br>12 | 2, 3, 4,<br>11, 12,<br>13, 14 | 2, 3, 12,<br>13 | 2, 3,12,<br>13, 14,<br>15 | _   | No connect. Can be connected to AVSS to avoid floating metal if desired.                                                                                                                                                                                           |

# 表 6-2. TPS7H500x-SP Bare Die Information - Applicable for All Devices

| DIE THICKNESS | BACKSIDE FINISH        | BACKSIDE POTENTIAL | BOND PAD<br>METALLIZATION<br>COMPOSITION | BOND PAD THICKNESS |

|---------------|------------------------|--------------------|------------------------------------------|--------------------|

| 15 mils       | Silicon with backgrind | GND                | Al (0.5% Cu)                             | 3000 nm            |

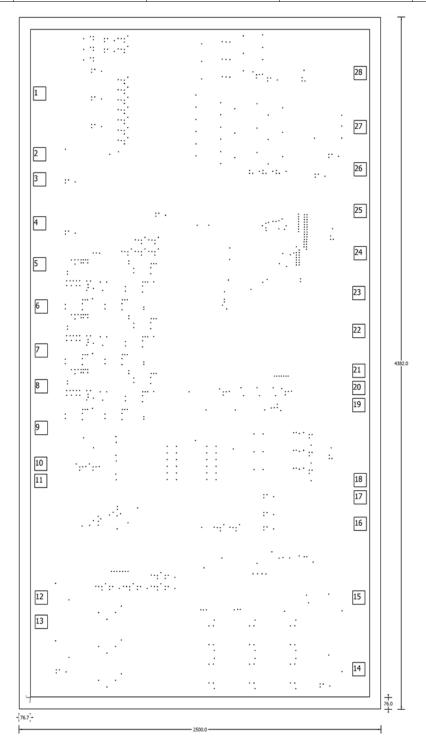

☑ 6-9. TPS7H500x-SP Bare Die Diagram - Applicable for All Devices

### 表 6-3. TPS7H5001-SP Bond Pad Coordinates in Microns

| DESCRIPTION | PAD NUMBER | X MIN   | Y MIN    | X MAX   | Y MAX    |

|-------------|------------|---------|----------|---------|----------|

| RT          | 1          | 21.33   | 3775.77  | 111.33  | 3865.77  |

| PS          | 2          | 21.33   | 3392.37  | 111.33  | 3482.37  |

| SP          | 3          | 21.33   | 3233.115 | 111.33  | 3323.115 |

| LEB         | 4          | 21.33   | 2955.015 | 111.33  | 3045.015 |

| HICC        | 5          | 21.33   | 2695.905 | 111.33  | 2785.905 |

| SYNC        | 6          | 32.13   | 2427.705 | 122.13  | 2517.705 |

| DCL         | 7          | 32.13   | 2149.515 | 122.13  | 2239.515 |

| NC          | 8          | 32.175  | 1923.165 | 122.175 | 2013.165 |

| EN          | 9          | 32.13   | 1660.275 | 122.13  | 1750.275 |

| VIN         | 10         | 28.665  | 1432.53  | 118.665 | 1522.53  |

| VIN         | 11         | 28.665  | 1325.475 | 118.665 | 1415.475 |

| OUTA        | 12         | 32.13   | 586.755  | 122.13  | 676.755  |

| OUTB        | 13         | 32.13   | 433.35   | 122.13  | 523.35   |

| SRB         | 14         | 2224.62 | 132.93   | 2314.62 | 222.93   |

| SRA         | 15         | 2224.62 | 586.755  | 2314.62 | 676.755  |

| AVSS        | 16         | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS        | 17         | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS        | 18         | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO        | 19         | 2224.62 | 1803.51  | 2314.62 | 1893.51  |

| VLDO        | 20         | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO        | 21         | 2224.62 | 2021.58  | 2314.62 | 2111.58  |

| CS_ILM      | 22         | 2224.62 | 2274.3   | 2314.62 | 2364.3   |

| FAULT       | 23         | 2224.62 | 2513.16  | 2314.62 | 2603.16  |

| REFCAP      | 24         | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC         | 25         | 2235.42 | 3033.36  | 2325.42 | 3123.36  |

| SS          | 26         | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE      | 27         | 2235.42 | 3563.64  | 2325.42 | 3653.64  |

| COMP        | 28         | 2235.42 | 3905.55  | 2325.42 | 3995.55  |

# 表 6-4. TPS7H5002-SP Bond Pad Coordinates in Microns

| DESCRIPTION | PAD NUMBER | X MIN   | Y MIN    | X MAX   | Y MAX    |

|-------------|------------|---------|----------|---------|----------|

| RT          | 1          | 21.33   | 3775.77  | 111.33  | 3865.77  |

| PS          | 2          | 21.33   | 3392.37  | 111.33  | 3482.37  |

| SP          | 3          | 21.33   | 3233.115 | 111.33  | 3323.115 |

| LEB         | 4          | 21.33   | 2955.015 | 111.33  | 3045.015 |

| HICC        | 5          | 21.33   | 2695.905 | 111.33  | 2785.905 |

| SYNC        | 6          | 32.13   | 2427.705 | 122.13  | 2517.705 |

| DCL         | 7          | 32.13   | 2149.515 | 122.13  | 2239.515 |

| NC          | 8          | 32.175  | 1923.165 | 122.175 | 2013.165 |

| EN          | 9          | 32.13   | 1660.275 | 122.13  | 1750.275 |

| VIN         | 10         | 28.665  | 1432.53  | 118.665 | 1522.53  |

| VIN         | 11         | 28.665  | 1325.475 | 118.665 | 1415.475 |

| OUTA        | 12         | 32.13   | 586.755  | 122.13  | 676.755  |

| NC          | 13         | 32.13   | 433.35   | 122.13  | 523.35   |

| NC          | 14         | 2224.62 | 132.93   | 2314.62 | 222.93   |

# 表 6-4. TPS7H5002-SP Bond Pad Coordinates in Microns (続き)

| DESCRIPTION | PAD NUMBER | X MIN   | Y MIN    | X MAX   | Y MAX    |

|-------------|------------|---------|----------|---------|----------|

| SRA         | 15         | 2224.62 | 586.755  | 2314.62 | 676.755  |

| AVSS        | 16         | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS        | 17         | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS        | 18         | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO        | 19         | 2224.62 | 1803.51  | 2314.62 | 1893.51  |

| VLDO        | 20         | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO        | 21         | 2224.62 | 2021.58  | 2314.62 | 2111.58  |

| CS_ILM      | 22         | 2224.62 | 2274.3   | 2314.62 | 2364.3   |

| FAULT       | 23         | 2224.62 | 2513.16  | 2314.62 | 2603.16  |

| REFCAP      | 24         | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC         | 25         | 2235.42 | 3033.36  | 2325.42 | 3123.36  |

| SS          | 26         | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE      | 27         | 2235.42 | 3563.64  | 2325.42 | 3653.64  |

| COMP        | 28         | 2235.42 | 3905.55  | 2325.42 | 3995.55  |

### 表 6-5. TPS7H5003-SP Bond Pad Coordinates in Microns

| DESCRIPTION | PAD NUMBER | X MIN   | Y MIN    | X MAX   | Y MAX    |

|-------------|------------|---------|----------|---------|----------|

| RT          | 1          | 21.33   | 3775.77  | 111.33  | 3865.77  |

| NC          | 2          | 21.33   | 3392.37  | 111.33  | 3482.37  |

| NC          | 3          | 21.33   | 3233.115 | 111.33  | 3323.115 |

| NC          | 4          | 21.33   | 2955.015 | 111.33  | 3045.015 |

| HICC        | 5          | 21.33   | 2695.905 | 111.33  | 2785.905 |

| SYNC        | 6          | 32.13   | 2427.705 | 122.13  | 2517.705 |

| DCL         | 7          | 32.13   | 2149.515 | 122.13  | 2239.515 |

| NC          | 8          | 32.175  | 1923.165 | 122.175 | 2013.165 |

| EN          | 9          | 32.13   | 1660.275 | 122.13  | 1750.275 |

| VIN         | 10         | 28.665  | 1432.53  | 118.665 | 1522.53  |

| VIN         | 11         | 28.665  | 1325.475 | 118.665 | 1415.475 |

| OUTA        | 12         | 32.13   | 586.755  | 122.13  | 676.755  |

| NC          | 13         | 32.13   | 433.35   | 122.13  | 523.35   |

| NC          | 14         | 2224.62 | 132.93   | 2314.62 | 222.93   |

| SRA         | 15         | 2224.62 | 586.755  | 2314.62 | 676.755  |

| AVSS        | 16         | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS        | 17         | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS        | 18         | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO        | 19         | 2224.62 | 1803.51  | 2314.62 | 1893.51  |

| VLDO        | 20         | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO        | 21         | 2224.62 | 2021.58  | 2314.62 | 2111.58  |

| CS_ILM      | 22         | 2224.62 | 2274.3   | 2314.62 | 2364.3   |

| FAULT       | 23         | 2224.62 | 2513.16  | 2314.62 | 2603.16  |

| REFCAP      | 24         | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC         | 25         | 2235.42 | 3033.36  | 2325.42 | 3123.36  |

| SS          | 26         | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE      | 27         | 2235.42 | 3563.64  | 2325.42 | 3653.64  |

### 表 6-5. TPS7H5003-SP Bond Pad Coordinates in Microns (続き)

| DESCRIPTION | PAD NUMBER | X MIN   | Y MIN   | X MAX   | Y MAX   |

|-------------|------------|---------|---------|---------|---------|

| COMP        | 28         | 2235.42 | 3905.55 | 2325.42 | 3995.55 |

### 表 6-6. TPS7H5004-SP Bond Pad Coordinates in Microns

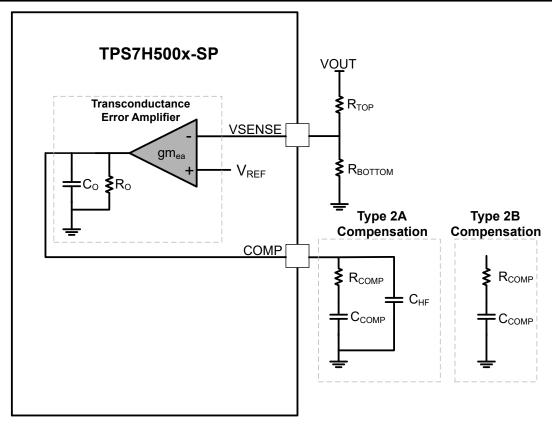

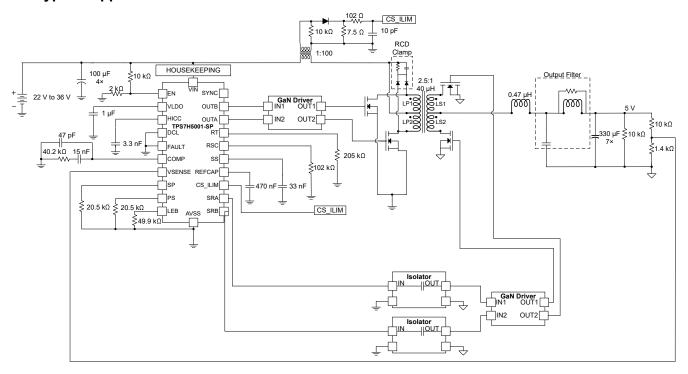

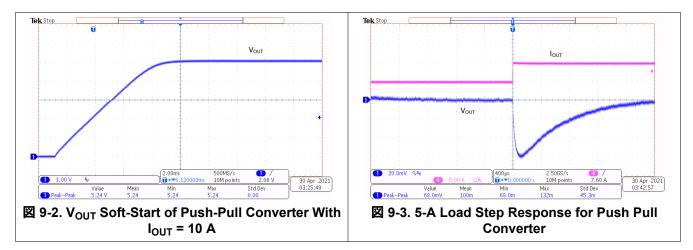

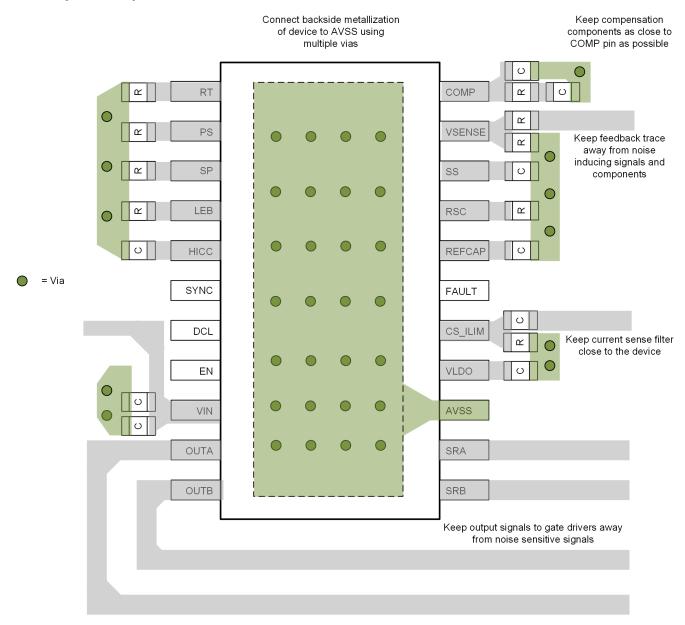

|             | 200.110    |         | ia i aa oooi amatoo iii iiiloi ono |         |          |  |  |