# TPS7H3024-SP および 耐放射線特性、14V、ウォッチドッグ タイマ付き 4 チャネルスーパーバイザ

## 1 特長

- 耐放射線性能:

- 吸収線量 (TID) 100krad(Si)までの放射線耐性保証 (RHA)

- シングルイベントラッチアップ (SEL)、シングルイベントバーンアウト (SEB)、シングルイベントゲートラップチャージ (SEGR) の最大線エネルギー付与 (LET) = 75MeV-cm<sup>2</sup>/mg に対する耐性

- シングルイベント機能割り込み (SEFI) およびシングルイベント過渡 (SET) の最大 LET = 75MeV-cm<sup>2</sup>/mg に対する耐性

- 広い電源入力電圧範囲 ( $V_{IN}$ ): 3V ~ 14V

- 最大 4 つの電圧レールを高精度で監視可能:

- TPS7H3024: 2 OV + 2 UV または 2 つのウインドウ (プッシュプル  $\overline{RESETx}$  付き)

- ウォッチドッグ タイマを使用して、プロセッサの一貫した実行を監視

- 単一抵抗によりプログラム可能なグローバル タイマ

- プログラム可能なウォッチドッグ タイムアウト

- 高精度のスレッショルド電圧とヒステリシス電流

- 全体で 599.7mV ±1% の  $V_{TH\_SENSEx}$ : 電圧、温度、放射線 (TID)

- 全体で 24μA ±3% の  $I_{HYS\_SENSEx}$ : 電圧、温度、放射線 (TID)

- 1.6V~7V のプログラマブル プルアップ電圧に対応するプッシュプル出力

- グローバル  $\overline{RESETx}$  プルアップドメイン ( $V_{PULL\_UP1}$ )

- 共通の PWRGD および  $\overline{WDO}$  プルアップドメイン ( $V_{PULL\_UP2}$ )

- すべての出力をリセットするための  $\overline{SR\_UVLO}$  入力

- 外部抵抗デバイスを用いた構成可能な低電圧ロッカウトとしても使用できます

- 軍用温度範囲 (-55°C~125°C) を供給可能

## 2 アプリケーション

- 衛星用電源システム (EPS)**

- 次のような複雑なデジタル プロセッサの電圧レールの監視: 宇宙アプリケーション向けの FPGA、SoC、AFE、電源システム

- 一貫性のあるプロセッサ実行の監視

## 3 説明

TPS7H3024-SP は、3V ~ 14V に対応する 4 チャネル放射線耐性付き電源スーパーバイザで、ウォッチドッグ機能を備えた集積デバイスです。正確な 599.7mV ±1% のスレッショルド電圧と 24μA ±3% のヒステリシス電流により、監視電圧をプログラム可能に設定できます。グローバル プログラマブル 遅延タイマは、1 本の抵抗によって設定されます。さらに、グローバル電源ツリーのステータスを監視するために、PWRGD 出力が提供されています。このデバイスには、正のエッジ検出ウォッチドッグ タイマも内蔵されており、外部プロセッサを監視して一貫性のある実行を行えます。 $\overline{SR\_UVLO}$  入力を使用することで、外部コントローラでフォルトを検出して緩和できます。

### 製品情報

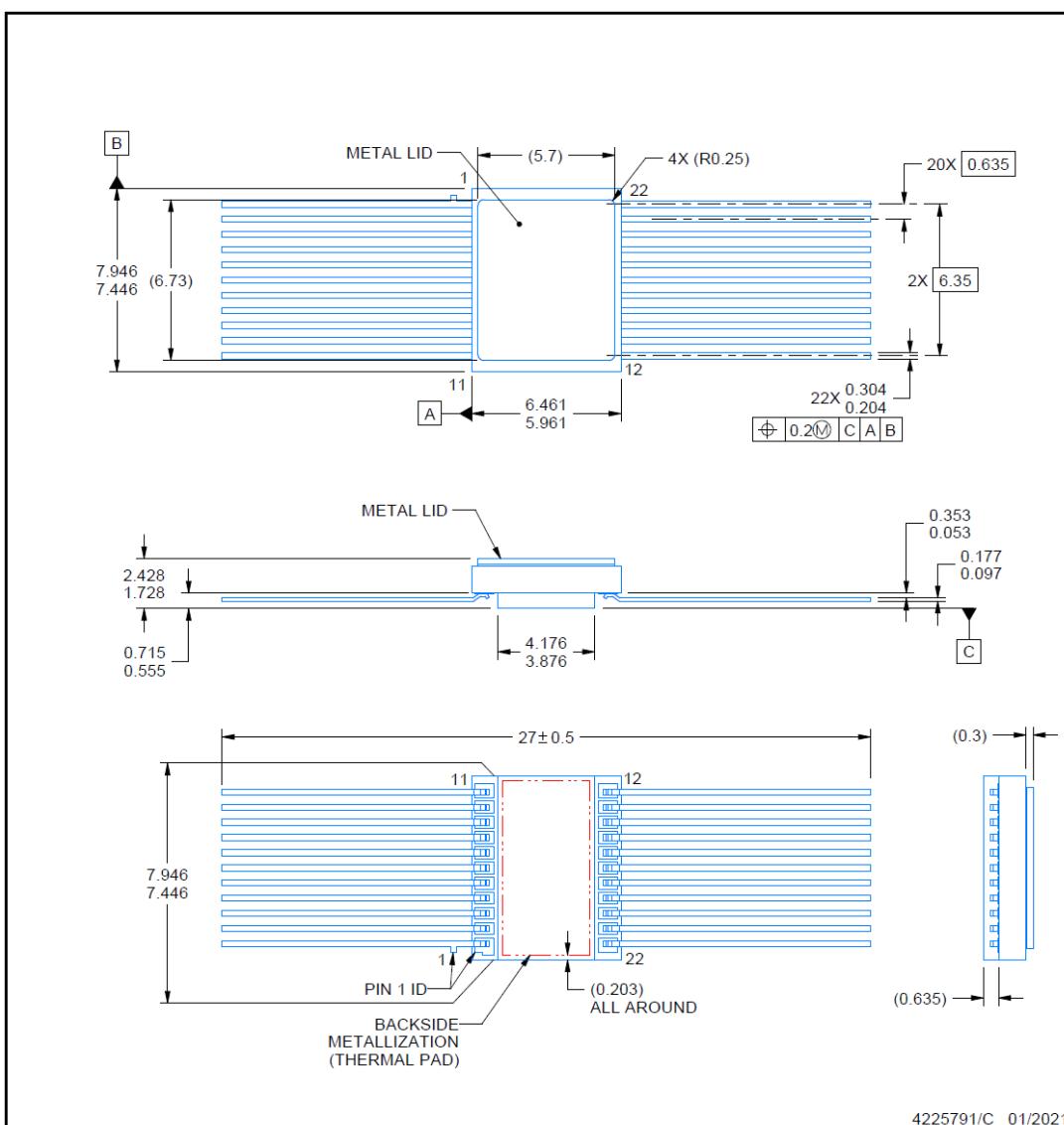

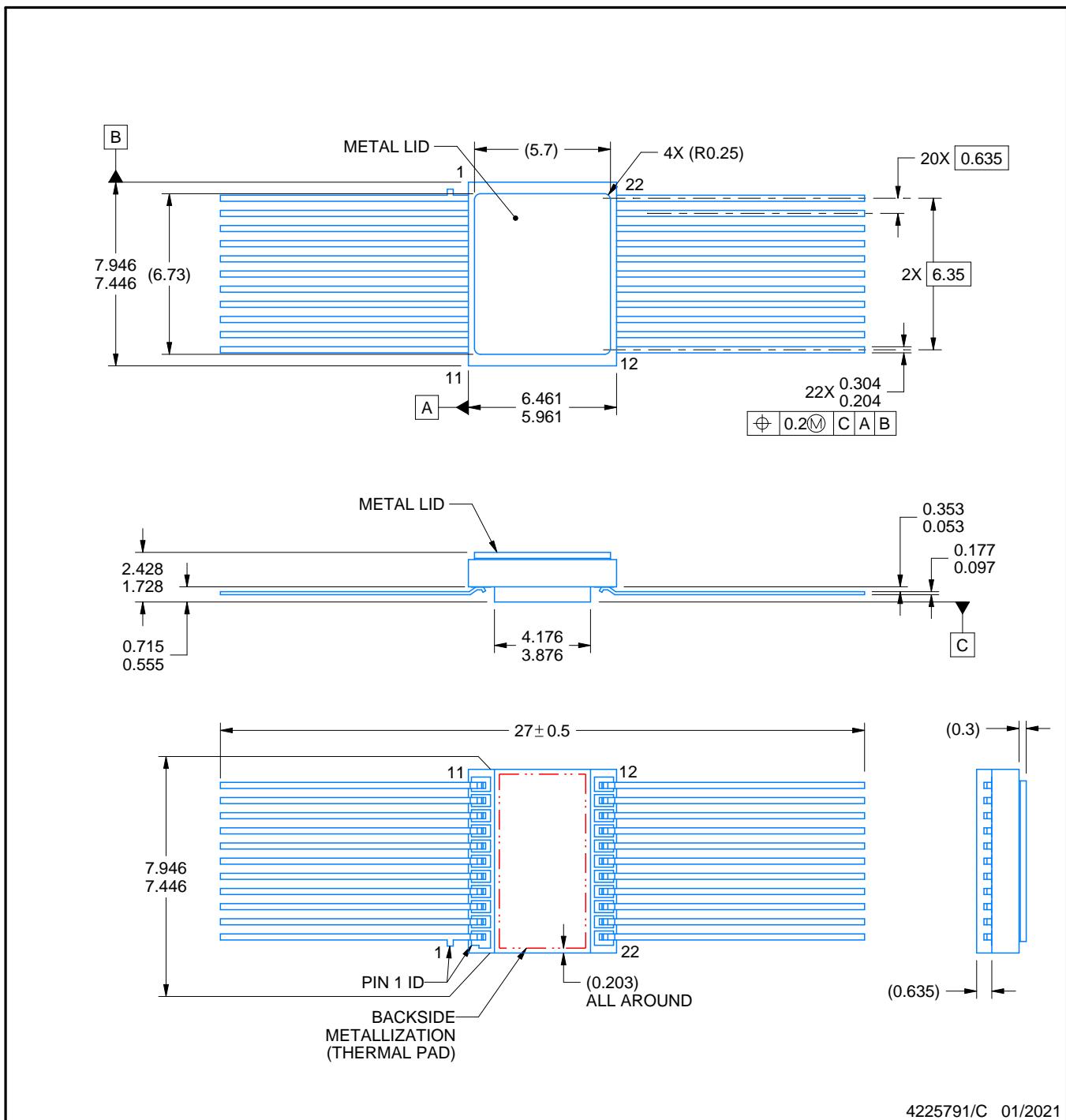

| 部品番号 (1)        | グレード          | パッケージ(2)                             |

|-----------------|---------------|--------------------------------------|

| 5962R2420601VXC | QMLV-RHA      | 22 ピンのセラミック (CFP)<br>6.21mm x 7.69mm |

| TPS7H3024HFT/EM | エンジニアリング サンプル | 質量 = 415.6mg                         |

(1) 詳細は、[デバイス オプション表](#)をご覧ください。

(2) 質量は公称値であり、本体サイズ(長さ×幅)は公称値であり、ピンは含まれません。

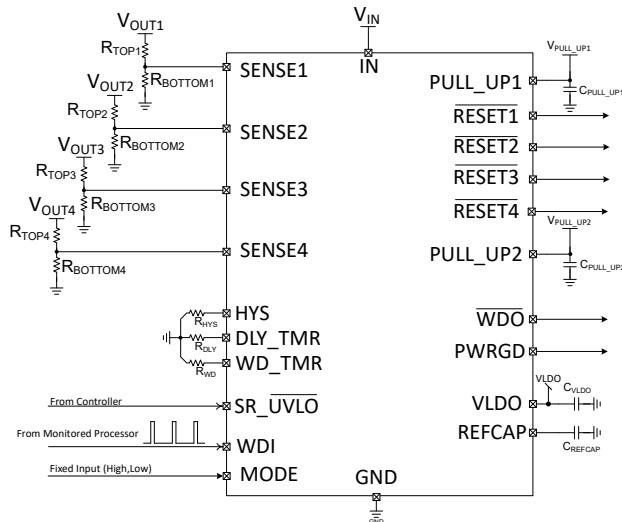

### 代表的なアプリケーション

**⚠️** このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                              |    |

|------------------|----|------------------------------|----|

| 1 特長.....        | 1  | 8.2 機能ブロック図.....             | 27 |

| 2 アプリケーション.....  | 1  | 8.3 機能説明.....                | 28 |

| 3 説明.....        | 1  | 8.4 デバイスの機能モード.....          | 43 |

| 4 デバイス比較表.....   | 3  | 9 アプリケーションと実装.....           | 45 |

| 5 ピン構成および機能..... | 4  | 9.1 アプリケーション情報.....          | 45 |

| 6 仕様.....        | 6  | 9.2 代表的なアプリケーション.....        | 45 |

| 6.1 絶対最大定格.....  | 6  | 9.3 電源に関する推奨事項.....          | 50 |

| 6.2 ESD 定格.....  | 6  | 9.4 レイアウト.....               | 51 |

| 6.3 推奨動作条件.....  | 7  | 10 デバイスおよびドキュメントのサポート.....   | 55 |

| 6.4 熱に関する情報..... | 7  | 10.1 ドキュメントのサポート.....        | 55 |

| 6.5 電気的特性.....   | 8  | 10.2 ドキュメントの更新通知を受け取る方法..... | 55 |

| 6.6 タイミング要件..... | 11 | 10.3 サポート・リソース.....          | 55 |

| 6.7 品質適合検査.....  | 12 | 10.4 商標.....                 | 55 |

| 6.8 代表的特性.....   | 13 | 10.5 静電気放電に関する注意事項.....      | 55 |

| 7 パラメータ測定情報..... | 19 | 10.6 用語集.....                | 55 |

| 8 詳細説明.....      | 25 | 11 改訂履歴.....                 | 55 |

| 8.1 概要.....      | 25 | 12 メカニカル、パッケージ、および注文情報.....  | 56 |

## 4 デバイス比較表

| ジェネリック型番     | 出力タイプ  | 機能                                    | 放射線定格 <sup>(1)</sup>                                                | グレード <sup>(2)</sup>            | パッケージ            | 発注用型番           |

|--------------|--------|---------------------------------------|---------------------------------------------------------------------|--------------------------------|------------------|-----------------|

| TPS7H3024-SP | プッシュプル | 2 UV +<br>2 OV<br>(または 2 つの<br>ウインドウ) | 100krad(Si) RLAT の TID、<br>75MeV-cm <sup>2</sup> /mg まで DSEE<br>フリー | QMLV-RHA                       | 22 ピン CFP<br>HFT | 5962R2420601VXC |

|              |        | なし                                    | なし                                                                  | エンジニアリング<br>モデル <sup>(3)</sup> |                  | TPS7H3024HFT/EM |

(1) TID は総電離線量、DSEE は破壊的シングル イベント効果です。詳細については、関連する TID レポートおよび各製品の SEE レポートを参照してください。

(2) 部品のグレードについて詳細は、[TI 部品のレーティング](#)をご覧ください。

(3) これらのユニットは、技術的な評価のみを目的としています。これらのユニットは、非準拠のフローで処理されています（バーンインがない、25°Cでのテストしか行わないなど）。これらのユニットは、認定、量産、放射線テスト、航空での使用には設計されていません。部品は、温度または動作寿命全体にわたる性能は規定されていません。

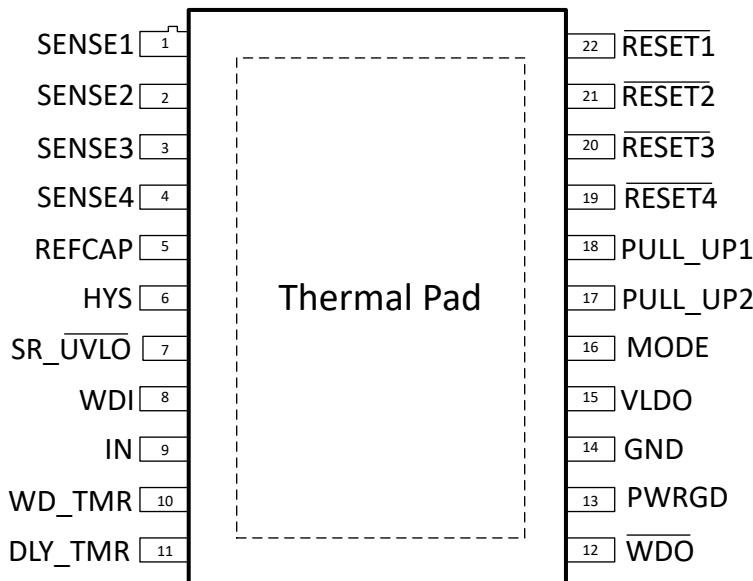

## 5 ピン構成および機能

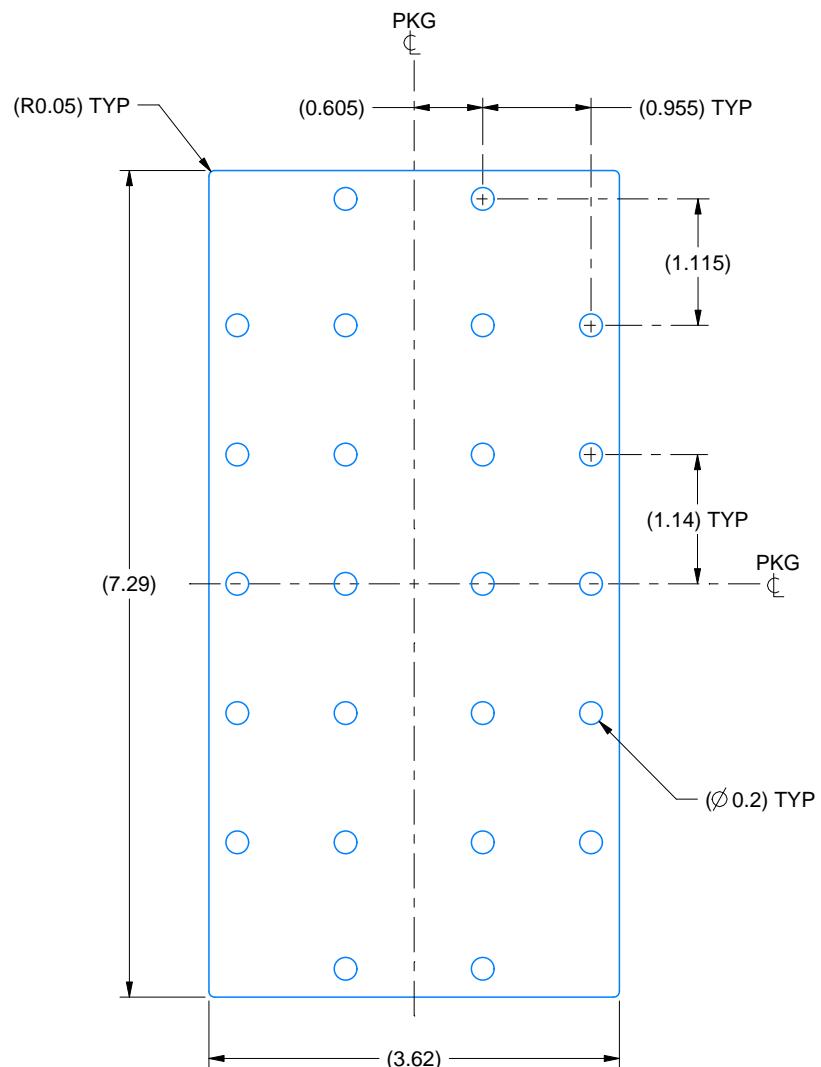

図 5-1. HFT パッケージ、22 ピン CFP (上面図)

表 5-1. ピンの機能

| ピン      |    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                               |

|---------|----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号 |                    |                                                                                                                                                                                                                                                                                                                  |

| SENSE1  | 1  | I                  | 目的の電圧レールを監視するために使用されるコンパレータの非反転入力。 $V_{ON1}$ 電圧と $V_{OFF1}$ 電圧を設定するには、監視対象のレールと GND との間に外付け分圧抵抗を接続し、中点を SENSE1 ピンに接続します。このピンで $V_{TH\_SENSEx}$ (599.7mV、標準値) を上回る電圧は、レギュレーション電圧レール ( $V_{ON1}$ ) と見なされます。 $V_{OFF1}$ は、 $I_{HYS}$ 電流、分圧抵抗、 $V_{TH\_SENSEx}$ の関数です。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| SENSE2  | 2  | I                  | 目的の電圧レールを監視するために使用されるコンパレータの非反転入力。 $V_{ON2}$ 電圧と $V_{OFF2}$ 電圧を設定するには、監視対象のレールと GND との間に外付け分圧抵抗を接続し、中点を SENSE2 ピンに接続します。このピンで $V_{TH\_SENSEx}$ (599.7mV、標準値) を上回る電圧は、レギュレーション電圧レール ( $V_{ON2}$ ) と見なされます。 $V_{OFF2}$ は、 $I_{HYS}$ 電流、分圧抵抗、 $V_{TH\_SENSEx}$ の関数です。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| SENSE3  | 3  | I                  | 目的の電圧レールを監視するために使用されるコンパレータの非反転入力。 $V_{ON3}$ 電圧と $V_{OFF3}$ 電圧を設定するには、監視対象のレールと GND との間に外付け分圧抵抗を接続し、中点を SENSE3 ピンに接続します。このピンで $V_{TH\_SENSEx}$ (599.7mV、標準値) を上回る電圧は、レギュレーション電圧レール ( $V_{ON2}$ ) と見なされます。 $V_{OFF3}$ は、 $I_{HYS}$ 電流、分圧抵抗、 $V_{TH\_SENSEx}$ の関数です。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| SENSE4  | 4  | I                  | 目的の電圧レールを監視するために使用されるコンパレータの非反転入力。 $V_{ON4}$ 電圧と $V_{OFF4}$ 電圧を設定するには、監視対象のレールと GND との間に外付け分圧抵抗を接続し、中点を SENSE4 ピンに接続します。このピンで $V_{TH\_SENSEx}$ (599.7mV、標準値) を上回る電圧は、レギュレーション電圧レール ( $V_{ON4}$ ) と見なされます。 $V_{OFF4}$ は、 $I_{HYS}$ 電流、分圧抵抗、 $V_{TH\_SENSEx}$ の関数です。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| REFCAP  | 5  | O                  | 1.2V 内部リファレンス。GND との間に 470nF の外付けコンデンサを必要とします。<br>このピンには、外部回路を追加して負荷を接続しないでください。                                                                                                                                                                                                                                 |

| HYS     | 6  | O                  | ヒステリシス。このピンと GND の間に 49.9kΩ 抵抗を接続して、SENSE1 と SENSE4 でのヒステリシス電流 (標準 24μA) をプログラムします。ユーザーには、0.1% 以上の許容差を持つ抵抗を使用することが推奨されます。                                                                                                                                                                                        |

| SR_UVLO | 7  | O                  | システムリセットと UVLO 入力。この入力を強制的に Low にして、すべての出力を Low にアサートします。 $V_{IN}$ と GND の間の分圧抵抗を使用して、本デバイスのターンオン レベルを設定できます。                                                                                                                                                                                                    |

**表 5-1. ピンの機能(続き)**

| ピン       |    | I/O <sup>(1)</sup> | 説明                                                                                                                                                            |

|----------|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号 |                    |                                                                                                                                                               |

| WDI      | 8  | I                  | ウォッチドッグ入力。この信号を Low から High に切り替えると、ウォッチドッグ タイマがクリアされます。ウォッチドッグ タイマが満了する前にこの入力が Low から High にトグルすると、WDO は High のままになり、それ以外の場合は Low にアサートされます。                 |

| IN       | 9  | I                  | デバイスへの入力電源。3 V ~ 14V の入力電圧範囲。0.1μF 以上のセラミックコンデンサを、ピンのできるだけ近くに接続してください。                                                                                        |

| WD_TMR   | 10 | I/O                | ウォッチドッグ タイマ。ウォッチドッグ タイムアウトを設定するために、56.2kΩ ~ 174kΩ の範囲の抵抗を GND に接続します。遅延時間は 0.52s~1.5s の範囲で調整できます。ウォッチドッグ タイマを無効にするには、このピンをフロートのままにしてください。                     |

| DLY_TMR  | 11 | I/O                | 遅延タイマ。�ルト解除遅延を設定するために、10.5kΩ ~ 1.18MΩ の範囲の抵抗を GND に接続します。遅延時間は、0.25ms ~ 25ms の範囲で調整できます。遅延を発生させないように、このピンはフロートのままにしてください。                                     |

| WDO      | 12 | O                  | ウォッチドッグ出力。プッシュプル出力。出力 high (VOH) レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                                                              |

| PWRGD    | 13 | O                  | パワーグッド。この出力は、すべてのレール (SENSE1 から SENS4) がレギュレーション中であることを示します。プッシュプル出力。VOH レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                      |

| GND      | 14 | —                  | グランド。                                                                                                                                                         |

| VLDO     | 15 | O                  | 内部レギュレータの出力。このピンは、少なくとも 1μF の外付けセラミック コンデンサを GND に接続する必要があります。この電圧は、負の電圧を監視する際に正のオフセットを生成するために使用できます。この LDO の最大負荷は 5mA です。このピンは過電流事象に対して保護されていません。            |

| モード      | 16 | I                  | 出力段の動作 (ウインドウ または UV + OV) を制御するための論理入力。詳細については、 <a href="#">セクション 8.3.4</a> を参照してください。この入力を動的に変更することはできません。MODE=0 は 2 UV + 2 OV に対応し、MODE=1 は 2 ウインドウに対応します。 |

| PULL_UP2 | 17 | I                  | PWRGD および WDO のプッシュプル出力のプルアップ電圧をプログラムするための入力電源電圧。1μF 以上のセラミックコンデンサを、ピンのできるだけ近くに接続してください。                                                                      |

| PULL_UP1 | 18 | I                  | RESET1 から RESET4 までのプッシュプル出力のグローバルプルアップ電圧をプログラムするための入力電源電圧。1μF 以上のセラミックコンデンサを、ピンのできるだけ近くに接続してください。                                                            |

| RESET4   | 19 | O                  | Reset 4。SENSE4 が故障のとき、RESET4 は Low にアサートされます。プッシュプル出力。VOH レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                                     |

| RESET3   | 20 | O                  | Reset 3。SENSE3 が故障のとき、RESET3 は Low にアサートされます。出力。VOH レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                                           |

| RESET2   | 21 | O                  | Reset 2。SENSE2 が故障のとき、RESET2 は Low にアサートされます。出力。VOH レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                                           |

| RESET1   | 22 | O                  | Reset 1。SENSE1 が故障のとき、RESET1 は Low にアサートされます。出力。VOH レベルは、PULL_UP2 入力電源電圧によって設定されます。                                                                           |

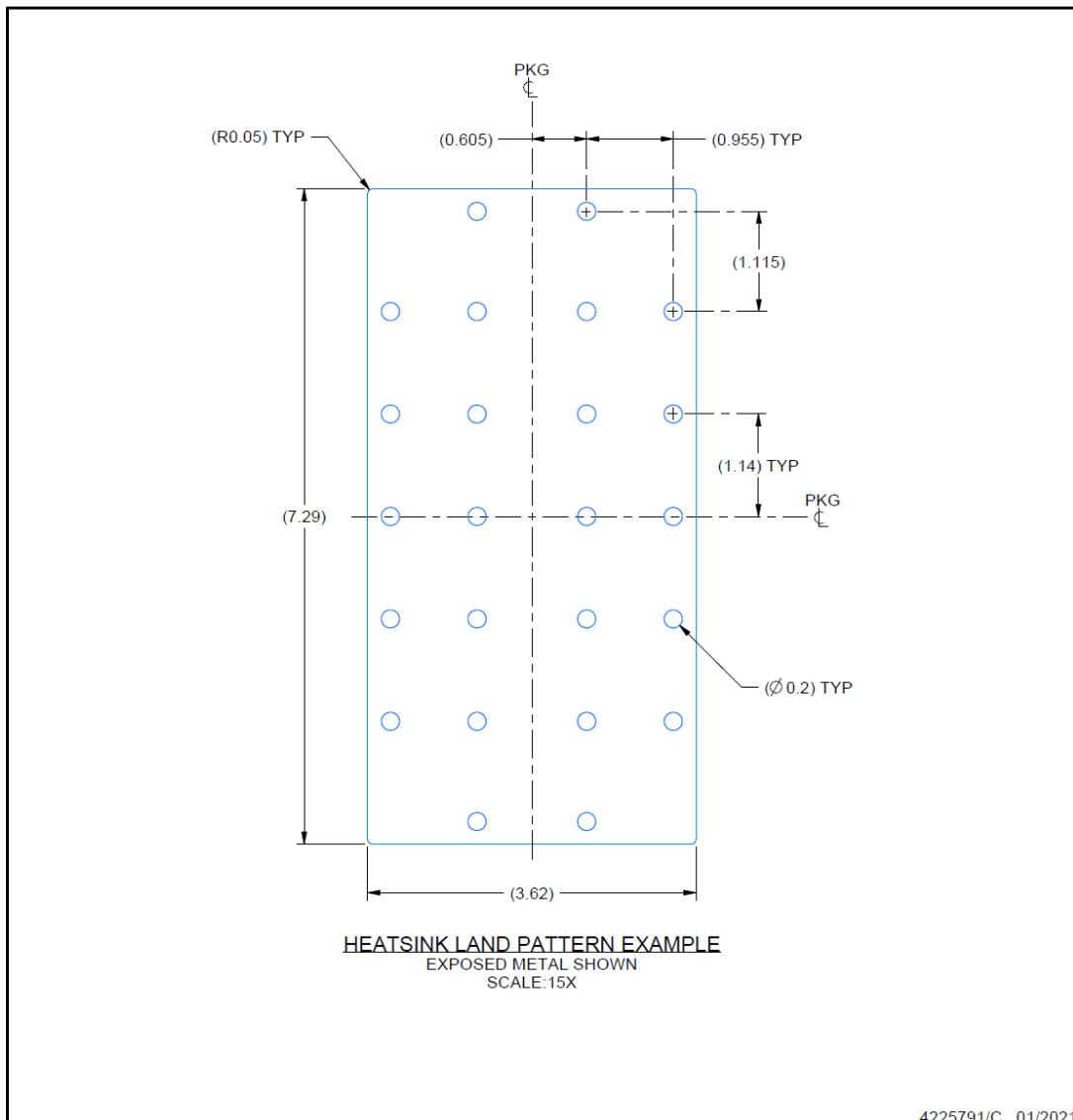

| サーマル パッド |    | —                  | 内部グランド。効果的な放熱のため、この金属サーマル パッドは大きなグランド プレーンに接続することを推奨します。                                                                                                      |

| 金属製ふた    | ふた | —                  | このふたは、シール リングを介してサーマル パッドと GND に内部接続されています。                                                                                                                   |

(1) I = 入力、O = 出力、I/O = 入力または出力、— = その他

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲(特に注記のない限り)(1) (2)

|       |                             | 最小値  | 最大値 | 単位 |

|-------|-----------------------------|------|-----|----|

| 入力電圧  | IN                          | -0.3 | 16  | V  |

|       | WDI、MODE                    | -0.3 | 7.5 |    |

|       | SENSE1、SENSE2、SENSE3、SENSE4 | -0.3 | 3.6 |    |

|       | PULL_UP1、PULL_UP2           | -0.3 | 7.5 |    |

|       | SR_UVLO                     | -0.3 | 7.5 |    |

|       | DLY_TMR、WD_TMR              | -0.3 | 3.6 |    |

| 出力電圧  | REFCAP                      | -0.3 | 2   | V  |

|       | VLDO                        | -0.3 | 3.6 |    |

|       | HYS                         | -0.3 | 3.6 |    |

|       | RESET1、RESET2、RESET3、RESET4 | -0.3 | 7.5 |    |

|       | PWRGD、WDOD                  | -0.3 | 7.5 |    |

| 出力電流  | RESET1、RESET2、RESET3、RESET4 | -20  | 20  | mA |

|       | PWRGD、WDOD                  | -20  | 20  |    |

| 接合部温度 | T <sub>J</sub>              | -55  | 150 | °C |

| 保存温度  | T <sub>stg</sub>            | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、GND を基準としたものです。

### 6.2 ESD 定格

|                  |      | 値                                                                | 単位    |

|------------------|------|------------------------------------------------------------------|-------|

| V <sub>ESD</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、すべてのピン <sup>(1)</sup>      | ±1000 |

|                  |      | 荷電デバイスモデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±250  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

動作温度範囲外 (特に記述のない限り)<sup>(1)</sup>

|            |                             | 最小値   | 公称値 | 最大値 | 単位   |

|------------|-----------------------------|-------|-----|-----|------|

| 入力電圧       | IN                          | 3     | 14  | 14  | V    |

|            | WDI、MODE                    | 0     | 7   | 7   |      |

|            | SENSE1、SENSE2、SENSE3、SENSE4 | 0     | 3.5 | 3.5 |      |

|            | PULL_UP1、PULL_UP2           | 1.6   | 7   | 7   |      |

|            | SR_UVLO                     | 0     | 7   | 7   |      |

| 出力電圧       | RESET1、RESET2、RESET3、RESET4 | 0     | 7   | 7   | V    |

|            | PWRGD、WD0                   | 0     | 7   | 7   |      |

| 出力電流       | RESET1、RESET2、RESET3、RESET4 | -10   | 10  | 10  | mA   |

|            | PWRGD、WD0                   | -10   | 10  | 10  |      |

| 接合部温度      | T <sub>J</sub>              | -55   | 125 | 125 | °C   |

| 入力電圧スルーレート | SR <sub>IN</sub>            | 0.001 | 10  | 10  | V/μs |

(1) すべての電圧値は、GND を基準としたものです。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TPS7H3024-SP | 単位   |

|-----------------------|-------------------|--------------|------|

|                       |                   | HFT (CFP)    |      |

|                       |                   | 22 ピン        |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 34.2         | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 7.7          | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 17.2         | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 16.9         | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 8.6          | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 17           | °C/W |

(1) 従来および最新の熱測定基準

の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準』(SPRA953) を参照してください。

## 6.5 電気的特性

$3V \leq V_{IN} \leq 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{WD\_TMR} = 56.2k\Omega$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ 、動作温度範囲 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )、において、特記がない限り適用されます。また、QML RHA デバイスに対するグループ E の放射線試験  $T_A = 25^{\circ}C$  も含まれます<sup>(1) (2)</sup>

| パラメータ                                                   | テスト条件                               | サブグループ <sup>(3)</sup>                                                           | 最小値             | 標準値   | 最大値   | 単位              |

|---------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|-----------------|-------|-------|-----------------|

| <b>電源電圧および電流</b>                                        |                                     |                                                                                 |                 |       |       |                 |

| $I_{Q\_IN}$                                             | $V_{IN}$ 静止電流                       | $V_{SR\_UVLO} > V_{TH\_SR\_UVLO\_RISING}$ (MAX)                                 | 1, 2, 3         | 1.5   | 2.5   | mA              |

| $I_{SD\_IN}$                                            | $V_{IN}$ シャットダウン電流                  | $V_{SR\_UVLO} = 0V$                                                             | 1, 2, 3         | 1.5   | 2.1   |                 |

| $UVLO_{RISE}$                                           | $V_{IN}$ 立ち上がり低電圧ロックアウト             |                                                                                 | 1, 2, 3         | 2.73  | 2.80  | 2.88            |

| $UVLO_{FALL}$                                           | $V_{IN}$ の立ち下がり定電圧ロックアウト            |                                                                                 | 1, 2, 3         | 2.58  | 2.65  | 2.72            |

| $V_{LDO}$                                               | 内部リニアレギュレータの出力電圧                    | $4V \leq V_{IN} \leq 14V$                                                       | 1, 2, 3         | 3.23  | 3.29  | 3.37            |

|                                                         |                                     | $V_{IN} = 3V$                                                                   | 1, 2, 3         | 98%   | 99%   | $\times V_{IN}$ |

| $VLDO_I_{MAX}$                                          | VLDO 最大電流                           | $3.65V \leq V_{IN} \leq 14V$ , $VLDO = 98.5\% \times VLDO_{(NOM)}$              | 1, 2, 3         |       | 5     | mA              |

| REFCAP                                                  | 内部バンドギャップ電圧                         |                                                                                 | 1, 2, 3         | 1.188 | 1.2   | 1.212           |

| $V_{POR\_IN}$                                           | IN パワーオンリセット電圧 <sup>(4)</sup>       | $1.6V \leq V_{PULL\_UPx} \leq 7V$ , $V_{OL} \leq 320mV$ ( $I_{RESETx} = -1mA$ ) | 1, 2, 3         | 1.42  | 2     |                 |

| $V_{POR\_PULL\_UPx}$                                    | PULL_UPx パワーオンリセット電圧 <sup>(5)</sup> | $V_{IN} = 0V$ , $V_{OL} \leq 320mV$ , $I_{RESETx} = -100\mu A$                  | 1, 2, 3         | 0.85  | 1.1   |                 |

| $V_{HYS}$                                               | HYS ピンの内部電圧                         | $R_{HYS} = 49.9k\Omega$                                                         | 1, 2, 3         | 1.164 | 1.2   | 1.236           |

| <b>SENSE1 から SENSE4, SR_UVLO, WDI、および MODE コンパレータ入力</b> |                                     |                                                                                 |                 |       |       |                 |

| $V_{TH\_SENSEx}$                                        | SENSEx のスレッショルド電圧                   |                                                                                 | 1, 2, 3         | 593.1 | 599.7 | 604.9           |

| $I_{HYS\_SENSEx}$                                       | SENSEx ヒステリシス電流                     | $V_{SENSEx} = 700mV$                                                            | 1, 2, 3         | 23.28 | 24    | 24.72           |

| $I_{LKG\_SENSEx}$                                       | SENSEx での入力リーケ電流                    | $V_{SENSEx} = 500mV$                                                            | 1, 2, 3         | 1     | 100   | nA              |

| $V_{TH\_SR\_UVLO\_RISING}$                              | $SR\_UVLO$ での立ち上がりスレッショルド電圧         |                                                                                 | 1, 2, 3         | 580   | 602   | 618             |

| $V_{TH\_SR\_UVLO\_FALLING}$                             | $SR\_UVLO$ での立ち下がりスレッショルド電圧         |                                                                                 | 1, 2, 3         | 475   | 499   | 517             |

| $I_{LKG\_SR\_UVLO}$                                     | $SR\_UVLO$ での入力リーケ電流                | $V_{SR\_UVLO} = 7V$                                                             | 1, 2, 3         | 2     | 100   | nA              |

| $V_{TH\_WDI\_RISING}$                                   | WDI の立ち上がりスレッショルド電圧                 |                                                                                 | 1, 2, 3         | 578   | 602   | 624             |

| $V_{TH\_WDI\_FALLING}$                                  | WDI の立ち下がりスレッショルド電圧                 |                                                                                 | 1, 2, 3         | 473   | 498   | 521             |

| $I_{LKG\_WDI}$                                          | WDI での入力リーケ電流                       | $V_{WDI} = 7V$                                                                  | 1, 2, 3         | 1.4   | 100   | nA              |

| $V_{TH\_MODE\_RISING}$                                  | MODE の立ち上がりスレッショルド電圧                |                                                                                 | 1, 2, 3<br>7, 8 | 576   | 600   | 623             |

| $V_{TH\_MODE\_FALLING}$                                 | MODE の立ち下がりスレッショルド電圧                |                                                                                 | 1, 2, 3<br>7, 8 | 475   | 498   | 520             |

| $I_{LKG\_MODE}$                                         | MODE での入力リーケ電流                      | $V_{MODE} = 7V$                                                                 | 1, 2, 3         | 1     | 100   | nA              |

## 6.5 電気的特性 (続き)

$3V \leq V_{IN} \leq 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{WD\_TMR} = 56.2k\Omega$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ 、動作温度範囲 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )、において、特記がない限り適用されます。また、QML RHA デバイスに対するグループ E の放射線試験  $T_A = 25^{\circ}C$  も含まれます<sup>(1) (2)</sup>

| パラメータ                                       | テスト条件                             |                                                                                      | サブグループ <sup>(3)</sup>             | 最小値               | 標準値 | 最大値     | 単位              |

|---------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------|-----------------------------------|-------------------|-----|---------|-----------------|

| <b>RESET1 から RESET4、PWRGD、WDO のプッシュプル出力</b> |                                   |                                                                                      |                                   |                   |     |         |                 |

| Pull_UPx_LKG                                | PULL_UP x リーク電流                   | $V_{PULL\_UPx} = 7V$ , $\overline{RESETx} = LOW$                                     | 1, 2, 3                           | 48                | 100 | $\mu A$ |                 |

| $V_{OL\_RESETx}$                            | Low レベル $\overline{RESETx}$ 出力電圧  | $1.6V \leq V_{PULL\_UP1} \leq 7V$                                                    | $I_{LOAD} = -2mA$                 | 1, 2, 3           | 5%  |         | $x$             |

|                                             |                                   |                                                                                      | $I_{LOAD} = -10mA$                | 1, 2, 3           | 23% |         |                 |

| $V_{OH\_RESETx}$                            | High レベル $\overline{RESETx}$ 出力電圧 | $1.6V \leq V_{PULL\_UP1} \leq 7V$                                                    | $I_{LOAD} = 2mA$                  | 1, 2, 3           | 95% |         | $V_{PULL\_UP1}$ |

|                                             |                                   |                                                                                      | $I_{LOAD} = 10mA$                 | 1, 2, 3           | 75% |         |                 |

| $V_{OL\_PWRGD}$                             | Low レベル PWRGD 出力電圧                | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                                    | $I_{LOAD} = -2mA$                 | 1, 2, 3           | 5%  |         | $x$             |

|                                             |                                   |                                                                                      | $I_{LOAD} = -10mA$                | 1, 2, 3           | 23% |         |                 |

| $V_{OH\_PWRGD}$                             | High レベル PWRGD 出力電圧               | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                                    | $I_{LOAD} = 2mA$                  | 1, 2, 3           | 95% |         | $V_{PULL\_UP2}$ |

|                                             |                                   |                                                                                      | $I_{LOAD} = 10mA$                 | 1, 2, 3           | 75% |         |                 |

| $V_{OL\_WDO}$                               | Low レベル $\overline{WDO}$ 出力電圧     | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                                    | $I_{LOAD} = -2mA$                 | 1, 2, 3           | 5%  |         | $x$             |

|                                             |                                   |                                                                                      | $I_{LOAD} = -10mA$                | 1, 2, 3           | 23% |         |                 |

| $V_{OH\_WDO}$                               | High レベル $\overline{WDO}$ 出力電圧    | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                                    | $I_{LOAD} = 2mA$                  | 1, 2, 3           | 95% |         |                 |

|                                             |                                   |                                                                                      | $I_{LOAD} = 10mA$                 | 1, 2, 3           | 75% |         |                 |

| SR <sub>RESETx_RISE</sub>                   | RESETx 立ち上がり出力電圧のスルーレート           | $V_{PULL\_UP1} の 10\% \sim 90\%$ ,<br>$R_{LOAD} = 50k\Omega$ ,<br>$C_{LOAD} = 100pF$ | $1.6V \leq V_{PULL\_UP1} \leq 7V$ | 7, 8<br>9, 10, 11 | 17  | 298     | $V/\mu s$       |

| SR <sub>PWRGD_RISE</sub>                    | PWRGD 立ち上がり出力電圧のスルーレート            |                                                                                      |                                   | 7, 8<br>9, 10, 11 | 17  | 298     |                 |

| SR <sub>WDO_RISE</sub>                      | WDO 立ち上がり出力電圧のスルーレート              |                                                                                      |                                   | 7, 8<br>9, 10, 11 | 17  | 298     |                 |

| SR <sub>RESETx_FALL</sub>                   | RESETx 立ち下がり出力電圧のスルーレート           | $V_{PULL\_UP1} の 90\% \sim 10\%$ ,<br>$R_{LOAD} = 50k\Omega$ ,<br>$C_{LOAD} = 100pF$ | $1.6V \leq V_{PULL\_UP1} \leq 7V$ | 7, 8<br>9, 10, 11 | 44  | 186     |                 |

| SR <sub>PWRGD_FALL</sub>                    | PWRGD 立ち下がり出力電圧のスルーレート            |                                                                                      |                                   | 7, 8<br>9, 10, 11 | 44  | 186     |                 |

| SR <sub>WDO_FALL</sub>                      | WDO 立ち下がり出力電圧のスルーレート              |                                                                                      |                                   | 7, 8<br>9, 10, 11 | 44  | 186     |                 |

| $R_{RESETx\_PULL\_UP}$                      | RESET PMOS ソース出力抵抗                | $I_{LOAD} = 2mA$                                                                     | $1.6V \leq V_{PULL\_UP1} < 3.3V$  | 1, 2, 3           | 20  | 40      | $\Omega$        |

|                                             |                                   |                                                                                      | $3.3V \leq V_{PULL\_UP1} \leq 7V$ | 1, 2, 3           | 9   | 20      |                 |

| $R_{PWRGD\_PULL\_UP}$                       | PWRGD PMOS ソース出力抵抗                | $I_{LOAD} = 2mA$                                                                     | $1.6V \leq V_{PULL\_UP2} < 3.3V$  | 1, 2, 3           | 20  | 40      |                 |

|                                             |                                   |                                                                                      | $3.3V \leq V_{PULL\_UP2} \leq 7V$ | 1, 2, 3           | 9   | 20      |                 |

| $R_{WDO\_PULL\_UP}$                         | WDO PMOS ソース出力抵抗                  | $I_{LOAD} = 2mA$                                                                     | $1.6V \leq V_{PULL\_UP2} < 3.3V$  | 1, 2, 3           | 20  | 40      |                 |

|                                             |                                   |                                                                                      | $3.3V \leq V_{PULL\_UP2} \leq 7V$ | 1, 2, 3           | 9   | 20      |                 |

| $R_{RESETx\_PULL\_DOWN}$                    | RESET NMOS シンク出力抵抗                | $I_{LOAD} = -2mA$ , $1.6V \leq V_{PULL\_UP1} \leq 7V$                                | 1, 2, 3                           |                   | 16  | 36      |                 |

| $R_{PWRGD\_PULL\_DOWN}$                     | PWRGD NMOS シンク出力抵抗                | $I_{LOAD} = -2mA$ , $1.6V \leq V_{PULL\_UP1} \leq 7V$                                | 1, 2, 3                           |                   | 16  | 36      |                 |

| $R_{WDO\_PULL\_DOWN}$                       | WDO NMOS シンク出力抵抗                  | $I_{LOAD} = -2mA$ , $1.6V \leq V_{PULL\_UP1} \leq 7V$                                | 1, 2, 3                           |                   | 16  | 36      |                 |

## 6.5 電気的特性 (続き)

$3V \leq V_{IN} \leq 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{WD\_TMR} = 56.2k\Omega$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ 、動作温度範囲 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )、において、特記がない限り適用されます。また、QML RHA デバイスに対するグループ E の放射線試験  $T_A = 25^{\circ}C$  も含まれます<sup>(1) (2)</sup>

| パラメータ                   | テスト条件           | サブグループ <sup>(3)</sup>        | 最小値     | 標準値  | 最大値  | 単位          |    |

|-------------------------|-----------------|------------------------------|---------|------|------|-------------|----|

| <b>熱保護</b>              |                 |                              |         |      |      |             |    |

| $T_{SD\_ENTER}$         | サーマルシャットダウン入口温度 |                              | 185     |      |      | $^{\circ}C$ |    |

| $T_{SD\_EXIT}$          | サーマルシャットダウン出口温度 |                              |         |      | 171  |             |    |

| <b>遅延機能とウォッチドッグ タイム</b> |                 |                              |         |      |      |             |    |

| $t_{DLY\_TMR}$          | 遅延時間            | $R_{DLY\_TMR} = 10.5k\Omega$ | 1, 2, 3 | 0.22 | 0.26 | 0.33        | ms |

|                         |                 | $R_{DLY\_TMR} = 619k\Omega$  | 1, 2, 3 | 11.3 | 12.5 | 13.7        |    |

|                         |                 | $R_{DLY\_TMR} = 1.18M\Omega$ | 1, 2, 3 | 21.3 | 23.7 | 26.2        |    |

| $t_{WD\_TMR}$           | ウォッチドッグ タイムアウト  | $R_{WD\_TMR} = 56.2k\Omega$  | 1, 2, 3 | 0.43 | 0.52 | 0.57        | s  |

|                         |                 | $R_{WD\_TMR} = 118k\Omega$   | 1, 2, 3 | 0.8  | 1    | 1.2         |    |

|                         |                 | $R_{WD\_TMR} = 174k\Omega$   | 1, 2, 3 | 1.34 | 1.5  | 1.7         |    |

- (1) RHA デバイスの詳細については、5962R24206 SMD (標準マイクロ回路図) を参照。

- (2) すべての電圧値は、GND を基準としたものです。

- (3) サブグループの定義については、「品質適合性検査」表を参照してください。

- (4)  $V_{POR\_IN}$  は、出力が制御された状態を保つために必要な  $V_{IN}$  の最小値で、 $1.6V \leq V_{PULL\_UPx} \leq 7V$  の場合の値です。 $V_{POR\_IN}$  を下回ると、出力状態は決定できません。

- (5)  $V_{POR\_PULL\_UPx}$  は出力が制御された状態を保つために必要な  $V_{PULL\_UPx}$  の最小値で、 $V_{IN} \leq 3V$  の場合の値です。 $V_{POR\_PULL\_UPx}$  を下回ると、出力状態は決定できません。

## 6.6 タイミング要件

$3V \leq V_{IN} \leq 14V$ 、 $R_{DLY\_TMR} = 10k\Omega$ 、 $R_{REG\_TMR} = 10k\Omega$ 、 $V_{PULL\_UP1} = 3.3V$ 、 $V_{PULL\_UP2} = 3.3V$ 、動作温度範囲 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )、において、特記がない限り適用されます。また、RHA デバイスに対するグループ E の放射線試験  $T_A = 25^{\circ}C$  も含まれます

(1)

| パラメータ                  | テスト条件                       | サブグループ <sup>(2)</sup>                                                                | 最小値     | 標準値  | 最大値                  | 単位 |

|------------------------|-----------------------------|--------------------------------------------------------------------------------------|---------|------|----------------------|----|

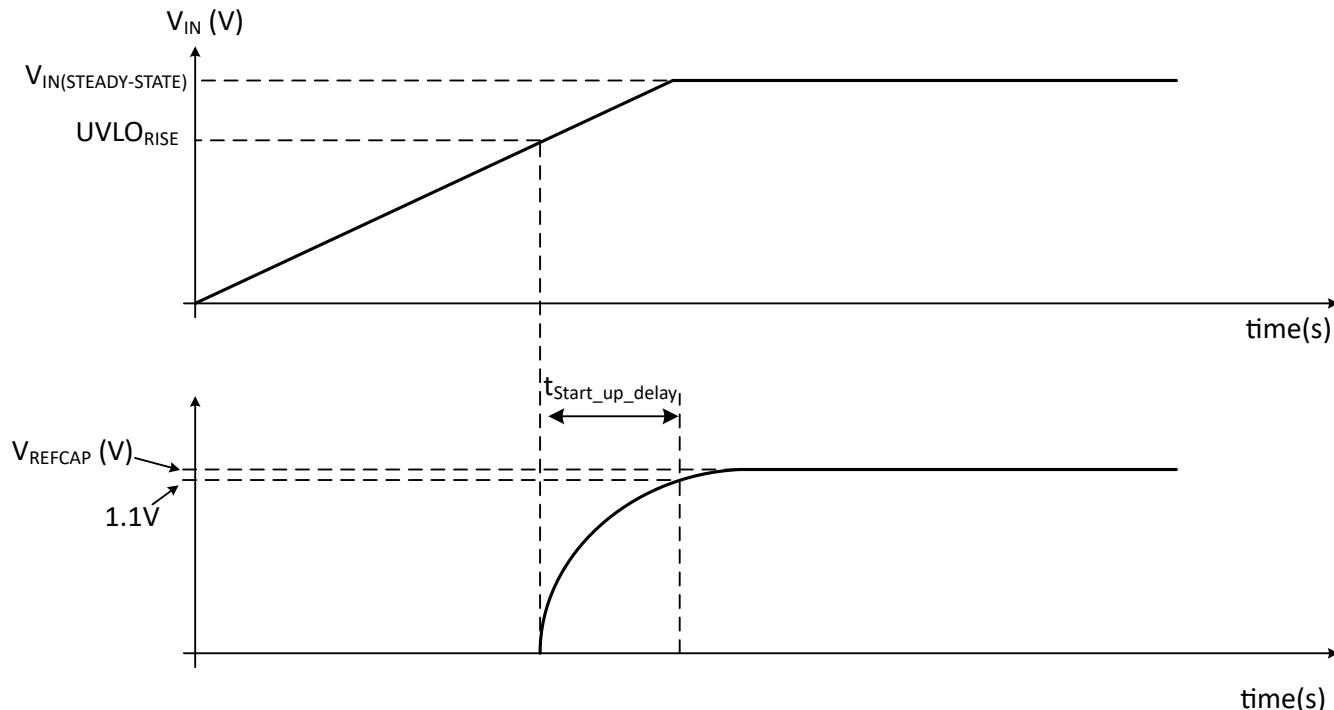

| $t_{START\_UP\_DLY}$   | 起動遅延時間 <sup>(3)</sup>       | $V_{REFCAP} \geq 1.1V$ 、図 7-1                                                        | 1, 2, 3 | 0.3  | 2.8                  | ms |

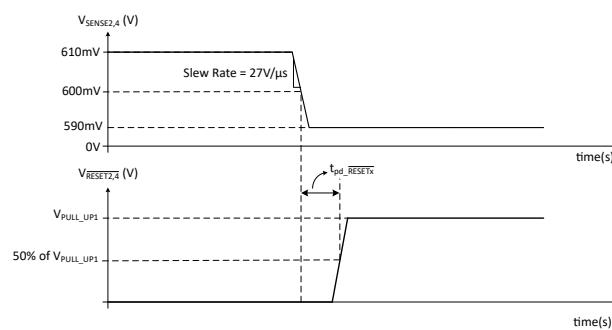

| $t_{pd\_RESETx}$       | RESET 伝搬遅延                  | DLY_TMR = オープン、<br>図 7-2 および 図 7-3 を参照してください                                         | 1, 2, 3 | 0.62 | 4.3                  | μs |

| $t_{pd\_PWRGD}$        | PWRGD 伝搬遅延                  | Dly_TMR = オープン、<br>図 7-4 を参照                                                         | 1, 2, 3 | 0.51 | 4.3                  | μs |

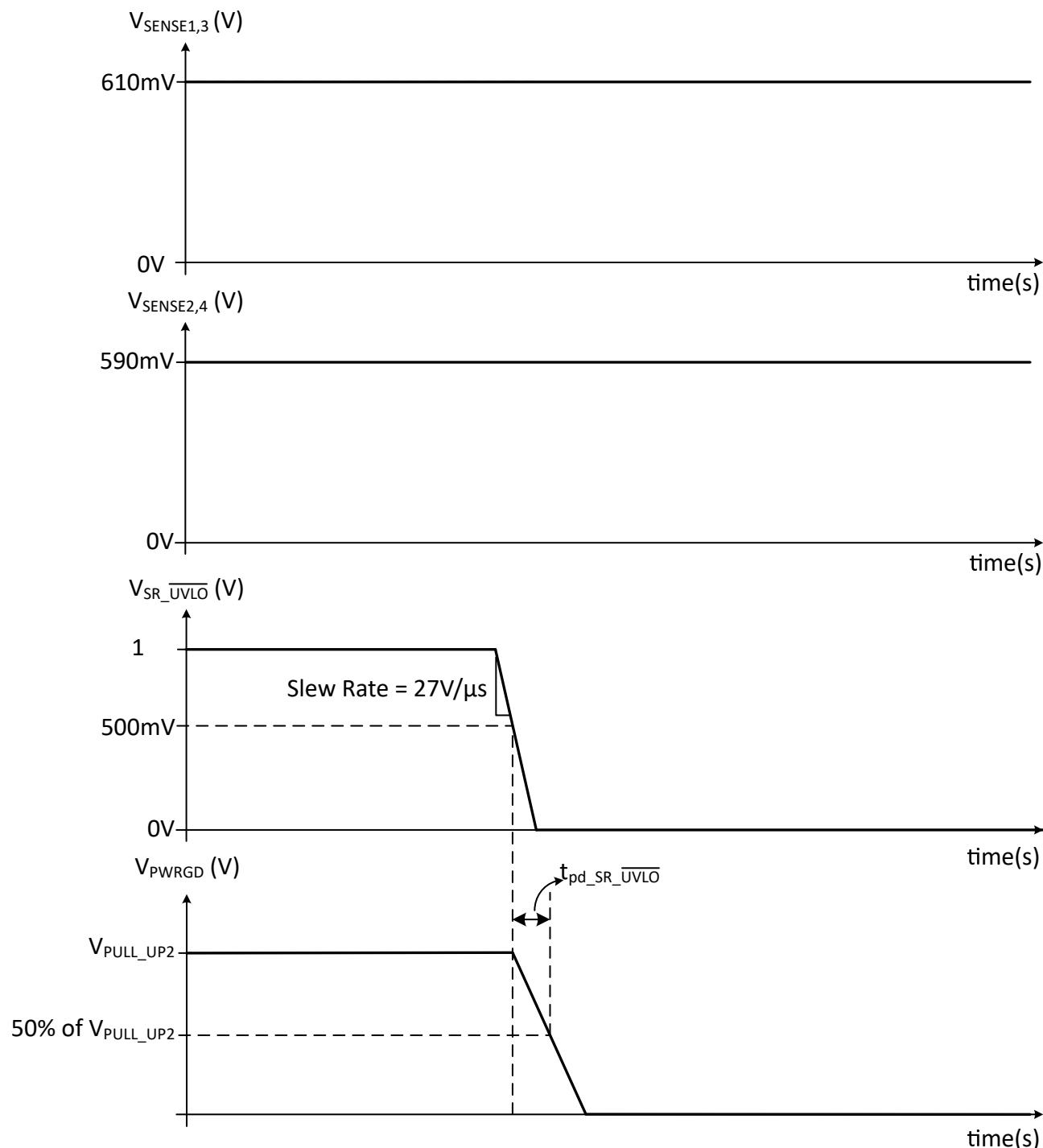

| $t_{pd\_SR\_UVLO}$     | SR_UVLO の伝搬遅延               | 図 7-5 をご覧ください                                                                        | 1, 2, 3 | 0.92 | 2                    | μs |

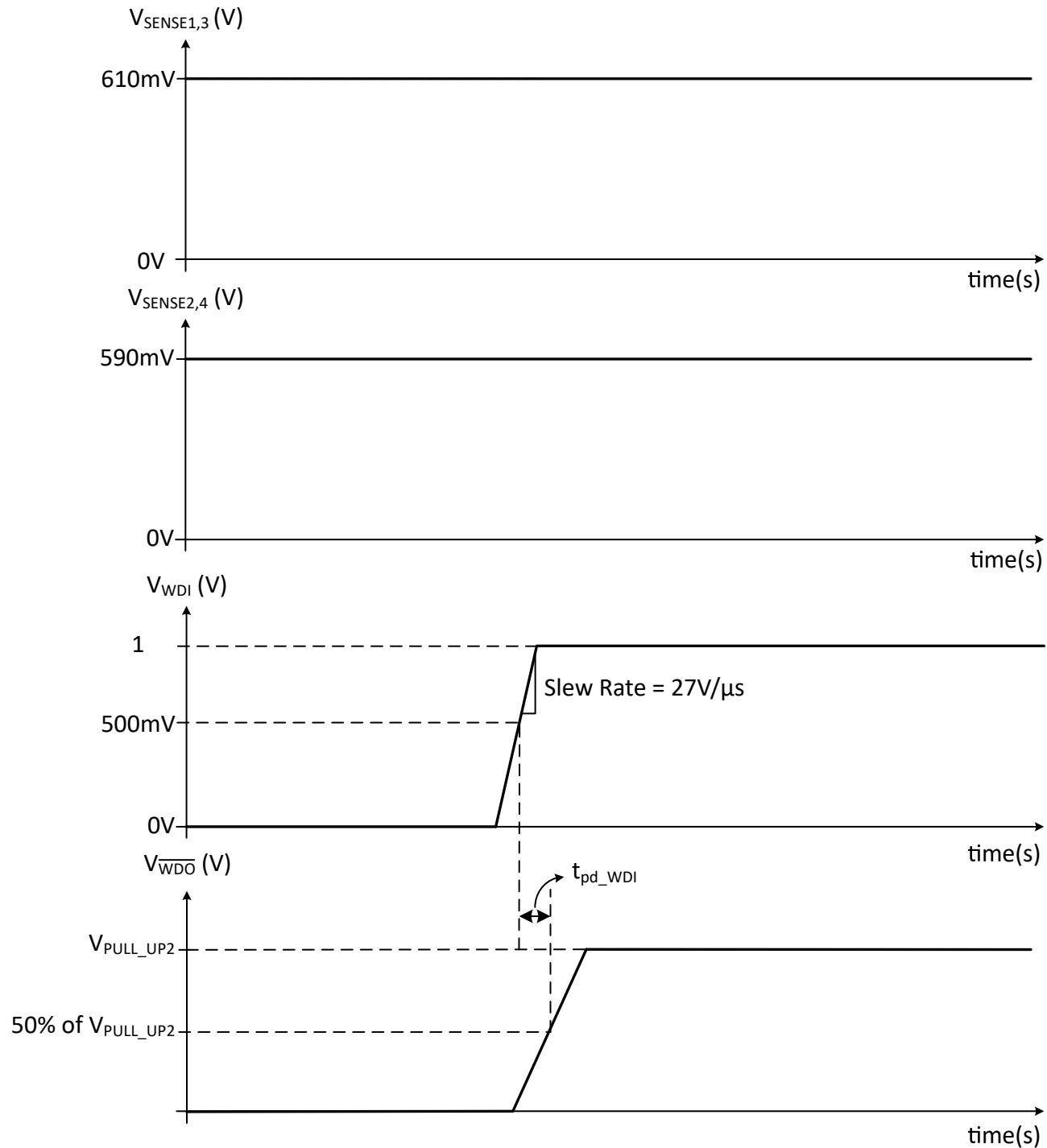

| $t_{pd\_WDI}$          | WDI 伝搬遅延                    | 図 7-6 をご覧ください<br>$t_{WD\_TMR} = 0.52s$<br>$t_{WD\_TMR} = 1s$<br>$t_{WD\_TMR} = 1.5s$ | 1, 2, 3 | 23   | 40                   | μs |

|                        |                             |                                                                                      |         | 47   | 80                   |    |

|                        |                             |                                                                                      |         | 68   | 116                  |    |

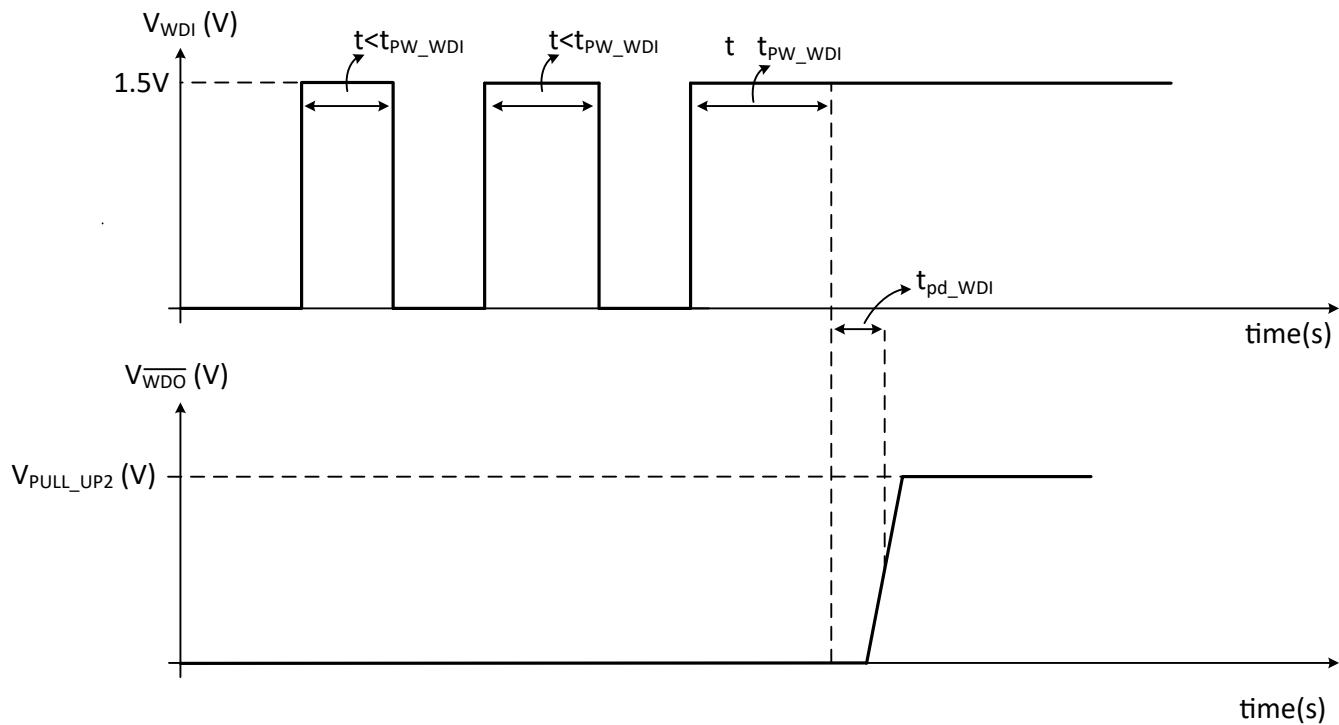

| $t_{PW\_WDI}$          | WDI 最小パルス幅                  | 図 7-7 をご覧ください                                                                        | 4, 5, 6 | 2    | $\times t_{WD\_OSC}$ |    |

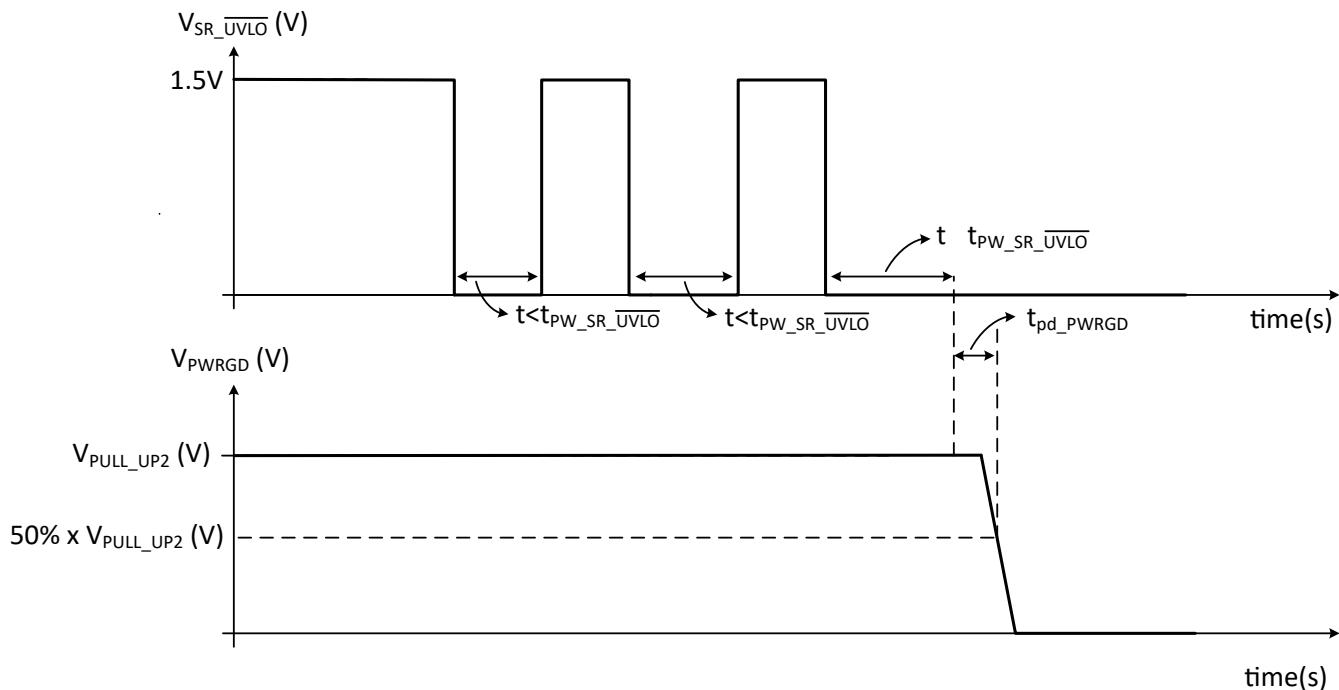

| $t_{PW\_SR\_UVLO}$     | SR_UVLO 有効なリセットの最小パルス幅      | 図 7-8 をご覧ください                                                                        | 4, 5, 6 | 0.61 | 1.1                  | μs |

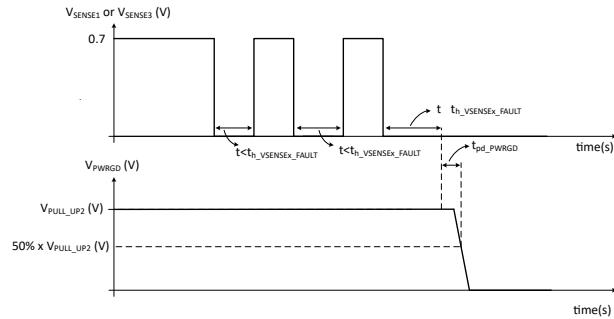

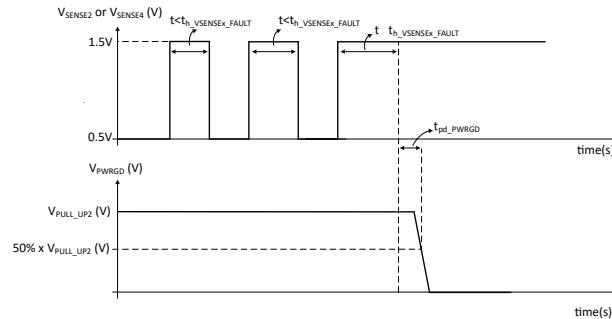

| $t_{h\_VENSEx\_FAULT}$ | 有効な�オルト検出の VSENSEx のホールド時間  | $C_{LOAD} = 100pF$ 、図 7-9 および<br>図 7-10 をご覧ください                                      | 4, 5, 6 | 0.56 | 2.2                  | μs |

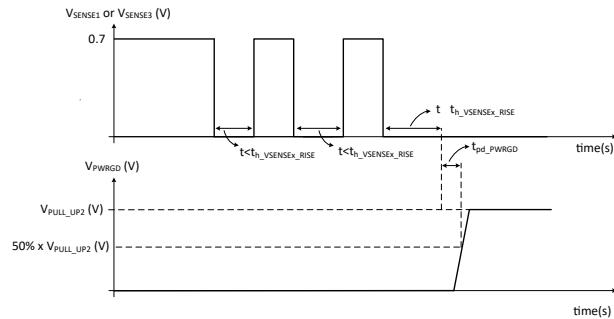

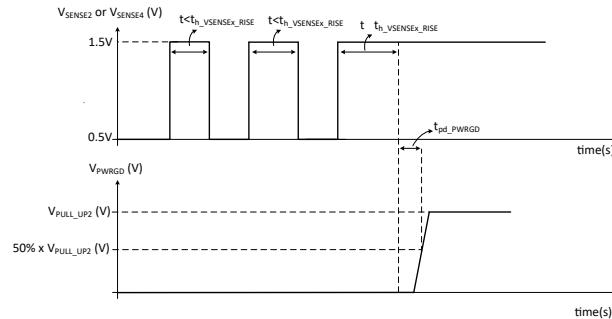

| $t_{h\_VENSEx\_RISE}$  | VSENSEx ホールド時間の立ち上がりスレッショルド | 図 7-11 および 図 7-12 をご覧ください                                                            | 4, 5, 6 |      | 3.7                  | μs |

(1) RHA デバイスの詳細については、5962R24206 SMD (標準マイクロ回路図) を参照してください。

(2) サブグループの定義については、「[品質適合性検査](#)」表を参照してください。

(3) 電源オンのとき、すべての 内部リファレンスが仕様範囲内に収まるように、 $V_{IN}$  は、少なくとも  $t_{Start\_up\_delay}$  の間、 $UVLO_{RISE(MAX)}$  以上でなければなりません。

## 6.7 品質適合検査

MIL-STD-883、方法 5005 - グループ A

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 1      | 静的テスト      | 25      |

| 2      | 静的テスト      | 125     |

| 3      | 静的テスト      | -55     |

| 4      | 動的テスト      | 25      |

| 5      | 動的テスト      | 125     |

| 6      | 動的テスト      | -55     |

| 7      | 機能テスト      | 25      |

| 8A     | 機能テスト      | 125     |

| 8B     | 機能テスト      | -55     |

| 9      | スイッチング テスト | 25      |

| 10     | スイッチング テスト | 125     |

| 11     | スイッチング テスト | -55     |

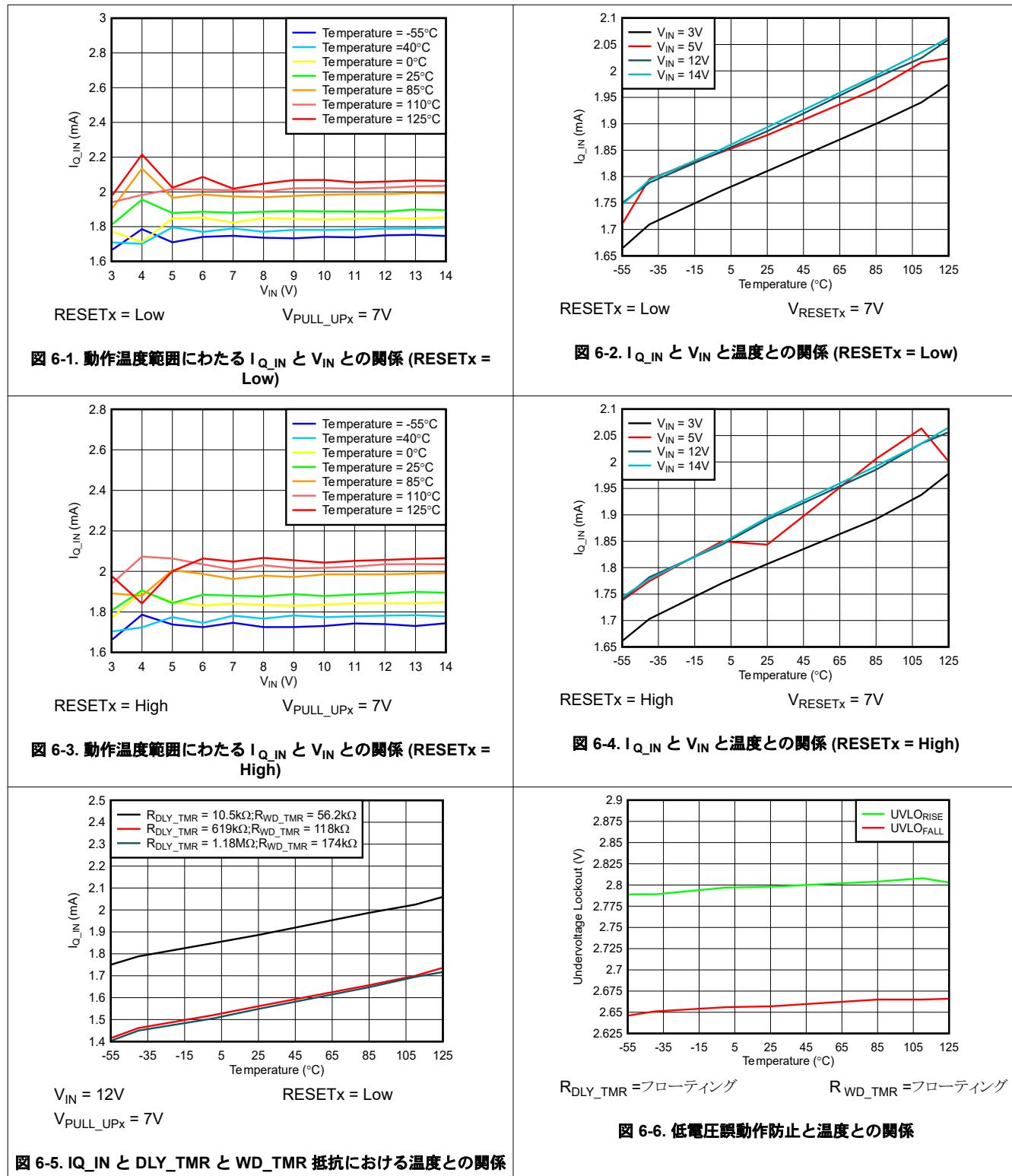

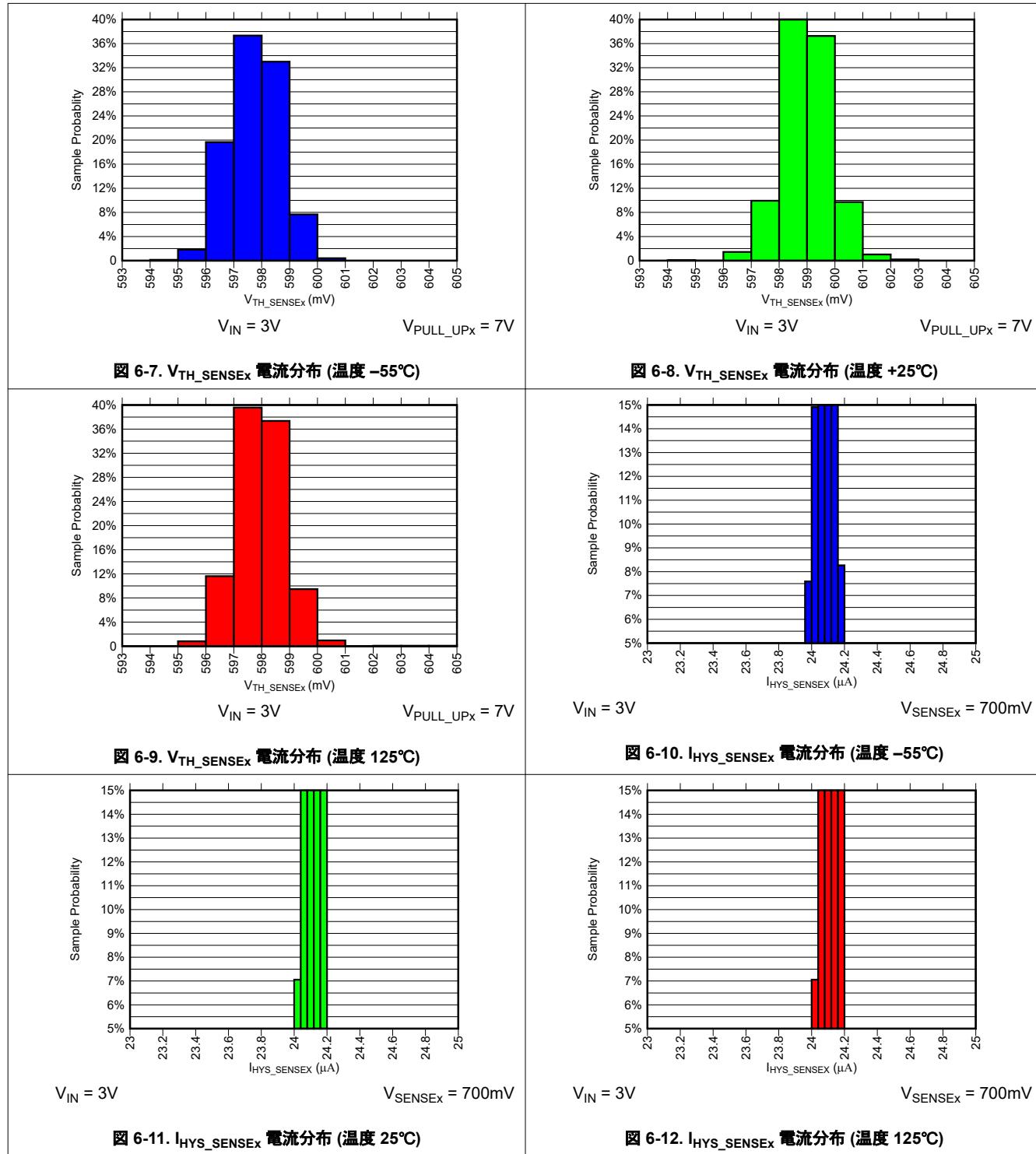

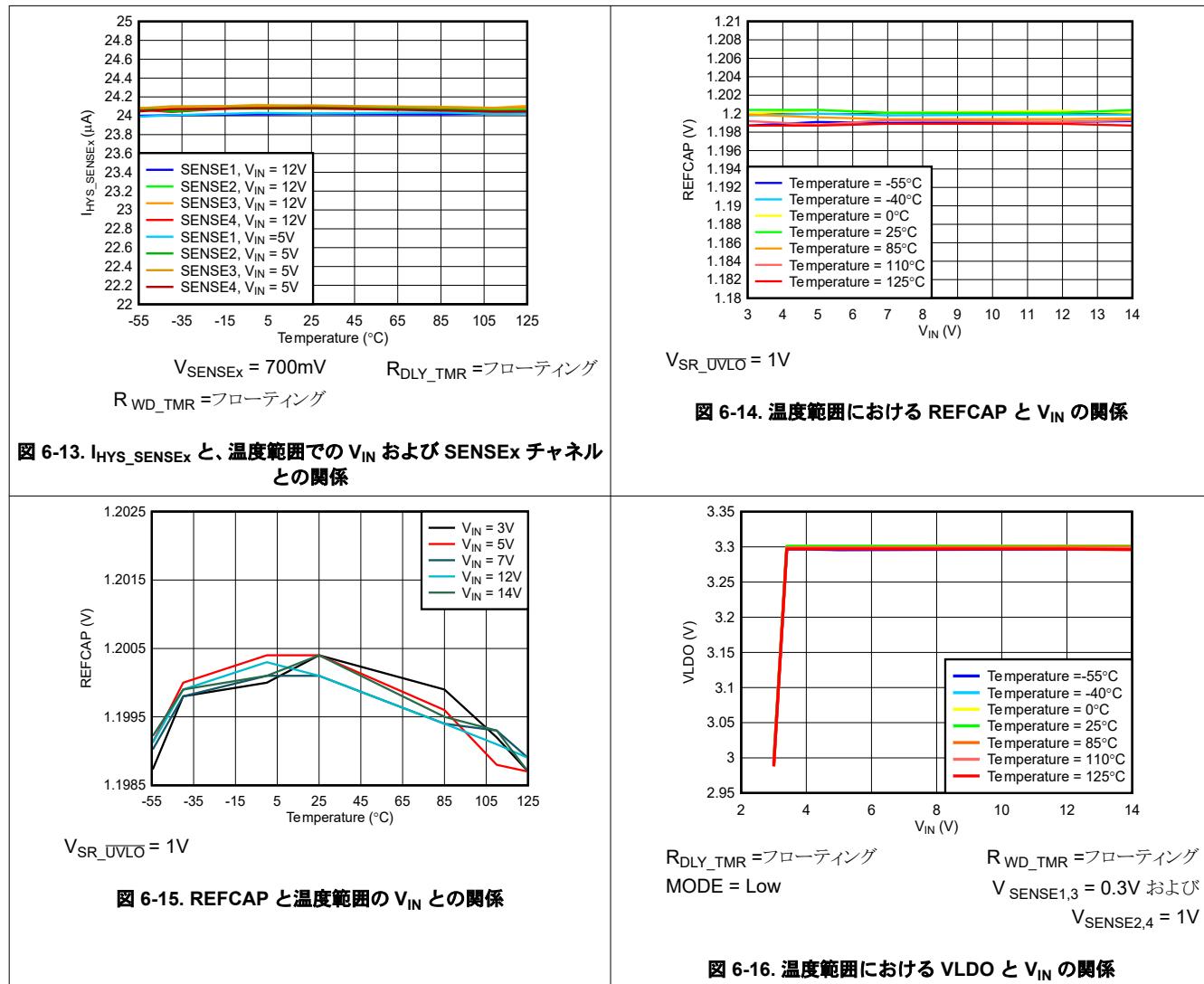

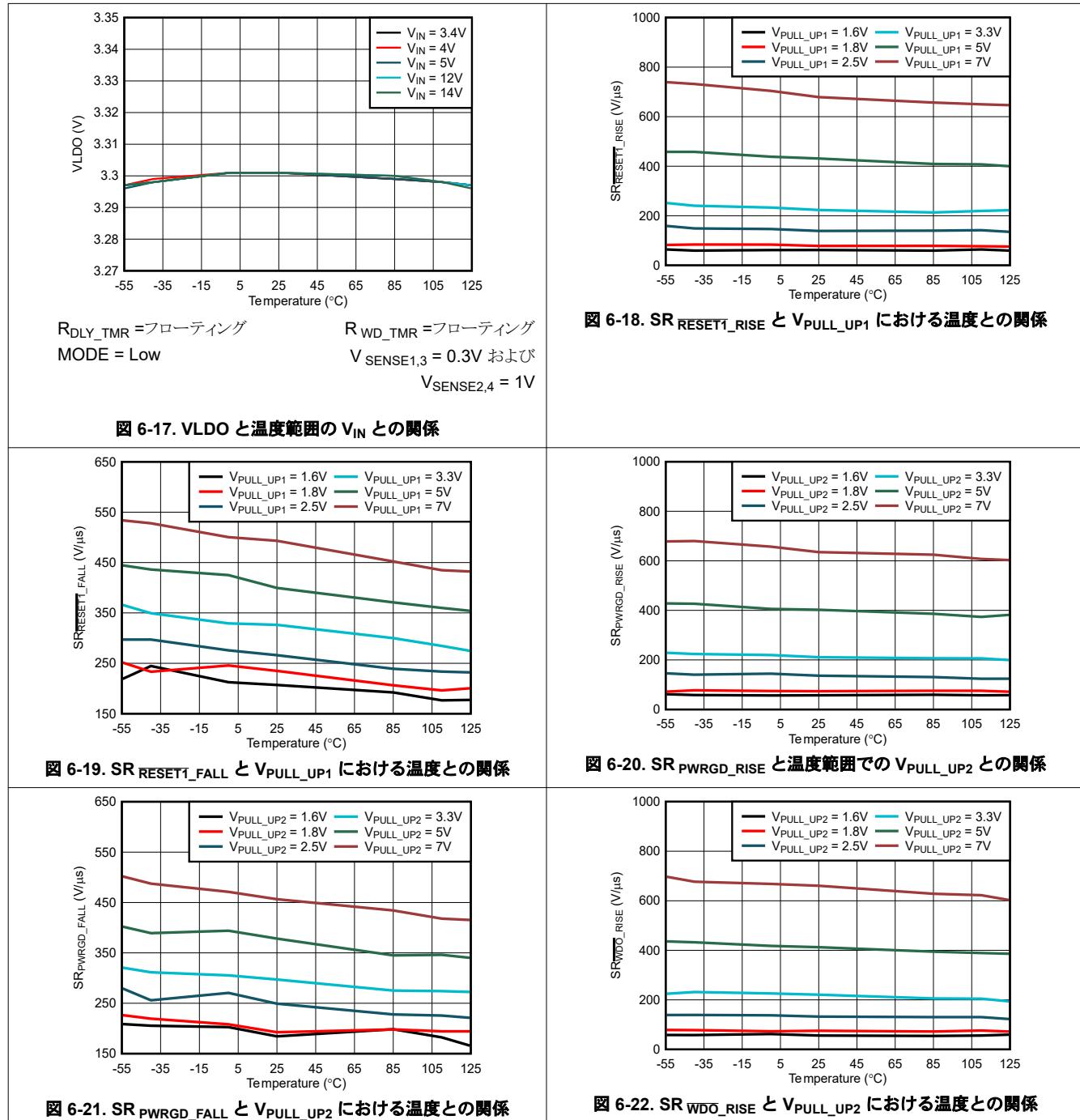

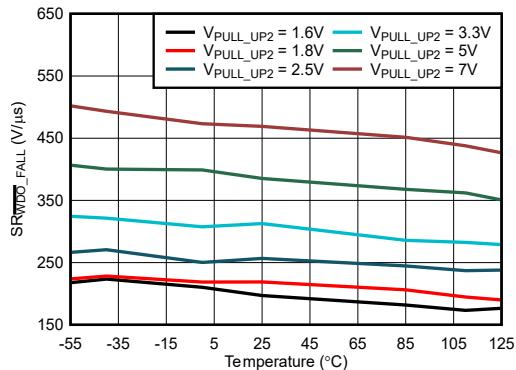

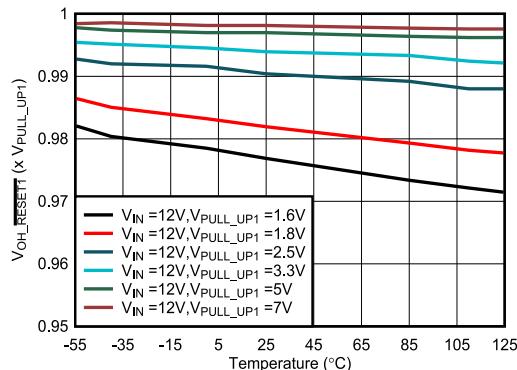

## 6.8 代表的特性

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

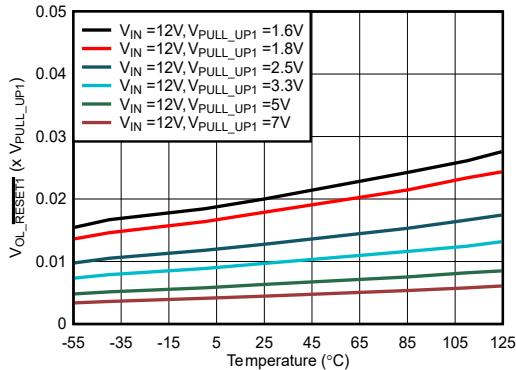

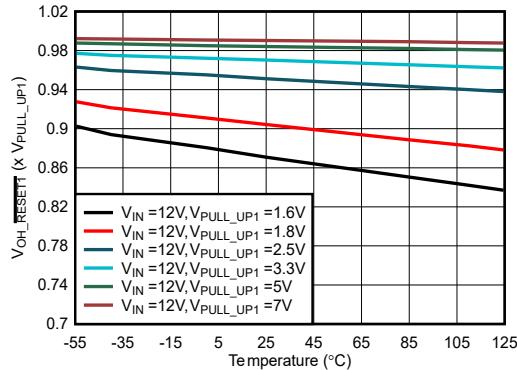

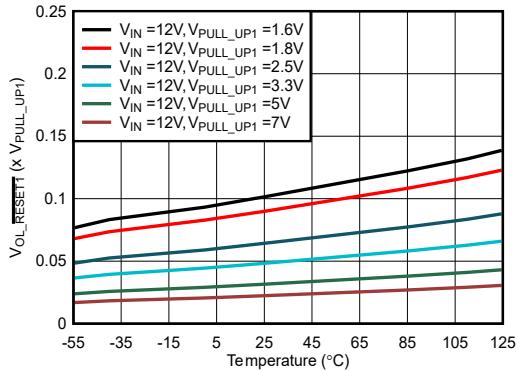

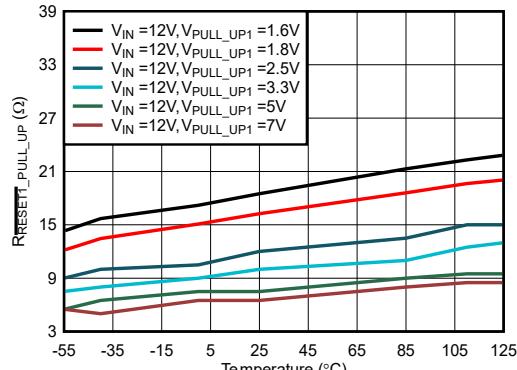

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

図 6-23. SR<sub>WD0\_FALL</sub> と V<sub>PULL\_UP2</sub> における温度との関係

図 6-24. RESET1 VOH 電圧 (V<sub>PULL\_UP1</sub> に対するパーセント) と I<sub>LOAD</sub> = 2mA における V<sub>PULL\_UP1</sub> 全域での温度の関係

図 6-25. RESET1 VOL 電圧 (V<sub>PULL\_UP1</sub> に対するパーセント) と I<sub>LOAD</sub> = 2mA における V<sub>PULL\_UP1</sub> 全域での温度の関係

図 6-26. RESET1 VOH 電圧 (V<sub>PULL\_UP1</sub> に対するパーセント) と I<sub>LOAD</sub> = 10mA における V<sub>PULL\_UP1</sub> 全域での温度の関係

図 6-27. RESET1 VOL 電圧 (V<sub>PULL\_UP1</sub> に対するパーセント) と I<sub>LOAD</sub> = 10mA における V<sub>PULL\_UP1</sub> 全域での温度の関係

図 6-28. RESET1 プルアップ抵抗と I<sub>LOAD</sub> = 2mA における V<sub>PULL\_UP1</sub> 全域での温度

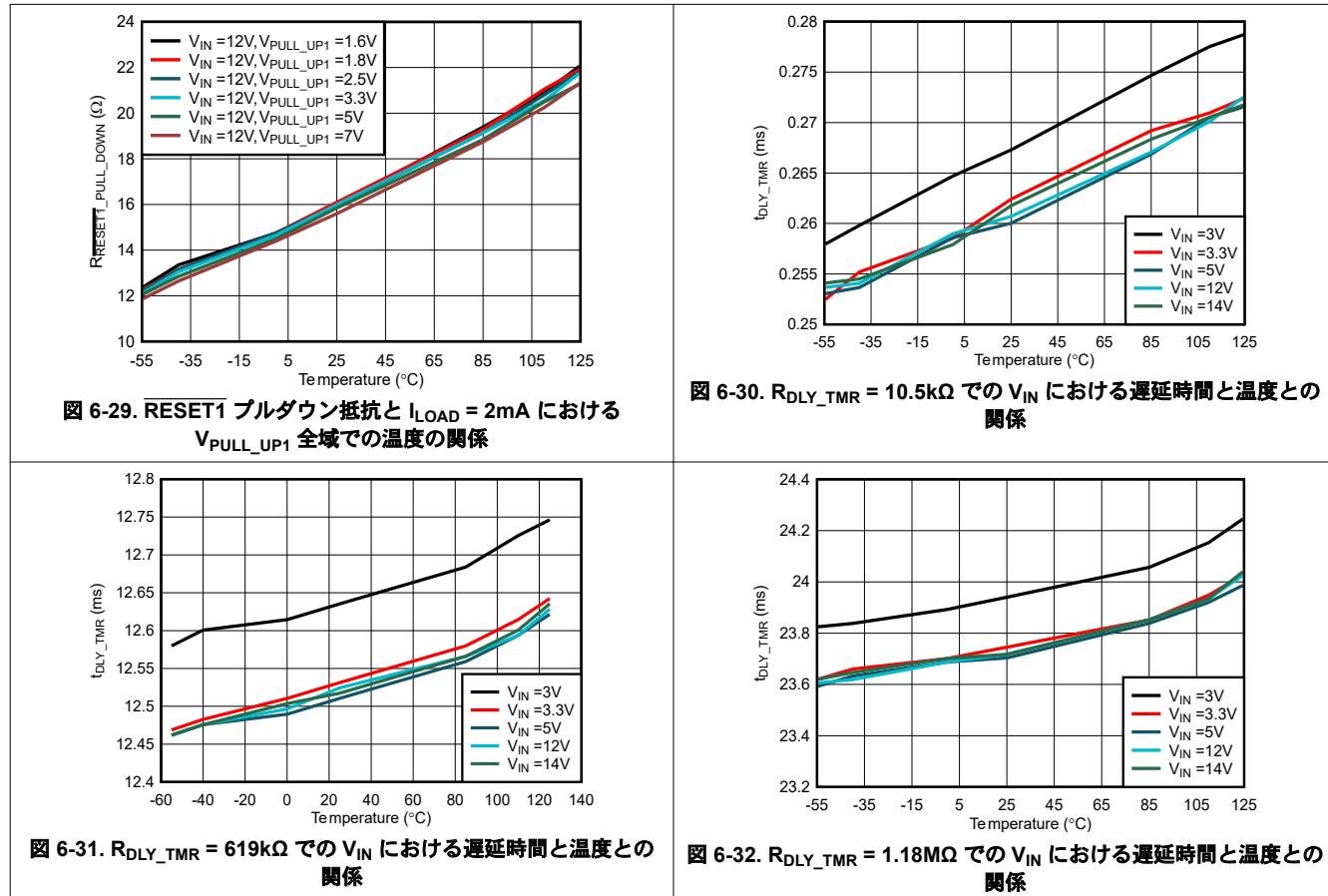

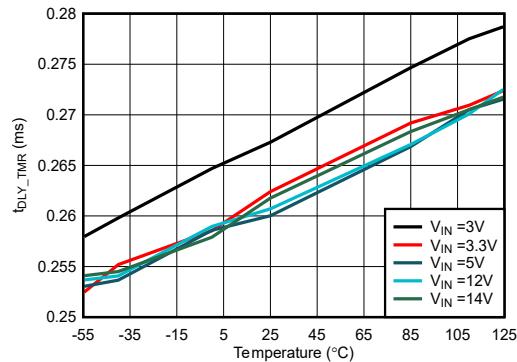

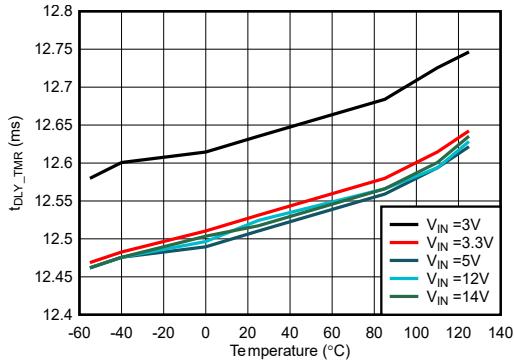

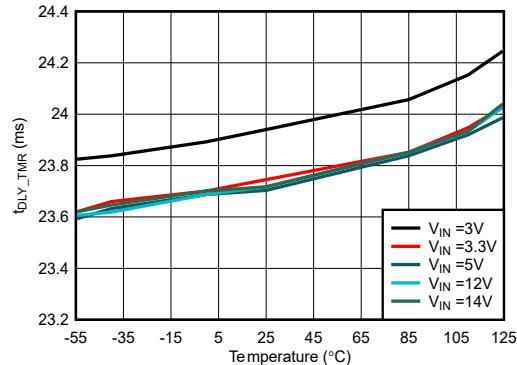

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{WD\_TMR} = 56.2\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $R_{HYS} = 49.9\text{k}\Omega$ 、MODE = ロジック Low (特に記述のない限り)。

図 6-29. RESET1 プルダウン抵抗と  $I_{LOAD} = 2\text{mA}$  における  $V_{PULL\_UP1}$  全域での温度の関係

図 6-30.  $R_{DLY\_TMR} = 10.5\text{k}\Omega$  での  $V_{IN}$  における遅延時間と温度との関係

図 6-31.  $R_{DLY\_TMR} = 619\text{k}\Omega$  での  $V_{IN}$  における遅延時間と温度との関係

図 6-32.  $R_{DLY\_TMR} = 1.18\text{M}\Omega$  での  $V_{IN}$  における遅延時間と温度との関係

## 7 パラメータ測定情報

MODE=0 の場合、特に指定がない限り、PWRGD 電圧を基準とするすべての測定において、SENSE<sub>x</sub> 電圧は非フォルト状態に強制されました。

A.  $V_{IN(STEADY-STATE)}$  の有効な動作電圧は 3V ~ 14V です

図 7-1.  $t_{Start\_up\_delay}$  時間測定

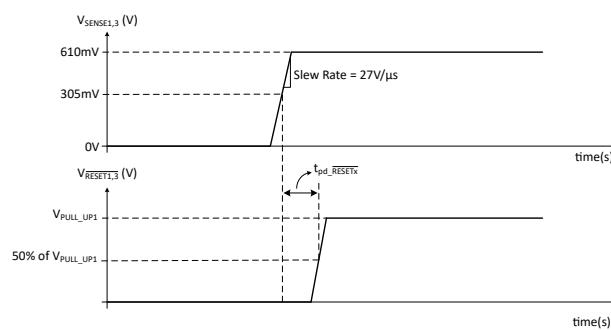

図 7-2. RESET1 および RESET3 の伝搬遅延

( $t_{pd\_RESETx}$ ) 時間測定

A.  $t_{pd\_RESETx}$  の場合、各 SENSE<sub>x</sub> の伝搬遅延は個別に測定されます。

図 7-3. RESET2 および RESET4 の伝搬遅延

( $t_{pd\_RESETx}$ ) 時間測定

図 7-4. PWRGD 伝搬遅延 ( $t_{pd\_PWRGD}$ )

図 7-5. SR\_UVLO 伝搬遅延 ( $t_{pd\_SR\_UVLO}$ )

A. MODE=0

図 7-6. WDI 伝搬遅延 ( $t_{pd\_WDI}$ )

A.  $V_{SENSE1,3} = 1.5V$ ,  $V_{SENSE2,4} = 0V$

図 7-7. WDI パルス幅 ( $t_{PW\_WDI}$ )

図 7-8. SR\_UVLO パルス幅 ( $t_{PW\_SR\_UVLO}$ )

A.  $t_{h\_VSENSEx\_FAULT}$  の間、各 SENSE $x$  は別々に測定されます。

**図 7-9. 有効なフォルト検出のための VSENSE1 および VSENSE3 ホールド時間 ( $t_{h\_VSENSEx\_FAULT}$ )**

A.  $t_{h\_VSENSEx\_FAULT}$  の間、各 SENSE $x$  は別々に測定されます。

**図 7-10. 有効なフォルト検出のための VSENSE2 および VSENSE4 ホールド時間 ( $t_{h\_VSENSEx\_FAULT}$ )**

A.  $t_{h\_VSENSEx\_FAULT}$  の間、各 SENSE $x$  は別々に測定されます。

**図 7-11. VSENSE1 および VSENSE3 立ち上がりリストショルド ホールド時間 ( $t_{h\_VSENSEx\_RISE}$ )**

A.  $t_{h\_VSENSEx\_FAULT}$  の間、各 SENSE $x$  は別々に測定されます。

**図 7-12. VSENSE2 および VSENSE4 立ち上がりリストショルド ホールド時間 ( $t_{h\_VSENSEx\_RISE}$ )**

## 8 詳細説明

### 8.1 概要

TPS7H3024 は、宇宙用途向けのウォッチドッグ タイマ機能を統合した、4 チャネル、3V～14V 対応の電圧監視回路です。アクティブ Low の **RESETx** 出力は、ディセーブル Low 入力付きのデバイス監視を容易にサポートします。このデバイスは、指定された構成において、従属レールの数を監視するように設定できます：

1. 2 つの低電圧 (UV) + 2 つの過電圧 (OV)。

2. 2 つのウインドウ。

この動作は、**MODE** ピンの論理値によって制御されます。詳細については、[表 8-1](#) を参照してください。

**表 8-1. TPS7H3024 の機能モード**

| 機能          | モード <sup>(1)</sup> |

|-------------|--------------------|

| 2 UV + 2 OV | 0 <sup>(2)</sup>   |

| 2 つのウインドウ   | 1 <sup>(3)</sup>   |

(1) モードは静的な入力であり、ユーザーは論理値を動的に変更しません。デバイスが起動したら、値はほとんど変化しません。

(2)  $0 = V_{\text{MODE}} < V_{\text{TH\_MODE\_FALLING (MIN)}}$

(3)  $1 = V_{\text{MODE}} > V_{\text{TH\_MODE\_RISING (MAX)}}$

**RESETx**、**PWRGD**、**WDO** のロジック High は、**PULL\_UPx** 入力電源を介して外部制御されます。ユーザは、少なくとも 1 つの  $1\mu\text{F}$  コンデンサを **PULL\_UPx** ピンのできるだけ近くに接続する必要があります。すべての **RESETx** 出力の論理 High レベルは **PULL\_UP1** 入力によって設定され、**PWRGD** と **WDO** のロジック High レベルは **PULL\_UP2** によって設定されます。**PULL\_UPx** の電圧範囲は 1.6V ~ 7V です。

**SENSEx** 入力はコンパレータの非反転入力に接続されており、これによって監視対象の電圧が次のように分類されます。

1. レギュレーション中。

2. レギュレーション範囲外。

低電圧および過電圧コンパレータの動作の詳細については、[セクション 8.3.3.3](#) を参照してください。これらの各入力はスレッショルド レベル 599.7mV(標準値)を備え、電圧、温度、放射線 (TID) 全体で  $\pm 1\%$  の精度を達成しています。ヒステリシス電圧スレッショルド レベルはユーザーが調整でき、 $R_{\text{TOPx}}$  抵抗とヒステリシス電流 ( $I_{\text{HYS\_SENSEx}}$ ) により決定されます。**SENSEx** の立ち上がり電圧が  $V_{\text{TH\_SENSEx}}$  スレッショルド (標準 599.7mV) を超えると、 $I_{\text{HYS\_SENSEx}}$  がアクティブになります。 $I_{\text{HYS}}$  は  $24\mu\text{A}$  で、電圧、温度、放射線 (TID) の全範囲で  $\pm 3\%$  の精度を維持します。さらに、このデバイスは **PWRGD** と呼ばれる出力を備えており、電源ツリー (システム全体) の状態を監視するために使用されます。

#### 注

過電圧コンパレータの場合、**RESETx** 出力は入力コンパレータの出力で論理的に反転されます。[図 8-13](#) を参照してください。

電圧監視機能に加えて、TPS7H3024 は立ち上がりエッジ検出型のウォッチドッグ タイマーを内蔵しています。ウォッチドッグ入力 (**WDI**) は、立上りエッジの電圧変化を検出します。ウォッチドッグ タイマ ロジックが **WDI** ピンで立ち上がり電圧を検出すると、ウォッチドッグ タイマがすでにアクティブな場合はタイマがクリアされ、最初に検出されたパルスである場合はカウントを開始します。**WDI** ピンで立ち上がりパルスが検出されると、システムはプログラムされたタイムアウト(標準で  $0.5\text{ms} \sim 1.5\text{ms}$ )までに再びタイマをクリアする必要があります。タイムアウト前にタイマがクリアされると、ウォッチドッグ出力 (**WDO**) は High に維持され、それ以外の場合は **WDO** は Low にアサートされます。通常、ウォッチドッグ タイマは、コヒーレントなプロセッサの実行を監視するために使用されます。通常、プロセッサは出力チャネルを使用して **WDI** に立ち上がりエッジ電圧を誘導し、**WDO** はノンマスカブル割り込みに接続されます。プロセッサがスタックした場合、**WDI** ピンはトグルしません。その結果、**WDO** が Low になり、プロセッサが既知の状態にリセットされます。

このデバイスには、2 つのプログラム可能なタイマが組み込まれています。

1. **Dly\_TMR:** フォルト終了遅延を設定します。監視対象の電圧変化状態が、レギュレーション範囲ではない状態からレギュレートされている状態になると、ユーザーによってプログラムされた遅延 (**DLY\_TMR** を使用) が終了すると、**RESETx** が High にアサートされます。このタイマは、 $10.5\text{k}\Omega$  を使用して  $1.18\text{M}\Omega$  抵抗に、それぞれ  $0.25\text{ms}$ ~ $25\text{ms}$  にプログラムできます。この遅延は、入力（「監視対象の電圧」）が「規定範囲内」から「規定範囲外」に変化する場合には適用されません。これは、異常ができるだけ早く伝達するためです。

2. **WD\_TMR:** ウオッチドッグタイマのタイムアウトを設定します。ウォッチドッグ入力が入力 (**WDI**) の立ち上がり電圧を検出すると、監視対象プロセスは、出力 (**WDO**) を High に維持するためにプログラムされたタイムアウトまでに別の立ち上がり電圧を供給する必要があり、そうでない場合は出力が Low になります。

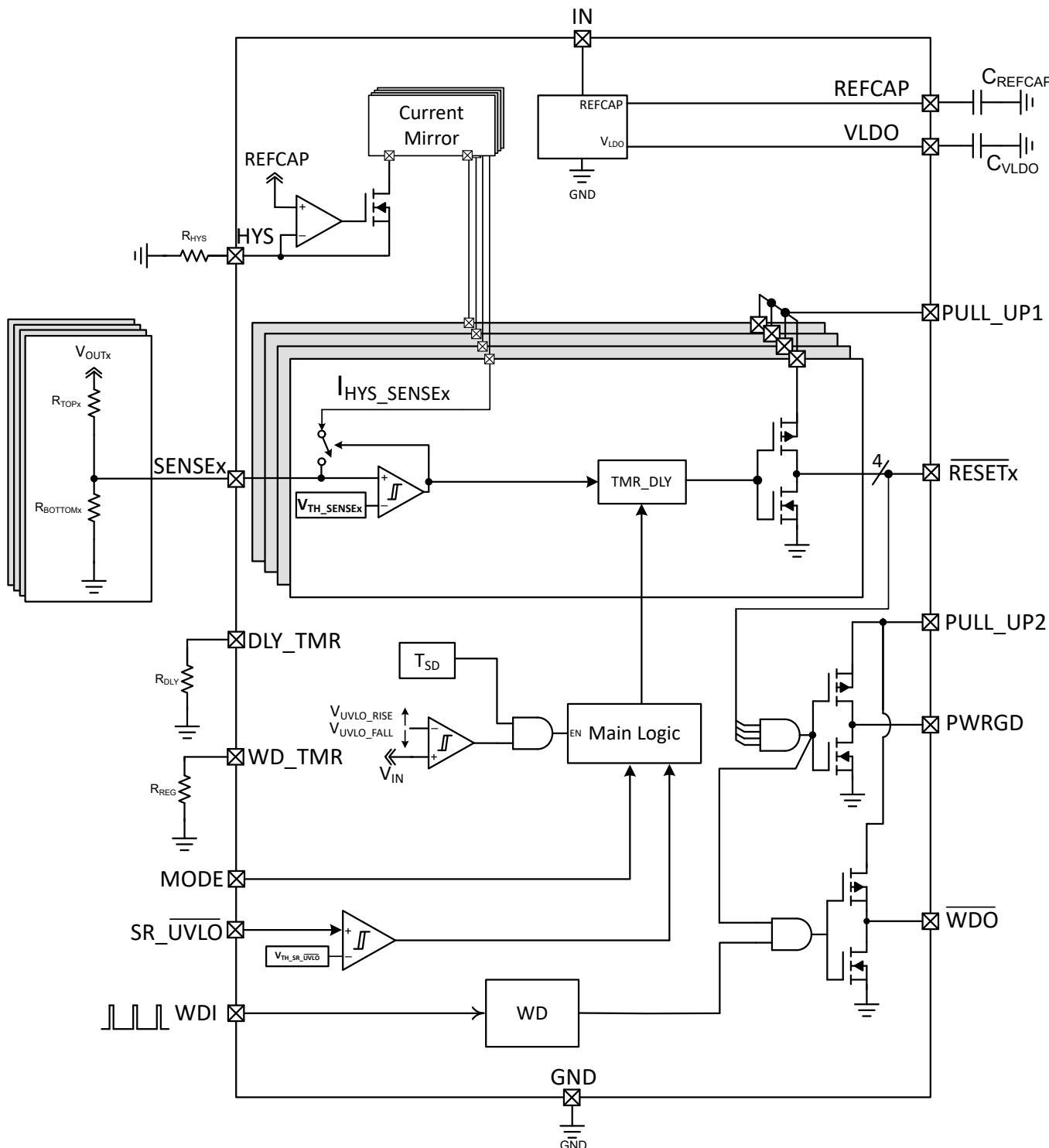

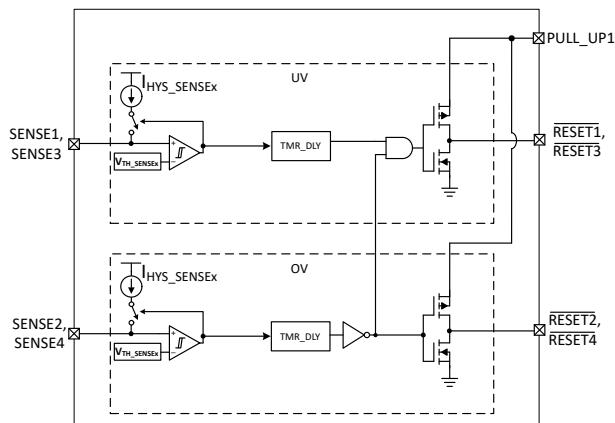

## 8.2 機能ブロック図

- A. 過電圧イベントを検出するために、RESET2 および RESET4 出力段は入力コンパレータの出力から論理的に反転されます。詳細については、[図 8-13](#) を参照してください。

- B. MODE = 1 の場合、RESET1 と RESET3 はウインドウ タイプになります。詳細については、[図 8-9](#) を参照してください。RESET2 および RESET4 は過電圧コンパレータ フラグです。

## 8.3 機能説明

### 8.3.1 入力電圧 (IN) VLDO およびREFCAP

定常状態動作中は、TPS7H3024 の入力電圧は 3V ~ 14V の間にする必要があります。 $V_{IN}$  と GND の間には、少なくとも  $0.1\mu F$  のバイパス キャパシタンスが必要です。入力バイパスコンデンサは、デバイスにできるだけ近くに配置します。IC が正しく動作するように、 $V_{IN}$  のスルーレートを  $10 V/\mu s$  から  $1 mV/\mu s$  の範囲に制御します。

$V_{IN}$  に印加される電圧は、内部レギュレータの入力として機能し、このレギュレータによって通常  $3.29V$  の VLDO 電圧が生成されます。入力電圧が  $3.65V$  未満の場合、VLDO レギュレータはドロップアウト状態になることがあります。VLDO の推奨容量は、 $1\mu F$  セラミックタイプです。VLDO は最大  $5mA$  の負荷に対応できます。

---

#### 注

VLDO 出力は短絡の条件に対して保護されていません。

---

電源投入時には、 $V_{IN}$  が  $UVLO_{RISE}$  を超えた後、少なくとも  $2.8ms$  ( $t_{Start\_up\_delay}$ ) 待機することが推奨されます。これは、すべての内部時定数を超えるようにして、基準が  $\pm 1\%$  の精度から外れないようにするためです。

各デバイスは、さまざまな制御ロジック ブロックで利用される  $1.2V$  の内部バンドギャップ リファレンスを生成します。これは、定常状態動作時に REFCAP ピンに印加される電圧です。この電圧は分圧され、次のコンパレータ入力用のリファレンス電圧として使用されます：

- SENSEx =  $599.7mV$  (標準値)

- 立ち上がり電圧時は  $SR\_UVLO = 602mV$  (標準値)、立ち下がり電圧時は  $489mV$ 。

- 立ち上がり電圧時には  $WDI = 602mV$  (標準値)、立ち下がり電圧時には  $498mV$ 。

- 立ち上がり電圧時には  $MODE = 600mV$  (標準値)、立ち下がり電圧時には  $498mV$ 。

$V_{TH\_SENSEx}$  基準電圧は、エラー アンプのオフセットを考慮して、 $\overline{RESETx}$  出力で測定され、電圧、温度、放射線の TID (シリコンの最大  $100krad$ ) 全体で  $1\%$  以内のレギュレーションを維持します。この厳格な基準電圧公差により、ユーザーは電圧レールを高精度で監視できます。

適切な電気的動作のために、またデバイスの堅牢な SET 性能を確保するために、REFCAP ピンで GND との間に  $470nF$  のコンデンサが必要です。

#### 8.3.1.1 低電圧ロックアウト ( $V_{POR\_IN} < V_{IN} < UVLO$ )

$V_{IN}$  の電圧が  $UVLO$  ( $2.79V$  標準値) 電圧未満で、パワーオンリセット電圧 ( $V_{POR\_IN}$ ,  $1.42V$ (標準値)) より高い場合、出力ピン ( $\overline{RESETx}$ ,  $PWRGD$ ,  $\overline{WDO}$ ) は、以下のデバイス入力ピンの電圧に関係なくロジック Low 状態になります：

- SENSEx

- $SR\_UVLO$

- WDI

- モード

#### 8.3.1.2 パワーオンリセット ( $V_{IN} < V_{POR\_IN}$ )

$V_{IN}$  の電圧がパワーオンリセット電圧 ( $V_{POR\_IN}$ ) より低い場合、出力信号は未定義となり、外部デバイスを正しいロジックレベルに設定するために依存してはいけません。

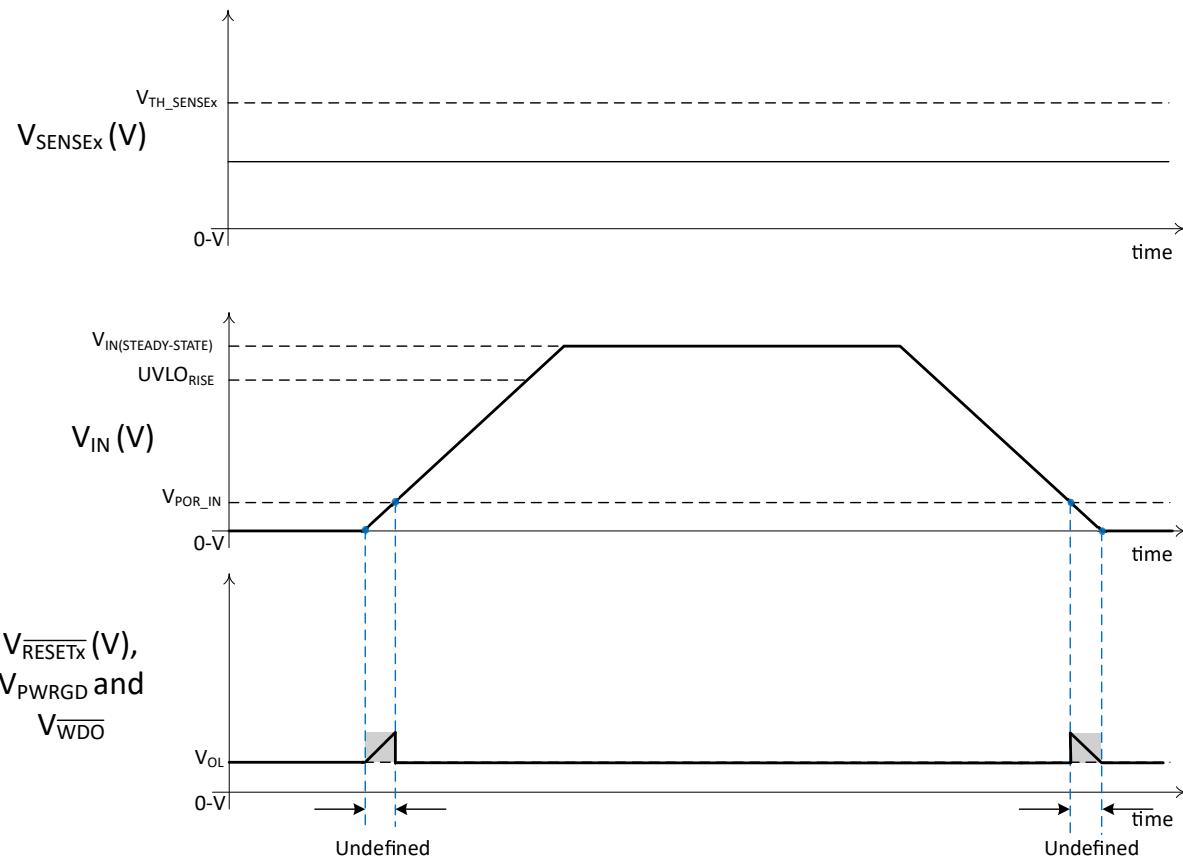

図 8-1 に、 $\overline{RESETx}$  出力と立ち上がり入力電圧 ( $V_{IN}$ ) との関係を示します。ご覧のように、 $V_{IN}$  が  $V_{POR\_IN}$  (標準値  $1.42V$ ) を下回ると、 $\overline{RESETx}$  は以下のようになります。このとき、出力は  $0V$  から  $V_{IN}$  まで任意の値になり得ます。

この例では、すべての入力コンパレータ (SENSEx) への入力電圧は  $V_{TH\_SENSEx}$  (標準値  $599.7mV$ ) を下回っています。このため、 $V_{IN}$  が  $UVLO_{RISE}$  ( $2.79V$ ) を上回った後も、 $\overline{RESETx}$ ,  $PWRGD$ ,  $\overline{WDO}$  は Low のままであります。

図 8-1.  $V_{IN} > V_{POR\_IN}$  の後、有効な Low 状態になる出力

A. この図では以下のようになります。

1. 有効な外部プルアップ電圧は、PULL\_UPx 入力 ( $1.6V \leq V_{PULL\_UPx} \leq 7V$ ) に接続されている。

2.  $V_{IN(STEADY-STATE)}$  の有効な  $V_{IN}$  電圧は、 $3V \sim 14V$  である。

3. このグラフでは、すべての入力が低電圧 (UV) タイプであると仮定します。

4.  $V_{OL}$  は以下を表す: $V_{OL\_RESETx}$ 、 $V_{OL\_PWRGD}$ 、 $V_{OL\_WDO}$ 、またはすべての出力の Low ロジック出力電圧です。

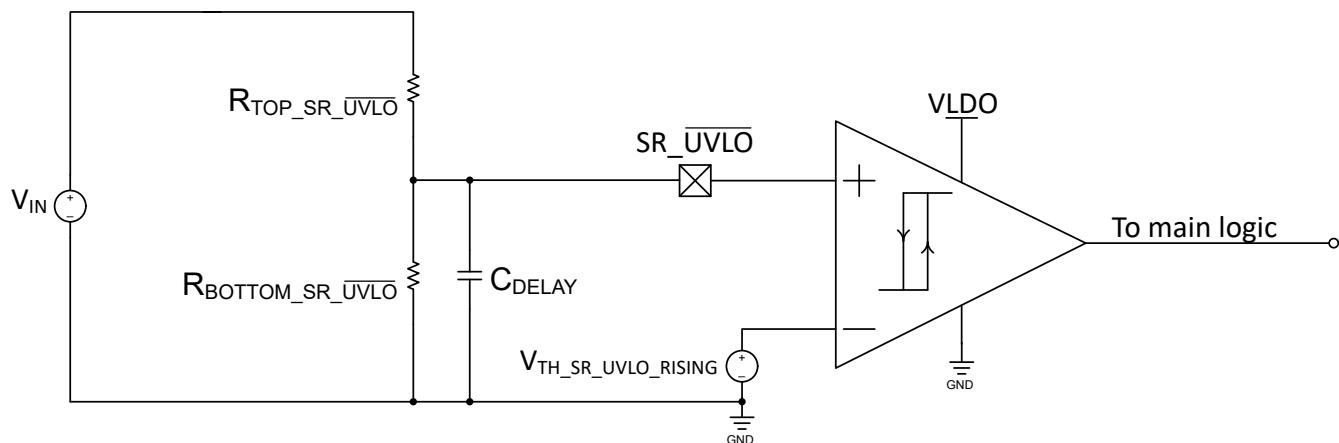

### 8.3.2 SR\_UVLO

The SR\_UVLO (システムリセットおよび低電圧ロックアウト) 入力ピンにより、外部コントローラはすべての出力を一度にアサート（または強制的に Low に）することで、外部フォルトを伝搬できます。SR\_UVLO が Low (<  $V_{TH\_SR\_UVLO\_FALLING}$ ) の場合、本デバイスはシャットダウンモードに移行し、すべての出力は強制的に論理的に Low になります。SR\_UVLO は高精度 ( $\pm 3.17\%$ ) コンパレータへの入力であり、立ち上がりスレッショルド電圧は  $V_{TH\_SR\_UVLO\_RISING} = 602\text{mV}$  であるため、設計者は必要に応じてこのピンを使用して外部低電圧誤動作防止を設定できます（図 8-2 を参照）。コンパレータには  $103\text{mV}$  の固定ヒステリシスが組み込まれています。

通常、設計者は、TPS7H3024 をイネーブルにする必要のある電圧を把握しています。この情報から、抵抗分圧器の値は式 1 を使って計算できます。通常、上側の抵抗は  $10\text{k}\Omega$  の値に固定されていますが、他の値は使用できます。より大きな値の抵抗を使用すると消費電力が最小限に抑えられますが、「弱い」プルアップにより、ノイズが出力信号に結合することができる場合があります。

$$R_{BOTTOM\_SR\_UVLO} = R_{TOP\_SR\_UVLO} \times \frac{V_{TH\_SR\_UVLO\_RISING}}{V_{IN\_UVLO\_DESIRED} - V_{TH\_SR\_UVLO\_RISING}} \quad (1)$$

ここで

- $V_{TH\_SR\_UVLO\_RISING}$  は、SR\_UVLO の立ち上がり電圧（標準値  $602\text{mV}$ ）の間の内部基準です。

- 設計者は、代表値を使用するのではなく中心値を使用することで、以下に示すように電圧、温度、放射線全体にわたる誤差を最小化できます：

$$\frac{V_{TH\_SR\_UVLO\_RISING(MIN)} + V_{TH\_SR\_UVLO\_RISING(MAX)}}{2} = \frac{0.580\text{V} + 0.618\text{V}}{2} = 0.599\text{V} \quad (2)$$

- $V_{IN\_UVLO\_DESIRED}$  は、 $V_{IN}$  の立ち上がり電圧の間デバイスをイネーブルするための必要な外部電圧です。

- $R_{TOP\_SR\_UVLO}$  は、抵抗分圧器に対して選択された上側の抵抗です。

設計者が実際の抵抗分圧器の値を把握したら、式 3 および 式 4 を使用して、外部低電圧ロックアウトの標準的な立ち上がり電圧および立ち下がり電圧を以下のように算出できます。

$$V_{IN\_UVLO\_RISING\_NOMINAL} (V) = \left( 1 + \frac{R_{TOP\_SR\_UVLO}}{R_{BOTTOM\_SR\_UVLO}} \right) \times V_{TH\_SR\_UVLO\_RISING} \quad (3)$$

$$V_{IN\_UVLO\_FALLING\_NOMINAL} (V) = \left( 1 + \frac{R_{TOP\_SR\_UVLO}}{R_{BOTTOM\_SR\_UVLO}} \right) \times V_{TH\_SR\_UVLO\_FALLING} \quad (4)$$

式 4 では、温度、電圧、放射線 (TID) 全体にわたってセンターを以下のように使用できます：

$$\frac{V_{TH\_SR\_UVLO\_FALLING(MIN)} + V_{TH\_SR\_UVLO\_FALLING(MAX)}}{2} = \frac{0.475\text{V} + 0.517\text{V}}{2} = 0.496\text{V} \quad (5)$$

起動中、デバイスは  $2.8\text{ms}(t_{START\_UP\_DELAY})$  以上にわたって安定した入力電圧 ( $UVLO_{RISE} \leq V_{IN} \leq 14$ ) を持っている必要があります。これは、すべての内部時定数を超えていることを確認するためです。これにより、 $V_{TH\_SENSEx}$  基準電圧がセトリングされ、精度は仕様範囲内 (1%) になります。 $V_{IN}$  が高速な立ち上がり電圧の場合、外付けの遅延容量を分圧抵抗に追加して、図 8-2 に示されているように、 $t_{START\_UP\_DELAY}$  が超えたあとでデバイスをイネーブルにできます。SR\_UVLO ピンの容量( $C_{DELAY}$ )を選択するには、式 6 を使用できます。

$$C_{DELAY} \left( F \right) > \frac{t_{DELAY}(\text{s})}{R_{TH}(\Omega) \times \ln \left( \frac{V_{TH}(V)}{V(t) - V_{TH}(V)} \right)} \quad (6)$$

ここで

- $t_{DELAY}$ (秒) は必要な遅延時間(秒)です( $V_{IN} > UVLO_{RISE}$  から少なくとも  $2.8\text{ms}$ )。

- $R_{TH}$  はテブナン等価抵抗であり、 $R_{TOP\_SR\_UVLO}$  と  $R_{BOTTOM\_SR\_UVLO}$  の並列接続による抵抗値 ( $\Omega$ ) です。

$$- R_{TH}(\Omega) = \frac{R_{TOP\_SR\_UVLO}(\Omega) \times R_{BOTTOM\_SR\_UVLO}(\Omega)}{R_{TOP\_SR\_UVLO}(\Omega) + R_{BOTTOM\_SR\_UVLO}(\Omega)} \quad (7)$$

- $V_{TH}$  はテブナン等価電圧であり、定常動作時の  $V_{SR\_UVLO}$  における電圧 ( $V$ ) です。

$$- V_{TH}(V) = \left( \frac{R_{BOTTOM\_SR\_UVLO}(\Omega)}{R_{TOP\_SR\_UVLO}(\Omega) + R_{BOTTOM\_SR\_UVLO}(\Omega)} \right) \times V_{IN}(V) \quad (8)$$

- $V(t)$  は  $SR\_UVLO$  の電圧 ( $V_{SR\_UVLO}$ ) で、シーケンスを開始します。この場合は 0.602V です。

– 溫度および電圧全体にわたり、式 2 に規定された中心値を使用できます。

図 8-2. メイン レールを監視して、シーケンスの立ち上げおよびシャット ダウンを自動的に開始します

### 8.3.3 SENSEx 入力

#### 8.3.3.1 $V_{TH\_SENSEx}$ および $V_{OUTx\_RISE}$

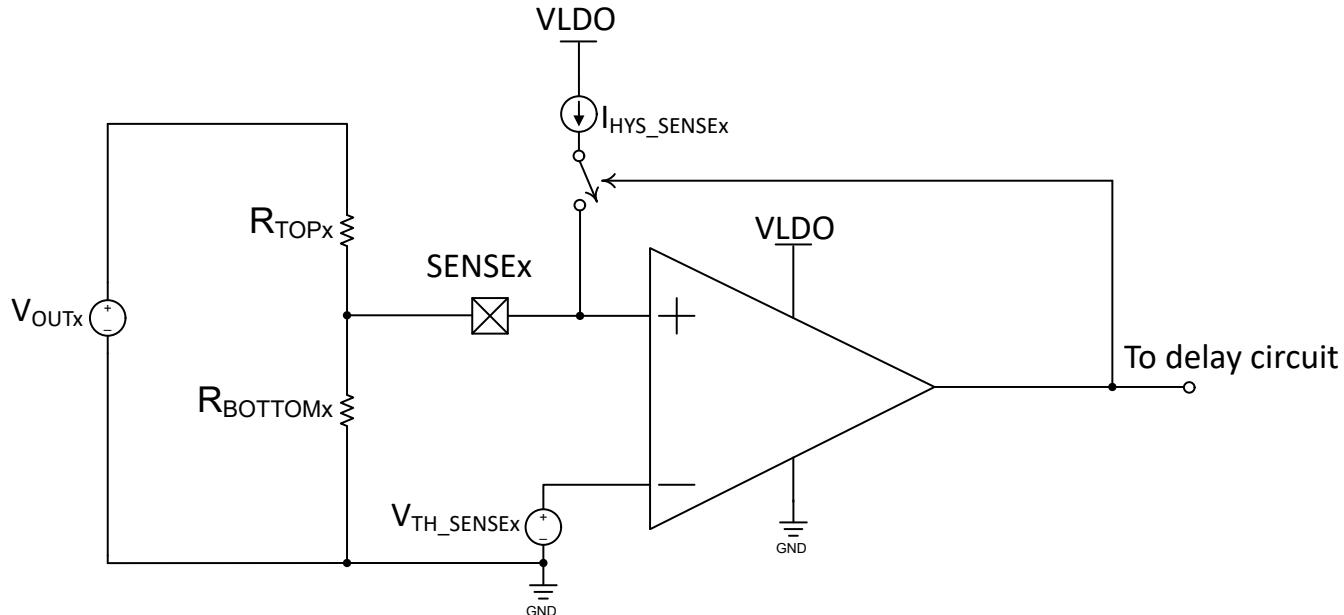

TPS7H3024 電圧スーパーバイザには 4 つの入力コンパレータが内蔵されており、標準で 599.7mV ( $V_{TH\_SENSEx}$ ) の正確な( $\pm 1\%$ ) スレッショルド電圧を備えています。 $V_{TH\_SENSEx}$  は、スレッショルドのコンパレータ オフセットを考慮して  $RESETx$  出力で測定されます。外付けの抵抗分圧器を調整して目的の電圧レール( $V_{OUTx}$ )を検出できるため、最大限の柔軟性が得られます。SENSEx 入力に接続されたコンパレータの概念図を、図 8-3 に示します。ご覧のように、検出した電圧レール( $V_{OUTx}$ )は(外付けの分圧抵抗  $R_{TOPx}$  と  $R_{BOTTOMx}$  を使用することにより)減衰され、 $V_{TH\_SENSEx}$  電圧と比較されます。寿命全体にわたってスレッショルド ( $V_{TH\_SENSEx}$ ) の良い精度を維持するため、定常状態の SENSEx 電圧を 1.6V 未満に維持することを推奨します。

#### 注

コンパレータ自体には、電圧ヒステリシスが組み込まれていません。ヒステリシスは、ヒステリシス電流 ( $I_{HYS\_SENSEx}$ ) と上側抵抗 ( $R_{TOPx}$ ) を使用して外部制御されます。詳細については、セクション 8.3.3.4 を参照してください。低電圧や過電圧タイプに応じて入力コンパレータは変化しません。過電圧は、出力段を駆動する信号を反転することにより実装されます。

図 8-3. SENSEx コンパレータ入力

監視対象のレール ( $V_{OUTx}$ ) の電圧が上昇するとき、ヒステリシス電流 ( $I_{HYS\_SENSEx}$ ) は SENSEx 入力に接続されません。SENSEx (減衰された  $V_{OUTx}$ ) が内部基準電圧 ( $V_{TH\_SENSEx}$ ) と比較されています。 $V_{SENSEx} > V_{TH\_SENSEx}$  の場合、電圧は次のように見なされます。

1. レギュレーション時: 低電圧チャネル (UV) の場合。

2. レギュレーションなし: 過電圧チャネル (OV)

単純な分圧器を使用する方法で、 $V_{OUTx}$  での立ち上がり電圧スレッショルド電圧を計算できます。

$$V_{OUTx\_RISE\_NOMINAL} \left( V \right) = \left( 1 + \frac{R_{TOPx}}{R_{BOTTOMx}} \right) \times V_{TH\_SENSEx} \quad (9)$$

ここで

- $V_{TH\_SENSEx}$  は、標準検出スレッショルド電圧で 599.7mV です。

- 温度全体にわたる監視電圧の誤差を最小限に抑えたい場合は、標準値の代わりに中央値を使用することができます:  $V_{TH\_SENSEx} = \frac{V_{TH\_SENSEx(MIN)} + V_{TH\_SENSEx(MAX)}}{2} = 599\text{mV}$

- $R_{TOPx}$  は上側の抵抗 ( $\Omega$ ) です。

- $R_{BOTTOMx}$  は下側の抵抗 ( $\Omega$ ) です。

どのようなシステムでも同様に、設計変数にはある程度のばらつき（または誤差）が存在します。この場合、上側の抵抗値および下側の抵抗値、ならびに **SENSEx** スレッショルド電圧 ( $V_{TH\_SENSEx}$ ) です。微分法（導関数法）を用いて総誤差を算出する場合（すべての変数が相関しておらず、かつ両方の抵抗が同じ許容誤差を持つと仮定）、 $V_{TH\_RISEx\_NOMINAL}$  の誤差は以下のように計算できます:

$$V_{OUTx\_RISE\_ERROR} \left( V \right) = \pm \sqrt{\frac{V_{TH\_SENSEx}^2 \times \left[ \left( 2 \times R_{TOL}^2 \times R_{TOPx}^2 \right) + \left( V_{TH\_SENSEx\_ACC}^2 \times \left( R_{TOPx} + R_{BOTTOMx} \right)^2 \right) \right]}{R_{BOTTOMx}^2}} \quad (10)$$

ここで

- $R_{TOL}$  は、抵抗の許容誤差（抵抗は上下とも同じ）の数値。例えば、許容誤差 0.1% の抵抗の場合、0.001 を使用。

- $V_{TH\_SENSEx\_ACC}$  は、**SENSEx** しきい値精度の数値（この場合は 0.01）。

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) です。

- $V_{TH\_SENSEx}$  は 0.599V（温度範囲全体の中央値）です。

式 9 と式 10 を使用して、立ち上がり電圧しきい値の範囲は、次のように計算できます:

$$V_{OUTx\_RISE} = V_{OUTx\_RISE\_NOMINAL} \pm V_{OUTx\_RISE\_ERROR} \quad (11)$$

#### 注

$V_{TH\_SENSEx}$  はシグマレータのオフセットを考慮する際の基準電圧で  $V_{TH\_SENSEx} = V_{REF} + V_{IOx}$  であることに注意してください。

必須ではありませんが、ノイズの多いアプリケーションでは、監視対象信号の過渡電圧に対する感度を低減するために、**SENSEx** 入力端に小容量のバイパスコンデンサを配置することが優れたアナログ設計の実践となります。

#### 8.3.3.2 $I_{HYS\_SENSEx}$ と $V_{OUTx\_FALL}$

TPS7H3024 には 24 $\mu$ A のヒステリシス電流が内蔵されており、精度は  $\pm 3\%$  です ( $R_{HYS} = 49.9\text{k}\Omega$  の場合)。ヒステリシス電流は、 $V_{HYS}/R_{HYS}$  とほぼ等価です。ヒステリシス電流の精度に最終的に影響するため、 $R_{HYS}$  抵抗には 0.1% の許容差を使用してください。この電流は、すべての **SENSEx** 入力において内部でミラーリングされます。このヒステリシス電流は、**SENSEx** 電圧がスレッショルド電圧 (599.7mV 1%、式 11 および図 8-3) を超えたときに有効になります。この電流 ( $I_{HYS\_SENSEx}$ ) に  $R_{TOPx}$  抵抗を乗算すると、**SENSEx** ノードに追加される電圧 ( $V_{HYS\_SENSEx}$ ) が誘導されます。これにより、ノード電圧（この場合は  $V_{SENSEx}$ ）が実質的に昇圧（またはインクリメント）されます。

$V_{OUTx}$  電圧が下降し、 $V_{OUT\_FALLx}$  よりも低くなった場合、その電圧は次のように見なされます。

1. レギュレーションなし: 低電圧チャネル (UV) の場合。

2. レギュレーション中: 過電圧チャネル (OV)。

ヒステリシス電圧は、次のように定義されます:

$$V_{HYS\_SENSEx\_NOMINAL} \left( V \right) = I_{HYS\_SENSEx} \times R_{TOPx} \quad (12)$$

ここで

- $I_{HYS\_SENSEx} = 24 \times 10^{-6}$  アンペア (または  $24\mu A$ )

- $R_{TOPx}$  単位はオーム ( $\Omega$ ) 単位です。

立ち下がり電圧スレッショルドは、次のようにで計算できます。

$$V_{OUTx\_FALL\_NOMINAL} (V) = V_{OUTx\_RISE\_NOMINAL} - V_{HYS\_SENSEx\_NOMINAL} \quad (13)$$

式 9 および式 13 を使用しますが

$$V_{OUTx\_FALL\_NOMINAL} (V) = \left[ \left( 1 + \frac{R_{TOPx}}{R_{BOTTOMx}} \right) \times V_{TH\_SENSEx} \right] - (I_{HYS\_SENSEx} \times R_{TOPx}) \quad (14)$$

ここで

- $V_{TH\_SENSEx}$  は、標準の検出しきい値電圧は  $0.599 V$  です。

- $I_{HYS\_SENSEx} = 24 \times 10^{-6}$  アンペア (または  $24\mu A$ )

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) 単位です。

$V_{OUTx\_FALL}$  エラーは、次の式で計算できます：

$$V_{TH\_FALLx\_ERROR} (V) = \pm \sqrt{\frac{A + B + C + D}{R_{BOTTOMx}^2}} \quad (15)$$

式 15 は、導関数法を用い、すべての変数が無相関であり、かつ両方の抵抗が同じ許容誤差を持つという仮定の下で算出されました。

ここで、方程式の項は次のとおりです。

$$A = I_{HYS\_SENSEx}^2 \times I_{HYS\_SENSEx\_ACC}^2 \times R_{TOPx}^2 \times R_{BOTTOMx}^2 \quad (16)$$

$$B = R_{TOL}^2 \times R_{TOPx}^2 \times V_{TH\_SENSEx}^2 \quad (17)$$

$$C = R_{TOL}^2 \times R_{TOPx}^2 \times [(I_{HYS\_SENSEx} \times R_{BOTTOMx}) - V_{TH\_SENSEx}]^2 \quad (18)$$

$$D = V_{TH\_SENSEx}^2 \times V_{TH\_SENSEx\_ACC}^2 \times (R_{TOPx} + R_{BOTTOMx})^2 \quad (19)$$

ここで

- $R_{TOL}$  は、抵抗の許容誤差 (抵抗は上下とも同じ) の数値。例えば、許容誤差  $0.1\%$  の抵抗の場合、 $0.001$  を使用。

- $V_{TH\_SENSEx\_ACC}$  は、SENSEx しきい値精度の数値 (この場合は  $0.01$ )。

- $I_{HYS\_SENSEx\_ACC}$  は、数値としてのヒステリシス電流精度 (この場合は  $0.03$ ) です。

- $V_{TH\_SENSEx}$  は、標準の検出しきい値電圧は  $0.599 V$  です。

- $I_{HYS\_SENSEx} = 24 \times 10^{-6} A$  (または  $24\mu A$ )

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) 単位です。

式 15 と式 14 を使用して、立ち下がり電圧範囲は次のように計算できます。

$$V_{OUTx\_FALL} = V_{OUTx\_FALL\_NOMINAL} \pm V_{OUTx\_FALL\_ERROR} \quad (20)$$

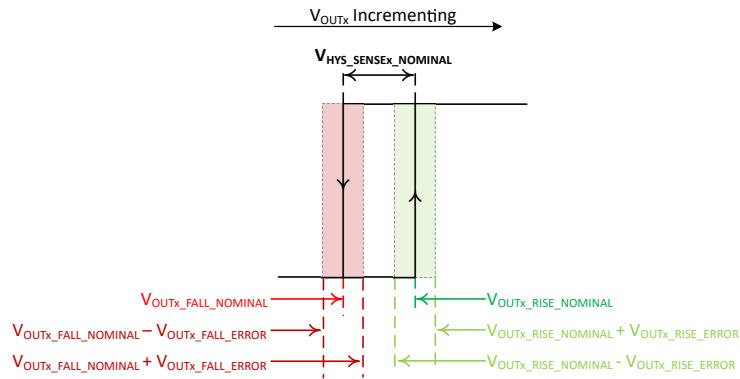

図 8-4 に、立ち上がり電圧と立ち下がり電圧の概念図を示します。この図には、 $V_{TH}$  の精度、 $I_{HYS}$  の精度、抵抗分割回路の許容誤差による電圧の誤差も記載されています。システム レベルでは、堅牢な設計を実現するために、これらの誤差を考慮する必要があります。

図 8-4. SENSE<sub>x</sub> コンパレータの立ち上がりおよび立ち下りにおけるしきい値電圧

### 8.3.3.3 入力から出力までのタイミング図

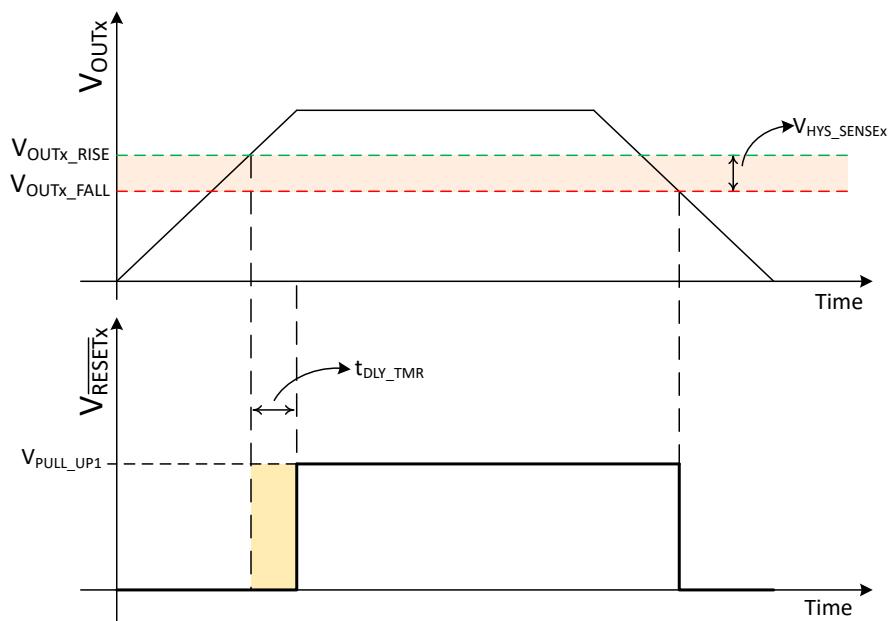

A. TPS7H3024 およびでは、MODE = 0 のとき、チャネル #1 (ピン #1) とチャネル #3 (ピン #3) は低電圧タイプです。

図 8-5. 低電圧チャネル (UV) の時間図

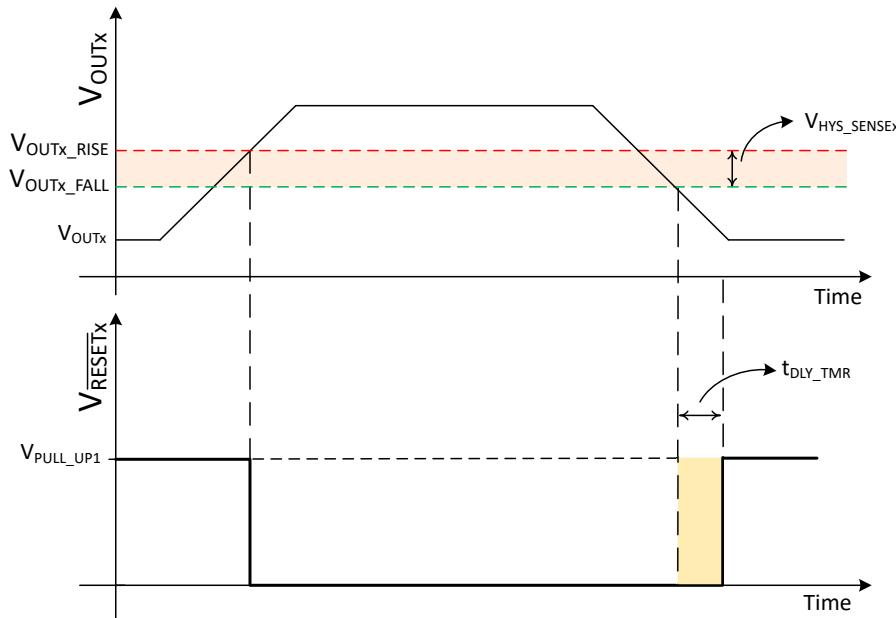

- A. では、MODE = 1 のとき、チャネル #2 (ピン#2) とチャネル #4 (ピン #4) は過電圧タイプです。

図 8-6. 過電圧チャネル (OV) の時間図

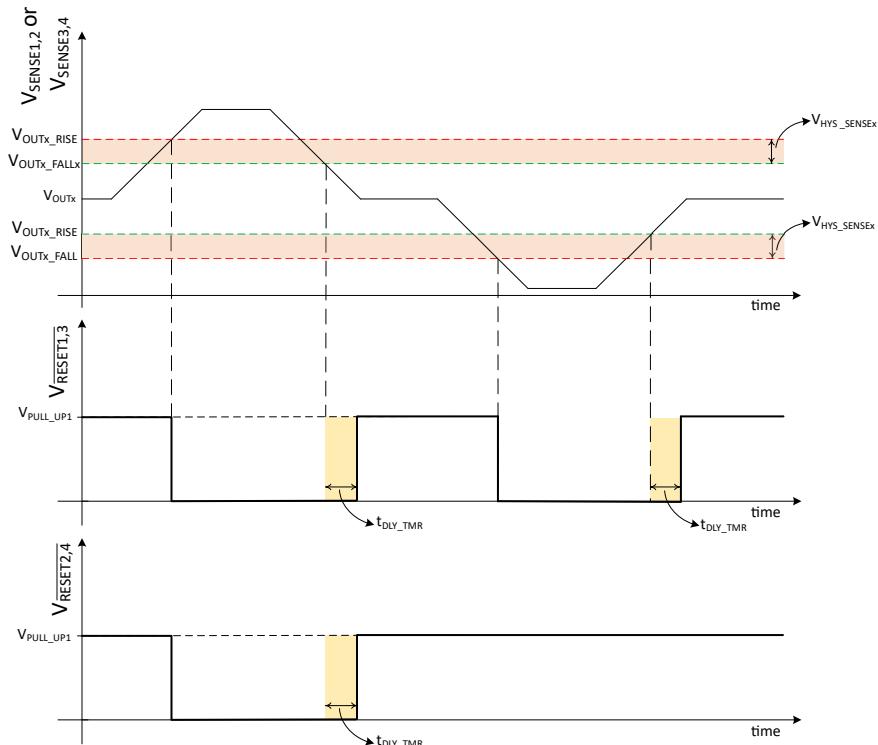

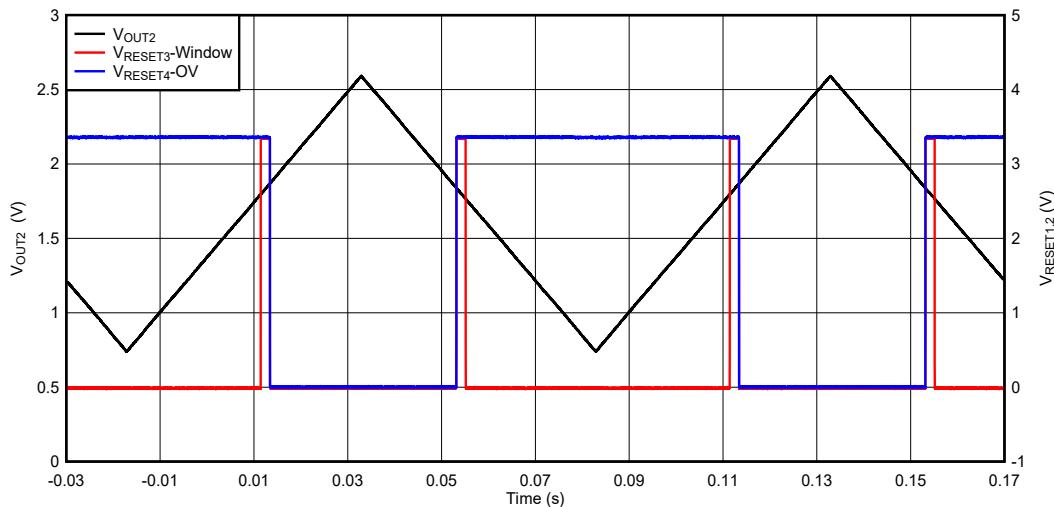

- A. TPS7H3024 では、MODE = 1 のとき、チャネル #1 (ピン 1) とチャネル #2 (ピン #2) は内部的にまたは「接続されて」ウィンドウ チャネルを作成し、チャネル #3 (ピン #3) とチャネル #4 (ピン #4) は OR 接続されて、2 番目のウィンドウ チャネルを作成します

B. 低電圧と過電圧の場合、V\_OUTx\_RISE、V\_OUTx\_FALL、V\_HYS\_SENSEx は、それぞれ異なる値である可能性があります。

図 8-7. ウィンドウ チャネルの時間図

### 8.3.3.4 上部および下部の抵抗分圧回路の設計式

システム レベルでは、設計者は  $V_{OUTx\_RISE}$  および  $V_{OUTx\_FALL}$  レベルを知っています（または選択します）。通常、これらの電圧は、監視対象の公称レール電圧( $V_{OUTx}$ )に対するパーセンテージとして選択されます。この情報が判明していれば、目的の目標レベルについて、抵抗の公称分割部品の値 ( $R_{TOPx}$  と  $R_{BOTTOMx}$ ) を計算することができます。[式 13](#) と [式 12](#) を使用して、上側の抵抗を計算できます。

$$R_{TOPx} = \frac{V_{OUTx\_RISE} - V_{OUTx\_FALL}}{I_{HYS\_SENSEx}} \quad (21)$$

下部の抵抗は、[式 9](#) から次のように計算できます。

$$R_{BOTTOMx} = \frac{R_{TOPx} \times V_{TH\_SENSEx}}{V_{OUTx\_RISE} - V_{TH\_SENSEx}} \quad (22)$$

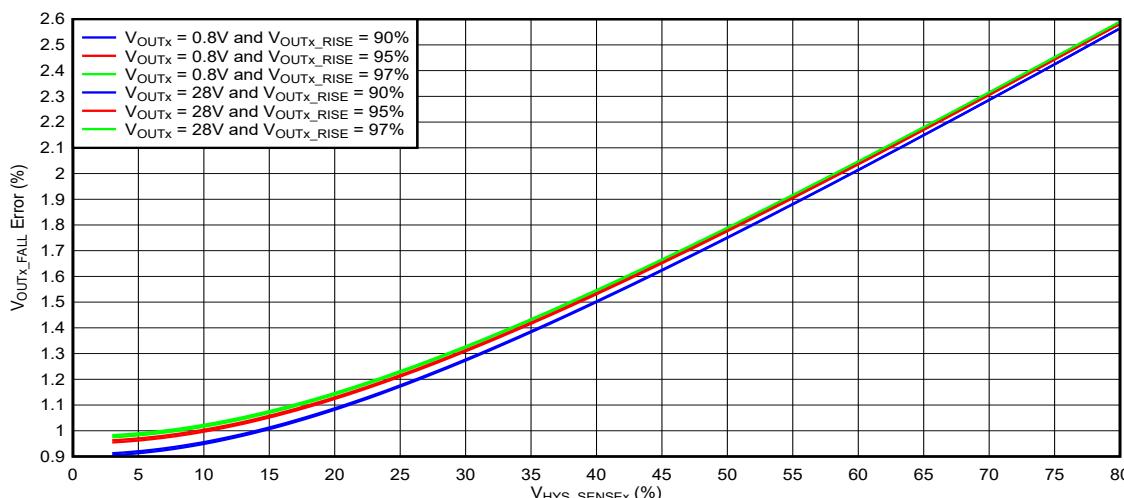

$V_{OUTx\_RISE}$  と  $V_{OUTx\_FALL}$  ( $V_{HYS\_SENSEx}$  と呼びます) の差が大きいほど、立ち下がり電圧の誤差が大きくなることに注意する必要があります。[図 8-8](#) に、さまざまなセンス ヒステリシス電圧 ( $V_{HYS\_SENSEx} = V_{OUTx\_RISE} - V_{OUTx\_Fall}$ ) の  $V_{OUTx\_Fall}$  エラーのプロットを示します。このプロットは、3 種類の  $V_{OUTx\_RISE}$  電圧（または、公称出力電圧のパーセンテージで 90%、95%、97%）と、2 種類の出力電圧（0.8V と 28V）に対して作成されています。グラフからわかるように、出力電圧は立ち下がり電圧誤差にほとんど影響を与えません（プロットで差を簡単に確認することはできません）。誤差（%単位）は約 1% ( $V_{HYS\_SENSEx} = 3\%$ ) から約 2.6% ( $V_{HYS\_SENSEx} = 80\%$  の場合) までに大きくなることがあります。

**図 8-8.  $V_{OUTx\_FALL}$  絶対誤差と  $V_{HYS\_SENSEx}$  との関係**

- A. このプロットには、[式 21](#) と [式 22](#) を使用して計算した上側抵抗と下側抵抗の差、および設計者が調達できる実際の抵抗値による  $V_{OUTx\_FALL}$  の誤差は含まれていません。

- B. 計算に使用する抵抗の許容誤差は 0.1%、 $V_{TH\_SENSEx}$  精度は 1%、 $I_{HYS\_SENSEx}$  精度は 3%です。

- C. このプロットでは、 $V_{HYS\_SENSEx}$  (%) が公称出力電圧 ( $V_{OUTx}$ ) をパーセンテージで表しています。

- D. このプロットでは、フルスケール電圧（または  $V_{OUTx}$ ）を基準にして  $V_{OUTx\_FALL}$  誤差 (%) が正規化されています。

### 8.3.4 モード

MODE ピンは、出力段の動作を変化させて以下を検出する入力です。

1. 低電圧 (UV)

2. 過電圧 (OV)

3. ウィンドウ

詳細については [表 8-1](#) および [セクション 8.3.5](#) を参照してください。

**注**

MODE は、VLDO に接続すると、論理 High に設定できます。絶縁保護のために直列抵抗を使用します。

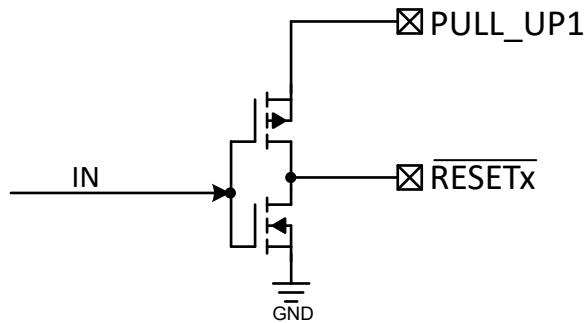

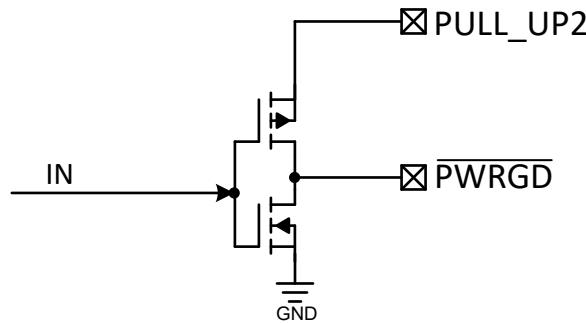

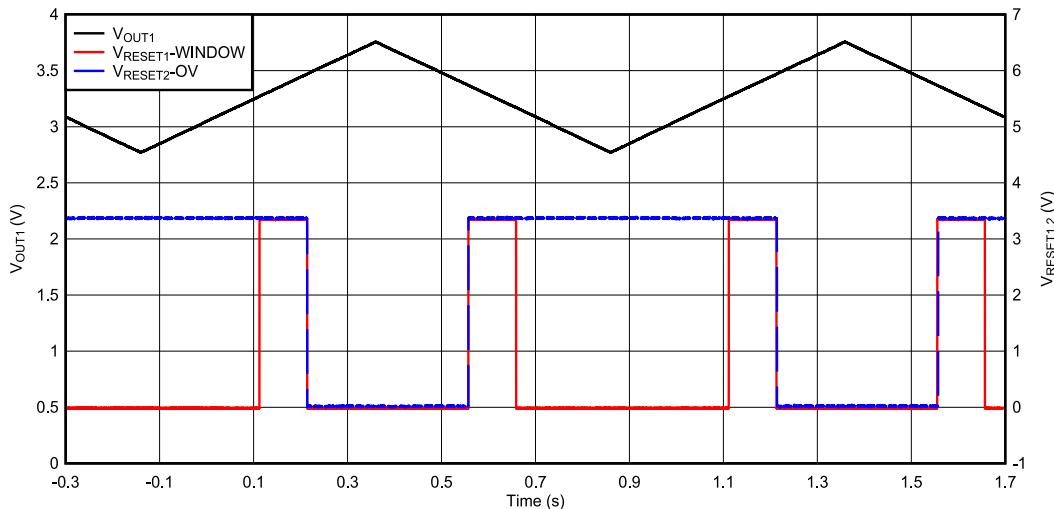

### 8.3.5 出力段 ( $\overline{\text{RESETx}}$ , $\overline{\text{PWRGD}}$ , $\overline{\text{WDO}}$ , $\overline{\text{PULL\_UP1}}$ , $\overline{\text{PULL\_UP2}}$ )

出力段 ( $\overline{\text{RESET1}}$  から  $\overline{\text{RESET4}}$ )、 $\overline{\text{PWRGD}}$ 、 $\overline{\text{WDO}}$  はプッシュプルタイプで供給されます。図 8-9 に示されているように、出力が過電圧タイプのとき、 $\overline{\text{RESETx}}$  は  $\text{SENSE}_x$  コンパレータの出力から論理的に反転されます (図 8-13 も参照)。

TPS7H3024 (プッシュプル出力)で、 $\text{MODE} = 1$  の場合、 $\text{SENSE1}$  (UV) と  $\text{SENSE2}$  (OV) は内部 A 接続され、出力が  $\overline{\text{RESET1}}$  出力を駆動するために使用されます。この場合、 $\overline{\text{RESET1}}$  はウインドウコンパレータの出力です。 $\overline{\text{RESET2}}$  は変更されないままで、 $\text{SENSE2}$  の OV フラグになります。ウインドウフラグと OV フラグの両方が利用可能なため、システムは出力を読み取って、システム内でどの種類のフォルト (UV または OV) が発生したかを判別できます。同様のことが、2 番目のウインドウコンパレータを構成する  $\text{SENSE3}$  および  $\text{SENSE4}$  にも当てはまります。

図 8-9. TPS7H3024 用ウインドウコンパレータ (MODE=1 の場合)

- A.  $\text{SENSE1}$  と  $\text{SENSE2}$  は 1 つ目のウインドウコンパレータチャネルを構成し、 $\text{SENSE3}$  と  $\text{SENSE4}$  は 2 つ目のウインドウコンパレータチャネルを構成します。

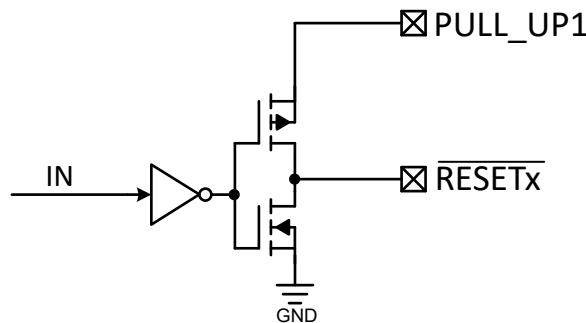

#### 8.3.5.1 プッシュプル出力

プッシュプル出力のプルアップ電圧は、ユーザが外部から供給します。 $\text{PULL\_UP1}$  (入力) はすべての  $\overline{\text{RESETx}}$  出力 ( $\overline{\text{RESET1}}$  から  $\overline{\text{RESET4}}$  まで) のプルアップ電圧ドメインです。 $\text{PULL\_UP2}$  (入力) は  $\overline{\text{PWRGD}}$  および  $\overline{\text{WDO}}$  出力のプルアップ電圧ドメインです。図 8-10 から 図 8-13 を参照してください。

**注**

IN、 $\text{PULL\_UP1}$  と  $\text{PULL\_UP2}$  の間にシーケンス要件はありません。

各出力段は、ハイサイド PMOS とローサイド NMOS の (CMOS) ペアで構成されています。PMOS 抵抗は通常  $9\Omega$  (最大値  $20\Omega$ )、NMOS は標準  $16\Omega$  (最大値  $36\Omega$ )、 $V_{\text{PULL\_UPx}} \geq 3.3\text{V}$  の場合。 $\text{PULL\_UP1}$  および  $\text{PULL\_UP2}$  の電圧範囲は  $1.6\text{V} \sim 7\text{V}$  であり、それぞれ独立してバイアスをかけることも、同じ電源レールに接続することも可能です。ただし、両方とも必ずバイアスをかける必要があります。PMOS レッグの出力抵抗は、 $\text{PULL\_UPx}$  電圧依存性を持ちます。 $\text{PULL\_UPx}$  電圧が低いほど、PMOS 抵抗は高くなります。

$V_{IN} < V_{POR\_IN}$  (最大電圧 2V) または  $V_{PULL\_UPx} > V_{POR\_PULL\_UPx}$  (最大 1.1V) のとき、出力は既知のプルダウン状態になります。この条件では、本デバイスが出力に  $100 \mu A$  の電流をシンクする場合、 $V_{OL} \leq 320mV$  で、出力のシンク能力が低下します。

- $\overline{RESETx}$

- PWRGD

- WDO

入力電圧が推奨範囲である 3V~14V の範囲内にある場合、各出力は  $\pm 10mA$  のフルドライブ能力を持ちます。

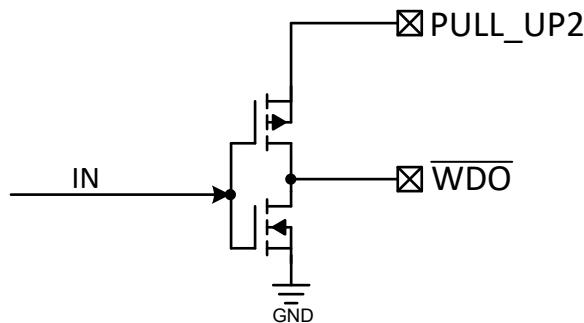

図 8-10. UV チャネル タイプの  $\overline{RESETx}$  プッシュプル出力段

図 8-11. UV チャネル タイプ用の PWRGD プッシュプル出力段

図 8-12. UV チャネル タイプ用の WDO プッシュプル出力段

A.  $\overline{RESETx}$ のみは、チャネルのタイプに以下のように依存します。UV または OV これは、MODE 入力ピンの論理値に依存します。

図 8-13. OV チャネル タイプの  $\overline{RESETx}$  プッシュプル出力段

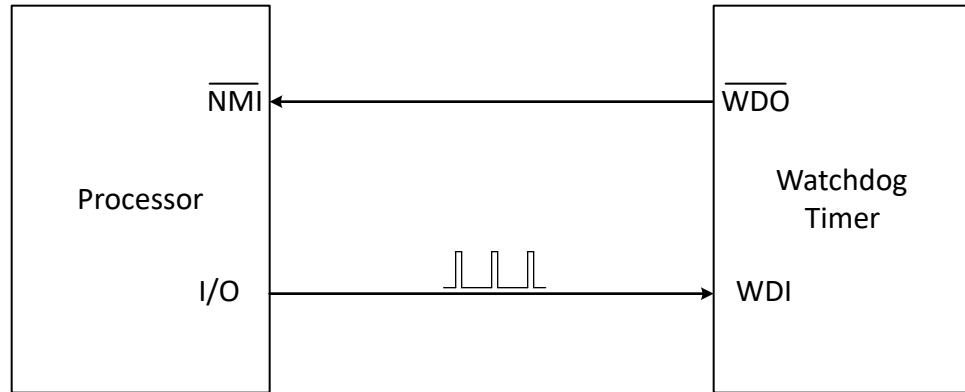

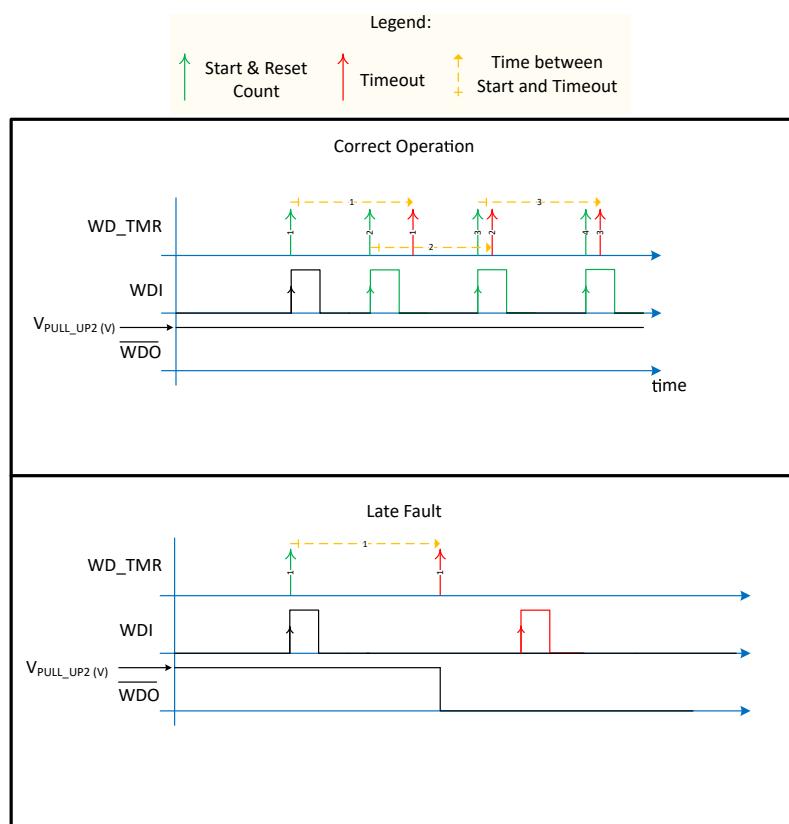

### 8.3.6 WDI

ウォッチドッグ入力 (WDI) ピンは、602mV の基準電圧 ( $V_{TH\_WDI\_RISING}$ ) を持つコンパレータの非反転入力の入力です。コンパレータには、ノイズ耐性を高めるために 104 mV (固定) のヒステリシス電圧が内蔵されています。ウォッチドッグステートマシンは、WDI ピンで立ち上がり電圧が検出されるたびにクリア (またはウォッチドッグ カウンタのリセット) を行います。ウォッチドッグ タイムアウトのばらつきを考慮するため、プロセッサが WDI 信号を送信する頻度を決定する際には、WD\_TMR の最小値を使用することを推奨します。例えば、WD\_TMR が 1s に設定されている場合、実際のタイムアウトは 0.8s から 1.2s の間になります。したがって、最悪の場合のばらつきを考慮して、WDI 信号はプロセッサから少なくとも 0.8s ごとに送信することを推奨します。WD\_TMR (またはタイムアウト) は、WD\_TMR 入力を使用して、ユーザーがプログラムすることができます。このタイマは 520ms~1.5s の範囲でプログラム可能です。詳細については、[セクション 8.3.7.2](#) を参照してください。

### 8.3.7 ユーザープログラマブル タイマ

TPS7H3024 には 2 つの調整可能なタイマがあります。

1. DLY\_TMR の代表的な範囲は 260μs から 23.37ms です。

2. WD\_TMR の代表的な範囲は 520ms から 1.5s です。

両方のタイマは、DLY\_TMR ピンと WD\_TMR ピンと GND との間に 1 つの抵抗によりプログラムされます。これらの抵抗は、タイマの内部発振器周波数をプログラムするために使用されます。DLY\_TMR ピンまたは WD\_TMR ピンをフローティングにすると、それぞれのタイマは無効になります。タイマをディセーブルすると、デバイスの静止電流 ( $I_Q\_IN$ ) が減ります。詳細については、[図 6-5](#) を参照してください。

#### 注

タイマ ピンの抵抗設定は、電源投入時に有効である必要があり、動的に変更できません。

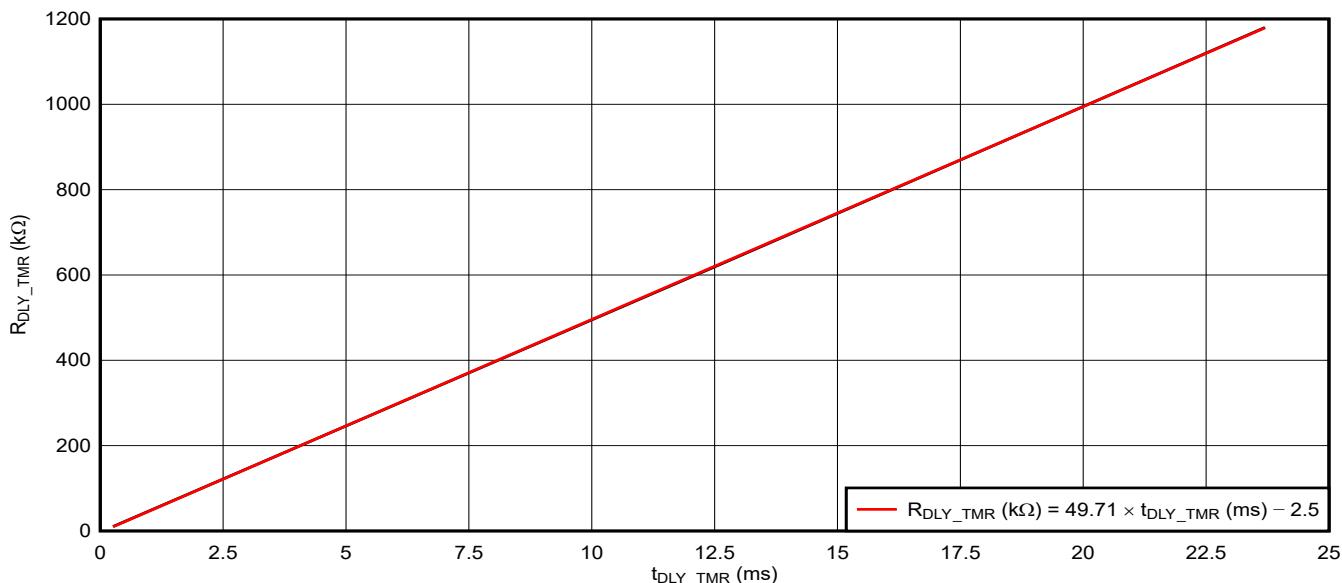

#### 8.3.7.1 DLY\_TMR

TPS7H3024 には、調整可能な時間遅延機能があります。DLY\_TMR ピンと GND の間に 1 つの抵抗を接続すると、遅延をプログラムできます。260μs から 23.7ms の遅延の場合、使用可能な抵抗 ( $R_{DLY}$ ) の値は 10.5kΩ と 1.18MΩ の間です。この遅延は、次のような故障状態からの復帰時にのみ有効です：

1. UV: 低電圧チャネル (UV) で、遅延は  $V_{OUTx}$  電圧が立ち上がり、 $V_{OUTx\_RISE}$  を横切るときに有効です。

2. OV: 過電圧チャネル (OV) では、遅延は  $V_{OUTx}$  電圧が立ち下がり、 $V_{OUTx\_FALL}$  を横切るときに有効です。

詳細については [図 8-5](#) と [図 8-6](#) を参照してください。

システムに対して遅延が望ましくない場合は、ピン (DLY\_TMR) をフローティングのままにしておくことができます。タイマをディセーブルすると、デバイスの消費電流が低減されます ( $I_Q\_IN$ )。遅延が望ましくない場合、 $V_{OUTx}$  が  $V_{OUTx\_RISE}$  と  $V_{OUTx\_FALL}$  を交差する間に、4.3μs (最大) 固有の伝搬遅延が観測されます。

DLY\_TMR 抵抗は、式 23 を使って選択できます。[図 8-14](#) に、DLY\_TMR 抵抗と遅延時間の線形的な傾向を示します。

$$R_{DLY\_TMR}(k\Omega) = [49.71 \times t_{DLY\_TMR}(\text{ms})] - 2.5 \quad (23)$$

さまざまな遅延時間の公称抵抗値を、[表 8-2](#) に示します。

**表 8-2. 標準的な DLY\_TMR 抵抗**

| 遅延 (ms) | $R_{DLY\_TMR}(k\Omega)$ |

|---------|-------------------------|

| 0.260   | 10.5                    |

| 12.5    | 619                     |

| 23.7    | 1180                    |

図 8-14. 全発振器範囲における  $R_{DLY\_TMR}$  と  $t_{DLY\_TMR}$  との関係

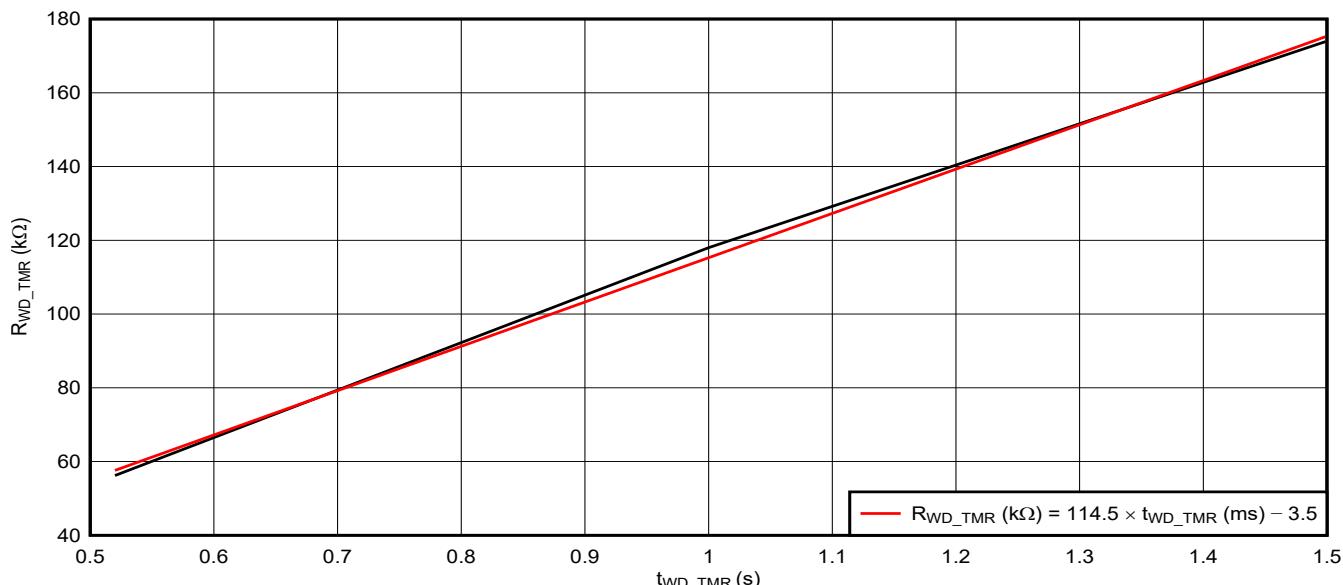

### 8.3.7.2 WD\_TMR

WD\_TMR は、内部ウォッチドッグ タイマのタイムアウトをプログラムする可変タイマです。ウォッチドッグタイマーは、プロセッサの一貫した動作を監視するために一般的に使用されます。故障により監視対象のプロセッサが停止した場合、WDI ピンは立ち上がりエッジを検出せず、WDO が Low にアサートされるため、プロセッサは既知の状態にリセットされます。図 8-15 に、監視対象プロセッサと TPS7H3024 との間の一般的な接続を示します。図 8-16 に、TPS7H3024 のプロセッサとウォッチドッグの間の正しいハンドシェイクと不適切な(遅いパルス)ハンドシェイクを示します。

ユーザーは、WD\_TMR ピンと GND との間に 1 つの抵抗を使用して WD\_TMR をプログラムできます。抵抗 ( $R_{WD}$ ) の範囲は、それぞれ 520ms~1.5s の時間の範囲に対して 56.2kΩ から 174kΩ の間です。ウォッチドッグ タイマを使用したくない場合は、このピンをフローティングのままにしてもかまいません。ウォッチドッグ タイマをディセーブルにすると、デバイスの静止電流 ( $I_Q\_IN$ ) が減少します。

#### 注

ウォッチドッグ タイマがディセーブルのとき (WD\_TMR ピンがフローティング)、WDO ピンは PWRGD と同等になります。

REG\_TMR 抵抗は、式 24 を使って計算できます。図 8-17 に、WD\_TMR 抵抗とウォッチドッグ タイマをクリアするために許容される時間(またはタイムアウト)との線形の傾向を示します。

$$R_{WD\_TMR}(k\Omega) = [114.5 \times t_{WD\_TMR}(s)] - 3.5 \quad (24)$$

表 8-3 に、さまざまな許容レギュレーション時間に対する標準抵抗値を示します。WDI ピンの最小パルス幅は、ウォッチドッグ オシレータ周期の 2 倍として規定されています。オシレータ周期は、式 25 を使って計算できます。

$$t_{WD\_OSC}(s) = \frac{t_{WD\_TMR}(s)}{57,344} \quad (25)$$

図 8-15. TPS7H3024 と監視対象プロセッサとの間のウォッチドッグタイマのハンドシェイク (代表値)

図 8-16. ウォッチドッグのタイミング図

表 8-3. 標準的な REG\_TMR 抵抗

| 許容レギュレーション時間 (s) | R <sub>REG_TMR</sub> (kΩ) |

|------------------|---------------------------|

| 0.52             | 56.2                      |

| 1                | 118                       |

| 1.5              | 174                       |

図 8-17. 全発振器範囲における  $R_{WD\_TMR}$  と  $t_{WD\_TMR}$  との関係

#### 8.4 デバイスの機能モード

表 8-4.  $V_{IN}$  および  $V_{PULL\_UPx}$  が推奨最小電圧より低い場合の  $\overline{RESETx}$ 、 $PWRGD$ 、および  $WDO$  の真理値表。

| SR_UVLO<br>(1) (2) | SENSEx<br>(3) (4) | RESETx | PWRGD | WDO | IN                          | PULL_UPx                                    |

|--------------------|-------------------|--------|-------|-----|-----------------------------|---------------------------------------------|

| 0 または 1            | 0 または 1           | 不定     | 不定    | 不定  | $V_{IN} < V_{POR\_IN}$      | $V_{PULL\_UPx} < V_{POR\_PULL\_UPx}$        |

|                    |                   | L      | L     | L   | $V_{IN} < V_{POR\_IN}$      | $V_{POR\_PULL\_UPx} < V_{PULL\_UPx} < 1.6V$ |

|                    |                   | L      | L     | L   | $V_{POR\_IN} < V_{IN} < 3V$ | $V_{PULL\_UPx} < V_{POR\_PULL\_UPx}$        |

|                    |                   | L      | L     | L   | $V_{POR\_IN} < V_{IN} < 3V$ | $1.6V < V_{PULL\_UPx} < 7V$                 |

表 8-5.  $V_{IN}$  および  $V_{PULL\_UPx}$  が推奨動作電圧範囲内にある場合の  $\overline{RESETx}$ 、 $PWRGD$ 、および  $WDO$  の真理値表

| SR_UVLO<br>(1) (2) | MODE<br>(5) (6) | SENSE1<br>(3) (4) | SENSE2<br>(3) (4) | SENSE3<br>(3) (4) | SENSE4<br>(3) (4) | RESET1 | RESET2 | RESET3 | RESET4 | PWRGD | WDO<br>(7) |

|--------------------|-----------------|-------------------|-------------------|-------------------|-------------------|--------|--------|--------|--------|-------|------------|

| 0                  | 0 または 1         | 0 または 1           | 0 または 1           | 0 または 1           | 0 または 1           | L      | L      | L      | L      | L     | L          |

**表 8-5.  $V_{IN}$  および  $V_{PULL\_UPx}$  が推奨動作電圧範囲内にある場合の  $\overline{RESETx}$ 、 $PWRGD$ 、および  $WDO$  の真理値表

(続き)**

| SR_UVLO<br>(1) (2) | MODE<br>(5) (6) | SENSE1<br>(3) (4) | SENSE2<br>(3) (4) | SENSE3<br>(3) (4) | SENSE4<br>(3) (4) | RESET1 | RESET2 | RESET3 | RESET4 | PWRGD | WDO<br>(7) |

|--------------------|-----------------|-------------------|-------------------|-------------------|-------------------|--------|--------|--------|--------|-------|------------|

| 0                  | 0               | 0                 | 0                 | 0                 | 0                 | L      | H      | L      | H      | L     | L          |

|                    |                 | 0                 | 0                 | 0                 | 1                 | L      | H      | L      | L      | L     | L          |

|                    |                 | 0                 | 0                 | 1                 | 0                 | L      | H      | H      | H      | L     | L          |

|                    |                 | 0                 | 0                 | 1                 | 1                 | L      | H      | H      | L      | L     | L          |

|                    |                 | 0                 | 1                 | 0                 | 0                 | L      | L      | L      | H      | L     | L          |

|                    |                 | 0                 | 1                 | 0                 | 1                 | L      | L      | L      | L      | L     | L          |

|                    |                 | 0                 | 1                 | 1                 | 0                 | L      | L      | H      | H      | L     | L          |

|                    |                 | 0                 | 1                 | 1                 | 1                 | L      | L      | H      | L      | L     | L          |

|                    |                 | 1                 | 0                 | 0                 | 0                 | H      | H      | L      | H      | L     | L          |

|                    |                 | 1                 | 0                 | 0                 | 1                 | H      | H      | L      | L      | L     | L          |

|                    |                 | 1                 | 0                 | 1                 | 0                 | H      | H      | H      | H      | H     | H          |

|                    |                 | 1                 | 0                 | 1                 | 1                 | H      | H      | H      | L      | L     | L          |

|                    |                 | 1                 | 1                 | 0                 | 0                 | H      | L      | L      | H      | L     | L          |

|                    |                 | 1                 | 1                 | 0                 | 1                 | H      | L      | L      | L      | L     | L          |

|                    |                 | 1                 | 1                 | 1                 | 0                 | H      | L      | H      | H      | L     | L          |

|                    |                 | 1                 | 1                 | 1                 | 1                 | H      | L      | H      | L      | L     | L          |

| 1                  | 1               | 0                 | 0                 | 0                 | 0                 | L      | H      | L      | H      | L     | L          |

|                    |                 | 0                 | 0                 | 0                 | 1                 | L      | H      | L      | L      | L     | L          |

|                    |                 | 0                 | 0                 | 1                 | 0                 | L      | H      | H      | H      | L     | L          |

|                    |                 | 0                 | 0                 | 1                 | 1                 | L      | H      | L      | L      | L     | L          |

|                    |                 | 0                 | 1                 | 0                 | 0                 | L      | L      | L      | H      | L     | L          |

|                    |                 | 0                 | 1                 | 0                 | 1                 | L      | L      | L      | L      | L     | L          |

|                    |                 | 0                 | 1                 | 1                 | 0                 | L      | L      | H      | H      | L     | L          |

|                    |                 | 0                 | 1                 | 1                 | 1                 | L      | L      | L      | L      | L     | L          |

|                    |                 | 1                 | 0                 | 0                 | 0                 | H      | H      | L      | H      | L     | L          |

|                    |                 | 1                 | 0                 | 0                 | 1                 | H      | H      | L      | L      | L     | L          |

|                    |                 | 1                 | 0                 | 1                 | 0                 | H      | H      | H      | H      | H     | H          |

|                    |                 | 1                 | 0                 | 1                 | 1                 | H      | H      | L      | L      | L     | L          |

|                    |                 | 1                 | 1                 | 0                 | 0                 | L      | L      | L      | H      | L     | L          |

|                    |                 | 1                 | 1                 | 0                 | 1                 | L      | L      | L      | L      | L     | L          |

|                    |                 | 1                 | 1                 | 1                 | 0                 | L      | L      | H      | H      | L     | L          |

|                    |                 | 1                 | 1                 | 1                 | 1                 | L      | L      | L      | L      | L     | L          |

(1)  $0 = V_{SR\_UVLO} < V_{TH\_SR\_UVLO\_FALLING}$ (2)  $1 = V_{SR\_UVLO} > V_{TH\_SR\_UVLO\_RISING}$ (3)  $0 = V_{SENSEx} < V_{TH\_SENSEx}$ (4)  $1 = V_{SENSEx} > V_{TH\_SENSEx}$ (5)  $0 = V_{MODE} < V_{TH\_MODE\_FALLING}$ (6)  $1 = V_{MODE} > V_{TH\_MODE\_RISING}$

(7) ウオッチドッグ タイマが期限切れになる前に、WDI に有効な立上りエッジ パルスが入力されることを前提としています。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

TPS7H3024 は、放射線耐性を強化した、ウォッチドッグ タイマ付きの 4 チャンネル電圧スーパーバイザです。このモジュールを使用して、FPGA、ASIC、AFE、各種電源システムの電源レール、プロセッサの一貫性のある実行を監視できます。

### 9.2 代表的なアプリケーション

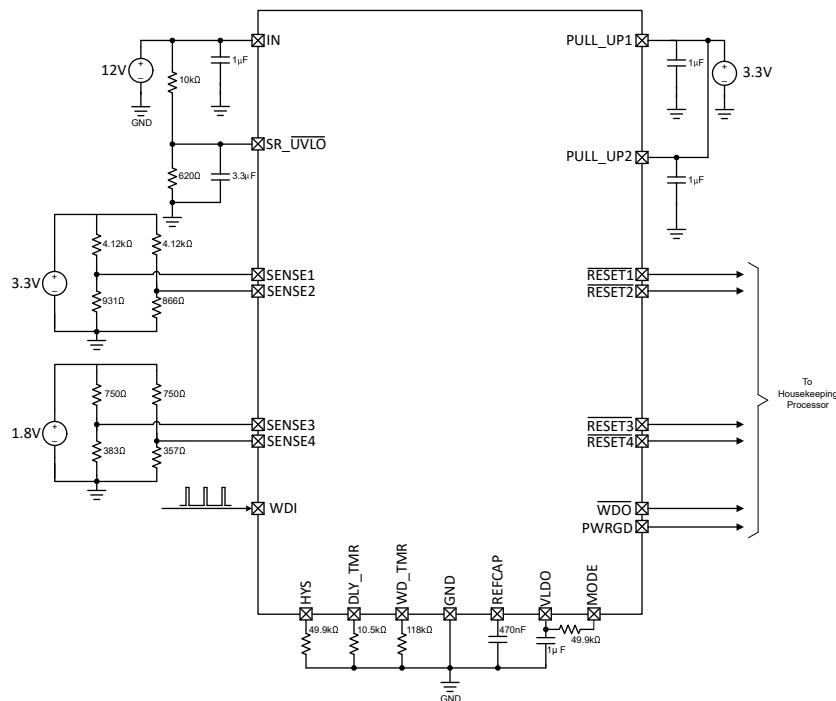

#### 9.2.1 ウィンドウ電圧モニタ

多くの最新システム(またはサブシステム)では、複数の電圧レールが必要な場合が多く、これを「電源ツリー」と呼びます。これらの電源ツリーは、信頼性の高い動作のために厳密な電圧仕様が求められることがよくあります。これらの仕様が満たされていない場合、信頼性の低い動作または永続的な誤動作が発生する可能性があります。信頼性の高い動作を可能にするために、電圧レールはリアルタイムで監視され、電源オフやローカル レギュレータの無効化などの是正処置がシステム全体に伝達されます。

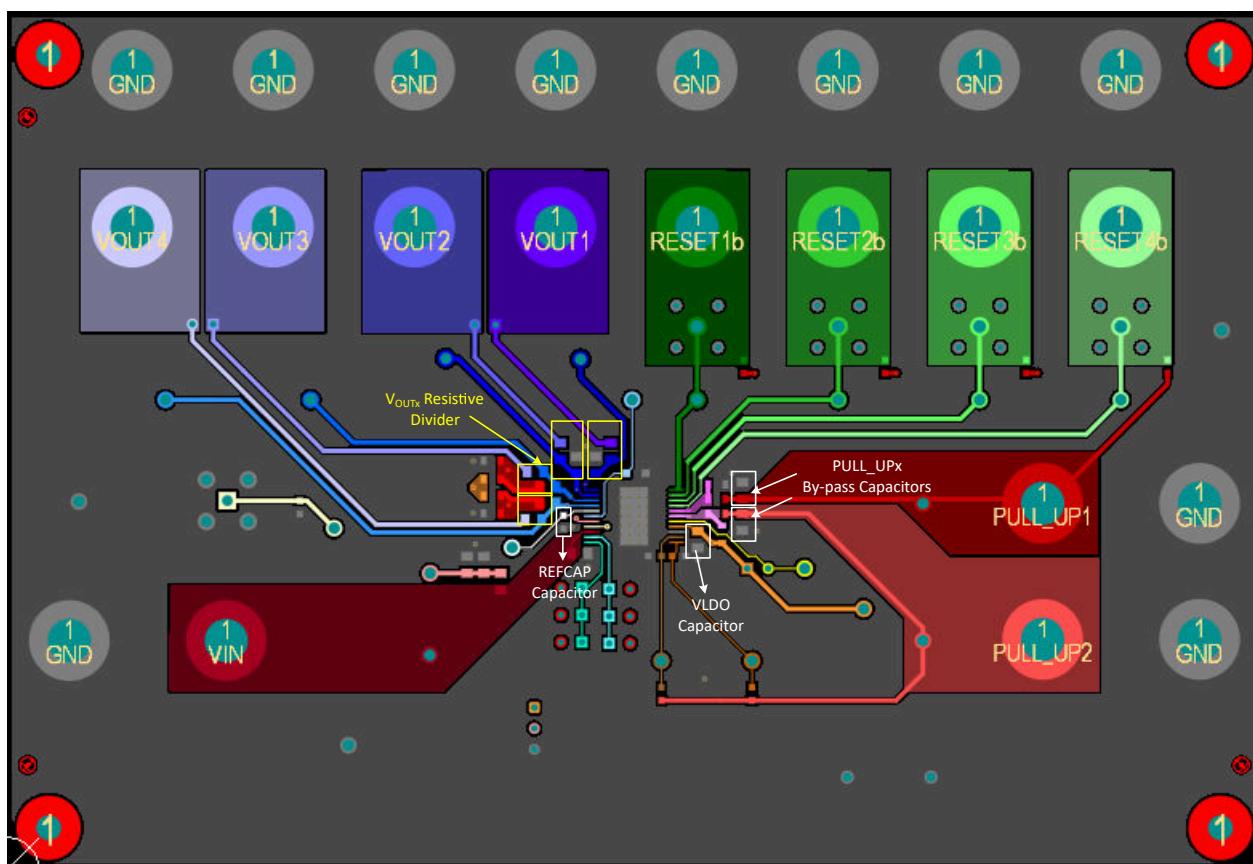

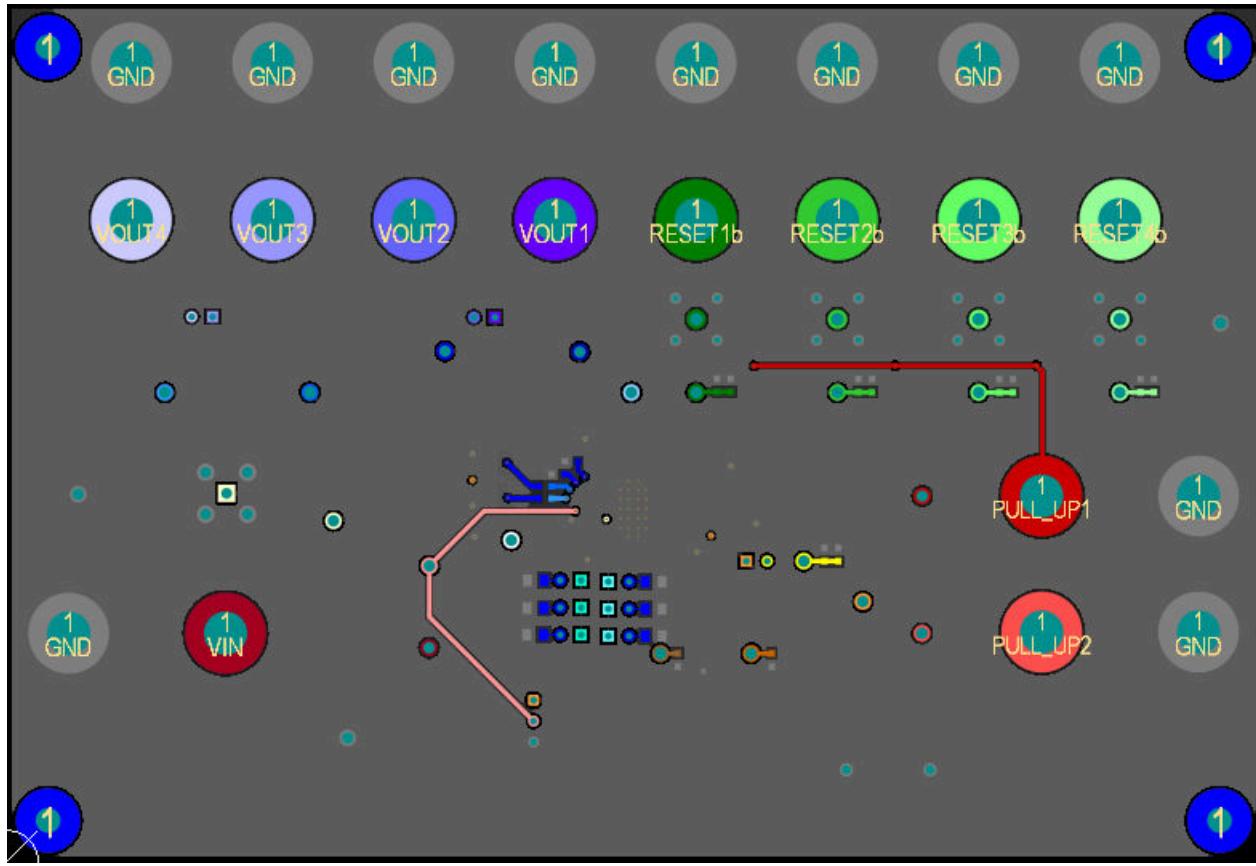

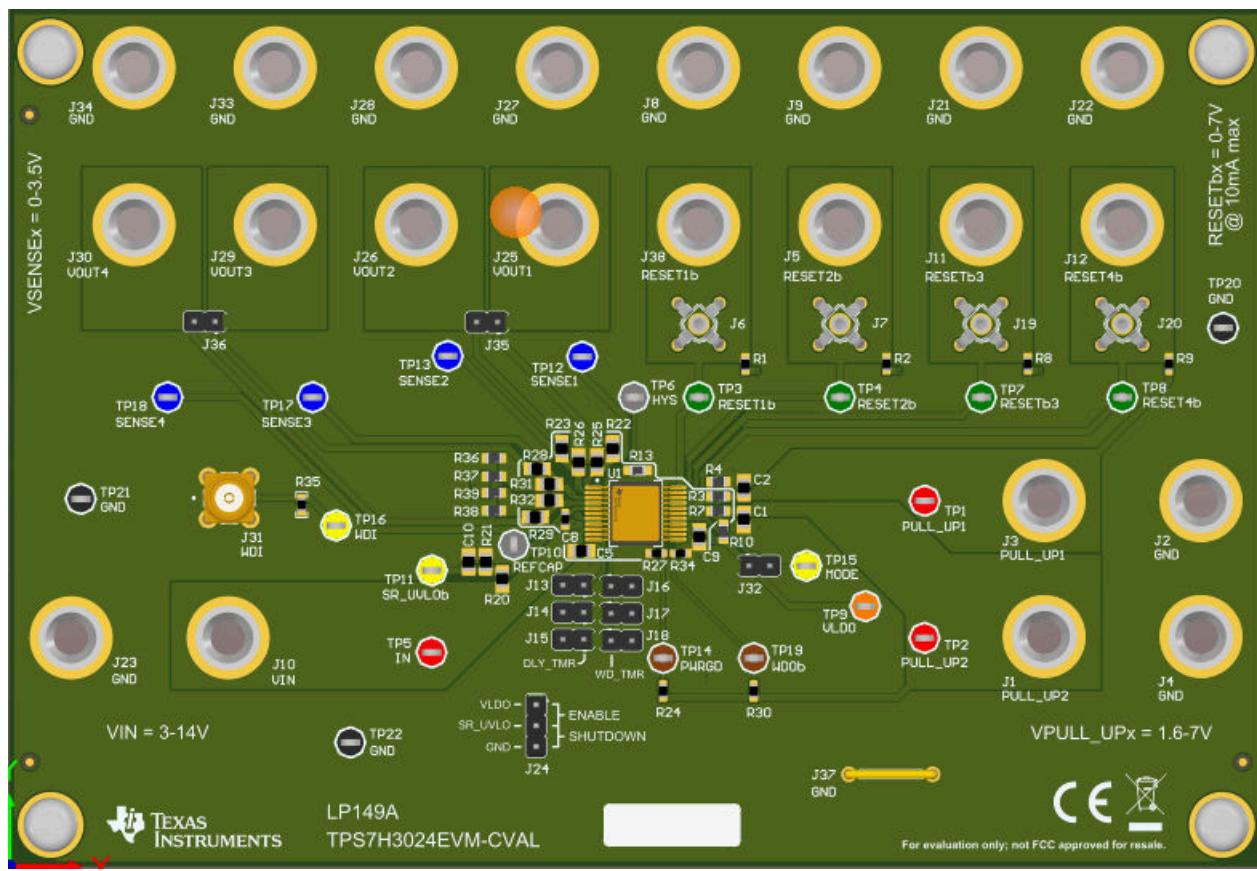

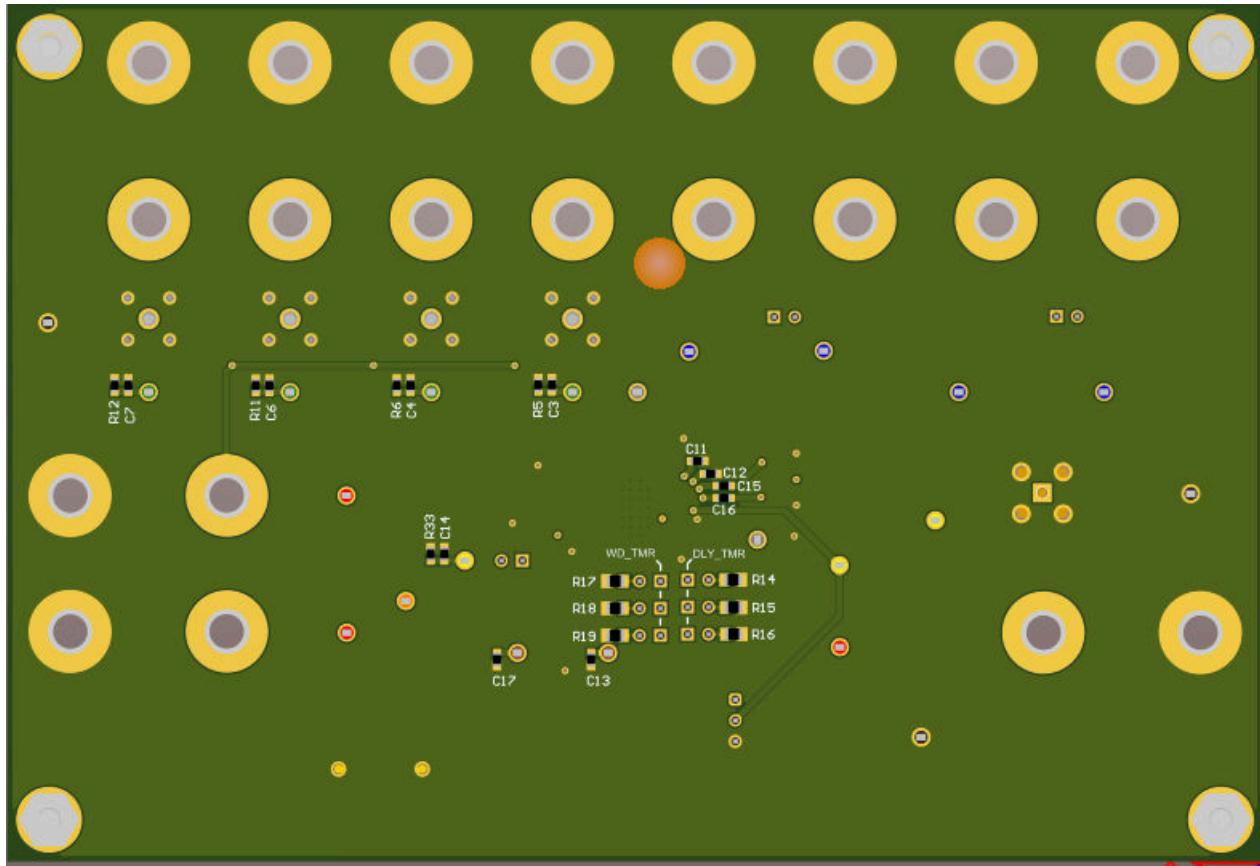

この例では、2 つの電圧レールがウィンドウトリガを使用して監視され、レールが仕様内で動作していることを確認します。以下に、設計手順と部品選定の詳細を示します。設計については、図 9-1 にまとめられています。

### 注

この例で示されているすべての計算値は、小数点以下 2 術に丸められていますが、センス分圧回路の下側の抵抗値のみは小数点以下 3 術に丸められています。

図 9-1. ウォッチドッグ タイマ付きウィンドウ電圧モニタ

### 9.2.1.1 設計要件

この設計では、信頼性の高い動作を確保するために、ウインドウコンパレータを使用して2つの電圧レールを監視する必要があります。ウインドウ監視方式が用いられているため、システム仕様の上限および下限が監視されます。また、ウォッチドッグを使用してプロセッサの一貫した実行も監視されます。スーパーバイザICは、SR\_UVLOピンを駆動する外付け抵抗分圧器を使用して、公称12Vレールの約86% (10.31V) を開始するように設定されます。

すべてのフラグはハウスキーピングプロセッサによって監視されるものとみなされ、WDOはプロセッサのノンマスク可能割り込みを駆動するために使用されます。すべての設計条件は、表9-1で定義されています。

**表9-1. 設計条件**

| パラメータ                   | 設計要件                                                                                                       | 設計結果                                                                                                                  |

|-------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| システムの公称電圧               | 12Vの入力電圧をスーパーバイザに監視し、電圧が10.3V(86%)を少なくとも2.8msの間上回ったときにICをイネーブルにします。電圧が8.5V(または71%)を下回ると、システムはディスエーブルになります。 | TPS7H3024は、SR_UVLOを使用することで外部から正確にイネーブルできます。内部基準電圧は、温度、電圧、TIDの全範囲にわたって3.1%の精度を維持します。誤差を最小限に抑えるために、0.1%の許容差を持つ抵抗を使用します。 |

| $V_{OUT1} = 3.3V$ (公称)  | 低電圧:<br>$V_{OUT1\_RISE\_UV} = 98\%$ および<br>$V_{OUT1\_FALL\_UV} = 95\%$                                     | $V_{OUT1\_RISE\_UV} = 3.25V$<br>$V_{OUT1\_FALL\_UV} = 3.15V$                                                          |

|                         | 過電圧:<br>$V_{OUT1\_RISE\_OV} = 105\%$ および<br>$V_{OUT1\_FALL\_OV} = 102\%$                                   | $V_{OUT1\_RISE\_OV} = 3.45V$<br>$V_{OUT1\_FALL\_OV} = 3.35V$                                                          |

| $V_{OUT2} = 1.8V$ (公称)  | 低電圧:<br>$V_{OUT2\_RISE\_UV} = 98\%$ および<br>$V_{OUT2\_FALL\_UV} = 97\%$                                     | $V_{OUT2\_RISE\_UV} = 1.77V$<br>$V_{OUT2\_FALL\_UV} = 1.75V$                                                          |

|                         | 過電圧:<br>$V_{OUT2\_RISE\_OV} = 103\%$ および<br>$V_{OUT2\_FALL\_OV} = 102\%$                                   | $V_{OUT2\_RISE\_OV} = 1.86V$<br>$V_{OUT2\_FALL\_OV} = 1.84V$                                                          |

| 故障状態から復帰している間でのRESETx遅延 | 公称260μsの遅延                                                                                                 | $R_{DLY\_TMR} = 10.5k\Omega$                                                                                          |

| ウォッチドッグのタイムアウト          | 公称1秒                                                                                                       | $R_{WD\_TMR} = 118k\Omega$                                                                                            |

### 9.2.1.2 詳細な設計手順

#### 9.2.1.2.1 入力電源とデカップリングコンデンサ

TPS7H3024には、次の三つの電源が必要です。

- INは、TPS7H3024 ICに電力を供給する入力電源です。この電源は、1μF以上、ピンにできるだけ近い場所でデカップリングする必要があります。この回路では、 $V_{IN} = 12V$ です。

- PULL\_UP1は、RESETx出力電圧をHIGH( $V_{OH}$ )にプログラムする入力電源です。これらの出力は、ハウスキーピングプロセッサに接続されています。この電源は、1μF以上、ピンにできるだけ近い場所でデカップリングする必要があります。このアプリケーションでは、 $V_{PULL\_UP1} = 3.3V$ です。

- PULL\_UP2は、PWRGDおよびWDO出力の出力電圧High( $V_{OH}$ )をプログラムする入力電源です。これらの出力はハウスキーピングプロセッサに接続され、特にWDOは通常WDIパルスを生成するプロセッサのノンマスカブルNMO入力に接続されます。この電源は、1μF以上、ピンにできるだけ近い場所でデカップリングする必要があります。このアプリケーションでは、 $V_{PULL\_UP1} = 3.3V$ です。

また、TPS7H3024には、良好な電気的特性および放射線耐性を得るためにデカップリングが必要な2つの安定化電圧出力を備えています。それらを以下に示します。

- REFCAP(1.2Vのリファレンス)は、以下のようすべての放射基準電圧を生成するためにデバイスで内部で使用されます。

- $V_{TH\_SENSE}$

- $I_{HYS\_SENSE}$

- $V_{TH\_SR\_UVLO}$

- $V_{TH\_WDI}$

- $V_{TH\_MODE}$

このリファレンスには、**470nF** のセラミック コンデンサをできるだけピンの近くに配置してデカップリングします。このピンには、外部に負荷を接続しないでください。

2. **VLDO** は、TPS7H3024 の内部回路に電力を供給するために使用される内部レギュレータの出力です。このレギュレータは、ピンにできるだけ近い **1μF** でデカップリングします。この **LDO** は最大 **5mA** まで負荷をかけることができます。この **LDO** は短絡に対する保護を備えていないことを理解しておくことが重要です。

### 9.2.1.2.2 SR\_UVLO スレッショルド

このアプリケーションでは、**SR\_UVLO** ピンを使用して **12V** の入力電源電圧を監視し、目的の電圧に達したときにデバイスをイネーブルします。

**IC** は、レール電圧が **10.26V** (標準公称電圧の **85.5%**) を超えるとイネーブルになります。**SR\_UVLO** のヒステリシス電圧は内部制御されているため、立ち下がり電圧は制御されません。しかし、計算値は **8.55V** (または公称電圧の **71.2%**、標準値) となります。TPS7H3024 には **2.8ms** (最大) の内部時定数 ( $t_{Start\_UP\_DELAY}$ ) があるため、**SR\_UVLO** ピンに **3.3μF** の遅延コンデンサが追加されます。このコンデンサは、 $V_{IN}$  が立ち上がりするときに **SR\_UVLO** ピンに遅延を発生させるため追加されます。このコンデンサにより、シーケンスを開始する **2** 番目の条件が追加されます。 $V_{IN} \geq 10.26V$  (標準値) が **2.8ms** 以上の間なら、**IC** がイネーブルになります。

**SR\_UVLO** の抵抗デバイダの上側抵抗を固定すると、設計要件に従って下側の抵抗を計算できます。上側の抵抗は **10kΩ** に固定されています。下側抵抗の式は式 1 を使用して、次のように計算されます。

$$V_{BOTTOM\_SR\_UVLO} = 10\text{k}\Omega \times \frac{0.599\text{V}}{10.26\text{V} - 0.599\text{V}} = 620\Omega \quad (26)$$

基準抵抗値が計算できたので、次に実際に使用する(実部品としての)抵抗を選定します。この場合、**0.1%** の許容誤差を持つ抵抗を使用して最も近い値を選定します(この特定のケースでは、基準抵抗と実際に使用する抵抗の値が同じです)

- $R_{BOTTOM\_SR\_UVLO} = 620\Omega$

実際に使用する抵抗値を用いて、スーパーバイザを有効化する上昇電圧および無効化する下降電圧を逆算することができます。式 4 と式 3 の使用:

$$V_{IN\_UVLO\_RISING\_NOMINAL}(V) = \left(1 + \frac{10\text{k}\Omega}{620\Omega}\right) \times 0.599\text{V} \cong 10.26\text{V} \quad (27)$$

$$V_{IN\_UVLO\_FALLING\_NOMINAL}(V) = \left(1 + \frac{10\text{k}\Omega}{620\Omega}\right) \times 0.496\text{V} \cong 8.50\text{V} \quad (28)$$

遅延コンデンサは、式 7、式 8、および式 6 を使って計算します。

$$R_{TH}(\Omega) = \frac{10\text{k}\Omega \times 620\Omega}{10\text{k}\Omega + 620\Omega} = 583.80\Omega \quad (29)$$

$$V_{TH}(\Omega) = \left(\frac{620\Omega}{10\text{k}\Omega + 620\Omega}\right) \times 12\text{V} = 0.70\text{V} \quad (30)$$

$$C_{DELAY}(F) \geq \frac{0.0028\text{s}}{582.8\Omega \times \ln\left(-\frac{0.7\text{V}}{0.599\text{V} - 0.7\text{V}}\right)} = 2.48\mu\text{F} \quad (31)$$

入力コンデンサには **3.3μF** のコンデンサを選びます。

### 9.2.1.2.3 SENSEx スレッショルド

SENSEx 入力は、システム レベルの境界（または制限値）に対して電圧レールを監視するために使用されます。この設計では、監視対象の出力電圧を次のように設定します。

1.  $V_{OUT1} = 3.3V$

2.  $V_{OUT2} = 1.8V$

各レールの  $V_{OUTx\_RISE}$  と  $V_{OUTx\_FALL}$  の設計は、表 9-2 で規定されています

**表 9-2. チャネルごとの立ち上がり/立ち下がり設計要件**

| チャネル | チャネル タイプ | $V_{OUTx\_NOM}$ (V) | $V_{ONx\_RISE}$ (%) | $V_{ONx\_RISE}$ (V) | $V_{ONx\_FALL}$ (%) | $V_{ONx\_FALL}$ (V) |