# TPS7H3014-SP および TPS7H3014-SEP 耐放射線特性、14V、4 チャネル シーケンサ

## 1 特長

- 耐放射線性能:

- QML 向け吸収線量 (TID) 100krad(Si)までの放射線耐性保証 (RHA)、SEP 向け 50krad(Si)

- シングル イベントランチアップ (SEL)、シングルイベントバーンアウト (SEB)、シングル イベントゲートラップチャージ (SEGR) の、最大線エネルギー付与 (LET) = 75MeV-cm<sup>2</sup>/mg (QML) および 43MeV-cm<sup>2</sup>/mg (SEP) に対する耐性

- シングル イベント機能割り込み (SEFI) およびシングル イベント過渡 (SET) の最大 LET = 75MeV-cm<sup>2</sup>/mg (QML) および 43MeV-cm<sup>2</sup>/mg (SEP) に対する耐性

- 広い電源入力電圧範囲 ( $V_{IN}$ ): 3V ~ 14V

- 単一のデバイスで最大 4 つの電圧レールのシーケンス制御と監視

- デイジーチェーン機能によりチャネル数を拡張

- 単一抵抗によりプログラム可能なグローバル タイマー:

- シーケンスのアップ / ダウン遅延

- レギュレーションまでのシーケンス アップ時間

- 逆順シーケンス ダウン

- 高精度のスレッショルド電圧とヒステリシス電流

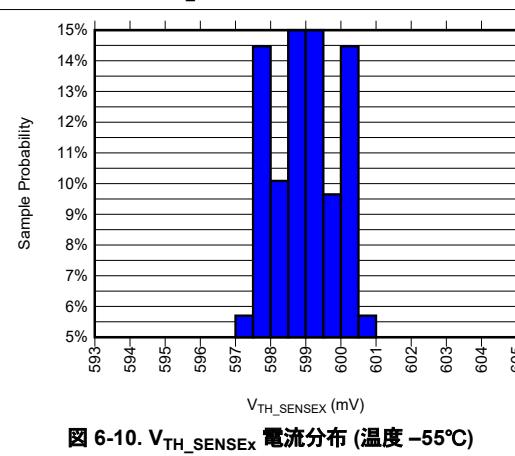

- 全体で 599mV ±1% の  $V_{TH\_SENSEx}$ : 電圧、温度、放射線 (TID)

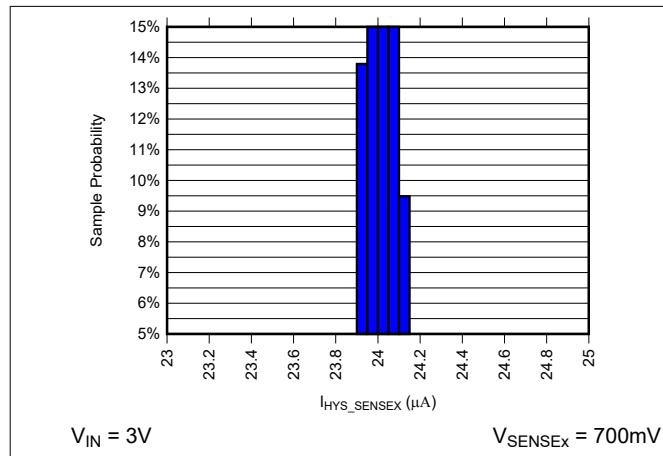

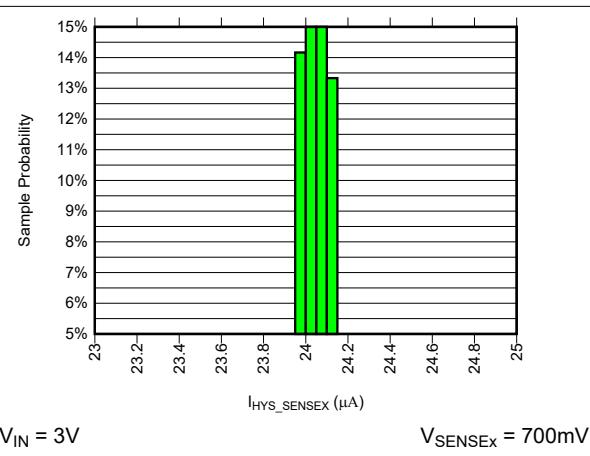

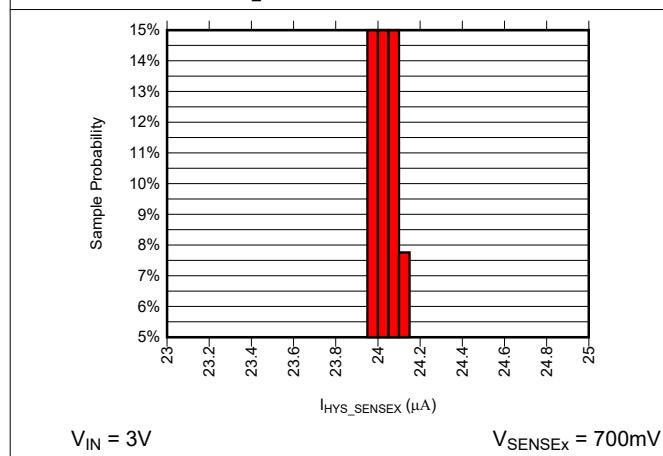

- 全体で 24μA ±3% の  $I_{HYS\_SENSEx}$ : 電圧、温度、放射線 (TID)

- 1.6V ~ 7V のプログラマブル プルアップ電圧に対応するプッシュプル出力

- グローバル EN<sub>x</sub> プルアップ ドメイン ( $V_{PULL\_UP1}$ )

- 共通の SEQ\_DONE および PWRGD プルアップ ドメイン ( $V_{PULL\_UP2}$ )

- ステートマシンに起因するフォルトを監視するための FAULT オープンドレイン出力

- ASTM E595 に準拠したガス排出試験済みのプラスチック パッケージ

- 軍用温度範囲 (-55°C ~ 125°C) を供給可能

## 2 アプリケーション

- 衛星用電源システム (EPS)

- 次のような複雑なデジタル プロセッサの制御シーケンスと監視: 宇宙アプリケーション向けの FPGA、SoC、AFE、電源システム

## 3 説明

TPS7H3014 は統合型、3V ~ 14V、4 チャネル、放射線耐性保証の電源シーケンサです。複数のデバイスをディジーチェーン構成で接続することにより、チャネル数を拡張できます。このデバイスは、アクティブ High ('ON') 入力搭載の集積回路 (IC) 向けに、シーケンス アップ / ダウン制御信号を提供します。さらに、SEQ\_DONE フラグと PWRGD フラグが、監視対象の電源ツリーのシーケンスと電源ステータスを監視するために提供されています。

正確な 599mV ±1% のスレッショルド電圧と 24μA ±3% ヒステリシス電流により、立ち上がりおよび立ち下がり監視電圧をプログラム可能です。立ち上がりおよび立ち下がり遅延時間は、単一の抵抗を使用してグローバルにプログラムされます。また、SENSE<sub>x</sub> の立ち上がり電圧を追跡するためのタイムトゥ レギュレーション タイマーが搭載されています。これらの機能に加えて、FAULT 検出ピンが組み込まれており、内部で生成されるフォルトを監視して、宇宙の電源シーケンス アプリケーションに対するシステムレベルの信頼性を向上させます。QML バリアント 5962R2320101VXC では、SMD (Standard Microcircuit Drawing) を利用できます。

### 製品情報

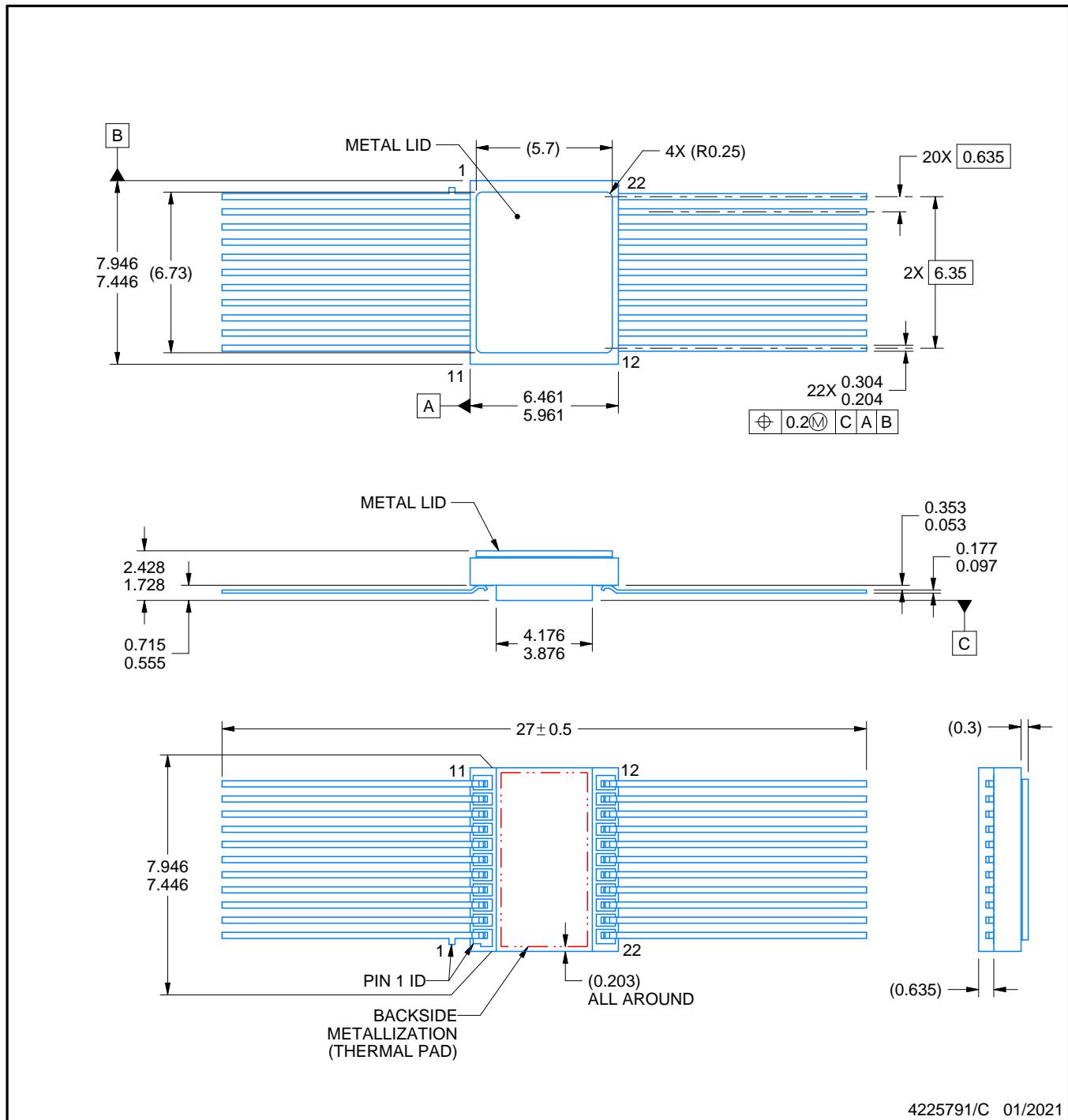

| 部品番号 (1)         | グレード (2)      | パッケージ(3)                                              |

|------------------|---------------|-------------------------------------------------------|

| 5962R2320101VXC  | QMLV-RHA      | 22 ピンのセラミック (CFP)<br>6.21mm x 7.69mm<br>質量 = 415.6mg  |

| TPS7H3014HFT/EM  | エンジニアリング サンプル |                                                       |

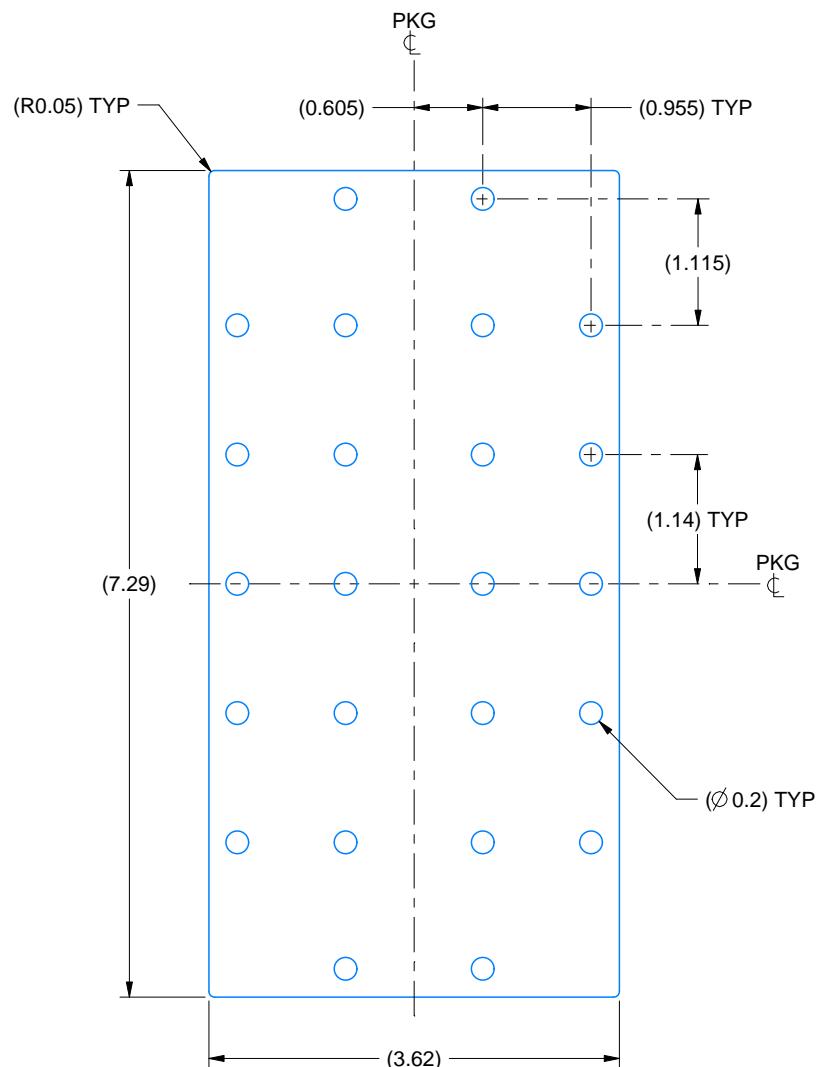

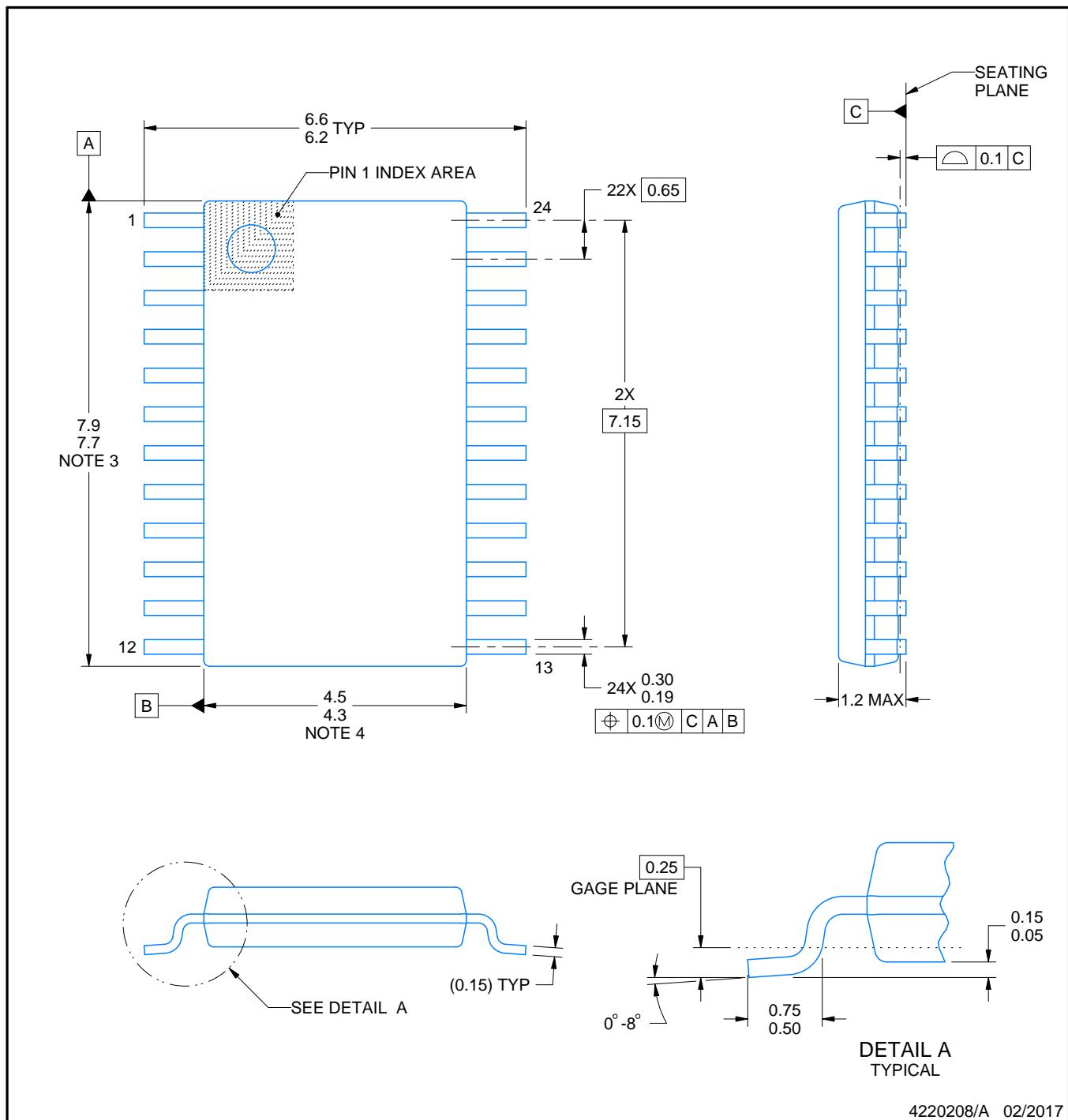

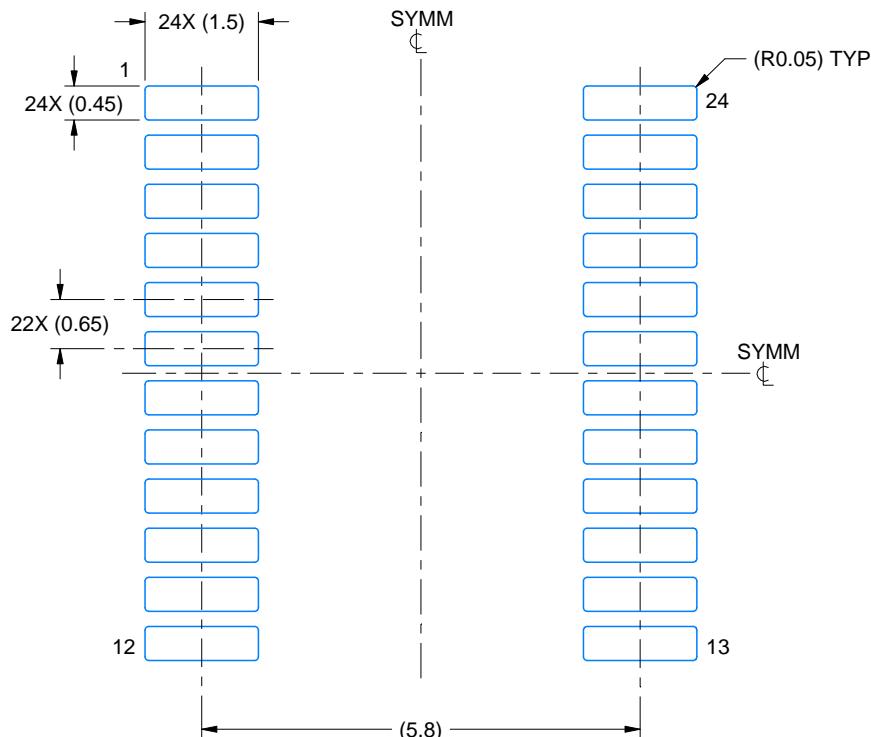

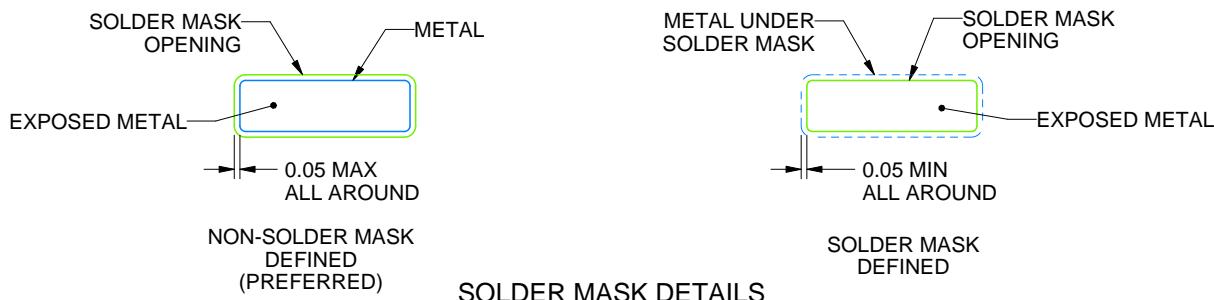

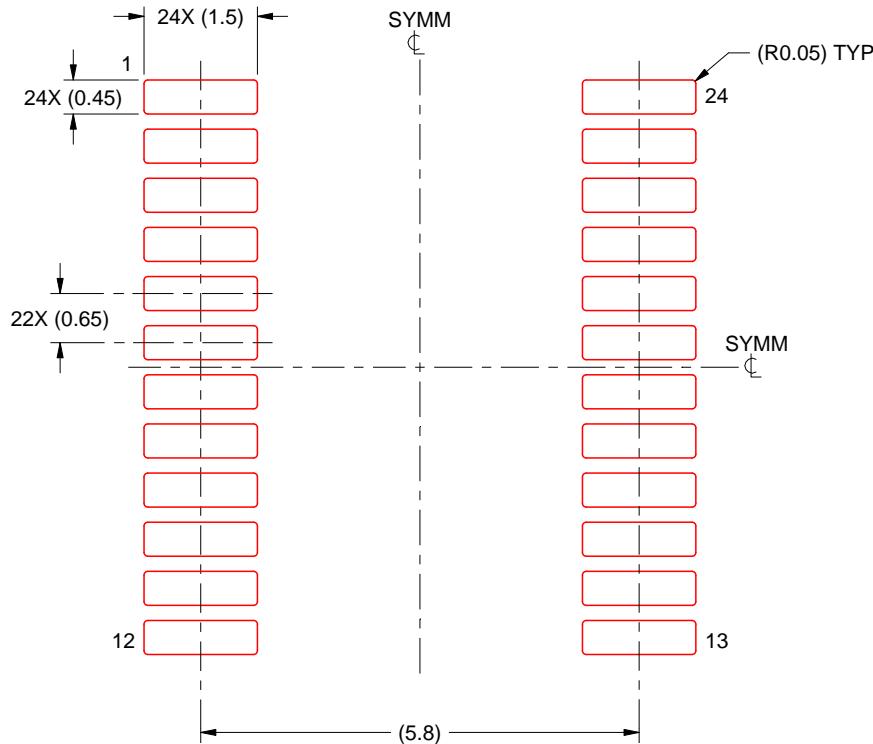

| TPS7H3014MPWTSEP | SEP           | 24 ピンのプラスチック (TSSOP)<br>4.4mm x 7.8mm<br>質量 = 102.3mg |

(1) 詳細は、「[デバイス オプション](#)」表をご覧ください。

(2) 部品のグレードについて詳細は、[SLYB235](#) をご覧ください。

(3) 寸法と質量は公称値です。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SNVSCE7](#)

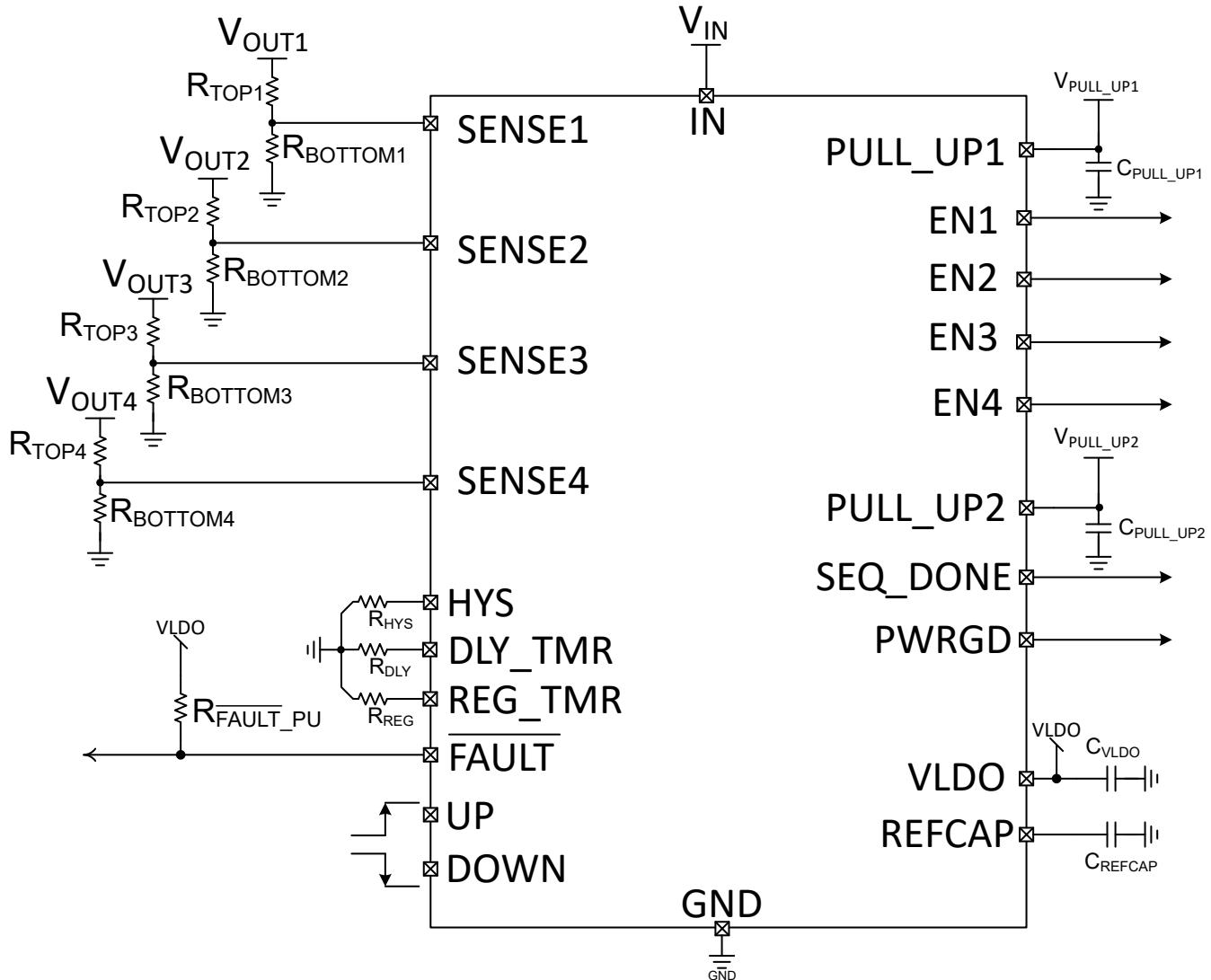

代表的なアプリケーション

## 目次

|              |    |                         |    |

|--------------|----|-------------------------|----|

| 1 特長         | 1  | 8.3 機能説明                | 26 |

| 2 アプリケーション   | 1  | 8.4 デイジー チェーン           | 43 |

| 3 説明         | 1  | 9 アプリケーションと実装           | 44 |

| 4 デバイスのオプション | 4  | 9.1 アプリケーション情報          | 44 |

| 5 ピン構成および機能  | 5  | 9.2 代表的なアプリケーション        | 44 |

| 6 仕様         | 8  | 9.3 外部要因によるシステム RESET   | 53 |

| 6.1 絶対最大定格   | 8  | 9.4 電源に関する推奨事項          | 53 |

| 6.2 ESD 定格   | 8  | 9.5 レイアウト               | 53 |

| 6.3 推奨動作条件   | 9  | 10 デバイスおよびドキュメントのサポート   | 56 |

| 6.4 熱に関する情報  | 9  | 10.1 ドキュメントのサポート        | 56 |

| 6.5 電気的特性    | 10 | 10.2 ドキュメントの更新通知を受け取る方法 | 56 |

| 6.6 タイミング要件  | 13 | 10.3 サポート・リソース          | 56 |

| 6.7 品質適合検査   | 13 | 10.4 商標                 | 56 |

| 6.8 代表的特性    | 14 | 10.5 静電気放電に関する注意事項      | 56 |

| 7 パラメータ測定情報  | 20 | 10.6 用語集                | 56 |

| 8 詳細説明       | 24 | 11 改訂履歴                 | 56 |

| 8.1 概要       | 24 | 12 メカニカル、パッケージ、および注文情報  | 57 |

| 8.2 機能ブロック図  | 25 |                         |    |

## 4 デバイスのオプション

| ジェネリック型番      | 放射線定格 <sup>(1)</sup>                                              | グレード <sup>(2)</sup>        | パッケージ          | 発注用製品型番          |

|---------------|-------------------------------------------------------------------|----------------------------|----------------|------------------|

| TPS7H3014-SP  | 100krad(Si) RLAT の TID、<br>75 MeV-cm <sup>2</sup> /mg まで DSEE フリー | QMLV-RHA                   | 22 ピン CFP HFT  | 5962R2320101VXC  |

|               | なし                                                                | エンジニアリングモデル <sup>(3)</sup> | 22 ピン CFP HFT  | TPS7H3014HFT/EM  |

| TPS7H3014-SEP | 50krad(Si) RLAT の TID、<br>43MeV-cm <sup>2</sup> /mg まで DSEE フリー   | 宇宙向けに強化されたプラスチック           | 24-ピン TSSOP PW | TPS7H3014MPWTSEP |

- (1) TID は総電離線量、DSEE は破壊的シングル イベント効果です。詳細については、関連する TID レポートおよび各製品の SEE レポートを参照してください。

- (2) 部品のグレードについて詳細は、[SLYB235](#) をご覧ください。

- (3) これらのユニットは、技術的な評価のみを目的としています。非準拠のフローで処理されています（バーンインがない、25°Cでのテストしか行わないなど）。これらのユニットは、認定、量産、放射線テスト、航空での使用には適していません。部品は、温度または動作寿命全体にわたる性能を保証されていません。

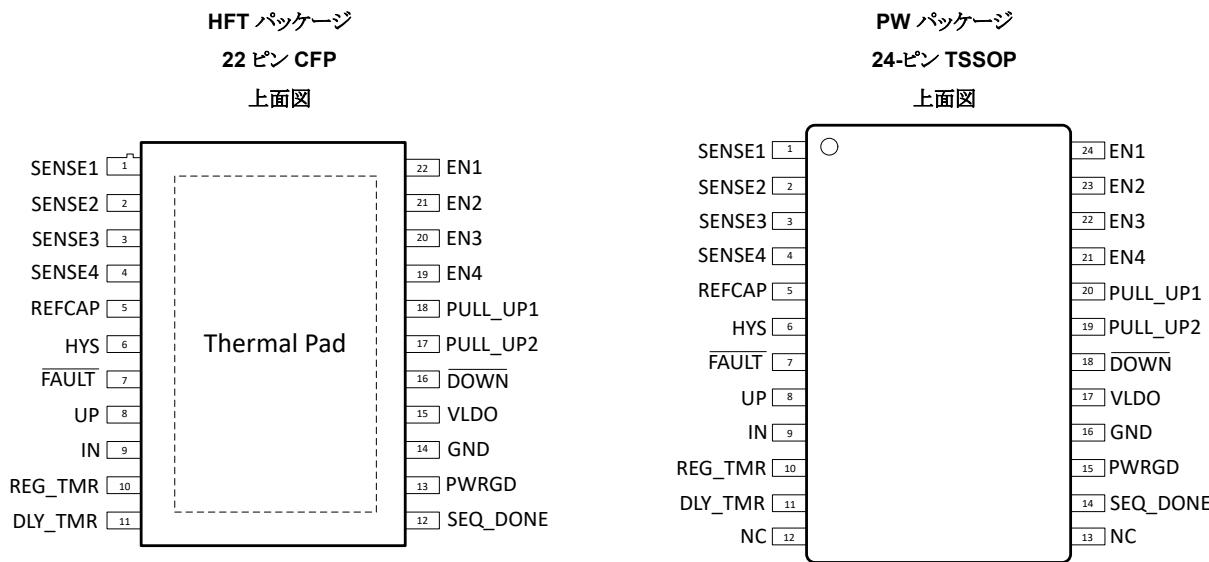

## 5 ピン構成および機能

表 5-1. ピンの機能

| ピン     |            | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                            |

|--------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | HFT (22)番号 |                    |                                                                                                                                                                                                                                                                                                               |

| SENSE1 | 1          | 1                  | パワーアップシーケンス/パワーダウンシーケンスを行うため、最初のレールのモニタリングに使用するコンパレータの非反転入力。モニタリング対象のレールと GND との間に外付けの抵抗分圧回路を接続し、その中間点を SENSE1 に接続して $V_{ON}$ および $V_{OFF}$ 電圧を設定します。このピンで 599mV(標準値)を上回る電圧は、安定化電圧レール( $V_{ON}$ )と見なされます。 $V_{OFF}$ は、 $I_{HYS}$ 電流と、分圧抵抗回路の上流側の抵抗によって設定されます。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。   |

| SENSE2 | 2          | 2                  | パワーアップシーケンス/パワーダウンシーケンスを行うため、2 番目のレールのモニタリングに使用するコンパレータの非反転入力。モニタリング対象のレールと GND との間に外付けの抵抗分圧回路を接続し、その中間点を SENSE2 に接続して $V_{ON}$ および $V_{OFF}$ 電圧を設定します。このピンで 599mV(標準値)を上回る電圧は、安定化電圧レール( $V_{ON}$ )と見なされます。 $V_{OFF}$ は、 $I_{HYS}$ 電流と、分圧抵抗回路の上流側の抵抗によって設定されます。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| SENSE3 | 3          | 3                  | パワーアップシーケンス/パワーダウンシーケンスを行うため、3 番目のレールのモニタリングに使用するコンパレータの非反転入力。モニタリング対象のレールと GND との間に外付けの抵抗分圧回路を接続し、その中間点を SENSE3 に接続して $V_{ON}$ および $V_{OFF}$ 電圧を設定します。このピンで 599mV(標準値)を上回る電圧は、安定化電圧レール( $V_{ON}$ )と見なされます。 $V_{OFF}$ は、 $I_{HYS}$ 電流と、分圧抵抗回路の上流側の抵抗によって設定されます。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| SENSE4 | 4          | 4                  | パワーアップシーケンス/パワーダウンシーケンスを行うため、4 番目のレールのモニタリングに使用するコンパレータの非反転入力。モニタリング対象のレールと GND との間に外付けの抵抗分圧回路を接続し、その中間点を SENSE4 に接続して $V_{ON}$ および $V_{OFF}$ 電圧を設定します。このピンで 599mV(標準値)を上回る電圧は、安定化電圧レール( $V_{ON}$ )と見なされます。 $V_{OFF}$ は、 $I_{HYS}$ 電流と、分圧抵抗回路の上流側の抵抗によって設定されます。 <a href="#">上部および下部の抵抗分圧回路の設計式</a> を参照してください。 |

| REFCAP | 5          | 5                  | O 1.2V 内部リファレンス。GND との間に 470nF の外付けコンデンサが必要です。このピンには、負荷をかけないでください。                                                                                                                                                                                                                                            |

| HYS    | 6          | 6                  | O ヒステリシス。このピンと GND の間に 50kΩ 抵抗を接続して、SENSE1 と SENSE4 でのヒステリシス電流(標準 24 μA)をプログラムします。精度を保つため、許容誤差 0.1% の抵抗を使用することを推奨します。                                                                                                                                                                                         |

表 5-1. ピンの機能 (続き)

| ピン       |            |            | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                               |

|----------|------------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | HFT (22)番号 | PW (24) 番号 |                    |                                                                                                                                                                                                                                  |

| FAULT    | 7          | 7          | O                  | 障害。オープンドレイン出力は、ステートマシンによって強制的に Low にされたもので、内部で生成された障害を示します。 $10\text{k}\Omega$ を使用してこのピンを VLDO にプルアップすることを推奨します。ただし、デバイスの動作中に値が変化せず安定している場合に限り、別の外部電圧源をプルアップとして使用することができます。                                                      |

| UP       | 8          | 8          | I                  | コンパレータの非反転入力。電圧が $599\text{mV}$ (標準値) を超えると立ち上がりエッジが発生し、パワーアップシーケンスが開始されます。このピンは、外部コントローラで駆動することも、外部の抵抗分割回路を介してメインレールに接続し、その中間点を UP ピンに接続してシーケンスを自動的に駆動させることもできます。ノイズ安定のために $100\text{mV}$ (標準値) の固定ヒステリシスが存在します。                |

| IN       | 9          | 9          | I                  | デバイスへの入力電源。3 V ~ 14 V の入力電圧範囲。 $0.1\mu\text{F}$ 以上のコンデンサを、ピンのできるだけ近くに接続してください。                                                                                                                                                   |

| REG_TMR  | 10         | 10         | I/O                | レギュレーション タイマの時間。 $10.5\text{k}\Omega$ と $1.18\text{M}\Omega$ の間の GND に抵抗を接続して、SENSE <sub>x</sub> レールがレギュレーションしきい値(V ON)に達するまでの許容時間を設定します。遅延時間は、 $0.25\text{ms} \sim 25\text{ms}$ の範囲で調整できます。この機能を無効にする場合は、このピンをフローティング状態にしてください。 |

| DLY_TMR  | 11         | 11         | I/O                | 遅延タイマ。 $10.5\text{k}\Omega$ と $1.18\text{M}\Omega$ の間の GND に抵抗を接続して、パワーアップおよびパワーダウンシーケンスの遅延時間を設定します。遅延時間は、 $0.25\text{ms} \sim 25\text{ms}$ の範囲で調整できます。システム上、遅延が不要であれば、このピンをフローティング状態にしてください。                                    |

| SEQ_DONE | 12         | 14         | O                  | シーケンスの完了。PULL_UP2 入力電源電圧によって $V_{OH}$ レベルを設定したプッシュプル出力。パワーアップまたはパワーダウンシーケンスの完了を示します。                                                                                                                                             |

| PWRGD    | 13         | 15         | O                  | パワーグッド。入力電源電圧 (PULL_UP2) により $V_{OH}$ レベルを設定したプッシュプル出力。すべてのレール (SENSE1 から SENSE4) が規定範囲内であることを示します。                                                                                                                              |

| GND      | 14         | 16         | —                  | グランド                                                                                                                                                                                                                             |

| VLDO     | 15         | 17         | O                  | 内部レギュレータの出力。GND との間に少なくとも $1\mu\text{F}$ の外部コンデンサが必要です。このレギュレータで許容される負荷は次のとおりです。 $10\text{k}\Omega$ 抵抗を使用した FAULT プルアップ、または必要に応じて SENSE2 と SENSE4 を直接接続することによる未使用チャネルのタンオフ。                                                      |

| DOWN     | 16         | 18         | I                  | コンパレータの非反転入力。電圧が $498\text{mV}$ (標準値) を下回ると、立ち下がりエッジが発生し、パワーダウンシーケンスが開始されます。このピンは、外部コントローラで駆動することも、外部の抵抗分割回路を介してメインレールに接続し、その中間点を DOWN ピンに接続してシーケンスを自動的に駆動させることもできます。ノイズ安定のために $100\text{mV}$ (標準値) の固定ヒステリシスが存在します。             |

| PULL_UP2 | 17         | 19         | I                  | SEQ_DONE および PWRGD のプッシュプル出力段のプルアップ電圧をプログラムするための入力電源電圧。 $1\mu\text{F}$ 以上のコンデンサを、ピンのできるだけ近くに接続してください。                                                                                                                            |

| PULL_UP1 | 18         | 20         | I                  | EN1 から EN4 のプッシュプル出力段のグローバル プルアップ電圧をプログラムするための入力電源電圧。 $1\mu\text{F}$ 以上のコンデンサを、ピンのできるだけ近くに接続してください。                                                                                                                              |

| EN4      | 19         | 21         | O                  | 有効化 4。PULL_UP1 入力電源電圧によって $V_{OH}$ レベルが設定されたプッシュプル出力。デバイスの論理イネーブル信号に接続して、SENSE4 によって制御、モニタします。                                                                                                                                   |

| EN3      | 20         | 22         | O                  | 有効化 3。PULL_UP1 入力電源電圧によって $V_{OH}$ レベルが設定されたプッシュプル出力。デバイスの論理イネーブル信号に接続して、SENSE3 によって制御、モニタします。                                                                                                                                   |

| EN2      | 21         | 23         | O                  | 有効化 2。PULL_UP1 入力電源電圧によって $V_{OH}$ レベルが設定されたプッシュプル出力。デバイスの論理イネーブル信号に接続して、SENSE2 によって制御、モニタします。                                                                                                                                   |

| EN1      | 22         | 24         | O                  | 有効化 1。PULL_UP1 入力電源電圧によって $V_{OH}$ レベルが設定されたプッシュプル出力。デバイスの論理イネーブル信号に接続して、SENSE1 によって制御、モニタします。                                                                                                                                   |

| NC       | —          | 12, 13     | —                  | 接続なし。このピンは内部接続されていません。電荷の蓄積を防ぐため、これらのピンを GND に接続することを推奨しますが、これらのピンはオープンのままにすることも、GND と $V_{IN}$ の範囲の任意の電圧に接続することもできます。                                                                                                           |

| サーマル パッド |            | —          | —                  | 内部グランド。効果的な放熱のため、この金属サーマル パッドは大きなグランド プレーンに接続することを推奨します。                                                                                                                                                                         |

**表 5-1. ピンの機能 (続き)**

| ピン    |            |            | I/O <sup>(1)</sup> | 説明                                          |

|-------|------------|------------|--------------------|---------------------------------------------|

| 名称    | HFT (22)番号 | PW (24) 番号 |                    |                                             |

| 金属製ふた | ふた         |            | —                  | このふたは、シール リングを介してサーマル パッドと GND に内部接続されています。 |

(1) I = 入力、O = 出力、I/O = 入力または出力、— = その他

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲(特に注記のない限り)(1) (2)

|       |                             | 最小値  | 最大値 | 単位 |

|-------|-----------------------------|------|-----|----|

| 入力電圧  | IN                          | -0.3 | 16  | V  |

|       | UP、DOWN                     | -0.3 | 7.5 |    |

|       | SENSE1、SENSE2、SENSE3、SENSE4 | -0.3 | 3.6 |    |

|       | PULL_UP1、PULL_UP2           | -0.3 | 7.5 |    |

|       | FAULT                       | -0.3 | 7.5 |    |

|       | DLY_TMR、REG_TMR             | -0.3 | 3.6 |    |

| 出力電圧  | VLDO                        | -0.3 | 3.6 | V  |

|       | EN1、EN2、EN3、EN4             | -0.3 | 7.5 |    |

|       | REFCAP                      | -0.3 | 2   |    |

|       | HYS                         | -0.3 | 3.6 |    |

|       | SEQ_DONE、PWRGD              | -0.3 | 7.5 |    |

| 出力電流  | EN1、EN2、EN3、EN4             | -20  | 20  | mA |

|       | SEQ_DONE、PWRGD              | -20  | 20  |    |

| 接合部温度 | T <sub>J</sub>              | -55  | 150 | °C |

| 保存温度  | T <sub>stg</sub>            | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、GND を基準としたものです。

### 6.2 ESD 定格

|                  |      | 値                                                                | 単位    |

|------------------|------|------------------------------------------------------------------|-------|

| V <sub>ESD</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、すべてのピン <sup>(1)</sup>      | ±2000 |

|                  |      | 荷電デバイスモデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

動作温度範囲全体に対し、 $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に注記のない限り)<sup>(1)</sup>

|            |                                | 最小値   | 公称値 | 最大値 | 単位         |

|------------|--------------------------------|-------|-----|-----|------------|

| 入力電圧       | IN                             | 3     |     | 14  | V          |

|            | UP, DOWN                       | 0     |     | 7   |            |

|            | SENSE1, SENSE2, SENSE3, SENSE4 | 0     |     | 3.5 |            |

|            | PULL_UP1, PULL_UP2             | 1.6   |     | 7   |            |

|            | FAULT                          | 0     |     | 7   |            |

| 出力電圧       | EN1, EN2, EN3, EN4             | 0     |     | 7   | V          |

|            | SEQ_DONE, PWRGD                | 0     |     | 7   |            |

| 出力電流       | EN1, EN2, EN3, EN4             | -10   |     | 10  | mA         |

|            | SEQ_DONE, PWRGD                | -10   |     | 10  |            |

|            | FAULT                          | -2    |     |     |            |

| 接合部温度      | $T_J$                          | -55   |     | 125 | °C         |

| 入力電圧スルーレート | $SR_{IN}$                      | 0.001 |     | 10  | V/ $\mu$ s |

(1) すべての電圧値は、GND を基準としたものです。

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | TPS7H3014-SEP | TPS7H3014-SP | 単位   |

|----------------------|-------------------|---------------|--------------|------|

|                      |                   | PW (TSSOP)    | HFT (CFP)    |      |

|                      |                   | 24 ピン         | 22 ピン        |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 66            | 34.2         | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | -             | 7.7          | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 33.8          | 17.2         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 16            | 16.9         | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 0.4           | 8.6          | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 33.3          | 17           | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 6.5 電気的特性

$3V \leq V_{IN} \leq 14V$ 、 $R_{DLY\_TMR} = 10.5k\Omega$ 、 $R_{REG\_TMR} = 10.5k\Omega$ 、 $C_{REFCAP} = 470nF$ 、 $C_{VLDO} = 1\mu F$ 、 $V_{PULL\_UP1} = 3.3V$ 、 $V_{PULL\_UP2} = 3.3V$ 、 $C_{PULL\_UP1} = 1\mu F$ 、 $C_{PULL\_UP2} = 1\mu F$  全体、動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )。特に注記のない限り、QML RHA デバイスの  $T_A = 25^{\circ}C$  でのグループ E 放射線テストを含みます<sup>(1) (2)</sup>

| パラメータ                                          | テスト条件                       |                                                                            | サブグループ <sup>(3)</sup> | 最小値     | 標準値  | 最大値   | 単位                     |

|------------------------------------------------|-----------------------------|----------------------------------------------------------------------------|-----------------------|---------|------|-------|------------------------|

| <b>電源電圧および電流</b>                               |                             |                                                                            |                       |         |      |       |                        |

| $I_{Q\_IN}$                                    | $V_{IN}$ 静止電流               | すべての出力がフローティング状態で、パワーアップおよびパワーダウンシーケンスを待機している状態。 <a href="#">状態図</a> を参照   | 1, 2, 3               | 2.5     | 4    | mA    |                        |

| $UVLO_{RISE}$                                  | $V_{IN}$ 立ち上がり低電圧ロックアウト     |                                                                            | 1, 2, 3               | 2.72    | 2.79 | 2.84  | V                      |

| $UVLO_{FALL}$                                  | $V_{IN}$ の立ち下がり定電圧ロックアウト    |                                                                            | 1, 2, 3               | 2.59    | 2.64 | 2.69  |                        |

| $V_{LDO}$                                      | 内部リニアレギュレータの出力電圧            | $5V \leq V_{IN} \leq 14V$                                                  | 1, 2, 3               | 3.19    | 3.29 | 3.38  | V                      |

|                                                |                             | $V_{IN} < 3.24V$                                                           | 1, 2, 3               | 97%     | 99%  |       | $\times V_{IN}$        |

| REFCAP                                         | 内部バンドギャップ電圧                 |                                                                            | 1, 2, 3               | 1.188   | 1.2  | 1.212 |                        |

| $V_{POR\_IN}$                                  | パワー オンリセット電圧 <sup>(4)</sup> | $1.6V \leq V_{PULL\_UPx} \leq 7V$ , $V_{OL} \leq 320mV$ , $I_{ENx} = -2mA$ | 1, 2, 3               | 1.41    | 2    |       | V                      |

| $V_{POR\_PULL\_UPx}$                           | パワー オンリセット電圧 <sup>(5)</sup> | $V_{IN} = 0V$ , $V_{OL} = 320mV$ で $I_{OUT} = -100\mu A$                   | 1, 2, 3               | 0.89    | 1.4  |       |                        |

| <b>SENSE1 ~ SENSE4, UP および DOWN コンパレータ入力</b>   |                             |                                                                            |                       |         |      |       |                        |

| $V_{TH\_SENSEx}$                               | SENSEx のスレッショルド電圧           |                                                                            | 1, 2, 3               | 593     | 599  | 605   | mV                     |

| $I_{HYS\_SENSEx}$                              | SENSEx ヒステリシス電流             | $V_{SENSEx} = 700mV$                                                       | 1, 2, 3               | 23.28   | 24   | 24.72 | $\mu A$                |

| $I_{LKG\_SENSEx}$                              | SENSEx での入力リーグ電流            | $V_{SENSEx} = 500mV$                                                       | 1, 2, 3               | 2       | 100  |       | nA                     |

| $V_{TH\_UP}$                                   | UP の立ち上がりスレッショルド電圧          |                                                                            | 1, 2, 3               | 580     | 598  | 615   | mV                     |

| $V_{TH\_DOWN}$                                 | DOWN のしきい値電圧の下降             |                                                                            | 1, 2, 3               | 483     | 498  | 512   | mV                     |

| $V_{HYS\_UP\_DOWN}$                            | UP および DOWN のヒステリシス電圧       |                                                                            | 1, 2, 3               | 100     |      |       | mV                     |

| $I_{LKG\_UP\_DOWN}$                            | UP および DOWN 時の入力リーグ電流       | $V_{UP} = V_{DOWN} = 500mV$                                                | 1, 2, 3               | 2       | 100  |       | nA                     |

| $V_{TURN\_OFF}$                                | チャネル 2, 3, 4 のターンオフ電圧       |                                                                            | 1, 2, 3               | 87%     | 89%  | 91%   | $\times VLDO$          |

| <b>EN1 ~ EN4, SEQ_DONE および PWRGD のプッシュプル出力</b> |                             |                                                                            |                       |         |      |       |                        |

| $V_{OL\_ENx}$                                  | Low レベル ENx 出力電圧            | $1.6V \leq V_{PULL\_UP1} \leq 7V$                                          | $I_{LOAD} = -2mA$     | 1, 2, 3 |      | 10%   | $\times V_{PULL\_UP1}$ |

|                                                |                             |                                                                            | $I_{LOAD} = -10mA$    | 1, 2, 3 |      | 25%   |                        |

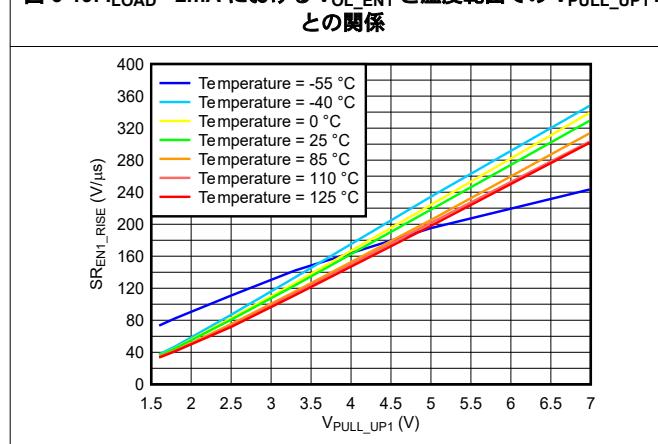

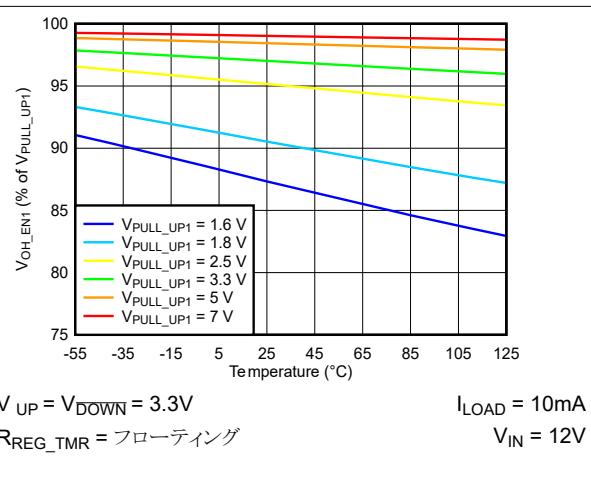

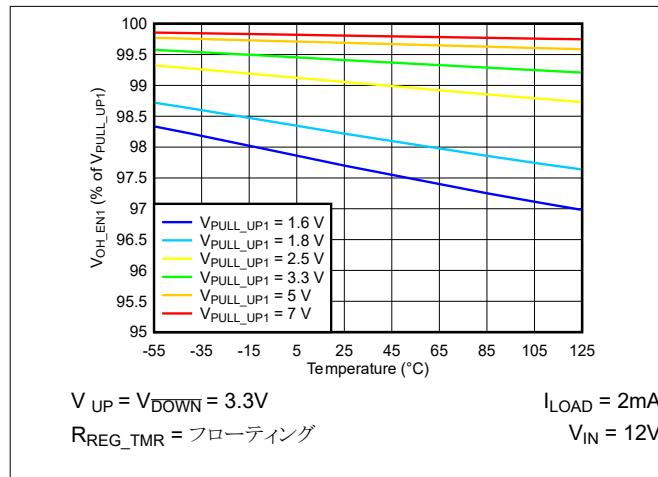

| $V_{OH\_ENx}$                                  | High レベル ENx 出力電圧           | $1.6V \leq V_{PULL\_UP1} \leq 7V$                                          | $I_{LOAD} = 2mA$      | 1, 2, 3 | 90%  |       |                        |

|                                                |                             |                                                                            | $I_{LOAD} = 10mA$     | 1, 2, 3 | 70%  |       |                        |

## 6.5 電気的特性 (続き)

$3V \leq V_{IN} \leq 14V$ 、 $R_{DLY\_TMR} = 10.5k\Omega$ 、 $R_{REG\_TMR} = 10.5k\Omega$ 、 $C_{REFCAP} = 470nF$ 、 $C_{VLDO} = 1\mu F$ 、 $V_{PULL\_UP1} = 3.3V$ 、 $V_{PULL\_UP2} = 3.3V$ 、 $C_{PULL\_UP1} = 1\mu F$ 、 $C_{PULL\_UP2} = 1\mu F$  全体、動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )。特に注記のない限り、QML RHA デバイスの  $T_A = 25^{\circ}C$  でのグループ E 放射線テストを含みます<sup>(1) (2)</sup>

| パラメータ                       |                           | テスト条件                                                                    |                                   | サブグループ <sup>(3)</sup> | 最小値 | 標準値 | 最大値                    | 単位 |

|-----------------------------|---------------------------|--------------------------------------------------------------------------|-----------------------------------|-----------------------|-----|-----|------------------------|----|

| $V_{OL\_SEQ\_DONE}$         | Low レベル SEQ_DONE 出力電圧     | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                        | $I_{LOAD} = -2mA$                 | 1, 2, 3               | 10% |     | $\times V_{PULL\_UP2}$ |    |

|                             |                           |                                                                          | $I_{LOAD} = -10mA$                | 1, 2, 3               | 25% |     |                        |    |

| $V_{OH\_SEQ\_DONE}$         | High レベル SEQ_DONE 出力電圧    | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                        | $I_{LOAD} = 2mA$                  | 1, 2, 3               | 90% |     |                        |    |

|                             |                           |                                                                          | $I_{LOAD} = 10mA$                 | 1, 2, 3               | 70% |     |                        |    |

| $V_{OL\_PWRGD}$             | Low レベル PWRGD 出力電圧        | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                        | $I_{LOAD} = -2mA$                 | 1, 2, 3               | 10% |     |                        |    |

|                             |                           |                                                                          | $I_{LOAD} = -10mA$                | 1, 2, 3               | 25% |     |                        |    |

| $V_{OH\_PWRGD}$             | High レベル PWRGD 出力電圧       | $1.6V \leq V_{PULL\_UP2} \leq 7V$                                        | $I_{LOAD} = 2mA$                  | 1, 2, 3               | 90% |     |                        |    |

|                             |                           |                                                                          | $I_{LOAD} = 10mA$                 | 1, 2, 3               | 70% |     |                        |    |

| $Pull\_UPx_{LKG}$           | PULL_UP x リーク電流           | $V_{PULL\_UPx} = 7V$                                                     | 1, 2, 3                           |                       | 48  | 121 | $\mu A$                |    |

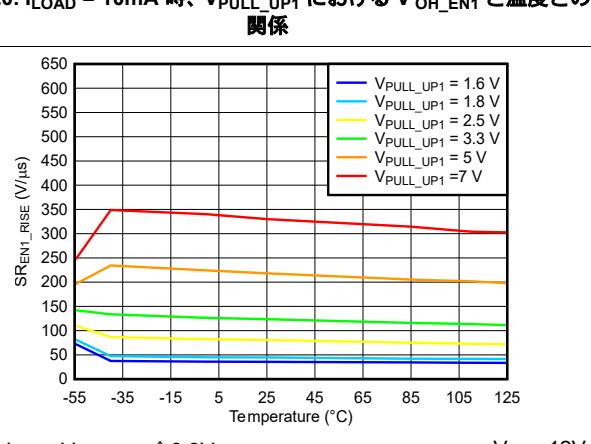

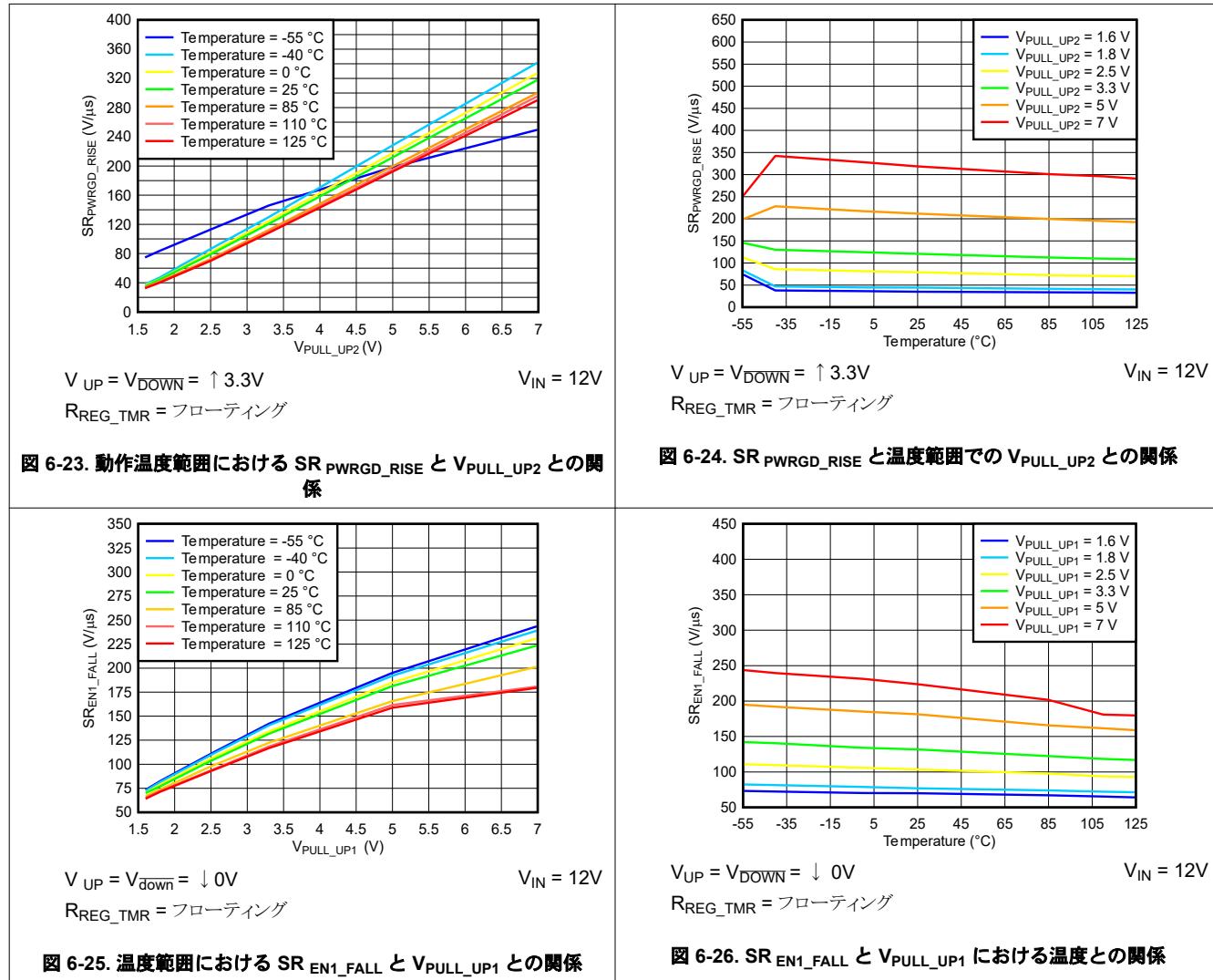

| $SR_{ENx\_RISE}$            | イネーブル立ち上がり出力電圧のスルーレート     | $V_{PULL\_UP1}$ の 10% ~ 90%、 $R_{LOAD} = 50k\Omega$ 、 $C_{LOAD} = 100pF$ | $1.6V \leq V_{PULL\_UP1} \leq 7V$ | 9, 10, 11             | 17  | 125 |                        |    |

| $SR_{SEQ\_DONE\_RISE}$      | SEQ_DONE 立ち上がり出力電圧スルーレート  | $V_{PULL\_UP2}$ の 10% ~ 90%、 $R_{LOAD} = 50k\Omega$ 、 $C_{LOAD} = 100pF$ | $1.6V \leq V_{PULL\_UP2} \leq 7V$ | 9, 10, 11             | 17  | 125 | $V/\mu s$              |    |

| $SR_{PWRGD\_RISE}$          | PWRGD 立ち上がり出力電圧のスルーレート    |                                                                          |                                   | 9, 10, 11             | 17  | 125 |                        |    |

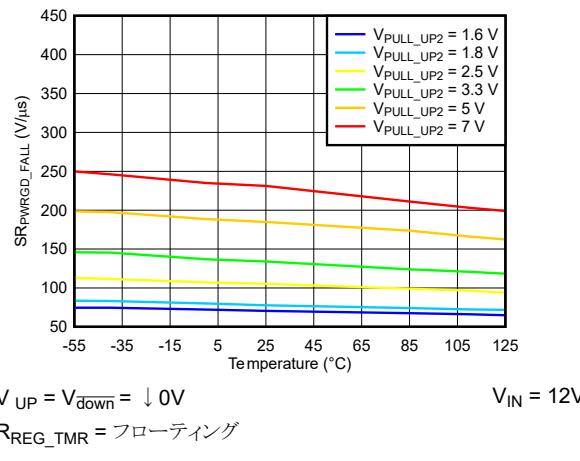

| $SR_{ENx\_FALL}$            | イネーブルの立ち下がり出力電圧スルーレート     | $V_{PULL\_UP1}$ の 90% ~ 10%、 $R_{LOAD} = 50k\Omega$ 、 $C_{LOAD} = 100pF$ | $1.6V \leq V_{PULL\_UP1} \leq 7V$ | 9, 10, 11             | 44  | 126 |                        |    |

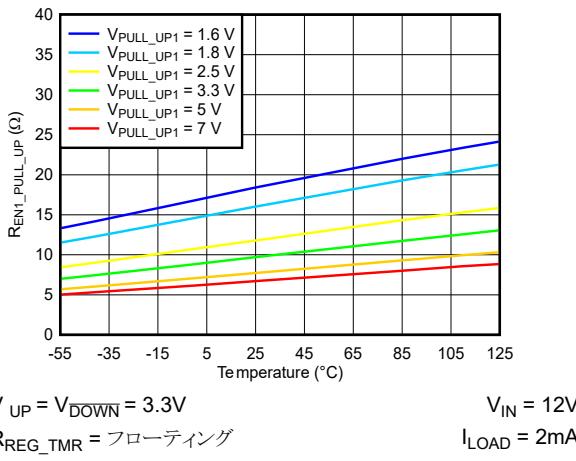

| $SR_{SEQ\_DONE\_FALL}$      | SEQ_DONE 立ち下がり出力電圧のスルーレート |                                                                          |                                   | 9, 10, 11             | 44  | 126 |                        |    |

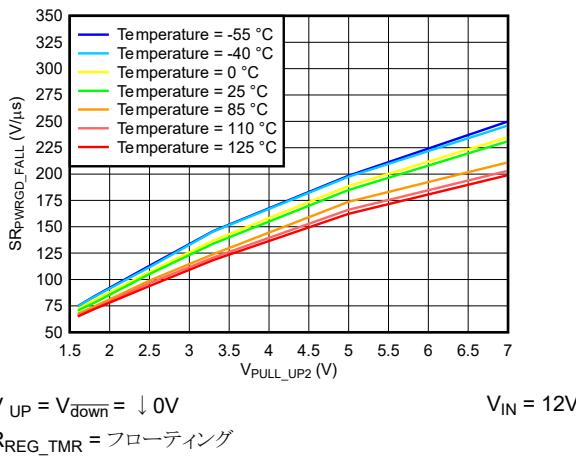

| $SR_{PWRGD\_FALL}$          | PWRGD 立ち下がり出力電圧のスルーレート    |                                                                          |                                   | 9, 10, 11             | 44  | 126 |                        |    |

| $R_{ENx\_PULL\_UP}$         | EN PMOS ソース出力抵抗           | $I_{LOAD} = 2mA$                                                         | $V_{PULL\_UP1} = 1.6V$            | 1, 2, 3               | 18  |     | $\Omega$               |    |

|                             |                           |                                                                          | $V_{PULL\_UP1} = 7V$              | 1, 2, 3               | 7   |     |                        |    |

| $R_{SEQ\_DONE\_PULL\_UP}$   | SEQ_DONE PMOS ソース出力抵抗     | $I_{LOAD} = 2mA$                                                         | $V_{PULL\_UP2} = 1.6V$            | 1, 2, 3               | 18  |     |                        |    |

|                             |                           |                                                                          | $V_{PULL\_UP2} = 7V$              | 1, 2, 3               | 7   |     |                        |    |

| $R_{PWRGD\_PULL\_UP}$       | PWRGD PMOS ソース出力抵抗        | $I_{LOAD} = 2mA$                                                         | $V_{PULL\_UP2} = 1.6V$            | 1, 2, 3               | 18  |     |                        |    |

|                             |                           |                                                                          | $V_{PULL\_UP2} = 7V$              | 1, 2, 3               | 7   |     |                        |    |

| $R_{ENx\_PULL\_DOWN}$       | EN NMOS シンク出力抵抗           | $I_{LOAD} = -2mA, 1.6V \leq V_{PULL\_UP1} \leq 7V$                       | 1, 2, 3                           |                       | 7   | 28  |                        |    |

| $R_{SEQ\_DONE\_PULL\_DOWN}$ | SEQ_DONE NMOS シンク出力抵抗     | $I_{LOAD} = -2mA, 1.6V \leq V_{PULL\_UP1} \leq 7V$                       | 1, 2, 3                           |                       | 7   | 28  |                        |    |

| $R_{PWRGD\_PULL\_DOWN}$     | PWRGD NMOS シンク出力抵抗        | $I_{LOAD} = -2mA, 1.6V \leq V_{PULL\_UP1} \leq 7V$                       | 1, 2, 3                           |                       | 7   | 28  |                        |    |

| <b>FAULT 出力</b>             |                           |                                                                          |                                   |                       |     |     |                        |    |

| $R_{FAULT\_PULL\_DOWN}$     | FAULT プルダウン抵抗             | $I_{FAULT} = 100\mu A$                                                   | 1, 2, 3                           | 131                   |     | 512 | $\Omega$               |    |

| $I_{LKG\_FAULT}$            | FAULT リーク電流               | $V_{FAULT} = 7V$                                                         | 1, 2, 3                           | 23                    |     | 600 | $nA$                   |    |

| <b>熱保護</b>                  |                           |                                                                          |                                   |                       |     |     |                        |    |

| $T_{SD\_ENTER}$             | サーマル シャットダウン入 口温度         |                                                                          |                                   | 177                   |     |     | $^{\circ}C$            |    |

| $T_{SD\_EXIT}$              | サーマル シャットダウン出 口温度         |                                                                          |                                   | 164                   |     |     |                        |    |

## 6.5 電気的特性 (続き)

$3V \leq V_{IN} \leq 14V$ 、 $R_{DLY\_TMR} = 10.5k\Omega$ 、 $R_{REG\_TMR} = 10.5k\Omega$ 、 $C_{REFCAP} = 470nF$ 、 $C_{VLDO} = 1\mu F$ 、 $V_{PULL\_UP1} = 3.3V$ 、 $V_{PULL\_UP2} = 3.3V$ 、 $C_{PULL\_UP1} = 1\mu F$ 、 $C_{PULL\_UP2} = 1\mu F$  全体、動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )。特に注記のない限り、QML RHA デバイスの  $T_A = 25^{\circ}C$  でのグループ E 放射線テストを含みます<sup>(1) (2)</sup>

| パラメータ                     | テスト条件         | サブグループ <sup>(3)</sup>        | 最小値       | 標準値   | 最大値   | 単位    |

|---------------------------|---------------|------------------------------|-----------|-------|-------|-------|

| <b>レギュレーション タイマの遅延と時間</b> |               |                              |           |       |       |       |

| $t_{DLY\_TMR}$            | 遅延時間          | $R_{DLY\_TMR} = 10.5k\Omega$ | 9, 10, 11 | 0.205 | 0.268 | 0.342 |

|                           |               | $R_{DLY\_TMR} = 619k\Omega$  | 9, 10, 11 | 10.77 | 12.5  | 14.14 |

|                           |               | $R_{DLY\_TMR} = 1.18M\Omega$ | 9, 10, 11 | 20    | 23.37 | 27.2  |

| $t_{REG\_TMR}$            | レギュレーションまでの時間 | $R_{REG\_TMR} = 10.5k\Omega$ | 9, 10, 11 | 0.197 | 0.264 | 0.34  |

|                           |               | $R_{REG\_TMR} = 619k\Omega$  | 9, 10, 11 | 10.8  | 12.4  | 14.1  |

|                           |               | $R_{REG\_TMR} = 1.18M\Omega$ | 9, 10, 11 | 20.3  | 23.63 | 27.2  |

- (1) RHA デバイスの詳細については、5962R2320101VXC SMD(標準マイクロ回路図)を参照。

- (2) すべての電圧値は、GND を基準としたものです。

- (3) サブグループの定義については、「品質適合性検査」表を参照。

- (4)  $V_{POR\_IN}$  は、出力が制御された状態を保つために必要な  $V_{IN}$  の最小値で、 $1.6V \leq V_{PULL\_UPx} \leq 7V$  の場合の値です。 $V_{POR\_IN}$  を下回ると、出力は決定できません。

- (5)  $V_{POR\_PULL\_UPx}$  は出力が制御された状態を保つために必要な  $V_{PULL\_UPx}$  の最小値で、 $V_{IN} \leq 3V$  の場合の値です。 $V_{POR\_PULL\_UPx}$  を下回ると、出力は決定できません。

## 6.6 タイミング要件

$3V \leq V_{IN} \leq 14V$ 、 $R_{DLY\_TMR} = 10.5k\Omega$ 、 $R_{REG\_TMR} = 10.5k\Omega$ 、 $C_{REFCAP} = 470nF$ 、 $C_{VLDO} = 1\mu F$ 、 $V_{PULL\_UP1} = 3.3V$ 、 $V_{PULL\_UP2} = 3.3V$ 、 $C_{PULL\_UP1} = 1\mu F$ 、 $C_{PULL\_UP2} = 1\mu F$  全体、動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )。特に注記のない限り、RHA デバイスの  $T_A = 25^{\circ}C$  でのグループ E 放射線テストを含みます<sup>(1)</sup>

| パラメータ                  |                                  | テスト条件                                                                  | サブグループ <sup>(2)</sup> | 最小値  | 標準値 | 最大値 | 単位      |

|------------------------|----------------------------------|------------------------------------------------------------------------|-----------------------|------|-----|-----|---------|

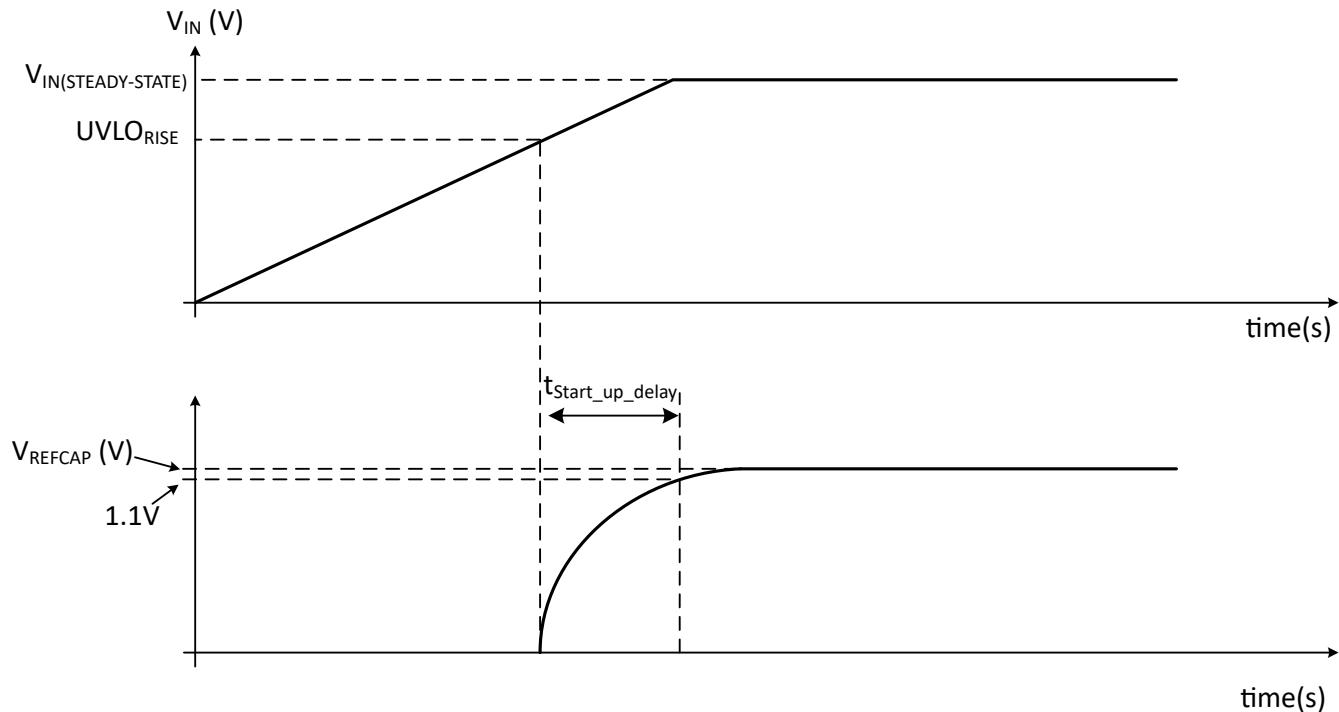

| $t_{Start\_up\_delay}$ | 起動遅延時間 <sup>(3)</sup>            | $V_{REFCAP} \geq 1.1V$ 、図 7-1                                          | 9, 10, 11             |      |     | 2.8 | ms      |

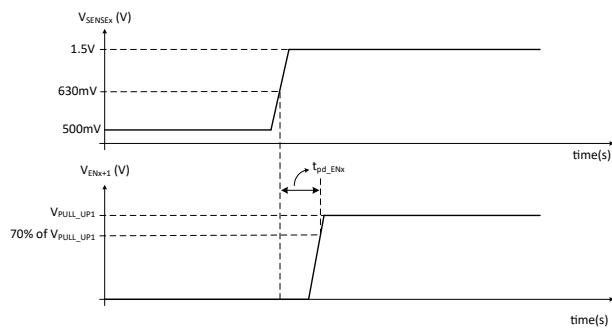

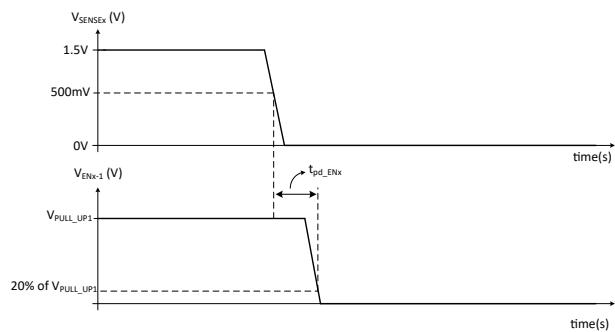

| $t_{pd\_ENx}$          | ENx 伝搬遅延                         | Dly_TMR = オープン、REG_TMR = オープン、図 7-2 および 図 7-3 を参照                      | 9, 10, 11             |      | 3.4 | 6.5 | $\mu s$ |

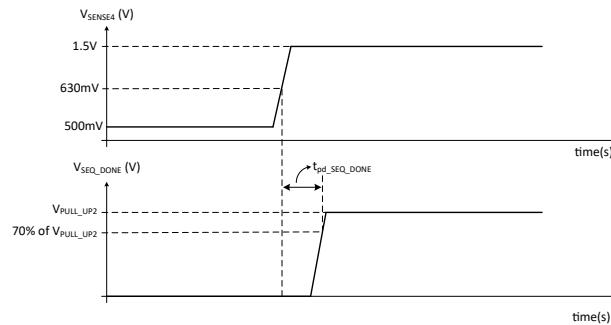

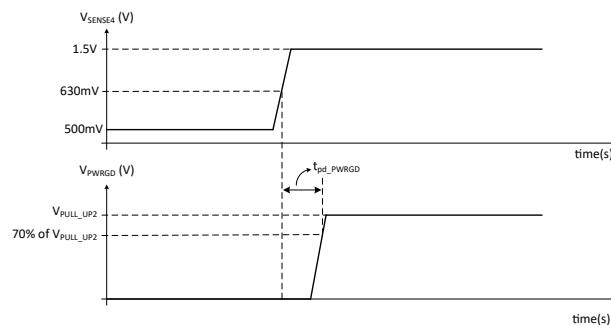

| $t_{pd\_SEQ\_DONE}$    | SEQ_DONE の伝搬遅延                   | Dly_TMR = オープン、REG_TMR = オープン、図 7-4 および 図 7-5 を参照                      | 9, 10, 11             |      | 3.4 | 6.5 |         |

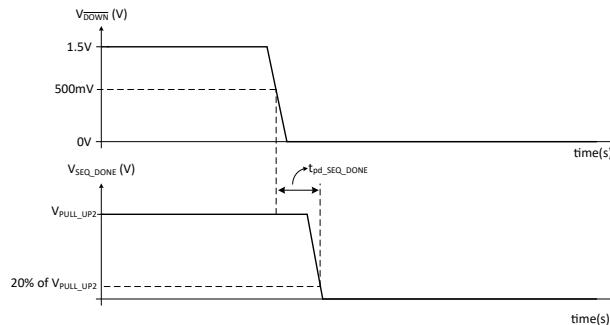

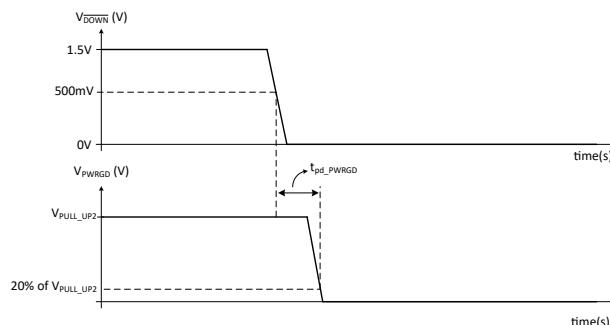

| $t_{pd\_PWRGD}$        | PWRGD 伝搬遅延                       | Dly_TMR = オープン、REG_TMR = オープン、図 7-6 および 図 7-7 を参照                      | 9, 10, 11             |      | 3.4 | 6.5 |         |

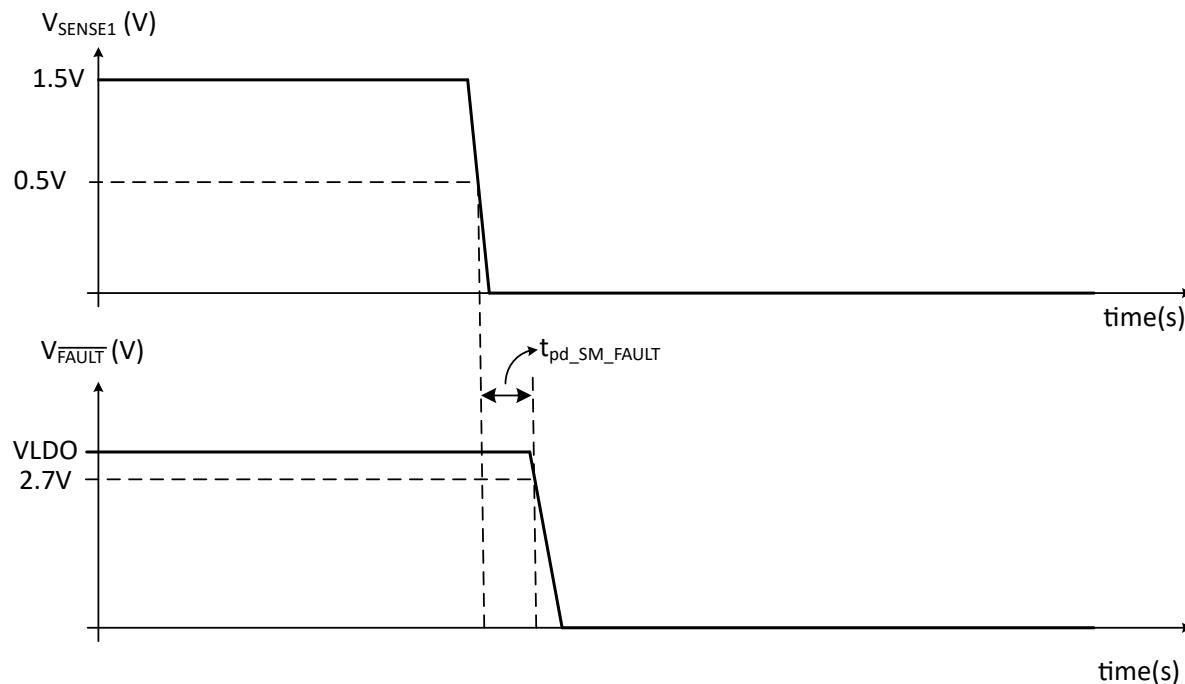

| $t_{pd\_SM\_FAULT}$    | ステートマシン障害の伝搬遅延                   | 「SENSE1 ↓ の 33%から 82% PWRGD ↓までのシーケンスダウン状態への待機」で、図 7-8 と 状態図を参照してください。 | 9, 10, 11             |      | 3.4 | 4.3 |         |

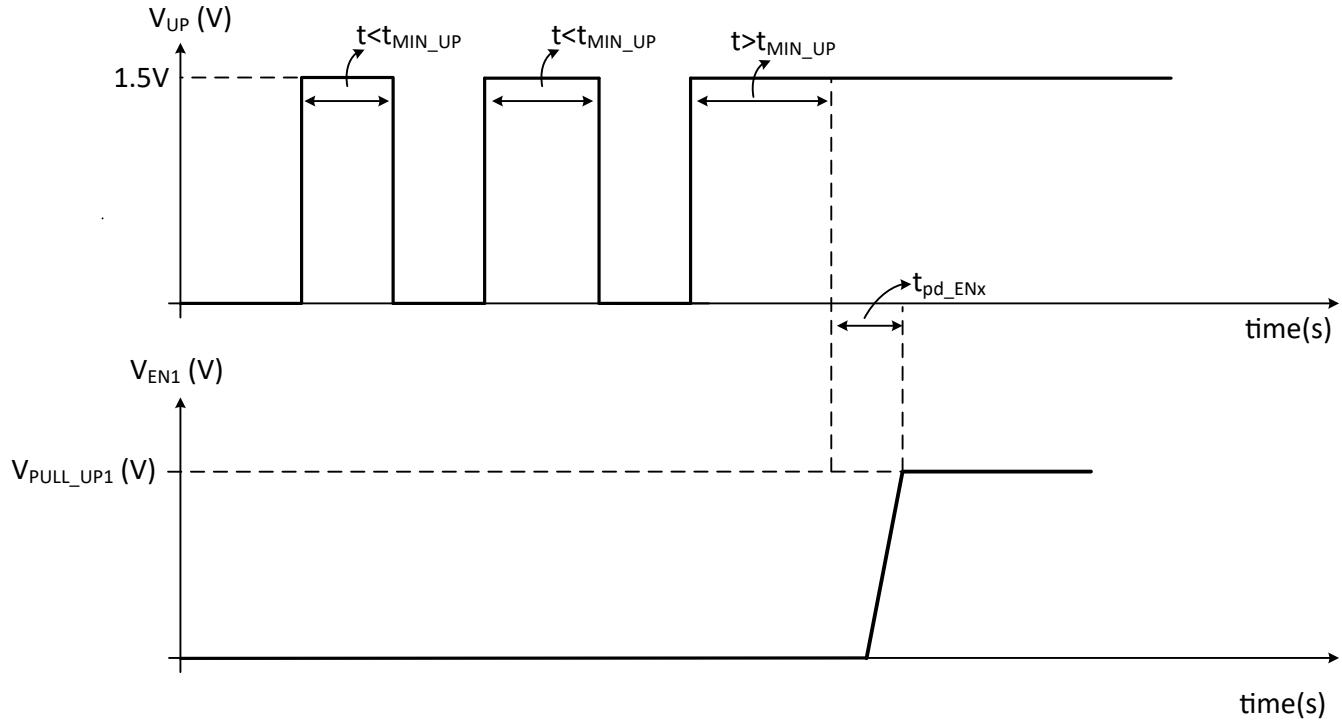

| $T_{MIN\_UP}$          | $V_{UP}$ の有効な UP に対する最小時間        | Dly_TMR = オープン、図 7-10 を参照                                              | 9, 10, 11             | 0.27 | 0.7 |     | $\mu s$ |

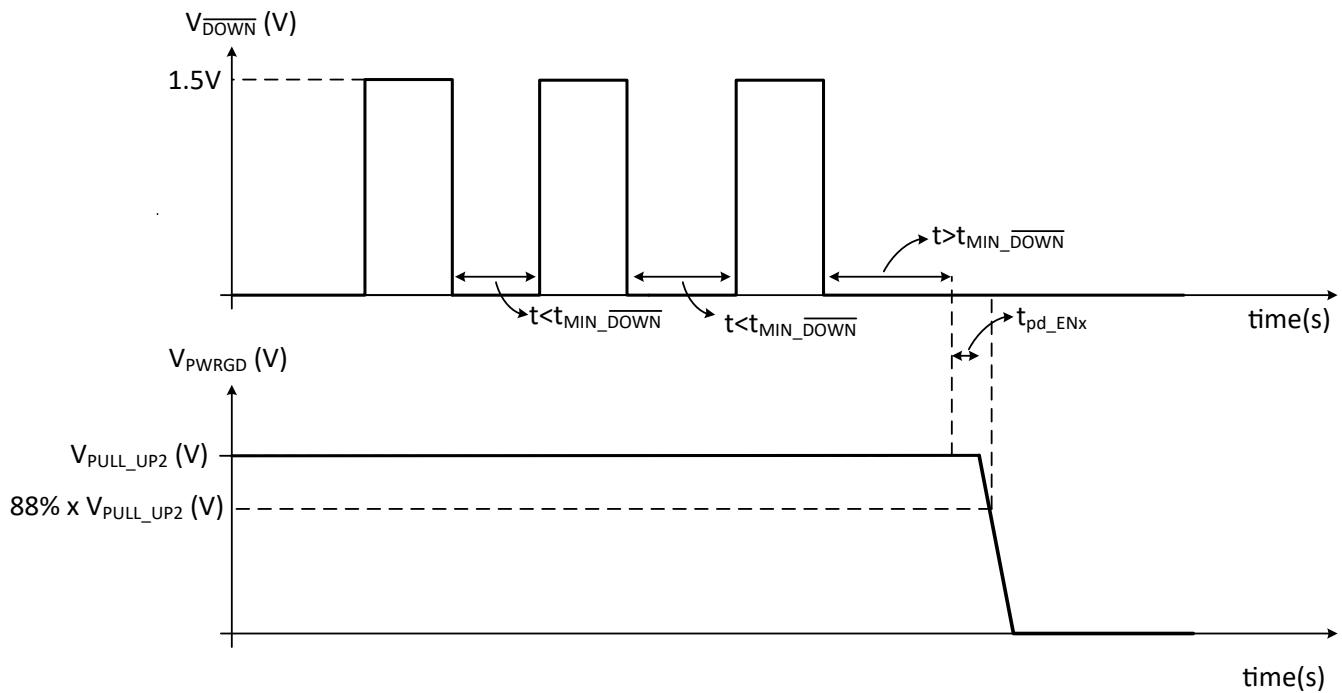

| $T_{MIN\_DOWN}$        | 有効な DOWN に対する $V_{DOWN}$ 起動の最小時間 | Dly_TMR = オープン、図 7-11 を参照                                              | 9, 10, 11             | 0.42 | 0.9 |     |         |

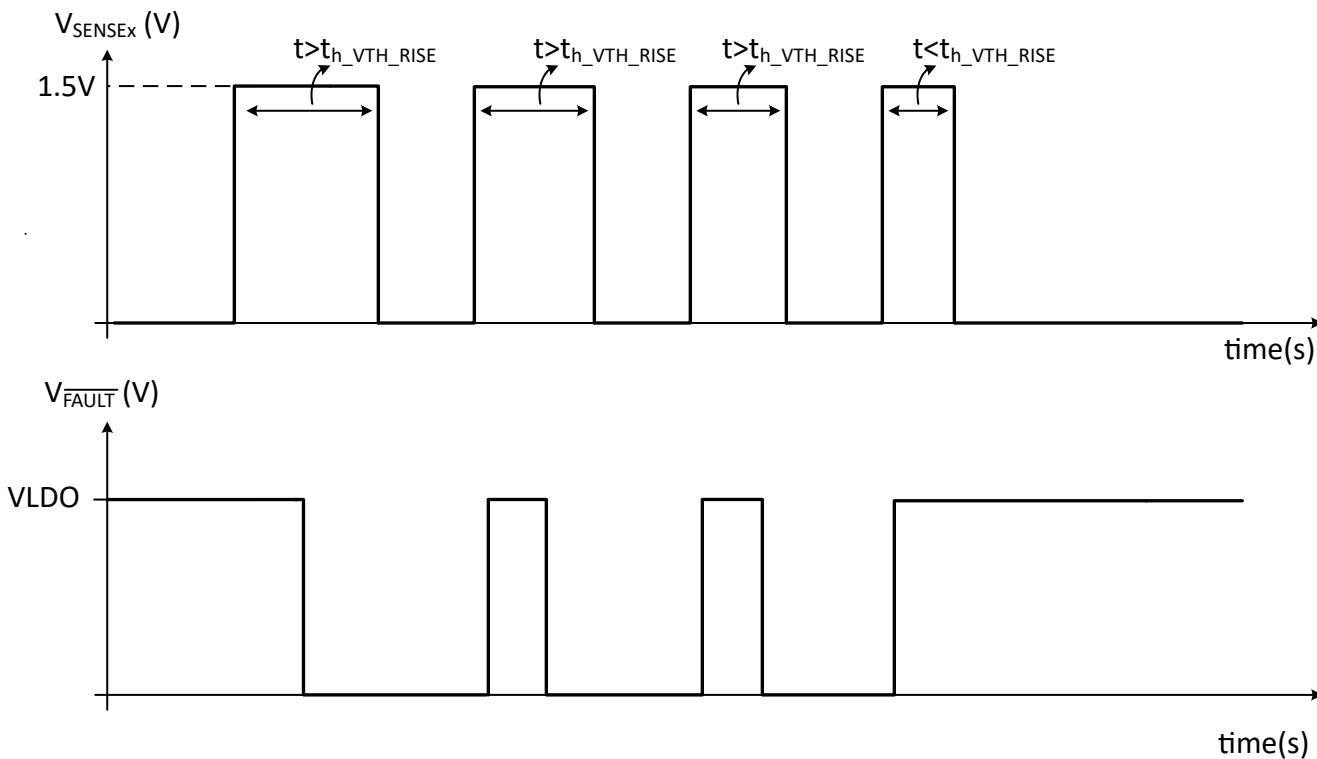

| $t_{h\_VTH\_RISE}$     | VSENSEx ホールド時間しきい値の上昇            | Dly_TMR = オープン、図 7-12 を参照                                              | 9, 10, 11             | 0.84 | 1.6 |     | $\mu s$ |

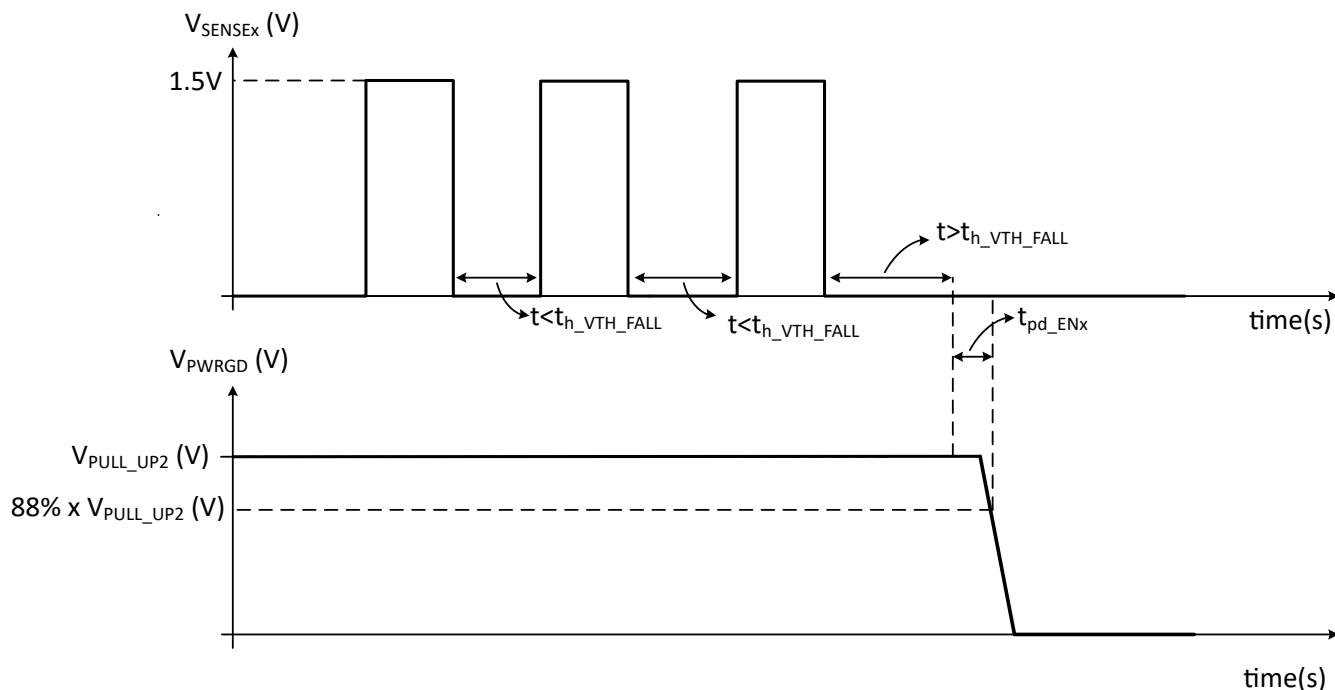

| $t_{h\_VTH\_FALL}$     | VSENSEx ホールド時間しきい値の下降            | Dly_TMR = オープン、図 7-13 を参照                                              | 9, 10, 11             | 0.35 | 1   |     | $\mu s$ |

(1) RHA デバイスの詳細については、5962R2320101VXC SMD (標準マイクロ回路図) を参照。

(2) サブグループの定義については、「品質適合性検査」表を参照。

(3) 電源オンのとき、すべての 内部リファレンスが仕様範囲内に収まるように、 $V_{IN}$  は、少なくとも  $t_{Start\_up\_delay}$  の間、 $V_{IN}$  (最小) 以上でなければなりません。

## 6.7 品質適合検査

MIL-STD-883、方法 5005 - グループ A

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 1      | 静的テスト      | 25      |

| 2      | 静的テスト      | 125     |

| 3      | 静的テスト      | -55     |

| 4      | 動的テスト      | 25      |

| 5      | 動的テスト      | 125     |

| 6      | 動的テスト      | -55     |

| 7      | 機能テスト      | 25      |

| 8A     | 機能テスト      | 125     |

| 8B     | 機能テスト      | -55     |

| 9      | スイッチング テスト | 25      |

| 10     | スイッチング テスト | 125     |

| 11     | スイッチング テスト | -55     |

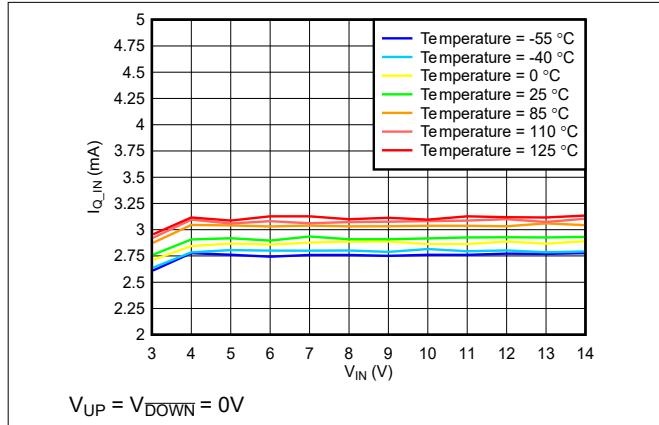

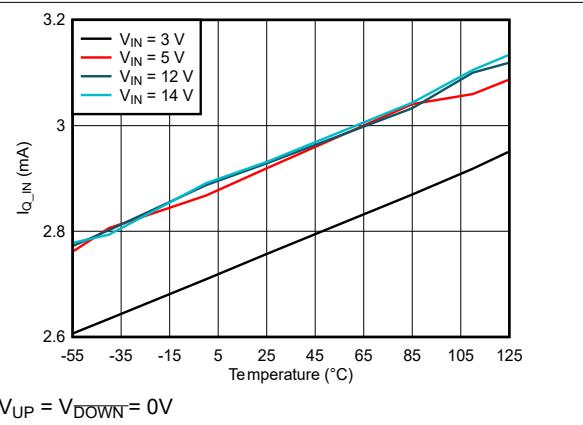

## 6.8 代表的特性

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ ,  $R_{REG\_TMR} = 10.5\text{k}\Omega$ ,  $V_{PULL\_UP1} = 3.3\text{V}$ ,  $V_{PULL\_UP2} = 3.3\text{V}$ ,  $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

図 6-1. パワーアップシーケンス待機状態における温度範囲での  $I_{Q\_IN}$  と  $V_{IN}$  との関係

図 6-2. パワーアップシーケンス待機状態における  $I_{Q\_IN}$  と温度範囲の  $V_{IN}$  との関係

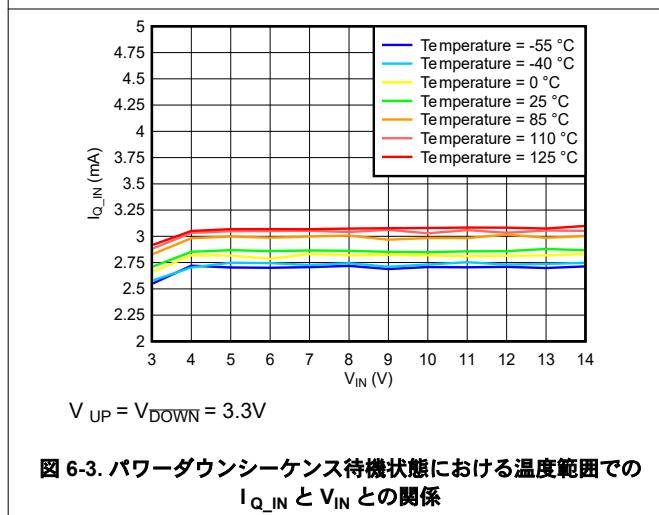

図 6-3. パワーダウンシーケンス待機状態における温度範囲での  $I_{Q\_IN}$  と  $V_{IN}$  との関係

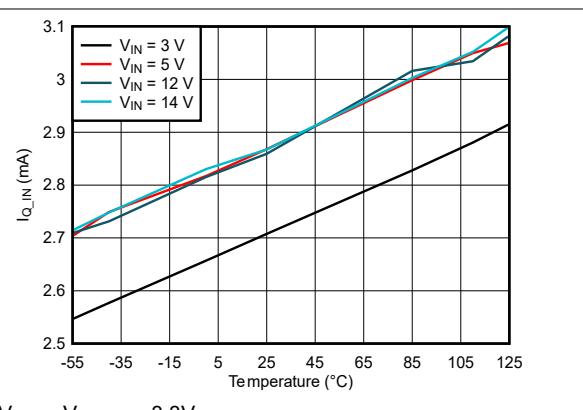

図 6-4. パワーダウンシーケンス待機状態における  $V_{IN}$  と温度範囲での  $I_{IN}$  との関係

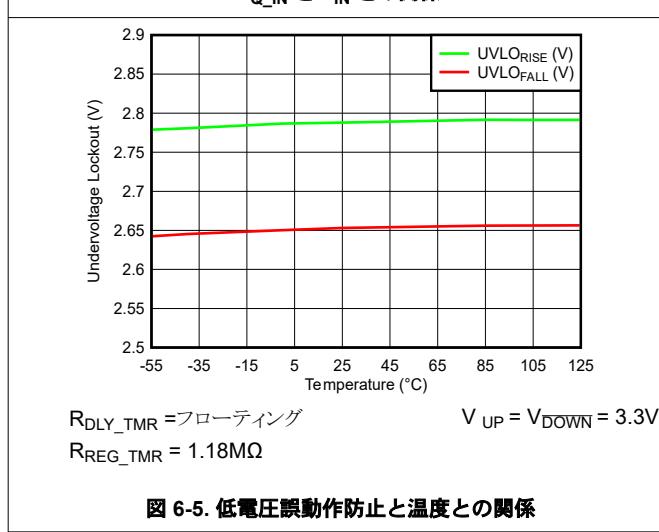

図 6-5. 低電圧誤動作防止と温度との関係

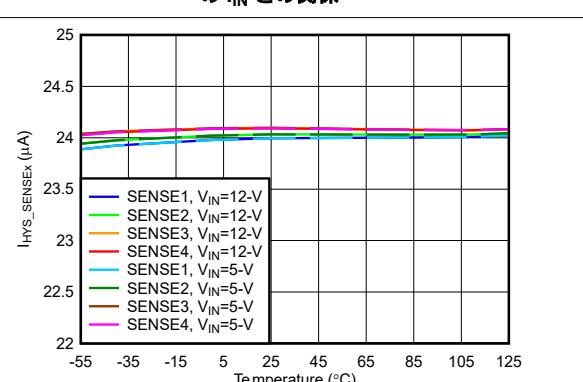

$V_{SENSEx} = 700\text{mV}$   $R_{REG\_TMR} = \text{フローティング}$

図 6-6.  $I_{HYS\_SENSEx}$  と、温度範囲での  $V_{IN}$  および SENSEx チャネルとの関係

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ 、 $R_{REG\_TMR} = 10.5\text{k}\Omega$ 、 $V_{PULL\_UP1} = 3.3\text{V}$ 、 $V_{PULL\_UP2} = 3.3\text{V}$ 、 $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

図 6-7. I<sub>HYS\_SENSEx</sub> 電流分布 (温度 -55°C)

図 6-8. I<sub>HYS\_SENSEx</sub> 電流分布 (温度 25°C)

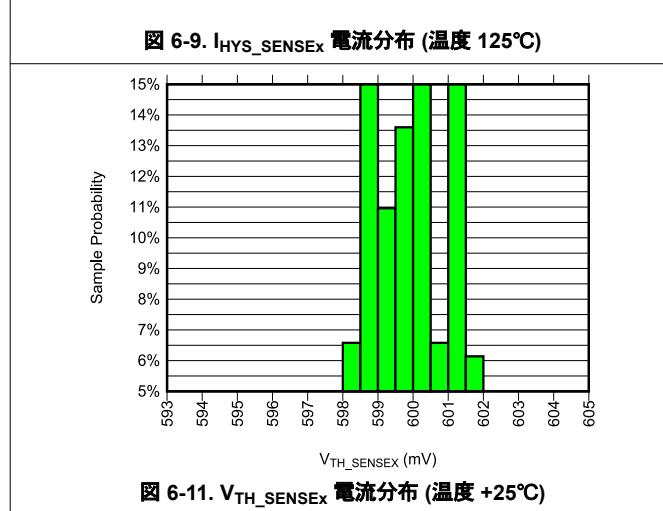

図 6-9. I<sub>HYS\_SENSEx</sub> 電流分布 (温度 125°C)

図 6-10. V<sub>TH\_SENSEx</sub> 電圧分布 (温度 -55°C)

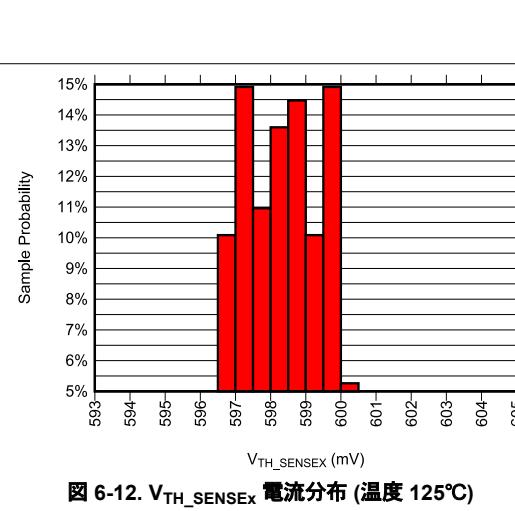

図 6-11. V<sub>TH\_SENSEx</sub> 電圧分布 (温度 +25°C)

図 6-12. V<sub>TH\_SENSEx</sub> 電圧分布 (温度 125°C)

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ ,  $R_{REG\_TMR} = 10.5\text{k}\Omega$ ,  $V_{PULL\_UP1} = 3.3\text{V}$ ,  $V_{PULL\_UP2} = 3.3\text{V}$ ,  $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

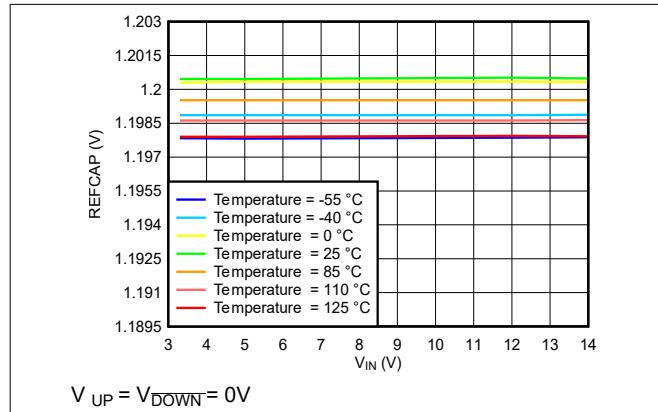

図 6-13. 温度範囲における REFCAP と  $V_{IN}$  との関係

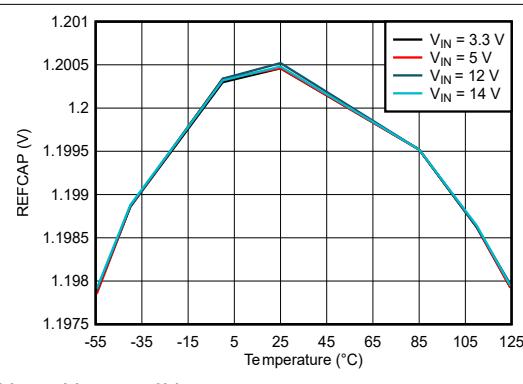

図 6-14. REFCAP と温度範囲の  $V_{IN}$  との関係

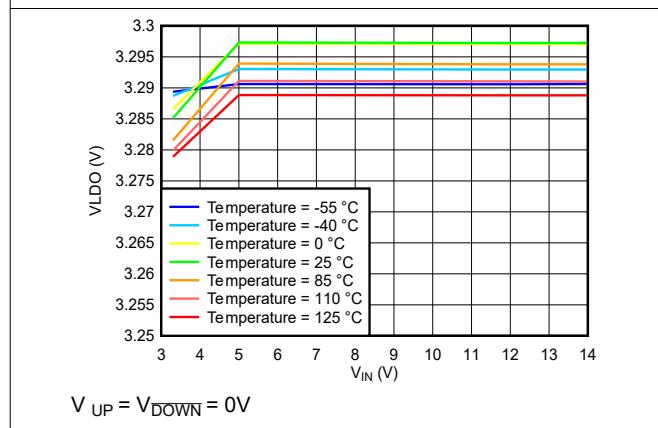

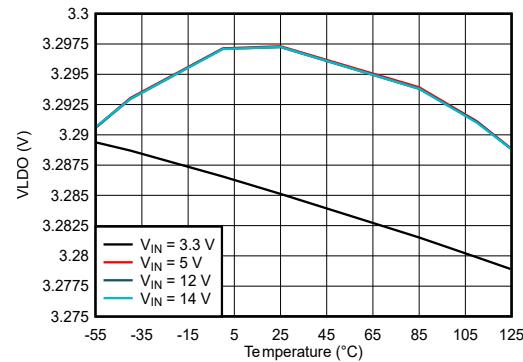

図 6-15. 温度範囲における VLDO と  $V_{IN}$  の関係

図 6-16. VLDO と温度範囲の  $V_{IN}$  との関係

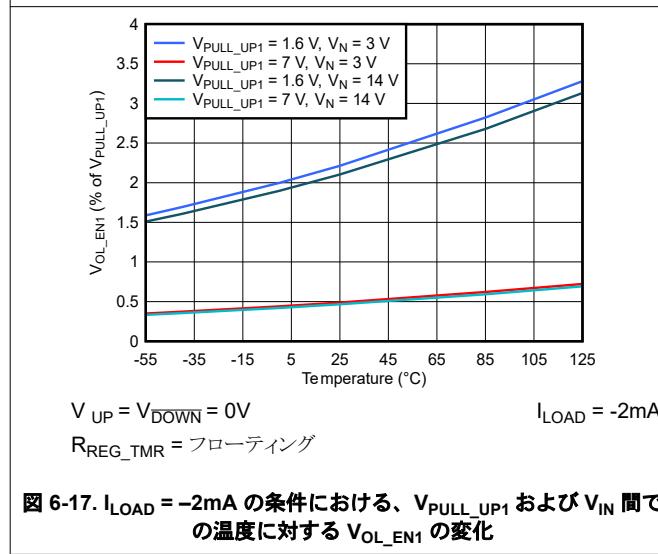

図 6-17.  $I_{LOAD} = -2\text{mA}$  の条件における、 $V_{PULL\_UP1}$  および  $V_{IN}$  間での温度に対する  $V_{OLENI}$  の変化

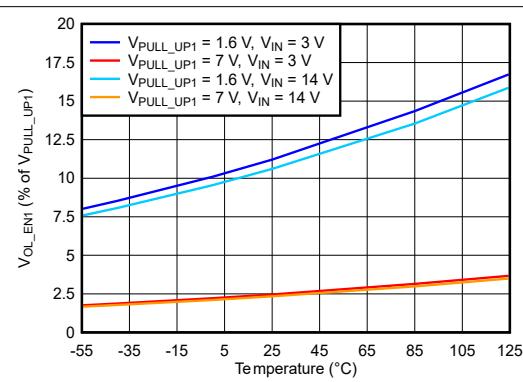

図 6-18.  $I_{LOAD} = -10\text{mA}$  の条件における、 $V_{PULL\_UP1}$  および  $V_{IN}$  間での温度に対する  $V_{OLENI}$  の変化

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ ,  $R_{REG\_TMR} = 10.5\text{k}\Omega$ ,  $V_{PULL\_UP1} = 3.3\text{V}$ ,  $V_{PULL\_UP2} = 3.3\text{V}$ ,  $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ ,  $R_{REG\_TMR} = 10.5\text{k}\Omega$ ,  $V_{PULL\_UP1} = 3.3\text{V}$ ,  $V_{PULL\_UP2} = 3.3\text{V}$ ,  $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

## 6.8 代表的特性 (続き)

$R_{DLY\_TMR} = 10.5\text{k}\Omega$ ,  $R_{REG\_TMR} = 10.5\text{k}\Omega$ ,  $V_{PULL\_UP1} = 3.3\text{V}$ ,  $V_{PULL\_UP2} = 3.3\text{V}$ ,  $V_{FAULT} = 10\text{k}\Omega$  の VLDO へのプルアップ、 $R_{HYS} = 50\text{k}\Omega$ 、 $C_{REFCAP} = 470\text{nF}$ 、 $C_{VLDO} = 1\mu\text{F}$ 、 $C_{PULL\_UP1} = 1\mu\text{F}$ 、 $C_{PULL\_UP2} = 1\mu\text{F}$ (特に注記のない限り)。

図 6-27. 溫度範囲における  $SR_{PWRGD\_FALL}$  と  $V_{PULL\_UP2}$  との関係

図 6-28.  $SR_{PWRGD\_FALL}$  と  $V_{PULL\_UP2}$  における温度との関係

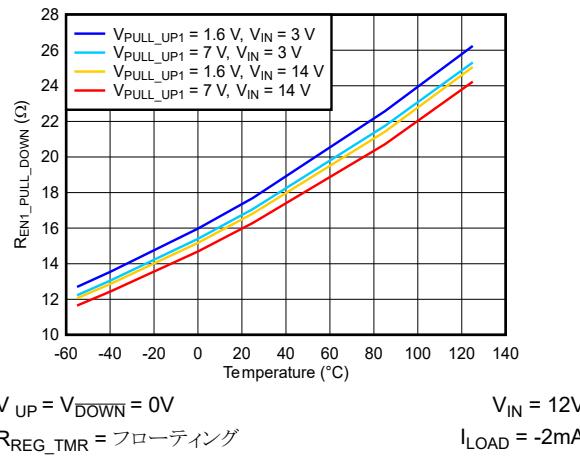

$I_{LOAD} = 2\text{mA}$

図 6-29.  $R_{EN1\_PULL\_UP}$  と温度範囲での  $V_{PULL\_UP1}$  との関係

$I_{LOAD} = -2\text{mA}$

図 6-30.  $R_{EN1\_PULL\_DOWN}$  と温度範囲での  $V_{PULL\_UP1}$  との関係

## 7 パラメータ測定情報

A.  $V_{IN(STEADY-STATE)}$ の有効な動作電圧は 3V ~ 14V です

図 7-1.  $t_{Start\_up\_delay}$  時間測定

図 7-2. ENx 伝搬遅延 ( $t_{pd\_ENx}$ ) 時間測定-立ち上がり電圧

図 7-3. ENx 伝搬遅延 ( $t_{pd\_ENx}$ ) 時間測定-立ち下がり電圧

図 7-4. SEQ\_DONE 伝搬遅延 ( $t_{pd\_SEQ\_DONE}$ ) 時間測定-立ち上がり電圧

図 7-5. SEQ\_DONE 伝搬遅延 ( $t_{pd\_SEQ\_DONE}$ ) 時間測定-立ち下がり電圧

図 7-6. PWRGD 伝搬遅延 ( $t_{pd\_PWRGD}$ ) 時間測定-立ち上り電圧

図 7-7. PWRGD 伝搬遅延 ( $t_{pd\_PWRGD}$ ) 時間測定-立ち下り電圧

- A. ステートマシンがパワーダウンシーケンス待機状態になると、 $V_{SENSE1}$  は Low になります。

- B. 見やすくするために、スルーレートは誇張されています。

図 7-8. ステートマシン検出障害の伝搬遅延 ( $t_{pd\_sm\_FAULT}$ )

図 7-9. 有効なパワーアップシーケンスコマンドの最小時間 ( $t_{MIN\_UP}$ )

図 7-10. 有効なパワーダウンシーケンスコマンドの最小時間 ( $t_{MIN\_DOWN}$ )

図 7-11. SENSEx ホールド時間の立ち上がりしきい値 ( $t_{h\_VTH\_RISE}$ )

図 7-12. SENSEx ホールド時間の立ち下がりしきい値 ( $t_{h\_VTH\_FALL}$ )

## 8 詳細説明

### 8.1 概要

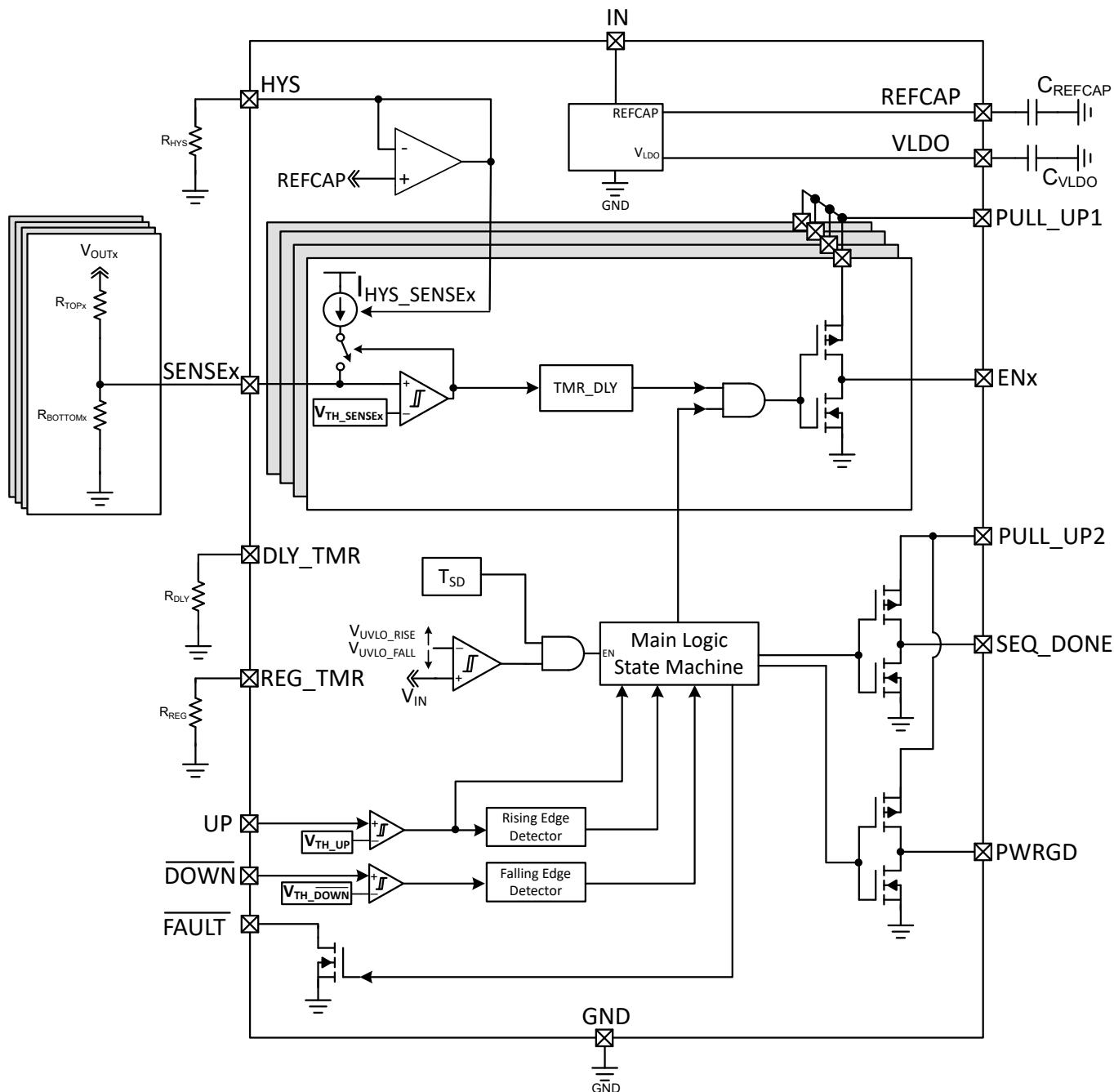

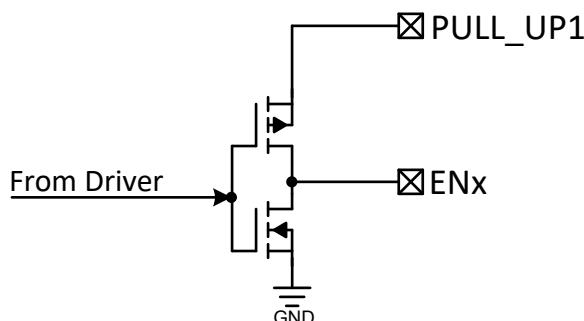

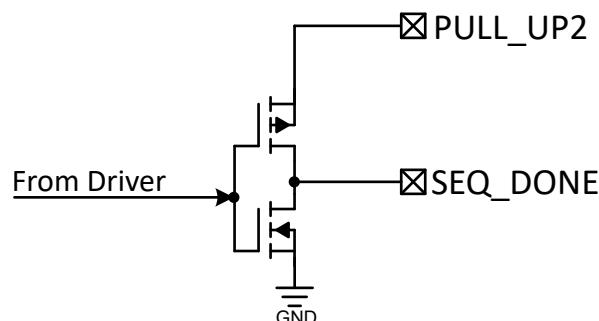

TPS7H3014 は、宇宙アプリケーション向けの 4 チャネル、3V ~ 14V のシーケンサおよびスーパーバイザです。このデバイスは、イネーブル ハイロジック入力を使用してデバイスを駆動することを想定しています。アプリケーションの場合、複数の IC をデイジーチェーン構成で接続することにより、必要に応じてチャネル数を増やすことができます。各出力はプッシュプルアーキテクチャを採用しています。これらの出力のロジック High は、ユーザーがプルアップ入力に電圧を供給することにより、外部から提供します。すべての EN<sub>x</sub> プッシュプル出力は、PULL\_UP1 ドメインに接続しますが、SEQ\_DONE と PWRGD は PULL\_UP2 ドメインに接続します。

SENSE<sub>x</sub> 入力は、コンパレータの非反転入力(低電圧)に接続されており、監視対象電源(V<sub>OUTx</sub>)のオン(規定範囲内)とオフ(期待範囲外)の電圧レベルを判定するために使用されます。これらの各入力は、しきい値レベル 599mV(標準値)により、電圧、温度、放射線(TID)全体で ±1% の精度を実現しています。ヒステリシス電圧のしきい値レベルは、ユーザーによる調整が可能で、R<sub>TOPx</sub> 抵抗とヒステリシス電流(I<sub>HYS</sub>)によって決まります。SENSE<sub>x</sub> の立ち上がり電圧がしきい値(標準 599mV)を超えると、I<sub>HYS</sub> がアクティブになり、監視対象の電圧レールが規定範囲内の状態であることが示されます。I<sub>HYS</sub> は、24μA で電圧、温度、放射線(TID)を通じて ±3% の精度です。

このデバイスには、次の 2 つのタイマーが内蔵されています。

1. **Dly\_TMR:**立ち上がりおよび立ち下がり EN<sub>x</sub> 遅延を設定します。パワーアップシーケンスの時に SENSE<sub>x-1</sub> がオン電圧を上回ると、DLY\_TMR 入力を使用してユーザーが設定した遅延が終了することにより、EN<sub>x</sub> が High にアサートされます。パワーダウンシーケンスの時も同様で、この場合、SENSE<sub>x</sub> が OFF 電圧を下回ると、タイマが満了した時点で EN<sub>x-1</sub> が Low にアサートされることになります。このタイマは、10.5kΩ ~ 1.18MΩ の抵抗を使用することにより、それぞれ 0.25ms ~ 25ms に設定できます。

2. **Reg\_TMR:**検出された電圧レールが、オンのしきい値(期待範囲)を上回る必要がある許容時間を設定します。EN<sub>x</sub> が High にアサートされると、SENSE<sub>x</sub> は、REG\_TMR を使用して、ユーザーが設定した時間が 599mV(標準値)を上回るまで上昇します。それ以外の場合は、EN<sub>x-1</sub> から逆方向シーケンスが開始されます。

デイジーチェーン構成ができるようにするために、デバイスには独立した UP ピンと DOWN ピンが用意されています。UP ピンのしきい値(V<sub>TH\_UP</sub>)は 599mV(標準値)で、DOWN ピンのしきい値(V<sub>TH\_DOWN</sub>)は 498mV です。ノイズ安定性のため、両方の入力コンパレータには 100mV 固定ヒステリシスが組み込まれています。これらのピンはエッジセンシティブであり、UP の立ち上がりエッジでパワーアップシーケンスが開始され、DOWN の立ち下がりエッジでパワーアップシーケンスが開始されます。

1 つのデバイスを使用して外部から駆動する場合、通常は両方のピン(UP および DOWN)が互いに接続されます。UP 入力と DOWN 入力には正確なしきい値があるため、(抵抗分圧回路を使用して)別のレールを正確に検出することで、シーケンスの UP および DOWN を開始することも、コントローラで外部から駆動することも可能です。V<sub>TH\_UP</sub> より高い電圧で駆動すると、デバイスはプログラムされた遅延時間(DLY\_TMR)の後、EN1 を High にアサートしてシーケンスを開始し、その後、SENSE1 は立ち上がり開始します。REG\_TMR が経過する前に SENSE1 がオン電圧を超えると、設定された遅延の後に EN2 が High にアサートされます。このプロセスは、SEQ\_DONE と PWRGD が High にアサートされるまで、それぞれ完全なパワーアップシーケンスとシステムパワー グッドが確認されるまで継続します。

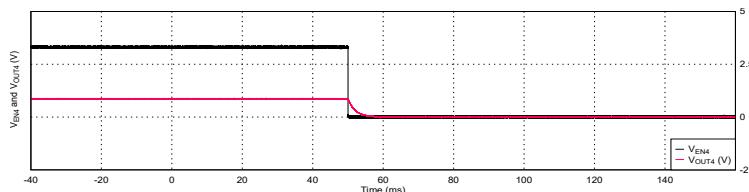

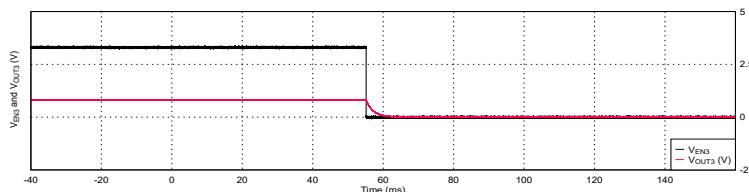

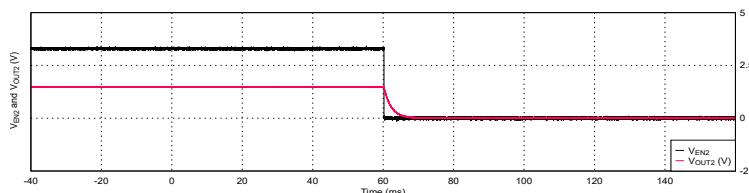

DOWN ピンが V<sub>TH\_DOWN</sub> より低い値で駆動すると、プログラムされた遅延が経過した後、デバイスは EN4 を強制的に Low にすることでパワーダウンシーケンスを開始します。この時点で、SENSE4 電圧は、設定したオフ電圧を下回るまで立ち下がりを続けます。この状態になると、プログラムされた遅延の後に EN3 が Low にアサートされます。これは、EN1 が強制的に Low になるまで継続されます。シーケンス制御されたデバイスの放電時間が不明なため、電源オフ時に REG\_TMR はアクティブになりません。

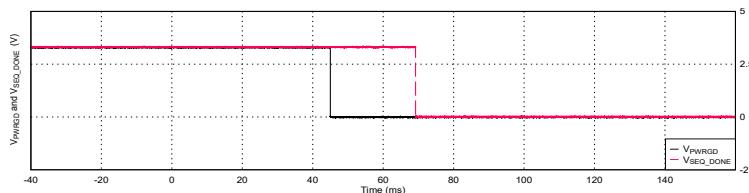

パワーアップシーケンスのとき、最後に使用されたチャネルがオン電圧しきい値を超え、プログラムされた DLY\_TMR (アクティブであると仮定) が経過した後、SEQ\_DONE と PWRGD が High にアサートされます。パワーダウンシーケンスのとき、V<sub>OUT1</sub> が OFF 電圧を下回り、DLY\_TMR が経過すると、SEQ\_DONE は強制的に Low になります。ただし、PWRGD は、コマンドによるパワーダウンシーケンスの直後、強制的に Low になります。

TPS7H3014 には、ステートマシンセクションで解説した包摂的な障害管理システムも搭載されています。

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 入力電圧 (IN) VLDO およびREFCAP

定常状態で動作しているとき、TPS7H3014 の入力電圧は 3V ~ 14V にしなければなりません。 $V_{IN}$  と GND の間には、0.1 $\mu$ F 以上のバイパスコンデンサが必要です。入力バイパスコンデンサは、シーケンス IC のきるだけ近くに配置する必要があります。は、IC が適切に動作するために、 $V_{IN}$  のスルーレートを 10V/ $\mu$ s ~ 1mV/ $\mu$ s の範囲で制御することを推奨します。

$V_{IN}$  に印加される電圧は、VLDO 電圧(通常 3.29V)を生成する内部レギュレータの入力として機能します。入力電圧が 3.29V(標準値)より低い場合、VLDO 電圧は  $V_{IN}$  電圧に追従します。VLDO の推奨容量は 1 $\mu$ F です。パワーアップおよびパワーダウンシーケンスの時に、未使用の SENSE2 ~ SENSE4 を VLDO に接続すれば、チャネル遅延をバイパスすることができます。10k $\Omega$  抵抗を介して FAULT ピンを VLDO にプルアップすることができますが、それ以外の場合、出力電流能力が制限されているので、このピンに外部負荷をかけることは推奨できません。電源投入時、ユーザーは、 $V_{IN} > UVLO_{RISE}$  となった後、2.8ms( $t_{Start\_up\_delay}$ )以上待機してからパワーアップシーケンスを開始する必要があります。これは、デバイスの内部時定数によるものです。

各デバイスは、さまざまな制御ロジック ブロックで利用される 1.2V の内部バンドギャップ リファレンスを生成します。これは、定常状態動作時に REFCAP ピンに印加される電圧です。この電圧は分圧され、コンパレータ入力 SENSE<sub>x</sub>(標準値 599mV)、UP(標準値 598mV)、DOWN(標準値 498mV)のリファレンス(基準電圧)を生成します。 $V_{TH\_SENSE_x}$  基準電圧は、エラーアンプのオフセットを考慮して EN<sub>x</sub> 出力で測定され、電圧、温度、放射線の TID(シリコンでは最大 100krad)全体にわたってレギュレーションを ±1% 以内に維持します。この厳格な基準電圧公差により、ユーザーは電圧レベルを高精度で監視できます。適切な電気的動作のために、またデバイスの堅牢なセット性能を確保するために、REFCAP ピンで GND との間に 470nF のコンデンサが必要です。

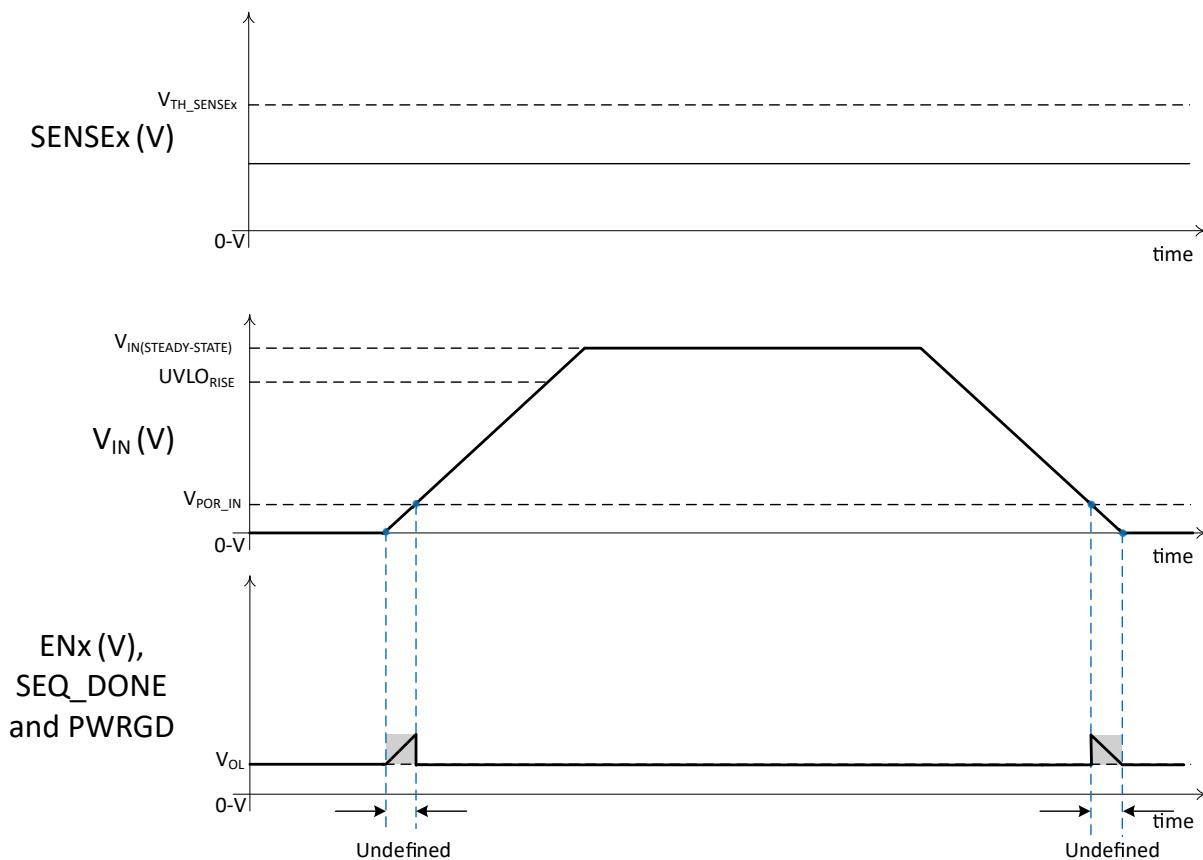

#### 8.3.1.1 低電圧ロックアウト ( $V_{POR\_IN} < V_{IN} < UVLO$ )

$V_{IN}$  の電圧が、UVLO(2.79V 標準値)電圧未満で、電源オン・リセット電圧( $V_{POR\_IN}$ 、1.41V 標準値)よりも高い場合、出力ピン(EN<sub>x</sub>、SEQ\_DONE、PWRGD)は、デバイスの入力電圧に関係なく、ロジック LOW 状態になります。この名称は次の通りです:

- SENCE<sub>x</sub>

- UP

- DOWN

#### 8.3.1.2 パワーオン リセット ( $V_{IN} < V_{POR\_IN}$ )

$V_{IN}$  の電圧が、パワーオン リセット電圧( $V_{POR\_IN}$ )を下回った場合、出力信号は不定となり、デバイスの正常な動作を保証するものではありません。

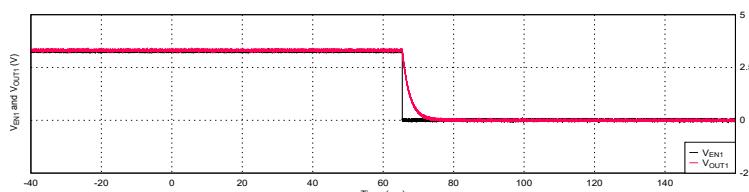

図 8-1 に、EN<sub>x</sub> 出力と立ち上がり入力電圧( $V_{IN}$ )との関係を示します。ご覧のように、 $V_{IN}$  が  $V_{POR\_IN}$ (標準値 1.41V)を下回ると、EN<sub>x</sub> は未定義になります。このとき、出力は 0V から  $V_{IN}$  まで任意の値になり得ます。この場合、すべての低電圧(UV)入力コンパレータ(SENSE<sub>x</sub>)への入力電圧は  $V_{TH\_SENSE_x}$ (599mV)を下回っています。したがって、(立ち上がりエッジの待機と合わせて)、 $V_{IN}$  が UVLO<sub>RISE</sub>(通常 2.79V)を上回った後も、EN<sub>x</sub>、SEQ\_DONE、PWRGD は Low のままでです。

**図 8-1.  $V_{IN} > V_{IN-MIN}$  後の有効な Low 状態における出力**

A. この図では以下のようになります。

1. 有効な外部プルアップ電圧は、PULL\_UPx 入力 ( $1.6V \leq V_{PULL\_UPx} \leq 7V$ ) に接続されている。

2.  $V_{IN(STEADY-STATE)}$  の有効な  $V_{IN}$  電圧は、 $3V \sim 14V$  である。

3.  $V_{FAULT}$  は、VLDO へのプルアップ(抵抗)である。

4. デバイスは:パワーアップシーケンス状態で待機中(詳細については、[ステート マシン](#)を参照)。

5.  $V_{OL}$  は以下を表す: $V_{OL\_ENx}$ 、 $V_{OL\_SEQ\_DONE}$ 、 $V_{OL\_PWRGD}$ 、またはすべての出力の Low ロジック出力電圧。

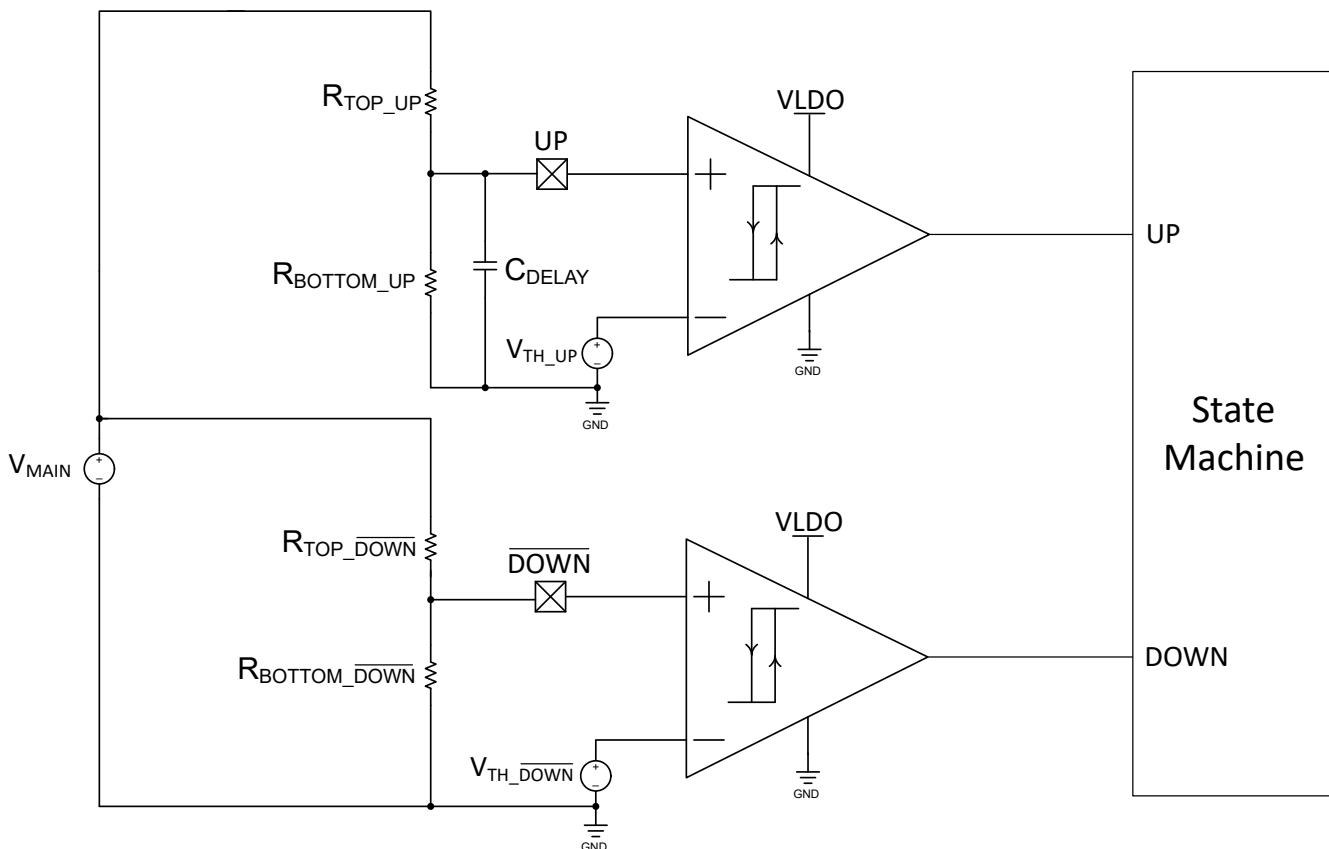

### 8.3.2 SENSEx 入力

#### 8.3.2.1 $V_{TH\_SENSEx}$ および $V_{ONx}$

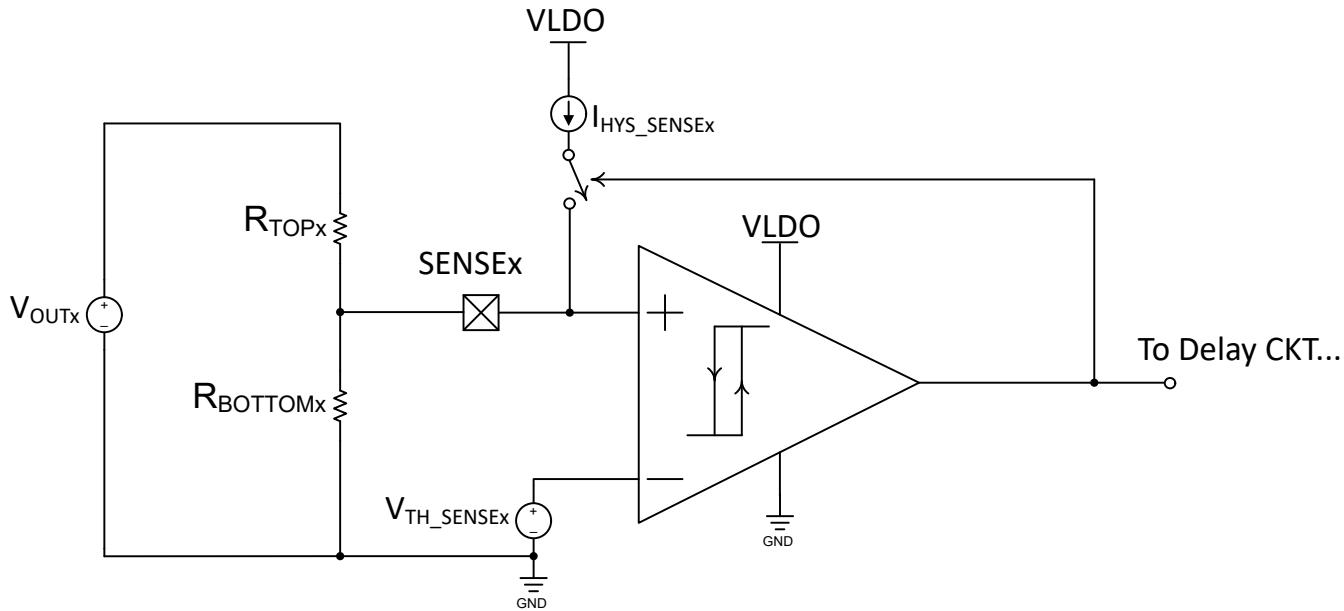

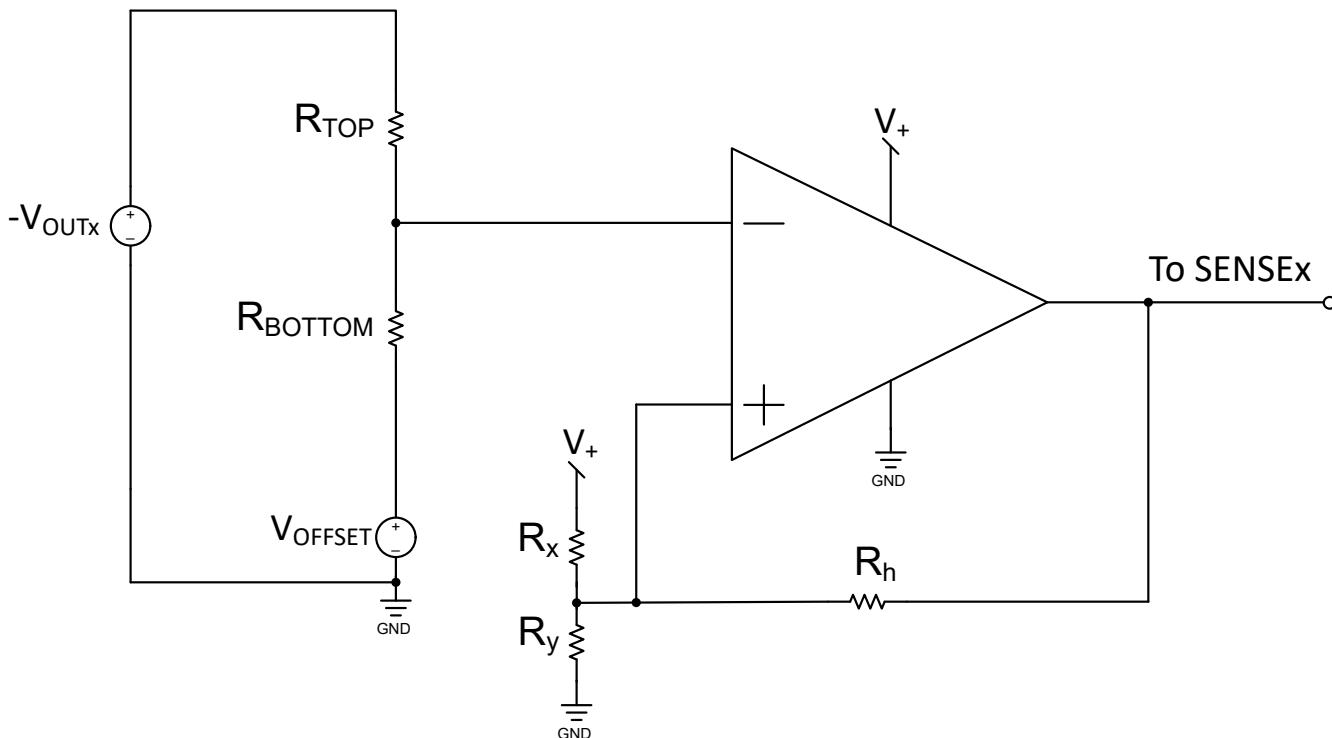

TPS7H3014 シーケンサには 4 つの低電圧(UV)コンパレータが内蔵されており、公称 599mV に対して高精度( $\pm 1\%$ )のしきい値電圧( $V_{TH\_SENSEx}$ )を確保しています。 $V_{TH\_SENSEx}$  は、しきい値のコンパレータオフセットを考慮して ENx 出力で測定します。任意の電圧レール( $V_{OUTx}$ )を検出するように外付け分圧抵抗回路を調整できるので、最大限のフレキシビリティをご提供できます。SENSEx 入力に接続されたコンパレータの概念図を、図 8-2 に示します。ご覧のように、検出した電圧レール( $V_{OUTx}$ )は(外付けの分圧抵抗  $R_{TOPx}$  と  $R_{BOTTOMx}$  を使用することにより)減衰され、 $V_{TH\_SENSEx}$  電圧と比較されます。しきい値電圧( $V_{TH\_SENSEx}$ )の精度を確保するため、定常状態の SENSEx 電圧を 1.6V 未満に維持することを推奨します。

図 8-2. SENSEx コンパレータ入力

監視対象レール( $V_{OUTx}$ )の電圧が上昇すると、ヒステリシス電流( $I_{HYS}$ )は SENSEx 入力に接続されません。このとき、SENSEx(減衰された  $V_{OUTx}$ )電圧を SENSEx しきい値電圧( $V_{TH\_SENSEx}$ )と比較します。 $V_{SENSEx} > V_{TH\_SENSEx}$  であれば、電圧は規定の制限範囲内と見なされます。簡単な分圧回路を使用すると、オン(規定範囲内)電圧を次のように計算できます:

$$V_{ONx\_NOMINAL} \left( V \right) = \left( 1 + \frac{R_{TOPx}}{R_{BOTTOMx}} \right) \times V_{TH\_SENSEx} \quad (1)$$

ここで

- $V_{TH\_SENSEx}$  は、イネーブルしきい値電圧で 599mV です。

他のシステムと同様に、設計上の変数にも多少の変動(または誤差)があります。この場合は、上部と下部の抵抗と SENSEx のしきい値電圧です。微分法を使用して合計誤差を計算します(また、これらの変数は相関していないと仮定)。両方の抵抗の許容誤差が同じであれば、 $V_{ONx}$  誤差は次のように計算できます:

$$V_{ONx\_ERROR} \left( V \right) = \pm \sqrt{\frac{V_{TH\_SENSEx}^2 \times \left[ \left( 2 \times R_{TOL}^2 \times R_{TOPx}^2 \right) + \left( V_{TH\_SENSEx\_ACC}^2 \times \left( R_{TOPx} + R_{BOTTOMx} \right)^2 \right) \right]}{R_{BOTTOMx}^2}} \quad (2)$$

ここで

- $R_{TOL}$  は、抵抗の許容誤差 (抵抗は上下とも同じ) の数値。例えば、許容誤差 0.1% の抵抗の場合、0.001 を使用。

- $V_{TH\_SENSEx\_ACC}$  は、SENSE $x$  しきい値精度の数値 (この場合は 0.01)。

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) です。

- $V_{TH\_SENSEx}$  は 0.599 V です。

式 1 と式 2 を使用すると、ON 電圧範囲は次のように計算できます:

$$V_{ONx} = V_{ONx\_NOMINAL} \pm V_{ONx\_ERROR} \quad (3)$$

**注**

$V_{TH\_SENSEx}$  は、コンパレータのオフセットを考慮する際の基準電圧であり、 $V_{TH\_SENSEx} = V_{REF} + V_{OFFSETx}$  であることを思い出してください。

このデバイスはマルチレールシステムのシーケンス制御を目的としているため、EN $x$  から SENSE $x$  への順序は、パワーアップシーケンスの昇順 (EN1 から EN4) とパワーダウンシーケンスダウンの降順 (EN4 から EN1) と定義されます。シーケンサのチャネルが不要な場合 (未使用)、チャネルを VLDO に接続して、パワーアップ/パワーダウンシーケンス中にチャネルをスキップすることができます。無効化したチャネルはすべて VLDO に接続することを推奨しますが、VLDO (最大) の 91% を超える外部電圧を使用するとチャネルは無効化されます (SENSE $x$  の電圧は 3.5V を超えることができません)。無効化できるのは、チャネル 2 ~ 4 だけです。各チャネルは、High (チャネル#4) から Low (チャネル#2) の順に無効化することを推奨します。チャネルは、チャネル数の少ないもの以降が無効になります。つまり、チャンネル#2 が無効になっている場合、チャンネル#3 と#4 も無効になります。すべての無効化されたチャネルを VLDO (または VLDO の 91% を超える電圧) に接続する必要があります。

**注**

無効化するチャネルは、電源オン時に有効である必要があり、パワーアップおよびパワーダウンシーケンス中に動的に変更しないでください。

SENSE2 ~ SENSE4 の任意の電圧  $> V_{TAN\_OFF}$  [VLDO (最大) の 91%] の場合、チャネルは無効 (またはターンオフ) になります。これにより、パワーアップおよびパワーダウンシーケンス中は、これらのチャネルの遅延 (TMR\_DLY で設定) が無効になります。

必須ではありませんが、ノイズの多いアプリケーションでは、監視対象信号の過渡電圧に対する感度を低減するために、SENSE $x$  入力端に小容量のバイパスコンデンサを配置することが優れたアナログ設計の実践となります。

### 8.3.2.2 $I_{HYS\_SENSEx}$ および $V_{OFFx}$

TPS7H3014 には 24 $\mu$ A のヒステリシス電流が組み込まれており、その精度は  $\pm 3\%$  です ( $R_{HYS} = 50\text{k}\Omega$  の場合)。ヒステリシス電流は、REFCAP/ $R_{HYS}$  と等価です。最終的にヒステリシス電流の精度に影響を及ぼすため、 $R_{HYS}$  の許容誤差は 0.1% を推奨します。

**注**

50 $\text{k}\Omega$  の代わりに、 $R_{HYS} = 49.9\text{k}\Omega$  の抵抗を使用することができます。この場合、公称電流  $I_{HYS\_SENSEx}$  は、24 $\mu$ A ではなく 24.05 $\mu$ A になります。

この電流は、すべての SENSE $x$  入力において内部でミラーリングされます。このヒステリシス電流は、SENSE $x$  電圧がしきい値電圧 (599mV  $\pm 1\%$ ) を上回ると、 $V_{OUTx} > V_{ONx}$  と同じ値 (式 3 と図 8-2 を参照) でアクティブになります。この電流 ( $I_{HYS}$ ) に  $R_{TOPx}$  抵抗を乗算すると、SENSE $x$  ノードに追加される電圧 ( $V_{HYSx}$ ) が誘導され、ノード電圧を効率的に上昇 (インクリメント)させます。パワーダウンシーケンスのとき、または  $V_{OUTx}$  がデクリメントして低電圧イベントとなった場合、規定範囲外 (または障害) と見なされるためには、電圧が  $V_{OFF}$  電圧を下回る必要があります。ヒステリシス電圧は、次のように定義されます:

$$V_{HYSx\_NOMINAL} \text{ (V)} = I_{HYS\_SENSEx} \times R_{TOPx} \quad (4)$$

ここで

- $I_{HYS\_SENSEx} = 24 \times 10^{-6}$  アンペア (または  $24\mu A$ )

- $R_{TOPx}$  単位はオーム ( $\Omega$ ) 単位です。

「オフ」電圧(または規定範囲外)電圧は、次のように計算することができます:

$$V_{OFFx\_NOMINAL} (V) = V_{ONx\_NOMINAL} - V_{HYSx\_NOMINAL} \quad (5)$$

式 1 および式 5 を使用しますが

$$V_{OFFx\_NOMINAL}(V) = \left[ \left( 1 + \frac{R_{TOPx}}{R_{BOTTOMx}} \right) \times V_{TH\_SENSEx} \right] - (I_{HYS\_SENSEx} \times R_{TOPx}) \quad (6)$$

ここで

- $V_{TH\_SENSEx}$  は、標準の検出しきい値電圧は  $0.599\text{V}$  です。

- $I_{HYS\_SENSEx} = 24 \times 10^{-6}$  アンペア (または  $24\mu A$ )

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) 単位です。

$V_{off}$  誤差(微分法を使用し、すべての変数が相關していないと仮定した場合)は、次のように計算できます。

$$V_{OFFx\_ERROR}(V) = \pm \sqrt{\frac{A+B+C+D}{R_{BOTTOMx}^2}} \quad (7)$$

ここで、方程式の項は次のとおりです。

$$A = I_{HYS\_SENSEx}^2 \times I_{HYS\_SENSEx\_ACC}^2 \times R_{TOPx}^2 \times R_{BOTTOMx}^2 \quad (8)$$

$$B = R_{TOL}^2 \times R_{TOPx}^2 \times V_{TH\_SENSEx}^2 \quad (9)$$

$$C = R_{TOL}^2 \times R_{TOPx}^2 \times [(I_{HYS\_SENSEx} \times R_{BOTTOMx}) - V_{TH\_SENSEx}]^2 \quad (10)$$

$$D = V_{TH\_SENSEx}^2 \times V_{TH\_SENSEx\_ACC}^2 \times (R_{TOPx} + R_{BOTTOMx})^2 \quad (11)$$

ここで

- $R_{TOL}$  は、抵抗の許容誤差(抵抗は上下とも同じ)の数値。例えば、許容誤差  $0.1\%$  の抵抗の場合、 $0.001$  を使用。

- $V_{TH\_SENSEx\_ACC}$  は、SENSEx しきい値精度の数値(この場合は  $0.01$ )。

- $I_{HYS\_SENSEx\_ACC}$  は、ヒステリシス電流精度の数値(この場合は  $0.03$ )。

- $V_{TH\_SENSEx}$  は、標準の検出しきい値電圧は  $0.599\text{V}$  です。

- $I_{HYS\_SENSEx} = 24 \times 10^{-6}$  アンペア (または  $24\mu A$ )

- $R_{TOPx}$  と  $R_{BOTTOMx}$  の単位はオーム ( $\Omega$ ) 単位です。

$$V_{OFFx} = V_{OFFx\_NOMINAL} \pm V_{OFFx\_ERROR} \quad (12)$$

式 6 と式 7 を使用すれば、オフ電圧範囲を次のように算出できます:

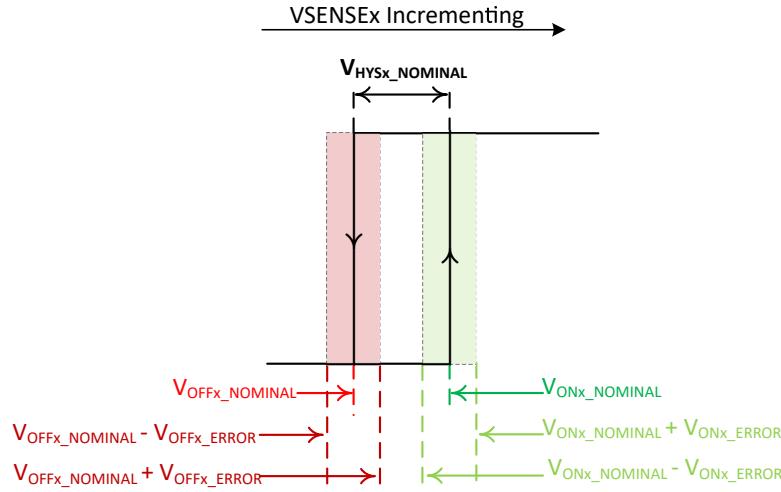

図 8-3 に、立ち上がり電圧と立ち下がり電圧の概念図を示します。この図には、 $V_{TH}$  の精度、 $I_{HYS}$  の精度、抵抗分割回路の許容誤差による電圧の誤差も記載されています。システムレベルでは、堅牢な設計を実現するために、これらの誤差を考慮する必要があります。

図 8-3. SENSE<sub>x</sub> コンパレータの立ち上がりおよび立ち下りにおけるしきい値電圧

#### 8.3.2.3 上部および下部の抵抗分圧回路の設計式

システムレベルでは、設計者が  $V_{ONx}$  および  $V_{OFFx}$  レベルを把握(または選択)します。通常、これらの電圧は、監視対象の公称レール電圧( $V_{OUTx}$ )に対するパーセンテージとして選択されます。この情報が判明していれば、目的の目標レベルに応じて抵抗分割回路の各構成部品の値( $R_{TOPx}$  と  $R_{BOTTOMx}$ )を計算することができます。式 5 と式 4 を使用して、上側の抵抗を計算できます。

$$R_{TOPx} = \frac{V_{ONx} - V_{OFFx}}{I_{HYS\_SENSEx}} \quad (13)$$

下部の抵抗は、式 1 から次のように計算できます。

$$R_{BOTTOMx} = \frac{R_{TOPx} \times V_{TH\_SENSEx}}{V_{ONx} - V_{TH\_SENSEx}} \quad (14)$$

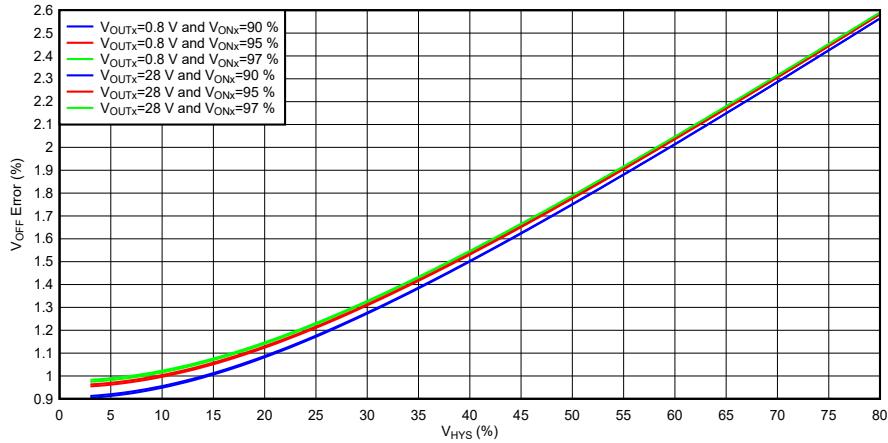

$V_{ONx}$  と  $V_{OFFx}$  ( $V_{HYSx}$  と呼びます) の乖離が大きくなれば、オフ電圧の誤差も大きくなることに注意してください。図 8-4 に、さまざまなヒステリシス電圧( $V_{HYSx} = V_{ONx} - V_{OFFx}$ )に対する  $V_{OFFx}$  のプロットを示します。このプロットは、3 つの異なる  $V_{ON}$  電圧(または次の公称出力電圧のパーセンテージ: 90、95、97%)、および 2 つの異なる出力電圧(0.8V と 28V)について作成されています。ご覧のとおり、出力電圧がオフ電圧の誤差に及ぼす影響はほとんどありません(ただし、プロットで差異を計ることはできません)。誤差(% 単位)は、約 1% ( $V_{HYS} = 3\%$  のとき)から約 2.6% ( $V_{HYS} = 80\%$  のとき)になります。

図 8-4.  $V_{OFFx}$  の誤差と  $V_{HYS}$  との関係

- A. このプロットには、式 13 と式 14 を使用して計算した上部の抵抗と下部の抵抗の差、および設計者が調達できる抵抗の実際の値との差による  $V_{OFFx}$  の誤差は含まれていません。

- B. 計算に使用する抵抗の許容誤差は 0.1%、 $V_{TH\_SENSEx}$  精度は 1%、 $I_{HYS\_SENSEx}$  精度は 3% です。

- C.  $V_{HYS}(\%)$  は、このプロットでは、乖離を公称出力電圧 ( $V_{OUTx}$ ) のパーセンテージとして表しています。

- D. このプロットでは、フルスケール電圧 ( $V_{OUTx}$ ) を基準にして、% 単位の  $V_{OFF}$  誤差を正規化しています。

### 8.3.3 出力段 (**ENx**, **SEQ\_DONE**, **PWRGD**, **PULL\_UP1**, **PULL\_UP2**)

出力段(**EN1** ~ **EN4**)、**SEQ\_DONE**、**PWRGD**はプッシュプル、アクティブ High タイプです。プッシュプル出力のプルアップ電圧は、ユーザが外部から供給します。**PULL\_UP1**(入力)はすべての **ENx** 出力(**EN1** から **EN4** へ)のプルアップ電圧ドメインで、**PULL\_UP2**(入力)は **SEQ\_DONE** 出力と **PWRGD** 出力のプルアップ電圧ドメインです。

#### 注

**IN**、**PULL\_UP1**、**PULL\_UP2** のシーケンス要件はありませんが、パワーアップおよびパワーダウンシーケンスに対するコマンドの前に、すべてにバイアスを印加する必要があります。

#### 注

TIでは、**PULL\_UPx** 入力を、ピンのできるだけ近くに配置して、 $1\mu\text{F}$  のセラミックコンデンサでデカップリングすることを推奨しています。これにより、出力(**ENx**, **PWRGD**, **SEQ\_DONE**)のクリーンな電圧信号を確保します。

各出力段は PMOS/NMOS(CMOS)ペアで構成されます。各レッグの出力抵抗は、 $V_{\text{PULL\_UP}x} > 3.3\text{V}$  の場合、標準値の  $7\Omega$  です。**PULL\_UP1** および **PULL\_UP2** の電圧範囲は  $1.6\text{V} \sim 7\text{V}$  で、電圧範囲は個別にバイアスすることも、同じ電圧レールに接続することができますが、いずれにしてもバイアスする必要があります。PMOS レッグの出力抵抗は、**PULL\_UPx** 電圧依存性を持ちます。**PULL\_UPx** 電圧が低いほど、PMOS 抵抗は高くなります。

$V_{\text{IN}} < V_{\text{POR\_IN}}$ かつ  $V_{\text{PULL\_UP}x} > V_{\text{POR\_PULL\_UP}x}$ (最大  $1.4\text{V}$ )の場合、出力は既知のプルダウン状態になります。この条件では、本デバイスが出力に  $100\ \mu\text{A}$  の電流をシンクする場合、 $V_{\text{OL}} \leq 320\text{mV}$  で、出力のシンク能力が低下します。

- **ENx**

- **PWRGD**

- **SEQ\_DONE**

入力電圧範囲が  $3\text{V} \sim 14\text{V}$  の推奨入力電圧範囲内にある場合、出力は、出力ごとに  $\pm 10\text{mA}$  の最大の能力を発揮します。

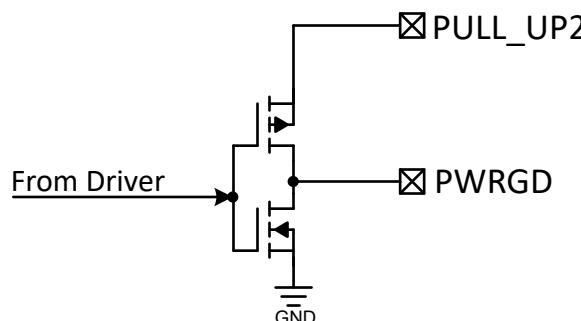

図 8-5. **ENx** プッシュプル出力段

図 8-6. **SEQ\_DONE** プッシュプル出力段

図 8-7. **PWRGD** プッシュプル出力段

### 8.3.4 ユーザープログラマブルタイマ

TPS7H3014 には、次のとおり、2 つのグローバル(またはすべての SENSE<sub>x</sub> チャネルに共通)調整可能タイマがあります:

- DLY\_TMR

- REG\_TMR

このタイマは、両方とも DLY\_TMR および REG\_TMR ピンと GND との間にある 1 つの抵抗を介してプログラムされます。これらの抵抗は、タイマの内部発振器周波数をプログラムするために使用されます。DLY\_TMR ピンまたは REG\_TMR ピンをフローティング状態にすると、それぞれタイマは無効化されます。タイマを無効化すると、デバイスの電流消費が低減されます( $I_{Q\_IN}$ )。両タイマのレンジは、250μs ~ 25ms です。

注

タイマの条件は、電源投入時に有効でなければならず、動的に変更することはできません。

図 8-8 に、UP/DOWN ピンが互いに接続され、障害が発生していないと仮定した場合のパワーアップおよびパワーダウンシーケンスを示します。DLY\_TMR はオレンジ色で、REG\_TMR 時間は矢印で表示されています(EN<sub>x</sub> から High に移行するまで)。

**図 8-8. パワーアップ/ダウン シーケンス**

- 大切なのは、 $t_{pd\_ENx}$ 、 $t_{pd\_pwrGd}$ 、 $t_{pd\_SEQ\_DONE}$  が青色で表示されていることです。これは、出力(ENx, PWRGD, SEQ\_DONE)の伝搬遅延です。DLY\_TMR(フローティング)を使用していない場合、出力信号はこの遅延の後に有効な状態に変化します。DLY\_TMRを使用する場合は、プログラムされたタイム間にこの時間を追加する必要があります。

- REG\_TMR が有効なのは、パワーアップシーケンスのときだけです。

### 8.3.4.1 DLY\_TMR

TPS7H3014 には、調整可能な時間遅延機能があります。DLY\_TMR ピンと GND の間に 1 つの抵抗を接続すると、遅延をプログラムできます。使用可能な抵抗 ( $R_{DLY}$ ) の値は、 $268\mu s$  から  $23.63ms$  までの遅延に対して、それぞれ  $10.5k\Omega$  から  $1.18M\Omega$  までとなります。パワーアップシーケンスの最中に、この遅延により、監視対象の電圧がユーザーがプログラムした時間に「オン」電圧 ( $V_{OUTx} > V_{ONx}$ ) を超えると、 $EN_{x+1}$ 、 $SEQ\_DONE$  と PWRGD が Low に保持されます。パワーダウンシーケンスの最中に、監視対象の電圧が「オフ」電圧 ( $V_{OUTx} < V_{OFFx}$ ) を下回ると、プログラムした遅延時間の間、 $EN_{x-1}$  および  $SEQ\_DONE$  が High に保持されます。

#### 注

パワーダウンシーケンスのとき、PWRGD は、 $V_{DOWN} < V_{TH\_DOWN}$  の直後に Low になります。

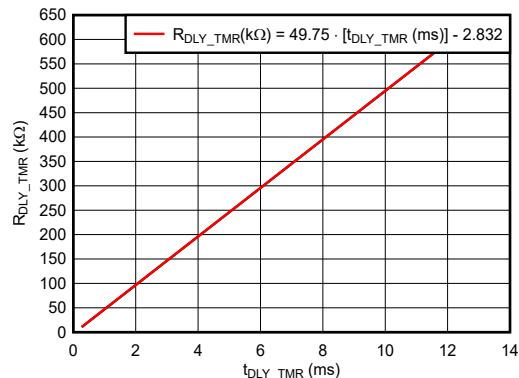

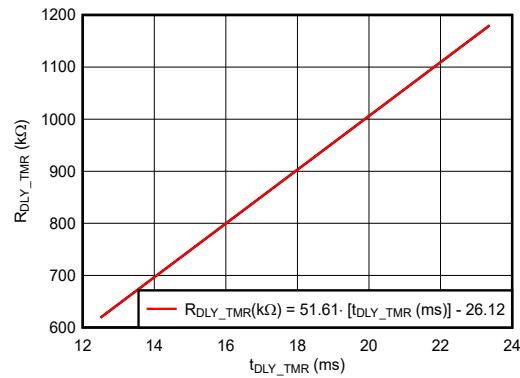

システムに対して遅延が望ましくない場合は、ピン (DLY\_TMR) をフローティングのままにしておくことができます。遅延が望ましくない場合であっても、パワーアップシーケンス中に、 $V_{OUTx}$  が  $V_{ONx}$  と  $EN_{x+1}$  を超えて High になるまでの間に、 $6.5\mu s$  (最大) の固有の伝搬遅延が観測されます。また、パワーダウンシーケンス中には、 $V_{OUTx}$  が  $V_{OFFx}$  を下回り、 $EN_{x-1}$  が強制的に Low になると、伝搬遅延が観測されます。パワーアップシーケンスアップ中では、 $V_{OUT4} > V_{ON4}$  のとき、 $SEQ\_DONE$  と PWRGD にもこの伝搬遅延が発生します。パワーダウンシーケンスのとき、伝搬遅延の後で  $V_{OUT1} < V_{OFF1}$  になると  $SEQ\_DONE$  は Low になり、パワーダウンシーケンスが指示されると、伝搬遅延の後で PWRGD が Low になります。図 8-8 では、伝搬遅延 ( $t_{pd\_ENx}$ 、 $t_{pd\_SEQ\_DONE}$ 、 $t_{pd\_PWRGD}$ ) は青色で、プログラミングされた遅延 ( $t_{DLY\_TMR}$ ) はオレンジ色で示されています。DLY\_TMR 抵抗は、式 15 または式 16 を使用して選択できます。図 8-9 と図 8-10 に、DLY\_TMR 抵抗と遅延時間の線形トレンドを示します。

$t_{DLY\_TMR}$  が  $0.268ms \sim 12.5ms$  の場合は、以下を使用します：

$$R_{DLY\_TMR}(k\Omega) = [49.75 \times t_{DLY\_TMR}(ms)] - 2.832 \quad (15)$$

$t_{DLY\_TMR}$  が  $12.5ms$  を超える場合は、以下を使用します：

$$R_{DLY\_TMR}(k\Omega) = [51.61 \times t_{DLY\_TMR}(ms)] - 26.12 \quad (16)$$

さまざまな遅延時間の公称抵抗値を、表 8-1 に示します。

表 8-1. 標準的な DLY\_TMR 抵抗

| $t_{DLY\_TMR}(ms)$ | $R_{DLY\_TMR}(k\Omega)$ |

|--------------------|-------------------------|

| 0.268              | 10.5                    |

| 12.5               | 619                     |

| 23.37              | 1180                    |

図 8-9.  $R_{DL.Y\_TMR}$  と  $t_{DL.Y\_TMR}$  との関係 (0.268ms ~ 12.5ms)

図 8-10.  $R_{DL.Y\_TMR}$  と  $t_{DL.Y\_TMR}$  との関係 (12.5ms ~ 23.37ms)

### 8.3.4.2 Reg\_TMR

REG\_TMR(レギュレーション・タイマ用)は、調整可能な時間モニタで、 $V_{OUTx} > V_{ONx}$ となるまでに要する時間を監視します。ユーザーは、REG\_TMRとGND間に1つの抵抗を配置すれば、REG\_TMRをプログラムすることができます。抵抗( $R_{REG}$ )の範囲は、264μs～23.63msに対して、それぞれ10.5kΩ～1.18MΩです。REG\_TMRをアクティブにしたくない場合は、このピンをフローティング状態にしておくことができます。この場合、 $V_{OUTx}$ では、 $V_{ONx}$ 電圧を超えるまでの時間が無限になります。REG\_TMRは、パワーアップシーケンスのときにのみアクティブになります。

#### 注

REG\_TMRがフローティングのままになっていて、 $V_{ONx}$ 電圧が交差しない場合、ステートマシンは無制限に待機状態を維持します。

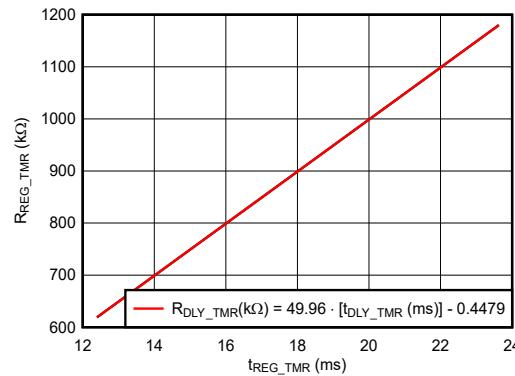

アクティブの場合、REG\_TMRは、ENx信号が強制的にHighになったときに、 $V_{OUTx}$ が $V_{ONx}$ 電圧を超えるまでに要する時間をモニタします。REG\_TMRが経過しても、 $V_{OUTx}$ が $V_{ONx}$ 電圧を超えていない場合は、[ステートマシンセクション](#)で説明しているように、従前にシーケンスしたレールからの逆方向のシーケンスが開始されます。[図8-8](#)に、ENxが強制的にHighになった時( $V_{OUTx}$ の立ち上がり開始)からのパワーアップシーケンス中のREG\_TMRアクティブを示します。この場合、 $V_{OUTx}$ は、タイマが経過する前に必ず $V_{ON}$ を超えます。[式17](#)および[式18](#)を使用してREG\_TMR抵抗を選択できます。[図8-11](#)または[図8-12](#)に、REG\_TMR抵抗と、レールがレギュレーション状態になることが許容されるレギュレーション時間との間の線形傾向( $V_{OUTx} > V_{ONx}$ )を示します。

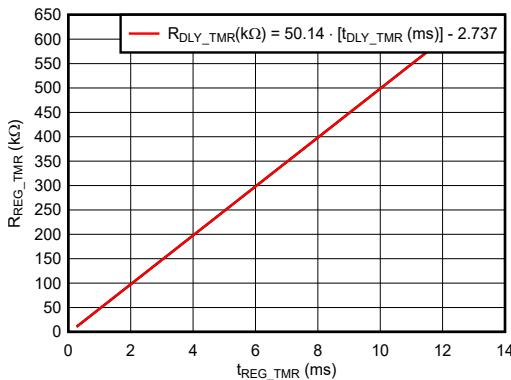

$t_{DLY\_TMR}$ が0.264ms～12.4msの間の場合は、以下を使用します：

$$R_{DLY\_TMR}(k\Omega) = [50.14 \times t_{DLY\_TMR}(ms)] - 2.737 \quad (17)$$

$t_{DLY\_TMR}$ が12.4msを超える場合は、以下を使用します：

$$R_{DLY\_TMR}(k\Omega) = [49.96 \times t_{DLY\_TMR}(ms)] - 0.4479 \quad (18)$$

[表8-2](#)に、さまざまな許容レギュレーション時間に対する標準抵抗値を示します。

表8-2. 標準的なREG\_TMR抵抗

| $t_{REG\_TMR}$ (ms) | $R_{REG\_TMR}$ (kΩ) |

|---------------------|---------------------|

| 0.264               | 10.5                |

| 12.4                | 619                 |

| 23.63               | 1180                |

図8-11.  $R_{REG\_TMR}$ と $t_{REG\_TMR}$ との関係、0.264msから12.4msまで 図8-12.  $R_{REG\_TMR}$ と $t_{REG\_TMR}$ との関係、12.4msから23.63msまで

### 8.3.5 UP および DOWN

UP ピンと DOWN ピンは、パワーアップまたはパワーダウンシーケンスを開始する入力です。どちらのピンにも、しきい値電圧  $V_{TH\_UP} = 599\text{mV}$  (UP 用)、および  $V_{TH\_DOWN} = 498\text{mV}$  (DOWN 用) の正確なコンパレータが組み込まれており、両入力の精度は、 $\pm 3\%$  です。

ノイズを安定させるため、両方のコンパレータには 100mV の固定ヒステリシスが組み込まれています。これらのピンのエッジは、次のようなコマンドを開始するために使用されます：

- UP の立ち上がりエッジによるパワーアップシーケンスの開始。

- Down の立ち下がりエッジによるパワーダウンシーケンスの開始。

また、UP 電圧は、FAULT(障害)時の発振を防止するためのラッチ方式としてステートマシンでも使用されます。障害状態から抜け出すには、UP 電圧をロジック Low にする必要があります。UP は 100mV のヒステリシスを持つコンパレータなので、 $V_{UP}$  が以前に  $V_{TH\_UP}$  を上回っていたかどうかに応じて、ロジック Low レベルは次のようになります。

- UP が、これまでに  $V_{TH\_UP}$  を上回っていない場合は、 $V_{TH\_UP} \leq 599\text{mV}$  (標準値)。

- UP が、以前に  $V_{UP\_TH}$  を超えたことがある場合は、 $V_{UP\_TH}$  (標準値 600mV) – 100mV  $\leq 500\text{mV}$  (標準値)。

これらの入力は、ハウスキーピング コントローラを使用して外部から駆動するか、電圧源に接続された抵抗分圧回路を介して駆動することができます。

これらの入力はエッジの影響を受けやすいため、パワーアップシーケンス コマンドを送信する前に、2.8ms ( $t_{Start\_up\_delay}$ ) 以上の安定した入力電圧 ( $UVLO_{RISE} < V_{IN} < 14\text{V}$ ) を確保することが重要です。これは、デバイスの内部時定数によるものです。パワーダウンシーケンスのときは、SEQ\_DONE フラグが LOW に設定されるまで、安定した入力電圧を維持して、すべてのレールのパワーダウンシーケンスが適切に制御されるようにすることが重要です。

UP ピンと DOWN ピンの両方に高精度の低電圧コンパレータがあるため、ユーザーは、抵抗分圧回路を使用してメイン電源レール ( $V_{MAIN}$ ) を監視するときに、システムが自動的にパワーアップおよびパワーダウンシーケンスを開始する電圧をプログラムすることができます。ただし、この場合、すでに説明したように、 $V_{IN}$  が安定したときに立ち上がり/立ち下がりエッジが確実に送信するようにすることが重要です。 $V_{MAIN}$  のスルーレートが高速の場合は、UP ピンと GND の間にコンデンサを追加して信号を遅延させることができます。

通常、パワーアップシーケンスを起動する電圧 ( $V_{UP\_IDEAL}$  と呼ばれます) および停止する電圧 ( $V_{DOWN\_IDEAL}$  と呼ばれます) は、設計者が把握しています。この情報とともに、式 19 および式 20 を使用して抵抗分圧回路の値を計算することができます。通常、上部の抵抗値は  $10\text{k}\Omega$  に固定されています。

$$R_{BOTTOM\_UP} = R_{TOP\_UP} \times \frac{V_{TH\_UP}}{V_{UP\_IDEAL} - V_{TH\_UP}} \quad (19)$$

$$R_{BOTTOM\_DOWN} = R_{TOP\_DOWN} \times \frac{V_{TH\_DOWN}}{V_{DOWN\_IDEAL} - V_{TH\_DOWN}} \quad (20)$$

ここで

- $V_{TH\_UP} = 598\text{mV}$  (標準値)

- $V_{TH\_DOWN} = 498\text{mV}$  (標準値)

設計者が実際の(実在する)抵抗分圧回路の値を把握していれば、式 21 と式 22 を使用してパワーアップおよびパワーダウンシーケンスの公称電圧は次のように算出できます：

$$V_{UP\_NOMINAL} (V) = \left( 1 + \frac{R_{TOP\_UP}}{R_{BOTTOM\_UP}} \right) \times V_{TH\_UP} \quad (21)$$

$$V_{DOWN\_NOMINAL} (V) = \left( 1 + \frac{R_{TOP\_DOWN}}{R_{BOTTOM\_DOWN}} \right) \times V_{TH\_DOWN} \quad (22)$$

希望に応じて、式 23 を使用することができる UP ピンの容量 ( $C_{DELAY}$ ) を選択します。

$$C_{DELAY} \left( F \right) > \frac{t_{DELAY}(s)}{R_{TH}(\Omega) \times \ln\left(-\frac{V_{TH}(V)}{V(t) - V_{TH}(V)}\right)} \quad (23)$$

ここで

- $t_{DELAY}$ (秒) は必要な遅延時間(秒)です( $V_{IN} > UVLO_{RISE}$  から少なくとも 2.8ms)。

- $R_{TH}$  は、テブナン等価抵抗です。この場合、 $R_{TOP}$  と  $R_{BOTTOM}$  の並列抵抗 ( $\Omega$ ) です。

$$- R_{TH}(\Omega) = \frac{R_{TOP}(\Omega) \times R_{BOTTOM}(\Omega)}{R_{TOP}(\Omega) + R_{BOTTOM}(\Omega)} \quad (24)$$

- $V_{TH}$  はテブナンの等価電圧です。この場合、定常駆動状態での  $V_{UP}$  電圧 (V) です。

$$- V_{TH}(V) = \left( \frac{R_{BOTTOM}(\Omega)}{R_{TOP}(\Omega) + R_{BOTTOM}(\Omega)} \right) \times V_{MAIN}(V) \quad (25)$$

- $V(t)$  は、パワーアップシーケンスを開始する UP 電圧 ( $V_{UP}$ ) です。この場合、598mV ±3% で、ボルト単位です。

図 8-13. メイン レールを監視して、シーケンスの立ち上げおよびシャット ダウンを自動的に開始します

### 8.3.6 フォルト

**FAULT** ピンはオープンドレイン出力で、ユーザーはステートマシンによって内部に故障が発生しているかどうかの監視に使用できます。10k $\Omega$  抵抗を介してこのピンを VLDO 出力にプルアップすることを推奨します。必要に応じて別の電圧源も利用できますが、その電圧が安定し、常に 1V を超えていることが重要です。このピンの最大電圧は 7V です。適切に動作させるには、パワーアップ/パワーダウンシーケンスの試験前にこの電圧が安定している必要があります。デバイスの動作中は常に 1V を上回っていなければなりません。[ステート マシン](#)で説明されているように、シーケンスの内部ステートマシンが故障を検出すると、オープンドレイン FET は強制的に Low になります。

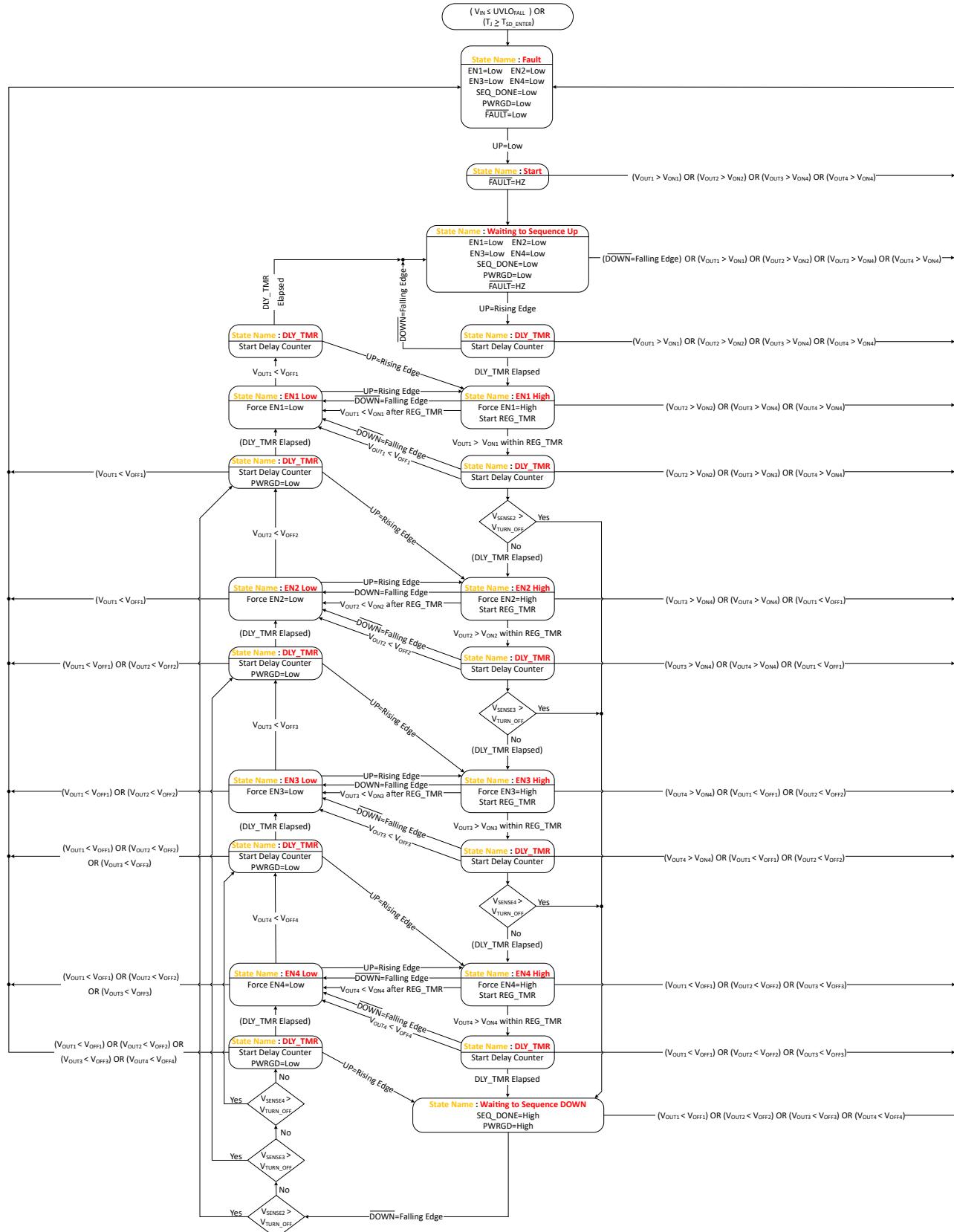

### 8.3.7 ステート マシン

TPS7H3014 には、包括的なステートマシンエンジンが組み込まれています。検出した入力の状態に応じて、3 つの結果が考えられます。

1. 次の場合、以前に良好とみなされた(強制的に High になった) ENx 信号から逆方向のシーケンスが開始されます。

- ENx が HIGH のとき、REG\_TMR で設定された時間内に、パワーアップシーケンスによって V<sub>OUTx</sub> が V<sub>ONx</sub> 電圧に到達しなかった場合。

- 以前に V<sub>ONx</sub> を超えた後、V<sub>OUTx</sub> は V<sub>OFFx</sub> を超えたが、V<sub>OUTx+1</sub> がまだ V<sub>ONx+1</sub> を超えていない場合。

- ユーザーは、パワーアップシーケンスの途中でパワーダウンシーケンスを指示します。

2. アウトオブオーダーが検出されると、すべての出力(ENx, SEQ\_DONE, PWRGD) は強制的に Low になります。これは、次のことを意味します:

- 少なくとも V<sub>OUTx+1</sub> がすでに規定範囲内(良好とみなされる)となっているときに、以前は良好とみなされたレール V<sub>OUTx</sub> が V<sub>OFFx</sub> を下回っている。

- ENx が HIGH でないとき、V<sub>OUTx</sub> > V<sub>ONx</sub> となっている。パワーアップシーケンスアップ中のみ有効。

---

#### 注

シーケンサでは、V<sub>ONx</sub> を監視対象の公称電圧に対するパーセンテージ(たとえば、V<sub>ONx</sub> = 0.8 × V<sub>OUTx</sub>) で設定するのが一般的です。パワーダウンシーケンスのとき、V<sub>OUTx</sub> ≥ V<sub>ONx</sub> となる時間があります。レール(V<sub>OUTx</sub>)の放電速度は TPS7H3014 では不明なため、この機能はパワーアップシーケンスのときに限って有効です。

3. 以下の場合、DLY\_TMR の経過後に、以前に強制的に Low にされた ENx 信号からパワーアップシーケンスが開始されます:

- ユーザーは、パワーダウンシーケンスの途中でパワーアップシーケンスを指示します。

図 8-14. TPS7H3014 のステートマシン図

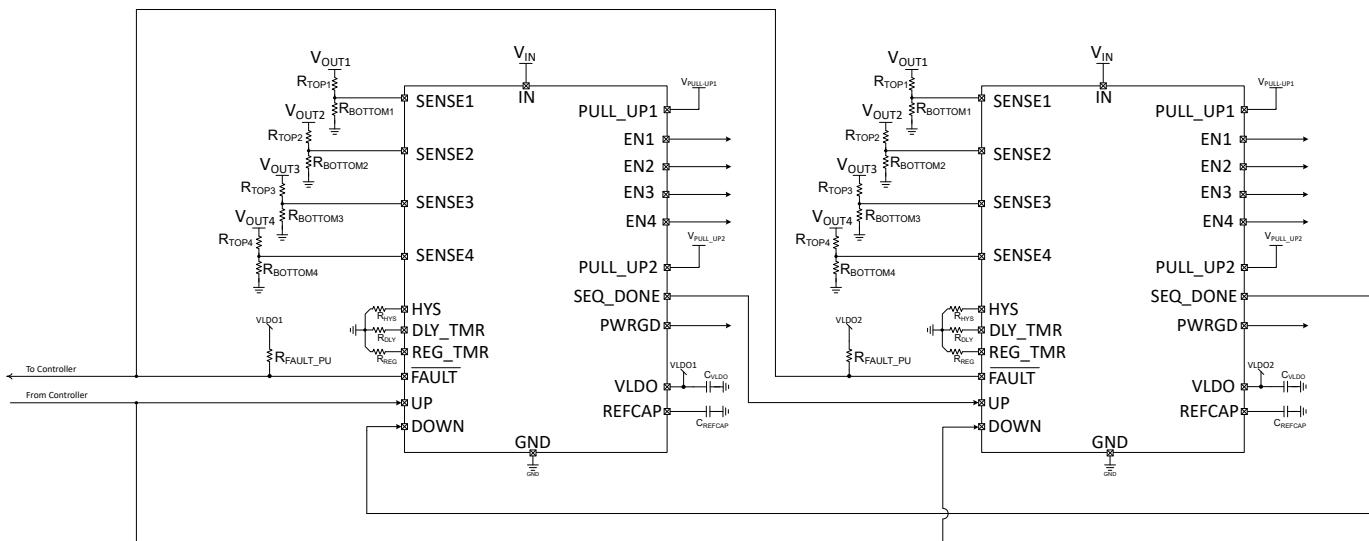

## 8.4 デイジーチェーン

TPS7H3014 には、最大 4 つの電圧レールをシーケンス制御/監視するための 4 つの入力チャネルが内蔵されています。ただし、このアプリケーションで 4 つ以上のチャネルが必要な場合は、必要に応じて複数のデバイスをデイジーチェーン接続できます。デイジーチェーン構成を、図 8-15 に示します。この場合、ここには 2 つのデバイスのみが表示されていますが、アプリケーションの必要に応じて複数の IC を構成することができます。

図 8-15. デイジーチェーン構成

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

TPS7H3014 は、耐放射線特性が強化された 4-チャネルのリニア レギュレータです。FPGA、ASIC、AFE、各種電源システムのシーケンス制御に利用できます。

### 9.2 代表的なアプリケーション

#### 9.2.1 自己完結型 – シーケンスアップ/ダウン

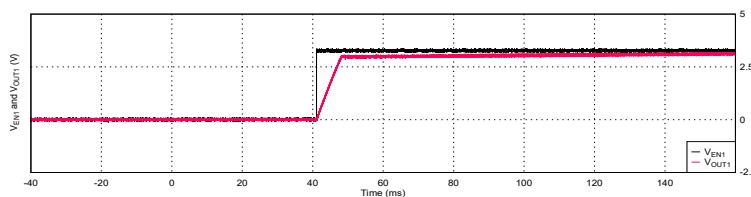

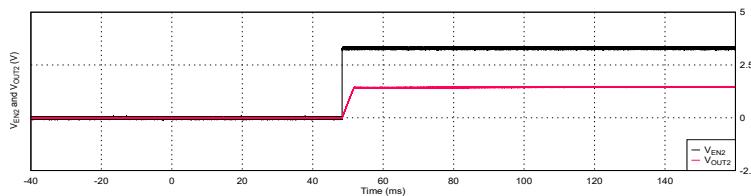

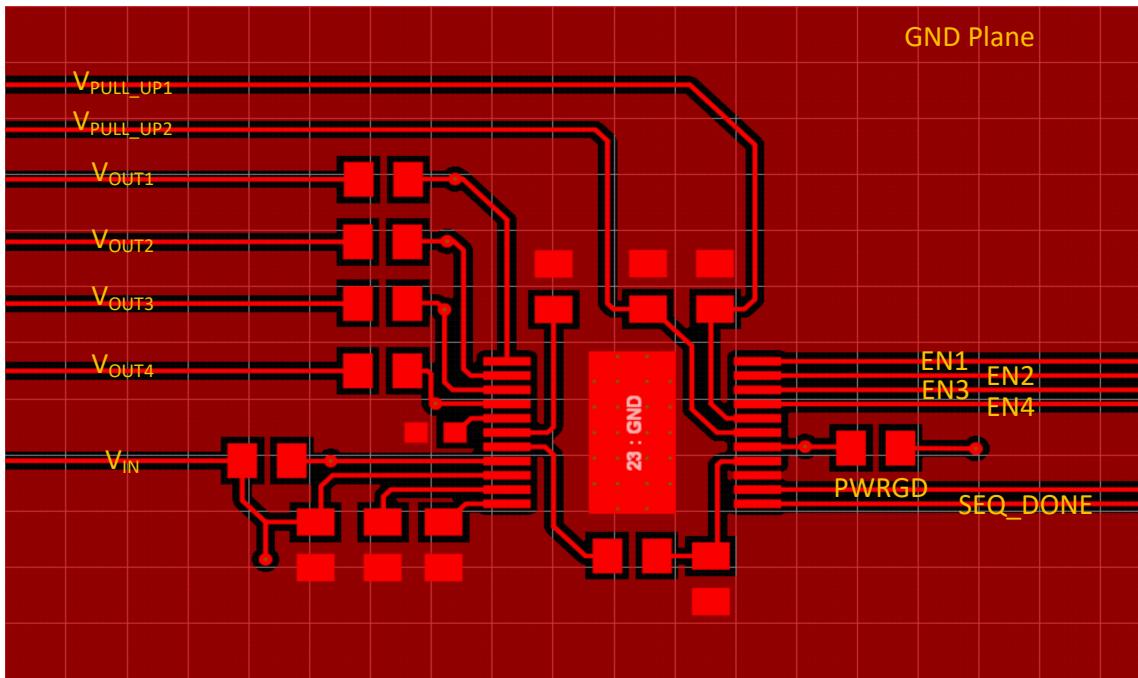

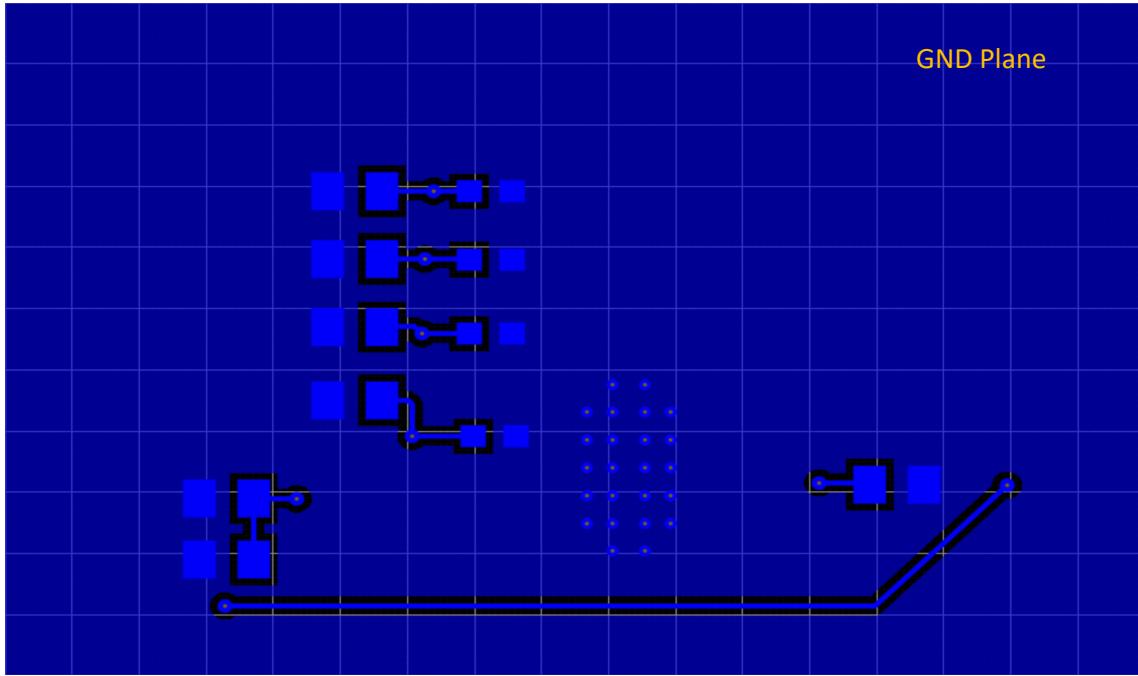

多くの最新システム(またはサブシステム)では、複数の電圧レールが必要な場合が多く、これを「電源ツリー」と呼びます。その場合、これらの電源ツリーでは、信頼性の高いシステム動作を保証するために必要なパワーアップシーケンスとその逆のパワーダウンシーケンスの手順について規定されていることがほとんどです。これらのシステムが、正しく動作するために侵害できないタイミング仕様を持つことは珍しくありません。この例では、EN<sub>x</sub> 出力と SENSE<sub>x</sub> 入力により、それぞれ 4 つの電圧レールがシーケンス制御され、監視されています。以下に、設計手順と部品選定の詳細を示します。設計については、図 9-1 にまとめられています。

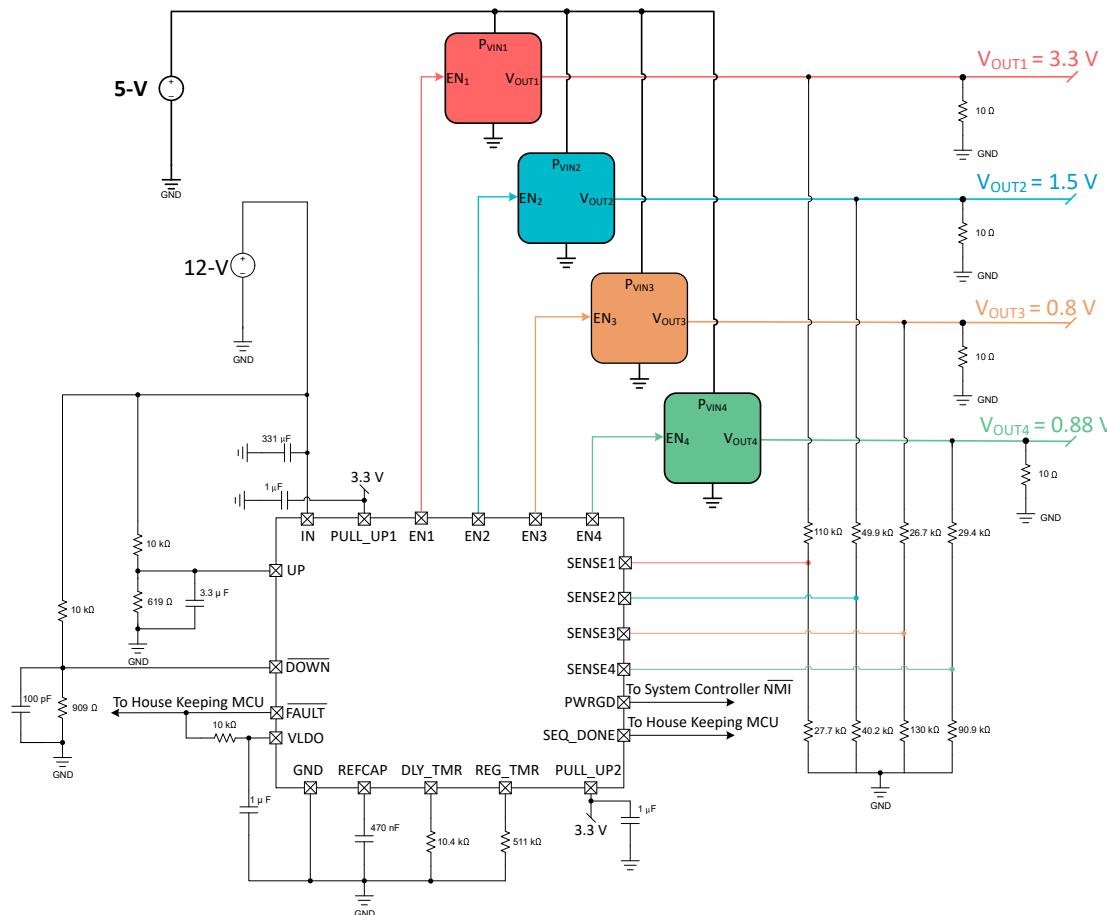

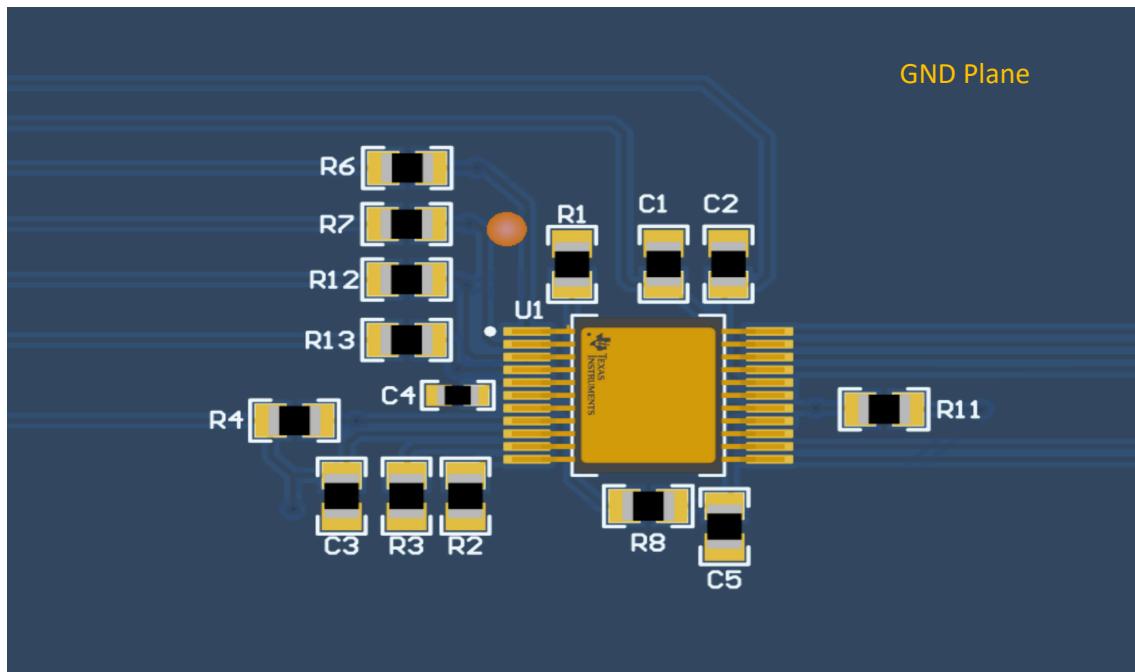

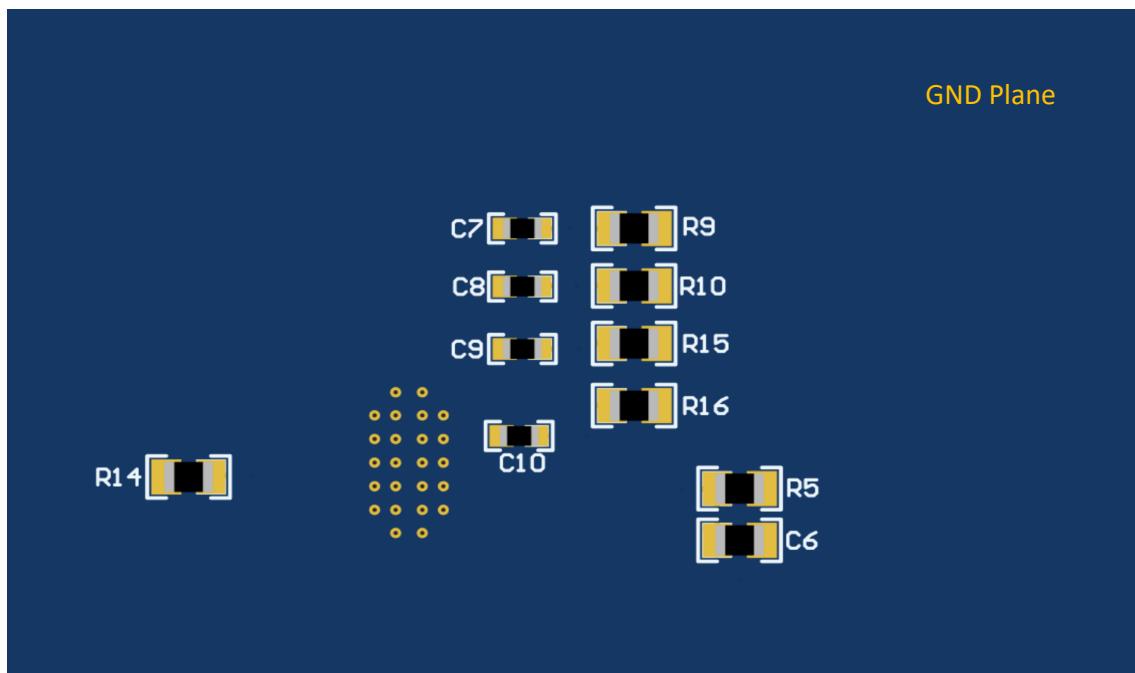

図 9-1. 4 つの電圧レールの電源ツリーを対象とした自己完結型のパワーアップ/パワーダウン シーケンスの設計

### 9.2.1.1 設計要件

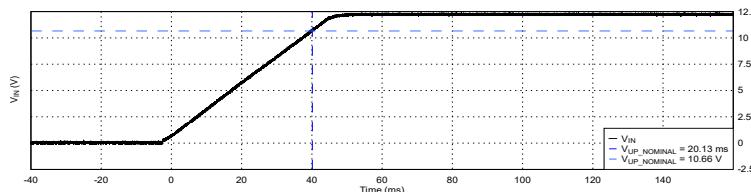

この設計では、4つの電圧レールの電圧をシーケンス制御する必要があります。TPS7H3014 の公称入力電圧は 12V であり、電圧が希望の目標電圧レベルに達すると、シーケンサがパワーアップおよびパワーダウンシーケンスを自動的に開始するように設定されています。すべての電圧レギュレータに対して、5V の公称電圧レールで電力を供給します。システムのハウスキーピング・マイクロコントローラは、VLDO にプルアップされた FAULT ピンの電圧を介して故障を監視できます。PWRGD は、システムのノンマスカブル割り込みが存在する場合はそれに接続されるフラグ、あるいは電源ツリーの状態を確認するために MCU によって監視されるフラグです。SEQ\_DONE は、パワーアップ/パワーダウンシーケンスが完了したかどうかをモニタすることもできます。すべての設計条件は、表 9-1 で定義されています。

**表 9-1. 設計条件**

| パラメータ                             | 設計要件                                                                                                     | 設計結果                                                                                                                                 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| システムの公称電圧                         | 12V の入力電圧を監視し、電圧が 3.7ms 以上 10.7V (88%) を上回るとパワーアップシーケンスを開始します。電圧が 6V (または 50%) を下回ると、パワーダウンシーケンスが開始されます。 | TPS7H3014 は、電圧を監視し抵抗分圧回路を使用してパワーアップおよびパワーダウンシーケンスを自動的に開始させることができます。UPDOWN の内部リファレンスの精度は、3% です。誤差を最小限に抑えるため、公差 0.1% の抵抗を使用することを推奨します。 |

| V <sub>OUT1</sub>                 | 公称 3.3V:<br>V <sub>ON</sub> = 90%、V <sub>OFF</sub> = 10%                                                 | V <sub>ON</sub> = 2.978V ± 29.97mV<br>V <sub>OFF</sub> = 0.338V ± 84.61mV<br>許容誤差 0.1% の抵抗を使用                                        |

| V <sub>OUT2</sub>                 | 公称 0.8V:<br>V <sub>ON</sub> = 90%、V <sub>OFF</sub> = 10%                                                 | V <sub>ON</sub> = 0.722V ± 7.22mV<br>V <sub>OFF</sub> = 0.081V ± 20.54mV<br>許容誤差 0.1% の抵抗を使用                                         |

| V <sub>OUT3</sub>                 | 公称 1.5V:<br>V <sub>ON</sub> = 90%、V <sub>OFF</sub> = 10%                                                 | V <sub>ON</sub> = 1.343V ± 13.47mV<br>V <sub>OFF</sub> = 0.145V ± 38.35mV<br>許容誤差 0.1% の抵抗を使用                                        |

| V <sub>OUT4</sub>                 | 公称 0.88V:<br>V <sub>ON</sub> = 90%、V <sub>OFF</sub> = 10%                                                | V <sub>ON</sub> = 0.793V ± 7.93mV<br>V <sub>OFF</sub> = 0.087V ± 22.6mV<br>許容誤差 0.1% の抵抗を使用                                          |

| パワーアップおよびパワーダウンシーケンス中の ENx 遅延     | 遅延は公称 0.268ms                                                                                            | R <sub>DLY_TMR</sub> = 10.4kΩ                                                                                                        |

| レールが V <sub>ONx</sub> に達するまでの許容時間 | レールが V <sub>ONx</sub> に達するまで、10.3ms (公称値) 待機                                                             | R <sub>REG_TMR</sub> = 511kΩ                                                                                                         |

### 9.2.1.2 詳細な設計手順

#### 9.2.1.2.1 入力電源とデカップリング コンデンサ

TPS7H3014 には、次の三つの電源が必要です。

- IN は、TPS7H3014 IC に電力を供給する入力電源です。この電源は、ピンのできるだけ近くに 1μF 以上のコンデンサを配置してデカップリングすることを推奨しています。この回路では、V<sub>IN</sub> = 12V です。

- PULL\_UP1 は、すべてのイネーブル出力(ENx)の出力電圧 HIGH(V<sub>OH</sub>)をプログラムするための入力電源です。これらの出力はレギュレータのイネーブル入力に接続され、パワーアップ/パワーダウンシーケンスを制御します。この電源は、ピンのできるだけ近くに 1μF 以上のコンデンサを配置してデカップリングすることを推奨しています。このアプリケーションでは、V<sub>PULL\_UP1</sub> = 3.3V です。これは、電子システムで使用される標準的な電圧であり、市販のほとんどのレギュレータのロジック入力に対応します。

- PULL\_UP2 は、PWRGD および SEQ\_DONE 出力の出力電圧 High(V<sub>OH</sub>)をプログラムする入力電源です。これらの出力は通常、システムコントローラ(通常は FPGA または ASIC)やハウスキーピング(維持管理)コントローラに接続されます。デイジーチェーン構成では、図 8-15 に示すように、SEQ\_DONE は後続の TPS7H3014 I.C. の UP に接続されます。この電源は、ピンのできるだけ近くに 1μF 以上のコンデンサを配置してデカップリングすることを推奨しています。このアプリケーションでは、V<sub>PULL\_UP1</sub> = 3.3V です。これは、コントローラ I/O の一般的な電圧です。

また、TPS7H3014 には、良好な電気的特性および放射線耐性を得るためにデカップリングが必要な 2 つの安定化電圧出力を備えています。それらを以下に示します。

- REFCAP(1.2V リファレンス)は、デバイス内部で次のとおりリファレンスによるすべてのレシオメトリック電圧を生成するため使用されます。

- $V_{TH\_SENSE}$

- $I_{HYS\_SENSE}$

- $V_{TH\_UP}$

- $V_{TH\_DOWN}$

このリファレンスには、470nF のセラミック コンデンサをできるだけピンの近くに配置してデカップリングします。このピンには、外部に負荷を接続しないでください。

- VLDO は、TPS7H3014 の内部回路に電力を供給するために使用される内部レギュレータの出力です。このレギュレータは、ピンのできるだけ近くに配置した 1μF 以上のコンデンサでデカップリングすることを推奨します。このレギュレータの有効な負荷は次のとおりです：

- 必要に応じてチャネル 2 ~ 4 をオフにします。

- $\overline{FAULT}$  オープンドレイン出力をプルアップします。

#### 9.2.1.2.2 昇圧/降圧スレッショルド

このアプリケーションでは、UP ピンと DOWN ピンを使用して 12V の入力電源電圧を監視します。レール電圧が 10.7 (標準)を上回ると、パワーアップシーケンスが開始され、電圧が 6V (標準)を下回ると停止します。TPS7H3014 の内部時定数( $t_{Start\_UP\_DELAY}$ )は 2.8ms (最大)であるため、3.3μF の遅延コンデンサを UP ピンに追加します。このコンデンサを追加すると、 $V_{IN}$  の立ち上がり時に UP ピンに遅延が発生します。このコンデンサにより、シーケンス開始に 2 番目の条件が追加され、 $V_{IN} \geq 10.7V$  (標準値) が 2.8ms 以上のとき、パワーアップシーケンスのコマンドが指示されます。

UP DOWN の抵抗分圧回路の上部抵抗を固定すれば、設計要件に従って下部の抵抗を計算することができます。いずれの場合も、上部抵抗は 10kΩ に固定されています。[式 19](#) と [式 20](#) の式を使用して、UP および DOWN の下部抵抗は次のように算出されます：

$$R_{BOTTOM\_UP} = 10 \text{ k}\Omega \times \frac{0.598 \text{ V}}{10.7 \text{ V} - 0.589 \text{ V}} \cong 594 \text{ }\Omega \quad (26)$$

$$R_{BOTTOM\_DOWN} = 10 \text{ k}\Omega \times \frac{0.498 \text{ V}}{6 \text{ V} - 0.498 \text{ V}} \cong 905 \text{ }\Omega \quad (27)$$

リファレンス抵抗が算出されたので、実際の(または現実の)抵抗を選択できます。この場合、次のとおり最も近い値の抵抗を選定するため許容誤差が 0.1% の抵抗を使用します：

- $R_{BOTTOM\_UP} = 619\Omega$

- $R_{BOTTOM\_DOWN} = 909\Omega$

実際の抵抗値を使用して公称電圧を逆算し、[式 21](#) と [式 22](#) を使用して、次のとおりパワーアップまたはパワーダウンシーケンスを開始できます：

$$V_{UP\_NOMINAL}(V) = \left(1 + \frac{10 \text{ k}\Omega}{619 \text{ }\Omega}\right) \times 12 \text{ V} \cong 10.66 \text{ V} \quad (28)$$

$$V_{DOWN\_NOMINAL}(V) = \left(1 + \frac{10 \text{ k}\Omega}{909 \text{ }\Omega}\right) \times 12 \text{ V} \cong 5.97 \text{ V} \quad (29)$$

遅延コンデンサは、次のとおり[式 23](#)、[式 24](#)、[式 25](#) を使って計算します。

$$R_{TH}(\Omega) = \frac{10 \text{ k}\Omega \times 619 \text{ }\Omega}{10 \text{ k}\Omega + 619 \text{ }\Omega} = 582.9 \text{ }\Omega \quad (30)$$

$$V_{TH}(\Omega) = \left(\frac{619 \text{ }\Omega}{10 \text{ k}\Omega + 619 \text{ }\Omega}\right) \times 12 \text{ V} = 0.7 \text{ V} \quad (31)$$

$$C_{\text{DELAY}} \left( F \right) \geq \frac{0.0028 \text{ s}}{582.9 \Omega \times \ln\left(-\frac{0.7 \text{ V}}{0.598 \text{ V} - 0.7 \text{ V}}\right)} = 2.49 \mu\text{F} \quad (32)$$

入力コンデンサには  $3.3\mu\text{F}$  のコンデンサを選びます。

### 9.2.1.2.3 SENSEx スレッショルド

SENSEx 入力を使用して、パワーアップおよびパワーダウンシーケンシングを行う電圧レールをモニタします。この設計では、シーケンス制御およびモニタする出力電圧は次のとおりです。

1.  $V_{\text{OUT1}} = 3.3\text{V}$

2.  $V_{\text{OUT2}} = 0.8\text{V}$

3.  $V_{\text{OUT3}} = 1.5\text{V}$

4.  $V_{\text{OUT4}} = 0.88\text{V}$

すべてのレールについて、 $V_{\text{ON}}$  と  $V_{\text{OFF}}$  は、公称電圧レールの 90% と 10% になるよう選択されます。式 13 と式 14 を使用して、上部と下部のリファレンス抵抗を計算し、0.1%（精度）の抵抗値を使用して最も近い抵抗値を選択できます。表 9-2 にリファレンスの（または計算上の）上部抵抗と下部抵抗を示します。表 9-3 に、アプリケーション用に選定した抵抗を示します。

**表 9-2. SENSEx のリファレンス電圧の公称抵抗値**

| チャネル | $V_{\text{ON}}$ (V) | $V_{\text{OFF}}$ (V) | $R_{\text{TOP}}$ (kΩ) <sup>(1)</sup> | $R_{\text{BOTTOM}}$ (kΩ) <sup>(1)</sup> |

|------|---------------------|----------------------|--------------------------------------|-----------------------------------------|

| 1    | 2.970               | 0.330                | 110.0                                | 27.8                                    |

| 2    | 1.350               | 0.150                | 50.0                                 | 39.9                                    |

| 3    | 0.720               | 0.080                | 26.7                                 | 132.0                                   |

| 4    | 0.792               | 0.088                | 29.3                                 | 91.0                                    |

(1) 数値は小数第 2 位で四捨五入されています。

チャネル 1（または SENSE1）の上部抵抗と下部抵抗の計算方法の例を以下に示します：

$$\frac{2.970 \text{ V} - 0.330 \text{ V}}{24 \mu\text{A}} = 110 \text{ k}\Omega \quad (33)$$

$$\frac{110 \text{ k}\Omega \times 0.599 \text{ V}}{2.970 \text{ V} - 0.599 \text{ V}} = 39.88 \text{ k}\Omega \quad (34)$$

**表 9-3. 許容誤差 0.1% の抵抗を使用して SENSEx の抵抗を選定**

| チャネル | $R_{\text{TOP}}$ (kΩ) | $R_{\text{BOTTOM}}$ (kΩ) |

|------|-----------------------|--------------------------|

| 1    | 110                   | 27.7                     |

| 2    | 49.9                  | 40.2                     |

| 3    | 26.7                  | 130                      |

| 4    | 29.4                  | 90.9                     |

実際の抵抗が判明したため、式 1、式 2、式 3、式 6、式 7、式 12 を使用して実際のオン/オフ公称電圧と誤差電圧を計算できます。誤差を使用すると、上部と下部の電圧を計算し、公称出力電圧を基準にして値を正規化することができます。

**表 9-4.  $V_{\text{ON}}$  公称値、統計値 (V およびパーセンテージ)**

| チャネル | $V_{\text{ON\_NOMINAL}}$ (V) <sup>(1)</sup> | $V_{\text{ON\_NOMINAL}}$ (%) <sup>(1) (4)</sup> | $V_{\text{ON\_ERROR}}$ (mV) <sup>(1)</sup> | $V_{\text{ON\_LSL}}$ (V) <sup>(1) (2)</sup> | $V_{\text{ON\_LSL}}$ (%) <sup>(1)</sup><br><sup>(2) (4)</sup> | $V_{\text{ON\_USL}}$ (V) <sup>(1) (3)</sup> | $V_{\text{ON\_USL}}$ (%) <sup>(1)</sup><br><sup>(3) (4)</sup> |

|------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|

| 1    | 2.978                                       | 90.232                                          | 29.966                                     | 2.948                                       | 89.325                                                        | 3.008                                       | 91.141                                                        |

| 2    | 1.343                                       | 89.502                                          | 13.466                                     | 1.329                                       | 88.605                                                        | 1.356                                       | 90.400                                                        |

| 3    | 0.722                                       | 90.253                                          | 7.222                                      | 0.715                                       | 89.350                                                        | 0.729                                       | 91.156                                                        |

表 9-4. V<sub>ON</sub> 公称値、統計値 (V およびパーセンテージ) (続き)

| チャネル | V <sub>ON_NOMINAL</sub> (V) <sup>(1)</sup> | V <sub>ON_NOMINAL</sub> (%) <sup>(1) (4)</sup> | V <sub>ON_ERROR</sub> (mV) <sup>(1)</sup> | V <sub>ON_LSL</sub> (V) <sup>(1) (2)</sup> | V <sub>ON_LSL</sub> (%) <sup>(1) (2) (4)</sup> | V <sub>ON_USL</sub> (V) <sup>(1) (3)</sup> | V <sub>ON_USL</sub> (%) <sup>(1) (3) (4)</sup> |

|------|--------------------------------------------|------------------------------------------------|-------------------------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------|------------------------------------------------|

| 4    | 0.793                                      | 90.084                                         | 7.932                                     | 0.785                                      | 89.182                                         | 0.801                                      | 90.985                                         |

(1) 数値は小数第 4 位で四捨五入されています。

(2) LSL は、仕様下限値、または最小値です。

(3) USL は、仕様上限値または最大値です。

(4) 数値は、そのレールの公称出力電圧に正規化されています。

表 9-5. V<sub>OFF</sub> 公称値、統計値 (V およびパーセンテージ)