# TPS7A56 6A、低 $V_{IN}$ 、低ノイズ、高精度、超低ドロップアウト (LDO) 電圧レギュレータ

## 1 特長

- 入力電圧範囲:

- BIAS なし: 1.1V ~ 6.0V

- BIAS あり: 0.7V ~ 6.0V

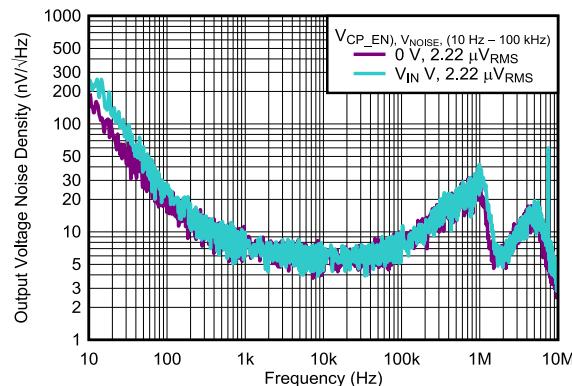

- 出力電圧ノイズ:  $2.45\mu V_{RMS}$

- ライン、負荷、温度の全範囲にわたって 1% (最大値) の精度

- 低いドロップアウト: 6 A 時に 90 mV

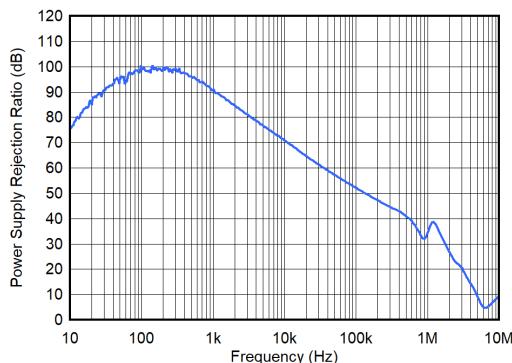

- 電源電圧変動除去比 (6A):

- 1kHz 時に 100dB

- 10kHz 時に 78dB

- 100kHz 時に 60dB

- 1MHz 時に 36dB

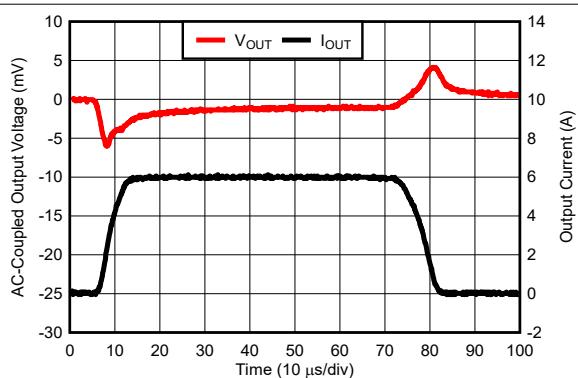

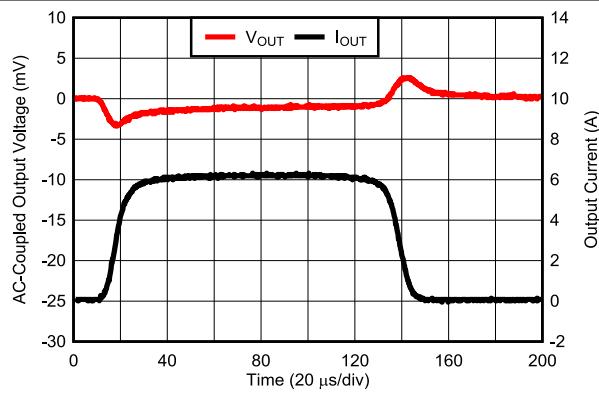

- 負荷過渡応答:

- 100mA~6A の負荷ステップで  $\pm 3mV$

- 可変出力電圧範囲: 0.5V ~ 5.0V

- 調整可能なソフトスタート突入電流制御

- BIAS レール:

- 内部チャージポンプまたは 3V~11V の外部レール

- 内部チャージポンプをディスエーブルにできる

- オープンドレインのパワー グッド (PG) 出力

- パッケージ:

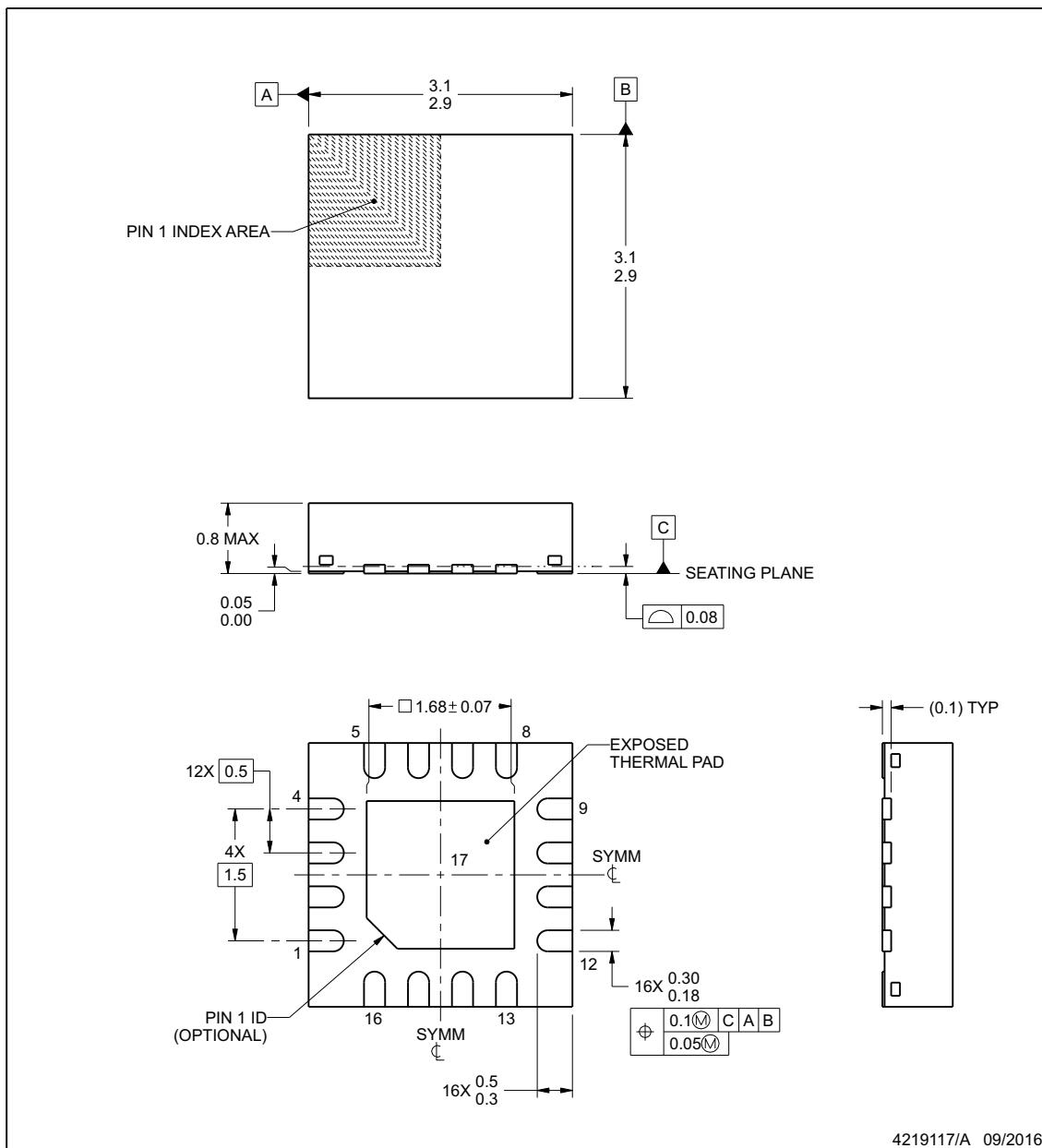

- 3mm × 3mm、16 ピン WQFN

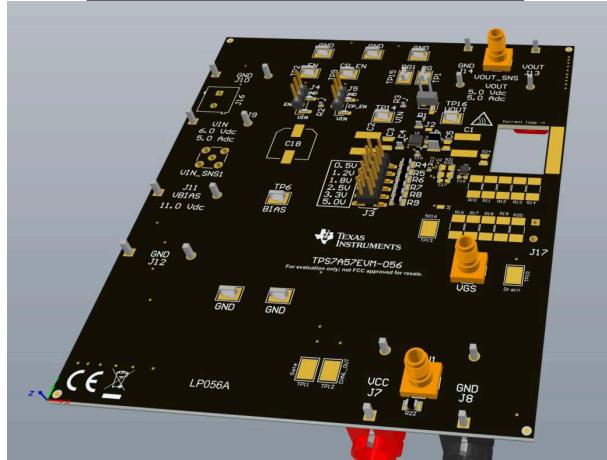

- EVM  $R_{\theta JA}$ : 21.9°C/W

## 2 アプリケーション

- マクロリモート無線ユニット (RRU)

- 屋外バックホール ユニット

- アクティブアンテナシステム (AAS) の mMIMO

- 超音波スキャナ

- 実験室およびフィールド向け計測機器

- センサ、画像処理、レーダー

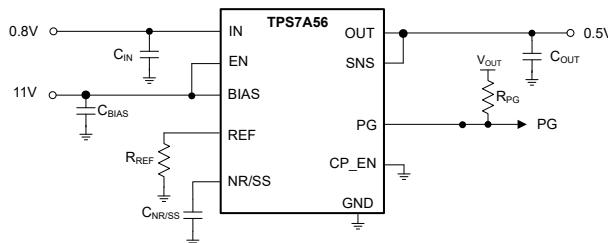

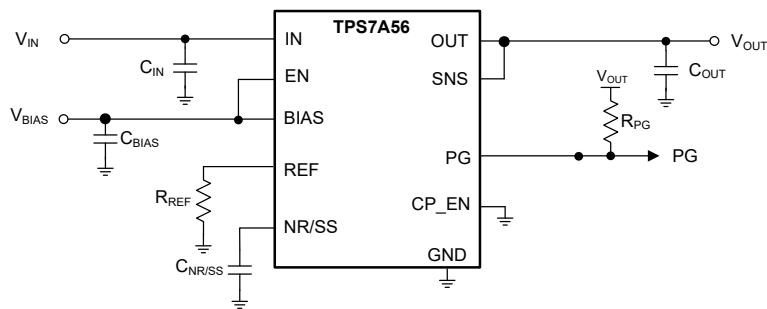

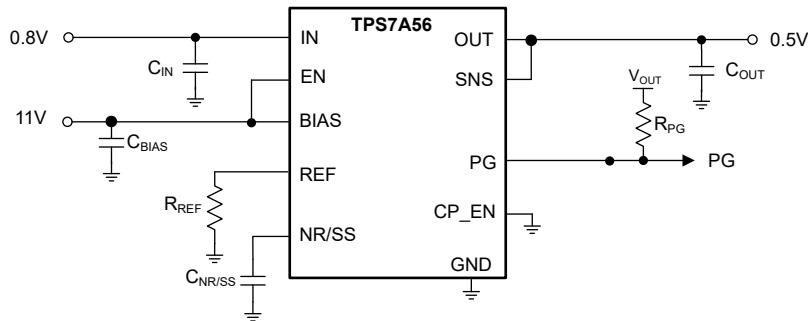

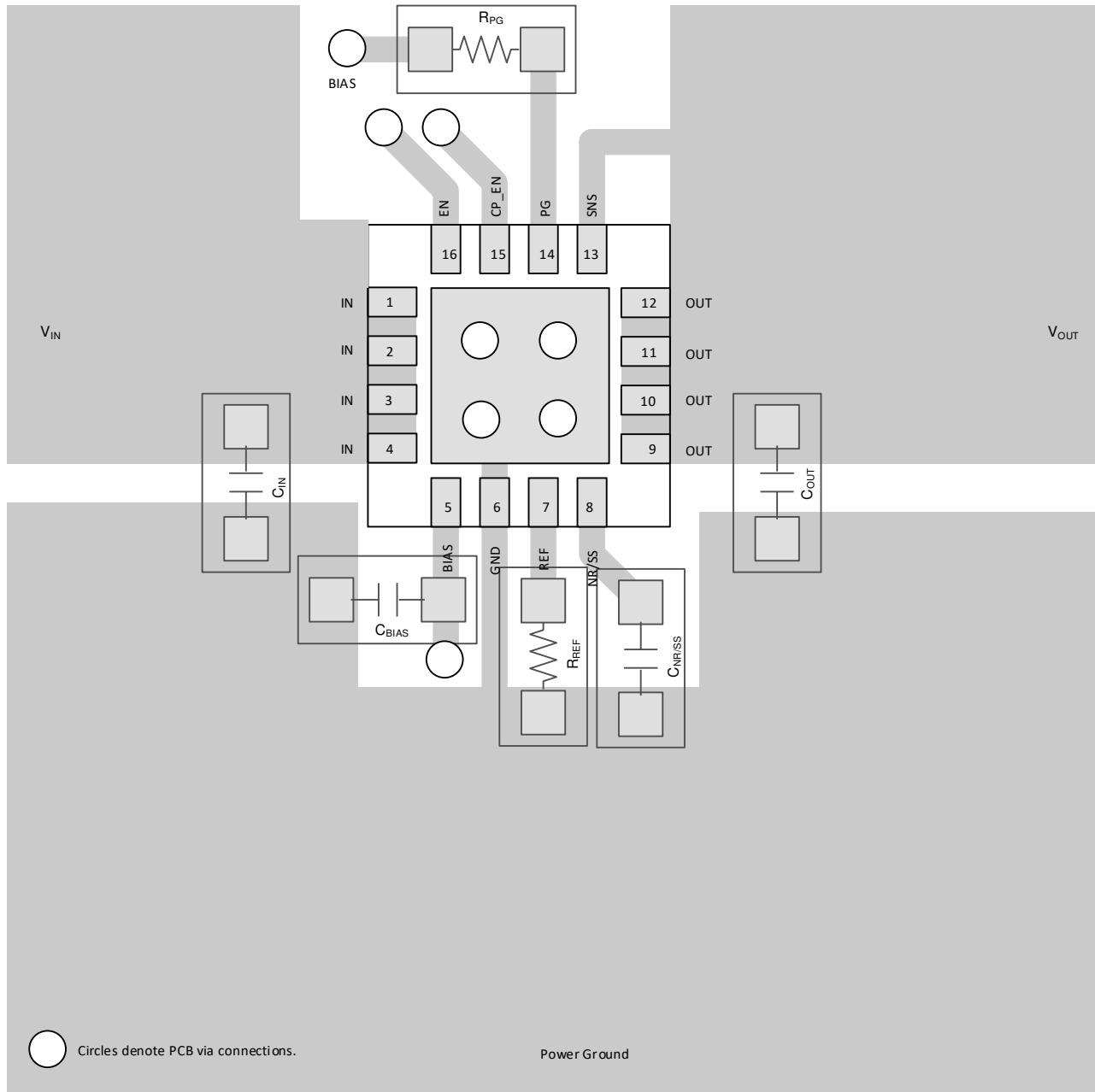

代表的なアプリケーション回路

## 3 説明

TPS7A56、低ノイズ ( $2.45\mu V_{RMS}$ ) で超低ドロップアウトのリニア レギュレータ (LDO) であり、出力電圧に依存せず 90mV のドロップアウトで最大 6A の電流を供給可能です。デバイスの出力電圧は、1 個の外付け抵抗を使って 0.5V~5V の範囲で調整可能です。低ノイズ、高 PSRR (36dB at 1MHz)、高出力電流能力の組み合わせにより、TPS7A56 はノイズに敏感なコンポーネントの電源用に設計されています。これらのコンポーネント (RF アンプ、レーダー センサー、SERDES、アナログ チップセットなど) は、レーダーの電力、通信、画像処理の用途に使用されています。

低入力、低出力 (LILO) 電圧で動作するデジタル負荷も、優れた精度、リモート センシング、過渡応答性能、ソフトスタート機能の恩恵を受け、システム全体の性能を最大限に引き出することができます。これらの負荷には、アプリケーション固有集積回路 (ASIC)、フィールド プログラマブル ゲート アレイ (FPGA)、デジタル信号プロセッサ (DSP) などが含まれます。汎用性、性能、フットプリントが小さいため、この LDO は大電流のアナログ負荷や、シリアルライザ / デシリアライザ (SerDes)、FPGA、DSP など、大電流アナログ負荷のための優れた選択肢となります。大電流アナログ負荷には、A/D コンバータ (ADC)、D/A コンバータ (DAC)、画像処理センサが含まれます。

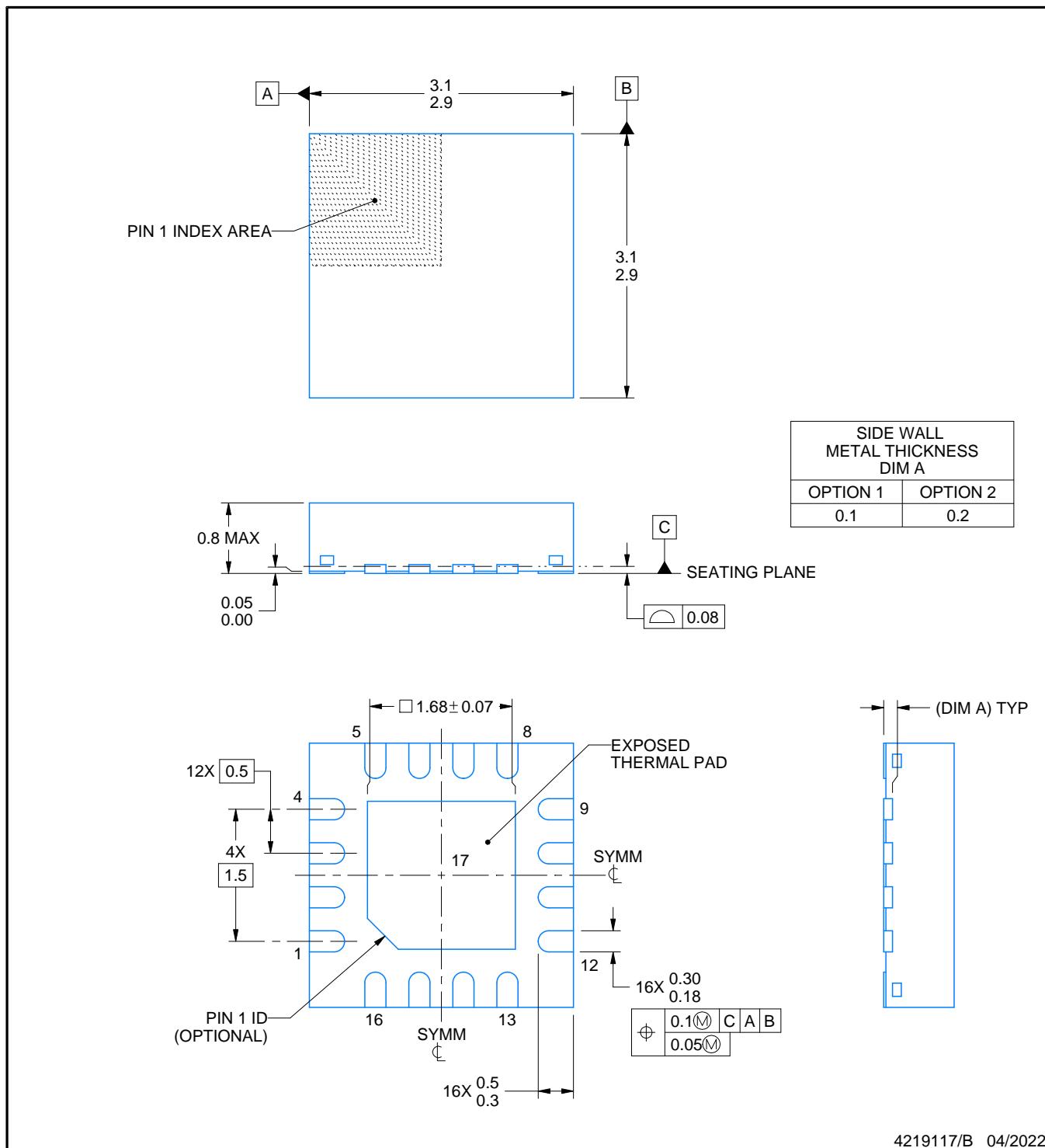

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| TPS7A56 | RTE (WQFN, 16)       | 3mm × 3mm                |

- (1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

(2) パッケージサイズ (長さ×幅) は公称値であり、ピンを含む場合もあります。

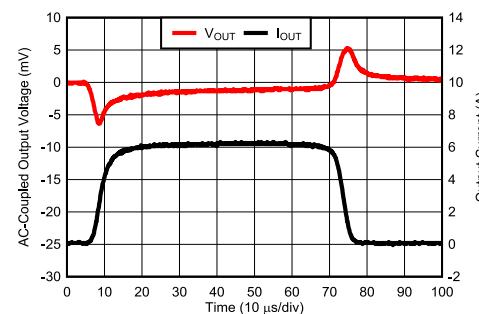

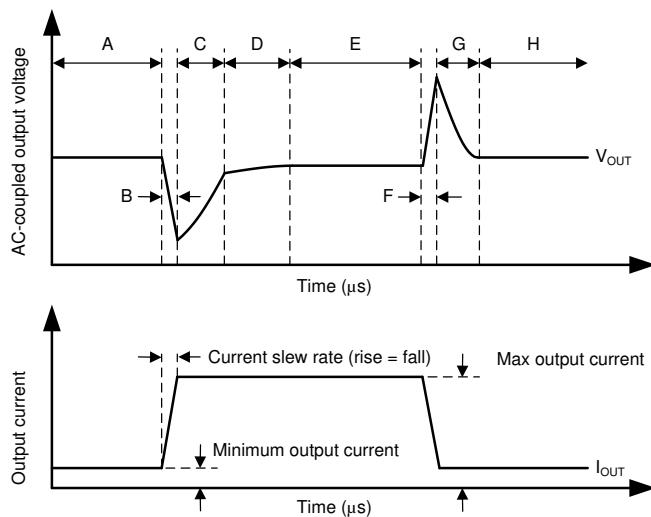

TPS7A56 の負荷過渡応答

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                          |           |                                     |           |

|--------------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b> .....        | <b>1</b>  | <b>7 アプリケーションと実装</b> .....          | <b>45</b> |

| <b>2 アプリケーション</b> .....  | <b>1</b>  | <b>7.1 アプリケーション情報</b> .....         | <b>45</b> |

| <b>3 説明</b> .....        | <b>1</b>  | <b>7.2 代表的なアプリケーション</b> .....       | <b>62</b> |

| <b>4 ピン構成および機能</b> ..... | <b>3</b>  | <b>7.3 電源に関する推奨事項</b> .....         | <b>63</b> |

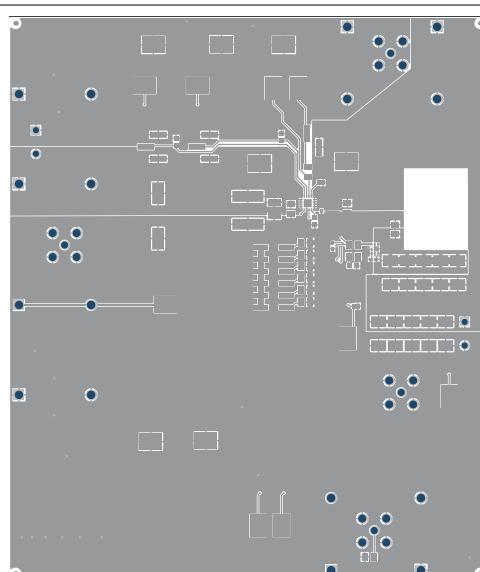

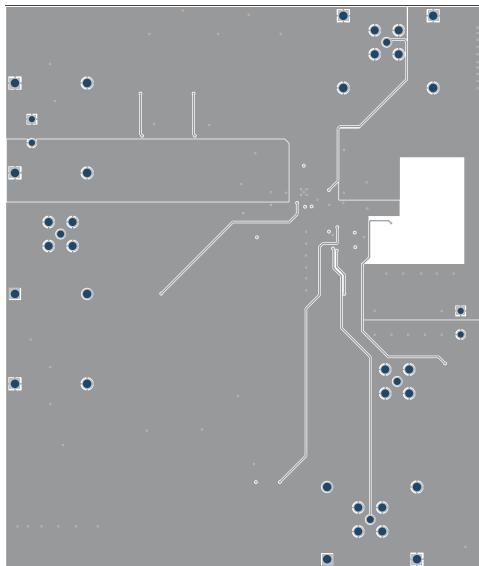

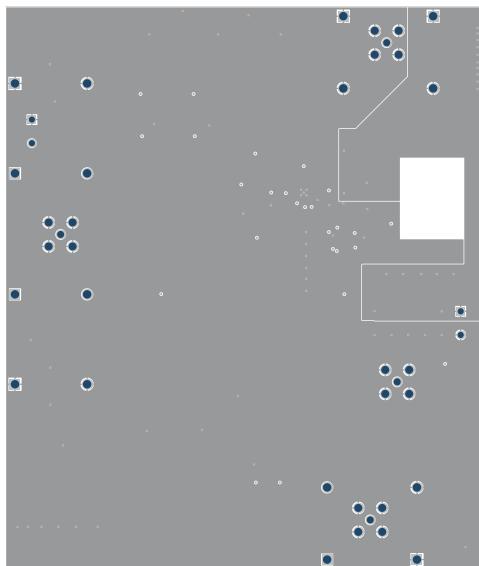

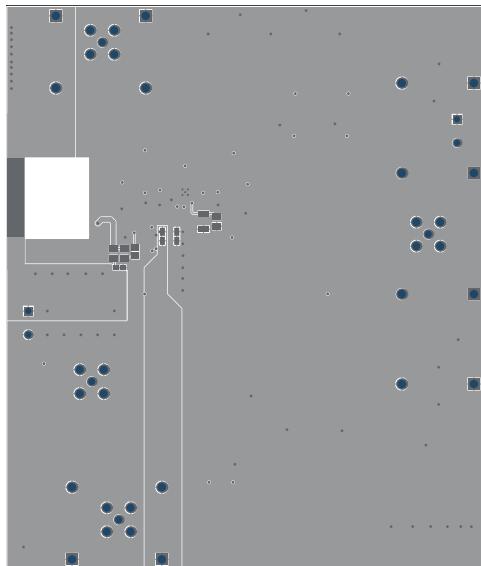

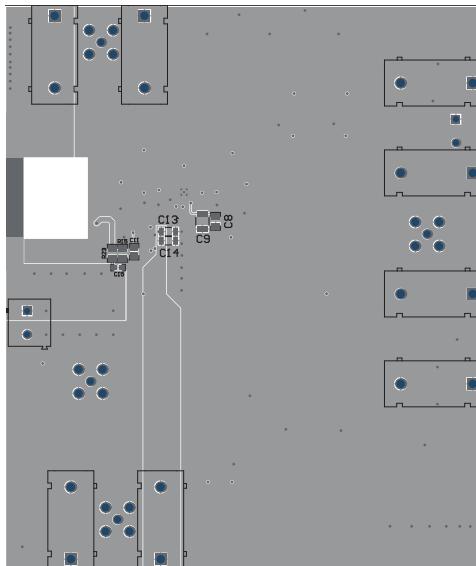

| <b>5 仕様</b> .....        | <b>4</b>  | <b>7.4 レイアウト</b> .....              | <b>63</b> |

| 5.1 絶対最大定格.....          | 4         | <b>8 デバイスおよびドキュメントのサポート</b> .....   | <b>65</b> |

| 5.2 ESD 定格.....          | 4         | <b>8.1 デバイス サポート</b> .....          | <b>65</b> |

| 5.3 推奨動作条件.....          | 5         | <b>8.2 ドキュメントのサポート</b> .....        | <b>65</b> |

| 5.4 熱に関する情報.....         | 5         | <b>8.3 ドキュメントの更新通知を受け取る方法</b> ..... | <b>65</b> |

| 5.5 電気的特性.....           | 6         | <b>8.4 サポート・リソース</b> .....          | <b>65</b> |

| 5.6 代表的特性.....           | 9         | <b>8.5 商標</b> .....                 | <b>65</b> |

| <b>6 詳細説明</b> .....      | <b>39</b> | <b>8.6 静電気放電に関する注意事項</b> .....      | <b>65</b> |

| 6.1 概要.....              | 39        | <b>8.7 用語集</b> .....                | <b>66</b> |

| 6.2 機能ブロック図.....         | 40        | <b>9 改訂履歴</b> .....                 | <b>66</b> |

| 6.3 機能説明.....            | 41        | <b>10 メカニカル、パッケージ、および注文情報</b> ..... | <b>66</b> |

| 6.4 デバイスの機能モード.....      | 43        | <b>10.1 メカニカル データ</b> .....         | <b>67</b> |

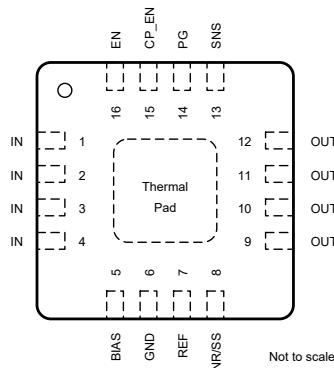

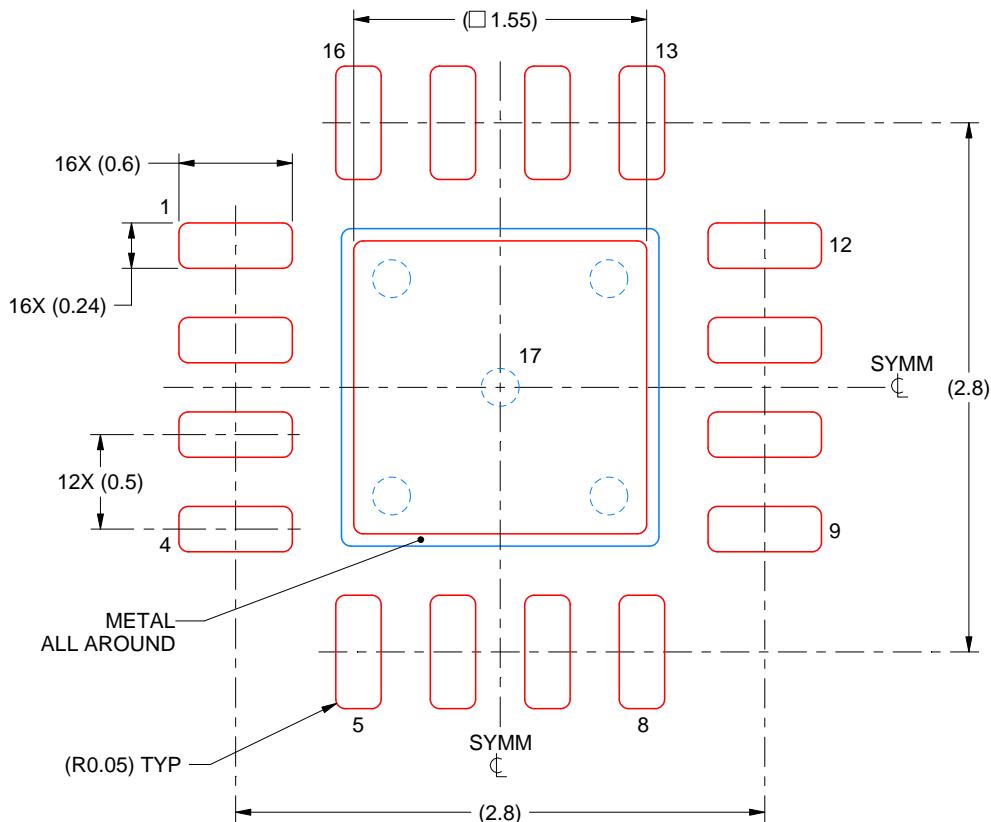

## 4 ピン構成および機能

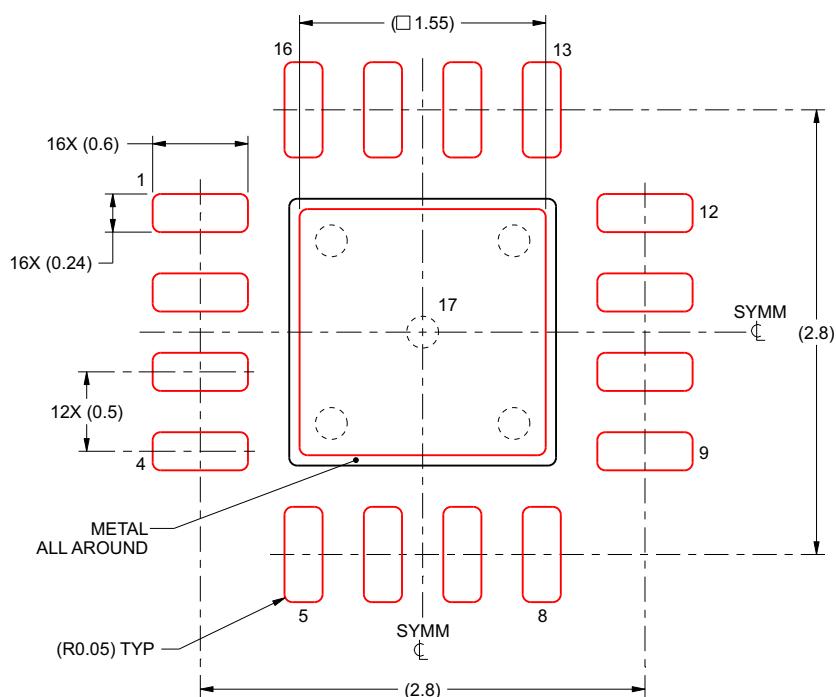

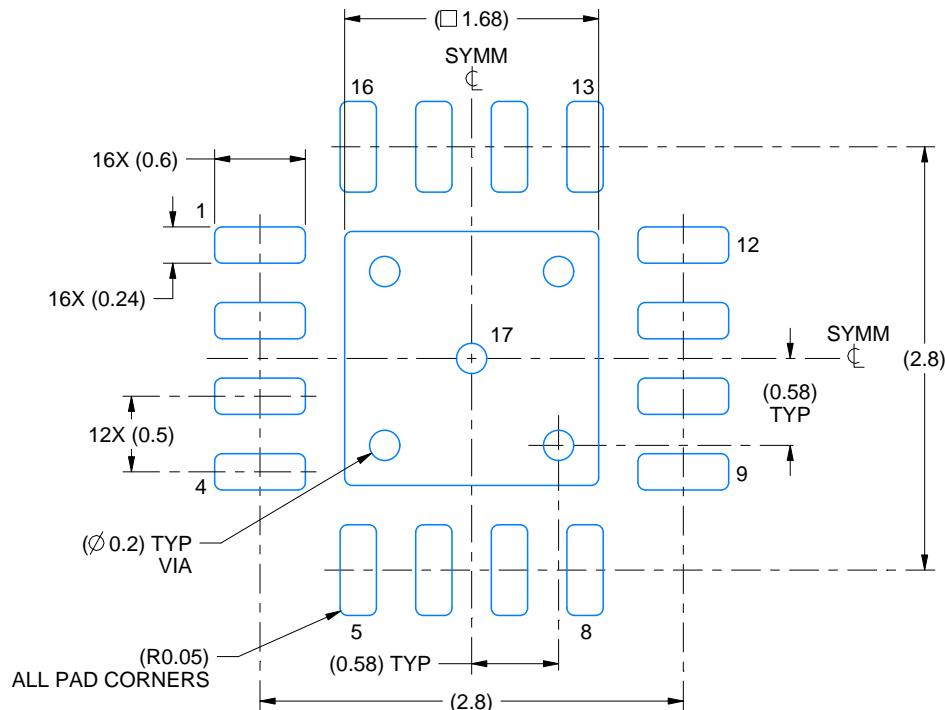

図 4-1. RTE パッケージ、16 ピン WQFN (上面図)

表 4-1. ピンの機能

| ピン       |            | 種類 <sup>(1)</sup> | 説明                                                                                                                                                   |

|----------|------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号         |                   |                                                                                                                                                      |

| BIAS     | 5          | I                 | BIAS 電源電圧ピン。追加情報については「 <a href="#">チャージポンプのイネーブルとBIAS レール</a> 」セクションを参照してください。                                                                       |

| CP_EN    | 15         | I                 | 充電イネーブルピン。追加情報については「 <a href="#">チャージポンプのイネーブルとBIAS レール</a> 」セクションを参照してください。                                                                         |

| EN       | 16         | I                 | イネーブルピン。追加情報については「 <a href="#">高精度のイネーブルとUVLO</a> 」セクションを参照してください。                                                                                   |

| GND      | 6          | GND               | グランドピン。追加情報については「 <a href="#">レイアウトのガイドライン</a> 」セクションを参照してください。                                                                                      |

| IN       | 1、2、3、4    | I                 | 入力電源電圧ピン。詳細については、「 <a href="#">入力および出力コンデンサの要件 (C<sub>IN</sub> および C<sub>OUT</sub>)</a> 」セクションを参照してください。                                             |

| NR/SS    | 8          | I/O               | ノイズ低減ピン。追加情報については、「 <a href="#">プログラム可能なソフトスタート (NR/SS ピン)</a> 」および「 <a href="#">ソフトスタート、ノイズ低減 (NR/SS ピン)、パワーグッド (PG ピン)</a> 」セクションを参照してください。        |

| OUT      | 9、10、11、12 | O                 | レギュレートされた出力ピン。詳細については「 <a href="#">出力電圧設定およびレギュレーション</a> 」および「 <a href="#">入力および出力コンデンサの要件 (C<sub>IN</sub> および C<sub>OUT</sub>)</a> 」セクションを参照してください。 |

| PG       | 14         | O                 | LDO の出力電圧用のオープンドレイン型パワーグッドインジケータピン。追加情報については「 <a href="#">パワーグッドピン (PG ピン)</a> 」セクションを参照してください。                                                      |

| REF      | 7          | I/O               | リファレンスピン。追加情報については「 <a href="#">出力電圧設定およびレギュレーション</a> 」セクションを参照してください。                                                                               |

| SNS      | 13         | I                 | 出力検出センスピン。追加情報については「 <a href="#">出力電圧設定およびレギュレーション</a> 」セクションを参照してください。                                                                              |

| サーマル パッド | —          | GND               | 最良の熱性能を得るために、パッドを GND に接続します。詳細については、「 <a href="#">レイアウト</a> 」セクションを参照してください。                                                                        |

(1) I = 入力、O = 出力、I/O = 入力または出力、GND = グランド。

## 5 仕様

### 5.1 絶対最大定格

動作接合部温度範囲を超過。すべての電圧は GND を基準とします (別段の記載がない限り)(1)

|    |                  | 最小値    | 最大値                | 単位 |

|----|------------------|--------|--------------------|----|

| 電圧 | BIAS             | -0.3   | 11.2               | V  |

|    | IN、PG、EN、, CP_EN | -0.3   | 6.5                |    |

|    | REF、NR/SS、SNS    | -0.3   | 6                  |    |

|    | OUT              | -0.3   | $V_{IN} + 0.3$ (2) |    |

| 電流 | OUT              | 内部的に制限 |                    | A  |

|    | PG (デバイスへのシンク電流) |        | 5                  | mA |

| 温度 | 動作時の接合部温度、 $T_J$ | -40    | 150                | °C |

|    | 保存、 $T_{stg}$    | -55    | 150                |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 絶対最大定格は  $V_{IN} + 0.3V$  または 6.0V のどちらか小さい方です。

### 5.2 ESD 定格

|             |      |                                             | 値          | 単位 |

|-------------|------|---------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠(1)    | $\pm 2000$ | V  |

|             |      | 荷電デバイス モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠(2) | $\pm 500$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

## 5.3 推奨動作条件

接合部動作温度範囲内 (特に記述のない限り)

|                |                        | 最小値 | 標準値 | 最大値  | 単位         |

|----------------|------------------------|-----|-----|------|------------|

| $V_{IN}$       | 入力電源電圧                 | 0.7 |     | 6    | V          |

| $V_{REF}$      | リファレンス電圧               | 0.5 |     | 5    | V          |

| $V_{OUT}$      | 出力電圧                   | 0.5 |     | 5    | V          |

| $V_{BIAS}$     | バイアス電圧                 | 3   |     | 11   | V          |

| $I_{OUT}$      | 出力電流                   | 0   |     | 6    | A          |

| $C_{IN}$       | 入力コンデンサ                | 4.7 | 10  | 1000 | $\mu$ F    |

| $C_{OUT}$      | 出力コンデンサ <sup>(1)</sup> | 22  |     | 3000 | $\mu$ F    |

| $C_{OUT\_ESL}$ | 出力コンデンサの ESL           | 2   |     | 20   | $m\Omega$  |

| $Z_{OUT\_ESL}$ | 合計インピーダンス ESL          | 0.2 |     | 1    | nH         |

| $C_{BIAS}$     | バイアスビンコンデンサ            | 0   | 1   | 100  | $\mu$ F    |

| $C_{NR/SS}$    | ノイズ低減コンデンサ             | 0.1 | 4.7 | 10   | $\mu$ F    |

| $R_{PG}$       | パワーグッドのブルアップ抵抗         | 10  |     | 100  | k $\Omega$ |

| $T_J$          | 接合部温度                  | -40 |     | 125  | °C         |

(1) 安定させるために、最低 15 $\mu$ F の実効出力キャパシタンスが必要です

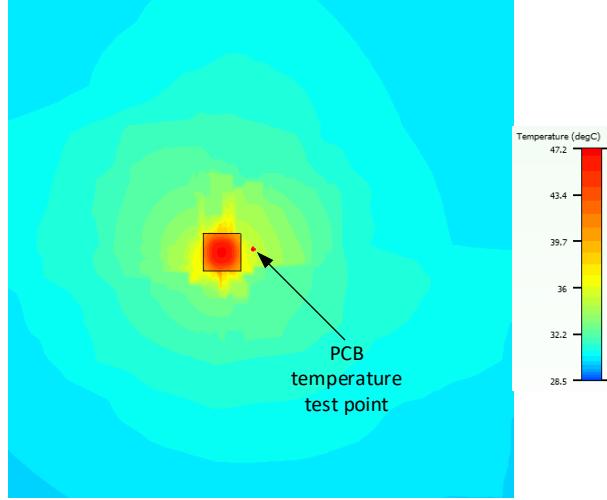

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | TPS7A56                      |                              | 単位   |

|----------------------|---------------------|------------------------------|------------------------------|------|

|                      |                     | RTE (WQFN)<br><sup>(2)</sup> | RTE (WQFN)<br><sup>(3)</sup> |      |

|                      |                     | 16 ピン                        | 16 ピン                        |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 40.3                         | 21.9                         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 39.3                         | –                            | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 14                           | –                            | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.5                          | 0.4                          | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 14.0                         | 11.9                         | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.8                          | –                            | °C/W |

- (1) 従来および新しい熱評価基準の詳細については、『[半導体およびIC パッケージの熱評価基準](#)』アプリケーション ノートを参照してください。

(2) JEDEC 規格 (2s2p) を使用して評価済みです。

(3) EVM を使用して評価します。

## 5.5 電気的特性

動作温度範囲全体 ( $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ )、 $V_{IN(\text{NOM})} = V_{OUT(\text{NOM})} + 0.4\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{EN} = 1.8\text{V}$ 、 $C_{IN} = 10\mu\text{F}$ 、 $C_{OUT} = 22\mu\text{F}$ 、 $C_{BIAS} = 0\text{nF}$ 、 $C_{NR/SS} = 100\text{nF}$ 、特に記載のない限り、SNS ピンは OUT ピンにショートされ、PG ピンは  $100\text{k}\Omega$  で  $V_{IN}$  プルアップされています。標準値は  $T_J = 25^{\circ}\text{C}$  です

| パラメータ                             |                                       | テスト条件                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 最小値 | 標準値  | 最大値  | 単位              |

|-----------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-----------------|

| $V_{UVLO(\text{IN})}$             | BIAS 付きの入力電源 UVLO                     | $V_{IN}$ 立ち上がり、 $V_{CP\_EN} = 1.8\text{V}$ ( $3\text{V} \leq V_{BIAS} \leq 11\text{V}$ ) および $V_{CP\_EN} = 0\text{V}$ ( $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ )                                                                                                                                                                                                                                                                                   |     | 0.67 | 0.7  | V               |

| $V_{HYS(UVLO\_IN)}$               | BIAS 付きの入力電源 UVLO ヒステリシス              | $V_{CP\_EN} = 1.8\text{V}$ ( $3\text{V} \leq V_{BIAS} \leq 11\text{V}$ ) および $V_{CP\_EN} = 0\text{V}$ ( $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ )                                                                                                                                                                                                                                                                                                   |     | 50   |      | mV              |

| $V_{UVLO(\text{IN})}$             | 入力電源 UVLO (BIAS なし)                   | $V_{IN}$ 立ち上がり、 $V_{CP\_EN} = 1.8\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 1.07 | 1.1  | V               |

| $V_{HYS(UVLO\_IN)}$               | 入力電源 UVLO ヒステリシス (BIAS なし)            | $V_{CP\_EN} = 1.8\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 50   |      | mV              |

| $V_{UVLO(BIAS)} - V_{REF}$        | CP なしでの $V_{REF}$ に対する BIAS UVLO      | $V_{BIAS}$ 立ち上がり、 $V_{CP\_EN} = 0\text{V}$ 、 $1.4\text{V} \leq V_{REF} \leq 5.2\text{V}$                                                                                                                                                                                                                                                                                                                                                                          |     | 2.1  | 2.95 | V               |

| $V_{HYS(UVLO\_BIAS - REF)}$       | CP なしの $V_{REF}$ ヒステリシスに対する BIAS UVLO | $V_{CP\_EN} = 0\text{V}$ 、 $1.4\text{V} \leq V_{REF} \leq 5.2\text{V}$                                                                                                                                                                                                                                                                                                                                                                                            |     | 240  |      | mV              |

| $V_{UVLO(BIAS)}$                  | CP による BIAS UVLO                      | $V_{BIAS}$ 立ち上がり、 $V_{CP\_EN} = 1.8\text{V}$ 、 $0.7\text{V} \leq V_{IN} < 1.1\text{V}$                                                                                                                                                                                                                                                                                                                                                                            |     | 2.8  | 2.95 | V               |

| $V_{HYS(UVLO\_BIAS)}$             | CP による BIAS UVLO ヒステリシス               | $V_{CP\_EN} = 1.8\text{V}$ 、 $0.7\text{V} \leq V_{IN} < 1.1\text{V}$                                                                                                                                                                                                                                                                                                                                                                                              |     | 115  |      | mV              |

| $I_{NR/SS}$                       | NR/SS 高速スタートアップ充電電流                   | $V_{NR/SS} = \text{GND}$ 、 $V_{IN} = 1.1\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 0.2  |      | mA              |

| $V_{OUT}$                         | 出力電圧精度 <sup>(1)</sup>                 | $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$ 、<br>$V_{CP\_EN} = 0\text{V}$ 、 $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(2)</sup> 、<br>$V_{CP\_EN} = 1.8\text{V}$ 、 $3\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(2)</sup> 、<br>$V_{CP\_EN} = 1.8\text{V}$ 、BIAS なし、 $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ |     | -1   | 1    | %               |

| $I_{REF}$                         | REF 電流ピン                              | $V_{IN} = 1.1\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、<br>$I_{LOAD} = 0\text{A}$ 、 $V_{BIAS} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                |     | 50   |      | $\mu\text{A}$   |

|                                   |                                       | $V_{CP\_EN} = 0\text{V}$ (CP ディセーブル)、<br>$0.7\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(1)</sup> <sup>(2)</sup> 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$                                                                                                                                                                                             |     | -1   | 1    | %               |

|                                   |                                       | $V_{CP\_EN} = 1.8\text{V}$ (CP イネーブル)、<br>$1.1\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(1)</sup> 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$ <sup>(2)</sup>                                                                                                                                                                                                                                                       |     | -1   | 1    |                 |

|                                   |                                       | $V_{CP\_EN} = 1.8\text{V}$ (CP イネーブル)、<br>$0.7\text{V} \leq V_{IN} \leq 6\text{V}$ 、 <sup>(1)</sup> $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$3\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、 $0\text{A} \leq I_{OUT} \leq 6\text{A}$                                                                                                                                                                                                                          |     | -1   | 1    |                 |

| $V_{OS}$                          | 出力オフセット電圧 ( $V_{NR/SS} - V_{OUT}$ )   | $V_{IN} = 0.7\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、<br>$V_{CP\_EN} = 1.8\text{V}$ 、 $3\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、<br>$V_{CP\_EN} = 0\text{V}$ 、 $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$                                                                                                                                                                                                                        |     | -1   | 1    | mV              |

|                                   |                                       | $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(1)</sup> <sup>(2)</sup> 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$V_{CP\_EN} = 1.8\text{V}$ 、 $3\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$                                                                                                                                                                                                                     |     | -2   | 2    |                 |

|                                   |                                       | $1.1\text{V} \leq V_{IN} \leq 6.0\text{V}$ <sup>(1)</sup> <sup>(2)</sup> 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$                                                                                                                                                                                                                                      |     | -2   | 2    |                 |

|                                   |                                       | $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ <sup>(1)</sup> <sup>(2)</sup> 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、<br>$V_{CP\_EN} = 0\text{V}$ 、 $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、<br>$0\text{A} \leq I_{OUT} \leq 6\text{A}$                                                                                                                                                                                                           |     | -2   | 2    |                 |

| $\Delta I_{REF(\Delta V_{BIAS})}$ | ライン レギュレーション: $\Delta I_{REF}$        | $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、 $V_{IN} = 0.7\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、<br>$V_{CP\_EN} = 0\text{V}$ 、 $I_{OUT} = 0\text{A}$                                                                                                                                                                                                                                                                                                    |     | 0.15 |      | $\text{nA/V}$   |

| $\Delta V_{OS(\Delta V_{BIAS})}$  | ライン レギュレーション: $\Delta V_{OS}$         | $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$ 、 $V_{IN} = 0.7\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、<br>$V_{CP\_EN} = 0\text{V}$ 、 $I_{OUT} = 0\text{A}$                                                                                                                                                                                                                                                                                                    |     | 0.06 |      | $\mu\text{V/V}$ |

| $\Delta I_{REF(\Delta V_{IN})}$   | ライン レギュレーション: $\Delta I_{REF}$        | $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、<br>$I_{OUT} = 0\text{A}$ 、 $V_{BIAS} = 0\text{V}$                                                                                                                                                                                                                                                                                                               |     | 0.03 |      | $\text{nA/V}$   |

| $\Delta V_{OS(\Delta V_{IN})}$    | ライン レギュレーション: $\Delta V_{OS}$         | $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、<br>$I_{OUT} = 0\text{A}$ 、 $V_{BIAS} = 0\text{V}$                                                                                                                                                                                                                                                                                                               |     | 0.01 |      | $\mu\text{V/V}$ |

## 5.5 電気的特性 (続き)

動作温度範囲全体 ( $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ )、 $V_{IN(\text{NOM})} = V_{OUT(\text{NOM})} + 0.4\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{EN} = 1.8\text{V}$ 、 $C_{IN} = 10\mu\text{F}$ 、 $C_{OUT} = 22\mu\text{F}$ 、 $C_{BIAS} = 0\text{nF}$ 、 $C_{NR/SS} = 100\text{nF}$ 、特に記載のない限り、SNS ピンは OUT ピンにショートされ、PG ピンは  $100\text{k}\Omega$  で  $V_{IN}$  プルアップされています。標準値は  $T_J = 25^\circ\text{C}$  です

| パラメータ                           |                               | テスト条件                                                                                                                                                                                                 | 最小値 | 標準値  | 最大値  | 単位                     |             |

|---------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------------------------|-------------|

| $\Delta V_{OS(\Delta I_{OUT})}$ | 負荷レギュレーション: $\Delta V_{OS}$   | $V_{IN} = 0.7\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $0\text{A} \leq I_{OUT} \leq 6\text{A}$ 、 $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$                         |     | 5    |      | $\mu\text{V}/\text{A}$ |             |

|                                 |                               | $V_{OUT} = 5.0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $0\text{A} \leq I_{OUT} \leq 6\text{A}$ 、 $V_{BIAS} = 0\text{V}$                                                                               |     | 175  |      |                        |             |

|                                 | $I_{REF}$ の変化と $V_{REF}$ との関係 | $0.5\text{V} \leq V_{REF} \leq 5.2\text{V}$ 、 $V_{IN} = 6\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$                                                      |     | 4.4  |      | $\text{nA}$            |             |

|                                 |                               | $V_{OS}$ の変化と $V_{REF}$ との関係                                                                                                                                                                          |     | 0.25 |      |                        |             |

| $V_{DO}$                        | ドロップアウト電圧 <sup>(3)</sup>      | $1.1\text{V} \leq V_{IN} \leq 5.3\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$                                                |     | 90   | 132  | $\text{mV}$            |             |

|                                 |                               | $1.1\text{V} \leq V_{IN} \leq 5.3\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +85^\circ\text{C}$                                                 |     |      | 120  |                        |             |

|                                 |                               | $0.0\text{V} \leq V_{IN} \leq 1.1\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 3\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$                       |     | 90   | 132  |                        |             |

|                                 |                               | $0.0\text{V} \leq V_{IN} \leq 1.1\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 3\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +85^\circ\text{C}$                        |     |      | 120  |                        |             |

|                                 |                               | $0.7\text{V} \leq V_{IN} \leq 5.3\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{IN} + 3.2\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$              |     | 90   | 132  |                        |             |

|                                 |                               | $0.7\text{V} \leq V_{IN} \leq 5.3\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{IN} + 3.2\text{V}$ 、 $-40^\circ\text{C} \leq T_J \leq +85^\circ\text{C}$               |     |      | 120  |                        |             |

| $I_{LIM}$                       | 出力電流制限                        | $V_{OUT}$ を $0.9 \times V_{OUT(\text{NOM})}$ で強制、 $V_{OUT(\text{NOM})} = 5.0\text{V}$ 、 $V_{IN} = V_{OUT(\text{NOM})} + 400\text{mV}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ | 6.2 | 7.2  | 8.4  | A                      |             |

| $I_{SC}$                        | 短絡電流制限                        | $R_{LOAD} = 10\text{m}\Omega$ 、フォールドバック動作時                                                                                                                                                            |     | 5    |      | A                      |             |

| $I_{BIAS}$                      | BIAS ピン電流                     | $V_{IN} = 6\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ 、 $V_{OUT} = 5.2\text{V}$                                                                |     | 1    | 1.5  | 2.5                    |             |

|                                 |                               | $V_{IN} = 0.7\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $3.0\text{V} \leq V_{BIAS} \leq 11\text{V}$                                                   |     | 8    | 11   | 18                     |             |

| $I_{GND}$                       | GND ピン電流                      | $V_{IN} = 6\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ 、 $V_{OUT} = 5.2\text{V}$                                                                |     | 3.5  | 5    | 8                      |             |

|                                 |                               | $V_{IN} = 5.6\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{OUT} = 5.0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$                                                                        |     |      | 18   |                        |             |

|                                 |                               | $V_{IN} = 1.1\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$                                                                        |     | 12   | 18   | 27                     |             |

|                                 |                               | $V_{IN} = 0.7\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $3\text{V} \leq V_{BIAS} \leq 11\text{V}$                                                     |     | 11   | 18   | 26                     |             |

|                                 |                               | $V_{IN} = 0.7\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{OUT} + 3.2\text{V} \leq V_{BIAS} \leq 11\text{V}$                                           |     | 5    | 7    | 12                     |             |

| $I_{SDN}$                       | シャットダウン GND ピン電流              | $PG = (\text{オーブン})$ 、 $V_{IN} = 6\text{V}$ 、 $V_{EN} = 0.4\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$                                                                            |     | 100  | 300  | $\mu\text{A}$          |             |

|                                 |                               | $PG = (\text{オーブン})$ 、 $V_{IN} = 6\text{V}$ 、 $V_{EN} = 0.4\text{V}$ 、 $V_{CP\_EN} = 0.4\text{V}$ 、 $V_{BIAS} = 11\text{V}$                                                                           |     |      | 150  |                        |             |

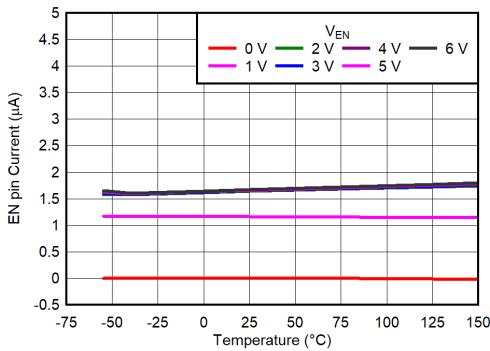

| $I_{EN}$                        | EN ピン電流                       | $V_{IN} = 6\text{V}$ 、 $0\text{V} \leq V_{EN} \leq 6\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$                                                                                   | -5  |      | 5    | $\mu\text{A}$          |             |

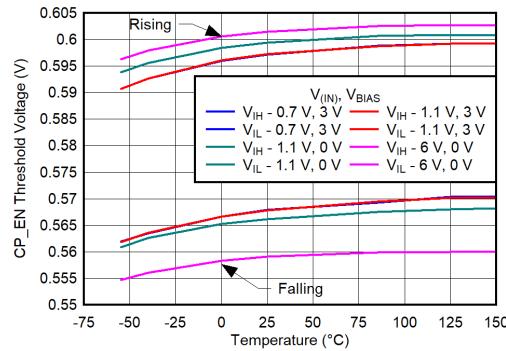

| $V_{IH(EN)}$                    | EN トリップ ポイントの立ち上がり (ターンオン)    | $V_{IN} = 1.1\text{V}$ ( $V_{CP\_EN} = 1.8\text{V}$ ) または $V_{BIAS} \geq 3\text{V}$ ( $V_{CP\_EN} = 0\text{V}$ )                                                                                      |     | 0.62 | 0.65 | 0.68                   | V           |

| $V_{HYS(EN)}$                   | EN トリップ ポイントヒステリシス            | $V_{IN} = 1.1\text{V}$ ( $V_{CP\_EN} = 1.8\text{V}$ ) または $V_{BIAS} \geq 3\text{V}$ ( $V_{CP\_EN} = 0\text{V}$ )                                                                                      |     |      | 40   |                        | $\text{mV}$ |

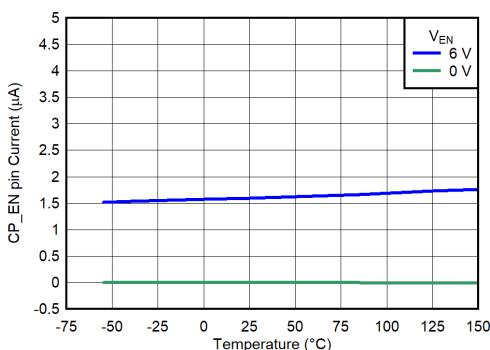

| $I_{CP\_EN}$                    | CP_EN ピンの電流                   | $V_{IN} = 6.0\text{V}$ 、 $0\text{V} \leq V_{CP\_EN} \leq 6\text{V}$                                                                                                                                   | -5  |      | 5    | $\mu\text{A}$          |             |

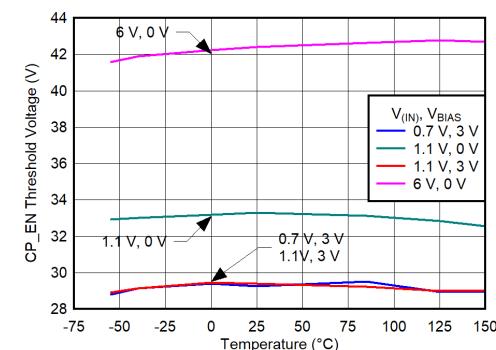

| $V_{IH(CP\_EN)}$                | CP_EN トリップ ポイントの立ち上がり (ターンオン) | $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $V_{EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $0.7\text{V} \leq V_{IN} \leq 1.1\text{V}$ 、 $V_{EN} = 1.8\text{V}$ 、 $V_{BIAS} = 3\text{V}$             |     | 0.57 | 0.6  | 0.63                   | V           |

| $V_{HYS(CP\_EN)}$               | CP_EN トリップ ポイントヒステリシス         | $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $V_{EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $0.7\text{V} \leq V_{IN} \leq 1.1\text{V}$ 、 $V_{EN} = 1.8\text{V}$ 、 $V_{BIAS} = 3\text{V}$             |     |      | 56   |                        | $\text{mV}$ |

## 5.5 電気的特性 (続き)

動作温度範囲全体 ( $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ )、 $V_{IN(\text{NOM})} = V_{OUT(\text{NOM})} + 0.4\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $V_{EN} = 1.8\text{V}$ 、 $C_{IN} = 10\mu\text{F}$ 、 $C_{OUT} = 22\mu\text{F}$ 、 $C_{BIAS} = 0\text{nF}$ 、 $C_{NR/SS} = 100\text{nF}$ 、特に記載のない限り、SNS ピンは OUT ピンにショートされ、PG ピンは  $100\text{k}\Omega$  で  $V_{IN}$  プルアップされています。標準値は  $T_J = 25^\circ\text{C}$  です

| パラメータ                     |                     | テスト条件                                                                                                                                                                                                                                                 | 最小値 | 標準値  | 最大値 | 単位                           |

|---------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------------------------------|

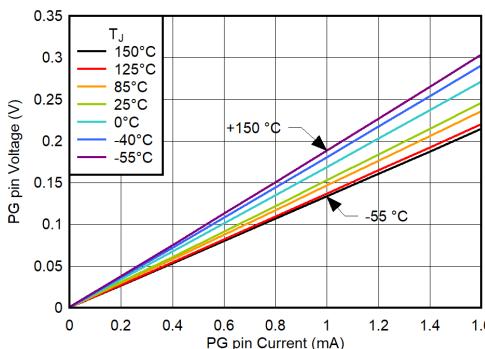

| $V_{IT(\text{PG})}$       | PG ピンのスレッショルド       | $V_{OUT}$ が低下して PG が Low に遷移する場合、 $V_{IN} = 1.1\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{OUT} < V_{IT(\text{PG})}$ 、 $I_{PG} = -1\text{mA}$ (デバイスへの電流)                                                                    | 87  | 90   | 93  | %                            |

| $V_{HYS(\text{PG})}$      | PG ピンのヒステリシス        | $V_{IN} = 1.1\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{OUT} < V_{IT(\text{PG})}$ 、 $I_{PG} = -1\text{mA}$ (デバイスへの電流)                                                                                                      |     | 2    |     | %                            |

| $V_{OL(\text{PG})}$       | PG ピンの Low レベル出力電圧  | $V_{IN} = 1.1\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{OUT} < V_{IT(\text{PG})}$ 、 $I_{PG} = -1\text{mA}$ (デバイスへの電流)                                                                                                      |     | 0.4  |     | V                            |

| $I_{LKG(\text{PG})}$      | PG ピンのリーク電流         | $V_{PG} = 6\text{V}$ 、 $V_{OUT} > V_{IT(\text{PG})}$ 、 $V_{IN} = 1.1\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$                                                                                                                   |     | 1    |     | $\mu\text{A}$                |

| PSRR                      | 電源リップル除去            | $f = 1\text{MHz}$ 、 $V_{IN} = 0.8\text{V}$ 、 $V_{OUT(\text{NOM})} = 0.5\text{V}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$                                               | 40  |      |     | dB                           |

|                           |                     | $f = 1\text{MHz}$ 、 $V_{IN} = 0.9\text{V}$ 、 $V_{OUT(\text{NOM})} = 0.5\text{V}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$                                               | 40  |      |     |                              |

|                           |                     | $f = 1\text{MHz}$ 、 $V_{IN} = 5.3\text{V}$ 、 $V_{OUT(\text{NOM})} = 5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$                                                           | 40  |      |     |                              |

|                           |                     | $f = 1\text{MHz}$ 、 $V_{IN} = 5.4\text{V}$ 、 $V_{OUT(\text{NOM})} = 5\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$                                                           | 36  |      |     |                              |

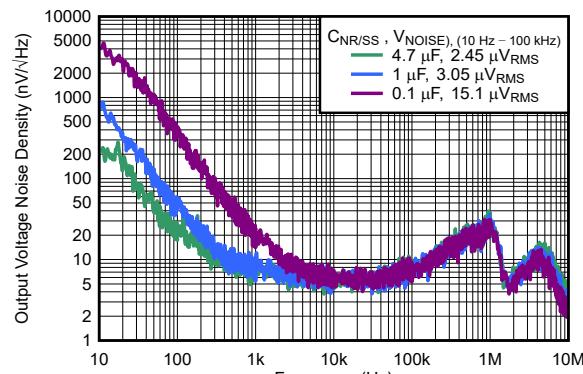

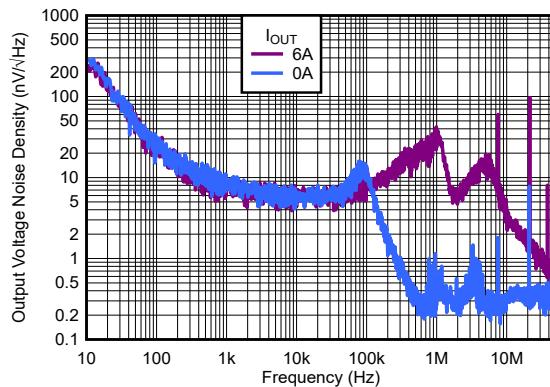

| $V_n$                     | 出力ノイズ電圧             | $BW = 10\text{Hz} \sim 100\text{kHz}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$ |     | 2.49 |     | $\mu\text{V}_{\text{RMS}}$   |

|                           |                     | $BW = 10\text{Hz} \sim 100\text{kHz}$ 、 $1.1\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$           |     | 2.49 |     |                              |

|                           | ノイズ スペクトル密度         | $f = 100\text{Hz}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$                    | 20  |      |     | $\text{nV}/\sqrt{\text{Hz}}$ |

|                           |                     | $f = 1\text{kHz}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$                     | 9   |      |     |                              |

|                           |                     | $f = 10\text{kHz}$ 、 $0.7\text{V} \leq V_{IN} \leq 6\text{V}$ 、 $0.5\text{V} \leq V_{OUT} \leq 5.2\text{V}$ 、 $I_{OUT} = 6\text{A}$ 、 $C_{NR/SS} = 4.7\mu\text{F}$ 、 $V_{CP\_EN} = 0\text{V}$ 、 $V_{BIAS} = V_{OUT} + 3.2\text{V}$                    | 6   |      |     |                              |

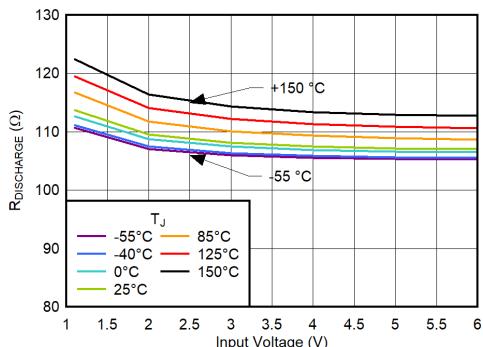

| $R_{DIS}$                 | 出力ピンのアクティブ放電抵抗      | $V_{IN} = 1.1\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{EN} = 0\text{V}$                                                                                                                                                   |     | 110  |     | $\Omega$                     |

| $R_{NR/SS\_DIS}$          | NR/SS ピンのアクティブ放電抵抗  | $V_{IN} = 1.1\text{V}$ 、 $V_{CP\_EN} = 1.8\text{V}$ 、 $V_{BIAS} = 0\text{V}$ 、 $V_{EN} = 0\text{V}$                                                                                                                                                   |     | 100  |     | $\Omega$                     |

| $T_{SD(\text{shutdown})}$ | サーマル シャットダウン温度      | シャットダウン、温度上昇                                                                                                                                                                                                                                          |     | 165  |     | $^\circ\text{C}$             |

| $T_{SD(\text{reset})}$    | サーマル シャットダウン リセット温度 | リセット、温度低下                                                                                                                                                                                                                                             |     | 150  |     | $^\circ\text{C}$             |

(1) 最大消費電力は  $2\text{W}$ 。

(2) バルスの最大消費電力によって制限されます。 $0\text{mA} \leq I_{OUT} \leq 2.5\text{A}$ 、 $V_{IN} = 6\text{V}$ 、 $0\text{mA} \leq I_{OUT} \leq 6\text{A}$ 、 $V_{IN} = 5.6\text{V}$  の場合。

(3)  $V_{REF} = V_{IN}$ 、 $V_{SNS} = 97\% \times V_{REF}$

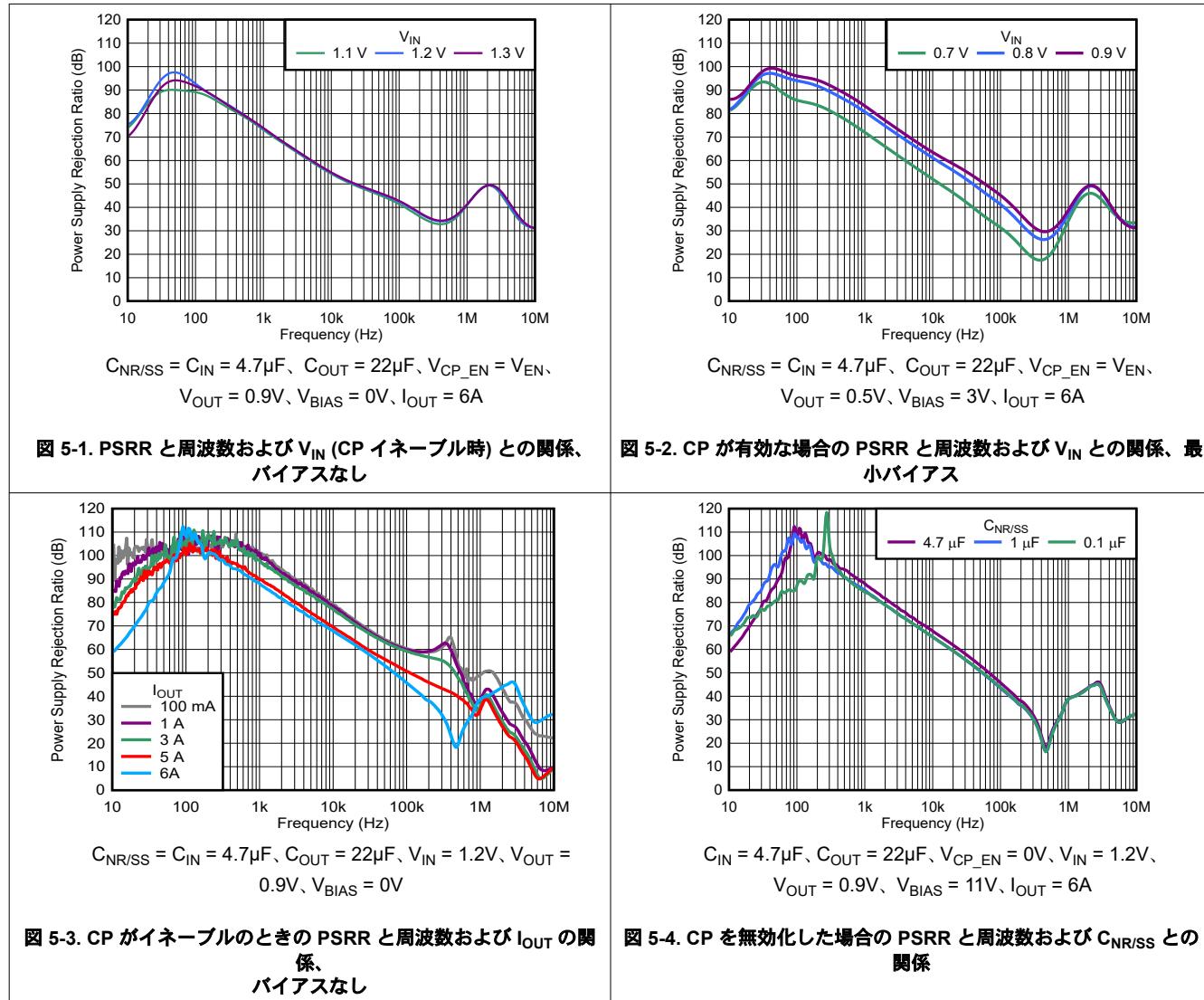

## 5.6 代表的特性

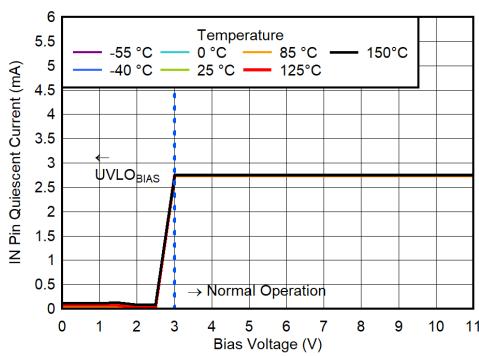

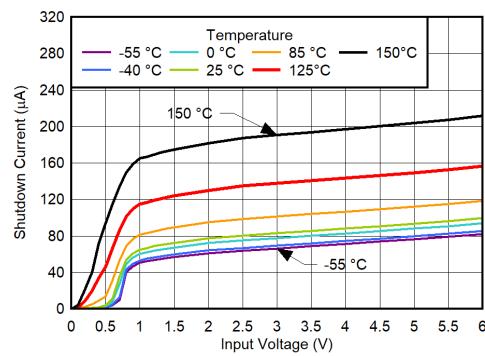

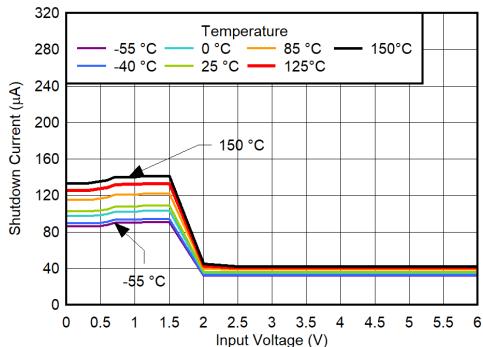

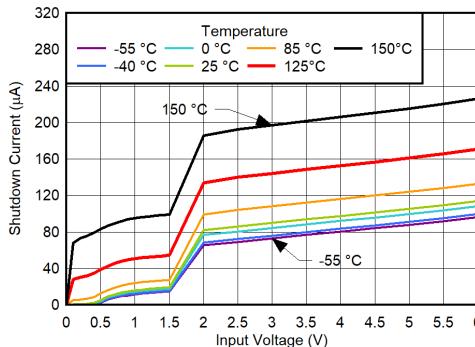

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-1. PSRR と周波数および  $V_{IN}$  (CP イネーブル時) との関係、バイアスなし

図 5-2. CP が有効な場合の PSRR と周波数および  $V_{IN}$  との関係、最小バイアス

図 5-3. CP がイネーブルのときの PSRR と周波数および  $I_{OUT}$  の関係、バイアスなし

図 5-4. CP を無効化した場合の PSRR と周波数および  $C_{NR/SS}$  との関係

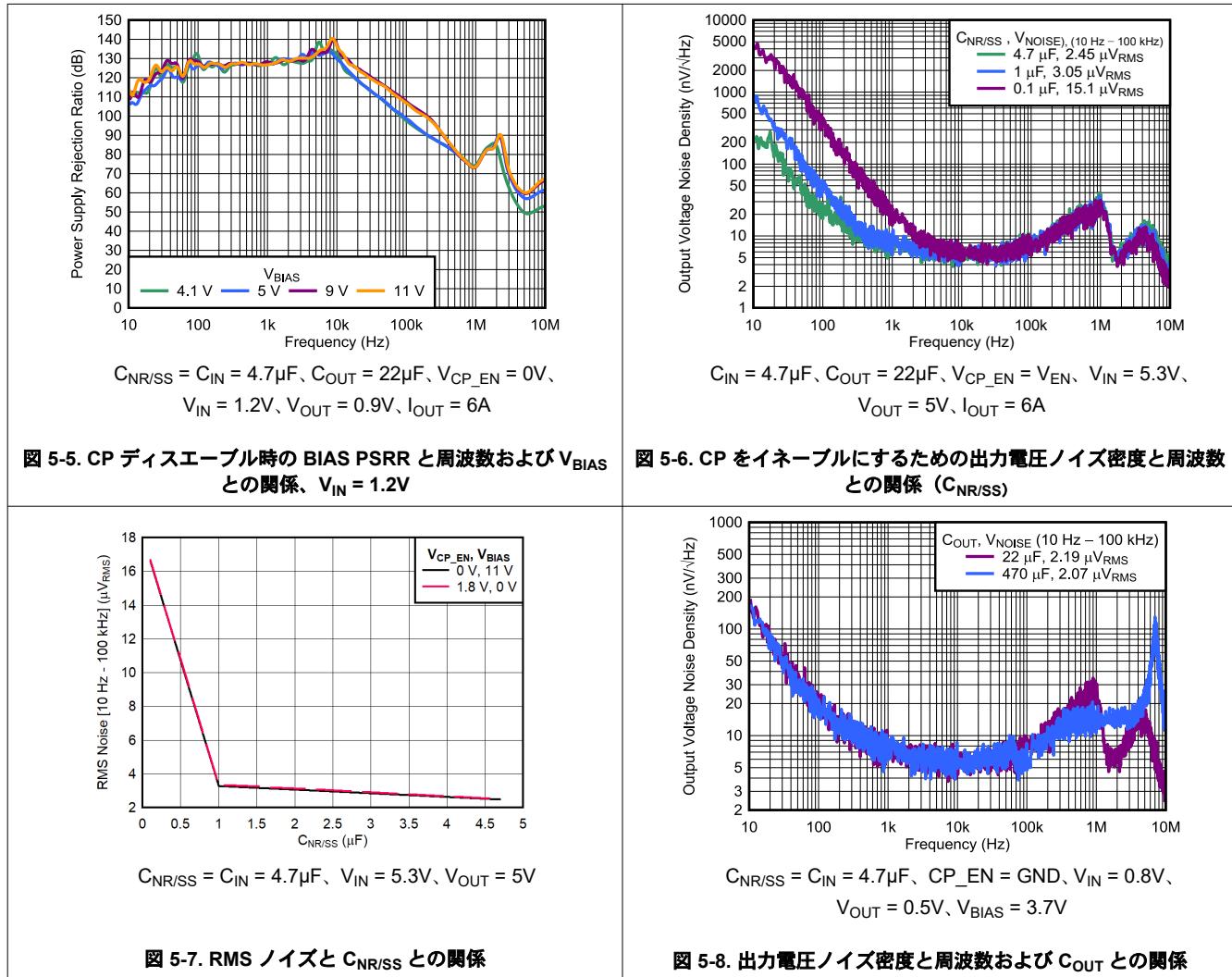

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

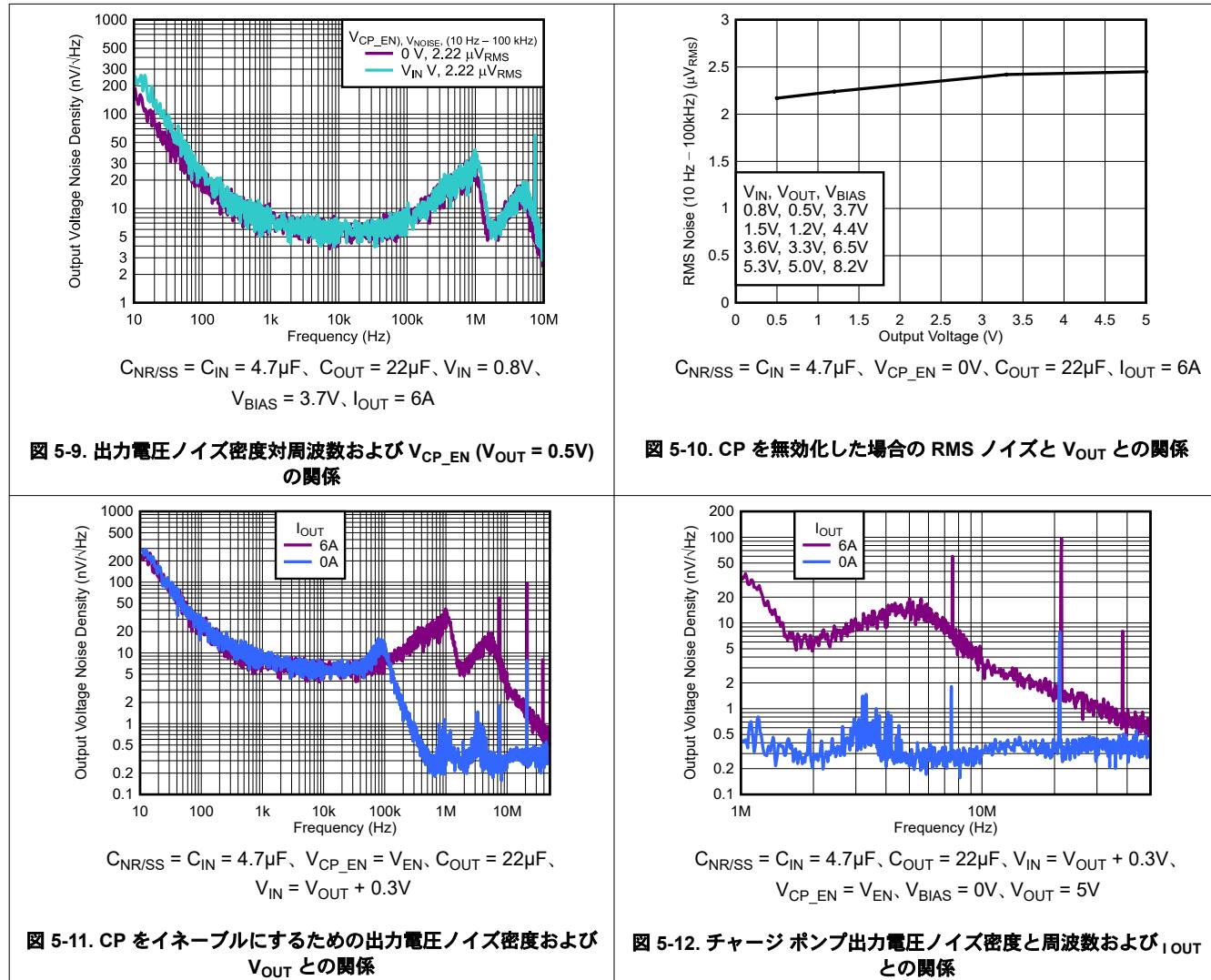

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

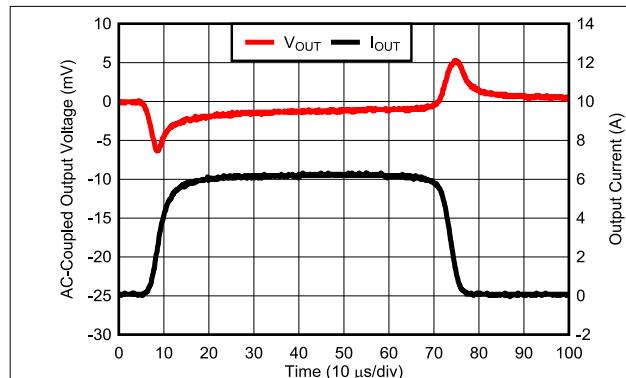

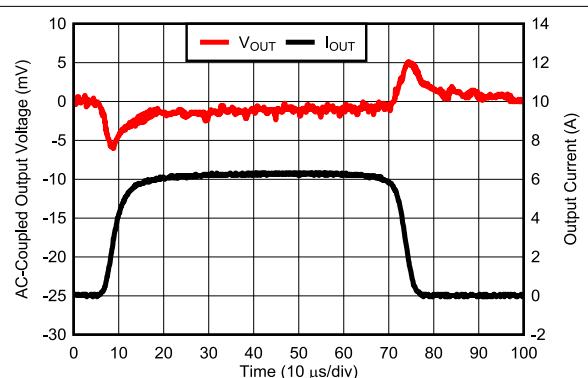

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

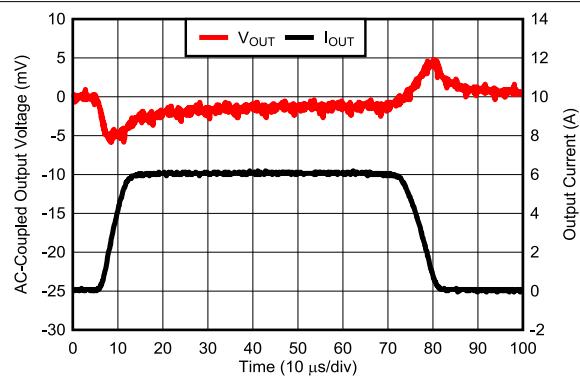

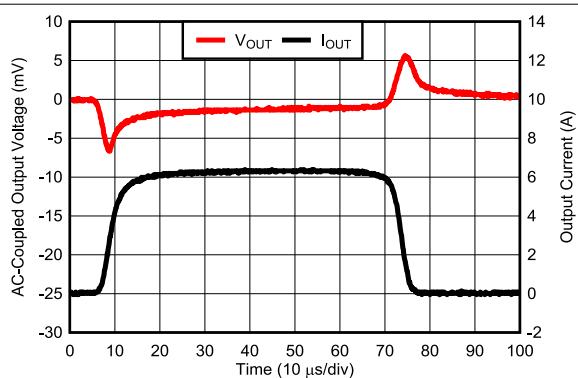

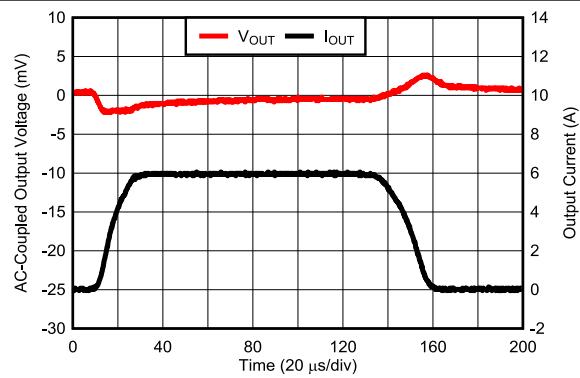

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 3V$ 、 $V_{IN} = 0.8V$ 、 $SR = 1A/\mu s$

図 5-13.  $V_{OUT} = 0.5V$  の負荷過渡、 $I_{OUT} = 100mA$  から  $6A$ 、CP はイネーブル

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 1.1V$ 、 $SR = 1A/\mu s$

図 5-14.  $V_{OUT} = 0.5V$  の負荷過渡、 $I_{OUT} = 100mA$  から  $6A$ 、CP はイネーブル

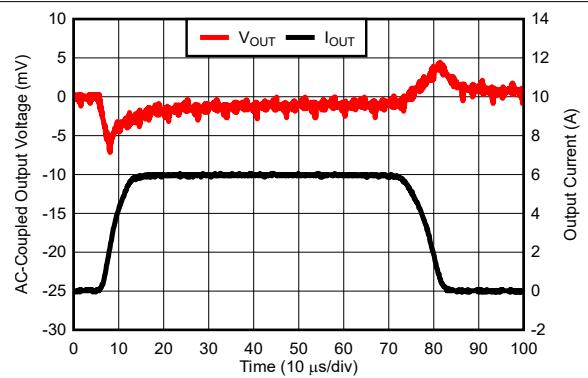

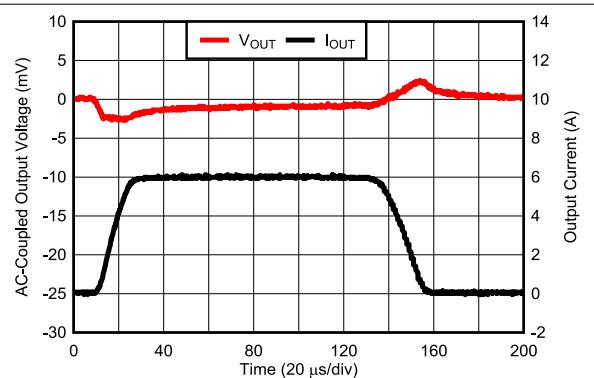

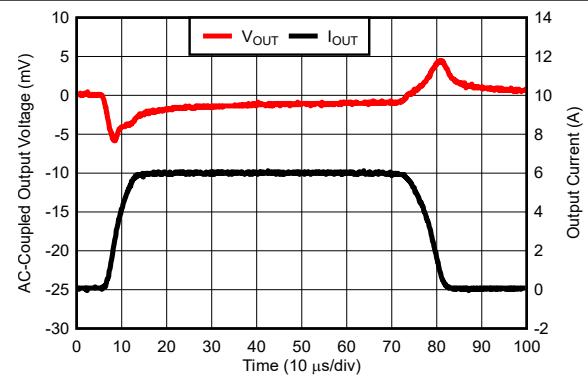

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 3.6V$ 、 $SR = 1A/\mu s$

図 5-15.  $V_{OUT} = 3.3V$  の負荷過渡、 $I_{OUT} = 100mA$  から  $6A$ 、CP はイネーブル

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 5.5V$ 、 $SR = 1A/\mu s$

図 5-16.  $V_{OUT} = 5.2V$  の負荷過渡、 $I_{OUT} = 100mA$  から  $6A$ 、CP はイネーブル

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

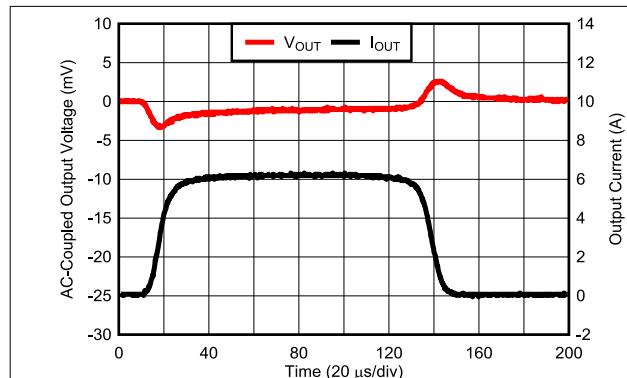

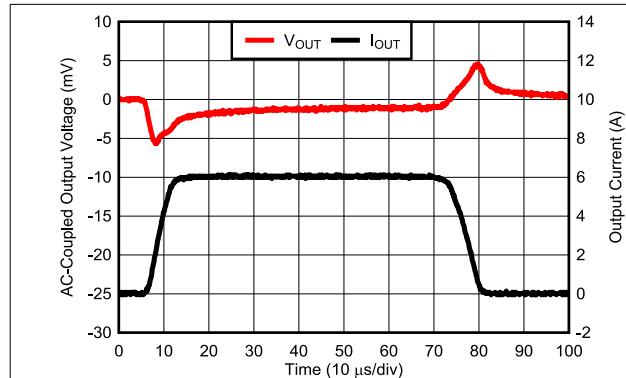

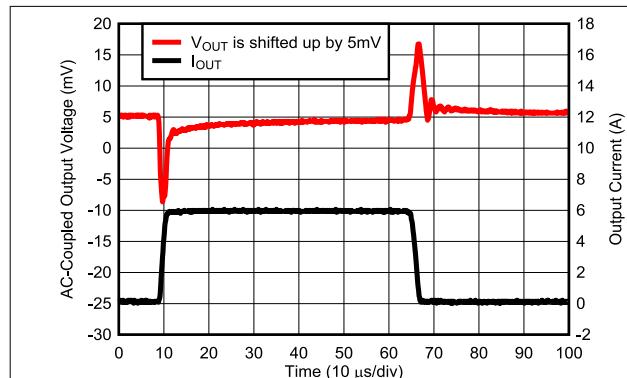

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 3.7V$ 、 $V_{IN} = 0.8V$

図 5-17.  $V_{OUT} = 0.5V$ 、 $I_{OUT} = 100mA$  から  $6A$  への負荷過渡、CP ディセーブル、SR =  $0.5A/\mu s$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 3.7V$ 、 $V_{IN} = 0.8V$

図 5-18.  $V_{OUT} = 0.5V$ 、 $I_{OUT} = 100mA$  から  $6A$  への負荷過渡、CP ディセーブル、SR =  $1A/\mu s$

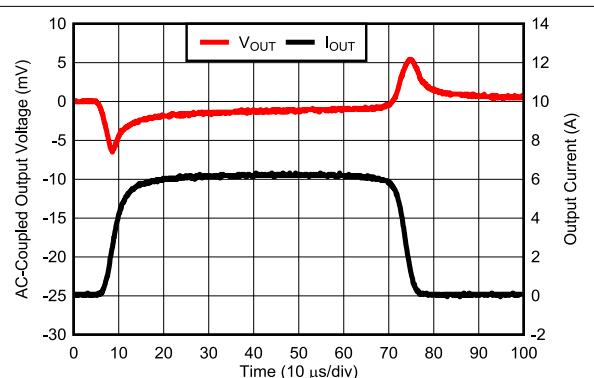

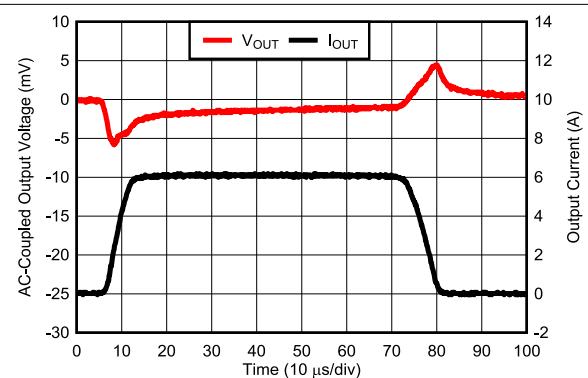

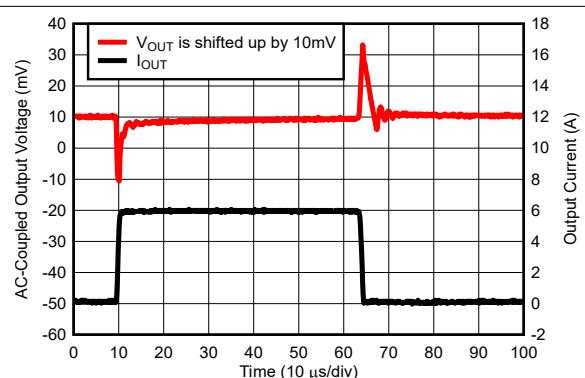

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 11V$ 、 $V_{IN} = 0.8V$

図 5-19.  $V_{OUT} = 0.5V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、SR =  $1A/\mu s$ 、 $V_{BIAS} = 11V$  での負荷過渡

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 6.5V$ 、 $V_{IN} = 3.6V$

図 5-20.  $V_{OUT} = 3.3V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、SR =  $0.5A/\mu s$ 、 $V_{BIAS} = 6.5V$  での負荷過渡

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-21.  $V_{OUT} = 3.3V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 1A/\mu s$ 、 $V_{BIAS} = 6.5V$  での負荷過渡

図 5-22.  $V_{OUT} = 3.3V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 1A/\mu s$ 、 $V_{BIAS} = 11V$  での負荷過渡

図 5-23.  $V_{OUT} = 5.2V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 0.5A/\mu s$ 、 $V_{BIAS} = 8.4V$  での負荷過渡

図 5-24.  $V_{OUT} = 5.2V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 1A/\mu s$ 、 $V_{BIAS} = 8.4V$  での負荷過渡

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-25.  $V_{OUT} = 5.2V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 5A/\mu s$ 、 $V_{BIAS} = 8.4V$  での負荷過渡

図 5-26.  $V_{OUT} = 5.2V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 10A/\mu s$ 、 $V_{BIAS} = 8.4V$  での負荷過渡

図 5-27.  $V_{OUT} = 5.2V$ 、 $I_{OUT} = 100mA$  から  $6A$  へ、CP ディセーブル、

$SR = 1A/\mu s$ 、 $V_{BIAS} = 11V$  での負荷過渡

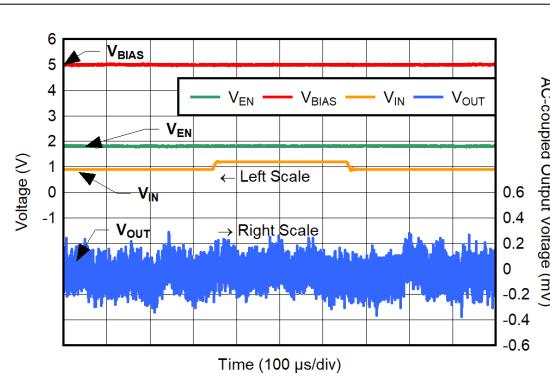

図 5-28.  $V_{IN}$  向け IN ライン過渡応答 ( $0.9V \sim 1.2V$ )

## 5.6 代表的特性 (続き)

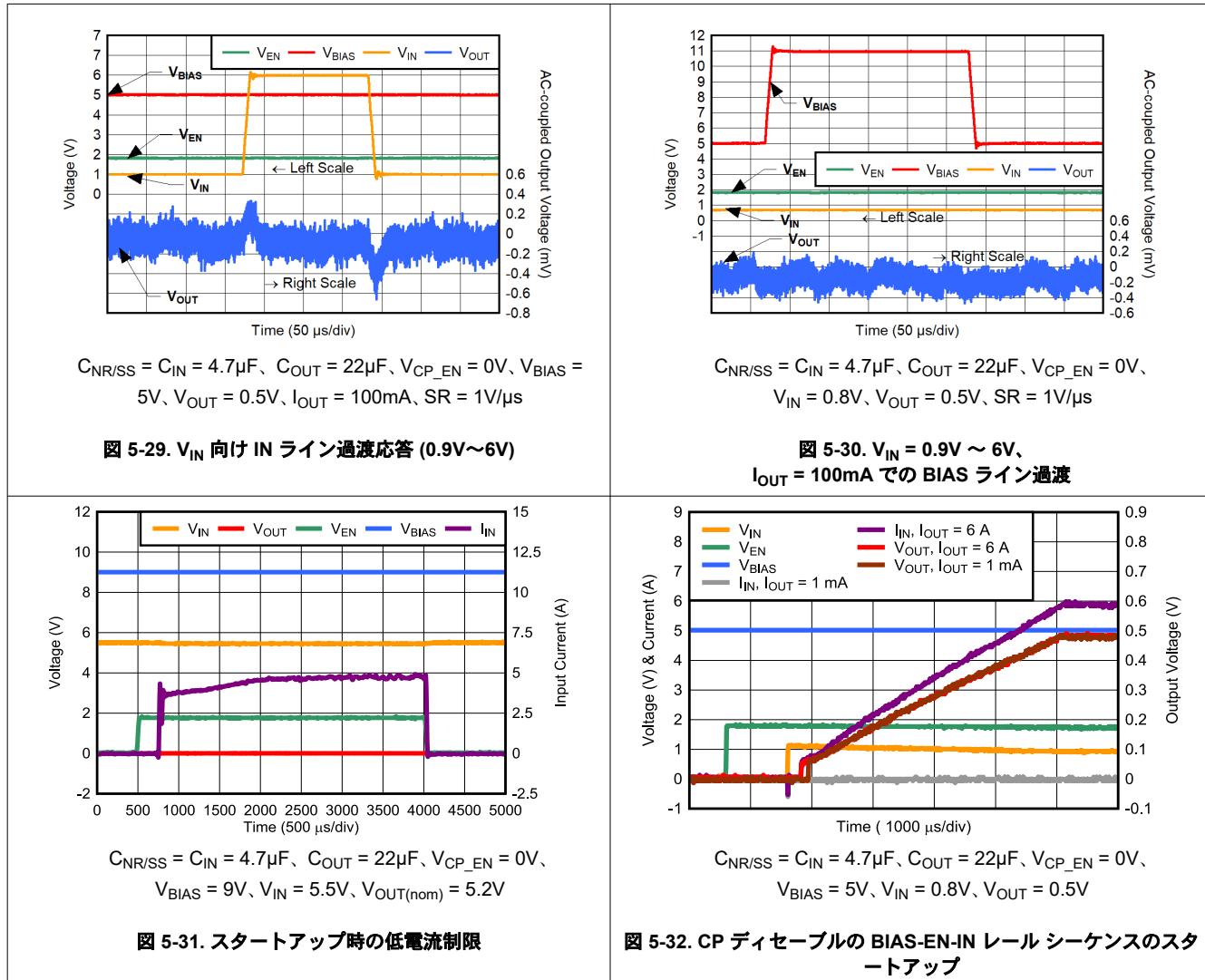

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

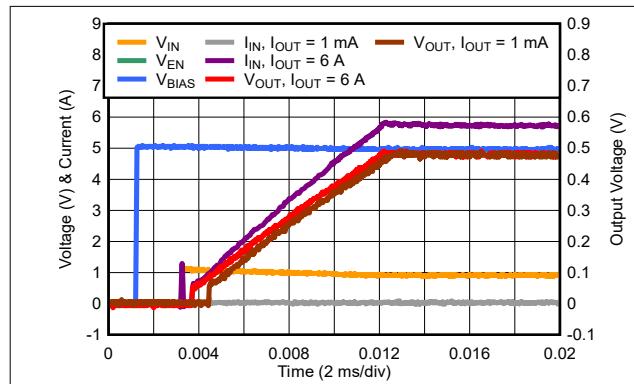

## 5.6 代表的特性 (続き)

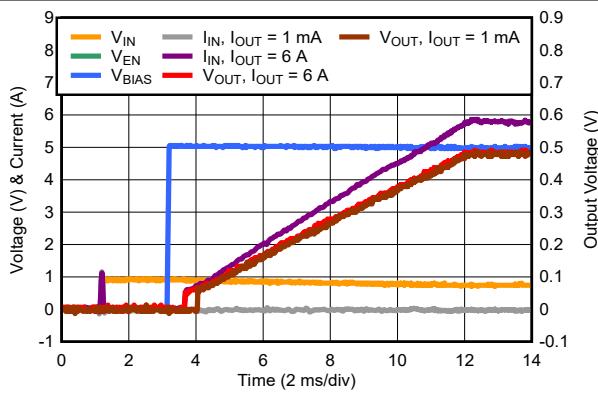

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

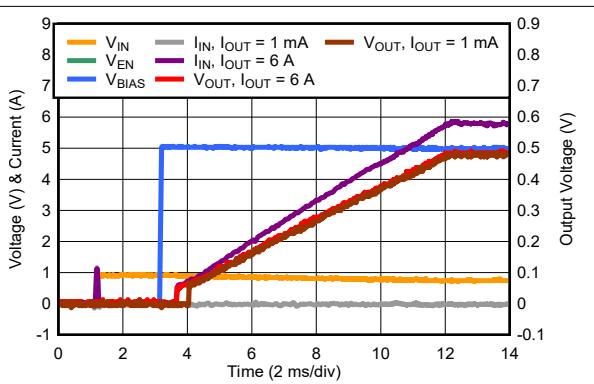

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 5V$ 、 $V_{IN} = 0.8V$ 、 $V_{OUT} = 0.5V$

図 5-33. CP ディセーブルの EN-BIAS-IN レール シーケンスのスタートアップ

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 5V$ 、 $V_{IN} = 0.8V$ 、 $V_{OUT} = 0.5V$

図 5-34. CP ディセーブルの EN-IN-BIAS レール シーケンスのスタートアップ

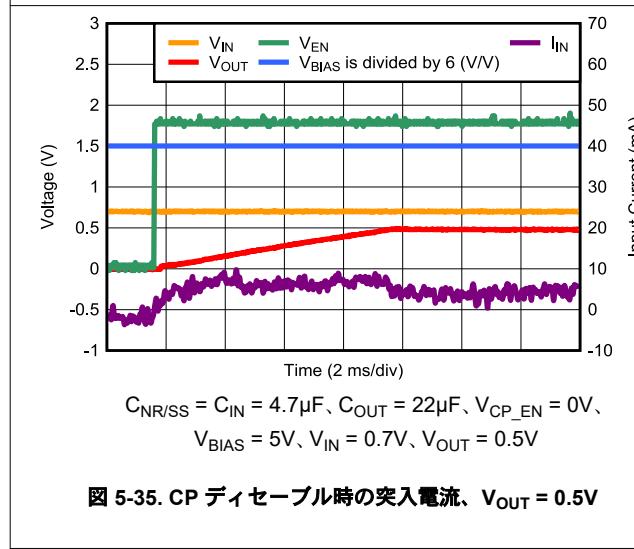

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 5V$ 、 $V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$

図 5-35. CP ディセーブル時の突入電流、 $V_{OUT} = 0.5V$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 5V$ 、 $V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$

図 5-36. CP ディセーブル時の突入電流、 $V_{OUT} = 0.5V$ 、最初の 500μs

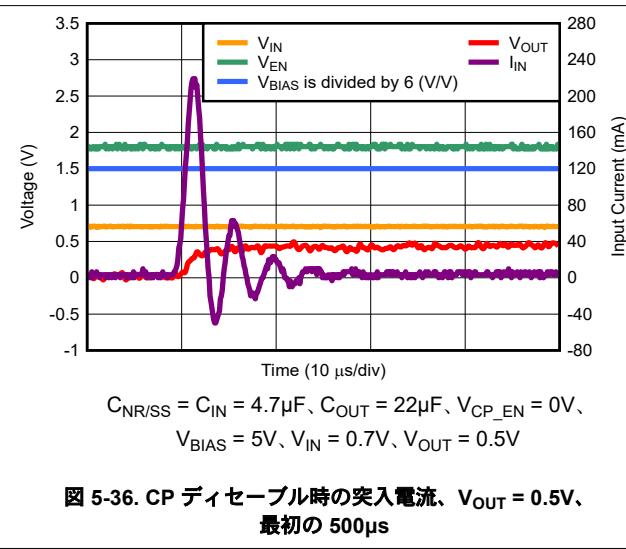

## 5.6 代表的特性 (続き)

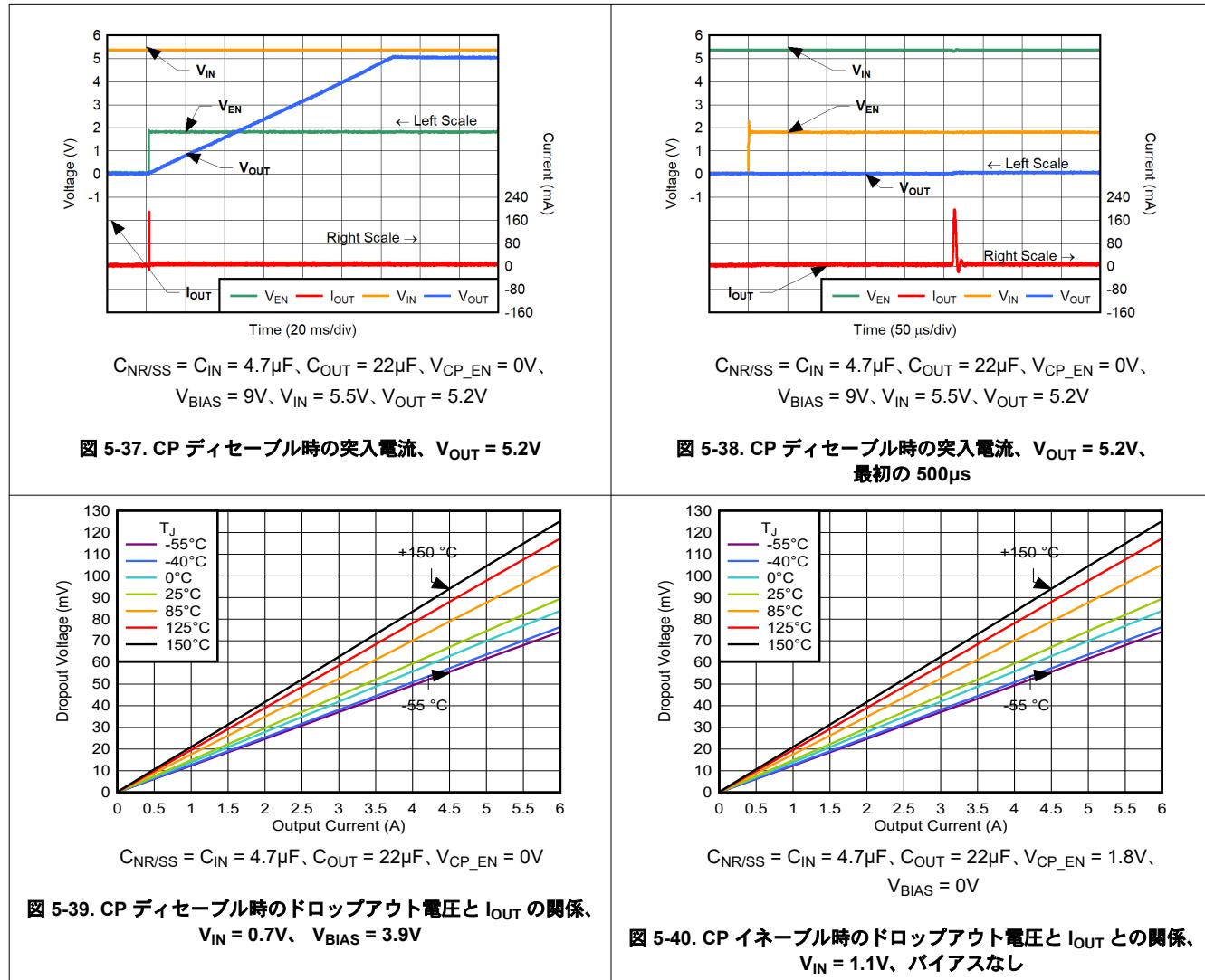

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$

図 5-41. 出力放電抵抗と  $V_{IN}$  の関係

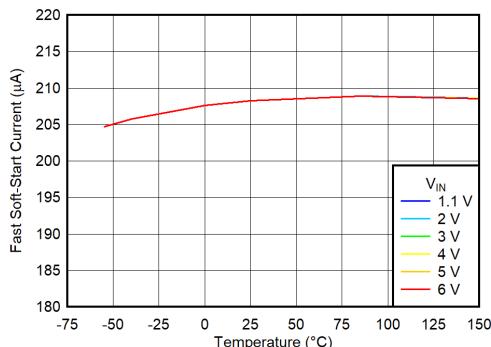

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 0V$

図 5-42. 高速ソフトスタート電流と温度および  $V_{IN}$  との関係

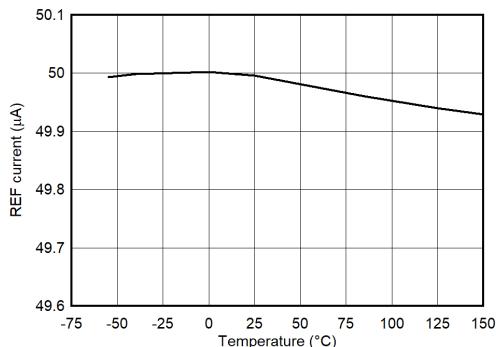

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 1.1V$

図 5-43. リファレンス電流と温度との関係

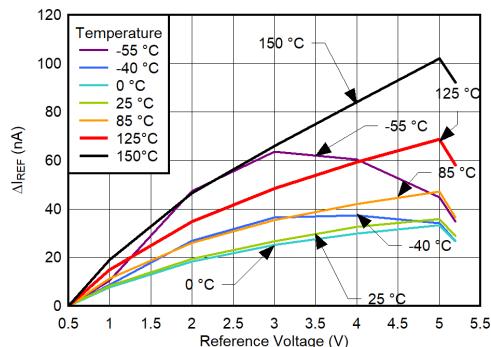

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 6V$ 、 $I_{OUT} = 0A$

図 5-44. 基準電流の変化と  $V_{REF}$  の関係

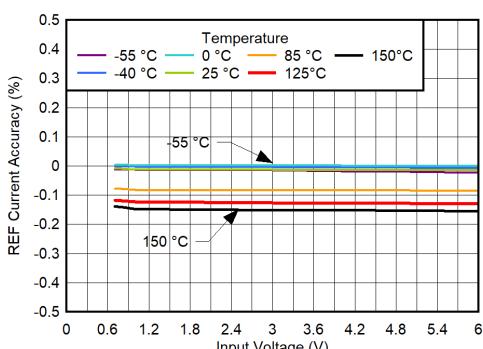

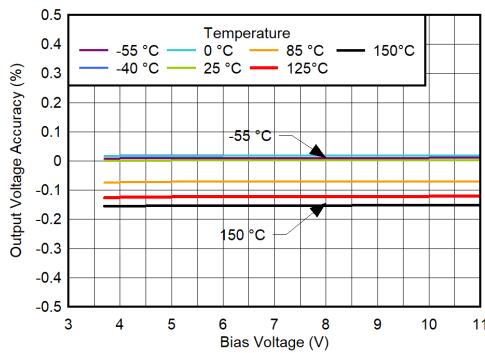

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{BIAS} = 3V$ 、 $V_{OUT} = 0.5V$

図 5-45. CP をイネーブルにするためのリファレンス電流精度と  $V_{IN}$  との関係

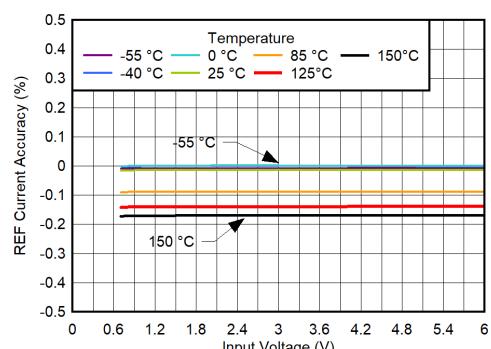

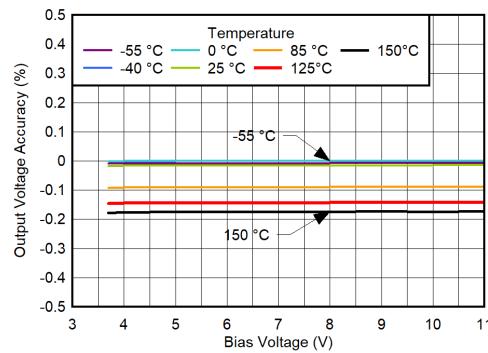

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 3.7V$ 、 $V_{OUT} = 0.5V$

図 5-46. CP ディスエーブル時のリファレンス電流精度と  $V_{IN}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

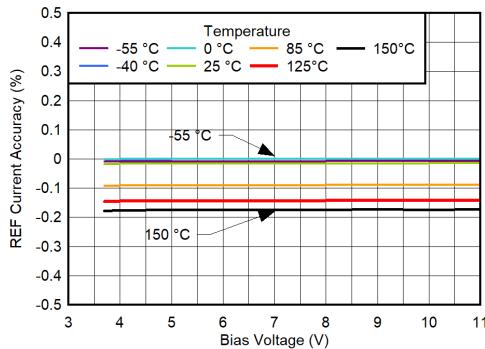

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$

図 5-47. CP ディスエーブル時の  $I_{OUT} = 0A$  でのリファレンス電流精度と  $V_{BIAS}$  との関係

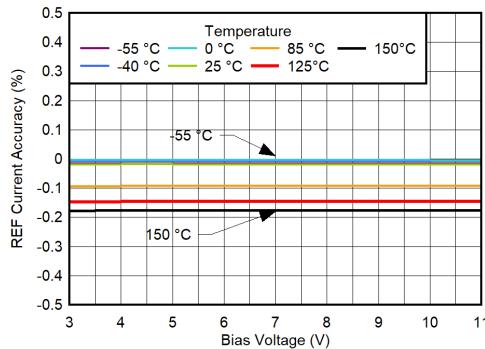

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$

図 5-48. CP イネーブル時の  $I_{OUT} = 0A$  のリファレンス電流精度と  $V_{BIAS}$  との関係

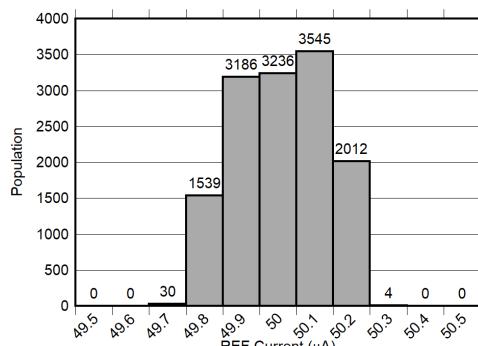

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-49.  $I_{REF}$  の分布

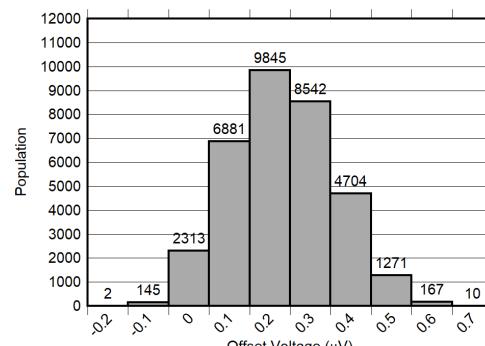

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-50.  $V_{OS}$  の分布

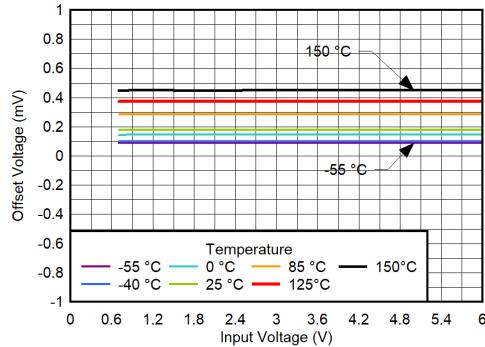

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 3.7V$ 、 $V_{OUT} = 0.5V$ 、 $I_{OUT} = 0A$

図 5-51. オフセット電圧と  $V_{IN}$  との関係

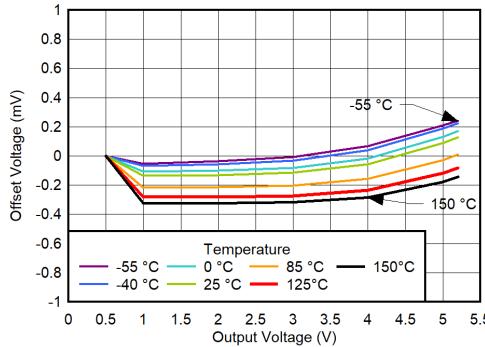

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 0V$ 、 $V_{IN} = 6V$ 、 $I_{OUT} = 0A$

図 5-52. オフセット電圧と  $V_{OUT}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

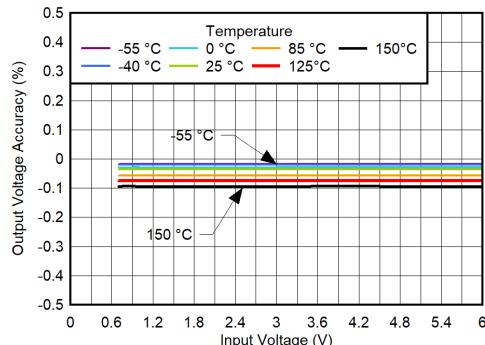

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 11V$ 、 $V_{OUT} = 0.5V$ 、 $I_{OUT} = 0A$

図 5-53. 出力電圧精度と  $V_{IN}$  との関係 ( $V_{BIAS} = 11V$ )、

CP ディセーブル時

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{BIAS} = 3.7V$ 、 $V_{OUT} = 0.5V$ 、 $I_{OUT} = 0A$

図 5-54. 出力電圧精度と  $V_{IN}$  との関係 ( $V_{BIAS} = 3.7V$ )、CP ディセーブル時

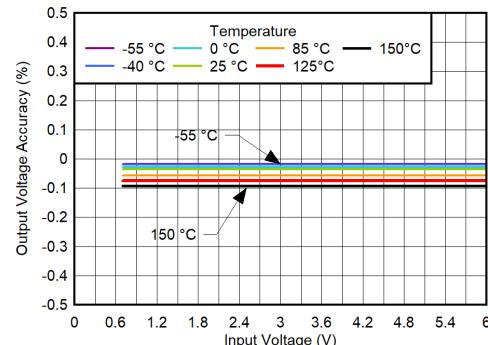

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{IN} = 6V$ 、

$V_{OUT} = 0.5V$ 、 $I_{OUT} = 0A$

図 5-55. 出力電圧精度と  $V_{BIAS}$  との関係 ( $V_{IN} = 6V$ )、

CP ディセーブル時

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、

$V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$ 、 $I_{OUT} = 0A$

図 5-56. 出力電圧精度と  $V_{BIAS}$  との関係 ( $V_{IN} = 0.7V$ )、CP ディセーブル時

## 5.6 代表的特性 (続き)

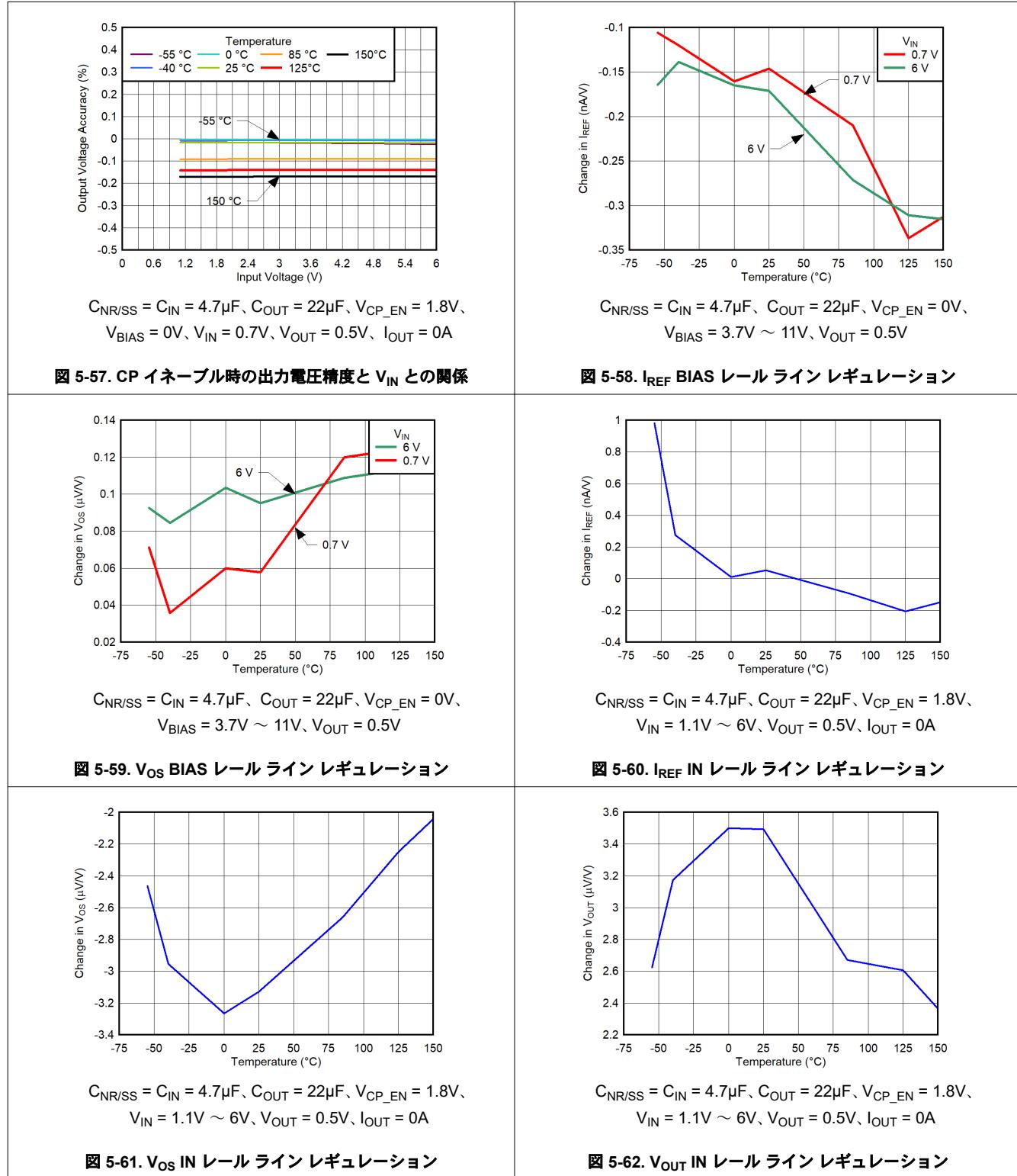

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

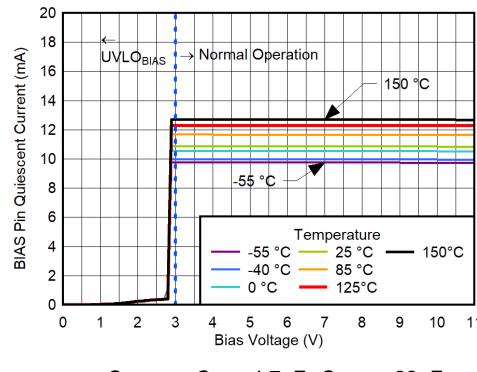

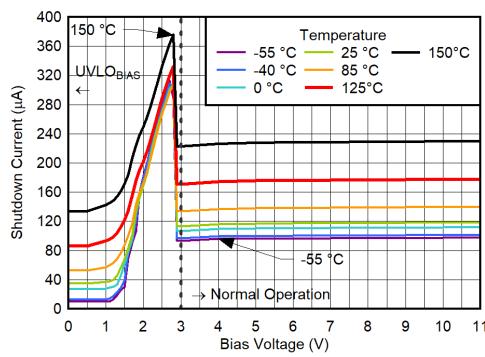

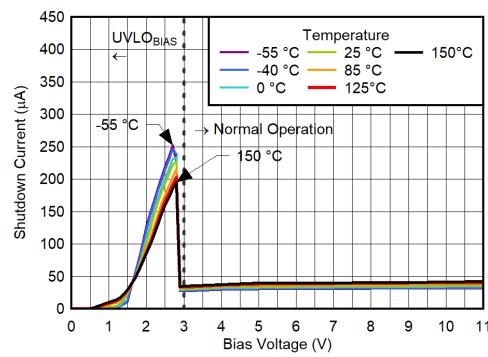

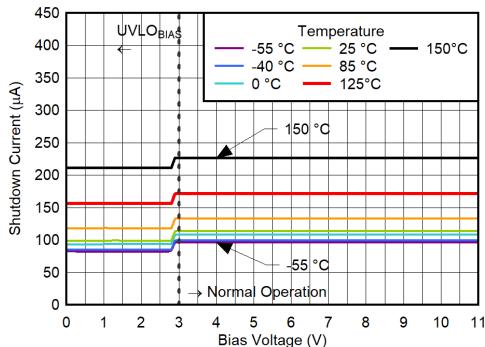

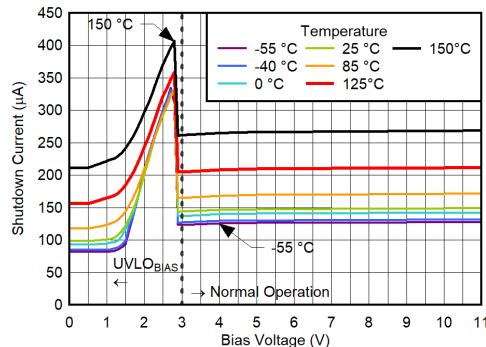

## 5.6 代表的特性 (続き)

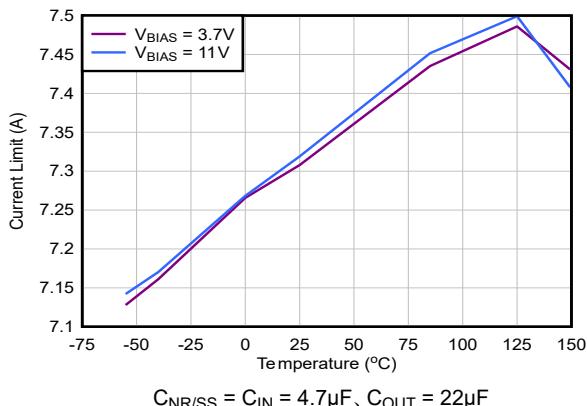

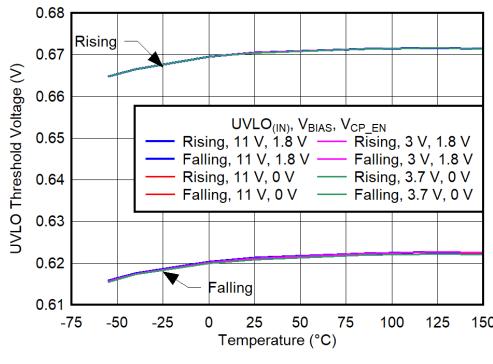

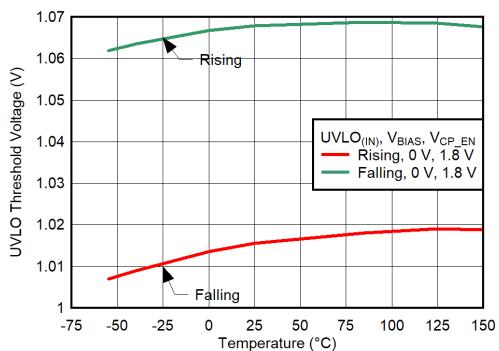

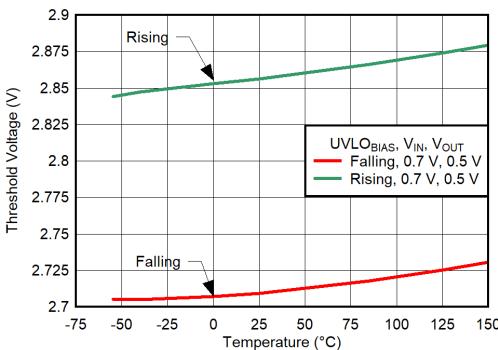

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

図 5-63.  $I_{LIMIT}$  vs 温度

図 5-64. UVLO<sub>IN</sub> スレッショルドと温度との関係 (BIAS レールあり)

図 5-65. UVLO<sub>IN</sub> スレッショルドと温度との関係 (BIAS レールなし)

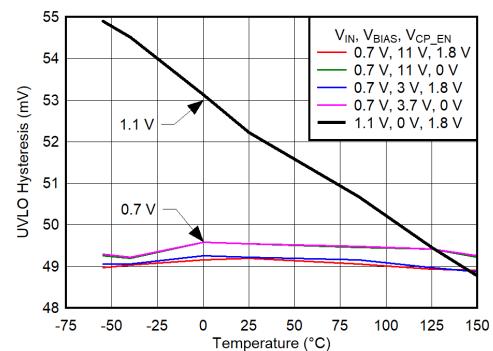

図 5-66. UVLO<sub>IN</sub> ヒステリシスと温度との関係

図 5-67. CP ディスエーブル時の UVLO<sub>BIAS</sub> スレッショルドと温度との関係

図 5-68. CP イネーブル時の UVLO<sub>BIAS</sub> スレッショルドと温度との関係

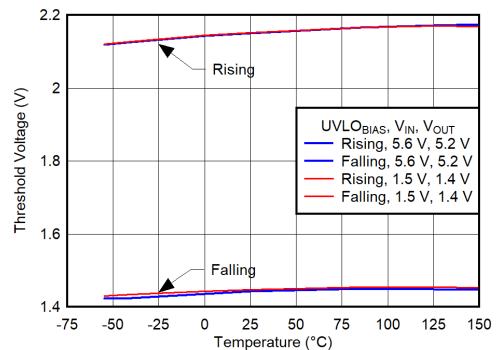

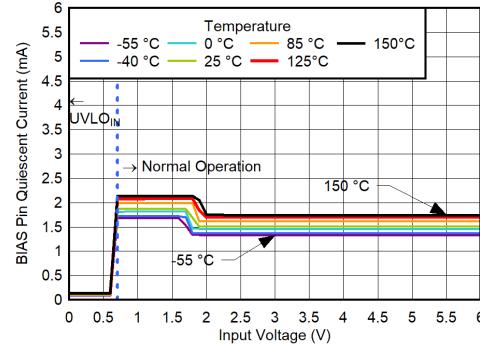

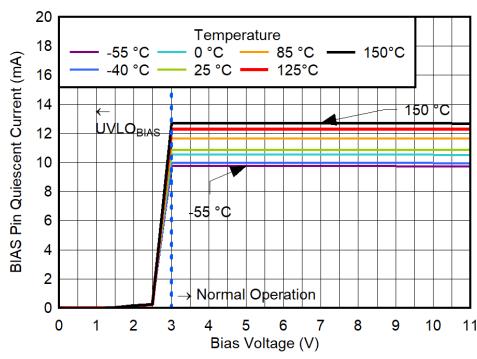

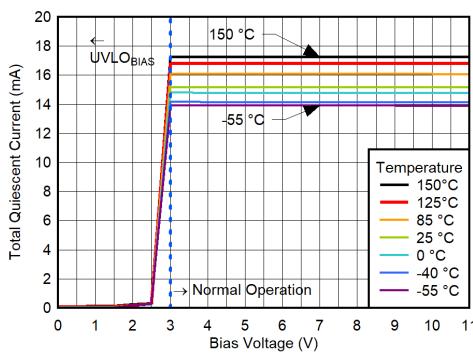

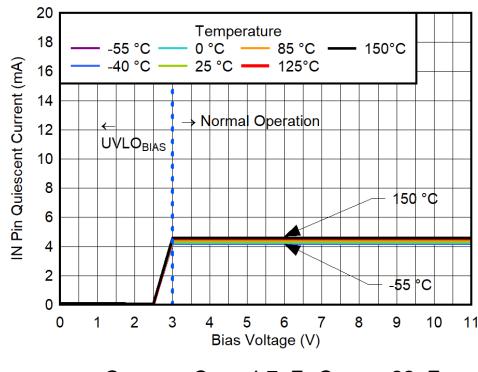

## 5.6 代表的特性 (続き)

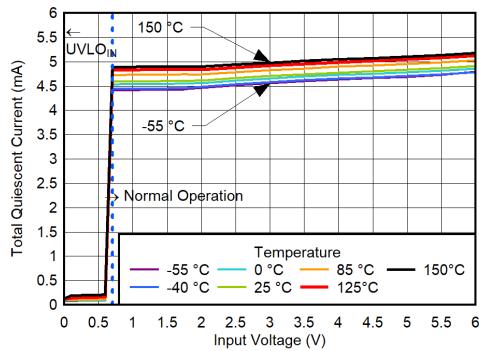

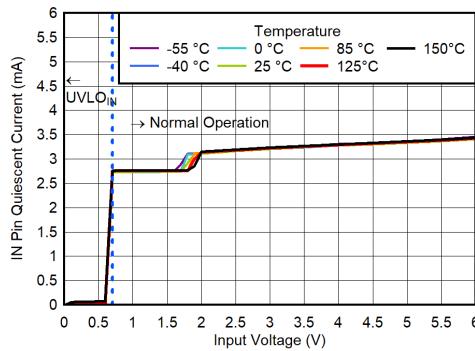

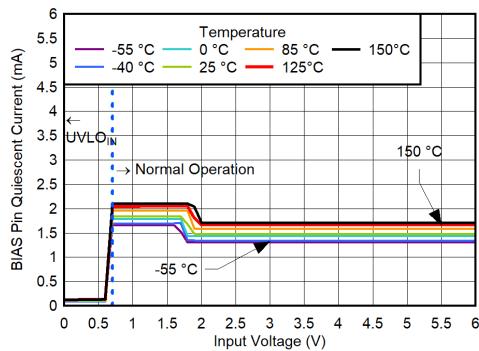

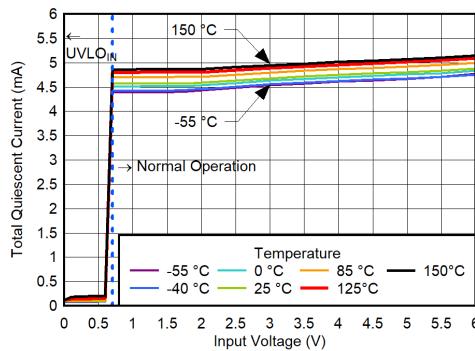

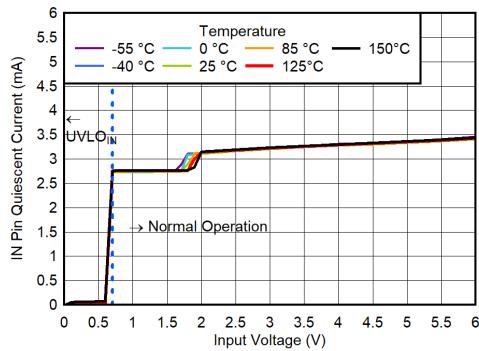

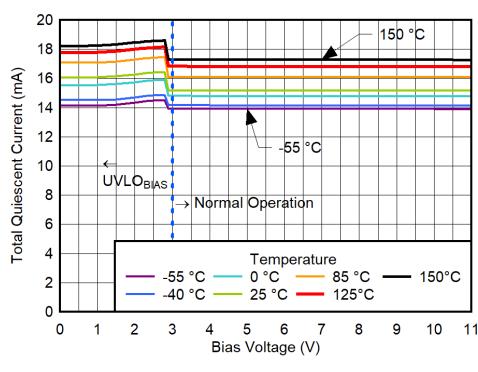

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

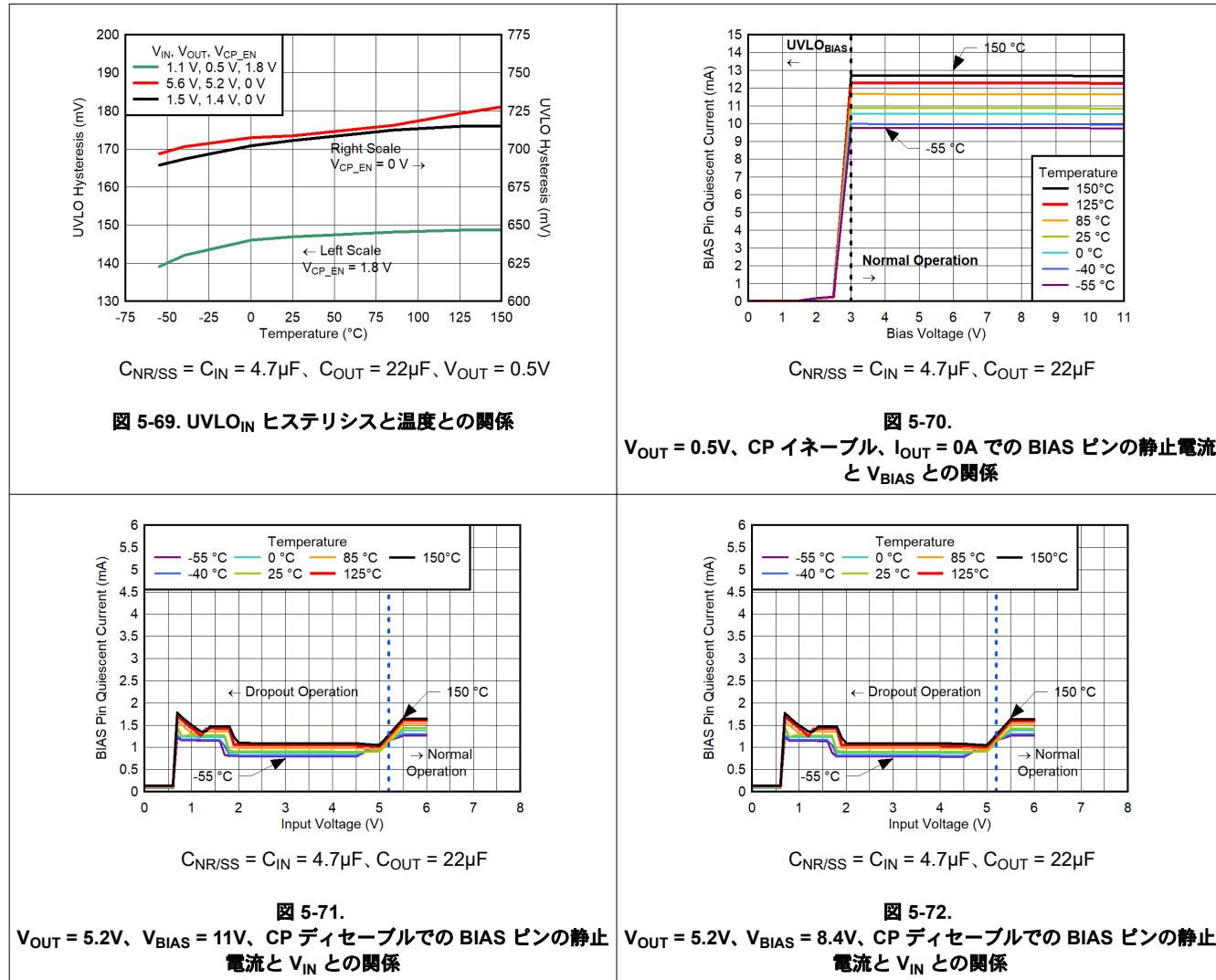

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

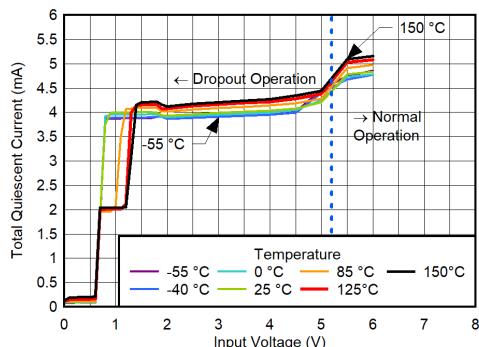

図 5-73.

$V_{OUT} = 5.2V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの BIAS ピンの合計

静止電流と  $V_{IN}$  との関係

図 5-74.  $V_{OUT} = 5.2V$ 、 $V_{BIAS} = 8.4V$ 、CP ディセーブルでの合計静止

電流と  $V_{IN}$  との関係

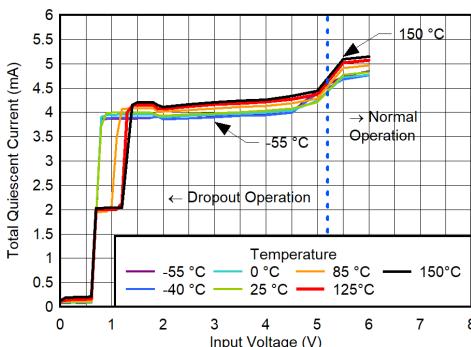

図 5-75. IN ピンの静止電流と  $V_{IN}$  との関係 ( $V_{OUT} = 5.2V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブル

図 5-76. IN ピンの静止電流と  $V_{IN}$  との関係 ( $V_{OUT} = 5.2V$ 、 $V_{BIAS} = 8.4V$ 、CP ディセーブル

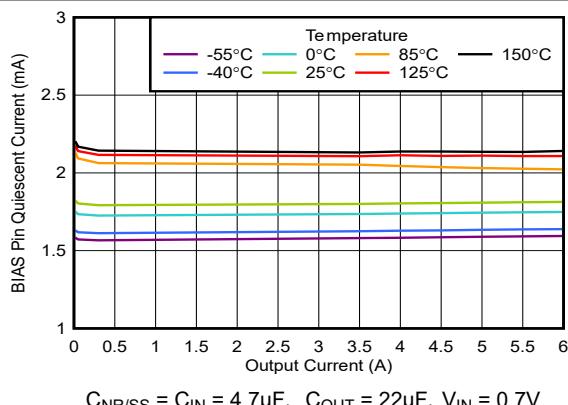

図 5-77.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの BIAS ピンの静止

電流と  $I_{OUT}$  との関係

図 5-78.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブル時の合計静止

電流と  $I_{OUT}$  との関係

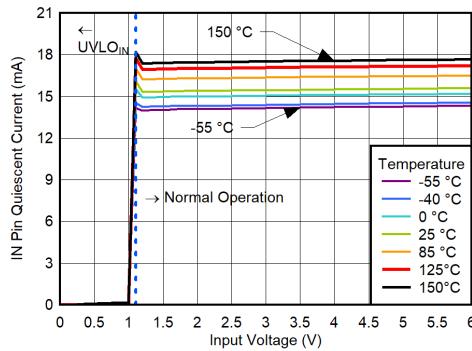

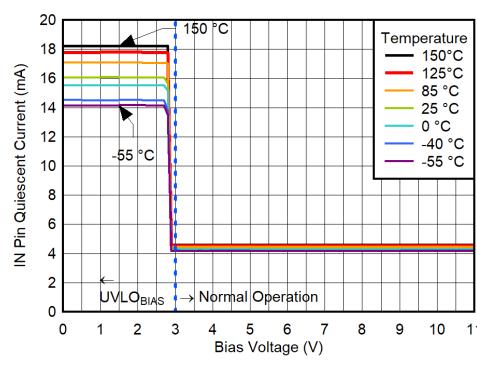

## 5.6 代表的特性 (続き)

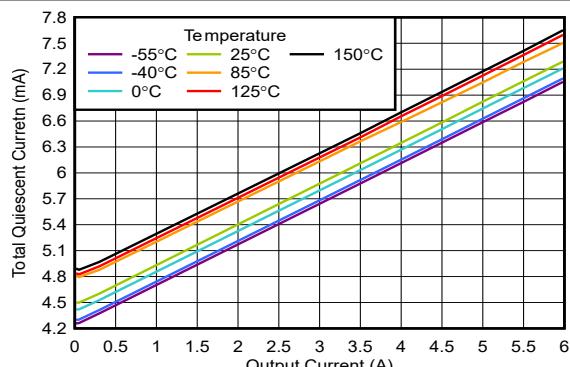

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-79. IN ピンの静止電流と  $I_{OUT}$  との関係 ( $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP はディセーブル)

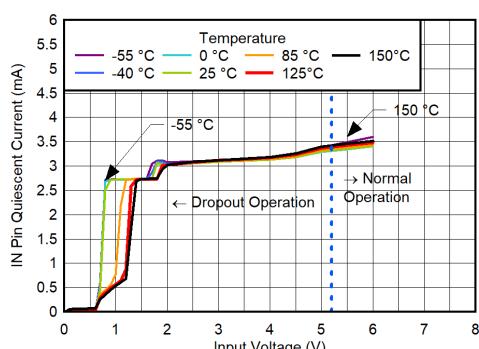

図 5-80.  $V_{OUT} = 0.5V$ 、

$V_{BIAS} = 11V$ 、CP ディセーブルでの BIAS ピン電流と  $V_{IN}$  との関係

図 5-81.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの合計静止電流と  $V_{IN}$  との関係

図 5-82. IN ピンの静止電流と  $V_{IN}$  との関係 ( $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブル)

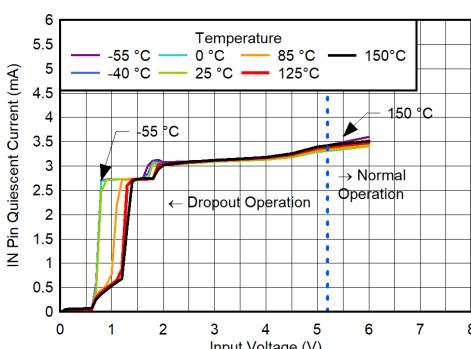

図 5-83.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3.7V$ 、CP ディセーブルでの BIAS ピンの静止電流と  $V_{IN}$  との関係

図 5-84.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3.7V$ 、CP ディセーブルでのビンの合計静止電流と  $V_{IN}$  との関係

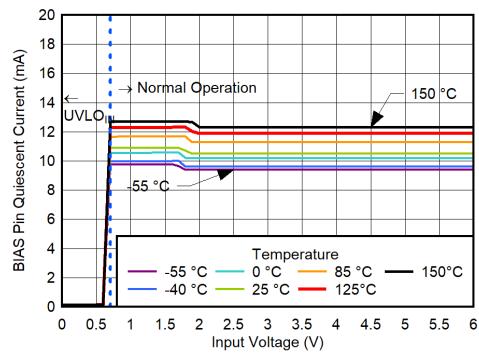

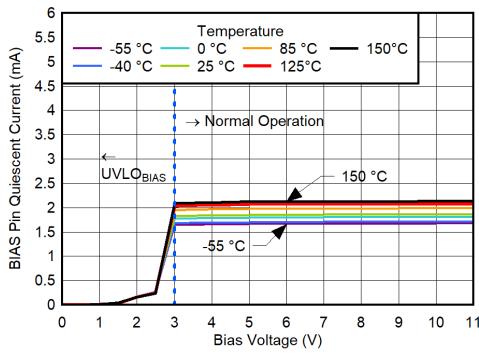

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

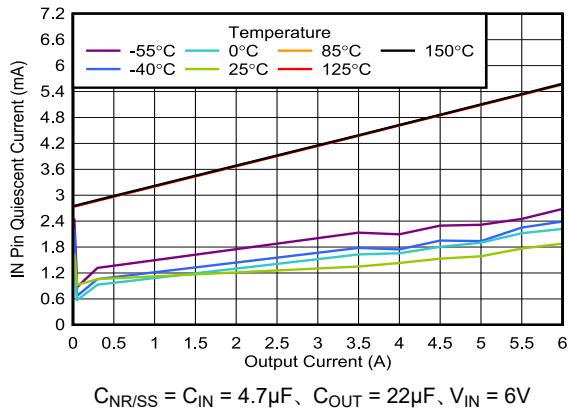

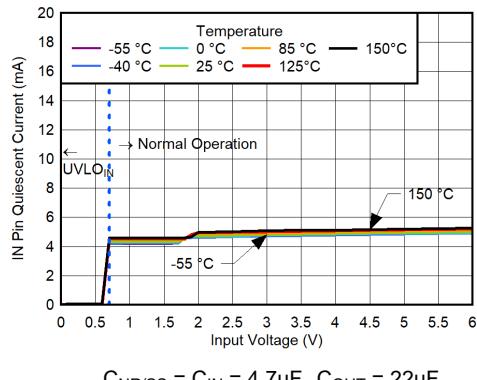

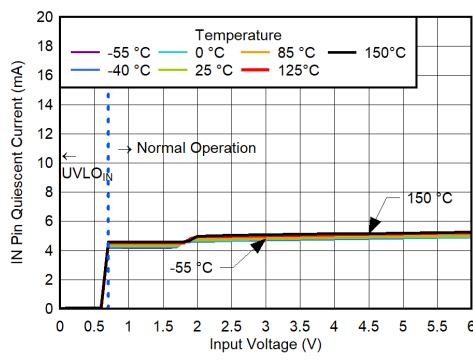

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-85. IN ピンの静止電流と  $V_{IN}$  との関係( $V_{OUT} = 0.5V$ )、 $V_{BIAS} = 3.7V$ 、CP ディセーブル

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-86.

$V_{OUT} = 0.5V$ 、 $BIAS$  なし、CP イネーブル、 $I_{OUT} = 0A$  での  $BIAS$  ピンの静止電流と  $V_{IN}$  との関係

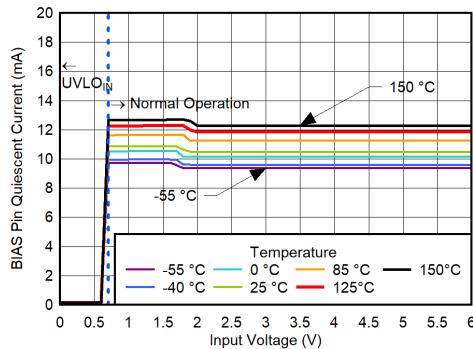

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-87.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブル、 $I_{OUT} = 0A$  での  $BIAS$  ピンの静止電流と  $V_{IN}$  との関係

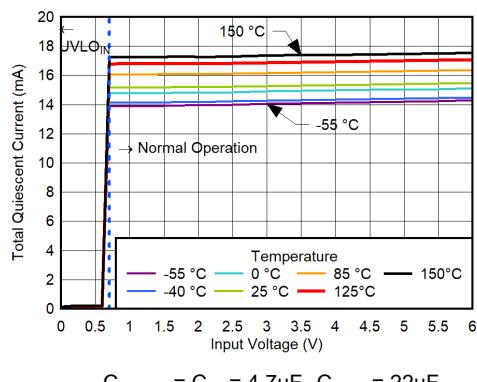

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-88.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブル、 $I_{OUT} = 0A$  での

合計静止電流と  $V_{IN}$  との関係

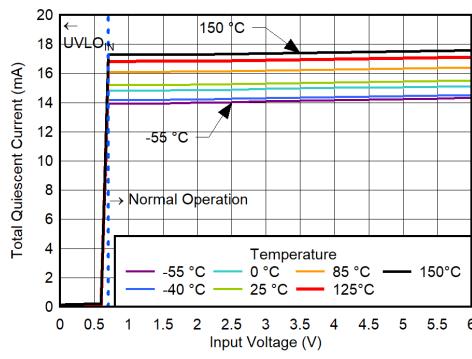

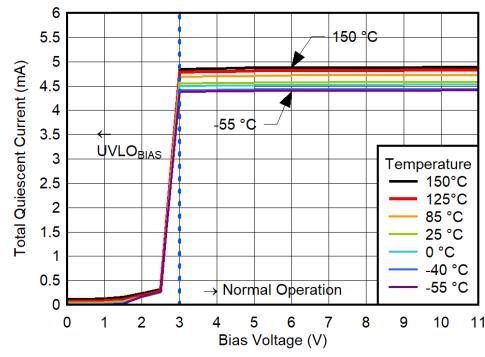

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-89. IN ピンの静止電流と  $V_{IN}$  との関係 ( $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブル、 $I_{OUT} = 0A$ )

図 5-90.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP イネーブル、 $I_{OUT} = 0A$  での BIAS ピンの静止電流と  $V_{IN}$  との関係

図 5-91.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP イネーブル、 $I_{OUT} = 0A$  での

合計静止電流と  $V_{IN}$  との関係

図 5-92. IN ピンの静止電流と  $V_{IN}$  との関係 ( $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP イネーブル、 $I_{OUT} = 0A$ )

図 5-93.

$V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP イネーブル、 $I_{OUT} = 0A$  での BIAS ピンの静止電流と  $V_{BIAS}$  との関係

図 5-94.  $V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP イネーブル、 $I_{OUT} = 0A$  での

合計静止電流と  $V_{BIAS}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

図 5-95. IN ピンの静止電流と  $V_{BIAS}$  との関係( $V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP イネーブル、 $I_{OUT} = 0A$ )

図 5-96.

$V_{OUT} = 0.5V$ 、 $V_{IN} = 1.1V$ 、CP イネーブル、 $I_{OUT} = 0A$  での BIAS ピンの静止電流と  $V_{BIAS}$  との関係

図 5-97.  $V_{OUT} = 0.5V$ 、 $V_{IN} = 1.1V$ 、CP イネーブル、 $I_{OUT} = 0A$  での合計静止電流と  $V_{BIAS}$  との関係

図 5-98.

$V_{OUT} = 0.5V$ 、 $V_{IN} = 1.1V$ 、CP イネーブル、 $I_{OUT} = 0A$  での IN ピン静止電流と BIAS 電圧との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

図 5-99.

$V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP ディセーブル、 $I_{OUT} = 0A$  での BIAS ピンの静止電流と  $V_{BIAS}$  との関係

図 5-100.  $V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP ディセーブル、 $I_{OUT} = 0A$  での合計静止電流と  $V_{BIAS}$  との関係

図 5-101. IN ピンの静止電流と  $V_{BIAS}$  との関係( $V_{OUT} = 0.5V$ 、 $V_{IN} = 0.7V$ 、CP イネーブル、 $I_{OUT} = 0A$ )

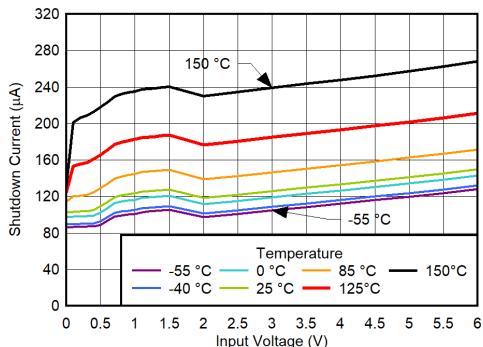

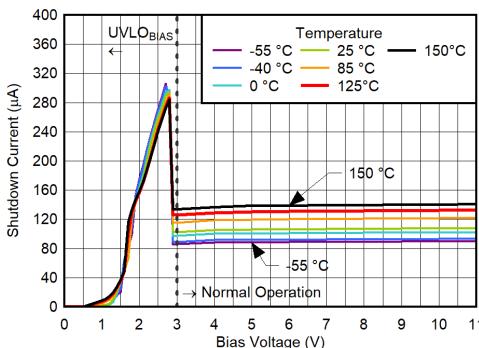

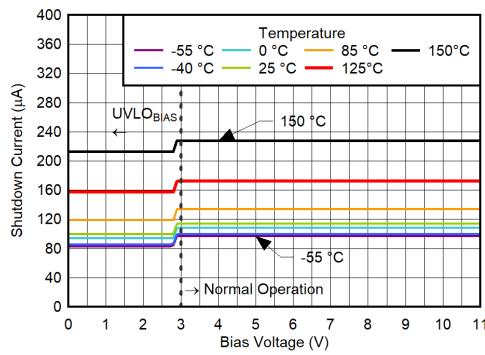

図 5-102.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 0V$ 、CP イネーブルの場合のシャットダウン電流と  $V_{IN}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

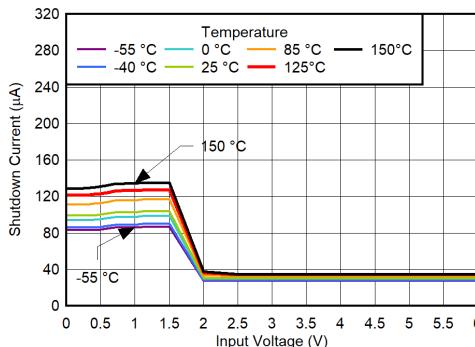

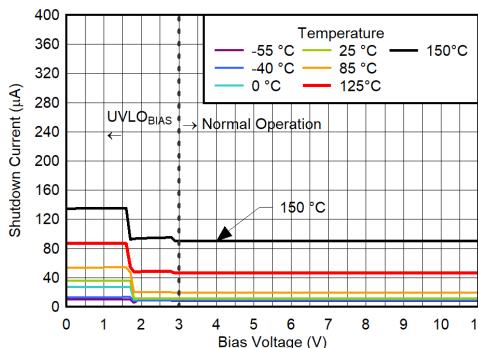

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0.4V$ 、

$V_{EN} = 0.4V$

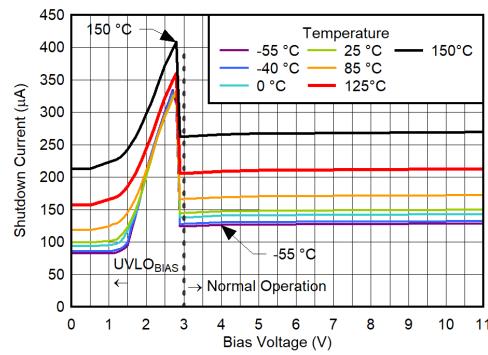

図 5-103.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの BIAS ピン シャットダウン電流と  $V_{IN}$  との関係

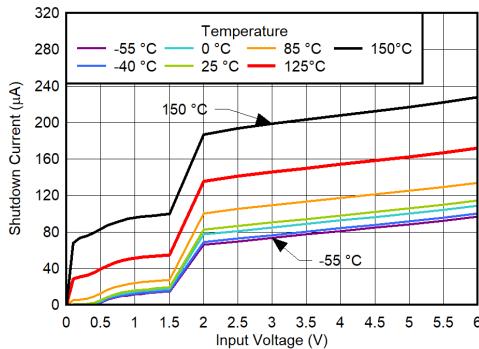

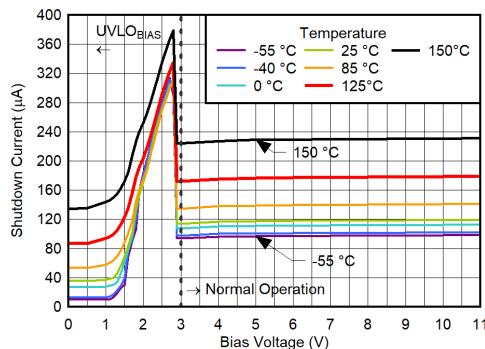

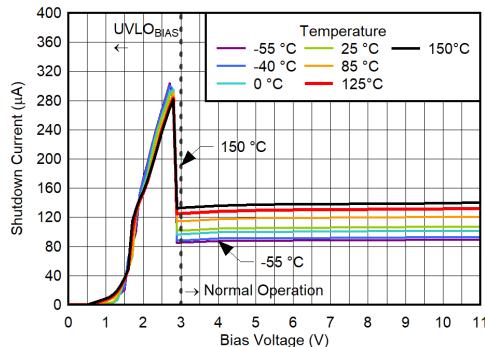

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0.4V$ 、

$V_{EN} = 0.4V$

図 5-104.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの IN ピン シャットダウン電流と  $V_{IN}$  との関係

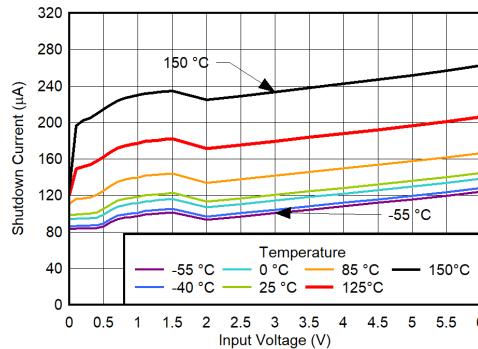

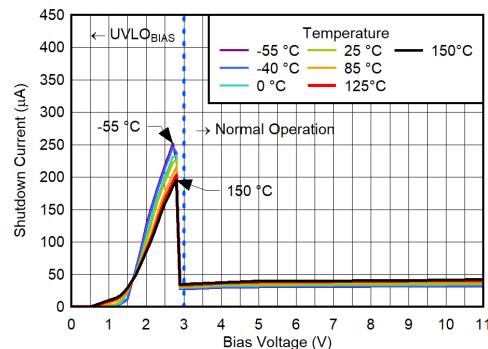

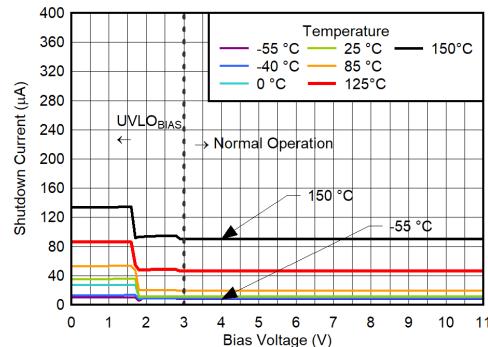

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0.4V$ 、

$V_{EN} = 0.4V$

図 5-105.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 11V$ 、CP ディセーブルでの合計シャットダウン電流と  $V_{IN}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{EN} = 0.4V$

図 5-106.

$V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブルでの BIAS ピン シャットダウン電流と  $V_{IN}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{EN} = 0.4V$

図 5-107.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブルでの IN ピンシャットダウン電流と  $V_{IN}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{EN} = 0.4V$

図 5-108.  $V_{OUT} = 0.5V$ 、 $V_{BIAS} = 3V$ 、CP イネーブルでの合計シャットダウン電流と  $V_{IN}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{EN} = 0.4V$

図 5-109.  $V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$ 、CP イネーブルでの BIAS ピンシャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、

$V_{EN} = 0.4V$

図 5-110.  $V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$ 、CP イネーブルでの IN ピンシャットダウン電流と  $V_{BIAS}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、 $V_{EN} = 0.4V$

図 5-111.  $V_{IN} = 0.7V$ 、 $V_{OUT} = 0.5V$ 、CP イネーブルでの合計シャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、 $V_{EN} = 0.4V$

図 5-112.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP イネーブルでの BIAS ピンシャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、 $V_{EN} = 0.4V$

図 5-113.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP イネーブルでの BIAS ピンシャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 1.8V$ 、 $V_{EN} = 0.4V$

図 5-114.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP イネーブルでの合計シャットダウン電流と  $V_{BIAS}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(nom)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-115.  $V_{IN} = 0.7V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルでの BIAS ピン シャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-116.  $V_{IN} = 0.7V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルでの IN ピン シャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-117.  $V_{IN} = 0.7V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルの場合の合計シャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-118.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルでの BIAS ピン シャットダウン電流と  $V_{BIAS}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(nom)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-119.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルでの IN ピンシャットダウン電流と  $V_{BIAS}$  との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{CP\_EN} = 0V$ 、 $V_{EN} = 0.4V$

図 5-120.  $V_{IN} = 6V$ 、 $V_{OUT(nom)} = 0.5V$ 、CP ディセーブルの場合の合計シャットダウン電流と  $V_{BIAS}$  との関係

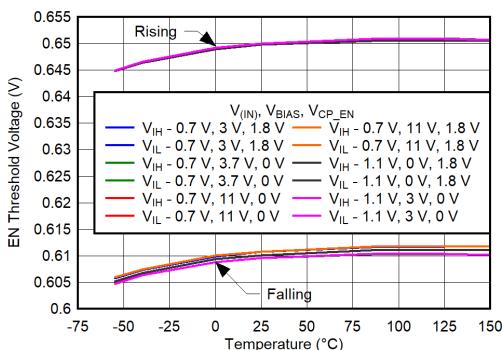

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-121. EN スレッショルド電圧と温度との関係 ( $V_{IN} = 0.7V$  および  $1.1V$ 、 $V_{OUT} = 0.5V$ )

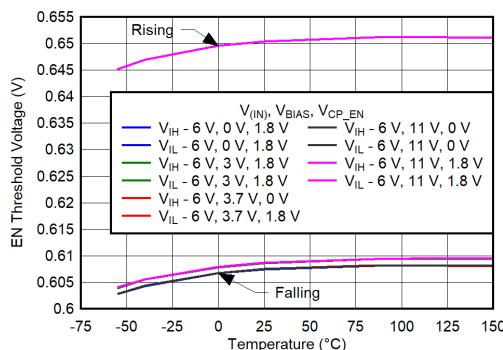

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-122. EN スレッショルド電圧と温度との関係 ( $V_{IN} = 6V$ 、 $V_{OUT} = 0.5V$ )

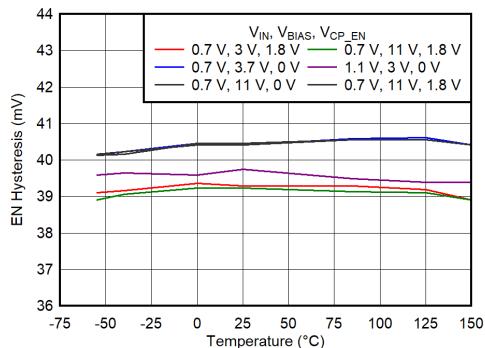

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-123. EN ヒステリシスと温度との関係 ( $V_{IN} = 0.7V$  および  $1.1V$ 、 $V_{OUT} = 0.5V$ )

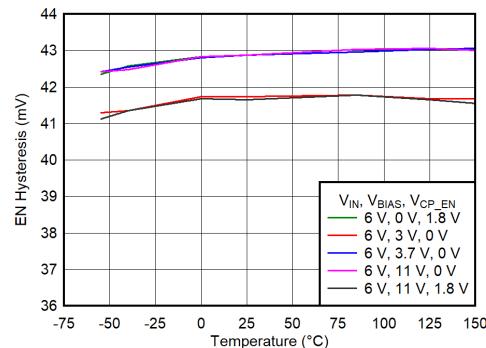

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-124. EN ヒステリシスと温度との関係 ( $V_{IN} = 6V$ 、 $V_{OUT} = 0.5V$ )

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

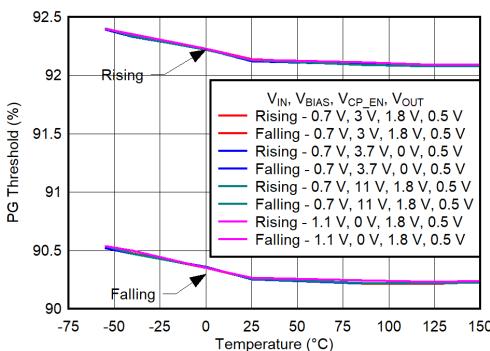

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-125. EN ピンの電流と温度との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-126. CP\_EN スレッショルド電圧と温度との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-127. CP\_EN ピンの電流と温度との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-128. CP\_EN ヒステリシスと温度との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-129. PG のスレッショルド電圧と温度との関係 ( $V_{IN} = 0.7V$  および  $1.1V$ )

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-130. PG スレッショルド電圧と温度との関係 ( $V_{IN} = 6V$ )

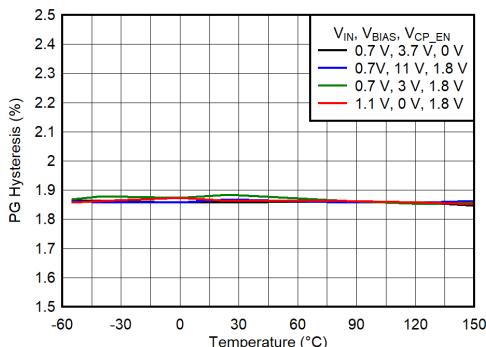

## 5.6 代表的特性 (続き)

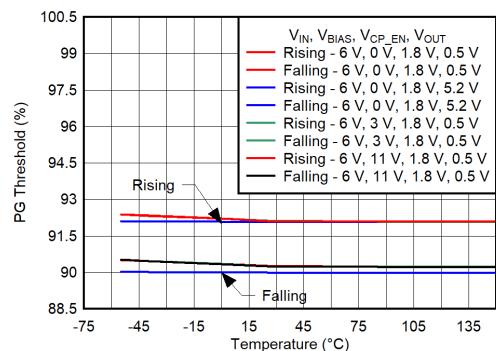

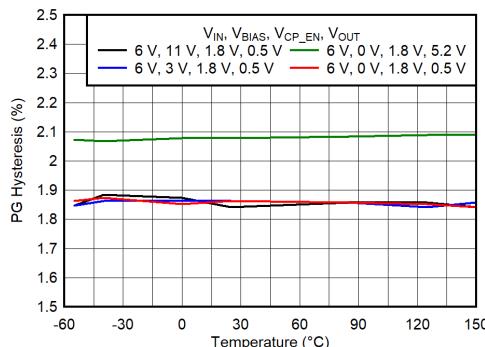

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^\circ C$

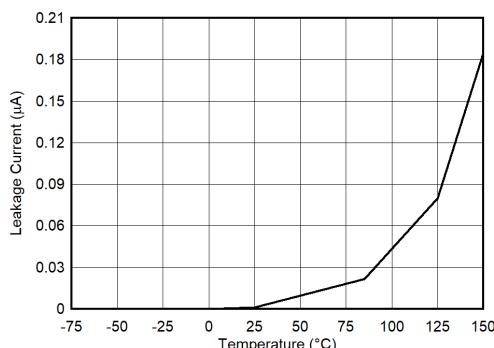

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-131. PG ヒステリシスと温度との関係 ( $V_{IN} = 0.7V$  および  $1.1V$ )

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-132. PG ヒステリシスと温度との関係 ( $V_{IN} = 6V$ )

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$

図 5-133. PG リーク電流と温度との関係

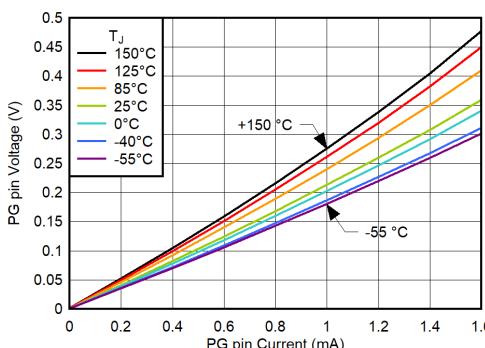

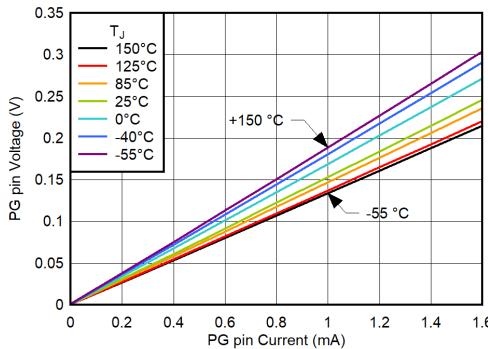

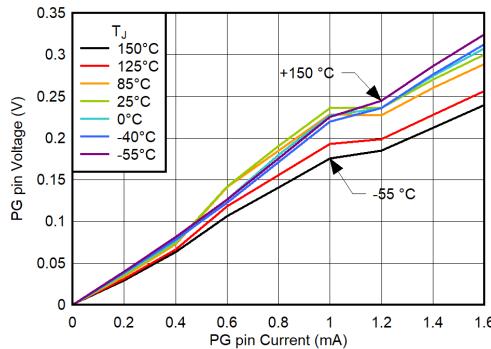

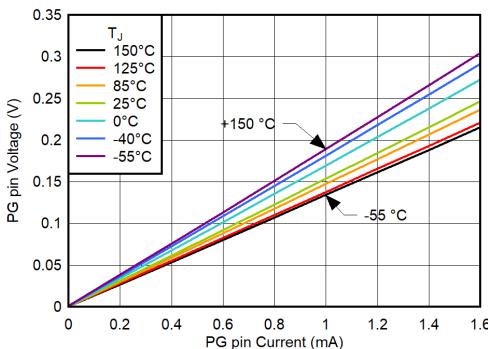

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{BIAS} = 0V$ 、

$V_{OUT} = 0.5V$ 、 $V_{CP\_EN} = 1.8V$

図 5-134.  $V_{IN} = 1.1V$ 、BIAS なしでの PG ピンの低レベル電圧と PG ピン電流との関係

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{BIAS} = 0V$ 、

$V_{OUT} = 0.5V$ 、 $V_{CP\_EN} = 1.8V$

図 5-135.  $V_{IN} = 6V$ 、BIAS なしでの PG ピンの低レベル電圧と PG ピン電流との関係

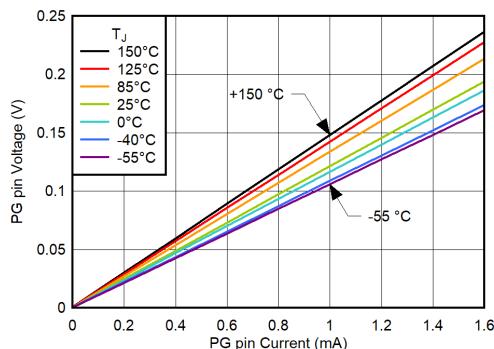

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{OUT} = 0.5V$

図 5-136. PG ピンの低レベル電圧と PG ピン電流との関係 ( $V_{IN} = 0.7V$ 、 $V_{BIAS} = 3.7V$ 、 $V_{CP\_EN} = 0V$ )

## 5.6 代表的特性 (続き)

$V_{IN} = V_{OUT(NOM)} + 0.4V$ 、 $V_{EN} = 1.8V$ 、 $V_{CP\_EN} = 1.8V$ 、 $C_{IN} = 10\mu F$ 、 $C_{NR/SS} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $C_{BIAS} = 0nF$ 、SNS ピンを OUT ピンに短絡、PG ピンを  $100k\Omega$  で  $V_{IN}$  にプルアップ(特に記述のない限り)。標準値は  $T_J = 25^{\circ}C$

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{OUT} = 0.5V$

図 5-137. PG ピンの低レベル電圧と PG ピン電流との関係 ( $V_{IN} = 0.7V$ 、 $V_{BIAS} = 11V$ 、 $V_{CP\_EN} = 0V$ )

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{OUT} = 0.5V$

図 5-138. PG ピンの低レベル電圧と PG ピン電流との関係 ( $V_{IN} = 0.7V$ 、 $V_{BIAS} = 3V$ 、 $V_{CP\_EN} = 1.8V$ )

$C_{NR/SS} = C_{IN} = 4.7\mu F$ 、 $C_{OUT} = 22\mu F$ 、 $V_{OUT} = 0.5V$

図 5-139. PG ピンの低レベル電圧と PG ピン電流との関係 ( $V_{IN} = 0.7V$ 、 $V_{BIAS} = 11V$ 、 $V_{CP\_EN} = 1.8V$ )

## 6 詳細説明

### 6.1 概要

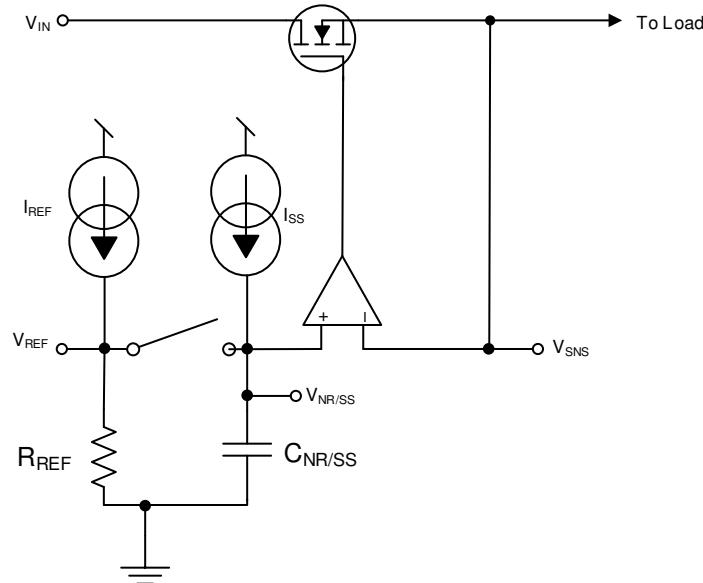

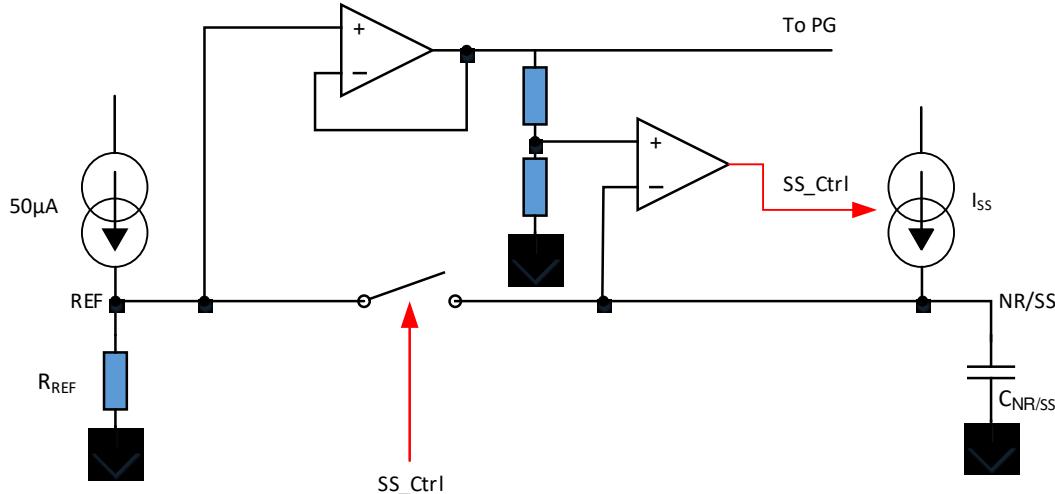

TPS7A56 は、低ノイズ(10Hz ~ 100kHz の帯域幅で  $2.45\mu\text{V}_{\text{RMS}}$ )、超高 PSRR(> 36dB ~ 1MHz)、高精度(1%)、超低ドロップアウト(LDO)リニア電圧レギュレータです。このデバイスの入力範囲は 0.7V ~ 6.0V、出力電圧範囲は 0.5V ~ 5.0V です。このデバイスは革新的な回路構成を採用しており、広い帯域幅と高いループゲインを実現しています。その結果、動作マージンが非常に小さい状況でも、超高 PSRR を達成します。このヘッドルームは  $[\text{V}_{\text{OpHr}} = (\text{V}_{\text{IN}} - \text{V}_{\text{OUT}})]$  として計算できます。概要として、このデバイスには 2 つの主な特長といくつかの副次的な機能があります。主な特長は、電流リファレンスとユニティゲイン LDO バッファです。副次的な特長には、調整可能なソフトスタート突入電流制御、高精度イネーブル、チャージポンプのイネーブル、PG ピンがあります。

電流リファレンスは、REF ピンにより制御されます。このピンは、1 本の抵抗で出力電圧を設定します。

NR/SS ピンは、立ち上がり時間を設定し、リファレンスや外付け設定抵抗によって発生するノイズをフィルタします。

ユニティゲイン LDO バッファが出力電圧を制御します。低ノイズ特性は出力電圧の上昇によって悪化せず、広帯域の PSRR を提供します。そのため、SNS ピンは負荷のリモートセンシング専用で使用されます。

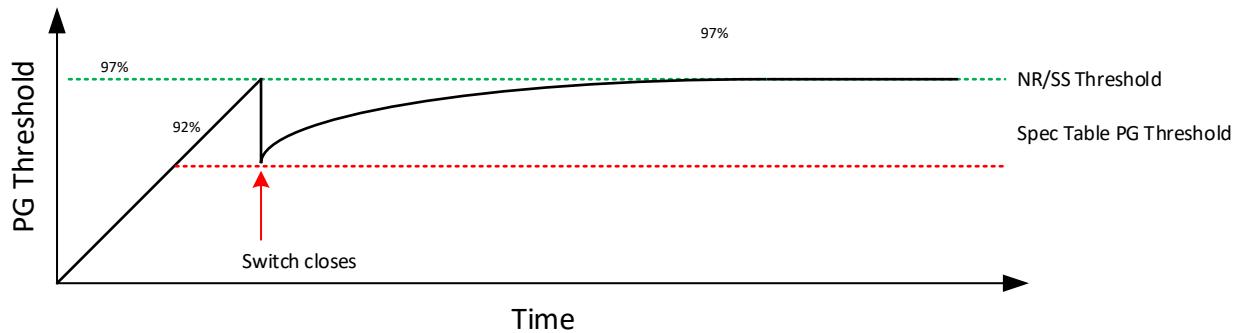

出力電圧を設定するには、標準値  $50\mu\text{A}$  の低ノイズ電流リファレンスを外付け抵抗( $R_{\text{REF}}$ )とともに使用します。このプロセスにより、出力電圧範囲を 0.5V ~ 5.0V に設定できます。低ノイズを実現し、ソフトスタート時の突入電流を抑制するために、NR/SS ピンに外付けコンデンサ  $C_{\text{NR/SS}}$  (通常は  $4.7\mu\text{F}$ ) を接続します。起動が完了し、REF と NR/SS 間のスイッチが閉じられると、 $C_{\text{NR/SS}}$  コンデンサが  $R_{\text{REF}}$  抵抗と並列に接続されます。この抵抗はバンドギャップノイズを減衰させ、出力電圧を設定します。このユニティゲインの LDO は、負荷変動や電源変動に対する応答性能を損なうことなく、広い周波数範囲にわたって非常に高い PSRR を提供します。

EN ピンは高精度イネーブル機能を設定するためのもので、このピンに接続された抵抗分圧回路によって、デバイスが起動する最適な入力電圧が選択されます。このデバイスには、3 つの独立した低電圧誤動作防止(UVLO)電圧があります。これらの電圧は、IN レールおよび BIAS レールに対する内部固定の UVLO スレッショルドと、EN ピンを使用して外部から調整可能な UVLO スレッショルドです。

CP\_EN ピンは、内部チャージポンプをイネーブル / ディエーブルします。TPS7A56 では、BIAS レールなしで 1.1V 未満で動作させることはできません。チャージポンプがディセーブルなら、OUT と BIAS の間の最小動作ヘッドルームが必要です。

このレギュレータは、電流制限機能および熱保護機能を備えており、 $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の範囲で完全に仕様が規定されています。また、このデバイスは熱効率に優れた  $3\text{mm} \times 3\text{mm}$  の 16 ピン WQFN パッケージで提供されます。

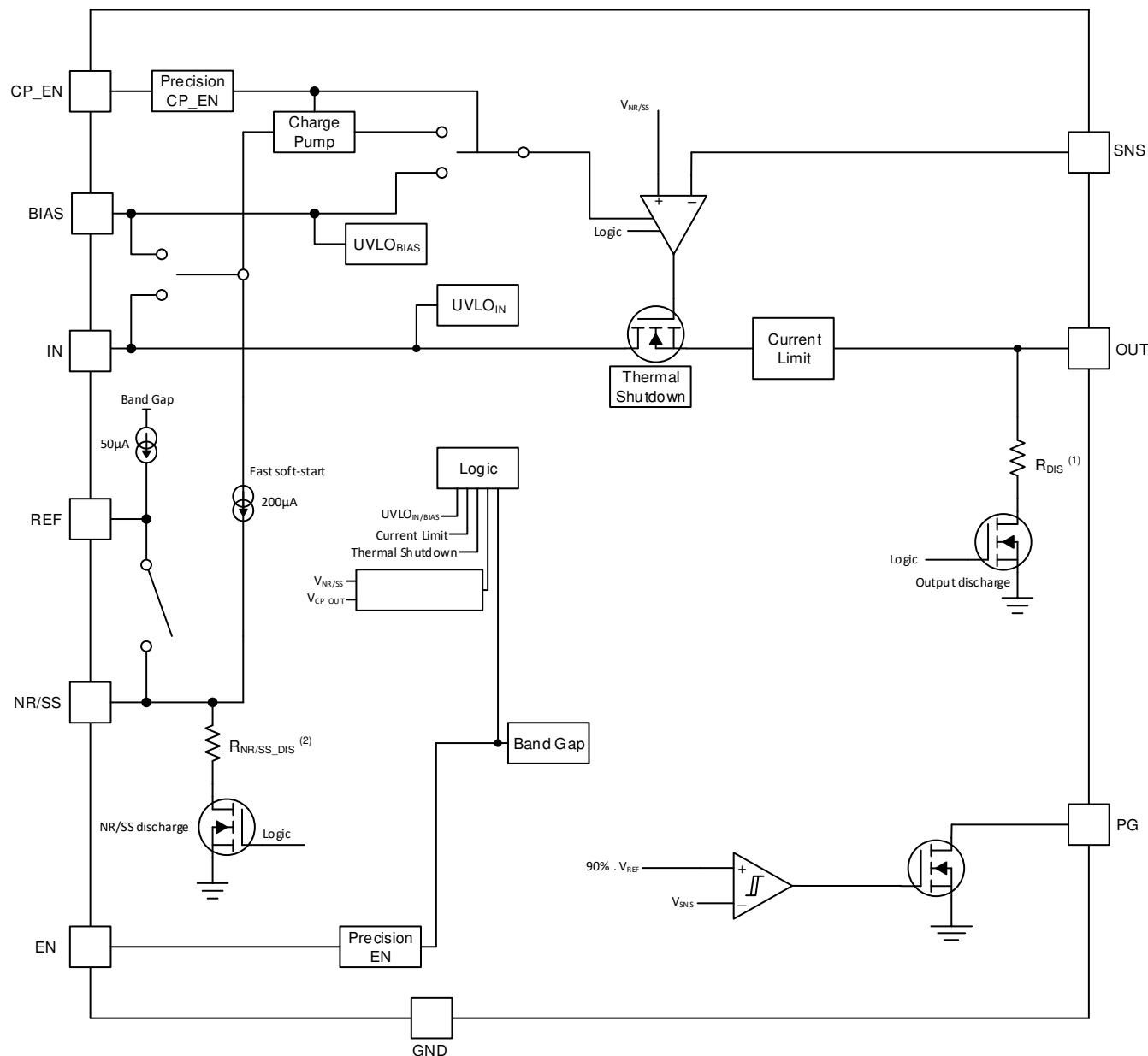

## 6.2 機能ブロック図

- A.  $R_{DIS}$  (出力ピンのアクティブ放電抵抗) の値を [電気的特性](#) の表で参照してください。

B.  $R_{NR/SS\_DIS}$  (NR/SS ピンのアクティブ放電抵抗) の値を [電気的特性](#) の表で参照してください。

## 6.3 機能説明

### 6.3.1 出力電圧設定およびレギュレーション

図 6-1 に、簡略化したレギュレーション回路を示します。入力信号 ( $V_{REF}$ ) は、内部電流源 ( $I_{REF}$ ) と外付け抵抗 ( $R_{REF}$ ) から生成されます。誤差アンプは常にユニティ ゲイン構成で動作するため、LDO 出力電圧は  $V_{REF}$  電圧によってプログラムされます。 $V_{REF}$  リファレンス電圧は、 $R_{REF}$  抵抗を駆動する内部の低ノイズ電流源から生成されます。 $V_{REF}$  は、ローパス フィルタ ( $C_{NR/SS} \parallel R_{REF}$ ) を使用することで、エラー アンプへの入力の帯域幅が非常に低くなるように設計されています。

ユニティ ゲイン構成は、SNS を OUT に接続することで実現されます。出力のトレース インダクタンスを最小限に抑え、 $C_{OUT}$  をできる限り出力の近くに接続します。

$$V_{OUT} = I_{REF} \times R_{REF}$$

図 6-1. 簡易レギュレーション回路

このユニティ ゲイン構成と、高精度の  $I_{REF}$  リファレンス電流により、このデバイスは非常に優れた出力電圧精度を実現できます。低いドロップアウト電圧 ( $V_{DO}$ ) によって、放熱が低減され、堅牢な性能を実現します。この機能の組み合わせにより、このデバイスは敏感なアナログ低電圧 ( $\leq 5.5V$ ) デバイスへの電力供給に最適な電圧源です。

### 6.3.2 低ノイズおよび超高電源除去比 (PSRR)

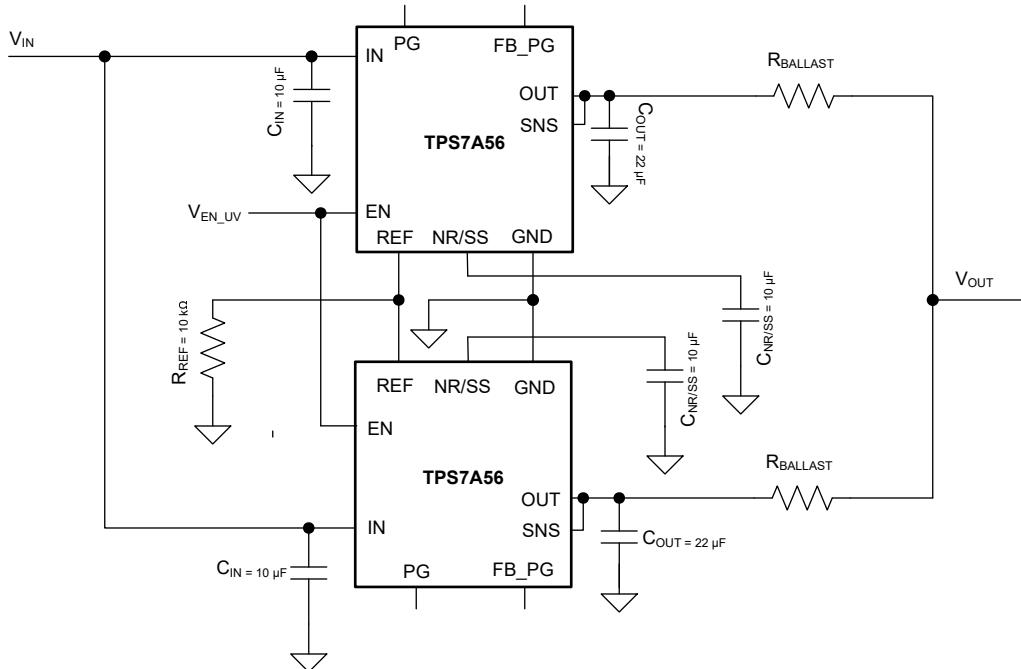

このデバイスのアーキテクチャは、高精度、高精密、低ノイズの電流リファレンスと、それに続く最先端の相補型金属酸化膜半導体 (CMOS) エラー アンプを備えています。この CMOS 誤差アンプは、 $V_{OUT} \geq 0.5V$  の場合、10kHz ノイズで  $6nV/\sqrt{Hz}$  です。従来世代の LDO とは異なり、このデバイスのユニティ ゲイン構成は、出力電圧範囲全体にわたって低ノイズを実現します。複数の TPS7A56 LDO を並列接続することで、ノイズのさらなる低減とより高い出力電流が実現されます。**並列接続により大出力電流と低ノイズを実現** セクションを参照してください。

### 6.3.3 プログラム可能なソフトスタート (NR/SS ピン)

このデバイスには、プログラム可能、単調、電流制御、ソフトスタート回路が搭載されています。この回路では  $C_{NR/SS}$  コンデンサを使用して、起動時の出力コンデンサおよび負荷への突入電流を最小限に抑えます。この回路は、出力電圧が設定値の少なくとも 90% に迅速に到達することが求められる用途において、起動時間を短縮します。詳細については、「**ソフトスタート、ノイズ低減 (NR/SS ピン)、パワーグッド (PG ピン)**」セクションを参照してください。

### 6.3.4 高精度のイネーブルと UVLO

回路の実装によっては、最大 3 つの独立した低電圧誤動作防止 (UVLO) 電圧回路がアクティブな可能性があります。入力電源 (IN ピン) およびバイアス電源 (BIAS ピン) には内部設定された UVLO があり、入力電圧が最小しきい値に達すると自動的に LDO を無効化します。高精度の EN 機能 (EN ピン) は、ユーザーがプログラム可能な UVLO としても機能します。このプログラマビリティには以下が含まれます。

1. 内部入力電源電圧 UVLO 回路により、入力電圧が十分高くないときはレギュレータがオンになるのを防止します。詳細については、「[電気的特性](#)」表を参照してください。

2. 内部バイアス電源の UVLO 回路により、バイアス電圧が十分に高くないときにレギュレータがオンになることが防止されます。詳細については、「[電気的特性](#)」表を参照してください。

3. 高精度のイネーブル回路により、他の電源からの抵抗分圧を用いて複数の電源のシーケンス制御を簡単に行うことができます。このイネーブル回路を使用することで、EN ピンに抵抗分圧を設け、デバイスが有効になる外部 UVLO 電圧を設定できます。詳細については、「[高精度イネーブル \(外部 UVLO\)](#)」セクションを参照してください。

### 6.3.5 チャージポンプのイネーブルと BIAS レール

本デバイスは、スイッチングノイズを一切許容できないシステム向けに、内部チャージポンプを無効化することが可能です。

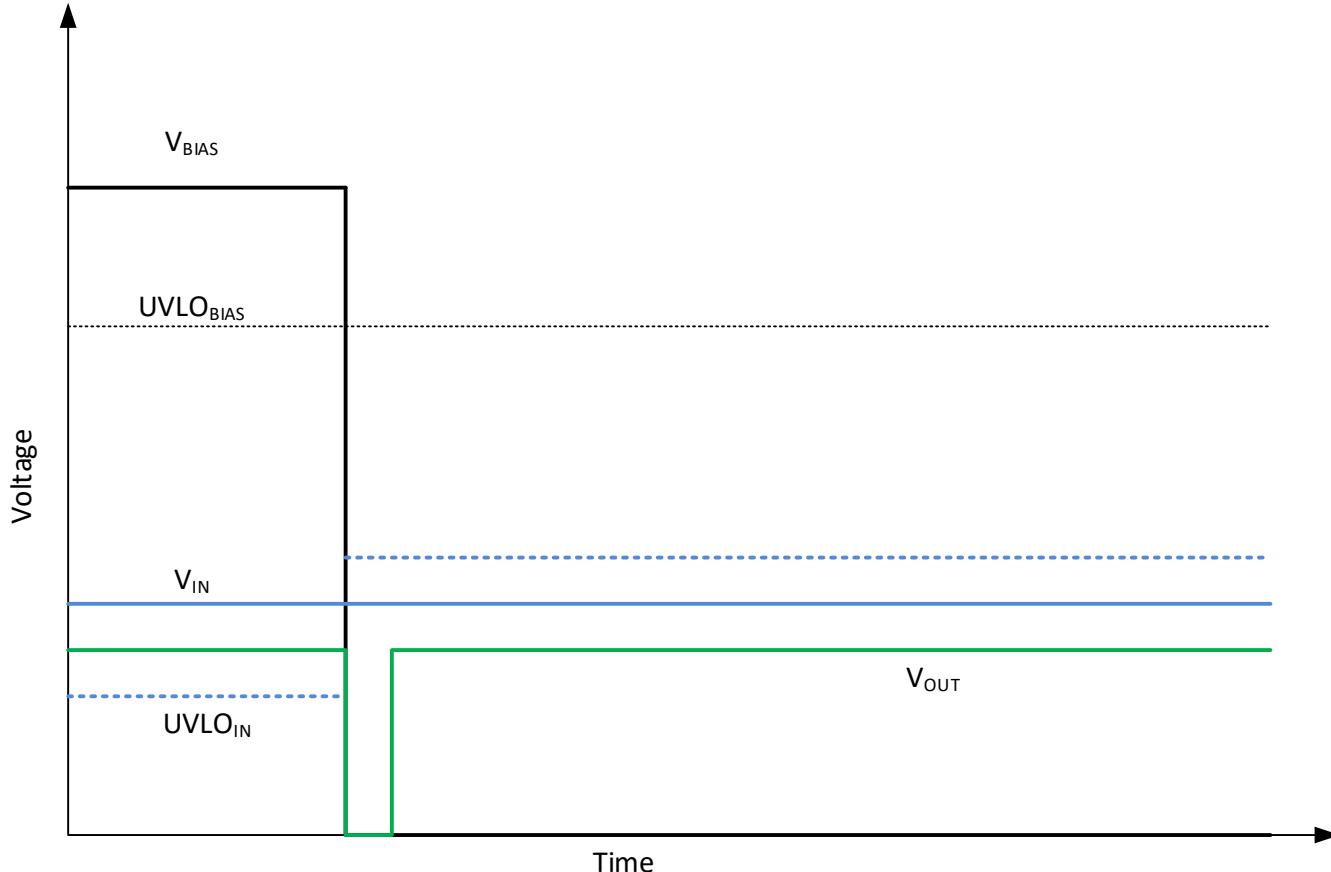

$V_{IN}$  が 1.1V 未満の場合、このレールは内部回路に必要な電流を供給するため、BIAS レールが必要です。チャージポンプは、有効または無効のいずれかの状態になります。チャージポンプを無効にする場合は、OUT から BIAS への十分な動作ヘッドルームを確保する必要があります。詳細については、「[低電圧誤動作防止 \(UVLO\) 動作](#)」セクションを参照してください。

$V_{IN}$  が 1.1V 以上の場合、CP\_EN ピンの接続によって内部回路への電力供給方法が決まります。CP\_EN が GND に接続されている場合 (CP が無効)、内部回路は BIAS レールから電力供給されます。詳細については、「[低電圧誤動作防止 \(UVLO\) 動作](#)」セクションを参照してください。CP\_EN が電源に接続されている場合 (CP が有効)、内部回路に必要な電流はすべて IN ピンから供給されます。このため、BIAS ピンはオープンのままになります。

### 6.3.6 パワーグッドピン (PG ピン)

PG ピンは、LDO が電力供給可能な状態であることを示す出力ピンです。このピンは、オープンドレイン構成で実装されています。起動フェーズ中、高速ソフトスタートが進行している間は、PG の電圧スレッショルドは REF 電圧によって設定されます。高速ソフトスタートが完了し、REF と NR/SS 間のスイッチが閉じられると、PG のスレッショルドは NR/SS 電圧によって設定されます。

[機能ブロック図](#) に示すように、SNS ピンの電圧を内部基準電圧と比較することで PG ピンが実装されています。このため、PG ピンは出力電圧状態を反映した電圧インジケータと見なされます。

PG ピンの実装については、[パワーグッド機能](#) セクションを参照してください。

### 6.3.7 アクティブ放電

内部ノードを迅速に放電するために、本デバイスには 2 つの内部プルダウン MOSFET (金属酸化膜半導体電界効果トランジスタ) が組み込まれています。1 番目のプルダウン MOSFET は、デバイスがディセーブルされて、出力コンデンサをアクティブに放電する際に、OUT からグランドに抵抗 ( $R_{DIS}$ ) を接続します。2 番目のプルダウン MOSFET は、デバイスがディスエーブルになると NR/SS ( $R_{NR/SS\_DIS}$ ) とグランドとの間に抵抗を接続し、NR/SS コンデンサを放電します。両方のプルダウン MOSFET は、以下のいずれかのイベントによってアクティブ化されます。

- EN ピンの電圧を  $V_{EN(LOW)}$  スレッショルドより低くする

- IN ピンの電圧が低電圧誤動作防止スレッショルド電圧  $V_{UVLO(IN)}$  を下回っている

- BIAS ピンの電圧が低電圧誤動作防止スレッショルド電圧  $V_{UVLO(BIAS)}$  を下回っている

**注**

低入力、低出力 (LILO) 動作時 ( $< 1.1V_{IN}$ ) に BIAS でブラウンアウトが発生すると、 $C_{NR/SS}$  の放電が不完全になります。適切なシステム シャットダウン手順を行うために、NR/SS ピンおよび OUT ピンの時定数を考慮します。

### 6.3.8 サーマル シャットダウン保護機能 ( $T_{SD}$ )

デバイスには、パス トランジスタの接合部温度 ( $T_J$ ) が  $T_{SD(shutdown)}$  (標準値) まで上昇したときにデバイスを無効化するサーマル シャットダウン保護回路が内蔵されています。サーマル シャットダウン ヒステリシスにより、温度が  $T_{SD(RESET)}$  (標準値) まで低下するとデバイスがリセットされます (オンになります)。

半導体ダイの熱時定数はかなり短いです。このため、サーマル シャットダウンに達した時点で、消費電力が低下するまで、デバイスはオンとオフを繰り返します。スタートアップ時の消費電力は、デバイス両端での大きな  $V_{IN} - V_{OUT}$  電圧降下が発生するか、大きな突入電流で大容量の出力コンデンサを充電することにより高くなります。条件によっては、サーマル シャットダウン保護機能により、起動が完了する前にデバイスが無効化されることがあります。

信頼性の高い動作を実現するには、接合部温度を [推奨動作条件](#) 表に記載された最大値に制限します。この最大温度を超えて動作すると、デバイスは動作仕様を超えます。本デバイスの内蔵保護回路は熱過負荷状態から保護するように設計されていますが、この回路は適切なヒートシンクの代わりとなるものではありません。デバイスをサーマル シャットダウン状態、または推奨される最大接合部温度を上回る状態で使用し続けると、長期的な信頼性が低下します。

## 6.4 デバイスの機能モード

### 6.4.1 通常動作

デバイスは、以下の条件が満たされたとき、公称出力電圧へのレギュレートを行います。

- 入力電圧が、公称出力電圧とドロップアウト電圧の合計 ( $V_{OUT(nom)} + V_{DO}$ ) よりも大きくなります。

- バイアス電圧は、公称出力電圧と OUT から BIAS 降下電圧の合計よりも大きくなります。この状況は、チャージ ポンプがディセーブルになった場合、または入力電圧が 1.1V を下回った場合に発生します。OUT から BIAS へのドロップアウト電圧は、 $V_{OUT(nom)} + V_{DO(BIAS)}$  として定義されます。

- 出力電流が、電流制限より小さい ( $I_{OUT} < I_{CL}$ )

- デバイスの接合部温度がサーマルシャットダウン温度未満 ( $T_J < T_{SD(shutdown)}$ ) です。

- EN ピンの電圧は以前に  $V_{IH(EN)}$  スレッショルド電圧を上回っており、イネーブル立ち下がりスレッショルドを下回るまでには低下していません。

表 6-1 は、すべての有効な動作モードをまとめ、内部バイアス電流を供給しているレールを示します。

**表 6-1. デバイスの機能モードの比較**

| 動作モード       | パラメータ                                                              |                                |                                  |                          |                    |                             |

|-------------|--------------------------------------------------------------------|--------------------------------|----------------------------------|--------------------------|--------------------|-----------------------------|

|             | $V_{IN}$                                                           | $V_{BIAS}$                     | $V_{CP\_EN}$                     | $V_{EN}$                 | $I_{OUT}$          | $T_J$                       |

| 通常モード       | $V_{IN} \geq V_{OUT(nom)} + V_{DO}$ および $V_{IN} \geq V_{UVLO(IN)}$ | $V_{BIAS} \geq V_{OUT} + 3.2V$ | $V_{CP\_EN} \geq V_{IH(CP\_EN)}$ | $V_{EN} \geq V_{IH(EN)}$ | $I_{OUT} < I_{CL}$ | シャットダウン用: $T_J < T_{SD}$    |

| ドロップアウト モード | $V_{IN(min)} < V_{IN} < V_{OUT(nom)} + V_{DO}$                     | $V_{BIAS} = V_{OUT} + 3.2V$    | $V_{CP\_EN} > V_{IH(CP\_EN)}$    | $V_{EN} > V_{IH(EN)}$    | $I_{OUT} < I_{CL}$ | シャットダウン用: $T_J < T_{SD}$    |

| 無効 モード      | $V_{IN} < V_{UVLO(IN)}$                                            | $V_{BIAS} < V_{BIAS(UVLO)}$    | $V_{CP\_EN} < V_{IL(CP\_EN)}$    | $V_{EN} < V_{IL(EN)}$    | -                  | シャットダウン用: $T_J \geq T_{SD}$ |

#### 6.4.2 ドロップアウト動作

入力電圧が、公称出力電圧と規定ドロップアウト電圧の和よりも低い場合、デバイスはドロップアウト モードで動作します。このモードでは、出力電圧は入力電圧に追従します。このモードでは、デバイスの過渡性能が大きく低下します。このモード中、パストランジスタは完全にオンに駆動されます。ドロップアウト中にライン過渡または負荷過渡事象が生じると、大きな出力電圧の偏差が発生する可能性があります。

##### 注

チャージポンプが無効の場合は、REF 電圧より高い最小の UVLO (BIAS) 電圧を維持します。3V の BIAS レール以上の電圧が必要です。ただし、この要件が必要となるのは、チャージポンプが有効で、かつ IN 電圧が 1.1V 未満の場合のみです。チャージポンプが有効で、IN 電圧が 1.1V 以上であれば、BIAS レールは不要です。

追加情報については、「[低電圧誤動作防止 \(UVLO\) 動作](#)」セクションを参照してください。

#### 6.4.3 ディセーブル

EN ピンの電圧を強制的に  $V_{IH(EN)}$  スレッショルド未満にすることで、デバイス出力をシャットダウンします（[電気的特性](#) 表を参照）。無効化されると、パストランジスタはオフになり、内部回路はシャットダウンされ、NR/SS ピンおよび OUT ピンの電圧はともに積極的にグランドへ放電されます。これらのピンの電圧は、IN ピンの電圧がダイオードの順方向電圧以上である場合、内部の放電回路によってグランドへ放電されます。

#### 6.4.4 電流制限動作

出力電流が最小電流制限 ( $I_{LIM(Min)}$ ) 以上の場合、デバイスは電流制限モードで動作します。電流制限はフォールドバック実装です。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

アプリケーションで LDO を正しく実装するには、アプリケーションの要件に依存します。このセクションでは、デバイスの主要な機能と、信頼性の高い設計を実現するための最適な実装方法について説明します。

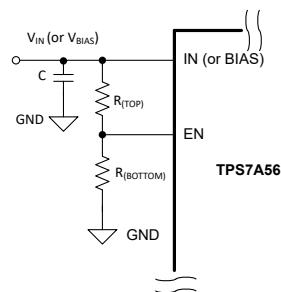

#### 7.1.1 高精度イネーブル(外部 UVLO)

高精度イネーブル回路 (EN ピン) は、デバイスのオン/オフを切り替えます。図 7-1 に示すように、この回路を使用して外部の低電圧誤動作防止 (UVLO) 電圧を設定します。この回路は、IN (またはチャージ ポンプがディセーブルされているときは BIAS)、EN、GND の間に分圧抵抗を使用してデバイスのオン / オフを切り替えます。

図 7-1. 高精度 EN を外部 UVLO として使用

入力電源電圧が十分に高くない場合にデバイスが起動しないようにするために、この外部 UVLO (低電圧ロックアウト) ソリューションを使用します。外部 UVLO により、デバイスはドロップアウト動作状態になります。このソリューションでは、他の電源からの抵抗デバイダを使用して複数の電源を簡単にシーケンシングすることができます。このピンには内部プルダウン抵抗がないため、EN ピンがフローティングになることはありません。この状態は、抵抗分圧回路を使用してデバイスを有効または無効にすることによる、もう一つの利点をもたらします。ただし、このピンの絶対最大定格を満たす必要がある場合は、EN ピンとグラウンドの間にゼナー ダイオードを配置します。

式 1 と式 2 を使用して正しい抵抗値を求めます。

$$V_{ON} = V_{OFF} \times [(V_{IH(EN)} + V_{HYS(EN)}) / V_{EN}] \quad (1)$$

$$R_{(TOP)} = R_{(BOTTOM)} \times (V_{ON} / V_{IH(EN)} - 1) \quad (2)$$

ここで

- $V_{OFF}$  は、レギュレータがオフになる入力またはバイアス電圧です

- $V_{ON}$  は、レギュレータがオンになる入力またはバイアス電圧です

### 注

EN ピンの入力電流  $I_{EN}$  では、影響は無視されます。

### 7.1.2 低電圧誤動作防止 (UVLO) 動作

各種動作モードの UVLO スレッショルドを、表 7-1 に示します。

表 7-1. 各種動作モードでの相対スレッショルド

| UVLO スレッショルド                   | チャージポンプがオフのときの<br>UVLO スレッショルド (標準値) | チャージポンプがオンの場合と<br>BIAS なしの場合の UVLO スレッショルド (標準値) | チャージポンプ オンおよび BIAS<br>での UVLO スレッショルド (標準値) |

|--------------------------------|--------------------------------------|--------------------------------------------------|---------------------------------------------|

| V <sub>UVLO/IN</sub> の立ち上がり    | 0.67V                                | 1.07V                                            | 0.67V                                       |

| V <sub>UVLO(BIAS)</sub> の立ち上がり | V <sub>REF</sub> + 2.1V              | 該当なし                                             | 最大 (V <sub>REF</sub> + 2.1V, 2.8V)          |

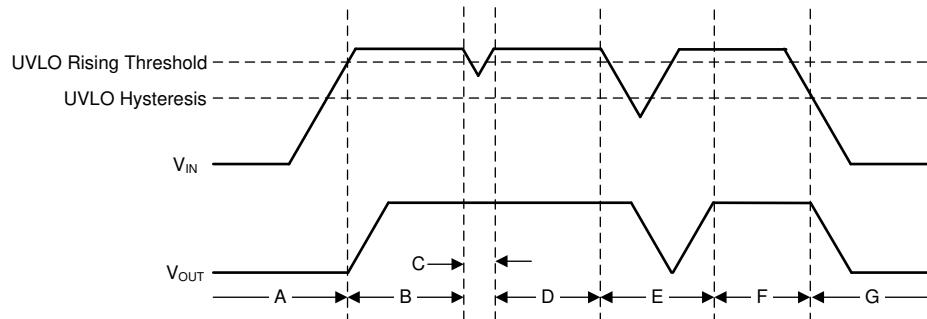

#### 7.1.2.1 UVLO での IN ピン

IN ピンの UVLO (UVLO (IN)) 回路により、入力電源が最小動作電圧範囲に達する前に、デバイスが確実にディセーブルに維持されます。また、この回路により、入力電源が低下した場合にデバイスが確実にシャットダウンされます。

UVLO (IN) 回路が完全にアサートされるまでの最小応答時間は数マイクロ秒です。この間、電圧が約 0.67V を下回るような下降過渡が発生すると、入力電源の UVLO (IN) が短時間アサートされます。しかし、UVLO (IN) 回路には、デバイス内部の回路を完全に放電させるだけの蓄積エネルギーがありません。したがって、OUT コンデンサと NR/SS コンデンサは潜在的に放電されます。

注

ライン下降過渡現象の影響により、オーバーシュート防止回路がトリガされます。この効果は、[高精度イネーブル \(外部 UVLO\)](#) セクションで提案するソリューションを使用することで簡単に軽減できます。

#### 7.1.2.2 BIAS UVLO

BIAS ピンの UVLO (UVLO (BIAS)) 回路により、入力電源が最小動作電圧範囲に達する前に、デバイスが確実にディセーブルに維持されます。この回路により、入力電源が低下した場合にデバイスが確実にシャットダウンされます。