TPS7A53A-Q1 JAJSPA7A - NOVEMBER 2022 - REVISED DECEMBER 2022

# TPS7A53A-Q1 車載グレード、3A、高精度、低ノイズ、LDO 電圧レギュレー

# 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:-40°C ≤ T<sub>Δ</sub> ≤ +125°C

- HBM ESD 分類レベル 2

- CDM ESD 分類レベル C4A

- 拡張接合部温度 (T」) 範囲:

- -40°C~+150°C

- 入力電圧範囲:

- IN:  $(V_{REF} + V_{DO}) \sim 6.0V$

- BIAS:  $(V_{OUT} + V_{DO(BIAS)}) \sim 6.0V$

- 低いドロップアウト: 130 mV / 3A

- 出力電圧ノイズ:5.6µV<sub>RMS</sub>

- 精度:ライン、負荷、温度の範囲全体にわたって

- 1.3% (最大)

- 電源リップル除去:

- 500kHz 時 40dB

- 調整可能なソフトスタート突入電流制御

- オープン・ドレインのパワー・グッド (PG) 出力

- パッケージ:

- ウェッタブル・フランク付きで高 CTE (12ppm/℃) の成形コンパウンドを使用した 4mm × 4mm、20 ピンの WQFN

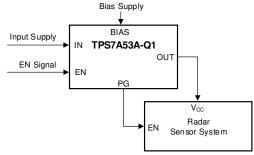

# 2 アプリケーション

- テレマティクス制御ユニット

- インフォテインメントおよびクラスタ

- 画像処理レーダー

RF コンポーネントの電源

## 3 概要

TPS7A53A-Q1 は低ノイズ (5.6 $\mu$ V<sub>RMS</sub>)、低ドロップアウト のリニア・レギュレータ (LDO) で、3A を供給でき、ドロップ アウトはわずか 130mV です。

低ノイズ (5.6µV<sub>RMS</sub>)、高 PSRR 、大出力電流の能力の 組み合わせにより、TPS7A53A-Q1 はレーダーの電源や インフォテインメント・アプリケーションなどに使用される、 電力ノイズに敏感な部品への電源供給に理想的です。こ のデバイスは高性能で、電源によって生成される位相ノイ ズとクロック・ジッタを制限するため、RFアンプ、レーダー・ センサ、チップセットの電源として有用です。このデバイス の性能の高さは、特に信号チェーン部品で有益です。 TPS7A53A-Q1 にはウェッタブル・フランク・オプションが あり、光学検査を容易に行えます。

ASIC (Application-Specific Integrated Circuit), FPGA (Field-Programmable Gate Array), DSP (Digital Signal Processor) などのデジタル負荷で低入力電圧、低出力 電圧 (LILO) 動作を必要とする場合、TPS7A53A-Q1 の 非常に優れた精度(負荷および温度の全範囲で1.3%)、 リモート・センシング、優れた過渡性能、ソフトスタート機能 により、最適なシステム性能が実現されます。

多用途な TPS7A53A-Q1 デバイスは、要求の厳しい多く のアプリケーションの部品として最適な選択肢です。

# パッケージ情報 (1)

| 部品番号        | パッケージ                              | 本体サイズ (公称)      |

|-------------|------------------------------------|-----------------|

| TPS7A53A-Q1 | ウェッタブル・フランク<br>付き<br>RTJ (WQFN、20) | 4.00mm × 4.00mm |

利用可能なパッケージについては、データシートの末尾にあるパ ッケージ・オプションについての付録を参照してください。

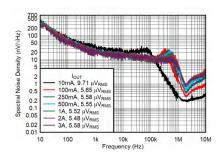

スペクトル・ノイズ密度と周波数および出力電流との

# **Table of Contents**

| 1 特長                                    | 1 | 7.4 Device Functional Modes                         | 17 |

|-----------------------------------------|---|-----------------------------------------------------|----|

| 2 アプリケーション                              |   | 8 Application and Implementation                    | 18 |

| - , , , , , , , , , , , , , , , , , , , |   | 8.1 Application Information                         | 18 |

| 4 Revision History                      |   | 8.2 Typical Application                             | 22 |

| 5 Pin Configuration and Functions       |   | 8.3 Power Supply Recommendations                    | 23 |

| 6 Specifications                        |   | 8.4 Layout                                          | 23 |

| 6.1 Absolute Maximum Ratings            |   | 9 Device and Documentation Support                  |    |

| 6.2 ESD Ratings                         |   | 9.1 Documentation Support                           | 25 |

| 6.3 Recommended Operating Conditions    |   | 9.2 Receiving Notification of Documentation Updates | 25 |

| 6.4 Thermal Information                 |   | 9.3 サポート・リソース                                       | 25 |

| 6.5 Electrical Characteristics          |   | 9.4 Trademarks                                      | 25 |

| 6.6 Typical Characteristics             |   | 9.5 Electrostatic Discharge Caution                 | 25 |

| 7 Detailed Description                  |   | 9.6 Glossary                                        |    |

| 7.1 Overview                            |   | 10 Mechanical, Packaging, and Orderable             |    |

| 7.2 Functional Block Diagram            |   | Information                                         | 25 |

| 7.3 Feature Description                 |   | 10.1 Mechanical Data                                | 26 |

|                                         |   |                                                     |    |

# **4 Revision History**

| CI | hanges from Revision * (November 2022) to Revision A (December 2022) | Pag |

|----|----------------------------------------------------------------------|-----|

| •  | ドキュメントのステータスを「事前情報」から「量産データ」に変更                                      |     |

Product Folder Links: TPS7A53A-Q1

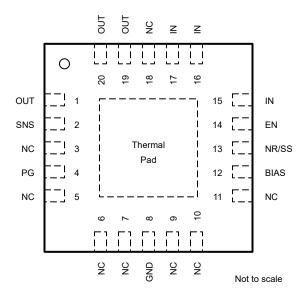

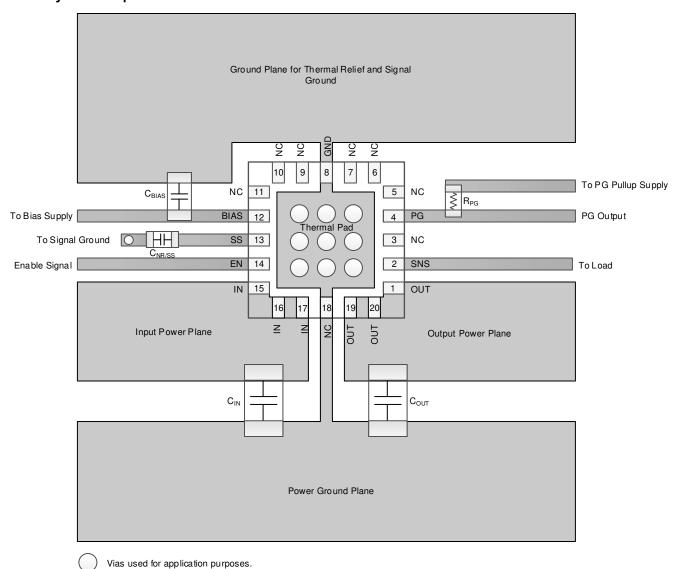

# **5 Pin Configuration and Functions**

図 5-1. RTJ Package (Fixed), 4-mm × 4-mm, 20-Pin WQFN (Top View)

表 5-1. Pin Functions

|           | PIN                            |      |                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | RTJ<br>(Fixed)                 | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

| BIAS      | 12                             | I    | BIAS supply voltage. This pin enables the use of low-input voltage, low-output (LILO) voltage conditions (that is, $V_{IN}$ = 1.3 V, $V_{OUT}$ = 1 V) to reduce power dissipation across the die. Using a BIAS voltage improves dc and ac performance for $V_{IN} \le 2.2$ V. A 0.1- $\mu$ F capacitor or larger must be connected between this pin and ground. |

| EN        | 14                             | I    | Enable pin. Driving this pin to logic high enables the device; driving this pin to logic low disables the device. If enable functionality is not required, this pin must be connected to IN or BIAS.                                                                                                                                                            |

| FB        | _                              | I    | Feedback pin connected to the error amplifier. Although not required, a 10-nF, feed-forward capacitor from FB to OUT (as close to the device as possible) maximizes ac performance. Using a feed-forward capacitor can disrupt PG (power-good) functionality.                                                                                                   |

| GND       | 8                              | _    | Ground pin. This pin must be connected to ground and the thermal pad with a low-impedance connection.                                                                                                                                                                                                                                                           |

| IN        | 15-17                          | I    | Input supply voltage pin. A 1- $\mu$ F or larger ceramic capacitor (0.5 $\mu$ F or greater of capacitance) from IN to ground reduces the impedance of the input supply. Place the input capacitor as close to the input as possible.                                                                                                                            |

| NC        | 3, 5, 6, 7,<br>9, 10,11,<br>18 | _    | No internal connection.                                                                                                                                                                                                                                                                                                                                         |

| SS        | 13                             | _    | Noise-reduction and soft-start pin. Connecting an external capacitor between this pin and ground enables the soft-start function.                                                                                                                                                                                                                               |

| OUT       | 1, 19, 20                      | 0    | Regulated output pin. A 10-µF or larger ceramic capacitor (5 µF or greater of capacitance) from OUT to ground is required for stability and must be placed as close to the output as possible. Minimize the impedance from the OUT pin to the load.                                                                                                             |

| PG        | 4                              | 0    | Active-high, power-good pin. An open-drain output indicates when the output voltage reaches $V_{\rm IT(PG)}$ of the target. The use of a feed-forward capacitor can disrupt PG (power-good) functionality.                                                                                                                                                      |

| SNS       | 2                              | I    | Sense pin connected to the error amplifier.                                                                                                                                                                                                                                                                                                                     |

| Thermal p | ad                             |      | Connect the thermal pad to a large-area ground plane. The thermal pad is internally connected to GND.                                                                                                                                                                                                                                                           |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)(1)

|             |                               | MIN        | MAX                   | UNIT |

|-------------|-------------------------------|------------|-----------------------|------|

|             | IN, BIAS, PG, EN              | -0.3       | 6.5                   | V    |

| Voltage     | OUT                           | -0.3       | V <sub>IN</sub> + 0.3 | V    |

|             | SS, FB                        | -0.3       | 6.5                   | V    |

| Current     | OUT                           | Internally | limited               | mA   |

| Current     | PG (sink current into device) | 0          | 1.5                   |      |

| Tomporatura | Junction, T <sub>J</sub>      | -40        | 150                   | °C   |

| Temperature | Storage, T <sub>stg</sub>     | -55        | 150                   | C    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                                            |  |                                                            | VALUE | UNIT |

|--------------------------------------------|--|------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge |  | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup>    | ±2000 | V    |

|                                            |  | Charged device model (CDM), per AEC specification Q100-011 | ±500  | ·    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                | MIN                                                         | NOM | MAX                               | UNIT |

|-------------------|--------------------------------|-------------------------------------------------------------|-----|-----------------------------------|------|

| V <sub>IN</sub>   | Input supply voltage           | V <sub>OUT</sub> + V <sub>DO</sub> (IN)                     |     | 6.0                               | V    |

| V <sub>EN</sub>   | Enable supply voltage          |                                                             | -   | 6.0                               | V    |

| V <sub>BIAS</sub> | BIAS supply voltage            | V <sub>OUT</sub> + V <sub>DO</sub><br>(BIAS) <sup>(1)</sup> |     | 6.0                               | V    |

| V <sub>OUT</sub>  | Output voltage                 | 0.8                                                         | ,   | V <sub>IN</sub> - V <sub>DO</sub> | V    |

| I <sub>OUT</sub>  | Output current                 | 0                                                           |     | 3                                 | Α    |

| C <sub>OUT</sub>  | Output capacitor (3)           | 10                                                          |     |                                   | μF   |

| C <sub>IN</sub>   | Input capacitor (1) (2)        | 1                                                           |     |                                   | μF   |

| C <sub>BIAS</sub> | Bias capacitor                 | 0.1                                                         | 1   |                                   | μF   |

| C <sub>SS</sub>   | Soft-start capacitor           | 0                                                           | 10  | 100                               | nF   |

| TJ                | Operating junction temperature | -40                                                         |     | 150                               | °C   |

- (1)  $V_{BIAS}$  has a minimum voltage of 1.7 V or  $V_{OUT} + V_{DO}$  ( $V_{BIAS}$ ), whichever is higher.

- (2) If  $V_{IN}$  and  $V_{BIAS}$  are connected to the same supply, the recommended minimum capacitor for the supply is 4.7  $\mu$ F.

- (3) A maximum capacitor derating of 25% is considered for minimum capacitance.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## **6.4 Thermal Information**

|                       |                                              | TPS7A53A-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTJ (VQFN)  | UNIT |

|                       |                                              | 20 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 42.5        | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 35.2        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 18.8        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.7         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.7        | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.9         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC package thermal metrics application report.

### 6.5 Electrical Characteristics

at  $V_{EN}$  = 1.1 V,  $V_{IN}$  =  $V_{OUT}$  + 0.3 V,  $C_{BIAS}$  = 0.1  $\mu$ F,  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu$ F,  $C_{NR}$  = 1 nF,  $I_{OUT}$  = 50 mA,  $V_{BIAS}$  = 5.0 V <sup>(5)</sup>, and  $T_{J}$  =  $-40^{\circ}$ C to 150°C (unless otherwise noted); typical values are at  $T_{J}$  = 25°C

| F                                         | PARAMETER                                        | TEST CONDITIONS                                                                                                                  | MIN  | TYP   | MAX | UNIT  |

|-------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|-------|

| V <sub>REF</sub>                          | Internal reference                               | Fixed 1 V only                                                                                                                   |      | 1.0   |     | V     |

| V <sub>NR/SS</sub>                        | NR/SS pin voltage                                | Fixed 1 V only <sup>(4)</sup>                                                                                                    |      | 1     |     | V     |

| V <sub>BIAS(UVLO)</sub>                   | Rising bias supply UVLO                          |                                                                                                                                  |      | 1.4   | 1.8 | V     |

| V <sub>BIAS(UVLO),HY</sub>                | Bias supply UVLO<br>hysteresis                   |                                                                                                                                  | 25   | 50    | 75  | mV    |

| Δν <sub>ουτ (Δνίν)</sub>                  | Accuracy (1) (6)                                 | $V_{OUT}$ + 2.5 V ≤ $V_{BIAS}$ ≤ 5.5 V, 50 mA ≤ $I_{OUT}$ ≤ 3 A, -40°C ≤ $I_{J}$ ≤ 125°C                                         | -1   | ±0.5  | 1   | %     |

| (=:)                                      | ·                                                | $V_{OUT} + 2.5 \text{ V} \le V_{BIAS} \le 5.5 \text{ V}, 50 \text{ mA} \le I_{OUT} \le 3 \text{ A}$                              | -1.3 | ±0.5  | 1.3 |       |

| ΔV <sub>OUT (ΔΙΟUΤ)</sub>                 | Line regulation                                  | $V_{OUT(nom)} + 0.3 \text{ V} \le V_{IN} \le 6.0 \text{ V}$                                                                      |      | 0.025 |     | %/V   |

| V <sub>OUT</sub>                          | Load regulation                                  | 50 mA ≤ I <sub>OUT</sub> ≤ 3 A                                                                                                   |      | 0.025 |     | %/A   |

| $V_{DO(IN)}$                              | V <sub>IN</sub> dropout voltage <sup>(2)</sup>   | $I_{OUT} = 3 \text{ A}, V_{BIAS} - V_{OUT(nom)} \ge 3.25 \text{ V}^{(3)}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ |      | 130   | 275 | mV    |

| - ( )                                     |                                                  | $I_{OUT} = 3 \text{ A}, V_{BIAS} - V_{OUT(nom)} \ge 3.25 \text{ V}^{(3)}$                                                        |      | 130   | 285 |       |

| V <sub>DO(BIAS)</sub>                     | V <sub>BIAS</sub> dropout voltage <sup>(2)</sup> | I <sub>OUT</sub> = 3 A, V <sub>IN</sub> = V <sub>BIAS</sub>                                                                      |      | 1.4   | 1.9 | V     |

| I <sub>CL</sub> (Fixed V <sub>OUT</sub> ) | Fixed V <sub>OUT</sub> , output current limit    | V <sub>OUT</sub> = 80% × V <sub>OUT(nom)</sub>                                                                                   | 4.0  | 4.7   | 5.5 | Α     |

| I <sub>BIAS</sub>                         | BIAS pin current                                 | I <sub>OUT</sub> = 50 mA                                                                                                         |      | 0.7   | 1.2 | mA    |

| I <sub>SHDN</sub>                         | Shutdown supply current (I <sub>GND</sub> )      | V <sub>EN</sub> ≤ 0.4 V, V <sub>IN</sub> = 1.25 V, V <sub>BIAS</sub> = 6 V                                                       |      | 1     | 25  | μΑ    |

| I <sub>FB/SNS</sub>                       | Feedback/sense pin current                       |                                                                                                                                  | -0.3 | 0.12  | 0.3 | μΑ    |

|                                           | Power-supply rejection                           | 1 kHz, I <sub>OUT</sub> = 2 A, V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                |      | 70    |     | dB    |

| PSRR                                      | (V <sub>IN</sub> to V <sub>OUT</sub> )           | 3 MHz, I <sub>OUT</sub> = 2 A, V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                |      | 27    |     | dB    |

| PORK                                      | Power-supply rejection                           | 1 kHz, I <sub>OUT</sub> = 2 A, V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                |      | 65    |     | dB    |

|                                           | (V <sub>BIAS</sub> to V <sub>OUT</sub> )         | 3 MHz, I <sub>OUT</sub> = 2 A, V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                |      | 28    |     | dB    |

| V <sub>n</sub>                            | Output noise voltage                             | BW = 10 Hz to 100 kHz, I <sub>OUT</sub> = 2 A, C <sub>SS</sub> = 1 nF                                                            |      | 7     |     | μVrms |

| t <sub>STR</sub>                          | Minimum startup time                             | C <sub>SS</sub> = 10 nF, V <sub>OUT</sub> = 1.0 V                                                                                |      | 2     |     | ms    |

| I <sub>SS</sub>                           | Soft-start charging current                      | t <sub>SS</sub> = 4.8 x V <sub>OUT(NOM)</sub> / 0.8 V, V <sub>OUT</sub> = 1.0 V                                                  |      | 6     |     | μΑ    |

| V <sub>EN(hi)</sub>                       | Enable input high level                          |                                                                                                                                  | 1.1  |       | 5.5 | V     |

| V <sub>EN(lo)</sub>                       | Enable input low level                           |                                                                                                                                  | 0    |       | 0.4 | V     |

| V <sub>EN(hys)</sub>                      | Enable pin hysteresis                            |                                                                                                                                  |      | 70    |     | mV    |

| V <sub>EN(dg)</sub>                       | Enable pin deglitch time                         |                                                                                                                                  |      | 15    |     | μs    |

# **6.5 Electrical Characteristics (continued)**

at  $V_{EN}$  = 1.1 V,  $V_{IN}$  =  $V_{OUT}$  + 0.3 V,  $C_{BIAS}$  = 0.1  $\mu$ F,  $C_{IN}$  =  $C_{OUT}$  = 10  $\mu$ F,  $C_{NR}$  = 1 nF,  $I_{OUT}$  = 50 mA,  $V_{BIAS}$  = 5.0 V <sup>(5)</sup>, and  $T_{J}$  =  $-40^{\circ}$ C to 150°C (unless otherwise noted); typical values are at  $T_{J}$  = 25°C

|                       | PARAMETER                | TEST CONDITIONS                                                      | MIN | TYP   | MAX  | UNIT              |  |

|-----------------------|--------------------------|----------------------------------------------------------------------|-----|-------|------|-------------------|--|

| I <sub>EN</sub>       | Enable pin current       | V <sub>EN</sub> = 5 V                                                |     | 0.1   | 0.25 | μA                |  |

| V <sub>IT</sub>       | PG trip threshold        | V <sub>OUT</sub> decreasing                                          | 85  | 90    | 94   | %V <sub>OUT</sub> |  |

| V <sub>HYS</sub>      | PG trip hysteresis       |                                                                      |     | 2.5   |      | %V <sub>OUT</sub> |  |

| V <sub>PG(lo)</sub>   | PG output low voltage    | I <sub>PG</sub> = 1 mA (sinking), V <sub>OUT</sub> < V <sub>IT</sub> |     |       | 0.3  | V                 |  |

| I <sub>PG(lkg)</sub>  | PG leakage current       | V <sub>PG</sub> = 5.25 V, V <sub>OUT</sub> > V <sub>IT</sub>         |     | 0.001 | 0.05 | μA                |  |

| R <sub>PULLDOWN</sub> | Output Pulldown resistor | V <sub>BIAS</sub> = 5 V, V <sub>EN</sub> = 0 V                       |     | 0.5   |      | kΩ                |  |

| т                     | Thermal shutdown         | Shutdown, temperature increasing                                     |     | 165   |      | - °C              |  |

| T <sub>SD</sub>       | temperature              | Reset, temperature decreasing                                        |     | 140   |      | C                 |  |

- (1) Adjustable devices tested at 0.8 V; resistor tolerance is not taken into account.

- Dropout is defined as the voltage from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  when  $V_{\text{OUT}}$  is 3% below nominal.

- (3) 3.25 V is a test condition of this device and can be adjusted by referring to Figure 6.

- For fixed voltage, NR/SS voltage is equal to output voltage.

- $V_{BIAS} = V_{DO\_MAX(BIAS)} + V_{OUT}$  for  $V_{OUT} \ge 3.1$ V. The device is not tested under conditions where  $V_{IN} > V_{OUT} + 0.85$  V and  $I_{OUT} = 3$  A, because the power dissipation is higher than the maximum rating of the package. Also, this accuracy specification does not apply on any application condition that exceeds the power dissipation limit of the package under test.

Product Folder Links: TPS7A53A-Q1

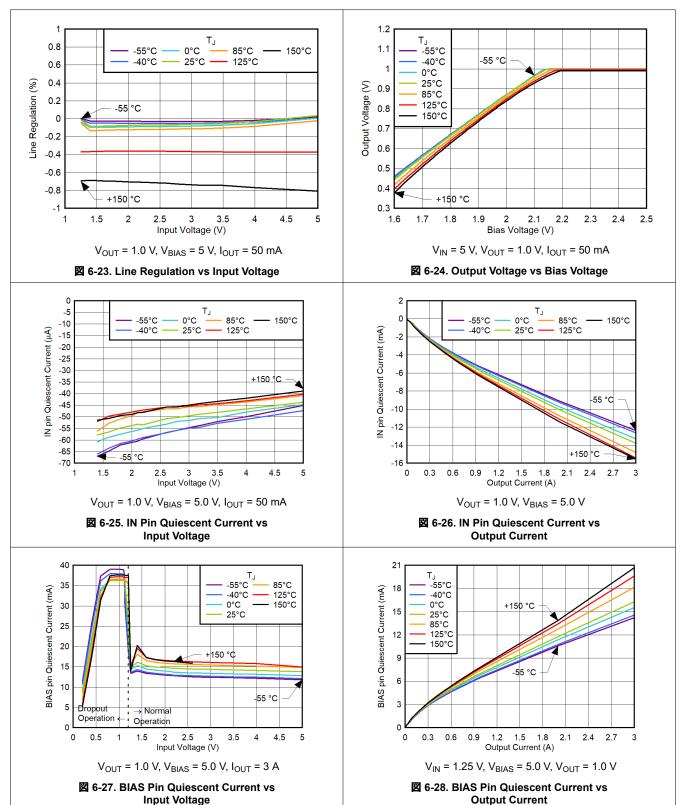

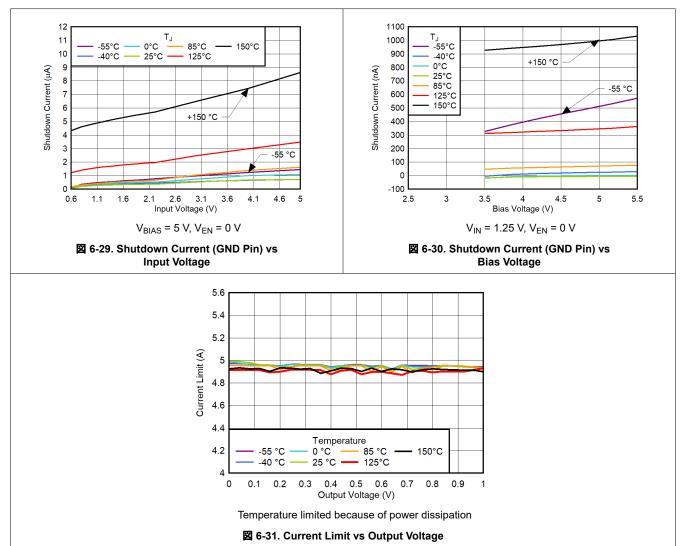

# **6.6 Typical Characteristics**

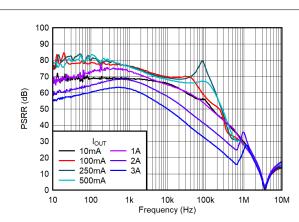

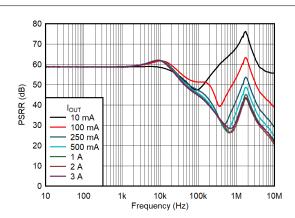

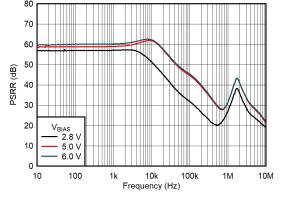

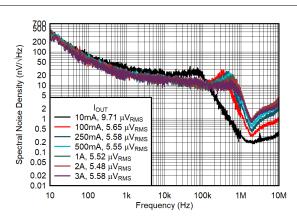

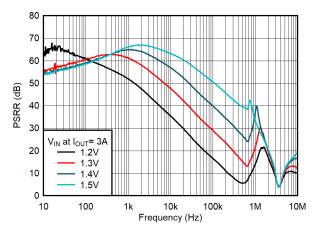

at  $T_A$  = 25°C,  $V_{IN}$  = 1.4 V or  $V_{IN}$  =  $V_{OUT(NOM)}$  + 0.3 V (whichever is greater),  $V_{BIAS}$  = open,  $V_{OUT(NOM)}$  = 0.8 V,  $V_{EN}$  = 1.1 V,  $C_{OUT}$  = 47  $\mu$ F,  $C_{NR/SS}$  = 0 nF,  $C_{FF}$  = 0 nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

70

$V_{IN}$  = 1.3 V,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{OUT}$  = 10  $\mu F,$  $C_{BIAS} = 0.1 \mu F, C_{SS} = 10 nF$

# 図 6-1. PSRR vs Frequency and I<sub>OUT</sub>

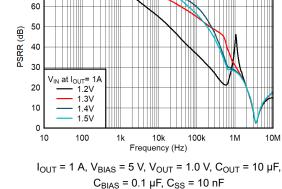

#### $\boxtimes$ 6-2. PSRR vs Frequency and $V_{IN}$ for $I_{OUT} = 1$ A

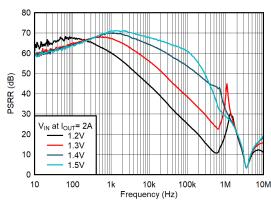

$I_{OUT}$  = 2 A,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{OUT}$  = 10  $\mu F,$  $C_{BIAS} = 0.1 \mu F, C_{SS} = 10 nF$

$\boxtimes$  6-3. PSRR vs Frequency and  $V_{IN}$  for  $I_{OUT} = 2$  A

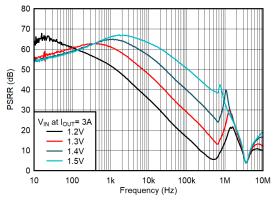

$I_{OUT}$  = 3 A,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{OUT}$  = 10  $\mu F,$  $C_{BIAS} = 0.1 \mu F$ ,  $C_{SS} = 10 nF$

### 図 6-4. PSRR vs Frequency and V<sub>IN</sub> for I<sub>OUT</sub> = 3 A

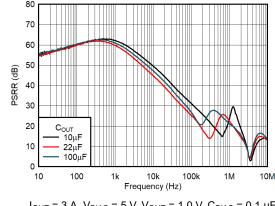

$I_{OUT}$  = 3 A,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{BIAS}$  = 0.1  $\mu$ F,  $C_{SS} = 10 \text{ nF}$

図 6-5. PSRR vs Frequency and Cout

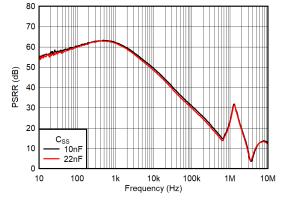

$I_{OUT}$  = 3 A,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{BIAS}$  = 0.1  $\mu$ F,  $C_{OUT} = 10 \mu F$

図 6-6. PSRR vs Frequency and C<sub>SS</sub>

at  $T_A$  = 25°C,  $V_{IN}$  = 1.4 V or  $V_{IN}$  =  $V_{OUT(NOM)}$  + 0.3 V (whichever is greater),  $V_{BIAS}$  = open,  $V_{OUT(NOM)}$  = 0.8 V,  $V_{EN}$  = 1.1 V,  $C_{OUT}$  = 47  $\mu$ F,  $C_{NR/SS}$  = 0 nF,  $C_{FF}$  = 0 nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

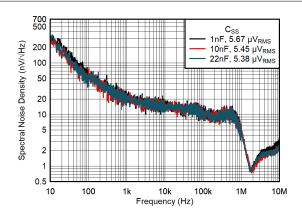

$V_{IN}$  =  $V_{EN}$  = 1.3 V,  $V_{BIAS}$  = 5 V,  $V_{OUT}$  = 1.0 V,  $C_{IN}$  = 10  $\mu F$ ,  $C_{OUT}$  = 10  $\mu F$ ,  $C_{SS}$  = 10 nF

## 図 6-7. BIAS PSRR vs Frequency and I<sub>OUT</sub>

$V_{IN}$  =  $V_{EN}$  = 1.3 V,  $V_{OUT}$  = 1.0 V,  $C_{IN}$  = 10  $\mu F,$   $C_{OUT}$  = 10  $\mu F,$   $C_{SS}$  = 10 nF

#### ☑ 6-8. BIAS PSRR vs Frequency and V<sub>BIAS</sub>

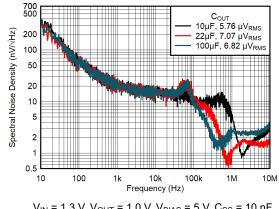

$V_{IN}$  = 1.3 V,  $V_{OUT}$  = 1.0 V,  $V_{BIAS}$  = 5 V,  $C_{OUT}$  = 10  $\mu F,$   $C_{SS}$  = 10 nF,  $C_{BIAS}$  = 0.1  $\mu F,$  RMS noise BW = 10 Hz to 100 kHz

###

$V_{IN}$  = 1.3 V,  $V_{OUT}$  = 1.0 V,  $C_{OUT}$  = 10  $\mu$ F,  $C_{SS}$  = 10 nF,  $C_{BIAS}$  = 0.1  $\mu$ F, RMS noise BW = 10 Hz to 100 kHz

#### 図 6-9. Spectral Noise Density vs Frequency and I<sub>OUT</sub>

$V_{IN}$  = 1.3 V,  $V_{OUT}$  = 1.0 V,  $V_{BIAS}$  = 5 V,  $C_{SS}$  = 10 nF,  $C_{BIAS}$  = 0.1  $\mu$ F, RMS noise BW = 10 Hz to 100 kHz

☑ 6-11. Spectral Noise Density vs Frequency and C<sub>OUT</sub>

$V_{IN}$  = 1.3 V,  $V_{OUT}$  = 1.0 V,  $V_{BIAS}$  = 5 V,  $C_{OUT}$  = 10  $\mu$ F,  $C_{BIAS}$  = 0.1  $\mu$ F, RMS noise BW = 10 Hz to 100 kHz

☑ 6-12. Spectral Noise Density vs Frequency and C<sub>SS</sub>

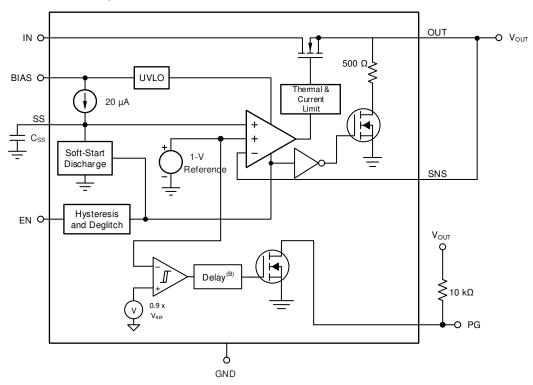

# 7 Detailed Description

### 7.1 Overview

The TPS7A53A-Q1 is a low-input, low-output (LILO), low-quiescent-current linear regulator optimized to support excellent transient performance. This regulator uses a low-current bias rail to power all internal control circuitry, allowing the n-type field effect transistor (NMOS) pass transistor to regulate very-low input and output voltages.

Using an NMOS-pass transistor offers several critical advantages for many applications. Unlike a p-channel metal-oxide-semiconductor field effect transistor (PMOS) topology device, the output capacitor has little effect on loop stability. This architecture allows the TPS7A53A-Q1 to be stable with any ceramic capacitor 10  $\mu$ F or greater. Transient response is also superior to PMOS topologies, particularly for low  $V_{IN}$  applications.

The TPS7A53A-Q1 features a programmable, voltage-controlled, soft-start circuit that provides a smooth, monotonic start-up and limits start-up inrush currents that can be caused by large capacitive loads. An enable (EN) pin with hysteresis and deglitch allows slow-ramping signals to be used for sequencing the device. The low  $V_{IN}$  and  $V_{OUT}$  capability allows for inexpensive, easy-to-design, and efficient linear regulation between the multiple supply voltages often required by processor-intensive systems.

# 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Enable and Shutdown

The enable (EN) pin is active high and compatible with standard digital-signaling levels. Setting  $V_{EN}$  below 0.4 V turns the regulator off, and setting  $V_{EN}$  above 1.1 V turns the regulator on. Unlike many regulators, the enable circuitry has hysteresis and deglitching for use with relatively slowly ramping analog signals. This configuration allows the device to be enabled by connecting the output of another supply to the EN pin. The enable circuitry typically has 70 mV of hysteresis and a deglitch circuit to help avoid on-off cycling as a result of small glitches in the  $V_{EN}$  signal.

The enable threshold is typically 0.75 V and varies with temperature and process variations. Temperature variation is approximately –1.2 mV/°C; process variation accounts for most of the remaining variation to the 0.4-V and 1.1-V limits. If precise turn-on timing is required, a fast rise-time signal must be used.

If not used, EN can be connected to BIAS. Place the connection as close as possible to the bias capacitor.

### 7.3.2 Active Discharge

The TPS7A53A-Q1 has an internal active pulldown circuits on the OUT pin.

This active discharge function uses an internal metal-oxide-semiconductor field-effect transistor (MOSFET) that connects a resistor (R<sub>PULLDOWN</sub>) to ground when the low-dropout resistor (LDO) is disabled in order to actively discharge the output voltage. The active discharge circuit is activated when the device is disabled by driving EN to logic low, when the voltage at IN or BIAS is below the UVLO threshold, or when the regulator is in thermal shutdown.

The discharge time after disabling the device depends on the output capacitance ( $C_{OUT}$ ) and the load resistance ( $R_L$ ) in parallel with the pulldown resistor.

The active pulldown circuit connects the output to GND through a  $500-\Omega$  resistor when the device is disabled.

$$T_{OUT} = (500 \times R_L / (500 + R_L) \times C_{OUT})$$

(1)

Do not rely on the active discharge circuit for discharging a large amount of output capacitance after the input supply has collapsed because reverse current can flow from the output to the input and can cause damage to the device. Limit reverse current to no more than 5% of the device-rated current.

Product Folder Links: TPS7A53A-Q1

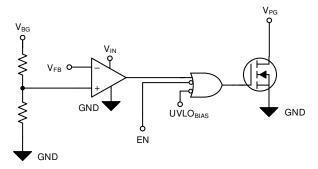

#### 7.3.3 Power-Good Output (PG)

The PG signal provides an easy solution to meet demanding sequencing requirements because PG signals when the output nears the nominal value. PG can be used to signal other devices in a system when the output voltage is near, at, or above the set output voltage  $(V_{OUT(nom)})$ .  $\boxtimes$  7-1 shows a simplified schematic.

The PG signal is an open-drain digital output that requires a pullup resistor to a voltage source and is active high. The PG circuit sets the PG pin into a high-impedance state to indicate that the power is good.

Using a large feed-forward capacitor ( $C_{FF}$ ) delays the output voltage and, because the PG circuit monitors the FB pin, the PG signal can indicate a false positive.

図 7-1. Simplified PG Circuit

#### 7.3.4 Internal Current Limit

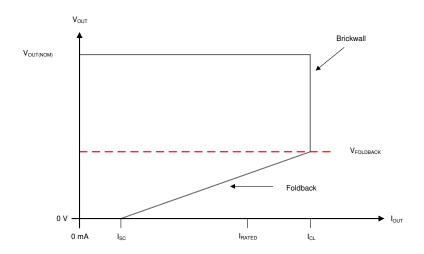

The device has an internal current-limit circuit that protects the regulator during transient high-load current faults or shorting events. The current limit is a hybrid brick-wall foldback scheme. The current limit transitions from a brick-wall scheme to a foldback scheme at the foldback voltage ( $V_{FOLDBACK}$ ). In a high-load current fault with the output voltage above  $V_{FOLDBACK}$ , the brick-wall scheme limits the output current to the current limit ( $I_{CL}$ ). When the voltage drops below  $V_{FOLDBACK}$ , a foldback current limit activates that scales back the current when the output voltage approaches GND. When the output is shorted, the device supplies a typical current called the short-circuit current limit ( $I_{SC}$ ).  $I_{CL}$  and  $I_{SC}$  are listed in the *Electrical Characteristics* table.

For this device, V<sub>FOLDBACK</sub> is approximately 60% × V<sub>OUT(nom)</sub>.

The output voltage is not regulated when the device is in current limit. When a current-limit event occurs, the device begins to heat up because of the increase in power dissipation. When the device is in a brick-wall current limit, the pass transistor dissipates power  $[(V_{IN} - V_{OUT}) \times I_{CL}]$ . When the device output is shorted and the output is below  $V_{FOLDBACK}$ , the pass transistor dissipates power  $[(V_{IN} - V_{OUT}) \times I_{SC}]$ . If thermal shutdown is triggered, the device turns off. When the device sufficiently cools down, the internal thermal shutdown circuit turns the device back on. If the output current fault condition continues, the device cycles between current limit and thermal shutdown. For more information on current limits, see the *Know Your Limits* application note.  $\boxtimes$  7-2 shows a diagram of the foldback current limit.

図 7-2. Foldback Current Limit

## 7.3.5 Thermal Shutdown Protection (T<sub>SD</sub>)

The internal thermal shutdown protection circuit disables the output when the thermal junction temperature ( $T_J$ ) of the pass transistor rises to the thermal shutdown temperature threshold,  $T_{SD(shutdown)\ (typical)}$ . The thermal shutdown circuit hysteresis makes sure that the LDO resets (turns on) when the temperature falls to  $T_{SD(reset)\ (typical)}$ .

The thermal time constant of the semiconductor die is fairly short; thus, the device can cycle on and off when thermal shutdown is reached until the power dissipation is reduced. Power dissipation during start up can be high from large  $V_{\text{IN}} - V_{\text{OUT}}$  voltage drops across the device or from high inrush currents charging large output capacitors. Under some conditions, the thermal shutdown protection disables the device before start up completes.

For reliable operation, limit the junction temperature to the maximum listed in the *Recommended Operating Conditions* table. Operation above this maximum temperature causes the device to exceed operational specifications. Although the internal protection circuitry is designed to protect against thermal overload conditions, this circuitry is not intended to replace proper heat sinking. Continuously running the regulator into thermal shutdown, or above the maximum recommended junction temperature, reduces long-term reliability.

#### 7.4 Device Functional Modes

表 7-1 shows the conditions that lead to the different modes of operation. See the *Electrical Characteristics* table for parameter values.

|                                                        | ₹ 7-1. Device Functional Mode Companison                             |                                                              |                                       |                                    |                                               |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|------------------------------------|-----------------------------------------------|--|--|

| OPERATING MODE                                         |                                                                      |                                                              |                                       |                                    |                                               |  |  |

| OPERATING MODE                                         | V <sub>IN</sub>                                                      | V <sub>BIAS</sub>                                            | V <sub>EN</sub>                       | I <sub>OUT</sub>                   | TJ                                            |  |  |

| Normal mode                                            | $V_{IN} \ge V_{OUT (nom)} + V_{DO(IN)}$ and $V_{IN} \ge V_{IN(min)}$ | $V_{BIAS} \ge V_{OUT} + V_{DO(BIAS)}$                        | $V_{EN} \ge V_{HI(EN)}$               | I <sub>OUT</sub> < I <sub>CL</sub> | T <sub>J</sub> < T <sub>SD</sub> for shutdown |  |  |

| Dropout mode                                           | $V_{IN(min)} < V_{IN} < V_{OUT}$ $(nom) + V_{DO(IN)}$                | V <sub>BIAS</sub> < V <sub>OUT</sub> + V <sub>DO(BIAS)</sub> | V <sub>EN</sub> > V <sub>HI(EN)</sub> | I <sub>OUT</sub> < I <sub>CL</sub> | T <sub>J</sub> < T <sub>SD</sub> for shutdown |  |  |

| Disabled mode (any true condition disables the device) | V <sub>IN</sub> < V <sub>UVLO(IN)</sub>                              | V <sub>BIAS</sub> < V <sub>BIAS(UVLO)</sub>                  | V <sub>EN</sub> < V <sub>LO(EN)</sub> | _                                  | T <sub>J</sub> ≥ T <sub>SD</sub> for shutdown |  |  |

表 7-1. Device Functional Mode Comparison

# 7.4.1 Normal Operation

The device regulates to the nominal output voltage when the following conditions are met:

- The input voltage is greater than the nominal output voltage plus the dropout voltage (V<sub>OUT(nom)</sub> + V<sub>DO(IN)</sub>)

- The bias voltage is greater than the nominal output voltage plus the dropout voltage (V<sub>OUT(nom)</sub> + V<sub>DO(BIAS)</sub>)

- The output current is less than the current limit (I<sub>OUT</sub> < I<sub>CL</sub>)

- The device junction temperature is less than the thermal shutdown temperature ( $T_J < T_{SD(shutdown)}$ )

- The enable voltage has previously exceeded the enable rising threshold voltage and has not yet decreased to less than the enable falling threshold

#### 7.4.2 Dropout Operation

If the input voltage is lower than the nominal output voltage plus the specified dropout voltage, but all other conditions are met for normal operation, the device operates in dropout mode. Similarly, if the bias voltage is lower than the nominal output voltage plus the specified dropout voltage, but all other conditions are met for normal operation, the device operates in dropout mode as well. In this mode, the output voltage tracks the input voltage. During this mode, the transient performance of the device becomes significantly degraded because the pass transistor is in the ohmic or triode region, and functions as a switch. Line or load transients in dropout can result in large output voltage deviations.

When the device is in a steady dropout state, defined as when the device is in dropout  $(V_{IN} < V_{OUT} + V_{DO(IN)})$  or  $V_{BIAS} < V_{OUT} + V_{DO(BIAS)}$  directly after being in normal regulation state, but not during start up), the pass transistor is driven into the ohmic or triode region. When the input voltage returns to a value greater than or equal to the nominal output voltage plus the dropout voltage  $(V_{OUT(NOM)} + V_{DO(IN)})$ , the output voltage can overshoot for a short time when the device pulls the pass transistor back into the linear region.

#### 7.4.3 Disabled

The output of the device can be shutdown by forcing the voltage of the enable pin to less than  $V_{IL(EN)}$  (see the *Electrical Characteristics* table). When disabled, the pass transistor is turned off, internal circuits are shutdown, and the output voltage is actively discharged to ground by an internal discharge circuit from the output to ground.

The device is disabled under the following conditions:

- The input or bias voltages are below the respective minimum specifications

- The enable voltage is less than the enable falling threshold voltage or has not yet exceeded the enable rising threshold

- The device junction temperature is greater than the thermal shutdown temperature

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 8.1 Application Information

The TPS7A53A-Q1 is a low-input, low-output (LILO), low-dropout regulator (LDO) that features soft-start capability. This regulator uses a low-current bias input to power all internal control circuitry, allowing the NMOS pass transistor to regulate very low input and output voltages.

Using an NMOS pass transistor offers several critical advantages for many applications. Unlike a PMOS topology device, the output capacitor has little effect on loop stability. This architecture allows stability with ceramic capacitors of 10  $\mu$ F or greater. Transient response is also superior to PMOS topologies, particularly for low  $V_{\text{IN}}$  applications.

A programmable voltage-controlled, soft-start circuit provides a smooth, monotonic start-up and limits start-up inrush currents that can be caused by large capacitive loads. An enable (EN) pin with hysteresis and deglitch allows slow-ramping signals to be used for sequencing the device. The low  $V_{IN}$  and  $V_{OUT}$  capability allows for inexpensive, easy-to-design, and efficient linear regulation between the multiple supply voltages often required by processor-intensive systems.

### 8.1.1 Input, Output, and Bias Capacitor Requirements

The device is designed to be stable for ceramic capacitor of values  $\geq$  10  $\mu$ F. The device is also stable with multiple capacitors in parallel, which can be of any type or value.

The capacitance required on the IN and BIAS pins strongly depends on the input supply source impedance. To counteract any inductance in the input, the minimum recommended capacitor for  $V_{IN}$  is 1  $\mu$ F and the minimum recommended capacitor for  $V_{BIAS}$  is 0.1  $\mu$ F. If  $V_{IN}$  and  $V_{BIAS}$  are connected to the same supply, the recommended minimum capacitor for  $V_{BIAS}$  is 4.7  $\mu$ F. Use good quality, low equivalent series resistance (ESR) and equivalent series inductance (ESL) capacitors on the input; ceramic X5R and X7R capacitors are preferred. Place these capacitors as close the pins as possible for optimum performance.

Low ESR and ESL capacitors improve high-frequency PSRR.

#### 8.1.2 Dropout Voltage

The TPS7A53A-Q1 offers very low dropout performance, making the device designed for high-current, low  $V_{IN}$  and low  $V_{OUT}$  applications. The low dropout allows the device to be used in place of a dc/dc converter and still achieve good efficiency.  $\npreceq$  2 provides a quick estimate of the efficiency.

Efficiency

$$\approx \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{\left[V_{\text{IN}} \times (I_{\text{IN}} + I_{\text{Q}})\right]} \approx \frac{V_{\text{OUT}}}{V_{\text{IN}}} \text{ at } I_{\text{OUT}} >> I_{\text{Q}}$$

(2)

This efficiency provides designers with the power architecture for applications to achieve the smallest, simplest, and lowest cost solutions.

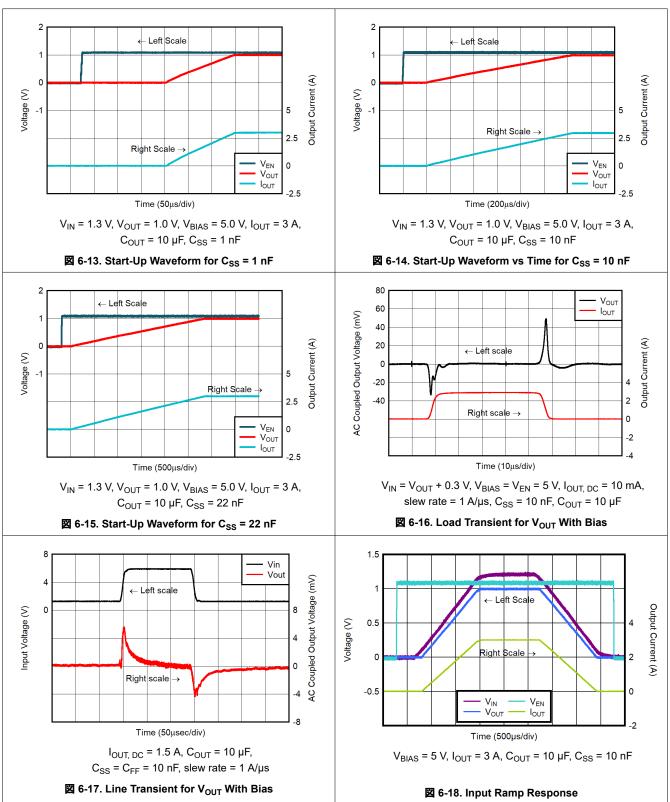

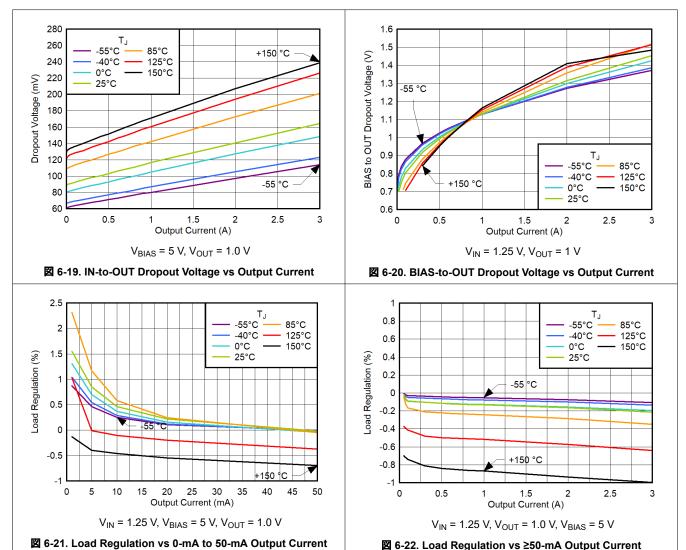

For this architecture, there are two different specifications for dropout voltage. The first specification (see  $\boxtimes$  6-19) is referred to as  $V_{IN}$  dropout and is used when an external bias voltage is applied to achieve low dropout. This specification assumes that  $V_{BIAS}$  is at least 2.8 V above  $V_{OUT}$ , which is the case for  $V_{BIAS}$  when powered by a 5.0-V rail with 5% tolerance and with  $V_{OUT}$  = 1.5 V. If  $V_{BIAS}$  is higher than  $V_{OUT}$  + 2.8 V, the  $V_{IN}$  dropout is less than specified.

注

2.8 V is a test condition of this device and can be adjusted by referring to the *Electrical Characteristics* table.

The second specification (illustrated in  $\boxtimes$  6-20) is referred to as  $V_{BIAS}$  dropout and applies to applications where IN and BIAS are tied together. This option allows the device to be used in applications where an auxiliary bias voltage is not available or low dropout is not required. Dropout is limited by BIAS in these applications because  $V_{BIAS}$  provides the gate drive to the pass transistor; therefore,  $V_{BIAS}$  must be 1.9 V above  $V_{OUT}$ . Because of this usage, having IN and BIAS tied together become a highly inefficient solution that can consume large amounts of power. Pay attention not to exceed the power rating of the device package.

### 8.1.3 Output Noise

The TPS7A53A-Q1 provides low output noise when a soft-start capacitor is used. When the device reaches the end of the soft-start cycle, the soft-start capacitor serves as a filter for the internal reference. By using a 10-nF, soft-start capacitor, the output noise is reduced by half and is typically 7.1  $\mu$ V<sub>RMS</sub> for a 1-V output (10 Hz to 100 kHz). Further increasing C<sub>SS</sub> has little effect on noise. Because most of the output noise is generated by the internal reference, the noise is a function of the set output voltage.  $\sharp$  3 gives the RMS noise with a 10-nF, soft-start capacitor:

$$V_{N}(\mu V_{RMS}) = 7.1 \cdot \left(\frac{\mu V_{RMS}}{V}\right) \cdot V_{OUT}(V)$$

(3)

The low output noise makes this LDO a good choice for powering transceivers, phase-locked loops (PLLs), or other noise-sensitive circuitry.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

## 8.1.4 Estimating Junction Temperature

By using the thermal metrics  $\Psi_{JT}$  and  $\Psi_{JB}$ , as shown in the *Thermal Information* table, the junction temperature can be estimated with corresponding formulas (given in  $\stackrel{*}{\precsim}$  4). For backwards compatibility, an older  $\theta_{JC(top)}$  parameter is listed as well.

$$\Psi_{JT}: \quad T_{J} = T_{T} + \Psi_{JT} \bullet P_{D}$$

$$\Psi_{JB}: \quad T_{J} = T_{B} + \Psi_{JB} \bullet P_{D}$$

(4)

where:

- P<sub>D</sub> is the power dissipation

- T<sub>T</sub> is the temperature at the center-top of the package

- T<sub>B</sub> is the PCB temperature measured 1 mm away from the package on the PCB surface

注

Both  $T_T$  and  $T_B$  can be measured on actual application boards using a thermo-gun (an infrared thermometer).

For more information about measuring  $T_T$  and  $T_B$ , see the *Using New Thermal Metrics* application note, available for download at www.ti.com.

For a more detailed discussion of why TI does not recommend using  $\theta_{JC(top)}$  to determine thermal characteristics, see the *Using New Thermal Metrics* application note, available for download at www.ti.com. For further information, see the *Semiconductor and IC Package Thermal Metrics* application note, also available on the TI website.

### 8.1.5 Soft Start, Sequencing, and Inrush Current

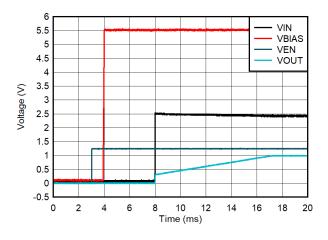

Soft-start refers to the ramp-up characteristic of the output voltage during LDO turn-on after EN and UVLO achieve threshold voltage. The soft start current is fixed for fixed output voltage versions.

Although the device does not have any sequencing requirement, following the sequencing order of BIAS, IN, and EN makes sure that the soft start starts from zero.

⊠ 8-1 shows an example of the device behavior when the EN pin is enabled prior to having either power supply up. Under this condition, the output jumps from 0 V to approximately 0.3 V almost instantly when the IN voltage is sufficient to power the circuit.

図 8-1. Sequencing and Soft-Start Behavior

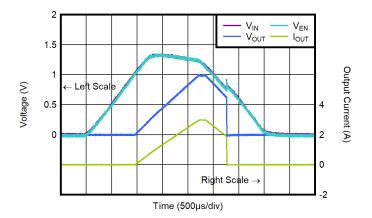

As shown in 🗵 8-2, connecting EN to IN, in conjunction with a slow input or output voltage ramp, can have undesired behavior in the application. For a smooth IN and OUT ramp, consider using the EN pin separate from the IN voltage.

図 8-2. V<sub>EN</sub> = V<sub>IN</sub> Behavior

Inrush current is defined as the current into the LDO at the IN pin during start-up. Inrush current then consists primarily of the sum of load current and the current used to charge the output capacitor. This current is difficult to measure because the input capacitor must be removed, which is not recommended. However,  $\pm$  5 can estimate this soft-start current:

$$I_{OUT(t)} = \left[\frac{C_{OUT} \times dV_{OUT}(t)}{dt}\right] + \left[\frac{V_{OUT}(t)}{R_{LOAD}}\right]$$

(5)

#### where:

- V<sub>OUT</sub>(t) is the instantaneous output voltage of the turn-on ramp

- dV<sub>OUT</sub>(t) / dt is the slope of the V<sub>OUT</sub> ramp

- R<sub>I OAD</sub> is the resistive load impedance

## 8.1.6 Power-Good Operation

For proper operation of the power-good circuit, the pullup resistor value must be between 10 k $\Omega$  and 100 k $\Omega$ . The lower limit of 10 k $\Omega$  results from the maximum pulldown strength of the power-good transistor, and the upper limit of 100 k $\Omega$  results from the maximum leakage current at the power-good node. If the pullup resistor is outside of this range, then the power-good signal can possibly not read a valid digital logic level.

The state of PG is only valid when the device operates above the minimum supply voltage. During short UVLO events and at light loads, power-good does not assert because the output voltage is sustained by the output capacitance.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

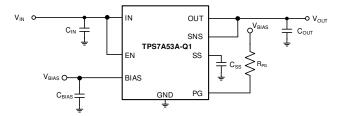

## 8.2 Typical Application

This section discusses the implementation of the fixed 1.0-V TPS7A53A-Q1 to regulate a 3-A load requiring good PSRR at high frequency with low noise. 🗵 8-3 provides a schematic for this typical application circuit.

図 8-3. Typical Fixed Voltage Application

#### 8.2.1 Design Requirements

For this design example, use the parameters listed in 表 8-1 as the input parameters.

| 2 o 1. Design i diameters   |                                                                  |  |  |  |

|-----------------------------|------------------------------------------------------------------|--|--|--|

| PARAMETER                   | DESIGN REQUIREMENT                                               |  |  |  |

| Input voltage               | 1.3 V, ±3%, provided by the dc/dc converter switching at 500 kHz |  |  |  |

| Bias voltage                | 5.0 V                                                            |  |  |  |

| Output voltage              | 1.0 V, ±1%                                                       |  |  |  |

| Output current              | 3.0 A (maximum), 10 mA (minimum)                                 |  |  |  |

| RMS noise, 10 Hz to 100 kHz | < 10 μV <sub>RMS</sub>                                           |  |  |  |

| PSRR at 500 kHz             | > 40 dB                                                          |  |  |  |

| Start-up time               | < 25 ms                                                          |  |  |  |

表 8-1. Design Parameters

# 8.2.2 Detailed Design Procedure

At 3.0 A and 1.0  $V_{OUT}$ , the dropout of the TPS7A53A-Q1 has a 285-mV maximum dropout over temperature; thus, a 300-mV headroom is sufficient for operation over both input and output voltage accuracy. At full load and high temperature on some devices, the TPS7A53A-Q1 can enter dropout if both the input and output supply are beyond the edges of the respective accuracy specification.

To satisfy the required start-up time and still maintain low noise performance, a 10-nF  $C_{SS}$  is selected.  $\stackrel{\prec}{\not\sim}$  6 calculates this value.

$$t_{SS} = (V_{SS} \times C_{SS}) / I_{SS}$$

(6)

At the 3.0-A maximum load, the internal power dissipation is 0.9 W and corresponds to a 38.3°C junction temperature rise for the RTJ package on a standard JEDEC board. With an 55°C maximum ambient temperature, the junction temperature is at 93.3°C.

Submit Document Feedback

#### 8.2.3 Application Curve

図 8-4. PSRR vs Frequency for V<sub>OUT</sub> = 1.0 V and I<sub>OUT</sub> = 3 A

# 8.3 Power Supply Recommendations

The TPS7A53A-Q1 is designed to operate from an input voltage up to 6.0 V, provided the bias rail is at least 1.3 V higher than the input supply and dropout requirements are met. The bias rail and the input supply must both provide adequate headroom and current for the device to operate normally. Connect a low output impedance power supply directly to the IN pin. This supply must have at least 1  $\mu$ F of capacitance near the IN pin for optimal performance. A supply with similar requirements must also be connected directly to the BIAS rail with a separate 0.1  $\mu$ F or larger capacitor. If the IN pin is tied to the BIAS pin, a minimum 4.7- $\mu$ F capacitor is required for performance. To increase the overall PSRR of the solution at higher frequencies, use a pi-filter or ferrite bead before the input capacitor.

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

#### 8.4.1.1 Board Lavout

For best overall performance, place all circuit components on the same side of the circuit board and as near as practical to the respective LDO pin connections. Place ground return connections to the input and output capacitor, and to the LDO ground pin as close to each other as possible, connected by a wide, component-side, copper surface. To avoid negative system performance, do not use of vias and long traces to the input and output capacitors. The grounding and layout scheme illustrated in  $\boxtimes$  8-5 minimizes inductive parasitics, and thereby reduces load-current transients, minimizes noise, and increases circuit stability.

To improve performance, use a ground reference plane, either embedded in the PCB or placed on the bottom side of the PCB opposite the components. This reference plane serves to provide accuracy of the output voltage, shield noise, and behaves similar to a thermal plane to spread (or sink) heat from the LDO device when connected to the thermal pad. In most applications, this ground plane is necessary to meet thermal requirements.

#### 8.4.1.2 RTJ Package — High CTE Mold Compound

The RTJ package uses a mold compound with a high coefficient of thermal expansion (CTE) of 12 ppm/°C. This mold compound allows for the CTE of the packaged device to more closely match the CTE of a conventional FR4 PCB (approximately 14 ppm/°C to 17 ppm/°C). This CTE match is important when considering the effects that temperature swings can induce on a board with large differences in CTE values. Package and board combinations with widely dissimilar CTEs can experience mechanical cracking or fracturing of the solder joints caused by frequent changes in temperature, and the corresponding differences in expansion. Devices with

normal mold compounds in similar packages typically have CTE values that are 25% lower than values found with the RTJ package.

## 8.4.2 Layout Example

図 8-5. Example Layout

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 9 Device and Documentation Support

## 9.1 Documentation Support

#### 9.1.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, TPS3702 High-Accuracy, Overvoltage and Undervoltage Monitor data sheet

- Texas Instruments, Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator application note

- · Texas Instruments, 6 A Current-Sharing Dual LDO design guide

## 9.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 9.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 9.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 9.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 9.6 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

# 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

### 10.1 Mechanical Data

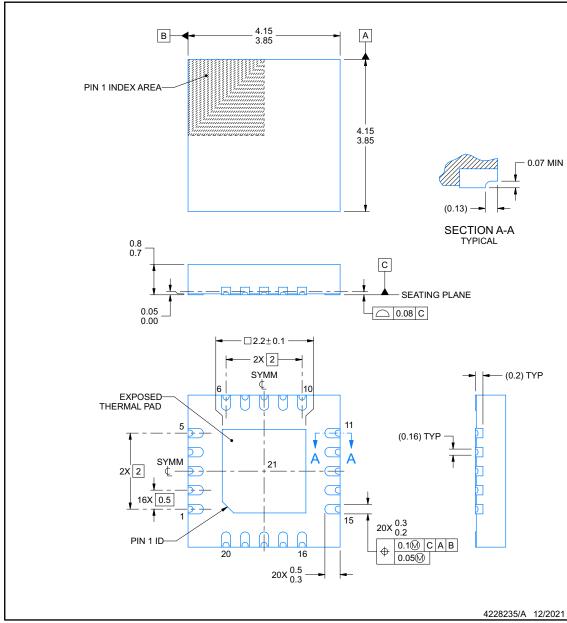

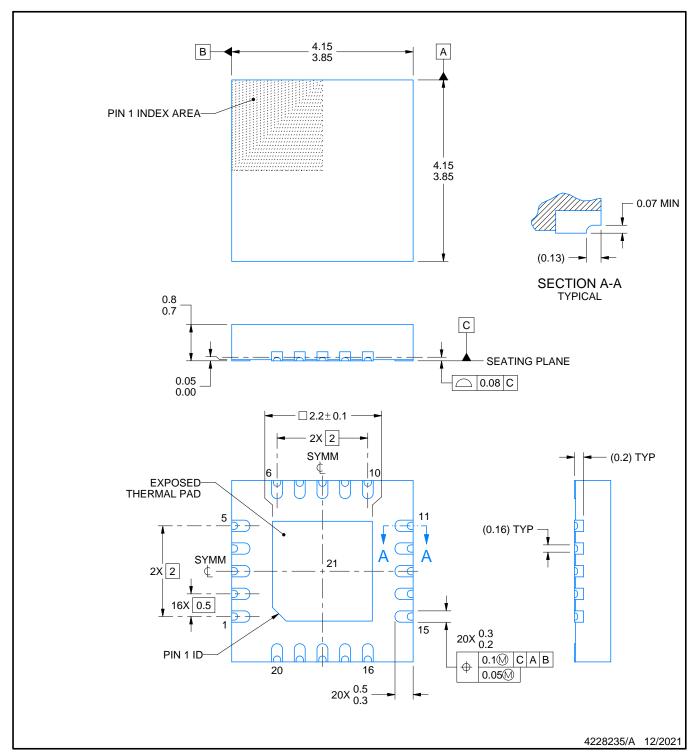

# RTJ0020L

## **PACKAGE OUTLINE**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

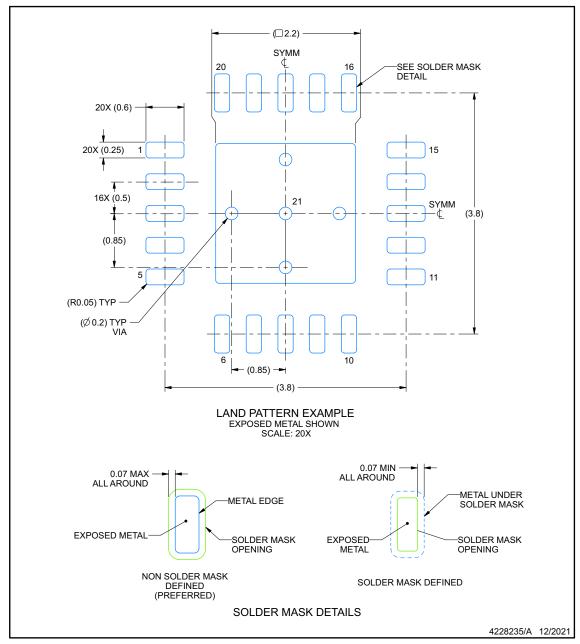

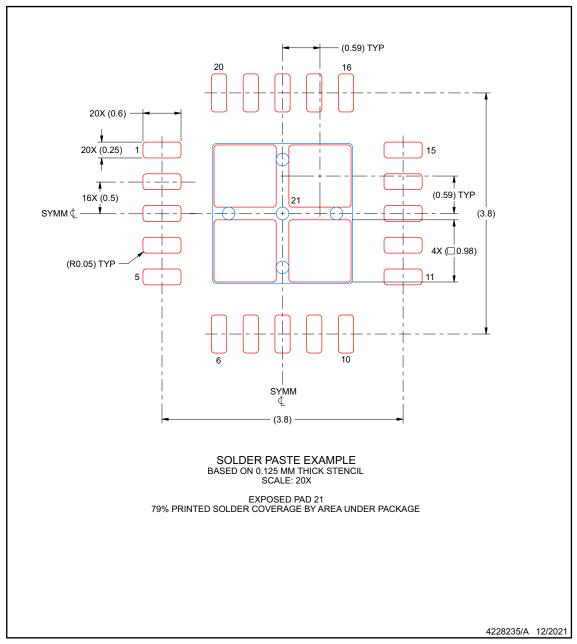

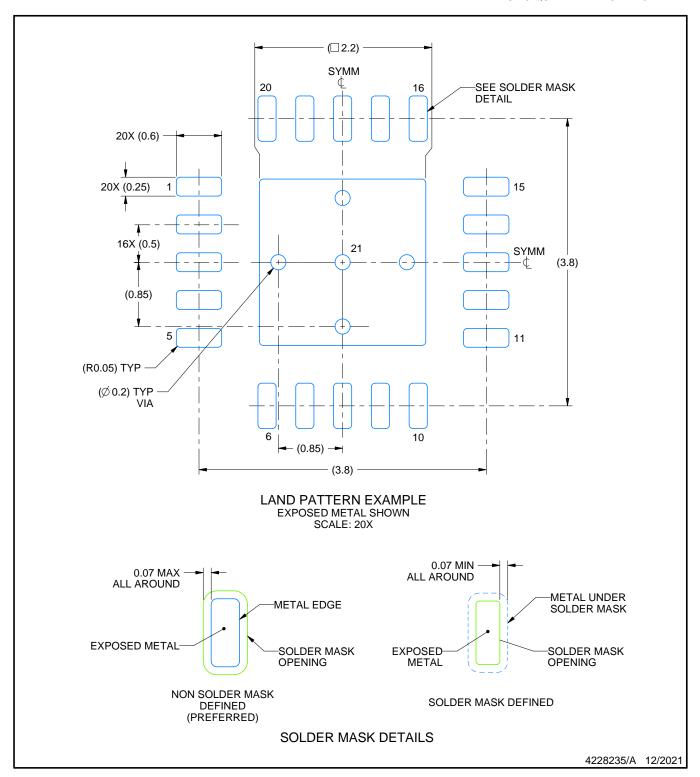

### **EXAMPLE BOARD LAYOUT**

# RTJ0020L

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

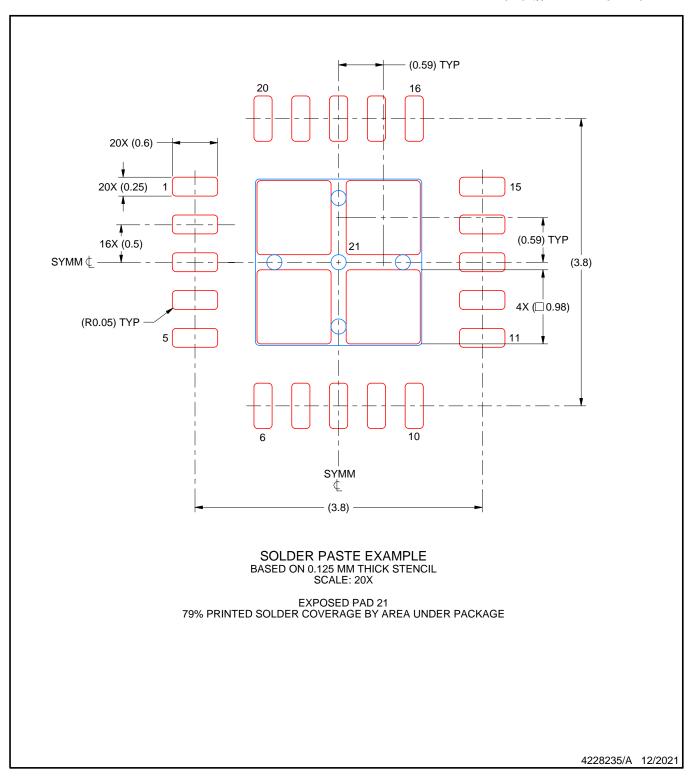

## **EXAMPLE STENCIL DESIGN**

# **RTJ0020L**

WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type | Package   Pins | Package qty   Carrier | RoHS (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|---------------|----------------|-----------------------|----------|-------------------------------|----------------------------|--------------|------------------|

| TPS7A5310AQWRTJRQ1    | Active        | Production    | QFN (RTJ)   20 | 3000   LARGE T&R      | Yes      | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 150   | 7A5310A          |

| TPS7A5310AQWRTJRQ1.A  | Active        | Production    | QFN (RTJ)   20 | 3000   LARGE T&R      | Yes      | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 150   | 7A5310A          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE MATERIALS INFORMATION

www.ti.com 30-Oct-2025

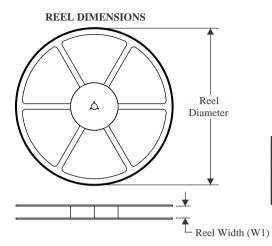

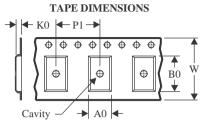

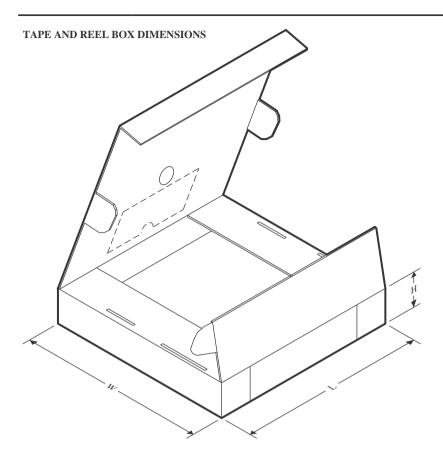

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | _   | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS7A5310AQWRTJRQ1 | QFN | RTJ                | 20 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q1               |

PACKAGE MATERIALS INFORMATION

www.ti.com 30-Oct-2025

### \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS7A5310AQWRTJRQ1 | QFN          | RTJ             | 20   | 3000 | 360.0       | 360.0      | 36.0        |

4 x 4, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

<sup>6.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月