## TPS7A21-Q1 車載対応、500mA、低ノイズ、低 $I_Q$ 、高 PSRR LDO

### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$

- 接合部温度:  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$

- 超低  $I_Q$ :  $6.5\mu\text{A}$

- 入力電圧範囲:  $2.0\text{V} \sim 6.0\text{V}$

- 出力電圧範囲:  $0.8\text{V} \sim 5.5\text{V}$  (50mV 刻み)

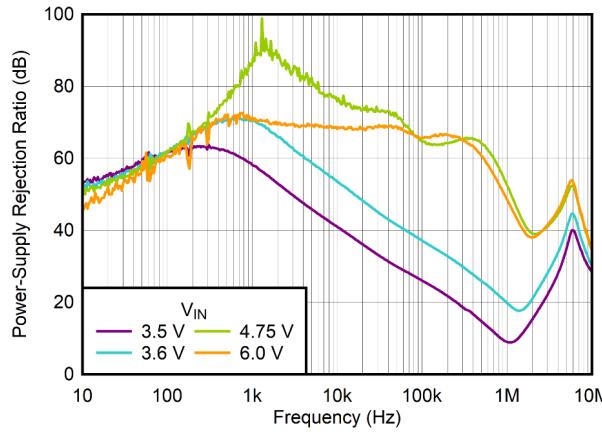

- 高 PSRR: 1kHz 時に 91dB

- 低い出力電圧ノイズ:  $7.7\mu\text{V}_{\text{RMS}}$

- 低いドロップアウト:

- $500\text{mA}$  ( $2.5\text{V}$   $\text{V}_{\text{OUT}}$ ) で  $265\text{mV}$  (最大値)

- スマート EN プルダウン

- 出力電圧許容誤差: 温度範囲全体で  $\pm 1\%$

- 幅広いセラミックコンデンサをサポート:

- $1\mu\text{F} \sim 200\mu\text{F}$

- パッケージ:

- $3\text{mm} \times 3\text{mm}$  ウエッタブル フランク VSON

- $2\text{mm} \times 2\text{mm}$  ウエッタブル フランク WSON

- $2\text{mm} \times 2\text{mm}$  WSON

### 2 アプリケーション

- DAS のカメラとレーダー

- オートモーティブ インフォテインメント

- テレマティクス システム

- ナビゲーション システム

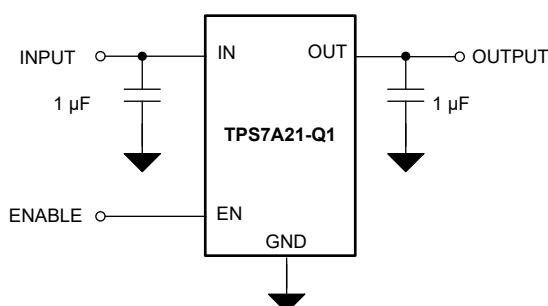

アプリケーション概略回路図

### 3 説明

TPS7A21-Q1 は、500mA の出力電流を供給できる小型の低ドロップアウト (LDO) リニア電圧レギュレータです。このデバイスは、低ノイズ、高 PSRR、および非常に優れた負荷およびライン過渡性能を特長とし、車載アプリケーションにおける RF やその他のアナログ回路の要件に対応できます。革新的な設計手法により、外部ノイズ バイパス コンデンサを追加しなくても低ノイズ性能を実現します。TPS7A21-Q1 の低静止電流は、低電力システムに最適な選択肢です。 $2.0\text{V} \sim 6.0\text{V}$  の入力電圧範囲と、 $0.8\text{V} \sim 5.5\text{V}$  の出力電圧範囲は、さまざまなシステム要件に対応しています。

内部のソフトスタート回路により突入電流を制御できるため、スタートアップ時の入力電圧降下を最小限に抑えることができます。LDO は小さなセラミック コンデンサでも安定して動作するため、設計全体を小型化できます。

内部で制御されるプルダウン抵抗を持つスマート イネーブル入力回路により、EN ピンが接続されていない場合でも、LDO はディセーブル状態に維持されます。また、この回路は、EN 入力をプルダウンするために必要な外付け部品を不要にするのにも役立ちます。

#### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup>     | パッケージ サイズ <sup>(2)</sup>       |

|------------|--------------------------|--------------------------------|

| TPS7A21-Q1 | DRB (ウェッタブル フランク VSON 8) | $3\text{mm} \times 3\text{mm}$ |

|            | DSG (ウェッタブル フランク WSON 8) | $2\text{mm} \times 2\text{mm}$ |

|            | DSG (WSON, 8)            | $2\text{mm} \times 2\text{mm}$ |

(1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>7 アプリケーションと実装</b>          | <b>18</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>7.1 アプリケーション情報</b>         | <b>18</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>7.2 代表的なアプリケーション</b>       | <b>21</b> |

| <b>4 ピン構成および機能</b> | <b>3</b>  | <b>7.3 電源に関する推奨事項</b>         | <b>23</b> |

| <b>5 仕様</b>        | <b>4</b>  | <b>7.4 レイアウト</b>              | <b>23</b> |

| 5.1 絶対最大定格         | 4         | 8.1 デバイス サポート                 | 25        |

| 5.2 ESD 定格         | 4         | 8.2 ドキュメントのサポート               | 25        |

| 5.3 推奨動作条件         | 4         | 8.3 ドキュメントの更新通知を受け取る方法        | 25        |

| 5.4 熱に関する情報        | 5         | 8.4 サポート・リソース                 | 25        |

| 5.5 電気的特性          | 5         | 8.5 商標                        | 25        |

| 5.6 代表的特性          | 7         | 8.6 静電気放電に関する注意事項             | 25        |

| <b>6 詳細説明</b>      | <b>14</b> | 8.7 用語集                       | <b>25</b> |

| 6.1 概要             | 14        | <b>9 改訂履歴</b>                 | <b>26</b> |

| 6.2 機能ブロック図        | 14        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>26</b> |

| 6.3 機能説明           | 15        |                               |           |

| 6.4 デバイスの機能モード     | 17        |                               |           |

|                    |           |                               |           |

|                    |           |                               |           |

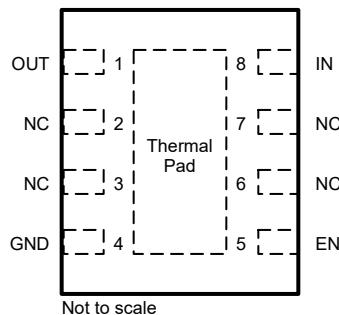

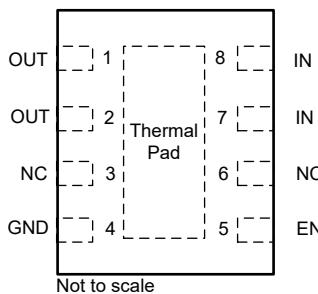

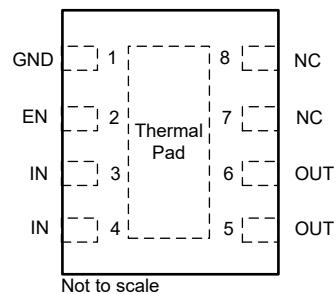

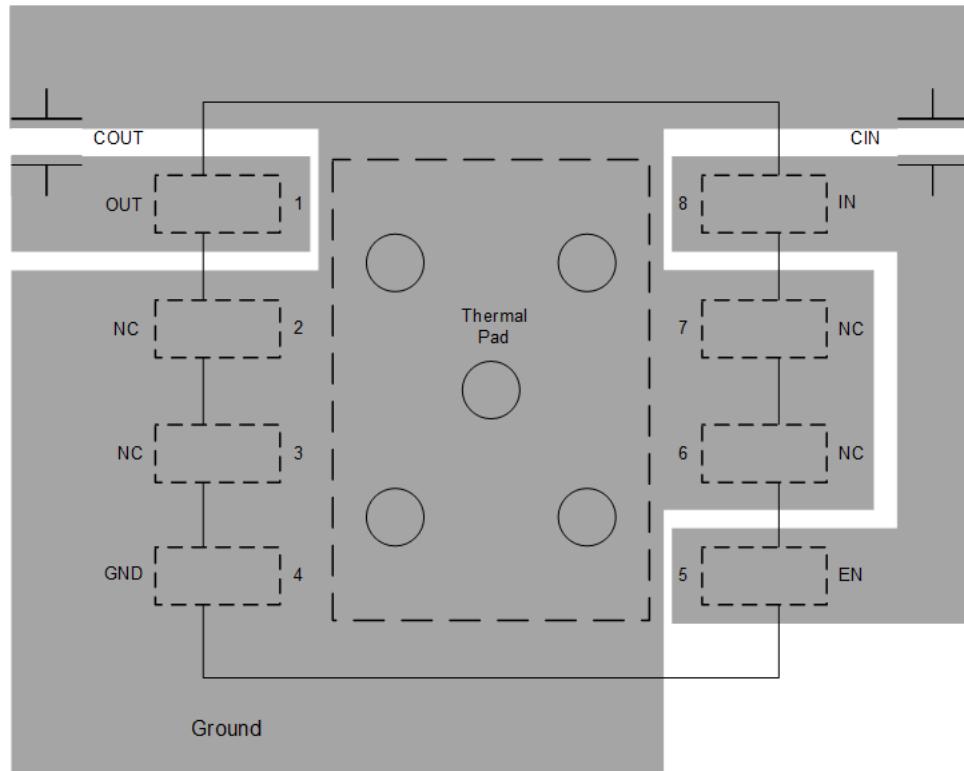

## 4 ピン構成および機能

図 4-1. DRB パッケージ、8 ピン固定 VSON (上面図)

図 4-2. DSG パッケージ (DSG0008B)、8 ピン固定 WSON (上面図)

図 4-3. DSG パッケージ (DSG0008A)、8 ピン固定 WSON C バージョン (上面図)

表 4-1. ピンの機能

| ピン       |            |          |                           | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                          |

|----------|------------|----------|---------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | DRB        | DSG0008B | DSG0008A<br>(C バージョ<br>ン) |                   |                                                                                                                                                                                             |

| EN       | 5          | 5        | 2                         | I                 | イネーブルピン。EN を $V_{EN(HI)}$ より高く駆動すると、レギュレータがオンになります。EN を $V_{EN(LO)}$ 未満に駆動すると、低ドロップアウトレギュレータ (LDO) がシャットダウン モードに移行します。                                                                      |

| GND      | 4          | 4        | 1                         | —                 | グランド ピン。                                                                                                                                                                                    |

| IN       | 8          | 7, 8     | 3, 4                      | I                 | 入力ピン。 <a href="#">推奨動作条件</a> 表および <a href="#">入出力コンデンサの要件</a> セクションに示されているように、最高の過渡応答を実現し、入力インピーダンスを最小化するには、推奨値またはそれ以上に大きい値のセラミック コンデンサを IN とグランドの間に接続します。入力コンデンサはデバイスの出力にできるだけ近い場所に配置します。  |

| NC       | 2, 3, 6, 7 | 3, 6     | 7, 8                      | —                 | 内部接続なし熱性能を向上させるために、このピンをグランドに接続してください。                                                                                                                                                      |

| OUT      | 1          | 1, 2     | 5, 6                      | O                 | レギュレートされた出力電圧ピン。低等価直列抵抗 (ESR) コンデンサをこのピンに接続します。最高の過渡応答を実現するには、公称推奨値またはそれ以上に大きい値のコンデンサを OUT と GND の間に接続します。内部ブルダウン抵抗により、レギュレータがシャットダウン モード ( $V_{EN} < V_{EN(Low)}$ ) のときに OUT に電荷が残るのを防ぎます。 |

| サーマル パッド |            |          |                           |                   | サーマル パッドは GND ノードに電気的に接続します。熱性能を向上させるために、GND プレーンに接続します。                                                                                                                                    |

(1) I = 入力、O = 出力、NC = 接続なし。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1) (3)</sup>

|                  |                       | 最小値                                              | 最大値 | 単位 |

|------------------|-----------------------|--------------------------------------------------|-----|----|

| V <sub>IN</sub>  | 入力電圧                  | -0.3                                             | 6.5 | V  |

| V <sub>OUT</sub> | 出力電圧                  | -0.3 V <sub>IN</sub> + 0.3 または 6.5 のいずれか<br>小さい方 |     | V  |

| V <sub>EN</sub>  | イネーブル入力電圧             | -0.3                                             | 6.5 | V  |

|                  | 最大出力電流 <sup>(3)</sup> | 内部的に制限                                           |     | A  |

| T <sub>J</sub>   | 動作時接合部温度              | -40                                              | 150 | °C |

| T <sub>stg</sub> | 保存温度                  | -65                                              | 150 | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、このような条件や、推奨動作条件に記載されている条件を超える条件でデバイスが機能するということを意味するわけではありません。推奨動作条件の範囲外ではあるが、絶対最大定格の範囲内で短時間動作している場合、デバイスは損傷を受けない可能性がありますが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

- (2) 電圧はすべて、GND ピンを基準にしています。

- (3) 内部のサーマル シャットダウン回路により、デバイスを永続的な損傷から保護します。

### 5.2 ESD 定格

|                    |      |                                                                                                                 | 値     | 単位 |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup><br>デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±2000 | V  |

|                    |      |                                                                                                                 | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                        | 最小値 | 公称値 | 最大値 | 単位 |

|------------------|------------------------|-----|-----|-----|----|

| V <sub>IN</sub>  | 入力電源電圧                 | 2.0 | 6.0 | V   |    |

| V <sub>EN</sub>  | イネーブル入力電圧              | 0   | 6.0 | V   |    |

| V <sub>OUT</sub> | 公称出力電圧範囲               | 0.8 | 5.5 | V   |    |

| I <sub>OUT</sub> | 出力電流                   | 0   | 500 | mA  |    |

| C <sub>IN</sub>  | 入力コンデンサ <sup>(2)</sup> |     | 1   |     | μF |

| C <sub>OUT</sub> | 出力コンデンサ <sup>(3)</sup> | 1   | 200 |     | μF |

| ESR              | 出力コンデンサの等価直列抵抗         |     | 100 |     | mΩ |

| T <sub>J</sub>   | 動作時接合部温度               | -40 | 150 | °C  |    |

- (1) 電圧はすべて、GND ピンを基準にしています。

- (2) LDO の安定性のために、入力コンデンサは必要ありません。しかし、ソース抵抗とインダクタンスの影響を打ち消すために、最小実効値が 0.47μF の入力コンデンサを推奨します。ソース抵抗とインダクタンスは、場合によって、特に負荷過渡現象がある場合には、リギングや発振などのシステムレベルの不安定性の症状を引き起こす可能性があります。

- (3) 100mΩまでのESR値での安定性のため、すべての温度および電圧条件にわたって、最小 0.4μF、最大 200μF の実効出力容量が必要です。ESR が 20mΩ以下に低下すると、実効出力容量は最小 0.3μF で安定して動作します。

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | TPS7A21-Q1    |               | 単位   |

|-----------------------|-------------------|---------------|---------------|------|

|                       |                   | DRB<br>(VSON) | DSG<br>(WSON) |      |

|                       |                   | 8 ピン          | 8 ピン          |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 58.9          | 77.7          | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 76.3          | 109.0         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 31.8          | 44.5          | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 6.3           | 7.2           | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 31.8          | 44.5          | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 13.3          | 17.0          | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』および『基板レイアウトが LDO の熱性能に及ぼす影響に関する実証的分析』アプリケーションノートを参照してください。

## 5.5 電気的特性

指定動作温度範囲内 ( $T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ )、 $V_{IN} = V_{OUT(NOM)} + 0.3\text{V}$  または  $2\text{V}$  (いずれか大きい方)、 $V_{EN} = 1.0\text{V}$ 、 $I_{OUT} = 1\text{mA}$ 、 $C_{IN} = 1\mu\text{F}$ 、 $C_{OUT} = 1\mu\text{F}$  (特に記述のない限り)、標準値はすべて  $T_J = 25^\circ\text{C}$  での値です

| パラメータ            |               | テスト条件                                                                                                                                                | 最小値                                                     | 標準値  | 最大値  | 単位            |

|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|---------------|

| $\Delta V_{OUT}$ | 出力電圧許容誤差      | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$1\text{mA} < I_{OUT} \leq 500\text{mA}$ ,<br>$V_{OUT} \geq 3.3\text{V}$               | -2.25                                                   | 1.5  |      | %             |

|                  |               | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$1\text{mA} < I_{OUT} \leq 500\text{mA}$ ,<br>$2.8\text{V} \leq V_{OUT} < 3.3\text{V}$ | -2.5                                                    | 1.5  |      |               |

|                  |               | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$I_{OUT} = 1\text{mA}$ ,<br>$V_{OUT} \geq 2.8\text{V}$                                 | -1                                                      | 1    |      |               |

|                  |               | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$1\text{mA} < I_{OUT} \leq 500\text{mA}$ ,<br>$V_{OUT} < 2.8\text{V}$                  | -70                                                     | 50   |      | mV            |

|                  |               | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$I_{OUT} = 1\text{mA}$ ,<br>$V_{OUT} < 2.8\text{V}$                                    | -50                                                     | 50   |      |               |

| $\Delta V_{OUT}$ | ライン レギュレーション  | $V_{IN} = (V_{OUT(NOM)} + 0.3\text{V}) \sim 6.0\text{V}$ ,<br>$I_{OUT} = 1\text{mA}$                                                                 | 0.03                                                    |      |      | %/V           |

| $\Delta V_{OUT}$ | ロード レギュレーション  | $I_{OUT} = 1\text{mA} \sim 500\text{mA}$                                                                                                             | 0.003                                                   |      |      | %/mA          |

| $I_{GND}$        | 静止時電流         | $V_{EN} = V_{IN}$ , $V_{IN} = 6.0\text{V}$ , $I_{OUT} = 0\text{mA}$                                                                                  | $T_J = 25^\circ\text{C}$                                | 6.5  | 9    | $\mu\text{A}$ |

|                  |               |                                                                                                                                                      | $T_J = -40^\circ\text{C} \sim 85^\circ\text{C}$         |      | 11   |               |

|                  |               |                                                                                                                                                      | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$        |      | 15   |               |

|                  |               |                                                                                                                                                      | $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$        |      | 18   |               |

|                  |               | $V_{EN} = V_{IN}$ , $V_{IN} = 6.0\text{V}$ , $I_{OUT} = 500\text{mA}$                                                                                |                                                         | 2300 | 3500 |               |

| $I_{SHTDWN}$     | シャットダウン電流     | $V_{EN} = 0\text{V}$ (ディスエーブル), $V_{IN} = 6.0\text{V}$ , $T_J = 25^\circ\text{C}$                                                                    | 0.15                                                    | 1    |      | $\mu\text{A}$ |

|                  |               | $V_{EN} = 0\text{V}$ (ディスエーブル), $V_{IN} = 6.0\text{V}$ , $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$                                            |                                                         |      | 10   |               |

| $I_{Q(DO)}$      | ドロップアウト時の静止電流 | $V_{IN} \leq V_{OUT(NOM)}$ , $I_{OUT} = 0\text{mA}$                                                                                                  | 7                                                       | 15   |      | $\mu\text{A}$ |

| $V_{DO}$         | ドロップアウト電圧     | $I_{OUT} = 500\text{mA}$ ,<br>$V_{OUT} = 95\% \times V_{OUT(NOM)}$                                                                                   | $0.8\text{V} \leq V_{OUT} < 1.0\text{V}$ <sup>(1)</sup> |      | 825  | $\text{mV}$   |

|                  |               |                                                                                                                                                      | $1.0\text{V} \leq V_{OUT} < 1.2\text{V}$ <sup>(1)</sup> |      | 605  |               |

|                  |               |                                                                                                                                                      | $1.2\text{V} \leq V_{OUT} < 1.5\text{V}$ <sup>(1)</sup> |      | 470  |               |

|                  |               |                                                                                                                                                      | $1.5\text{V} \leq V_{OUT} < 2.5\text{V}$                |      | 355  |               |

|                  |               |                                                                                                                                                      | $2.5\text{V} \leq V_{OUT} \leq 5.5\text{V}$             |      | 265  |               |

| $I_{CL}$         | 出力電流制限        | $V_{OUT} = 0.9 \times V_{OUT(NOM)}$                                                                                                                  | 650                                                     | 1060 | 1500 | $\text{mA}$   |

| $I_{SC}$         | 回路短絡時の電流制限    | $V_{OUT} = 0\text{V}$                                                                                                                                |                                                         | 325  |      | $\text{mA}$   |

## 5.5 電気的特性 (続き)

指定動作温度範囲内 ( $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ )、 $V_{\text{IN}} = V_{\text{OUT(NOM)}} + 0.3\text{V}$  または  $2\text{V}$  (いずれか大きい方)、 $V_{\text{EN}} = 1.0\text{V}$ 、 $I_{\text{OUT}} = 1\text{mA}$ 、 $C_{\text{IN}} = 1\mu\text{F}$ 、 $C_{\text{OUT}} = 1\mu\text{F}$  (特に記述のない限り)、標準値はすべて  $T_J = 25^{\circ}\text{C}$  での値です

| パラメータ                      |                   | テスト条件                                                                                   | 最小値                             | 標準値  | 最大値  | 単位                         |

|----------------------------|-------------------|-----------------------------------------------------------------------------------------|---------------------------------|------|------|----------------------------|

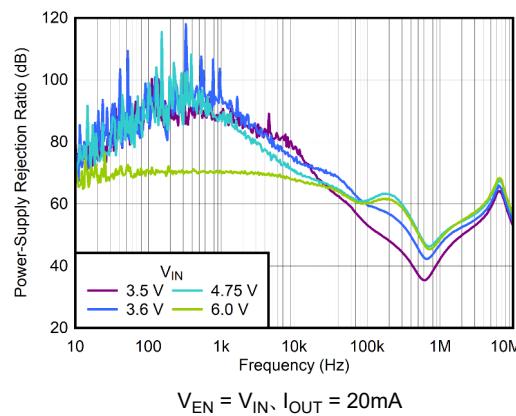

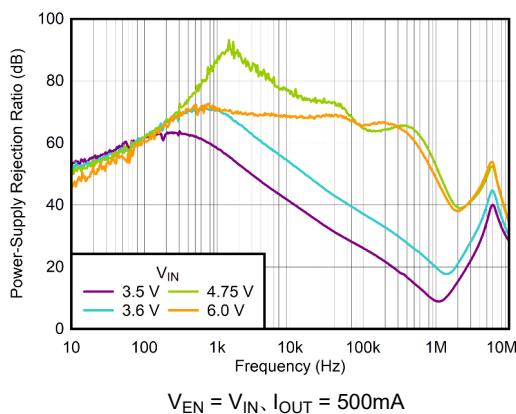

| PSRR                       | 電源除去比             | $I_{\text{OUT}} = 20\text{mA}$ ,<br>$V_{\text{IN}} = V_{\text{OUT}} + 1.0\text{V}$      | $f = 100\text{Hz}$              | 90   |      | dB                         |

|                            |                   |                                                                                         | $f = 1\text{kHz}$               | 91   |      |                            |

|                            |                   |                                                                                         | $f = 10\text{kHz}$              | 71   |      |                            |

|                            |                   |                                                                                         | $f = 100\text{kHz}$             | 61   |      |                            |

|                            |                   |                                                                                         | $f = 1\text{MHz}$               | 50   |      |                            |

|                            |                   | $I_{\text{OUT}} = 500\text{mA}$ ,<br>$V_{\text{IN}} = V_{\text{OUT}} + 1.0\text{V}$     | $f = 100\text{Hz}$              | 65   |      |                            |

|                            |                   |                                                                                         | $f = 1\text{kHz}$               | 85   |      |                            |

|                            |                   |                                                                                         | $f = 10\text{kHz}$              | 79   |      |                            |

|                            |                   |                                                                                         | $f = 100\text{kHz}$             | 44   |      |                            |

|                            |                   |                                                                                         | $f = 1\text{MHz}$               | 50   |      |                            |

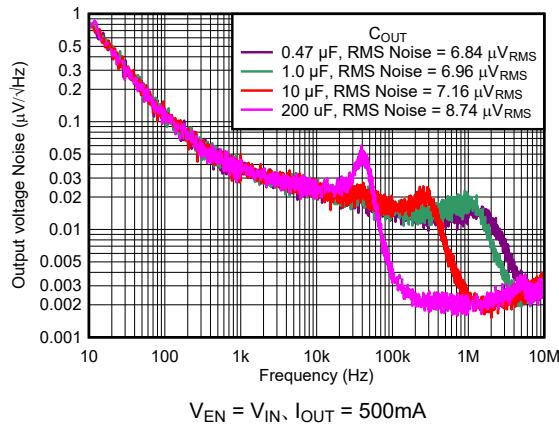

| $V_N$                      | 出力ノイズ電圧           | $BW = 10\text{Hz} \sim 100\text{kHz}$ ,<br>$V_{\text{OUT}} = 2.8\text{V}$               | $I_{\text{OUT}} = 500\text{mA}$ | 7.7  |      | $\mu\text{V}_{\text{RMS}}$ |

|                            |                   |                                                                                         | $I_{\text{OUT}} = 1\text{mA}$   | 10   |      |                            |

| $R_{\text{PULLDOWN}}$      | 出力自動放電プルダウン抵抗     | $V_{\text{IN}} = 2\text{V}$ , $V_{\text{EN}} < V_{\text{IL}}$ (出力ディスエーブル)               |                                 | 150  |      | $\Omega$                   |

| $T_{\text{SD}}$            | サーマル シャットダウン立ち上がり | $T_J$ 立ち上がり                                                                             |                                 | 165  |      | $^{\circ}\text{C}$         |

|                            | サーマル シャットダウン立ち下がり | $T_J$ 立ち下がり                                                                             |                                 | 140  |      |                            |

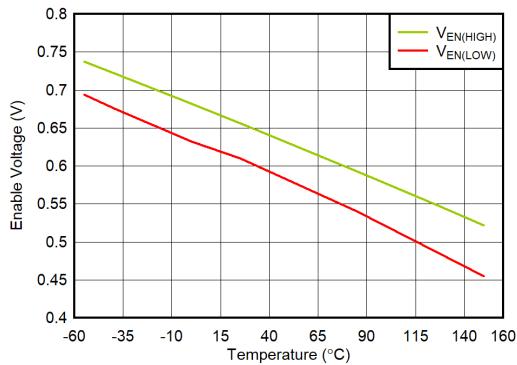

| $V_{\text{EN(LOW)}}$       | Low 入力スレッショルド     | $V_{\text{IN}} = 2.0\text{V} \sim 6.0\text{V}$ ,<br>$V_{\text{EN}}$ は出力が無効化されるまで立ち下がります |                                 | 0.3  |      | $\text{V}$                 |

| $V_{\text{EN(HI)}}$        | High 入力スレッショルド    | $V_{\text{IN}} = 2.0\text{V} \sim 6.0\text{V}$ ,<br>$V_{\text{EN}}$ は出力が有効化されるまで立ち上がります |                                 | 0.9  |      | $\text{V}$                 |

| $V_{\text{UVLO}}$          | UVLO スレッショルド      | $V_{\text{IN}}$ 立ち上がり                                                                   | 1.11                            | 1.32 | 1.63 | $\text{V}$                 |

|                            |                   | $V_{\text{IN}}$ 立ち下がり                                                                   | 1.05                            | 1.27 | 1.57 |                            |

| $V_{\text{UVLO(HYST)}}$    | UVLO ヒステリシス       |                                                                                         |                                 | 50   |      | $\text{mV}$                |

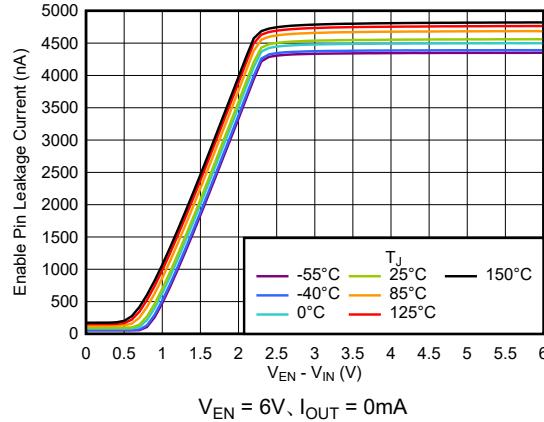

| $I_{\text{EN}}$            | EN ビンのリーク電流       | $V_{\text{EN}} = 6.0\text{V}$ , $V_{\text{IN}} = 6.0\text{V}$                           |                                 | 100  | 300  | $\text{nA}$                |

| $R_{\text{EN(PULL-DOWN)}}$ | スマートイネーブルのプルダウン抵抗 |                                                                                         |                                 | 440  |      | $\text{k}\Omega$           |

| $t_{\text{ON}}$            | ターンオン時間           | $V_{\text{EN}} > V_{\text{IH}}$ から $V_{\text{OUT}}$ まで = $V_{\text{OUT(NOM)}}$ の 95%    | 120                             | 200  | 280  | $\mu\text{s}$              |

- (1) UVLO スレッショルドを下回っている、または極端に近い電圧での  $V_{\text{OUT}}$  のドロップアウト電圧は、直接測定されません。表示された値は、シミュレーションにより検証されています。

## 5.6 代表的特性

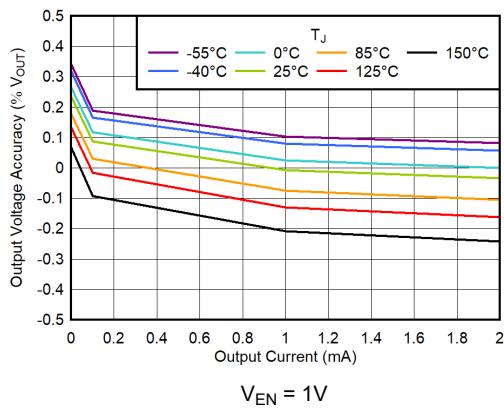

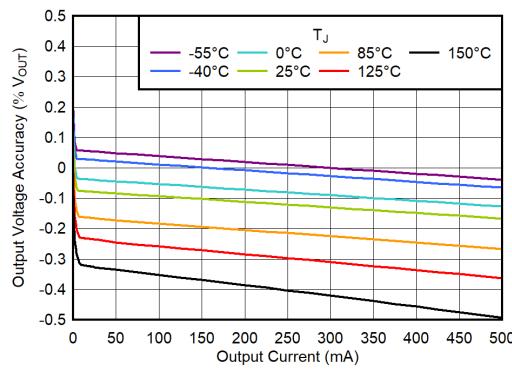

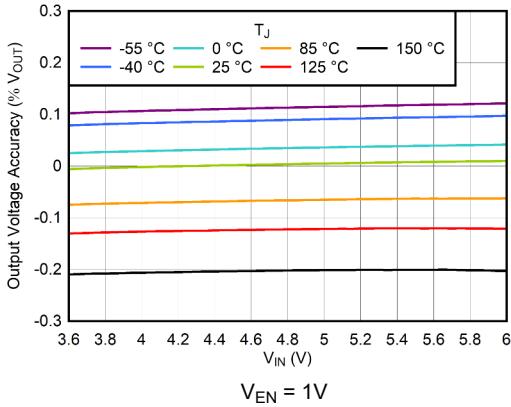

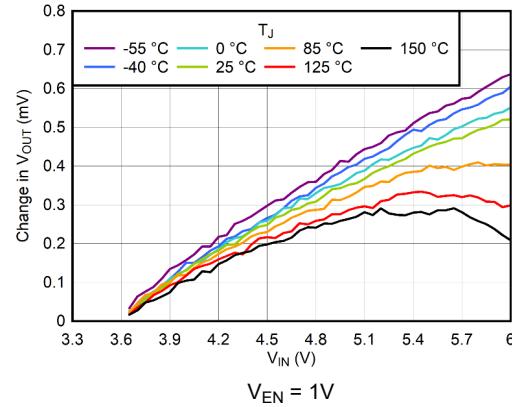

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^{\circ}C$  (特に記述のない限り)

図 5-1. 出力電圧精度と  $I_{OUT}$  との関係

図 5-2. 出力電圧精度と  $I_{OUT}$  との関係

図 5-3. 出力電圧精度と  $V_{IN}$  との関係

図 5-4. ライン レギュレーションと  $V_{IN}$  との関係

図 5-5. ロード レギュレーションと  $I_{OUT}$  との関係

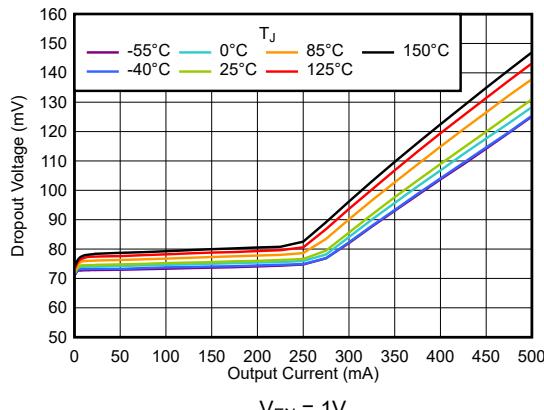

図 5-6. ドロップアウト電圧と  $I_{OUT}$  との関係

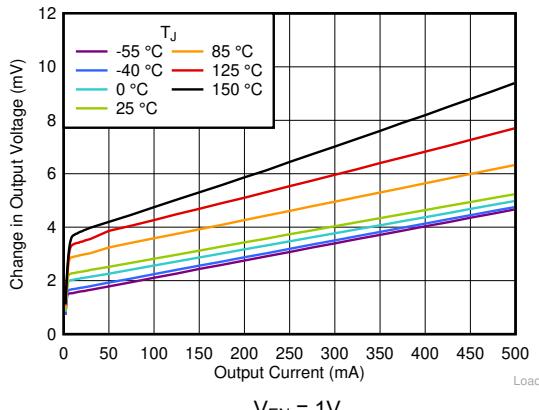

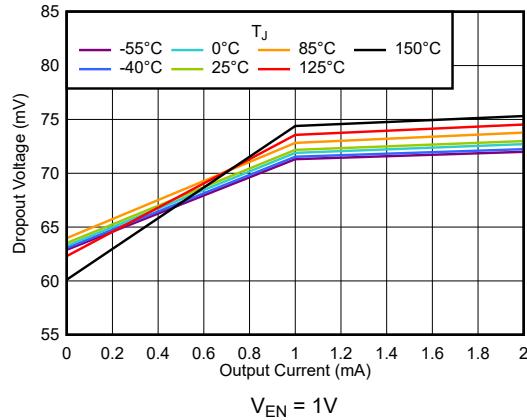

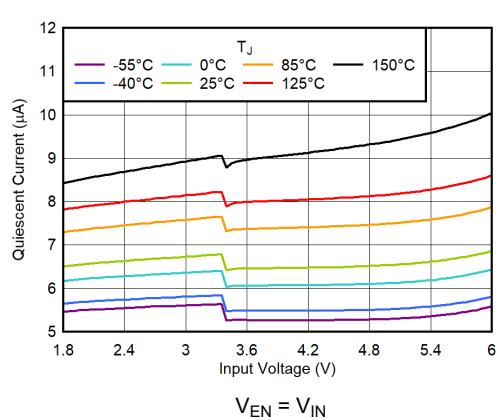

## 5.6 代表的特性 (続き)

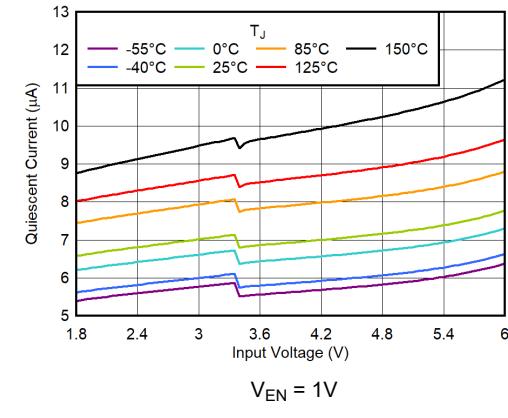

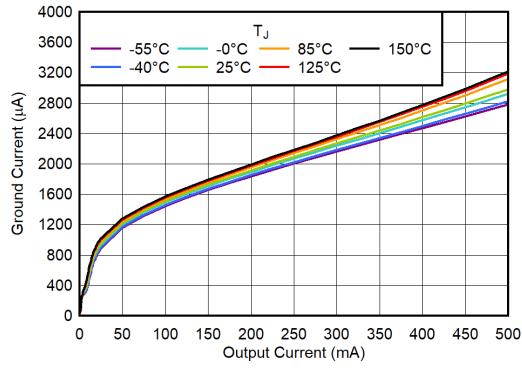

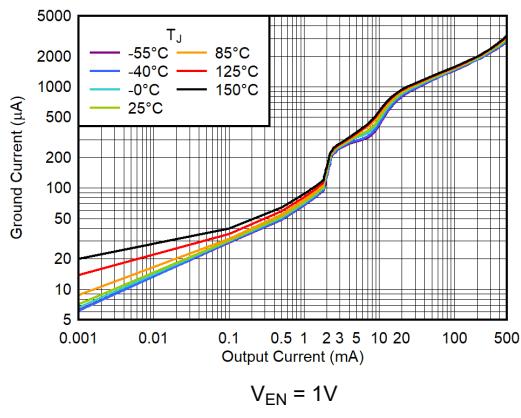

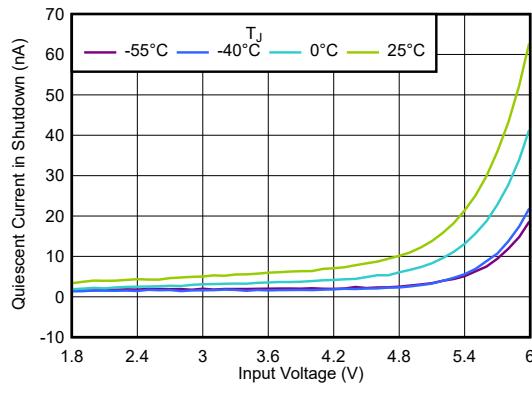

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^{\circ}C$  (特に記述のない限り)

図 5-7. ドロップアウト電圧と  $I_{OUT}$  との関係

図 5-8.  $I_Q$  と  $V_{IN}$  との関係

図 5-9.  $I_Q$  と  $V_{IN}$  との関係

図 5-10.  $I_{GND}$  と  $I_{OUT}$  との関係

図 5-11.  $I_{GND}$  と  $I_{OUT}$  との関係

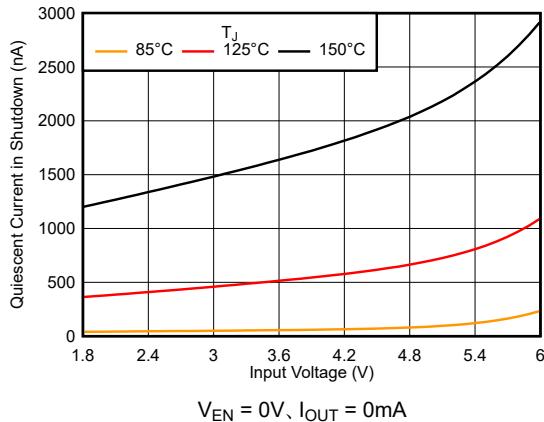

図 5-12. シャットダウン電流と  $V_{IN}$  との関係

## 5.6 代表的特性 (続き)

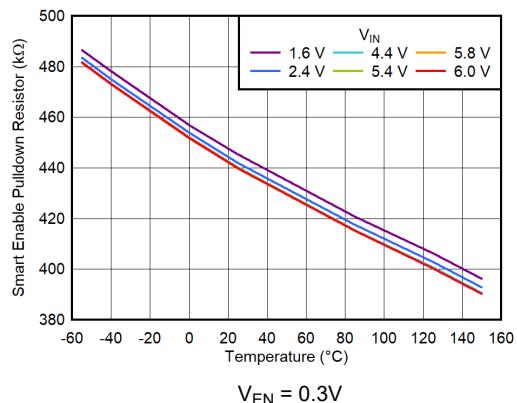

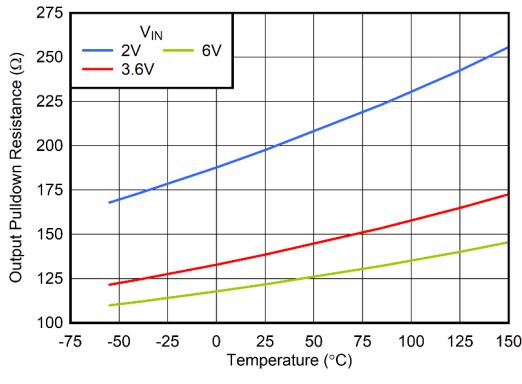

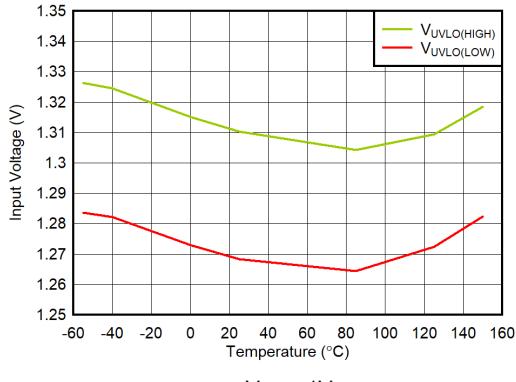

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^\circ C$  (特に記述のない限り)

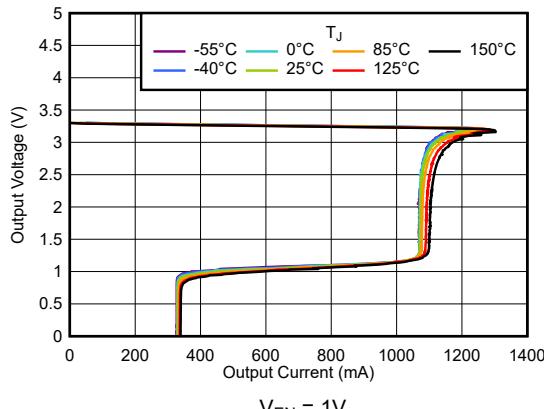

図 5-13. シャットダウン電流と  $V_{IN}$  との関係

図 5-14. フォールドバック電流制限

図 5-15. イネーブル ロジック スレッショルドと温度との関係

図 5-16. イネーブル ピンのリーク電流と  $V_{EN} - V_{IN}$  との関係

図 5-17. スマートイネーブル プルダウン抵抗と温度および  $V_{IN}$  との関係

図 5-18. 出力プルダウン抵抗と温度および  $V_{IN}$  との関係

## 5.6 代表的特性 (続き)

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^\circ C$  (特に記述のない限り)

$V_{EN} = 1V$

図 5-19.  $V_{IN}$  UVLO スレッショルドと温度との関係

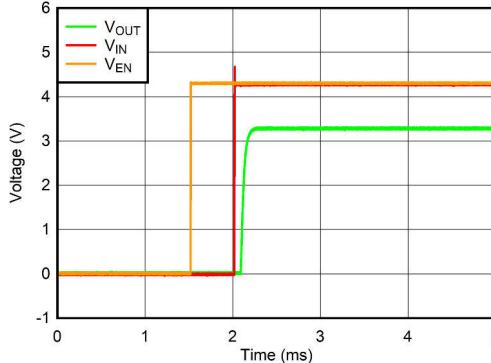

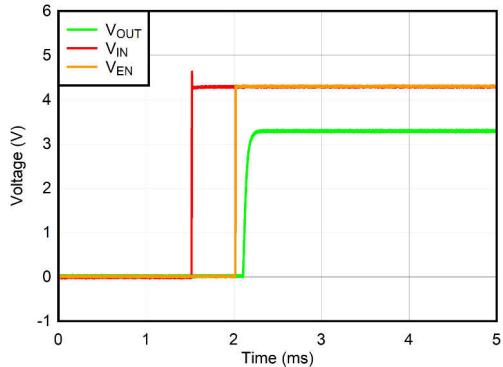

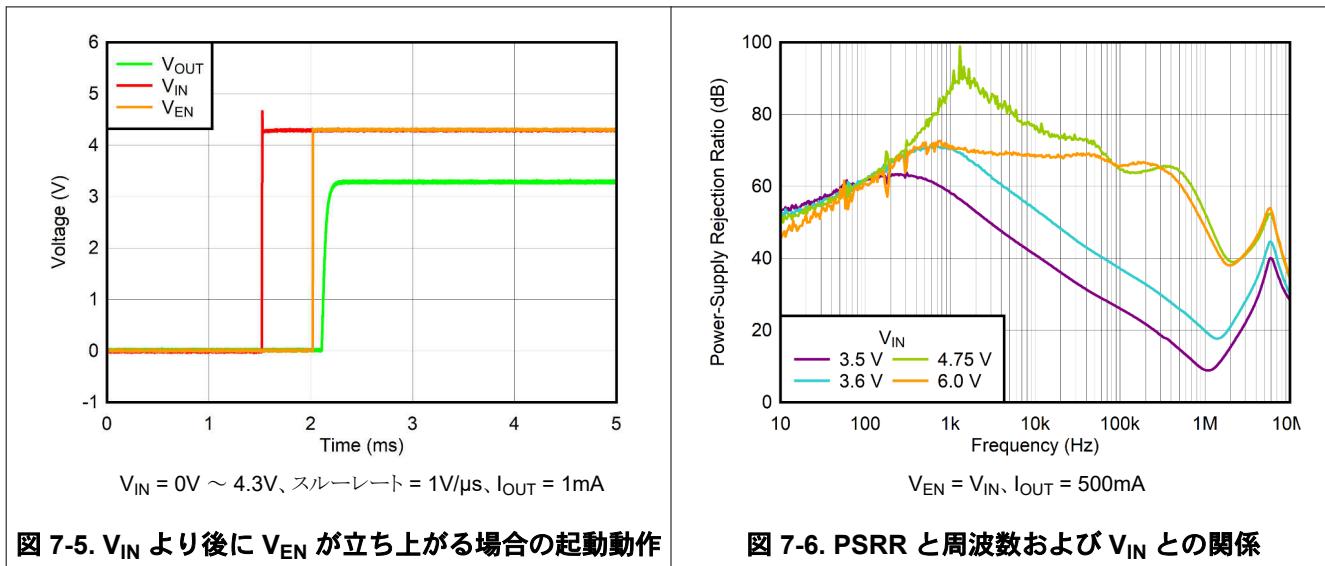

$V_{IN} = 0V \sim 4.3V$ 、スルーレート =  $1V/\mu s$ 、 $I_{OUT} = 500mA$

図 5-20.  $V_{IN}$  より前に  $V_{EN}$  が立ち上がる場合の起動動作

$V_{IN} = 0V \sim 4.3V$ 、スルーレート =  $1V/\mu s$ 、 $I_{OUT} = 0mA$

図 5-21.  $V_{IN}$  より後に  $V_{EN}$  が立ち上がる場合の起動動作

$V_{IN} = 0V \sim 4.3V$ 、スルーレート =  $1V/\mu s$ 、 $I_{OUT} = 500mA$

図 5-22.  $V_{IN}$  より後に  $V_{EN}$  が立ち上がる場合の起動動作

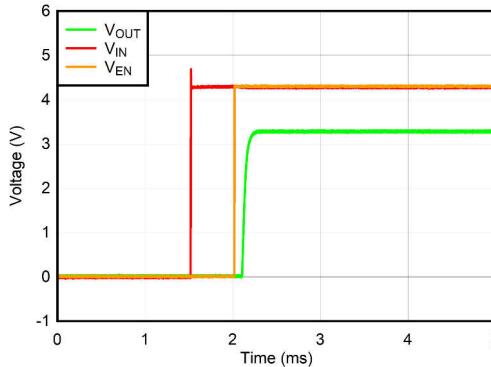

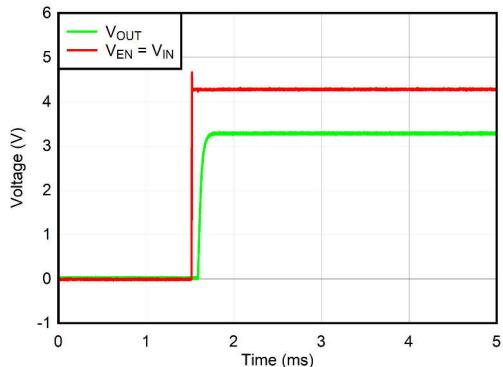

$V_{IN} = 0V \sim 4.3V$ 、スルーレート =  $1V/\mu s$ 、 $I_{OUT} = 500mA$

図 5-23.  $V_{EN} = V_{IN}$  によるスタートアップ

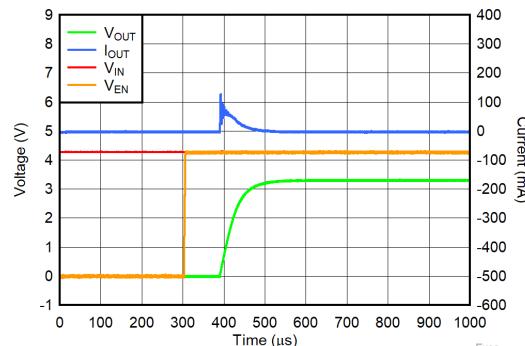

$V_{IN} = 4.3V$ 、 $V_{EN} = 0V \sim 4.3V$ 、スルーレート =  $1V/\mu s$ 、

$I_{OUT} = 0mA$ 、 $C_{OUT} = 1\mu F$

図 5-24. スタートアップ突入電流

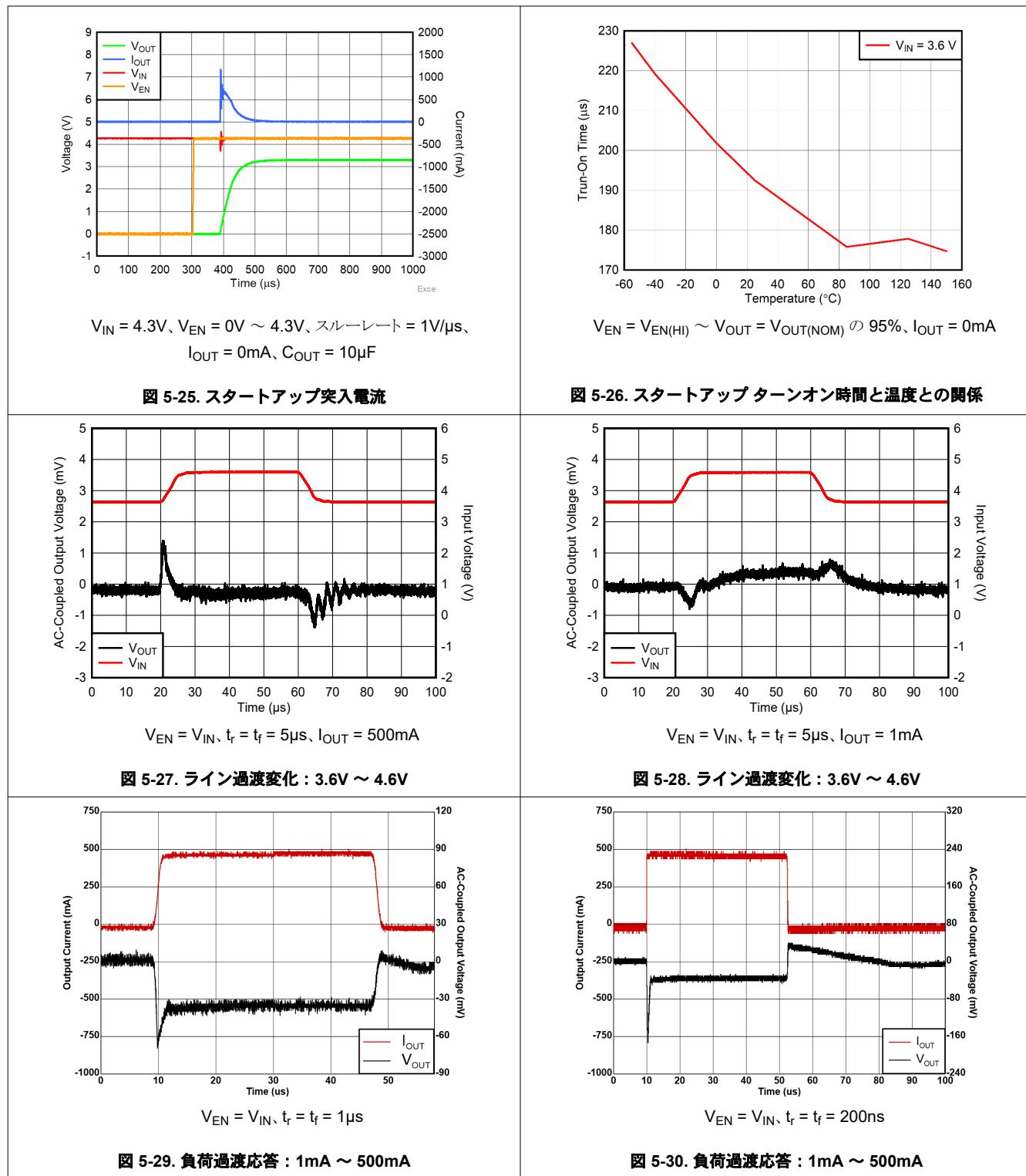

## 5.6 代表的特性 (続き)

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^\circ C$  (特に記述のない限り)

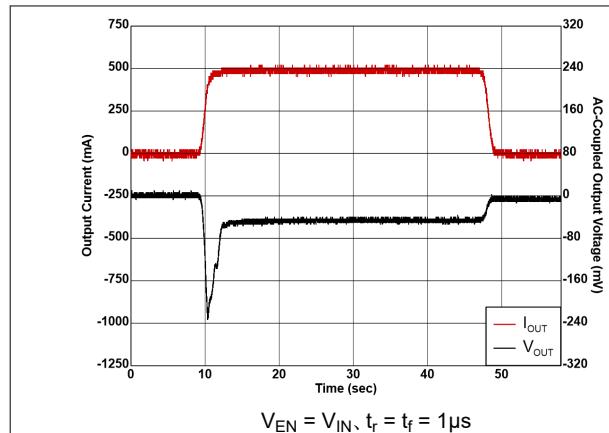

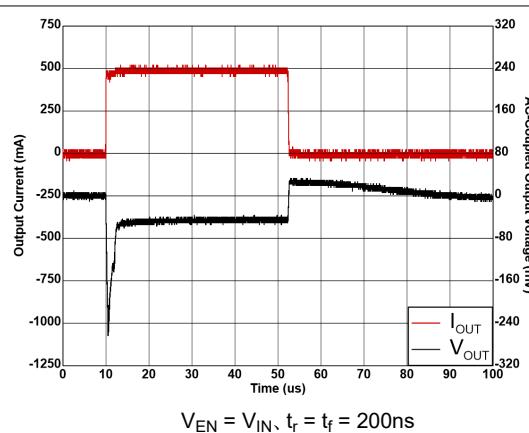

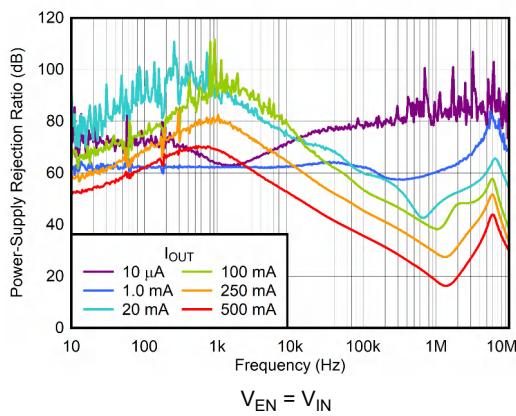

## 5.6 代表的特性 (続き)

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^\circ C$  (特に記述のない限り)

図 5-31. 負荷過渡応答 : 0mA ~ 500mA

図 5-32. 負荷過渡応答 : 0mA ~ 500mA

図 5-33. PSRR と周波数および  $I_{OUT}$  との関係

図 5-34. PSRR と周波数および  $V_{IN}$  との関係

図 5-35. PSRR と周波数および  $V_{IN}$  との関係

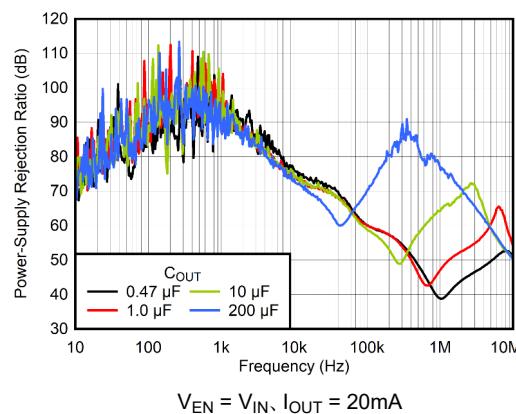

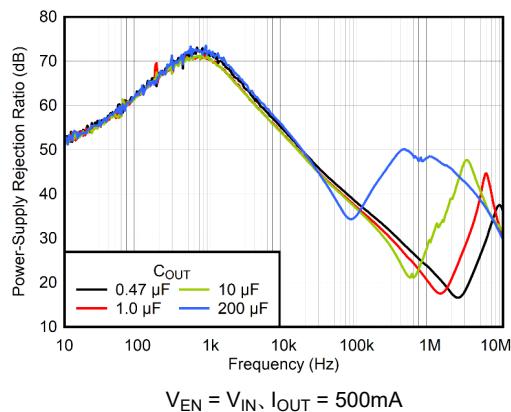

図 5-36. PSRR と周波数および  $C_{OUT}$  との関係

## 5.6 代表的特性 (続き)

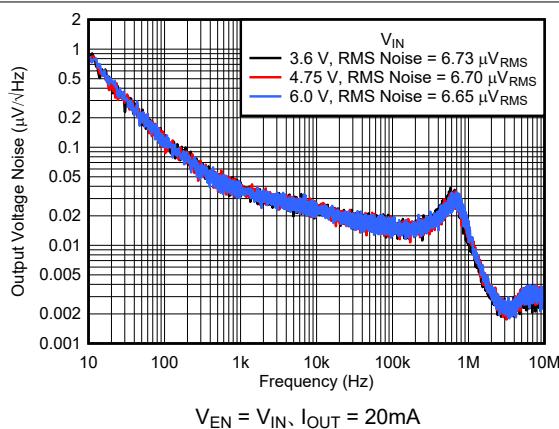

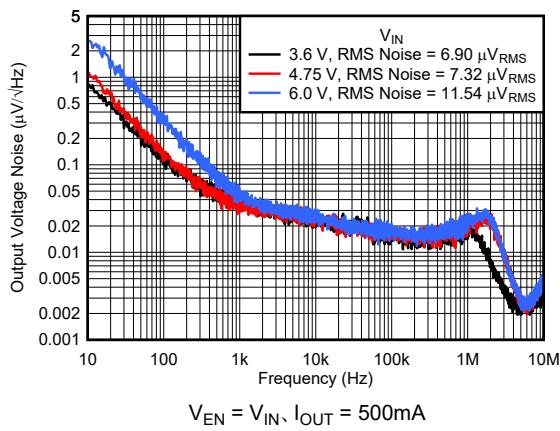

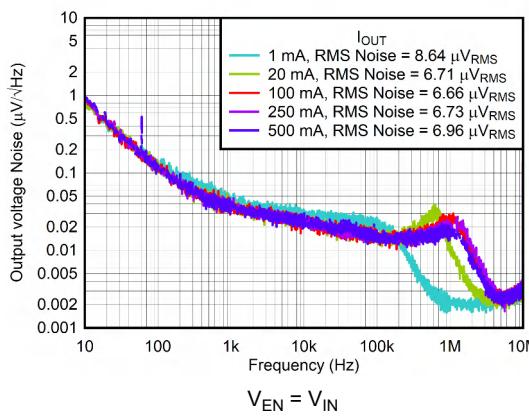

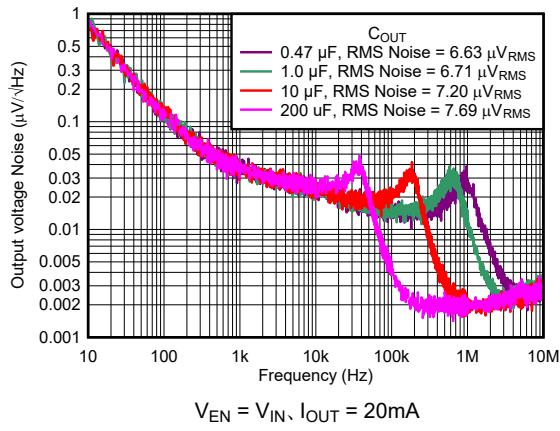

$V_{IN} = 3.6V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 1mA$ 、 $C_{IN} = 1\mu F$ 、 $C_{OUT} = 1\mu F$ 、 $T_A = 25^\circ C$  (特に記述のない限り)

図 5-37. PSRR と周波数および  $C_{OUT}$  との関係

図 5-38. ノイズと周波数および  $V_{IN}$  との関係

図 5-39. ノイズと周波数および  $V_{IN}$  との関係

図 5-40. ノイズと周波数および  $I_{OUT}$  との関係

図 5-41. ノイズと周波数および  $C_{OUT}$  との関係

図 5-42. ノイズと周波数および  $C_{OUT}$  との関係

## 6 詳細説明

### 6.1 概要

感度の高い RF 回路およびアナログ回路の要件を満たすよう設計された TPS7A21-Q1 は、低ノイズ、高 PSRR、低静止電流、ラインおよび負荷の優れた過渡応答といった特徴を備えています。TPS7A21-Q1 は、個別のノイズ フィルタ コンデンサを必要とせずに、優れたノイズ性能を実現できます。

TPS7A21-Q1 は、 $1\mu\text{F}$  入力コンデンサ 1 個と、 $1\mu\text{F}$  セラミック出力コンデンサ 1 個で正常に動作するように設計されています。すべての動作電圧および温度条件にわたって、実効出力容量が少なくとも  $0.4\mu\text{F}$  であることを確認します。

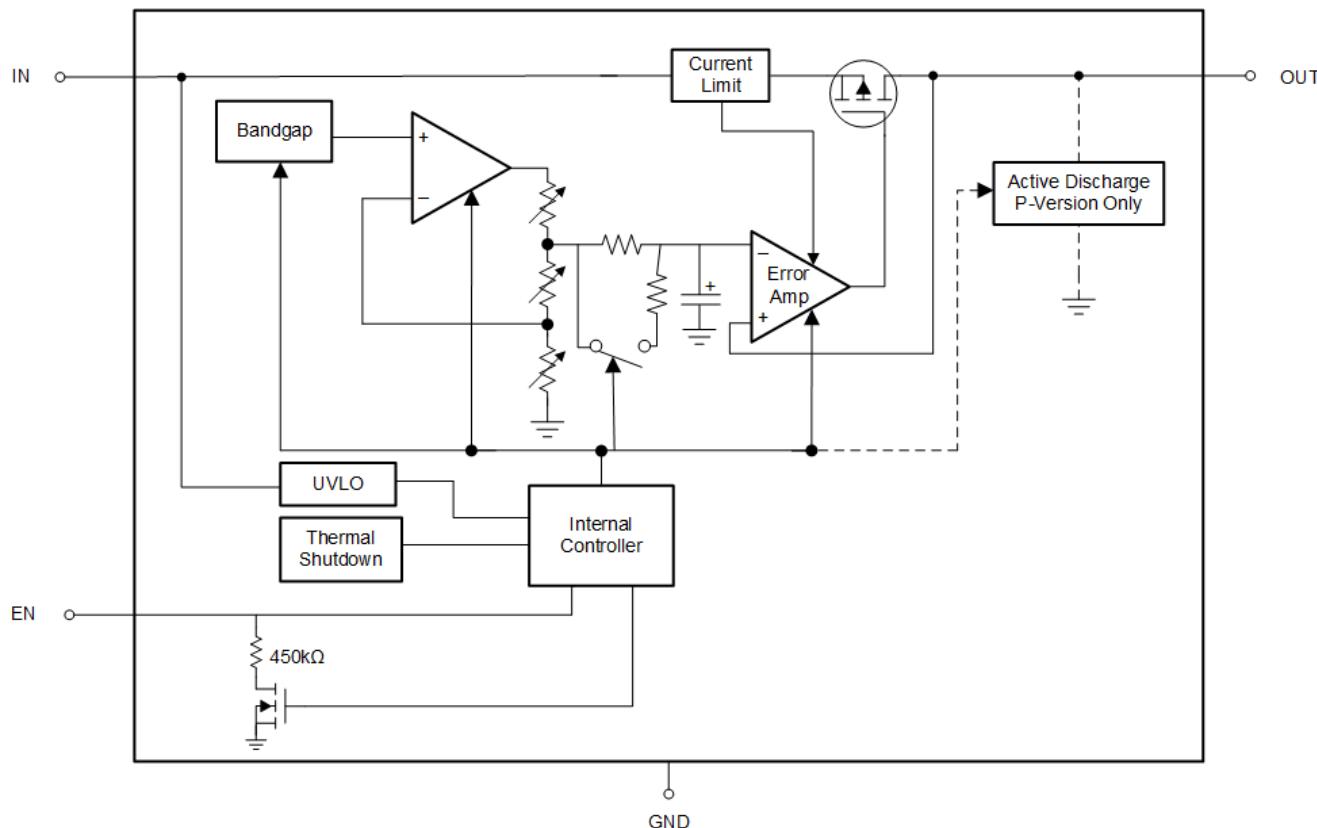

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 スマートイネーブル(EN)

イネーブルピン(EN)はアクティブHighです。ENに印加される電圧が $V_{EN(HI)}$ を上回ると、出力が有効になり、印加電圧が $V_{EN(LOW)}$ を下回ると、出力が無効になります。出力電圧の外部制御が必要な場合は、ENをINに接続します。このデバイスは、静止電流を低減するスマートイネーブル回路を搭載しています。イネーブルピンの電圧が $V_{EN(HI)}$ 以上に駆動されると、出力が有効になり、スマートイネーブル機能の内部プルダウン抵抗( $R_{EN(PULLDOWN)}$ )が切り離されます。イネーブルピンがフローティング状態の場合、 $R_{EN(PULLDOWN)}$ が接続され、イネーブルピンをLowにプルダウンすることで出力を無効化します。スマートプルダウンは、静止電流の低減に加えて、電流駆動能力が制限されたソースからENを駆動した場合でも、ロジックレベルを適切に維持するのに役立ちます。[電気的特性](#)表に、 $R_{EN(PULLDOWN)}$ の値を示します。

### 6.3.2 低い出力ノイズ

TPS7A21-Q1リファレンス電圧での内部ノイズは、出力バッファ段に渡される前に、1次ローパスRCフィルタによって低減されます。ローパスRCフィルタは、-3dBカットオフ周波数が約0.1Hzです。スタートアップ中、フィルタ抵抗はバイパスされるため、出力の立ち上がり時間が短縮されます。出力電圧が公称値に達すると、フィルタは通常動作を開始します。

### 6.3.3 アクティブ放電

このレギュレータにはMOSFET(金属酸化膜半導体電界効果トランジスタ)が内蔵されており、このMOSFETが無効化されていて、出力電圧をアクティブに放電しようとするときに、出力ピンとグランドピンの間にプルダウン抵抗を接続します。INの電圧がプルダウンMOSFETをオンにするのに十分な高さであることを確認します。 $V_{IN}$ が低すぎて、プルダウンMOSFETに十分な $V_{GS}$ を供給できない場合、プルダウン回路はアクティブになりません。アクティブ放電回路は、イネーブルピンによって、またはINの電圧が低電圧誤動作防止(UVLO)スレッショルドを下回ることによって有効になります。

入力電源が低下した後で、大きな出力キャパシタンスを放電する場合には、アクティブ放電回路に依存しないでください。逆電流が出力側から入力側へ流れる可能性があります。この逆電流の流れは、デバイスに損傷を与える可能性があります。そのような過渡逆電流は、デバイスの定格電流の5%以下に制限します。

### 6.3.4 ドロップアウト電圧

ドロップアウト電圧( $V_{DO}$ )は、パストランジスタが完全にオンとなる定格出力電流( $I_{RATED}$ )において、入力電圧から出力電圧を引いた値( $V_{IN} - V_{OUT}$ )として定義されます。 $I_{RATED}$ は、[推奨動作条件](#)表に記載されている最大 $I_{OUT}$ です。パストランジスタは、抵抗領域すなわち動作の三極管領域で動作し、スイッチとして機能します。ドロップアウト電圧は、出力電圧がレギュレーションのままであると予想される、プログラムされた公称出力電圧よりも大きな最小入力電圧を間接的に指定します。入力電圧が出力レギュレーションをサポートするために必要な値よりも低下すると、出力電圧も同様に低下します。

CMOSレギュレータの場合、ドロップアウト電圧はパストランジスタのドレインソース間オン抵抗( $R_{DS(ON)}$ )によって決まります。したがって、リニアレギュレータが定格電流よりも低い値で動作する場合、その電流に対するドロップアウト電圧はそれに応じてスケーリングされます。[式1](#)により、デバイスの $R_{DS(ON)}$ を計算します。

$$R_{DS(ON)} = \frac{V_{DO}}{I_{RATED}} \quad (1)$$

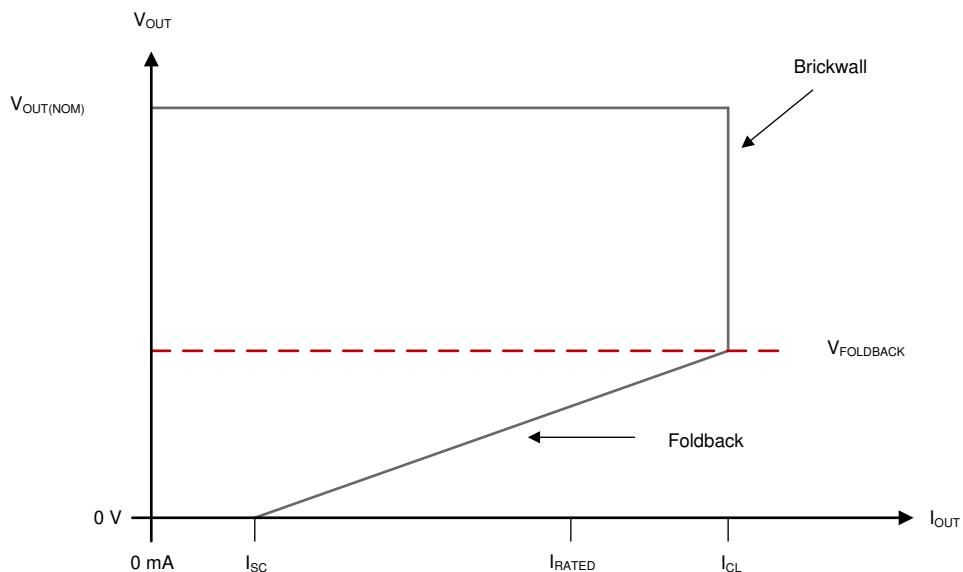

### 6.3.5 フォールドバック電流制限

TPS7A21-Q1には、内部に電流制限回路があり、過渡的な高負荷電流障害または短絡イベントの時にレギュレータを保護します。電流制限は、ブリックウォールフォールドバック方式です。フォールドバック電圧( $V_{FOLDBACK}$ )では、電流制限はブリックウォール方式からフォールドバック方式に遷移します。

出力電圧が $V_{FOLDBACK}$ を上回った際の高負荷電流障害では、ブリックウォール方式により、出力電流が電流制限( $I_{CL}$ )に制限されます。出力電圧が $V_{FOLDBACK}$ を下回ると、フォールドバック電流制限が有効になり、出力電圧がGNDに近

付くと電流を小さくします。出力が短絡したとき、デバイスは 短絡電流制限 ( $I_{SC}$ ) と呼ばれる標準的な電流を供給します。 $I_{CL}$  と  $I_{SC}$  は、「[電気的特性](#)」表に記載されています。

デバイスが電流制限されている場合、出力電圧はレギュレートされません。電流制限イベントが発生すると、消費電力の増加によりレギュレータが発熱し始めます。デバイスがブリックウォール電流制限にある場合、パストランジスタは電力  $[(V_{IN} - V_{OUT}) \times I_{CL}]$  を消費します。出力が短絡され、出力が  $V_{FOLDBACK}$  を下回ると、パストランジスタは電力  $[(V_{IN} - V_{OUT}) \times I_{SC}]$  を消費します。サーマルシャットダウンがトリガされると、デバイスはオフになります。デバイスの温度が下がると、内蔵のサーマルシャットダウン回路によってデバイスがオンに戻ります。出力電流フォルト状態が継続すると、デバイスは電流制限とサーマルシャットダウンを繰り返します。電流制限の詳細については、「[制限の把握](#)」アプリケーションノートを参照してください。

図 6-1 は、フォールドバック電流制限の図を示しています。

図 6-1. フォールドバック電流制限

### 6.3.6 低電圧誤動作防止

入力電圧を監視する独立した低電圧ロックアウト (UVLO) 回路を備えており、出力電圧のオンおよびオフを制御された一定の動作で行えるようにします。負荷過渡中に入力電圧が低下した場合 (デバイスの出力がイネーブルのとき)、UVLO にはヒステリシスが組み込まれているため、不要なターンオフを防止できます。

### 6.3.7 過熱保護機能 ( $T_{SD}$ )

接合部温度  $T_J$  がシャットダウン温度スレッショルド  $T_{SD}$  まで上昇すると、サーマルシャットダウンにより出力が無効になります。サーマルシャットダウン回路のヒステリシスにより、再度オンにする前に、温度がより低い温度まで下がる必要があります。半導体ダイの熱時定数はかなり短いです。このため、サーマルシャットダウンに達した時点で、消費電力が低下するまで、デバイスはオンとオフを繰り返します。

スタートアップ時にデバイス両端で大きな  $V_{IN} - V_{OUT}$  電圧降下が発生するか、大きな突入電流によって大容量の出力コンデンサが充電されるため、電力消費が高くなります。条件によっては、サーマルシャットダウン保護機能により、起動が完了する前にデバイスが無効化されることがあります。

信頼性の高い動作を実現するには、接合部温度を「[推奨動作条件](#)」表に記載された最大値に制限します。この最大温度を超えて動作すると、レギュレータは動作仕様を超えます。

サーマル シャットダウン回路は一時的な熱過負荷状態から保護するように設計されていますが、この回路は適切な熱設計の代わりとなるものではありません。レギュレータをサーマル シャットダウン状態、または推奨される最大接合部温度を上回る状態で使用し続けると、長期的な信頼性が低下します。

## 6.4 デバイスの機能モード

### 6.4.1 デバイスの機能モードの比較

表 6-1 に、各種の動作モードにつながる条件を示します。パラメータ値については、[電気的特性](#) 表を参照してください。

**表 6-1. デバイスの機能モードの比較**

| 動作モード                             | パラメータ                                                       |                           |                          |                             |

|-----------------------------------|-------------------------------------------------------------|---------------------------|--------------------------|-----------------------------|

|                                   | $V_{IN}$                                                    | $V_{EN}$                  | $I_{OUT}$                | $T_J$                       |

| 通常動作                              | $V_{IN} > V_{OUT(nom)} + V_{DO}$ および $V_{IN} > V_{IN(min)}$ | $V_{EN} \geq V_{EN(HI)}$  | $I_{OUT} < I_{OUT(max)}$ | $T_J < T_{SD(shutdown)}$    |

| ドロップアウト動作                         | $V_{IN(min)} < V_{IN} < V_{OUT(nom)} + V_{DO}$              | $V_{EN} \geq V_{EN(HI)}$  | $I_{OUT} < I_{OUT(max)}$ | $T_J < T_{SD(shutdown)}$    |

| ディスエーブル<br>(条件が真の場合、デバイスはディスエーブル) | $V_{IN} < V_{UVLO}$                                         | $V_{EN} \leq V_{EN(LOW)}$ | 該当なし                     | $T_J \geq T_{SD(shutdown)}$ |

### 6.4.2 通常動作

デバイスは、以下の条件が満たされたとき、公称出力電圧へのレギュレートを行います。

- 入力電圧が、公称出力電圧とドロップアウト電圧の和 ( $V_{OUT(nom)} + V_{DO}$ ) よりも大きい

- 出力電流が、電流制限より小さい ( $I_{OUT} < I_{CL}$ )

- デバイスの接合部温度がサーマル シャットダウンの温度を下回っている ( $T_J < T_{SD}$ )

- イネーブル電圧が以前にイネーブル立ち上がりスレッショルド電圧を超えていて、まだイネーブル立ち下がりスレッショルドよりも低くなっていない

### 6.4.3 ドロップアウト動作

入力電圧が、公称出力電圧と規定ドロップアウト電圧の和よりも小さいが、通常動作の他の条件がすべて満たされているとき、デバイスはドロップアウト モードで動作します。このモードでは、出力電圧は入力電圧に追従します。このモードでは、パストランジスタがオーム領域または三極管領域にあり、スイッチとして機能するため、デバイスの過渡性能が大幅に低下します。ドロップアウト中にライン過渡または負荷過渡事象が生じると、大きな出力電圧の偏差が発生します。

デバイスが定的なドロップアウト状態にあるとき (起動中ではないが、通常のレギュレーション状態になった直後に、デバイスがドロップアウト状態 ( $V_{IN} < V_{OUT(NOM)} + V_{DO}$ ) になったときとして定義される)、パストランジスタはオーム領域または三極管領域に駆動されます。入力電圧が公称出力電圧とドロップアウト電圧 ( $V_{OUT(NOM)} + V_{DO}$ ) を加えた値以上に戻ると、デバイスがパストランジスタをリニア領域にプルバックする間に、出力電圧が短時間オーバーシュートすることができます。

出力電流が約 200mA より小さい場合、ドロップアウト電圧曲線の勾配は大電流の場合よりも小さくなります。このスロープは、LDO がドロップアウト状態のときに優れた性能を維持するのに役立ちます。

### 6.4.4 ディセーブル

イネーブル ピンの電圧を強制的に  $V_{EN(LOW)}$  未満にして、デバイスの出力をシャットダウンします。無効化されると、パストランジスタがオフになり、内部回路がシャットダウンされ、出力電圧は内部放電回路によって出力からグランドへアクトライブに放電されます。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

#### 7.1.1 推奨されるコンデンサの種類

このデバイスは、入出力に低等価直列抵抗 (ESR) のセラミックコンデンサを使用することで安定するように設計されています。積層セラミックコンデンサは、多くのタイプのアプリケーションの業界標準になっており、推奨されますが、適切な判断のもとに使用する必要があります。X7R、X5R、C0G 定格の誘電体材料を使用したセラミックコンデンサは、温度範囲全体にわたって良好な容量の安定性を実現しますが、Y5V 定格のコンデンサの使用は、静電容量の変動が大きいため推奨されません。

選択したセラミックコンデンサの種類にかかわらず、実効静電容量は動作電圧と温度によって変化します。性能を確認するには、メーカーのデータシートを参照してください。一般に、実効静電容量は 50% 程度減少すると予想されます。「[推奨動作条件](#)」表に推奨される入力および出力コンデンサは、公称値の約 50% の実効静電容量を表しています。

#### 7.1.2 入出力コンデンサの要件

入力コンデンサなしで LDO が安定しますが、設計上の適切な方法は、少なくとも「[推奨動作条件](#)」表に規定されている公称値と同じ値で、IN と GND の間にコンデンサを接続することです。入力コンデンサは、リアクティブな入力ソースに対抗し、過渡応答、入力リップル、PSRR を改善します。ソースインピーダンスが  $0.5\Omega$  を超える場合には、これが推奨されます。ソース抵抗とインダクタンスが十分に高い場合、IN と GND の間に容量が不十分な場合、システム全体の不安定性（リングングや持続的な発振を含む）やその他の性能低下の影響を受けやすくなります。立ち上がり時間の高速な負荷またはライン過渡事象が大きく存在する場合、または LDO が入力電源から数センチ以上離れている場合には、最小値よりも大きいコンデンサが必要です。

適切な値の出力コンデンサは、安定性の確保と動的性能の向上に役立ちます。「[推奨動作条件](#)」表に記載されている範囲内の出力コンデンサを使用します。

#### 7.1.3 負荷過渡応答

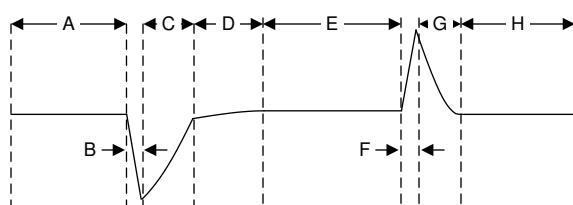

負荷ステップ過渡応答とは、LDO の出力電圧が負荷電流の変動に対してどのように応答し、出力電圧のレギュレーションを維持するかを示すものです。負荷過渡応答中には、軽負荷から重負荷への遷移、および重負荷から軽負荷への遷移の 2 つの重要な遷移があります。図 7-1 に示す領域は、以下のように分類されます。A、E、H の各領域で、出力電圧が定常状態にあることを示しています。

図 7-1. 負荷過渡波形

軽負荷から重負荷への遷移中の動作:

- 初期の電圧降下は、出力コンデンサの電荷の消耗および出力コンデンサまでの寄生インピーダンスによって生じるもの（領域 B）

- 電圧降下からの回復は、LDO が供給電流を増加させることによって起こり、出力電圧のレギュレーションへつながります（領域 C）

重負荷から軽負荷への遷移時には、以下のようなことが起こります:

- 初期の電圧上昇は、LDO が大きな電流を供給することによって生じ、その結果、出力コンデンサの電荷が増加します（領域 F）

- 電圧上昇からの回復は、LDO が供給電流を減少させることと、負荷が出力コンデンサを放電することによって生じます（領域 G）

出力容量が大きいと、負荷過渡時のピークは小さくなりますが、デバイスの応答時間は遅くなります。DC 負荷が大きくなることでもピークは小さくなります。これは、遷移の振幅が小さくなり、出力コンデンサに対してより大きな電流の放電経路が確保されるためです。

#### 7.1.4 低電圧誤動作防止 (UVLO) 動作

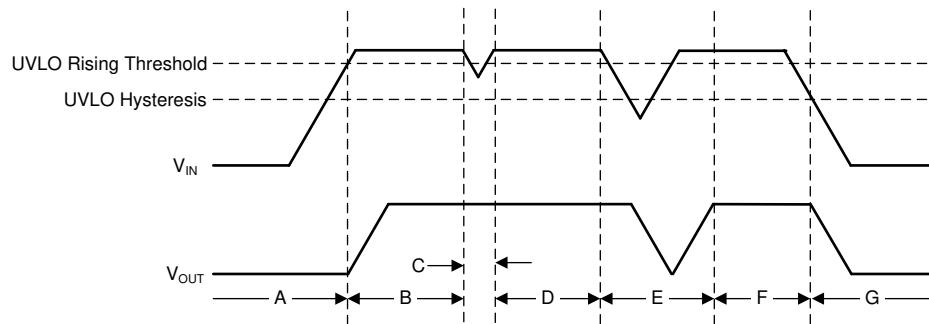

UVLO 回路により、入力電源が最小動作電圧範囲に達する前にデバイスがディスエーブル状態を維持し、入力電源が急激に低下した場合にデバイスが確実にシャットダウンされます。図 7-2 に、各種入力電圧イベントに対する UVLO 回路の応答を示します。この図は、次の領域に分かれています:

- 領域 A: 入力が UVLO 立ち上がりスレッショルドに達するまで、デバイスは起動しません。

- 領域 B: 通常動作、レギュレーション デバイス。

- 領域 C: UVLO 立ち下がりスレッショルドを上回るブラウンアウト イベント (UVLO 立ち上がりスレッショルド - UVLO ヒステリシス)。出力は規定の範囲から外れますが、デバイスは有効なままで。

- 領域 D: 通常動作、レギュレーション デバイス。

- 領域 E: UVLO 立ち下がりスレッショルドを下回るブラウンアウト イベント。ほとんどの場合、デバイスはディセーブルされており、負荷およびアクティブ放電回路によって出力が低下します。入力電圧が UVLO の立ち上がりスレッショルドに達すると、デバイスは再びイネーブル状態になり、通常の起動シーケンスに移行します。

- 領域 F: 通常動作の後、入力電圧が UVLO の下降スレッショルドまで低下します。

- 領域 G: 入力電圧が UVLO 立ち下がりスレッショルド 0V を下回ると、デバイスはディスエーブルになります。負荷およびアクティブ放電回路によって出力が低下します。

図 7-2. UVLO の標準動作

#### 7.1.5 消費電力 ( $P_D$ )

回路の信頼性を確保するには、デバイスの電力消費、プリント回路基板 (PCB) 上の回路の位置、および熱プレーンの正しいサイズを適切に考慮する必要があります。レギュレータ周辺の PCB エリアには、熱的ストレスを増加させる他の発熱デバイスをできるだけ配置しないようにしてください。

1 次近似として、レギュレータの消費電力は、入力と出力の電圧差と負荷条件に依存します。式 2 を使用して、 $P_D$  を概算します：

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} \quad (2)$$

システム電圧レールを適切に選択することで、消費電力を最小限に抑えることができるため、より高い効率を実現できます。適切に選択することで、入出力電圧差の最小値が得られます。TPS7A21-Q1 のドロップアウトが小さいため、広い範囲の出力電圧にわたって最大の効率を実現します。

このデバイスの主な放熱経路は、パッケージのサーマル パッドを通じたものです。そのため、サーマル パッドはデバイス下の銅パッド領域に確実にはんだ付けします。このパッド領域にはめつきビアのアレイがあり、熱を内部層のプレーンや基板裏面の銅プレーンへと伝導します。

最大許容接合部温度 ( $T_J$ ) によって、デバイスの最大消費電力が決まります。式 3 によれば、消費電力と接合部温度は、PCB とデバイス パッケージを組み合わせた接合部から周囲への熱抵抗 ( $R_{\theta JA}$ )、および周囲空気の温度 ( $T_A$ ) に最も関連します。

$$T_J = T_A + (R_{\theta JA} \times P_D) \quad (3)$$

式 4 は出力電流用に式 3 を並べ替えたものです。

$$I_{OUT} = (T_J - T_A) / [R_{\theta JA} \times (V_{IN} - V_{OUT})] \quad (4)$$

残念ながら、この熱抵抗 ( $R_{\theta JA}$ ) は、特定の PCB 設計に組み込まれている熱拡散能力に大きく依存するため、合計の銅箔面積、銅箔の重量、およびプレーンの位置によって変化します。[熱に関する情報](#) テーブルに記録されている  $R_{\theta JA}$  は JEDEC 規格、PCB、銅の拡散領域によって決まり、パッケージの放熱性能の相対的な単位としてのみ使用されます。適切に設計された熱レイアウトの場合、 $R_{\theta JA}$  は実際には、パッケージの接合部からケース(底面)までの熱抵抗 ( $R_{\theta JC(bot)}$ ) と PCB 銅による熱抵抗の寄与の合計になります。

### 7.1.6 推定接合部温度

現在、JEDEC 規格では、典型的な PCB 基板アプリケーションで回路内にある LDO の接合部温度を推定するために、psi ( $\Psi$ ) の熱指標を使用することを推奨しています。これらの指標は、厳密には熱抵抗ではありませんが、接合部温度を実用的かつ相対的に推定する手段として用いられます。これらの psi 指標は、銅の広がり面積に対して大きく影響を受けないことが確認されています。主要な熱特性指標 ( $\Psi_{JT}$  および  $\Psi_{JB}$ ) は、式 5 に従って使用され、[熱に関する情報](#) 表に示されています。

$$\Psi_{JT} : T_J = T_T + \Psi_{JT} \times P_D \text{ and } \Psi_{JB} : T_J = T_B + \Psi_{JB} \times P_D \quad (5)$$

ここで

- $P_D$  は、[消費電力 \(P\\_D\)](#) セクションで説明されているように消費される電力です

- $T_T$  は、デバイス パッケージの中央上部の温度

- $T_B$  は、デバイス パッケージから 1mm の位置で、パッケージのエッジの中心で測定された PCB 表面温度

### 7.1.7 連続動作の推奨領域

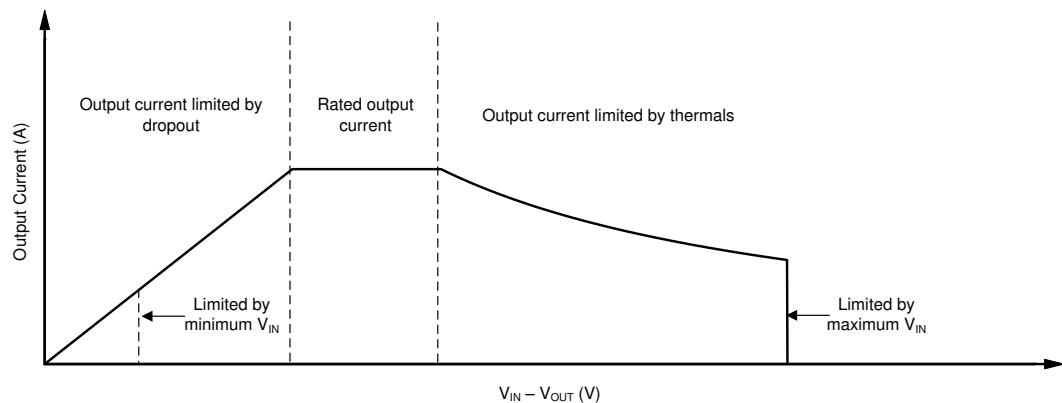

LDO の動作領域は、ドロップアウト電圧、出力電流、接合部温度、入力電圧によって制限されます。リニア レギュレータの連続動作の推奨領域を 図 7-3 に示し、これらは以下の部品で構成されています：

- ドロップアウト電圧は、与えられた出力電流レベルにおける入力と出力との間の最小差動電圧 ( $V_{IN} - V_{OUT}$ ) を制限します。詳細については、「[ドロップアウト動作](#)」セクションを参照してください。

- 定格出力電流は、推奨される最大出力電流レベルを制限します。この定格を超えると、デバイスが仕様外になります。

- 定格接合部温度によって、デバイスの最大接合部温度が制限されます。この定格を超えると、デバイスが仕様の範囲外になり、長期的な信頼性が低下します。

- 図 7-3 の 3 番目の領域で勾配の形状を確認できます。LDO の最大定格接合部温度が LDO 全体の消費電力によって制御されるため、スロープは非線形になります。したがって、 $V_{IN} - V_{OUT}$  が増加すると、出力電流は減少します。

- 定格入力電圧範囲によって、 $V_{IN} - V_{OUT}$  の最小値と最大値の両方が決まります。

図 7-3 は、JEDEC 標準の高熱伝導率基板上で、このデバイスの推奨動作領域を示しています。使用されている基板の  $R_{\theta JA}$  は [熱に関する情報](#) 表に示されています。

図 7-3. 連続動作領域の説明

## 7.2 代表的なアプリケーション

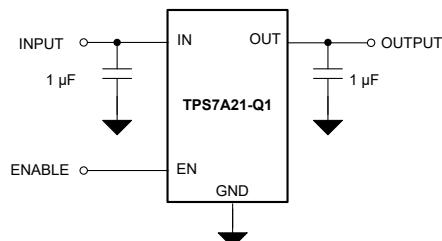

図 7-4 に、TPS7A21-Q1 の代表的なアプリケーション回路を示します。一部のアプリケーションで必要な場合は、入力および出力容量を  $1\mu F$  の最小値を上回るように増やします。

図 7-4. TPS7A21-Q1 の代表的なアプリケーション

## 7.2.1 設計要件

表 7-1 に、一般的なアプリケーション回路の設計要件をまとめます。

**表 7-1. 設計パラメータ**

| 設計パラメータ | 数値の例        |

|---------|-------------|

| 入力電圧範囲  | 3.6V ~ 4.2V |

| 出力電圧    | 3.3V        |

| 出力電流    | 350mA       |

| 最大周囲温度  | 125°C       |

## 7.2.2 詳細な設計手順

この設計例では、3.3V 出力バージョン (TPS7A2133PQWDRBRQ1) を選択します。公称 3.6V の入力電源を想定しています。最小  $1.0\mu\text{F}$  の入力コンデンサを使用して、ソースと LDO 入力との間の抵抗およびインダクタンスの影響を最小限に抑えます。安定性と優れた負荷過渡応答を実現するために、最小  $1.0\mu\text{F}$  の出力コンデンサを使用します。ドロップアウト電圧 ( $V_{DO}$ ) は、3.3V の出力電圧と 500mA 出力電流で最大 150mV 未満なので、入力電圧 3.6V と最大出力電流 350mA でのドロップアウトの問題はありません。

### 7.2.2.1 電力散逸とデバイス動作

任意のパッケージにおける許容消費電力は、電源 (デバイスの接合部) から最終的な放熱先である周囲環境へ熱を伝達するデバイスの能力の指標です。したがって、消費電力は周囲温度およびダイ接合部と周囲空気との間の各種インターフェイスを通る熱抵抗に依存します。

式 6 で、特定のパッケージでのデバイスの最大許容消費電力を計算します：

$$P_{D-MAX} = ((T_{J-MAX} - T_A) / R_{\theta JA}) \quad (6)$$

式 7 は、デバイスで実際に消費される電力を表します：

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} \quad (7)$$

この 2 つの式は、熱を考慮した結果として許容される最大電力消費、デバイス両端の電圧降下、デバイスの連続電流能力との関係を示します。この 2 つの式を使用して、アプリケーションのデバイスの最適な動作条件を決定します。

消費電力を低減 ( $P_D$ ) または優れたパッケージ熱抵抗 ( $R_{\theta JA}$ ) を使用するアプリケーションでは、最大周囲温度 ( $T_{A-MAX}$ ) を増やすことができます。

消費電力が高いアプリケーションまたはパッケージからの熱抵抗が低いアプリケーションでは、必要に応じて、最大周囲温度 ( $T_{A-MAX}$ ) をディレーティングする必要があります。式 8 に示されているよう、 $T_{A-MAX}$  は動作時の最大接合部温度 ( $T_{J-MAX-OP} = 150^\circ\text{C}$ )、アプリケーションのデバイス パッケージの最大許容消費電力 ( $P_{D-MAX}$ )、およびアプリケーションのデバイスまたはパッケージの接合部から周囲への熱抵抗 ( $R_{\theta JA}$ ) に依存します：

$$T_{A-MAX} = (T_{J-MAX-OP} - (R_{\theta JA} \times P_{D-MAX})) \quad (8)$$

または、 $T_{A-MAX}$  をディレーティングできない場合は、 $P_D$  の値を下げないでください。この削減は、最小  $V_{IN}$  が満たされている限り、 $V_{IN}-V_{OUT}$  項の  $V_{IN}$  を削減することによって、または  $I_{OUT}$  項を削減することによって、あるいはこの 2 つの組み合わせによって実現されます。

### 7.2.3 アプリケーション曲線

## 7.3 電源に関する推奨事項

この LDO は、 $2.0V \sim 5.5V$  の入力電源電圧範囲で動作するように設計されています。入力電源が十分に安定しており、不要なノイズが含まれていないことを確認します。TPS7A21-Q1 の出力電圧が適切に安定化され、動的性能が最適になるように、入力電源を少なくとも  $V_{OUT} + 0.3V$  に設定します。 $1\mu F$  の最小コンデンサ値は、IN ピンから 1cm 以内にする必要があります。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

TPS7A21-Q1 の動的性能は、PCB レイアウトに依存します。標準的な LDO に適した PCB レイアウト手法により、TPS7A21-Q1 の PSRR、ノイズ、過渡性能が低下する可能性があります。

$C_{IN}$  と  $C_{OUT}$  を TPS7A21-Q1 と同じ PCB 側で、パッケージのできるだけ近くに配置することで、最高の性能が得られます。 $C_{IN}$  と  $C_{OUT}$  のグランド接続は、実用的にできるだけ広く短く銅のパターンを使って、TPS7A21-Q1 のグランドピンに配線します。

長いパターン長、狭いパターン幅、ビアを介した接続を使用しないでください。これらの接続によって寄生インダクタンスと抵抗が追加され、特に過渡条件の発生時に性能が低下します。

#### 7.4.2 レイアウト例

図 7-7. 代表的な DRB レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 デバイスの命名規則

| 製品 <sup>(1)</sup> <sup>(2)</sup> | V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS7A21xx(x)(C)PQ(W)yyyzQ1       | <p><b>xx(x)</b> は公称出力電圧です。出力電圧の分解能が 100mV の場合、注文番号に 2 桁が使用されます。それ以外の場合は 3 桁が使用されます（例：28 = 2.8V, 125 = 1.25V）。</p> <p><b>C</b>（存在する場合）は、代替のピン構成を示します。</p> <p><b>P</b> はアクティブ出力放電機能を表します。TPS7A21 のバリエントはすべて、デバイスのディスエーブル時に出力をアクティブに放電します。</p> <p><b>Q</b> は、AEC-Q100 規格のグレード 1 に準拠したデバイスであることを表すものです。</p> <p><b>W</b>（存在する場合）は、ウェッタブル フランクを採用したパッケージであることを表します。</p> <p><b>yyy</b> はパッケージ指定子です。</p> <p><b>Z</b> はパッケージ数量です。R は 3,000 ピースのリールです。</p> <p><b>Q1</b> は、車載グレード（AEC-Q100）デバイスであることを表すものです。</p> |

- (1) 最新のパッケージと発注情報については、このデータシートの末尾にあるパッケージ オプションの付録を参照するか、[www.ti.com](http://www.ti.com) にあるデバイスの製品フォルダをご覧ください。

(2) 出力電圧は、0.8V から 5.5V まで、50mV 刻みで設定できます。詳細と入手可能性については、工場にお問い合わせください。

### 8.2 ドキュメントのサポート

#### 8.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『QFN/SON の PCB 実装』アプリケーション レポート

### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.7 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision C (June 2024) to Revision D (June 2025) | Page |

|---------------------------------------------------------------|------|

| • 8 ピン DSG デバイス ステータスを「事前情報」から「量産データ」に変更.....                 | 1    |

---

| Changes from Revision B (February 2024) to Revision C (June 2024)       | Page |

|-------------------------------------------------------------------------|------|

| • ウェッタブル フランク WSON (DGS) パッケージを「事前情報」から「量産データ」に変更 .....                 | 1    |

| • 出力電圧の許容誤差を「 $1mA I_{OUT}$ で $\pm 1\%$ 」から「温度範囲全体で $\pm 1\%$ 」に変更..... | 1    |

| • 「概要」セクションから出力電圧の最大許容誤差の説明を削除.....                                     | 1    |

| • 冗長電圧許容誤差を訂正。.....                                                     | 5    |

| • EN ピンの最大リーク電流を 250nA から 300nA に変更。.....                               | 5    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| PS7A21105PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 21105P              |

| PS7A21105PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 21105P              |

| S7A21105PQWDSSGRQ1    | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3JAH                |

| S7A21105PQWDSSGRQ1.A  | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3JAH                |

| TPS7A2109PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J6H                |

| TPS7A2109PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J6H                |

| TPS7A2110PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2110P              |

| TPS7A2110PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2110P              |

| TPS7A2110PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J5H                |

| TPS7A2110PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J5H                |

| TPS7A2112PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2112P              |

| TPS7A2112PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2112P              |

| TPS7A2112PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J7H                |

| TPS7A2112PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J7H                |

| TPS7A2115PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2115P              |

| TPS7A2115PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2115P              |

| TPS7A2115PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J4H                |

| TPS7A2115PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J4H                |

| TPS7A2118CPQDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | 35RH                |

| TPS7A2118CPQDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | 35RH                |

| TPS7A2118PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2118P              |

| TPS7A2118PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2118P              |

| TPS7A2118PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 35QH                |

| TPS7A2118PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 35QH                |

| TPS7A2128PQWDRBRQ1    | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2128P              |

| TPS7A2128PQWDRBRQ1.A  | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2128P              |

| TPS7A2128PQWDSSGRQ1   | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J2H                |

| TPS7A2128PQWDSSGRQ1.A | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J2H                |

| TPS7A2131PQDSSGRQ1    | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | 3MJH                |

| Orderable part number              | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS7A2131PQDSGRQ1.A                | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | 3MJH                |

| <a href="#">TPS7A2131PQWDSGRQ1</a> | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J8H                |

| TPS7A2131PQWDSGRQ1.A               | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J8H                |

| <a href="#">TPS7A2133PQWDRBRQ1</a> | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2133P              |

| TPS7A2133PQWDRBRQ1.A               | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2133P              |

| <a href="#">TPS7A2133PQWDSGRQ1</a> | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J9H                |

| TPS7A2133PQWDSGRQ1.A               | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J9H                |

| <a href="#">TPS7A2150PQWDRBRQ1</a> | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2150P              |

| TPS7A2150PQWDRBRQ1.A               | Active        | Production           | SON (DRB)   8  | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | A2150P              |

| <a href="#">TPS7A2150PQWDSGRQ1</a> | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J3H                |

| TPS7A2150PQWDSGRQ1.A               | Active        | Production           | WSON (DSG)   8 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 3J3H                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS7A21-Q1 :**

- Catalog : [TPS7A21](#)

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

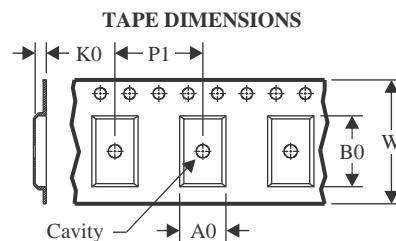

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

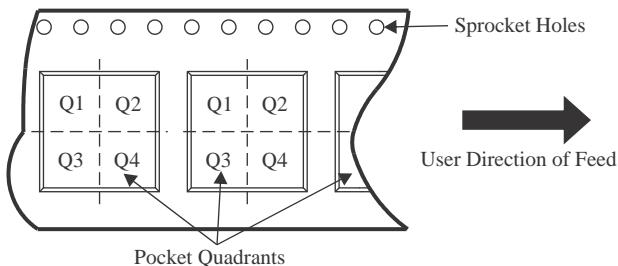

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| PS7A21105PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| S7A21105PQWDSGRQ1  | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2109PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2110PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2110PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2112PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2112PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2115PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2115PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2118CPQDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2118PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2118PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2128PQWDRBRQ1 | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2128PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2131PQDSGRQ1  | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2131PQWDSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| Device              | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS7A2133PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2133PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

| TPS7A2150PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS7A2150PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.2     | 2.2     | 1.2     | 4.0     | 8.0    | Q2            |

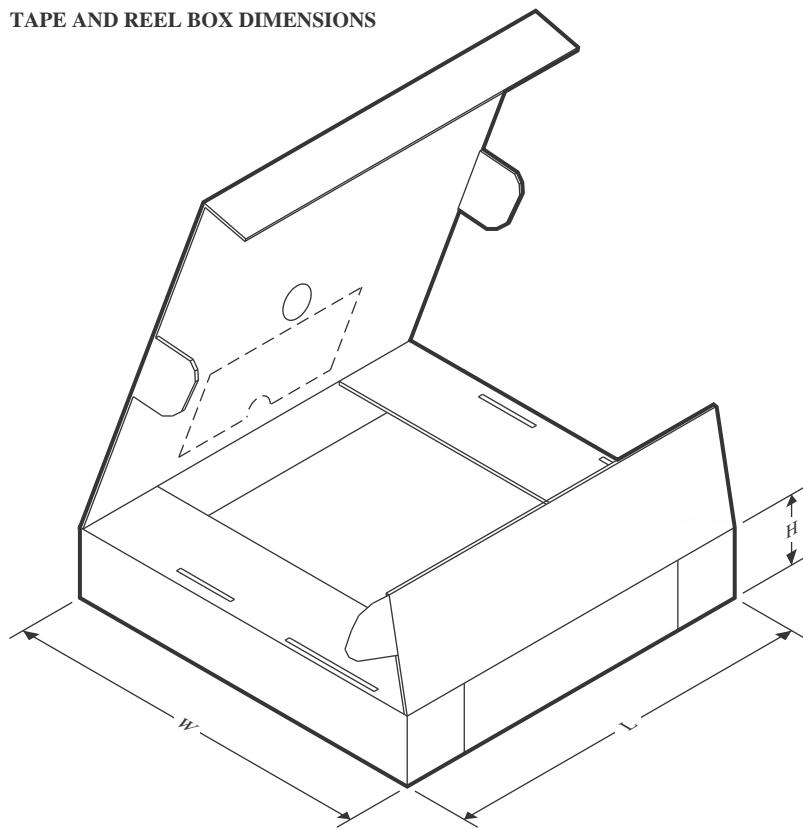

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| PS7A21105PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| S7A21105PQWDSSGRQ1  | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2109PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2110PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2110PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2112PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2112PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2115PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2115PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2118CPQDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2118PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2118PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2128PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2128PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2131PQDSSGRQ1  | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2131PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| TPS7A2133PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2133PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| Device              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS7A2150PQWDRBRQ1  | SON          | DRB             | 8    | 5000 | 367.0       | 367.0      | 35.0        |

| TPS7A2150PQWDSSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

## GENERIC PACKAGE VIEW

**DRB 8**

**VSON - 1 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4203482/L

**DRB0008J**

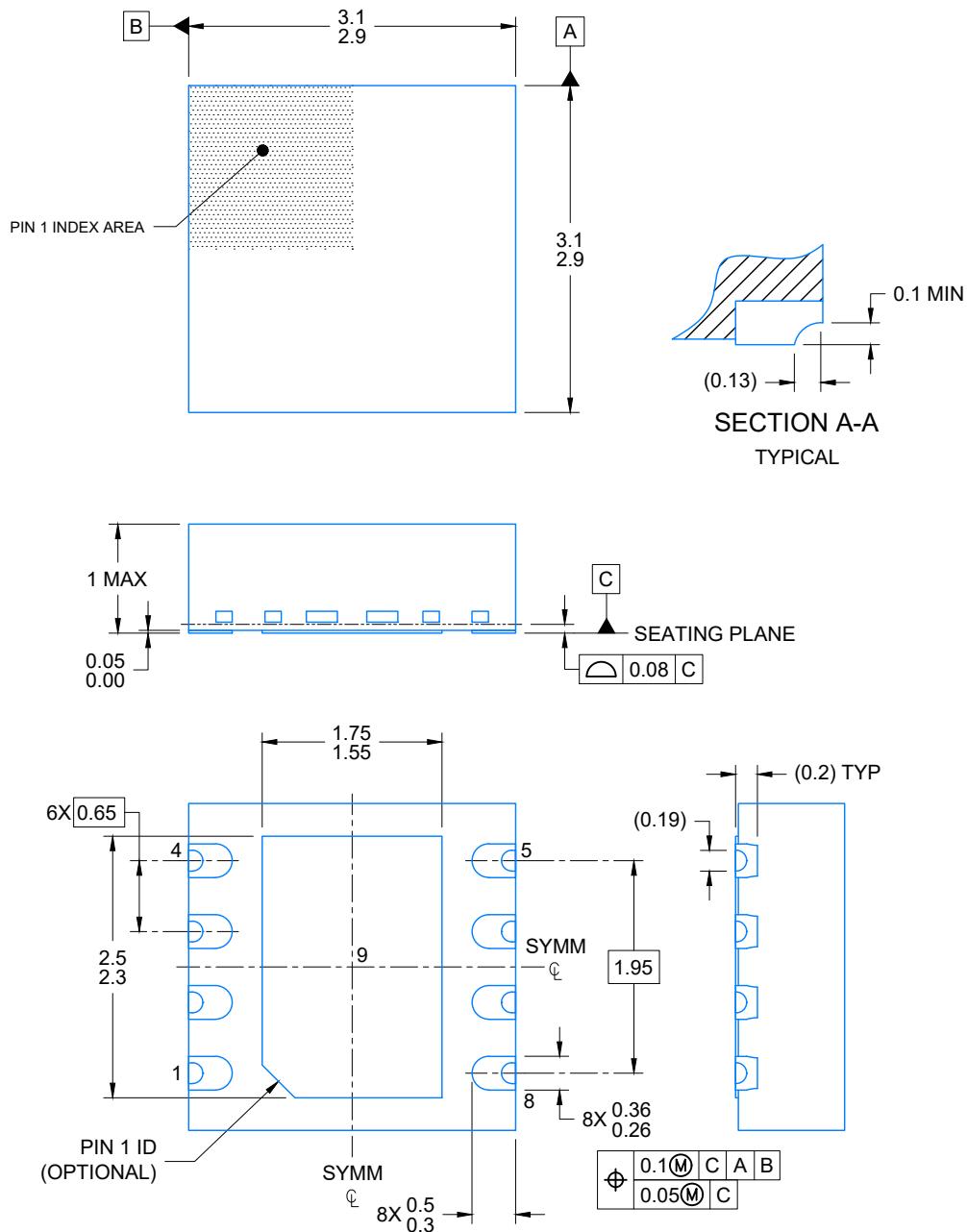

**PACKAGE OUTLINE

VSON - 1 mm max height**

PLASTIC QUAD FLAT PACK- NO LEAD

4225036/A 06/2019

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

**DRB0008J**

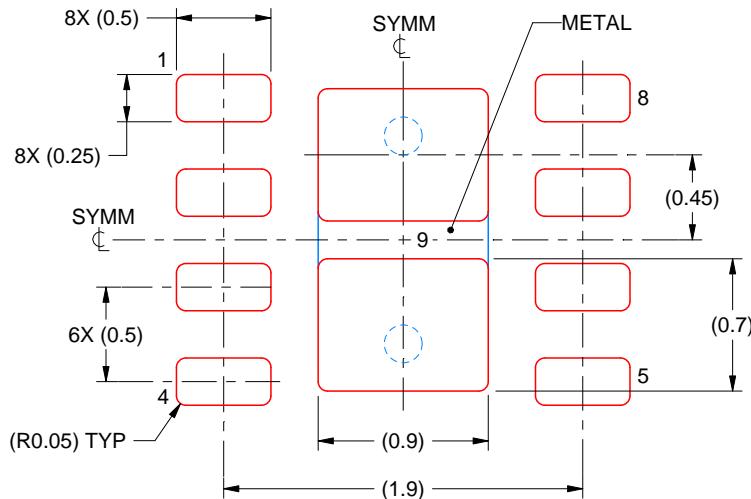

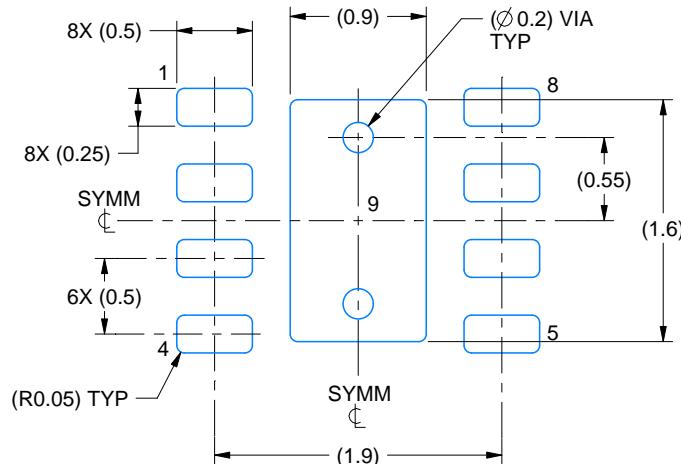

# EXAMPLE BOARD LAYOUT

**VSON - 1 mm max height**

PLASTIC QUAD FLAT PACK- NO LEAD

## LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

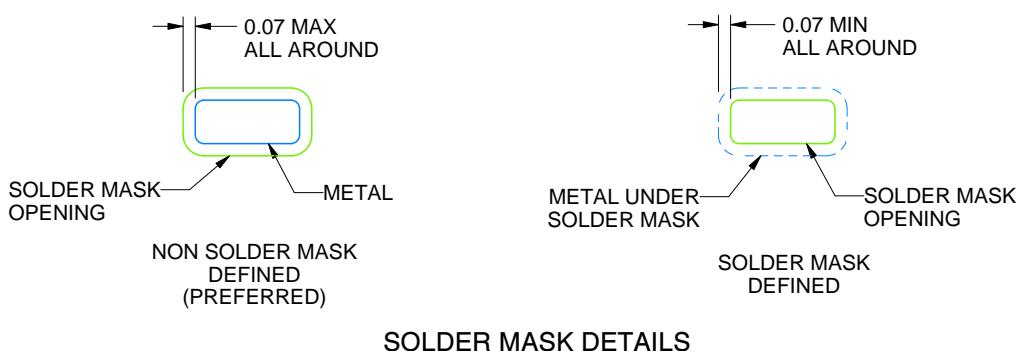

## SOLDER MASK DETAILS

4225036/A 06/2019

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

VSON - 1 mm max height

DRB0008J

PLASTIC QUAD FLAT PACK- NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD

81% PRINTED COVERAGE BY AREA

SCALE: 20X

4225036/A 06/2019

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# GENERIC PACKAGE VIEW

**DSG 8**

**WSON - 0.8 mm max height**

**2 x 2, 0.5 mm pitch**

**PLASTIC SMALL OUTLINE - NO LEAD**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224783/A

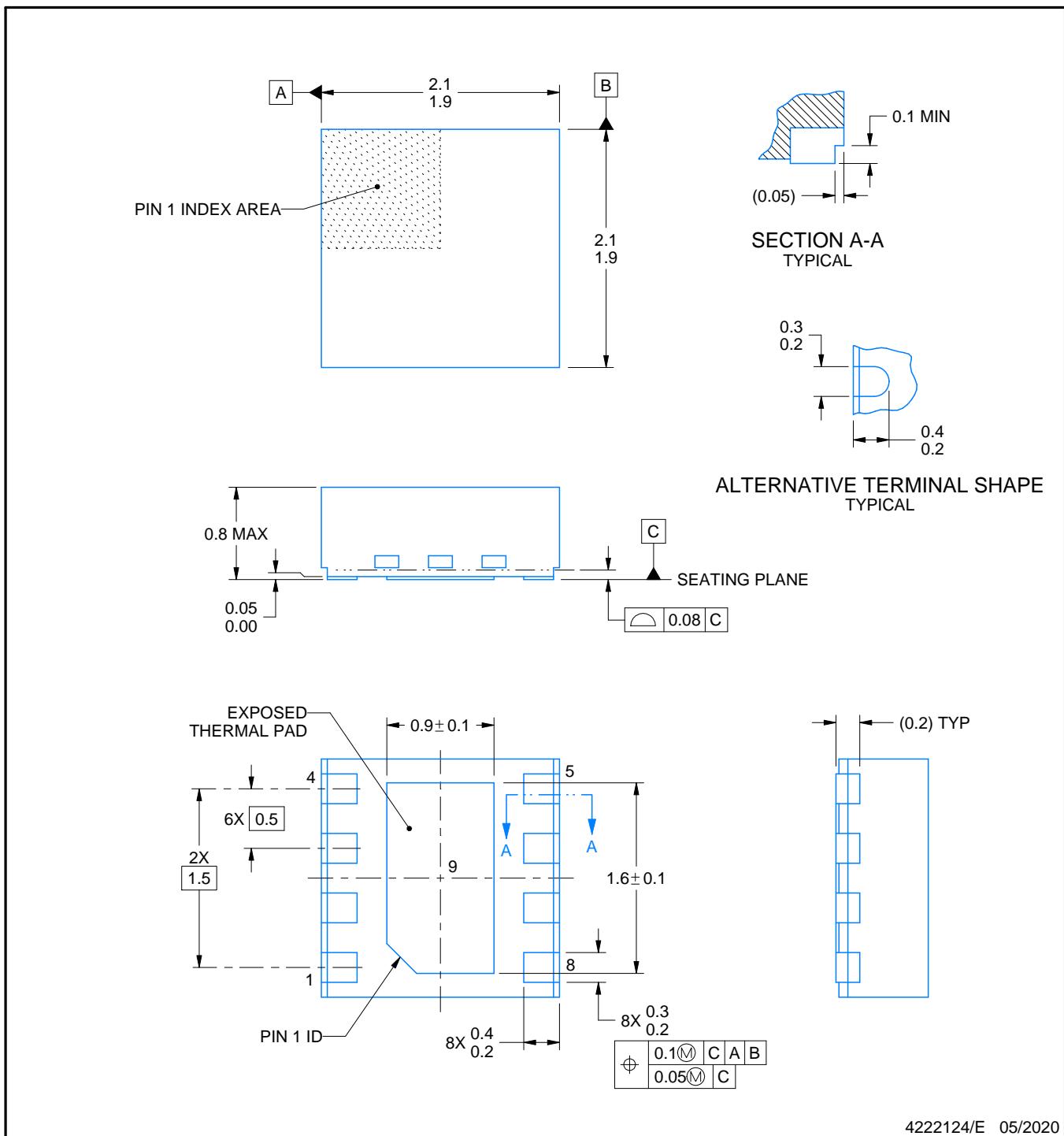

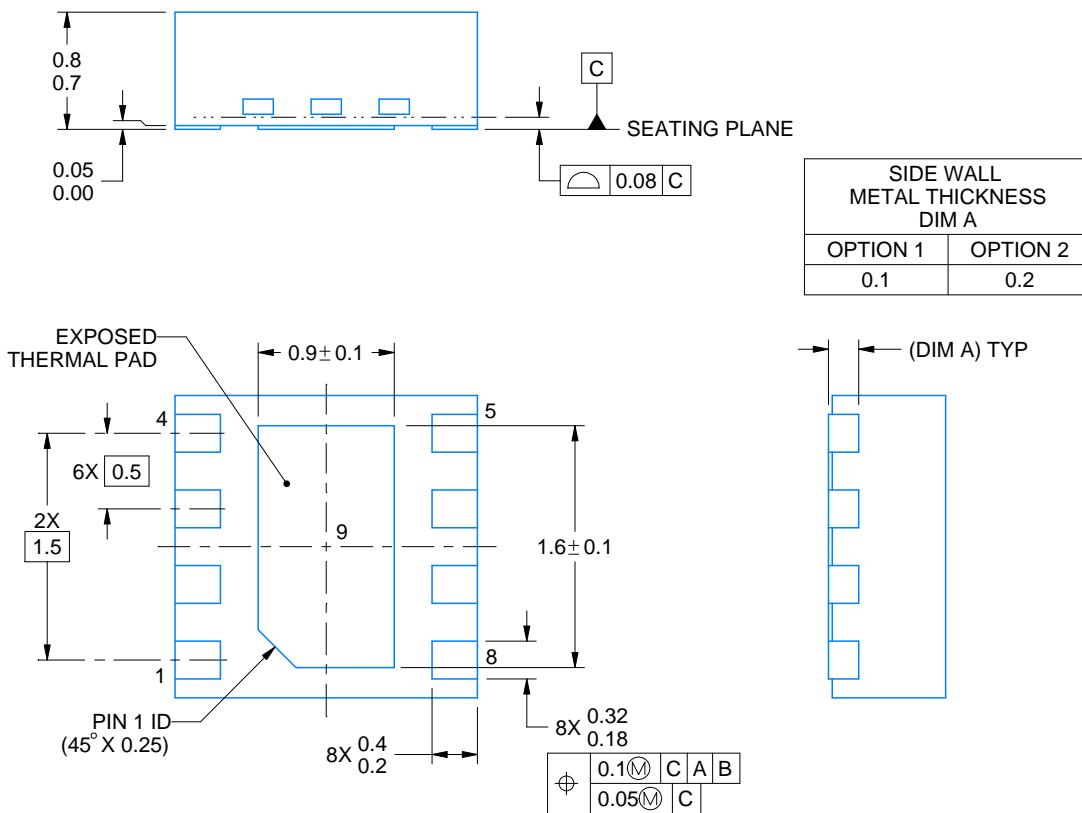

# PACKAGE OUTLINE

**DSG0008B**

**WSON - 0.8 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

4222124/E 05/2020

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

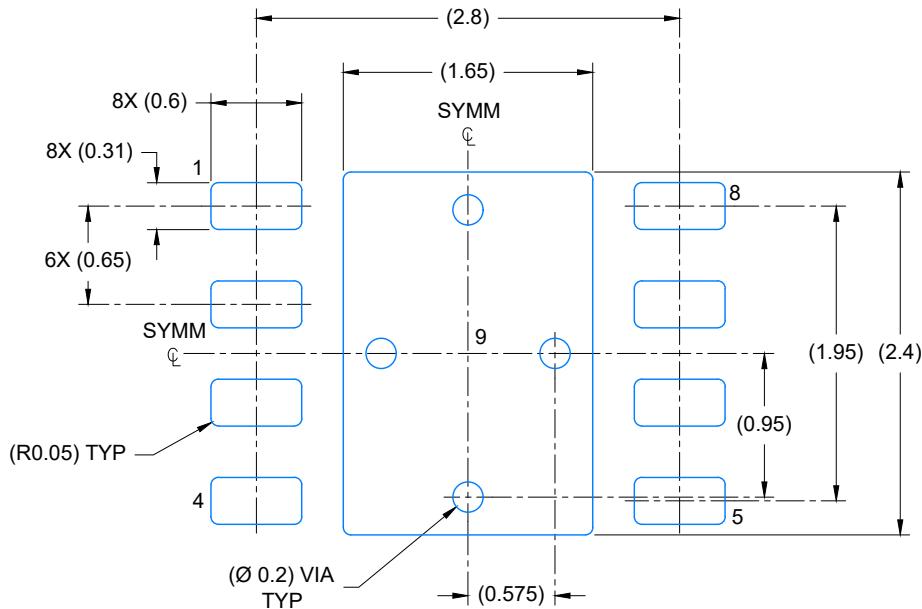

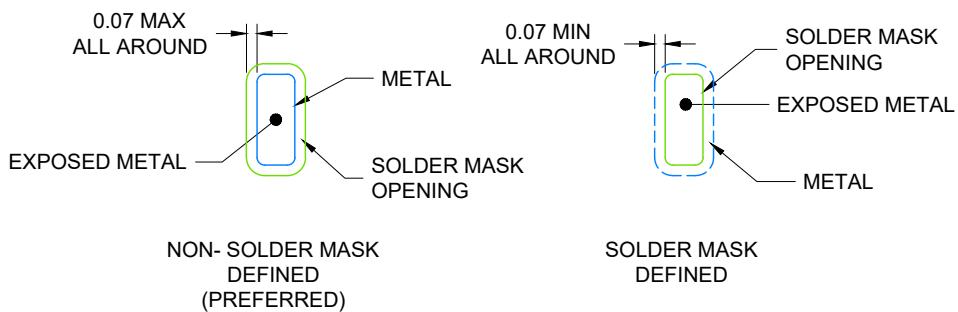

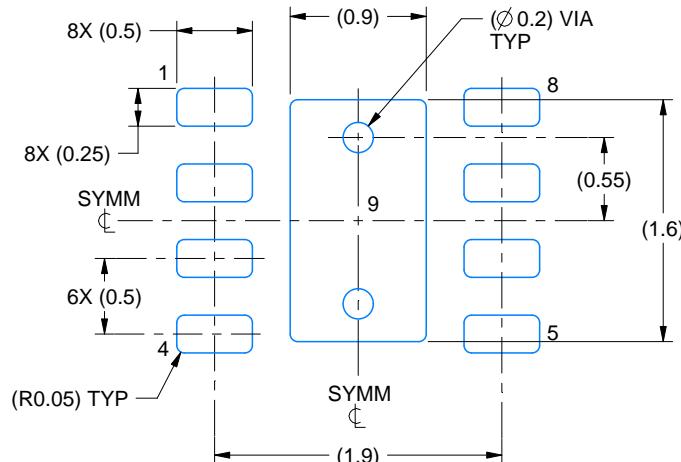

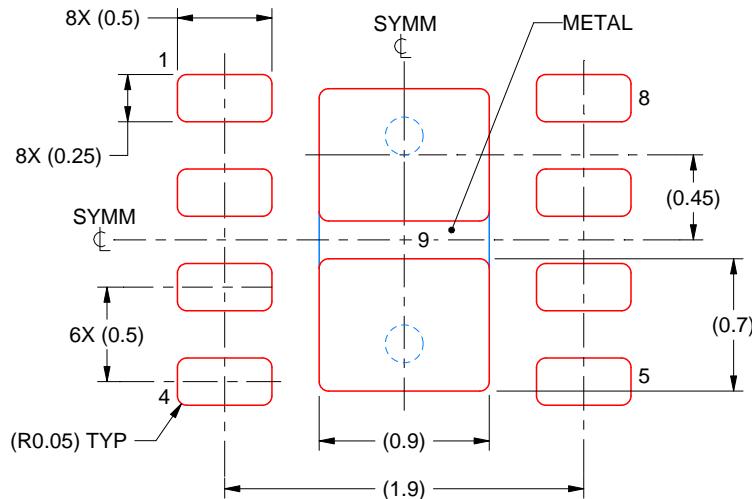

# EXAMPLE BOARD LAYOUT

DSG0008B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:20X

SOLDER MASK DETAILS

4222124/E 05/2020

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

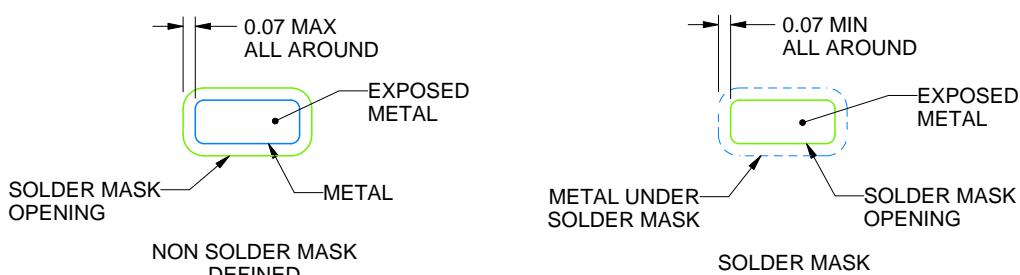

# EXAMPLE STENCIL DESIGN

DSG0008B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 9:

87% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:25X

4222124/E 05/2020

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

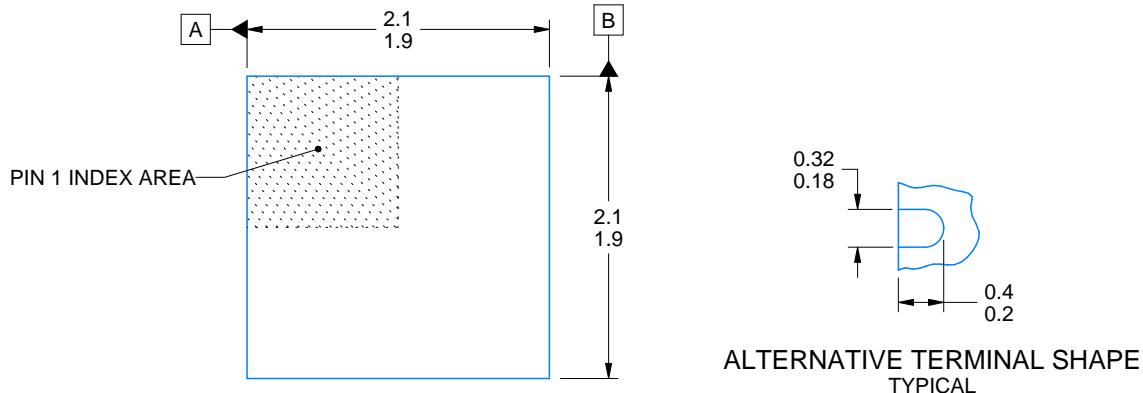

# PACKAGE OUTLINE

**DSG0008A**

**WSON - 0.8 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

4218900/E 08/2022

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

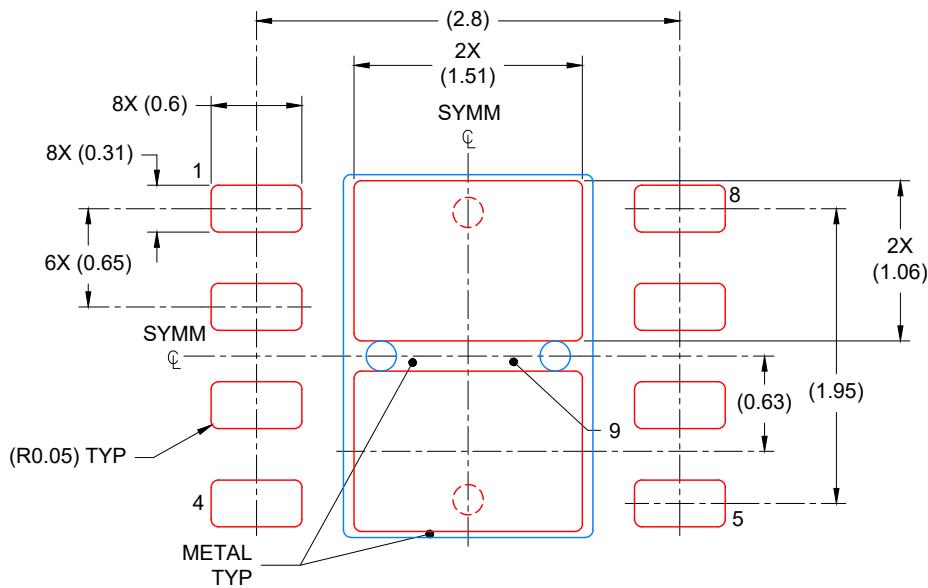

# EXAMPLE BOARD LAYOUT

DSG0008A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

SCALE:20X

SOLDER MASK DETAILS

4218900/E 08/2022

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

DSG0008A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 9:

87% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:25X

4218900/E 08/2022

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月