## 低入力電圧、1A、スーパーバイザ付き 低ドロップアウト・リニア・レギュレータ

### 特 長

- 出力電流：1A

- 固定出力モデル（1.5V、1.6V、1.8V、2.5V）と可変出力モデル（1.2V～5.5V）

- 入力電圧：最小1.8V

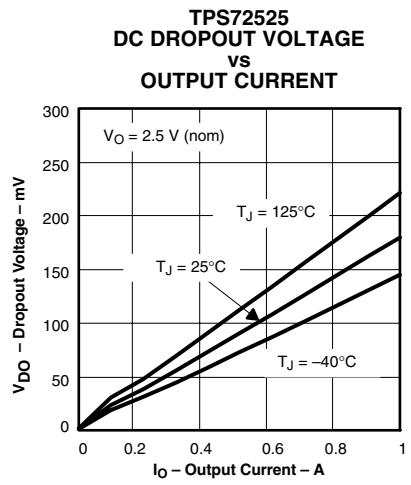

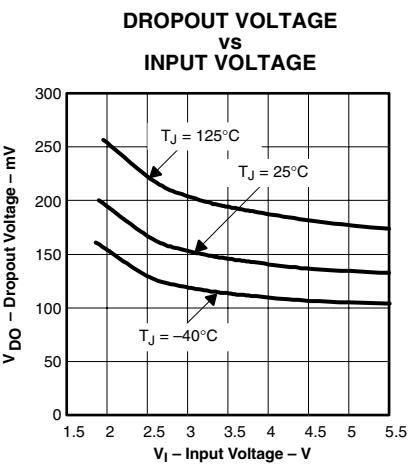

- 低ドロップアウト電圧：1Aで170mV（TPS72525）

- 任意の種類/容量の出力コンデンサで安定

- RESET遅延時間50msのスーパーバイザ（SVS）を内蔵（固定出力電圧製品のみ）

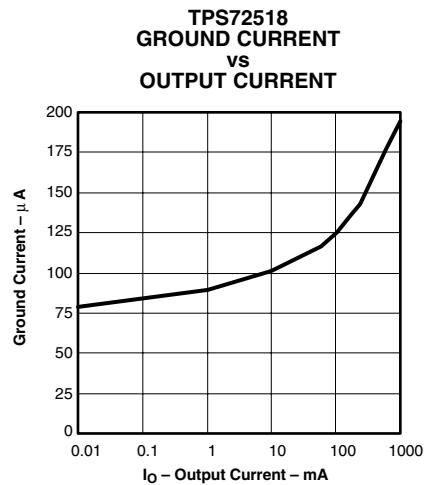

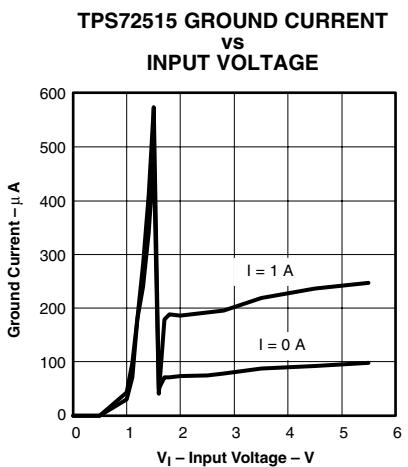

- 全負荷時210μAの低グランド電流（TPS72525）

- スタンバイ電流：1μA以下

- 全入力電圧範囲、全負荷電流範囲、全温度範囲（ $T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ ）に対する出力電圧公差： $\pm 2\%$

- UVLO（低入力電圧時誤動作防止）

- 過熱保護と過電流保護

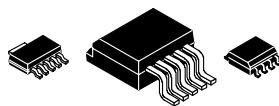

- 5リードSOT223-5、DDPAK、および8ピンSOP（TPS72501のみ）表面実装パッケージ

### アプリケーション

- PCIカード

- モデム・バンク

- テレコム・ボード

- DSP、FPGA、およびマイクロプロセッサ用電源

- 携帯型、バッテリー駆動アプリケーション

### 概 要

TPS725xxファミリーの1A低ドロップアウト（LDO）リニア・レギュレータには、最新のDSP、FPGA、およびマイクロコントローラへの電源供給に一般的に使用される各固定電圧のモデルが用意されています。また、1.22V～5.5Vの可変電圧モデルもあります。内蔵のスーパーバイザ回路により、出力がレギュレーション範囲より低下した場合に、アクティブ・ローのRESET信号が生成されます。コンデンサ無し、または任意の種類と容量の出力コンデンサを使用できるため、ユーザが必要な過渡特性に応じて出力容量を調整できます。その結果、同じ出力電流を供給可能な他のレギュレータと比較して、TPS725xxファミリーのレギュレータを使用すれば、スタンダードアロンの電源ソリューション、またはスイッチ・モード電源用のポスト・レギュレータを容易に実現できます。

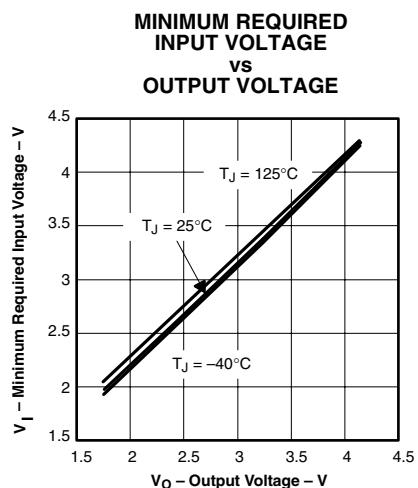

これらのレギュレータは、高電流のアプリケーションに理想的です。TPS725xxファミリーは、幅広い入力電圧範囲（1.8V～6V）で動作し、ドロップアウト電圧が非常に低くなっています（1Aで170mV）。

グランド電流は全負荷時で210μA（標準）、無負荷時には80μA

注：TPS72501では、RESETの代わりにFBとなります。DCKおよびKTTパッケージでは、タブがGNDとなります。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ（日本TI）が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

未満まで低下します。スタンバイ時の電流は1μA以下です。

各レギュレータ・モデルは、SOT223-5、D (TPS72501のみ)、またはDDPAKパッケージで供給されます。低い入力電圧および放熱パッドを備えたパッケージの製品では、2.5V以上の最小入力電圧や高い自己消費電流を必要とする同等製品に比べ、放熱能力が大きく、より高い効率を実現できます。これらの機能により、TPS725xxファミリーは、バッテリー駆動の携帯型機器に対しても最適な電源ソリューションとなります。

安定動作のための出力コンデンサは必須ではありませんが、10μFの出力コンデンサを使用する事により過渡応答特性および出力ノイズ特性が向上します。

最小出力電流の制限を持ち無負荷で使用できないいくつかのレギュレータとは異なり、TPS725ファミリーは出力負荷電流

0mAでも安定して動作します。低ノイズ特性と、高電流動作、および容易な放熱により、本ファミリーは、テレコム・ボード、モデム・バンクなどのノイズに敏感なアプリケーションに理想的です。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## 製品情報

| T <sub>J</sub> | 電圧 <sup>(1)</sup> | SOT223-5 <sup>(2)</sup> | 記号      | DDPAK <sup>(3)</sup> | D <sup>(4)</sup> | 記号       |

|----------------|-------------------|-------------------------|---------|----------------------|------------------|----------|

| -40°C ~ 125°C  | 可変 (1.2V~5V)      | TPS72501DCQ             | PS72501 | TPS72501KTT          | TPS72501D        | TPS72501 |

|                | 1.5 V             | TPS72515DCQ             | PS72515 | TPS72515KTT          | —                | TPS72515 |

|                | 1.6 V             | TPS72516DCQ             | PS72516 | TPS72516KTT          | —                | TPS72516 |

|                | 1.8 V             | TPS72518DCQ             | PS72518 | TPS72518KTT          | —                | TPS72518 |

|                | 2.5 V             | TPS72525DCQ             | PS72525 | TPS72525KTT          | —                | TPS72525 |

(1) ご要望に応じて、他の電圧オプションも提供可能です。

(2) リール(2500個)での発注には部品番号の末尾にRを付けてください(例: TPS72501DCQR)。

(3) 1リールあたり50個の供給の場合は、部品番号の末尾にTを追加します(例: TPS72501KTTT)。

1リールあたり500個の供給の場合は、部品番号の末尾にRを追加します(例: TPS72501KTTR)。

(4) 部品番号の末尾にRまたはT(2500または500)を付けてください(例: TPS72501DR)。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                                    |                          | 単位 |

|------------------------------------|--------------------------|----|

| 入力電圧、V <sub>I</sub> <sup>(2)</sup> | -0.3~7                   | V  |

| 電圧範囲(EN、FB)                        | -0.3~V <sub>I</sub> +0.3 | V  |

| OUT、RESETの電圧                       | 6                        | V  |

| ESD定格、HBM                          | 2                        | kV |

| 連続合計消費電力                           | 「定格消費電力」の表を参照してください。     |    |

| 動作接合部温度範囲、T <sub>J</sub>           | -50~150                  | °C |

| 最大接合部温度範囲、T <sub>J</sub>           | 150                      | °C |

| 保存温度、T <sub>stg</sub>              | -65~150                  | °C |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) すべての電圧値は回路のグランド端子を基準としています。

## 推奨動作条件

|                                    | MIN | NOM | MAX | 単位 |

|------------------------------------|-----|-----|-----|----|

| 入力電圧、V <sub>I</sub> <sup>(1)</sup> | 1.8 | 6   | —   | V  |

| 連続出力電流、I <sub>O</sub>              | 0   | 1   | —   | A  |

| 動作接合部温度、T <sub>J</sub>             | -40 | 125 | —   | °C |

(1) 最小 V<sub>I</sub> = V<sub>O</sub>(公称) + V<sub>DO</sub> です。

## パッケージ定格消費電力

| パッケージ  | 基板                    | $R_{\theta JC}$ | $R_{\theta JA}$ |

|--------|-----------------------|-----------------|-----------------|

| DDPAK  | High K <sup>(1)</sup> | 2 °C/W          | 23 °C/W         |

| SOT223 | Low K <sup>(2)</sup>  | 15 °C/W         | 53 °C/W         |

| D-8    | High K <sup>(1)</sup> | 39.4 °C/W       | 55 °C/W         |

(1) このデータを得るために使用したJEDEC High-K(2s2p)基板のデザインは、3インチ×3インチ(7.5cm×7.5cm)の多層基板で、内部に1オンスの電源およびグランド・プレーンを持ち、基板の上面および底面に2オンスの銅トレースを形成しています。

(2) このデータを得るために使用したJEDEC Low-K(1s)基板のデザインは、上面に3オンスの銅トレースを形成した3インチ×3インチ(7.5cm×7.5cm)の片面基板です。

## 電気的特性

推奨動作温度範囲内、 $V_I = V_O(\text{typ}) + 1V$ 、 $I_O = 1mA$ 、EN = IN、 $C_O = 1\mu F$ 、 $C_I = 1\mu F$ (特に記述のない限り)

| パラメータ                                                                    |                                                    | 測定条件                                 |                              | MIN         | TYP         | MAX   | 単位      |

|--------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------|------------------------------|-------------|-------------|-------|---------|

| $V_O$ バンドギャップ電圧リファレンス                                                    |                                                    |                                      |                              | 1.177       | 1.220       | 1.263 | V       |

| $V_O$ 出力電圧                                                               | TPS72501<br>可変                                     | $0 \mu A < I_O < 1 A$ <sup>(1)</sup> | $1.22 V \leq V_O \leq 5.5 V$ | 0.965 $V_O$ | 1.035 $V_O$ |       | V       |

|                                                                          | TPS72515                                           | $T_J = 25^\circ C$                   |                              |             | 1.5         |       |         |

|                                                                          |                                                    | $0 \mu A < I_O < 1 A$                | $1.8 V \leq V_I \leq 5.5 V$  | 1.47        | 1.53        |       |         |

|                                                                          | TPS72516                                           | $T_J = 25^\circ C$                   |                              |             | 1.6         |       |         |

|                                                                          |                                                    | $0 \mu A < I_O < 1 A$                | $2.6 V \leq V_I \leq 5.5 V$  | 1.568       | 1.632       |       |         |

|                                                                          | TPS72518                                           | $T_J = 25^\circ C$                   |                              |             | 1.8         |       |         |

|                                                                          |                                                    | $0 \mu A < I_O < 1 A$                | $2.8 V \leq V_I \leq 5.5 V$  | 1.764       | 1.836       |       |         |

|                                                                          | TPS72525                                           | $T_J = 25^\circ C$                   |                              |             | 2.5         |       |         |

|                                                                          |                                                    | $0 \mu A < I_O < 1 A$                | $3.5 V \leq V_I \leq 5.5 V$  | 2.45        | 2.55        |       |         |

|                                                                          |                                                    |                                      |                              |             |             |       |         |

| I グランド電流                                                                 | $I_O = 0 \mu A$                                    |                                      |                              | 75          | 120         |       | $\mu A$ |

|                                                                          | $I_O = 1 A$                                        |                                      |                              | 210         | 300         |       |         |

| EN < 0.4 V                                                               |                                                    | $T_J = 25^\circ C$                   |                              | 0.2         |             |       | $\mu A$ |

|                                                                          |                                                    |                                      |                              |             | 1           |       |         |

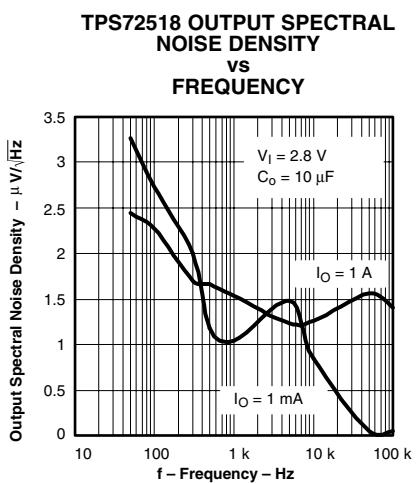

| $V_n$ 出力ノイズ電圧                                                            | $BW = 200 Hz$ to $100 kHz$ ,<br>$T_J = 25^\circ C$ | $C_O = 10 \mu F$ , $I_O = 1 mA$      |                              | 150         |             |       | $\mu V$ |

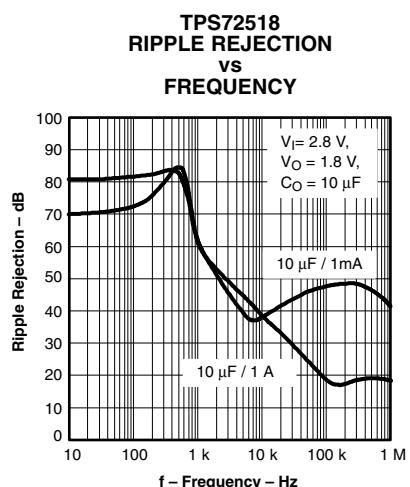

| PSRR リップル除去                                                              | $f = 1 kHz$ , $C_O = 10 \mu F$                     | $T_J = 25^\circ C$                   |                              | 60          |             |       | dB      |

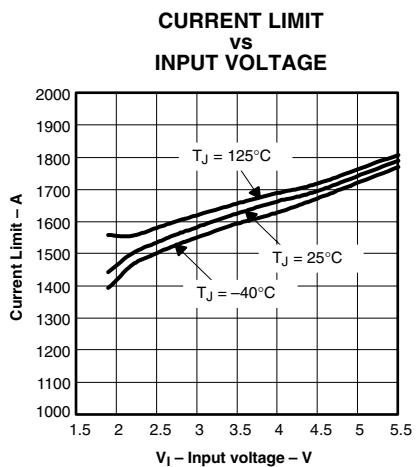

| 電流制限 <sup>(2)</sup>                                                      |                                                    |                                      |                              | 1.1         | 1.6         | 2.3   | A       |

| 出力電圧ライン・レギュレーション <sup>(ΔV<sub>O</sub>/V<sub>O</sub>)<sup>(3)</sup></sup> | $V_O + 1 V < V_I \leq 5.5 V$                       |                                      |                              | -0.15       | 0.02        | 0.15  | %/V     |

| 出力電圧負荷レギュレーション                                                           | $0 \mu A < I_O < 1 A$                              |                                      |                              | -0.25       | 0.05        | 0.25  | %/A     |

| $V_{IH}$ EN “High” レベル入力 <sup>(2)</sup>                                  |                                                    |                                      |                              | 1.3         |             |       | V       |

| $V_{IL}$ EN “Low” レベル入力 <sup>(2)</sup>                                   |                                                    |                                      |                              | -0.2        |             | 0.4   |         |

| $I_I$ EN入力電流                                                             | $EN = 0 V$ or $V_I$                                |                                      |                              | 0.01        | 100         |       | nA      |

| $I_{(FB)}$ フィードバック電流                                                     | TPS72501                                           | $V_{(FB)} = 1.22$                    |                              | -100        | 100         |       | nA      |

| UVLOスレッシュホールド                                                            | $V_{CC}$ 立ち上がり                                     |                                      |                              | 1.45        | 1.57        | 1.70  | V       |

| UVLOヒステリシス                                                               | $T_J = 25^\circ C$ , $V_{CC}$ 立ち上がり                |                                      |                              | 50          |             |       | mV      |

| UVLOデグリッチ                                                                | $T_J = 25^\circ C$ , $V_{CC}$ 立ち上がり                |                                      |                              | 10          |             |       | $\mu s$ |

| UVLO遅延                                                                   | $T_J = 25^\circ C$ , $V_{CC}$ 立ち上がり                |                                      |                              | 100         |             |       | $\mu s$ |

(1) 測定に使用した最小IN動作電圧は $V_O(\text{typ}) + 1V$ です。

(2) 測定条件には、出力電圧 $V_O = V_O - 15\%$ およびパルス幅 = 10msが含まれます。

(3)  $V_{Imin}$ は、 $(V_O + 1)$ と1.8Vのうち大きいほうになります。

$$\text{ライン・レギュレーション (mV)} = (\%/\text{V}) \times \frac{V_O(5.5 \text{ V} - V_{Imin})}{100} \times 1000$$

## 電気的特性

推奨動作温度範囲内、 $V_I = V_O(\text{typ}) + 1V$ 、 $I_O = 1\text{mA}$ 、EN = IN、 $C_O = 1\mu\text{F}$ 、 $C_i = 1\mu\text{F}$ (特に記述のない限り)

| パラメータ    |                                      | 測定条件              |                          | MIN  | TYP | MAX | 単位            |

|----------|--------------------------------------|-------------------|--------------------------|------|-----|-----|---------------|

| $V_{DO}$ | ドロップアウト電圧<br>TPS72525 <sup>(4)</sup> | $I_O = 1\text{A}$ | $T_J = 25^\circ\text{C}$ |      | 170 |     | mV            |

|          |                                      | $I_O = 1\text{A}$ |                          |      |     | 280 |               |

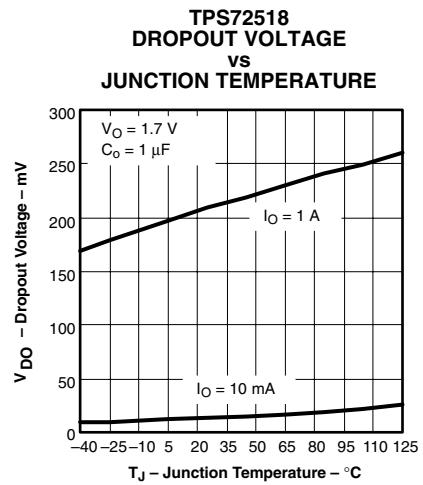

|          | TPS72518 <sup>(4)</sup>              | $I_O = 1\text{A}$ | $T_J = 25^\circ\text{C}$ |      | 210 |     |               |

|          |                                      | $I_O = 1\text{A}$ |                          |      |     | 320 |               |

| RESET    | 有効なRESETの最小入力電圧                      |                   |                          | 1.3  |     |     | V             |

|          | トリップ・スレッシュホールド電圧                     |                   |                          | 90   | 93  | 96  | % $V_O$       |

|          | ヒステリシス電圧                             |                   |                          | 10   |     |     | mV            |

|          | $t_{(\text{RESET})}$ 遅延時間            |                   |                          | 25   | 50  | 75  | ms            |

|          | 立ち上がりエッジ・デグリッチ                       |                   |                          | 10   |     |     | $\mu\text{s}$ |

|          | 出力“Low”電圧(700 $\mu\text{A}$ 時)       |                   |                          | -0.3 |     | 0.4 | V             |

|          | リーコ電流                                |                   |                          | 100  |     |     | nA            |

(4) ドロップアウト電圧は、 $V_I = V_O + 1V$ で測定された値よりも $V_O$ が100mV下回ったときの、 $V_O$ と $V_I$ の電圧差として定義されます。

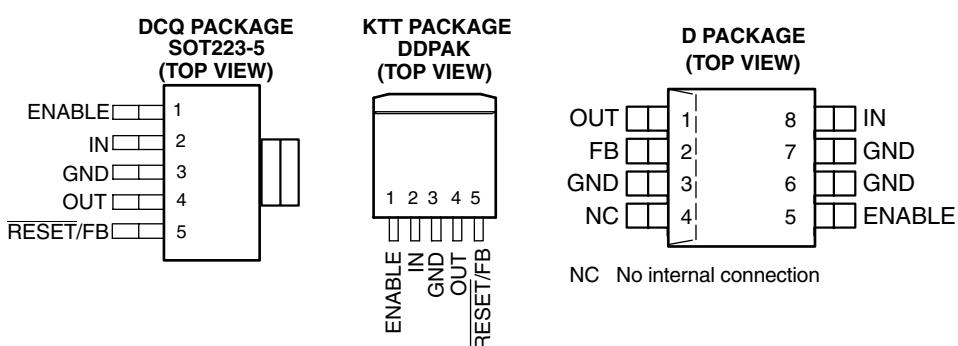

## 機能ブロック図 - 可変出力モデル

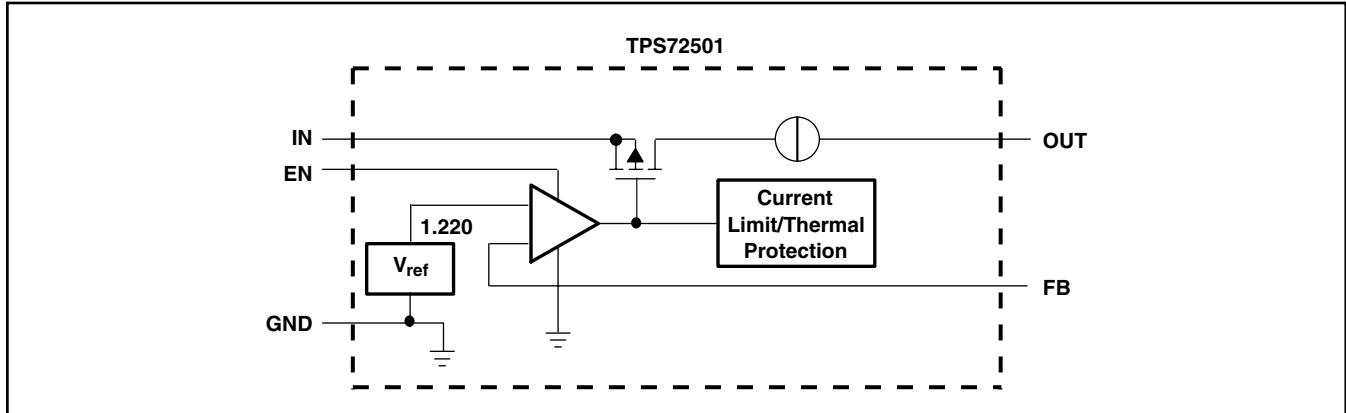

## 機能ブロック図 - 固定出力モデル

## ピン機能

| 端子       |         |             | I/O | 説明                                                                                                                                                                                        |

|----------|---------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号(D)   | 番号(DCQ、KTT) |     |                                                                                                                                                                                           |

| ENABLE   | 5       | 1           | I   | イネーブル入力                                                                                                                                                                                   |

| FB       | 2       |             |     | フィードバック                                                                                                                                                                                   |

| GND      | 3, 6, 7 | 3           |     | グランド                                                                                                                                                                                      |

| IN       | 8       | 2           | I   | 入力電源電圧                                                                                                                                                                                    |

| RESET/FB | —       | 5           | O/I | この端子は、可変出力電圧製品TPS72501ではフィードバック入力端子です。他のすべての固定出力電圧製品では、この端子はRESET出力端子となります。ブルアップ抵抗と共に使用することで、このオープン・ドレイン出力は、レギュレータの出力電圧がその公称出力電圧を5%以上下回ったときに、アクティブ・ローのRESET信号を発生します。RESET遅延時間は、標準で50msです。 |

| NC       | 4       | —           |     | 接続なし                                                                                                                                                                                      |

| OUT      | 1       | 4           | O   | 安定化出力電圧                                                                                                                                                                                   |

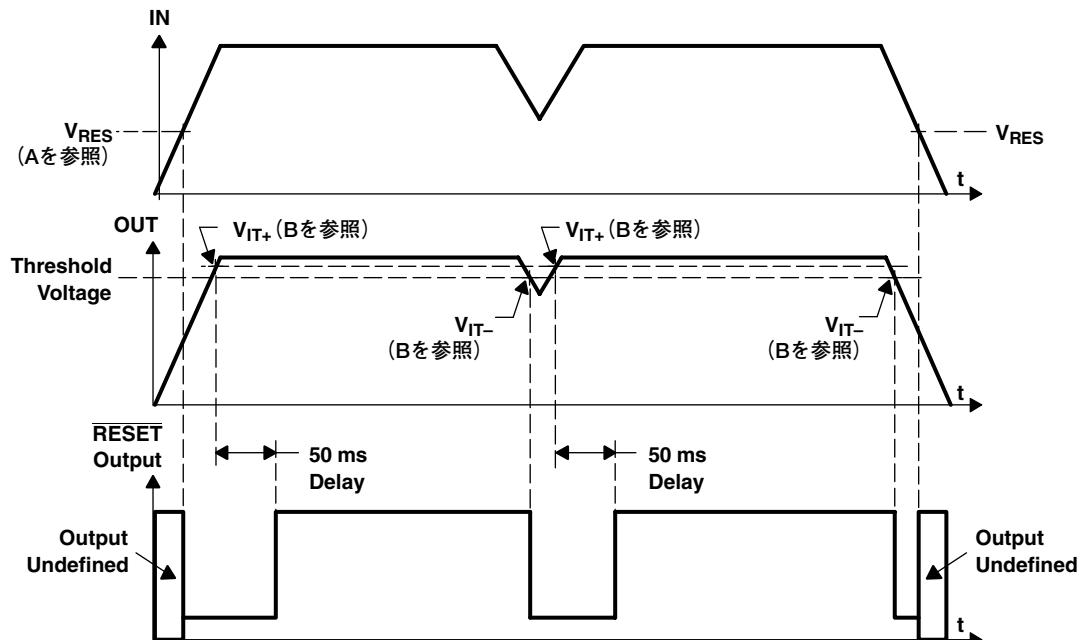

## リセット・タイミング図

注： A.  $V_{RES}$ は、 $\overline{RESET}$ が有効となる最小入力電圧です。記号 $V_{RES}$ は現在、EIAまたはJEDEC標準の半導体記号体系には含まれていません。

B.  $V_{IT-}$  ト里ップ電圧は、出力電圧より標準で7%低い電圧です( $93\%V_O$ )。 $V_{IT-} \sim V_{IT+}$ は、ヒステリシス電圧です。

## 代表的特性

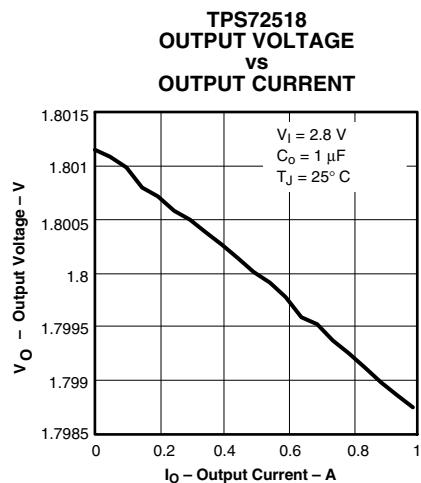

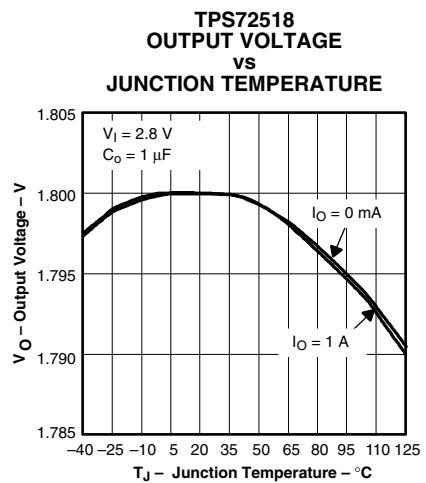

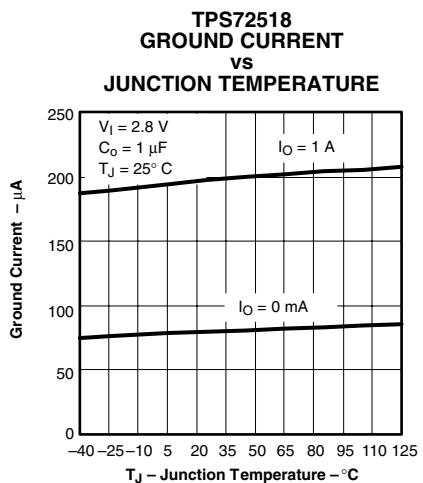

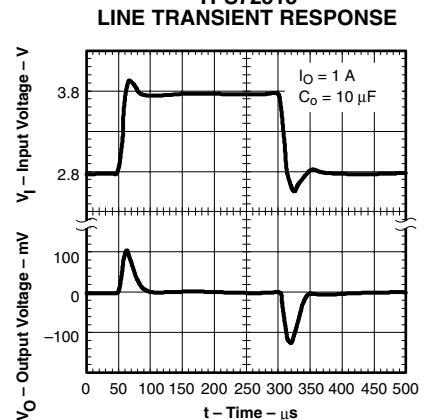

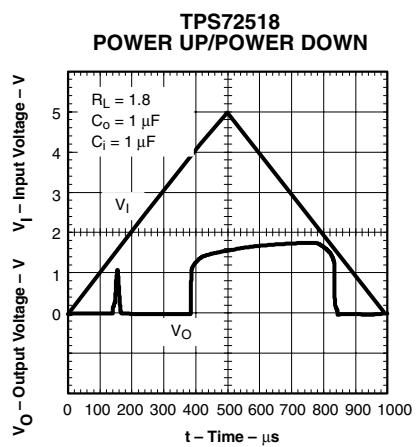

図 1

図 2

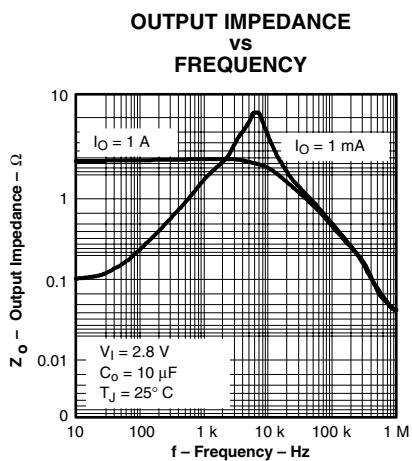

図 3

図 4

図 5

図 6

図 7

図 8

図 9

## 代表的特性

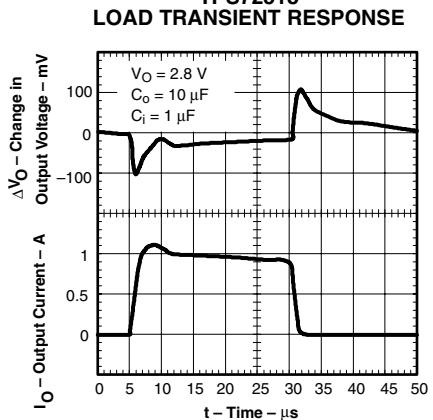

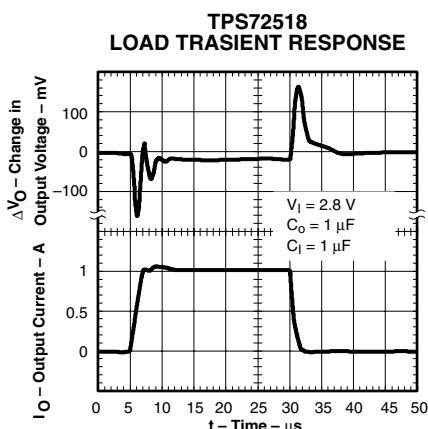

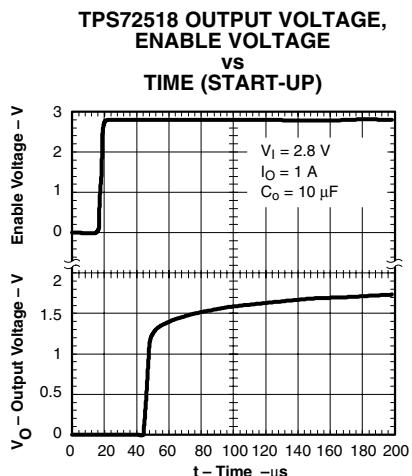

図 10

図 11

図 12

図 13

図 14

図 15

図 16

図 17

図 18

## アプリケーション情報

TPS725xxファミリーの低ドロップアウト(LOD)レギュレータには、幅広い範囲のアプリケーションで利用するための機能が多機能搭載されています。非常に低い入力電圧(1.8V以上)と低いドロップアウト電圧(全負荷時200mV)で動作することにより、高効率のスタンダードアロン電源や、バッテリーまたはスイッチ・モード電源のポスト・レギュレータとして活用できます。アクティブ・ローのRESET、さらには1Aの出力電流により、TPS725xxファミリーは、プロセッサおよびFPGA電源への電源供給に理想的です。また、出力ノイズが低い( $10\mu\text{F}$ の出力コンデンサで標準 $150\mu\text{VRMS}$ )ため、テレコム機器での使用にも最適です。

## 外部コンデンサ要件

安定性向上のため、INとGNDの間に、 $1\mu\text{F}$ 以上のセラミック入力バイパス・コンデンサをTPS725xxに近づけて配置する必要があります。過渡応答、ノイズ除去、およびリップル除去性能を向上させるために、さらに $10\mu\text{F}$ 以上の低ESRコンデンサを追加することを推奨します。立ち上がりの速い大きな負荷過渡電流が予期される場合や、本製品の配置が電源供給元から数インチも離れている場合、特に、最小入力電圧の1.8Vで使用する場合には、より大容量の低ESR入力コンデンサが必要となる場合があります。

安定動作のための出力コンデンサは必須ではありませんが、 $10\mu\text{F}$ の出力コンデンサを使用すると過渡応答および出力ノイズ特性が向上します。

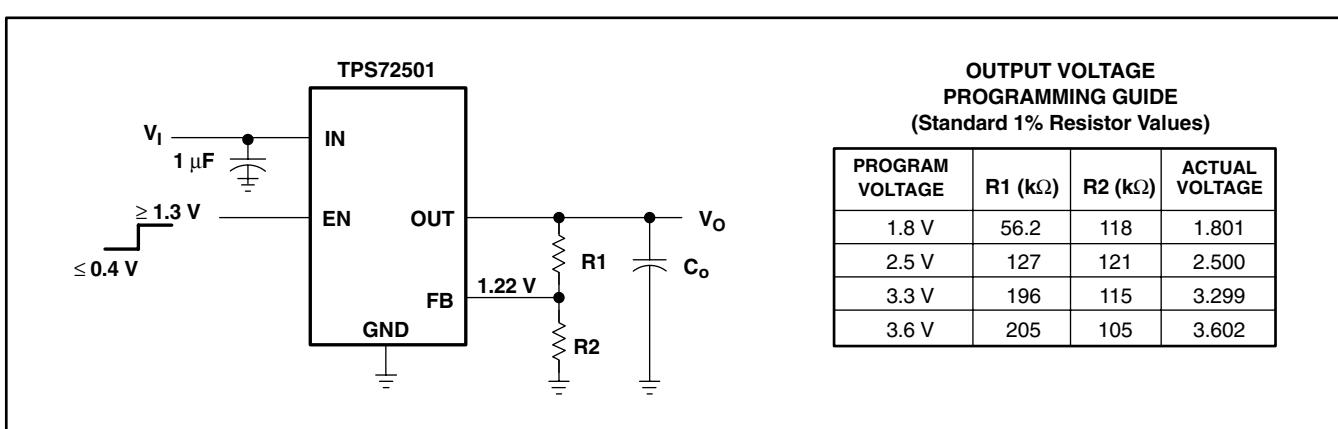

## TPS72501可変LDOレギュレータのプログラミング

TPS72501可変レギュレータの出力電圧は、図19に示すように、外部に抵抗デバイダを使用して設定します。出力電圧は次の式で計算されます。

$$V_O = V_{ref} \times \left(1 + \frac{R1}{R2}\right) \quad (1)$$

ここで、

- $V_{FB} = V_{REF} = 1.22\text{V}$ (標準)

( $V_{REF}$ の誤差については、電気的特性を参照)

抵抗R1およびR2は、デバイダ電流が約 $10\mu\text{A}$ となるように選択する必要があります。それより小さな値の抵抗を使用しても、本質的なメリットではなく、消費電力が大きくなります。それより大きな抵抗値は、FBピンでのリーク電流によって出力電圧の誤差が増加するため、避けてください。推奨される設計手順は、デバイダ電流が $10\mu\text{A}$ になるよう $R2 = 120\text{k}\Omega$ を選択してから、次の式でR1を計算することです。

$$R1 = \left( \frac{V_O}{V_{ref}} - 1 \right) \times R2 \quad (2)$$

## レギュレータの保護

TPS725xxの制御素子にはバック・ダイオードが内蔵され、入力電圧が出力電圧よりも低下した場合(パワーダウン時など)に、逆方向電流を安全に流します。電流は出力から入力へと逆流しますが、内蔵された電流制限起動は動作しません。長時間の逆電圧状態が予想される場合は、外部での電流制限が必要となる場合もあります。

TPS725xxは、過電流制限および過熱保護機能も内蔵しています。通常動作時、TPS725xxは出力電流を約1.6Aに制限します。電流制限がかかると、出力電圧は過電流状態が終了するまで直線的に低下します。電流制限はデバイス全体の障害を防ぐように設計されていますが、パッケージの定格消費電力を超えないよう注意が必要です。デバイスの温度が $165^\circ\text{C}$ を超えると、過熱保護回路によってデバイスがシャットダウンされます。デバイスの温度が $145^\circ\text{C}$ 以下まで低下すると、レギュレータの動作が再開されます。

図 19. TPS72501可変LDOレギュレータのプログラミング

## 熱特性について

LDOリニア・レギュレータが発する熱量は、動作中に負荷の回路が消費する電力の量に直接比例します。すべてのICには、最大許容接合部温度( $T_{Jmax}$ )が規定され、それを超えると通常の動作が保証されません。システム設計者は、動作時の接合部温度( $T_J$ )が最大接合部温度( $T_{Jmax}$ )を超えないように動作環境を設計する必要があります。熱特性を改善するために設計者が使用できる2つの主要な環境変数は、エアフローと外部ヒートシンクです。ここでは、設計者のために、特定の電力レベルで動作するリニア・レギュレータに対して適切な動作環境を決定する方法を説明します。

一般に、リニア・レギュレータによって消費される最大予想電力( $P_{D(max)}$ )は、次のように計算されます。

$$P_{D(max)} = \left( V_{I(avg)} - V_{O(avg)} \right) \times I_{O(avg)} + V_{I(avg)} \times I_{(Q)} \quad (3)$$

ここで

- $V_{I(avg)}$ は、平均入力電圧です。

- $V_{O(avg)}$ は、平均出力電圧です。

- $I_{O(avg)}$ は、平均出力電流です。

- $I_{(Q)}$ は、無信号時電流です。

TIのほとんどのLDOレギュレータでは、無信号時電流は平均出力電流と比較してずっと小さいため、 $V_{I(avg)} \times I_{(Q)}$ の項は無視できます。動作接合部温度は、周囲温度( $T_A$ )に、レギュレータの消費電力による温度上昇を加算することで計算されます。温度上昇は、最大予想消費電力に、接合部 - ケース間の熱抵抗( $R_{\theta JC}$ )、ケース-ヒートシンク間の熱抵抗( $R_{\theta CS}$ )、ヒートシンク周囲空間間の熱抵抗( $R_{\theta SA}$ )の合計を乗算することで求められます。熱抵抗は、物体がどのくらい効率的に熱を放散できるかを表す指標です。一般に、デバイスのパッケージが大きいほど、放散に利用できる表面積が大きくなり、熱抵抗は低くなります。

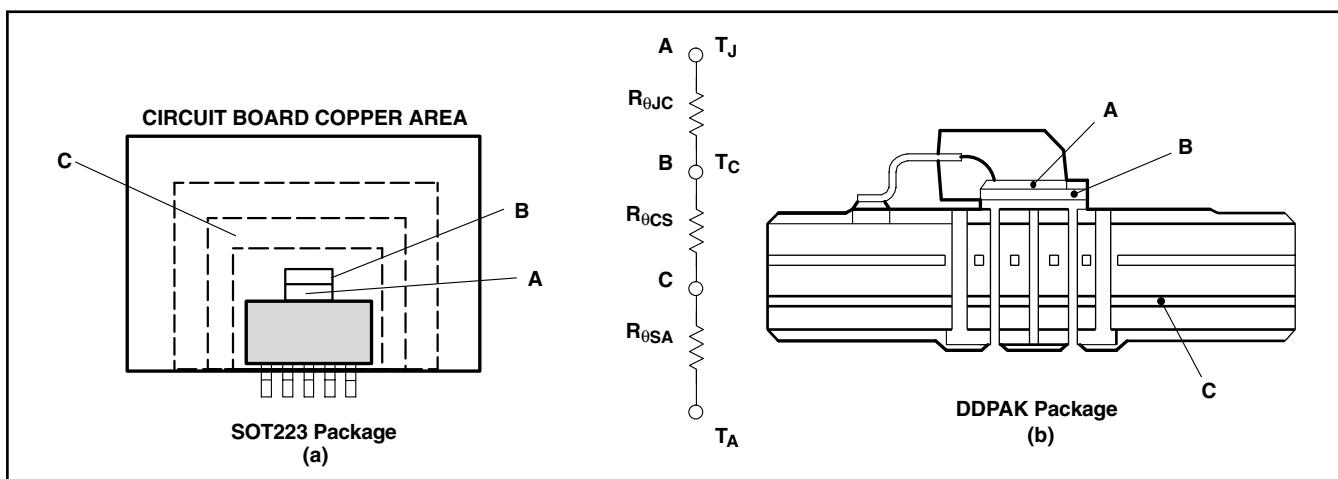

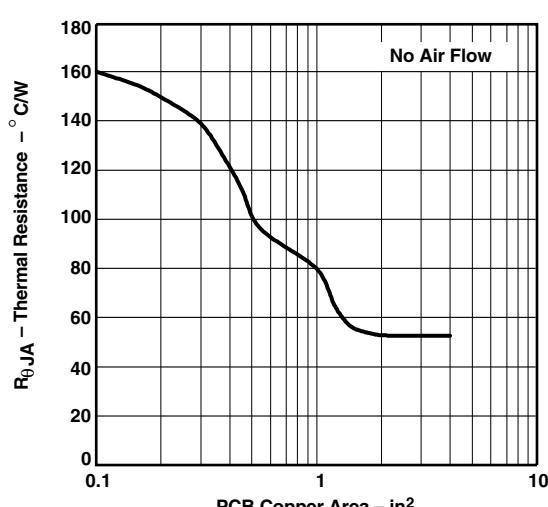

図20に、(a) JEDEC Low-K基板に実装されたSOT223パッケージ、および(b) JEDEC High-K基板に実装されたDDPAKパッケージについて、この3つの熱抵抗を示します。

図 20. 热抵抗

これらの計算を式(4)にまとめます。

$$T_J = T_A + P_{D(max)} \times (R_{\theta JC} + R_{\theta CS} + R_{\theta SA}) \quad (4)$$

$R_{\theta JC}$ は各レギュレータに固有の値で、パッケージ、リード・フレーム、およびダイ・サイズによって決まり、レギュレータのデータシートに記載されています。 $R_{\theta SA}$ は、ヒートシンクの種類およびサイズの関数となります。例えば、黒色のラジエータ形ヒートシンクの場合、 $R_{\theta SA}$ 値は、非常に大きなヒートシンクでは $5^{\circ}\text{C}/\text{W}$ 、非常に小さなヒートシンクでは $50^{\circ}\text{C}/\text{W}$ となります。 $R_{\theta CS}$ は、パッケージとヒートシンクの接合方法により決定される値となります。例えば、SOT223パッケージのヒートシンクの取り付けにサーマル・コンパウンドを使用した場合、 $R_{\theta CS}$ は $1^{\circ}\text{C}/\text{W}$ が妥当な値です。

パッケージの外部に黒色のラジエータ形ヒートシンクが取り付けられていない場合でも、レギュレータが実装される基板により、ピンの半田接続を通してある程度の熱の拡散が行われます。DDPAKやSOT223パッケージなど、いくつかのパッケージでは、パッケージ直下の銅パターンまたは回路基板の内層のグランド・プレーンをヒートシンクとして使用し、熱特性を向上させることができます。コンピュータを使った熱拡散のモデリングにより、(異なる種類の回路基板、異なる種類およびサイズのヒートシンク、異なるエアフローなど)各種の動作環境におけるICの熱特性を非常に正確に近似計算することができます。これらのモデルを使用し、3つの熱抵抗の合計を、接合部 - 周囲間の1つの熱抵抗( $R_{\theta JA}$ )にできます。この $R_{\theta JA}$ は、コンピュータ・モデルで使用された特定の動作環境でのみ有効な値です。

式(4)は、式(5)のように簡略化できます。

$$T_J = T_A + P_{D(max)} \times R_{\theta JA} \quad (5)$$

式(5)を変形して、式(6)が導かれます。

$$R_{\theta JA} = \frac{T_J - T_A}{P_{D(max)}} \quad (6)$$

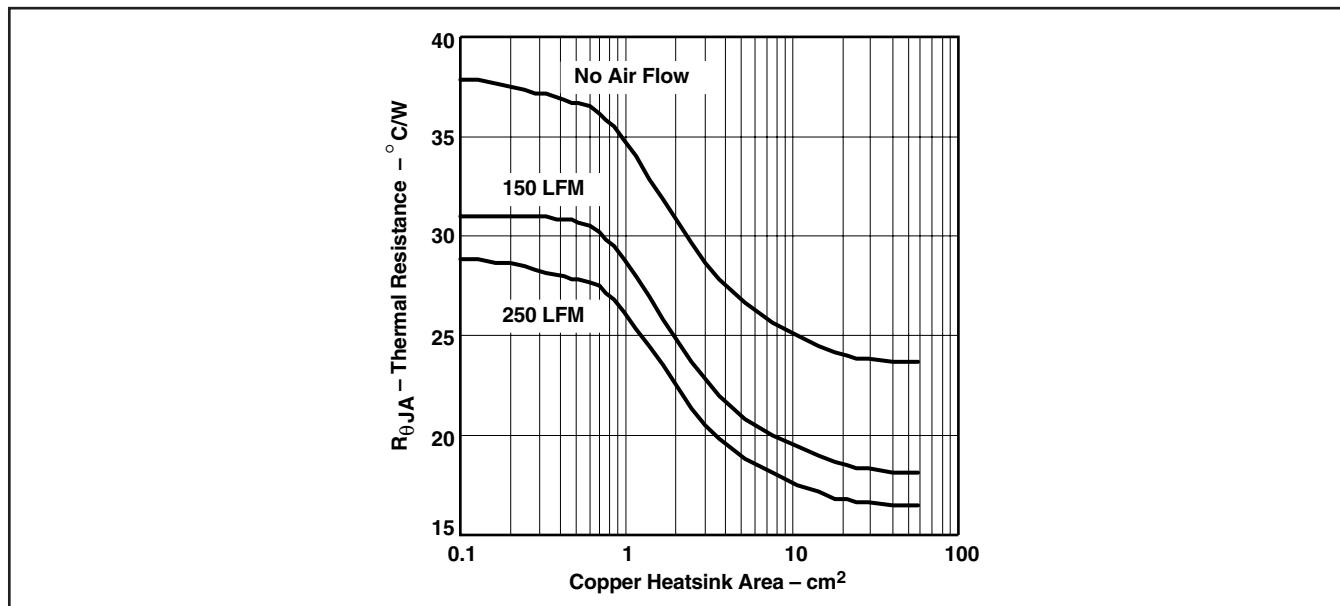

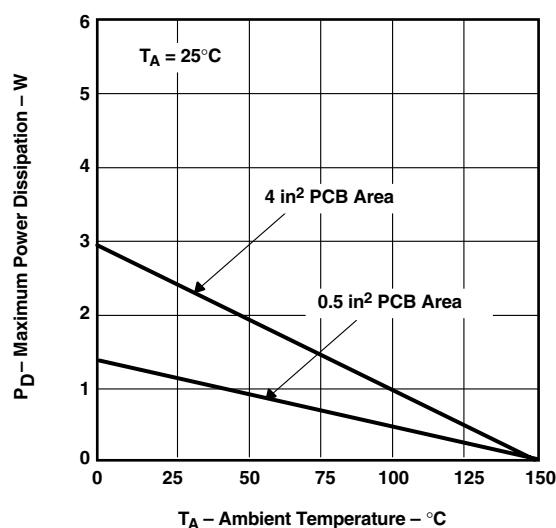

式(5)と、図21および図24に示すコンピュータ・モデルにより生成された曲線を使用すれば、特定の周囲温度、消費電力、および動作環境に対して、必要なヒートシンクの熱抵抗と基板面積を容易に求める事ができます。

## DDPAKの消費電力

DDPAKパッケージは、表面実装アプリケーションにおいて高い消費電力による発熱を効果的に放熱させる事を可能とします。DDPAKパッケージの寸法は、データシート巻末のメカニカル・データ・セクションに記載されています。DDPAKパッケージの直下に銅プレーンを配置する事によりパッケージの熱特性を向上させる事ができます。

ここでは説明のために、DDPAKパッケージのTPS72525を選択しています。この例では、平均入力電圧が5V、出力電圧が2.5V、平均出力電流が1A、周囲温度が55°C、エアフローが150LFM、および動作環境は下記に示すとおりです。自己消費電流は小さいので無視して計算すると、最大平均電力は次のようにになります。

$$P_D \text{max} = (5 - 2.5) \text{ V} \times 1 \text{ A} = 2.5 \text{ W} \quad (7)$$

式(6)の $T_J$ に $T_{J\text{max}}$ を代入すると、式(8)が得られます。

$$R_{\theta JA}^{\text{max}} = (125 - 55) \text{ }^{\circ}\text{C} / 2.5 \text{ W} = 28 \text{ }^{\circ}\text{C/W} \quad (8)$$

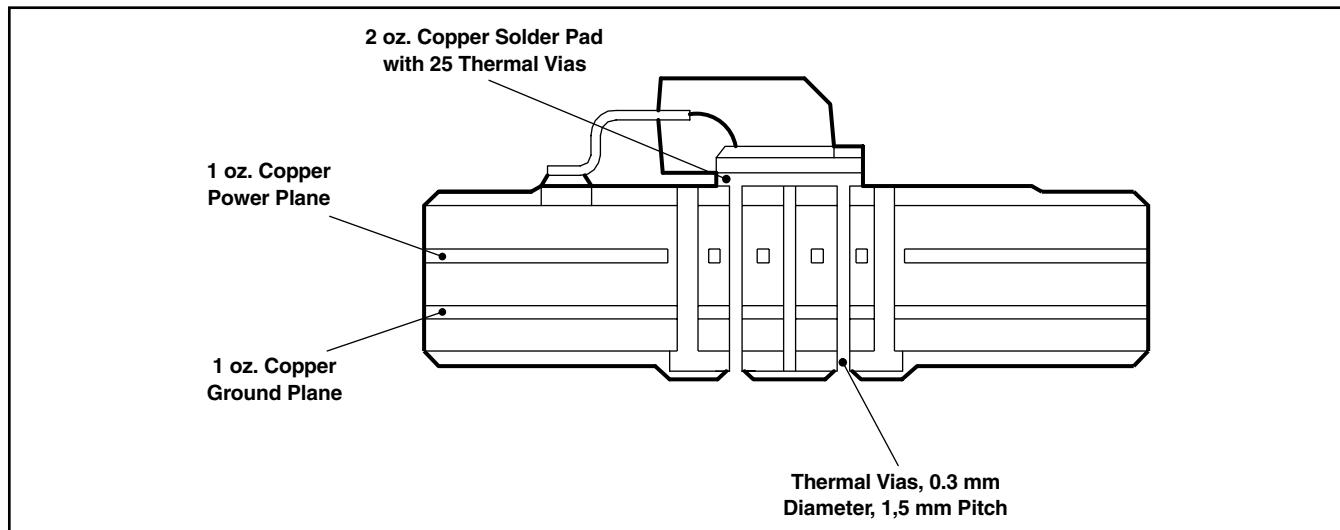

図21「DDPAKの熱抵抗対銅ヒートシンク面積」から、デバイスが2.5Wを消費するためには1cm<sup>2</sup>のグランド・プレーンが必要です。図21を得るためにコンピュータ・モデルで使用した動作環境は、標準JEDEC High-K (2S2P) 基板で、1オンスの内部銅プレーンおよびグランド・プレーンから構成されています。パッケージは、2オンスの銅パッドに半田付けされます。このパッドは、サーマル・ビアを通して1オンスのグランド・プレーンに接続されます。図22に、コンピュータ・モデルで使用した動作環境の側面図を示します。

図 21. DDPAKの熱抵抗対銅ヒートシンク面積

図 22. DDPAKの熱抵抗

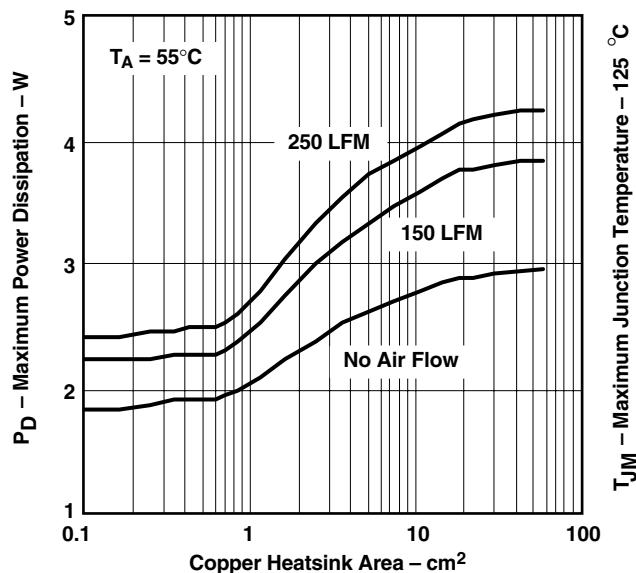

図23. 最大消費電力 対 銅ヒートシンク面積

図23のデータを使用し、式(6)を変形すると、グランド・プレーン面積および特定の周囲温度に対する最大消費電力を計算できます。

無視して計算すると、最大平均電力は次のようにになります。

$$P_{D\max} = (3.3 - 2.5) V \times 1 A = 800 \text{ mW} \quad (9)$$

式(6)の $T_J$ に $T_{J\max}$ を代入すると、式(10)が得られます。

$$R_{\theta JA\max} = (125 - 55)^\circ\text{C} / 800 \text{ mW} = 87.5^\circ\text{C/W} \quad (10)$$

図24「SOT223の熱抵抗対PCB面積」から、デバイスが800mWを消費するためには0.55 in<sup>2</sup>のグランド・プレーンが必要です。図24を得るために使用した動作環境は、1オンスの銅プレーンを持つ両面基板から構成されています。パッケージは、基板上面の1オンスの銅パッドに半田付けされます。このパッドは、サーマル・ビアを通して1オンスの裏面のグランド・プレーンに接続されます。

図24. SOT223の熱抵抗対PCB面積

図24のデータを使用し、式(6)を変形すると、グランド・プレーン面積および特定の周囲温度に対する最大消費電力を計算できます(図25)。

図 25. SOT223の消費電力

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins             | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS72501DCQ           | Obsolete      | Production           | SOT-223 (DCQ)   6          | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | PS72501             |

| TPS72501DCQR          | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72501             |

| TPS72501DCQR.B        | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72501             |

| TPS72501DCQRG4        | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72501             |

| TPS72501KTTR          | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72501        |

| TPS72501KTTR.B        | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72501        |

| TPS72515DCQ           | Obsolete      | Production           | SOT-223 (DCQ)   6          | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | PS72515             |

| TPS72515DCQR          | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72515             |

| TPS72515DCQR.B        | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72515             |

| TPS72515KTTR          | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72515        |

| TPS72515KTTR.B        | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72515        |

| TPS72516DCQ           | Obsolete      | Production           | SOT-223 (DCQ)   6          | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | PS72516             |

| TPS72516DCQR          | Obsolete      | Production           | SOT-223 (DCQ)   6          | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | PS72516             |

| TPS72516KTTT          | Obsolete      | Production           | DDPAK/<br>TO-263 (KTT)   5 | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | TPS<br>72516        |

| TPS72518KTTR          | Obsolete      | Production           | DDPAK/<br>TO-263 (KTT)   5 | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | TPS<br>72518        |

| TPS72525DCQ           | Obsolete      | Production           | SOT-223 (DCQ)   6          | -                     | -           | Call TI                              | Call TI                           | -40 to 125   | PS72525             |

| TPS72525DCQR          | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72525             |

| TPS72525DCQR.B        | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72525             |

| TPS72525DCQRG4        | Active        | Production           | SOT-223 (DCQ)   6          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | PS72525             |

| TPS72525KTTR          | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72525        |

| TPS72525KTTR.B        | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72525        |

| TPS72525KTTRG3        | Active        | Production           | DDPAK/<br>TO-263 (KTT)   5 | 500   LARGE T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | TPS<br>72525        |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

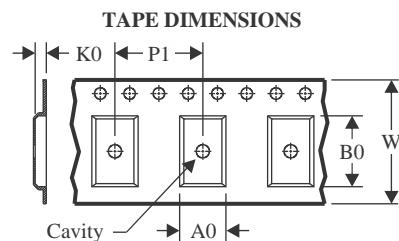

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

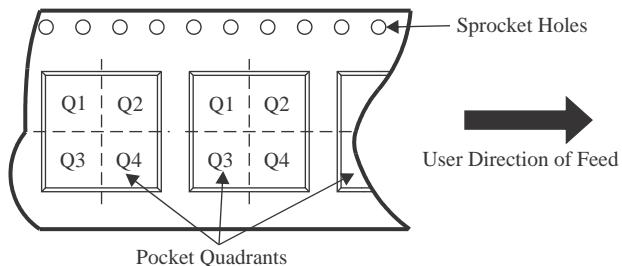

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type     | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|------------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS72501DCQR | SOT-223          | DCQ             | 6    | 2500 | 330.0              | 12.4               | 7.1     | 7.45    | 1.88    | 8.0     | 12.0   | Q3            |

| TPS72501KTTR | DDPAK/<br>TO-263 | KT              | 5    | 500  | 330.0              | 24.4               | 10.9    | 16.1    | 4.9     | 16.0    | 24.0   | Q2            |

| TPS72515DCQR | SOT-223          | DCQ             | 6    | 2500 | 330.0              | 12.4               | 7.1     | 7.45    | 1.88    | 8.0     | 12.0   | Q3            |

| TPS72515KTTR | DDPAK/<br>TO-263 | KT              | 5    | 500  | 330.0              | 24.4               | 10.9    | 16.1    | 4.9     | 16.0    | 24.0   | Q2            |

| TPS72525DCQR | SOT-223          | DCQ             | 6    | 2500 | 330.0              | 12.4               | 7.1     | 7.45    | 1.88    | 8.0     | 12.0   | Q3            |

| TPS72525KTTR | DDPAK/<br>TO-263 | KT              | 5    | 500  | 330.0              | 24.4               | 10.9    | 16.1    | 4.9     | 16.0    | 24.0   | Q2            |

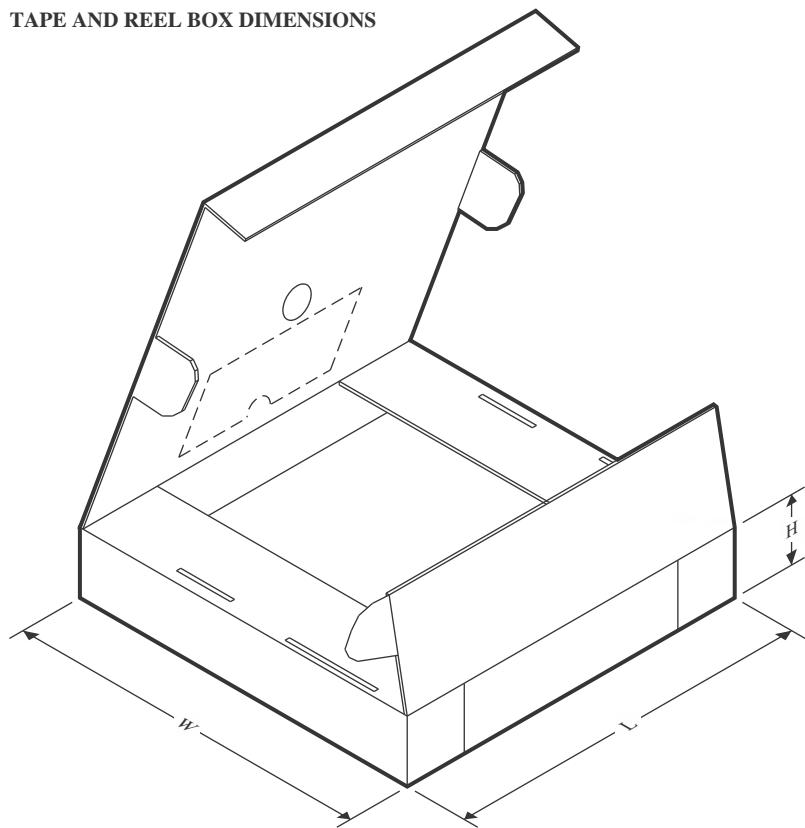

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS72501DCQR | SOT-223      | DCQ             | 6    | 2500 | 346.0       | 346.0      | 29.0        |

| TPS72501KTTR | DDPAK/TO-263 | KTT             | 5    | 500  | 356.0       | 356.0      | 45.0        |

| TPS72515DCQR | SOT-223      | DCQ             | 6    | 2500 | 346.0       | 346.0      | 29.0        |

| TPS72515KTTR | DDPAK/TO-263 | KTT             | 5    | 500  | 356.0       | 356.0      | 45.0        |

| TPS72525DCQR | SOT-223      | DCQ             | 6    | 2500 | 346.0       | 346.0      | 29.0        |

| TPS72525KTTR | DDPAK/TO-263 | KTT             | 5    | 500  | 356.0       | 356.0      | 45.0        |

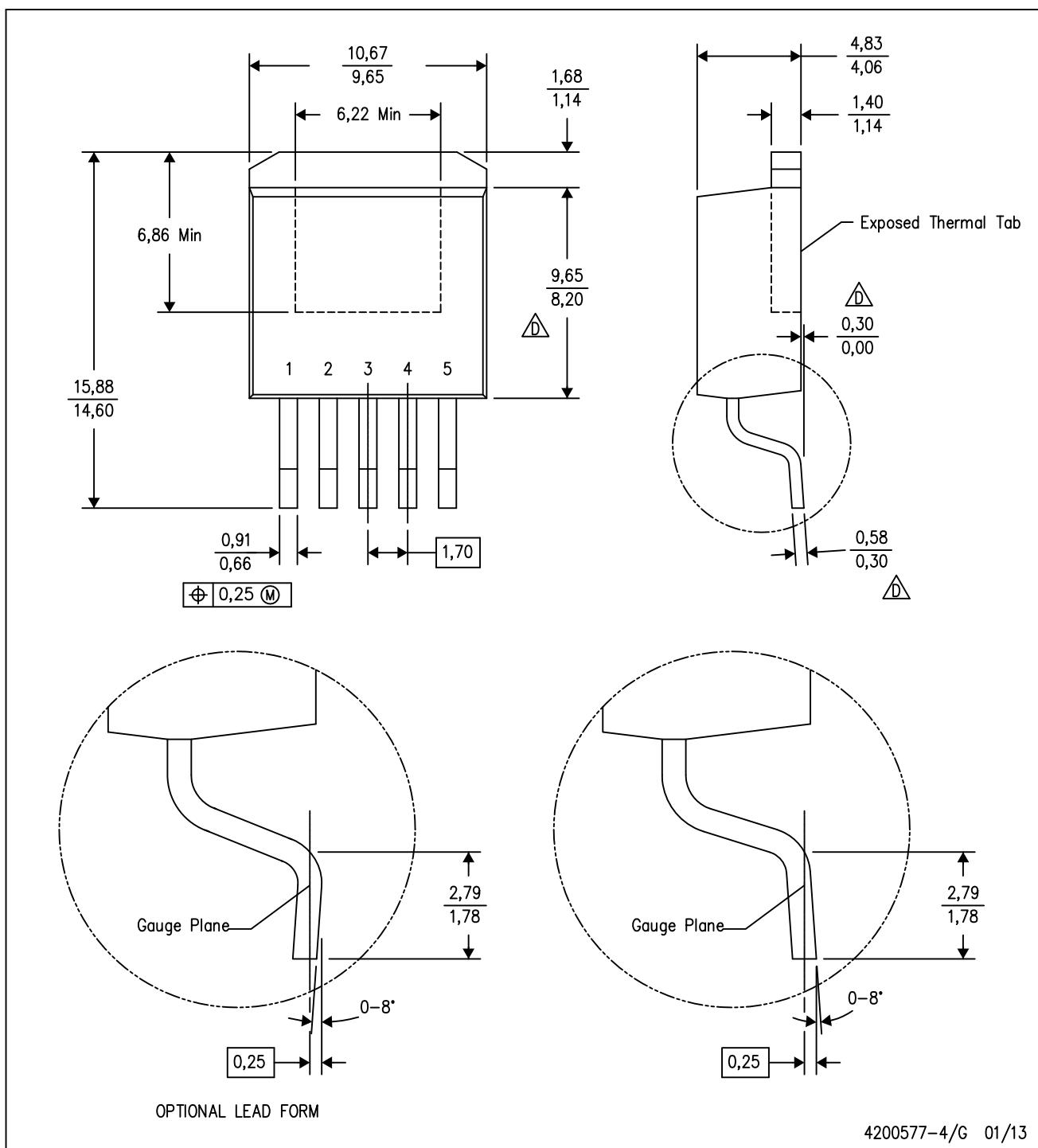

## MECHANICAL DATA

KTT (R-PSFM-G5)

PLASTIC FLANGE-MOUNT PACKAGE

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusion. Mold flash or protrusion not to exceed 0.005 (0,13) per side.

- Falls within JEDEC TO-263 variation BA, except minimum lead thickness, maximum seating height, and minimum body length.

KTT (R-PSFM-G5)

PLASTIC FLANGE-MOUNT PACKAGE

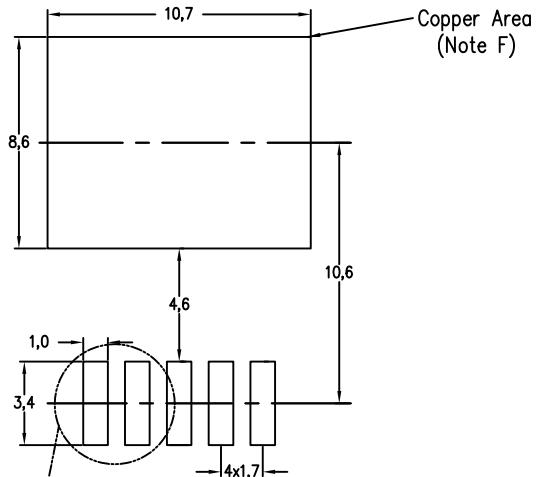

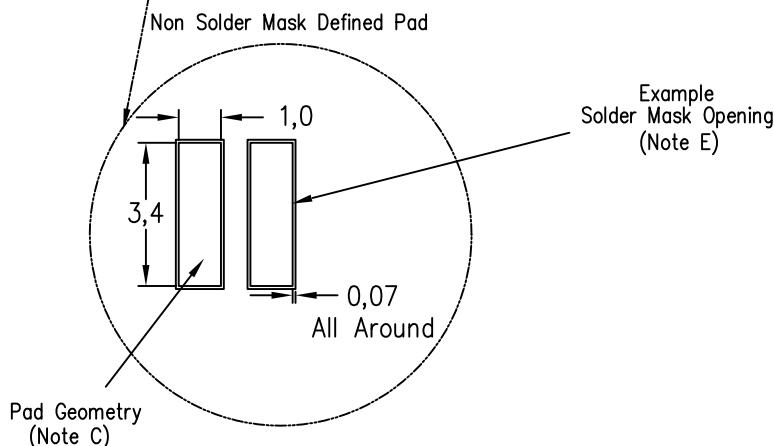

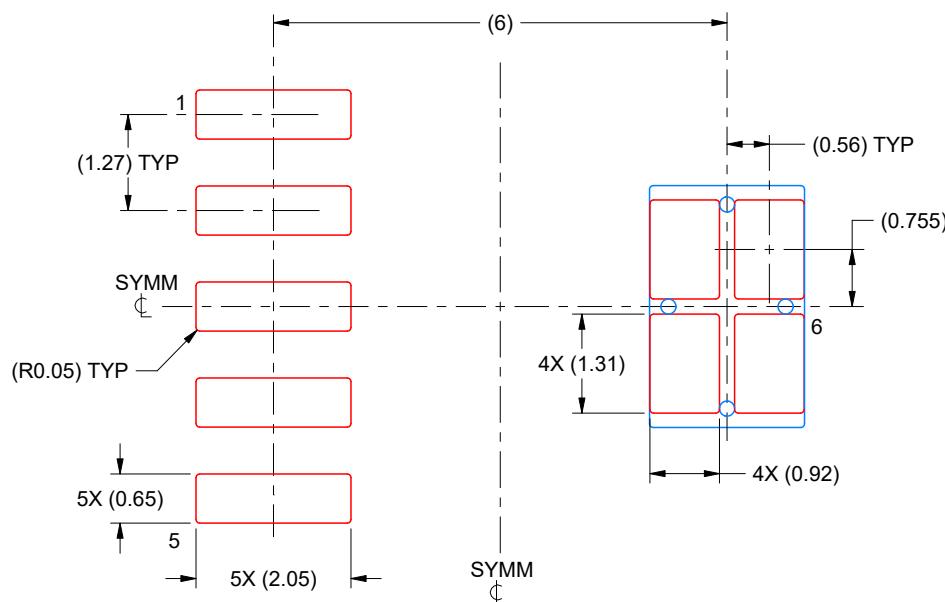

Example Board Layout

(Note C)Example Stencil Design

(Note D)

4208208-3/C 08/12

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-SM-782 is recommended for alternate designs.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- This package is designed to be soldered to a thermal pad on the board. Refer to the Product Datasheet for specific thermal information, via requirements, and recommended thermal pad size. For thermal pad sizes larger than shown a solder mask defined pad is recommended in order to maintain the solderable pad geometry while increasing copper area.

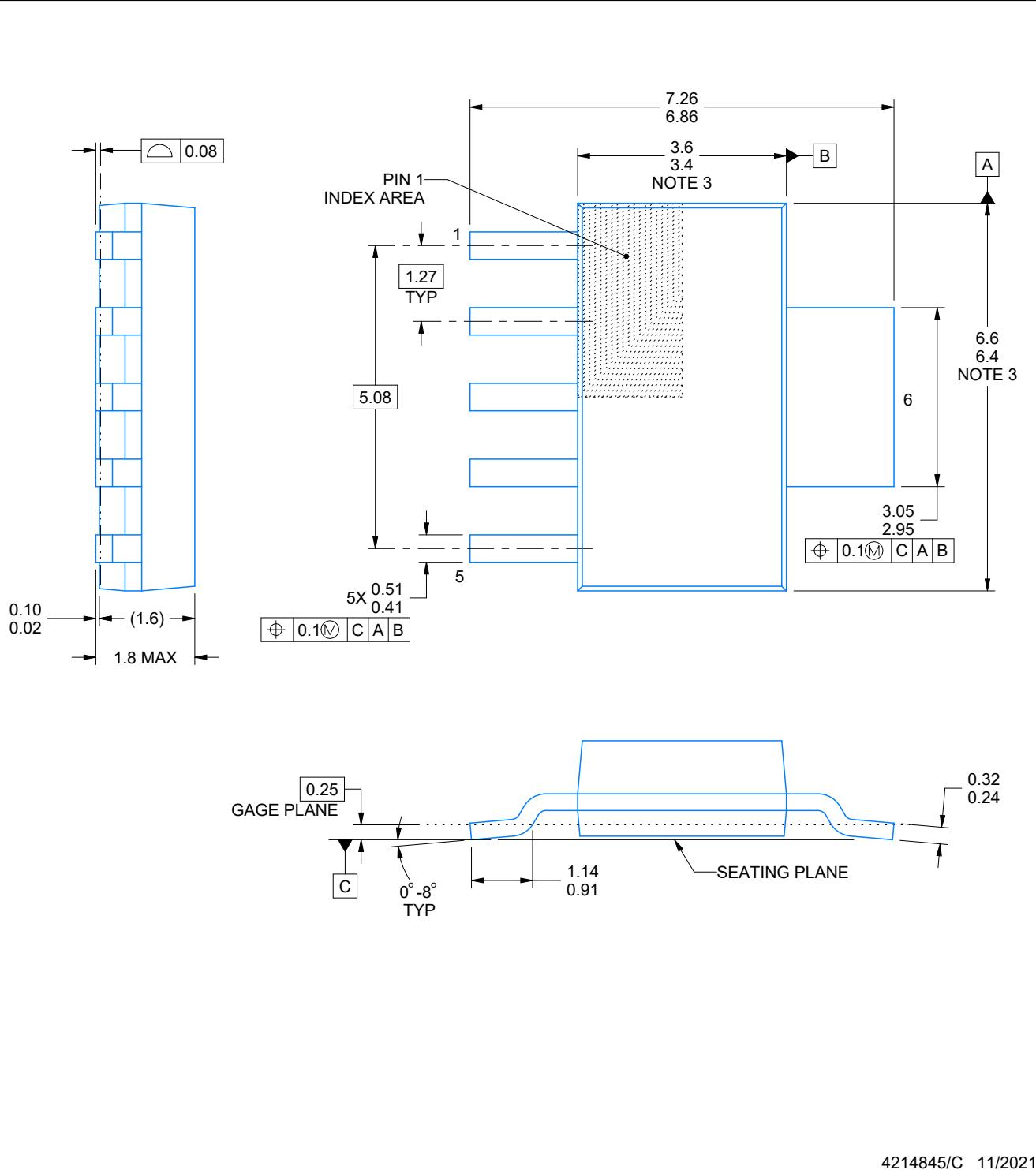

# PACKAGE OUTLINE

## SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

**DCQ0006A**

4214845/C 11/2021

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

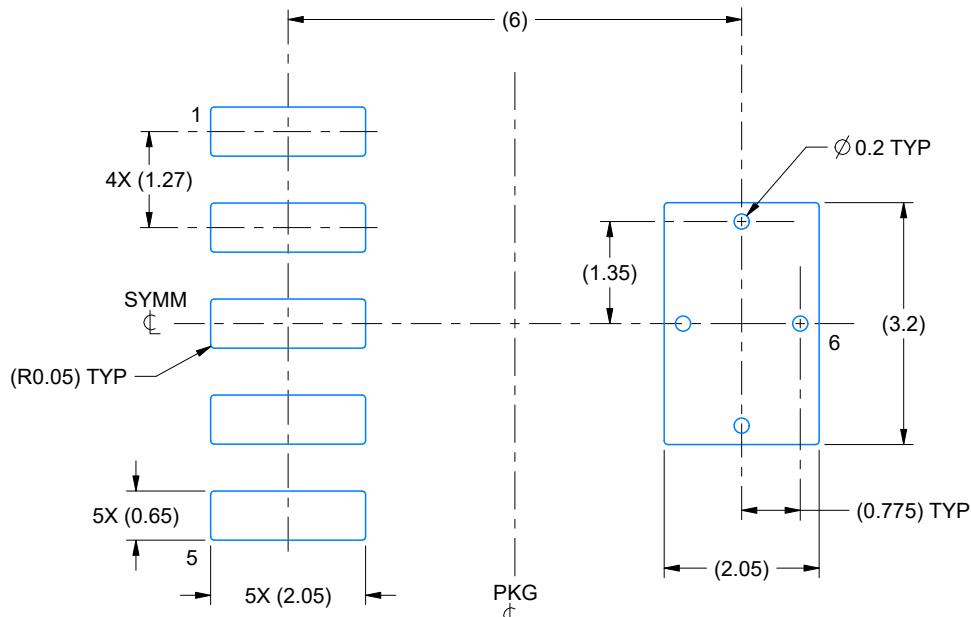

# EXAMPLE BOARD LAYOUT

DCQ0006A

SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

SOLDER MASK DETAILS

4214845/C 11/2021

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

6. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

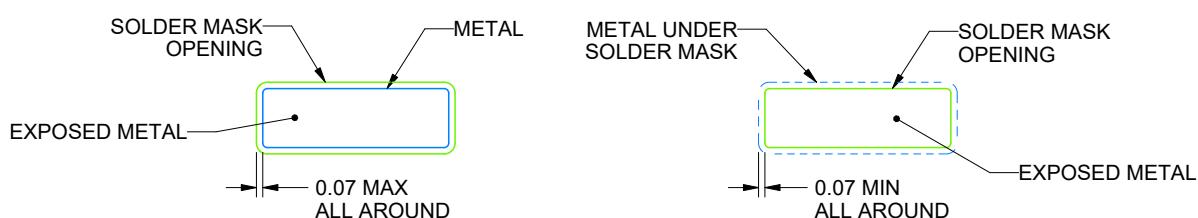

# EXAMPLE STENCIL DESIGN

DCQ0006A

SOT - 1.8 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4214845/C 11/2021

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月