**TPS65235-1** JAJSCX2F - JANUARY 2017 - REVISED MAY 2023

# TPS65235-1 LNB 電圧レギュレータ、I<sup>2</sup>C インターフェイス搭載

# 1 特長

LNB および I<sup>2</sup>C インターフェイス用の完全な統合ソリ ューション

Ordering &

**g**uality

- DiSEqC 2.x および DiSEqC 1.x 互換

- 5V、12V、15V の電源レールに対応

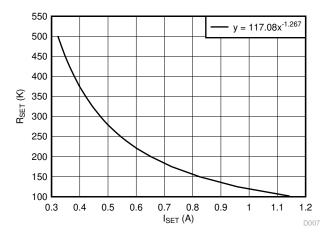

- 外付け抵抗により 1000mA までの高精度出力電流制 限を設定可能

- 昇圧スイッチ・ピーク電流制限は LDO 電流制限に比

- 140m $\Omega$  の低  $R_{ds(on)}$  内部電力スイッチ付き昇圧コンバ

- 昇圧スイッチング周波数は 1MHz または 500kHz を 選択可能

- 強制 PWM モードにより可聴周波数のノイズを回避

- I<sup>2</sup>C 以外のアプリケーション用の専用イネーブル・ピン

- VLNB 出力用のプッシュプル出力段付き低ドロップア ウト(LDO)レギュレータ

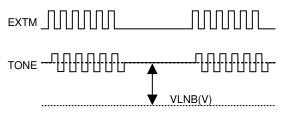

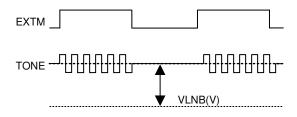

- 高精度の 22kHzトーン・ジェネレータ内蔵、外部トー ン入力もサポート

- 外部の 44kHz および 22kHzトーン入力をサポート

- ソフトスタートおよび 13V から 18V への電圧遷移時間 を調整可能

- 650mV~750mV の 22kHzトーン振幅選択

- EN LOW 時に I<sup>2</sup>C レジスタヘアクセス可能

- 動的な短絡保護

- 出力電圧レベル、DiSEqCトーン入力および出力、電 流レベル、ケーブル接続の診断

- 過熱保護機能を搭載

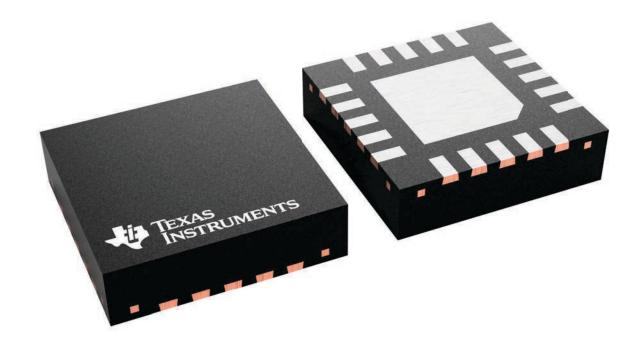

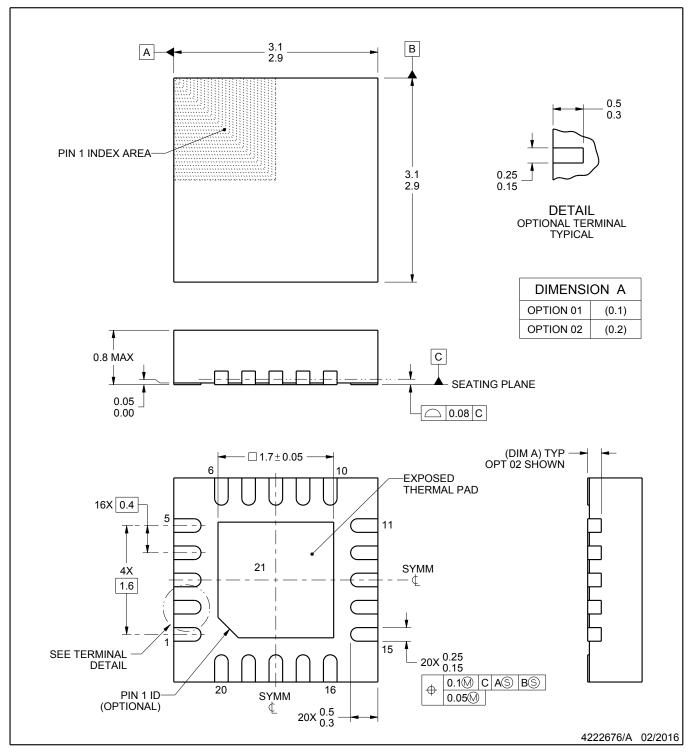

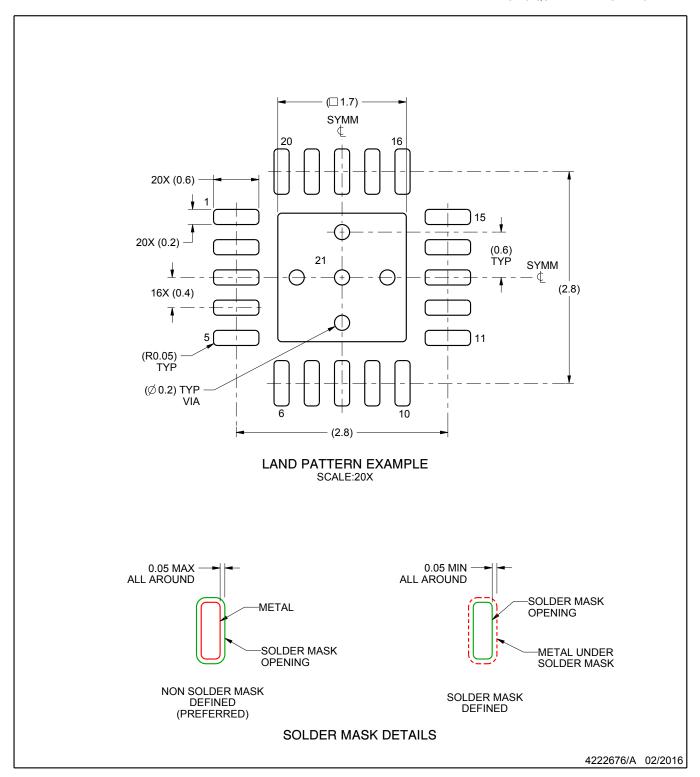

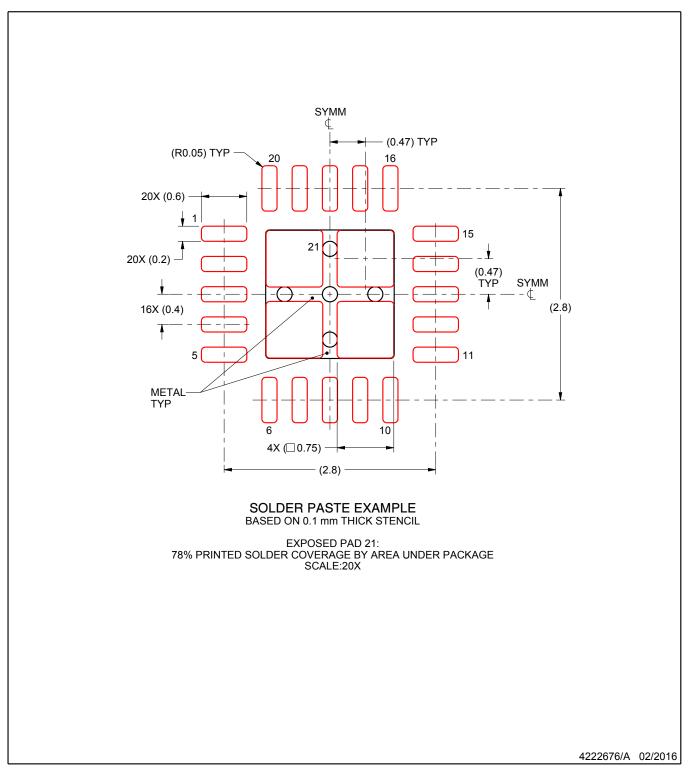

- 20 ピン WQFN 3mm × 3mm (RUK) パッケージ

# 2 アプリケーション

- セットトップ・ボックスの衛星放送受信機

- テレビの衛星放送受信機

- PC カードの衛星放送受信機

- 衛星放送テレビ

## 3 概要

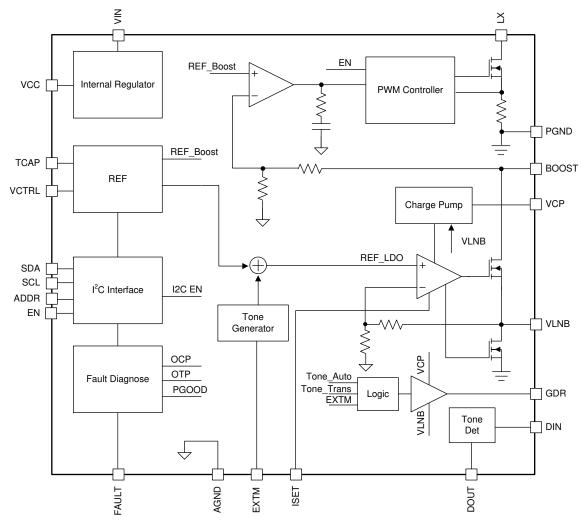

TPS65235-1 は、 $I^2C$  インターフェイスを搭載したモノリシ ック電圧レギュレータで、アナログおよびデジタルの衛星 放送受信機用に設計されており、13V~18V 電源および 22kHzトーン信号を、皿型アンテナの LNB ダウン・コンバ ータ、またはマルチスイッチ・ボックスへ供給します。このデ バイスは、最小の部品数、低消費電力、単純な設計で、 I<sup>2</sup>C 標準インターフェイスを備えた、包括的なソリューショ ンを提供します。

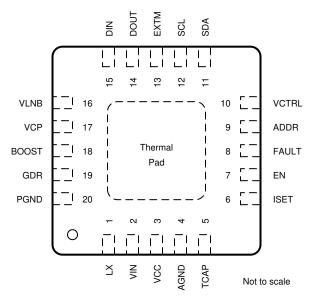

TPS65235-1 は、電力効率が高いという特長があります。 昇圧コンバータには 140mΩ のパワー MOSFET が内蔵 されており、スイッチング周波数として 1MHz または 500kHz を選択できます。リニア・レギュレータでのドロップ アウト電圧は 0.8V で、電力損失を最小化できます。 TPS65235-1 は、複数の方法で 22kHz 信号を生成でき ます。プッシュプル出力段を備えた内蔵のリニア・レギュレ ータは、22kHzトーン信号を生成し、負荷がゼロのときで も出力に重畳されます。リニア・レギュレータの電流制限 は、外付け抵抗により ±10% の精度でプログラム可能で す。I<sup>2</sup>C で読み取られる幅広い診断情報をシステム監視 に使用可能です。

TPS65235-1 は、特に VIN が VLNB 出力に近いか超え ている場合、可聴周波数のノイズを回避するために、 FCCM モードで特別な設計が使用されています。

TPS65235-1 は、22kHzトーン検出回路および出力イン ターフェイスにより、先進的な DiSEqC 2.x 規格をサポート しています。

# パッケージ情報 <sup>(1)</sup>

| 部品番号       | パッケージ          | 本体サイズ (公称)      |  |  |

|------------|----------------|-----------------|--|--|

| TPS65235-1 | RUK (WQFN, 20) | 3.00mm x 3.00mm |  |  |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

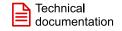

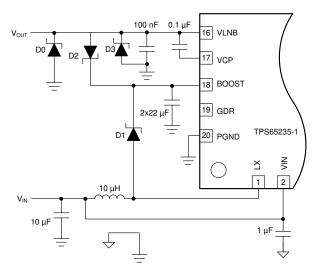

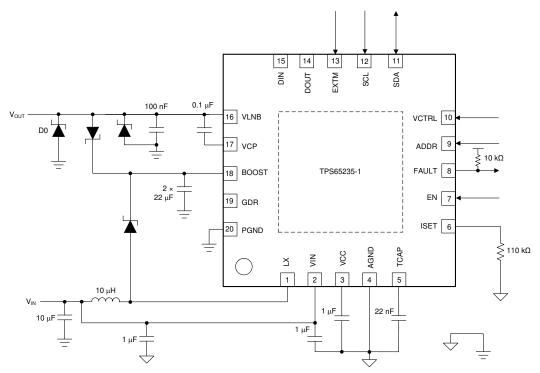

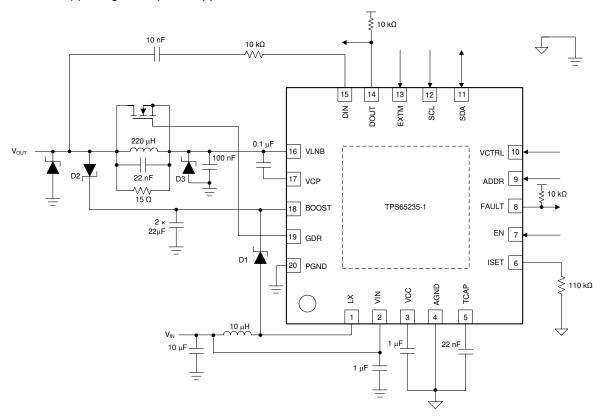

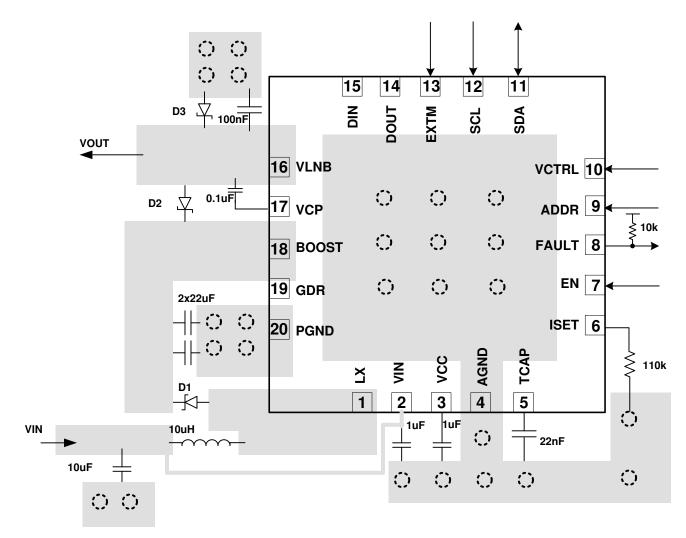

簡略回路図

# **Table of Contents**

| 1 特長                                                                                                     | 1 7.5 Programming                     | 20                                |

|----------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|

| 2アプリケーション                                                                                                |                                       | s22                               |

| 3 概要                                                                                                     | 0.4                                   | Implementation25                  |

| 4 Revision History                                                                                       |                                       | formation25                       |

| 5 Pin Configuration and Functions                                                                        |                                       | eation25                          |

| 6 Specifications                                                                                         |                                       | Recommendations31                 |

| 6.1 Absolute Maximum Ratings                                                                             |                                       | 31                                |

| 6.2 ESD Ratings                                                                                          | 0 Davidsa and Dass                    | ımentation Support33              |

| 6.3 Recommended Operating Conditions                                                                     |                                       | ort33                             |

| 6.4 Thermal Information                                                                                  | 000                                   | on Support33                      |

| 6.5 Electrical Characteristics                                                                           |                                       | 更新通知を受け取る方法33                     |

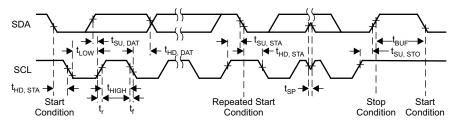

| 6.6 Timing Requirements                                                                                  |                                       | -733                              |

| 6.7 Typical Characteristics                                                                              |                                       |                                   |

| 7 Detailed Description                                                                                   |                                       | 関する注意事項33                         |

| 7.1 Overview                                                                                             |                                       | <ul><li>(表) の任息事項</li></ul>       |

| 7.1 Overview                                                                                             |                                       |                                   |

|                                                                                                          |                                       | ckaging, and Orderable            |

| 7.3 Feature Description                                                                                  |                                       | 34                                |

| <b>4 Revision History</b><br>資料番号末尾の英字は改訂を表しています。                                                        |                                       |                                   |

| Changes from Revision E (May 2021) to                                                                    |                                       | Page                              |

| <ul><li>ドキュメント全体を通して数式のフォーマット</li></ul>                                                                  |                                       |                                   |

|                                                                                                          |                                       |                                   |

| Updated the ADDR pin voltage range for                                                                   |                                       |                                   |

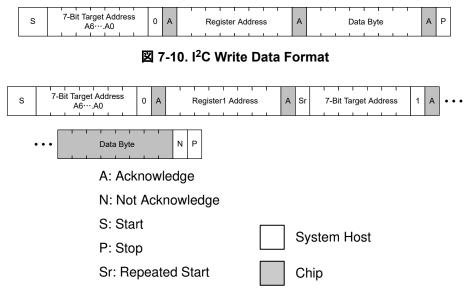

| Changed all instances of legacy termino                                                                  | ogy to controller and target wher     | e 1ºC is mentioned20              |

| Changes from Revision D (July 2019) to                                                                   | Revision E (May 2021)                 | Page                              |

| <ul><li>文書全体にわたって表、図、相互参照の採</li></ul>                                                                    |                                       | 1                                 |

|                                                                                                          |                                       |                                   |

| Changes (Glop) him and max values him                                                                    |                                       |                                   |

| <ul> <li>Changed I<sub>(rev_dis)</sub> min and max values</li> </ul>                                     |                                       |                                   |

| Changes from Revision C (July 2018) to                                                                   | Revision D (July 2019)                | Page                              |

| Changed V <sub>(drop)</sub> at TONEAMP = 0b Fron                                                         |                                       |                                   |

| 1.1 in the <i>Electrical Characteristics</i>                                                             |                                       | 6                                 |

| • Changed V <sub>(drop)</sub> at TONEAMP = 1b Fror                                                       | 1000000000000000000000000000000000000 | 1.12 To: MIN = 0.65 TYP = 0.9 MAX |

| = 1.2 in the Electrical Characteristics                                                                  |                                       | 6                                 |

| Changes from Revision B (June 2018) to                                                                   |                                       | Page                              |

| • Changed the GDR TONE_TRANS = 1b<br>Electrical Characteristics                                          |                                       |                                   |

| Electrical Criaracteristics                                                                              |                                       |                                   |

| Changes from Revision A (January 2017                                                                    | · · · · · · · · · · · · · · · · · · · | <i>,</i>                          |

| <ul> <li>Changed bit 4 (T125) in 表 7-8 From: 0b<br/>From: 1b = Die temperature &lt; 125°C To:</li> </ul> |                                       |                                   |

| From: 10 - Die temperature < 125 C 10:                                                                   |                                       | 24                                |

| Changes from Revision * (January 2017)                                                                   | -                                     |                                   |

| Changed the VCP values From: VLNB to                                                                     |                                       |                                   |

| <ul> <li>Changed the GDR values From: VLNB t</li> </ul>                                                  |                                       |                                   |

| • Changed the A <sub>(tone)</sub> TONEAMP = 0b val                                                       | ies From: MIN = 667 TYP = 700         | MAX = 746 To: MIN = 617 TYP =     |

| 650 MAY - 606 in the Electrical Charact                                                                  | eristics                              | 6                                 |

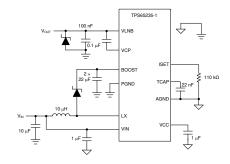

# **5 Pin Configuration and Functions**

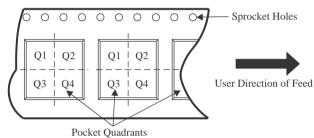

図 5-1. RUK Package 20-Pin WQFN With Exposed Thermal Pad Top View

表 5-1. Pin Functions

| NO. NAME |             | TYPE(1) | DESCRIPTION                                                                                                                                                                                                 |  |  |

|----------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |             | ITPE    |                                                                                                                                                                                                             |  |  |

| 1        | LX          | I       | Switching node of the boost converter                                                                                                                                                                       |  |  |

| 2        | VIN         | S       | Input of internal linear regulator                                                                                                                                                                          |  |  |

| 3        | VCC         | 0       | Internal 6.3-V power supply. Connect a 1- $\mu$ F ceramic capacitor from this pin to ground. When $V_{IN}$ is 5 V, connect the VCC pin to the VIN pin.                                                      |  |  |

| 4        | AGND        | S       | Analog ground. Connect all ground pins and power pad together.                                                                                                                                              |  |  |

| 5        | TCAP        | 0       | Connect a capacitor to this pin to set the rise time of the LNB output.                                                                                                                                     |  |  |

| 6        | ISET        | 0       | Connect a resistor to this pin to set the LNB output current limit.                                                                                                                                         |  |  |

| 7        | EN          | 1       | Enable this pin to enable the VLNB output. pull this pin to ground to disable the output. The output is then pulled to ground, and, when the EN pin is low, the I <sup>2</sup> C interface can be accessed. |  |  |

| 8        | FAULT       | 0       | Open drain output pin, it goes low if any fault flag is set.                                                                                                                                                |  |  |

| 9        | ADDR        | I       | Connect a different resistor to this pin to set different I <sup>2</sup> C addresses (see the 表 7-4 table).                                                                                                 |  |  |

| 10       | VCTRL       | 1       | Voltage level at this pin to set the output voltage (see the 表 7-3).                                                                                                                                        |  |  |

| 11       | SDA         | I/O     | I <sup>2</sup> C compatible bidirectional data                                                                                                                                                              |  |  |

| 12       | SCL         | I       | I <sup>2</sup> C compatible clock input                                                                                                                                                                     |  |  |

| 13       | EXTM        | I       | External modulation logic input pin that activates the 22-kHz tone output. The feeding signal can be 22-kHz tone or logic high or low.                                                                      |  |  |

| 14       | DOUT        | 0       | Tone detection output                                                                                                                                                                                       |  |  |

| 15       | DIN         | I       | Tone detection input                                                                                                                                                                                        |  |  |

| 16       | VLNB        | 0       | Output of the power supply connected to satellite receiver or switch                                                                                                                                        |  |  |

| 17       | VCP         | 0       | Gate drive supply voltage and output of charge pump. Connect a capacitor between this pin and the VLNB pin.                                                                                                 |  |  |

| 18       | BOOST       | 0       | Output of the boost regulator and Input voltage of the internal linear regulator                                                                                                                            |  |  |

| 19       | GDR         | 0       | Control the gate of the external MOSFET for DiSEqc 2.x support                                                                                                                                              |  |  |

| 20       | PGND        | S       | Power ground for the boost converter                                                                                                                                                                        |  |  |

|          | Thermal Pad |         | The thermal pad must be soldered to the printed circuit board (PCB) for optimal thermal performance. Use thermal vias on the PCB to enhance power dissipation.                                              |  |  |

(1) I = input, O = output, I/O = input and output, S = power supply

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                              | MIN  | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------------|------|-----|------|

|                                       | VIN, LX, BOOST, VLNB                                         | 1    | 30  |      |

|                                       | VCP, GDR (referenced to VLNB pin)                            | -0.3 | 7   |      |

| Voltage                               | VCC, EN, ADDR, FAULT, SCL, SDA, VCTRL, EXTM, DOUT, DIN, TCAP | -0.3 | 7   | V    |

|                                       | ISET                                                         | -0.3 | 3.6 |      |

|                                       | PGND                                                         | -0.3 | 0.3 |      |

| Operating junction tempe              | ng junction temperature, T <sub>J</sub>                      |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub> |                                                              | -55  | 150 |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                     |                                                                                | VALUE | UNIT     |

|--------------------|---------------------|--------------------------------------------------------------------------------|-------|----------|

| V <sub>(ESD)</sub> |                     | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 | V        |

|                    | O) discharge Charge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | <b>v</b> |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                                | MIN | NOM MAX | UNIT |

|-----------------|--------------------------------|-----|---------|------|

| V <sub>IN</sub> | Input operating voltage        | 4.5 | 20      | V    |

| T <sub>A</sub>  | Operating junction temperature | -40 | 125     | °C   |

### 6.4 Thermal Information

|                        | THERMAL METRIC(1)                            | RUK (WQFN) | UNIT |

|------------------------|----------------------------------------------|------------|------|

|                        |                                              | 20 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 44.8       | °C/W |

| R <sub>0JC(top)</sub>  | Junction-to-case (top) thermal resistance    | 47.3       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 16.5       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.4       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 3.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $\text{V}_{\text{IN}}$  = 12 V,  $\text{f}_{\text{SW}}$  = 1 MHz (unless otherwise noted)

|                            | PARAMETER                                                | TEST CONDITIONS                                                                    | MIN   | TYP  | MAX   | UNIT |

|----------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------|-------|------|-------|------|

| INPUT SUPI                 | PLY                                                      |                                                                                    |       |      |       |      |

| V <sub>IN</sub>            | Input voltage range                                      |                                                                                    | 4.5   | 12   | 20    | V    |

| I <sub>DD(SDN)</sub>       | Shutdown supply current                                  | EN = 0b                                                                            | 90    | 120  | 150   | μA   |

| I <sub>LDO(Q)</sub>        | LDO quiescent current                                    | EN = 1b, I <sub>O</sub> = 0 A, V <sub>VLNB</sub> = 18.2 V                          | 1.5   | 5    | 8.5   | mA   |

|                            |                                                          | V <sub>IN</sub> rising                                                             | 4.15  | 4.3  | 4.45  | V    |

| UVLO                       | V <sub>IN</sub> undervoltage lockout                     | Hysteresis                                                                         | 280   | 480  | 550   | mV   |

| OUTPUT VC                  | DLTAGE                                                   |                                                                                    |       |      |       |      |

|                            |                                                          | V <sub>(ctrl)</sub> = 1, I <sub>O</sub> = 500 mA                                   | 18    | 18.2 | 18.4  | V    |

|                            |                                                          | V <sub>(ctrl)</sub> = 0, I <sub>O</sub> = 500 mA                                   | 13.25 | 13.4 | 13.55 | V    |

| V <sub>OUT</sub>           | Regulated output voltage                                 | SCL = 1b, V <sub>(ctrl)</sub> = 1, I <sub>O</sub> = 500 mA (Non I <sup>2</sup> C)  | 19.18 | 19.4 | 19.62 | V    |

|                            |                                                          | SCL = 1b, V <sub>(ctrl)</sub> = 0, I <sub>O</sub> = 500 mA (Non I <sup>2</sup> C)  | 14.44 | 14.6 | 14.76 | V    |

|                            | 0.1.1.1.1.1.1.11.11                                      | R <sub>(SET)</sub> = 200 kΩ, Full temperature                                      | 580   | 650  | 720   | mA   |

| I <sub>(OCP)</sub>         | Output short circuit current limit                       | T <sub>J</sub> = 25°C                                                              | 629   | 650  | 688   | mA   |

| f <sub>SW</sub>            | Boost switching frequency                                | f = 1 MHz                                                                          | 977   | 1060 | 1134  | kHz  |

| I <sub>(limitsw)</sub> (1) | Switching current limit                                  | $V_{IN}$ = 12 V, $V_{OUT}$ = 18.2 V, $R_{(SET)}$ = 200 $k\Omega$                   |       | 3    |       | А    |

| R <sub>ds(on)_LS</sub>     | On resistance of low side FET                            | V <sub>IN</sub> = 12 V                                                             | 90    | 140  | 210   | mΩ   |

|                            |                                                          | I <sub>O</sub> = 500 mA, TONEAMP = 0b                                              | 0.44  | 0.8  | 1.15  | V    |

| $V_{(drop)}$               | Linear regulator voltage dropout                         | I <sub>O</sub> = 500 mA, TONEAMP = 1b                                              | 0.55  | 0.9  | 1.2   | V    |

| I <sub>(cable)</sub>       | Cable good detection current threshold                   | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 13.4 V or 18.2 V                        | 0.9   | 5    | 8.8   | mA   |

| I <sub>(rev)</sub>         | Reverse bias current                                     | EN = 1b, V <sub>VLNB</sub> = 21 V                                                  | 49    | 58   | 65    | mA   |

| I <sub>(rev_dis)</sub>     | Disabled reverse bias current                            | EN = 0b, V <sub>VLNB</sub> = 21 V                                                  | 2.9   | 4.6  | 6.3   | mA   |

| LOGIC SIGN                 | NALS                                                     |                                                                                    |       |      |       |      |

|                            | Enable threshold (V <sub>(EN)</sub> ), high              |                                                                                    | 1.6   |      |       | V    |

|                            | Enable threshold (V <sub>(EN)</sub> ), low               |                                                                                    |       |      | 0.8   | V    |

| L                          | Enable internal pullup current                           | V <sub>(EN)</sub> = 1.5 V                                                          | 5     | 6    | 7     | μA   |

| I <sub>(EN)</sub>          | Enable internal pullup current                           | V <sub>(EN)</sub> = 1 V                                                            | 2     | 3    | 4     | μA   |

| V <sub>(VCTRL_H)</sub>     | VCTRL logic threshold level for high-level input voltage |                                                                                    | 2     |      |       | V    |

| V <sub>(VCTRL_L)</sub>     | VCTRL logic threshold level for low-level input voltage  |                                                                                    |       |      | 0.8   | V    |

| V <sub>(EXTM_H)</sub>      | EXTM logic threshold level for high-level input voltage  |                                                                                    | 2     |      |       | V    |

| V <sub>(EXTM_L)</sub>      | EXTM logic threshold level for low-level input voltage   |                                                                                    |       |      | 0.8   | V    |

| V <sub>OL(FAULT)</sub>     | FAULT output low voltage                                 | FAULT open drain, I <sub>OL</sub> = 1 mA                                           |       |      | 0.4   | V    |

| TONE                       |                                                          |                                                                                    |       |      |       |      |

| f <sub>(tone)</sub>        | Tone frequency                                           | 22-kHz tone output                                                                 | 20    | 22   | 24    | kHz  |

| Δ., .                      | Tone amplitude                                           | 0 mA $\leq$ I <sub>O</sub> $\leq$ 500 mA, C <sub>O</sub> = 100 nF,<br>TONEAMP = 0b | 617   | 650  | 696   | mV   |

| A <sub>(tone)</sub>        | ione ampillude                                           | $0 \text{ mA} \le I_O \le 500 \text{ mA}, C_O = 100 \text{ nF},$<br>TONEAMP = 1b   | 703   | 750  | 803   | mV   |

| D <sub>(tone)</sub>        | Tone duty cycle                                          |                                                                                    | 45%   | 50%  | 55%   |      |

| _                          | Future of top a input for a constant                     | 22-kHz tone output                                                                 | 17.6  | 22   | 26.4  | kHz  |

| f <sub>(EXTM)</sub>        | External tone input frequency range                      | 44-kHz tone output                                                                 | 35.2  | 44   | 52.8  | kHz  |

-40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, V<sub>IN</sub> = 12 V, f<sub>SW</sub> = 1 MHz (unless otherwise noted)

| PARAMETER                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                      | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MAX                                                                               | UNIT                                                                                     |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| ECTION                                |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |                                                                                          |

| Tone detector frequency capture range | 0.4-V <sub>PP</sub> sine wave                                                                                                                                                                                                                                                                                                                                                        | 17.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26.4                                                                              | kHz                                                                                      |

| Tone detector input amplitude         | Sine wave, 22 kHz                                                                                                                                                                                                                                                                                                                                                                    | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.5                                                                               | V                                                                                        |

| DOUT output voltage                   | Tone present, I <sub>load</sub> = 2 mA                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.4                                                                               | V                                                                                        |

| Pyraga EET gata valtaga I NP          | TONE_TRANS = 1b, V <sub>(LNB)</sub> = 18.2 V                                                                                                                                                                                                                                                                                                                                         | 23.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24.33                                                                             | V                                                                                        |

| bypass FET gate voltage, LINB         | TONE_TRANS = 0b, V <sub>(LNB)</sub> = 18.2 V                                                                                                                                                                                                                                                                                                                                         | 18.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18.23                                                                             | V                                                                                        |

| SHUT-DOWN (JUNCTION TEMPERATURE       | )                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |                                                                                          |

| Thermal protection trip point         | Temperature rising                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   | °C                                                                                       |

| Thermal protection hysteresis         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                   | °C                                                                                       |

| BACK FAULT STATUS                     |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |                                                                                          |

|                                       | Feedback voltage UVP low                                                                                                                                                                                                                                                                                                                                                             | 94%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97.1%                                                                             |                                                                                          |

| DCCOD trip lovels                     | Feedback voltage UVP high                                                                                                                                                                                                                                                                                                                                                            | 93%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94.5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95.5%                                                                             |                                                                                          |

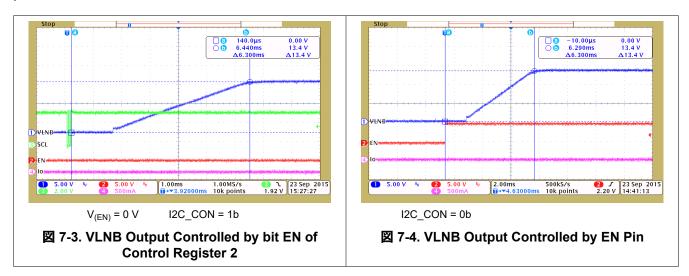

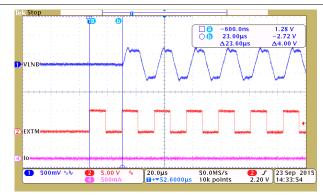

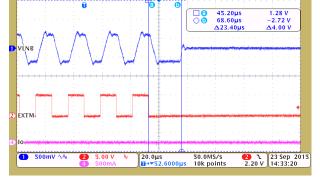

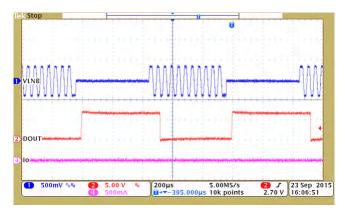

| PGOOD trip levels                     | Feedback voltage OVP high                                                                                                                                                                                                                                                                                                                                                            | 104%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 106.6%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 108%                                                                              |                                                                                          |