🕳 Order

Now

Support & Community

**TPS652170**

JAJSHL2-JUNE 2019

# TPS652170 プログラム可能なバッテリ駆動システム用 PMIC

## 1 特長

充電器および電源パス

INSTRUMENTS

Texas

- 電源パスで **2A** の出力電流

- リニア充電器:最大充電電流 700mA

- 20V 許容の USB および AC 入力

- サーマル・レギュレーション、安全タイマ

- 温度検出入力

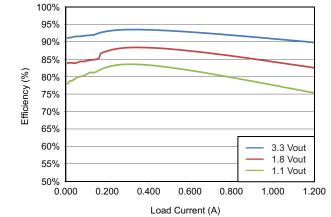

- 降圧コンバータ (DCDC1、DCDC2、DCDC3)

- スイッチング FET を内蔵した 3 つの降圧コンバー

- 2.25MHz の固定周波数動作

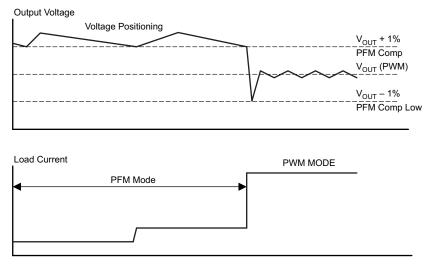

- 軽負荷電流時のパワー・セーブ・モード

- PWM モード時の出力電圧精度:**±2%**

- 100% デューティ・サイクル動作による最小のドロップアウト電圧

- コンバータごとの静止電流:15µA (標準値)

- ディセーブル時にグランドへパッシブ放電

- LDO レギュレータ (LDO1、LDO2)

- 2 つの調整可能 LDO

- LDO2 は DCDC3 をトラッキングするよう構成可能

静止電流:15µA (標準値)

- 負荷スイッチ (LDO3、LDO4)

- 2 つの独立負荷スイッチ、LDO として構成可能

- WLED ドライバ

- 調光制御用に PWM を内部生成

- 38V の開路 LED 保護

- 最大 10 個の LED を持つストリング 2 つをサポート、各 25mA

- 内部のローサイド電流シンク

- 保護

- 低電圧誤動作防止およびバッテリ・フォルト・コンパ レータ

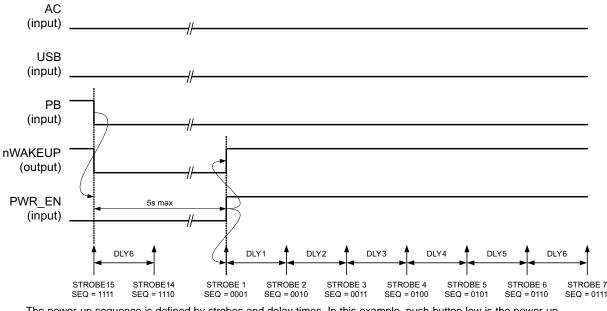

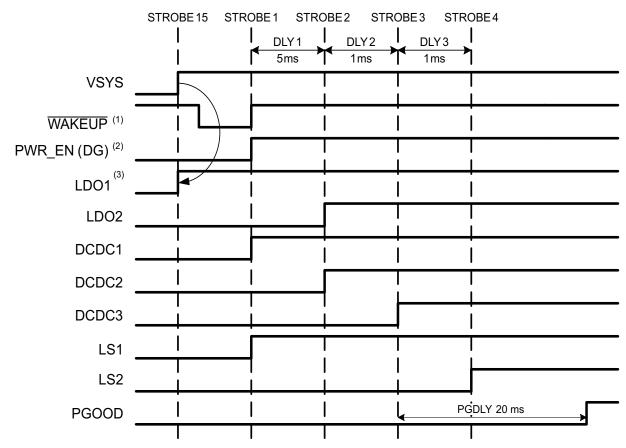

- 常時オンのプッシュボタン・モニタ

- ハードウェアのリセット・ピン

- パスワード保護付き I<sup>2</sup>C レジスタ

- ・ インターフェイス

- I<sup>2</sup>C インターフェイス (アドレス 0x24)

- パスワード保護付き I<sup>2</sup>C レジスタ

- 2 アプリケーション

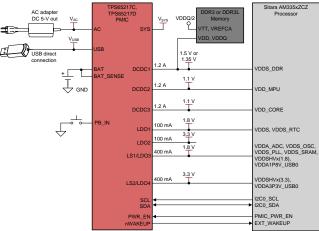

- Sitara™AM335x プロセッサの電源

- ボータブル・ナビゲーション・システム

- タブレット・コンピュータ

- 5V 産業用機器

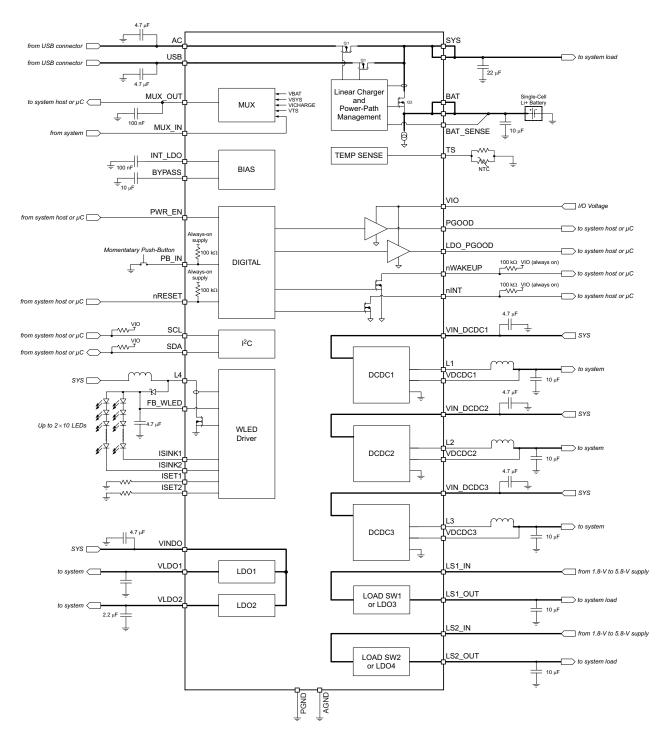

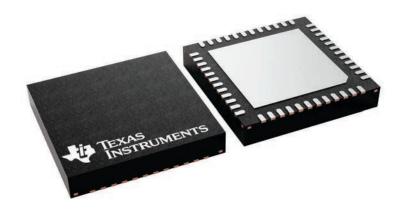

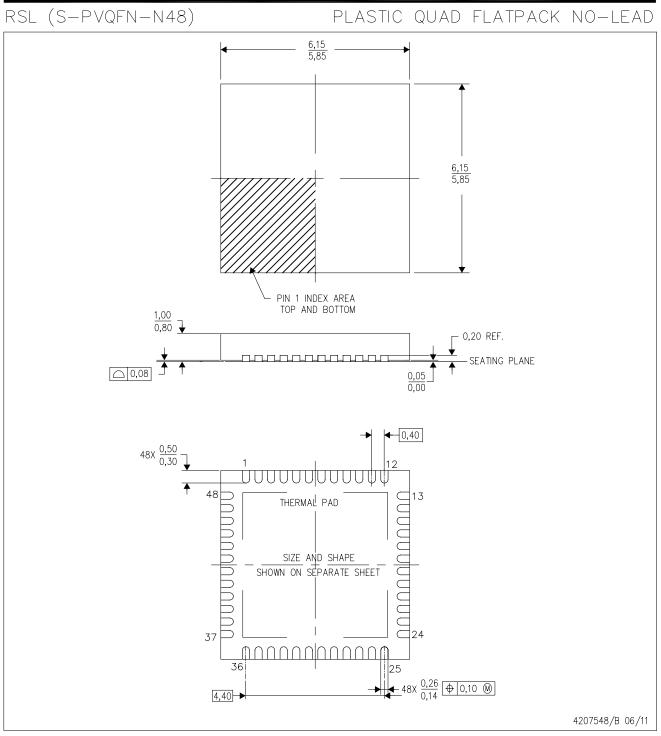

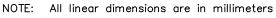

TPS652170 はシングルチップの電力管理 IC (PMIC) で あり、携帯用や 5V ライン電源のアプリケーションで AM335x ARM<sup>®</sup> Cortex<sup>®</sup>-A8プロセッサの電源に使用す ることに特化して設計されています。PMICデバイスには、 単一のリチウムイオンおよびリチウムポリマー・バッテリ用の リニア・バッテリ充電器、デュアル入力の電源パス、3つの 降圧コンバータ、4つの低ドロップアウト(LDO)レギュレー タ、および最大10個のLEDを持つストリング2つに電力を 供給する高効率の昇圧コンバータが内蔵されています。こ のシステムは、USBポート、5V ACアダプタ、リチウムイオ ン・バッテリのどのような組み合わせでも電力を供給できま す。このデバイスは-40℃~+105℃の温度範囲で動作が 規定されているため、産業用アプリケーションに適してい ます。3つの高効率2.25MHz降圧コンバータが、システム のコア電圧、メモリ、I/O電圧を供給できます。TPS652170 は、0.4mm ピッチの 48 ピン・リードレス・パッケージ (6mm × 6mm VQFN) で供給されます。

### 製品情報<sup>(1)</sup>

| 2010/10/10 |           |               |  |  |  |  |

|------------|-----------|---------------|--|--|--|--|

| 型番         | パッケージ     | 本体サイズ(公称)     |  |  |  |  |

| TPS652170  | VQFN (48) | 6.00mm×6.00mm |  |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

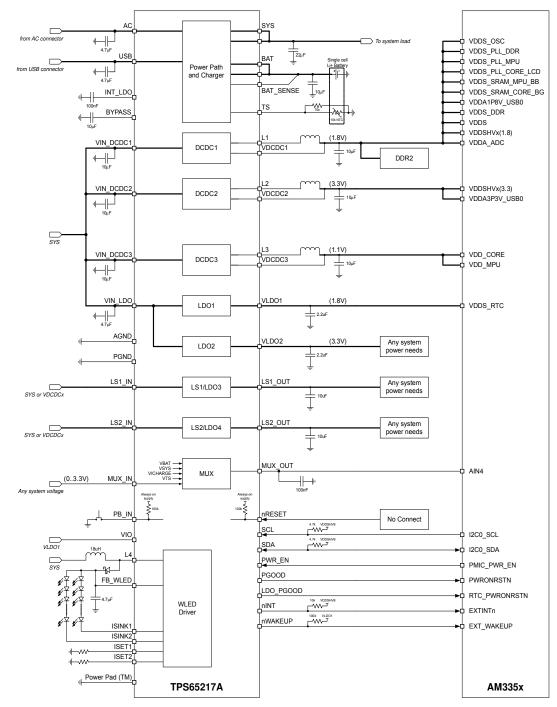

### アプリケーション概略図

Copyright © 2018, Texas Instruments Incorporated

3 概要 TPS652170 はシングルチップ

Texas Instruments

www.ti.com

# 目次

| 1 | 特長   | <u>.</u>                             | 1              |

|---|------|--------------------------------------|----------------|

| 2 | アプ   | ゜リケーション                              | 1              |

| 3 | 概要   | Ŧ<br>                                | 1              |

| 4 | 改訂   | 「履歴                                  | 2              |

| 5 | Pin  | Configuration and Functions          | 3              |

| 6 | Spe  | cifications                          | 5              |

|   | 6.1  | Absolute Maximum Ratings             | 5              |

|   | 6.2  | ESD Ratings                          | <mark>5</mark> |

|   | 6.3  | Recommended Operating Conditions     |                |

|   | 6.4  | Thermal Information                  | 6              |

|   | 6.5  | Electrical Characteristics           | <mark>6</mark> |

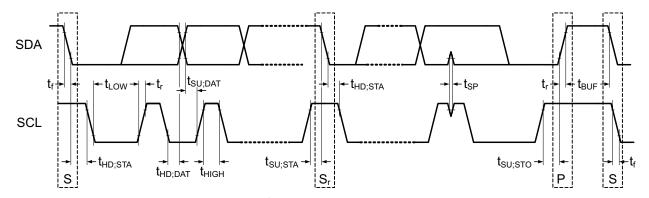

|   | 6.6  | I <sup>2</sup> C Timing Requirements | 13             |

|   | 6.7  | Typical Characteristics              | 14             |

| 7 | Deta | ailed Description                    | 15             |

|   | 7.1  | Overview                             | 15             |

|   | 7.2  | Functional Block Diagram             | 16             |

|   | 7.3  | Feature Description                  | 17             |

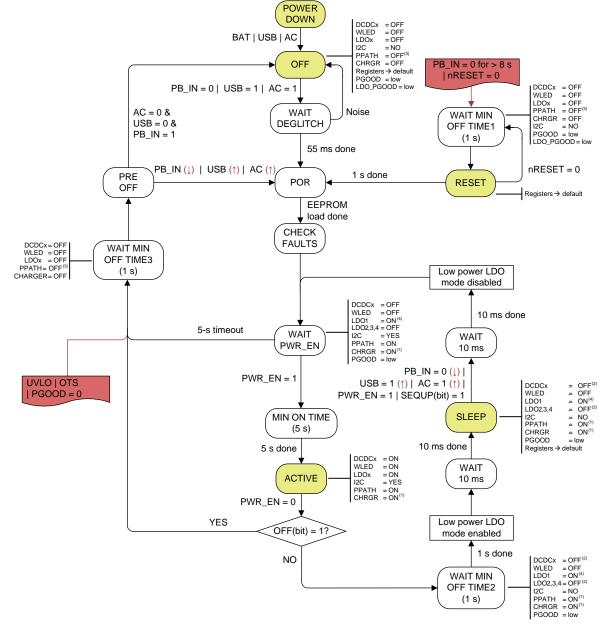

|   | 7.4  | Device Functional Modes              | 37             |

|   |      |                                      |                |

|   |      |                                      |                |

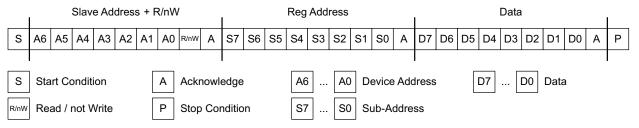

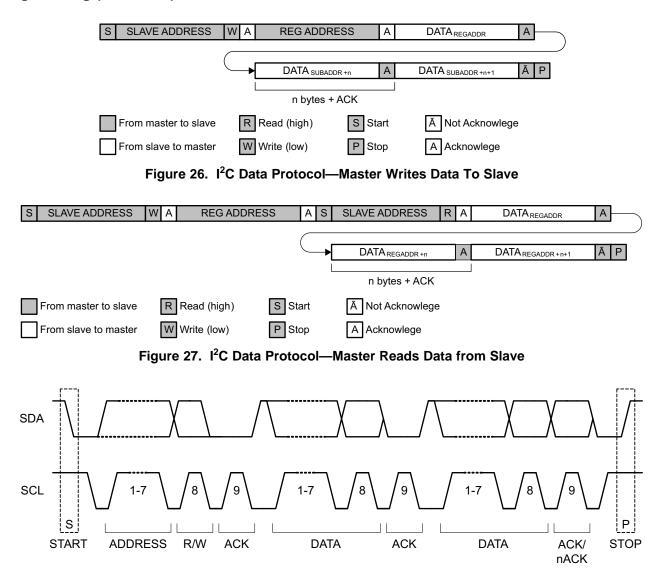

|    | 7.5  | Programming                | 39 |

|----|------|----------------------------|----|

|    | 7.6  | Register Maps              | 42 |

| 8  | Appl | ication and Implementation | 71 |

|    | 8.1  | Application Information    | 71 |

|    | 8.2  | Typical Application        | 72 |

| 9  | Pow  | er Supply Recommendations  | 79 |

| 10 | Layo | out                        | 80 |

|    | 10.1 | Layout Guidelines          | 80 |

|    | 10.2 | Layout Example             | 80 |

| 11 |      | イスおよびドキュメントのサポート           |    |

|    | 11.1 | デバイス・サポート                  | 81 |

|    | 11.2 | ドキュメントのサポート                | 81 |

|    | 11.3 |                            |    |

|    | 11.4 | コミュニティ・リソース                |    |

|    | 11.5 | 商標                         | 81 |

|    | 11.6 | 静電気放電に関する注意事項              |    |

|    | 11.7 | Glossary                   |    |

| 12 | メカニ  | ニカル、パッケージ、および注文情報          | 82 |

|    |      |                            |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付         | リビジョン | 注  |

|------------|-------|----|

| 2019 年 6 月 | *     | 初版 |

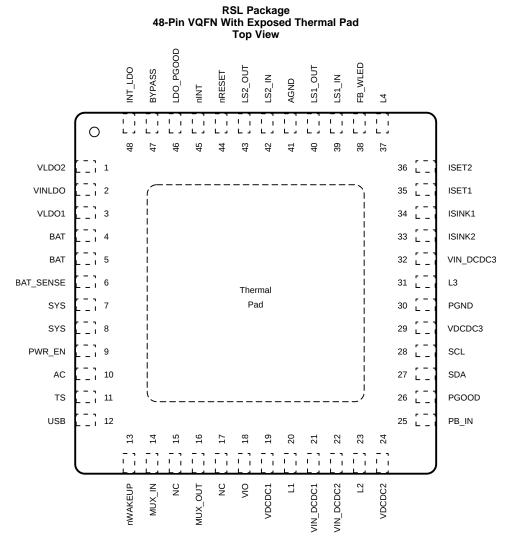

# 5 Pin Configuration and Functions

NC - No internal connection

#### **Pin Functions**

| PIN       |      | 1/0 | DESCRIPTION                                                                                                     |

|-----------|------|-----|-----------------------------------------------------------------------------------------------------------------|

| NAME      | NO.  | 1/0 | DESCRIPTION                                                                                                     |

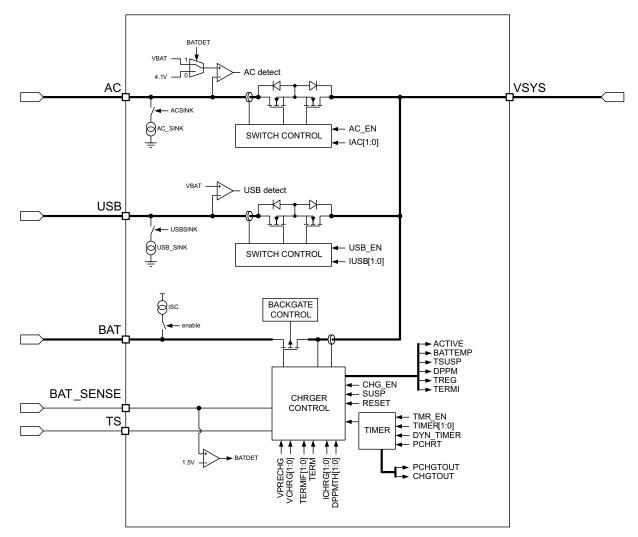

| AC        | 10   | I   | AC-adapter input to power path. Connect this pin to an external dc supply.                                      |

| AGND      | 41   | —   | Analog ground (GND). Connect the AGND pin to the ground plane.                                                  |

| BAT       | 4, 5 | I/O | Battery charger output. Connect these pins to the battery.                                                      |

| BAT_SENSE | 6    | I   | Battery-voltage sense input. Connect the BAT_SENSE pin to the BAT pin directly at the battery terminal.         |

| BYPASS    | 47   | 0   | Internal bias voltage (2.25 V). TI does not recommend connecting any external load to this pin.                 |

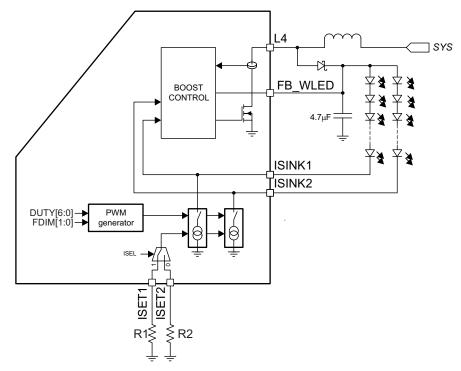

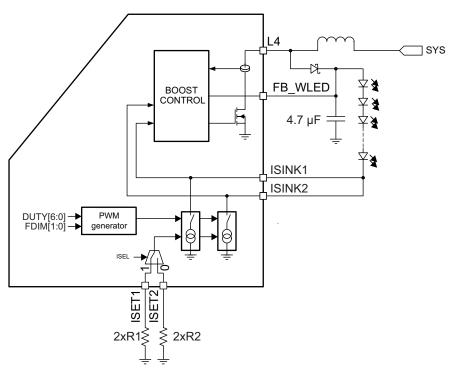

| FB_WLED   | 38   | I   | Feedback pin for the WLED boost converter. This pin is also connected to the anode of the WLED strings.         |

| INT_LDO   | 48   | 0   | Internal bias voltage (2.3 V). TI does not recommend connecting any external load to this pin.                  |

| ISET1     | 35   | I   | Low-level WLED current set. Connect this pin to a resistor to ground to set the WLED low-level current value.   |

| ISET2     | 36   | I   | High-level WLED current set. Connect this pin to a resistor to ground to set the WLED high-level current value. |

# Pin Functions (continued)

| PIN       |        |     |                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |  |

| ISINK1    | 34     | I   | Input to the WLED current SINK1. Connect this pin to the cathode of the WLED string. Current through the SINK1 pin equals current through the ISINK2 pin. If only one WLED string is used, short the ISINK1 and ISINK2 pins together.                                                                                                              |  |

| ISINK2    | 33     | I   | Input to the WLED current SINK2. Connect this pin to the cathode of the WLED string. Current through the SINK1 pin equals current through the ISINK2 pin. If only one WLED string is used short the ISINK1 and ISINK2 pins together.                                                                                                               |  |

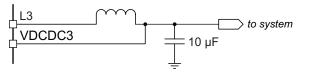

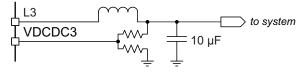

| L1        | 20     | 0   | Switch pin for DCDC1. Connect this pin to the respective inductor.                                                                                                                                                                                                                                                                                 |  |

| L2        | 23     | 0   | Switch pin for DCDC2. Connect this pin to the respective inductor.                                                                                                                                                                                                                                                                                 |  |

| L3        | 31     | 0   | Switch pin for DCDC3. Connect this pin to the respective inductor.                                                                                                                                                                                                                                                                                 |  |

| L4        | 37     | 0   | Switch pin of the WLED boost converter. Connected this pin to the respective inductor.                                                                                                                                                                                                                                                             |  |

| LDO_PGOOD | 46     | 0   | Power-good signal for the LDO regulator (LDO1 and LDO2 only). This pin is a push-pull output. This pin is pulled low when either the LDO1 or LDO2 regulator is out of regulation.                                                                                                                                                                  |  |

| LS1_IN    | 39     | I   | Input voltage pin for load switch 1 (LS1) or LDO3                                                                                                                                                                                                                                                                                                  |  |

| LS1_OUT   | 40     | 0   | Output voltage pin for load switch 1 (LS1) or LDO3                                                                                                                                                                                                                                                                                                 |  |

| LS2_IN    | 42     | I   | Input voltage pin for load switch 2 (LS2) or LDO4                                                                                                                                                                                                                                                                                                  |  |

| LS2_OUT   | 43     | 0   | Output voltage pin for load switch 2 (LS2) or LDO4                                                                                                                                                                                                                                                                                                 |  |

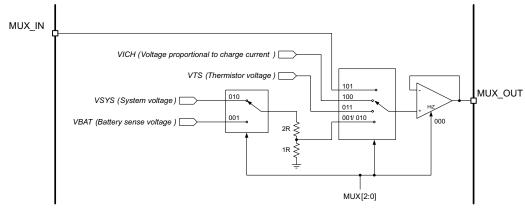

| MUX_IN    | 14     | 0   | Input to analog multiplexer                                                                                                                                                                                                                                                                                                                        |  |

| MUX_OUT   | 16     | 0   | Output pin of analog multiplexer                                                                                                                                                                                                                                                                                                                   |  |

| NC        | 15, 17 |     | Not used                                                                                                                                                                                                                                                                                                                                           |  |

| nINT      | 45     | 0   | Interrupt output. This pin is an active-low, open-drain output. This pin is pulled low if an interrupt bit is set. The output goes high after the bit causing the interrupt in the INT register is read. The interrupt sources can be masked in the INT register, such that no interrupt is generated when the corresponding interrupt bit is set. |  |

| nRESET    | 44     | I   | Reset pin. This pin is an active-low input. Pulling this pin low causes the PMIC to shut down. When this pin returns to a high voltage level, the PMIC powers up in its default state after a 1-s delay.                                                                                                                                           |  |

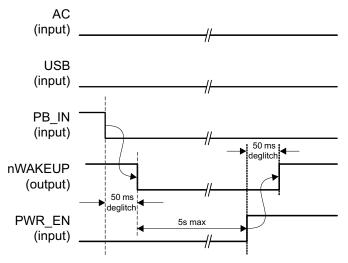

| nWAKEUP   | 13     | 0   | Signal to the host to indicate a power-on event. This pin is an active-low, open-drain output.                                                                                                                                                                                                                                                     |  |

| PB_IN     | 25     | I   | Push-button monitor input. This pin is typically connected to a momentary switch to ground. This pin is an active-low input.                                                                                                                                                                                                                       |  |

| PGND      | 30     |     | Power ground. Connect this pin to the ground plane.                                                                                                                                                                                                                                                                                                |  |

| PGOOD     | 26     | 0   | Power-good output. This pin is a push-pull output. This pin is pulled low when any of the power rails are out of regulation.                                                                                                                                                                                                                       |  |

| PWR_EN    | 9      | I   | Enable input for the DCDC1, DCDC2, and DCDC3 converters, and the LDO1, LDO2, LDO3, and LDO4 regulators. Pull this pin high to start the power-up sequence.                                                                                                                                                                                         |  |

| SCL       | 28     | I   | Clock input for the I <sup>2</sup> C interface                                                                                                                                                                                                                                                                                                     |  |

| SDA       | 27     | I/O | Data line for the I <sup>2</sup> C interface                                                                                                                                                                                                                                                                                                       |  |

| SYS       | 7, 8   | 0   | System voltage pin and output of the power path. All voltage regulators are typically powered from this output.                                                                                                                                                                                                                                    |  |

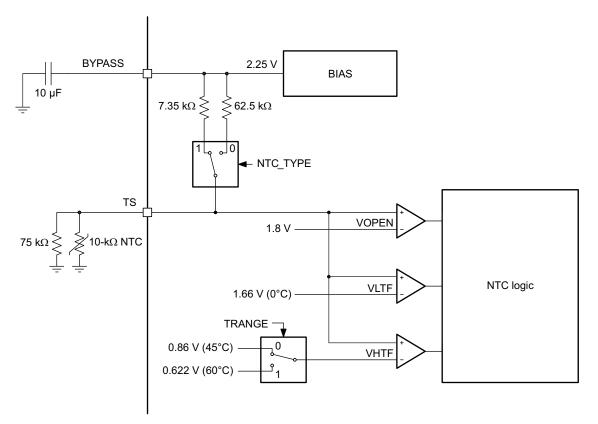

| TS        | 11     | I   | Temperature sense input. Connect this pin to the NTC thermistor to sense the battery temperature. This pin works with $10-k\Omega$ and $100-k\Omega$ thermistors. For more information, see the <i>Battery-Pack Temperature Monitoring</i> section.                                                                                                |  |

| USB       | 12     | I   | USB voltage input to power path. Connect this pin to an external voltage from a USB port.                                                                                                                                                                                                                                                          |  |

| VDCDC1    | 19     | I   | DCDC1 output and feedback voltage-sense input                                                                                                                                                                                                                                                                                                      |  |

| VDCDC2    | 24     | I   | DCDC2 output and feedback voltage-sense input                                                                                                                                                                                                                                                                                                      |  |

| VDCDC3    | 29     | I   | DCDC3 output and feedback voltage-sense input                                                                                                                                                                                                                                                                                                      |  |

| VINLDO    | 2      | I   | Input voltage for LDO1 and LDO2                                                                                                                                                                                                                                                                                                                    |  |

| VIN_DCDC1 | 21     | I   | Input voltage for DCDC1. This pin must be connected to the SYS pin.                                                                                                                                                                                                                                                                                |  |

| VIN_DCDC2 | 22     | I   | Input voltage for DCDC2. This pin must be connected to the SYS pin.                                                                                                                                                                                                                                                                                |  |

| VIN_DCDC3 | 32     | I   | Input voltage for DCDC3. This pin must be connected to the SYS pin.                                                                                                                                                                                                                                                                                |  |

| VIO       | 18     | I   | Output-high supply for output buffers                                                                                                                                                                                                                                                                                                              |  |

| VLDO1     | 3      | 0   | Output voltage of LDO1                                                                                                                                                                                                                                                                                                                             |  |

#### **Pin Functions (continued)**

| PIN         |     | I/O | DESCRIPTION                                                                        |  |

|-------------|-----|-----|------------------------------------------------------------------------------------|--|

| NAME        | NO. | 1/0 |                                                                                    |  |

| VLDO2       | 1   | 0   | Output voltage of LDO2                                                             |  |

| Thermal pad |     |     | Power-ground connection for the PMIC. Connect the thermal pad to the ground plane. |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                  |                                             |                                      | MIN  | MAX  | UNIT |

|------------------|---------------------------------------------|--------------------------------------|------|------|------|

|                  | Supply voltage (with respect to DCND)       | BAT                                  | -0.3 | 7    | V    |

|                  | Supply voltage (with respect to PGND)       | USB, AC                              | -0.3 | 20   | V    |

|                  |                                             | All pins unless specified separately | -0.3 | 7    |      |

|                  | Input/output voltage (with respect to PGND) | ISINK                                | -0.3 | 20   | V    |

|                  | ( GND)                                      | L4, FB_WLED                          | -0.3 | 44   |      |

|                  | Absolute voltage difference between SYS     | 0.3                                  | 0.3  | V    |      |

|                  | Terminal current                            | SYS, USB, BAT                        | 3000 | 3000 | mA   |

|                  | Source or Sink current                      | PGOOD, LDO_PGOOD                     | 6    | 6    | mA   |

|                  | Sink current                                | nWAKEUP, nINT                        | 2    | 2    | mA   |

| TJ               | Operating junction temperature              |                                      | 125  | 125  | °C   |

| T <sub>A</sub>   | Operating ambient temperature               |                                      | -40  | 105  | °C   |

| T <sub>stg</sub> | Storage temperature                         |                                      | -65  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

### 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                                                               | MIN  | NOM | MAX | UNIT |

|-------------------------------------------------------------------------------|------|-----|-----|------|

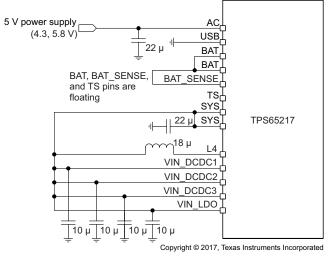

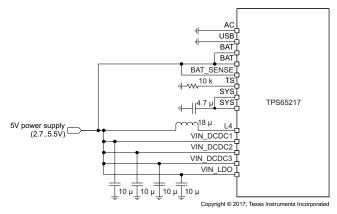

| Supply voltage, USB, AC                                                       | 4.3  |     | 5.8 | V    |

| Supply voltage, BAT                                                           | 2.75 |     | 5.5 | V    |

| Input current from AC                                                         |      |     | 2.5 | А    |

| Input current from USB                                                        |      |     | 1.3 | А    |

| Battery current                                                               |      |     | 2   | А    |

| Input voltage range for DCDC1, DCDC2, and DCDC3                               | 2.7  |     | 5.8 | V    |

| Input voltage range for LDO1, LDO2                                            | 1.8  |     | 5.8 | V    |

| Input voltage range for LS1 or LDO3, LS2, or LDO4 configured as LDOs          | 2.7  |     | 5.8 | V    |

| Input voltage range for LS1 or LDO3, LS2, or LDO4 configured as load switches | 1.8  |     | 5.8 | V    |

| Output voltage range for LDO1                                                 | 1    |     | 3.3 | V    |

| Output voltage range for LDO2                                                 | 0.9  |     | 3.3 | V    |

| Output voltage range for LS1 or LDO3, LS2, or LDO4                            | 1.8  |     | 3.3 | V    |

### **Recommended Operating Conditions (continued)**

over operating ambient temperature range (unless otherwise noted)

|                                                                                    | MIN | NOM MAX | UNIT |

|------------------------------------------------------------------------------------|-----|---------|------|

| Output current DCDC1                                                               | 0   | 1.2     | А    |

| Output current DCDC2                                                               | 0   | 1.2     | А    |

| Output current DCDC3                                                               | 0   | 1.2     | А    |

| Output current LDO1, LDO2                                                          | 0   | 100     | mA   |

| Output current LS1 or LDO3, LS2 or LDO4 configured as load switches <sup>(1)</sup> | 0   | 200     | mA   |

(1) When LS1 (LDO3) and LS2 (LDO4) are configured as LDO regulators, the maximum output current can also be configured as 200 mA or 400 mA.

#### 6.4 Thermal Information

|                       |                                              | TPS652170  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSL (VQFN) | UNIT |

|                       |                                              | 48 PINS    |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 30.4       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 16.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.6        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 5.6        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$V_{BAT}$  = 3.6 V ±5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                      | PARAMETER                                                      | TEST CONI                                                                                       | DITIONS                         | MIN  | TYP                                        | MAX | UNIT |

|----------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|------|--------------------------------------------|-----|------|

| INPUT VOL            | TAGE AND CURRENTS                                              |                                                                                                 |                                 |      |                                            |     |      |

|                      |                                                                | USB or AC supply connect                                                                        | ted                             | 0    |                                            | 5.5 | V    |

| V <sub>BAT</sub>     | Battery input voltage range                                    | USB and AC not connected                                                                        | ed                              | 2.75 |                                            | 5.5 | V    |

| V <sub>AC</sub>      | AC adapter input voltage range                                 | Valid range for charging                                                                        |                                 | 4.3  |                                            | 5.8 | V    |

| V <sub>USB</sub>     | USB input voltage range                                        | Valid range for charging                                                                        |                                 | 4.3  |                                            | 5.8 | V    |

|                      |                                                                |                                                                                                 | UVLO[1:0] = 00b                 |      | 2.73                                       |     |      |

|                      |                                                                | Measured in respect to                                                                          | UVLO[1:0] = 01b                 |      | 2.89                                       |     |      |

| .,                   | Undervoltage lockout                                           | $V_{BAT}$ ; supply falling;<br>$V_{AC} = V_{USB} = 0 V$                                         | UVLO[1:0] = 10b                 |      | 3.18                                       |     | V    |

| V <sub>UVLO</sub>    |                                                                |                                                                                                 | UVLO[1:0] = 11b                 |      | 3.3                                        |     |      |

|                      | UVLO accuracy                                                  |                                                                                                 |                                 | -2%  |                                            | 2%  |      |

|                      | UVLO deglitch time <sup>(1)</sup>                              |                                                                                                 |                                 | 4    |                                            | 6   | ms   |

| V <sub>OFFSET</sub>  | AC and USB UVLO offset                                         | $V_{BAT} < V_{UVLO}$ ; Device shut<br>$V_{USB}$ drop below $V_{UVLO}$ +                         |                                 |      | 200                                        |     | mV   |

| I <sub>OFF</sub>     | OFF current,<br>Total current into VSYS, VINDCDCx,<br>VINLDO   | All rails disabled, $T_A = 27^\circ$                                                            | Ċ                               |      | 6                                          |     | μA   |

| I <sub>SLEEP</sub>   | Sleep current,<br>Total current into VSYS, VINDCDCx,<br>VINLDO | LDO1 and LDO2 enabled.<br>All other rails disabled.<br>$V_{SYS} = 4 V$ , $T_A = 0.105^{\circ}C$ | , no load.                      |      | 80                                         | 106 | μA   |

| V                    | AC and USP voltage detection threshold                         | $V_{BAT} > V_{UVLO}$ , AC and US<br>$_{USB} - V_{BAT} > V_{IN(DT)}$                             | B valid when V <sub>AC-</sub>   | 190  |                                            |     | mV   |

| V <sub>IN(DT)</sub>  | AC and USB voltage-detection threshold                         | $V_{BAT} < V_{UVLO}$ , AC and USI > $V_{IN(DT)}$                                                | B valid when $V_{AC-USB}$       | 4.3  |                                            |     | V    |

| V <sub>IN(NDT)</sub> | AC and USB voltage-removal detection                           | $V_{BAT} > V_{UVLO}$ , AC and US $V_{AC/USB} - V_{BAT} < V_{IN(DT)}$                            | B invalid when                  |      |                                            | 125 | mV   |

|                      | threshold                                                      | $V_{BAT} < V_{UVLO}$ , AC and USI<br>USB < $V_{IN(DT)}$                                         | B invalid when V <sub>AC-</sub> |      | V <sub>UVLO</sub> +<br>V <sub>OFFSET</sub> |     | V    |

(1) Not tested in production

# **Electrical Characteristics (continued)**

# $V_{BAT}$ = 3.6 V ±5%, $T_{\rm J}$ = 27°C (unless otherwise noted)

|                         | PARAMETER                                                           | TEST CONDITIONS                                                                         | MIN  | TYP  | MAX  | UNIT         |

|-------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|--------------|

| t <sub>RISE</sub>       | $V_{AC}$ , $V_{USB}$ rise time                                      | Voltage rising from 100 mV to 4.5 V. If rise time is exceeded, device may not power up. |      |      | 50   | ms           |

| t <sub>DG(DT)</sub>     | Power detected deglitch <sup>(1)</sup>                              | AC or USB voltage increasing                                                            |      | 22.5 |      | ms           |

| V <sub>IN(OVP)</sub>    | Input overvoltage detection threshold                               | USB and AC input                                                                        | 5.8  | 6    | 6.4  | V            |

| POWER PAT               | TH TIMING                                                           |                                                                                         |      |      |      |              |

| t <sub>SW(PSEL)</sub>   | Switching from AC to USB <sup>(1)</sup>                             |                                                                                         |      |      | 150  | μs           |

| POWER PAT               | TH MOSFET CHARACTERISTICS                                           |                                                                                         |      |      |      |              |

| V <sub>DO, AC</sub>     | AC input switch dropout voltage                                     | IAC[1:0] = 11b (2.5 A), I <sub>SYS</sub> = 1 A                                          |      | 150  |      | mV           |

| V <sub>DO, USB</sub>    | USB input switch dropout voltage                                    | IUSB[1:0] = 01b (500 mA), I <sub>SYS</sub> = 500 mA                                     |      | 100  |      | mV           |

| VDO, USB                | COD input switch dropout voltage                                    | IUSB[1:0] = 10b (1300 mA), I <sub>SYS</sub> = 800 mA                                    |      | 160  |      | IIIV         |

| V <sub>DO, BAT</sub>    | Battery switch dropout voltage                                      | $V_{BAT} = 3 V$ , $I_{BAT} = 1 A$                                                       |      | 60   |      | mV           |

| POWER PAT               | TH INPUT CURRENT LIMITS                                             |                                                                                         |      |      |      |              |

|                         |                                                                     | IAC[1:0] = 00b                                                                          | 90   |      | 130  |              |

| 1                       | Input current limit; AC pin                                         | IAC[1:0] = 01b                                                                          | 480  |      | 580  | mA           |

| ACLMT                   | inpat ourient innit, AO pill                                        | IAC[1:0] = 10b                                                                          | 1000 | 1500 |      | iii/A        |

|                         |                                                                     | IAC[1:0] = 11b                                                                          | 2000 | 2500 |      |              |

|                         |                                                                     | IUSB[1:0] = 00b                                                                         | 90   |      | 100  |              |

| l                       | Input current limit: LISP nin                                       | IUSB[1:0] = 01b                                                                         | 460  |      | 500  | m^           |

| USBLMT                  | Input current limit; USB pin                                        | IUSB[1:0] = 10b                                                                         | 1000 | 1300 |      | mA           |

|                         |                                                                     | IUSB[1:0] = 11b                                                                         | 1500 | 1800 |      |              |

| I <sub>BAT</sub>        | Battery load current <sup>(1)</sup>                                 |                                                                                         |      |      | 2    | А            |

| POWER PAT               | TH BATTERY SUPPLEMENT DETECTION                                     | · · · · · · · · · · · · · · · · · · ·                                                   |      |      |      |              |

| V <sub>BSUP</sub>       | Battery supplement threshold                                        | $V_{SYS} \le V_{BAT} - VBSUP1,$<br>$V_{SYS}$ falling IUSB[1:0] = 10b                    |      | 40   |      | mV           |

|                         | Battery supplement hysteresis                                       | V <sub>SYS</sub> rising                                                                 |      | 20   |      |              |

| POWER PAT               | TH BATTERY PROTECTION                                               |                                                                                         |      |      |      |              |

| V <sub>BAT(SC)</sub>    | BAT pin short-circuit detection threshold                           |                                                                                         | 1.3  | 1.5  | 1.7  | V            |

| I <sub>BAT(SC)</sub>    | Source current for BAT pin short-circuit detection                  |                                                                                         |      | 7.5  |      | mA           |

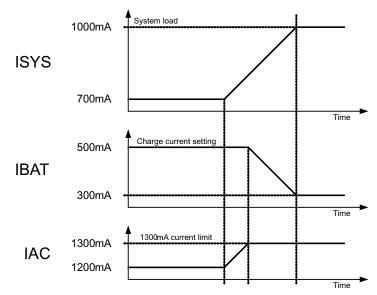

| INPUT BASE              | ED DYNAMIC POWER PATH MANAGEMEN                                     | Г (DPPM)                                                                                |      |      |      |              |

| V <sub>DPPM</sub>       | Threshold at which DPPM loop is<br>enabled                          | I <sup>2</sup> C selectable                                                             | 3.5  |      | 4.25 | V            |

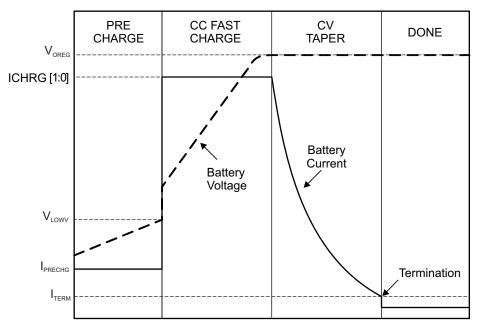

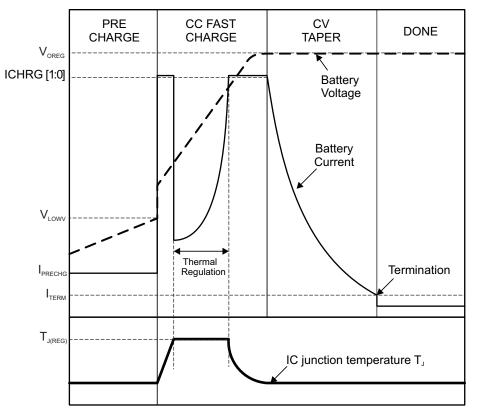

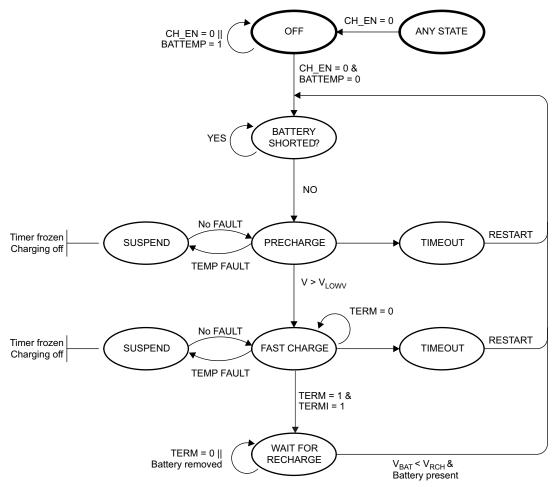

| BATTERY C               | HARGER                                                              |                                                                                         |      |      |      |              |

| N/                      | Battery charger voltage                                             | I <sup>2</sup> C selectable                                                             | 4.1  |      | 4.25 | V            |

| V <sub>OREG</sub>       | Battery charger accuracy                                            |                                                                                         | -2%  |      | 1%   | V            |

|                         | Precharge to fast-charge transition                                 | VPRECHG = 0b                                                                            |      | 2.9  |      |              |

| V <sub>LOWV</sub>       | threshold                                                           | VPRECHG = 1b                                                                            |      | 2.5  |      | V            |

| t <sub>DGL1(LOWV)</sub> | Deglitch time on precharge to fast-charge transition <sup>(1)</sup> |                                                                                         |      | 25   |      | ms           |

| t <sub>DGL2(LOWV)</sub> | Deglitch time on fast-charge to precharge transition <sup>(1)</sup> |                                                                                         |      | 25   |      | ms           |

|                         |                                                                     | ICHRG[1:0] = 00b                                                                        |      | 300  |      |              |

|                         | Battery fast charge current range                                   | ICHRG[1:0] = 01b                                                                        |      | 400  |      | <i>w</i> - ^ |

| I <sub>CHG</sub>        | $V_{OREG} > V_{BAT} > V_{LOWV},$<br>$V_{IN} = V_{USB} = 5 V$        | ICHRG[1:0] = 10b                                                                        | 450  | 500  | 550  | mA           |

|                         |                                                                     | ICHRG[1:0] = 11b                                                                        |      | 700  |      |              |

|                         |                                                                     | ICHRG[1:0] = 00b                                                                        |      | 30   |      |              |

|                         |                                                                     | ICHRG[1:0] = 01b                                                                        |      | 40   |      |              |

| IPRECHG                 | Precharge current                                                   | ICHRG[1:0] = 10b                                                                        | 25   | 50   | 75   | mA           |

|                         |                                                                     |                                                                                         |      |      |      |              |

Texas Instruments

www.ti.com

# **Electrical Characteristics (continued)**

# $V_{BAT}$ = 3.6 V ±5%, $T_{\rm J}$ = 27°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                                                                  | TEST COND                                                                          | TIONS             | MIN  | TYP  | MAX                | UNIT             |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------|------|------|--------------------|------------------|

|                        |                                                                                                                                                                            | TERMIF[1:0] = 00b                                                                  |                   |      | 2.5% |                    |                  |

|                        | Charge current value for termination                                                                                                                                       | TERMIF[1:0] = 01b                                                                  |                   | 3%   | 7.5% | 10%                |                  |

| TERM                   | detection threshold (fraction of I <sub>CHG</sub> )                                                                                                                        | TERMIF[1:0] = 10b                                                                  |                   |      | 15%  |                    |                  |

|                        |                                                                                                                                                                            | TERMIF[1:0] = 11b                                                                  |                   |      | 18%  |                    |                  |

| t <sub>DGL(TERM)</sub> | Deglitch time, termination detected <sup>(1)</sup>                                                                                                                         |                                                                                    |                   |      | 125  |                    | ms               |

| V <sub>RCH</sub>       | Recharge detection threshold                                                                                                                                               | Voltage below V <sub>OREG</sub>                                                    |                   | 150  | 100  | 70                 | mV               |

| t <sub>DGL(RCH)</sub>  | Deglitch time, recharge threshold detected <sup>(1)</sup>                                                                                                                  |                                                                                    |                   |      | 125  |                    | ms               |

| BAT(DET)               | Sink current for battery detection                                                                                                                                         | $T_J = 27^{\circ}C$                                                                |                   | 3    | 7.5  | 10                 | mA               |

| t <sub>det</sub>       | Battery detection timer. $I_{BAT(DET)}$ is pulled from the battery for $t_{DET}$ . If BAT voltage stays above $V_{RCH}$ threshold the battery is connected. <sup>(1)</sup> | V <sub>BAT</sub> < V <sub>RCH;</sub>                                               |                   |      | 250  |                    | ms               |

| t <sub>CHG</sub>       | Charge safety timer <sup>(1)</sup>                                                                                                                                         | Safety timer range, thermal active, selectable by I <sup>2</sup> C                 | and DPPM not      | 4    |      | 8                  | h                |

|                        |                                                                                                                                                                            | Pre charge timer, thermal                                                          | PCHRGT = 0b       |      | 30   | 60                 |                  |

| t <sub>PRECHG</sub>    | Precharge timer <sup>(1)</sup>                                                                                                                                             | and DPPM loops not active, selectable by I <sup>2</sup> C                          | PCHRGT = 1b       |      | 60   |                    | min              |

| BATTERY N              | TC MONITOR                                                                                                                                                                 |                                                                                    | •                 |      |      | U. J.              | -                |

| t <sub>THON</sub>      | Thermistor power on time at charger off, sampling mode on                                                                                                                  |                                                                                    |                   |      | 10   |                    | ms               |

| t <sub>THOFF</sub>     | Thermistor power sampling period at<br>charger off, sampling mode on                                                                                                       |                                                                                    |                   |      | 1    |                    | S                |

|                        | Pullup resistor from thermistor to Internal                                                                                                                                | NTC_TYPE = 1 (10-kΩ NT                                                             | C)                |      | 7.35 |                    | 10               |

| R <sub>NTC_PULL</sub>  | LDO, I <sup>2</sup> C selectable                                                                                                                                           | NTC_TYPE = 0 (100-kΩ NTC)                                                          |                   |      | 60.5 |                    | kΩ               |

|                        | Accuracy                                                                                                                                                                   | $T_A = 27^{\circ}C$                                                                |                   | -3%  |      | 3%                 |                  |

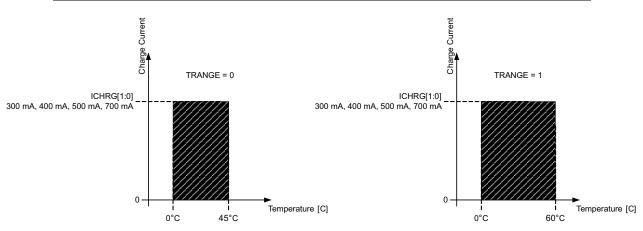

|                        |                                                                                                                                                                            | Temperature falling                                                                |                   |      | 1660 |                    |                  |

| V <sub>LTF</sub>       | Low-temperature failure threshold                                                                                                                                          | Temperature rising                                                                 |                   |      | 1610 |                    | mV               |

|                        |                                                                                                                                                                            | Temperature falling                                                                |                   |      | 910  |                    |                  |

| N/                     | High-temperature failure threshold                                                                                                                                         | Temperature rising                                                                 | nperature falling |      | 860  |                    |                  |

| V <sub>HTF</sub>       |                                                                                                                                                                            | Temperature falling                                                                |                   |      | 667  |                    | mV               |

|                        |                                                                                                                                                                            | Temperature rising                                                                 | TRANGE = 1b       |      | 622  |                    |                  |

| V <sub>DET</sub>       | Thermistor detection threshold                                                                                                                                             |                                                                                    |                   | 1750 |      | 1850               | mV               |

| t <sub>BATDET</sub>    | Thermistor not detected. Battery not present deglitch <sup>(1)</sup>                                                                                                       |                                                                                    |                   |      | 26   |                    | ms               |

| THERMAL R              | EGULATION                                                                                                                                                                  |                                                                                    |                   |      |      |                    |                  |

| T <sub>J(REG)</sub>    | Temperature regulation limit, temperature<br>at which charge current is decreased                                                                                          |                                                                                    |                   | 111  |      | 123                | °C               |

| DCDC1 (BUC             | СК)                                                                                                                                                                        | L                                                                                  |                   |      |      |                    |                  |

| V <sub>IN</sub>        | Input voltage range                                                                                                                                                        | VIN_DCDC1 pin                                                                      |                   | 2.7  |      | $V_{SYS}$          | V                |

| Q,SLEEP                | Quiescent current in SLEEP mode                                                                                                                                            | No load, $V_{SYS} = 4 V$ , $T_A = 2$                                               | 5°C               |      | 30   |                    | μA               |

|                        |                                                                                                                                                                            | External resistor divider (XA                                                      | ADJ1 = 1b)        | 0.6  |      | V <sub>IN</sub>    |                  |

|                        | Output voltage range                                                                                                                                                       | $I^2C$ selectable in 25-mV ste<br>(XADJ1 = 0b)                                     | ps                | 0.9  |      | 1.8 <sup>(2)</sup> | V                |

| V <sub>OUT</sub>       | DC output voltage accuracy                                                                                                                                                 | $V_{IN} = V_{OUT} + 0.3 V \text{ to } 5.8 V$<br>0 mA ≤ $I_{OUT} \le 1.2 \text{ A}$ | ,                 | -2%  |      | 3%                 |                  |

|                        | Power-save mode (PSM) ripple voltage                                                                                                                                       | $I_{OUT} = 1 \text{ mA, PFM mode}$<br>L = 2.2 µH, C <sub>OUT</sub> = 20 µF         |                   |      | 40   |                    | mV <sub>pp</sub> |

| олт                    | Output current range                                                                                                                                                       |                                                                                    |                   | 0    |      | 1.2                | А                |

|                        | High-side MOSFET on-resistance                                                                                                                                             | V <sub>IN</sub> = 2.7 V                                                            |                   |      | 170  |                    |                  |

| DS(on)                 | Low-side MOSFET on-resistance                                                                                                                                              | V <sub>IN</sub> = 2.7 V                                                            |                   |      | 120  |                    | mΩ               |

|                        | High-side MOSFET leakage current                                                                                                                                           | V <sub>IN</sub> = 5.8 V                                                            |                   |      |      | 2                  |                  |

| LEAK                   | Low-side MOSFET leakage current                                                                                                                                            | V <sub>DS</sub> = 5.8 V                                                            |                   |      |      | 1                  | μA               |

(2) Contact factory for 3.3-V option.

# **Electrical Characteristics (continued)**

$V_{BAT}$  = 3.6 V ±5%,  $T_{J}$  = 27°C (unless otherwise noted)

|                      | PARAMETER                                        | TEST CONDITIONS                                                                   | MIN  | TYP         | MAX                | UNIT             |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|------|-------------|--------------------|------------------|

| I <sub>LIMIT</sub>   | Current limit (high- and low-side MOSFET).       | 2.7 V < V <sub>IN</sub> < 5.8 V                                                   |      | 1.6         |                    | А                |

| f <sub>SW</sub>      | Switching frequency                              |                                                                                   | 1.95 | 2.25        | 2.55               | MHz              |

| V <sub>FB</sub>      | Feedback voltage                                 | XADJ = 1b                                                                         |      | 600         |                    | mV               |

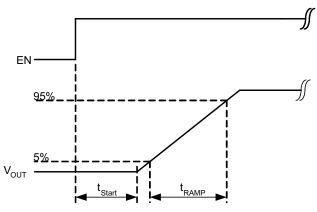

| t <sub>SS</sub>      | Soft-start time                                  | Time to ramp $V_{\text{OUT}}$ from 5% to 95%, no load                             |      | 750         |                    | μs               |

| R <sub>DIS</sub>     | Internal discharge resistor at L1 <sup>(3)</sup> |                                                                                   |      | 250         |                    | Ω                |

| L                    | Inductor                                         |                                                                                   | 1.5  | 2.2         |                    | μH               |

| 0                    | Output capacitor                                 | Ceramic                                                                           | 10   | 22          |                    | μF               |

| C <sub>OUT</sub>     | ESR of output capacitor                          |                                                                                   |      | 20          |                    | mΩ               |

| DCDC2 (B             | UCK)                                             |                                                                                   |      |             |                    |                  |

| V <sub>IN</sub>      | Input voltage range                              | VIN_DCDC2 pin                                                                     | 2.7  |             | V <sub>SYS</sub>   | V                |

| I <sub>Q,SLEEP</sub> | Quiescent current in SLEEP mode                  | No load, $V_{SYS} = 4 V$ , $T_A = 25^{\circ}C$                                    |      | 30          |                    | μA               |

|                      |                                                  | External resistor divider (XADJ2 = 1b)                                            | 0.6  |             | V <sub>IN</sub>    |                  |

|                      | Output voltage range                             | I <sup>2</sup> C selectable in 25-mV steps<br>(XADJ2 = 0b)                        | 0.9  |             | 3.3                | V                |

| V <sub>OUT</sub>     | DC output voltage accuracy                       | $V_{IN} = V_{OUT} + 0.3 V \text{ to } 5.8 V;$<br>0 mA ≤ I <sub>OUT</sub> ≤ 1.2 A  | -2%  |             | 3%                 |                  |

|                      | Power-save mode (PSM) ripple voltage             | $I_{OUT} = 1 \text{ mA, PFM mode}$<br>L = 2.2 µH, C <sub>OUT</sub> = 20 µF        |      | 40          |                    | mV <sub>pp</sub> |

| I <sub>OUT</sub>     | Output current range                             |                                                                                   | 0    |             | 1.2                | А                |

|                      | High-side MOSFET on-resistance                   | V <sub>IN</sub> = 2.7 V                                                           |      | 170         |                    |                  |

| r <sub>DS(on)</sub>  | Low-side MOSFET on-resistance                    | V <sub>IN</sub> = 2.7 V                                                           |      | 120         |                    | mΩ               |

|                      | High-side MOSFET leakage current                 | V <sub>IN</sub> = 5.8 V                                                           |      |             | 2                  |                  |

| I <sub>LEAK</sub>    | Low-side MOSFET leakage current                  | $V_{\rm DS} = 5.8 \text{ V}$                                                      |      |             | 1                  | μA               |

| I <sub>LIMIT</sub>   | Current limit (high and low side MOSFET).        | 2.7 V < V <sub>IN</sub> < 5.8 V                                                   |      | 1.6         |                    | A                |

| f <sub>SW</sub>      | Switching frequency                              |                                                                                   | 1.95 | 2.25        | 2.55               | MHz              |

| V <sub>FB</sub>      | Feedback voltage                                 | XADJ = 1b                                                                         |      | 600         |                    | mV               |

| t <sub>SS</sub>      | Soft-start time                                  | Time to ramp V <sub>OUT</sub> from 5% to 95%, no load                             |      | 750         |                    | μs               |

| R <sub>DIS</sub>     | Internal discharge resistor at L2                |                                                                                   |      | 250         |                    | Ω                |

| L                    | Inductor                                         |                                                                                   | 1.5  | 2.2         |                    | μH               |

|                      | Output capacitor                                 | Ceramic                                                                           | 10   | 22          |                    | μF               |

| C <sub>OUT</sub>     | ESR of output capacitor                          |                                                                                   |      | 20          |                    | mΩ               |

| DCDC3 (B             |                                                  |                                                                                   |      |             |                    |                  |

| V <sub>IN</sub>      | Input voltage range                              | VIN DCDC3 pin                                                                     | 2.7  |             | V <sub>SYS</sub>   | V                |

|                      | Quiescent current in SLEEP mode                  | No load, $V_{SYS} = 4 \text{ V}, T_A = 25^{\circ}\text{C}$                        | 2.1  | 30          | • 515              | μA               |

| Q,SLEEP              |                                                  | External resistor divider (XADJ3 = 1b)                                            | 0.6  | 00          | V <sub>IN</sub>    | μ, ι             |

|                      | Output voltage range                             | $I^2C$ selectable in 25-mV steps<br>(XADJ3 = 0b)                                  | 0.9  |             | 1.5 <sup>(2)</sup> | V                |

| V <sub>OUT</sub>     | DC output voltage accuracy                       | $V_{IN} = V_{OUT} + 0.3 V \text{ to } 5.8 V;$<br>0 mA ≤ I <sub>OUT</sub> ≤ 1.2 A  | -2%  |             | 3%                 |                  |

|                      | Power save mode (PSM) ripple voltage             | $I_{OUT} = 1 \text{ mA}, \text{PFM mode}$<br>L = 2.2 µH, C <sub>OUT</sub> = 20 µF |      | 40          |                    | mV <sub>pp</sub> |

| IOUT                 | Output current range                             |                                                                                   | 0    |             | 1.2                | А                |

| -                    | High-side MOSFET on-resistance                   | V <sub>IN</sub> = 2.7 V                                                           |      | 170         |                    |                  |

| r <sub>DS(on)</sub>  | Low side MOSFET on-resistance                    | $V_{\rm IN} = 2.7 \text{ V}$                                                      |      | 120         |                    | mΩ               |

|                      | High-side MOSFET leakage current                 | V <sub>IN</sub> = 5.8 V                                                           |      | -           | 2                  |                  |

| I <sub>LEAK</sub>    | Low-side MOSFET leakage current                  | $V_{\rm DS} = 5.8 \text{ V}$                                                      |      |             | 1                  | μA               |

|                      | Current limit (high- and low-side                |                                                                                   |      |             |                    |                  |

| f                    | MOSFET).                                         | 2.7 V < V <sub>IN</sub> < 5.8 V                                                   | 1.95 | 1.6<br>2.25 | 2.55               | A<br>MH7         |

| f <sub>SW</sub>      | Switching frequency                              | YAD L. 4L                                                                         | C6.1 |             | 2.00               | MHz              |

| V <sub>FB</sub>      | Feedback voltage                                 | XADJ = 1b                                                                         |      | 600         |                    | mV               |

(3) Can be factory disabled.

Texas Instruments

# **Electrical Characteristics (continued)**

# $V_{BAT}$ = 3.6 V ±5%, $T_{\rm J}$ = 27°C (unless otherwise noted)

|                      | PARAMETER                                            | TEST CONDITIONS                                                                                                            | MIN   | TYP | MAX  | UNIT  |

|----------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-------|

| t <sub>SS</sub>      | Soft-start time                                      | Time to ramp $V_{\text{OUT}}$ from 5% to 95%, no load                                                                      |       | 750 |      | μs    |

| R <sub>DIS</sub>     | Internal discharge resistor at L1, L2                |                                                                                                                            |       | 250 |      | Ω     |

| L                    | Inductor                                             |                                                                                                                            | 1.5   | 2.2 |      | μH    |

| C <sub>OUT</sub>     | Output capacitor                                     | Ceramic                                                                                                                    | 10    | 22  |      | μF    |

| 0001                 | ESR of output capacitor                              |                                                                                                                            |       | 20  |      | mΩ    |

| LDO1, LDC            | 02                                                   | 1                                                                                                                          | 1     |     |      |       |

| V <sub>IN</sub>      | Input voltage range                                  |                                                                                                                            | 1.8   |     | 5.8  | V     |

| I <sub>Q,SLEEP</sub> | Quiescent current in SLEEP mode                      | No load, $V_{SYS} = 4 V$ , $T_A = 25^{\circ}C$                                                                             |       | 5   |      | μA    |

|                      | Output voltage range                                 | LDO1, I <sup>2</sup> C selectable                                                                                          | 1     |     | 3.3  | V     |

|                      |                                                      | LDO2, I <sup>2</sup> C selectable                                                                                          | 0.9   |     | 3.3  | v     |

|                      | DC output voltage accuracy                           | $\begin{split} I_{OUT} = 10 \text{ mA},  V_{\text{IN}} > V_{OUT} + 200 \text{ mV}, \\ V_{OUT} > 0.9 \text{ V} \end{split}$ | -2%   |     | 2%   |       |

| V <sub>OUT</sub>     | Line regulation                                      | $V_{IN}$ = 2.7 V - 5.5 V, $V_{OUT}$ = 1.2 V,<br>$I_{OUT}$ = 100 mA                                                         | -1%   |     | 1%   |       |

|                      | Load regulation                                      | $I_{OUT}$ = 1 mA - 100 mA, $V_{OUT}$ = 1.2 V, $V_{\rm IN}$ = 3.3 V                                                         | -1%   |     | 1%   |       |

|                      |                                                      | $I_{OUT}$ = 0 mA - 1 mA, $V_{OUT}$ = 1.2 V, $V_{\rm IN}$ = 3.3 V                                                           | -2.5% |     | 2.5% |       |

| lour                 | Output current range                                 | SLEEP state                                                                                                                | 0     |     | 1    | mA    |

| IOUT                 | Calput current range                                 | ACTIVE state                                                                                                               | 0     |     | 100  | 111/4 |

| I <sub>SC</sub>      | Short circuit current limit                          | Output shorted to GND                                                                                                      | 100   | 250 |      | mA    |

| V <sub>DO</sub>      | Dropout voltage                                      | $I_{OUT} = 100 \text{ mA}, V_{IN} = 3.3 \text{ V}$                                                                         |       |     | 200  | mV    |

| R <sub>DIS</sub>     | Internal discharge resistor at output                |                                                                                                                            |       | 430 |      | Ω     |

| C <sub>OUT</sub>     | Output capacitor                                     | Ceramic                                                                                                                    |       | 2.2 |      | μF    |

| 0001                 | ESR of output capacitor                              |                                                                                                                            |       | 20  |      | mΩ    |

| LS1 OR LD            | DO3, AND LS2 OR LDO4, CONFIGURED AS                  | LDOs                                                                                                                       | 1     |     |      |       |

| V <sub>IN</sub>      | Input voltage range                                  |                                                                                                                            | 2.7   |     | 5.8  | V     |

| I <sub>Q,SLEEP</sub> | Quiescent current in SLEEP mode                      | No load, $V_{SYS} = 4 V$ , $T_A = 25^{\circ}C$                                                                             |       | 30  |      | μA    |

|                      | Output voltage range                                 | LS1LDO3 = 1b, LS2LDO4 = 1b<br>$I^2C$ selectable                                                                            | 1.5   |     | 3.3  | V     |

| V <sub>OUT</sub>     | DC output voltage accuracy                           | $I_{OUT}$ = 10 mA, $V_{IN}$ > $V_{OUT}$ + 200 mV,<br>$V_{OUT}$ > 1.8 V                                                     | -2%   |     | 2%   |       |

| VOUT                 | Line regulation                                      | $V_{\rm IN}$ = 2.7 V - 5.5 V, $V_{\rm OUT}$ = 1.8 V, $I_{\rm OUT}$ = 200 mA                                                | -1%   |     | 1%   |       |

|                      | Load regulation                                      | $I_{OUT}$ = 1 mA - 200 mA, $V_{OUT}$ = 1.8 V, $V_{\rm IN}$ = 3.3 V                                                         | -1%   |     | 1%   |       |

| V <sub>DO</sub>      | Dropout voltage                                      | I <sub>OUT</sub> = 200 mA, V <sub>IN</sub> = 3.3 V                                                                         |       |     | 200  | mV    |

| R <sub>DIS</sub>     | Internal discharge resistor at output <sup>(3)</sup> |                                                                                                                            |       | 375 |      | Ω     |

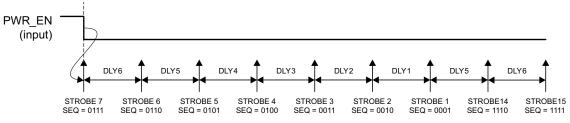

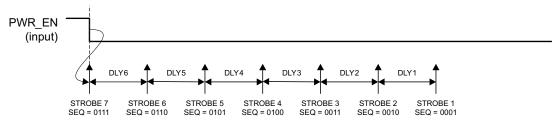

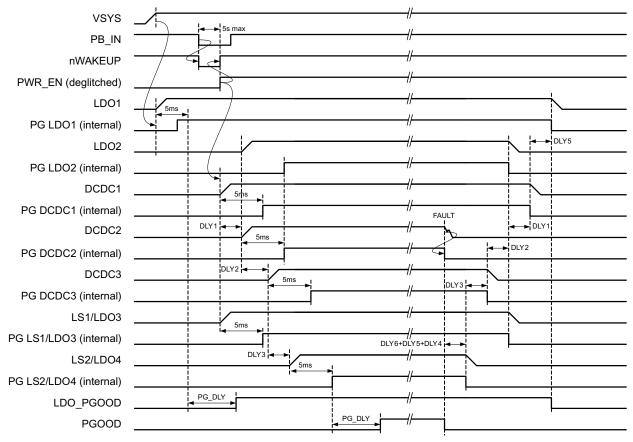

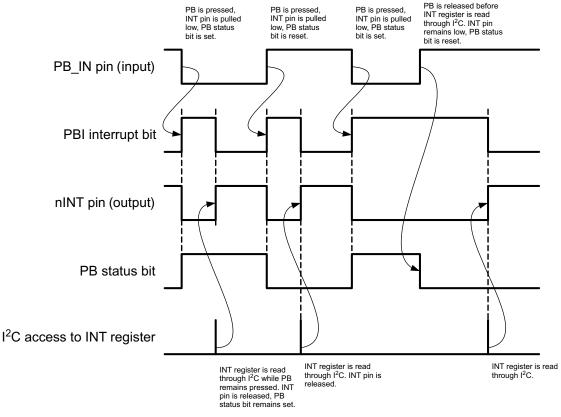

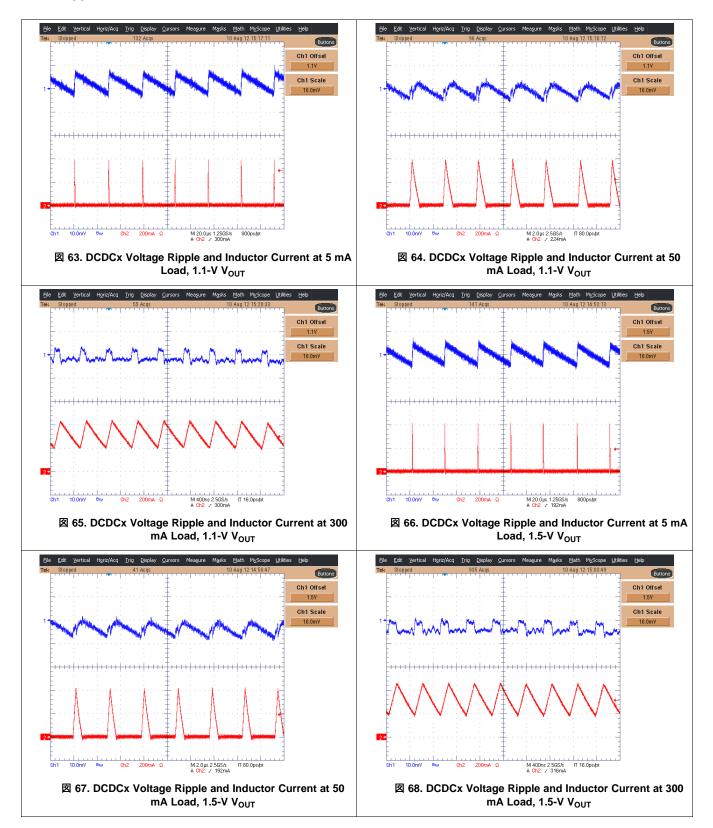

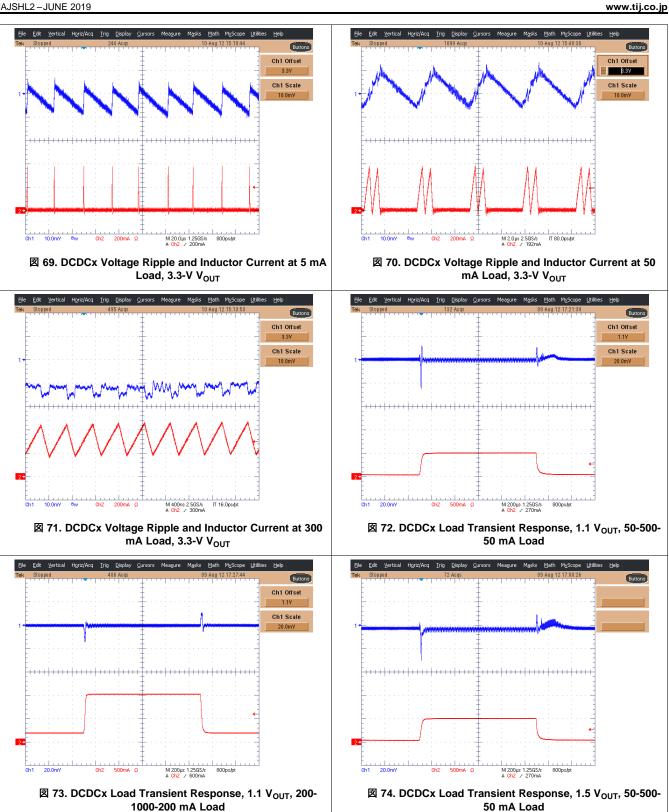

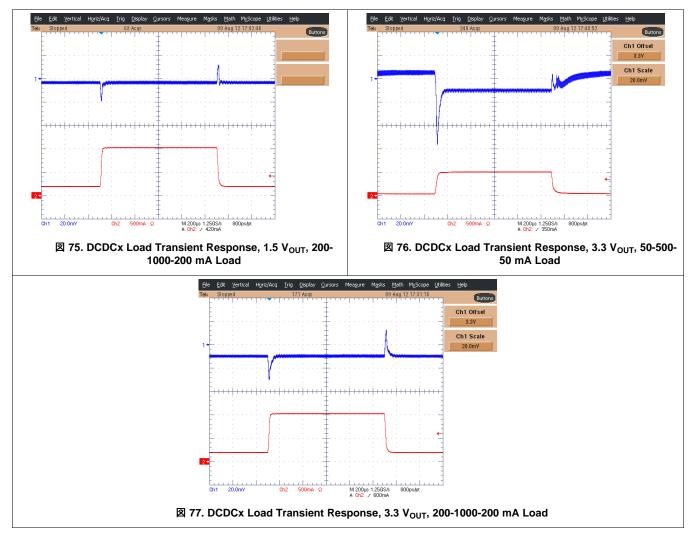

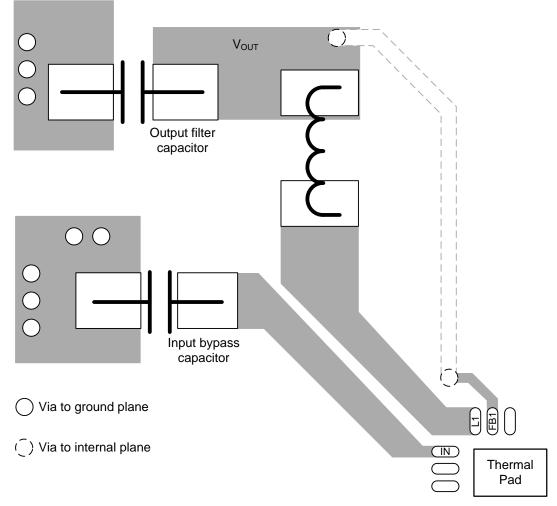

|                      | Output capacitor                                     | Ceramic                                                                                                                    | 8     | 10  | 12   | μF    |