# TPS62901 1.5mm × 2mm QFN パッケージ封止、3V～17V、高効率、低 $I_Q$ 、降圧コンバータ

## 1 特長

- 高効率で、広いデューティサイクルと広い負荷範囲に対応

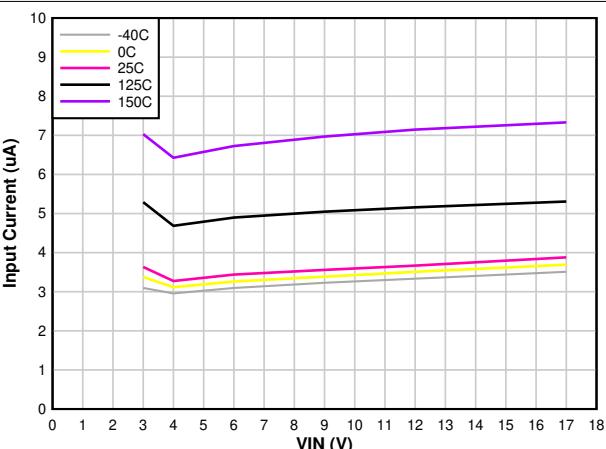

- $I_Q$ : 4 $\mu$ A (代表値)

- 2.5MHz と 1.0MHz から選択可能なスイッチング周波数

- $R_{DS(ON)}$ : ハイサイド 62m $\Omega$ 、ローサイド 22m $\Omega$

- 自動効率向上 (AEE)

- 1.5mm × 2.0mm、0.5mm ピッチの小型 VQFN パッケージ

- 最大 1A の連続出力電流

- 40°C～150°C の範囲で ±0.9% の帰還電圧精度

- 構成可能な出力電圧:

- $V_{FB}$  外部分圧器: 0.6V～5.5V

- $V_{SET}$  内部分圧器: 0.4V～5.5V の 16 通りの選択肢

- 100% モードを備えた DCS-Control トポロジ

- きわめてフレキシブルで優れた使いやすさ

- 単層ルーティング用に最適化されたピン配置

- 高精度インエーブル入力

- 強制 PWM または自動パワーセーブ モード

- パワーグッド出力

- 選択可能なアクティブ出力放電

- 可変ソフトスタートおよびトラッキング

- 外部ブートストラップ コンデンサ不要

- WEBENCH® Power Designer により、TPS62901 を使用するカスタム設計を作成

## 2 アプリケーション

- ファクトリ・オートメーションおよび制御

- ビル・オートメーション

- データ・センターおよびエンタープライズ・コンピューティング

- モーター・ドライブ・システム

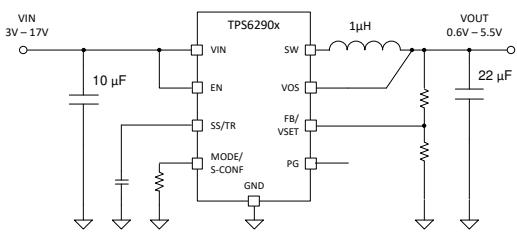

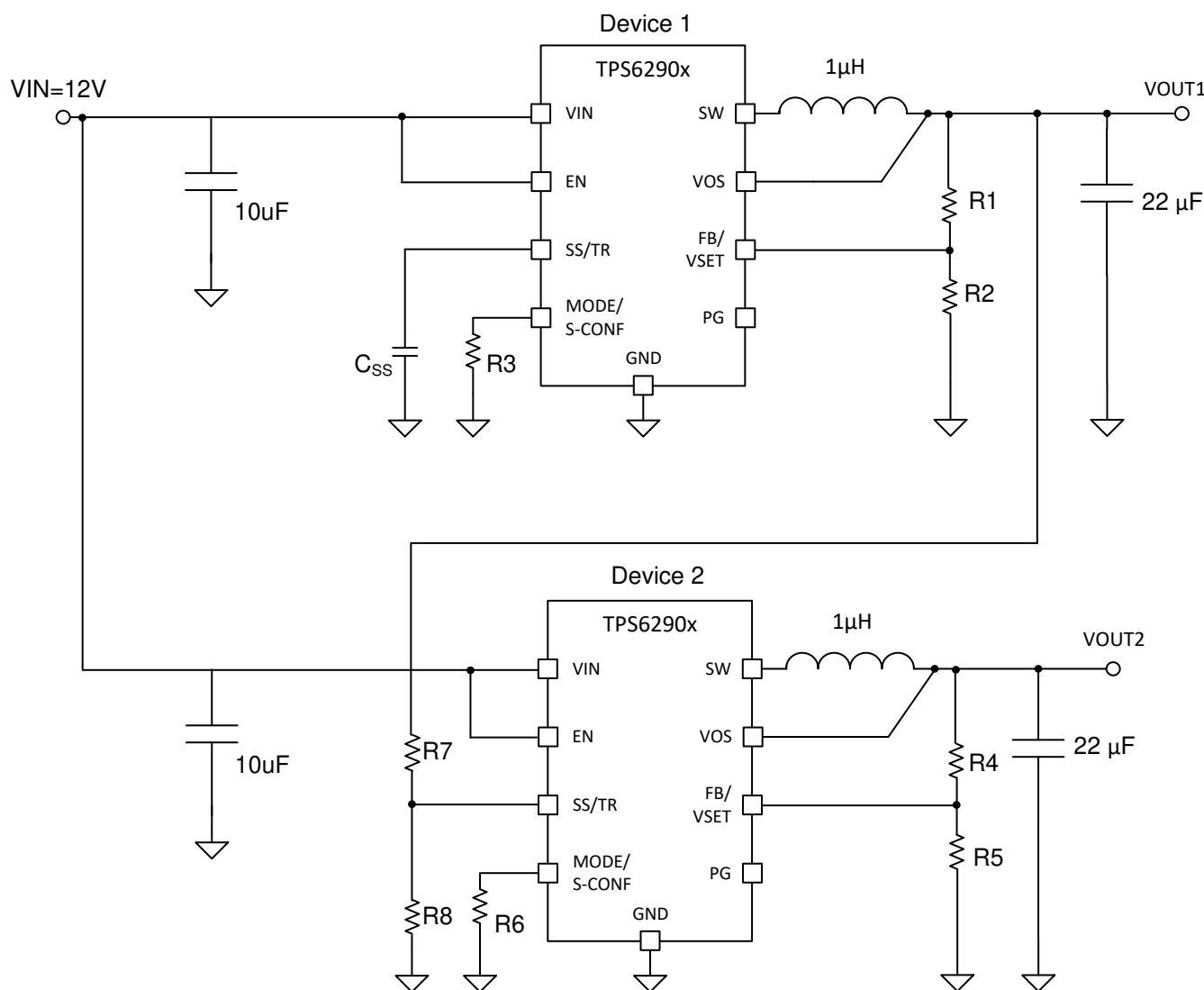

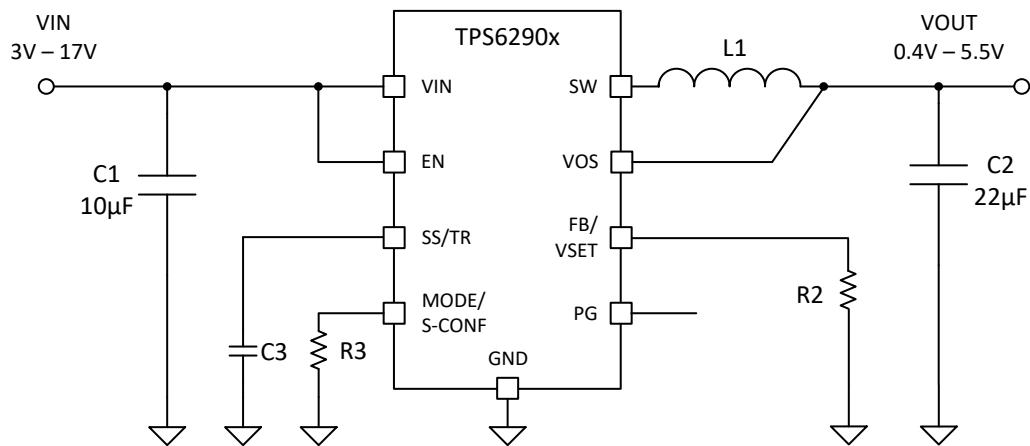

概略回路図

- PD (パワー・デリバリー)

- PC とノート PC

## 3 概要

TPS62901 は、使いやすく、高効率、小型、フレキシブルな同期整流式降圧 DC/DC コンバータです。スイッチング周波数を 2.5MHz ないしは 1.0MHz から選択できるため、小型のインダクタが使用可能であり、高速な過渡応答を実現します。このデバイスは、DCS-Control トポロジにより ±1% の高い  $V_{OUT}$  精度をサポートしています。3V～17V の広い入力電圧レンジで動作するため、12V 電源レール、シングルセルまたはマルチセルのリチウムイオン、5V または 3.3V レールなど、各種の公称入力に対応します。

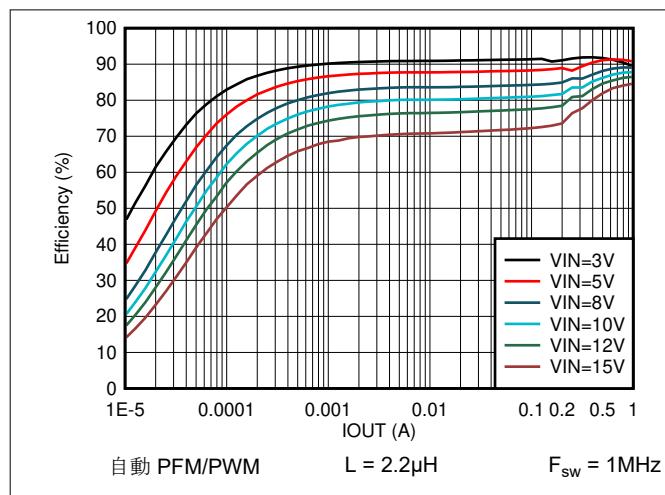

TPS62901 は、軽負荷時には自動的にパワーセーブ モードに移行し (自動 PFM/PWM 選択時)、高効率を維持します。また、非常に小さな負荷でも高い効率を実現するため、静止電流は 4 $\mu$ A (代表値) と小さくなっています。AEE がイネーブルの場合、 $V_{IN}$ 、 $V_{OUT}$ 、負荷電流の全体にわたる高効率を実現します。このデバイスは、内部および外部分圧器、スイッチング周波数、出力電圧放電、自動パワー セーブ モードまたは強制 PWM 動作を設定する MODE/S-CONF 入力を備えています。

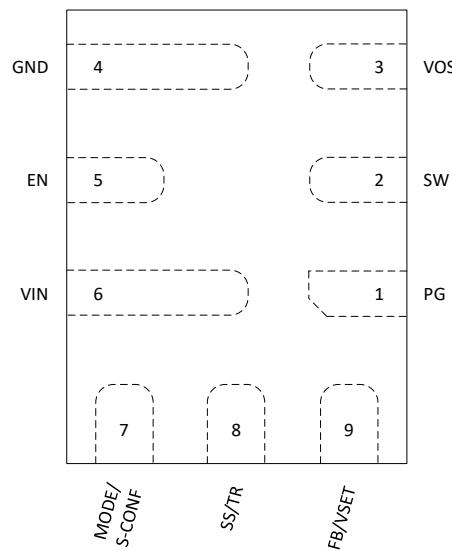

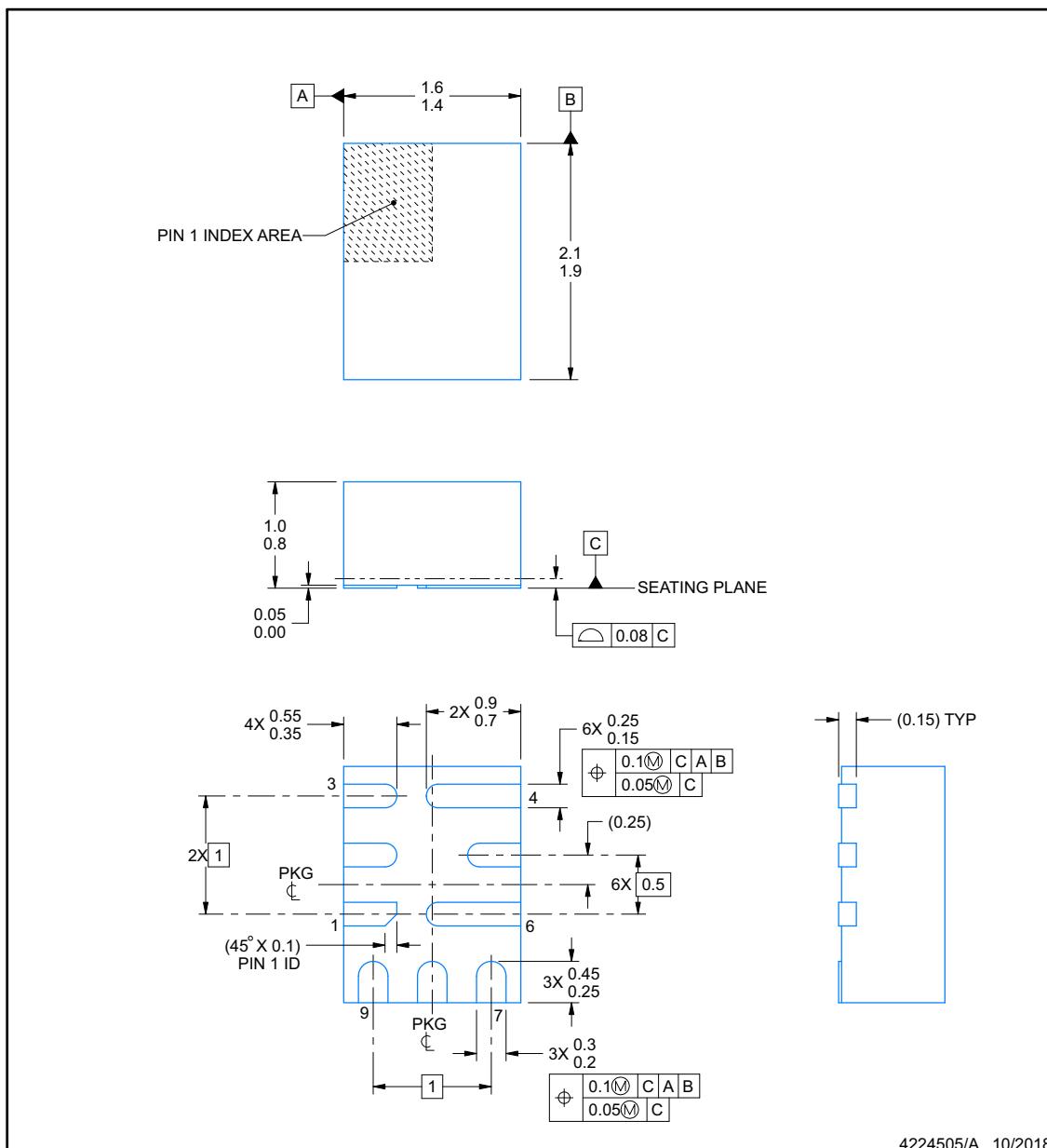

このデバイスは、サイズが 1.50mm × 2.00mm、ピッチが 0.5mm の小型 9 ピン VQFN パッケージで供給されます。

## パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| TPS62901 | RPJ (VQFN-HR, 9)     | 1.50mm × 2.00mm          |

- (1) 供給されているすべてのパッケージについては、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

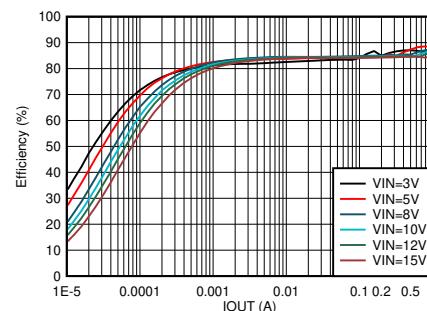

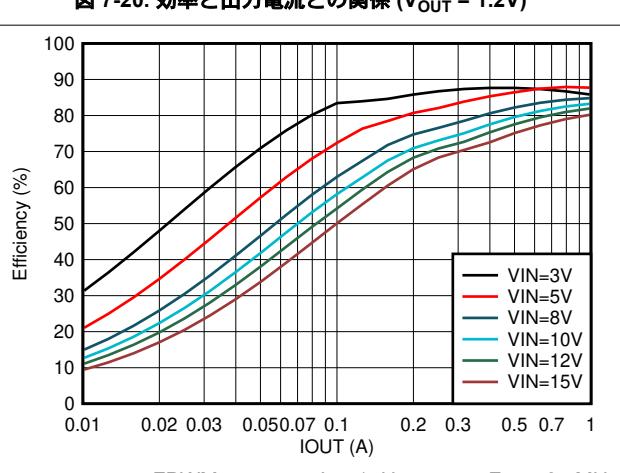

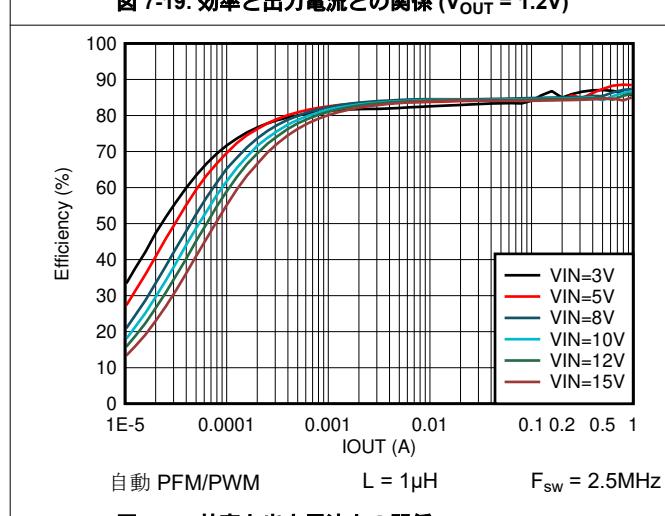

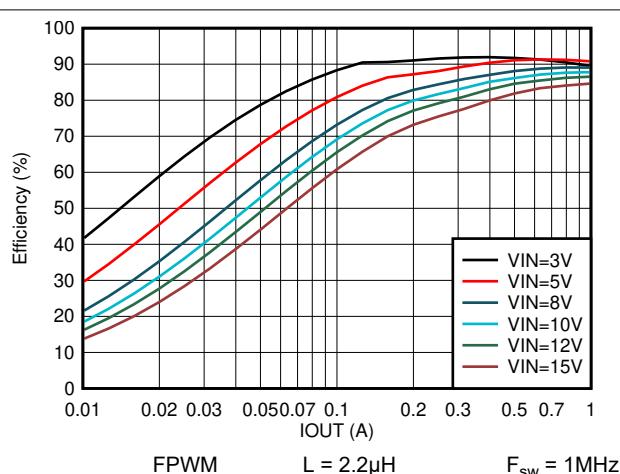

効率と出力電流との関係 (2.5MHz、1μH、自動 PFM/PWM で  $V_O = 1.2V$ )

## 目次

|                    |          |                                  |           |

|--------------------|----------|----------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b> | <b>7 アプリケーションと実装</b>             | <b>17</b> |

| <b>2 アプリケーション</b>  | <b>1</b> | <b>7.1 アプリケーション情報</b>            | <b>17</b> |

| <b>3 概要</b>        | <b>1</b> | <b>7.2 代表的なアプリケーション - 可変出力電圧</b> | <b>17</b> |

| <b>4 ピン構成および機能</b> | <b>3</b> | <b>7.3 システム例</b>                 | <b>38</b> |

| <b>5 仕様</b>        | <b>4</b> | <b>7.4 電源に関する推奨事項</b>            | <b>40</b> |

| 5.1 絶対最大定格         | 4        | <b>7.5 レイアウト</b>                 | <b>41</b> |

| 5.2 ESD 定格         | 4        | <b>8 デバイスおよびドキュメントのサポート</b>      | <b>43</b> |

| 5.3 推奨動作条件         | 4        | <b>8.1 デバイスのサポート</b>             | <b>43</b> |

| 5.4 熱に関する情報        | 5        | <b>8.2 ドキュメントの更新通知を受け取る方法</b>    | <b>43</b> |

| 5.5 電気的特性          | 5        | <b>8.3 サポート・リソース</b>             | <b>43</b> |

| 5.6 代表的特性          | 7        | <b>8.4 商標</b>                    | <b>43</b> |

| <b>6 詳細説明</b>      | <b>8</b> | <b>8.5 静電気放電に関する注意事項</b>         | <b>43</b> |

| 6.1 概要             | 8        | <b>8.6 用語集</b>                   | <b>43</b> |

| 6.2 機能ブロック図        | 8        | <b>9 改訂履歴</b>                    | <b>44</b> |

| 6.3 機能説明           | 9        | <b>10 メカニカル、パッケージ、および注文情報</b>    | <b>44</b> |

| 6.4 デバイスの機能モード     | 14       |                                  |           |

## 4 ピン構成および機能

図 4-1. 9 ピン RPJ VQFN パッケージ (上面図、デバイス ピンは裏側)

表 4-1. ピンの機能

| ピン |                 | タイプ | 説明                                                                                                                                                                                                                  |

|----|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称              |     |                                                                                                                                                                                                                     |

| 1  | PG              | O   | オープンドレインのパワー グッド出力。High = $V_{OUT}$ は準備ができます。Low = $V_{OUT}$ は公称 レギュレーション値を下回っています。このピンはプルアップ抵抗を必要とします。                                                                                                             |

| 2  | SW              |     | コンバータのスイッチ ピン。内部パワー スイッチに接続されています。SW と出力コンデンサとの間にインダクタを接続します。                                                                                                                                                       |

| 3  | VOS             | I   | 出力電圧検出ピン。出力コンデンサの正のピンに直接接続します。                                                                                                                                                                                      |

| 4  | GND             |     | グラウンド ピン。このピンを共通グラウンド プレーンに直接接続する必要があります。                                                                                                                                                                           |

| 5  | EN              | I   | イネーブル入力ピンロジック Low に接続すると、本デバイスは無効化されます。High にプルすると、本デバイスは有効化されます。このピンを未接続のままにしないでください。                                                                                                                              |

| 6  | VIN             | I   | 電源入力ピン。必ず入力コンデンサを、VIN ピンと GND ピンとの間に、本デバイスにできるだけ近づけて接続します。                                                                                                                                                          |

| 7  | MODE/<br>S-CONF | I   | デバイス モード選択 (自動 PWM/PWM または強制 PFM 動作) および SmartConfig™ アプリケーション ピン。 <a href="#">表 6-1</a> に従ってデバイスを構成するため、High、Low、または抵抗に接続します。このピンを未接続のままにしないでください。                                                                 |

| 8  | SS/TR           | I   | ソフトスタート / トランкиング ピン。このピンと GND との間に接続する外付けコンデンサにより、内部基準電圧の立ち上がり時間が設定されます。このピンは、トランкиングとシーケンシングの入力としても使用できます。このピンをフローティングにすると、最も速いランプアップ時間を実現できます。                                                                   |

| 9  | FB/<br>VSET     | I   | デバイス構成に依存 ( <a href="#">セクション 6.3.1</a> を参照) <ul style="list-style-type: none"> <li>FB: 電圧フィードバック入力。抵抗分圧器の出力をこのピンに接続します。</li> <li>VSET: 出力電圧設定ピン。<a href="#">表 6-2</a> に従って出力電圧を選択するため、GND との間に抵抗を接続します。</li> </ul> |

## 5 仕様

### 5.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) (1)

|                  |                       | 最小値  | 最大値                   | 単位 |

|------------------|-----------------------|------|-----------------------|----|

| 電圧 (2)           | VIN、EN、PG、MODE/S-CONF | -0.3 | 18                    | V  |

|                  | SW (DC)               | -0.3 | V <sub>IN</sub> + 0.3 |    |

|                  | SW (AC、10ns 未満) (3)   | -3.0 | 23                    |    |

|                  | FB/VSET、SS/TR、VOS     | -0.3 | 6                     |    |

| T <sub>J</sub>   | 接合部温度                 | -40  | 150                   | °C |

| T <sub>stg</sub> | 保管温度                  | -65  | 150                   | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗示するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、回路のグランドを基準としたものです。

- (3) スイッチング動作時。

### 5.2 ESD 定格

|                    |      |                                                | 値     | 単位 |

|--------------------|------|------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 (1)      | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 (2) | ±500  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                      |                     | 最小値 | 公称値 | 最大値     | 単位 |

|----------------------|---------------------|-----|-----|---------|----|

| V <sub>I</sub>       | 入力電圧範囲              | 3.0 | 17  |         | V  |

| V <sub>O</sub>       | 出力電圧範囲              | 0.4 |     | 5.5     | V  |

| C <sub>I</sub>       | 実効入力容量              | 3   | 10  |         | μF |

| C <sub>O</sub>       | 実効出力容量 (2.5MHz を選択) | 10  | 22  | 100 (1) | μF |

| C <sub>O</sub>       | 実効出力容量 (1.0MHz を選択) | 6   | 22  | 50 (1)  | μF |

| I <sub>OUT</sub>     | 出力電流                | 0   |     | 1       | A  |

| I <sub>SINK_PG</sub> | PG ピンのシンク電流         |     |     | 1       | mA |

| T <sub>J</sub>       | 接合部温度 (2)           | -40 |     | 150     | °C |

- (1) これは、本デバイスの出力に直接接続されたコンデンサに対応する値です。そのコンデンサが直列抵抗を持っている場合、より大きい容量値が許容されます。

- (2) 接合部温度が 125°Cを超えると、動作寿命が短くなります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TPS6290x  |                 | 単位   |  |

|-----------------------|-------------------|-----------|-----------------|------|--|

|                       |                   | VQFN 9 ピン |                 |      |  |

|                       |                   | JEDEC PCB | TPS6290xEVM-069 |      |  |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 97.2      | 73.5            | °C/W |  |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 74.4      | N/A             | °C/W |  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 25        | N/A             | °C/W |  |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 2.7       | 4.3             | °C/W |  |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 24.7      | 28              | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 5.5 電気的特性

V<sub>I</sub> = 3V~17V、T<sub>J</sub> = -40°C~+150°C、標準値は V<sub>I</sub> = 12.0V および T<sub>A</sub> = 25°C (特に記述のない限り)

| パラメータ                 | テスト条件                         | 最小値                                                                                    | 標準値   | 最大値   | 単位   |    |

|-----------------------|-------------------------------|----------------------------------------------------------------------------------------|-------|-------|------|----|

| <b>電源</b>             |                               |                                                                                        |       |       |      |    |

| I <sub>Q_PSM</sub>    | 動作時の静止電流(パワーセーブモード)           | I <sub>out</sub> = 0mA、デバイスはスイッチングしていません。                                              |       | 4     | μA   |    |

| I <sub>Q_PWM</sub>    | 動作時の静止電流(PWMモード)              | V <sub>IN</sub> = 12V、V <sub>OUT</sub> = 1.2V、I <sub>out</sub> = 0mA、デバイスはスイッチングしています。 |       | 8     | mA   |    |

| I <sub>SD</sub>       | V <sub>IN</sub> ピンへのシャットダウン電流 | EN = 0V                                                                                |       | 0.27  | 3.5  | μA |

| V <sub>UVLO</sub>     | 低電圧誤動作防止                      | V <sub>IN</sub> の立ち上がり                                                                 | 2.85  | 2.925 | 3.0  | V  |

|                       | 低電圧誤動作防止                      | V <sub>IN</sub> の立ち下がり                                                                 | 2.7   | 2.775 | 2.85 | V  |

| V <sub>UVLO_HYS</sub> | 低電圧誤動作防止ヒステリシス                | ヒステリシス                                                                                 |       | 150   | mV   |    |

| <b>制御およびインターフェイス</b>  |                               |                                                                                        |       |       |      |    |

| I <sub>LKG</sub>      | ENの入力リーク電流                    | EN = 12V                                                                               | 10    | 300   | nA   |    |

| V <sub>IH_MODE</sub>  | MODE/S-CONFピンのHighレベル入力電圧     |                                                                                        | 1.0   |       | V    |    |

| T <sub>SD</sub>       | サーマルシャットダウンスレッショルド            | T <sub>J</sub> 立ち上がり                                                                   | 170   |       | °C   |    |

|                       | サーマルシャットダウンのヒステリシス            | ヒステリシス                                                                                 | 20    |       |      |    |

| V <sub>IH</sub>       | ENピンのHighレベル入力電圧              |                                                                                        | 0.97  | 1.0   | 1.03 | V  |

| V <sub>IL</sub>       | ENピンのLowレベル入力電圧               |                                                                                        | 0.87  | 0.9   | 0.93 | V  |

| R <sub>EN_PD</sub>    | スマートイネーブルの内部プルダウン抵抗           | EN = Low                                                                               |       | 0.5   | MΩ   |    |

| V <sub>PG</sub>       | パワー グッドスレッショルド                | V <sub>FB</sub> の立ち上がり。公称V <sub>FB</sub> を基準とします。                                      | 93.5% | 96%   | 99%  |    |

|                       |                               | V <sub>FB</sub> の立ち下がり。公称V <sub>FB</sub> を基準とします。                                      | 88.5% | 93%   | 96%  |    |

|                       |                               | ヒステリシス                                                                                 | 1.5%  | 3.5%  | 6%   |    |

| V <sub>PGOL</sub>     | PGピンのLowレベル出力電圧               | I <sub>SINK</sub> = 1mA                                                                |       | 0.4   | V    |    |

| I <sub>PG_LKG</sub>   | PGピンへの入力リーク電流                 | V <sub>PG</sub> = 5V                                                                   | 15    | 550   | nA   |    |

| t <sub>PG_DLY</sub>   | パワー グッド遅延時間                   | V <sub>FB</sub> の立ち下がり                                                                 | 32    |       | μs   |    |

| R <sub>SET</sub>      | S-CONF/VSET抵抗の許容誤差            |                                                                                        | -4    | +4    | %    |    |

| C <sub>SET</sub>      | S-CONF/VSETピンに接続される容量の最大値     |                                                                                        |       | 30    | pF   |    |

| <b>パワー スイッチ</b>       |                               |                                                                                        |       |       |      |    |

| I <sub>LKG_SW</sub>   | SWピンへのリーク電流                   | V <sub>SW</sub> = V <sub>OS</sub> = 5.5V                                               | 2     | 7     | μA   |    |

## 5.5 電気的特性 (続き)

$V_I = 3V \sim 17V$ 、 $T_J = -40^\circ C \sim +150^\circ C$ 、標準値は  $V_I = 12.0V$  および  $T_A = 25^\circ C$  (特に記述のない限り)

| パラメータ              |                     | テスト条件                                                                          | 最小値     | 標準値    | 最大値 | 単位        |

|--------------------|---------------------|--------------------------------------------------------------------------------|---------|--------|-----|-----------|

| $R_{DS\_ON}$       | ハイサイド FET オン抵抗      | $V_{IN} > 4V$ 、 $I_{SW} = 500mA$                                               | 62      | 111    |     | $m\Omega$ |

|                    | ローサイド FET オン抵抗      | $V_{IN} > 4V$ 、 $I_{SW} = 500mA$                                               | 22      | 40     |     |           |

| $I_{LIM}$          | ハイサイド FET 電流制限値     | TPS62901                                                                       | 1.5     | 1.8    | 2.3 | A         |

|                    | ローサイド FET 電流制限値     | TPS62901                                                                       | 1.2     | 1.6    | 2.0 | A         |

| $I_{LIM\_SINK}$    | ローサイド FET シングル電流制限値 |                                                                                | 1.3     | 1.7    | 2.5 | A         |

| $f_{SW}$           | スイッチング周波数           | 2.5MHz 選択                                                                      | 2.5     |        |     | MHz       |

| $T_{ON(MIN)}$      | 最小オン時間              |                                                                                | 50      |        |     | ns        |

| $f_{SW}$           | スイッチング周波数           | 1.0MHz 選択                                                                      | 1.0     |        |     | MHz       |

| D                  | デューティ サイクル          |                                                                                |         |        | 1   |           |

| <b>出力</b>          |                     |                                                                                |         |        |     |           |

| $V_{O\_Reg1}$      | 出力電圧レギュレーション        | VSET 構成を選択。 $T_J = 25^\circ C$ 。                                               | -0.9%   | +0.9%  |     |           |

| $V_{O\_Reg2}$      | 出力電圧レギュレーション        | VSET 構成を選択。 $0^\circ C < T_J < 85^\circ C$                                     | -1.1%   | +1.1%  |     |           |

| $V_{O\_Reg3}$      | 出力電圧レギュレーション        | VSET 構成を選択。 $-40^\circ C < T_J < 150^\circ C$                                  | -1.25%  | +1.25% |     |           |

| $V_{FB}$           | フィードバック レギュレーション電圧  | 可変構成を選択                                                                        | 0.6     |        |     | V         |

| $V_{FB\_Reg1}$     | フィードバック電圧レギュレーション   | FB オプションを選択。 $T_J = 25^\circ C$ 。                                              | -0.6%   | +0.6%  |     |           |

| $V_{FB\_Reg2}$     | フィードバック電圧レギュレーション   | FB オプションを選択。 $0^\circ C < T_J < 85^\circ C$                                    | -0.65%  | +0.65% |     |           |

| $V_{FB\_Reg3}$     | フィードバック電圧レギュレーション   | FB オプションを選択。 $-40^\circ C < T_J < 150^\circ C$                                 | -0.9%   | +0.9%  |     |           |

| $I_{FB}$           | FB ピンへの入力リーク電流      | 可変構成、 $V_{FB} = 0.6V$                                                          | 1       | 70     | nA  |           |

| $T_{delay}$        | 起動遅延時間              | $I_O = 0mA$ 、EN = High からスイッチング開始までの時間、可変構成を選択。                                | 600     | 1400   |     | $\mu s$   |

|                    | 起動遅延時間              | $I_O = 0mA$ 、EN = High からスイッチング開始までの時間、VSET 構成を選択。標準値は VSET 構成の最初の選択肢に基づいています。 | 650     | 1850   |     | $\mu s$   |

| $T_{SS}$           | ソフトスタート時間           | $T_{delay}$ 後に $I_O = 0mA$ 、最初のスイッチング パルスから $V_O$ 目標値まで。TR/SS ピン = オープン        | 150     | 200    |     | $\mu s$   |

| $I_{SS}$           | SS/TR ソース電流         |                                                                                | 2.3     | 2.5    | 2.7 | $\mu A$   |

| $V_{FB}/V_{SS/TR}$ | トラッキング ゲイン、可変構成     |                                                                                | 0.75    |        |     |           |

| $V_{FB}/V_{SS/TR}$ | トラッキング ゲインの許容誤差     |                                                                                | $\pm 8$ |        |     | mV        |

| $R_{DISCH}$        | アクティブ放電抵抗           | 放電 = オン - オプションを選択、EN = Low、                                                   | 7.5     | 20     |     | $\Omega$  |

## 5.6 代表的特性

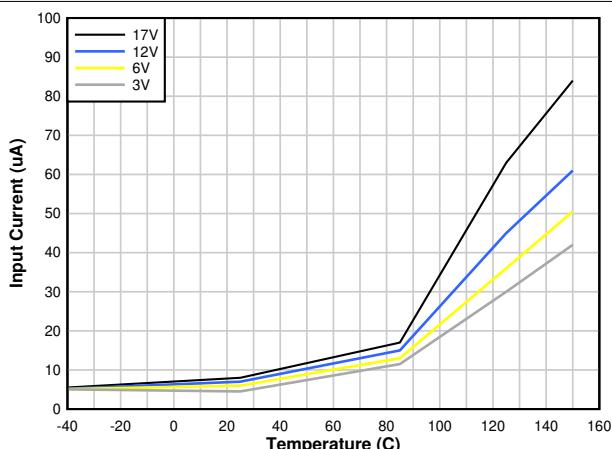

図 5-1. 静止電流 (標準値) と  $V_{IN}$  との関係

図 5-2. 静止電流 (最大値) と温度との関係

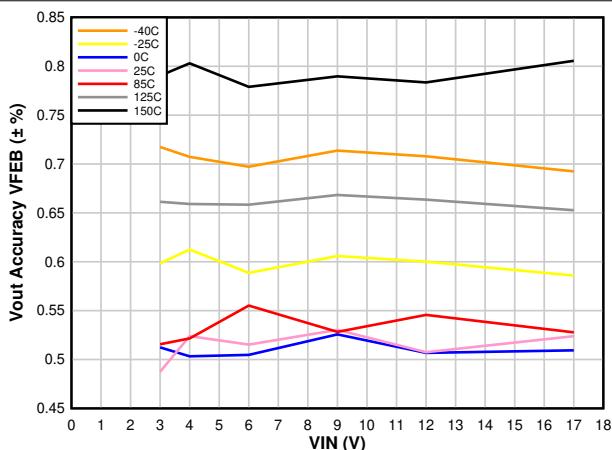

図 5-3. シャットダウン電流 (標準値)

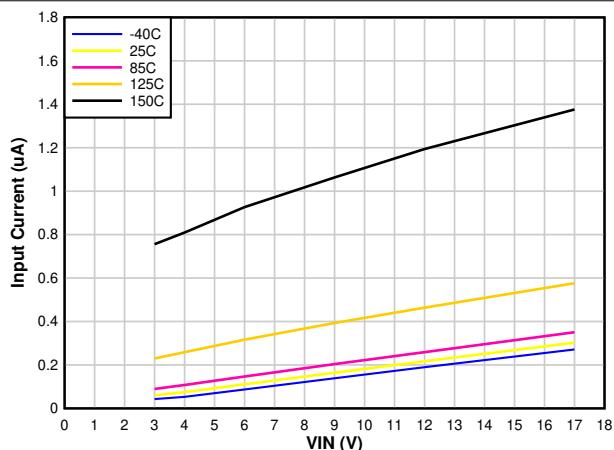

図 5-4. 出力電圧精度 - VFEB を選択

## 6 詳細説明

### 6.1 概要

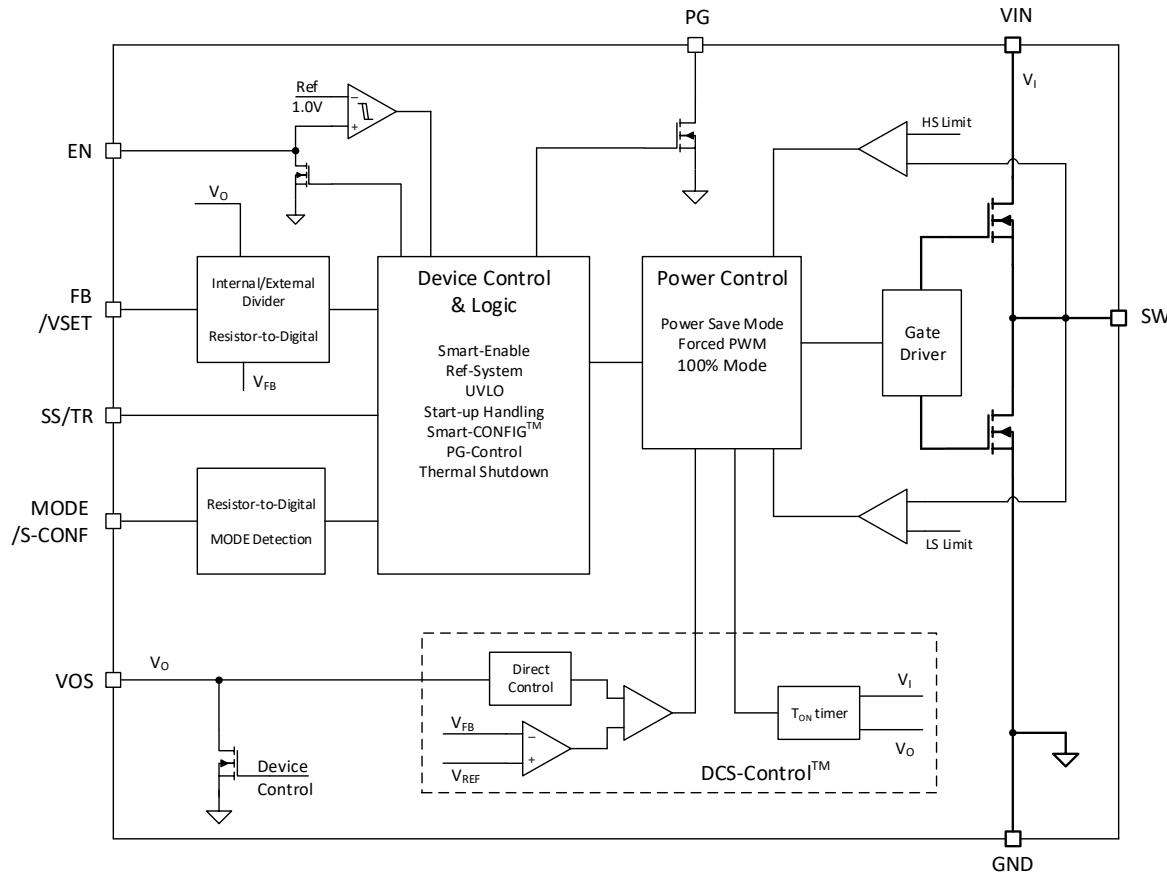

TPS62901 同期整流式スイッチ モード パワー コンバータは、DCS-Control (パワーセーブ モードにシームレスに遷移できる直接制御) を採用しています。DCS-Control は、ヒステリシス、電圧モード、電流モード制御の利点を兼ね備えた先進のレギュレーショントポロジです。この制御ループは、出力電圧の変化に関する情報を受け取り、その情報を直接、高速コンパレータ段に送ります。制御ループにより、スイッチング周波数が設定されます。この周波数は、定常動作条件では一定であり、動的な負荷の変化に対して即座に応答します。高精度の DC 負荷レギュレーションを実現するため、電圧帰還ループを使用しています。内部的に補償された制御ネットワークは、小型外付け部品と低 ESR コンデンサを使った高速で安定した動作を実現します。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 モード選択とデバイス構成のための MODE/S-CONF

本デバイスは、MODE/S-CONF (SmartConfig アプリケーション) を使って、1 つの入力に 2 つの機能を持たせています。これは、本デバイスの動作を次の 2 つの方法でカスタマイズするために使用できます。

- 従来のように High レベルまたは Low レベルでデバイスモード (PFM または AEE 動作付き自動 PWM) を選択します。

- MODE/S-CONF ピンに 1 つの抵抗を接続することで、デバイス構成 (スイッチング周波数、内部 / 外部フィードバック、出力放電、PFM/PWM モード) を選択します。

起動シーケンス中、内部 OTP を読み出した後、ソフトスタートでスイッチングを開始する前に、本デバイスはこのピンを解釈します。本デバイスが High または Low レベルを読み出した場合、動的モード変更が有効化され、動作中の PWM/PWM モード変更が可能になります。本デバイスが抵抗値を読み出した場合、動作中はそれ以上の解釈は行われず、デバイスモードまたはその他の構成はその後変更されません。

#### 注

MODE/S-CONF ピンはフローティング状態のままにすることはできません。表 6-1 に従って本デバイスを構成するため、High、Low、または 1 つの抵抗にピンを接続します。

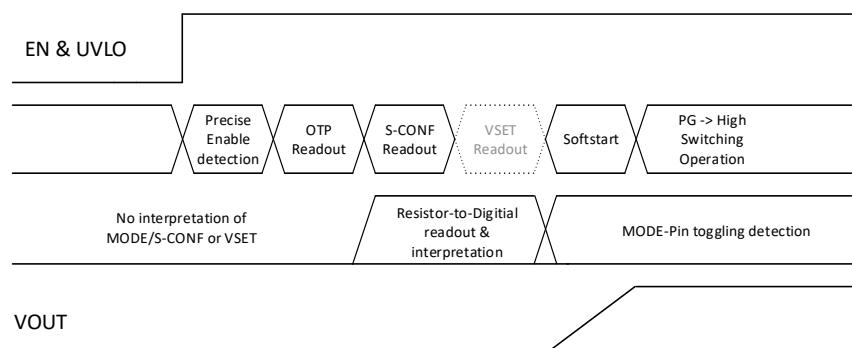

図 6-1. S-CONF と VSET の解釈フロー

表 6-1. SmartConfig™ アプリケーションの設定表

| #            | レベルまたは抵抗値 [ $\Omega$ ] (1) | FB/VSET ピン | $f_{sw}$ (MHz) | 出力放電 | MODE (自動または強制 PWM) | 動的モード変更 |

|--------------|----------------------------|------------|----------------|------|--------------------|---------|

| レベルによる選択肢の設定 |                            |            |                |      |                    |         |

| 1            | GND                        | 外部 FB      | 2.5            | あり   | AEE 付き自動 PFM/PWM   | 有効      |

| 2            | High ( $> V_{IH\_MODE}$ )  | 外部 FB      | 2.5            | あり   | 強制 PWM             |         |

| 抵抗による選択肢の設定  |                            |            |                |      |                    |         |

| 3            | 7.15k                      | 外部 FB      | 2.5            | なし   | AEE 付き自動 PFM/PWM   | 無効      |

| 4            | 8.87k                      | 外部 FB      | 2.5            | なし   | 強制 PWM             |         |

| 5            | 11.0k                      | 外部 FB      | 1              | あり   | 自動 PFM/PWM         |         |

| 6            | 13.7k                      | 外部 FB      | 1              | あり   | 強制 PWM             |         |

| 7            | 16.9k                      | 外部 FB      | 1              | なし   | 自動 PFM/PWM         |         |

| 8            | 21.0k                      | 外部 FB      | 1              | なし   | 強制 PWM             |         |

| 9            | 26.1k                      | VSET       | 2.5            | あり   | AEE 付き自動 PFM/PWM   |         |

| 10           | 32.4k                      | VSET       | 2.5            | あり   | 強制 PWM             |         |

| 11           | 40.2k                      | VSET       | 2.5            | なし   | AEE 付き自動 PFM/PWM   |         |

| 12           | 49.9k                      | VSET       | 2.5            | なし   | 強制 PWM             |         |

| 13           | 61.9k                      | VSET       | 1              | あり   | 自動 PFM/PWM         |         |

| 14           | 76.8k                      | VSET       | 1              | あり   | 強制 PWM             |         |

| 15           | 95.3k                      | VSET       | 1              | なし   | 自動 PFM/PWM         |         |

| 16           | 118k                       | VSET       | 1              | なし   | 強制 PWM             |         |

(1) E96 抵抗シリーズ、1% の精度、 $\pm 200\text{ppm}/^\circ\text{C}$ 以下の温度係数

### 6.3.2 可変 $V_O$ 動作 (外付け分圧器)

TPS62901 は、MODE/S-CONF ピンを使うことで、FB/VSET ピンをフィードバック・ピンとして使用し、外付け抵抗分圧器で  $V_O$  を検出する従来型の構成に設定できます。TPS62901 は、16 種類の固定出力電圧構成に設定することもできます。これらの電圧は、FB/VSET ピンと GND との間の外付け抵抗によって設定されます。この構成では、本デバイスの VOS 端子で  $V_O$  が直接検出されます。

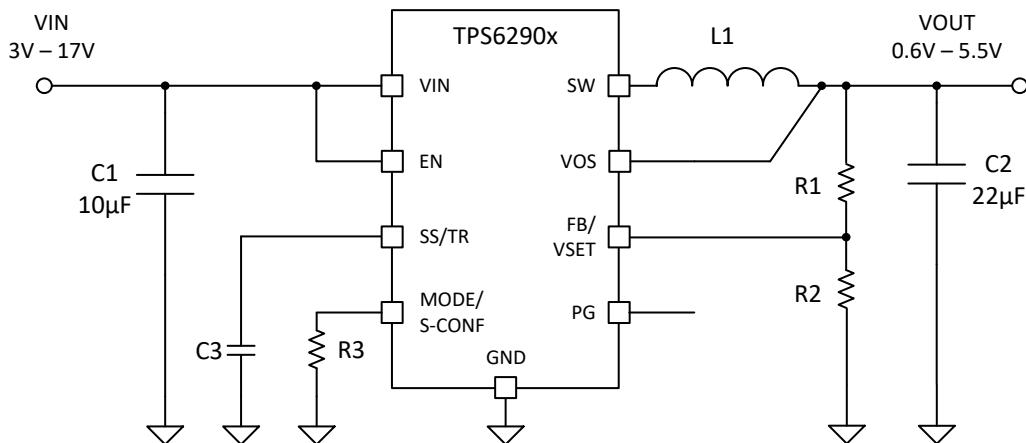

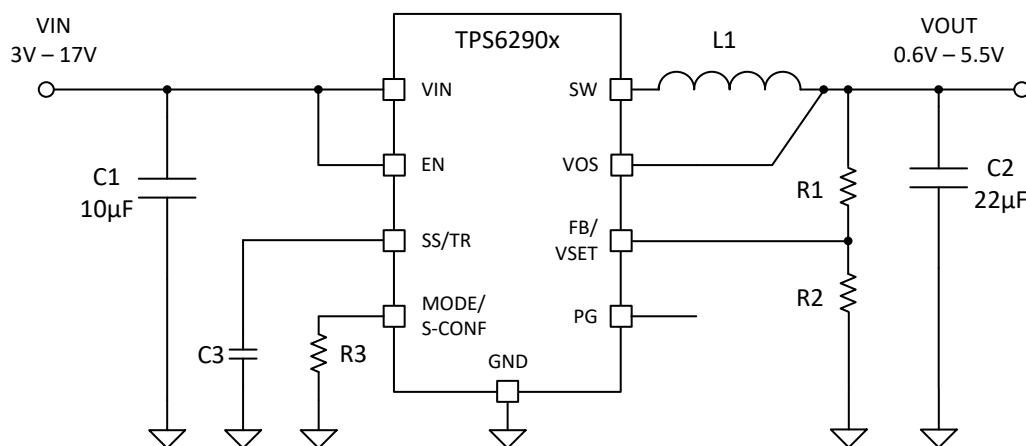

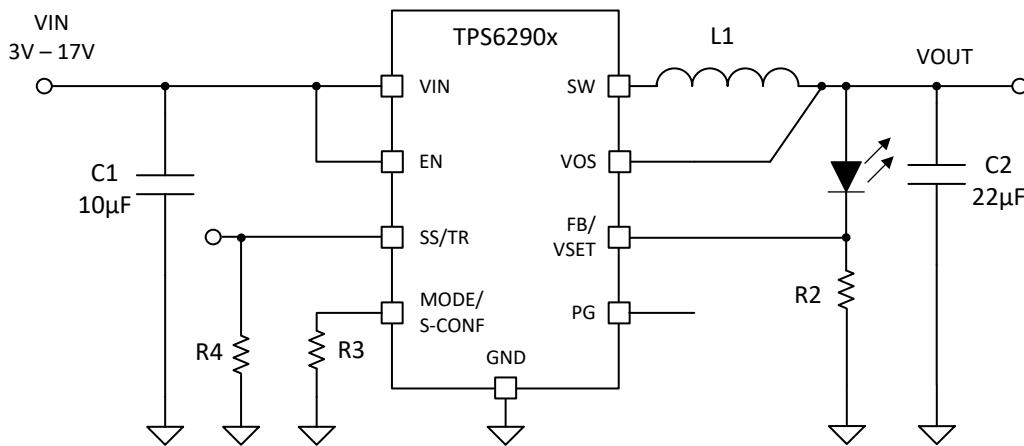

本デバイスが従来型の可変  $V_O$  動作で動作するよう構成されている場合、FB/VSET ピンがフィードバック・ピンとして使われ、外付け分圧器回路を通して  $V_O$  を FB/VSET ピンで検出する必要があります。図 6-2 に、この構成の代表的な回路を示します。

図 6-2. 可変  $V_O$  動作の回路図

### 6.3.3 設定可能な $V_O$ 動作 (VSET と内部分圧器)

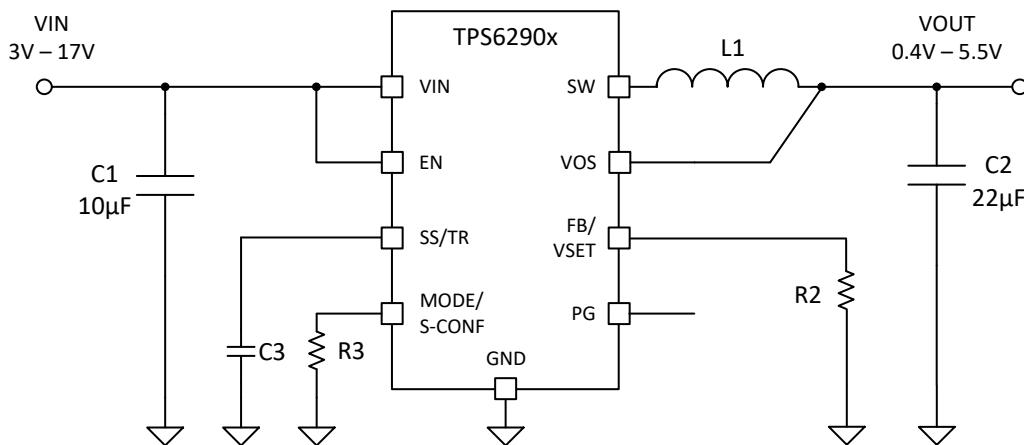

本デバイスが VSET 動作を行なうように構成されている場合、内部抵抗分圧器によって、VOS ピンを通してのみ  $V_O$  が検出されます。 $V_O$  の目標値は、VSET ピンと GND との間に接続された外付け抵抗によって設定されます。図 6-3 に、この構成の代表的な回路を示します。

図 6-3. 設定可能な  $V_O$  動作の回路図

表 6-2. VSET の選択表

| #  | 抵抗値 [Ω]           | $V_O$ の目標値 [V] |

|----|-------------------|----------------|

| 1  | GND               | 1.2            |

| 2  | 4.64k             | 0.4            |

| 3  | 5.76k             | 0.6            |

| 4  | 7.15k             | 0.8            |

| 5  | 8.87k             | 1.0            |

| 6  | 11.0k             | 1.1            |

| 7  | 13.7k             | 1.3            |

| 8  | 16.9k             | 1.35           |

| 9  | 21.0k             | 1.8            |

| 10 | 26.1k             | 1.9            |

| 11 | 40.2k             | 2.5            |

| 12 | 61.9k             | 3.8            |

| 13 | 76.8k             | 5.0            |

| 14 | 95.3k             | 5.1            |

| 15 | 118.0k            | 5.5            |

| 16 | 249.00k 以上 / オープン | 3.3            |

### 6.3.4 ソフトスタート / トラッキング (SS/TR)

SS/TR ピンを使用すると、ソフトスタート動作の調整と外部電圧の追跡が可能です。動作の詳細については、セクション 7.2.2.6 を参照してください。

内蔵ソフトスタート回路は、起動時の出力電圧の傾きを制御します。これにより、過剰な突入電流を防止し、出力電圧の立ち上がり時間を確実に制御できます。また、インピーダンスが高い電源またはバッテリによる望ましくない電圧降下も防止できます。動作を開始させるため、EN を High に設定すると、本デバイスは遅延の後にスイッチングを開始し、その後内部基準電圧、したがって  $V_O$  が、SS/TR ピンに接続された外付けコンデンサで制御される傾きで上昇します。

SS/TR ピンに何も接続されていない場合、本デバイスは、内部的に制限される最も速い速度で起動します（このピンを外部から Low にプルすることはできません）。

シャットダウン（EN = GND）、低電圧誤動作防止、サーマル・シャットダウンのいずれかに本デバイスが設定されると、適切な Low レベルを確保するため、内部の抵抗が SS/TR ピンをプルダウンします。これらの状態から復帰すると、SS/TR の接続で設定された起動シーケンスが新たに実行されます。

SS/TR に印加される電圧は、マスタ電圧を追跡するために使えます。強制 PWM モードでは、出力電圧はこの電圧に追従して上昇および下降します。PFM モードでは、出力電圧は負荷電流に基づいて低下します。

### 6.3.5 高精度のスレッショルドを持つスマート イネーブル

TPS62901 のイネーブル ピンに印加される電圧は、固定の立ち上がりスレッショルド電圧とコンパレータで比較されます。そのため、ゆっくり変化する電圧でもイネーブル ピンを駆動でき、また、外部 RC ネットワークを使ってパワーアップ遅延を実現することもできます。

高精度のイネーブル 入力を使うと、イネーブル ピンの入力に抵抗分圧器を追加することで、低電圧誤動作防止機能を設定できます。

イネーブル入力の立ち下がりエッジのスレッショルドは、立ち上がりエッジのスレッショルドよりも低く設定されています。イネーブル入力が立ち上がりスレッショルドを上回ると、TPS62901 は動作を開始します。正しく動作させるには、EN ピンを終端し、フローティング状態のままにしないようにします。EN ピンを Low にプルすると、本デバイスはシャットダウンします。このモードでは、内部のハイサイドおよびローサイド MOSFET がターンオフし、内部制御回路全体がオフになります。

本デバイスが無効化されると、内部抵抗によって EN ピンが GND にプルダウンされ、ピンがフローティングにならないようになっています（本デバイスが有効化されると、そのプルダウンは切り離されます）。これにより、EN ピンを安全に Low レベルに駆動できない場合に、本デバイスが制御されていない状態で起動することを防止できます。EN を Low にすると、本デバイスはシャットダウン モードに入ります。EN を High レベルに設定すると、本デバイスはターンオンします。内部制御ロジックと基準電圧が起動すると、プルダウン制御回路は EN ピンのプルダウン抵抗を切り離します。EN を Low レベルに設定すると、本デバイスはシャットダウン モードに移行し、プルダウン抵抗が再度有効化されます。

### 6.3.6 パワー グッド (PG)

TPS62901 には、出力電圧が目標値に達し、本デバイスの準備が整ったかどうかを示すため、パワー グッド (PG) 機能が内蔵されています。PG 信号は、スタートアップ時の複数のレールのシーケンシングに使用できます。PG ピンは、推奨入力電圧レベルに合致する任意の電圧に接続されたプルアップ抵抗を必要とするオープンドレイン出力です。EN、UVLO (低電圧誤動作防止)、サーマル シャットダウンにより本デバイスがターンオフされると、PG は Low になります。PG ピンが Low に維持されるには、V<sub>IN</sub> が印加され続けている必要があります。

パワー グッド出力を使用しない場合、このピンを GND に接続するか、オープンのままにすることを推奨します。

表 6-3. パワー グッド インジケータの機能表

| ロジック信号                       |       |              |                      | PG のステータス |

|------------------------------|-------|--------------|----------------------|-----------|

| V <sub>I</sub>               | EN ピン | サーマル シャットダウン | V <sub>O</sub>       |           |

| V <sub>I</sub> > UVLO        | High  | なし           | 目標の V <sub>O</sub>   | 高インピーダンス  |

|                              |       |              | V <sub>O</sub> < 目標値 | Low       |

|                              | Low   | あり           | X                    | Low       |

|                              | X     | X            | X                    | Low       |

| 1.8V < V <sub>I</sub> < UVLO | X     | X            | X                    | Low       |

| V <sub>I</sub> < 1.8V        | X     | X            | X                    | 未定義       |

### 6.3.7 低電圧誤動作防止 (UVLO)

入力電圧が低下した場合、低電圧誤動作防止機能が両方のパワー FET をオフにすることで、本デバイスの誤動作を防止します。本デバイスは、立ち上がり UVLO スレッショルドを上回る電圧では完全に動作し、電源電圧低下スレッショルドを入力電圧が下回ると、オフになります。

### 6.3.8 電流制限および短絡保護

TPS62901 は、過負荷および短絡イベントに対して保護されています。インダクタ電流がハイサイド FET の電流制限値 ( $I_{LIMH}$ ) を上回ると、インダクタ電流を減少させるため、ハイサイド スイッチがターンオフし、ローサイド スイッチがターンオンします。ローサイド FET の電流がローサイド FET の電流制限スレッショルドを下回った場合にのみ、ハイサイド FET は再度ターンオンします。

内部伝搬遅延が原因で、その間に実際の電流が静的電流制限値を上回ることがあります。動的な電流制限値は、次の式 1 で与えられます。

$$I_{peak(typ)} = I_{LIMH} + \frac{V_L}{L} \times t_{PD} \quad (1)$$

ここで、

- $I_{LIMH}$  は、[電気的特性](#)に規定されているハイサイド FET の静的電流制限値

- $L$  は、ピーク電流時の実効インダクタンス

- $V_L$  は、インダクタの両端の電圧 ( $V_{IN} - V_{OUT}$ )

- $t_{PD}$  は、50ns (標準値) の内部伝搬遅延

特に、入力電圧が高く、かつ使用しているインダクタンスが非常に小さい場合、電流が静的制限値を上回ることがあります。ハイサイド スイッチの動的ピーク電流は、次のように計算できます。

$$I_{peak(typ)} = I_{LIMH} + \frac{V_{IN} - V_{OUT}}{L} \times 50\text{ ns} \quad (2)$$

### 6.3.9 サーマル・シャットダウン

本デバイスの接合部温度  $T_J$  は内蔵の温度センサによって監視されています。 $T_J$  が上昇し、サーマル・シャットダウン・スレッショルド  $T_{SD}$  を上回ると、本デバイスはシャットダウンします。ハイサイドとローサイドの両方のパワー FET がターンオフし、PG が Low に遷移します。 $T_J$  がヒステリシスを下回ると、コンバータはソフトスタートを発端に、通常動作に復帰します。PFM スキップが一時的に停止している間、サーマル・シャットダウン機能は無効化されています。シャットダウンまたはリストートは、スイッチング・サイクル中にのみトリガされます。[セクション 6.4.3](#) を参照してください。

## 6.4 デバイスの機能モード

### 6.4.1 パルス幅変調 (PWM) 動作

TPS62901 には、このセクションで説明する強制 PWM モードと、[セクション 6.4.3](#) で説明した PWM/PWM という 2 つの動作モードがあります。

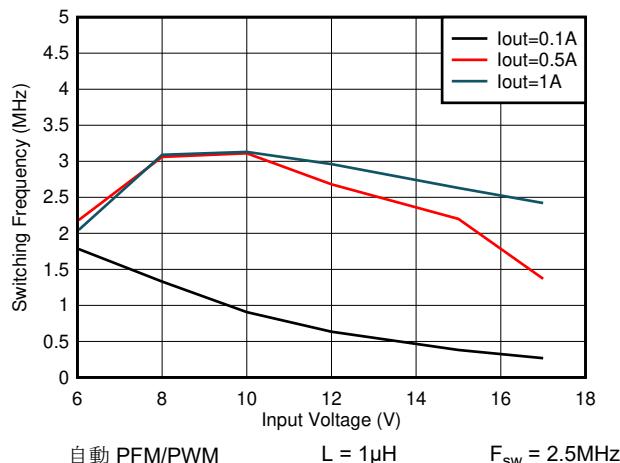

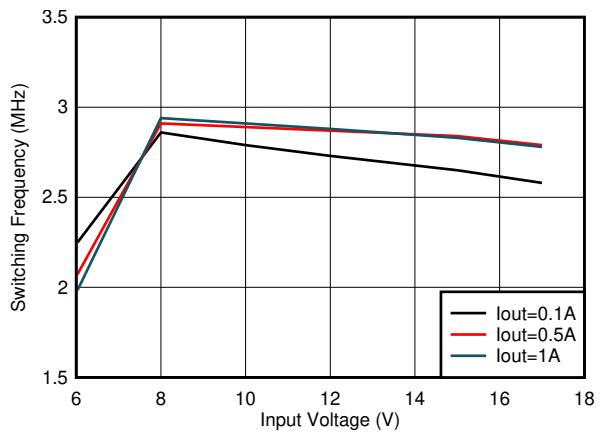

PWM モードになるように MODE/S-CONF ピンを設定すると、TPS62901 は公称スイッチング周波数 2.5/1.0MHz の連続導通モード (CCM) のパルス幅変調で動作します。PWM の周波数変動は制御されており、 $V_{IN}$ 、 $V_{OUT}$ 、インダクタンスに依存します。強制 PWM モードでのオン時間は次の式 3 で与えられます。

$$TON = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{sw}} \quad (3)$$

### 6.4.2 AEE (自動効率拡張) 機能

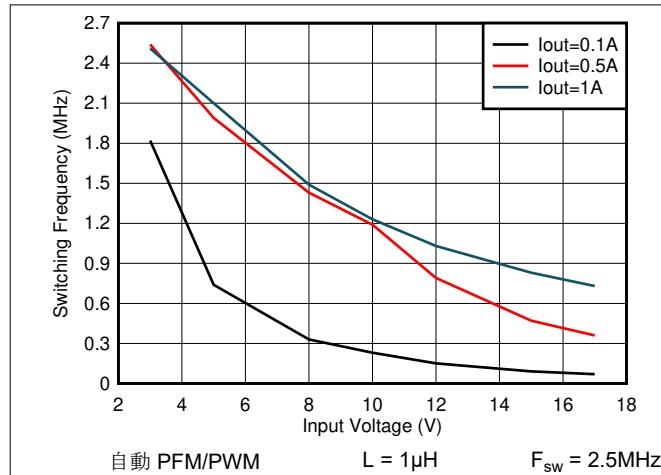

AEE モードになるように MODE/S-CONF ピンを設定すると、TPS62901 はコンバータのスイッチング周波数を自動的に調整することで、入力電圧および出力電圧の全範囲にわたって最大の効率を実現します。これは、コンバータのオフ時間の予測値を設定することで実現されます。スイッチ・モード・コンバータの効率は、変換時の電力損失によって決まります。 $V_{OUT}$  が減少した場合、 $V_{IN}$  が増加した場合、またはその両方の場合、効率は低下します ([式 4](#) を参照)。デューティ・サイクル範囲 ( $V_{OUT}/V_{IN}$  比) の全体にわたって高い効率を維持するため、リップル電流を維持しながらスイッチング周波数が調整されます。

$$F_{sw} (MHz) = 10 \times V_{OUT} \times \frac{V_{IN} - V_{OUT}}{V_{IN}^2} \quad (4)$$

TPS62901 の AEE 機能は、入力電圧と出力電圧に応じてパワーセーブ・モードのオン時間 (TON) を調整し、最大効率を維持します。定常動作でのオン時間は、[式 5](#) を使って推定できます。

$$TON = 100 \times \frac{VIN}{VIN - VOUT} [ns] \quad (5)$$

[式 6](#) に、インダクタ・リップル電流、スイッチング周波数、デューティ・サイクルの関係を示します。

$$\Delta I_L = V_{OUT} \times \left( \frac{1-D}{L \times f_{sw}} \right) = V_{OUT} \times \left( \frac{1 - \left( \frac{V_{OUT}}{V_{IN}} \right)}{L \times f_{sw}} \right) \quad (6)$$

各種デューティ・サイクルでスイッチング損失を減らし高い効率を維持することで、効率は向上します。一方、リップル電流の振幅は、電流制限に達することなく、最大出力電流を供給できるほど十分小さく維持されます。特に、固定周波数コンバータの効率を大幅に低下させる  $V_{OUT}$  値の低下の際に、AEE 機能は各種デューティ・サイクルでの効率を向上させます。またこの機能は、高い  $V_{IN}$  から低い  $V_{OUT}$  への変換の際の非常に小さいデューティ・サイクルを補償します。そのような変換の場合、その他のトポロジでは制御範囲が制限されます。

### 6.4.3 パワーセーブ モード動作 (自動 PFM/PWM)

パワーセーブ モード (自動 PFM/PWM/PWM) になるように MODE/S-CONF ピンが構成されている場合、出力電流がインダクタリップル電流の 1/2 より大きい限り、本デバイスは PWM モードで動作します。軽負荷時に高い効率を維持するため、本デバイスは不連続導通モード (DCM) との境界でパワーセーブ モードに移行します。この移行は、出力電流がインダクタリップル電流の 1/2 より小さくなった場合に行われます。負荷電流が減少すると、滑らかにパワーセーブ モードに移行します。これにより、軽負荷動作時の高い効率が確保されます。インダクタ電流が不連続である限り、本デバイスはパワーセーブ モードにとどまります。

パワーセーブ モードでは、スイッチング周波数は負荷電流に比例して低下し、高い効率を維持します。パワーセーブ モードの開始と終了は、どちらの方向にも滑らかに行われます。

2.5MHz が選択されている場合、AEE 機能を使用して最高の効率を維持するため、TPS62901 は、スイッチングの調整に加えて、入力電圧と出力電圧に応じてパワーセーブ モードのオン時間 (TON) を調整します ([セクション 6.4.2](#) を参照)。

パワーセーブ モードでは、TON 時間は式 3 (1MHz の場合) と式 5 (2.5MHz、AEE が有効化されている場合) を使って推定できます。

出力電圧が非常に小さい場合、スイッチング損失を制限するため、約 50ns の最小オン時間が維持されます。これにより動作周波数がその公称値から低減され、高い効率が維持されます。TON を使って、パワーセーブ モードでのピーク インダクタ電流の標準値が次の式 7 で近似されます。

$$ILPSM_{(peak)} = \frac{(VIN - VOUT)}{L} \times TON \quad (7)$$

TPS62901 のデューティサイクルを制限するオフ時間には最小値が存在します。V<sub>OUT</sub> より 15% (標準値) 大きい値よりも V<sub>IN</sub> が小さい場合、負荷電流にかかわらず、TPS62901 はパワーセーブ モードに移行しません。本デバイスは、PWM モードで出力レギュレーションを維持します。

パワーセーブ モードでの出力電圧リップルは、次の式 8 で与えられます。

$$\Delta V = \frac{L \times VIN^2}{200 \times C} \left( \frac{1}{VIN - VOUT} + \frac{1}{VOUT} \right) \quad (8)$$

ここで、

- L は実効インダクタンス

- C は実効出力容量

#### 6.4.4 100% デューティ サイクルでの動作

PWM モードで動作する降圧コンバータのデューティサイクルは、D = V<sub>OUT</sub>/V<sub>IN</sub> で与えられます。入力電圧が出力電圧に近づき、オフ時間が短くなると、デューティサイクルは増加します。80ns (標準値) の最小オフ時間に達すると、TPS62901 は、100% モードに近付きながら、スイッチング周波数を下げます。100% モードに入ると、ハイサイド スイッチが連続的にオン状態に維持されます。出力電圧が内部設定点を下回っている限り、ハイサイド スイッチはターンオンされたままになります。そのため、入力と出力の電圧差が小さくても変換できます (たとえば、バッテリ駆動アプリケーションで非常に長い動作時間を実現できます)。100% デューティサイクル モードでは、ローサイド FET は遮断されています。

出力電圧レギュレーションを維持するための入力電圧の最小値は、負荷電流と出力電圧レベルに応じて、次のように計算できます。

$$VIN_{(min)} = VOUT + IOUT(R_{DS(on)} + RL) \quad (9)$$

ここで、

- I<sub>OUT</sub> は出力電流

- R<sub>DS(on)</sub> はハイサイド FET のオン状態の抵抗

- R<sub>L</sub> は、使用しているインダクタの DC 抵抗

#### 6.4.5 出力放電機能

放電機能の目的は、本デバイスが（イネーブル入力によって）無効化されつつある際に出力電圧の設定されたダウンランプを確保することだけでなく、本デバイスがターンオフした際に出力電圧を約 0V に維持することです。出力放電機能は、電源電圧が印加されてから、TPS62901 が少なくとも 1 回（イネーブル入力によって）有効化された後にのみ機能します。内部放電抵抗は VOS ピンに接続されています。本デバイスが無効化された場合、サーマルシャットダウンが作動した場合、低電圧誤動作防止が作動した場合のいずれかに、放電機能は即座に有効化されます。放電機能の動作を維持するために必要な電源電圧の最小値は 2V（標準値）です。

#### 6.4.6 負荷にバイアスが印加された状態での起動

TPS62901 は、出力にバイアスが印加された状態で起動できます。内部のソフトスタートランプがフィードバック電圧以上である場合にのみ、本デバイスはスイッチングを開始します。フィードバックピンが公称値よりも高い電圧にバイアスされている場合、フィードバックピンの電圧が目標値まで下がらない限り、TPS62901 はスイッチングを開始しません。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPS62901 デバイスは、使いやすく、高効率、小型、フレキシブルな同期整流式降圧 DC/DC コンバータです。3V~17V の広い入力電圧レンジで動作するため、12V 電源レール、シングル セルまたはマルチ セルのリチウムイオン、5V または 3.3V レールなど、各種の入力に対応します。

### 7.2 代表的なアプリケーション - 可変出力電圧

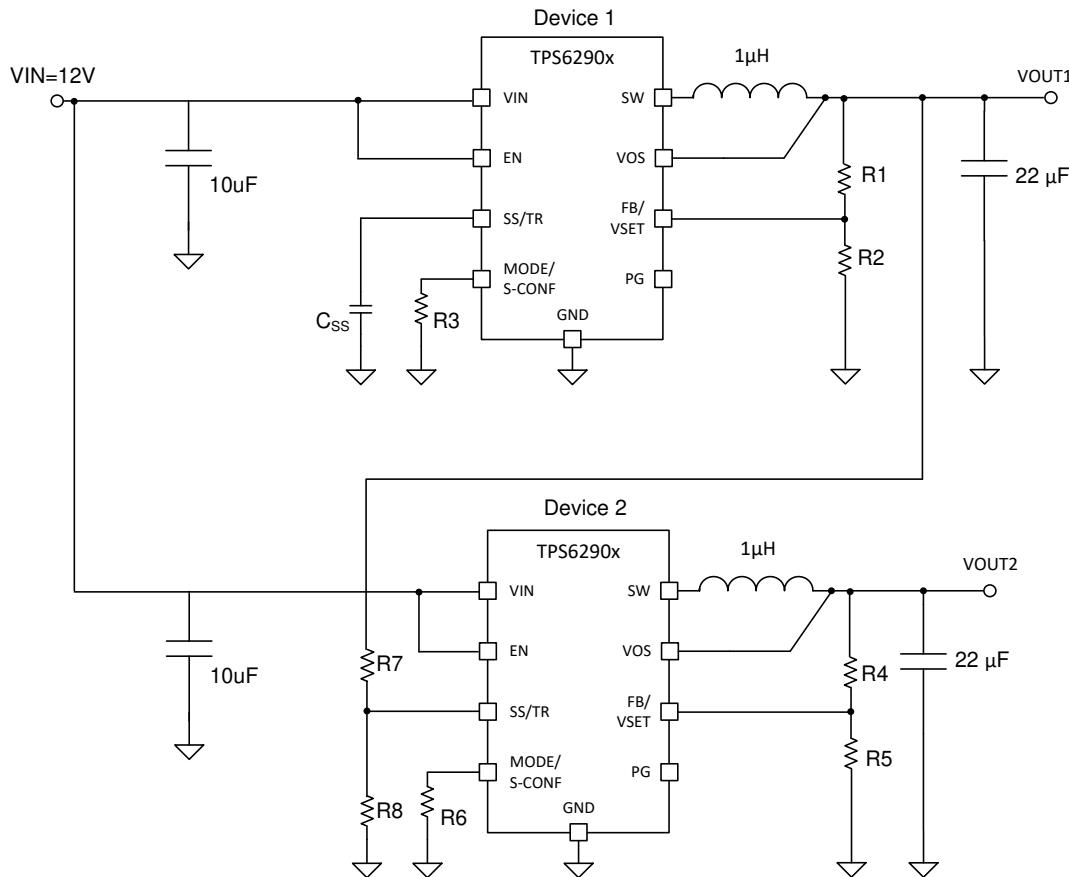

図 7-1. 代表的なアプリケーション回路

#### 7.2.1 設計要件

表 7-1. 部品表

| 記号   | 説明                                       | 製造元                         |

|------|------------------------------------------|-----------------------------|

| IC   | 17V、3A 降圧コンバータ                           | TPS6290x シリーズ、テキサス・インスツルメンツ |

| L    | 1µH インダクタ                                | XGL4020-102、Coilcraft       |

| CIN  | 10µF、25V、セラミック、0805                      | C3216X7R1E106M160AE、TDK     |

| COUT | 22µF、16V、セラミック、0805                      | C2012X7S1A226M125AC、TDK     |

| CSS  | ソフトスタート時間に依存 (セクション 7.2.2.5.3 を参照)       | 16V、セラミック、X7R               |

| R1   | V <sub>OUT</sub> に依存 (セクション 7.2.2.2 を参照) | 標準 1% 金属皮膜                  |

| R2   | V <sub>OUT</sub> に依存 (セクション 7.2.2.2 を参照) | 標準 1% 金属皮膜                  |

| R3   | デバイス設定に依存 (セクション 6.3.1 を参照)              | 標準 1% 金属皮膜                  |

#### 7.2.2 詳細な設計手順

##### 7.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS62901 デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と一緒に参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 7.2.2.2 出力電圧の設定

TPS62901 の出力電圧は可変です。 $V_{OUT}$  と GND との間に接続された抵抗分圧器を使って、本デバイスの出力電圧を 0.6V~5.5V に設定できます。FB ピンの電圧は 600mV にレギュレートされています。[式 10](#) から、抵抗分圧器の選択によって出力電圧の値が設定されます。2μA 以上の電流を許容できる抵抗値を選択することを推奨します。これは、R2 の値が 400kΩ を超えないことを意味します。設計の精度と信頼性を高めるため、より小さい抵抗値を推奨します。

$$R_1 = R_2 \times \left( \frac{V_{OUT}}{V_{FB}} - 1 \right) \quad (10)$$

$V_{FB} = 0.6V$  (標準値) の場合:

表 7-2. 出力電圧の設定

| 公称出力電圧 | R1     | R2     | 出力電圧の正確な値 |

|--------|--------|--------|-----------|

| 0.75V  | 24.9kΩ | 100kΩ  | 0.749V    |

| 1.2V   | 100kΩ  | 100kΩ  | 1.2V      |

| 1.5V   | 150kΩ  | 100kΩ  | 1.5V      |

| 1.8V   | 200kΩ  | 100kΩ  | 1.8V      |

| 2.0V   | 49.9kΩ | 21.5kΩ | 1.992V    |

| 2.5V   | 100kΩ  | 31.6kΩ | 2.498V    |

| 3.0V   | 100kΩ  | 24.9kΩ | 3.009V    |

| 3.3V   | 113kΩ  | 24.9kΩ | 3.322V    |

| 5.0V   | 182kΩ  | 24.9kΩ | 4.985V    |

### 7.2.2.3 外付け部品の選択

外付け部品は、アプリケーションのニーズだけでなく、デバイスの制御ループの安定性基準も満たしている必要があります。TPS62901 は、特定の範囲内の外部部品で動作するよう最適化されています。LC 出力フィルタのインダクタと容量とともに考慮する必要があります。これらは二重極 (ダブル ポール) を生成し、コンバータのコーナー周波数を設定します ([セクション 7.2.2.7](#) を参照)。表 7-3 を使用すると、出力フィルタ部品の選択が容易になります。表 7-3 の値は公称値です。実効的な容量は、+20% または -50% 変化するものと考えました。

表 7-3. LC 出力フィルタの推奨される組み合わせ

|       | 4.7μF | 10μF | 22μF             | 47μF | 100μF            | 200μF            |

|-------|-------|------|------------------|------|------------------|------------------|

| 1μH   |       | ✓    | ✓ <sup>(1)</sup> | ✓    | ✓                | ✓ <sup>(3)</sup> |

| 1.5μH |       | ✓    | ✓                | ✓    | ✓ <sup>(3)</sup> |                  |

**表 7-3. LC 出力フィルタの推奨される組み合わせ (続き)**

|       | 4.7μF | 10μF | 22μF             | 47μF | 100μF            | 200μF |

|-------|-------|------|------------------|------|------------------|-------|

| 2.2μH |       | ✓    | ✓ <sup>(2)</sup> | ✓    | ✓ <sup>(3)</sup> |       |

(1) この LC の組み合わせは標準値であり、2.5MHz のスイッチング周波数を使用するほとんどのアプリケーションに推奨されます。

(2) この LC の組み合わせは標準値であり、1MHz のスイッチング周波数を使用するほとんどのアプリケーションに推奨されます。

(3) 動作を安定させるため、出力容量は 10mΩ 以上の ESR を持っている必要があります。セクション 7.3.2 も参照してください。

### 7.2.2.4 インダクタの選択

TPS62901 は、 $1\mu\text{H}$  (公称値) のインダクタを使うように設計されています。インダクタ電流リップルを低減するためにより大きな値も使えますが、効率と過渡応答に悪影響を及ぼす可能性があります。 $1\mu\text{H}$  より小さい値は、低出力電流または無出力電流時の強制 PWM モードでのより大きな負のインダクタ電流の原因となる大きなインダクタ電流リップルを引き起します。したがって、入力電圧が高く出力電圧が低い場合のように、インダクタの両端の電圧が大きい場合、 $1\mu\text{H}$  より小さい値は推奨されません。強制 PWM モードでの小さい出力電流は、負の電流制限を超える可能性があるより大きな負のピークインダクタ電流の原因となります。出力電流が小さく(またはゼロであり)、かつインダクタ値が小さい場合、出力電圧はもはやレギュレートされません。その他の LC 組み合わせの詳細については、[SLVA463](#) を参照してください。

インダクタの選択は、インダクタリップル電流、出力リップル電圧、PWM から PFM への遷移点、効率など、各種の要因に影響されます。また、選択されたインダクタは、適切な飽和電流と DC 抵抗 (DCR) の定格を満たしている必要があります。[式 11](#) を使って、最大インダクタ電流を計算できます。

$$I_{L(\max)} = I_{OUT(\max)} + \frac{\Delta I_{L(\max)}}{2} \quad (11)$$

$$\Delta I_{L(\max)} = V_{OUT} \times \left( 1 - \frac{V_{OUT}}{V_{IN(\max)}} \right) \frac{L_{(\min)} \times f_{sw}}{(12)}$$

ここで、

- $I_{L(\max)}$  はインダクタ電流の最大値

- $\Delta I_{L(\max)}$  は、ピークツーピークインダクタリップル電流の最大値

- $L_{(\min)}$  は実効インダクタ値の最小値

- $f_{sw}$  は実際の PWM スイッチング周波数

- $V_{OUT}$  は出力電圧

- $V_{IN(\max)}$  は最大出力電圧の期待値

実際の動作条件を使用して最大インダクタ電流を計算すると、必要なインダクタ飽和電流の最小値が求まります。約 20% のマージンを追加することを推奨します。リップル電流が小さくするために、インダクタの値を大きくすることは有効ですが、過渡応答時間が長くなり、サイズも大きくなります。以下のインダクタは、TPS62901 と組み合わせて使用した実績があり、これらのインダクタを使うことを推奨します。

**表 7-4. インダクター一覧**

| タイプ                  | インダクタンス [ $\mu\text{H}$ ] | 電流 [A] <sup>(1)</sup> | 寸法 (LxBxH) [mm] | 製造元            |

|----------------------|---------------------------|-----------------------|-----------------|----------------|

| XGL4020-102ME        | 1.0 $\mu\text{H}$ , ±20%  | 8.8                   | 4.0x4.0x2.1     | Coilcraft      |

| DFE252012F-1R0M      | 1.0 $\mu\text{H}$ , ±20%  | 4.7                   | 2.5x2.5x1.2     | Murata (村田製作所) |

| CIGT252010TM1R0MLE   | 1.0 $\mu\text{H}$ , ±20%  | 5.3                   | 2.5x2.5x1.0     | Samsung        |

| TFM252010ALM-1R0MTAA | 1.0 $\mu\text{H}$ , ±20%  | 4.7                   | 2.5x2.0x1.0     | TDK            |

| XEL5030-222ME        | 2.2 $\mu\text{H}$ , ±20%  | 9.7                   | 5.3x5.5x3.1     | Coilcraft      |

| XGL4020-222ME        | 2.2 $\mu\text{H}$ , ±20%  | 6.2                   | 4.0x4.0x2.1     | Coilcraft      |

(1) 30% 低下時の  $I_{SAT}$

インダクタの値は、パワーセーブ モードに移行する負荷電流も決定します。

$$I_{load(PSM)} = \frac{1}{2} \Delta I_L \quad (13)$$

### 7.2.2.5 コンデンサの選択

#### 7.2.2.5.1 出力コンデンサ

出力コンデンサの推奨値は  $22\mu F$  です。TPS62901 は、等価直列抵抗 (ESR) の小さいセラミックコンデンサを出力コンデンサとして使用できるアキテクチャを採用しています。出力電圧リップルを低減するため、これらのコンデンサを使うことを推奨します。高い周波数まで低抵抗が維持され、温度による静電容量の変動が小さい X7R または X5R 誘電体を使うことを推奨します。大きな値を使うと、電圧リップルが小さくなり、パワーセーブ モードでの DC 出力精度が向上するなどの利点があります ([SLVA463](#) を参照)。

パワーセーブ モードでは、出力電圧リップルは出力容量、出力コンデンサの ESR、ESL、ピークインダクタ電流に依存します。セラミックコンデンサを使うと、小さな ESR、ESL、および低リップルが得られます。出力コンデンサは、本デバイスのできるだけ近くに配置する必要があります。

セラミックコンデンサは DC バイアス効果が大きいため、出力電圧が大きい場合、実効的な容量を確認する必要があります。

#### 7.2.2.5.2 入力コンデンサ

より大きい値を使うと入力電流リップルがさらに低減されるとはいっても、ほとんどのアプリケーションで  $10\mu F$  (公称値) は十分な大きさであり、この値が推奨されます。入力コンデンサは、入力電圧の過渡イベントを和らげ、また、コンバータが電源の影響を受けないようにします。最良のフィルタ処理を行うため、低 ESR の積層セラミックコンデンサ (MLCC) を推奨します。また、このコンデンサは、VIN と GND との間に、これらのピンにできるだけ近づけて配置する必要があります。

表 7-5. コンデンサのリスト

| タイプ (1)             | 静電容量 (公称値) [ $\mu F$ ] | 定格電圧 [V] | サイズ  | 製造元 |

|---------------------|------------------------|----------|------|-----|

| C3216X7R1E106K160AB | 10                     | 25       | 0805 | TDK |

| C2012X7S1A226M125AC | 22                     | 10       | 0805 | TDK |

(1)  $I_{RMS}$  (40°C 上昇時) と  $I_{SAT}$  (30% 低下時) の小さい方。

#### 7.2.2.5.3 ソフトスタートコンデンサ

SS/TR ピンと GND との間にコンデンサを接続すると、出力電圧の起動時の傾きを設定できます。

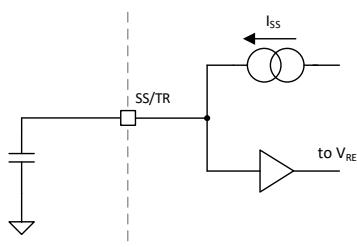

図 7-2. ソフトスタート動作の概略回路図

外部容量を充電するために定電流源が内蔵されています。ソフトスタートのランプ時間の標準値は次の式で与えられます。

$$T_{SS} = \frac{C_{SS}}{I_{SS}} \times V_{REF} + 55 \quad (14)$$

ここで、

- $C_{SS}$  は、SS/TR ピンに接続する必要がある容量 (単位は pF)

- $T_{SS}$  はソフトスタートランプ時間の目標値 (単位は  $\mu s$ )

- $I_{SS}$  は SS/TR のソース電流 (単位は  $\mu A$ 、「電気的特性」を参照)

- $V_{REF}$  はフィードバックレギュレーション電圧 ( $V_{FB}/0.75$ 、単位は V、「電気的特性」を参照)

外部  $C_{ss}$  容量が 680pF 未満である場合またはピンがオープンである場合でも、実現可能な最も速いランプ時間は 150μs (標準値) です。突入電流を低減するためにソフトスタート時間を 1ms 未満にすることは通常推奨されません。

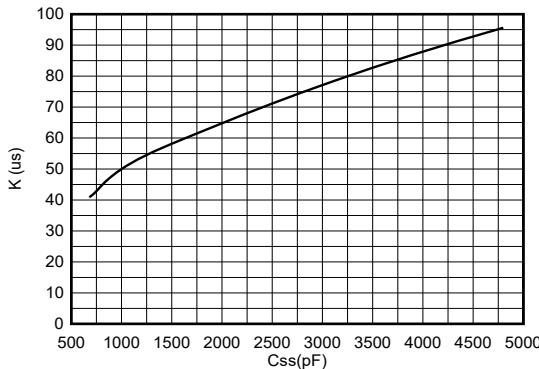

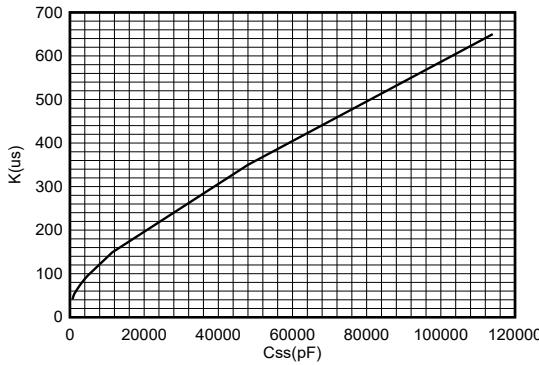

ソフトスタート時間には変動があります。より正確な構成を実現するには、以下の最大値と最小値の式を考慮する必要があります。

$$T_{SS\_max} = \frac{C_{SS\_max}}{I_{SS\_min}} \times V_{REF\_max} + 160 \quad (15)$$

$$T_{SS\_min} = \frac{C_{SS\_min}}{I_{SS\_max}} \times V_{REF\_min} - K \quad (16)$$

K は  $C_{ss}$  の値と相関関係にあり、単位は μs です。この相関曲線を [図 7-3](#) と [図 7-4](#) に示します。

図 7-3. K と  $C_{ss}$  との相関曲線 (680pF~4800pF)

図 7-4. K と  $C_{ss}$  との相関曲線 (4800pF~114000pF)

### 7.2.2.6 トラッキング機能

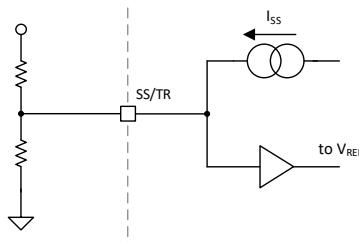

トラッキング機能が必要な場合、SS/TR ピンを外部のトラッキング電圧に接続することで、この目的に使用できます。出力電圧は、「電気的特性」に規定されたゲインとオフセット (標準値) で、その電圧に追従します。

図 7-5. トラッキング動作の概略回路図

$$V_{FB} = 0.75 \times V_{SS/TR} \quad (17)$$

SS/TR ピンの電圧が 0.8V を上回ると、内部電圧がクランプされ、本デバイスは通常のレギュレーションに移行します。これは、入力電圧が推奨動作条件の範囲内にある限り、立ち上がりトラッキング電圧と立ち下がりトラッキング電圧に対して同じように作用します。PFM モードで SS/TR ピンの電圧を下げた場合、本デバイスは出力から電流をシンクしなくなります。このため、負荷が軽い場合、結果として生じる出力電圧の低下は SS/TR ピンの電圧の低下よりも遅くなる可能性があります。外部電圧で SS/TR ピンを駆動する場合は、SS/TR ピンの定格電圧である 6V を超えないようにしてください。SS/TR ピンは、EN = 0 のとき、GND に抵抗を介して内部的に接続されます。

入力電圧が低電圧誤動作防止スレッショルド電圧を下回ると、トラッキング電圧にかかわらず、出力電圧はゼロになります。図 7-6 に、トラッキング機能を使うことでレシオメトリックおよび同時シーケンシングを行うように本デバイスを接続する方法を示します。システム例のセクション 7.3.3 を参照してください。

図 7-6. レシオメトリックおよび同時起動の回路図

R7 と R8 の抵抗分圧器を使用して、VOUT2 のランプ レートを、VOUT1 より高速、VOUT1 より低速、VOUT1 と同じに変更できます。

デバイス 1 の VOUT の PG ピンをデバイス 2 の EN ピンに接続することで、順次起動されます。PG にはプルアップ抵抗が必要です。レシオメトリック起動シーケンスは、両方の電源が同じソフトスタートコンデンサを共有している場合に行われます。[式 14](#) に、ソフトスタート時間と示します。ただし、SS/TR 電流を 2 倍にする必要があります。これらとその他のトラッキングおよびシーケンシング回路の詳細については、[SLVA470](#) を参照してください。

#### 注

FB ピンの電圧がその標準値である 0.6V よりも小さい場合、出力電圧精度は仕様よりも広い許容誤差を持つ可能性があります。SS/TR ピンから流れ出る 2.5μA の電流も、特に、SS/TR ピンに高抵抗の外部分圧器を接続した場合、トラッキング機能に影響を及ぼします。

#### 7.2.2.7 出力フィルタとループ安定性

TPS62901 ファミリのデバイスは、[式 18](#) で計算されるコーナー周波数に対応する L-C フィルタの組み合わせにより安定化するように内部的に補償されます。

$$f_{LC} = \frac{1}{2\pi\sqrt{L \cdot C}} \quad (18)$$

インダクタンスとセラミック コンデンサの実績のある公称値を[セクション 7.2.2.3](#) に示します。これらの値を使うことを推奨します。別の値を使っても動作しますが、影響を受けるループの安定性に注意する必要があります。詳細な LC 安定性マトリクスを含む詳細については、[SLVA463](#) を参照してください。

TPS62901 デバイスには、VOS ピンと FB ピンとの間に接続された 3pF のフィードフォワード コンデンサが内蔵されています。このコンデンサは周波数動作に影響を及ぼし、フィードバック分圧器の抵抗と相まって、[式 19](#) と[式 20](#) に従って、制御ループに極とゼロを形成します。

$$f_{zero} = \frac{1}{2\pi \times R_1 \times 3pF} \quad (19)$$

$$f_{pole} = \frac{1}{2\pi \times 3pF} \times \left( \frac{1}{R_1} \times \frac{1}{R_2} \right) \quad (20)$$

TPS62901 デバイスは、極とゼロが特定の位置に存在しなくても安定しますが、アプリケーションの特定の要求に合わせてそれらの位置を調整すると、パワーセーブ モード時の性能の向上、過渡応答の改善、またはそれらの両方を実現できます。外付けのフィードフォワード コンデンサを追加することもできます。安定性と過渡応答との関係の最適化の詳細については、[SLVA289](#) と [SLVA466](#) を参照してください。

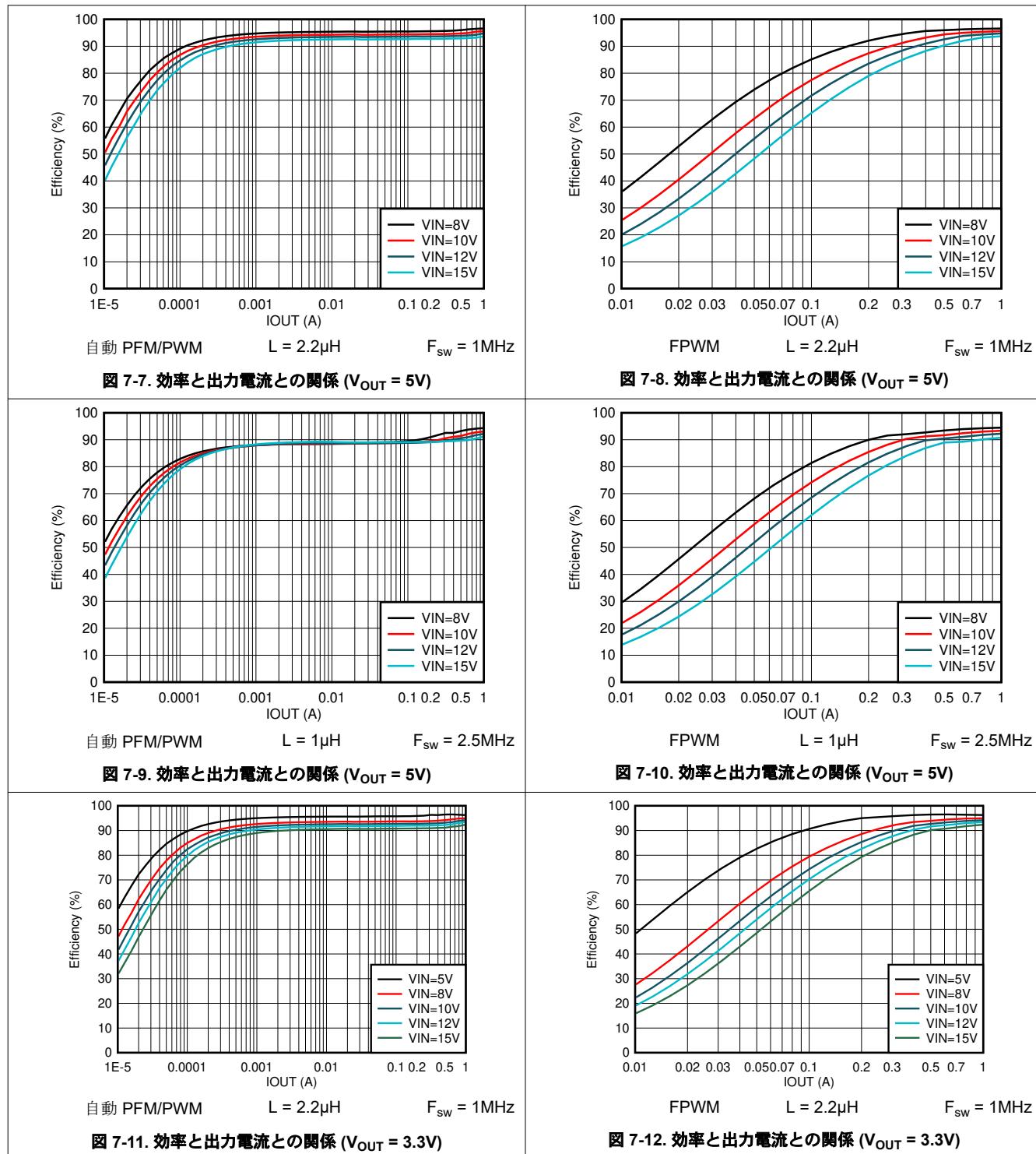

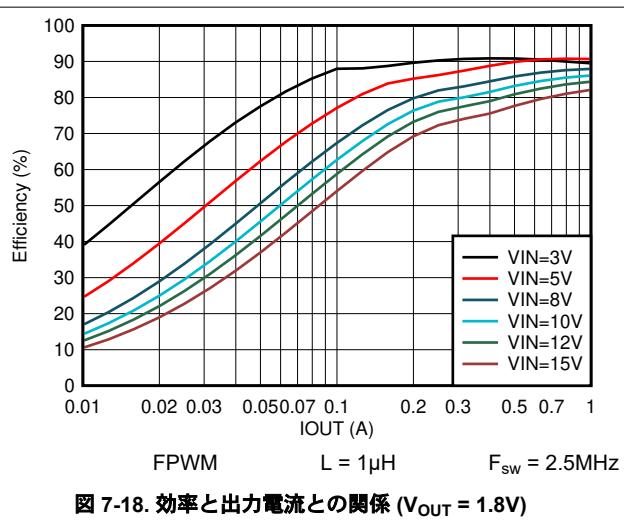

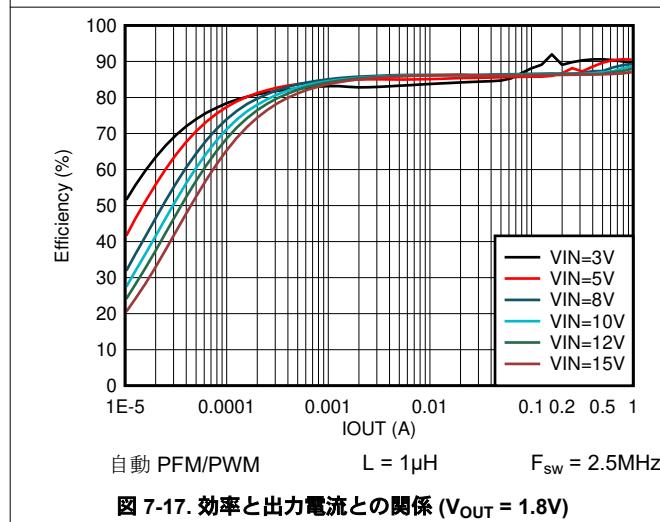

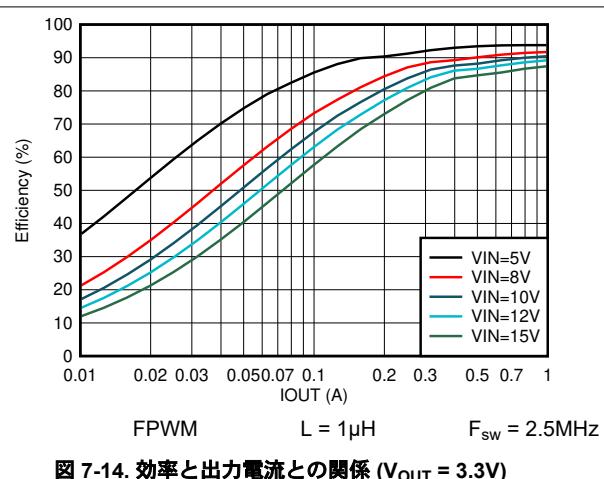

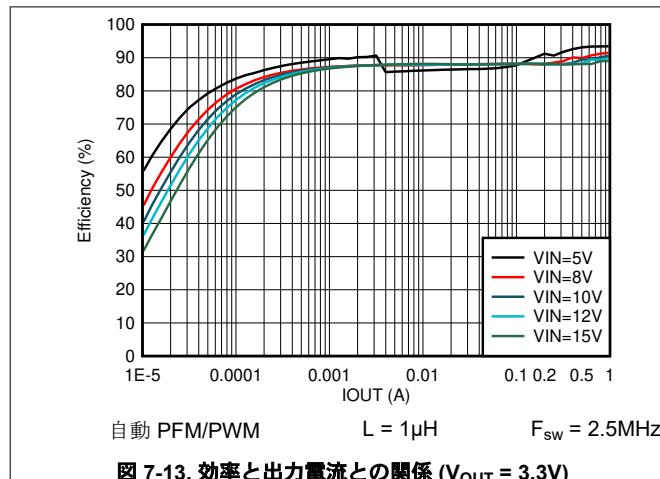

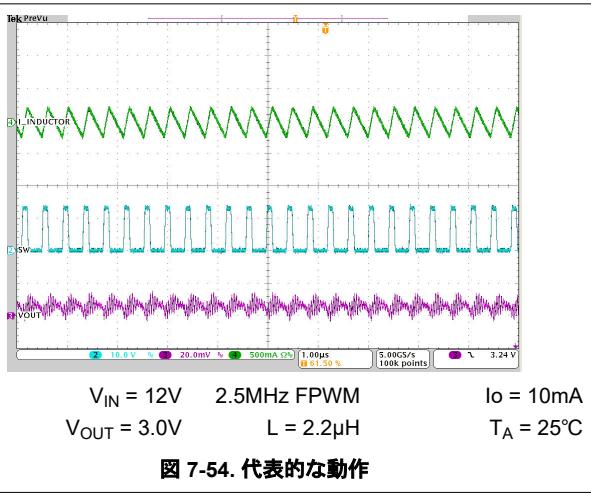

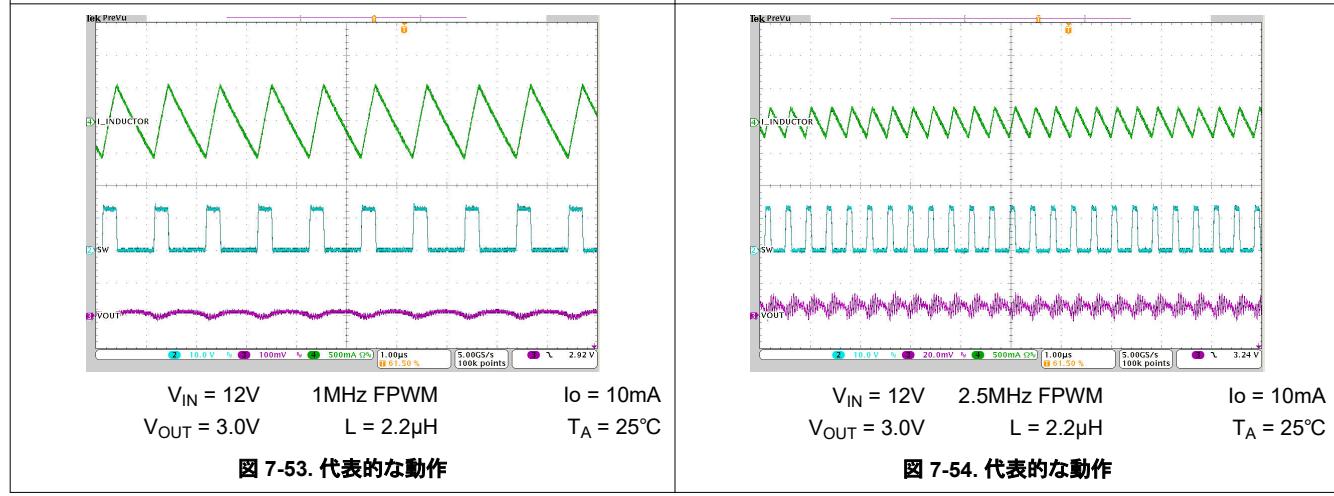

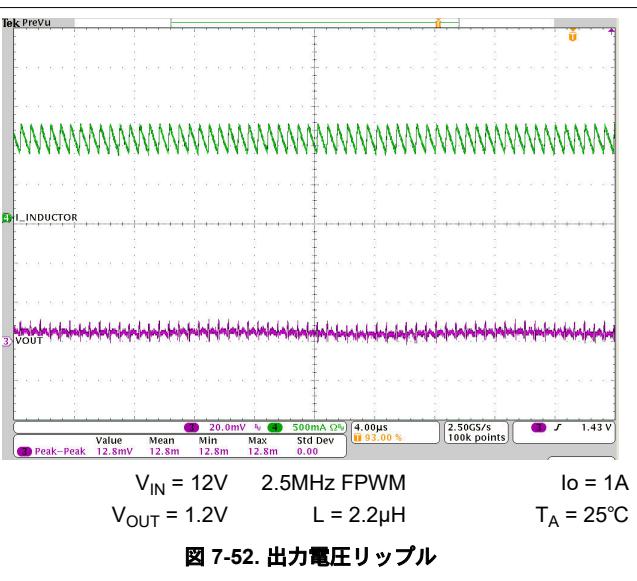

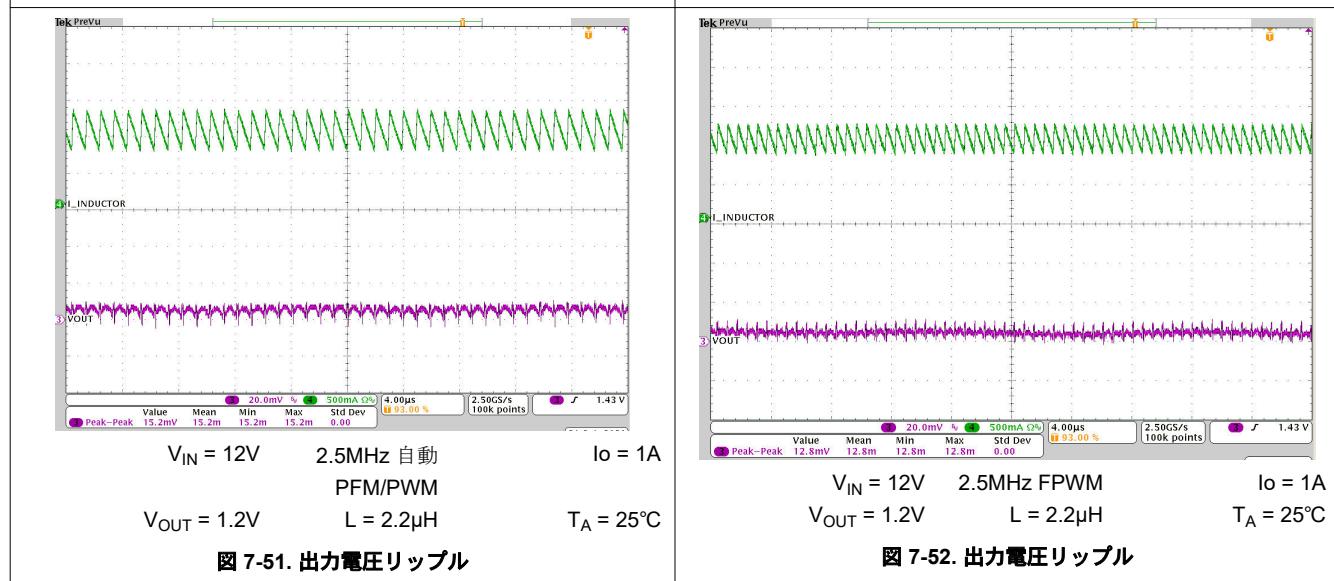

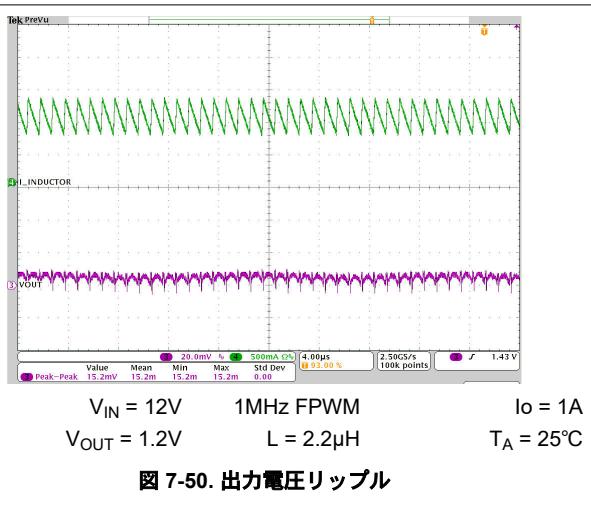

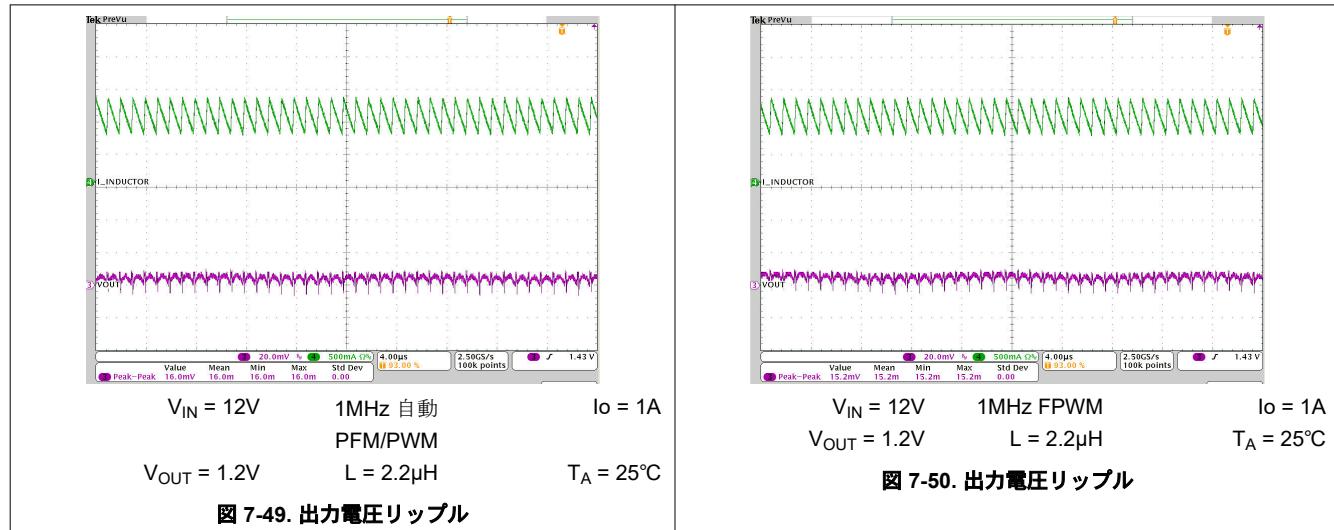

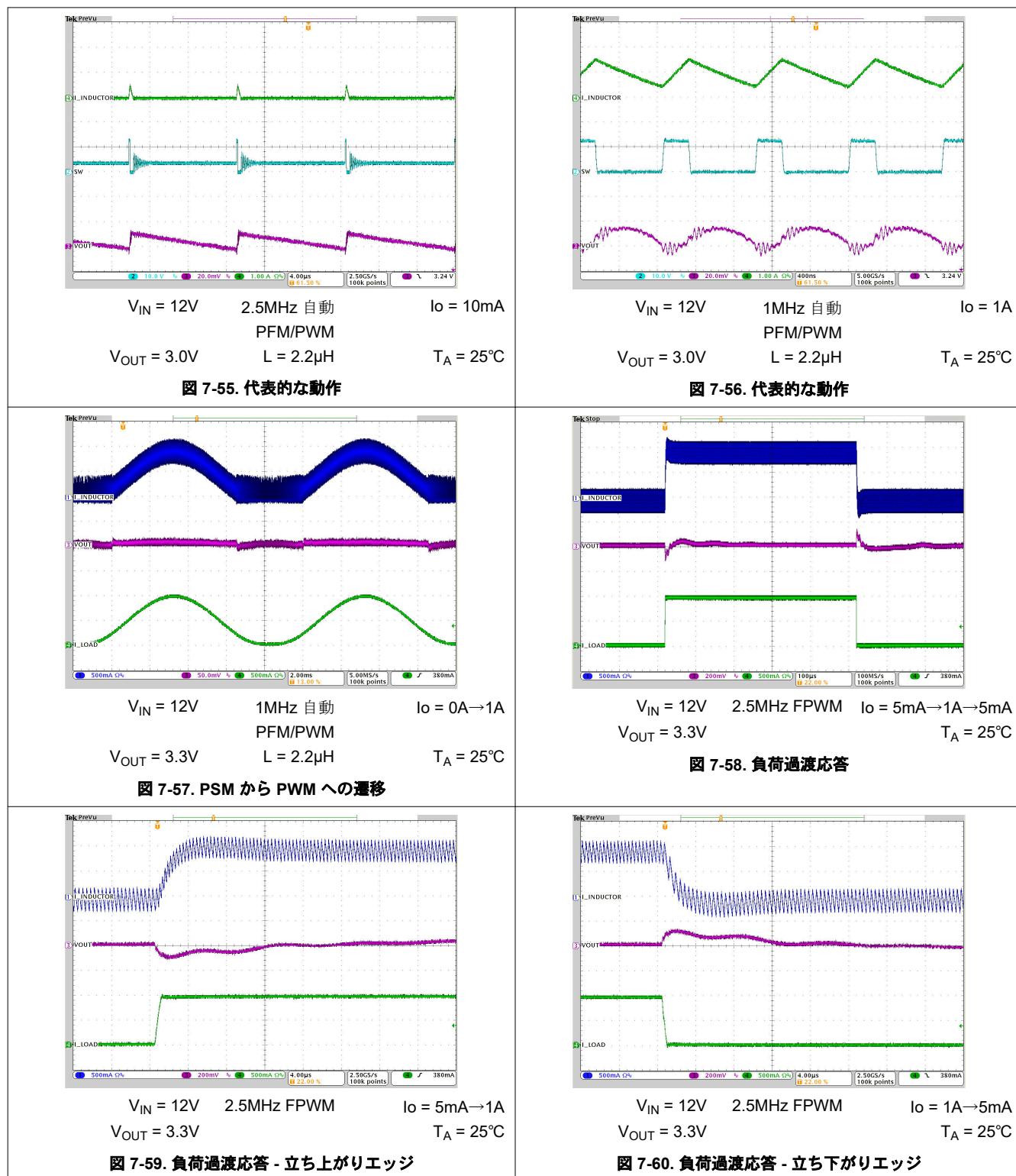

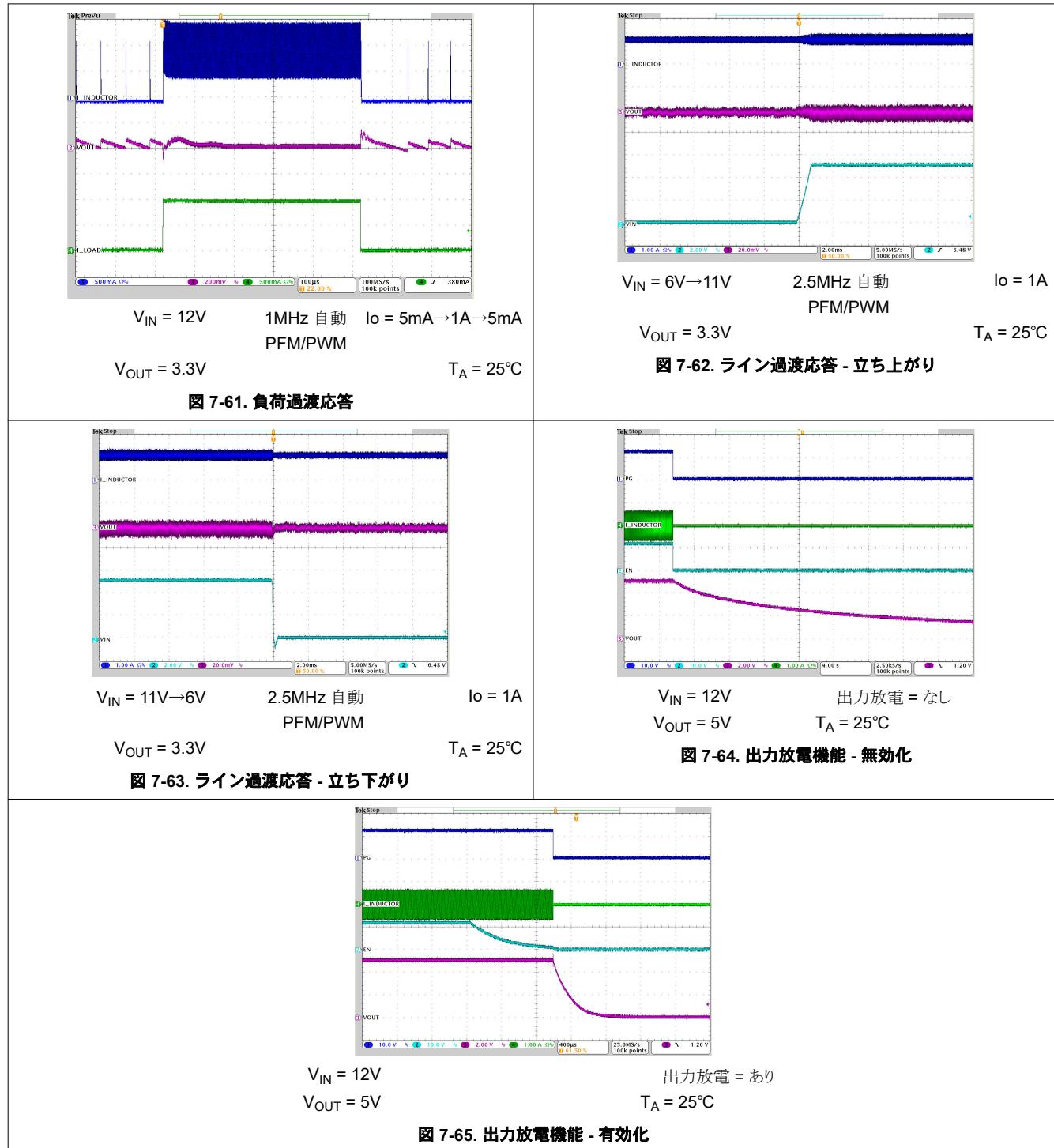

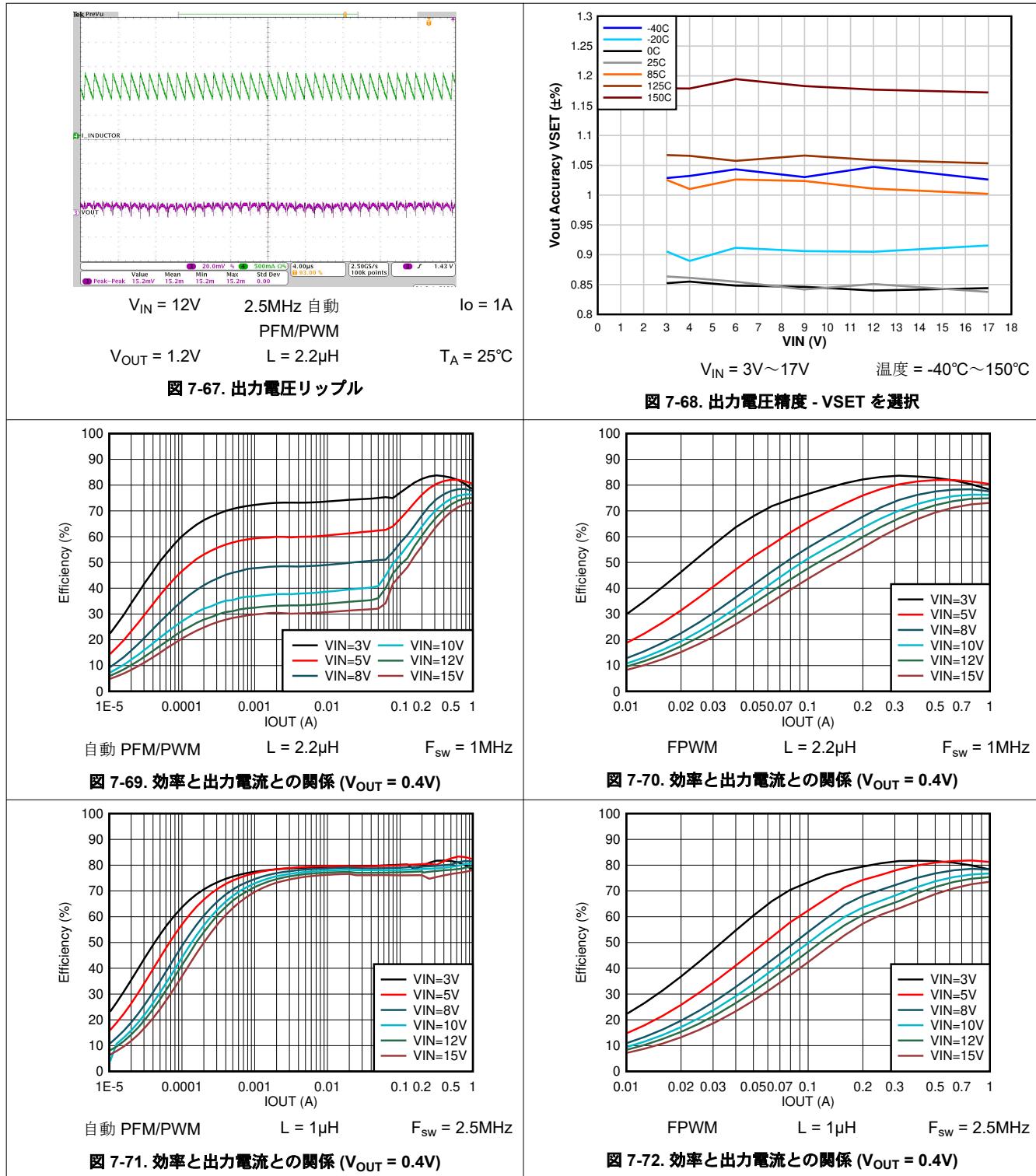

### 7.2.3 アプリケーション曲線

### 7.2.3 アプリケーション曲線(続き)

### 7.2.3 アプリケーション曲線 (続き)

### 7.2.3 アプリケーション曲線 (続き)

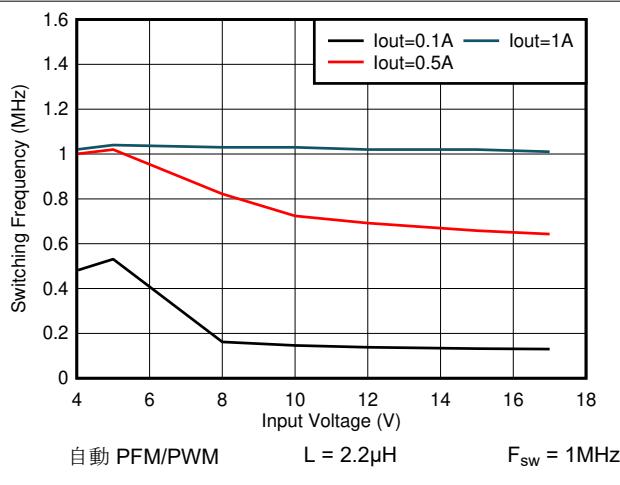

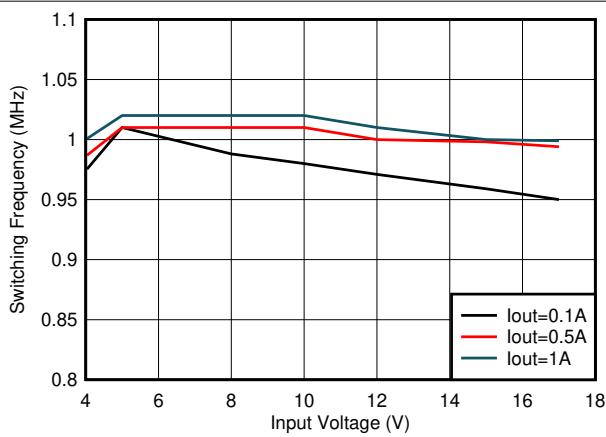

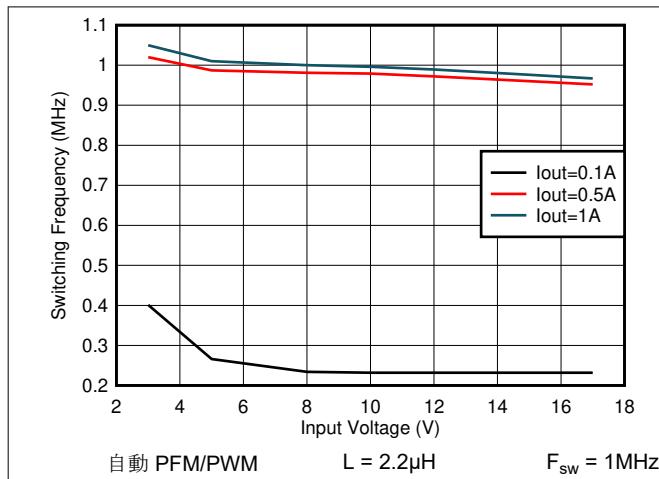

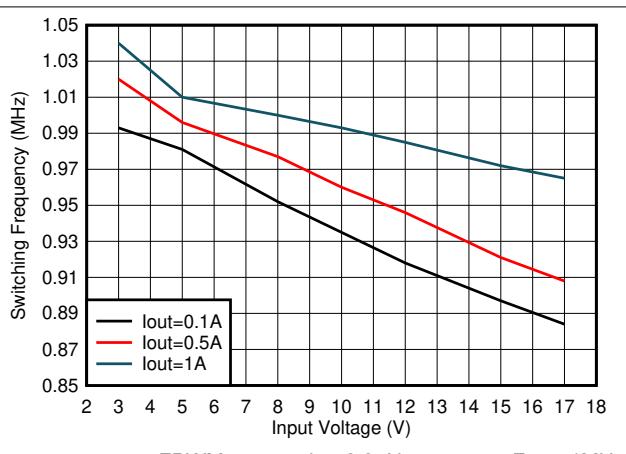

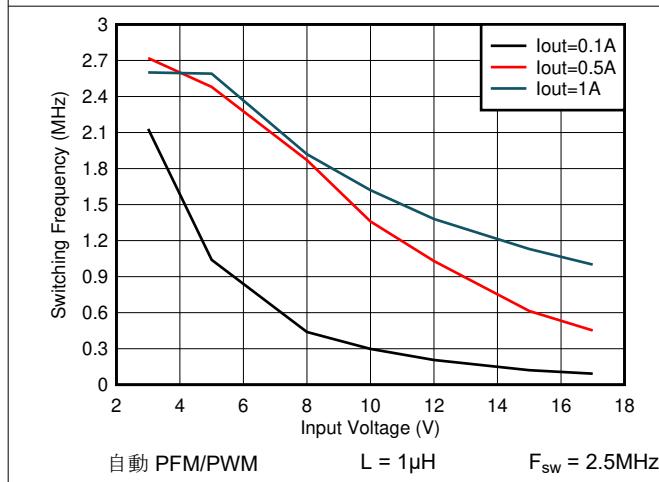

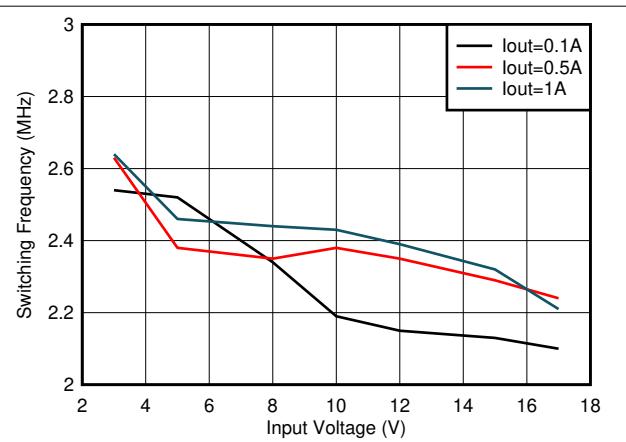

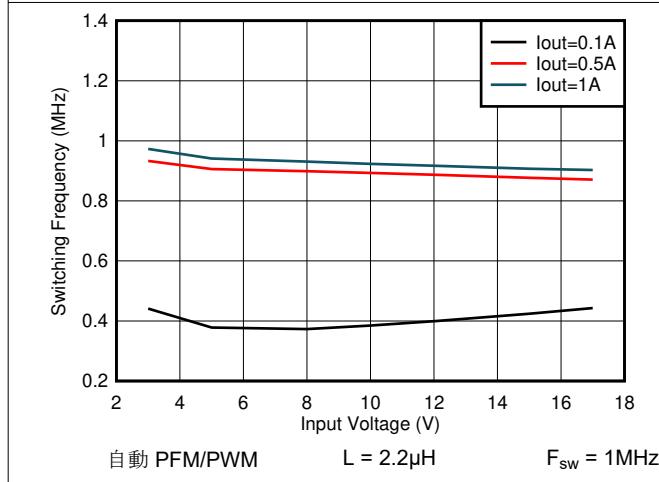

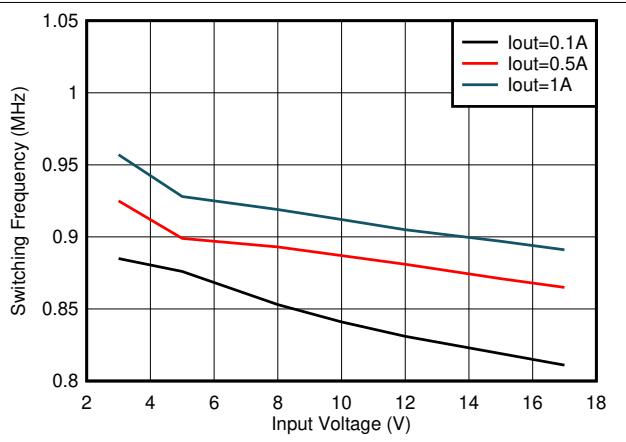

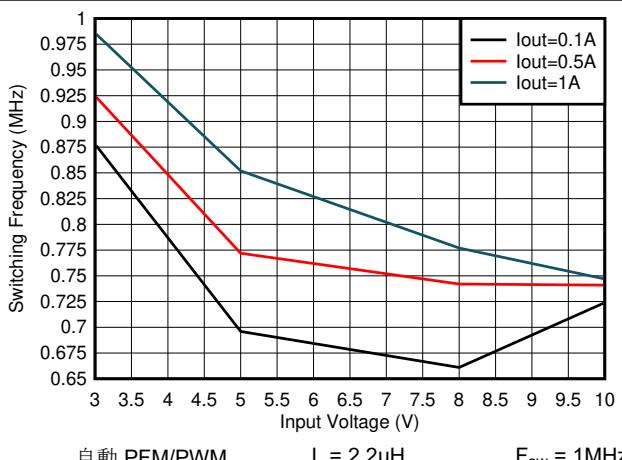

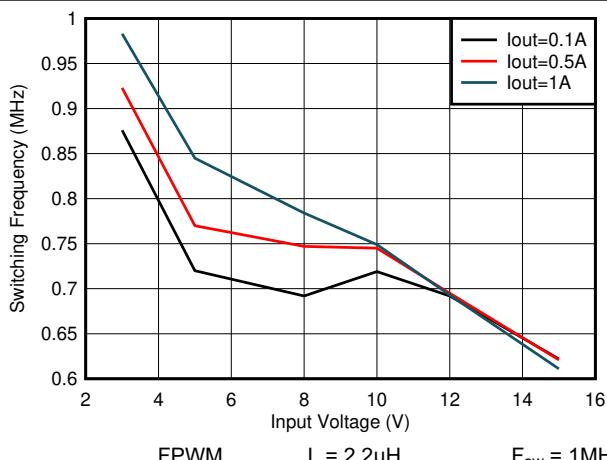

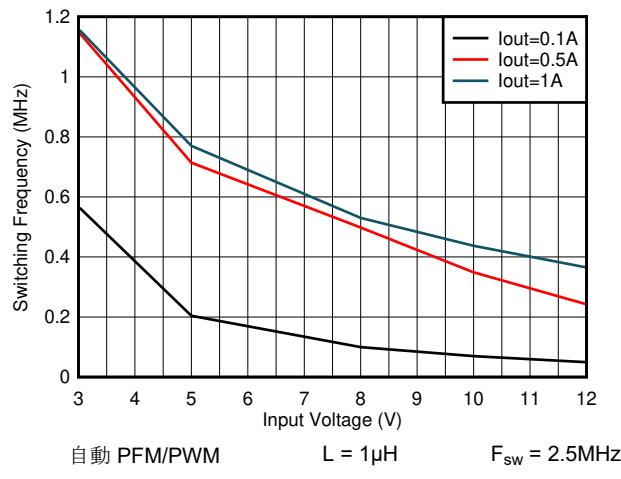

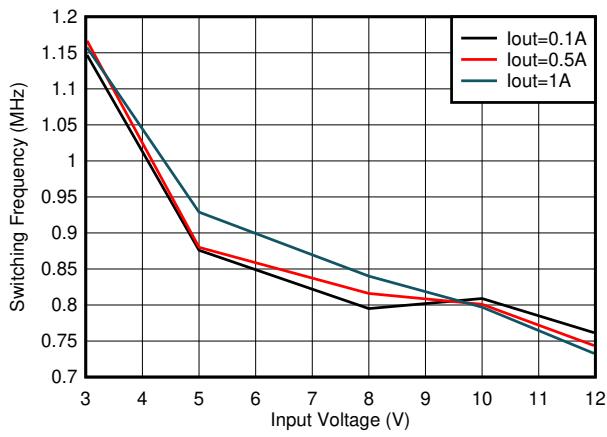

図 7-25. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 5\text{V}$ )図 7-26. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 5\text{V}$ )図 7-27. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 3.3\text{V}$ )図 7-28. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 3.3\text{V}$ )図 7-29. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 3.3\text{V}$ )図 7-30. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 3.3\text{V}$ )

### 7.2.3 アプリケーション曲線 (続き)

図 7-31. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.8\text{V}$ )

図 7-32. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.8\text{V}$ )

図 7-33. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.8\text{V}$ )

図 7-34. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.8\text{V}$ )

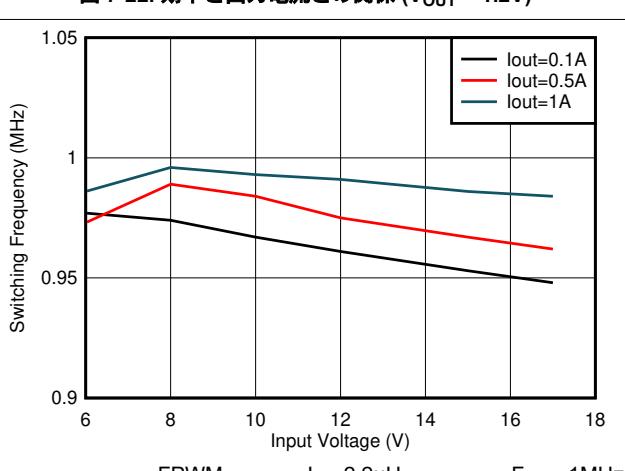

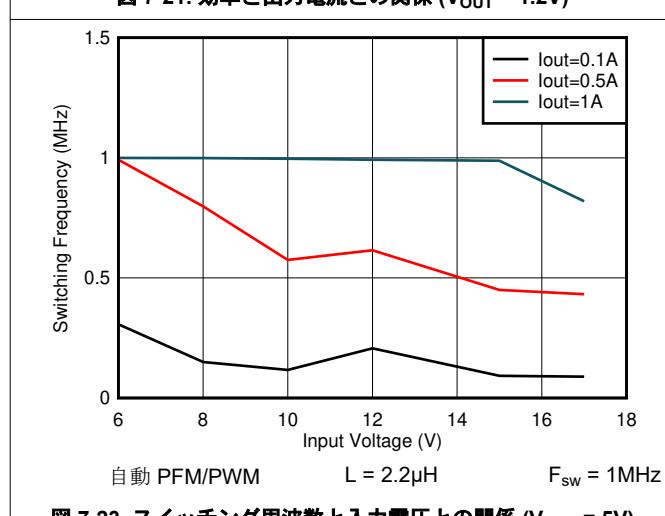

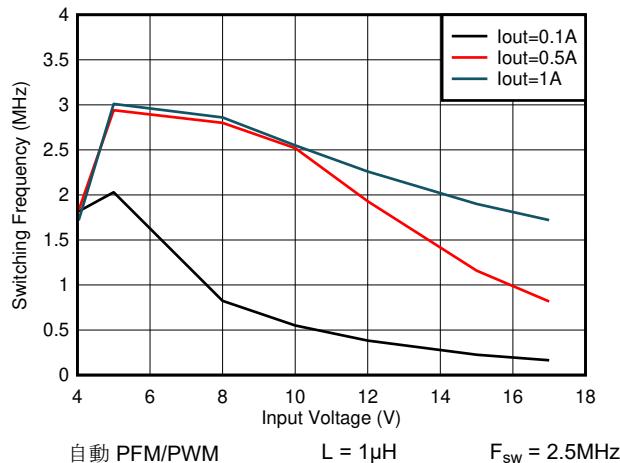

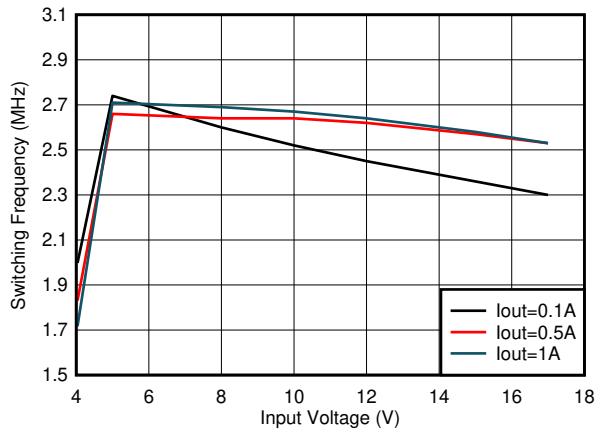

図 7-35. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.2\text{V}$ )

図 7-36. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.2\text{V}$ )

### 7.2.3 アプリケーション曲線 (続き)

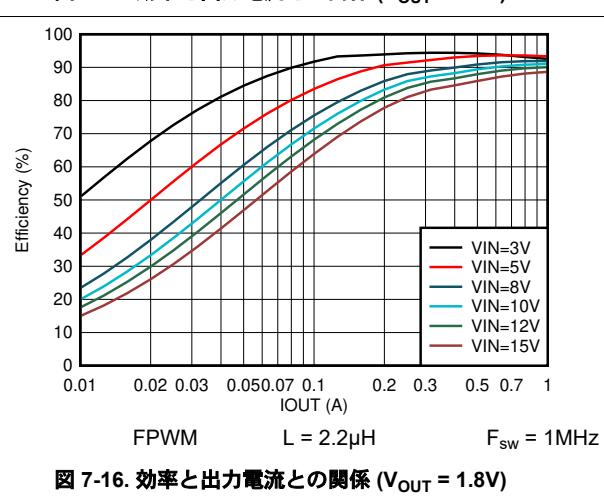

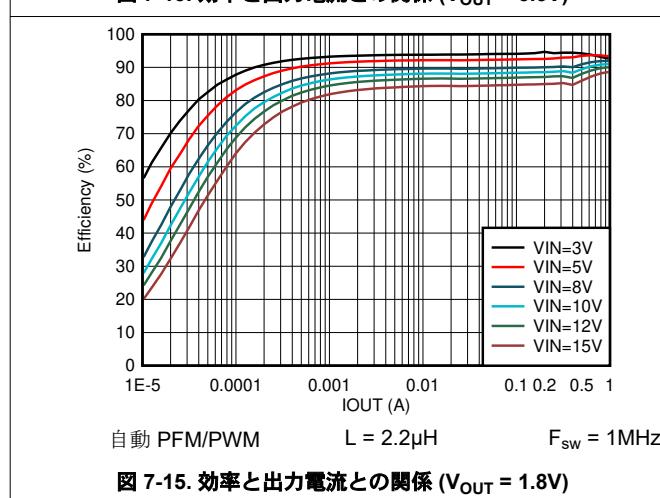

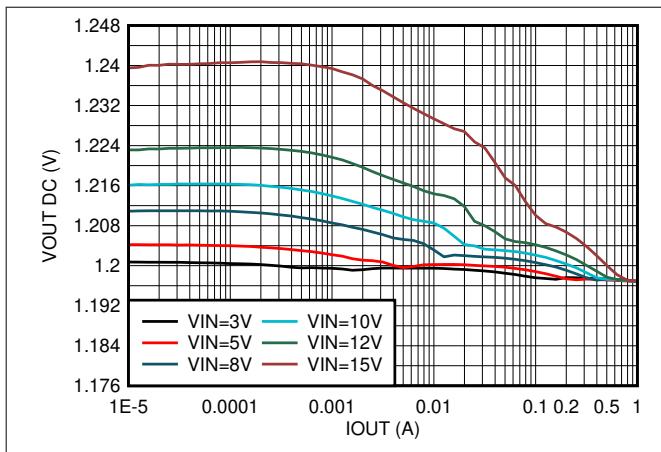

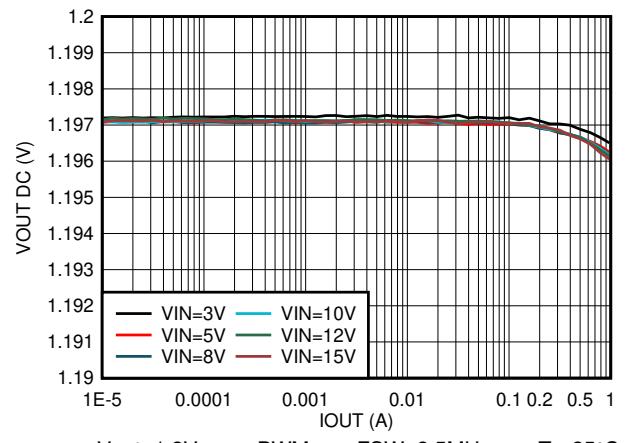

図 7-37. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.2\text{V}$ )図 7-38. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 1.2\text{V}$ )図 7-39. 出力電圧と出力電流との関係 ( $V_{OUT} = 3.3\text{V}$ )図 7-40. 効率と出力電流との関係 ( $V_{OUT} = 1.8\text{V}$ )

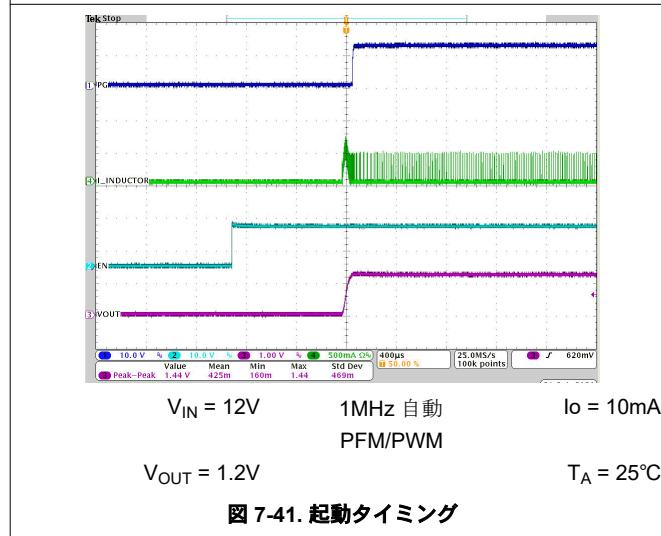

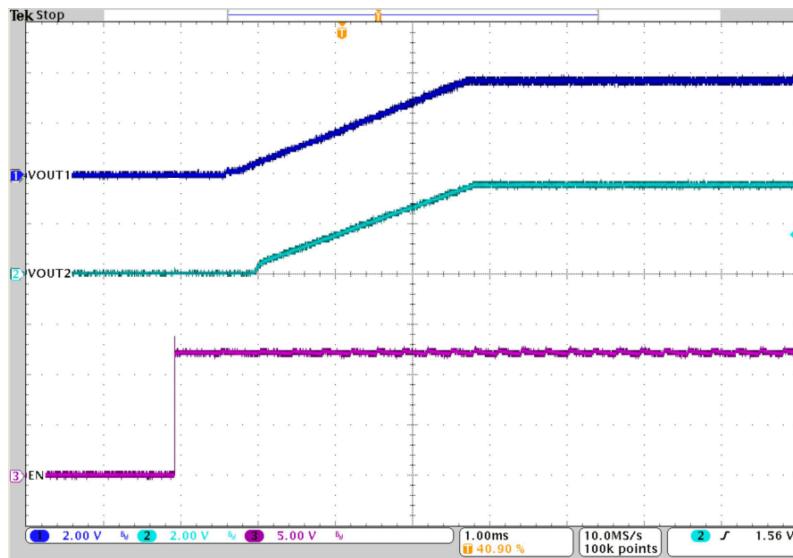

図 7-41. 起動タイミング

図 7-42. 起動タイミング

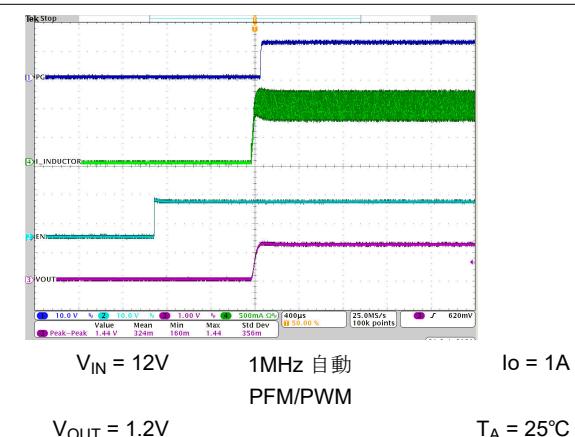

### 7.2.3 アプリケーション曲線(続き)

### 7.2.3 アプリケーション曲線(続き)

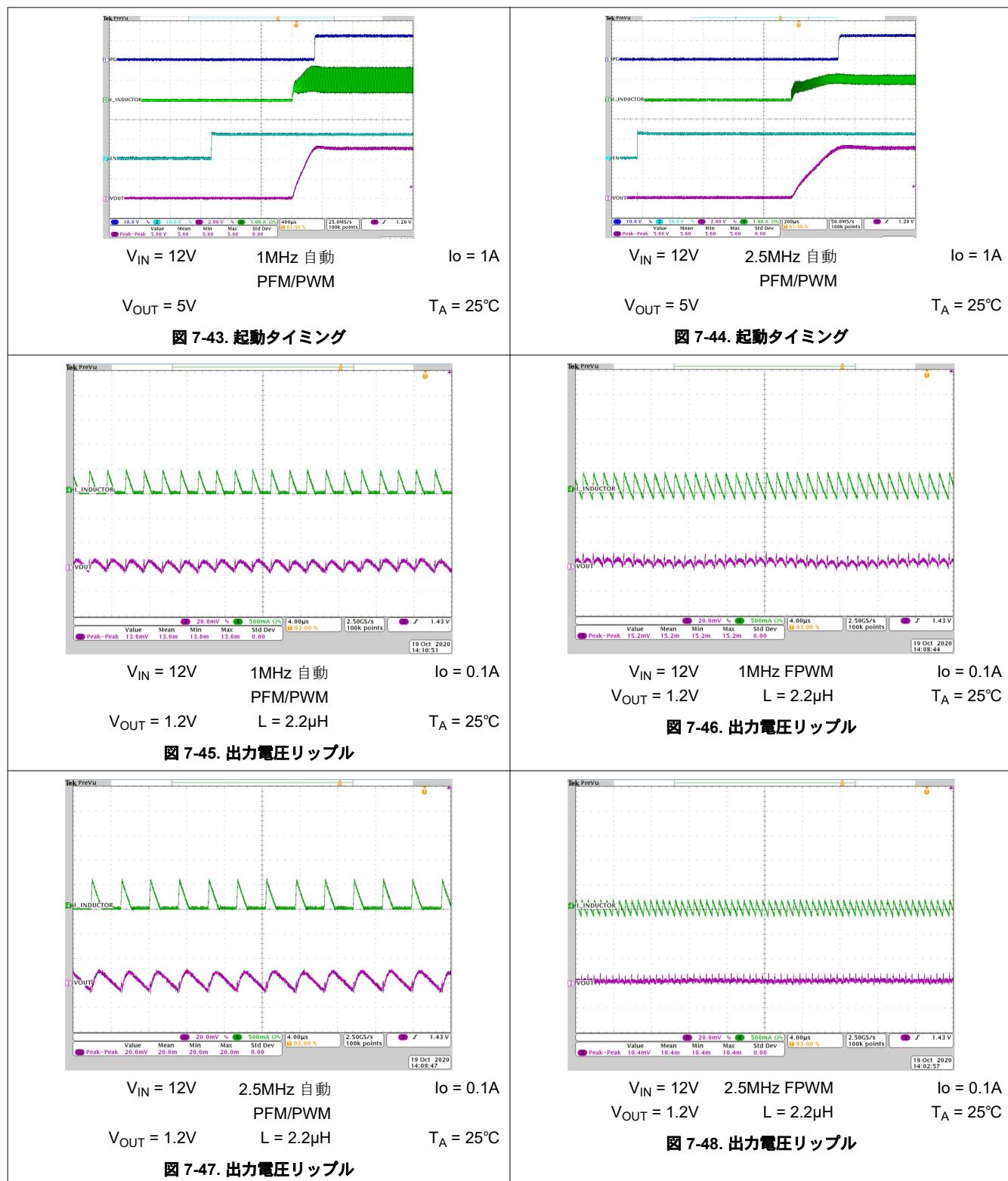

### 7.2.3 アプリケーション曲線(続き)

### 7.2.3 アプリケーション曲線(続き)

### 7.2.4 VSET を使った設定可能な $V_O$ の代表的なアプリケーション

図 7-66. 代表的なアプリケーション回路 (VSET)

#### 7.2.4.1 設計要件

VSET を使うと、FB/VSET ピンとグランドとの間に接続した 1 つの抵抗のみを使って出力電圧を設定できます。表 6-2 に、16 通りの使用可能な選択肢を示します。

#### 7.2.4.2 詳細な設計手順

VSET オプションは、MODE/S-CONF ピンを使用して選択する必要があります。本デバイスが VSET 動作を行うように構成されると、内部抵抗分圧器によって、VOS ピンを通してのみ  $V_O$  が検出されるようになります。 $V_O$  の目標値は、FB/VSET と GND との間に接続された外付け抵抗 R2 によって設定されます。

### 7.2.4.3 アプリケーション曲線

### 7.2.4.3 アプリケーション曲線(続き)

図 7-73. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 0.4\text{V}$ )

図 7-74. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 0.4\text{V}$ )

図 7-75. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 0.4\text{V}$ )

図 7-76. スイッチング周波数と入力電圧との関係 ( $V_{OUT} = 0.4\text{V}$ )

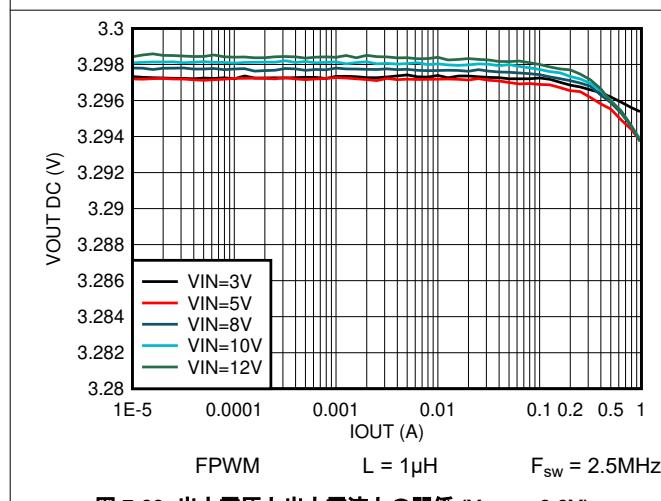

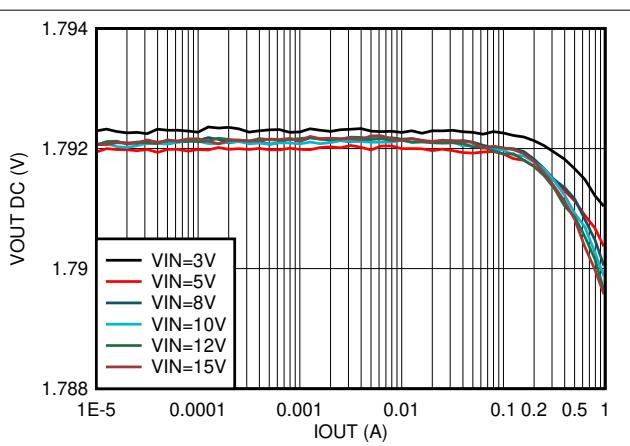

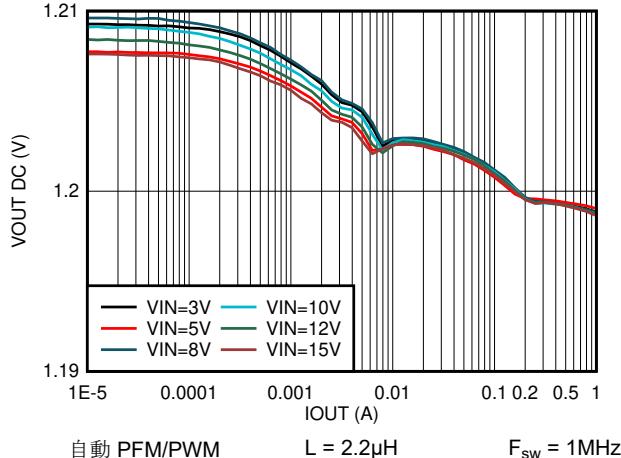

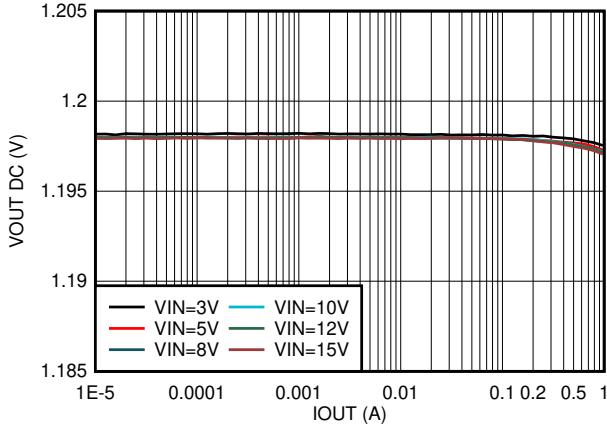

図 7-77. 出力電圧と出力電流との関係 ( $V_{OUT} = 1.2\text{V}$ )

図 7-78. 出力電圧と出力電流との関係 ( $V_{OUT} = 1.2\text{V}$ )

### 7.2.4.3 アプリケーション曲線(続き)

図 7-79. 出力電圧と出力電流との関係 ( $V_{OUT} = 1.2\text{V}$ )図 7-80. 出力電圧と出力電流との関係 ( $V_{OUT} = 1.2\text{V}$ )

## 7.3 システム例

### 7.3.1 LED の電源

TPS62901 はパワー LED 用電源として使用できます。SS/TR ピンを使用することで、公称値よりも低い電圧に FB ピンを簡単に設定できます。これにより、検出抵抗での電圧降下が小さくなり、過剰な電力損失が防止されます。このピンは  $2.5\mu\text{A}$  を供給するため、式 21 に従って、フィードバックピンの電圧を外付け抵抗で調整できます。LED の電流に比例するこの電圧降下は、LED を駆動するのに適したレベルに出力電圧 (アノード電圧) をレギュレートするために使われます。TPS62901 は、アナログ調光と PWM 調光の両方をサポートしています。図 7-81 に、アナログ調光を使ってテストされたアプリケーション回路を示します。

図 7-81. 1 つのパワー LED の電源

SS/TR の抵抗により、FB 電圧が決まります。式 21 を使って、 $R_{SS/TR} = R4 = 162\text{k}\Omega$  によって FB 電圧は  $304\text{mV}$  に設定されます。これにより、良好な精度を維持したまま、R4 の損失を、公称値 ( $0.6\text{V}$ ) のフィードバック電圧を使った場合の半分に低減しています。

$$V_{FB} = 0.75 \times 2.5\mu A \times R_{SS/TR} \quad (21)$$

これで本デバイスは、抵抗  $R_2$  で設定された定電流を  $FB/VSET$  から GND に供給するようになりました。最小入力電圧定格は、使用する LED が必要とする順方向電圧に応じて設定する必要があります。詳細については、[SLVA451](#) を参照してください。

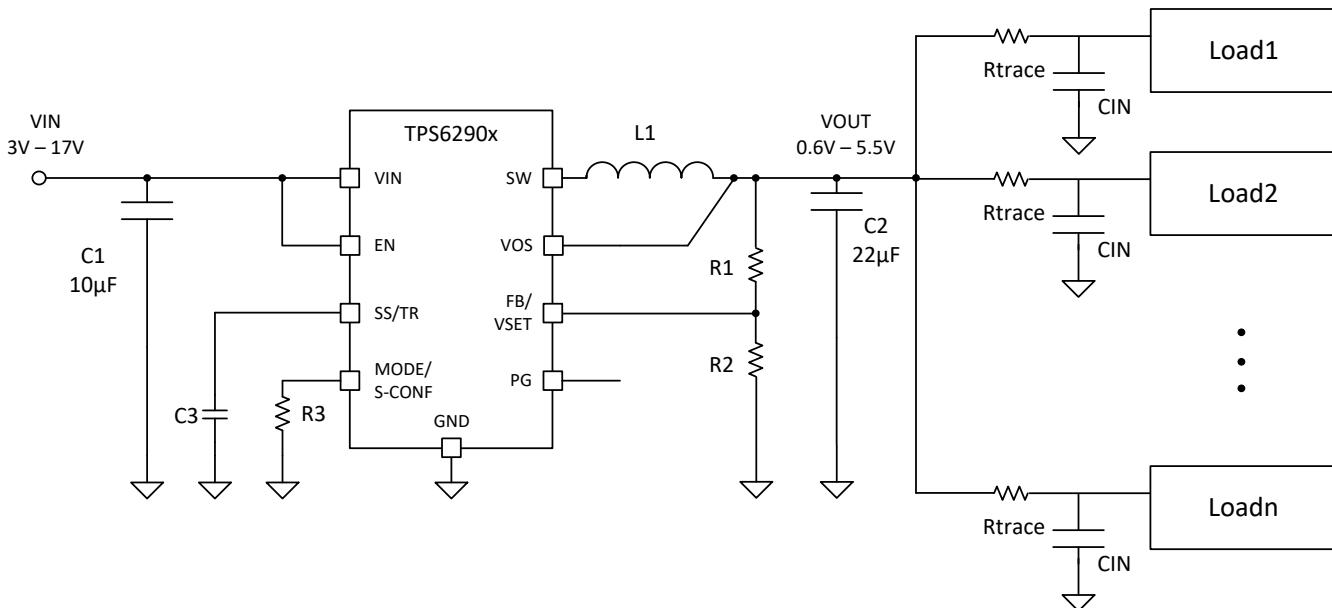

### 7.3.2 複数の負荷への電力供給

TPS62901 を使って複数の負荷回路に電力を供給するアプリケーションでは、出力の総容量が非常に大きくなる場合があります。出力電圧を適切にレギュレートするには、**VOS** ピンに適切な AC 信号レベルが存在している必要があります。タンタルコンデンサは、**VOS** ピンの出力電圧リップルを十分な大きさに維持するのに十分な大きさの ESR を持っています。低 ESR のセラミックコンデンサを使用すると、出力電圧リップルが小さくなりすぎる可能性があるため、本デバイスの出力に直接大きな容量を接続することは推奨しません。複数の負荷回路とそれに関連する入力コンデンサが PCB 上に存在する場合、これらの負荷は通常、基板全体にわたって分布しています。これにより、適切なレギュレーションに必要な、**VOS** ピン上で十分な大きさの AC 信号が維持されるのに十分な大きさのトレース抵抗 ( $R_{trace}$ ) がもたらされます。

分布した負荷の総トレース抵抗は少なくとも  $10m\Omega$  です。以下の使用事例での総容量 ( $n \times C_{in}$ ) は  $32 \times 47\mu F$  のセラミック X7R コンデンサでした。

図 7-82. 複数負荷

### 7.3.3 電圧トラッキング

デバイス 2 は、**SS/TR** ピンに印加される電圧に追従します。**SS/TR** が  $0.8V$  に上昇すると、 $V_{FB}$  の  $0.6V$  基準電圧に従い、出力電圧が上昇します。

デバイス 1 の  $3.8V$  をトラッキングするには、デバイス 1 の分圧器の出力が  $0.6V$  のときに、デバイス 2 の **SS/TR** の抵抗分圧器で  $0.8V$  を出力する必要があります。**SS/TR** ピンからの  $2.5\mu A$  の出力電流には、 $R_7$  と  $R_8$  で形成される抵抗分圧器のオフセット電圧が伴います。したがって、 $R_7 // R_8$  の等価抵抗は  $15k\Omega$  未満に維持する必要があります。

図 7-83. トラッキングの例

図 7-84. トラッキング

## 7.4 電源に関する推奨事項

TPS62901 の電源は、TPS62901 の電源電圧、出力電圧、出力電流に応じた定格電流を必要とします。

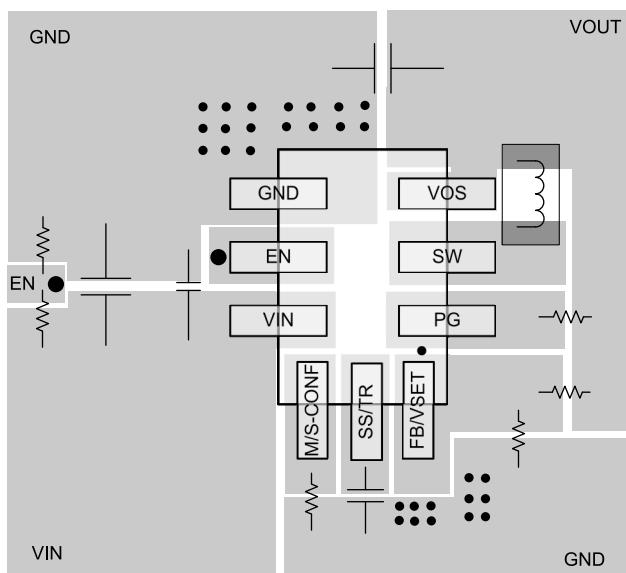

## 7.5 レイアウト

### 7.5.1 レイアウトのガイドライン

さらに高いスイッチング周波数でスイッチモード電源を動作させるには、適切なレイアウトが非常に重要です。したがって、確実に動作させ、仕様に規定された性能を達成するため、TPS62901 の PCB レイアウトでは細心の注意が必要です。レイアウトが不適切な場合、レギュレーション性能の低下（ラインと負荷の両方）、安定性と精度の低下、EMI 放射の増加、ノイズの増加などの問題につながる可能性があります。

一般的な外部グランド接続を行うように設計された TPS62901 の推奨レイアウトについては、図 7-85 を参照してください。入力コンデンサは、VIN ピンと GND ピンとの間に、TPS62901 にできるだけ近づけて配置する必要があります。また、VOS ピンは、出力コンデンサの VOUT に最も短い経路で接続します。

$di/dt$  の大きいループの経路は、インダクタンスと抵抗が小さくなるようにします。そのため、スイッチング負荷電流が流れる経路は、できるだけ短く、かつ幅広ぐする必要があります。 $dv/dt$  の大きいトレースの経路は、（その他のすべてのノードに対する）容量が小さくなるようにします。そのため、入力および出力容量を IC ピンにできる限り近づけて配置し、長距離にわたる並列配線や狭いトレースを避ける必要があります。交流電流を流すループに囲まれた領域から放射されるエネルギーは、その領域の面積に比例するため、その面積をできるだけ小さくする必要があります。

敏感なノード（FB、VOS など）は、短い配線で接続し、 $dv/dt$  の大きい信号（SW など）に近づけないようにする必要があります。敏感なノードは、出力電圧に関する情報を伝達するため、（出力コンデンサの）実際の出力電圧のできるだけ近くに接続する必要があります。SS/TR ピンのコンデンサと FB 抵抗（R1、R2）は、IC の近くに配置し、これらのピンとシステムグランドプレーンに直接接続する必要があります。VSET を使用して出力電圧をスケーリングする場合、VSET 抵抗にも同じことが当てはまります。

このパッケージでは、電力を放散する目的でピンを使用します。VIN および GND ピンのサーマルビアは、PCB を通して熱を拡散させるのに有効です。

デジタル入力 EN と MODE/S-CONF のどちらかを  $V_{IN}$  の入力電源電圧に接続する必要がある場合、回路図に示すように、入力コンデンサに直接接続する必要があります。

推奨レイアウトは EVM に実装されており、ユーザーズガイド SNVU745 に記載されています。

### 7.5.2 レイアウト例

図 7-85. レイアウト

### 7.5.2.1 热に関する注意事項

一般に、低背でファイン・ピッチの表面実装パッケージに IC を実装する場合は、消費電力に特別な注意が必要です。热結合、エアフロー、追加ヒートシンク、対流面、他の放熱部品の存在など、システムに依存する多くの問題により、特定の部品の消費電力制限が左右されます。

热特性強化の 3 つの方法を以下のリストに示します。

- PCB 設計の放熱性能の改善。例:銅箔の厚さ、サーマル・ビア、層数の増加

- システムへのエアフローの導入

热パラメータの使い方の詳細については、以下のアプリケーション・ノートを参照してください。热特性のアプリケーション・ノート ([SZZA017](#), [SPRA953](#))

TPS62901 の設計上の動作時接合部温度 ( $T_J$ ) の最大値は 150°C です。したがって、最大出力電力は、パッケージとその周囲の PCB 構造によって与えられる総熱抵抗で放散できる電力損失によって制限されます。パッケージの熱抵抗が決まっている場合、周囲の銅箔の面積を広げ、IC を熱的に適切に接続することで、総熱抵抗を下げることができます。放熱性を改善するため、上層のメタルを使って、広く太いメタル・ラインでデバイスを接続することを推奨します。内部のグラウンド層を IC の直下のビアに接続することで、放熱性を高めることができます。

短絡または過負荷状態が発生した場合、本デバイスは内部的な電力損失を制限することで保護されます。

本デバイスは、150°C の接合部温度での長期認定に対応しています。HotRod パッケージのディレーティングと寿命の詳細については、以下のアプリケーション・ノート [SPRACS3](#) を参照してください。

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイスのサポート

#### 8.1.1 開発サポート

##### 8.1.1.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS62901 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と一緒に参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になります。

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

SmartConfig™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

| Changes from Revision * (March 2021) to Revision A (January 2024) | Page |

|-------------------------------------------------------------------|------|

| • 商標の情報を更新.....                                                   | 1    |

| • ESD 定格を更新して、CDM 試験が JS-002 に準拠したことを明示.....                      | 4    |

| • ソフトスタート時間の標準値を式 14 で更新.....                                     | 21   |

| • VREF の定義を更新.....                                                | 21   |

| • 「突入電流を考慮して、ソフトスタート時間を 1ms 未満に設定することは通常推奨しない」旨の注釈を追加.....        | 21   |

| • 式 15、式 16 によるソフトスタート時間の最大および最小値の計算を追加。.....                     | 21   |

| • 「高精度ソフトスタートタイミング」セクションを削除.....                                  | 39   |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## PACKAGE OUTLINE

**RPJ0009A**

**VQFN-HR - 1 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

4224505/A 10/2018

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

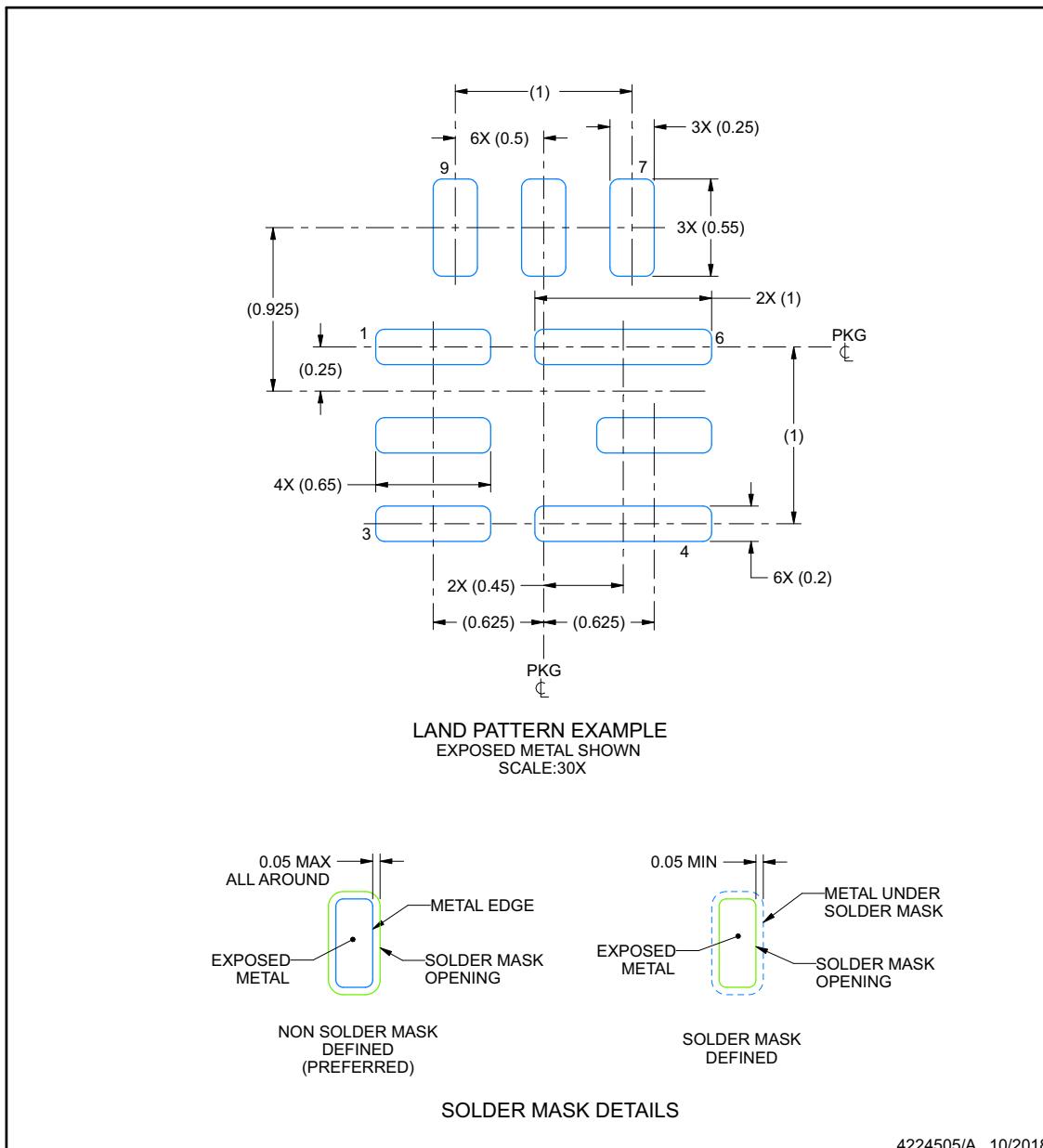

## EXAMPLE BOARD LAYOUT

**RPJ0009A**

**VQFN-HR - 1 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

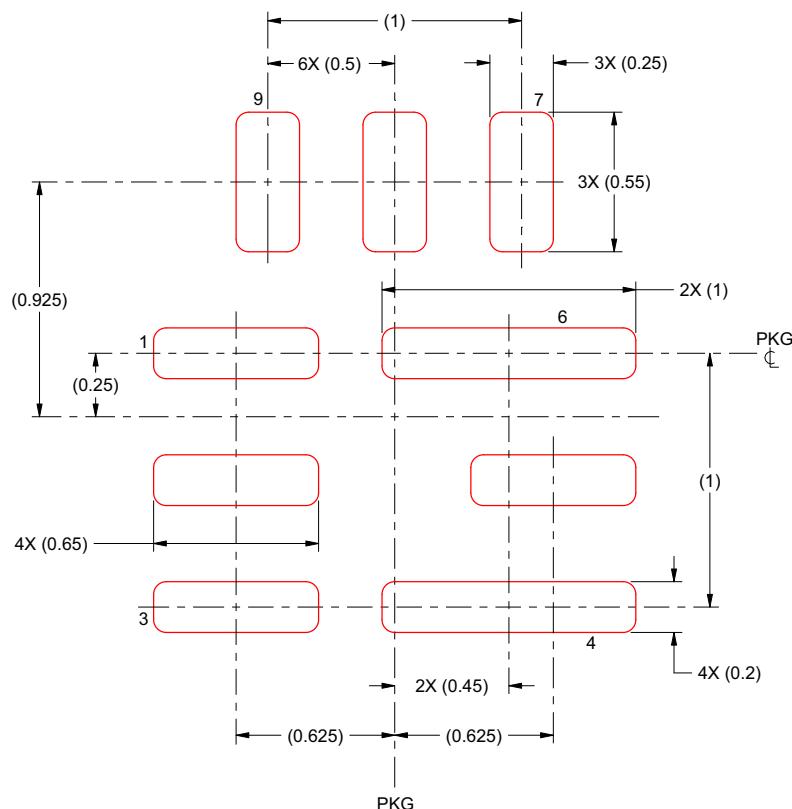

## EXAMPLE STENCIL DESIGN

**RPJ0009A**

**VQFN-HR - 1 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:40X

4224505/A 10/2018

NOTES: (continued)

- For alternate stencil design recommendations, see IPC-7525 or board assembly site preference.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS62901RPJR          | Active        | Production           | VQFN-HR (RPJ)   9 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | FQ8                 |

| TPS62901RPJR.A        | Active        | Production           | VQFN-HR (RPJ)   9 | 3000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 150   | FQ8                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS62901 :**

- Automotive : [TPS62901-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

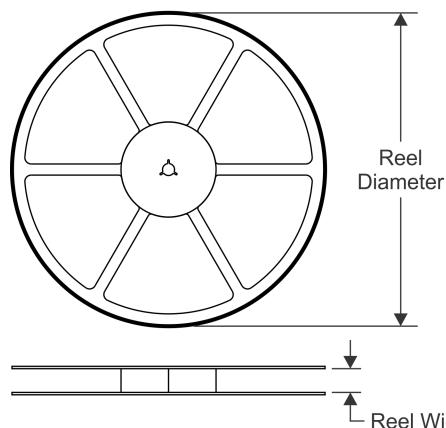

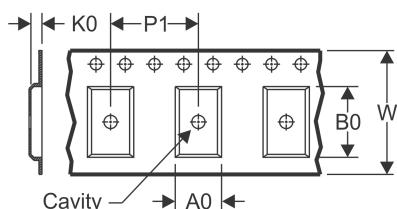

## TAPE AND REEL INFORMATION

### REEL DIMENSIONS

### TAPE DIMENSIONS

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

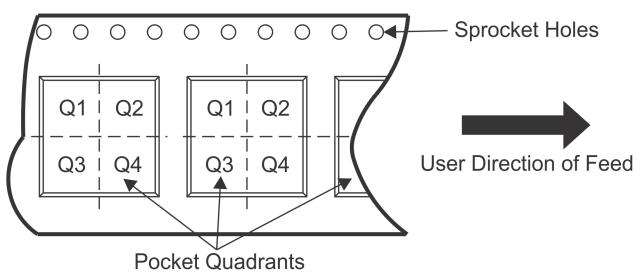

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS62901RPJR | VQFN-HR      | RPJ             | 9    | 3000 | 180.0              | 8.4                | 1.75    | 2.25    | 1.0     | 4.0     | 8.0    | Q1            |

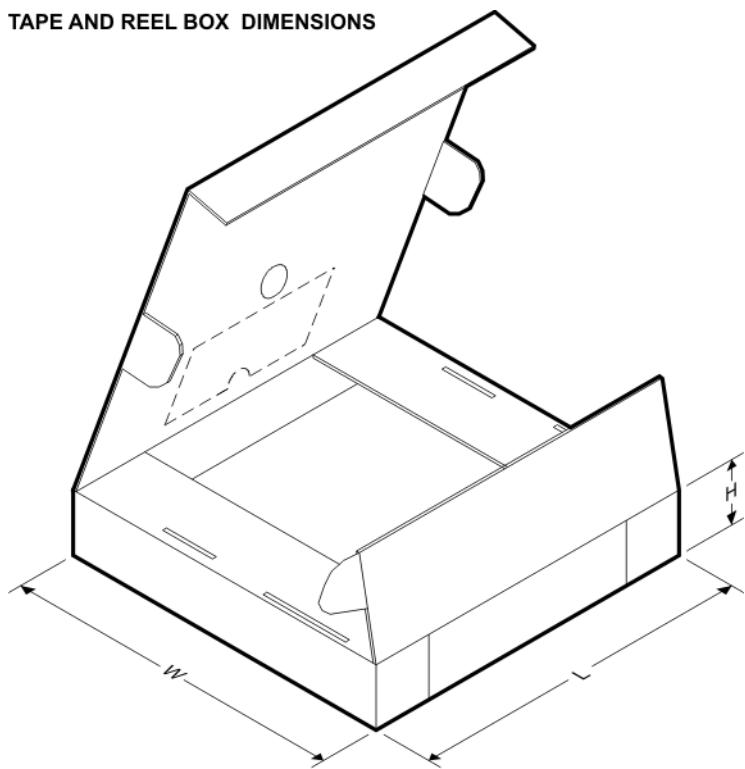

## TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS62901RPJR | VQFN-HR      | RPJ             | 9    | 3000 | 210.0       | 185.0      | 35.0        |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月