# TPS6287x 2.7V ~ 6V 入力、6A、9A、12A、15A、高速過渡スタッカブル同期 降圧コンバータ、I<sup>2</sup>C インターフェイスとリモートセンス機能搭載

## 1 特長

- インダクタ内蔵パワー モジュールとして提供:

[TPSM8287A06](#)、[TPSM8287A10](#)、[TPSM8287A12](#)、[TPSM8287A15](#)

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- 2.7V ~ 6V の入力電圧範囲

- 6A、9A、12A、15A のピン互換デバイス ファミリ

- 4 つの出力電圧範囲:

- 0.4V ~ 0.71875V (1.25mV 刻み)

- 0.4V ~ 1.0375V (2.5mV 刻み)

- 0.4V ~ 1.675V (5mV 刻み)

- 0.8V ~ 3.35V (10mV 刻み)

- ±1% の出力電圧精度

- 差動リモートセンシング

- 7mΩ/4.5mΩ のパワー MOSFET を内蔵

- 可変外部補償

- パワー セーブまたは強制 PWM 動作

- 外部クロックへの同期またはスペクトラム拡散動作を選択可能

- I<sup>2</sup>C 互換インターフェイス: 最高 1MHz

- 出力電流能力を強化するためのスタッカブル

- サーマル警告およびサーマル シャットダウン

- アクティブ出力放電

- ウインドウ コンバーティによるパワー グッド出力

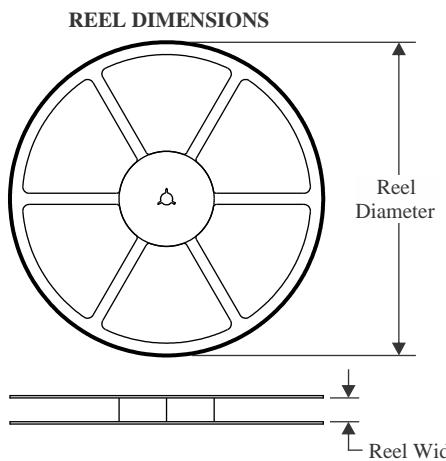

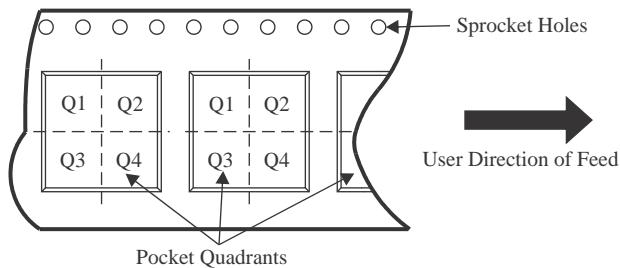

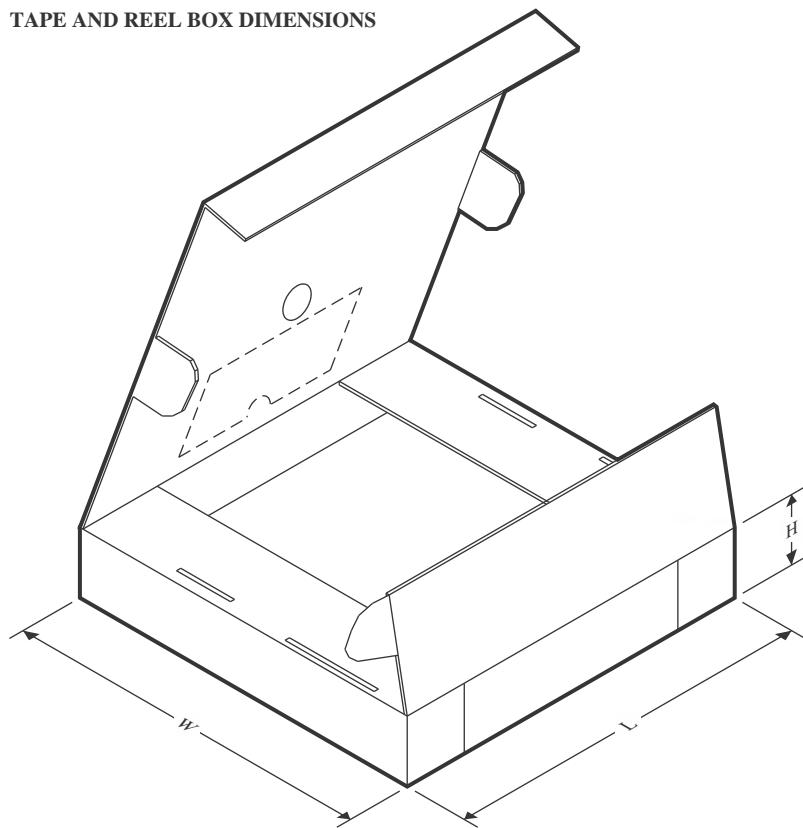

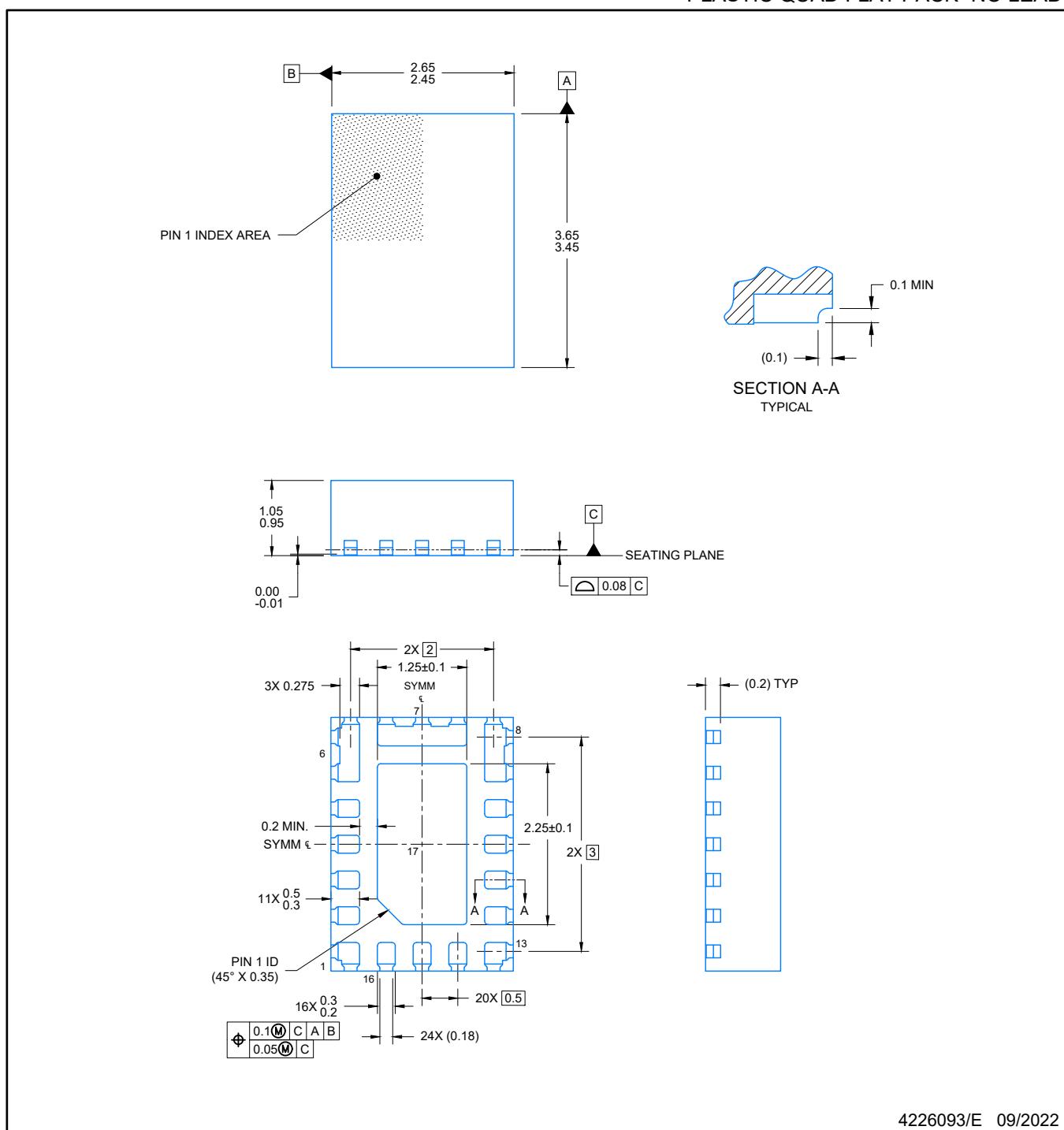

- ウェッタブル フランク付き 2.55mm × 3.55mm × 1mm VQFN パッケージで供給されます

- 40°C ~ 125°C の接合部温度範囲 (T<sub>J</sub>)

## 2 アプリケーション

- 光ネットワーク、ストレージ

- FPGA、ASIC、デジタルコア電源

- DDR メモリ電源

### 製品情報

| 部品番号     | 電流定格 <sup>(1)</sup> | パッケージ <sup>(2)</sup> |

|----------|---------------------|----------------------|

| TPS62870 | 6A                  | RXS (VQFN-FCRLF、16)  |

| TPS62871 | 9A                  |                      |

| TPS62872 | 12A                 |                      |

| TPS62873 | 15A                 |                      |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) 「[デバイスのオプション](#)」表を参照してください。

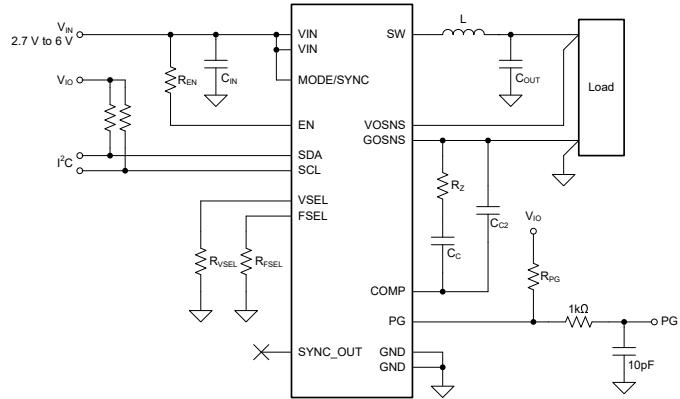

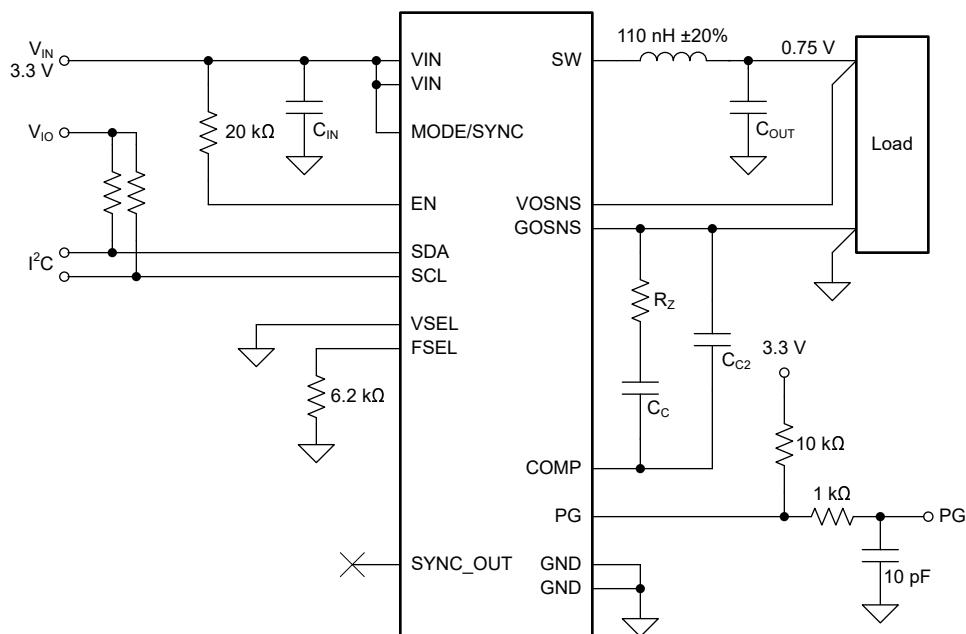

TPS6287x の概略回路図

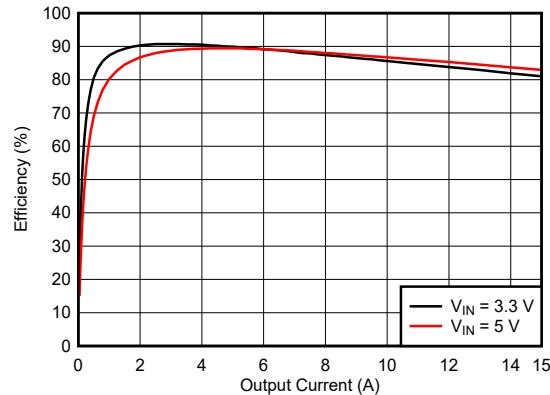

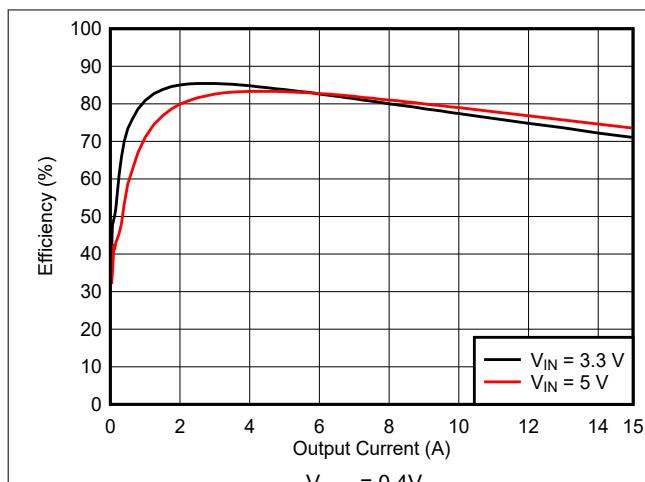

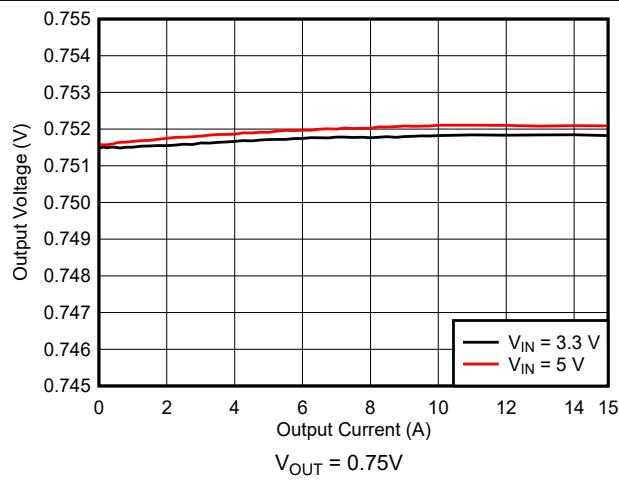

効率と出力電流との関係

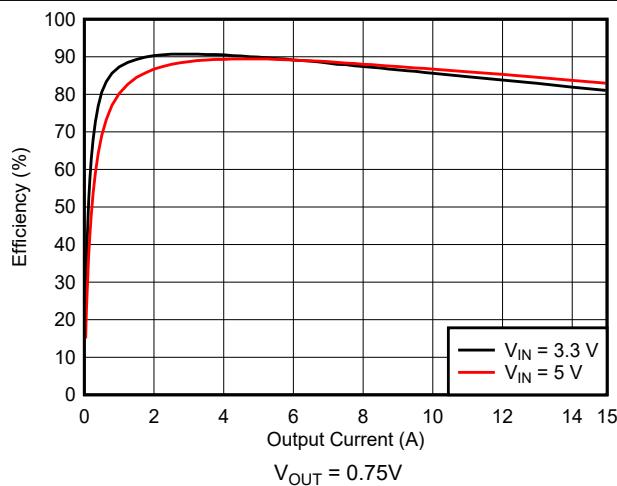

V<sub>OUT</sub> = 0.75V, FPWM, f<sub>SW</sub> = 2.25MHz

### 3 説明

TPS6287x は、差動リモート センシング機能を搭載したピン互換の 6A、9A、12A、15A 同期整流降圧 DC/DC コンバータのファミリです。各電流定格に、I<sup>2</sup>C インターフェイス付きのフル機能のデバイス バリエーションと I<sup>2</sup>C インターフェイスなしの制限機能付きデバイス バリエーションがあります。すべてのデバイスは、高い効率と使いやすさを特長としています。低抵抗の電源スイッチにより、高い周囲温度でも最大 15A の連続出力電流を供給できます。

これらのデバイスをスタック モードで動作させることで、大きな出力電流を供給することや、消費電力を複数のデバイスに分散することが可能です。

TPS6287x ファミリは、高速過渡をサポートする固定周波数 DCS 制御方式を実装します。デバイスは、最大効率を達成するパワーセーブ モード、または最高の過渡性能と最小の出力電圧リップルを実現する強制 PWM モードで動作できます。

リモート センシング機能は、POL (ポイント オブ ロード) での電圧レギュレーションを可能にし、あらゆる動作条件において ±1% 以内の DC 電圧精度を実現します。

スイッチング周波数は、FSEL ピンに接続した抵抗により選択できます。スイッチング周波数は 1.5MHz、2.25MHz、2.5MHz、3.0MHz のいずれかに設定できます。または、同じ周波数範囲の外部クロックに同期させることができます。

I<sup>2</sup>C 互換インターフェイスを使うと、各種の制御、監視、警告機能 (電圧の監視、温度に関連する警告など) を実現できます。出力電圧は、アプリケーションの性能要求に負荷の消費電力が適合するように、I<sup>2</sup>C 互換インターフェイスを使って素早く調整できます。デフォルトの起動電圧は、VSEL ピンに接続した抵抗により選択できます。

## 目次

|                                       |    |                         |    |

|---------------------------------------|----|-------------------------|----|

| 1 特長                                  | 1  | 7.4 デバイスの機能モード          | 33 |

| 2 アプリケーション                            | 1  | 7.5 プログラミング             | 34 |

| 3 説明                                  | 2  | 8 レジスタ マップ              | 38 |

| 4 デバイスのオプション                          | 4  | 9 アプリケーションと実装           | 44 |

| 5 ピン構成および機能                           | 6  | 9.1 アプリケーション情報          | 44 |

| 6 仕様                                  | 8  | 9.2 代表的なアプリケーション        | 44 |

| 6.1 絶対最大定格                            | 8  | 9.3 設計のベスト プラクティス       | 54 |

| 6.2 ESD 定格                            | 8  | 9.4 電源に関する推奨事項          | 55 |

| 6.3 推奨動作条件                            | 8  | 9.5 レイアウト               | 55 |

| 6.4 熱に関する情報                           | 9  | 10 デバイスおよびドキュメントのサポート   | 57 |

| 6.5 電気的特性                             | 9  | 10.1 デバイス サポート          | 57 |

| 6.6 I <sup>2</sup> C インターフェイス タイミング特性 | 12 | 10.2 ドキュメントの更新通知を受け取る方法 | 57 |

| 6.7 タイミング要件                           | 13 | 10.3 サポート・リソース          | 57 |

| 6.8 代表的特性                             | 14 | 10.4 商標                 | 57 |

| 7 詳細説明                                | 15 | 10.5 静電気放電に関する注意事項      | 57 |

| 7.1 概要                                | 15 | 10.6 用語集                | 57 |

| 7.2 機能ブロック図                           | 16 | 11 改訂履歴                 | 57 |

| 7.3 機能説明                              | 16 | 12 メカニカル、パッケージ、および注文情報  | 58 |

## 4 デバイスのオプション

| 部品番号            | 出力電流 | 起動電圧と I <sup>2</sup> C アドレス <sup>(1)</sup><br>(2) (3) | VSEL 設定        | 拡散スペクトラム クロック処理 | ソフトスタート時間     |

|-----------------|------|-------------------------------------------------------|----------------|-----------------|---------------|

| TPS62873Z0WRXSR | 15A  | 0.800V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 0.800V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62873Z1WRXSR | 15A  | 0.600V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 0.900V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62873Z2WRXSR | 15A  | 0.500V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 1.050V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62873Z4WRXSR | 15A  | 0.850V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 1.000V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62873Z5WRXSR | 15A  | 0.400V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 0.400V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62872Z0WRXSR | 12A  | 0.800V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 0.800V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62872Z2WRXSR | 12A  | 0.500V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 1.050V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62872Z4WRXSR | 12A  | 0.850V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 1.000V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62871Z0WRXSR | 9A   | 0.800V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 0.800V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| TPS62871Z2WRXSR | 9A   | 0.500V, 0x40                                          | 6.2kΩ から GND へ | デフォルト設定 = オフ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                          | GND への短絡       |                 |               |

|                 |      | 0.875V, 0x42                                          | VIN への短絡       |                 |               |

|                 |      | 1.050V, 0x43                                          | 47kΩ から VIN へ  |                 |               |

| 部品番号            | 出力電流 | 起動電圧と I <sup>2</sup> C アドレス <sup>(1)</sup><br><sup>(2)</sup> <sup>(3)</sup> | VSEL 設定        | 拡散スペクトラム クロ<br>ック処理 | ソフト スタート時間    |

|-----------------|------|-----------------------------------------------------------------------------|----------------|---------------------|---------------|

| TPS62871Z4WRXSR | 9A   | 0.850V, 0x40                                                                | 6.2kΩ から GND へ | デフォルト設定 = オ<br>フ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                                                | GND への短絡       |                     |               |

|                 |      | 0.875V, 0x42                                                                | VIN への短絡       |                     |               |

|                 |      | 1.000V, 0x43                                                                | 47kΩ から VIN へ  |                     |               |

| TPS62870Z0WRXSR | 6A   | 0.800V, 0x40                                                                | 6.2kΩ から GND へ | デフォルト設定 = オ<br>フ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                                                | GND への短絡       |                     |               |

|                 |      | 0.875V, 0x42                                                                | VIN への短絡       |                     |               |

|                 |      | 0.800V, 0x43                                                                | 47kΩ から VIN へ  |                     |               |

| TPS62870Z4WRXSR | 6A   | 0.850V, 0x40                                                                | 6.2kΩ から GND へ | デフォルト設定 = オ<br>フ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                                                | GND への短絡       |                     |               |

|                 |      | 0.875V, 0x42                                                                | VIN への短絡       |                     |               |

|                 |      | 1.000V, 0x43                                                                | 47kΩ から VIN へ  |                     |               |

| TPS62873Z6WRXSR | 15A  | 0.500V, 0x40                                                                | 6.2kΩ から GND へ | デフォルト設定 = オ<br>フ    | デフォルト設定 = 1ms |

|                 |      | 0.750V, 0x41                                                                | GND への短絡       |                     |               |

|                 |      | 0.875V, 0x42                                                                | VIN への短絡       |                     |               |

|                 |      | 0.500V, 0x43                                                                | 47kΩ から VIN へ  |                     |               |

(1) I<sup>2</sup>C アドレスは、選択した起動電圧にリンクされます。起動電圧と I<sup>2</sup>C アドレスを別々に選択することはできません。

(2) VSEL ピンを使用して、デバイスが使用する 4 つの起動電圧のいずれかを選択できます。詳細については、表 7-5 および 表 7-10 を参照してください。

(3) その他の起動電圧または I<sup>2</sup>C アドレス オプションについては、TI にお問い合わせください

特に記述のない限り、I<sup>2</sup>C のないデバイス バリアントは、I<sup>2</sup>C のあるデバイス バリアントと同じデフォルト設定で動作します。

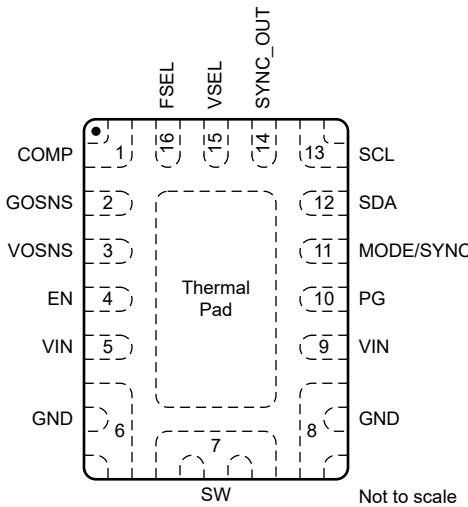

## 5 ピン構成および機能

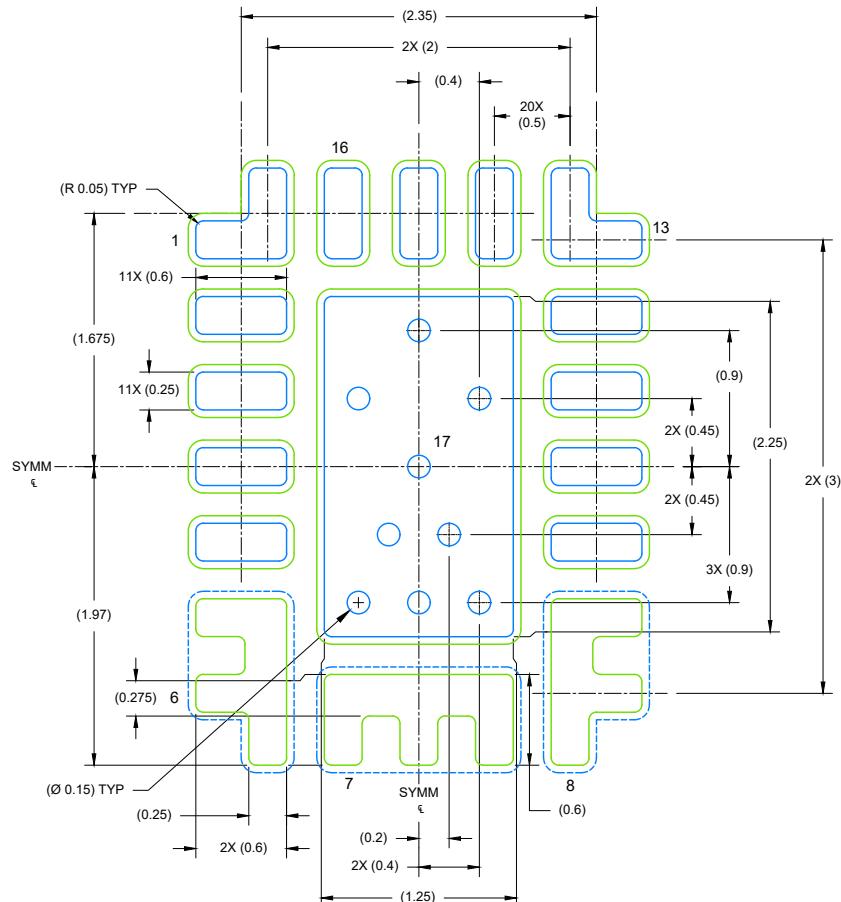

図 5-1. 16 ピン RXS VQFN パッケージ (上面図)

表 5-1. ピンの機能

| ピン        |      | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                        |

|-----------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号   |                    |                                                                                                                                                                                                                                                                                                           |

| COMP      | 1    | —                  | デバイス補償入力。このピンと GOSNSとの間に抵抗とコンデンサによって、制御ループの補償が定義されます。<br>スタッック動作では、スタッキングされたすべてのデバイスの COMP ピンを互いに接続し、共通の COMP ノードと GOSNSとの間に抵抗とコンデンサを接続します。                                                                                                                                                               |

| GOSNS     | 2    | I                  | 出力グランド検出 (差動出力電圧センシング)                                                                                                                                                                                                                                                                                    |

| VOSNS     | 3    | I                  | 出力電圧検出 (差動出力電圧センシング)                                                                                                                                                                                                                                                                                      |

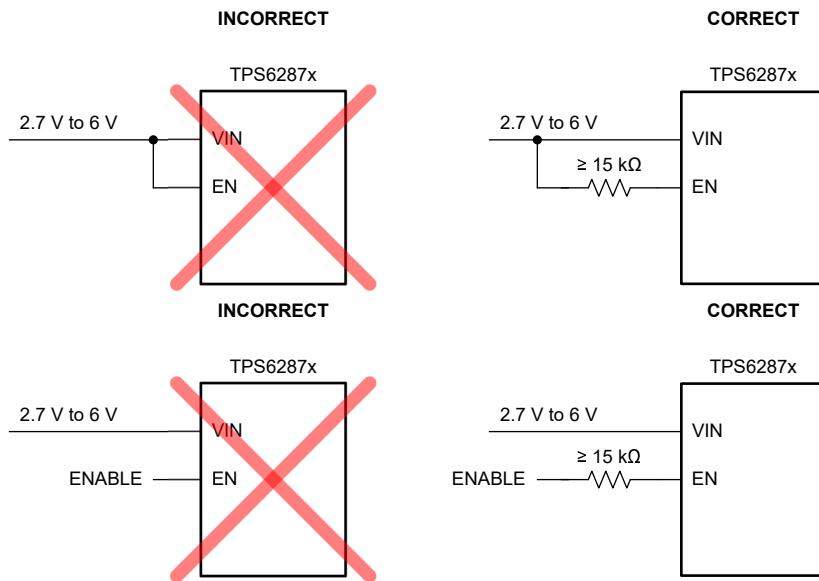

| EN        | 4    | I                  | 製品のイネーブルピンです。ユーザーは、少なくとも $15\text{k}\Omega$ の直列抵抗を使用してこのピンに接続する必要があります。このピンが low ロジック レベルになるとデバイスは無効化され、このピンが high ロジック レベルになるとデバイスが有効化されます。このピンを未接続のままにしないでください。<br>スタッキング動作を行う場合は、すべてのデバイスの EN ピンを相互に接続し、それらを電源電圧またはプロセッサの GPIO に抵抗を介して接続します。詳細については、セクション 7.3.17 を参照してください。                            |

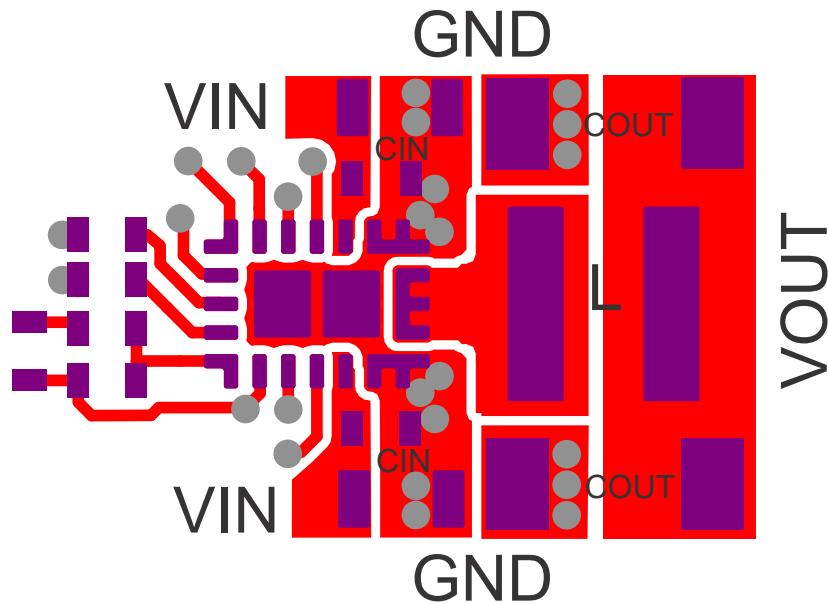

| VIN       | 5, 9 | P                  | 電源入力。入力コンデンサは、デバイスの VIN ピンと GND ピンの間にできる限り近づけて (パッケージの両面に) 配置してください                                                                                                                                                                                                                                       |

| GND       | 6, 8 | GND                | グランド ピン                                                                                                                                                                                                                                                                                                   |

| SW        | 7    | O                  | このピンはコンバータのスイッチ ピンであり、内部パワー MOSFET に接続されています。                                                                                                                                                                                                                                                             |

| PG        | 10   | I/O                | オープンドレインのパワー グッド出力。「パワーグッド」でないときは低インピーダンス、「パワーグッド」のときはハイインピーダンスになります。このピンは、単一のデバイス動作で使用されていない場合は、オーブンのままにすることも、GND に接続することもできます。<br>スタッキング動作では、スタッキングされたすべてのデバイスの PG ピンを相互接続します。スタッキング動作の 1 次側コンバータの PG ピンのみがオープンドレイン出力です。スタッキングモードで 2 次側コンバータとして定義されたデバイスの場合、このピンは入力ピンです。詳細については、セクション 7.3.17 を参照してください。 |

| MODE/SYNC | 11   | I                  | このピンが Low になると、デバイスはパワーセーブモードで動作します。ピンが high にプルされる場合、デバイスは強制 PWM モードで動作します。このピンを未接続のままにしないでください。モードピンを使用して、デバイスを外部クロックに同期することもできます。                                                                                                                                                                      |

| SDA       | 12   | I/O                | I <sup>2</sup> C シリアル データ ピン。フロー ティングのままにしないでください。プルアップ 抵抗をロジック high レベルに接続します。<br>スタッキング動作での 2 次側デバイスと I <sup>2</sup> C のないデバイス バリエントの場合は、GND に接続します。                                                                                                                                                    |

| SCL       | 13   | I                  | I <sup>2</sup> C シリアル クロック ピン。このピンをフロー ティングのままにしないでください。プルアップ 抵抗を論理 high レベルに接続します。<br>スタッキング動作での 2 次側デバイスと I <sup>2</sup> C のないデバイス バリエントの場合は、このピンを GND に接続します。                                                                                                                                          |

**表 5-1. ピンの機能 (続き)**

| ピン           |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                            |

|--------------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号 |                    |                                                                                                                                                                                                                                                                                                                                               |

| SYNC_OUT     | 14 | O                  | スタック モードでの同期用の内部クロック出力ピン。このピンはシングルデバイス動作用にフローティングのままにします。スタック動作では、このピンをデイジーチェーン内の次のデバイスの MODE/SYNC ピンに接続します。このピンを <b>TPS6287x</b> 以外のデバイスに接続しないでください。<br>スタートアップ時に、このピンを使用して、スタック動作でデバイスを 2 次側コンバータとして動作させる必要があるかどうかを識別します。このピンと GND との間に $47\text{k}\Omega$ 抵抗を接続して、スタック動作でセカンダリコンバータを定義します。詳細については、 <a href="#">セクション 7.3.17</a> を参照してください。 |

| VSEL         | 15 | —                  | スタートアップ時の出力電圧選択ピン。抵抗、または GND もしくは $V_{IN}$ への短絡によって、選択される出力電圧が決まります。 <a href="#">セクション 7.3.6.2</a> を参照してください。                                                                                                                                                                                                                                 |

| FSEL         | 16 | —                  | 周波数選択ピン。抵抗または GND や $V_{IN}$ への短絡によって、フリーランニング スイッチング周波数が決まります。 <a href="#">セクション 7.3.6.2</a> を参照してください。                                                                                                                                                                                                                                      |

| 露出したサーマル パッド |    | —                  | 適切な熱抵抗と機械的安定性を実現するため、サーマル パッドは GND に半田付けする必要があります。                                                                                                                                                                                                                                                                                            |

(1) I = 入力、O = 出力、P = 電源、GND = グランド

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) (1)

|           |                               | 最小値  | 最大値            | 単位 |

|-----------|-------------------------------|------|----------------|----|

| 電圧 (2)    | VIN <sup>(4)</sup>            | -0.3 | 6.5            | V  |

|           | SW (DC)                       | -0.3 | $V_{IN} + 0.3$ |    |

|           | SW (AC, 10ns 未満) (3)          | -3   | 10             |    |

|           | VOSNS                         | -0.3 | 3.8            |    |

|           | SCL, SDA                      | -0.3 | 5.5            |    |

|           | FSEL, VSEL, EN, MODE/SYNC, PG | -0.3 | 6.5            |    |

|           | GOSNS                         | -0.3 | 0.3            |    |

|           | COMP                          | -0.3 | $V_{IN}$       |    |

| 電流        | SYNC_OUT                      | -1   | 1              | mA |

|           | COMP                          | -1   | 1              |    |

|           | PG                            |      | 5              |    |

|           | SDA                           |      | 9              |    |

|           | EN                            |      | 1              |    |

| $T_J$     | 接合部温度                         | -40  | 150            | °C |

| $T_{stg}$ | 保存温度                          | -65  | 150            | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、GND ピンを基準としたものです。

- (3) スイッチング動作時。

- (4) このピンの電圧は、絶対最大定格 6.5V を短時間にわたって超えることができますが、8V 未満に維持する必要があります。VIN を 8V に 100ms さらすことは、室温でのデバイスの経年劣化約 8 時間に相当します。

### 6.2 ESD 定格

|             |      |                                                           | 値     | 単位 |

|-------------|------|-----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | ±2000 | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|           |      |          | 最小値 | 公称値                                        | 最大値 | 単位 |

|-----------|------|----------|-----|--------------------------------------------|-----|----|

| $V_{IN}$  | 入力電圧 | VIN      | 2.7 | 6                                          | V   |    |

|           |      | SDA, SCL |     | 5                                          |     |    |

| $V_{OUT}$ | 出力電圧 |          | 0.4 | 3.35V または $(V_{IN} - 1.4V)$ <sup>(1)</sup> |     | V  |

## 6.3 推奨動作条件 (続き)

動作温度範囲内 (特に記述のない限り)

|           |                            |                                                               | 最小値 | 公称値 | 最大値            | 単位            |

|-----------|----------------------------|---------------------------------------------------------------|-----|-----|----------------|---------------|

| $I_{OUT}$ | 出力電流                       | TPS62870                                                      |     |     | 6              | A             |

|           |                            | TPS62871                                                      |     |     | 9              |               |

|           |                            | TPS62872                                                      |     |     | 12             |               |

|           |                            | TPS62873                                                      |     |     | 15             |               |

| $L$       | インダクタンス                    |                                                               | 110 |     | 330            | nH            |

|           |                            | $f_{SW} \geq 2.25\text{MHz}$ および $V_{OUT} \leq 1.675\text{V}$ | 55  |     | 330            |               |

| $C_{IN}$  | 入力容量 (ピンごと) <sup>(2)</sup> | VIN                                                           | 5   | 10  |                | $\mu\text{F}$ |

| $C_{OUT}$ | 出力容量 <sup>(2)</sup>        |                                                               | 40  |     | <sup>(3)</sup> |               |

| $C_{PAR}$ | 寄生容量                       | VSEL、FSEL                                                     |     |     | 100            | pF            |

|           |                            | SYNC_OUT                                                      |     |     | 20             |               |

|           | 抵抗の誤差                      | VSEL、FSEL                                                     |     |     | $\pm 2\%$      |               |

| $T_J$     | 動作時接合部温度                   |                                                               | -40 |     | 125            | °C            |

(1) いざれか小さいほうの値。

(2) 「実効」容量。

(3) 推奨される最大出力キャパシタンスは、アプリケーションの特定の動作条件によって異なります。しかし、通常は数ミリアラッドまでの出力キャパシタンス値が可能です。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | TPS6287x    |           | 単位   |

|-----------------------------|---------------------|-------------|-----------|------|

|                             |                     | RXS (JEDEC) | RXS (EVM) |      |

|                             |                     | 16 ピン       | 16 ピン     |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 43.2        | 28        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 19.2        | 該当なし      | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 7.7         | 該当なし      | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.5         | 1.5       | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 7.7         | 9.3       | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 | 6.3         | 該当なし      | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

動作時接合部温度 ( $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ) および  $V_{IN} = 2.7\text{V} \sim 6\text{V}$ 、 $V_{IN} = 3.3\text{V}$  および  $T_J = 25^\circ\text{C}$  の場合の標準的な値 (特に記載のない限り)。

| パラメータ     |                           | テスト条件 |                                                                                                                      | 最小値 | 標準値  | 最大値 | 単位            |

|-----------|---------------------------|-------|----------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------|

| <b>電源</b> |                           |       |                                                                                                                      |     |      |     |               |

| $I_Q$     | 電源電流 (VIN)                | 動作    | $EN = \text{high}$ 、 $I_{OUT} = 0\text{mA}$ 、 $V_{(SW)} = 0\text{V}$ 、1 次側動作、デバイスのスイッチングなし、 $T_J = 25^\circ\text{C}$ |     | 1.75 | 3   | mA            |

|           |                           | スタンバイ | $EN = \text{low}$ 、 $V_{(SW)} = 0\text{V}$ 、 $T_J = 25^\circ\text{C}$                                                |     | 16.5 | 40  | $\mu\text{A}$ |

| $V_{IT+}$ | 正方向の UVLO スレッショルド電圧 (VIN) |       |                                                                                                                      | 2.5 | 2.6  | 2.7 | V             |

| $V_{IT-}$ | 負方向の UVLO スレッショルド電圧 (VIN) |       |                                                                                                                      | 2.4 | 2.5  | 2.6 | V             |

| $V_{hys}$ | UVLO ヒステリシス電圧 (VIN)       |       |                                                                                                                      | 90  |      |     | mV            |

| $V_{IT+}$ | 正方向の OVLO スレッショルド電圧 (VIN) |       |                                                                                                                      | 6.1 | 6.3  | 6.5 | V             |

## 6.5 電気的特性 (続き)

動作時接合部温度 ( $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ) および  $V_{IN} = 2.7\text{V} \sim 6\text{V}$ ,  $V_{IN} = 3.3\text{V}$  および  $T_J = 25^\circ\text{C}$  の場合の標準的な値 (特に記載のない限り)。

| パラメータ              |                                                           | テスト条件                                                                           | 最小値  | 標準値 | 最大値  | 単位          |

|--------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|------|-----|------|-------------|

| $V_{IT-}$          | 負方向の OVLO スレッショルド電圧 ( $V_{IN}$ )                          |                                                                                 | 6.0  | 6.2 | 6.4  | V           |

| $V_{hys}$          | OVLO ヒステリシス電圧 ( $V_{IN}$ )                                |                                                                                 | 85   |     |      | mV          |

| $V_{IT-}$          | 負方向のパワーオンリセットスレッショルド                                      |                                                                                 | 1.4  |     |      | V           |

| $T_{SD}$           | サーマル シャットダウン スレッショルド温度                                    | $T_J$ 立ち上がり                                                                     | 170  |     |      | °C          |

|                    | サーマル シャットダウンヒステリシス                                        |                                                                                 | 20   |     |      | °C          |

| $T_W$              | 過熱警告のスレッショルド温度                                            | $T_J$ 立ち上がり                                                                     | 150  |     |      | °C          |

|                    | 過熱警告ヒステリシス                                                |                                                                                 | 20   |     |      | °C          |

| 制御とインターフェイス        |                                                           |                                                                                 |      |     |      |             |

| $V_{IT+}$          | 正方向の入力スレッショルド電圧 (EN)                                      |                                                                                 | 0.97 | 1.0 | 1.03 | V           |

| $V_{IT-}$          | 負方向の入力スレッショルド電圧 (EN)                                      |                                                                                 | 0.87 | 0.9 | 0.93 | V           |

| $V_{hys}$          | ヒステリシス電圧 (EN)                                             |                                                                                 | 95   |     |      | mV          |

| $I_{IH}$           | High レベル入力電流 (EN)                                         | $V_{IH} = V_{IN}$ 、内部プルダウン抵抗は無効                                                 |      | 200 |      | nA          |

| $I_{IL}$           | Low レベル入力電流 (EN)                                          | $V_{IL} = 0\text{V}$ 、内部プルダウン抵抗は無効                                              | -200 |     |      | nA          |

| $V_{IH}$           | High レベル入力電圧 (SDA, SCL, MODE/ SYNC, VSEL, FSEL, SYNC_OUT) |                                                                                 | 0.8  |     |      | V           |

| $V_{IL}$           | Low レベル入力電圧 (SDA, SCL, MODE/ SYNC, VSEL, FSEL, SYNC_OUT)  |                                                                                 |      | 0.4 |      | V           |

| $V_{OL}$           | Low レベル出力電圧 (SDA)                                         | $I_{OL} = 3\text{mA}$                                                           |      | 0.4 |      | V           |

|                    |                                                           | $I_{OL} = 9\text{mA}$                                                           |      | 0.4 |      | V           |

|                    |                                                           | $I_{OL} = 5\text{mA}$                                                           |      | 0.2 |      | V           |

| $I_{OH}$           | High レベル出力電流 (SDA, SCL)                                   | $V_{OH} = 3.3\text{V}$                                                          |      | 200 |      | nA          |

| $I_{IL}$           | Low レベル入力電圧 (MODE/SYNC)                                   | $V_{IL} = 0\text{V}$                                                            | -150 | 150 |      | nA          |

| $I_{IH}$           | High レベル入力電圧 (MODE/SYNC)                                  | $V_{IH} = V_{IN}$                                                               |      | 3   |      | μA          |

| $I_{IL}$           | Low レベル入力電圧 (SYNC_OUT)                                    | $V_{IL} = 0\text{V}$                                                            | -250 |     |      | nA          |

| $I_{IH}$           | High レベル入力電圧 (SYNC_OUT)                                   | $V_{IH} = 2\text{V}$                                                            |      | 150 |      | nA          |

| $C_{IN\_SDA\_SCL}$ | SDA および SCL ピンの寄生入力容量                                     |                                                                                 |      | 10  |      | pF          |

| $t_{d(EN)1}$       | EN を $V_{IN}$ に接続したときのイネーブル遅延時間                           | EN が high になった時点からデバイスがスイッチングを開始する時点までを測定<br>$SR_{VIN} = 1\text{V}/\mu\text{s}$ |      | 175 | 500  | μs          |

| $t_{d(EN)2}$       | $V_{IN}$ がすでに印加されているときのイネーブル遅延時間                          | EN が High になった時点からデバイスがスイッチングを開始する時点までを測定                                       |      |     | 100  | μs          |

| $t_{d(RAMP)}$      | 出力電圧ランプタイム                                                | デバイスがスイッチングを開始してから、PG 信号が立ち上がるまでの時間を測定                                          | 0.35 | 0.5 | 0.65 | ms          |

|                    |                                                           |                                                                                 | 0.7  | 1   | 1.3  | ms          |

|                    |                                                           |                                                                                 | 1.4  | 2   | 2.6  | ms          |

|                    |                                                           |                                                                                 | 2.8  | 4   | 5.2  | ms          |

|                    | 外部周波数にロックする時間                                             |                                                                                 |      | 50  |      | μs          |

|                    | 内部プルアップ抵抗 (VSEL, FSEL)                                    |                                                                                 | 5.5  |     | 9    | kΩ          |

|                    | 内部プルダウン抵抗 (VSEL, FSEL)                                    |                                                                                 | 1.3  |     | 2.2  | kΩ          |

| $V_{T+}$           | 正方向のパワーグッドスレッショルド電圧 (出力低電圧)                               |                                                                                 | 94   | 96  | 98   | % $V_{OUT}$ |

| $V_{T-}$           | 負方向のパワーグッドスレッショルド電圧 (出力低電圧)                               |                                                                                 | 92   | 94  | 96   | % $V_{OUT}$ |

## 6.5 電気的特性 (続き)

動作時接合部温度 ( $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ ) および  $V_{IN} = 2.7\text{V} \sim 6\text{V}$ ,  $V_{IN} = 3.3\text{V}$  および  $T_J = 25^\circ\text{C}$  の場合の標準的な値 (特に記載のない限り)。

| パラメータ           |                              | テスト条件                                                                               | 最小値           | 標準値  | 最大値   | 単位               |

|-----------------|------------------------------|-------------------------------------------------------------------------------------|---------------|------|-------|------------------|

| $V_{T+}$        | 正方向のパワーグッド スレッショルド電圧 (出力過電圧) |                                                                                     | 104           | 106  | 108   | % $V_{OUT}$      |

| $V_{T-}$        | 負方向のパワーグッド スレッショルド電圧 (出力過電圧) |                                                                                     | 102           | 104  | 106   | % $V_{OUT}$      |

| $V_{OL}$        | Low レベル出力電圧 (PG)             | $I_{OL} = 1\text{mA}$                                                               |               | 0.3  |       | V                |

| $I_{OH}$        | High レベル出力電流 (PG)            | $V_{OH} = 3.3\text{V}$                                                              |               | 200  |       | nA               |

| $V_{IH}$        | High レベル入力電圧 (PG)            | スタック動作で 2 次側デバイスとして構成されたデバイス                                                        | 0.8           |      |       | V                |

| $V_{IL}$        | Low レベル入力電圧 (PG)             | スタック動作で 2 次側デバイスとして構成されたデバイス                                                        |               | 0.4  |       | V                |

| $I_{IH}$        | High レベル入力電流 (PG)            | スタック動作で 2 次側デバイスとして構成されたデバイス                                                        |               | 1    |       | $\mu\text{A}$    |

| $I_{IL}$        | Low レベル入力電流 (PG)             | スタック動作で 2 次側デバイスとして構成されたデバイス                                                        | -1            |      |       | $\mu\text{A}$    |

| $t_{d(PG)}$     | グリッチ除去時間 (PG)                | PG ピンの High から Low、または Low から High への遷移                                             | 34            | 40   | 46    | $\mu\text{s}$    |

| <b>出力</b>       |                              |                                                                                     |               |      |       |                  |

| $V_{OUT}$       | 出力精度                         | $V_{IN} \geq V_{OUT} + 1.4\text{V}$                                                 | -1            | 1    |       | %                |

| $I_{IB}$        | 入力バイアス電流 (GOSNS)             | $V_{(GOSNS)} = -100\text{mV} \sim 100\text{mV}$                                     | -6            |      |       | $\mu\text{A}$    |

| $I_{IB}$        | 入力バイアス電流 (VOSNS)             | $V_{(VOSNS)} = 3.3\text{V}$ , $V_{IN} = 6\text{V}$                                  |               | 6    |       | $\mu\text{A}$    |

| $V_{ICR}$       | 同相入力範囲 (GOSNS)               |                                                                                     | -100          | 100  |       | mV               |

|                 | 定電流モードでの出力放電電流               | $V_{(VOSNS)} = 2\text{V}$                                                           | 50            | 115  | 200   | mA               |

| $R_{DIS}$       | 抵抗放電モードでの出力放電抵抗              | $V_{(VOSNS)} \leq 0.5\text{V}$                                                      |               | 6    |       | $\Omega$         |

| $f_{SW}$        | スイッチング周波数 (SW)               | $f_{SW} = 1.5\text{MHz}$ , PWM 動作、 $V_{IN} 3.3\text{V}$ , $V_{OUT} = 0.75\text{V}$  | 1.35          | 1.5  | 1.65  | MHz              |

|                 |                              | $f_{SW} = 2.25\text{MHz}$ , PWM 動作、 $V_{IN} 3.3\text{V}$ , $V_{OUT} = 0.75\text{V}$ | 2.025         | 2.25 | 2.475 |                  |

|                 |                              | $f_{SW} = 2.5\text{MHz}$ , PWM 動作、 $V_{IN} 3.3\text{V}$ , $V_{OUT} = 0.75\text{V}$  | 2.25          | 2.5  | 2.75  |                  |

|                 |                              | $f_{SW} = 3\text{MHz}$ , PWM 動作、 $V_{IN} 3.3\text{V}$ , $V_{OUT} = 0.75\text{V}$    | 2.7           | 3    | 3.3   |                  |

| $f_{mod}$       | スペクトラム拡散掃引の周波数               |                                                                                     | $f_{sw}/2048$ |      |       | kHz              |

| $\Delta f_{SW}$ | スペクトラム拡散動作時のスイッチング周波数の変動     |                                                                                     | $\pm 10\%$    |      |       |                  |

| $T$             | エミュレート電流時定数                  |                                                                                     | 12.5          |      |       | $\mu\text{s}$    |

| $r_{DS(on)}$    | ハイサイド FET の静的オン状態抵抗          | $V_{IN} = 3.3\text{V}$                                                              | 7             | 16   |       | $\text{m}\Omega$ |

| $r_{DS(on)}$    | ローサイド FET の静的オン状態抵抗          | $V_{IN} = 3.3\text{V}$                                                              |               | 4.1  | 9.4   | $\text{m}\Omega$ |

| $I_{(SW)(off)}$ | ハイサイド FET のオフ状態電流            | $V_{IN} = 6\text{V}$ , $V_{(SW)} = 0\text{V}$ , $T_J = 25^\circ\text{C}$            | -1            |      |       | $\mu\text{A}$    |

|                 | ローサイド FET オフ状態電流             | $V_{IN} = 6\text{V}$ , $V_{(SW)} = 6\text{V}$ , $T_J = 25^\circ\text{C}$            |               | 100  |       |                  |

| $I_{LIM}$       | ハイサイド FET 順方向スイッチ電流制限、DC     | TPS62870                                                                            | 9             | 12   | 14    | A                |

|                 |                              | TPS62871                                                                            | 12            | 16   | 18    |                  |

|                 |                              | TPS62872                                                                            | 15            | 20   | 22    |                  |

|                 |                              | TPS62873                                                                            | 18            | 24   | 26    |                  |

|                 | ローサイド FET 負電流制限、DC           |                                                                                     | 7.5           | 12   |       | A                |

## 6.6 I<sup>2</sup>C インターフェイス タイミング特性

| パラメータ             |                             | テスト条件        | 最小値                            | 標準値  | 最大値 | 単位  |

|-------------------|-----------------------------|--------------|--------------------------------|------|-----|-----|

| $f_{SCL}$         | SCL クロック周波数                 | スタンダード モード   |                                | 100  |     | kHz |

|                   |                             | ファスト モード     |                                | 400  |     |     |

|                   |                             | ファスト モード プラス |                                | 1000 |     |     |

| $t_{HD}; t_{STA}$ | (繰り返し) START 条件のホールド時間      | スタンダード モード   | 4                              |      |     | μs  |

|                   |                             | ファスト モード     | 0.6                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.26                           |      |     |     |

| $t_{LOW}$         | SCL クロック Low 期間             | スタンダード モード   | 4.7                            |      |     | μs  |

|                   |                             | ファスト モード     | 1.3                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.5                            |      |     |     |

| $t_{HIGH}$        | SCL クロックの High の時間          | スタンダード モード   | 4                              |      |     | μs  |

|                   |                             | ファスト モード     | 0.6                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.26                           |      |     |     |

| $t_{SU}; t_{STA}$ | 反復開始条件のセットアップ時間             | スタンダード モード   | 4.7                            |      |     | μs  |

|                   |                             | ファスト モード     | 0.6                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.26                           |      |     |     |

| $t_{HD}; t_{DAT}$ | データ ホールド時間                  | スタンダード モード   | 0                              | 3.45 |     | μs  |

|                   |                             | ファスト モード     | 0                              | 0.9  |     |     |

|                   |                             | ファスト モード プラス | 0                              |      |     |     |

| $t_{SU}; t_{DAT}$ | データ セットアップ時間                | スタンダード モード   | 250                            |      |     | ns  |

|                   |                             | ファスト モード     | 100                            |      |     |     |

|                   |                             | ファスト モード プラス | 50                             |      |     |     |

| $t_r$             | SDA 信号と SCL 信号の両方の立ち上がり時間   | スタンダード モード   |                                | 1000 |     | ns  |

|                   |                             | ファスト モード     | 20                             | 300  |     |     |

|                   |                             | ファスト モード プラス |                                | 120  |     |     |

| $t_f$             | SDA 信号と SCL 信号の両方の立ち下がり時間   | スタンダード モード   |                                | 300  |     | ns  |

|                   |                             | ファスト モード     | $20 \times V_{DD}/5.5V$<br>(1) | 300  |     |     |

|                   |                             | ファスト モード プラス | $20 \times V_{DD}/5.5V$<br>(1) | 120  |     |     |

| $t_{SU}; t_{STO}$ | 停止条件のセットアップ時間               | スタンダード モード   | 4                              |      |     | μs  |

|                   |                             | ファスト モード     | 0.6                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.26                           |      |     |     |

| $t_{BUF}$         | STOP 条件と START 条件の間のバスフリー時間 | スタンダード モード   | 4.7                            |      |     | μs  |

|                   |                             | ファスト モード     | 1.3                            |      |     |     |

|                   |                             | ファスト モード プラス | 0.5                            |      |     |     |

| $C_b$             | 各バスラインの容量性負荷                | スタンダード モード   |                                | 400  |     | pF  |

|                   |                             | ファスト モード     |                                | 400  |     |     |

|                   |                             | ファスト モード プラス |                                | 550  |     |     |

(1) VDD は SDA と SCL のプルアップ電圧

## 6.7 タイミング要件

|              |                                 |                               | 最小値 | 公称値 | 最大値 | 単位  |

|--------------|---------------------------------|-------------------------------|-----|-----|-----|-----|

| $f_{(SYNC)}$ | 同期クロック周波数範囲 (MODE/SYNC)         | 公称値 $f_{SW} = 1.5\text{MHz}$  | 1.3 |     | 2.0 | MHz |

| $f_{(SYNC)}$ | 同期クロック周波数範囲 (MODE/SYNC)         | 公称値 $f_{SW} = 2.25\text{MHz}$ | 1.8 |     | 2.7 | MHz |

| $f_{(SYNC)}$ | 同期クロック周波数範囲 (MODE/SYNC)         | 公称値 $f_{SW} = 2.5\text{MHz}$  | 2.0 |     | 3.0 | MHz |

| $f_{(SYNC)}$ | 同期クロック周波数範囲 (MODE/SYNC)         | 公称値 $f_{SW} = 3.0\text{MHz}$  | 2.5 |     | 3.3 | MHz |

| $D_{(SYNC)}$ | 同期クロック デューティ サイクル範囲 (MODE/SYNC) |                               | 45% |     | 55% |     |

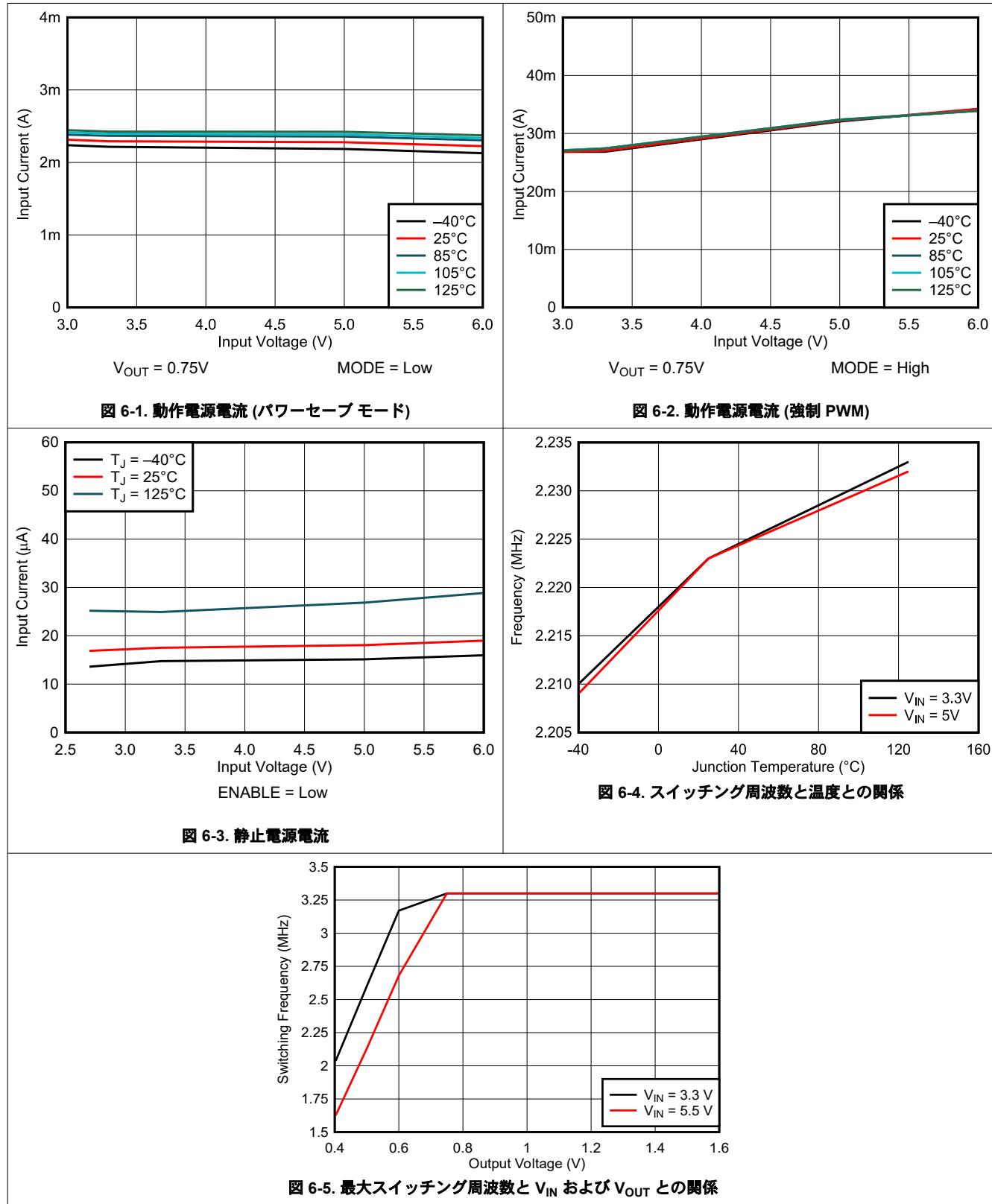

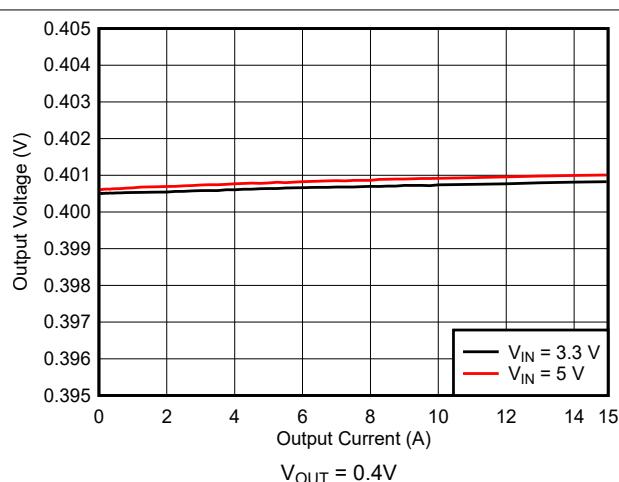

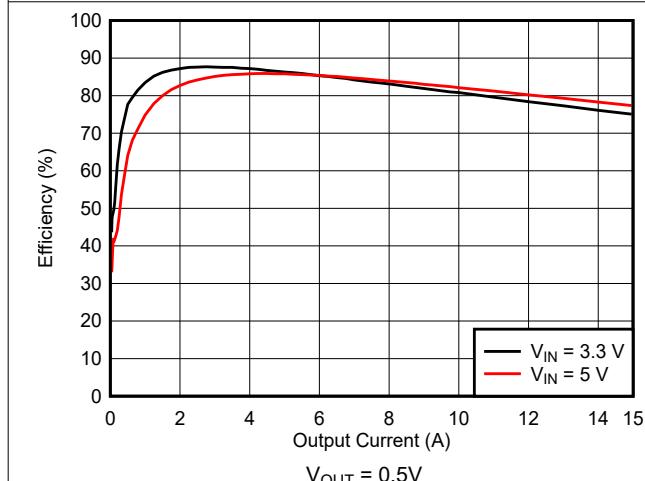

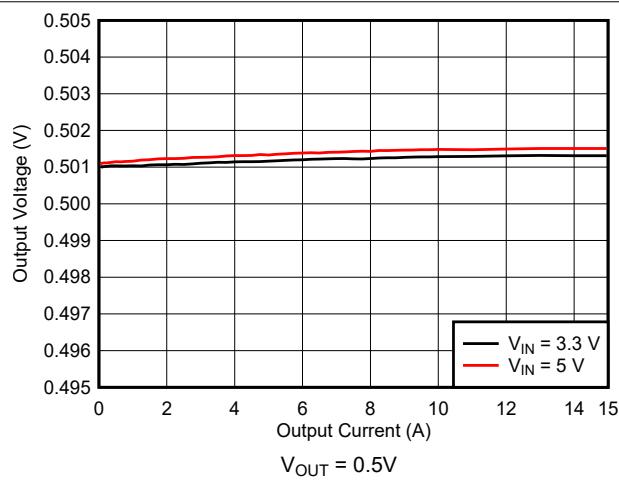

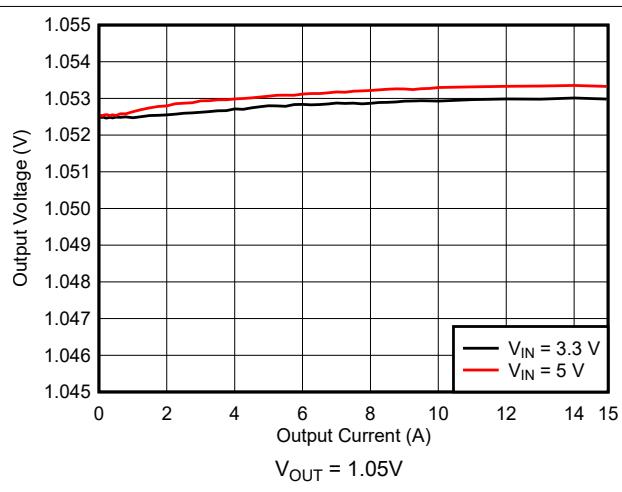

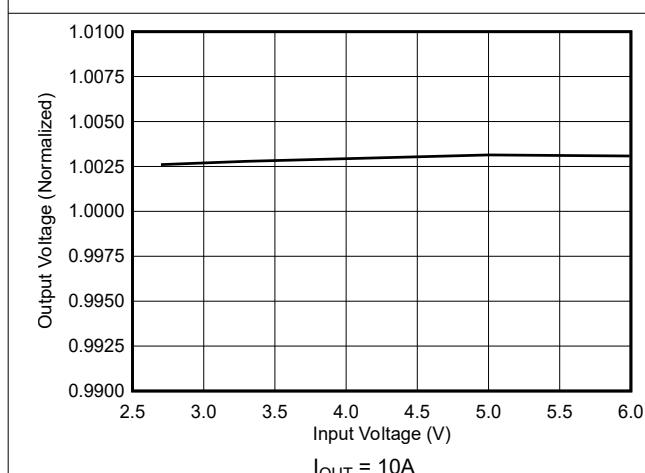

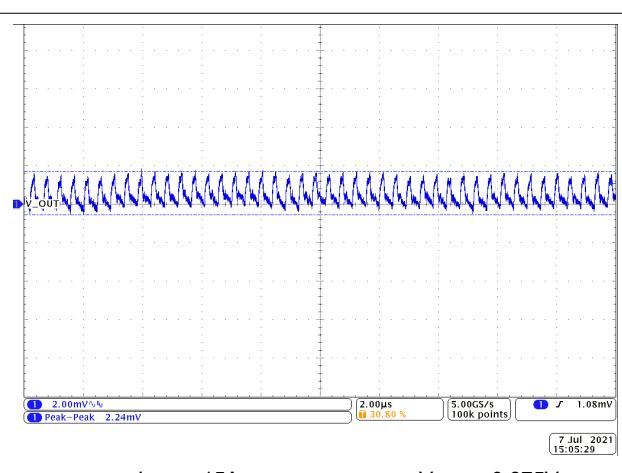

## 6.8 代表的特性

## 7 詳細説明

### 7.1 概要

TPS6287x デバイスは同期整流降圧型（バック）DC/DC コンバータです。これらのデバイスは固定周波数の DCS-Control トポロジを使用して、高速過渡応答を実現します。低出力電圧リップル、高い DC 精度、差動リモート センシングにより、これらのデバイスは最新の高性能プロセッサのコアを供給するのに最適です。

このファミリのデバイスには、6A、9A、12A、15A のデバイスが含まれています。出力電流能力をさらに高めるために、ユーザーは「スタック」で複数のデバイスを組み合わせることができます。たとえば、2 つの TPS62873 デバイスをスタックすると、30A の電流容量になります。1 つのデバイスが電流制限に過度に早く移行しないように、スタックの各デバイスの電流定格は同じにする必要があります。

各電流定格には、I<sup>2</sup>C インターフェイスを備えたフル機能のデバイスと、I<sup>2</sup>C インターフェイスのない制限機能のデバイスがあります（「[デバイスのオプション](#)」を参照）。以下の点を除き、I<sup>2</sup>C のあるデバイス バリアントとまったく同じように、I<sup>2</sup>C のないデバイス バリアントを使用できます。

- 未使用の SCL および SDA ピンを GND に接続する必要があります。

- ユーザーは、（固定された）工場出荷時のパラメータ設定および I<sup>2</sup>C デバイス バリアントでプログラム可能な機能を認識する必要があります。

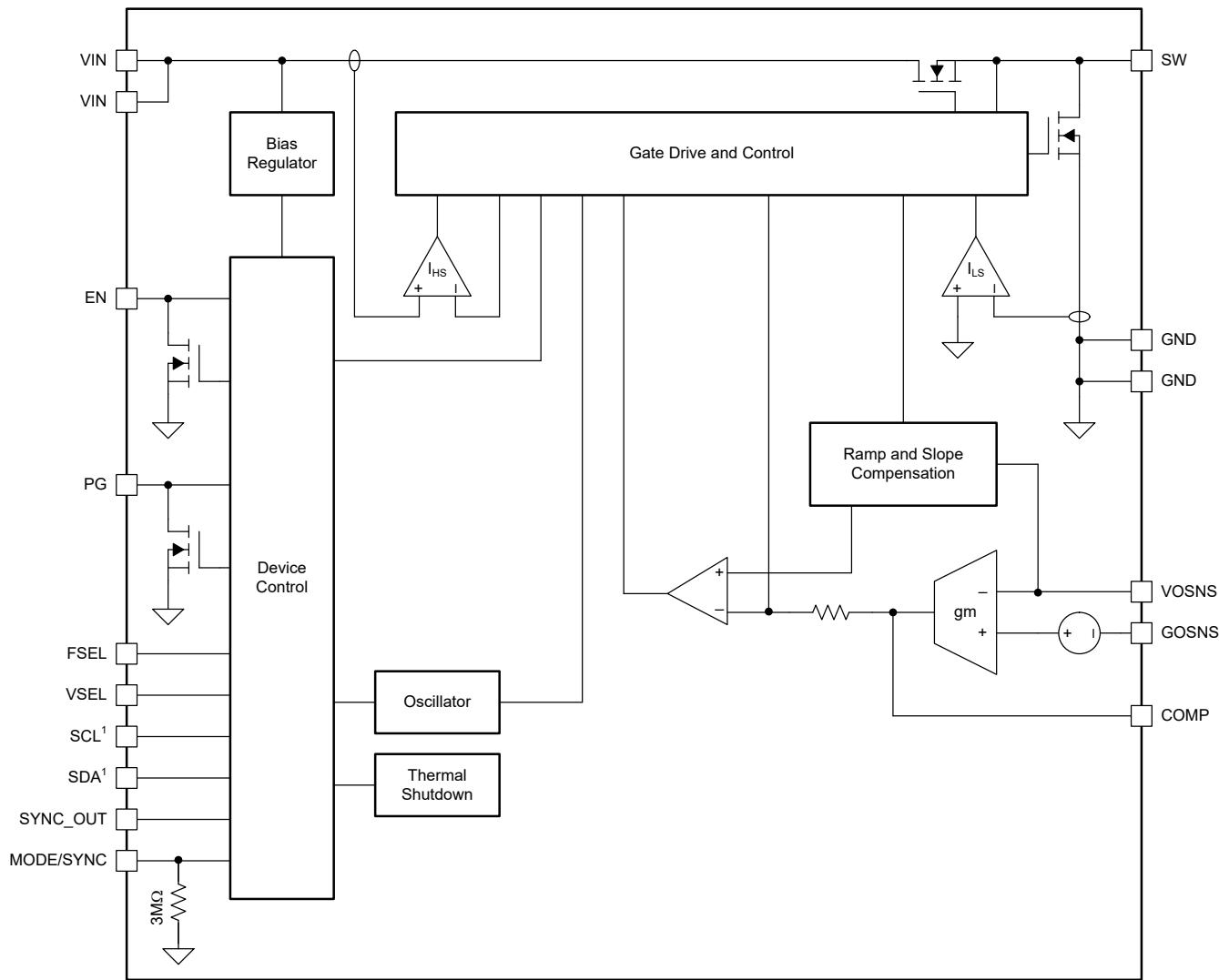

## 7.2 機能ブロック図

1. In device variants without I<sup>2</sup>C the SDA and SCL pins are internally connected, but the functionality of these pins is deactivated.

## 7.3 機能説明

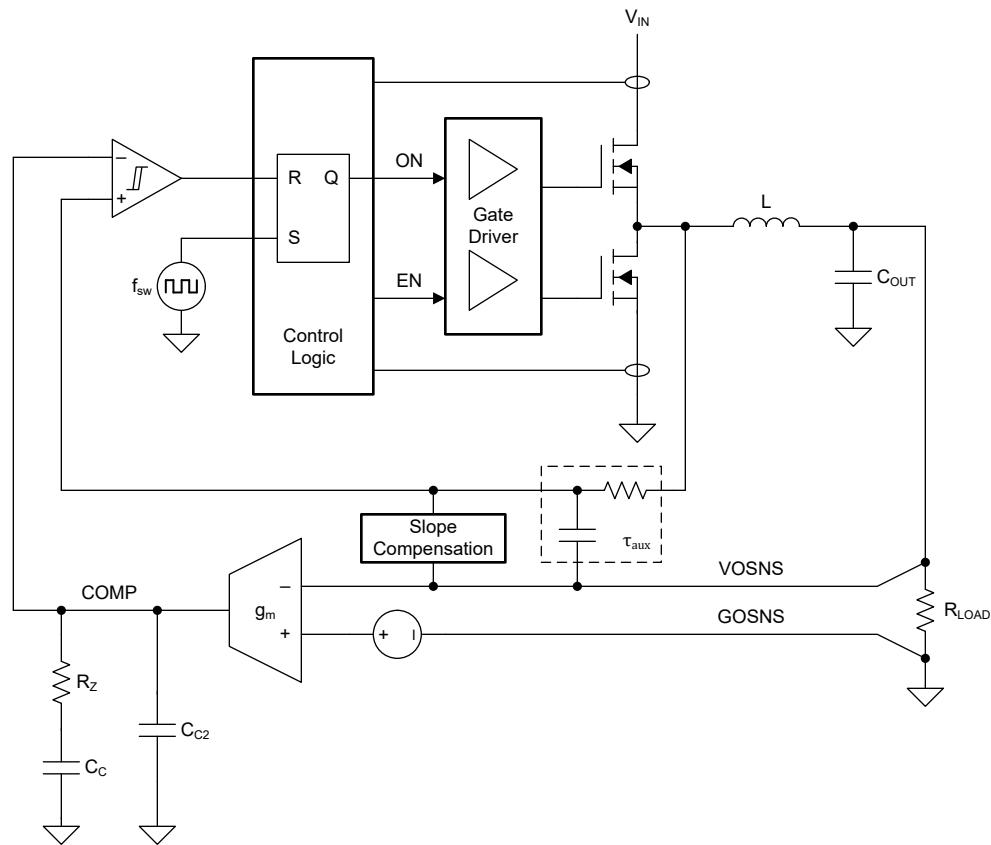

### 7.3.1 固定周波数の DCS-Control トポロジ

図 7-1 に、TPS6287x デバイスで使用されている固定周波数 DCS-Control トポロジの簡略ブロック図を示します。このトポロジは、内部でエミュレートされた電流ループ、中間の直接帰還ループ、外部の電圧レギュレーション ループで構成されています。このトポロジの詳細については、[SLYT846](#) を参照してください。

図 7-1. 固定周波数の DCS-Control トポロジ(簡略図)

### 7.3.2 強制 PWM モードとパワーセーブ モード

デバイスは、出力をレギュレートするための 3 つの方法でインダクタ電流を制御できます。

- ・ 連続インダクタ電流を使用するパルス幅変調 (PWM-CCM)

- ・ 不連続インダクタ電流によるパルス幅変調 (PWM-DCM)

- ・ 不連続インダクタ電流およびパルススキップによるパルス周波数変調 (PFM - DCM)

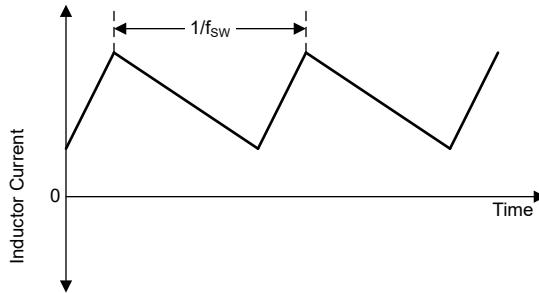

PWM-CCM でのオン時間は 式 1 で与えられます。出力電圧が非常に小さい場合、約 50ns の最小オン時間 ( $t_{on, min}$ ) により、スイッチング周波数が設定値から低下します。最小オン時間に達した場合でも、本デバイスはオフ時間を延長することで適切な出力電圧レギュレーションを維持します。

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \times f_{SW}} \quad (1)$$

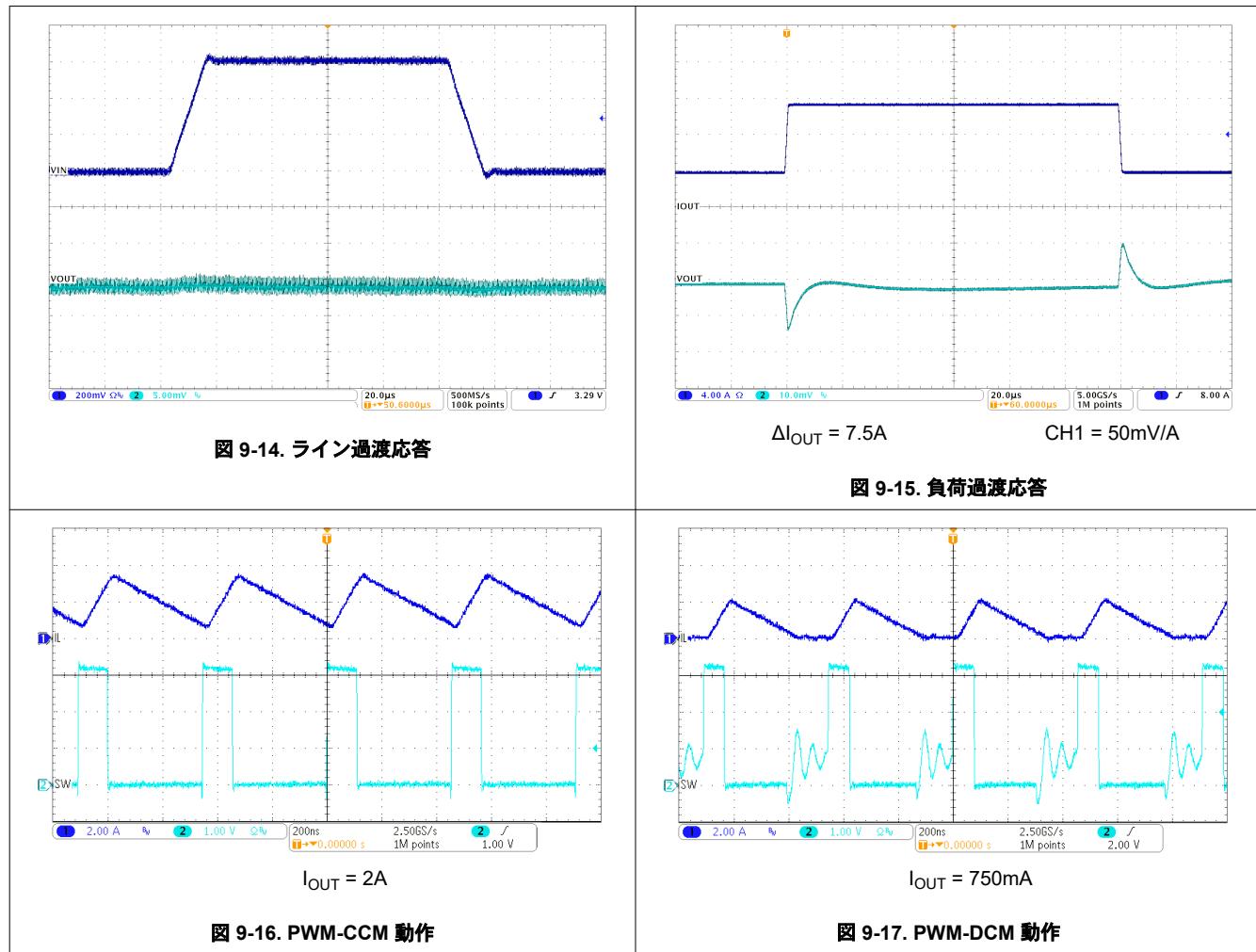

PWM-CCM 動作中、デバイスは一定の周波数でスイッチングを行い、インダクタ電流は連続的です (図 7-2 を参照)。PWM 動作は、最小の出力電圧リップルと最高の過渡性能を達成します。

図 7-2. 連続導通モード (PWM-CCM) 電流波形

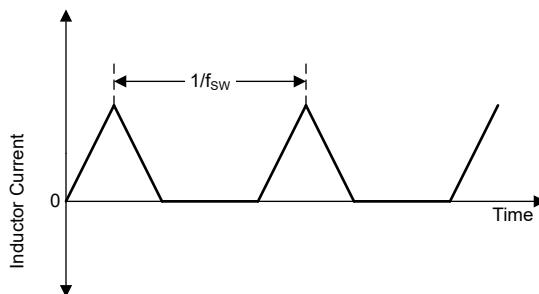

PWM-DCM 動作中、デバイスは一定の周波数でスイッチングを行い、インダクタ電流は不連続です (図 7-3 を参照)。このモードでは、デバイスはピーク インダクタ電流を制御し、選択したスイッチング周波数を維持しながら、出力のレギュレーションを維持することができます。

デバイスが PWM-DCM になる出力電流スレッショルドを計算するには、式 2 を使用します。

$$I_{OUT(PCM-DCM)} = \frac{(V_{IN} - V_{OUT})}{2L} t_{ON} \quad (2)$$

$t_{ON}$  になります (式 1 に基づく)。

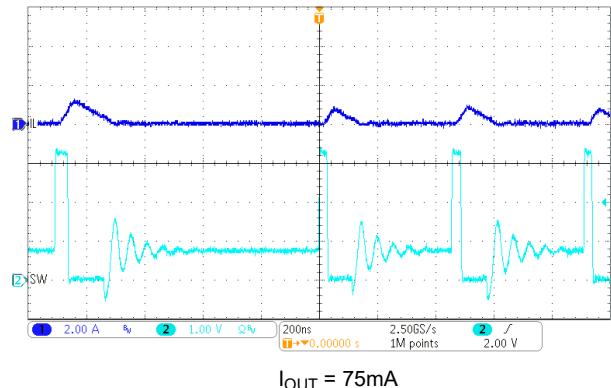

図 7-3. 不連続導通モード (PCM/DCM) 電流波形

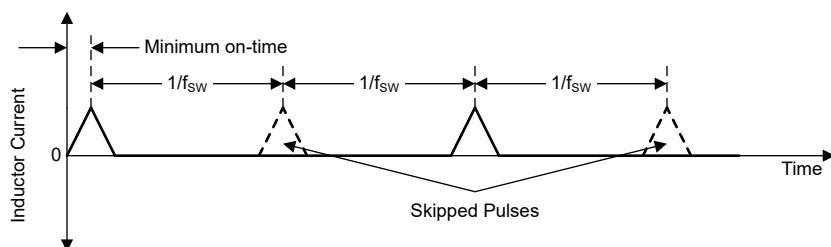

PFM-DCM 動作中、デバイスはピーク インダクタ電流を一定に維持し (コンバータの最小オン時間に対応するレベル)、パルスをスキップして出力をレギュレートします (図 7-4 を参照)。PFM - DCM 動作中に発生するスイッチング パルスは、内部クロックに同期されます。

図 7-4. 不連続導通モード (PFM-DCM) 電流波形

デバイスが PWM-DCM から PFM-DCM に変化する出力電流スレッショルドを計算するには、式 3 を使用します。

$$I_{OUT(PFM-DCM)} = \frac{V_{IN} \times t_{ON\_min\_PFM}}{2} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L} \quad (3)$$

$t_{ON\_min\_PFM}$  は PFM—DCM における約 20ns の最小オン時間です。

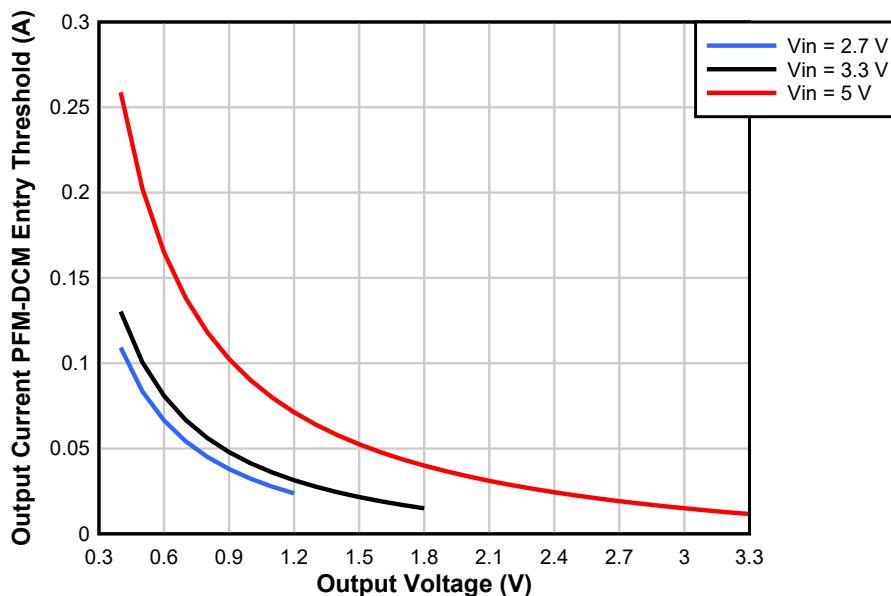

図 7-5 に、スイッチング周波数が 2.25MHz の場合に、このスレッショルドが通常  $V_{IN}$  と  $V_{OUT}$  によってどのように変化するかを示します。

$$f_{SW} = 2.25\text{MHz} \text{ and } L = 110\text{nH}$$

図 7-5. 出力電流 PFM-DCM エントリ スレッショルド

ユーザーは、強制 PWM (FPWM) モードまたはパワーセーブ モード (PSM) のいずれかを使用するようにデバイスを構成できます。

- 強制 PWM モードでは、デバイスは常に PWM-CCM を使用します。

- パワーセーブ モードでは、このデバイスは中負荷および高負荷で PWM-CCM、低負荷で PWM-DCM、非常に低負荷で PFM -DCM を使用します。各種動作モード間の遷移はシームレスに行われます。

表 7-1 に、本デバイスの動作モードを制御する MODE/SYNC ピンの機能表と CONTROL1 レジスタの FPWMEN ビットを示します。

表 7-1. FPWM モードとパワーセーブ モードの選択

| MODE/SYNC ピン | FPWMEN ビット | 動作モード | 注記                  |

|--------------|------------|-------|---------------------|

| Low          | 0          | PSM   | スタック構成では使用しないでください。 |

|              | 1          | FPWM  |                     |

| High         | X          | FPWM  |                     |

| 同期クロック       | X          | FPWM  |                     |

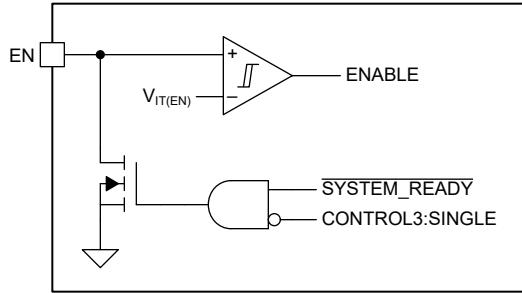

### 7.3.3 高精度イネーブル

イネーブル (EN) ピンは双方で、2 つの機能を持ちます。

- 入力として、EN はデバイスの DC/DC コンバータを有効化/無効化します。

- 出力として、EN はスタック構成内の他のデバイスに対して SYSTEM\_READY 信号を提供します。

図 7-6. 機能ブロック図を有効にする

EN ピンに接続された内部オープンドレイントランジスタがあるため、低インピーダンスのソースからこのピンを直接駆動しないでください。代わりに、抵抗を使用して、EN ピンに流れる電流を制限します (セクション 9 を参照)。

VIN ピンに電源が初めて供給されると、デバイスは非揮発メモリからデフォルトのレジスタ設定を読み込み、VSEL、FSEL、および SYNC\_OUT ピンの状態を読み取るまで、EN ピンを low に保持します。また、サーマル シャットダウンや過電圧ロックアウトなどの故障が発生した場合も、デバイスは EN を Low にプルします。スタック構成では、すべてのデバイスが共通のイネーブル信号を共有します。これは、スタック内の「すべての」デバイスが初期化を完了するまで、スタック内の DC/DC コンバータのスイッチングを開始できないことを意味します。同様に、スタック内の 1 つ以上のデバイスに故障が発生すると、スタック内のすべてのコンバータが無効化されます (セクション 7.3.17 を参照)。

スタンダード (非スタック) アプリケーションでは、ユーザーが CONTROL3 レジスタで SINGLE = 1 を設定すると、EN ピンのアクティブ プルダウンを無効にすることができます。SINGLE = 1 の場合 (デバイスの初期化中に EN ピンは「常に」プルダウンされる)、フォルト条件は EN ピンに影響を与えません。スタックアプリケーションでは、SINGLE = 0 であることを確認してください。

内部 SYSTEM\_READY 信号が low のとき (つまり、初期化が完了し、フォルト条件がないとき)、内部オープンドレイントランジスタはハイインピーダンスであり、EN ピンは標準入力と同様に機能します。EN ピンが high レベルになると、デバイスの DC/DC コンバータが有効になります。low レベルは DC/DC コンバータを無効化します (I<sup>2</sup>C インターフェイスは、デバイスが初期化を完了するとすぐに有効になり、内部 ENABLE または SYSTEM\_READY 信号の状態には影響されません)。

EN ピンが Low レベルになると、デバイスは強制的にシャットダウンします。シャットダウン中、電力段の MOSFET がオフになり、内部制御回路が無効化され、デバイスの消費電流は 20 $\mu$ A (標準値) のみです。

EN ピンの立ち上がりしきい値電圧は 1.0V、立ち下がりしきい値電圧は 0.9V です。スレッショルド電圧の許容誤差は  $\pm 30\text{mV}$  であるため、ユーザーは EN ピンを使用して正確なオン/オフ制御を実現できます。

VIN ピンに電力が供給されても、EN ピンのトグルは負荷されたデフォルトのレジスタ設定をリセットしません。

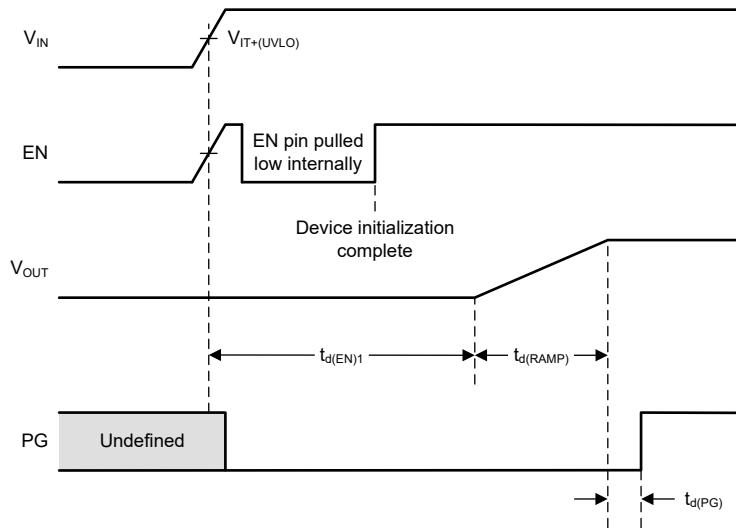

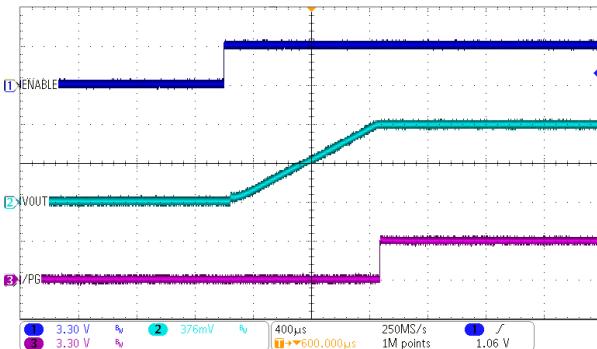

#### 7.3.4 スタートアップ

VIN ピンの電圧が正方向の UVLO スレッショルドを超えると、デバイスは次のように初期化されます。

- デバイスは、EN ピンを Low にプルします。

- デバイスは、内部リファレンス電圧を無効にします。

- デバイスは VSEL、FSEL、および SYNC\_OUT ピンの状態を読み取ります。

- デバイスは、デフォルト値をデバイスのレジスタにロードします。

初期化が完了すると、デバイスは I<sup>2</sup>C 通信を有効にし、EN ピンを解放します。これで、EN ピンを制御する外部回路によってデバイスの動作が決定されます。

- EN ピンが low になると、デバイスは無効化されます。ユーザーはデバイス レジスタへの書き込みと読み取りはできませんが、DC/DC コンバータは動作しません。

- EN ピンが high の場合、デバイスは有効です。ユーザーはデバイス レジスタへの書き込みと読み取りを行うことができ、少しの遅延の後に DC/DC コンバータが出力の立ち上げを開始します。

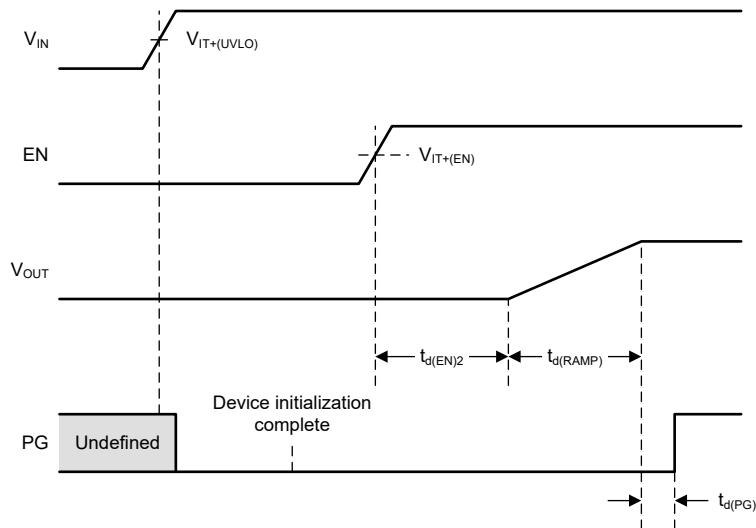

図 7-7 に、EN ピンが抵抗を経由して  $V_{IN}$  にプルアップされたときのスタートアップ シーケンスを示します。

図 7-7. EN が  $V_{IN}$  にプルアップされたときのスタートアップタイミング

図 7-8 に、外部信号が EN ピンに接続されている場合のスタートアップ シーケンスを示します。

図 7-8. 外部信号が EN ピンに接続されている場合のスタートアップタイミング

CONTROL2 レジスタの SSTIME[1:0] ビットを使用して、ソフトスタートランプの持続時間を選択します。

- $t_d(RAMP) = 500\mu s$

- $t_d(RAMP) = 1ms$  (デフォルト)

- $t_d(RAMP) = 2ms$

- $t_d(RAMP) = 4ms$

ユーザーが以下のようにプログラムしている場合は、デバイスのソフトスタート シーケンスがすでに開始されたとき、ソフトスタート シーケンスが完了するまで、デバイスは新しい値を無視します。

- 新しい出力電圧設定ポイント(VSET[7:0])

- 出力電圧範囲 (VRANGE[1:0])

- ソフトスタート時間 (SSTIME[1:0]) 設定

ソフトスタート中に VSET[7:0] の値をユーザーが変更すると、デバイスは最初にソフトスタートシーケンスが開始した時点の VSET[7:0] の値に上昇します。そして、ソフトスタートが完了すると、デバイスは新しい値まで上昇または下降します。

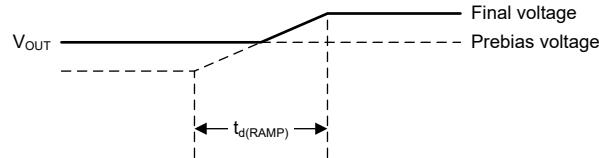

デバイスはプリバイアス出力の起動ができます。この場合、内部電圧ランプの一部のみが外部から検出されます (図 7-9 を参照)。

図 7-9. プリバイアス出力の起動

スタートアップ ランプ中は、他の構成設定や動作条件に関係なく、デバイスは「常に」DCM で動作することに注意してください。

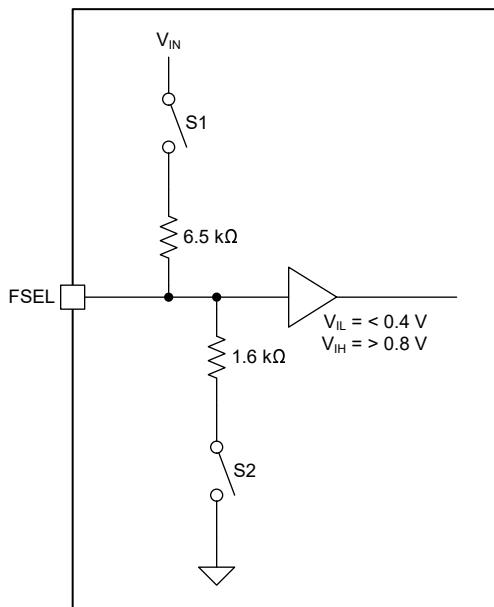

### 7.3.5 スイッチング周波数の選択

デバイスの初期化時に、デバイスの抵抗/デジタル コンバータによって FSEL ピンの状態が決定され、表 7-2 に従って DC/DC コンバータのスイッチング周波数が設定されます。

表 7-2. スイッチング周波数の選択肢

| FSEL ピン <sup>(1)</sup>   | スイッチング周波数 |

|--------------------------|-----------|

| GND への短絡                 | 1.5MHz    |

| 6.2kΩ から GND へ           | 2.25MHz   |

| 47kΩ を V <sub>IN</sub> へ | 2.5MHz    |

| V <sub>IN</sub> への短絡     | 3MHz      |

(1) 信頼性の高い電圧設定を得るため、FSEL ピンに接続された浮遊電流バスが存在しないこと、および FSEL ピンと GND の間の寄生容量が 100pF 未満であることを確認します。

図 7-10 に、FSEL ピンの状態を検出するために使用される R2D コンバータの簡略ブロック図を示します (同一の回路が VSEL ピンの状態の検出にも使用されます。セクション 7.3.6.2 を参照)。

図 7-10. FSEL R2D コンバータの機能ブロック図

FSEL ピンの状態の検出は次のように動作します。

最上位ビット (MSB) を検出するため、回路は S1 と S2 を開き、FSEL ピンに high または low レベルが接続されているかどうかを入力バッファが検出します。

最下位ビット (LSB) を検出する場合：

- MSB が 0 の場合、回路は S1 を閉じます。入力バッファが high レベルを検出すると、 $LSB = 1$  になります。回路が low レベルを検出すると、 $LSB = 0$  になります。

- MSB が 1 の場合、回路は S2 を閉じます。入力バッファが low レベルを検出すると、 $LSB = 0$  になります。回路が high レベルを検出すると、 $LSB = 1$  になります。

### 7.3.6 出力電圧設定

#### 7.3.6.1 出力電圧範囲

このデバイスは、4 つの電圧範囲に対応しています。CONTROL2 レジスタの VRANGE[1:0] ビットは、アクティブにする範囲を制御します (表 7-3 を参照)。デバイス初期化後のデフォルトの出力電圧範囲は 0.4V ~ 1.675V で、5mV 刻みです。

表 7-3. 電圧レンジ

| VRANGE[1:0] | 電圧レンジ                       |

|-------------|-----------------------------|

| 0b00        | 0.4V ~ 0.71875V (1.25mV 刻み) |

| 0b01        | 0.4V ~ 1.0375V (2.5mV 刻み)   |

| 0b10        | 0.4V ~ 1.675V (5mV 刻み)      |

| 0b11        | 0.8V ~ 3.3V (10mV 刻み)       |

VRANGE[1:0] ビットの変更の後には、VSET[7:0] ビットの値が変化しない場合でも、VSET レジスタに書き込む必要があります。このシーケンスは、デバイスが新しい電圧範囲の使用を開始するために必要です。

0.8V ~ 3.35V の範囲に切り替えると、デバイスは内部リファレンスを 0.4V ~ 0.8V の範囲で切り替えます。変更中に発生する可能性のある出力電圧のオーバーシュートまたはアンダーシュートを防止するには、新しい範囲と古い範囲の両方で発生する出力電圧で VRANGE の変更を行う必要があります、VSET[7:0] ビットを新しい範囲と古い範囲の両方で同じ出力電圧に設定する必要があります。

正常に動作させるには、入力電圧は選択した出力電圧よりも 1.4V 以上高い必要があります。

I<sup>2</sup>C のないデバイス バリエントでは、出力電圧範囲は工場出荷時に 0.4V ~ 1.675V に設定されています。

#### 7.3.6.2 出力電圧の設定ポイント

選択した範囲と一緒に、VSET レジスタの VSET[7:0] ビットは、デバイスの出力電圧設定点を制御します (表 7-4 を参照)。

表 7-4. 起動時の電圧設定

| VRANGE[1:0] | 出力電圧の設定ポイント               |

|-------------|---------------------------|

| 0b00        | 0.4V + VSET[7:0] × 1.25mV |

| 0b01        | 0.4V + VSET[7:0] × 2.5mV  |

| 0b10        | 0.4V + VSET[7:0] × 5mV    |

| 0b11        | 0.8V + VSET[7:0] × 10mV   |

初期化時、デバイスは VSEL ピンの状態を読み取り、表 7-5 に従ってデフォルトの出力電圧を選択します。VSEL ピンはデバイスの I<sup>2</sup>C ターゲットアドレスも選択することに注意してください (表 7-10 を参照)。

表 7-5. デフォルトの出力電圧の設定ポイント

| VSEL ピン <sup>(1)</sup>     | 部品番号       | VSET[7:0] | 出力電圧の設定ポイント |

|----------------------------|------------|-----------|-------------|

| GND に 6.2kΩ                | TPS6287xZ0 | 0x50      | 800mV       |

|                            | TPS6287xZ1 | 0x28      | 600mV       |

|                            | TPS6287xZ2 | 0x14      | 500mV       |

|                            | TPS6287xZ4 | 0x5A      | 850mV       |

|                            | TPS6287xZ5 | 0x00      | 400mV       |

| GND への短絡                   | すべて        | 0x46      | 750mV       |

| V <sub>IN</sub> への短絡       | すべて        | 0x5F      | 875mV       |

| 47 kΩ から V <sub>IN</sub> へ | TPS6287xZ0 | 0x50      | 800mV       |

|                            | TPS6287xZ1 | 0x64      | 900mV       |

|                            | TPS6287xZ2 | 0x82      | 1050mV      |

|                            | TPS6287xZ4 | 0x78      | 1000mV      |

|                            | TPS6287xZ5 | 0x00      | 400mV       |

(1) 信頼性の高い電圧設定を得るため、VSEL ピンに接続された浮遊電流バスが存在しないこと、および VSEL ピンと GND の間の寄生容量が 100pF 未満であることを確認します。

デバイスがすでにソフトスタート シーケンスを開始している状態で、ユーザーが新しい出力電圧設定値 (VSET[7:0])、出力電圧範囲 (VRANGE[1:0])、またはソフトスタート時間 (SSTIME[1:0]) を設定しても、デバイスはソフトスタート シーケンスが完了するまでその新しい値を無視します。ソフトスタート中に VSET[7:0] の値をユーザーが変更すると、デバイスは最初にソフトスタート シーケンスが開始した時点の VSET[7:0] の値に上昇します。ソフトスタートが完了すると、新しい値まで上昇または下降します。

ユーザーが EN 信号が low の間に VSET[7:0]、VRAMP[1:0]、または SSTIME[1:0] を変更した場合、デバイスは次回ユーザーがデバイスを有効化したときに新しい値を使用します。

起動時、出力電圧は、VSEL ピンで設定された目標値まで上昇すると、I<sup>2</sup>C インターフェイス経由でデバイスにプログラムされた新しい値まで上昇または下降します。

### 7.3.6.3 デフォルト以外の出力電圧の設定ポイント

デフォルトの電圧範囲や電圧設定値の組み合わせがアプリケーションに適切でない場合は、ユーザーはデバイスを有効にする前に、I<sup>2</sup>C によってこれらの設定を変更することができます。その後、ユーザーが EN ピンを high にすると、デバイスは所望の起動電圧で立ち上ります。

ユーザーが「デバイスのランプ中」に I<sup>2</sup>C を使用してデバイス設定を変更した場合は、ランプが完了するまでの変更は無視されることに注意してください。

### 7.3.6.4 ダイナミック電圧スケーリング

DC/DC コンバータがデバイスの動作中に出力電圧の設定ポイントを変更すると、デバイスは制御された方法で新しい電圧設定へと上昇または下降します。

CONTROL1 レジスタの VRAMP[1:0] ビットは、DVS 中にデバイスがある電圧から別の電圧に上昇するときのスルーレートを設定します (表 7-6 を参照)。

表 7-6. 動的電圧 スケーリング スルーレート

| VRAMP[1:0] | DVS スルーレート         |

|------------|--------------------|

| 0b00       | 10mV/μs (0.5μs/刻み) |

| 0b01       | 5mV/μs (1μs/刻み)    |

| 0b10       | 1.25mV/μs (5μs/刻み) |

| 0b11       | 0.5mV/μs (10μs/刻み) |

出力をより高い電圧に上げるには、追加の出力電流が必要になることに注意してください。そのため、DVS 中、コンバータは次の式で求められる合計出力電流を生成する必要があります。

$$I_{OUT} = I_{OUT(DC)} + C_{OUT} \frac{dV_{OUT}}{dt} \quad (4)$$

ここで、

- $I_{OUT}$  はより高い電圧に上昇している間にコンバータが生成する必要がある合計電流です。

- $I_{OUT(DC)}$  は DC 負荷電流です。

- $C_{OUT}$  は合計出力キャパシタンスです。

- $dV_{OUT}/dt$  は出力電圧のスルーレートです (0.5mV/μs ~ 10mV/μs の範囲でプログラマブル)。

正常に動作させるには、DVS 中の合計出力電流がデバイスの電流制限を超えないことを確認してください。

### 7.3.7 補償 (COMP)

COMP ピンは、外部補償ネットワークの接続ポイントです。代表的なアプリケーションでは、GOSNS に対する直列接続の抵抗とコンデンサで十分です。直列接続の抵抗は、広範囲の動作条件に対してループ応答を最適化するのに十分な範囲も提供します。

複数のデバイスをスタック構成で使用する場合、すべてのデバイスは共通の補償回路を共有し、COMP ピンによってデバイス間の電流共有が等しくなります (セクション 7.3.17 を参照)。

### 7.3.8 モード選択およびクロック同期 (MODE/SYNC)

MODE/SYNC ピンに High レベルが印加されると、強制 PWM 動作が選択されます。MODE/SYNC ピンが low レベルになると、パワーセーブ動作が選択され、デバイスは負荷条件に応じて PWM と PFM の間を自動的に遷移します。

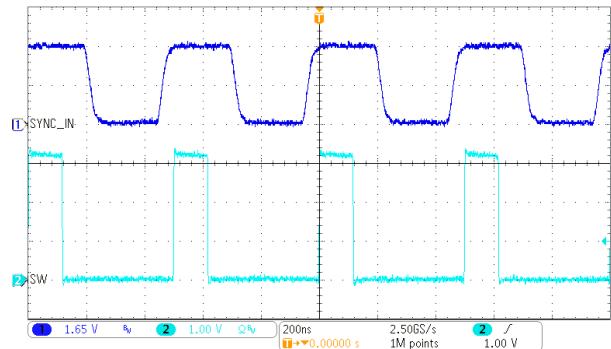

ユーザーが MODE/SYNC ピンに有効なクロック信号を印加すると、デバイスはスイッチング サイクルを外部クロックに同期させ、強制 PWM 動作を自動的に選択します。

MODE/SYNC ピンは CONTROL1 レジスタの FPWMEN ビットと論理 OR されます (表 7-1 を参照)。

複数のデバイスをスタック構成で使用する場合、2 次側デバイスの MODE/SYNC ピンはクロック信号の入力として機能します (セクション 7.3.17 を参照)。

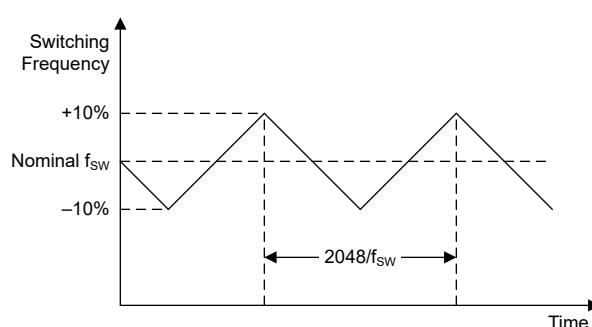

### 7.3.9 スペクトラム拡散クロック処理 (SSC)

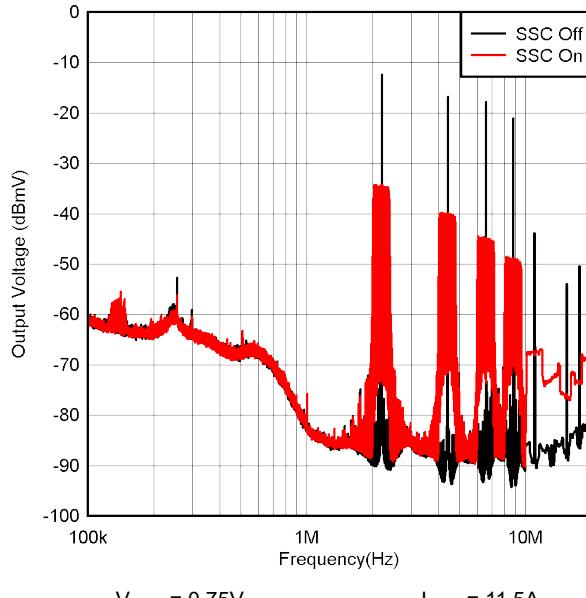

このデバイスはスペクトラム拡散クロック機能を備え、電磁干渉 (EMI) を低減できます。SSC 機能がアクティブのとき、デバイスは公称値の  $\pm 10\%$  までスイッチング周波数を変調します。周波数変調は三角波特性を持っています (図 7-11 を参照)。

図 7-11. スペクトラム拡散クロック処理の動作

SSC 機能を使用するには、次のことを確認します。

- CONTROL1 レジスタの SSCEN = 1。

- クロックが外部クロックに同期していないこと。

TI は、SSC を使用する場合は FPWM 動作を推奨しますが、PSM 動作で SSC を使用できます。SSC 機能を無効化するには、CONTROL1 レジスタで **SCCEN = 0** であることを確認します。

スタック構成の複数のデバイスで SSC 機能を使用するには、1 次側コンバータが内部発振器から動作し、すべての 2 次側コンバータが 1 次側クロックに同期するようにします (図 7-15 を参照)。

### 7.3.10 出力放電

このデバイスには出力放電機能が備わっており、デバイスが無効化された際に出力電圧が一定の速度で低下するようにし、デバイスがオフの間も出力電圧を 0V 付近に保ちます。CONTROL1 レジスタで **DISCHEN = 1** のとき、出力放電機能は有効にされます。出力放電機能はデフォルトで有効になっています。

有効になっている場合、デバイスは以下の条件下で出力を放電します：

- EN ピンには low レベルが印加されている。

- CONTROL1 レジスタの **SWEN = 0**。

- サーマルシャットダウンイベントが発生します。

- UVLO イベントが発生します。

- OVLO イベントが発生します。

出力放電機能は、ユーザーが電源投入後に一度でもデバイスを有効化しない限り使用できません。電源オフ時、デバイスは内部電源電圧が約 1.8V を上回っている限り、出力の放電を継続します。

### 7.3.11 低電圧誤動作防止 (UVLO)

デバイスには低電圧誤動作防止機能があり、電源電圧が低すぎて正常な動作ができない場合、デバイスは無効化されます。UVLO 機能の負方向スレッショルドは 2.5V (標準値) です。電源電圧がこの値を下回ると、デバイスはスイッチングを停止します。CONTROL1 レジスタで **DISCHEN = 1** の場合、出力放電をオンにします。また、EN ピンが Low になり、スタッ�内の他のすべてのデバイスが無効になります。デバイスは自動的にスイッチングを再開します。電源電圧が 2.6V (標準値) を上回ると、デバイスは新しいソフトスタートシーケンスを開始します。

### 7.3.12 過電圧誤動作防止 (OVLO)

デバイスには過電圧ロックアウト機能があり、電源電圧が高すぎて正常な動作ができない場合、DC/DC コンバータが無効になります。OVLO 機能の正方向スレッショルドは 6.3V (標準値) です。電源電圧がこの値を超えると、デバイスはスイッチングを停止し、CONTROL1 レジスタで **DISCHEN = 1** に設定されている場合は、出力放電機能が有効になります。

デバイスは自動的にスイッチングを再開します。電源電圧が 6.2V (標準値) を下回ると、デバイスは新しいソフトスタートシーケンスを開始します。

### 7.3.13 過電流保護

#### 7.3.13.1 サイクル単位の電流制限

ピーク インダクタ電流がハイサイド電流制限のしきい値を超えると、デバイスはハイサイド スイッチをオフにし、ローサイドスイッチをオンにしてインダクタ電流を減少させます。デバイスは、インダクタ電流がローサイド電流制限のしきい値を下回った場合にのみ、再びハイサイド スイッチをオンにします。

なお、電流制限コンパレータの伝播遅延により、実際の電流制限スレッショルドは、「電気的特性」に記載された DC 値より大きくなる場合があります。実際には、次の式で電流制限を求められます。

$$I_L = I_{LIMH} + \left( \frac{V_{IN} - V_{OUT}}{L} \right) \times t_{pd} \quad (5)$$

ここで

- $I_L$  はインダクタ電流です。

- $I_{LIMH}$  は DC で測定されるハイサイド電流制限スレッショルドです。

- $V_{IN}$  は入力電圧

- $V_{OUT}$  は出力電圧です。

- $L$  は、ピーク電流レベルでの実効インダクタンスです。

- $t_{pd}$  は電流制限コンパレータの伝播遅延です (通常は 50ns)。

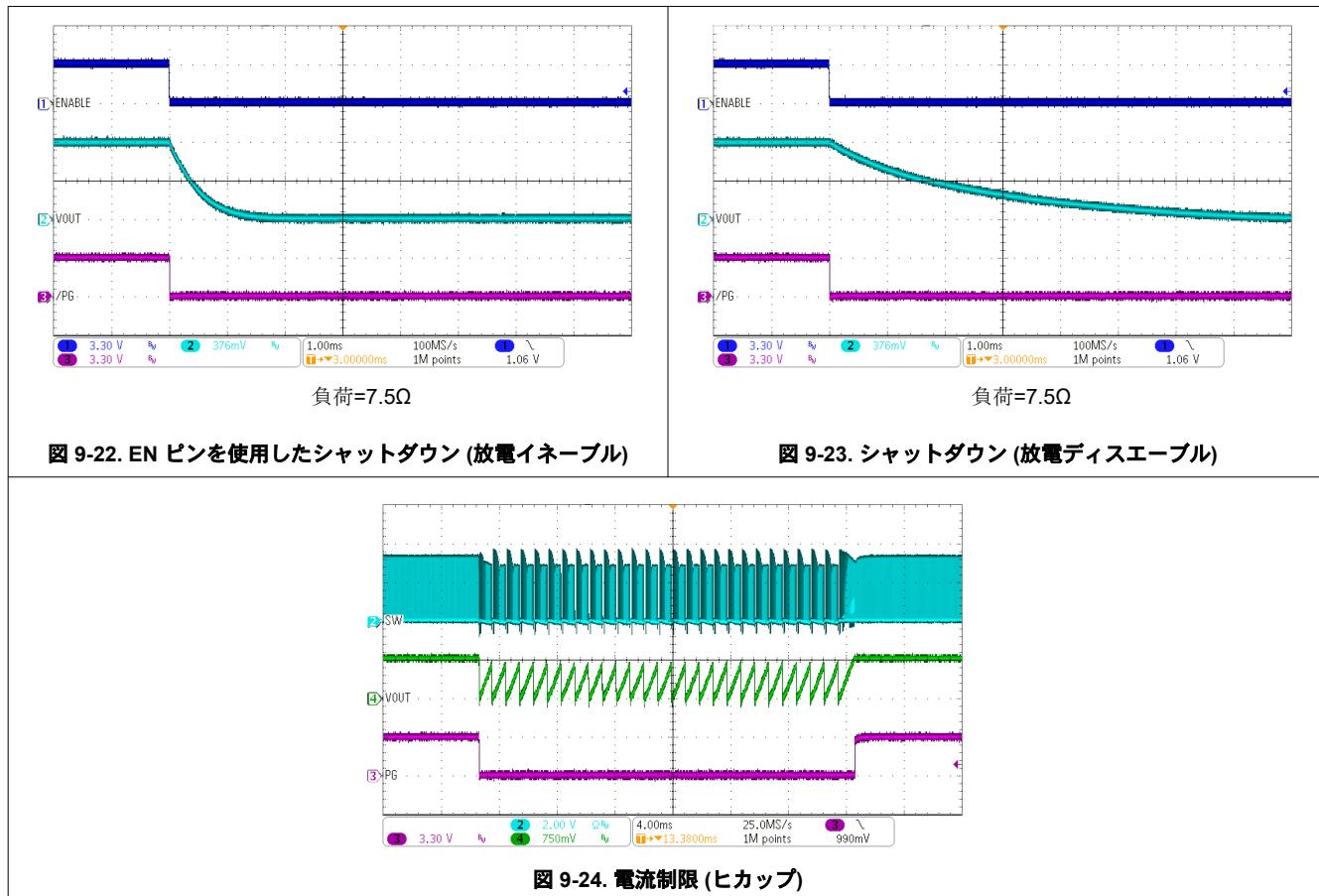

### 7.3.13.2 ヒカップ モード

ヒカップ動作を有効にするには、CONTROL1 レジスタが HICCUPEN = 1 であることを確認します。

ヒカップ動作が有効になり、ハイサイドスイッチ電流が連続 32 スイッチングサイクルでハイサイド電流制限スレッショルドを超えると、デバイスは次の動作を行います。

- 128 $\mu$ s のスイッチングを停止します。その後、デバイスは自動的にスイッチングを再開します (デバイスは新しいソフトスタートシーケンスを開始)。

- STATUS レジスタの HICCUP ビットをセットする。

- PG ピンを low にします過負荷状態が解消され、デバイスが正常に起動して出力電圧をレギュレートできるまで、PG ピンは Low のまま維持されます。パワーグッド機能にはグリッチ除去回路があり、パワーグッド信号の立ち上がりエッジを 40 $\mu$ s (標準値) 遅延させることに注意してください。

ヒカップ動作は、出力過負荷状態が存在する限り、電流制限内の 32 サイクルで繰り返されます。その後、128 $\mu$ s の一時停止と、ソフトスタートが試みられます。

過負荷状態が解消されたときにユーザーが STATUS レジスタを読み取ると、デバイスは HICCUP ビットをクリアします。

### 7.3.13.3 電流制限モード

電流制限モードを有効にするには、CONTROL1 レジスタが HICCUPEN = 0 であることを確認します。

電流制限動作が有効になっているとき、過負荷状態が存在する間、デバイスはハイサイドスイッチの電流をサイクルごとに制限します。デバイスが連続 4 回以上のスイッチング サイクルにわたってハイサイド スイッチ電流を制限する場合、デバイスは STATUS レジスタで ILIM = 1 に設定します。

過負荷状態が解消された後にユーザーが STATUS レジスタを読み取ると、デバイスは ILIM ビットをクリアします。

### 7.3.14 パワーグッド (PG)

パワーグッド (PG) ピンは双方向で、次の 2 つの機能を備えています。

- スタンドアロン構成の場合、またスタック構成の主要デバイスでは、PG ピンはコンバータまたはスタックのステータスを示すオーブンドレイン出力です。

- スタック構成におけるセカンダリ デバイスでは、PG ピンは入力として機能し、ソフトスタートシーケンスが完了し、スタック内のすべてのコンバータが DCM スイッチングから CCM スイッチングに切り替え可能な状態であることを示します。

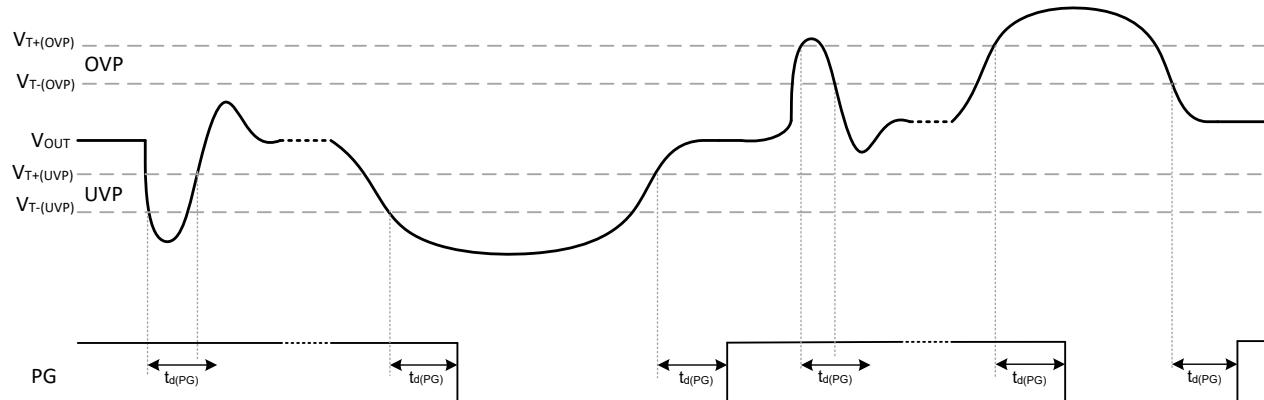

図 7-12. PG のタイミング

### 7.3.14.1 スタンドアロンまたは 1 次側デバイスの動作

PG ピンの主な目的は、出力電圧がレギュレート状態であるかどうかを示すことですが、PG ピンはデバイスがサーマルシャットダウン状態でも無効化状態でも示されます。表 7-7 に、スタンドアロンまたは 1 次側デバイスにおける PG ピンの動作をまとめます。

表 7-7. パワーグッド機能表

| $V_{IN}$                                 | EN | $V_{OUT}$                                                 | ソフトスタート | PGBLNKDVS         | $T_J$          | PG        |

|------------------------------------------|----|-----------------------------------------------------------|---------|-------------------|----------------|-----------|

| $V_{IN} < 2V$                            | X  | X                                                         | X       | X                 | X              | 未定義       |

| $V_{IT-(UVLO)} \geq V_{IN} \geq 2V$      | X  | X                                                         | X       | X                 | X              | Low       |

| $V_{IT-(OVLO)} > V_{IN} > V_{IT+(UVLO)}$ | H  | X                                                         | X       | X                 | X              | Low       |

|                                          |    | X                                                         | アクティブ   | X                 | X              | Low       |

|                                          |    | $V_{OUT} > V_{T+(OVP)} \text{ or } V_{OUT} < V_{T-(UVP)}$ |         | 0                 | X              | Low       |

|                                          |    | X                                                         |         | 1<br>(DVS 非アクティブ) | X              | Low       |

|                                          |    | $V_{T-(OVP)} > V_{OUT} > V_{T+(UVP)}$                     |         | 1<br>(DVS アクティブ)  | $T_J < T_{SD}$ | ハイインピーダンス |

|                                          |    | X                                                         | X       | X                 |                | ハイインピーダンス |

| $V_{IN} > V_{IT+(OVLO)}$                 | X  | X                                                         | X       | X                 | $T_J > T_{SD}$ | Low       |

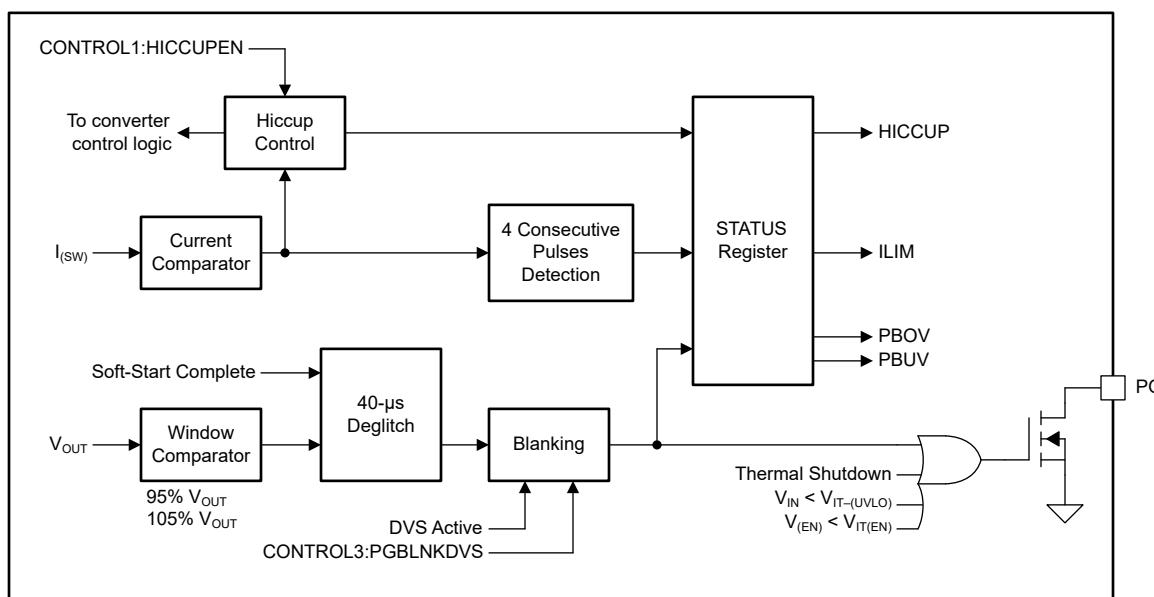

図 7-13 に、スタンドアロンまたは 1 次側デバイスのパワーグッド機能の機能ブロック図を示します。ウインドウコンパレータは出力電圧を監視し、出力電圧が公称出力電圧の 95% 未満（標準値）または公称電圧の 105% を上回る場合、コンパレータの出力が High になります。ウインドウコンパレータの出力はグリッチ除去されます：標準のグリッチ除去時間は 40 $\mu$ s。その後、オープンドレインの PG ピンの駆動に使用されます。

図 7-13. パワーグッド機能のブロック図 (スタンドアロンまたは 1 次側デバイス)

低電圧または過電圧出力イベントが発生すると、デバイスはそれぞれ STATUS レジスタで PBUV ビットまたは PBOV ビットを設定します。パワーバッド状態が解消された後にユーザーが STATUS レジスタを読み取ると、デバイスは PBOV および PBUV ビットをクリアします。

DVS 動作時は、ウインドウ コンパレータの電圧リファレンスはランプ出力電圧の設定点に追従します。DVS が FPWM モードの間、PG は通常 low になりません。これは、DVS ランプに従って出力電圧をアクティブに上昇または下降させて駆動するためです。パワーセーブ モードでは、出力電圧を引き下げるほど十分な負荷がなく、それがウインドウ コンパレータの制限内に留まるほど十分な速度でない場合、PG がランプダウン時に low になる可能性があります。FPWM モードとパワーセーブ モードの両方で、CONTROL3 レジスタに PGBLNKDVS = 1 を設定すると、デバイスは DVS ランプ時間中 (CONTROL1 レジスタに VRAMP[1:0] ビットで設定) パワーグッド ウインドウ コンパレータの出力を無視し、PG ピンをハイインピーダンスに維持します。DVS 時間が経過すると、PG は再度ウインドウ コンパレータの出力を反映します。

PG ピンは、以下の場合ウインドウ コンパレータの出力に関係なく常に low であることに注意してください。

- デバイスがサーマルシャットダウン中

- デバイスが無効化されている

- デバイスは低電圧誤動作防止または過電圧誤動作防止 (UVLO または OVLO) 状態にある

- デバイスがソフトスタート状態にある

小さな RC フィルタ (たとえば、 $1\text{k}\Omega + 10\text{pF}$ ) を PG ピンに追加して、高周波信号をフィルタします。

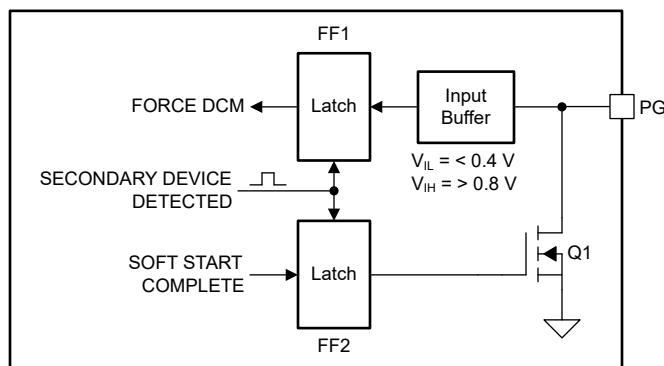

### 7.3.14.2.2 次デバイスの動作

図 7-14 に、2 次側デバイスにおけるパワーグッド機能の機能ブロック図を示します。初期化中、デバイスは FF1 および FF2 をリセットし、これによって PG ピンがプルダウンされ、デバイスが DCM で動作するように強制されます。デバイスがソフトスタートを完了すると、FF2 がリセットされ、Q1 がオフになります。しかし、スタック構成では、すべてのデバイスが同じ PG 信号を共有するため、スタック内の「すべての」デバイスがソフトスタートを完了するまで PG ピンは low のままになります。その場合 FF1 がリセットされコンバータが CCM で動作します。

図 7-14. パワーグッド機能のブロック図 (2 次側デバイス)

### 7.3.15 リモート センス

このデバイスには VOSNS と GOSNS の 2 つのピンがあり、出力電圧をリモートで検出できます。リモートセンシングにより、コンバータはポイント・オブ・ロードで出力電圧を直接検出し、出力電圧レギュレーションの精度を向上できます。

### 7.3.16 热警告およびシャットダウン

このデバイスは、2 レベルの過熱検出機能を備えています。

接合部温度が過熱警告スレッショルド  $150^\circ\text{C}$  (標準値) を上回ると、デバイスは STATUS レジスタの TWARN ビットを設定します。接合部温度が TWARN スレッショルド  $130^\circ\text{C}$  (標準値) を下回っているときにユーザーが STATUS レジスタを読み取ると、デバイスは TWARN ビットをクリアします。

接合部温度が  $170^\circ\text{C}$  (標準値) のサーマル シャットダウンのスレッショルドを上回ると、デバイスは次の動作を行います。

- スイッチングを停止する

- EN ピンをプルダウンする (CONTROL3 レジスタで SINGLE = 0 の場合)

- 出力放電を有効にする (CONTROL1 レジスタで DISCHEN = 1 の場合)

- STATUS レジスタの TSHUT ビットをセットする

- PG ピンを low にします

接合部温度が 150°C (標準値) のサーマル シャットダウンのスレッショルドを下回ると、デバイスは次の動作を行います。

- 新しいソフトスタート シーケンスから開始して、再度スイッチングを開始する

- EN ピンをハイ インピーダンス状態に設定する

- PG ピンをハイ インピーダンス状態に設定する

接合部温度が TSHUT スレッショルド 150°C (標準値) を下回っているときにユーザーが STATUS レジスタを読み取ると、デバイスは TSHUT ビットをクリアします。

すべてのデバイスが共通のイネーブル信号を共有するスタック構成では、1 つのデバイスのサーマル シャットダウン条件により、スタック全体が無効化されます。熱いデバイスが冷却されると、スタック全体が自動的に再びスイッチングを開始します。

### 7.3.17 スタック動作

ユーザーは「スタック」と呼ばれる方法で複数のデバイスを並列に接続することができます。たとえば、これにより、出力電流能力を高めたり、デバイスの接合部温度を下げたりすることができます。スタックは、1 つのプライマリデバイスと 1 つ以上のセカンダリデバイスで構成されます。初期化時に、各デバイスは SYNC\_OUT ピンを監視して、1 次側デバイスまたは 2 次側デバイスとして動作する必要があるかを判断します。

- SYNC\_OUT ピンとグランドの間に 47kΩ の抵抗を接続すると、そのデバイスは セカンダリ デバイスとして動作します。

- SYNC\_OUT ピンがハイ インピーダンス状態の場合、そのデバイスはプライマリ デバイスとして動作します。

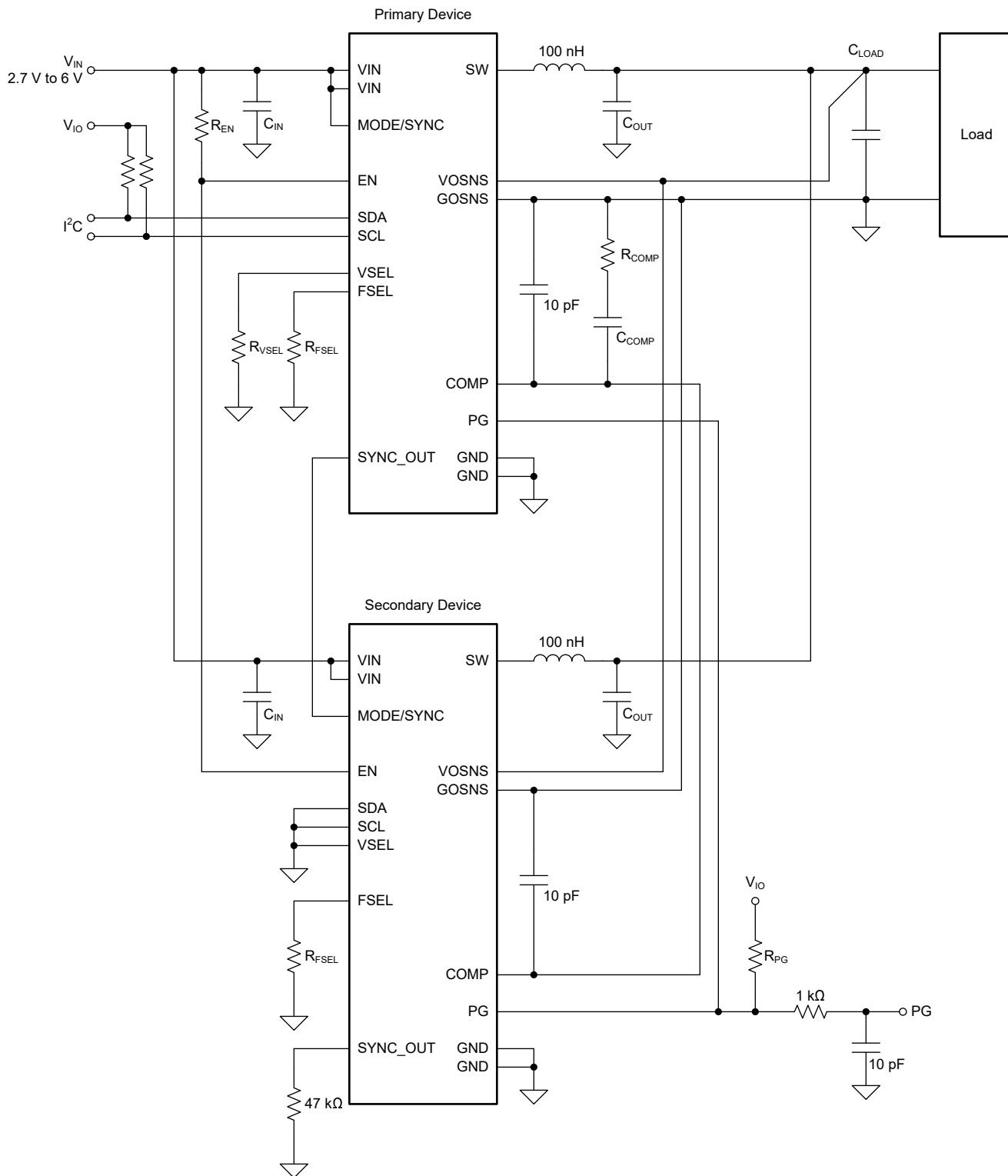

図 7-15 に、2 個の TPS6287x デバイスをスタックした推奨相互接続を示します。

図 7-15. 2 個の TPS6287x デバイスをスタックした構成

注意すべき重要なポイントは次のとおりです。

- スタック内のすべてのデバイスは共通のイネーブル信号を共有しています。この信号は、 $15\text{k}\Omega$  以上の抵抗でプルアップする必要があります。

- スタック内のすべてのデバイスは共通のパワーグッド信号を共有しており、この信号は  $V_{sub}(IH\_PG)$  より高いロジック high レベルにプルアップする必要があります。PG 出力を使用しない場合でも、PG ピンは接続またはプルアップする必要があります。

- スタック内のすべてのデバイスは共通の補償信号を共有します。

- すべてのセカンダリ デバイスは、SYNC\_OUT ピンとグランドの間に  $47\text{k}\Omega$  抵抗を接続する必要があります。

- 各デバイスのリモート センスピン (VOSNS および GOSNS) は接続する必要があります (これらのピンをフローティングのままにしないでください)。

- 各デバイスは、同じスイッチング周波数に設定する必要があります。

- プライマリ デバイスは強制 PWM 動作用に構成する必要があります (セカンダリ デバイスは自動的に強制 PWM 動作用に構成されます)。

- スタック構成は、外部クロックとの同期またはスペクトラム拡散クロック処理をサポートできます。

- デフォルトの出力電圧の設定には、1 次側デバイスの VSEL ピンのみが使用されます。2 次側デバイスの VSEL ピンは使わず、グランドに接続する必要があります。

- セカンダリ デバイスの SDA および SCL ピンは使わず、グランドに接続する必要があります。

- スタック構成ではデイジーチェーン接続されたクロック信号を使用し、各デバイスは隣接するデバイスに対して約  $140^\circ$  の位相差を持ってスイッチング動作を行います。クロック信号をデイジーチェーン接続するには、プライマリ デバイスの SYNC\_OUT ピンを最初のセカンダリ デバイスの MODE/SYNC ピンに接続します。最初のセカンダリ デバイスの SYNC\_OUT ピンを、2 番目のセカンダリ デバイスの MODE/SYNC ピンに接続します。スタック内のすべてのデバイスに対してこの接続方式を続行し、デバイスをデイジーチェーン接続します。

- ヒップ過電流保護は、スタック構成で使用しないでください。

スタック構成では、共通イネーブル信号は SYSTEM\_READY 信号としても機能します (セクション 7.3.3 を参照)。デバイスの起動時またはフォルトの発生時に、スタック内の各デバイスが EN ピンを Low にすることができます。そのため、すべてのデバイスがスタートアップ シーケンスを完了し、フォルトがない場合のみ、スタックが有効になります。いずれか 1 つのデバイスに故障が発生した場合、その故障状態が存在している限り、スタック全体が無効化します。

起動中、イネーブル信号 (SYSTEM\_READY) が Low になっている間、プライマリ コンバータは COMP ピンを Low にします。イネーブル信号が High になると、プライマリ デバイスは COMP ピンをアクティブに制御し、スタック内のすべてのコンバータが COMP 電圧に従います。スタートアップ時に、スタック内の各デバイスは、本デバイスが初期化される間、PG ピンを low にします。初期化が完了すると、スタック内の 2 次側の各デバイスは PG ピンを高インピーダンス状態にし、PG 信号の状態は 1 次側デバイスのみが制御します。PG ピンは、スタックが立ち上がりシーケンスを完了し、出力電圧が規定範囲内に達したときに High になります。スタック内の 2 次側コンバータは、パワーグッド信号の立ち上がりエッジを検出すると、DCM 動作から CCM 動作に切り替わります。スタックが正常に起動すると、プライマリ デバイスは通常の方法でパワーグッド信号を制御します。スタック構成では、個々のデバイスにのみ影響する故障と、すべてのデバイスに影響するその他の故障があります。たとえば、1 つのデバイスが電流制限に入った場合、そのデバイスのみが影響を受けます。しかし、1 つのデバイスにサーマル シャットダウンまたは低電圧誤動作防止イベントが発生すると、共有のイネーブル (SYSTEM\_READY) 信号により、すべてのデバイスが無効化されます。

### スタック動作中の機能

デバイス機能の一部はスタック動作中は使用できないか、プライマリ コンバータでのみ使用できます。表 7-8 に、スタック動作時に使用できる機能をまとめます。

表 7-8. スタック動作中の機能

| 機能                  | 1 次側デバイス | 2 次側デバイス | 注記                 |

|---------------------|----------|----------|--------------------|

| UVLO                | あり       | あり       | 共通のイネーブル信号         |

| OVLO                | あり       | あり       | 共通のイネーブル信号         |

| OCP — 電流制限          | あり       | あり       | 個人向け               |

| OCP — ヒップ OCP       | なし       | なし       | スタック操作中は使用しないでください |

| サーマル シャットダウン        | あり       | あり       | 共通のイネーブル信号         |

| パワーグッド (ウンドウ コンバータ) | あり       | なし       | プライマリ デバイスのみ       |

**表 7-8. スタック動作中の機能 (続き)**

| 機能                        | 1 次側デバイス             | 2 次側デバイス         | 注記                                 |

|---------------------------|----------------------|------------------|------------------------------------|

| I <sup>2</sup> C インターフェイス | あり                   | なし               | プライマリ デバイスのみ                       |

| DVS                       | I <sup>2</sup> C 経由で | なし               | プライマリ デバイスのみで制御される電圧ループ            |

| SSC                       | I <sup>2</sup> C 経由で | はい、プライマリ デバイス経由で | プライマリ デバイスからセカンダリ デバイスへのデイジーチェーン接続 |

| SYNC                      | あり                   | はい、プライマリ デバイス経由で | 1 次側デバイスに適用される同期クロック               |

| 高精度イネーブル                  | なし                   | なし               | バイナリイネーブルのみ                        |

| 出力放電                      | I <sup>2</sup> C 経由で | あり               | セカンダリ デバイスでは常に有効になっています            |

### スタック動作中の故障処理

スタック構成では、個々のデバイスにのみ影響する故障と、すべてのデバイスに影響するその他の故障があります。たとえば、1 つのデバイスが電流制限に入った場合、そのデバイスのみが影響を受けます。1 つのデバイスにサーマル シャットダウンまたは低電圧誤動作防止イベントが発生すると、共有のイネーブル (SYSTEM\_READY) 信号により、すべてのデバイスが無効化されます。表 7-9 に、TPS6287x デバイスのスタック動作中のフォルト処理を示します。

**表 7-9. スタック動作中の故障処理**

| フォルト条件       | デバイスの応答              | システムの応答         |

|--------------|----------------------|-----------------|

| UVLO         |                      |                 |

| OVLO         |                      |                 |

| サーマル シャットダウン | イネーブル信号が Low にプルされる  | 新しいソフトスタート      |

| 電流制限         | イネーブル信号は High に維持される | エラー アンプがクランプされる |

## 7.4 デバイスの機能モード

### 7.4.1 パワーオン リセット

電源電圧が POR スレッショルド 1.4V (標準値) 未満のときに、デバイスは POR モードで動作します。

POR モードでは、どの機能も利用できず、デバイスのレジスタの内容は無効です。

電源電圧が POR スレッショルドを上回ると、デバイスは POR モードを終了し、UVLO モードに移行します。

### 7.4.2 低電圧誤動作防止

電源電圧が POR スレッショルドと UVLO スレッショルドの間にあるとき、デバイスは UVLO モードで動作します。

デバイスが POR モードから UVLO モードに移行した場合、利用できる機能はありません。デバイスがスタンバイモードから UVLO モードに移行する場合は、出力放電機能が利用可能です。デバイスのレジスタの内容は UVLO モードで有効です。

電源電圧が POR スレッショルドを下回ると、デバイスは UVLO モードを終了し、POR モードに移行します。電源電圧が UVLO スレッショルドを上回ると、デバイスは UVLO モードを終了し、スタンバイモードに移行します。

### 7.4.3 スタンバイ

電源電圧が UVLO スレッショルドよりも高く (およびデバイスの初期化が完了し)、次のいずれかの条件が満たされている場合、デバイスはスタンバイ モードで動作します。

- EN ピンには low レベルが印加されている。

- CONTROL1 レジスタの SWEN = 0。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも高くなっている。

- 電源電圧が OVLO スレッショルドを超えている。

デバイスは、デバイスのパワーオン リセット後に電源電圧が UVLO スレッショルド電圧を超えて上昇すると、指定された期間  $t_{d(EN)}1$  (標準値 175 $\mu$ s、最大値 500 $\mu$ s) 中に初期化されます。電源電圧が UVLO スレッショルドを下回り、POR スレッショルドを下回らない場合、電源電圧が再度上昇しても、デバイスは再初期化されません。初期化中に、デバイスは FSEL、VSEL、および SYNC\_OUT ピンの状態を読み取ります。

デバイスの初期化が完了した後、スタンバイ モードでは以下の機能が使用可能になります。

- I<sup>2</sup>C インターフェイス

- 出力放電

- パワー グッド

電源電圧が UVLO スレッショルドを下回ると、デバイスはスタンバイモードから UVLO モードに移行します。次のすべての条件が満たされると、デバイスはスタンバイモードを終了し、オンモードに移行します。

- EN ピンには high レベルが印加されている。

- CONTROL1 レジスタの SWEN = 1。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドより低くなっている。

- 電源電圧が OVLO スレッショルドを下回っている。

#### 7.4.4 オン

電源電圧が UVLO スレッショルドより高く、次のすべての条件が成立する場合、デバイスはオン モードで動作します。

- EN ピンには high レベルが印加されている。

- CONTROL1 レジスタの SWEN = 1。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドより低くなっている。

- 電源電圧が OVLO スレッショルドを下回っている。

すべての機能はオン モードで使用できます。

電源電圧が UVLO スレッショルドを下回ると、デバイスはオン モードを維持し、UVLO モードに移行します。次のいずれかの条件に該当する場合、デバイスはオン モードを終了します。

- EN ピンには low レベルが印加されている。

- CONTROL1 レジスタの SWEN = 0。

- デバイスの接合部温度がサーマル シャットダウンのスレッショルドよりも高くなっている。

- 電源電圧が OVLO スレッショルドを超えている。

## 7.5 プログラミング

### 7.5.1 シリアルインターフェイスの説明

I<sup>2</sup>C は、Philips Semiconductor (現在の NXP Semiconductors)によって開発された 2 線式シリアル インターフェースです (2014 年 4 月 4 日付の I<sup>2</sup>C-Bus 仕様とユーザーマニュアル改訂 6 を参照)。バスは、プルアップ構造を持つデータライン (SDA) とクロック ライン (SCL) で構成されます。バスが アイドルのときは、SDA ラインと SCL ラインの両方が High にプルされます。I<sup>2</sup>C 互換のデバイスはすべて、オープン ドレインの I/O ピンである SDA および SCL を介して I<sup>2</sup>C バスに接続します。コントローラ (通常はマイクロコントローラまたはデジタル信号プロセッサ) がバスを制御します。コントローラは SCL 信号とデバイス アドレスを生成します。コントローラは、データ転送の開始と停止を示す特定の条件も生成します。「ターゲット」は、コントローラの制御下でバス上でデータを受信、送信、または両方を実行します。

TPS6287x デバイスはターゲットとして動作し、以下の転送「モード」で I<sup>2</sup>C-Bus 仕様で定義されているように動作します。スタンダード モード (100Kbps)、ファスト モード (400Kbps)、ファスト モード プラス (1Mbps)。このインターフェイスにより、電源設計の柔軟性が向上し、ほとんどの機能を瞬時のアプリケーション要件に応じて新しい値にプログラムできます。入力電圧が 1.4V を上回っている限り、レジスタの内容はそのまま維持されます。

スタンダード モードとファスト モードのデータ転送プロトコルはまったく同じであるため、このデータシートではこれらのモードを F/S モードと呼びます。このデバイスは 7 ビットアドレスをサポートしています。ゼネラルコールアドレスはサポートされていません。

電源投入時の VSEL ピンの状態により、デバイスの I<sup>2</sup>C ターゲットアドレスが定義されます (表 7-10 を参照)。VSEL ピンは、デバイスのデフォルトの起動電圧も設定することに注意してください (表 7-4 を参照)。

**表 7-10. I<sup>2</sup>C インターフェイス ターゲットアドレスの選択**

| VSEL ピン                  | I <sup>2</sup> C ターゲットアドレス <sup>(1)</sup> |

|--------------------------|-------------------------------------------|

| 6.2kΩ から GND へ           | 0x40                                      |

| GND への短絡                 | 0x41                                      |

| V <sub>IN</sub> への短絡     | 0x42                                      |

| 47kΩ を V <sub>IN</sub> へ | 0x43                                      |

(1) I<sup>2</sup>C アドレスを使用可能。このパラメータはデバイス番号によって異なります。セクション 4 の「デバイスのオプション」表を参照

TI では、I<sup>2</sup>C エンジンが確実にリセットされるように、I<sup>2</sup>C コントローラは、SDA および SCL プルアップ電圧の初期パワーアップ後に I<sup>2</sup>C バス上で STOP 条件を開始することをお勧めしています。

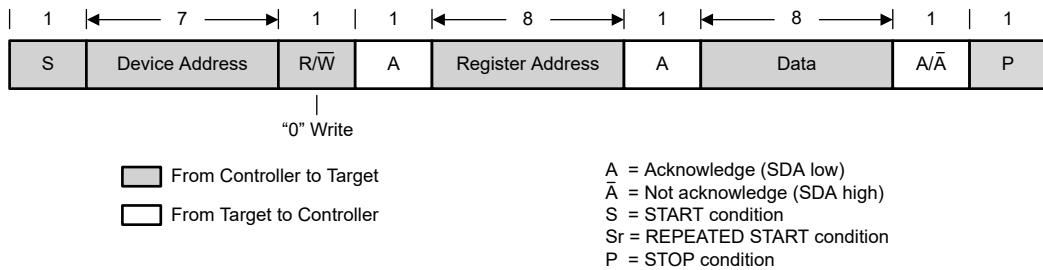

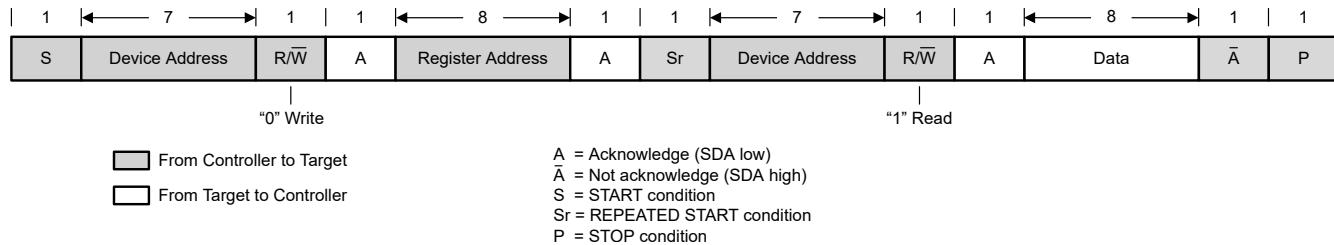

### 7.5.2 スタンダードモード、ファストモード、ファストモードプラスのプロトコル

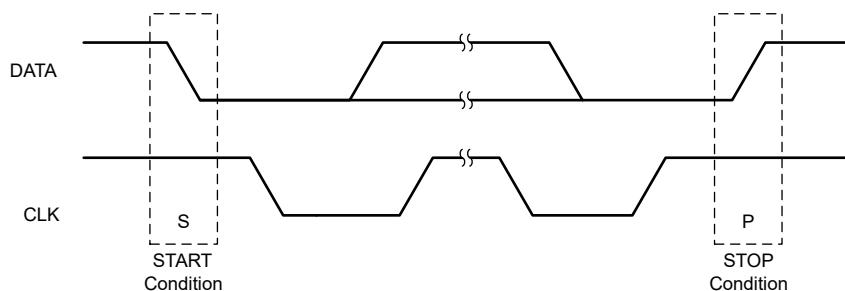

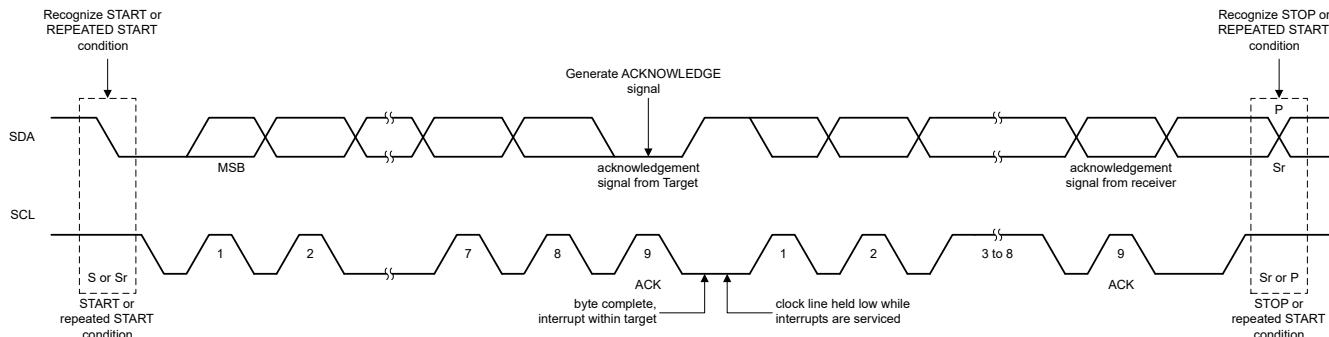

コントローラは、スタート条件を生成することでデータ転送を開始します。スタート条件は、図 7-16 に示すように、SCL が High のときに SDA ラインで High から Low への遷移が発生するときです。すべての I<sup>2</sup>C 互換デバイスは、スタート条件を認識する必要があります。

**図 7-16. 開始条件と停止条件**

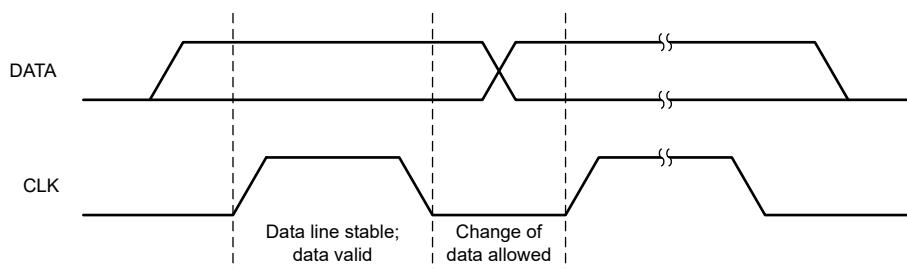

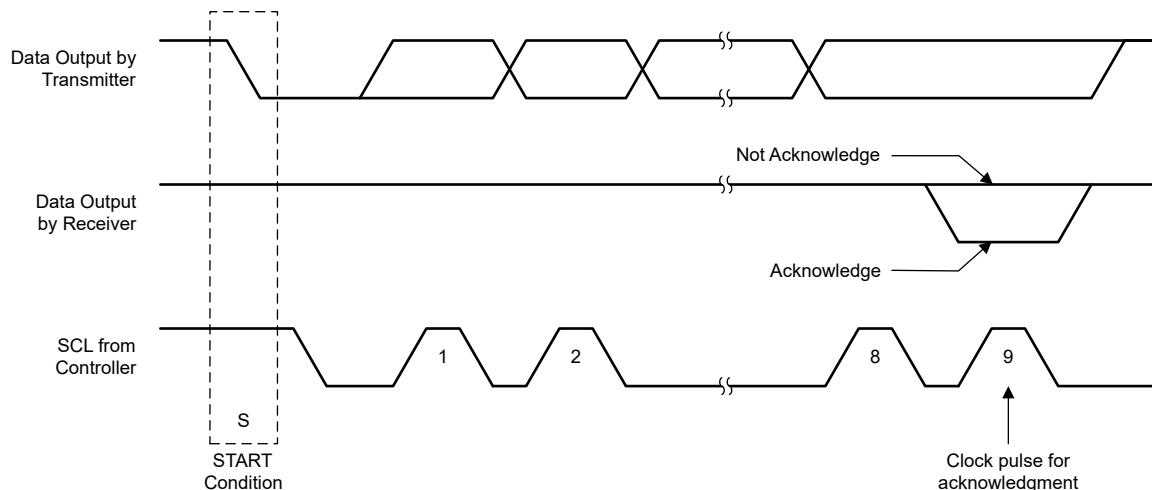

次に、コントローラは SCL パルスを生成し、7 ビットのアドレスと読み取り/書き込み方向ビット R/W を SDA ライン上で送信します。すべての送信中、コントローラはデータが有効であることを確認します。有効なデータ条件では、クロック パルスの High 期間中、SDA ラインのデータが安定している必要があります (図 7-17 を参照)。すべてのデバイスは、コントローラによって送信されたアドレスを認識して、そのアドレスを内部の固定アドレスと比較します。一致するアドレスを持つターゲット デバイスだけが、9 回目の SCL サイクルの High 期間全体の間 SDA ラインを Low にすることで、アクリソジを生成します (図 7-18 を参照)。この確認を検出すると、コントローラはターゲットとの通信リンクが確立されたことを認識します。

**図 7-17. シリアルインターフェイスでのビット転送**

コントローラは、データをターゲットへ送信するか (R/W ビット 0)、ターゲットからデータを受信するため (R/W ビット 1)、さらに SCL サイクルを生成します。どちらの場合も、コントローラから送信されたデータに対してターゲットがアクリソジを返す必要があります。したがって、アクリソジ信号は、どちらが受信側かに応じて、コントローラが生成する場合とターゲット

が生成する場合があります。8ビットのデータと1ビットのアクノリッジから構成される9ビットの有効なデータシーケンスを、必要なだけ続けることができます。