TPS62865, TPS62867 JAJSLM0 - MARCH 2021

# TPS62865/TPS62867 2.4V~5.5V 入力、4A および 6A 同期整流降圧コンバータ、 1.5 x 2.5mm QFN パッケージ

## 1 特長

- DCS-Controlトポロジにより、高速過渡応答を実現

- $11m\Omega$  および  $10.5m\Omega$  のパワー MOSFET を内蔵

- ±1% の出力電圧精度

- 動作時の静止電流:4µA

- 入力電圧範囲:2.4V~5.5V

- 可変出力電圧範囲: 0.6V~V<sub>IN</sub>

- 固定 (外付け抵抗で選択可能) および可変出力電圧

- 2.4MHz のスイッチング周波数

- 強制 PWM またはパワーセーブ・モード

- 出力電圧放電

- 100% デューティ・サイクル・モード

- ヒカップ短絡保護機能

- パワー・グッド・インジケータとウィンドウ・コンパレータ

- サーマル・シャットダウン

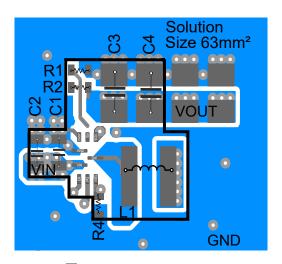

- 最小 30mm<sup>2</sup> のソリューション・サイズ が可能

- 1.5Mm×2.5mm の QFN、0.5mm ピッチで供給

- WEBENCH® Power Designer により、TPS62865 を 使用するカスタム設計を作成

- WEBENCH® Power Designer により、TPS62867 を 使用するカスタム設計を作成

# 2 アプリケーション

- FPGA、CPU、ASIC、ビデオ・チップセット用のコア電

- マシン・ビジョン・カメラ

- IP ネットワーク・カメラ

- ソリッドステート・ドライブ

- 光モジュール

- マルチファンクション・プリンタ

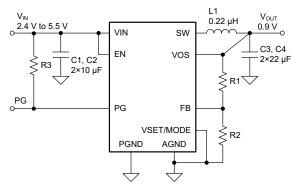

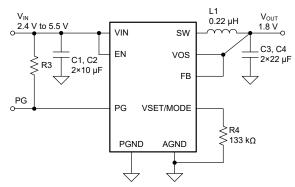

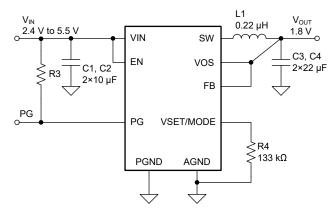

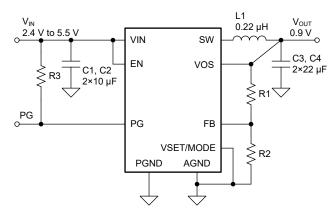

代表的なアプリケーション回路図 - 可変出力電圧

# 3 概要

TPS62865 および TPS62867 は、高効率で柔軟性が高 く高電力密度のソリューションを実現する高周波数同期整 流降圧コンバータです。中負荷から重負荷では PWM モ ードで動作し、軽負荷時には自動的にパワーセーブ・モ ードへ移行するので、負荷電流の全範囲にわたって高効 率が維持されます。このデバイスは、強制的に PWM モー ドで動作させ、出力電圧リップルを最小化することもできま す。DCS-Control アーキテクチャと相まって、優れた負荷 過渡性能と厳格な出力電圧精度を実現します。このデバ イスは、パワー・グッド信号と、内部のソフトスタート回路を 備えています。100% モードで動作可能です。フォルト保 護としては、ヒカップ短絡保護機能と、サーマル・シャットダ ウンが内蔵されています。

# 製品情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)         |

|----------|----------------------|--------------------|

| TPS62865 | QFN (9)              | 1.5 × 2.5 × 1mm    |

| TPS62867 | QFN (9)              | 1.5 ^ 2.5 ^ 111111 |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

代表的なアプリケーション回路図 - 固定出力電圧

# **Table of Contents**

| 1 特長                                 | 1 | 8.4 Device Functional Modes             | 10               |

|--------------------------------------|---|-----------------------------------------|------------------|

| 2 アプリケーション                           |   | 9 Application and Implementation        | 12               |

| 3 概要                                 |   | 9.1 Application Information             | 12               |

| 4 Revision History                   |   | 9.2 Typical Application                 | 12               |

| 5 Device Options                     |   | 10 Power Supply Recommendations         | 19               |

| 6 Pin Configuration and Functions    |   | 11 Layout                               | <mark>2</mark> 0 |

| 7 Specifications                     |   | 11.1 Layout Guidelines                  | 20               |

| 7.1 Absolute Maximum Ratings         |   | 11.2 Layout Example                     | 20               |

| 7.2 ESD Ratings                      |   | 12 Device and Documentation Support     | 22               |

| 7.3 Recommended Operating Conditions |   | 12.1 Device Support                     |                  |

| 7.4 Thermal Information              |   | 12.2 Documentation Support              | <mark>22</mark>  |

| 7.5 Electrical Characteristics       |   | 12.3 サポート・リソース                          | <mark>22</mark>  |

| 7.6 Typical Characteristics          |   | 12.4 Trademarks                         | <mark>22</mark>  |

| 8 Detailed Description               |   | 12.5 静電気放電に関する注意事項                      | 22               |

| 8.1 Overview                         |   | 12.6 用語集                                | 23               |

| 8.2 Functional Block Diagram         |   | 13 Mechanical, Packaging, and Orderable |                  |

| 8.3 Feature Description              |   | Information                             | 23               |

| •                                    |   |                                         |                  |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE       | REVISION | NOTES           |

|------------|----------|-----------------|

| March 2021 | *        | Initial Release |

# **5 Device Options**

| PART NUMBER <sup>(1)</sup> | OUTPUT CURRENT |

|----------------------------|----------------|

| TPS62865                   | 4 A            |

| TPS62867                   | 6 A            |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

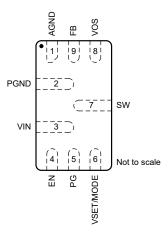

# **6 Pin Configuration and Functions**

図 6-1. 9-Pin RQY QFN Package (Top View)

表 6-1. Pin Functions

| PIN       |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AGND      | 1   | Analog ground pin                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FB        | 9   | Feedback pin. For the fixed output voltage versions, the pin must be connected to the output directly.                                                                                                                                                                                                                                                                                                                                    |

| vos       | 8   | Output voltage sense pin. This pin must be directly connected to the output capacitor.                                                                                                                                                                                                                                                                                                                                                    |

| PGND      | 2   | Power ground pin                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SW        | 7   | Switch pin of the power stage                                                                                                                                                                                                                                                                                                                                                                                                             |

| VIN       | 3   | Power supply input voltage pin                                                                                                                                                                                                                                                                                                                                                                                                            |

| EN        | 4   | Device enable pin. To enable the device, this pin needs to be pulled high. Pulling this pin low disables the device. Do not leave floating.                                                                                                                                                                                                                                                                                               |

| VSET/MODE | 6   | Voltage Set pin In fixed output voltage applications, connect a resistor between this pin and GND to set the output voltage (see 表 8-2). After start-up, connect this pin to a high level to enable forced-PWM operation, or to a low level to enable power-save mode. In adjustable output voltage applications, connect this pin to a high level to enable forced-PWM operation, or to a low level to enable power-save mode operation. |

| PG        | 5   | Power-good open-drain output pin. The pullup resistor can be connected to voltages up to 5.5 V. If unused, leave it floating.                                                                                                                                                                                                                                                                                                             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

See (1)

|                        |                                         | MIN  | MAX                   | UNIT |

|------------------------|-----------------------------------------|------|-----------------------|------|

|                        | VIN, EN, VOS, FB, PG, VSET/MODE         | -0.3 | 6                     |      |

| Voltage <sup>(2)</sup> | SW (DC)                                 | -0.3 | V <sub>IN</sub> + 0.3 | V    |

|                        | SW (AC, less than 10 ns) <sup>(3)</sup> | -2.5 | 10                    |      |

| I <sub>SINK_PG</sub>   | Sink current at PG                      |      | 1                     | mA   |

| T <sub>J</sub>         | Junction temperature                    | -40  | 150                   | °C   |

| T <sub>stg</sub>       | Storage temperature                     | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values are with respect to network ground terminal.

- (3) While switching

# 7.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Over operating junction temperature range (unless otherwise noted)

|                  |                                 | MIN | NOM MAX         | UNIT  |

|------------------|---------------------------------|-----|-----------------|-------|

| V <sub>IN</sub>  | Supply Voltage Range            | 2.4 | 5.5             | V     |

| V <sub>OUT</sub> | Output Voltage Range            | 0.6 | V <sub>IN</sub> | V     |

| SR               | Slew rate at VIN <sup>(1)</sup> | -10 |                 | mV/μs |

|                  | Output current, TPS62865        |     | 4               | ۸     |

| IOUT             | Output current, TPS62867        |     | 6               | A     |

| T <sub>J</sub>   | Junction temperature            | -40 | 125             | °C    |

(1) The falling slew rate of V<sub>IN</sub> must be limited if V<sub>IN</sub> goes below V<sub>UVLO</sub>.

# 7.4 Thermal Information

|                       |                                              | TPS        | TPS6286x           |      |  |

|-----------------------|----------------------------------------------|------------|--------------------|------|--|

|                       | THERMAL METRIC(1)                            | JEDEC 51-7 | TPS62867EVM-121    | UNIT |  |

|                       |                                              | 9 PINS     | 9 PINS             |      |  |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 90.9       | 60.3               | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 68.2       | n/a <sup>(2)</sup> | °C/W |  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 25.0       | n/a <sup>(2)</sup> | °C/W |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.9        | 3.3                | °C/W |  |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 24.7       | 31.5               | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Not applicable to an EVM

# 7.5 Electrical Characteristics

$T_J$  = -40°C to 125°C, and  $V_{IN}$  = 2.4 V to 5.5 V. Typical values are at  $T_J$  = 25°C and  $V_{IN}$  = 5 V, unless otherwise noted.

|                                               | PARAMETER                                              | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY                                        | •                                                      |                                                                                                          |      |      |      |      |

| IQ                                            | Quiescent current                                      | EN = High, no load, device not switching                                                                 |      | 4    | 10   | μA   |

| I <sub>Q_VOS</sub>                            | Operating quiescent current into VOS pin               | EN = High, no load, device not switching, V <sub>VOS</sub> = 1.8 V                                       |      | 8    |      | μΑ   |

| I <sub>SD</sub>                               | Shutdown current                                       | EN = Low, $T_J = -40^{\circ}\text{C}$ to 85°C                                                            |      | 0.24 | 1    | μA   |

|                                               | Hardward Lades Advantage                               | V <sub>IN</sub> rising                                                                                   | 2.2  | 2.3  | 2.4  | V    |

| $V_{UVLO}$                                    | Undervoltage lockout threshold                         | V <sub>IN</sub> falling                                                                                  | 2.1  | 2.2  | 2.3  | V    |

| <b>-</b>                                      | Thermal shutdown threshold                             | T <sub>J</sub> rising                                                                                    |      | 150  |      | °C   |

| $T_{JSD}$                                     | Thermal shutdown hysteresis                            | T <sub>J</sub> falling                                                                                   |      | 20   |      | °C   |

| LOGIC II                                      | NTERFACE                                               |                                                                                                          |      |      |      |      |

| V <sub>IH</sub>                               | High-level input threshold voltage at EN and VSET/MODE |                                                                                                          | 0.84 |      |      | V    |

| V <sub>IL</sub>                               | Low-level input threshold voltage at EN and VSET/MODE  |                                                                                                          |      | -    | 0.4  | V    |

| I <sub>EN,LKG</sub>                           | Input leakage current into EN pin                      |                                                                                                          |      | 0.01 | 0.1  | μA   |

|                                               | IP, POWER GOOD                                         |                                                                                                          |      |      |      |      |

| t <sub>Delay</sub>                            | Enable delay time                                      | Time from EN high to device starts switching 249-k $\Omega$ resistor connected between VSET/MODE and GND | 420  | 700  | 1100 | μs   |

| t <sub>Ramp</sub>                             | Output voltage ramp time                               | Time from device starts switching to power good                                                          | 0.8  | 1    | 1.5  | ms   |

|                                               | Power good lower threshold                             | V <sub>VOS</sub> referenced to V <sub>OUT</sub> nominal                                                  | 85%  | 91%  | 96%  |      |

| $V_{PG}$                                      | Power good upper threshold                             | V <sub>VOS</sub> referenced to V <sub>OUT</sub> nominal                                                  | 103% | 111% | 120% |      |

| $V_{PG,OL}$                                   | Low-level output voltage                               | I <sub>sink</sub> = 1 mA, PG pin version                                                                 |      |      | 0.36 | V    |

| t <sub>PG,DLY</sub> Power good deglitch delay |                                                        | Rising and falling edges                                                                                 |      | 34   |      | μs   |

| OUTPUT                                        | Γ                                                      |                                                                                                          |      |      |      |      |

| V <sub>OUT</sub>                              | Output voltage accuracy                                | Fixed voltage operation, FPWM, no load, T <sub>J</sub> = 0°C to 85°C                                     | -1%  |      | 1%   |      |

|                                               |                                                        | Fixed voltage operation, FPWM, no load                                                                   | -2%  |      | 2%   |      |

| $V_{FB}$                                      | Feedback voltage                                       | Adjustable voltage operation                                                                             | 594  | 600  | 606  | mV   |

| I <sub>FB,LKG</sub>                           | Input leakage into FB pin                              | Adjustable voltage operation, V <sub>FB</sub> = 0.6 V                                                    |      | 0.01 | 0.4  | μΑ   |

| I <sub>VOS,LKG</sub>                          | Input leakage current into VOS pin                     | Output discharge disabled, V <sub>VOS</sub> = 1.8 V                                                      |      | 0.2  | 2.5  | μΑ   |

| R <sub>DIS</sub>                              | Output discharge resistor at VOS pin                   |                                                                                                          |      | 3.5  |      | Ω    |

|                                               | Load regulation                                        | V <sub>OUT</sub> = 0.9 V, FPWM                                                                           |      | 0.04 |      | %/A  |

| POWER                                         | SWITCH                                                 |                                                                                                          |      |      |      |      |

| D                                             | High-side FET on-resistance                            |                                                                                                          |      | 11   |      | mΩ   |

| R <sub>DS(on)</sub>                           | Low-side FET on-resistance                             |                                                                                                          |      | 10.5 |      | mΩ   |

|                                               | High-side FET forward current limit                    | TPS62865                                                                                                 | 5    | 5.5  | 6    | Α    |

|                                               | ingn-side FET forward current limit                    | TPS62867                                                                                                 | 7    | 7.7  | 8.5  | Α    |

| I <sub>LIM</sub>                              | Low aids EET farward surrent limit                     | TPS62865                                                                                                 |      | 4.5  |      | Α    |

|                                               | Low-side FET forward current limit                     | TPS62867                                                                                                 |      | 6.5  |      | Α    |

|                                               | Low-side FET negative current limit                    | TPS62865, TPS62867                                                                                       |      | -3   |      | Α    |

| f <sub>SW</sub>                               | PWM switching frequency                                | I <sub>OUT</sub> = 1 A, V <sub>OUT</sub> = 0.9 V                                                         |      | 2.4  |      | MHz  |

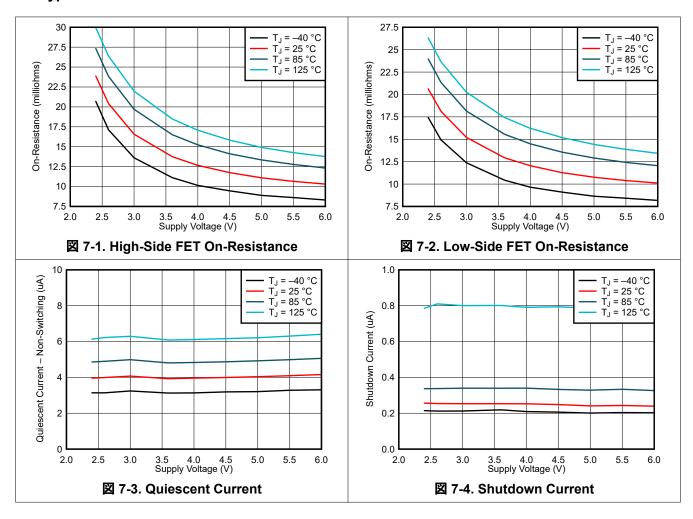

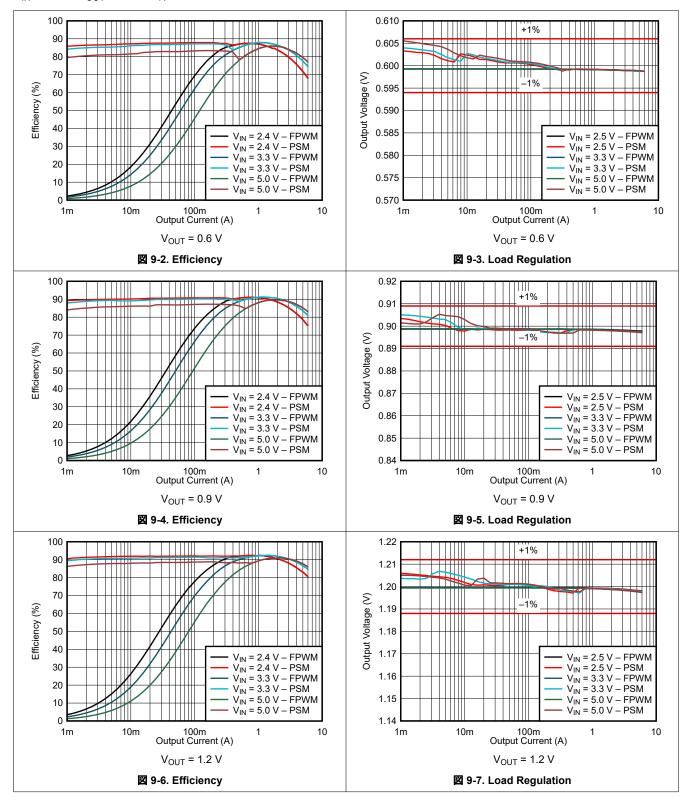

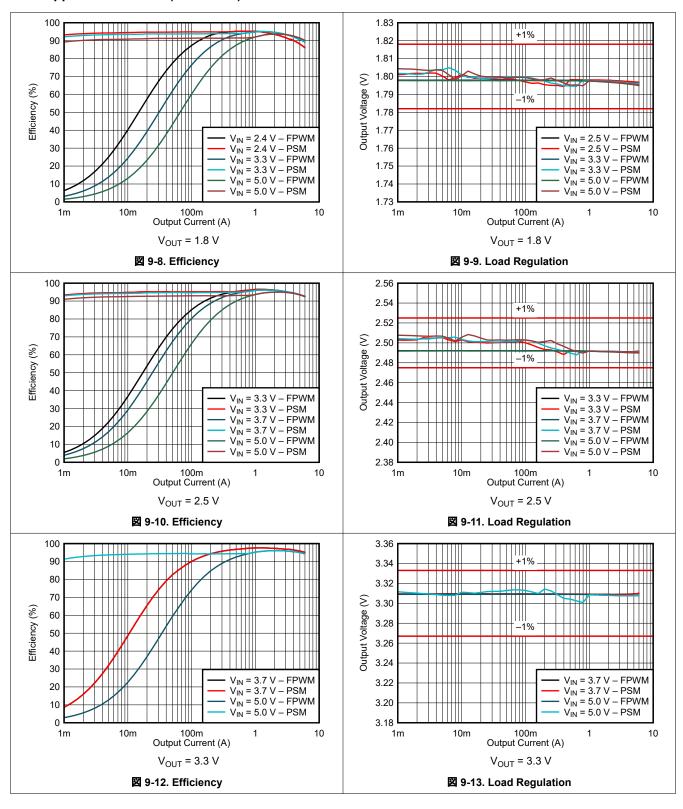

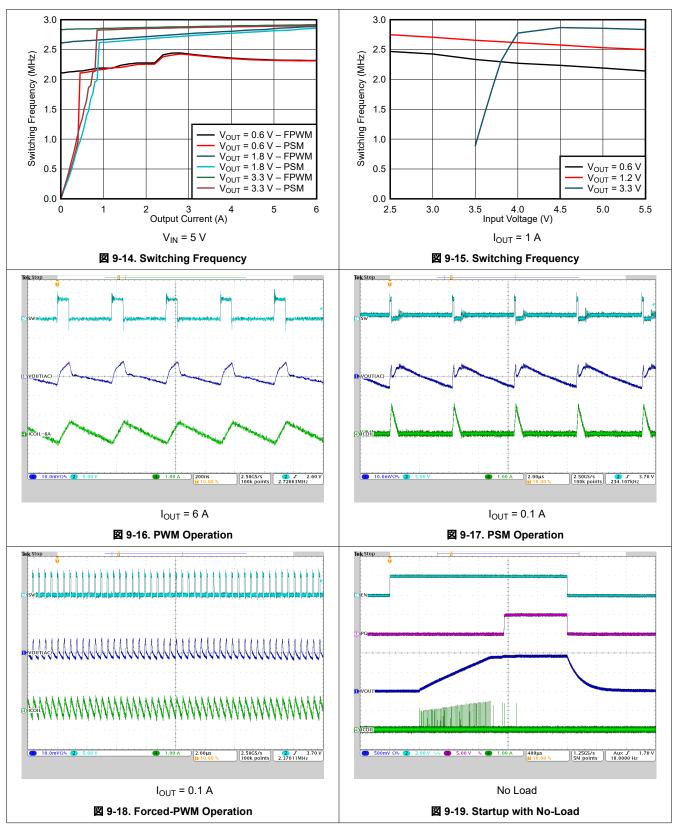

# 7.6 Typical Characteristics

# **8 Detailed Description**

#### 8.1 Overview

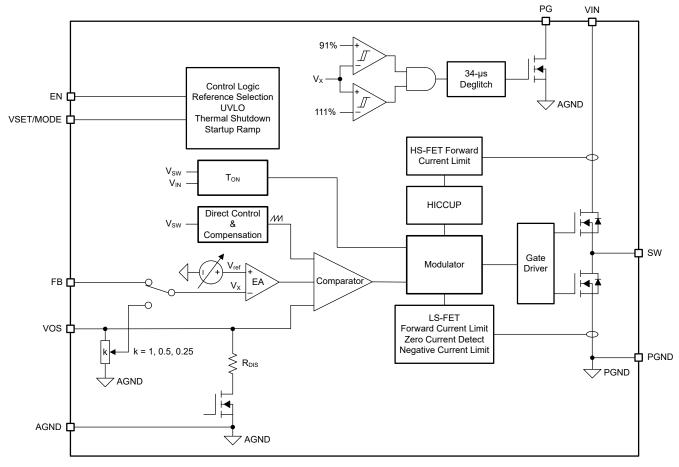

The TPS62865 and TPS62867 synchronous step-down converters use the DCS-Control (Direct Control with Seamless transition into Power Save Mode) topology. This is an advanced regulation topology that combines the advantages of hysteretic and current-mode control schemes.

The DCS-Control topology operates in PWM (pulse width modulation) mode for medium to heavy load conditions and in Power Save Mode at light load currents. In PWM mode, the converter operates with its 2.4-MHz nominal switching frequency, having a controlled frequency variation over the input voltage range. Since DCS-Control supports both operation modes (PWM and PFM) within a single building block, the transition from PWM mode to Power Save Mode is seamless and does not affect on the output voltage. The devices offer both excellent DC voltage and superior load transient regulation combined with very low output voltage ripple.

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Power Save Mode

As the load current decreases, the device enters Power Save Mode (PSM) operation. PSM occurs when the inductor current becomes discontinuous, which is when it reaches 0 A during a switching cycle. Power Save Mode is based on a fixed on-time architecture, as shown in 式 1.

$$t_{\rm ON} = \frac{V_{\rm OUT}}{V_{\rm IN}} \times 416 \, \rm ns \tag{1}$$

In Power Save Mode, the output voltage rises slightly above the nominal output voltage. This effect is minimized by increasing the output capacitor or inductor value.

When  $V_{IN}$  decreases to typically 15% above  $V_{OUT}$ , the TP6286x does enter Power Save Mode, regardless of the load current. The device maintains output regulation in PWM mode.

#### 8.3.2 Forced PWM Mode

Connecting the VSET/MODE pin to logic high after the start-up, the device switches at 2.4 MHz, even with a light load. This reduces the output voltage ripple and allows simple filtering of the switching frequency for noise-sensitive applications. Efficiency at light load is lower in Forced PWM mode (FPWM).

#### 8.3.3 100% Duty Cycle Mode Operation

There is no limitation for small duty cycles since even at very low duty cycles, the switching frequency is reduced as needed to always ensure a proper regulation.

If the output voltage level comes close to the input voltage, the device enters 100% mode. While the high-side switch is constantly turned on, the low-side switch is switched off. The difference between  $V_{IN}$  and  $V_{OUT}$  is determined by the voltage drop across the high-side MOSFET and the DC resistance of the inductor. The minimum  $V_{IN}$  that is needed to maintain a specific  $V_{OUT}$  value is estimated as:

$$V_{IN,MIN} = V_{OUT} + (R_{DS(ON)} + R_L)I_{OUT,MAX}$$

(2)

#### where

- V<sub>IN,MIN</sub> is the minimum input voltage to maintain an output voltage

- I<sub>OUT,MAX</sub> is the maximum output current

- R<sub>DS(on)</sub> is the high-side FET ON-resistance

- R<sub>L</sub> is the inductor ohmic resistance (DCR)

#### 8.3.4 Soft Start

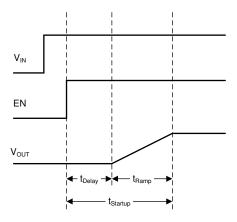

After enabling the device, there is a 700- $\mu$ s (typical) enable delay ( $t_{delay}$ ) before the device starts switching. After the enable delay, an internal soft start-up circuitry ramps up the output voltage with a period of 1 ms ( $t_{Ramp}$ ). This avoids excessive inrush current and creates a smooth output voltage rise-slope. It also prevents excessive voltage drops of primary cells and rechargeable batteries with high internal impedance. The device is able to start into a pre-biased output capacitor. It starts with the applied bias voltage and ramps the output voltage to its nominal value.

図 8-1. Start-up Sequence

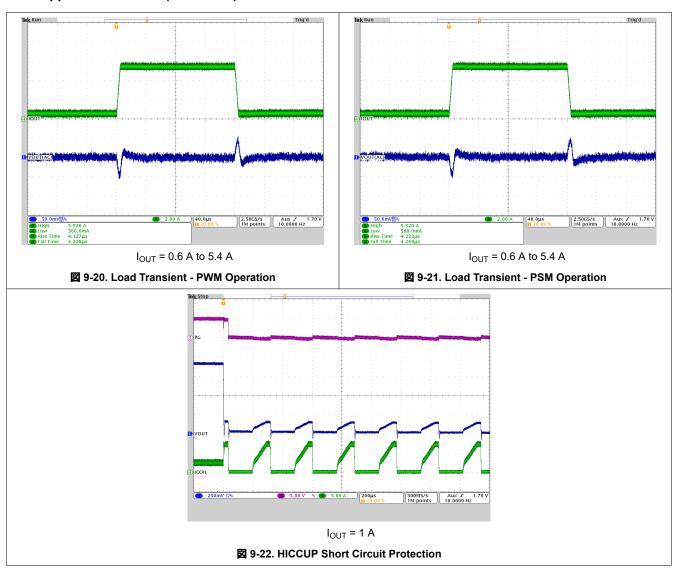

#### 8.3.5 Switch Current Limit and HICCUP Short-Circuit Protection

The switch current limit prevents the device from high inductor current and from drawing excessive current from the battery or input voltage rail. Excessive current might occur with a shorted or saturated inductor or a heavy load or shorted output circuit condition. If the inductor current reaches the threshold I<sub>LIM</sub>, cycle by cycle, the high-

side MOSFET is turned off and the low-side MOSFET is turned on, while the inductor current ramps down to the low-side MOSFET current limit.

When the high-side MOSFET current limit is triggered 32 times, the device stops switching. The device then automatically re-starts with an internal soft start-up after a typical delay time of 128 µs has passed. This is named HICCUP short-circuit protection. The device repeats this mode until the high load condition disappears.

#### 8.3.6 Undervoltage Lockout

To avoid mis-operation of the device at low input voltages, undervoltage lockout (UVLO) is implemented when the input voltage is lower than  $V_{UVLO}$ . The device stops switching and the output voltage discharge is active when the device is in UVLO. When the input voltage recovers, the device automatically returns to operation with an internal soft start-up.

#### 8.3.7 Thermal Shutdown

When the junction temperature exceeds  $T_{JSD}$ , the device goes into thermal shutdown, stops switching, and activates the output voltage discharge. When the device temperature falls below the threshold by the hysteresis, the device returns to normal operation automatically with an internal soft start-up. During thermal shutdown, the internal register values are kept.

#### 8.4 Device Functional Modes

### 8.4.1 Enable and Disable (EN)

The device is enabled by setting the EN pin to a logic high. In shutdown mode (EN = low), the internal power switches and the entire control circuitry are turned off. An internal switch smoothly discharges the output through the VOS pin in shutdown mode. Do not leave the EN pin floating.

#### 8.4.2 Power Good (PG)

The device has an open-drain power-good pin, which is specified to sink up to 1 mA. The power-good output requires a pullup resistor connecting to any voltage rail less than 5.5 V. The PG has a deglitch delay of 34 µs.

The PG signal can be used for sequencing of multiple rails by connecting it to the EN pin of other converters. Leave the PG pin unconnected when not used.

|                      | PG PIN                                                               |           |

|----------------------|----------------------------------------------------------------------|-----------|

| Enable               | $0.9 \times V_{OUT\_NOM} \le V_{VOS} \le 1.1 \times V_{OUT\_NOM}$    | Hi-Z      |

| Lilable              | $V_{VOS}$ < 0.9 × $V_{OUT\_NOM}$ or $V_{VOS}$ > 1.1 × $V_{OUT\_NOM}$ | Low       |

| Shutdown             | EN = low                                                             | Low       |

| Thermal shutdown     | $T_{J} > T_{JSD}$                                                    | Low       |

| UVLO                 | 1.8 V < V <sub>IN</sub> < V <sub>UVLO</sub>                          | Low       |

| Power supply removal | V <sub>IN</sub> < 1.8 V                                              | Undefined |

表 8-1. PG Function Table

## 8.4.3 Voltage Setting and Mode Selection (VSET/MODE)

During the enable delay ( $t_{Delay}$ ), the device configuration is set by an external resistor connected to the VSET/MODE pin through an internal R2D (resistor to digital) converter.  $\frac{1}{2}$  8-2 shows the options.

The R2D converter has an internal current source that applies current through the external resistor and an internal ADC that reads back the resulting voltage level. Depending on the level, the output voltage is set. Once this R2D conversion is finished, the current source is turned off to avoid current flowing through the external resistor. Ensure that there is no additional current path or capacitance greater than 30 pF from this pin to GND during R2D conversion. Otherwise, a false value is set.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

表 8-2. Voltage Selection Table

| RESISTOR (E96 SERIES, ±1% ACCURACY) AT VSET/MODE PIN | FIXED OR ADJUSTABLE OUTPUT VOLTAGE |

|------------------------------------------------------|------------------------------------|

| 249 kΩ or logic high                                 | adjustable                         |

| 205 kΩ                                               | 3.30 V                             |

| 162 kΩ                                               | 2.50 V                             |

| 133 kΩ                                               | 1.80 V                             |

| 105 kΩ                                               | 1.50 V                             |

| 86.6 kΩ                                              | reserved                           |

| 68.1 kΩ                                              | 1.35 V                             |

| 56.2 kΩ                                              | 1.20 V                             |

| 44.2 kΩ                                              | 1.10 V                             |

| 36.5 kΩ                                              | 1.05 V                             |

| 28.7 kΩ                                              | 1.00 V                             |

| 23.7 kΩ                                              | 0.95 V                             |

| 18.7 kΩ                                              | 0.90 V                             |

| 15.4 kΩ                                              | 0.85 V                             |

| 12.1 kΩ                                              | 0.80 V                             |

| 10 kΩ or logic low                                   | adjustable                         |

When the device is set as a fixed output voltage converter, then FB pin must be connected to the output directly. Refer to  $\boxtimes$  8-2.

図 8-2. Fixed Start-up Output Voltage Application Circuit

After the start-up period ( $t_{Startup}$ ), a different operation mode can be selected. When VSET/MODE is high, the device operates in forced PWM mode, otherwise the device operates in power save mode.

# 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 9.1 Application Information

The following section discusses the design of the external components to complete the power supply design for several input and output voltage options by using typical applications as a reference.

## 9.2 Typical Application

図 9-1. Typical Application

# 9.2.1 Design Requirements

For this design example, use the parameters listed in 表 9-1 as the input parameters.

DESIGN PARAMETER

EXAMPLE VALUE

Input voltage

2.4 V to 5.5 V

Output voltage

0.9 V

Maximum output current

6 A

表 9-1. Design Parameters

表 9-2 lists the components used for the example.

#### 表 9-2. List of Components

| REFERENCE | DESCRIPTION                                                               | MANUFACTURER <sup>(1)</sup> |  |  |  |

|-----------|---------------------------------------------------------------------------|-----------------------------|--|--|--|

| C1, C2    | C1, C2 10 μF, ceramic capacitor, 10 V, X7R, size 0603,GRM188Z71A106KA73   |                             |  |  |  |

| C3, C4    | C3, C4 22 μF, ceramic capacitor, 6.3 V, X7R, size 0805, GRM21BZ70J226ME44 |                             |  |  |  |

| L1        | 0.22 μH, power inductor, XAL4020-221ME (12 A, 5.81 mΩ)                    | Coilcraft                   |  |  |  |

| R1        | Depending on the output voltage, chip resistor, 1/16 W, 1%, size 0402     | Std                         |  |  |  |

| R2        | 100 kΩ, chip resistor, 1/16 W, 1%, size 0402                              | Std                         |  |  |  |

| R3        | 100 kΩ, chip resistor, 1/16 W, 1%, size 0402                              | Std                         |  |  |  |

(1) See the *Third-party Products* disclaimer.

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS62865 device with the WEBENCH® Power Designer.

Click here to create a custom design using the TPS62867 device with the WEBENCH® Power Designer.

- Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Setting The Output Voltage

The output voltage is set by an external resistor divider according to 式 3:

$$R1 = R2\left(\frac{V_{OUT}}{V_{FB}} - 1\right) = R2\left(\frac{V_{OUT}}{0.6 \text{ V}} - 1\right)$$

(3)

R2 must not be higher than 200  $k\Omega$  to achieve high efficiency at light load while providing acceptable noise sensitivity.

For the fixed output versions, connect the FB pin to the output. R1 and R2 are not needed.

#### 9.2.2.3 Output Filter Design

The inductor and the output capacitor together provide a low-pass filter. To simplify this process,  $\frac{1}{8}$  9-3 outlines possible inductor and capacitor value combinations for most applications. Checked cells represent combinations that are proven for stability by simulation and lab testing. Further combinations must be checked for each individual application.

表 9-3. Matrix of Output Capacitor and Inductor Combinations

| NOMINAL L [µH] <sup>(2)</sup> | NOMINAL C <sub>OUT</sub> [µF] <sup>(3)</sup> |              |        |     |  |  |

|-------------------------------|----------------------------------------------|--------------|--------|-----|--|--|

| ΙΚΟΙΝΙΙΚΑΣ Σ [μ11]            | 10                                           | 2 × 22 or 47 | 3 × 22 | 150 |  |  |

| 0.22                          |                                              | +(1)         | +      | +   |  |  |

- This LC combination is the standard value and recommended for most applications.

- (2) Inductor tolerance and current derating is anticipated. The effective inductance can vary by 20% and -30%.

- (3) Capacitance tolerance and bias voltage derating is anticipated. The effective capacitance can vary by 20% and -50%.

#### 9.2.2.4 Inductor Selection

The main parameter for the inductor selection is the inductor value, then the saturation current of the inductor. To calculate the maximum inductor current under static load conditions,  $\pm 4$  is given.

$$I_{L,MAX} = I_{OUT,MAX} + \frac{\Delta I_L}{2}$$

$$\Delta I_{L} = V_{OUT} \left( \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f_{SW}} \right)$$

(4)

where

- I<sub>OUT,MAX</sub> is the maximum output current

- ΔI<sub>L</sub> is the inductor current ripple

- f<sub>SW</sub> is the switching frequency

- L is the inductor value

It is recommended to choose a saturation current for the inductor that is approximately 20% to 30% higher than  $I_{L,MAX}$ . In addition, DC resistance and size must also be taken into account when selecting an appropriate inductor.  $\frac{1}{2}$  9-4 lists recommended inductors.

表 9-4. List of Recommended Inductors

| INDUCTANCE [µH] <sup>(1)</sup> | CURRENT RATING<br>[A] | DIMENSIONS<br>[L × W × H mm] | DC RESISTANCE [mΩ] | PART NUMBER              |

|--------------------------------|-----------------------|------------------------------|--------------------|--------------------------|

| 0.22                           | 18.7                  | 4 × 4 × 2                    | 5.81               | Coilcraft, XAL4020-221ME |

| 0.24                           | 6.6                   | 2 × 1.6 × 1.2                | 13                 | Murata, DFE201612E-R24M  |

(1) See the Third-party Products disclaimer.

#### 9.2.2.5 Capacitor Selection

The input capacitor is the low-impedance energy source for the convertersm which helps to provide stable operation. A low-ESR multilayer ceramic capacitor is recommended for the best filtering and must be placed between VIN and GND as close as possible to those pins. For most applications,  $8 \, \mu F$  of effective <sup>1</sup> capacitance is sufficient, however, a larger value reduces input current ripple.

The architecture of the device allows the use of tiny ceramic output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended. To keep its low resistance up to high frequencies and to get narrow capacitance variation with temperature, TI recommends using X7R or X5R dielectrics. The recommended typical output capacitor value is 30 µF of effective <sup>1</sup> capacitance. This capacitance can vary over a wide range as outlined in the output filter selection table.

Submit Document Feedback

<sup>1</sup> The effective capacitance is the capacitance after tolerance, temperature, and DC bias effects have been considered.

#### 9.2.3 Application Curves

$V_{IN}$  = 5.0 V,  $V_{OUT}$  = 0.9 V,  $T_A$  = 25 °C, BOM =  $\frac{1}{8}$  9-2, unless otherwise noted.

#### 9.2.3 Application Curves (continued)

# 9.2.3 Application Curves (continued)

# 9.2.3 Application Curves (continued)

# 10 Power Supply Recommendations

The device is designed to operate from an input voltage supply range from 2.4 V to 5.5 V. Ensure that the input power supply has a sufficient current rating for the application.

## 11 Layout

# 11.1 Layout Guidelines

A proper layout is critical for the operation of any switched mode power supply, especially at high switching frequencies. The PCB layout of the TPS62865 and TPS62867 devices requires careful attention to ensure best performance. A poor layout can lead to issues like bad line and load regulation, instability, increased EMI radiation, and noise sensitivity. Refer to the *Five Steps to a Great PCB Layout for a Step-Down Converter* technical brief for a detailed discussion of general best practices. The following are specific recommendations for the TPS62865 and TPS62867:

- The input capacitor or capacitors must be placed as close as possible to the VIN and PGND pins of the

device. This is the most critical component placement. Route the input capacitor or capacitors directly to the

VIN and PGND pins, avoiding vias.

- Place the output inductor close to the SW pins. Minimize the copper area at the switch node.

- Place the output capacitor or capacitors ground close to the PGND pin and route it directly, avoiding vias.

Minimize the length of the connection from the inductor to the output capacitor. Connect the VOS pin directly to the output capacitor.

- Sensitive traces, such as the connections to the VOS, FB, and VSEL pins, must be connected with short traces and be routed away from any noise source, such as the SW pin.

- Make the connections from the input voltage of the system and the connection to the load as wide as possible to minimize voltage drops.

- Have a solid ground plane between PGND and the input and output capacitor ground connections.

- The sensitive signal ground connections for the feedback voltage divider must be connected to a separate signal ground trace.

## 11.2 Layout Example

図 11-1. Layout Example

#### 11.2.1 Thermal Considerations

After the layout recommendations for component placement and routing have been followed, the PCB design must focus on thermal performance. Thermal design is important and must be considered to remove the heat generated in the device during operation. The device junction temperature must stay below its maximum rated temperature of 125°C for correct operation.

Use wide traces and planes, especially to the PGND, VIN, and VOUT pins, and use vias to internal planes to improve the power dissipation capability of the design. If the application allows it, use airflow in the system to further improve cooling.

The *Thermal Information* table provides the thermal parameters of the device and its package based on the JEDEC standard 51-7. See the *Semiconductor and IC Package Thermal Metrics* application report for a detailed

explanation of each parameter. In addition to the JEDEC standard, the thermal information table also contains the thermal parameters of the EVM. The EVM better reflects a real-world PCB design with thicker traces connecting to the device.

# 12 Device and Documentation Support

# 12.1 Device Support

## 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 12.1.2 Development Support

#### 12.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS62865 device with the WEBENCH® Power Designer.

Click here to create a custom design using the TPS62867 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## **12.2 Documentation Support**

## 12.2.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs application report

- Texas Instruments, Semiconductor and IC Package Thermal Metrics application report

#### 12.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接 得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得るこ とができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するも のではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うこと を推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずか に変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

# 12.6 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

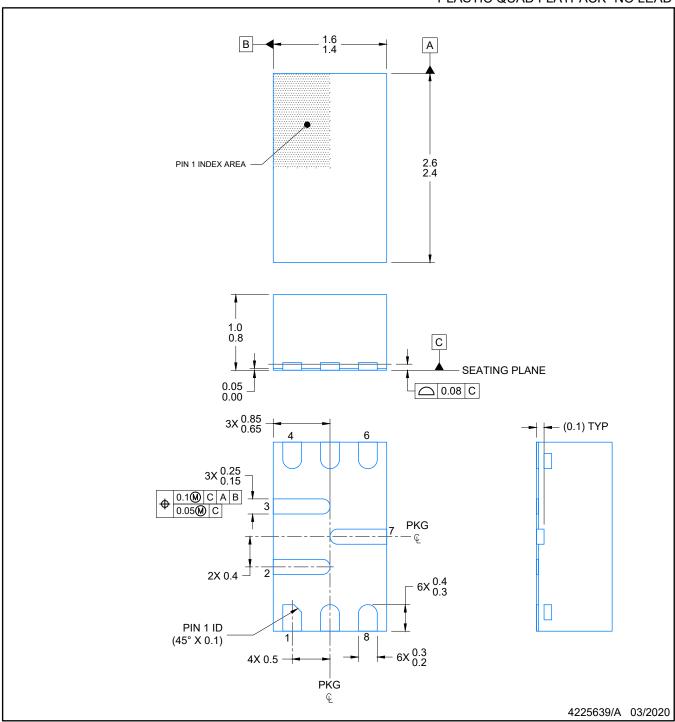

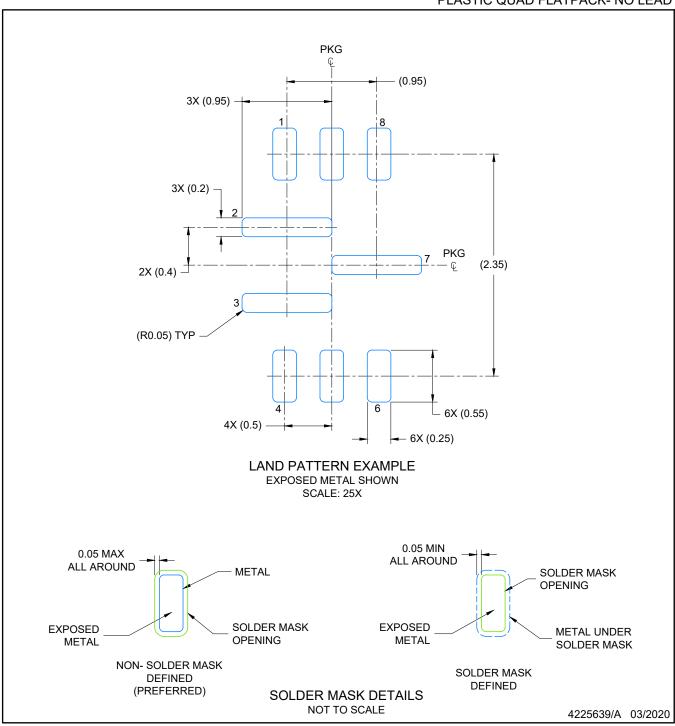

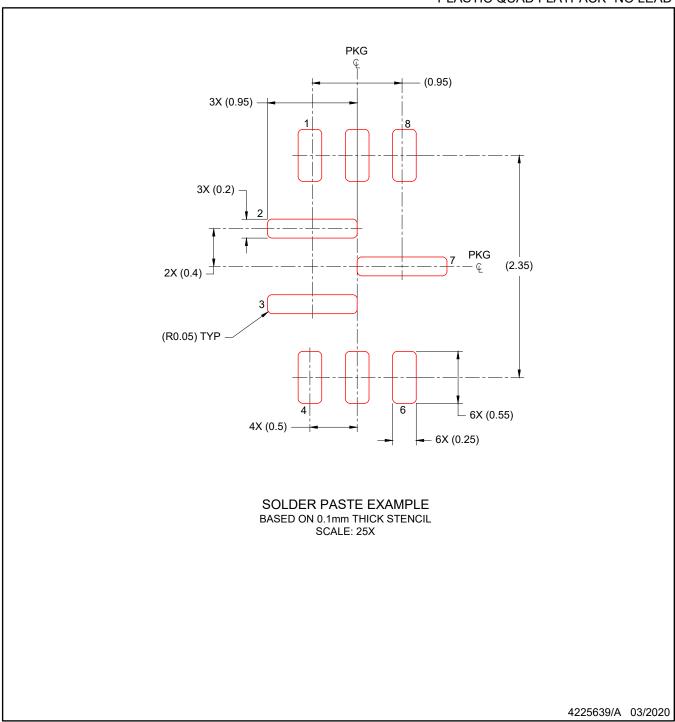

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                   |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                   |                       |      | (4)           | (5)                 |              |              |

| TPS62865RQYR          | Active | Production    | VQFN-HR (RQY)   9 | 3000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 2EAH         |

| TPS62865RQYR.A        | Active | Production    | VQFN-HR (RQY)   9 | 3000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 2EAH         |

| TPS62867RQYR          | Active | Production    | VQFN-HR (RQY)   9 | 3000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 2DWH         |

| TPS62867RQYR.A        | Active | Production    | VQFN-HR (RQY)   9 | 3000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -40 to 125   | 2DWH         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

PLASTIC QUAD FLATPACK- NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- 3. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 4. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月