## 2.25MHz 2x800mA デュアル降圧型コンバータ 小型3×3mm QFNパッケージ

### 特長

- 効率：95% (最大)

- $V_{IN}$ 入力電圧範囲：2.5V ~ 6V

- 2.25MHz固定周波数動作

- 出力電流：2 x 800mA

- 出力電圧可変範囲：0.6V ~  $V_{IN}$

- EasyScale™オプションによる1ピンのシリアル・インターフェイスにより、動作中に出力電圧の変更が可能

- 軽負荷電流時パワーセーブ・モードで動作

- 180°逆位相動作

- 出力電圧精度： $\pm 1\%$  (PWMモード時)

- 静止時電流 (両コンバータ合計) : 32  $\mu$ A (Typ)

- 100%のデューティ・サイクル動作が可能で、最小のドロップアウトを実現

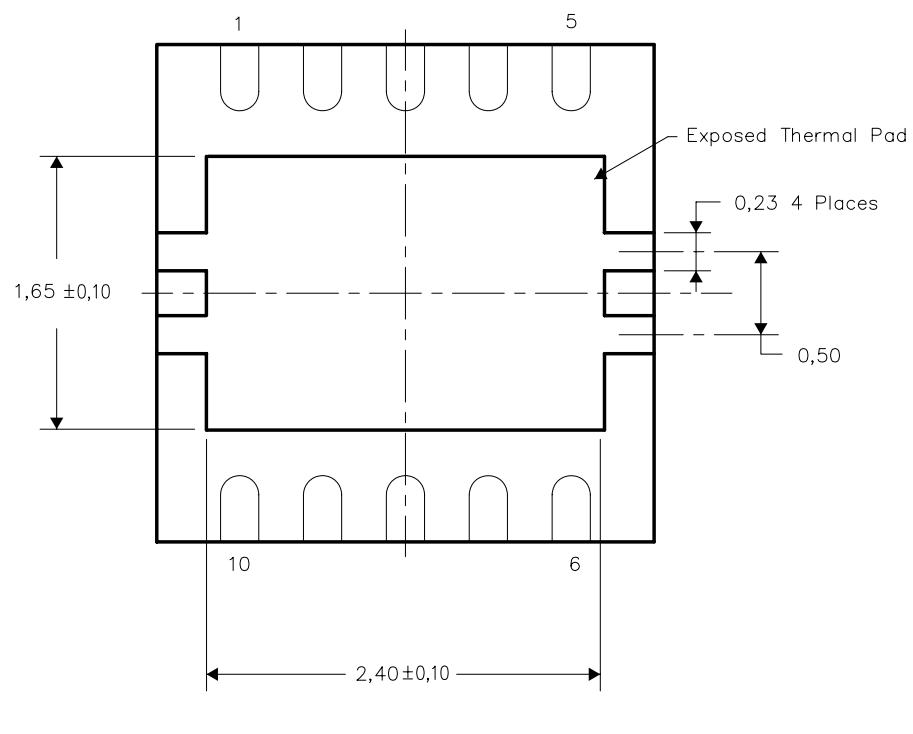

- 10ピンQFNパッケージ (3×3mm)

### アプリケーション

- 携帯電話、スマート・フォン 0

- PDA、ポケットPC

- OMAP™およびローパワーDSPの電源

- ポータブル・メディア・プレーヤー

- デジタル・ラジオ

- デジタル・カメラ

### 概要

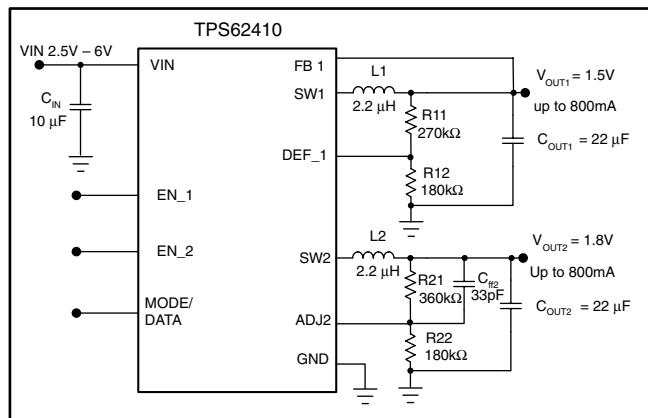

TPS62410は、デュアルチャネルの同期整流方式降圧型DC/DCコンバータで、バッテリー駆動のポータブル用途のアプリケーションに最適です。TPS62410は、入力電源として、単一セルのリチウム・イオン・バッテリー、3セルのニッケル水素/ニッカド・バッテリーを使用することが可能で、出力には独立した2系統を持っています。このデバイスは、入力が標準の3.3Vまたは5V電圧レールでの動作にも適しています。

TPS62410は入力電圧が2.5V~6Vの範囲であるため、スマート・フォン、PDA、その他のポータブル機器のような携帯型機器の電源に理想的なデバイスです。

EasyScale™シリアル・インターフェイスにより、出力電圧を動作時も変更することができるため、ローパワーDSPやプロセッサの電源のデジタル出力可変に対応しています。

EasyScale, OMAP, PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

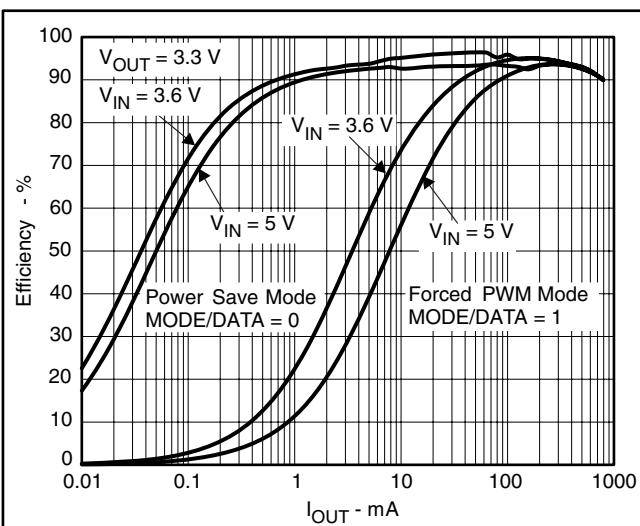

TPS62410は2.25MHzの固定スイッチング周波数で動作し、全負荷電流範囲にわたって高効率を維持するよう、軽負荷電流時にはパワーセーブ・モード動作になります。低ノイズが求められるアプリケーションには、MODE/DATAピンを“H”レベルにすることで固定周波数でスイッチングする固定PWMモードとすることができます。シャットダウン・モードでは、自己消費電流は1.2 $\mu$ A(Typ)に低減します。本デバイスを用いることで、小型のインダクタ及びコンデンサを使用することができる所以、機器そのものの小型化に寄与します。

TPS62410のパッケージは10ピンのリードレス・パッケージ(3×3mm QFN)です。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

### 製品情報<sup>(1)</sup>

| T <sub>A</sub> | 製品名<br>(1) | 初期出力電圧<br>(2) |            | 出力電流  | QFN (1)<br>パッケージ | 注文番号        | パッケージ<br>マーキング |

|----------------|------------|---------------|------------|-------|------------------|-------------|----------------|

| -40°C to 85°C  | TPS62410   | OUT1          | Adjustable | 800mA | DRC              | TPS62410DRC | CAT            |

|                |            | OUT2          |            | 800mA |                  |             |                |

(1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト([www.ti.com](http://www.ti.com))をご覧ください。

### 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                                                       |                      | 値                                      | 単位      |

|-------------------------------------------------------|----------------------|----------------------------------------|---------|

| Input voltage range on V <sub>IN</sub> <sup>(2)</sup> |                      | -0.3 ~ 7                               | V       |

| Voltage range on EN, MODE/DATA, DEF_1                 |                      | -0.3 ~ V <sub>IN</sub> + 0.3, $\leq$ 7 | V       |

| Maximum Current into MODE/DATA                        |                      | 500                                    | $\mu$ A |

| Voltage on SW1, SW2                                   |                      | -0.3 ~ 7                               | V       |

| Voltage on ADJ2, FB1                                  |                      | -0.3 ~ V <sub>IN</sub> + 0.3, $\leq$ 7 | V       |

| ESD rating <sup>(3)</sup>                             | HBM Human body model | 2                                      | kV      |

|                                                       | Charge device model  | 1                                      | kV      |

|                                                       | Machine model        | 200                                    | V       |

| T <sub>J(max)</sub> Maximum junction temperature      |                      | 150                                    | °C      |

| T <sub>A</sub> Operating ambient temperature range    |                      | -40 ~ 85                               | °C      |

| T <sub>stg</sub> Storage temperature range            |                      | -65 ~ 150                              | °C      |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) 全ての電圧値は回路のグランド端子を基準にしています。

(3) 人体モデルは1.5k $\Omega$ の抵抗を介して各ピンに100pFのコンデンサで放電します。マシン・モデルは各ピンに直接200pFのコンデンサで放電します。

### 損失定格

| パッケージ | R <sub>θJA</sub> | 電力定格 T <sub>A</sub> ≤25°C | 軽減係数 T <sub>A</sub> = 25°C |

|-------|------------------|---------------------------|----------------------------|

| DRC   | 49°C/W           | 2050mW                    | 21mW/°C                    |

### 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                                               | MIN | NOM             | MAX | 単位 |

|-----------------------------------------------|-----|-----------------|-----|----|

| V <sub>IN</sub> Supply voltage                | 2.5 | 6               | V   |    |

| Output voltage range for adjustable voltage   | 0.6 | V <sub>IN</sub> | V   |    |

| T <sub>A</sub> Operating ambient temperature  | -40 | 85              | °C  |    |

| T <sub>J</sub> Operating junction temperature | -40 | 125             | °C  |    |

## 電気的特性

$V_{IN} = 3.6V$ ,  $V_{OUT} = 1.8V$ ,  $EN = V_{IN}$ ,  $MODE = GND$ ,  $L = 2.2\mu H$ ,  $C_{OUT} = 20\mu F$ ,  $T_A = -40^{\circ}C \sim 85^{\circ}C$  typical values are at  $T_A = 25^{\circ}C$  (特に記述がない限り)

| パラメータ                   | 測定条件                                                                        | MIN                                                                                                    | TYP               | MAX      | 単位      |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|----------|---------|

| <b>SUPPLY CURRENT</b>   |                                                                             |                                                                                                        |                   |          |         |

| $V_{IN}$                | Input voltage range                                                         |                                                                                                        | 2.5               | 6.0      | V       |

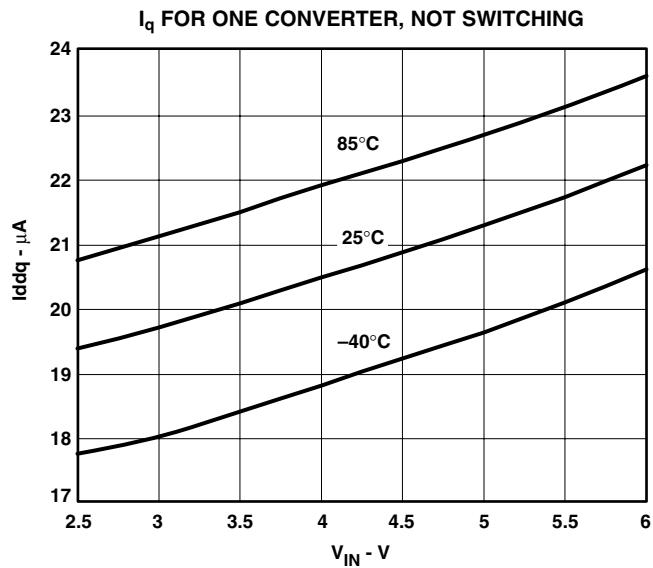

|                         |                                                                             | One converter, $I_{OUT} = 0mA$ . PFM mode enabled (Mode = 0) device not switching, EN1 = 1 OR EN2 = 1  | 19                | 29       | $\mu A$ |

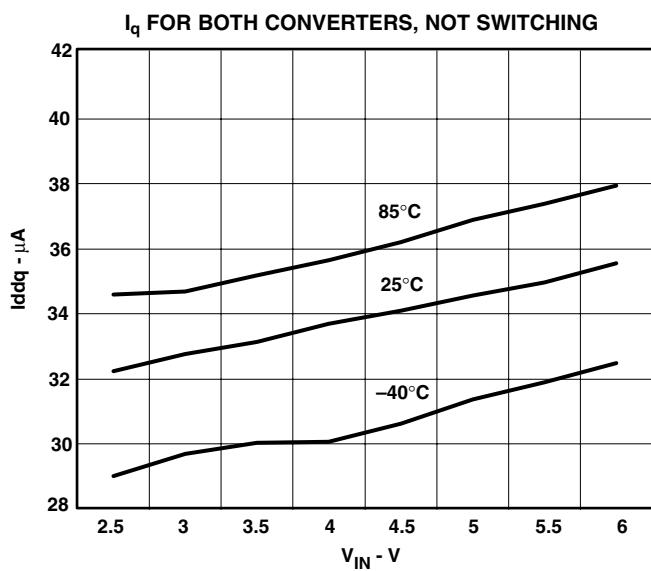

| $I_Q$                   | Operating quiescent current                                                 | Two converter, $I_{OUT} = 0mA$ . PFM mode enabled (Mode = 0) device not switching, EN1 = 1 AND EN2 = 1 | 32                | 48       | $\mu A$ |

|                         |                                                                             | $I_{OUT} = 0mA$ , MODE/DATA = GND, for one converter, $V_{OUT} 1.575V^{(1)}$                           | 23                |          | $\mu A$ |

|                         |                                                                             | $I_{OUT} = 0mA$ , MODE/DATA = $V_{IN}$ , for one converter, $V_{OUT} 1.575V^{(1)}$                     | 3.6               |          | mA      |

| $I_{SD}$                | Shutdown current                                                            | EN1, EN2 = GND, $V_{IN} = 3.6V^{(2)}$                                                                  | 1.2               | 3        | $\mu A$ |

|                         |                                                                             | EN1, EN2 = GND, $V_{IN}$ ramped from 0V to 3.6V <sup>(3)</sup>                                         | 0.1               | 1        |         |

| $V_{UVLO}$              | Undervoltage lockout threshold                                              | Falling                                                                                                | 1.5               | 2.35     | V       |

|                         |                                                                             | Rising                                                                                                 |                   | 2.4      |         |

| <b>ENABLE EN1, EN2</b>  |                                                                             |                                                                                                        |                   |          |         |

| $V_{IH}$                | High-level input voltage, EN1, EN2                                          |                                                                                                        | 1.2               | $V_{IN}$ | V       |

| $V_{IL}$                | Low-level input voltage, EN1, EN2                                           |                                                                                                        | 0                 | 0.4      | V       |

| $I_{IN}$                | Input bias current, EN1, EN2                                                | EN1, EN2 = GND or $V_{IN}$                                                                             | 0.05              | 1.0      | $\mu A$ |

| <b>DEF_1 INPUT</b>      |                                                                             |                                                                                                        |                   |          |         |

| $I_{IN}$                | Input bias current DEF_1                                                    | DEF_1 = GND or $V_{IN}$                                                                                | 0.01              | 1.0      | $\mu A$ |

| <b>MODE/DATA</b>        |                                                                             |                                                                                                        |                   |          |         |

| $V_{IH}$                | High-level input voltage, MODE/DATA                                         |                                                                                                        | 1.2               | $V_{IN}$ | V       |

| $V_{IL}$                | Low-level input voltage, MODE/DATA                                          |                                                                                                        | 0                 | 0.4      | V       |

| $I_{IN}$                | Input bias current, MODE/DATA                                               | MODE/DATA = GND or $V_{IN}$                                                                            | 0.01              | 1.0      | $\mu A$ |

| $V_{OH}$                | Acknowledge output voltage high                                             | Open drain, via external pullup resistor                                                               |                   | $V_{IN}$ | V       |

| $V_{OL}$                | Acknowledge output voltage low                                              | Open drain, sink current 500 $\mu A$                                                                   | 0                 | 0.4      | V       |

| <b>INTERFACE TIMING</b> |                                                                             |                                                                                                        |                   |          |         |

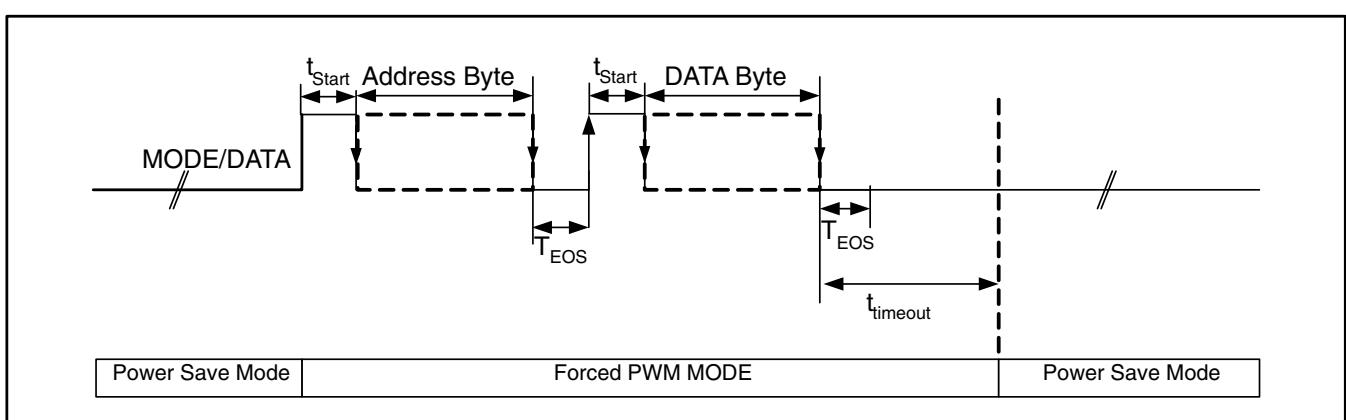

| $t_{Start}$             | Start time                                                                  |                                                                                                        | 2                 |          | $\mu s$ |

| $t_{H\_LB}$             | High time low bit, logic 0 detection                                        | Signal level on MODE/DATA pin is $> 1.2V$                                                              | 2                 | 200      | $\mu s$ |

| $t_{L\_LB}$             | Low time low bit, logic 0 detection                                         | Signal level on MODE/DATA pin $< 0.4V$                                                                 | 2x<br>$t_{H\_LB}$ | 400      | $\mu s$ |

| $t_{L\_HB}$             | Low time high bit, logic 1 detection                                        | Signal level on MODE/DATA pin $< 0.4V$                                                                 | 2                 | 200      | $\mu s$ |

| $t_{H\_LB}$             | High time high bit, logic 1 detection                                       | Signal level on MODE/DATA pin is $> 1.2V$                                                              | 2x<br>$t_{L\_HS}$ | 400      | $\mu s$ |

| $T_{EOS}$               | End of Stream                                                               | $T_{EOS}$                                                                                              | 2                 |          | $\mu s$ |

| $t_{ACKN}$              | Duration of acknowledge condition (MODE/DATA line pulled low by the device) | $V_{IN} 2.5V$ to 6V                                                                                    | 400               | 520      | $\mu s$ |

| $t_{valACK}$            | Acknowledge valid time                                                      |                                                                                                        |                   | 2        | $\mu s$ |

| $t_{timeout}$           | Timeout for entering power save mode                                        | MODE/DATA Pin changes from high to low                                                                 |                   | 520      | $\mu s$ |

(1) デバイスは出力無負荷でスイッチングしており、L 値は3.3 $\mu H$ 、値にはコイルによる損失が含まれています。

(2) この値はデバイスが一度イネーブルになった(EN1またはEN2 = “H” レベル)後で、電源電圧 $V_{IN}$ がパワー・ダウンしていない場合に有効です。

(3) この値はデバイスがディスエーブル(EN1及びEN2 = “L” レベル)で電源電圧 $V_{IN}$ が供給を開始した時に有効です。値はデバイスが最初にイネーブル(EN1またはEN2 = “H” レベル)になるまで有効です。最初のイネーブルの後に、この注(3)による制約が有効となります。

## 電気的特性

$V_{IN} = 3.6V$ ,  $V_{OUT} = 1.8V$ ,  $EN = V_{IN}$ ,  $MODE = GND$ ,  $L = 2.2\mu H$ ,  $C_{OUT} = 20\mu F$ ,  $T_A = -40^{\circ}C \sim 85^{\circ}C$  typical values are at  $T_A = 25^{\circ}C$  (特に記述がない限り)

| パラメータ               |                                                                                         | 測定条件                                                                                                                |          | MIN                   | TYP      | MAX  | 単位          |

|---------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|-----------------------|----------|------|-------------|

| <b>POWER SWITCH</b> |                                                                                         |                                                                                                                     |          |                       |          |      |             |

| $R_{DS(ON)}$        | P-Channel MOSFET On-resistance, Converter 1,2                                           | $V_{IN} = V_{GS} = 3.6V$                                                                                            |          | 280                   | 620      |      | $m\Omega$   |

| $I_{LK\_PMOS}$      | P-Channel leakage current                                                               | $V_{DS} = 6.0V$                                                                                                     |          |                       | 1        |      | $\mu A$     |

| $R_{DS(ON)}$        | N-Channel MOSFET On-resistance Converter 1,2                                            | $V_{IN} = V_{GS} = 3.6V$                                                                                            |          | 200                   | 450      |      | $m\Omega$   |

| $I_{LK\_SW1/SW2}$   | Leakage Current into SW1/SW2 Pin                                                        | Includes N-Chanel leakage current, $V_{IN} = \text{open}$ , $V_{SW} = 6.0V$ , $EN = GND$ <sup>(4)</sup>             |          | 6                     | 7.5      |      | $\mu A$     |

| $I_{LIMF}$          | Forward Current Limit PMOS and NMOS                                                     | $2.5V \leq V_{IN} \leq 6.0V$                                                                                        |          | 1.0                   | 1.2      | 1.38 | A           |

| $T_{SD}$            | Thermal shutdown                                                                        | Increasing junction temperature                                                                                     |          | 150                   |          |      | $^{\circ}C$ |

|                     | Thermal shudown hysteresis                                                              | Decreasing junction temperature                                                                                     |          | 20                    |          |      | $^{\circ}C$ |

| <b>OSCILLATOR</b>   |                                                                                         |                                                                                                                     |          |                       |          |      |             |

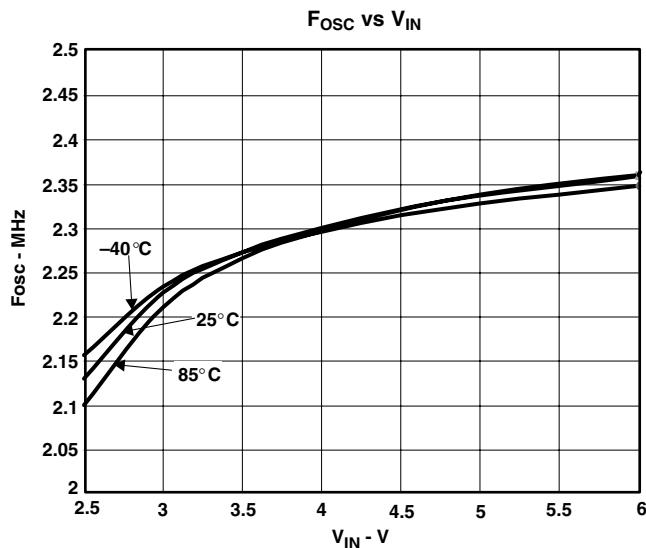

| $f_{SW}$            | Oscillator frequency                                                                    | $2.5V \leq V_{IN} \leq 6.0V$                                                                                        |          | 2.0                   | 2.25     | 2.5  | MHz         |

| <b>OUTPUT</b>       |                                                                                         |                                                                                                                     |          |                       |          |      |             |

| $V_{OUT}$           | Adjustable output votage range                                                          |                                                                                                                     |          | 0.6                   | $V_{IN}$ |      | V           |

| $V_{ref}$           | Reference voltage                                                                       |                                                                                                                     |          | 600                   |          |      | $mV$        |

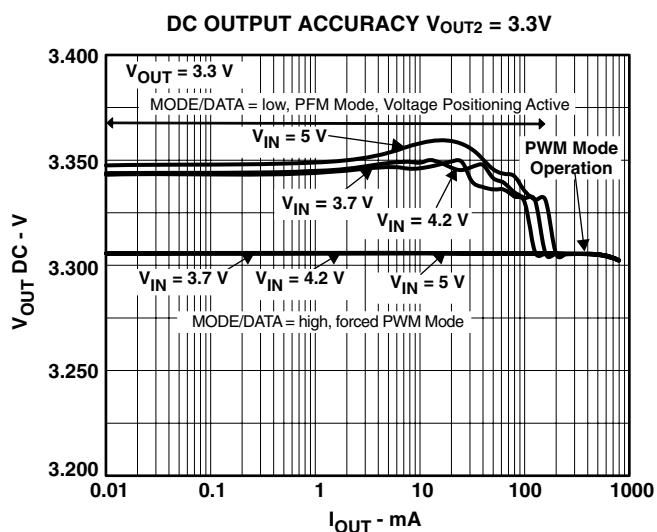

| $V_{OUT}$ (PFM)     | DC output voltage accuracy PFM mode, adjustable and fixed output voltage <sup>(5)</sup> | Voltage positioning active, MODE/DATA = GND, device operating in PFM mode, $VIN = 2.5V$ to $5.0V$ <sup>(6)(7)</sup> | $-1.5\%$ | $1.01 \times V_{OUT}$ | 2.5%     |      |             |

| $V_{OUT}$           |                                                                                         | MODE/DATA = GND; device operating in PWM Mode $VIN = 2.5V$ to $6.0V$ <sup>(7)</sup>                                 | $-1\%$   | 0%                    | 1%       |      |             |

|                     |                                                                                         | $V_{IN} = 2.5V$ to $6.0V$ , Mode/Data = $V_{IN}$ , Fixed PWM operation, $0mA < I_{OUT} < I_{OUTMAX}$ <sup>(8)</sup> | $-1\%$   | 0%                    | 1%       |      |             |

|                     | DC output voltage load regulation                                                       | PWM operation mode                                                                                                  |          |                       | 0.5      |      | %/A         |

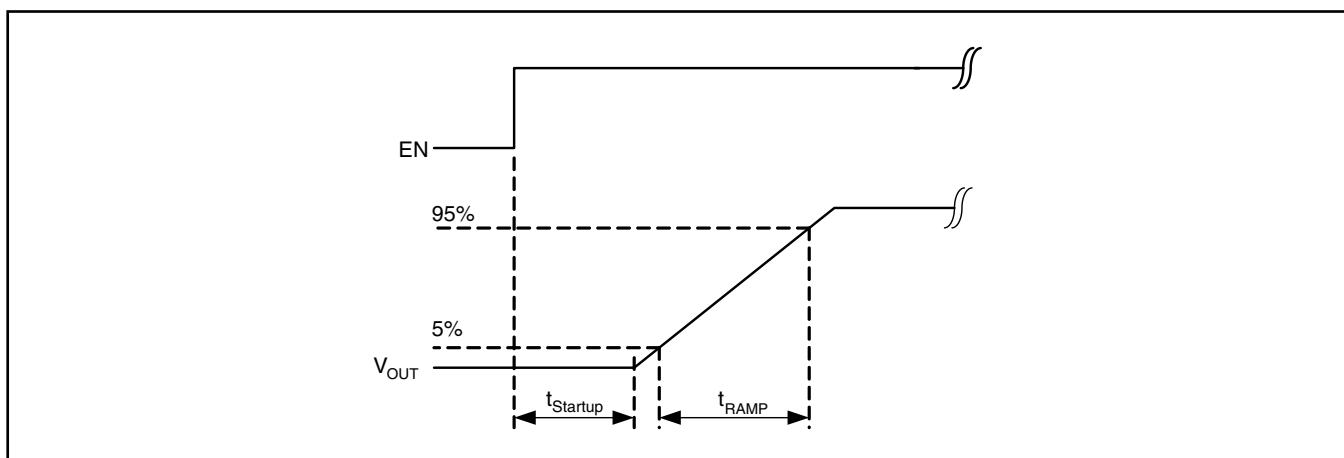

| $t_{Start\ up}$     | Start-up time                                                                           | Activation time to start switching <sup>(9)</sup>                                                                   |          | 170                   |          |      | $\mu s$     |

| $t_{Ramp}$          | $V_{OUT}$ Ramp UP time                                                                  | Time to ramp from 5% to 95% of $V_{OUT}$                                                                            |          | 750                   |          |      | $\mu s$     |

(4) SW1ピンとSW2ピンには $1M\Omega$ の内部抵抗がGNDに接続されています。

(5) 出力電圧の仕様には外部の電圧調整用の抵抗による誤差は含まれていません。

(6) 構成は $L = 2.2\mu H$ (Typ),  $C_{OUT} = 20\mu F$ (Typ)です。パラメータ測定情報を参照してください。PFMモード時の出力電圧リップルは出力コンデンサの実効容量により決まります。出力コンデンサが大きいと出力電圧精度が高くなります。

(7) パワーセーブ・モードで動作中には、標準的に $I_{PSM} = V_{IN}/32\Omega$ を超えるとPWMモードに移行します。

(8)  $V_{OUT} > 2.2V$ の場合、 $V_{IN\ min} = V_{OUT} + 0.3V$

(9) この起動時間が得られるのは、2つコンバータのうちの1つがシャットダウン・モード( $EN2 = 0$ )からアクティブ・モード( $EN2 = 1$ )になり、かつ、もう1つのコンバータが既にイネーブル(例えば、 $EN = 1$ )である場合です。また、2つのコンバータともシャットダウン・モード( $EN1 = EN2 = 0$ )からアクティブ・モード( $EN1 / EN2$ の両方、またはいずれかが1)になった場合では、内部回路が動くまでにさらに $80\mu s$ (Typ)の時間が必要です。 $t_{Start}$ 経過後、コンバータはスイッチングを開始し、 $V_{OUT}$ を上昇させます。

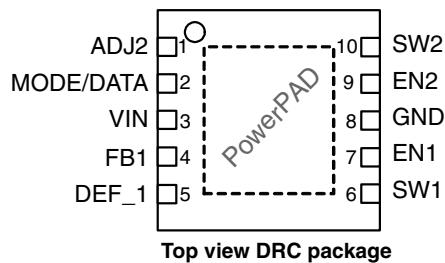

## ピン配置

## ピン機能

| 端子        | NAME | NO.<br>(QFN) | I/O | 説明                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADJ2      | 1    | 1            | I   | コンバータ2の出力電圧設定用入力端子。出力電圧可変バージョン(TPS62410)では、VOUT2-ADJ2間にGND-ADJ2間に分圧抵抗を外付けして、出力電圧を0.6V~VINの間に設定してください。コンバータ2に対してEasyScale™インターフェイスを通して電圧制御が行われる場合にも、このピンは出力に直接接続しなければなりません。                                                                                                                                                                                                                                    |

| MODE/DATA | 2    | 2            | I   | <p>このピンには2つの機能があります。</p> <ol style="list-style-type: none"> <li>動作モードの選択：“L”レベルの場合、軽負荷時にデバイスがPFMモードで動作し、重負荷時に自動的にPWMモードとなる「パワーセーブ・モード」となります。このピンを“H”レベルにすると、デバイスは全負荷範囲にわたり固定PWMモードで動作します。</li> <li>EasyScale™インターフェイス機能：2つのコンバータの出力電圧を変更するための1線式のシリアル・インターフェイス。このピンは、必要に応じて認証状態を出力するためのオープン・ドレイン出力機能も持っています。オープン・ドレインのシンク可能な電流は、500μAまでとなっています。このインターフェイスは、EN1かEN2のいずれか一方が“H”レベルの場合、アクティブな状態となります。</li> </ol> |

| VIN       | 3    | 1            | I   | デバイスの電源電圧であり、電圧範囲が2.5V~6Vのバッテリーに接続します。                                                                                                                                                                                                                                                                                                                                                                        |

| FB1       | 4    | 1            | I   | コンバータ1の直接フィードバック電圧検出入力で、直接Vout1に接続します。内部位相補償コンデンサがこのピンと誤差増幅器の間に内蔵されています。出力電圧固定タイプの場合、またはインターフェイスが使用された場合、このピンは内部の電圧検出抵抗に接続されます。                                                                                                                                                                                                                                                                               |

| DEF_1     | 5    | I/O          |     | <p>このピンはコンバータ1の出力電圧を決めます。TPS62410では外付けの抵抗を介した出力電圧設定用のアナログ入力として動作します。固定出力電圧製品ではこのピンはデフォルト固定出力電圧から選択するデジタル入力として動作します。</p> <p>TPS62410の場合、出力電圧を設定するために、このピンに外付けで抵抗を接続する必要があります。</p>                                                                                                                                                                                                                              |

| SW1       | 6    |              |     | コンバータ1のスイッチ・ピン。インダクタ1に接続します。                                                                                                                                                                                                                                                                                                                                                                                  |

| EN1       | 7    | I            |     | コンバータ1のイネーブル入力で、アクティブ“H”。                                                                                                                                                                                                                                                                                                                                                                                     |

| GND       | 8    | I            |     | 両方のコンバータのグランド・ピンで、このピンはPowerPad™に接続します。                                                                                                                                                                                                                                                                                                                                                                       |

| EN2       | 9    | I/O          |     | コンバータ2のイネーブル入力で、アクティブ“H”。                                                                                                                                                                                                                                                                                                                                                                                     |

| SW2       | 10   |              |     | コンバータ2のスイッチ・ピン。インダクタ2に接続します。                                                                                                                                                                                                                                                                                                                                                                                  |

| PowerPAD™ |      |              |     | GNDに接続します。                                                                                                                                                                                                                                                                                                                                                                                                    |

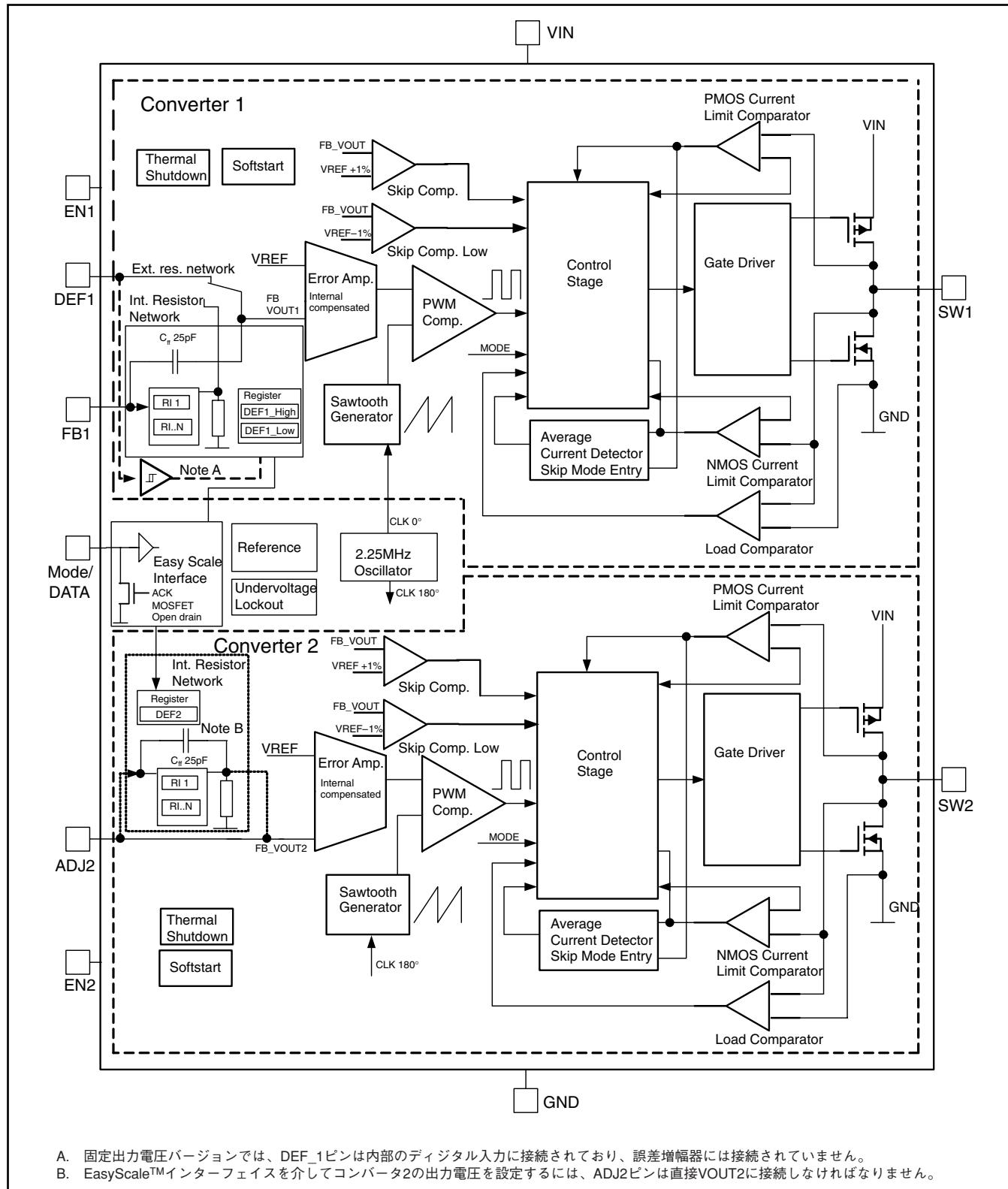

## 機能ブロック図

A. 固定出力電圧バージョンでは、DEF\_1ピンは内部のデジタル入力に接続されており、誤差増幅器には接続されていません。

B. EasyScale™インターフェイスを介してコンバータ2の出力電圧を設定するには、ADJ2ピンは直接VOUT2に接続しなければなりません。

## パラメータ測定情報

## 代表的特性

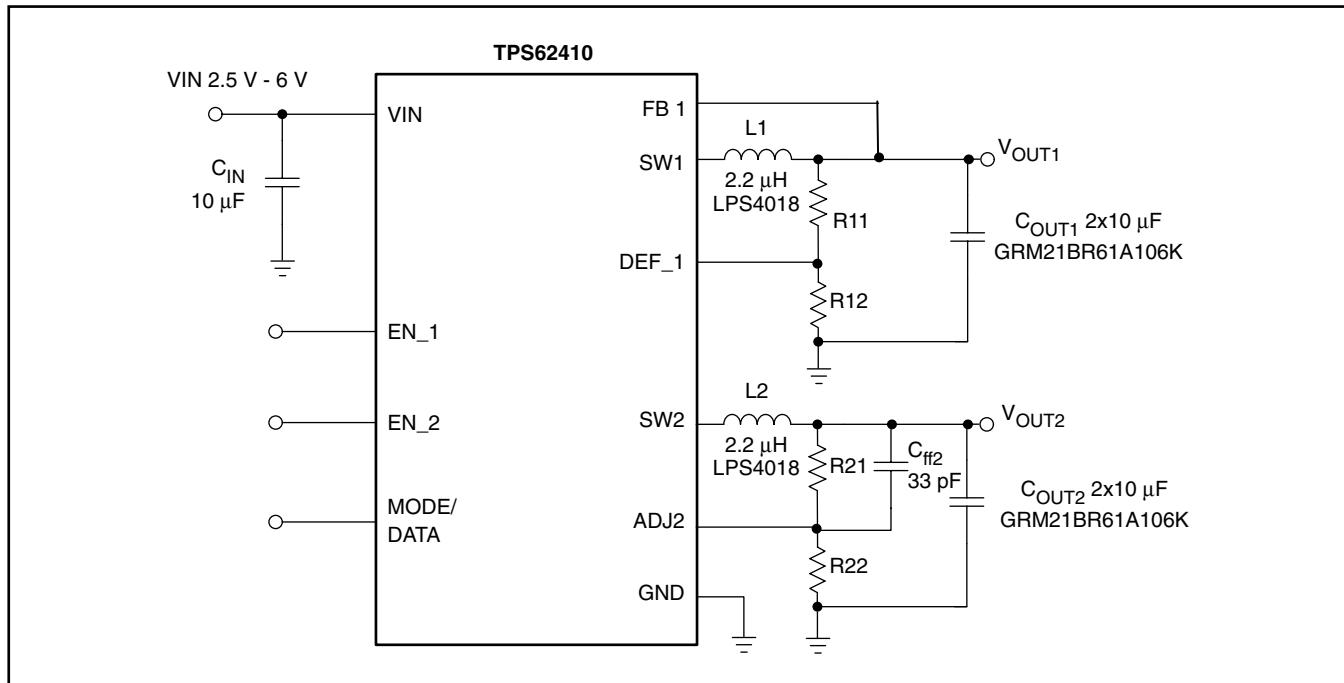

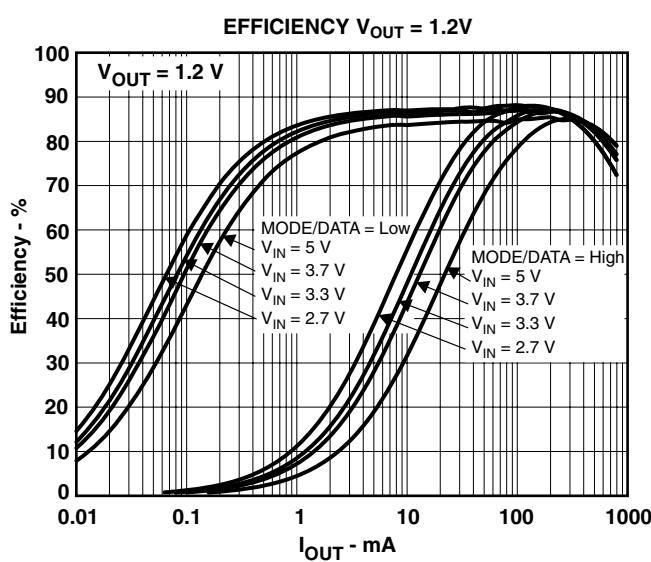

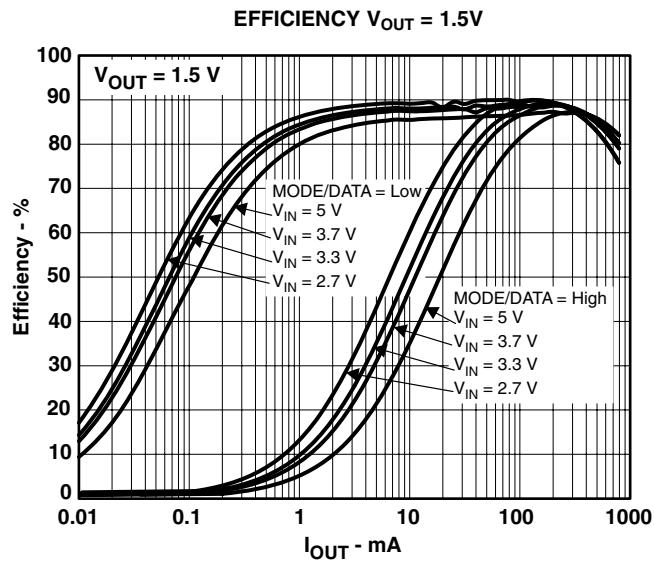

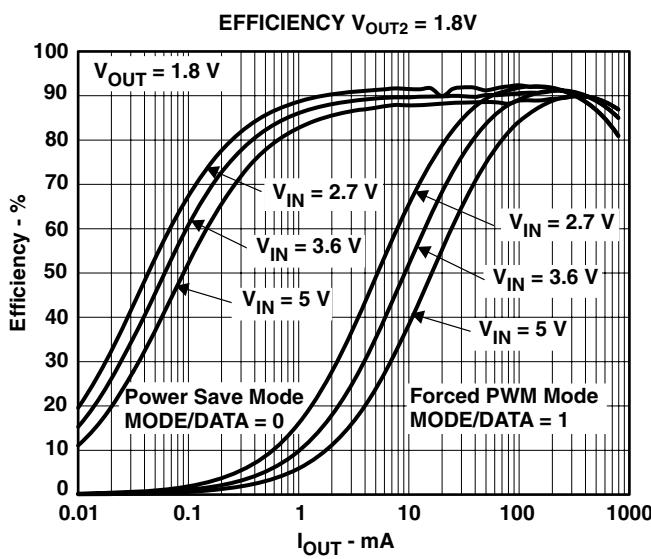

グラフおよび図一覧

|                                                                             | 図 NO. |

|-----------------------------------------------------------------------------|-------|

| Efficiency $V_{OUT1} = 1.2V$                                                | 1     |

| Efficiency $V_{OUT1} = 1.5V$                                                | 2     |

| Efficiency $V_{OUT2} = 1.8V$                                                | 3     |

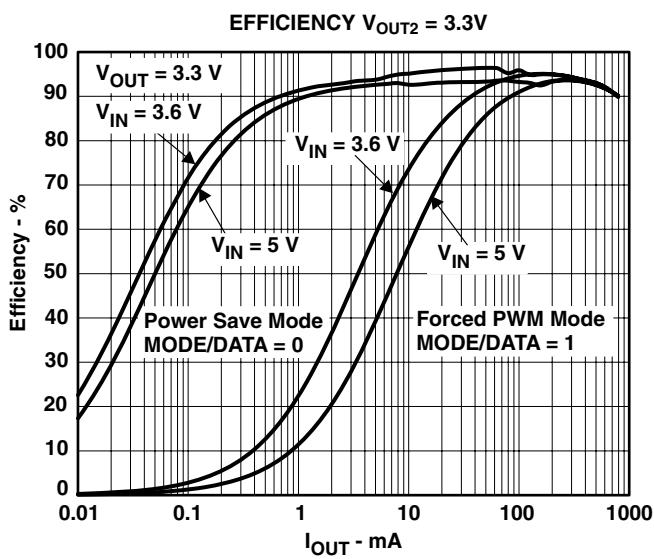

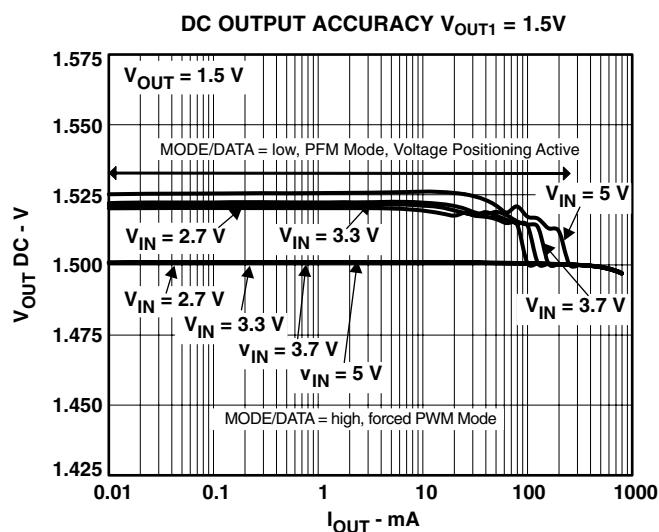

| Efficiency $V_{OUT2} = 3.3V$                                                | 4     |

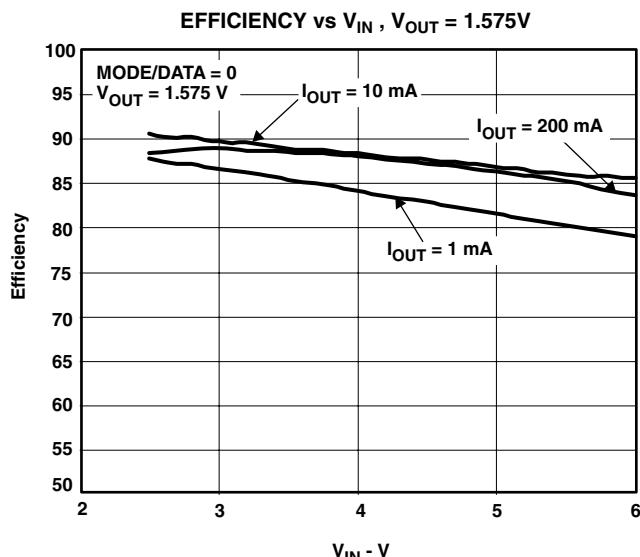

| Efficiency<br>vs $V_{IN}$                                                   | 5, 6  |

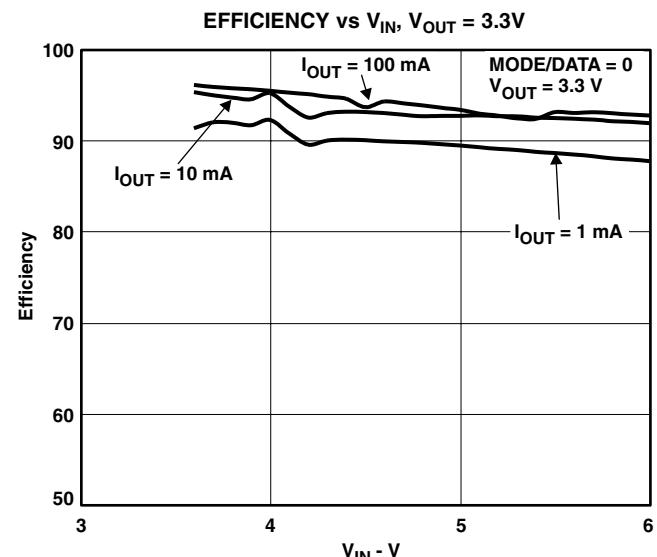

| DC Output Accuracy $V_{OUT1} = 1.5V$                                        | 7     |

| DC Output Accuracy $V_{OUT2} = 3.3V$                                        | 8     |

| $F_{osc}$<br>vs $V_{IN}$                                                    | 9     |

| $I_q$ for one converter                                                     | 10    |

| $I_q$ for both converters, not switching                                    | 11    |

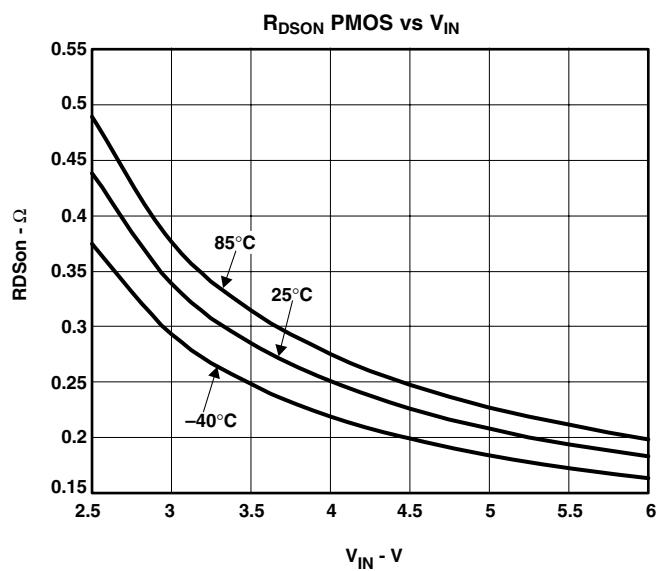

| $R_{DSON}$ PMOS<br>vs $V_{IN}$                                              | 12    |

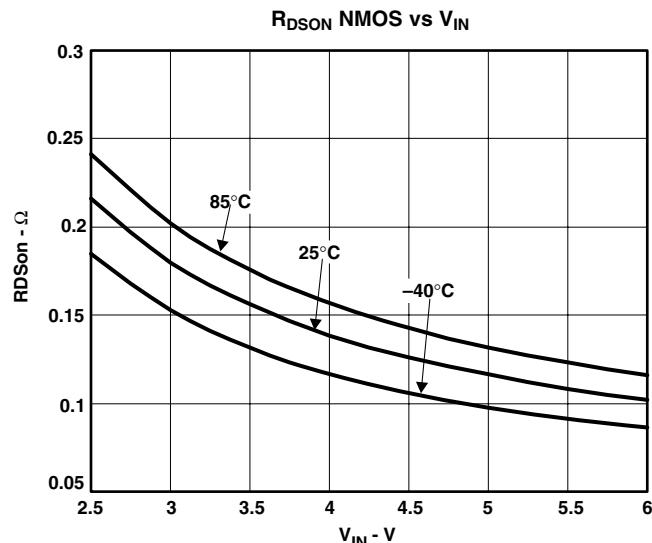

| $R_{DSON}$ NMOS<br>vs $V_{IN}$                                              | 13    |

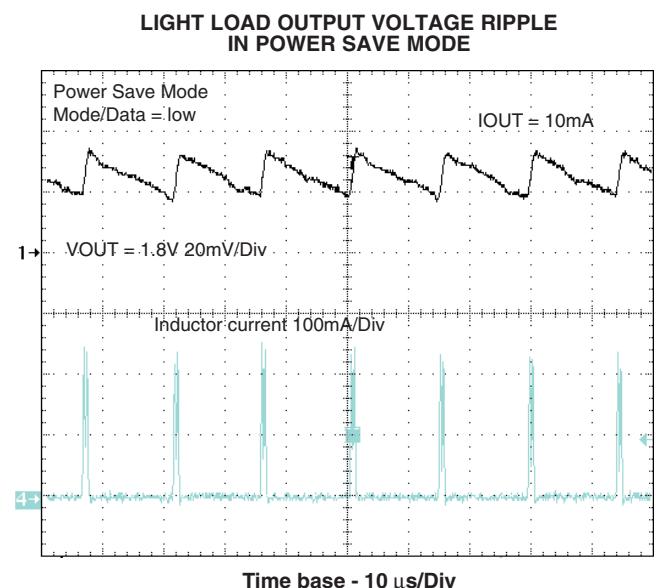

| Light Load Output Voltage Ripple in Power Save Mode                         | 14    |

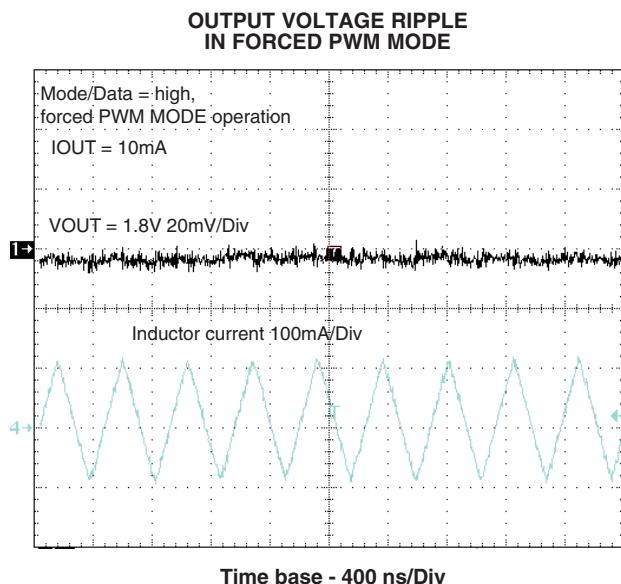

| Output Voltage Ripple in Forced PWM Mode                                    | 15    |

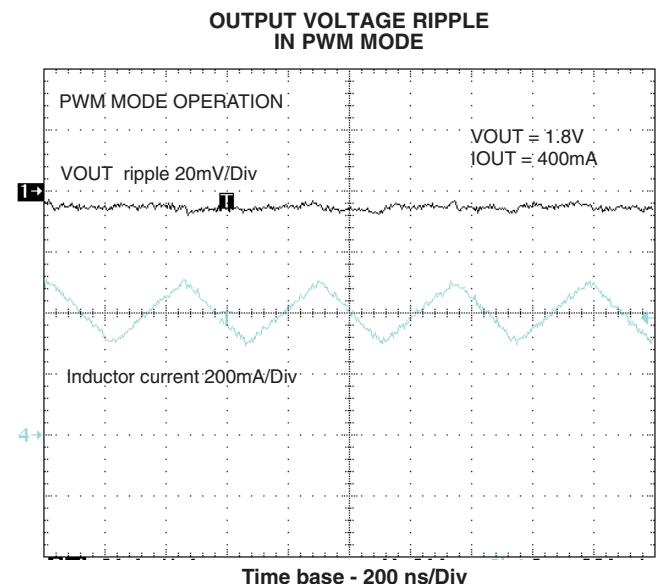

| Output Voltage Ripple in PWM Mode                                           | 16    |

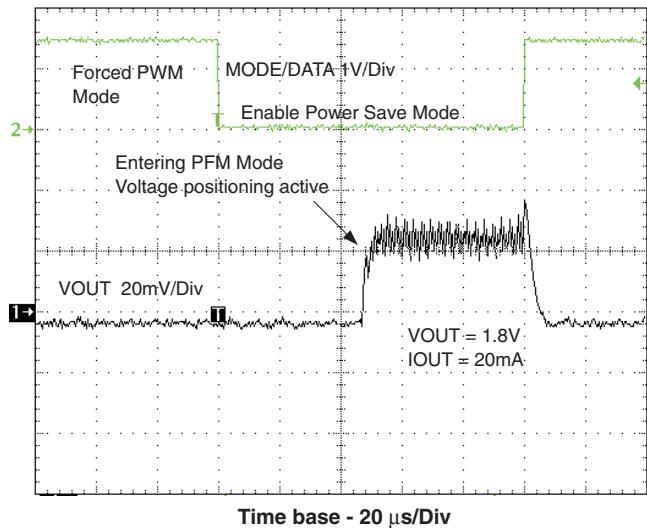

| Forced PWM/ PFM Mode Transition                                             | 17    |

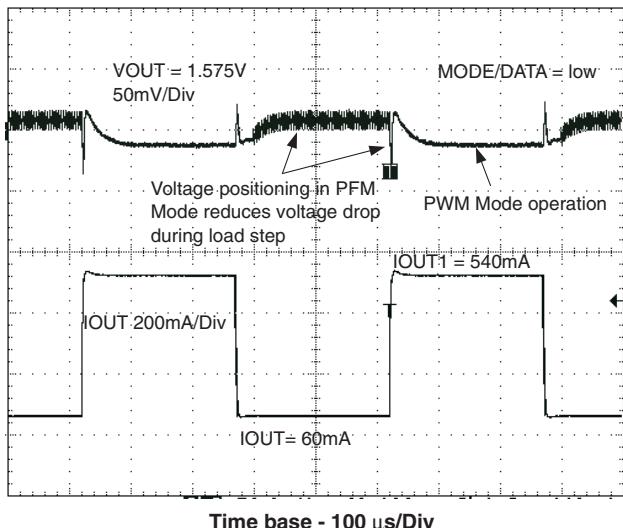

| Load Transient Response PFM/PWM                                             | 18    |

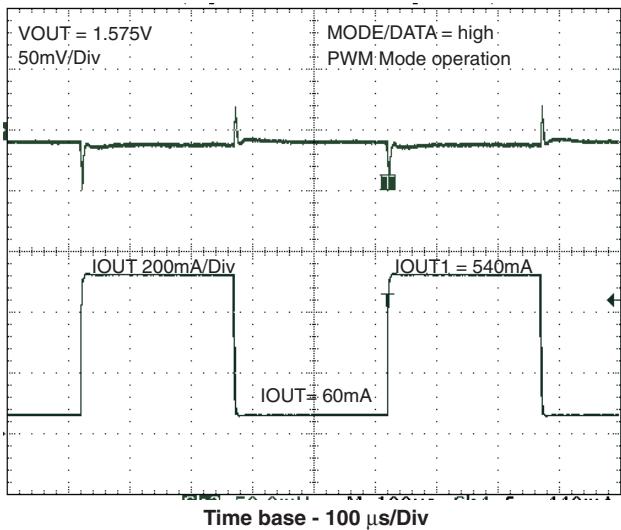

| Load Transient Response PWM Operation                                       | 19    |

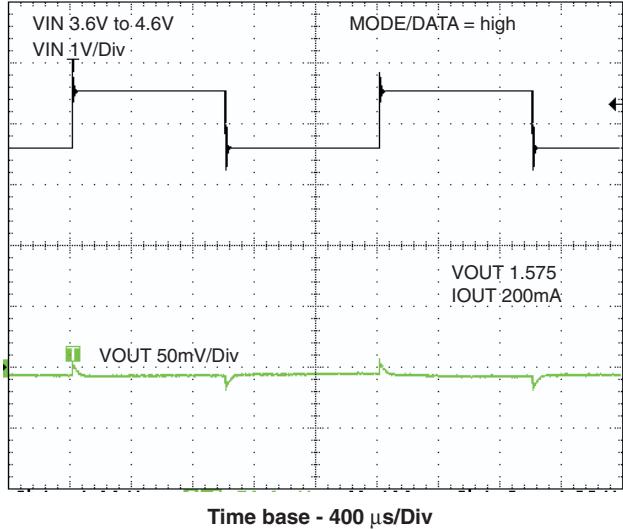

| Line Transient Response                                                     | 20    |

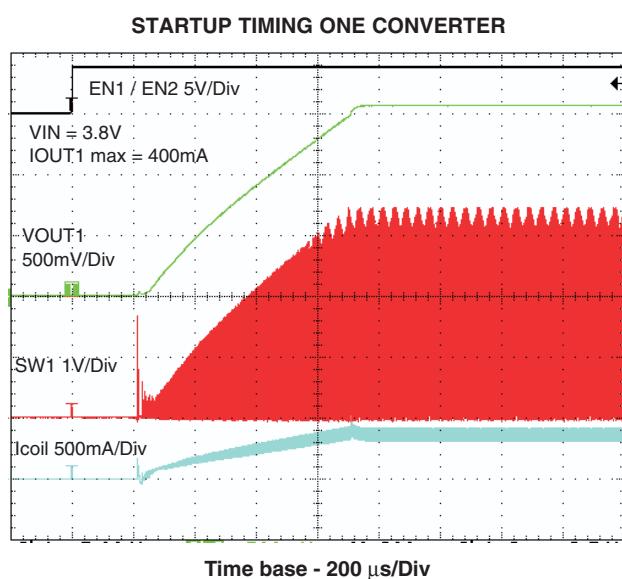

| Startup Timing One Converter                                                | 21    |

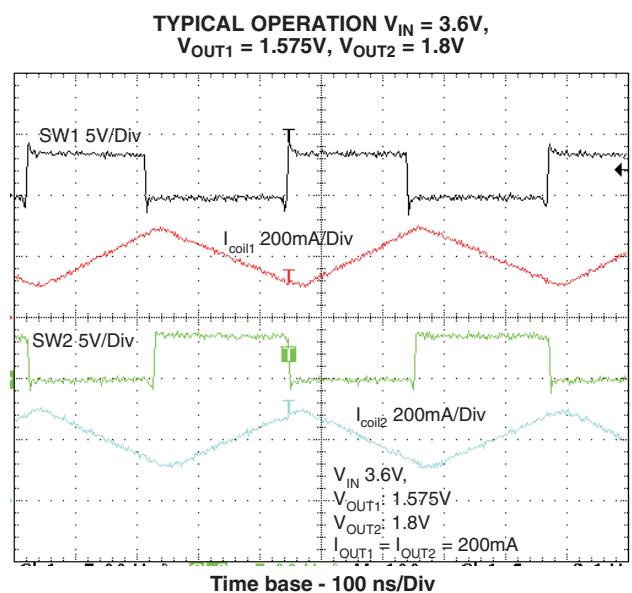

| Typical Operation $V_{IN} = 3.6V$ , $V_{OUT1} = 1.575V$ , $V_{OUT2} = 1.8V$ | 22    |

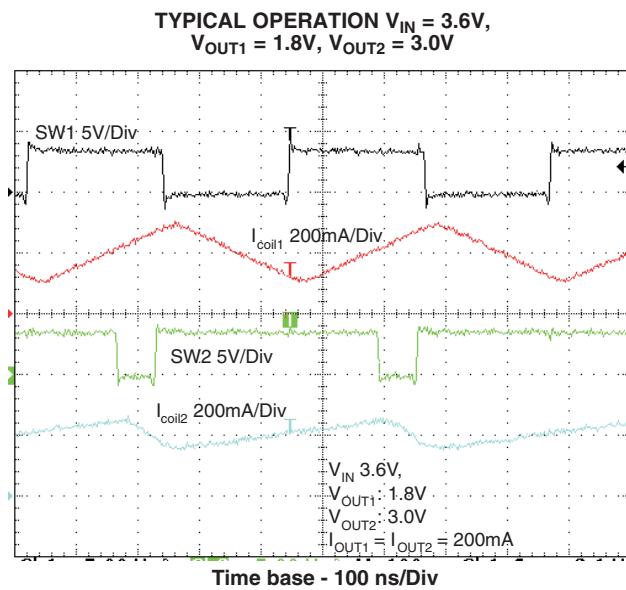

| Typical Operation $V_{IN} = 3.6V$ , $V_{OUT1} = 1.8V$ , $V_{OUT2} = 3.0V$   | 23    |

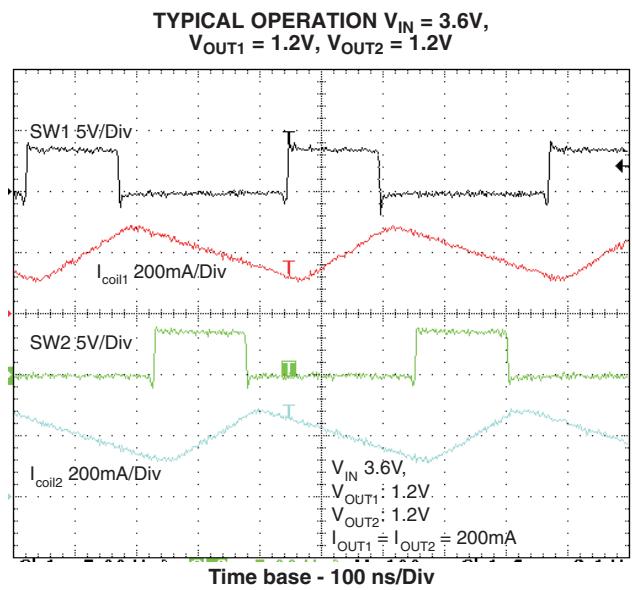

| Typical Operation $V_{IN} = 3.6V$ , $V_{OUT1} = 1.2V$ , $V_{OUT2} = 1.2V$   | 24    |

| Dynamic Voltage Positioning                                                 | 25    |

## 代表的特性

|                                                             | 図NO.   |

|-------------------------------------------------------------|--------|

| Soft Start                                                  | 26     |

| EasyScale Protocol Overview                                 | 27     |

| EasyScale Protocol Without Acknowledge                      | 28     |

| EasyScale Protocol Including Acknowledge                    | 29     |

| EasyScale – Bit Coding                                      | 30     |

| MODE/DATA PIN: Mode Selection                               | 31     |

| MODE/DATA Pin: Power Save Mode / Interface Communication    | 32     |

| Typical Application Circuit 1.5V / 2.85V Adjustable Outputs | 33, 34 |

| Layout Diagram                                              | 35     |

| PCB Layout                                                  | 36     |

図 1

図 2

図 3

図 4

## 代表的特性

図 5

図 6

図 7

図 8

## 代表的特性

図 9

図 10

図 11

図 12

## 代表的特性

図 13

図 14

図 15

図 16

## 代表的特性

FORCED PWM/PFM MODE TRANSITION

図 17

LOAD TRANSIENT RESPONSE PFM/PWM

図 18

LOAD TRANSIENT RESPONSE PWM OPERATION

図 19

LINE TRANSIENT RESPONSE

図 20

## 代表的特性

図 21

図 22

図 23

図 24

**$V_{OUT1}$  CHANGE WITH EASYSCALE**

## 詳細説明

### 動作

TPS62410には2つの同期式降圧型コンバータが内蔵されています。このコンバータは中～大負荷電流範囲において、2.25MHzの固定周波数のパルス幅変調(PWM)で動作します。パワーセーブ・モードがイネーブルの場合、コンバータは軽負荷時に自動的にパワーセーブ・モードとなり、PFM(パルス周波数変調)で動作します。PWM動作時、入力電圧フィードフォワードをもつ独自の高速応答電圧モード制御を行うことで、良好なライン及び負荷レギュレーションが得られ、小型の入力/出力セラミック・コンデンサを使用することが可能になります。クロック信号から作られる各スイッチング・サイクルの始まりでは、PチャネルのMOSFETスイッチがオンとなりインダクタ電流が上昇します。その後コンパレータが反転し、コントロール・ロジックがスイッチをオフにします。

各コンバータはそれぞれに2つの電流制限を内蔵しており、1つはPチャネルMOSFETに、もう1つはNチャネルMOSFETを持っています。PチャネルMOSFETの電流がその電流制限に達した時、PチャネルMOSFETはオフになり、NチャネルMOSFETはオンになります。NチャネルMOSFETの電流がNMOSの電流制限スレッシュホールドを超えると、電流がその制限値より低くなるまでNチャネルMOSFETはオフのままであります。2つのDC/DCコンバータは互いに同期して動作します。コンバータ1とコンバータ2の間に180°の位相差を作ることで、入力リップル電流が減少します。

### コンバータ1

出力電圧可変タイプのTPS62410では、DEF\_1ピンはアナログ入力として機能し、コンバータ1の出力電圧をDEF\_1ピンの外付け抵抗で設定することができます。この場合、出力電圧を0.6V～VINの範囲で設定できます。FB1ピンはコンバータ1の出力電圧VOUT1に直接接続します。こうすることで出力電圧が直接フィードバックループに接続されます。

また、コンバータ1の出力電圧はEasyScale™シリアル・インターフェイスを使っても変更することができます。これにより、デバイスは出力電圧を調整するのに高い柔軟性をもつことになります。この場合、デバイスは内部の抵抗を使用します。

### コンバータ2

出力電圧可変タイプのTPS62410では、コンバータ2の出力電圧はADJ2ピンに接続される外付けの分圧抵抗で設定されます。この抵抗には、33pFのフィードフォワード・コンデンサを付加します。

EasyScale™インターフェイスを介してコンバータ2の出力電圧を変更することもできます。この場合も、ADJ2ピンはコンバータ2の出力電圧VOUT2に直接接続しなければなりません。TPS62410では外付け抵抗を接続してはなりません。

### パワーセーブ・モード

パワーセーブ・モードはMODE/DATAピンを“L”レベルにセットすることで両方のコンバータに対しイネーブルになります。コンバータの負荷電流が減少すると、このコンバータは自動的にパワーセーブ・モード動作になります。コンバータのパワーセーブ・モードへの移行はもう一方のコンバータの動作状態とは無関係に行われます。パワーセーブ・モード時、コンバータはPFMモードで動作してスイッチング周波数を落とし、最小の自己消費電流で動作することで高効率を維持します。PFMモード時の出力電圧はVOUT(Typ)の1.01倍となります。この電圧調整機能により突然の負荷増大により生じる電圧降下による影響を最小限に抑えられます。

軽負荷時のコンバータ効率を最適化するために、平均インダクタ電流を監視しています。PWMモードで動作中にインダクタ電流があるスレッシュホールド値より低下した場合、デバイスの動作はPWMモードからパワーセーブ・モードに移行します。出力電流の標準スレッシュホールド電流値はVINに依存し、各コンバータについて式(1)で計算することができます。

式(1) : PFMモードになる平均出力電流のスレッシュホールド

$$I_{\text{OUT\_PFM\_enter}} = \frac{V_{\text{IN}}_{\text{DCDC}}}{32 \Omega} \quad (1)$$

式(2) : PFMモードから出る平均出力電流のスレッシュホールド

$$I_{\text{OUT\_PFM\_leave}} = \frac{V_{\text{IN}}_{\text{DCDC}}}{24 \Omega} \quad (2)$$

パワーセーブ・モード時の出力電圧リップルを小さくするために、出力電圧はシングル・スレッシュホールド・コンパレータ(スキップ・コンパレータ)で監視されています。出力電圧がスキップ・コンパレータのスレッシュホールド(skip comp標準1.01 × VOUT)より低下すると、そのコンバータは1μs(Typ)の最小時間でスイッチングを開始し、電流を負荷と出力コンデンサに供給します。その結果、出力電圧は上昇し、スキップ・コンパレータのスレッシュホールド(skip comp)で再び反転するまで、デバイスはスイッチングを続けます。スキップコンパレータの再反転で全てのスイッチング動作は停止し、自己消費電流は最小となります。負荷には、出力電圧がスレッシュホールドより低下するまでの間出力コンデンサから電流が供給されます。そしてデバイスは再びスイッチングを開始します。

パワーセーブ・モードからPWMモードへ移行するのは、出力電流がIOUT\_PFM\_leave値を越えた場合、または出力電圧が、“スキップ・コンパレータ・ロー(Skip Comp Low)スレッシュホールド”と呼ばれるもう一つのコンパレータ・スレッシュホールドより低下した場合です。このスキップ・コンパレータ・ローのスレッシュホールドはVoutの標準値2%に設定されており、負荷変動時パワーセーブ・モードからPWMモードへの高速の移行を可能にしています。

パワーセーブ・モードでは、静止時自己消費電流は1つのコンバータで19 $\mu$ A (Typ) にまで低減され、両方でも32 $\mu$ A (Typ) にまで低減します。このシングル・スキップ・コンパレータ・スレッシュホールド法を用いることで、パワーセーブ・モードでの出力電圧リップルを極めて小さくすることができます。リップルの大きさは、コンパレータの遅延と出力コンデンサの大きさにより変わります。出力コンデンサの容量を増やすと出力リップルを小さくできます。パワーセーブ・モードはMODE/DATAピンを“H”レベルにセットすることによりディスエーブルすることができます。その場合、2つのコンバータは固定PWMモードで動作します。パワーセーブ・モードのイネーブル/ディスエーブルは両方のコンバータに適用されます。

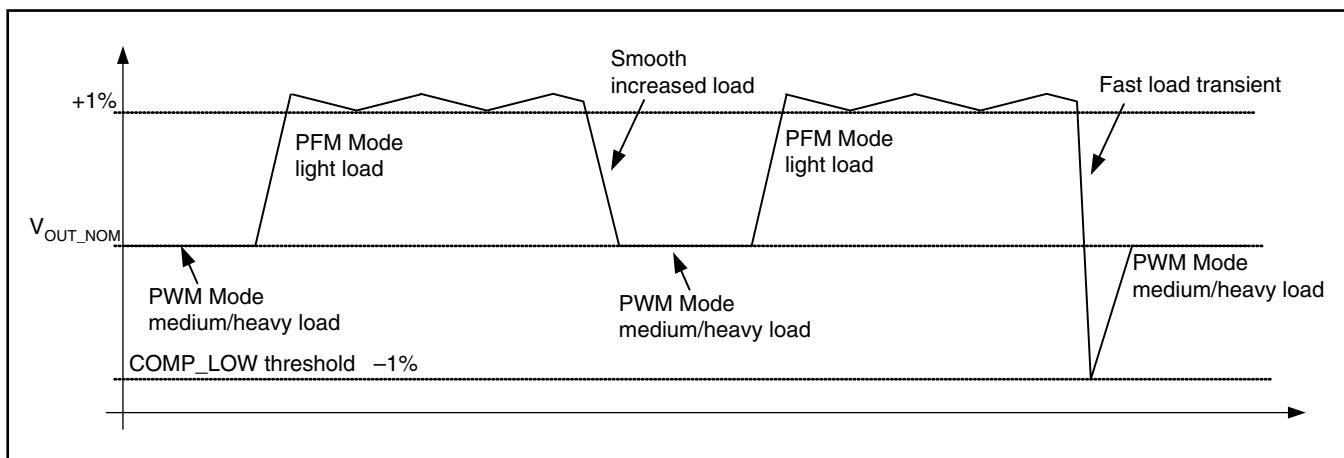

### ダイナミック電圧ポジショニング

この機能により、軽負荷から重負荷/重負荷から軽負荷といった負荷変動時の電圧アンダーシュート/オーバーシュートが低減されます。この機能はパワーセーブ・モード動作時にアクティブになります。負荷変動時の電圧降下と起動時の電圧上昇の両方に対しさらなる余裕が生まれます。この機能により負荷過渡応答特性が改善されます。

コンバータがPFMモードで動作する軽負荷時、出力電圧は標準値より1% (Typ) 高い電圧でリギュレーションされます。軽負荷から重負荷へ急速な負荷変動があり、出力電圧が標準値の-2%に設定されているスキップ・コンパレータ・ローのスレッシュホールドに達すると動作モードはPWMモードに変わります。また、重負荷から軽負荷への負荷変化の時は、ローサイドのNチャネルのスイッチをオンにするアクティブ・リギュレーションにより電圧のオーバーシュートも最小限に抑えられます。

### ソフトスタート

2つのコンバータは内部に起動時の突入電流を制限するソフトスタート回路をもっています。ソフトスタート時、出力電圧の上昇は図26のように制御されます。

図 25. Dynamic Voltage Positioning

図 26. Soft Start

## 100%デューティ・サイクルの低ドロップアウト動作

本コンバータは100%デューティ・サイクル・モードを持っているので、低い入出力電圧差でも動作できます。このモードでは、Pチャネル・スイッチは常にオンになっています。これは特にバッテリー駆動のアプリケーションで有用で、バッテリーの全電圧範囲を最大限に活用することで最長の動作時間を得られます。レギュレーションを維持するための最小入力電圧は負荷電流と出力電圧により決まり、以下の式で計算することができます。

$$V_{IN_{min}} = V_{OUT_{max}} + I_{OUT_{max}} \times (RDS_{ON_{max}} + R_L) \quad (3)$$

但し、

$I_{OUT_{max}}$  = 最大出力電流 + インダクタ・リップル電流

$RDS_{ON_{max}}$  = Pチャネル・スイッチの最大オン抵抗

$R_L$  = インダクタの直流抵抗

$V_{OUT_{max}}$  = 標準出力電圧 + 最大出力電圧の最大公差

負荷電流が減少すると、デバイスは負荷に応じてパワー段が間欠的に動作するパルス・スキップ動作に自動的に切り替わります。周期的なサイクル動作により、スイッチング損失は最小になります。デバイスは最小の静止電流で動作するため、高効率が維持されます。

## 低電圧ロックアウト

低電圧ロックアウト回路は、低入力電圧時にコンバータをディスエーブルにし、デバイスの誤動作やバッテリーの過放電を防止します。低電圧ロックアウトのスレッシュホールドは標準で1.5V、最大で2.35Vです。デフォルトのレジスタ値がインターフェイス経由で上書きされた場合、電源電圧が低電圧ロックアウトのスレッシュホールドより低下しない限り、レジスタREG\_DEF\_1\_HIGH、REG\_DEF\_1\_LOW、REG\_DEF\_2に設定された値は有効のままです。このときコンバータがディスエーブルかどうかは無関係です。

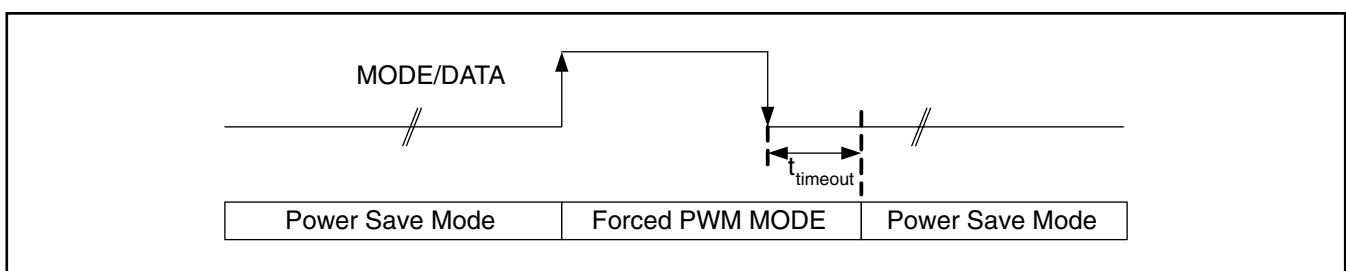

## モード選択

MODE/DATAピンにより、固定PWMモードとパワーセーブ・モードからモード選択を行うことができます。このモード選択は2つのコンバータに対して有効となります。さらに、このピンは多機能ピンで、(モード選択に加えて)出力電圧を設定するためのシリアル・データをホストから受け取ります。これについてはEasyScale<sup>TM</sup>インターフェイスの項で説明します。

このピンをGNDに接続するとPWMモードとパワーセーブ・モードの自動切換動作がイネーブルになります。コンバータは中～重負荷では固定周波数のPWMモードで動作し、軽負荷時にはPFMモードに自動的に切り替わって動作し、広い負荷電流範囲にわたって高効率を維持します。

MODE/DATAピンを“H”レベルにすると、2つのコンバータとも軽負荷時でも常にPWMモードで動作します。この利点は、コンバータが固定周波数で動作することにより、ノイズに敏感なアプリケーションの場合に、スイッチング周波数帯のフィルタが簡素化できることです。このモードでは、効率は軽負荷

時にパワーセーブ・モードに比べて低くなります。さらなる柔軟性をもたせるため、動作中にパワーセーブ・モードから固定PWMモードに切り替えることができます。コンバータの動作を個別のシステム要件に適合させることで、効率的なパワー・マネジメントが可能になります。

動作モードが固定PWMモード(MODE/DATAピン=“H”レベル)からパワーセーブ・モード・イネーブル(MODE/DATAピン=“L”レベル)に変更された場合、パワーセーブ・モードは最大520μsの遅延時間t<sub>timeout</sub>の後イネーブルになります。

固定PWMモード動作はMODE/DATAピンが1にセットされると直ちにイネーブルになります。

## イネーブル

このデバイスは、コンバータごとに個別のENピンをもっているので、それぞれを独立して起動させることができます。EN1やEN2が“H”レベルにセットされた場合、対応するコンバータは前述のようにソフトスタートにより起動します。

EN1とEN2を“L”レベルにすると、デバイスはシャットダウンし、静止電流はわずか1.2μA(Typ)となります。このモードでは、Pチャネル及びNチャネルMOSFETはオフになり、全ての内部コントロール回路もオフに切り替わります。正常動作を行うにはEN1ピンとEN2ピンは終端処理をしなければならず、フローティングにしておいてはいけません。

## DEF\_1ピンの機能

DEF\_1ピンはコンバータ1の専用ピンで可変出力電圧設定のアナログ入力として機能します。このピンに抵抗を外付けし、デフォルトの出力電圧を0.6V～V<sub>IN</sub>の間で任意に設定することができます。

## 180°の逆位相動作

PWMモードでは、それぞれのコンバータはPMOS(ハイサイド)トランジスタが180°逆位相でターンオンします。このことにより、2つのコンバータのハイサイド・スイッチが同時にオンすることがなくなり、入力電流が平滑化されます。この機能により電源から流れ込むサージ電流が低減します。

## 短絡保護

両出力とも短絡保護機能を持っており、その短絡電流値は最大出力電流 = I<sub>LIMF</sub> (PMOS、NMOSとも)に等しくなっています。PMOSスイッチがその電流制限に達すると、PMOSスイッチはオフになり、NMOSスイッチがオンになります。NMOSの電流がNMOS電流制限値より低くなるとPMOSのみが再びオンになります。

## サーマル・シャットダウン

接合部温度T<sub>J</sub>が150°C(Typ)を越えるとデバイスはサーマル・シャットダウン状態になります。このモードでは、PチャネルMOSFETとNチャネルMOSFETはオフになります。接合部温度がサーマル・シャットダウンのヒステリシスより低くなると、動作を再開します。

# EasyScale™：出力電圧のダイナミック調整用1ピンのシリアル・インターフェイス

## 概要

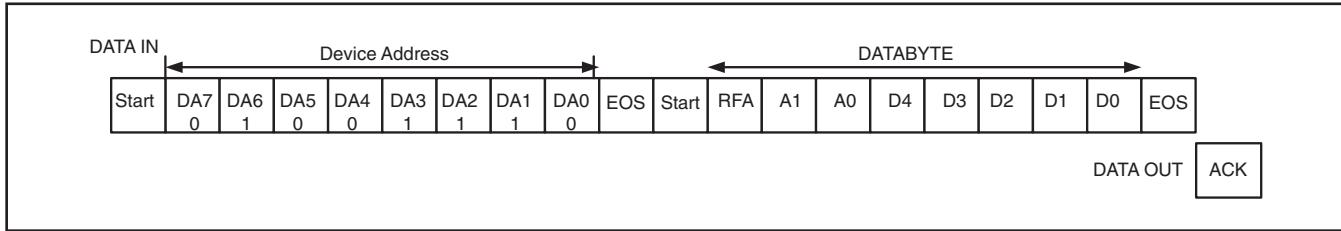

EasyScaleは単純であるにもかかわらず高い柔軟性をもっており、1ピンのインターフェイスで2つのDC/DCコンバータの出力電圧を設定することができます。このインターフェイスはマスター/スレーブ構成に基づいており、マスターがマイクロコントローラやアプリケーション・プロセッサであるのが一般的です。図27と表2にプロトコルの概要を示します。プロトコルは、デバイス特有のアドレス・バイトとデータ・バイトにより構成されています。デバイス特有のアドレス・バイトは4E(16進)固定です。データ・バイトは情報用の5ビット、アドレスの2ビット、RFAの1ビットで構成されています。RFAビットが“H”レベルにセットされていると、“認証”的応答が要求されます。“認証”的応答は、データプロトコルが正しく受信された場合のみスレーブから出力されます。

EasyScale™の利点は、他の1ピンだけのインターフェイスと比べて、そのビット検出がビット転送レートにほとんど依存していないということです。つまり、1.7kbit/sec～160kbit/sec間のビット・レートを自動的に検出することができるということです。さらに、このインターフェイスはMODE/DATAとピンを共有しているため、ピンの追加をせずに済んでいます。

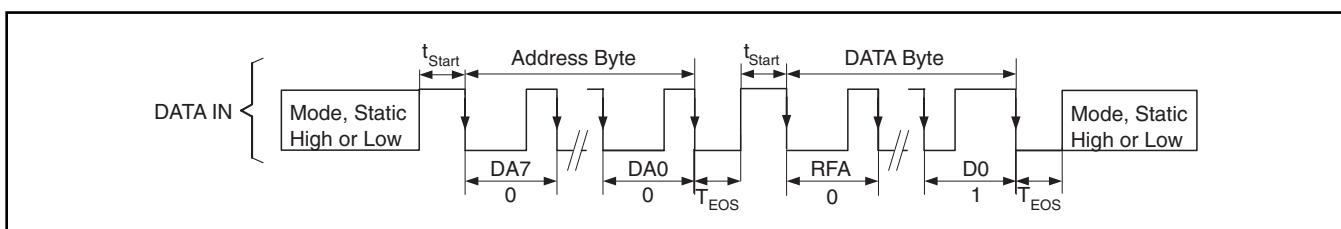

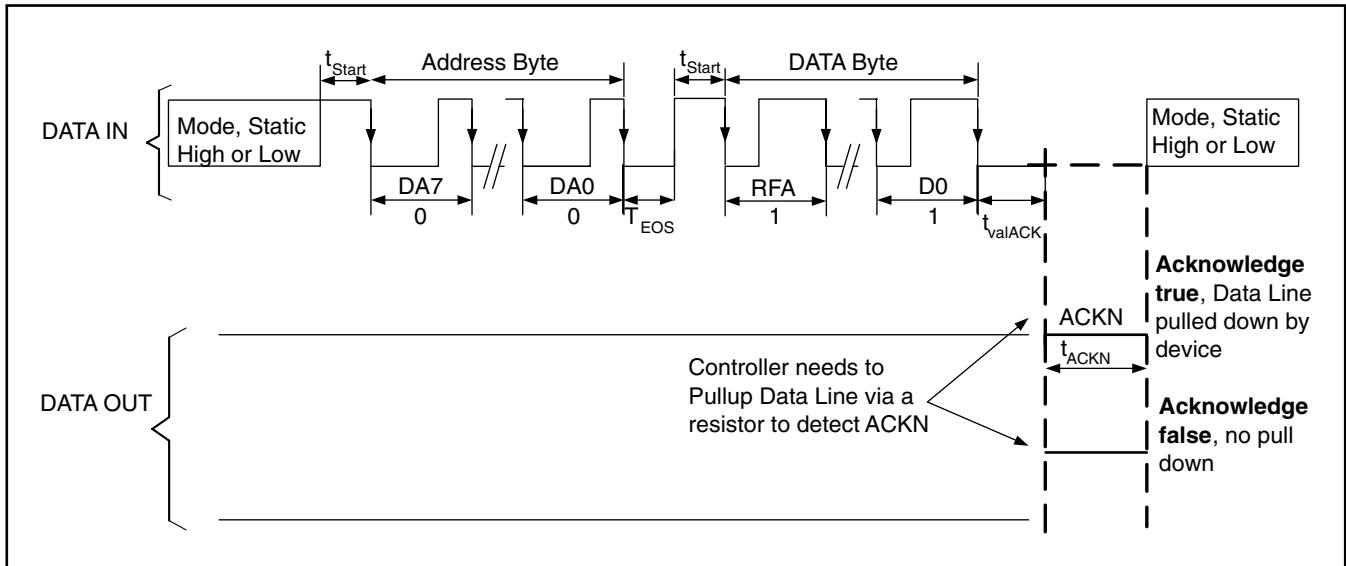

## プロトコル

全てのビットはMSB先頭/LSB最終で転送されます。図28に認証要求がない場合のプロトコル(ビットRFA = 0)、図29に認証要求がある場合のプロトコル(ビットRFA = 1)を示します。

デバイス・アドレス・バイト/データ・バイトの送信を開始する前に、スタート状態を作る必要があります。このためには、MODE/DATAピンは、ビット転送が立下りエッジで開始する前に少なくとも $t_{Start}$ の間“H”レベルに保持しておく必要があります。MODE/DATAラインが既に“H”レベルである場合(強制PWMモードのとき)は、デバイスのアドレス・バイトの前にスタート状態を作る必要はありません。

各バイトの送信は、少なくとも $T_{EOS}$ 間のエンド・オブ・ストリーム状態を保持して終了することが必要です。

## アドレスで選択可能なレジスタ

TPS62410では5ビットのデータ・コンテンツをもつ2つのレジスタがアドレスにより選択可能です。5ビットのデータ・コンテンツにより、各々のレジスタに32種の値を設定することができます。表1はDEF\_1ピンが外部に抵抗が接続されアナログ入力として機能している時のアドレスで選択可能なレジスタを示します。

| REGISTER       | DESCRIPTION                                  | A1 | A0 | D4 | D3 | D2 | D1 | D0 |

|----------------|----------------------------------------------|----|----|----|----|----|----|----|

| REG_DEF_1_High | Not available in TPS62410 adjustable version | 0  | 1  |    |    |    |    |    |

| REG_DEF_1_Low  | Converter 1 output voltage setting           | 0  | 0  |    |    |    |    |    |

| REG_DEF_2      | Converter 2 output voltage                   | 1  | 0  |    |    |    |    |    |

|                | Don't use                                    | 1  | 1  |    |    |    |    |    |

表1. Addressable Registers for Adjustable Output Voltage Devices

コンバータ1の出力電圧は表3の値に従い設定されます。コンバータ2で設定可能な電圧を表4に示します。これらの出力電圧を生成するために高精度の内蔵分圧抵抗が使用され、外付け抵抗が不要となり(ボード・スペースの削減)、高い出力電圧精度が実現可能となります。

少なくとも1つのコンバータがイネーブル(EN1またはEN2が“H”レベル)になると、インターフェイスはアクティブになります。起動時間 $t_{Start}$ (170μs)経過後、インターフェイスはデータ受信の準備が整います。

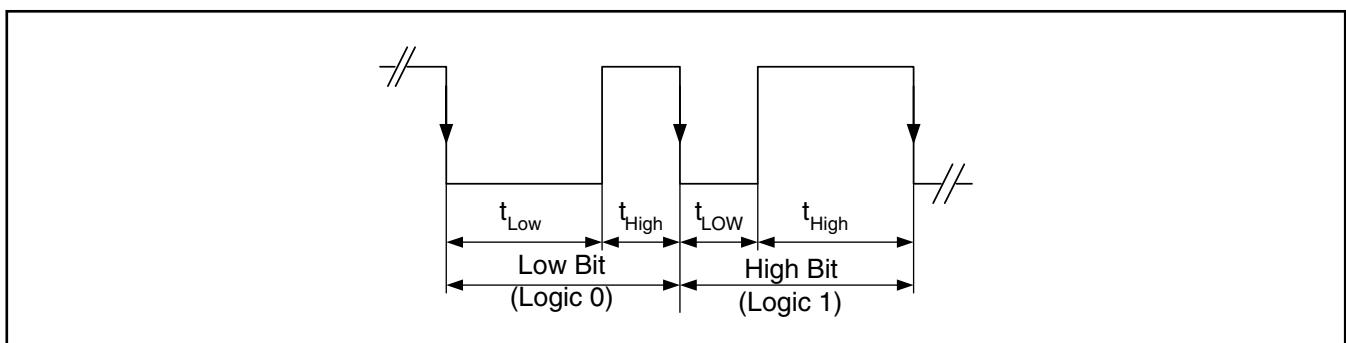

## ビットのディコード

ビットの検出はPWM動作に基づいて行われ、その規準は $t_{Low}$ と $t_{High}$ の時間の比率となります。これは以下のように簡素化することができます。

“H”レベル・ビット： $t_{High} > t_{Low}$ で、 $t_{High}$ が $t_{Low}$ の2倍より大。

図30参照。

“L”レベル・ビット： $t_{Low} > t_{High}$ で、 $t_{Low}$ が $t_{High}$ の2倍より大。

図30参照。

ビットの検出はMODE/DATAピンの立下りエッジで開始し、次の立下りエッジで終了します。 $t_{Low}$ と $t_{High}$ の関係により、0または1が検出されます。

## 認証

認証は以下の場合にのみ出力されます。

- ・認証がRFAビットの設定により要求された。

- ・転送されたデバイス・アドレスがデバイスのデバイス・アドレスに一致した。

- ・16ビットが正しく受信された。

この時、デバイスは内部のACKN-MOSFETをオンにし、MODE/DATAピンを最大520μsの $t_{ACKN}$ の間“L”レベルにします。認証状態は、内部遅延時間 $t_{valACK}$ 経過後に有効となります。このことは、プロトコルの最後の立下りエッジが検出されてから $t_{valACK}$ の後、内部のACKN-MOSFETがオンになるということを意味しています。マスター・コントローラはこの間ラインを“L”レベルに保持します。

マスター・デバイスは $t_{valACK}$ 後、MODE/DATAピンを解放して入力に設定することにより0を読み込み認証状態を検出することができます。

デバイス・アドレスが有効でない場合、またはプロトコルが正しく受信されない場合、非認証状態が適用されるため、内部のMOSFETはオンにはならず、外付けのプルアップ抵抗により $t_{valACK}$ 後にMODE/DATAピンは“H”レベルになります。MODE/DATAピンは認証状態が終了した後再び使用することができます。

注：認証は、マスター・デバイスがオープン・ドレイン出力をもつている場合にのみ要求することができます。

プッシュプル出力段の場合は、MODE/DATAラインに直列に電流を500 $\mu$ Aに制限する抵抗を挿入することを推奨します。これは、誤って認証が要求されたときに、内部のACKN-MOSFETを保護するためです。

## モードの選択

MODE/DATAピンはインターフェイスとモード選択の2つの機能に使用されるため、デバイスは、ビット列をデコーディングするのか、動作モードを変更するのかを判断する必要があります。

デバイスはMODE/DATAピンが“H”レベルになると、直ちに固定PWMモードになります。また、プロトコルの受信時間も固定PWMモードのままです。

デバイスは、MODE/DATAピンの立ち下りエッジでビットのデコーディングを開始します。MODE/DATAピンが少なくとも $t_{timeout}$ の間“L”レベルのままであると、デバイスは内部でタイムアウト状態になり、パワーセーブ・モード動作がイネーブルになります。

PFMへのモード変更のための立下りエッジは最初のビットとして認識されるため、この間に送られたプロトコルは無視されてしまいます。この場合、最初にプロトコルを送り、次にプロトコルの終わりでパワーセーブ・モードに変更することを推奨します。

図 27. Easy Scale Protocol Overview

| BYTE                | BIT NUMBER | NAME | TRANSMISSION DIRECTION | DESCRIPTION                                                                                                                                                     |

|---------------------|------------|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Address Byte | 7          | DA7  | IN                     | 0 MSB device address                                                                                                                                            |

|                     | 6          | DA6  | IN                     | 1                                                                                                                                                               |

|                     | 5          | DA5  | IN                     | 0                                                                                                                                                               |

|                     | 4          | DA4  | IN                     | 0                                                                                                                                                               |

|                     | 3          | DA3  | IN                     | 1                                                                                                                                                               |

|                     | 2          | DA2  | IN                     | 1                                                                                                                                                               |

|                     | 1          | DA1  | IN                     | 1                                                                                                                                                               |

|                     | 0          | DA0  | IN                     | 0 LSB device address                                                                                                                                            |

| Databyte            | 7(MSB)     | RFA  | IN                     | リクエスト・フォー・認証。“H”レベルであるとデバイスにより認証状態が適用されます。                                                                                                                      |

|                     | 6          | A1   |                        | Address Bit 1                                                                                                                                                   |

|                     | 5          | A0   |                        | Address Bit 0                                                                                                                                                   |

|                     | 4          | D4   |                        | Data Bit 4                                                                                                                                                      |

|                     | 3          | D3   |                        | Data Bit 3                                                                                                                                                      |

|                     | 2          | D2   |                        | Data Bit 2                                                                                                                                                      |

|                     | 1          | D1   |                        | Data Bit 1                                                                                                                                                      |

|                     | 0(LSB)     | D0   |                        | Data Bit 0                                                                                                                                                      |

|                     |            | ACK  | OUT                    | 認証状態でアクティブ0。この状態はRFAビットがセットされている場合にのみ適用されます。オープン・ドレイン出力で、ラインはホストによりプルアップ抵抗で“H”レベルにすることが必要です。<br>この機能はマスターがオープン・ドレイン出力をもっている場合にのみ使用できます。プッシュプル出力の場合認証状態は要求できません。 |

表 2. EasyScale<sup>TM</sup>のビット説明

図 28. Easy Scale Protocol Without Acknowledge

图 29. Easy Scale Protocol Including Acknowledge

图 30. Easy Scale – Bit Coding

图 31. MODE/DATA PIN : Mode Selection

图 32. MODE/DATA Pin : Power Save Mode/Interface Communication

|    | TPS62410 OUTPUT VOLTAGE [V]<br>REGISTER REG_DEF_1_LOW                             | D4 | D3 | D2 | D1 | D0 |

|----|-----------------------------------------------------------------------------------|----|----|----|----|----|

| 0  | <b><math>V_{OUT1}</math> Adjustable Output With Resistor Network on DEF_1 Pin</b> | 0  | 0  | 0  | 0  | 0  |

|    | <b>0.6V with DEF_1 Pin connected to <math>V_{OUT1}</math></b>                     |    |    |    |    |    |

| 1  | 0.825                                                                             | 0  | 0  | 0  | 0  | 1  |

| 2  | 0.85                                                                              | 0  | 0  | 0  | 1  | 0  |

| 3  | 0.875                                                                             | 0  | 0  | 0  | 1  | 1  |

| 4  | 0.9                                                                               | 0  | 0  | 1  | 0  | 0  |

| 5  | 0.925                                                                             | 0  | 0  | 1  | 0  | 1  |

| 6  | 0.95                                                                              | 0  | 0  | 1  | 1  | 0  |

| 7  | 0.975                                                                             | 0  | 0  | 1  | 1  | 1  |

| 8  | 1.0                                                                               | 0  | 1  | 0  | 0  | 0  |

| 9  | 1.025                                                                             | 0  | 1  | 0  | 0  | 1  |

| 10 | 1.050                                                                             | 0  | 1  | 0  | 1  | 0  |

| 11 | 1.075                                                                             | 0  | 1  | 0  | 1  | 1  |

| 12 | 1.1                                                                               | 0  | 1  | 1  | 0  | 0  |

| 13 | 1.125                                                                             | 0  | 1  | 1  | 0  | 1  |

| 14 | 1.150                                                                             | 0  | 1  | 1  | 1  | 0  |

| 15 | 1.175                                                                             | 0  | 1  | 1  | 1  | 1  |

| 16 | 1.2                                                                               | 1  | 0  | 0  | 0  | 0  |

| 17 | 1.225                                                                             | 1  | 0  | 0  | 0  | 1  |

| 18 | 1.25                                                                              | 1  | 0  | 0  | 1  | 0  |

| 19 | 1.275                                                                             | 1  | 0  | 0  | 1  | 1  |

| 20 | 1.3                                                                               | 1  | 0  | 1  | 0  | 0  |

| 21 | 1.325                                                                             | 1  | 0  | 1  | 0  | 1  |

| 22 | 1.350                                                                             | 1  | 0  | 1  | 1  | 0  |

| 23 | 1.375                                                                             | 1  | 0  | 1  | 1  | 1  |

| 24 | 1.4                                                                               | 1  | 1  | 0  | 0  | 0  |

| 25 | 1.425                                                                             | 1  | 1  | 0  | 0  | 1  |

| 26 | 1.450                                                                             | 1  | 1  | 0  | 1  | 0  |

| 27 | 1.475                                                                             | 1  | 1  | 0  | 1  | 1  |

| 28 | 1.5                                                                               | 1  | 1  | 1  | 0  | 0  |

| 29 | 1.525                                                                             | 1  | 1  | 1  | 0  | 1  |

| 30 | 1.55                                                                              | 1  | 1  | 1  | 1  | 0  |

| 31 | 1.575                                                                             | 1  | 1  | 1  | 1  | 1  |

表3. アナログ入力としてピンDEF\_1を用いたコンバータ1の選択可能出力電圧(TPS62410)

|    | OUTPUT VOLTAGE [V]<br>FOR REGISTER REG_DEF_2                            | D4 | D3 | D2 | D1 | D0 |

|----|-------------------------------------------------------------------------|----|----|----|----|----|

| 0  | <b>V<sub>OUT2</sub> Adjustable Output With Resistor Network on ADJ2</b> | 0  | 0  | 0  | 0  | 0  |

|    | <b>0.6V with ADJ2 Pin connected to V<sub>OUT2</sub></b>                 |    |    |    |    |    |

| 1  | 0.85                                                                    | 0  | 0  | 0  | 0  | 1  |

| 2  | 0.9                                                                     | 0  | 0  | 0  | 1  | 0  |

| 3  | 0.95                                                                    | 0  | 0  | 0  | 1  | 1  |

| 4  | 1.0                                                                     | 0  | 0  | 1  | 0  | 0  |

| 5  | 1.05                                                                    | 0  | 0  | 1  | 0  | 1  |

| 6  | 1.1                                                                     | 0  | 0  | 1  | 1  | 0  |

| 7  | 1.15                                                                    | 0  | 0  | 1  | 1  | 1  |

| 8  | 1.2                                                                     | 0  | 1  | 0  | 0  | 0  |

| 9  | 1.25                                                                    | 0  | 1  | 0  | 0  | 1  |

| 10 | 1.3                                                                     | 0  | 1  | 0  | 1  | 0  |

| 11 | 1.35                                                                    | 0  | 1  | 0  | 1  | 1  |

| 12 | 1.4                                                                     | 0  | 1  | 1  | 0  | 0  |

| 13 | 1.45                                                                    | 0  | 1  | 1  | 0  | 1  |

| 14 | 1.5                                                                     | 0  | 1  | 1  | 1  | 0  |

| 15 | 1.55                                                                    | 0  | 1  | 1  | 1  | 1  |

| 16 | 1.6                                                                     | 1  | 0  | 0  | 0  | 0  |

| 17 | 1.7                                                                     | 1  | 0  | 0  | 0  | 1  |

| 18 | 1.8                                                                     | 1  | 0  | 0  | 1  | 0  |

| 19 | 1.85                                                                    | 1  | 0  | 0  | 1  | 1  |

| 20 | 2.0                                                                     | 1  | 0  | 1  | 0  | 0  |

| 21 | 2.1                                                                     | 1  | 0  | 1  | 0  | 1  |

| 22 | 2.2                                                                     | 1  | 0  | 1  | 1  | 0  |

| 23 | 2.3                                                                     | 1  | 0  | 1  | 1  | 1  |

| 24 | 2.4                                                                     | 1  | 1  | 0  | 0  | 0  |

| 25 | 2.5                                                                     | 1  | 1  | 0  | 0  | 1  |

| 26 | 2.6                                                                     | 1  | 1  | 0  | 1  | 0  |

| 27 | 2.7                                                                     | 1  | 1  | 0  | 1  | 1  |

| 28 | 2.8                                                                     | 1  | 1  | 1  | 0  | 0  |

| 29 | 2.85                                                                    | 1  | 1  | 1  | 0  | 1  |

| 30 | 3.0                                                                     | 1  | 1  | 1  | 1  | 0  |

| 31 | 3.3                                                                     | 1  | 1  | 1  | 1  | 1  |

表 4. コンバータ2の選択可能出力電圧(V<sub>OUT</sub>にADJ2を接続)

## アプリケーション情報

### 出力電圧の設定

#### コンバータ1出力電圧可変タイプの初期値電圧の設定

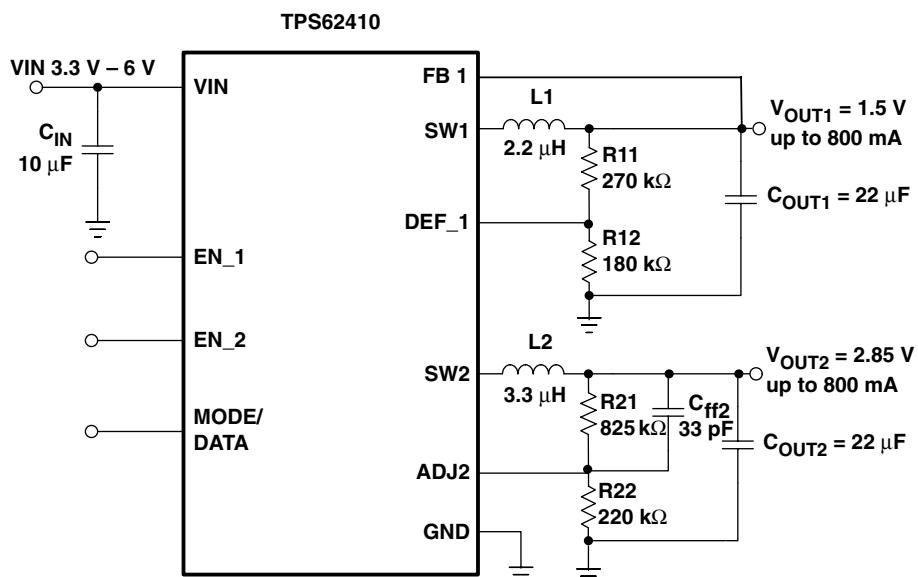

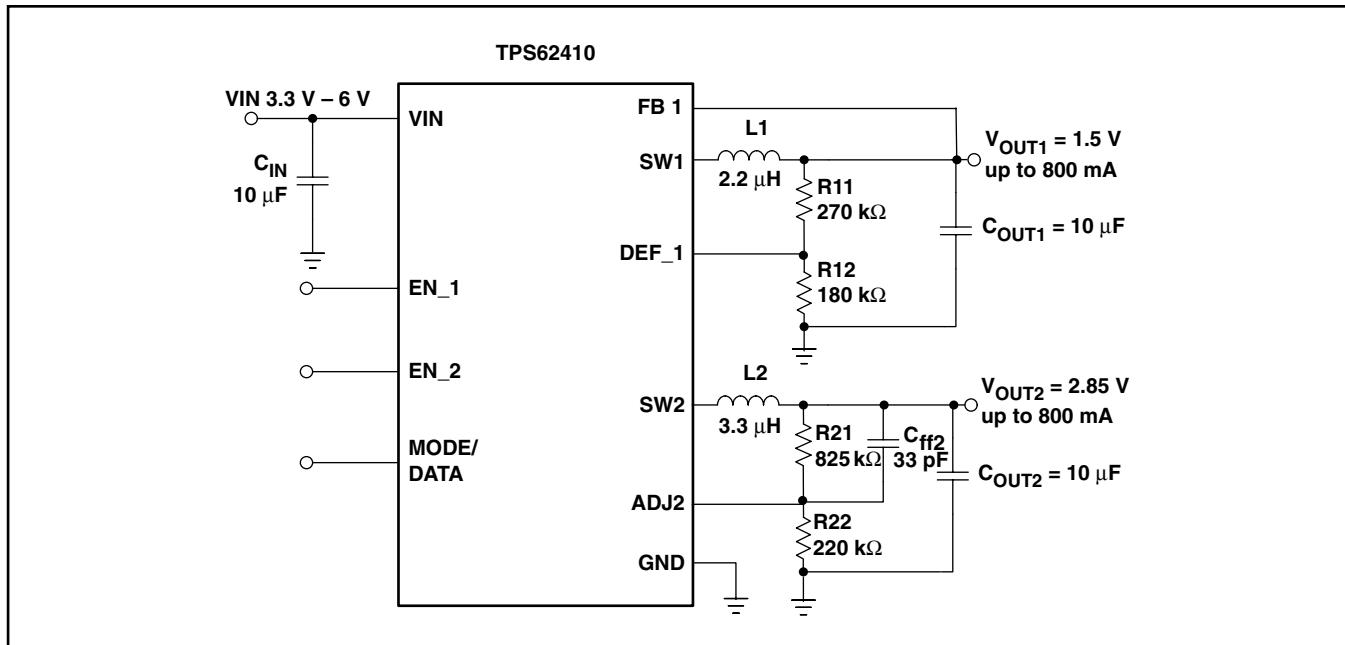

出力電圧は以下の式で計算することができます。

$$V_{OUT} = V_{REF} \times \left( 1 + \frac{R_{11}}{R_{12}} \right)$$

内部基準電源電圧  $V_{REF}$  は標準値 0.6V

### コンバータ2

コンバータ2の出力電圧初期値は外付け抵抗回路で設定することができます。抵抗値の選択方法はコンバータ2もコンバータ1と同じです。33pFのフィードフォワード・コンデンサ  $C_{ff2}$  の追加が良好な負荷応答特性を実現するのに必要となります。出力電圧は以下の式で計算することができます。

$$V_{OUT} = V_{REF} \times \left( 1 + \frac{R_{21}}{R_{22}} \right)$$

内部基準電源電圧  $V_{REF}$  は標準値 0.6V

ADJ2の配線はインダクタやSW2の配線などのノイズ源から離して配置してください。コンバータ2を通信で制御する場合はADJ2と  $V_{out2}$  を直接接続してください。

動作時の無効電流を最小にするには、 $R_{12}$ を180kΩ～360kΩの範囲内で選択することを推奨します。ただし、 $R_{12}$ と $R_{11}$ の合計は1MΩを越えてはいけません。出力電圧が3.3Vを超える場合は $R_{12}$ に180kΩより低い抵抗を使用する事をお勧めします。DEF\_1ラインはインダクタまたはSW1ラインなどのノイズ源から離して配線します。FB1ラインは出力コンデンサに直接接続してください。このピンにはフィードフォワード用のコンデンサが内蔵されているので外部にフィードフォワード用のコンデンサは不要です。

図 33. Typical Application Circuit 1.5V/2.85V Adjustable Outputs, low PFM Voltage ripple Optimized

図 34. Typical Application Circuit 1.5V/2.85V Adjustable Outputs

## 出力フィルタの設計 (インダクタと出力コンデンサ)

デバイスは、2.2μH～4.7μHのインダクタと10μF～22μFの出力コンデンサでの動作に対して最適化されています。2.2μHのインダクタを使用する場合は22μFのコンデンサを推奨します。

### インダクタの選択

選択するインダクタは、その直流抵抗と飽和電流の定格が明確となっていることが必要です。インダクタの直流抵抗はコンバータの効率に直接影響するため、効率を最大にするには最小の直流抵抗をもつインダクタを選択しなければなりません。

式(6)で定負荷条件下での最大インダクタ電流が計算されます。インダクタが飽和しあはじめる電流値は、式(7)で計算される最大インダクタ電流値よりも大きくななければなりません。重負荷過渡時に、インダクタ電流は式(7)で計算される値より上昇するため、これを推奨します。

$$\Delta I_L = V_{out} \times \frac{1 - \frac{V_{out}}{V_{in}}}{L \times f} \quad (6)$$

$$I_{Lmax} = I_{outmax} + \frac{\Delta I_L}{2} \quad (7)$$

但し、

$f$  = スイッチング周波数 (標準2.25MHz)

$L$  = インダクタ値

$\Delta I_L$  = peak-to-peak インダクタ・リップル電流

$I_{Lmax}$  = 最大インダクタ電流

インダクタ電流が最大となるのはVinが最大の時です。

開磁路型のインダクタは飽和しにくい特性を持っており、通常同程度の閉磁路型のインダクタに比べてより大きなインダクタ電流が流せます。

より安全な方法は、使用するコンバータの最大スイッチ電流と同じ電流定格のインダクタを選択することです。考慮しておくことは、インダクタごとにコア材が異なり、この差が効率に影響を及ぼすということです。使用可能なインダクタについて、表5と代表的アプリケーション回路を参照してください。

| 寸法 [mm <sup>3</sup> ] | インダクタ・タイプ | メーカー      |

|-----------------------|-----------|-----------|

| 2.8x2.6x1.4           | VLF3014   | TDK       |

| 3x3x1.4               | LPS3015   | Coilcraft |

| 3.9x3.9x1.7           | LPS4018   | Coilcraft |

表 5. インダクタ・リスト

## 出力コンデンサの選択

本コンバータは、高度な高速応答電圧モード制御を採用しており、重負荷過渡時にも出力電圧に大きなアンダーシュートやオーバーシュートがなく、出力コンデンサも標準値が $10\mu\text{F}$ の極めて小さなセラミック・コンデンサを使用することができます。セラミックのX7RまたはX5R特性のものは低ESRで、出力電圧リップルを最小に出来るのでこれを推奨します。出力コンデンサにセラミックを使用した場合は、コンデンサの定格RMSリップル電流は常にアプリケーションによる電流要求を満足していかなければなりません。RMSリップル電流は以下の式で計算されます。

$$I_{\text{RMSCout}} = V_{\text{out}} \times \frac{1 - \frac{V_{\text{out}}}{V_{\text{in}}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}} \quad (8)$$

インダクタ方式のDCDCコンバータが定格負荷電流でPWMモードで動作している時の出力電圧リップルは、電圧スパイク(出力コンデンサのESRにより生じる)と電圧リップル(出力コンデンサを充放電することにより生じる)の合計となります。

$$\Delta V_{\text{out}} = V_{\text{out}} \times \frac{1 - \frac{V_{\text{out}}}{V_{\text{in}}}}{L \times f} \times \left( \frac{1}{8 \times C_{\text{out}} \times f} + \text{ESR} \right) \quad (9)$$

但し、出力電圧リップルが最大となるのは、入力電圧 $V_{\text{in}}$ が最大の時です。

軽負荷の時、コンバータはパワーセーブ・モードで動作し、出力電圧リップルは出力コンデンサの値に依存します。出力電圧リップルは内部コンパレータの遅延時間と外付けのコンデンサ容量で決まります。 $22\mu\text{F}$ のような大きな出力コンデンサを使用すると、PFMモードでの電圧リップルが最小限に抑えられ、PFMモードでの直流出力電圧精度が高くなります。

## 入力コンデンサの選択

原理的に降圧型コンバータは入力がパルス状の電流となるため、低ESRの入力コンデンサが必要とされます。そうでないと、デバイスの誤動作やシステムの他の回路への干渉を引き起こす可能性のある大きな電圧変動が生じることがあります。容量としては、 $10\mu\text{F}$ の入力コンデンサで十分です。

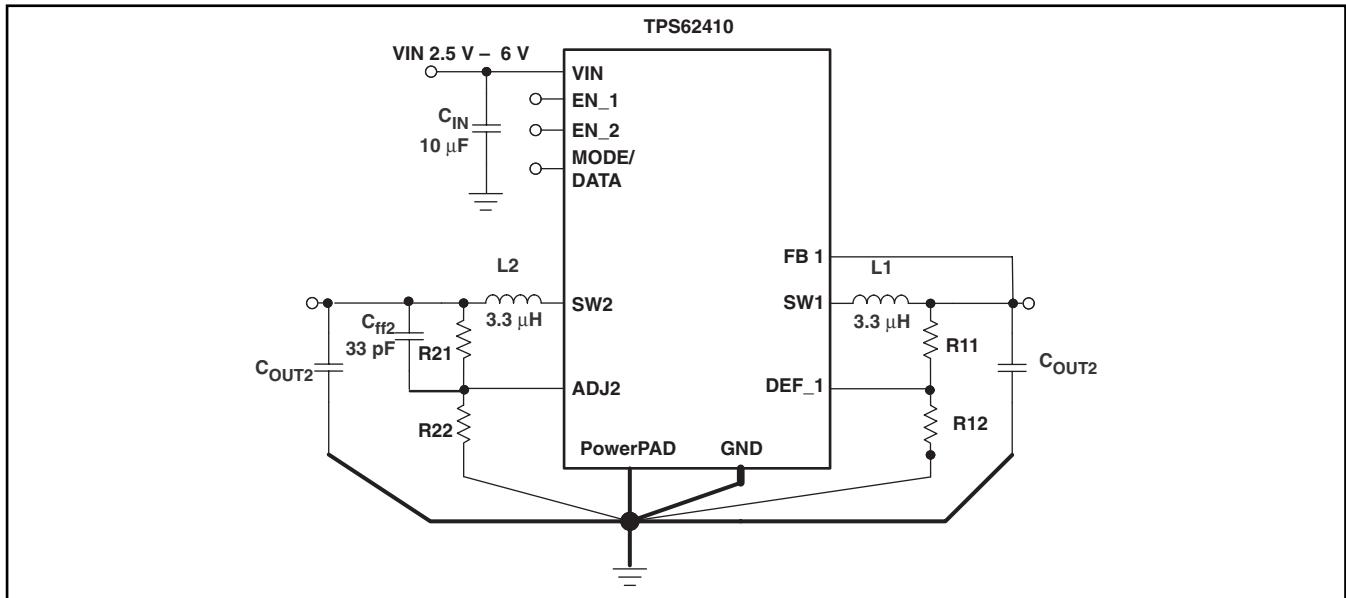

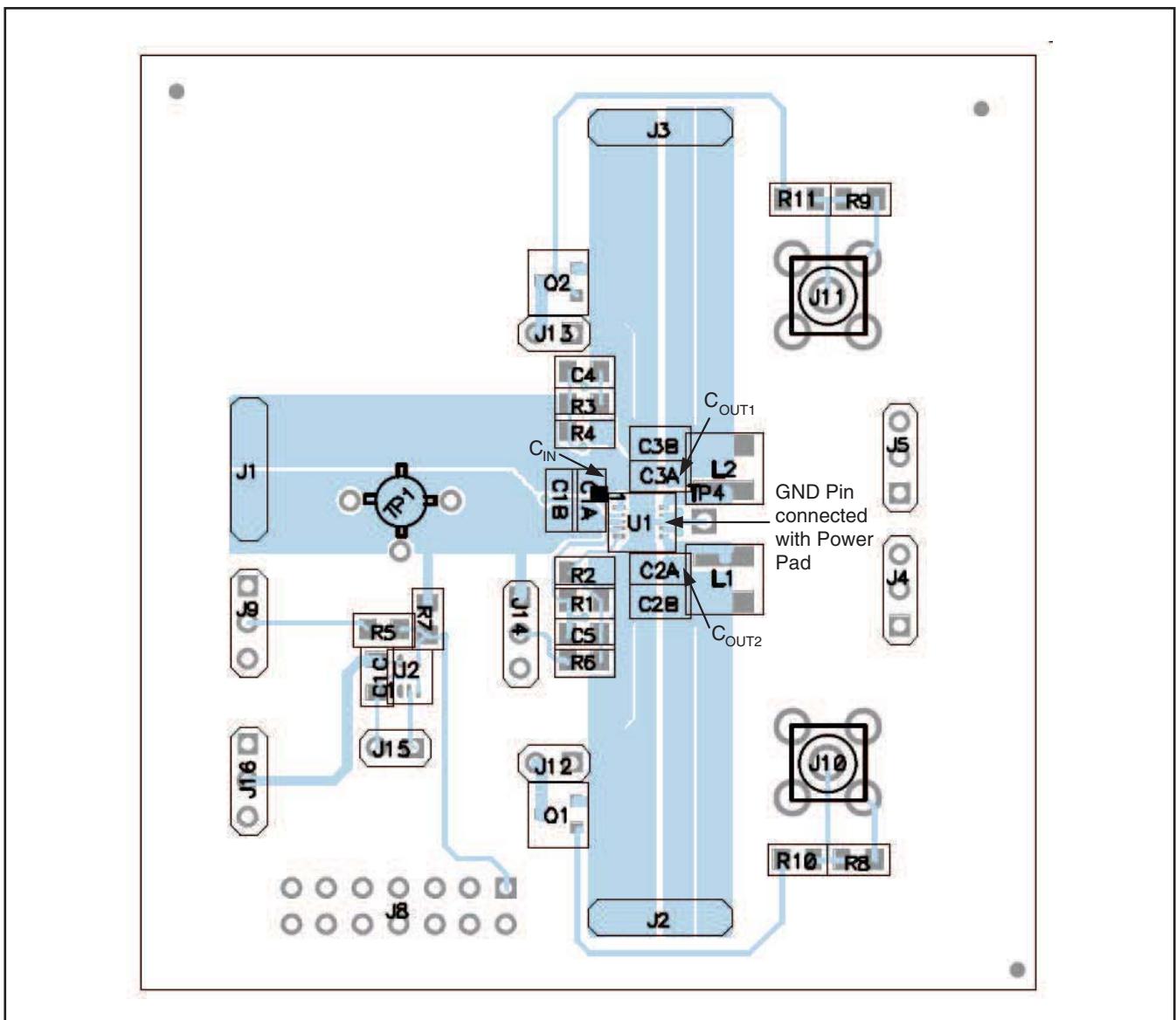

## レイアウトについての考察

すべてのスイッチング電源において、基板レイアウトは重要な設計ポイントとなります。デバイスを正常に機能させるには、基板レイアウトに十分注意を払う必要があります。本来の性能を得るために基板レイアウトには気を付けなければなりません。レイアウトに注意せずに設計すると、EMI問題はもちろんのこと、ライン/負荷レギュレーションが悪くなったり、安定性の問題が生じることもあります。また、低インダクタンス/低インピーダンスのグランド・パスを備えることも重要であるため、図35に太線で示されているように大電流パターンには太く短い配線を使用してください。

入力コンデンサは、ICのピンに出来るだけ近づけて配置しなければいけません。インダクタや出力コンデンサも同様です。

デバイスのGNDピンは基板上のPowerPADランドに接続し、このパッドを一点接地するポイントとして考えます。グランド・ノイズの影響を最小限に押さえるため、2つのコンバータで共有のパワー用グランドとそれから分離されたシグナル用グランドを持っています。これらのグランド・ノードを全てICの底面のPowerPADで一点接地により接続します。GNDピンへのパターンは、グランド・ノイズを回避するためできるだけ短くしておきます。そうすることで、小信号成分も出力コンデンサの大電流も同じGNDパターンを使うことが可能となります。出力電圧の検出ライン(FB1、DEF\_1、ADJ2)は出力コンデンサの直近に接続し、ノイズの多い部品や配線(例、SWライン)から離して引かなければなりません。EasyScale™インターフェイスを高い転送レートで動作させる場合、MODE/DATAの配線はADJ2ピンへの容量結合を避けるため、ADJ2ラインから離して引かなければなりません。MODE/DATAピンとADJ2ピン間にグランドのガードリングを設けると生じる可能性の高いノイズ結合の問題が回避されます。

図 35. Layout Diagram

図 36. PCB Layout

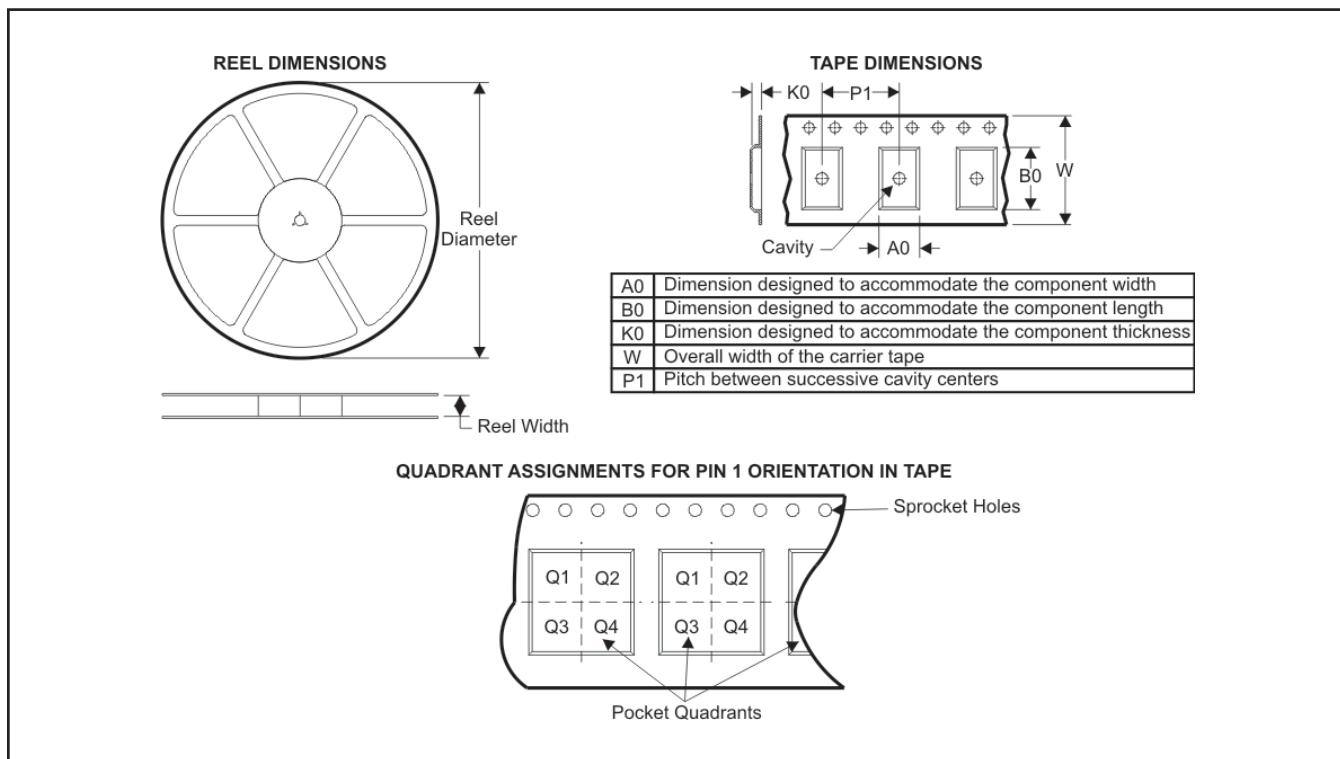

## パッケージ・マテリアル情報

### テープおよびリール・ボックス情報

| Device       | Package | Pins | Site    | Reel Diameter (mm) | Reel Width (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|---------|------|---------|--------------------|-----------------|---------|---------|---------|---------|--------|---------------|

| TPS62410DRCR | DRC     | 10   | SITE 41 | 330                | 12              | 3.3     | 3.3     | 1.1     | 8       | 12     | Q2            |

| TPS62410DRCT | DRC     | 10   | SITE 41 | 180                | 12              | 3.3     | 3.3     | 1.1     | 8       | 12     | Q2            |

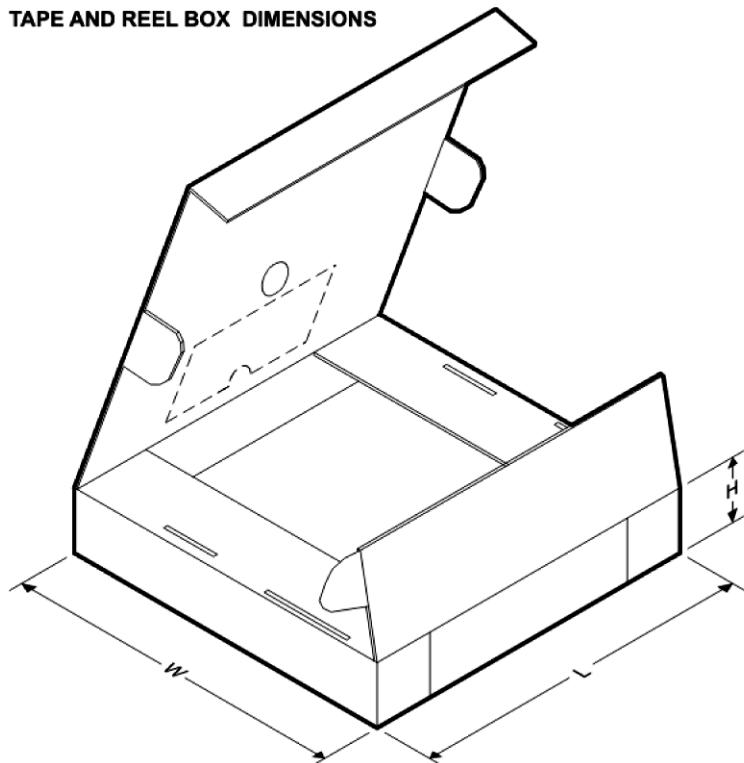

## パッケージ・マテリアル情報

TAPE AND REEL BOX DIMENSIONS

| Device       | Package | Pins | Site    | Length (mm) | Width (mm) | Height (mm) |

|--------------|---------|------|---------|-------------|------------|-------------|

| TPS62410DRCR | DRC     | 10   | SITE 41 | 346.0       | 346.0      | 29.0        |

| TPS62410DRCT | DRC     | 10   | SITE 41 | 190.5       | 212.7      | 31.75       |

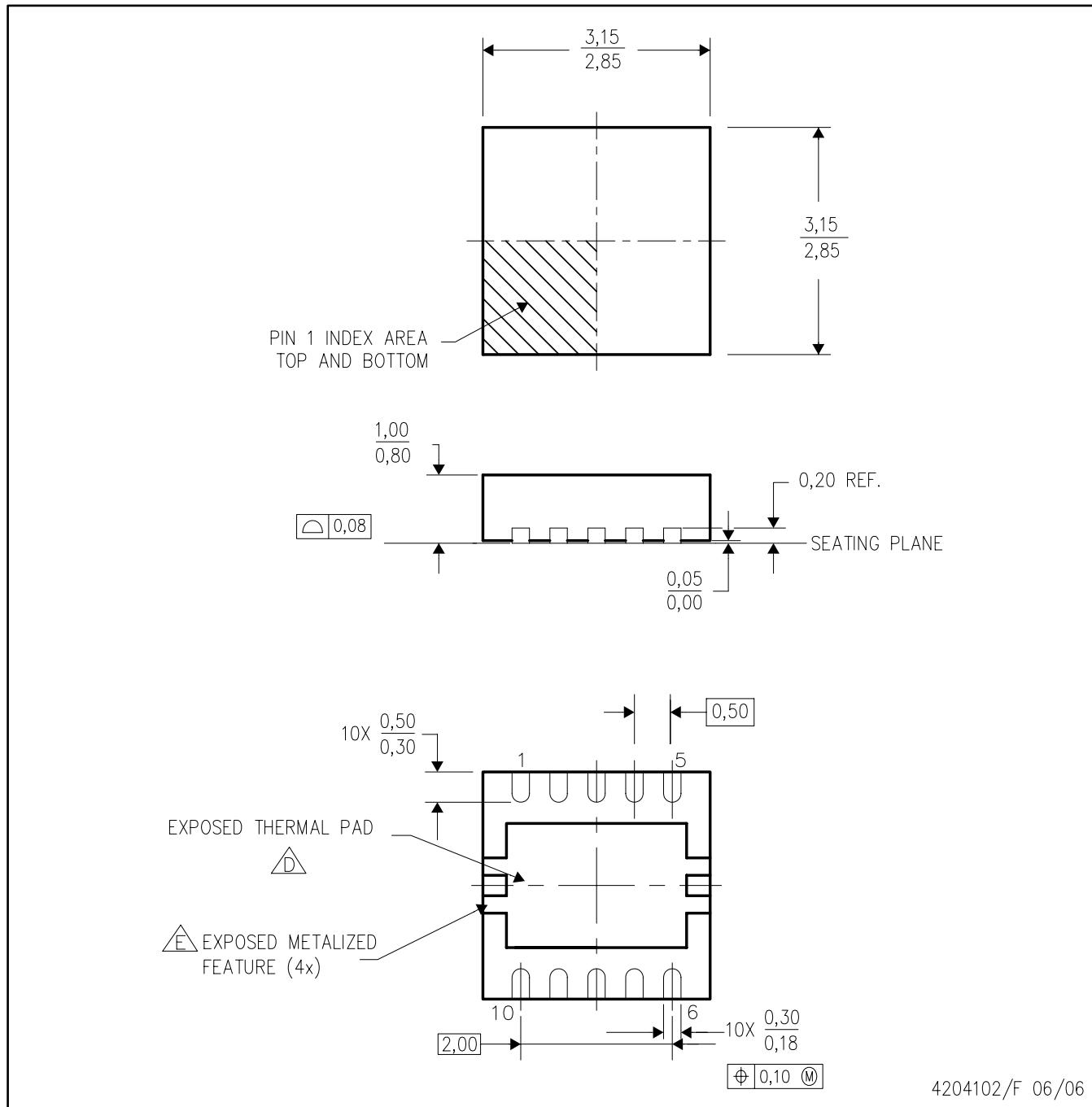

# メカニカル・データ

DRC (S-PDSO-N10)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

C. Small Outline No-Lead (SON) package configuration.

The package thermal pad must be soldered to the board for thermal and mechanical performance.

See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

E. Metalized features are supplier options and may not be on the package.

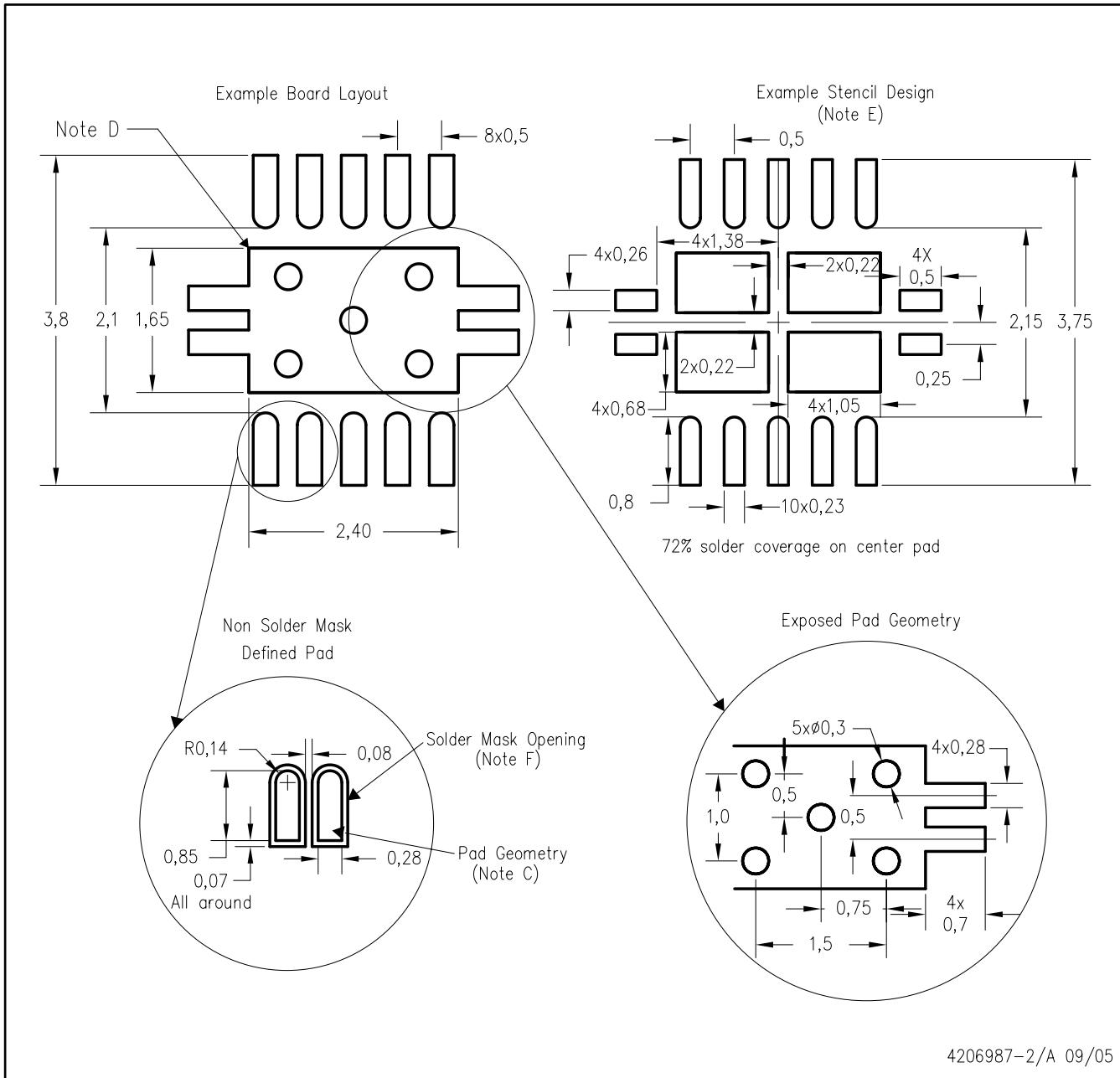

# サーマルパッド・メカニカル・データ

## DRC (S-PDSO-N10)

### 熱特性について

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板 (PCB) に直接はんだ付けされなければなりません。はんだ付けの後、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはデバイスの電気回路図に示されている銅プレーンに直接接続するか、あるいは、PCBに設計された特別なヒートシンク構造に接続することができます。この設計により、集積回路 (IC) からの熱移動が最適化されます。

クワッド・フラットパック・ノーリード (QFN) パッケージとその利点についての情報はアプリケーション・レポート “Quad Flatpack No-Lead Logic Packages” TI文献番号SCBA017を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージの露出サーマル・パッドの寸法は以下の図に示されています。

注：寸法はすべてミリメートル単位です。

露出サーマル・パッドの寸法

# LAND PATTERN

DRC (S-PDSO-N10)

- NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SCBA017, SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

(SLVS737)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS62410DRCR          | Active        | Production           | VSON (DRC)   10 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

| TPS62410DRCR.B        | Active        | Production           | VSON (DRC)   10 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

| TPS62410DRCRG4        | Active        | Production           | VSON (DRC)   10 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

| TPS62410DRCT          | Active        | Production           | VSON (DRC)   10 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

| TPS62410DRCT.B        | Active        | Production           | VSON (DRC)   10 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

| TPS62410DRCTG4        | Active        | Production           | VSON (DRC)   10 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | CAT                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS62410 :**

- Automotive : [TPS62410-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月