# TPS62097 2A 高効率降圧コンバータ、iDCS-Control、強制 PWM モード、スイッ チング周波数選択機能付き

#### 1 特長

- 新製品:TPS62851x、6V、0.5A/1A/2A 降圧コンバー タ、SOT583 パッケージ

- iDCS-control トポロジ

- 強制 PWM またはパワー・セーブ・モード

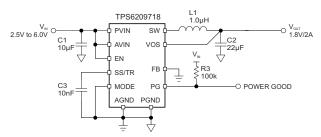

- 最大 97% の効率

- 2.5V~6.0Vの入力電圧

- 出力電圧は 0.8V~V<sub>IN</sub> まで可変

- 1.8V~3.3V の固定出力電圧

- ±1% の出力電圧精度

- ヒカップ短絡保護機能

- ソフト・スタートアップをプログラム可能

- 出力電圧トラッキング

- 選択可能なスイッチング周波数

- 100% デューティ・サイクル動作による最小のドロップ アウト電圧

- 出力放電

- パワー・グッド出力

- サーマル・シャットダウン保護機能

- 動作時接合部温度:-40℃~125℃

- 2mm × 2mm の VQFN パッケージで供給

#### 2 アプリケーション

- モーター・ドライブ

- プログラマブル・ロジック・コントローラ (PLC)

- ソリッド・ステート・ドライブ (SSD)

- ポイント・オブ・ロード (POL) レギュレータ

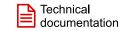

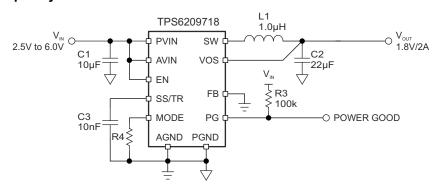

1.8V 出力、PWM/PSM モードのアプリケーション

#### 3 概要

TPS62097 デバイスは同期整流降圧コンバータで、高効 率とノイズが重要なアプリケーションに最適化されていま す。このデバイスは、広い出力電流範囲にわたって高い 効率で変換を行うことを主眼としています。コンバータは、 中負荷から高負荷では PWM モードで動作し、軽負荷時 には自動的にパワー・セーブ・モードの動作に移行しま す。スイッチング周波数は外付け抵抗により 1.5MHz~ 2.5MHz の範囲で選択できます。iDCS-Control は、固定 スイッチング周波数を使い低ノイズ動作に適した強制 PWM モードで動作させることができます。

システム電源レールの要件に対処するため、内部補償回 路は 150µF を超えるものも含め、多くの外部出力コンデ ンサの値を選択できます。スタートアップ時の突入電流を 制御するため、デバイスは SS/TR ピンに接続される外付 けコンデンサにより、ソフト・スタートアップをプログラムでき ます。SS/TR ピンは、電圧トラッキング構成にも使用され ます。デバイスには短絡保護、パワー・グッド、サーマル・ シャットダウン機能が搭載されています。このデバイスは、 2mm × 2mm の VQFN パッケージで供給されます。

新製品 TPS62851x は低 BOM コスト、小さい総ソリュー ション・サイズ、その他の特長を備えています。

#### 製品情報

| 部品番号       | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |  |  |  |  |

|------------|----------------------|---------------|--|--|--|--|

| TPS62097   |                      |               |  |  |  |  |

| TPS6209718 | VQFN (11)            | 2.0mm × 2.0mm |  |  |  |  |

| TPS6209733 |                      |               |  |  |  |  |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

1.8V 出力、PWM/PSM モードの効率

### **Table of Contents**

| 1 特長                               | 1 | 8.4 Device Function Modes               | 8                |

|------------------------------------|---|-----------------------------------------|------------------|

| 2アプリケーション                          |   | 9 Application and Implementation        | 12               |

| 3 概要                               |   | 9.1 Application Information             | 1 <mark>2</mark> |

| 4 Revision History                 |   | 9.2 1.2-V Output Application            | 12               |

| 5 Device Options                   |   | 10 Power Supply Recommendations         | 20               |

| 6 Pin Configuration and Functions  |   | 11 Layout                               | <mark>2</mark> 1 |

| 7 Specifications                   |   | 11.1 Layout Guidelines                  | <mark>2</mark> 1 |

| 7.1 Absolute Maximum Ratings       |   | 11.2 Layout Example                     | <mark>2</mark> 1 |

| 7.2 ESD Ratings                    |   | 12 Device and Documentation Support     | <mark>22</mark>  |

| 7.3 Recommend Operating Conditions |   | 12.1 Device Support                     | <mark>22</mark>  |

| 7.4 Thermal Information            |   | 12.2 サポート・リソース                          | <mark>22</mark>  |

| 7.5 Electrical Characteristics     | 5 | 12.3ドキュメントの更新通知を受け取る方法                  | <u>22</u>        |

| 7.6 Typical Characteristics        |   | 12.4 Trademarks                         | 22               |

| 8 Detailed Description             |   | 12.5 静電気放電に関する注意事項                      | <mark>22</mark>  |

| 8.1 Overview                       |   | 12.6 用語集                                |                  |

| 8.2 Functional Block Diagram       |   | 13 Mechanical, Packaging, and Orderable |                  |

| 8.3 Feature Description            |   | Information                             | 22               |

| •                                  |   |                                         |                  |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | Changes from Revision * (December 2015) to Revision A (January 2021) | Page |

|---|----------------------------------------------------------------------|------|

| • | 新しいデバイス (TPS62851x) へのリンクを追加                                         | 1    |

| • | TI Web サイトの関連アプリケーションのページへのリンクを追加                                    | 1    |

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                            | 1    |

# **5 Device Options**

| PART NUMBER <sup>(1)</sup> | OUTPUT VOLTAGE | PACKAGE MARKING |

|----------------------------|----------------|-----------------|

| TPS62097                   | Adjustable     | ZFZ5            |

| TPS6209718                 | 1.8V           | ZGB5            |

| TPS6209733                 | 3.3V           | ZGC5            |

<sup>(1)</sup> For detailed ordering information, please check the Mechanical, Packaging, and Orderable Information section at the end of this datasheet.

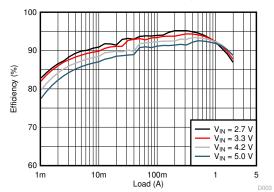

# **6 Pin Configuration and Functions**

図 6-1. 11-Pin VQFN RWK Package (Top View)

表 6-1. Pin Functions

| PII   | N                                                                                                                                                                            |     |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.                                                                                                                                                                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|       |                                                                                                                                                                              |     |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PGND  | 1                                                                                                                                                                            |     | Power ground pin                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| SW    | 2                                                                                                                                                                            | PWR | Switch pin. It is connected to the internal MOSFET switches. Connect the external inductor between this terminal and the output capacitor.                                                                                                                                                                                                                        |  |  |  |

| vos   | 3                                                                                                                                                                            | I   | Output voltage sense pin. This pin must be directly connected to the output capacitor.                                                                                                                                                                                                                                                                            |  |  |  |

| FB    | 4                                                                                                                                                                            | I   | redback pin. For the fixed output voltage versions, this pin is recommended to be connected to AGND for proved thermal performance. The pin also can be left floating as an internal 400-kΩ resistor is connected tween this pin and AGND for fixed output voltage versions. For the adjustable output voltage version, a resistor vider sets the output voltage. |  |  |  |

| PG    | 5                                                                                                                                                                            | 0   | Power-good open-drain output pin. The pullup resistor should not be connected to any voltage higher than 6 V. If it is not used, leave the pin floating.                                                                                                                                                                                                          |  |  |  |

| EN    | 6                                                                                                                                                                            | I   | Enable pin. To enable the device, this pin needs to be pulled high. Pulling this pin low disables the device. This pin has an internal pulldown resistor of typically $375 \text{ k}\Omega$ when the device is disabled.                                                                                                                                          |  |  |  |

| PVIN  | 7                                                                                                                                                                            | PWR | Power input supply pin                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| AVIN  | 8                                                                                                                                                                            | I   | Analog input supply pin. Connect it to the PVIN pin together.                                                                                                                                                                                                                                                                                                     |  |  |  |

| SS/TR | TR 9 I Soft start-up and voltage tracking pin. A capacitor is connected to this pin to set the soft start-up time. Leaving this pin floating sets the minimum start-up time. |     | Soft start-up and voltage tracking pin. A capacitor is connected to this pin to set the soft start-up time. Leaving this pin floating sets the minimum start-up time.                                                                                                                                                                                             |  |  |  |

| MODE  | 10                                                                                                                                                                           | I   | Mode selection pin. Connect this pin to AGND to enable Power Save Mode with automatic transition between PWM and Power Save Mode. Connect this pin to an external resistor or leave floating to enable forced PWM mode only. See 表 8-1.                                                                                                                           |  |  |  |

| AGND  | 11                                                                                                                                                                           |     | Analog ground pin                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                |                                    | MIN  | MAX                   | UNIT |

|--------------------------------|------------------------------------|------|-----------------------|------|

| Voltage at Pins <sup>(2)</sup> | AVIN, PVIN, EN, VOS, PG            | -0.3 | 6.0                   | V    |

|                                | MODE, SS/TR, SW                    | -0.3 | V <sub>IN</sub> +0.3V |      |

|                                | FB                                 | -0.3 | 3.0                   |      |

| Sink current                   | PG                                 | 0    | 1.0                   | mA   |

| Temperature                    | Operating Junction, T <sub>J</sub> | -40  | 150                   | °C   |

|                                | Storage, T <sub>stg</sub>          | -65  | 150                   |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|      |               |                                                              | VALUE | UNIT  |

|------|---------------|--------------------------------------------------------------|-------|-------|

| V    | Electrostatic | Human Body Model (HBM) ESD stress voltage <sup>(1)</sup>     | ±2000 | V     |

| VESD | discharge     | Charged Device Model (CDM) ESD stress voltage <sup>(2)</sup> | ±500  | \ \ \ |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommend Operating Conditions

Over operating free-air temperature range, unless otherwise noted.

|                  |                                | MIN | MAX             | UNIT |

|------------------|--------------------------------|-----|-----------------|------|

| V <sub>IN</sub>  | Input voltage range            | 2.5 | 6.0             | V    |

| $V_{PG}$         | Pull-up resistor voltage       | 0   | 6.0             | V    |

| V <sub>OUT</sub> | Output voltage range           | 0.8 | V <sub>IN</sub> | V    |

| I <sub>OUT</sub> | Output current range           | 0   | 2.0             | А    |

| TJ               | Operating junction temperature | -40 | 125             | °C   |

#### 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | TPS62097xx<br>RWK (11 TERMINALS) | UNITS |

|-----------------------|----------------------------------------------|----------------------------------|-------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 83.4                             | °C/W  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 61.0                             | °C/W  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 19.9                             | °C/W  |

| Ψлт                   | Junction-to-top characterization parameter   | 4.4                              | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 19.9                             | °C/W  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0                              | °C/W  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953

Product Folder Links: TPS62097

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 7.5 Electrical Characteristics

$T_J$  = -40°C to 125°C, and  $V_{IN}$  = 2.5V to 6.0V. Typical values are at  $T_J$  = 25°C and  $V_{IN}$  = 3.6V, unless otherwise noted.

|                     | PARAMETER                                         | TEST CONDITIONS                                                                                    | MIN   | TYP  | MAX  | UNIT  |  |

|---------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|------|------|-------|--|

| SUPPLY              | ,                                                 |                                                                                                    |       |      |      |       |  |

|                     | 0 :                                               | EN = High, Device not switching, T <sub>J</sub> = -40°C to 85°C                                    |       | 40   | 57   |       |  |

| lQ                  | Quiescent current into AVIN, PVIN                 | EN = High, Device not switching                                                                    |       | 40   | 65   | μA    |  |

|                     | Shutdown current into AVIN, PVIN                  | EN = Low, $T_J = -40^{\circ}$ C to 85°C                                                            |       | 0.7  | 3    |       |  |

| I <sub>SD</sub>     |                                                   | EN = Low                                                                                           |       | 0.7  | 10   | μA    |  |

| .,                  | Under voltage lock out threshold                  | V <sub>IN</sub> falling                                                                            | 2.2   | 2.3  | 2.4  | .,    |  |

| $V_{UVLO}$          |                                                   | V <sub>IN</sub> rising                                                                             | 2.3   | 2.4  | 2.5  | V     |  |

|                     | Thermal shutdown threshold                        | T <sub>J</sub> rising                                                                              |       | 160  |      | °C    |  |

| $T_{JSD}$           | Thermal shutdown hysteresis                       | T <sub>J</sub> falling                                                                             |       | 20   |      | °C    |  |

| LOGIC I             | NTERFACE (EN, MODE)                               |                                                                                                    |       |      |      |       |  |

| V <sub>H EN</sub>   | High-level input voltage, EN pin                  |                                                                                                    | 2.0   | 1.6  |      | V     |  |

| $V_{L_{EN}}$        | Low-level input voltage, EN pin                   |                                                                                                    |       | 1.3  | 1.0  | V     |  |

| I <sub>EN,LKG</sub> | Input leakage current into EN pin                 | EN = High                                                                                          |       | 0.01 | 0.9  | μA    |  |

| R <sub>PD</sub>     | Pull-down resistance at EN pin                    | EN = Low                                                                                           |       | 375  |      | kΩ    |  |

| V <sub>H_MO</sub>   | High-level input voltage, MODE pin                |                                                                                                    | 1.2   |      |      | V     |  |

| V <sub>L_MO</sub>   | Low-level input voltage, MODE pin                 |                                                                                                    |       |      | 0.4  | V     |  |

| I <sub>MO,LKG</sub> | Input leakage current into MODE pin               | MODE = High                                                                                        |       | 0.01 | 0.16 | μA    |  |

| -                   | TARTUP, POWER GOOD (SS/TR, PG)                    |                                                                                                    |       |      |      | •     |  |

| I <sub>SS</sub>     | Soft startup current                              |                                                                                                    | 5.5   | 7.5  | 9.5  | μA    |  |

|                     | Voltage tracking gain factor                      | V <sub>FB</sub> / V <sub>SS/TR</sub>                                                               |       | 1    |      | •     |  |

|                     | Power good threshold                              | V <sub>OUT</sub> rising, referenced to V <sub>OUT</sub> nominal                                    | 92    | 95   | 98   |       |  |

| $V_{PG}$            |                                                   | V <sub>OUT</sub> falling, referenced to V <sub>OUT</sub> nominal                                   | 87    | 90   | 92   | %     |  |

| $V_{PG,OL}$         | Low-level output voltage, PG pin                  | I <sub>sink</sub> = 1mA                                                                            |       |      | 0.4  | V     |  |

| I <sub>PG,LKG</sub> | Input leakage current into PG pin                 | V <sub>PG</sub> = 5.0V                                                                             |       | 0.01 | 1.6  | μA    |  |

| OUTPU1              |                                                   | 176 0.01                                                                                           |       |      |      | F     |  |

|                     |                                                   | PWM mode, No load                                                                                  | -1.0  |      | 1.0  |       |  |

| $V_{OUT}$           | Output voltage accuracy<br>TPS6209718, TPS6209733 | PSM mode <sup>(1)</sup>                                                                            | -1.0  |      | 2.1  | %     |  |

|                     |                                                   | PWM mode                                                                                           | 792   | 800  | 808  |       |  |

| $V_{FB}$            | Feedback reference voltage                        | PSM mode <sup>(1)</sup>                                                                            | 792   | 800  | 817  | mV    |  |

| I <sub>FB,LKG</sub> | Input leakage current into FB pin                 | V <sub>FB</sub> = 0.8V                                                                             | 702   | 0.01 | 0.1  | μA    |  |

| R <sub>DIS</sub>    | Output discharge resistor                         | EN = Low, V <sub>OUT</sub> = 1.8V                                                                  |       | 165  | 0.1  | Ω     |  |

| פוטיי               | Line regulation                                   | I <sub>OUT</sub> = 0.5A, V <sub>OUT</sub> = 1.8V <sup>(1)</sup>                                    |       | 0.02 |      | %/V   |  |

|                     | Load regulation                                   | PWM mode, V <sub>OUT</sub> = 1.8V <sup>(1)</sup>                                                   |       | 0.2  |      | %/A   |  |

| POWER               | SWITCH                                            | 1 *************************************                                                            |       | 0.2  |      | 70/71 |  |

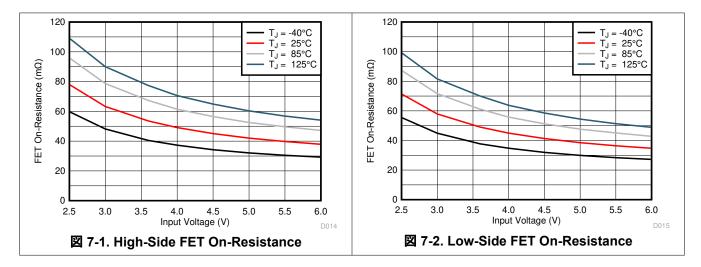

| OWER                |                                                   | I <sub>SW</sub> = 500mA, V <sub>IN</sub> = 5.0V                                                    |       | 40   | 73   |       |  |

|                     | High-side FET on-resistance                       | I <sub>SW</sub> = 500mA, V <sub>IN</sub> = 3.6V                                                    |       | 50   | 96   | mΩ    |  |

| R <sub>DS(on)</sub> |                                                   |                                                                                                    |       |      | 68   |       |  |

|                     | Low-side FET on-resistance                        | $I_{SW} = 500 \text{mA}, V_{IN} = 5.0 \text{V}$<br>$I_{SW} = 500 \text{mA}, V_{IN} = 3.6 \text{V}$ |       | 40   |      | ⊣ mΩ  |  |

|                     |                                                   | ISW - SUUTTIA, VIN - S.OV                                                                          | 2.4   | 50   | 85   |       |  |

| I <sub>LIMF</sub>   | High-side FET forward current limit               | V = 5.0V                                                                                           | 3.1   | 3.6  | 4.2  | Α     |  |

|                     | Law did FET was 1                                 | $V_{\rm IN} = 5.0V$                                                                                | 3.3   | 3.6  | 3.9  |       |  |

| LIMN                | Low-side FET negative current limit               | Forced PWM mode                                                                                    | -1.25 | -1.1 | -0.7 | Α     |  |

<sup>(1)</sup> Conditions: L = 1  $\mu$ H, C<sub>OUT</sub> = 22  $\mu$ F, Switching Frequency = 2.0 MHz

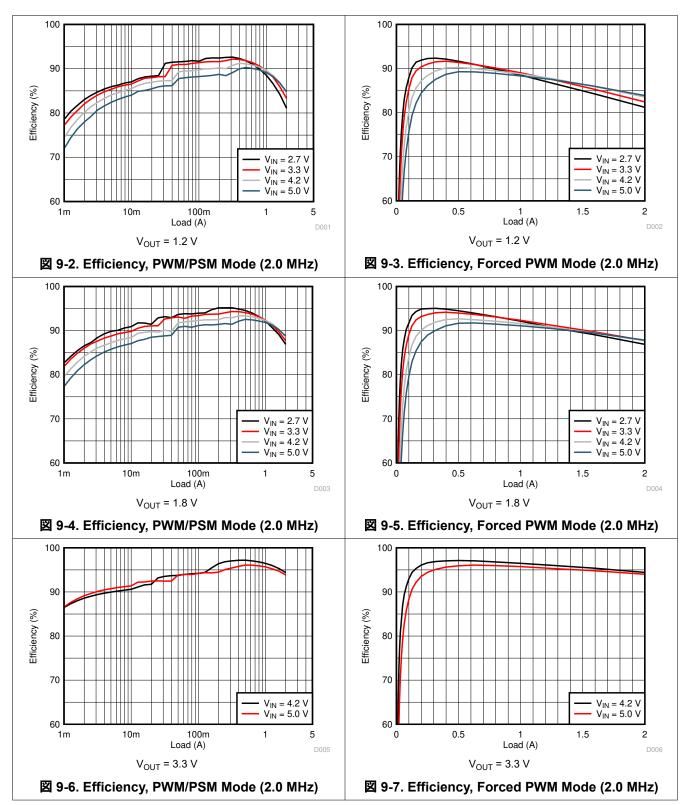

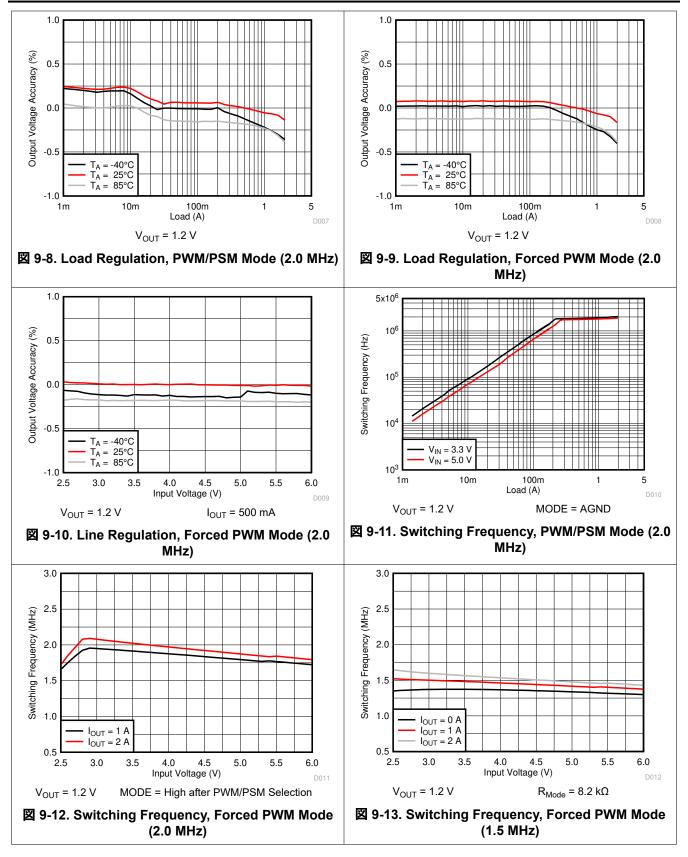

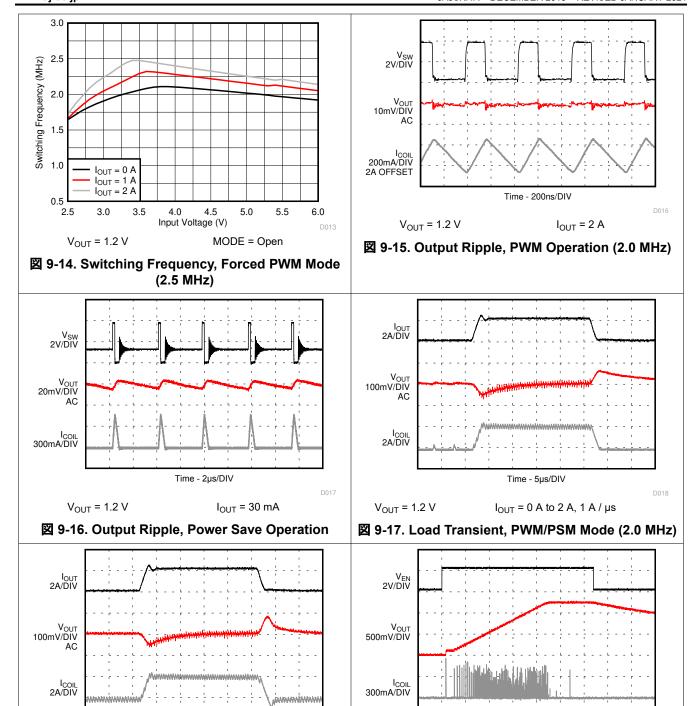

### 7.6 Typical Characteristics

# **8 Detailed Description**

#### 8.1 Overview

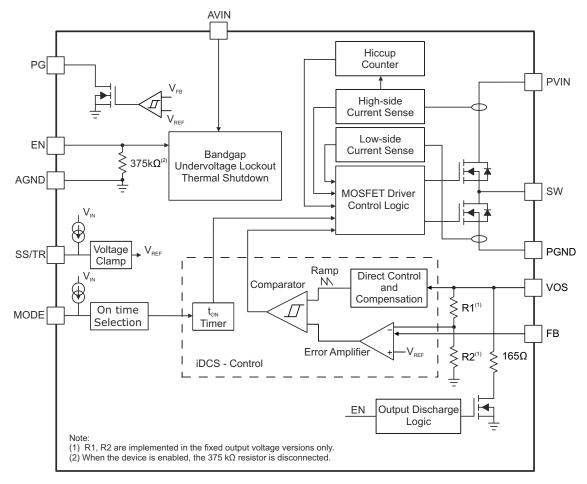

The TPS62097 synchronous step-down converter is based on the iDCS-Control (Industrial Direct Control with Seamless transition into Power Save Mode) topology. The control topology not only keeps the advantages of DCS-Control, but also provides other features:

- · Forced PWM mode over the whole load range

- Selectable PWM switching frequency

- 1% output voltage accuracy

- Output voltage sequencing and tracking

The iDCS-Control topology operates in PWM (Pulse Width Modulation) mode for medium to heavy load conditions and in Power Save Mode (PSM) at light load conditions. Or it forces the device in fixed frequency PWM mode only operation for the whole load range.

In PWM mode, the device operates with a predictive on-time switching pulse. A quasi-fixed switching frequency over the input and output voltage range is achieved by using an input and output voltage feedforward to set the on-time, as shown in 表 8-1. The converter enters Power Save Mode, reducing the switching frequency and minimizing current consumption, to achieve high efficiency over the entire load current range. Since iDCS-Control supports both operation modes within a single building block, the transition from PWM mode to Power Save Mode is seamless and without effects on the output voltage.

#### 8.2 Functional Block Diagram

Copyright © 2021 Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 100% Duty Cycle Mode

The device offers a low input to output voltage dropout by entering 100% duty cycle mode when the input voltage reaches the level of the output voltage. In this mode, the high-side MOSFET switch is constantly turned on and the low-side MOSFET is switched off. The minimum input voltage to maintain output regulation, depending on the load current and output voltage, is calculated as:

$$V_{\text{IN(min)}} = V_{\text{OUT(min)}} + I_{\text{OUT}} \times (R_{\text{DS(on)}} + R_{\text{L}}) \tag{1}$$

#### where

- V<sub>IN(min)</sub> = Minimum input voltage to maintain a minimum output voltage

- I<sub>OUT</sub> = Output current

- R<sub>DS(on)</sub> = High side FET on-resistance

- R<sub>I</sub> = Inductor ohmic resistance (DCR)

When the device operates close to 100% duty cycle mode, the TPS62097 cannot enter Power Save Mode regardless of the load current if the input voltage decreases to typically 15% above the output voltage. The device maintains output regulation in PWM mode.

#### 8.3.2 Switch Current Limit and Hiccup Short Circuit Protection

The switch current limit prevents the devices from high inductor current and from drawing excessive current from the battery or input voltage rail. Excessive current might occur with a shorted/saturated inductor or a heavy load/ shorted output circuit condition. If the inductor current reaches the threshold I<sub>LIMF</sub>, the high-side MOSFET is turned off and the low-side MOSFET is turned on to ramp down the inductor current. Once this switch current limit is triggered 32 times, the devices stop switching and enable the output discharge. The devices then automatically start a new start-up after a typical delay time of 100 µs has passed. This is HICCUP short circuit protection and is implemented to reduce the current drawn during a short circuit condition. The devices repeat this mode until the high load condition disappears.

When the device is in forced PWM mode, the negative current limit of the low-side MOSFET is active. The negative current limit prevents excessive current from flowing back through the inductor to the input.

#### 8.3.3 Undervoltage Lockout (UVLO)

To avoid mis-operation of the device at low input voltages, an undervoltage lockout is implemented, which shuts down the devices at voltages lower than  $V_{UVLO}$  with a hysteresis of 100 mV.

#### 8.3.4 Thermal Shutdown

The device goes into thermal shutdown and stops switching once the junction temperature exceeds T<sub>JSD</sub>. Once the device temperature falls below the threshold by 20°C, the device returns to normal operation automatically.

#### 8.4 Device Function Modes

#### 8.4.1 Enable and Disable (EN)

The device is enabled by setting the EN pin to a logic high. Accordingly, shutdown mode is forced if the EN pin is pulled low with a shutdown current of typically  $0.7~\mu A$ .

In shutdown mode, the internal power switches as well as the entire control circuitry are turned off. An internal resistor of 165  $\Omega$  discharges the output through the VOS pin smoothly. The output discharge function also works when thermal shutdown, undervoltage lockout, or HICCUP short circuit protection are triggered.

An internal pulldown resistor of 375 k $\Omega$  is connected to the EN pin when the EN pin is low. The pulldown resistor is disconnected when the EN pin is high.

#### 8.4.2 Power Save Mode and Forced PWM Mode (MODE)

The MODE pin is a multi-functional pin that allows the device operation in forced PWM mode or PWM/PSM mode, and to select the PWM switching frequency.

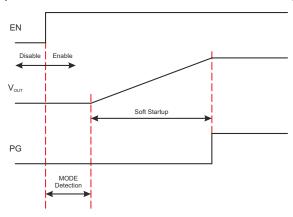

Once the EN pin is pulled high, the IC enables internal circuit blocks and prepares to ramp the output up. The period between the rising edge of the EN pin and the beginning of the power stage switching is called the MODE detection time, typically 50  $\mu$ s. During the MODE detection time period, shown in  $\mathbb{Z}$  8-1, the PWM switching frequency and operating mode are set by the MODE pin status, as shown in  $\mathbb{Z}$  8-1.

The PWM switching frequency cannot be changed after the detection time period. Only when the device is set in PWM/PSM mode during the MODE detection time period (MODE = AGND), it is possible to switch between PWM/PSM and forced PWM operation modes by toggling the MODE pin with a GPIO pin of a microcontroller, for example. The other four MODE pin selections force the device in PWM mode only.

図 8-1. Power-up Sequence

表 8-1. Switching Frequency and Mode Selection

| TYPICAL PWM<br>SWITCHING<br>FREQUENCY<br>(MHZ) | RESISTANCE AT MODE<br>PIN<br>(E24 EIA VALUE) | TOGGLE MODE PIN<br>AFTER MODE DETECTION | ON-TIME EQUATION                                              | OPERATING<br>MODE |

|------------------------------------------------|----------------------------------------------|-----------------------------------------|---------------------------------------------------------------|-------------------|

| 1.50                                           | 8.2 kΩ ±5%                                   | No                                      | $t_{ON}$ = 667 ns x $V_{OUT} / V_{IN}$                        | Forced PWM        |

| 1.75                                           | 18 kΩ ±5%                                    | No                                      | $t_{ON}$ = 571 ns x $V_{OUT} / V_{IN}$                        | Forced PWM        |

| 2.00                                           | AGND                                         | Yes                                     | t <sub>ON</sub> = 500 ns x V <sub>OUT</sub> / V <sub>IN</sub> |                   |

| 2.25                                           | 39 kΩ ±5%                                    | No                                      | $t_{ON}$ = 444 ns x $V_{OUT} / V_{IN}$                        | Forced PWM        |

| 2.50                                           | 75 kΩ ±5% or Open                            | No                                      | $t_{ON}$ = 400 ns x $V_{OUT} / V_{IN}$                        | Forced PWM        |

Connecting the MODE pin to AGND with a resistor or leaving the MODE pin open forces the device into PWM mode for the whole load range. The device operates with a fixed switching frequency that allows simple filtering of the switching frequency for noise sensitive applications. In forced PWM mode, the efficiency is lower than that of PSM at light load.

Connecting the MODE pin to the AGND pin enables Power Save Mode with an automatic transition between PWM and Power Save Mode. As the load current decreases and the inductor current becomes discontinuous, the device enters Power Save Mode operation automatically. In Power Save Mode, the switching frequency is reduced and estimated by  $\precsim$  2. In Power Save Mode, the output voltage rises slightly above the nominal output voltage, as shown in Load Regulation, PWM/PSM Mode (2.0 MHz). This effect is minimized by increasing the output capacitor.

$$f_{PSM} = \frac{2 \times I_{OUT}}{t_{ON}^2 \times \frac{V_{IN}}{V_{OUT}} \times \frac{V_{IN} - V_{OUT}}{L}}$$

(2)

Copyright © 2021 Texas Instruments Incorporated

When the device operates close to 100% duty cycle mode, the TPS62097 cannot enter Power Save Mode regardless of the load current if the input voltage decreases to typically 15% above the output voltage. The device maintains output regulation in PWM mode.

#### 8.4.3 Soft Start-up (SS/TR)

The TPS62097 programs its output voltage ramp rate with the SS/TR pin. Connecting an external capacitor to SS/TR enables output soft start-up to reduce inrush current from the input supply. The device charges the capacitor voltage to the input supply voltage with a constant current of typically 7.5  $\mu$ A. The FB pin voltage follows the SS/TR pin voltage until the internal reference voltage of 0.8 V is reached. The soft start-up time is calculated using  $\pm$  3. Keep the SS/TR pin floating to set the minimum start-up time.

$$t_{SS} = C_{SS/TR} \times \frac{0.8V}{7.5\mu A} \tag{3}$$

An active pulldown circuit is connected to the SS/TR pin. It discharges the external soft start-up capacitor in case of disable, UVLO, thermal shutdown, and HICCUP short circuit protection.

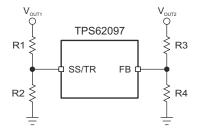

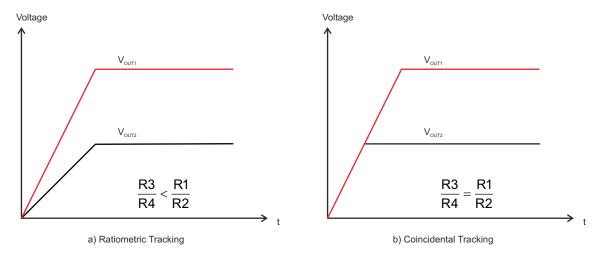

#### 8.4.4 Voltage Tracking (SS/TR)

The SS/TR pin is externally driven by another voltage source to achieve output voltage tracking. The application circuit is shown in  $\boxtimes$  8-2. From 0 V to 0.8 V, the internal reference voltage to the internal error amplifier follows the SS/TR pin voltage. When the SS/TR pin voltage is above 0.8 V, the voltage tracking is disabled and the FB pin voltage is regulated at 0.8 V. The device achieves ratiometric or coincidental (simultaneous) output tracking, as shown in  $\boxtimes$  8-3.

図 8-2. Output Voltage Tracking

図 8-3. Voltage Tracking Options

The R2 value should be set properly to achieve accurate voltage tracking by taking 7.5  $\mu$ A soft start-up current into account. 1  $k\Omega$  or smaller is a sufficient value for R2.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

www.tij.co.jp

For decreasing SS/TR pin voltage, the device does not sink current from the output when the device is in PSM, so the resulting decreases of the output voltage can be slower than the SS/TR pin voltage if the load is light. When driving the SS/TR pin with an external voltage, do not exceed the voltage rating of the SS/TR pin which is  $V_{IN} + 0.3 V.$

#### 8.4.5 Power Good (PG)

The TPS62097 has a power-good output. The PG pin goes high impedance once the output voltage is above 95% of the nominal voltage and is driven low once the output voltage falls below typically 90% of the nominal voltage. The PG pin is an open-drain output and is specified to sink up to 1 mA. The power-good output requires a pullup resistor connected to any voltage rail less than 6 V. The PG pin goes low when the device is disabled or in thermal shutdown. When the devices are in UVLO, the PG pin is high impedance.

The PG signal can be used for sequencing of multiple rails by connecting it to the EN pin of other converters. Leave the PG pin floating when not used.

# 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 9.1 Application Information

The following section discusses the design of the external components to complete the power supply design of the TPS62097.

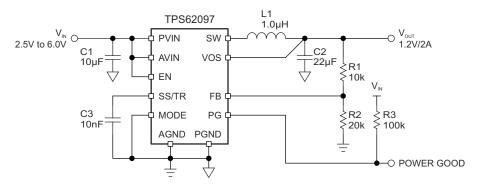

#### 9.2 1.2-V Output Application

図 9-1. 1.2-V Output Application Schematic

#### 9.2.1 Design Requirements

For this design example, use the following as the input parameters.

DESIGN PARAMETER

EXAMPLE VALUE

Input voltage range

2.5 V to 6 V

Output voltage

1.2 V

Output current

2.0 A

Output voltage ripple

< 30 mV</td>

表 9-1. Design Parameters

表 9-2 lists the components used for the example.

| REFERENCE | DESCRIPTION                                                          | MANUFACTURER |

|-----------|----------------------------------------------------------------------|--------------|

| C1        | 10 μF, Ceramic Capacitor, 6.3 V, X7R, size 0805, C2012X7R0J106M125AB | TDK          |

| C2        | 22 μF, Ceramic Capacitor, 6.3 V, X7S, size 0805, C2012X7S1A226M125AC | TDK          |

| C3        | 10 nF, Ceramic Capacitor, 6.3 V, X7R, size 0603, GRM188R70J103KA01   | Murata       |

| L1        | 1 μH, Shielded, 5.4 A, XFL4020-102MEB                                | Coilcraft    |

| R1        | Depending on the output voltage, 1% accuracy                         | Std          |

| R2        | 20 kΩ, 1% accuracy                                                   | Std          |

| R3        | 100 Ωk, 1% accuracy                                                  | Std          |

Product Folder Links: TPS62097

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Setting the Output Voltage

The output voltage is set by an external resistor divider according to 式 4:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R1}{R2}\right) = 0.8 \text{ V} \times \left(1 + \frac{R1}{R2}\right)$$

(4)

R2 should not be higher than 20 k $\Omega$  to reduce noise coupling into the FB pin and improve the output voltage regulation.  $\boxtimes$  9-1 shows the external resistor divider value for 1.2-V output. Choose additional resistor values for other outputs. A feedforward capacitor is not required.

The fixed output voltage versions, TPS6209718 and TPS6209733, do not need the external resistor divider. TI recommends to connect the FB pin to AGND for improved thermal performance.

#### 9.2.2.2 Output Filter Design

The inductor and the output capacitor together provide a low-pass filter. To simplify the selection process, 表 9-3 outlines possible inductor and capacitor value combinations for most applications.

NOMINAL L [μH]<sup>(2)</sup>

10

22

47

100

150

0.47

1 +(1) + + + +

2.2

表 9-3. Output Capacitor / Inductor Combinations

- (1) Typical application configuration. Other '+' mark indicates recommended filter combinations. Other values may be acceptable in applications but should be fully tested by the user. Refer to the application note SLVA710.

- (2) Inductor tolerance and current de-rating is anticipated. The effective inductance can vary by +20% and -30%. The required effective inductance is 500-nH minimum.

- (3) Capacitance tolerance and bias voltage de-rating is anticipated. The effective capacitance can vary by 20% and -50%.

#### 9.2.2.3 Inductor Selection

The main parameters for the inductor selection are the inductor value and the saturation current. To calculate the maximum inductor current under static load conditions,  $\pm 5$  is given.

$$I_{L,MAX} = I_{OUT,MAX} + \frac{\Delta I_L}{2}$$

$$\Delta I_{L} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f_{SW}}$$

(5)

Where:

$I_{OUT,MAX}$  = Maximum output current  $\Delta I_L$  = Inductor current ripple  $f_{SW}$  = Switching frequency L = Inductor value

TI recommends to choose the saturation current for the inductor 20% to 30% higher than the  $I_{L,MAX}$ , out of  $\precsim 5$ . A higher inductor value is also useful to lower ripple current but increases the transient response time as well. The following inductors are recommended to be used in designs.

Copyright © 2021 Texas Instruments Incorporated

#### 表 9-4. List of Recommended Inductors

| INDUCTANCE<br>[µH] | CURRENT RATING<br>[A] | DIMENSIONS<br>L x W x H [mm <sup>3</sup> ] | DC RESISTANCE<br>[mΩ TYP] | PART NUMBER <sup>(1)</sup>    |

|--------------------|-----------------------|--------------------------------------------|---------------------------|-------------------------------|

| 1                  | 5.4                   | 4.0x4.0x2.0                                | 11                        | COILCRAFT XFL4020-102ME       |

| 1                  | 5.3                   | 2.5x2.0x1.2                                | 33                        | TOKO DFE252012F-1R0M          |

| 1                  | 3.4                   | 2.0x1.2x1.0                                | 62                        | TOKO DFE201210S-1R0M          |

| 1                  | 5.1                   | 3.0x3.0x1.2                                | 43                        | TAIYO YUDEN MDMK3030T1R0MM    |

| 1                  | 4.2                   | 2.5x2.0x1.2                                | 43                        | CYNTEC SDEM25201B-1R0MS-79    |

| 1                  | 2.6                   | 2.5x2.0x1.2                                | 48                        | Murata LQH2HPN1R0NJR          |

| 1                  | 6.6                   | 3.0x3.0x1.2                                | 42                        | Wurth Electronics 74438334010 |

<sup>(1)</sup> See Third-Party Products Disclaimer

#### 9.2.2.4 Capacitor Selection

The input capacitor is the low impedance energy source for the converters which helps to provide stable operation. A low-ESR multilayer ceramic capacitor is required for best filtering and should be placed between PVIN and PGND as close as possible to those pins. For most applications, a 10-µF capacitor is sufficient, though a larger value reduces input current ripple.

The architecture of the TPS62097 allows the use of tiny ceramic output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended. To keep its low resistance up to high frequencies and to get narrow capacitance variation with temperature, TI recommends to use X7R or X5R dielectrics. The recommended typical output capacitor value is 22  $\mu$ F and can vary over a wide range as outlined in  $\frac{1}{8}$  9-4.

Ceramic capacitors have a DC-Bias effect, which has a strong influence on the final effective capacitance. Choose the right capacitor carefully in combination with considering its package size and voltage rating. Ensure that the input effective capacitance is at least 5  $\mu$ F and the output effective capacitance is at least 10  $\mu$ F.

Product Folder Links: TPS62097

#### 9.2.3 Application Performance Curves

$T_A = 25$ °C,  $V_{IN} = 3.6$  V, unless otherwise noted.

図 9-18. Load Transient, Forced PWM Mode (2.0 MHz)

Time - 5µs/DIV

$I_{OUT}$  = 0 A to 2 A, 1 A /  $\mu$ s

図 9-19. Startup and Shutdown without Load

V<sub>OUT</sub> = 1.2 V

Time - 250µs/DIV

$V_{OUT}$  = 1.2 V

R<sub>OUT</sub> = No Load

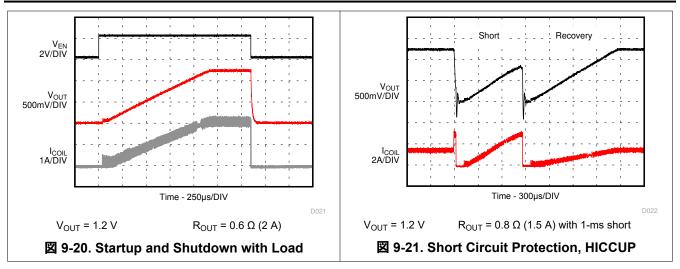

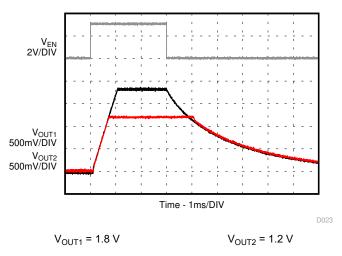

#### 9.2.4 Coincidental Voltage Tracking

図 9-22. 1.8-V and 1.2-V Coincidental Voltage Tracking Schematic

#### 9.2.4.1 Design Requirements

For this design example, use the following as the input parameters.

表 9-5. Design Parameters FER

| DESIGN PARAMETER                                          | EXAMPLE VALUE |  |  |  |  |

|-----------------------------------------------------------|---------------|--|--|--|--|

| Input voltage range                                       | 2.5 V to 6 V  |  |  |  |  |

| Output voltage 1                                          | 1.8 V         |  |  |  |  |

| Output voltage 2                                          | 1.2 V         |  |  |  |  |

| Output voltage 2 follows output voltage 1 coincidentally. |               |  |  |  |  |

#### 9.2.4.2 Detailed Design Procedure

Set 1 k $\Omega$  for R2 and 0.5 k $\Omega$  for R1. Connect the two converters as shown in  $\boxtimes$  9-22. Set up two converters in forced PWM mode.

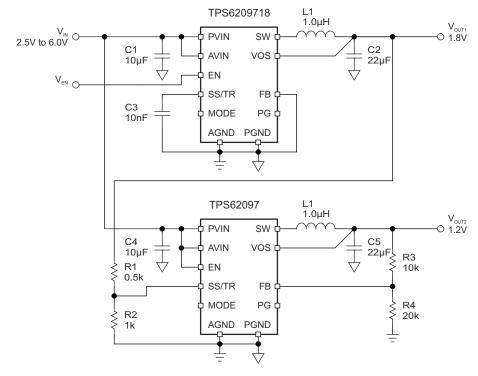

#### 9.2.4.3 Application Performance Curve

$T_A = 25$ °C,  $V_{IN} = 5.0$  V, unless otherwise noted.

図 9-23. Coincidental Tracking Waveform

#### 9.2.5 Switching Frequency Selection

図 9-24. Switching Frequency Selection by an External Resistor

#### 9.2.5.1 Design Requirements

For this design example, use the following as the input parameters.

DESIGN PARAMETEREXAMPLE VALUEInput voltage range2.5 V to 6 VOutput voltage 11.8 VSwitching Frequency Selection1.5 MHz, 2.0 MHz, or 2.5 MHz

表 9-6. Design Parameters

#### 9.2.5.2 Detailed Design Procedure

Set  $8.2~k\Omega$  and  $75~k\Omega$  for 1.5-MHz, 2.0-MHz, and 2.5-MHz switching frequency. R4 uses the standard E24 series resistor values.

Copyright © 2021 Texas Instruments Incorporated

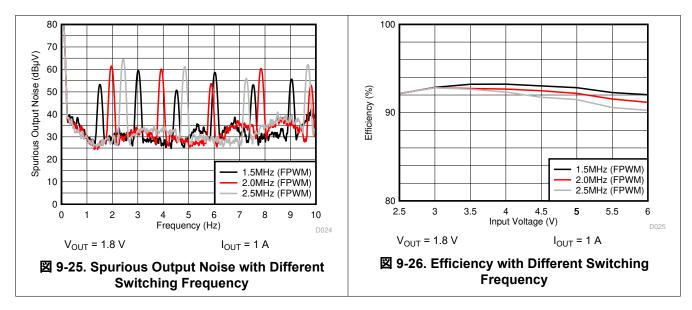

#### 9.2.5.3 Application Performance Curves

$T_A = 25$ °C,  $V_{IN} = 5.0$ , unless otherwise noted.

#### 10 Power Supply Recommendations

The devices are designed to operate from an input voltage supply range between 2.5 V and 6 V. The average input current of the TPS62097 is calculated as:

$$I_{IN} = \frac{1}{\eta} \times \frac{V_{OUT} \times I_{OUT}}{V_{IN}}$$

(6)

Ensure that a power supply has a sufficient current rating for the application.

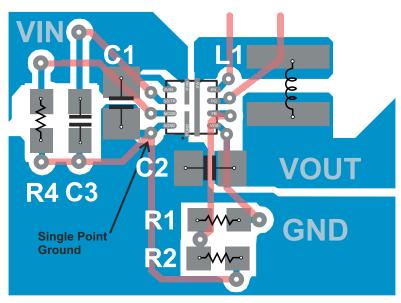

#### 11 Layout

#### 11.1 Layout Guidelines

- TI recommends to place all components as close as possible to the IC. Specifically, the input capacitor placement must be closest to the PVIN and PGND pins of the device.

- The low side of the input and output capacitors must be connected directly to the PGND pin to avoid a ground potential shift.

- Use the terminal of the input capacitor as the common node for AVIN and PVIN, AGND, and PGND. It helps reduce the noise coupling into the internal analog circuit blocks. Do not use a solid plane pour to connect these nodes.

- Use wide and short traces for the main current paths to reduce the parasitic inductance and resistance.

- The sense trace connected to VOS pin is a signal trace. Special care should be taken to avoid noise being induced. By a direct routing, parasitic inductance can be kept small. Keep the trace away from SW nodes.

- Refer to the 🗵 11-1 for an example of component placement, routing, and thermal design.

#### 11.2 Layout Example

図 11-1. TPS62097 PCB Layout

#### 11.2.1 Thermal Information

Implementation of integrated circuits in low-profile and fine pitch surface mount packages typically requires special attention to power dissipation. Many system dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

セクション 7.4 provides the thermal metric of the device on the TPS62097 EVM after considering the PCB design of real applications. The big copper planes connecting to the pads of the IC on the PCB board improve the thermal performance of the device. For more details on how to use the thermal parameters, see the application notes: Thermal Characteristics Application Notes SZZA017 and SPRA953.

Copyright © 2021 Texas Instruments Incorporated

#### 12 Device and Documentation Support

#### 12.1 Device Support

#### 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 12.2 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「*更新の通知を受け取る」をクリック*して登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 12.6 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

9-Nov-2025

www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins     | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|--------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                    |                       |      | (4)                           | (5)                        |              |                  |

| TPS6209718RWKR        | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | Call TI   Sn                  | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209718RWKR.A      | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209718RWKR.B      | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209718RWKT        | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | Call TI   Sn                  | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209718RWKT.A      | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209718RWKT.B      | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZGB5             |

| TPS6209733RWKR        | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS6209733RWKR.A      | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS6209733RWKR.B      | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS6209733RWKT        | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS6209733RWKT.A      | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS6209733RWKT.B      | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125   | ZGC5             |

| TPS62097RWKR          | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | Call TI   Sn                  | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

| TPS62097RWKR.A        | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

| TPS62097RWKR.B        | Active | Production    | VQFN-HR (RWK)   11 | 3000   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

| TPS62097RWKT          | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | Call TI   Sn                  | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

| TPS62097RWKT.A        | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

| TPS62097RWKT.B        | Active | Production    | VQFN-HR (RWK)   11 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | ZFZ5             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

(5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS62097:

Automotive: TPS62097-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Feb-2025

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS + K0 - P1 - B0 W Cavity - A0 -

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

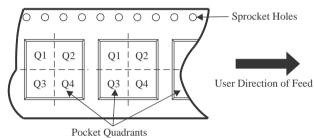

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS6209718RWKR | VQFN-<br>HR     | RWK                | 11 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS6209718RWKT | VQFN-<br>HR     | RWK                | 11 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS6209733RWKR | VQFN-<br>HR     | RWK                | 11 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS6209733RWKT | VQFN-<br>HR     | RWK                | 11 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

www.ti.com 3-Feb-2025

#### \*All dimensions are nominal

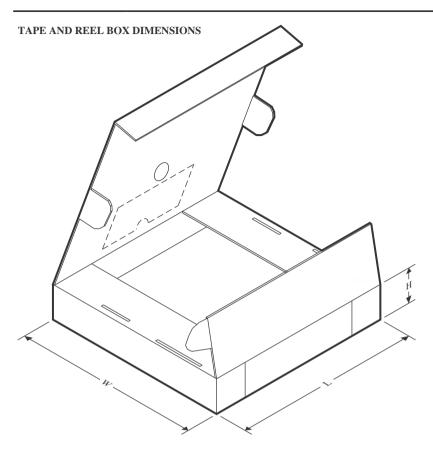

| Device         | Package Type Package Drawing |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|------------------------------|-----|------|------|-------------|------------|-------------|

| TPS6209718RWKR | VQFN-HR                      | RWK | 11   | 3000 | 341.0       | 182.0      | 80.0        |

| TPS6209718RWKT | VQFN-HR                      | RWK | 11   | 250  | 341.0       | 182.0      | 80.0        |

| TPS6209733RWKR | VQFN-HR                      | RWK | 11   | 3000 | 341.0       | 182.0      | 80.0        |

| TPS6209733RWKT | VQFN-HR                      | RWK | 11   | 250  | 341.0       | 182.0      | 80.0        |

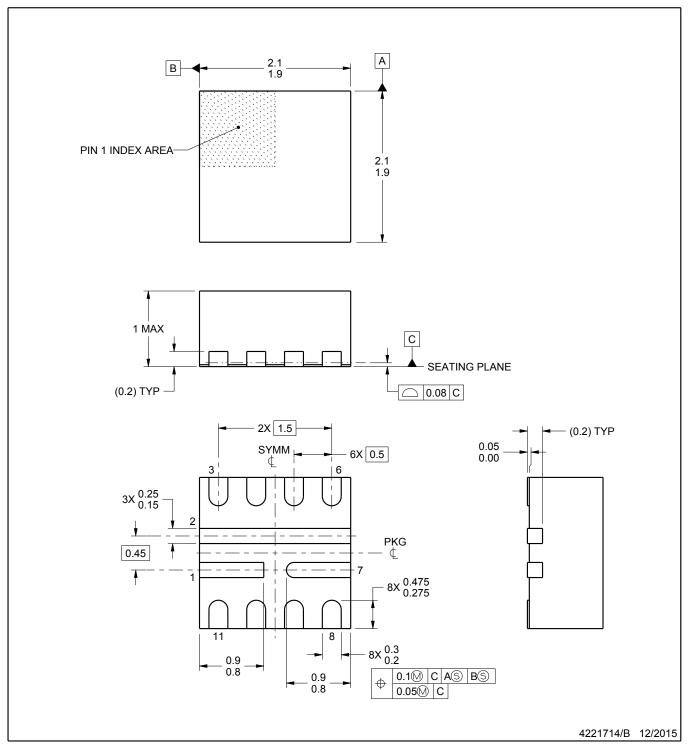

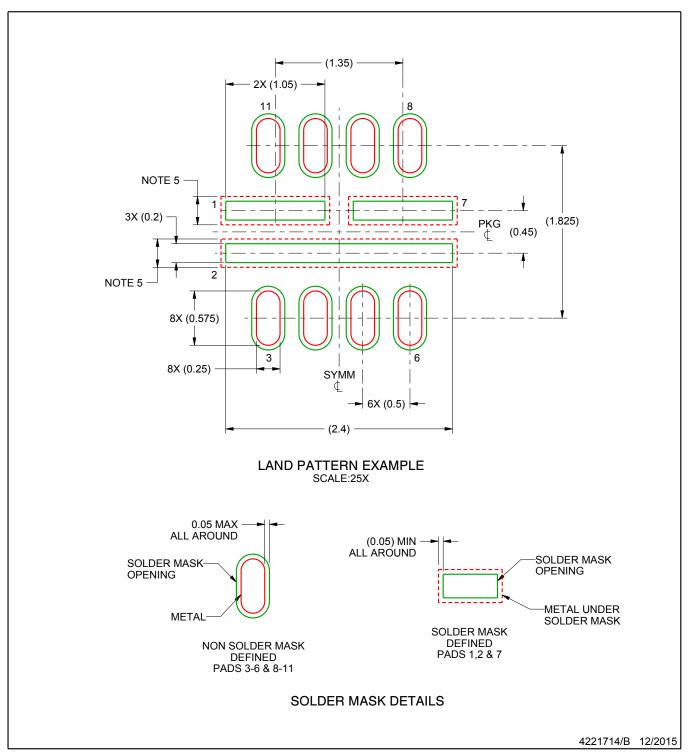

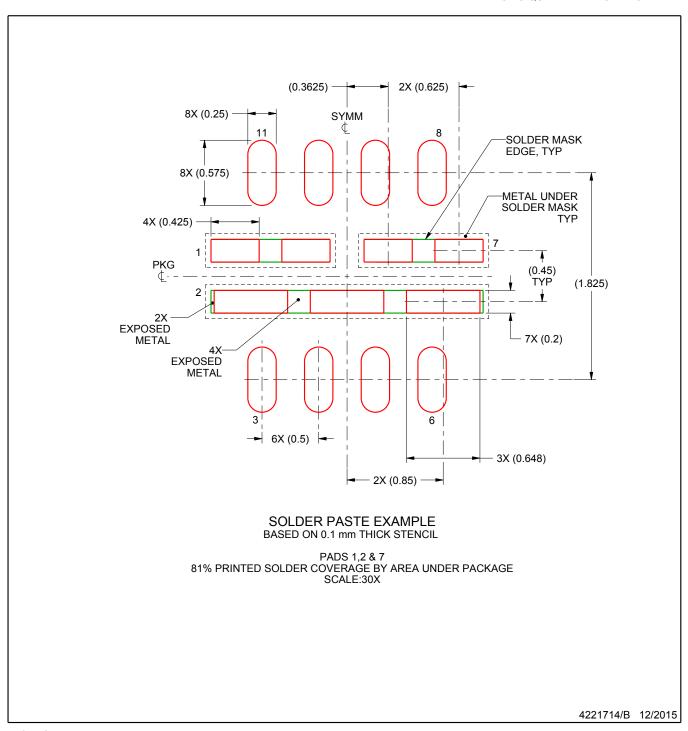

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Package pin numbers 1, 2, and 7 must be soldered to the printed circuit board for thermal and mechanical performance.

- Refer to product data sheet for specific thermal pad and via recommendations.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271). 5. Size of metal pad may vary due to creepage requirements.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月