## 3MHz、1.6A降圧型コンバータ (2×2 SON/パッケージ)

### 特 長

- 高スイッチング周波数3MHz

- $V_{IN}$ の電圧範囲は2.7V ~ 6V

- 出力電流 1.6A

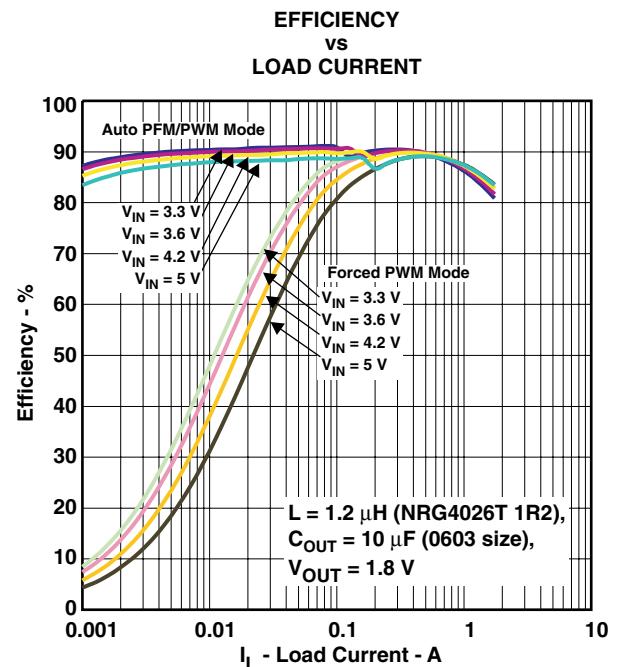

- 最高効率97%

- パワーセーブ・モードと3MHz固定周波数PWMモード

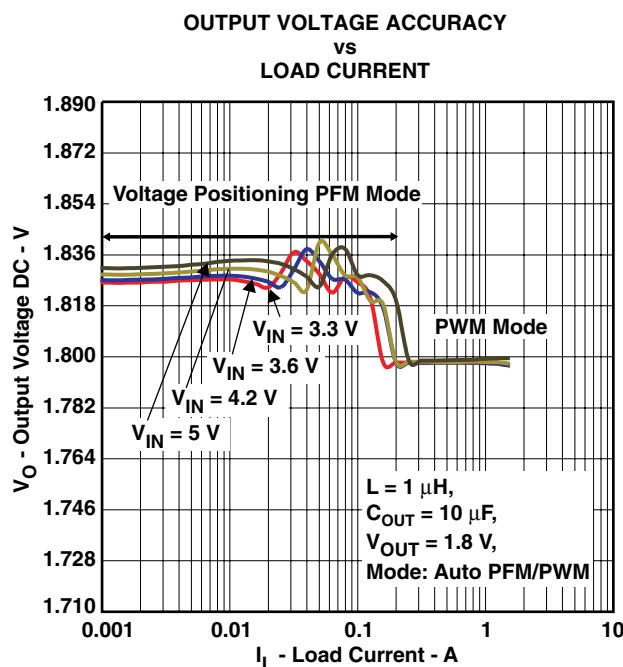

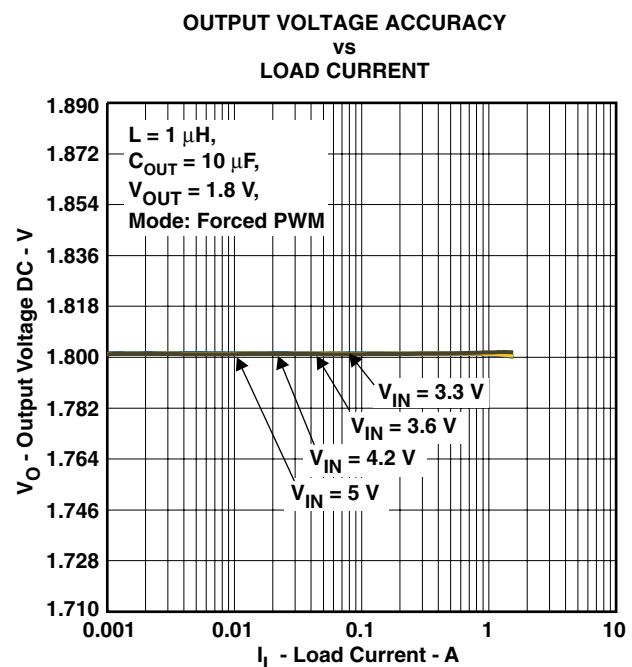

- PWMモードでの出力電圧精度： $\pm 1.5\%$

- 出力コンデンサの放電機能

- 無負荷時自己消費電流：18μA（標準値）

- 100%デューティ・サイクル動作により最小の入出力電位差

- 出力電圧ポジショニング

- クロック周波数のデザリング

- 高さ1mm未満の電源を構築可能

- 2×2×0.75mmのSONパッケージで供給

### アプリケーション

- POL電源

- ノートPC、ポケットPC

- 携帯用メディア・プレーヤー

- DSP電源

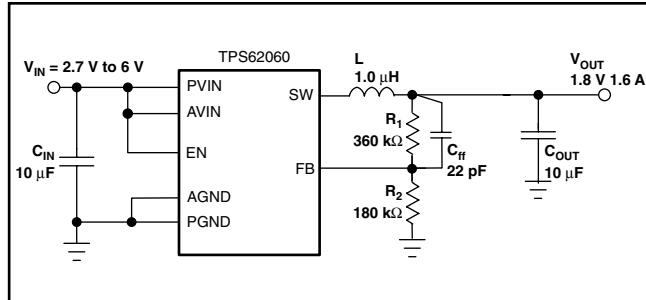

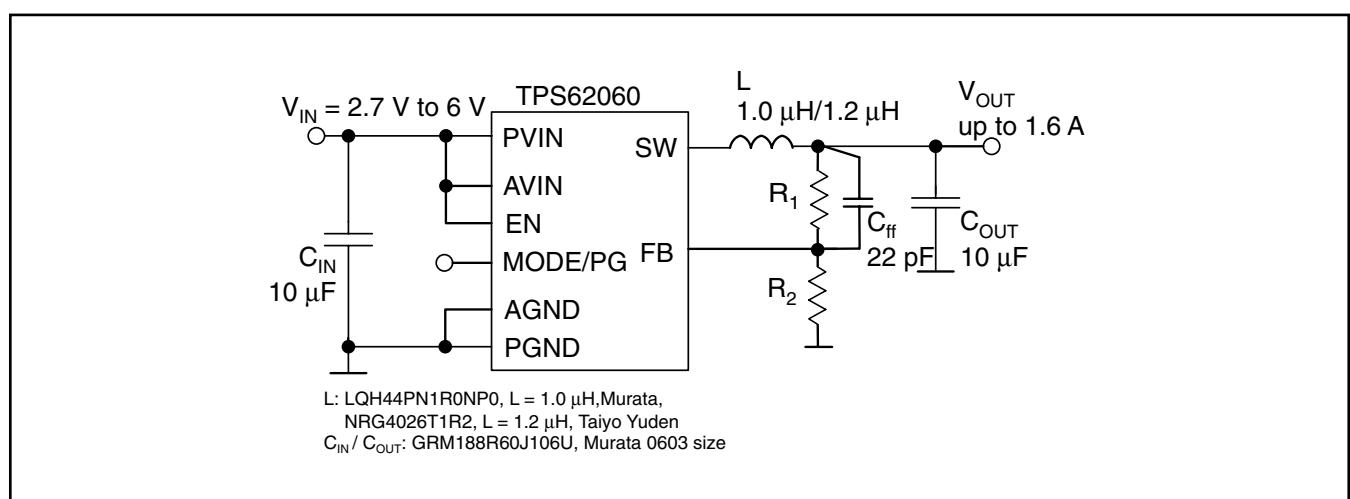

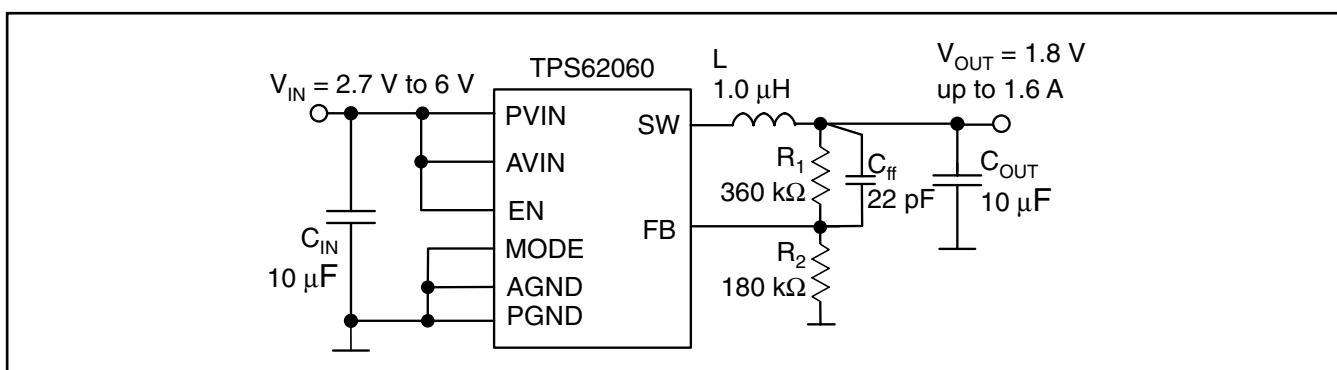

### TYPICAL APPLICATION CIRCUIT

### 概 要

TPS62060は高効率の同期整流方式の降圧型DC/DCコンバータです。本製品は最大1.6Aの出力電流を供給できます。

本製品は2.7V~6Vの入力電圧範囲を備え、5Vや3.3Vのシステム電源からの降圧電源に最適です。TPS62060は、3MHzの固定スイッチング周波数で動作し、軽負荷電流時にはパワーセーブ・モードに自動的に切り替わり、広い負荷電流範囲にわたって高効率を維持します。パワーセーブ・モードは出力のリップル電圧が最小になるように最適化されています。さらに低ノイズが要求されるアプリケーションの場合、本製品はMODEピンを“High”にすることで、強制的に固定周波数PWMモードにすることができます。

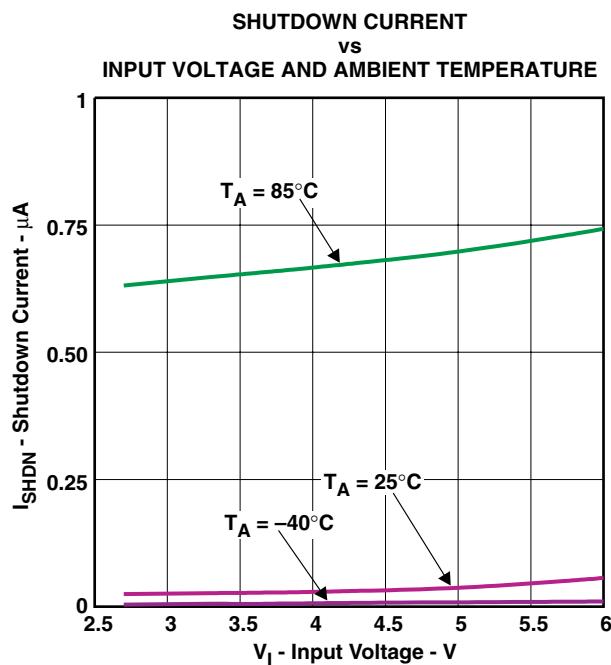

シャットダウン・モードでは、自己消費電流が1μA未満に低下し、内部回路により出力コンデンサは放電されます。

TPS62060は、1.0μHの小型のインダクタと10μFの小型出力コンデンサを使用して小さなソリューション・サイズで高い出力性能を実現しています。

TPS62060は8ピンの2×2×0.75mmのSONパッケージで提供されます。

PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## 製品情報<sup>(1)</sup>

| T <sub>A</sub> | PART NUMBER <sup>(2)</sup> | OUTPUT VOLTAGE <sup>(3)</sup> | FUNCTION   |               | MAXIMUM OUTPUT CURRENT | PACKAGE DESIGNATOR | ORDERING    | PACKAGE MARKING |

|----------------|----------------------------|-------------------------------|------------|---------------|------------------------|--------------------|-------------|-----------------|

|                |                            |                               | MODE       | Power Good PG |                        |                    |             |                 |

| -40°C ~ 85°C   | TPS62060                   | Adjustable                    | Selectable | No            | 1.6A                   | DSG                | TPS62060DSG | OFA             |

|                | TPS6206x <sup>(3)</sup>    | Adjustable                    | no         | yes           | 1.6A                   | DSG                |             | -               |

(1) 最新のパッケージおよびご発注情報については、最新の英文データシート末尾の“Package Addendum”を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com))をご覧ください。

(2) DSG(SON-8)パッケージはテーブ・リールとして供給されます。デバイス・タイプの末尾にRを付けてください。個数はリール当たり3000個です。

(3) その他の固定出力電圧オプションについては、TIにお問い合わせください。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                                                                         |                  | VALUE              |                          | 単位 |

|-------------------------------------------------------------------------|------------------|--------------------|--------------------------|----|

|                                                                         |                  | MIN                | MAX                      |    |

| Voltage Range <sup>(2)</sup>                                            | AVIN, PVIN       | -0.3               | 7                        | V  |

|                                                                         | EN, MODE, FB     | -0.3               | V <sub>IN</sub> +0.3 < 7 |    |

|                                                                         | SW               | -0.3               | 7                        |    |

| Current (source)                                                        | Peak output      | Internally limited |                          | A  |

| Electrostatic Discharge (HBM) QSS 009-105 (JESD22-A114A) <sup>(3)</sup> |                  | 2                  |                          | kV |

| Electrostatic Discharge (CDM) QSS 009-147 (JESD22-C101B.01)             |                  | 1                  |                          |    |

| Electrostatic Discharge (Machine model)                                 |                  | 200                |                          | V  |

| Temperature                                                             | T <sub>J</sub>   | -40                | 125                      | °C |

|                                                                         | T <sub>stg</sub> | -65                | 150                      | °C |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) すべての電圧値は回路のグランド端子を基準としています。

(3) HBM(Human Body Model)は、100pFのコンデンサから1.5kΩの抵抗を経由して各ピンに放電した場合です。マシン・モデルは、200pFのコンデンサから各ピンに直接放電した場合です。

## 許容損失<sup>(1)(2)</sup>

| PACKAGE | R <sub>θJA</sub> | POWER RATING<br>T <sub>A</sub> = ≤ 25°C | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C |

|---------|------------------|-----------------------------------------|------------------------------------------------|

| DSG     | 75°C/W           | 1300 mW                                 | 13 mW/°C                                       |

(1) 最大許容損失はT<sub>J(max)</sub>とθ<sub>JA</sub>及びT<sub>A</sub>の関数となります。最高の使用環境温度における最大許容損失はP<sub>D</sub> = (T<sub>J(max)</sub> - T<sub>A</sub>) / θ<sub>JA</sub>で計算出来ます。

(2) この熱データはhigh-K基板(JEDEC標準規格のJESD51-7による4層基板)で測定された値です。

## 推奨動作条件

|                                                    |  | MIN | NOM      | MAX | 単位      |

|----------------------------------------------------|--|-----|----------|-----|---------|

| $V_{IN}$ , Supply voltage                          |  | 2.7 | 6        |     | V       |

| $P_{VIN}$                                          |  |     |          |     |         |

| Output current capability                          |  |     | 1600     |     | mA      |

| Output voltage range for adjustable voltage        |  | 0.8 | $V_{IN}$ |     | V       |

| L Effective Inductance Range                       |  | 0.7 | 1.0      | 1.6 | $\mu H$ |

| $C_{OUT}$ Effective Output Capacitance Range       |  | 4.5 | 10       | 22  | $\mu F$ |

| $T_A$ Operating ambient temperature <sup>(1)</sup> |  | -40 | 85       |     | °C      |

| $T_J$ Operating junction temperature               |  | -40 | 125      |     | °C      |

(1) 損失が大きな場合やパッケージからの熱抵抗が高いアプリケーションの場合、使用可能な環境温度の最高値が低下します。

最高環境温度( $T_A(max)$ )は最高ジャンクション温度( $T_J(max)$ )、アプリケーションにおいてディバイスで発生する最大損失( $P_{D(max)}$ )、およびジャンクション - 周囲空間の間の熱抵抗( $\theta_{JA}$ )に依存し、以下の式で計算できます： $T_A(max) = T_J(max) - (\theta_{JA} \times P_{D(max)})$

## 電気的特性

Over full operating ambient temperature range, typical values are at  $T_A = 25^\circ C$ . Unless otherwise noted, specifications apply for condition  $V_{IN} = EN = 3.6V$ . External components  $C_{IN} = 10\mu F$  0603,  $C_{OUT} = 10\mu F$  0603,  $L = 1.0\mu H$ , see the parameter measurement information.

| パラメータ                                                          | テスト条件                                                                        | MIN  | TYP  | MAX  | 単位         |

|----------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|------------|

| <b>SUPPLY</b>                                                  |                                                                              |      |      |      |            |

| $V_{IN}$ Input voltage range                                   |                                                                              | 2.7  | 6    |      | V          |

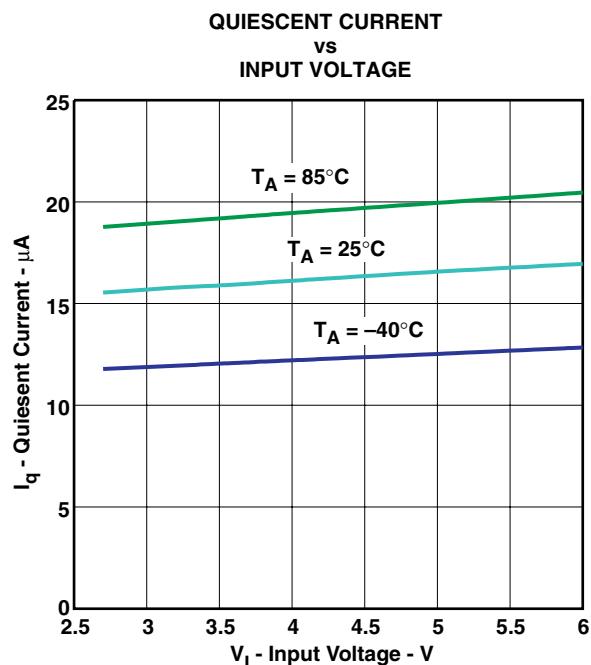

| $I_Q$ Operating quiescent current                              | $I_{OUT} = 0 mA$ , device operating in PFM mode and not device not switching |      | 18   | 25   | $\mu A$    |

| $I_{SD}$ Shutdown current                                      | $EN = GND$ , current into AVIN and PVIN                                      | 0.1  | 1    |      | $\mu A$    |

| $V_{UVLO}$ Undervoltage lockout threshold                      | Falling                                                                      | 1.73 | 1.78 | 1.83 | V          |

|                                                                | Rising                                                                       | 1.9  | 1.95 | 1.99 |            |

| <b>ENABLE, MODE</b>                                            |                                                                              |      |      |      |            |

| $V_{IH}$ High level input voltage                              | $2.7 V \leq V_{IN} \leq 6 V$                                                 | 1.0  | 6    |      | V          |

| $V_{IL}$ Low level input voltage                               | $2.7 V \leq V_{IN} \leq 6 V$                                                 | 0    | 0.4  |      | V          |

| $I_{IN}$ Input bias current                                    | Pin tied to GND or VIN                                                       |      | 0.01 | 1    | $\mu A$    |

| <b>POWER SWITCH</b>                                            |                                                                              |      |      |      |            |

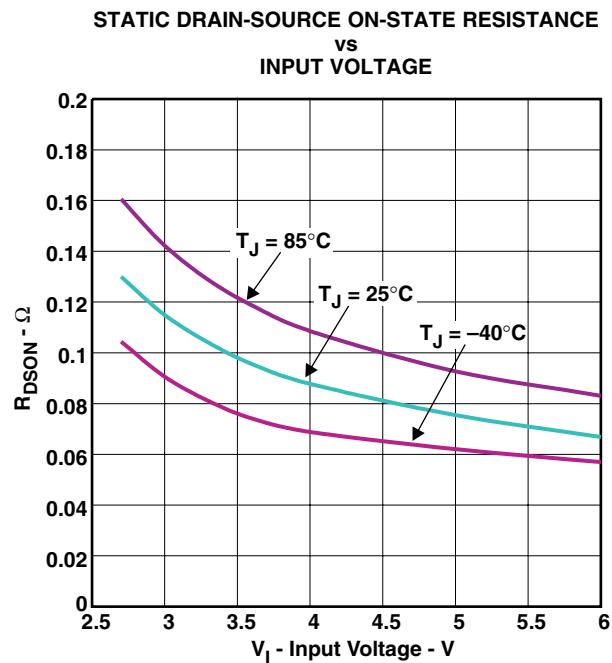

| $R_{DS(on)}$ High-side MOSFET on-resistance                    | $V_{IN} = 3.6 V^{(1)}$                                                       | 120  | 180  |      | $m\Omega$  |

|                                                                | $V_{IN} = 5.0 V^{(1)}$                                                       | 95   | 150  |      |            |

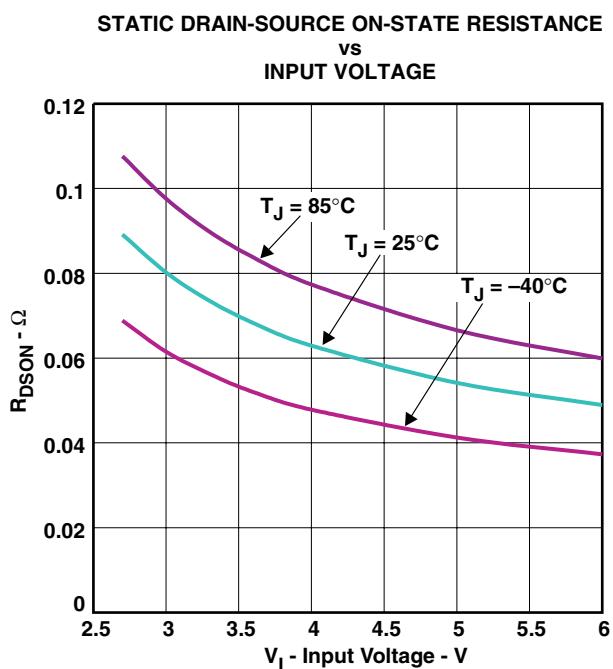

| $R_{DS(on)}$ Low-side MOSFET on-resistance                     | $V_{IN} = 3.6 V^{(1)}$                                                       | 90   | 130  |      | $m\Omega$  |

|                                                                | $V_{IN} = 5.0 V^{(1)}$                                                       | 75   | 100  |      |            |

| $I_{LIMF}$ Forward current limit MOSFET high-side and low-side | $2.7V \leq V_{IN} \leq 6 V$                                                  | 1800 | 2250 | 2700 | mA         |

| $T_{SD}$                                                       | Thermal shutdown                                                             | 150  |      |      | $^\circ C$ |

|                                                                | Thermal shutdown hysteresis                                                  | 10   |      |      |            |

| <b>OSCILLATOR</b>                                              |                                                                              |      |      |      |            |

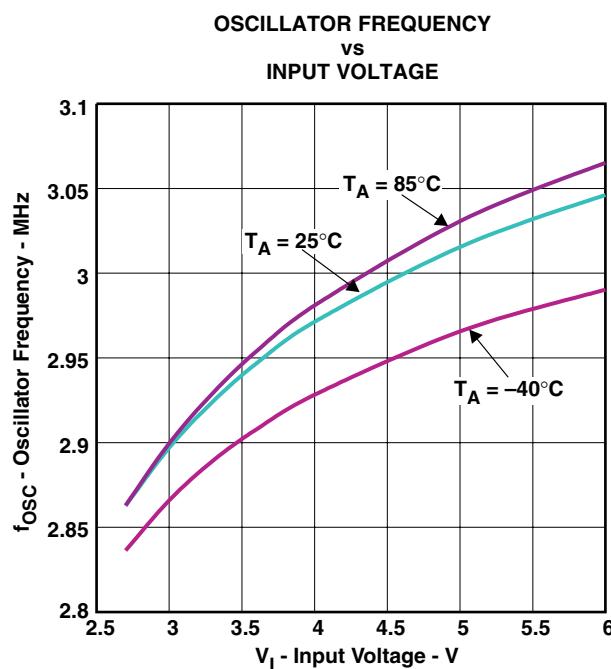

| $f_{SW}$ Oscillator frequency                                  | $2.7 V \leq V_{IN} \leq 6 V$                                                 | 2.6  | 3    | 3.4  | MHz        |

(1) 最大値は $T_J = 85^\circ C$ の時に適用されます。

## 電気的特性

Over full operating ambient temperature range, typical values are at  $T_A$  for condition  $V_{IN} = EN = 3.6V$ . External components  $C_{IN} = 10\mu F$  0603,  $C_{OUT} = 10\mu F$  0603,  $L = 1.0\mu H$ , see the parameter measurement information.

| パラメータ             |                                                   | テスト条件                                                                                  | MIN | TYP   | MAX   | 単位   |

|-------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-------|------|

| <b>OUTPUT</b>     |                                                   |                                                                                        |     |       |       |      |

| $V_{ref}$         | Reference voltage                                 |                                                                                        |     | 600   | mV    |      |

| $V_{FB(PWM)}$     | Feedback voltage PWM Mode                         | PWM operation, MODE = $V_{IN}$ ,<br>2.7 V $\leq V_{IN} \leq 6$ V, 0 mA load            |     | -1.5% | 0%    | 1.5% |

| $V_{FB(PFM)}$     | Feedback voltage PFM mode,<br>Voltage Positioning | device in PFM mode, voltage positioning active <sup>(2)</sup>                          |     | 1%    |       |      |

| $V_{FB}$          | Load regulation                                   |                                                                                        |     | -0.5  | %/A   |      |

|                   | Line regulation                                   |                                                                                        |     | 0     | %/V   |      |

| $R_{(Discharge)}$ | Internal discharge resistor                       | Activated with $EN = GND$ , 2.0V $\leq V_{IN} \leq 6$ V, 0.8 $\leq V_{OUT} \leq 3.6$ V |     | 75    | 200   | 1450 |

| $t_{START}$       | Start-up time                                     | Time from active EN to reach 95% of $V_{OUT}$                                          |     | 500   | \mu s |      |

(2) PFMモードでは内部基準電圧は標準で  $1.01 \times V_{ref}$  に設定されます。パラメータ測定情報を参照してください。

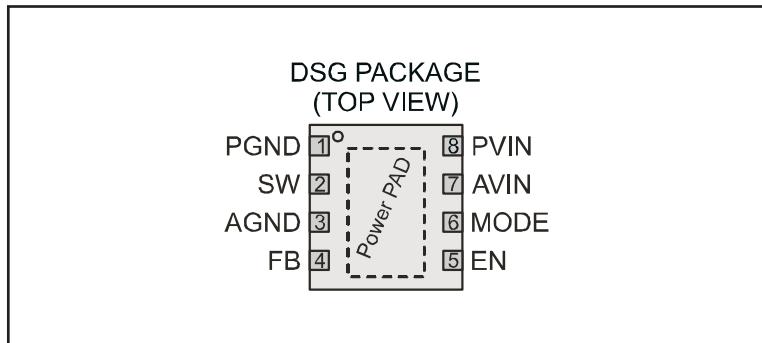

## ピン配置

## 端子機能

| TERMINAL  |                  | I/O | 説明                                                                                                                  |

|-----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.<br>SON 2x2-8 |     |                                                                                                                     |

| PGND      | 1                | PWR | 出力段の電源GNDピンです。                                                                                                      |

| SW        | 2                | OUT | スイッチ・ピンで内部MOSFETスイッチに接続しています。このピンと出力コンデンサの間に外部インダクタを接続します。                                                          |

| AGND      | 3                | IN  | 内部制御回路用のアナログGNDピンです。                                                                                                |

| FB        | 4                | IN  | 内部レギュレーション・ループ用のフィードバック・ピン。このピンに、外部の抵抗デバイダを接続します。固定出力電圧オプションの場合、このピンを出力コンデンサに直接接続します。                               |

| EN        | 5                | IN  | デバイスのイネーブル・ピンです。このピンを“Low”にすると、デバイスが強制的にシャットダウン・モードに入ります。このピンを“High”にすると、デバイスがイネーブルになります。このピンは終端する必要があります。          |

| MODE      | 6                | IN  | MODE : MODEピンを“High”にすると、デバイスは強制的に固定周波数PWMモードで動作します。MODEピンを“Low”にすると、パワーセーブ・モードが有効になり、PFMモードと固定周波数PWMモードを自動的に遷移します。 |

| AVIN      | 7                | IN  | 制御回路用アナログ電源入力。PVINと入力コンデンサに接続します。                                                                                   |

| PVIN      | 8                | PWR | 出力段の $V_{IN}$ 電源入力ピン。                                                                                               |

| Power PAD |                  |     | 高い放熱特性の為に、このパッドは基板のランドパターンにはんだ付けする必要があります。<br>このパッドは製品のGNDとして扱います。                                                  |

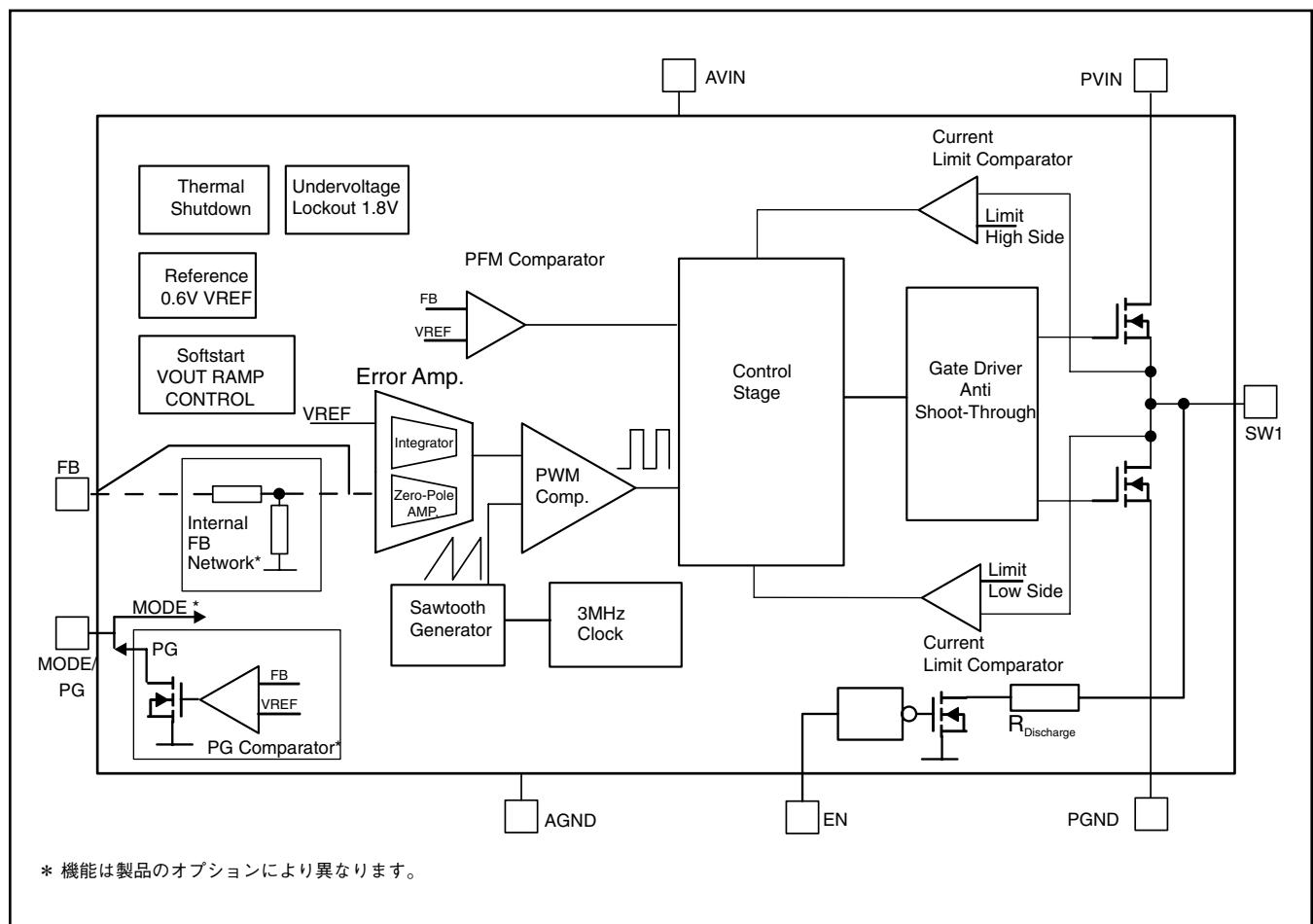

## 機能ブロック図

## パラメータ測定情報

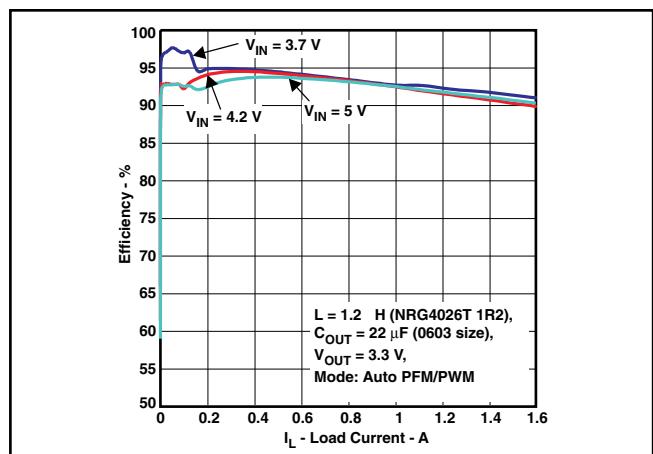

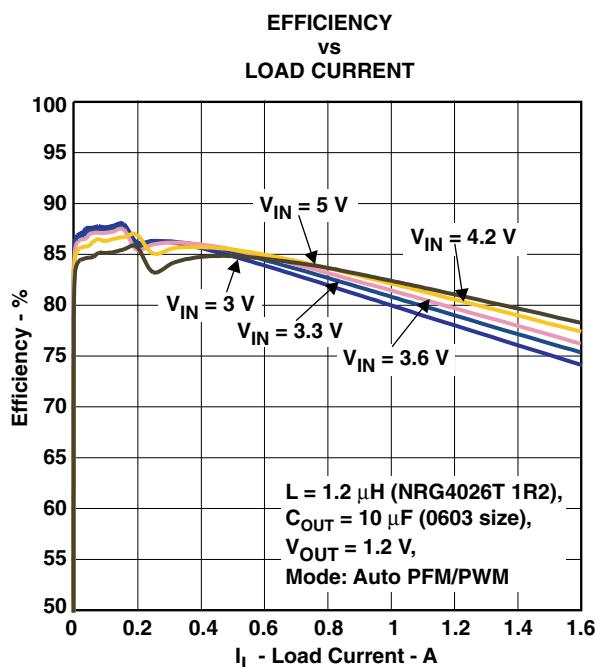

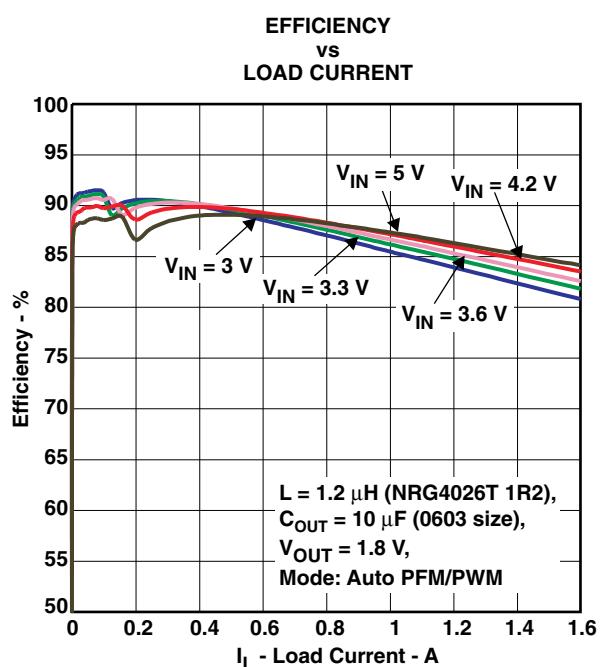

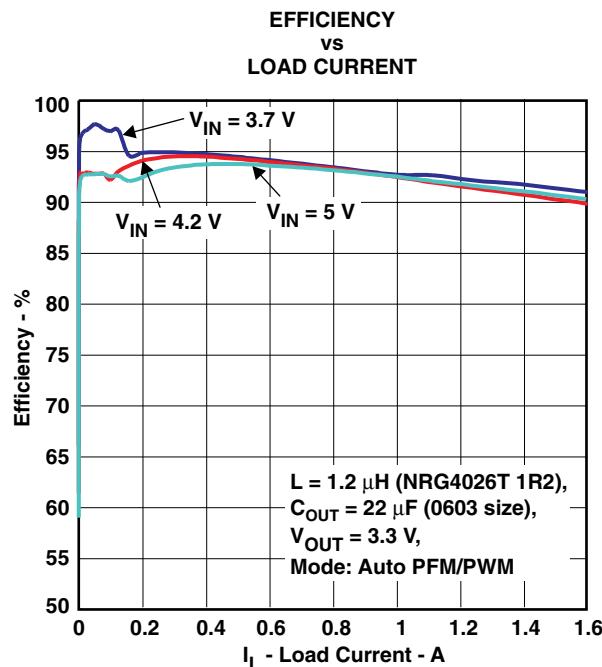

## 代表的特性

|                                         |                                                                                                          | 図    |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------|------|

| η Efficiency                            | Load Current, $V_{OUT} = 1.2$ V, Auto PFM/PWM Mode, Linear Scale                                         | 図 1  |

|                                         | Load Current, $V_{OUT} = 1.8$ V, Auto PFM/PWM Mode, Linear Scale                                         | 図 2  |

|                                         | Load Current, $V_{OUT} = 3.3$ V, PFM/PWM Mode, Linear Scale                                              | 図 3  |

|                                         | Load Current, $V_{OUT} = 1.8$ V, Auto PFM/PWM Mode vs. Forced PWM Mode, Logarithmic Scale                | 図 4  |

| Output Voltage Accuracy                 | Load Current, $V_{OUT} = 1.8$ V, Auto PFM/PWM Mode                                                       | 図 5  |

|                                         | Load Current, $V_{OUT} = 1.8$ V, Forced PWM Mode                                                         | 図 6  |

| Shutdown Current                        | Input Voltage and Ambient Temperature                                                                    | 図 7  |

| Quiescent Current                       | Input Voltage                                                                                            | 図 8  |

| Oscillator Frequency                    | Input Voltage                                                                                            | 図 9  |

| Static Drain-Source On-State Resistance | Input Voltage, Low-Side Switch                                                                           | 図 10 |

|                                         | Input Voltage, High-Side Switch                                                                          | 図 11 |

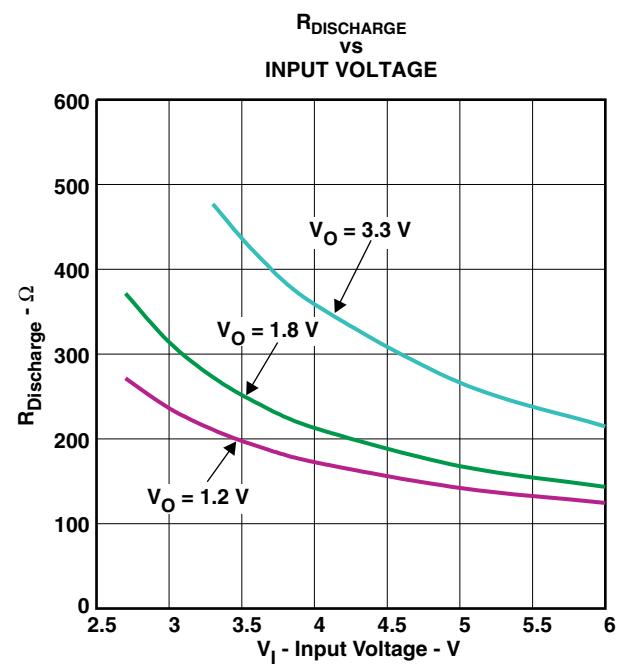

| $R_{DISCHARGE}$                         | Input Voltage vs. $V_{OUT}$                                                                              | 図 12 |

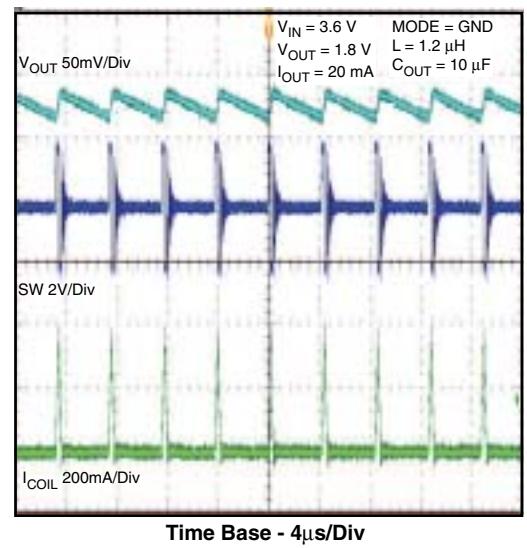

| Typical Operation                       | PWM Mode, $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V, 500 mA, $L = 1.2 \mu\text{H}$ , $C_{OUT} = 10\mu\text{F}$ | 図 13 |

|                                         | PFM Mode, $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V, 20 mA, $L = 1.2 \mu\text{H}$ , $C_{OUT} = 10\mu\text{F}$  | 図 14 |

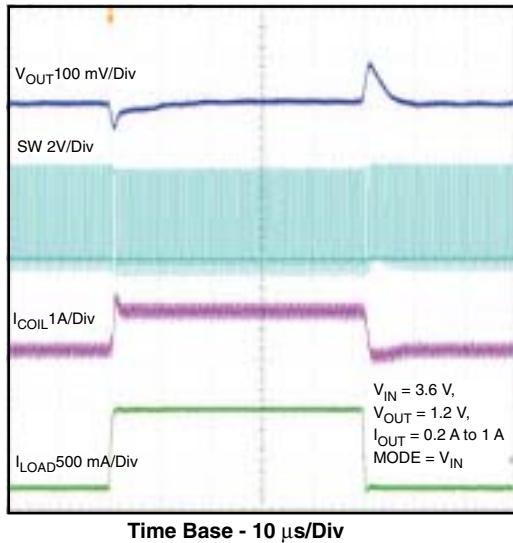

| Load Transient                          | PWM Mode, $V_{IN} = 3.6$ V, $V_{OUT} = 1.2$ V, 0.2 mA to 1 A                                             | 図 15 |

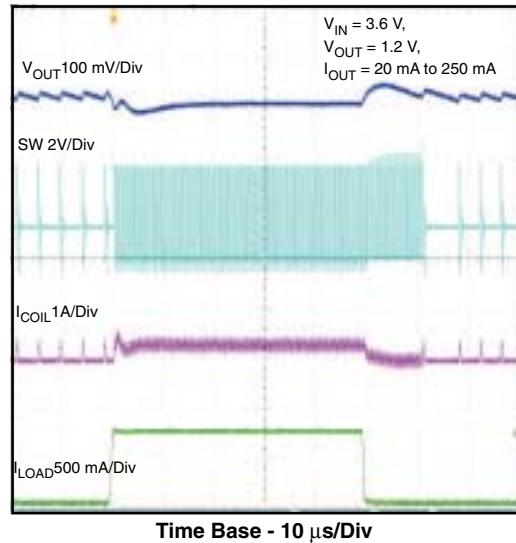

|                                         | PFM Mode, $V_{IN} = 3.6$ V, $V_{OUT} = 1.2$ V, 20 mA to 250 mA                                           | 図 16 |

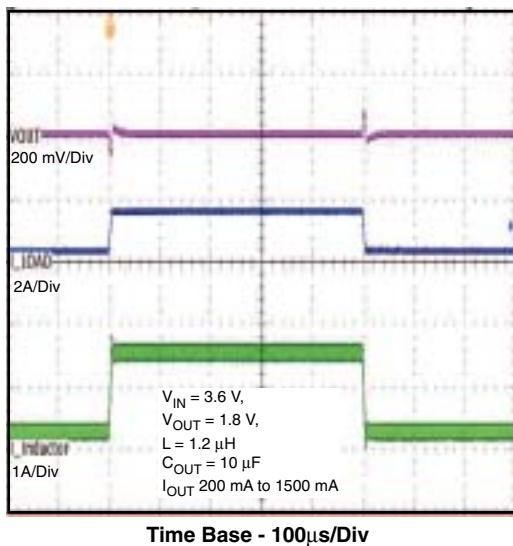

|                                         | $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V, 200 mA to 1500 mA                                                   | 図 17 |

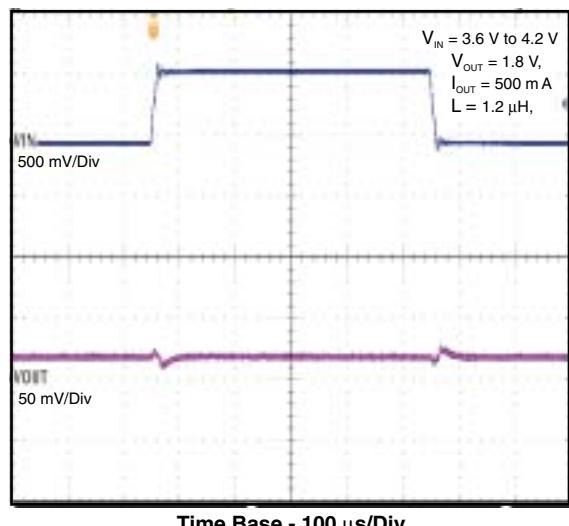

| Line Transient                          | PWM Mode, $V_{IN} = 3.6$ V to 4.2 V, $V_{OUT} = 1.8$ V, 500 mA                                           | 図 18 |

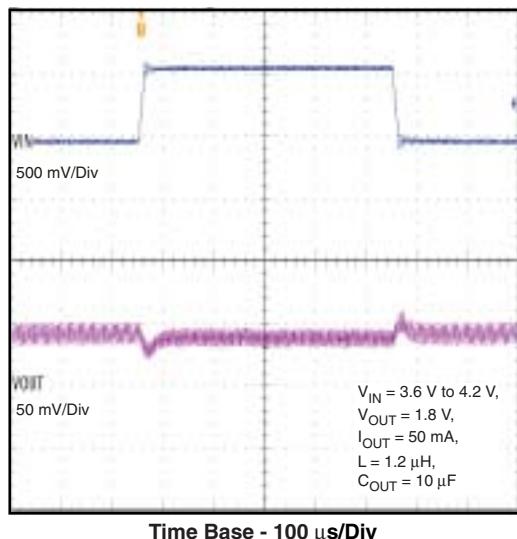

|                                         | PFM Mode, $V_{IN} = 3.6$ V to 4.2 V, $V_{OUT} = 1.8$ V, 500 mA                                           | 図 19 |

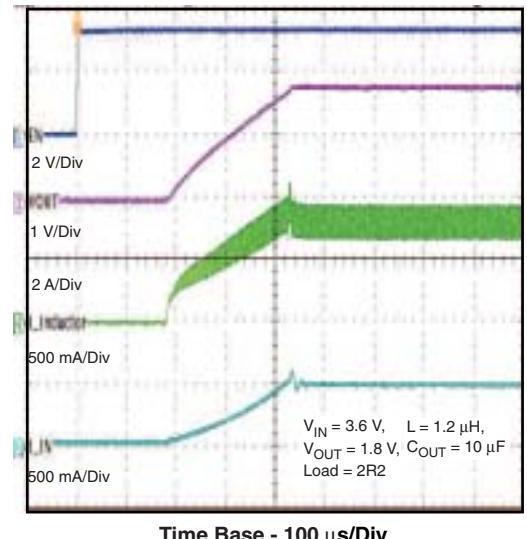

| Startup into Load                       | $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V, Load = $2.2\Omega$                                                  | 図 20 |

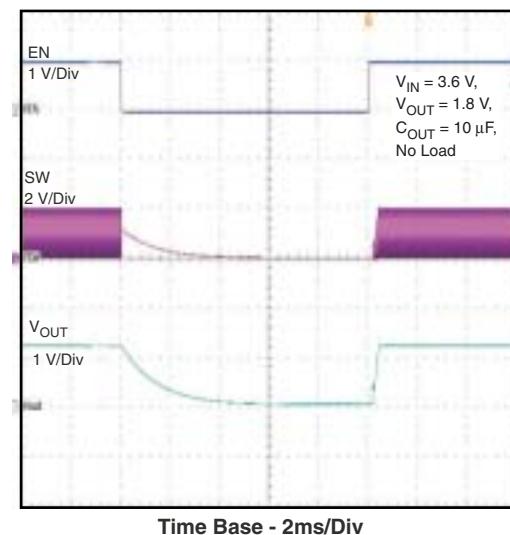

| Output Discharge                        | $V_{IN} = 3.6$ V, $V_{OUT} = 1.8$ V, No Load                                                             | 図 21 |

表 1. グラフ一覧

図 1.  $V_{OUT} = 1.2$  V, Auto PFM/PWM Mode, Linear Scale

図 2.  $V_{OUT} = 1.8$  V, Auto PFM/PWM Mode, Linear Scale

## 代表的特性

图3.  $V_{OUT} = 3.3$  V, Auto PFM/PWM Mode, Linear Scale

图4. Auto PFM/PWM Mode vs. Forced PWM Mode, Logarithmic Scale

图5. Auto PFM/PWM Mode

图6. Forced PWM Mode

## 代表的特性

図 7

図 8

図 9

図 10. Low-Side Switch

## 代表的特性

图 11. High-Side Switch

图 12

图 13. Typical Operation (PWM Mode)

图 14. Typical Operation (PFM Mode)

## 代表的特性

図 15. Load Transient Response PWM Mode 0.2A to 1A

図 16. Load Transient PFM Mode 20mA to 250mA

図 17. Load Transient Response 200mA to 1500mA

図 18. Line Transient Response PWM Mode

## 代表的特性

図 19. Line Transient PFM Mode

図 20. Startup Into Load –  $V_{OUT}$  1.8V

図 21. Output Discharge

# 詳細説明

## 動作

TPS62060降圧型コンバータは、中程度から重負荷の負荷電流では標準3MHzの固定周波数パルス幅変調(PWM)により動作します。軽負荷電流の場合は、自動的にパワーセーブ・モードになり、PFM(パルス周波数変調)モードで動作します。

PWM動作では、入力電圧フィードフォワードを持つ独自の高速応答特性の電圧モード制御方式により、入力と出力のセラミック・コンデンサが小容量の場合でも、優れたライン・レギュレーションおよびロード・レギュレーションを、実現することができます。クロック信号によって開始された各クロック・サイクルの冒頭で、ハイサイドMOSFETスイッチがオンになります。すると、入力コンデンサからの電流がハイサイドMOSFETスイッチを経由してインダクタに流れ、さらに出力コンデンサ、負荷へと流れます。このフェーズの間、PWMコンパレータがトリップして制御ロジックによりスイッチがオフになるまで、電流は上昇を続けます。ハイサイドMOSFETスイッチの電流が過電流制限値を超えた場合も、電流制限コンパレータがこのスイッチをオフにします。貫通電流を阻止するデッドタイムが経過した後、ローサイドMOSFET整流器がオンになり、インダクタ電流が下降します。この結果、インダクタからの電流は継続して出力コンデンサと負荷に流れます。この電流はローサイドMOSFET整流器を経由してインダクタに戻ります。

クロック信号により次のサイクルが開始され、再びローサイドMOSFET整流器がオフになり、ハイサイドMOSFETスイッチがオンになります。

## パワーセーブ・モード

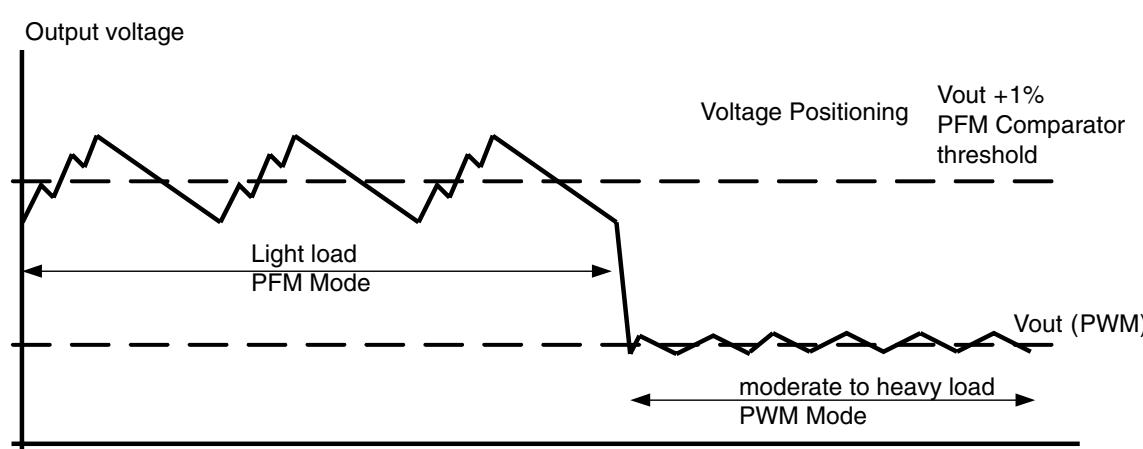

TPS62060ではパワーセーブ・モードは、MODEピンを“Low”レベルに設定することによりイネーブルになります。負荷電流が減少すると、コンバータは自動的にパワーセーブ・モード動作に移行します。パワーセーブ・モードでは、スイッチングがスキップされます。自己消費電流を最小限に抑え、高効率を維持するために、PFMモードにより低い周波数で動作します。コンバータは出力電圧を標準時の電圧より標準で1%高く設定します。このボルテージ・ポジショニングの機能により、急激

な負荷電流の増加による出力電圧のドロップを最小限に抑えることができます。

ローサイドMOSFETスイッチのインダクタ電流が0になる、つまり不連続モードになると、PWMモードからPFMモードへの移行が発生します。

パワーセーブ・モードでは、PFMコンパレータを使用して出力電圧を監視します。出力電圧がPFMコンパレータのスレッショルド電圧(公称値 $V_{OUT}$ )を下回ると、デバイスはPFMパルス電流駆動を開始します。ハイサイドMOSFETスイッチがオンになり、インダクタ電流が上昇します。オン時間が満了すると、このスイッチがオフになります。インダクタ電流が0になるまでの間、ローサイドMOSFETがオンになります。

コンバータにより、出力コンデンサおよび負荷に効率的に電流が供給されます。供給電流が負荷電流を上回ると、出力電圧が上昇します。出力電圧がPFMコンパレータ・スレッショルド以上になると、スイッチングが停止され、スリープ・モードに入ります。スリープ・モード時の自己消費電流は、標準で $18\mu A$ です。

出力電圧がPFMコンパレータ・スレッショルドよりもまだ低い場合、PFMコンパレータ・スレッショルドに到達するまで、一連のPFMパルス電流がさらに生成されます。負荷電流により出力電圧が降下してPFMコンパレータ・スレッショルドを下回ると、スイッチングが再開されます。

出力電流がPFMモードでサポートできなくなった場合、PFMモードからPWMモードに移行します。

## ダイナミック・ボルテージ・ポジショニング

この機能により軽負荷から重負荷への負荷変動、およびその逆の場合も同様に発生する、出力電圧のアンダーシュートやオーバーシュートを軽減することができます。これはパワーセーブモードにおいて出力電圧をその標準値から1%高い電圧にレギュレーションすることにより達成されています。この機能により、負荷急増による電圧低下や負荷急減による電圧上昇の両方において電圧マージンを増加させることができます。

図 22. パワーセーブ・モード動作と自動動作モード遷移

## 100%デューティ・サイクル時の低ドロップアウト動作

入力電圧が低下して公称出力電圧に近づくと、デバイスは100%デューティ・サイクル・モードへの移行を開始します。出力電圧を維持するために、1サイクルまたはそれ以上の間、ハイサイドMOSFETスイッチが100%オンの状態になります。

VINがさらに低下すると、ハイサイドMOSFETスイッチが継続したオン状態になります。この結果、コンバータでの入力電圧と出力電圧の電位差が最小となります。この機能はバッテリの全電圧範囲を最大限に活用することで最長の動作時間を実現できるため、バッテリ駆動のアプリケーションで特に有用です。

レギュレーションを維持するための最小入力電圧は負荷電流と出力電圧に依存し、次の式で計算できます。

$$V_{IN\min} = V_{O\max} + I_{O\max} \times (R_{DS(on)\max} + R_L)$$

ここで、各変数の意味は次のとおりです。

$I_{O\max}$  = 最大出力電流にインダクタのリップル電流を加算したピーク電流値

$R_{DS(on)\max}$  = ハイサイドMOSFETスイッチの最大 $R_{DS(on)}$

$R_L$  = インダクタのDC抵抗

$V_{O\max}$  = 公称出力電圧に出力電圧の最大許容差を加えた値

## 低電圧ロックアウト (UVLO)

低電圧ロックアウト回路により、入力電圧が低いときのデバイスの誤動作やバッテリの過放電を防止します。VINが低電圧ロックアウト・スレッショルド電圧 (UVLO) 以下まで低下するとコンバータの出力段をディスエーブルにします。低電圧ロックアウト・スレッショルドは、VINの立ち下がり時で標準1.78Vです。VINが上昇して製品が再起動する低電圧ロックアウト・スレッショルドは標準で1.95Vです。

## 出力コンデンサの放電

EN = GNDにすると製品はシャットダウン・モードになり、全ての内部回路はディスエーブル状態となります。出力コンデンサの電荷を放電させるために内蔵された抵抗によりSWピンはPGNDと接続されます。

## モード選択

MODEピンを使用して、固定PWMモードとパワーセーブ・モードを切り替えることができます。

このピンをGNDに接続すると、パワーセーブ・モードがイネーブルになります。PWMモードとPFMモードの間を自動的に移行するようになります。MODEピンを“High”にすると、軽負荷電流の場合でもコンバータが固定周波数PWMモードで動作するようになります。これにより、ノイズの影響を受けやすいアプリケーションでスイッチング周波数を簡単にフィルタリングできます。このモードでは、軽負荷時の効率はパワーセーブ・モードの場合よりも低くなります。

MODEピンの状態は、動作中に変更できます。コンバータの動作モードをシステムの動作状態による要件に応じて設定変更することで、効率的な電源管理が可能になります。

## イネーブル

ENピンを“High”に設定することで、デバイスがイネーブルになります。最初に内部基準電源が起動し、内部のアナログ回路が安定状態となります。その後ソフトスタートが起動し出力電圧が上昇を開始します。出力電圧は製品がイネーブルになってから $t_{START}$ で規定された標準500μs以内に設定値の95%に達します。EN入力を使用して、さまざまなDC/DCコンバータを含むシステムの電源立ち上げシーケンスを制御できます。ENピンを別のコンバータの出力に接続することで、ENピンを“High”にして、電源レールのシーケンシングを実行できます。ENピンをGNDにすると、デバイスはシャットダウン・モードに移行し、すべての回路がディスエーブルになります。SWピンは内部の抵抗によりPGNDに接続されて出力の電荷を放電します。

## ソフトスタート

TPS62060には、出力電圧の上昇を制御するソフトスタート回路が内蔵されています。入力電圧が低電圧ロックアウト電圧VUVLO以上の電圧のときにコンバータがイネーブルになると、出力電圧は通常250μsの時間をかけて公称値の5%から95%まで上昇します。

これにより、電圧上昇中にコンバータ内の突入電流が抑制され、バッテリや高い内部インピーダンスを持つ電源の使用時に発生する可能性がある入力電圧の降下を防止します。

ソフトスターの時、出力電圧が設定値の1/3に達するまでの間、電流制限値を $I_{LIMF}$ の標準値の1/3に減少させます。出力電圧がこのスレッショルドに達すると製品はその標準の電流制限値 $I_{LIMF}$ で動作します。

## 内部電流制限とフォールドバック型(フの字型)電流制限による短絡保護

通常動作時ハイサイドおよびローサイドのMOSFETスイッチは、最大電流制限 $I_{LIMF}$ により保護されます。ハイサイドMOSFETスイッチが電流制限値を超えると、ハイサイドMOSFETスイッチがオフになります。ローサイドMOSFETスイッチがオンになります。ローサイドMOSFETスイッチの電流が減少して電流制限値 $I_{LIMF}$ を下回るまで、ハイサイドMOSFETスイッチは再びオンにはなりません。本製品は内部電流制限 $I_{LIMF}$ までのインダクタピーク電流を供給することができます。

スイッチ電流制限が動作して過負荷状態あるいは負荷短絡状態により出力電圧が設定出力電圧の1/3以下まで低下すると直ちにフォールドバック電流制限に移行します。この時、スイッチの電流制限値は標準値 $I_{LIMF}$ の1/3の値となります。

この短絡保護機能は起動時にも動作するために、本製品は出力電圧が設定電圧の1/3を超えるまでの間に標準電流制限値 $I_{LIMF}$ の1/3以上の電流を供給しません。この起動条件はコンバータの出力に電流シンク型の負荷(モーターなどの負性抵抗の負荷)が接続される場合には考慮する必要があります。

## クロック・ディザリング

高周波領域でのスイッチ周波数の高調波によるノイズを低減させる為に、TPS62060ファミリー製品はクロック・ディザリング回路を内蔵しています。クロック周波数は標準で6nsのクロック・ディザが発生するようにサブクロックによりわずかに周波数変調されています。

## サーマル・シャットダウン

接合部温度 $T_J$ が150°C(標準値)を超えると、デバイスはサーマル・シャットダウン状態になります。このモードでは、ハイサイドMOSFETおよびローサイドMOSFETがオフになります。接合部温度がサーマル・シャットダウン・ヒステリシス温度を下回ると、デバイスは動作を再開します。

## アプリケーション情報

### 出力電圧設定

出力電圧は次のように計算できます。

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right)$$

ここで、内部リファレンス電圧 $V_{REF}$ は標準で0.6Vです。

帰還デバイダ回路を流れる電流を小さくするには、 $R_2$ を120kΩから360kΩの間にします。 $R_1$ と $R_2$ の合計値は、回路のノイズ耐性を維持するために、1MΩ未満にしてください。負荷過渡応答特性を最適化するために、外部フィードフォワード・コンデンサ $C_{ff}$ が必要です。より低い抵抗値を使用することも可能ですが、この場合には以下の式を使用して $C_{ff}$ の値を調整する必要があります。

フィードフォワード・ネットワークのコーナー

$$f_c = \frac{1}{2 \times \pi \times R_2 \times C_{ff}} = 35\text{kHz}$$

周波数これより、フィードフォワード・コンデンサは次の様に計算できます。

$$C_{ff} = \frac{1}{2 \times \pi \times R_2 \times 35\text{kHz}}$$

## 出力フィルタの設計(インダクタおよび出力コンデンサ)

TPS62060の内部位相補償は以下のコーナー周波数のLC出力フィルタに適合するように最適化されています。

$$f_c = \frac{1}{2 \times \pi \times \sqrt{(1\mu\text{H} \times 10\mu\text{F})}} = 50\text{kHz}$$

本製品は標準で1.0μHから1.2μHのインダクタと10μFから22μFの小型のX5RかX7Rのセラミック・コンデンサで動作します。インダクタとコンデンサのリストを参照してください。本製品は1.0μHのインダクタと10μFの出力コンデンサに最適化されています。

### インダクタの選択

インダクタの値は、リップル電流に直接影響します。選択するインダクタは、DC抵抗と飽和電流の定格を満たしている必要があります。インダクタのリップル電流( $\Delta I_L$ )は、インダクタンスが高いほど小さくなり、入力電圧が高いほど大きくなります。

式(1)では、静的な負荷条件でのPWMモードの最大インダクタ電流を計算します。インダクタの飽和電流は、式(2)で計算される最大インダクタ電流よりも大きく設定する必要があります。これは、大きな負荷過渡応答の際にはインダクタ電流がこの計算値を上回るためです。

$$\Delta I_L = V_{out} \times \frac{1 - \frac{V_{out}}{V_{in}}}{L \times f} \quad (1)$$

$$I_{Lmax} = I_{outmax} + \frac{\Delta I_L}{2} \quad (2)$$

ここで、各変数の意味は次のとおりです。

$f$ =スイッチング周波数(標準2.25MHz)

$L$ =インダクタの値

$\Delta I_L$ =ピーク・ツー・ピークのインダクタ・リップル電流

$I_{Lmax}$ =最大インダクタ

電流さらに用心深い手法では、コンバータの最大スイッチ電流制限に基づいてのみ、インダクタの電流定格を選択します。

より大きなリップル電流が許容できるならより小さなインダ

図 23. TPS62060可変出力電圧1.8V設定

クタン値を選択できます、しかしこの結果より大きな出力リップル電圧とより大きなコア損失が発生し、出力可能な最大電流能力も減少します。

コイルで発生する総損失は、DC/DCコンバータの効率に大きく影響します。総損失は直流抵抗 $R_{(DC)}$ による抵抗損と、次に示す周波数に依存する要素によって構成されます。

- コア材料での損失(特に高スイッチング周波数で生じる、磁気ヒステリシス損)

- 表皮効果による導体内で追加される損失(高周波数での電流偏移)

- 近接する巻線間での磁界損失(近接効果)

- 放射損失

| DIMENSIONS [mm <sup>3</sup> ] | INDUCTANCE μH | INDUCTOR TYPE         | SUPPLIER    |

|-------------------------------|---------------|-----------------------|-------------|

| 3.2 x 2.5 x 1.2 max           | 1.0           | MIPSAZ3225D           | FDK         |

| 3.2 x 2.5 x 1.0 max           | 1.0           | LQM32PN (MLCC)        | Murata      |

| 3.7 x 4 x 1.8 max             | 1.0           | LQH44 (wire wound)    | Murata      |

| 4.0 x 4.0 x 2.6 max           | 1.2           | NRG4026T (wire wound) | Taiyo Yuden |

| 3.5 x 3.7 x 1.8 max           | 1.2           | DE3518(wire wound)    | TOKO        |

表2. インダクタ一覧

## 出力コンデンサの選択

TPS62060は最先端の高速応答電圧モード制御方式を使用しているため、小容量のセラミック・コンデンサを使用することができます。低ESR値のセラミック・コンデンサは出力電圧リップルが最小となるため、これを推奨します。出力コンデンサには、X7RまたはX5R型の誘電体が必須となります。Y5VおよびZ5U型の誘電体のコンデンサは、温度によって容量が大幅に変動(減少)するだけでなく、高い周波数での抵抗成分が大きくなりますので使用しないで下さい。殆どのアプリケーションでは標準で10μFから22μFのコンデンサが最適です。サイズの小さなセラミック・コンデンサではDCバイアス特性により実効容量が減少します。この為に、2V以上の出力電圧の場合は22μFのコンデンサを使用します。コンデンサのリストを参照してください。

DC/DCコンバータの出力に接続された負荷のシステムが追加のセラミック・コンデンサを持っている場合、推奨される実効容量範囲を超えない値となる様に出力容量 $C_{OUT}$ を減少させる必要があります。この場合後述するループ安定性の検証が必要となります。

公称負荷電流では、デバイスはPWMモードで動作し、RMSリップル電流は次の式(3)で計算されます。

$$I_{RMSOut} = V_{out} \times \frac{1 - \frac{V_{out}}{V_{in}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}} \quad (3)$$

## 入力コンデンサの選択

原理的にバック・コンバータに入力される電流はパルス電流となります。そのため、入力電圧を最適にフィルタリングして高い入力電圧スパイクによって他の回路に干渉する可能性を減らすには、低ESRの入力コンデンサが必要となります。ほとんどのアプリケーションでは、10μFのセラミック・コンデンサをお勧めします。入力電圧を最適にフィルタリングするために、入力コンデンサの容量は無制限に増やすことができます。

小容量のセラミック入力コンデンサのみを使用する場合には注意が必要です。入力にセラミック・コンデンサを使用している場合に、長いワイヤを通して(ACアダプタなどから)電源を供給すると、出力での負荷のステップ変動や入力での電源電圧のステップ変動により $V_{IN}$ ピンでリンギングが生じる可能性があります。このリンギングは出力に誘導される場合があり、ループ不安定性と誤解されたり、最大定格を超えて部品に損傷を与えることもあります。

| CAPACITANCE | TYPE            | SIZE [mm <sup>3</sup> ] | SUPPLIER |

|-------------|-----------------|-------------------------|----------|

| 10μF        | GRM188R60J106M  | 0603: 1.6 x 0.8 x 0.8   | Murata   |

| 22μF        | GRM188R60G226M  | 0603: 1.6 x 0.8 x 0.8   | Murata   |

| 22μF        | CL10A226MQ8NRNC | 0603: 1.6 x 0.8 x 0.8   | Samsung  |

| 10μF        | CL10A106MQ8NRNC | 0603: 1.6 x 0.8 x 0.8   | Samsung  |

表3. コンデンサー一覧

## ループ安定性の確認

回路と安定性の評価の第一歩は定常動作時の以下の信号波形の状態の観測からです。

- スイッチングノード: SW

- インダクタ電流:  $I_L$

- 出力リップル電圧:  $V_{OUT(AC)}$

これらは、スイッチングコンバータを評価するとき、測定する必要がある基本信号です。

スイッチング波形が大きなジッタを持っている場合、出力電圧やインダクタ電流が発振状態になっている場合は制御ループが不安定になっている可能性があります。これは基板レイアウトの問題や間違ったLCフィルタ部品の組み合わせの結果としてたびたび発生します。制御ループの評価の次のステップは負荷過渡応答のテストです。アプリケーションでの負荷過渡の発生からPチャネルMOSFETがONするまでの遅延時間の間、出力コンデンサは負荷で必要とされる電流を供給する必要があります。負荷変動により $V_{OUT}$ は直ちに $\Delta I_{(LOAD)} \times ESR$ の電圧シフトが発生します。ESRは $C_{OUT}$ の等価直列抵抗です。 $\Delta I_{(LOAD)}$ は出力コンデンサ $C_0$ の充電あるいは放電を開始し、 $V_{OUT}$ を設定値まで回復させる為の電圧エラー帰還信号を生成します。製品が中負荷から高負荷電流のPWMモードで動作している時がもっとも簡単に動作状態を理解することができます。

この電圧回復時間の間、 $V_{OUT}$ の応答時間、オーバーシュートやリンギングを観測することにより、コンバータの安定性を評価するのに役立ちます。リンギングの発生が全く無ければ通常45°以上の位相余裕があります。

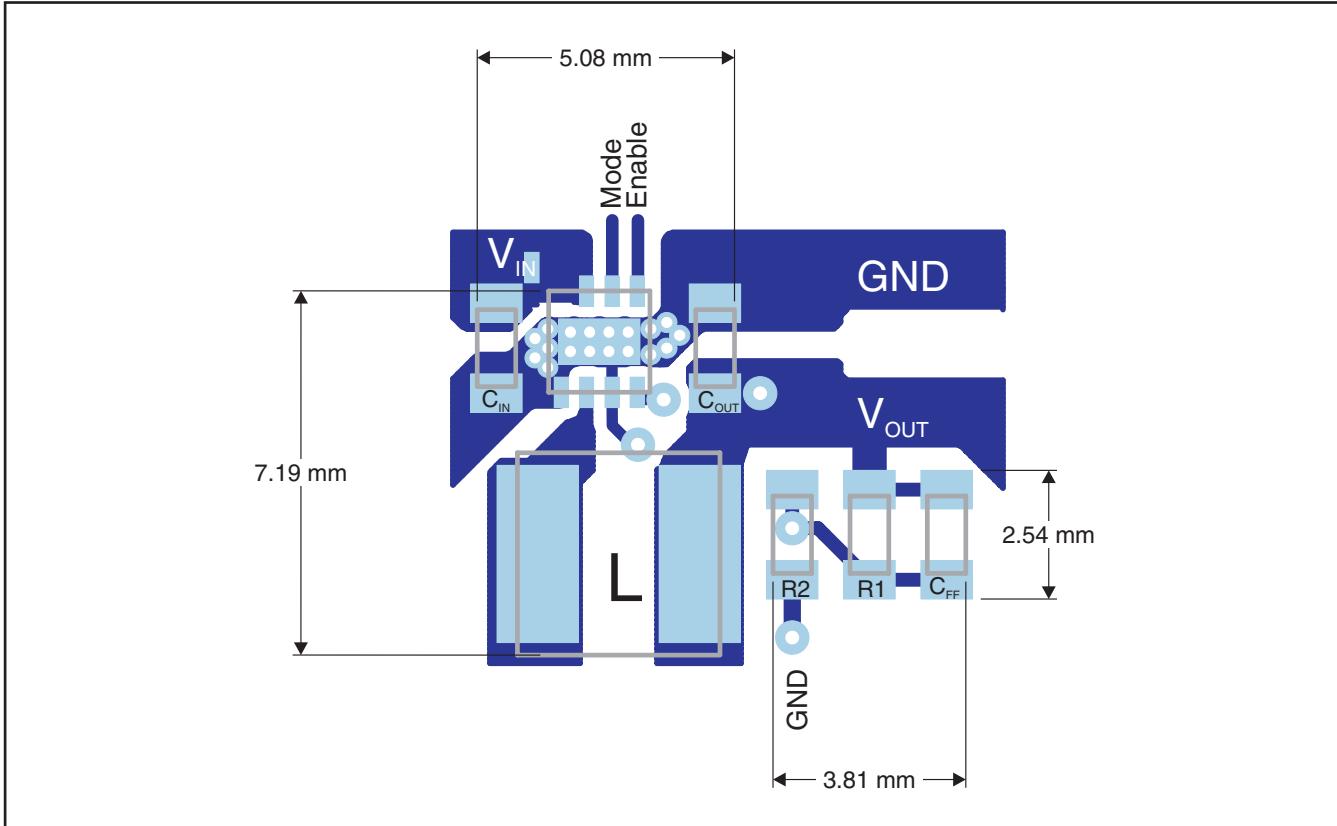

## レイアウトについての考察

図 24. 基板レイアウト

すべてのスイッチング電源において、レイアウトは設計での重要なステップとなります。デバイスが適切に機能するように、PCBレイアウトに注意を払う必要があります。仕様に規定された特性を得るには、基板のレイアウトを注意して行ってください。レイアウトに注意しなければ、ラインや負荷のレギュレーションがうまくいかない場合や、安定性の問題やEMIの問題が生じる場合もあります。低インダクタンス、低インピーダンスのグランド・パスを使用することが重要です。そのため、メインの電流パスには幅広く短い配線パターンを使用してください。入力コンデンサはインダクタや出力コンデンサと同様にICのピンから最短距離で配置しなければなりません。

デバイスのGNDピンを基板のPowerPAD™部に接続し、このパッドを一点アースの基準点として使用します。グランド・ノイズの影響を小さくするために、電源GNDノードは共通で使用し、別のノードを信号GNDとして使用します。FBの抵抗分圧回路は出力コンデンサに接続する必要があります。FB回路の配線はノイズの発生源となるような部品や配線(例えばSWの配線)を避けるようにレイアウトします。

本コンバータのパッケージは非常に小さく、電源全体を小さく作れるためにPCBでのレイアウトによる熱設計は非常に重要です。優れた放熱能力を確保するには4層以上の多層基板を使用することを推奨します。ICのPowerPADは適切な熱結合を確保する為に必ず基板のパワーパッド領域にはんだ付けする必要があります。優れた熱特性を得る為に基板のパワーパッド領域は内層のGNDプレーンと充分な数のビアで結合しておく必要があります。評価キットの説明書を参照してください。

# パッケージ情報

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins Qty | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL            | Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|----------|-------------|-------------------------|------------------|----------------|--------------------------|

| TPS62060DSGR     | ACTIVE                | WSON         | DSG             | 8        | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

| TPS62060DSGT     | ACTIVE                | WSON         | DSG             | 8        | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

(1) マーケティング・ステータスは次のように定義されています。

**ACTIVE** : 製品デバイスが新規設計用に推奨されています。

**LIFEBUY** : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

**NRND** : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

**PREVIEW** : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

**OBSOLETE** : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

**TBD** : Pb-Free/Green変換プランが策定されていません。

**Pb-Free (RoHS)** : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

**Pb-Free (RoHS Exempt)** : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS)と考えられます。

**Green (RoHS & no Sb/Br)** : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項** : このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパートの購入価格の合計金額を超える責任は負いかねます。

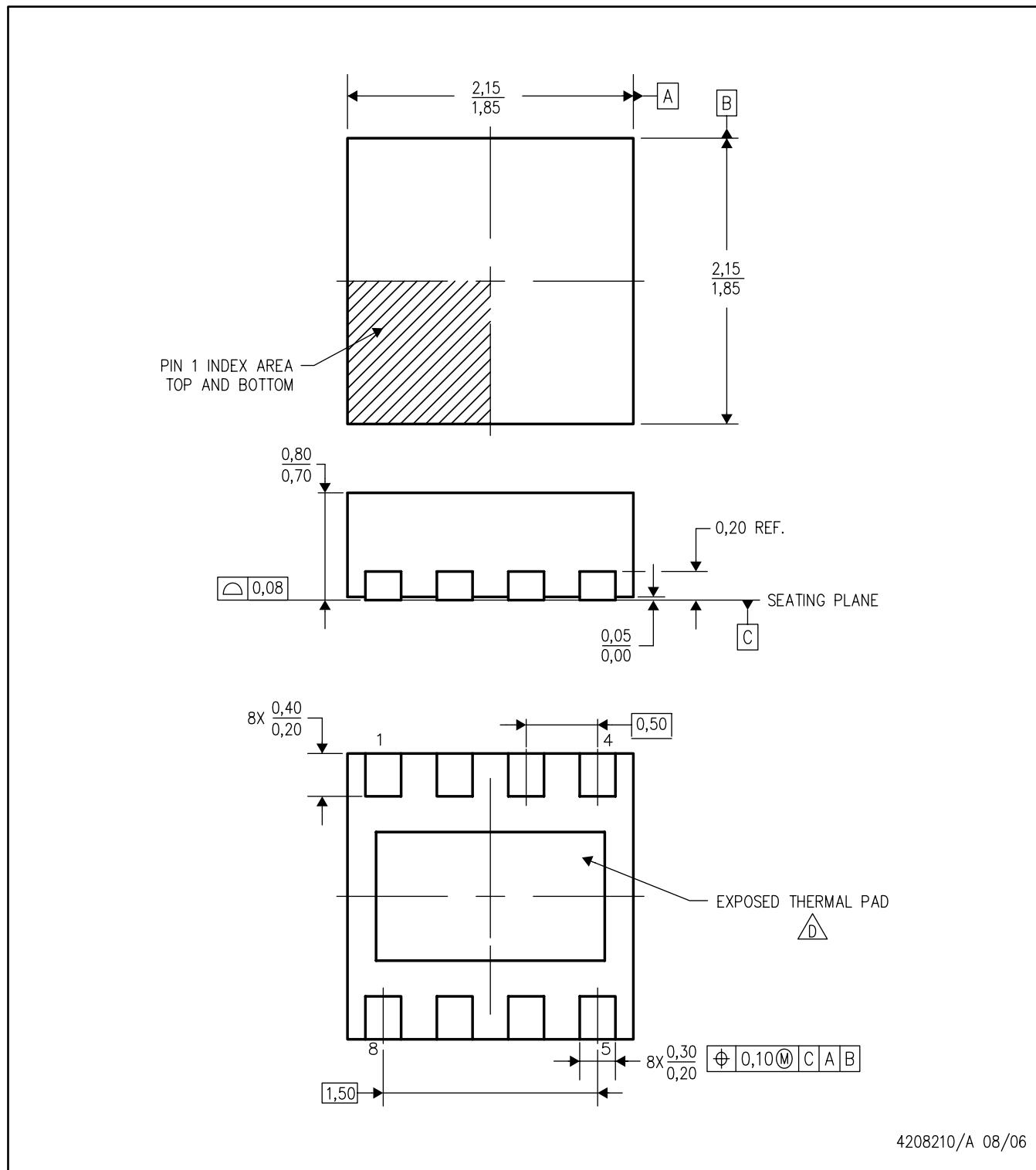

# メカニカル・データ

DSG (S-PDSO-N8)

PLASTIC SMALL OUTLINE

4208210/A 08/06

注：A. 直線寸法はすべてミリメートル単位です。寸法および許容誤差は、ASME Y14.5M-1994によります。

B. 本図は予告なしに変更することがあります。

C. QFN(クアド・フラットパック・ノーリード)パッケージ構造。

△パッケージのサーマルパッドは、熱的および機械的特性を得るために基板に半田付けする必要があります。

露出サーマルパッドの寸法に関する詳細は、製品データシートをご覧ください。

E. JEDEC MO-229に準拠します。

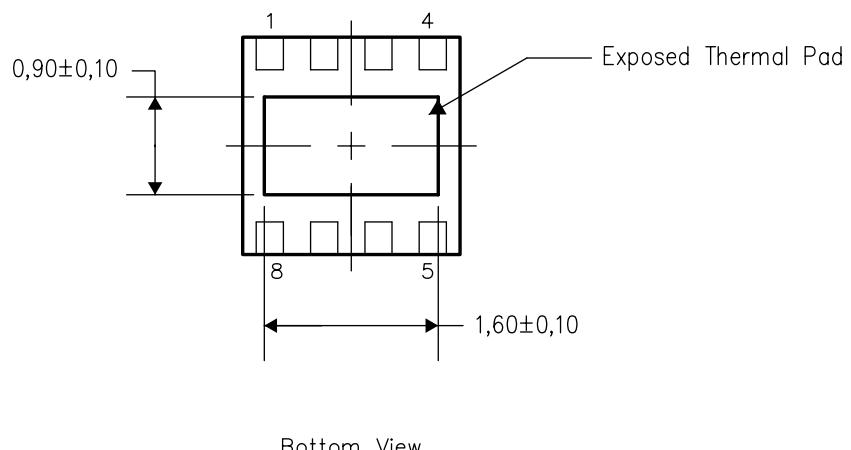

# サーマルパッド・メカニカル・データ

DSG (S-PDSO-N8)

## 熱的特性に関する資料

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板(PCB)に直接はんだ付けされなければなりません。はんだ付けされることにより、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはグランドまたは電源プレーン(どちらか当てはまる方)、またはもう1つの方法としてPCBに設計された特別なヒートシンク構造に直接接続することができます。この設計により、集積回路(IC)からの熱の移動が最適化されます。

クワッド・フラットパック・ノーリード(QFN)パッケージとその利点についての情報はアプリケーション・レポート“Quad Flatpack No-Lead Logic Packages” TI文献番号SCBA017を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージのサーマル・パッドの寸法は以下の図に示されています。

注：全ての線寸法の単位はミリメートルです。

サーマル・パッド寸法図

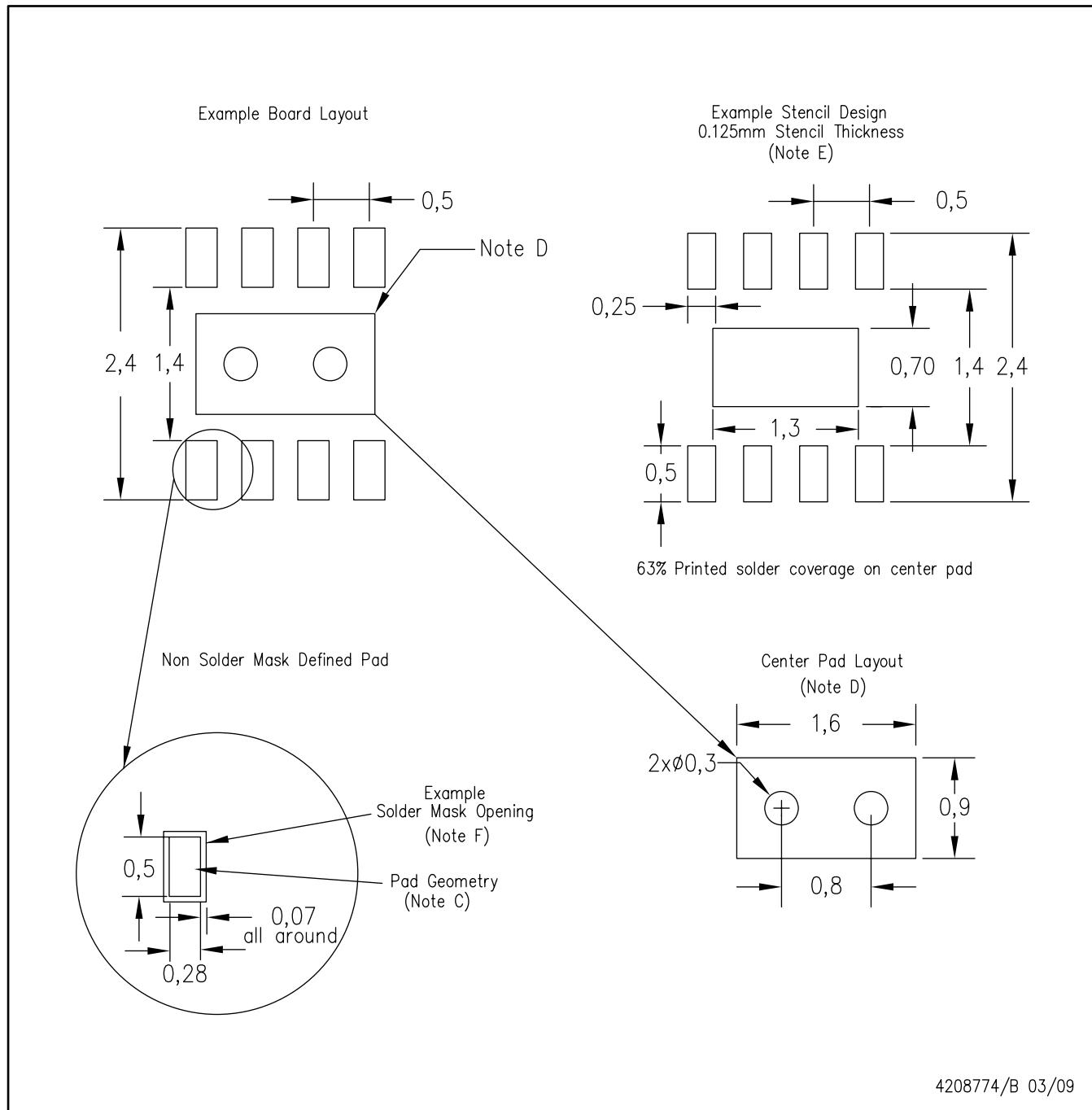

# ランド・パターン

DSG (S-PWSON-N10) Minimized Design

- 注： A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLUA271)を参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

F. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

(SLVSA95)

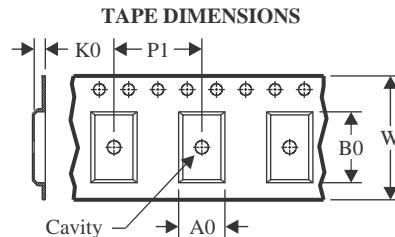

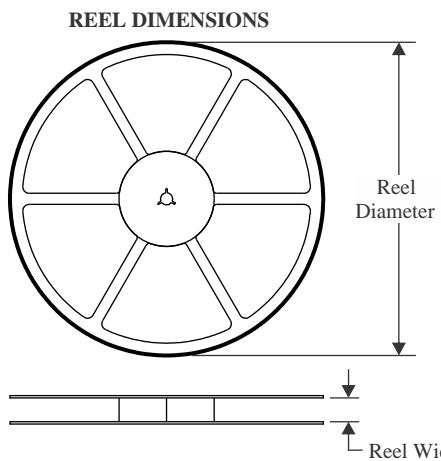

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

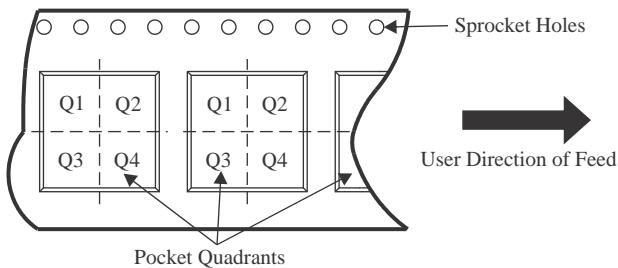

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS62060DSGR   | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS62060DSGR   | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS62060DSGRG4 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS62060DSGT   | WSON         | DSG             | 8    | 250  | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TPS62060DSGT   | WSON         | DSG             | 8    | 250  | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

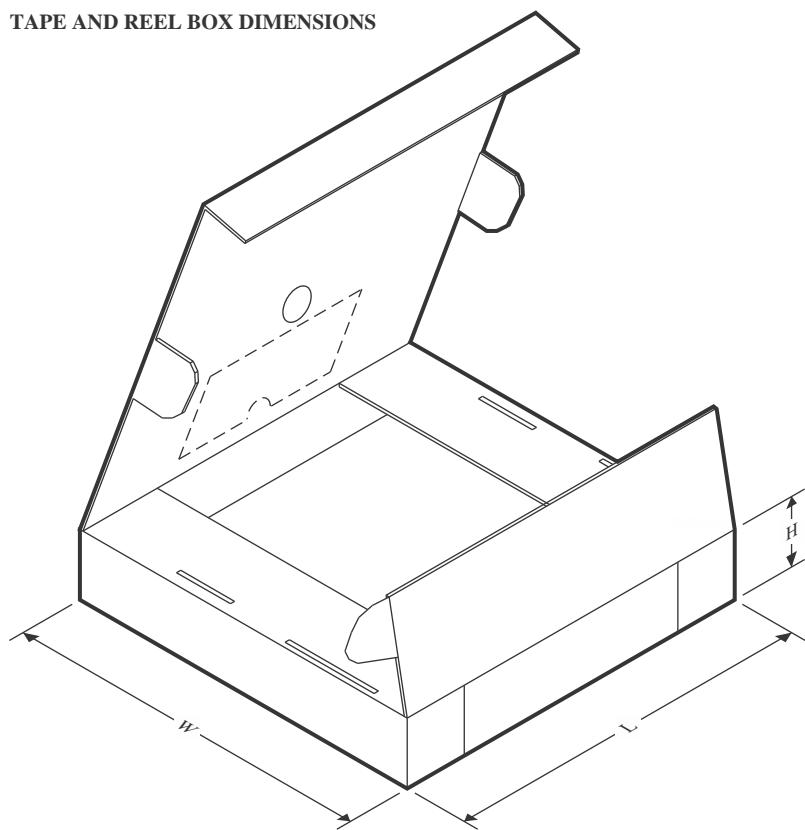

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS62060DSGR   | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62060DSGR   | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62060DSGRG4 | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62060DSGT   | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62060DSGT   | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月