# TPS56C215 3.8V ~ 17V 入力、12A、同期整流型降圧 SWIFT™ コンバータ

## 1 特長

- 7.8mΩ および 3.2mΩ の MOSFET を内蔵

- 12A の連続  $I_{OUT}$  をサポート

- 外部 5.0V バイアスなしで 4.5V のスタートアップ

- 温度範囲全体にわたって ±1% 精度の 0.6V 基準電圧

- 出力電圧範囲: 0.6V ~ 5.5V

- セラミック出力コンデンサに対応

- D-CAP3™ 制御モードによる高速過渡応答

- 厳しい出力電圧リップルに対する強制連続導通モード(FCCM)、または、軽負荷時に効率を向上する自動スキップ Eco-mode のいずれかを選択可能

- $F_{SW}$  として 400kHz、800kHz、1.2MHz を選択可能

- プリバイアス出力への単調スタートアップ

- 2 つの調整可能な電流制限設定、ヒップ再起動機能付き

- 外部 5V バイアスによる効率向上 (オプション)

- 可変ソフトスタート、デフォルトのソフトスタート時間は 1ms

- 動作時接合部温度: -40°C ~ 150°C

- 小型 3.5mm × 3.5mm HotRod™ QFN パッケージ

- 8A TPS56215 とピン互換

- WEBENCH® Power Designer により、TPS56C215 を使用するカスタム設計を作成

## 2 アプリケーション

- サーバー、クラウド・コンピューティング、ストレージ

- テレコムおよびネットワーキング、ポイント・オブ・ロード (POL)

- IPC、ファクトリ・オートメーション、PLC、テスト測定

- ハイエンド DTV

## 3 説明

TPS56C215 は、適応型オン時間 D-CAP3 制御モードを備えた小型でモノリシックな 12A 同期整流降圧コンバータです。このデバイスは、低  $R_{DS(on)}$  のパワー MOSFET を内蔵して高効率を実現し、外付け部品数が最小になるため、スペースの制約が厳しい電力システムでも使いやすくなっています。競争力の高い機能として、非常に正確な基準電圧、高速な負荷過渡応答、自動スキップ モードの動作による軽負荷時の高効率、可変の電流制限、外部補償が不要なことが挙げられます。強制連続導通モードにより、高性能 DSP や FPGA に求められる厳しい電圧レギュレーション精度要件を満たすことができます。TPS56C215 は放熱特性の優れた 18 ピン HotRod QFN パッケージで供給され、-40°C ~ 150°C の接合部温度で動作するよう設計されています。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| TPS56C215 | RNN (VQFN-HR, 18)    | 3.5mm × 3.5mm            |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は標準値であり、該当する場合はビンを含みます。

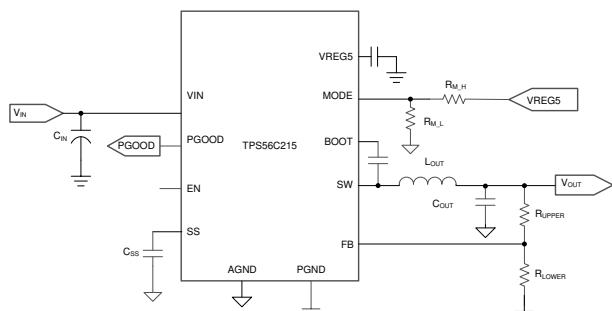

代表的なアプリケーション

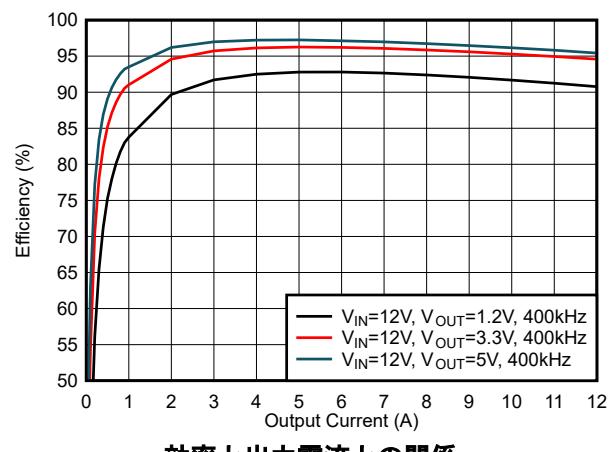

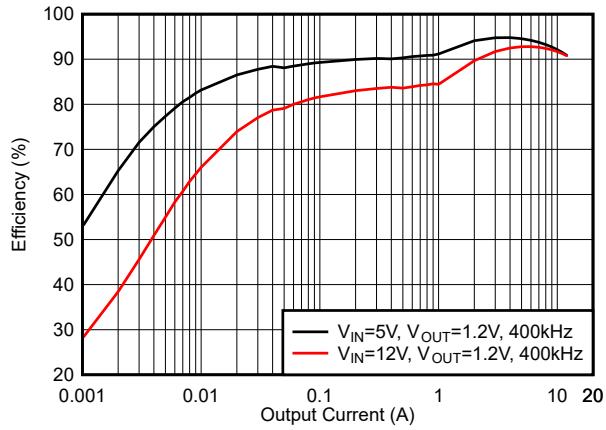

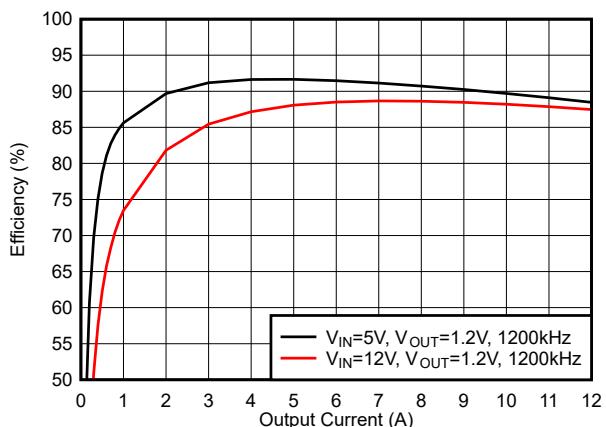

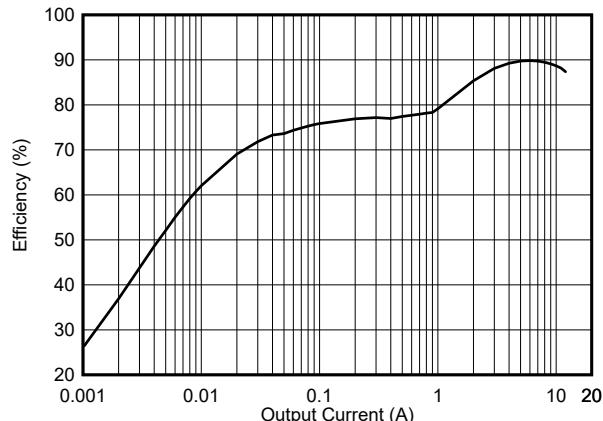

効率と出力電流との関係

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                             |    |

|------------------|----|-----------------------------|----|

| 1 特長.....        | 1  | 6.4 デバイスの機能モード.....         | 20 |

| 2 アプリケーション.....  | 1  | 7 アプリケーションと実装.....          | 21 |

| 3 説明.....        | 1  | 7.1 アプリケーション情報.....         | 21 |

| 4 ピン構成および機能..... | 3  | 7.2 代表的なアプリケーション.....       | 21 |

| 5 仕様.....        | 4  | 7.3 電源に関する推奨事項.....         | 25 |

| 5.1 絶対最大定格.....  | 4  | 7.4 レイアウト.....              | 25 |

| 5.2 ESD 定格.....  | 4  | 8 デバイスおよびドキュメントのサポート.....   | 29 |

| 5.3 推奨動作条件.....  | 4  | 8.1 デバイス サポート.....          | 29 |

| 5.4 熱に関する情報..... | 5  | 8.2 ドキュメントの更新通知を受け取る方法..... | 30 |

| 5.5 電気的特性.....   | 5  | 8.3 サポート・リソース.....          | 30 |

| 5.6 タイミング要件..... | 6  | 8.4 商標.....                 | 30 |

| 5.7 代表的特性.....   | 7  | 8.5 静電気放電に関する注意事項.....      | 30 |

| 6 詳細説明.....      | 13 | 8.6 用語集.....                | 30 |

| 6.1 概要.....      | 13 | 9 改訂履歴.....                 | 31 |

| 6.2 機能ブロック図..... | 14 | 10 メカニカル、パッケージ、および注文情報..... | 32 |

| 6.3 機能説明.....    | 14 | 10.1 パッケージ マーキング.....       | 32 |

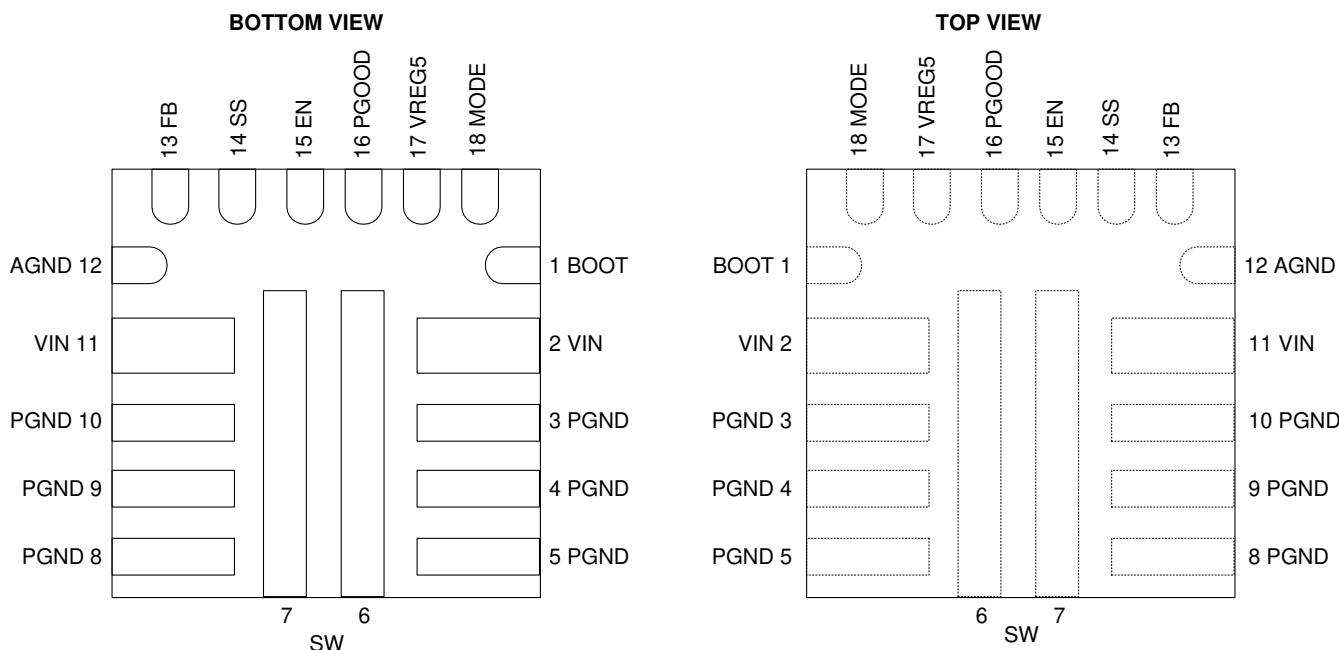

## 4 ピン構成および機能

図 4-1. RNN パッケージ、18 ピン VQFN

表 4-1. ピンの機能

| ピン    |              | タイプ <sup>(1)</sup> | 説明                                                                                                           |

|-------|--------------|--------------------|--------------------------------------------------------------------------------------------------------------|

| 名称    | 番号           |                    |                                                                                                              |

| BOOT  | 1            | I                  | ハイサイド MOSFET のゲート駆動電圧用電源入力です。BOOT と SW の間にブートストラップ コンデンサを接続します。                                              |

| VIN   | 2.11         | P                  | 制御回路の入力電源ピン。VIN と PGND の間に入力デカッピング コンデンサを接続します。                                                              |

| PGND  | 3、4、5、8、9、10 | G                  | コントローラ回路および内部回路用のパワー GND 端子です。短い配線で AGND に接続します。                                                             |

| SW    | 6、7          | O                  | スイッチ ノード端子です。出力インダクタをこのピンに接続します。                                                                             |

| AGND  | 12           | G                  | 内部アナログ回路のグラウンド。AGND を PGND プレーンに短い配線で接続します。                                                                  |

| FB    | 13           | I                  | コンバータの帰還入力。出力電圧と AGND 間の分圧抵抗回路の中点に接続します。                                                                     |

| SS    | 14           | O                  | ソフトスタート時間選択ピン。外付けコンデンサを接続するとソフトスタート時間が設定され、外部コンデンサを接続しない場合は、1ms でコンバータが起動します。                                |

| EN    | 15           | I                  | イネーブル入力制御ピンを開放状態になるとコンバータが有効化されます。このピンは、VIN と EN の間にある分圧抵抗の中点に接続することで、入力 UVLO の調整にも使用できます。                   |

| PGOOD | 16           | O                  | オープンドレインのパワー グッド インジケータであり、出力電圧が PGOOD スレッショルドを外れた場合、過電圧、デバイスがサーマルシャットダウン、EN シャットダウン、またはソフトスタート中は Low になります。 |

| VREG5 | 17           | I/O                | 4.7V 内部 LDO 出力であり、5V 外部入力で駆動することができます。このピンは、内部回路およびゲートドライバに電圧を供給します。4.7μF コンデンサを使用して、このピンをバイパスしてください。        |

| モード   | 18           | I                  | スイッチング周波数、電流制限選択、軽負荷動作モードの選択用のピンです。このピンは VREG5 と AGND 間の分圧抵抗に接続し、表 6-3 に示す各種モードオプションを選択します。                  |

(1) I = 入力、P = 電源、G = グランド、O = 出力

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|          |                                 | 最小値  | 最大値  | 単位 |

|----------|---------------------------------|------|------|----|

| 入力電圧     | V <sub>IN</sub>                 | -0.3 | 20   | V  |

|          | SW                              | -2   | 19   |    |

|          | SW (10ns 過渡)                    | -5   | 25   |    |

|          | V <sub>IN</sub> -SW             |      | 22   |    |

|          | V <sub>IN</sub> -SW (10ns 過渡応答) |      | 25   |    |

|          | EN                              | -0.3 | 6.5  |    |

|          | BOOT-SW                         | -0.3 | 6.5  |    |

|          | BOOT-SW (10ns 過渡応答)             | -0.3 | 7.5  |    |

|          | BOOT                            | -0.3 | 25.5 |    |

|          | SS、MODE、FB                      | -0.3 | 6.5  |    |

| 出力電圧     | VREG5                           | -0.3 | 6    | V  |

|          | PGOOD                           | -0.3 | 6.5  |    |

|          | I <sub>OUT</sub>                |      | 14   |    |

| 動作時接合部温度 | T <sub>J</sub>                  | -40  | 150  | °C |

| 保存温度     | T <sub>stg</sub>                | -55  | 150  | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、「推奨動作条件」に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 105°C 接合部温度での 100k パワーオン時間という TI の信頼性要件を満たすため、100% デューティ動作下で出力電流が連続して 14A を超えないようにし、半田付けのエレクトロマイグレーション故障を防ぐ必要があります。連続出力電流が 14A 未満であれば、より高い接合部温度や、より長いパワーオン時間を実現できます。

### 5.2 ESD 定格

|                         |                                                         | 値     | 単位 |

|-------------------------|---------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

|                         | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±500  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|          |                   | 最小値  | 公称値  | 最大値  | 単位 |

|----------|-------------------|------|------|------|----|

| 入力電圧     | V <sub>IN</sub>   | 3.8  | 17   | 17   | V  |

|          | SW                | -1.8 | 17   | 17   | V  |

|          | BOOT              | -0.1 | 23.5 | 23.5 | V  |

|          | VREG5             | -0.1 | 5.2  | 5.2  | V  |

| 出力電流     | I <sub>LOAD</sub> | 0    | 12   | 12   | A  |

| 動作時接合部温度 | T <sub>J</sub>    | -40  | 150  | 150  | °C |

## 5.4 热に関する情報

|                             | 热評価基準 <sup>(1)</sup> | RNN (VQFN-HR) | 単位   |

|-----------------------------|----------------------|---------------|------|

|                             |                      | 18 ピン         |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗         | 29.5          | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗    | 17.0          | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗         | 8.6           | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ     | 0.4           | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ     | 8.6           | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗    | 0.5           | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{IN} = 12\text{V}$  (特に記述のない限り)

| パラメータ            |                    | 条件                                                          | 最小値   | 標準値   | 最大値    | 単位 |

|------------------|--------------------|-------------------------------------------------------------|-------|-------|--------|----|

| <b>電源電流</b>      |                    |                                                             |       |       |        |    |

| $I_{IN}$         | $V_{IN}$ 電源電流      | $T_J = 25^{\circ}\text{C}$ 、 $V_{EN} = 5\text{V}$ 、非スイッチング時 | 146   |       |        | μA |

| $I_{VINSDN}$     | $V_{IN}$ シャットダウン電流 | $T_J = 25^{\circ}\text{C}$ 、 $V_{EN} = 0\text{V}$           | 9.3   |       |        | μA |

| <b>論理スレッショルド</b> |                    |                                                             |       |       |        |    |

| $V_{ENH}$        | EN H レベル スレッショルド電圧 |                                                             | 1.175 | 1.225 | 1.3    | V  |

| $V_{ENL}$        | EN L レベル スレッショルド電圧 |                                                             | 1.025 | 1.104 | 1.15   | V  |

| $V_{ENHYS}$      |                    |                                                             | 0.121 |       |        | V  |

| $I_{ENp1}$       | EN プルアップ電流         | $V_{EN} = 1.0\text{V}$                                      | 0.35  | 1.91  | 2.95   | μA |

| $I_{ENp2}$       |                    | $V_{EN} = 1.3\text{ V}$                                     | 3     | 4.197 | 5.5    | μA |

| <b>帰還電圧</b>      |                    |                                                             |       |       |        |    |

| $V_{FB}$         | FB 電圧              | $T_J = 25^{\circ}\text{C}$                                  | 598   | 600   | 602    | mV |

|                  |                    | $T_J = 0^{\circ}\text{C} \sim 85^{\circ}\text{C}$           | 597.5 | 600   | 602.5  | mV |

|                  |                    | $T_J = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}$         | 594   | 600   | 602.5  | mV |

|                  |                    | $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$        | 594   | 600   | 606    | mV |

| <b>LDO 電圧</b>    |                    |                                                             |       |       |        |    |

| $V_{REG5}$       | LDO 出力電圧           | $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$        | 4.58  | 4.7   | 4.83   | V  |

| $ILIM5$          | LDO 出力電流制限         | $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$        | 100   | 150   | 200    | mA |

| <b>MOSFET</b>    |                    |                                                             |       |       |        |    |

| $R_{DS(on)H}$    | ハイサイド スイッチ抵抗       | $T_J = 25^{\circ}\text{C}$ 、 $V_{REG5} = 4.7\text{V}$       | 7.8   |       |        | mΩ |

| $R_{DS(on)L}$    | ローサイド スイッチ抵抗       | $T_J = 25^{\circ}\text{C}$ 、 $V_{REG5} = 4.7\text{V}$       | 3.2   |       |        | mΩ |

| <b>ソフトスタート</b>   |                    |                                                             |       |       |        |    |

| $I_{ss}$         | ソフトスタート充電電流        | $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$        | 4.9   | 6     | 7.1    | μA |

| <b>電流制限</b>      |                    |                                                             |       |       |        |    |

| $I_{OCL}$        | 電流制限(ローサイドソーシング)   | ILIM-1 オプション、バレー電流                                          | 9.775 | 11.5  | 13.225 | A  |

|                  |                    | ILIM オプション、バレー電流                                            | 11.73 | 13.8  | 15.87  | A  |

|                  | 電流制限(ローサイド負方向)     | バレー電流                                                       | 4     |       |        | A  |

| <b>パワーグッド</b>    |                    |                                                             |       |       |        |    |

## 5.5 電気的特性 (続き)

$T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ ,  $V_{IN} = 12\text{V}$  (特に記述のない限り)

| パラメータ                             |                                        | 条件                                         | 最小値                | 標準値 | 最大値 | 単位 |

|-----------------------------------|----------------------------------------|--------------------------------------------|--------------------|-----|-----|----|

| $V_{PGOODTH}$                     | PGOOD スレッショルド                          | $V_{FB}$ 立ち下がり (故障)                        | 84%                |     |     |    |

|                                   |                                        | $V_{FB}$ 立ち上がり (良好)                        | 93%                |     |     |    |

|                                   |                                        | $V_{FB}$ 立ち上がり (故障)                        | 116%               |     |     |    |

|                                   |                                        | $V_{FB}$ 立ち下がり (良好)                        | 108%               |     |     |    |

| <b>出力低電圧および過電圧保護</b>              |                                        |                                            |                    |     |     |    |

| $V_{OVP}$                         | 出力 OVP スレッショルド                         | OVP 検出                                     | 121% ×<br>$V_{FB}$ |     |     |    |

| $V_{UVP}$                         | 出力 UVP スレッショルド                         | ヒップアップ検出                                   | 70% ×<br>$V_{FB}$  |     |     |    |

| <b>サーマル シャットダウン</b>               |                                        |                                            |                    |     |     |    |

| $T_{SDN}$                         | サーマル シャットダウンのスレッショルド                   | シャットダウン温度                                  | 160                |     |     | °C |

|                                   |                                        | ヒステリシス                                     | 15                 |     |     | °C |

| <b>UVLO</b>                       |                                        |                                            |                    |     |     |    |

| UVLO                              | UVLO スレッショルド                           | $V_{REG5}$ 立ち上がり電圧                         | 4.25               |     |     | V  |

|                                   |                                        | $V_{REG5}$ 立ち下がり電圧                         | 3.52               |     |     | V  |

|                                   |                                        | $V_{REG5}$ ヒステリシス                          | 730                |     |     | mV |

| UVLO、<br>$V_{REG5} = 4.7\text{V}$ | UVLO スレッショルド、 $V_{REG5} = 4.7\text{V}$ | $V_{IN}$ 立ち上がり電圧、 $V_{REG5} = 4.7\text{V}$ | 3.32               |     |     | V  |

|                                   |                                        | $V_{IN}$ 立ち下がり電圧、 $V_{REG5} = 4.7\text{V}$ | 3.24               |     |     | V  |

|                                   |                                        | $V_{IN}$ ヒステリシス、 $V_{REG5} = 4.7\text{V}$  | 80                 |     |     | mV |

## 5.6 タイミング要件

| パラメータ                        |                        | 条件                                                                          | 最小値 | 標準値 | 最大値 | 単位   |

|------------------------------|------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| <b>ON-TIME TIMER CONTROL</b> |                        |                                                                             |     |     |     |      |

| $t_{ON}$                     | SW オン時間 <sup>(1)</sup> | $V_{IN} = 12\text{V}$ , $V_{OUT} = 3.3\text{V}$ , $F_{SW} = 800\text{kHz}$  | 310 | 340 | 380 | ns   |

| $t_{ON\ min}$                | SW 最小オン時間              | $V_{IN} = 17\text{V}$ , $V_{OUT} = 0.6\text{V}$ , $F_{SW} = 1200\text{kHz}$ |     | 60  |     | ns   |

| $t_{OFF}$                    | SW 最小オフ時間              | $25^\circ\text{C}$ , $V_{FB} = 0.5\text{V}$                                 |     |     | 310 | ns   |

| <b>ソフトスタート</b>               |                        |                                                                             |     |     |     |      |

| $t_{SS}$                     | ソフト スタート時間             | 内部ソフトスタート時間                                                                 |     | 1.2 |     | ms   |

| <b>出力低電圧および過電圧保護</b>         |                        |                                                                             |     |     |     |      |

| $t_{UVPDEL}$                 | SS 時間にに対する出力ヒップアップ遅延   | UVP 検出                                                                      |     | 1   |     | サイクル |

| $t_{UVPEN}$                  | SS 時間にに対する出力ヒップアップ有効遅延 | UVP 検出                                                                      |     | 14  |     | サイクル |

(1) 設計により規定されています。

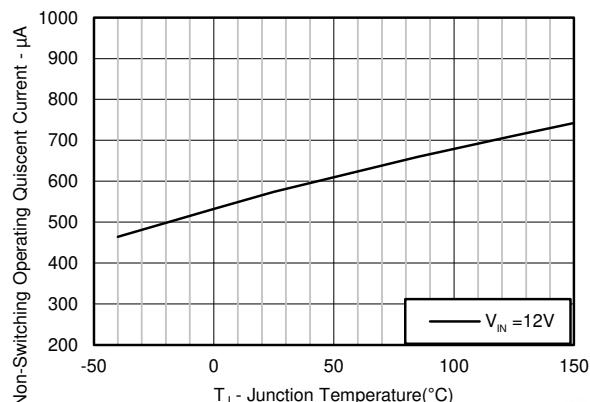

## 5.7 代表的特性

図 5-1. 静止電流と温度との関係

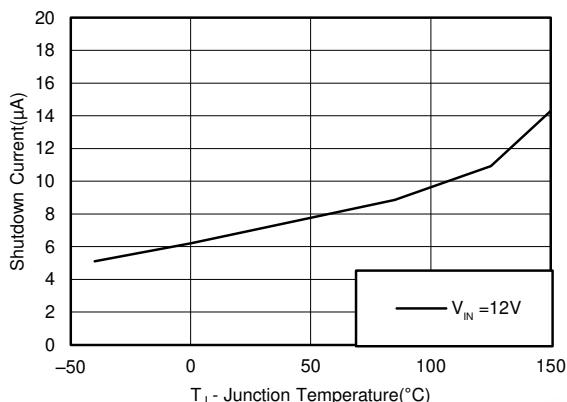

図 5-2. シャットダウン電流と温度との関係

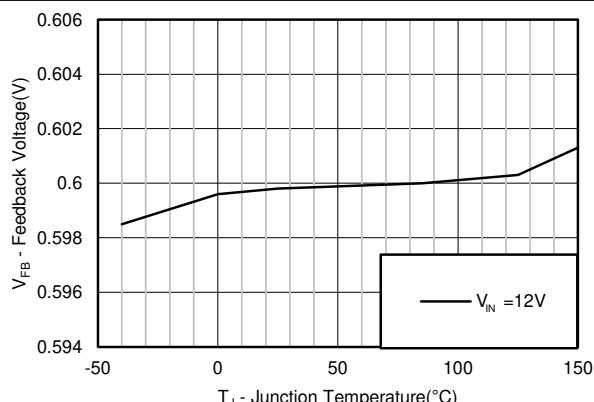

図 5-3. 帰還電圧と温度との関係

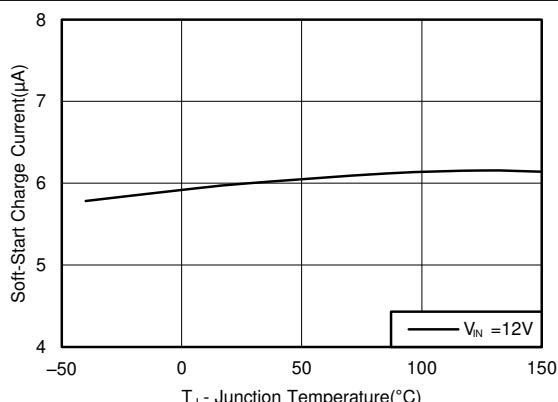

図 5-4. ソフトスタート充電電流と温度との関係

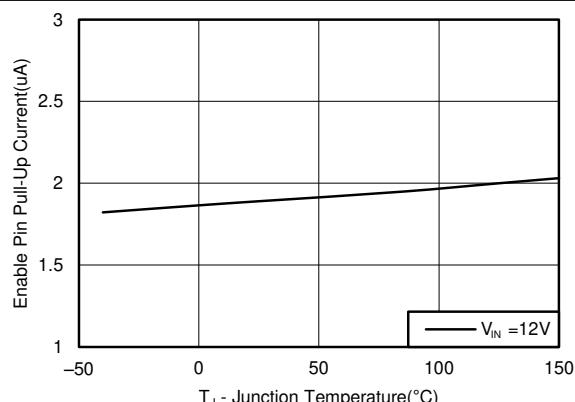

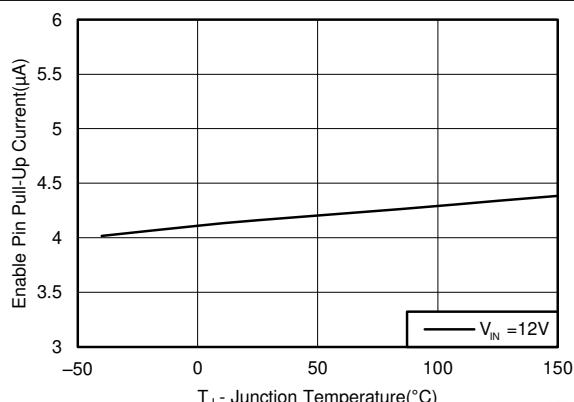

図 5-5. イネーブル プルアップ電流、V<sub>EN</sub> = 1.0V

図 5-6. イネーブル プルアップ電流、V<sub>EN</sub> = 1.3V

## 5.7 代表的特性 (続き)

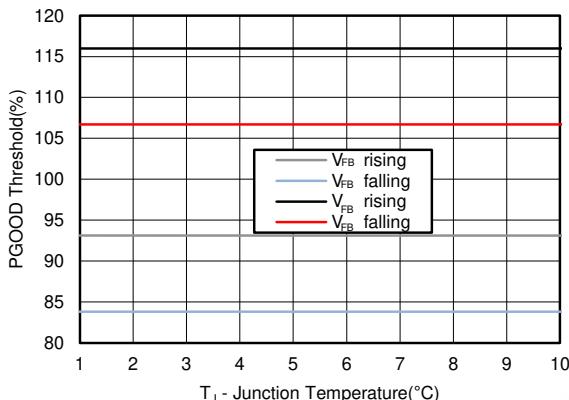

図 5-7. PGOOD スレッショルドと温度との関係

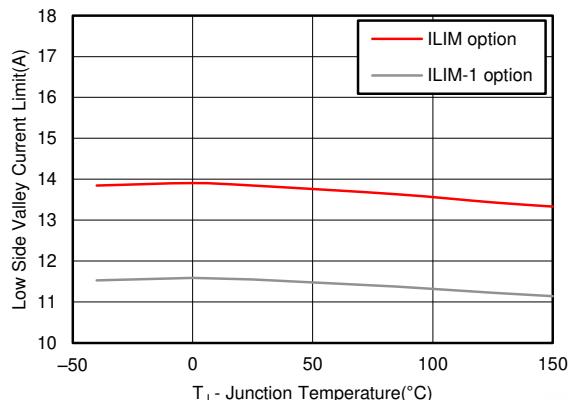

図 5-8. 電流制限と温度との関係

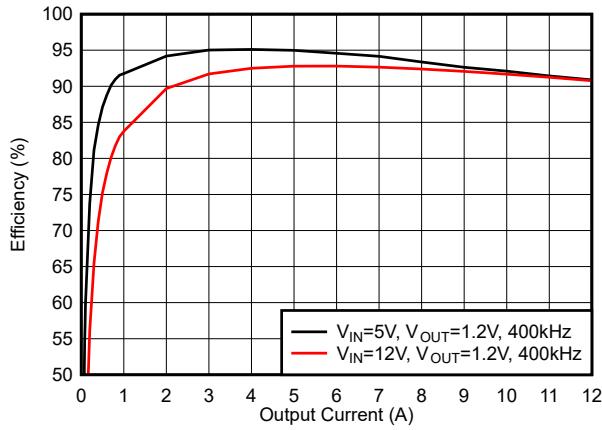

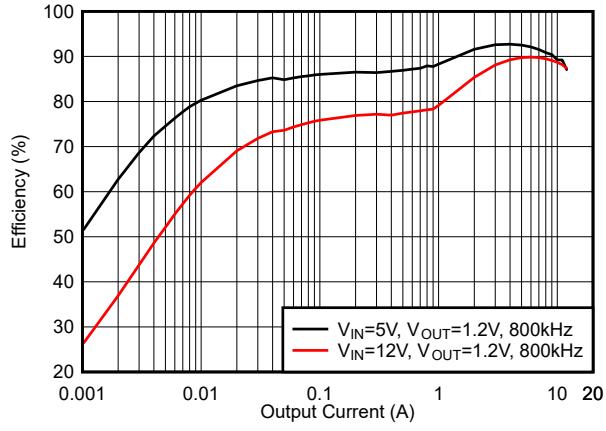

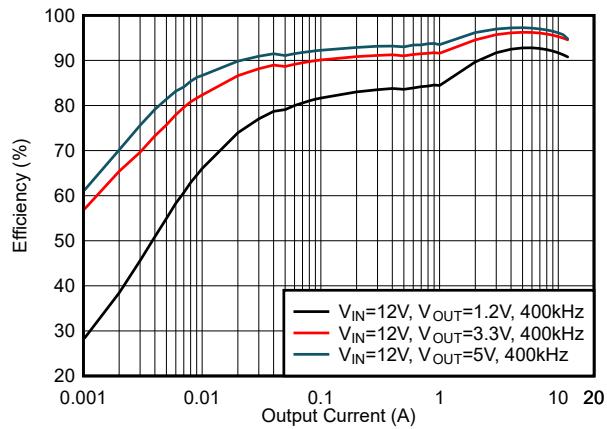

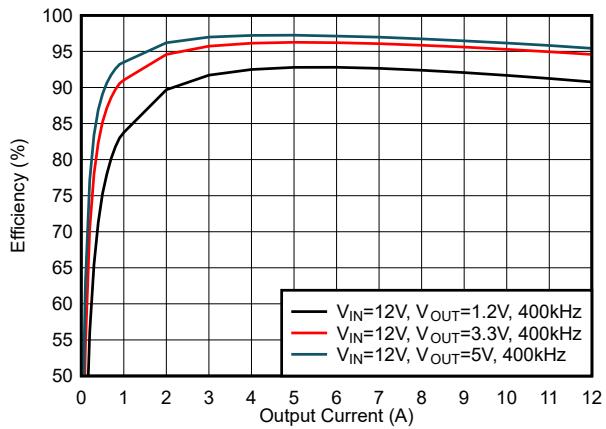

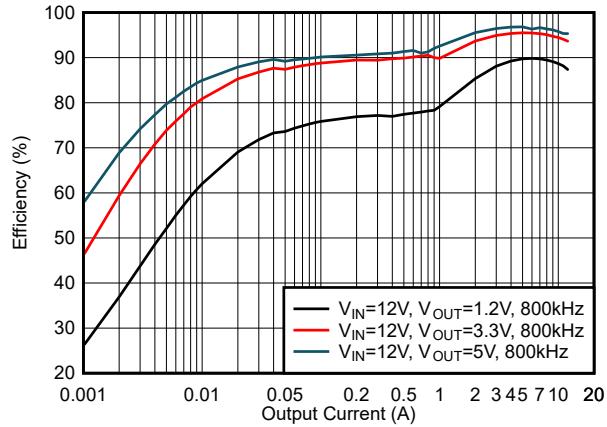

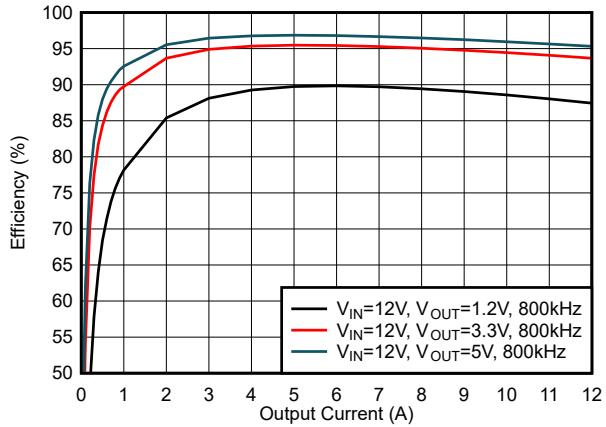

図 5-9. 効率 : DCM モード、f<sub>sw</sub> = 400kHz図 5-10. 効率 : FCCM モード、f<sub>sw</sub> = 400kHz図 5-11. 効率 : DCM モード、f<sub>sw</sub> = 800kHz図 5-12. 効率 : FCCM モード、f<sub>sw</sub> = 800kHz

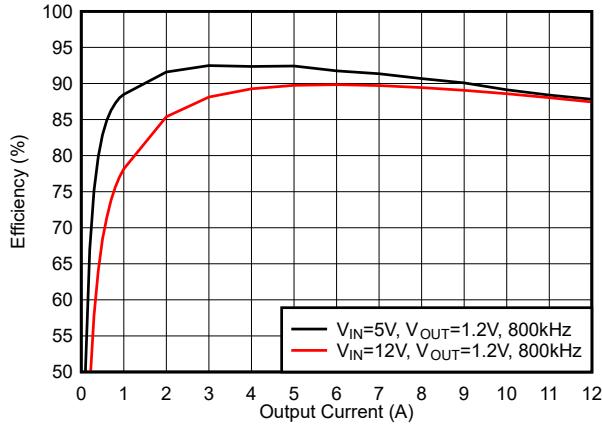

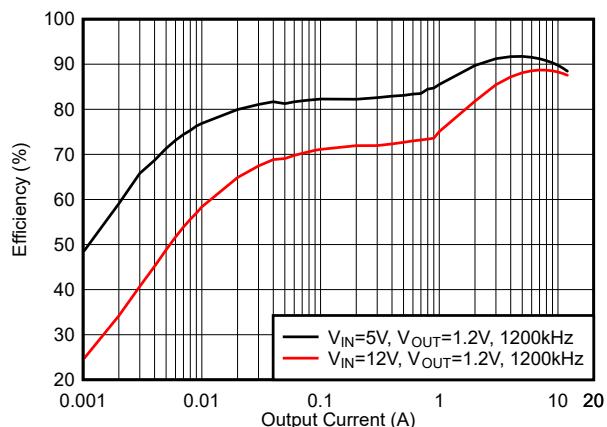

## 5.7 代表的特性 (続き)

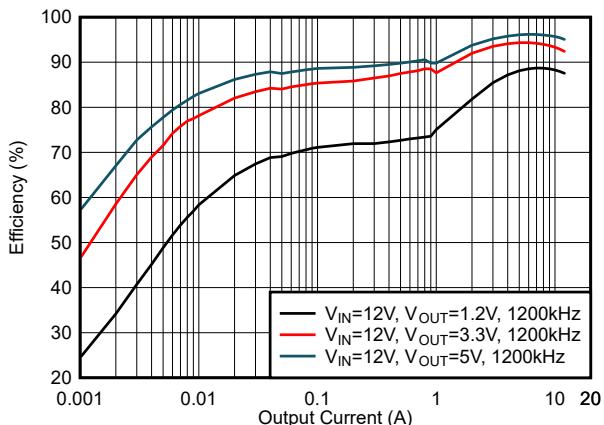

図 5-13. 効率 : DCM モード、 $f_{SW} = 1200\text{kHz}$

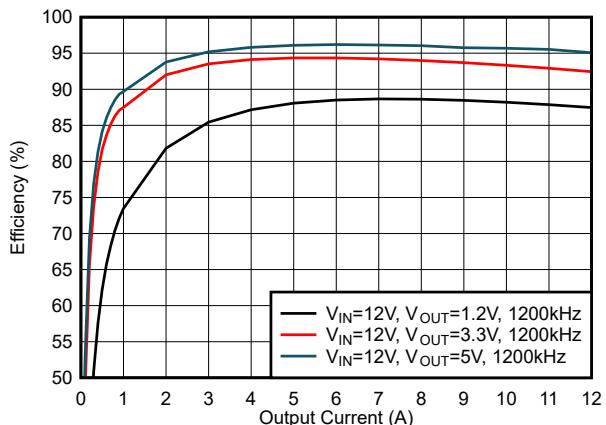

図 5-14. 効率 : FCCM モード、 $f_{SW} = 1200\text{kHz}$

図 5-15. 効率 : DCM モード、 $f_{SW} = 400\text{kHz}$

図 5-16. 効率 : FCCM モード、 $f_{SW} = 400\text{kHz}$

図 5-17. 効率 : DCM モード、 $f_{SW} = 800\text{kHz}$

図 5-18. 効率 : FCCM モード、 $f_{SW} = 800\text{kHz}$

## 5.7 代表的特性 (続き)

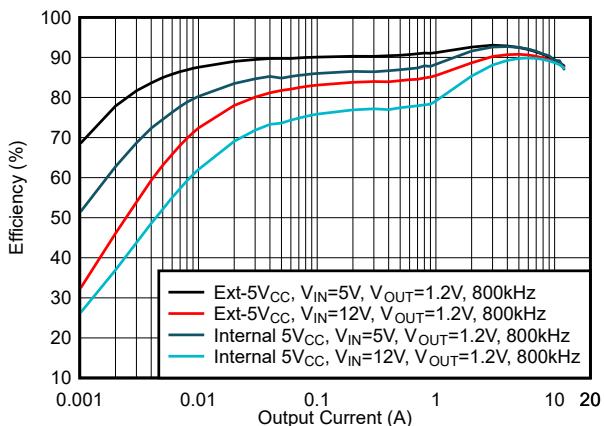

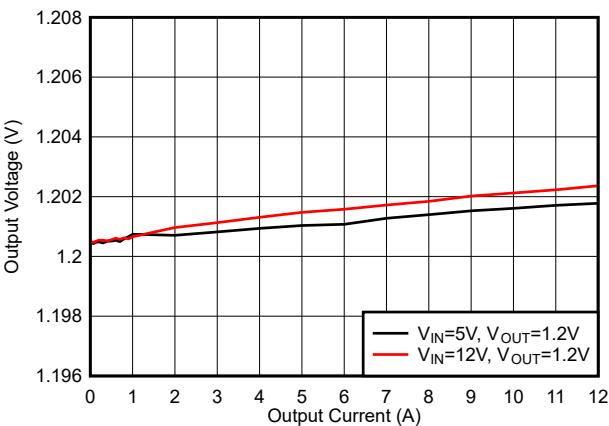

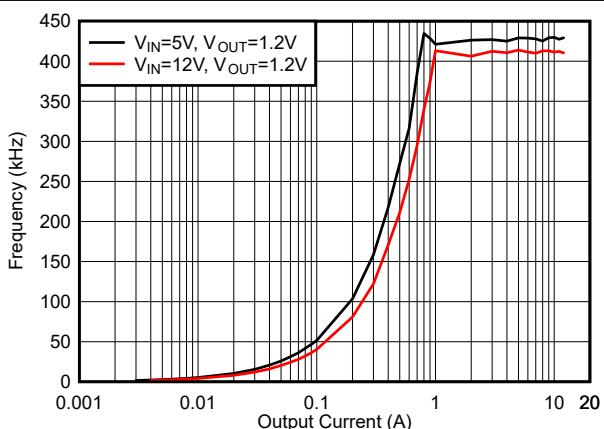

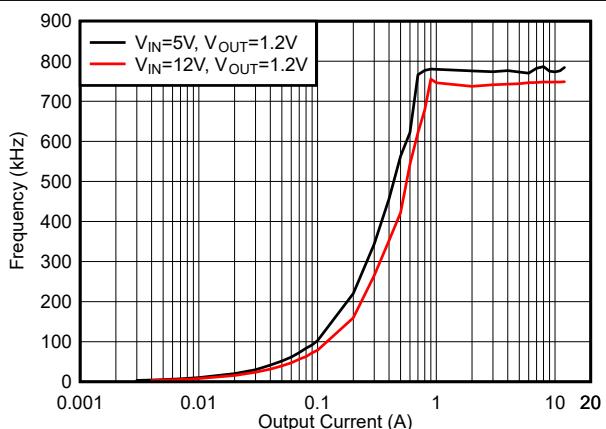

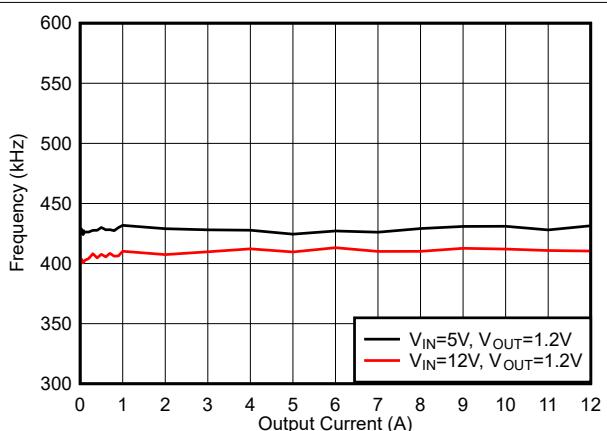

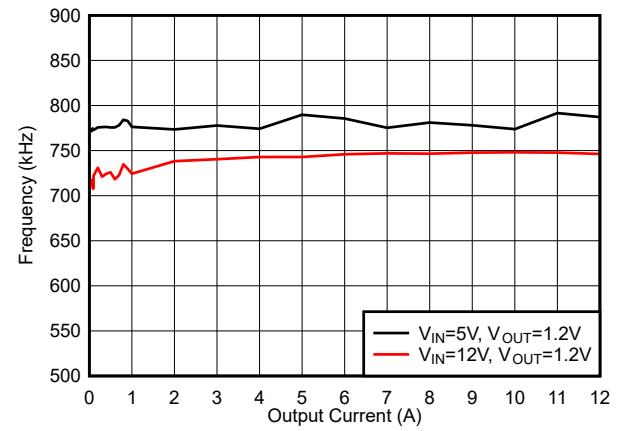

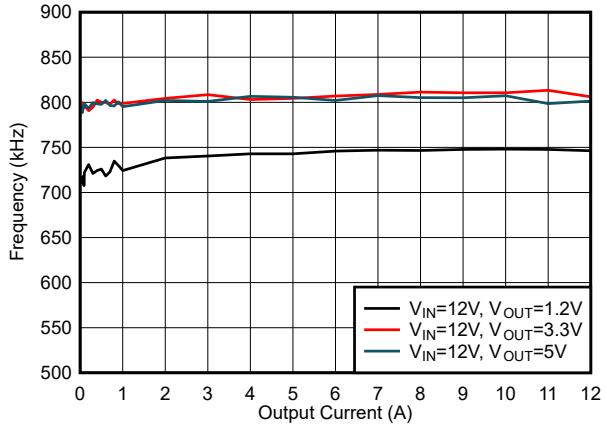

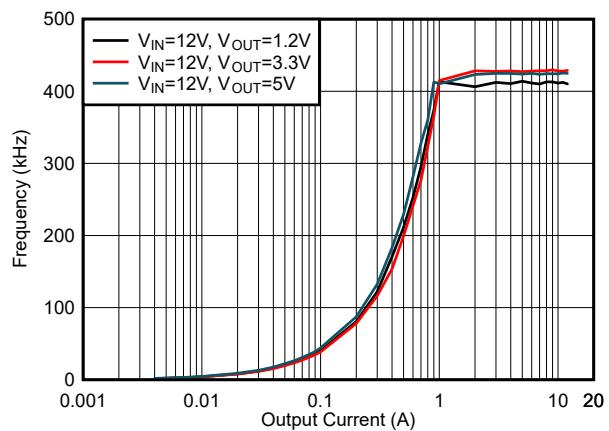

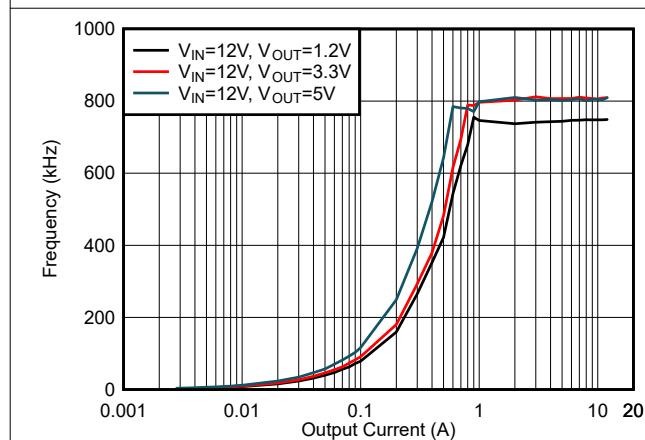

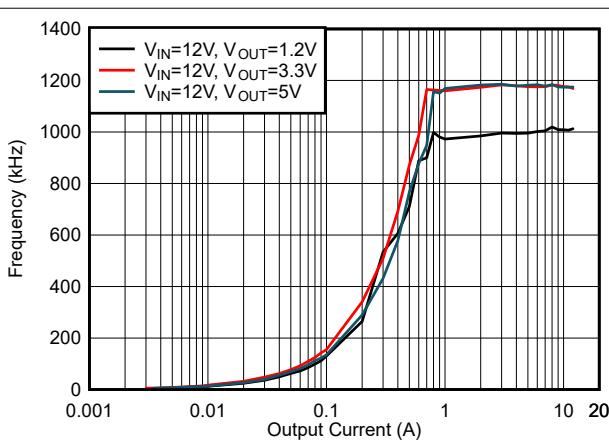

図 5-19. 効率 : DCM モード、 $f_{sw} = 1200\text{kHz}$ 図 5-20. 効率 : FCCM モード、 $f_{sw} = 1200\text{kHz}$ 図 5-21. 効率 : 外部 VCC と内部 VCC との関係、DCM モード、 $f_{sw} = 800\text{kHz}$ 図 5-22. 負荷レギュレーション :  $f_{sw} = 800\text{kHz}$ 図 5-23.  $f_{sw}$  負荷レギュレーション : モード = DCM、 $f_{sw} = 400\text{kHz}$ 図 5-24.  $f_{sw}$  負荷レギュレーション : モード = DCM、 $f_{sw} = 800\text{kHz}$

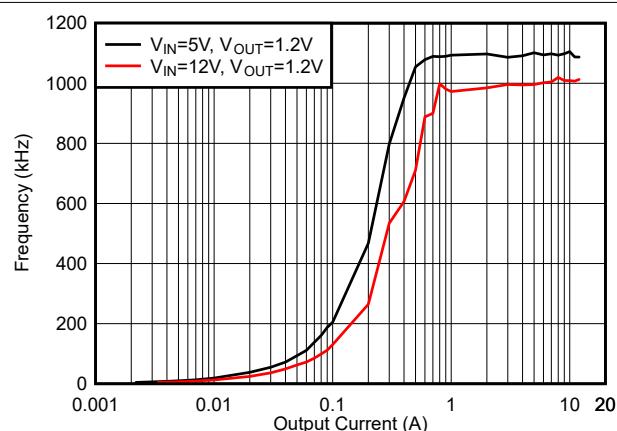

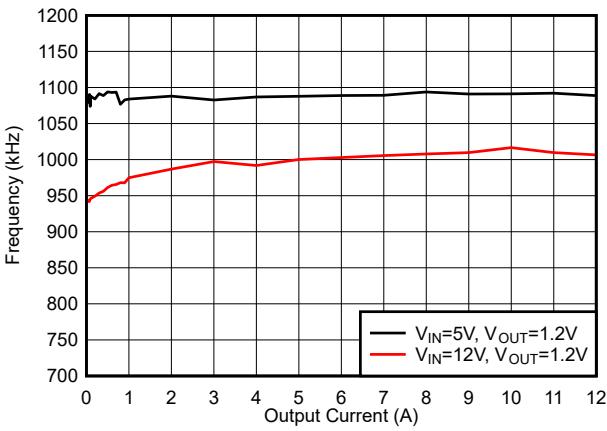

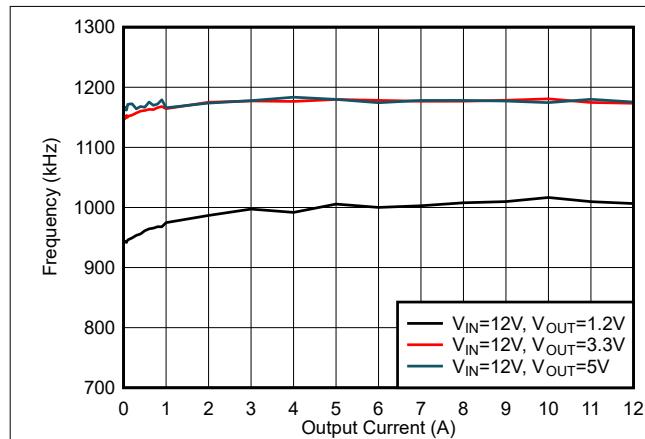

## 5.7 代表的特性 (続き)

図 5-25.  $F_{SW}$  負荷レギュレーション: モード = DCM、 $F_{SW} = 1200\text{kHz}$

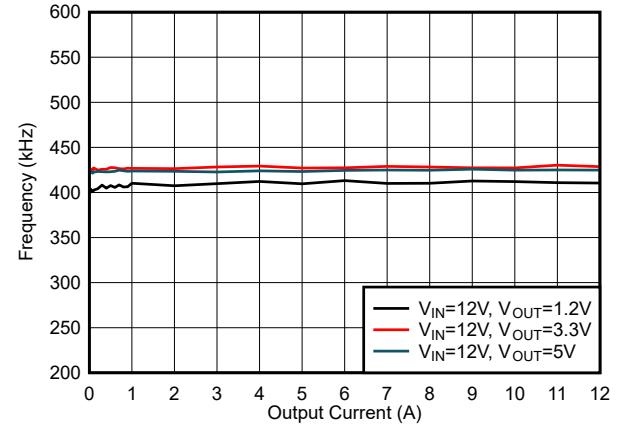

図 5-26.  $F_{SW}$  負荷レギュレーション: モード = FCCM、 $F_{SW} = 400\text{kHz}$

図 5-27.  $F_{SW}$  負荷レギュレーション: モード = FCCM、 $F_{SW} = 800\text{kHz}$

図 5-28.  $F_{SW}$  負荷レギュレーション: モード = FCCM、 $F_{SW} = 1200\text{kHz}$

図 5-29.  $F_{SW}$  負荷レギュレーション: モード = FCCM、 $F_{SW} = 400\text{kHz}$

図 5-30.  $F_{SW}$  負荷レギュレーション: モード = FCCM、 $F_{SW} = 800\text{kHz}$

## 5.7 代表的特性 (続き)

図 5-31.  $F_{SW}$  負荷レギュレーション : モード = FCCM、 $F_{SW} = 1200\text{kHz}$

図 5-32.  $F_{SW}$  負荷レギュレーション : モード = DCM、 $F_{SW} = 400\text{kHz}$

図 5-33.  $F_{SW}$  負荷レギュレーション : モード = DCM、 $F_{SW} = 800\text{kHz}$

図 5-34.  $F_{SW}$  負荷レギュレーション : モード = DCM、 $F_{SW} = 1200\text{kHz}$

## 6 詳細説明

### 6.1 概要

TPS56C215 は、3.8V から 17V の入力電圧 ( $V_{IN}$ ) で動作可能な高密度の同期整流降圧型コンバータです。このデバイスは  $7.8\text{m}\Omega$  および  $3.2\text{m}\Omega$  MOSFET を内蔵し、最大 12A の高効率を実現できます。D-CAP3 制御モードを採用し、外部補償部品なしで高速な過渡応答と、高精度な帰還電圧を実現します。この制御トポロジは、高負荷時の FCCM 動作モードと軽負荷時の DCM/Eco-mode 動作との間でシームレスな切り替えを実現します。DCM/Eco-mode を使用すると、TPS56C215 は軽負荷時でも高効率を維持できます。TPS56C215 は、POSCAP や SP-CAP など等価直列抵抗 (ESR) の低い出力コンデンサにも、ESR の非常に低いセラミックコンデンサにも対応可能です。

TPS56C215 は 3 つの選択可能なスイッチング周波数 ( $F_{SW}$ ) (400 kHz, 800 kHz, 1200 kHz) を備え、高効率やサイズの小型化を重視した設計に柔軟に対応できます。電流制限は 2 段階から選択できます。これらのオプションはすべて、MODE ピンで適切な電圧を選択することで構成されます。

TPS56C215 は、4.7V 内部 LDO を搭載し、すべての内部回路へのバイアス電源を生成します。VREG5 ピンに外部電圧を印加して内部 LDO を上書き駆動することで、コンバータの効率をさらに向上させることができます。低電圧誤動作防止 (UVLO) 回路は VREG5 ピンの電圧を監視し、入力電圧低下時に内部回路を保護します。デバイスの EN ピンには内部プルアップ電流源があり、このピンが開放時でもデバイスを有効化できます。

ソフトスタート時間は、SS ピンにコンデンサを接続することで選択できます。本デバイスは、出力短絡、低電圧、過温度状態から保護されています。

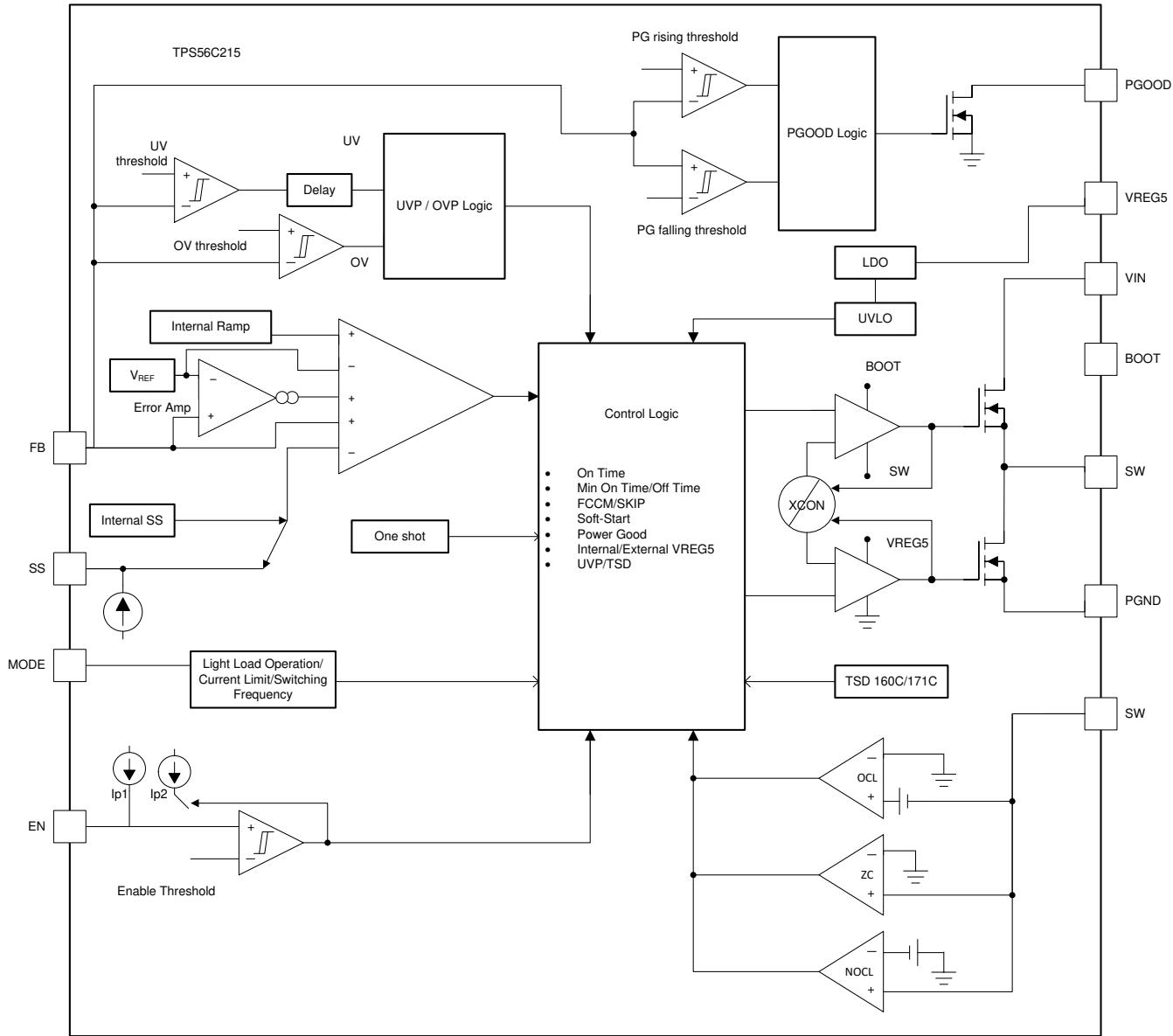

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 PWM動作とD-CAP3™制御モード

TPS56C215 は、適応型オン時間 PWM 制御を使用して、独自の D-CAP3 制御モードを使用して動作するため、高速な負荷過渡応答により外部部品数を抑えながら、高い出力電圧精度を維持できます。各スイッチング サイクルの開始時に、ハイサイド MOSFET は内部ワンショット タイマで設定されたオン時間だけオンになります。このオン時間は、コンバータの入力電圧、コンバータの出力電圧、擬似固定周波数に基づいて設定されるため、このタイプの制御トポロジは適応型オン時間制御と呼ばれます。ワンショット タイマは、帰還電圧 ( $V_{FB}$ ) が内部リファレンス電圧 ( $V_{REF}$ ) を下回るとリセットされ、再度オンになります。内部でランプ波形が生成され、FB ピンに供給されることで出力電圧リップルをシミュレートします。これにより、多層セラミックコンデンサ (MLCC) などの超低 ESR 出力コンデンサの使用が可能になります。DCAP3 制御トポロジでは、外部の電流センス ネットワークやループ補償回路は不要です。

TPS56C215 は、出力電圧の高精度化を実現するエラー アンプを内蔵しています。このエラーアンプは、他の D-CAP3 モデルには搭載されていません。内部で補償されるすべての制御トポロジには、制御トポロジがサポートできる出力フィルタの範囲があります。TPS56C215 で使用される出力フィルタは、ローパス L-C 回路です。この L-C フィルタは、式 1 に記載された二重極があります。

$$f_P = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}} \quad (1)$$

低周波数では、出力設定点分圧抵抗回路、および TPS56C215 の内部ゲインによって、全体のループ ゲインが設定されます。低周波域の L-C 二重極では、位相は 180 度の同相になります。出力フィルタ周波数では、ゲインは -40dB/dec レートで減衰し、位相も急激に低下します。内部リップル生成回路によって高周波ゼロ点が導入されることで、ゲインの減衰が -40dB/dec から -20dB/dec に低減され、ゼロ点周波数で 1 dec 上で位相が 90 度まで上昇します。内部リップル注入による高周波ゼロ点位置は、選択したスイッチング周波数に応じて表 6-1 に示すように変化します。出力フィルタに使用するインダクタとコンデンサは、この高周波数ゼロから得られる位相ブーストによって安定性要件のための十分な位相マージンが確保されるように、二重極を高周波数ゼロに十分近く配置する必要があります。システム全体のクロスオーバー周波数は通常、スイッチング周波数 ( $F_{SW}$ ) の 1/5 未満に設定する必要があります。

表 6-1. リップル注入ゼロ点

| スイッチング周波数 (kHz) | ゼロ位置 (kHz) |

|-----------------|------------|

| 400             | 17.8       |

| 800             | 27.1       |

| 1200            | 29.8       |

表 6-2 に、セクション 5.7 の効率曲線のプロットに使用したインダクタ値と型番を示します。

表 6-2. インダクタ値

| $V_{OUT}$ (V) | $F_{SW}$ (kHz) | $L_{OUT}$ (μH) | WÜRTH 型番 <sup>(1)</sup> |

|---------------|----------------|----------------|-------------------------|

| 1.2           | 400            | 1.2            | 744325120               |

|               | 800            | 0.68           | 744311068               |

|               | 1200           | 0.47           | 744314047               |

| 3.3           | 400            | 2.4            | 744325240               |

|               | 800            | 1.5            | 7443552150              |

|               | 1200           | 1.2            | 744325120               |

| 5.5           | 400            | 3.3            | 744325330               |

|               | 800            | 2.4            | 744325240               |

|               | 1200           | 1.5            | 7443552150              |

(1) サード パーティー製品の免責事項をご覧ください。

### 6.3.2 Eco モード制御

TPS56C215 は、Eco-mode 制御を備えた設計で、軽負荷時の高効率を実現しています。このオプションは、表 6-3 に示すように MODE ピンで選択できます。出力電流が重負荷状態から減少すると、インダクタ電流も減少します。出力電流が十分に減少すると、インダクタ電流の谷がゼロレベルに達します。これは連続導通モードと不連続導通モードの境界に当たります。インダクタ電流がゼロと検出されると、ローサイド MOSFET がオフになります。負荷電流がさらに減少すると、コンバータは不連続導通モードで動作します。オン時間は、連続導通モード時とほぼ同じに保たれます。負荷電流が小さい場合、出力の放電時間が長くなるため、オフ時間が長くなります。Eco-mode 動作への遷移が発生する軽負荷電流 ( $I_{OUT(LL)}$ ) は、式 2 を使用して算出できます。

$$I_{OUT(LL)} = \frac{1}{2 \times L_{OUT} \times F_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \quad (2)$$

アプリケーション要件を確認した後、インダクタのピーク ツー ピーク リップル電流が  $I_{OUT(max)}$  (アプリケーションのピーク電流) の約 20% ~ 30% になるように出力インダクタンス ( $L_{OUT}$ ) を設計してください。バレー電流が負のローサイド電流制限に達しないようにインダクタのサイズを適切に調整することが重要です。

### 6.3.3 4.7V LDO

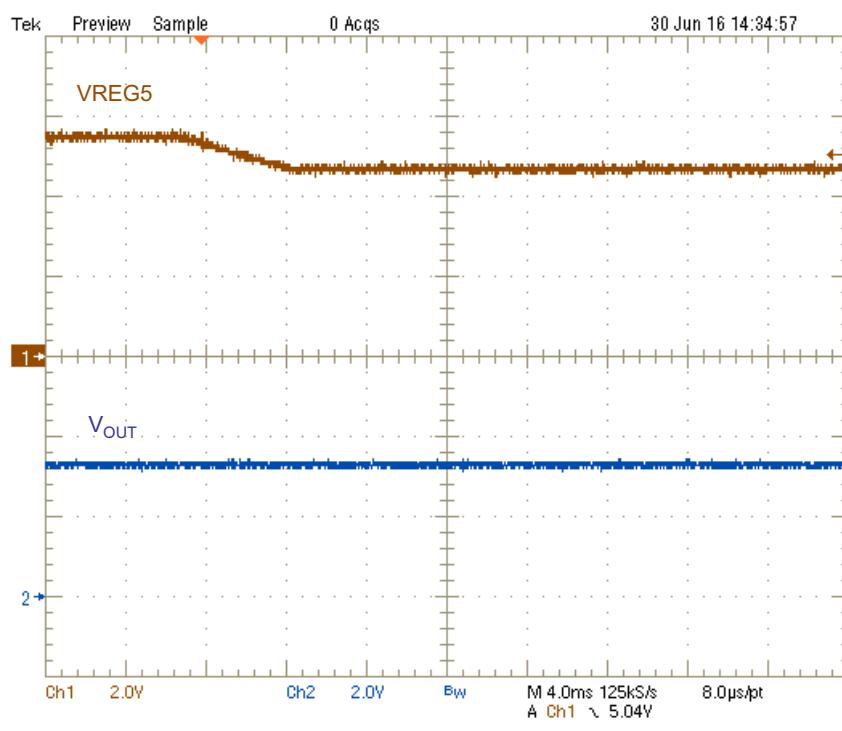

VREG5 ピンは、すべての内部回路と MOSFET ゲートドライバのバイアスを生み出す内部 4.7V リニア レギュレータの出力です。VREG5 ピンは、 $4.7\mu F$  コンデンサでバイパスする必要があります。内部 LDO の出力電圧より高い外部電圧を印加すると、内部 LDO は外部レールに切り替わり、より高い電圧を検出すると、内部 LDO は外部レールに切り替わります。これにより、静止電流が入力電源ではなく外部レールから供給されるため、コンバータの効率が向上します。UVLO 回路は VREG5 ピンの電圧を監視し、VREG5 が UVLO スレッショルドを下回ると出力を無効にします。VREG5 レールに外部バイアスを使用する場合、任意のパワーアップおよびパワーダウン シーケンスを適用できますが、VREG5 レールに放電パスが存在し、VREG5 から LDO の内部電流制限 (ILIM5) を超える電流が流れると、VREG5 LDO がオフになります。TPS56C215 の出力がシャットダウンされることを理解しておくことが重要です。このような条件がなければ、外部 VREG5 レールがオフになった場合、VREG5 の電圧は数ナノ秒で内部 LDO 電圧 (通常 4.7V) に切り替わります。**図 6-1** は、TPS56C215 の出力が変化しないまま VREG5 への外部バイアスが無効化されているときに、VREG5 電圧が 5.5V の外部バイアスから 4.7V の内部 LDO 出力へと遷移する様子を示しています。

**図 6-1. VREG5 の遷移**

### 6.3.4 MODE の選択

TPS56C215 には MODE ピンがあり、電流制限、スイッチング周波数、軽負荷動作の組み合わせで 12 種類の動作状態を選択できます。このデバイスは、ILIM-1 と ILIM の 2 種類の電流制限で動作可能であり、それぞれ 10A と 12A の出力連続電流に対応します。TPS56C215 は、インダクタのバレー電流を電流制限スレッショルドと比較するように設計されているため、出力電流はバレー電流にインダクタリップル電流の 1/2 を加えた値になることを理解してください。たとえば、ILIM 電流制限を選択した場合、OCL スレッショルドは最小 11.73A になり、過電流状態にならずにコンバータから 12A を出力するためには、インダクタのピーク ツー ピーク リップル電流が最低 0.54A 必要になります。TPS56C215 は 400kHz、800kHz、1200kHz の 3 種類の周波数で動作でき、Eco-mode と FCCM モードのどちらかも選択できます。デバイスは起動時に MODE ピンの電圧を読み取り、表 6-3 に記載された MODE オプションのいずれかにラッチします。

MODE ピンの電圧は、VREG5 と AGND の間に接続された分圧抵抗のセンター タップにこのピンを接続することで設定できます。1% 抵抗器を用いた上側抵抗 ( $R_{M\_H}$ ) と下側抵抗 ( $R_{M\_L}$ ) のガイドラインを表 6-3 に示します。内部的にこの電圧を基準として MODE オプションを判別しているため、MODE ピンの電圧は必ず VREG5 レールから供給してください。MODE ピンの設定は、VIN の電源を再投入した場合にのみリセットできます。

**表 6-3. MODE ピンの抵抗設定**

| $R_{M\_L}$ (kΩ) | $R_{M\_H}$ (kΩ) | 軽荷動作 | 電流制限   | 周波数 (kHz) |

|-----------------|-----------------|------|--------|-----------|

| 5.1             | 300             | FCCM | ILIM-1 | 400       |

| 10              | 200             | FCCM | ILIM   | 400       |

| 20              | 160             | FCCM | ILIM-1 | 800       |

| 20              | 120             | FCCM | ILIM   | 800       |

| 51              | 200             | FCCM | ILIM-1 | 1200      |

| 51              | 180             | FCCM | ILIM   | 1200      |

| 51              | 150             | DCM  | ILIM-1 | 400       |

| 51              | 120             | DCM  | ILIM   | 400       |

| 51              | 91              | DCM  | ILIM-1 | 800       |

| 51              | 82              | DCM  | ILIM   | 800       |

| 51              | 62              | DCM  | ILIM-1 | 1200      |

| 51              | 51              | DCM  | ILIM   | 1200      |

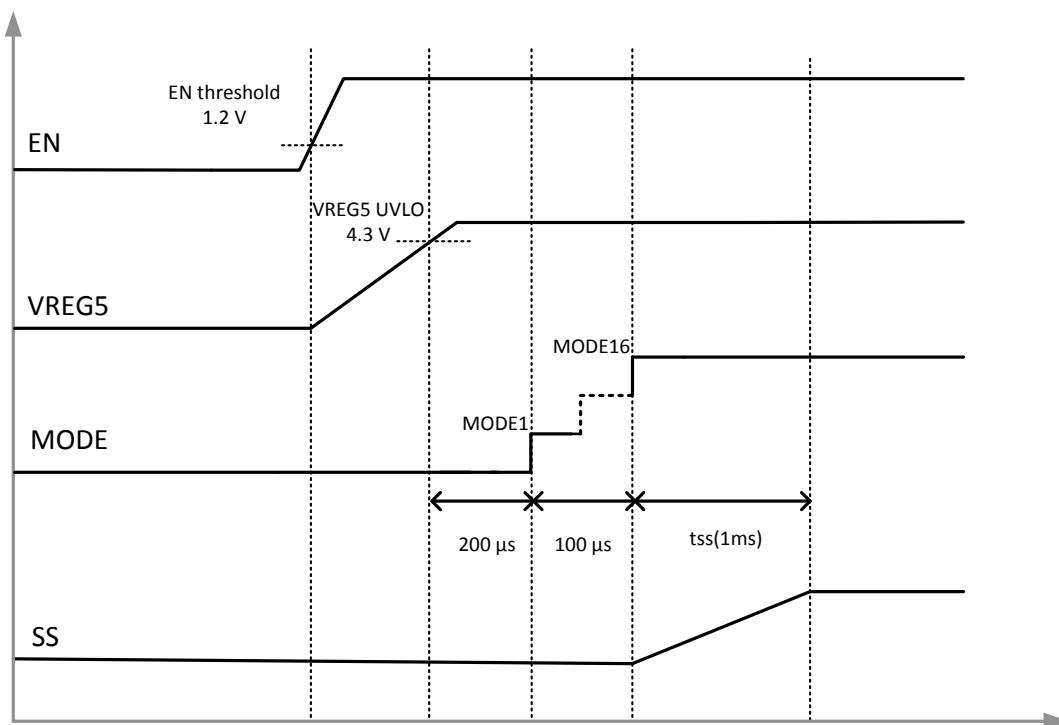

図 6-2 は、EN ピン電圧が EN ターンオン スレッショルドを超えた後のデバイスの代表的なスタートアップ シーケンスを示しています。VREG5 ピンの電圧が UVLO 立ち上がりスレッショルドを超えると、最初の MODE 設定の読み取るに 100μs、その後最後のモード設定完了までに約 100μs かかります。MODE 設定の読み取りが完了すると、出力電圧が上昇を開始します。

**図 6-2. パワーアップ シーケンス**

### 6.3.5 ソフトスタートおよびプリバイアス付きソフトスタート

TPS56C215 は、SS ピンにコンデンサを接続することでソフトスタート時間を調整できます。EN ピンが High になると、ソフトスタート充電電流 ( $I_{SS}$ ) が、SS と AGND 間に接続された外付けコンデンサ ( $C_{SS}$ ) の充電を開始します。本デバイスは、内部ソフトスタート電圧、または外部ソフトスタート電圧のいずれか低い方を基準としてトラッキングします。ソフトスタート時間 ( $T_{SS}$ ) の計算式は、式 3 に示されています。

$$T_{SS(S)} = \frac{C_{SS} \times V_{REF}}{I_{SS}} \quad (3)$$

ここで、

- $V_{REF}$  は 0.6V、 $I_{SS}$  は 6μA です

スタートアップ時に出力コンデンサがプリバイアスされている場合には、内部リファレンス電圧が帰還電圧  $V_{FB}$  より大きくなるまで、スイッチングおよび電圧上昇は開始されません。この方式により、コンバータはレギュレーション点までスムーズに上昇します。

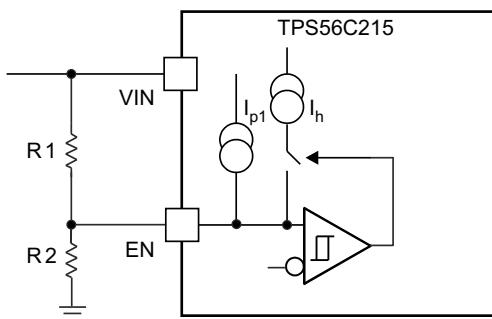

### 6.3.6 イネーブルおよび調整可能な UVLO

EN ピンはデバイスのターンオン / ターンオフを制御します。EN ピン電圧が約 1.2V のターンオン スレッショルドを上回るとデバイスはスイッチングを開始し、EN ピン電圧が約 1.1V のターンオフ スレッショルドを下回るとスイッチングを停止します。ユーザー・アプリケーションで異なるターンオン ( $V_{START}$ ) とターンオフ スレッショルド ( $V_{STOP}$ ) が必要な場合、VIN と EN の間に分圧抵抗を接続することにより、図 6-3 に示すように EN ピンを設定できます。EN ピンにはプルアップ電流  $I_{p1}$  があり、ピン開放時にデフォルト状態が設定されます。EN ピン電圧がターンオン スレッショルドを超えると、この電流は  $I_{p2}$  に増加します。UVLO スレッショルドは、式 4 および式 5 を使用して設定できます。

図 6-3. 可変の VIN 低電圧誤動作防止

$$R1 = \frac{V_{START} \left( \frac{V_{ENFALLING}}{V_{ENRISING}} \right) - V_{STOP}}{I_{p1} \left( 1 - \frac{V_{ENFALLING}}{V_{ENRISING}} \right) + I_h} \quad (4)$$

$$R2 = \frac{R1 \times V_{ENFALLING}}{V_{STOP} - V_{ENFALLING} + R1 I_{p2}} \quad (5)$$

ここで、

- $I_{p2} = 4.197\mu A$

- $I_{p1} = 1.91\mu A$

- $I_h = 2.287\mu A$

- $V_{ENRISING} = 1.225V$

- $V_{ENFALLING} = 1.104V$

### 6.3.7 パワー グッド

Power Good (PGOOD) ピンはオープンドレイン出力です。FB ピン電圧が内部基準電圧( $V_{REF}$ ) の 93% ~ 107% になると、PGOOD はデアサートされ、200 $\mu$ s デグリッチ時間後にオープンになります。TI は、VREG5 へのプルアップ用として、10k $\Omega$  の抵抗を推奨しています。FB ピン電圧が  $V_{UVP}$  未満または  $V_{OVP}$  しきい値を超えた場合、サーマル シャットダウン時、またはソフト スタート中は、PGOOD ピンは Low に引き下げられます。

### 6.3.8 電流保護と低電圧保護

出力過電流制限 (OCL) は、サイクル毎のバレー検出制御回路を使用して実現されています。スイッチ電流は、OFF 状態時にローサイド FET のドレイン - ソース間電圧を測定することで監視されます。この電圧は、スイッチ電流に比例します。ハイサイド FET スイッチのオン時間中、スイッチ電流は入力電圧、出力電圧、オン時間、出力インダクタ値によって決定される直線的なレートで増加します。ローサイド FET スイッチのオン時間中は、この電流はリニアに減少します。スイッチ電流の平均値はが、負荷電流  $I_{OUT}$  です。ローサイド FET のドレイン - ソース間電圧が電流制限に比例する電圧を上回った場合、ローサイド FET は電流レベルが OCL レベル未満になるまでオンのまま保持され、出力可能な電流が制限されます。負荷要求がコンバータの供給能力を上回るため、電流が制限されると出力電圧が低下する傾向があります。出力電圧が目標電圧の 68% を下回ると、UVP コンパレータがこれを検出し、1 ×  $t_{SS}$  の待機時間後にデバイスをシャットダウンします。デバイスは、14 ×  $t_{SS}$  のヒップアップ時間経過後に再起動します。このバレー検出制御方式では、負荷電流は、OCL スレッショルドよりもピークツーピーク インダクタリップル電流の 1/2 分だけ高くなります。過電流状態が解消されると、出力電圧はレギュレーション値に復帰します。起動中に OCL 状態が発生した場合、デバイスは 1 ソフト スタート サイクルの待機時間なしで直ちにヒップアップモードに移行します。

### 6.3.9 過渡応答の強化

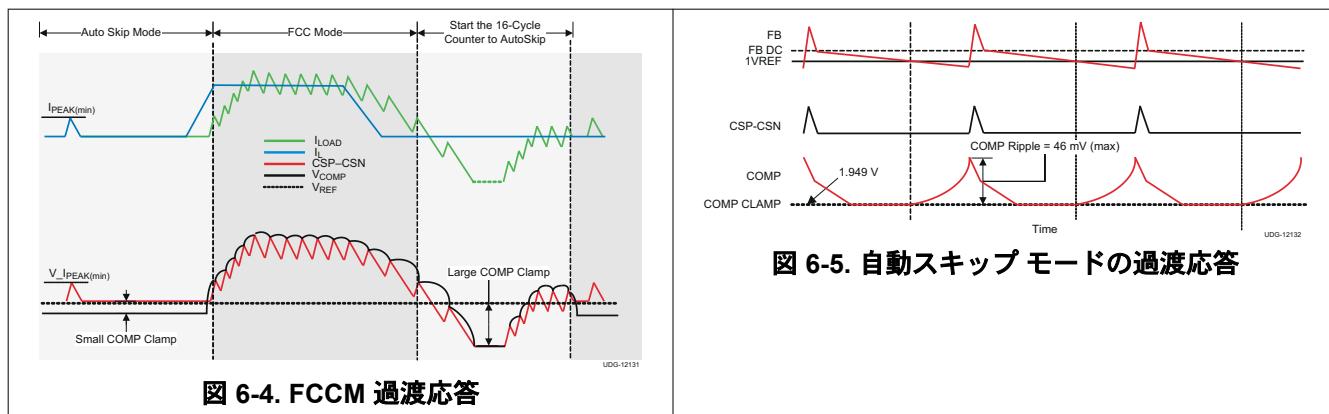

PSM デグリッチ機能は、デバイスが連続導通モード (CCM) の重負荷状態から不連続導通モード (DCM) の軽負荷状態に遷移する際に作動します。この遷移中、システムは強制連続導通モード (FCCM) で 16 サイクル動作してから DCM に切り替わります。この機能は、DCM 動作中の負荷変動時に高速な応答を実現するために設計されています。

図 6-4 には、負荷解放時および COMP ピンの動的位置決め時の 16 サイクルおよび 32 サイクルの FCCM 動作が示されています。図 6-5 には、動的 COMP ピン クランプによる定常状態の自動スキップ モード動作が示されています。

### 6.3.10 UVLO 保護

低電圧誤動作防止 (UVLO) 機能は、内部 VREG5 レギュレータの電圧を監視します。VREG5 電圧が UVLO スレッショルド電圧を下回ると、デバイスはシャットダウンします。この保護機能は非ラッチ方式です。

### 6.3.11 サーマル シャットダウン

本デバイスは、内部ダイの温度を監視します。この温度がサーマル シャットダウン スレッショルド値 ( $T_{SDN}$  通常 160°C) を超えると、デバイスはシャットダウンします。これは非ラッチ方式の保護です。起動時にデバイス温度が 160°C より高い場合、デバイスはスイッチングを開始せず、MODE 設定も読み込まれません。起動後にデバイス温度が  $T_{SDN}$  スレッショルド

を超えると、デバイスはグランドへの **SS** リセットでスイッチングを停止し、内部放電スイッチをオンにして出力電圧を迅速に放電します。温度がサーマル シャットダウン スレッショルドを下回ると、本デバイスはスイッチングを再開しますが、**MODE** 設定は再度読み込まれません。

### 6.3.12 出力電圧放電

本デバイスは  $500\Omega$  の放電スイッチを内蔵し、出力過電圧、出力低電圧、TSD、VREG5 電圧が UVLO 未満、EN ピン電圧 ( $V_{EN}$ ) がターンオン スレッショルド未満の場合など、いずれかのフォールト時に SW ノードを介して出力  $V_{OUT}$  を放電します。

## 6.4 デバイスの機能モード

### 6.4.1 軽負荷動作

MODE ピンが FCCM モードに設定されている場合、軽負荷時でもコンバータは連続導通モード (FCCM) で動作します。FCCM 動作中は、負荷範囲全体でスイッチング周波数 ( $F_{SW}$ ) がほぼ一定に保たれます。これは軽負荷時での効率低下を犠牲にしてもスイッチング周波数と出力電圧リップルを厳密に制御する必要があるアプリケーション向けに設計されています。MODE ピンが DCM/Eco-mode に設定されている場合、インダクタリップル電流のパレーがゼロを下回ると、デバイスはパルススキップ モードに入ります。Eco-mode では、軽負荷時にスイッチング周波数を下げることで、より高い効率を維持します。

### 6.4.2 スタンバイ動作

TPS56C215 は、EN ピンを Low にすることでスタンバイ モードに移行できます。スタンバイ状態のデバイスは、 $7\mu A$  のシャットダウン電流で動作します。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

図 7-1 の回路図は TPS56C215 の代表的なアプリケーション例を示しています。この設計は、4.5V ~ 17V の入力電圧範囲を 1.2V へ降圧し、最大連続出力電流 12A に対応します。

### 7.2 代表的なアプリケーション

図 7-1. アプリケーション回路図

#### 7.2.1 設計要件

表 7-1. 設計パラメータ

| パラメータ                    |           | 条件        | 最小値 | 標準値     | 最大値 | 単位                  |

|--------------------------|-----------|-----------|-----|---------|-----|---------------------|

| V <sub>OUT</sub>         | 出力電圧      |           |     | 1.2     |     | V                   |

| I <sub>OUT</sub>         | 出力電流      |           |     | 12      |     | A                   |

| ΔV <sub>OUT</sub>        | 過渡応答      | 9A 負荷ステップ |     | 40      |     | mV                  |

| V <sub>IN</sub>          | 入力電圧      |           | 4.5 | 12      | 17  | V                   |

| V <sub>OUT(ripple)</sub> | 出力電圧リップル  |           |     | 20      |     | mV <sub>(P-P)</sub> |

|                          | 入力電圧開始    | 入力電圧立ち上がり |     | 内蔵 UVLO |     | V                   |

|                          | 入力電圧停止    | 入力電圧立ち下がり |     | 内蔵 UVLO |     | V                   |

| F <sub>sw</sub>          | スイッチング周波数 |           |     | 1.2     |     | MHz                 |

| 動作モード                    |           |           |     | DCM     |     |                     |

| T <sub>A</sub>           | 周囲温度      |           |     | 25      |     | °C                  |

#### 7.2.2 詳細な設計手順

##### 7.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS56C215 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (VIN)、出力電圧 (VOUT)、出力電流 (IOUT) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 7.2.2.2 外付け部品の選択

#### 7.2.2.2.1 出力電圧設定点

アプリケーションの出力電圧を変更するには、帰還回路の上側抵抗値を変更する必要があります。この抵抗値を変更することで、出力電圧を 0.6V 以上に変更できます。[式 6](#) を参照してください。

$$V_{OUT} = 0.6 \times \left( 1 + \frac{R_{UPPER}}{R_{LOWER}} \right) \quad (6)$$

#### 7.2.2.2.2 スイッチング周波数およびモードの選択

スイッチング周波数、電流制限、スイッチングモード (DCM または FCCM) は、MODE ピンに接続された VREG5 から GND への分圧器によって設定されます。MODE の構成例については、[表 6-3](#) を参照してください。スイッチング周波数の選択は、高効率と小型設計とのトレードオフになります。スイッチング周波数が低いと、全体の効率は高くなりますが、外付け部品は比較的大きくなります。スイッチング周波数が高いほどスイッチング損失が増加し、効率や放熱性能が悪化します。本設計では、スイッチング周波数は 1.2 MHz、スイッチングモードは DCM、出力電流は 12A を選択しています。

#### 7.2.2.2.3 インダクタの選択

インダクタリップル電流は、出力コンデンサによってフィルタリングされます。インダクタのリップル電流が大きいほど、出力コンデンサのリップル電流定格はインダクタのリップル電流よりも大きくなればならないことを意味します。推奨インダクタ値については、[表 7-2](#) を参照してください。

インダクタを流れる RMS 電流およびピーク電流は、[式 7](#) および [式 8](#) を用いて算出できます。インダクタの定格がこの電流に対応できるものであることを確認してください。

$$I_{L(rms)} = \sqrt{I_{OUT}^2 + \frac{1}{12} \times \left( \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times L_{OUT} \times F_{SW}} \right)^2} \quad (7)$$

$$I_{L(peak)} = I_{OUT} + \frac{I_{OUT(ripple)}}{2} \quad (8)$$

過渡状態、短絡状態時には、インダクタ電流がデバイスの電流制限値まで増加する可能性があるため、電流制限時のピーク電流を上回る飽和電流に対応するインダクタを選択することが安全です。

#### 7.2.2.2.4 出力コンデンサの選択

インダクタ選定後、出力コンデンサを最適化する必要があります。[DCAP3](#) では、レギュレータがデューティ比の変化に対して 1 サイクル以内で応答するため、大きな出力容量を必要とせずに優れた過渡応答性能を得ることができます。推奨出力容量の範囲を [表 7-2](#) に示します

セラミック コンデンサは非常に低い ESR を備えていますが、それ以外の場合は、コンデンサの最大 ESR を  $V_{OUT(ripple)}$  /  $I_{OUT(ripple)}$  未満にする必要があります。

**表 7-2. 推奨部品値**

| $V_{OUT}$ (V) | $R_{LOWER}$ (kΩ) | $R_{UPPER}$ (kΩ) | $F_{sw}$ (kHz) | $L_{OUT}$ (μH) | $C_{OUT(min)}$ (μF) | $C_{OUT(max)}$ (μF) | $C_{FF}$ (pF) |

|---------------|------------------|------------------|----------------|----------------|---------------------|---------------------|---------------|

| 0.6           | 10               | 0                | 400            | 0.68           | 300                 | 500                 | -             |

|               |                  |                  | 800            | 0.47           | 100                 | 500                 | -             |

|               |                  |                  | 1200           | 0.33           | 88                  | 500                 | -             |

| 1.2           |                  | 10               | 400            | 1.2            | 100                 | 500                 | -             |

|               |                  |                  | 800            | 0.68           | 88                  | 500                 | -             |

|               |                  |                  | 1200           | 0.47           | 88                  | 500                 | -             |

| 3.3           |                  | 45.3             | 400            | 2.4            | 88                  | 500                 | 100 ~ 220     |

|               |                  |                  | 800            | 1.5            | 88                  | 500                 | 100 ~ 220     |

|               |                  |                  | 1200           | 1.2            | 88                  | 500                 | 100 ~ 220     |

| 5.5           |                  | 82.5             | 400            | 3.3            | 88                  | 500                 | 100 ~ 220     |

|               |                  |                  | 800            | 2.4            | 88                  | 500                 | 100 ~ 220     |

|               |                  |                  | 1200           | 1.5            | 88                  | 700                 | 100 ~ 220     |

#### 7.2.2.2.5 入力コンデンサの選択

必要な最小入力容量は、式 9 に示されています。

$$C_{IN(min)} = \frac{I_{OUT} \times V_{OUT}}{V_{IN(ripple)} \times V_{IN} \times F_{SW}} \quad (9)$$

TI は、入力電圧ピンに、40μF の高品質 X5R または X7R 入力デカップリング コンデンサを使用することを推奨します。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。コンデンサのリップル電流定格をアプリケーションの最大入力電流リップルよりも大きくする必要があります。入力リップル電流は、式 10 で計算できます。

$$I_{CIN(rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN(min)}} \times \frac{(V_{IN(min)} - V_{OUT})}{V_{IN(min)}}} \quad (10)$$

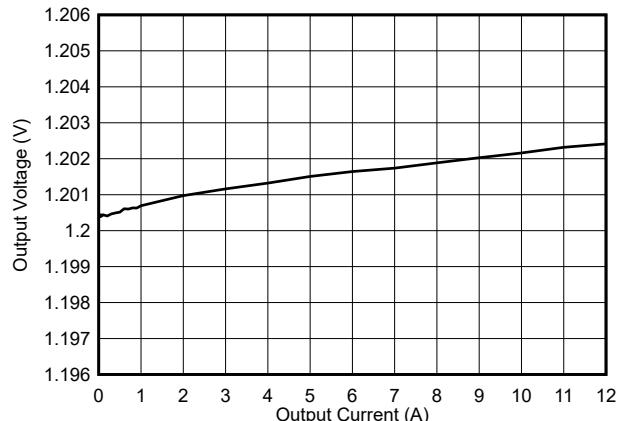

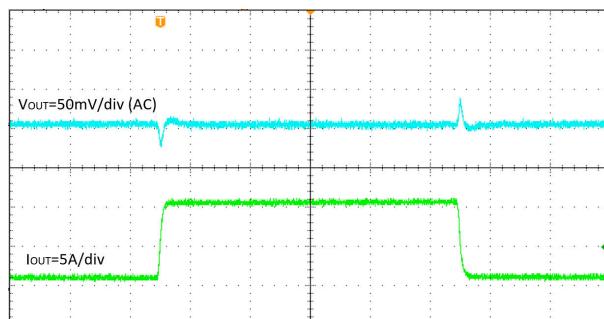

### 7.2.3 アプリケーション曲線

図 7-2 から 図 7-8 は 図 7-1 の回路に適用されます。 $V_{IN} = 12\text{ V}$ ,  $f_{SW} = 800\text{ kHz}$ ,  $T_a = 25^\circ\text{C}$  特に指定がない限り。

図 7-2. 効率

図 7-3. ロード レギュレーション

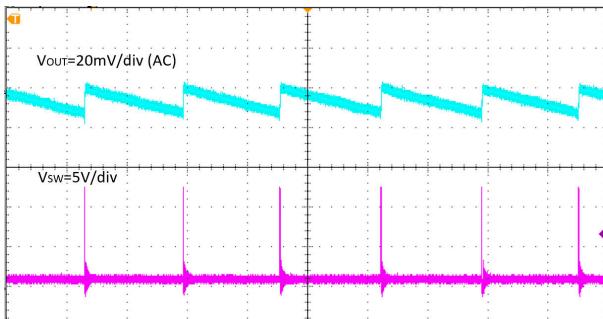

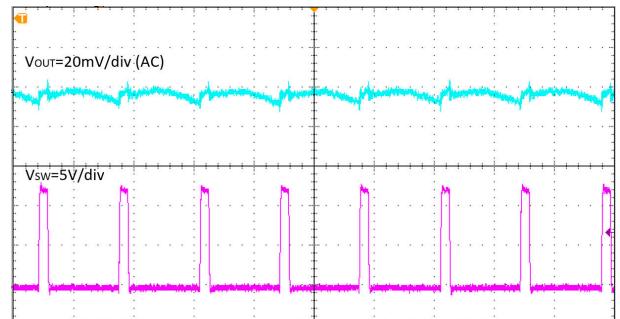

図 7-4. 出力電圧リップル、 $I_{OUT} = 10\text{mA}$ 、時間 = 80μS/div

図 7-5. 出力電圧リップル、 $I_{OUT} = 12\text{A}$ 、時間 = 1μS/div

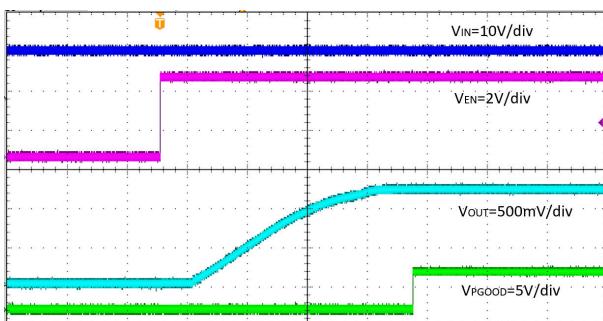

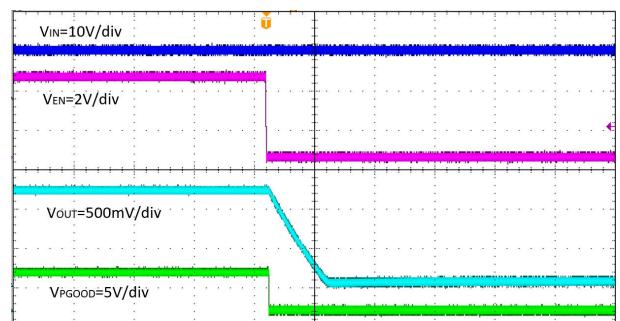

図 7-6. EN 立ち上がりに対するスタートアップ、時間 = 2ms/div

図 7-7. EN 立ち下がりに対するシャットダウン、時間 = 200μS/div

図 7-8. 過渡応答、負荷ステップ = 3A – 9A – 3A、スルーレート設定 = 2.5A/ $\mu\text{s}$ 、時間 = 100 $\mu\text{s}/\text{div}$

## 7.3 電源に関する推奨事項

TPS56C215 は、安定化された DC 電源による動作を前提に設計されています。入力電圧範囲は 3.8 ~ 17V です。TPS56C215 は降圧コンバータです。適切に動作させるには、入力電源電圧は目的の出力電圧よりも高い必要があります。入力電源電流は、目的の出力電流に適したものでなければなりません。入力電源が TPS56C215 回路から離れている場合は、追加の入力バルクコンデンサを推奨します。推奨値は 100 $\mu\text{F}$  ~ 470 $\mu\text{F}$  です。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

- 良好な熱特性と最大限のグランドプレーンを確保するために、4 層 または 6 層の PCB を推奨します。3 インチ × 3 インチ、2 オンス銅箔の 4 層 PCB を例として使用しています。

- IC の両側に等しい同じ値のコンデンサを配置することを推奨します。コンデンサは、VIN を挟んでできる限り近づけて配置します。

- 内層 1 はグランド層で、PGND と AGND のネットタイがあります

- 内層 2 には、VIN 銅箔領域があり、最上層の VIN と接続されています。デバイス直下の VIN や PGND、入力コンデンサ付近に複数のビアを配置し、寄生インダクタンスの提言を熱特性を向上させます

- 最下層は GND で、BOOT 配線経路があります。

- フィードバックはノイズの少ない AGND を基準とし、スイッチノードから離して配線してください。

- VIN 配線の幅を広くとり、配線インピーダンスを低減します。

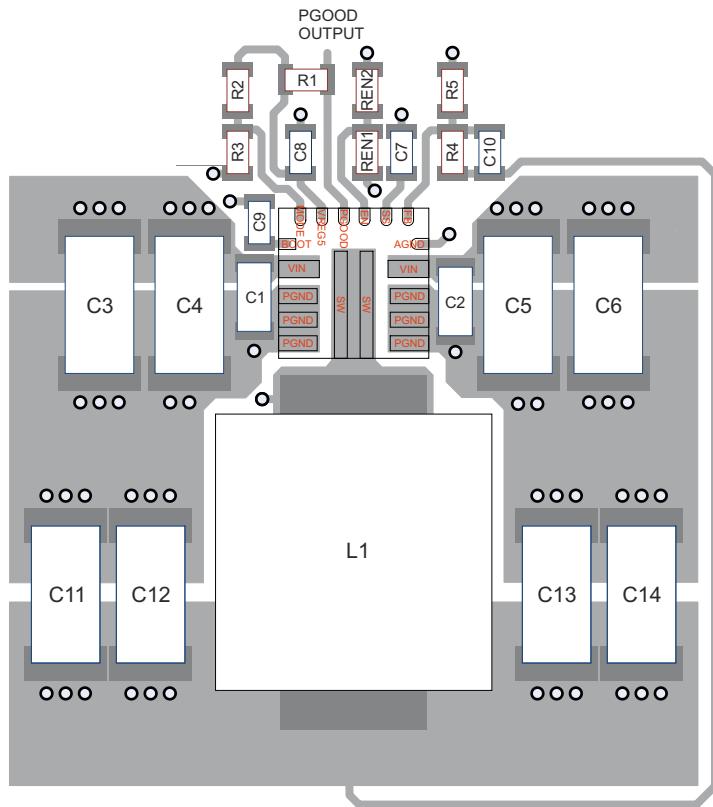

### 7.4.2 レイアウト例

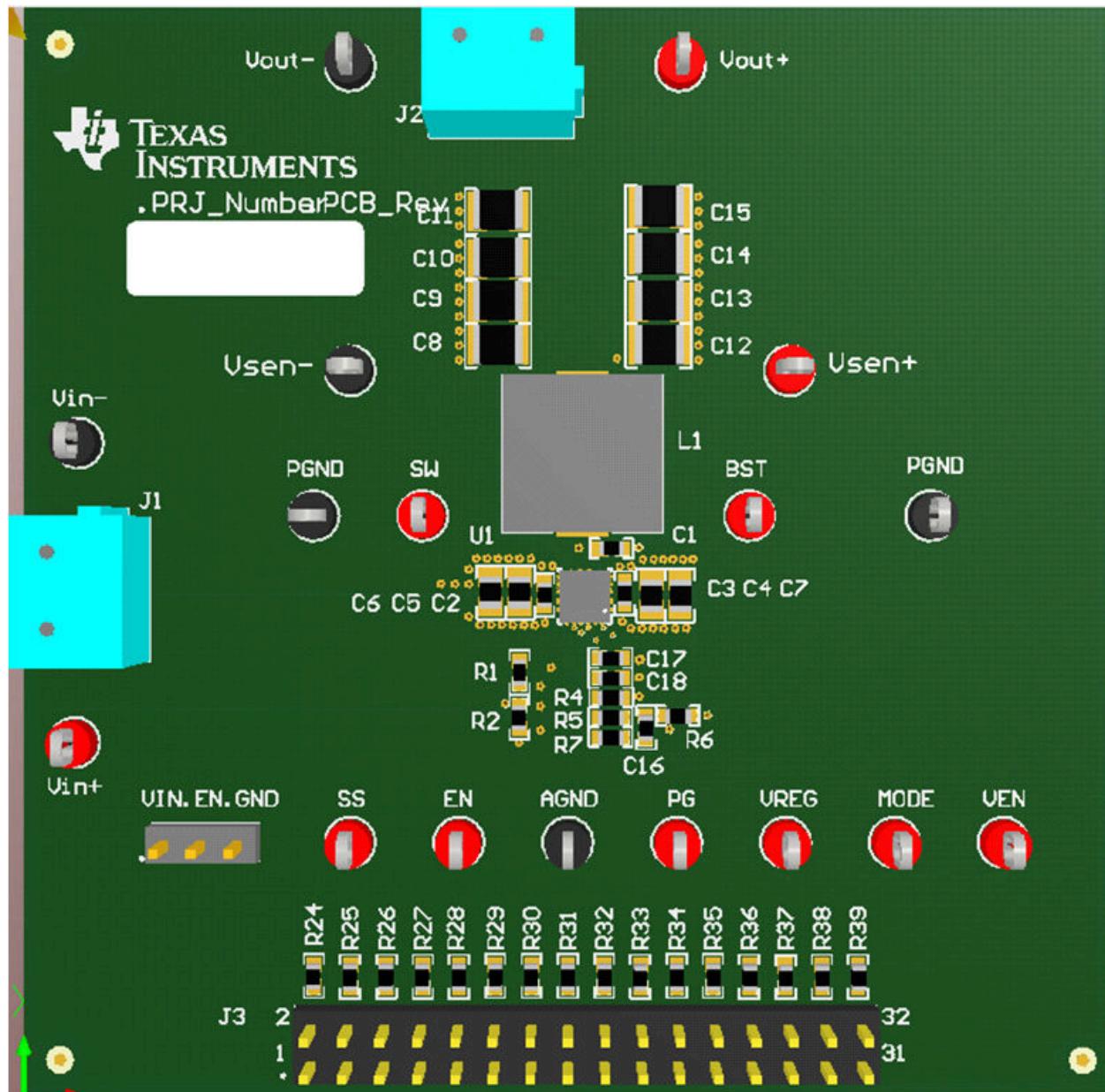

図 7-9 は、推奨される上面レイアウトを示しています。部品参照指定子は、図 7-1 に示す回路と同じです。図 7-1 の回路には EN 用分圧抵抗は使用されていませんが、参照用にレイアウトに示しています。

図 7-9. 上面レイアウト

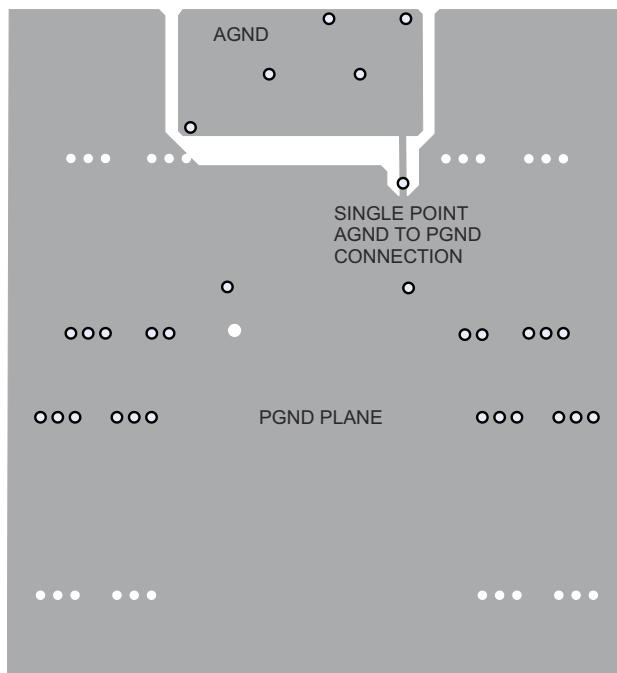

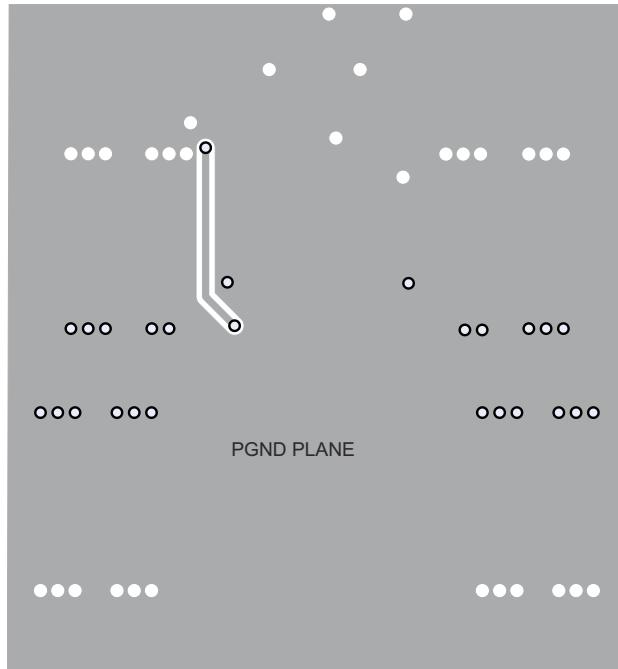

図 7-10 は、第 1 内層の推奨レイアウトを示しています。この図は、大きな PGND プレーンと小さな ANGD アイランドで構成されています。AGND と PGND 循環電流を低減するために 1 点で接続されています。

図 7-10. 中間層 1 レイアウト

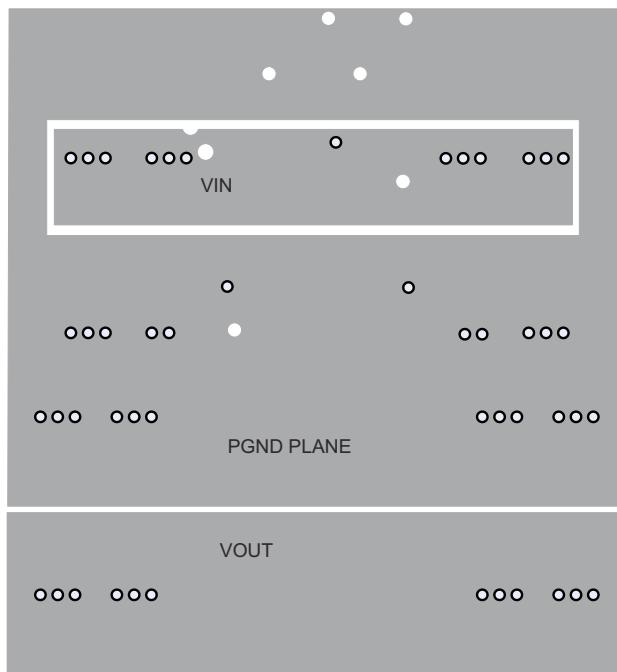

図 7-11 は、第 2 内層の推奨レイアウトを示しています。この図は、大きな PGND プレーン、上面の 2 つの  $V_{IN}$  銅箔領域を接続するための小さな銅箔領域、および 2 番目の  $V_{OUT}$  銅箔領域で構成されています。

図 7-11. 中間層 2 レイアウト

図 7-12 は、最下層の推奨レイアウトを示しています。この図は、大きな PGND プレーンと、BOOT コンデンサを SW ノードに接続するためのパターンで構成されています。

図 7-12. 最下層レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インストルメンツの出版物は、単独またはテキサス・インストルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 8.1.2 開発サポート

システム検証用評価モジュールは、図 8-1 に示されています。

図 8-1. システム検証用 EVM ボード

### 8.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS56C215 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (VIN)、出力電圧 (VOUT)、出力電流 (IOUT) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になります。

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

SWIFT™, D-CAP3™, HotRod™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision G (August 2024) to Revision H (June 2025)</b>                                                                                                        | <b>Page</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • MOSFET の値を $13.5\text{m}\Omega$ および $4.5\text{m}\Omega$ から $7.8\text{m}\Omega$ および $3.2\text{m}\Omega$ に変更.....                                                             | 1           |

| • 「機能」リストに WEBENCH リンクを追加.....                                                                                                                                                | 1           |

| • デバイスの最新データを含むように効率と出力電流との関係図を更新.....                                                                                                                                        | 1           |

| • $R_{DS(on)H}$ を $13.5\text{m}\Omega$ から $7.8\text{m}\Omega$ に、 $R_{DS(on)L}$ を $4.5\text{m}\Omega$ から $3.2\text{m}\Omega$ に、 $t_{UVOPEN}$ のヒップ時間から 7 サイクルから 14 サイクルに更新..... | 5           |

| • $I_{IN}$ の代表値を $600\mu\text{A}$ から $146\mu\text{A}$ に変更し、 $I_{IN}$ 最大値を削除.....                                                                                              | 5           |

| • $I_{VINSDN}$ の代表値を $7\mu\text{A}$ から $9.3\mu\text{A}$ に変更.....                                                                                                              | 5           |

| • $V_{PGOODTH}$ VFB の立ち下がり(良好)値を 107% から 108% に変更.....                                                                                                                        | 5           |

| • $V_{UVP}$ の値を 68% から 70% に変更.....                                                                                                                                           | 5           |

| • UVLO VREG5 立ち上がり電圧値を $4.3\text{V}$ から $4.25\text{V}$ に変更.....                                                                                                               | 5           |

| • UVLO VREG5 立ち下がり電圧値を $3.57\text{V}$ から $3.52\text{V}$ に変更.....                                                                                                              | 5           |

| • UVLO VREG5 = $4.7\text{V}$ の VIN 立ち下がり電圧 (VREG5 = $4.7\text{V}$ ) の値を $3.26\text{V}$ から $3.24\text{V}$ に変更.....                                                             | 5           |

| • UVLO VREG5 = $4.7\text{V}$ の VIN ヒステリシス (VREG5 = $4.7\text{V}$ ) の値を $60\text{mV}$ から $80\text{mV}$ に変更.....                                                                | 5           |

| • $t_{ON}$ の最小値を $54\text{ns}$ から $60\text{ns}$ に変更.....                                                                                                                      | 6           |

| • $t_{SS}$ の値を $1.045\text{ms}$ から $1.2\text{ms}$ に変更.....                                                                                                                    | 6           |

| • デバイスの最新データを反映するため、図 5-9 を図 5-34 に更新.....                                                                                                                                    | 7           |

| • ハイサイド RDS (ON) と温度の関係、およびローサイド RDS (ON) と温度の関係の図を削除.....                                                                                                                    | 7           |

| • MOSFET の値を $13.5\text{m}\Omega$ から $7.8\text{m}\Omega$ に、 $4.5\text{m}\Omega$ から $3.2\text{m}\Omega$ に変更.....                                                               | 13          |

| • 表 6-1 の「ゼロ位置」の値を $7.1$ から $17.8$ 、 $14.3$ から $27.1$ 、 $21.4$ から $29.8$ に変更.....                                                                                             | 14          |

| • 待機時間を $1\text{ms}$ から $1 \times t_{SS}$ に、ヒップ時間を $7\text{ms}$ から $14 \times t_{SS}$ に変更.....                                                                                | 19          |

| • 「過渡応答の強化」セクションを追加.....                                                                                                                                                      | 19          |

| • 「WEBENCH® ツールを使用したカスタム設計」セクションを追加.....                                                                                                                                      | 21          |

| • デバイスの最新データを含めるように「アプリケーション曲線」を更新.....                                                                                                                                       | 24          |

| • 「WEBENCH® ツールを使用したカスタム設計」セクションを追加.....                                                                                                                                      | 30          |

| <b>Changes from Revision F (August 2023) to Revision G (August 2024)</b> | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| • 製品ラインアップを更新し、説明を「テキサス・インスツルメンツ最小」から「小型」に変更.....                        | 1           |

| • $T_{SDN}$ VREG5 仕様を削除.....                                             | 5           |

| • SW オン時間パラメータに「設計値」の注を追加.....                                           | 6           |

| • 「境界外動作」セクションを削除.....                                                   | 14          |

| • 「サーマル シャットダウン」セクションを更新.....                                            | 19          |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

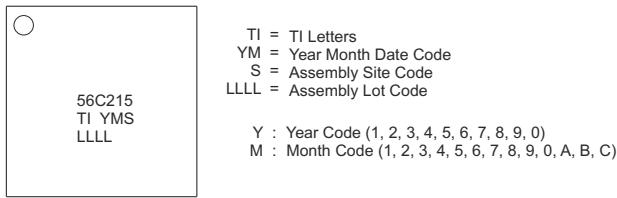

### 10.1 パッケージ マーキング

図 10-1. 記号表記

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins     | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|--------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS56C215RNNR</a> | Active        | Production           | VQFN-HR (RNN)   18 | 3000   LARGE T&R      | Yes         | Call TI   Sn                         | Level-2-260C-1 YEAR               | -40 to 125   | 56C215              |

| TPS56C215RNNR.A               | Active        | Production           | VQFN-HR (RNN)   18 | 3000   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | 56C215              |

| <a href="#">TPS56C215RNNT</a> | Active        | Production           | VQFN-HR (RNN)   18 | 250   SMALL T&R       | Yes         | Call TI   Sn                         | Level-2-260C-1 YEAR               | -40 to 125   | 56C215              |

| TPS56C215RNNT.A               | Active        | Production           | VQFN-HR (RNN)   18 | 250   SMALL T&R       | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | 56C215              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

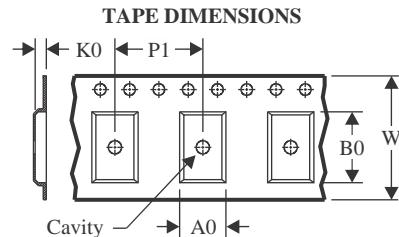

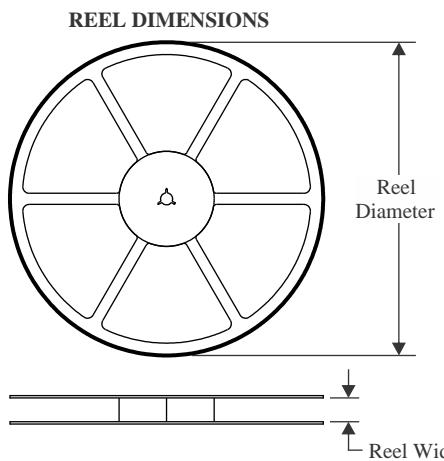

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS56C215RNRR | VQFN-HR      | RNN             | 18   | 3000 | 330.0              | 12.4               | 3.75    | 3.75    | 1.15    | 8.0     | 12.0   | Q1            |

| TPS56C215RNNT | VQFN-HR      | RNN             | 18   | 250  | 180.0              | 12.4               | 3.75    | 3.75    | 1.15    | 8.0     | 12.0   | Q1            |

| TPS56C215RNNT | VQFN-HR      | RNN             | 18   | 250  | 180.0              | 12.4               | 3.75    | 3.75    | 1.15    | 8.0     | 12.0   | Q1            |

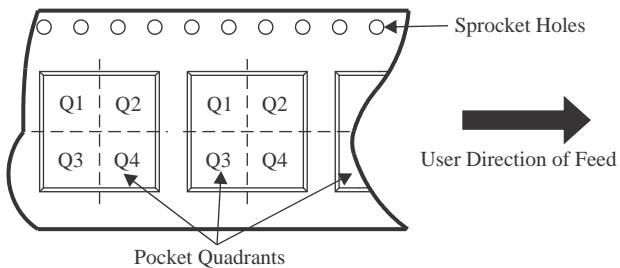

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS56C215RNRR | VQFN-HR      | RNN             | 18   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS56C215RNNT | VQFN-HR      | RNN             | 18   | 250  | 213.0       | 191.0      | 35.0        |

| TPS56C215RNNT | VQFN-HR      | RNN             | 18   | 250  | 210.0       | 185.0      | 35.0        |

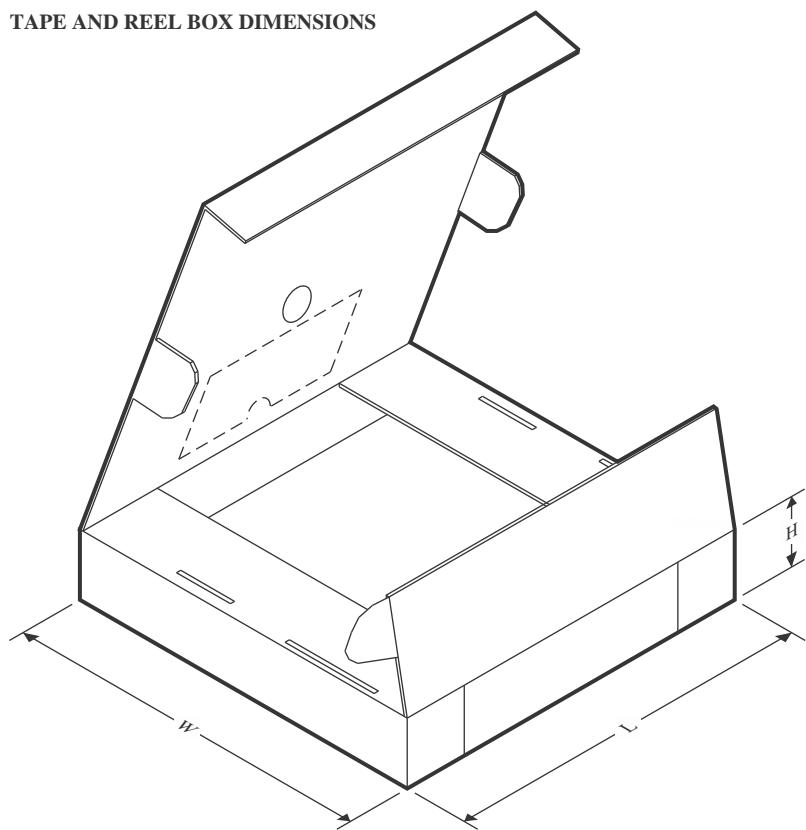

## **PACKAGE OUTLINE**

RNN0018A

## **VQFN-HR - 1 mm max height**

## PLASTIC QUAD FLATPACK - NO LEAD

4222688/E 03/2021

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

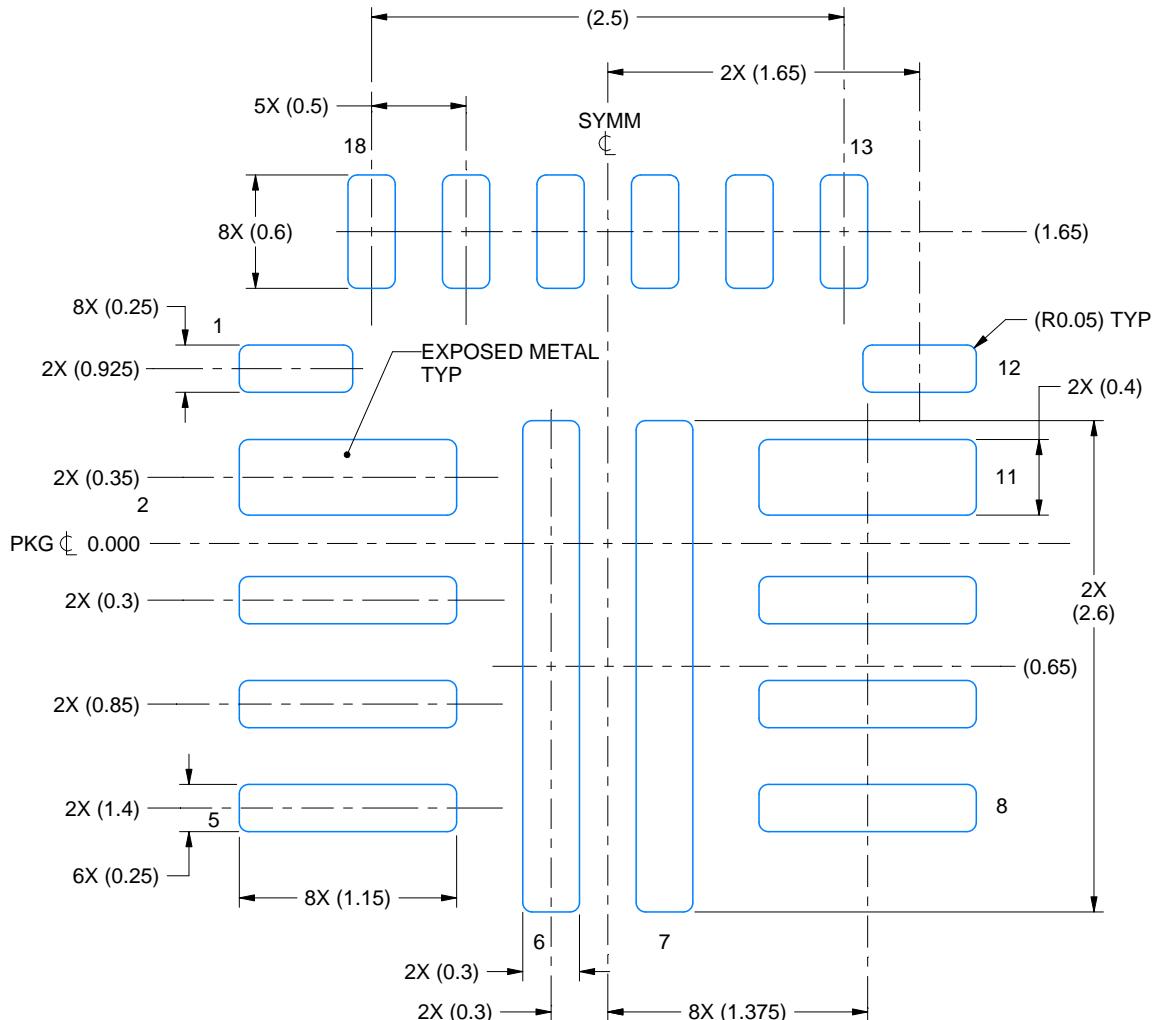

## **EXAMPLE BOARD LAYOUT**

RNN0018A

**VQFN-HR - 1 mm max height**

#### **PLASTIC QUAD FLATPACK - NO LEAD**

**LAND PATTERN EXAMPLE**

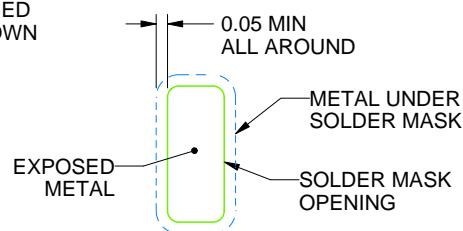

SOLDER MASK DEFINED

EXPOSED METAL SHOWN

SCALE:25X

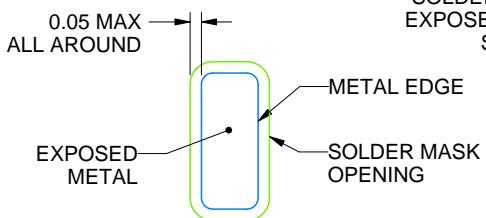

NON SOLDER MASK

DEFINED

(PREFERRED)

## SOLDER MASK DETAILS

#### NOTES: (continued)

3. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

4. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

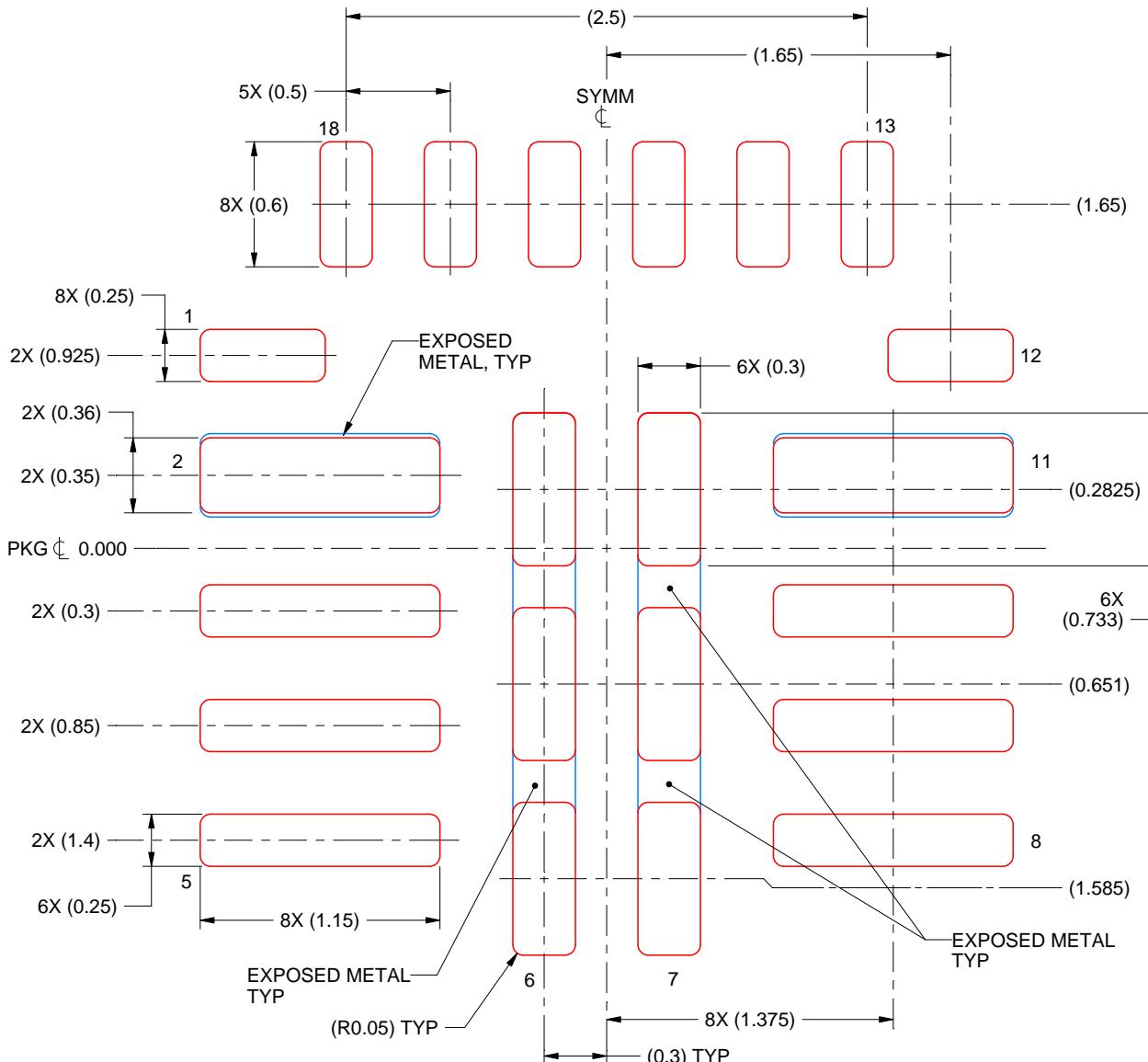

# EXAMPLE STENCIL DESIGN

RNN0018A

VQFN-HR - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

PADS 6 & 7: 83% - PADS 2 & 11: 90%

SCALE:30X

4222688/E 03/2021

NOTES: (continued)

5. For alternate stencil design recommendations, see IPC-7525 or board assembly site preference.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月