TPS54A20 SLVSCQ8A – DECEMBER 2015 – REVISED APRIL 2016

# TPS54A20 8-V to 14-V Input, 10-A, up to 10-MHz SWIFT™ Step Down Converter

#### 1 Features

- Two-phase, Synchronous Series Capacitor Buck Converter

- Automatic Current Balancing Between Phases

- 2-MHz to 5-MHz Per Phase Switching Frequency

- 14-ns Minimum On-Time

- 0.51-V to 2-V Output Voltage Range with ±0.5% Feedback Reference Voltage

- Input Overvoltage Lockout for 17-V Surge Protection

- Adjustable Current Limit with Auto Restart (Hiccup)

- · Synchronizes to an External Clock

- Fixed Frequency in Steady State

- Adaptive On-Time Control

- Internal Feedback Loop Compensation

- Internal Gate Drive LDO with External Supply Option

- EN Pin Allowing for Adjustable Input UVLO

- Selectable Soft-Start Time

- Monotonic Startup with Pre-biased Output

- Output Power Good Indicator (Open Drain)

- Output Overvoltage/Undervoltage Protection

#### 2 Applications

- Telecom, base station, and communications equipment

- Storage, SSD, DDR memory, switches, hubs, routers, and other networking equipment

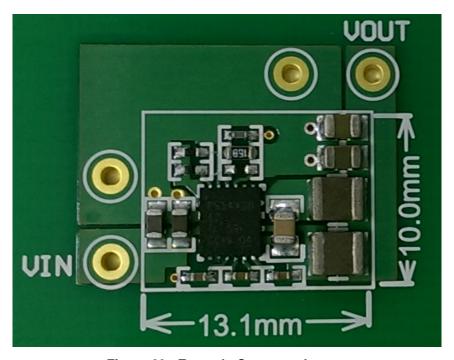

- Low profile/Backside board mounting (< 2 mm height)

#### 3 Description

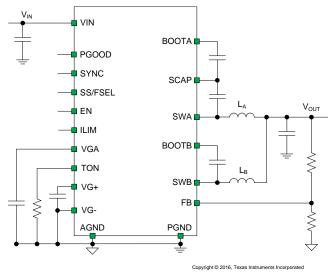

The TPS54A20 is a two-phase, synchronous series capacitor buck converter designed for small size, low voltage applications from a 12-V input rail. This topology uniquely merges a switched capacitor circuit with a two phase buck converter. Advantages include automatic current balancing between the inductors, lower switching losses which enable high frequency (HF) operation, and voltage step-down through the series capacitor. Small, low profile inductors used with the TPS54A20 significantly reduce total solution area and height. An adaptive on-time control architecture provides fast transient response and accurate voltage regulation at up to 10-MHz operating frequency. Fixed frequency operation during steady state is maintained through the use of a phase lock loop (PLL) to lock switching signals to a reference oscillator.

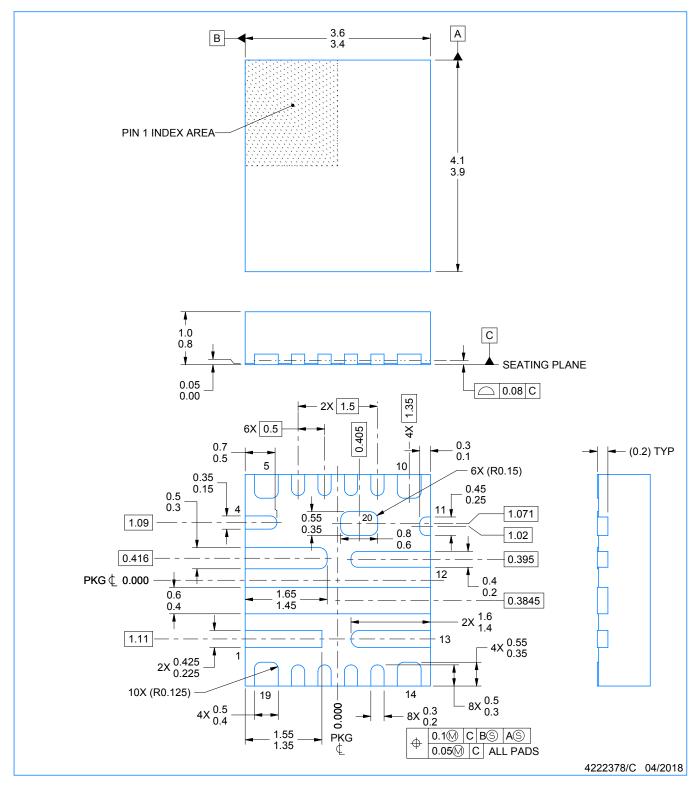

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE        | BODY SIZE (NOM) |

|-------------|----------------|-----------------|

| TPS54A20    | VQFN (20 pins) | 3.5 mm x 4 mm   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

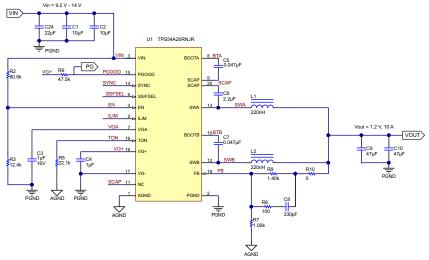

## Simplified Schematic

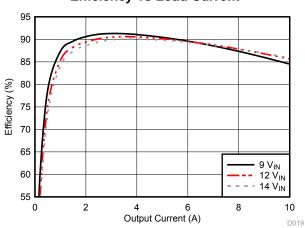

#### **Efficiency vs Load Current**

1.8  $V_{OUT}$ , 2 MHz per phase, External VG+, 3.2 x 2.5 x 1.2 mm inductors

# **Table of Contents**

| 1 | Features 1                           |    | 7.3 Feature Description              | 16 |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                       | 8  | Application and Implementation       | 22 |

| 3 | Description 1                        |    | 8.1 Application Information          | 22 |

| 4 | Revision History2                    |    | 8.2 Typical Application              | 23 |

| 5 | Pin Configuration and Functions      | 9  | Power Supply Recommendations         | 31 |

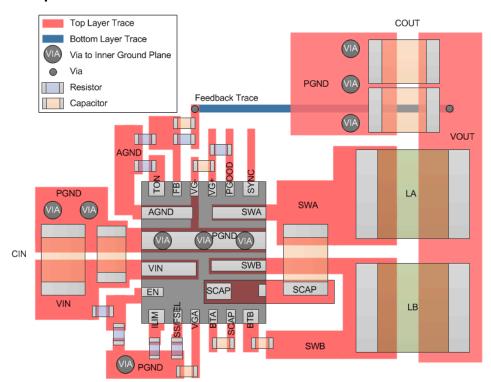

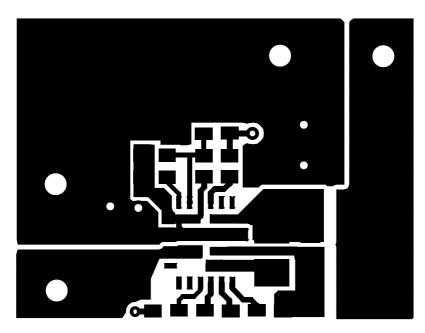

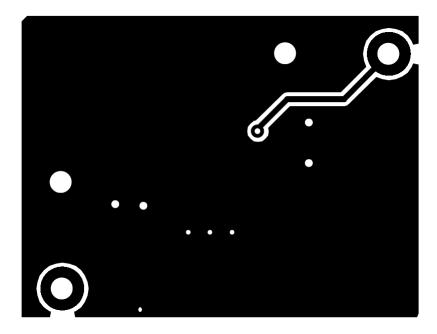

| 6 | Specifications4                      | 10 | Layout                               | 32 |

| • | 6.1 Absolute Maximum Ratings         |    | 10.1 Layout Guidelines               | 32 |

|   | 6.2 ESD Ratings                      |    | 10.2 Layout Example                  | 33 |

|   | 6.3 Recommended Operating Conditions | 11 | Device and Documentation Support     | 35 |

|   | 6.4 Thermal Information              |    | 11.1 Documentation Support           | 35 |

|   | 6.5 Electrical Characteristics       |    | 11.2 Community Resources             | 35 |

|   | 6.6 Timing Requirements              |    | 11.3 Trademarks                      | 35 |

|   | 6.7 Typical Characteristics8         |    | 11.4 Electrostatic Discharge Caution | 35 |

| 7 | Detailed Description                 |    | 11.5 Glossary                        |    |

| • | 7.1 Overview                         | 12 | Mechanical, Packaging, and Orderable | 35 |

|   | 7.2 Functional Block Diagram         |    | IIIOIIIIauoii                        |    |

# 4 Revision History

| Changes from Original (December 2015) to Revision A |                                              |   |  |

|-----------------------------------------------------|----------------------------------------------|---|--|

| •                                                   | Changed the device status to Production data | 1 |  |

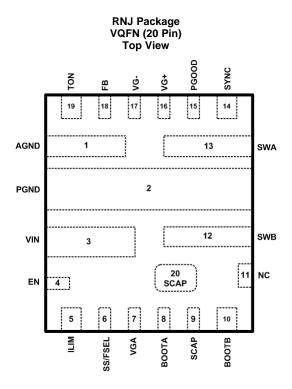

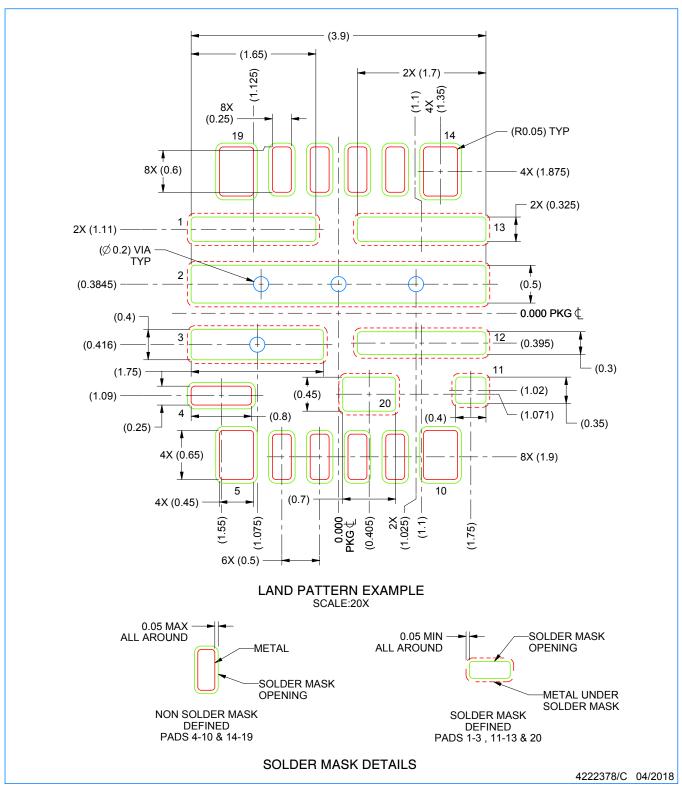

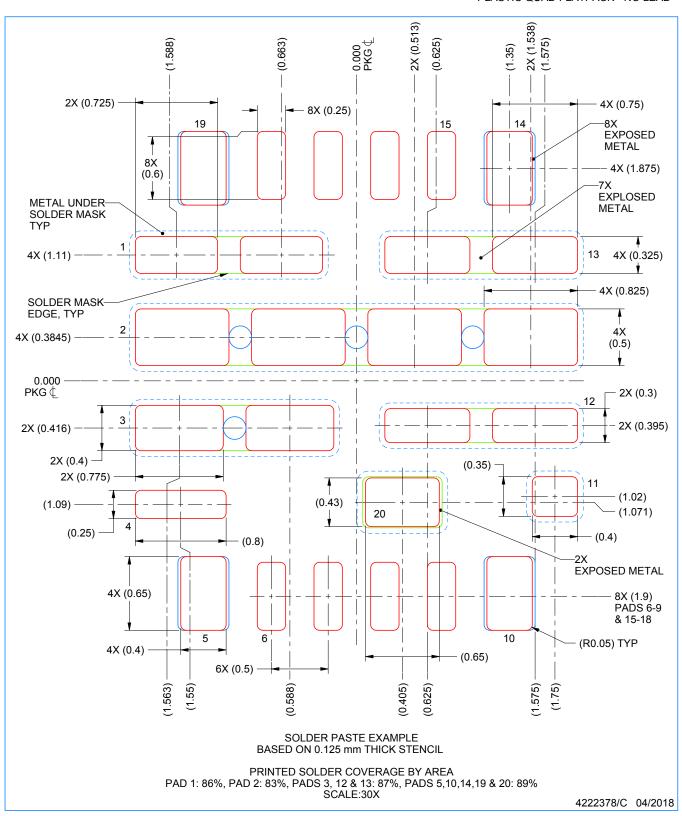

# 5 Pin Configuration and Functions

#### **Pin Functions**

|         | PIN  | (4)                |                                                                                                                                                                                                                                                                                                                                        |

|---------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

| AGND    | 1    | G                  | Analog signal ground of the IC. AGND should be connected to PGND and VG- at a single point on PCB (e.g. underneath the IC).                                                                                                                                                                                                            |

| воота   | 8    | S                  | Bootstrap capacitor node for phase A high-side MOSFET gate driver. Connect the bootstrap capacitor from this pin to the SCAP pin (pin 9).                                                                                                                                                                                              |

| воотв   | 10   | S                  | Bootstrap capacitor node for phase B high-side MOSFET gate driver. Connect the bootstrap capacitor from this pin to the SWB pin.                                                                                                                                                                                                       |

| EN      | 4    | 1                  | Enable pin. Floating this pin will enable the IC. Pull below 1.23V to enter shutdown mode. Can also be used to adjust the input undervoltage lockout above 8 V with two resistors.                                                                                                                                                     |

| FB      | 18   | I                  | Feedback pin for voltage regulation. Connect this pin to the center tap of a resistor divider to set the output voltage.                                                                                                                                                                                                               |

| ILIM    | 5    | I                  | Current limit programming pin. A resistor between this pin and ground sets the current limit. If no resistor is included, the default load current limit is 15 A.                                                                                                                                                                      |

| NC      | 11   |                    | No connect. This pin is not electrically connected to the IC and is included for board level reliability (BLR) purposes. Connect this pin to the SCAP trace.                                                                                                                                                                           |

| PGND    | 2    | G                  | Power ground of the IC. PGND should be connected to AGND and VG- at a single point on PCB (e.g. underneath the IC). Thermal vias to internal ground planes should be added beneath this pin.                                                                                                                                           |

| PGOOD   | 15   | 0                  | Power good indicator. This pin is an open-drain output and will assert low if the output voltage is greater than ±5% away from the desired value or due to thermal shutdown, over-voltage/under-voltage, EN shutdown, or during soft start. A pull-up resistor can be connected between PGOOD and VG+ or an external logic supply pin. |

| SCAP    | 9,20 | 0                  | Series capacitor pin. Connect a ceramic capacitor from pin 20 to the SWA pin.                                                                                                                                                                                                                                                          |

| SS/FSEL | 6    | I                  | Soft start/frequency select pin. Connect a resistor from this pin to ground to set the soft-start time and the switching frequency. If no resistor is provided, the default setting of 4MHz oscillator frequency and 512µs soft start time is used.                                                                                    |

| SWA     | 13   | 0                  | Switching node for phase A. Connect an inductor from this pin to the output capacitors.                                                                                                                                                                                                                                                |

| SWB     | 12   | 0                  | Switching node for phase B. Connect an inductor from this pin to the output capacitors.                                                                                                                                                                                                                                                |

| SYNC    | 14   | 1                  | External clock synchronization pin. An external clock signal can be connected to this pin to synchronize the oscillator frequency (within ±10% of the nominal frequency set via SS/FSEL).                                                                                                                                              |

(1) I = Input, O = Output, S = Supply, G = Ground Return

#### Pin Functions (continued)

|      | PIN      |        | DESCRIPTION .                                                                                                                                                                                                                                                             |  |  |  |

|------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME | NO.      | 1/0(*/ | DESCRIPTION                                                                                                                                                                                                                                                               |  |  |  |

| TON  | TON 19 I |        | On-time selection. An external resistor from this pin to the AGND pin programs the nominal on-time of the high side switches.                                                                                                                                             |  |  |  |

| VG+  | 16       | S      | Gate driver positive supply pin. Connect a bypass capacitor from this pin to VG To improve converter efficiency, the internal regulator can be overridden by connecting an external 5V supply to this pin. This supply rail also provides power to the control circuitry. |  |  |  |

| VG-  | 17       | G      | Gate driver supply return pin. VG- should be connected to PGND and AGND at a single point on PCB (e.g. underneath the IC).                                                                                                                                                |  |  |  |

| VGA  | 7        | S      | High side phase A gate driver supply pin. Connect a bypass capacitor from this pin to ground.                                                                                                                                                                             |  |  |  |

| VIN  | 3        | 1      | The power input pin to the IC. Connect VIN to a supply voltage between 8 V and 14 V.                                                                                                                                                                                      |  |  |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                       |                                                 |                                   | MIN  | MAX              | UNIT |

|-----------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|------|------------------|------|

|                                                                       | Dawer Conversion VIN                            | DC w.r.t. PGND, switching         | -0.3 | 15               | V    |

|                                                                       | Power Conversion, VIN                           | DC w.r.t. PGND, non-switching     | -0.3 | 17               | V    |

| Input Voltage  Output Voltage  Voltage  Input Current  Output Current | De etetere V                                    | DC with respect to PGND           | -0.3 | 22               | V    |

|                                                                       | Bootstrap, V <sub>(BOOTA)</sub>                 | DC with respect to SCAP           |      | 6                | V    |

|                                                                       | Do atation V                                    | DC with respect to PGND           | -0.3 | 14               | V    |

| Innut Voltage                                                         | Bootstrap, V <sub>(BOOTB)</sub>                 | DC with respect to SWB            |      | 6                | V    |

|                                                                       | Bias Supply, VG                                 | DC with respect to PGND           | -0.3 | 6                | V    |

|                                                                       | Series Capacitor Node Voltage, $V_{(SCAP)}$     | DC with respect to PGND           | -0.3 | 16               |      |

|                                                                       | Switch Node Voltage, V <sub>(SWA,</sub>         | DC with respect to PGND           | -1   | 9                | V    |

|                                                                       | SWB)                                            | Pulse < 10 ns                     | -4   | 14               |      |

|                                                                       | Feedback, V <sub>(FB)</sub>                     |                                   | -0.3 | 3                | V    |

| Output Voltage                                                        | Bias Supply, V <sub>(VGA)</sub>                 | DC with respect to PGND           | -0.3 | 15               | V    |

| Voltage                                                               | Enable Voltage, V <sub>(EN)</sub>               | Enable Voltage, V <sub>(EN)</sub> |      |                  |      |

|                                                                       | Soft Start/Freq. Select, V <sub>(SS/FSEI)</sub> | -0.3                              | 3    |                  |      |

|                                                                       | Power Good Voltage, V <sub>(PGOOD)</sub>        |                                   | -0.3 | 6                | V    |

|                                                                       | External Sync Clock Voltage, V(S                | SYNC)                             | -0.3 | 6                | V    |

|                                                                       | Current Limit/Mode Select, V(ILIM               | 1)                                | -0.3 | 3                |      |

|                                                                       | On Time Pin Voltage, V <sub>(TON)</sub>         |                                   | -0.3 | 3                |      |

| lanut Currant                                                         | Power Conversion, I <sub>(VIN)</sub>            |                                   |      | 6                | Α    |

| input Current                                                         | Bias Supply, I <sub>(VG)</sub>                  |                                   |      | 100              | mA   |

| Voltage Input Current                                                 | Switch Node A, I <sub>(SWA)</sub>               |                                   |      | Current<br>Limit | Α    |

|                                                                       | Switch Node B, I <sub>(SWB)</sub>               |                                   |      | Current<br>Limit | Α    |

| Operating Junction                                                    | Temperature, T <sub>J</sub>                     |                                   | -40  | 125              | °C   |

| Storage temperature                                                   | e, T <sub>stq</sub>                             |                                   | -65  | 150              | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|             |                         |                                                                               | VALUE | TINU |

|-------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                      | MIN | NOM MAX            | UNIT |

|------------------|----------------------|-----|--------------------|------|

| $V_{IN}$         | Input Voltage        | 8   | 14                 | V    |

| V <sub>OUT</sub> | Output Voltage       | 0.5 | V <sub>IN</sub> /5 | V    |

| I <sub>OUT</sub> | Output Current       | 0   | 10                 | Α    |

| TJ               | Junction Temperature | -40 | 125                | °C   |

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | RNJ               | LINUT |

|----------------------|----------------------------------------------|-------------------|-------|

|                      | THERMAL METRIC**                             | 20 PINS           | UNIT  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 25 <sup>(2)</sup> | °C/W  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 13.4              | °C/W  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 4.9               | °C/W  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2               | °C/W  |

| ΨЈВ                  | Junction-to-board characterization parameter | 4.7               | °C/W  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.0               | °C/W  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) Tested on four layer evaluation board.

#### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                                                                              | TEST CONDITIONS                                              | MIN    | TYP     | MAX    | UNIT     |

|-----------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------|--------|---------|--------|----------|

| SUPPLY          | VOLTAGE (VIN PIN)                                                                      |                                                              |        |         |        |          |

| V <sub>IN</sub> | VIN Operating                                                                          |                                                              | 8      | 12      | 14     | V        |

|                 | VIN Input UVLO Voltage                                                                 | VIN rising                                                   | 7.4    | 7.65    | 7.95   | V        |

|                 | VIN UVLO hysteresis                                                                    | 1 3                                                          |        | 250     |        | mV       |

|                 |                                                                                        | VIN rising                                                   |        | 15.4    | 15.8   | V        |

|                 | VIN Input OVLO Voltage                                                                 | VIN falling                                                  | 14.1   | 14.8    |        | V        |

|                 | VIN OVLO hysteresis                                                                    | T. T. T. Samuely                                             |        | 600     |        | mV       |

|                 | Shutdown                                                                               | EN < 0.4 V, V <sub>IN</sub> = 12 V, T <sub>A</sub> = 25°C    |        | 47      |        | μA       |

| IQ              | Operating into VIN                                                                     | FB = 0.53 V, $V_{IN}$ = 12 V, $T_A$ = 25°C                   |        | 6       |        | mA       |

|                 | E (EN PIN)                                                                             | 1 B = 0.00 V, V <sub>IN</sub> = 12 V, 1 <sub>A</sub> = 20 0  |        |         |        | 1117 (   |

| LIVADEL         | Enable threshold                                                                       |                                                              | 1.17   | 1.23    | 1.27   | V        |

|                 | Litable titleshold                                                                     | Enable threshold + 50 mV                                     | 1.17   | -4      | 1.21   | μA       |

|                 | Input current                                                                          | Enable threshold – 50 mV                                     |        |         |        |          |

| VOLTAC          | DE DEFEDENCE                                                                           | Enable threshold – 50 mV                                     |        | _1      |        | μA       |

| VULTAG          | GE REFERENCE                                                                           | T 25°C                                                       | 0.5054 | 0.500   | 0.5400 | 17       |

|                 | Voltage Reference                                                                      | T <sub>A</sub> = 25°C                                        | 0.5054 | 0.508   | 0.5106 | V        |

|                 |                                                                                        | -40°C < T <sub>J</sub> < 125°C                               | 0.5029 | 0.508   | 0.5131 | V        |

| FREQUE          | ENCY                                                                                   | T                                                            |        |         |        |          |

|                 |                                                                                        | $R_{(SS/FSEL)}$ = Open, 71.5 k $\Omega$ , or 48.7 k $\Omega$ | 3.6    | 4       | 4.4    | MHz      |

| $f_{OSC}$       | Oscillator Frequency                                                                   | $R_{(SS/FSEL)} = Short or 35.7 k\Omega$                      | 6.3    | 7       | 7.7    | MHz      |

|                 |                                                                                        | $R_{(SS/FSEL)}$ = 21.5 kΩ, 15.4 kΩ, or 8.66 kΩ               | 9      | 10      | 11     | MHz      |

| SYNC            |                                                                                        |                                                              |        |         |        |          |

|                 | Minimum Input Clock Pulsewidth                                                         |                                                              |        |         | 20     | ns       |

|                 | SYNC high threshold                                                                    |                                                              |        |         | 2      | V        |

|                 | SYNC low threshold                                                                     |                                                              | 0.8    |         |        | V        |

|                 | Frequency sync range                                                                   |                                                              |        | ±10     |        | % nomina |

|                 | Last SYNC falling/rising edge to return to resistor timing mode if SYNC is not present | 10 MHz: 400 ns<br>7 MHz: 571 ns<br>4 MHz : 1 µs              |        | 4       |        | Cycles   |

| I OW-SIF        | DE A MOSFET                                                                            | - 1/11/12. Τ μο                                              |        |         |        |          |

| 2011 011        | On resistance                                                                          | VG = 5 V, Measured at pins                                   |        | 6.8     | 10.5   | mΩ       |

| I OW-SIE        | DE B MOSFET                                                                            | VO = 5 V, Measured at pins                                   |        | 0.0     | 10.5   | 11122    |

| LO11-011        | On resistance                                                                          | VG = 5 V, Measured at pins                                   |        | 9.3     | 14.8   | mΩ       |

| HIGH-SII        | DE MOSFETS                                                                             | vo = o v, measured at pms                                    |        | 0.0     | 14.0   | 11132    |

| 111011-011      | On resistance                                                                          | Vgs = 5 V, Measured at pins                                  |        | 27      | 50     | mΩ       |

|                 | SW rise time 10% to 90%                                                                | VIN = 12 V                                                   |        | 2       | 30     |          |

|                 | SW fall time 90% to 10%                                                                | VIN = 12 V<br>VIN = 12 V                                     |        | 2       |        | ns       |

| CURREN          | NT LIMIT                                                                               | VIIV = 12 V                                                  |        |         |        | ns       |

| CURKEN          | NI LIMII                                                                               | 45A Lood Trip D. Onco                                        | 40.7   | 40.0    | 40.0   |          |

|                 | Peak Switch LSA Current Limit                                                          | ~15A Load Trip, R <sub>(ILIM)</sub> = Open                   | 12.7   | 16.3    | 19.9   | Α        |

|                 |                                                                                        | ~11.25A Load Trip, $R_{(ILIM)} = 47 \text{ k}\Omega$         | 9.9    | 12.7    | 15.5   |          |

|                 | Peak Switch LSB Current Limit                                                          | ~15A Load Trip, R <sub>(ILIM)</sub> = Open                   | 6.8    | 8.7     | 10.6   | Α        |

|                 |                                                                                        | ~11.25A Load Trip, $R_{(ILIM)} = 47 \text{ k}\Omega$         | 5.3    | 6.8     | 8.3    |          |

|                 | Overcurrent protection scheme                                                          |                                                              |        | Hiccup  |        |          |

|                 | OCP cycle count to trip fault                                                          |                                                              |        | 3       |        | Cycles   |

|                 | , ,                                                                                    |                                                              |        |         |        |          |

|                 | Fault hiccup wait time                                                                 | 10 MHz: 13.1 ms<br>7 MHz: 18.7 ms                            |        | 131,072 |        | Cycles   |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                     | MIN | TYP     | MAX  | UNIT              |

|----------------------------------|-----------------------------------------------------|-----|---------|------|-------------------|

| INTERNAL REGULATOR (VG LDO)      | ,                                                   |     |         |      |                   |

| Output Voltage                   | 0 mA ≤ I <sub>VG</sub> ≤ 100 mA                     | 4.4 | 4.8     | 5    | V                 |

| Current Limit                    |                                                     | 100 | 140     |      | mA                |

| Nominal Operating Current        | Fosc = 10 MHz, I <sub>LOAD</sub> = 10A              |     | 60      |      | mA                |

| DYNAMIC REGULATOR (VGA LDO)      |                                                     |     |         |      |                   |

| Outrot Valtage                   |                                                     |     |         | 15   | V                 |

| Output Voltage                   | VIN = 12 V                                          |     | 10.5    |      | V                 |

| SERIES CAP MONITOR               |                                                     |     |         |      |                   |

| Low Voltage Fault Trip           |                                                     |     | 35      | 38   | %VIN              |

| Nominal Voltage                  |                                                     |     | 50      |      |                   |

| High Voltage Fault Trip          |                                                     | 62  | 65      |      |                   |

| Capacitor Precharge Current      |                                                     | 5.5 | 10      | 14.5 | mA                |

| POWER GOOD                       | ,                                                   | •   |         | ·    |                   |

|                                  | V <sub>FB</sub> falling (Fault), UVP                |     | 90      |      |                   |

| V throobold                      | V <sub>FB</sub> rising (Good)                       |     | 95      |      | 0/1/              |

| V <sub>FB</sub> threshold        | V <sub>FB</sub> rising (Fault), OVP                 |     | 110     |      | %V <sub>REI</sub> |

|                                  | V <sub>FB</sub> falling (Good)                      |     | 105     |      |                   |

| PGOOD sink current               | $V_{(PGOOD)} = 0.4 \text{ V}$                       |     | 2.7     |      | mA                |

| PGOOD pin leakage current        | $V_{FB} = V_{REF}, V_{(PGOOD)} = 5 V$               |     |         | 1    | μΑ                |

| Minimum $V_{IN}$ for valid PGOOD | V <sub>(PGOOD)</sub> ≤ 0.5 V at 100 μA              |     | 1.2     | 2.75 | V                 |

| THERMAL SHUTDOWN                 |                                                     |     |         |      |                   |

| Thermal shutdown set threshold   |                                                     |     | 135     |      | °C                |

| Thermal shutdown hysteresis      |                                                     |     | 20      |      | °C                |

| Thermal shutdown hiccup time     | 10 MHz: 13.1 ms<br>7 MHz: 18.7 ms<br>4 MHz: 32.8 ms |     | 131,072 |      | Cycles            |

## 6.6 Timing Requirements

| o.o mining Kequirements                                      | <u> </u>                   |     |     |     |      |

|--------------------------------------------------------------|----------------------------|-----|-----|-----|------|

|                                                              |                            | MIN | NOM | MAX | UNIT |

| ENABLE (EN PIN)                                              |                            | •   |     | •   |      |

| Enable to Start Switching time                               | 1 μF series cap, VIN = 12V |     | 625 |     | μs   |

| SYNC                                                         |                            | ·   |     |     |      |

| Lock in time                                                 |                            |     | 30  |     | μs   |

| HIGH-SIDE MOSFETS                                            |                            | ·   |     |     |      |

| SW minimum ON pulse width                                    |                            |     | 14  |     | ns   |

| SW minimum OFF pulse width                                   |                            |     | 10  |     | ns   |

| Non-Overlap Time between HS FET Off and LS FET On (deadtime) | Face FMII- VIN 40 V        |     | 3   |     | ns   |

| Non-Overlap Time between LS FET Off and HS FET On (deadtime) | Fsw = 5 MHz, VIN = 12 V    |     | 3   |     | ns   |

# TEXAS INSTRUMENTS

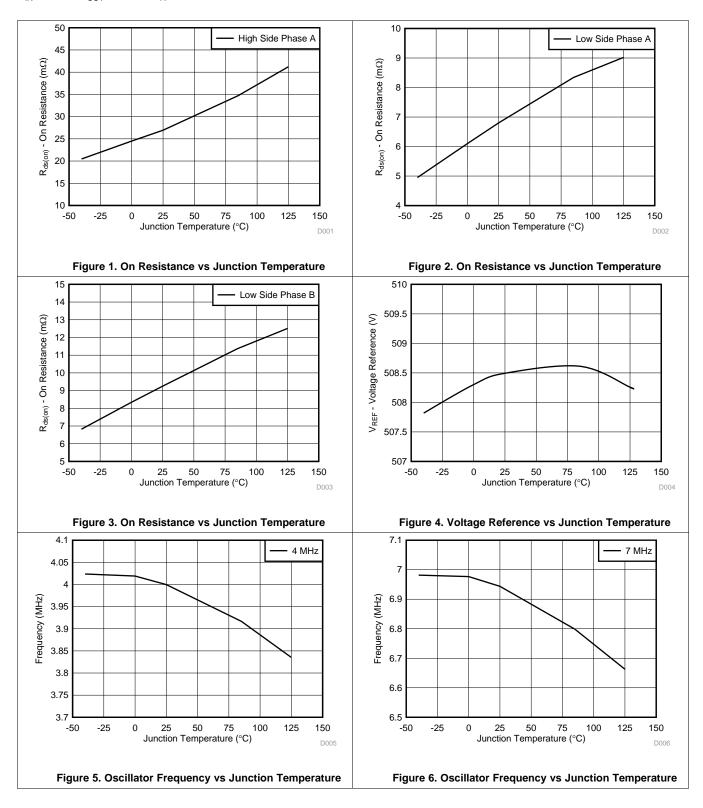

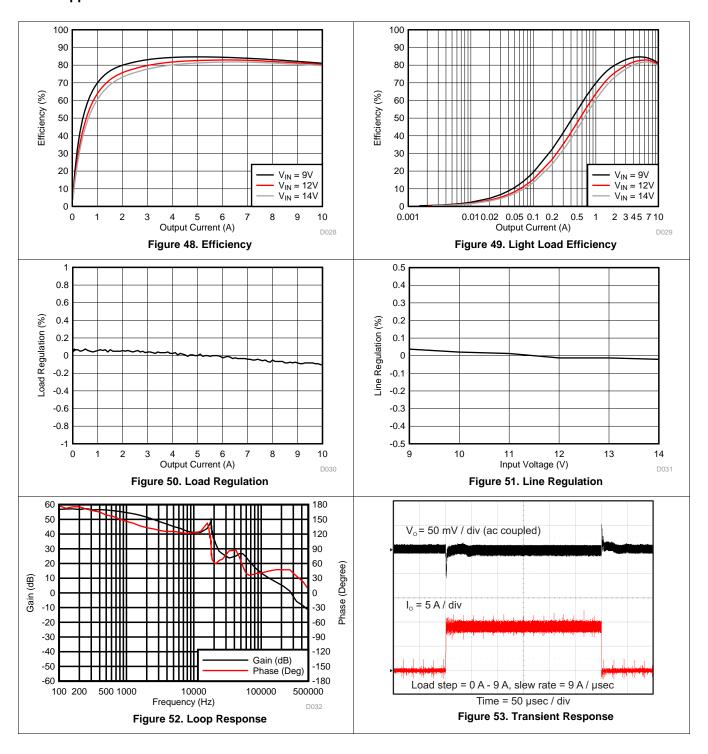

#### 6.7 Typical Characteristics

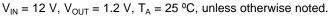

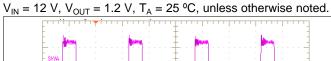

$V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $T_A$  = 25 °C, unless otherwise noted.

Submit Documentation Feedback

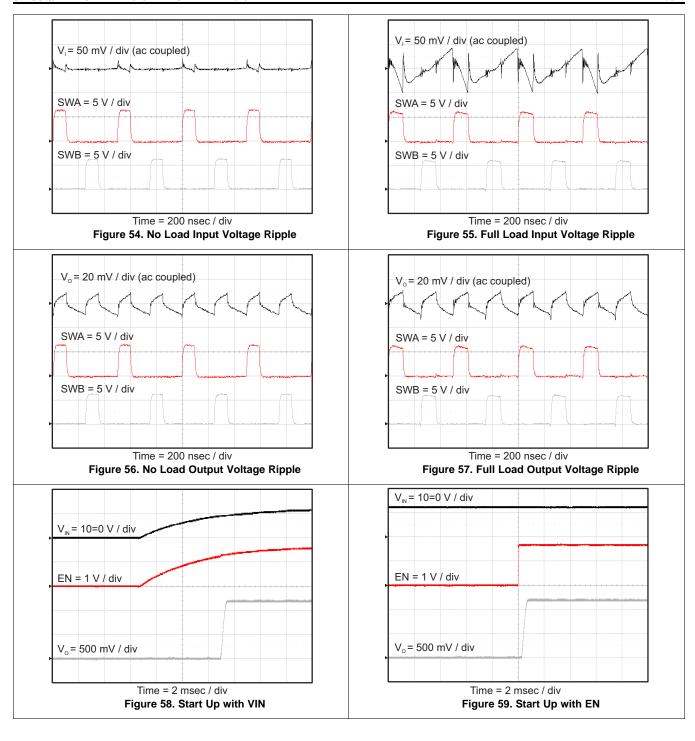

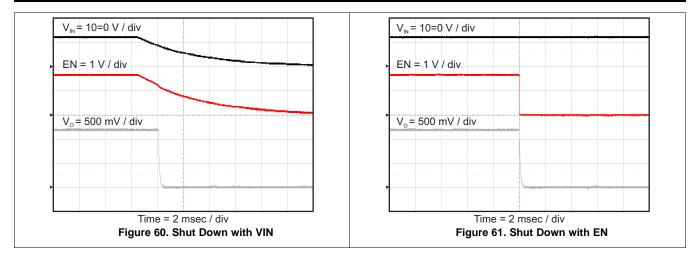

#### **Typical Characteristics (continued)**

$V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $T_A$  = 25 °C, unless otherwise noted.

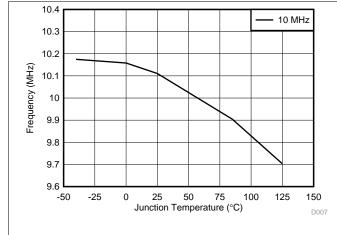

Figure 7. Oscillator Frequency vs Junction Temperature

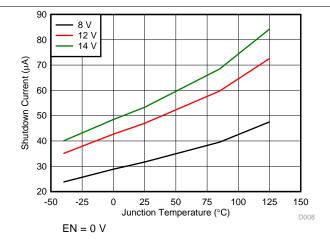

Figure 8. Shutdown Current vs Junction Temperature

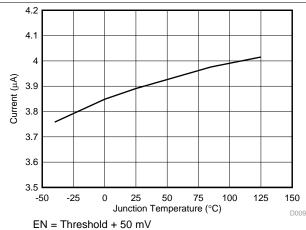

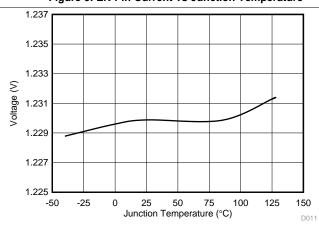

Figure 9. EN Pin Current vs Junction Temperature

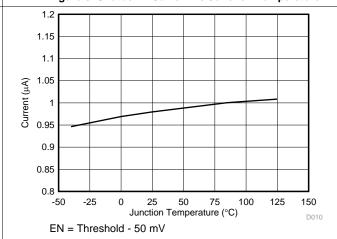

Figure 10. EN Pin Current vs Junction Temperature

Figure 11. EN Pin Threshold vs Junction Temperature

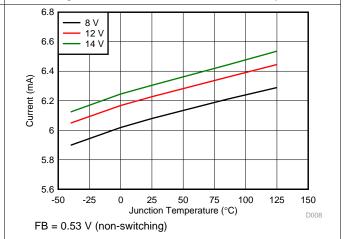

Figure 12. Non-Switching Operating Current vs Junction Temperature

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

$V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $T_A$  = 25 °C, unless otherwise noted.

16 15.5 15 14.5 Current (A) 15 A Limit 14 11.25 A Limit 13.5 13 12.5 12 -25 50 75 125 150 -50 25 100 Junction Temperature (°C) D014

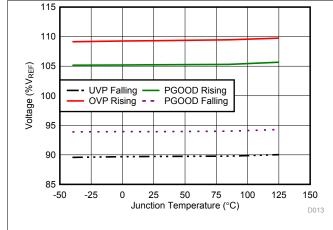

Figure 13. PGOOD and Under/Overvoltage Protection

Threshold vs Junction Temperature

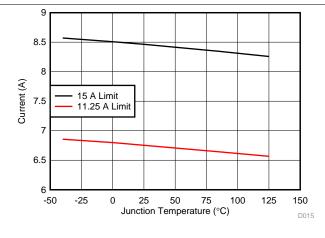

Figure 14. Phase A Low-Side MOSFET Current Limit vs Junction Temperature

Figure 15. Phase B Low-Side MOSFET Current Limit vs Junction Temperature

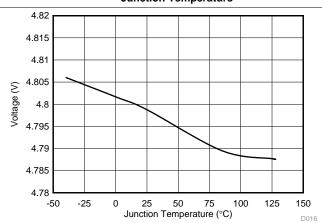

Figure 16. Internal Gate Drive Voltage (VG) vs Junction Temperature

Figure 17. Undervoltage Lockout Threshold vs Junction Temperature

Figure 18. Overvoltage Lockout Threshold vs Junction Temperature

Submit Documentation Feedback

#### **Typical Characteristics (continued)**

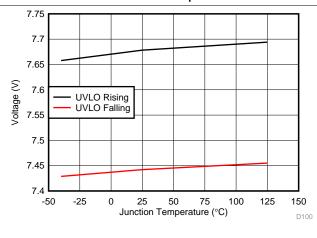

$V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $T_A$  = 25 °C, unless otherwise noted. 95 90 90 85 85 Efficiency (%) 80 80 Efficiency 75 75 70 70 65 65 1.8 V<sub>OUT</sub> 1.2 V<sub>OUT</sub> 60 External VG+ 60 0.8 V<sub>OUT</sub> Internal VG+ 55 55 0 Output Current (A) Output Current (A) D022 f<sub>sw</sub> = 2 MHz per phase 3.2 x 2.5 x 1.2 mm f<sub>sw</sub> = 2 MHz per phase External 3.2 x 2.5 x 1.2 mm inductors inductors Figure 19. Efficiency vs Output Current for Gate Drive Figure 20. Efficiency vs Output Current for Output Voltage Supply 0.4 40 8 V<sub>IN</sub> 12 V<sub>IN</sub> 14 V<sub>IN</sub> 35 0.3 30 0.2 Load Regulation (%V<sub>O</sub>) Temperature Rise (°C) 0.1 25 20 15 -0.1 10 -0.2 5 -0.30 -0.4 0 10 10 Output Current (A) Output Current (A) D024 3.2 x 2.5 x 1.2 mm No air flow  $f_{sw} = 2 MHz per phase$ inductors Figure 22. Load Regulation Figure 21. Case Temperature Rise vs Output Current 0.4 0 A Recommended 5 A Theoretical 0.3 3.5 - 10 A 0.2 Max Output Voltage (V) Line Regulation (%V<sub>O</sub>) 3 0.1 2.5 -0.1 1.5 -0.2 -0.3 -0.4 0.5

Copyright © 2015–2016, Texas Instruments Incorporated

12

Input Voltage (V)

Figure 23. Line Regulation

8

Submit Documentation Feedback

12

14

14

8

10

Input Voltage (V)

Figure 24. Max Output Voltage vs Input Voltage

# TEXAS INSTRUMENTS

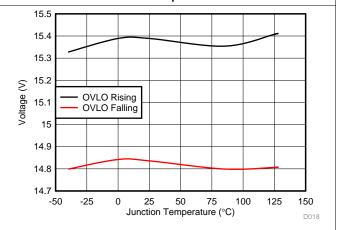

#### **Typical Characteristics (continued)**

$V_{IN}$  = 12 V,  $V_{OUT}$  = 1.2 V,  $T_A$  = 25 °C, unless otherwise noted.

Submit Documentation Feedback

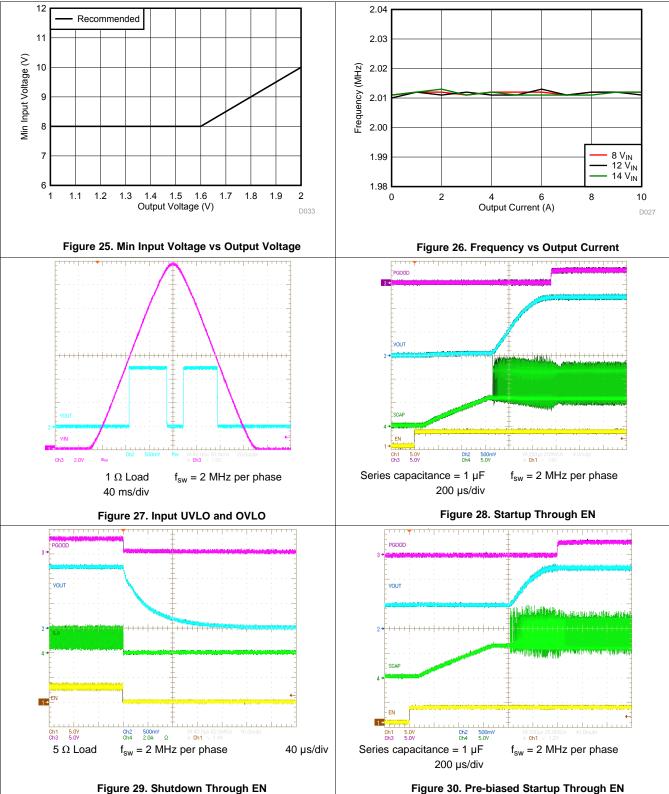

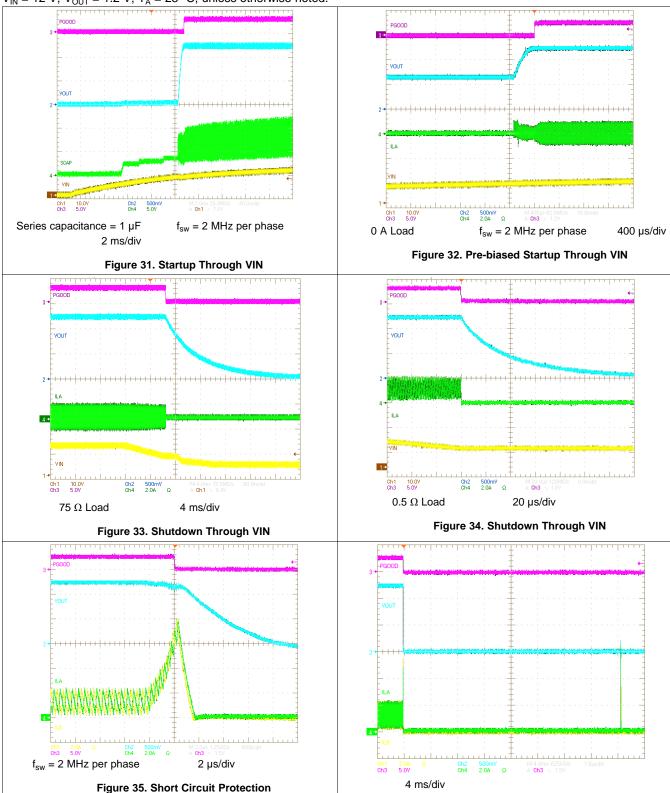

#### **Typical Characteristics (continued)**

Copyright © 2015–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Figure 36. Short Circuit Hiccup Restart

# **ISTRUMENTS**

#### **Typical Characteristics (continued)**

Ch1 1.0A Ω Ch2 1.0V M 10.0 μs 250MS π 4.0 ms/pt Ch3 2.0V Ch4 1.0A Ω A Ch3 7.168V 3.2 MHz SYNC clock

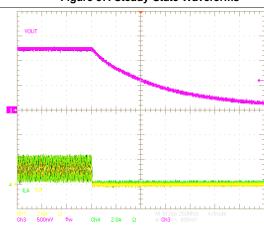

Figure 37. Steady-State Waveforms

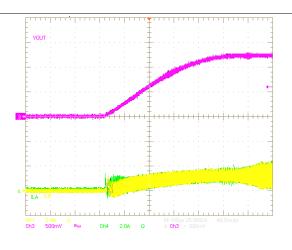

Figure 38. External SYNC Add/Remove

Figure 39. Thermal Shutdown

Figure 40. Thermal Shutdown Recovery

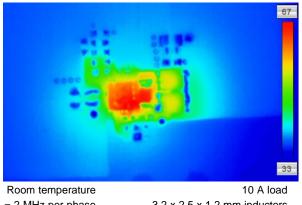

f<sub>sw</sub> = 2 MHz per phase

3.2 x 2.5 x 1.2 mm inductors

No air flow Four layer board

Figure 41. Thermal Image

Submit Documentation Feedback

#### 7 Detailed Description

#### 7.1 Overview

The TPS54A20 is a 14-V, 10-A, synchronous series capacitor step-down (buck) converter with four integrated N-channel MOSFETs. To improve performance during line and load transients the TPS54A20 implements an adaptive on-time control scheme which does not require external compensation components. The selectable switching frequencies are 2 MHz, 3.5 MHz, or 5 MHz per phase which allows for efficiency and size optimization when selecting the output filter components. A resistor to ground on the TON pin sets the nominal high side switch on-time based on the desired output voltage.

The TPS54A20 contains an internal oscillator for steady-state, fixed frequency operation that is set through the SS/FSEL pin. The controller operates at twice the per phase switching frequency (that is, 4 MHz, 7 MHz, or 10 MHz) and the oscillator is set accordingly. An external synchronization clock can also be provided via the SYNC pin.

The TPS54A20 starts up safely into loads with pre-biased outputs (non-zero volts at startup). The device implements an internal under voltage lockout (UVLO) feature on the VIN pin with a nominal starting voltage of 7.65 V. The total operating current for the TPS54A20 is approximately 6 mA when not switching and under no load. When the TPS54A20 is disabled by pulling the EN pin low, the supply current is typically less than 50 µA.

The integrated MOSFETs allow for high-efficiency, high-density power supply designs with continuous output currents up to 10 A. The MOSFETs are sized to optimize efficiency for low duty cycle applications operating around 2 MHz per phase switching frequency.

The TPS54A20 reduces the external component count by integrating the bootstrap recharge circuit. Capacitors connected between the BOOTA/BOOTB and SCAP/SWB pins (respectively) supply the gate drive voltage for the integrated high-side MOSFETs. The output voltage can be stepped down to as low as the 0.5-V voltage reference ( $V_{REF}$ ).

The TPS54A20 has a power good comparator (PGOOD) which monitors the output voltage through the FB pin. The PGOOD pin is an open-drain MOSFET which is pulled low when the FB pin voltage is less than 95% or greater than 105% of the reference voltage ( $V_{REF}$ ). The PGOOD pin floats (de-asserted) when the FB pin voltage is between 95% to 105% of  $V_{RFF}$ . The PGOOD pin is held low during startup or when a fault occurs.

The EN pin is used to provide power supply sequencing during power up. Soft start times for each frequency can be selected through the SS/FSEL pin. Soft start helps to minimize inrush currents.

The device current limit can be set via the ILIM pin. Two selectable current limits are provided.

The control scheme implemented is an adaptive on-time control. The on-time is adjusted based on input voltage and oscillator frequency. An internal phase lock loop (PLL) ensures fixed-frequency operation of the converter over the entire load range and adapts the on-time accordingly.

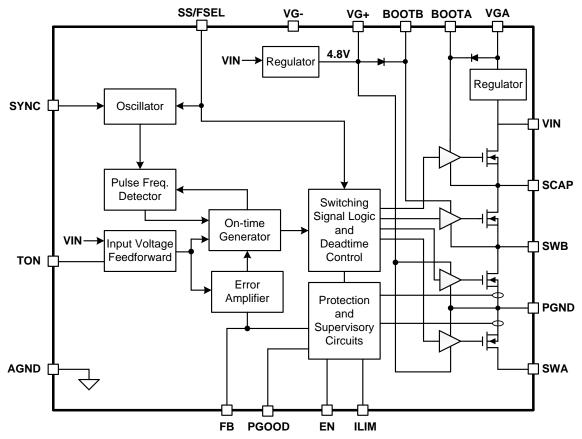

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

#### 7.3.1 Frequency Selection

The oscillator frequency of this converter can be selected to be one of three options: 4, 7, or 10 MHz. The per phase switching frequency of the converter is half the oscillator frequency (that is, 2, 3.5, or 5 MHz per phase). The internal oscillator frequency is selected by programming the SS/FSEL pin. The resistor programming information is shown in Table 1. The frequency setting is latched in at power up and cannot be changed during operation. Cycling the input power or the EN pin will reset the frequency setting.

#### 7.3.2 External Clock Syncronization

An external clock can be connected to the SYNC pin. The external clock signal overrides the internal oscillator and is used as the system clock. This feature enables the user to synchronize the switching events to a master clock on their board and reduce/manage the ripple on the input capacitors. The internal phase locked loop (PLL) has been implemented to allow synchronization at frequencies between ±10% of the nominal oscillator frequency programmed on the SS/FSEL pin. This allows the user to easily switch from the internal oscillator mode to the external clock mode. Before the external clock is present or after it is removed, the device with default to the internal oscillator setting as programmed on the SS/FSEL pin.

To implement the synchronization feature, connect a square wave clock signal to the SYNC pin with a duty cycle between 20% and 80%. The clock signal amplitude must transition lower than 0.8 V and higher than 2 V. The start of the switching cycle is synchronized to the rising edge of the SYNC pin. The device can be configured for operation in applications where both an internal oscillator mode and an external synchronization clock mode are needed. Before the external clock is present, the device functions with the internal oscillator and the switching

#### **Feature Description (continued)**

frequency is set by the R<sub>SS/FSEL</sub> resistor. When the external clock is present, the SYNC mode overrides the internal oscillator. The first time the SYNC pin is pulled above the SYNC high threshold (2 V), the device switches from the internal oscillator mode to the SYNC mode and the PLL starts to lock onto the frequency of the external clock. When the external SYNC clock is removed, the converter will transition back to the internal oscillator after 4 internal clock cycles.

#### 7.3.3 Adjusting the Output Voltage

The output voltage is set by connecting a resistor divider network from the output voltage to the FB pin of the device and to AGND. It is recommended that the lower divider resistor maintain a range between 1 k $\Omega$  and 10 k $\Omega$ . To change the output voltage of a design, it is necessary to select the value of the upper resistor. Equation 2 can be used to select the upper resistor. Selecting the value of the upper resistor can change the output voltage between 0.508 V and 2 V. The minimum output setpoint voltage cannot be less than the reference voltage of 0.508 V. The maximum output voltage can be limited by minimum input voltage as shown in Figure 24. The recommended minimum input voltage should be at least five times the output voltage as shown in Figure 25. This is due to the nature of the series capacitor buck converter.

#### 7.3.4 Soft Start

Soft start is an important feature that limits current inrush into the converter and reduces the load on the bus converter that supplies this device. During soft start, the internal reference voltage is slowly ramped up to the nominal internal reference voltage (~0.5 V). This slowly increases the commanded output voltage of the converter and reduces the initial surge in current. PGOOD remains low during soft start, the PLL is not active, and output UVP/OVP faults are disabled. After the soft start interval is complete, the converter operates with normal operating conditions and PGOOD will no longer be held low when the output is within bounds.

Soft-start time is programmed with an external resistor on SS/FSEL pin (or by shorting to ground or by leaving the pin open). There are multiple soft-start time options per operating frequency available to the user through the SS/FSEL pin. The soft-start setting is latched in at power up or when the EN pin voltage is set high. Resistors used for programing the SS/FSEL pin must have ±1% or lower tolerance. The following frequencies and soft start times can be programmed on the SS/FSEL pin.

| R <sub>SS/FSEL</sub> (kΩ) | F <sub>OSC</sub> (MHz) | F <sub>SW</sub> (MHz) | Soft Start Time (µs) | Hiccup Time (ms) |

|---------------------------|------------------------|-----------------------|----------------------|------------------|

| 71.5                      | 4                      | 2                     | 64                   | 32.8             |

| Open                      | 4                      | 2                     | 512                  | 32.8             |

| 48.7                      | 4                      | 2                     | 4096                 | 32.8             |

| 35.7                      | 7                      | 3.5                   | 36.6                 | 18.7             |

| Short                     | 7                      | 3.5                   | 293                  | 18.7             |

| 21.5                      | 10                     | 5                     | 25.6                 | 13.1             |

| 15.4                      | 10                     | 5                     | 205                  | 13.1             |

| 8.66                      | 10                     | 5                     | 1638                 | 13.1             |

Table 1. Frequency and Soft Start Resistor Selection

#### 7.3.5 Startup into Pre-biased Outputs

The device prevents the low-side MOSFETs from discharging a pre-biased output. During pre-biased startup, the low-side MOSFETs do not turn on until after the phase A high-side MOSFET has started switching. The high-side MOSFETs do not start switching until the internal soft-start reference voltage exceeds the voltage at the FB pin. It is required to first apply the gate driver supply voltage (VG+) before starting up into pre-biased loads. Alternatively, 6.8 µF bypass capacitance or more can be used.

#### 7.3.6 Power Good (PGOOD)

The Power Good (PGOOD) pin is an open drain output. After startup when the FB pin is typically between 95% and 105% of the internal voltage reference, the PGOOD pin pull-down is de-asserted and the pin floats. It is recommended to use a pullup resistor between the values of  $10~\mathrm{k}\Omega$  and  $100~\mathrm{k}\Omega$  to a voltage source that is  $5.5~\mathrm{V}$  or less. The PGOOD is in a defined state once the VIN input voltage is greater than approximately 1.2 V but with reduced current sinking capability. The PGOOD achieves full current sinking capability once the VIN input voltage is above the input UVLO. The PGOOD pin is pulled low when the FB pin voltage is typically lower than 95% or greater than 105% of the nominal internal reference voltage. A resistor-capacitor (RC) filter can be connected to the PGOOD pin to filter out PGOOD being pulled low during large load transients if low output capacitance is used. The PGOOD pin is also pulled low if a fault is detected, the EN pin is pulled low, or the converter is performing its soft-start power up sequence.

#### 7.3.7 Overcurrent Protection

The device protects itself from an overcurrent condition by a current limit detector. The device senses inductor currents using the low side MOSFETs. After three sequential overcurrent measurements are made (in phase A or B), the over current flag is triggered, the converter switches are turned off, and PGOOD is pulled low. The converter attempts to restart after a hiccup interval counter has expired (that is, 32.8 ms, 18.7 ms, or 13.1 ms when in 4 MHz, 7 MHz, or 10 MHz mode, respectively). This provides a hiccup response to an overcurrent condition.

The two overcurrent trip points are based on two full load applications of 7.5 A or 10 A. The overcurrent trip points correspond to the load demanding 1.5 times the full load current (11.25 A and 15 A, respectively). This provides enough margin for brief overshoots in inductor currents during a load transient while at the same time protecting against short circuits or other potentially catastrophic faults on the output. The table below lists the resistor values for programming the ILIM pin to select the desired overcurrent limit. Programming resistors with up to ±5% variation can be used. The current limit selection is latched in at power up and cannot be changed without cycling power input or the EN pin voltage.

**Table 2. Current Limit Selection**

| $R_{ILIM}$ ( $k\Omega$ ) | Load Current Limit (A) |

|--------------------------|------------------------|

| Open                     | 15                     |

| 47                       | 11.25                  |

#### 7.3.8 Light Load Operation

The converter operates in forced continuous conduction mode (FCCM) under light load conditions. When operating in FCCM, the high side and low side MOSFETs are turned on and off in a complementary fashion and negative inductor current is allowed for part of the switching cycle. The switching frequency remains constant in FCCM.

#### 7.3.9 Output Undervoltage/Overvoltage Protection

The device incorporates an output undervoltage/overvoltage protection (UVP/OVP) circuit to prevent damage to the load. This fault can be triggered during large, fast load transients if insufficient output capacitance is used. The UVP/OVP feature compares the FB pin voltage to internal thresholds. If the FB pin voltage is lower than 90% or greater than 110% of the nominal internal reference voltage, the converter is turned off (i.e. power MOSFETs are turned OFF), a fault is triggered, and the PGOOD pin is pulled low. When the fault hiccup interval is complete, the converter will attempt to restart.

#### 7.3.10 Input Undervoltage/Overvoltage Lockout

The device incorporates an input undervoltage/overvoltage lockout (UVLO/OVLO) circuit. The converter will not operate if the input voltage is below the UVLO threshold. The OVLO circuit protects the converter if the input bus voltage flies higher than the input voltage rating of the device while it is switching. When the input voltage crosses the input rising OVLO trip threshold, the converter turns off all the switches (makes them high impedance) and PGOOD is pulled low. When the input voltage drops lower than the falling OVLO threshold, the converter restarts using the normal soft-start sequence. This feature increases the maximum input voltage the device can sustain without being damaged due to a fault in the system.

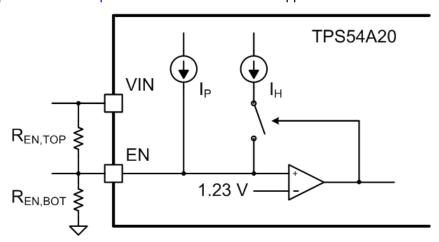

#### 7.3.11 Enable and Adjusting Undervoltage Lockout

The EN pin provides electrical on and off control of the device. Once the EN pin voltage exceeds the threshold voltage, the device starts operation. If the EN pin voltage is pulled below the threshold voltage, the regulator stops switching and enters a low power state. There is no voltage hysteresis in the EN threshold. The rising and falling voltage thresholds occur at the same level.

The EN pin has an internal hysteretic current source. This allows the user to float the EN pin for self-enabling the device or to design the ON and OFF threshold input voltages with a resistor divider at the EN pin. If an application requires controlling the EN pin, use open drain or open collector output logic to interface with the pin.

The EN pin can be configured as shown in Figure 42. The EN pin has a 1  $\mu$ A pull-up current  $i_P$  which sets the current source value before the start-up sequence. The device includes the second 3  $\mu$ A current source  $i_H$  which is activated when the EN threshold voltage has been exceeded. To achieve clean transitions between the OFF and ON states, it is recommended that the turn OFF threshold is no less than 7.75 V, and the turn ON threshold is no less than 8 V on the VIN pin. It is also recommended to set the UVLO hysteresis to be greater than 500mV in order to avoid repeated chatter during start up or shut down. The value of  $R_{EN(TOP)}$  and  $R_{EN(BOT)}$  can be calculated using Equation 18 and Equation 19 as described in the applications section.

Figure 42. Adjustable VIN Undervoltage Lockout

#### 7.3.12 Series Capacitor Monitoring

The series capacitor voltage is preconditioned and monitored during operation. The series capacitor is located between the source of the high-side MOSFET and the drain of the low-side MOSFET in Phase A. After the input voltage is above UVLO and the EN pin is high, the series capacitor is precharged. A 10 mA current source charges the series capacitor up to half the input voltage. When the series capacitor precharge is complete, the soft start sequence begins. The delay due series capacitor precharge can be calculated using Equation 1.

$$t_{pc} = \frac{C_t \times V_{IN}}{2 \times I_{pc}} \tag{1}$$

Here  $C_t$  is the series capacitance,  $I_{DC}$  is the precharge current, and  $V_{IN}$  is the input voltage.

The voltage monitor is continuously tracking the status of the series capacitor. Its function is to ensure the series capacitor voltage, measured differentially between the SCAP pin and the SWA pin, stays within predefined thresholds. These thresholds are relative to the VIN voltage with respect to PGND and set at 35% and 65% of VIN. If the voltage monitor indicates a voltage outside of these thresholds has occurred, a fault is triggered and following actions are taken based on which threshold has been crossed.

#### 7.3.12.1 Dropping Below 35% Threshold

The 35% of VIN threshold detects a series capacitor undervoltage fault. Once the 35% threshold is breached, a fault is triggered, the converter shuts down, and PGOOD is pulled low. After the fault hiccup time is complete, the converter will start up in the normal manner. The start up sequence begins with pre-charging the series capacitor to half the input voltage and is followed by the soft start.

#### 7.3.12.2 Rising Above 65% Threshold

The 65% of VIN threshold indicates a series capacitor overvoltage fault has occurred. Once the 65% threshold is breached, a fault is triggered, the converter shuts down, PGOOD is pulled low, and an internal bleed resistor is connected to the SCAP to reduce the series capacitor voltage. After the fault hiccup time is complete, the converter will start up in the normal manner.

#### 7.3.13 Thermal Shutdown

The die temperature is continuously monitored to ensure it is within limits. The thermal shutdown (TSD) fault is triggered when the die temperature exceeds the rising temperature threshold. This interrupts switching by making the switches high impedance. The fault state persists until the die temperature cools down to below the falling temperature threshold. The converter then automatically goes through the normal soft start sequence.

#### 7.3.14 Phase A Power Stage

Phase A implements a bootstrap driver for the high-side MOSFET, an LDO, a low-side driver and a low-side current monitor. Additional logic is included to implement deadtime control and overcurrent protection.

An LDO is implemented to manage the high-side bootstrap driver. This LDO is unique to this topology given the high-side driver is referenced to the SCAP pin and not to the conventional switch node of a buck converter. A conventional bootstrap circuit will not work because the SCAP pin is never connected to PGND during operation. The LDO is designed to produce an output voltage at the VGA pin. This allows a nominal enhancement of around 5V about the VIN rail. The bootstrap capacitor charges when the phase A low side switch is on. An external decoupling capacitor is required on the VGA pin.

The low-side MOSFET current is monitored using a sense FET configuration. This circuit enables the driver to monitor the current delivered in Phase A for overcurrent protection. In the case of overcurrent, a fault flag is set if the current detected exceeds the current limit threshold. Adjustment of this threshold is accomplished via programming the ILIM pin.

#### 7.3.15 Phase B Power Stage

Phase B implements a bootstrap driver for the high-side MOSFET, a low-side driver and a low-side current monitor. Additional logic is included to implement deadtime control and overcurrent protection.

No additional LDO function is required for Phase B as the bootstrap capacitor is charged directly from the VG input rail. A conventional bootstrap circuit is used in phase B.

The overcurrent protection operates in the same manner as Phase A.

#### 7.3.16 Internal Gate Drive Regulator

There is an internal linear regulator that generates a 4.8 V supply rail on the VG+ pin. The input comes from the VIN pin. The VG+ supply rail is used to power the gate drivers of phase A low side switch and phase B switches. It also is the input to another regulator that generates the internal supply rails used by the controller. To improve converter efficiency, an external 5V supply is recommended to be connected to the VG+ pin, thereby overriding the internal 4.8 V regulator. The VG+ supply requires external decoupling capacitance connected between the VG+ and VG- pins. The VG- pin must be connected to AGND and PGND. It is recommended to make this connection directly beneath the device.

#### 7.3.17 Voltage Feed Forward

The input voltage feed forward (VFF) circuit adapts the nominal on-time of the converter in response to changes in the input voltage. The VFF provides a control signal to the on-time generator based on the value of the resistor placed on the TON pin and the input voltage.

#### 7.3.18 Internal Oscillator

The internal oscillator provides a default system clock for the converter. The oscillator can be programmed to run at 4 MHz, 7 MHz, or 10 MHz depending on the resistor connected to the SS/FSEL pin. Synchronization to an external clock is allowed. If provided, an external synchronization clock signal is passed through to the oscillator block and bypasses internal oscillator.

#### 7.3.19 Pulse Frequency Detector

The pulse frequency detector is an important block used to create a phase lock loop (PLL). This portion of the PLL accepts two clock signals and delivers a control signal. The PLL control is held inactive during startup and is activated once soft start is complete. The control signal is delivered to the on-time generator to make small adjustments in the on-time such that the frequency and phase of the switching signals match the reference clock (internal or external SYNC).

#### 7.3.20 On-Time Generator

The on-time generator provides the on-time pulse for high side switches of the converter. The nominal on-time is programmed from the TON pin. The control signal generated by the VFF circuit is proportional to the on-time required by the converter and is adjusted for input voltage variation. Fine adjustment of the on-time comes from pulse frequency detector which enables fixed frequency operation in steady state.

#### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The TPS54A20 is a two-phase, synchronous series capacitor buck converter optimized for small size, low voltage applications from a 12 V input rail. See (SLVA750) for a more detailed introduction to the series capacitor buck converter topology.

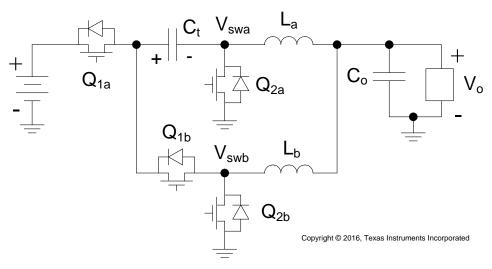

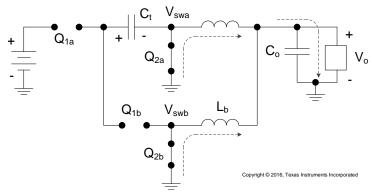

#### 8.1.1 Two-Phase Series Capacitor Buck Converter Topology

The series capacitor buck converter topology uniquely merges a switched capacitor converter and a buck converter. Only one extra capacitor (the series capacitor) is needed as compared to a conventional two-phase buck converter. Advantages include automatic current balancing between the inductors (inductor current sensing and a current sharing loop are not required), lower switching losses which enable high frequency (HF) operation, and voltage step-down through the series capacitor. The on-time of both high side switches is double that of a regular buck converter. This is particularly helpful in high frequency, high conversion ratio applications. The schematic of the converter topology and the converter switch states are shown below.

Figure 43. Two-Phase Series Capacitor Buck Converter Topology

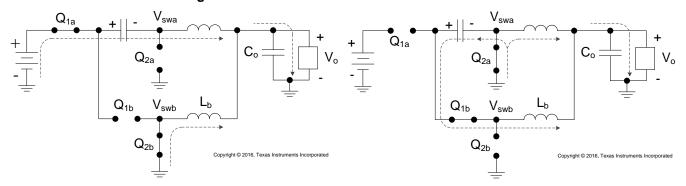

#### 8.1.2 Converter Switch Configurations

Product Folder Links: TPS54A20

Figure 44. Phase A High Side MOSFET On

Figure 45. Phase B High Side MOSFET On

## **Application Information (continued)**

Figure 46. Phase A/B Low Side MOSFET On

## 8.2 Typical Application

Copyright © 2016, Texas Instruments Incorporated

Figure 47. Typical Application

#### 8.2.1 Design Requirements

**Table 3. Design Parameters**

|                          | PARAMETER             | CONDITIONS            | MIN | TYP | MAX | UNIT         |

|--------------------------|-----------------------|-----------------------|-----|-----|-----|--------------|

| V <sub>OUT</sub>         | Output voltage        |                       |     | 1.2 |     | ٧            |

| I <sub>OUT</sub>         | Output current        |                       |     | 10  |     | Α            |

| $\Delta V_{OUT}$         | Transient response    | 9-A load step         |     | 60  |     | mV           |

| V <sub>IN</sub>          | Input voltage         |                       | 9.2 | 12  | 14  | V            |

| V <sub>OUT(ripple)</sub> | Output voltage ripple |                       |     | 20  |     | $mV_{(P-P)}$ |

|                          | Start input voltage   | Input voltage rising  |     | 9.4 |     | V            |

|                          | Stop input voltage    | Input voltage falling |     | 9.2 |     | ٧            |

| f <sub>SW</sub>          | Switching frequency   |                       |     | 2   |     | MHz          |

| T <sub>A</sub>           | Ambient temperature   |                       |     | 25  |     | °C           |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Output Voltage

Before beginning design, ensure that the series capacitor buck converter can be used in the application. It is recommended to use this converter when the minimum input voltage is at least five times greater than the target output voltage. If this recommendation is not followed, output voltage dropout can occur at heavy load conditions and poor transient response to load increases can result.

The output voltage is set by connecting a resistor divider network from the output voltage to the FB pin of the device and to AGND. It is recommended that the lower divider resistor maintain a range between 1  $k\Omega$  and 10  $k\Omega$ . To change the output voltage of a design, it is necessary to select the value of the upper resistor. The value of R<sub>TOP</sub> for a specific output voltage can be calculated using Equation 2.

$$R_{(TOP)} = \frac{R_{(BOT)}x(V_{OUT} - V_{REF})}{V_{REF}}$$

(2)

For the example design, 1 k $\Omega$  was selected for R<sub>BOT</sub> (R7). Using Equation 2, R<sub>TOP</sub> (R9) is calculated as 1.4 k $\Omega$ . It is recommended to use resistors with ±1% or less variation.

A capacitor can be connected in parallel with the upper resistor to provide additional phase boost near the converter's crossover frequency. See (SLVA289) for more details and design guidelines. For this design, 330 pF in series with 100  $\Omega$  is used. The values were optimized based on measured loop performance.

#### 8.2.2.2 Switching Frequency

A key design step is to decide on a switching frequency for the regulator. There is a tradeoff between higher and lower switching frequencies. Higher switching frequencies may produce a smaller solution size using lower valued inductors and smaller output capacitors compared to a power supply that switches at a lower frequency. However, the higher switching frequency creates extra switching loss, which reduces the converter's efficiency and thermal performance. In this design, a moderate switching frequency of 2 MHz per phase is selected to achieve both a small solution size and a high efficiency operation. Refer to Table 1 for the SS/FSEL programming resistor selection.

#### 8.2.2.3 On-Time

The TON pin requires a resistor to set the nominal on-time and to support the input voltage feedforward circuit. The resistance value used also influences the internal ramp in the controller. As a starting point, Equation 3 is recommended for selecting the TON resistor.

$$R_{(TON)} = 3 k + 15 k x V_{OUT}$$

The  $R_{TON}$  resistor (R5) is calculated to be 21 k $\Omega$ . The selected value for this design example is 22.1 k $\Omega$ . During startup, the converter uses the nominal on-time programmed through TON. The phase lock loop (PLL) is only activated after startup is complete. When the PLL is engaged, the on-time is adjusted. If the nominal on-time programmed through the TON pin is not close to the on-time when the PLL is engaged, the SYNC range of the device may be reduced. The TON resistor can also be adjusted to tune the controller. Lowering the  $R_{TON}$  value will increase the internal ramp height. This will reduce the converter's sensitivity to noise and jitter but it will also reduce the transient response capabilities of the converter.

#### 8.2.2.4 Inductor Selection

To calculate the value of the output inductors, use Equation 4.  $K_{IND}$  is a coefficient that represents the amount of inductor ripple current relative to the maximum output current. The inductor ripple current is filtered by the output capacitor. In general, the inductor ripple value is at the discretion of the designer; however,  $K_{IND}$  is normally from 0.1 to 0.4 for the majority of applications.

$$L = \frac{2 \times V_{OUT} \times (V_{IN(MAX)} - 2 \times V_{OUT})}{K_{(IND)} \times I_{OUT} \times V_{IN(MAX)} \times F_{SW}}$$

(4)

For this design example, use  $K_{IND} = 0.4$  and the inductor value is calculated to be 249 nH. For this design, the nearby standard value of 220 nH was chosen. For the output filter inductor, it is generally recommended that the RMS current and saturation current ratings not be exceeded. The current ripple, RMS, and peak inductor current are calculated in Equation 5, Equation 6, and Equation 7.

$$\Delta I_{L} = \frac{2 \times V_{OUT} \times \left(V_{IN(MAX)} - 2 \times V_{OUT}\right)}{L \times V_{IN(MAX)} \times F_{SW}}$$

(5)

$$I_{L(RMS)} = \sqrt{\left(\frac{I_{OUT}}{2}\right)^2 + \frac{1}{12} \times \left(\Delta I_L\right)^2}$$

(6)

$$I_{L(PEAK)} = \frac{I_{OUT}}{2} + \frac{\Delta I_L}{2}$$

(7)

For this design, the RMS inductor current is calculated to be 5.04 A and the peak inductor current is 6.13 A. The chosen inductor is 220 nH with a saturation current rating of 8.2 A and a dc current rating of 7.6 A.

The current flowing through each inductor is the inductor ripple current plus half the output current. During power up, faults, or transient load conditions, the inductor current can increase above the peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than half the load current limit rather than the peak inductor current in steady state. Many inductors today have soft saturation characteristics that may be able to ride through a transient that pushes current beyond the saturation rating specified in the datasheet. An example list of inductors that have been tested to work with the TPS54A20 are shown in Table 4. Inductors not listed below can also be used with this device.

| Inductance (nH) | Saturation Current<br>Rating (A) | Dimensions<br>[L x W x H] (mm) | DCR Typ/Max (mΩ) Type |                  | Vendor           |

|-----------------|----------------------------------|--------------------------------|-----------------------|------------------|------------------|

| 220 ±20%        | 9.3                              | 3.2 x 2.5 x 1.2                | 9 / 12                | HMLW32251B-R22MS | CYNTEC           |

| 330 ±20%        | 7.5                              | 3.2 x 2.5 x 1.2                | 13 / 16               | HMLW32251B-R33MS | CYNTEC           |

| 220 ±30%        | 8.2                              | 3.2 x 2.5 x 1.2                | 7.5 / 10.5            | MLA-FY12NR22N-M3 | MAGLAYERS        |

| 330 ±30%        | 7.5                              | 3.2 x 2.5 x 1.2                | 13.5 / 16             | MLA-FY12NR33N-M3 | MAGLAYERS        |

| 220 ±20%        | 8.7                              | 3.2 x 2.5 x 1.2                | 9.4 / 11.6            | MCMK3225TR22MG   | TAIYO YUDEN      |

| 330 ±20%        | 10.4                             | 3.2 x 2.5 x 1.2                | 11.2 / 13.8           | MCMK3225TR33MG   | TAIYO YUDEN      |

| 250 ±30%        | 12                               | 3.2 x 2.5 x 1.5                | 10 / 12.5             | 74479290125      | WURTH ELECTRONIK |

| 330 ±30%        | 12.4                             | 4.1 x 4.1 x 2.1                | 6 / 7.2               | 744383560033     | WURTH ELECTRONIK |

| 220 ±20%        | 10.1                             | 3.5 x 3.2 x 1.5                | 7.8 / 8.9             | XEL3515-221      | COILCRAFT        |

| 350 ±20%        | 8.2                              | 3.5 x 3.2 x 1.5                | 11.6 / 13.4           | XEL3515-351      | COILCRAFT        |

| 330 ±20%        | 8.5                              | 2.5 x 2.0 x 1.2                | 14 / 19               | DFE252012F-R33M  | TOKO             |

**Table 4. Example Inductor List**

#### 8.2.2.5 Output Capacitor Selection

For most applications, the primary consideration for selecting the value of the output capacitor is how the regulator responds to a large change in load current. The output capacitance may also be selected based on output voltage ripple or closed-loop bandwidth design objectives.

The output capacitance required to maintain an output voltage ripple  $\Delta V_{OUT}$  during steady-state operation can be estimated using Equation 8.

$$C_{O} > \frac{\Delta I_{L}}{16 x f_{SW} x \Delta V_{OUT}}$$

(8)

The desired response to a large change in the load current is typically the most stringent criteria. The output capacitor needs to supply the load with current when the regulator cannot. This situation would occur if there are desired hold-up times for the regulator where the output capacitor must hold the output voltage above a certain level for a specified amount of time after the input power is removed. The regulator is also temporarily not able to supply sufficient output current if there is a large, fast change in the load current such as a transition from no load to full load. The output capacitor must be sized to supply the extra current to the load until the control loop responds to the load change. The minimum output capacitance required for a load increase can be estimated using Equation 9.

$$C_{O} > \frac{2 \times L \times (\Delta I_{OUT})^{2}}{(V_{IN} - 4 \times V_{OUT}) \times \Delta V_{OUT}}$$

(9)

In low voltage applications, the inductor slew rate during a load step decrease is sometimes slower than its slew rate during a load step increase. The minimum output capacitance required for a load decrease can be estimated using Equation 10 for a given tolerable amount of overshoot in the output voltage.

$$C_{O} > \frac{L \times (\Delta I_{OUT})^{2}}{4 \times V_{OUT} \times \Delta V_{OUT}}$$

(10)

Here  $\Delta I_{OUT}$  is the change in output current and  $\Delta V_{OUT}$  is the allowable change in the output voltage. For this design example, the transient load response is specified as a 3% change in V<sub>OUT</sub> for a load step of 5A. For this example,  $\Delta I_{OUT}$  = 5 A and  $\Delta V_{OUT}$  = 0.03 x 1.2 = 0.036 V. Based on these design parameters, a minimum capacitance of 93 µF is calculated using Equation 9. This value does not take the ESR of the output capacitor into account in the output voltage change. For ceramic capacitors, the ESR is usually small enough to ignore in this calculation. Additional capacitance de-ratings for aging, temperature and DC bias should be factored in which also increases this minimum value. For this design example, two 47 μF, 6.3 V rated, ceramic capacitors with 3 m $\Omega$  of ESR are selected.

#### 8.2.2.6 Input Capacitor Selection

The TPS54A20 requires a high quality ceramic, type X5R or X7R, input decoupling capacitor of at least 4.7 µF of effective capacitance on the VIN input voltage pin. Additional bulk capacitance may also be required for the VIN input. The value of a ceramic capacitor varies significantly over temperature and the amount of DC bias applied to the capacitor. The capacitance variations due to temperature can be minimized by selecting a dielectric material that is stable over temperature. X5R and X7R ceramic dielectrics are usually selected for power regulator capacitors because they have a high capacitance to volume ratio and are fairly stable over temperature. The capacitor must also be selected with the DC bias taken into account. The capacitance value of a capacitor decreases as the DC bias across a capacitor increases. For this example design, a ceramic capacitor with at least a 25-V voltage rating is selected to support the maximum input voltage. The input capacitance value impacts the input ripple voltage of the regulator. The minimum input capacitance can be estimated using Equation 11.

$$C_{\text{IN(MIN)}} = \frac{2 \times I_{\text{OUT}} \times V_{\text{OUT}} \left( V_{\text{IN(MIN)}} - 2 \times V_{\text{OUT}} \right)}{f_{\text{SW}} \times V_{\text{IN(MIN)}}^2 \times \Delta V_{\text{IN}}}$$

(11)