**TPS548B27**

JAJSM99A - JULY 2021 - REVISED JULY 2021

# TPS548B27 2.7V~16V 入力、20A 同期整流降圧コンバータ、 リモート・センス、3V内部LDOおよびヒカップ電流制限付き

# 1 特長

- 入力範囲:4V~16V、最大 20A、外部バイアスなし

- 入力範囲: 2.7V~16V、最大 20A、外部バイアス (3.13V~3.6V) あり

- 出力電圧範囲:0.6V~5.5V

- 7.7mΩ および 2.4mΩ の MOSFET を内蔵し、20A の 連続出力電流に対応

- きわめて高速な負荷ステップ応答を実現する D-CAP3 ™ 制御モード

- すべての出力コンデンサでセラミック・コンデンサの使 用をサポート

- 差動リモート・センス、V<sub>RFF</sub> = 0.6V ±1% (-40℃~ +125℃の接合部温度)

- 自動スキップ Eco-mode により軽負荷時の効率を向

- 電流制限を RTRIP でプログラム可能

- スイッチング周波数をピンで選択可能:600kHz、 800kHz、1MHz

- 高い出力精度を達成するための差動リモート・センス

- ソフトスタート時間をプログラム可能

- トラッキング用の外部リファレンス入力

- プリバイアス付きスタートアップ機能

- オープン・ドレインのパワー・グッド出力

- OC、UV、OV フォルトのヒカップ

- 4mm × 3mm、19ピン VQFN-FCRLF パッケージ

- 適用除外なしで RoHS に完全準拠

### BOOT 19 18 VIN $V_{OUT}$ 7 EN SW 1 TPS548B27 16 VCC Vosns+ FB 6 8 PGOOD 3 MODE Vosns-VSNS-2 TRIP SS/ REFIN AGND **PGND** アプリケーション概略

# 2 アプリケーション

- ラック・サーバーとブレード・サーバー

- ハードウェア・アクセラレータおよびアドイン・カード

- データ・センター向けスイッチ

- 産業用 PC

# 3 概要

TPS548B27 デバイスは、適応型オン時間 D-CAP3 制御 モードを備えた小型で高効率の同期整流降圧コンバータ です。外部補償が不要なので、本デバイスは使いやすく、 外付け部品をほとんど必要としません。このデバイスは、ス ペースに制約のあるデータ・センター・アプリケーションに 適しています。

TPS548B27 デバイスは、差動リモート・センス、高性能の 内蔵 MOSFET、動作時接合部温度の全範囲にわたって 高精度 (±1%) の 0.6V 基準電圧を備えています。このデ バイスは、高速な負荷過渡応答、精密な負荷レギュレーシ ョンとライン・レギュレーション、スキップ・モードまたは FCCM 動作、プログラム可能なソフトスタートを特長として います。

TPS548B27 は鉛フリー・デバイスです。RoHS に完全準 拠しています (適用除外なし)。

#### 魁品情報

| 4DÇHH ITI TIA |                      |                 |  |  |  |

|---------------|----------------------|-----------------|--|--|--|

| 部品番号          | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |  |  |  |

| TPS548B27     | VQFN-FCRLF (19)      | 4.00mm × 3.00mm |  |  |  |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

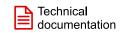

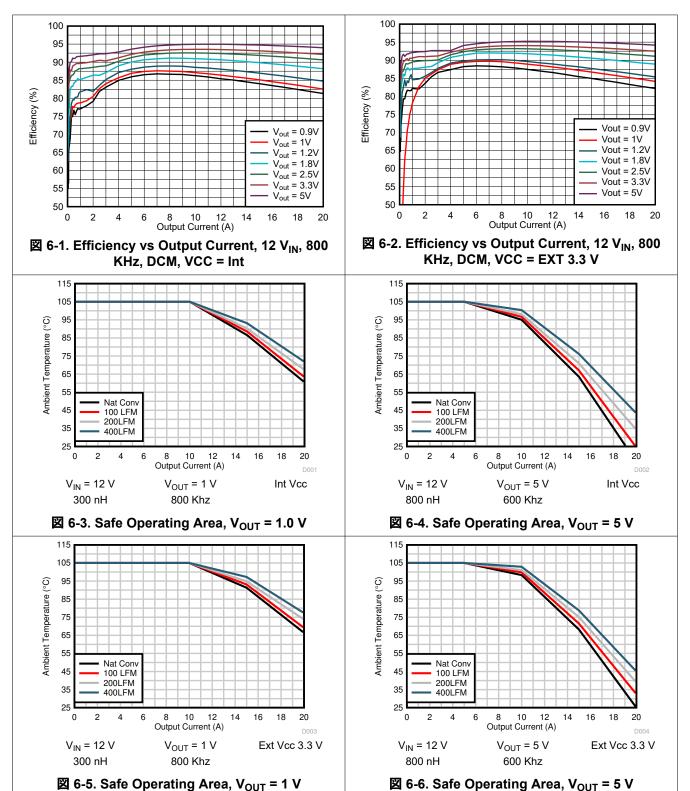

効率と出力電流との関係

# **Table of Contents**

| 1 特長                                 | 1 | 8 Application and Implementation                  | 25     |

|--------------------------------------|---|---------------------------------------------------|--------|

| 2アプリケーション                            |   | 8.1 Application Information                       |        |

| 3 概要                                 |   | 8.2 Typical Application                           | 25     |

| 4 Revision History                   |   | 9 Power Supply Recommendations                    | 35     |

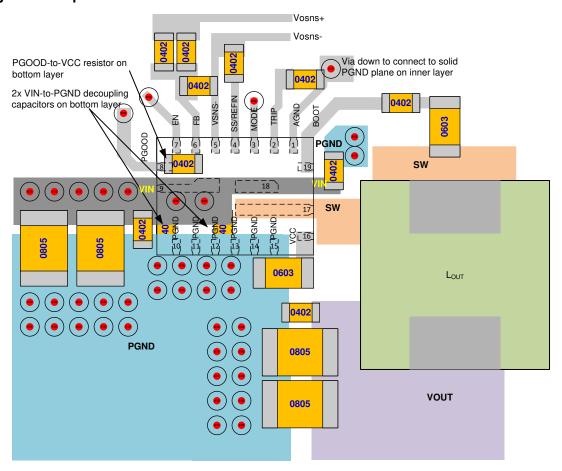

| 5 Pin Configuration and Functions    |   | 10 レイアウト                                          | 35     |

| 6 Specifications                     |   | 10.1 Layout Guidelines                            | 35     |

| 6.1 Absolute Maximum Ratings         |   | 10.2 Layout Example                               | 36     |

| 6.2 ESD Ratings                      |   | 11 Device and Documentation Support               | 37     |

| 6.3 Recommended Operating Conditions |   | 11.1 Device Support                               | 37     |

| 6.4 Thermal Information              |   | 11.2 Documentation Support                        | 37     |

| 6.5 Electrical Characteristics       |   | 11.3 サポート・リソース                                    | 37     |

| 6.6 Typical Characteristics          |   | 11.4 Receiving Notification of Documentation Upda | tes 37 |

| 7 Detailed Description               |   | 11.5 Trademarks                                   | 37     |

| 7.1 Overview                         |   | 11.6 Electrostatic Discharge Caution              | 37     |

| 7.2 Functional Block Diagram         |   | 11.7 Glossary                                     | 37     |

| 7.3 Feature Description              |   | 12 Mechanical, Packaging, and Orderable           |        |

| 7.4 Device Functional Modes          |   | Information                                       | 38     |

|                                      |   |                                                   |        |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | Changes from Revision * (July 2021) to Revision A (July 2021) |   |

|---|---------------------------------------------------------------|---|

| • | 図 3-1 を更新                                                     | 1 |

| • | Corrected package designator in セクション 5                       | 3 |

| • | Corrected package designator in セクション 6.4                     | 6 |

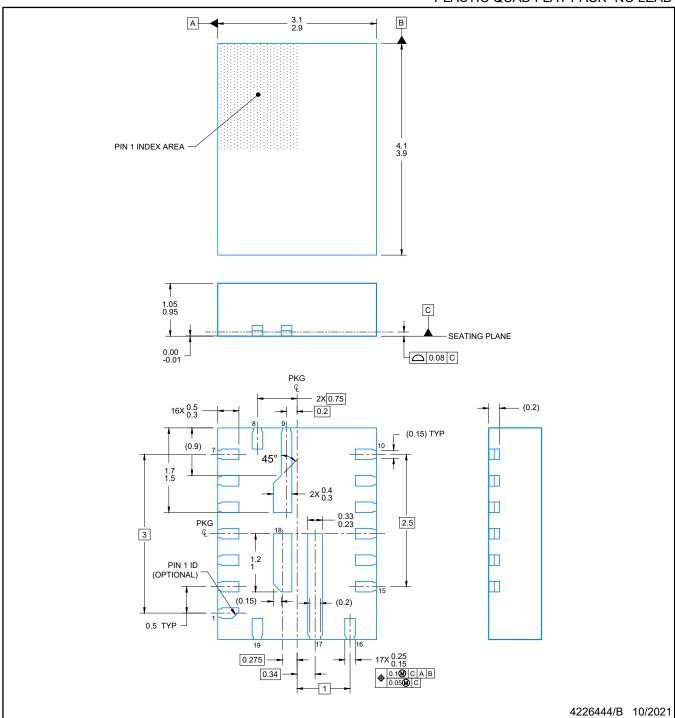

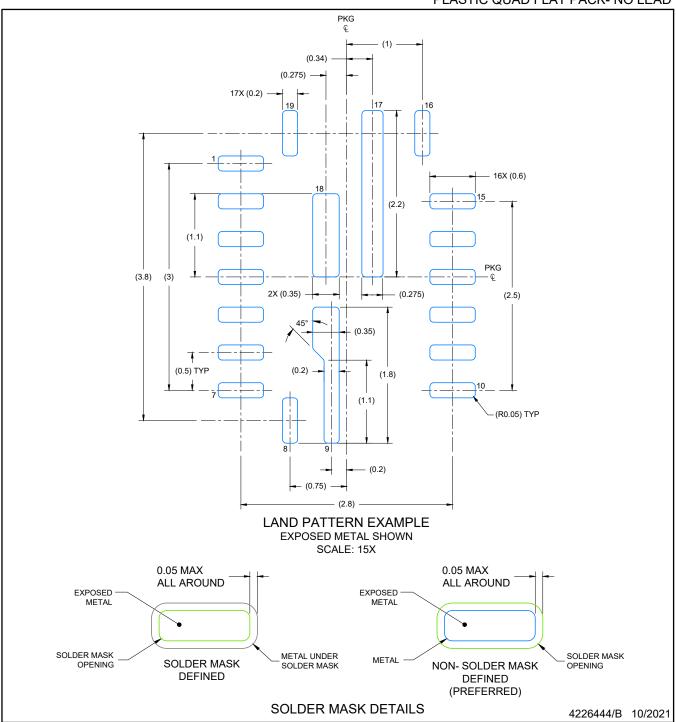

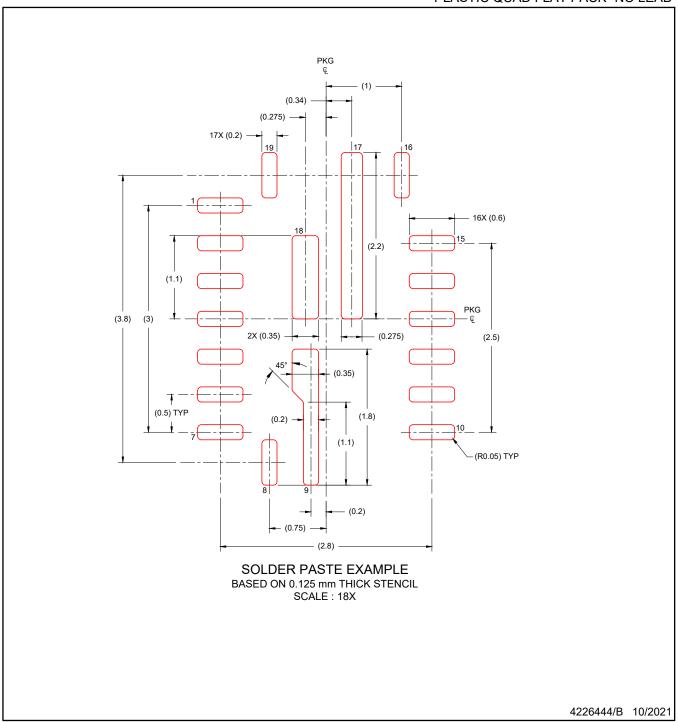

# **5 Pin Configuration and Functions**

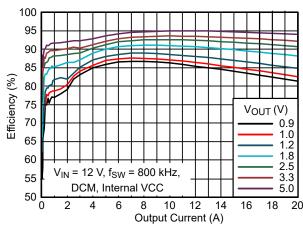

図 5-1. RYL Package, 19-Pin VQFN-FCRLF (Top View)

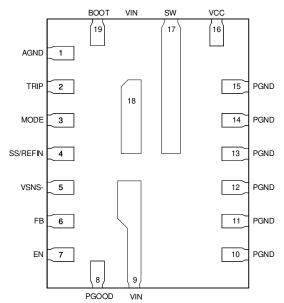

図 5-2. RYL Package, 19-Pin VQFN-FCRLF (Bottom View)

表 5-1. Pin Functions

| NAME                                                                                        | NO.                   | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------------------------------------------------------------------|-----------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| воот                                                                                        | 19                    | I/O                | Supply rail for the high-side gate driver (boost terminal). Connect the bootstrap capacitor from this pin to SW node.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AGND                                                                                        | 1                     | G                  | Ground pin. Reference point for the internal control circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| TRIP                                                                                        | 2                     | I/O                | Current limit setting pin. Connect a resistor to AGND to set the current limit trip point. ±1% tolerance resistor is highly recommended. See セクション 7.3.9 for details on the OCL setting.                                                                                                                                                                                                                                                                                                                                          |  |

| MODE                                                                                        | 3                     | I                  | The MODE pin sets the Forced Continuous Conduction mode (FCCM) or Skip mode operation. It also selects the operating frequency by connecting a resistor from the MODE pin to AGND. ±1% tolerance resistor is recommended. See 表 7-1 for details.                                                                                                                                                                                                                                                                                  |  |

| SS/REFIN                                                                                    | 4                     | I/O                | Dual-function pin Soft-start function: Connecting a capacitor to the VSNS- pin programs the soft-start time. Minimum soft-start time (1.5 ms) is fixed internally. A minimum 1-nF capacitor is required for this pin to avoid overshoot during the charge of the soft-start capacitor. REFIN function: The device always looks at the voltage on this SS/REFIN pin as the reference for the control loop. The internal reference voltage can be overridden by an external DC voltage source on this pin for tracking application. |  |

| VSNS-                                                                                       | 5                     | 1                  | The return connection for a remote voltage sensing configuration. It is also used as ground for the internal reference. Short to AGND for a single-end sense configuration.                                                                                                                                                                                                                                                                                                                                                       |  |

| FB                                                                                          | 6                     | 1                  | Output voltage feedback input. A resistor divider from V <sub>OUT</sub> to VSNS– (tapped to FB pin) sets the output voltage.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| EN 7 I before start-up                                                                      |                       | I                  | Enable pin (EN). The Enable pin turns the DC/DC switching converter on or off. Floating the EN pin before start-up disables the converter. The maximum recommended operating condition for the EN pin is 5.5 V. <i>Do not</i> connect the EN pin to the VIN pin directly.                                                                                                                                                                                                                                                         |  |

| PGOOD 8 O Open-drain power-good status signal. When FB v PGOOD goes low after a 2-µs delay. |                       | 0                  | Open-drain power-good status signal. When FB voltage moves outside the specified limits, PGOOD goes low after a 2-µs delay.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| VIN                                                                                         | 9,18                  | Р                  | Power-supply input pins for both integrated power MOSFET pair and the internal LDO. Place the decoupling input capacitors from the VIN pins to the PGND pins as close as possible.                                                                                                                                                                                                                                                                                                                                                |  |

| PGND                                                                                        | 10,11,12,13<br>,14,15 | G                  | Power ground of the internal low-side MOSFET. At least six PGND vias are required to be placed as close as possible to the PGND pins. This minimizes parasitic impedance and lowers thermal resistance.                                                                                                                                                                                                                                                                                                                           |  |

# 表 5-1. Pin Functions (continued)

| NAME NO. I/O <sup>(1)</sup>                                   |    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------------------------------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VCC                                                           | 16 | I/O                | Internal 3-V LDO output. An external bias with 3.3-V or higher voltage can be connected to this pin to save the power losses on the internal LDO. The voltage source on this pin powers both the internal circuitry and gate driver. Requires a 2.2-µF, at least 6.3-V, rating ceramic capacitor from the VCC pin to the PGND pins as the decoupling capacitor and the placement is required to be as close as possible. |  |  |

| SW 17 O Output switching terminal of the power converter. Con |    | 0                  | Output switching terminal of the power converter. Connect this pin to the output inductor.                                                                                                                                                                                                                                                                                                                               |  |  |

(1) I = Input, O = Output, P = Supply, G = Ground

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

Over operating junction temperature range (unless otherwise noted) (1)

|                    |                                       | MIN  | MAX     | UNIT |  |

|--------------------|---------------------------------------|------|---------|------|--|

|                    | VIN                                   | -0.3 | -0.3 18 |      |  |

|                    | VIN – SW, DC                          | -0.3 | 18      |      |  |

|                    | VIN – SW, < 10-ns transient           | -1.5 | 25      |      |  |

|                    | SW - PGND, DC                         | -0.3 | 18      |      |  |

|                    | SW – PGND, < 10-ns transient          | -5   | 21.5    |      |  |

| Din veltage        | BOOT – PGND                           | -0.3 | 22      | V    |  |

| Pin voltage        | BOOT – SW                             | -0.3 | 4       | V    |  |

|                    | VCC                                   | -0.3 | 4       |      |  |

|                    | EN, PGOOD                             | -0.3 | 6       |      |  |

|                    | MODE                                  | -0.3 | 4       | 1    |  |

|                    | TRIP, SS/REFIN, FB                    | -0.3 | 3       |      |  |

|                    | VSNS-                                 | -0.3 | 0.3     |      |  |

| Sinking current    | Power-good sinking current capability |      | 10      | mA   |  |

| Operating junction | on temperature, T <sub>J</sub>        | -40  | 150     | °C   |  |

| Storage tempera    | ature, T <sub>stg</sub>               | -55  | 150     | C    |  |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)   | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

Over operating junction temperature range (unless otherwise noted)

|                    |                                                                                       | MIN  | NOM MAX | UNIT |

|--------------------|---------------------------------------------------------------------------------------|------|---------|------|

|                    | Input voltage range when the VCC pin is powered by a valid external bias              | 2.7  | 16      |      |

| V <sub>IN</sub>    | Input voltage range when using the internal VCC LDO                                   | 4.0  | 16      |      |

| - IIN              | Minimum $V_{\text{IN}}$ before enabling the converter when using the internal VCC LDO | 3.3  |         |      |

| V <sub>OUT</sub>   | Output voltage range                                                                  | 0.6  | 5.5     |      |

|                    | External VCC bias                                                                     | 3.13 | 3.6     | V    |

|                    | BOOT to SW                                                                            | -0.1 | 3.6     |      |

| Din voltogo        | EN, PGOOD                                                                             | -0.1 | 5.5     |      |

| Pin voltage        | MODE                                                                                  | -0.1 | VCC     |      |

|                    | TRIP, SS/REFIN, FB                                                                    | -0.1 | 1.5     |      |

|                    | VSNS- (refer to AGND)                                                                 | -50  | 50      | mV   |

| I <sub>PG</sub>    | Power-good input current capability                                                   | 0    | 10      | mA   |

| IL <sub>PEAK</sub> | Maximum peak inductor current                                                         |      | 28      | Α    |

|                    | Minimum R <sub>TRIP</sub>                                                             | 0    |         | Ω    |

| TJ                 | Operating junction temperature                                                        | -40  | 125     | °C   |

### **6.4 Thermal Information**

|                       |                                              | TPS5                 | TPS548B27             |      |  |  |

|-----------------------|----------------------------------------------|----------------------|-----------------------|------|--|--|

| THERMAL METRIC(1)     |                                              | RYL<br>(VQFN, JEDEC) | RYL<br>(VQFN, TI EVM) | UNIT |  |  |

|                       |                                              | 19 PINS              | 19 PINS               |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 49.0                 | 24.1                  | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 23.0                 | Not applicable (2)    | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.2                  | Not applicable (2)    | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5                  | 0.7                   | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 9.0                  | 8.7                   | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Not applicable to an EVM layout.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# **6.5 Electrical Characteristics**

$T_1 = -40$ °C to +125°C. VCC = 3 V (unless otherwise noted)

|                           | PARAMETER                                       | TEST CONDITIONS                                                                                                                                                                  | MIN  | TYP  | MAX   | UNIT |

|---------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| SUPPLY                    |                                                 |                                                                                                                                                                                  |      |      |       |      |

| I <sub>Q(VIN)</sub>       | V <sub>IN</sub> quiescent current               | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 2 V, V <sub>FB</sub> = V <sub>INTREF</sub> + 50 mV (non-switching), no external bias on the VCC pin                                    |      | 910  | 1007  | μA   |

| I <sub>SD(VIN)</sub>      | V <sub>IN</sub> shutdown supply current         | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 0 V, no external bias on the VCC pin                                                                                                   |      | 9.5  | 20    | μΑ   |

| UVLO                      | ·                                               |                                                                                                                                                                                  |      |      |       |      |

| VIN <sub>UVLO(rise)</sub> | VIN UVLO rising threshold                       | V <sub>IN</sub> rising, V <sub>CC</sub> = 3.3-V external bias                                                                                                                    | 2.1  | 2.4  | 2.7   | V    |

| VIN <sub>UVLO(fall)</sub> | VIN UVLO falling threshold                      | V <sub>IN</sub> falling, VCC = 3.3-V external bias                                                                                                                               | 1.55 | 1.85 | 2.15  | V    |

| ENABLE                    | ·                                               |                                                                                                                                                                                  |      |      |       |      |

| V <sub>EN(rise)</sub>     | EN voltage rising threshold                     | EN rising, enable switching                                                                                                                                                      | 1.17 | 1.22 | 1.27  | V    |

| V <sub>EN(fall)</sub>     | EN voltage falling threshold                    | EN falling, disable switching                                                                                                                                                    | 0.97 | 1.02 | 1.07  | V    |

| V <sub>EN(hyst)</sub>     | EN voltage hysteresis                           |                                                                                                                                                                                  |      | 0.2  |       | V    |

| V <sub>EN(LKG)</sub>      | Input leakage current into the EN pin           | V <sub>EN</sub> = 3.3 V                                                                                                                                                          |      | 0.5  | 5     | μΑ   |

|                           | EN internal pulldown resistance                 | EN pin to AGND, EN floating disables the converter.                                                                                                                              |      | 6500 |       | kΩ   |

| INTERNAL LDO              | (VCC PIN)                                       |                                                                                                                                                                                  |      |      |       |      |

| VCC <sub>UVLO(rise)</sub> | V <sub>CC</sub> UVLO rising threshold           | V <sub>CC</sub> rising                                                                                                                                                           | 2.80 | 2.87 | 2.94  | .,   |

| VCC <sub>UVLO(fall)</sub> | V <sub>CC</sub> UVLO falling threshold          | V <sub>CC</sub> falling                                                                                                                                                          | 2.62 | 2.70 | 2.77  | V    |

| VCC <sub>UVLO(hys)</sub>  | V <sub>CC</sub> UVLO hysteresis                 |                                                                                                                                                                                  |      | 0.17 |       | V    |

|                           | V <sub>CC</sub> LDO dropout voltage, 20-mA load | T <sub>J</sub> = 25°C, V <sub>IN</sub> = 4.0 V, I <sub>VCC(Load)</sub> = 20 mA, nonswitching                                                                                     |      |      | 1.037 | V    |

|                           | V <sub>CC</sub> LDO short-circuit current limit | V <sub>IN</sub> = 12 V, all temperature                                                                                                                                          | 52   | 105  | 158   | mA   |

|                           | FB threshold to turn off VCC LDO                | VCC LDO turn-off is controlled by FB voltage during EN shutdown event.                                                                                                           |      | 90   | 146   | mV   |

| REFERENCE V               | OLTAGE                                          |                                                                                                                                                                                  |      |      |       |      |

| I <sub>FB(LKG)</sub>      | Input leakage current into FB pin               | V <sub>FB</sub> = V <sub>INTREF</sub>                                                                                                                                            |      | 1    | 40    | nA   |

| SWITCHING FR              | EQUENCY                                         |                                                                                                                                                                                  |      |      |       |      |

|                           |                                                 | $T_J$ = 25°C, $V_{IN}$ = 12 V, $V_{OUT}$ = 1.25 V, $R_{MODE}$ = 0 Ω to AGND                                                                                                      | 0.5  | 0.6  | 0.7   |      |

| $f_{SW}$                  | SW switching frequency, FCCM operation          | $T_J$ = 25°C, $V_{IN}$ = 12 V, $V_{OUT}$ = 1.25 V, $R_{MODE}$ = 30.1 kΩ to AGND                                                                                                  | 0.6  | 0.7  | 0.8   | MHz  |

|                           |                                                 | $T_J$ = 25°C, $V_{IN}$ = 12 V, $V_{OUT}$ = 1.25 V, $R_{MODE}$ = 60.4 kΩ to AGND                                                                                                  |      | 0.85 | 1.0   |      |

| START-UP                  |                                                 |                                                                                                                                                                                  |      |      |       |      |

|                           | EN to first switching delay, internal LDO       | The delay from EN goes high to the first SW rising edge with internal LDO configuration. $C_{VCC}$ = 2.2 $\mu$ F, $C_{SS/REFIN}$ = 220 nF                                        |      | 0.93 | 2     | ms   |

|                           | EN to first switching delay, external VCC bias  | The delay from EN goes high to the first SW rising edge with external VCC bias configuration. VCC bias should reach regulation before EN ramp up. C <sub>SS/REFIN</sub> = 220 nF |      | 0.55 | 0.9   | ms   |

| t <sub>ss</sub>           | Internal fixed soft-start time                  | V <sub>O</sub> rising from 0 V to 95% of final setpoint, C <sub>SS/REFIN</sub> = 1 nF                                                                                            | 1    | 1.5  |       | ms   |

|                           | SS/REFIN sourcing current                       | V <sub>SS/REFIN</sub> = 0 V                                                                                                                                                      |      | 36   |       | μΑ   |

|                           | SS/REFIN sinking current                        | V <sub>SS/REFIN</sub> = 1 V                                                                                                                                                      |      | 12   |       | μΑ   |

# **6.5 Electrical Characteristics (continued)**

$T_J = -40$ °C to +125°C, VCC = 3 V (unless otherwise noted)

|                            | PARAMETER                                              | TEST CONDITIONS                                                                                                  | MIN  | TYP    | MAX  | UNIT |

|----------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|--------|------|------|

| BOOT CIRCUIT               |                                                        |                                                                                                                  |      |        |      |      |

| I <sub>BOOT(LKG)</sub>     | BOOT leakage current                                   | T <sub>J</sub> = 25°C, V <sub>BOOT-SW</sub> = 3.3 V                                                              |      | 35     | 50   | μΑ   |

| V <sub>BOOT-SW(UV_F)</sub> | BOOT-SW UVLO falling threshold                         | T <sub>J</sub> = 25°C, V <sub>IN</sub> = 12 V, V <sub>BOOT-SW</sub> falling                                      |      | 2.0    |      | V    |

| OVERCURRENT                | PROTECTION                                             |                                                                                                                  |      |        |      |      |

| I <sub>NOCL</sub>          | Negative current limit threshold                       | All V <sub>IN</sub> s                                                                                            | -12  | -10    | -8   | Α    |

| I <sub>zc</sub>            | Zero-cross detection current threshold, open loop      | V <sub>IN</sub> = 12 V, VCC = internal LDO                                                                       |      | 400    |      | mA   |

| OUTPUT OVP A               | ND UVP                                                 |                                                                                                                  |      |        |      |      |

| V <sub>OVP</sub>           | Output overvoltage-protection (OVP) threshold voltage  |                                                                                                                  | 113% | 116%   | 119% |      |

| t <sub>OVP(delay)</sub>    | Output OVP response delay                              | With 100-mV overdrive                                                                                            |      | 400    |      | ns   |

| V <sub>UVP</sub>           | Output undervoltage-protection (UVP) threshold voltage |                                                                                                                  | 77%  | 80%    | 83%  |      |

| t <sub>UVP(delay)</sub>    | Output UVP filter delay                                |                                                                                                                  |      | 68     |      | μs   |

| POWER GOOD                 |                                                        |                                                                                                                  |      |        |      |      |

|                            |                                                        | PGOOD high, FB rising                                                                                            | 89%  | 92.5%  | 95%  |      |

| $V_{PGTH}$                 | PGOOD threshold                                        | PGOOD low, FB rising                                                                                             | 113% | 116%   | 119% |      |

|                            |                                                        | PGOOD low, FB falling                                                                                            | 77%  | 80%    | 83%  |      |

|                            | OOB (out-of-bounds) threshold                          | PGOOD high, FB rising                                                                                            | 103% | 105.5% | 108% |      |

| $I_{PG}$                   | PGOOD sink current                                     | V <sub>PGOOD</sub> = 0.4 V, V <sub>IN</sub> = 12 V, VCC = internal LDO                                           |      |        | 17   | mA   |

| $V_{PG(low)}$              | PGOOD low-level output voltage                         | I <sub>PGOOD</sub> = 5.5 mA, V <sub>IN</sub> = 12 V, VCC = internal LDO                                          |      |        | 400  | mV   |

| t <sub>PGDLY(rise)</sub>   | Delay for PGOOD from low to high                       |                                                                                                                  |      | 1.06   | 1.33 | ms   |

| t <sub>PGDLY(fall)</sub>   | Delay for PGOOD from high to low                       |                                                                                                                  |      | 0.5    | 5    | μs   |

| I <sub>PG(LKG)</sub>       | PGOOD leakage current when pulled high                 | $T_J = 25$ °C, $V_{PGOOD} = 3.3$ V, $V_{FB} = V_{INTREF}$                                                        |      |        | 5    | μΑ   |

|                            | PGOOD clamp low-level output                           | $V_{IN}$ = 0 V, VCC = 0 V, $V_{EN}$ = 0 V,<br>PGOOD pulled up to 3.3 V through a<br>100-kΩ resistor              |      | 710    | 850  | mV   |

|                            | voltage                                                | V <sub>IN</sub> = 0 V, VCC = 0 V, V <sub>EN</sub> = 0 V,<br>PGOOD pulled up to 3.3 V through a<br>10-kΩ resistor |      | 850    | 1000 | mV   |

|                            | Min VCC for valid PGOOD output                         | V <sub>PGOOD</sub> ≤ 0.4 V                                                                                       |      |        | 1.5  | V    |

| OUTPUT DISCH               | ARGE                                                   |                                                                                                                  |      |        | 1    |      |

| R <sub>Dischg</sub>        | Output discharge resistance                            | V <sub>IN</sub> = 12 V, VCC = internal LDO, V <sub>SW</sub> = 0.5 V, power conversion disabled                   |      | 70     |      | Ω    |

| THERMAL SHUT               | rdown                                                  |                                                                                                                  |      |        |      |      |

| T <sub>SDN</sub>           | Thermal shutdown threshold <sup>(1)</sup>              | Temperature rising                                                                                               | 150  | 165    |      | °C   |

| T <sub>HYST</sub>          | Thermal shutdown hysteresis <sup>(1)</sup>             |                                                                                                                  |      | 30     |      | °C   |

<sup>(1)</sup> Specified by design. Not production tested.

Submit Document Feedback

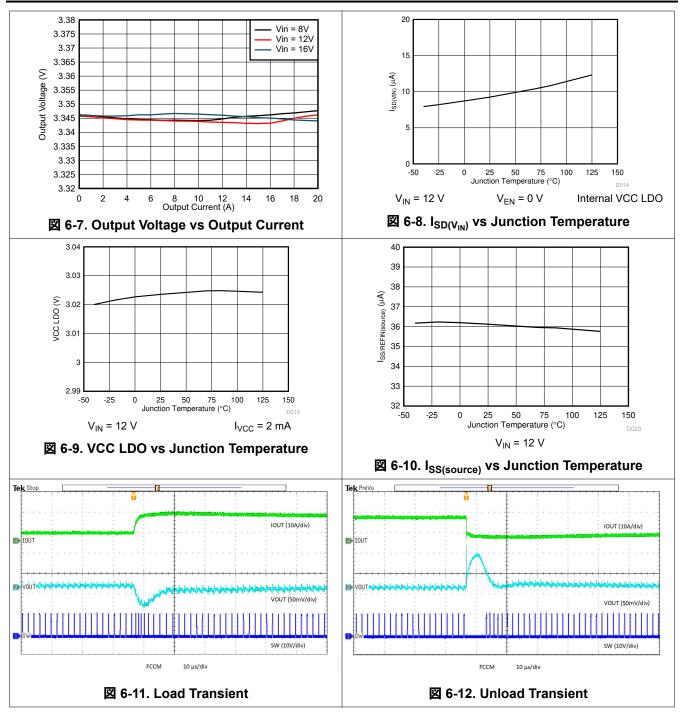

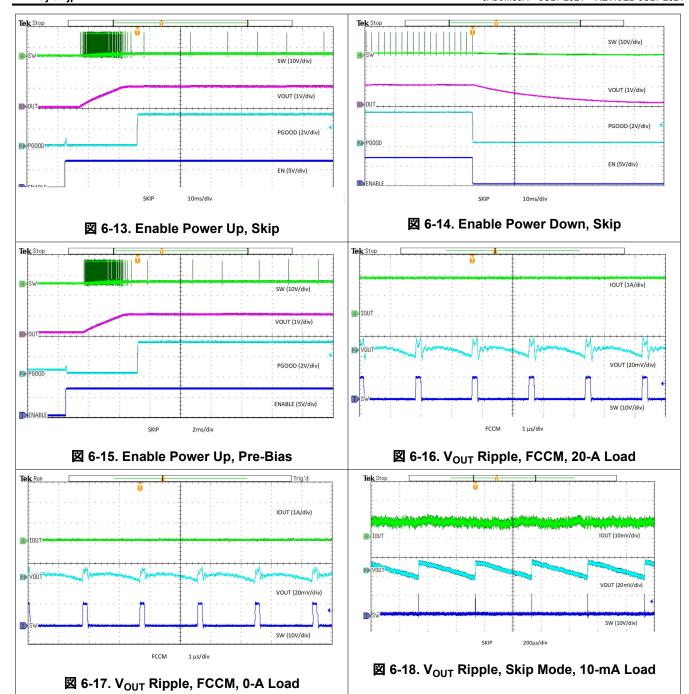

# **6.6 Typical Characteristics**

# 7 Detailed Description

### 7.1 Overview

The TPS548B27 device is a high-efficiency, single-channel, small-sized, synchronous-buck converter. The device suits low output voltage point-of-load applications with 20-A or lower output current in server, storage, and similar computing applications. The TPS548B27 features proprietary D-CAP3 mode control combined with adaptive on-time architecture. This combination builds modern low-duty-ratio and ultra-fast load-step-response DC/DC converters in an ideal fashion. The output voltage ranges from 0.6 V to 5.5 V. The conversion input voltage ranges from 2.7 V to 16 V, and the VCC input voltage ranges from 3.13 V to 3.6 V. The D-CAP3 mode uses emulated current information to control the modulation. An advantage of this control scheme is that it does not require a phase-compensation network outside, which makes the device easy to use and also allows low external component count. Another advantage of this control scheme is that it supports stable operation with all low-ESR output capacitors (such as ceramic capacitor and low-ESR polymer capacitor). Adaptive on-time control tracks the preset switching frequency over a wide range of input and output voltages while increasing switching frequency as needed during load-step transient.

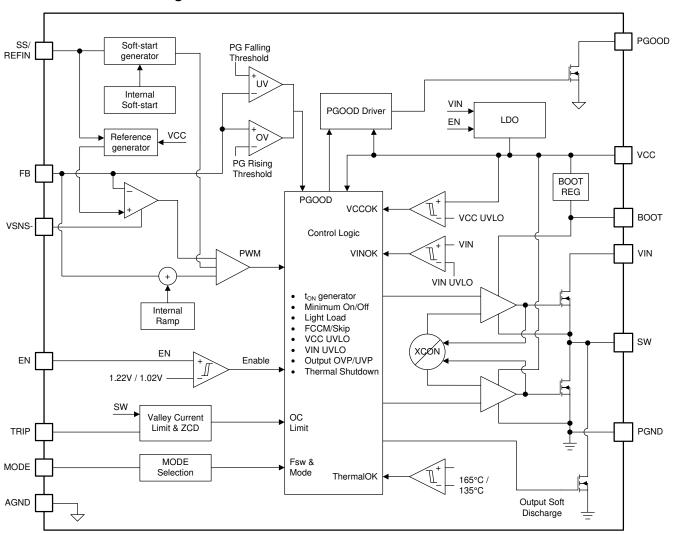

## 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Internal VCC LDO and Using External Bias on VCC Pin

The TPS548B27 has an internal 3.0-V LDO, featuring input from VIN and output to VCC. When the EN voltage rises above the enable threshold (typically 1.22 V), the internal LDO is enabled and starts regulating output voltage on the VCC pin. The VCC voltage provides the bias voltage for the internal analog circuitry and also provides the supply voltage for the gate drives.

The VCC pin needs to be bypassed with a 2.2-µF, at least 6.3-V rating, ceramic capacitor. An external bias that is above the output voltage of the internal LDO can override the internal LDO. This enhances the efficiency of the converter because the VCC current now runs off this external bias instead of the internal linear regulator.

The VCC UVLO circuit monitors the VCC pin voltage and disables the whole converter when VCC falls below the VCC UVLO falling threshold. Maintaining a stable and clean VCC voltage is required for a smooth operation of the device.

Considerations when using an external bias on the VCC pin are as follows:

- When the external bias is applied on the VCC pin early enough (for example, before EN signal comes in), the internal LDO will be always forced off and the internal analog circuits will have a stable power supply rail at their power enable.

- (Not recommended) When the external bias is applied on the VCC pin late (for example, after EN signal

comes in), any power-up and power-down sequencing can be applied as long as there is no excess current

pulled out of the VCC pin. It is important to understand that an external discharge path on the VCC pin, which

can pull a current higher than the current limit of the internal LDO from the VCC pin, can potentially turn off

VCC LDO, thereby shutting down the converter output.

- A good power-up sequence is when at least one of VIN UVLO rising threshold or EN rising threshold is satisfied later than the VCC UVLO rising threshold. For example, a practical power-up sequence is: VIN is applied first, then the external bias applied, and then EN signal goes high.

#### 7.3.2 Enable

When the EN pin voltage rises above the enable threshold voltage (typically 1.22 V) and  $V_{IN}$  rises above the  $V_{IN}$  UVLO rising threshold, the device enters its internal power-up sequence. The EN to first switching delay is specified in the Start-up section in the Electrical Characteristics table.

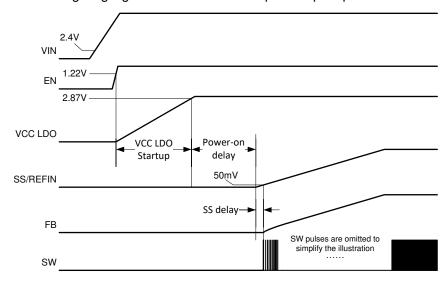

When using the internal VCC LDO, the internal power-up sequence includes three sequential steps. During the first period, the VCC voltage is charged up on a VCC bypass capacitor by an 11-mA current source. The length of this VCC LDO start-up time varies with the capacitance on the VCC pin. However, if the V<sub>IN</sub> voltage ramps up very slowly, the VCC LDO output voltage will be limited by the V<sub>IN</sub> voltage level, thus the VCC LDO start-up time can be extended longer. Since the VCC LDO start-up time is relatively long, the internal V<sub>INTREF</sub> build-up happens and finishes during this period. Once the VCC voltage crosses above VCC UVLO rising threshold (typically 2.87 V), the device moves to the second step, power-on delay. The MODE pin setting detection, SS/REFIN pin detection, and control loop initialization are finished within this 285-µs delay. Soft-start ramp starts when the 285-µs power-on delay finishes. During the soft-start ramp power stage, switching does not happen until the SS/REFIN pin voltage reaches 50 mV. This introduces a SS delay that varies with the external capacitance on the SS/REFIN pin.

$\boxtimes$  7-1 shows an example where the V<sub>IN</sub> UVLO rising threshold is satisfied earlier than the EN rising threshold. In this scenario, the V<sub>CC</sub> UVLO rising threshold becomes the gating signal to start the internal power-up sequence, and the sequence between VIN and EN does not matter.

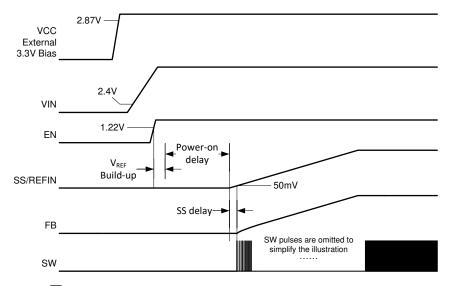

When using an external bias on the VCC pin, the internal power-up sequence still includes three sequential steps. The first period is much shorter since VCC voltage is built up already. A 100-µs period allows the internal references to start up and reach regulation points. This 100-µs period includes not only the 0.6-V V<sub>INTREF</sub>, but also all of the other reference voltages for various functions. The device then moves to the second step, power-on delay. The MODE pin setting detection, SS/REFIN pin detection, and control loop initialization are finished within this 285-µs delay. Soft-start ramp starts when the 285-µs power-on delay finishes. During the soft-start ramp power stage, switching does not happen until the SS/REFIN pin voltage reaches 50 mV. This introduces a SS delay that varies with the external capacitance on the SS/REFIN pin.

$\boxtimes$  7-2 shows an example where the V<sub>IN</sub> UVLO rising threshold and EN rising threshold are satisfied later than the V<sub>CC</sub> UVLO rising threshold. In this scenario, the VIN UVLO rising threshold or EN rising threshold, whichever is satisfied later, becomes the gating signal to start the internal power-up sequence.

図 7-1. Internal Power-Up Sequence Using Internal LDO

図 7-2. Internal Power-Up Sequence Using External Bias

The EN pin has an internal filter to avoid unexpected ON or OFF due to small glitches. The time constant of this RC filter is 5  $\mu$ s. For example, when applying a 3.3-V voltage source on the EN pin that jumps from 0 V to 3.3 V with an ideal rising edge, the internal EN signal will reach 2.086 V after 5  $\mu$ s, which is 63.2% of applied 3.3-V voltage level.

A internal pulldown resistor is implemented between the EN pin and AGND pin. To avoid impact to the EN rising/falling threshold, this internal pulldown resistor is set to 6.5 M $\Omega$ . With this pulldown resistor, floating the EN pin before start-up keeps the device under disabled state. During nominal operation when the power stage switches, this large internal pulldown resistor may not have enough noise immunity to hold EN the pin low.

The maximum recommended operating condition for the EN pin is 5.5 V. *Do not* connect the EN pin to the VIN pin directly.

### 7.3.3 Output Voltage Setting

The output voltage is programmed by the voltage-divider resistors,  $R_{FB\_HS}$  and  $R_{FB\_LS}$ . Connect  $R_{FB\_HS}$  between the FB pin and the positive node of the load, and connect  $R_{FB\_LS}$  between the FB pin and VSNS- pin. The recommended  $R_{FB\_LS}$  value is 10 k $\Omega$ , ranging from 1 k $\Omega$  to 20 k $\Omega$ . Determine  $R_{FB\_HS}$  by using  $\vec{x}$  1.

$$R_{FB\_HS} = \frac{V_O - V_{INTREF}}{V_{INTREF}} \times R_{FB\_LS}$$

(1)

The FB accuracy is determined by two elements. The first element is the accuracy of the internal 600-mV reference, which will be applied to the SS/REFIN pin unless an external  $V_{REF}$  is applied. The TPS548B27 device offers  $\pm 0.5\%$   $V_{INTREF}$  accuracy from a 0°C to 85°C temperature range, and  $\pm 1.0\%$   $V_{INTREF}$  accuracy from a -40°C to 125°C temperature range. The second element is the SS/REFIN-to-FB accuracy, which tells the user how accurately the control loop regulates FB node to SS/REFIN pin. The TPS548B27 offers  $\pm 0.6\%$  SS/REFIN-to-FB accuracy from a -40°C to 125°C temperature range. For example, when operating from a 0°C to 85°C temperature range, the total FB accuracy is  $\pm 1.1\%$ , which includes the impact from chip junction temperature and also the variation from part to part.

To improve the overall  $V_{OUT}$  accuracy, using a  $\pm 1\%$  accuracy or better resistor for the FB voltage divider is highly recommended.

Regardless of remote sensing or single-end sensing connection, the FB voltage divider,  $R_{FB\_HS}$  and  $R_{FB\_LS}$ , should be always placed as close as possible to the device.

#### 7.3.3.1 Remote Sense

The TPS548B27 offers remote sense function through the FB and VSNS- pins. Remote sense function compensates a potential voltage drop on the PCB traces, helping maintain  $V_{OUT}$  tolerance under steady-state operation and load transient event. Connecting the FB voltage divider resistors to the remote location allows sensing to the output voltage at a remote location. The connections from the FB voltage divider resistors to the remote location should be a pair of PCB traces with at least 12-mil trace width, and should implement Kelvin sensing across a high bypass capacitor of 0.1  $\mu$ F or higher. The ground connection of the remote sensing signal must be connected to the VSNS- pin. The  $V_{OUT}$  connection of the remote sensing signal must be connected to the feedback resistor divider with the lower feedback resistor,  $R_{FB\_LS}$ , terminated at the VSNS- pin. To maintain stable output voltage and minimize the ripple, the pair of remote sensing lines should stay away from any noise sources such as inductor and SW nodes, or high frequency clock lines. It is recommended to shield the pair of remote sensing lines with ground planes above and below.

Single-ended  $V_O$  sensing is often used for local sensing. For this configuration, connect the higher FB resistor,  $R_{FB\ HS}$ , to a high-frequency local bypass capacitor of 0.1  $\mu F$  or higher, and short VSNS– to AGND.

The recommended VSNS- operating range (refer to AGND pin) is -50 mV to +50 mV.

# 7.3.4 Internal Fixed Soft Start and External Adjustable Soft Start

The TPS548B27 implements a circuit to allow both internal fixed soft start and external adjustable soft start. The internal soft-start time is typically 1.5 ms. The soft-start time can be increased by adding a soft-start (SS) capacitor between the SS/REFIN and VSNS- pins. The total SS capacitor value can be determined by  $\stackrel{>}{\propto}$  2. The device follows the longer SS ramp among the internal SS time and the SS time determined by the external SS capacitors. The recommended maximum SS capacitor is 1  $\mu$ F. A minimum 1-nF SS capacitor is required.

The device does not require a capacitor from the SS/REFIN pin to AGND, thus it is not recommended to place a capacitor from the SS/REFIN pin to AGND. If both  $C_{SS/REFIN}$ -to-VSNS— and  $C_{SS/REFIN}$ -to-AGND capacitors exist, place  $C_{SS/REFIN}$ -to-VSNS— more closely with shortest trace back to the VSNS— pin.

$$C_{SS}(nF) = \frac{t_{SS}(ms) \times 36(\mu A)}{V_{INTREF}(V)}$$

(2)

The TPS548B27 provides an analog input pin (SS/REFIN) to accept an external reference. When an external voltage signal is applied between the SS/REFIN pin and VSNS- pin, it acts as the reference voltage, thus FB voltage follows this external voltage signal exactly. Applying this external reference to the SS/REFIN pin before the EN high signal is recommended. The external reference must be equal to or higher than the internal reference level to ensure correct power-good thresholds during soft start.

With an external reference applied, the internal fixed soft-start controls the output voltage ramp during start-up. After soft start finishes, the external voltage signal can be in a range of 0.5 V to 1.2 V.

When driving the SS/REFIN pin with an external resistor divider, the resistance should be low enough so that the external voltage source can overdrive the internal current source.

### 7.3.5 External REFIN For Output Voltage Tracking

The TPS548B27 provides an analog input pin (SS/REFIN) to accept an external reference (a DC voltage source). The device always looks at the voltage on this SS/REFIN pin as the reference for the control loop. When an external voltage reference is applied between the SS/REFIN pin and VSNS- pin, it acts as the reference voltage, so the FB voltage follows this external voltage reference exactly. The same ±0.6% SS/REFIN-to-FB accuracy from the -40°C to 125°C temperature range applies here too.

In the middle of internal power-on delay, a detection circuit senses the voltage on the SS/REFIN pin to tell whether an active DC voltage source is applied. Before the detection happens, the SS/REFIN pin tries to discharge any energy on SS/REFIN capacitors through an internal 120- $\Omega$  resistor to AGND. This discharge lasts for 125  $\mu$ s. Then, within a 32- $\mu$ s window, the detection circuit compares the SS/REFIN pin voltage with an internal reference equal to 89% of V<sub>INTREF</sub>. This discharge operation ensures a SS capacitor with left-over energy will not be wrongly detected as a voltage reference. If the external voltage reference fails to supply sufficient current and hold voltage level higher than 89% of V<sub>INTREF</sub>, the SS/REFIN detection circuit will provide the wrong detection result.

If the detection result is that SS/REFIN pin voltage falls below 89% of  $V_{INTREF}$ , which means no external reference is connected, the device first uses the internal fixed  $V_{INTREF}$  as the reference for the PGOOD,  $V_{OUT}$  OVP, and  $V_{OUT}$  UVP thresholds. On this configuration, given the SS/REFIN pin sees a soft-start ramp on this pin, the slower ramp along with the internal fixed soft start and the external soft start determine the start-up of FB. Once both the internal and external soft-start ramp finishes, the power-good signal becomes high after a 1.06-ms internal delay. The whole internal soft-start ramp takes 2 ms to finish. The external soft-start done signal goes high when FB reaches a threshold equal to  $V_{INTREF}$  – 50 mV. The device waits for the PGOOD status transition from low to high, then starts using the SS/REFIN pin voltage, instead of the internal  $V_{INTREF}$  as the reference for PGOOD,  $V_{OUT}$  OVP, and  $V_{OUT}$  UVP threshold.

If the detection result is that the SS/REFIN pin voltage holds higher than 89% of  $V_{\rm INTREF}$ , which means an active DC voltage source is used as an external reference, the device always uses the SS/REFIN pin voltage instead of the internal  $V_{\rm INTREF}$  as the reference for the PGOOD,  $V_{\rm OUT}$  OVP, and  $V_{\rm OUT}$  UVP thresholds. On this configuration, since the SS/REFIN pin sees a DC voltage and no soft-start ramp on this pin, the internal fixed soft start is used for start-up. Once the internal soft-start ramp finishes, the power-good signal becomes high after a 1.06-ms internal delay. The whole internal soft-start ramp takes 2 ms to finish because the soft-start ramp goes beyond  $V_{\rm INTREF}$ .

On this external REFIN configuration, applying a stabilized DC external reference to the SS/REFIN pin before the EN high signal is recommended. During the internal power-on delay, the external reference should be capable of holding the SS/REFIN pin equal to or higher than 89% of  $V_{INTREF}$ , so that the device can correctly detect the external reference and choose the right thresholds for power good,  $V_{OUT}$  OVP, and  $V_{OUT}$  UVP. After the power-good status goes from low to high, the external reference can be set in a range from 0.5 V to 1.2 V. To overdrive the SS/REFIN pin during nominal operation, the external reference has to be able to sink more than 36- $\mu$ A current if the external reference is lower than the internal  $V_{INTREF}$ , or source more than 12- $\mu$ A current if the external reference is higher than the internal  $V_{INTREF}$ . When driving the SS/REFIN pin by an external reference through a resistor divider, the resistance of the divider should be low enough to provide the sinking, or sourcing current capability.

Product Folder Links: TPS548B27

Submit Document Feedback

The configuration of applying EN high signal first, then applying an external ramp on the SS/REFIN pin as a tracking reference can be achieved, as long as design considerations for power good,  $V_{OUT}$  OVP, and  $V_{OUT}$  UVP have been taken. Please contact Texas Instruments for detailed information about this configuration.

If the external voltage source must transition up and down between any two voltage levels, the slew rate must be no more than 1 mV/µs.

# 7.3.6 Frequency and Operation Mode Selection

The TPS548B27 provides forced CCM operation for tight output ripple application and auto-skip Eco-mode for high light-load efficiency. The TPS548B27 allows users to select the switching frequency and operation mode by connecting a resistor from the MODE pin to AGND pin.  $\frac{1}{8}$  7-1 lists the resistor values for the switching frequency and operation mode selection. TI recommends  $\pm 1\%$  tolerance resistors with a typical temperature coefficient of  $\pm 100$  ppm/°C.

The MODE state will be set and latched during the internal power-on delay period. Changing the MODE pin resistance after the power-on delay will not change the status of the device. The internal circuit will set the MODE pin status to 600 kHz / Skip mode if the MODE pin is left open during the power-on delay period.

To make sure the internal circuit detects the desired option correctly, *do not* place any capacitor on the MODE pin.

| St 1-1: MODE 1 III ocioculon |                                 |                                                                |  |  |  |

|------------------------------|---------------------------------|----------------------------------------------------------------|--|--|--|

| MODE PIN<br>CONNECTIONS      | OPERATION MODE UNDER LIGHT LOAD | SWITCHING FREQUENCY<br>(f <sub>SW</sub> ) (kHz) <sup>(1)</sup> |  |  |  |

| Short to VCC                 | Skip mode                       | 600                                                            |  |  |  |

| 243 kΩ ± 10% to AGND         | Skip mode                       | 800                                                            |  |  |  |

| 121 kΩ ± 10% to AGND         | Skip mode                       | 1000                                                           |  |  |  |

| 60.4 kΩ ±10% to AGND         | Forced CCM                      | 1000                                                           |  |  |  |

| 30.1 kΩ ±10% to AGND         | Forced CCM                      | 800                                                            |  |  |  |

| Short to AGND                | Forced CCM                      | 600                                                            |  |  |  |

表 7-1. MODE Pin Selection

### 7.3.7 D-CAP3 Control

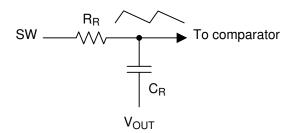

☑ 7-3. Internal RAMP Generation Circuit

The TPS548B27 uses D-CAP3 mode control to achieve fast load transient while maintaining the ease-of-use feature. The D-CAP3 control architecture includes an internal ripple generation network enabling, the use of very low-ESR output capacitors such as multi-layered ceramic capacitors (MLCC), and low-ESR polymer capacitors. No external current sensing network or voltage compensators are required with D-CAP3 control architecture. The role of the internal ripple generation network is to emulate the ripple component of the inductor current information and then combine it with the voltage feedback signal to regulate the loop operation. The amplitude of the ramp is determined by  $V_{IN}$ ,  $V_{OUT}$ , operating frequency, and the R-C time-constant of the internal ramp circuit. At different switching frequency settings (see  $\gtrsim$  7-1), the R-C time-constant varies to maintain relatively constant ramp amplitude. Also, the device uses internal circuitry to cancel the DC offset caused by an injected ramp, and significantly reduces the DC offset caused by the output ripple voltage, especially under light load condition.

<sup>(1)</sup> Switch frequency is based on 3.3 V<sub>OUT</sub>. Frequency varies with V<sub>OUT</sub>.

For any control topologies supporting no external compensation design, there is a minimum range, maximum range, or both, of the output filter it can support. The output filter used with the TPS548B27 is a low-pass L-C circuit. This L-C filter has a double pole that is described in 式 3.

$$f_{p} = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}}$$

(3)

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the TPS548B27. The low frequency L-C double pole has a 180-degree drop in phase. At the output filter frequency, the gain rolls off at a -40-dB per decade rate and the phase drops rapidly. The internal ripple generation network introduces a high-frequency zero that reduces the gain roll off from -40-dB to -20-dB per decade and increases the phase by 90 degrees per decade above the zero frequency.

After identifying the application requirements, the output inductance should be designed so that the inductor peak-to-peak ripple current is approximately between 15% and 40% of the maximum output current.

The inductor and capacitor selected for the output filter must be such that the double pole of 式 3 is located no higher than 1/30th of operating frequency. Choose very small output capacitance leads to relative high frequency L-C double pole, allowing overall loop gain to stay high until the L-C double frequency. Given the zero from the internal ripple generation network is relatively high frequency as well, the loop with very small output capacitance may have too high crossover frequency, which is not desired. Use 表 7-2 to help locate the internal zero based on the selected switching frequency.

表 7-2. Locating the Zero

| SWITCHING FREQUENCIES (f <sub>SW</sub> ) (kHz) | ZERO (f <sub>Z</sub> ) LOCATION (kHz) |

|------------------------------------------------|---------------------------------------|

| 600                                            | 84.5                                  |

| 800                                            | 84.5                                  |

| 1000                                           | 106                                   |

In general, where reasonable (or smaller) output capacitance is desired, the output ripple requirement and load transient requirements can be used to determine the necessary output capacitance for stable operation.

For the maximum output capacitance recommendation, select the inductor and capacitor values so that the L-C double pole frequency is no less than 1/100th of operating frequency. With this starting point, verify the small signal response on the board making sure the phase margin at the loop crossover is greater than 50 degrees.

The actual maximum output capacitance can go higher as long as phase margin is greater than 50 degrees. However, small signal measurement (bode plot) should be done to confirm the design.

If MLCC is used, consider the derating characteristics to determine the final output capacitance for the design. For example, when using an MLCC with specifications of 10  $\mu$ F, X5R and 6.3 V, the derating by DC bias and AC bias are 80% and 50%, respectively. The effective derating is the product of these two factors, in this case, 40% and 4  $\mu$ F. Consult with capacitor manufacturers for specific characteristics of the capacitors to be used in the system/applications.

For higher output voltage at or above 2 V, additional phase boost can be required to secure sufficient phase margin due to phase delay/loss for higher output voltage (large on time (t<sub>ON</sub>)) setting in a fixed-on-time topology based operation. A feedforward capacitor placed in parallel with R<sub>FB\_HS</sub> is found to be very effective to boost the phase margin at loop crossover. Refer to the *Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor* application report for details.

Besides boosting the phase, a feedforward capacitor feeds more  $V_{OUT}$  node information into the FB node by the AC coupling. This feedforward during load transient event enables the control loop a faster response to  $V_{OUT}$  deviation. However, this feedforward during steady state operation also feeds more  $V_{OUT}$  ripple and noise into FB. High ripple and noise on FB usually leads to more jitter, or even double pulse behavior. To determine the final feedforward capacitor value, impacts to phase margin, load transient performance, and ripple and noise on

FB should be all considered. Using frequency analysis equipment to measure the crossover frequency and the phase margin is recommended.

#### 7.3.8 Low-Side FET Zero-Crossing

The TPS548B27 uses a zero-crossing circuit to perform the zero inductor-current detection during Skip mode operation. The function compensates the inherent offset voltage of the Z-C comparator and delay time of the Z-C detection circuit. The zero-crossing threshold is set to a positive value to avoid negative inductor current. As a result, the device delivers better light-load efficiency.

#### 7.3.9 Current Sense and Positive Overcurrent Protection

For a buck converter, during the on time of the high-side FET, the switch current increases at a linear rate determined by input voltage, output voltage, the on time, and the output inductor value. During the on time of the low-side FET, this current decreases linearly. The average value of the switch current equals to the load current.

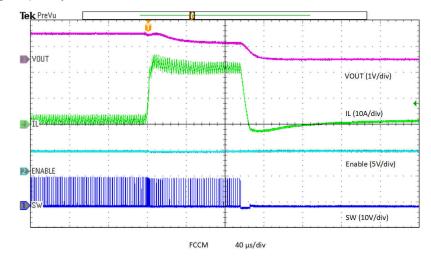

The output overcurrent limit (OCL) in the TPS548B27 device is implemented using a cycle-by-cycle valley current detect control circuit. The inductor current is monitored during the on time of the low-side FET by measuring the low-side FET drain-to-source current. If the measured drain-to-source current of the low-side FET is above the current limit threshold, the low-side FET stays ON until the current level becomes lower than the current limit threshold. This type of behavior reduces the average output current sourced by the device. During an overcurrent condition, the current to the load exceeds the current to the output capacitors. Thus, the output voltage tends to decrease. Eventually, when the output voltage falls below the undervoltage-protection threshold (80%), the UVP comparator detects it and shuts down the device after a wait time of 68 µs. The device then enters a hiccup sleep period for approximately 14 ms. After this waiting period, the device attempts to start up again. Z 7-4 shows the cycle-by-cycle valley current limit behavior as well as the wait time before the device shuts down.

If an OCL condition happens during start-up, the device still has cycle-by-cycle current limit based on low-side valley current. After soft start is finished, the UV event which is caused by the OC event, shuts down the device and enters Hiccup mode with a wait time of 68 µs.

The resistor, R<sub>TRIP</sub>, connected from the TRIP pin to AGND sets current limit threshold. A ±1% tolerance resistor is highly recommended because a worse tolerance resistor provides less accurate OCL threshold. 式 4 calculates the R<sub>TRIP</sub> for a given overcurrent limit threshold on the device. To simplify the calculation, use a constant,  $K_{OCI}$ , to replace the value of 12 × 10<sup>4</sup>.  $\stackrel{1}{

m I}$  4 calculates the overcurrent limit threshold for a given  $R_{TRIP}$ value. The tolerance of K<sub>OCL</sub> is listed in セクション 6.5 to help the user analyze the tolerance of the overcurrent limit threshold.

To protect the device from unexpected connection on the TRIP pin, an internal fixed OCL clamp is implemented. This internal OCL clamp limits the maximum valley current on LS FET when TRIP pin has too small resistance to AGND, or is accidentally shorted to ground.

$$R_{TRIP} = \frac{12 \times 10^{4}}{I_{OCLIM} - \frac{1}{2} \times \frac{(V_{IN} - V_{O}) \times V_{O}}{V_{IN}} \times \frac{1}{L \times f_{SW}}} = \frac{K_{OCL}}{I_{OCLIM} - \frac{1}{2} \times \frac{(V_{IN} - V_{O}) \times V_{O}}{V_{IN}} \times \frac{1}{L \times f_{SW}}}$$

(4)

#### where

- I<sub>OCLIM</sub> is overcurrent limit threshold for load current in A

- $R_{TRIP}$  is TRIP resistor value in  $\Omega$

- K<sub>OCL</sub> is a constant for the calculation

- V<sub>IN</sub> is input voltage value in V

- V<sub>O</sub> is output voltage value in V

- L is output inductor value in µH

- f<sub>SW</sub> is switching frequency in MHz

$$I_{OCLIM} = \frac{K_{OCL}}{R_{TRIP}} + \frac{1}{2} \times \frac{\left(V_{IN} - V_{O}\right) \times V_{O}}{V_{IN}} \times \frac{1}{L \times f_{SW}}$$

# TEXAS INSTRUMENTS www.tij.co.jp

#### where

- I<sub>OCLIM</sub> is overcurrent limit threshold for load current in A

- R<sub>TRIP</sub> is TRIP resistor value in Ω

- K<sub>OCL</sub> is a constant for the calculation

- V<sub>IN</sub> is input voltage value in V

- V<sub>O</sub> is output voltage value in V

- L is output inductor value in μH

- f<sub>SW</sub> is switching frequency in MHz

図 7-4. Overcurrent Protection

#### 7.3.10 Low-Side FET Negative Current Limit

The device has a fixed, cycle-by-cycle negative current limit. Similar with the positive overcurrent limit, the inductor current is monitored during the on time of the low-side FET. To prevent too large negative current flowing through the low-side FET, when the low-side FET detects a -10-A current (typical threshold), the device turns off the low-side FET, then turns on the high-side FET for a proper on time (determined by  $V_{IN}/V_O/f_{SW}$ ). After the high-side FET on time expires, the low-side FET turns on again.

The device should not trigger the -10-A negative current limit threshold during nominal operation, unless a small inductor value that is too small is chosen or the inductor becomes saturated. This negative current limit is utilized to discharge output capacitors during an output OVP or an OOB event. See セクション 7.3.12 and セクション 7.3.13 for details.

#### 7.3.11 Power Good

The device has power-good output that indicates high when the converter output is within the target. The power-good output is an open-drain output and must be pulled up to the VCC pin or an external voltage source (< 5.5 V) through a pullup resistor (typically 30.1 k $\Omega$ ). The recommended power-good pullup resistor value is 1 k $\Omega$  to 100 k $\Omega$ .

Once both the internal and external soft-start ramp finishes, the power-good signal becomes high after a 1.06-ms internal delay. The whole internal soft-start ramp takes 2 ms to finish. The external soft-start done signal goes high when FB reaches threshold equal to  $V_{INTREF}$  – 50 mV. If the FB voltage drops to 80% of the  $V_{INTREF}$  voltage or exceeds 116% of the  $V_{INTREF}$  voltage, the power-good signal latches low after a 2- $\mu$ s internal delay. The power-good signal can only be pulled high again after re-toggling EN or a reset of VIN.

If the input supply fails to power up the device, for example VIN and VCC both stay at zero volts, the PG pin clamps low by itself when this pin is pulled up through an external resistor.

Once VCC voltage level rises above the minimum VCC threshold for valid PGOOD output (maximum 1.5 V), internal power-good circuit is enabled to hold the PGOOD pin to the default status. By default, PGOOD is pulled

low and this low-level output voltage is no more than 400 mV with 5.5-mA sinking current. The power-good function is fully activated after the soft-start operation is completed.

#### 7.3.12 Overvoltage and Undervoltage Protection

The device monitors a resistor-divided feedback voltage to detect overvoltage and undervoltage events. When the FB voltage becomes lower than 80% of the  $V_{INTREF}$  voltage, the UVP comparator detects and an internal UVP delay counter begins counting. After the 68- $\mu$ s UVP delay time, the device enters Hiccup mode and restarts with a sleep time of 14 ms. The UVP function enables after the soft-start period is complete.

When the FB voltage becomes higher than 116% of the  $V_{INTREF}$  voltage, the OVP comparator detects and the circuit latches OFF the high-side MOSFET driver and turns on the low-side MOSFET until reaching a negative current limit  $I_{NOCL}$ . Upon reaching the negative current limit, the low-side FET is turned off, and the high-side FET is turned on again, for a proper on time (determined by  $V_{IN}/V_O/f_{SW}$ ). The device operates in this cycle until the output voltage is pulled down under the UVP threshold voltage for 68  $\mu$ s. After the 68- $\mu$ s UVP delay time, the device enters hiccup mode and re-starts with a sleep time of 14 ms.

During the  $68-\mu s$  UVP delay time, if the output voltage becomes higher than the UV threshold, thus is not qualified for a UV event, the timer will be reset to zero. When the output voltage triggers the UV threshold again, the timer of the  $68~\mu s$  restarts.

### 7.3.13 Out-Of-Bounds (OOB) Operation

The device has an out-of-bounds (OOB) overvoltage protection that protects the output load at a much lower overvoltage threshold of 5% above the  $V_{INTREF}$  voltage. OOB protection does not trigger an overvoltage fault, so the device is on non-latch mode after an OOB event. OOB protection operates as an early no-fault overvoltage-protection mechanism. During the OOB operation, the controller operates in forced CCM mode. Turning on the low-side FET beyond the zero inductor current quickly discharges the output capacitor, thus helps the output voltage to fall quickly towards the setpoint. During the operation, the cycle-by-cycle negative current limit is also activated to ensure the safe operation of the internal FETs.

### 7.3.14 Output Voltage Discharge

When the device is disabled through EN, it enables the Output Voltage Discharge mode. This mode forces both high-side and low-side FETs to latch off, but turns on the discharge FET, which is connected from SW to PGND, to discharge the output voltage. Once the FB voltage drops below 90 mV, the discharge FET is turned off.

The output voltage discharge mode is activated by any of the following fault events:

- 1. EN pin goes low to disable the converter.

- 2. Thermal shutdown (OTP) is triggered.

- V<sub>CC</sub> UVLO (falling) is triggered.

- 4. V<sub>IN</sub> UVLO (falling) is triggered.

#### 7.3.15 UVLO Protection

The device monitors the voltage on both the VIN and the VCC pins. If the VCC pin voltage is lower than the VCC<sub>UVLO</sub> falling threshold voltage, the device shuts off. If the VCC voltage increases beyond the VCC<sub>UVLO</sub> rising threshold voltage, the device turns back on. VCC UVLO is a non-latch protection.

When the VIN pin voltage is lower than the  $VIN_{UVLO}$  falling threshold voltage but the VCC pin voltage is still higher than  $VCC_{UVLO}$  rising threshold voltage, the device stops switching and discharges SS/REFIN pin. Once the VIN voltage increases beyond the  $VIN_{UVLO}$  rising threshold voltage, the device re-initiates the soft start and switches again.  $V_{IN}$  UVLO is a non-latch protection.

#### 7.3.16 Thermal Shutdown

The device monitors internal junction temperature. If the temperature exceeds the threshold value (typically 165°C), the device stops switching and discharges the SS/REFIN pin. When the temperature falls approximately 30°C below the threshold value, the device turns back on with a re-initiated soft start. Thermal shutdown is a non-latch protection.

#### 7.4 Device Functional Modes

### 7.4.1 Auto-Skip Eco-mode Light Load Operation

While the MODE pin is pulled to VCC directly or connected to the AGND pin through a resistor larger than 121  $k\Omega$ , the device automatically reduces the switching frequency at light-load conditions to maintain high efficiency. This section describes the operation in detail.

As the output current decreases from heavy load condition, the inductor current also decreases until the rippled valley of the inductor current touches zero level. Zero level is the boundary between the Continuous-conduction and Discontinuous-conduction modes. The synchronous MOSFET turns off when this zero inductor current is detected. As the load current decreases further, the converter runs into Discontinuous-conduction mode (DCM). The on time is maintained to a level approximately the same as during Continuous-conduction mode operation so that discharging the output capacitor with a smaller load current to the level of the reference voltage requires more time. The transition point to the light-load operation  $I_{O(LL)}$  (for example, the threshold between Continuous-and Discontinuous-conduction mode) is calculated as shown in  $\not \equiv 5$ .

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(5)

where

f<sub>SW</sub> is the switching frequency

Only using ceramic capacitors is recommended for Skip mode.

#### 7.4.2 Forced Continuous Conduction Mode

When the MODE pin is tied to the AGND pin through a resistor less than 60.4  $k\Omega$ , the controller operates in Continuous-conduction mode (CCM) during light-load conditions. During CCM, the switching frequency maintained to an almost constant level over the entire load range which is suitable for applications requiring tight control of the switching frequency at the cost of lower efficiency.

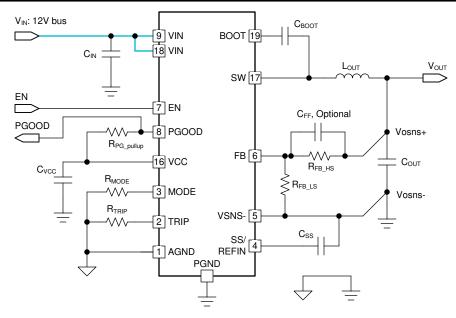

#### 7.4.3 Powering the Device from a 12-V Bus

The device works well when powering from a 12-V bus with a single  $V_{IN}$  configuration. As a single  $V_{IN}$  configuration, the internal LDO is powered by a 12-V bus and generates a 3.0-V output to bias the internal analog circuitry and powers up the gate drives. The  $V_{IN}$  input range under this configuration is 4 V to 16 V for up to 20-A load current.  $\boxtimes$  7-5 shows an example for this single  $V_{IN}$  configuration.

VIN and EN are the two signals to enable the part. For start-up sequence, any sequence between the VIN and EN signals can power the device up correctly.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

図 7-5. Single V<sub>IN</sub> Configuration for a 12-V Bus

### 7.4.4 Powering the Device from a 3.3-V Bus