# TPS548A23 4V ~ 16V 入力、12A、リモートセンス 同期整流降圧コンバータ 搭載

## 1 特長

- 4V ~ 16V 入力電圧範囲

- 3.1V ~ 5.3V の外部 VCC バイアスをサポート

- 8.4mΩ および 3.3mΩ MOSFET ( $V_{VCC} = 3.3V$ )

- 12A 連続出力電流

- 効率と放熱性能向けに最適化された 19 ピン WQFN-HR パッケージ

- 内部フィードバックで  $\pm 1.25\%$  の出力電圧精度、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$

- 出力電圧範囲: 0.5V ~ 5.5V

- 差動リモートセンス

- D-CAP4 による超高速負荷ステップ応答

- すべての出力コンデンサでセラミックコンデンサの使用をサポート

- 軽負荷時の高効率を実現する自動スキップ Eco モードを選択可能

- バレー電流制限をプログラム可能

- 600kHz、800kHz、1.0MHz、1.2MHz、で選択可能なスイッチング周波数

- ソフトスタート時間をプログラム可能

- プリバイアス付きスタートアップ機能

- オープンドレインのパワー グッド出力

- 過電圧および低電圧フォルト保護

- 3mm × 3mm (0.4mm ピンピッチ)、19 ピン QFN パッケージ

- 20A TPS548B23 とピン互換

## 2 アプリケーション

- ラック サーバーとブレード サーバー

- データセンター向けスイッチ

- ワイヤレス インフラ

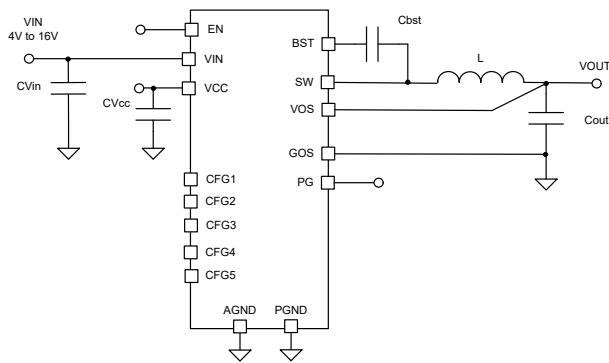

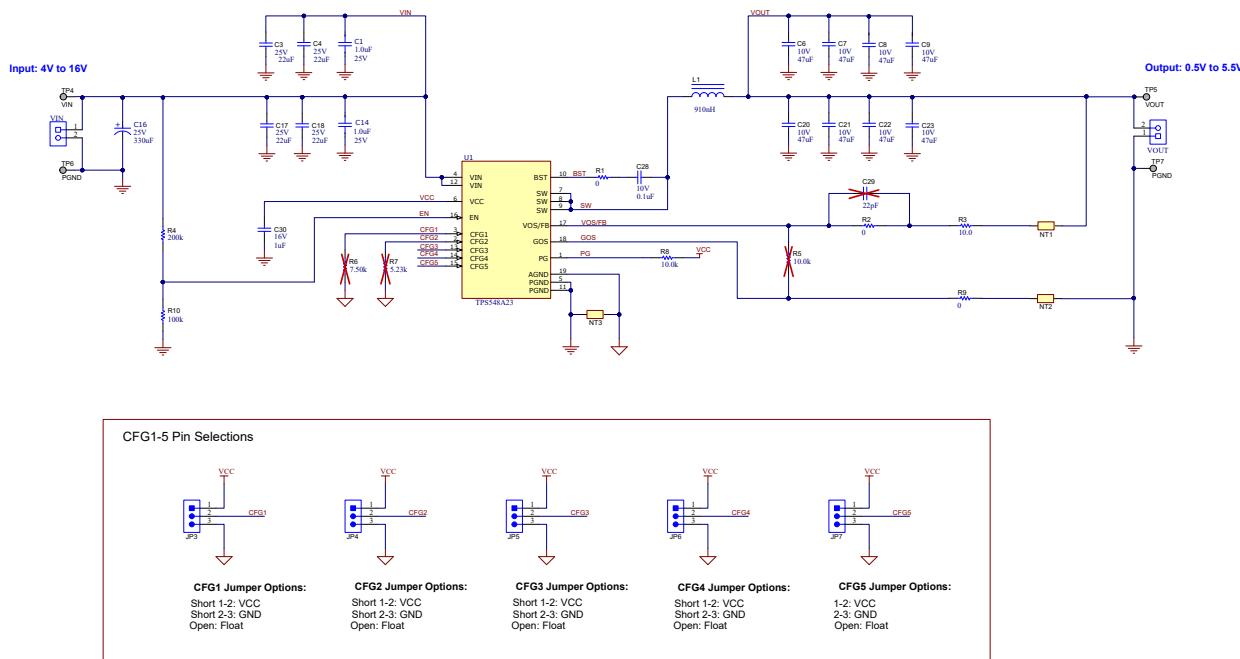

概略回路図

## 3 説明

TPS548A23 デバイスは、適応型オン時間 D-CAP4 制御モードを備えた小型で高効率の同期整流降圧コンバータです。この制御方式により、外部補償ネットワークを必要とせずに、出力電圧範囲全体にわたって低い最小オン時間と高速負荷過渡応答を実現できます。このデバイスは外部補償が不要のため使いやすく、外部部品をほとんど必要としません。このデバイスは、スペースに制約のあるデータセンター アプリケーションに適した設計になっています。

The TPS548A23 デバイスは、差動リモートセンス、高性能の内蔵 MOSFET、外部フィードバック用に  $\pm 1.0\%$  のリファレンス電圧を備えており、内部リファレンス電圧を使用して  $\pm 1.25\%$  の出力電圧精度に対応しています。このデバイスの特長は、正確な負荷およびライン レギュレーションと、Eco モードまたは強制連続導通モード (FCCM) 動作です。複数のピnstラップ オプションを使用して、過電流制限、フォルト応答、内部または外部のフィードバック、出力電圧の選択、スイッチング周波数、ソフトスタート時間を設定できます。

内蔵の 3.0V LDO は、VCC ピンを介して 3.1V ~ 5.3V の外部電源でオーバードライブできるため、効率向上と消費電力低減を実現できます。

TPS548A23 デバイスは鉛フリー デバイスです。RoHS に準拠しています (適用除外なし)。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| TPS548A23 | VAN (WQFN-HR, 19)    | 3mm × 3mm                |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 6.4 デバイスの機能モード         | 26 |

| 2 アプリケーション  | 1  | 7 アプリケーションと実装          | 27 |

| 3 説明        | 1  | 7.1 アプリケーション情報         | 27 |

| 4 ピン構成および機能 | 3  | 7.2 代表的なアプリケーション       | 27 |

| 5 仕様        | 5  | 7.3 電源に関する推奨事項         | 34 |

| 5.1 絶対最大定格  | 5  | 7.4 レイアウト              | 35 |

| 5.2 ESD 定格  | 5  | 8 デバイスおよびドキュメントのサポート   | 37 |

| 5.3 推奨動作条件  | 5  | 8.1 ドキュメントのサポート        | 37 |

| 5.4 熱に関する情報 | 6  | 8.2 ドキュメントの更新通知を受け取る方法 | 37 |

| 5.5 電気的特性   | 6  | 8.3 サポート・リソース          | 37 |

| 5.6 代表的特性   | 9  | 8.4 商標                 | 37 |

| 6 詳細説明      | 15 | 8.5 静電気放電に関する注意事項      | 37 |

| 6.1 概要      | 15 | 8.6 用語集                | 37 |

| 6.2 機能ブロック図 | 15 | 9 改訂履歴                 | 37 |

| 6.3 機能説明    | 16 | 10 メカニカル、パッケージ、および注文情報 | 38 |

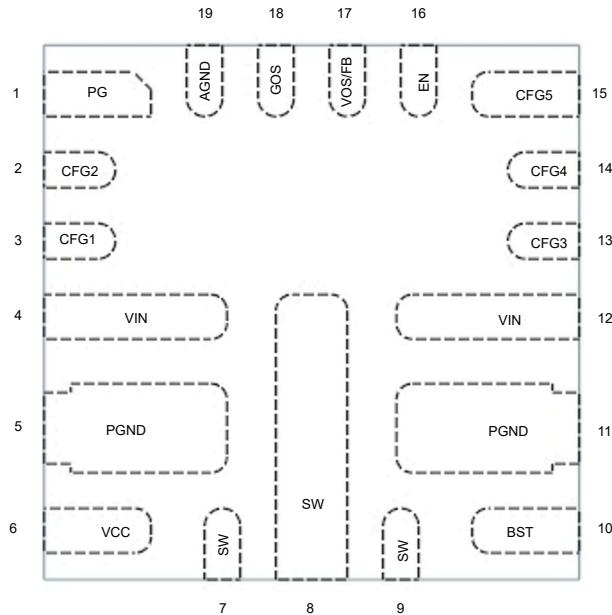

## 4 ピン構成および機能

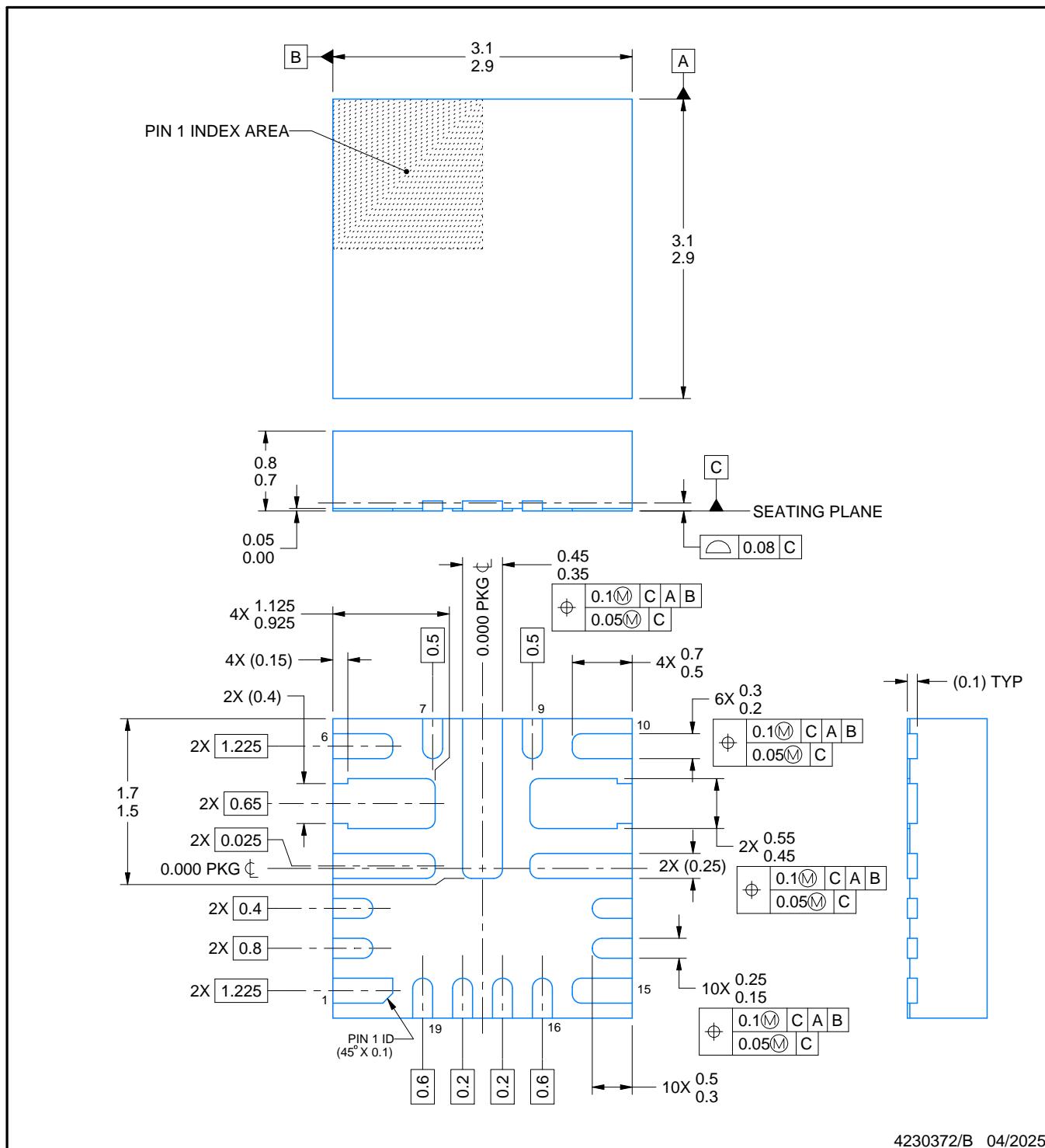

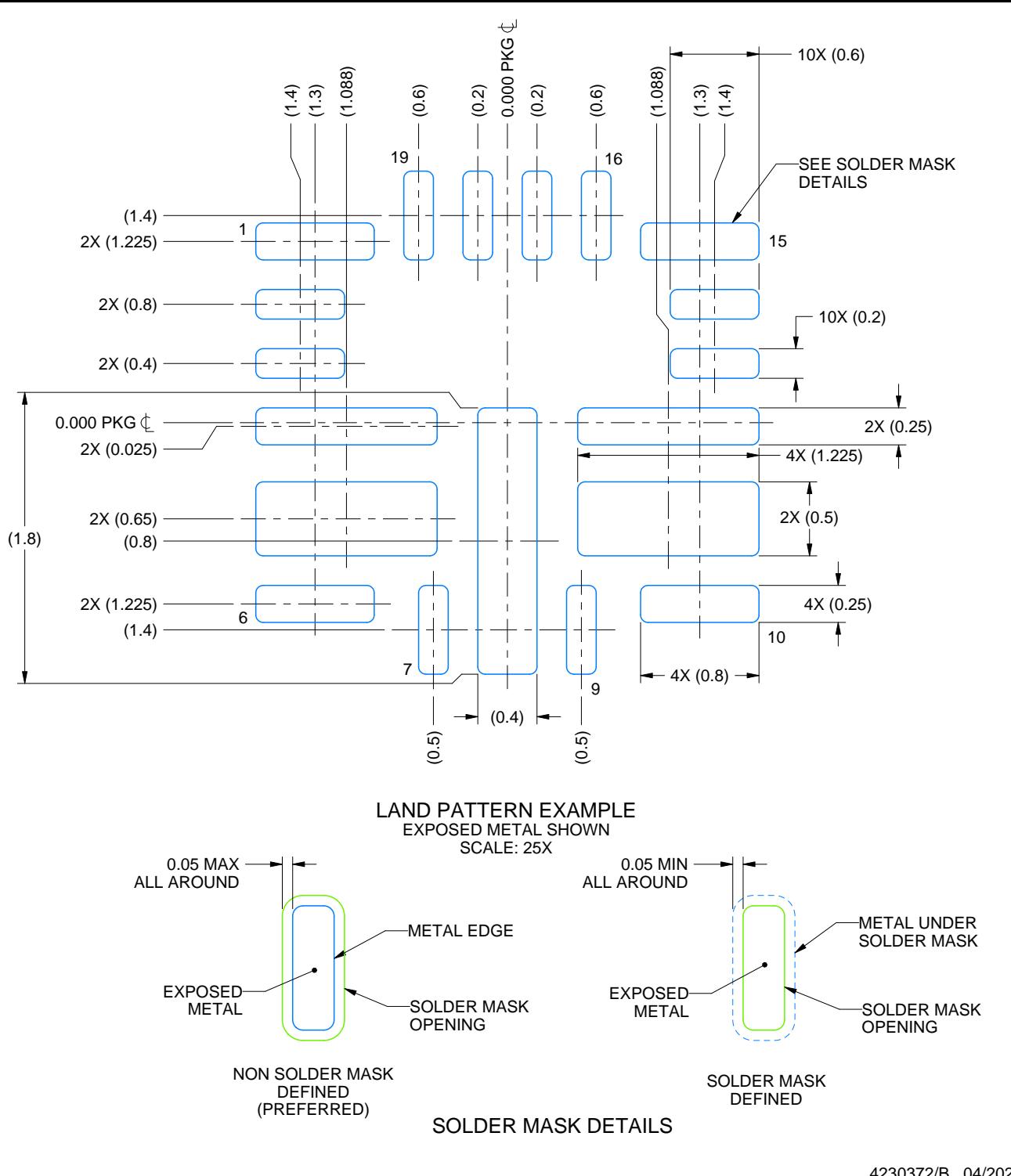

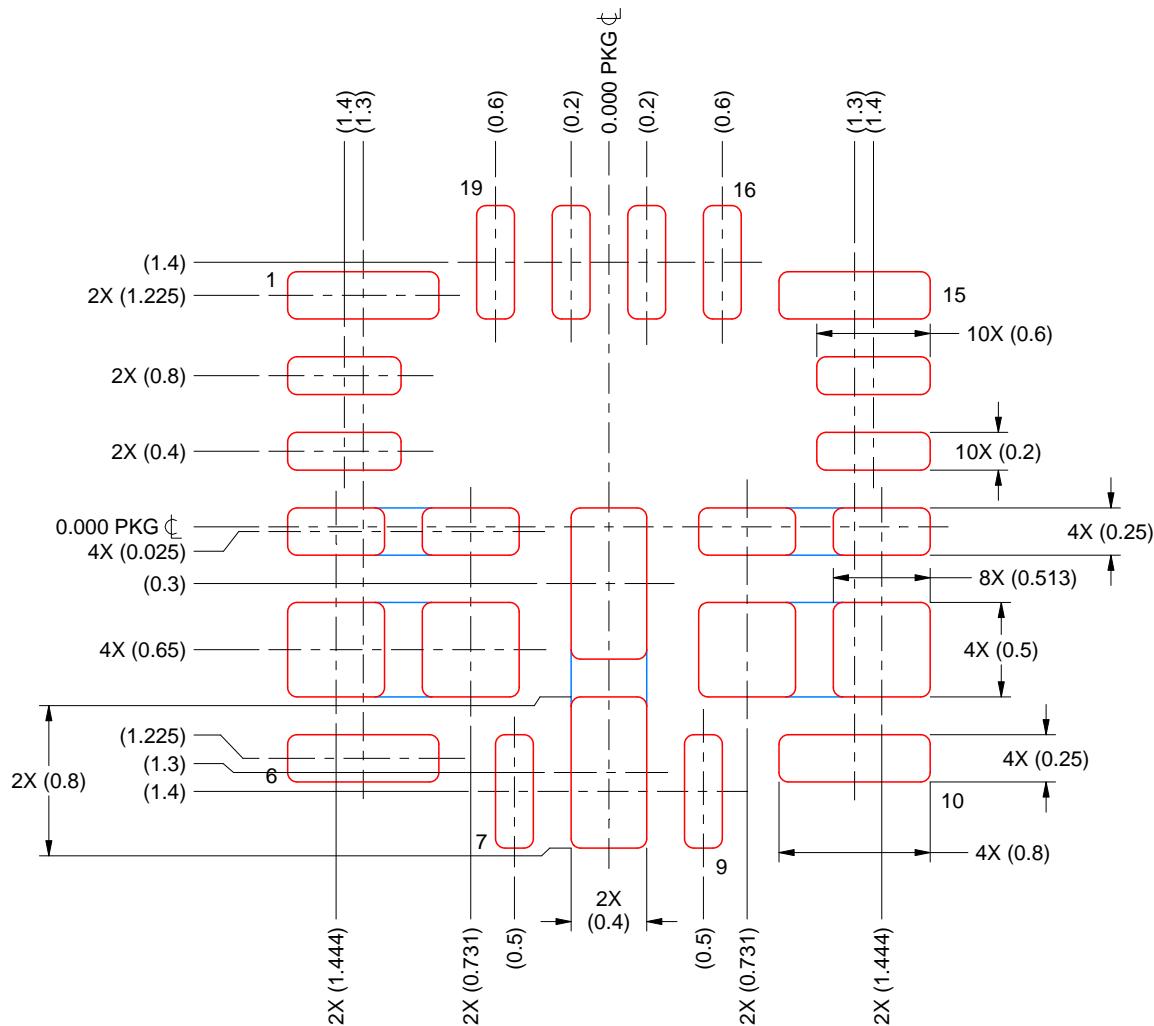

図 4-1. VAN パッケージ、19 ピン、3mm×3mm (0.4mm

ピンピッチ) WQFN-HR (上面図)

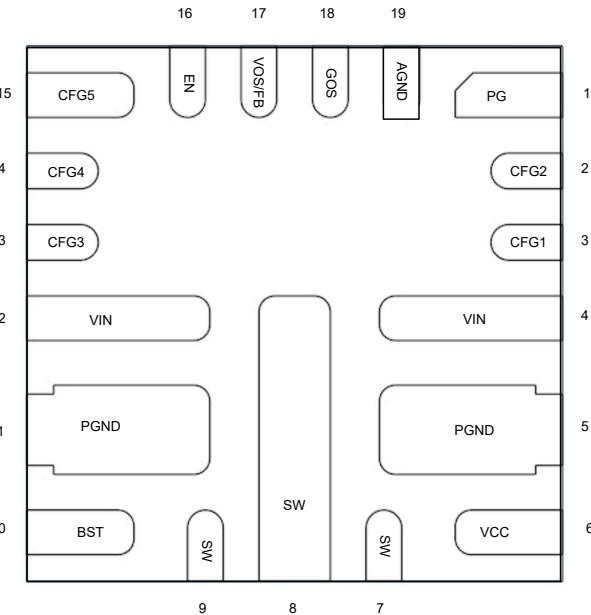

図 4-2. VAN パッケージ、19 ピン、3mm×3mm (0.4mm

ピンピッチ) WQFN-HR (底面図)

表 4-1. ピンの機能

| ピン     |       | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                             |

|--------|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | なし    |                    |                                                                                                                                                                                                                |

| PG     | 1     | O                  | オープンドレインのパワー グッド ステータス信号。外付けプルアップ抵抗を電圧源に接続します。FB 電圧が指定された制限値を外れると、指定された遅延の後に PG が Low になります。                                                                                                                   |

| CFG2   | 2     | I                  | マルチファンクション選択ピン。AGND、VCC、またはフローティングに接続します。このピンにより、動作周波数と過電流制限のいずれかが選択されます。外部 FB 動作用に構成している場合、このピンと AGND の間に抵抗を接続することで OCP 制限が設定されます。                                                                            |

| CFG1   | 3     | I                  | マルチファンクション選択ピン。AGND、VCC、またはフローティングに接続します。このピンにより、動作周波数と過電流制限のいずれかが選択されます。外部 FB 動作用に設定されている場合、このピンと AGND の間に抵抗を接続すると、スイッチング周波数、SS 時間が選択されます。                                                                    |

| VIN    | 4、12  | P                  | 電力段 MOSFET および内部 LDO の電源入力ピン。デカップリング入力コンデンサを VIN ピンから PGND ピンにできるだけ近づけて配置します。各 VIN から IC に近い PGND にコンデンサを接続する必要があります。                                                                                          |

| PGND   | 5、11  | G                  | 電力段のグラントリターン。このピンは内部でローサイド MOSFET のソースに接続されます。できるだけ多くのビアを PGND ピンの下、できるだけ PGND ピンの近くに配置します。この動作により、寄生インピーダンスが最小限に抑えられ、熱抵抗も低下します。                                                                               |

| VCC    | 6     | P                  | 内部 3V LDO 出力。内部 LDO での電力損失を抑えるために、このピンに 3.1V ~ 5.3V の外部バイアスを接続することができます。このピンの電圧源は、内部回路とゲートドライバの両方に電力を供給します。<br>1μF、> 6.3V 定格のセラミックコンデンサを使用して、VCC ピンから PGND にバイパスします。このコンデンサは、VCC ピンと PGND ピンのできるだけ近くに配置してください。 |

| SW     | 7、8、9 | O                  | パワー コンバータの出力スイッチング端子。このピンを出力インダクタに接続します。                                                                                                                                                                       |

| BST    | 10    | I/O                | 内蔵のハイサイド MOSFET ゲートドライバ用電源 (ブースト端子)。このピンと SW ノードとの間にブーストストラップコンデンサを接続します。                                                                                                                                      |

| CFG3   | 13    | I                  | マルチファンクション選択ピン。CFGx を AGND、VCC、またはフローティングに接続すると、出力電圧の設定/構成 (内部または外部 FB) と強制連続導通モード (FCCM) またはスキップモード動作が選択されます。                                                                                                 |

| CFG4   | 14    | I                  |                                                                                                                                                                                                                |

| CFG5   | 15    | I                  |                                                                                                                                                                                                                |

| EN     | 16    | I                  | イネーブル ピン。イネーブル ピンは、DC/DC スイッチング コンバータのオン/オフを切り替えます。起動前に EN ピンをフローティングにすると、コンバータは無効化されます。EN ピンに印加する推奨最大電圧は 5.5V です。TI は、EN ピンを VIN ピンに直接接続することは推奨していません。                                                        |

| VOS/FB | 17    | I                  | 出力電圧フィードバック入力。差動リモートセンス回路の正入力。負荷側の Vout センス ポイントに接続。外部フィードバック用に構成した場合、VOUT から GOS (FB ピンにタップ) への分圧抵抗により出力電圧が設定されます。                                                                                            |

| GOS    | 18    | I                  | 差動リモートセンス回路の負入力。負荷付近のグラントリターン センス ポイントに接続します。                                                                                                                                                                  |

| AGND   | 19    | G                  | 内部制御回路用のアナログ グラントリターンとリファレンス電圧                                                                                                                                                                                 |

(1) I = 入力、O = 出力、P = 電源、G = グラント

## 5 仕様

### 5.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |                       | 最小値  | 最大値  | 単位 |

|------------------|-----------------------|------|------|----|

| ピン電圧             | VIN                   | -0.3 | 19   | V  |

| ピン電圧             | SW – PGND, DC         | -0.3 | 19   | V  |

| ピン電圧             | SW – PGND, 過渡 < 10ns  | -3   | 21   | V  |

| ピン電圧             | VIN – SW, DC          | -0.3 | 19   | V  |

| ピン電圧             | VIN – SW, 過渡 < 10 ns  | -3   | 25   | V  |

| ピン電圧             | BOOT – PGND           | -0.3 | 24.5 | V  |

| ピン電圧             | BOOT – SW             | -0.3 | 5.5  | V  |

| ピン電圧             | EN                    | -0.3 | 7    | V  |

| ピン電圧             | VOS/FB, PG, CFGx, VCC | -0.3 | 6    | V  |

| ピン電圧             | GOS, PGND             | -0.3 | 0.3  | V  |

| シンク電流            | PG                    |      | 15   | mA |

| T <sub>J</sub>   | 動作時接合部温度              | -40  | 150  | °C |

| T <sub>stg</sub> | 保存温度                  | -55  | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      |                                                          | 値     | 単位 |

|--------------------|------|----------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                    |               |                                           | 最小値  | 公称値             | 最大値             | 単位 |

|--------------------|---------------|-------------------------------------------|------|-----------------|-----------------|----|

| V <sub>IN</sub>    | 入力電圧範囲        | VIN                                       | 4    | 16              | 16              | V  |

| V <sub>VCC</sub>   | 外部バイアス範囲      | VCC, V <sub>IN</sub> ≤ 16V                | 3.1  | 5.3             | 5.3             | V  |

| V <sub>GOS</sub>   | ピン電圧          | V <sub>GOS</sub> と V <sub>AGND</sub> との関係 | -0.1 | 0.1             | 0.1             | V  |

|                    |               | EN, PG, VOS/FB                            | -0.1 | 5.5             | 5.5             | V  |

| V <sub>OUT</sub>   | ピン電圧          | CFGx                                      | 0    | V <sub>CC</sub> | V <sub>CC</sub> | V  |

| V <sub>OUT</sub>   | 出力電圧範囲        | V <sub>OUT</sub>                          | 0.5  | 5.5             | 5.5             | V  |

| I <sub>PG</sub>    | パワーグッド シンク電流  | PG                                        |      | 10              | 10              | mA |

| I <sub>OUT</sub>   | 出力電流          | SW                                        |      | 12              | 12              | A  |

| I <sub>LPEAK</sub> | 最大ピーク インダクタ電流 | SW                                        |      | 21              | 21              | A  |

| T <sub>J</sub>     | 動作時接合部温度      |                                           | -40  | 150             | 150             | °C |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                    | TPS548A23                  |                                      | 単位   |

|-----------------------|--------------------|----------------------------|--------------------------------------|------|

|                       |                    | VAN (WQFN-HR, JEDEC レイアウト) | VAN (WQFN-HR, アプリケーションレイアウト、6 層 PCB) |      |

|                       |                    | 19 ピン                      | 19 ピン                                |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗       | 59                         | 19.0 <sup>(2)</sup>                  | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗  | 36                         | 該当なし <sup>(3)</sup>                  | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗       | 13.6                       | 該当なし <sup>(3)</sup>                  | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ   | 1.9                        | 該当なし <sup>(3)</sup>                  | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ   | 13.5                       | 該当なし <sup>(3)</sup>                  | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)までの熱抵抗 | n/a                        | 該当なし <sup>(3)</sup>                  | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

(2) デバイス内消費 1.0W の TPS548B23EVM で測定しました。

(3) 熱テストまたはシミュレーション設定は、アプリケーション レイアウトには適用できません。

## 5.5 電気的特性

T<sub>J</sub> = -40°C ~ +150°C、V<sub>VCC</sub> = 3.3V (外部)、V<sub>VIN</sub> = 4V ~ 16V。代表値は、T<sub>J</sub> = 25°C および V<sub>VIN</sub> = 12V (特に記述のない限り)。

| パラメータ                             |                             | テスト条件                                                                                                                                        | 最小値  | 標準値  | 最大値  | 単位 |

|-----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| <b>電源</b>                         |                             |                                                                                                                                              |      |      |      |    |

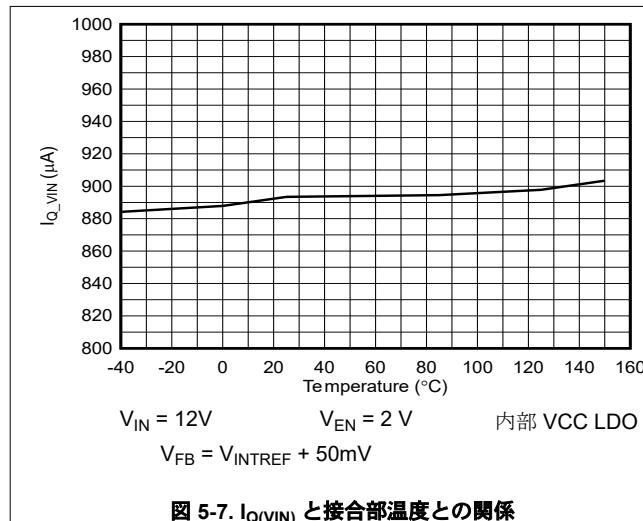

| I <sub>Q(VIN)</sub>               | VIN 静止電流                    | 非スイッチング、V <sub>EN</sub> = 2V、V <sub>FB</sub> = V <sub>FB_REG</sub> + 50mV、VCC ピンに外部バイアスなし                                                    |      | 970  |      | μA |

| I <sub>Q(VIN)</sub>               | 外部 VCC バイアスでの VIN 静止電流      | T <sub>J</sub> = 25°C、V <sub>IN</sub> = 12V、V <sub>EN</sub> = 2V、V <sub>FB</sub> = V <sub>FB_REG</sub> + 10mV (スイッチングなし)、VCC ピンの 3.3V 外部バイアス |      | 230  | 290  | μA |

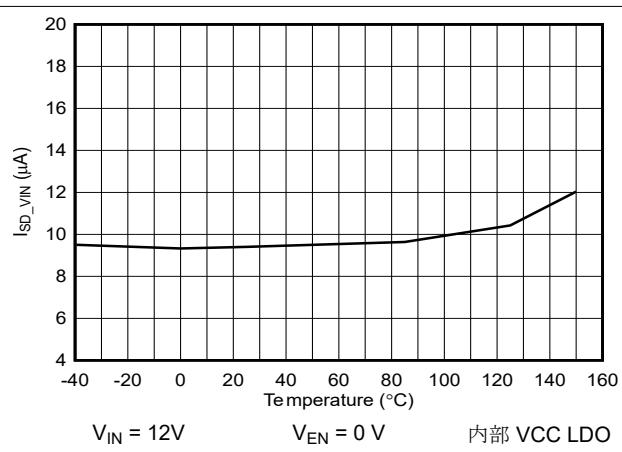

| I <sub>SD(VIN)</sub>              | VIN のシャットダウン時消費電流           | V <sub>IN</sub> = 12V、V <sub>EN</sub> = 0V、VCC ピンの外部バイアスなし                                                                                   |      | 9.5  | 20   | μA |

| I <sub>Q(VCC)</sub>               | VCC 静止電流                    | T <sub>J</sub> = 25°C、V <sub>IN</sub> = 12V、V <sub>EN</sub> = 2V、V <sub>FB</sub> = V <sub>FB_REG</sub> + 10mV (スイッチングなし)、VCC ピンの 3.3V 外部バイアス |      | 860  |      | μA |

| I <sub>SD(VCC)</sub>              | VCC シャットダウン電流               | V <sub>EN</sub> = 0V、V <sub>IN</sub> = 0V、VCC ピンに 3.3V 外部バイアス                                                                                |      | 90   |      | μA |

| I <sub>VCC</sub>                  | VCC 外部バイアス電流 <sup>(1)</sup> | T <sub>J</sub> = 25°C、V <sub>IN</sub> = 12V、V <sub>EN</sub> = 2V、レギュラースイッチング、f <sub>SW</sub> = 600kHz、VCC ピンに 3.3V 外部バイアス                    |      | 10   |      | mA |

| I <sub>VCC</sub>                  | VCC 外部バイアス電流 <sup>(1)</sup> | T <sub>J</sub> = 25°C、V <sub>IN</sub> = 12V、V <sub>EN</sub> = 2V、レギュラースイッチング、f <sub>SW</sub> = 1200kHz、VCC ピンに 3.3V 外部バイアス                   |      | 16   |      | mA |

| <b>内部 LDO (VCC)</b>               |                             |                                                                                                                                              |      |      |      |    |

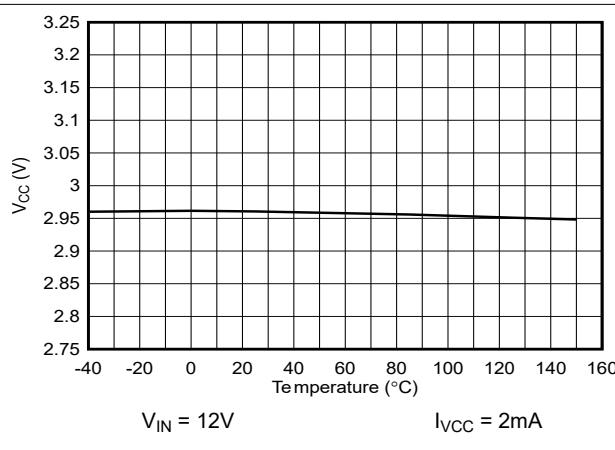

| V <sub>VCC</sub>                  | 内部 LDO 出力電圧                 |                                                                                                                                              | 2.85 | 3.0  | 3.1  | V  |

| I <sub>VCC</sub>                  | 内部 LDO 短絡電流制限               | V <sub>VIN</sub> = 12V                                                                                                                       |      | 210  |      | mA |

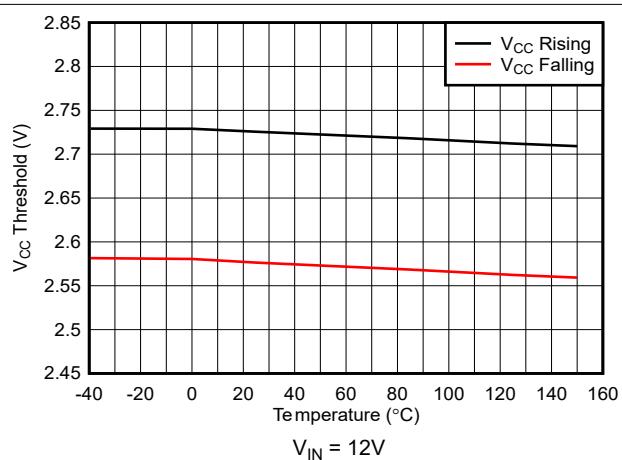

| V <sub>C<sub>UVLO(R)</sub></sub>  | VCC UVLO 立ち上がりスレッショルド       | V <sub>VIN</sub> = 4V                                                                                                                        |      | 2.73 | 2.85 | V  |

| V <sub>C<sub>UVLO(F)</sub></sub>  | VCC UVLO 立ち下がりスレッショルド       | V <sub>VIN</sub> = 4V                                                                                                                        |      | 2.58 |      | V  |

| V <sub>C<sub>UVLO(H)</sub></sub>  | VCC UVLO ヒステリシス             | V <sub>VIN</sub> = 4V                                                                                                                        |      | 0.15 |      | V  |

|                                   | VCC LDO をオフにする FB スレッショルド   | V <sub>FB</sub> 立ち下がり、EN = 0V                                                                                                                |      | 50   | 85   | mV |

| <b>UVLO</b>                       |                             |                                                                                                                                              |      |      |      |    |

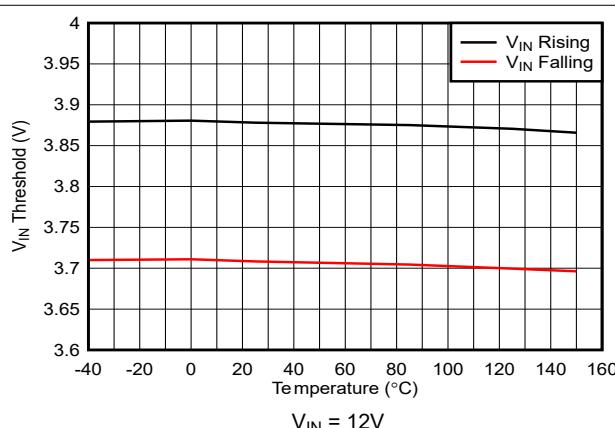

| V <sub>IN<sub>UVLO(R)</sub></sub> | VIN UVLO 立ち上がりスレッショルド       | V <sub>IN</sub> 立ち上がり                                                                                                                        |      | 3.88 | 3.95 | V  |

| V <sub>IN<sub>UVLO(F)</sub></sub> | VIN UVLO 立ち下がりスレッショルド       | V <sub>IN</sub> 立ち下がり                                                                                                                        |      | 3.71 | 3.78 | V  |

| V <sub>IN<sub>UVLO(H)</sub></sub> | VIN UVLO ヒステリシス             |                                                                                                                                              |      | 0.17 |      | V  |

| <b>イネーブル</b>                      |                             |                                                                                                                                              |      |      |      |    |

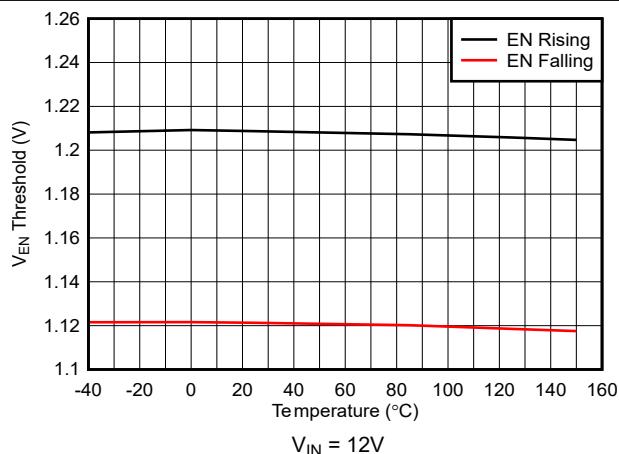

| V <sub>EN(R)</sub>                | EN 電圧立ち上がりスレッショルド           | EN 立ち上がり、スイッチングはイネーブル                                                                                                                        | 1.15 | 1.2  | 1.25 | V  |

| V <sub>EN(F)</sub>                | EN 電圧立ち下がりスレッショルド           | EN 立ち下がり、スイッチングはディスエーブル                                                                                                                      | 1.06 | 1.12 | 1.18 | V  |

| V <sub>EN(H)</sub>                | EN 電圧ヒステリシス                 |                                                                                                                                              |      | 80   |      | mV |

## 5.5 電気的特性 (続き)

$T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 、 $V_{\text{VCC}} = 3.3\text{V}$  (外部)、 $V_{\text{VIN}} = 4\text{V} \sim 16\text{V}$ 。代表値は、 $T_J = 25^{\circ}\text{C}$  および  $V_{\text{VIN}} = 12\text{V}$  (特に記述のない限り)。

| パラメータ                       |                                  | テスト条件                                                                                             | 最小値     | 標準値   | 最大値    | 単位               |

|-----------------------------|----------------------------------|---------------------------------------------------------------------------------------------------|---------|-------|--------|------------------|

| $I_{\text{EN(Hys)}}$        | EN ピン ヒステリシス電流                   | $\text{EN} > V_{\text{EN(R)}}$                                                                    | 2.0     | 5     | 7.5    | $\mu\text{A}$    |

|                             | EN 内部プルダウン抵抗                     | EN ピンを AGND に接続                                                                                   | 0.74    | 1     | 1.27   | $\text{M}\Omega$ |

| $V_{\text{ENSTB(R)}}$       | EN スタンバイ立ち上がりスレッショルド             | EN 立ち上がり、内部 LDO 有効、スイッチングなし                                                                       |         | 0.7   |        | $\text{V}$       |

| $V_{\text{ENSTB(F)}}$       | EN スタンバイ立ち下がりスレッショルド             | EN 立ち下がり、内部 LDO 無効                                                                                | 0.3     | 0.6   |        | $\text{V}$       |

| ピンストラップ                     |                                  |                                                                                                   |         |       |        |                  |

| CFGx_high                   | CFGx ロジック High 出力電圧レベル           | $V_{\text{CC}} = 5.0\text{V}$                                                                     | 4.2     | 4.4   |        | $\text{V}$       |

|                             |                                  | $V_{\text{CC}} = 3.3\text{V}$                                                                     | 2.4     | 2.85  |        | $\text{V}$       |

| CFGx_low                    | CFGx ロジック Low 電圧レベル              | $V_{\text{CC}} = 5.0\text{V}$                                                                     | 0.5     | 0.6   |        | $\text{V}$       |

|                             |                                  | $V_{\text{CC}} = 3.3\text{V}$                                                                     | 0.3     | 0.4   |        | $\text{V}$       |

| スタートアップ                     |                                  |                                                                                                   |         |       |        |                  |

| $t_{\text{SS}}$             | ソフトスタート時間                        | $V_{\text{FB}} 10\% \sim 90\%, t_{\text{SS}} = 1\text{ms}$ 設定                                     | 1       |       |        | $\text{ms}$      |

|                             |                                  | $V_{\text{FB}} 10\% \sim 90\%, t_{\text{SS}} = 2\text{ms}$ 設定                                     | 2       |       |        | $\text{ms}$      |

|                             |                                  | $V_{\text{FB}} 10\% \sim 90\%, t_{\text{SS}} = 3\text{ms}$ 設定                                     | 3       |       |        | $\text{ms}$      |

| $t_{\text{EN\_DLY}}$        | EN High からスイッチング開始までの遅延          | $V_{\text{CC}}$ に外部バイアスなし                                                                         | 1300    | 2000  |        | $\mu\text{s}$    |

| リファレンス電圧 (FB)               |                                  |                                                                                                   |         |       |        |                  |

| $V_{\text{VOS\_REG}}$       | 出力電圧レギュレーション精度                   | 内部フィードバック構成、 $T_J = 0^{\circ}\text{C} \sim +85^{\circ}\text{C}$                                   | -0.9 %  |       | +0.9%  |                  |

|                             |                                  | 内部フィードバック構成                                                                                       | -1.25 % |       | +1.25% |                  |

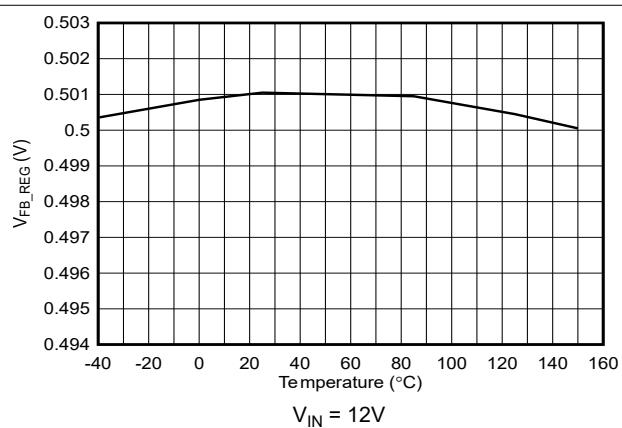

| $V_{\text{FB\_REG}}$        | フィードバック レギュレーション電圧               | 外部フィードバック構成、 $T_J = 0^{\circ}\text{C} \sim 85^{\circ}\text{C}$                                    | 498.5   | 501   | 503.5  | $\text{mV}$      |

|                             |                                  | 外部フィードバック構成                                                                                       | 495     | 500   | 505    | $\text{mV}$      |

| $I_{\text{FB(LKG)}}$        | FB の入力リーク電流                      | $V_{\text{FB}} = V_{\text{FB\_REG}}$                                                              |         |       | 250    | $\text{nA}$      |

| 差動リモートセンスアンプ                |                                  |                                                                                                   |         |       |        |                  |

| $I_{\text{GOSNS}}$          | GOS ピンから流れ出すリーク電流                | $V_{\text{GOS}} - V_{\text{AGND}} = 100\text{ mV}$                                                |         |       | 80     | $\mu\text{A}$    |

| スイッチング周波数                   |                                  |                                                                                                   |         |       |        |                  |

| $f_{\text{SW(FCCM)}}$       | スイッチング周波数、FCCM 動作                | $V_{\text{VIN}} = 12\text{V}, V_{\text{OUT}} = 3.3\text{V}, f_{\text{SW}} = 600\text{ kHz, 負荷なし}$ | 510     | 600   | 690    | $\text{kHz}$     |

|                             |                                  | $V_{\text{VIN}} = 12\text{V}, V_{\text{OUT}} = 3.3\text{V}, f_{\text{SW}} = 800\text{ kHz, 負荷なし}$ | 680     | 800   | 920    | $\text{kHz}$     |

|                             |                                  | $V_{\text{VIN}} = 12\text{V}, V_{\text{OUT}} = 3.3\text{V}, f_{\text{SW}} = 1.0\text{ MHz, 負荷なし}$ | 850     | 1000  | 1150   | $\text{kHz}$     |

|                             |                                  | $V_{\text{VIN}} = 12\text{V}, V_{\text{OUT}} = 3.3\text{V}, f_{\text{SW}} = 1.2\text{ MHz, 負荷なし}$ | 1020    | 1200  | 1380   | $\text{kHz}$     |

| 電力段                         |                                  |                                                                                                   |         |       |        |                  |

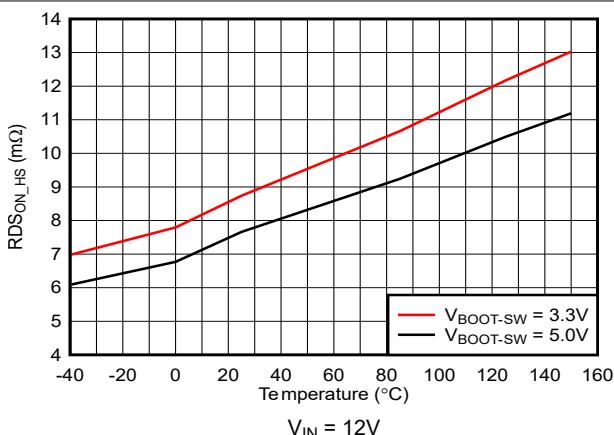

| $R_{\text{DSON(HS)}}$       | ハイサイド MOSFET オン抵抗                | $V_{\text{BOOT-SW}} = 5.0\text{V}$                                                                |         | 7.5   |        | $\text{m}\Omega$ |

|                             |                                  | $V_{\text{BOOT-SW}} = 3.3\text{V}$                                                                |         | 8.4   |        | $\text{m}\Omega$ |

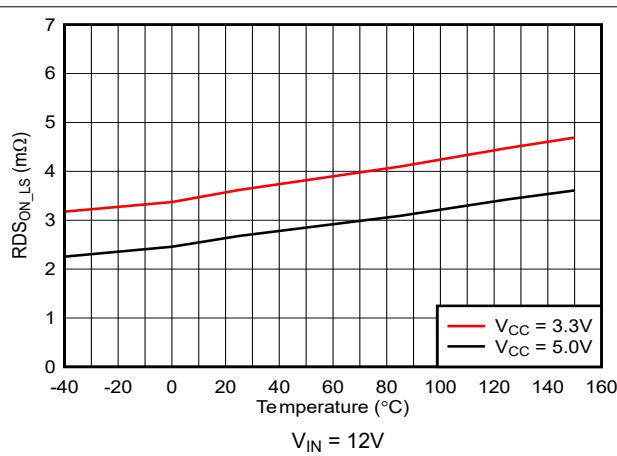

| $R_{\text{DSON(LS)}}$       | ローサイド MOSFET オン抵抗                | $V_{\text{VCC}} = 5.0\text{V}$                                                                    |         | 2.7   |        | $\text{m}\Omega$ |

|                             |                                  | $V_{\text{VCC}} = 3.3\text{V}$                                                                    |         | 3.3   |        | $\text{m}\Omega$ |

| $t_{\text{ON(min)}}$        | 最小 ON パルス幅 <a href="#">(1)</a>   |                                                                                                   |         | 40    |        | $\text{ns}$      |

| $t_{\text{OFF(min)}}$       | 最小 OFF パルス幅 <a href="#">(1)</a>  |                                                                                                   |         |       | 150    | $\text{ns}$      |

|                             | SW ピンの出力放電抵抗                     | $V_{\text{IN}} = 12\text{V}, V_{\text{SW}} = 1\text{V}$ 、電力変換無効                                   |         | 75    |        | $\Omega$         |

| $I_{\text{BOOT(LKG)}}$      | BOOT ピンへのリーク電流                   | $V_{\text{BOOT-SW}} = 3.3\text{V}$ 、有効、スイッチングなし。                                                  |         | 23    | 30     | $\mu\text{A}$    |

| パワーグッド                      |                                  |                                                                                                   |         |       |        |                  |

| $V_{\text{PGTH(RISE\_OV)}}$ | パワーグッド スレッショルド                   | FB 立ち上がり、PG High から Low                                                                           | 113%    | 116%  | 119%   |                  |

| $V_{\text{PGTH(RISE\_UV)}}$ | パワーグッド スレッショルド                   | FB 立ち上がり、PG low から high                                                                           | 89%     | 92.5% | 95%    |                  |

| $V_{\text{PGTH(FALL\_UV)}}$ | パワーグッド スレッショルド                   | FB 立ち下り、PG high から low                                                                            | 77%     | 80%   | 83%    |                  |

| $t_{\text{PG\_DLY}}$        | スタートアップ時に PG 遅延が low から high に変化 | タイミング図を参照してください                                                                                   |         | 1.1   | 1.5    | $\text{ms}$      |

|                             | PG 遅延が high から low に変化           |                                                                                                   |         | 4     | 6.2    | $\mu\text{s}$    |

## 5.5 電気的特性 (続き)

$T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 、 $V_{VCC} = 3.3\text{V}$  (外部)、 $V_{VIN} = 4\text{V} \sim 16\text{V}$ 。代表値は、 $T_J = 25^{\circ}\text{C}$  および  $V_{VIN} = 12\text{V}$  (特に記述のない限り)。

| パラメータ         |                                                | テスト条件                                                                                                                           | 最小値 | 標準値  | 最大値 | 単位            |

|---------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------|

| $I_{PG(LKG)}$ | オープンドレイン出力が high の PG ピンのリード電流                 | $V_{PG} = 4.5\text{V}$                                                                                                          |     | 6    |     | $\mu\text{A}$ |

|               | PG ピン出力 Low レベル電圧                              | $I_{PG} = 7\text{ mA}$                                                                                                          |     | 500  |     | $\text{mV}$   |

|               | $VIN$ および $VCC$ が Low のとき、PG ピンは Low レベルを出力します | $V_{VIN} = 0\text{V}$ 、 $V_{VCC} = 0\text{V}$ 、 $V_{EN} = 0\text{V}$ 、PG は $100\text{k}\Omega$ の抵抗を介して $3.3\text{V}$ にプルアップされます |     | 850  |     | $\text{mV}$   |

|               | $VIN$ および $VCC$ が Low のとき、PG ピンは Low レベルを出力します | $V_{VIN} = 0\text{V}$ 、 $V_{VCC} = 0\text{V}$ 、 $V_{EN} = 0\text{V}$ 、PG は $10\text{k}\Omega$ の抵抗を介して $3.3\text{V}$ にプルアップされます  |     | 1000 |     | $\text{mV}$   |

### 過電流保護

|               |                                         |                                                                                   |      |      |      |                  |

|---------------|-----------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------------------|

|               | OC 制限上限クランプ                             | $LS$ FET のバレー電流、 $CFG3-5 = GND$ 、 $0\Omega \leq R_{ILIM} \leq 4.32\text{k}\Omega$ | 11.5 | 13   | 14.5 | A                |

| $I_{LS(OC)}$  | ローサイド バレー電流制限 (外部フィードバック構成)             | $LS$ FET のバレー電流、 $R_{ILIM} = 5.25\text{k}\Omega$                                  | 9.0  | 10.4 | 11.8 | A                |

| $I_{LS(OC)}$  | ローサイド バレー電流制限 (外部フィードバック構成)             | $LS$ FET のバレー電流、 $R_{ILIM} = 10.5\text{k}\Omega$                                  | 4.4  | 5.2  | 6.0  | A                |

| $I_{ILIM}$    | $ILIM$ ピンの抵抗範囲                          | $LS$ FET のバレー電流、 $R_{ILIM} = 20.0\text{k}\Omega$                                  | 2    | 2.7  | 3.4  | A                |

| $I_{ILIM}$    | $ILIM$ ピンの抵抗範囲                          |                                                                                   | 0    | 20   |      | $\text{k}\Omega$ |

| $I_{LS(OC)}$  | ローサイド バレー電流制限 (内部フィードバック構成)             | $LS$ FET のバレー電流、 $CFG3-5 = VCC$ 、 $CFG1 = VCC$                                    | 11.5 | 13   | 14.5 | A                |

| $I_{LS(OC)}$  |                                         | $LS$ FET のバレー電流、 $CFG3-5 = VCC$ 、 $CFG1 = GND$                                    | 9    | 10   | 11   | A                |

| $I_{LS(OC)}$  |                                         | $LS$ FET のバレー電流、 $CFG3-5 = VCC$ 、 $CFG1 = \text{Float}$                           | 6    | 7    | 8    | A                |

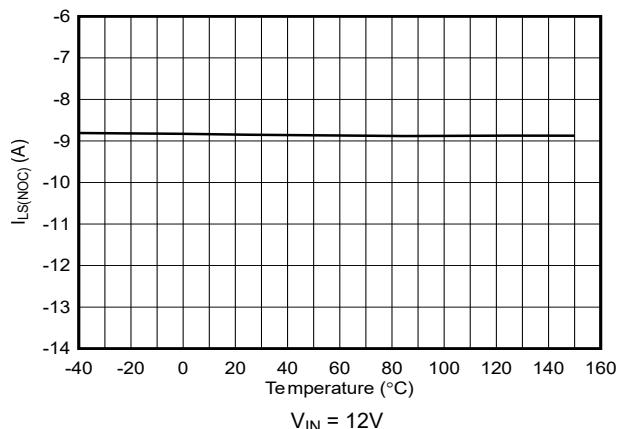

| $I_{LS(NOC)}$ | 上限側負の電流制限                               | $LS$ FET のシンク電流制限                                                                 |      | -9   | -7.5 | A                |

| $I_{ZC}$      | DCM、オープンループに入るゼロ交差検出電流スレッショルド           | $V_{IN} = 12\text{V}$                                                             |      | -750 |      | $\text{mA}$      |

| $I_{ZC(HYS)}$ | DCM、オープンループに入った後のゼロ交差検出電流スレッショルド ヒステリシス | $V_{IN} = 12\text{V}$                                                             |      | 1000 |      | $\text{mA}$      |

### 出力 OVP と UVP

|              |                        |                   |      |              |      |               |

|--------------|------------------------|-------------------|------|--------------|------|---------------|

| $V_{OVP}$    | 過電圧保護 (OVP) のスレッショルド電圧 | $V_{FB}$ の立ち上がり   | 113% | 116%         | 119% |               |

| $t_{OVPDLY}$ | OVP 遅延                 | 100mV オーバードライブの場合 |      | 650          |      | ns            |

| $V_{UVP}$    | 低電圧保護 (UVP) スレッショルド電圧  | $V_{FB}$ の立ち下がり   | 77%  | 80%          | 83%  |               |

| $t_{UVPDLY}$ | UVP フィルタ遅延             |                   |      | 70           |      | $\mu\text{s}$ |

|              | ヒップ待機時間                | ヒップモード有効          |      | 14× $t_{SS}$ |      | ms            |

### サーマル シャットダウン

|              |                          |      |  |     |  |                    |

|--------------|--------------------------|------|--|-----|--|--------------------|

| $T_{J(SD)}$  | サーマル シャットダウンのスレッショルド (1) | 温度上昇 |  | 165 |  | $^{\circ}\text{C}$ |

| $T_{J(HYS)}$ | サーマル シャットダウンヒステリシス (1)   |      |  | 15  |  | $^{\circ}\text{C}$ |

- (1) このパラメータは参考用にのみ提供されており、テキサス インスツルメンツの製品保証においてテキサス インスツルメンツが発行するデバイス仕様の一部に含まれないものとします。

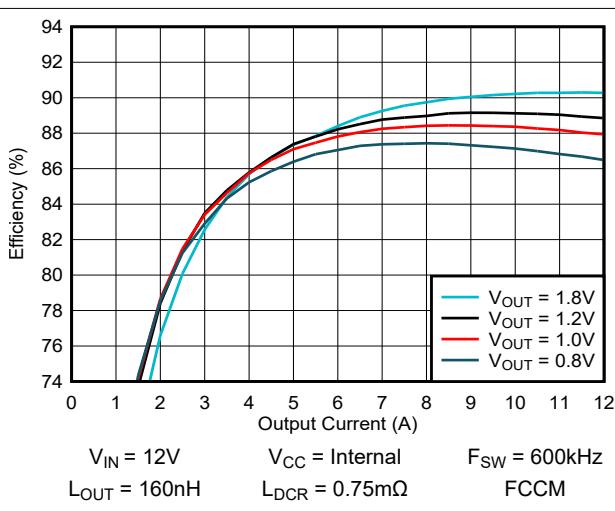

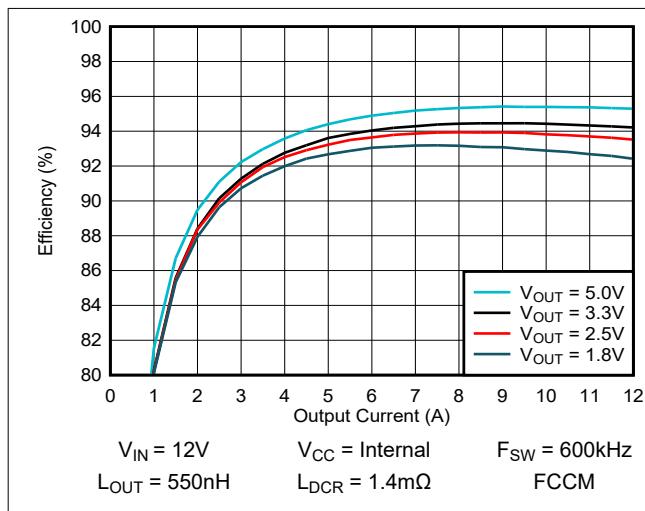

## 5.6 代表的特性

## 5.6 代表的特性 (続き)

## 5.6 代表的特性 (続き)

図 5-13. V<sub>EN</sub> ピン スレッショルドと接合部温度との関係

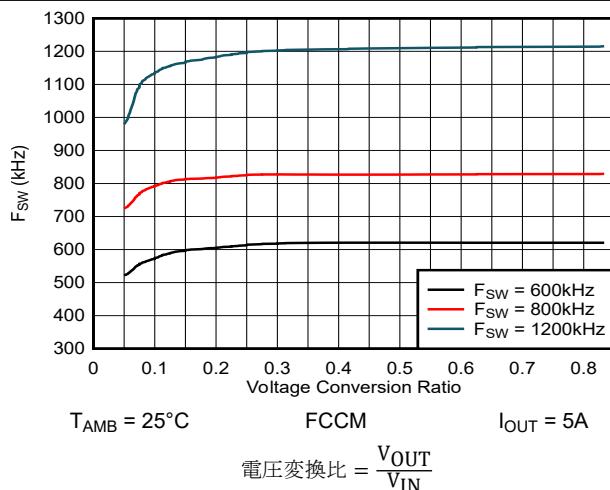

図 5-14. スイッチング周波数と電圧変換比との関係

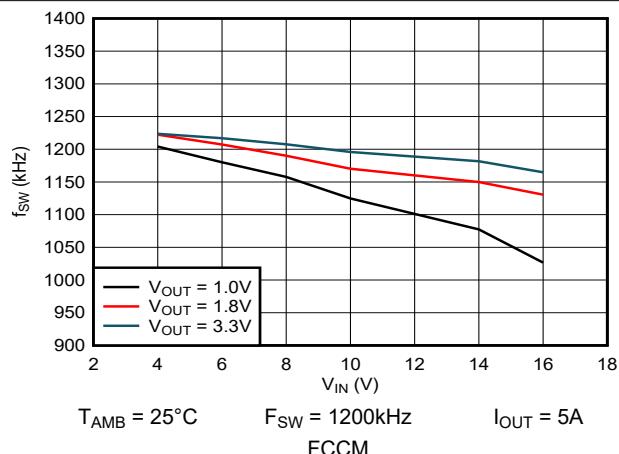

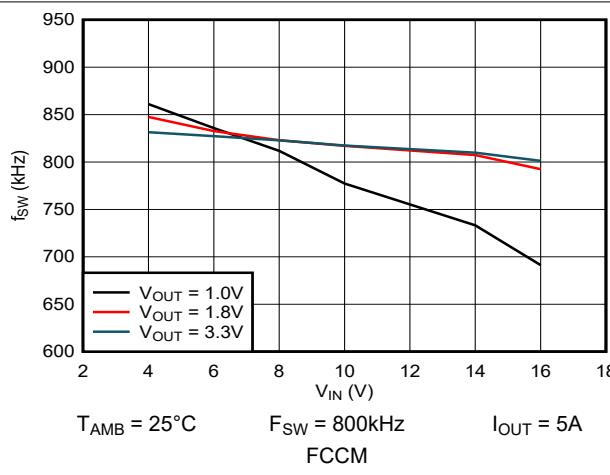

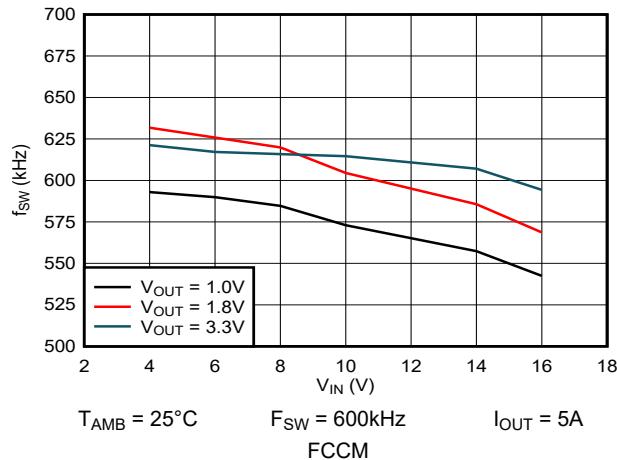

図 5-15. スイッチング周波数と入力電圧との関係

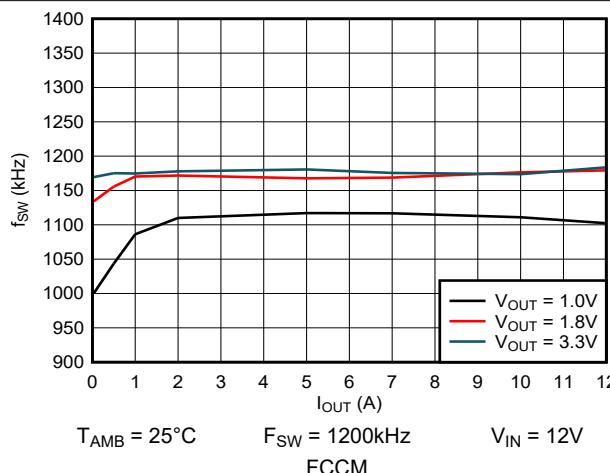

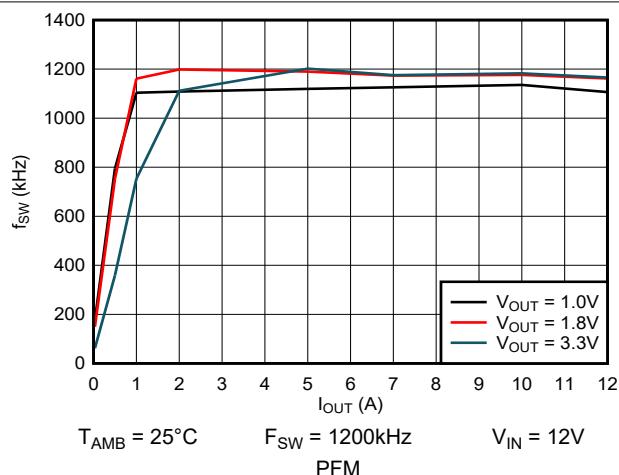

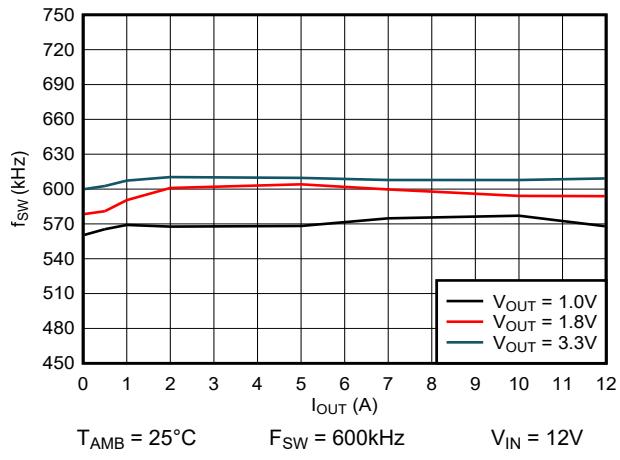

図 5-16. スイッチング周波数 対 出力電流

図 5-17. スイッチング周波数 対 出力電流

図 5-18. スイッチング周波数と入力電圧との関係

## 5.6 代表的特性 (続き)

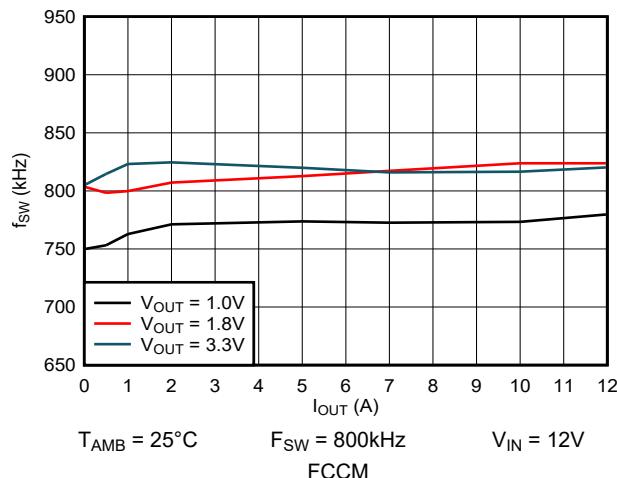

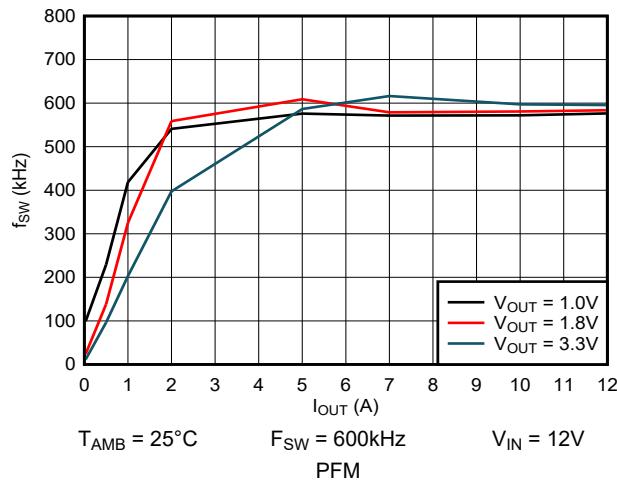

図 5-19. スイッチング周波数 対 出力電流

図 5-20. スイッチング周波数 対 出力電流

図 5-21. スイッチング周波数と入力電圧との関係

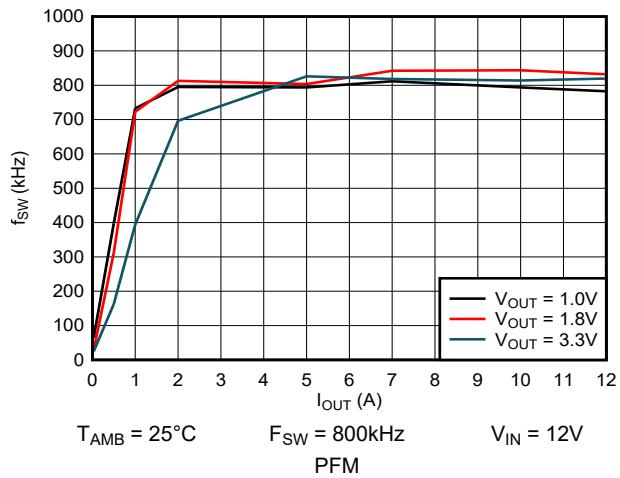

図 5-22. スイッチング周波数 対 出力電流

図 5-23. スイッチング周波数 対 出力電流

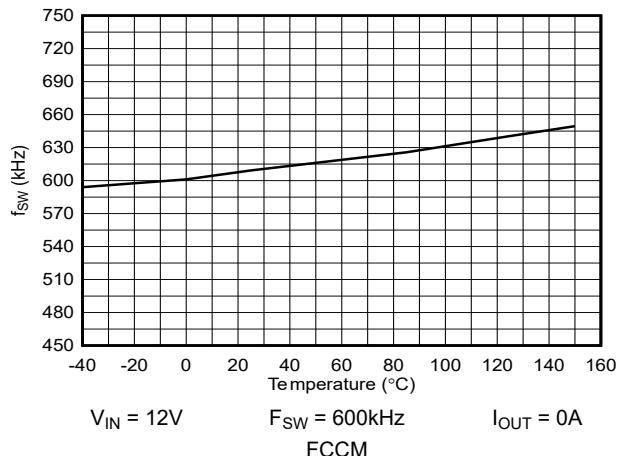

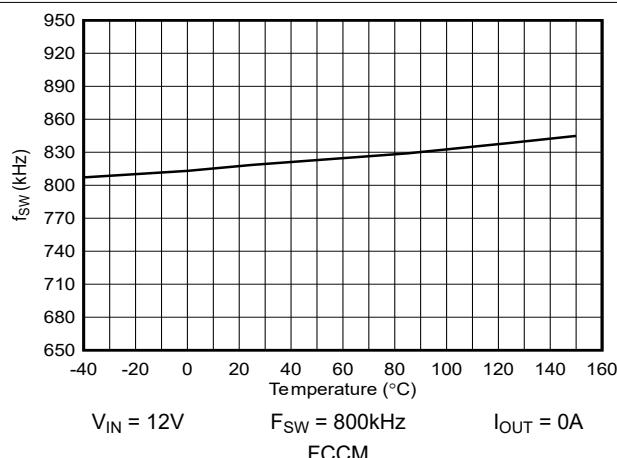

図 5-24. スイッチング周波数と接合部温度との関係

## 5.6 代表的特性 (続き)

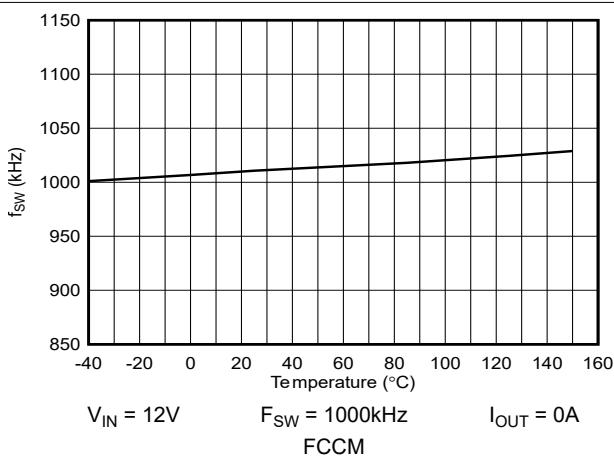

図 5-25. スイッチング周波数と接合部温度との関係

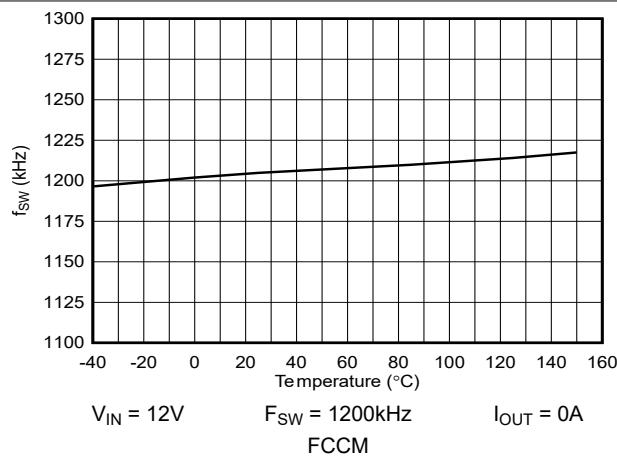

図 5-26. スイッチング周波数と接合部温度との関係

図 5-27. スイッチング周波数と接合部温度との関係

図 5-28.  $R_{DSon(HS)}$  と接合部温度との関係

図 5-29.  $R_{DSon(LS)}$  と接合部温度との関係

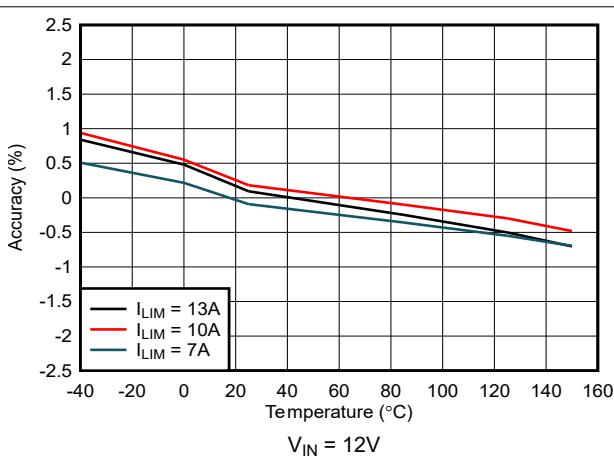

図 5-30. ローサイドドライバ電流制限精度 (内部) と接合部温度との関係

## 5.6 代表的特性 (続き)

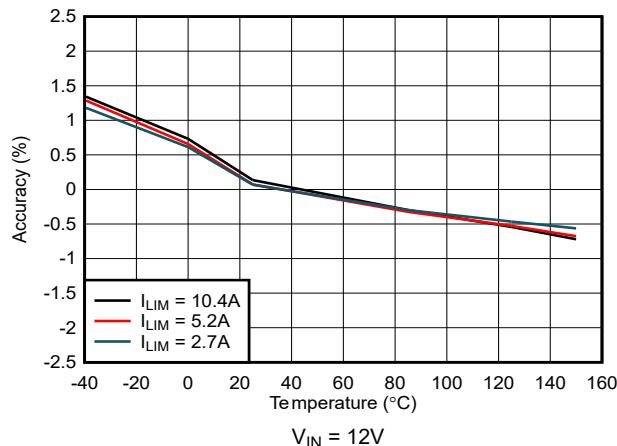

図 5-31. ローサイドバレー電流制限精度 (外部) と接合部温度との関係

図 5-32. ローサイド負過電流制限と接合部温度との関係

## 6 詳細説明

### 6.1 概要

TPS548A23 デバイスは、高効率のシングル チャネル小型同期整流 降圧コンバータです。このデバイスは、サーバー、ストレージ、および同様のコンピューティング アプリケーションにおける 12A または以下の出力電流の低出力電圧ポイントオブ ロード アプリケーション向けに設計されています。TPS548A23 は、独自の D-CAP4 モード制御と適応型オン時間アーキテクチャを採用しています。この組み合わせにより、低デューティ比で超高速の負荷ステップ応答を持つ最新の DC/DC コンバータを優れた方法で構築できます。帰還分圧器で設定される出力電圧の範囲は、0.5 ~ 5.5V です。変換入力電圧の範囲は 4V ~ 16V、VCC 入力電圧の範囲は 3.1V ~ 5.3V です。D-CAP4 変調器は、エミュレートされた電流情報を使用して変調を制御します。D-CAP4 変調器により、異なる出力電圧によるループゲイン変動が低減され、より高い出力電圧のアプリケーションで優れた過渡応答が得られます。この制御方式の利点として、この制御方式に外部位相補償回路が必要ないことが挙げられます。そのため、デバイスは使いやすく、外付け部品数も少なくて済みます。この制御方式のもう 1 つの利点は、この制御方式が、すべての低 ESR 出力コンデンサ (セラミック コンデンサや低 ESR ポリマー コンデンサなど) で安定して動作できることです。最後に、適応型オン時間制御は、広い範囲の入力電圧および出力電圧にわたってプリセットされたスイッチング周波数を追跡すると同時に、負荷ステップ過渡が発生した際に必要に応じてスイッチング周波数を上昇させます。

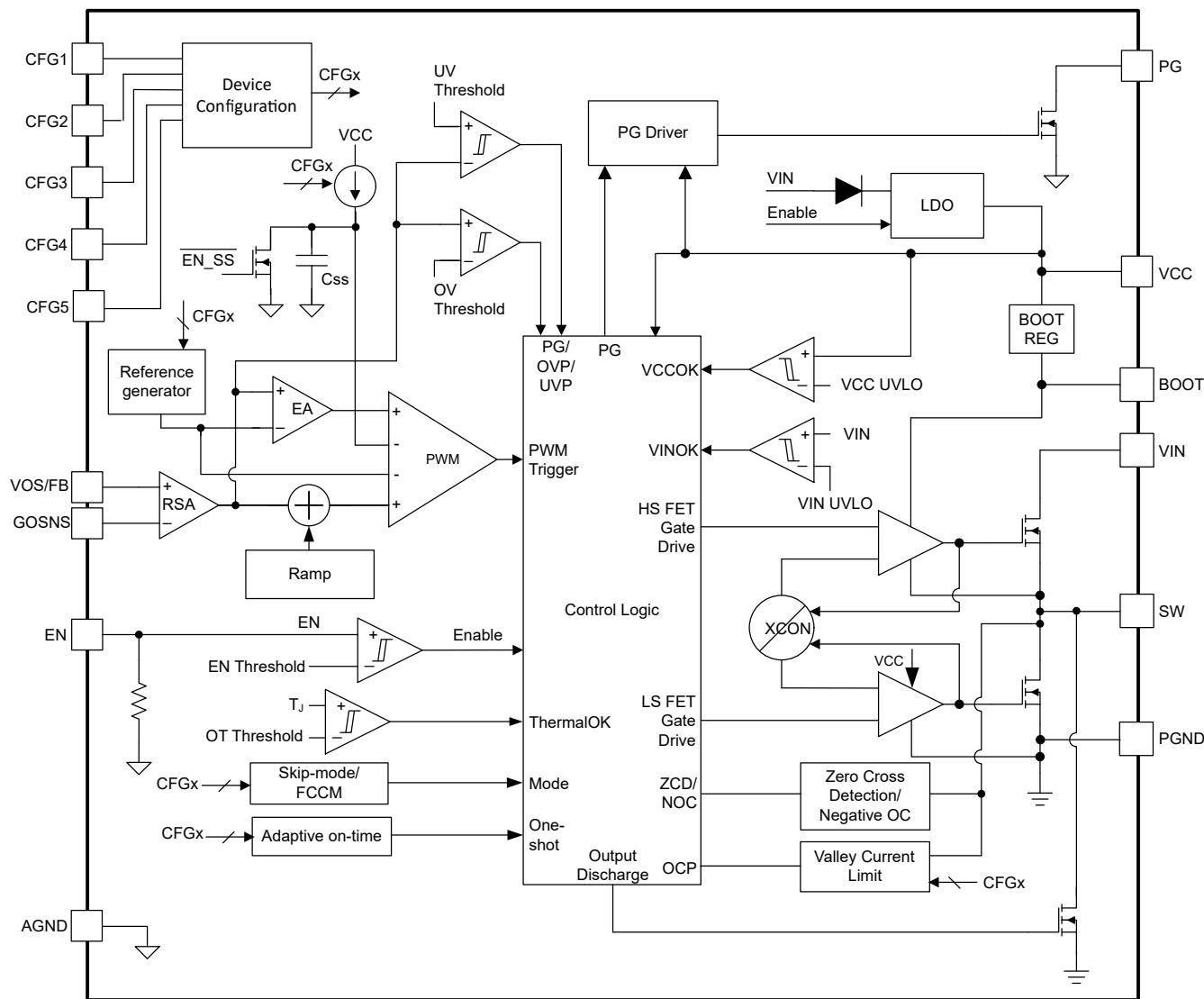

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 D-CAP4 制御

デバイスは D-CAP4 制御を使用して、使いやすさを維持しながら高速の負荷過渡応答を実現します。D-CAP4 制御アーキテクチャには、内部のリップル生成回路が含まれ、多層セラミック コンデンサ (MLCC) や低 ESR 高分子コンデンサなどの超低 ESR 出力コンデンサを使用できます。D-CAP4 制御アーキテクチャでは、外部の電流検出回路や電圧補償回路は不要です。内部リップル生成回路の役割は、インダクタ電流情報のリップル成分をエミュレートし、電圧帰還信号と組み合わせることでループ動作を制御することです。

D-CAP4 制御アーキテクチャにより、 $V_{OUT}$  全体のループ ゲイン変動が低減され、1 つのランプ設定で出力電圧範囲全体にわたって高速負荷過渡応答を実現できます。内部ランプ回路の R-C 時定数によって、ランプのゼロ周波数が設定されます。これは、他の R-C ベースの内部ランプ生成アーキテクチャと同様です。また、ループ ゲインの変動が小さくなるため、フィード フォワード コンデンサの必要性も緩和され、過渡応答を最適化できます。ランプ振幅は  $V_{IN}$  によって変化し、入力電圧 (一般に入力電圧フィードフォワードと呼ばれます) 全体にわたるループ ゲインの変動を最小限に抑えます。最後に、デバイスは、注入されたランプに起因する dc オフセットを補正するために内部回路を使用しており、特に軽負荷電流の場合、出力リップル電圧に起因する dc オフセットを大幅に低減します。

外部補償を使用しない制御トポロジでは、サポートできる出力フィルタには、最小範囲、最大範囲、またはその両方が存在します。代表的な降圧コンバータで使用する出力フィルタは、ローパス L-C 回路です。この L-C フィルタには、式 1 に説明されているように、二重極があります。

$$f_p = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}} \quad (1)$$

低周波数では、出力設定点分圧抵抗回路、およびデバイスの内部ゲインによって、全体のループ ゲインが設定されます。低周波数の L-C 二重極には、180 度の位相降下があります。出力フィルタ周波数では、10 進数毎にゲインが  $-40\text{dB}$  ロール オフし、位相は急速に減少します。内部リップル生成回路によって高周波数のゼロが導入されることで、ゲインのロール オフが 10 進数毎に  $-40\text{dB}$  から  $-20\text{dB}$  に減り、位相はゼロ周波数より 10 進数毎に 90 度増加します。

出力フィルタ用に選択されたインダクタとコンデンサは、式 1 の  $f_p$  重極が 表 6-1 で指定された値より高くならないようにする必要があります、その後、式 2 を使用するアプリケーションの公称デューティサイクルに基づいて調整されます。式 2 は  $f_{P(TABLE)}$  を拡大します。これは、デューティサイクルが増加すると D-CAP4 ランプのゲインが減少し、最大 L-C ダブル ポールも増加するためです。

$$f_{P(MAX)} = f_{P(TABLE)} \times \left( 1 + \left( \frac{V_{OUT}}{V_{IN(\text{typ})}} \right)^2 \right) \quad (2)$$

表 6-1. 最大 L-C 重極

| スイッチング周波数 (kHz) | 最大 L-C 重極周波数 (kHz) |

|-----------------|--------------------|

| 600             | 14.9               |

| 800             | 19.9               |

| 1000            | 24.9               |

| 1200            | 29.9               |

各設定についてこれらのガイドラインに違反する L-C の重極周波数も可能ですが、測定時にアプリケーションで検証する必要があります。

アプリケーション要件を特定した後、出力インダクタンスは通常、インダクタのピークツーピーク リップル電流がアプリケーションの最大出力電流の約 15% ~ 40% になるように設計されます。非常に小さい出力容量を選択すると、高周波の L-C 重極が発生し、L-C 重極周波数まで全体のループ ゲインは高く維持されます。内部リップル生成回路のゼロも比較的高い周波数であるため、出力容量が非常に小さいループではクロスオーバー周波数が高くなりすぎ、不安定性が発生する可能性があります。一般に、妥当な (より小さな) 出力容量が求められる場合には、出力リップル要件と負荷過渡要件を使用して、安定動作に必要な出力容量を決定できます。

MLCC を使用する場合は、設計の最終的な出力容量を決定する際に、ディレーティング特性を考慮します。たとえば、 $10\mu\text{F}$ 、X5R、6.3V の仕様を持つ MLCC を使用する場合には、DC バイアスおよび AC バイアスによるディレーティングがそれぞれ 80% および 50% となります。実効的なディレーティングは、この 2 つの係数の積であり、この場合は 40%、 $4\mu\text{F}$  となります。アプリケーションで使用するコンデンサの具体的な特性については、コンデンサのメーカーに確認してください。

簡略化されたルールとして、TI は、ESR ゼロを持つ出力コンデンサが L-C 重極周波数の 10 倍未満になっている場合、安定性のために L-C の重極周波数を計算するときは無視することを推奨します。L-C 重極周波数は、低 ESR MLCC のみを使用して再計算する必要があります。混在タイプの出力コンデンサを使用する際のより正確な解析を行うため、TI ではシミュレーションまたは測定を推奨します。

最大出力容量に関する推奨値を得るには、L-C の二重極周波数が動作周波数の 1/100 以上になるように、インダクタとコンデンサの値を選択します。この出発点で、次の基準を使用して基板上の小信号応答を確認します。ループ クロスオーバーでの位相マージンが 45 度より大きい。位相マージンが 45 度より大きい限り、実際の最大出力容量はさらに大きくなる可能性があります。ただし、小信号測定 (ボード線図) を実行して設計を確認する必要があります。

L-C の二重極が動作周波数の 1/100 付近にある大型出力フィルタの場合は、追加の位相ブーストが必要になることがあります。 $R_{FB\_HS}$  と並列にフィードフォワード コンデンサを配置すると、位相が増幅されます。『[フィードフォワード コンデンサ付きの内部的に補正される dc-dc コンバータの過渡応答の最適化](#)』アプリケーション ノートも参照してください。

位相を増幅する以外に、フィードフォワード コンデンサは AC 結合を通じてより多くの  $V_{OUT}$  ノード情報を FB ノードに供給します。このフィードフォワードにより、負荷過渡イベント時に、 $V_{OUT}$  偏差に対する制御ループの応答を短縮できます。ただし、定常状態動作時のこのフィードフォワードにより、より多くの  $V_{OUT}$  リップルやノイズが FB に送られます。FB 上の高いリップルとノイズは通常、ジッタの増加、またはダブル パルス動作につながります。最終的なフィードフォワード コンデンサの値が、FB 上の位相マージン、負荷過渡性能、リップル、ノイズに与える影響をすべて考慮してください。TI は、周波数解析機器を使用してクロスオーバー周波数と位相マージンを測定することを推奨します。

### 6.3.2 内部 VCC LDO と VCC ピンへの外部バイアスの使用

TPS548A23 には内部 3.0V LDO があり、VIN からの入力を受け入れ、VCC への出力を備えています。EN 電圧が有効化スレッショルド ( $V_{ENSTB(R)}$ ) を上回ると、内部 LDO が有効になり、VCC ピンの出力電圧のレギュレーションが開始されます。VCC 電圧は、内部アナログ回路にバイアス電圧を提供し、ゲートドライバに電源電圧も供給します。

VCC ピンは  $1\mu\text{F}$  6.3V 以上の定格セラミック コンデンサを使用してバイパスします。内部 LDO の出力電圧より高い外部バイアスによって、内部 LDO がオーバーライドされる可能性があります。このオーバーライドにより、VCC 電流が、内部リニア レギュレータではなくこの外部バイアスで動作するため、コンバータの効率が向上します。3.1V ~ 5.3V の外部バイアスを使用すると、内蔵パワー MOSFET の  $R_{DS(on)}$  を低減することで効率を向上させることができます。

VCC UVLO 回路は VCC ピンの電圧を監視し、VCC が VCC UVLO 立ち下がりスレッショルドを下回ると、コンバータ全体を無効にします。デバイスをスムーズに動作させるには、安定的でクリーンな VCC 電圧を維持する必要があります。

VCC ピンに外部バイアスを使用する際の検討事項を以下に示します。

- 外部バイアスが VCC ピンに十分早く(たとえば、EN 信号が入力される前)適用されると、内部 LDO パス デバイスは常にオフになり、内部アナログ回路は電源有効時に安定した電源レールを確保できます。

- この考慮事項は推奨されていません。VCC ピンに外部バイアスが後後に印加される場合(EN 信号が入った後など)、VCC ピンから過剰な電流が引き出されない限り、パワーアップ シーケンスおよびパワーダウン シーケンスを適用できます。このシーケンスでは、内部 VCC LDO の電流制限よりも大きく電流が流れる可能性がある VCC ピンの外部放電パスに注意してください。内部 VCC LDO の電流制限を超える負荷は、VCC 電圧を Low にして、UVLO 経由で VCC LDO をオフにし、コンバータ出力がシャットダウンされる可能性があります。

- 良好なパワーアップ シーケンスとは、VIN UVLO 立ち上がりスレッショルドよりも後で EN 立ち上がりスレッショルドの少なくとも 1 つまたは VCC UVLO 立ち上がりスレッショルドが満たされている状態のことです。例えば、実用的なパワー アップ シーケンスは次のとおりです。最初に VIN を印加した後に外部バイアスを印加し、次に EN 信号が High になります。

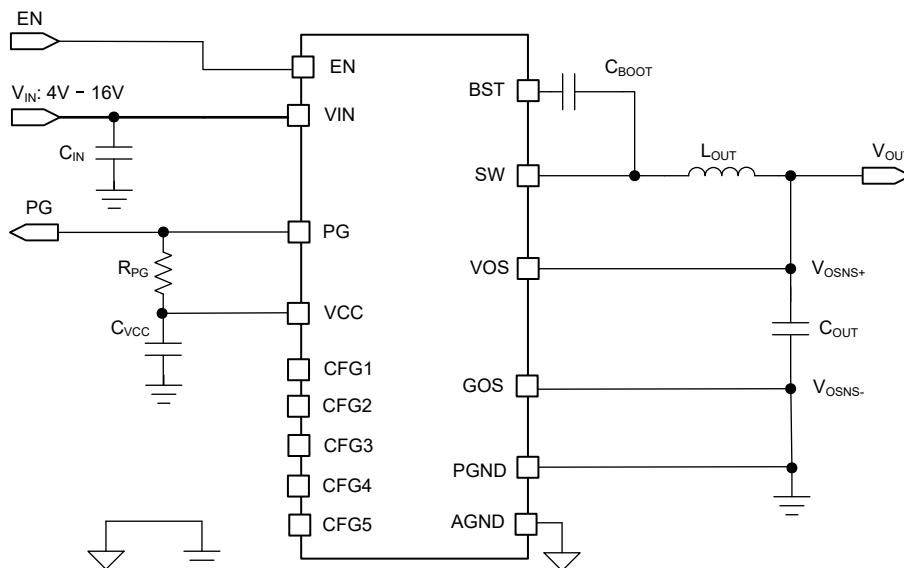

## 6.3.2.1 シングルバスからデバイスへの電力供給

デバイスは、単一の  $V_{IN}$  構成で電源が供給されると正常に動作します。シングル  $V_{IN}$  構成では、内部 LDO は通常 5V または 12V バスから電力を供給され、内部アナログ回路とパワー MOSFET ゲートドライバにバイアスをかける 3V 出力を生成します。この構成での  $V_{IN}$  入力範囲は、最大 12A の負荷電流に対して 4V ~ 16V です。図 6-1 に、この単一  $V_{IN}$  構成の例を示します。

$V_{IN}$  と EN はデバイスを有効化するための 2 つの信号です。起動シーケンスの場合、 $V_{IN}$  信号と EN 信号との間の任意のシーケンスによってデバイスに正しく電源を供給することができます。

図 6-1. 12V バスを使用するシングル  $V_{IN}$  構成

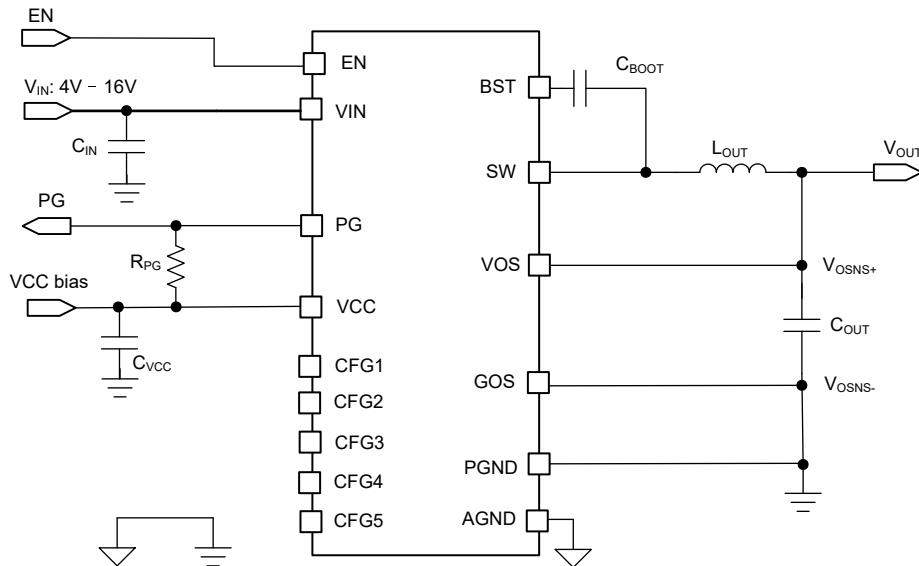

## 6.3.2.2 分割レール構成によるデバイスへの電力供給

メイン  $V_{IN}$  バスとは異なるレベルの外部バイアスを  $VCC$  ピンに印加する場合、メイン  $V_{IN}$  バスと  $VCC$  バイアスの両方を使用して分割レールにデバイスを構成できます。有効な  $VCC$  バイアスを  $VCC$  ピンに接続すると、内部 LDO がオーバーライドされ、内部 LDO での電力損失が低減されます。この構成は、システム レベル全体の効率を向上させますが、有効な  $VCC$  バイアスが必要です。 $VCC$  バイアスには、3.3V または 5.0V レールが一般的な選択肢です。 $VCC$  バイアスが安定している場合、この構成での推奨  $V_{IN}$  入力範囲は 4V ~ 16V のままです。

外部バイアスのノイズは、内部アナログ回路に影響を及ぼします。正常な動作を確保するために、クリーンで低ノイズの外部バイアス、および  $VCC$  ピンから PGND ピンへの十分なローカル デカッピング コンデンサが必要です。図 6-2 に、この分割レール構成の例を示します。

公称動作時の  $VCC$  外部バイアス電流は、バイアス電圧レベルと動作周波数によっても変化します。たとえば、デバイスをスキップ モードに設定すると、軽負荷状態で周波数が低下したときに、 $VCC$  ピンが外部バイアスから引き出す電流が少なくなります。FCCM 動作時の  $VCC$  外部バイアス電流の標準値を、に示します。外部バイアスにこの電流を供給する必要があります。そうしないと、外部バイアス電圧が低下し、内部 LDO がオーバーライドできなくなります。

分割レール構成では、 $V_{IN}$ 、 $VCC$  バイアス、EN が部品を有効にする信号です。スタートアップ シーケンスについては、 $VCC$  UVLO 立ち上がりスレッショルドよりも後で、 $VIN$  UVLO 立ち上がりスレッショルドまたは EN 立ち上がりスレッショルドの少なくとも一つを満たすことを推奨します。実用的なスタートアップシーケンスの例は次のとおりです。

1.  $V_{IN}$  を印加

2. 外部  $VCC$  バイアスを印加

3. EN 信号が High に遷移

同様に、パワーダウンシーケンスについては、TI は、外部 VCC バイアス電源がオフになる前に、VIN UVLO 立ち下がりスレッショルドまたは EN 立ち下がりスレッショルドの少なくとも一つを満たすことを推奨します。最初に外部 VCC バイアス電源がオフになると、デバイスの内部 LDO が VCC 電圧を 3.0V 未満に低下させるのを防止し、外部 VCC バイアス電源から電力を供給される他の回路によって負荷を供給します。

図 6-2. 外部 VCC バイアスを使用した分割レール構成

### 6.3.3 マルチファンクション構成 (CFG1-5) ピン

マルチファンクション構成ピン (CFG 1-5) により、デバイスは各種の動作モードに構成できます。CFG1-2 ピンは、デバイススイッチング周波数、過電流スレッショルド、ソフトスタート時間、ヒカッピングまたはラッチアップ故障回復動作の設定に使用され、CFG3-5 ピンは内部または外部フィードバックのための機能を選択し、FCCM または PFM 動作を選択できます。

注

CFG3-5 ピンを使用して、内部または外部のフィードバック動作を選択すると、CFG1-2 ピンの機能が変更されます。セクション 6.3.3.1 および セクション 6.3.3.2 も参照してください。

CFGx の状態は、内部の電源オン遅延期間中に設定およびラッピングされます。電源オン遅延後に CFGx ピンを変更しても、デバイスの状態は変化しません。

#### 6.3.3.1 マルチファンクション構成 (CFG1-2) ピン (内部フィードバック)

CFG 3-5 ピンによる内部帰還動作にデバイスを構成した場合 (表 6-4 を参照)、CFG1-2 ピンを次の表に基づいて High (VCC)、Low (GND) に接続するか、フローティングのままにすることで、スイッチング周波数と電流制限をプログラムします。

注

デバイスが内部帰還動作に構成されている場合、ソフトスタート時間は、1ms に設定され、故障回復はヒカッピング用に構成されます。

表 6-2. CFG 1-2 ピンの選択 (内部フィードバック構成)

| CFG1 | パレー OCP (A) | CFG2 | スイッチング周波数 (f <sub>sw</sub> ) (kHz) <sup>(1)</sup> |

|------|-------------|------|---------------------------------------------------|

| VCC  | 13          | VCC  | 600                                               |

| GND  | 10          | GND  | 800                                               |

表 6-2. CFG 1-2 ピンの選択 (内部フィードバック構成) (続き)

| CFG1 | バレー OCP (A) | CFG2 | スイッチング周波数<br>( $f_{sw}$ ) (kHz) <sup>(1)</sup> |

|------|-------------|------|------------------------------------------------|

| 浮動   | 7           | 浮動   | 1200                                           |

(1) スイッチング周波数は、3.3V の出力電圧に基づいています。周波数は出力電圧によって変化します。

### 6.3.3.2 マルチファンクション構成 (CFG1-2) ピン (外部フィードバック)

デバイスが CFG 3-5 ピンによる外部フィードバック動作作用に構成されている場合 (表 6-4 を参照)、CFG1-2 ピンと AGND の間に抵抗を接続することで、スイッチング周波数、故障回復モード、過電流レッショルド、およびソフトスタート時間をプログラムします。デバイスの動作範囲全体で正確に検出するには、許容誤差  $\pm 1\%$  の抵抗と温度係数  $\pm 100\text{ppm}/^\circ\text{C}$  (標準値) が必要です。

スイッチング周波数、故障回復モード、ソフトスタート時間は、次の表に基づいて CFG1 ピンと AGND との間に抵抗を接続することでプログラムされます。

表 6-3. CFG1 ピン選択表 (外部フィードバック構成)

| AGND への CFG1 ピン<br>抵抗 (k $\Omega$ ) | スイッチング周波数 ( $f_{sw}$ ) (kHz) <sup>(1)</sup> | 故障回復モード | ソフトスタート時間<br>(ms) |

|-------------------------------------|---------------------------------------------|---------|-------------------|

| 0 (GND)                             | 600                                         | ヒップ     | 1                 |

| 4.99                                | 800                                         | ヒップ     | 1                 |

| 7.50                                | 1000                                        | ヒップ     | 1                 |

| 10.5                                | 1200                                        | ヒップ     | 1                 |

| 13.3                                | 600                                         | ラッチオフ   | 1                 |

| 16.9                                | 800                                         | ラッチオフ   | 1                 |

| 21.0                                | 1000                                        | ラッチオフ   | 1                 |

| 24.9                                | 1200                                        | ラッチオフ   | 1                 |

| 30.1                                | 600                                         | ヒップ     | 2                 |

| 35.7                                | 800                                         | ヒップ     | 2                 |

| 42.2                                | 1000                                        | ヒップ     | 2                 |

| 48.7                                | 1200                                        | ヒップ     | 2                 |

| 56.2                                | 600                                         | ラッチオフ   | 2                 |

| 64.9                                | 800                                         | ラッチオフ   | 2                 |

| 75.0                                | 1000                                        | ラッチオフ   | 2                 |

| 86.6                                | 1200                                        | ラッチオフ   | 2                 |

| 102                                 | 600                                         | ヒップ     | 3                 |

| 118                                 | 800                                         | ヒップ     | 3                 |

| 137                                 | 1000                                        | ヒップ     | 3                 |

| 158                                 | 1200                                        | ヒップ     | 3                 |

| 182                                 | 600                                         | ラッチオフ   | 3                 |

| 210                                 | 800                                         | ラッチオフ   | 3                 |

| 243                                 | 1000                                        | ラッチオフ   | 3                 |

| $\geq 280$ (FLOAT)                  | 1200                                        | ラッチオフ   | 3                 |

(1) スイッチング周波数は、3.3V の出力電圧に基づいています。周波数は出力電圧によって変化します。

バレー過電流保護は、式 4 に基づいて CFG2 と AGND との間に抵抗 ( $R_{ILIM}$ ) を使用してプログラムされます。

$$I_{LIM\_VALLEY} = \frac{K_{OCL}}{R_{ILIM}} \quad (3)$$

$$R_{ILIM} = \frac{K_{OCL}}{I_{LIM\_VALLEY}} \quad (4)$$

ここで、

- $I_{LIM\_VALLEY}$  は、A における負荷電流のバレー過電流制限スレッショルドです

- $R_{ILIM}$  は  $ILIM$  抵抗値 ( $\Omega$ ) です

- $K_{OCL}$  は、計算における定数  $54.4 \times 10^3$  です

さらに、式 6 を使用して、特定の  $I_{LIM\_VALLEY}$  設定の最大出力電流を計算します。

$$I_{OUT\_MAX} = I_{LIM\_VALLEY} + \frac{1}{2} \times I_{RIPPLE} \quad (5)$$

$$I_{OUT\_MAX} = I_{LIM\_VALLEY} + \frac{1}{2} \times \frac{(V_{IN} - V_0) \times V_0}{V_{IN}} \times \frac{1}{L \times f_{SW}} \quad (6)$$

ここで、

- $I_{OUT\_MAX}$  は A における最大出力電流です

- $I_{LIM\_VALLEY}$  は、A における負荷電流のバレー過電流制限スレッショルドです

- $V_{IN}$  は入力電圧値 (V) です

- $V_0$  は出力電圧値 (V) です

- $L$  は出力インダクタの値 ( $\mu$ H) です

- $f_{SW}$  はスイッチング周波数 (MHz) です

#### 注

TI は、抵抗の許容誤差が小さいほど OCL スレッショルドの精度が低くなるため、テキサス インスツルメンツでは  $\pm 1\%$  の許容誤差を持つ抵抗を推奨します。

$ILIM$  ピンへの予期しない接続からデバイスを保護するために、内部の固定 OCL クランプが実装されています。この内部 OCL クランプは、 $ILIM$  ピンが AGND への抵抗が小さすぎる場合や、誤ってグランドに短絡した場合に、ローサイド MOSFET の最大バレー電流を 13A に制限します。

#### 6.3.3.3 マルチファンクション構成 (CFG3-5) ピン

CFG3-5 ピンは、以下の表に基づいてデバイスの出力電圧構成と、FCCM または PFM 動作を選択します。

表 6-4. CFG 3-5 ピン選択表

| CFG3 | CFG4 | CFG5 | $V_{FB}$ 構成 | $V_{OUT}$ (V) | $f_{SW}$ モード |

|------|------|------|-------------|---------------|--------------|

| VCC  | VCC  | VCC  | 内部          | 5.0           | FCCM         |

| VCC  | GND  | VCC  | 内部          | 3.3           | FCCM         |

| VCC  | 浮動   | VCC  | 内部          | 2.5           | FCCM         |

| VCC  | VCC  | GND  | 内部          | 1.8           | FCCM         |

| VCC  | GND  | GND  | 内部          | 1.5           | FCCM         |

| VCC  | 浮動   | GND  | 内部          | 1.2           | FCCM         |

| VCC  | VCC  | 浮動   | 内部          | 1.1           | FCCM         |

| VCC  | GND  | 浮動   | 内部          | 1.05          | FCCM         |

| VCC  | 浮動   | 浮動   | 内部          | 1.0           | FCCM         |

| GND  | VCC  | VCC  | 内部          | 0.95          | FCCM         |

| GND  | GND  | VCC  | 内部          | 0.9           | FCCM         |

| GND  | 浮動   | VCC  | 内部          | 0.85          | FCCM         |

| GND  | VCC  | GND  | 内部          | 0.8           | FCCM         |

| GND  | GND  | GND  | 外部          | 0.5           | FCCM         |

| GND  | 浮動   | GND  | 内部          | 5.0           | PFM          |

| GND  | VCC  | 浮動   | 内部          | 3.3           | PFM          |

| GND  | GND  | 浮動   | 内部          | 2.5           | PFM          |

| GND  | 浮動   | 浮動   | 内部          | 1.8           | PFM          |

表 6-4. CFG 3-5 ピン選択表 (続き)

| CFG3 | CFG4 | CFG5 | V <sub>FB</sub> 構成 | V <sub>OUT</sub> (V) | F <sub>SW</sub> モード |

|------|------|------|--------------------|----------------------|---------------------|

| 浮動   | VCC  | VCC  | 内部                 | 1.5                  | PFM                 |

| 浮動   | GND  | VCC  | 内部                 | 1.2                  | PFM                 |

| 浮動   | 浮動   | VCC  | 内部                 | 1.1                  | PFM                 |

| 浮動   | VCC  | GND  | 内部                 | 1.0                  | PFM                 |

| 浮動   | GND  | GND  | 内部                 | 0.95                 | PFM                 |

| 浮動   | 浮動   | GND  | 内部                 | 0.9                  | PFM                 |

| 浮動   | VCC  | 浮動   | 内部                 | 0.85                 | PFM                 |

| 浮動   | GND  | 浮動   | 内部                 | 0.8                  | PFM                 |

| 浮動   | 浮動   | 浮動   | 外部                 | 0.5                  | PFM                 |

### 6.3.4 イネーブル

EN ピンの電圧が有効スレッショルド電圧 (V<sub>EN(R)</sub>) を上回り、VIN が VIN UVLO 立ち上がりスレッショルドを上回ると、デバイスは内部パワーアップシーケンスに入ります。

EN ピンには内部フィルタがあり、小グリッチによる予期しないオン/オフを防止します。この RC フィルタの時定数は 2μs です。たとえば、理想的な立ち上がりエッジで 0V から 3.3V にジャンプする EN ピンに 3.3V 電圧ソースを印加すると、内部の EN 信号は 2μs の後で 2.1V に達します。これは、印加されている 3.3V 電圧レベルの 63.2% です。

EN ピンと AGND ピンの間に内部プルダウン抵抗が実装されています。このプルダウン抵抗により、起動前に EN ピンをフローティングにすると、デバイスは無効状態に維持されます。EN ピンの分圧抵抗を使用して、デバイスがスタートアップシーケンスを開始する入力電圧を上昇させることができます。外付け分圧抵抗を使用する場合は、内部プルダウン抵抗を考慮する必要があります。EN の立ち上がりおよび立ち下がりスレッショルドへの影響を低減するために、この内部プルダウン抵抗は 1MΩ です。電力段が切り替わるときの公称動作中、この大きな内部プルダウン抵抗は、EN ピンを Low に保持するのに十分なノイズ耐性を備えられないため、デバイスが無効状態に移行するのに十分なレベルになりません。

外付けの分圧抵抗が EN ピンに接続されている場合、EN 電圧が立ち上がりスレッショルドを超えると追加の 5μA 電流源がアクティブになり、有効立ち下がりスレッショルド電圧 (V<sub>EN(F)</sub>) と外付け抵抗に基づいて、プログラム可能なヒステリシスを提供します。

EN ピンの推奨動作条件は最大 5.5V です。VIN が 5.5V を超える可能性がある場合は、EN ピンを VIN ピンに直接接続しないでください。

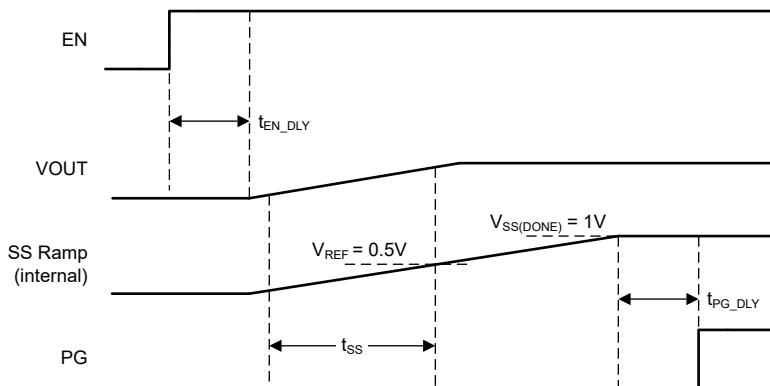

### 6.3.5 ソフトスタート

デバイスは、内部フィードバック動作に構成すると、1ms の内部固定ソフトスタート時間と、外部フィードバック動作に構成する場合に選択可能な (1ms, 2ms, 3ms) ソフトスタート時間を実装します。

ヒップモードが有効な場合、SS 時間によって、再起動試行の前のヒップ待機時間も設定されます。故障が発生した後でヒップ応答がトリガされると、内部タイマがヒップ待機時間を 14×t<sub>SS</sub> に設定します。

### 6.3.6 パワーグッド

デバイスには、パワーグッド (PG または PGOOD) 出力があり、これが high になり、コンバータ出力がレギュレーション状態になったことを示します。パワーグッド出力はオープンドレイン出力であり、high にするには、プルアップ抵抗 (通常 30.1kΩ) を介して VCC ピンまたは外部電圧源 (< 5.5V) にプルアップする必要があります。パワーグッド プルアップ抵抗の推奨値は、1kΩ から 100kΩ への接続です。

#### 注

外部電圧源を使用して PG ピンをプルアップするシステムでは、この同じ外部電圧源を使用して VCC ピンをバイアスすることを推奨します。

ソフトスタート ランプが完了すると、内部遅延 t<sub>PG\_DLY</sub> の後で、パワーグッド信号が High になります。SS 電圧が V<sub>SS(DONE)</sub> に達すると、内部ソフトスタート完了信号が High になり、ソフトスタートランプが完了したことを示します。FB 電圧が V<sub>REF</sub> 電圧の 80% まで低下した場合、または V<sub>REF</sub> 電圧の 116% を超えた場合、内部で 4μs の遅延後、パワーグ

ップ信号が **Low** にラッピングされます。パワーグッド信号は、**EN** を再度切り替えるか、**VIN** がリセットされた後でのみ再度 **High** にできます。

**OV** イベントによってソフトスタート中に **FB** 電圧が **OV** スレッショルドを超えたが、ソフトスタートが完了する前に **FB** 電圧が **OV** スレッショルドを下回った場合、**FB** が **OV** スレッショルドを超えるか、または **UV** スレッショルドを下回るまで、パワーグッド信号は **Low** をラッピングしません。**OV** または **UV** イベントは、ソフトスタートランプが完了した後に、パワーグッド信号が **Low** にラッピングされる必要があります。しかし、ソフトスタート中に **FB** が **OV** スレッショルドを超えると、**OV** フォルトがトリガされ、デバイスの応答（セクション 6.3.7 を参照）は通常、出力電圧を **UV** スレッショルドよりも低くします。

入力電源がデバイスの電源投入に失敗した場合（たとえば、**VIN** と **VCC** は両方とも **0V** のまま）、このピンが外部抵抗を介してプルアップされると、パワーグッドピンは **電気的特性** の「パワーグッド」セクションで指定された **low** レベルにクランプされます

図 6-3. EN、SS、および PG のタイミング図

### 6.3.7 過電圧および低電圧保護

このデバイスは、抵抗分割されたフィードバック電圧を監視して、過電圧および低電圧イベントを検出します。OVP 機能は、出力が有効になると有効になります。UVP 機能は、ソフトスタートの完了後に有効になります。

ソフトスタートが完了した後で、**FB** 電圧が **V<sub>REF</sub>** 電圧の **80%** を下回ると、UVP コンパレータはトリップし、内部 UVP 遅延カウンタがカウントを開始します。70 UVP 遅延時間の後で、選択した故障回復モードに応じて、デバイスはソフトスタート期間の **14** 倍のスリープ時間後にヒップアップ（一時中断）して再起動するか、ハイサイドとローサイドの両方の **MOSFET** をラッピングオフします。ラッピングオフ障害は、**VIN** をリセットするか、**EN** ピンを切り替えることでクリアできます。

出力が有効のとき、UVP コンパレータをクリアするには、**FB** 電圧を **PG** の **low** から **high** へのスレッショルドである **92.5%** を上回る必要があります。**FB** 電圧がソフトスタート周期の終了までに **92.5%** スレッショルドを超えていた場合、デバイスは低電圧イベントに応答します。

UVP 遅延時間中に、**FB** 電圧が **PG** の **Low** から **High** へのスレッショルドである **92.5%** を上回ると、低電圧イベントがクリアされ、タイマはゼロにリセットされます。出力電圧が **80%** UVP スレッショルドを再度下回ると、**70μs** のタイマが再起動します。

**FB** 電圧が **V<sub>REF</sub>** 電圧の **116%** より高くなると、OVP コンパレータがトリップし、回路が故障状態をラッピングして、**PG** ピンを **Low** に駆動します。負の電流制限 **I<sub>NOCL</sub>** に達するまで、ハイサイド **MOSFET** がオフになり、ローサイド **MOSFET** がオンになります。負の電流制限に達すると、ローサイド **MOSFET** がオフになり、適切なオン時間 (**V<sub>O</sub> / V<sub>IN</sub> / f<sub>SW</sub>** で決定) のため、ハイサイド **MOSFET** が再度オンになります。デバイスは、UVP スレッショルド未満に出力電圧がプルダウンされるまで、このモードで動作します。その後、デバイスは上記のように低電圧イベントに応答します。

出力が有効になる前に過電圧状態（**High** プリバイアス出力など）が発生した場合、デバイスはソフトスタート周期の開始時に、上記のように過電圧イベントに応答します。デバイスは、UVP が有効になるまでソフトスタート周期が完了するまで待機します。また、選択された故障回復モードに応じて、デバイスをヒップアップして再起動するか、ソフトスタート期間の **14** 倍のスリープ時間後に再起動するか、オフにラッピングされます。

### 6.3.8 出力電圧設定(外部フィードバック構成)

CFG 3-5 ピンのすべてをフローティングまたは GNDing にすることで、デバイスは外部帰還動作用に構成され、出力電圧は分圧抵抗によってプログラムされます。 $R_{FB\_T}$  と  $R_{FB\_B}$  でプログラムされます。 $R_{FB\_T}$  は、FB ピンと負荷の正ノードの間に接続し、 $R_{FB\_B}$  を FB ピンと GOS ピンの間に接続します。FB ピンは内部リファレンス ( $V_{REF}$ ) に調整されます。推奨される  $R_{FB\_B}$  の値は  $10\text{k}\Omega$  で、 $1\text{k}\Omega$  から  $20\text{k}\Omega$  までの範囲です。 $R_{FB\_T}$  を決定するには、式 7 を使用します。

$$R_{FB\_T} = \frac{V_O - V_{FB\_REG}}{V_{FB\_REG}} \times R_{FB\_B} \quad (7)$$

$V_{OUT}$  全体の精度を向上させるには、FB 分圧器に  $\pm 1\%$  以内の精度の抵抗を使用することを強く推奨します。リモートセンシングやシングルエンドセンシングにかかわらず、FB 分圧器  $R_{FB\_T}$  および  $R_{FB\_B}$  は、常にデバイスのできるだけ近くに配置する必要があります。

### 6.3.9 リモートセンス

デバイスは、GOS/FB ピンと VOS ピンの間にリモートセンスアンプを内蔵しています。リモートセンス機能は、PCB トレース上の電圧降下を補正し、定常動作および負荷過渡イベント時の  $V_{OUT}$  精度を維持するのに役立ちます。

FB ピンに接続されるパターン長を最小限に抑えるため、FB 分圧抵抗(使用する場合)は、デバイスの近くに配置する必要があります。FB 電圧分周抵抗と GOS ピンからリモートロケーションへの接続は、 $0.1\mu\text{F}$  以上のバイパスコンデンサを介したケルビン検出を備えた PCB トレースペアである必要があります。安定した出力電圧を維持し、リップルを最小限に抑えるには、インダクタや SW ノード、高周波クロックラインなどのノイズ源から、1 対のリモート検出ラインを離して配置する必要があります。リモート検出ラインのペアを上下のグランドプレーンでシールドすることを TI は推奨します。

シングルエンド  $V_{OUT}$  センシングは多くの場合、ローカルセンシングに使用されます。この構成では、より高い FB 抵抗  $R_{FB\_HS}$  を  $0.1\mu\text{F}$  以上の高周波ローカルバイパスコンデンサに接続し、GOS を AGND に短絡します。

推奨される GOS 動作範囲(AGND ピンを基準とする)は  $-100\text{mV} \sim +100\text{mV}$  です。

### 6.3.10 ローサイド MOSFET のゼロ交差センシング

デバイスでは、ゼロ交差(ZC)回路を使用して、スキップモード動作時にゼロインダクタ電流検出を行います。ZC スレッショルドは、ローサイド MOSFET がオフになる前に小さな負の値に設定され、不連続導通モード(DCM)動作に入ります。DCM に入った後、ZC スレッショルドヒステリシスは DCM に入った後にスレッショルドを小さな正の値に増加させます。結果として、デバイスの軽負荷効率が向上します。

デバイスが DCM を終了できるように負荷電流が十分増加した場合、ZC 回路は DCM に戻る前に、ZC スレッショルドを下回る負のインダクタ電流の連続 16 サイクルを検出する必要があります。DCM を終了するのに必要なのは、ZC 検出なしの 1 サイクルのみです。

出力が有効のとき、デバイスがソフトスタートしている間、最初の 32 スイッチングサイクル中にも ZC 回路が有効になります。デバイスが FCCM に構成されている場合、ZC は無効化され、ソフトスタートの完了時にデバイスは FCCM に遷移します。ソフトスタート完了の説明については、[ソフトスタート](#)を参照してください。高出力プリバイアスでのスタートアップ時などに、ソフトスタートの実行前に少なくとも 32 スイッチングサイクルがない場合、ソフトスタートが完了してから最初のハイサイド MOSFET のオン時間が完了するまで、ZC は無効なりません。

### 6.3.11 電流センスと正の過電流保護の各機能

降圧コンバータの場合、ハイサイド MOSFET のオン時間中、スイッチ電流は入力電圧、出力電圧、オン時間、出力インダクタ値によって決定される直線的なレートで増加します。ローサイド MOSFET のオン時間中は、この電流はリニアに減少します。スイッチ電流の平均値は、負荷電流と等しくなります。

デバイス内の出力過電流制限(OCL)は、サイクル毎のバレー電流検出制御回路を使用して実現されています。インダクタ電流は、ローサイド MOSFET のオン時間中に、ローサイド MOSFET のドレイン - ソース電流を測定することによって監視されます。ローサイド MOSFET の測定されたドレイン - ソース間電流が電流制限スレッショルドを超えている場合、

電流レベルが電流制限スレッショルドよりも低くなるまでローサイド MOSFET はオンのままになります。この種の動作により、デバイスから供給される平均出力電流が低減されます。

過電流状態の間、負荷に流れる電流は出力コンデンサに流れる電流を上回っています。したがって、出力電圧は低下する傾向があります。最終的に、出力電圧が低電圧保護スレッショルド (80%) を下回ると、UVP コンパレータがその低下を検出し、70μs の待機時間後にデバイスをシャットダウンします。故障回復構成に応じて、デバイスはヒップまたはラッチオフのいずれかを起こします ([過電圧および低電圧保護](#)を参照してください)。

#### 注

起動中に OCL 状態が発生した場合、デバイスはローサイドのバレー電流に基づくサイクル単位の電流制限が続けますが、UVP コンパレータはソフトスタートが完了するまでデバイスをシャットダウンしません。

現在制限されている保護スレッショルドの設定については、[セクション 6.3.3](#) を参照してください。

### 6.3.12 ローサイド MOSFET 負電流制限

このデバイスには、固定のサイクル単位の負の過電流制限 ( $I_{LS(NOC)}$ ) があります。正の過電流制限と同様に、ローサイド MOSFET のオン時間中にインダクタ電流が監視されます。ローサイド MOSFET に過大な負電流が流れないよう、デバイスがローサイド MOSFET を通過して -9 A 電流 (標準スレッショルド) を検出すると、ローサイド MOSFET がオフになり、ワンショットタイマ ( $V_{IN}/V_{OUT}/f_{SW}$  で決定) で設定されたオン時間の間ハイサイド MOSFET をオンにします。ハイサイド MOSFET のオン時間が経過すると、ローサイド MOSFET が再度オンになります。

小さすぎるインダクタ値が選択された場合、またはインダクタが飽和しない限り、公称動作中に -9 A の負電流制限スレッショルドをデバイスがトリガしてはいけません。この負の電流制限を使用して、出力 OVP イベント後に出力コンデンサを放電します。[過電圧および低電圧](#)も参照してください。

### 6.3.13 出力電圧放電

EN によりデバイスが無効になると、出力電圧放電モードは有効になります。このモードでは、ハイサイド MOSFET とローサイド MOSFET の両方が強制的にラッチオフされますが、SW から PGND に接続された内部放電 MOSFET がオンになり、出力電圧が放電されます。FB 電圧が 50mV を下回ると、放電 MOSFET と内部 VCC LDO がオフになります。

EN ピンが Low になってコンバータが無効になり、VCC 電圧が放電スイッチをオンにするのに十分な間、出力電圧放電モードがアクティブになります。

### 6.3.14 UVLO 保護

このデバイスは、VIN ピンと VCC ピンの両方の電圧を監視します。VCC ピンの電圧が  $V_{CC_{UVLO}}$  立ち下がりスレッショルド電圧よりも低い場合、デバイスはシャットオフします。VCC 電圧が  $V_{CC_{UVLO}}$  立ち上がりスレッショルド電圧を超えると、デバイスは再びオンになります。VCC UVLO は非ラッチ方式の保護です。

VIN ピンの電圧が  $V_{IN_{UVLO}}$  立ち下がりスレッショルド電圧よりも低いにもかかわらず、VCC ピンの電圧が  $V_{CC_{UVLO}}$  立ち上がりスレッショルド電圧よりも高い場合、デバイスはスイッチングを停止し、SS ピンを放電します。VIN 電圧が  $V_{IN_{UVLO}}$  立ち上がりスレッショルド電圧を上回ると、デバイスはソフトスタートを再度開始し、再度スイッチングを行います。VIN UVLO は非ラッチ方式の保護です。

### 6.3.15 サーマル シャットダウン

デバイスは内部接合部温度を監視します。温度がスレッショルド (通常 165°C) を超えると、デバイスはスイッチングを停止し、SS ピンを放電します。温度がスレッショルド値を約 15°C 下回ると、デバイスは再起動されたソフトスタートでオンに戻ります。サーマル シャットダウンは非ラッチ方式の保護です。

## 6.4 デバイスの機能モード

### 6.4.1 自動スキップ (PFM) エコモード軽負荷動作

CFG3-5 ピン、を通じてスキップ (PFM) モードが選択されると、デバイスは軽負荷状態でスイッチング周波数を自動的に下げて高効率を維持します。PFM モードの選択方法については、[多機能構成 \(CFG3-5\) ピンセクション](#)を参照してください。

出力電流が重負荷状態から減少すると、インダクタ電流も減少し、インダクタリップル電流バーがゼロ交差スレッショルド ([ローサイド MOSFET ゼロ交差](#)) に達するまで続きます。ゼロ交差スレッショルドは、連続導通モードと不連続導通モード間の境界を設定します。このゼロ交差スレッショルドが検出されると、同期 MOSFET がオフになります。負荷電流がさらに減少すると、コンバータは不連続導通モード (DCM) に入ります。オン時間は連続導通モード動作中とほぼ同じレベルに維持されるため、出力コンデンサを小さな負荷電流でリファレンス電圧レベルまで放電するには、より長い時間を要します。軽負荷動作  $I_{OUT(LL)}$  への遷移点 (例:連続導通モードと不連続導通モードの境界) を計算するには、[式 8](#) を使用します。

出力リップルを低くするため、TI は、スキップ モードで動作する設計にはセラミック出力コンデンサのみを使用することを推奨します。

$$I_{OUT(LL)} = \frac{1}{2} \times \frac{(V_{IN} - V_0) \times V_0}{V_{IN}} \times \frac{1}{L \times f_{SW}} \quad (8)$$

### 6.4.2 強制連続導通モード

FCCM モードを選択した場合 CFG3-5 ピン、本コントローラは軽負荷状態で連続導通モード (CCM) で動作します。FCCM モードの選択方法については、[多機能構成 \(CFG3-5\) ピンセクション](#)を参照してください。

FCCM 中、スイッチング周波数は負荷範囲全体にわたってほぼ一定のレベルに維持されます。これは、軽負荷効率の低下を犠牲にしてスイッチング周波数と出力リップルを厳密に制御する必要があるアプリケーション向けに設計されています。標準的な軽負荷動作の境界を計算するには、[式 8](#) を使用します。負荷電流の計算された値を下回ると、デバイスは FCCM で動作します。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPS548A23 デバイスは、高効率のシングル チャネル小型同期整流 降圧コンバータです。このデバイスは、サーバー、ストレージ、および同様のコンピューティング アプリケーションにおける 12A または以下の出力電流の低出力電圧ポイントオブ ロード アプリケーション向けに設計されています。TPS548A23 は、独自の D-CAP4 モード制御と適応型オン時間アーキテクチャを採用しています。この組み合わせにより、低デューティ比で超高速の負荷ステップ応答を持つ最新の DC/DC コンバータを優れた方法で構築できます。出力電圧範囲は、0.5V ~ 5.5V です。変換入力電圧の範囲は 4V ~ 16V、VCC 入力電圧の範囲は 3.1V ~ 5.3V です。D-CAP4 モードは、エミュレートされた電流情報を使用して変調を制御します。この制御方式の利点として、この制御方式に外部位相補償回路が必要ないことが挙げられます。そのため、デバイスは使いやすく、外付け部品数も少なくて済みます。この制御方式のもう 1 つの利点は、この制御方式が、すべての低 ESR 出力コンデンサ (セラミックコンデンサや低 ESR ポリマー コンデンサなど) で安定して動作できることです。適応型オン時間制御は、広い範囲の入力電圧および出力電圧にわたってプリセットされたスイッチング周波数を追跡すると同時に、負荷ステップ過渡が発生した際に必要に応じてスイッチング周波数を上昇させます。

### 7.2 代表的なアプリケーション

の回路図は TPS548A23 の代表的なアプリケーション例を示しています。この例では、8V ~ 16V の入力電圧範囲を最大出力電流 12A で 3.3V に変換する設計手順について説明します。

図 7-1. アプリケーション回路図

## 7.2.1 設計要件

この設計では、次の表に示すパラメータを使用します。

**表 7-1. 設計例の仕様**

| 仕様                     | テスト条件                                            |      | 最小値  | 標準値  | 最大値  | 単位   |

|------------------------|--------------------------------------------------|------|------|------|------|------|

| $V_{IN}$ 電圧範囲          |                                                  |      | 8    | 12   | 16   | V    |

| 入力電流                   | $V_{IN} = 8V$ 、 $I_{OUT} = 12A$                  |      |      | 5.55 |      | A    |

| $V_{IN}$ スタート電圧        | EN ピン抵抗デバイダで設定                                   |      |      | 3.84 |      | V    |

| 出力電圧の設定ポイント            |                                                  |      |      | 3.3  |      | V    |

| 出力電流範囲                 | $V_{IN} = 8V \rightarrow 16V$                    |      | 0    |      | 12   | A    |

| 負荷過渡応答                 | $I_{OUT} = 0A \sim 10A$                          | 電圧変化 |      | -99  |      | mV   |

|                        | $I_{OUT} = 10A \sim 0A$                          | 電圧変化 |      | 99   |      | mV   |

| 出力リップル電圧               | $I_{OUT} = 12A$                                  |      |      | 16   |      | mVPP |

| ソフトスタート時間              | スイッチング開始から $V_{FB} = 0.5V$ 、 $t_{SS} = 2ms$ 設定まで |      | 1.4  | 2    | 2.6  | ms   |

| 電流制限                   | CFG1 ピン選択による $OCP = 13A$ の設定                     |      | 11.5 | 13   | 14.5 | A    |

| スイッチング周波数 ( $f_{SW}$ ) | CFG2 ピンの選択による $f_{SW} = 800kHz$ 設定               |      |      | 800  |      | kHz  |

| IC ケース温度               | $I_{OUT} = 12A$ 、15 分間の浸漬                        |      |      | 52.7 |      | °C   |

## 7.2.2 詳細な設計手順

外部部品の選択は、D-CAP4 モードを使用した簡単なプロセスです。外部部品は以下の手順で選択します。

### 7.2.2.1 出力電圧設定値

CFG3-5 ピンは、表 6-4 に基づいてデバイスの出力電圧構成と、FCCM または PFM 動作を選択します。この設計では、内部 FB 構成オプションを使用します。

表 6-4 で使用可能なものの外の出力電圧が必要な場合は、外部フィードバック構成により、電圧分割抵抗 R1 および R2 によって出力電圧をプログラムできます。R1 は FB ピンと出力の間に接続し、R2 を FB ピンと GOS の間に接続します。推奨 R2 値は  $10k\Omega$  ですが、 $1k\Omega \sim 20k\Omega$  の範囲内で別の値に設定することもできます。R1 を決定するには、式 9 を使用します。

$$R1 = R2 \times \left( \frac{V_{OUT}}{0.5V} - 1 \right) \quad (9)$$

### 7.2.2.2 スイッチング周波数の選択

この設計では、内部フィードバック モードを使用し、CFG2 ピンを VCC (600kHz) または GND (800kHz) に接続するか、フローティング (1.2MHz) のままにすることで、スイッチング周波数が設定されます。表 6-2 も参照してください。

外部フィードバック構成を使用する場合、CFG1 ピンを使用して 4 つのスイッチング周波数 (600kHz、800kHz、1MHz、1.2MHz) から選択できます。外部フィードバックモードでの CFG1 ピン構成の使用方法の詳細については、表 6-3 も参照してください。

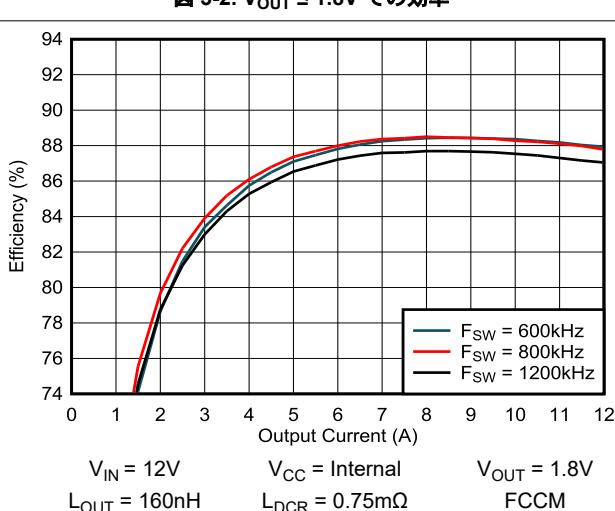

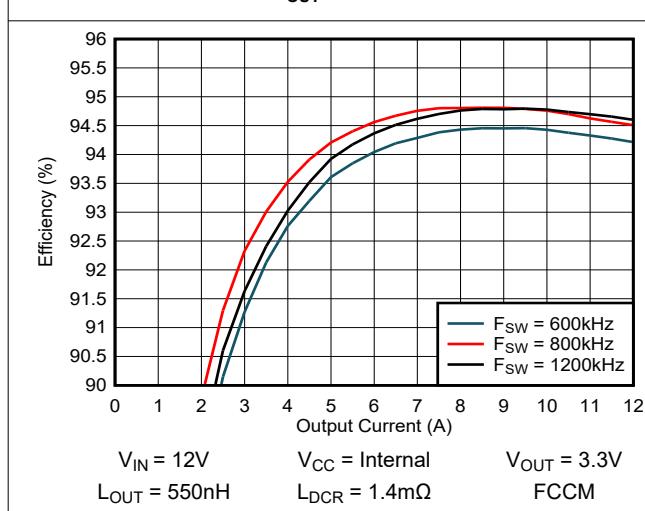

スイッチング周波数の選択は、高効率と小型設計とのトレードオフになります。スイッチング周波数が低いと、全体の効率は高くなりますが、外付け部品は比較的大きくなります。スイッチング周波数が高いほどスイッチング損失が増加し、効率や放熱性能が悪化します。この設計では、CFG2 ピンを AGND に接続し、スイッチング周波数を 800kHz に設定します。

降圧コンバータのスイッチング周波数を選択するときは、最小オン時間と最小オフ時間を考慮する必要があります。式 10 では、最小オン時間によって制限される前の最大  $f_{SW}$  を計算します。D-CAP4 制御によりコンバータの最小オン時間制限に達すると、実効スイッチング周波数が変化して出力電圧がレギュレートされたままになります。この計算では、コンバータの抵抗性電圧降下を無視して、ワーストケースの推定が行われます。

$$f_{SW(max)} = \frac{V_{OUT}}{V_{IN(max)}} \times \frac{1}{t_{ON\_MIN}} = \frac{3.3\text{ V}}{16\text{ V}} \times \frac{1}{40\text{ ns}} = 5156\text{ kHz} \quad (10)$$

式 11 では、最小オフ時間によって制限される前の最大  $f_{SW}$  を計算します。D-CAP4 制御によるコンバータの最小オフ時間制限に達すると、動作デューティサイクルは増加し、出力電圧は入力電圧に応じて低下し始めます。この式では、次の手順で選択されたインダクタの DC 抵抗  $R_{DCR}$  が必要なため、この予備計算では  $1.4\text{ m}\Omega$  の抵抗を想定しています。最小オフ時間によって制限される最大  $f_{SW}$  付近で動作する場合は、式 12 を使用する際に温度による抵抗の変動を考慮する必要があります。選択した  $800\text{ kHz}$  の  $f_{SW}$  は、計算された 2 つの最大値を下回っています。

$$f_{SW(max)} = \frac{V_{IN(min)} - V_{OUT} - I_{OUT(max)} \times (R_{DCR} + R_{DS(ON)_HS})}{t_{OFF\_MIN(max)} \times (V_{IN(min)} - I_{OUT(max)} \times (R_{DS(ON)_HS} - R_{DS(ON)_LS}))} \quad (11)$$

$$f_{SW(max)} = \frac{8\text{ V} - 3.3\text{ V} - 12\text{ A} \times (1.4\text{ m}\Omega + 9.5\text{ m}\Omega)}{150\text{ ns} \times (8\text{ V} - 12\text{ A} \times (9.5\text{ m}\Omega - 3.3\text{ m}\Omega))} = 3843\text{ kHz} \quad (12)$$

### 7.2.2.3 インダクタの選択

出力インダクタ ( $L_{OUT}$ ) を計算するには、式 13 を使用します。出力コンデンサは、インダクタのリップル電流 ( $I_{IND(ripple)}$ ) をフィルタリングします。したがって、大きなインダクタ リップル電流を選択すると、それ以上のリップル電流定格を持つ出力コンデンサが必要となるため、出力コンデンサの選択に影響が及びます。リップル電流が大きいと、出力リップル電圧が増加しますが、信号対雑音比が向上し、動作の安定に役立ちます。一般的に言って、バランスのとれた性能を得るには、インダクタンス値はリップル電流を最大出力電流のおよそ  $15\% \sim 40\%$  に設定する必要があります。

この設計では、インダクタ リップル電流を  $12\text{ A}$  の出力電流の  $30\%$  に設定しています。スイッチング周波数が  $800\text{ kHz}$  で、最大  $V_{IN}$  は  $16\text{ V}$ 、出力電圧が  $3.3\text{ V}$  の場合、これらのパラメータに基づいて、式 13 は  $0.91\mu\text{H}$  のインダクタンスを計算します。最も近い標準値  $0.91\mu\text{H}$  が選択されます。

$$L = \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{I_{RIPPLE} \times V_{IN(max)} \times f_{SW}} = \frac{(16\text{ V} - 3.3\text{ V}) \times 3.3\text{ V}}{0.3 \times 12\text{ A} \times 16\text{ V} \times 800\text{ kHz}} = 0.91\mu\text{H} \quad (13)$$

インダクタは良好な効率を達成するために Low DCR が必要です。また、ピーク インダクタ電流から飽和までの間に十分な余裕が必要です。インダクタ電流リップルを見積るには、式 14 を使用します。この設計では、CFG1 ピンを VCC に接続することで、 $I_{OC(valley)}$  は  $13\text{ A}$  に設定されるため、最大  $V_{IN}$  におけるピークインダクタ電流は式 15 で  $13.8\text{ A}$  と計算されます。

$$I_{RIPPLE} = \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{L \times V_{IN(max)} \times f_{SW}} = \frac{(16\text{ V} - 3.3\text{ V}) \times 3.3\text{ V}}{0.91\mu\text{H} \times 16\text{ V} \times 800\text{ kHz}} = 3.6\text{ A} \quad (14)$$

$$I_{L(Peak)} = I_{OUT} + \frac{I_{RIPPLE}}{2} = 12\text{ A} + \frac{3.6\text{ A}}{2} = 13.8\text{ A} \quad (15)$$

$$I_{L(RMS)} = \sqrt{I_{OUT}^2 + \frac{I_{RIPPLE}^2}{12}} = \sqrt{12\text{ A}^2 + \frac{3.6\text{ A}^2}{12}} = 12.04\text{ A} \quad (16)$$

### 7.2.2.4 出力コンデンサの選択

出力コンデンサの値を選択する際には、主に 3 つの検討事項があります。

1. 安定性

2. 定常状態の出力電圧リップル

3. 負荷電流の変化に対するレギュレータの過渡応答

まず、これら 3 つの要件に基づいて最小出力容量を計算します。式 17 では、安定性要件を満たすための、LC 重極を表 6-1 の  $f_{P(MAX)}$  未満に維持するための最小容量を計算しています。この要件は、LC の重極を内部ゼロに近く維持するのに役立ちます。式 18 では、定常状態の出力電圧リップル要件である  $16\text{ mV}$  を満たすための最小容量を計算しています。

す。これらの計算は CCM 動作用であり、出力コンデンサの ESR または ESL に起因する出力電圧リップルの一部は含まれていません。

$$C_{OUT\_STABILITY} > \left( \frac{1}{2\pi \times f_P(TABLE) \times \left( 1 + \left( \frac{V_{OUT}}{V_{IN(TYP)}} \right)^2 \right)} \right)^2 \times \frac{1}{L_{OUT}} = \left( \frac{1}{2\pi \times 19.9\text{kHz} \times \left( 1 + \left( \frac{3.3\text{V}}{12\text{V}} \right)^2 \right)} \right)^2 \times \frac{1}{0.91\mu\text{H}} \quad (17)$$

$$= 61\mu\text{F}$$

$$C_{OUT\_RIPPLE} > \frac{I_{RIPPLE}}{8 \times V_{RIPPLE} \times f_{SW}} = \frac{3.6\text{A}}{8 \times 16\text{mV} \times 800\text{kHz}} = 35.2\mu\text{F} \quad (18)$$

式 20 と式 21 は、10A ステップで 99mV の過渡応答要件を満たす最小静電容量を計算します。これらの式は、負荷ステップ後にインダクタ電流が上昇または下降している間、出力電圧を一定に保持するために必要な出力容量を計算します。

$$C_{OUT\_UNDERSHOOT} > \frac{L \times I_{STEP}^2 \times \left( \frac{V_{OUT}}{V_{IN(\min)} \times f_{SW}} + t_{OFF\_MIN(max)} \right)}{2 \times V_{TRANS} \times V_{OUT} \times \left( \frac{V_{IN(\min)} - V_{OUT}}{V_{IN(\min)} \times f_{SW}} - t_{OFF\_MIN(max)} \right)} \quad (19)$$

$$C_{OUT\_UNDERSHOOT} > \frac{0.91\mu\text{H} \times 10\text{A}^2 \times \left( \frac{3.3\text{V}}{8\text{V} \times 800\text{kHz}} + 150\text{ns} \right)}{2 \times 99\text{mV} \times 3.3\text{V} \times \left( \frac{8\text{V} - 3.3\text{V}}{8\text{V} \times 800\text{kHz}} - 150\text{ns} \right)} = 158.6\mu\text{F} \quad (20)$$

$$C_{OUT\_OVERSHOOT} > \frac{L \times I_{STEP}^2}{2 \times V_{TRANS} \times V_{OUT}} = \frac{0.91\mu\text{H} \times 10\text{A}^2}{2 \times 99\text{mV} \times 3.3\text{V}} = 139.3\mu\text{F} \quad (21)$$

オーバーシュート要件を満たすために必要な出力容量は最大値であるため、この例では必要な最小出力容量が設定されます。安定性要件では、最大出力容量を制限することもできます。式 22 は、推奨最大出力容量を計算します。この計算では、LC の重極が  $f_{SW}$  の 1/100 よりも高く維持されます。

$$C_{OUT\_STABILITY} < \left( \frac{50}{\pi \times f_{SW}} \right)^2 \times \frac{1}{L} = \left( \frac{50}{\pi \times 800\text{kHz}} \right)^2 \times \frac{1}{0.91\mu\text{H}} = 435\mu\text{F} \quad (22)$$

より大きな出力容量を使用することも可能ですが、ボード線図または過渡応答測定で安定性を確認する必要があります。選択する出力容量は、8 × 47μF、10V のセラミックコンデンサです。セラミックコンデンサを使用する場合は、DC バイアス効果と AC バイアス効果により容量をディレーティングする必要があります。選択したコンデンサは公称値で 48% までディレーティングし、実効的な総容量は 180μF となります。この実効容量は、最小要件と最大要件を満たします。

このアプリケーションではすべてセラミックコンデンサを使用するため、リップルと過渡に対する ESR の影響は無視されました。非セラミックコンデンサを使用する場合、まず、ESR は、リップル要件を満たすために式 23 で計算された値よりも低く、過渡要件を満たすために式 24 よりも低くなければなりません。より正確な計算を行う場合、または複数の出力コンデンサを使用する場合は、出力コンデンサのインピーダンスを使用して、リップルと過渡要件を満たすかどうかを判定する必要があります。

$$R_{ESR\_RIPPLE} < \frac{V_{RIPPLE}}{I_{RIPPLE}} = \frac{26\text{mV}}{3.6\text{A}} = 7.2\text{m}\Omega \quad (23)$$

$$R_{ESR\_TRANS} < \frac{V_{TRANS}}{I_{STEP}} = \frac{99\text{mV}}{10\text{A}} = 9.9\text{m}\Omega \quad (24)$$

### 7.2.2.5 入力コンデンサ ( $C_{IN}$ ) の選択

このデバイスでは、電力段をバイパスするため、VIN ピンと PGND ピンの両方のペアの間に入力バイパスコンデンサを接続する必要があります。バイパスコンデンサは、レイアウトが可能な限り IC のピンのできるだけ近くに配置する必要があります。

ります。セラミック容量の少なくとも  $20\mu\text{F}$  (公称値) と、2つの高周波セラミックバイパスコンデンサが必要です。必要な高周波バイパスを提供し、**VIN** ピンと **SW** ピンのパワーステージ全体の高周波オーバーシュートとアンダーシュートを低減するには、 $0.1\mu\text{F} \sim 1\mu\text{F}$  のコンデンサを、デバイスのボードの同じ側にある **VIN** ピン 4 と 12 の両方にできるだけ近づけて配置する必要があります。テキサスインスツルメンツは、入力電圧リップルを最小限に抑えるため、各 **VIN** ピンにできるだけ近づけてバイパスキャパシタンスを  $1\mu\text{F}$  以上にすることを推奨します。セラミックコンデンサには、高い容量/体積比と温度範囲全体にわたって安定した特性を持つため、X6S 以上の高品質の誘電体を使用する必要があります。この要件に加えて、過渡条件時の入力電圧の変動を最小限に抑えるため、アプリケーションによっては入力に応じて大きなバルク容量が必要となる場合があります。

式 25 を使用して、特定の入力リップル目標を満たすために必要な入力容量を計算します。推奨される目標入力電圧リップルは最小入力電圧の 5% で、この例では  $400\text{mV}$  です。計算された入力容量は  $9.1\mu\text{F}$ 。この例では、 $2 \times 10\mu\text{F}$  のセラミックコンデンサを使用して、これら 2 つの要件を満たしています。

$$C_{\text{IN}} > \frac{V_{\text{OUT}} \times I_{\text{OUT}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}(\text{min})}\right)}{f_{\text{SW}} \times V_{\text{IN}}(\text{min}) \times V_{\text{IN\_RIPPLE}}} = \frac{3.3\text{V} \times 12\text{A} \times \left(1 - \frac{3.3\text{V}}{8\text{V}}\right)}{800 \text{kHz} \times 8\text{V} \times 400\text{mV}} = 9.1\mu\text{F} \quad (25)$$

コンデンサの RMS 電流定格をアプリケーションの最大入力電流 RMS よりも大きくする必要があります。式 27 を使用して、入力コンデンサがサポートする必要がある入力 RMS 電流を計算します。結果はこの例では、 $5.9\text{A}$  です。セラミック入力コンデンサの電流定格は、この値よりも大きいです。

$$I_{\text{CIN}(\text{RMS})} = \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}(\text{min})} \times \left( \frac{(V_{\text{IN}}(\text{min}) - V_{\text{OUT}})}{V_{\text{IN}}(\text{min})} \times I_{\text{OUT}}^2 + \frac{I_{\text{RIPPLE}}^2}{12} \right)} \quad (26)$$

$$I_{\text{CIN}(\text{RMS})} = \sqrt{\frac{3.3\text{V}}{8\text{V}} \times \left( \frac{(8\text{V} - 3.3\text{V})}{8\text{V}} \times 12^2 + \frac{3.6^2}{12} \right)} = 5.9\text{A} \quad (27)$$

低入力電圧と高電流などの入力にバルク容量を必要とするアプリケーションの場合、TI はアナログ設計ジャーナルの [降圧コンバータの入力コンデンサの選択方法](#) に記載されている選択プロセスを推奨しています。

#### 7.2.2.6 VCC バイパスコンデンサ

レイアウトが可能な限り、**VCC** ピンをできるだけ近くに配置した  $1.0\mu\text{F}$  (6.3V 以上の定格)、X5R セラミックバイパスコンデンサが必要です。0402 パッケージなど、可能な限り最小サイズのコンデンサを使用して、**VCC** ピンから **PGND** ピンまでのループを最小限に抑えます。

#### 7.2.2.7 BOOT コンデンサ

レイアウトの許す限り、**BOOT** ピンと **SW** ピンの間に、少なくとも  $0.1\mu\text{F}$ 、10V、X5R のセラミックバイパスコンデンサがピンのできるだけ近くに配置されている必要があります。

#### 7.2.2.8 PG プルアップ抵抗

**PG** ピンはオープンドレインであるため、このピンを使用する場合はプルアップ抵抗が必要です。推奨される値は  $1\text{k}\Omega \sim 100\text{k}\Omega$  です。

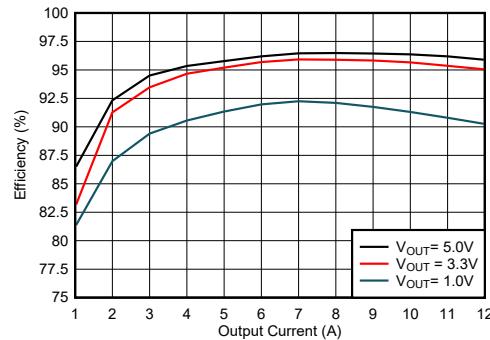

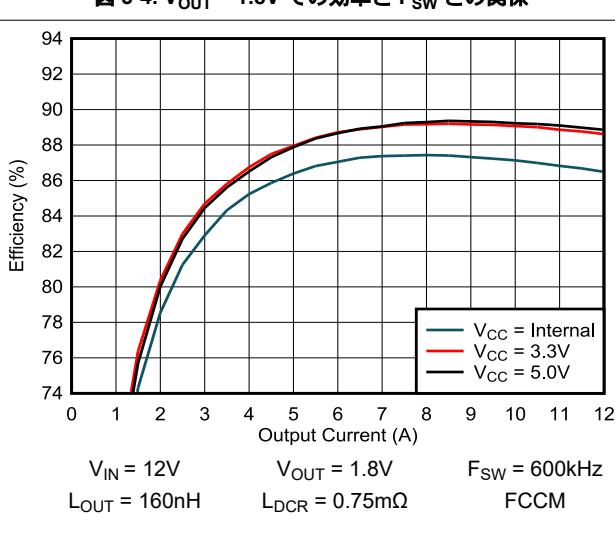

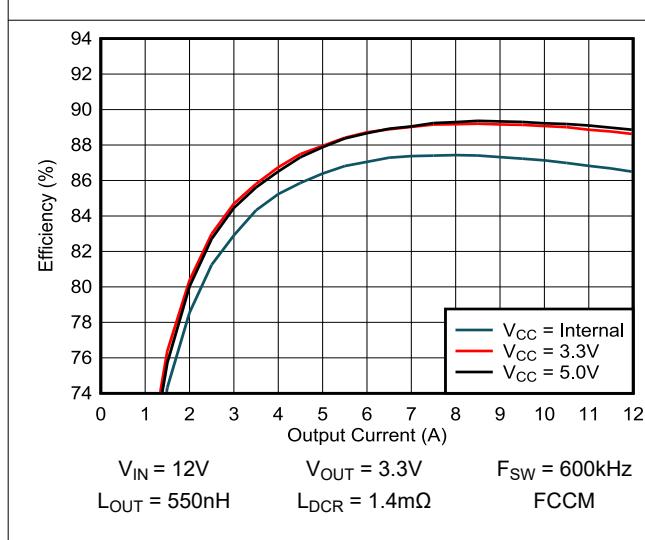

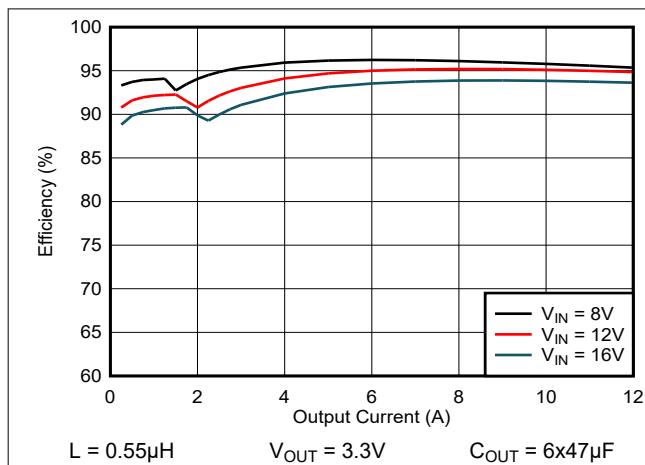

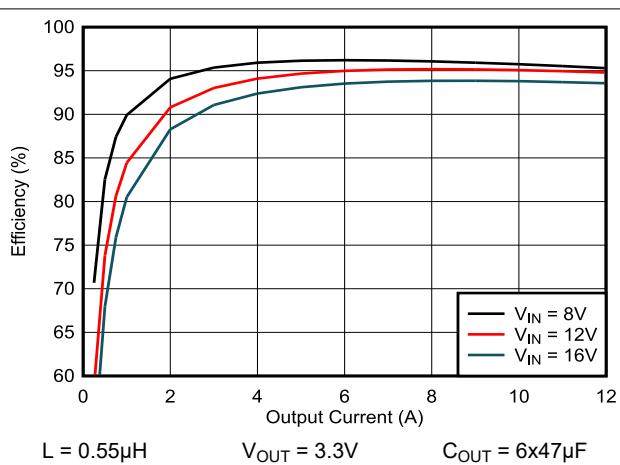

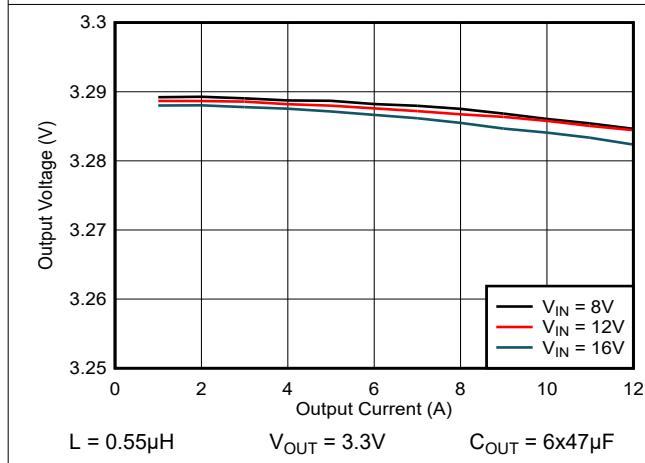

### 7.2.3 アプリケーション曲線

図 7-2. 効率 - PFM モード

図 7-3. 効率 - FCCM モード

図 7-4. ロード レギュレーション

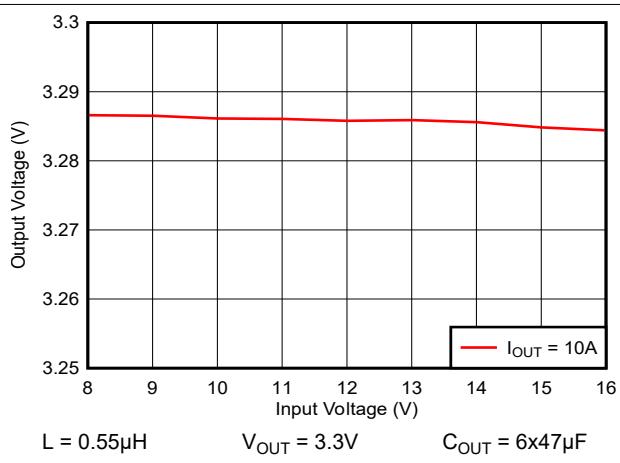

図 7-5. ライン レギュレーション

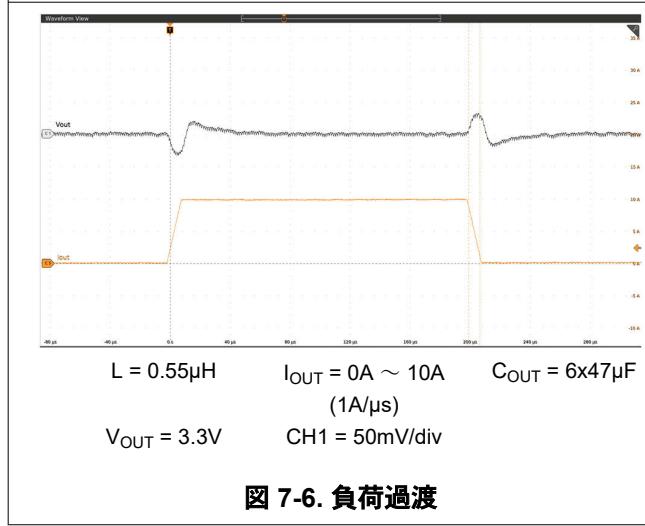

図 7-6. 負荷過渡

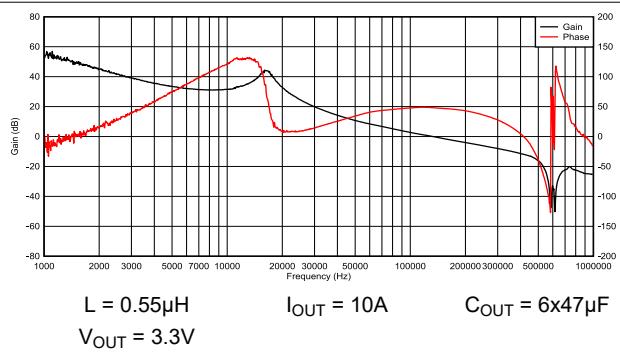

図 7-7. 周波数応答

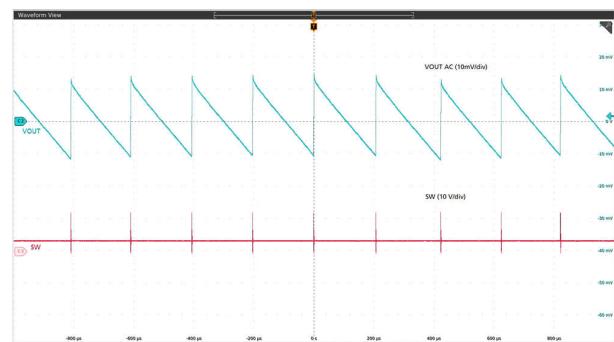

$L = 0.55\mu\text{H}$        $I_{\text{OUT}} = 10\text{mA}$        $C_{\text{OUT}} = 6 \times 47\mu\text{F}$

$V_{\text{OUT}} = 3.3\text{V}$

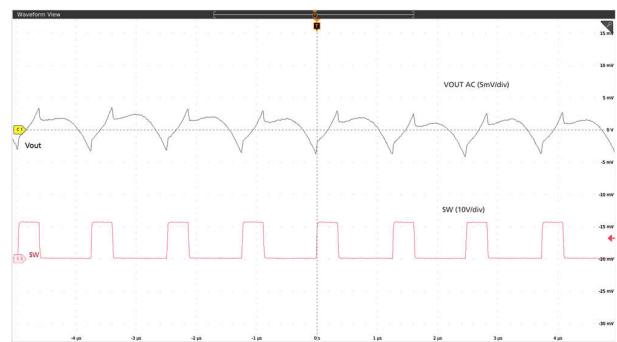

図 7-8. 出力電圧リップル – PFM モード

$L = 0.55\mu\text{H}$        $I_{\text{OUT}} = 12\text{A}$        $C_{\text{OUT}} = 6 \times 47\mu\text{F}$

$V_{\text{OUT}} = 3.3\text{V}$

図 7-9. 出力電圧リップル、FCCM モード

$I_{\text{OUT}} = 10\text{A}$

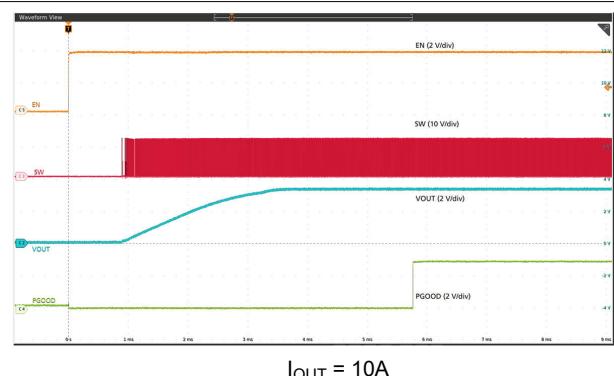

図 7-10. EN によるスタートアップ

$I_{\text{OUT}} = 10\text{A}$

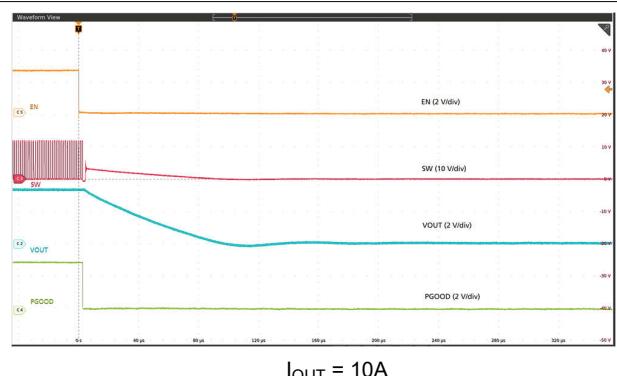

図 7-11. EN によるシャットダウン

### 7.3 電源に関する推奨事項

デバイスは、4V ~ 16V の入力電源電圧範囲で動作するように設計されています。両方の入力電源 (VIN と VCC バイアス) が適切に調整されている必要があります。入力電源 (VIN および VCC バイアス) の適切なバイパスも、PCB レイアウトや接地方式と同様に、ノイズ性能にとって重要です。レイアウトの推奨事項を参照してください。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

このデバイスを使用して設計を開始する前に、以下を考慮してください。

- VIN、PGND、および SW のパターンを可能な限り広く配置し、トレースインピーダンスを低減、放熱を改善してください。

- 電源部品 (入力 / 出力コンデンサ、インダクタ、IC を含む) は、PCB の上面に配置します。小信号パターンをノイズの多い電源ラインから遮蔽 / 絶縁するために、少なくとも 1 つのソリッドなグランド内部プレーンを挿入します。

- パワー MOSFET の堅牢性を確保するには、VIN デカップリングコンデンサの配置が重要です。各ピン (ピン 4 と 12) に  $1\mu\text{F}$  /25V/0402 セラミック高周波バイパスコンデンサを接続する必要があり、隣接する PGND ピン (それぞれピン 5 とピン 11) に接続します。残りのセラミック入力キャパシタンスは、これらの高周波バイパスコンデンサの隣に配置します。残りの入力キャパシタンスは基板の反対側に配置できますが、IC のピンとコンデンサ間のインピーダンスを最小限に抑えるため、可能な限り多くのビアを使用してください。

- できるだけ多くのビアを PGND ピンの下と近くに配置します。この動作により、寄生インピーダンスが最小限に抑えられ、熱抵抗も低下します。

- 両方の VIN ピンの近くにビアを使用し、内部層を経由してこれらのビア間を低インピーダンスで接続します。各 VIN ピンの下にビアを配置することもできます。

- VCC のデカップリング コンデンサは、PGND (ピン 5) に短い間隔で、デバイスのできるだけ近くに配置します。VCC デカップリング ループが小さくなっていることを確認し、12mil 以上の幅のトレースを使用して接続を配線します。

- BOOT コンデンサを、BOOT ピンと SW ピンのできるだけ近くに配置します。接続には 12mil 以上の幅のトレースを使用します。

- SW ピンとインダクタの高電圧側を接続する PCB トレースは、スイッチ ノードとして定義されます。このスイッチ ノードは、できる限り短く、幅広くする必要があります。

- 外部帰還を使用する場合は、シングルエンド センシングやリモート センシングに関係なく、FB パターンの距離を最小限に抑えるため、常にデバイスの近くに帰還抵抗を配置します。

- リモート センシングの場合、FB 電圧分割抵抗からリモート ロケーションへの接続は PCB トレースの差動ペアである必要があります、 $0.1\mu\text{F}$  以上のバイパスコンデンサを介してケルビン センシングを実装する必要があります。リモート 検出信号のグランド接続を GOS 端子に接続する必要があります。リモート センシング信号の  $V_{\text{OUT}}$  接続は、下側のフィードバック抵抗を GOS ピンに終端したフィードバック抵抗分周器に接続する必要があります。安定した出力電圧を維持し、リップルを最小限に抑えるには、インダクタや SW ノード、高周波クロック ラインなどのノイズ源から、1 対のリモート検出ラインを離して配置する必要があります。リモート検出ラインのペアを上下のグランドプレーンでシールドすることを TI は推奨します。

- シングルエンド センシングの場合、FB ピンと出力電圧間の上部フィードバック抵抗を  $0.1\mu\text{F}$  以上の高周波ローパス出力バイパスコンデンサに接続し、GOS を AGND に短いトレースで短絡します。

- AGND ピン (ピン 19) をデバイスの下にある PGND ピン (ピン 5 とピン 11) に接続します。

- カッピングを制限するため、PG 信号やその他のノイズの多い信号は、VOS /FB や GOS などのノイズに敏感な信号の近くにアプリケーションで配線しないでください。

- レイアウトの推奨事項については、[レイアウト例](#)を参照してください。

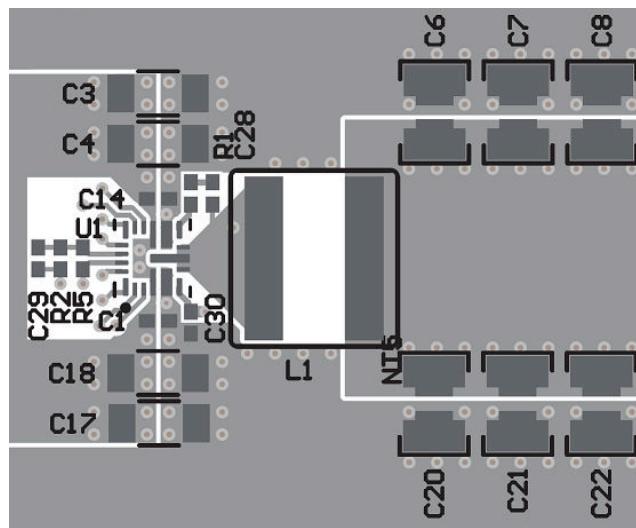

#### 7.4.2 レイアウト例

図 7-12. レイアウトに関する推奨事項

詳細なレイアウト例については、[TPS548B23 降圧コンバータ評価基板 EVM ユーザーガイド](#)を参照してください。

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

- テキサス・インスツルメンツ、フィードフォワードコンデンサ付きの内部的に補正される DC-DC コンバータの過渡応答の最適化アプリケーションノート

- テキサス・インスツルメンツ、ラックサーバーおよびデータセンター アプリケーションにおける VR13.HC 用の非絶縁型ポイントオブロードソリューションアプリケーションノート

- テキサス・インスツルメンツ、TPS548B23 降圧コンバータ評価基板 EVM ユーザー ガイド

- テキサス・インスツルメンツ、降圧コンバータの入力コンデンサの選択方法アナログ設計ジャーナル

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

| 日付            | 改訂 | 注      |

|---------------|----|--------|

| November 2025 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins     | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS548A23VANR         | Active        | Production           | WQFN-HR (VAN)   19 | 5000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | T48A23              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.