# TPS546D24 2.95V~16V、40A、最大4xスタッカブル、PMBus®降圧コンバータ

## 1 特長

- 分割レール対応：2.95V~16V PVIN、2.95V~18V AVIN（4V<sub>IN</sub> VDD5によるスイッチング）

- 4.5mΩ/0.9mΩのMOSFET内蔵

- 平均電流モード制御、内部補償を選択可能

- 2x、3x、4xスタッカブルで最大160Aのカレント・シェア（電流共有）、出力ごとに1つのアドレスをサポート

- 選択可能な出力：ピン・ストラップで0.6V~5.5V、PMBusのVOUT\_COMMANDで0.25V~5.5V

- 豊富なPMBusコマンド・セット、V<sub>OUT</sub>、I<sub>OUT</sub>、内部ダイ温度のテレメトリー

- 内蔵FB分圧器による差動リモート・センシングで1%未満のV<sub>OUT</sub>誤差（T<sub>J</sub>=-40°C~+150°C）を実現

- PMBusによるAVSおよびマージニング機能

- MSELピンによるPMBusデフォルト値のピン設定

- 225kHz~1.5MHzで12のスイッチング周波数を選択可能（8つのピン・ストラップ・オプション）

- 周波数同期入力/同期出力

- プリバイアス出力をサポート

- 強結合インダクタをサポート

- 7mm×5mm×1.5mm、40ピンQFN、ピッチ=0.5mm

- WEBENCH® Power Designer**により、TPS546D24を使用するカスタム設計を作成

## 2 アプリケーション

- データ・センター・スイッチ、ラック・サーバー

- アクティブ・アンテナ・システム、リモート無線/ベースバンド・ユニット

- 自動試験装置、CT、PET、MRI

- ASIC、SoC、FPGA、DSPコア、I/O電圧

## 3 概要

TPS546D24は高度に統合された非絶縁型DC/DCコンバータであり、7mm×5mmのパッケージで高周波動作と40Aの電流出力を実現します。2個、3個、4個のTPS546D24を相互に接続して、単一出力で最大160Aを供給できます。VDD5ピンを介して外部5V電源で内蔵5V LDOをオーバードライブできるため、コンバータの効率向上と消費電力低減が可能です。

TPS546D24は入力フィードフォワードによる独自の固定周波数電流モード制御を採用しており、内部補償部品を選択可能であるため、システム・サイズを最小化し、幅広い出力容量で安定性を確保できます。

### 製品情報<sup>(1)</sup>

| 型番        | パッケージ          | 本体サイズ(公称)     |

|-----------|----------------|---------------|

| TPS546D24 | LQFN-CLIP (40) | 7.00mm×5.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

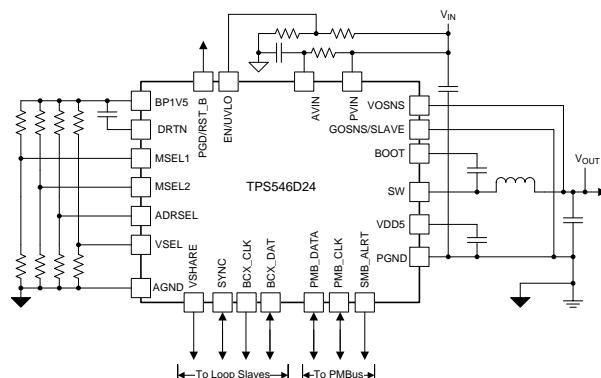

### アプリケーション概略図

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

## 目次

|                                         |   |                              |   |

|-----------------------------------------|---|------------------------------|---|

| 1 特長 .....                              | 1 | 7.1 デバイス・サポート .....          | 6 |

| 2 アプリケーション .....                        | 1 | 7.2 ドキュメントの更新通知を受け取る方法 ..... | 6 |

| 3 概要 .....                              | 1 | 7.3 コミュニティ・リソース .....        | 7 |

| 4 改訂履歴 .....                            | 2 | 7.4 商標 .....                 | 7 |

| 5 概要(続き) .....                          | 3 | 7.5 静電気放電に関する注意事項 .....      | 7 |

| 6 Pin Configuration and Functions ..... | 4 | 7.6 Glossary .....           | 7 |

| 7 デバイスおよびドキュメントのサポート .....              | 6 | 8 メカニカル、パッケージ、および注文情報 .....  | 7 |

## 4 改訂履歴

2018年11月発行のものから更新

Page

- |                            |   |

|----------------------------|---|

| • 生産データを用いたデータシートの初版 ..... | 1 |

|----------------------------|---|

## 5 概要（続き）

1MHzクロックをサポートするPMBusインターフェイスは、出力電圧、出力電流、内部ダイ温度などの主要パラメータを監視するためだけでなく、コンバータを設定するための便利な標準化されたデジタル・インターフェイスを提供します。フォルト条件への応答は、システム要件に応じて、再起動、ラッチオフ、無視のいずれかに設定できます。スタックしたデバイス間のバックチャネル通信により、1つの出力レールに電力供給するすべてのTPS546D24コンバータが1つのアドレスを共有できるため、システム・ソフトウェア/ファームウェア設計を簡素化できます。出力電圧、スイッチング周波数、ソフトスタート時間、過電流フォルト制限などの主要なパラメータは、PMBus通信を使わないでBOM選定で設定することもでき、プログラムなしでのパワーオンをサポートしています。

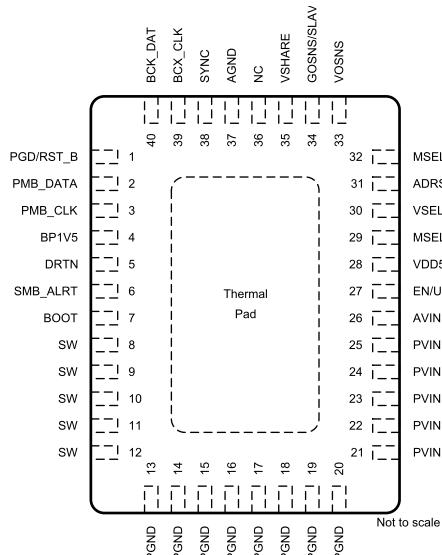

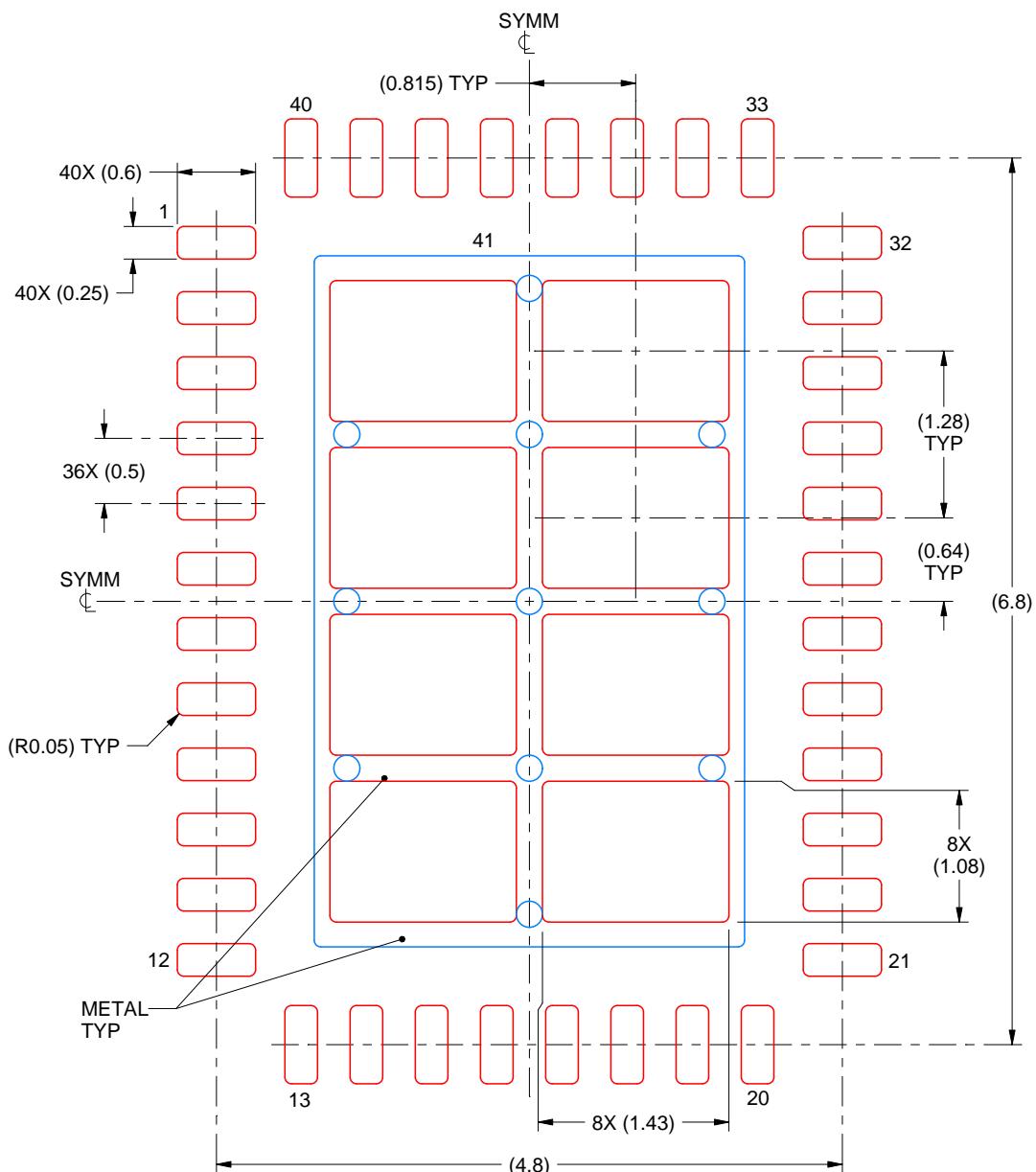

## 6 Pin Configuration and Functions

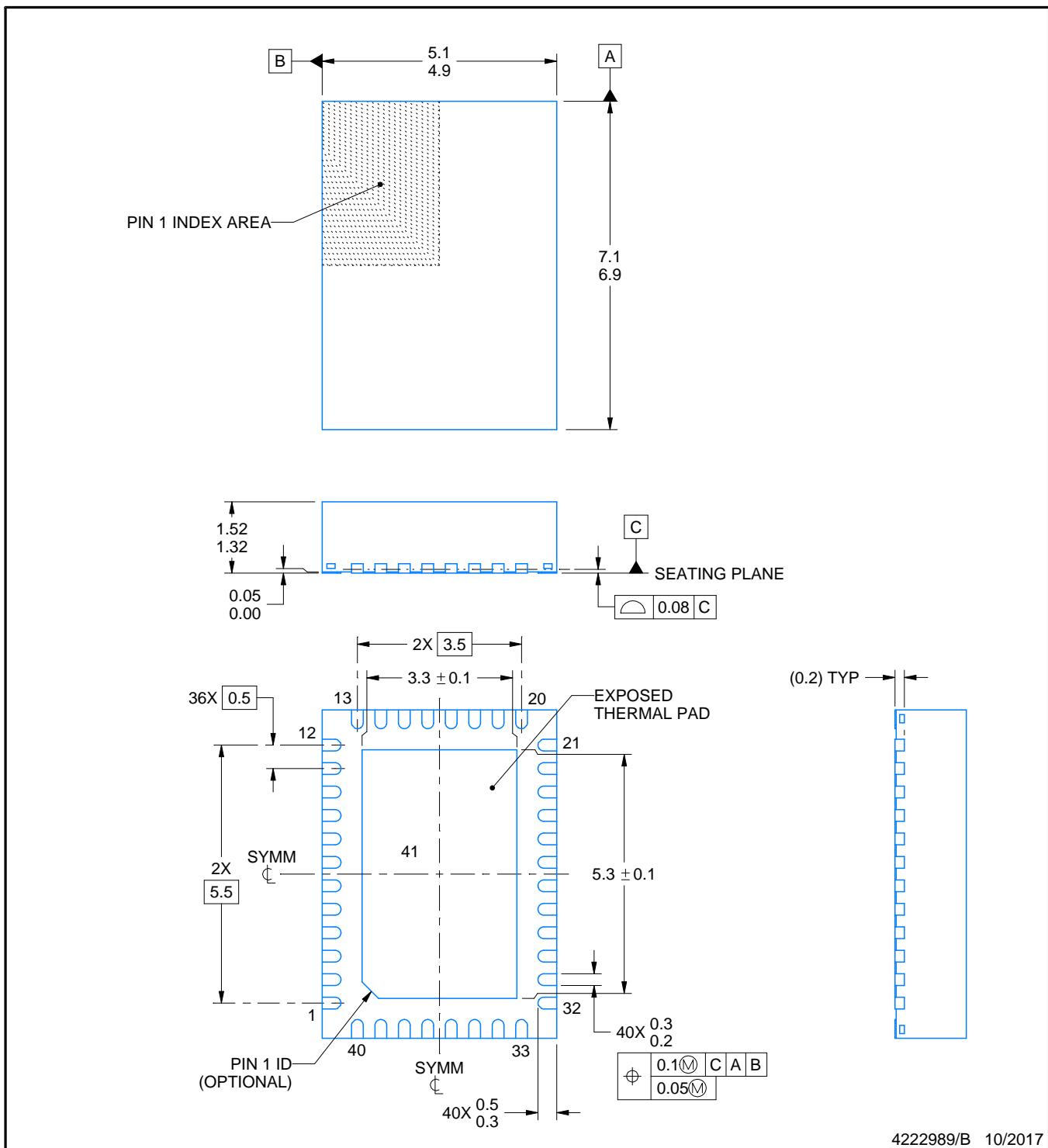

**RVF Package**

**40-Pin LQFN-CLIP With Exposed Thermal Pad**

**Top View**

### Pin Functions

| PIN |           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                       |

|-----|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      |     |                                                                                                                                                                                                                                                                                   |

| 1   | PGD/RST_B | I/O | Open-drain power good or reset#, As determined by user accessible bit (See in PMBUS Command detailed descriptions) . The default pin function is an open drain power-good indicator.                                                                                              |

| 2   | PMB_DATA  | I/O | PMBus DATA pin. See PMBus specification.                                                                                                                                                                                                                                          |

| 3   | PMB_CLK   | I   | PMBus CLK pin. See PMBus specification.                                                                                                                                                                                                                                           |

| 4   | BP1V5     | O   | Output of the 1.5-V internal regulator. This regulator powers the digital circuitry and should be bypassed with a minimum of 1 $\mu$ F to DRTN. BP1V5 is not designed to power external circuit.                                                                                  |

| 5   | DRTN      | —   | Digital bypass return for bypass capacitor for BP1V5. Internally Connected to AGND. Do not Connect to PGND or AGND.                                                                                                                                                               |

| 6   | SMB_ALRT  | O   | SMBus alert pin. See SMBus specification.                                                                                                                                                                                                                                         |

| 7   | BOOT      | I   | Bootstrap pin for the internal flying high side driver. Connect a typical 100 nF from this pin to SW. To reduce the voltage spike at SW, an optional BOOT resistor of up to 8 $\Omega$ may be placed in series with the BOOT capacitor to slow down turn-on of the high-side FET. |

| 8   | SW        | I/O | Switched power output of the device. Connect the output averaging filter and bootstrap to this group of pins.                                                                                                                                                                     |

| 9   |           |     |                                                                                                                                                                                                                                                                                   |

| 10  |           |     |                                                                                                                                                                                                                                                                                   |

| 11  |           |     |                                                                                                                                                                                                                                                                                   |

| 12  |           |     |                                                                                                                                                                                                                                                                                   |

| 13  | PGND      | —   | Power stage ground return. These pins are internally connected to the thermal pad.                                                                                                                                                                                                |

| 14  |           |     |                                                                                                                                                                                                                                                                                   |

| 15  |           |     |                                                                                                                                                                                                                                                                                   |

| 16  |           |     |                                                                                                                                                                                                                                                                                   |

| 17  |           |     |                                                                                                                                                                                                                                                                                   |

| 18  |           |     |                                                                                                                                                                                                                                                                                   |

| 19  |           |     |                                                                                                                                                                                                                                                                                   |

| 20  |           |     |                                                                                                                                                                                                                                                                                   |

**Pin Functions (continued)**

| <b>PIN</b> |             | <b>I/O</b> | <b>DESCRIPTION</b>                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>NO.</b> | <b>NAME</b> |            |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21         | PVIN        | I          | Input power to the power stage. Low-impedance bypassing of these pins to PGND is critical.                                                                                                                                                                                                                                                                                                       |

| 22         |             |            |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23         |             |            |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24         |             |            |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25         |             |            |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 26         | AVIN        | I          | Input power to the controller. Bypass with a minimum 1- $\mu$ F ceramic capacitor to PGND. If AVIN is connected to the same input as PVIN or VDD5, a minimum 10- $\mu$ s R-C filter is recommended to reduce switching noise on AVIN.                                                                                                                                                            |

| 27         | EN/UVLO     | I          | Enable switching as the PMBus CONTROL pin. EN/UVLO can also be connected to a resistor divider to program input voltage UVLO.                                                                                                                                                                                                                                                                    |

| 28         | VDD5        | O          | Output of the 5-V internal regulator. This regulator powers the driver stage of the controller and should be bypassed with a minimum of 4.7 $\mu$ F to PGND at the thermal pad. Low impedance bypassing of this pin to PGND is critical.                                                                                                                                                         |

| 29         | MSEL2       | I          | Connect this pin to a resistor divider between BP1V5 and AGND for different options of soft-start time, overcurrent fault limit, and multi-phase information. See section                                                                                                                                                                                                                        |

| 30         | VSEL        | I          | Connect this pin to a resistor divider between BP1V5 and AGND for different options of internal voltage feedback divider and default output voltage. See section.                                                                                                                                                                                                                                |

| 31         | ADRSEL      | I          | Connect this pin to a resistor divider between BP1V5 and AGND for different options of PMBus addresses and frequency sync (including determination of SYNC pin as SYNC IN or SYNC OUT function). See section.                                                                                                                                                                                    |

| 32         | MSEL1       | I          | Connect this pin to a resistor divider between BP1V5 and AGND for different options of switching frequency and internal compensation parameters. See section.                                                                                                                                                                                                                                    |

| 33         | VOSNS       | I          | The positive input of the remote sense amplifier. For a standalone device or the loop master device in a multi-phase configuration, connect VOSNS pin to the output voltage at the load. For the loop slave device in a multi-phase configuration, the remote sense amplifier is not required for output voltage sensing or regulation, this pin can be left floating.                           |

| 34         | GOSNS/SLAVE | I          | The negative input of the remote sense amplifier for loop master device or should be pulled up high to indicate loop slave. For standalone device or the loop master device in a multi-phase configuration, connect GOSNS pin to the ground at the load. For the loop slave device in a multi-phase configuration, the GOSNS pin must be pulled up to BP1V5 to indicate the device a loop slave. |

| 35         | VSHARE      | I/O        | Voltage sharing signal for multi-phase operation. For stand-alone device, the VSHARE pin must be left floating.                                                                                                                                                                                                                                                                                  |

| 36         | NC          | -          | Not internally connected. Pin can be left floating or connected to PGND at the thermal pad.                                                                                                                                                                                                                                                                                                      |

| 37         | AGND        | -          | Analog ground return for controller. Connect the AGND pin directly to the thermal pad on the PCB board.                                                                                                                                                                                                                                                                                          |

| 38         | SYNC        | I/O        | For frequency synchronization, can be programmed as SYNC IN or SYNC OUT pin by ADRSEL pin or the PMBus Command. The SYNC pin can be left floating when not used.                                                                                                                                                                                                                                 |

| 39         | BCX_CLK     | I/O        | Clock for back-channel communications between stacked devices.                                                                                                                                                                                                                                                                                                                                   |

| 40         | BCX_DAT     | I/O        | Data for back-channel communications between stacked devices.                                                                                                                                                                                                                                                                                                                                    |

| —          | Thermal pad | —          | Package thermal pad, internally connected to PGND. The thermal pad must have adequate solder coverage for proper operation.                                                                                                                                                                                                                                                                      |

## 7 デバイスおよびドキュメントのサポート

### 7.1 デバイス・サポート

#### 7.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供される場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワークの製品またはサービスの是認の表明を意味するものではありません。

#### 7.1.2 開発サポート

##### 7.1.2.1 WEBENCH®ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designerにより、TPS546D24を使用するカスタム設計を作成できます。

- 最初に、入力電圧( $V_{IN}$ )、出力電圧( $V_{OUT}$ )、出力電流( $I_{OUT}$ )の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットで出力する。

- 設計のレポートをPDFで印刷し、設計を共有する。

WEBENCHツールの詳細は、[www.ti.com/WEBENCH](http://www.ti.com/WEBENCH)でご覧になれます。

##### 7.1.2.2 Texas Instruments Fusion Digital Power Designer

TPS546D24はテキサス・インスツルメンツのDigital Power Designerでサポートされています。Fusion Digital Power Designerはグラフィカル・ユーザー・インターフェイス(GUI)で、テキサス・インスツルメンツ製のUSB-to-GPIOアダプタを使用し、PMBus経由でデバイスを設定および監視するために使用できます。

Texas Instruments Fusion Digital Power Designerソフトウェア・パッケージをダウンロードするには、このリンクをクリックしてください。

### 7.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 7.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™オンライン・コミュニティ** *TIのE2E ( Engineer-to-Engineer )* コミュニティ。エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てるることができます。

**設計サポート** *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

## 7.4 商標

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

PMBus is a registered trademark of System Management Interface Forum, Inc..

All other trademarks are the property of their respective owners.

## 7.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

## 7.6 Glossary

[SLYZ022 — TI Glossary](#).

This glossary lists and explains terms, acronyms, and definitions.

## 8 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。これらのデータは、予告なしに、このドキュメントの更新なしに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins       | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS546D24RVFR</a> | Active        | Production           | LQFN-CLIP (RVF)   40 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS546D24           |

| TPS546D24RVFR.A               | Active        | Production           | LQFN-CLIP (RVF)   40 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS546D24           |

| TPS546D24RVFR.B               | Active        | Production           | LQFN-CLIP (RVF)   40 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| <a href="#">TPS546D24RVFT</a> | Active        | Production           | LQFN-CLIP (RVF)   40 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS546D24           |

| TPS546D24RVFT.A               | Active        | Production           | LQFN-CLIP (RVF)   40 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS546D24           |

| TPS546D24RVFT.B               | Active        | Production           | LQFN-CLIP (RVF)   40 | 250   SMALL T&R       | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

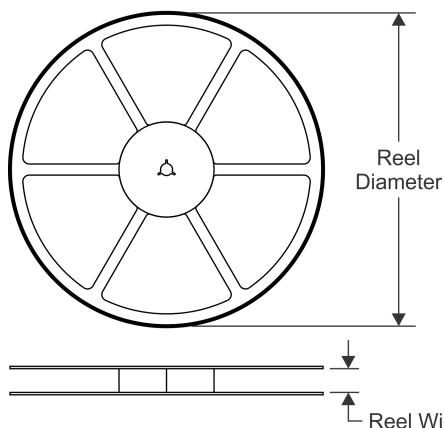

## TAPE AND REEL INFORMATION

### REEL DIMENSIONS

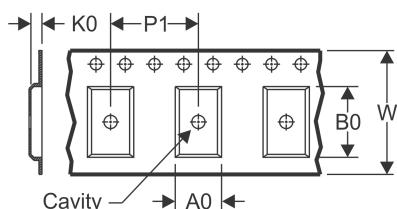

### TAPE DIMENSIONS

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

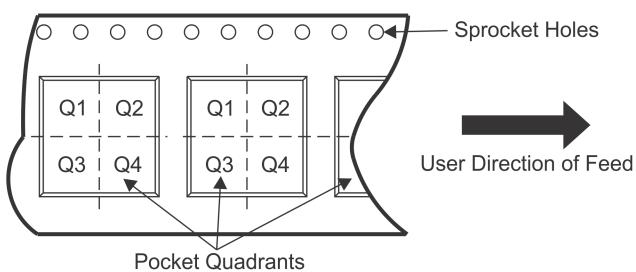

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS546D24RVFR | LQFN-CLIP    | RVF             | 40   | 2500 | 330.0              | 16.4               | 5.35    | 7.35    | 1.7     | 8.0     | 16.0   | Q1            |

| TPS546D24RVFT | LQFN-CLIP    | RVF             | 40   | 250  | 180.0              | 16.4               | 5.35    | 7.35    | 1.7     | 8.0     | 16.0   | Q1            |

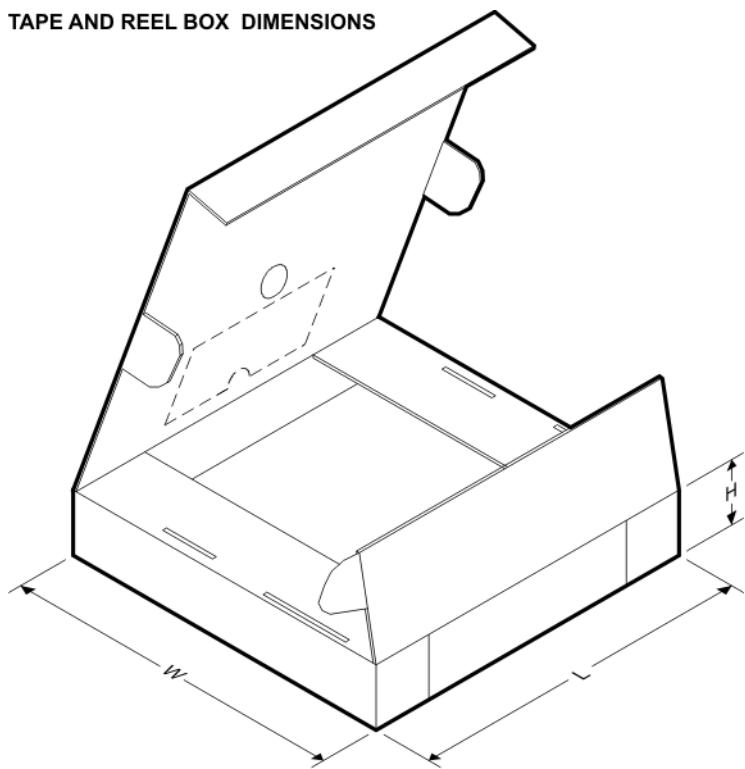

## TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS546D24RVFR | LQFN-CLIP    | RVF             | 40   | 2500 | 367.0       | 367.0      | 38.0        |

| TPS546D24RVFT | LQFN-CLIP    | RVF             | 40   | 250  | 210.0       | 185.0      | 35.0        |

## GENERIC PACKAGE VIEW

**RVF 40**

**LQFN-CLIP - 1.52 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4211383/D

**RVF0040A**

## PACKAGE OUTLINE

**LQFN-CLIP - 1.52 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

4. Reference JEDEC registration MO-220.

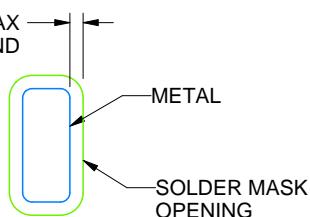

0.07 MAX

ALL AROUND

NON SOLDER MASK

DEFINED

(PREFERRED)

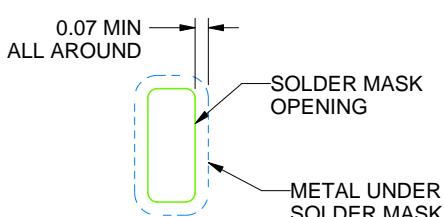

0.07 MIN

ALL AROUND

SOLDER MASK

DEFINED

#### SOLDER MASK DETAILS

4222989/B 10/2017

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

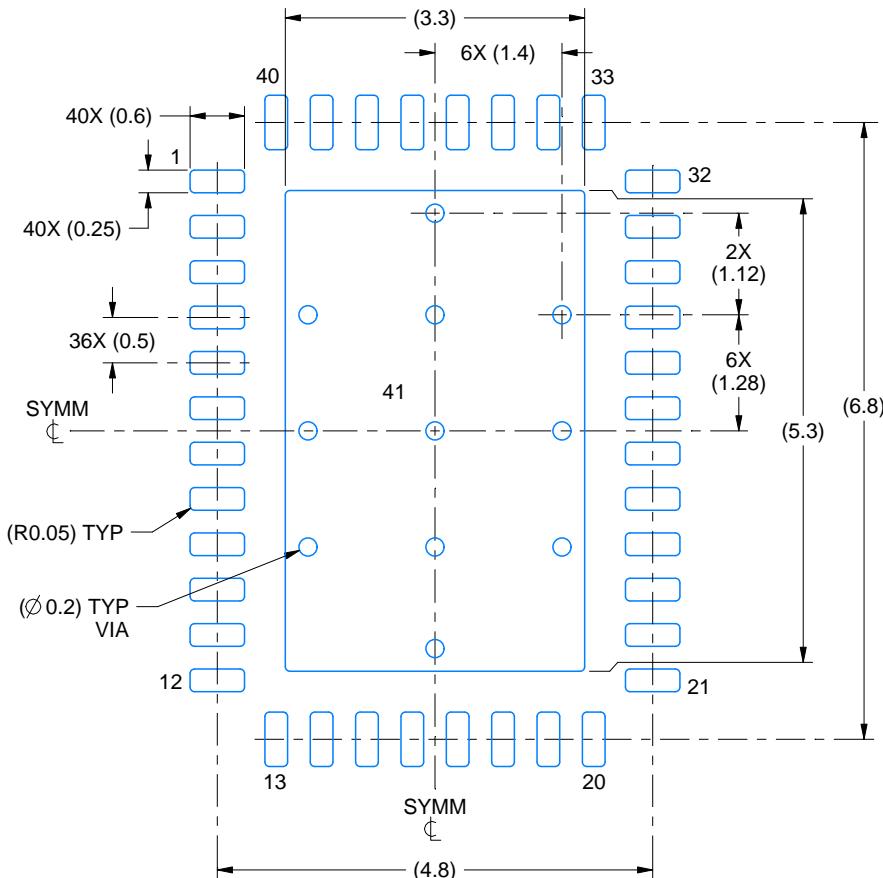

## EXAMPLE STENCIL DESIGN

**RVF0040A**

## LQFN-CLIP - 1.52 mm max height

#### **PLASTIC QUAD FLATPACK - NO LEAD**

## SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD

71% PRINTED SOLDER COVERAGE BY AREA

SCALE:18X

4222989/B 10/2017

## NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月