## FET内蔵(SWIFT™)、4A出力、 シングル同期整流降圧型スイッチャ

### 特 長

- D-CAP2™モードによる高速過渡応答

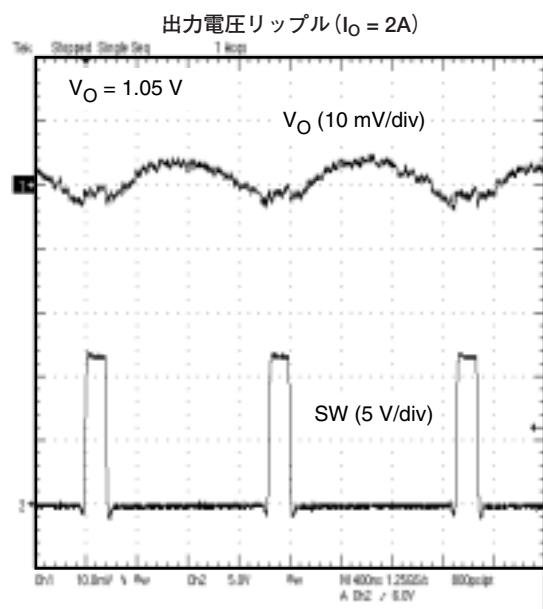

- 出力リップルが低く、セラミック出力コンデンサを使用可能

- 幅広いVIN入力電圧範囲：4.5V～18V

- 出力電圧範囲：0.76V～5.5V

- 低デューティ・サイクルのアプリケーションに対して最適化された高効率の内蔵FET

- 65mΩ(ハイサイド)および55mΩ(ローサイド)

- 高効率、シャットダウン時10μA未満

- 高い初期バンドギャップ・リファレンス精度

- 調整可能なソフト・スタート

- プリバイアス付きソフト・スタート

- スイッチング周波数(f<sub>SW</sub>)：700kHz

- サイクル毎の過電流制限

- パワー・グッド出力

### アプリケーション

- 幅広い範囲の低電圧システム用アプリケーション

- デジタル・テレビ用電源

- 高精細Blu-ray Disc™プレーヤー

- ネットワーク・ホーム・ターミナル

- デジタル・セットトップ・ボックス(STB)

### 概 要

TPS54425は、適応型オン時間D-CAP2™モードに対応した同期整流バック・コンバータです。TPS54425を採用することで、各種機器の電源バス・レギュレータに対して、コスト効果が高く、部品数の少ない、低スタンバイ電流のソリューションを実現できます。TPS54425の主制御ループではD-CAP2™モード制御を使用し、外部補償部品なしで非常に高速な過渡応答が得られます。また、TPS54425には、POSCAP/SP-CAPなどの低ESR(等価直列抵抗)出力コンデンサだけでなく、超低ESRのセラミック・コンデンサにも対応できる、独自の回路が採用されています。このデバイスは、4.5V～18VのVIN入力で動作します。出力電圧は、0.76V～5.5Vの範囲でプログラミングできます。また、調整可能なソフト・スタート時間と、パワー・グッド機能も備えています。TPS54425は14ピンのHTSSOPパッケージで提供され、-40°C～85°Cの温度範囲で動作するように設計されています。

SWIFT, D-CAP2, PowerPADは、テキサス・インスツルメンツの登録商標です。

Blu-ray Discは、Blu-ray Disc Association社の登録商標です。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に對応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

ESDはこの集積回路にダメージを与えることがあります。テキサス・インスツルメンツ社は、全ての集積回路に適切なESD対策が行われることを推奨します。この適切な取扱いや取付け手順が守られない場合には、素子にダメージを与えることがあります。

ESDが与えるダメージには、素子へ微妙な性能劣化から完全な素子故障まで様々な症状に及びます。非常に些細なパラメータの変化でもその素子の仕様を満足しなくなることがあります。高詳細な集積回路はさらにESDによる影響を受けやすい場合があります。

## 製品情報<sup>(1)</sup>

| T <sub>A</sub> | パッケージ <sup>(2) (3)</sup>    | オーダー可能な部品番号  | ピン | 出荷形態    |

|----------------|-----------------------------|--------------|----|---------|

| −45°C ~ 85°C   | PowerPAD™<br>(HTSSOP) – PWP | TPS54425PWP  | 14 | チューブ    |

|                |                             | TPS54425PWPR |    | テープ・リール |

(1) 最新のパッケージおよびご発注情報については、このデータシートの巻末にある「付録：パッケージ・オプション」を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

(2) パッケージ図面、熱特性データ、記号の意味については、[www.ti.com/packaging](http://www.ti.com/packaging)を参照してください。

(3) すべてのパッケージ・オプションがCu NiPdAuリード/ポール仕上げとなっています。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                   |                                | VALUE                      | 単位    |

|-------------------|--------------------------------|----------------------------|-------|

| V <sub>I</sub>    | VIN1, VIN2 EN                  | −0.3 ~ 20                  | V     |

|                   | VBST                           | −0.3 ~ 26                  | V     |

|                   | VBST (10 ns transient)         | −0.3 ~ 28                  | V     |

|                   | VFB VO, SS, PG                 | −0.3 ~ 6.5                 | V     |

|                   | SW1, SW2                       | −2 ~ 20                    | V     |

|                   | SW1, SW2 (10 ns transient)     | −3 ~ 22                    | V     |

| V <sub>O</sub>    | VREG5                          | −0.3 ~ 6.5                 | V     |

|                   | PGND1, PGND2                   | −0.3 ~ 0.3                 | V     |

| V <sub>diff</sub> | Voltage from GND to POWERPAD   | −0.2 ~ 0.2                 | V     |

| ESD rating        | Electrostatic discharge        | Human Body Model (HBM)     | 2 kV  |

|                   |                                | Charged Device Model (CDM) | 500 V |

| T <sub>J</sub>    | Operating junction temperature | −40 ~ 150                  | °C    |

| T <sub>stg</sub>  | Storage temperature            | −55 ~ 150                  | °C    |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 熱特性について

| THERMAL METRIC <sup>(1)</sup> |                                              | TPS54425 | 単位<br>°C/W |

|-------------------------------|----------------------------------------------|----------|------------|

|                               |                                              | PWP      |            |

|                               |                                              | 14 PINS  |            |

| θ <sub>JA</sub>               | Junction-to-ambient thermal resistance       | 55.6     | °C/W       |

| θ <sub>JCtop</sub>            | Junction-to-case (top) thermal resistance    | 51.3     |            |

| θ <sub>JB</sub>               | Junction-to-board thermal resistance         | 26.4     |            |

| ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 1.8      |            |

| ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 20.6     |            |

| θ <sub>JCbot</sub>            | Junction-to-case (bottom) thermal resistance | 4.3      |            |

(1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|          |                                |                            | MIN  | MAX | 単位 |

|----------|--------------------------------|----------------------------|------|-----|----|

| $V_{IN}$ | Supply input voltage range     |                            | 4.5  | 18  | V  |

| $V_I$    | Input voltage range            | VBST                       | -0.3 | 24  | V  |

|          |                                | VBST (10 ns transient)     | -0.3 | 27  |    |

|          |                                | SS, PG                     | -0.1 | 5.7 |    |

|          |                                | EN                         | -0.1 | 18  |    |

|          |                                | VO, VFB                    | -0.1 | 5.5 |    |

|          |                                | SW1, SW2                   | -1.8 | 18  |    |

|          |                                | SW1, SW2 (10 ns transient) | -3   | 21  |    |

|          |                                | PGND1, PGND2               | -0.1 | 0.1 |    |

| $V_O$    | Output voltage range           | VREG5                      | -0.1 | 5.7 | V  |

| $I_O$    | Output Current range           | $I_{VREG5}$                | 0    | 10  | mA |

| $T_A$    | Operating free-air temperature |                            | -40  | 85  | °C |

| $T_J$    | Operating junction temperature |                            | -40  | 150 | °C |

## 電気的特性

動作温度範囲内、 $V_{IN} = 12V$ (特に記述のない限り)

| パラメータ                                                       |                                          | テスト条件                                                                                 | MIN | TYP       | MAX | 単位 |

|-------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------|-----|-----------|-----|----|

| <b>SUPPLY CURRENT</b>                                       |                                          |                                                                                       |     |           |     |    |

| $I_{VIN}$                                                   | Operating - non-switching supply current | $V_{IN}$ current, $T_A = 25^\circ C$ , EN = 5 V,<br>$V_{FB} = 0.8 V$                  | 850 | 1300      |     | μA |

| $I_{VINSNDN}$                                               | Shutdown supply current                  | $V_{IN}$ current, $T_A = 25^\circ C$ , EN = 0 V                                       | 1.8 | 10        |     | μA |

| <b>LOGIC THRESHOLD</b>                                      |                                          |                                                                                       |     |           |     |    |

| $V_{ENH}$                                                   | EN high-level input voltage              | EN                                                                                    | 2   |           |     | V  |

| $V_{ENL}$                                                   | EN low-level input voltage               | EN                                                                                    |     | 0.4       |     | V  |

| <b><math>V_{FB}</math> VOLTAGE AND DISCHARGE RESISTANCE</b> |                                          |                                                                                       |     |           |     |    |

| $V_{FBTH}$                                                  | $V_{FB}$ threshold voltage               | $T_A = 25^\circ C$ , $V_O = 1.05 V$ , continuous mode                                 | 757 | 765       | 773 | mV |

|                                                             |                                          | $T_A = 0^\circ C$ to $85^\circ C$ , $V_O = 1.05 V$ , continuous mode <sup>(1)</sup>   | 753 |           | 777 |    |

|                                                             |                                          | $T_A = -40^\circ C$ to $85^\circ C$ , $V_O = 1.05 V$ , continuous mode <sup>(1)</sup> | 751 |           | 779 |    |

| $I_{VFB}$                                                   | $V_{FB}$ input current                   | $V_{FB} = 0.8 V$ , $T_A = 25^\circ C$                                                 | 0   | $\pm 0.1$ |     | μA |

| $R_{Dischg}$                                                | $V_O$ discharge resistance               | EN = 0 V, $V_O = 0.5 V$ , $T_A = 25^\circ C$                                          | 50  | 100       |     | Ω  |

| <b><math>V_{REG5}</math> OUTPUT</b>                         |                                          |                                                                                       |     |           |     |    |

| $V_{VREG5}$                                                 | $V_{REG5}$ output voltage                | $T_A = 25^\circ C$ , $6 V < V_{IN} < 18 V$ ,<br>$0 < I_{VREG5} < 5 mA$                | 5.3 | 5.5       | 5.7 | V  |

| $V_{LN5}$                                                   | Line regulation                          | $6.0 V < V_{IN} < 18 V$ , $I_{VREG5} = 5 mA$                                          |     | 20        |     | mV |

| $V_{LD5}$                                                   | Load regulation                          | $0 mA < I_{VREG5} < 5 mA$                                                             |     | 100       |     | mV |

| $I_{VREG5}$                                                 | Output current                           | $V_{IN} = 6 V$ , $V_{REG5} = 4 V$ , $T_A = 25^\circ C$                                | 70  |           |     | mA |

| <b>MOSFET</b>                                               |                                          |                                                                                       |     |           |     |    |

| $R_{ds0nh}$                                                 | High side switch resistance              | $25^\circ C$ , $V_{BST} - SW1,2 = 5.5 V$                                              | 63  |           |     | mΩ |

| $R_{ds0nl}$                                                 | Low side switch resistance               | $25^\circ C$                                                                          | 55  |           |     | mΩ |

(1) 実製品の検査は行っていません。

## 電気的特性

動作温度範囲内、 $V_{IN} = 12V$ (特に記述のない限り)

| パラメータ                                                 |                            | テスト条件                                                               | MIN   | TYP  | MAX         | 単位      |  |

|-------------------------------------------------------|----------------------------|---------------------------------------------------------------------|-------|------|-------------|---------|--|

| <b>CURRENT LIMIT</b>                                  |                            |                                                                     |       |      |             |         |  |

| $I_{OCL}$                                             | Current limit              | $L_{OUT} = 1.5 \mu H^{(2)}$ , $T_A = -20^{\circ}C \sim 85^{\circ}C$ | 4.7   | 5.4  | 7.5         | A       |  |

| <b> THERMAL SHUTDOWN</b>                              |                            |                                                                     |       |      |             |         |  |

| $T_{SDN}$                                             | Thermal shutdown threshold | Shutdown temperature <sup>(2)</sup>                                 | 165   |      | $^{\circ}C$ |         |  |

|                                                       |                            | Hysteresis <sup>(2)</sup>                                           | 30    |      |             |         |  |

| <b>ON-TIME TIMER CONTROL</b>                          |                            |                                                                     |       |      |             |         |  |

| $T_{ON}$                                              | On time                    | $V_{IN} = 12 V$ , $V_O = 1.05 V$                                    | 145   |      | ns          |         |  |

| $T_{OFF(MIN)}$                                        | Minimum off time           | $T_A = 25^{\circ}C$ , $V_{FB} = 0.7 V$                              | 260   |      | 310         | ns      |  |

| <b>SOFT START</b>                                     |                            |                                                                     |       |      |             |         |  |

| $I_{SSC}$                                             | SS charge current          | $V_{SS} = 0 V$                                                      | 1.4   | 2.0  | 2.6         | $\mu A$ |  |

| $I_{SSD}$                                             | SS discharge current       | $V_{SS} = 0.5 V$                                                    | 0.1   | 0.2  | mA          |         |  |

| <b>POWER GOOD</b>                                     |                            |                                                                     |       |      |             |         |  |

| $V_{THPG}$                                            | PG threshold               | $V_{FB}$ rising (good)                                              | 85    | 90   | 95          | %       |  |

|                                                       |                            | $V_{FB}$ falling (fault)                                            | 85    |      | %           |         |  |

| $I_{PG}$                                              | PG sink current            | PG = 0.5 V                                                          | 2.5   | 5    | mA          |         |  |

| <b>OUTPUT UNDERVOLTAGE AND OVERVOLTAGE PROTECTION</b> |                            |                                                                     |       |      |             |         |  |

| $V_{OVP}$                                             | Output OVP trip threshold  | OVP detect                                                          | 115   | 120  | 125         | %       |  |

| $T_{OVPDEL}$                                          | Output OVP prop delay      |                                                                     | 10    |      | $\mu s$     |         |  |

| $V_{UVP}$                                             | Output UVP trip threshold  | UVP detect                                                          | 60    | 65   | 70          | %       |  |

|                                                       |                            | Hysteresis                                                          | 10    |      | %           |         |  |

| $T_{UVPDEL}$                                          | Output UVP delay           |                                                                     | 0.25  |      | ms          |         |  |

| $T_{UVPEN}$                                           | Output UVP enable delay    | Relative to soft-start time                                         | x 1.7 |      |             |         |  |

| <b>UVLO</b>                                           |                            |                                                                     |       |      |             |         |  |

| $V_{UVLO}$                                            | UVLO threshold             | Wake up $V_{REG5}$ voltage                                          | 3.55  | 3.8  | 4.05        | V       |  |

|                                                       |                            | Hysteresis $V_{REG5}$ voltage                                       | 0.23  | 0.35 | 0.47        |         |  |

(2) 実製品の検査は行っていません。

## 製品情報

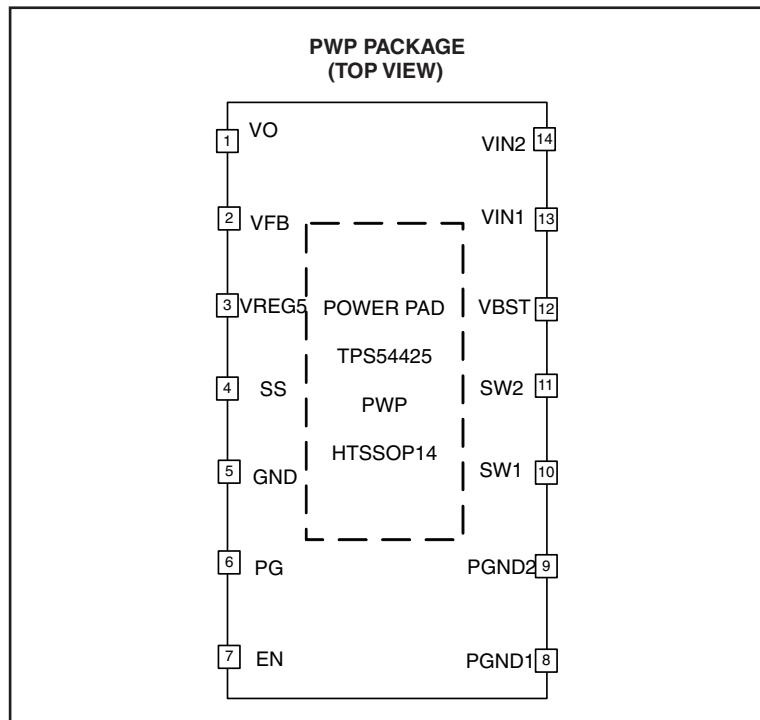

### ピン機能

| ピン          |        | 説明                                                                                                        |

|-------------|--------|-----------------------------------------------------------------------------------------------------------|

| 名前          | 番号     |                                                                                                           |

| VO          | 1      | コンバータの出力に接続します。この端子は、オン時間の調整に使用されます。                                                                      |

| VFB         | 2      | コンバータの帰還入力。帰還分圧抵抗回路を使用して出力電圧に接続します。                                                                       |

| VREG5       | 3      | 5.5V電源出力。GNDとの間にコンデンサ(標準1μF)を接続する必要があります。ENが“Low”的とき、VREG5は非アクティブです。                                      |

| SS          | 4      | ソフト・スタート制御。GNDとの間に外付けコンデンサを接続する必要があります。                                                                   |

| GND         | 5      | 信号グランド・ピン。                                                                                                |

| PG          | 6      | オープン・ドレインのパワー・グッド出力。                                                                                      |

| EN          | 7      | イネーブル制御入力。ENはアクティブ・ハイであり、デバイスをイネーブルにする場合はプルアップする必要があります。                                                  |

| PGND1,PGND2 | 8, 9   | ローサイドMOSFETのグランド・リターン。電流コンパレータの入力としても機能します。PGNDとGNDは、ICの近くでまとめて確実に接続する必要があります。                            |

| SW1, SW2    | 10, 11 | ハイサイドNFETおよびローサイドNFET用のスイッチ・ノード接続。電流コンパレータへの入力としても機能します。                                                  |

| VBST        | 12     | ハイサイドNFETゲート・ドライバの電源入力(昇圧端子)。このピンと、対応するSW1, SW2ピンとの間に、コンデンサを接続します。VREG5ピンとVBSTピンの間には、内部でPNダイオードが接続されています。 |

| VIN1, VIN2  | 13, 14 | パワー入力であり、ハイサイドNFETのドレインに接続されています。制御回路用の5V内部リニア・レギュレータの電源入力です。                                             |

| PowerPAD™   | 裏側     | パッケージのサーマル・パッド。適切な放熱を実現するために、半田付けする必要があります。PGNDに接続してください。                                                 |

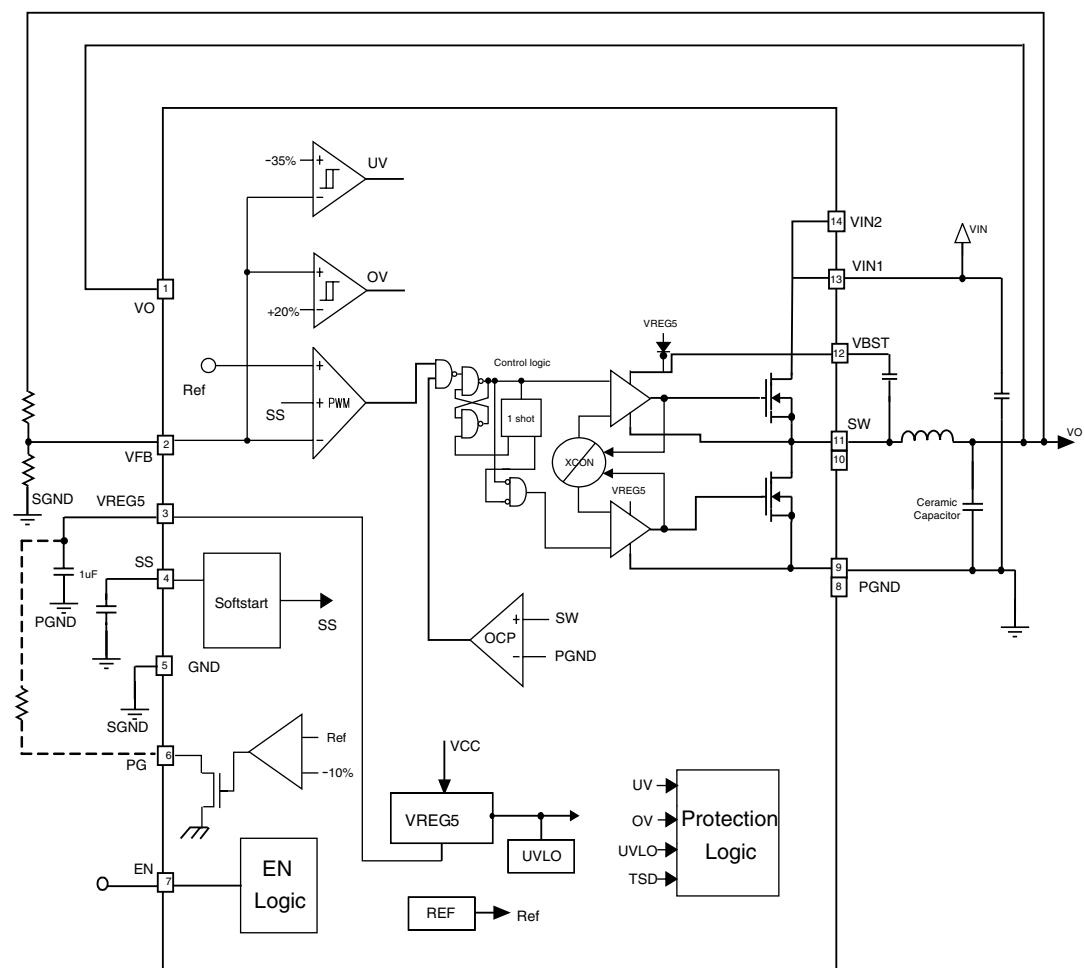

## 機能ブロック図

## 概要

TPS54425は、2つのNチャネルMOSFETを内蔵した、4Aの同期整流降圧型(バック)コンバータです。D-CAP2™モード制御を使用して動作します。D-CAP2™制御の高速過渡応答により、特定レベルの性能を満たすために必要な出力容量が小さくて済みます。独自の内部回路により、セラミックおよび特殊なポリマー・タイプを含めた低ESR出力コンデンサを使用可能です。

## 詳細説明

### PWM動作

TPS54425のメイン制御ループは、独自のD-CAP2™モード制御をサポートする適応型オン時間パルス幅変調(PWM)コントローラとなっています。D-CAP2™モード制御は、一定オン時間制御を、擬似固定周波数で外部部品数の少ない構成を可能にする内部補償回路と組み合わせたもので、低ESRコンデンサとセラミック出力コンデンサの両方を使用できます。出力にほとんどリップルがない状態でも安定して動作します。

各サイクルの開始時に、ハイサイドMOSFETがオンになります。内部のワンショット・タイマが終了すると、このMOSFETがオフになります。このワンショット・タイマの時間は、入力電圧範囲内で擬似固定周波数が維持されるように、コンバータの入力電圧(VIN)と出力電圧(VO)によって設定されます。そのため、これは適応型オン時間制御と呼ばれます。帰還電圧がリファレンス電圧を下回ると、ワンショット・タイマがリセットされ、ハイサイドMOSFETが再度オンになります。出力リップルをシミュレートするために、リファレンス電圧に内部ランプが追加され、これにより、D-CAP2™モード制御ではESRによる出力リップルが不要になります。

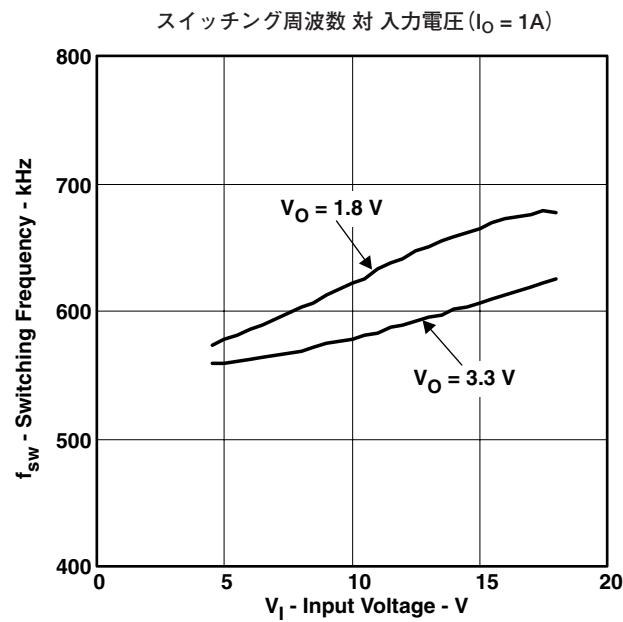

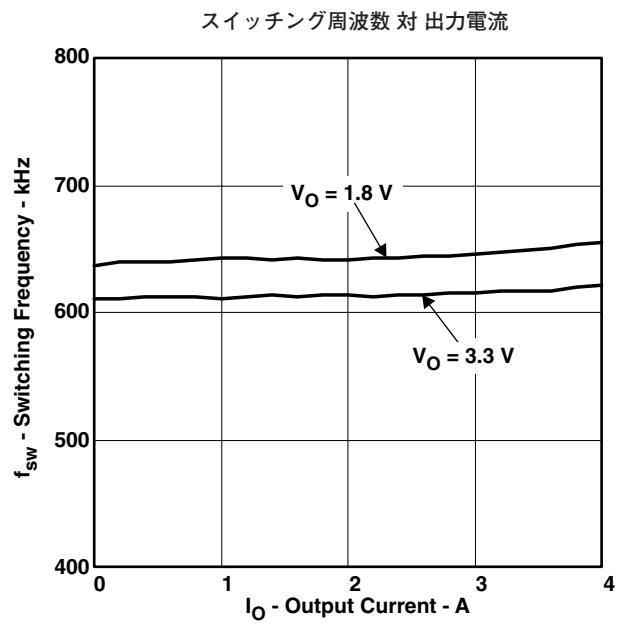

### PWM周波数と適応型オン時間制御

TPS54425は、適応型オン時間制御方式を採用し、専用の発振器は内蔵していません。入力電圧および出力電圧を使用してオン時間ワンショット・タイマを設定することにより、700kHzの擬似定周波数で動作します。オン時間は、入力電圧に逆比例し、出力電圧に比例するため、デューティ比がVOUT/VINのとき周波数は一定となります。

### ソフト・スタートおよびプリバイアス付き ソフト・スタート

ソフト・スタート機能は調整可能です。ENピンが“High”になると、SSピンとGNDの間に接続されているコンデンサの充電が2μAの電流によって開始されます。スタートアップ中には出力電圧のスムーズな制御が維持されます。スロー・スタート時間は式(1)で計算されます。VFB電圧は0.765V、SSピンのソース電流は2μAです。

$$T_{SS}(\text{ms}) = \frac{C_6(\text{nF}) \cdot V_{ref}}{I_{SS}(\mu\text{A})} = \frac{C_6(\text{nF}) \cdot 0.765}{2} \quad (1)$$

出力がプリバイアスされている状態で、スタートアップ中に出力から電流が引き抜かれるのを防止するために、TPS54425には独自の回路が搭載されています。ソフト・スタートでプリバイアス・レベルよりも高い電圧が指定される(内部ソフト・スタートが帰還電圧V<sub>FB</sub>よりも大きくなる)と、コントローラは、最初のローサイドFETゲート・ドライバ・パルスを狭いオン時間で開始することにより、ゆっくりと同期整流を起動します。次に、そのオン時間が(1 - D)で示される時間と一致するまで(Dはコンバータのデューティ・サイクル)、オン時間をサイクルごとにインクリメントします。この方式により、プリバイアス出力の初期シンクを防ぐとともに、出力電圧(VO)は立ち上がり後スムーズにレギュレーション状態まで上昇し、また、制御ループがプリバイアス・スタートアップから通常モード動作へと遷移するために十分な時間が確保されます。

### パワー・グッド

TPS54425は、パワー・グッド出力を備えています。パワー・グッド機能はソフト・スタートの終了後に起動されます。ソフト・スタート時間の1.7倍の時間が経過した後でパワー・グッド機能が有効となります。出力電圧が目標値の90%以上に達すると、内部のコンパレータによりパワー・グッド状態が検出され、パワー・グッド信号が“High”になります。パワー・グッド出力PGは、オープン・ドレイン出力です。帰還電圧が目標値の85%を下回った場合、内部で5μsの遅延が加えられた後、パワー・グッド信号が“Low”になります。

### VREG5

VREG5は、TPS54425で使用される内部生成電圧源です。これは入力電圧から直接生成され、入力電圧が5.6Vを超えるときには公称5.5Vにレギュレーションされます。VREG5レギュレータの出力が、内部UVLO機能への入力となります。TPS54425が機能するためには、VREG5がUVLOウェイクアップ・スレッショルド電圧(標準3.8V)を上回っている必要があります。VREG5出力の適切なレギュレーションのために、TPS54425のピン3とパワー・グランドとの間に1.0μFのコンデンサを接続します。VREG5出力電圧は外部でも使用でき、標準で最大70mAをソースできます。TPS54425のENピンがオープンまたは“Low”的場合、VREG5出力はディスエーブルになります。

### 出力放電制御

TPS54425では、ENが“Low”的場合、または保護機能(OVP、UVP、UVLO、過熱保護)によってコントローラがオフになった場合、出力が放電されます。VOとPGNDの間に接続されている内部の50Ω MOSFETを使用して出力を放電します。出力に負電圧が生じることを避けるために、出力放電中は内部ローサイドMOSFETがオンになりません。

## 電流保護

出力電流は、サイクル毎の過電流制限御によって制限され、オフ状態中のインダクタ電流が監視されます。インダクタ電流が過電流トリップ・レベルを超えている間、オフ状態が維持されます。高精度と低コストを両立するために、温度補償付きの内部MOSFET  $R_{DS(on)}$  センス機能がサポートされています。

インダクタ電流は、PGNDピンとSW1/SW2ピンの間の電圧によってモニタされます。過電流状態では、負荷への電流が高出力コンデンサへの電流より大きくなるため、通常は出力電圧が低下します。最終的には、出力電圧が低電圧保護スレッショルドを下回り、シャットダウンされます。

## 過電圧/低電圧保護

TPS54425では、抵抗で分割された帰還電圧を監視することで、過電圧と低電圧を検出しています。帰還電圧が目標電圧の120%を超過すると、OVPコンパレータの出力が“High”になります。ハイサイドMOSFETドライバがオフ、ローサイドMOSFETがオンとしてラッチされます。帰還電圧が目標電圧の65%より低くなると、UVPコンパレータ出力が“High”になります。内部のUVP遅延カウンタが動作を開始します。250μs経過後、上側と下側の両方の内部MOSFETがオフにラッチされます。この機能は、約(1.7 × ソフト・スタート時間)後にイネーブルになります。

## UVLO保護

低電圧ロックアウト保護(UVLO)は、 $V_{REG5}$ ピンの電圧を監視します。 $V_{REG5}$ の電圧がUVLOスレッショルド電圧を下回ると、TPS54425がオフになります。これは、非ラッチ方式の保護です。

## 過熱シャットダウン

TPS54425は、自身の温度を監視しています。温度がスレッショルド値(標準165°C)を超えると、デバイスがシャットダウンされます。これは非ラッチ方式の保護です。

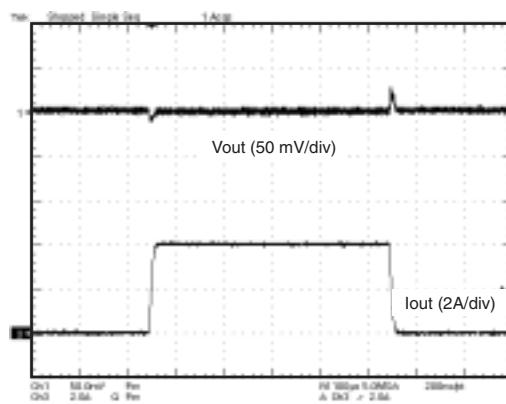

## 標準的特性

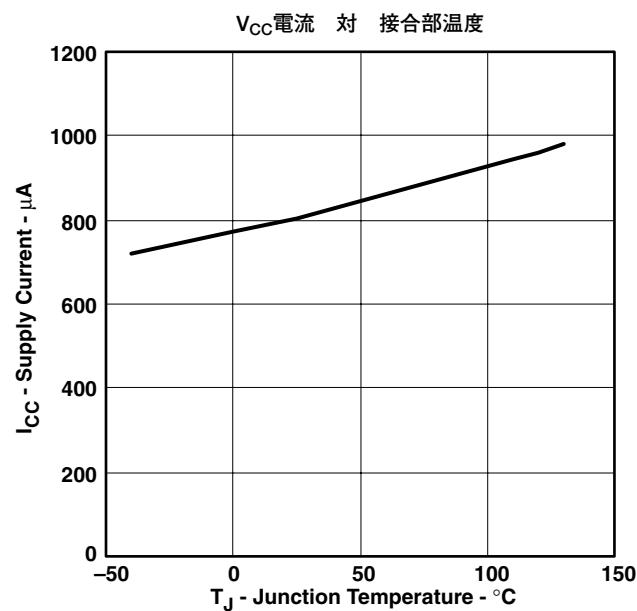

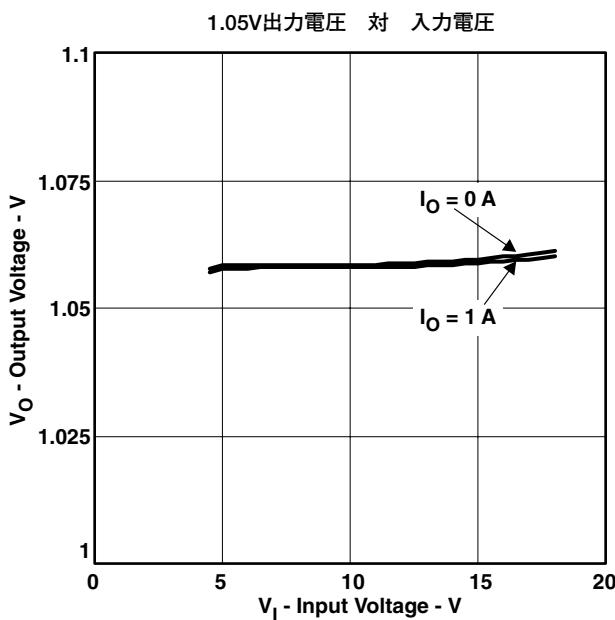

図 1

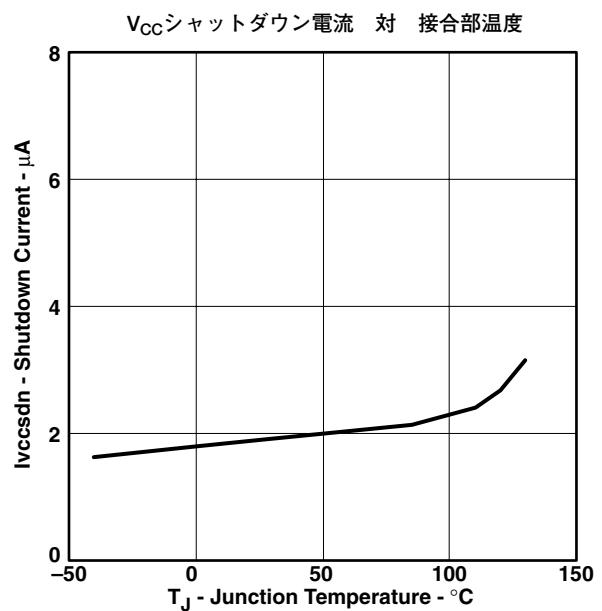

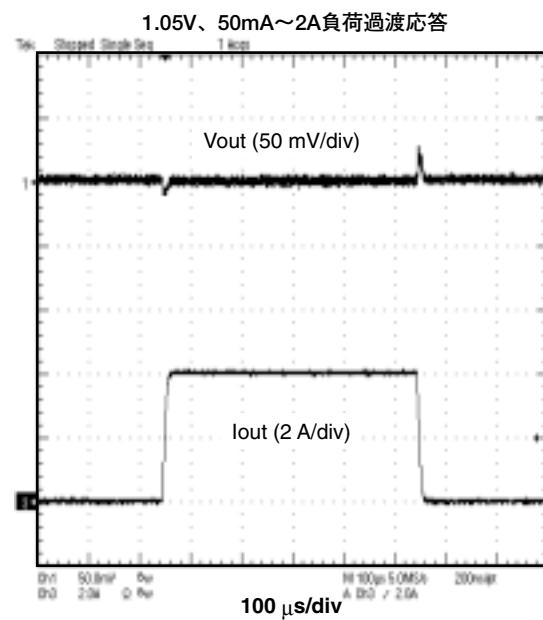

図 2

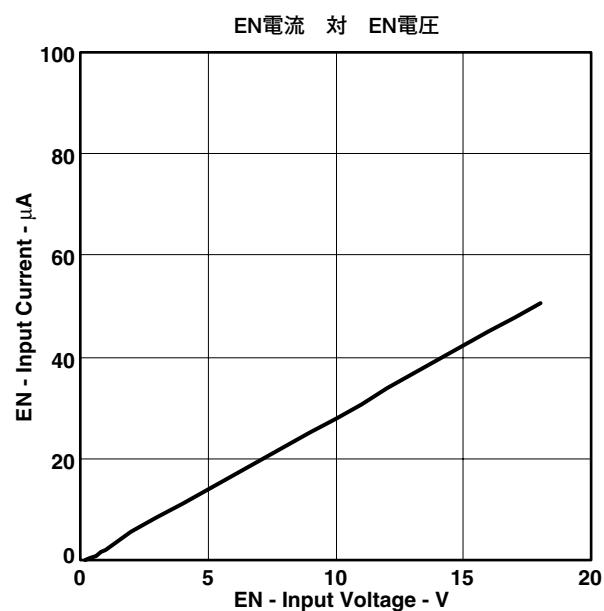

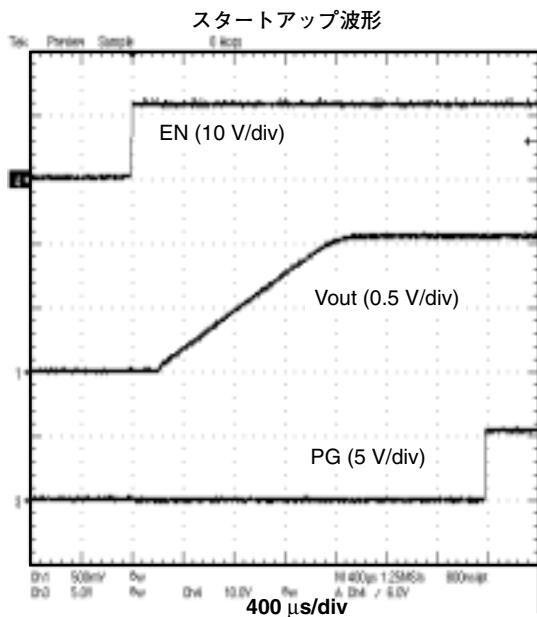

図 3

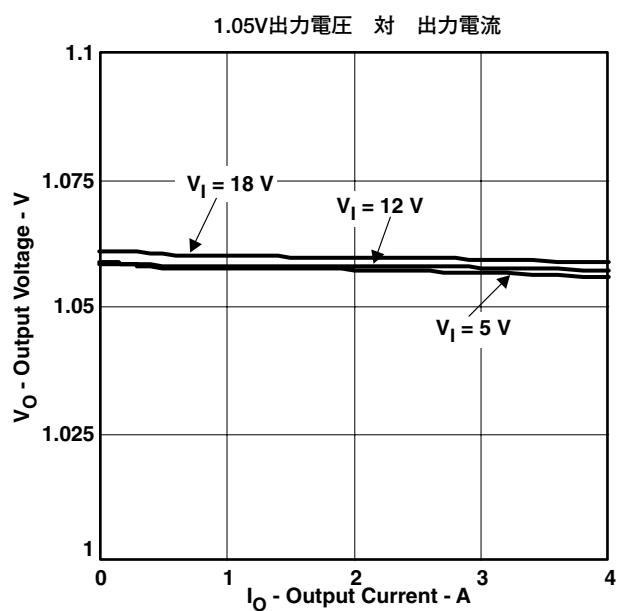

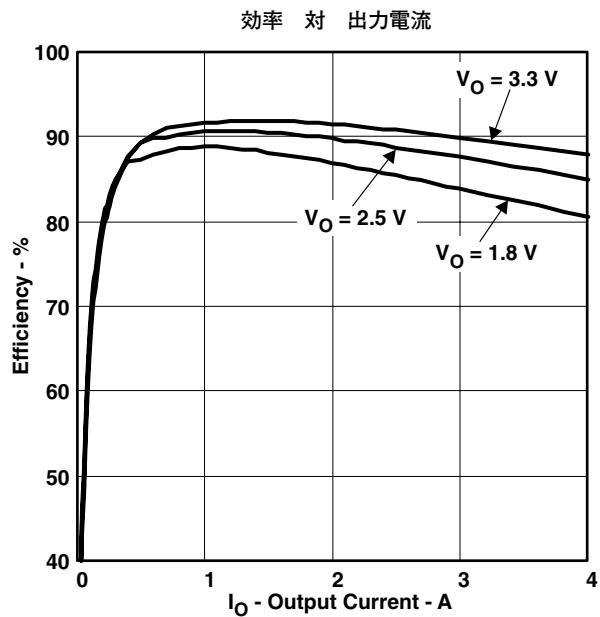

図 4

## 標準的特性

図 5

図 6

図 7

図 8

## 標準的特性

図 9

図 10

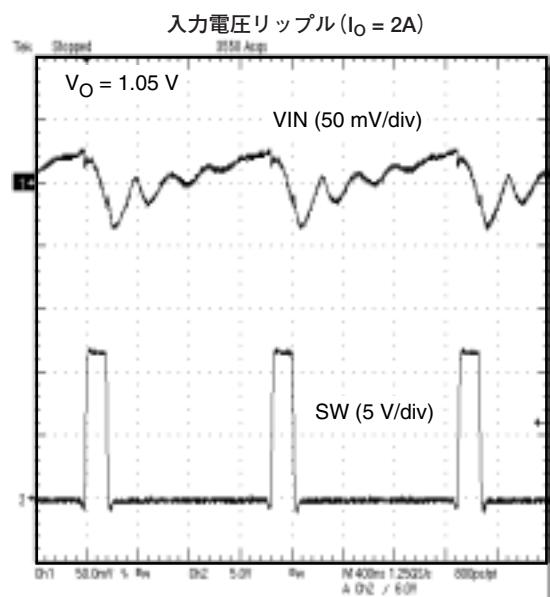

図 11

図 12

# 設計ガイド

## ステップ毎の設計手順

設計プロセスを開始するには、いくつかのアプリケーション・パラメータについて知っておく必要があります。

- 入力電圧範囲

- 出力電圧

- 出力電流

- 出力電圧リップル

- 入力電圧リップル

## 出力電圧抵抗の選択

出力電圧は、出力ノードとVFBピンとの間の抵抗分圧回路によって設定されます。公差1%以内の分圧抵抗を使用することを推奨します。式(2)および式(3)を使用して $V_{OUT}$ を計算します。

非常に軽い負荷での効率を向上させるには、より大きな値の抵抗の使用を考慮します。ただし、抵抗が大きすぎると、ノイズの影響を受けやすくなり、VFB入力電流からの電圧誤差が目立つようになります。

出力電圧が0.76V~2.5Vの場合：

$$V_{OUT} = 0.765 \cdot \left(1 + \frac{R_1}{R_2}\right) \quad (2)$$

出力電圧が2.5V以上の場合：

$$V_{OUT} = (0.763 + 0.0017 \cdot V_{OUT\_SET}) \cdot \left(1 + \frac{R_1}{R_2}\right) \quad (3)$$

ここで

$V_{OUT\_SET}$  = 目標の $V_{OUT}$ 電圧

## 出力フィルタの選択

TPS54425で使用する出力フィルタは、LC回路です。このLCフィルタは、下記の周波数に二重極を持ちます。

$$F_P = \frac{1}{2\pi \sqrt{L_{OUT} \times C_{OUT}}} \quad (4)$$

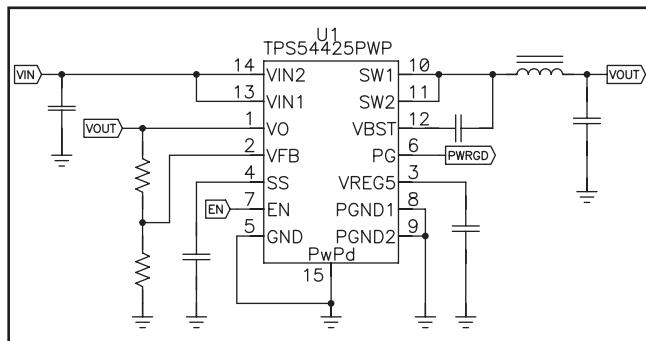

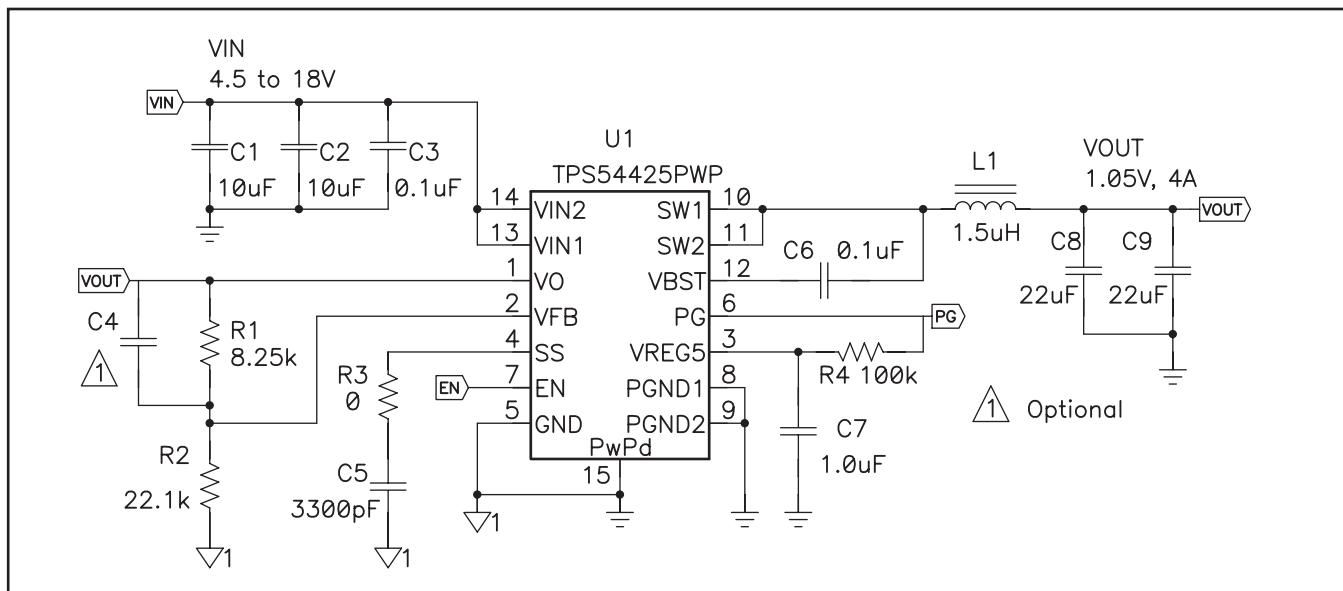

図 13. 設計例の回路図

低周波数では、出力設定点分圧抵抗回路、およびTPS54425の内部ゲインによって、全体のループ・ゲインが設定されます。低周波数での位相は180度です。出力フィルタの極周波数では、ディケードごとにゲインが-40dBロールオフし、位相は急速に減少します。D-CAP2<sup>TM</sup>によって高周波数のゼロが導入されることで、ゲインのロールオフがディケードあたり-20dBに減り、位相はゼロ周波数の1ディケード上で90度に増加します。出力フィルタに使用するインダクタとコンデンサは、式(4)の二重極が高周波ゼロより低く、かつ(位相ブーストが得られ、高周波ゼロによって回路安定化のための十分な位相マージンが確保されるように)十分近い値となるよう選択する必要があります。この要件を満足するための推奨値を表1に示します。

DCゲインは出力電圧に依存するため、出力電圧が高くなると必要なインダクタ値も増加します。1.8V以上の高出力電圧では、R1と並列にフィードフォワード・コンデンサ(C4)を追加することにより、追加の位相ブーストを実現できます。

インダクタのピーク・ツー・ピーク・リップル電流、ピーク電流、およびRMS電流は、式(5)、式(6)、および式(7)で求めることができます。インダクタの飽和電流定格は、ピーク電流の計算値より大きい必要があります。RMSまたは加熱電流定格は、RMS電流の計算値より大きい必要があります。

$f_{SW}$ には700kHzを使用します。選択したインダクタが、式(6)のピーク電流および式(7)のRMS電流の定格を満たすことを確認してください。

$$I_{Ip-p} = \frac{V_{OUT}}{V_{IN(max)}} \cdot \frac{V_{IN(max)} - V_{OUT}}{L_O \cdot f_{SW}} \quad (5)$$

$$I_{Ipeak} = I_O + \frac{I_{Ip-p}}{2} \quad (6)$$

$$I_{Lo(RMS)} = \sqrt{I_O^2 + \frac{1}{12} I_{Ip-p}^2} \quad (7)$$

この設計例では、ピーク電流の計算値が4.47A、RMS電流の計算値が4.009Aです。ここでは、インダクタとしてTDKのSPM6530-1R5M100を使用し、ピーク電流定格は11.5A、RMS電流定格は11Aです。

コンデンサの値とESRによって、出力電圧リップルの大きさが決まります。TPS54425は、セラミックまたは他の低ESRコンデンサとともに使用するよう設計されています。推奨値の範囲は22μF~68μFです。出力コンデンサに対して必要なRMS電流定格は、式(8)で求められます。

$$I_{CO(RMS)} = \frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{\sqrt{12} \cdot V_{IN} \cdot L_O \cdot f_{SW}} \quad (8)$$

この設計では、出力コンデンサとしてTDKのC3216X5R0J226M(22μF)を2個使用します。標準ESRはそれぞれ2mΩです。RMS電流の計算値は0.271Aであり、各出力コンデンサの定格は4Aです。

## 入力コンデンサの選択

TPS54425には、入力デカップリング・コンデンサと、アプリケーションによってはパルク・コンデンサが必要となります。デカップリング・コンデンサには、10μF以上のセラミック・コンデンサを推奨します。過電流制限機能の安定性を向上させるため、ピン14とグランドの間に0.1μFのコンデンサを追加することを推奨します。コンデンサの電圧定格は、最大入力電圧よりも大きい必要があります。

## ブーストストラップ・コンデンサの選択

適切な動作のためには、VBSTピンとSWピンの間に0.1μFのセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

## VREG5コンデンサの選択

適切な動作のためには、VREG5ピンとGNDピンの間に1.0μFのセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

| 出力電圧(V) | R1(kΩ) | R2(kΩ) | C4(pF) <sup>(1)</sup> | L1(μH) | C8 + C9(μF) |

|---------|--------|--------|-----------------------|--------|-------------|

| 1       | 6.81   | 22.1   |                       | 1.5    | 22 - 68     |

| 1.05    | 8.25   | 22.1   |                       | 1.5    | 22 - 68     |

| 1.2     | 12.7   | 22.1   |                       | 1.5    | 22 - 68     |

| 1.8     | 30.1   | 22.1   | 10 - 22               | 2.2    | 22 - 68     |

| 2.5     | 49.9   | 22.1   | 10 - 22               | 2.2    | 22 - 68     |

| 3.3     | 73.2   | 22.1   | 10 - 22               | 2.2    | 22 - 68     |

| 5       | 121    | 22.1   | 10 - 22               | 3.3    | 22 - 68     |

表1. 推奨部品値

(1) オプション

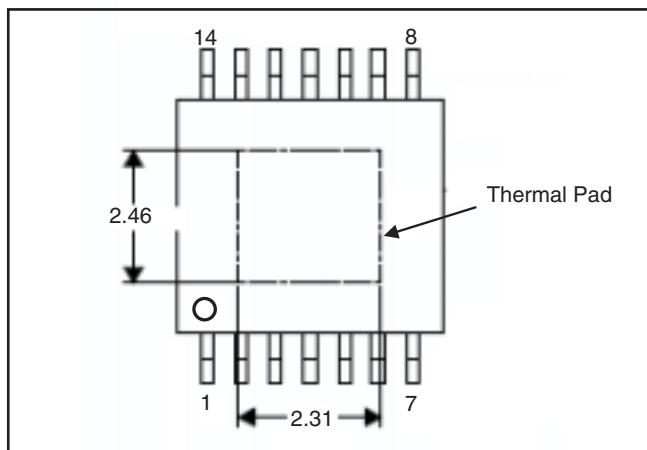

## 熱特性について

このPowerPAD™パッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。サーマル・パッドは、プリント基板(PCB)に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD™パッケージについての追加情報およびその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD™ Thermally Enhanced Package』(TI文献番号SLMA002)およびアプリケーション・ブリーフ『PowerPAD™ Made Easy』(TI文献番号SLMA004)を参照してください。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

図 14. サーマル・パッドの寸法

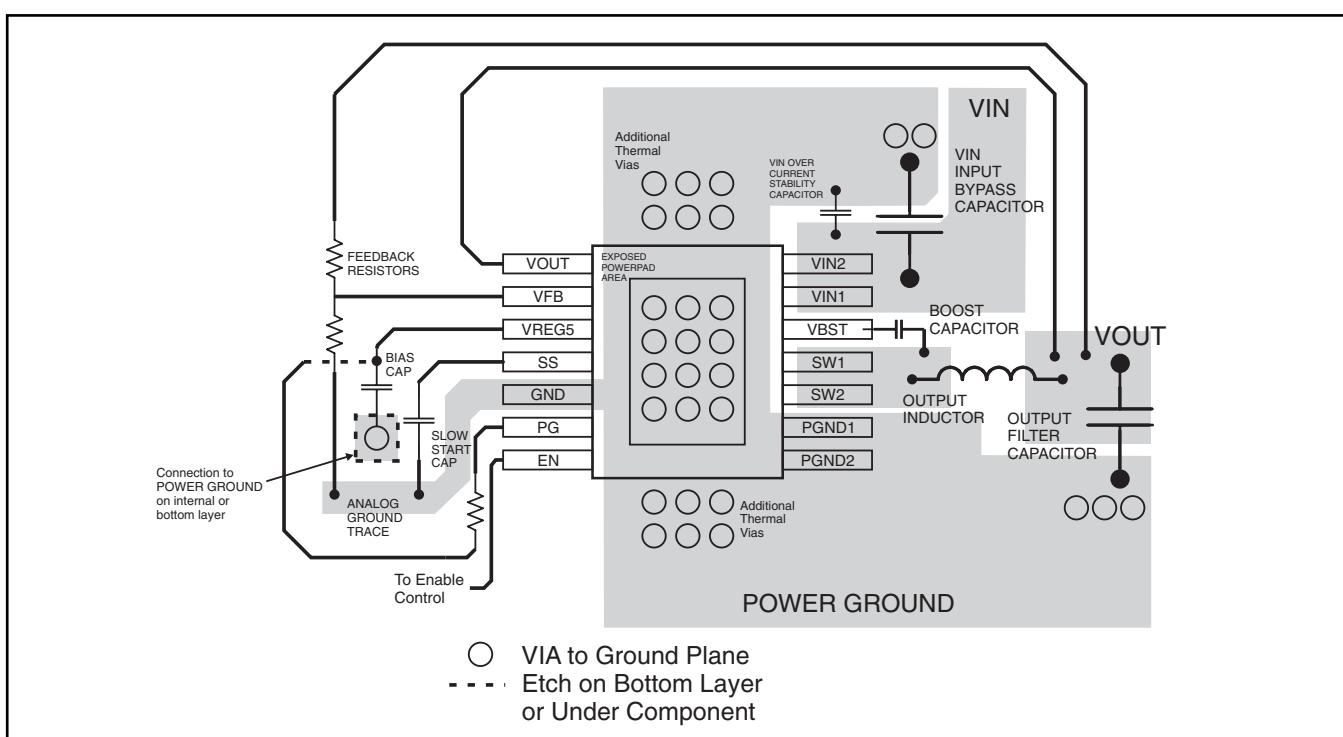

## レイアウトについての考慮事項

1. 入力スイッチング電流ループは可能な限り小さくします。

2. 寄生容量およびインダクタンスを低減し、放射を最小限に抑えるために、SWノードは物理的に可能な限り小さく、かつ短くします。出力とデバイスの帰還ピンとの間に、ケルビン接続を使用してください。

3. アナログ部品と非スイッチング部品は、スイッチング部品から離して配置します。

4. 信号グランドと電源グランドは一点接続します。

5. デバイスの下をスイッチング電流が流れないようにしてください。

6. VINおよびPGNDのパターン・ラインを幅広くします。

7. デバイスの露出したパッドは、PGNDに半田付けする必要があります。

8. VREG5コンデンサは、デバイスの近くに配置し、PGNDに接続する必要があります。

9. 出力コンデンサは、PGNDの幅広いパターンに接続する必要があります。

10. 電圧帰還ループはできる限り短くし、可能であればグランド・シールドを使用します。

11. VFBピンに接続される分圧回路の下側の抵抗は、SGNDに接続する必要があります。

12. VIN、SW、およびPGND接続に対しては、十分なビアを設けることを推奨します。

13. VIN、SW、およびPGNDのPCBパターンは、可能な限り幅広くします。

14. VINコンデンサは、可能な限りデバイスの近くに配置します。

図 15. PCB レイアウト

(SLVSA84B)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS54425PWP           | Active        | Production           | HTSSOP (PWP)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWP.A         | Active        | Production           | HTSSOP (PWP)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWP.B         | Active        | Production           | HTSSOP (PWP)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPR          | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPR.A        | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPR.B        | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPRG4        | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPRG4.A      | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

| TPS54425PWPRG4.B      | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | PS54425             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

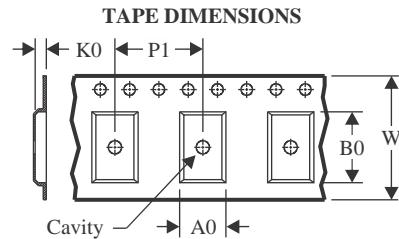

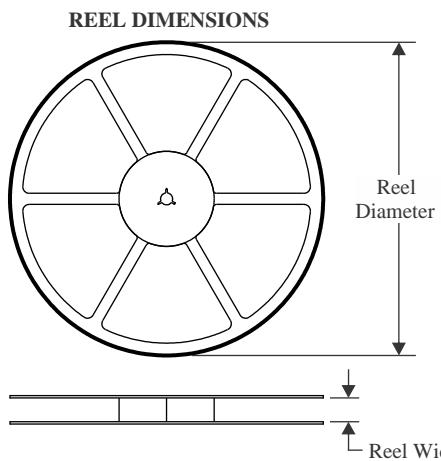

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

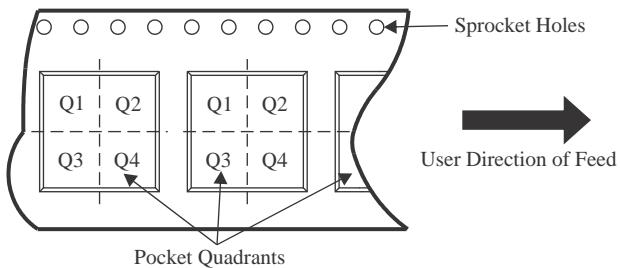

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54425PWPR   | HTSSOP       | PWP             | 14   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TPS54425PWPRG4 | HTSSOP       | PWP             | 14   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

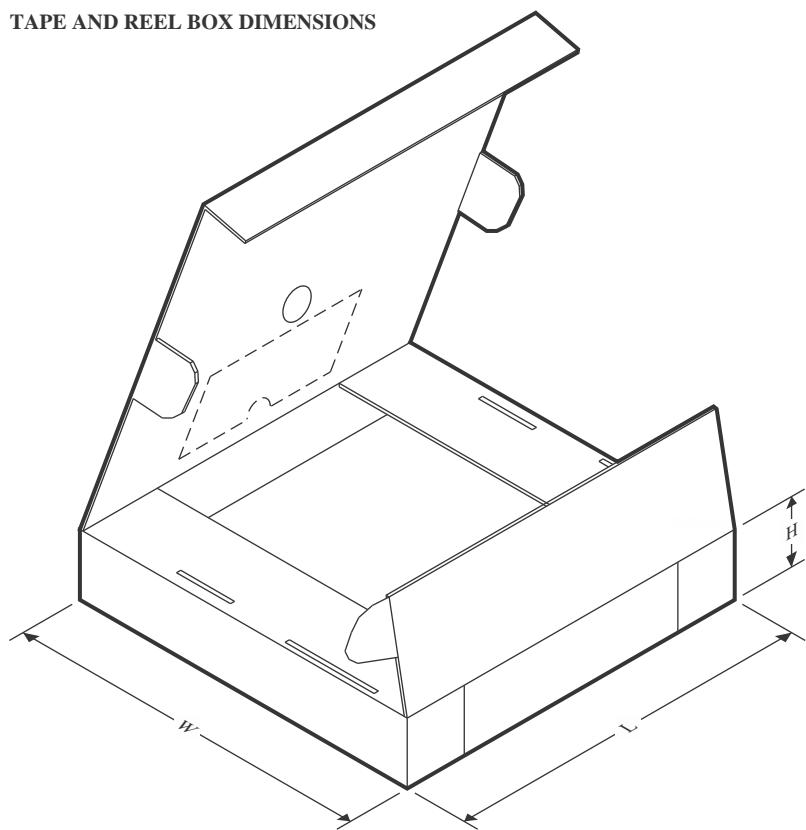

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54425PWPR   | HTSSOP       | PWP             | 14   | 2000 | 353.0       | 353.0      | 32.0        |

| TPS54425PWPRG4 | HTSSOP       | PWP             | 14   | 2000 | 353.0       | 353.0      | 32.0        |

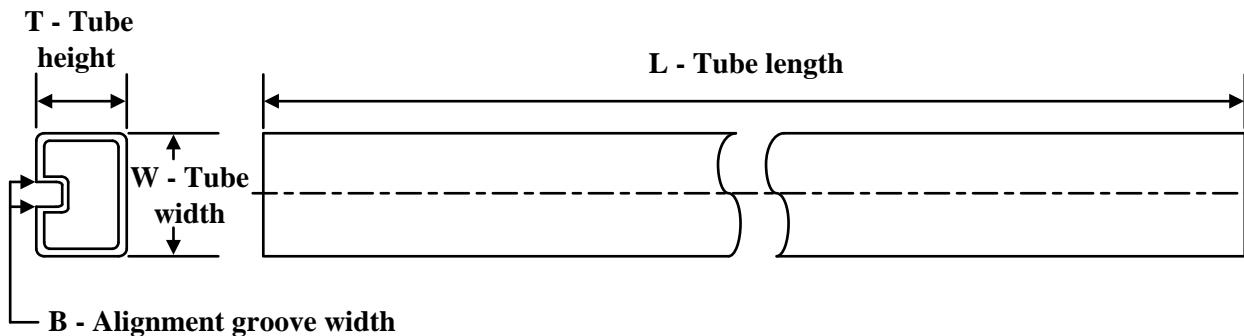

## TUBE

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54425PWP   | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54425PWP   | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54425PWP.A | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54425PWP.A | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54425PWP.B | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54425PWP.B | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600         | 3.5    |

## GENERIC PACKAGE VIEW

**PWP 14**

**PowerPAD TSSOP - 1.2 mm max height**

**4.4 x 5.0, 0.65 mm pitch**

**PLASTIC SMALL OUTLINE**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224995/A

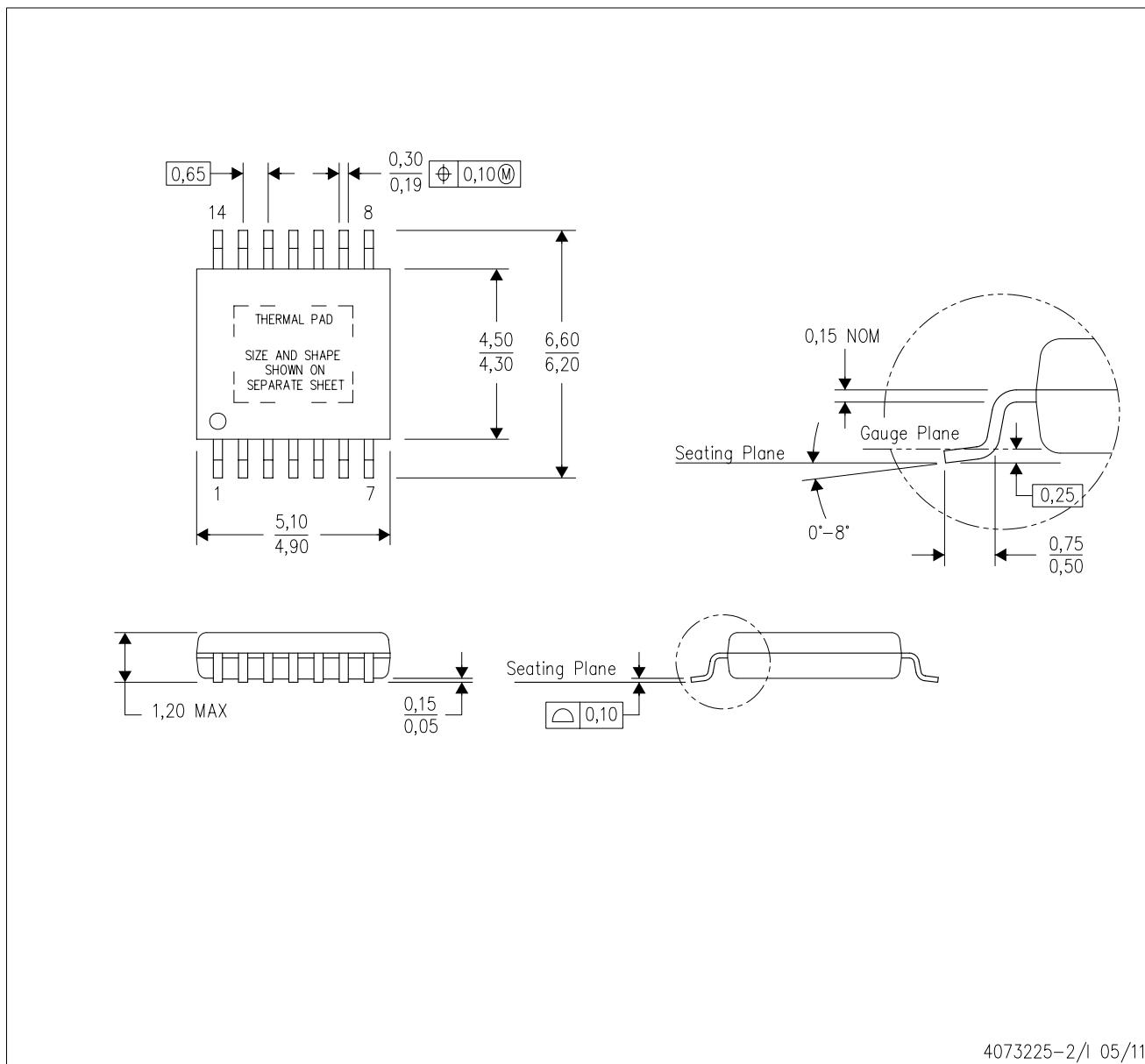

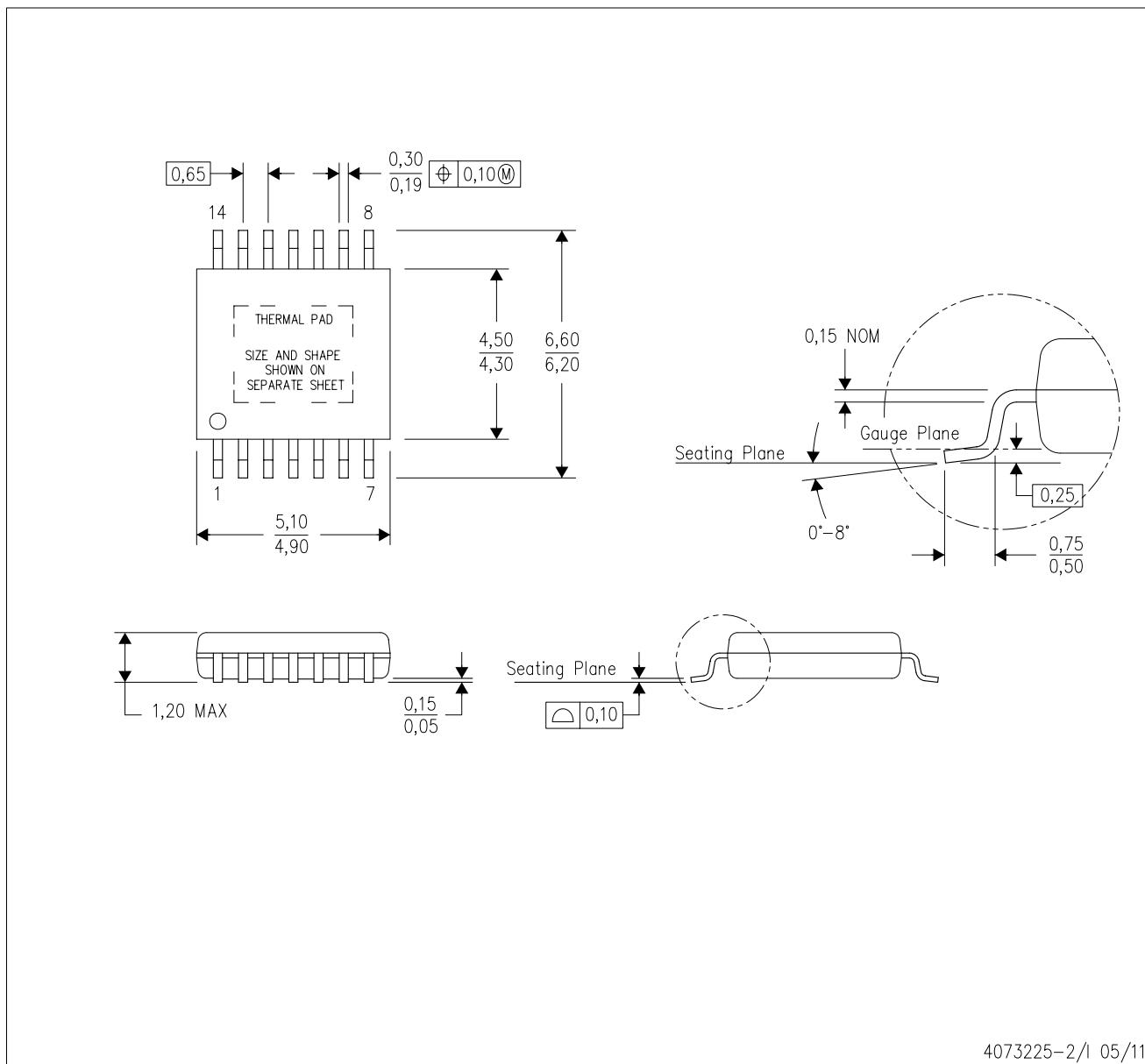

## MECHANICAL DATA

PWP (R-PDSO-G14)

PowerPAD™ PLASTIC SMALL OUTLINE

4073225-2/1 05/11

- NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

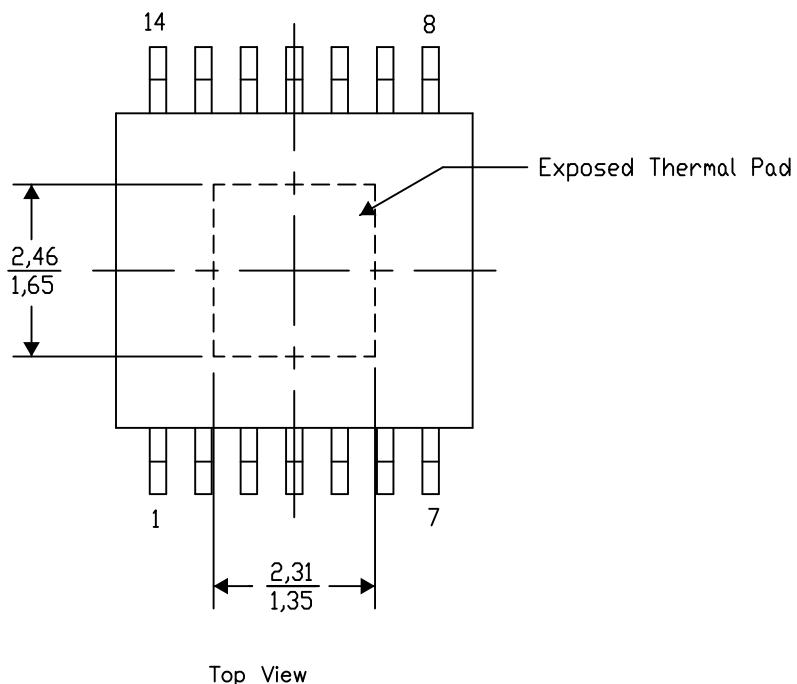

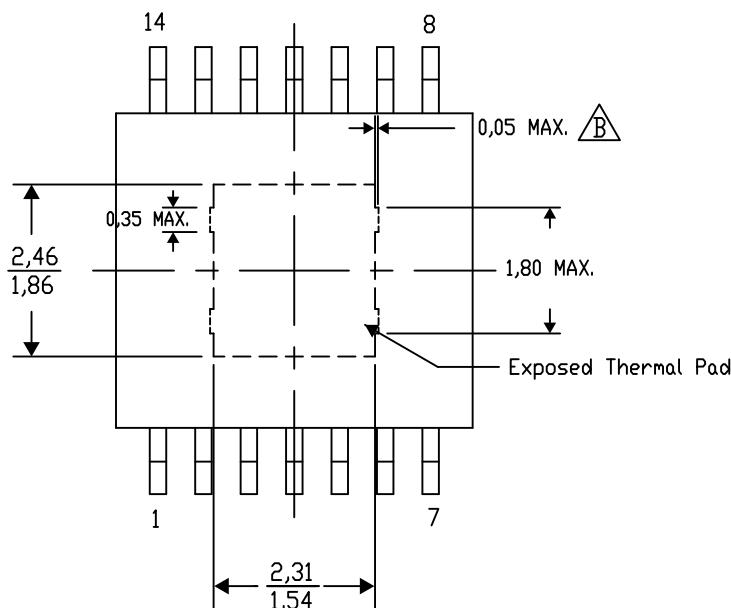

# THERMAL PAD MECHANICAL DATA

PWP (R-PDSO-G14)

PowerPAD™ SMALL PLASTIC OUTLINE

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

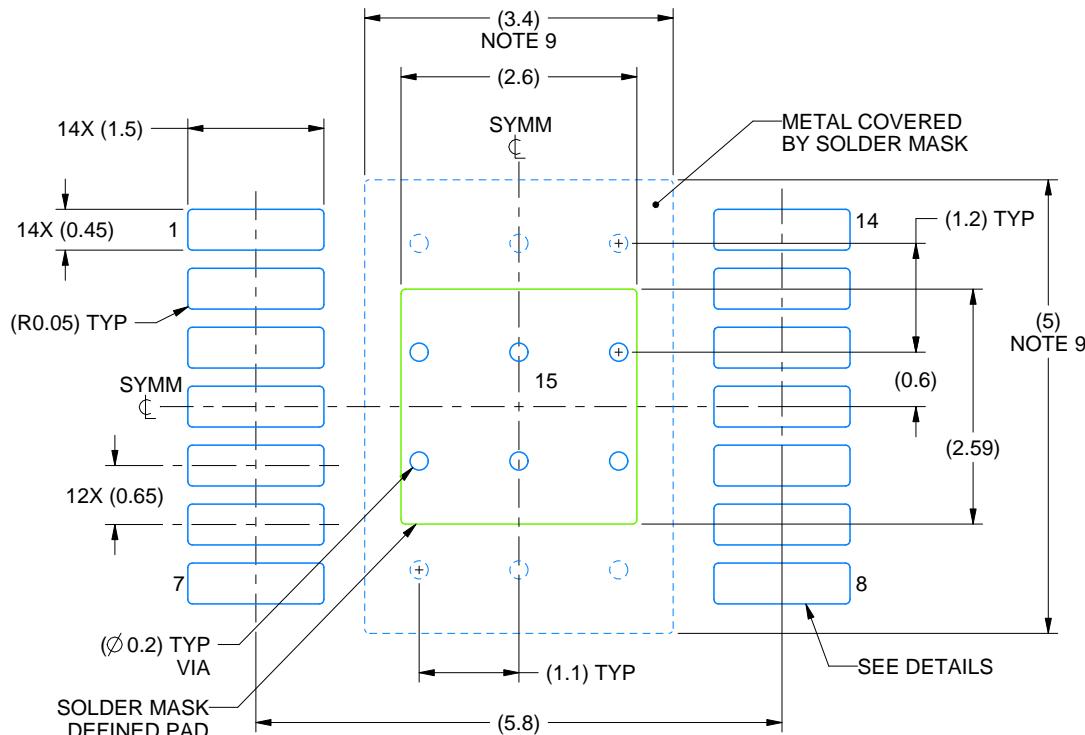

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-2/AO 01/16

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

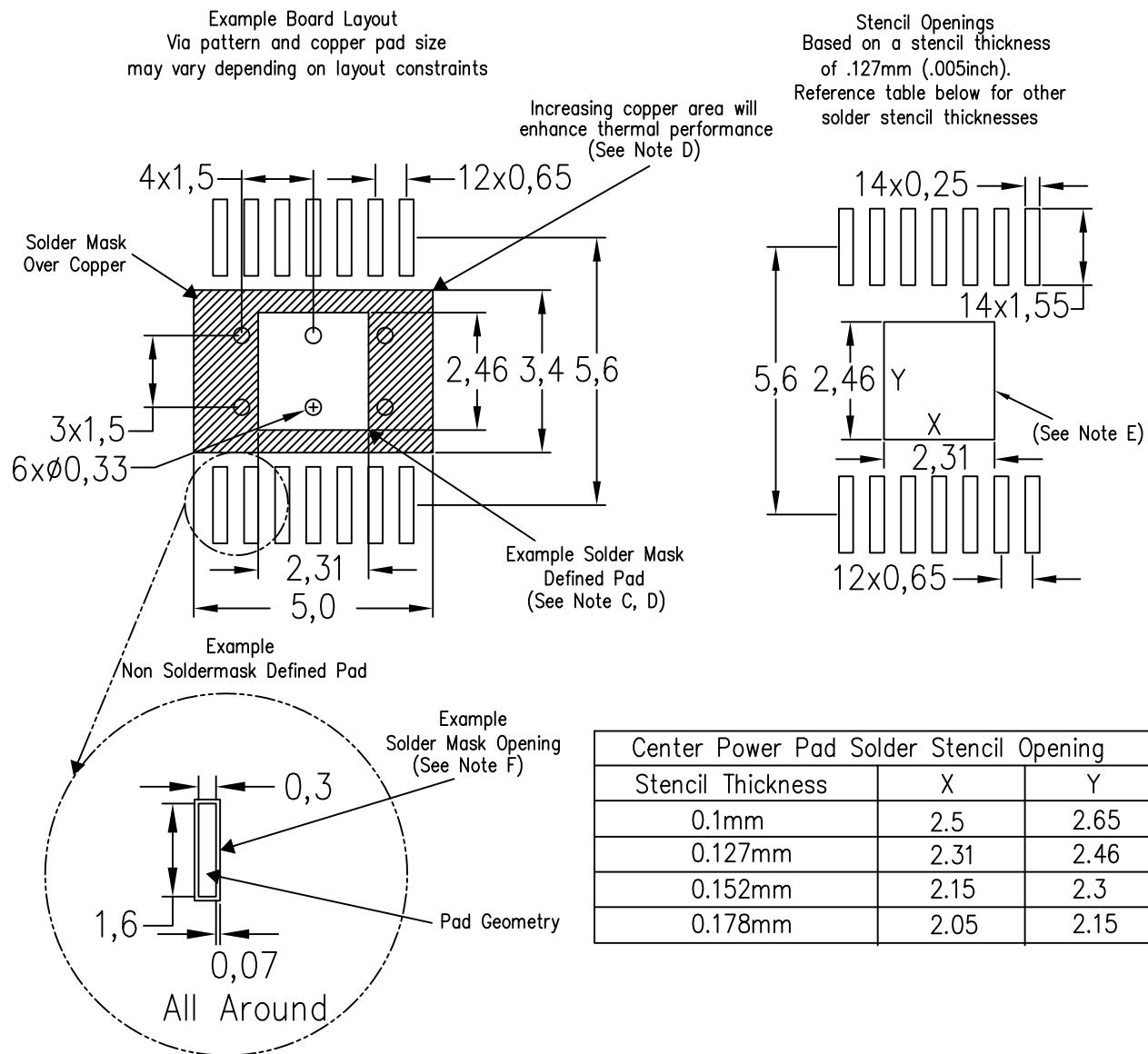

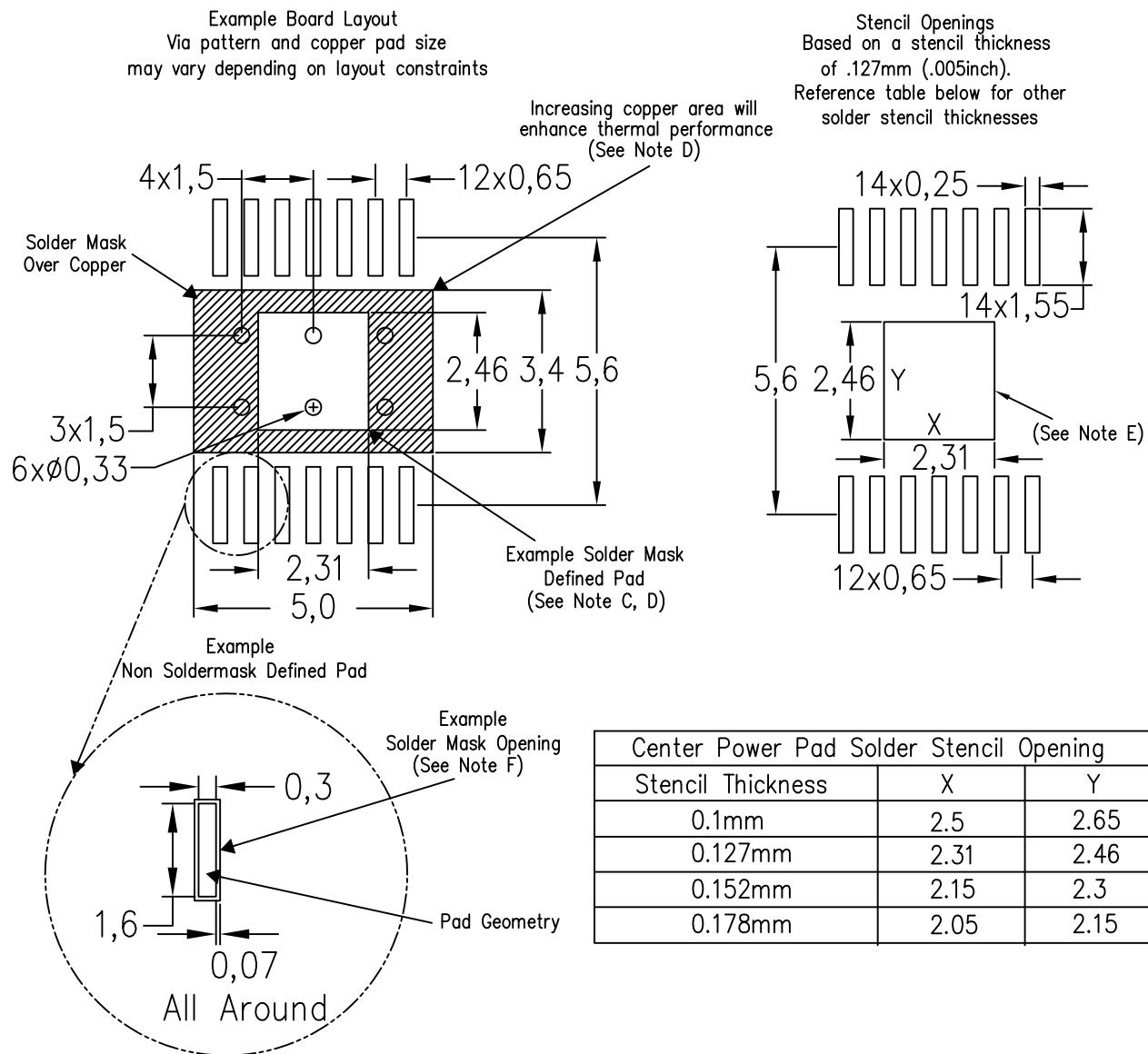

# LAND PATTERN DATA

PWP (R-PDSO-G14)

PowerPAD™ PLASTIC SMALL OUTLINE

4207609-2/W 09/15

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>. Publication IPC-7351 is recommended for alternate designs.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## MECHANICAL DATA

PWP (R-PDSO-G14)

PowerPAD™ PLASTIC SMALL OUTLINE

4073225-2/1 05/11

- NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# THERMAL PAD MECHANICAL DATA

PWP (R-PDSO-G14)

PowerPAD™ SMALL PLASTIC OUTLINE

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-44/AO 01/16

NOTE: A. All linear dimensions are in millimeters

Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

# LAND PATTERN DATA

PWP (R-PDSO-G14)

PowerPAD™ PLASTIC SMALL OUTLINE

4207609-2/W 09/15

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>. Publication IPC-7351 is recommended for alternate designs.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

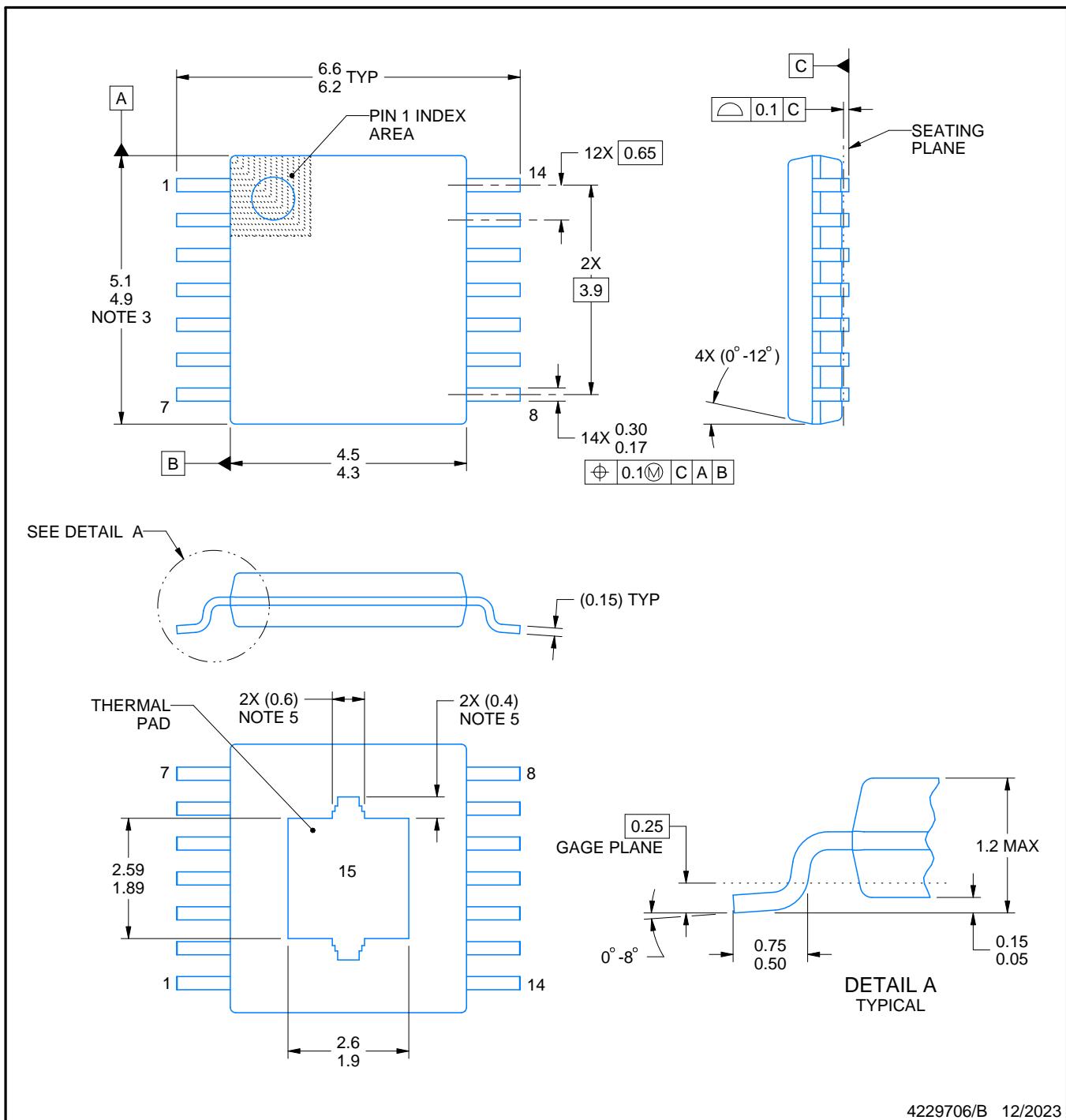

## **PACKAGE OUTLINE**

PWP0014K

# **PowerPAD™ TSSOP - 1.2 mm max height**

## SMALL OUTLINE PACKAGE

## NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ or may not be present.

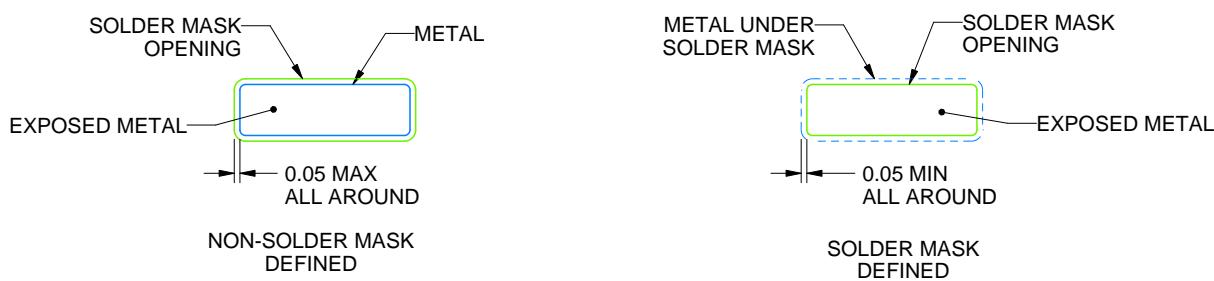

# EXAMPLE BOARD LAYOUT

PWP0014K

PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 12X

SOLDER MASK DETAILS

4229706/B 12/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

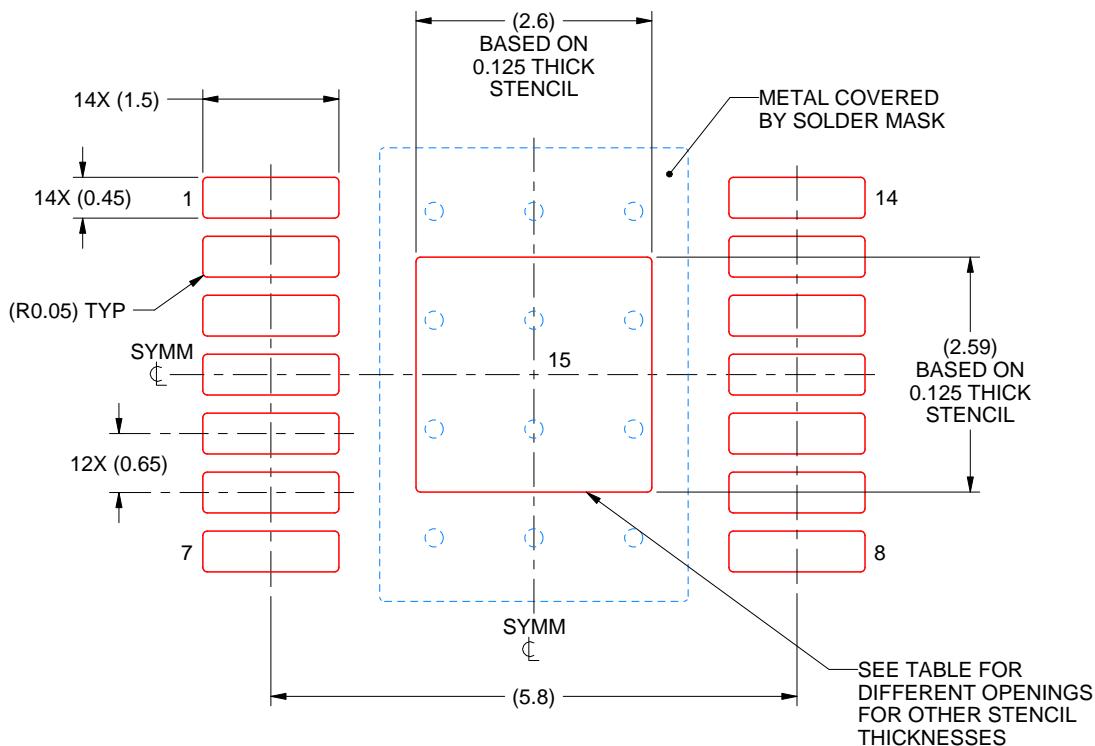

# EXAMPLE STENCIL DESIGN

PWP0014K

PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 12X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.91 X 2.90            |

| 0.125             | 2.60 X 2.59 (SHOWN)    |

| 0.15              | 2.37 X 2.36            |

| 0.175             | 2.20 X 2.19            |

4229706/B 12/2023

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月