# TPS543B25E 4V～18V 入力、25A 同期整流 SWIFT™ 降圧コンバータ、内部補償型高度電流モード制御付き

## 1 特長

- 固定周波数、内部補償、高度な電流モード (ACM) 制御

- 6.5mΩ および 2mΩ の MOSFET を内蔵

- 入力電圧範囲: 4V ~ 18V

- 出力電圧範囲: 0.5V ~ 7V

- 真の差動リモートセンスアンプ (RSA)

- 制御ループ性能を最適化する 3 つの選択可能な PWM ランプオプション

- 5 つの選択可能なスイッチング周波数: 500kHz、750kHz、1MHz、1.5MHz、2.2MHz

- 外部クロックに同期可能

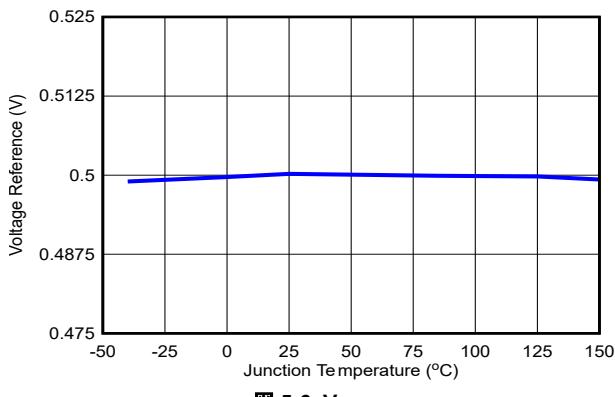

- 全温度範囲にわたって 0.5V、±0.5% の電圧リファレンス精度

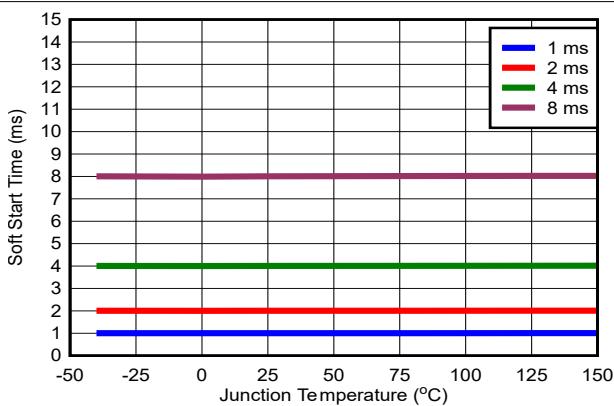

- 選択可能なソフトスタート時間: 1ms、2ms、4ms、8ms

- プリバイアス出力への単調スタートアップ

- 25A および 20A 動作をサポートする選択可能な電流制限

- 可変入力低電圧誤動作防止を利用可能

- パワー グッド出力監視

- 出力過電圧、出力低電圧、入力低電圧、過電流、過熱保護

- 動作時接合部温度: -55°C ~ 150°C

- 2.5mm × 4.5mm の 17 ピン WQFN-FCRLF パッケージ、0.5mm ピッチ

- 鉛フリー (RoHS 準拠)

- 20A - [TPS543B22](#)、16A - [TPS543A26](#)、および 12A - [TPS543A22](#) とピン互換

- SIMPLIS モデルが利用可能

- [WEBENCH® Power Designer](#) により、TPS543B25E を使用するカスタム設計を作成

## 2 アプリケーション

- 航空

- 電子戦

- ソフトウェア無線

- 追尾フロントエンド

## 3 説明

TPS543B25E は、高効率、18V、25A の同期降圧コンバーターです。このデバイスは、内部補償された固定周波数 ACM 制御アーキテクチャを採用しており、常に強制連続導通モード (FCCM) で動作し、0.5V ~ 7V の出力電圧を生成します。本デバイスは、最大 2.2MHz のスイッチング周波数で動作しながら高い効率を実現できるため、小さいソリューション サイズが求められる設計に最適です。固定周波数コントローラは 500kHz ~ 2.2MHz で動作でき、SYNC ピンを使用して外部クロックに同期できます。追加機能として、高精度の電圧リファレンス、2 線式のリモート検出、選択可能なソフトスタート時間、プリバイアス出力への単調なスタートアップ、選択可能な電流制限、EN ピンにより調整可能な低電圧ロックアウト (UVLO)、各種の故障保護があります。

TPS543B25E は小型の 2.5mm × 4.5mm の HotRod™ WQFN-FCRLF パッケージで供給されます。

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| TPS543B25E | RYS (WQFN-FCRLF、17)  | 4.50mm × 2.50mm          |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSILO](#)

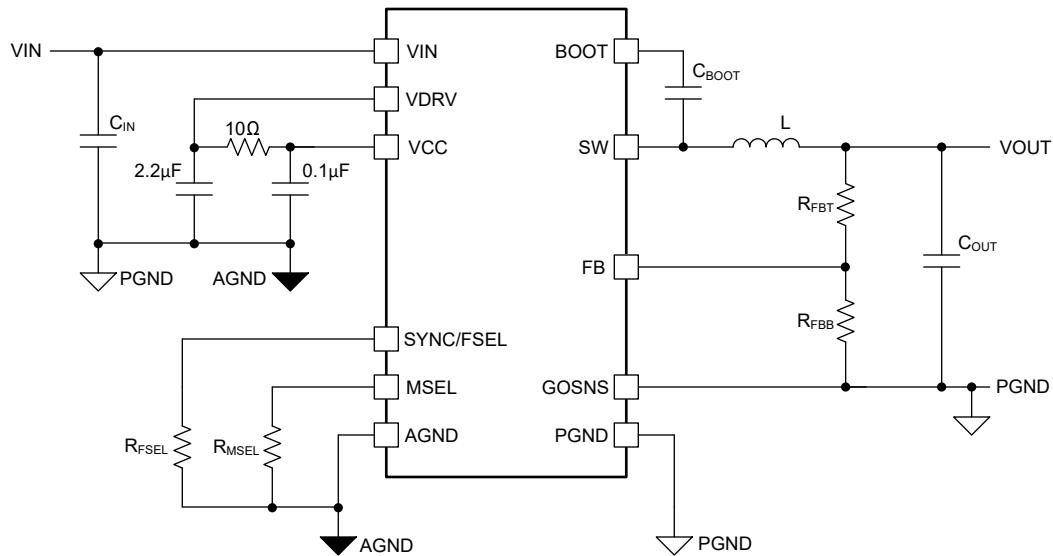

TPS543B25E のアプリケーション概略図

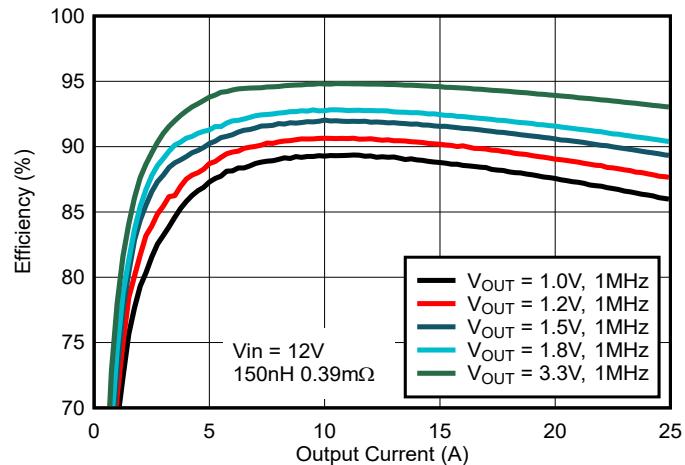

代表的なアプリケーションの効率

## 目次

|                 |    |                        |    |

|-----------------|----|------------------------|----|

| 1 特長            | 1  | 6.4 デバイスの機能モード         | 22 |

| 2 アプリケーション      | 1  | 7 アプリケーションと実装          | 23 |

| 3 説明            | 1  | 7.1 アプリケーション情報         | 23 |

| 4 ピン構成および機能     | 4  | 7.2 代表的なアプリケーション       | 23 |

| 5 仕様            | 5  | 7.3 電源に関する推奨事項         | 34 |

| 5.1 絶対最大定格      | 5  | 7.4 レイアウト              | 34 |

| 5.2 ESD Ratings | 5  | 8 デバイスおよびドキュメントのサポート   | 36 |

| 5.3 推奨動作条件      | 5  | 8.1 デバイス サポート          | 36 |

| 5.4 熱に関する情報     | 6  | 8.2 ドキュメントの更新通知を受け取る方法 | 36 |

| 5.5 電気的特性       | 6  | 8.3 サポート・リソース          | 36 |

| 5.6 代表的特性       | 8  | 8.4 商標                 | 36 |

| 6 詳細説明          | 11 | 8.5 静電気放電に関する注意事項      | 36 |

| 6.1 概要          | 11 | 8.6 用語集                | 36 |

| 6.2 機能ブロック図     | 11 | 9 改訂履歴                 | 37 |

| 6.3 機能説明        | 11 | 10 メカニカル、パッケージ、および注文情報 | 37 |

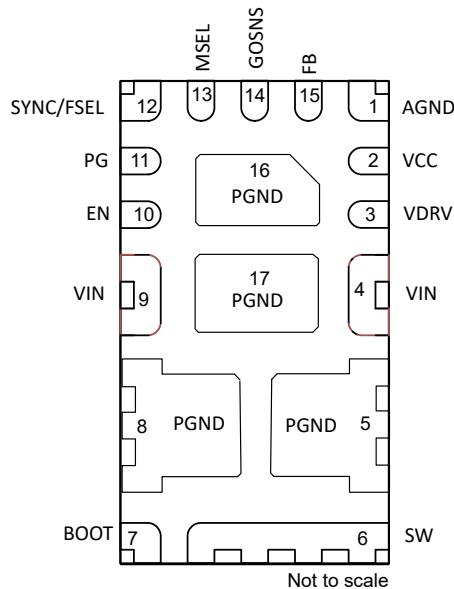

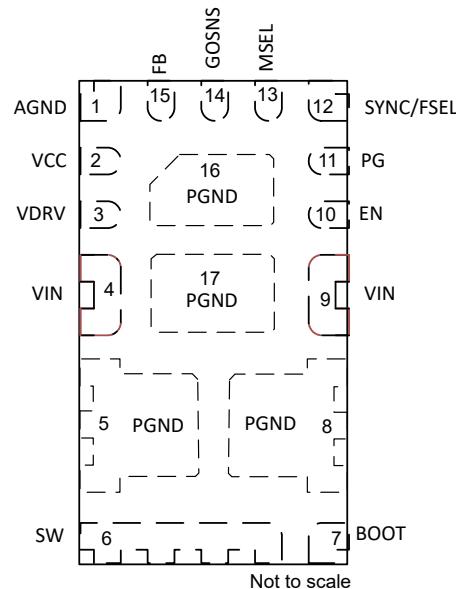

## 4 ピン構成および機能

図 4-1. 17 ピン WQFN-FCRLF RYS パッケージ (底面図)

図 4-2. 17 ピン WQFN-FCRLF RYS パッケージ (上面図)

表 4-1. ピンの機能

| ピン        | 種類 <sup>(1)</sup> | 説明                                                                                                               |

|-----------|-------------------|------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号                |                                                                                                                  |

| AGND      | 1                 | — 内部アナログ回路のグラウンドリターン                                                                                             |

| VCC       | 2                 | I アナログ制御回路の電源。VDRV からこのピンに $10\Omega$ の抵抗を接続し、 $0.1\mu\text{F}$ コンデンサで AGND にバイパスします。                            |

| VDRV      | 3                 | O 5V の内部レギュレータ出力とドライバへの内部接続。これらのピンを PGND との間に $2.2\mu\text{F}$ コンデンサを使用してバイパスします。セクション 6.3.2 を参照してください。          |

| VIN       | 4, 9              | I 電力段への入力電力。これらのピンから PGND への低インピーダンスのバイパスが重要です。各 VIN から IC に近い PGND に $1\mu\text{F}$ コンデンサを接続する必要があります。          |

| PGND      | 5, 8, 16, 17      | — 電力段のグラウンドリターン。このピンは内部でローサイド MOSFET のソースに接続されます。                                                                |

| SW        | 6                 | O コンバータのスイッチ ノード。このピンを出力インダクタに接続します。                                                                             |

| BOOT      | 7                 | I 内蔵のハイサイド MOSFET ゲートドライバ用電源。このピンと SW との間にコンデンサを接続します。                                                           |

| EN        | 10                | I イネーブル ピン。浮動または High に接続してイネーブル、外部信号を使用してイネーブル/ディスエーブルするか、抵抗デバイダで入力低電圧ロックアウトを調整します。セクション 6.3.3 を参照してください。       |

| PG        | 11                | O オープンドレインのパワーグッド インジケータセクション 6.3.10 を参照してください。                                                                  |

| SYNC/FSEL | 12                | I 周波数選択と外部クロック同期。接地への抵抗により、デバイスのスイッチング周波数が設定されます。このピンに外部クロックを印加して、スイッチング周波数を同期することもできます。セクション 6.3.5.3 を参照してください。 |

| MSEL      | 13                | I グランドに接続された抵抗により、電流制限、ソフトスタートレート、PWM ランプ振幅を選択します。セクション 6.3.9 を参照してください。                                         |

| GOSNS     | 14                | I グランドセンスのリターンと差動リモートセンスアンプへの入力                                                                                  |

| FB        | 15                | I 帰還ピンと出力電圧レギュレーションのための差動リモートセンスアンプへの入力。このピンを抵抗デバイダの中間点に接続して、出力電圧を設定します。セクション 6.3.6 を参照してください。                   |

(1) I = 入力、O = 出力

## 5 仕様

### 5.1 絶対最大定格

外気温度範囲内での動作 (特に記述のない限り) [\(1\)](#) [\(2\)](#)

|                  |                         | 最小値  | 最大値 | 単位 |

|------------------|-------------------------|------|-----|----|

| ピン電圧             | VIN                     | -0.3 | 20  | V  |

| ピン電圧             | SW、DC                   | -0.3 | 20  | V  |

| ピン電圧             | SW、過渡 20ns              | -5   | 22  | V  |

| ピン電圧             | VIN から SW、DC            | -0.3 | 20  | V  |

| ピン電圧             | VIN から SW、過渡 20ns       | -6   | 25  | V  |

| ピン電圧             | BOOT                    | -0.3 | 25  | V  |

| ピン電圧             | BOOT から SW へ            | -0.3 | 6   | V  |

| ピン電圧             | EN、PG、MSEL、SYNC/FSEL、FB | -0.3 | 6   | V  |

| ピン電圧             | VCC、VDRV                | -0.3 | 6   | V  |

| ピン電圧             | GOSNS                   | -0.3 | 0.3 | V  |

| シンク電流            | PG                      |      | 5   | mA |

| 動作時接合部温度         | T <sub>J</sub>          | -55  | 150 | °C |

| T <sub>stg</sub> |                         | -55  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、PGND を基準としたものです。

### 5.2 ESD Ratings

|                    |      |                                                               | 値     | 単位 |

|--------------------|------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <a href="#">(1)</a>     | ±2000 | V  |

| V <sub>(ESD)</sub> | 静電放電 | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <a href="#">(2)</a> | ±500  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                  |            |                         | 最小値  | 公称値 | 最大値 | 単位 |

|------------------|------------|-------------------------|------|-----|-----|----|

| V <sub>IN</sub>  | ピン電圧       | 入力電圧範囲                  | 4    | 18  | 18  | V  |

| V <sub>OUT</sub> | 出力電圧範囲     |                         | 0.5  | 7   | 7   | V  |

|                  | ピン電圧       | SW ~ PGND               | -0.1 | 18  | 18  | V  |

|                  | ピン電圧       | EN、FB、PG、MSEL、SYNC/FSEL | -0.1 | 5.5 | 5.5 | V  |

|                  | ピン電圧       | GOSNS                   | -0.3 | 0.3 | 0.3 | V  |

| I <sub>OUT</sub> | 出力電流範囲     |                         |      |     | 25  | A  |

| I <sub>PG</sub>  | パワーグッド入力電流 |                         |      | 2   | 5   | mA |

| T <sub>J</sub>   | 動作時接合部温度   |                         | -55  | 150 | 150 | °C |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TPS543B25E             |                         | 単位   |

|-----------------------|-------------------|------------------------|-------------------------|------|

|                       |                   | RYS (WQFN-FCRLF、JEDEC) | RYS (WQFN-FCRLF、TI EVM) |      |

|                       |                   | 17 ピン                  | 17 ピン                   |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 33.9                   | 18.6                    | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 10.6                   | 該当なし <sup>(2)</sup>     | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 5.5                    | 該当なし <sup>(2)</sup>     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.8                    | 1.3                     | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 5.5                    | 6.6                     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

(2) EVM レイアウトには適用されません。

## 5.5 電気的特性

T<sub>j</sub> = -55°C ~ +150°C、V<sub>VIN</sub> = 4V ~ 18V (特に記述のない限り)

| パラメータ                    | テスト条件                                        | 最小値                                                                         | 標準値                    | 最大値                    | 単位    |

|--------------------------|----------------------------------------------|-----------------------------------------------------------------------------|------------------------|------------------------|-------|

| <b>電源電圧</b>              |                                              |                                                                             |                        |                        |       |

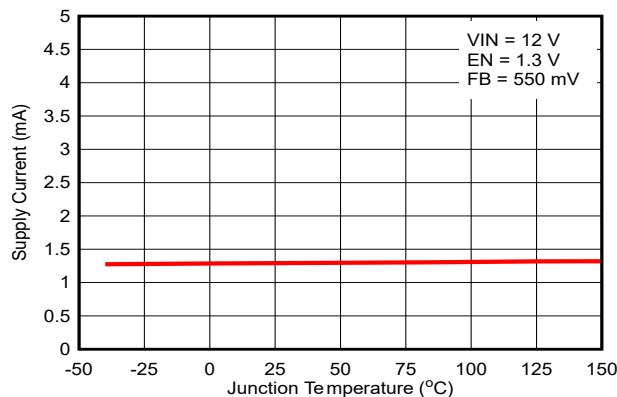

| I <sub>Q(VIN)</sub>      | V <sub>VIN</sub> 動作時非スイッチング電源電流              | V <sub>EN</sub> = 1.3V、V <sub>FB</sub> = 550mV、V <sub>VIN</sub> = 12V、1MHz  | 1200                   | 1600                   | μA    |

| V <sub>VIN</sub> UVLO(R) | VIN UVLO 立ち上がりスレッショルド                        | V <sub>VIN</sub> 立ち上がり                                                      | 3.8                    | 4.00                   | 4.2   |

| V <sub>VIN</sub> UVLO(H) | VIN UVLO ヒステリシス                              |                                                                             | 150                    |                        | mV    |

| <b>内部 LDO</b>            |                                              |                                                                             |                        |                        |       |

| V <sub>VDRV</sub>        | 内部リニアレギュレータの出力電圧                             | V <sub>VIN</sub> = 12V、I <sub>VDRV</sub> = 25mA                             | 4.5                    |                        | V     |

|                          | 内部リニアレギュレータ短絡電流制限                            | V <sub>VIN</sub> = 12V                                                      | 150                    |                        | mA    |

| V <sub>C</sub> UVLO(R)   | VCC UVLO 立ち上がりスレッショルド                        |                                                                             | 3.4                    |                        | V     |

| V <sub>C</sub> UVLO(H)   | VCC UVLO ヒステリシス                              |                                                                             | 0.4                    |                        | V     |

| <b>イネーブル</b>             |                                              |                                                                             |                        |                        |       |

| V <sub>EN(R)</sub>       | EN 電圧立ち上がりスレッショルド                            | EN 立ち上がり、スイッチングはイネーブル                                                       | 1.2                    | 1.25                   | V     |

| V <sub>EN(F)</sub>       | EN 電圧立ち下がりスレッショルド                            | EN 立ち下がり、スイッチングはディスエーブル                                                     | 1.05                   | 1.1                    | V     |

| V <sub>EN(H)</sub>       | EN 電圧ヒステリシス                                  |                                                                             | 100                    |                        | mV    |

|                          | EN ピンソース電流                                   | V <sub>EN</sub> = 1.1V                                                      | 1.75                   |                        | μA    |

|                          | EN ピンソース電流                                   | V <sub>EN</sub> = 1.3V                                                      | 11.6                   |                        | μA    |

|                          | EN HIGH からスイッチング開始までの遅延 <sup>(1)</sup>       | EN 0V から 3V までの立ち上がり                                                        | 1                      |                        | ms    |

| <b>基準電圧</b>              |                                              |                                                                             |                        |                        |       |

| V <sub>FB</sub>          | 帰還電圧                                         | T <sub>j</sub> = -40°C ~ 150°C                                              | 497.5                  | 500                    | 502.5 |

| I <sub>FB(LKG)</sub>     | FB ピンへの入力リーケ電流                               | V <sub>FB</sub> = 500mV、非スイッチング、V <sub>VIN</sub> = 12V、V <sub>EN</sub> = 0V | 3                      |                        | nA    |

| <b>リモートセンスアンプ</b>        |                                              |                                                                             |                        |                        |       |

| I <sub>LEAK(GOSNS)</sub> | GOSNS ピンから流れ出す電流                             |                                                                             | 85                     | 90                     | 95    |

| V <sub>IRNG(GOSNS)</sub> | GOSNS の同相電圧(レギュレーション用)                       | AGND+/-V <sub>GOSNS</sub>                                                   | -100                   |                        | 100   |

| <b>スイッチング周波数および発振器</b>   |                                              |                                                                             |                        |                        |       |

| f <sub>SW</sub>          | スイッチング周波数                                    | R <sub>FSEL</sub> = 24.3kΩ ~ AGND                                           | 450                    | 500                    | 550   |

| f <sub>SW</sub>          | スイッチング周波数                                    | R <sub>FSEL</sub> = 17.4kΩ ~ AGND                                           | 675                    | 750                    | 825   |

| f <sub>SW</sub>          | スイッチング周波数                                    | R <sub>FSEL</sub> = 11.8kΩ ~ AGND                                           | 900                    | 1000                   | 1100  |

| f <sub>SW</sub>          | スイッチング周波数                                    | R <sub>FSEL</sub> = 8.06kΩ ~ AGND                                           | 1350                   | 1500                   | 1650  |

| <b>同期</b>                |                                              |                                                                             |                        |                        |       |

| V <sub>IL(sync)</sub>    | Low レベル入力電圧                                  |                                                                             |                        | 0.8                    | V     |

| F <sub>SYNC(range)</sub> | ループの安定性に悪影響を及ぼさない周波数<br>同期範囲。 <sup>(1)</sup> |                                                                             | F <sub>CLK</sub> - 20% | F <sub>CLK</sub> + 20% |       |

## 5.5 電気的特性 (続き)

$T_J = -55^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 、 $V_{\text{VIN}} = 4\text{V} \sim 18\text{V}$  (特に記述のない限り)

| パラメータ                       |                                     | テスト条件                                                                                           | 最小値  | 標準値               | 最大値 | 単位                 |

|-----------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------|------|-------------------|-----|--------------------|

| <b>ソフトスタート</b>              |                                     |                                                                                                 |      |                   |     |                    |

| $t_{\text{SS1}}$            | ソフトスタート時間 0 ~ 100% $V_{\text{OUT}}$ | $R_{\text{MSEL}} = 1.78\text{k}\Omega$                                                          | 1    |                   |     | ms                 |

| $t_{\text{SS2}}$            | ソフトスタート時間 0 ~ 100% $V_{\text{OUT}}$ | $R_{\text{MSEL}} = 2.21\text{k}\Omega$                                                          | 2    |                   |     | ms                 |

| $t_{\text{SS3}}$            | ソフトスタート時間 0 ~ 100% $V_{\text{OUT}}$ | $R_{\text{MSEL}} = 2.74\text{k}\Omega$                                                          | 4    |                   |     | ms                 |

| $t_{\text{SS4}}$            | ソフトスタート時間 0 ~ 100% $V_{\text{OUT}}$ | $R_{\text{MSEL}} = 3.32\text{k}\Omega$                                                          | 8    |                   |     | ms                 |

| <b>電力段</b>                  |                                     |                                                                                                 |      |                   |     |                    |

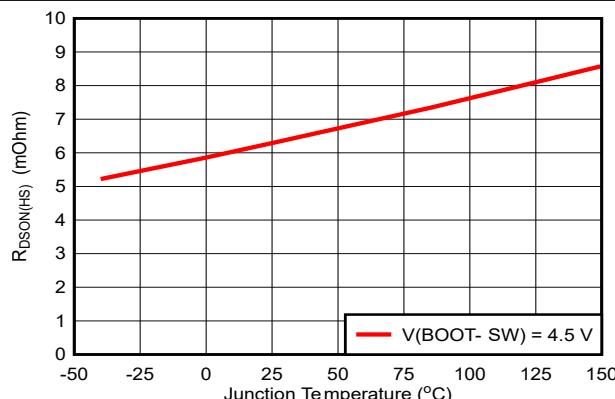

| $R_{\text{DS(on)HS}}$       | ハイサイド MOSFET オン抵抗                   | $T_J = 25^{\circ}\text{C}$ 、 $V_{\text{VIN}} = 12\text{V}$ 、 $V_{\text{BOOT-SW}} = 4.5\text{V}$ | 6.5  |                   |     | $\text{m}\Omega$   |

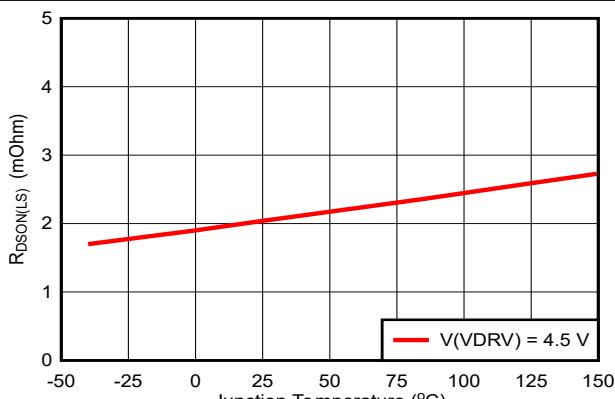

| $R_{\text{DS(on)LS}}$       | ローサイド MOSFET オン抵抗                   | $T_J = 25^{\circ}\text{C}$ 、 $V_{\text{VDRV}} = 4.5\text{V}$                                    | 2.0  |                   |     | $\text{m}\Omega$   |

| $V_{\text{VIN(TH\_r)}}$     | $V_{\text{IN}}$ スロットル立ち上がりスレッショルド   | $T_J = 25^{\circ}\text{C}$ $V_{\text{IN}}$ の立ち上がり時にハイサイドゲート駆動を弱める                               | 16   |                   |     | V                  |

| $V_{\text{VIN(TH\_f)}}$     | $V_{\text{IN}}$ スロットル立ち下がりスレッショルド   | $T_J = 25^{\circ}\text{C}$ $V_{\text{IN}}$ 立ち下がり時にハイサイドゲート駆動を回復する                               | 15.5 |                   |     | V                  |

| $V_{\text{BOOT-SW(UV\_R)}}$ | BOOT-SW UVLO 立ち上がりスレッショルド           | $V_{\text{BOOT-SW}}$ 立ち上がり                                                                      | 3.2  |                   |     | V                  |

| $V_{\text{BOOT-SW(UV\_F)}}$ | BOOT-SW UVLO 立ち上がりスレッショルド           | $V_{\text{BOOT-SW}}$ 立ち下がり                                                                      | 2.8  |                   |     | V                  |

| $T_{\text{ON(min)}}$        | 最小 ON パルス幅                          |                                                                                                 | 22   | 28                | ns  |                    |

| $T_{\text{OFF(min)}}$       | 最小 OFF パルス幅 (1)                     |                                                                                                 |      | 115               | ns  |                    |

| <b>電流センスおよび過電流保護</b>        |                                     |                                                                                                 |      |                   |     |                    |

| <b>出力過電圧および低電圧保護</b>        |                                     |                                                                                                 |      |                   |     |                    |

| $V_{\text{OVP}}$            | 過電圧保護 (OVP) のスレッショルド電圧              | $V_{\text{FB}}$ 立ち上がり                                                                           | 120% |                   |     | $V_{\text{REF}}$   |

| $V_{\text{UVP}}$            | 低電圧保護 (UVP) スレッショルド電圧               | $V_{\text{FB}}$ 立ち下がり                                                                           | 80%  |                   |     | $V_{\text{REF}}$   |

| <b>パワーグッド</b>               |                                     |                                                                                                 |      |                   |     |                    |

| $I_{\text{PG(LKG)}}$        | オープンドレイン出力が High のときの PG ピンへのリーキ電流  | $V_{\text{PG}} = 4.7\text{V}$                                                                   |      | 5                 |     | $\mu\text{A}$      |

| $V_{\text{PG(low)}}$        | PG low レベル出力電圧                      | $I_{\text{PG}} = 2\text{mA}$ 、 $V_{\text{IN}} = 12\text{V}$                                     |      | 0.6               |     | V                  |

|                             | 有効な PG 出力の最小 $V_{\text{IN}}$        | $EN = 0\text{V}$ 、PG を 5V にプルアップ                                                                |      | 1                 |     | V                  |

|                             | PG 遅延が low から high に変化              |                                                                                                 |      | 201               |     | us                 |

|                             | PG 遅延が high から low に変化              |                                                                                                 |      | 11                |     | $\mu\text{s}$      |

| <b>HICCUP</b>               |                                     |                                                                                                 |      |                   |     |                    |

|                             | 再スタート前のヒップ時間                        |                                                                                                 |      | $7*t_{\text{SS}}$ |     | ms                 |

| <b>出力放電</b>                 |                                     |                                                                                                 |      |                   |     |                    |

| $R_{\text{Dischg}}$         | 出力放電抵抗                              | $V_{\text{VIN}} = 12\text{V}$ 、 $V_{\text{SW}} = 0.5\text{V}$ 、電力変換無効。                          | 100  |                   |     | $\Omega$           |

| <b>サーマルシャットダウン</b>          |                                     |                                                                                                 |      |                   |     |                    |

| $T_{\text{J(SD)}}$          | サーマルシャットダウンのスレッショルド (1)             | 温度上昇                                                                                            | 165  | 175               |     | $^{\circ}\text{C}$ |

| $T_{\text{J(HYS)}}$         | サーマルシャットダウンヒステリシス (1)               |                                                                                                 | 12   |                   |     | $^{\circ}\text{C}$ |

(1) 設計により規定されています。

## 5.6 代表的特性

図 5-1. ハイサイド FET の  $R_{ds_{ON}}$

図 5-2. ローサイド FET の  $R_{ds_{ON}}$

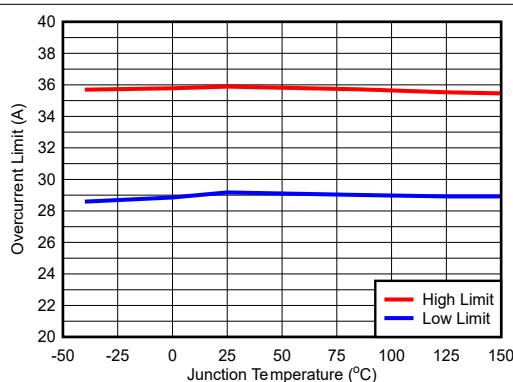

図 5-3. 過電流制限

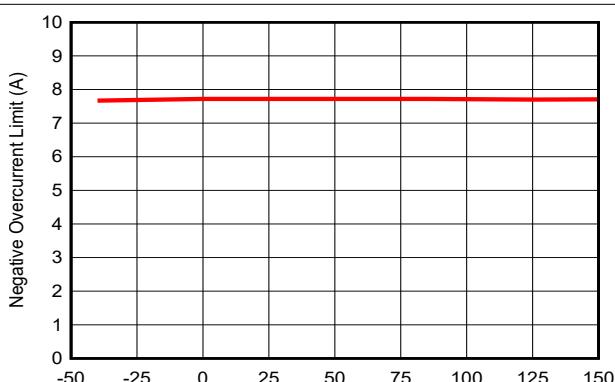

図 5-4. 負の過電流制限

図 5-5. イネーブル電圧

図 5-6.  $V_{REF}$

## 5.6 代表的特性 (続き)

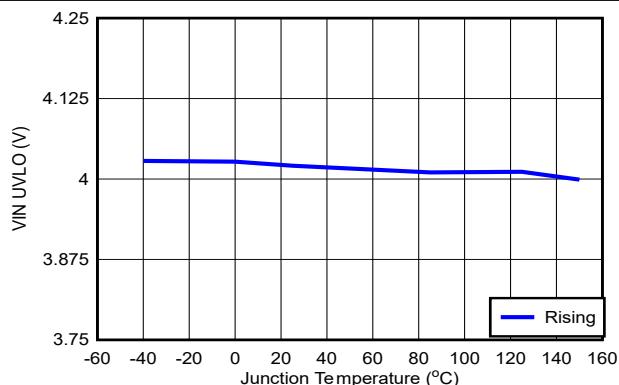

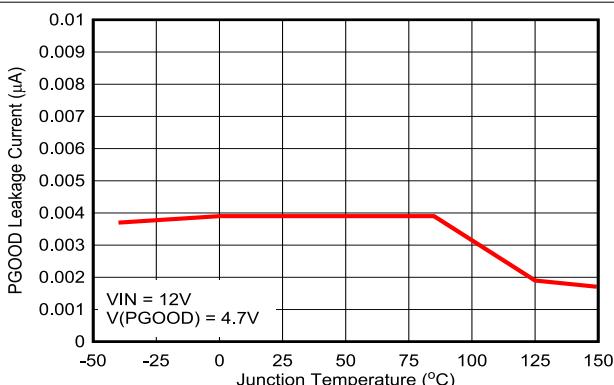

図 5-7. V<sub>IN</sub> UVLO

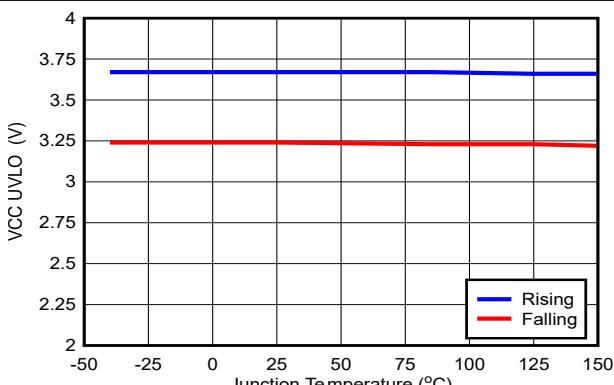

図 5-8. V<sub>CC</sub> UVLO

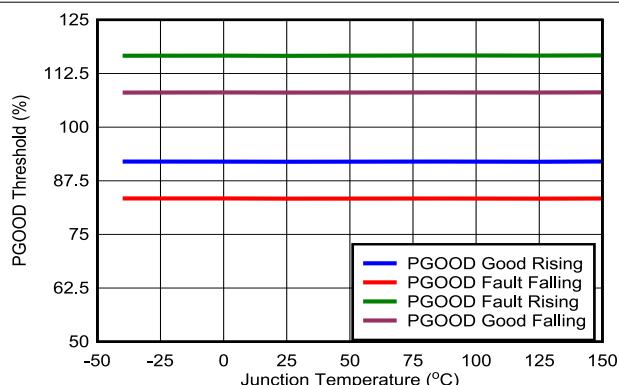

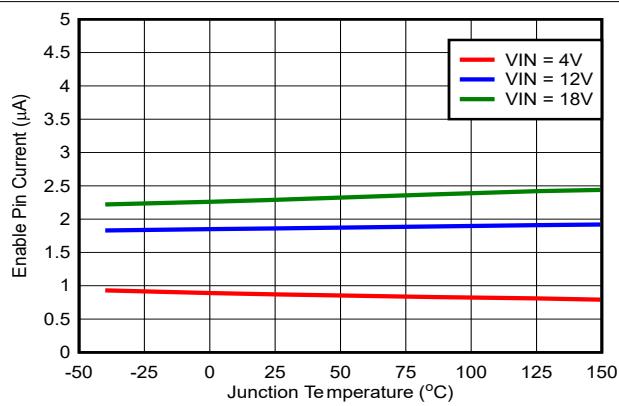

図 5-9. PG スレッショルド

図 5-10. PG リーク電流

図 5-11. 異なる VIN でのイネーブルピン電流

図 5-12. ソフトスタート

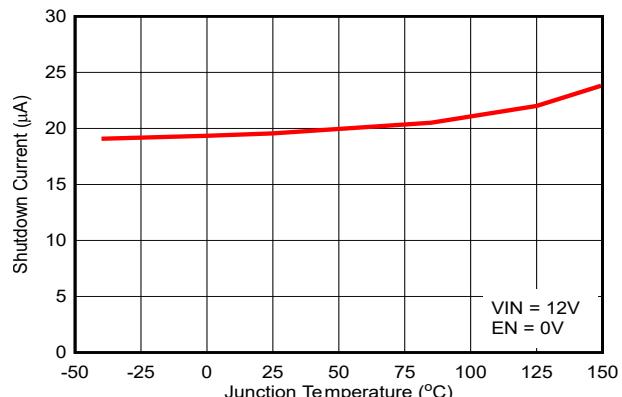

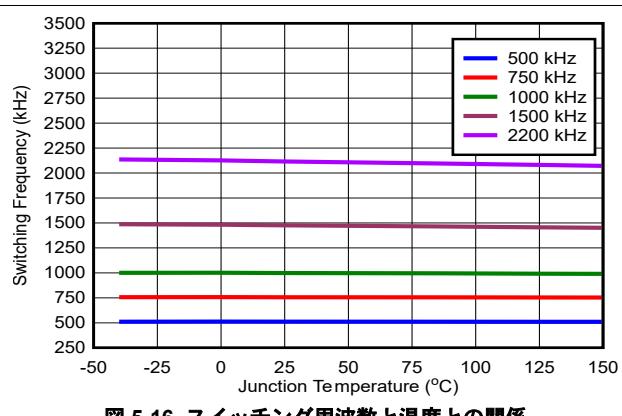

## 5.6 代表的特性 (続き)

図 5-13. 非スイッチング時の電源電流

図 5-14. シャットダウン時の電源電流

図 5-15. VDRV と温度との関係

図 5-16. スイッチング周波数と温度との関係

## 6 詳細説明

### 6.1 概要

TPS543B25E は、25A クラスで高性能な同期式のバックコンバーターで、2 つの内蔵 N チャネル MOSFET を搭載しています。TPS543B25E は、最大動作接合部温度が 150°C であるため、ワイヤレスインフラなどの高周囲温度アプリケーション向けに設計されています。入力電圧範囲は 4V ~ 18V で、出力電圧範囲は 0.5V ~ 7V です。このデバイスは、固定周波数の高度な電流モード制御アーキテクチャを採用し、500kHz から 2.2MHz までの範囲で 5 つのスイッチング周波数選択設定を行うことで、出力フィルタ部品を選択する際、効率とサイズ最適化を実現します。デバイスのスイッチング周波数は、FSEL/SYNC ピンに適用される外部クロックと同期させることができます。

高度な電流モードは、複雑な外部補償回路設計を必要とせずに、安定した静的および過渡動作を実現するピーク電流モード制御トポロジーのエミュレーションです。ACM には、インダクタ電流情報をエミュレートする内部ランプ生成回路が搭載されており、マルチレイヤードセラミックコンデンサ (MLCC) などの低 ESR 出力コンデンサの使用を可能にしています。また、内部ランプは高い信号対雑音比を実現し、優れたノイズ耐性を実現します。TPS543B25E は、AGND にシングル抵抗を接続するだけで、さまざまなインダクタと出力コンデンサの組み合わせに対して内部帰還ループを最適化するための 3 つのランプオプションを備えています (詳細については [セクション 6.3.7.2](#) を参照ください)。TPS543B25E は使いやすく、外付け部品の数を最小限に抑えつつ、高速な負荷過渡応答を実現します。また、固定周波数変調は、EMI ノイズを抑制するための容易なフィルター設計も提供します。

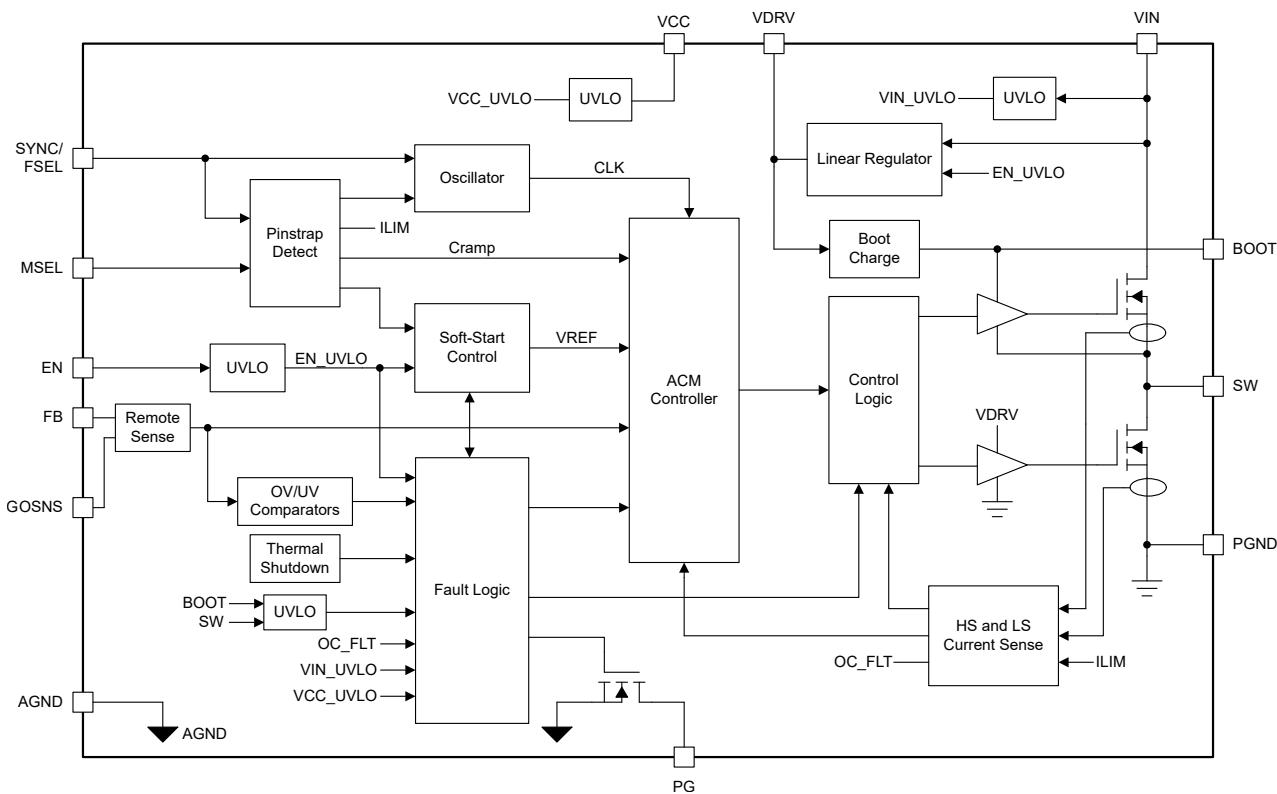

### 6.2 機能ブロック図

### 6.3 機能説明

#### 6.3.1 VIN ピンおよびVIN UVLO

VIN ピン電圧は、本デバイスの内部制御回路に電源を供給し、電力段に入力電圧を供給します。VIN の入力電圧は、4V ~ 18V の範囲です。本デバイスでは、VIN ピンに内部 UVLO 回路を実装します。VIN ピンの電圧が内部の VIN UVLO スレッショルドを下回ると、本デバイスは無効になります。スタートアップ時の内部 VIN UVLO スレッショルドは 3.95V (標準値) で、ヒステリシスは 150mV です。

デバイスを有効にするための 2 番目の手段は、EN ピンに接続することで提供されます。詳細については、[セクション 6.3.3](#) を参照してください。

### 6.3.2 内部リニア レギュレータとバイパス

VDRV ピンは、内部 (4.5V 公称) リニアレギュレータ (LDO) の出力と、MOSFET ドライバに内部で接続されています。セラミック コンデンサを使用して VDRV を PGND にバイパスします。TI は、 $2.2\mu\text{F} \sim 10\mu\text{F}$  の値を推奨しています。VCC ピンは内部制御回路 ソースです。VDRV と VCC の間に  $10\Omega$  抵抗を接続し、セラミックコンデンサを使用して VCC から AGND へバイパスします ( $0.1\mu\text{F}$  を推奨)。

図 6-1. デバイスのバイパス

VDRV 以外のソースで VCC を駆動することは意図していません。

VDRV を外部ソースや負荷に接続することは意図していません。

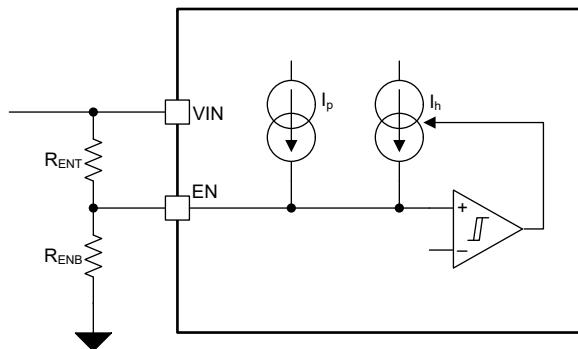

### 6.3.3 イネーブルおよび調整可能な UVLO

EN ピンは、デバイスの電気的オン/オフ制御に使用します。EN ピンの電圧が立ち上がりスレッショルド電圧を超えると、デバイスはスタートアップ シーケンシングを開始します。EN ピンの電圧がスレッショルド電圧よりも下回ると、レギュレータはスイッチングを停止し、低動作時電流状態になります。EN ピンには内部プルアップ電流ソース ( $I_P$ ) があるため、ピンをフローティングにしてデバイスをデフォルトで有効にすることができます。EN ピンに接続された回路のリーク電流が最小 EN プルアップ電流を超えないようにしてください。超えた場合、デバイスは起動できません。アプリケーションで ENABLE ピンのデジタル制御が必要な場合は、ピンとのインターフェイスに、オープンドレインまたはオープンコレクタ出力ロジックを使用してください。

または、[図 6-2](#) に示すように、VIN から EN ピンに外付け抵抗デバイダを追加して可変 UVLO を調整することもできます。EN ピン プルアップ ヒステリシス電流 ( $I_h$ ) は、EN ピンがイネーブル スレッショルドを超えた後にピン ソース電流を増加させることによって、UVLO 機能の電圧ヒステリシスを制御するために使用されます。UVLO スレッショルドは、[式 1](#) および [式 2](#) を使用し計算できます。可変 UVLO 機能を使用する場合、テキサス・インスツルメンツは 500mV 以上のヒステリシスを推奨します。入力電圧スルーレートが非常に遅いアプリケーションでは、EN ピンからグランドにコンデンサを配置して、入力電圧のノイズをフィルタリングできます。

図 6-2. EN を使用した可変 UVLO

$$R_{ENT} = \frac{V_{START} \times \left( \frac{V_{ENFALLING}}{V_{ENRISING}} \right) - V_{STOP}}{I_p \times \left( 1 - \frac{V_{ENFALLING}}{V_{ENRISING}} \right) + I_h} \quad (1)$$

$$R_{ENB} = \frac{R_{ENT} \times V_{ENFALLING}}{V_{STOP} - V_{ENFALLING} + R_{ENT} \times (I_p + I_h)} \quad (2)$$

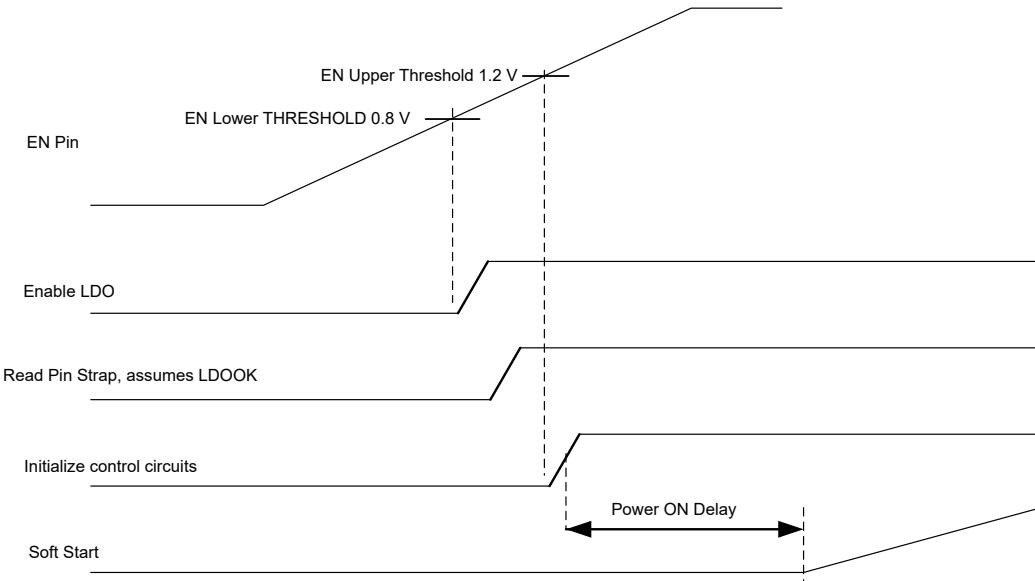

#### 6.3.3.1 スタートアップ時の内部イベント シーケンス

TPS543B25E のイネーブル機能には、2 つのスレッショルドレベル機能があります。EN ピンの電圧が内部スタートアップスレッショルド (約 0.8V) を下回ると、デバイスは低消費電力のシャットダウンモードとなります。EN ピンの電圧がこのスレッショルドを上回ると、内部リニア レギュレータ (LDO) が有効となり、外部 VDRV コンデンサを充電します。VCC が VDRV に接続され、VCC ピンの電圧が UVLO スレッショルド (約 3.6V) を超えると、TPS543B25E は、MSEL ピン (セクション 6.3.9 を参照) と SYNC/FSEL ピン (セクション 6.3.5.3 を参照) の設定に従ってピンストラップ構成を読み取り、スタンバイ状態に移行します。

VIN UVLO (約 4V) と VCC UVLO スレッショルドの両方を超えると、第 2 の EN ピンのスレッショルドがアクティブになります。したがって、EN ピンが (通常 1.2V) のスレッショルド上限を上回ると、TPS543B25E はパワーオン遅延 (通常 64μs) を実施し、制御ループ回路を初期化します。パワーオン遅延の後、電力段はイネーブルとなり、ソフトスタートが開始されます。

図 6-3. モーターのスタートアップシーケンス

イネーブル信号が急速に上昇する場合、EN の立ち上がりからソフトスタートの開始までの遅延時間は、デバイスの電力供給と初期化（リニア レギュレータの起動、VCC UVLO 超過、ピンストラップレベルの読み取り、フィードバック回路の初期化など）に必要な時間による関数となり、最大 1ms (通常) を要することがあります。

#### 6.3.4 スイッチング周波数の選択

デバイスのスイッチング周波数は、SYNC/FSEL ピンから AGND に抵抗 ( $R_{FSEL}$ ) を接続することで選択されます。周波数のオプションと、対応するプログラミング抵抗は [表 6-1](#) に一覧表示されています。許容誤差 1% 以下の抵抗を使用してください。

表 6-1. スイッチング周波数の選択

| $R_{FSEL}$ で許容される公称範囲は、(1%) (k $\Omega$ ) です | 推奨 E96 標準値は、(1%) (k $\Omega$ ) です | 推奨 E12 標準値は、(1%) (k $\Omega$ ) です | $f_{sw}$ (kHz) |

|----------------------------------------------|-----------------------------------|-----------------------------------|----------------|

| $\geq 24.0$                                  | 24.3                              | 27.0                              | 500            |

| 17.4 ~ 18.0                                  | 17.4                              | 17.8                              | 750            |

| 11.8 ~ 12.1                                  | 11.8                              | 12.1                              | 1000           |

| 8.06 ~ 8.25                                  | 8.06                              | 8.25                              | 1500           |

| $\leq 5.11$                                  | 4.99                              | 4.75                              | 2200           |

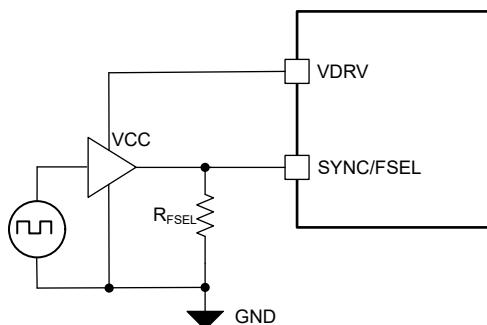

#### 6.3.5 外部クロックへのスイッチング周波数の同期

TPS543B25E は、20% ~ 80% のデューティ サイクルで SYNC/FSEL ピンに方形波クロック信号を適用することで同期できます。外部クロックは、本デバイスの起動前または動作中に適用できます。本デバイスが起動する前に外部クロックが適用される場合、SYNC/FSEL から AGND へのレジスタは不要です。デバイスが起動した後に外部クロックが適用される場合、クロック周波数は SYNC/FSEL 抵抗によって設定された周波数の  $\pm 20\%$  以内である必要があります。デバイスの起動後に外部クロックが適用されると、デバイスは外部クロックパルスによる連続する 4 回のスイッチングサイクルをカウントした後、この外部クロックとの同期を開始します。[セクション 6.3.5.2](#) を参照してください。

クロック周波数の 20% を超える範囲を検出するための内部回路はありませんが、クロック周波数は LC 設計の安定性範囲外にあるため、同期クロックが SYNC/FSEL 抵抗によって設定された周波数の  $\pm 20\%$  以内となっていることをお客様が確認していただく必要があります。

### 6.3.5.1 内部 PWM 発振周波数

外部クロックが存在する場合、本デバイスはスイッチング周波数をクロックに同期させます。外部クロックが存在しない場合、本デバイスはデフォルトで内部 PWM 発振器周波数に設定されます。

外部クロック信号が印加される前にデバイスが起動する場合、内部 PWM 発振器の周波数は、 $R_{FSEL}$  抵抗によって設定されます（[セクション 6.3.5.3](#) に基づく）。デバイスは、外部クロックが適用されるか、または外部クロックが存在しないときに、この周波数でスイッチングを行います。

本デバイスの起動前に外部クロック信号が印加される場合、 $R_{FSEL}$  抵抗は不要です。その後、デバイスは外部クロック周波数をデコードし、内部 PWM 発振器の周波数を選択します。

**表 6-2. 内部発振器周波数のデコード**

| 外部同期クロック周波数 (kHz) | デコードされた内部 PWM 発振器周波数 (kHz) |

|-------------------|----------------------------|

| 400 ~ 600         | 500                        |

| 600 ~ 857         | 750                        |

| 857 ~ 1200        | 1000                       |

| 1200 ~ 1810       | 1500                       |

| 1810 ~ 2640       | 2200                       |

外部同期クロック周波数範囲のスレッショルドの許容誤差は約  $\pm 5\%$  です。外部クロック周波数がこの許容範囲内の場合、内部 PWM 発振器の周波数を、そのスレッショルドの上または下の周波数としてデコードできます。同期クロックが失われた場合に使用されるのは内部周波数であるため、TI は、どちらの周波数でも安定性を確保できるよう、出力 LC フィルタとランプを選択することを推奨します。[表 6-3](#) は、デコードスレッショルドの許容範囲を示します。外部クロックがこれらの範囲のいずれかになる場合、TI は、可能な内部 PWM 発振器周波数の両方に対するコンバータの安定性を確保するようコンバータを設計することを推奨します。

**表 6-3. 周波数デコードスレッショルド**

| 最小値 (kHz) | 標準値 (kHz) | 最大値 (kHz) |

|-----------|-----------|-----------|

| 570       | 600       | 630       |

| 814       | 857       | 900       |

| 1140      | 1200      | 1260      |

| 1736      | 1810      | 1884      |

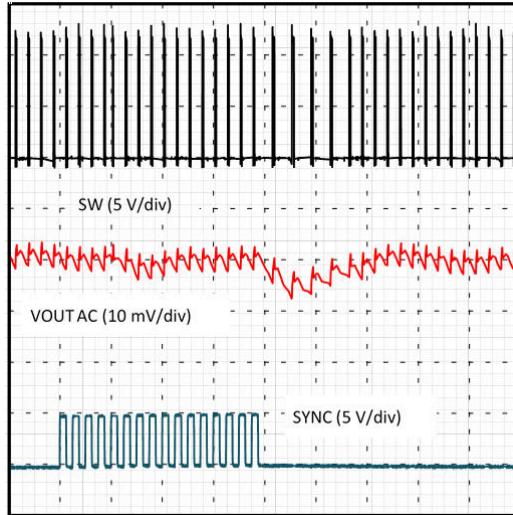

### 6.3.5.2 同期の損失

動作中に同期が失われた場合、デバイスは同期クロックが戻るまで、デフォルトの内部 PWM 発振器周波数を使用します。クロックが検出されなくなると、デバイスは 4 サイクル連続して内部クロック周波数の 70% でスイッチングを行います。クロックパルスなしで 4 サイクル連続で経過した後、デバイスは通常の内部 PWM 発振器周波数で動作します。

図 6-4. クロック同期遷移

### 6.3.5.3 SYNC/FSEL ピンとのインターフェイス

アプリケーションで同期クロックとの同期が必要であるが、デバイスが有効になる前にクロックが利用できない場合、テキサスインスツルメンツは、 $R_{FSEL}$  値を適切に検出できるように高インピーダンスバッファを推奨します。図 6-5 に、推奨される実装を示しています。 $R_{FSEL}$  値を適切に検出するためには、バッファ出力へのリーク電流は  $5\mu\text{A}$  未満である必要があります。デバイスが  $R_{FSEL}$  値を検出する前に、デバイスの VDRV 出力からバッファに電力を供給し、VCC 電圧が利用可能であり、バッファ出力が高インピーダンスであることを確認します。VDRV ピンからバッファに電力を供給するときは、VDRV ピンへの外部負荷は  $2\text{mA}$  未満である必要があります。

図 6-5. SYNC (同期)/ FSEL ピンのバッファとのインターフェイス

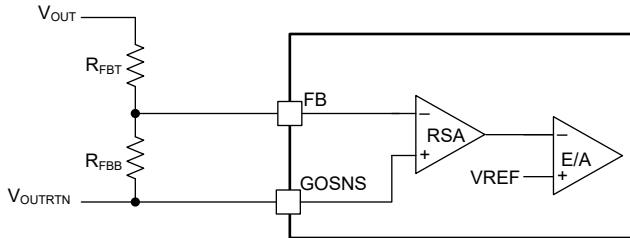

### 6.3.6 リモート センス アンプと出力電圧の調整

専用の高速、低オフセットの計測タイプ アンプを使用して、出力電圧のリモート センシングを実施しています。以下で説明する出力電圧設定分圧抵抗を出力電圧検知ポイントから GOSNS ピンに接続します。中心点は FB ピンに接続します。GOSNS ピンは、負荷の近くの場所で、コンバータの出力電圧のリターンに接続するようにします。

図 6-6 に示すように、出力電圧は、コンバータ出力 ( $V_{out}$ ) と FB ピンとの間の分圧抵抗回路によってプログラミングされます。公差 1% 以内の分圧抵抗を使用します。

図 6-6. FB 抵抗デバイダ

下側抵抗 (通常は  $10\text{k}\Omega$ ) の固定値から開始して、この [式 3](#) を使用して分周器の上側抵抗を計算します。

$$R_{FBT} = R_{FBB} \times \left( \frac{V_{OUT}}{V_{REF}} - 1 \right) \quad (3)$$

### 6.3.7 ループ補償のガイドライン

TPS543B25E は、ほとんどのアプリケーションに内部帰還ループ補償を提供するため、高度な電流モード制御 (ACM) アーキテクチャを採用しています。 $V_{IN}$ 、デューティサイクル、およびローサイド FET 電流情報を生成し、内部検出インダクタのバレー電流による寄与と組み合わせた内部ランプを適用することで、ACM は出力 LC フィルタの 1 つのポールをキャンセルし、位相補償を行いループの安定性を確保します。内部補償方式と同様に、特定の設計ガイドラインに従う必要があります。以下のセクションで、コンバータ設計のガイドラインを説明します。

#### 6.3.7.1 出力フィルタ インダクタのトレードオフ

出力インダクタの選択は、コンバータを設計する際に最も重要な選択肢の 1 つです。以下のリストは、インダクタンスの値を決定する際の検討事項の要点をまとめたものです。その他の検討事項については、[セクション 7](#) を参照してください。

まずは、インダクタの値を全負荷の 30% から 50% の範囲 リップル電流 ( $\Delta I$ ) となるように設定します。

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}} \quad (4)$$

- インダクタの値の選択は、負荷過渡応答と直接相関します。インダクタの値が大きすぎると、負荷過渡応答が不十分になる可能性があります。

- リップル電流は、コンバータが電流制限に入る DC 負荷電流に影響を及ぼします。全負荷時のピークバレー電流が、電流制限スレッショルドより十分なマージンで下回っていることを確認します。推奨される範囲は、電流制限スレッショルドの 60% ~ 80% です。

- リップル電流は、コンバータの RMS 損失に影響を及ぼします。リップル電流が大きくなるほど、RMS 損失は大きくなります。

#### 6.3.7.2 ランプ コンデンサの選択

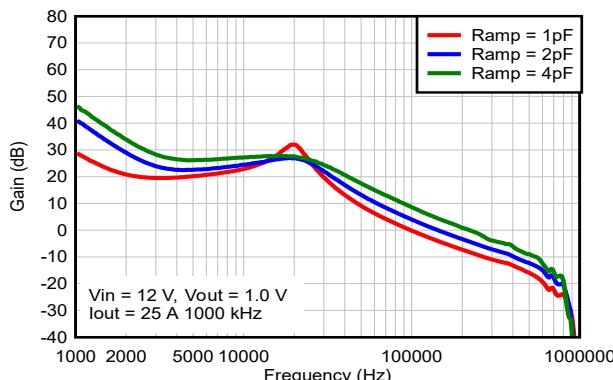

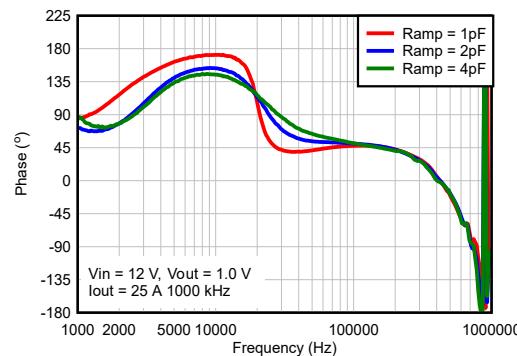

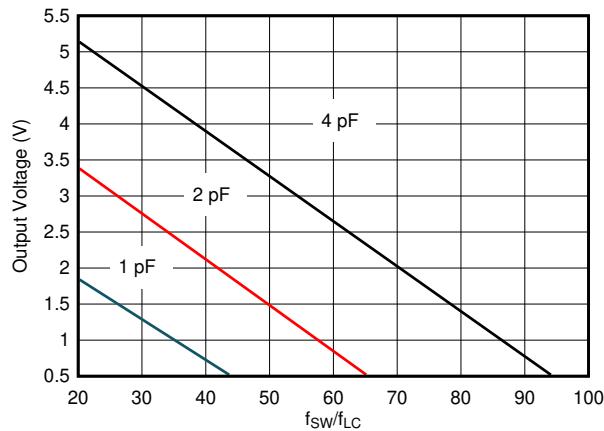

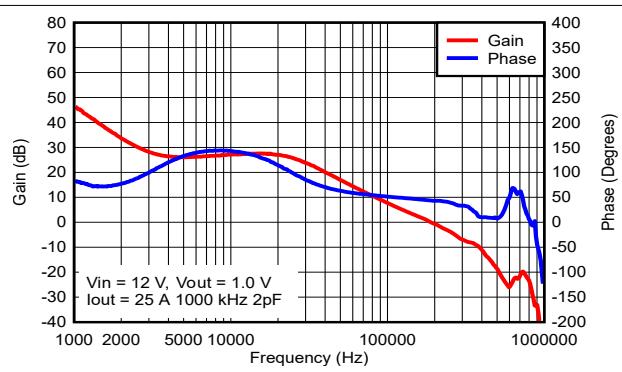

TPS543B25E は、入力電圧、デューティサイクル、およびローサイド FET 電流情報を使用して、内部ランプを生成します。ランプの振幅は、内部ランプ生成コンデンサ  $C_{RAMP}$  によって決定されます。 $C_{RAMP}$  の 3 つの値は、MSEL ピンの AGND への抵抗を使用して選択できます ([セクション 6.3.9](#) を参照)。コンデンサの選択肢は  $1\text{pF}$ 、 $2\text{pF}$ 、 $4\text{pF}$  です。ランプコンデンサが大きいほど、ランプ振幅は小さくなり、制御ループ帯域幅が広くなります。以下の図は、[図 7-1](#) の回路図における各ランプ設定によってループがどのように変化するかを示しています。

多くのアプリケーションでは、 $4\text{pF}$  の  $C_{RAMP}$  値で最適な性能を発揮しますが、ユーザーはループゲインと位相を測定して、特定のアプリケーションに最適な  $C_{RAMP}$  値を決定する必要があります。

- 最初に、[式 5](#) と [表 6-4](#) を使用して、ランプ時定数を計算します。

$$\tau_{CRAMP} = \frac{C_{RAMP} \times 10^6}{\text{Lookup1} - \text{Lookup2} \times \frac{V_{OUT}}{V_{IN}}} \quad (5)$$

表 6-4. ランプ選択ルックアップ値

| $f_{SW}$ (kHz) | LOOKUP1 の値 | LOOKUP2 の値 |

|----------------|------------|------------|

| 500            | 0.372      | 0.297      |

| 750            | 0.548      | 0.445      |

| 1000           | 0.719      | 0.594      |

| 1500           | 1.04       | 0.891      |

| 2200           | 1.46       | 1.31       |

2. 次に、ランプコンデンサの電圧を計算して、 $C_{RAMP}$  に選択したコンデンサによってランプ振幅が 1.25V を超えないようにします。これにより、負荷過渡中にランプがグランドに対して飽和しないようにします。

$$V_{CRAMP} = \frac{V_{IN} \times (t_{ON} + 100\text{ns})}{\tau_{CRAMP}} \quad (6)$$

- $C_{RAMP}$  容量が大きいほど、ループゲインは最大になります。

- $C_{RAMP}$  容量が小さいと、出力コンデンサが少なくて済むため、クロスオーバー周波数が高くなります。

図 6-7 および 図 6-8 は、セクション 7 の回路図における各ランプ設定によってループがどのように変化するかを示しています。

図 6-7. ループゲインとランプ設定との関係

図 6-8. ループ位相とランプ設定との関係

### 6.3.7.3 出力コンデンサの選択

- 使用するコンデンサの ESR ゼロ周波数を、予測されるクロスオーバー周波数の 5 倍以上にする必要があります。このようにして、ESR がループゲインに及ぼす影響を、管理可能なレベルまで小さくします。

$$f_{ESR\_ZERO} = \frac{1}{2\pi \times R_{ESR} \times C} \quad (7)$$

- 出力キャパシタンスの大きさは、コンバータの閉ループ帯域幅に直接影響を及ぼします。容量や帯域幅が小さすぎると、安定性を維持するには高すぎる場合があります。

- 出力キャパシタンスの大きさは、負荷降下中の出力電圧のオーバーシュートに直接影響します。容量が不足していると、出力インダクタに蓄積されたエネルギーが急激な負荷減少時に出力電圧の過電圧を引き起こす可能性があります。

- 出力キャパシタンスのインピーダンス（コンデンサのインピーダンスと ESR を追加した場合）は、コンバータの出力リップルノイズに影響を及ぼします。インピーダンスが高すぎる（容量が不足している、ESR が高すぎる、または両方が原因）と、システム要件を上回る出力リップルが発生する可能性があります。

$$V_{RIPPLE} = \Delta I \times \left( R_{ESR} + \frac{1}{2\pi \times f_{SW} \times C} \right) \quad (8)$$

### 6.3.7.4 優れた過渡応答を実現する設計方法

以下のコンバータ補償を設計する方法で、負荷過渡応答を最適化できます。

- 過渡応答の目標を満たすために必要な出力インピーダンスを計算します。この式では、負荷ステップ過渡がコンバータの BW よりも高速であることを仮定しています。

$$Z_{OUT\_REQUIRED} = \frac{\text{delta\_V}_{OUT}}{\text{delta\_I}_{OUT}} \quad (9)$$

- 出力インダクタンスの値を選択します。

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}} \quad (10)$$

- 過渡応答の目標を満たすために必要なコンバータの出力インピーダンスを計算します。

$$Z_{OUT\_CONVERTER} = \frac{\left(0.00135 + \frac{L}{\tau_{CRAMP}}\right)}{34} \times \frac{V_{OUT}}{V_{REF}} \quad (11)$$

$Z_{OUT\_CONVERTER}$  が、手順 1 で得られた  $Z_{OUT\_REQUIRED}$  より小さいことを確認してください。また、 $C_{RAMP}$  の電圧が許容範囲内にあることを再確認してください(前のセクションを参照)。大きすぎる場合は、より大きな  $C_{RAMP}$  値を使用します。

- インピーダンス要件を満たすために必要な最小出力キャパシタンスを計算します。

$$C_{OUT\_MIN} = \frac{1}{2\pi \times Z_{OUT\_CONVERTER} \times f_{CO\_DESIRED}} \quad (12)$$

ここで、

- $f_{CO\_DESIRED}$  は、望まれるコンバータの閉ループクロスオーバー周波数で、通常はコンバータのスイッチング周波数  $1/8$  から  $1/4$  です。

- 必要な出力コンデンサの数を計算します。前のセクションから、**ESR** のガイドラインを使用してコンデンサのタイプと値を選択し、この式で必要なコンデンサの数を求めます。コンデンサの インピーダンス(選択したクロスオーバー周波数における **ESR** + キャパシタンスのインピーダンス)が使用されていることに注意してください。

$$Z_{CAPACITOR} = R_{ESR\_CAPACITOR} + \frac{1}{2\pi \times C_{CAPACITOR} \times f_{CO}} \quad (13)$$

$$N_{CAPACITORS} = \frac{Z_{CAPACITOR}}{Z_{OUT\_CONVERTER}} \quad (14)$$

- TI.com のツールの 1 つを使用し、設計の値でシミュレーションを行ってください。

### 6.3.8 ソフトスタートおよびプリバイアス出力スタートアップ

起動中、デバイスはリファレンス電圧をゼロから最終値まで徐々に増加させるため、コンバータの突入電流が減少します。ソフトスタート時間には 4 つのオプションがあります。この時間は、リファレンスが 0.5V まで上昇するのに要する時間です。

- 1ms

- 2ms

- 4ms

- 8ms

ソフトスタート時間は、MSEL ピンの AGND への抵抗によって選択します。[セクション 6.3.9](#) を参照してください。

起動前にプリバイアス出力状態が発生した場合、デバイスは電流が output から放電されることを防ぎます。単調なプリバイアススタートアップ中、SS ピンの電圧が FB ピンの電圧より高くなり、ハイサイド MOSFET がスイッチングを開始するまで、ローサイド MOSFET は電流をシンクできません。唯一の例外は、BOOT-SW 電圧が UVLO レッショルドを下回った場合です。BOOT-SW UVLO 中は、ローサイド MOSFET がオンになり BOOT コンデンサを充電できます。ローサイド

MOSFET の逆電流保護機能は、ハイサイド MOSFET がスイッチング開始した後、デバイスに追加の保護層を提供します。

### 6.3.9 MSEL ピン

ランプの振幅、ソフトスタート時間、電流制限の設定は、MSEL から AGND までのシングル抵抗  $R_{MSEL}$  を使用してプログラムできます。表 6-5 に、使用可能なオプションに対応する抵抗値を示します。許容誤差 1% 以下の抵抗を使用してください。「High」および「Low」設定に対応する電流制限スレッショルドについては、セクション 6.3.11.1 を参照してください。

表 6-5. MSEL ピンの選択

| $R_{MODE}$ (kΩ) | 電流制限 | $C_{RAMP}$ (pF) | ソフトスタート時間 (ms) |

|-----------------|------|-----------------|----------------|

| 1.78            | High | 1               | 1              |

| 2.21            | High | 1               | 2              |

| 2.74            | High | 1               | 4              |

| 3.32            | High | 1               | 8              |

| 4.02            | High | 2               | 1              |

| 4.87            | High | 2               | 2              |

| 5.9             | High | 2               | 4              |

| 7.32            | High | 2               | 8              |

| 9.09            | High | 4               | 1              |

| 11.3            | High | 4               | 2              |

| 14.3            | High | 4               | 4              |

| 18.2            | High | 4               | 8              |

| 22.1            | Low  | 1               | 1              |

| 26.7            | Low  | 1               | 2              |

| 33.2            | Low  | 1               | 4              |

| 40.2            | Low  | 1               | 8              |

| 49.9            | Low  | 2               | 1              |

| 60.4            | Low  | 2               | 2              |

| 76.8            | Low  | 2               | 4              |

| 102             | Low  | 2               | 8              |

| 137             | Low  | 4               | 1              |

| 174             | Low  | 4               | 2              |

| 243             | Low  | 4               | 4              |

| 412             | Low  | 4               | 8              |

### 6.3.10 パワーグッド (PG)

TPS543B25E PG ピンはオープンドレイン出力であり、High 信号を出力するための外部プルアップ抵抗が必要です。FB ピンが内部電圧リファレンスの 92% ~ 108% の間となった後、ソフトスタートが完了し、256μs のグリッチ除去時間が経過すると、PG ピンがデアサートされ、ピンがフローティングとなります。TI は、5.5V 以下の電圧源との間に抵抗値が 10kΩ ~ 100kΩ のプルアップ抵抗を配置することを推奨します。PG は、VIN 入力電圧が 1V を上回っているが、電流シンク能力が低くなった後に定義された状態となります。FB が公称内部リファレンス電圧の 84% を下回るか、116% を超える場合は、8μs グリッチ除去時間の後に、PG ピンは Low となります。VIN が UVLO を下回った場合、EN ピンが Low となるか、デバイスがサーマルシャットダウンに移行すると、PG は即座に Low となります。

### 6.3.11 出力過負荷保護

TPS543B25E は、ハイサイド MOSFET とローサイド MOSFET の両方をサイクルごとに電流制限することにより、出力過負荷 (つまり過電流) イベントから保護します。過電流状態が継続すると、デバイスはヒップモードに入ります。正のインダクタ電流および負のインダクタ電流の状況では、各種の保護機能が起動します。

#### 6.3.11.1 正のインダクタ電流保護

ノイズを安定させるための短いブランкиング時間後に導通するハイサイド MOSFET で電流が検出されます。ハイサイド過電流スレッショルドを超えると、ハイサイド MOSFET が直ちにオフになります。ローサイド MOSFET がオンになります。ハイサイド MOSFET は電流がローサイド MOSFET 過電流スレッショルドを下回るまでオフに戻らないため、これにより、短絡状態が発生した場合にピーク電流が実質的に制限されます。ハイサイド過電流が連続 15 サイクルにわたって検出されると、このデバイスはヒップモードに入ります。

ローサイド MOSFET でも、ノイズが安定するように、短いブランкиング時間の後に導通している間に電流が検出されます。コントローラから次の入力 PWM 信号を受信したときにローサイド過電流スレッショルドを超えると、デバイスはその PWM パルスの処理をスキップします。ローサイド過電流スレッショルドを超えるまで、デバイスはハイサイド MOSFET を再度オフにしません。ローサイド過電流スレッショルドを連続 15 サイクルにわたって超えたままの場合、デバイスはヒップに移行します。ハイサイドとローサイドの過電流イベント用に 2 つの独立したカウンターがあります。オフ時間が短すぎると、ローサイド過電流がトリップできません。ただし、ローサイド過電流は、ハイサイドピーク過電流制限を超えた後にトリップを開始します。ピーク電流制限を超えると、オン時間が短くなり、オフ時間が延長されるためです。

ハイサイドとローサイドの正の過電流スレッショルドは、MSEL ピンを使用してプログラム可能です。2 組のスレッショルド (‘High’と‘Low’) が利用可能で、詳細は [表 6-6](#) にまとめられています。これらのスレッショルドの値は、DC 電流での開ループ測定により、正確に指定されます。実際のアプリケーションでは、インダクタ電流の増加率 (ランプレート) は、インダクタの両端の電圧 ( $V_{IN} - V_{OUT}$ ) およびインダクタンス値に依存します。このランプレートと電流検出回路の遅延が組み合わさることで、仕様値とわずかに異なる値が生じます。ハイサイド過電流制限が影響を受ける電流は、仕様よりもわずかに高くなる場合があり、ローサイド過電流制限が効果を発揮する電流は、仕様よりもわずかに低くなる場合があります。

**表 6-6. 過電流スレッショルド**

| MSEL 電流制限の設定 | ハイサイド過電流の標準値 (A) | ローサイド過電流の標準値 (A) |

|--------------|------------------|------------------|

| High         | 36               | 27.5             |

| Low          | 29               | 22               |

#### 6.3.11.2 負のインダクタ電流保護

ノイズを安定させるための短いブランкиング時間後に導通すると、ローサイド MOSFET で負の電流が検出されます。ローサイドの負の過電流スレッショルドを超えると、ローサイド MOSFET は直ちにオフになります。次のハイサイド MOSFET のターンオンは、クロックと PWM コンパレータによって決定されます。負の過電流スレッショルドの最小値は 7A です。正のインダクタ電流保護と同様に、電流検出コンパレータがトリップしたときのインダクタ電流の実際の値は電流ランプレートの関数です。その結果、負のインダクタ電流制限が効果を発揮する電流は、仕様よりもわずかに負の値になる可能性があります。

### 6.3.12 出力過電圧および低電圧保護

TPS543B25E には、出力過電圧および低電圧保護機能が組み込まれています。過電圧が検出された場合、デバイスは再起動を試みる前に出力電圧を安全なレベルまで放電しようとします。過電圧スレッショルドを超えると、ローサイド負の過電流スレッショルドに達するまで、ローサイド MOSFET がオフになります。この時点で、インダクタ電流がゼロになるまで、ハイサイド MOSFET はオフ状態を維持します。その後、ローサイド負の過電流スレッショルドに達するまで、ローサイド MOSFET は再度オフになります。出力電圧が PG ウィンドウに戻るまでこのプロセスが繰り返されます。この後、デバイスは再起動し、ソフトスタートサイクルを実行します。デバイスは、ヒップ時間を持たずに再起動します。

低電圧状態が検出されると、デバイスはヒップ状態になり、7 回のソフトスタートサイクルを経たのちに再起動します。低電圧保護は、ソフトスタートの完了後に有効になります。

### 6.3.13 過熱保護

ダイの温度が  $165^{\circ}\text{C}$  を超えると、デバイスはオフになります。ダイ温度がヒステリシスレベル (通常は  $12^{\circ}\text{C}$ ) 未満に低下すると、デバイスは再起動します。温度がヒステリシスレベルを下回るまで、デバイスはスイッチを切り替えたり、再起動を試みるためのヒックアップを行いません。温度がヒステリシスレベルを下回ると、デバイスはヒップを実行せずに再起動します。

### 6.3.14 出力電圧放電

TPS543B25E が有効化されているが、故障状態によりハイサイド FET とローサイド FET が無効化されている場合、出力電圧放電モードが有効になり、SW から PGND への放電 FET がオンになり、出力電圧が放電されます。オルトが解消された後、またはヒップが終了するまでの待機時間の後に、コンバータがスイッチングを再開する準備が整った時点での放電 FET はオフになります。

出力電圧放電モードは、次のいずれか故障事象によってアクティブになります。

- ハイサイドまたはローサイドの正の過電流

- サーマル シャットダウン

- 出力電圧低電圧

- VIN UVLO

## 6.4 デバイスの機能モード

### 6.4.1 強制連続導通モード

TPS543B25E は、通常動作時に強制連続導通モード (FCCM) で動作します。

### 6.4.2 ソフトスタート時の不連続導通モード

ソフトスタートの開始時に、コンバータは最初の 16 PWM サイクルにわたって不連続導通モード (DCM) で動作します。この期間中、ゼロ交差検出コンパレータを使用して、電流が 0 アンプに達した際にローサイド MOSFET をオフにし、出力のプライバイス状態の放電を防止します。DCM の 16 サイクル終了後、コンバーターは残りの起動期間および定格運転に移行するため、FCCM モードに入ります。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPS543B25E は、4V ~ 18V の入力と 25A の負荷値を想定して設計した、同期整流降圧コンバータです。この手順では、セラミック出力コンデンサを使用した高周波スイッチング レギュレータの設計を示しています。

### 7.2 代表的なアプリケーション

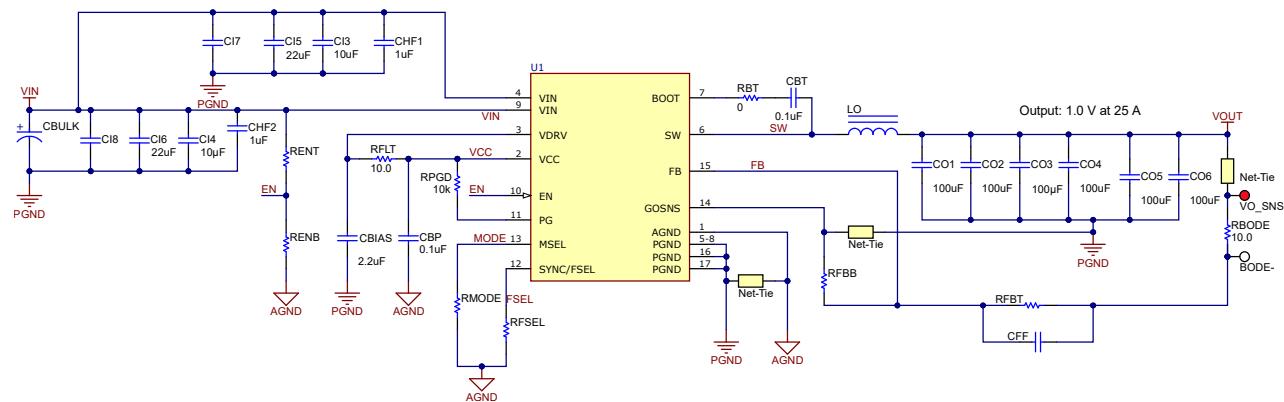

#### 7.2.1 1MHz アプリケーションでの 1.0V 出力

図 7-1. 12V 入力と 1.0V 出力での、1MHz 回路図

#### 7.2.1.1 設計要件

この設計例では、表 7-1 に示すパラメータを使用します。

表 7-1. 設計パラメータ

| パラメータ                  | 数値の例                 |

|------------------------|----------------------|

| 入力電圧範囲 ( $V_{IN}$ )    | 4.5 ~ 18V、公称 12V     |

| 出力電圧 ( $V_{OUT}$ )     | 1.0V                 |

| 出力電流定格 ( $I_{OUT}$ )   | 25A                  |

| スイッチング周波数 ( $f_{sw}$ ) | 1000kHz              |

| 定常状態の出力リップル電圧          | 10mV                 |

| 出力電流負荷ステップ             | 12.5A                |

| 過渡応答                   | $\pm 50mV (\pm 5\%)$ |

#### 7.2.1.2 詳細な設計手順

##### 7.2.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS543B25E デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 7.2.1.2.2 スイッチング周波数

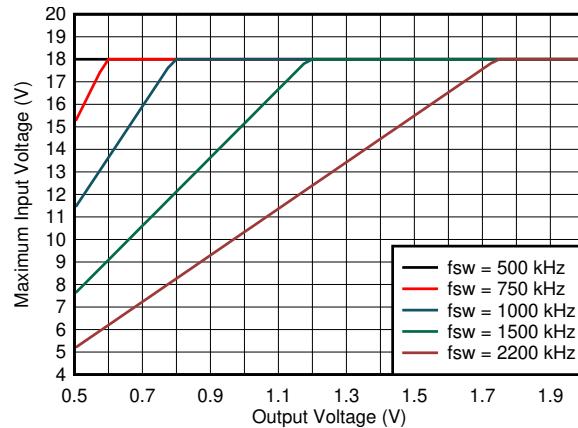

最初のステップは、スイッチング周波数を決定することです。TPS543B25E は、500kHz から 2.2MHz までの 5 つの異なる周波数で動作できます。 $f_{sw}$  は、FSEL ピンとグランドとの間にある抵抗の値により設定されます。一般には、可能な限り高いスイッチング周波数が求められます。なぜなら、この周波数によって設計サイズが最小になるからです。スイッチング周波数が高ければ、低い周波数でスイッチングする電源と比較して、インダクタと出力コンデンサを小型化できます。高いスイッチング周波数を選択することによる主なトレードオフは、スイッチング電力損失の増加です。これにより、レギュレータの効率が低下します。

特定のアプリケーションの最大スイッチング周波数は、レギュレータの最小オン時間によって制限され、最大  $f_{sw}$  は 式 15 を使って推定できます。このアプリケーションでは、最大最小オン時間である 40ns、最大入力電圧 18.0V を使用すると、最大スイッチング周波数は 1389kHz となります。選択するスイッチング周波数には、許容誤差も考慮する必要があります。設計サイズと効率のバランスを考慮し、100kHz のスイッチング周波数が選択されました。周波数を 1000kHz に設定するには、選択した FSEL 抵抗は、表 6-1 に基づき 11.8kΩ となります。

$$f_{sw}(\max) = \frac{1}{tonmin} \times \frac{V_{OUT}}{V_{IN}(\max)} \quad (15)$$

図 7-2 は、各 FSEL 周波数の最大推奨入力電圧と出力電圧との関係を示します。このグラフは、最大最小オン時間 40ns を使用し、スイッチング周波数の許容誤差である 10% も含んでいます。

図 7-2. 最大入力電圧と出力電圧の関係

### 7.2.1.2.3 出力インダクタの選択

出力インダクタを計算するには、式 16 を使用します。 $K_{IND}$  は、最大出力電流に対するインダクタのリップル電流の量を表す比です。インダクタリップル電流は、出力コンデンサによってフィルタリングされます。したがって、大きなインダクタリップル電流を選択すると、それ以上のリップル電流定格を持つ出力コンデンサが必要となるため、出力コンデンサの選択に

影響が及びます。小さなインダクタ リップル電流を選択すると、過渡応答性能 劣させる可能性があります。インダクタリップル  $K_{IND}$  は、ほとんどのアプリケーションにおいて 0.1 から 0.4 の範囲にあり、ピーク ツ ピークの間リップル電流の範囲は 2A から 8A となります。ターゲット  $I_{RIPPLE}$  は 1A 以上である必要があります。

この設計例では、 $K_{IND} = 0.2$  を使用し、インダクタ値は 0.183 $\mu$ H と計算されます。インダクタンスが 0.150 $\mu$ H のインダクタが選択されます。インダクタの RMS (実効値) 電流および飽和電流定格を超えないようにしてください。RMS およびピークインダクタ電流は、式 18 および 式 19 から求められます。この設計では、RMS インダクタ電流は 25.96 A で、ピークインダクタ電流は 28.498A です。選択したインダクタは、SLR1050A-151KEC です。インダクタの飽和電流定格は、51A、RMS 電流定格は、56.7A、標準的な DC 直列抵抗は 0.39m $\Omega$  です。

インダクタを流れるピーク電流は、インダクタ リップル電流プラス出力電流です。パワーアップ時、障害発生時、または負荷過渡状態中は、インダクタ電流が 式 19 で計算されたピーク インダクタ電流レベルを超えて増加する場合があります。過渡状態では、インダクタ電流がデバイスのスイッチ電流制限まで増加する場合があります。この理由により、最も保守的なアプローチは、定常状態のピークインダクタ電流ではなく、スイッチ電流制限に基づいてインダクタの電流定格を指定することです。

$$L1 = \frac{(V_{IN} - V_{OUT})}{I_0 \times K_{IND}} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}} \quad (16)$$

$$I_{ripple} = \frac{(V_{INMAX} - V_{OUT})}{L1} \times \frac{V_{OUT}}{V_{INMAX} \times f_{SW}} \quad (17)$$

$$I_{L_{rms}} = \sqrt{I_0^2 + \frac{1}{12} \times \left( \frac{(V_{INMAX} - V_{OUT})}{L1} \times \frac{V_{OUT}}{V_{INMAX} \times f_{SW}} \right)^2} \quad (18)$$

$$I_{L_{peak}} = I_{OUT} + \frac{I_{ripple}}{2} \quad (19)$$

#### 7.2.1.2.4 出力コンデンサ

出力コンデンサの値を選択する際には、主に 2 つの検討事項があります。それらは出力電圧リップルと、レギュレータが負荷電流の大きな変化にどのように反応するかです。出力キャパシタンスは、これらの基準のうちより厳しいものに基づいて選択する必要があります。

負荷電流の大きな変化に対する望ましい応答は最初の基準であり、通常最も厳格な要件です。レギュレータは、負荷電流の大きく、速い増加または減少に対してはすぐには応答しません。出力コンデンサは、レギュレータが負荷ステップに応答するまで、供給または電荷を吸収します。制御ループは出力電圧の変化を検出し、負荷の変化に対応してピークスイッチ電流を調整する必要があります。最小出力キャパシタンス力は、ループ帯域幅の推定値に基づいて選択します。通常、ループ帯域幅は  $f_{SW} / 10$  付近です。式 20 により、必要な最小出力キャパシタンスを推定します。

この例では、負荷過渡応答は、負荷ステップが 12.5A のときに  $V_{OUT}$  が 5% 変化するものと指定されています。したがって、 $\Delta I_{OUT}$  は 12.5A であり、 $\Delta V_{OUT}$  は 50mV です。このターゲットを使用すると、最小キャパシタンスは 398 $\mu$ F となります。この値は、出力電圧の変化について出力コンデンサの ESR を考慮していません。セラミック コンデンサの場合、ESR の影響は無視できるほど小さい場合があります。アルミ電解コンデンサやタンタル コンデンサの場合は、ESR が大きいため、負荷ステップの計算に含める必要があります。

$$C_{OUT} > \frac{\Delta I_{OUT}}{\Delta V_{OUT}} \times \frac{1}{2\pi \times \frac{f_{SW}}{10}} \quad (20)$$

ここで、

- $\Delta I_{OUT}$  は出力電流の変化量を表します。

- $\Delta V_{OUT}$  は出力電圧の許容変化量を表します。

ループ帯域幅に加えて、インダクタ電流のスルーレートを制限することで、レギュレータが負荷ステップに反応する速度を制限することができます。低デューティサイクルのアプリケーションでは、負荷が低下した後にインダクタ電流が低下するまでの時間が制限因子となる場合があります。式 21 は、負荷下降後の出力電圧の変化を制限するために必要な最小出力キャパシタンスを推定します。選択した  $0.150\mu\text{H}$  のインダクタンスを使用すると、最小キャパシタンスは  $234\mu\text{F}$  になります。

$$C_{\text{OUT}} > \frac{L_{\text{OUT}} \times \Delta I_{\text{OUT}}^2}{2 \times \Delta V_{\text{OUT}} \times V_{\text{OUT}}} \quad (21)$$

式 22 で、出力電圧リップル仕様を満たすために必要な最小出力キャパシタンスを計算します。この場合、最大定常状態出力電圧リップルは  $10\text{mV}$  になります。この要件下で、式 22 容量は  $88\mu\text{F}$  となります。

$$C_{\text{O}} > \frac{1}{8 \times f_{\text{SW}}} \times \frac{V_{\text{ORIPPLE}}}{I_{\text{RIPPLE}}} \quad (22)$$

ここで、

- $\Delta I_{\text{OUT}}$  は出力電流の変化量を表します。

- $\Delta V_{\text{OUT}}$  は出力電圧の許容変化量を表します。

- $f_{\text{SW}}$  は、レギュレータのスイッチング周波数です。

- $V_{\text{ORIPPLE}}$  は、最大許容定常状態の出力電圧リップルです。

- $I_{\text{RIPPLE}}$  は、インダクタリップル電流です。

最後に、アプリケーションに厳格な負荷過渡応答や出力リップルの要件がない場合は、MODE ピンで最も低いゲインランプ設定時でも制御ループが安定するように、一定の最小キャパシタンスが必要です。式 23 は、ループの安定性に必要な最小キャパシタンスを推定します。式 23 は、LC 周波数をスイッチング周波数に対して最小値に保つことで、最小のキャパシタンスを設定します。最小ゲインランプ設定が  $1\text{pF}$  での制限と出力電圧との対比については、図 7-3 を参照してください。出力が  $1\text{V}$  の場合、最小比は 35 であり、この比を使用すると、式 23 は最小キャパシタンスの  $207\mu\text{F}$  となります。

$$C_{\text{OUT}} > \left( \frac{\text{Ratio}}{2\pi \times f_{\text{SW}}} \right)^2 \times \frac{1}{L_{\text{OUT}}} \quad (23)$$

式 24 は、出力コンデンサが持つことができる最大合計 ESR を計算し、この結果が出力電圧リップル仕様を満たすための ESR が  $6\text{m}\Omega$  未満でなければならないことを示します。この場合、セラミックコンデンサを使用しますが、並列接続されたセラミックコンデンサの合計 ESR は、リップルを満たすために必要な値よりもはるかに小さくなります。コンデンサには、過剰な熱を発生させずに故障することなく処理できるリップル電流の限界があります。インダクタリップル電流に対して対応可能な出力コンデンサを指定する必要があります。コンデンサデータシートには、最大リップル電流の RMS 値が指定されています。式 25 を使用して、出力コンデンサがサポートしなければならない RMS リップル電流を計算できます。このアプリケーションでは、式 25 は  $1.2\text{A}$  を生成し、セラミックコンデンサのリップル電流定格は通常、この式よりもはるかに高くなります。

$$R_{\text{ESR}} < \frac{V_{\text{ORIPPLE}}}{I_{\text{RIPPLE}}} \quad (24)$$

$$I_{\text{CORMS}} = \frac{V_{\text{OUT}} \times (V_{\text{INMAX}} - V_{\text{OUT}})}{\sqrt{12} \times V_{\text{INMAX}} \times L_1 \times f_{\text{SW}}} \quad (25)$$

X5R および X7R セラミック誘電体はキャパシタンスとの体積比が高く、温度に対してかなり安定しているため、選択した X5R および X7R セラミック誘電体は電力レギュレータコンデンサとして同等です。出力コンデンサは、DC バイアスと AC 電圧の定格減衰を考慮して選択する必要があります。DC 電圧バイアスと AC RMS 電圧によるセラミックコンデンサのディレーティングキャパシタンス値は、通常、コンデンサメーカーの Web サイトに掲載されています。このアプリケーション例では、ESR が  $3m\Omega$  の  $100\mu F$ 、 $10V$ 、X5R、1210 のセラミックコンデンサが 6 個使用されています。6 個の並列コンデンサを使用する場合、コンデンサのメーカーの Web サイトを使用したディレーティング後の実効出力キャパシタンスの推定値は  $570\mu F$  です。1V では DC バイアスのディレーティングが約 -5% です。図 7-8 に示すように、ループのクロスオーバ一周波数が  $f_{SW} / 10$  の推定値を上回っていたため、計算された最小値よりも小さく使用できました。

### 7.2.1.2.5 入力コンデンサ

入力デカップリング セラミックコンデンサのタイプ X5R、X7R、または IC にできるだけ近くに配置されている VIN から PGND までと同等のものが必要です。少なくとも  $66\mu F$  以上のキャパシタンスが必要であり、一部のアプリケーションではバルク容量が必要になる場合があります。テキサスインスツルメンツは、入力電圧リップルを最小限に抑えるため、各 VIN ピンにできるだけ近づけてバイパスキャパシタンスを  $1\mu F$  以上にすることを推奨します。 $1\mu F$  のコンデンサを、デバイスの基板の同一面にある VIN ピン 4 と 9 のできるだけ近い位置に配置し、VIN ピンと SW ピンにおける高周波のオーバーシュートとアンダーシュートを低減するための高周波バイパス回路を構成する必要があります。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。コンデンサは、最大 RMS 入力電流よりも大きなリップル電流定格を有する必要があります。RMS 入力電流は、式 26 を使用して計算できます。

この設計例では、最大入力電圧をサポートするために、少なくとも  $25V$  の電圧定格を持つセラミックコンデンサが必要です。 $22\mu F$ 、1210、X7R、 $25V$ 、 $10\mu F$  の 2 個、0805、X7S、 $25V$ 、および  $1\mu F$  の 2 個、0402 または 0603、X7R  $25V$  の 2 個のコンデンサを並列接続して、IC の両側の VIN ピンから PGND ピンまでの近くに配置することが選択されました。コンデンサメーカーの Web サイトに基づき、合計セラミック入力容は公称入力電圧  $12V$  で  $25\mu F$  まで低下します。追加の  $100\mu F$  のセラミック容量と  $220\mu F$  のアルミ電解も、ラボベンチトップ電源に接続する際の長いリードをバイパスするために使用されます。

入力キャパシタンスの値によって、レギュレータの入力リップル電圧が決まります。入力リップル電圧は、式 26 を使って計算できます。最大の入力リップルは、デューティサイクルが 50% により近い状態で動作している時発生します。起こりります。 $I_{OUT(MAX)} = 25A$ 、 $C_{IN} = 25\mu F$ 、 $f_{SW} = 1000kHz$  の公称設計例の値を使用すると、 $12V$  の公称入力での入力電圧リップルは  $76.4mV$  となり、 $4.5V$  の最小入力で RMS 入力リップル電流は  $10.39A$  となります。

$$I_{CINRMS} = I_{OUT} \times \sqrt{\frac{(V_{INMIN} - V_{OUT})}{V_{INMIN}} \times \frac{V_{OUT}}{V_{INMIN}}} \quad (26)$$

$$\Delta V_{IN} = \frac{I_{OUTMAX} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \frac{V_{OUT}}{V_{IN}}}{C_{IN} \times f_{SW}} \quad (27)$$

### 7.2.1.2.6 調整可能な低電圧誤動作防止

システムの低電圧誤動作防止 (UVLO) は、 $R_{ENT}$  および  $R_{ENB}$  の外付け分割電圧を使用して調整します。UVLO には 2 つのスレッショルドがあり、1 つは入力電圧が上昇している時のパワーアップ中に適用され、もう 1 つは入力電圧の低下している時のパワーダウンまたはブランアウト中に適用されます。この設計例では、入力電圧が  $4.5V$  を超えた後 (UVLO を開始または有効にして)、電源がオンになり、スイッチングを開始するように設定されています。レギュレータがスイッチングを開始した後、レギュレータは入力電圧が  $3.95V$  を下回るまでその動作を継続します (UVLO が停止またはディスエーブル)。この例では、EN 抵抗デバイスによって設定されるスタートおよびストップの電圧が、内部固定 VIN UVLO よりも多くのヒステリシスを持つように選択されています。

式 1 と 式 2 を使用して、上限と下限の抵抗値を計算できます。これらの式が機能するためには、EN ピンの電圧ヒステリシスにより、 $V_{START}$  を  $1.1 \times V_{STOP}$  でなければなりません。規定された電圧では、 $R_{ENT}$  に使用される標準抵抗値は  $16.9k\Omega$ 、 $R_{ENB}$  に使用される標準抵抗値は  $6.04k\Omega$  です。

### 7.2.1.2.7 出力電圧抵抗の選択

出力電圧は、出力ノードから FB ピンまでの  $R_{FBT}$  と  $R_{FBB}$  で構成される抵抗デバイダによって設定されます。許容誤差 1% 以内の抵抗値を使用します。この設計例では、 $R_{FBB}$  に  $4.99\text{k}\Omega$  を選択しています。式 28 から、 $R_{FBT}$  は  $4.99\text{k}\Omega$  と計算されます。この抵抗は、標準的な 1% 抵抗値です。

$$R_{FBT} = R_{FBB} \times \left( \frac{V_{OUT}}{V_{REF}} - 1 \right) \quad (28)$$

PCB レイアウトで セクション 7.4.1 に推奨される AGND から PGND への接続を使用していない場合、帰還ピンのノイズが最大負荷時の出力電圧レギュレーションを劣化させる可能性があります。 $1.00\text{k}\Omega$  のより小さな  $R_{FBB}$  を使用すると、このノイズの影響を最小限に抑えることができます。

### 7.2.1.2.8 ブートストラップコンデンサの選定

適切な動作のためには、BOOT ピンと SW ピンの間に  $0.1\mu\text{F}$  のセラミックコンデンサを接続する必要があります。DC バイアスのディレーティングを最小限に抑えるため、コンデンサの定格は  $10\text{V}$  以上にする必要があります。

BOOT コンデンサと直列に抵抗を追加で、ハイサイド MOSFET のターンオンを低速にし、SW ピンのオーバーシュートの立ち上がりエッジのオーバーシュートを低減できます。この動作には、電力損失の増加と効率の低下というトレードオフが伴います。ベストプラクティスとして、プロトタイプの設計に  $0\Omega$  のプレースホルダを配置します。これは、PCB レイアウトの寄生インダクタンスが通常よりも SW ピンでの電圧オーバーシュートが大きくなる場合に備えてください。この方法により、電圧をデバイスの定格内に維持し、SW ノードの高周波ノイズを低減することができます。

### 7.2.1.2.9 VDRV および VCC コンデンサの選択

適切な動作のためには、VDRV ピンと PGND ピンの間に  $2.2\mu\text{F}$  のセラミックコンデンサを接続する必要があります。DC バイアスのディレーティングを最小限に抑えるため、コンデンサの定格は  $10\text{V}$  以上にする必要があります。VDRV ピンは、内部リニアレギュレータの出力とゲートドライバへの電源です。VCC ピンはアナログ制御回路の電源であり、VCC から AGND に  $0.1\mu\text{F}$  および  $10\text{V}$  定格以上のセラミックコンデンサを接続する必要があります。VDRV と VCC ピンの間に  $10\Omega$  の 0402 抵抗を接続する必要があります。

### 7.2.1.2.10 PGOOD プルアップ抵抗

$10\text{k}\Omega$  抵抗は、FB 条件が満たされたときにパワーグッド信号をプルアップするために使用されます。プルアップ電圧源は、PGOOD ピンの絶対最大値である  $6\text{V}$  より低くする必要があります。

### 7.2.1.2.11 電流制限の選択

MODE ピンを使用して、2 つの電流制限設定を選択します。最小値が最大定常状態ピーク電流の 1.1 倍以上の電流制限設定を選択します。この選択は、部品の許容誤差と負荷過渡に対するマージンを確保するために行います。この設計では、高い電流制限設定を選択するために、最小電流制限が  $7.45\text{A}$  を超える必要があります。

### 7.2.1.2.12 ソフトスタート時間の選択

MODE ピンを使用し、4 種類のソフトスタート時間から選択します。これは、レギュレータの出力電圧に対して特定のタイミング要件が負荷にある場合に便利です。出力キャパシタンスが非常に大きく、出力キャパシタンスを出力電圧レベルまで迅速に充電するために大きな電流が必要な場合には、長いソフトスタート時間を使用することも有用です。コンデンサを充電するために必要な大電流は、入力電源からの過大な電流引き込みにより、電流制限に達したり、入力電圧レールが低下したりする可能性があります。出力電圧のスルーレートを制限することで、その両方の問題を解決できます。この設計例では、ソフトスタート時間を  $1.0\text{ms}$  に設定しています。このソフトスタート時間により、出力コンデンサを公称出力電圧まで充電するために必要な電流はわずか  $0.14\text{A}$  です。

### 7.2.1.2.13 ランプ選択および制御ループの安定性

3つの異なるランプ設定から、MODE ピンを使用して選択します。優れたランプ設定は、 $V_{OUT}$ 、 $f_{SW}$ 、 $L_{OUT}$ 、 $C_{OUT}$  に依存します。開始するには、式 29 を使用して LC ダブルポール周波数を計算します。次に、 $f_{SW}$  と  $f_{LC}$  の間の比を計算します。この比率と出力電圧に基づいて、図 7-3 を使用して推奨ランプ設定を選択します。出力が 1V の場合、TI は約 35 から 58 の比に対して 1pF のランプ、約 58 から 86 の比に対して 2pF のランプ、約 86 より大きい比に対して 4pF のランプを推奨します。一般に、設計でサポート可能な最大のランプコンデンサを使用します。ランプコンデンサを大きくすると過渡応答が改善されますが、安定性マージンが減少したり、オン時間ジッタが増加したりする可能性があります。

この設計では、 $f_{LC}$  は 17.5kHz であり、比は 57 となり、1pF と 2pF のランプ設定の境界にあります。ベンチ評価により、2pF のランプで十分な安定性マージンを持つ設計が得られたため、この設定が最良の過渡応答が得られる設定として選択されました。図 7-3 で指定されている推奨ランプ設定には、潜在的な部品の許容差および動作条件ごとの変動を考慮するためのマージンが含まれているため、この例に示すように、より高いランプ設定を使用することも可能です。

$$f_{LC} = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}} \quad (29)$$

図 7-3. 推奨ランプ設定

フィードフォワードコンデンサ ( $C_{FF}$ ) を上側帰還抵抗 ( $R_{FBT}$ ) と並列に使用し、制御ループにゼロを追加して、位相ブーストを行います。位相マージン要件を満たすためにゼロが必要になる可能性があるため、このコンデンサに対応するプレースホルダを差し込みます。このコンデンサには、ゼロより高い周波数のポールも追加されます。ポール周波数とゼロ周波数は独立していないため、ゼロ位置を選択した後、ポールも固定されます。このゼロは、式 30 で  $C_{FF}$  の値を計算することにより、 $f_{SW} 1/4$  に配置されます。計算値は 128pF ですが、この値を最も近い標準値である 120pF に切り下げます。

AC 応答のベンチ測定を使用して、この設計例のフィードフォワードコンデンサを 180pF に増やし、過渡応答を向上させました。

$$C_{FF} = \frac{1}{\pi \times R_{FBT} \times \frac{f_{SW}}{2}} \quad (30)$$

より大きなフィードフォワードコンデンサを使用して過渡応答をさらに改善しますが、すべての動作条件で最小  $-9\text{dB}$  のゲインマージンが得られるように注意してください。フィードフォワードコンデンサは、出力のノイズを **FB** ピンに注入します。この追加のノイズは、スイッチングノードでのオンタイムジッターの増加を引き起こす可能性があります。ゲインマージンが小さすぎると、広いパルスと狭いパルスの動作が繰り返し発生する可能性があります。フィードフォワードコンデンサと直列に  $100\Omega$  の抵抗を追加すると、優れた選択肢でない PCB レイアウトの場合に **FB** ピンへのノイズの影響を低減できます。この抵抗値は、値が大きくなるほどフィードフォワードポールとゼロが近づき、フィードフォワードコンデンサが供給する位相ブーストが劣化するため、値を小さく保つ必要があります。

ポリマーやタンタルなど、より高い ESR 出力コンデンサを使用する場合は、ESR ゼロ ( $f_{\text{ESR}}$ ) を考慮する必要があります。ESR ゼロは、[式 31](#) を使って計算できます。ESR ゼロ周波数が  $f_{\text{SW}}$  の推定帯域幅の  $1/10$  未満である場合、この周波数はゲインマージンと位相マージンに影響を及ぼす可能性があります。**FB** ピンと接地との間に直列に R-C を接続して、必要に応じて制御ループにポールを追加できます。この設計ではすべてセラミックコンデンサを使用しているため、ESR ゼロの影響は無視されます。

$$f_{\text{ESR}} = \frac{1}{2 \times \pi \times C_{\text{OUT}} \times R_{\text{ESR}}} \quad (31)$$

#### 7.2.1.2.14 MODE ピン

モード抵抗を  $4.87\text{k}\Omega$  に設定し、大電流制限設定、 $2.0\text{ms}$  のソフトスタート、 $2\text{pF}$  のランプを選択します。MODE ピン設定の全一覧については、[表 6-5](#) を参照してください。

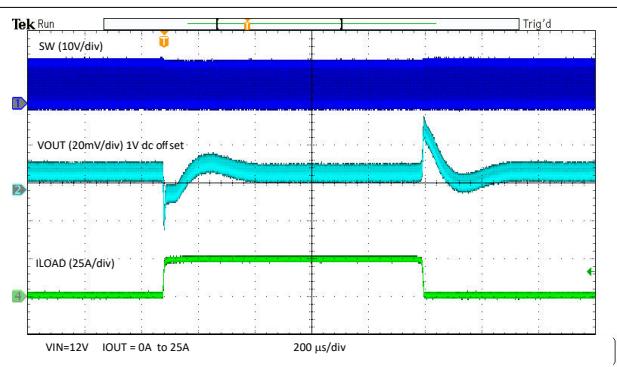

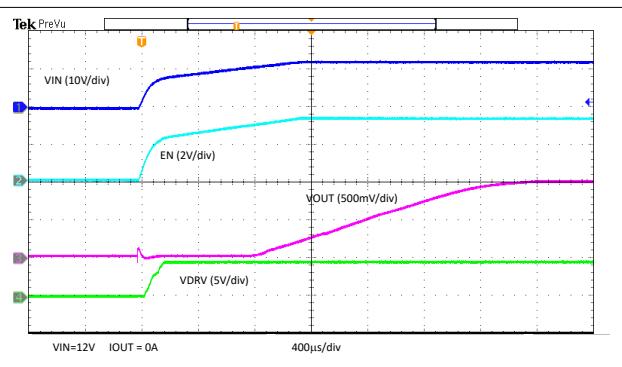

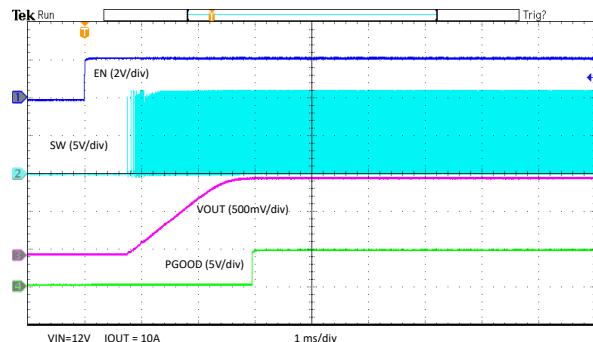

### 7.2.1.3 アプリケーション曲線

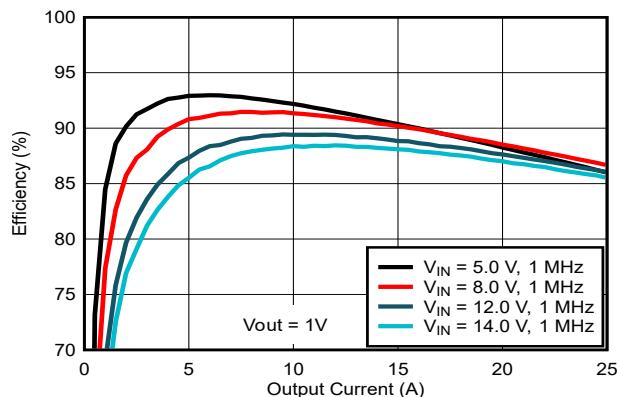

図 7-4. 効率曲線

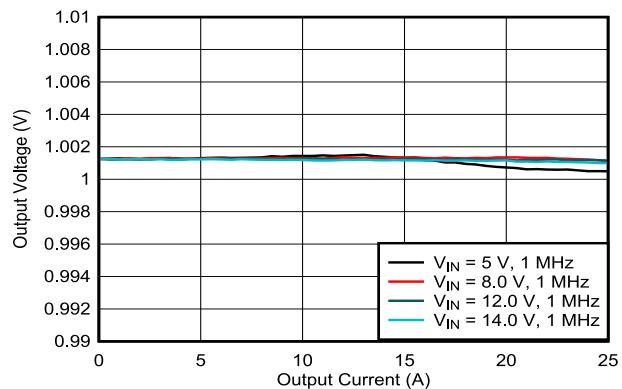

図 7-5. ロードレギュレーション

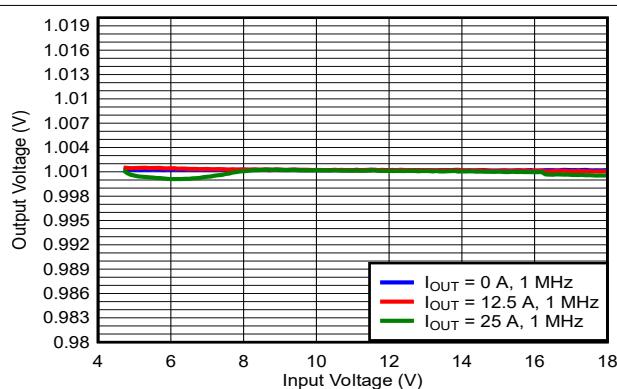

図 7-6. ラインレギュレーション

図 7-7. ポード線図

図 7-8. 負荷過渡

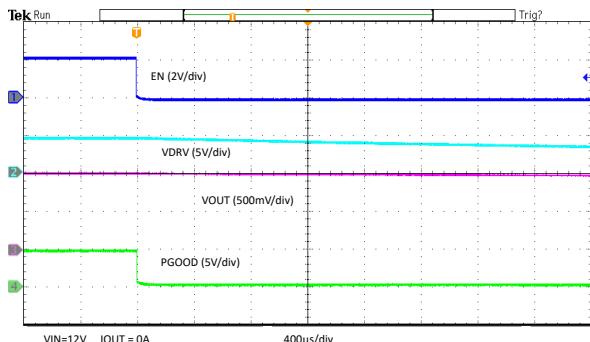

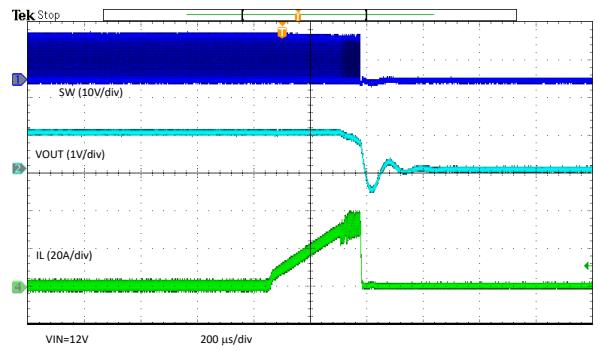

図 7-9. BP5 測定時の EN スタートアップ

図 7-10. SW 測定時の EN スタートアップ

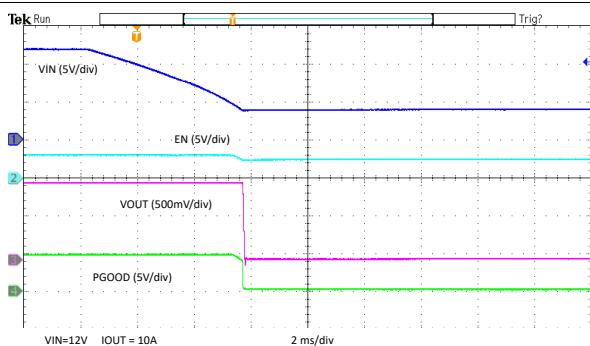

図 7-11. EN シャットダウン

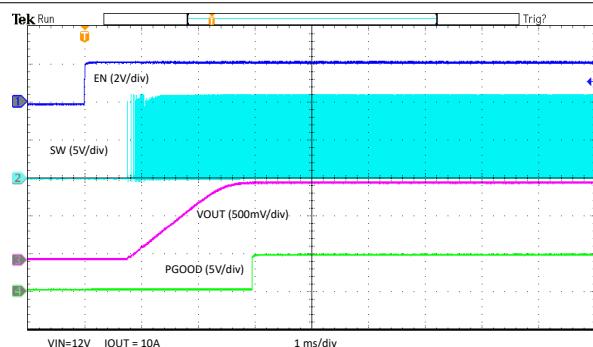

図 7-12. 負荷状態での EN スタートアップ

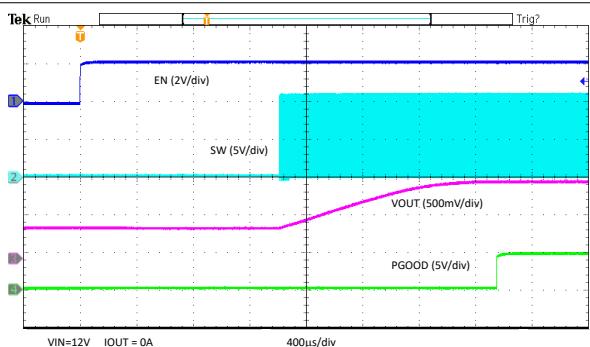

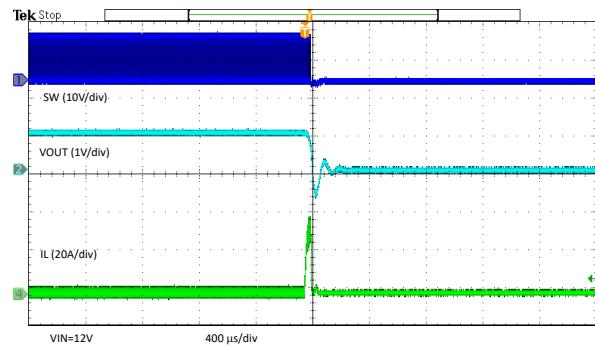

図 7-13. 0.5V プリバイアスでの EN スタートアップ

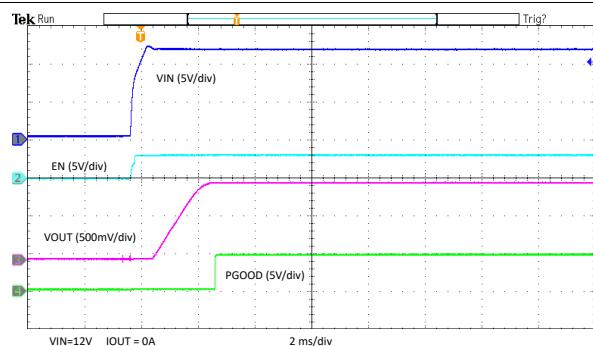

図 7-14.  $V_{IN}$  でのスタートアップ

図 7-15.  $V_{IN}$  シャットダウン

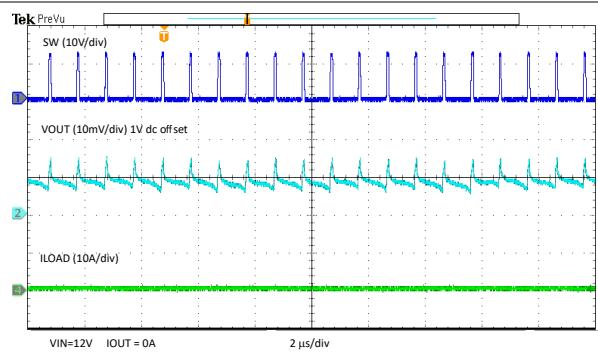

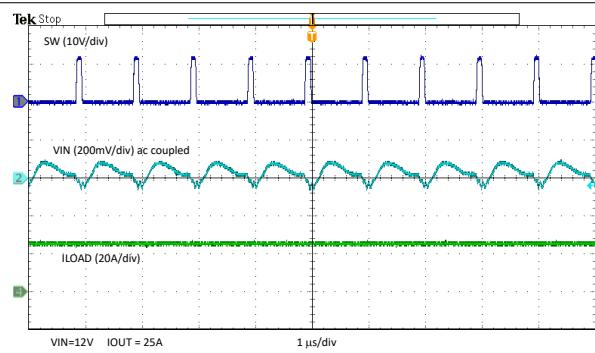

図 7-16. 無負荷時での出力リップル

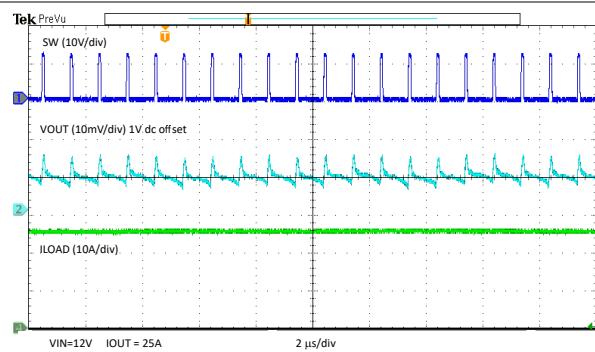

図 7-17. 全負荷時での出力リップル

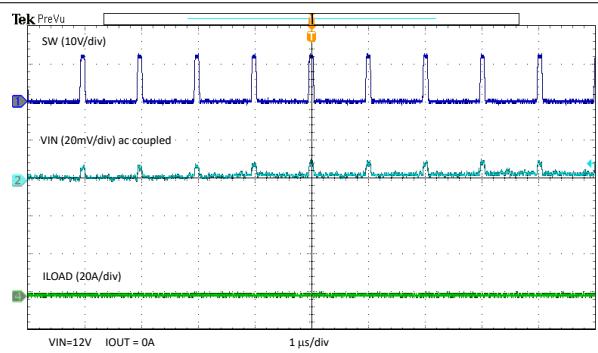

図 7-18. 無負荷時での入力リップル

図 7-19. 全負荷時での入力リップル

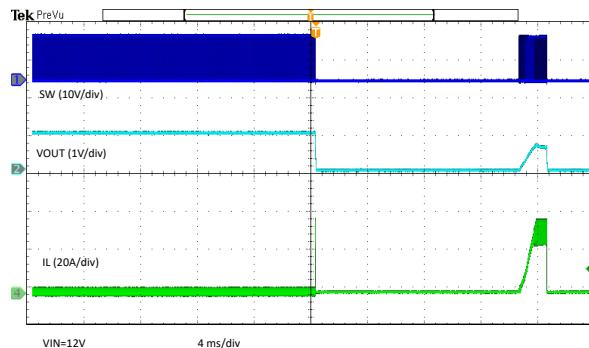

図 7-20. 過負荷での過電流保護

図 7-21. 短絡での過電流保護

図 7-22. ヒカップと回復時の過電流保護

## 7.3 電源に関する推奨事項

TPS543B25E は、4V ~ 18V の入力電源電圧範囲で動作するように設計されています。この電源電圧には適切なレギュレーションが行われる必要があります。入力電源の適切なバイパスは、適切な電気的性能を確保するために不可欠であり、PCB レイアウトとグラウンド方式も同様に重要です。最低  $10\mu\text{F}$  (ディレーティング後) のセラミックコンデンサ (タイプ X5R またはそれ以上) をデバイスの近くに配置する必要があります。テキサス・インスツルメンツでは、セラミック入力容量をデバイスの両側にある VIN ピンと PGND ピンの間に均等に分割し、デバイスの両側に少なくとも  $5\mu\text{F}$  のセラミック容量を形成することを推奨しています。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

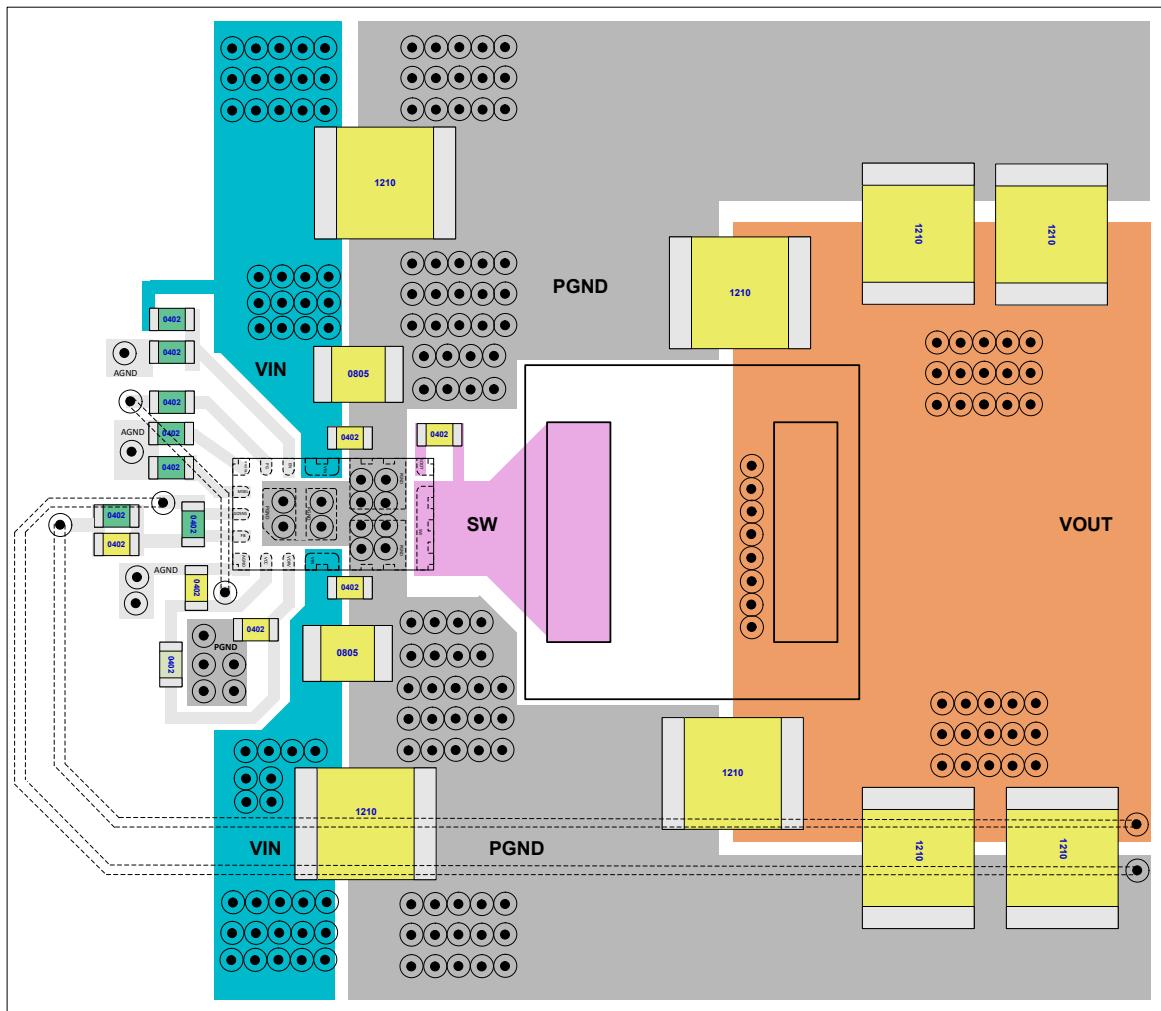

レイアウトは、優れた電源設計のために重要な要素です。PCB レイアウト例については、図 7-23 を参照してください。レイアウトに関する主なガイドラインは次のとおりです。

- VIN、PGND、および SW のパターンを可能な限り広く配置し、トレースインピーダンスを低減、放熱を改善してください。VIN および PGND パターンのインピーダンスを低減するため、その他の層にビアおよびトレースを使用します。

- PGND ピンの近くに複数のビアを使用し、デバイスの直下の層を使用してそれらを互いに接続することで、ノイズを最小限に抑え、放熱に役立ちます。

- 両方の VIN ピンの近くにビアを使用し、内部層を経由してこれらのビア間を低インピーダンスで接続します。

- 各  $1\mu\text{F}/25\text{V}/X6\text{R}$  以上の誘電セラミックコンデンサを各 VIN ピンと PGND ピンの間に配置し、PCB の同じ側でデバイスにできるだけ近い位置に配置してください。残りのセラミック入力キャパシタンスは、これらの高周波バイパスコンデンサの隣に配置します。残りの入力キャパシタンスは基板の反対側に配置できますが、IC のピンとコンデンサ間のインピーダンスを最小限に抑えるため、可能な限り多くのビアを使用してください。

- SW ノード配線の長さを最小限に抑えるため、インダクタをできる限りデバイスの近くに配置します。

- BOOT-SW コンデンサを、BOOT ピンと SW ピンのできるだけ近くに配置します。BOOT コンデンサには、 $0.1\mu\text{F}/16\text{V}/X6\text{R}$  以上の誘電セラミックコンデンサを使用します。

- $2.2\mu\text{F}/10\text{V}/X6\text{R}$  またはそれ以上の誘電セラミックコンデンサを、VDRV と PGND ピンのできるだけ近くに配置します。

- VDRV から VCC に  $10\Omega$  の抵抗を接続し、VCC から AGND に  $0.1\mu\text{F}/10\text{V}/X6\text{R}$  以上の誘電セラミックコンデンサを接続します。

- FB 分圧の底部の抵抗を IC の FB ピンと GOSNS ピンのできるだけ近くに配置します。また、上側帰還抵抗とフィードフォワードコンデンサは IC の近くに配置します。FB 分圧は、希望のギュレーションポイント点の出力電圧に接続します。

- 最上層の AGND アイランドにビアを使用して、内部層の AGND レイヤアイランドに接続します。内部層の AGND アイランドを PGND に 1 点で接続します。

- FSEL および MODE 抵抗を、静かな AGND アイランドに戻します。

#### 7.4.2 レイアウト例

図 7-23. PCB レイアウト例

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 開発サポート

##### 8.1.1.1 WEBENCH® ツールによるカスタム設計

ここをクリック すると、WEBENCH Power Designer により、TPS543B25E デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (VIN)、出力電圧 (VOUT)、出力電流 (IOUT) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

SWIFT™, HotRod™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

| 日付        | 改訂 | 注      |

|-----------|----|--------|

| July 2025 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS543B25VRYSR        | Active        | Production           | WQFN-FCRLF<br>(RYS)   17 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -55 to 150   | T54B25E             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

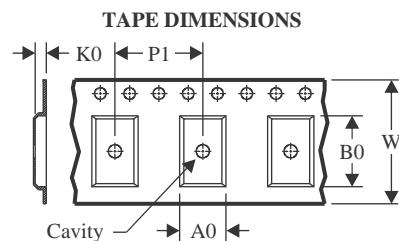

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

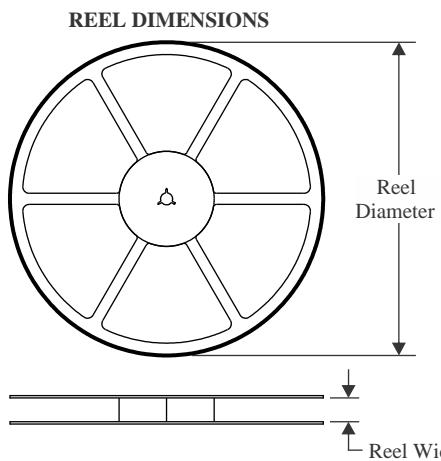

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS543B25VRYSR | WQFN-FCRLF   | RYS             | 17   | 5000 | 330.0              | 12.4               | 2.8     | 4.8     | 0.9     | 8.0     | 12.0   | Q1            |

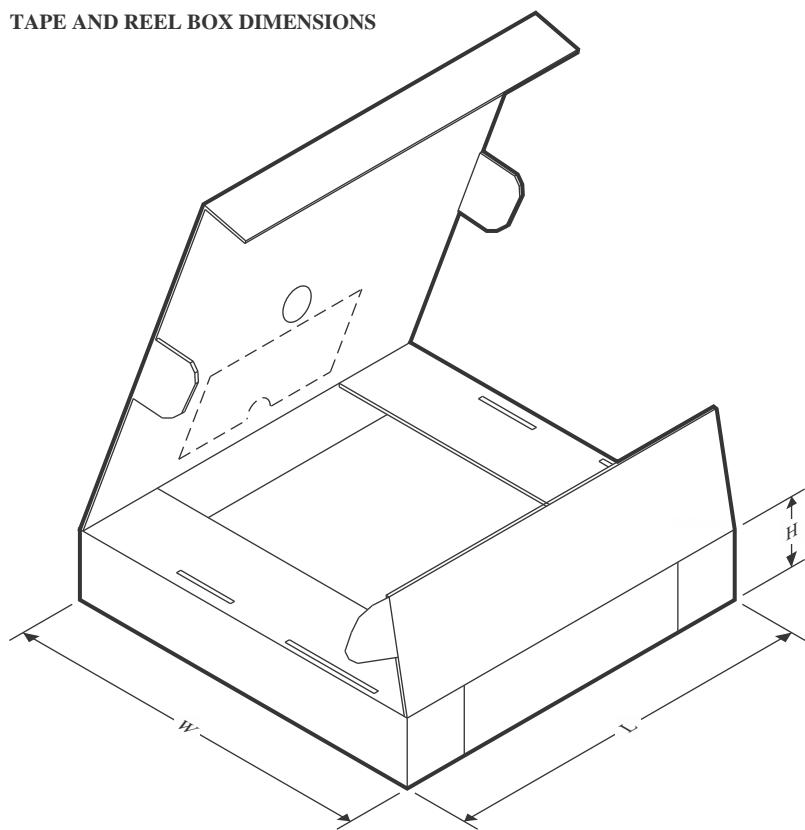

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS543B25VRYSR | WQFN-FCRLF   | RYS             | 17   | 5000 | 367.0       | 367.0      | 35.0        |

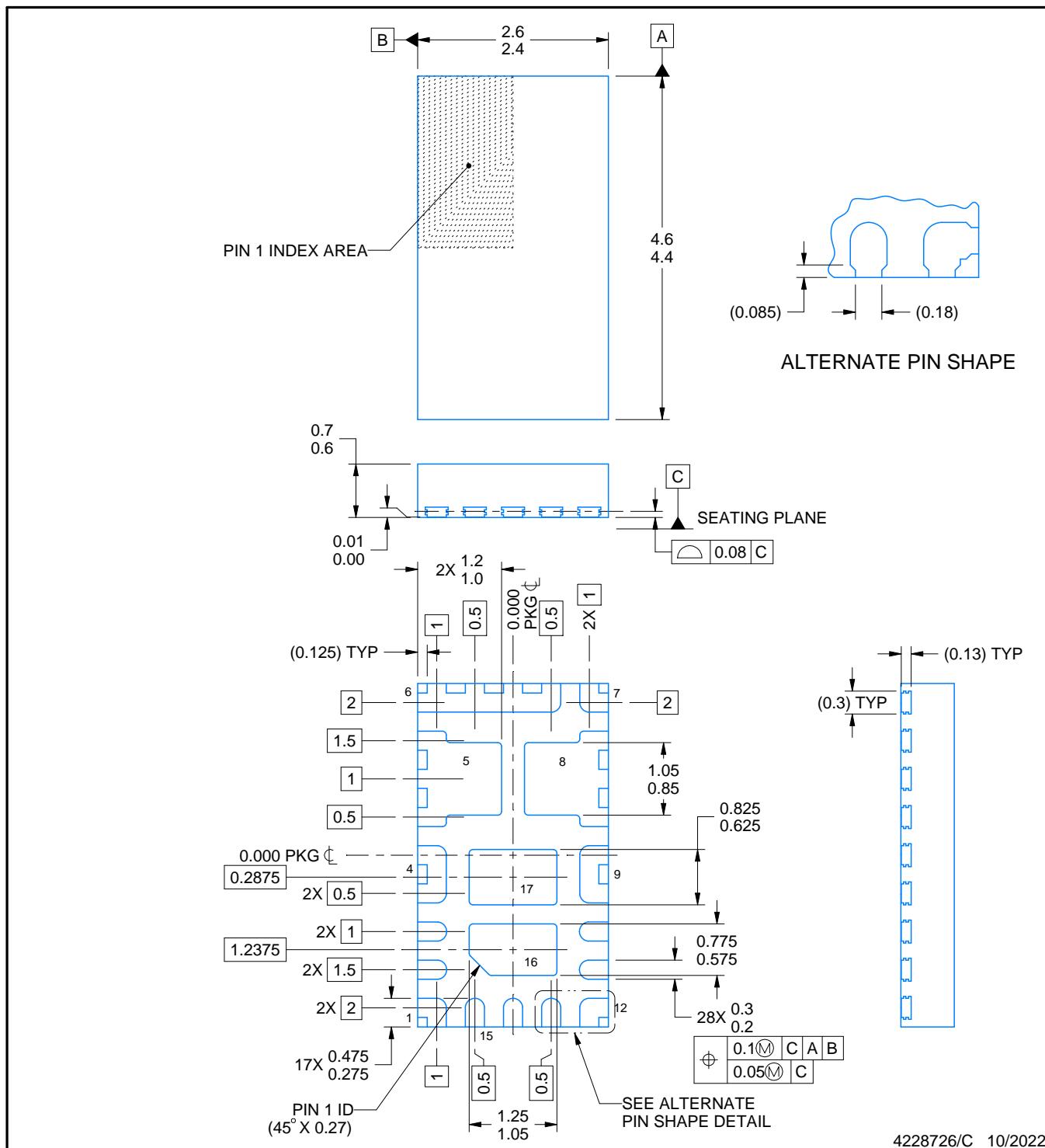

## PACKAGE OUTLINE

**RYS0017A**

## **WQFN-FCRLF - 0.7 mm max height**

**PLASTIC QUAD FLATPACK - NO LEAD**

4228726/C 10/2022

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

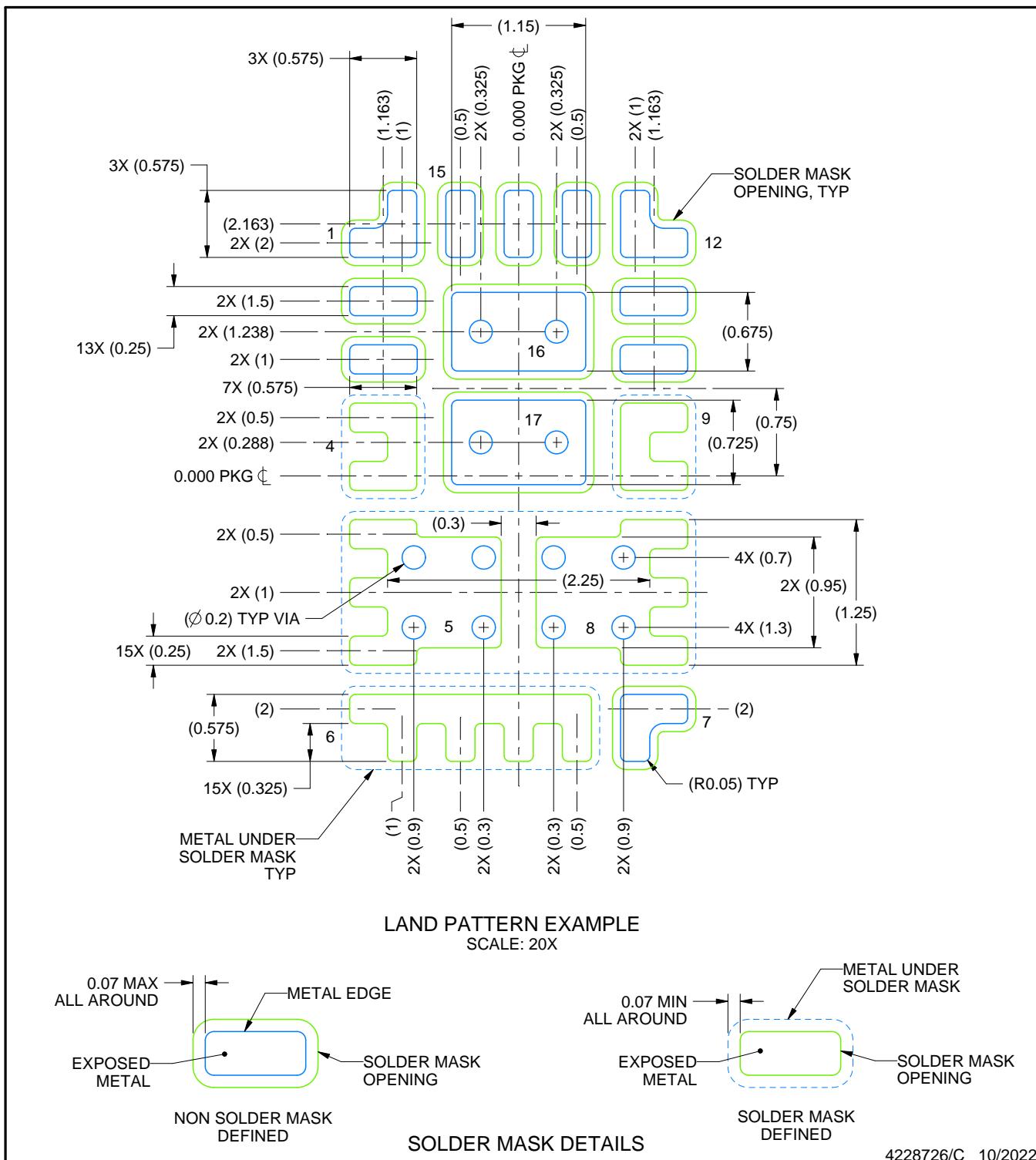

# EXAMPLE BOARD LAYOUT

RYS0017A

WQFN-FCRLF - 0.7 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

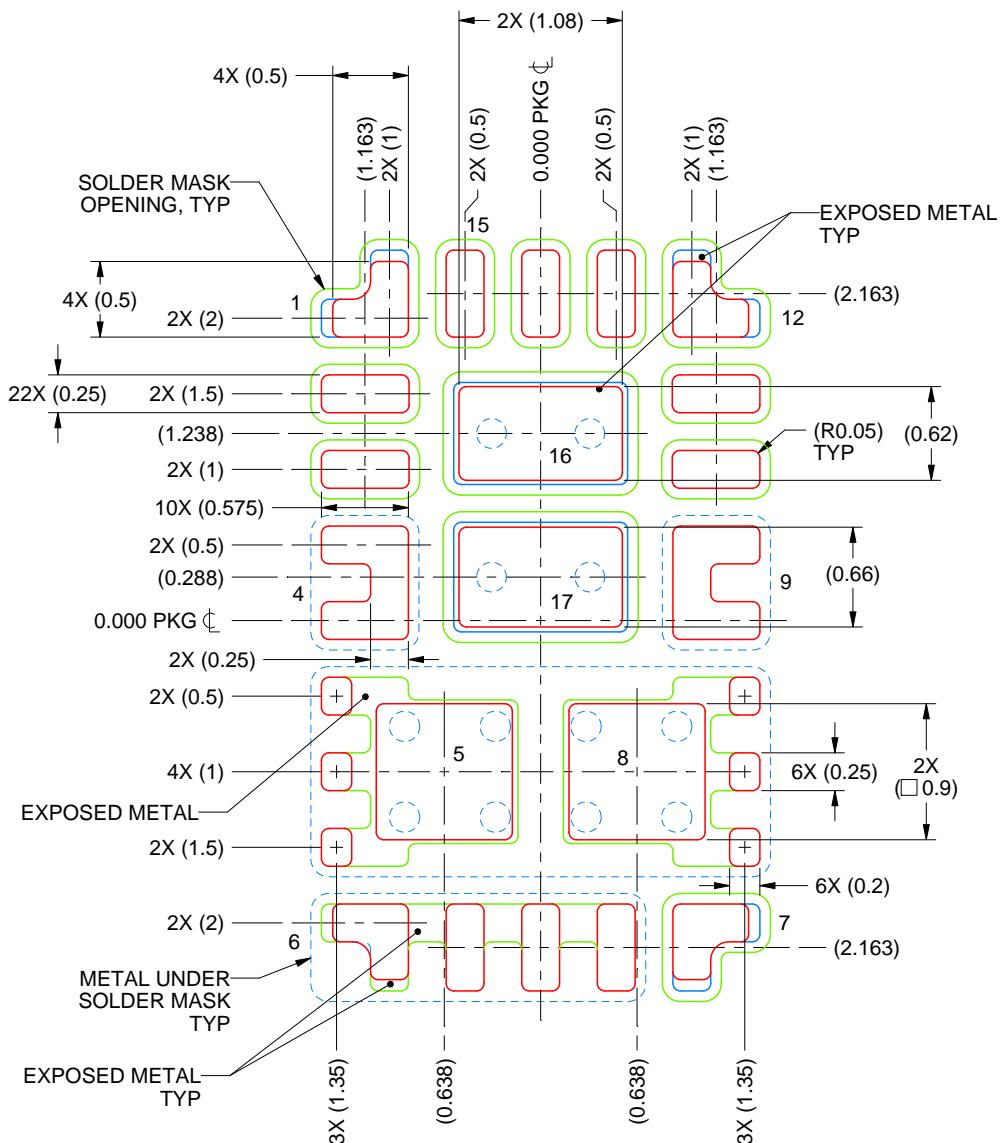

# EXAMPLE STENCIL DESIGN

RYS0017A

WQFN-FCRLF - 0.7 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月