# **TPS54350**

JAJS001A

# 4.5V~20V入力、3A出力 FET内蔵同期式PWM スイッチャ(SWIFT™)

#### 特 乍

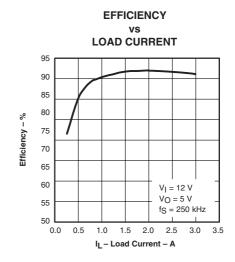

- オン抵抗100mΩ、ピーク電流4.5AのMOSFETスイッ チ内蔵により3A連続出力電流時高効率を実現

- 外付けローサイドMOSFETまたはダイオードを使用

- 出力電圧の調整可能(0.891V、1%基準電圧内蔵)

- 外部クロックに同期

- 180° 位相ずれの同期動作が可能

- 広範囲なPWM周波数 固定250kHz/500kHz、 可变250kHz~700kHz

- スロースタート機能内蔵

- ピーク電流制限とサーマル・シャットダウンによる負 荷の保護

- 調整可能な低電圧ロックアウト

- 16ピンTSSOP PowerPAD™パッケージ

# アプリケーション

- 産業/商用低電力システム

- LCDモニター/ TV

- コンピュータ周辺装置

- 高性能DSP、FPGA、ASIC、マイクロプロセッサ向 けポイント・オブ・ロード・レギュレーション

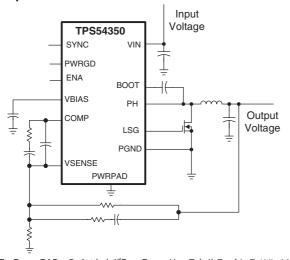

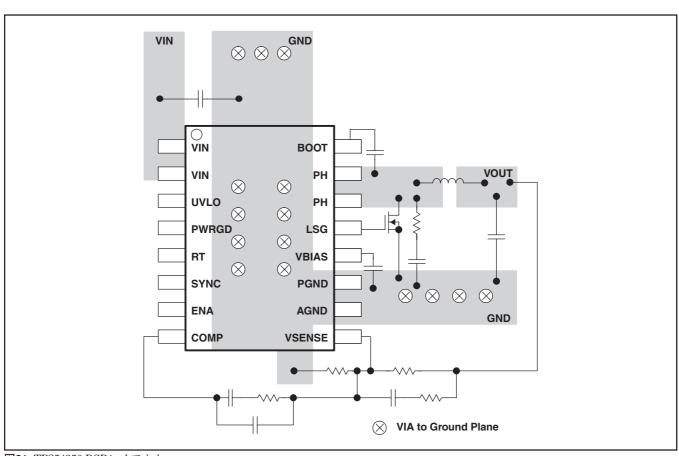

# Simplified Schematic

## 要

TPS54350は、中程度の出力電流の同期式バックPWMコンバー タで、ハイサイドMOSFETやオプションの外付けローサイド MOSFET用ゲート・ドライバを内蔵しています。特長として、出 力フィルタ/インダクタを選択する際に過渡状態下で最大の性能 と柔軟性を可能にする高性能の電圧誤差増幅器を内蔵していま す。TPS54350は、入力電圧が4.5Vに達するまで起動を防止する 低電圧ロックアウト回路、突入電流を制限するスロースタート回 路、出力状態を示すパワー・グッド出力をもっています。同期回 路は180°の位相ずれが簡単に実現できるよう入力または出力とし て構成することができます。

TPS54350は、熱特性を改善した16ピンのTSSOP(PWP) PowerPAD™パッケージで供給されています。TIは評価モジュー ルとSWIFT™デザイナー・ソフトウェアツールを提供しており、 装置の短期間の開発サイクルにおいて高性能な電源設計が迅速に 行なわれることを支援しています。

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資 料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための 補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料 をご確認下さい

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかか わらず、更新以前の情報に基づいて発生した問題や障害等につきまして は如何なる責任も負いません。

SLVS456C 翻訳版

最新の英語版資料

http://focus.ti.com/lit/ds/symlink/tps54350.pdf

# 静電気放電対策

これらのデバイスは、限定的な ESD(静電破壊) 保護機能を内蔵しています。保存時または取り扱い時は、MOS ゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## 製品情報

| T <sub>A</sub> | 出力電圧                  | パッケージ                | PART NUMBER |

|----------------|-----------------------|----------------------|-------------|

| -40°C to 85°C  | Adjustable to 0.891 V | Plastic HTSSOP (PWP) | TPS54350PWP |

(1)PWPパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(すなわち、TPS54350PWPR)

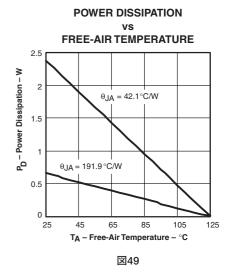

## パッケージ定格消費電力

| パッケージ                                 | THERMAL IMPEDANCE JUNCTION-TO-AMBIENT | T <sub>A</sub> = 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 16-Pin PWP with solder <sup>(1)</sup> | 42.1°C/W                              | 2.36                                  | 1.31                                  | 0.95                                  |

| 16-Pin PWP without solder             | 151.9°C/W                             | 0.66                                  | 0.36                                  | 0.26                                  |

- (1) 消費電力曲線については図46を参照してください。

- (2) テスト・ボードの条件は以下の通りです。

- 1. 厚さ:0.062インチ

- 2. サイズ:3インチx3インチ

- 3. はんだ付け用にPCBの上面と底面に重量2オンスの銅配線

- 4. はんだ付け用にPCBの上面と底面に銅領域

- 5. 電源及びグランド・プレーンは重量1オンス(厚さ0.036mm)

- 6. サーマル·ビアは直径0.33mm、ピッチ1.5mm

- 7. 電源プレーンは熱的に分離

詳細についてはTI技術資料SLMA002を参照してください。

## 絶対最大定格

動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                                              |                                | 単位                     |

|--------------------------------------------------------------|--------------------------------|------------------------|

|                                                              | VIN                            | −0.3 V ~ 21.5 V        |

|                                                              | VSENSE                         | −0.3 V ~ 8.0 V         |

| Input voltage range, V <sub>I</sub>                          | UVLO                           | −0.3 V ~ 8.0 V         |

| input voltage range, v <sub>l</sub>                          | SYNC                           | $-0.3~V\sim4.0~V$      |

|                                                              | ENA                            | $-0.3~V\sim4.0~V$      |

|                                                              | BOOT                           | VI(PH) + 8.0 V         |

|                                                              | VBIAS                          | −0.3 ~ 8.5 V           |

|                                                              | LSG                            | −0.3 ~ 8.5 V           |

|                                                              | SYNC                           | −0.3 ~ 4.0 V           |

| Output voltage range, V <sub>O</sub>                         | RT                             | −0.3 ~ 4.0 V           |

|                                                              | PWRGD                          | −0.3 ~ 6.0 V           |

|                                                              | COMP                           | −0.3 ~ 4.0 V           |

|                                                              | PH                             | −1.5 V ~ 22 V          |

|                                                              | PH                             | Internally Limited (A) |

| Source current, I <sub>O</sub>                               | LSG (Steady State Current)     | 10 mA                  |

|                                                              | COMP, VBIAS                    | 3 mA                   |

|                                                              | SYNC                           | 5 mA                   |

|                                                              | LSG (Steady State Current)     | 100 mA                 |

| Sink current, I <sub>S</sub>                                 | PH (Steady State Current)      | 500 mA                 |

|                                                              | COMP                           | 3 mA                   |

|                                                              | ENA, PWRGD                     | 10 mA                  |

| Voltage differential                                         | AGND to PGND                   | ±0.3 V                 |

| Operating virtual junction temperature range, T <sub>J</sub> |                                | -40°C ∼ +150°C         |

| Storage temperature, T <sub>stg</sub>                        |                                | −65°C ~ +150°C         |

| Lead temperature 1,6 mm (1/16                                | inch) from case for 10 seconds | 260°C                  |

(1)絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 推奨動作条件

|                                                 | MIN | NOM | MAX | 単位 |

|-------------------------------------------------|-----|-----|-----|----|

| Input voltage range, V <sub>I</sub>             | 4.5 |     | 20  | ٧  |

| Operating junction temperature, T <sub>,1</sub> | -40 |     | 125 | °C |

## 電気的特性

T<sub>J</sub> = -40°C to 125°C, VIN = 4.5 V to 20 V (特に記述のない限り)

|          | パラメータ                                                      | 条件                                                                        | MIN      | TYP   | MAX   | 単位  |

|----------|------------------------------------------------------------|---------------------------------------------------------------------------|----------|-------|-------|-----|

| SUPPLY   | CURRENT                                                    |                                                                           |          |       |       |     |

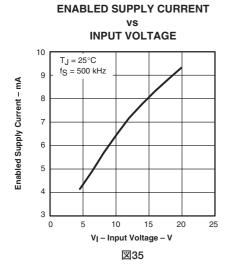

| IQ       | Quiescent current                                          | Operating Current, PH Pin open,<br>No external low side MOSFET, RT = Hi-Z |          | 5     |       | mA  |

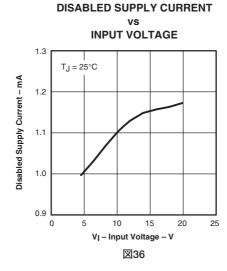

|          |                                                            | Shutdown, ENA = 0 V                                                       |          | 1.0   |       | mA  |

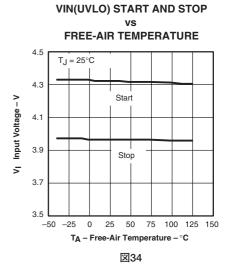

|          | Start threshold voltage                                    |                                                                           |          | 4.32  | 4.49  | ٧   |

| VIN      | Stop threshold voltage                                     |                                                                           | 3.69     | 3.97  |       | ٧   |

|          | Hysteresis                                                 |                                                                           |          | 350   |       | mV  |

| UNDER V  | OLTAGE LOCK OUT (UVLO PIN)                                 |                                                                           | •        |       |       |     |

|          | Start threshold voltage                                    |                                                                           |          | 1.20  | 1.24  | V   |

| UVLO     | Stop threshold voltage                                     |                                                                           | 1.02     | 1.10  |       | ٧   |

|          | Hysteresis                                                 |                                                                           |          | 100   |       | mV  |

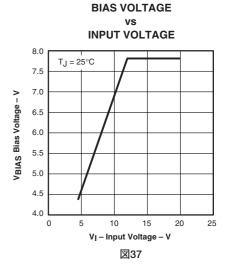

| BIAS VOI | LTAGE (VBIAS PIN)                                          |                                                                           | <u>'</u> |       |       | •   |

|          |                                                            | I <sub>VBIAS</sub> = 1 mA, VIN ≥12 V                                      | 7.5      | 7.8   | 8.0   |     |

| VBIAS    | Output voltage                                             | I <sub>VBIAS</sub> = 1 mA, VIN = 4.5 V                                    | 4.4      | 4.47  | 4.5   | ٧   |

| REFERE   | NCE SYSTEM ACCURACY                                        | ,                                                                         |          |       |       |     |

|          |                                                            | T <sub>J</sub> = 25°C                                                     | 0.888    | 0.891 | 0.894 | V   |

|          | Reference voltage                                          |                                                                           | 0.882    | 0.891 | 0.899 | ٧   |

| OSCILLA  | TOR (RT PIN)                                               | •                                                                         |          |       |       | •   |

|          |                                                            | RT Grounded                                                               | 200      | 250   | 300   |     |

|          | Internally set PWM switching frequency                     | RT Open                                                                   | 400      | 500   | 600   | kHz |

|          | Externally set PWM switching frequency                     | RT = 100 kΩ(1% resistor to AGND)                                          | 425      | 500   | 575   | kHz |

| FALLING  | EDGE TRIGGERED BIDIRECTIONAL SYNC SYS                      | TEM (SYNC PIN)                                                            |          |       |       | •   |

|          | SYNC out low-to-high rise time (10%/90%) <sup>(1)</sup>    | 25 pF to ground                                                           |          | 200   | 500   | ns  |

|          | SYNC out high-to-low fall time (90%/10%) <sup>(1)</sup>    | 25 pF to ground                                                           |          | 5     | 10    | ns  |

|          | Falling edge delay time <sup>(1)</sup>                     | Delay from rising edge to rising edge of PH pins, see Figure 19           |          | 180   |       | ۰   |

|          | Minimum input pulsewidth <sup>(1)</sup>                    | RT = 100 kΩ                                                               |          | 100   |       | ns  |

|          | Delay (falling edge SYNC to rising edge PH) <sup>(1)</sup> | RT = 100 kΩ                                                               |          | 360   |       | ns  |

|          | SYNC out high level voltage                                | 50 kΩ resistor to ground, no pullup resistor                              | 2.5      |       |       | V   |

|          | SYNC out low level voltage                                 |                                                                           |          |       | 0.6   | V   |

|          | SYNC in low level threshold                                |                                                                           | 0.8      |       |       | V   |

|          | SYNC in high level threshold                               |                                                                           |          |       | 2.3   | V   |

|          |                                                            | Percentage of programmed frequency                                        | -10%     |       | 10%   |     |

|          | SYNC in frequency range <sup>(1)</sup>                     |                                                                           | 225      |       | 770   | kHz |

<sup>(1)</sup>設計で保証されており、テストはされていません。

## 電気的特性

$T_J$  =  $-40^{\circ}$ C to 125°C, VIN = 4.5 V to 20 V (特に記述のない限り)

|                      | パラメータ                                                              | 条 件                                                  | MIN  | TYP  | MAX  | 単位   |

|----------------------|--------------------------------------------------------------------|------------------------------------------------------|------|------|------|------|

| FEED - FC            | DRWARD MODULATOR (INTERNAL SIGNAL)                                 |                                                      |      |      |      |      |

|                      | Modulator gain                                                     | VIN = 12 V, T <sub>J</sub> = 25°C                    |      | 8    |      | V/V  |

|                      | Modulator gain variation                                           |                                                      | -25% |      | 25%  |      |

|                      | Minimum controllable ON time(1)                                    |                                                      |      | 180  |      | ns   |

|                      | Maximum duty factor <sup>(1)</sup>                                 | VIN = 4.5 V                                          | 80%  | 86%  |      |      |

| ERROR AI             | MPLIFIER (VSENSE AND COMP PINS)                                    |                                                      |      |      |      |      |

|                      | Error amplifier open loop voltage gain <sup>(1)</sup>              |                                                      | 60   | 80   |      | dB   |

|                      | Error amplifier unity gain bandwidth <sup>(1)</sup>                |                                                      | 1.0  | 2.8  |      | MHz  |

|                      | Input bias current, VSENSE pin                                     |                                                      |      |      | 500  | nA   |

| COMP                 | Output voltage slew rate (symmetric) <sup>(1)</sup>                |                                                      |      | 1.5  |      | V/μs |

| ENABLE (I            | ENA PIN)                                                           |                                                      |      |      |      |      |

|                      | Disable low level input voltage                                    |                                                      |      |      | 0.5  | V    |

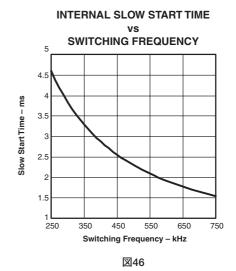

|                      | Internal along starting (100/ to 000/)                             | $f_S = 250 \text{ kHz}, RT = \text{ground}^{(1)}$    |      | 4.6  |      |      |

|                      | Internal slow-start time (10% to 90%)                              | $f_S = 500 \text{ kHz}, RT = Hi-Z^{(1)}$             |      | 2.3  |      | ms   |

|                      | Pullup current source                                              |                                                      | 1.8  | 5    | 10   | μА   |

|                      | Pulldown MOSFET                                                    | II(ENA)=1 mA                                         |      | 0.1  |      | V    |

| POWER G              | OOD (PWRGD PIN)                                                    | •                                                    | •    |      |      |      |

|                      | Power good threshold                                               | Rising voltage                                       |      | 97%  |      |      |

|                      | 5:                                                                 | f <sub>S</sub> = 250 kHz                             |      | 4    |      |      |

|                      | Rising edge delay <sup>(1)</sup>                                   | f <sub>S</sub> = 500 kHz                             |      | 2    |      | ms   |

|                      | Output saturation voltage                                          | I <sub>sink</sub> = 1 mA, VIN > 4.5 V                |      | 0.05 |      | V    |

| PWRGD                | Output saturation voltage                                          | I <sub>sink</sub> = 100 μA, VIN = 0 V                |      | 0.76 |      | V    |

|                      | Open drain leakage current                                         | Voltage on PWRGD = 6 V                               |      |      | 3    | μА   |

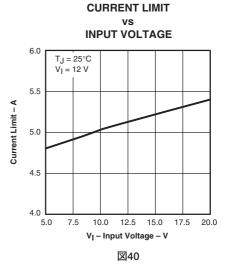

| CURRENT              | LIMIT                                                              | •                                                    | •    |      |      |      |

|                      | Current limit                                                      | VIN = 12 V                                           | 3.3  | 4.5  | 6.5  | А    |

|                      | Current limit Hiccup Time(1)                                       | f <sub>S</sub> = 500 kHz                             |      | 4.5  |      | ms   |

| THERMAL              | SHUTDOWN                                                           | •                                                    | •    |      |      |      |

|                      | Thermal shutdown trip point <sup>(1)</sup>                         |                                                      |      | 165  |      | °C   |

|                      | Thermal shutdown hysteresis <sup>(1)</sup>                         |                                                      |      | 7    |      | °C   |

| LOW SIDE             | MOSFET DRIVER (LSG PIN)                                            | •                                                    | •    |      |      |      |

|                      | Turn on rise time, (10%/90%) <sup>(1)</sup>                        | VIN = 4.5 V, Capacitive load = 1000 pF               |      | 15   |      | ns   |

|                      | Deadtime <sup>(1)</sup>                                            | VIN = 12 V                                           |      | 60   |      | ns   |

|                      | D: ON :                                                            | VIN = 4.5 V sink/source                              |      | 7.5  |      |      |

| Driver ON resistance |                                                                    | VIN = 12 V sink/source                               | 5    |      |      | Ω    |

| OUTPUT P             | POWER MOSFETS (PH PIN)                                             | •                                                    |      |      |      | -    |

|                      | Phase node voltage when disabled                                   | DC conditions and no load, ENA = 0 V                 |      | 0.5  |      | V    |

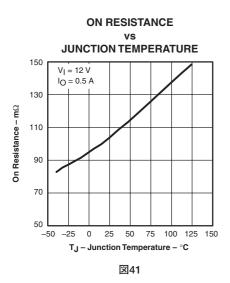

|                      | V II                                                               | VIN = 4.5 V, Idc = 100 mA                            |      | 1.13 | 1.42 | .,   |

|                      | Voltage drop, low side FET and diode                               | VIN = 12 V, Idc = 100 mA                             |      | 1.08 | 1.38 | V    |

|                      | (0)                                                                | VIN = 4.5 V, BOOT–PH = 4.5 V, I <sub>O</sub> = 0.5 A |      | 150  | 300  | _    |

|                      | r <sub>DS(ON)</sub> , high side power MOSFET switch <sup>(2)</sup> | VIN = 12 V, BOOT–PH = 8 V, I <sub>O</sub> = 0.5 A    |      | 100  | 200  | mΩ   |

<sup>(1)</sup>設計で保証されており、テストはされていません。

<sup>(2)</sup>VINピンからPHピンの抵抗

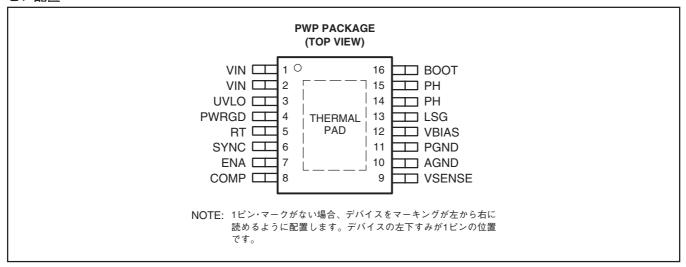

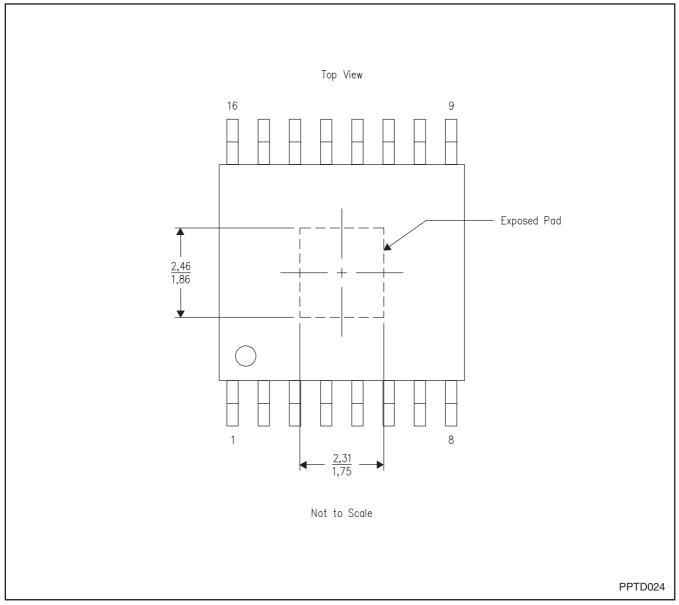

## ピン配置

## ピン構成

| NO.    | 端子<br>NAME | 機能                                                                                                                                                                                                    |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | VIN        | 入力電源電圧で4.5V~20V。この端子は低ESRで10μFのセラミック・キャパシタでバイパスしてください。                                                                                                                                                |

| 3      | UVLO       | 低電圧ロックアウト端子。VINからこの端子に抵抗性の分圧器を外付けすると内部のデフォルトのVINスタート/ストップ・スレッシュホールドが無効になります。                                                                                                                          |

| 4      | PWRGD      | パワー・グッド出力端子でオープン・ドレイン出力です。この端子が "L" レベルであると出力は設定出力電圧より下であることを表します。PWRGDコンパレータの出力には立上がりエッジ・フィルタが内蔵されています。                                                                                              |

| 5      | RT         | 周波数設定端子。スイッチング周波数を設定するためRTからAGNDに抵抗を接続してください。RT端子をグランドに接続するか、またはフローティングの場合には、周波数は内部であらかじめ設定されている周波数に設定されます。                                                                                           |

| 6      | SYNC       | 双方向同期I/O端子。SYNC端子は、RT端子がフローティングまたは "L" レベルに接続されている場合出力です。出力はPHの立ち上が<br>りエッジと逆相の立ち下がりエッジ信号です。SYNCは、RTに抵抗が使用されている時、立ち下りエッジ信号に接続することでシステム・クロックに同期させる入力としても使用できます。アプリケーション情報の項の "180° 位相ずれの同期" を参照してください。 |

| 7      | ENA        | イネーブル端子。0.5Vより低いとデバイスはスイッチングを停止します。フローティングでイネーブルになります。                                                                                                                                                |

| 8      | COMP       | 誤差増幅器出力。COMP端子からVSENSE端子に周波数補償回路を接続します。                                                                                                                                                               |

| 9      | VSENSE     | 誤差増幅器の反転入力。                                                                                                                                                                                           |

| 10     | AGND       | アナログ・グランド。敏感なアナログ・グランド回路に内部で接続されています。PGNDとPowerPAD™に接続してください。                                                                                                                                         |

| 11     | PGND       | 電源グランドでノイズの多い内部グランド。LSGドライバ出力からの帰還電流がPGNDに戻ってきます。AGNDとPowerPAD™に接続してください。                                                                                                                             |

| 12     | VBIAS      | 8.0Vの内部バイアス電圧。VBIAS端子には1.0μFのバイパス用セラミック・キャパシタが必要です。                                                                                                                                                   |

| 13     | LSG        | オプションのローサイドMOSFET用ゲート駆動端子。より高効率の同期式バック・コンバータの構成にするにはNチャネルのMOSFET<br>を接続してください。そうでなければ、オープンにして、グランドからPH端子にショットキー・ダイオードを接続します。                                                                          |

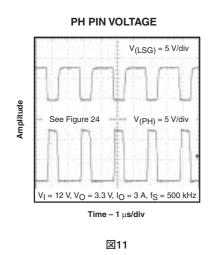

| 14, 15 | PH         | 位相ノード。外付けのLCフィルタを接続してください。                                                                                                                                                                            |

| 16     | BOOT       | ハイサイド·ゲート·ドライバ用ブートストラップ·キャバシタ接続端子。BOOT端子からPH端子に0.1μFのセラミック·キャパシタを接続します。                                                                                                                               |

|        | PowerPAD™  | 適切な動作を行うにはPGND及びAGND端子をむき出しのこのパッドに接続しなければなりません。図21のPCBレイアウト例を参照してください。                                                                                                                                |

# アプリケーション情報

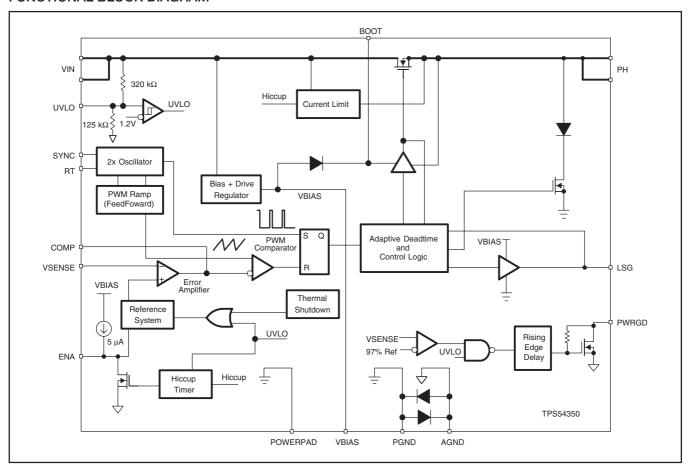

## **FUNCTIONAL BLOCK DIAGRAM**

## 詳細説明

## 低電圧ロックアウト(UVLO)

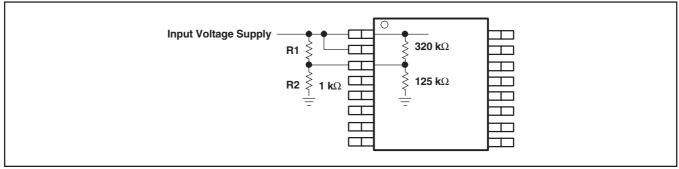

低電圧ロックアウト (UVLO)系にはVINからAGNDに分圧器が内蔵されています。スタート/ストップ値のデフォルトはVIN標示で表1に示されています。内部のUVLOスレッシュホールドはVINからグランドに抵抗デバイダを外付けすることで無効にできます。内部のデバイダ値は、上側の抵抗が約320k $\Omega$ 、下側の抵抗は約125k $\Omega$ です。分割比(ひいてはデフォルトのスタート/ストップ値)は非常に正確ですが、内部抵抗の絶対値は15%ほど変動する可能性があります。外部からUVLOスレッシュホールドを調整する場合に高い精度が要求されるならば、UVLOスレッシュホールドを設定する外付け抵抗にはより小さな値のものを選択してください。下側の抵抗には1k $\Omega$ (図1のR2参照)を使用することを推奨します。いかなる状態でもUVLOピンを直接VINに接続しないでください。

UVLO用抵抗を選択する際の式は以下のとおりです。

$$R1 = \frac{VIN(start) \times 1 k\Omega}{1.24 V} - 1k\Omega$$

(1)

$$VIN(stop) = \frac{(R1 + 1 k\Omega) \times 1.02 V}{1 k\Omega}$$

(2)

4.49Vより高い低電圧ロックアウト(UVLO)スレッシュホールドを必要とするアプリケーションには、スタート電圧のスレッシュホールドを調整するため、図1のように外付け抵抗を使用することができます。例えば、約7.8VのUVLOスタート電圧を必要とするアプリケーションでは式(1)を使うと、R1の計算結果はもっとも近い標準抵抗値5.36k $\Omega$ となります。式(2)を使うと入力電圧のストップ・スレッシュホールドの計算結果は6.48Vとなります。

|             | スタート電圧のスレッシュホールド | ストップ電圧のスレッシュホールド |

|-------------|------------------|------------------|

| VIN (デフォルト) | 4.49             | 3.69             |

| UVLO        | 1.24             | 1.02             |

表1. スタート/ストップ電圧のスレッシュホールド

図1. 外付けUVLO機能を用いる回路

## イネーブル(ENA)及び内部スロースタート

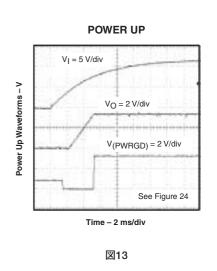

ENAピンの電圧が0.5Vを越えると、TPS54350は動作を開始します。TPS54350は基準電圧を1150スイッチング・サイクルでその最終値まで上昇させるディジタル式のスロースタートを内蔵しています。内部スロースタート時間(10% – 90%)は以下の式で概算されます。

$$T_{SS\_INTERNAL(ms)} = \frac{1.15k}{f_{s(kHz)}}$$

(3)

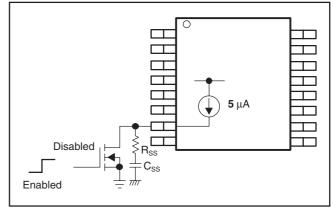

TPS54350デバイスが通常のレギュレーション状態にあると、ENAピンは"H"レベルです。ENAピンが0.5Vのストップ・スレッシュホールドより低くなった場合、スイッチングは停止し、内部のスロースタートはリセットされます。アプリケーションでTPS54350がディスエーブルになるよう要求される場合は、ENAピンとのインターフェイスにはオープン・ドレインまたはオープン・コレクタの出力ロジックを使用してください(図2参照)。ENAピンは内部にプルアップされた電流源をもっています。外付けのプルアップ抵抗は使用しないでください。

## スロースタート時間の延長

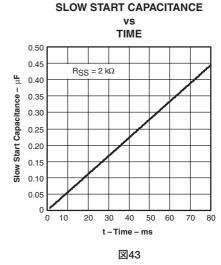

大きな値の出力容量を使用するアプリケーションでは、起動時電流が制限電流を越えるのを防ぐためスロースタート時間を長くすることが必要となる場合があります。電流制限回路は、ハイサイドMOSFETの電流が電流制限のスレッシュホールドを越えた時、ハイサイドMOSFETをディスエーブルにし、内部基準電圧を短期間リセットするよう設計されています。出力容量及び負荷電流により起動時電流が電流制限のスレッシュホールドを越えると、電源出力は設定出力電圧には達しません。スロースタート時間を延ばし、起動時電流を低減するために、抵抗とキャパシタをENAピンに外付けすることができます。このスロースタート用の容量は以下の式を使って計算されます。

$$C_{SS}(\mu F) = 5.55^{e-3} T_{SS}(ms)$$

抵抗 $R_{SS}$ は $2k\Omega$ でなければならず、またスロースタート用キャパシタは $0.47\mu F$ より小さくなくてはなりません。

図2. ENAピンへのインターフェイス

### スイッチング周波数(RT)

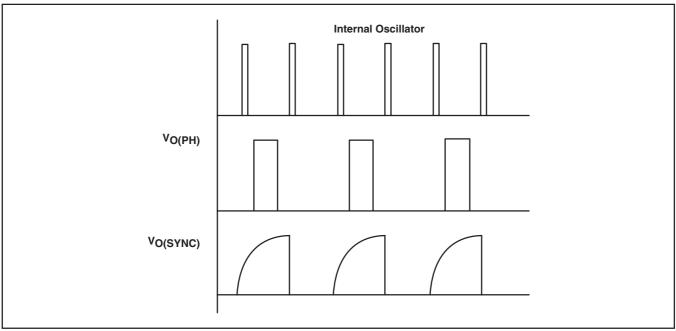

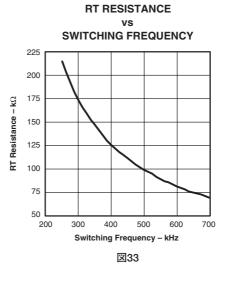

TPS54350はPWMスイッチング周波数の2倍で動作する内部発振器をもっています。内部発振器の周波数はRTピンでコントロールされます。RTピンをグランドに接続するとPWMスイッチング周波数は250kHzのデフォルト周波数に設定されます。RTピンをフローティングにするとPWMスイッチング周波数は500kHzに設定されます。

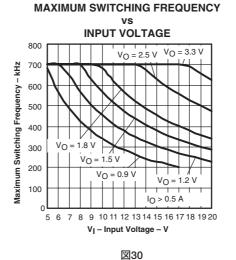

RTからAGNDに抵抗を接続すると以下の式に従い周波数が設定されます(図30も参照してください)。

$$RT(k\Omega) = \frac{46000}{f_{s(kHz)} - 35.9}$$

(4)

RTピンはSYNCピンの機能をコントロールします。RTピンがフローティング、またはグランドに接続された場合、SYNCは出力となります。スイッチング周波数がRTからAGNDに接続される抵抗を使ってプログラムされると、SYNCは入力として機能します。

内部電圧ランプの充電電流は設定周波数に比例して増加し、周波数の設定点に関係なくフィードフォワード変調定数(Km = 8)を維持します。

| スイッチング周波数                 | SYNCピン        | RTピン                                                                                                |

|---------------------------|---------------|-----------------------------------------------------------------------------------------------------|

| 250kHz (内部設定) SYNC出力信号を生成 |               | AGND                                                                                                |

| 500kHz (内部設定)             | SYNC出力信号を生成   | フローティング                                                                                             |

| 250kHz~700kHz (外部設定)      | GNDへの10kΩ抵抗接続 | R = $215k\Omega\sim69k\Omega$                                                                       |

| 外部同期周波数                   | 同期信号          | 他のTPS54350の同期出力信号を使用する場合RTがフローティングで110k $\Omega$ 、グランドで237k $\Omega$ 。外部同期周波数の90%~110%に相当するRT抵抗を使用。 |

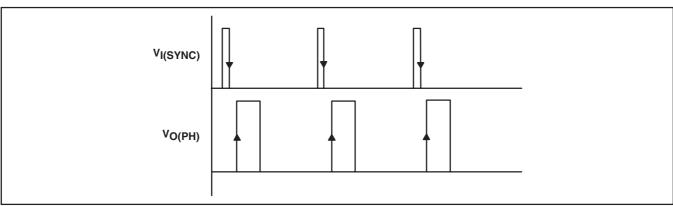

## 180° 位相ずれの同期(SYNC)

SYNCピンは、前項での説明したように入力または出力として構成できます。入力として動作する場合、SYNCピンは立下りエッジでトリガされる信号です(図3、4、19参照)。一方、出力として動作する場合、信号の立下りエッジはPHピンの立上がりエッジと約180°位相がずれます。従って、システムで2つのTPS54350デバイスが動作する場合、入力キャパシタを共有でき、単一ユニットの周波数の2倍でリップル電流が流れます。

180° 位相がずれた2つのTPS54350デバイスを動作させる場合、RMS総入力電流は低減するため、必要とされる入力容量は下がり、効率は上がります。

TPS54350を外部信号と同期させる場合、RTピンのタイミング 抵抗は発振器が同期周波数の90%から110%で動作するようにプログラムされるよう設定しなければなりません。

Note:出力電圧10V以上での設計で、同期入力は使用しないで下 さい。

### パワー・グッド(PWRGD)

VSENSEピンは内部基準信号と比較され、VSENSEが97%より高く他に異常がないと、PWRGDピンはハイ・インピーダンスとなります。PWRGDピンが "L" レベルであると異常を示します。PWRGDピンは設計上プルダウンが脆弱であり、デバイスに電源が供給されていない時でも異常を示します。TPS54350に電源が供給され、何か異常フラグがセットされると、TPS54350はPWRGDピンを "L" レベルにすることで出力は有効ではないことを表します。以下の事象の一つまたはその組み合わせが起こった場合に出力は有効ではないことを示します。

- VSENSEピンが規定範囲外

- 過電流

- サーマル・シャットダウン

- UVLO低電圧

- 入力電圧なし(脆弱なプルダウン)

図3. SYNC入力波形

図4. SYNC出力波形

- スロースタート時

- VBIASが低電圧

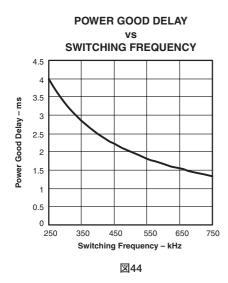

PWRGDピンがハイ・インピーダンス(つまり、出力有効)を示した後、VSENSEピンが規定範囲外であるとある時間遅延の後PWRGDピンが "L" レベル(つまり、出力無効)になります。この時間遅延はスイッチング周波数の関数で、以下の式(5)で計算されます。

$$T_{\text{delay}} = \frac{1000}{f_{\text{s(kHz)}}} \text{ ms}$$

(5)

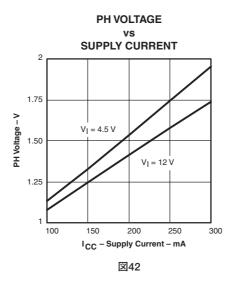

## バイアス電圧(VBIAS)

VBIASレギュレータは内部アナログ回路とローサイドのゲート・ドライバ用に安定した電源を供給します。外部アプリケーション回路で使用するために最大1mAの電流を流すことができます。VBIASピンには1.0μFのバイパス・キャパシタを接続しなければなりません。温度に対し特性値が安定しているため、X7RまたはX5Rクラスの特性の誘電体セラミック・キャパシタを推奨します。

## ブートストラップ電圧(BOOT)

BOOTキャパシタはVBIASキャパシタから1サイクルごとに電荷を取得します。動作させるにはBOOTピンからPHピンへのキャパシタが必要です。ハイサイド・ドライバへのブートストラップ接続には $0.1\mu$ Fのバイパス・キャパシタを用いなければなりません。

## 誤差増幅器

VSENSEピンは誤差増幅器の反転入力です。誤差増幅器は 1.5mAの駆動能力をもち、最小開ループ電圧利得60dBで2MHzの 単一利得帯域幅をもつ真の電圧増幅器です。

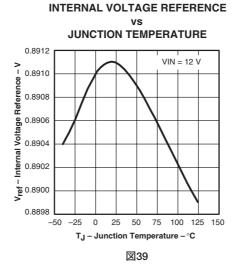

### 基準電圧

基準電圧系では温度に対し安定なバンドギャップ回路の出力をスケーリングすることで高精度の基準信号を生成します。量産テスト時には、バンドギャップ回路とスケーリング回路はボルテージ・フォロワのように接続された増幅器により誤差増幅器の出力で0.891Vが出力されるようトリミングされます。このトリミングにより、スケーリング回路及び誤差増幅器の回路のオフセット誤差がキャンセルされ、レギュレーションが改善されます。

## PWMコントロール及びフィードフォワード

誤差増幅器の出力、発振器、電流制限回路からの信号はPWM コントロール・ロジックにより処理されます。内部ブロック図を参照すると、このコントロール・ロジックにはPWMコンパレータ、PWMラッチ、アダプティブ・デッドタイム・コントロール・ロジックが含まれています。電流制限スレッシュホールド電圧より低い定常状態動作では、PWMコンパレータの出力と発振器の連続パルスが交互にPWMラッチのリセットとセットを行います。

PWMラッチがリセットされると、ローサイド・ドライバと内蔵 のプルダウンMOSFETは発振器のパルス幅で設定される最小期 間の間オン状態のままです。この期間で、PWMランプはその下限電圧まで急速に放電します。ランプが再充電し始めると、ローサイド・ドライバはオフになり、ハイサイドFETがオンになります。PWMのピーク・ランプ電圧は一定の変調器と8V/Vのパワー段利得を維持するため入力電圧に反比例します。

PWMランプ電圧が誤差増幅器の出力電圧を越えると、PWM コンパレータはラッチをリセットするため、ハイサイドFETがオフ、ローサイドFETはオンになります。ローサイド・ドライバは、発振器の次のパルスがPWMランプを放電するまでオン状態を保持します。

過渡状態では、誤差増幅器の出力はPWMランプの下限電圧より下またはPWMピーク電圧より上である可能性があります。誤差増幅器の出力が高いと、PWMラッチはリセットされず、ハイサイドFETは発振器のパルスがハイサイドFETをオフに、内部ローサイドFETとドライバをオンにするようコントロール・ロジックに信号を送るまでオン状態を保持します。このデバイスは出力電圧がレギュレーションの設定点に達するまでその最大デューティ・サイクルで動作し、VSENSEの電圧は内部基準電圧とほぼ同じ電圧に設定されます。一方、誤差増幅器の出力が低いと、PWMラッチは絶えずリセットされ、ハイサイドFETはオンになりません。内部ローサイドFETとローサイド・ドライバは、VSENSE電圧がPWMコンパレータに状態を変えさせる程度に減少するまでオン状態を保持します。TPS54350は出力がレギュレーションの設定点に達するまで外付けのローサイドFETに電流をシンクすることができます。

最小オン時間は180nsで設計されています。内部でのスロースタートの間で、内部基準電圧は0Vから0.891Vに上昇します。最初のスロースタートの間では、内部基準電圧は非常に小さいため、内部基準電圧が上昇するまで最小オン時間により実際の出力電圧が予め設定された電圧より少し大きくなるので、いくつかのパルスが飛ばされてしまいます。

## デッドタイム・コントロール

アダプティブ・デッドタイム・コントロールにより、ドライバのターンオン時間を能動的にコントロールすることによってスイッチング過渡時シュートスルー電流が内蔵のハイサイドMOSFETや外付けのローサイドMOSFETに流れることが防止されます。ハイサイド・ドライバはローサイドMOSFETのゲート電圧が1Vより低くなるまでオンになりません。一方、ローサイド・ドライバはハイサイドMOSFETのゲート電圧が1Vより低くなるまでオンにはなりません。

## ローサイド・ゲート・ドライバ(LSG)

LSGはローサイド・ゲート・ドライバの出力です。このMOSFET ドライバは100mAの電流能力をもち、このアプリケーションに適したもっとも一般的なMOSFETのゲート駆動を行うことができます。アプリケーションに最適なMOSFETを見つけるには SWIFTデザイナー・ソフトウェアツールを使用してください。 LSGピンはローサイドMOSFETのゲートに直接接続してください。ゲート抵抗は結果としてターンオン時間が遅すぎることになる可能性があるため使用しないでください。

### 内蔵プルダウンMOSFET

TPS54350にはPHからPGNDに一組のダイオード/MOSFETがあります。内蔵のMOSFETは外部のショットキー・ダイオードのみが使用される場合の軽負荷の連続導通モード動作用に設計されています。このデバイスの組み合わせにより、負荷電流がインダクタの境界電流より下に低下する状況下でインダクタ電流は連続的に流れ続けます。ローサイドのショットキー・ダイオードのみを使用するアプリケーションでインダクタを選択するには注意を払わなければなりません。インダクタのリップル電流は軽負荷時内蔵のローサイドMOSFETを流れるため、インダクタンス値はそのピーク電流がハイサイドFETのターンオフ時間で0.3Aより低い値に制限されるよう選択してください。インダクタンスの最小値は以下の式を使って計算されます。

$$L(H) = \frac{VO \times \left(1 - \frac{VO}{VI}\right)}{f_s \times 0.6}$$

(6)

### サーマル・シャットダウン

このデバイスは接合部温度が165℃を越えるとサーマル・シャットダウンを用いてMOSFETドライバとコントローラをオフにします。デバイスは接合部温度がサーマル・シャットダウンのトリップ点より7℃下がると自動的に再起動し、スロースタート回路のコントロールの下で立上がります。

### 過電流保護

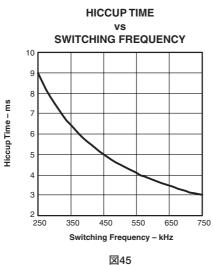

過電流保護はハイサイドMOSFETのドレイン/ソース間電圧を検出することにより行われ、過電流スレッシュホールド・リミットに相当する電圧レベルと比較されます。ドレイン/ソース間電圧が100ns以上過電流スレッシュホールド・リミットを越えると、ENAピンは "L" レベルに、ハイサイドMOSFETはディスエーブルになり、内部のディジタル方式のスロースタートは0Vにリセットされます。ENAはおおよそ以下の式で計算される時間 "L" レベルに保持されます。

$$T_{\text{HICCUP(ms)}} = \frac{2250}{f_{\text{s(kHz)}}} \tag{7}$$

この一時的な中断時間が終わるとENAピンは開放され、コンバータは内部スロースタートを開始します。

### 出力電圧の設定

TPS54350の出力電圧は抵抗デバイダ回路を用いて出力電圧をVSENSEピンにフィードバックさせることで設定することができます。図24のアプリケーション回路では、このデバイダ回路は抵抗R1とR2から構成されています。必要とされる出力電圧を生成するための抵抗値を計算するには、以下の式を用いてください。

$$R2 = \frac{R1 \times 0.891}{V_O - 0.891} \tag{8}$$

R1を固定値として、必要とされるR2の値を計算します。R1が固定値の $10k\Omega$ とすると、以下の表からいくつかの一般的な出力電圧に対する適切なR2の値が求められます。

| 出力電圧(V) | R2值(kΩ) |

|---------|---------|

| 1.2     | 28.7    |

| 1.5     | 14.7    |

| 1.8     | 9.76    |

| 2.5     | 5.49    |

| 3.3     | 3.74    |

### 出力電圧の制限

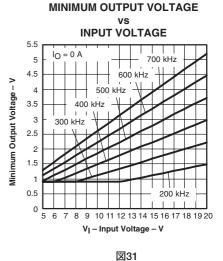

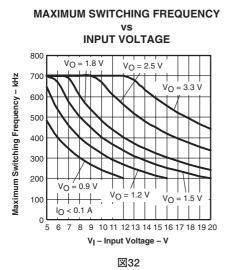

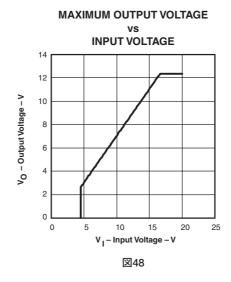

TPS54350の内部設計により、任意の与えられた入力電圧に対して出力電圧には上限と下限の両方が存在します。さらに、出力電圧の設定点範囲の下側の境界も動作周波数に依存します。出力電圧の設定点の上限はデバイスの最大デューティ・サイクルで制限され、図48に示されています。下限は最小のコントロール可能なオン時間で制限されますが、この時間は220nsです。所定の入力電圧と動作周波数範囲に対するおおよその最小出力電圧は図29に、いくつかの一般的な出力電圧に対する最大動作周波数対入力電圧は図30に示されています。

これら2つの図に示されている曲線は出力電流が0.5Aより大きい場合に有効です。出力電流が無負荷(0A)へと減少してゆくにつれ、最小出力電圧は減少してゆきます。負荷電流が100mAより小さなアプリケーションでは、図31と図32で示されている曲線が適用されます。これらの曲線に表示されているすべてのデータは近似であり、目的の設定点に対し実際の動作周波数には20%程度の狂いが起こり得ることを考慮してください。

# 代表的特性

# 代表的特性

# POWER DOWN $V_{\parallel} = 5 \text{ V/div}$ $V_{O} = 2 \text{ V/div}$ $V_{(PWRGD)} = 2 \text{ V/div}$ See Figure 24 Time - 2 ms/div

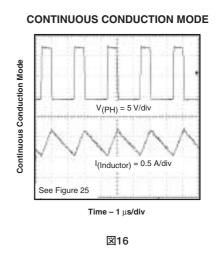

## DISCONTINUOUS CONDUCTION MODE

図17 図18

# アプリケーション情報

## PCBレイアウト

2つのVINピンはプリント基板(PCB)上で互いに接続し、低ESR のセラミック・キャパシタでバイパスしなければなりません。こ の時、バイパス·キャパシタの接続、VINピン、TPS54350のグ ランド・ピンで形成されるループ領域を最小限に抑えるような注 意が必要です。推奨最小バイパス容量は10μF セラミックのX5R またはX7R誘電体で、その最適な配置位置はVINピン、AGND ピン、PGNDピンにもっとも近いところです。図21のボード·レ イアウト例を参照してください。AGNDピンとPGNDピンはICの ピンでPCBのグランド・プレーンに接続します。ローサイド MOSFETのソースとショットキー·ダイオードのアノードは直接 PCBのグランド・プレーンに接続します。2つのPHピンは互いに 接続し、ローサイドMOSFETのドレインまたは外付けショット キー·ダイオードのカソードに引き廻します。PHの接続はスイッ チング・ノードであるため、MOSFET(またはダイオード)はPH ピンに近づけて置き、また過度の容量結合を防ぐためPCBの導体 領域は最小限に抑えてください。14ピンと15ピンの推奨導体幅は

0.050インチから0.075インチで1オンスの銅です。銅のランド・パターン長は0.2インチ以上にならないようにしてください。

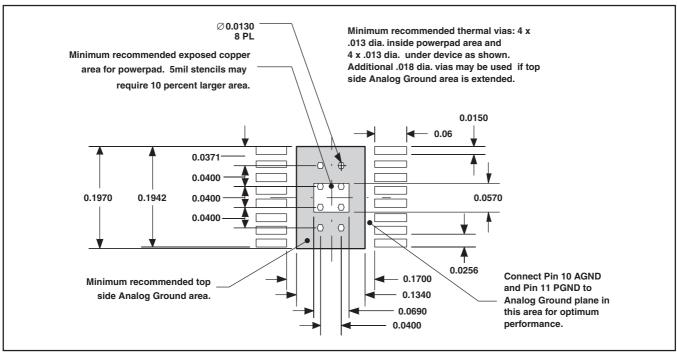

全定格負荷で動作を行うには、アナログ・グランドのプレーン は十分な熱放散面積を備えていなければなりません。周囲の温度 とエアフローにもより、強制ではありませんが、3インチx3イン チの銅プレーンを推奨します。ほとんどのアプリケーションでは 内部に大きな領域のグランド・プレーンをもつことができ、 PowerPAD™はこの利用可能な最大領域に接続しなければなりま せん。下層または上層の別の領域も熱放散の手助けとなり、3Aま たはそれ以上での動作が求められる場合には利用可能な領域はす べて使用しなければなりません。PowerPAD™のむき出しの領域 からアナログ・グランド・プレーン層へはビアの中でのはんだの ウィッキング(ボイド)を避けるため直径0.013インチのビアを使っ て接続しなければなりません。PowerPAD™領域には4つのビ ア、及びパッド領域の外側とパッケージの真下に4つの追加ビア がなければなりません。熱特性を向上させるのに推奨するこれ以 上の追加ビアはデバイス・パッケージの下以外の領域に置くこと が必要です。

図21. TPS54350 PCBレイアウト

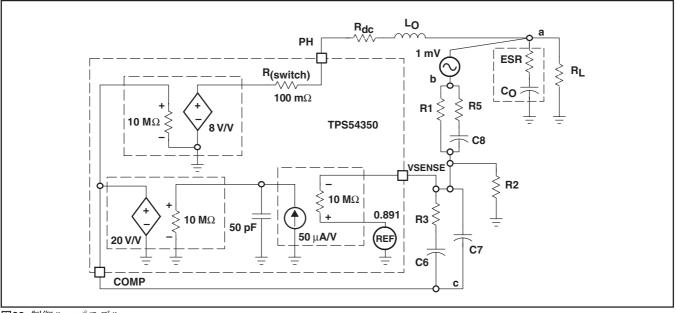

## ループ応答のモデル

図23に、周波数応答とダイナミック負荷応答を調べるため回路シミュレーション・プログラムでモデル化可能なTPS54350のコントロール・ループの等価モデルを示します。TPS54350の誤差増幅器は80dB(10000V/V)の開ループ利得をもつ電圧増幅器です。誤差増幅器は図23に示されるように出力に抵抗とキャパシタをもつ電圧制御の理想電流源を使ってモデル化することができます。TPS54350はフィードフォワード補償回路を内蔵しており、入力電圧の変化がループの総伝達関数に与える影響を除去します。

フィードフォワード利得は8V/Vの利得をもつ電圧制御の理想電圧源としてモデル化されます。ノードaとbの間の1mVのAC電圧は周波数応答の測定のためコントロール・ループを効果的に分

割します。プロットb/cはパワー段の小信号応答を示しています。プロットc/aは周波数補償の小信号応答を示しています。プロットa/bはループ全体の小信号応答を示します。ダイナミック負荷応答はRLを時間領域の解析で適切な負荷ステップ振幅とステップ・レートをもつ電流源に置き換えることで調べることができます。

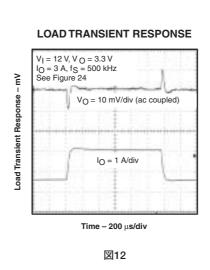

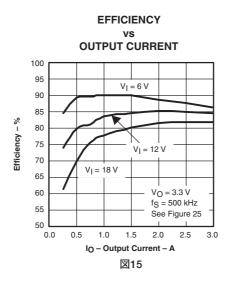

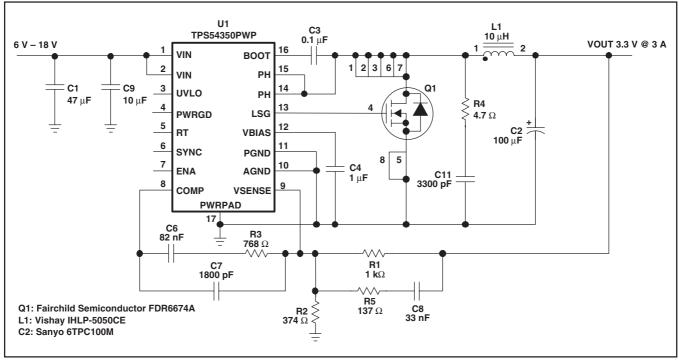

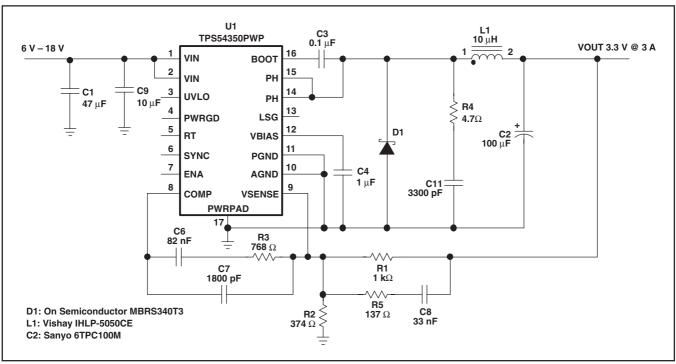

図24にTPS54350の代表的なアプリケーション回路図を示します。TPS54350は、標準出力電圧3.3V時最大3Aの出力電流を供給することができます。熱特性を適切にするには、デバイスの真下のむき出しのPowerPAD™をプリント基板にはんだ付けしなければなりません。

図22. 熱特性を考慮したPowerPAD™ レイアウト

図23. 制御ループモデル

図24.12Vから3.3Vを作るアプリケーション回路

## 設計手順

以下の設計手順はTPS54350の部品値を選択するのに利用することができます。また、設計全体にSWIFTデザイナー・ソフトウェアを使用することもできます。SWIFTデザイナー・ソフトウェアでは設計時反復設計手順が用いられ、また部品の総合データベースにアクセスします。この項では設計手順を簡略化して説明します。

## 設計手順

設計手順に着手するにはいくつかのパラメータを決めなければなりません。設計者は以下のことについて知っておく必要があります。

- 入力電圧範囲

- 出力電圧

- 入力リップル電圧

- 出力リップル電圧

- 出力電流定格

- 動作周波数

この設計例では、入力パラメータとして以下を使用します。

| 設計パラメータ  | 用例值      |

|----------|----------|

| 入力電圧範囲   | 6 V∼18 V |

| 出力電圧     | 3.3 V    |

| 入力リップル電圧 | 300 mV   |

| 出カリップル電圧 | 30 mV    |

| 出力電流定格   | 3 A      |

| 動作周波数    | 500 kHz  |

(注)その他制約条件として、設計は小型/薄型部品で行われています。

## スイッチング周波数

スイッチング周波数はRTピンを使って設定されます。RTピンをグランドに接続するとPWMスイッチング周波数は250kHzのデフォルト周波数に設定されます。RTピンをフローティングにするとPWMスイッチング周波数は500kHzに設定されます。RTからAGNDに抵抗を接続することで、250kHz~700kHzの範囲で周波数が設定できます。適切なRTの値を決めるには以下の式(9)を使用してください。

$$RT(k\Omega) = \frac{46000}{f_s(kHz) - 35.9}$$

(9)

この回路例ではRTは未接続であり周波数は500kHzに設定されています。

## 入力キャパシタ

TPS54350には入力デカップリング・キャパシタと、アプリケーションによっては、入力バルク・キャパシタが必要です。デカップリング・キャパシタC9の最小値は10μFです。高品質のセラミックX5RまたはX7Rタイプを推奨します。定格電圧は最大入力電圧より大きくなければなりません。さらに、特にTPS54350回路が入力電圧源から約2インチ以内に配置されていないとバルク容量がいくつか必要となることがあります。このキャパシタの値は重要ではありませんが、これはリップル電圧を含む最大入力電圧に対処するような定格で、入力リップル電圧が許容できるよう出力をフィルタしなければなりません。

入力リップル電圧は以下の式(10)で概算できます。

$$\Delta V_{\rm IN} = \frac{I_{\rm OUT(MAX)} \times 0.25}{C_{\rm BULK} \times f_{\rm sw}} + \left(I_{\rm OUT(MAX)} \times {\rm ESR}_{\rm MAX}\right) \quad (10)$$

但し、 $I_{OUT(MAX)}$ は最大負荷電流、 $f_{SW}$ はスイッチング周波数、 $C_{BULK}$ はバルク・キャパシタ値、 $ESR_{MAX}$ はバルク・キャパシタの最大直列抵抗です。

また、最大RMSリップル電流も調べることが必要です。最悪 条件の場合について、これは以下の式(11)で概算できます。

$$I_{CIN} = \frac{I_{OUT(MAX)}}{2} \tag{11}$$

この場合、入力リップル電圧は140mV、RMSリップル電流は1.5Aとなります。入力キャパシタ上の最大電圧はVINの最大値に ΔVIN/2に加えた値になります。選択したバルク・キャパシタ及びバイパス・キャパシタの定格はそれぞれ25Vで、合わせたリップル電流の受容能力は3Aより大きく、両方とも十分なマージンがあります。非常に重要なことは、いかなる環境下でも電圧及び電流の最大定格を越えないことです。

## 出力フィルタ部品

出力フィルタL1とC2の2つの部品を選択することが必要です。 TPS54350は外部で補償されるデバイスですので広範囲のフィル タ部品のタイプ及び値が対応しています。

## インダクタの選択

出力インダクタの最小値を計算するには以下の式(12)を使用 します。

$$L_{MIN} = \frac{V_{OUT(MAX)} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(max)} \times K_{IND} \times I_{OUT} \times F_{SW}}$$

(12)

$K_{\rm IND}$ は最大出力電流に対するインダクタのリップル電流量を表す係数です。セラミックなど低ESRの出力キャパシタを使用した設計では $K_{\rm IND}$  = 0.3を使用してください。ESRの高い出力キャパシタを使用する場合は、 $K_{\rm IND}$  = 0.2を使うとより良好な結果がもたらされます。

この設計例では、 $K_{IND}$  = 0.2が使われており、最小インダクタ値の計算結果は8.98 $\mu$ Hです。これより高い標準値は $10\mu$ Hで、この設計ではこれを使用します。

出力フィルタ・インダクタについては、定格RMS電流と定格飽和電流を越えないことが重要です。RMSインダクタ電流は以下の式(13)から求められます。

$$I_{L(RMS)} = \sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times \left(\frac{V_{OUT} \times \left(V_{IN(MAX)} - V_{OUT}\right)}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.8}\right)^2}$$

(13)

また、ピーク・インダクタ電流は以下の式(14)で決まります。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times \left(V_{IN(MAX)} - V_{OUT}\right)}{1.6 \times V_{IN(MAX)} \times L_{OUT} \times F_{SW}} \tag{14}$$

この設計では、RMSインダクタ電流は3.01A、ピーク・インダクタ電流は3.34Aです。選択したインダクタはVishay IHLP5050CE-01で10μHです。このインダクタの定格飽和電流は14A、定格RMS電流は7Aで、楽にこれら要件に適合しています。このデバイスは薄型であるため選択されましたが、より低い定格のインダクタを使用することもできます。一般的に、TPS54350とともに使用されるインダクタ値は6.8μHから47μHの範囲です。

### キャパシタの選択

出力キャパシタの重要な設計要因は、定格DC電圧、定格リップル電流、等価直列抵抗(ESR)です。定格DC電圧と定格リップル電流は越えることはできません。ESRはそれがインダクタ電流とともに出力リップル電圧量を決めるため重要です。出力キャパシタの実際の値は重要ではありませんが、いくつか実用上の制限が

あります。設計上の閉ループの設定クロスオーバー周波数と出力フィルタLCのコーナー周波数との間の関係について配慮してください。一般的に、閉ループのクロスオーバー周波数をスイッチング周波数の1/5より下に保持することが望ましいことです。この設計での500kHz周波数のような高いスイッチング周波数では、TPS54350の内部回路の制限により実際上の最大クロスオーバー周波数は約50kHzに制限されます。さらに、補償回路の十分な位相利得を可能にするには、LCのコーナー周波数はクロスオーバー周波数より約1/10程度下にしなければなりません。このことにより、出力フィルタの最小キャパシタ値は以下の式のように制限されます。

$$C_{OUT} = \frac{1}{L_{OUT}} \times \left(\frac{K}{2\pi f_{CO}}\right)^2 \tag{15}$$

但し、Kは $f_{LC}$ と $f_{CO}$ 間にまたがる周波数乗数です。Kは5と15の間ですが、10の差がありますが通常は10です。設定クロスオーバー周波数が50kHz、インダクタ値が10 $\mu$ Hの場合には、出力キャパシタの最小値は100 $\mu$ Hになります。選択する出力キャパシタの定格は、設定出力電圧にリップル電圧の1/2を加えた値より大きくなければなりません。また、軽減量も含めなければなりません。出力キャパシタの最大RMSリップル電流は以下の式(16)で求められます。

$$I_{\text{COUT}(\text{RMS})} = \frac{1}{\sqrt{12}} \times \left( \frac{V_{\text{OUT}} \times (V_{\text{IN}(\text{MAX})} - V_{\text{OUT}})}{V_{\text{IN}(\text{MAX})} \times I_{\text{OUT}} \times F_{\text{SW}} \times N_{\text{C}}} \right)$$

(16)

但し、NCは並列出力キャパシタの数です。

出力キャパシタの最大ESRは初めの設計パラメータに規定された許容出力リップル量で決まります。出力リップル電圧はインダクタのリップル電流に出力フィルタのESRを掛けたものであるため、キャパシタのデータシートに記載されている規定最大ESRは以下の式(17)で求められます。

$$ESR_{MAX} = N_{C} \times \left( \frac{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.8}{V_{OUT} \times \left(V_{IN(MAX)} - V_{OUT}\right)} \right) \times \Delta V_{p-p(MAX)}$$

(17)

但し、 $\Delta V_{PP}$ は設定ピーク間出力リップル電圧です。この設計例では、設計目標が小型化であるため、出力キャパシタには $100\mu F$ が1つC2として選択されています。RMSリップル電流の計算結果は156mA、必要となる最大ESRは59m $\Omega$ です。これらの要件に適合するキャパシタはSanyo Poscap 6TPC100Mで、定格6.3V、最大ESRは45m $\Omega$ 及び定格リップル電流は1.7Aです。別に0.1 $\mu F$ のセラミックの小型バイパス・キャパシタも使用されています。

その他のキャパシタのタイプも、アプリケーションの必要性に よっては、TPS54350とよく機能するものもあります。

### 補償部品

TPS54350とともに外部補償を使用すると広範囲の出力フィルタの構成が可能になります。広い範囲の誘電体のキャパシタ値とタイプが対応しています。設計例では、R1, R3, R5, C6, C7, C8から成るタイプ3の補償が使用されています。さらに、R1とともにR2が出力電圧を設定する分圧回路を形成しています。これら部品の参照番号はSWIFTデザイナー・ソフトウェアで使用されているのと同じです。補償回路を設計するには多くの方法があります。この手順ではもっとも多くの出力フィルタの組み合わせで良好な結果をもたらす比較的単純な手順を概説します。著しく高い閉

ループのクロスオーバー周波数、セラミックのような小さな値で低ESRの出力キャパシタの設計を行う時、またはデザイナーが設計手順に自信がもてない場合にはSWIFTデザイナー・ソフトウェアを使用することを推奨します。TPS54350の補償回路を設計する際には、いくつかの要因を考慮する必要があります。補償済の誤差増幅器の利得は増幅器の開ループ利得特性で制限されるべきではなく、また、スイッチング周波数時に過大な利得をもたらしてはいけません。また、閉ループのクロスオーバー周波数はスイッチング周波数の1/5より下に設定し、クロスオーバー時の位相余裕は45°より大きくなければなりません。ここで概説されている一般的な手順では、ループ補償の理論について詳細には述べていませんがこれら要件に合致する結果がもたらされています。

最初に以下の式(18)を使って出力フィルタLCのコーナー周波数を計算します。

$$f_{\rm LC} = \frac{1}{2\pi \sqrt{L_{\rm OUT} C_{\rm OUT}}} \tag{18}$$

設計例では $f_{IC}$  = 5033Hzになります。

閉ループのクロスオーバー周波数はf<sub>LC</sub>より高く、スイッチング周波数の1/5より下でなければなりません。また、誤差増幅器が設定利得を提供しないかもしれないため、クロスオーバー周波数は50kHzを越えてはなりません。この設計では、クロスオーバー周波数には30kHzを選択しました。この値は、安定性を保証するためになお適切な位相ブーストを可能にしながら、比較的広いループ帯域幅であるという理由で選択されました。

次に、3.3Vの出力電圧に対するR2抵抗値を以下の式(19)を使って計算します。

$$R2 = \frac{R1 \times 0.891}{V_{OUT} - 0.891} \tag{19}$$

TPS54350のどの設計でもR1値は1.0k $\Omega$ から始めます。よってR2は374 $\Omega$ になります。

これから、補償回路の極とゼロを設定する補償部品値を計算することができます。R1>R5、C6>C7と仮定すると、極及びゼロの位置は以下の式(20)から式(23)で求められます。

$$f_{Z1} = \frac{1}{2\pi R_3 C_6}$$

(20)

$$f_{Z2} = \frac{1}{2\pi R1C8}$$

(21)

$$f_{\rm P1} = \frac{1}{2\pi R5C8}$$

(22)

$$f_{P2} = \frac{1}{2\pi R^3 C^7}$$

(23)

さらに、以下の周波数で単一利得をもつ原点の極があります。

$$f_{\text{INT}} = \frac{1}{2\pi \text{RIC6}} \tag{24}$$

この極は補償済誤差増幅器の総利得を設定するのに使用され、 閉ループのクロスオーバー周波数を決定します。R1は1kΩで与え られ、クロスオーバー周波数は30kHzに選択されているため、求 めるf<sub>INT</sub>は以下の式(25)で計算できます。

$$f_{\text{INT}} = \frac{10^{-0.9} \times f_{\text{CO}}}{2} \tag{25}$$

また、C6の値は以下の式(26)で求められます。

$$C6 = \frac{1}{2\pi R1 f_{\text{INT}}} \tag{26}$$

最初のゼロ $f_{Z1}$ は出力フィルタLCのコーナー周波数の1/2に置かれるため、R3は以下の式(27)から計算できます。

$$R3 = \frac{1}{\pi C6f_{LC}} \tag{27}$$

2番目のゼロ $f_{Z2}$ は出力フィルタLCのコーナー周波数に置かれるため、C8は以下の式(28)から計算できます。

$$C8 = \frac{1}{2\pi R1 f_{1C}} \tag{28}$$

最初の極 $f_{P1}$ は出力フィルタのESRゼロ周波数に合致するよう置きます。この周波数は以下の式(29)から求められます。

$$f_{\rm ESR} = \frac{1}{2\pi R_{\rm ESR} C_{\rm OUT}} \tag{29}$$

但し、R<sub>ESR</sub>は出力キャパシタの等価直列抵抗です。

この場合、ESRゼロ周波数は35.4kHzで、R5は以下の式(30) から計算できます。

$$R5 = \frac{1}{2\pi C8 f_{ESR}} \tag{30}$$

最後の極は、スイッチング周波数でほとんど利得がないよう十分な減衰をさせながら、クロスオーバー周波数で位相を過度に減少させない、閉ループのクロスオーバー周波数より十分に高い周波数に置かれます。この回路のf<sub>P2</sub>極位置は閉ループのクロスオーバー周波数の4倍に設定され、最後の補償部品値C7は以下の式(31)より導かれます。

$$C7 = \frac{1}{8\pi R_3 f_{CO}} \tag{31}$$

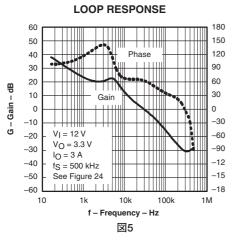

これらキャパシタは標準値という制限範囲内でのみ有効であることに注意してください。そのため、各々のキャパシタにはもっとも近い標準値を選択します。この設計での測定閉ループ応答を図5に示します。

## バイアス及びブートストラップ・キャパシタ

すべてのTPS54350の設計にはブートストラップ・キャパシタC3 とバイアス・キャパシタC4が必要です。ブートストラップ・キャパシタは0.1μFでなければならず、PHピンとBOOTピンの間に置かれます。バイアス・キャパシタはVBIASピンとAGNDピンの間に接続されます。その値は1.0μFでなければなりません。両方のキャパシタとも温度安定性のため高品質セラミック・タイプX7RまたはX5Rクラスの誘電体なければなりません。それらはできるだけデバイスの接続ピンの近くに置きます。

### ローサイドFET

TPS54350は外付けのローサイドMOSFETを使用して動作するよう設計されており、LSGピンがそのゲート駆動出力を供給します。そのドレインをPHピンに、ゲートをLSGに接続してください。TPS54350のゲート駆動回路はこのアプリケーションに適したもっとも一般的なNチャネルMOSFETに適合するよう設計され

ています。SWIFTデザイナー・ソフトウェアはローサイド MOSFETを選択するための全設計パラメータを計算するのに使用できます。多くの設計で許容できる解をもたらすのに適用できる簡略ガイドラインがいくつかあります。

選択するFETはアプリケーションの絶対最大定格に適合する必要があります。

ドレイン/ソース間電圧( $V_{DS}$ )はPHピンの最大電圧 $V_{INMAX}$ +0.5Vより高くなければなりません。

ゲート/ソース間電圧( $V_{GS}$ )は8Vより高くなければなりません。ドレイン電流( $I_{DD}$ )は1.1 x  $I_{OUTMAX}$ より高くなければなりません。ドレイン/ソース間のオン抵抗( $I_{DSON}$ )はできるだけ小さくすべきで、 $30m\Omega$ より下が望ましい値です。 $I_{DSON}$ が小さいと高効率の設計が実現します。注意すべき重要なことはローサイドFETのオン時間は通常ハイサイドFETのオン時間より長いことです。そのため、ローサイドFETのパラメータに注意を払うと総効率が著しく改善します。

総ゲート電荷( $Q_g$ )は50nCより低くなければなりません。今一度、 $Q_g$ が低い特性であると高効率が実現できます。

また、選択したデバイスが電力損失を放散することができるか も調べてください。

この設計では、Fairchild FDR6674A定格30VでNチャネル MOSFETがローサイドFETとして使用されています。この特殊なFETは特にローサイド同期整流器として使用するよう設計されています。

## パワー・グッド

TPS54350はパワー・グッド出力ピンPWRGDを備えています。この出力はオープン・ドレイン出力で、3.3Vまたは5Vのロジック電源にプルアップすることを意図しています。このアプリケーションでは10kΩのプルアップ抵抗で良好に機能します。絶対最大電圧は6Vですので、最大入力電圧が6Vを越える場合、このプルアップ抵抗をVINに接続しないよう注意が必要です。

## スナバ回路

図24のアプリケーション回路図のR4とC11はスナバ回路を構成しています。スナバは、内蔵ハイサイドFETがオンになった時位相ノードのオーバーシュートやリンギングを低減するために含まれています。リンギングの周波数と振幅は寄生効果の大きさに依存しますので、これらの部品値は設計レイアウトでの実測をもとに選択することが最善となります。スナバ設計のより詳細な情報については文献番号SLUP100を参照してください。

図25に、ローサイドFETの代わりにクランプ・ダイオードが使用されているアプリケーションを示します。TPS54350は、回路が軽負荷動作時連続モードで動作し続けるよう、プルダウンFETを内蔵しています。クランプ・ダイオードにはMotorola MBRS340T3またはその同等品の3A、40V規格のショットキー・ダイオードを推奨します。

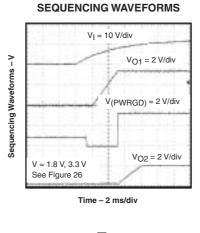

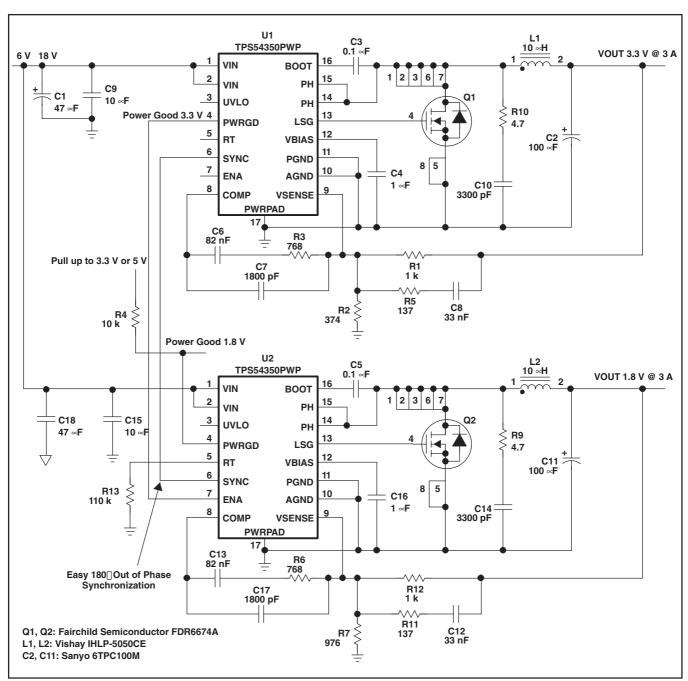

図26は2つのTPS54350を使用した電源シーケンスの例です。 U1は3.3V出力を生成するのに使用され、一方、U2の電圧出力は

図25. ショットキ·ダイオード3.3V電源回路

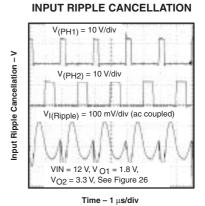

通常マイクロプロセッサやFPGA用のI/O電圧及びコア電圧である1.8Vに設定されています。この回路では、3.3V電源が最初に起動するよう設計されています。3.3V電源がレギュレーションの範囲内に入った後1.8V電源が上昇し始めるよう、U1のPWRGDピンはU2のENAピンに接続されています。U1のRTピンはフローティングであるため、SYNCピンは出力です。この同期信号がU2のSYNCピンに入ります。U2のRTピンから110k $\Omega$ がグランドに接続されており、このデバイスのSYNCピンは入力として機能します。1.8V電源は3.3V電源に同期して動作し、それらのスイッチング・ノードのリンギング・エッジは位相が約180° ずれているため入

力電圧リップルの低減を可能にしています。この波形については 図19を参照してください。

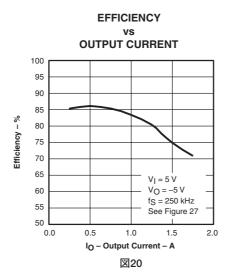

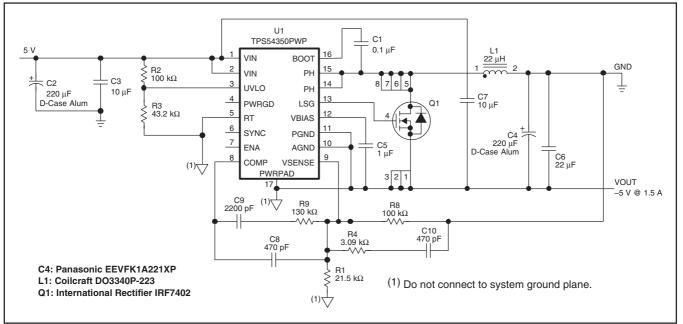

図27ではTPS54350が反転電源として構成されています。通常はグランドに接続されるピンが-5V出力です。バック・コンバータでは通常、出力であるLC出力フィルタの出力がグランドに接続されています。追加で10μFのキャパシタC7が出力からVINに必要です。

図26. シーケンス動作を持つ3.3V/1.8V電源回路

図27.5Vから-5V/1.5Aを作るインバーティング電源回路

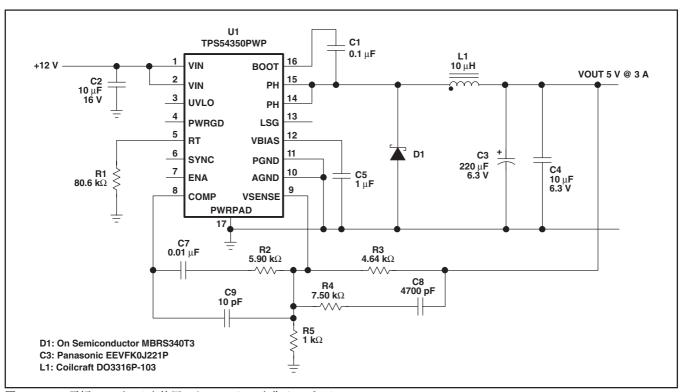

図28. アルミ電解コンデンサを使用した12Vから5Vを作るアプリケーション

図28は安価な出力フィルタ部品を使用した入力12V/出力5Vの例です。

## MINIMUM OUTPUT VOLTAGE **INPUT VOLTAGE** 5.5 I<sub>O</sub> > 0.5 A 5 4.5 700 kHz Minimum Output Voltage 3.5 600 kHz -500 kHz 3 2.5 400 kHz 1.5 0.5 300 kHz 200 kHz 8 9 10 11 12 13 14 15 16 17 18 19 20 V<sub>I</sub> - Input Voltage - V 図29

## **POWER GOOD THRESHOLD** JUNCTION TEMPERATURE 98.0 PWRGD - Power Good Threshold - % 97.5 97.0 96.5 -25 25 50 75 100 125 -50 0 T<sub>J</sub> – Junction Temperature – °C 図38

## FREE-AIR TEMPERATURE **MAXIMUM OUTPUT CURRENT** TJ= 1251C 120 T<sub>A</sub> – Free-Air Temperature – °C 100 80 60 40 20 0 0.5 2.5 0 1.5 2 3 I O - Output Current - A 図47

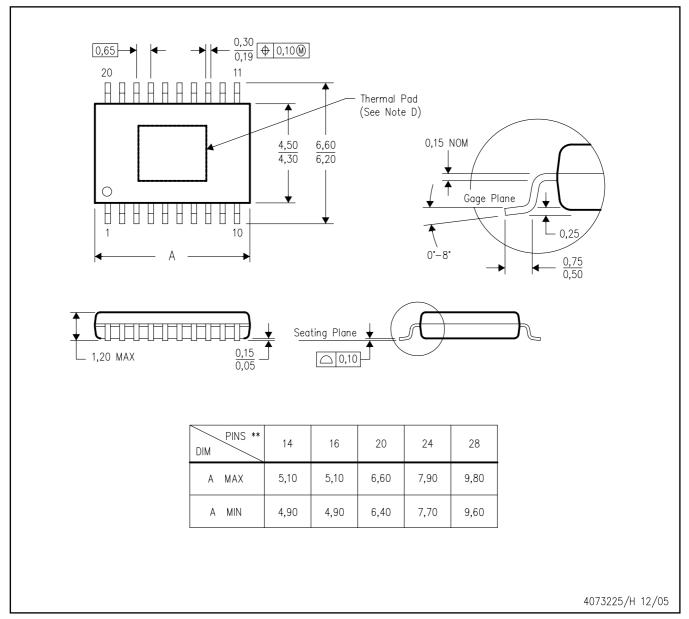

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. PowerPAD™パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ "PowerPAD™ Thermally Enhanced Package" TI文献番号SLMA002及びアプリケーション・ブリーフ "PowerPAD™ Made Easy" TI文献番号SLMA004を参照してください。いずれもホームページ www.ti.comで入手できます。

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS54350PWP      | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54350PWPG4    | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54350PWPR     | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54350PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

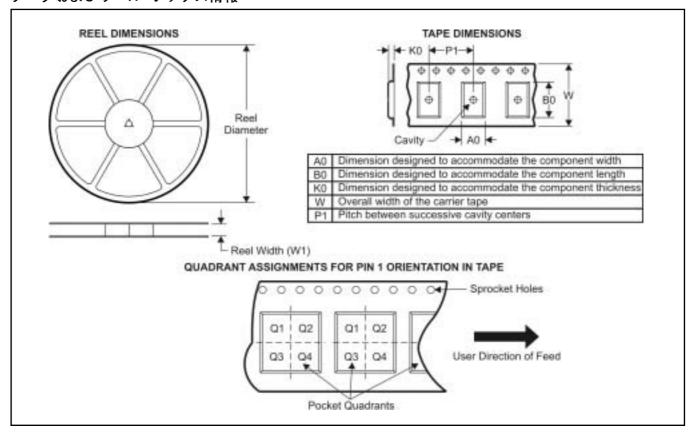

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

## \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS54350PWPR | HTSSOP          | PWP                | 16   | 2000 | 330.0                    | 12.4                     | 6.67    | 5.4     | 1.6     | 8.0        | 12.0      | Q1               |

# パッケージ・マテリアル情報

## \*All dimensions are nominal

| Device       | PackageType | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|-------------|-----------------|------|------|-------------|------------|-------------|

| TPS54350PWPR | HTSSOP      | PWP             | 16   | 2000 | 346.0       | 346.0      | 29.0        |

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">https://www.ti.com</a>.

- E. Falls within JEDEC MO-153

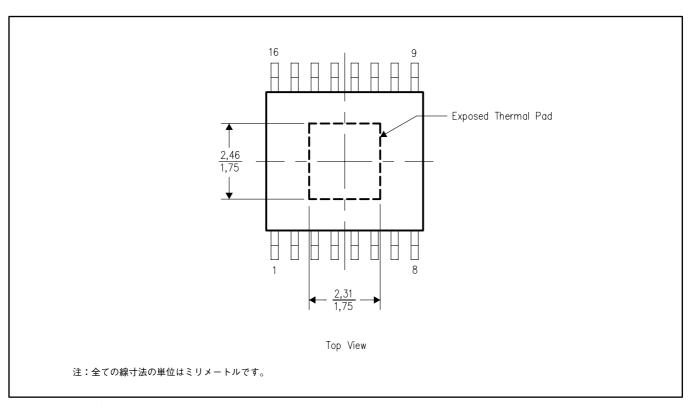

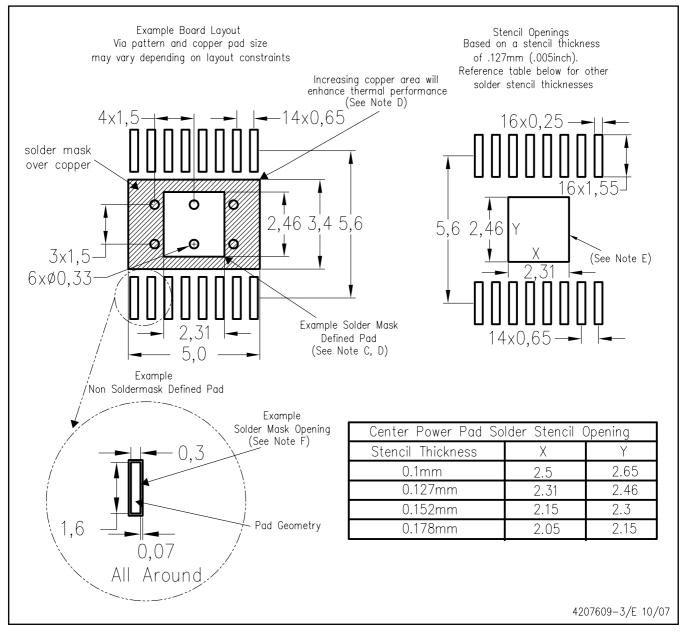

## THERMAL PAD MECHANICAL DATA

## 熱情報

このPowerPAD<sup>TM</sup>パッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板 (PCB) に直接はんだ付けされなければなりません。はんだ付けの後、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはデバイスの電気回路図に示されている銅プレーンに直接接続するか、あるいは、PCBに設計された特別なヒートシンク構造に接続することができます。この設計により、集積回路(IC)からの熱移動が最適化されます。

PowerPAD<sup>TM</sup>パッケージの追加情報及びその熱放散能力の利用法についてはテクニカル・ブリーフ "PowerPAD<sup>TM</sup> Thermally Enhanced Package" TI文献番号SLMA002とアプリケーション・ブリーフ "PowerPAD<sup>TM</sup> Made Easy" TI文献番号SLMA004を参照してください。両方の文献ともホームページwww.ti.comで入手できます。

このパッケージの露出サーマル・パッドの寸法は以下の図に 示されています。

サーマル・パッド寸法図

## PWP (R-PDSO-G16) PowerPAD™

注:A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. カスタマは中央のはんだマスク規定パッドを変更しないよう回路ボードの製作図面に注釈をつけなければなりません。

- D. このパッケージはボードのサーマル・パッドにはんだ付けされるよう設計されています。個別の熱情報、ビアの要件、推奨するボード・レイアウトについてはテクニカル・ブリーフ "PowerPAD™ Thermally Enhanced Package" TI文献番号SLMA002とSLMA004、及びプロダクト・データシートを参照してください。これらの文献はホームページwww.ti.comで入手できます。出版番号IPC-7351は設計代案についての推奨です。

- E. レーザーカットの開口部に台形の壁をつけ、角に丸みをつけるとペースト離れがよくなります。カスタマはステンシルの設計についてボード製作側に提案しなければなりません。このステンシル設計例は50%容積の金属を基にはんだペーストを積んでいます。その他の推奨ステンシルについてはIPC-7525を参照してください。

- F. カスタマは信号パッド間及びパッド回りのはんだマスクの許容値についてボード製作側に連絡しなければなりません。

(SLVS456)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

## 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上