## TPS54331 3A、28V 入力の降圧 DC/DC コンバータ、Eco-mode 付き

### 1 特長

- 3.5~28V の入力電圧範囲

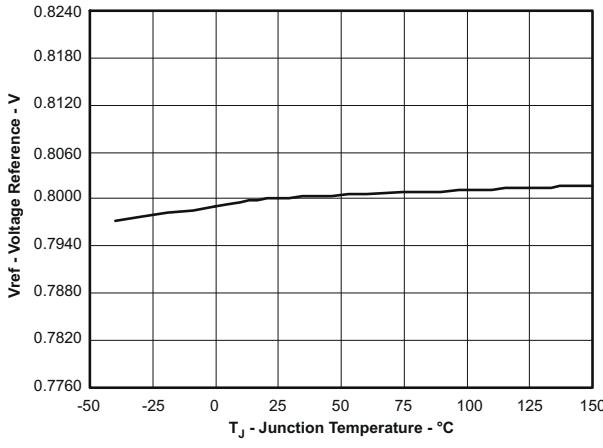

- 出力電圧を最低 0.8V まで変更可能

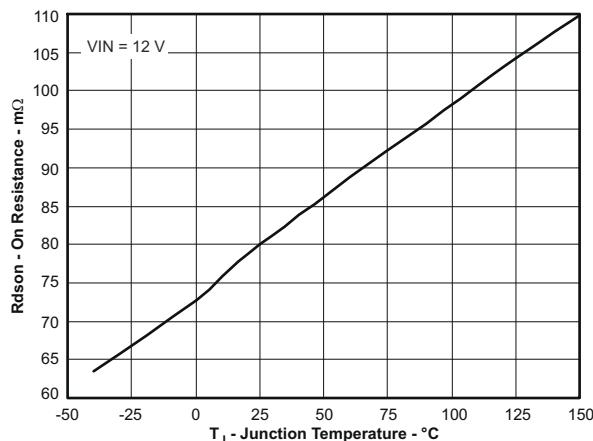

- 80mΩ のハイサイド MOSFET を内蔵し、最大 3A の連続出力電流に対応

- パルス・スキップ Eco-mode による高い軽負荷効率

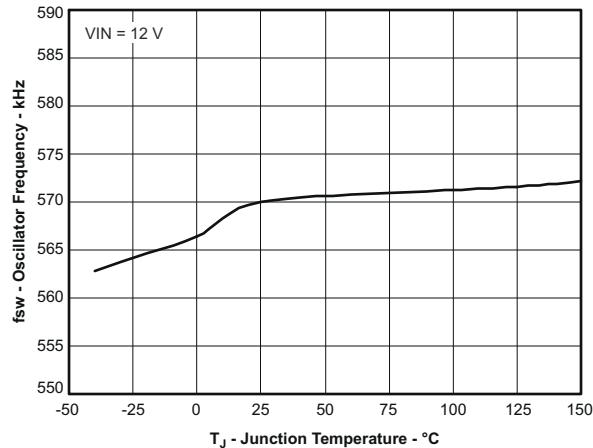

- 570kHz の固定スイッチング周波数

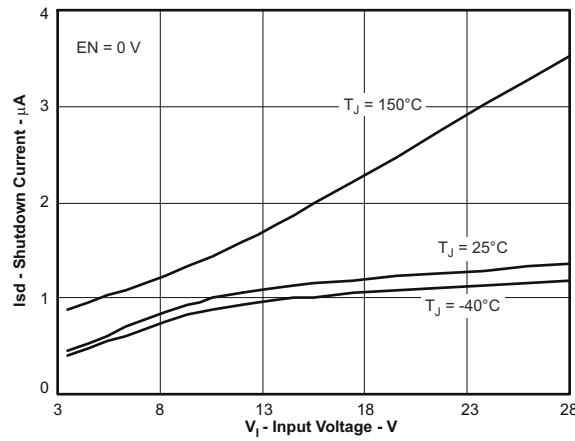

- 標準値 1µA のシャットダウン時静止電流

- 可変スロー・スタートにより突入電流を制限

- UVLO スレッショルドをプログラム可能

- 過電圧過渡保護

- サイクル単位の電流制限、周波数フォールドバック、およびサーマル・シャットダウン保護

- 使いやすい SOIC8 パッケージまたは放熱特性に優れた SOIC8 PowerPAD™ 集積回路パッケージで供給

- WEBENCH® Power Designer により、TPS54331 を使用するカスタム設計を作成

- 30 VIN コンバータに TPS62933 を使用して高周波数、低 IQ、高 EMI を実現

### 2 アプリケーション

- セットアップ・ボックス、CPE、LCD ディスプレイ、周辺機器、バッテリ充電器などの民生用アプリケーション

- 産業用 およびカーオーディオ用電源

- 5V、12V、24V の分散型電源システム

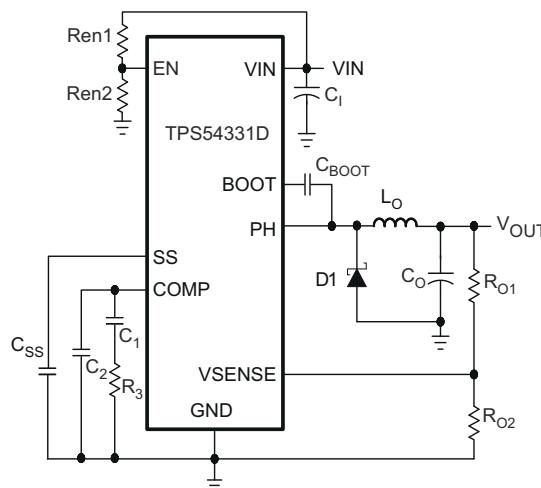

概略回路図

### 3 概要

TPS54331 は、低  $R_{DS(on)}$  のハイサイド MOSFET を内蔵した、28V、3A の非同期降圧コンバータです。軽負荷時には、パルスをスキップする Eco-mode 機能が自動的にオンになります。また、シャットダウン時の電源電流が 1µA と低いため、バッテリ駆動アプリケーションに使用できます。内部スロープ補償による電流モード制御により、外部補償計算が単純化され、セラミック出力コンデンサを使用しながら部品点数を減らすことができます。分圧抵抗を使用して、入力低電圧誤動作防止のヒステリシスをプログラムできます。過電圧過渡保護回路により、起動時および過渡状態での電圧オーバーシュートが制限されます。サイクル単位の電流制限方式、周波数フォールドバック、およびサーマル・シャットダウンにより、過負荷状況下でデバイスおよび負荷を保護します。TPS54331 デバイスは、8 ピン SOIC パッケージと 8 ピン SO PowerPAD 集積回路パッケージで供給され、熱性能を向上させるため内部的に最適化されています。

#### パッケージ情報

| 部品番号     | パッケージ (1)            | パッケージ・サイズ (2)  |

|----------|----------------------|----------------|

| TPS54331 | D (SOIC, 8)          | 4.90 mm × 6 mm |

|          | DDA (SO PowerPAD, 8) |                |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ・サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

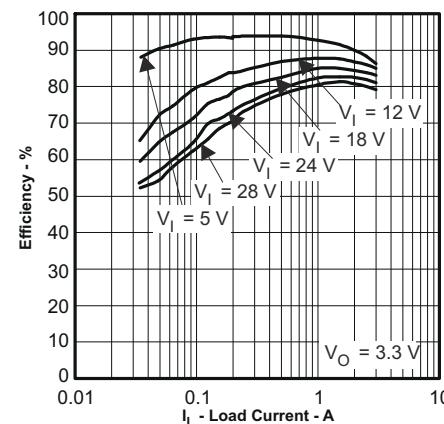

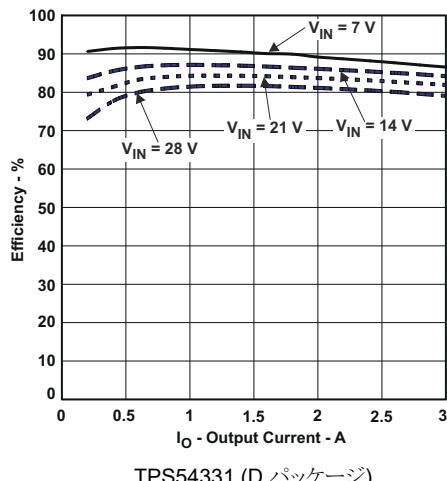

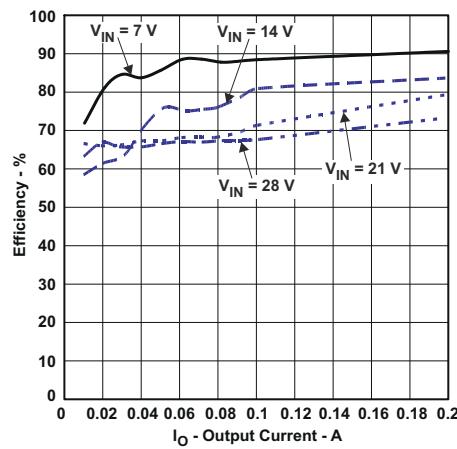

TPS54331 (D パッケージ) の効率

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|              |    |                        |    |

|--------------|----|------------------------|----|

| 1 特長         | 1  | 7.3 機能説明               | 10 |

| 2 アプリケーション   | 1  | 7.4 デバイスの機能モード         | 13 |

| 3 概要         | 1  | 8 アプリケーションと実装          | 14 |

| 4 改訂履歴       | 2  | 8.1 アプリケーション情報         | 14 |

| 5 ピン構成および機能  | 3  | 8.2 代表的なアプリケーション       | 14 |

| 6 仕様         | 4  | 8.3 電源に関する推奨事項         | 26 |

| 6.1 絶対最大定格   | 4  | 8.4 レイアウト              | 26 |

| 6.2 ESD 定格   | 4  | 9 デバイスおよびドキュメントのサポート   | 29 |

| 6.3 推奨動作条件   | 4  | 9.1 デバイスのサポート          | 29 |

| 6.4 熱に関する情報  | 5  | 9.2 サポート・リソース          | 29 |

| 6.5 電気的特性    | 5  | 9.3 ドキュメントの更新通知を受け取る方法 | 29 |

| 6.6 スイッチング特性 | 6  | 9.4 商標                 | 29 |

| 6.7 代表的特性    | 7  | 9.5 静電気放電に関する注意事項      | 29 |

| 7 詳細説明       | 9  | 9.6 用語集                | 29 |

| 7.1 概要       | 9  | 10 メカニカル、パッケージ、および注文情報 | 29 |

| 7.2 機能ブロック図  | 10 |                        |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision G (July 2022) to Revision H (September 2023) | Page |

|--------------------------------------------------------------------|------|

| • 「特長」に TPS62933 の情報を追加                                            | 1    |

| • 商標の情報を更新                                                         | 1    |

| • 「パッケージ情報」表の列のタイトルを「本体サイズ」から「パッケージ・サイズ」に変更                        | 1    |

| • 保管温度を「絶対最大定格」表に移動                                                | 4    |

| • 表のタイトルを「取り扱い定格」から「ESD 定格」に変更                                     | 4    |

| Changes from Revision F (October 2014) to Revision G (July 2022) | Page |

|------------------------------------------------------------------|------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新                                      | 1    |

| • 式 2 を更新                                                        | 10   |

| Changes from Revision E (February 2012) to Revision F (October 2014)                                                                                | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • 「取り扱い定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加 | 1    |

| • $I_{L(RMS)}$ および $I_{L(PK)}$ のインダクタ電流の式を更新                                                                                                        | 17   |

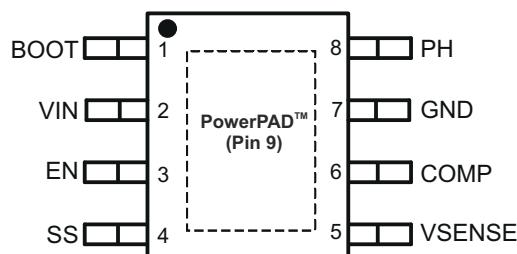

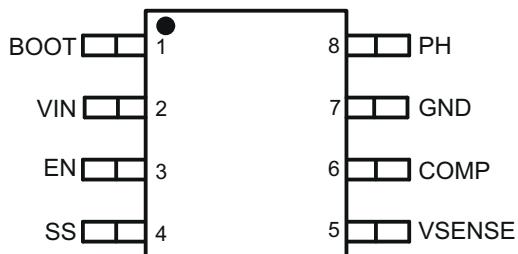

## 5 ピン構成および機能

図 5-1. 8 ピン SOIC D パッケージ (上面図)

図 5-2. 8 ピン SO PowerPAD™ 集積回路 DDA パッケージ (上面図)

表 5-1. ピンの機能

| ピン |          | I/O | 説明                                                                                                                    |

|----|----------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称       |     |                                                                                                                       |

| 1  | BOOT     | O   | BOOT ピンと PH ピンとの間に $0.1\mu F$ のブートストラップ・コンデンサが必要です。このコンデンサの電圧が最小要件を下回った場合、ハイサイド MOSFET はコンデンサがリフレッシュされるまで強制的にオフになります。 |

| 2  | VIN      | I   | このピンは、3.5V~28V の入力電源電圧です。                                                                                             |

| 3  | EN       | I   | このピンはイネーブル・ピンです。1.25V 未満になるとディセーブル、フローティングにするとイネーブルになります。2 つの抵抗を使用して入力低電圧誤動作防止をプログラミングすることを推奨します。                     |

| 4  | SS       | I   | このピンはスロー・スタート・ピンです。このピンに接続する外部コンデンサによって、出力の立ち上がり時間が設定されます。                                                            |

| 5  | VSENSE   | I   | このピンは、相互コンダクタンス (gm) エラー・アンプの反転ノードです。                                                                                 |

| 6  | COMP     | O   | このピンはエラー・アンプの出力で、PWM コンパレータへの入力です。このピンに周波数補償部品を接続します。                                                                 |

| 7  | GND      | —   | グランド・ピン                                                                                                               |

| 8  | PH       | O   | PH ピンは、内部ハイサイド・パワー MOSFET のソースです。                                                                                     |

| 9  | PowerPAD | —   | PowerPAD は DDA パッケージのみに搭載されています。正常に動作させるには、GND ピンを露出したパッドに接続する必要があります。                                                |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                          |                             | 最小値  | 最大値 | 単位 |

|--------------------------|-----------------------------|------|-----|----|

| 入力電圧                     | VIN                         | -0.3 | 30  | V  |

|                          | EN                          | -0.3 | 6   |    |

|                          | BOOT                        |      | 38  |    |

|                          | VSENSE                      | -0.3 | 3   |    |

|                          | COMP                        | -0.3 | 3   |    |

|                          | SS                          | -0.3 | 3   |    |

| 出力電圧                     | BOOT-PH                     |      | 8   | V  |

|                          | PH                          | -0.6 | 30  |    |

|                          | PH (グランドから負のピークまで 10ns で遷移) |      | -5  |    |

| ソース電流                    | EN                          | 100  | μA  |    |

|                          | BOOT                        | 100  | mA  |    |

|                          | VSENSE                      | 10   | μA  |    |

|                          | PH                          | 9    | A   |    |

| シンク電流                    | VIN                         | 9    | A   | μA |

|                          | COMP                        | 100  |     |    |

|                          | SS                          | 200  |     |    |

| 動作時の接合部温度、T <sub>J</sub> |                             | -40  | 150 | °C |

| 保管温度範囲、T <sub>stg</sub>  |                             | -65  | 150 | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、上記の値または推奨動作条件を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD 定格

|                    |       | 最小値                                                            | 最大値  | 単位  |    |

|--------------------|-------|----------------------------------------------------------------|------|-----|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | -2   | 2   | kV |

|                    |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | -500 | 500 | V  |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |          | 最小値 | 最大値 | 単位 |

|-----------------|----------|-----|-----|----|

| 動作入力電圧 (VIN ピン) |          | 3.5 | 28  | V  |

| T <sub>J</sub>  | 動作時接合部温度 | -40 | 150 | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>                          | D     | DDA  | 単位                          |

|-----------------------------------------------|-------|------|-----------------------------|

|                                               | 8 ピン  | 8 ピン |                             |

| $R_{\theta JA}$ 接合部から周囲への熱抵抗                  | 116.3 | 48.7 | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(\text{top})}$ 接合部からケース(上面)への熱抵抗 | 53.7  | 52.4 |                             |

| $R_{\theta JB}$ 接合部から基板への熱抵抗                  | 57.1  | 25.5 |                             |

| $\Psi_{JT}$ 接合部から上面への特性パラメータ                  | 12.9  | 8.4  |                             |

| $\Psi_{JB}$ 接合部から基板への特性パラメータ                  | 56.5  | 25.2 |                             |

| $R_{\theta JC(\text{bot})}$ 接合部からケース(底面)への熱抵抗 | —     | 2.3  |                             |

(1) 従来および新しい熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポート、SPRA953 を参照してください。

## 6.5 電気的特性

$T_A = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{VM} = 3.5 \sim 28\text{V}$  (特に記述のない限り)

| パラメータ                                | テスト条件                                                                                 | 最小値     | 標準値  | 最大値   | 単位                 |

|--------------------------------------|---------------------------------------------------------------------------------------|---------|------|-------|--------------------|

| <b>電源電圧 (VIN ピン)</b>                 |                                                                                       |         |      |       |                    |

| 内部の低電圧誤動作防止のスレッショルド                  | 立ち上がりと立ち下がり                                                                           |         | 3.5  |       | V                  |

| シャットダウン時の電源電流                        | $EN = 0\text{V}$ 、 $VIN = 12\text{V}$ 、 $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ | 1       | 4    |       | $\mu\text{A}$      |

| 動作時 - スイッチングなしの電源電流                  | $VSENSE = 0.85\text{V}$                                                               | 110     | 190  |       | $\mu\text{A}$      |

| <b>ENABLE と UVLO (EN ピン)</b>         |                                                                                       |         |      |       |                    |

| イネーブルのスレッショルド                        | 立ち上がりと立ち下がり                                                                           | 1.25    | 1.35 |       | V                  |

| 入力電流                                 | イネーブルのスレッショルド - 50mV                                                                  |         | -1   |       | $\mu\text{A}$      |

| 入力電流                                 | イネーブルのスレッショルド + 50mV                                                                  |         | -4   |       | $\mu\text{A}$      |

| <b>電圧リファレンス</b>                      |                                                                                       |         |      |       |                    |

| 電圧リファレンス                             |                                                                                       | 0.772   | 0.8  | 0.828 | V                  |

| <b>ハイサイド MOSFET</b>                  |                                                                                       |         |      |       |                    |

| オン抵抗                                 | $BOOT-PH = 3\text{V}$ 、 $VIN = 3.5\text{V}$                                           | 115     | 200  |       | $\text{m}\Omega$   |

|                                      | $BOOT-PH = 6\text{V}$ 、 $VIN = 12\text{V}$                                            | 80      | 150  |       |                    |

| <b>エラー・アンプ</b>                       |                                                                                       |         |      |       |                    |

| エラー・アンプの相互コンダクタンス ( $gm$ )           | $-2\mu\text{A} < I_{(\text{COMP})} < 2\mu\text{A}$ 、 $V_{(\text{COMP})} = 1\text{V}$  | 92      |      |       | $\mu\text{mhos}$   |

| エラー・アンプの DC ゲイン <sup>(1)</sup>       | $VSENSE = 0.8\text{V}$                                                                | 800     |      |       | V/V                |

| エラー・アンプのユニティ・ゲイン帯域幅 <sup>(1)</sup>   | COMP から GND ピンへの 5pF の容量                                                              | 2.7     |      |       | MHz                |

| エラー・アンプのソースおよびシンク電流                  | $V_{(\text{COMP})} = 1\text{V}$ 、100mV オーバードライブ                                       | $\pm 7$ |      |       | $\mu\text{A}$      |

| スイッチ電流から COMP への相互インダクタ<br>ンス        | $VIN = 12\text{V}$                                                                    | 12      |      |       | A/V                |

| <b>パルス・スキップ ECO-MODE</b>             |                                                                                       |         |      |       |                    |

| パルス・スキップ Eco-mode のスイッチ電流<br>スレッショルド |                                                                                       | 160     |      |       | $\text{mA}$        |

| <b>電流制限</b>                          |                                                                                       |         |      |       |                    |

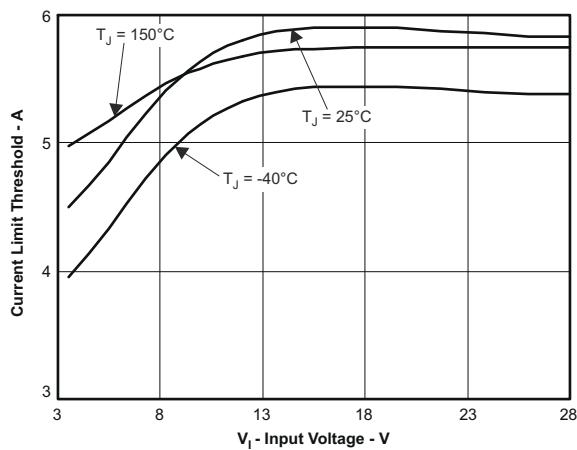

| 電流制限スレッショルド                          | $VIN = 12\text{V}$                                                                    | 3.5     | 5.8  |       | A                  |

| <b>サーマル・シャットダウン</b>                  |                                                                                       |         |      |       |                    |

| サーマル・シャットダウン                         |                                                                                       | 165     |      |       | $^{\circ}\text{C}$ |

| <b>スロー・スタート (SS ピン)</b>              |                                                                                       |         |      |       |                    |

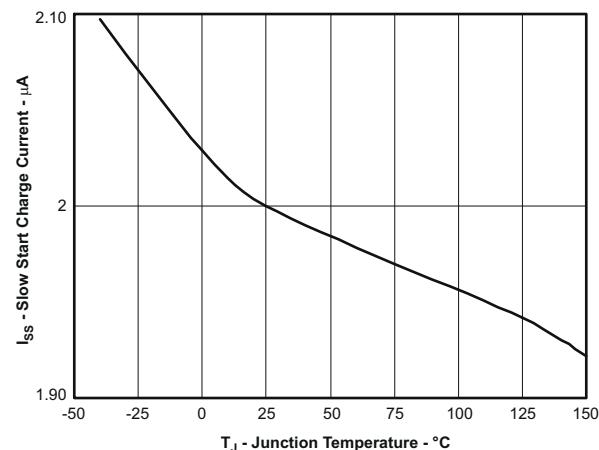

| 充電電流                                 | $V_{(\text{SS})} = 0.4\text{V}$                                                       | 2       |      |       | $\mu\text{A}$      |

$T_A = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{VM} = 3.5 \sim 28\text{V}$  (特に記述のない限り)

| パラメータ                | テスト条件                    | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------|--------------------------|-----|-----|-----|----|

| SS から VSENSE へのマッチング | $V_{(SS)} = 0.4\text{V}$ | 10  |     |     | mV |

(1) 設計により規定

## 6.6 スイッチング特性

$T_A = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{VM} = 3.5 \sim 28\text{V}$  (特に記述のない限り)

| パラメータ                        | テスト条件                                   | 最小値 | 標準値 | 最大値 | 単位  |

|------------------------------|-----------------------------------------|-----|-----|-----|-----|

| <b>スイッチング周波数</b>             |                                         |     |     |     |     |

| スイッチング周波数                    | $V_{IN} = 12\text{V}, 25^\circ\text{C}$ | 456 | 570 | 684 | kHz |

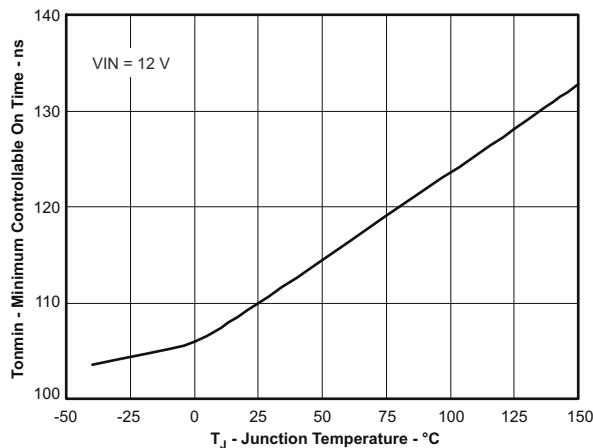

| 最小の制御可能なオン時間                 | $V_{IN} = 12\text{V}, 25^\circ\text{C}$ |     | 105 | 130 | ns  |

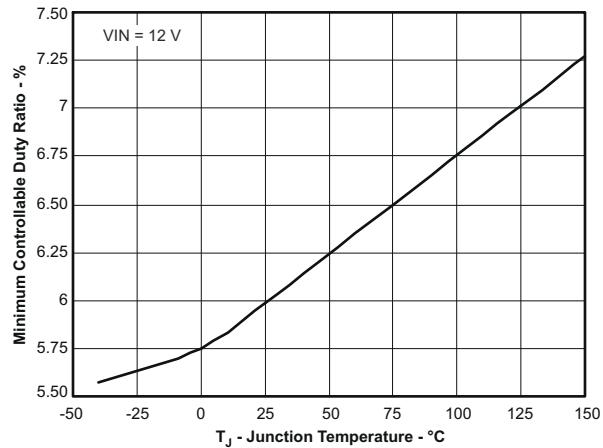

| 制御可能な最大デューティ比 <sup>(1)</sup> | BOOT-PH = 6V                            | 90% | 93% |     |     |

## 6.7 代表的特性

図 6-1. オン抵抗と接合部温度との関係

図 6-2. シャットダウン時の静止電流と入力電圧との関係

図 6-3. スイッチング周波数と接合部温度との関係

図 6-4. 電圧リファレンスと接合部温度との関係

図 6-5. 制御可能な最小オン時間と接合部温度との関係

図 6-6. 制御可能な最小デューティ比と接合部温度との関係

図 6-7. SS 充電電流と接合部温度との関係

図 6-8. 電流制限スレッショルドと入力電圧との関係

## 7 詳細説明

### 7.1 概要

TPS54331 デバイスは、ハイサイド N チャネル MOSFET を内蔵した、28V、3A の降圧 (バック) コンバータです。ラインおよび負荷の過渡状態における性能を向上させるため、定周波数の電流モード制御が実装されており、出力容量の低減と、外部周波数補償設計の単純化を実現しています。TPS54331 デバイスのスイッチング周波数は、570kHz にプリセットされています。

TPS54331 デバイスは、通常動作のため最低 3.5V の入力電圧を必要とします。EN ピンには内部プルアップ電流源があり、入力低電圧誤動作防止 (UVLO) を 2 個の外付け抵抗により調整可能です。また、このプルアップ電流は、EN ピンがフローティングのときにデバイスが動作するためのデフォルト状態を提供します。無負荷で非スイッチング時の動作電流は、標準値 110µA です。デバイスがディセーブル時の電源電流は、標準値 1µA です。

80mΩ のハイサイド MOSFET を内蔵しており、最大 3A の連続出力電流で高効率の電源を設計できます。

TPS54331 デバイスはブート再充電ダイオードを内蔵しているため、外付け部品数を低減できます。内蔵ハイサイド MOSFET のバイアス電圧は、BOOT ピンから PH ピンの間の外付けコンデンサによって供給されます。このブート・コンデンサ電圧は UVLO 回路によって監視され、標準値 2.1V のプリセットされたスレッショルドを下回ると、ハイサイド MOSFET がオフになります。出力電圧は、リファレンス電圧と同じ値まで降圧させることができます。

外部コンデンサを追加することにより、TPS54331 のスロー・スタート時間を調整でき、柔軟な出力フィルタ選択が可能になります。

軽負荷での効率を向上させるため、ピーク・インダクタ電流が標準 160mA を下回ると、TPS54331 デバイスは特別なパルス・スキップ Eco-mode に入ります。

周波数フォールドバックにより、起動時および過電流時にスイッチング周波数が低くなり、インダクタ電流を制御しやすくなります。サーマル・シャットダウン機能により、フォルト状況での保護が強化されます。

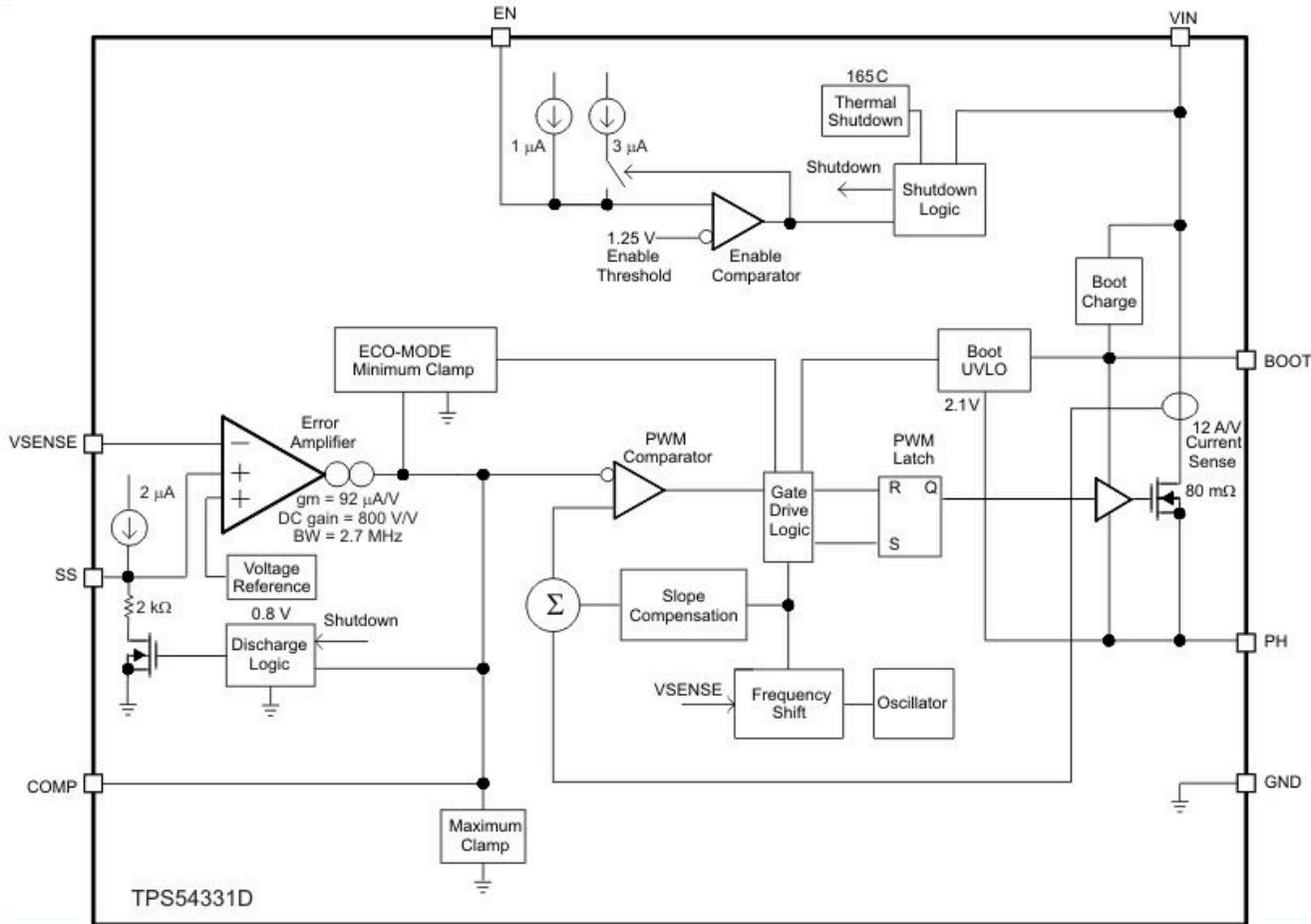

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 固定周波数 PWM 制御

TPS54331 デバイスは、固定周波数のピーク電流モード制御を使用します。TPS54331 デバイスの内部スイッチング周波数は、 $570\text{kHz}$  に固定されています。

### 7.3.2 電圧リファレンス ( $V_{REF}$ )

電圧リファレンス・システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで、 $\pm 2\%$  の初期精度を持つ電圧リファレンス（全温度範囲で  $\pm 3.5\%$ ）を生成します。標準の電圧リファレンスは、 $0.8\text{V}$  に設計されています。

### 7.3.3 ブートストラップ電圧 (BOOT)

TPS54331 デバイスにはブート・レギュレータが内蔵されており、ハイサイド MOSFET のゲート駆動電圧を提供するため、BOOT ピンと PH ピンとの間に  $0.1\mu F$  のセラミック・コンデンサが必要です。温度および電圧に対して安定した特性を持っている、X7R または X5R グレードの誘電体を持つセラミック・コンデンサをお勧めします。ドロップアウトを改善するため、TPS54331 デバイスは、BOOT ピンから PH ピンへの電圧が標準値  $2.1\text{V}$  より大きければ、100% のデューティ・サイクルで動作するよう設計されています。

### 7.3.4 イネーブル、および可変の入力低電圧誤動作防止 (VIN UVLO)

EN ピンには内部プルアップ電流源があり、EN ピンがフローティングで動作しているとき、デバイスがデフォルト条件になります。

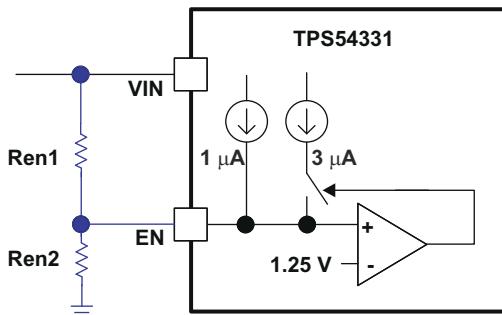

VIN ピンの電圧が内部の VIN UVLO スレッショルドを下回ると、TPS54331 デバイスはディセーブルになります。VIN 電圧が ( $V_{OUT} + 2V$ ) を超えない限り、外部 VIN UVLO を使用してヒステリシスを追加することをお勧めします。VIN UVLO 電圧をヒステリシスも含めて調整するには、図 7-1 に示すように、EN ピンに接続された外部回路を使用します。EN ピンの電圧が 1.25V を超えると、3μA のヒステリシスが追加されます。式 1 と式 2 を使用して、求められる VIN UVLO スレッショルド電圧に必要な抵抗の値を計算します。 $V_{STOP}$  スレッショルドは、常に 3.5V を上回る必要があります。

図 7-1. 可変の入力低電圧誤動作防止

$$Ren1 = \frac{V_{START} - V_{STOP}}{3\mu A} \quad (1)$$

ここで、

- $V_{START}$  は、入力開始スレッショルド電圧です。

- $V_{STOP}$  は、入力停止スレッショルド電圧です。

$$Ren2 = \frac{V_{EN}}{\frac{V_{STOP} - V_{EN}}{Ren1} + 4\mu A} \quad (2)$$

ここで、

- $V_{EN}$  は、イネーブル・スレッショルド電圧の 1.25V です。

### 7.3.5 SS ピンを使用したプログラム可能なスロー・スタート

スロー・スタート時間は内部で実装されていないため、外部でスロー・スタート時間をプログラミングすることを強くお勧めします。TPS54331 デバイスでは、SS ピン電圧または内部電圧リファレンスの低い方の電圧を、エラー・アンプに供給される電源のリファレンス電圧として使用し、それに従って出力のレギュレーションを行います。SS ピンとグランドとの間のコンデンサ ( $C_{SS}$ ) により、スロー・スタート時間が実装されます。TPS54331 には、外部のスロー・スタート・コンデンサを充電する 2μA の内部プルアップ電流源が内蔵されています。スロー・スタート時間 (10% から 90% へ) を計算するには、式 3 を使用します。

$$T_{SS}(\text{ms}) = \frac{C_{SS}(\text{nF}) \times V_{REF}(\text{V})}{I_{SS}(\mu A)} \quad (3)$$

ここで、

- $V_{REF}$  は 0.8V です。

- $I_{SS}$  は 2μA です。

良好なスタートアップ動作を保証するには、スロー・スタート時間を 1ms～10ms の範囲内にする必要があります。スロー・スタート・コンデンサの値は、27nF を超えないようにしてください。

通常動作中に、入力電圧が VIN UVLO スレッショルドを下回るか、EN ピンが 1.25V 未満になるか、サーマル・シャットダウンのイベントが発生した場合、TPS54331 デバイスはスイッチングを停止します。

### 7.3.6 エラー・アンプ

TPS54331 デバイスは、エラー・アンプとして相互コンダクタンス・アンプを内蔵しています。エラー・アンプは、VSENSE の電圧を、エラー・アンプの入力に印加された内部の実効電圧リファレンスと比較します。エラー・アンプの相互コンダクタンスは、通常動作時で  $92\mu\text{A/V}$  です。周波数補償部品は、COMP ピンとグランドとの間に接続されます。

### 7.3.7 勾配補償

50% を超えるデューティ・サイクルでの動作時に低調波発振を防ぐため、TPS54331 デバイスは、スイッチ電流信号への補償ランプである勾配補償を内蔵しています。

### 7.3.8 電流モード補償設計

TPS54331 デバイスを使用する設計の作業を簡素化するため、一般的なアプリケーションの標準的な設計を表 7-1 に示します。セラミック出力コンデンサを使用する設計では、安定性解析を実行するときにセラミック出力容量の適切なディレーティングをお勧めします。これは、印加された電圧が増加すると、実際のセラミック容量が公称値から大幅に低下するためです。セクション 8.2.2 の詳細なガイドラインを参照するか、WEBENCH ソフトウェア・ツール ([www.TI.com/WEBENCH](http://www.TI.com/WEBENCH)) を使用してください。

**表 7-1. 代表的な設計 (概略回路図を参照)**

| $V_{IN}$<br>(V) | $V_{OUT}$<br>(V) | $f_{SW}$<br>(kHz) | $L_o$<br>( $\mu\text{H}$ ) | $C_o$                                      | $R_{o1}$<br>( $\text{k}\Omega$ ) | $R_{o2}$<br>( $\text{k}\Omega$ ) | $C_2$<br>( $\text{pF}$ ) | $C_1$<br>( $\text{pF}$ ) | $R_3$<br>( $\text{k}\Omega$ ) |

|-----------------|------------------|-------------------|----------------------------|--------------------------------------------|----------------------------------|----------------------------------|--------------------------|--------------------------|-------------------------------|

| 12              | 5                | 570               | 6.8                        | セラミック $33\mu\text{F}, \times 2$            | 10                               | 1.91                             | 39                       | 4700                     | 49.9                          |

| 12              | 3.3              | 570               | 6.8                        | セラミック $47\mu\text{F}, \times 2$            | 10                               | 3.24                             | 47                       | 1000                     | 29.4                          |

| 12              | 1.8              | 570               | 4.7                        | セラミック $100\mu\text{F}$                     | 10                               | 8.06                             | 68                       | 5600                     | 29.4                          |

| 12              | 0.9              | 570               | 3.3                        | セラミック $100\mu\text{F}, \times 2$           | 10                               | 80.6                             | 56                       | 5600                     | 29.4                          |

| 12              | 5                | 570               | 6.8                        | アルミニウム $330\mu\text{F}, 160\text{m}\Omega$ | 10                               | 1.91                             | 68                       | 120                      | 29.4                          |

| 12              | 3.3              | 570               | 6.8                        | アルミニウム $470\mu\text{F}, 160\text{m}\Omega$ | 10                               | 3.24                             | 82                       | 220                      | 10                            |

| 12              | 1.8              | 570               | 4.7                        | SP $100\mu\text{F}, 15\text{m}\Omega$      | 10                               | 8.06                             | 68                       | 5600                     | 29.4                          |

| 12              | 0.9              | 570               | 3.3                        | SP $330\mu\text{F}, 12\text{m}\Omega$      | 10                               | 80.6                             | 100                      | 1200                     | 49.9                          |

### 7.3.9 過電流保護および周波数シフト

TPS54331 デバイスには電流モード制御が実装されており、COMP ピンの電圧を使用してハイサイド MOSFET をサイクル毎でオフにできます。各サイクルでは、スイッチ電流と COMP ピンの電圧が比較されます。ピーク・インダクタ電流が COMP ピンの電圧を超えると、ハイサイド・スイッチがオフになります。過電流状況によって出力電圧が Low になると、エラー・アンプによって COMP ピンが High に駆動され、スイッチ電流が増加します。COMP ピンは内部で最大値にクランプされ、出力電流を制限します。

TPS54331 デバイスは、短絡発生時にも堅牢な保護機能を備えています。出力短絡時に、出力インダクタに過電流暴走が発生する可能性があります。TPS54331 デバイスは、短絡状態のときスイッチング周波数を下げてオフ時間を増やすことで、この問題を解決します。VSENSE ピンの電圧が  $0\text{V}$  から  $0.8\text{V}$  に上昇すると、スイッチング周波数の分周は 1、2、4、8 に変化します。スイッチング周波数と VSENSE ピン電圧との関係を、表 7-2 に示します。

**表 7-2. スイッチング周波数の条件**

| スイッチング周波数  | VSENSE ピン電圧                                    |

|------------|------------------------------------------------|

| 570kHz     | $\text{VSENSE} \geq 0.6\text{V}$               |

| 570kHz / 2 | $0.6\text{V} > \text{VSENSE} \geq 0.4\text{V}$ |

| 570kHz / 4 | $0.4\text{V} > \text{VSENSE} \geq 0.2\text{V}$ |

| 570kHz / 8 | $0.2\text{V} > \text{VSENSE}$                  |

### 7.3.10 過電圧過渡保護

TPS54331 デバイスには、出力障害状態からの復帰や強い無負荷過渡で発生する出力電圧オーバーシュートを最小限に抑える、過電圧過渡保護 (OVTP) 回路が組み込まれています。OVTP 回路には、VSENSE ピン電圧を内部レッショルドと比較する過電圧コンパレータが内蔵されています。VSENSE ピンの電圧が  $109\% \times V_{REF}$  を上回ると、ハイサイド MOSFET が強制的にオフになります。VSENSE ピンの電圧が  $107\% \times V_{REF}$  を下回ると、ハイサイド MOSFET が再度イネーブルになります。

### 7.3.11 サーマル・シャットダウン

このデバイスは、接合部温度が  $165^{\circ}\text{C}$  を超えた場合にデバイス自身を保護する、サーマル・シャットダウン機能を内蔵しています。接合部温度がサーマル・トリップ・レッショルドを超えると、サーマル・シャットダウン機能によってデバイスのスイッチングが強制的に停止されます。ダイの温度が  $165^{\circ}\text{C}$  を下回ると、デバイスはパワーアップ・シーケンスを再び開始します。

## 7.4 デバイスの機能モード

### 7.4.1 Eco-mode

TPS54331 デバイスは、軽負荷時の効率を向上させるため、負荷電流が小さいときには、パルスをスキップする Eco-mode で動作するよう設計されています。ピーク・インダクタ電流が標準値  $160\text{mA}$  を下回ると、COMP ピンの電圧が標準  $0.5\text{V}$  まで低下し、デバイスは Eco-mode に入ります。デバイスが Eco-mode で動作中は、COMP ピンの電圧が内部で  $0.5\text{V}$  にクランプされ、ハイサイド内蔵 MOSFET のスイッチングを防ぎます。COMP ピンの電圧が  $0.5\text{V}$  を超えて Eco-mode を終了するためには、ピーク・インダクタ電流が  $160\text{mA}$  を上回る必要があります。内蔵の電流コンパレータはピーク・インダクタ電流のみを捕捉するため、Eco-mode に入るときの平均負荷電流は、アプリケーションおよび外部出力フィルタによって異なります。

### 7.4.2 $V_{IN} < 3.5\text{V}$ での動作

このデバイスは、 $3.5\text{V}$  を超える入力電圧での動作が推奨されます。VIN UVLO スレッショルドの標準値は規定されておらず、UVLO 電圧以上の入力電圧であれば動作可能です。実際の UVLO 電圧より低い入力電圧では、デバイスはスイッチしません。EN ピンが外部でプルアップされた場合、またはフローティングのままになっている場合、VIN ピンが UVLO スレッショルドを超えるとデバイスはアクティブになります。スロー・スタート・シーケンスが開始されると、スイッチングが開始されます。

### 7.4.3 EN 制御による動作

イネーブル・レッショルド電圧は、標準値  $1.25\text{V}$  です。EN ピンをこれより低い電圧に保持すると、デバイスはディセーブルされ、VIN ピンが UVLO スレッショルド以上であってもスイッチングは禁止されます。この状態では、IC の静止電流が減少します。VIN ピンが UVLO スレッショルドより高いとき、EN 電圧がスレッショルドを上回ると、デバイスはアクティブになります。スイッチングがイネーブルされ、スロー・スタート・シーケンスが開始されます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPS54331 デバイスは通常、3.5V~28V の電圧をそれより低い電圧に変換するための降圧コンバータとして使用されます。回路の設計や分析に役立つ WEBENCH ソフトウェアが用意されています。

設計の他の要求については、以下のデバイスを参照してください。

| パラメータ                | TPS54231 | TPS54232 | TPS54233 | TPS54331              | TPS54332     |

|----------------------|----------|----------|----------|-----------------------|--------------|

| I <sub>O</sub> (最大値) | 2A       | 2A       | 2A       | 3A                    | 3.5A         |

| 入力電圧範囲               | 3.5~28V  | 3.5~28V  | 3.5~28V  | 3.5~28V               | 3.5~28V      |

| スイッチング周波数 (標準値)      | 570kHz   | 1000kHz  | 285kHz   | 570kHz                | 1000kHz      |

| スイッチの電流制限 (最小値)      | 2.3A     | 2.3A     | 2.3A     | 3.5A                  | 4.2A         |

| ピンとパッケージ             | 8SOIC    | 8SOIC    | 8SOIC    | 8SOIC<br>8SO PowerPAD | 8SO PowerPAD |

### 8.2 代表的なアプリケーション

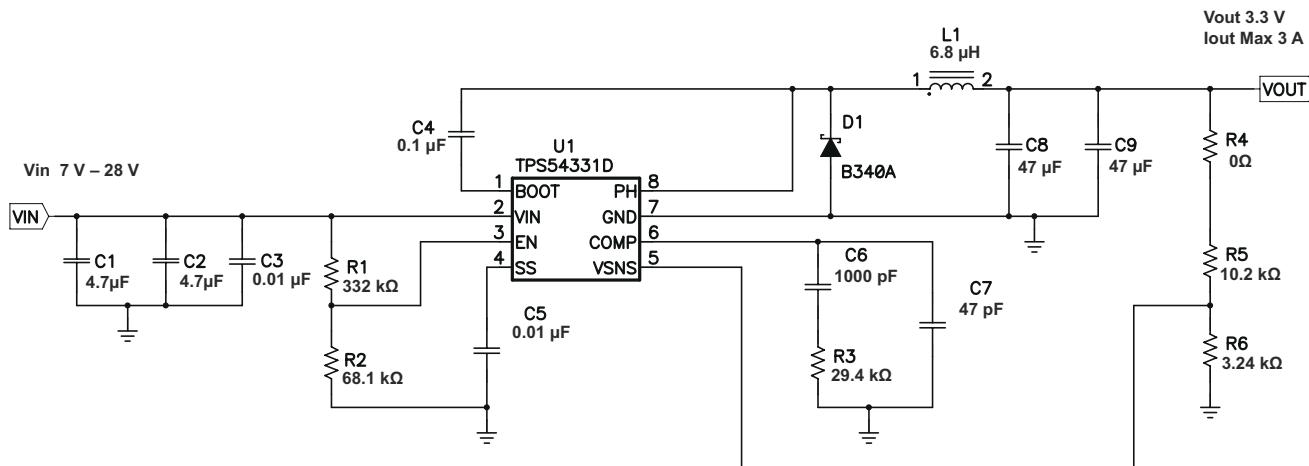

図 8-1. 代表的なアプリケーション回路図

#### 8.2.1 設計要件

この設計例では、表 8-1 に示されている値を入力パラメータとして使用します。

表 8-1. 設計パラメータ

| 設計パラメータ  | 値の例   |

|----------|-------|

| 入力電圧範囲   | 7~28V |

| 出力電圧     | 3.3V  |

| 入力リップル電圧 | 300mV |

| 出力リップル電圧 | 30mV  |

| 出力電流定格   | 3A    |

表 8-1. 設計パラメータ (続き)

| 設計パラメータ | 値の例    |

|---------|--------|

| 動作周波数   | 570kHz |

## 8.2.2 詳細な設計手順

以下の設計手順を使用して TPS54331 デバイスの部品値を選択できます。または、WEBENCH ソフトウェアを使用して完全な設計を生成することもできます。WEBENCH ソフトウェアは、反復的な設計手順を使用し、包括的な部品データベースにアクセスして設計を生成します。ここでは、設計手順について簡単に説明します。

### 8.2.2.1 WEBENCH® ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH Power Designer により、カスタム設計を作成できます。

1. 最初に、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{OUT}$  の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化し、この設計と、テキサス・インスツルメンツによる他の可能なソリューションとを比較します。

3. WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格や部品の在庫情報と併せて参照できます。

4. ほとんどの場合、ユーザーは次の操作を実行できます。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱性能を把握する。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットでエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

### 8.2.2.2 スイッチング周波数

TPS54331 デバイスのスイッチング周波数は、570kHz に固定されています。

### 8.2.2.3 出力電圧の設定点

TPS54331 デバイスの出力電圧は、分圧抵抗回路を使用して外部で調整可能です。[図 8-1](#) に示すように、この分圧回路は R5 と R6 で構成されています。出力電圧と分圧抵抗との関係は、[式 4](#) と [式 5](#) で与えられます。

$$R6 = \frac{R5 \times V_{REF}}{V_{OUT} - V_{REF}} \quad (4)$$

$$V_{OUT} = V_{REF} \times \left( \frac{R5}{R6} + 1 \right) \quad (5)$$

R5 の値として、約 10kΩ を選択します。R5 をわずかに増加または減少させると、標準の値の抵抗を使用するときに、より近い出力電圧マッチングが得られる場合があります。この設計では、 $R4 = 10.2\text{k}\Omega$ 、 $R = 3.24\text{k}\Omega$  で、出力電圧は 3.31V になります。 $0\Omega$  抵抗 R4 は、安定性テストで制御ループを切断するための便利な場所として用意されています。

### 8.2.2.4 入力コンデンサ

TPS54331 デバイスには入力デカップリング・コンデンサが必要で、アプリケーションによってはバルク入力コンデンサも必要になります。デカップリング・コンデンサの標準推奨値は  $10\mu\text{F}$  です。高品質の X5R または X7R セラミック・タイプをお勧めします。電圧定格は、最大入力電圧よりも大きい必要があります。他の要件をすべて満たしていれば、より小さい値も使用できます。ただし、多くの回路は  $10\mu\text{F}$  で適切に動作することが示されています。また、TPS54331 回路が入力電圧源から約 2 インチ以上離れている場合は特に、多少のバルク容量が必要になる場合があります。このコンデンサの値はそれほど重大ではありませんが、リップル電圧を含めた最大入力電圧を処理できる定格が必要で、入力リップル電圧が許容範囲に収まるよう出力をフィルタリングできることも必要です。この設計では、入力デカップリング・コンデンサに 2 個の  $4.7\mu\text{F}$  コンデンサを使用しています。これらのコンデンサは、定格 50V の X7R 誘電体です。等価直列抵抗 (ESR) は約  $2\text{m}\Omega$ 、電流定格は 3A です。また、高周波フィルタリングのために、小さな  $0.01\mu\text{F}$  コンデンサも使用されています。

入力リップル電圧を計算するには、[式 6](#) を使用します。

$$\Delta V_{IN} = \frac{I_{OUT(MAX)} \times 0.25}{C_{BULK} \times F_{SW}} + (I_{OUT(MAX)} \times ESR_{MAX}) \quad (6)$$

ここで、

- $I_{OUT(MAX)}$  は最大負荷電流です。

- $F_{SW}$  はスイッチング周波数です。

- $C_{BULK}$  はバルク・コンデンサの値です。

- $ESR_{MAX}$  はバルク・コンデンサの最大直列抵抗です。

最大 RMS リップル電流も確認する必要があります。ワーストケース条件について、式 7 を使用して最大 RMS 入力リップル電流である  $I_{CIN(RMS)}$  を計算します。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{2} \quad (7)$$

この場合、入力リップル電圧は 143mV、RMS リップル電流は 1.5A になります。

### 注

実際の入力電圧リップルは、レイアウトに関連する寄生成分と、電圧源の出力インピーダンスの影響を大きく受けます。

この回路の実際の入力電圧リップルは表 8-1 に示してあり、計算された値よりも大きくなっています。それでも、測定値は仕様の入力制限である 300mV を下回っています。入力コンデンサの両端の最大電圧は  $V_{IN(MAX)} + \Delta V_{IN} / 2$  です。選択したバルクおよびバイパス・コンデンサはそれぞれ定格 50V で、リップル電流容量は 3A を上回り、ともに十分なマージンが得られます。どのような環境であっても、電圧と電流の最大定格を超えないようにすることが重要です。

#### 8.2.2.5 出力フィルタ部品

出力フィルタとして、L1 と C2 の 2 つの部品を選択する必要があります。TPS54331 は外部補償デバイスなので、幅広い種類および値のフィルタ部品をサポートできます。

##### 8.2.2.5.1 インダクタの選択

出力インダクタの最小値を計算するには、式 8 を使用します。

$$L_{MIN} = \frac{V_{OUT(MAX)} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times K_{IND} \times I_{OUT} \times F_{SW}} \quad (8)$$

ここで、

- $K_{IND}$  は、最大出力電流に対するインダクタのリップル電流の量を示す係数です。

一般に、この値は設計者の裁量で決定しますが、以下のガイドラインを使用できます。セラミックなどの低 ESR 出力コンデンサを使用した設計では、最大  $K_{IND} = 0.3$  の値を使用できます。より ESR の高い出力コンデンサを使用する場合は、 $K_{IND} = 0.2$  が適切です。

この設計例では、 $K_{IND} = 0.3$  を使用し、最小インダクタ値は 5.7μH と計算されます。この設計では、大きな値として 6.8μH が選択されています。

出力フィルタ・インダクタの場合、RMS 電流および飽和電流定格を超えないようにしてください。式 9 を使用して、インダクタのリップル電流 ( $I_{LPP}$ ) を計算します。

$$I_{LPP} = \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times I_{OUT} \times F_{SW} \times 0.8} \quad (9)$$

RMS インダクタ電流を計算するには、式 10 を使用します。

$$I_{L(RMS)} = \sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times I_{LPP}^2} \quad (10)$$

ピーク・インダクタ電流を計算するには、式 11 を使用します。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{I_{LPP}}{2} \quad (11)$$

この設計では、RMS インダクタ電流は 3.01A、ピーク・インダクタ電流は 3.47A です。選択したインダクタは Sumida CDRH103-6R8、6.8μH です。このインダクタの飽和電流定格は 3.84A、RMS 電流定格は 3.6A で、これらの要件を満たしています。他の設計要件を満足していれば、設計者が許容するリップル電流の大きさに合わせて、これより小さい値や大きい値のインダクタを使用できます。大きな値のインダクタは AC 電流が小さくなり、出力電圧リップルが減少します。小さな値のインダクタは AC 電流が大きくなり、出力電圧リップルが増加します。一般に、TPS54331 デバイスで使用するインダクタの値は 6.8μH~47μH の範囲内です。

### 8.2.2.6 コンデンサの選択

出力コンデンサの設計で重要な要因は、DC 電圧定格、リップル電流定格、および等価直列抵抗 (ESR) です。DC 電圧定格とリップル電流定格を超えないようにしてください。ESR とインダクタ電流によって出力リップル電圧が決まるため、ESR は重要です。出力キャパシタの実際の値は重要ではありませんが、実用上の制限がいくつかあります。設計で求められる閉ループのクロスオーバー周波数と、出力フィルタの LC コーナー周波数との間の関係に注意してください。一般に、閉ループのクロスオーバー周波数は、スイッチング周波数の 1/5 未満に維持することが求められます。この設計では、スイッチング周波数が 570kHz など高い値なので、TPS54331 デバイスの内部回路の制限により、実際の最大クロスオーバー周波数は約 25kHz に制限されます。一般に、閉ループのクロスオーバー周波数は、負荷インピーダンスと出力コンデンサによって決定されるコーナー周波数よりも高くする必要があります。コンデンサの最小値の制限は、式 12 で計算します。

$$C_0(MIN) = \frac{1}{2 \times \pi \times R_0 \times f_{CO(MAX)}} \quad (12)$$

ここで、

- $R_0$  は出力負荷インピーダンス ( $V_o/I_o$ ) です。

- $f_{CO(MAX)}$  は、目的のクロスオーバー周波数です。

求められる最大クロスオーバーが 25kHz の場合、出力コンデンサの最小値は約 5.8μF です。この値は、出力リップル電圧要件を満たしていない可能性があります。出力リップル電圧は、出力フィルタ容量の充電と放電による電圧変化と、出力フィルタ・コンデンサの ESR にリップル電流を乗じた電圧変化という、2 つの成分で構成されます。出力リップル電圧を推定するには、式 13 を使用します。

$$V_{OPP} = I_{LPP} \times \left( \frac{(D - 0.5)}{4 \times F_{SW} \times C_0} + R_{ESR} \right) \quad (13)$$

出力コンデンサの最大 ESR は、設計の初期パラメータの仕様で許容される出力リップルの量から決定できます。ESR の出力リップル電圧への寄与分は、インダクタのリップル電流に出力フィルタの ESR を乗じた値です。したがって、式 14 を使用して、コンデンサのデータシートに記載されている最大指定 ESR を計算します。

$$ESR_{MAX} = \frac{V_{OPP(MAX)}}{I_{LPP}} - \frac{(D - 0.5)}{4 \times F_{SW} \times C_0} \quad (14)$$

ここで、

- $V_{OPP(MAX)}$  は求められるピーク・ツー・ピーク出力リップルです。

式 15 を使用して、最大 RMS リップル電流を計算します。

$$I_{COUT(RMS)} = \frac{1}{\sqrt{2}} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times N_C} \right) \quad (15)$$

ここで、

- $N_C$  は並列に配置された出力コンデンサの数です。

この設計例では、C8 と C9 に  $47\mu F$  のセラミック出力コンデンサを 2 個選択しています。これらのコンデンサは、定格  $6.3V$ 、最大 ESR  $2m\Omega$ 、リップル電流定格

$3A$  を超える TDK C3216X5R0J476MT です。計算される合計 RMS リップル電流の値は  $161mA$  (各  $80.6mA$ )、必要な最大合計 ESR は  $43m\Omega$  です。これらの出力コンデンサは要件を広いマージンで上回っているため、信頼性が高く高性能の設計を実現します。

### 注

出力が求められる  $3.3V$  で動作している場合、回路の実際の容量はカタログの値よりも小さくなる可能性があります。

選択する出力コンデンサは、求められる出力電圧にリップル電圧の半分を加算した値よりも電圧の定格が大きい必要があります。ディレーティングした量もこの計算に含める必要があります。アプリケーションによっては、その他のタイプのコンデンサを TPS54331 デバイスとともに使用しても、的確に動作します。

#### 8.2.2.7 補償部品

TPS54331 デバイスで使用される外部補償により、幅広い出力フィルタ構成が可能になります。広範なコンデンサの値と誘電体の種類がサポートされています。この設計例では、セラミック X5R 誘電体出力コンデンサを使用していますが、他の種類のコンデンサもサポートされています。

TPS54331 デバイスでは、Type II 補償方式をお勧めします。補償部品は、出力フィルタ部品で求められる閉ループ・クロスオーバー周波数と位相マージンを設定するために選択されます。Type II 補償には、DC ゲイン成分、低周波数の極、中周波数のゼロ極のペアという特性があります。

DC ゲインを計算するには、式 16 を使用します。

$$G_{DC} = \frac{V_{GGM} \times V_{REF}}{V_0} \quad (16)$$

ここで、

- $V_{GGM}$  は  $800$  です。

- $V_{REF}$  は  $0.8V$  です。

低周波数の極を計算するには、式 17 を使用します。

$$F_{P0} = \frac{1}{2 \times \pi \times R_{00} \times C_Z} \quad (17)$$

中周波数のゼロを計算するには、式 18 を使用します。

$$F_{Z1} = \frac{1}{2 \times \pi \times R_Z \times C_Z} \quad (18)$$

中周波数の極を計算するには、式 19 を使用します。

$$F_{P1} = \frac{1}{2 \times \pi \times R_Z \times C_P} \quad (19)$$

最初のステップは、閉ループのクロスオーバー周波数を選択することです。一般に、閉ループのクロスオーバー周波数は、最小動作周波数の  $1/8$  を下回る必要があります。ただし、TPS54331 デバイスでは、最大の閉ループ・クロスオーバー周波数が  $25kHz$  を超えないことをお勧めします。2 番目のステップは、クロスオーバー・ネットワークに必要なゲインと位相ブーストを計算することです。定義上、補償ネットワークのゲインは、変調器と出力フィルタのゲインの逆数にする必要があります。この設計例では、ESR ゼロが閉ループのクロスオーバー周波数よりもはるかに高い場合、変調器と出力フィルタのゲインを式 20 で概算できます。

$$\text{Gain} = -20 \times \log(2 \times \pi \times R_{\text{SENSE}} \times f_{\text{CO}} \times C_0) \quad (20)$$

ここで、

- $R_{\text{SENSE}}$  は  $1\Omega/12$  です。

- $f_{\text{CO}}$  は閉ループのクロスオーバー周波数です。

- $C_0$  は出力容量です。

位相損失は式 21 で計算します。

$$PL = \alpha \times \tan(2 \times \pi \times f_{\text{CO}} \times R_{\text{ESR}} \times C_0) - \alpha \times \tan(2 \times \pi \times f_{\text{CO}} \times R_0 \times C_0) \quad (21)$$

ここで、

- $R_{\text{ESR}}$  は、出力コンデンサの等価直列抵抗です。

- $R_0$  は  $V_0 / I_0$  です。

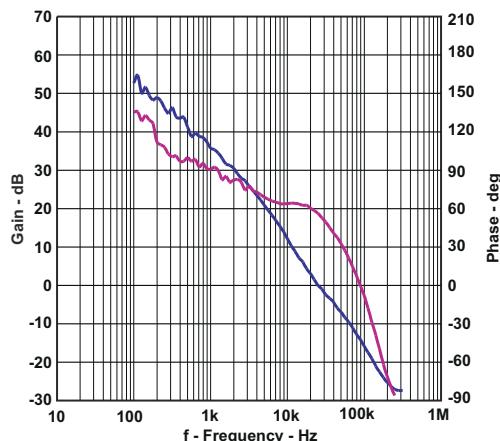

回路で測定される全体のループ応答を、図 8-7 に示します。実際の閉ループのクロスオーバー周波数は、約  $25\text{kHz}$  において意図した周波数よりも高くなります。これは主に、出力フィルタ部品の実際の値の変動と、内部フィードフォワード・ゲイン回路の公差の変動が原因です。全体として、この設計は位相マージンが 60 度より大きく、ラインと負荷の変動性のあらゆる組み合わせについて完全に安定しています。

位相損失が判明したので、位相マージン要件を満たすために必要な位相ブーストの量を決定できます。式 22 を使用して、必要な位相ブーストを計算します。

$$PB = (PM - 90\text{deg}) - PL \quad (22)$$

ここで、

- $PM$  は求められる位相マージンです。

補償ネットワークのゼロ極ペアは、意図した閉ループ周波数の周囲に対称的に配置され、クロスオーバー・ポイントで最大の位相ブーストを実現します。分離の量は、式 23 で計算できます。式 24 と式 25 を使用して、得られるゼロ周波数と極周波数を計算します。

$$k = \tan\left(\frac{PB}{2} + 45\text{deg}\right) \quad (23)$$

$$F_{Z1} = \frac{f_{\text{CO}}}{k} \quad (24)$$

$$F_{P1} = f_{\text{CO}} \times k \quad (25)$$

低周波数の極は、クロスオーバー周波数のゲインが変調器と出力フィルタのゲインの逆数と等しくなるように設定されます。極とゼロとの関係によって確立される関係のため、式 26 を使用して  $R_Z$  の値を計算します。

$$R_Z = \frac{2 \times \pi \times f_{\text{CO}} \times V_0 \times C_0 \times R_{OA}}{G_{\text{MCOMP}} \times V_{GGM} \times V_{REF}} \quad (26)$$

ここで、

- $V_0$  は出力電圧です。

- $C_0$  は出力容量です。

- $f_{\text{CO}}$  は求められるクロスオーバー周波数です。

- $R_{OA}$  は  $8M\Omega$  です。

- $G_{\text{MCOMP}}$  は  $12\text{A/V}$  です。

- $V_{GGM}$  は  $800$  です。

- $V_{REF}$  は  $0.8\text{V}$  です。

$R_Z$  の値が判明している場合、式 27 と式 28 を使用して  $C_Z$  および  $C_P$  の値を計算します。

$$C_Z = \frac{1}{2 \times \pi \times F_{Z1} \times R_Z} \quad (27)$$

$$C_P = \frac{1}{2 \times \pi \times F_{P1} \times R_Z} \quad (28)$$

この設計では、2 つの  $47\mu F$  出力コンデンサを使用します。セラミック・コンデンサの場合、コンデンサに DC バイアス電圧が印加されているときの実際の出力容量は定格値未満で、これは DC/DC コンバータで発生します。実際の出力容量は、 $54\mu F$  まで小さくできます。合計 ESR は約  $0.001\Omega$  です。

式 20 と式 21 を使用すると、出力段のゲインと位相損失は次の値になります。

- ゲイン =  $-2.26\text{dB}$

- PL =  $-83.52$  度

式 22 で 70 度の位相マージンを実現するには、63.52 度の位相ブーストが必要です。

式 23、式 24、式 25 を使用して、ゼロおよび極の周波数が次のように算出されます。

- $F_{Z1} = 5883\text{Hz}$

- $F_{P1} = 106200\text{Hz}$

式 26、式 27、式 28 を使用して、 $R_Z$ 、 $C_Z$ 、 $C_P$  の値を計算します。

$$R_Z = \frac{2 \times \pi \times 25000 \times 3.3 \times 54 \times 10^{-6} \times 8 \times 10^6}{12 \times 800 \times 0.8} = 29.2\text{k}\Omega \quad (29)$$

$$C_Z = \frac{1}{2 \times \pi \times 6010 \times 29200} = 928\text{pF} \quad (30)$$

$$C_P = \frac{1}{2 \times \pi \times 103900 \times 29200} = 51\text{pF} \quad (31)$$

図 8-1 を参照し、 $R3$ 、 $C6$ 、 $C7$  の標準値を使用すると、次の値が算出されます。

- $R3 = 29.4\text{k}\Omega$

- $C6 = 1000\text{pF}$

- $C7 = 47\text{pF}$

### 8.2.2.8 ブートストラップ・コンデンサ

TPS54331 の設計では、常にブートストラップ・コンデンサ  $C4$  が必要です。ブートストラップ・コンデンサの値は  $0.1\mu F$  にする必要があります。ブートストラップ・コンデンサは、**PH** ピンと **BOOT** ピンの間に接続します。温度安定性のために、**X7R** または **X5R** グレードの誘電体を使用した高品質セラミック・コンデンサを使用してください。

### 8.2.2.9 キャッチ・ダイオード

TPS54331 デバイスは、**PH** ピンと **GND** ピンとの間に外付けのキャッチ・ダイオードを接続して動作するよう設計されています。選択するダイオードは、アプリケーションの絶対最大定格を満たす必要があります。逆電圧は、**PH** ピンの最大電圧である  $V_{IN(MAX)} + 0.5V$  よりも高い必要があります。ピーク電流は、 $I_{OUT(MAX)}$  にピーク・ツー・ピーク・インダクタ電流の半分を加えた値よりも大きい必要があります。高い効率を得るために、順方向電圧降下は小さい必要があります。一般に、キャッチ・ダイオードの導通時間は、ハイサイド FET のオン時間よりも長いため、ダイオードのパラメータに注意を払うことで、全体の効率を大きく向上させることができます。また、選択したデバイスが電力損失を減らせるかを確認します。この設計では、**Diodes, Inc.** の **B340A** を選択しています。このダイオードは、逆方向電圧が  $40V$ 、順方向電流が  $3A$ 、順方向電圧降下が  $0.5V$  です。

### 8.2.2.10 出力電圧の制限

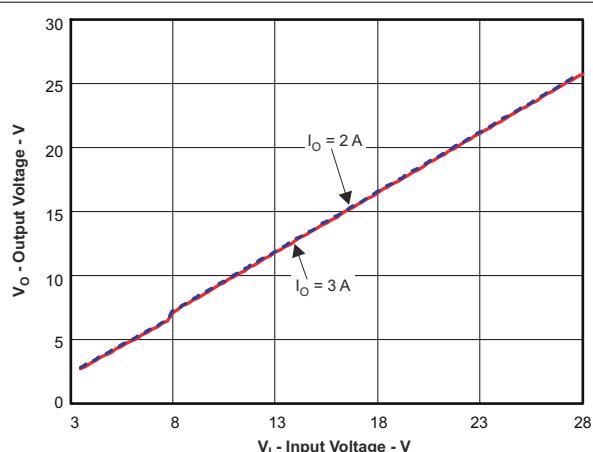

TPS54331 デバイスは、内部設計の関係で、任意の入力電圧について出力電圧の上限と下限がどちらも存在します。出力電圧の設定ポイントの上限は、最大デューティ・サイクルの  $91\%$  に制限され、式 32 で求められます。

$$V_{O(MAX)} = 0.91 \times ((V_{IN(MIN)} - I_{O(MAX)} \times R_{DS(ON)MAX}) + V_D) - (I_{O(MAX)} \times R_L) - V_D \quad (32)$$

ここで、

- $V_{IN(MIN)}$  は最小入力電圧です。

- $I_{O(MAX)}$  は最大負荷電流です。

- $V_D$  はキャッチ・ダイオードの順方向電圧です。

- $R_L$  は出力インダクタの直列抵抗です。

この式では、内部ハイサイド FET について最大のオン抵抗を想定しています。

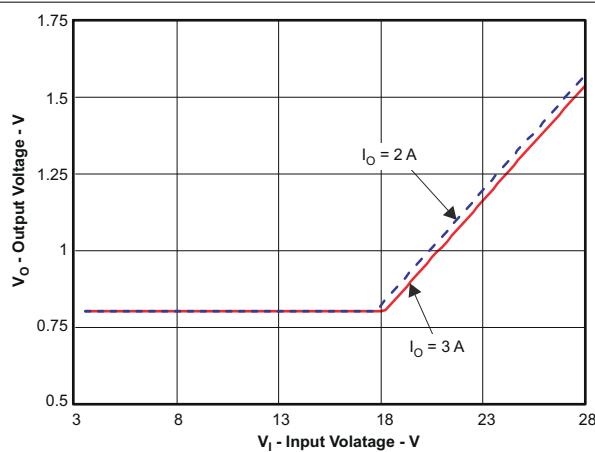

下限は、最小制御可能オン時間 (最大で 130ns) によって制限されます。式 33 を使用して、与えられた入力電圧と最小負荷電流について、最小出力電圧の概算値を計算します。

$$V_{O(MIN)} = 0.089 \times ((V_{IN(MAX)} - I_{O(MIN)} \times R_{DS(ON)MIN}) + V_D) - (I_{O(MIN)} \times R_L) - V_D \quad (33)$$

ここで、

- $V_{IN(MAX)}$  は最大入力電圧です。

- $I_{O(MIN)}$  は最小負荷電流です。

- $V_D$  はキャッチ・ダイオードの順方向電圧です。

- $R_L$  は出力インダクタの直列抵抗です。

式 33 でのハイサイド FET の公称オン抵抗が想定されています。式 33 は、動作周波数設定ポイントのワーストケース変動を示しています。デバイスの動作制限付近で動作する設計の場合、正しい機能を保証するために慎重な確認が必要です。

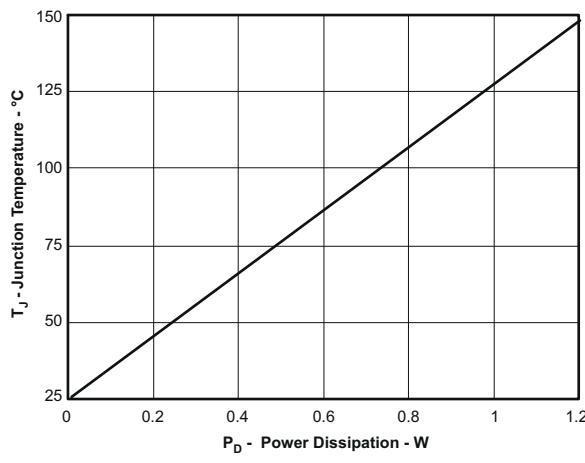

### 8.2.2.11 消費電力の推定

以下の式は、連続導通モード (CCM) 動作でのデバイスの消費電力を推定する方法を示しています。デバイスが不連続導通モード (DCM) またはパルス・スキップ Eco-mode で動作している場合は、これらの式を使用しないでください。

デバイスの消費電力には以下が含まれます。

#### 1. 導通損失:

$$P_{con} = I_{OUT}^2 \times R_{DS(on)} \times V_{OUT} / V_{IN}$$

ここで

- $I_{OUT}$  は出力電流 (A) です。

- $R_{DS(on)}$  はハイサイド MOSFET のオン抵抗 ( $\Omega$ ) です。

- $V_{OUT}$  は出力電圧 (V) です。

- $V_{IN}$  は入力電圧 (V) です。

#### 2. スイッチング損失:

$$P_{sw} = 0.5 \times 10^{-9} \times V_{IN}^2 \times I_{OUT} \times f_{sw}$$

ここで

- $f_{sw}$  はスイッチング周波数 (Hz) です。

#### 3. ゲート電荷損失:

$$P_{gc} = 22.8 \times 10^{-9} \times f_{sw}$$

#### 4. 静止時電流損失

$$P_q = 0.11 \times 10^{-3} \times V_{IN}$$

したがって、次のようになります。

$$P_{tot} = P_{con} + P_{sw} + P_{gc} + P_q$$

ここで

- $P_{tot}$  は合計デバイス消費電力 (W) です。

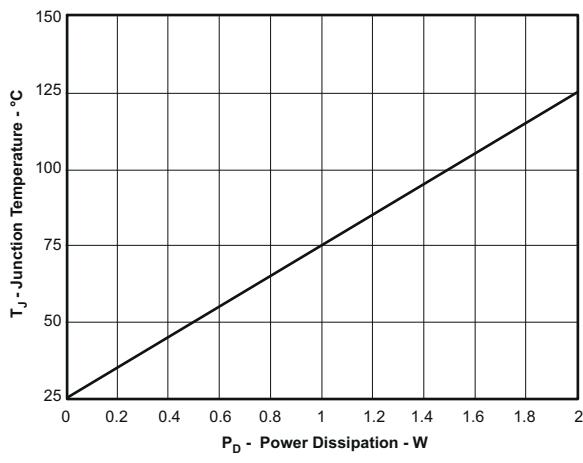

与えられた  $T_A$  に対して:

$$T_J = T_A + R_{th} \times P_{tot}$$

ここで

- $T_J$  は接合部温度 ( $^{\circ}\text{C}$ ) です。

- $T_A$  は周囲温度 ( $^{\circ}\text{C}$ ) です。

- $R_{th}$  はパッケージの熱抵抗 ( $^{\circ}\text{C}/\text{W}$ ) です。

与えられた  $T_{JMAX} = 150^{\circ}\text{C}$  に対して:

$$T_{A\text{MAX}} = T_{JMAX} - R_{th} \times P_{tot}$$

ここで

- $T_{JMAX}$  は最大接合部温度 ( $^{\circ}\text{C}$ ) です。

- $T_{A\text{MAX}}$  は最大周囲温度 ( $^{\circ}\text{C}$ ) です。

### 8.2.3 アプリケーション曲線

TPS54331 (D パッケージ)

図 8-2. 効率

TPS54331 (D パッケージ)

図 8-3. 低電流効率

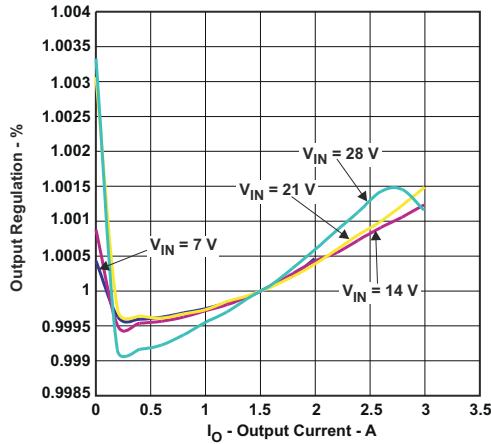

TPS54331 (D パッケージ)

図 8-4. 負荷レギュレーション

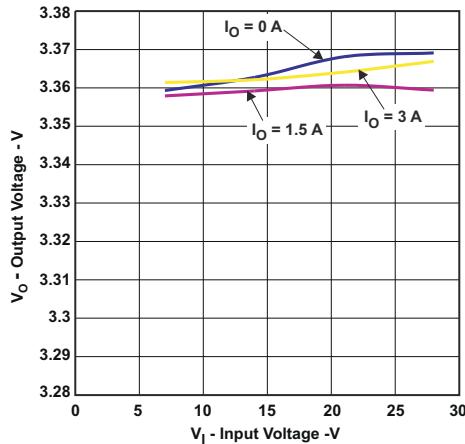

TPS54331 (D パッケージ)

図 8-5. ライン・レギュレーション

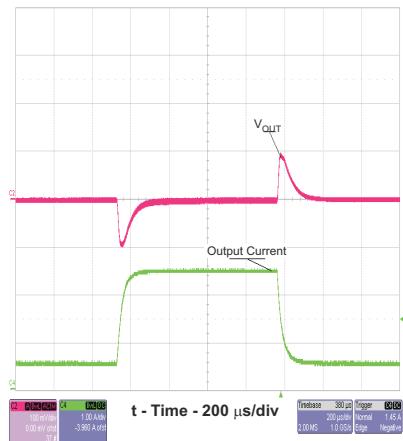

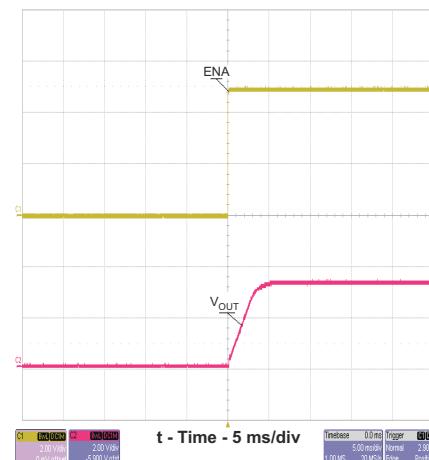

図 8-6. 過渡応答

図 8-7. ループ応答

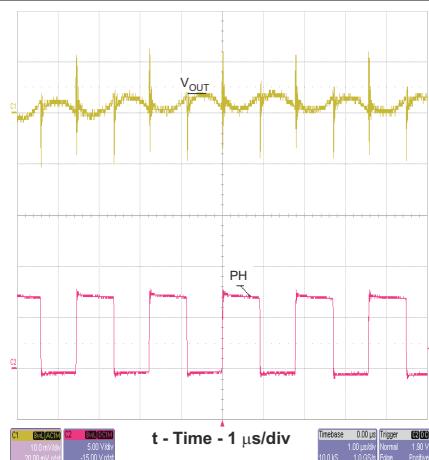

図 8-8. 出力リップル

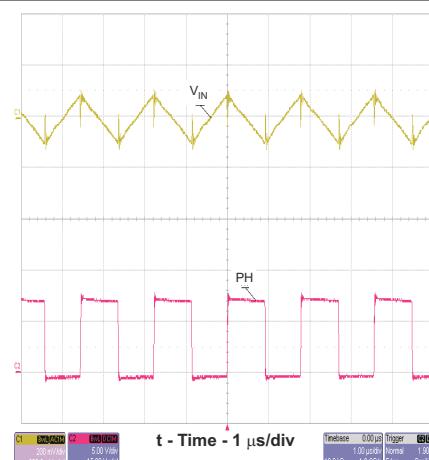

図 8-9. 入力リップル

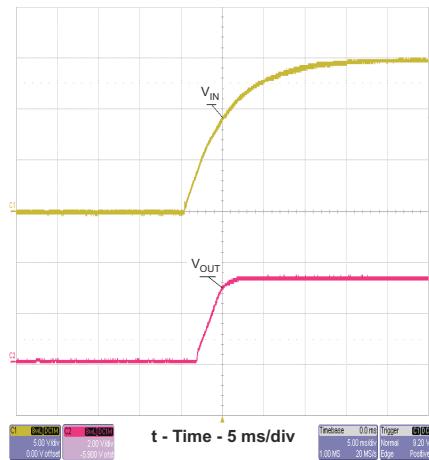

図 8-10. スタートアップ

図 8-11. イネーブルとスタートアップとの時間的な関係

図 8-12. 標準的な最小出力電圧と入力電圧との関係

図 8-13. 標準的な最大出力電圧と入力電圧との関係

TPS54331 (D パッケージ)

TPS54331 (D パッケージ)

図 8-14. 最大消費電力と接合部温度との関係

図 8-15. 最大消費電力と接合部温度との関係

## 8.3 電源に関する推奨事項

このデバイスは、3.5V～28V の入力電源電圧範囲で動作するよう設計されています。この入力電源には適切なレギュレーションが行われる必要があります。入力電源がコンバータから数インチ以上離れている場合は、セラミック・バイパス・コンデンサに加えて追加のバルク容量が必要となることがあります。通常は、100μF の電解コンデンサを使用します。

## 8.4 レイアウト

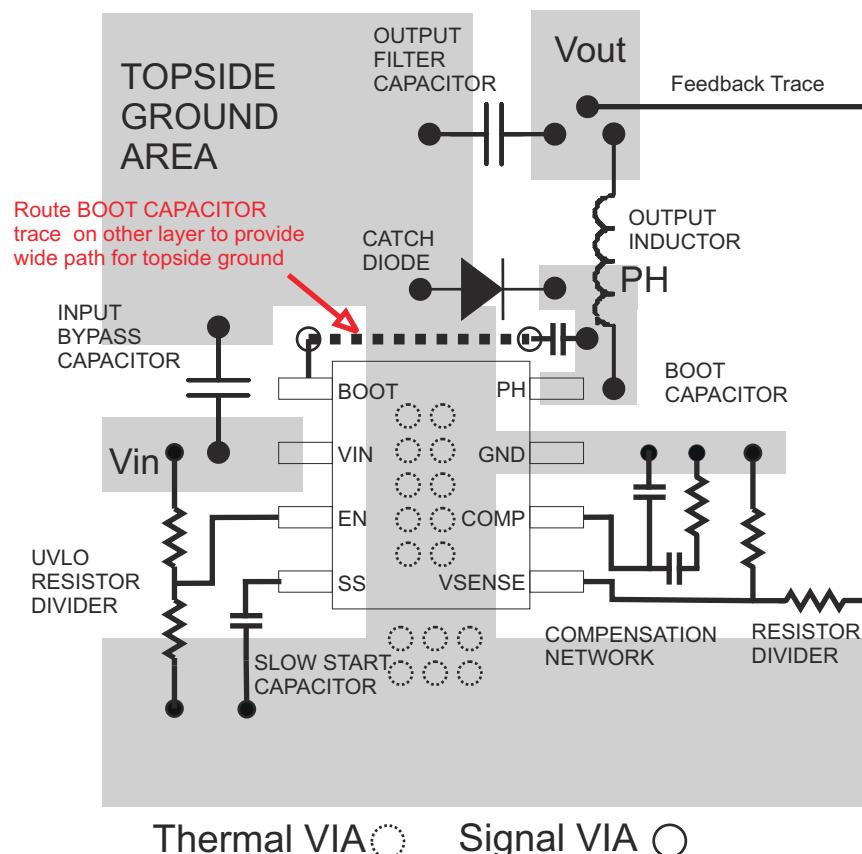

### 8.4.1 レイアウトのガイドライン

VIN ピンは、低 ESR のセラミック・バイパス・コンデンサを使用してグランドにバイパスする必要があります。バイパス・コンデンサ接続、VIN ピン、およびキャッチ・ダイオードのアノードによって形成されるループ領域は、最小限に抑えるよう注意が必要です。推奨される標準のバイパス・コンデンサは、X5R または X7R 誘電体を使用した 10μF のセラミック・コンデンサで、VIN ピン、およびキャッチ・ダイオードのアノードのソースにできる限り近づけて配置するのが最適です。PCB レイアウトの例を、図 8-16 に示します。GND ピンは、デバイスのピンで PCB グランド・プレーンに接続する必要があります。ローサイド MOSFET のソースは、入出力コンデンサのグランド側とキャッチ・ダイオードのアノードを接続するために使用する、上面 PCB のグランド領域に直接接続する必要があります。PH ピンは、キャッチ・ダイオードのカソード、および出力インダクタに配線します。PH 接続はスイッチング・ノードなので、キャッチ・ダイオードと出力インダクタは PH ピンのごく近くに配置し、過度の容量性カップリングを避けるため PCB 導体の面積は最小にします。全定格負荷で動作するには、上面のグランド領域に十分な熱放散面積が必要です。TPS54331 デバイスは、GND ピンがダイからの放熱を行う導電性パスとして機能するよう、ヒューズ付きリード・フレームを使用しています。多くのアプリケーションでは、内部またはバックサイドのグランド・プレーンのより広い領域を使用できます。また、デバイスの下または隣接する複数のビアを使用して、上面のグランド領域をこれらの領域に接続することで、熱を放散できます。追加の外部部品は図に示されるように配置できます。別のレイアウト方法で許容可能な性能を得ることもできますが、このレイアウトは良好な結果が得られることが示されており、ガイドラインを意図したものです。

#### 8.4.2 レイアウト例

図 8-16. TPS54331 のデバイス D の基板レイアウト

#### 8.4.3 電磁干渉 (EMI) に関する考慮事項

多くのアプリケーションにおいて EMI に対する懸念が高まる中で、TPS54331 デバイスの内部設計にも EMI を低減する機能が搭載されています。ハイサイド MOSFET のゲート駆動は、PH ピンの電圧のリングギングを低減するよう設計されています。内部の IC レールは、ノイズ感度を下げるため絶縁されています。また、パッケージ・ボンド・ワイヤ方式を使用して、寄生成分の影響を低減しています。

最高の EMI 性能を得るには、外部部品の選択と基板レイアウトが同じように重要です。EMI の潜在的な問題を防止するために、[セクション 8.2.2](#) に示す手順に従います。

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイスのサポート

#### 9.1.1 開発サポート

##### 9.1.1.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH Power Designer により、カスタム設計を作成できます。

1. 最初に、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{OUT}$  の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化し、この設計と、テキサス・インスツルメンツによる他の可能なソリューションとを比較します。

3. WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格や部品の在庫情報と併せて参照できます。

4. ほとんどの場合、ユーザーは次の操作を実行できます。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱性能を把握する。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットでエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用している場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS54331D</a>    | Active        | Production           | SOIC (D)   8             | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331D.A                  | Active        | Production           | SOIC (D)   8             | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331D.B                  | Active        | Production           | SOIC (D)   8             | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| <a href="#">TPS54331DDA</a>  | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| TPS54331DDA.A                | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| TPS54331DDA.B                | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| <a href="#">TPS54331DDAR</a> | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| TPS54331DDAR.A               | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| TPS54331DDAR.B               | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 54331               |

| TPS54331DG4                  | Active        | Production           | SOIC (D)   8             | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| <a href="#">TPS54331DR</a>   | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331DR.A                 | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331DR.B                 | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331DRG4                 | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| <a href="#">TPS54331GDR</a>  | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331GDR.A                | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

| TPS54331GDR.B                | Active        | Production           | SOIC (D)   8             | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 54331               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS54331 :**

- Automotive : [TPS54331-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

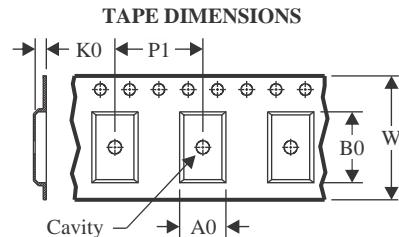

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

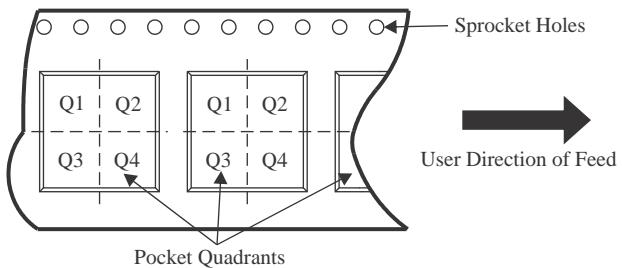

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54331DDAR | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| TPS54331DR   | SOIC         | D               | 8    | 2500 | 330.0              | 12.5               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| TPS54331GDR  | SOIC         | D               | 8    | 2500 | 330.0              | 12.5               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

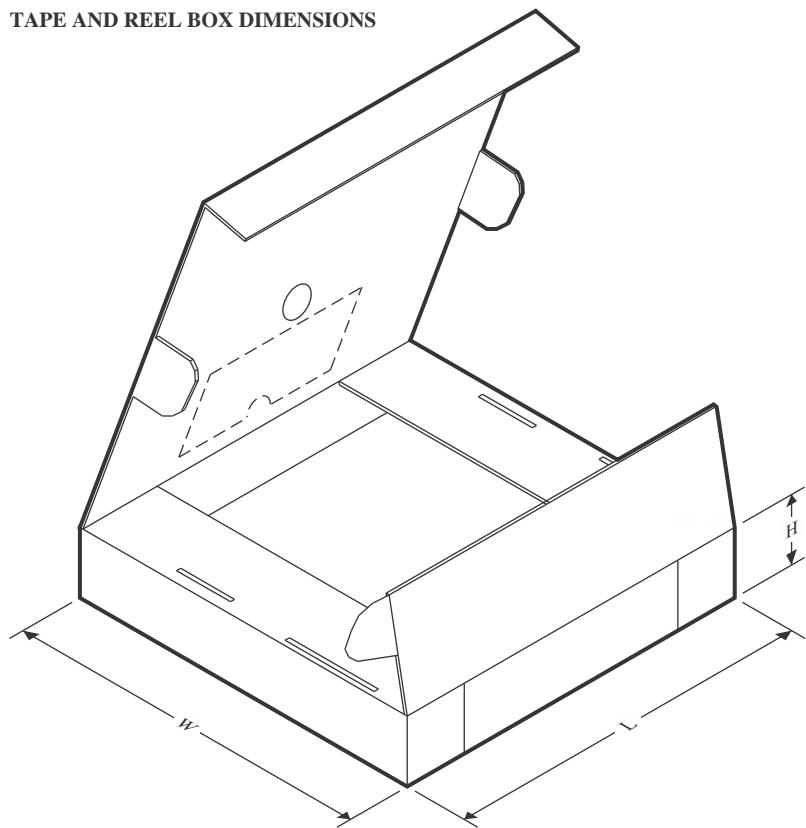

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54331DDAR | SO PowerPAD  | DDA             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| TPS54331DR   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| TPS54331GDR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

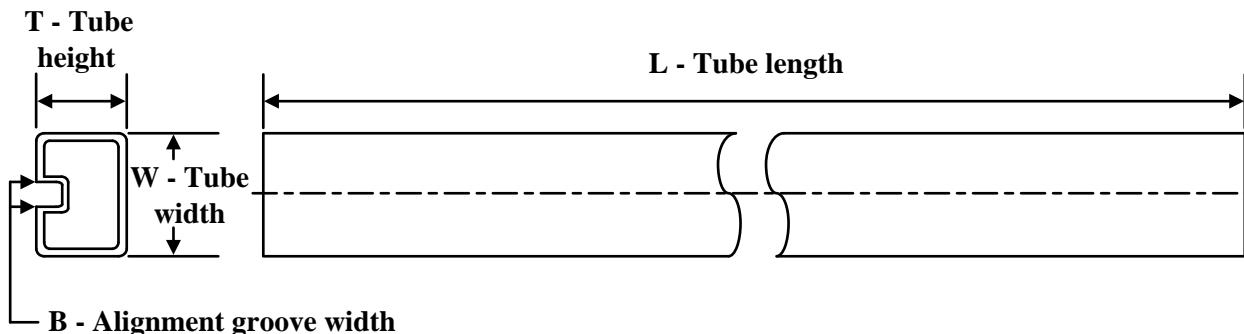

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54331D     | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54331D.A   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54331D.B   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54331DDA   | DDA          | HSOIC        | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| TPS54331DDA.A | DDA          | HSOIC        | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| TPS54331DDA.B | DDA          | HSOIC        | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| TPS54331DG4   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

## GENERIC PACKAGE VIEW

DDA 8

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4202561/G

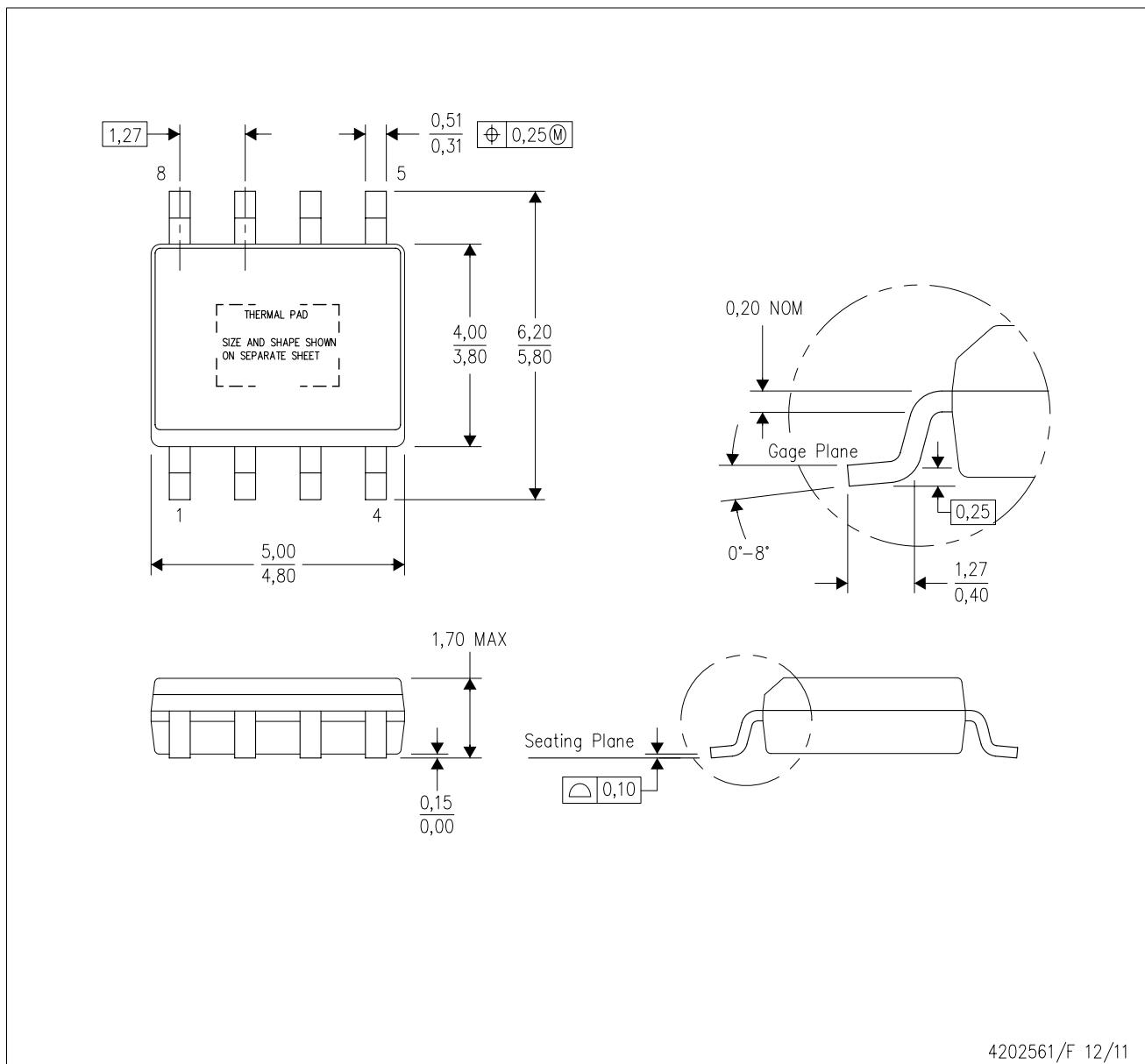

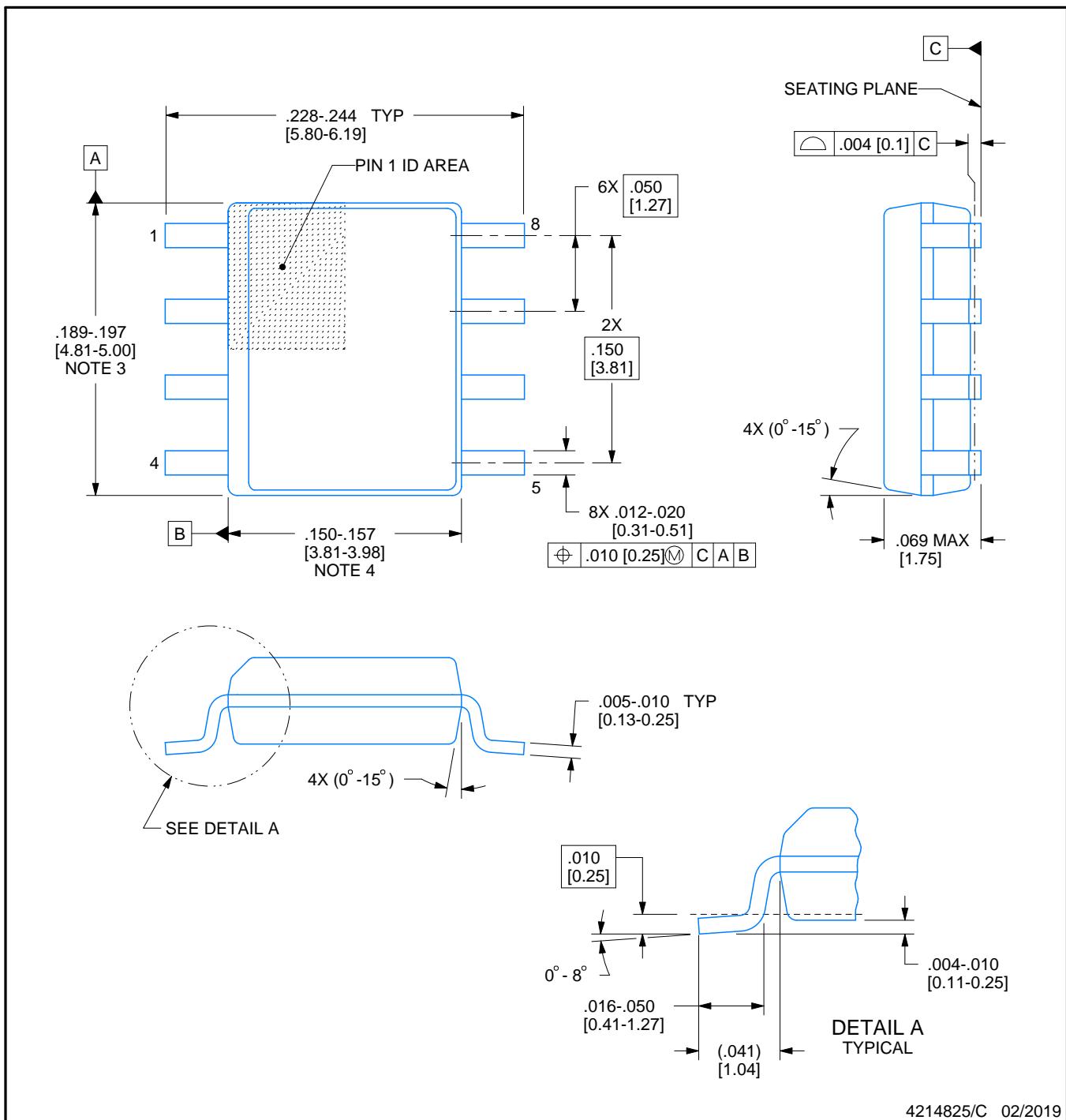

## MECHANICAL DATA

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL-OUTLINE

4202561/F 12/11

- NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. This package complies to JEDEC MS-012 variation BA

PowerPAD is a trademark of Texas Instruments.

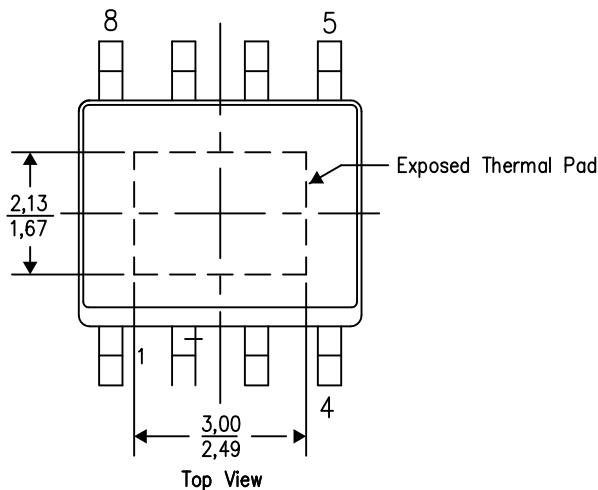

# THERMAL PAD MECHANICAL DATA

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL OUTLINE

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206322-5/L 05/12

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

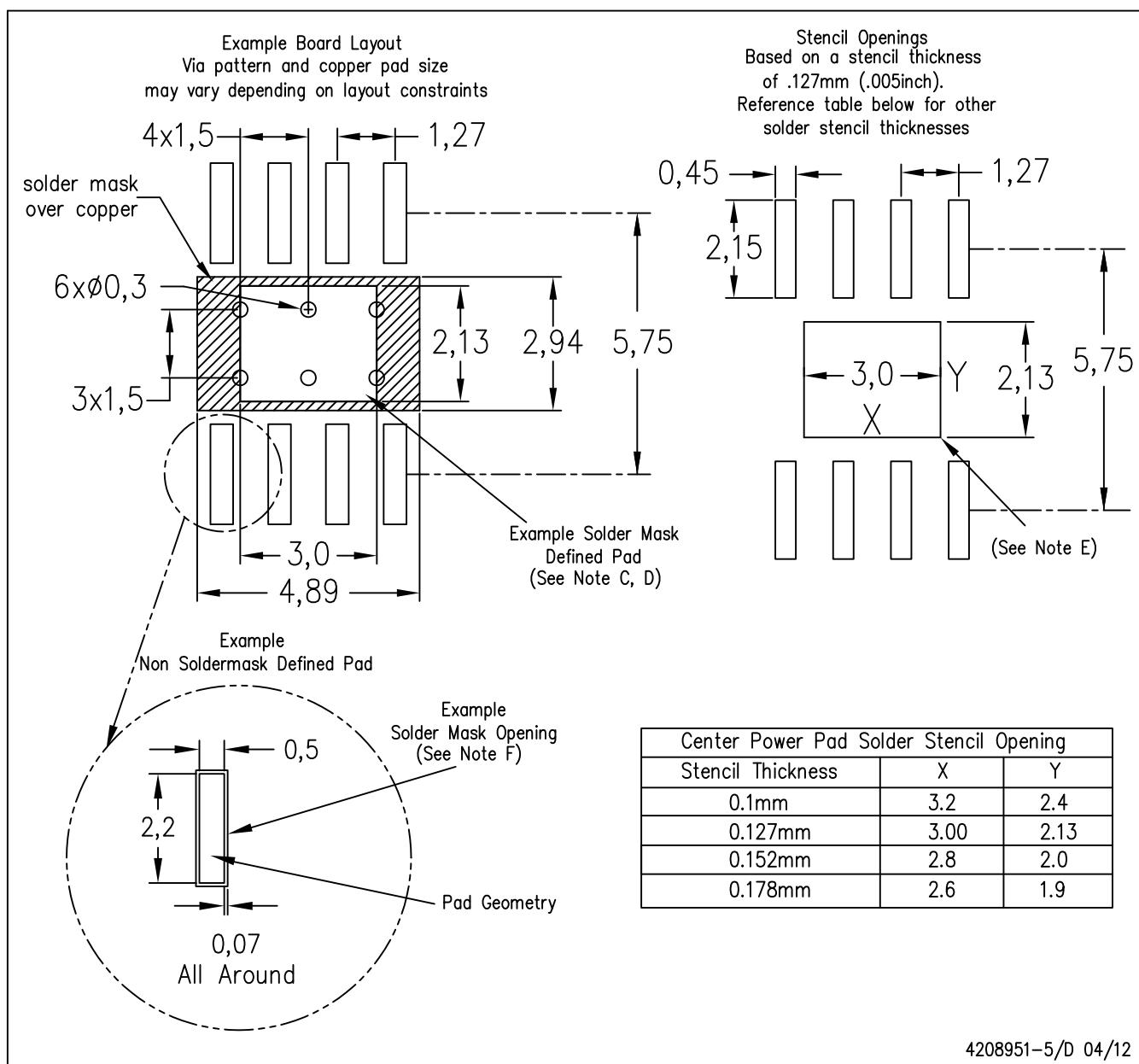

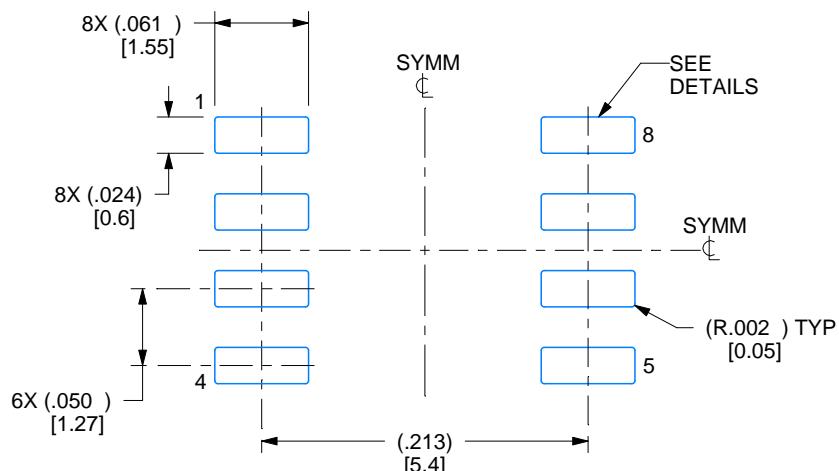

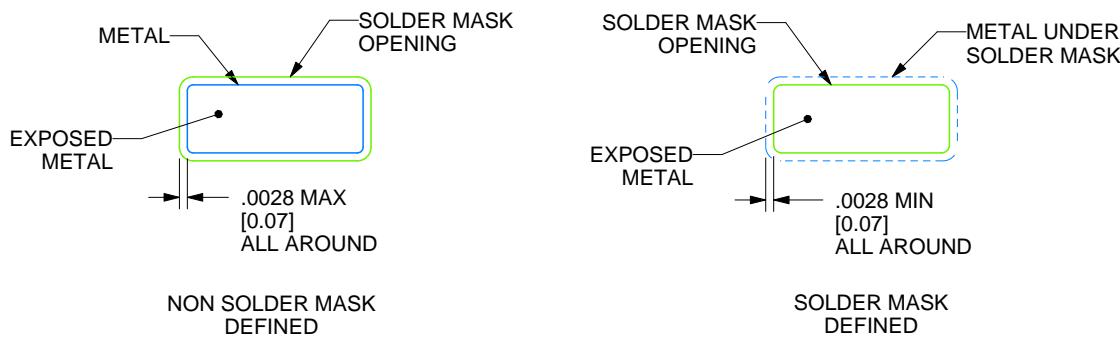

# LAND PATTERN DATA

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL OUTLINE

4208951-5/D 04/12

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>. Publication IPC-7351 is recommended for alternate designs.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

D0008A

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

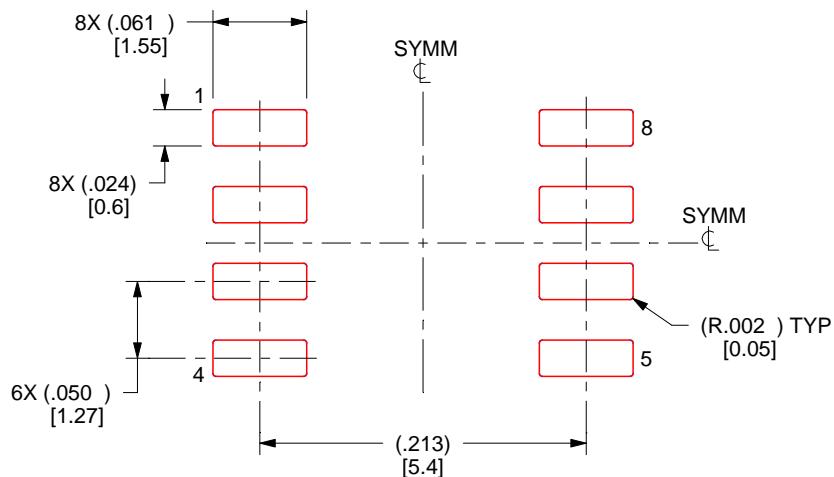

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月