**TPS54319**

www.tij.co.jp JAJS493

# FET内蔵(SWIFT™)、2.95V~6V入力、3A出力、 2MHz、同期整流降圧型スイッチャ

# 特長

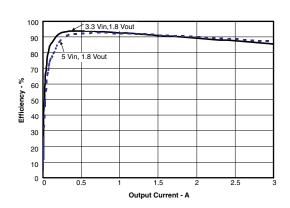

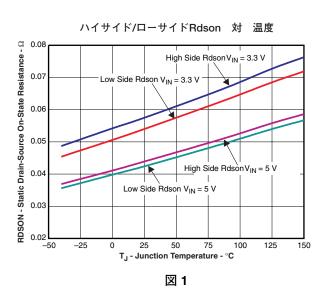

- 2個の45mΩ (typ) MOSFETにより3A負荷で高効率を 実現

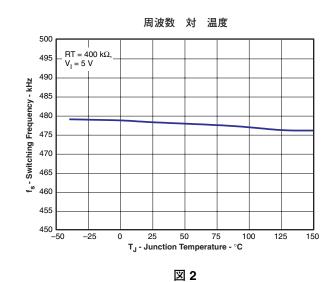

- スイッチング周波数:300kHz~2MHz

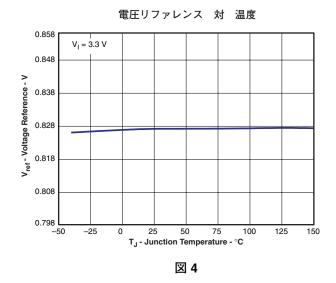

- 電圧リファレンス: 0.8V±3.0% (0°C~85°C)

- 外部クロックに同期

- 調整可能なスロー・スタート/シーケンシング

- パワー・グッド出力:UV、OV

- 動作接合部温度範囲:-40℃~150℃

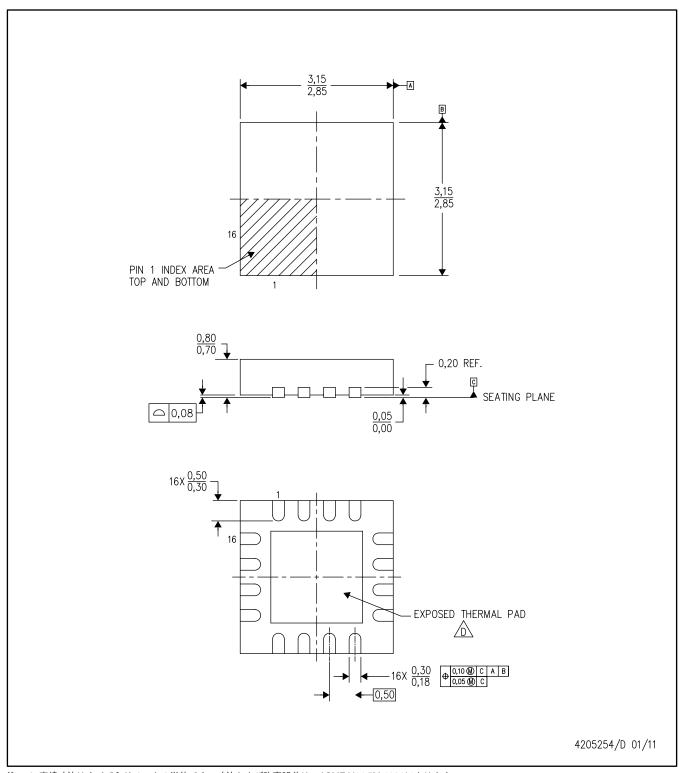

- 3mm×3mmの熱特性強化型16ピンQFN

- TPS54318とピン·コンパチブル

# アプリケーション

- 低電圧、高密度の電源システム

- セットトップ・ボックス、LCDディスプレイ、 CPE機器など、民生用アプリケーションのポイン ト・オブ・ロード (POL) レギュレーション

# 概要

TPS54319は、2個のMOSFETを内蔵した、フル機能の6V、3A同期整流降圧型電流モード・コンバータです。

MOSFETを内蔵し、電流モード制御の実装によって外部部品数を減らし、最大2MHzのスイッチング周波数によりインダクタのサイズを小さく抑え、3mm×3mmの小さな熱特性強化型QFNパッケージでICの占有面積を最小限にすることにより、小サイズの設計を可能にしています。

TPS54319は、温度に対して±3.0%の高精度な電圧リファレンス (VREF)により、各種の負荷に対して正確なレギュレーションを実現します。

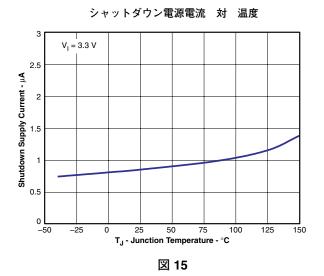

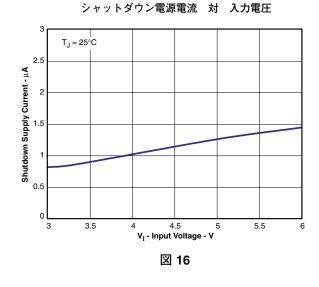

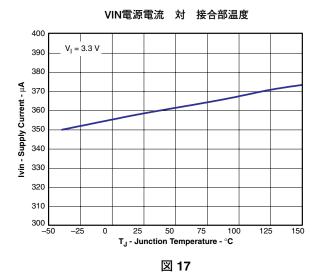

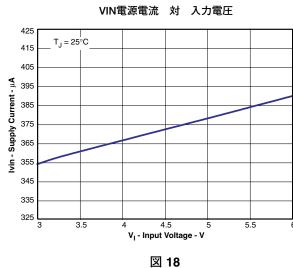

内蔵の $45m\Omega$  MOSFETおよび $360\mu$ A (typ) の消費電流により、効率を最大限に高めています。イネーブル・ピンを使用してシャットダウン・モードに入ることで、シャットダウン時には消費電流を $2\mu$ Aまで低減できます。

低電圧ロックアウトは内部で2.6Vに設定されていますが、イネーブル・ピンの抵抗回路でスレッショルドをプログラミングすることにより、さらに高い電圧に設定できます。起動時の出

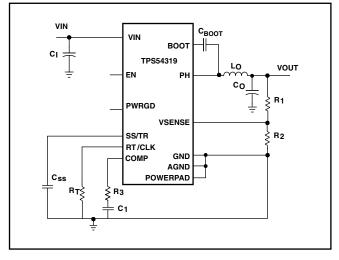

#### 回路概略図

SWIFT, SwitcherProは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLVSA83 翻訳版

力電圧の上昇は、スロー・スタート・ピンによって制御されます。 オープン・ドレインのパワー・グッド信号は、出力が公称電圧の 93%~107%の範囲内であることを示します。

周波数フォールドバックと過熱シャットダウン機能によって、過電流状態時にデバイスを保護します。

TPS54319は、SwitcherPro™ソフトウェア・ツール (www.ti.com/switcherpro)でサポートされています。

SWIFT™関連のドキュメントについては、TIのWebサイト www.ti.com/swiftをご覧ください。

# 静電気放電対策

ESDはこの集積回路にダメージを与えることがあります。テキサス・インスツルメンツ社は、全ての集積回路に適切なESD対策が行われることを推奨します。この適切な取扱いや取付け手順が守られない場合には、素子にダメージを与えることがあります。

ESDが与えるダメージには、素子へ微妙な性能劣化から完全な素子故障まで様々な症状に及びます。非常に些細なパラメータの変化でもその素子の仕様を満足しなくなることがあり、高詳細な集積回路はさらにESDによる影響を受けやすい場合があります。

# 製品情報(1)

| T <sub>J</sub> | パッケージ               | 部品番号        |  |  |

|----------------|---------------------|-------------|--|--|

| –40°C ∼ 150°C  | $3 \times 3$ mm QFN | TPS54319RTE |  |  |

<sup>(1)</sup> 最新のパッケージ情報とご発注情報については、このデータシートの巻末にある「付録:パッケージ・オプション」を参照するか、またはTIのWebサイト (www.ti.comまたはwww.tij.co.jp) をご覧ください。

#### 絶対最大定格(1)

|                    |                                                        | VAL  | .UE    | 774 KT |

|--------------------|--------------------------------------------------------|------|--------|--------|

|                    |                                                        | MIN  | MAX    | 単位     |

| Input voltage      | VIN                                                    | -0.3 | 7      |        |

|                    | EN                                                     | -0.3 | 7      |        |

|                    | воот                                                   |      | PH + 7 |        |

|                    | VSENSE                                                 | -0.3 | 3      |        |

|                    | COMP                                                   | -0.3 | 3      | V      |

|                    | PWRGD                                                  | -0.3 | 7      |        |

|                    | SS/TR                                                  | -0.3 | 3      |        |

|                    | RT/CLK                                                 | -0.3 | 6      |        |

| Output voltage     | воот-рн                                                |      | 7      |        |

|                    | PH                                                     | -0.6 | 7      | V      |

|                    | PH 10 ns Transient                                     | -2   | 10     |        |

| Source current     | EN                                                     |      | 100    | μА     |

|                    | RT/CLK                                                 |      | 100    | μА     |

| Sink current       | COMP                                                   |      | 100    | μА     |

|                    | PWRGD                                                  |      | 10     | mA     |

|                    | SS/TR                                                  |      | 100    | μΑ     |

| Electrostatic disc | charge (HBM) QSS 009-105 (JESD22-A114A) <sup>(2)</sup> |      | 1      | kV     |

| Electrostatic disc | charge (CDM) QSS 009-147 (JESD22-C101B.01)             |      | 500    | V      |

| Temperature        | Tj                                                     | -40  | 150    | °C     |

|                    | T <sub>stg</sub>                                       | -65  | 150    | °C     |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「電気的特性」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

<sup>(2)</sup> HBM (Human Body Model) は、100pFのコンデンサから1.5kΩの抵抗を経由して各ピンに放電した場合です。マシン・モデルは、200pFのコンデンサから各ピンに直接放電した場合です。

# 熱特性について

|                           | THERMAL METRIC <sup>(1)(2)</sup>                          | TPS54319      | 24 /± |

|---------------------------|-----------------------------------------------------------|---------------|-------|

|                           | THERMAL METRIC (1)                                        | RTE (16-PINS) | 単位    |

| $\theta_{JA}$             | Junction-to-ambient thermal resistance (standard board)   | 51.7          |       |

| $\theta_{JA}$             | Junction-to-ambient thermal resistance (custom board) (3) | 37.0          |       |

| ΨJT                       | Junction-to-top characterization parameter                | 0.8           |       |

| ΨЈВ                       | Junction-to-board characterization parameter              | 19.2          | °C/W  |

| $\theta_{\text{JC(top)}}$ | Junction-to-case(top) thermal resistance                  | 69.3          |       |

| θ <sub>JC(bottom)</sub>   | Junction-to-case(bottom) thermal resistance               | 6.2           |       |

| $\theta_{JB}$             | Junction-to-board thermal resistance                      | 22            |       |

- (1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』 (SPRA953) を参照してください。

- (SPHA953) を参照しくくたさい。

(2) 特定の周囲温度TAでの電力定格は、接合部温度150℃で決定されます。これは、歪が大きく増加し始める温度です。詳細については、このデータシートのアプリケーション情報の「消費電力の見積もり」を参照してください。

(3) テスト・ボードの条件は以下の通りです。

(a) サイズ:2インチ×2インチ、4層、厚さ0.062インチ

(b) PCBの上面に重量2オンスの銅配線

- - (c) 内部の2層および最下層に重量2オンスの銅のグランド・プレーン (d) デバイス・パッケージ下に4つのサーマル・ビア (10mil)

## 電気的特性

T<sub>J</sub> = -40°C~150°C、VIN = 2.95V~6V(特に記述のない限り)

| DESCRIPTION                                             | CONDITIONS                                            | MIN   | TYP        | MAX   | 単位       |  |

|---------------------------------------------------------|-------------------------------------------------------|-------|------------|-------|----------|--|

| SUPPLY VOLTAGE (VIN PIN)                                |                                                       |       |            |       |          |  |

| Operating input voltage                                 |                                                       | 2.95  |            | 6     | V        |  |

| Internal under voltage lockout threshold                |                                                       |       | 2.6        | 2.8   | V        |  |

| Shutdown supply current                                 | EN = 0 V, 25°C, 2.95 V ≤ VIN ≤ 6 V                    |       | 2          | 5     | μΑ       |  |

| Quiescent Current - Iq                                  | VSENSE = 0.9 V, VIN = 5 V, 25°C, RT = 400 k $\Omega$  |       | 360        | 575   | μΑ       |  |

| ENABLE AND UVLO (EN PIN)                                |                                                       |       |            |       |          |  |

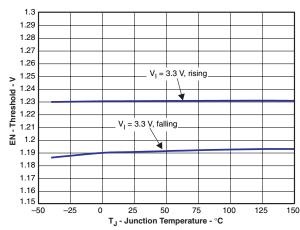

| Enable threshold                                        | Rising                                                |       | 1.25       |       | V        |  |

|                                                         | Falling                                               |       | 1.18       |       |          |  |

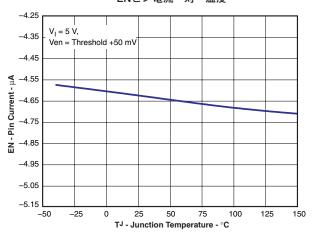

| Innut oursent                                           | Enable threshold + 50 mV                              |       | -4.6       |       | ^        |  |

| Input current                                           | Enable threshold – 50 mV                              |       | -1.2       |       | μΑ       |  |

| VOLTAGE REFERENCE (VSENSE PIN)                          |                                                       |       |            |       |          |  |

| Voltage Reference                                       | 2.95 V ≤ VIN ≤ 6 V, 0°C <t<sub>J &lt; 85°C</t<sub>    | 0.802 | 0.827      | 0.852 | V        |  |

| MOSFET                                                  |                                                       |       |            |       |          |  |

| High side and professions                               | BOOT-PH= 5 V                                          |       | 45         | 81    | 0        |  |

| High side switch resistance                             | BOOT-PH= 2.95 V                                       |       | 64         | 110   | mΩ       |  |

| Low side switch resistance                              | VIN= 5 V                                              |       | 42         | 81    | 31<br>mΩ |  |

| Low side switch resistance                              | VIN= 2.95 V                                           |       | 59         | 110   | 11152    |  |

| ERROR AMPLIFIER                                         |                                                       |       |            |       |          |  |

| Input current                                           |                                                       |       | 7          |       | nA       |  |

| Error amplifier transconductance (gm)                   | $-2 \mu A < I(COMP) < 2 \mu A, V(COMP) = 1 V$         |       | 245        |       | μmhos    |  |

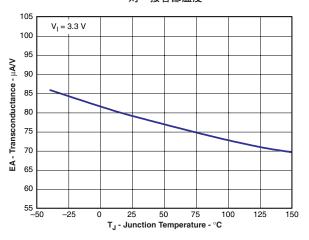

| Error amplifier transconductance (gm) during slow start | -2 μA < I(COMP) < 2 μA, V(COMP) = 1 V, Vsense = 0.4 V |       | 79         |       | μmhos    |  |

| Error amplifier source/sink                             | V(COMP) = 1 V, 100 mV overdrive                       |       | +20<br>-20 |       | μΑ       |  |

| COMP to Iswitch gm                                      |                                                       |       | 18         |       | A/V      |  |

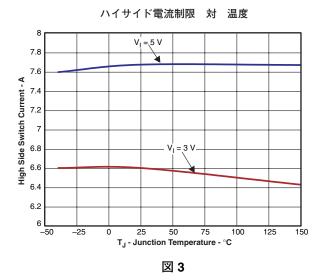

| CURRENT LIMIT                                           |                                                       |       |            | ·     |          |  |

| Current limit threshold                                 | 3V                                                    | 4.2   | 6.6        |       | Α        |  |

| THERMAL SHUTDOWN                                        |                                                       |       |            |       |          |  |

| Thermal Shutdown                                        |                                                       |       | 165        |       | °C       |  |

| Hysteresis                                              |                                                       |       | 15         |       | °C       |  |

# 電気的特性

T<sub>J</sub> = -40°C~150°C、VIN = 2.95V~6V(特に記述のない限り)

| DESCRIPTION                                 | CONDITIONS                                                 | MIN | TYP | MAX  | 単位     |

|---------------------------------------------|------------------------------------------------------------|-----|-----|------|--------|

| TIMING RESISTOR AND EXTERNAL CLOCK          | (RT/CLK PIN)                                               |     |     |      |        |

| Switching frequency range using RT mode     |                                                            | 300 |     | 2000 | kHz    |

| Switching frequency                         | Rt = 400 kΩ                                                | 400 | 500 | 600  | kHz    |

| Switching frequency range using CLK mode    |                                                            | 300 |     | 2000 | kHz    |

| Minimum CLK pulse width                     |                                                            | 75  |     |      | ns     |

| RT/CLK voltage                              | $R(RT/CLK) = 400k\Omega$                                   |     | 0.5 |      | V      |

| RT/CLK high threshold                       |                                                            |     | 1.6 | 2.2  | V      |

| RT/CLK low threshold                        |                                                            | 0.4 | 0.6 |      | V      |

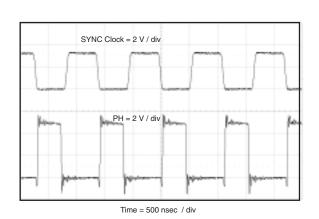

| RT/CLK falling edge to PH rising edge delay | Measure at 500 kHz with RT resistor in series              |     | 90  |      | ns     |

| PLL lock in time                            | Measure at 500 kHz                                         |     | 14  |      | μs     |

| PH (PH PIN)                                 |                                                            |     |     |      |        |

| Minimum On time                             | Measured at 50% points on PH, IOUT = 3 A                   |     | 65  |      |        |

|                                             | Measured at 50% points on PH, VIN = 5 V, IOUT = 0 A        |     | 120 |      | ns     |

| Minimum Off time                            | Prior to skipping off pulses, BOOT-PH = 2.95 V, IOUT = 3 A | 60  |     |      | ns     |

| Rise Time                                   | VIN. 5 V O A                                               | 2.5 |     |      | \//    |

| Fall Time                                   | VIN = 5 V, 3 A                                             | 2   |     |      | V/ns   |

| BOOT (BOOT PIN)                             |                                                            |     |     |      |        |

| BOOT Charge Resistance                      | VIN = 5 V                                                  |     | 16  |      | Ω      |

| BOOT-PH UVLO                                | VIN = 2.95 V                                               |     | 2.2 |      | V      |

| SLOW START AND TRACKING (SS/TR PIN)         |                                                            |     |     |      |        |

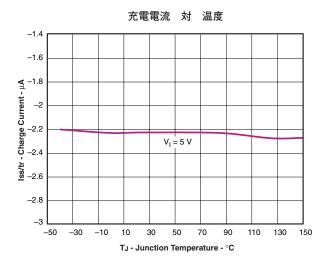

| Charge Current                              | V(SS/TR) = 0.4 V                                           |     | 2.2 |      | μΑ     |

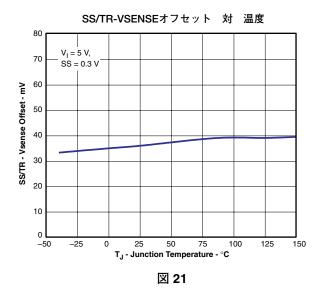

| SS/TR to VSENSE matching                    | V(SS/TR) = 0.4 V                                           |     | 35  |      | mV     |

| SS/TR to reference crossover                | 98% normal                                                 |     | 1.1 |      | V      |

| SS/TR discharge voltage (Overload)          | VSENSE = 0 V                                               |     | 46  |      | mV     |

| SS/TR discharge current (Overload)          | VSENSE = 0 V, V(SS/TR) = 0.4 V                             |     | 325 |      | μΑ     |

| POWER GOOD (PWRGD PIN)                      |                                                            |     |     |      |        |

|                                             | VSENSE falling (Fault)                                     |     | 91  |      | % Vref |

| VSENSE threshold                            | VSENSE rising (Good)                                       |     | 93  |      | % Vref |

| VSENSE tillesiloid                          | VSENSE rising (Fault)                                      |     | 107 |      | % Vref |

|                                             | VSENSE falling (Good)                                      |     | 105 |      | % Vref |

| Hysteresis                                  | VSENSE falling                                             |     | 2   |      | % Vref |

| Output high leakage                         | VSENSE = VREF, V(PWRGD) = 5.5 V                            |     | 2   |      | nA     |

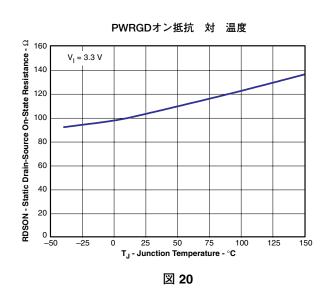

| On resistance                               |                                                            |     | 100 | 200  | Ω      |

| Output low                                  | I(PWRGD) = 3.0 mA                                          |     | 0.3 | 0.6  | V      |

| Minimum VIN for valid output                | V(PWRGD) < 0.5 V at 100 μA                                 |     | 1.2 | 1.6  | V      |

# 製品情報

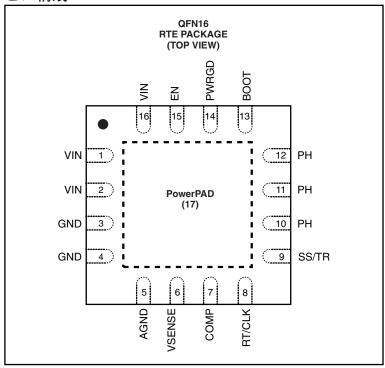

# ピン構成

# ピン機能

| ピン       |               | ≅ <b>X</b> □ <b>□</b>                                                                                                |  |  |  |  |  |  |

|----------|---------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 名前       | 番号            | · 説明                                                                                                                 |  |  |  |  |  |  |

| AGND     | 5             | アナログ・グランドは、デバイスの近くでGNDに電気的に接続する必要があります。                                                                              |  |  |  |  |  |  |

| BOOT     | 13            | BOOTとPHの間にブートストラップ・コンデンサが必要です。このコンデンサの電圧がBOOT UVLOに対して必要な最小値を下回った場合、出力はコンデンサがリフレッシュされるまで強制的にオフになります。                 |  |  |  |  |  |  |

| COMP     | 7             | 誤差増幅器の出力、および出力スイッチ電流コンパレータの入力。このピンに周波数補償部品を接続します。                                                                    |  |  |  |  |  |  |

| EN       | 15            | イネーブル・ピン、内部プルアップ電流源。ディスエーブルにするには、1.2V未満にプルダウンします。イネーブルにするには、フローティングにします。2個の抵抗を追加して、オン/オフ・スレッショルドの設定(UVLOの調整)に使用できます。 |  |  |  |  |  |  |

| GND      | 3, 4          | パワー・グランド。このピンは、IC直下のパワー・パッドに直接電気的に接続する必要があります。                                                                       |  |  |  |  |  |  |

| PH       | 10, 11,<br>12 | 内部ハイサイド・パワーMOSFETのソース、および内部ローサイド (同期) 整流MOSFETのドレイン。                                                                 |  |  |  |  |  |  |

| PowerPAD | 17            | 適切な動作のためには、GNDピンを露出したパワー・パッドに接続する必要があります。このパワー・パッドは、<br>複数のビアを使用して内部のPCBグランド・プレーンに接続することで、優れた熱特性が得られます。              |  |  |  |  |  |  |

| PWRGD    | 14            | 過熱シャットダウン、過電流、過電圧/低電圧、またはENシャットダウンによって出力電圧が規定値を外れた場合にアサートされる、オープン・ドレイン出力です。                                          |  |  |  |  |  |  |

| RT/CLK   | 8             | タイミング抵抗または外部クロック入力ピン。                                                                                                |  |  |  |  |  |  |

| SS/TR    | 9             | スロー·スタートおよびトラッキング。このピンに接続する外部コンデンサによって、出力電圧の立ち上がり時間<br>が設定されます。このピンは、トラッキングにも使用できます。                                 |  |  |  |  |  |  |

| VIN      | 1, 2, 16      | 入力電源電圧、2.95V~6V。                                                                                                     |  |  |  |  |  |  |

| VSENSE   | 6             | トランスコンダクタンス (gm) 誤差増幅器の反転ノード。                                                                                        |  |  |  |  |  |  |

#### トランスコンダクタンス (スロー・スタート) 対 接合部温度

#### 図 9

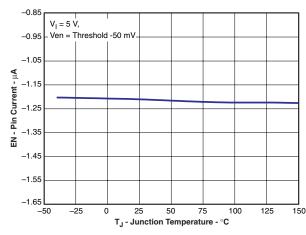

#### ENピン電流 対 温度

図 11

図 13

#### ENピン電圧 対 温度

図 10

#### ENピン電流 対 温度

図 12

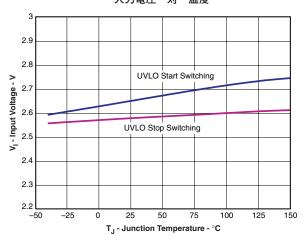

# 入力電圧 対 温度

図 14

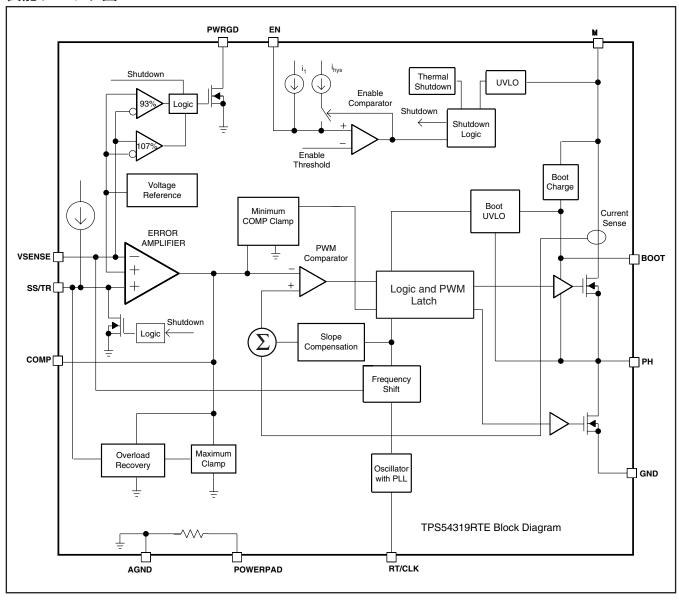

# 概要

TPS54319は、2個のNチャネルMOSFETを内蔵した、6V、3Aの同期整流降圧型(バック)コンバータです。ラインおよび負荷の過渡状態における性能を向上させるため、定周波数のピーク電流モード制御で動作し、出力容量の低減、外部周波数補償設計の単純化を実現しています。スイッチング周波数の範囲が300kHz~2000kHzと広いため、出力フィルタ部品の選択時に効率およびサイズを最適化できます。スイッチング周波数は、RT/CLKピンからグランドへの抵抗を使用して調整します。RT/CLKピンには内部フェーズ・ロック・ループ(PLL)が備えられ、パワー・スイッチをオンにするタイミングを外部システム・クロックの立ち下がりエッジに同期させることができます。

TPS54319の標準スタートアップ電圧はデフォルトで2.6Vです。ENピンの内部プルアップ電流源を使用して、入力電圧の低電圧ロックアウト (UVLO) を2個の外部抵抗により調整可能です。また、このプルアップ電流は、ENピンがフローティングのときにデバイスが動作するためのデフォルト状態を提供します。TPS54319の合計動作電流は、無負荷の非スイッチング時で360μA (typ)です。デバイスがディスエーブル時の消費電流は、5μA未満です。

45mΩの内蔵MOSFETにより、最大3Aの連続出力電流で高効率の電源設計が可能になります。

TPS54319は、ブート再充電ダイオードを内蔵し、外部部品数を低減できます。内蔵ハイサイドMOSFETのバイアス電圧

は、BOOT-PHピン間のコンデンサによって供給されます。このブート・コンデンサ電圧はUVLO回路によって監視され、内部設定されたスレッショルドを下回ると、ハイサイドMOSFETがオフになります。このBOOT回路により、TPS54319は100%のデューティ・サイクルで動作できます。出力電圧は、0.827Vのリファレンスと同じ値まで降圧させることができます。

TPS54319には、2%のヒステリシスを持つパワー·グッド·コンパレータ (PWRGD) があります。

この過電圧パワー・グッド・コンパレータを利用して、過度の出力過電圧を最小限に抑えています。レギュレーション出力電圧が公称電圧の107%を超えると、過電圧コンパレータが作動してハイサイドMOSFETがオフになり、出力電圧が105%を下回るまでオンになりません。

SS/TR(スロー・スタート/トラッキング)ピンは、パワーアップ時に突入電流を最小限に抑え、電源シーケンシングを構成するために使用できます。スロー・スタート用に、このピンには小容量のコンデンサを接続します。SS/TRピンが出力のパワーアップ前に放電されることで、過熱障害、UVLO障害、またはディスエーブル状態の後に、再起動を繰り返すことが可能になります。

周波数フォールドバック回路の使用により、起動時および過電流障害時にスイッチング周波数が低くなり、インダクタ電流の制限に役立ちます。

# 詳細説明

# 固定周波数PWM制御

TPS54319は、調整可能な固定周波数のピーク電流モード制御を使用します。COMPピンを駆動する誤差増幅器により、出力電圧がVSENSEピンの外付け抵抗を通して内部電圧リファレンスと比較されます。内部発振器により、ハイサイド・パワー・スイッチのオン動作が開始され、誤差増幅器の出力がハイサイド・パワー・スイッチ電流と比較されます。パワー・スイッチ電流がCOMP電圧レベルに達すると、ハイサイド・パワー・スイッチがオフになり、ローサイド・パワー・スイッチがオンになります。出力電流が増加および減少すると、COMPピン電圧も増加および減少します。デバイスではCOMPピン電圧を最大レベルにクランプすることで電流制限を実現しています。また、過渡応答特性の向上のために最小クランプも実装しています。

#### スロープ補償と出力電流

TPS54319は、スイッチ電流信号に補償ランプを追加します。このスロープ補償により、高いデューティ・サイクルでの低調波発振を防いでいます。使用可能なピーク・インダクタ電流は、デューティ・サイクルの範囲全体にわたって一定です。

# ブートストラップ電圧 (BOOT) と低ドロップアウト動作

TPS54319にはブート・レギュレータが内蔵され、ハイサイド MOSFETのゲート駆動電圧を提供するために、BOOTピンと PHピンの間に小さなセラミック・コンデンサが必要です。セラミック・コンデンサの値は、0.1μFとしてください。温度および電圧に対して安定した特性を持つため、X7RまたはX5Rクラスの誘電体を持つ電圧定格10V以上のセラミック・コンデンサを推奨します。

ドロップ・アウトを改善するため、TPS54319は、BOOT-PHピン間の電圧が2.2V以上であれば、100%のデューティ・サイクルで動作するよう設計されています。BOOT-PH間の電圧が2.2Vを下回ると、UVLO回路によってハイサイドMOSFETはオフになり、ローサイドMOSFETが導通します。BOOTピンからソースされる電源電流は非常に低いため、ハイサイドMOSFETはコンデンサのリフレッシュに必要な時間よりも多くのスイッチング・サイクルにわたってオンに保持でき、結果として、スイッチング・レギュレータの実効的なデューティ・サイクルが非常に大きくなります。

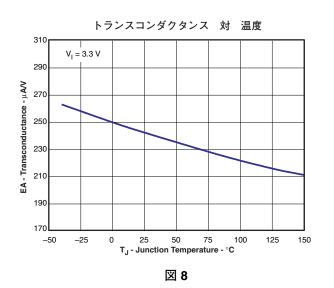

#### 誤差増幅器

TPS54319は、トランスコンダクタンス・アンプを内蔵しています。誤差増幅器は、VSENSEの電圧を、SS/TRピンの電圧または内部の0.827V電圧リファレンスのいずれか低い方と比較します。誤差増幅器のトランスコンダクタンスは、通常動作時には245μA/Vです。VSENSEピンの電圧が0.827V未満で、デバイスがSS/TR電圧を使用してレギュレーションを行っている場合、gmは標準で79μA/V以上、245μA/V未満となります。周波数補償部品をCOMPピンとグランドの間に配置します。

### 電圧リファレンス

電圧リファレンス・システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで、温度に対して±3.0%の高い精度を持つ電圧リファレンスを生成します。このバンドギャップ回路とスケーリング回路により、誤差増幅器の非反転入力に0.827Vが生成されます。

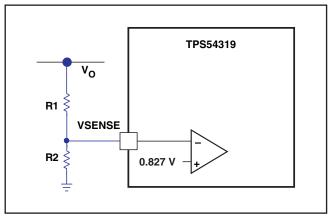

## 出力電圧の調整

出力電圧は、出力ノードとVSENSEピンとの間の分圧抵抗によって設定されます。公差1%以内の分圧抵抗を使用することを推奨します。最初はR1抵抗に100kΩを使用し、式(1)を使ってR2を計算します。負荷が非常に軽いときの効率を向上させるには、より大きな値の抵抗の使用を検討します。値が大きすぎると、レギュレータがノイズの影響を受けやすくなり、VSENSE入力電流からの電圧誤差が目立つようになります。

$$R2 = R1 \times \left( \frac{0.827 \text{ V}}{\text{V}_{\text{O}} - 0.827 \text{V}} \right) \tag{1}$$

図 22. 分圧回路

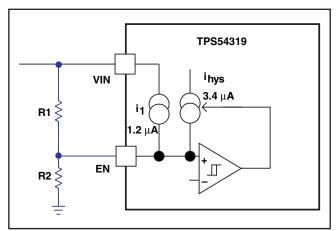

# イネーブルと低電圧ロックアウトの調整

VINピンの電圧が2.6Vを下回ると、TPS54319はディスエーブルになります。アプリケーションで、低電圧ロックアウト (UVLO)の電圧を高める必要がある場合は、図23のようにENピンを使用し、2個の外付け抵抗で入力電圧UVLOを調整します。ENピンには内部プルアップ電流源があり、ENピンがフローティングのときにTPS54319が動作するデフォルト状態を提供します。ENピンの電圧が1.25Vを超えると、3.4 $\mu$ Aのヒステリシスが追加されます。ENピンが1.18V未満になると、この3.4 $\mu$ Aは取り除かれます。この追加電流により、入力電圧のヒステリシスを実現できます。

図 23. 可変低電圧ロックアウト

R1 =

$$\frac{0.944 \times V_{START} - V_{STOP}}{3.47 \times 10^{-6}}$$

(\Omega)

$$R2 = \frac{1.18 \cdot R1}{V_{STOP} - 1.18 + 4.6 \times 10^{-6} \cdot R1} (\Omega)$$

(3)

### スロー・スタート/トラッキング・ピン

TPS54319は、SS/TRピンの電圧または内部リファレンス電圧のいずれか低い方の電圧でレギュレーションを行います。SS/TRピンとグランド間のコンデンサにより、スロー・スタート時間が実装されます。TPS54319には、外部のスロー・スタート・コンデンサを充電する2.2µAのプルアップ電流源が内蔵されています。必要なスロー・スタート・コンデンサの値は式(4)で計算されます。ここで、Tssは必要なスロー・スタート時間(ms)、Issは内部スロー・スタート充電電流(2.2µA)、Vrefは内部電圧リファレンス(0.827V)です。

$$Css(nF) = \frac{Tss(mS) \times Iss(\mu A)}{Vref(V)}$$

(4)

通常動作中に、VINがUVLOを下回るか、ENピンが1.2V未満にプルダウンされるか、または過熱シャットダウンが発生した場合、TPS54319はスイッチングを停止します。VINがUVLOを

上回るか、ENが解除("High"に設定)されるか、または過熱シャットダウンが終了した場合、SS/TRが40mV未満まで放電されてからパワーアップ・シーケンスを再び開始します。VSENSE電圧は、35mVのオフセットで内部電圧リファレンスの85%までSS/TRピン電圧に追従します。SS/TR電圧が内部リファレンス電圧の85%を上回ると、実効的なシステム・リファレンスがSS/TR電圧から内部電圧リファレンスへと遷移するため、オフセットが増加します。

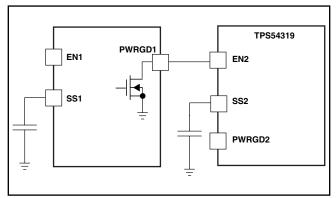

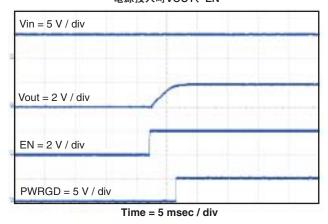

### シーケンシング

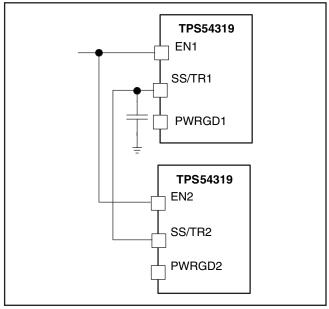

SS/TR、EN、およびPWRGDピンを使用して、多くの一般的な電源シーケンシング方法を実装できます。他のデバイスのパワーオン・リセット・ピンのオープン・ドレインまたはオープン・コレクタ出力を使用すれば、シーケンシャルな方法を実装できます。図24に、シーケンシャルなスタートアップ方法を示します。TPS54319のENピンにパワー・グッドを結合し、1次電源がレギュレーションに達した時点で2次電源をイネーブルにします。

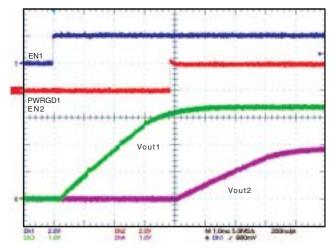

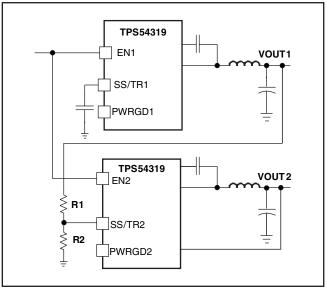

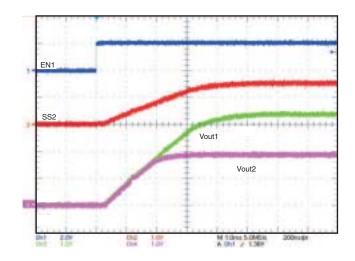

SS/TRピンを互いに接続すれば、レシオメトリックなスタートアップを実現できます。各レギュレータの出力は同時に上昇してレギュレーションに達します。スロー・スタート時間を計算する際には、式(4)でプルアップ電流源を2倍にする必要があります。レシオメトリックなスタートアップ方法を図26に示します。

図 24. シーケンシャルなスタートアップ

図 25. ENおよびPWRGDを使用した シーケンシャル・スタートアップ

図 26. レシオメトリックなスタートアップ・シーケンスの回路図

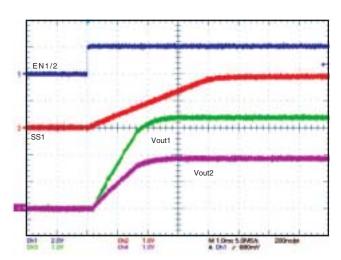

図 27. Vout1がVout2に先行する レシオメトリックなスタートアップ

図28に示すようなR1とR2の抵抗回路を、トラッキングが必 要な電源または他の電圧リファレンス源の出力に接続すること で、レシオメトリックな同時電源シーケンシングを実装できま す。式(5)と式(6)を使用して、Vout1の少し前か少し後、また は同時にVout2を開始するようトラッキング抵抗を計算できま す。式(7)は、Vout1とVout2の電圧差を示します。変数ΔVは、 同時シーケンシングでは0Vです。スロー·スタート回路の SS/TR - VSENSE間の固有のオフセット(Vssoffset)、およびプ ルアップ電流源(Iss)とトラッキング抵抗によって生成される オフセットの影響を最小限に抑えるため、VssoffsetおよびIss が変数として式に含まれています。Vout2がレギュレーション に達したときにVout2の電圧がVout1の電圧よりわずかに大きく なるように、レシオメトリックなスタートアップを設計するに は、式(5)~式(7)で $\Delta$ Vに負の数を使用します。Vout2がレギュ レーションに達したときにVout2がVout1よりわずかに低くなる アプリケーションでは、式(7)は正の数となります。EN、 UVLO、または過熱シャットダウン障害後には、起動前に SS/TRピンを40mV未満にプルダウンする必要があるため、デ

バイスが障害後に確実に再起動できるようトラッキング抵抗を慎重に選択する必要があります。デバイスが障害から回復できるようにするには、式(5)で計算されるR1の値が式(8)の計算値よりも大きくなる必要があります。SS/TRの電圧が公称リファレンス電圧の85%を超えると、スロー・スタート回路がレギュレーション・リファレンスを徐々に内部電圧リファレンスへと移行させ、Vssoffsetが大きくなります。図27に示すように、内部電圧リファレンスへと完全に移行するには、SS/TRピンの電圧が1.1Vより大きくなる必要があります。

$$R1 = \frac{Vout2 + \Delta V}{Vref} \times \frac{Vssoffset}{Iss}$$

(5)

$$R2 = \frac{Vref \times R1}{Vout2 + \Delta V - Vref}$$

(6)

$$\Delta V = Vout1 - Vout2 \tag{7}$$

$$R1 > 2930 \times Vout1 - 145 \times \Delta V \tag{8}$$

図 28. レシオメトリック/同時スタートアップ・シーケンス

**図 29**. SS/TRピンの結合によるレシオメトリックな スタートアップ

# 一定のスイッチング周波数、 およびタイミング抵抗(RT/CLKピン)

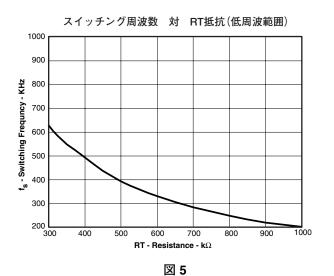

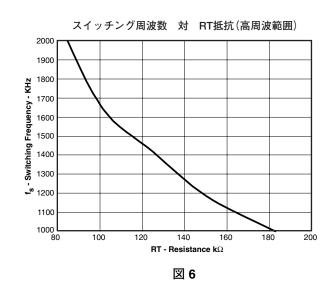

TPS54319のスイッチング周波数は、RT/CLKピンに最大  $700k\Omega \sim$ 最小 $85k\Omega o$ 抵抗を接続することで、 $300kHz \sim 2000kHz$ という広い範囲にわたって調整可能です。スイッチング周波数を設定するために、このピンとグランドの間に外部抵抗を接続すると、内部アンプによってこのピンが固定電圧に保持されます。RT/CLKの電圧は標準で0.5Vです。特定のスイッチング周波数に対するタイミング抵抗を決定するには、図5および図6の曲線を用いるか、または式(9)を使用します。

RT

$$(k\Omega) = \frac{311890}{\text{Fsw(kHz)}^{1.0793}}$$

(9)

$$Fsw(kHz) = \frac{133870}{RT(k\Omega)^{0.9393}}$$

(10)

ソリューション・サイズを小さくするには、一般にスイッチング周波数をできるだけ高く設定しますが、効率、最大入力電圧、および最小制御可能オン時間の間でトレードオフを考慮する必要があります。

最小制御可能オン時間は、全電流負荷時で標準65ns、無負荷時120nsであり、これによって最大動作入力電圧および出力電圧が制限されます。

# 過電流保護

TPS54319には、サイクル毎の電流制限があります。各スイッチング・サイクル中に、ハイサイド・スイッチ電流がCOMPピンの電圧と比較されます。スイッチ電流が瞬間的にCOMP電圧レベルを超えた場合、ハイサイド・スイッチがオフになります。過電流状態で出力電圧が低下すると、スイッチ電流が増加しながら、誤差増幅器によってCOMPピンが"High"になります。誤差増幅器の出力は内部でクランプされます。このクランプは、スイッチ電流の制限として機能します。

図30.システム・クロックとの同期

## 周波数シフト

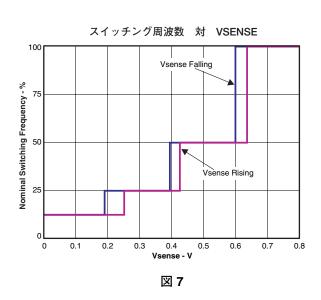

高いスイッチング周波数で動作し、過電流状態での保護を提供するために、TPS54319には周波数シフト機能が実装されています。周波数シフトが実装されていない場合、過電流状態中にローサイドMOSFETが、インダクタの電流を低減するのに十分なだけ長い時間オフにならず、電流暴走が発生する可能性があります。周波数シフトを行うと、過電流状態中、VSENSEピンの電圧が0.827Vから0Vへと低下する間、スイッチング周波数が100%、50%、25%、12.5%と段階的に低下することで、ローサイドMOSFETがインダクタ電流の低減に十分なだけ長い時間オフになります。スタートアップ時には、VSENSEの電圧が0Vから0.827Vへと上昇するにつれて、スイッチング周波数が上昇します。詳細については、図7を参照してください。

## 逆方向過電流保護

TPS54319には、ローサイドMOSFETの電圧を検出することによるローサイド電流保護機能があります。コンバータがローサイドFETを通して電流をシンクしているときに、逆方向電流が2A(typ)を超えた場合には、制御回路によってローサイドMOSFETがオフになります。この追加保護機能を実装することで、パワー・サイクル中やプリバイアス出力へのスタートアップ中に、コンバータを過電流から保護できます。

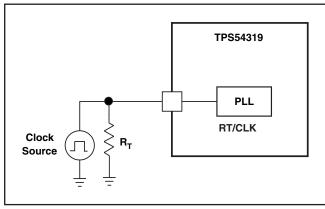

#### RT/CLKピンによる同期

RT/CLKピンを使用して、コンバータを外部システム・クロックに同期させることができます。図30を参照してください。システムに同期機能を実装するには、75ns以上のオン時間でRT/CLKピンに方形波を接続します。このピンをPLLの上限スレッショルドより高くプルアップすると、モード遷移が発生し、ピンは同期入力となります。内部アンプはディスエーブルになり、このピンは内部PLLへのハイ・インピーダンス・クロック入力となります。クロック・エッジが停止すると、内部アンプが再イネーブルされ、モードは抵抗で設定される周波数に戻ります。このピンに入力する方形波の振幅は、0.6V以下および1.6V以上(typ)の間で遷移する必要があります。同期周波数範囲は300kHz~2000kHzです。PHの立ち上がりエッジは、RT/CLKピンの立ち下がりエッジに同期します。

図 31. システム・クロックへの同期波形

#### パワー·グッド (PWRGDピン)

PWRGDピン出力は、オープン・ドレインMOSFETです。 VSENSEが公称内部リファレンス電圧の91%を下回るか107%を上回るかして障害状態になると、この出力は"Low"になります。スレッショルド電圧には2%のヒステリシスがあるため、VSENSE電圧が内部リファレンス電圧の93%を超えるかまたは105%を下回ると、PWRGD出力MOSFETがオフになります。6V未満の電圧源に対して $1k\Omega\sim100k\Omega$ のプルアップ抵抗を使用することを推奨します。VIN入力電圧が1.2Vを超えると、PWRGDは有効な状態となります。

# 過電圧過渡保護

TPS54319には、出力障害状態や強い無負荷過渡事象からの回復時に電圧オーバーシュートを最小限に抑える、過電圧過渡保護 (OVTP) 回路が備えられています。OVTP機能では、VSENSEピンの電圧を内部電圧リファレンスの107%であるOVTPスレッショルドと比較する回路を実装することにより、出力のオーバーシュートを最小限に抑えます。VSENSEピンの電圧がOVTPスレッショルドより高い場合は、ハイサイドMOSFETがディスエーブルになり、出力に電流が流れるのを防いで、出力オーバーシュートを抑えます。VSENSE電圧がOVTPスレッショルドを下回ると、次のクロック・サイクルでハイサイドMOSFETがオンになります。

# 過熱シャットダウン

このデバイスは、接合部温度が165℃を超えた場合にデバイス自身を保護する、過熱シャットダウン機能を内蔵しています。接合部温度が過熱トリップ・スレッショルドを超えると、デバイスのスイッチングが強制的に停止されます。接合部温度が150℃を下回ると、デバイスはSSピンを40mV未満まで放電し、パワーアップ・シーケンスを再び開始します。過熱シャットダウンのヒステリシスは15℃です。

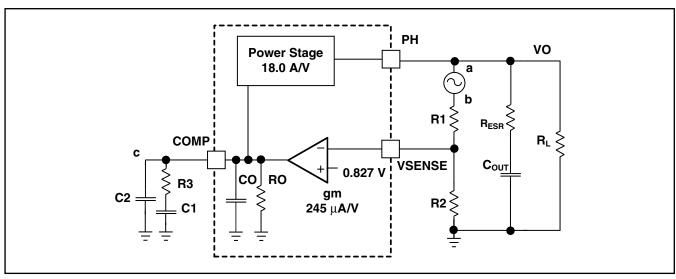

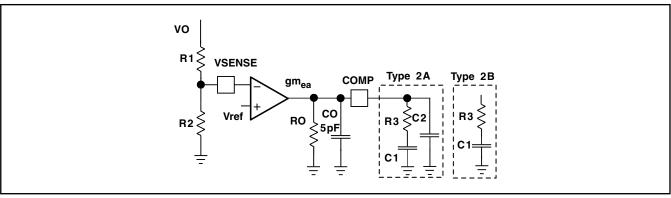

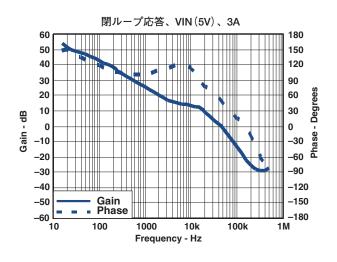

# ループ応答の小信号モデル

図32に、周波数応答と動的負荷応答をチェックするために回路シミュレーション・プログラムでモデル化できる、TPS54319 制御ループの等価モデルを示します。誤差増幅器は、gmが  $245\mu$ A/Vのトランスコンダクタンス・アンプです。この誤差増幅器は、理想的な電圧制御電流源を使用してモデル化できます。抵抗RoおよびコンデンサCoにより、増幅器の開ループ・ゲインと周波数応答がモデル化されます。ノードaとbの間の1mVの AC電圧源は、周波数応答測定のために制御ループを実質的に分断します。a/cのプロットにより、周波数補償の小信号応答が示されます。a/bのプロットは、ループ全体の小信号応答を示します。時間ドメイン分析で適切な負荷ステップ振幅およびステップ・レートを持つ電流源を、 $R_L$ の代わりに使用すれば、動的ループ応答をチェックできます。

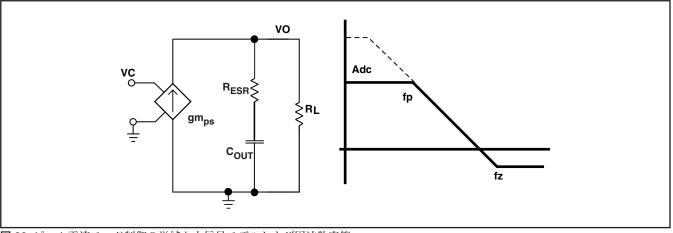

#### ピーク電流モード制御の単純な小信号モデル

図32に、周波数補償の設計方法を理解するために使用できる、 単純な小信号モデルを示します。TPS54319のパワー段は、出 力コンデンサおよび負荷抵抗に電流を供給する電圧制御電流源 (デューティ・サイクル変調器)として近似できます。制御-出力 間の伝達関数は式(11)に示され、DCゲイン、1つの支配的な 極、および1つのESRゼロで構成されます。スイッチ電流の変 化とCOMPピン電圧(図32のノードc)の変化との比が、パワー 段のトランスコンダクタンスです。TPS54319のgmは18.0A/V です。パワー段周波数応答の低周波ゲインは、式(12)に示す ように、トランスコンダクタンスと負荷抵抗の積です。負荷電 流が増加または減少すると、低周波ゲインはそれぞれ減少また は増加します。この負荷に対する変化は一見問題となりそうで すが、支配的な極は負荷電流とともに移動します(式(13)を 参照)。それらの組み合わせによる効果は、図33の右側に点線 で示されています。負荷電流が減少すると、ゲインが増加して 極周波数が低下するため、負荷状態の変化に対して0dBクロス オーバー周波数は一定に保たれ、周波数補償の設計が容易にな ります。

図 32. ループ応答の小信号モデル

図 33. ピーク電流モード制御の単純な小信号モデルおよび周波数応答

$$\frac{\text{vo}}{\text{vc}} = \text{Adc} \times \frac{\left(1 + \frac{\text{s}}{2\pi \times fz}\right)}{\left(1 + \frac{\text{s}}{2\pi \times fp}\right)}$$

(11)

$$Adc = gm_{ps} \times R_{L}$$

(12)

$$fp = \frac{1}{C_{OUT} \times R_{L} \times 2\pi}$$

(13)

$$fz = \frac{1}{C_{OUT} \times R_{ESR} \times 2\pi}$$

(14)

# 周波数補償の小信号モデル

TPS54319では、誤差増幅器にトランスコンダクタンス・アンプを使用し、一般的に使用される周波数補償回路のうち2つを容易にサポートします。それらの補償回路を図34に示します。タイプ2の回路は、低ESRの出力コンデンサを使用した高帯域電源設計に最もよく使用されます。タイプ2Aでは、高周波ノイズの減衰のために1つの高周波極が追加されています。

図 34. 周波数補償の種類

TPS54319のループ補償の設計ガイドラインを次に示します。

1. 式(15)と式(16)を使用して、変調回路の極(fpmod)および ESRゼロ(fz1)を計算する必要があります。コンデンサの定格に対する出力電圧の比率が高い場合は、出力コンデンサ (Cout)のディレーティングが必要な場合があります。コンデンサ値のディレーティングについては、コンデンサの製造元から提供される情報に従ってください。式(17)と式(18)使用して、クロスオーバー周波数fcの開始点を見積もります。式(17)は変調回路の極とESRゼロの相乗平均であり、式(18)は変調回路の極とスイッチング周波数の平均です。式(17)と式(18)で低い方の値を、最大クロスオーバー周波数として使用します。

$$fp \mod = \frac{Ioutmax}{2\pi \times Vout \times Cout}$$

(15)

$$fz \bmod = \frac{1}{2\pi \times Resr \times Cout}$$

(16)

$$f_{\rm C} = \sqrt{f \, \mathsf{p} \, \mathsf{mod} \, \times f \, \mathsf{z} \, \mathsf{mod}} \tag{17}$$

$$f_{\rm C} = \sqrt{f \, \text{p mod} \times \frac{f \, \text{sw}}{2}} \tag{18}$$

2. R3は次の式で求められます。

$$R3 = \frac{2\pi \times fc \times Vo \times C_{OUT}}{gm_{ea} \times Vref \times gm_{ps}}$$

(19)

ここで、 $gm_{ea}$ は増幅器のゲイン (245 $\mu$ A/V)、 $gm_{ps}$ はパワー 段のゲイン (18A/V)です。

3. 支配的な極  $fp = 1 / (C_{OUT} \times RL \times 2\pi)$  に補償用のゼロを配置します。C1は次の式で求められます。

$$C1 = \frac{R_L \times C_{OUT}}{B3}$$

(20)

4. C2はオプションです。これは、CoのESRからのゼロを キャンセルするために使用できます。

$$C2 = \frac{Resr \times C_{OUT}}{R3}$$

(21)

# アプリケーション情報

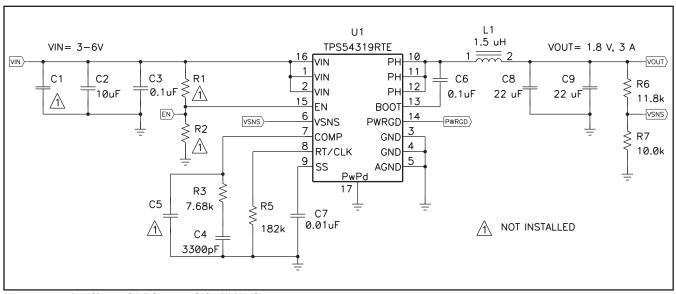

# 設計ガイドーステップ毎の設計手順

この例では、セラミック出力コンデンサを使用した高周波スイッチング・レギュレータ設計の詳細を示します。この設計は、HPA375評価モジュール(EVM)として提供されています。設計プロセスを開始するには、いくつかのパラメータがわかっている必要があります。これらのパラメータは一般に、システム・レベルで決定されます。この例では、以下に示す既知のパラメータを使用して開始します。

| 出力電圧             | 1.8 V              |  |  |  |

|------------------|--------------------|--|--|--|

| 過渡応答、1~2Aの負荷ステップ | $\Delta$ Vout = 5% |  |  |  |

| 最大出力電流           | 3 A                |  |  |  |

| 入力電圧             | 公称5V。3V~5V         |  |  |  |

| 出力電圧リップル         | < 30 mV p-p        |  |  |  |

| スイッチング周波数(Fsw)   | 1000 kHz           |  |  |  |

#### スイッチング周波数の選択

最初の手順は、レギュレータのスイッチング周波数を決定することです。一般には、可能な限り高いスイッチング周波数を選択します。それによってソリューション・サイズを最小にできるからです。高いスイッチング周波数では、低周波数でスイッチングする電源と比較して、低い値のインダクタと小さな出力コンデンサを使用できます。ただし、スイッチング周波数が高いと、スイッチング損失が増加し、コンバータの性能に悪影響を与えます。コンバータは、300kHz~2MHzで動作可能です。ソリューション・サイズの縮小が重点的な目標である場合を除き、1MHzという中程度のスイッチング周波数を選択することで、小さなソリューション・サイズと高効率動作を両立できます。式(9)を使用して、R5は180kΩと計算されます。この設計では、標準の1%値である182kΩを選択しています。

#### 出力インダクタの選択

選択したインダクタは、TPS54319の入力電圧範囲全体にわたって機能します。出力インダクタの値を計算するには、式(22)を使用します。 $K_{IND}$ は、最大出力電流を基準としたインダクタ・リップル電流の大きさを表す係数です。インダクタ・リップル電流は、出力コンデンサによってフィルタリングされます。したがって、大きなインダクタ・リップル電流を選択すると、それ以上のリップル電流定格を持つ出力コンデンサが必要となるため、出力コンデンサの選択に影響が及びます。一般に、インダクタ・リップル値は設計者の裁量で決定しますが、ほとんどのアプリケーションでは、 $K_{IND}$ は通常 $0.1\sim0.3$ です。

この設計例では、 $K_{\text{IND}}$  = 0.3を使用し、インダクタ値は 1.36 $\mu$ Hと計算されます。この設計では、最も近い標準値として 1.5 $\mu$ Hが選択されています。出力フィルタ・インダクタについて は、RMS電流および飽和電流の定格を超えないことが重要です。 RMSおよびピーク・インダクタ電流は、式 (24) および式 (25) で求めることができます。

この設計では、RMSインダクタ電流は3.01A、ピーク・インダクタ電流は3.72Aです。選択したインダクタは、CoilcraftのXLA4020-152ME\_です。このインダクタの飽和電流定格は9.6A、RMS電流定格は7.5Aです。

インダクタを流れる電流は、インダクタ・リップル電流 + 出力電流です。パワーアップ時、障害発生時、または負荷過渡状態中は、インダクタ電流が上記で計算されたピーク・インダクタ電流レベルを超えて増加する場合があります。過渡状態では、インダクタ電流がデバイスのスイッチ電流制限まで増加する場合があります。この理由により、最も保守的なアプローチは、ピーク・インダクタ電流ではなく、スイッチ電流制限以上の飽和電流定格を持つインダクタを指定することです。

図 35. UVLOを調整した高周波の1.8V出力電源設計

$$L1 = \frac{Vinmax - Vout}{Io \times Kind} \times \frac{Vout}{Vinmax \times fsw}$$

(22)

Iripple =

$$\frac{\text{Vinmax} - \text{Vout}}{\text{L1}} \times \frac{\text{Vout}}{\text{Vinmax} \times f\text{sw}}$$

(23)

ILrms =

$$\sqrt{\log^2 + \frac{1}{12} \times \left( \frac{\text{Vo} \times (\text{Vinmax} - \text{Vo})}{\text{Vinmax} \times \text{L1} \times f\text{sw}} \right)^2}$$

(24)

$$ILpeak = lout + \frac{Iripple}{2}$$

(25)

#### 出力コンデンサ

出力コンデンサ値の選択については、3つの主要な考慮事項があります。出力コンデンサは、変調器の極、出力電圧リップル、および負荷電流の大きな変化に対するレギュレータの応答を決定します。出力容量は、これら3つの条件のうち最も厳しいものに基づいて選択する必要があります。

最初の条件は、負荷電流の大きな変化に対して求められる応 答です。レギュレータが電流を供給できないときには、出力コン デンサが負荷に電流を供給する必要があります。この状況は、 レギュレータに対して保持時間要件があり、入力電力の停止後 に指定された時間だけ、出力コンデンサが出力電圧を特定のレ ベルより高く保持する必要がある場合に発生します。無負荷か ら全負荷への遷移時など、負荷の電流需要に大きく高速な変化 が発生した場合、レギュレータは一時的に十分な出力電流を供 給できなくなります。通常、レギュレータでは、制御ループが 負荷電流および出力電圧の変化を検知して、その変化に合わせ てデューティ・サイクルを調整するまでに、2クロック・サイク ル以上を必要とします。出力コンデンサの大きさは、制御ルー プが負荷の変化に応答するまでの間、負荷に追加の電流を供給 できるように決定する必要があります。出力容量は、出力電圧の 降下を許容範囲内に抑えながら、2クロック・サイクルにわたって 電流の差分を供給するのに十分な大きさでなければなりません。 そのために必要な最小の出力容量を式(26)に示します。

この例では、負荷過渡応答が、0A (無負荷) から1.5A (50%負荷) までの負荷ステップに対するV outの5%の変化と指定されています。この例では、 $\Delta I$  out = 1.5 - 0 = 1.5A、およU  $\Delta V$  out =  $0.05 \times 1.8 = 0.090 V$  です。これらの値を使用して、 $33 \mu F$  の最小容量が得られます。この値は、出力電圧の変化について出力コンデンサのE SR を考慮していません。セラミック・コンデンサの場合、E SR は通常十分に小さいため、この計算では無視できます。

式(27)は、出力電圧リップル仕様を満足するために必要な最小の出力容量を計算します。ここで、fswはスイッチング周波数、Vrippleは最大許容出力電圧リップル、Irippleはインダクタ・リップル電流です。この場合、最大出力電圧リップルは30mVです。この要件により、式(27)から2.3uFが得られます。

$$Co > \frac{2 \times \Delta lout}{fsw \times \Delta Vout}$$

(26)

$$Co > \frac{1}{8 \times fsw} \times \frac{1}{\frac{Voripple}{Iripple}}$$

(27)

ここで、ΔIoutは出力電流の変化、Fswはレギュレータのスイッチング周波数、ΔVoutは出力電圧の許容される変化です。

式 (28) は、出力電圧リップル仕様を満足するために出力コンデンサに許容される最大ESRを計算します。式 (28) より、ESR は55m $\Omega$ 未満とする必要があります。ここでは、セラミック・コンデンサのESRが55m $\Omega$ よりずっと小さくなります。

エージング、温度、およびDCバイアスに対して、追加の容量ディレーティングを考慮する必要があるため、この最小値は増加します。この例では、 $3m\Omega$ のESRを持つ $22\mu$ F、10VのX5Rセラミック・コンデンサが2個使用されます。

一般に、コンデンサでは、障害や過熱を発生させずに処理できるリップル電流の大きさに制限があります。インダクタ・リップル電流に対して対応可能な出力コンデンサを指定する必要があります。一部のコンデンサのデータシートでは、最大リップル電流のRMS(2乗平均平方根)値が指定されています。出力コンデンサで処理できる必要のあるRMSリップル電流値は、式(29)で計算できます。このアプリケーションでは、式(29)により333mAが得られます。

Resr <

$$\frac{\text{Voripple}}{\text{Iripple}}$$

(28)

$$Icorms = \frac{Vout \times (Vinmax - Vout)}{\sqrt{12} \times Vinmax \times L1 \times fsw}$$

(29)

## 入力コンデンサ

TPS54319は、4.7 µF以上の実効容量を持つ高品質のセラミック (タイプX5RまたはX7R) 入力デカップリング・コンデンサを必要とし、アプリケーションによってはバルク容量も必要とします。実効容量には、DCバイアスの影響も含まれます。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。また、コンデンサのリップル電流定格は、TPS54319の最大入力電流リップルよりも大きい必要があります。入力リップル電流は、式(30)で計算できます。

セラミック・コンデンサの値は、温度およびコンデンサに印加されるDCバイアスの大きさによって大きく変化します。温度による容量の変化は、温度に対して安定な誘電体を選択することで最小限に抑えることができます。X5RおよびX7Rセラミック誘電体は、容量/体積比が大きく、温度に対してかなり安定しているため、パワー・レギュレータのコンデンサとして一般に選択されます。また、出力コンデンサはDCバイアスも考慮して選択する必要があります。コンデンサ両端にかかるDCバイアスが増加すると、コンデンサの容量値は減少します。

この設計例では、最大入力電圧に対応するために10V以上の電圧定格を持つセラミック・コンデンサが必要です。この例では、10μFと0.1μFの10Vコンデンサをそれぞれ1個ずつ並列に使用しています。入力容量の値によって、レギュレータの入力リップル電圧が決まります。入力電圧リップルは、式(31)で計算できま

す。設計例の値であるIoutmax = 3A、Cin =  $10\mu$ F、Fsw = 1MHzを使用すると、76mVの入力電圧リップル、および1.47AのRMS入力リップル電流が得られます。

$$Icirms = Iout \times \sqrt{\frac{Vout}{Vinmin} \times \frac{(Vinmin - Vout)}{Vinmin}}$$

(30)

$$\Delta V in = \frac{loutmax \times 0.25}{Cin \times fsw}$$

(31)

### スロー・スタート・コンデンサ

スロー・スタート・コンデンサは、パワーアップ中に出力電圧がその公称設定値に達するまでにかかる最小の時間を決定します。これは、負荷に対して制御された電圧スルー・レートが必要である場合に有用です。また、出力容量が非常に大きく、コンデンサを出力電圧レベルまですばやく充電するのに大きな電流を必要とするような場合にも、利用されます。コンデンサの充電に必要な大きな電流によってTPS54319が電流制限に達したり、入力電源からの過剰な電流によって入力電圧レールが降下したりする場合があります。出力電圧のスルー・レートを制限することで、その両方の問題を解決できます。

スロー・スタート・コンデンサの値は式(32)を使って計算できます。この例の回路では、出力コンデンサ値が44μFで、1.8Vまでの充電に大きな電流を必要としないため、スロー・スタート時間はそれほど重要ではありません。この回路ではスロー・スタート時間が任意値の4msに設定され、10nFのコンデンサが必要となります。TPS54319では、Issは2.2μA、Vrefは0.827Vです。

$$Css(nF) = \frac{Tss(ms) \times Iss(\mu A)}{Vref(V)}$$

(32)

# ブートストラップ・コンデンサの選択

適切な動作のためには、BOOTピンとPHピンの間に0.1μFのセラミック・コンデンサを接続する必要があります。X5R以上の誘電体を持つセラミック・コンデンサの使用を推奨します。コンデンサの電圧定格は10V以上である必要があります。

# 出力電圧および帰還抵抗の選択

この設計例では、R6に100k $\Omega$ が選択されています。式 (33) を使用して、R7は80k $\Omega$ と計算されます。最も近い標準1%抵抗は、80.5k $\Omega$ です。

$$R7 = \frac{Vref}{Vo - Vref} R6 \tag{33}$$

TPS54319の内部設計により、与えられた入力電圧に対して最小出力電圧制限が存在します。出力電圧は、内部リファレンス電圧0.827Vより低くなることはできません。0.827V以上では、出力電圧は最小制御可能オン時間によって制限される場合があります。この例での最小出力電圧は、式(34)で与えられます。

$Voutmin = Ontimemin \times Fsmax \times (Vinmax - Ioutmin$

$$\times 2 \times RDS$$

) – Ioutmin  $\times (RL + RDS)$  (34)

ここで

Voutmin = 実現可能な最小出力電圧

Ontimemin = 最小制御可能オン時間

(標準65ns。無負荷時120ns)

Fsmax = 最大スイッチング周波数(公差を含む)

Vinmax = 最大入力電圧

Ioutmin = 最小負荷電流

RDS = 最小ハイサイドMOSFETオン抵抗 (45~64mΩ)

RL = 出力インダクタの直列抵抗

また、実現可能な最大出力電圧は最小オフ時間によって制限 されます。最大出力電圧は、式(35)で求められます。

Voutmax =  $(1 - Ontimemin \times Fsmax) \times$

(Vinmin – Ioutmax  $\times$  2  $\times$  RDS) – Ioutmax  $\times$  (RL + RDS)

(35)

ここで

Voutmax = 実現可能な最大出力電圧

Offtimeman = 最大オフ時間 (標準60ns)

Fsmax = 最大スイッチング周波数(公差を含む)

Vinmin = 最小入力電圧

Ioutmax = 最大負荷電流

RDS = 最小ハイサイドMOSFETオン抵抗 (81~110mΩ)

RL = 出力インダクタの直列抵抗

#### 補僧

DC/DCレギュレータの補償には業界でいくつかの手法が使用されています。ここで説明する方法は、計算が簡単で、高い位相マージンを得ることができます。ほとんどの条件に対して、レギュレータの位相マージンは60°~90°となります。ここに示す方法では、TPS54319内部のスロープ補償による影響は無視しています。スロープ補償が無視されるため、実際のクロスオーバー周波数は、計算で使用されるクロスオーバー周波数よりも通常は低くなります。より詳細な設計には、SwitcherProソフトウェアを使用してください。

最初に、式(36)と式(37)を使用して、変調回路の極(fpmod) およびESRゼロ (fz1) を計算する必要があります。1.8Vの出力 は10Vのコンデンサ定格に対して比率が小さいため、Coutに対 してディレーティングは必要ありません。コンデンサ定格に対 する出力の比率が高い場合は、コンデンサの製造元から提供さ れる情報に従って、コンデンサ値をディレーティングします。 式 (38) と式 (39) を使用して、クロスオーバー周波数fcの開始 点を見積もります。この設計例では、fpmod = 6.03kHz、およ びfzmod = 1210kHzです。式 (38) は変調回路の極とESRゼロの 相乗平均であり、式(39)は変調回路の極とスイッチング周波 数の平均です。式 (38) から85.3kHz、式 (39) から54.9kHzが得 られます。式(38)と式(39)で低い方の値を、クロスオーバー 周波数の近似値として使用します。この例では、fcが56kHzで す。次に、補償部品を計算します。コンデンサと直列の抵抗を 使用して、補償用のゼロを生成します。この2つの部品と並列 に別のコンデンサを接続することにより、(必要に応じて)補償 用の極を形成します。

$$fp \mod = \frac{loutmax}{2\pi \times Vout \times Cout}$$

(36)

$$fz \bmod = \frac{1}{2\pi \times Resr \times Cout}$$

(37)

$$f_{\mathbb{C}} = \sqrt{f_{\mathbb{P}} \mod \times f_{\mathbb{Z}} \mod}$$

(38)

$$f_{C} = \sqrt{f_{p} \mod \times \frac{f_{sw}}{2}}$$

(39)

補償設計の手順を次に示します。

1. 予想されるクロスオーバー周波数を設定します。式 (40) を使用して、補償回路の抵抗値を計算します。この例では、予想されるクロスオーバー周波数 (fc) は56kHzです。パワー段ゲイン ( $gm_{ps}$ ) は18A/V、誤差増幅器のゲイン ( $gm_{ea}$ ) は $245\mu A/V$ です。

$$R3 = \frac{2\pi \times fc \times Vo \times Co}{Gm \times Vref \times Vl_{gm}}$$

(40)

2. 負荷抵抗と出力コンデンサによって形成される極に補償用 のゼロを配置します。補償回路のコンデンサは式(41)で 計算できます。

$$C3 = \frac{Ro \times Co}{R3}$$

(41)

3. 高周波ノイズを減衰させるため、追加の極を配置できます。 このアプリケーションでは、極の追加は不要です。

上記の手順から、補償回路には7.68k $\Omega$ の抵抗と3300pFのコンデンサが含まれます。

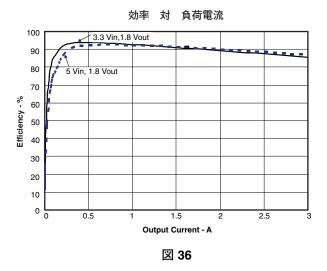

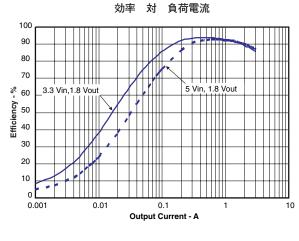

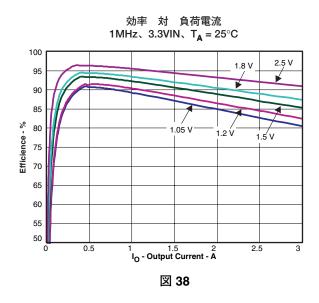

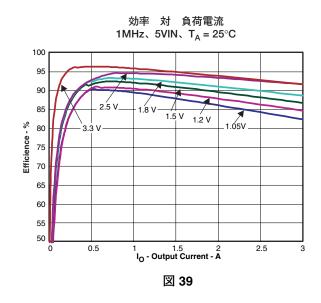

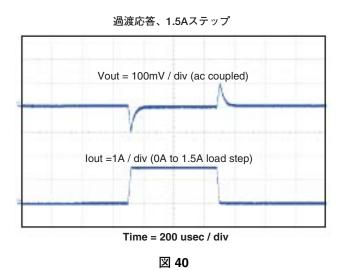

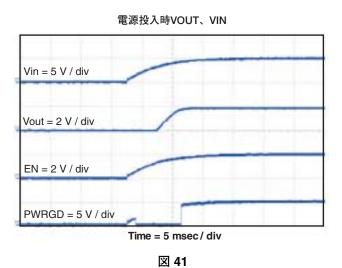

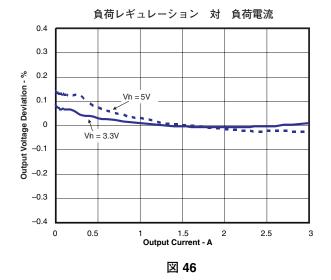

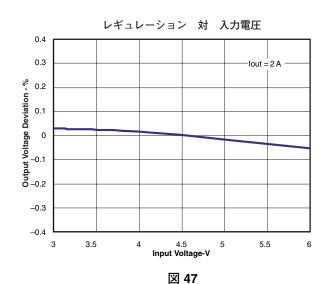

# アプリケーション曲線

図 37

# アプリケーション曲線

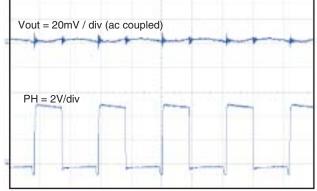

出力リップル、3A

Time = 500 nsec / div

図 43

# 図 42

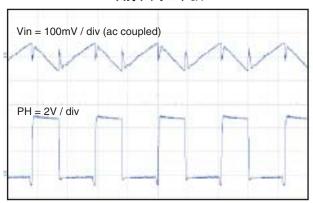

#### 入力リップル、3A

Time = 500 nsec / div

図 44

図 45

#### 消費電力の見積もり

以下の式は、連続導通モード (CCM) 動作でのICの消費電力を見積もる方法を示しています。ICの消費電力 (Ptot) には、導通損失 (Pcon)、デッド・タイム損失 (Pd)、スイッチング損失 (Psw)、ゲート駆動損失 (Pgd)、および消費電流損失 (Pq) が含まれます。

$Pcon = Io^2 \times R_{DS \text{ on Temp}}$

$Pd = f_{sw} \times Io \times 0.7 \times 40 \times 10^{-9}$

$Psw = 1/2 \times V_{in} \times Io \times f_{sw} \times 8 \times 10^{-9}$

$Pgd = 2 \times V_{in} \times f_{sw} \times 2 \times 10^{-9}$

$Pq = V_{in} \times 360 \times 10^{-6}$

ここで

Io = 出力電流(A)

$R_{DS\_on\_Temp}$  = 与えられた温度でのハイサイドMOSFETのオン抵抗 ( $\Omega$ )

V<sub>in</sub> = 入力電圧 (V)

$f_{sw}$  = スイッチング周波数 (Hz)

したがって、次のようになります。

Ptot = Pcon + Pd + Psw + Pgd + Pq

与えられたTAに対して:

$TJ = TA + Rth \times Ptot$

与えられたTJMAX = 150°Cに対して:

$TAmax = TJ max - Rth \times Ptot$

ここで

Ptot = 合計デバイス消費電力(W)

TA = 周囲温度 (°C)

TJ = 接合部温度 (°C)

Rth = パッケージの熱抵抗 (°C/W)

TJMAX = 最大接合部温度 (°C)

TAMAX = 最大周囲温度 (°C)

レギュレータ回路には、インダクタのACおよびDC損失、およびパターン抵抗による追加の電力損失があり、レギュレータ全体の効率に影響を与えます。

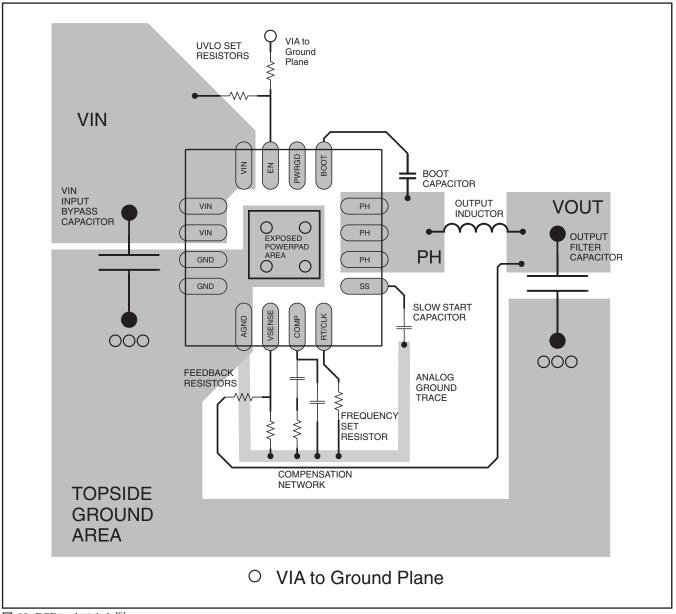

#### レイアウト

レイアウトは、優れた電源設計のために重要な要素です。高速で変化する電流または電圧を通す信号パスがいくつかあるため、浮遊インダクタンスや寄生容量によってノイズが発生したり、電源の性能が低下したりする可能性があります。バイパス・コンデンサ接続とVINピンによって形成されるループの面積は、最小限に抑えるよう注意が必要です。PCBレイアウト例については、図48を参照してください。GNDピンとAGNDピンは、ICの下部にあるパワー・パッドに直接接続する必要があります。パワー・パッドは、ICの直下にある複数のビアを使用して内部のPCBグランド・プレーンに接続します。さらに追加のビアを使用して、上面のグランド領域を入力および出力コンデンサ付近の内部プレーンに接続できます。全定格負荷で動作を行うには、上面のグランド領域と内部の追加グランド・プレーンが合わせて十分な熱放散面積を備えていなければなりません。

入力バイパス·コンデンサは、できる限りICに近づけて配置 します。PHピンは、出力インダクタに接続する必要がありま す。PH接続はスイッチング・ノードであるため、出力インダク タはPHピンにごく近づけて配置し、過度の容量性カップリン グを避けるためにPCB導体の面積はできるだけ小さくしてくだ さい。ブート・コンデンサもデバイスに近づけて配置する必要が あります。帰還用分圧抵抗、補償部品、スロー・スタート・コン デンサ、周波数設定抵抗の各アナログ・グランド接続はノイズ に敏感であるため、図に示すように別個のアナログ・グランド・ パターンに接続する必要があります。RT/CLKピンは特にノイ ズの影響を受けやすいため、RTの抵抗はICにできるだけ近づ けて配置し、最短のパターンで配線する必要があります。追加 の外部部品は図に示されるように配置できます。別のPCBレイ アウトでも許容される性能を得ることは可能ですが、このレイ アウトは良好な結果が得られることが実証済みであり、ガイド ラインとして示しています。

図 48. PCBレイアウト例

# パッケージ情報

#### 製品情報

| Orderable<br>Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Packag<br>Qty | <sup>e</sup> Eco Plan <sup>(2)</sup> | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|---------------------|-----------------------|-----------------|--------------------|------|---------------|--------------------------------------|----------------------|------------------------------|-----------------------------|

| TPS54319RTER        | ACTIVE                | WQFN            | RTE                | 16   | 3000          | Green (RoHS<br>& no Sb/Br)           | CU NIPDAU            | Level-2-260C-1 YEAR          | Purchase Samples            |

| TPS54319RTET        | ACTIVE                | WQFN            | RTE                | 16   | 250           | Green (RoHS<br>& no Sb/Br)           | CU NIPDAU            | Level-2-260C-1 YEAR F        | Request Free Samples        |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨

していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

Green (RoHS & no Sb/Br): TIにおける "Green"は、"Pb-Free"(RoHS互換)に加えて、臭素(Br) およびアンチモン(Sb) をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

<sup>(3)</sup> MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

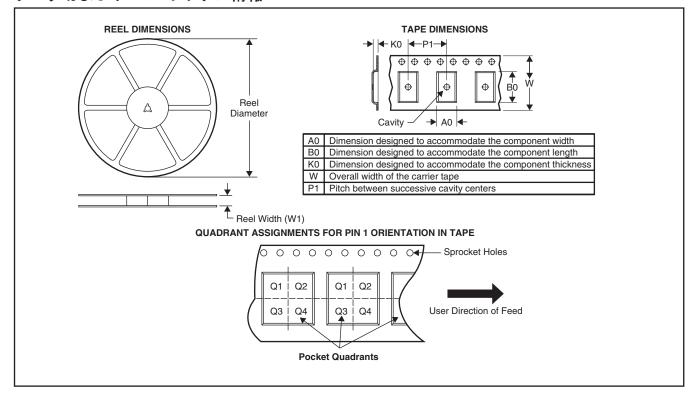

# パッケージ・マテリアル情報

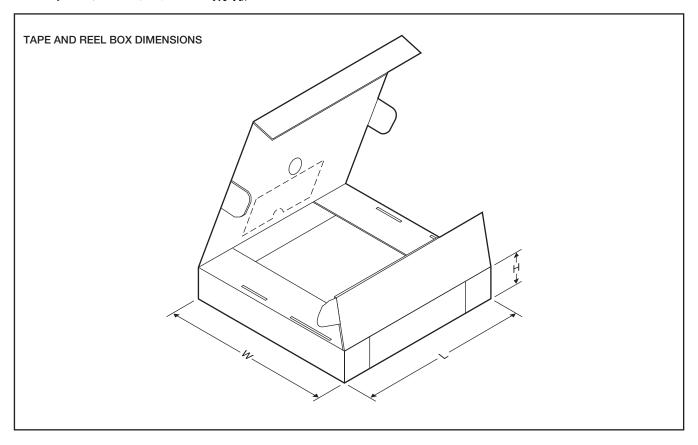

# テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS54319RTER | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS54319RTET | WQFN            | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

# パッケージ・マテリアル情報

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54319RTER | WQFN         | RTE             | 16   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS54319RTET | WQFN         | RTE             | 16   | 250  | 190.5       | 212.7      | 31.8        |

#### RTE (S-PWQFN-N16)

- 注: A. 直線寸法はすべてミリメートル単位です。寸法および許容誤差は、ASME Y14.5M-1994によります。

B. 本図は予告なしに変更することがあります。

C. QFN(クゥアド・フラットパック・ノーリード)パッケージ構造。

ハッケージのサーマルパッドは、熱的および機構的特性を得るために基板に半田付けする必要があります。

露出サーマルパッドの寸法に関する詳細は、製品データシートをご覧ください。

- E. JEDEC MO-220に準拠します。

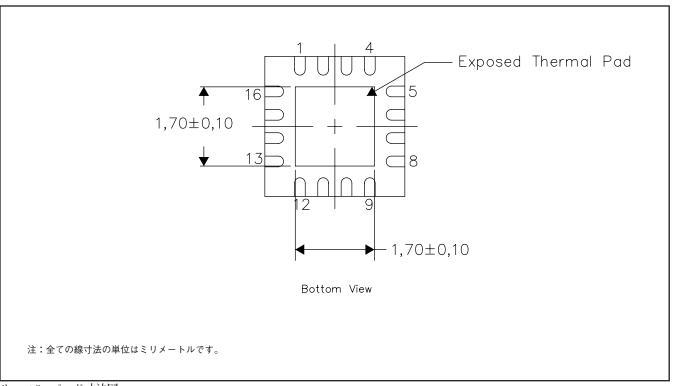

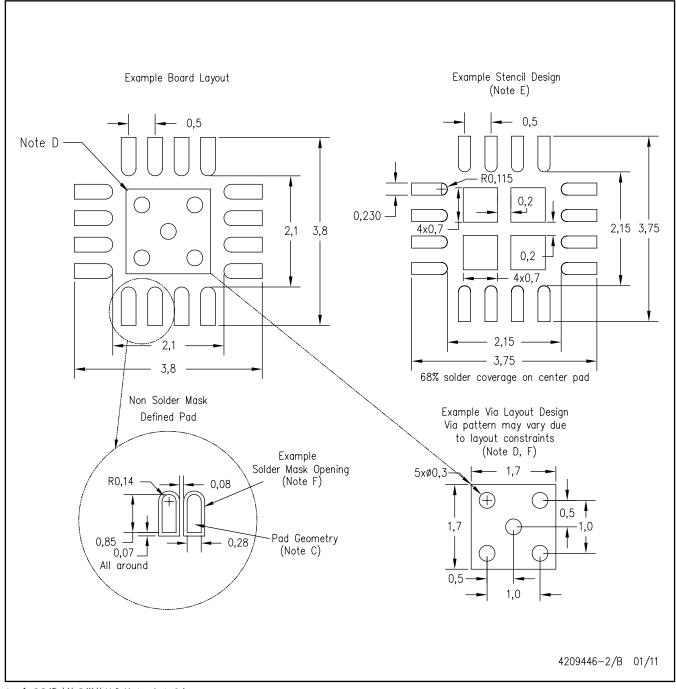

# サーマルパッド・メカニカル・データ

#### RTE (S-PWQFN-N16)

#### 熱特性について

このパッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板 (PCB) をヒートシンクとして使用できるように、PCBに直接半田付けする必要があります。また、サーマル・ピアを使用して、サーマル・パッドをグランド・プレーンまたはPCB内に設計された特別なヒートシンク構造に直接接続することができます。この設計により、ICからの熱伝導が最適化されます。

QFN (Quad Flatpack No-Lead) パッケージとその利点については、アプリケーション・レポート 『Quad Flatpack No-Lead Logic Packages』 (Texas Instruments文献番号SLUA271) を参照してください。このドキュメントは、ホームページwww.ti.comで入手できます。

このパッケージの露出したサーマル·パッドの寸法を次の図に示します。

サーマル・パッド 寸法図

#### PLASTIC QUAD FLATPACK NO-LEAD

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。 C. 代替設計については、資料IPC-7351を推奨します。

- このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。熱に関する具体的な情報、ビア要件、 および推奨基板レイアウトについては、アプリケーション・ノート 『Quad Flat-Pack Packages』(TI文献番号SLUA271) および製品データシートを参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

- E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。ステンシル設計上の考慮事項については、IPC 7525を参照してください。F. 半田マスクの許容差については、基板組み立て拠点にお問い合わせください。

(SLVSA83)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上