## TPS543x 3A、広入力範囲、降圧コンバータ

## 1 特長

- 広い入力電圧範囲:

- TPS5430: 5.5V~36V

- TPS5431: 5.5V~23V

- 最大 3A の連続 (4A のピーク) 出力電流

- 100mΩ の MOSFET スイッチを内蔵し、最大 95% の高効率を実現

- 広い出力電圧範囲: 1.5% の初期精度で最低 1.22V まで調整可能

- 内部補償により外付け部品の数を最小化

- 500kHz の固定スイッチング周波数により、フィルタを小型化

- 入力電圧フィードフォワードにより、ライン・レギュレーションと過渡応答を向上

- 過電流制限、過電圧保護、サーマル シャットダウンによりシステムを保護

- 動作時の接合部温度範囲: -40°C~125°C

- 熱特性が強化された小型 8 ピン SO PowerPAD™ 集積回路パッケージで供給

- WEBENCH® Power Designer により、TPS5430 を使用するカスタム設計を作成

## 2 アプリケーション

- 民生用: セットトップボックス、DVD、LCD ディスプレイ

- 工業用および車載オーディオ用の電源

- バッテリチャージャ、ハイパワー LED 電源

- 12V および 24V 分散型電源システム

## 3 概要

TPS543x は、低抵抗のハイサイド N チャネル MOSFET を内蔵した大出力電流の PWM コンバータです。記載されている特長以外に、過渡条件で電圧レギュレーションの精度を維持できる高性能な電圧誤差増幅器、入力電圧が 5.5V に達するまで起動を抑える低電圧誤動作防止回路、突入電流を制限するように内部的に設定されるスロースタート回路、過渡応答を改善するための電圧フィード・フォワード回路などの特長があります。ENA ピンを使用すると、シャットダウン時の供給電流を 15µA (標準値) に低減できます。また、アクティブ HIGH イネーブル、過電流制限、過電圧保護、サーマル シャットダウンの機能も備えています。設計の複雑性を低減し、外付け部品数を減らすために、TPS543x の帰還ループは内部的に補償されます。TPS5431 は、最大 23V の電源レールで動作するように設計されています。TPS5430 は、24V バスを含む各種電源をレギュレートします。

TPS543x デバイスは、熱特性が強化された使いやすい 8 ピン SOIC PowerPAD 集積回路パッケージで供給されます。TI は評価基板とデザイナー ソフトウェア・ツールを提供し、短い開発サイクルで、高性能な電源設計を迅速に行えるよう支援しています。

## 製品情報

| 部品番号    | パッケージ (1)     | 入力電圧     |

|---------|---------------|----------|

| TPS5430 | DDA (HSOP, 8) | 5.5V~36V |

| TPS5431 |               | 5.5V~23V |

(1) 詳細については、[セクション 10](#) を参照してください。

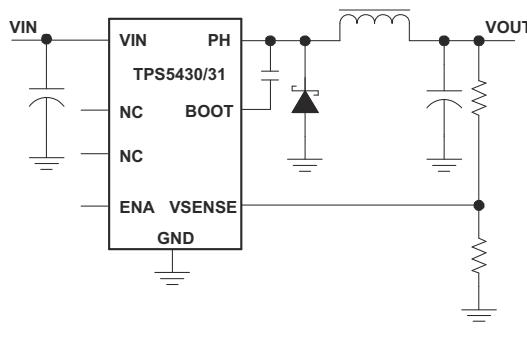

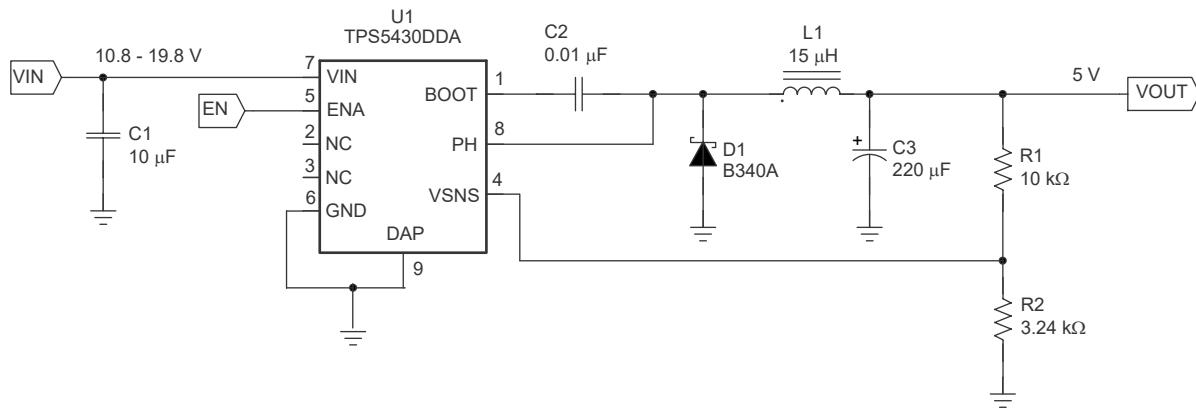

Simplified Schematic

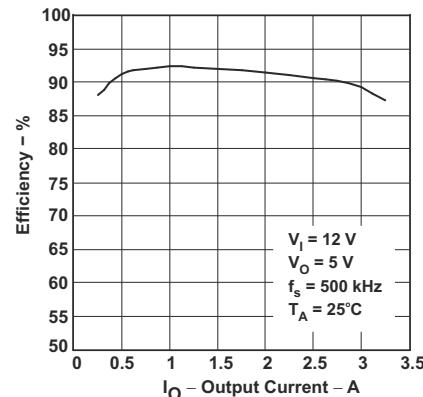

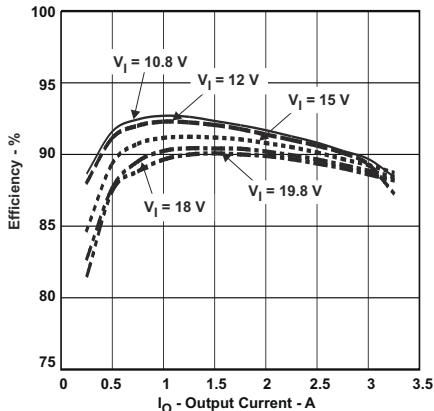

Efficiency vs Output Current

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                         |          |                               |           |

|-------------------------|----------|-------------------------------|-----------|

| <b>1 特長</b>             | <b>1</b> | 6.4 デバイスの機能モード                | <b>10</b> |

| <b>2 アプリケーション</b>       | <b>1</b> | <b>7 アプリケーションと実装</b>          | <b>12</b> |

| <b>3 概要</b>             | <b>1</b> | 7.1 アプリケーション情報                | <b>12</b> |

| <b>4 ピン構成および機能</b>      | <b>3</b> | 7.2 代表的なアプリケーション              | <b>13</b> |

| <b>5 仕様</b>             | <b>4</b> | 7.3 電源に関する推奨事項                | <b>25</b> |

| 5.1 絶対最大定格              | 4        | 7.4 レイアウト                     | <b>25</b> |

| 5.2 ESD Ratings         | 4        | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>27</b> |

| 5.3 推奨動作条件              | 4        | 8.1 デバイスのサポート                 | <b>27</b> |

| 5.4 熱に関する情報 (DDA パッケージ) | 4        | 8.2 ドキュメントの更新通知を受け取る方法        | <b>27</b> |

| 5.5 電気的特性               | 5        | 8.3 サポート・リソース                 | <b>27</b> |

| 5.6 代表的特性               | 6        | 8.4 商標                        | <b>27</b> |

| <b>6 詳細説明</b>           | <b>8</b> | 8.5 静電気放電に関する注意事項             | <b>27</b> |

| 6.1 概要                  | 8        | 8.6 用語集                       | <b>28</b> |

| 6.2 機能ブロック図             | 8        | <b>9 Revision History</b>     | <b>28</b> |

| 6.3 機能説明                | 9        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>29</b> |

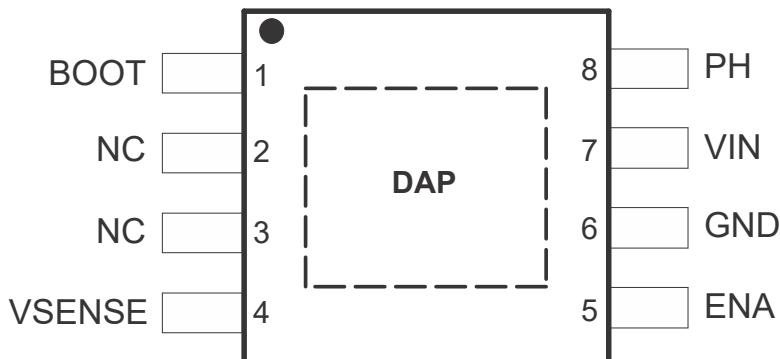

## 4 ピン構成および機能

図 4-1. DDA パッケージ 8 ピン SOIC (サーマル パッド付き) 上面図

表 4-1. ピンの機能

| ピン     |      | タイプ | 説明                                                                                    |

|--------|------|-----|---------------------------------------------------------------------------------------|

| 名称     | 番号   |     |                                                                                       |

| BOOT   | 1    | O   | ハイサイド FET ゲートドライバ用ブースト キャパシタ接続端子。BOOT ピンと PH ピンの間に $0.01\mu\text{F}$ の低 ESR キャパシタを接続。 |

| NC     | 2, 3 | —   | 内部未接続                                                                                 |

| VSENSE | 4    | I   | レギュレータ用フィードバック電圧検出端子。出力電圧デバイダに接続。                                                     |

| ENA    | 5    | I   | オン / オフ制御。0.5V 以下でスイッチング停止。この端子がフローティングでイネーブル。                                        |

| GND    | 6    | —   | グランド。DAP に接続。                                                                         |

| VIN    | 7    | —   | 電源入力。VIN ピンと GND ピン間に高品質、低 ESR のセラミック・キャパシタをできるだけデバイス パッケージの近くで接続する。                  |

| PH     | 8    | I   | ハイサイド パワー MOSFET のソース。外部インダクタおよびダイオードに接続される。                                          |

| DAP    |      | —   | 適切な動作のためには、GND ピンを露出したパッドに接続する必要があります。                                                |

## 5 仕様

### 5.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り) (1)

|                  |                                | 最小値  | 最大値    | 単位 |

|------------------|--------------------------------|------|--------|----|

| 入力電圧             | VIN (2) を GND に接続、TPS5430      | -0.3 | 40     | V  |

| 入力電圧             | VIN を GND に接続、TPS5431          | -0.3 | 25     | V  |

| 入力電圧             | ENA から GND へ                   | -0.3 | 7      | V  |

| 入力電圧             | VSENSE から GND へ                | -0.3 | 3      | V  |

| 出力電圧             | BOOT から PH へ                   | -0.3 | 6      | V  |

| 出力電圧             | PH から GND へ、(定常状態) (2)、TPS5430 | -0.6 | 40     | V  |

| 出力電圧             | PH から GND へ、(定常状態)、TPS5431     | -0.6 | 25     | V  |

| 出力電圧             | PH から GND へ、(過渡 10ns 未満)       | -1.2 |        | V  |

| ソース電流            | PH                             |      | 内部的に制限 |    |

| ソース電流            | PH リーク電流                       |      | 10     | μA |

| T <sub>J</sub>   | 動作時の仮想接合部温度                    | -40  | 150    | °C |

| T <sub>stg</sub> | 保管温度                           | -65  | 150    | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) VIN ピン電圧を絶対最大定格に近づけると、PH ピン電圧が絶対最大定格を越えることがあります。

### 5.2 ESD Ratings

| V <sub>(ESD)</sub> | 静電放電 |                                             | 値     | 単位 |

|--------------------|------|---------------------------------------------|-------|----|

|                    |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 (1)   | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠(2) | ±750  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                |                | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|----------------|-----|-----|-----|----|

| 入力電圧           | 入力電圧範囲、TPS5430 | 5.5 | 36  | 36  | V  |

| 入力電圧           | 入力電圧範囲、TPS5431 | 5.5 | 23  | 23  | V  |

| T <sub>J</sub> | 動作時接合部温度       | -40 | 125 | 125 | °C |

### 5.4 热に関する情報 (DDA パッケージ)

| 熱評価基準(1)              |                               | TPS543X     | 単位   |

|-----------------------|-------------------------------|-------------|------|

|                       |                               | DDA (HSOIC) |      |

|                       |                               | 8 ピン        |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗 (TPS5430EVM) (2) | 45          | °C/W |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗 (JESD 51-7) (3)  | 42.3        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗           | 46          | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗                  | 15          | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ              | 5.2         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ              | 15.3        | °C/W |

| 熱評価基準 <sup>(1)</sup> |  | TPS543X           |  | 単位                            |  |

|----------------------|--|-------------------|--|-------------------------------|--|

|                      |  | DDA (HSOIC)       |  |                               |  |

|                      |  | 8 ピン              |  |                               |  |

| $R_{\theta JC(bot)}$ |  | 接合部からケース(底面)への熱抵抗 |  | 6 $^{\circ}\text{C}/\text{W}$ |  |

- (1) 従来と新規の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』を参照してください。

- (2) 基板レイアウトと追加情報については、『EVM ユーザー ガイド』を参照してください。熱設計情報については、「最大周囲温度」セクションを参照してください。

- (3) この表に示す  $R_{\theta JA}$  の値は他のパッケージとの比較にのみ有効であり、設計目的に使用することはできません。これらの値は JESD 51-7 に従って計算され、4 層 JEDEC 基板上でシミュレーションされています。これらは、実際のアプリケーションで得られた性能を表すものではありません。たとえば、EVM  $R_{\theta JA} = \text{TBD } ^{\circ}\text{C}/\text{W}$  です。設計情報については、「最大周囲温度」セクションを参照してください。

## 5.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、 $V_{IN} = 5.5\text{V} \sim 36\text{V}$ 。標準値は  $T_J = 25^{\circ}\text{C}$ 、 $V_{IN} = 12\text{V}$  のときです (特に記述のない限り)。

| パラメータ                 |                                     | テスト条件                                                | 最小値   | 標準値   | 最大値           | 単位                 |

|-----------------------|-------------------------------------|------------------------------------------------------|-------|-------|---------------|--------------------|

| <b>電源電圧 (VIN ピン)</b>  |                                     |                                                      |       |       |               |                    |

| $I_Q(VIN)$            | VIN 静止電流                            | 非スイッチング、 $V_{SENSE} = 2\text{V}$ 、PH ピン オープン         | 2     | 4.4   | mA            |                    |

| $I_{SD(VIN)}$         | VIN のシャットダウン時消費電流                   | シャットダウン、ENA = 0V                                     | 15    | 50    | $\mu\text{A}$ |                    |

| <b>UVLO</b>           |                                     |                                                      |       |       |               |                    |

| $V_{IN(UVLO(R))}$     | VIN UVLO 立ち上がりスレッショルド               | $V_{VIN}$ 立ち上がり                                      | 5.3   | 5.5   | V             |                    |

| $V_{IN(UVLO(H))}$     | VIN UVLO ヒステリシス                     |                                                      | 0.35  |       | V             |                    |

| <b>電圧リファレンス</b>       |                                     |                                                      |       |       |               |                    |

| $V_{FB}$              | FB 電圧                               | $T_J = 25^{\circ}\text{C}$                           | 1.202 | 1.221 | 1.239         | V                  |

| $V_{FB}$              | FB 電圧                               | $T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ | 1.196 | 1.221 | 1.245         | V                  |

| <b>発振器</b>            |                                     |                                                      |       |       |               |                    |

| $f_{SW}$              | スイッチング周波数                           |                                                      | 400   | 500   | 600           | kHz                |

| $t_{ON(min)}$         | 最小 ON パルス幅                          |                                                      | 150   | 200   | ns            |                    |

| $D_{MAX}$             | 最大デューティ サイクル                        | $f_{SW} = 500\text{kHz}$                             | 87%   | 89%   |               |                    |

| <b>イネーブル (ENA ピン)</b> |                                     |                                                      |       |       |               |                    |

| $V_{EN(R)}$           | ENA 電圧立ち上がりスレッショルド                  |                                                      |       | 1.3   |               | V                  |

| $V_{EN(F)}$           | ENA 電圧立ち下がりスレッショルド                  |                                                      | 0.5   |       |               | V                  |

| $V_{EN(H)}$           | ENA 電圧ヒステリシス                        |                                                      | 325   |       |               | mV                 |

| $t_{SS}$              | 内部スロースタート時間 (0~100%)                |                                                      | 5.4   | 8     | 10            | ms                 |

| <b>過電流保護</b>          |                                     |                                                      |       |       |               |                    |

| $I_{HS(OC)}$          | ハイサイド ピーク電流制限                       |                                                      | 4.0   | 5.0   | 6.0           | A                  |

|                       | 再スタート前のヒップアップ時間                     |                                                      | 13    | 16    | 20            | ms                 |

| <b>出力 MOSFET</b>      |                                     |                                                      |       |       |               |                    |

| $R_{DS(on(HS))}$      | ハイサイド MOSFET オン抵抗                   | $V_{IN} = 12\text{V}$ 、 $V_{BOOT-SW} = 4.5\text{V}$  | 100   | 230   |               | $\text{m}\Omega$   |

| $R_{DS(on(HS))}$      | ハイサイド MOSFET オン抵抗                   | $V_{IN} = 5.5\text{V}$ 、 $V_{BOOT-SW} = 4.0\text{V}$ | 125   |       |               | $\text{m}\Omega$   |

| <b>サーマル シャットダウン</b>   |                                     |                                                      |       |       |               |                    |

| $T_{J(SD)}$           | サーマル シャットダウンのスレッショルド <sup>(1)</sup> | 温度上昇                                                 | 135   | 162   |               | $^{\circ}\text{C}$ |

| $T_{J(HYS)}$          | サーマル シャットダウン ヒステリシス <sup>(1)</sup>  |                                                      | 14    |       |               | $^{\circ}\text{C}$ |

- (1) パラメータは、設計、統計分析、相関パラメータの製造試験によって規定されています。実製品の検査は行っていません。

## 5.6 代表的特性

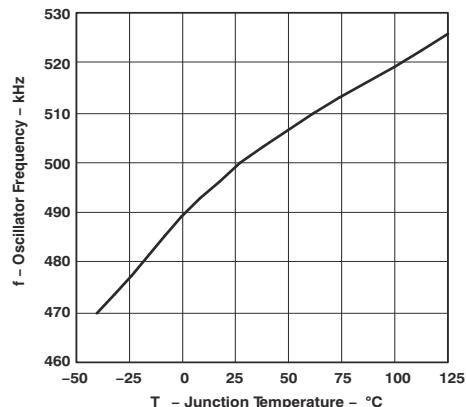

図 5-1. 発振周波数 対 接合部温度

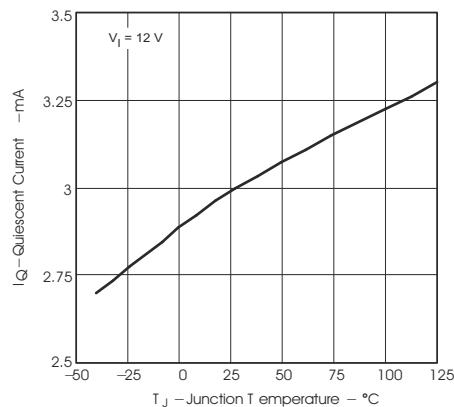

図 5-2. 非スイッチング時の静止電流 対 接合部温度

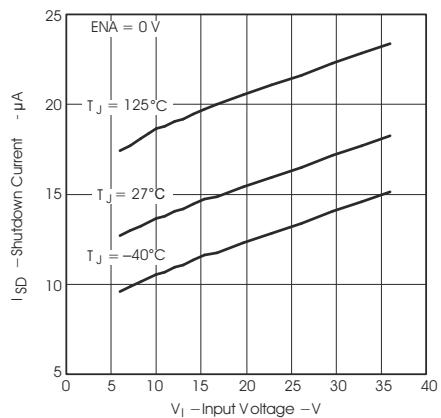

図 5-3. シャットダウン時の静止電流 対 入力電圧

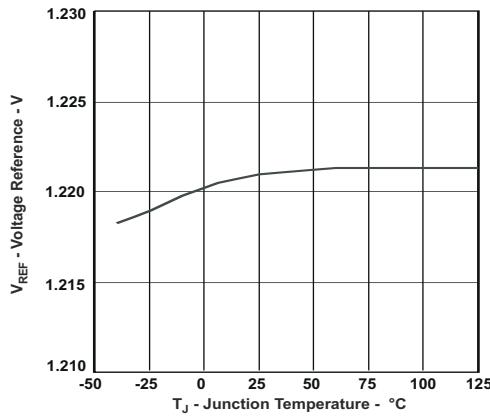

図 5-4. 電圧リファレンス 対 接合部温度

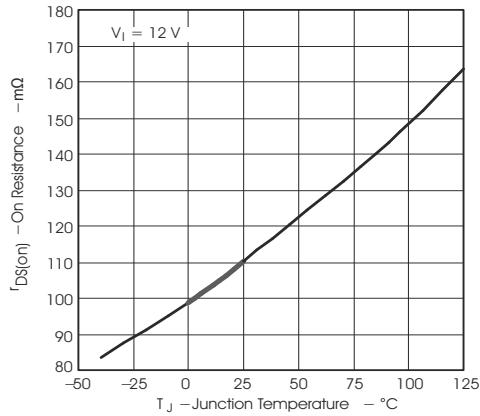

図 5-5. オン抵抗 対 接合部温度

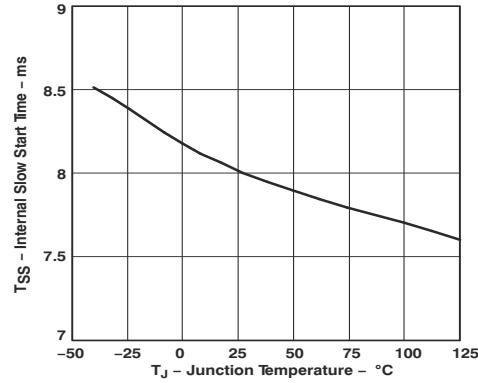

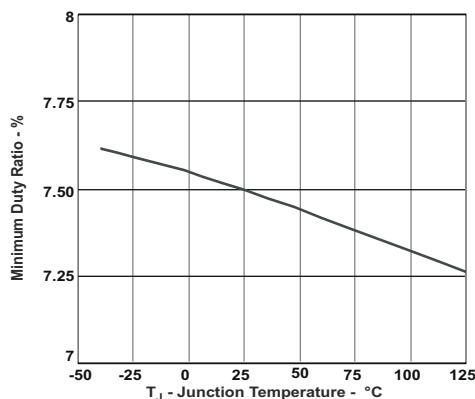

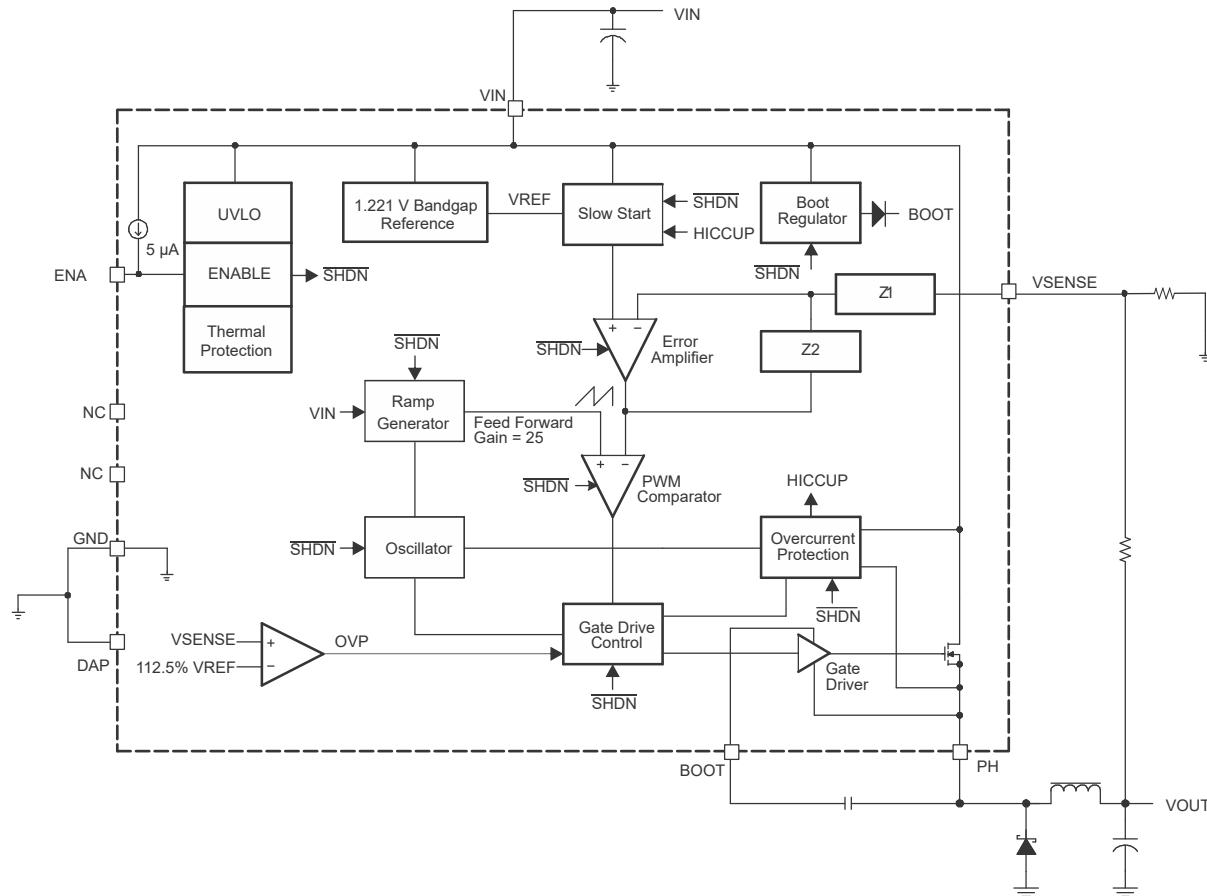

図 5-6. 内部スロースタート時間 対 接合部温度

図 5-7. 制御可能な最小オン時間 対 接合部温度

図 5-8. 制御可能な最小デューティ比 対 接合部温度

## 6 詳細説明

### 6.1 概要

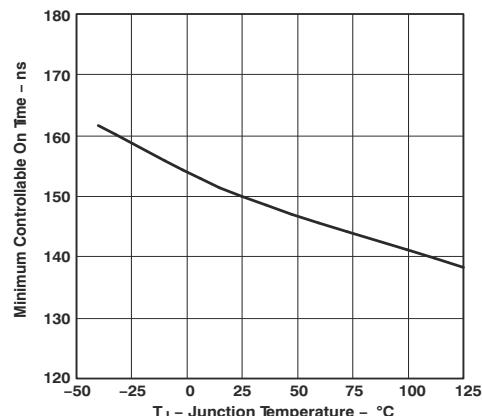

TPS543x は、ハイサイド N チャネル MOSFET 内蔵の 3A 降圧 (バック) レギュレータです。TPS5431 は最大 23V、TPS5430 は最大 36V の電源レールで動作するように設計されています。これらのデバイスは、電圧フィード フォワードによる定周波数の電圧制御モードを実装しており、ライン レギュレーションとライン過渡応答を改善しています。補償機能を内蔵しているため、設計が簡単であり、外付け部品数を減らせます。

内蔵の 100mΩ ハイサイド MOSFET は、3A の連続電流を負荷に供給できる高効率の電源設計をサポートします。内蔵ハイサイド MOSFET に対するゲート駆動バイアス電圧は、BOOT ピンと PH ピンの間に接続されるブートストラップ キャパシタによって供給されます。TPS543x は、ブートストラップ再充電ダイオードを内蔵しているため、外付け部品数を削減できます。

TPS543x のデフォルトの入力スタートアップ電圧は 5.3V (標準値) です。ENA ピンを使用して TPS543x をディスエーブルにすると、消費電流は 15µA に低減されます。ENA 端子がフローティングになると、内部プルアップ電流源によって動作がイネーブルになります。TPS543x には内部スロースタート回路が搭載され、起動中に出力の上昇を低速にすることで、突入電流と出力電圧オーバーシュートを低減します。最小出力電圧は、1.221V の内部帰還リファレンスに等しくなります。過電圧保護 (OVP) コンパレータにより、出力の過渡過電圧が最小限に抑えられます。OVP コンパレータが作動すると、ハイサイド MOSFET はオフになり、出力電圧が目標値の 112.5% を下回るまでオンになりません。

サイクル単位の内蔵過電流保護機能は、内蔵ハイサイド MOSFET のピーク電流を制限します。連続的な過電流フォルト条件が発生した場合、TPS543x は hiccup モードの過電流制限に移行します。過熱保護機能は、デバイスを過熱から保護します。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 発振周波数

内部的なフリー・ランニング・オシレータは、PWM スイッチング周波数を 500kHz に設定します。500kHz のスイッチング周波数では、出力リップルが同じ条件でもインダクタンスが低くなるため、出力インダクタ・サイズが小さくなります。

### 6.3.2 基準電圧

基準電圧システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで高精度の基準信号を生成します。量産テスト時に、バンドギャップ回路とスケーリング回路は、室温で出力が 1.221V になるようにトリミングされます。

### 6.3.3 イネーブル (ENA) と内部スロースタート時間

ENA ピンは、レギュレータの電気的なオン / オフを制御します。ENA ピンの電圧がスレッショルド電圧を超えると、レギュレータが動作を開始し、内部スロースタートが上昇し始めます。ENA ピンの電圧がスレッショルド電圧よりも低くなると、レギュレータはスイッチングを停止し、内部スロースタートはリセットされます。ENA ピンがグランドまたは 0.5V より低い電圧に接続されると、レギュレータはディスエーブルになり、シャットダウン・モードがアクティブになります。シャットダウン・モードでの TPS543x の静止時電流は 15µA (標準) です。

ENA ピンには内部プルアップ電流源があるため、ユーザーは ENA ピンをオープンにすることができます。アプリケーションで ENA ピンの制御が必要な場合は、ピンとのインターフェイスにオープン・ドレインまたはオープン・コレクタの出力ロジックを使用してください。起動時の突入電流を制限するために、内部スロースタート回路を使用して、基準電圧を 0V から最終値まで直線的に上昇させます。内部スロースタート時間は 8ms (標準) です。

### 6.3.4 低電圧誤動作防止 (UVLO)

TPS543x は、VIN (入力電圧) が UVLO スタート・スレッショルド電圧よりも低いときにデバイスをディスエーブルの状態に維持するために、低電圧誤動作防止回路を内蔵しています。電源の立ち上がり時には、VIN が UVLO スタート・スレッショルド電圧を超えるまで、内部回路は非アクティブ状態に保持され、内部スロースタートは接地されます。UVLO スタート・スレッショルド電圧に達すると、内部スロースタートがリリースされ、デバイスは起動を開始します。デバイスは、VIN が UVLO ストップ・スレッショルド電圧より低くなるまで動作します。UVLO コンパレータのヒステリシスは 350 mV (標準) です。

### 6.3.5 ブースト・キャパシタ (BOOT)

0.01µF の低 ESR セラミック・キャパシタが、BOOT ピンと PH ピン間に接続されます。このキャパシタは、ハイサイド MOSFET にゲート駆動電圧を供給します。温度に対して容量値が安定しているため、X7R または X5R クラスをお勧めします。

### 6.3.6 出力フィードバック (VSENSE) と内部補償

レギュレータの出力電圧は、外部の抵抗デバイダ回路の中心電圧を VSENSE ピンにフィードバックすることで設定されます。定常状態の動作では、VSENSE ピンの電圧は、基準電圧の 1.221V と同じになります。

TPS543x には、レギュレータの設計を簡潔にするために内部補償が装備されています。TPS543x では電圧モード制御が採用されているため、クロスオーバー周波数と位相マージンが高くなるようにタイプ 3 の補償回路がチップ上に設計されており、高い安定性を実現しています。詳細については、「アプリケーション」セクションの「内部補償回路」を参照してください。

### 6.3.7 電圧フィード・フォワード

内蔵のボルテージ・フィード・フォワードにより、入力電圧が変化しても DC 出力段のゲインは一定になります。これにより、安定性の分析が非常に簡単になり、過渡応答が大幅に改善されます。ボルテージ・フィード・フォワードにより、ピーク・ランプ電圧が入力電圧とは逆方向に変化するため、以下の式のように、モジュレータおよび出力段のゲインはフィード・フォワード・ゲインで一定になります。

$$\text{Feed Forward Gain} = \frac{V_{IN}}{\text{Ramp}_{pk-pk}} \quad (1)$$

TPS543x のフィード・フォワード・ゲインは 25 (標準値) です。

### 6.3.8 パルス幅変調 (PWM) 制御

レギュレータには、固定周波数のパルス幅モジュレータ (PWM) 制御方式が採用されています。まず、帰還電圧 (VSENSE ピン電圧) は、誤差電圧を生成する高ゲイン誤差増幅器および補償回路により、一定の基準電圧と比較されます。次に、誤差電圧は、PWM コンパレータにより、ランプ電圧と比較されます。この方式により、誤差電圧の大きさは、パルス幅 (デューティ・サイクル) に変換されます。最後に、PWM 出力がゲート駆動回路に送られ、ハイサイド MOSFET のオン時間が制御されます。

### 6.3.9 過電流保護

過電流保護は、ハイサイド MOSFET のドレイン-ソース間の電圧を検出することで実行されます。ドレイン-ソース間の電圧は、過電流スレッショルド制限値に相当する電圧レベルと比較されます。ドレイン-ソース間の電圧が過電流スレッショルド制限値を超えた場合、過電流インジケータがセットされます。システムは、ターンオン・ノイズによる誤作動を回避するために、各サイクルの最初のリーディング・エッジ・プランギング時間内は過電流インジケータを無視します。

過電流インジケータがセットされると、過電流保護がトリガされます。ハイサイド MOSFET は、伝播遅延の後、サイクルの残り時間の間オフになります。この過電流保護モードは、サイクルごとの電流制限と呼ばれます。

短絡などの深刻な過負荷条件が発生した場合、サイクルごとの電流制限を使用しても過電流を抑制できないことがあります。その場合、電流制限の 2 番目のモード、つまり hiccup モードの電流制限が使用されます。hiccup モードの過電流保護中は、基準電圧は接地され、ハイサイド MOSFET は hiccup 期間の間オフになります。hiccup 期間が完了すると、レギュレータはスロー スタート回路の制御により再起動されます。

### 6.3.10 過電圧保護

TPS543x には過電圧保護 (OVP) 回路があり、出力故障状態から復帰するときの電圧オーバーシュートが最小限に抑えられます。OVP 回路には、VSENSE ピンの電圧と  $112.5\% \times V_{REF}$  のスレッショルドを比較する過電圧コンパレータがあります。VSENSE ピンの電圧がこのスレッショルドより高くなると、ハイサイド MOSFET が強制的にオフにされます。VSENSE ピンの電圧がこのスレッショルドより低くなると、ハイサイド MOSFET が再びオンになります。

### 6.3.11 サーマル・シャットダウン

TPS543x が過熱状態にならないように、サーマル・シャットダウン回路を内蔵しています。接合部温度がサーマル・シャットダウンのトリップ・ポイントを超えると、基準電圧は接地され、ハイサイド MOSFET はオフになります。接合部温度がサーマル・シャットダウンのトリップ・ポイントを  $14^\circ\text{C}$  下回った時点で、本製品はスロースタート回路の制御により自動的に再起動されます。

## 6.4 デバイスの機能モード

### 6.4.1 最小入力電圧付近での動作

TPS543x は、5.5V を超える入力電圧で動作させることを推奨します。標準の VIN UVLO スレッショルドは 5.3V であり、UVLO 電圧以上の入力電圧であれば動作は可能です。実際の UVLO 電圧より低い入力電圧では、デバイスはスイッチングを行いません。EN がフローティングになっているか、または外部で 1.3V を超える電圧にプルアップされている場合、 $V_{(VIN)}$  が UVLO スレッショルドを超えた時点で TPS543x はアクティブになります。スイッチングがイネーブルになり、スロースタートシーケンスが開始されます。TPS543x は、内部スロースタート時間全体にわたって、内部リファレンス電圧を 0V から最終値まで直線的に上昇させます。

### 6.4.2 ENA 制御による動作

イネーブル・スタートのスレッショルド電圧は最大 1.3V です。ENA が最小ストップ・スレッショルド電圧の 0.5V 未満に保持されると、TPS543x は ディスエーブルされ、VIN が UVLO スレッショルドを超えてスイッチングは禁止されます。この

状態では、静止時電流は減少します。 $V_{(VIN)}$  が UVLO スレッショルドよりも高いときに ENA の電圧が最大スタート・スレッショルドを上回ると、デバイスはアクティブになります。スイッチングがイネーブルになり、スロースタート・シーケンスが開始されます。TPS543x は、内部スロースタート時間全体にわたって、内部リファレンス電圧を 0V から最終値まで直線的に上昇させます。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPS543x は、ハイサイド MOSFET を内蔵した 3A の降圧型レギュレータです。このデバイスは通常、最大出力電流 3A で高い DC 電圧から低い DC 電圧に変換するために使用します。アプリケーションの例として、セットトップボックス、DVD、LCD およびプラズマディスプレイ、ハイパワー LED 電源、カー オーディオ、バッテリチャージャ、その他の 12V および 24V 分散電源システム用の、高密度ポイントオブロード レギュレータが挙げられます。TPS543x の部品の値を選択するには、以下の設計手順を使用します。この手順は、高周波スイッチング レギュレータの設計例を示しています。あるいは、WEBENCH® ソフトウェアを使用して完全な設計を生成することもできます。WEBENCH ソフトウェアは、反復的な設計手順を使用し、包括的な部品データベースにアクセスして設計を生成します。

設計プロセスを開始するには、いくつかのパラメータを決定する必要があります。設計者は、以下を知っている必要があります。

- 入力電圧範囲

- 出力電圧

- 入力リップル電圧

- 出力リップル電圧

- 出力電流定格

- 動作周波数

## 7.2 代表的なアプリケーション

### 7.2.1 12V 入力から 5.0V 出力

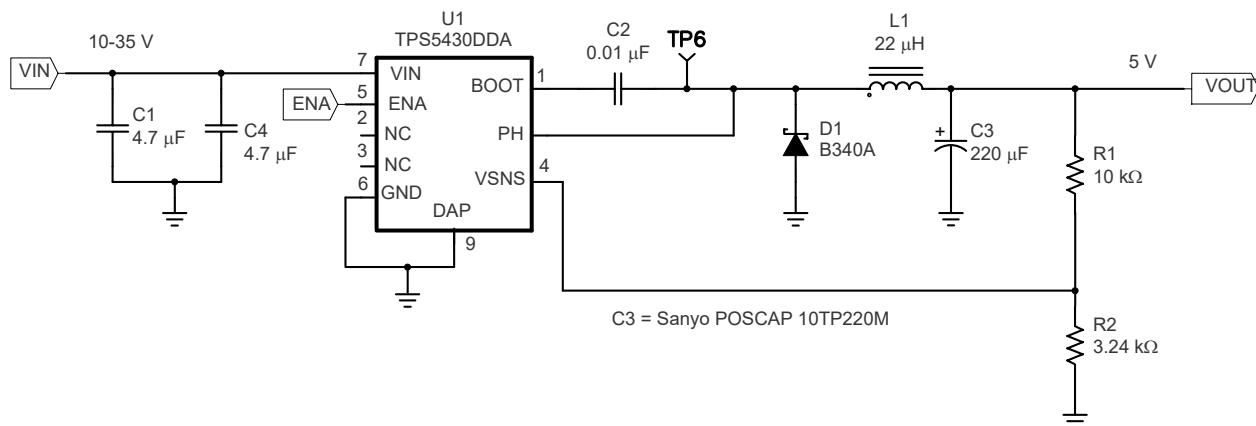

図 7-1 に、TPS5430 の代表的なアプリケーションの回路図を示します。TPS5430 は、公称出力電圧 5V で最大 3A の出力電流を供給できます。適切な放熱性能を得るには、デバイスの下に露出した DAP をプリント基板に半田付けする必要があります。

図 7-1. アプリケーション回路、12V 入力から 5.0V 出力

#### 7.2.1.1 設計要件

ここで説明する設計の例で使用している入力パラメータは、以下のとおりです。

| 設計パラメータ <sup>(1)</sup> | 設計値例        |

|------------------------|-------------|

| 入力電圧範囲                 | 10.8V~19.8V |

| 出力電圧                   | 5V          |

| 入力リップル電圧               | 300mV       |

| 出力リップル電圧               | 30mV        |

| 出力電流定格                 | 3A          |

| 動作周波数                  | 500kHz      |

(1) その他の設計条件としては、小さなサイズで、部品の厚みを薄くするように設定することです。

### 7.2.1.2 詳細な設計手順

次の設計手順に従って、TPS5430 の部品の値を選択できます。ここでは、設計手順について簡単に説明します。

#### 7.2.1.2.1 WEBENCH® ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer により、TPS5430 デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

#### 7.2.1.2.2 スイッチング周波数

TPS5430 のスイッチング周波数は、内部的に 500kHz に設定されています。スイッチング周波数を調整することはできません。

#### 7.2.1.2.3 入力キャパシタ

TPS5430 には入力デカップリング・キャパシタが必要で、アプリケーションによってはバルク入力キャパシタも必要です。デカップリング コンデンサ (C1) の推奨値は  $10\mu F$  です。高品質のセラミック・タイプである X5R または X7R が必要です。一部のアプリケーションでは、入力電圧定格と電流リップル定格を超えない限り、値の小さいデカップリング・キャパシタを使用できます。電圧定格は、最大入力電圧 (リップルを含む) よりも高くなればなりません。

この入力リップル電圧は、[式 2](#) で概算することができます。

$$\Delta V_{IN} = \frac{I_{OUT(MAX)} \times 0.25}{C_{BULK} \times f_{SW}} + (I_{OUT(MAX)} \times ESR_{MAX}) \quad (2)$$

ここで、 $I_{OUT(MAX)}$  は最大負荷電流、 $f_{SW}$  はスイッチング周波数、 $C_{IN}$  は入力キャパシタの値、 $ESR_{MAX}$  は入力キャパシタの最大直列抵抗です。

最大 RMS リップル電流についても確認する必要があります。ワーストケース条件の値は、[式 3](#) で概算することができます。

$$I_{CIN} = \frac{I_{OUT(MAX)}}{2} \quad (3)$$

この場合、入力リップル電圧は  $156\text{mV}$ 、RMS リップル電流は  $1.5\text{A}$  になります。入力キャパシタ両端の最大電圧は、 $V_{IN} \text{ max} + \Delta V_{IN}/2$  となります。選択した入力デカップリング キャパシタは定格が  $25\text{V}$ 、リップル電流容量が  $3\text{A}$  以上であり、十分な余裕があります。いかなる状況でも、電圧および電流の最大定格を超えないことが非常に重要です。

TPS5430 の回路が入力電圧源から約 2 インチ以内に配置されていない場合は、バルク容量の追加が必要になる場合があります。このコンデンサの値はそれほど重大ではありませんが、リップル電圧を含めた最大入力電圧を処理できる定格が必要で、入力リップル電圧が許容範囲に収まるよう出力をフィルタリングできることも必要です。

#### 7.2.1.2.4 出力フィルタ部品

出力フィルタとして L1 と C2 の 2 つの部品を選択する必要があります。TPS5430 は内部補償デバイスであるため、フィルタ部品のタイプと値の範囲に制限がかかります。

##### 7.2.1.2.4.1 インダクタの選択

出力インダクタの最小値を計算するには、式 4 を使用します。

$$L_{MIN} = \frac{V_{OUT(MAX)} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times K_{IND} \times I_{OUT} \times F_{SW}} \quad (4)$$

$K_{IND}$  は、最大出力電流に対するインダクタのリップル電流量を表す係数です。インダクタのリップル電流量を決定するには、3 つの要因を考慮する必要があります。この要因とは、ピーク・ツー・ピークのリップル電流が出力リップル電圧の振幅に影響を与えること、リップル電流がピーク・スイッチ電流に影響を与えること、さらに回路が不連続になるポイントがリップル電流量によって決定されることです。TPS5430 を使用する設計では、 $K_{IND}$  が 0.2 から 0.3 である場合に、良い結果を得ることができます。適切な出力キャパシタと組み合わせたときに、低出力リップル電圧が得られ、ピーク・スイッチ電流は電流制限設定ポイントよりも十分に低くなります。また、動作が不連続になる前に、相対的に低い負荷電流をソースすることができます。

この設計例では、 $K_{IND} = 0.2$  を使用し、最小インダクタ値は  $12.5\mu H$  と計算されます。次に高い標準値は  $15\mu H$  で、この設計ではこれを使用しています。

出力フィルタ インダクタについては、RMS 電流および飽和電流の定格を超えないことが重要です。RMS インダクタ電流は、式 5 から求められます。

$$I_{L(RMS)} = \sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.8} \right)^2} \quad (5)$$

ピーク・インダクタ電流は 式 6 で決定されます。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{1.6 \times V_{IN(MAX)} \times L_{OUT} \times F_{SW}} \quad (6)$$

この設計では、RMS インダクタ電流は  $3.003A$ 、ピーク インダクタ電流は  $3.31A$  です。選択したインダクタは、Sumida CDRH104R-150  $15\mu H$  です。このインダクタの飽和電流定格は  $3.4A$ 、RMS 電流定格は  $3.6A$  であり、これらの要件を十分に満足します。より低い定格のインダクタを使用することもできますが、このデバイスを選択したのは、薄型部品であるためです。一般に、TPS5430 で使用するインダクタの値は、 $10\mu H$ ~ $100\mu H$  の範囲内です。

### 7.2.1.2.4.2 キャパシタの選択

出力キャパシタの設計で重要な要因は、DC 電圧定格、リップル電流定格、および等価直列抵抗 (ESR) です。DC 電圧定格とリップル電流定格は、超えることができません。ESR とインダクタ・リップル電流によって出力リップル電圧が決まるため、ESR は重要です。出力キャパシタの実際の値は重要ではありませんが、実用上の制限がいくつかあります。設計上の目的とする閉ループのクロスオーバー周波数と、出力フィルタの LC コーナー周波数との関係に注意してください。内部補償の設計の観点から、閉ループのクロスオーバー周波数は 3kHz~30kHz の範囲内に維持することをお勧めします。この周波数の範囲では、十分な位相ブーストが得られ、動作が安定します。この設計例では、目的とする閉ループのクロスオーバー周波数が 2590Hz~24kHz の範囲内であり、出力キャパシタの ESR ゼロよりも低いことを想定しています。これらの条件では、閉ループのクロスオーバー周波数は、以下の式によって LC コーナー周波数に関連付けられます。

$$f_{CO} = \frac{f_{LC}^2}{85 V_{OUT}} \quad (7)$$

また、出力フィルタの出力キャパシタの要求値は、以下の値になります。

$$C_{OUT} = \frac{1}{3357 \times L_{OUT} \times f_{CO} \times V_{OUT}} \quad (8)$$

目的のクロスオーバーが 18kHz で 15μH のインダクタを使用している場合、出力キャパシタの計算値は 220μF になります。ESR ゼロがループ クロスオーバーよりも大きくなるように、キャパシタのタイプを選択する必要があります。最大 ESR は次の式で計算されます。

$$ESR_{MAX} = \frac{1}{2\pi \times C_{OUT} \times f_{CO}} \quad (9)$$

出力キャパシタの最大 ESR は、設計の初期パラメータの指定に従って、出力リップルの量も決定します。出力リップル電圧は、インダクタのリップル電流に出力フィルタの ESR を乗じた値です。キャパシタのデータシートに記載されている最大 ESR の仕様が、許容可能な出力リップル電圧を満たすことを確認してください。

$$V_{PP\ (MAX)} = \frac{ESR_{MAX} \times V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{N_C \times V_{IN(MAX)} \times L_{OUT} \times F_{SW}} \quad (10)$$

ここで、

- $\Delta V_{PP}$  は要求されるピーク・ツー・ピーク出力リップルです。

- $N_C$  は並列に配置された出力キャパシタの数です。

- $F_{SW}$  はスイッチング周波数です。

この設計例では、単一の 220μF 出力キャパシタを C3 として選択しています。計算で求めた RMS リップル電流は 143mA であり、必要な最大 ESR は 40mΩ です。これらの要件を満たすコンデンサは、定格 10V、最大 ESR 40mΩ、リップル電流定格 3A の Sanyo Poscap 10TPB220M です。追加の小さな 0.1μF セラミック バイパス コンデンサも使用できますが、この設計には含まれていません。

出力キャパシタの最小 ESR も考慮する必要があります。最適な位相マージンを得るために、ESR が最小になるときの ESR ゼロは、24kHz および 54kHz の内部補償の極よりも極端に高くならないようにしてください。

選択する出力キャパシタは、目的の出力電圧とリップル電圧の半分を加算した値よりも高い定格にする必要があります。ディレーティングした量もこの計算に含める必要があります。出力キャパシタの最大 RMS リップル電流は、式 11 で求められます。

$$I_{COUT(RMS)} = \frac{1}{\sqrt{12}} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times N_C} \right) \quad (11)$$

ここで、

- $N_C$  は並列に配置された出力キャパシタの数です。

- $F_{SW}$  はスイッチング周波数です。

アプリケーションによっては、その他のタイプのキャパシタを TPS5430 と併用することができます。

#### 7.2.1.2.5 出力電圧設定点

TPS5430 の出力電圧は、VSENSE ピンと出力との間に接続される抵抗デバイダ ( $R1$  と  $R2$ ) によって設定されます。以下の 式 12 を使用して、出力電圧が 5V のときの  $R2$  の抵抗値を計算します。

$$R2 = \frac{R1 \times 1.221}{V_{OUT} - 1.221} \quad (12)$$

TPS5430 の設計は、10k $\Omega$  の  $R1$  値から開始します。次に、 $R2$  を 3.24k $\Omega$  にします。

#### 7.2.1.2.6 ブートコンデンサ

ブートストラップコンデンサは 0.01 $\mu$ F とする必要があります。

#### 7.2.1.2.7 キャッチダイオード

TPS5430 は、PH と GND との間の外部キャッチダイオードを使用して動作する仕様になっています。選択するダイオードは、アプリケーションの絶対最大定格を満足する必要があります。逆方向電圧は、PH ピンの最大電圧 ( $V_{IN(MAX)} + 0.5V$ ) よりも高くなればならず、ピーク電流は、 $I_{OUT(MAX)} + (\text{ピークツーピーク インダクタ電流の } 1/2)$  よりも大きくなればなりません。高い効率を得るには、順方向電圧降下を小さくする必要があります。一般に、キャッチダイオードの導通時間は、ハイサイド FET のオン時間よりも長いため、ダイオードのパラメータに注意を払うことで、全体の効率を大きく向上させることができます。また、選択するダイオードが電力損失の要件に対応していることを確認します。この設計では、Diodes, Inc. の B340A を選択しています。このダイオードは、逆方向電圧が 40V、順方向電流が 3A、順方向電圧降下が 0.5V です。

#### 7.2.1.2.8 詳細情報

##### 7.2.1.2.8.1 出力電圧の制限

TPS543x の内部設計により、任意の与えられた入力電圧に対して、出力電圧の上限と下限が設定されます。出力電圧設定点の上限は、最大デューティ・サイクルの 87% に制限され、以下の式で求められます。

$$V_{OUTMAX} = 0.87 \times \left( (V_{INMIN} - I_{OMAX} \times 0.230) + V_D \right) - (I_{OMAX} \times R_L) - V_D \quad (13)$$

ここで、

- $V_{INMIN}$  = 最小入力電圧

- $I_{OMAX}$  = 最大負荷電流

- $V_D$  = キャッチダイオードの順方向電圧

- $R_L$  = 出力インダクタの直列抵抗

この式では、内部のハイサイド FET に対する最大オン抵抗を想定しています。

下限は、最小制御可能オン時間 (最大で 200ns) によって制限されます。特定の入力電圧と最小負荷電流に対応する最小出力電圧の概数は、次の式で求めることができます。

$$V_{OUTMIN} = 0.12 \times \left( (V_{INMAX} - I_{OMIN} \times 0.110) + V_D \right) - \left( I_{OMIN} \times R_L \right) - V_D \quad (14)$$

ここで、

- $V_{INMAX}$  = 最大入力電圧

- $I_{OMIN}$  = 最小負荷電流

- $V_D$  = キャッチ ダイオードの順方向電圧

- $R_L$  = 出力インダクタの直列抵抗

#### 7.2.1.2.8.2 内部補償回路

回路の例で使用されている設計の式は、TPS543x を使用する回路の生成に使用できます。これらの設計は特定の前提条件に基づいており、ほとんどの場合 ESR 値が制限範囲内になっている出力キャパシタが選択されています。別のタイプのキャパシタを使用する場合にも、TPS543x の内部補償に適合する可能性があります。以下の式 式 15 で内部電圧モード・タイプ III の補償回路の公称周波数応答を求めるできます。

$$H(s) = \frac{\left(1 + \frac{s}{2\pi \times Fz1}\right) \times \left(1 + \frac{s}{2\pi \times Fz2}\right)}{\left(\frac{s}{2\pi \times Fp0}\right) \times \left(1 + \frac{s}{2\pi \times Fp1}\right) \times \left(1 + \frac{s}{2\pi \times Fp2}\right) \times \left(1 + \frac{s}{2\pi \times Fp3}\right)} \quad (15)$$

ここで、

- $f_{p0} = 2165\text{Hz}$ ,  $f_{z1} = 2170\text{Hz}$ ,  $f_{z2} = 2590\text{Hz}$

- $f_{p1} = 24\text{kHz}$ ,  $f_{p2} = 54\text{kHz}$ ,  $f_{p3} = 440\text{kHz}$

- $f_{p3}$  は、理想的でない寄生容量の影響を表します。

この情報と目的の出力電圧、フィード・フォワード・ゲインおよび出力フィルタ特性を組み合わせると、閉ループの伝達関数が導かれます。

#### 7.2.1.2.8.3 熱に関する計算

以下の式は、連続導通モード動作でのデバイスの消費電力を見積もる方法を示しています。デバイスが不連続モードで動作していて、その負荷が軽い場合には、この式は使用しないでください。

**導通損失:**  $P_{con} = I_{OUT}^2 \times R_{ds(on)} \times V_{OUT}/V_{IN}$

**スイッチング損失:**  $P_{sw} = V_{IN} \times I_{OUT} \times 0.01$

**静止時電流損失:**  $P_q = V_{IN} \times 0.01$

**全体の損失:**  $P_{tot} = P_{con} + P_{sw} + P_q$

**与えられた  $T_A \Rightarrow$  予測接合部温度:**  $T_J = T_A + R_{th} \times P_{tot}$

**与えられた  $T_{JMAX} = 125^\circ\text{C} \Rightarrow$  予測最大周囲温度:**  $T_{AMAX} = T_{JMAX} - R_{th} \times P_{tot}$

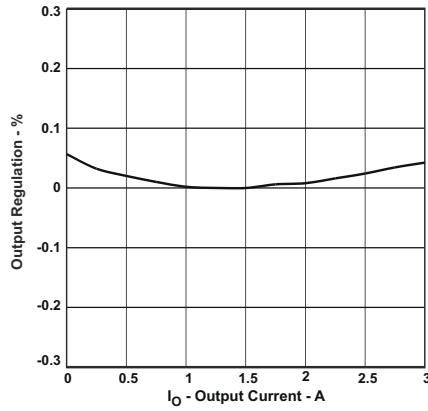

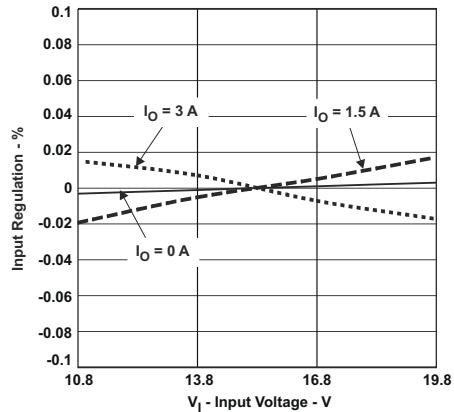

### 7.2.1.3 アプリケーション曲線

特性グラフ(図7-2から図7-8まで)は、図7-1の回路に適用可能です。 $T_a = 25^\circ\text{C}$  (特に記述のない限り)

図 7-2. 効率 対 出力電流

図 7-3. 出力レギュレーション % 対 出力電流

図 7-4. 入力レギュレーション % 対 入力電圧

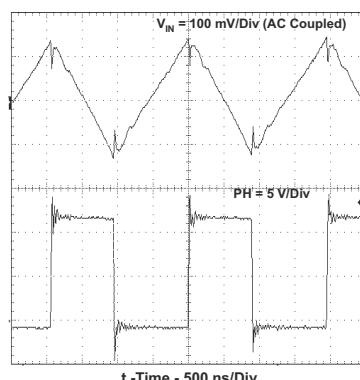

図 7-5. 入力電圧リップルと PH ノード、 $I_O = 3\text{ A}$

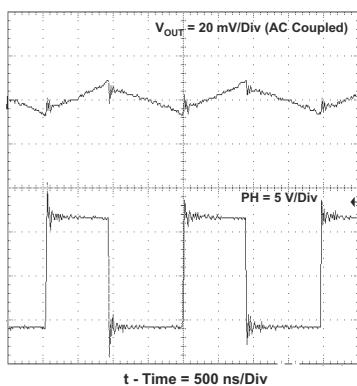

図 7-6. 出力電圧リップルと PH ノード、 $I_O = 3\text{ A}$

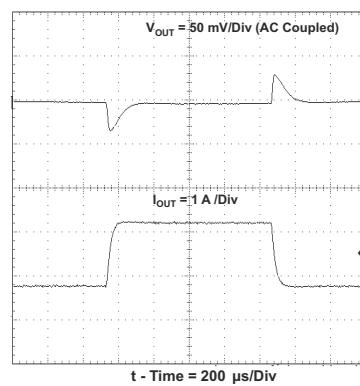

図 7-7. 過渡応答、 $I_O$  は 0.75A から 2.25A までステップ増加

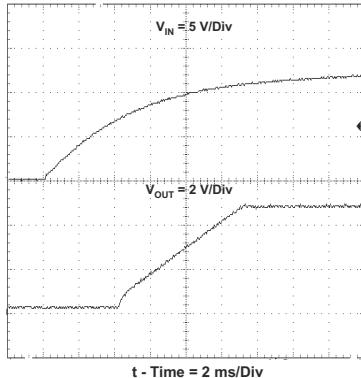

図 7-8. 起動波形、 $V_{IN}$  および  $V_{OUT}$

### 7.2.2 TPS5430 を使用した広い入力電圧範囲

図 7-9 に、TPS5430 の広い入力電圧範囲を使用するアプリケーション回路を示します。

図 7-9. 10V～35V 入力から 5V 出力へのアプリケーション回路

### 7.2.2.1 設計要件

この設計例では、入力パラメータとして以下の値を使用します。この回路の設計には、より大きな値の出力インダクタと、より低い閉ループ・クロスオーバー周波数も使用しています。

| 設計パラメータ  | 設計値例    |

|----------|---------|

| 入力電圧範囲   | 10V～35V |

| 出力電圧     | 5V      |

| 入力リップル電圧 | 300mV   |

| 出力リップル電圧 | 30mV    |

| 出力電流定格   | 3A      |

| 動作周波数    | 500kHz  |

### 7.2.2.2 詳細な設計手順

この設計手順は、セクション 7.2.1.2 の設計例で示したものと似ています。

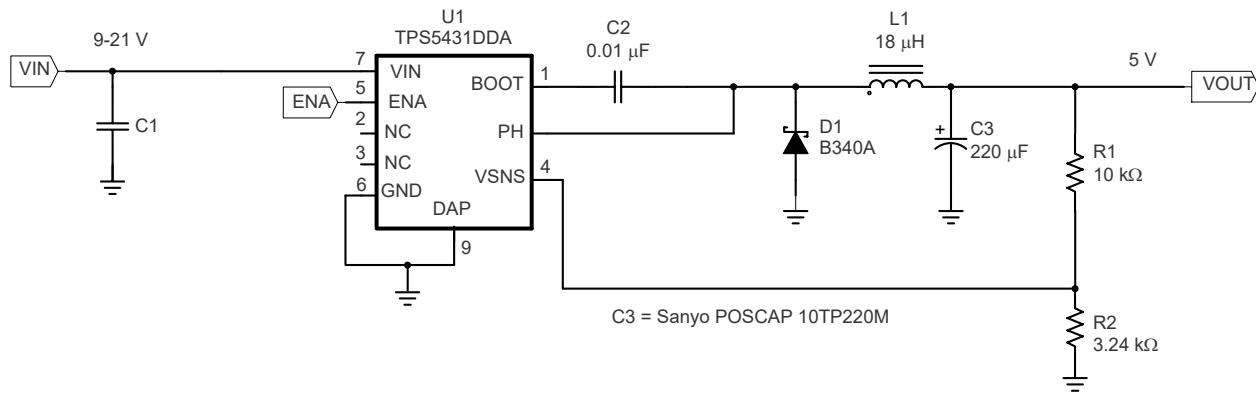

### 7.2.2.3 TPS5431 を使用した広い入力電圧範囲

図 7-10 に、TPS5431 の広い入力電圧範囲を使用するアプリケーション回路を示します。

図 7-10. 9V~21V 入力から 5V 出力へのアプリケーション回路

#### 7.2.2.3.1 設計要件

この設計例では、入力パラメータとして以下の値を使用します。この回路の設計には、より大きな値の出力インダクタと、より低い閉ループ・クロスオーバー周波数も使用しています。

| 設計パラメータ  | 設計値    |

|----------|--------|

| 入力電圧範囲   | 9V~21V |

| 出力電圧     | 5V     |

| 入力リップル電圧 | 300mV  |

| 出力リップル電圧 | 30mV   |

| 出力電流定格   | 3A     |

| 動作周波数    | 500kHz |

#### 7.2.2.3.2 詳細な設計手順

この設計手順は、セクション 7.2.1.2 の設計例で示したものと似ています。

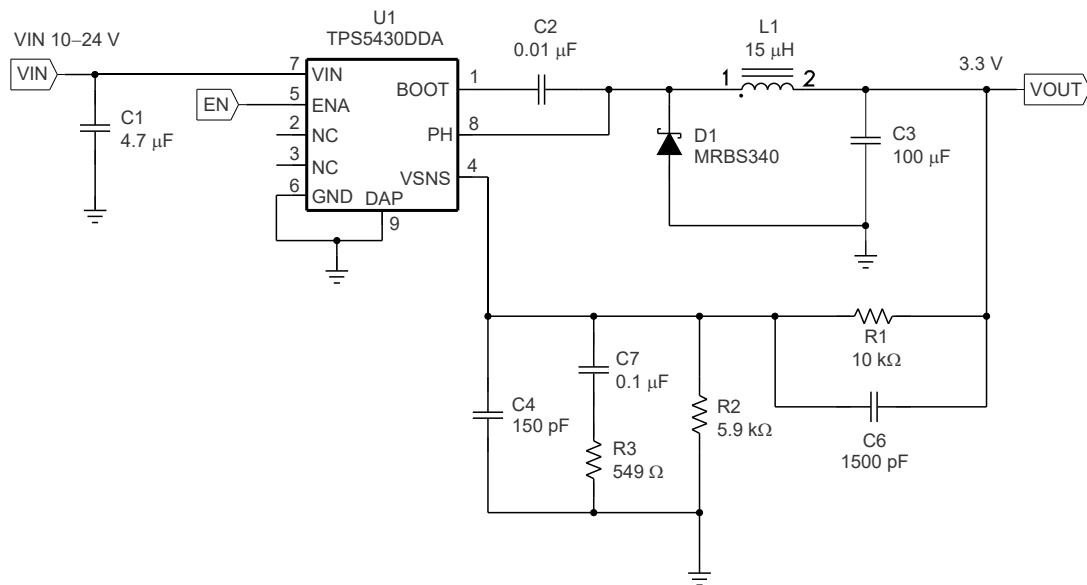

### 7.2.3 セラミック出力フィルタ キャパシタを使用する回路

図 7-11 に、入力フィルタと出力フィルタでいずれもセラミック キャパシタを採用したアプリケーション回路を示します。

図 7-11. セラミック出力フィルタ キャパシタ回路

#### 7.2.3.1 設計要件

この設計例では、入力パラメータとして以下の値を使用します。この回路の設計には、セラミック出力フィルタ・キャパシタも使用しています。

| 設計パラメータ  | 設計値     |

|----------|---------|

| 入力電圧範囲   | 10V~24V |

| 出力電圧     | 3.3V    |

| 入力リップル電圧 | 300mV   |

| 出力電流定格   | 3A      |

| 動作周波数    | 500kHz  |

#### 7.2.3.2 詳細な設計手順

設計パラメータは、セクション 7.2.1.2 の設計例で使用されているパラメータと同様ですが、設計例と比べると、出力フィルタ・キャパシタの値が大きく、回路を安定させるために追加された内部補償部品の設計が異なっています。

### 7.2.3.2.1 出力フィルタ部品の選択

式 11 を使用する場合、インダクタの最小値は  $12\mu\text{H}$  です。この設計例では、 $15\mu\text{H}$  の値が選択されています。

セラミック出力フィルタ キャパシタを使用する場合は、推奨される LC 共振周波数を  $7\text{kHz}$  以下にする必要があります。出力インダクタはすでに  $15\mu\text{H}$  のものを選択したため、出力キャパシタの最小値は次のように制限されます。

$$C_O (\text{MIN}) \geq \frac{1}{(2\pi \times 7000)^2 \times L_O} \quad (16)$$

キャパシタの最小値は  $34\mu\text{F}$  と計算されます。この回路でこれより大きな値のキャパシタを使用すると、より良い過渡応答を実現できます。C3 には  $100\mu\text{F}$  の出力コンデンサを 1 個使用しています。セラミック キャパシタの実際の静電容量が、印加電圧により減少することに注意してください。この例では、出力電圧が  $3.3\text{V}$  に設定されており、この影響を最小限に抑えています。

### 7.2.3.2.2 外部補償回路

セラミック出力キャパシタを使用する場合は、閉ループ システムを安定させるために付加的な回路が必要です。この回路の場合、外付けコンポーネントは R3、C4、C6、および C7 です。これらのコンポーネントの値を決定するには、まず、出力フィルタの LC 共振周波数を計算します。

$$F_{LC} = \frac{1}{2\pi \sqrt{L_O \times C_O (\text{EFF})}} \quad (17)$$

この例では、実効共振周波数は  $4109\text{Hz}$  と計算できます。

R1、R2、R3、C5、C6、および C7 によって構成される回路には 2 つの極と 2 つのゼロ点があり、これらを使用してフィードバック回路の全体的な応答をカスタマイズし、セラミック出力キャパシタの使用に対応します。極とゼロ点の場所は、次の式で求めることができます。

$$F_{p1} = 500000 \times \frac{V_O}{F_{LC}} \quad (18)$$

$$F_{z1} = 0.7 \times F_{LC} \quad (19)$$

$$F_{z2} = 2.5 \times F_{LC} \quad (20)$$

最後の極は非常に高い周波数に位置するので、考慮に値しません。式 20 で定義されている 2 番目のゼロ点 (fz2) は、周波数の倍値に 2.5 を使用します。場合によっては、この値を多少高くするか低くする必要があります。2.3~2.7 の範囲の値で適切に動作します。式 12 を使用して計算を行う際に、R1 と R2 の値を  $3.3\text{V}$  の出力電圧に対応させて固定します。この設計では、 $R1 = 10\text{k}\Omega$ 、 $R2 = 5.90\text{k}\Omega$  にしています。 $F_{p1} = 401\text{Hz}$ 、 $F_{z1} = 2876\text{Hz}$ 、 $F_{z2} = 10.3\text{kHz}$  の場合、R3、C6、C7 の値は 式 21、式 22、および 式 23 を使用して決定されます。

$$C7 = \frac{1}{2\pi \times F_{p1} \times (R1 \parallel R2)} \quad (21)$$

$$R3 = \frac{1}{2\pi \times F_{z1} \times C7} \quad (22)$$

$$C6 = \frac{1}{2\pi \times F_{z2} \times R1} \quad (23)$$

この設計では、最も近い標準値を使用し、C7 を  $0.1\mu\text{F}$ 、R3 を  $549\Omega$ 、C6 を  $1500\text{pF}$  にしています。C4 を追加すると、負荷レギュレーションの性能が向上します。C4 は、2 番目の極に対応する周波数のポイントで C6 と実質的に並列になるため、C6 に対して相対的に小さい値、つまり C6 の値の  $1/10$  未満にする必要があります。この例では、 $150\text{pF}$  で適切に動作します。

TPS5430、TPS5431、その他の広電圧範囲デバイスの外部補償の詳細については、『[TPS5410/20/30/31 でのアルミニウム / セラミック出力コンデンサの使用](#)』アプリケーション レポートを参照してください。

## 7.3 電源に関する推奨事項

TPS5430 は、 $5.5\text{V} \sim 36\text{V}$  の入力電源電圧範囲で動作するように設計されています。TPS5431 は、 $5.5\text{V} \sim 23\text{V}$  の入力電源電圧範囲で動作するように設計されています。この入力電源は、入力電源電圧範囲内に維持する必要があります。入力電源が TPS543x コンバータから数インチ以上離れている場合は、セラミック バイパス キャパシタに加えて追加のバルク容量が必要となることがあります。通常は、 $100\mu\text{F}$  の電解コンデンサを使用します。

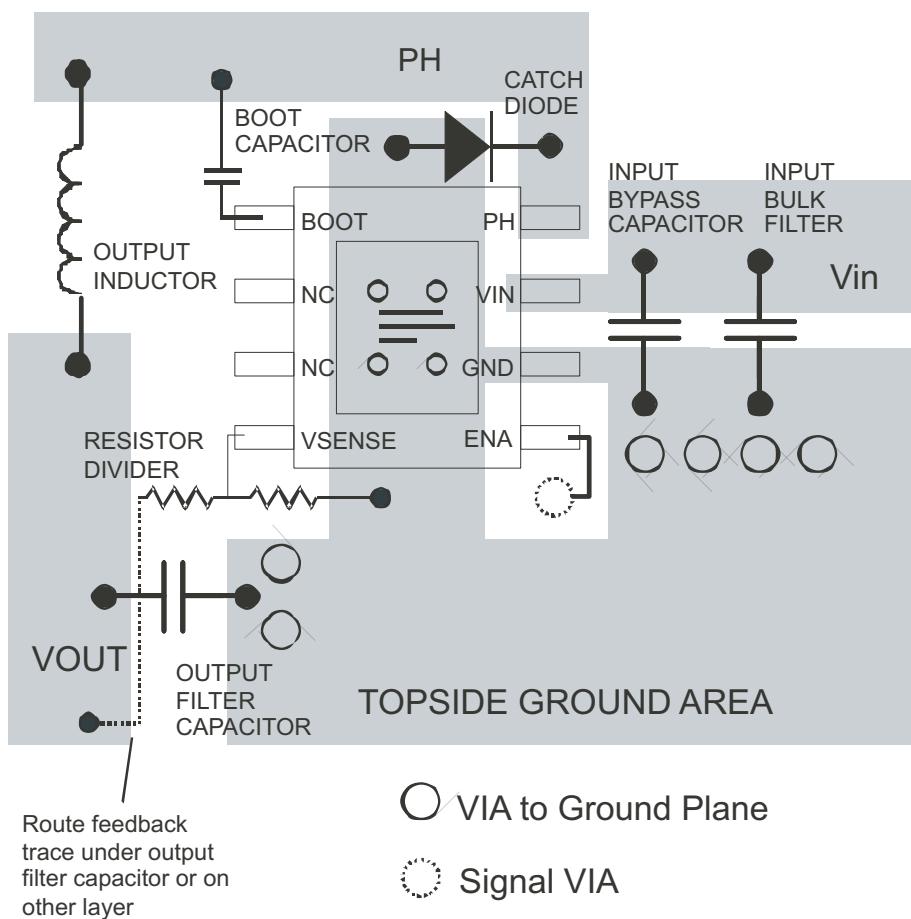

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

低 ESR のセラミック・バイパス・キャパシタを、VIN ピンに接続します。バイパス キャパシタ接続、VIN ピン、および TPS543x のグランド ピンによって形成されるループ領域を最小限に抑えるように注意する必要があります。そのためには、VIN パターンに隣接するデバイスの下のトップサイド グランド領域を広げ、バイパス・キャパシタができるだけ VIN ピンに近づけて設置するのが最善の方法です。推奨される最小のバイパス・キャパシタは、X5R または X7R クラスの誘導体が使用されている  $4.7\mu\text{F}$  のセラミック・キャパシタです。

IC 直下のトップ層には、DAP に接続するための露出した領域を持つグランド領域が必要です。ビアを使用して、このグランド領域を任意の内部グランド プレーンに接続します。入力および出力フィルタコンデンサのグランド側にも、追加のビアを使用します。GND ピンは、以下に示すように、デバイスの下のグランド領域に接続することによって PCB のグランドに接続する必要があります。

PH ピンは、出力インダクタ、キャッチ・ダイオード、およびブート キャパシタに接続する必要があります。PH の接続はスイッチング ノードであるため、インダクタは PH ピンのすぐ近くに配置し、PCB 導体の面積をできるだけ小さくして過度の容量性カップリングを避ける必要があります。キャッチ ダイオードもデバイスの近くに配置し、出力電流ループ領域の面積を最小化する必要があります。図に示すように、位相ノードと BOOT ピンの間にはブート・キャパシタを接続します。ブート・キャパシタは IC に近づけて配置し、導体パターンはできるだけ短くしてください。図に示すように部品を配置し接続すると正常に動作しますが、これとは別の接続を行うことも可能です。

VOUT パターンと GND の間には、図に示すように出力フィルタ・キャパシタを接続します。PH ピン、Lout、Cout、および GND によって形成されるループは、実用上適切な範囲でなるべく小さくすることが重要です。

出力電圧を設定するために、抵抗デバイダ回路を使用して、VOUT パターンを VSENSE ピンに接続します。このパターンは、PH パターンから少し離して配線してください。IC パッケージのサイズとデバイスのピン配置の関係で、このパターンを出力キャパシタの下に配線しなければならない場合があります。出力キャパシタの下に配線できない場合は、別の層上に配線します。

図 7-12 に示すようなグランド接続方法を使用している場合は、別の層へのビア接続を使用して ENA ピンに配線します。

### 7.4.2 レイアウト例

図 7-12. 設計レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイスのサポート

#### 8.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 8.1.2 開発サポート

##### 8.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS5430 デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する。

- 設計のレポートを PDF で印刷し、設計を共有する。

WEBENCH ツールの詳細は、[www.ti.com/WEBENCH](http://www.ti.com/WEBENCH) でご覧になれます。

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision J (July 2022) to Revision K (January 2024)</b>                                                                                                                                                                                                                                        | <b>Page</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • データシート全体にわたって WEBENCH® のリンクを更新 PowerPAD™ パッケージに言及する場合に「集積回路」を追加。MOSFET 抵抗を $110\text{m}\Omega$ から $100\text{m}\Omega$ に変更。 $I_Q$ を $18\mu\text{A}$ から $15\mu\text{A}$ に変更。.....                                                                                                                              | 1           |

| • 「ピン構成」の図のタイトルを「DDA パッケージ 8 ピン SOIC (サーマル パッド付き) 上面図」に変更し、そのタイトルを正しい位置に移動。「PowerPAD」を「DAP」に変更。.....                                                                                                                                                                                                           | 3           |

| • 特定のパラメータ名を含まず、最小および最大列を含む新しい形式に「絶対最大定格」表を更新。ヘッダーに $T_J$ を含める。信号名の代わりにピン名を使う。BOOT 電圧と PH 電圧を出力電圧として表示。脚注を更新し、注 2 を削除。.....                                                                                                                                                                                    | 4           |

| • BOOT と PH の間の電圧の絶対最大定格を $10\text{V}$ から $6\text{V}$ に変更。.....                                                                                                                                                                                                                                                | 4           |

| • PH と GND の間の電圧の絶対最大定格 (過渡 $10\text{ns}$ 未満) を $-4\text{V}$ から $-1.2\text{V}$ に変更。.....                                                                                                                                                                                                                       | 4           |

| • CDM ESD を $\pm 1500\text{V}$ から $\pm 750\text{V}$ に変更.....                                                                                                                                                                                                                                                   | 4           |

| • 推奨動作条件の「V」を「入力電圧」に変更。.....                                                                                                                                                                                                                                                                                   | 4           |

| • JEDEC 規格の情報を含む現行のテキサス・インスツルメンツ規格に合わせて熱に関する情報の脚注を更新。カスタム基板情報を EVM R <sub>θJA</sub> 情報に変更.....                                                                                                                                                                                                                 | 4           |

| • $R_{\theta\text{JC}(\text{top})}$ を $46.4$ から $46$ に、 $R_{\theta\text{JB}}$ を $20.8$ から $15$ に、 $\Psi_{JT}$ を $4.9$ から $5.2$ に、 $\Psi_{JB}$ を $20.7$ から $15.3$ に、 $R_{\theta\text{JC}(\text{bot})}$ を $0.8$ から $6$ に変更。.....                                                                                 | 4           |

| • 代表的な仕様の EC 表のヘッダーに条件を追加、パラメータ名と、パラメータの説明で使われるピン名を追加。脚注を追加。.....                                                                                                                                                                                                                                              | 5           |

| • $V_{FB}$ のテスト条件を「 $I_O = 0\text{A} \sim 3\text{A}$ 」から「 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 」に変更、 $r_{DS(\text{ON})}$ を $R_{DS(\text{ON})(\text{HS})}$ に変更、 $R_{DS(\text{ON})(\text{HS})}$ のテスト条件を「 $V_{IN} = 5.5\text{V}$ 」から「 $V_{IN} = 5.5\text{V}$ , $V_{BOOT-SW} = 4.0\text{V}$ 」に変更。..... | 5           |

| • $I_Q$ の名前を $I_{SD(VIN)}$ (ENA が Low の場合) および $I_{Q(VIN)}$ (チップがアクティブの場合) に変更。.....                                                                                                                                                                                                                           | 5           |

| • $D_{\text{MAX}}$ のテスト条件「 $f_{SW} = 500\text{kHz}$ 」と 2 番目の $R_{DS(\text{ON})(\text{HS})}$ 仕様のテスト条件「 $V_{IN} = 12\text{V}$ , $V_{BOOT-SW} = 4.5\text{V}$ 」を追加。.....                                                                                                                                           | 5           |

| • $I_{Q(VIN)}$ の標準値を $3\text{mA}$ から $2\text{mA}$ に、 $I_{SD(VIN)}$ の標準値を $18\mu\text{A}$ から $15\mu\text{A}$ に、 $V_{INUVLO(H)}$ を $330\text{mV}$ から $0.35\text{V}$ に、 $V_{EN(H)}$ を $450\text{mV}$ から $325\text{mV}$ に変更。.....                                                                                  | 5           |

| • $V_{IN} = 5\text{V}$ (標準値) の $R_{DS(\text{ON})}$ を $150\text{m}\Omega$ から $125\text{m}\Omega$ に、 $V_{IN} = 12\text{V}$ の $R_{DS(\text{ON})}$ を $110\text{m}\Omega$ から $100\text{m}\Omega$ に変更。.....                                                                                                          | 5           |

| • 「概要」の「 $110\text{m}\Omega$ ハイサイド MOSFET」を「 $100\text{m}\Omega$ ハイサイド MOSFET」に、 $18\mu\text{A}$ を $15\mu\text{A}$ に変更。.....                                                                                                                                                                                   | 8           |

| • 「イネーブル (ENA) と内部スロースタート時間」セクションのシャットダウン電流を $18\mu\text{A}$ から $15\mu\text{A}$ に変更。.....                                                                                                                                                                                                                      | 9           |

| • UVLO の説明の UVLO ヒステリシスを $330\text{mV}$ から $350\text{mV}$ に変更。.....                                                                                                                                                                                                                                            | 9           |

| • 図 7-1 の TPS5430DDA パッケージ図の「PwPd」を「DAP」に、回路の説明の「露出 PowerPAD™」を「DAP」に変更。.....                                                                                                                                                                                                                                  | 13          |

| • 図 7-9 の TPS5430DDA パッケージ図の「PwPd」を「DAP」に変更。.....                                                                                                                                                                                                                                                              | 21          |

| • 図 7-10 の TPS5431DDA パッケージ図の「PwPd」を「DAP」に変更。.....                                                                                                                                                                                                                                                             | 22          |

| • 図 7-11 の TPS5430DDA パッケージ図の「PwPd」を「DAP」に変更。.....                                                                                                                                                                                                                                                             | 23          |

| • 「レイアウトのガイドライン」の「PowerPAD」を「DAP」に変更 .....                                                                                                                                                                                                                                                                     | 25          |

| <b>Changes from Revision I (April 2017) to Revision J (July 2022)</b> | <b>Page</b> |

|-----------------------------------------------------------------------|-------------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新。.....                                     | 1           |

| Changes from Revision H (April 2016) to Revision I (March 2017) | Page |

|-----------------------------------------------------------------|------|

| • WEBENCH® モデルを追加.....                                          | 1    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

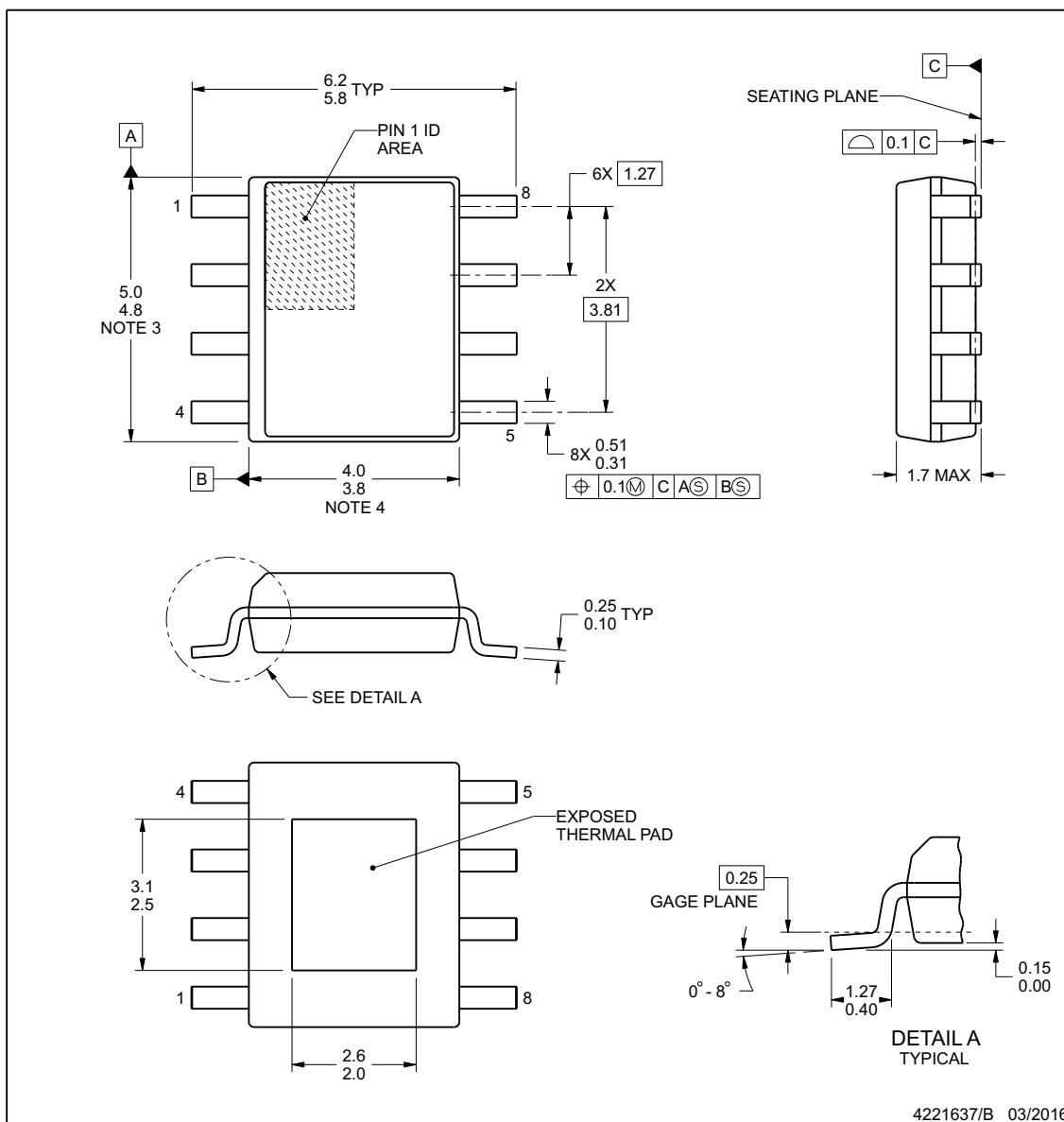

## PACKAGE OUTLINE

DDA0008J

## PowerPAD™ SOIC - 1.7 mm max height

## PLASTIC SMALL OUTLINE

PowerPAD is a trademark of Texas Instruments.

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012, variation BA.

www.ti.com

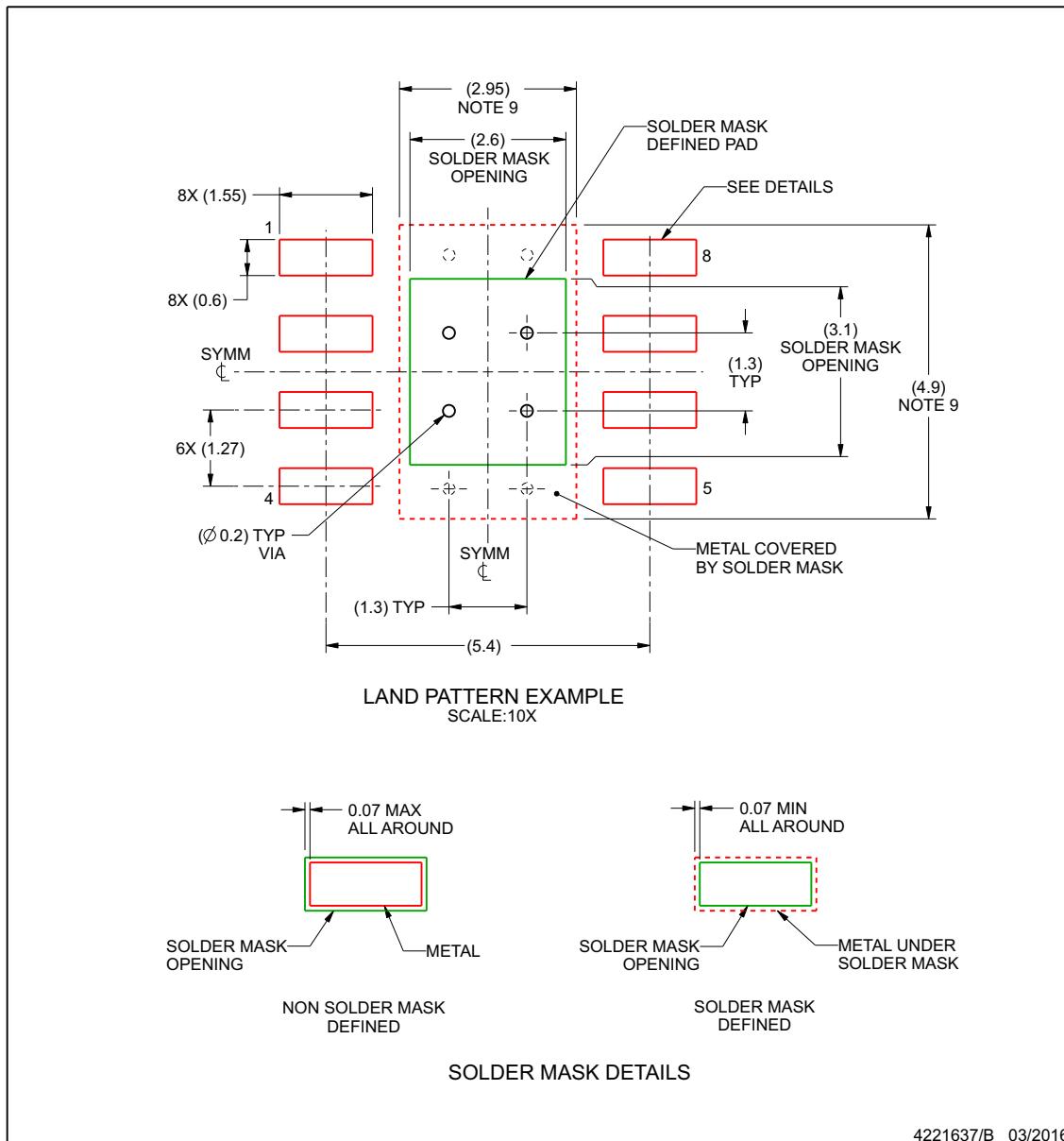

## EXAMPLE BOARD LAYOUT

**DDA0008J**

## PowerPAD™ SOIC - 1.7 mm max height

## PLASTIC SMALL OUTLINE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

www.ti.com

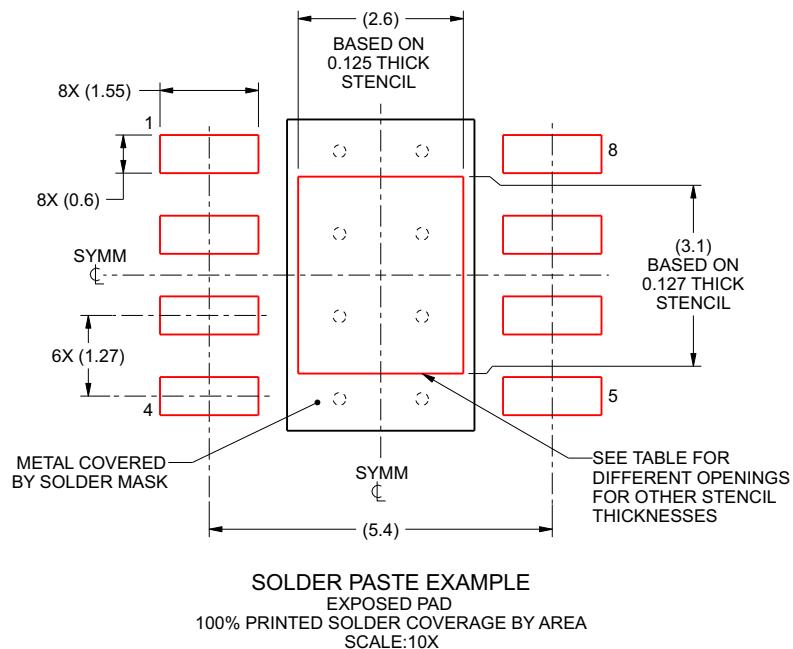

## EXAMPLE STENCIL DESIGN

**DDA0008J**

**PowerPAD™ SOIC - 1.7 mm max height**

PLASTIC SMALL OUTLINE

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.91 X 3.47            |

| 0.125             | 2.6 X 3.1 (SHOWN)      |

| 0.150             | 2.37 X 2.83            |

| 0.175             | 2.20 X 2.62            |

4221637/B 03/2016

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

[www.ti.com](http://www.ti.com)

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS5430DDA            | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDA.A          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDA.B          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDAG4          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDAR           | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDAR.A         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDAR.B         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5430DDARG4         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5430                |

| TPS5431DDA            | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDA.A          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDA.B          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDAG4          | Active        | Production           | SO PowerPAD (DDA)   8 | 75   TUBE             | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDAR           | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDAR.A         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDAR.B         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

| TPS5431DDARG4         | Active        | Production           | SO PowerPAD (DDA)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug   Nipda            | Level-1-260C-UNLIM                | -40 to 125   | 5431                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

**(2) Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

**(3) RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

**(4) Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**(5) MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

**(6) Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS5430 :**

- Automotive : [TPS5430-Q1](#)

- Enhanced Product : [TPS5430-EP](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

- Enhanced Product - Supports Defense, Aerospace and Medical Applications

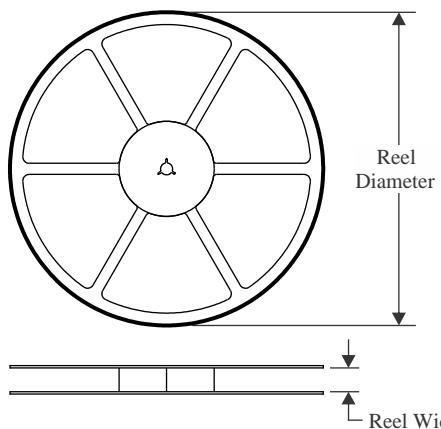

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

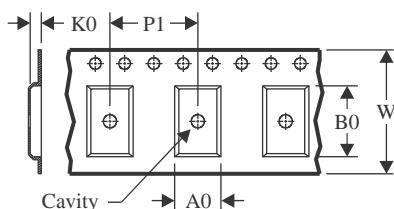

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

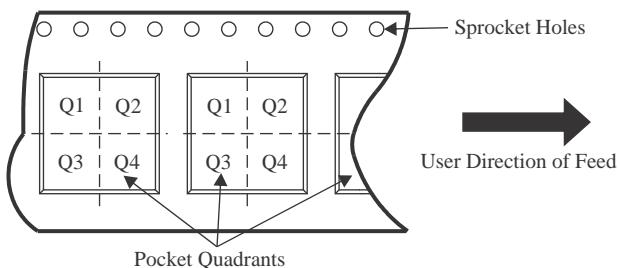

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS5430DDAR | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.8               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

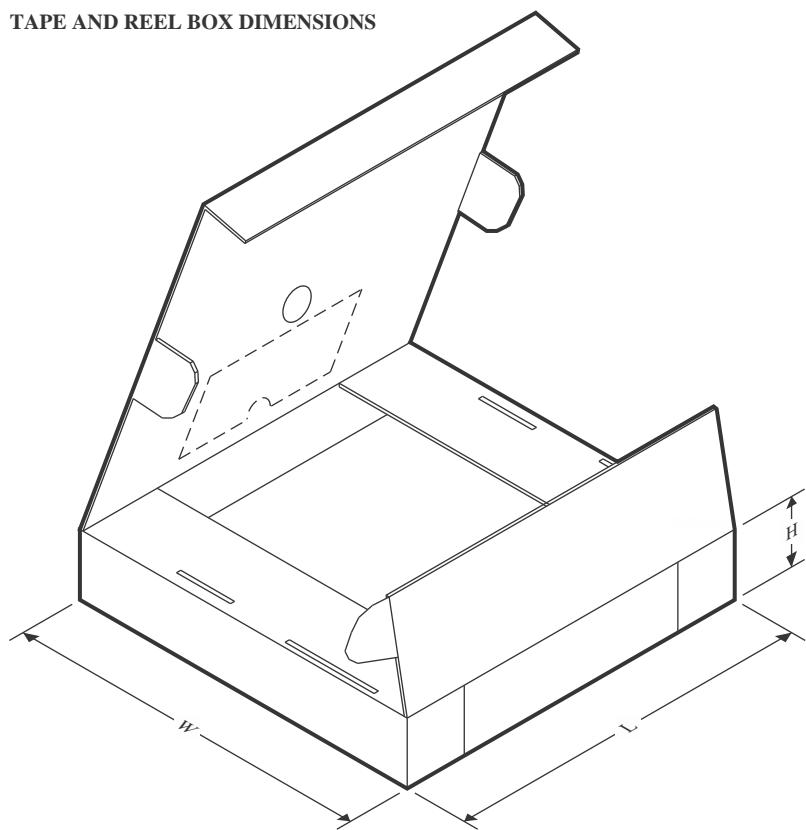

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS5430DDAR | SO PowerPAD  | DDA             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

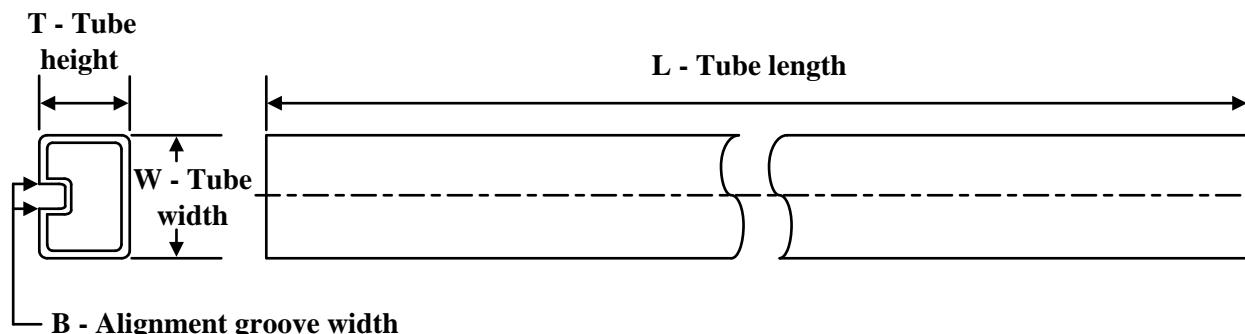

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ  | L (mm) | W (mm) | T (μm) | B (mm) |

|---------------|--------------|--------------|------|------|--------|--------|--------|--------|

| TPS5430DDA    | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDA    | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5430DDA    | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5430DDA.A  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5430DDA.A  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDA.A  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5430DDA.B  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDA.B  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5430DDA.B  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5430DDAG4  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5430DDAG4  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDAG4  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5430DDAR   | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDAR.A | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDAR.B | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5430DDARG4 | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDA    | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5431DDA    | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5431DDA    | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDA.A  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5431DDA.A  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDA.A  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5431DDA.B  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDA.B  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5431DDA.B  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5431DDAG4  | DDA          | HSOIC        | 8    | 75   | 506.6  | 8      | 3940   | 4.32   |

| TPS5431DDAG4  | DDA          | HSOIC        | 8    | 75   | 517    | 7.87   | 635    | 4.25   |

| TPS5431DDAG4  | DDA          | HSOIC        | 8    | 75   | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDAR   | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

---

| Device        | Package Name | Package Type | Pins | SPQ  | L (mm) | W (mm) | T (μm) | B (mm) |

|---------------|--------------|--------------|------|------|--------|--------|--------|--------|

| TPS5431DDAR.A | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDAR.B | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

| TPS5431DDARG4 | DDA          | HSOIC        | 8    | 2500 | 508    | 12.19  | 510    | 7.88   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月