## Eco-mode™ 搭載、2A、28V入力、 降圧型SWIFT™ DC/DCコンバータ

### 特 長

- 入力電圧範囲：3.5V～28V

- 可変出力電圧：最小0.8V

- 内蔵の80mΩハイサイドMOSFETにより最大2Aの連続出力電流をサポート

- パルス・スキップEco-mode™により軽負荷で高い効率を実現

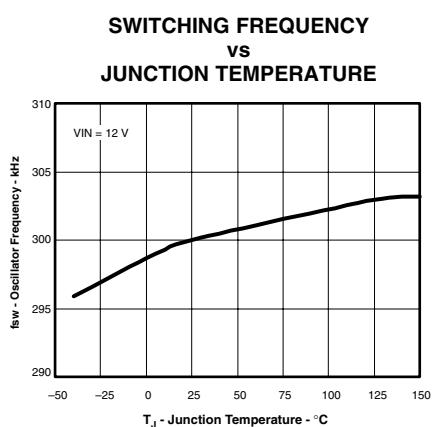

- 固定スイッチング周波数：300kHz

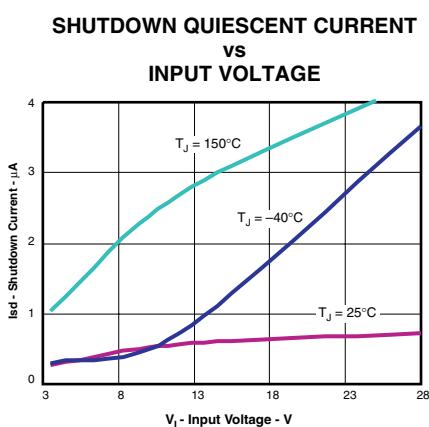

- シャットダウン時静止電流：標準1μA

- 可変スロー・スタートで突入電流を制限

- プログラミング可能なUVLOスレッショルド

- 過電圧過渡保護

- サイクル毎の電流制限、周波数フォールド・バック、および過熱シャットダウン保護

- 使いやすいSOIC8パッケージで供給

- SwitcherPro™ソフトウェア・ツールによるサポート (<http://focus.ti.com/docs/tools/folders/print/switcherpro.html>)

- SWIFT™関連のドキュメントについては、TIのWebサイト[www.ti.com/swift](http://www.ti.com/swift)をご覧ください。

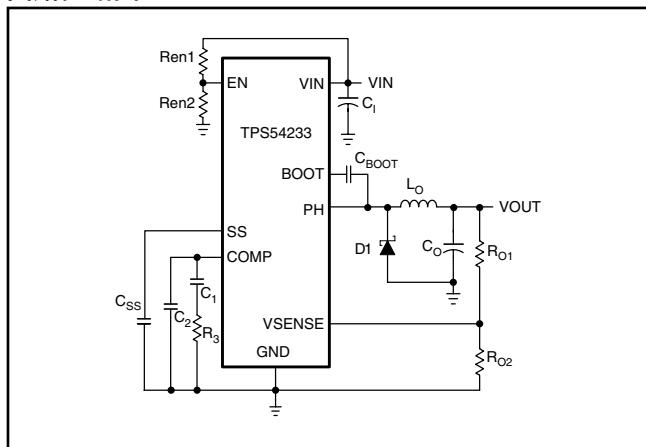

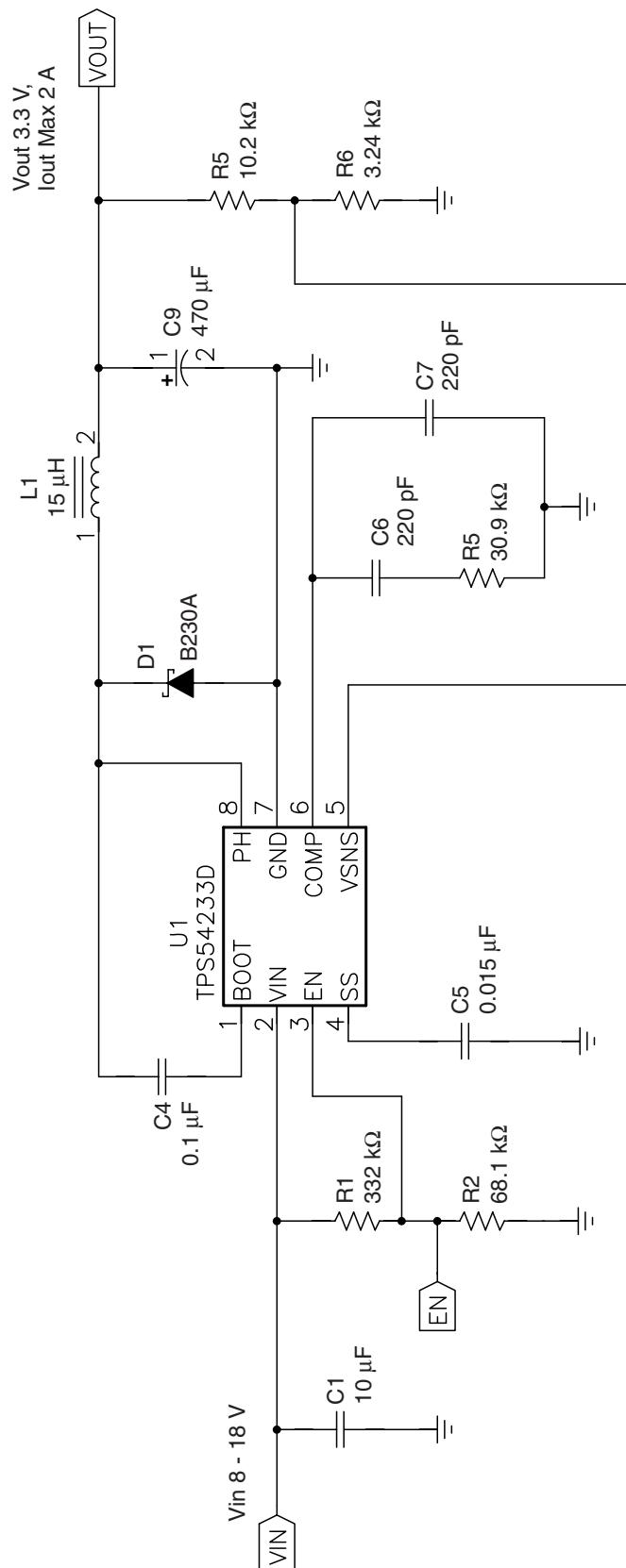

### 回路概略図

### ア プ リ ケ シ ョ ン

- セットトップ・ボックス、CPE機器、LCDディスプレイ、周辺機器、バッテリ充電器などの民生用アプリケーション

- 産業用およびカー・オーディオ用電源

- 5V、12V、24Vの分散型電源システム

### 概 要

TPS54233は、 $R_{DS(on)}$ のハイサイドMOSFETを内蔵した、28V、2Aの非同期バック・コンバータです。軽負荷時にはパルスをスキップするEco-mode™機能が自動的にオンになり、高効率動作を維持します。また、シャットダウン時電源電流が1μAと低いため、バッテリ駆動アプリケーションに使用できます。内部スロープ補償による電流モード制御により、外部補償が単純化され、セラミック出力コンデンサを使用しながら部品点数を減らすことができます。分圧抵抗を使用して、入力低電圧ロックアウトのヒステリシスをプログラミングできます。過電圧過渡保護回路により、起動時および過渡状態での電圧オーバーシュートが制限されます。また、サイクル毎の電流制御方式、周波数フォールド・バック、および過熱シャットダウンにより、過負荷状況下でデバイスおよび負荷を保護します。TPS54233は、熱特性向上のために内部で最適化された8ピンSOICパッケージで供給されます。

SWIFT、Eco-mode、SwitcherPro、PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

各種の設計ニーズに対しては、以下を参照してください。

|                     | TPS54231   | TPS54232   | TPS54233   | TPS54331   | TPS54332      |

|---------------------|------------|------------|------------|------------|---------------|

| I <sub>O</sub> (最大) | 2A         | 2A         | 2A         | 3A         | 3.5A          |

| 入力電圧範囲              | 3.5V - 28V    |

| スイッチング周波数(標準)       | 570kHz     | 1000kHz    | 300kHz     | 570kHz     | 1000kHz       |

| スイッチ電流制限(最小)        | 2.3A       | 2.3A       | 2.3A       | 3.5A       | 4.2A          |

| ピン/パッケージ            | 8SOIC      | 8SOIC      | 8SOIC      | 8SOIC      | 8SO PowerPAD™ |

## 製品情報<sup>(1)</sup>

| T <sub>J</sub> | パッケージ   | スイッチング周波数 | 部品番号 <sup>(2)</sup> |

|----------------|---------|-----------|---------------------|

| -40°C ~ 150°C  | 8ピンSOIC | 300 kHz   | TPS54233D           |

(1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

(2) Dパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(すなわち、TPS54233DR)。レイアウト情報についてはこのデータシートの「アプリケーション情報」を参照してください。

## 絶対最大定格<sup>(1)</sup>

動作温度範囲内(特に記述のない限り)

|                                |                                                   | VALUE     | 単位 |

|--------------------------------|---------------------------------------------------|-----------|----|

| Input Voltage                  | VIN                                               | -0.3 ~ 30 | V  |

|                                | EN                                                | -0.3 ~ 6  |    |

|                                | BOOT                                              | 38        |    |

|                                | VSENSE                                            | -0.3 ~ 3  |    |

|                                | COMP                                              | -0.3 ~ 3  |    |

|                                | SS                                                | -0.3 ~ 3  |    |

| Output Voltage                 | BOOT-PH                                           | 8         | V  |

|                                | PH                                                | -0.6 ~ 30 |    |

|                                | PH (10 ns transient from ground to negative peak) | -5        |    |

| Source Current                 | EN                                                | 100       | µA |

|                                | BOOT                                              | 100       | mA |

|                                | VSENSE                                            | 10        | µA |

|                                | PH                                                | 6         | A  |

| Sink Current                   | VIN                                               | 6         | A  |

|                                | COMP                                              | 100       | µA |

|                                | SS                                                | 200       |    |

| Electrostatic Discharge        | Human body model (HBM)                            | 2         | kV |

|                                | Charged device model (CDM)                        | 500       | V  |

| Operating Junction Temperature |                                                   | -40 ~ 150 | °C |

| Storage Temperature            |                                                   | -65 ~ 150 | °C |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

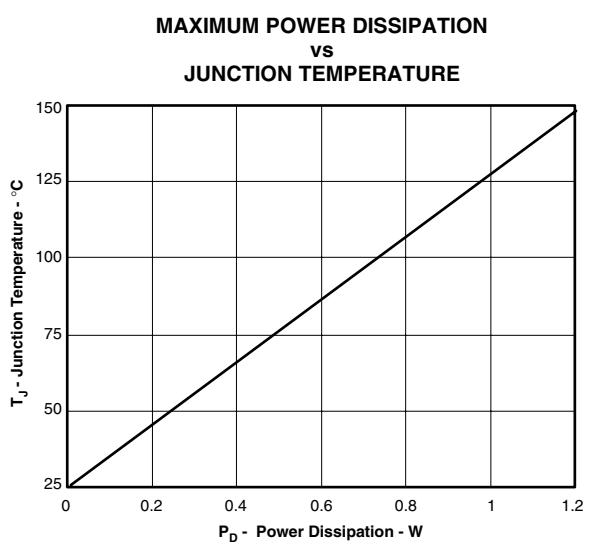

## パッケージ定格消費電力<sup>(1) (2) (3)</sup>

| PACKAGE | THERMAL IMPEDANCE<br>JUNCTION TO AMBIENT | PSEUDO THERMAL IMPEDANCE<br>JUNCTION TO TOP |

|---------|------------------------------------------|---------------------------------------------|

| SOIC8   | 100°C/W                                  | 5°C/W                                       |

- (1) 最大消費電力は過電流保護により制限されることがあります。

(2) 特定の周囲温度 $T_A$ での電力定格は、接合部温度150°Cで決定されます。これは、歪が大きく増加し始める温度です。

最高の性能および長期的な信頼性を得るには、PCBの熱管理で接合部温度を150°C以下に保持するようにしてください。

詳細については、このデータ・シートのアプリケーション情報の「消費電力の見積もり」を参照してください。

(3) テスト・ボードの条件は以下の通りです。

(a) サイズ：2インチ×1.5インチ、2層、厚さ0.062インチ

(b) PCBの上面および底面に重量2オンスの銅配線

(c) デバイス・パッケージ下に6つのサーマル・ピア

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                                       | MIN | TYP | MAX | 単位 |

|---------------------------------------|-----|-----|-----|----|

| Operating Input Voltage on (VIN pin)  | 3.5 | 28  | V   |    |

| Operating junction temperature, $T_J$ | -40 | 150 | °C  |    |

## 電気的特性

$T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{IN} = 3.5\text{V} \sim 28\text{V}$ (特に記述のない限り)

| DESCRIPTION                                         | テスト条件                                                                                   | MIN   | TYP  | MAX   | 単位    |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|-------|-------|

| <b>SUPPLY VOLTAGE (VIN PIN)</b>                     |                                                                                         |       |      |       |       |

| Internal undervoltage lockout threshold             | Rising and Falling                                                                      |       | 3.5  |       | V     |

| Shutdown supply current                             | EN = 0V, VIN = 12V, $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$                       |       | 1    | 4     | μA    |

| Operating – non switching supply current            | VSENSE = 0.85 V                                                                         |       | 75   | 110   | μA    |

| <b>ENABLE AND UVLO (EN PIN)</b>                     |                                                                                         |       |      |       |       |

| Enable threshold                                    | Rising and Falling                                                                      | 1.25  | 1.35 |       | V     |

| Input current                                       | Enable threshold – 50 mV                                                                | –1    |      |       | μA    |

| Input current                                       | Enable threshold + 50 mV                                                                | –4    |      |       | μA    |

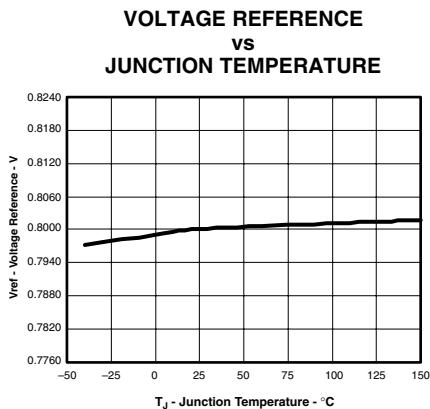

| <b>VOLTAGE REFERENCE</b>                            |                                                                                         |       |      |       |       |

| Voltage reference                                   |                                                                                         | 0.772 | 0.8  | 0.828 | V     |

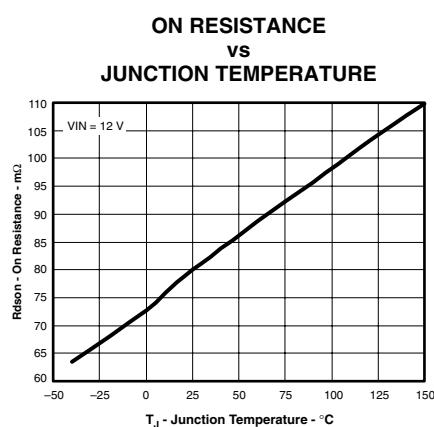

| <b>HIGH-SIDE MOSFET</b>                             |                                                                                         |       |      |       |       |

| On resistance                                       | BOOT-PH = 3 V, VIN = 3.5 V                                                              | 115   | 200  |       | mΩ    |

|                                                     | BOOT-PH = 6 V, VIN = 12 V                                                               | 80    | 150  |       |       |

| <b>ERROR AMPLIFIER</b>                              |                                                                                         |       |      |       |       |

| Error amplifier transconductance (gm)               | $-2 \mu\text{A} < I_{(\text{COMP})} < 2 \mu\text{A}$ , $V_{(\text{COMP})} = 1 \text{V}$ | 92    |      |       | μmhos |

| Error amplifier DC gain <sup>(1)</sup>              | VSENSE = 0.8 V                                                                          | 800   |      |       | V/V   |

| Error amplifier unity gain bandwidth <sup>(1)</sup> | 5 pF capacitance from COMP to GND pins                                                  | 2.7   |      |       | MHz   |

| Error amplifier source/sink current                 | $V_{(\text{COMP})} = 1 \text{V}$ , 100 mV overdrive                                     | ±7    |      |       | μA    |

| Switch current to COMP transconductance             | VIN = 12 V                                                                              | 9     |      |       | A/V   |

| <b>SWITCHING FREQUENCY</b>                          |                                                                                         |       |      |       |       |

| TPS54233 Switching Frequency                        | VIN = 12V                                                                               | 210   | 300  | 390   | kHz   |

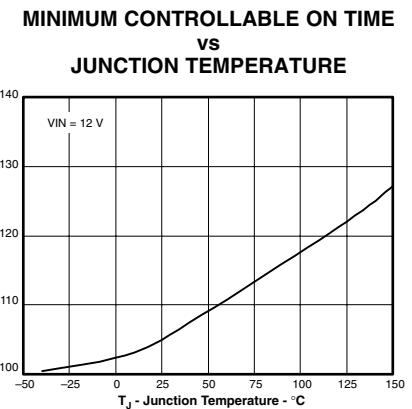

| Minimum controllable on time                        | VIN = 12V, 25°C                                                                         |       | 105  | 130   | ns    |

| Maximum controllable duty ratio <sup>(1)</sup>      | BOOT-PH = 6 V                                                                           | 90%   | 93%  |       |       |

| <b>PULSE SKIPPING ECO-MODE™</b>                     |                                                                                         |       |      |       |       |

| Pulse skipping Eco-mode™ switch current threshold   |                                                                                         | 100   |      |       | mA    |

| <b>CURRENT LIMIT</b>                                |                                                                                         |       |      |       |       |

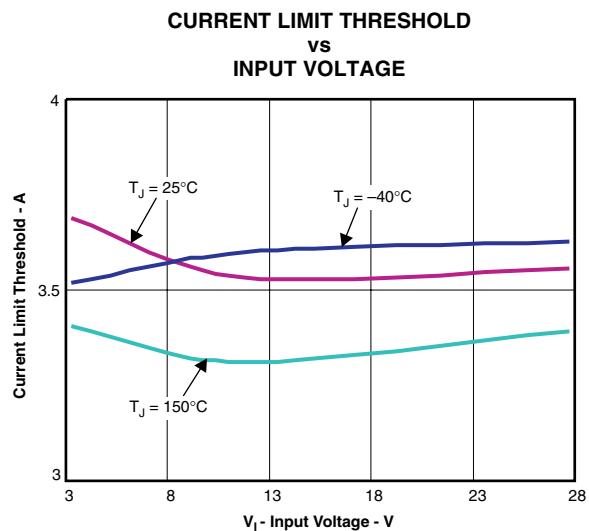

| Current limit threshold                             | VIN = 12 V                                                                              | 2.3   | 3.5  |       | A     |

(1) 設計で規定されています。

## 電気的特性

$T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{IN} = 3.5\text{V} \sim 28\text{V}$  (特に記述のない限り)

| DESCRIPTION                | テスト条件                     | MIN | TYP | MAX | 単位            |

|----------------------------|---------------------------|-----|-----|-----|---------------|

| <b>THERMAL SHUTDOWN</b>    |                           |     |     |     |               |

| Thermal Shutdown           |                           | 165 |     |     | °C            |

| <b>SLOW START (SS PIN)</b> |                           |     |     |     |               |

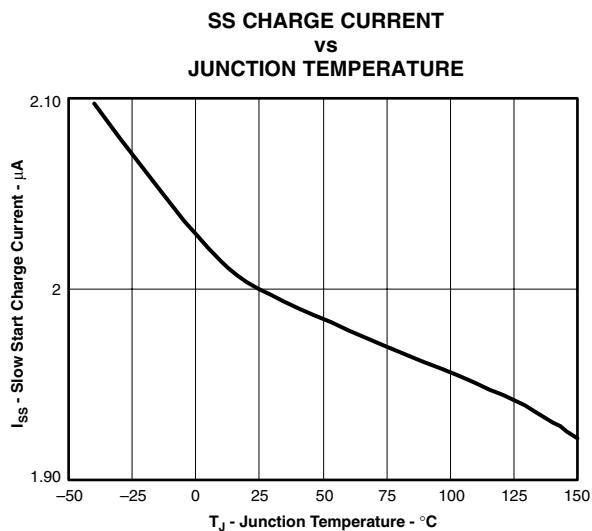

| Charge current             | $V_{(SS)} = 0.4\text{ V}$ | 2   |     |     | $\mu\text{A}$ |

| SS to VSENSE matching      | $V_{(SS)} = 0.4\text{ V}$ | 10  |     |     | mV            |

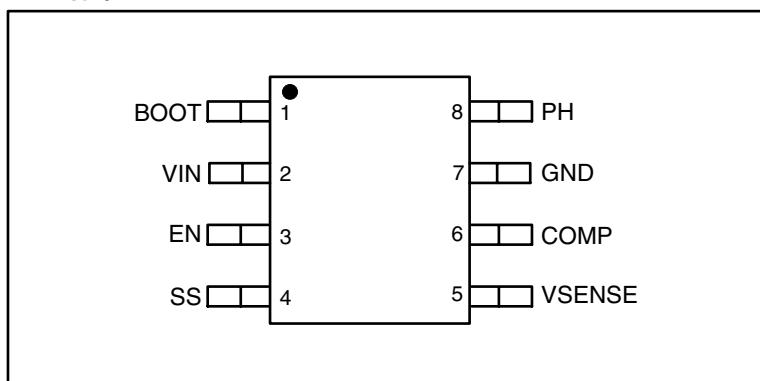

## 製品情報

### ピン配置

## 端子機能

| 端子     |    | 説明                                                                                                                |

|--------|----|-------------------------------------------------------------------------------------------------------------------|

| 名前     | 番号 |                                                                                                                   |

| BOOT   | 1  | BOOTとPHの間に $0.1\mu\text{F}$ のブートストラップ・コンデンサが必要です。このコンデンサの電圧が最小要件を下回った場合、ハイサイドMOSFETはコンデンサがリフレッシュされるまで強制的にオフになります。 |

| VIN    | 2  | 入力電源電圧、 $3.5\text{V} \sim 28\text{V}$                                                                             |

| EN     | 3  | イネーブル・ピン。ディスエーブルにするには、 $1.25\text{V}$ 未満にプルダウンします。イネーブルにするには、フローティングにします。2つの抵抗を使用して入力低電圧ロックアウトをプログラミングすることを推奨します。 |

| SS     | 4  | スロー・スタート・ピン。このピンに接続する外部コンデンサによって、出力の立ち上がり時間が設定されます。                                                               |

| VSENSE | 5  | gm誤差増幅器の反転ノード。                                                                                                    |

| COMP   | 6  | 誤差増幅器の出力、およびPWMコンパレータの入力。このピンに周波数補償部品を接続します。                                                                      |

| GND    | 7  | グランド。                                                                                                             |

| PH     | 8  | 内部ハイサイド・パワーMOSFETのソース。                                                                                            |

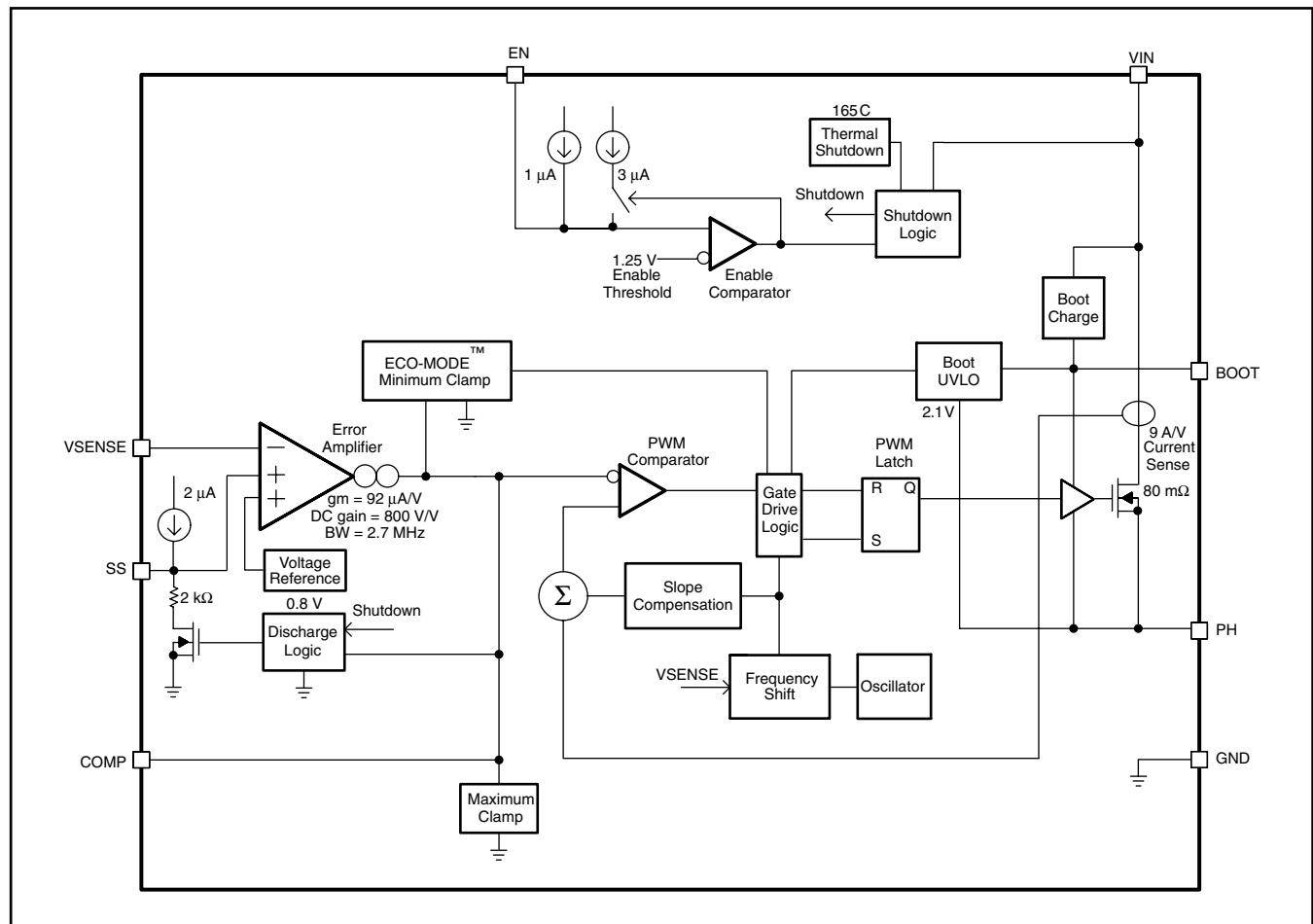

## 機能ブロック図

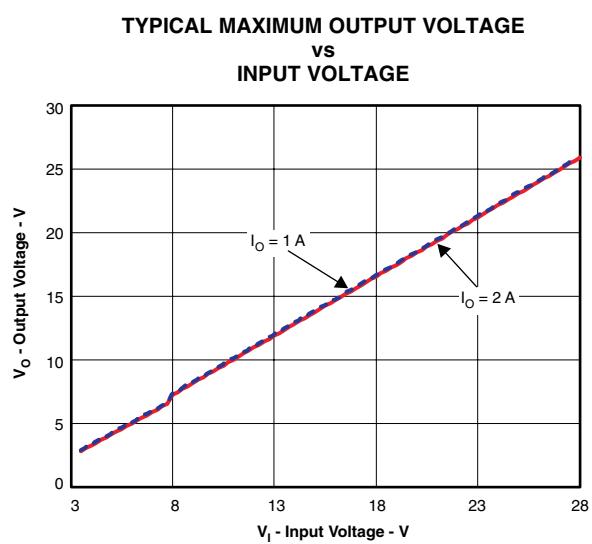

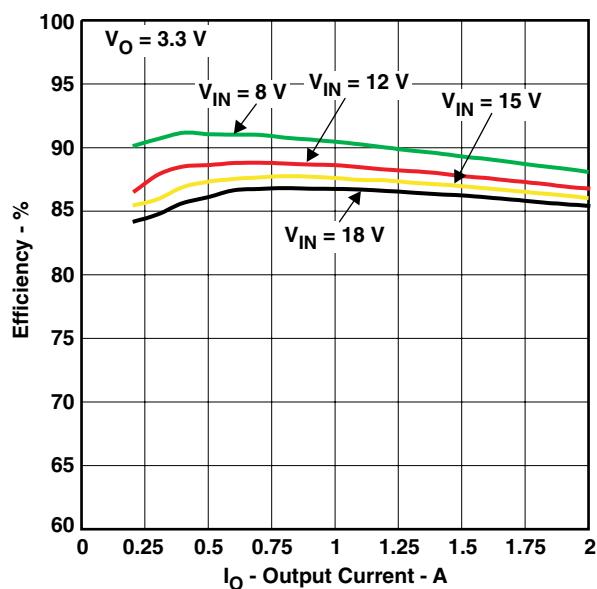

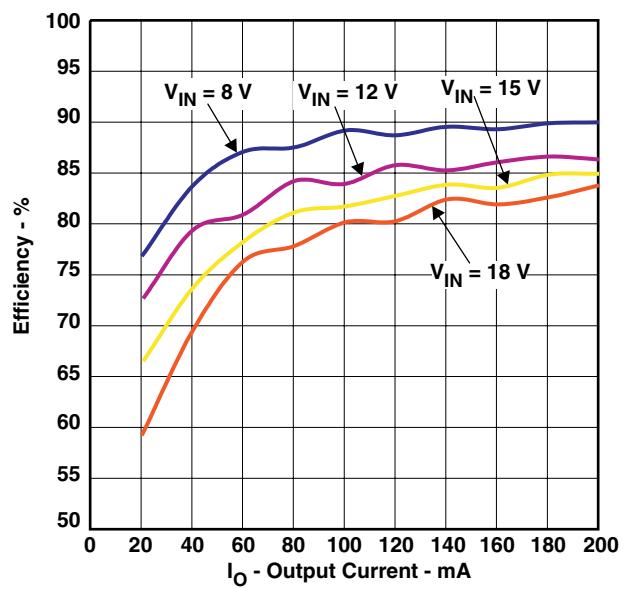

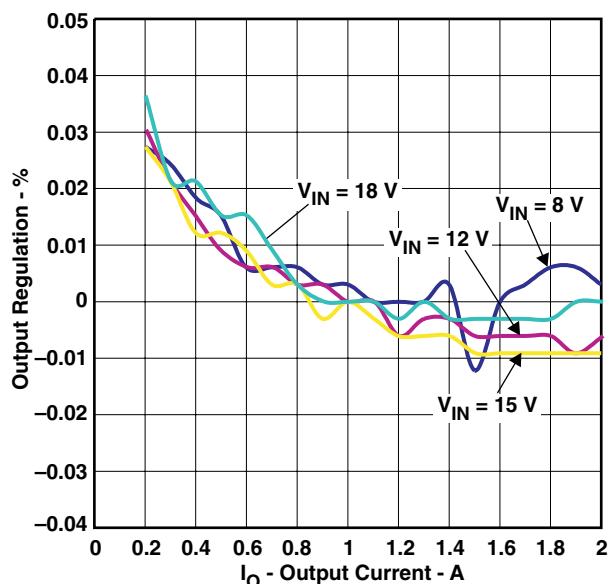

## 代表的特性

### 特性曲線

図 1

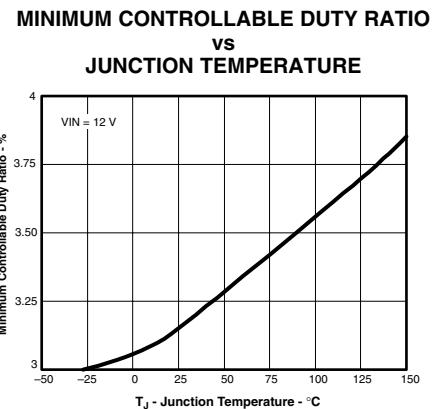

図 2

図 3

## 代表的特性

### 特性曲線

図 4

図 5

図 6

図 7

図 8

### 補助的なアプリケーション曲線

図 9

図 10

## 概要

TPS54233は、ハイサイドNチャネルMOSFETを内蔵した、28V、2Aの降圧型(バック)コンバータです。ラインおよび負荷の過渡状態における性能を向上させるため、定周波数の電流モード制御で動作し、出力容量の低減、外部周波数補償設計の単純化を実現しています。TPS54233はスイッチング周波数が300kHzにプリセットされています。

TPS54233が正常に動作するには、最低3.5Vの入力電圧が必要です。ENピンの内部プルアップ電流源を使用して、入力電圧低電圧ロックアウト(UVLO)を2つの外部抵抗により調整可能です。また、このプルアップ電流は、ENピンがフローティングのときにデバイスが動作するためのデフォルト状態を提供します。無負荷で非スイッチング時の動作電流は、標準で75μAです。デバイスがディスエーブル時の電源電流は、標準で1μAです。

内蔵の80mΩハイサイドMOSFETにより、最大2Aの連続出力電流で高効率の電源設計が可能になります。

TPS54233は、ブート再充電ダイオードを内蔵し、外部部品数を低減できます。内蔵ハイサイドMOSFETのバイアス電圧は、BOOT-PHピン間の外部コンデンサによって供給されます。このブート・コンデンサ電圧はUVLO回路によって監視され、標準2.1Vの内部設定されたスレッショルドを下回ると、ハイサイドMOSFETがオフになります。出力電圧は、リファレンス電圧と同じ値まで降圧させることができます。

外部コンデンサを追加することにより、TPS54233のスロー・スタート時間を調整でき、柔軟な出力フィルタ選択が可能になります。

軽負荷での効率を向上させるため、ピーク・インダクタ電流が標準100mAを下回ると、TPS54233は特別なパルス・スキップEco-mode<sup>TM</sup>に入ります。

周波数フォールドバックにより、起動時および過電流時にスイッチング周波数が低くなり、インダクタ電流を制御しやすくなります。過熱シャットダウン機能により、障害状況での保護が強化されています。

## 詳細説明

### 固定周波数PWM制御

TPS54233は、固定周波数のピーク電流モード制御を使用します。TPS54233の内部スイッチング周波数は、300kHzに固定されています。

### Eco-mode<sup>TM</sup>

TPS54233は、軽負荷時の効率を向上させるため、負荷電流が小さいときには、パルスをスキップするEco-mode<sup>TM</sup>で動作するよう設計されています。ピーク・インダクタ電流が標準100mAを下回ると、COMPピンの電圧が標準0.5Vまで低下し、デバイスはEco-mode<sup>TM</sup>に入れます。デバイスがEco-mode<sup>TM</sup>で動作中は、COMPピンの電圧が内部で0.5Vにクランプされ、ハイサイド内蔵MOSFETのスイッチングを防ぎます。COMPピンの電圧が0.5Vを超えてEco-mode<sup>TM</sup>を終了するためには、ピーク・インダクタ電流が100mAを上回る必要があります。内蔵の電流コンバレータはピーク・インダクタ電流のみを捕捉するため、Eco-mode<sup>TM</sup>に入るときの平均負荷電流は、アプリケーションおよび外部出力フィルタによって異なります。

### 電圧リファレンス( $V_{ref}$ )

電圧リファレンス・システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで、±2%の初期精度を持つ電圧リファレンス(温度に対して±3.5%)を生成します。標準の電圧リファレンスは、0.8Vに設計されています。

### ブートストラップ電圧(BOOT)

TPS54233にはブート・レギュレータが内蔵され、ハイサイドMOSFETのゲート駆動電圧を提供するために、BOOTピンとPHピンの間に0.1μFのセラミック・コンデンサが必要です。温度および電圧に対して安定した特性を持つため、X7RまたはX5Rクラスの誘電体を持つセラミック・コンデンサを推奨します。ドロップ・アウトを改善するため、TPS54233は、BOOT-PHピン間の電圧が標準2.1V以上であれば、100%のデューティ・サイクルで動作するよう設計されています。

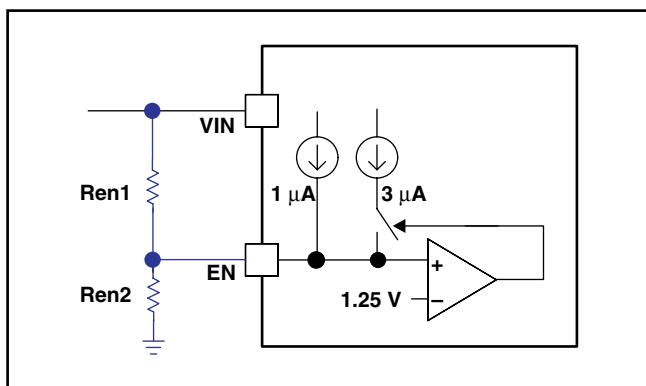

## イネーブル、および可変入力低電圧ロックアウト (VIN UVLO)

ENピンには内部プルアップ電流源があり、ENピンがフローティングのときにTPS54233が動作するデフォルト状態を提供します。

VINピンの電圧が内部のVIN UVLOスレッショルドを下回ると、TPS54233はディスエーブルになります。VINが( $V_{OUT} + 2V$ )より大きい場合を除き、外部VIN UVLOを使用してヒステリシスを追加することを推奨します。ヒステリシス付きのVIN UVLO電圧を調整するには、図11に示すように、ENピンに接続した外部回路を使用します。ENピンの電圧が1.25Vを超えると、 $3\mu A$ のヒステリシスが追加されます。目的のVIN UVLOスレッショルド電圧を得るために必要な抵抗値は、式(1)および式(2)で計算します。 $V_{START}$ は入力開始スレッショルド電圧、 $V_{STOP}$ は入力停止スレッショルド電圧、 $V_{EN}$ はイネーブル・スレッショルド電圧(1.25V)です。 $V_{STOP}$ は常に、3.5Vより大きい必要があります。

図 11. 可変入力低電圧ロックアウト

$$Ren1 = \frac{V_{START} - V_{STOP}}{3 \mu A} \quad (1)$$

$$Ren2 = \frac{V_{EN}}{\frac{V_{START} - V_{EN}}{Ren1} + 1 \mu A} \quad (2)$$

## SSピンを使用したプログラミング可能なスロー・スタート

スロー・スタート時間は内部設定されていないため、外部でスロー・スタート時間をプログラムすることを推奨します。TPS54233では、SSピン電圧または内部電圧リファレンスの低い方の電圧を、誤差増幅器に供給される電源リファレンス電圧として使用し、それに従って出力のレギュレーションを行います。SSピンとグランド間のコンデンサ( $C_{SS}$ )により、スロー・スタート時間が実装されます。TPS54233には、外部のスロー・スタート・コンデンサを充電する $2\mu A$ のプルアップ電流源が内蔵されています。スロー・スタート時間(10%~90%)は式(3)で計算されます。 $V_{ref}$ は0.8Vであり、 $I_{SS}$ 電流は $2\mu A$ です。

$$T_{SS}(ms) = \frac{C_{SS}(nF) \times V_{ref}(V)}{I_{SS}(\mu A)} \quad (3)$$

良好なスタートアップ動作を保証するには、スロー・スタート時間を1ms~10msの範囲内にする必要があります。スロー・スタート・コンデンサは、 $27nF$ 以下にしてください。

通常動作中に、入力電圧がVIN UVLOスレッショルドを下回るか、ENピンが1.25V未満にプルダウンされるか、または過熱シャットダウンが発生した場合、TPS54233はスイッチングを停止します。

## 誤差増幅器

TPS54233は、誤差増幅器としてトランスコンダクタンス・アンプを内蔵しています。誤差増幅器は、VSENSEの電圧を、誤差増幅器の入力に印加された内部の実効電圧リファレンスと比較します。誤差増幅器のトランスコンダクタンスは、通常動作時には $92\mu A/V$ です。周波数補償部品をCOMPピンとグランドの間に接続します。

## スロープ補償

50%を超えるデューティ・サイクルでの動作時に低調波発振を防ぐため、TPS54233には、スイッチ電流信号への補償ランプであるスロープ補償を内蔵しています。

| VIN (V) | V <sub>OUT</sub> (V) | F <sub>sw</sub> (kHz) | L <sub>o</sub> (μH) | C <sub>o</sub> | R <sub>O1</sub> (kΩ) | R <sub>O2</sub> (kΩ) | C <sub>2</sub> (pF) | C <sub>1</sub> (pF) | R <sub>3</sub> (kΩ) |

|---------|----------------------|-----------------------|---------------------|----------------|----------------------|----------------------|---------------------|---------------------|---------------------|

| 12      | 5                    | 300                   | 22                  | セラミック47μF      | 10                   | 1.91                 | 68                  | 1800                | 21                  |

| 12      | 3.3                  | 300                   | 15                  | セラミック47μF      | 10.2                 | 3.24                 | 47                  | 4700                | 21                  |

| 12      | 1.8                  | 300                   | 10                  | セラミック100μF×2   | 10                   | 8.06                 | 100                 | 4700                | 21                  |

| 12      | 0.9                  | 300                   | 6.8                 | セラミック100μF×2   | 10                   | 80.6                 | 100                 | 4700                | 21                  |

| 12      | 5                    | 300                   | 22                  | アルミ330μF/160mΩ | 10                   | 1.91                 | 56                  | 220                 | 40.2                |

| 12      | 3.3                  | 300                   | 15                  | アルミ470μF/160mΩ | 10.2                 | 3.24                 | 220                 | 220                 | 30.9                |

| 12      | 1.8                  | 300                   | 10                  | SP 220μF/12mΩ  | 10                   | 8.06                 | 100                 | 4700                | 40.2                |

| 12      | 0.9                  | 300                   | 6.8                 | SP 220μF/12mΩ  | 10                   | 80.6                 | 100                 | 1800                | 21                  |

表1. 標準的な設計(1ページの概略回路図を参照)

## 電流モード補償設計

TPS54233を使用した設計作業を単純化するために、一般的なアプリケーションに対する標準設計を表1に示します。セラミック・コンデンサを使用した設計での安定動作の解析においては、容量値の適切なディレーティングを考慮することが推奨されます。これは、セラミック・コンデンサの実際の容量値が、バイアス電圧が増すことによって標準容量値より低下していくためです。高度な設計を行う場合は、詳しいガイドラインとして「アプリケーション情報」の「ステップ毎の設計手順」を参照するか、またはSwitcherPro™ Softwareツール (<http://focus.ti.com/docs/toolsw/folders/print/switcherpro.html>) を利用できます。

## 過電流保護および周波数シフト

TPS54233は、電流モード制御を実装し、COMPピンの電圧を使用してハイサイドMOSFETをサイクル毎にオフにすることができます。各サイクルで、スイッチ電流とCOMPピン電圧が比較されます。ピーク・インダクタ電流がCOMPピン電圧と交差すると、ハイサイド・スイッチがオフになります。過電流状態で出力電圧が低下すると、誤差增幅器によってCOMPピンが“High”になり、スイッチ電流が増加します。COMPピンは内部で最大値にクランプされ、出力電流を制限しています。

TPS54233は、短絡発生時にも堅牢な保護機能を備えています。出力に短絡が発生すると、出力インダクタで過電流暴走が起こる可能性があります。TPS54233は、短絡状態中にスイッチング周波数を下げてオフ時間を増加させることで、この問題を解決します。VSENSEピンの電圧が0Vから0.8Vに上昇する際、スイッチング周波数は8、4、2、および1で分周されます。スイッチング周波数とVSENSEピン電圧の関係を表2に示します。

| スイッチング周波数   | VSENSEピン電圧                  |

|-------------|-----------------------------|

| 300 kHz     | VSENSE $\geq$ 0.6 V         |

| 300 kHz / 2 | 0.6 V > VSENSE $\geq$ 0.4 V |

| 300 kHz / 4 | 0.4 V > VSENSE $\geq$ 0.2 V |

| 300 kHz / 8 | 0.2 V > VSENSE              |

表2. スイッチング周波数の状態

## 過電圧過渡保護

TPS54233には、出力障害状態や強い無負荷過渡事象からの回復時に出力電圧のオーバーシュートを最小限に抑える、過電圧過渡保護(OVTP)回路が備えられています。OVTP回路には、VSENSEピン電圧を内部スレッショルドと比較する過電圧コンバレータが内蔵されています。VSENSEピンの電圧が109%  $\times$  V<sub>ref</sub>を上回ると、ハイサイドMOSFETが強制的にオフになります。VSENSEピンの電圧が107%  $\times$  V<sub>ref</sub>を下回ると、ハイサイドMOSFETが再度イネーブルになります。

## 過熱シャットダウン

TPS54233は、接合部温度が165°Cを超えた場合にデバイス自身を保護する、過熱シャットダウン機能を内蔵しています。接合部温度が過熱トリップ・スレッショルドを超えると、デバイスのスイッチングが強制的に停止されます。接合部温度が165°Cを下回ると、デバイスは電源投入シーケンスを再び開始します。

図 12. 標準的なアプリケーション回路図

# アプリケーション情報

## ステップ毎の設計手順

TPS54233の部品値を選択するには、以下の設計手順を使用できます。または、SwitcherPro™ソフトウェアを使用して完全な設計を生成することもできます。SwitcherPro™ソフトウェアは、反復的な設計手順を使用し、包括的な部品データベースにアクセスして設計を生成します。ここでは、設計プロセスを単純化して説明します。

設計プロセスを開始するには、いくつかのパラメータを決定する必要があります。設計者は、以下を知っている必要があります。

- 入力電圧範囲

- 出力電圧

- 入力リップル電圧

- 出力リップル電圧

- 出力電流定格

- 動作周波数

この設計例では、入力パラメータとして以下の値を使用します。

| 設計パラメータ  | 実例値      |

|----------|----------|

| 入力電圧範囲   | 8V ~ 18V |

| 出力電圧     | 3.3 V    |

| 入力リップル電圧 | 300 mV   |

| 出力リップル電圧 | 100 mV   |

| 出力電流定格   | 2 A      |

| 動作周波数    | 300 kHz  |

表3. 設計パラメータ

## スイッチング周波数

TPS54233のスイッチング周波数は、300kHzに固定されています。

## 出力電圧設定

TPS54233の出力電圧は、分圧抵抗回路を使用して外部で調整可能です。図12のアプリケーション回路では、この分圧抵抗回路はR5およびR6から構成されています。出力電圧と分圧抵抗の関係は、式(4)と式(5)で与えられます。

$$R6 = \frac{R5 \times V_{REF}}{V_{OUT} - V_{REF}} \quad (4)$$

$$V_{OUT} = V_{REF} \times \left[ \frac{R5}{R6} + 1 \right] \quad (5)$$

R5には、約10kΩを選択します。R5をわずかに増加または減少させると、標準値の抵抗を使用するときに、より近い出力電圧マッチングが得られる場合があります。この設計では、R5 = 10.2kΩおよびR6 = 3.24kΩで、出力電圧は3.31Vとなります。0Ω抵抗R4は、安定性試験で制御ループを切断するために用意されています。

## 入力コンデンサ

TPS54233には、入力デカップリング・コンデンサと、アプリケーションによってはバルク入力コンデンサが必要となります。デカップリング・コンデンサの標準推奨値は10μFです。高品質のX5RまたはX7Rセラミック・タイプを推奨します。電圧定格は、最大入力電圧よりも大きい必要があります。他の要件がすべて満足されれば、それより小さい値も使用できます。ただし、各種の回路が10μFでうまく動作することが示されています。TPS54233の回路が入力電圧源から約2インチ以内に配置されていない場合は、バルク容量の追加が必要になる場合があります。このコンデンサの値はそれほど重大ではありませんが、リップル電圧を含めた最大入力電圧を処理できる定格が必要であり、また、入力リップル電圧が許容範囲に収まるよう出力をフィルタリングできる必要があります。この設計では、入力デカップリング・コンデンサに2個の4.7μFコンデンサを使用しています。これらは、定格50VのX7Rタイプです。等価直列抵抗(ESR)は約2mΩであり、電流定格は3Aです。また、高周波フィルタリングのために、小さな0.01μFコンデンサも使用されています。

この入力リップル電圧は、式(6)で概算できます。

$$\Delta V_{IN} = \frac{I_{OUT(MAX)} \times 0.25}{C_{BULK} \times f_{SW}} + (I_{OUT(MAX)} \times ESR_{MAX}) \quad (6)$$

ここで、 $I_{OUT(MAX)}$ は最大負荷電流、 $f_{SW}$ はスイッチング周波数、 $C_{BULK}$ はバルク・コンデンサ値、 $ESR_{MAX}$ はバルク・コンデンサの最大直列抵抗です。

最大RMSリップル電流も確認する必要があります。ワースト・ケース条件の値を式(7)で概算できます。

$$I_{CIN} = \frac{I_{OUT(MAX)}}{2} \quad (7)$$

この場合、入力リップル電圧は143mV、RMSリップル電流は1.5Aとなります。また、実際の入力電圧リップルは、レイアウトに関連した寄生成分および電圧源の出力インピーダンスによって大きな影響を受けることにも注意してください。この回路の実際の入力電圧リップルは「設計パラメータ」に示しており、計算値よりも大きくなっています。それでも、この測定値は仕様の入力制限300mVを下回っています。入力コンデンサ両端の最大電圧は、 $V_{IN\ max} + \Delta V_{IN}/2$ になります。選択したバルクおよびバイパス・コンデンサはそれぞれ定格50Vであり、リップル電流容量は3Aを上回り、ともに十分なマージンが得られます。電圧および電流の最大定格はいかなる状況でも超えないことが重要です。

## 出力フィルタ部品

出力フィルタに対しては、2つの部品L1およびC2を選択する必要があります。TPS54233は外部補償デバイスであるため、幅広い種類および値のフィルタ部品をサポートできます。

### インダクタの選択

出力インダクタの最小値を計算するには、式(8)を使用します。

$$L_{MIN} = \frac{V_{OUT(MAX)} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times K_{IND} \times I_{OUT} \times F_{SW}} \quad (8)$$

$K_{IND}$ は、最大出力電流を基準としたインダクタ・リップル電流の大きさを表す係数です。この値は設計者の裁量で決定しますが、以下のガイドラインに従うことができます。セラミックなどの低ESR出力コンデンサを使用した設計では、最大 $K_{IND} = 0.3$ の値を使用できます。よりESRの高い出力コンデンサを使用する場合は、 $K_{IND} = 0.2$ が適切です。

この設計例では、 $K_{IND} = 0.3$ を使用し、最小インダクタ値は $14.97\mu H$ と計算されます。この設計では、最も近い値として $15\mu H$ が選択されています。

出力フィルタ・インダクタについては、RMS電流および飽和電流の定格を超えないことが重要です。RMSインダクタ電流は式(9)で求めることができます。

$$I_{L(RMS)} = \sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.7} \right)^2} \quad (9)$$

そして、ピーク・インダクタ電流は式(10)で決定できます。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{1.4 \times V_{IN(MAX)} \times L_{OUT} \times F_{SW}} \quad (10)$$

この設計では、RMSインダクタ電流は2.02A、ピーク・インダクタ電流は2.43Aです。選択したインダクタは、Coilcraft製のMSS1038-153ML  $15\mu H$ です。このインダクタの飽和電流定格は3.86A、RMS電流定格は3.8Aであり、これらの要件を十分に満足します。他の設計要件が満足されていれば、設計者が求めるリップル電流の大きさに合わせて、これより小さい値や大きい値のインダクタを使用できます。大きな値のインダクタを使用すると、AC電流が減少して出力電圧リップルが低下します。小さな値のインダクタを使用すると、AC電流および出力電圧リップルが増加します。TPS54233で使用するインダクタ値は、 $6.8\mu H$ ~ $47\mu H$ の範囲内です。

### コンデンサの選択

出力コンデンサについての設計で重要な要素は、DC電圧定格、リップル電流定格、および等価直列抵抗 (ESR) です。DC電圧およびリップル電流の定格を超えてはなりません。ESRは、インダクタ電流とともに出力リップル電圧の大きさを決定する要素として重要です。出力コンデンサの実際の値は、それほど重大ではありませんが、実用的な制限値は存在します。設計で必要な閉ループ・クロスオーバー周波数と、出力フィルタのLCコーナー周波数との関係を考慮します。一般に、閉ループ・クロスオーバー周波数は、スイッチング周波数の1/5未満に保持することを推奨します。この設計での300kHzのような高いスイッチング周波数の場合は、TPS54233の内部回路制限により、実質の最大クロスオーバー周波数が約25kHzに制限されます。一般に、閉ループ・クロスオーバー周波数は、負荷インピーダンスと出力コンデンサによって決まるコーナー周波数よりも高くする必要があります。これにより、出力フィルタの最小コンデンサ値が次の値に制限されます。

$$C_{O\_min} = 1 / (2 \times \pi \times R_O \times f_{CO\_max}) \quad (11)$$

ここで、 $R_O$ は出力負荷インピーダンス ( $V_O/I_O$ )、 $f_{CO}$ は目的のクロスオーバー周波数です。目的の最大クロスオーバー25kHzに対し、出力コンデンサの最小値は約 $3.8\mu F$ となります。この値は出力リップル電圧要件を満足しない可能性があります。出力リップル電圧は、2つの成分から構成されます。出力フィルタ容量の充電/放電による電圧の変化と、出力フィルタ・コンデンサのESRとリップル電流との積による電圧の変化です。出力リップル電圧は次の式で見積もることができます。

$$V_{OPP} = I_{LPP} \left[ \frac{(D - 0.5)}{4 \times F_{SW} \times C_O} + R_{ESR} \right] \quad (12)$$

また、出力コンデンサの最大ESRは、初期設計パラメータで指定される許容出力リップルの大きさによって決まるため、コンデンサのデータシートに記載されている最大仕様ESRは式(13)で与えられます。

$$ESR_{max} = \frac{V_{OPPmax}}{I_{LPP}} - \frac{(D - 0.5)}{4 \times F_{SW} \times C_O} \quad (13)$$

ここで、 $\Delta V_{pp}$ は、目的のピーク・ツー・ピーク出力リップルです。

100mVp-pのリップル要件を満足するために、C9として1個の $470\mu F$ アルミ電解出力コンデンサを選択しています。このコンデンサは、Panasonic製のEEVFK1A471Pであり、定格10V、最大ESR  $160m\Omega$ 、リップル電流定格600mAです。

最大RMS出力リップル電流は、式(14)で計算できます。

$$I_{COUT(RMS)} = \frac{1}{\sqrt{12}} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times N_C} \right) \quad (14)$$

ここで、 $N_C$ は並列出力コンデンサの個数です。

合計RMSリップル電流の計算値は216mAであり、必要な最大合計ESRは43mΩです。これらの出力コンデンサは、大きな余裕を持って要件を満足し、信頼性の高い、高性能設計を実現できます。選択する出力コンデンサの定格電圧は、目的の出力電圧 + (リップル電圧の1/2)よりも大きい必要があります。該当する場合は、ディレーティングの量も含めなければなりません。

アプリケーションのニーズに応じて、他の種類のコンデンサもTPS54233とともに使用できます。

## 補償部品

TPS54233の外部補償には、幅広い範囲の出力フィルタ構成を使用できます。さまざまなコンデンサ値および誘電体タイプがサポートされます。設計例では、セラミックX5Rタイプの出力コンデンサを使用していますが、他のタイプもサポートされています。

TPS54233には、タイプIIの補償方式を推奨します。補償部品は、出力フィルタ部品に対して目的の閉ループ・クロスオーバー周波数および位相マージンが得られるように選択します。タイプII補償は、DCゲイン成分、低周波数の極、および中周波数のゼロ/極ペアという特性を持っています。

DCゲインは、式(15)で決定されます。

$$G_{DC} = \frac{V_{ggm} \times V_{REF}}{V_O} \quad (15)$$

ここで

$$V_{ggm} = 800$$

$$V_{REF} = 0.8V$$

低周波数の極は、式(16)で決定されます。

$$V_{PO} = 1 / (2 \times \pi \times R_{OO} \times C_Z) \quad (16)$$

中周波数のゼロは、式(17)で決定されます。

$$F_{Z1} = 1 / (2 \times \pi \times R_Z \times C_Z) \quad (17)$$

中周波数の極は、式(18)で決定されます。

$$F_{P1} = 1 / (2 \times \pi \times R_Z \times C_P) \quad (18)$$

最初の手順は、閉ループ・クロスオーバー周波数の選択です。一般に、閉ループ・クロスオーバー周波数は、最小動作周波数の1/2未満にする必要がありますが、TPS54233では、最大閉ループ・クロスオーバー周波数を25kHz以下にすることを推奨します。次に、クロスオーバー・ネットワークに必要なゲインおよび位相ブーストを計算します。定義上、補償ネットワークのゲインは、変調回路と出力フィルタのゲインの逆数である必要があります。この設計例では、ESRゼロが閉ループ・クロスオーバー周波数より低いため、変調回路と出力フィルタのゲインは、式(19)で近似できます。

$$\text{Gain} = 20 \log \left( \frac{R_O}{R_{SENSE}} \right) - 20 \log \left( \frac{R_O}{R_{ESR}} \right) \quad (19)$$

ここで

$$R_{SENSE} = 1\Omega / 9$$

$$R_O = V_O / I_O$$

$$R_{ESR} = \text{出力コンデンサの等価直列抵抗}$$

位相損失は、式(20)で求められます。

$$PL = a \tan (2 \times \pi \times F_{CO} \times R_{ESR} \times C_O) - a \tan (2 \times \pi \times F_{CO} \times R_O \times C_O) \quad (20)$$

ここで

$$R_{ESR} = \text{出力コンデンサの等価直列抵抗}$$

$$R_O = V_O / I_O$$

位相損失がわかれば、位相マージン要件を満足するために必要な位相ブーストの量を決定できます。必要な位相ブーストは、式(21)で求められます。

$$PB = (PM - 90\text{deg}) - PL \quad (21)$$

ここで、 $PM$  = 目的の位相マージンです。

クロスオーバー点で最大の位相ブーストを得るために、補償ネットワークのゼロ/極ペアは、目的の閉ループ周波数を中心に対称的に配置します。間隔は式(22)で決定され、結果のゼロおよび極周波数は式(23)と式(24)で求められます。

$$k = \tan \left( \frac{PB}{2} + 45\text{deg} \right) \quad (22)$$

$$F_{Z1} = \frac{F_{CO}}{k} \quad (23)$$

$$F_{P1} = F_{CO} \times k \quad (24)$$

低周波数の極は、クロスオーバー周波数でのゲインが、変調回路と出力フィルタのゲインの逆数に等しくなるよう設定されます。極とゼロの関係から確立される関係により、 $R_Z$ の値は式(25)から直接求めることができます。

$$R_Z = \frac{V_O \times R_{OA} \times 0.98}{GM_{COMP} \times V_{ggm} \times V_{REF} \times R_{ESR}} \quad (25)$$

ここで

$V_O$  = 出力電圧

$R_{OA}$  = 8.696 MΩ

$GM_{COMP}$  = 9 A/V

$V_{ggm}$  = 800

$V_{REF}$  = 0.8 V

$R_{ESR}$  = 出力コンデンサの等価直列抵抗

$R_Z$ がわかれば、 $C_Z$ と $C_P$ は式(26)および式(27)を使用して計算できます。

$$C_Z = \frac{1}{2 \times \pi \times F_{Z1} \times R_Z} \quad (26)$$

$$C_P = \frac{1}{2 \times \pi \times F_{P1} \times R_Z} \quad (27)$$

この設計では、470μFの出力コンデンサを1個使用しています。ESRは約0.160Ωです。目的の閉ループ・クロスオーバー周波数は22000Hzです。

式(19)と式(20)により、出力段のゲインと位相損失は次のようにになります。

ゲイン = -3.114 dB

および

$PL = -4.96^\circ$

60°の位相余裕に対しては、式(21)により位相ブーストが必要であるため、Kを1に等しく設定できます。

式(22)、式(23)、および式(24)を使用して、以下のゼロおよび極周波数が求められます。

$F_{Z1}$  = 22000 Hz

および

$F_{P1}$  = 22000 Hz

$R_Z$ 、 $C_Z$ 、および $C_P$ は、式(25)、式(26)、および式(27)を使用して計算します。

$$R_Z = \frac{2.5 \times 8.696 \times 10^6 \times 0.98}{9 \times 800 \times 0.8 \times 0.160} = 30.5 \text{ k}\Omega \quad (28)$$

$$C_Z = \frac{1}{2 \times \pi \times 22000 \times 30500} = 237 \text{ pF} \quad (29)$$

$$C_P = \frac{1}{2 \times \pi \times 22000 \times 30500} = 237 \text{ pF} \quad (30)$$

図12のアプリケーション回路図で、 $R_3$ 、 $C_6$ 、 $C_7$ に標準値を使用すると次のようになります。

$R_3 = 30.9 \text{ k}\Omega$

$C_6 = 220 \text{ pF}$

$C_7 = 220 \text{ pF}$

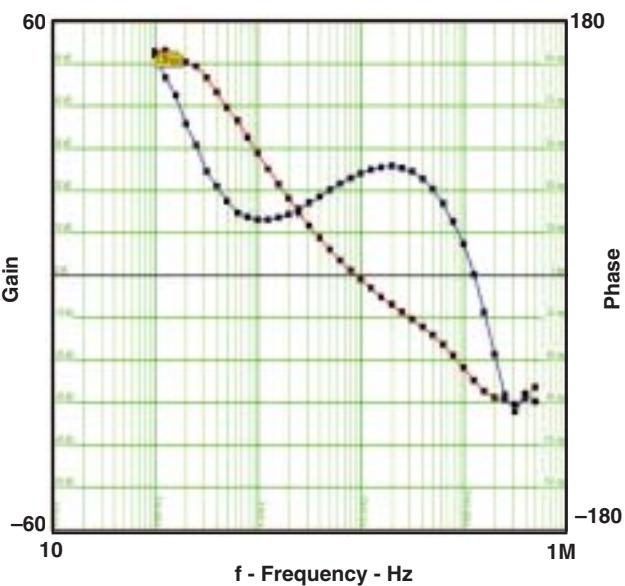

この回路の全体的なループ応答の測定結果を図12に示しています。25kHz付近で、実際の閉ループ・クロスオーバー周波数が意図した値よりも高いことに注意してください。これは主に、出力フィルタ部品の実際の値のばらつき、および内部フィードフォワード・ゲイン回路の公差のばらつきによるものです。設計全体としては、60度以上の位相マージンが得られ、ラインおよび負荷変動のあらゆる組み合わせに対して、完全に安定となります。

## ブートストラップ・コンデンサ

TPS54233の設計では、常にブートストラップ・コンデンサ $C_4$ が必要です。ブートストラップ・コンデンサは0.1μFとする必要があります。ブートストラップ・コンデンサは、PHピンとBOOTピンの間に接続します。温度安定性のために、X7RまたはX5Rクラスの誘電体を使用した高品質セラミック・コンデンサを使用してください。

## キャッチ・ダイオード

TPS54233は、PHとGNDの間に外付けのキャッチ・ダイオードを接続して動作するよう設計されています。選択するダイオードは、アプリケーションの絶対最大定格を満足する必要があります。逆方向電圧は、PHピンの最大電圧( $V_{INMAX} + 0.5\text{V}$ )よりも高くなければなりません。ピーク電流は、 $I_{OUTMAX} + (\text{ピーク} \cdot \text{ツー} \cdot \text{ピーク} \cdot \text{インダクタ電流の}1/2)$ よりも大きい必要があります。高い効率を得るために、順方向電圧降下は小さい必要があります。一般に、キャッチ・ダイオードの導通時間は、ハイサイドFETのオン時間よりも長いため、ダイオードのパラメータに注意を払うことで、全体の効率を大きく向上させることができます。また、選択するダイオードが電力損失の要件に対応していることを確認します。この設計では、Diodes, Inc.のB340Aを選択しています。このダイオードは、逆方向電圧が40V、順方向電流が3A、順方向電圧降下が0.5Vです。

## 出力電圧制限

TPS54233の内部設計により、与えられた入力電圧に対して上限と下限の出力電圧制限が存在します。出力電圧設定点の上限は、最大デューティ・サイクル91%によって制限され、式(31)で与えられます。

$$V_{O\max} = 0.91 \times ((V_{IN\ min} - I_{O\ max} \times R_{DS(on)\ max}) + V_D) - (I_{O\ max} \times R_L) - V_D \quad (31)$$

ここで

$V_{IN\ min}$  = 最小入力電圧

$I_{O\ max}$  = 最大負荷電流

$V_D$  = キャッチ・ダイオードの順方向電圧

$R_L$  = 出力インダクタの直列抵抗

この式では、内部ハイサイドFETの最大のオン抵抗を仮定しています。

下限は、最小制御可能オン時間(最大で160ns)によって制限されます。与えられた入力電圧および最小負荷電流に対する最小出力電圧は、式(32)で概算できます。

$$V_{O\min} = 0.051 \times ((V_{IN\ max} - I_{O\ min} \times R_{in}) + V_D) - (I_{O\ min} \times R_L) - V_D \quad (32)$$

ここで

$V_{IN\ max}$  = 最大入力電圧

$I_{O\ min}$  = 最小負荷電流

$V_D$  = キャッチ・ダイオードの順方向電圧

$R_L$  = 出力インダクタの直列抵抗

この式では、ハイサイドFETのオン抵抗の公称値を仮定し、動作周波数設定点のワースト・ケースの変動を想定しています。デバイスの動作制限付近で動作する設計の場合、適切な機能を保証するために慎重な確認が必要となります。

## 消費電力の見積もり

以下の式は、連続導通モード動作でのデバイスの消費電力を見積もる方法を示しています。デバイスが非連続導通モード(DCM)またはパルス・スキップEco-mode™で動作している場合は、これらの式を使用しないでください。

デバイスの消費電力には以下が含まれます。

- 1) 導通損失 :  $P_{con} = I_{out}^2 \times R_{DS(on)} \times V_{OUT}/VIN$

- 2) スイッチング損失 :  $P_{sw} = 0.5 \times 10^{-9} \times VIN^2 \times I_{OUT} \times F_{sw}$

- 3) ゲート・チャージ損失 :  $P_{gc} = 22.8 \times 10^{-9} \times F_{sw}$

- 4) 無信号時電流損失 :  $P_q = 0.075 \times 10^{-3} \times VIN$

ここで

$I_{OUT}$  = 出力電流 (A)

$R_{DS(on)}$  = ハイサイドMOSFETのオン抵抗 ( $\Omega$ )

$V_{OUT}$  = 出力電圧 (V)

$VIN$  = 入力電圧 (V)

$F_{sw}$  = スイッチング周波数 (Hz)

したがって、次のようにになります。

$$P_{tot} = P_{con} + P_{sw} + P_{gc} + P_q$$

与えられた  $T_A$  に対して、 $T_J = T_A + R_{th} \times P_{tot}$

与えられた  $T_{JMAX} = 150^\circ C$  に対して、

$$T_{AMAX} = T_{JMAX} - R_{th} \times P_{tot}$$

ここで

$P_{tot}$  = 合計デバイス消費電力 (W)

$T_A$  = 周囲温度 ( $^\circ C$ )

$T_J$  = 接合温度 ( $^\circ C$ )

$R_{th}$  = パッケージの熱抵抗 ( $^\circ C/W$ )

$T_{JMAX}$  = 最大接合部温度 ( $^\circ C$ )

$T_{AMAX}$  = 最大周囲温度 ( $^\circ C$ )

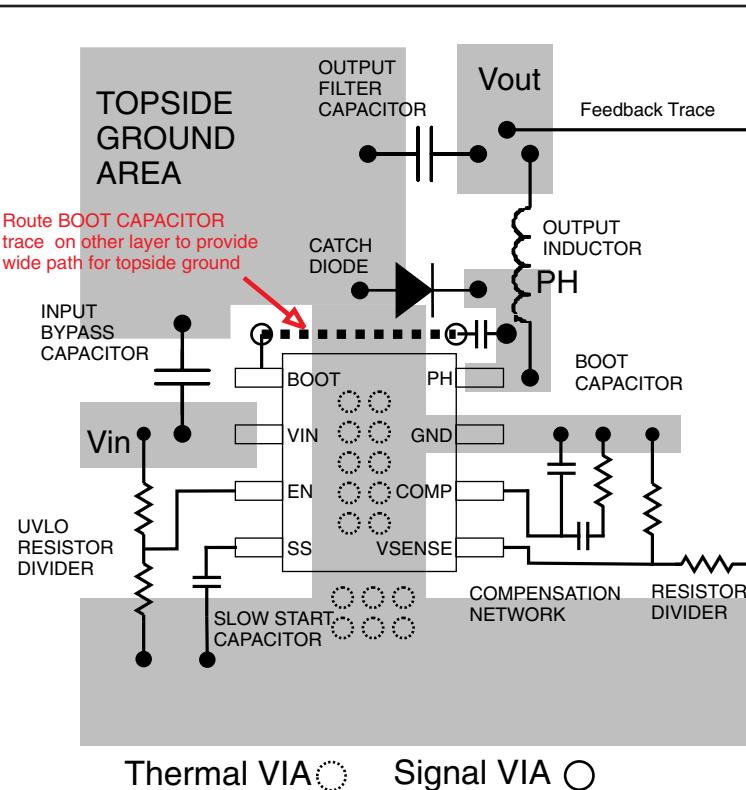

## PCBレイアウト

VINピンは、低ESRのセラミック・バイパス・コンデンサを使用してグランドにバイパスする必要があります。バイパス・コンデンサ接続、VINピン、およびキャッチ・ダイオードのアノードによって形成されるループ領域は、最小限に抑えるよう注意が必要です。推奨される標準のバイパス容量は、X5RまたはX7R誘電体を使用した $10\mu F$ のセラミック・コンデンサであり、VINピン、およびキャッチ・ダイオードのアノードのソースにできる限り近づけて配置するのが最適です。PCBレイアウト例については、図13を参照してください。GNDピンは、ICのピン部分でPCBグランド・プレーンに接続する必要があります。ローサイドMOSFETのソースは、上面のPCBグランド領域に直接接続する必要があります。このグランド領域は、入力および出力コンデンサのグランド側、およびキャッチ・ダイオードのアノードを互いに接続するために使用されます。PHピンは、キャッチ・ダイオードのカソード、および出力インダクタに配線します。PH接続はスイッチング・ノードであるため、キャッチ・ダイオードおよび出力インダクタはPHピンにごく近づけて配置し、過度の容量性カップリングを避けるためにPCB導体の面積はできるだけ小さくしてください。全定格負荷で動作を行うには、上面のグランド領域が十分な熱放散面積を備えていなければなりません。TPS54233は溶着リード・フレームを使用しているため、GNDピンはチップから放熱するための伝導経路として機能します。多くのアプリケーションでは、より大きな面積の内部または背面

面のグランド・プレーンを使用でき、デバイスの下または隣接の複数のビアを使用してそれらの領域に上面のグランド領域を接続することで、放熱性能を向上できます。追加の外部部品は図に示されるように配置できます。別のレイアウト方法でも許容される性能を得ることは可能ですが、このレイアウトは良好な結果が得られることが実証済みであり、ガイドラインとして示しています。

## 回路面積の見積もり

図12の設計で使用される部品に対して見積もられるプリント基板面積は、 $0.72\text{in}^2$ です。この面積には、テスト・ポイントおよびコネクタは含まれません。

## 電磁干渉(EMI)に関する考慮事項

EMIに対する懸念がますます高まる中で、TPS54233の内部設計でもEMIを低減するための方策が講じられています。ハイサイドMOSFETのゲート駆動は、PHピンの電圧のリンギングを低減するよう設計されています。内部のICレールは、ノイズへの耐性を高めるために絶縁されています。また、パッケージ・ボンド・ワイヤ方式を使用して、寄生成分の影響を低減しています。

最高のEMI性能を得るには、外部部品の選択と基板レイアウトが同じように重要です。潜在的なEMI問題を防ぐために、前述の「ステップ毎の設計手順」に従ってください。

図 13. TPS54233の基板レイアウト

## アプリケーション曲線

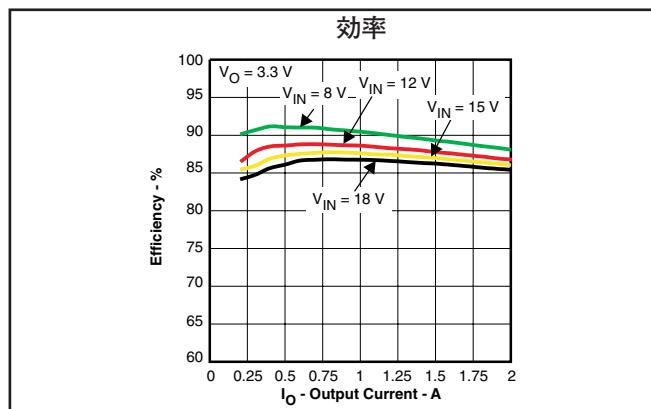

図 14. TPS54233の効率

図 15. TPS54233の低電流効率

図 16. TPS54233の負荷レギュレーション

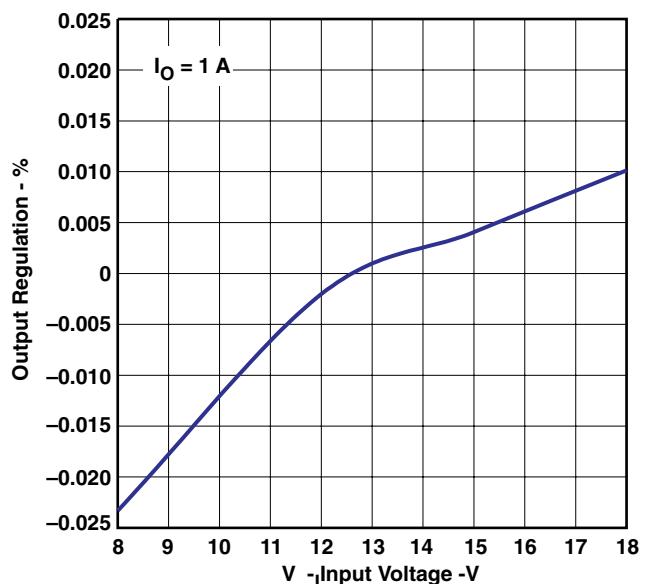

図 17. TPS54233のライン・レギュレーション

## アプリケーション曲線

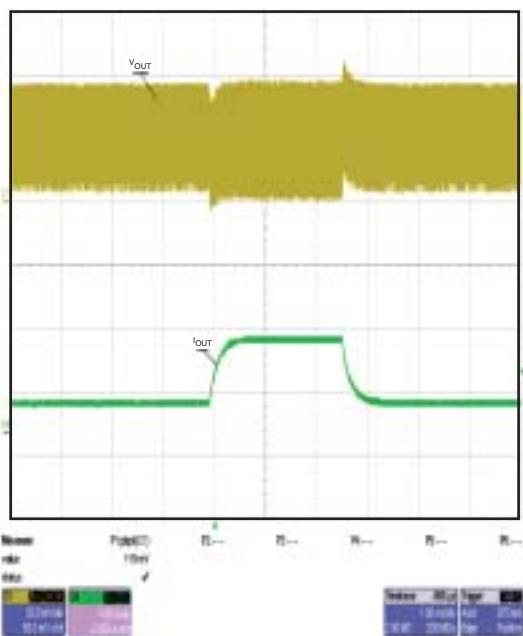

図 18. TPS54233の過渡応答

図 19. TPS54233のループ応答

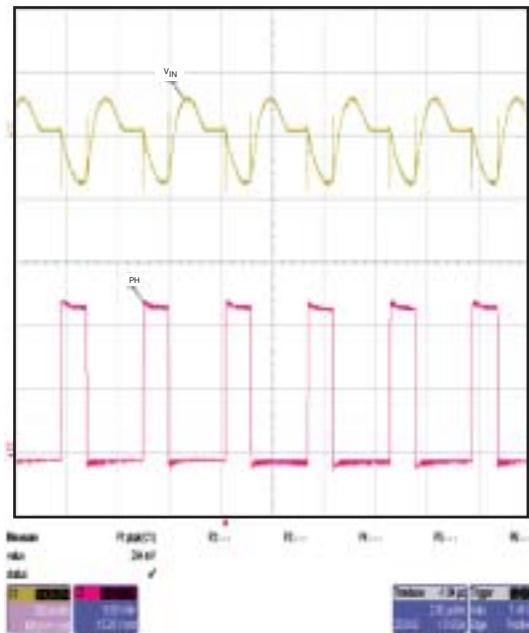

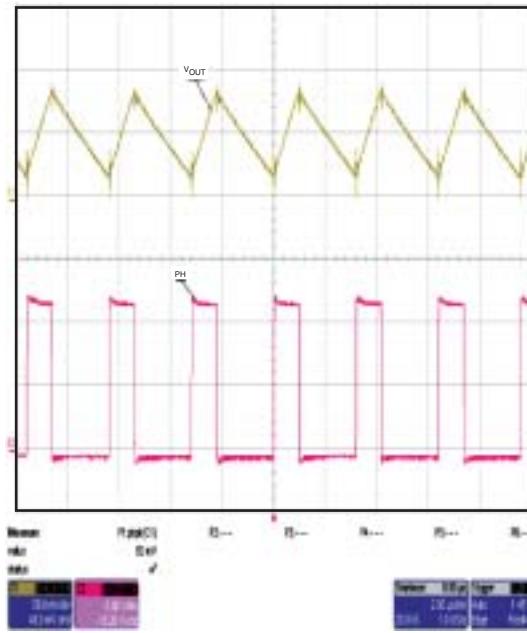

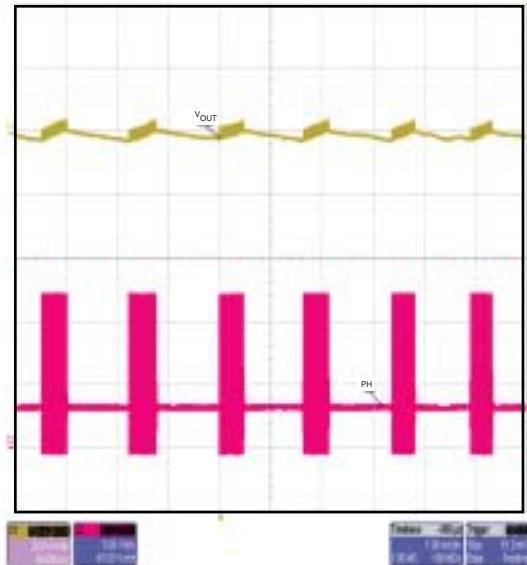

図 20. TPS54233の入力リップル

図 21. TPS54233の出力リップル

## アプリケーション曲線

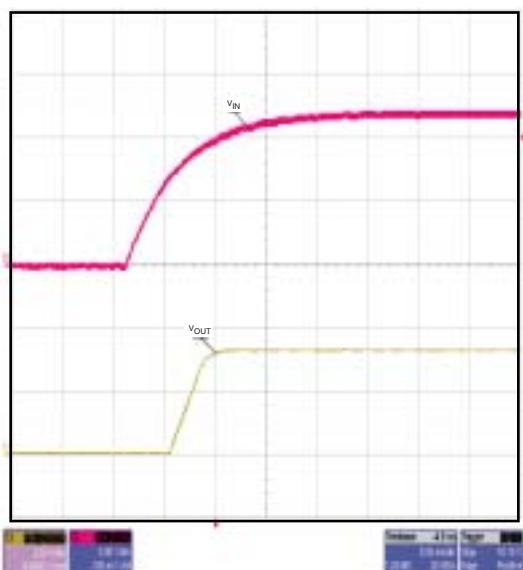

図 22. TPS54233のスタートアップ

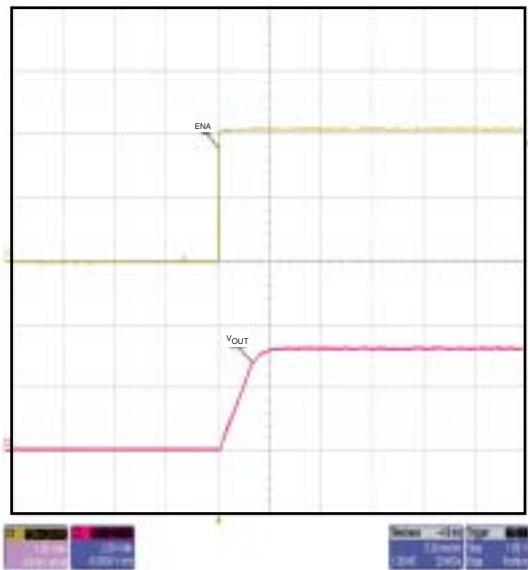

図 23. TPS54233のスタートアップ(イネーブル信号による)

図 24. TPS54233のEco-mode™動作

# パッケージ・オプション

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| TPS54233D        | ACTIVE                | SOIC         | D               | 8    | 75          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS54233DG4      | ACTIVE                | SOIC         | D               | 8    | 75          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS54233DR       | ACTIVE                | SOIC         | D               | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS54233DRG4     | ACTIVE                | SOIC         | D               | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS) : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS)と考えられます。

Green (RoHS & no Sb/Br) : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項：このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となったTIパートの購入価格の合計金額を超える責任は負いかねます。

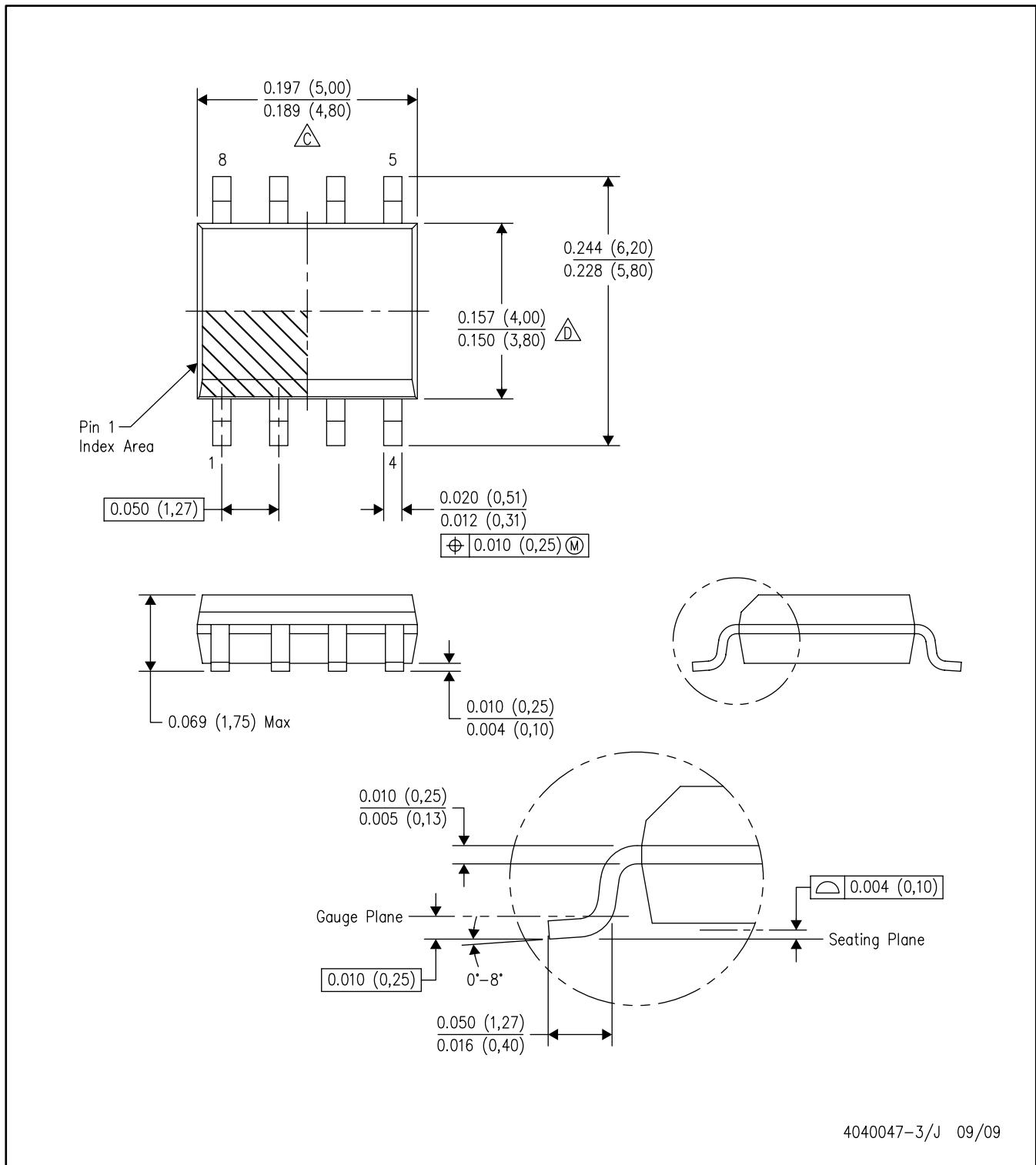

# メカニカル・データ

D (R-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

注：A. すべての直線寸法はインチ(mm)単位です。

B. この図面は、予告なく変更される可能性があります。

△ モールドの突起、突出部、ゲートのバリは、どの端でも 0.006 インチ(0.15mm)以下とします。

△ リード間の突起は、どの側でも 0.017 インチ(0.43mm)以下とします。

E. JEDEC MS-012 variation AA に準拠。

(SLUS859A)

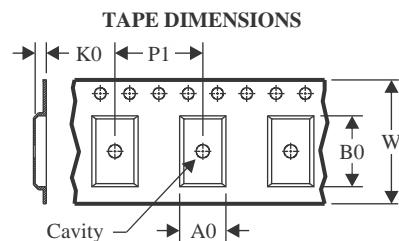

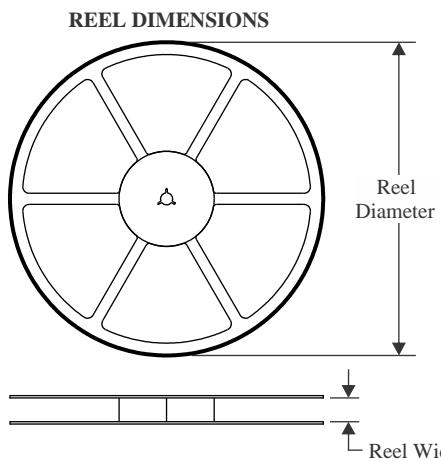

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

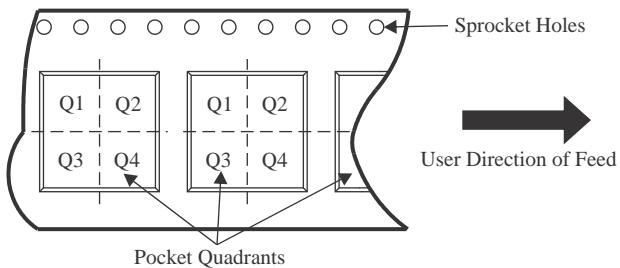

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54233DR | SOIC         | D               | 8    | 2500 | 330.0              | 12.5               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

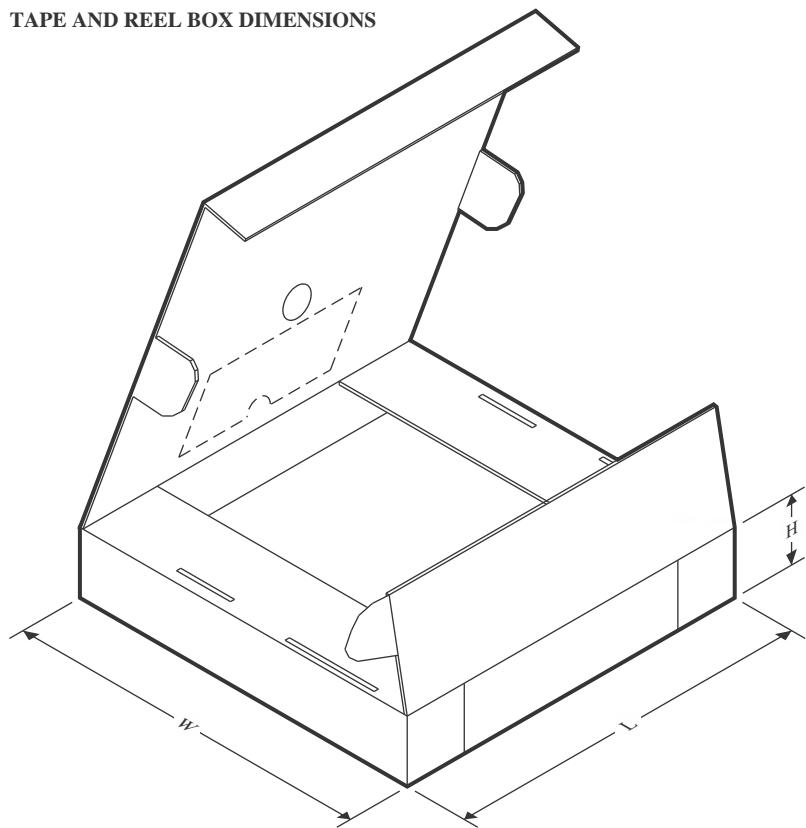

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54233DR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

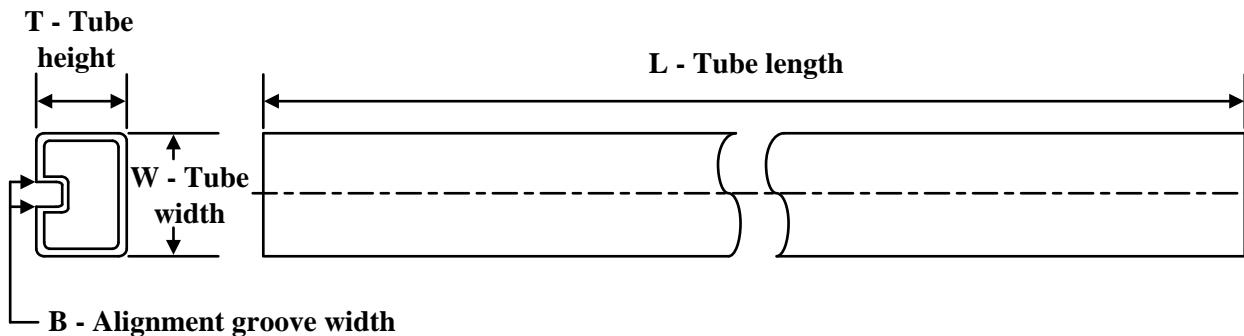

**TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54233D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54233D.A | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月