# **TPS54160A**

www.tij.co.jp JAJSBP9

# Eco-mode™搭載、1.5A、60V、 降圧型SWIFT™ DC/DCコンバータ

# 特長

- 入力電圧範囲: 3.5V~60V

- ハイサイドMOSFET: 200mΩ

- パルス・スキップEco-mode™により軽負荷で高い効率を実現

- TPS54160よりも厳密なイネーブル・スレッショルドに よってUVLO電圧の精度を向上

- 調整可能なUVLO電圧およびヒステリシス

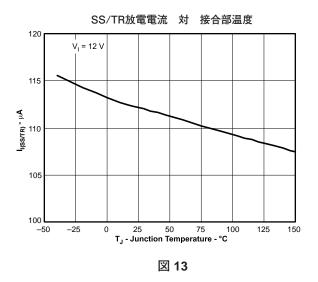

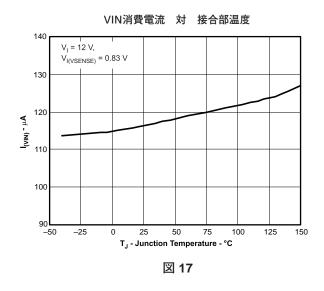

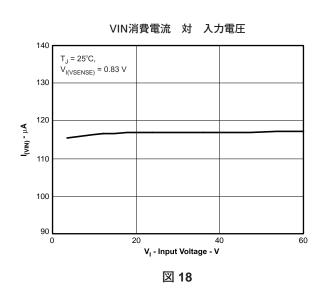

- 動作時静止電流:116μA

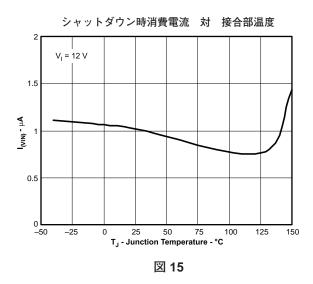

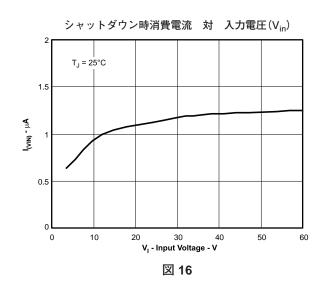

- シャットダウン時電流:1.3µA

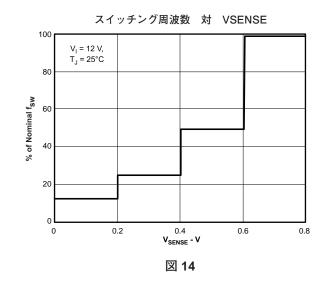

- スイッチング周波数:100kHz~2.5MHz

- 外部クロックに同期

- 調整可能なスロー・スタート/シーケンシング

- パワー・グッド出力: UV、OV

- 内部電圧リファレンス: 0.8V

- MSOP10および3mm × 3mmのVSON-10パッケージ (PowerPAD™付き)

- WEBBENCH®およびSwitcherPro™ソフトウェア・ ツールによるサポート

- SWIFT™関連のドキュメントについては、TIのWebサイトhttp://www.ti.com/swiftをご覧ください。

# アプリケーション

- 12V、24Vおよび48Vの産業用および民生用低電力 システム

- アフターマーケット用車載アクセサリ:ビデオ、 GPS、エンターテインメント

# 概要

TPS54160Aは、ハイサイドMOSFETを内蔵した60V、1.5A の降圧型レギュレータです。電流モード制御により、外部補償が単純化され、柔軟な部品選択が可能になります。低リップルのパルス・スキップ・モードを使用すると、無負荷でのレギュレーション出力時の消費電流を116μAまで低減できます。また、イネーブル・ピンにより、シャットダウン時消費電流を1.3μAまで低減できます。

低電圧誤動作防止は内部で2.5Vに設定されていますが、イネーブル・ピンを使用してさらに高い電圧に設定することができます。出力電圧のスタートアップ・ランプはスロー・スタート・ピンで制御され、このピンはシーケンシング/トラッキング用としても使用可能です。オープン・ドレインのパワー・グッド信号は、出力が公称電圧の94%~107%の範囲内であることを示

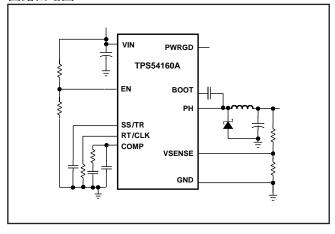

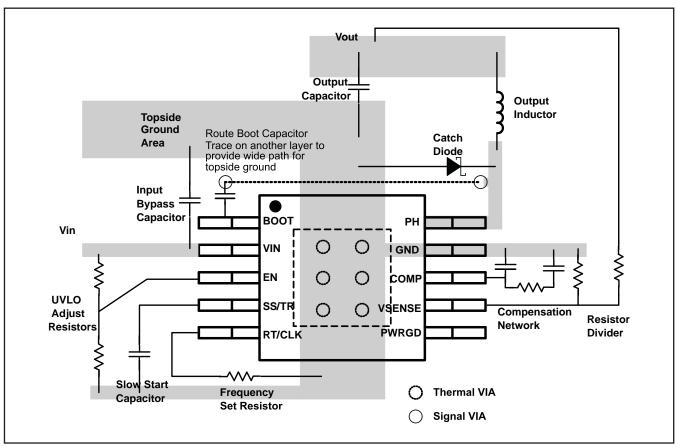

#### 回路概略図

Eco-Mode, PowerPAD, SwitcherPro, SWIFTは、テキサス・インスツルメンツの登録商標です。 WEBBENCHは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。

朝山から東村でしてと使用してい。 製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLVSB56A 翻訳版

最新の英語版資料 http://www.ti.com/lit/gpn/tps54160a

#### します。

スイッチング周波数の範囲が広いため、効率および外部部 品のサイズを最適化できます。周波数フォールドバックと過熱 シャットダウン機能によって、過負荷状態時にデバイスを保護 します。

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵 しています。保存時または取り扱い時に、MOSゲートに対する静電 破壊を防止するために、リード線どうしを短絡しておくか、デバイス を導電性のフォームに入れる必要があります。

### 製品情報(1)

| T <sub>J</sub> | パッケージ   | 部品番号          |

|----------------|---------|---------------|

| 4090 - 45090   | MSOP-10 | TPS54160ADGQ  |

| −40°C ~ 150°C  | VSON-10 | TPS54160ADRCR |

表 1.

# 絶対最大定格(1)

動作温度範囲内(特に記述のない限り)

|                                                          |                                       | VA               | VALUE    |    |

|----------------------------------------------------------|---------------------------------------|------------------|----------|----|

|                                                          |                                       | MIN              | MAX      |    |

|                                                          | VIN                                   | -0.3             | 65       |    |

|                                                          | EN (2)                                | -0.3             | 5        |    |

|                                                          | воот                                  |                  | 73       |    |

| lancit caltana                                           | VSENSE                                | -0.3             | 3        | V  |

| Input voltage                                            | COMP                                  | -0.3             | 3        | V  |

|                                                          | PWRGD                                 | -0.3             | 6        |    |

|                                                          | SS/TR                                 | -0.3             | 3        |    |

|                                                          | RT/CLK                                | -0.3             | 3.6      |    |

| Output voltage                                           | PH-BOOT                               |                  | 8        |    |

|                                                          | PH                                    | -0.6             | 65       | V  |

|                                                          | PH, 10-ns Transient                   | -2               | 65       |    |

| Voltage Difference                                       | PAD to GND                            |                  | ±200     | mV |

|                                                          | EN                                    |                  | 100      | μА |

|                                                          | BOOT                                  |                  | 100      | mA |

| Source current                                           | VSENSE                                |                  | 10       | μΑ |

|                                                          | PH                                    | PH Current Limit |          | Α  |

|                                                          | RT/CLK                                |                  | 100      | μΑ |

|                                                          | VIN                                   | Curre            | nt Limit | Α  |

| Sink current                                             | COMP                                  |                  | 100      | μΑ |

| Sink current                                             | PWRGD                                 |                  | 10       | mA |

|                                                          | SS/TR                                 |                  | 200      | μΑ |

| Electrostatic Discharge (HBM) QSS 009-105 (JESD22-A114A) |                                       |                  | 2        | kV |

| Electrostatic Discharge                                  | e (CDM) QSS 009-147 (JESD22-C101B.01) |                  | 500      | V  |

| Operating junction tem                                   | perature                              | -40              | 150      | °C |

| Storage temperature                                      |                                       | -65              | 150      | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて 示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(1) 詳細については、このデータシートの「イネーブルおよび低電圧誤動作防止の調整」を参照してください。

<sup>(1)</sup> 最新のパッケージ情報とご発注情報については、このデータシートの巻末にある「付録:パッケージ・オプション」を参照するか、 またはTIのWebサイト(www.ti.comまたはwww.tij.co.jp)をご覧ください。

# 熱特性について

|                  | THERMAL METRIC (1)                                     | TPS5         | <b>**</b>     |        |

|------------------|--------------------------------------------------------|--------------|---------------|--------|

|                  | THERMAL METRIC                                         | DGQ (10 PIN) | DRC (10 PINS) | 単位     |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (standad board) | 62.5         | 40            |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance              | 83           | 65            |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance                   | 28           | 8             | 90.444 |

| ψյτ              | Junction-to-top characterization parameter             | 1.7          | 0.6           | °C/W   |

| ΨЈВ              | Junction-to-board characterization parameter           | 20.1         | 7.5           |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance           | 21           | 7.8           |        |

<sup>(1)</sup> 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

# 電気的特性

$T_{J} = -40^{\circ}C \sim 150^{\circ}C$ 、VIN = 3.5V $\sim$ 60V(特に記述のない限り)

| パラメータ                                                      | テスト条件                                                                        | MIN   | TYP    | MAX   | 単位    |

|------------------------------------------------------------|------------------------------------------------------------------------------|-------|--------|-------|-------|

| SUPPLY VOLTAGE (VIN PIN)                                   |                                                                              |       |        |       |       |

| Operating input voltage                                    |                                                                              | 3.5   |        | 60    | V     |

| Internal undervoltage lockout threshold                    | No voltage hysteresis, rising and falling                                    |       | 2.5    |       | V     |

| Shutdown supply current                                    | EN = 0 V, 25°C, 3.5 V ≤ VIN ≤ 60 V                                           |       | 1.3    | 4     |       |

| Operating : nonswitching supply current                    | VSENSE = 0.83 V, VIN = 12 V, 25°C                                            |       | 116    | 136   | μΑ    |

| ENABLE AND UVLO (EN PIN)                                   |                                                                              |       |        |       |       |

| Enable threshold voltage                                   | No voltage hysteresis, rising and falling                                    | 1.11  | 1.25   | 1.36  | V     |

| lanut gurrant                                              | Enable threshold +50 mV                                                      |       | -3.8   |       | ^     |

| Input current                                              | Enable threshold –50 mV                                                      |       | -0.9   |       | μΑ    |

| Hysteresis current                                         |                                                                              | 1.91  | 2.95   | 3.99  | μΑ    |

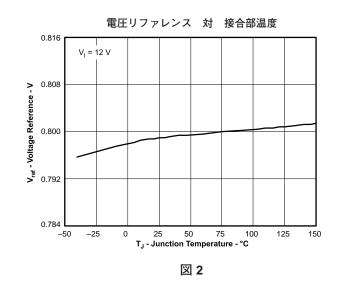

| VOLTAGE REFERENCE                                          |                                                                              |       |        |       |       |

| Voltage reference                                          | $T_J = 25$ °C                                                                | 0.792 | 8.0    | 0.808 | V     |

| voltage reference                                          |                                                                              | 0.784 | 8.0    | 0.816 | "     |

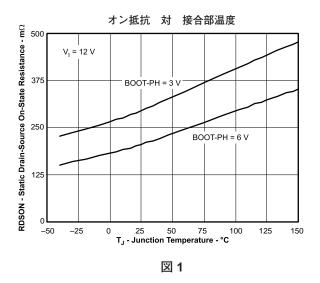

| HIGH-SIDE MOSFET                                           |                                                                              | •     |        |       |       |

| On-resistance                                              | VIN = 3.5 V, BOOT-PH = 3 V                                                   |       | 300    |       | mΩ    |

| Off-resistance                                             | VIN = 12 V, BOOT-PH = 6 V                                                    |       | 200    | 410   | 11152 |

| ERROR AMPLIFIER                                            |                                                                              | ·     |        |       |       |

| Input current                                              |                                                                              |       | 50     |       | nA    |

| Error amplifier transconductance $(g_M)$                   | $-2 \mu A < I_{(COMP)} < 2 \mu A, V_{(COMP)} = 1 V$                          |       | 97     |       | μMhos |

| Error amplifier transconductance $(g_M)$ during slow start | $-2 \mu A < I_{(COMP)} < 2 \mu A, V_{(COMP)} = 1 V,$<br>$V_{VSENSE} = 0.4 V$ | 26    |        |       | μMho  |

| Error amplifier dc gain                                    | V <sub>VSENSE</sub> = 0.8 V                                                  |       | 10,000 |       | V/V   |

| Error amplifier bandwidth                                  |                                                                              |       | 2700   |       | kHz   |

| Error amplifier source/sink                                | V <sub>(COMP)</sub> = 1 V, 100-mV overdrive                                  |       | ±7     |       | μΑ    |

| COMP to switch current transconductance                    |                                                                              |       | 6      |       | A/V   |

# 電気的特性

$T_J = -40^{\circ}C \sim 150^{\circ}C$ 、VIN = 3.5V $\sim$ 60V(特に記述のない限り)

|                     | パラメータ                                       | テスト条件                                                        | MIN | TYP  | MAX  | 単位  |

|---------------------|---------------------------------------------|--------------------------------------------------------------|-----|------|------|-----|

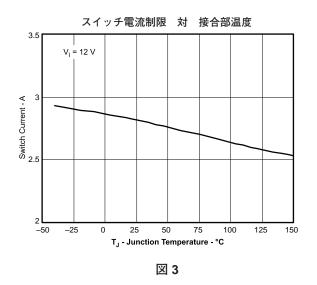

| CURRENT             | T LIMIT                                     |                                                              |     |      |      |     |

|                     | Current limit threshold                     | VIN = 12 V, T <sub>J</sub> = 25°C                            | 1.8 | 2.7  |      | Α   |

| THERMAL             | SHUTDOWN                                    |                                                              |     |      |      |     |

|                     | Thermal shutdown                            |                                                              |     | 182  |      | °C  |

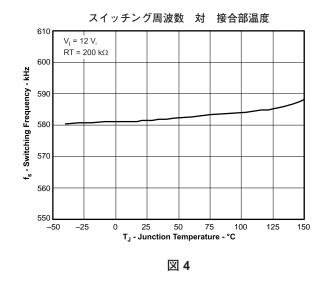

| TIMING R            | ESISTOR AND EXTERNAL CLOCK (R               | T/CLK PIN)                                                   |     |      |      |     |

|                     | Switching frequency range using RT mode     |                                                              | 100 |      | 2500 | kHz |

| f <sub>SW</sub>     | Switching frequency                         | $R_T = 200 \text{ k}\Omega$                                  | 450 | 581  | 720  | kHz |

|                     | Switching frequency range using CLK mode    |                                                              | 300 |      | 2200 | kHz |

|                     | Minimum CLK input pulse width               |                                                              |     | 40   |      | ns  |

|                     | RT/CLK high threshold                       |                                                              |     | 1.9  | 2.2  | V   |

|                     | RT/CLK low threshold                        |                                                              | 0.5 | 0.7  |      | V   |

|                     | RT/CLK falling edge to PH rising edge delay | Measured at 500 kHz with RT resistor in series               |     | 60   |      | ns  |

|                     | PLL lock in time                            | Measured at 500 kHz                                          |     | 100  |      | μS  |

| SLOW ST             | ART AND TRACKING (SS/TR)                    |                                                              |     |      |      |     |

|                     | Charge current                              | $V_{SS/TR} = 0.4 \text{ V}$                                  |     | 2    |      | μΑ  |

|                     | SS/TR-to-VSENSE matching                    | $V_{SS/TR} = 0.4 \text{ V}$                                  |     | 45   |      | mV  |

|                     | SS/TR-to-reference crossover                | 98% nominal                                                  |     | 1.0  |      | V   |

|                     | SS/TR discharge current (overload)          | VSENSE = 0 V, V(SS/TR) = 0.4 V                               |     | 112  |      | μΑ  |

|                     | SS/TR discharge voltage                     | VSENSE = 0 V                                                 |     | 54   |      | mV  |

| POWER G             | GOOD (PWRGD PIN)                            |                                                              |     |      |      |     |

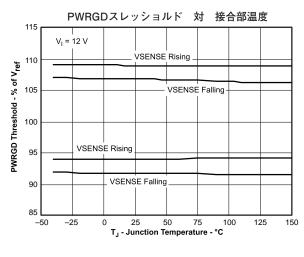

|                     |                                             | VSENSE falling                                               |     | 92%  |      |     |

| V <sub>VSENSE</sub> | VSENSE threshold                            | VSENSE rising                                                |     | 94%  |      |     |

| VVSENSE             | VOLINGE threshold                           | VSENSE rising                                                |     | 109% |      |     |

|                     |                                             | VSENSE falling                                               |     | 107% |      |     |

|                     | Hysteresis                                  | VSENSE falling                                               |     | 2%   |      |     |

|                     | Output high leakage                         | VSENSE = $V_{REF}$ , $V_{(PWRGD)}$ = 5.5 V, 25°C             |     | 10   |      | nA  |

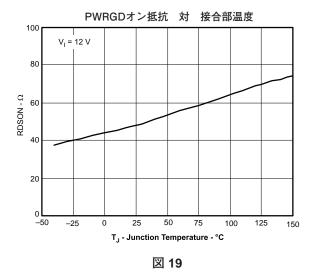

|                     | On resistance                               | I <sub>(PWRGD)</sub> = 3 mA, VSENSE < 0.79 V                 |     | 50   |      | Ω   |

|                     | Minimum VIN for defined output              | $V_{(PWRGD)} < 0.5 \text{ V}, I_{(PWRGD)} = 100 \mu\text{A}$ |     | 0.95 | 1.5  | V   |

# 製品情報

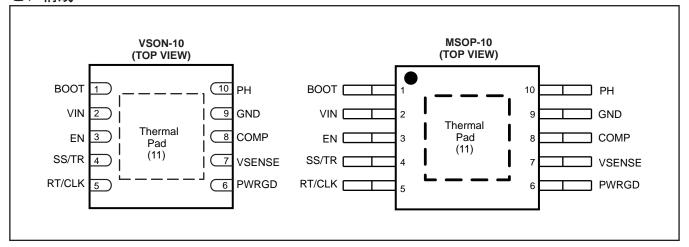

# ピン構成

# ピン機能

| ピン           |    | 1/0 | = 4 00                                                                                                                                                                                                                                              |

|--------------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名前           | 番号 | 1/0 | 説 明<br>                                                                                                                                                                                                                                             |

| воот         | 1  | 0   | BOOTとPHの間にブートストラップ・コンデンサが必要です。このコンデンサの電圧がデバイスに対して必要な最小値を下回った場合、出力はコンデンサがリフレッシュされるまで強制的にオフになります。                                                                                                                                                     |

| COMP         | 8  | 0   | 誤差増幅器の出力、および出力スイッチ電流コンパレータの入力。<br>このピンに周波数補償部品を接続します。                                                                                                                                                                                               |

| EN           | 3  | ı   | イネーブル・ピン、内部プルアップ電流源。ディスエーブルにするには、1.2V未満にプルダウンします。<br>イネーブルにするには、フローティングにします。2個の抵抗を使用して入力の低電圧誤動作防止を調整し<br>ます。                                                                                                                                        |

| GND          | 9  | -   | グランド                                                                                                                                                                                                                                                |

| PH           | 10 | I   | 内部ハイサイド・パワーMOSFETのソース。                                                                                                                                                                                                                              |

| サーマル・<br>パッド | 11 | -   | 適切な動作のためには、GNDピンをプリント基板上の露出したパッドに電気的に接続する必要があります。                                                                                                                                                                                                   |

| PWRGD        | 6  | 0   | 過熱シャットダウン、ドロップアウト、過電圧、またはENシャットダウンによって出力電圧が規定値を外れた場合にアサートされる、オープン・ドレイン出力です。                                                                                                                                                                         |

| RT/CLK       | 5  | I   | タイミング抵抗接続および外部クロック入力端子。スイッチング周波数を設定するために、このピンとグランドの間に外付け抵抗を接続すると、内部アンプによってこのピンが固定電圧に保持されます。このピンをPLLの上限スレッショルドより高くプルアップすると、モード遷移が発生し、ピンは同期入力となります。内部アンプはディスエーブルになり、このピンは内部PLLへのハイ・インピーダンス・クロック入力となります。クロック・エッジが停止すると、内部アンプが再イネーブルされ、モードは抵抗設定機能に戻ります。 |

| SS/TR        | 4  | I   | スロー・スタートおよびトラッキング入力。このピンに接続する外部コンデンサによって、出力の立ち上がり時間が設定されます。このピンの電圧は内部リファレンスよりも優先されるため、トラッキングおよびシーケンシングにも使用できます。                                                                                                                                     |

| VIN          | 2  | I   | 入力電源電圧、3.5V~60V。                                                                                                                                                                                                                                    |

| VSENSE       | 7  | I   | トランスコンダクタンス(gm)誤差増幅器の反転ノード。                                                                                                                                                                                                                         |

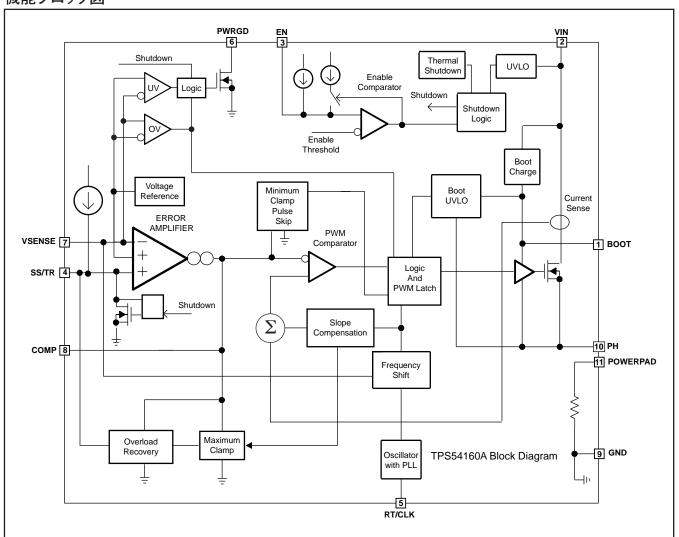

# 機能ブロック図

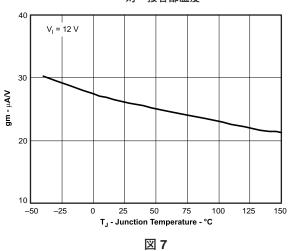

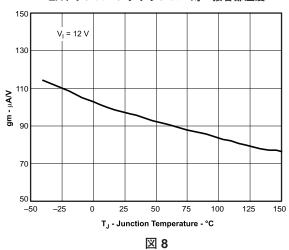

スロー・スタート中のEAトランスコンダクタンス 対 接合部温度

## EAトランスコンダクタンス 対 接合部温度

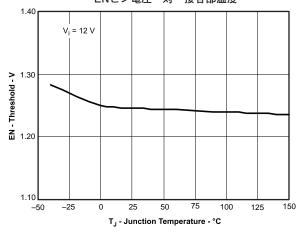

ENピン電圧 対 接合部温度

図 9

図 10

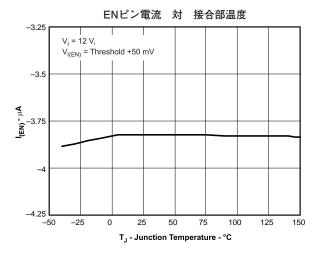

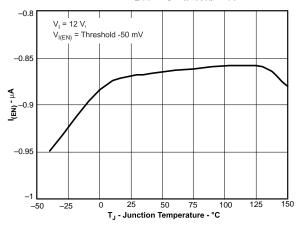

#### ENピン電流 対 接合部温度

図 11

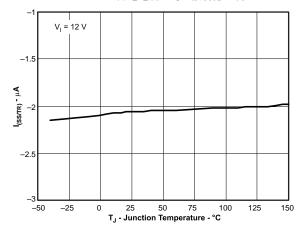

#### SS/TR充電電流 対 接合部温度

図 12

図 20

## 概要

TPS54160Aは、ハイサイドNチャネルMOSFETを内蔵した、60V、1.5Aの降圧型 (バック) レギュレータです。ラインおよび 負荷の過渡状態における性能を向上させるため、定周波数の電流モード制御で動作し、出力容量の低減、外部周波数補償設計の簡易化を実現しています。スイッチング周波数の範囲が100kHz~2500kHzと広いため、出力フィルタ部品の選択時に効率およびサイズを最適化できます。スイッチング周波数は、RT/CLKピンからグランドへの抵抗を使用して調整します。RT/CLKピンには内部フェーズ・ロック・ループ(PLL)が備えられ、パワー・スイッチをオンにするタイミングを外部システム・クロックの立ち下がりエッジに同期させることができます。

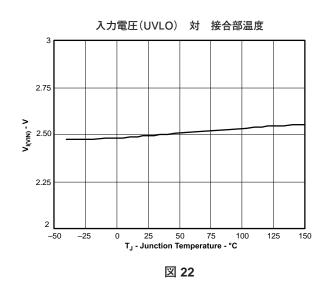

TPS54160Aのスタートアップ電圧はデフォルトで約2.5Vです。 ENピンの内部プルアップ電流源を使用して、入力低電圧誤動作 防止 (UVLO)のスレッショルドを2つの外部抵抗により調整可能です。また、このプルアップ電流によってデフォルト状態を設定できます。 ENピンがフローティングになると、デバイスが動作します。 無負荷で非スイッチング時の動作電流は116μAです。 デバイスがディスエーブル時の消費電流は、1.3μAです。

内蔵の200mΩハイサイドMOSFETにより、1.5Aの連続電流を負荷に供給できる高効率の電源設計が可能になります。TPS54160Aは、ブート再充電ダイオードを内蔵し、外部部品数を低減できます。内蔵ハイサイドMOSFETのバイアス電圧は、BOOT-PHピン間のコンデンサによって供給されます。このブート・コンデンサ電圧はUVLO回路によって監視され、内部設定されたスレッショルドを下回ると、ハイサイドMOSFETがオフになります。このブートUVLOにより、TPS54160Aは高いデューティ・サイクルで動作が可能です。出力電圧は、0.8Vのリファレンスと同じ値まで降圧させることができます。

TPS54160Aはパワー・グッド・コンパレータ(PWRGD)を備え、これはレギュレーション出力電圧が公称出力電圧の92%未満または109%を超えたときにアサートされます。PWRGDピンはオープン・ドレイン出力であり、VSENSEピンの電圧が公称出力電圧の94%~107%の範囲内のときにデアサートされ、プルアップ抵抗を使用した場合にはHighに遷移します。

TPS54160Aでは、OVパワー・グッド・コンパレータを利用して、過度の出力過電圧 (OV) を最小限に抑えています。OVコンパレータが作動すると、ハイサイドMOSFETはオフになり、出力電圧が107%を下回るまでオンになりません。

SS/TR(スロー・スタート/トラッキング)ピンは、パワーアップ時に突入電流を最小限に抑え、電源シーケンシングを構成するために使用できます。スロー・スタート時間を調整するには、このピンに小容量のコンデンサを接続します。電源シーケンシングの要件が重要である場合には、このピンに分圧抵抗を接続できます。SS/TRピンは、出力のパワーアップ前に放電されます。この放電によって、過熱障害、UVLO障害、またはディスエーブル状態の後に、再起動を繰り返すことが可能になります。

また、TPS54160Aは、過負荷回復回路によって過負荷状態時にスロー・スタート・コンデンサを放電します。過負荷回復回路は、過負荷状態が解消されると、出力を障害電圧から公称レギュレーション電圧へとスロー・スタートさせます。周波数フォールドバック回路により、起動時および過電流障害時にスイッチング周波数が低下し、インダクタ電流を制御しやすくなります。

### 詳細説明

### 固定周波数PWM制御

TPS54160Aは、調整可能な固定周波数のピーク電流モード制御を使用します。COMPピンを駆動する誤差増幅器により、出力電圧がVSENSEピンの外付け抵抗を通して内部電圧リファレンスと比較されます。内部発振器により、ハイサイド・パワー・スイッチのオン動作が開始され、誤差増幅器の出力がハイサイド・パワー・スイッチ電流と比較されます。パワー・スイッチ電流がCOMP電圧レベルに達すると、パワー・スイッチがオフになります。出力電流が増加および減少すると、COMPピン電圧も上昇および下降します。デバイスではCOMPピン電圧を最大レベルにクランプすることで電流制限を行っています。また、COMPピンの最小クランプによってEco-mode™を実現しています。

## スロープ補償出力電流

TPS54160Aは、スイッチ電流信号に補償ランプを追加します。このスロープ補償により、低調波発振を防いでいます。使用可能なピーク・インダクタ電流は、デューティ・サイクルの範囲全体にわたって一定です。

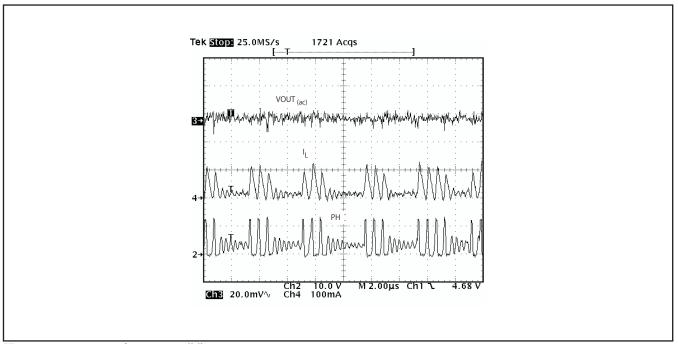

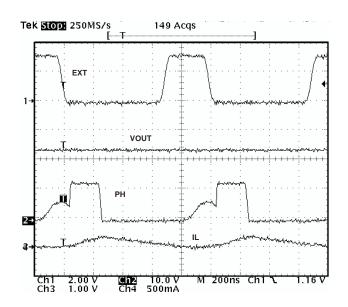

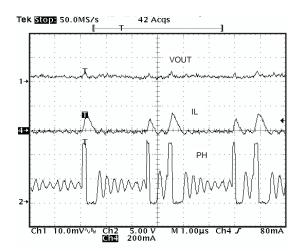

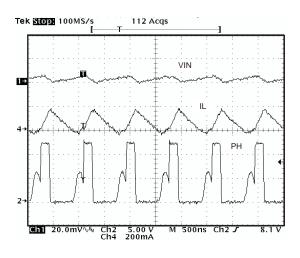

#### パルス・スキップEco-mode

COMPピンの電圧が最小クランプ値になると、TPS54160A はパルス·スキップ·モードに入ります。TPS54160Aは、軽負 荷電流時にはパルス・スキップ・モードで動作して効率を向上さ せます。パルス・スキップ・モード中のピーク・スイッチ電流は、 50mAまたはピーク・インダクタ電流のいずれか大きい方の値に なります。ピーク・インダクタ電流は、最大オン時間、入力電 圧、出力電圧、およびインダクタ値の関数です。負荷電流が低 く、出力電圧がレギュレーション内のとき、デバイスはスリー プ·モードに入り、静止時入力電流はわずか116µAとなります。 デバイスがスリープ・モードの間、出力電力は出力コンデンサ から供給されます。負荷電流が減少するにつれ、出力コンデン サから負荷電流を供給する時間が増加し、スイッチング周波数 が低下して、ゲート駆動損失およびスイッチング損失が減少し ます。出力電圧が低下すると、TPS54160Aはスリープ・モード から抜け、パワー・スイッチがオンになって出力コンデンサが 再充電されます(図25を参照)。スリープ・モード中、内部PLL は動作を継続します。軽負荷時にパルス・スキップ・モードで動 作している間は、外部クロック信号に同期してスイッチング遷 移が行われます。

図 25. パルス・スキップ・モードの動作

## ブートストラップ電圧(BOOT)

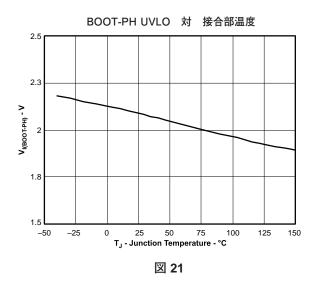

TPS54160Aにはブート・レギュレータが内蔵され、ハイサイ ドMOSFETのゲート駆動電圧を提供するために、BOOTピン とPHピンの間に小さなセラミック・コンデンサが必要です。こ のセラミック・コンデンサの値は、0.1uFとしてください。温度 および電圧に対して安定した特性を持つため、X7RまたはX5R クラスの誘電体を持つセラミック・コンデンサを推奨します。 ドロップアウトを改善するため、TPS54160Aは、BOOT-PH ピン間の電圧が2.1Vより高ければ、100%のデューティ・サイ クルで動作するよう設計されています。BOOT-PH間の電圧が 2.1Vを下回ると、UVLO回路によってハイサイドMOSFETが オフになることで、ローサイド・ダイオードが導通してBOOT コンデンサのリフレッシュが行われます。BOOTコンデンサか らソースされる電源電流は低いため、ハイサイドMOSFETは リフレッシュ時間よりも多くのスイッチング・サイクルにわたっ てオンに保持でき、結果として、ブート・レギュレータ・システ ムによる実効的なデューティ・サイクル制限が高くなります。

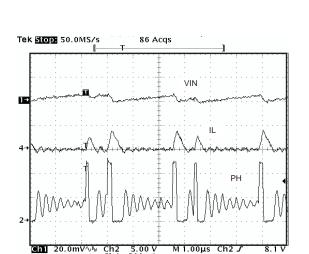

#### 低ドロップアウト動作

レギュレータのドロップアウト時のデューティ・サイクルは、主に、パワーMOSFET、インダクタ、ローサイド・ダイオード、プリント基板抵抗のそれぞれにおける電圧降下によって決まります。入力電圧が低下する動作状態では、デューティ・サイクルの100%にわたって出力レギュレーションを維持するように、またはBOOT-PH間の電圧が2.1Vを下回るまでの間、ハイサイドMOSFETをオンに保持できます。

ハイサイドがオフになると、ローサイド・ダイオードが導通し、BOOTコンデンサが再充電されます。このブート・コンデンサの再充電時間中は、ハイサイドMOSFETがオンになるまでインダクタ電流が減少します。再充電時間は前のスイッチング・サイクルの標準的なハイサイド・オフ時間よりも長いため、インダクタ電流リップルが増加し、結果として出力でのリップル電圧が増加します。再充電時間は、入力電圧、ブート・コンデンサ値、および内部ブート再充電ダイオードのインピーダンスの関数となります。

負荷電流の流れない時間が長くなる最大デューティ・サイクルのアプリケーションでは、注意が必要です。入力電圧と出力電圧の差が3V未満であるアプリケーションで、BOOTコンデンサ両端の電圧が2.1Vのスレッショルドを下回ると、ハイサイドMOSFETはオフになりますが、PHピンをプルダウンしてブート・コンデンサを再充電するために十分な電流がインダクタに流れません。ブート・コンデンサが2.1V未満であるためレギュレータはスイッチングせず、入力電圧と出力電圧の差が2.1Vに達するまで出力コンデンサは放電を続けます。ブート低電圧誤動作防止のスレッショルドを超えた時点で、デバイスは目的の出力電圧に達するまでスイッチングを行います。

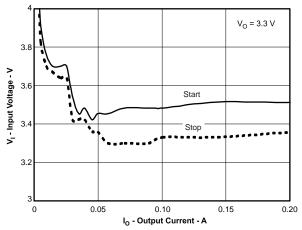

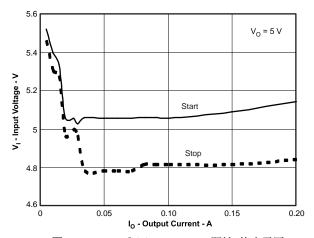

図26および図27に、開始および停止電圧を示します。電圧は 負荷電流に対してプロットされています。開始電圧は、1%以 内の出力レギュレーションに必要な入力電圧として定義されま す。停止電圧は、出力が5%低下するかまたはスイッチングが停止するときの入力電圧として定義されます。

図 26. 3.3Vアプリケーションの開始/停止電圧

図 27. 5.0Vアプリケーションの開始/停止電圧

### 誤差増幅器

TPS54160Aは、誤差増幅器としてトランスコンダクタンス・アンプを内蔵しています。誤差増幅器は、VSENSEの電圧を、SS/TRピンの電圧または内部の0.8V電圧リファレンスのいずれか低い方と比較します。誤差増幅器のトランスコンダクタンス(gm)は、通常動作時には97μΑ/Vです。スロー・スタート動作時には、トランスコンダクタンスは通常動作時の値よりずっと低くなります。VSENSEピンの電圧が0.8V未満で、デバイスがSS/TR電圧を使用してレギュレーションを行っている場合、トランスコンダクタンスは26μΑ/Vとなります。

COMPピンとグランドとの間に周波数補償部品 (コンデンサ、および直列接続の抵抗とコンデンサ) が追加されます。

#### 電圧リファレンス

電圧リファレンス・システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで、温度に対して±2%の高い精度を持つ電圧リファレンスを生成します。

## 出力電圧の調整

出力電圧は、出力ノードとVSENSEピンとの間の分圧抵抗によって設定されます。公差1%以内の分圧抵抗を使用することを推奨します。最初はR2抵抗に10kΩを使用し、式(1)を使ってR1を計算します。軽負荷時の効率を向上させるには、より大きな値の抵抗の使用を検討します。値が大きすぎると、レギュレータがノイズの影響を受けやすくなり、VSENSE入力電流からの電圧誤差が目立つようになります。

$$R1 = R2 \times \left(\frac{(Vout - 0.8V)}{0.8 V}\right)$$

(1)

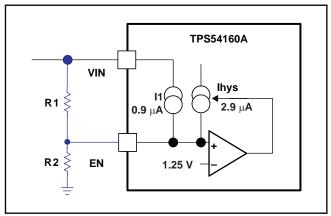

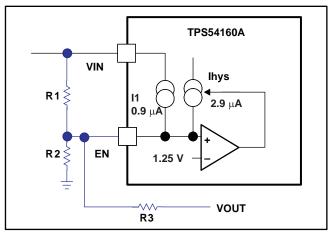

## イネーブルおよび低電圧誤動作防止の調整

VINピンの電圧が2.5Vを下回ると、TPS54160Aはディスエーブルになります。アプリケーションで、より高い値での低電圧誤動作防止 (UVLO)を必要とする場合は、図28のようにENピンを使用し、2個の外付け抵抗で入力電圧UVLOを調整します。UVLO調整抵抗の使用は必須ではありませんが、一貫したパワーアップ動作を実現するために強く推奨します。ENピンには $0.9\mu$ Aの内部プルアップ電流源IIがあり、ENピンがフローティングのときにTPS54160Aが動作するデフォルト状態を提供します。ENピンの電圧が1.25Vを超えると、 $2.9\mu$ AのヒステリシスIhysが追加されます。この追加電流により、入力電圧のヒステリシスを実現できます。入力電圧の外部ヒステリシスは、式(2)を使って設定します。入力スタート電圧は、式(3)を使って設定します。

図 28. 調整可能な低電圧誤動作防止(UVLO)

$$R1 = \frac{V_{START} - V_{STOP}}{I_{HYS}}$$

(2)

$$R2 = \frac{V_{ENA}}{\frac{V_{START} - V_{ENA}}{R1} + I_1}$$

(3)

入力電圧ヒステリシスを追加するもう1つの手法を図29に示します。前の方法で抵抗値が高く、より広い電圧ヒステリシスが必要である場合に、この方法を使用できます。抵抗R3は、追加のヒステリシス電流をENピンに供給します。

図 29. 追加ヒステリシスの提供

$$R1 = \frac{V_{START} - V_{STOP}}{I_{HYS} + \frac{V_{OUT}}{R3}}$$

(4)

$$R2 = \frac{V_{ENA}}{\frac{V_{START} - V_{ENA}}{R1} + I_1 - \frac{V_{ENA}}{R3}}$$

(5)

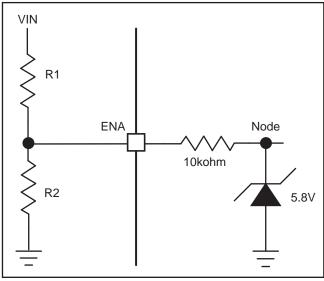

ENピン上に直接、5Vを超える低インピーダンス電圧源を接続しないでください。分圧抵抗を使用して開始および停止電圧を調整する場合、 $V_{\rm EN}>5$ Vのときには、 ${\rm EN}$ ピンに直接コンデンサを配置しないでください。ノード電圧(図30を参照)は、5.8V以下に維持する必要があります。このツェナー・ダイオードは、最大 $100\mu$ Aをシンクできます。 $V_{\rm IN}$ 電圧源のインピーダンスが高く、 ${\rm EN}$ ピンに $100\mu$ A以上をソースしない場合は、 ${\rm EN}$ ピンの電圧を5V以上にできます。

図 30. ノード電圧

## スロー・スタート/トラッキング・ピン(SS/TR)

TPS54160Aでは、SS/TRピン電圧または内部電圧リファレンスのいずれか低い方の電圧を電源リファレンス電圧として使用し、それに従って出力のレギュレーションを行います。SS/TRピンとグランド間のコンデンサにより、スロー・スタート時間が実装されます。TPS54160Aには、外部のスロー・スタート・コンデンサを充電する $2\mu$ Aのプルアップ電流源が内蔵されています。スロー・スタート時間  $(10\% \sim 90\%)$  は式 (6) で計算されます。電圧リファレンス  $(V_{REF})$  は0.8Vで、スロー・スタート電流  $(I_{SS})$  は $2\mu$ Aです。スロー・スタート・コンデンサは、 $0.47\mu$ F未満、0.47nF以上とする必要があります。

$$C_{SS}(nF) = \frac{t_{SS}(ms) \times I_{SS}(\mu A)}{V_{REF}(V) \times 0.8}$$

(6)

パワーアップ時、TPS54160Aは、適切なパワーアップを保証するために、スロー・スタート・ピンが放電されて40mVを下回るまでスイッチングを開始しません(図31を参照)。

また、通常動作中、VINピンの電圧がVIN UVLOを下回るか、ENピンが1.25V未満にプルダウンされるか、または過熱シャットダウン事象が発生した場合、TPS54160Aはスイッチングを停止し、SS/TRは40mVまで放電される必要があります。

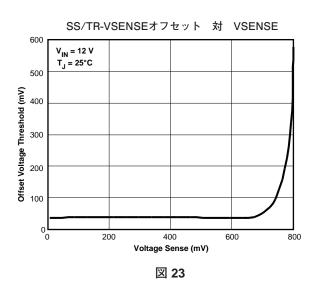

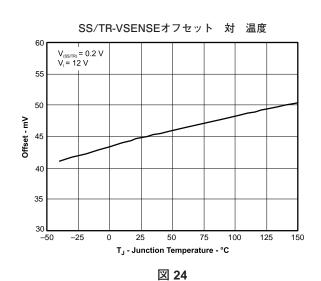

VSENSE電圧は、45mVのオフセットで内部電圧リファレンスの85%までSS/TRピン電圧に追従します。SS/TR電圧が内部リファレンス電圧の85%を上回ると、実効的なシステム・リファレンスがSS/TR電圧から内部電圧リファレンスへと遷移するため、オフセットが増加します(図23を参照)。SS/TR電圧は、1.7Vでクランプされるまで直線的に上昇します。

図 31. 起動時のSS/TRピンの動作

# 過負荷回復回路

TPS54160Aは、過負荷回復 (OLR) 回路を備えています。OLR回路は、過負荷状態が解消されると、出力を過負荷電圧から公称レギュレーション電圧へとスロー・スタートさせます。誤差増幅器が障害状態から高電圧状態へと変化すると、OLR回路は100μAの内部プルダウンを使用して、SS/TRピンをVSENSEピン電圧よりわずかに高い電圧まで放電します。障害状態が解消されると、出力は障害電圧から公称出力電圧へとスロー・スタートします。

図 32. シーケンシャルなスタートアップ・シーケンスの回路図

図 **34**. SS/TRピンの結合によるレシオメトリックなスタートアップの回路図

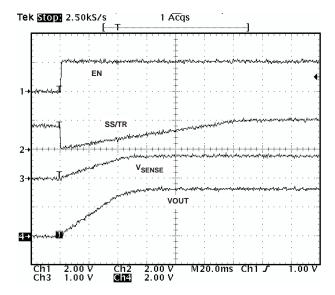

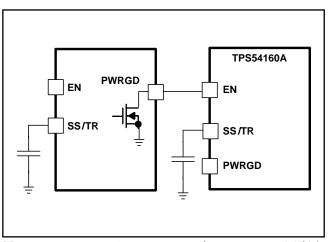

### シーケンシング

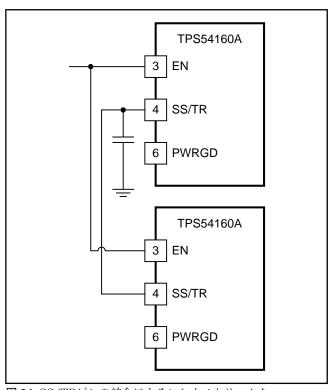

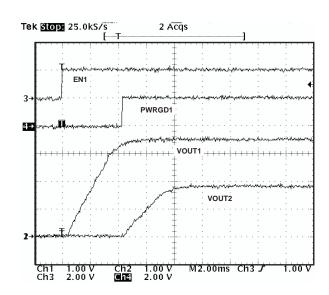

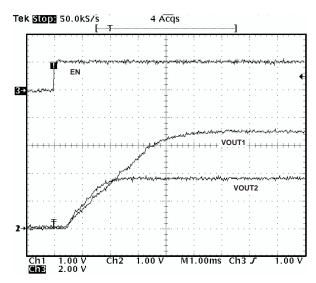

SS/TR、EN、およびPWRGDピンを使用して、多くの一般的な電源シーケンシング方法を実装できます。他のデバイスのパワーオン・リセット・ピンのオープン・ドレイン出力を使用すれば、シーケンシャルな方法を実装できます。図32に、2個のTPS54160Aデバイスを使用したシーケンシャルな方法を示します。TPS54160AのENピンにパワー・グッドを結合し、1次電源がレギュレーションに達した時点で2次電源をイネーブルにします。必要に応じて、2次電源のENピンに1nFのセラミック・コンデンサを接続することにより、1msのスタートアップ遅延を実現できます。図32の結果を図33に示します。

図 **33**. ENおよびPWRGDを使用したシーケンシャル・ スタートアップ

図 **35**. SS/TRピンの結合によるレシオメトリックな スタートアップ

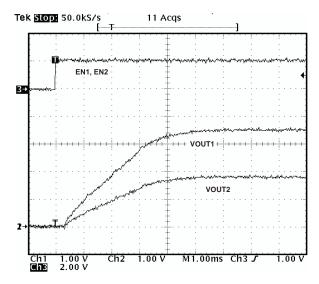

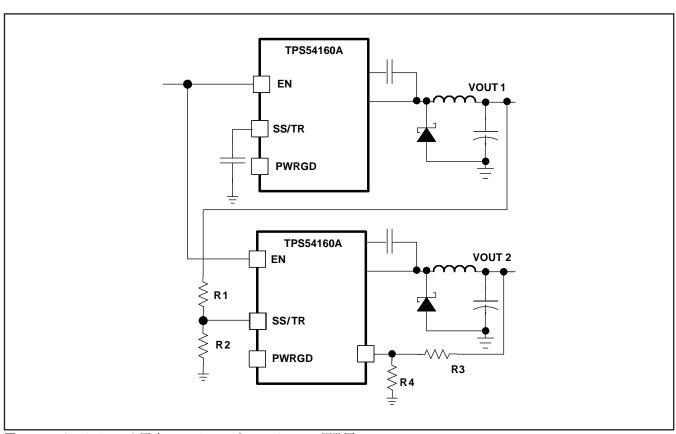

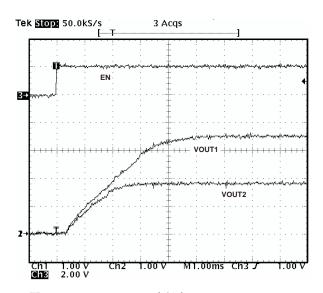

図34に、SS/TRピンを互いに接続することによるレシオメトリックなスタートアップ・シーケンスの方法を示します。各レギュレータの出力は同時に上昇してレギュレーションに達します。スロー・スタート時間を計算する際には、式(6)でプルアップ電流源を2倍にする必要があります。図34の結果を図35に示します。

図36に示すようなR1とR2の抵抗回路を、トラッキングが必要な電源または他の電圧リファレンス源の出力に接続することで、レシオメトリックな同時電源シーケンシングを実装できます。式 (7)と式 (8) を使用して、 $V_{OUT1}$ の少し前か少し後、または同時に $V_{OUT2}$ を開始するようトラッキング抵抗を計算できます。式 (9) は、公称出力レギュレーションの95%での $V_{OUT1}$ と $V_{OUT2}$ の電圧差です。

変数  $\Delta V$ は、同時シーケンシングでは0 Vです。スロー・スタート回路のSS/TR-VSENSE間の固有のオフセット  $(V_{SS(offset)})$ 、およびプルアップ電流源  $(I_{SS})$ とトラッキング抵抗によって生成されるオフセットの影響を最小限に抑えるため、 $V_{SS(offset)}$ および $I_{SS}$ が変数として式に含まれています。

$V_{OUT2}$ がレギュレーションに達したときに $V_{OUT2}$ の電圧が $V_{OUT1}$ の電圧よりわずかに大きくなるように、レシオメトリックなスタートアップを設計するには、式 (7)~式 (9)で $\Delta V$ に負の数を使用します。 $V_{OUT2}$ がレギュレーションに達したときに $V_{OUT2}$ が $V_{OUT1}$ よりわずかに低くなるアプリケーションでは、式 (9) は正の数となります。

EN、UVLO、または過熱シャットダウン障害後には、起動前にSS/TRピンを40mV未満にプルダウンする必要があるため、デバイスが障害後に確実に再起動できるようトラッキング抵抗を慎重に選択する必要があります。デバイスが障害から回復できるようにするには、式(7)で計算されるR1の値が式(10)の計算値よりも大きくなる必要があります。

SS/TRの電圧が公称リファレンス電圧の85%を超えると、スロー・スタート回路がレギュレーション・リファレンスを徐々に内部電圧リファレンスへと移行させ、 $V_{SS(offset)}$ が大きくなります。図23に示すように、内部電圧リファレンスへと完全に移行するには、SS/TRピンの電圧が1.3Vより大きくなる必要があります。

図 **36**. レシオメトリックな同時スタートアップ・シーケンスの回路図

$$R1 = \frac{V_{OUT2} + \Delta V}{V_{REF}} + \frac{V_{SS(offset)}}{I_{SS}}$$

(7)

$$R2 = \frac{V_{REF} \times R1}{V_{OUT2} + \Delta V - V_{REF}}$$

(8)

$$\Delta V = V_{OUT1} - V_{OUT2} \tag{9}$$

$$R1 > 2800 \times V_{OUT1} - 180 \times \Delta V \tag{10}$$

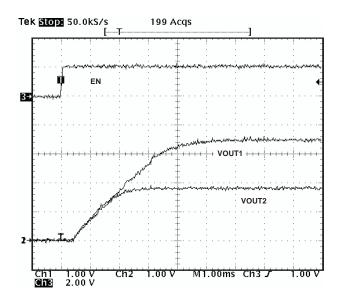

図 37.  $V_{OUT2}$ が $V_{OUT1}$ に先行するレシオメトリックなスタートアップ

図 38.  $V_{OUT1}$ が $V_{OUT2}$ に先行するレシオメトリックなスタートアップ

図39. トラッキング抵抗による同時スタートアップ

# 一定のスイッチング周波数、およびタイミング 抵抗(RT/CLKピン)

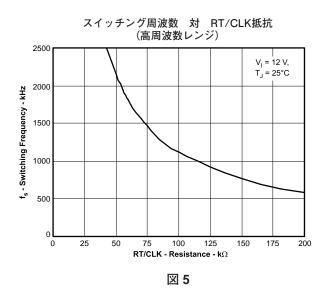

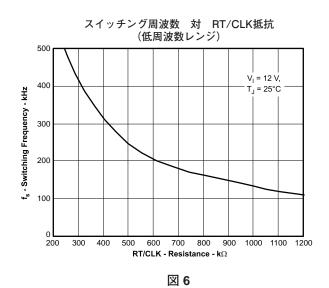

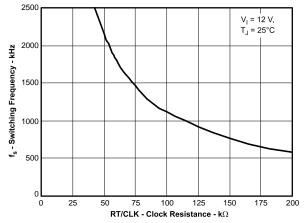

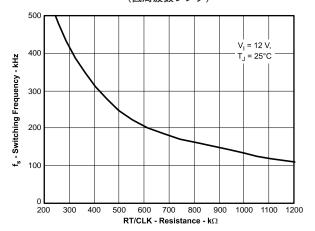

TPS54160Aのスイッチング周波数は、RT/CLKピンに抵抗を接続することで、約100kHz~2500kHzという広い範囲にわたって調整可能です。RT/CLKピンの電圧は標準で0.5Vであり、スイッチング周波数を設定するにはグランドとの間に抵抗を接続する必要があります。特定のスイッチング周波数に対するタイミング抵抗を決定するには、式(11)を用いるか、図40または図41の曲線を使用します。ソリューション・サイズを小さくするには、一般にスイッチング周波数をできるだけ高く設定しますが、電源効率、最大入力電圧、および最小制御可能オン時間の間でトレードオフを考慮する必要があります。

最小制御可能オン時間は標準で130nsであり、これによって 最大動作入力電圧が制限されます。

最大スイッチング周波数は、周波数シフト回路によっても制限されます。最大スイッチング周波数については、以下で詳しく説明します。

$$R_{RT}(k\Omega) = \frac{206033}{f_{SW}(kHz)^{1.0888}}$$

(11)

### スイッチング周波数 対 RT/CLK抵抗 (高周波数レンジ)

図 40. 高周波数レンジのタイミング抵抗

### 過電流保護および周波数シフト

TPS54160Aは、電流モード制御を実装し、COMPピンの電圧を使用してハイサイドMOSFETをサイクル毎にオフにすることができます。各サイクルで、スイッチ電流とCOMPピン電圧が比較されます。ピーク・スイッチ電流がCOMP電圧と交差すると、ハイサイド・スイッチがオフになります。過電流状態で出力電圧が低下すると、スイッチ電流が増加しながら誤差増幅器によってCOMPピンがHighになります。誤差増幅器の出力は内部でクランプされ、スイッチ電流の制限として機能します。

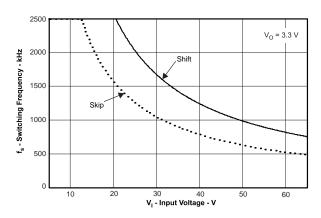

高い入力電圧での最大動作スイッチング周波数を高めるために、TPS54160Aでは周波数シフトを実装しています。 VSENSEピンの電圧が0Vから0.8Vに上昇する際、スイッチング周波数は8、4、2、および1で分周されます。

デバイスではデジタル周波数シフトを実装することで、通常動作時および障害状態時に外部クロックとの同期を可能にしています。スイッチング周波数は8分周のみが可能なため、デバイスが動作しながら周波数シフト保護も得られる最大の入力電圧制限が存在します。

短絡発生時(特に、高入力電圧アプリケーションの場合)には、制御ループに有限の最小制御可能オン時間が存在し、出力は低電圧となります。スイッチのオン時間中は、高い入力電圧と最小オン時間により、インダクタ電流がピーク電流制限まで上昇します。スイッチのオフ時間中は、インダクタは通常、上昇したのと同じ分だけ下降するために十分なオフ時間と出力電圧を得られません。周波数シフトを行うことで、オフ時間が実質的に増加するため、電流の下降が可能となります。

#### スイッチング周波数 対 RT/CLK抵抗 (低周波数レンジ)

図 41. 低周波数レンジのRT

### スイッチング周波数の選択

選択されるスイッチング周波数は、式 (12)と式 (13)の2つの値のうち小さい方の値となる必要があります。式 (12)は、最小制御可能オン時間によって設定される最大スイッチング周波数制限です。スイッチング周波数をこの値以上に設定すると、レギュレータがスイッチング・パルスをスキップします。

式(13)は、周波数シフト保護によって設定される最大スイッチング周波数制限です。高い入力電圧で十分な出力短絡保護を実現するには、スイッチング周波数をf<sub>SW(maxshift)</sub>より小さく設定する必要があります。式(13)で最大スイッチング周波数を計算するには、出力電圧が公称電圧から0Vまで減少する際に、周波数シフトに対応してf<sub>DIV</sub>整数が1から8まで増加することを考慮に入れる必要があります。

図42では、実線が周波数シフトに関する標準の安全動作領域を示し、出力電圧は0Vと仮定し、インダクタの抵抗が $0.1\Omega$ 、FETのオン抵抗が $0.2\Omega$ 、ダイオードの電圧降下が0.5Vです。点線は、パルスのスキップを避けるための最大スイッチング周波数です。これらの式をスプレッドシートまたは他のソフトウェアに入力するか、またはSwitcherPro設計ソフトウェアを使用してスイッチング周波数を決定します。

$$f_{\text{SW(maxskip)}} = \frac{1}{t_{\text{ON}}} \times \left( \frac{I_{\text{L}} \times R_{\text{dc}} + V_{\text{OUT}} + V_{\text{d}}}{V_{\text{IN}} - I_{\text{L}} \times R_{\text{DS(on)}} + V_{\text{d}}} \right)$$

(12)

$$f_{\text{SWshift}} = \frac{f_{\text{DIV}}}{t_{\text{ON}}} \times \left( \frac{I_{\text{L}} \times R_{\text{dc}} + V_{\text{OUT(sc}}) + V_{\text{d}}}{V_{\text{IN}} - I_{\text{L}} \times R_{\text{DS(on)}} + V_{\text{d}}} \right)$$

(13)

$I_L$  インダクタ電流  $R_{dc}$  インダクタ抵抗  $V_{IN}$  最大入力電圧  $V_{OUT}$  出力電圧

$V_{OUT(sc)}$  短絡時の出力電圧  $V_{OUT(sc)}$  短絡時の出力電圧  $V_{OUT(sc)}$  ダイオードの電圧降下  $V_{OUT(sc)}$  スイッチのオン抵抗  $V_{OUT(sc)}$  最小制御可能オン時間  $V_{OUT(sc)}$  分周数  $V_{OUT(sc)}$  分周数  $V_{OUT(sc)}$  ない。

図 42. 最大スイッチング周波数 対 入力電圧

#### RT/CLKピンへのインターフェイス方法

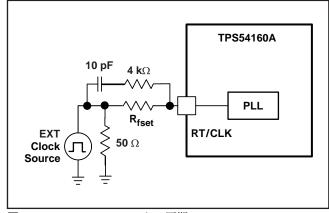

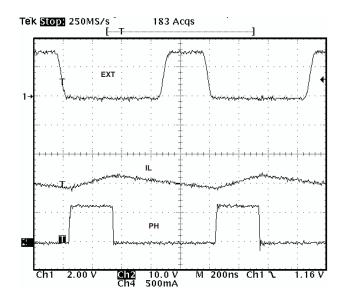

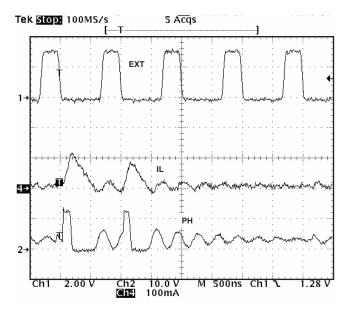

RT/CLKピンを使用して、レギュレータを外部システム・ク ロックに同期させることができます。同期機能を実装するに は、図43に示す回路ネットワークを通してRT/CLKピンに方 形波を接続します。方形波の振幅はRT/CLKピン上で0.5V未 満および2.2V以上で遷移する必要があり、オン時間が40ns以 上、オフ時間が40ns以上となる必要があります。同期周波数範 囲は300kHz~2200kHzです。PHの立ち上がりエッジは、RT/ CLKピン信号の立ち下がりエッジに同期します。外部同期回 路は、同期信号がオフになったとき、RT/CLKピンとグラン ドの間にデフォルトの周波数設定抵抗が接続されるよう設計す る必要があります。図43に示すような周波数設定抵抗を50Ωの 抵抗を介してグランドに接続することを推奨します。この抵 抗によって、スイッチング周波数が外部CLK周波数に近い値 に設定される必要があります。同期信号は10pFのセラミック・ コンデンサを通してRT/CLKピンおよび4kΩの直列抵抗にAC 結合することを推奨します。この直列抵抗により、重負荷アプ リケーションで外部クロックと同期する場合に、および同期か らRTモードに遷移するアプリケーションで、PHジッタが低減 されます。CLKがCLKスレッショルドを最初に超えたときに、 デバイスはRT抵抗周波数からPLLモードへと切り替わります。 PLLが外部信号へのロックを開始すると、内部の0.5V電圧源が 切り離され、CLKピンがハイ・インピーダンスになります。レ ギュレータはPLLを備えているため、スイッチング周波数は外 付け抵抗で設定された周波数よりも高くまたは低くできます。 デバイスは抵抗モードからPLLモードに遷移した後、PLLが 100マイクロ秒以内にCLK周波数へとロックするまで、スイッ チング周波数を上昇または下降させます。

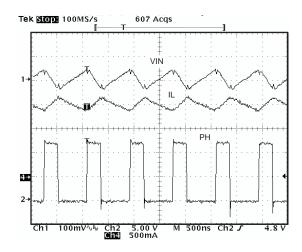

デバイスがPLLモードから抵抗モードに遷移すると、スイッチング周波数がCLK周波数から150kHzへと低下した後、0.5Vの電圧が再印加され、抵抗によりスイッチング周波数が設定されます。VSENSEピンの電圧が0Vから0.8Vに上昇する際、スイッチング周波数は8、4、2、および1で分周されます。デバイスではデジタル周波数シフトを実装することで、通常動作時および障害状態時に外部クロックとの同期を可能にしています。図44、図45、および図46に、連続導通モード(ccm)、不連続導通モード(dcm)、およびパルス・スキップ・モード(psm)での外部システム・クロックとの同期を示します。

図 43. システム・クロックとの同期

**図 44.** ccmでの同期プロット

図 45. dcmでの同期プロット

図 46. PSMでの同期プロット

# パワー・グッド (PWRGDピン)

PWRGDピンは、オープン・ドレイン出力です。VSENSE ピンが内部電圧リファレンスの94%~107%になると、PWRGD ピンはデアサートされてフローティングになります。5.5V未満の電圧源に対して10kΩ~100kΩのプルアップ抵抗を使用することを推奨します。VIN入力電圧が1.5Vを超えると、PWRGDは、電流シンク能力は低いですが有効となります。VIN入力電圧が3Vに近づくと、PWRGDは完全な電流シンク能力を持つようになります。

VSENSEが公称入力リファレンス電圧の92%を下回るか、または109%を上回ると、PWRGDピンはLowになります。また、UVLOまたは過熱シャットダウンがアサートされるか、ENピンがLowになった場合にも、PWRGDはLowになります。

#### 過電圧過渡保護

TPS54160Aには、小さな出力容量の電源設計で、出力障害 状態からの回復時や強い無負荷過渡事象時に発生する電圧オー バーシュートを最小限に抑える、過電圧過渡保護 (OVTP)回 路が備えられています。例えば、電源出力が過負荷となった場 合、誤差増幅器によって実際の出力電圧が内部リファレンス電 圧と比較されます。VSENSEピンの電圧が内部リファレンス 電圧よりも一定時間にわたって低くなった場合、誤差増幅器の 出力が高い電圧にクランプされます。これにより、最大出力電 流が要求されます。この状態が解消されると、レギュレータ の出力が上昇し、誤差増幅器の出力は定常状態のデューティ・ サイクルに遷移します。一部のアプリケーションでは、電源 出力の電圧が誤差増幅器の出力よりも速く応答する場合があ り、これは実際、出力のオーバーシュートにつながる可能性が あります。OVTP機能では、値の小さい出力コンデンサの使用 時に、VSENSEピンの電圧を内部電圧リファレンスの109%で あるOVTPスレッショルドと比較する回路を実装することによ り、出力のオーバーシュートを最小限に抑えます。VSENSE ピンの電圧がOVTPスレッショルドより高い場合は、ハイサイ ドMOSFETがディスエーブルになり、出力に電流が流れるの を防いで、出力オーバーシュートを抑えます。VSENSE電圧が OVTPスレッショルドを下回ると、次のクロック・サイクルで ハイサイドMOSFETがオンになります。

#### 過熱シャットダウン

このデバイスは、接合部温度が182℃を超えた場合にデバイス自身を保護する、過熱シャットダウン機能を内蔵しています。接合部温度が過熱トリップ・スレッショルドを超えると、デバイスのスイッチングが強制的に停止されます。接合部温度が182℃を下回ると、デバイスはSS/TRピンを放電して電源投入シーケンスを再び開始します。

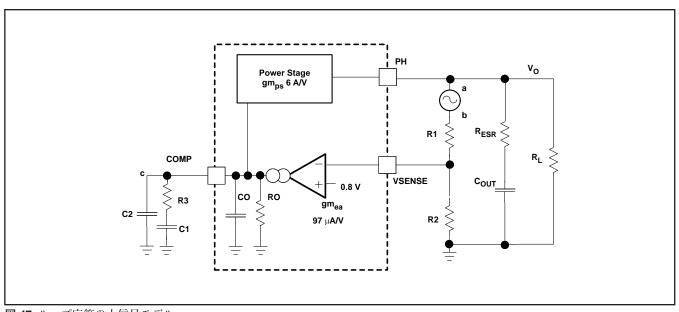

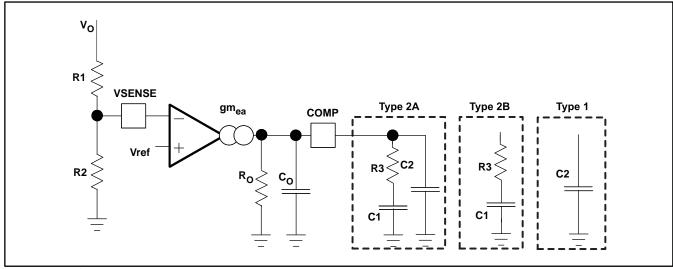

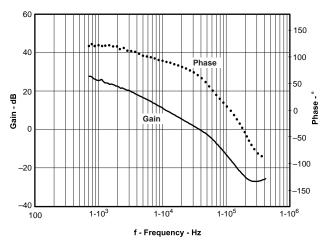

## ループ応答の小信号モデル

図47に、周波数応答と動的負荷応答をチェックするために回路シミュレーション・プログラムでモデル化できる、TPS54160A制御ループの等価モデルを示します。誤差増幅器は、 $gm_{EA}$ が $97\mu A/V$ のトランスコンダクタンス・アンプです。この誤差増幅器は、理想的な電圧制御電流源を使用してモデル化できます。抵抗 $R_0$ およびコンデンサ $C_0$ により、増幅器の開ループ・ゲインと周波数応答がモデル化されます。ノードaとbの間の1mVのAC電圧源は、周波数応答測定のために制御ループを実質的に分断します。c/aのプロットにより、周波数補償の小信号応答を示します。 $R_L$ の代わりに、時間ドメイン分析で適切な負荷ステップ振幅およびステップ・レートを持つ電流源を使用すれば、動的ループ応答をチェックできます。この等価モデルは、連続導通モードの設計に対してのみ有効です。

図 47. ループ応答の小信号モデル

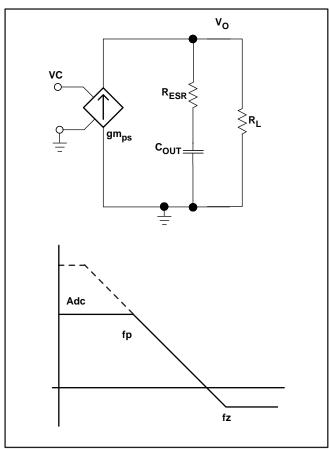

## ピーク電流モード制御の単純な小信号モデル

図48に、周波数補償の設計方法を理解するために使用できる、単純な小信号モデルを示します。TPS54160Aのパワー段は、出力コンデンサおよび負荷抵抗に電流を供給する電圧制御電流源(デューティ・サイクル変調器)として近似できます。制御-出力間の伝達関数は式(14)に示され、DCゲイン、1つの支配的な極、および1つのESRゼロで構成されます。スイッチ電流の変化とCOMPピン電圧(図47のノードc)の変化との比が、パワー段のトランスコンダクタンスです。TPS54160AのgmpSは6A/Vです。パワー段周波数応答の低周波ゲインは、式(15)に示すように、トランスコンダクタンスと負荷抵抗の積です。

負荷電流が増加または減少すると、低周波ゲインはそれぞれ減少または増加します。この負荷に対する変化は一見問題となりそうですが、幸い、支配的な極は負荷電流とともに移動します(式(16)を参照)。それらの組み合わせによる効果は、図48の下側に点線で示されています。負荷電流が減少すると、ゲインが増加して極周波数が低下するため、負荷状態の変化に対して0dBクロスオーバー周波数は一定に保たれ、周波数補償の設計が容易になります。選択する出力コンデンサの種類によって、ESRゼロが周波数補償設計に大きな影響を与えるかどうかが決まります。ESRの高いアルミ電解コンデンサを使用すると、低周波では位相マージンがESRゼロから増加するため、ループ全体の安定化に必要な周波数補償部品の数が少なくて済む可能性があります(式(17)を参照)。

図 48. ピーク電流モード制御の単純な小信号モデル および周波数応答

$$\frac{V_{OUT}}{V_{C}} = Adc \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P}}\right)}$$

(14)

$$Adc = gm_{ps} \times R_{L}$$

(15)

$$f_{\mathsf{P}} = \frac{1}{\mathsf{C}_{\mathsf{OUT}} \times \mathsf{R}_{\mathsf{L}} \times 2\pi} \tag{16}$$

$$f_{Z} = \frac{1}{C_{OUT} \times R_{ESR} \times 2\pi}$$

(17)

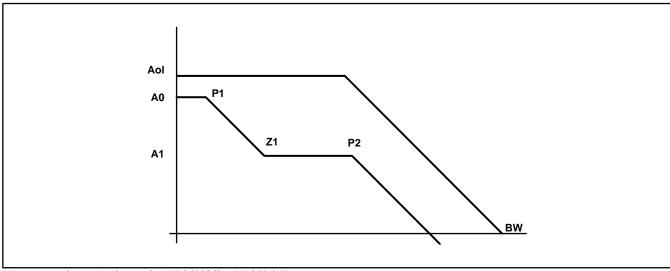

# 周波数補償の小信号モデル

TPS54160Aでは、誤差増幅器にトランスコンダクタンス・アンプを使用し、一般的に使用される周波数補償回路のうち3つを標準でサポートしています。タイプ2A、タイプ2B、およびタイプ1の補償回路を図49に示します。タイプ2の回路は、低ESRの出力コンデンサを使用した高帯域電源設計で実装されるのが最も一般的です。タイプ1の回路は、高ESRのアルミ電解コンデンサまたはタンタル・コンデンサを使用した電源設計で用いられます。式 (18) および式 (19) は、増幅器の周波数応答を図49の小信号モデルにどのように関連付けるかを示しています。開ループ・ゲインおよび帯域幅は、図49の $R_0$ および $C_0$ を使用してモデル化されます。低ESRの出力コンデンサとともにタイプ2A回路を使用した設計例については、「アプリケーション情報 | を参照してください。

式 (18)~式 (27) は、所望の方法を用いて補償を行う方への 参考として記載しています。規定の方法を使用する場合には、 「アプリケーション情報」で説明する方法に従うか、またはス イッチング情報を参考にしてください。

図 49. 周波数補償の種類

図 50. タイプ2Aおよびタイプ2B周波数補償の周波数応答

$$Ro = \frac{Aol(V/V)}{gm_{ea}}$$

(18)

$$Z1 = \frac{1}{2\pi \times R3 \times C1}$$

$$C_{OUT} = \frac{gm_{ea}}{2\pi \times BW \text{ (Hz)}}$$

(19)

$$P2 = \frac{1}{2\pi \times R3 \mid \mid Ro \times (C2 + Co)} \text{ type 2a}$$

(25)

$P2 = \frac{1}{2\pi \times R3 \mid \mid Ro \times Co} \text{ type 2b}$

$P2 = \frac{1}{2\pi \times Ro \times (C2 + Co)} \text{ type 1}$

$$EA = A0 \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z1}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P1}}\right) \times \left(1 + \frac{s}{2\pi \times f_{P2}}\right)}$$

(20)

$$A0 = gm_{ea} \times Ro \times \frac{R2}{R1 + R2}$$

(21)

A1 =

$$gm_{ea} \times Ro| | R3 \times \frac{R2}{R1 + R2}$$

(22)

$$P1 = \frac{1}{2\pi \times Ro \times C1} \tag{23}$$

(24)

(26)

(27)

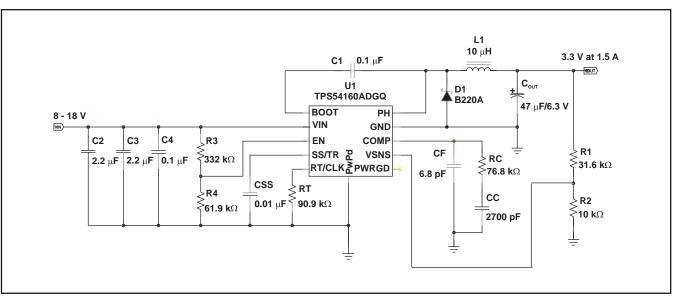

# アプリケーション情報

# 設計ガイドーステップ毎の設計手順

この例では、セラミック出力コンデンサを使用した高周波スイッチング・レギュレータ設計の詳細を示します。設計プロセスを開始するには、いくつかのパラメータがわかっている必要があります。これらのパラメータは一般に、システム・レベルで決定されます。この例では、以下に示す既知のパラメータを使用して開始します。

| 出力電圧               | 3.3V                          |

|--------------------|-------------------------------|

| 過渡応答、0~1.5Aの負荷ステップ | $\Delta V_{\text{out}} = 4\%$ |

| 最大出力電流             | 1.5 A                         |

| 入力電圧               | 12V公称、8V~18V                  |

| 出力電圧リップル           | < 33 mV <sub>pp</sub>         |

| 開始入力電圧(VIN上昇時)     | 7.7 V                         |

| 停止入力電圧(VIN下降時)     | 6.7 V                         |

### スイッチング周波数の選択

最初の手順は、レギュレータのスイッチング周波数を決定することです。一般に、ユーザは可能な限り高いスイッチング周波数を選択します。それによってソリューション・サイズを最小にできるからです。高いスイッチング周波数では、低周波数

でスイッチングする電源と比較して、低い値のインダクタと小さな出力コンデンサを使用できます。選択可能なスイッチング 周波数は、内部パワー・スイッチの最小オン時間、入力電圧と 出力電圧、および周波数シフト制限によって制限されます。

レギュレータの最大スイッチング周波数を求めるには、式 (12) と式 (13)を使用し、2つの式のうち小さい方の値を選択します。これらの値よりも高いスイッチング周波数を使用すると、パルスのスキップが発生したり、短絡時に過電流保護が機能しなかったりします。

TPS54160Aでの標準の最小オン時間 $t_{onmin}$ は130nsです。この例では、出力電圧が3.3Vで最大入力電圧が18Vであるため、式 (12)でインダクタ抵抗、オン抵抗、およびダイオード電圧を含めると、最大1600kHzのスイッチング周波数を設定できます。設計で短絡発生時に過電流暴走が問題とならないようにするには、式 (13)または図42の実線の曲線を使用して最大スイッチング周波数を決定します。18Vから少し余裕を見て最大入力電圧を20Vとし、ダイオード電圧を0.5V、インダクタ抵抗を100m $\Omega$ 、スイッチ抵抗を200m $\Omega$ 、電流制限値を2.7Aと仮定すると、最大スイッチング周波数は約2500kHzとなります。

2つの値のうち小さい方を選択し、多少の余裕を取って、1200kHzのスイッチング周波数を使用します。特定のスイッチング周波数に対するタイミング抵抗を決定するには、式(11)を用いるか、図40の曲線を使用します。

スイッチング周波数は、図51に示される抵抗 $R_t$ によって設定されます。

図 51. UVLOを調整した高周波の3.3V出力電源設計

# 出力インダクタの選択(Lo)

出力インダクタの最小値を計算するには、式 (28)を使用します。

K<sub>IND</sub>は、最大出力電流を基準としたインダクタ・リップル電流の大きさを表す係数です。

インダクタ・リップル電流は、出力コンデンサによってフィルタリングされます。したがって、大きなインダクタ・リップル電流を選択すると、それ以上のリップル電流定格を持つ出力コンデンサが必要となるため、出力コンデンサの選択に影響が及びます。一般に、インダクタ・リップル値は設計者の裁量で決定しますが、以下のガイドラインに従うことができます。

セラミックなどの低ESR出力コンデンサを使用した設計では、最大 $K_{IND}$  = 0.3の値を使用できます。よりESRの高い出力コンデンサを使用する場合は、 $K_{IND}$  = 0.2が適切です。インダクタ・リップル電流はPWM制御システムの一部であるため、信頼性の高い動作のためにはインダクタ・リップル電流が常に100mAを上回っている必要があります。入力電圧範囲の広いレギュレータでは、大きい側でインダクタ・リップル電流を選択するのが最善です。これにより、最小の入力電圧でもインダクタが適度なリップル電流を持つことができます。

この設計例では、 $K_{\rm IND}=0.2$ を使用し、最小インダクタ値は 7.6 $\mu$ Hと計算されます。この設計では、最も近い標準値として  $10\mu$ Hが選択されています。出力フィルタ・インダクタについては、RMS電流および飽和電流の定格を超えないことが重要です。 RMSおよびピーク・インダクタ電流は、式 (30) および式 (31) で求めることができます。

この設計では、RMSインダクタ電流は1.506A、ピーク・インダクタ電流は1.62Aです。選択したインダクタは、MSS6132-103です。このインダクタの飽和電流定格は1.64A、RMS電流定格は1.9Aです。

一連の式で示されるように、リップル電流が小さいとレギュレータの出力電圧リップルが減少しますが、より大きなインダクタンスが必要になります。より大きなリップル電流を選択するとレギュレータの出力電圧リップルが増加しますが、インダクタンスの値が小さくて済みます。

インダクタを流れる電流は、インダクタ・リップル電流 + 出力電流です。パワーアップ時、障害発生時、または負荷過渡状態中は、インダクタ電流が上記で計算されたピーク・インダクタ電流レベルを超えて増加する場合があります。過渡状態では、インダクタ電流がデバイスのスイッチ電流制限まで増加する場合があります。この理由により、最も保守的なアプローチは、ピーク・インダクタ電流ではなく、スイッチ電流制限以上の飽和電流定格を持つインダクタを指定することです。

$$L_{O(min)} = \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN(max)} \times f_{SW}}$$

(28)

$$I_{RIPPLE} = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times L_{O} \times f_{SW}}$$

(29)

$$I_{L(rms)} = \sqrt{\left(I_{OUT}\right)^{2} + \frac{1}{12} \times \left(\frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{V_{IN(max)} \times L_{O} \times f_{SW}}\right)^{2}}$$

(30)

$$I_{L(peak)} = I_{OUT} + \frac{I_{RIPPLE}}{2}$$

(31)

### 出力コンデンサ

出力コンデンサ値の選択については、3つの主要な考慮事項があります。出力コンデンサは、変調器の極、出力電圧リップル、および負荷電流の大きな変化に対するレギュレータの応答を決定します。出力容量は、これら3つの条件のうち最も厳しいものに基づいて選択する必要があります。

最初の条件は、負荷電流の大きな変化に対して求められる応 答です。レギュレータが電流を供給できないときには、出力 コンデンサが負荷に電流を供給する必要があります。この状況 は、レギュレータに対して保持時間要件があり、入力電力の停 止後に指定された時間だけ、出力コンデンサが出力電圧を特定 のレベルより高く保持する必要がある場合に発生します。ま た、無負荷から全負荷への遷移時など、負荷の電流需要に大き く高速な変化が発生した場合、レギュレータは一時的に十分な 出力電流を供給できなくなります。通常、レギュレータでは、 制御ループが負荷電流および出力電圧の変化を検知して、その 変化に合わせてデューティ・サイクルを調整するまでに、2ク ロック・サイクル以上を必要とします。出力コンデンサの大き さは、制御ループが負荷の変化に応答するまでの間、負荷に追 加の電流を供給できるように決定する必要があります。出力容 量は、出力電圧の降下を許容範囲内に抑えながら、2クロック・サ イクルにわたって電流の差分を供給するのに十分な大きさでなけ ればなりません。そのために必要な最小の出力容量を式(32)に 示します。

ここで、 $\Delta I_{OUT}$ は出力電流の変化、 $f_{sw}$ はレギュレータのスイッチング周波数、 $\Delta V_{OUT}$ は出力電圧の許容される変化です。この例では、負荷過渡応答が、0A(無負荷)から1.5A(全負荷)までの負荷ステップに対する $V_{OUT}$ の4%の変化と指定されています。この例では、 $\Delta I_{OUT}=1.5-0=1.5A$ 、および $\Delta V_{OUT}=0.04\times3.3=0.132$ Vです。これらの値を使用して、 $18.9\mu$ Fの最小容量が得られます。この値は、出力電圧の変化について出力コンデンサのESRを考慮していません。セラミック・コンデンサの場合、ESRは通常十分に小さいため、この計算では無視できます。アルミ電解コンデンサおよびタンタル・コンデンサの場合は、ESRが比較的高いので考慮に入れる必要があります。

レギュレータのキャッチ・ダイオードは電流をシンクできな いため、負荷電流が急速に減少すると、インダクタに蓄積され たエネルギーによって出力電圧にオーバーシュートが発生しま す (図52を参照)。また、出力コンデンサは、高負荷電流から低 負荷電流への遷移時に、インダクタに蓄積されたエネルギーを 吸収できるだけの容量を持つ必要があります。出力コンデンサ に蓄積された余分なエネルギーにより、コンデンサの電圧は上 昇します。コンデンサの容量は、これらの過渡期間中に所定の 出力電圧を保持できるような大きさでなければいけません。出 力電圧オーバーシュートを所定の値に保持するための最小容量 は式(33)で計算します。ここで、Lはインダクタの値、IOHは 重負荷時の出力電流、IOI は軽負荷時の出力電流、Vfは最終的 なピーク出力電圧、Viはコンデンサ電圧の初期値です。この例 では、ワーストケースの負荷ステップは1.5Aから0Aです。この 負荷遷移中は出力電圧が上昇し、仕様に規定された最大値は出 力電圧の4%です。これにより、 $Vf = 1.04 \times 3.3 = 3.432$ となり ます。Viはコンデンサ電圧の初期値であり、これは公称出力電 圧の3.3Vです。式 (33) にこれらの値を使用すると、25.3μFの 最小容量が得られます。

式 (34) は、出力電圧リップル仕様を満足するために必要な最小の出力容量を計算します。ここで、fswはスイッチング周波数、 $V_{OUT(ripple)}$ は最大許容出力電圧リップル、 $I_{ripple}$ はインダクタ・リップル電流です。式 (34) により、 $0.7\mu$ Fが得られます。

式 (35) は、出力電圧リップル仕様を満足するために出力コンデンサに許容される最大ESRを計算します。式 (35) より、ESRは $147m\Omega$ 未満とする必要があります。

無負荷過渡状態中に出力電圧のレギュレーションを維持するための、出力コンデンサに対する最も厳しい条件は、25.3µFの容量です。

エージング、温度、およびDCバイアスに対して、追加の容量ディレーティングを考慮する必要があるため、この最小値は増加します。この例では、ESRが $5m\Omega$ の $47\mu$ F/6.3V X7Rセラミック・コンデンサを使用します。

一般に、コンデンサでは、障害や過熱を発生させずに処理できるリップル電流の大きさに制限があります。インダクタ・リップル電流に対して対応可能な出力コンデンサを指定する必要があります。一部のコンデンサのデータシートでは、最大リップル電流の2乗平均平方根 (RMS)値が指定されています。出力コンデンサで処理できる必要のあるRMSリップル電流値は、式 (36)で計算できます。このアプリケーションでは、式 (36)により64.8mAが得られます。

$$C_{\text{OUT}} > \frac{2 \times \Delta I_{\text{OUT}}}{f_{\text{SW}} \times \Delta V_{\text{OUT}}}$$

(32)

$$C_{OUT} > L_O \times \frac{\left( (l_{OH})^2 - (l_{OL})^2 \right)}{\left( (V_f)^2 - (V_i)^2 \right)}$$

(33)

$$C_{OUT} > \frac{1}{8 \times f_{SW}} \times \frac{1}{\left(\frac{V_{OUT(ripple)}}{I_{RIPPLE}}\right)}$$

(34)

$$R_{ESR} = \frac{V_{OUT(ripple)}}{I_{RIPPLE}}$$

(35)

$$I_{COUT(rms)} = \frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{\sqrt{12} \times V_{IN(max)} \times L_{O} \times f_{SW}}$$

(36)

## キャッチ・ダイオード

TPS54160Aでは、PHピンとGNDの間に外付けのキャッチ・ダイオードが必要です。選択するダイオードは、Vinmax以上の逆方向電圧定格を持つ必要があります。ダイオードのピーク電流定格は、最大インダクタ電流よりも大きくなければなりません。また、順方向電圧は低い必要があります。ショットキー・ダイオードは順方向電圧が低いため、一般にキャッチ・ダイオードとして優れた選択肢となります。ダイオードの順方向電圧が低いほど、レギュレータの効率は高くなります。

一般に、ダイオードの電圧および電流定格が高いと、順方向電圧は高くなります。設計例の入力電圧は最大18Vなので、逆方向電圧が最低20Vであるダイオードを選択します。

この設計例では、順方向電圧の低いB220Aショットキー・ダイオードを選択します。このダイオードは、小さなデバイスよりも優れた熱特性を持つ大きなパッケージ・サイズで提供されています。B220Aの標準順方向電圧は0.50Vです。

また、このダイオードは、適切な電力定格を持つ必要があります。このダイオードは、内部パワー・スイッチのオフ時間中に出力電流を導通させます。内部スイッチのオフ時間は、最大入力電圧、出力電圧、およびスイッチング周波数の関数です。オフ時間中の出力電流とダイオードの順方向電圧の積が、ダイオードの導通損失に等しくなります。高いスイッチ周波数では、ダイオードのAC損失を考慮に入れる必要があります。ダイオードのAC損失は、接合部容量の充放電および逆方向回復によって生じます。ダイオードの合計の電力損失(導通損失 + AC損失)は、式 (37) で求められます。

B220Aの接合部容量は120pFです。式 (37)により、選択する ダイオードの損失は0.632Wです。この電力損失により、実装 手法に応じて、入力電圧が18Vおよび負荷電流が1.5Aのときに 16Cの温度上昇がダイオードに生じます。

電源が軽負荷電流やスリープ・モードで動作する時間が長い場合には、リーク電流が低く順方向電圧降下がやや大きなダイオードの使用を検討してください。

$$P_{D} = \frac{\left(V_{IN(max)} - V_{OUT}\right) \times I_{OUT} \times Vfd}{V_{IN(max)}} + \frac{C_{j} \times f_{SW} \times \left(V_{IN} + Vfd\right)^{2}}{2}$$

(37)

### 入力コンデンサ

TPS54160Aは、3μF以上の実効容量を持つ高品質のセラミック(タイプX5RまたはX7R)入力デカップリング・コンデンサを必要とし、アプリケーションによってはバルク容量も必要とします。実効容量には、DCバイアスの影響も含まれます。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。また、コンデンサのリップル電流定格は、TPS54160Aの最大入力電流リップルよりも大きい必要があります。入力リップル電流は、式(38)で計算できます。

セラミック・コンデンサの値は、温度およびコンデンサに印加されるDCバイアスの大きさによって大きく変化します。温度による容量の変化は、温度に対して安定な誘電体を選択することで最小限に抑えることができます。X5RおよびX7Rセラミック誘電体は、容量/体積比が大きく、温度に対してかなり安定しているため、パワー・レギュレータのコンデンサとして一般に選択されます。また、出力コンデンサはDCバイアスも考慮して選択する必要があります。コンデンサ両端にかかるDCバイアスが増加すると、コンデンサの容量値は減少します。

この設計例では、最大入力電圧に対応するために20V以上の電圧定格を持つセラミック・コンデンサが必要です。セラミック・コンデンサの一般的な標準電圧定格としては4V、6.3V、10V、16V、25V、50V、100Vがあるため、25Vのコンデンサを選択します。この例では、 $2.2\mu$ F、25Vのコンデンサを2個並列に使用しています。高電圧コンデンサの一覧を表2に示します。入力容量の値によって、レギュレータの入力リップル電圧が決まります。入力電圧リップルは、式 (39) で計算できます。設計例の値である

- $I_{OUT(max)} = 1.5A$

- $C_{IN} = 4.4 \mu F$

- fsw = 1200kHz

を使用すると、71mVの入力電圧リップル、および0.701Aの RMS入力リップル電流が得られます。

$$I_{CI(rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN(min)}} \times \frac{\left(V_{IN(min)} - V_{OUT}\right)}{V_{IN(min)}}}$$

(38)

$$\Delta V_{IN} = \frac{I_{OUT(max)} \times 0.25}{C_{IN} \times f_{SW}}$$

(39)

#### スロー・スタート・コンデンサ

スロー・スタート・コンデンサは、パワーアップ中に出力電圧がその公称設定値に達するまでにかかる最小の時間を決定します。これは、負荷に対して制御された電圧スルー・レートが必要である場合に有用です。また、出力容量が非常に大きく、コンデンサを出力電圧レベルまで充電するのに大きな電流を必要とするような場合にも、利用されます。コンデンサの充電に必要な大きな電流によってTPS54160Aが電流制限に達したり、入力電源からの過剰な電流によって入力電圧レールが降下したりする場合があります。出力電圧のスルー・レートを制限することで、その両方の問題を解決できます。

スロー・スタート時間は、レギュレータが過剰な電流を引き込むことなく出力コンデンサを出力電圧まで充電できるよう十分に長くする必要があります。式 (40)を使用すると、出力コンデンサCoutを出力電圧Voutの10%から90%まで、平均スロー・スタート電流Issavgで充電するために必要な、最小のスロー・スタート時間tssを求めることができます。この例では、平均入力電流0.125Aで47μFの出力コンデンサを3.3Vまで充電するために、1msのスロー・スタート時間が必要です。

スロー・スタート時間がわかれば、式 (6) を使用してスロー・スタート・コンデンサ値を計算できます。この例の回路では、出力コンデンサ値が $47\mu$ Fで、3.3Vまでの充電に大きな電流を必要としないため、スロー・スタート時間はそれほど重要ではありません。この回路ではスロー・スタート時間が任意値の1mSに設定され、3.3nFのコンデンサが必要となります。

$$t_{SS} > \frac{C_{OUT} \times V_{OUT} \times 0.8}{I_{SS(avg)}}$$

(40)

| メーカー    | 値(μF)     | EIAサイズ | 電圧(V) | 誘電体 | 名称             |  |

|---------|-----------|--------|-------|-----|----------------|--|

| Mussets | 1.0 ~ 2.2 | 1210   | 100   |     | CDM203.II 7    |  |

|         | 1.0 ~ 4.7 | 1210   | 50    |     | GRM32シリース      |  |

| Murata  | 1.0       | 1206   | 100   |     | CDM213.II      |  |

|         | 1.0 ~ 2.2 | 1206   | 50    |     | GRM31シリース      |  |

| Vishay  | 1.0 ~ 1.8 | 2220   | 50    |     |                |  |

|         | 1.0 ~ 1.2 | 2220   | 100   | X7R | VJ X7Rシリース     |  |

|         | 1.0 ~ 3.9 | 2225   | 50    |     | VJ X/HJ·J·-    |  |

|         | 1.0 ~ 1.8 | 2225   | 100   |     |                |  |

|         | 1.0 ~ 2.2 | 1812   | 100   |     | CシリーズC453      |  |

| TDK     | 1.5 ~ 6.8 | 1012   | 50    |     | U J J - X U 45 |  |

| IDK     | 1.0. ∼2.2 | 1210   | 100   |     | CシリーズC322      |  |

|         | 1.0 ~ 3.3 | 1210   | 50    |     | 099-20322      |  |

|         | 1.0 ~ 4.7 | 1210   | 50    |     |                |  |

| AVX     | 1.0       | 1210   | 100   |     | VZD 託電仕 S.II   |  |

|         | 1.0 ~ 4.7 | 1010   | 50    |     | X7R誘電体シリー      |  |

|         | 1.0 ~ 2.2 | 1812   | 100   |     |                |  |

表 2. コンデンサの種類

### ブートストラップ・コンデンサの選択

適切な動作のためには、BOOTピンとPHピンの間に $0.1\mu$ Fのセラミック・コンデンサを接続する必要があります。X5R以上の誘電体を持つセラミック・コンデンサの使用を推奨します。コンデンサの電圧定格は10V以上である必要があります。

### 低電圧誤動作防止の設定点

低電圧誤動作防止 (UVLO)は、TPS54160AのENピンに接続した外部分圧回路を使用して調整できます。UVLOには2つのスレッショルドがあり、1つは入力電圧が上昇するパワーアップ中に適用され、もう1つは入力電圧が下降するパワーダウンまたはブラウンアウト中に適用されます。この設計例では、入力電圧が7.7V以上に上昇 (イネーブル)したときに、電源がオンになりスイッチングを開始する必要があります。レギュレータがスイッチングを開始した後は、入力電圧が6.7Vを下回る (UVLO停止)までの間、スイッチングを継続する必要があります。

プログラミング可能なUVLO電圧およびイネーブル電圧は、ENピンに接続された $V_{\rm IN}$ ーグランド間の分圧抵抗を使用して設定されます。式 (2) および式 (3) を使用して、必要な抵抗値を計算できます。このアプリケーション例では、7.7Vおよび6.7Vの開始および停止電圧を生成するために、 $V_{\rm IN}$ とENの間に332k $\Omega$ 、ENとグランドの間に61.9k $\Omega$ が必要となります。

### 出力電圧および帰還抵抗の選択

この設計例では、R2に10.0k $\Omega$ が選択されています。式 (1)を使用して、R1は31.25k $\Omega$ と計算されます。最も近い標準1%抵抗は、31.6k $\Omega$ です。VSENSEピンのリーク電流があるため、出力電圧の精度を維持するには、帰還回路を流れる電流が1 $\mu$ Aより大きい必要があります。この要件により、R2の最大値は800k $\Omega$ に等しくなります。より高い抵抗値を選択すると、静止時電流が減少し、低出力電流での効率が向上しますが、ノイズ耐性の問題が生じる場合があります。

#### 補償

DC/DCレギュレータの補償には業界でいくつかの手法が使用されています。ここで説明する方法では、高い位相マージンを得ることができます。ほとんどの条件に対して、レギュレータの位相マージンは60°~90°となります。ここに示す方法では、TPS54160A内部のスロープ補償による影響は無視しています。スロープ補償が無視されるため、実際のクロスオーバー周波数は、計算で使用されるクロスオーバー周波数よりも通常は低くなります。

より詳細な設計には、SwitcherProソフトウェアを使用してください。

未補償のレギュレータには、出力コンデンサと負荷抵抗による標準で300Hz~3kHzの支配的な極と、誤差増幅器による極があります。また、出力コンデンサおよびESRにより、1つのゼロが存在します。ゼロ周波数は、2つの極のいずれよりも高くなっています。

未補償のままでは、誤差増幅器と変調器によって生成される2重の極によってレギュレータが不安定になります。レギュレータを安定させるには、1つの極をキャンセルする必要があります。1つの設計アプローチとして、変調器の極に補償用の

ゼロを配置する方法があります。そして、変調器の極よりも高いクロスオーバー周波数を選択します。誤差増幅器のゲインは、目的のクロスオーバー周波数が得られるように計算できます。補償用のゼロを生成するためのコンデンサは、誤差増幅器の出力インピーダンスとともに低周波数の極を形成し、クロスオーバー周波数を通して-1のスロープを提供します。次に、出力コンデンサのESRに起因するゼロをキャンセルするために補償用の極を追加します。ESRゼロがスイッチング周波数よりも高い周波数に位置する場合、そのESRゼロは無視できます。

この方法でTPS54160Aを補償する場合は、最初に次の式を用いて変調器の極とゼロを計算します。

$$f_{P(\text{mod})} = \frac{I_{\text{OUT}(\text{max})}}{2 \times \pi \times V_{\text{OUT}} \times C_{\text{OUT}}}$$

(41)

ここで

- ・ I<sub>OUT(max)</sub>は最大出力電流です。

- C<sub>OUT</sub>は出力容量です。

- V<sub>OUT</sub>は公称出力電圧です。

$$f_{Z(\text{mod})} = \frac{1}{2 \times \pi \times R_{\text{ESR}} \times C_{\text{OUT}}}$$

(42)

設計例では、変調器の極が1.5kHz、ESRゼロが338kHzに位置します。

次に、制御ループの帯域幅を決定するクロスオーバー周波数を選択します。クロスオーバー周波数は、変調器の極より5倍以上高い周波数に位置する必要があります。また、クロスオーバー周波数は、その周波数で得られる誤差増幅器のゲインが適切な補償のために十分高い値となるよう選択する必要があります。

式(47)を使用すると、ESRゼロが目的のクロスオーバー周波数よりも高い周波数に位置する場合の、最大クロスオーバー周波数を計算できます。これは通常、セラミック・コンデンサまたは低ESRのタンタル・コンデンサの場合です。アルミ電解コンデンサやタンタル・コンデンサでは一般にESRが高いため、変調器のゼロは低い周波数に生成されます。

この例のアプリケーションでは、ESRの低い  $(10 \text{m}\Omega)$  セラミック・コンデンサを使用しているため、ゼロは338kHzに位置します。

この値は標準のクロスオーバー周波数よりもずっと高いため、 最大クロスオーバー周波数は式(43)と式(46)から求められます。

式 (46)を使用すると最小クロスオーバー周波数として7.6kHzが得られ、式 (43)では最大クロスオーバー周波数として45.3kHzが得られます。

この範囲から、45kHzのクロスオーバー周波数を任意に選択します。

セラミック・コンデンサに対しては、式(43)を使用します。

$$f_{C(max)} \le 2100 \sqrt{\frac{f_{P(mod)}}{V_{OUT}}}$$

(43)

タンタルまたはアルミ・コンデンサに対しては、式 (44)を使用します。

$$f_{\mathsf{C}(\mathsf{max})} \le \frac{51442}{\sqrt{\mathsf{V}_{\mathsf{OUT}}}} \tag{44}$$

すべてのケースについて、式(45)および式(46)を使用します。

$$f_{\mathsf{C}(\mathsf{max})} \le \frac{f_{\mathsf{SW}}}{5} \tag{45}$$

$$f_{\mathsf{C}(\mathsf{min})} \ge 5 \times f_{\mathsf{P}(\mathsf{mod})} \tag{46}$$

クロスオーバー周波数fcが選択されると、クロスオーバー周波数での変調器のゲインが求められます。クロスオーバー周波数での変調器のゲインは、式 (47)で計算します。

$$G_{MOD(fc)} = \frac{gm_{(PS)} \times R_{LOAD} \times (2\pi \times f_C \times C_{OUT} \times R_{ESR} + 1)}{2\pi \times f_C \times C_{OUT} \times (R_{LOAD} + R_{ESR}) + 1}$$

(47)

この例では、クロスオーバー周波数での変調器のゲインが 0.542となります。次に、補償部品を計算します。コンデンサと直列の抵抗を使用して、補償用のゼロを生成します。この 2つの部品と並列に別のコンデンサを接続することで、補償用の極を形成します。ただし、これらの部品の値の計算は、ESRゼロがクロスオーバー周波数より高いか低いかによって異なります。セラミックまたは低ESRタンタル出力コンデンサの場合は、ゼロは通常、クロスオーバー周波数よりも高く配置されます。アルミ電解コンデンサやタンタル・コンデンサでは、変調器のゼロは通常、クロスオーバー周波数よりも低い周波数に位置します。変調器のゼロがクロスオーバー周波数よりも高い場合(セラミック・コンデンサ)は、次のようになります。

$$R_{C} = \frac{V_{OUT}}{G_{MOD(fc)} \times gm_{(EA)} \times V_{REF}}$$

(48)

$$C_{C} = \frac{1}{2\pi \times R_{C} \times f_{P(mod)}}$$

(49)

$$Cf = \frac{C_{OUT} \times R_{ESR}}{R_{C}}$$

(50)

変調器のゼロがクロスオーバー周波数よりも低い場合 (アルミまたはタンタル・コンデンサ)は、次のようになります。

$$R_{C} = \frac{V_{OUT}}{G_{MOD(fc)} \times f_{Z(mod)} \times gm_{(EA)} \times V_{REF}}$$

(51)

$$C_{C} = \frac{1}{2\pi \times R_{C} \times f_{P(mod)}}$$

(52)

$$Cf = \frac{1}{2\pi \times R_{C} \times f_{Z(mod)}}$$

(53)

この例の場合、ESRゼロはクロスオーバー周波数と比較して高い周波数に位置するため、式 (50) ~式 (53) を使用して補償部品を計算します。この例では、部品の計算値が次のようになります。

- $R_C = 76.2k\Omega$

- $C_C = 2710 pF$

- Cf = 6.17pF

Cfコンデンサの計算値は標準値でないため、2700pFを使用します。 $C_C$ には6.8pFを使用します。抵抗 $R_C$ は、クロスオーバー周波数を決定する誤差増幅器のゲインを設定します。 $R_C$ の計算値は標準値でないため、76.8k $\Omega$ を使用します。

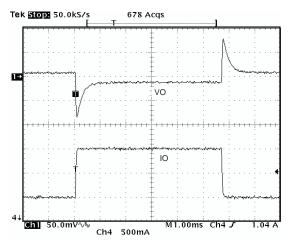

# アプリケーション曲線

図 52. 負荷過渡応答

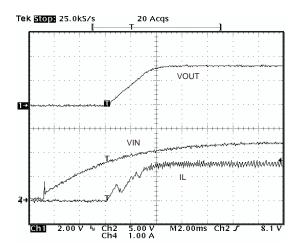

図 54. VINパワーアップ

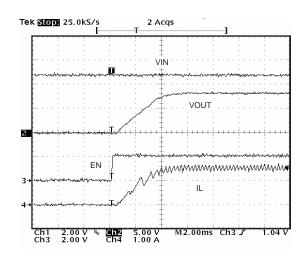

図 53. ENによるスタートアップ

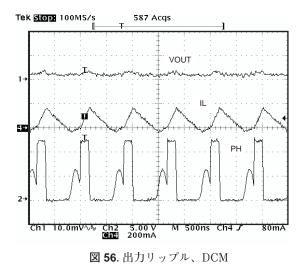

**図 55**. 出力リップルCCM

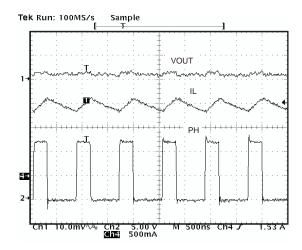

**図 57**. 出力リップル、PSM

# アプリケーション曲線

**図 58**. 入力リップルCCM

**図 60**. 入力リップルPSM

図 62. ループ全体の周波数応答

**図 59**. 入力リップルDCM

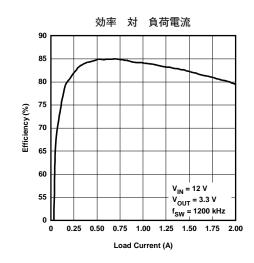

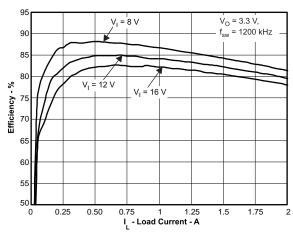

図 61. 効率 対 負荷電流

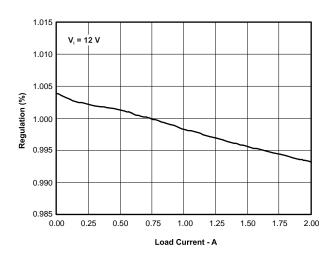

図 63. レギュレーション 対 負荷電流

# アプリケーション曲線

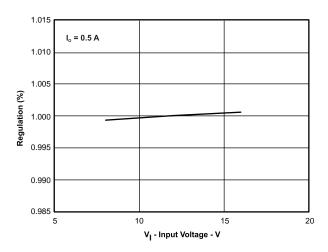

図 64. レギュレーション 対 入力電圧

## 消費電力の見積もり

以下の式は、連続導通モード(CCM)動作でのデバイスの消費電力を見積もる方法を示しています。デバイスが不連続導通モード(DCM)で動作している場合は、これらの式を使用しないでください。

デバイスの消費電力には、導通損失 (Pcon)、スイッチング損失 (Psw)、ゲート駆動損失 (Pgd)、および消費電流 (Pq) が含まれます。

$$P_{COND} = (I_{OUT})^{2} \times R_{DS(on)} \times \left(\frac{V_{OUT}}{V_{IN}}\right)$$

(54)

$$P_{SW} = (V_{IN})^2 \times f_{SW} \times I_{OUT} \times 0.25 \times 10^{-9}$$

(55)

$$P_{GD} = V_{IN} \times 3 \times 10^{-9} \times f_{SW} \tag{56}$$

$$P_{Q} = 116 \times 10^{-6} \times V_{IN}$$

(57)

#### ここで

- I<sub>OUT</sub> = 出力電流 (A)

- ・  $R_{\mathrm{DS(on)}}$  = ハイサイドMOSFETのオン抵抗  $(\Omega)$

- V<sub>OUT</sub> = 出力電圧 (V)

- V<sub>IN</sub> = 入力電圧 (V)

- f<sub>SW</sub> = スイッチング周波数 (Hz)

$$P_{TOT} = P_{COND} + P_{SW} + P_{GD} + P_{Q}$$

(58)

与えられたTAに対して:

$$T_{J} = T_{A} + R_{TH} \times P_{TOT} \tag{59}$$

与えられたT<sub>JMAX</sub> = 150℃に対して:

$$T_{A(max)} = T_{J(max)} - R_{TH} \times P_{TOT}$$

(60)

#### ここで

- P<sub>TOT</sub> = 合計デバイス消費電力 (W)

- T<sub>A</sub> = 周囲温度 (℃)

- · T<sub>J</sub> = 接合部温度 (℃)

- R<sub>TH</sub> = パッケージの熱抵抗 (℃/W)

- T<sub>J(max)</sub> = 最大接合部温度 (℃)

- T<sub>A(max)</sub> = 最大周囲温度 (℃)

レギュレータ回路には、インダクタのACおよびDC損失、キャッチ・ダイオードおよびパターン抵抗による追加の電力損失があり、レギュレータ全体の効率に影響を与えます。

#### レイアウト

レイアウトは、優れた電源設計のために重要な要素です。高速で変化する電流または電圧を通す信号パスがいくつかあるため、浮遊インダクタンスや寄生容量によってノイズが発生したり、電源の性能が低下したりする可能性があります。これらの問題をなくすために、VINピンは、X5RまたはX7R誘電体を使用した低ESRのセラミック・バイパス・コンデンサを使用してグランドにバイパスする必要があります。バイパス・コンデンサ接続、VINピン、およびキャッチ・ダイオードのアノードによって形成されるループ領域は、最小限に抑えるよう注意が必要です。PCBレイアウト例については、図65を参照してください。GNDピンは、デバイスの下部にあるパワー・パッドに直接接続する必要があります。

パワー・パッドは、デバイスの直下にある複数のビアを使用して内部のPCBグランド・プレーンに接続します。PHピンは、キャッチ・ダイオードのカソード、および出力インダクタに配

線します。PH接続はスイッチング・ノードであるため、キャッチ・ダイオードおよび出力インダクタはPHピンに近づけて配置し、過度の容量性カップリングを避けるためにPCB導体の面積はできるだけ小さくしてください。全定格負荷で動作を行うには、上面のグランド領域が十分な熱放散面積を備えていなければなりません。RT/CLKピンはノイズの影響を受けやすいため、RTの抵抗はデバイスにできるだけ近づけて配置し、最短のパターンで配線する必要があります。追加の外部部品は図に示されるように配置できます。別のPCBレイアウトでも許容される性能を得ることは可能ですが、このレイアウトは良好な結果が得られることが実証済みであり、ガイドラインとして示しています。

図 65. PCBレイアウト例

## パッケージ情報

#### 製品情報

| Orderable<br>Device | Status <sup>(1)</sup> | Package<br>Type   | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|---------------------|-----------------------|-------------------|--------------------|------|----------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPS54160ADGQ        | _                     | MSOP-<br>PowerPAD | DGQ<br>)           | 10   | 80             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TPS54160ADGQF       | _                     | MSOP-<br>PowerPAD | DGQ<br>)           | 10   | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TPS54160ADRCR       | ACTIVE                | SON               | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TPS54160ADRCT       | ACTIVE                | SON               | DRC                | 10   | 500            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

(1)マーケティング・ステータスは次のように定義されています。

ACTIVE: 製品デバイスが新規設計用に推奨されています。

LIFEBUY: TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND: 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW: デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free(RoHS)、Pb-Free(RoHS Expert)およびGreen(RoHS & no Sb/Br)があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free" (鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green(RoHS & no Sb/Br)**: TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン(Sb) をベースとした難燃材を含まない (均質な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

<sup>(3)</sup>MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

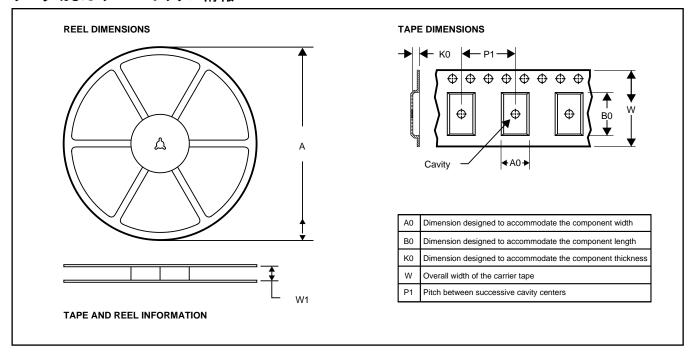

# パッケージ・マテリアル情報

# テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device        | Package<br>Type       | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS54160ADGQR | MSOP-<br>Power<br>PAD | DGQ                | 10   | 2500 | 330.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| TPS54160ADRCR | SON                   | DRC                | 10   | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

| TPS54160ADRCT | SON                   | DRC                | 10   | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

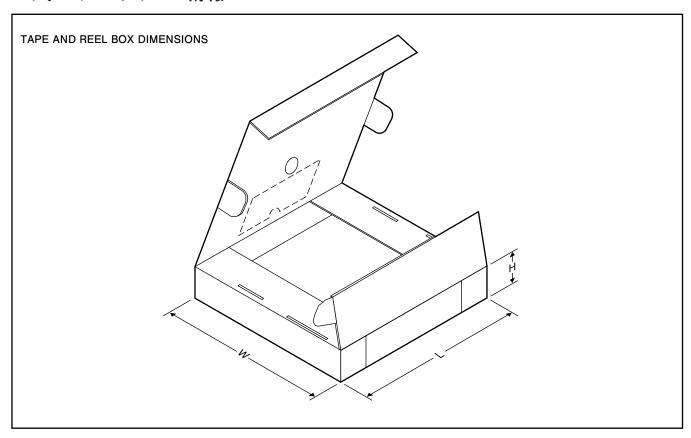

# パッケージ・マテリアル情報

### \*All dimensions are nominal

| Device        | Package Type  | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|---------------|-----------------|------|------|-------------|------------|-------------|

| TPS54160ADGQR | MSOP-PowerPAD | DGQ             | 10   | 2500 | 346.0       | 346.0      | 35.0        |

| TPS54160ADRCR | SON           | DRC             | 10   | 3000 | 346.0       | 346.0      | 35.0        |

| TPS54160ADRCT | SON           | DRC             | 10   | 250  | 203.0       | 203.0      | 35.0        |

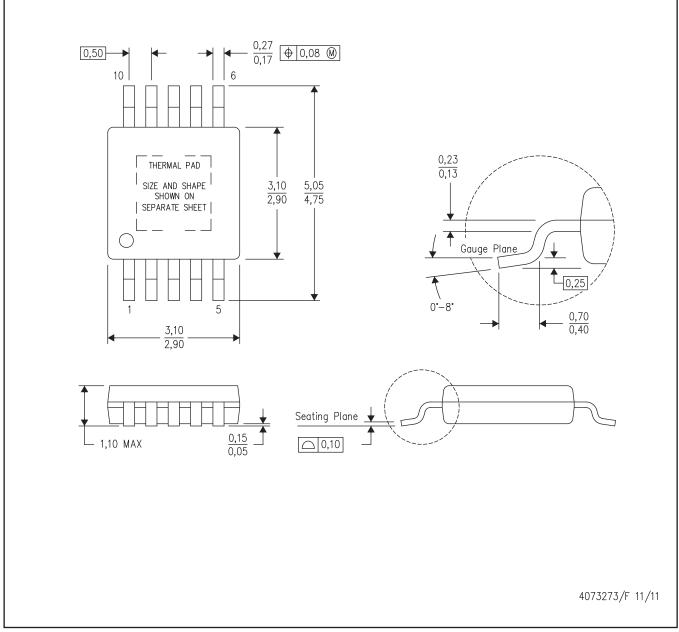

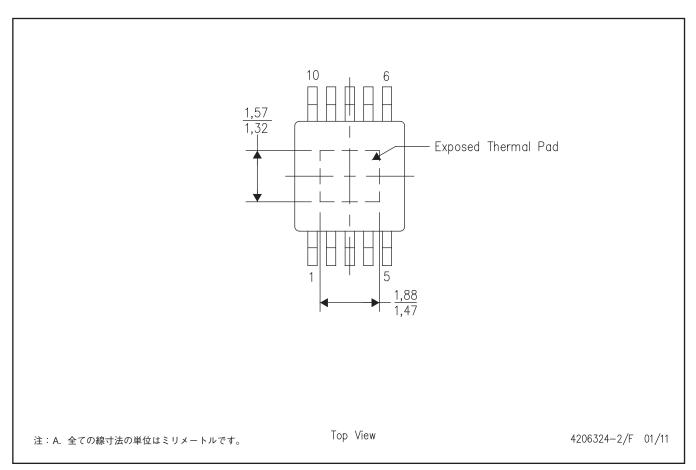

### DGQ(S-PDSO-G10)

- 注:A. 直線寸法はすべてミリメートル単位です。

- B. 本図は予告なしに変更することがあります。 C. ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。 推奨基板レイアウトについては、 テクニカル・ブリーフ 『PowerPAD Thermally Enhanced Package』 (TI文献番号SLMA002) を参照してください。 これらの ドキュメントは、ホームページwww.ti.comで入手できます。

- E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

- F. JEDEC MO-187 バリエーションBA-Tに適合しています。

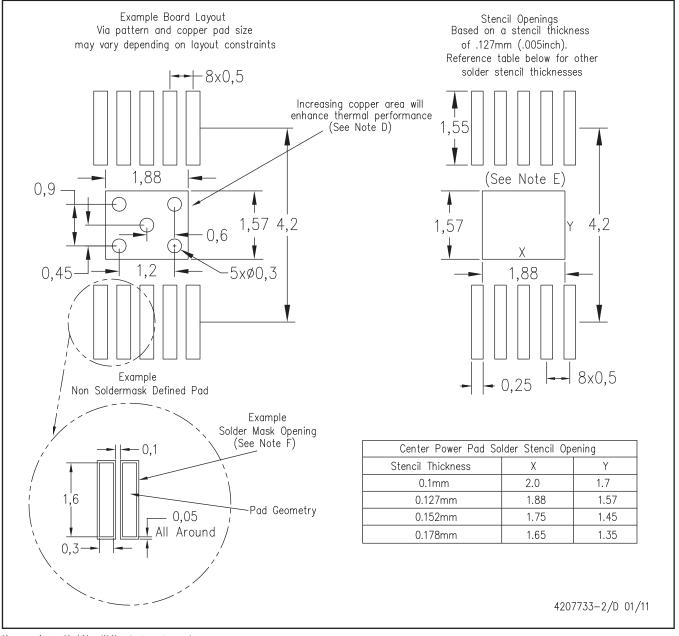

# サーマルパッド・メカニカル・データ

#### DGQ(S-PDSO-G10)

#### 熱的特性に関する資料

このPowerPAD™パッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板 (PCB)に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD<sup>™</sup>パッケージについての追加情報およびその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002) およびアプリケーション・ブリーフ『PowerPAD Made Easy』(TI文献番号SLMA004) を参照してください。いずれもホームページwww.ti.comで入手できます。

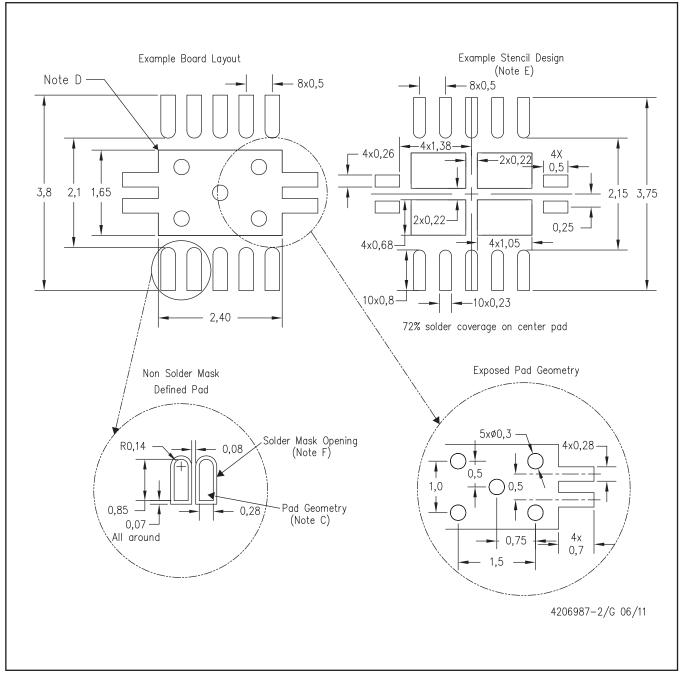

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

サーマル・パッド寸法図

### PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

- 注:A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 中央の半田マスク定義パッドを変更しないように、回路基板組み立て図に注記を書き込んでください。

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ 「PowerPAD Thermally Enhanced Package」(TI文献番号SLMA002, SLMA004)を参照してください。これらのドキュメントは、ホームページ www.ti.comで入手できます。代替設計については、資料IPC-7351を推奨します。

- E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て 拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の 推奨事項については、IPC-7525を参照してください。

- F. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

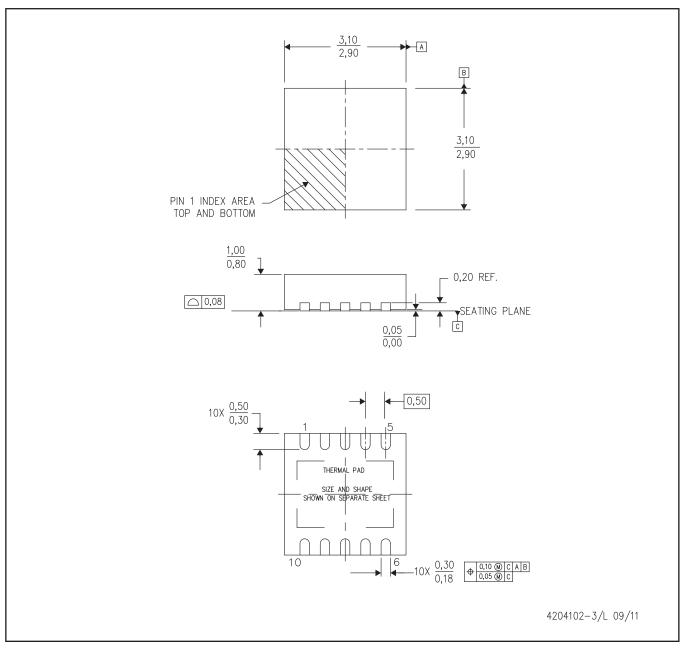

### DRC(S-PVSON-N10)

- 注:A. 全ての線寸法の単位はミリメートルです。寸法と許容差はASME Y14.5M- 1994に従っています。

- B. 図は予告なく変更することがあります。

- C. SON(Small Outline No-Lead) パッケージ構成

- D. 最良の熱特性および機械的特性を得るには、パッケージのサーマル・パッドを基板に半田付けする必要があります。

- E. 露出したサーマル・パッドの寸法に関する詳細は、製品データシートを参照してください。

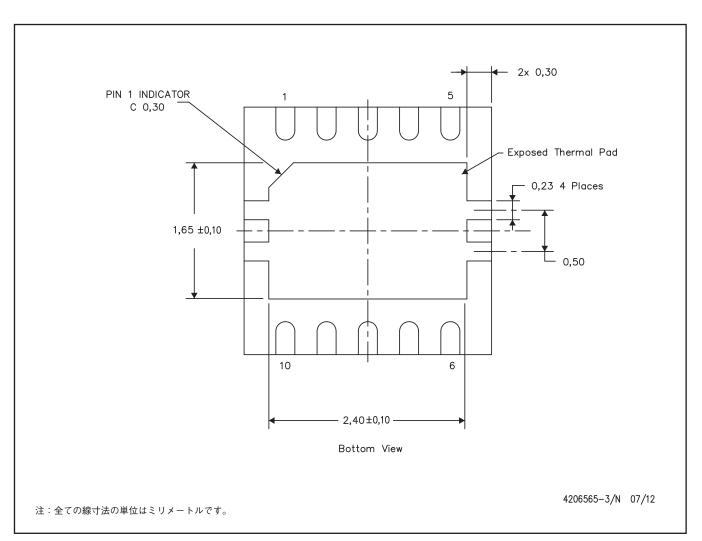

# サーマルパッド・メカニカル・データ

#### DRC(S-PVSON-N10)

#### 熱的特性に関する資料

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板(PCB)に直接はんだ付けされなければなりません。はんだ付けされることにより、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはグランドまたは電源プレーン(どちらか当てはまる方)、またはもう1つの方法としてPCBに設計された特別なヒートシンク構造に直接接続することができます。この設計により、集積回路(IC)からの熱の移動が最適化されます。

クワッド・フラットパック・ノーリード(QFN)パッケージとその利点についての情報はアプリケーション・レポート "QuadFlatpack No-Lead Logic Packages" TI文献番号SLUA271を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージのサーマル・パッドの寸法は以下の図に示されています。

サーマル・パッド寸法図

- 注:A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 代替設計には、IPC-7351規格を推奨します。

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。熱に関する具体的な情報、ビア要件、および推奨基板レイアウトについては、アプリケーション・ノート『Quad Flat-Pack Packages』(TI文献番号SLUA271) および製品データシートを参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

- および製品データシートを参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。ステンシル設計上の考慮事項については、IPC 7525を参照してください。

- F. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

(SLVSB56A)

# ご注意

Texas Instruments Incorporated 及びその関連会社(以下総称してTIといいます)は、最新のJESD46に従いその半導体製品及びサービスを修正し、改善、改良、その他の変更をし、又は最新のJESD48に従い製品の製造中止またはサービスの提供を中止する権利を留保します。お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての半導体製品は、ご注文の受諾の際に提示されるTIの標準販売契約約款に従って販売されます。

TIは、その製品が、半導体製品に関するTIの標準販売契約約款に記載された保証条件に従い、販売時の仕様に対応した性能を有していることを保証します。検査及びその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、適用される法令によってそれ等の実行が義務づけられている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援又はお客様の製品の設計について責任を負うことはありません。TI 製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI 製部品を使用したお客様の製品及びアプリケーションに関連する危険を最小のものとするため、適切な設計上及び操作上の安全対策は、お客様にてお取り下さい。

TIは、TIの製品又はサービスが使用されている組み合せ、機械装置、又は方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品又はサービスを使用することについてライセンスを与えるとか、保証又は是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない、又はTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブック又はデータ・シートの中にある情報の重要な部分の複製は、その情報に一切の変更を加えること無く、且つその情報と関連する全ての保証、条件、制限及び通知と共になされる限りにおいてのみ許されるものとします。TIは、変更が加えられて文書化されたものについては一切責任を負いません。第三者の情報については、追加的な制約に服する可能性があります。

TIの製品又はサービスについて TI が提示したパラメーターと異なる、又は、それを超えてなされた説明で当該 TI 製品又はサービスを再販売することは、関連する TI 製品又はサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TI は、そのような説明については何の義務も責任も負いません。

TI からのアプリケーションに関する情報提供又は支援の一切に拘わらず、お客様は、ご自身の製品及びご自身のアプリケーションにおける TI 製品の使用に関する法的責任、規制、及び安全に関する要求事項の全てにつき、これをご自身で遵守する責任があることを認め、且つそのことに同意します。お客様は、想定される不具合がもたらす危険な結果に対する安全対策を立案し実行し、不具合及びその帰結を監視し、害を及ぼす可能性のある不具合の可能性を低減し、及び、適切な治癒措置を講じるために必要な専門的知識の一切を自ら有することを表明し、保証します。お客様は、TI 製品を安全でないことが致命的となるアプリケーションに使用したことから生じる損害の一切につき、TI 及びその代表者にその全額の補償をするものとします。

TI 製品につき、安全に関連するアプリケーションを促進するために特に宣伝される場合があります。そのような製品については、TIが目的とするところは、適用される機能上の安全標準及び要求事項を満たしたお客様の最終製品につき、お客様が設計及び製造ができるようお手伝いをすることにあります。それにも拘わらず、当該TI 製品については、前のパラグラフ記載の条件の適用を受けるものとします。

FDA クラスIII(又は同様に安全でないことが致命的となるような医療機器)へのTI 製品の使用は、TIとお客様双方の権限ある役員の間で、そのような使用を行う際について規定した特殊な契約書を締結した場合を除き、一切認められていません。

TIが軍需対応グレード品又は「強化プラスティック」製品として特に指定した製品のみが軍事用又は宇宙航空用アプリケーション、若しくは、軍事的環境又は航空宇宙環境にて使用されるように設計され、かつ使用されることを意図しています。お客様は、TIがそのように指定していない製品を軍事用又は航空宇宙用に使う場合は全てご自身の危険負担において行うこと、及び、そのような使用に関して必要とされるすべての法的要求事項及び規制上の要求事項につきご自身のみの責任により満足させることを認め、且つ同意します。

TIには、主に自動車用に使われることを目的として、ISO/TS 16949の要求事項を満たしていると特別に指定した製品があります。当該指定を受けていない製品については、自動車用に使われるようには設計されてもいませんし、使用されることを意図しておりません。従いまして、前記指定品以外のTI製品が当該要求事項を満たしていなかったことについては、TIはいかなる責任も負いません。

Copyright © 2013, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40°C、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上