JAJSBU0F - JULY 2012 - REVISED NOVEMBER 2020

# TPS54020 軽負荷効率向上、小型、10A、4.5V~17V 入力、SWIFT™ 同期整流降圧 型コンバータ

# 1 特長

- 動作時の接合部温度範囲: -40℃~+150℃

- 8mΩ/6mΩ の MOSFET を内蔵

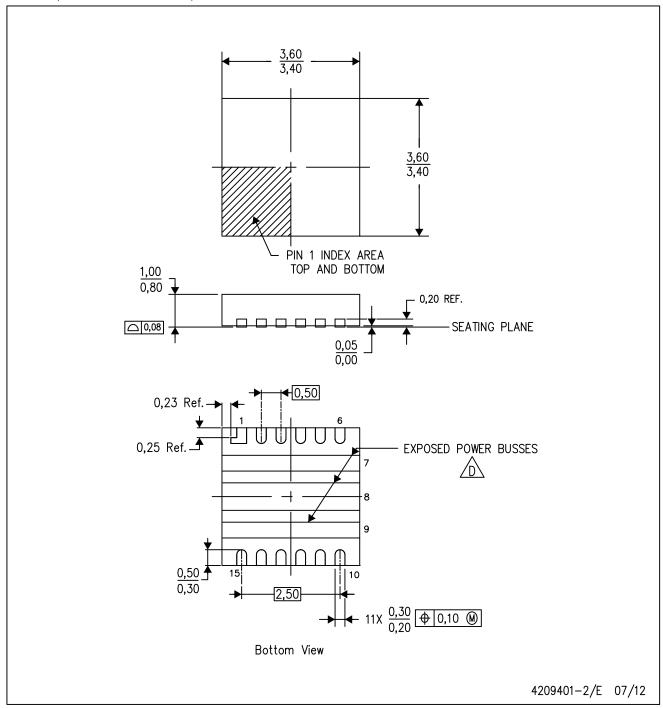

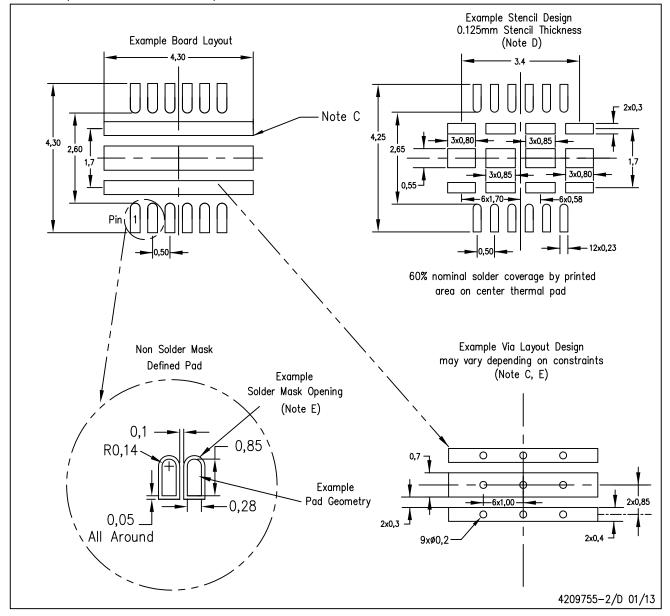

- 放熱特性の優れた 3.5mm × 3.5mm HotRod™ パッ ケージ

- ピーク電流モード制御

- Eco-mode<sup>™</sup> パルス・スキップによる効率の向上

- 両方の MOSFET に対する過電流保護

- 選択可能な過電流保護方式

- 選択可能な過電流保護レベル

- 分割電源レール: 1.6V~17V (PVIN)

- 電圧リファレンス: 0.6V、精度 ±1%

- 200kHz~1.2MHz のスイッチング周波数

- 外部クロックに同期

- 出力をプリバイアスした状態で起動

- 過熱保護および過電圧保護

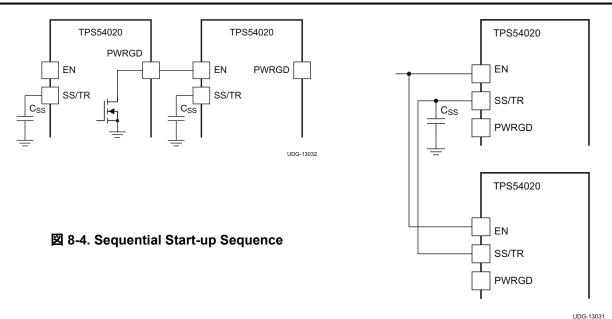

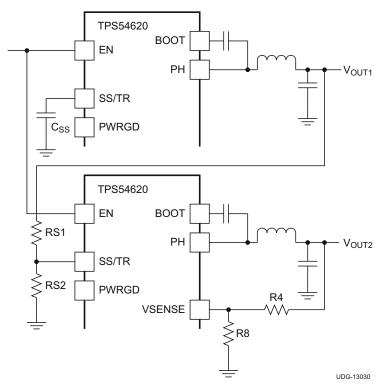

- 調整可能なソフト・スタートおよび電源シーケンス

- 低電圧および過電圧用パワー・グッド出力モニタ

- SYNC OUT 機能により位相差 180°の出力クロッ ク信号を提供

- SWIFT™ ドキュメントと WEBENCH については Web ページを参照

- WEBENCH® Power Designer により、TPS54020 を使用するカスタム設計を作成

# 2 アプリケーション

- 無線インフラストラクチャおよび有線通信機器

- 試験/測定機器

- 航空宇宙/防衛

- 産業用アプリケーションの DSP と FPGA のポイ ント・オブ・ロード (POL)

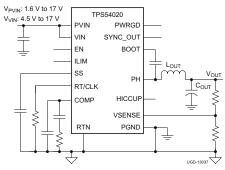

アプリケーション概略回路図

### 3 概要

TPS54020 は 10A、4.5V~17V 入力の SWIFT コンバ ータです。画期的な 3.5mm × 3.5mm の HotRod パッ ケージにより、高密度の降圧設計を最適化できます。 TPS54020 は必要な機能をすべて搭載したコンバータ です。

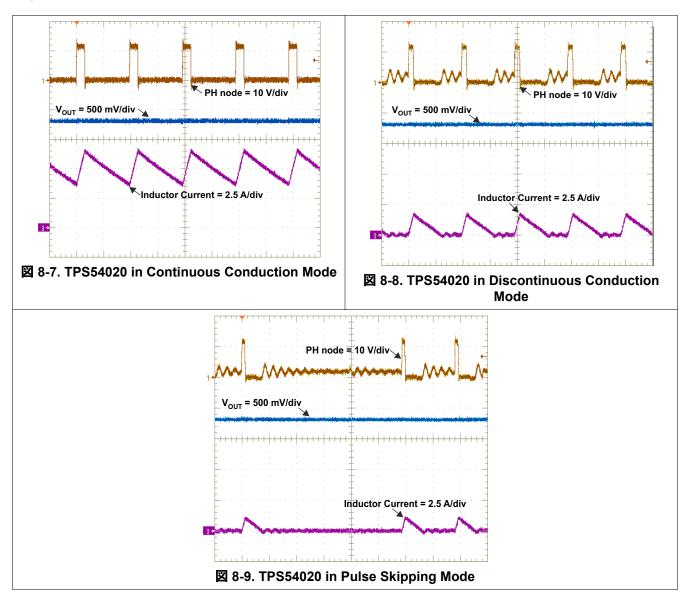

ハイサイドおよびローサイド MOSFET の画期的な統 合とパッケージングによって高効率を実現しており、 高負荷条件では連続電流モード (CCM) で動作し、軽負 荷時にはパルスをスキップしながら Eco-mode に遷 移して効率を高めます。

両方の MOSFET に対する電流制限により、デバイス およびシステムを保護できます。ハイサイド MOSFET ではサイクルごとの電流制限によって過負 荷状況に対する保護を提供し、ローサイド MOSFET ではゼロ電流検出機能により、軽負荷動作時にローサ イド MOSFET がオフになります。3 つの電流制限ス レッショルドから選択可能なため、さまざまな用途に 対応します。ヒカップまたはサイクルごとの過電流保 護方式も選択できます。

サーマル・シャットダウン保護機能により、ダイ温度 がサーマル・シャットダウン・トリップ・ポイントを 超えるとスイッチングはディセーブルになり、設定さ れた温度ヒステリシスの分だけ温度が低下し、シャッ トダウン・ヒカップ時間が経過するとスイッチングは イネーブルになります。

#### 魁品情報

|          | 4DC HH IIJ TIA                  |                 |  |

|----------|---------------------------------|-----------------|--|

| 部品番号     | パッケージ <sup>(1)</sup> (1ペ<br>ージ) | 本体サイズ (公称)      |  |

| TPS54020 | VQFN (15)                       | 3.50mm × 3.50mm |  |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

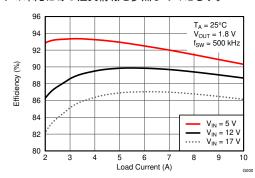

効率と負荷電流との関係

# **Table of Contents**

| 1 特長                                                                                                   | 1                  | 9 Application and Implementation                                    | 23             |

|--------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------|----------------|

| 2 アプリケーション                                                                                             |                    | 9.1 Application Information                                         |                |

| 3 概要                                                                                                   | 1                  | 9.2 Typical Application                                             |                |

| 4 Revision History                                                                                     | <mark>2</mark>     | 10 Power Supply Recommendations                                     | 36             |

| 5 Description (Continued)                                                                              |                    | 11 Layout                                                           | 37             |

| 6 Pin Configuration and Functions                                                                      |                    | 11.1 Layout Guidelines                                              |                |

| 7 Specifications                                                                                       |                    | 11.2 Layout Examples                                                | 38             |

| 7.1 Absolute Maximum Ratings (1)                                                                       |                    | 12 Device and Documentation Support                                 | 40             |

| 7.2 ESD Ratings                                                                                        |                    | 12.1 Device Support                                                 |                |

| 7.3 Recommended Operating Conditions                                                                   |                    | 12.2 Documentation Support                                          |                |

| 7.4 Thermal Information                                                                                |                    | 12.3 Receiving Notification of Documentation U                      |                |

|                                                                                                        |                    | 12.4 Support Resources                                              |                |

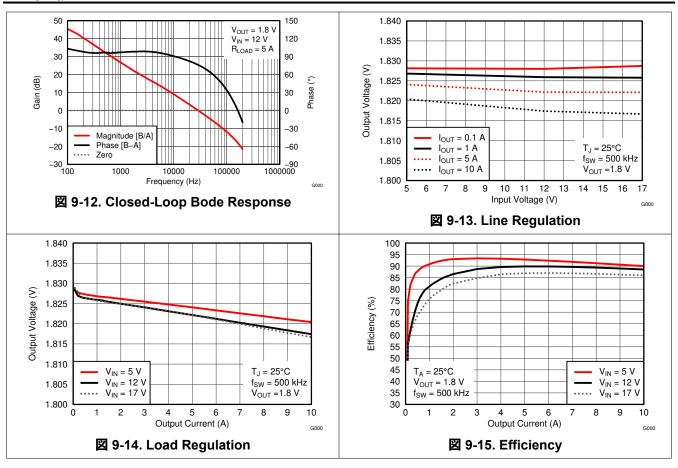

| 7.6 Typical Characteristics                                                                            |                    | 12.6 Electrostatic Discharge Caution                                |                |

| 8.1 Overview                                                                                           |                    | 12.7 Glossary                                                       |                |

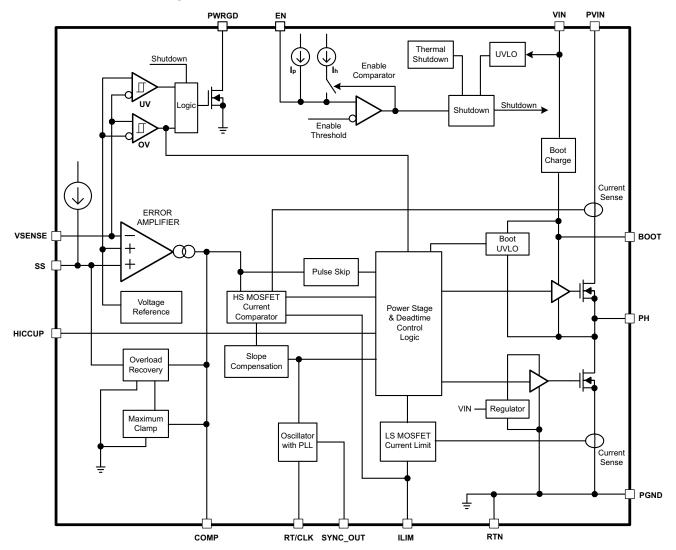

| 8.2 Functional Block Diagram                                                                           |                    | 13 Mechanical, Packaging, and Orderable                             | 40             |

| 8.3 Feature Description                                                                                |                    | Information                                                         | 41             |

| 8.4 Device Functional Modes                                                                            |                    |                                                                     |                |

| Changes from Revision E (March 2019) to Revis     文書全体にわたって表、図、相互参照の採番方法                               |                    |                                                                     | Page1          |

| <ul><li>「アプリケーション」を更新</li></ul>                                                                        |                    |                                                                     |                |

| Removed 1000 V/V MIN specification for error a                                                         |                    |                                                                     |                |

| Changed low-side switch sinking current limit un                                                       |                    |                                                                     |                |

|                                                                                                        |                    |                                                                     |                |

| Increased MAX specification for low-side switch                                                        | SINKIN             | g current limit from -0.8 A to -1.15 A                              | b              |

| Changes from Revision D (December 2014) to R                                                           |                    | <u> </u>                                                            | Page           |

| • WEBENCH のリンクを追加                                                                                      |                    |                                                                     | 1              |

| <ul> <li>Changed symbols in セクション 7.4; changed R</li> </ul>                                            | $R_{	heta JA}$ fro | m 16.6°C/W to 25°C/W                                                | 6              |

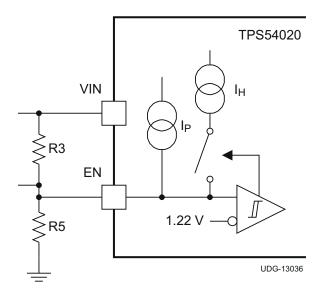

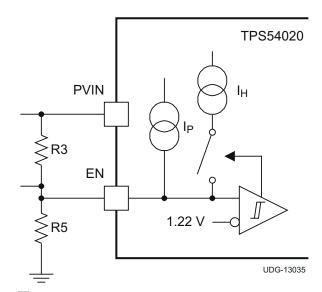

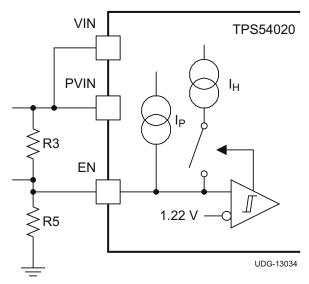

| <ul> <li>Changed "I<sub>IN(EN)</sub>" to "I<sub>P</sub>" and added "V<sub>EN</sub> below to</li> </ul> | thresho            | old"; added "I <sub>H</sub> " and "V <sub>FN</sub> above threshold" | <mark>6</mark> |

| <ul> <li>Added 2 sentences to end of セクション 8.3.12</li> </ul>                                           |                    |                                                                     |                |

| Changed "proper operation of the device" to "state                                                     |                    |                                                                     |                |

| • Changed 式 5 and 式 8                                                                                  |                    |                                                                     |                |

|                                                                                                        |                    |                                                                     |                |

| • Added paragraph to end of セクション 8.3.13                                                               |                    |                                                                     |                |

| Deleted "and the low-side MOSFET is turned Of                                                          |                    |                                                                     |                |

| Changed last sentence of first paragraph in                                                            | クション               | × 8.3.14                                                            | 19             |

| Changes from Revision C (March 2013) to Revis                                                          |                    |                                                                     | Page           |

| • 「ピン構成および機能」セクション、「取り扱い<br>機能モード」セクション、「アプリケーションと<br>「レイアウト」セクション、「デバイスおよびド・<br>ジ、および注文情報」セクションを追加    | ≤実装」<br>キュメ        | ーセクション、「電源に関する推奨事項」セク:<br>ントのサポート」セクション、「メカニカル、                     | ション、<br>パッケー   |

| Changes from Revision B (February 2013) to Re                                                          |                    | · · · · · · · · · · · · · · · · · · ·                               |                |

| <ul> <li>Deleted Note 2 from the Thermal Information tal</li> </ul>                                    | ble                |                                                                     | 5              |

| · Added VIN internal UVLO threshold and VIN inte                                                       | ernal U            | VLO hysteresis rows                                                 | <mark>6</mark> |

| • Changed OVERVIEW paragraph "The TPS5402                                                              |                    | •                                                                   |                |

|       | IN   | 5    | IK |

|-------|------|------|----|

| www.t | ij.c | o.jı | 0  |

| Changes from Revision A (September 2012) to Revision B (February 2013)                                                                                                                                                                | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Changed the Input Voltage and Power Input Voltage Pins (VIN and PVIN) section     Changed the DETAILED DESCRIPTION section     Changed the DESIGN EXAMPLE section  Changes from Revision * (July 2011) to Revision A (September 2012) | 14   |

| Changed the DETAILED DESCRIPTION section                                                                                                                                                                                              | 20   |

| Changed the DESIGN EXAMPLE section                                                                                                                                                                                                    | 26   |

| Changes from Revision * (July 2011) to Revision A (September 2012)                                                                                                                                                                    | Page |

| • デバイスを「製品プレビュー」から「量産」に変更                                                                                                                                                                                                             | 1    |

|                                                                                                                                                                                                                                       |      |

# **5 Description (Continued)**

The SS pin controls the output voltage start-up ramp and allows for selectable soft-start times. Power supply sequencing is also available by configuring the enable (EN) and the open-drain power-good (PWRGD) pins.

Two TPS54020 devices may be synchronized 180° out-of-phase by using the SYNC\_OUT and CLK pins.

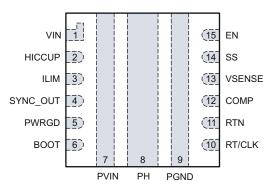

# **6 Pin Configuration and Functions**

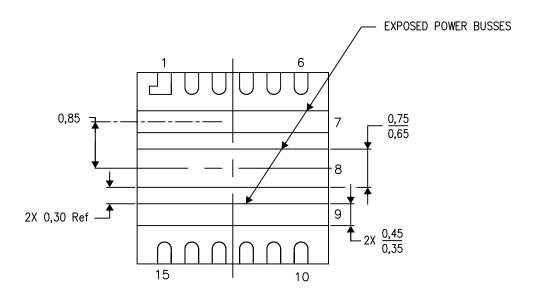

図 6-1. 15-Pin VQFN RUW Package (Top View)

表 6-1. Pin Functions

| PIN                                                                                                                                        |     | I/O <sup>(1)</sup>                                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                       | NO. | 1/0(-/                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                              |

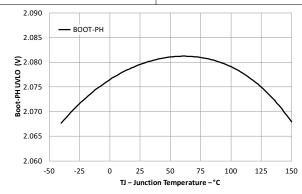

| воот                                                                                                                                       | 6   | S                                                                                                                                                                   | A bootstrap capacitor is required between BOOT and PH. If the voltage on this capacitor is below the minimum required by the high-side MOSFET (BOOT UVLO), the PH node is forced low so that the capacitor is refreshed. |

| COMP                                                                                                                                       | 12  | 0                                                                                                                                                                   | Error amplifier current output, and input to the output switch current comparator. Connect frequency compensation to this pin.                                                                                           |

| EN 15 I A divider network must be used to implement an undervoltage lockout f reduce quiescent current, this pin must be pulled to ground. |     | A divider network must be used to implement an undervoltage lockout function. To disable switching and reduce quiescent current, this pin must be pulled to ground. |                                                                                                                                                                                                                          |

| HICCUP                                                                                                                                     | 2   | 0                                                                                                                                                                   | Overcurrent protection scheme select pin                                                                                                                                                                                 |

| ILIM                                                                                                                                       | 3   | 0                                                                                                                                                                   | Current limit threshold select pin                                                                                                                                                                                       |

| PGND                                                                                                                                       | 9   | G                                                                                                                                                                   | Power Ground. Return for the low-side MOSFET                                                                                                                                                                             |

| PH                                                                                                                                         | 8   | 0                                                                                                                                                                   | Switch node                                                                                                                                                                                                              |

| PVIN                                                                                                                                       | 7   | I                                                                                                                                                                   | Power input. Supplies the power switches of the power converter                                                                                                                                                          |

| PWRGD                                                                                                                                      | 5   | 0                                                                                                                                                                   | Power-good fault pin. Asserts low if output voltage is out of regulation due to thermal shutdown, dropout, overvoltage, EN shutdown, or during soft start.                                                               |

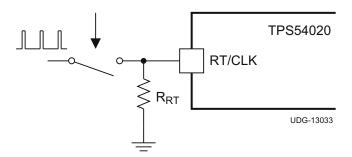

| RT/CLK                                                                                                                                     | 10  | I/O                                                                                                                                                                 | Automatically selects between RT mode and CLK mode. An external timing resistor adjusts the switching frequency of the device. In CLK mode, the device synchronizes to an external clock.                                |

| RTN                                                                                                                                        | 11  | G                                                                                                                                                                   | Return for control circuitry                                                                                                                                                                                             |

| SS                                                                                                                                         | 14  | I/O                                                                                                                                                                 | Soft-start pin. An external capacitor connected to this pin sets the internal voltage reference rise time. The voltage on this pin overrides the internal reference. It can be used for sequencing.                      |

| SYNC_OU<br>T                                                                                                                               | 4   | 0                                                                                                                                                                   | Synchronization output provides a clock signal 180° out-of-phase with the power switch.                                                                                                                                  |

| VIN                                                                                                                                        | 1   | ı                                                                                                                                                                   | Supplies the control circuitry of the power converter                                                                                                                                                                    |

| VSENSE                                                                                                                                     | 13  | I                                                                                                                                                                   | Inverting node of the transconductance (gm) error amplifier                                                                                                                                                              |

(1) I = Input, O = Output, S = Supply, G = Ground Return

Product Folder Links: TPS54020

# 7 Specifications

# 7.1 Absolute Maximum Ratings (1)

over operating free-air temperature range (unless otherwise noted)

|                        |                                             | MIN  | MAX              | UNIT |  |

|------------------------|---------------------------------------------|------|------------------|------|--|

|                        | VIN, PVIN                                   | -0.3 | 20               |      |  |

|                        | EN                                          | -0.3 | 6                |      |  |

| Input voltage          | BOOT                                        | -0.3 | 27               | V    |  |

|                        | COMP, HICCUP, ILIM, SS/TR, SYNC_OUT, VSENSE | -0.3 | 3                |      |  |

|                        | PWRGD, RT/CLK                               | -0.3 | 6                |      |  |

|                        | воот-рн                                     | 0    | 7.5              |      |  |

| Output voltage         | PH                                          | -1   | 20               | V    |  |

|                        | PH (10-ns transient)                        | -3   | 20               |      |  |

|                        | RT/CLK                                      | -100 | 100              | μΑ   |  |

| Source current         | PH                                          |      | Current<br>Limit | Α    |  |

|                        | PH                                          |      | Current<br>Limit | А    |  |

| Sink current           | PVIN                                        |      | Current<br>Limit | A    |  |

|                        | COMP                                        | -200 | 200              | μA   |  |

|                        | PWRGD                                       | -0.1 | 5                | mA   |  |

| Operating junction tem | perature, T <sub>J</sub>                    | -40  | 150              | °C   |  |

| Storage temperature,   | Г <sub>stg</sub>                            | -65  | 150              | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under セクション 7.3 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                 |      | MIN | MAX | UNIT |

|-------------------------------------------------|------|-----|-----|------|

| Operating junction temperature – T <sub>J</sub> |      | -40 | 150 | °C   |

| Control input voltage                           | VIN  | 4.5 | 17  | V    |

| Power stage input voltage                       | PVIN | 1.6 | 17  | V    |

Copyright © 2020 Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.4 Thermal Information

|                       |                                              | TPS54020          |      |

|-----------------------|----------------------------------------------|-------------------|------|

|                       | THERMAL METRIC <sup>(2)</sup>                | RUW (VQFN)        | UNIT |

|                       |                                              | 15 PINS           |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 25 <sup>(1)</sup> | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 28.8              | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 19.0              | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.7               | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.9              | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.3               | °C/W |

<sup>(1)</sup> Applicable only to the EVM in free space with no airflow.

# 7.5 Electrical Characteristics

$T_J = -40$ °C to +150°C,  $V_{IN} = 4.5$  V to 17 V,  $P_{VIN} = 4.5$  V to 17 V (unless otherwise noted)

|                  | PARAMETER                                                | CONDITIONS                                                    | MIN      | TYP   | MAX   | UNIT |

|------------------|----------------------------------------------------------|---------------------------------------------------------------|----------|-------|-------|------|

| SUPPLY           | VOLTAGE (VIN AND PVIN PINS)                              |                                                               |          |       |       |      |

|                  | PVIN operating input voltage                             |                                                               | 1.6      |       | 17    | V    |

|                  | VIN operating input voltage                              |                                                               | 4.5      |       | 17    | V    |

|                  | VIN internal UVLO threshold                              | VIN Rising                                                    |          | 4     | 4.5   | V    |

|                  | VIN internal UVLO hysteresis                             |                                                               |          | 150   |       | mV   |

|                  | VIN shutdown supply current                              | V <sub>EN</sub> = 0 V                                         |          | 2     | 10    | μΑ   |

|                  | VIN operating – nonswitching supply current              | V <sub>VSENSE</sub> = 610 mV                                  |          | 600   | 1000  | μA   |

| ENABLE           | AND UVLO (EN PIN)                                        |                                                               |          |       |       |      |

| ·                | Enable threshold                                         | Rising                                                        |          | 1.22  | 1.26  | V    |

| $V_{EN}$         | Enable infestioid                                        | Falling                                                       | 1.10     | 1.17  |       | V    |

| l <sub>P</sub>   | Input current V <sub>EN</sub> below threshold            | V <sub>EN</sub> = 1.1 V                                       |          | -1.15 |       | μΑ   |

| I <sub>H</sub>   | Added hysteresis current V <sub>EN</sub> above threshold | V <sub>EN</sub> = 1.3 V                                       |          | -3.3  |       | μΑ   |

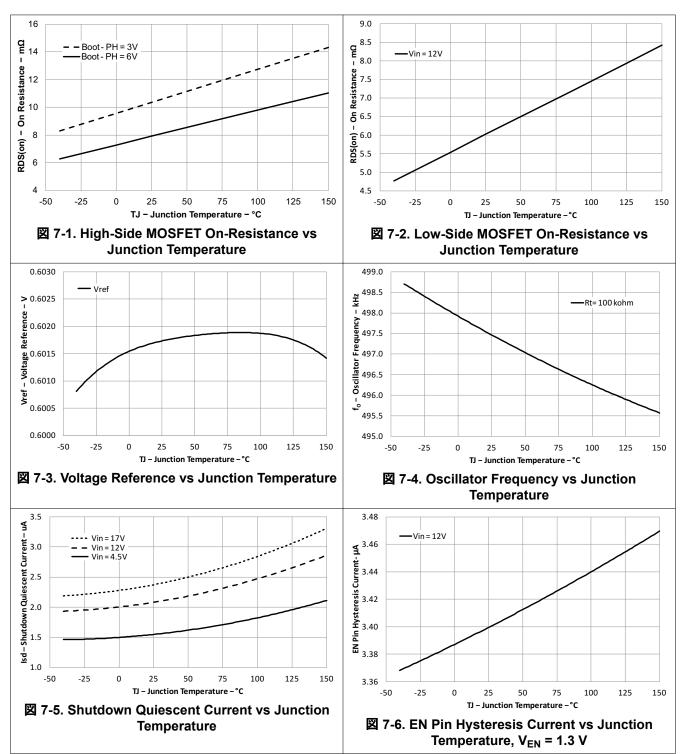

| VOLTAG           | EREFERENCE                                               |                                                               |          |       |       |      |

| V <sub>REF</sub> | Voltage reference                                        | 0 A ≤ I <sub>OUT</sub> ≤ 10 A, −40°C ≤ T <sub>A</sub> ≤ 150°C | 0.594    | 0.6   | 0.606 | V    |

| MOSFET           | г                                                        |                                                               | <u>'</u> |       |       |      |

| DRVH             | High-side switch resistance                              | BOOT-PH = 3 V                                                 |          | 9.5   | 18    | mΩ   |

| DKVH             | night-side switch resistance                             | BOOT-PH = 6 V <sup>(1)</sup>                                  |          | 8     | 14    | mΩ   |

| DRVL             | Low-side switch resistance <sup>(1)</sup>                | V <sub>VIN</sub> = 12 V                                       |          | 6     | 11    | mΩ   |

| ERROR            | AMPLIFIER                                                |                                                               | ,        |       |       |      |

|                  | Error amplifier input bias current                       | V <sub>VIN</sub> = 12 V                                       |          | 50    |       | nA   |

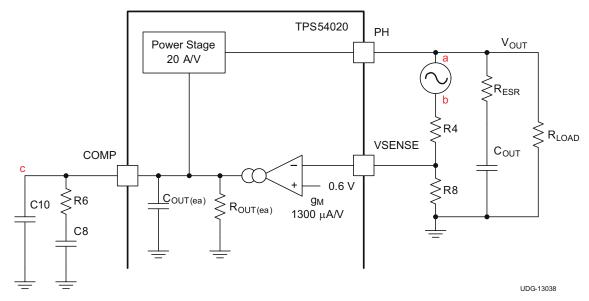

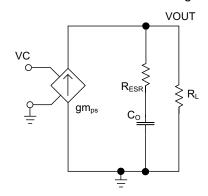

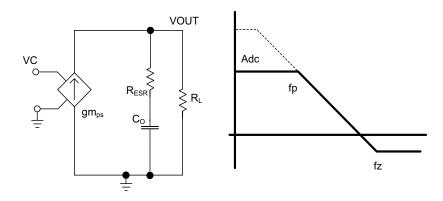

| 9м               | Error amplifier transconductance                         | $-2 \mu A < I_{COMP} < 2 \mu A, V_{COMP} = 1 V$               |          | 1300  |       | μS   |

|                  | Error amplifier dc gain                                  | V <sub>VSENSE</sub> = 0.6 V                                   |          | 3000  |       | V/V  |

|                  | Error amplifier source/sink                              | V <sub>COMP</sub> = 1 V, 100 mV Overdrive                     |          | ±100  |       | μΑ   |

|                  | Start switching threshold                                | V <sub>COMP</sub>                                             |          | 0.27  |       | V    |

|                  |                                                          | I <sub>ILIM</sub> = NC                                        |          | 20    |       |      |

| 9м               | COMP to I <sub>SWITCH</sub> transconductance             | I <sub>ILIM</sub> = RTN                                       |          | 17    |       | A/V  |

|                  |                                                          | 499 kΩ (1%) between ILIM and RTN                              |          | 13    |       |      |

Product Folder Links: TPS54020

<sup>(2)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

www.tij.co.jp

$T_1 = -40^{\circ}C$  to +150°C.  $V_{IN} = 4.5$  V to 17 V.  $P_{VIN} = 4.5$  V to 17 V (unless otherwise noted)

|                      | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS                                                                | MIN  | TYP                    | MAX   | UNIT   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------------------------|-------|--------|

| CURREN               | IT LIMIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |      |                        |       |        |

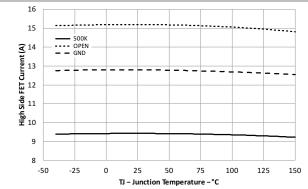

|                      | Little and the second s | I <sub>ILIM</sub> = NC                                                    | 13.4 | 15.1                   | 16.5  |        |

|                      | High-side switch current limit threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>ILIM</sub> = RTN                                                   | 11.2 | 12.75                  | 14    | Α      |

|                      | High-side switch current limit threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 499 kΩ (1%) between ILIM and RTN                                          | 8.3  | 9.4                    | 10.2  | Α      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>ILIM</sub> = NC                                                    | 11   | 13                     | 15    | Δ.     |

|                      | Low-side switch sourcing current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sub>ILIM</sub> = RTN                                                   | 9    | 10.5                   | 12    | Α      |

|                      | Low-side switch sourcing current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 499 kΩ (1%) between ILIM and RTN                                          | 6.5  | 8                      | 9.5   | Α      |

|                      | Low-side switch sinking current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -ve current denotes current sourced from PH pin                           |      | -0.2                   | -1.15 | Α      |

|                      | Overcurrent protection scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (HICCUP = RTN)                                                            |      | Cycle-<br>by-<br>cycle |       |        |

|                      | Hiccup delay before re-start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | HICCUP OPEN                                                               |      | 16384                  |       | Cycles |

|                      | Hiccup wait time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | HICCUP OPEN                                                               |      | 128                    |       | Cycles |

| THERMA               | AL SHUTDOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '                                                                         |      |                        |       |        |

|                      | Thermal shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |      | 175                    |       | °C     |

|                      | Thermal shutdown hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |      | 10                     |       | °C     |

|                      | Thermal shutdown hiccup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |      | 16384                  |       | Cycles |

| TIMING F             | RESISTOR AND EXTERNAL CLOCK (RT/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LK PIN)                                                                   |      |                        |       |        |

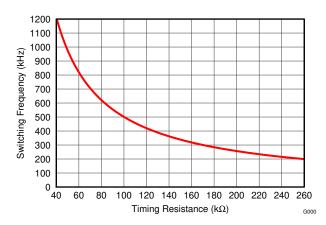

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $R_{RT/CLK} = 250 \text{ k}\Omega (1\%)$                                  | 185  | 205                    | 230   |        |

|                      | Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R <sub>RT/CLK</sub> = 100 kΩ (1%)                                         | 475  | 500                    |       | kHz    |

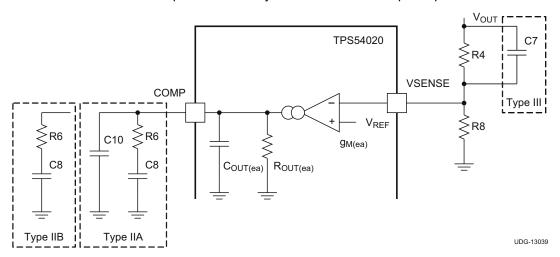

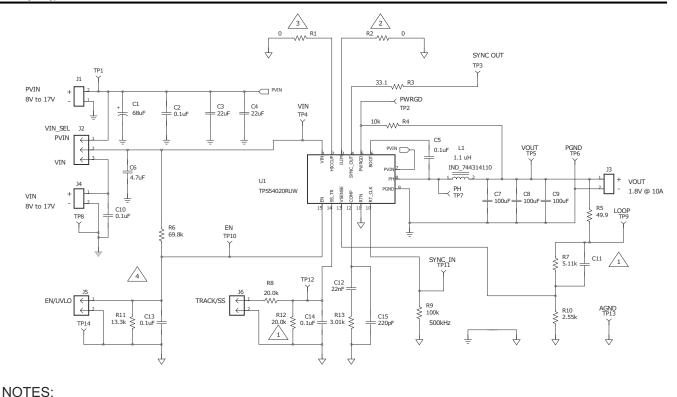

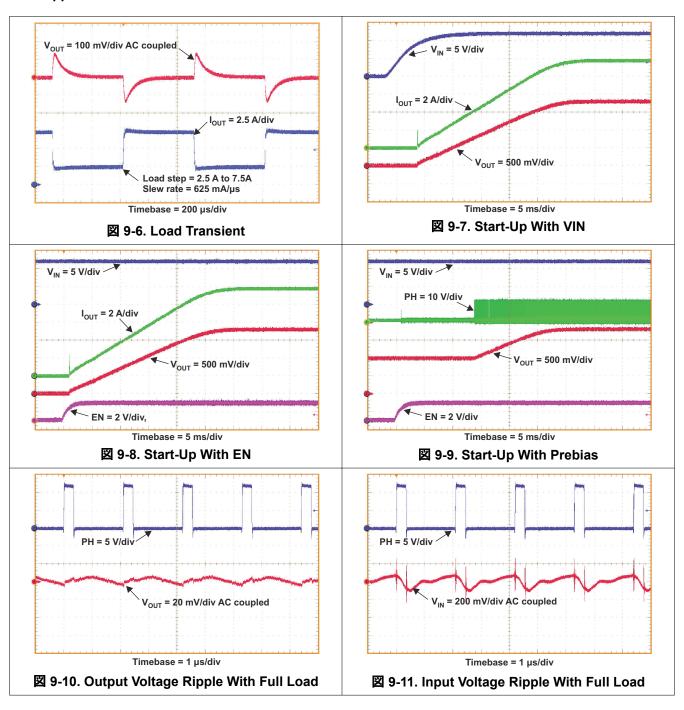

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R <sub>RT/CLK</sub> = 50 kΩ (1%)                                          | 890  | 990                    |       |        |