# 0.5A、42V入力、降圧型SWIFT™コンバータ

## 特 長

- 入力電圧範囲：3.5V～42V

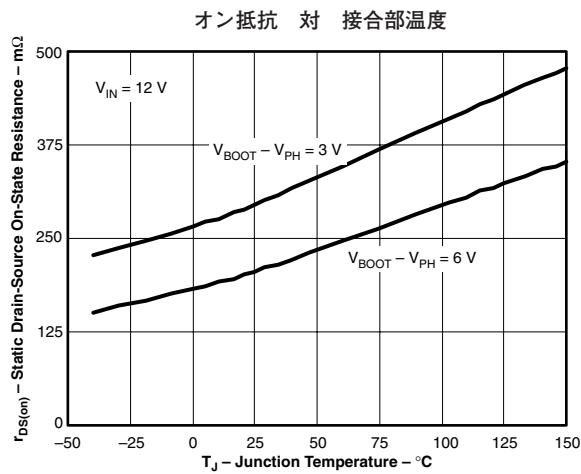

- ハイサイドMOSFET：200mΩ

- パルス・スキップEco-mode™制御方式により軽負荷で高い効率を実現

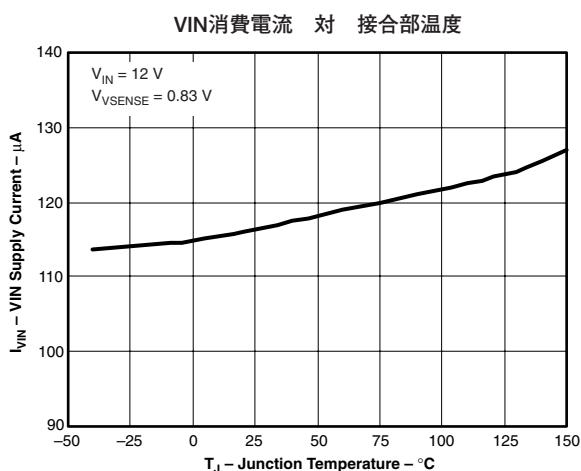

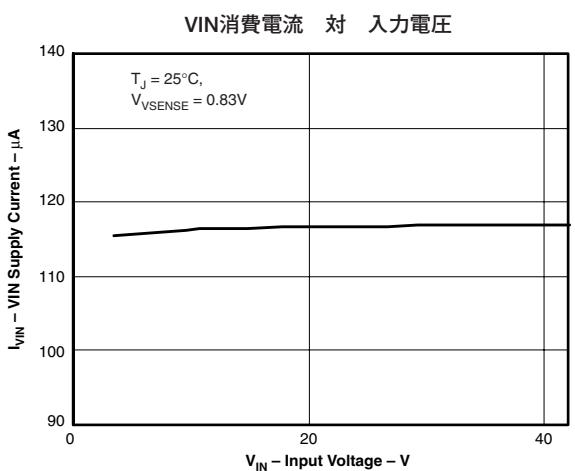

- 動作時静止電流：116μA

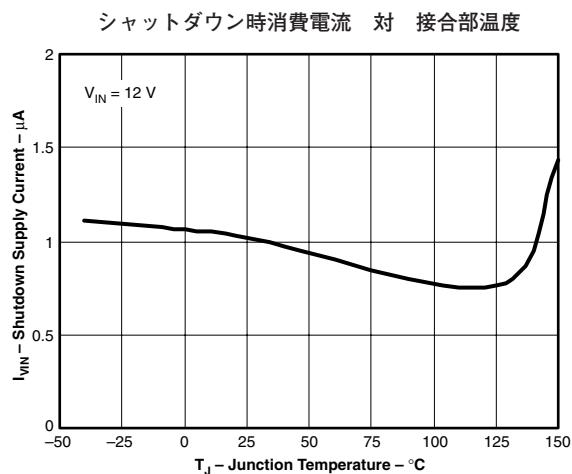

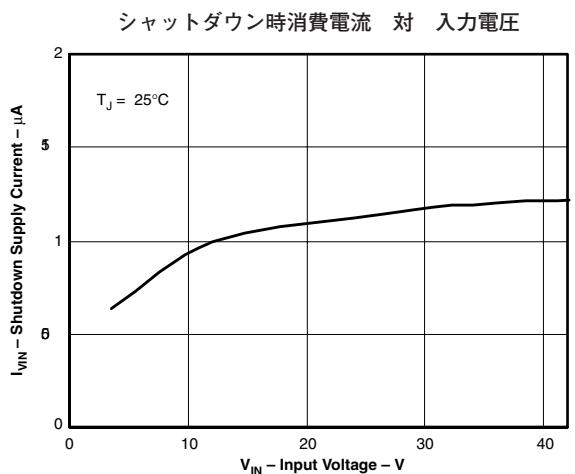

- シャットダウン時電流：1.3μA

- スイッチング周波数：100kHz～2.5MHz

- 外部クロックに同期

- 調整可能なスロー・スタート/シーケンシング

- パワー・グッド出力：UV、OV

- 調整可能なUVLO電圧およびヒステリシス

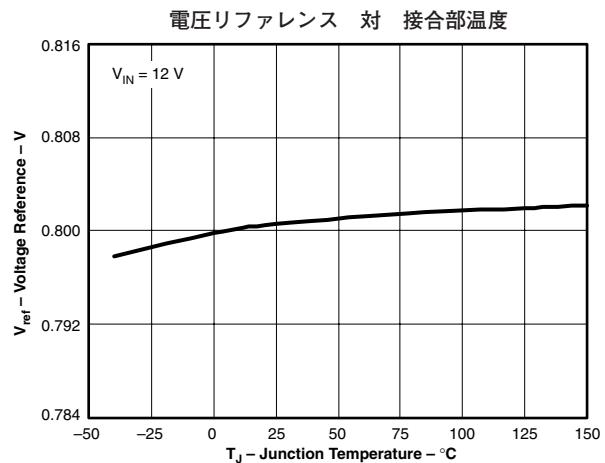

- 内部電圧リファレンス：0.8V±3.5%

- MSOP10 PowerPAD™パッケージ

- SwitcherPro™ソフトウェア・ツールに対応

([www.tij.co.jp/switcherpro](http://www.tij.co.jp/switcherpro))

- SWIFT™パワー製品のドキュメントについては、

TIのWebサイト [www.tij.co.jp/swiftdoc](http://www.tij.co.jp/swiftdoc) をご覧ください。

## ア プ リ ケ ー シ ョ ン

- 12Vおよび24Vの産業用および民生用低電力システム

- Eメーター

## 概 要

TPS5401は、ハイサイドMOSFETを内蔵した、42V、0.5Aの降圧型レギュレータです。電流モード制御により、外部補償が単純化され、柔軟な部品選択が可能になります。低リップルのパルス・スキップ・モードを使用すると、無負荷でレギュレーション電圧出力時の消費電流を116μAまで低減できます。また、イネーブル・ピンが“Low”的ときには、シャットダウン時消費電流1.3μAまで低減されます。

低電圧ロックアウトは内部で2.5Vに設定されていますが、イネーブル・ピンを使用してさらに高い電圧に設定することができます。出力電圧のスタートアップ・ランプはスロー・スタート・ピンで制御され、このピンはシーケンシング/トラッキング用としても使用可能です。オープン・ドレインのパワー・グッド信号は、出力が公称電圧の94%～107%の範囲内であることを

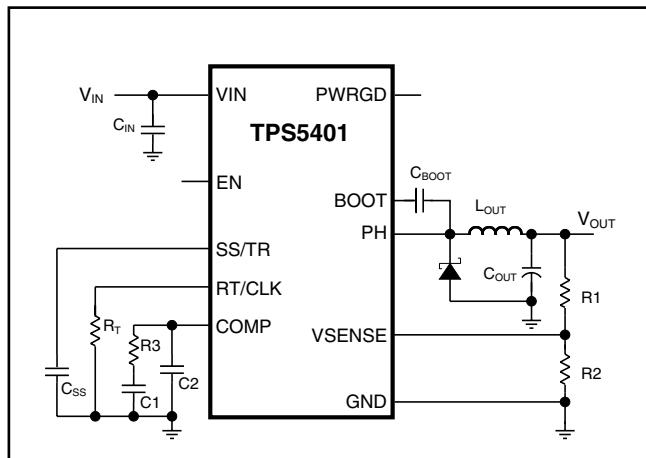

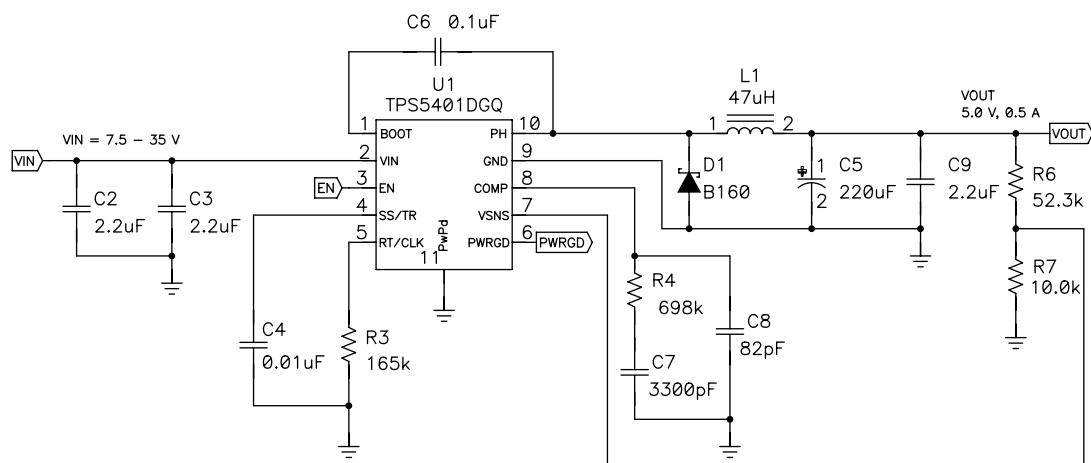

## 回路概略図

Eco-Mode, PowerPAD, SwitcherPro, SWIFTは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

示します。

スイッチング周波数の範囲が広いため、効率および外部部品のサイズを最適化できます。周波数フォールドバックと過熱シャットダウン機能によって、過負荷状態時にデバイスを保護します。

TPS5401は、熱特性が強化された10ピンMSOP PowerPADパッケージで提供されます。

## 静電気放電対策

ESDはこの集積回路にダメージを与えることがあります。テキサス・インスツルメンツ社は、全ての集積回路に適切なESD対策が行われることを推奨します。この適切な取扱いや取付け手順が守られない場合には、素子にダメージを与えることがあります。

ESDが与えるダメージには、素子へ微妙な性能劣化から完全な素子故障まで様々な症状に及びます。非常に些細なパラメータの変化でもその素子の仕様を満足しなくなることがあります。高詳細な集積回路はさらにESDによる影響を受けやすい場合があります。

## オーダー情報<sup>(1)</sup>

| T <sub>J</sub> | パッケージ    | 部品番号 <sup>(2)</sup> |

|----------------|----------|---------------------|

| -40°C ~ 150°C  | 10ピンMSOP | TPS5401DGQ          |

(1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

(2) DGQパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(すなわち、TPS5401DGQR)。

## 絶対最大定格<sup>(1)</sup>

動作温度範囲内 (特に記述のない限り)

|                                                             |                     | VALUE         |      | 単位 |

|-------------------------------------------------------------|---------------------|---------------|------|----|

|                                                             |                     | MIN           | MAX  |    |

| Input voltage                                               | VIN                 | -0.3          | 47   | V  |

|                                                             | EN                  | -0.3          | 5    |    |

|                                                             | BOOT                |               | 55   |    |

|                                                             | VSENSE              | -0.3          | 3    |    |

|                                                             | COMP                | -0.3          | 3    |    |

|                                                             | PWRGD               | -0.3          | 6    |    |

|                                                             | SS/TR               | -0.3          | 3    |    |

|                                                             | RT/CLK              | -0.3          | 3.6  |    |

| Output voltage                                              | BOOT - PH           |               | 8    | V  |

|                                                             | PH                  | -0.6          | 47   |    |

|                                                             | PH, 10-ns transient | -2            | 47   |    |

| Voltage difference                                          | Thermal pad to GND  |               | ±200 | mV |

| Source current                                              | EN                  |               | 100  | µA |

|                                                             | BOOT                |               | 100  | mA |

|                                                             | VSENSE              |               | 10   | µA |

|                                                             | PH                  | Current limit |      | A  |

|                                                             | RT/CLK              |               | 100  | µA |

| Sink current                                                | VIN                 | Current limit |      | A  |

|                                                             | COMP                |               | 100  | µA |

|                                                             | PWRGD               |               | 10   | mA |

|                                                             | SS/TR               |               | 200  | µA |

| Electrostatic discharge (HBM) QSS 009-105 (JESD22-A114A)    |                     |               | 1    | kV |

| Electrostatic discharge (CDM) QSS 009-147 (JESD22-C101B.01) |                     |               | 500  | V  |

| Operating junction temperature                              |                     | -40           | 150  | °C |

| Storage temperature                                         |                     | -65           | 150  | °C |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 熱特性について

| THERMAL METRIC <sup>(1)</sup> |                                              | TPS5401        | 単位   |

|-------------------------------|----------------------------------------------|----------------|------|

|                               |                                              | MSOP (10 PINS) |      |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance       | 68             | °C/W |

| $\theta_{JC(\text{top})}$     | Junction-to-case(top) thermal resistance     | 63.3           | °C/W |

| $\theta_{JB}$                 | Junction-to-board thermal resistance         | 44.6           | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 1.4            | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 22.8           | °C/W |

| $\theta_{JC(\text{bottom})}$  | Junction-to-case(bottom) thermal resistance  | 25.6           | °C/W |

(1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

## 電気的特性

$T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ 、 $V_{IN} = 3.5\text{V} \sim 42\text{V}$  (特に記述のない限り)

| パラメータ                           | テスト条件                                                         | MIN                                                                                                               | TYP  | MAX   | 単位                |

|---------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-------|-------------------|

| <b>SUPPLY VOLTAGE (VIN PIN)</b> |                                                               |                                                                                                                   |      |       |                   |

| $V_{IN}$                        | Operating input voltage                                       |                                                                                                                   | 3.5  | 42    | V                 |

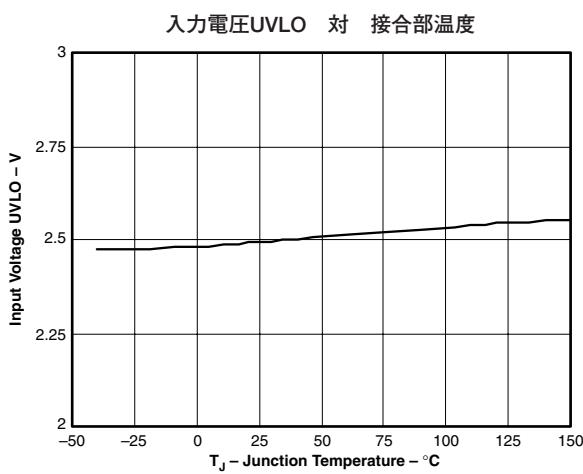

|                                 | Internal undervoltage lockout threshold                       | No voltage hysteresis, rising and falling                                                                         |      | 2.5   | V                 |

|                                 | Shutdown supply current                                       | $V_{EN} = 0\text{ V}$                                                                                             |      | 1.3   | 4                 |

|                                 | Operating: nonswitching supply current                        | $V_{VSENSE} = 0.83\text{ V}$ , $V_{IN} = 12\text{ V}$ , $25^\circ\text{C}$                                        |      | 116   | 136 $\mu\text{A}$ |

| <b>ENABLE AND UVLO (EN PIN)</b> |                                                               |                                                                                                                   |      |       |                   |

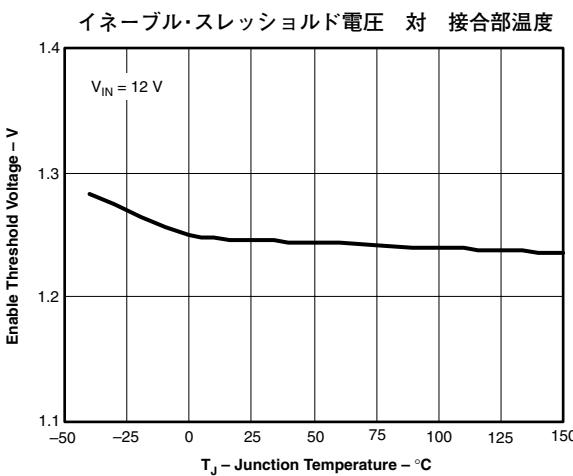

| Enable threshold voltage        | No voltage hysteresis, rising and falling, $25^\circ\text{C}$ | 0.9                                                                                                               | 1.25 | 1.55  | V                 |

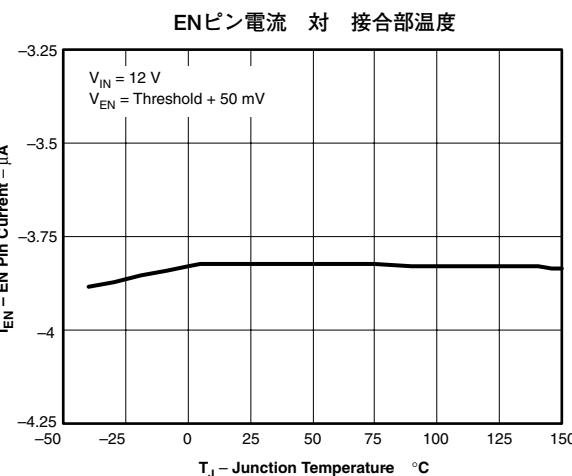

| Input current                   | Enable threshold 50 mV                                        |                                                                                                                   | -3.8 |       | $\mu\text{A}$     |

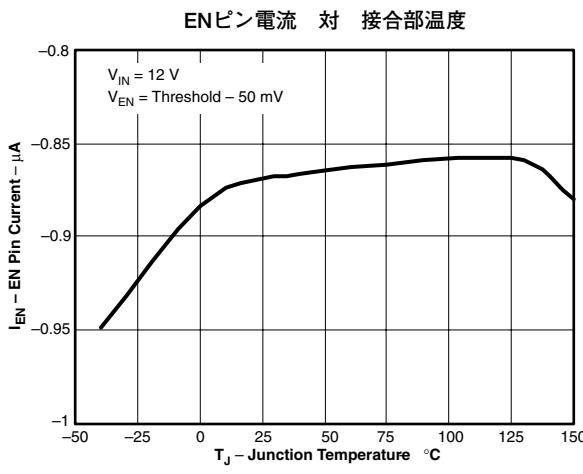

|                                 | Enable threshold -50 mV                                       |                                                                                                                   | -0.9 |       |                   |

| Hysteresis current              |                                                               |                                                                                                                   | -2.9 |       | $\mu\text{A}$     |

| <b>VOLTAGE REFERENCE</b>        |                                                               |                                                                                                                   |      |       |                   |

| $V_{ref}$                       | Voltage reference                                             | 0.772                                                                                                             | 0.8  | 0.828 | V                 |

| <b>HIGH-SIDE MOSFET</b>         |                                                               |                                                                                                                   |      |       |                   |

| On-resistance                   | $V_{IN} = 3.5\text{ V}$ , $V_{BOOT} - V_{PH} = 3\text{ V}$    |                                                                                                                   | 300  |       | $\text{m}\Omega$  |

|                                 | $V_{IN} = 12\text{ V}$ , $V_{BOOT} - V_{PH} = 6\text{ V}$     |                                                                                                                   | 200  | 410   |                   |

| <b>ERROR AMPLIFIER</b>          |                                                               |                                                                                                                   |      |       |                   |

| Input current                   |                                                               | 50                                                                                                                |      |       | nA                |

| $gm_{EA}$                       | Error amplifier transconductance                              | $-2\text{ }\mu\text{A} < I_{COMP} < 2\text{ }\mu\text{A}$ , $V_{COMP} = 1\text{ V}$                               | 97   |       | $\mu\text{Mhos}$  |

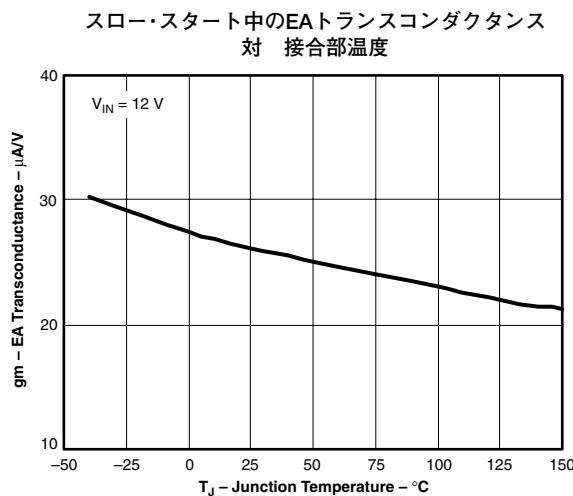

|                                 | Error amplifier transconductance during slow-start            | $-2\text{ }\mu\text{A} < I_{COMP} < 2\text{ }\mu\text{A}$ , $V_{COMP} = 1\text{ V}$ , $V_{VSENSE} = 0.4\text{ V}$ | 26   |       | $\mu\text{Mhos}$  |

| Error amplifier dc gain         | $V_{VSENSE} = 0.8\text{ V}$                                   | 10,000                                                                                                            |      |       | V/V               |

| Error amplifier bandwidth       |                                                               | 2700                                                                                                              |      |       | kHz               |

| Error amplifier source/sink     | $V_{COMP} = 1\text{ V}$ , 100 mV overdrive                    |                                                                                                                   | ±7   |       | $\mu\text{A}$     |

| $gm_{PS}$                       | COMP to switch current transconductance                       |                                                                                                                   | 1.9  |       | A/V               |

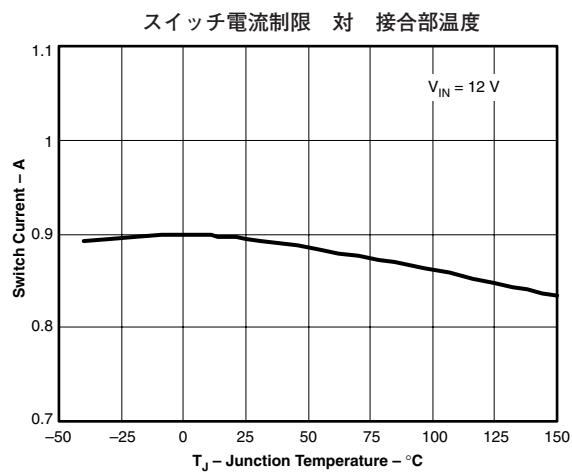

| <b>CURRENT LIMIT</b>            |                                                               |                                                                                                                   |      |       |                   |

| Current limit threshold         | $V_{IN} = 12\text{ V}$ , $T_J = 25^\circ\text{C}$             | 0.6                                                                                                               | 0.94 |       | A                 |

| <b>THERMAL SHUTDOWN</b>         |                                                               |                                                                                                                   |      |       |                   |

| Thermal shutdown                |                                                               |                                                                                                                   | 182  |       | °C                |

## 電気的特性

$T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、 $V_{IN} = 3.5\text{V} \sim 42\text{V}$  (特に記述のない限り)

| パラメータ                                                  | テスト条件                                                                       | MIN  | TYP  | MAX | 単位            |

|--------------------------------------------------------|-----------------------------------------------------------------------------|------|------|-----|---------------|

| <b>TIMING RESISTOR AND EXTERNAL CLOCK (RT/CLK PIN)</b> |                                                                             |      |      |     |               |

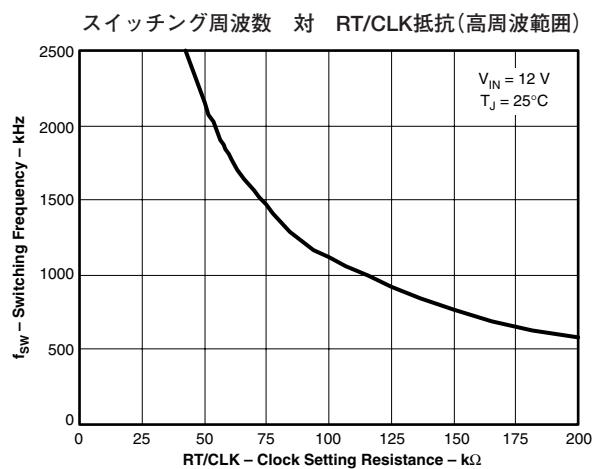

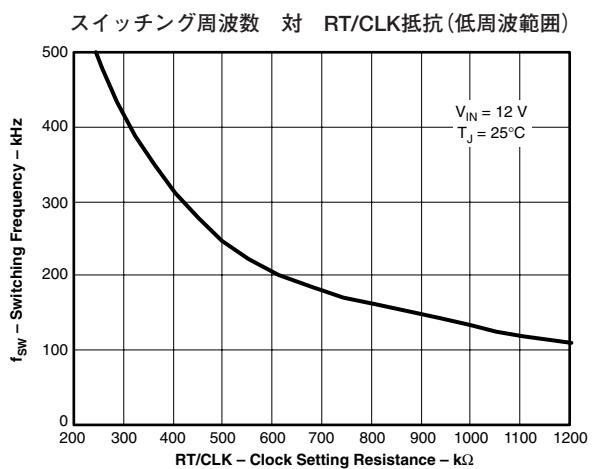

| Switching-frequency range using RT mode                |                                                                             | 100  | 2500 |     | kHz           |

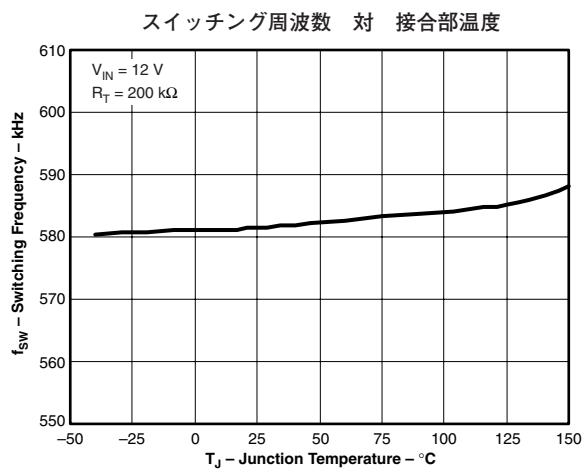

| $f_{SW}$                                               | $R_T = 200 \text{ k}\Omega$                                                 | 450  | 581  | 720 | kHz           |

| Switching-frequency range using CLK mode               |                                                                             | 300  | 2200 |     | kHz           |

| Minimum CLK input pulse width                          |                                                                             | 40   |      |     | ns            |

| RT/CLK high threshold                                  |                                                                             | 1.9  | 2.2  |     | V             |

| RT/CLK low threshold                                   |                                                                             | 0.5  | 0.7  |     | V             |

| RT/CLK falling edge to PH rising edge delay            | Measured at 500 kHz with $R_T$ resistor in series                           | 60   |      |     | ns            |

| PLL lock-in time                                       | Measured at 500 kHz                                                         | 100  |      |     | $\mu\text{s}$ |

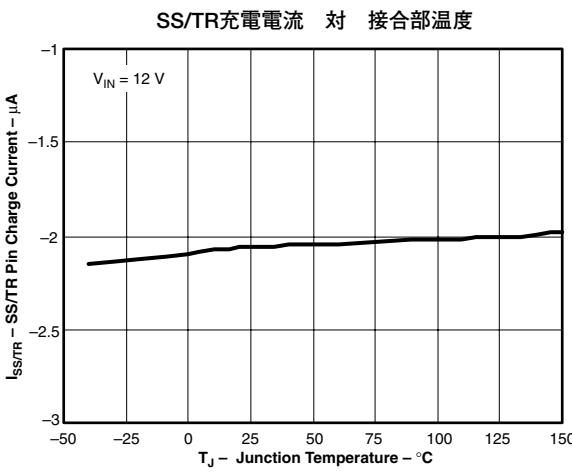

| <b>SLOW-START AND TRACKING (SS/TR PIN)</b>             |                                                                             |      |      |     |               |

| Charge current                                         | $V_{SS/TR} = 0.4 \text{ V}$                                                 | 2    |      |     | $\mu\text{A}$ |

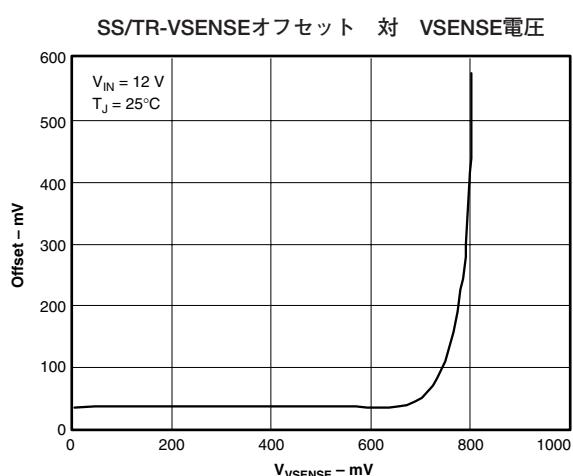

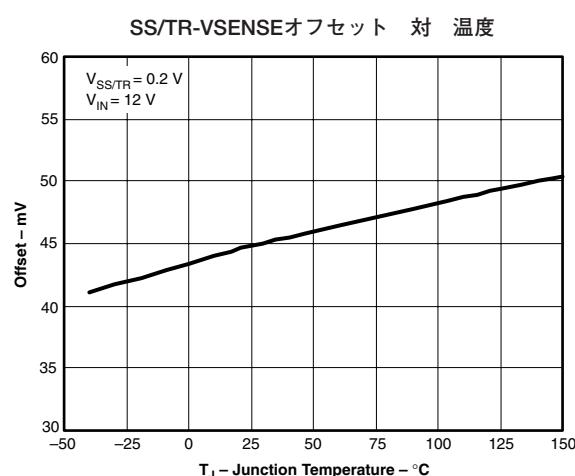

| SS/TR-to-VSENSE matching                               | $V_{SS/TR} = 0.4 \text{ V}$                                                 | 45   |      |     | mV            |

| SS/TR-to-reference crossover                           | 98% nominal                                                                 | 1    |      |     | V             |

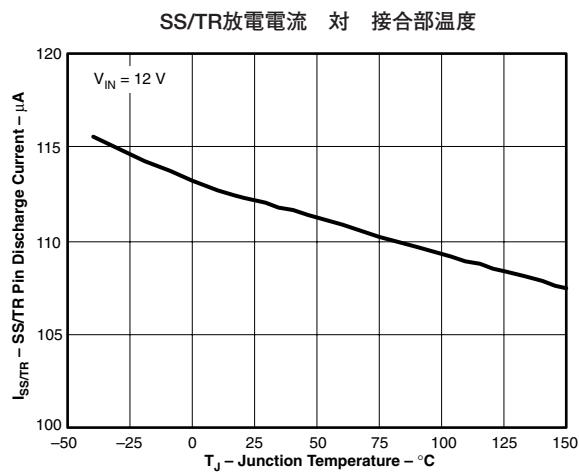

| SS/TR discharge current (overload)                     | $V_{VSENSE} = 0 \text{ V}$ , $V_{SS/TR} = 0.4 \text{ V}$                    | 112  |      |     | $\mu\text{A}$ |

| SS/TR discharge voltage                                | $V_{VSENSE} = 0 \text{ V}$                                                  | 54   |      |     | mV            |

| <b>POWER GOOD (PWRGD PIN)</b>                          |                                                                             |      |      |     |               |

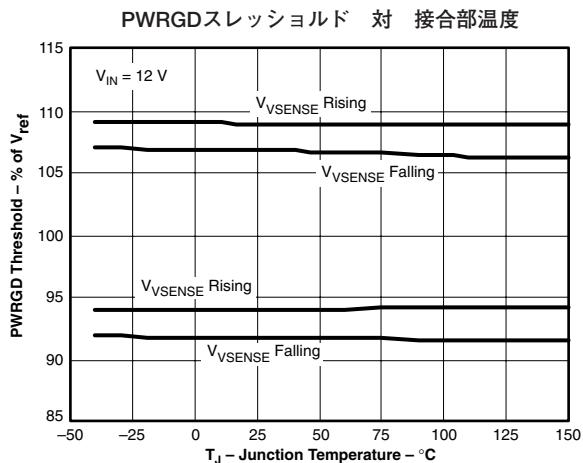

| VSENSE low threshold                                   | $V_{VSENSE}$ falling                                                        | 92%  |      |     | $V_{ref}$     |

|                                                        | $V_{VSENSE}$ rising                                                         | 94%  |      |     |               |

| VSENSE high threshold                                  | $V_{VSENSE}$ rising                                                         | 109% |      |     | $V_{ref}$     |

|                                                        | $V_{VSENSE}$ falling                                                        | 107% |      |     |               |

| Hysteresis                                             | $V_{VSENSE}$ falling                                                        | 2%   |      |     |               |

| Output-high leakage                                    | $V_{VSENSE} = V_{ref}$ , $V_{PWRGD} = 5.5 \text{ V}$ , $25^{\circ}\text{C}$ | 10   |      |     | nA            |

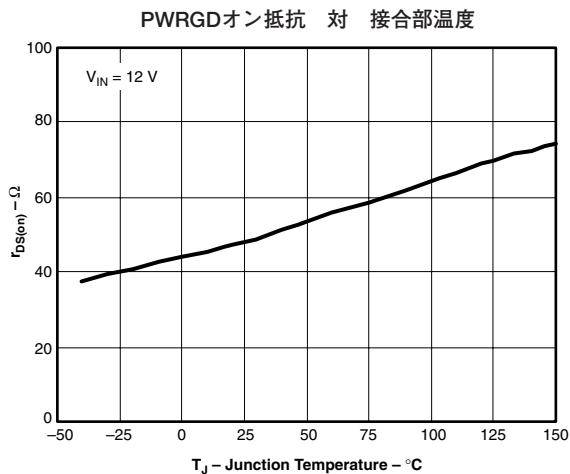

| On-resistance                                          | $I_{PWRGD} = 3 \text{ mA}$ , $V_{VSENSE} < 0.77 \text{ V}$                  | 50   |      |     | $\Omega$      |

| Minimum $V_{IN}$ for defined output                    | $V_{PWRGD} < 0.5 \text{ V}$ , $I_{PWRGD} = 100 \mu\text{A}$                 | 0.95 | 1.5  |     | V             |

# 製品情報

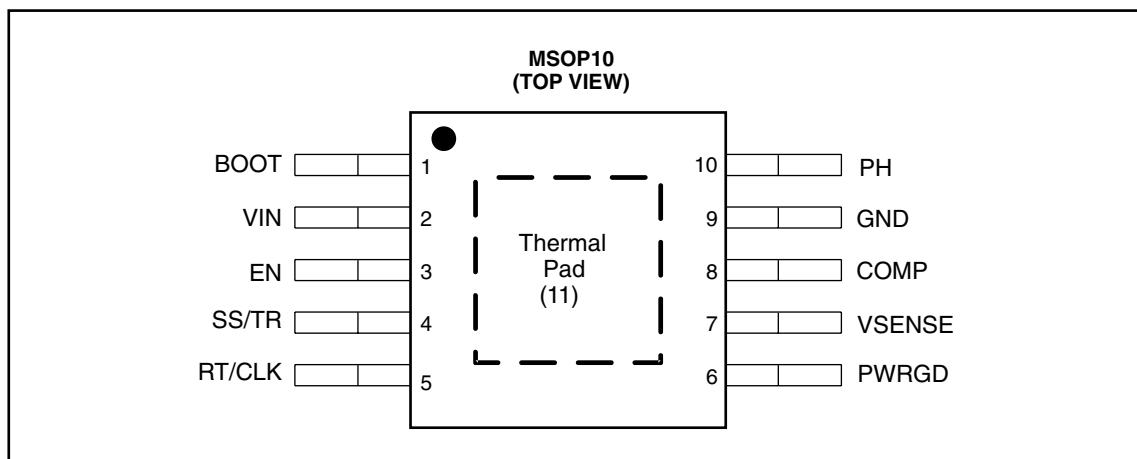

## ピン構成

## ピン機能

| ピン<br>名前      | 番号 | I/O | 説明                                                                                                                                                                                                                                                 |

|---------------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

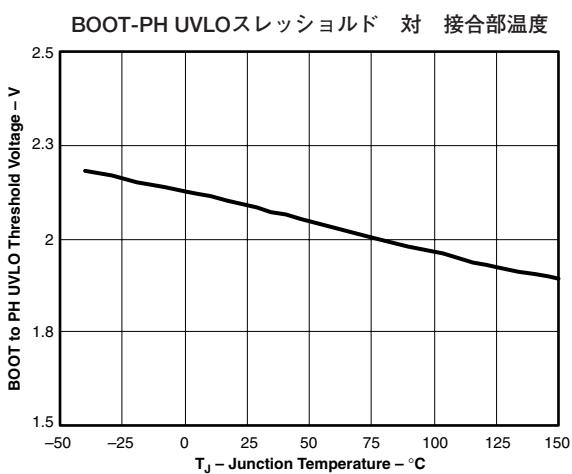

| BOOT          | 1  | O   | BOOTとPHの間にブートストラップ・コンデンサが必要です。このコンデンサの電圧が出力カーデバイスに対して必要な最小値を下回った場合、出力はコンデンサがリフレッシュされるまで強制的にオフになります。                                                                                                                                                |

| COMP          | 8  | O   | 誤差増幅器の出力、および出力スイッチ電流コンパレータの入力。このピンに周波数補償部品を接続します。                                                                                                                                                                                                  |

| EN            | 3  | I   | イネーブル・ピン、内部ブルアップ電流源。ディスエーブルにするには、1.2V未満にブルダウンします。イネーブルにするには、フローティングにします。2つの抵抗を使用して入力低電圧ロックアウトを調整します。                                                                                                                                               |

| GND           | 9  | -   | グランド                                                                                                                                                                                                                                               |

| PH            | 10 | I   | 内部ハイサイド・パワーMOSFETのソース                                                                                                                                                                                                                              |

| PWRGD         | 6  | O   | 過熱シャットダウン、ドロップアウト、過電圧、またはENシャットダウンによって出力電圧が規定値を外れた場合にアサートされる、オープン・ドレイン出力です。                                                                                                                                                                        |

| RT/CLK        | 5  | I   | タイミング抵抗接続および外部クロック入力端子。スイッチング周波数を設定するために、このピンとグランドの間に外部抵抗を接続すると、内部アンプによってこのピンが固定電圧に保持されます。このピンをPLLの上限スレッショルドより高くブルアップすると、モード遷移が発生し、ピンは同期入力となります。内部アンプはディスエーブルになり、このピンは内部PLLへのハイ・インピーダンス・クロック入力となります。クロック・エッジが停止すると、内部アンプが再イネーブルされ、モードは抵抗設定機能に戻ります。 |

| SS/TR         | 4  | I   | スロー・スタートおよびトラッキング。このピンに接続する外部コンデンサによって、出力の立ち上がり時間が設定されます。このピンの電圧は内部リファレンスよりも優先されるため、トラッキングおよびシーケンシングにも使用できます。                                                                                                                                      |

| サーマル・パッド (11) | -  |     | 適切な動作のためには、GNDピンをプリント基板上のサーマル・パッドに電気的に接続する必要があります。                                                                                                                                                                                                 |

| VIN           | 2  | I   | 入力電源電圧、3.5V~42V                                                                                                                                                                                                                                    |

| VSENSE        | 7  | I   | トランスコンダクタンス(gm)誤差増幅器の反転ノード。                                                                                                                                                                                                                        |

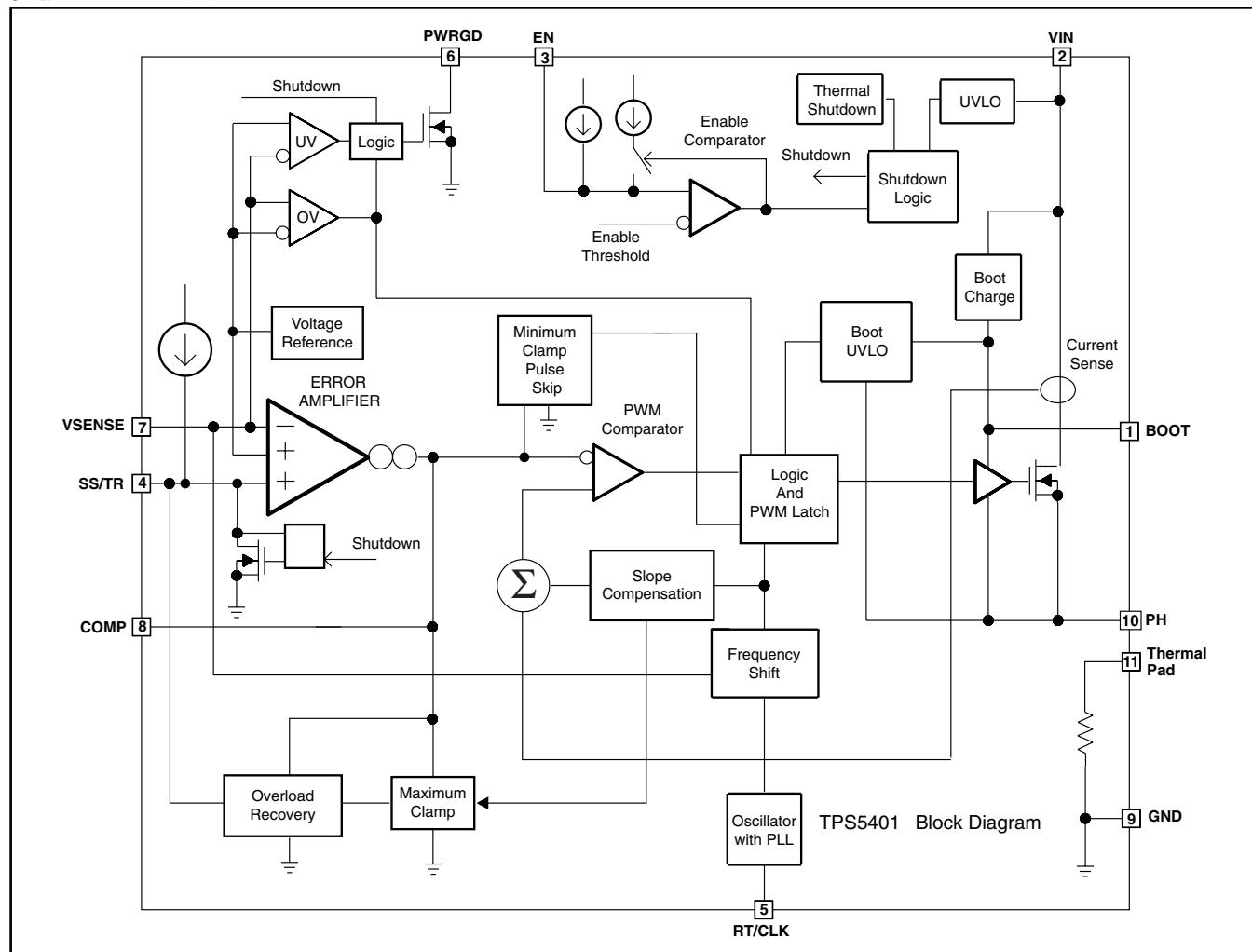

## 機能ブロック図

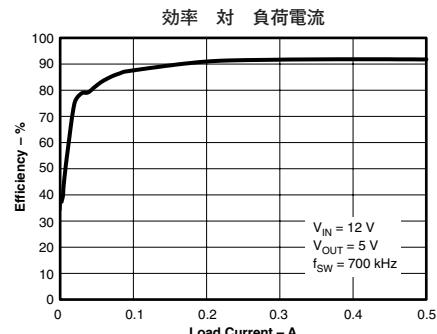

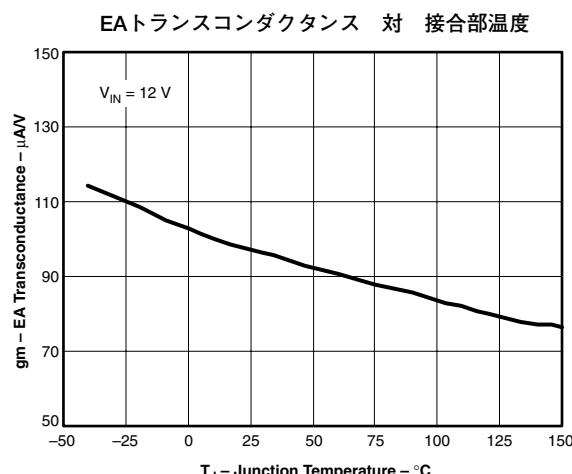

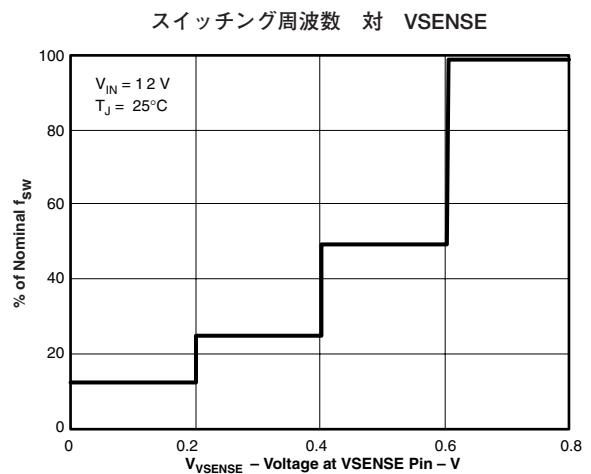

## 標準的特性

図 1

図 2

図 3

図 4

図 5

図 6

## 標準的特性

図 7

図 8

図 9

図 10

図 11

図 12

## 標準的特性

図 13

図 14

図 15

図 16

図 17

図 18

## 標準的特性

図 19

図 20

図 21

図 22

図 23

図 24

## 概要

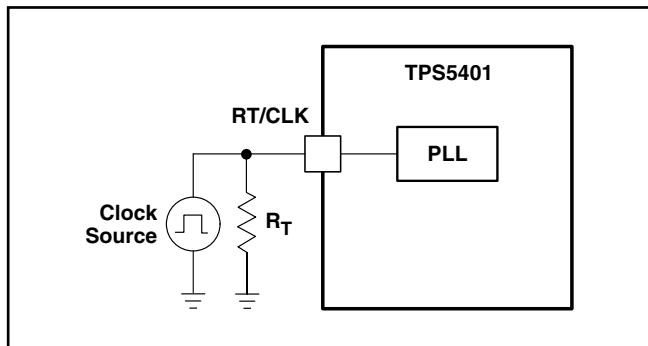

TPS5401は、ハイサイドNチャネルMOSFETを内蔵した、42V、0.5Aの降圧型(バック)レギュレータです。ラインおよび負荷の過渡状態における性能を向上させるため、定周波数の電流モード制御で動作し、出力容量の低減、外部周波数補償設計の簡易化を実現しています。スイッチング周波数の範囲が100kHz～2500kHzと広いため、出力フィルタ部品の選択時に効率およびサイズを最適化できます。スイッチング周波数は、RT/CLKピンからグランドへの抵抗を使用して調整します。RT/CLKピンには内部フェーズ・ロック・ループ(PLL)が備えられ、パワー・スイッチをオンにするタイミングを外部システム・クロックの立ち下がりエッジに同期させることができます。

TPS5401のスタートアップ電圧はデフォルトで約2.5Vです。ENピンの内部プルアップ電流源を使用して、入力低電圧ロックアウト(UVLO)のスレッショルドを2つの外部抵抗により調整可能です。また、このプルアップ電流によってデフォルト状態を設定できます。ENピンがフローティングになると、デバイスが動作します。無負荷で非スイッチング時の動作電流は116μAです。デバイスがディスエーブル時の消費電流は、1.3μAです。

内蔵の200mΩハイサイドMOSFETにより、0.5Aの連続電流を負荷に供給できる高効率の電源設計が可能になります。TPS5401は、ブート再充電ダイオードを内蔵し、外部部品数を低減できます。内蔵ハイサイドMOSFETのバイアス電圧は、BOOTピン - PHピン間のコンデンサによって供給されます。このブート・コンデンサ電圧はUVLO回路によって監視され、内部設定されたスレッショルドを下回ると、ハイサイドMOSFETがオフになります。このブートUVLOにより、TPS5401は高いデューティ・サイクルで動作が可能です。出力電圧は、0.8Vのリファレンスと同じ値まで降圧させることができます。

TPS5401はパワー・グッド・コンパレータ(PWRGD)を備え、これはレギュレーション出力電圧が公称出力電圧の92%未満または109%を超えたときにアサートされます。PWRGDピンはオープン・ドレイン出力であり、VSENSEピンの電圧が公称出力電圧の94%～107%の範囲内のときにデアサートされ、プルアップ抵抗を使用した場合には“High”に遷移します。

TPS5401では、OVパワー・グッド・コンパレータを利用して、過度の出力過電圧(OV)を最小限に抑えています。OVコンパレータが作動すると、ハイサイドMOSFETはオフになり、出力電圧が107%を下回るまでオンになりません。

SS/TR(スロー・スタート/トラッキング)ピンは、パワーアップ時に突入電流を最小限に抑え、電源シーケンシングを構成するために使用できます。スロー・スタート時間調整には、このピンに小容量のコンデンサを接続します。電源シーケンシングの要件が重要である場合には、このピンに分圧抵抗を接続できます。SS/TRピンは、出力のパワーアップ前に放電されます。この放電によって、過熱障害、UVLO障害、またはディスエーブル状態の後に、再起動を繰り返すことが可能になります。

また、TPS5401は、過負荷回復回路によって過負荷状態時にスロー・スタート・コンデンサを放電します。過負荷回復回路は、過負荷状態が解消されると、出力を障害電圧から公称レギュレーション電圧へとスロー・スタートさせます。周波数フォールドバック回路により、起動時および過電流障害時にスイッチング周波数が低くなり、インダクタ電流を制御しやすくなります。

## 詳細説明

### 固定周波数PWM制御

TPS5401は、調整可能な固定周波数のピーク電流モード制御を使用します。COMPピンを駆動する誤差増幅器により、出力電圧がVSENSEピンの外付け抵抗を通して内部電圧リファレンスと比較されます。内部発振器により、ハイサイド・パワー・スイッチのオン動作が開始され、誤差増幅器の出力がハイサイド・パワー・スイッチ電流と比較されます。パワー・スイッチ電流がCOMP電圧で設定されたレベルに達すると、パワー・スイッチがオフになります。出力電流が増加および減少すると、COMPピン電圧も増加および減少します。デバイスではCOMPピン電圧を最大レベルにクランプすることで電流制限を実現しています。また、COMPピンの最小クランプによってEco-mode制御方式を実現しています。

### スロープ補償出力電流

TPS5401は、スイッチ電流信号に補償ランプを追加します。このスロープ補償により、低調波発振を防いでいます。使用可能なピーク・インダクタ電流は、デューティ・サイクルの範囲全体にわたって一定です。

### パルス・スキップEco-mode制御方式

TPS5401は、軽負荷電流時にはパルス・スキップEco-mode制御方式で動作し、スイッチング損失やゲート駆動損失の低減によって効率を向上させます。出力電圧がレギュレーション範囲内のときに、任意のスイッチング・サイクルの終わりでピーク・スイッチ電流がパルス・スキップ電流スレッショルドを下回っている場合、TPS5401はEco-mode制御方式に切り替わるよう設計されています。この電流スレッショルドは、公称COMP電圧(500mV)に対応した電流レベルです。

Eco-mode制御方式では、COMPピンの電圧が500mVにクランプされ、ハイサイドMOSFETがディスエーブルになります。負荷電流がさらに低下、または出力電圧がさらに上昇しても、COMPピンはこのクランプ電圧レベルを下回りません。

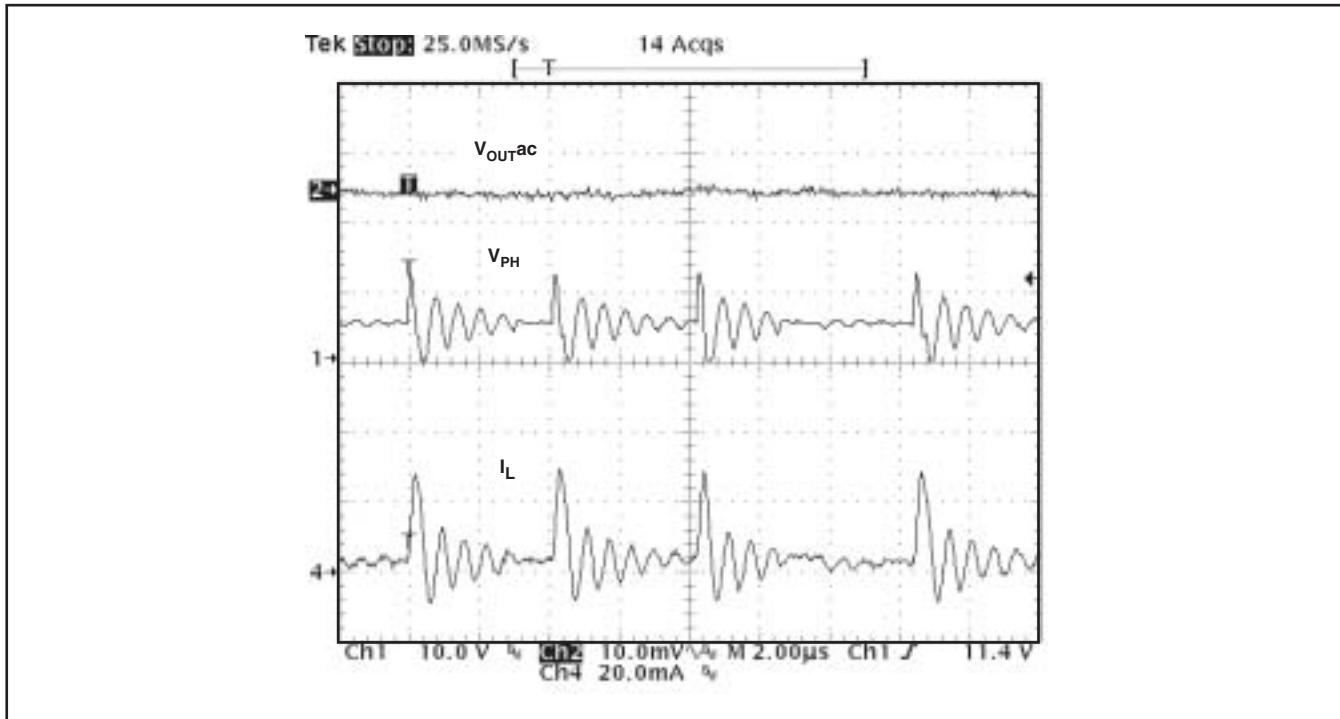

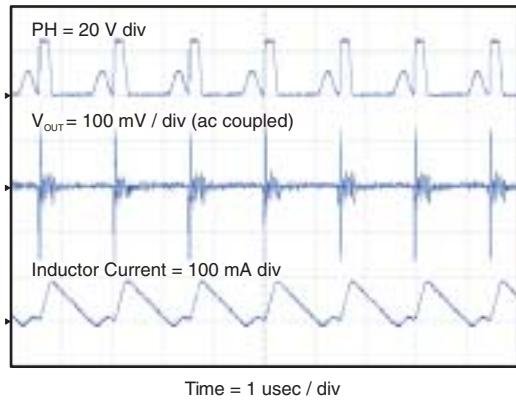

デバイスはスイッチングを停止しているため、出力電圧は低下始めます。電圧制御ループによって出力電圧の低下が補償されるため、COMPピンの電圧は上昇を開始します。このとき、ハイサイドMOSFETがイネーブルとなり、次のスイッチング・サイクルでスイッチング・パルスが開始されます。ピーク電流は、COMPピンの電圧によって設定されます。出力電圧がレギュレーション値に再上昇した後(図25)、ピーク・スイッチ電流は減少し始め、さらに減少してEco-modeスレッショルドを下回ると、デバイスは再度Eco-mode制御に入ります。

Eco-mode制御方式での動作時には、TPS5401は(平均電流や負荷電流ではなく)ピーク電流をセンスするため、デバイスがEco-mode制御に入る負荷電流は出力インダクタ値によって異なります。例えば、図40の回路は、出力電流が約20mAになるとEco-mode制御に入ります。負荷電流が低く、出力電圧がレギュレーション内のとき、デバイスはスリープ・モードに入り、静止時入力電流はわずか116μAとなります。スリープ・モード

図 25. パルス・スキップ・モードの動作

中、内部PLLは動作を継続します。軽負荷時にパルス・スキップ・モードで動作している間は、外部クロック信号に同期してスイッチング遷移が行われます。

## 低ドロップアウト動作とブートストラップ電圧 (BOOT)

TPS5401にはブート・レギュレータが内蔵され、ハイサイドMOSFETのゲート駆動電圧を提供するために、BOOTピンとPHピンの間に小さなセラミック・コンデンサが必要です。BOOTコンデンサは、ハイサイドMOSFETがオフでローサイド・ダイオードが導通しているときにリフレッシュされます。セラミック・コンデンサの値は、 $0.1\mu\text{F}$ としてください。温度および電圧に対して安定した特性を持つため、X7RまたはX5Rクラスの誘電体を持つ電圧定格10V以上のセラミック・コンデンサを推奨します。

ドロップ・アウトを改善するため、TPS5401は、BOOT-PHピン間に電圧が2.1V以上であれば、100%のデューティ・サイクルで動作するよう設計されています。BOOT-PH間に電圧が2.1Vを下回ると、UVLO回路によってハイサイドMOSFETがオフになることで、ローサイド・ダイオードが導通してBOOTコンデンサの電荷がリフレッシュされます。BOOTコンデンサからソースされる電源電流は低いため、ハイサイドMOSFETはコンデンサのリフレッシュに必要な時間よりも多くのスイッチング・サイクルにわたってオンに保持でき、結果として、スイッチング・レギュレータの実効的なデューティ・サイクルが大きくなります。

レギュレータのドロップアウト時の実効デューティ・サイクルは、主に、パワーMOSFET、インダクタ抵抗、ローサイド・ダイオード、プリント基板抵抗のそれぞれにおける電圧降下に

よって影響を受けます。入力電圧が低下し、レギュレータが連続動作モードで動作している状態では、BOOT-PH間に電圧が2.1Vを下回るまで、出力レギュレーションを維持するように、デューティ・サイクルの100%にわたってハイサイドMOSFETをオンに保持できます。

軽負荷または無負荷での最大デューティ・サイクルのアプリケーションでは、注意が必要です。BOOTコンデンサ両端の電圧が2.1VのUVLOスレッショルドを下回ると、ハイサイドMOSFETがオフになりますが、PHピンをプルダウンしてBOOTコンデンサを再充電するほど十分なインダクタ電流は得られない可能性があります。BOOTコンデンサの電圧が2.1V未満であるため、レギュレータのハイサイドMOSFETはスイッチングを停止します。それにより、入力電圧と出力電圧の差が2.1Vを超えるまで出力コンデンサの電圧は低下し続けます。差が2.1Vを超えてBOOT UVLOスレッショルドを上回ると、デバイスは目的の出力電圧に達するまで再度スイッチングを開始します。この動作状況が、入力電圧または負荷電流が上昇するまで継続します。ENピンの抵抗による可変VIN UVLO機能を使用して、アプリケーションの最小負荷時のBOOT UVLOトリガ条件を上回るようVIN停止電圧を調整することを推奨します。

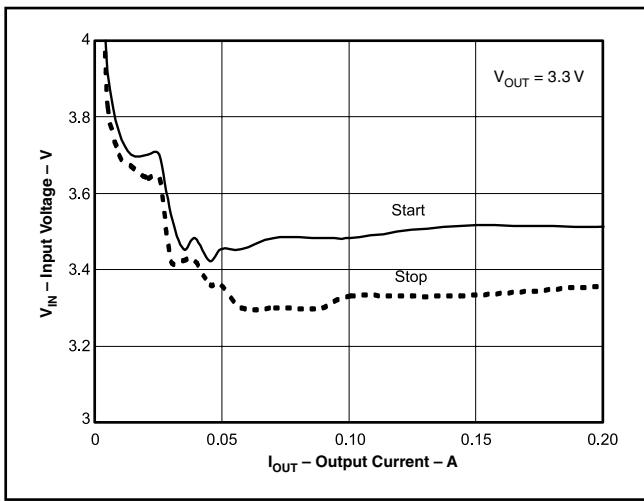

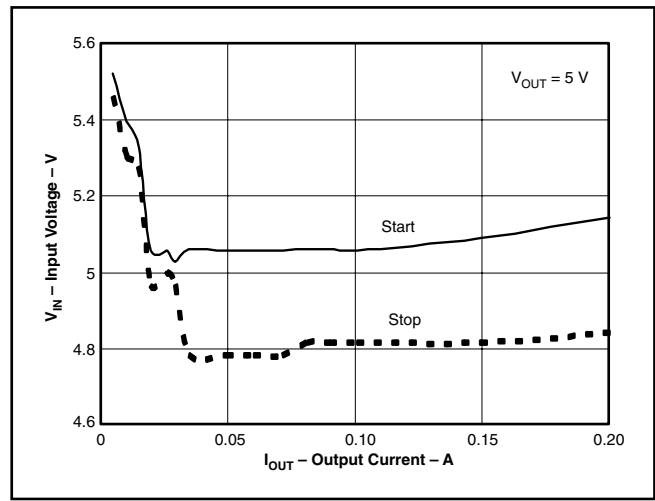

標準的な3.3Vおよび5V出力アプリケーションでの開始および停止電圧をそれぞれ図26および図27に示します。電圧は負荷電流に対してプロットされています。開始電圧は、3.5%以内の出力レギュレーションに必要な入力電圧として定義されます。停止電圧は、出力が5%低下するかまたはスイッチングが停止するときの入力電圧として定義されます。

図 26. 3.3V アプリケーションの開始/停止電圧

図 27. 5V アプリケーションの開始/停止電圧

高デューティ・サイクルの状況では、BOOTコンデンサが再充電されて出力のリップル電圧が増加する間、インダクタの電流リップルが増加します。これは、スイッチングが毎サイクル発生するときに、ブート・コンデンサの再充電時間が標準的なハイサイド・オフ時間よりも長いためです。

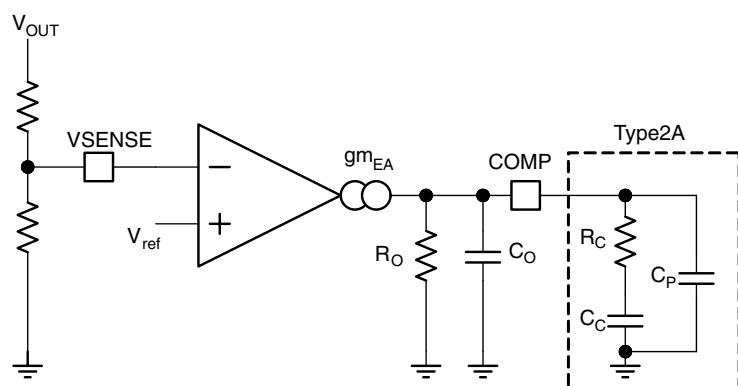

## 誤差増幅器

TPS5401は、誤差増幅器としてトランスコンダクタンス・アンプを内蔵しています。誤差増幅器は、VSENSEの電圧を、SS/TRピンの電圧または内部の0.8V電圧リファレンスのいずれか低い方と比較します。誤差増幅器のトランスコンダクタンス( $gm$ )は、通常動作時には97 $\mu$ A/Vです。スロー・スタート動作時には、トランスコンダクタンスは通常動作時の $gm$ よりもずっと低くなります。VSENSEピンの電圧が0.8V未満で、デバイスがSS/TR電圧を使用してレギュレーションを行っている場合、 $gm$ は26 $\mu$ A/Vとなります。

COMPピンとグランドとの間に周波数補償部品(直列抵抗およびコンデンサ)が追加されます。

## 電圧リファレンス

電圧リファレンス・システムは、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで、温度に対して $\pm 3.5\%$ の高い精度を持つ電圧リファレンスを生成します。

## 出力電圧の調整

出力電圧は、出力ノードとVSENSEピンとの間の分圧抵抗によって設定されます。公差1%以内の分圧抵抗を使用することを推奨します。最初はR2抵抗に10k $\Omega$ を使用し、式(1)を使ってR1を計算します。軽負荷時の効率を向上させるには、より大きな値の抵抗の使用を検討します。値が大きすぎると、レギュレータがノイズの影響を受けやすくなり、VSENSE入力電流からの電圧誤差が目立つようになります。

$$R1 = R2 \times \left( \frac{V_{OUT} - 0.8V}{0.8V} \right) \quad (1)$$

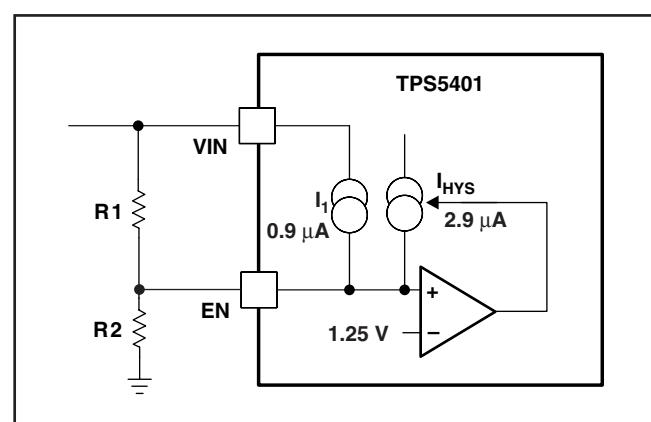

## 低電圧ロックアウトのイネーブルおよび調整

VINピンの電圧が2.5Vを下回ると、TPS5401はディスエーブルになります。アプリケーションで、より高い値での低電圧ロックアウト(UVLO)を必要とする場合は、図28のようにENピンを使用し、2個の外付け抵抗で入力電圧UVLOを調整します。UVLO調整抵抗の使用は必須ではありませんが、一貫したパワーアップ動作を実現するために強く推奨します。ENピンには0.9 $\mu$ Aの内部プルアップ電流源 $I1$ があり、ENピンがフローティングのときにTPS5401が動作するデフォルト状態を提供します。ENピンの電圧が1.25Vのイネーブル・スレッショルド電圧( $V_{ENA}$ )を超えると、2.9 $\mu$ Aのヒステリシス(IHYS)が追加されます。この追加電流により、入力電圧のヒステリシスを実現できます。入力電圧の外部ヒステリシスは、式(2)を使って設定します。入力スタート電圧は、式(3)を使って設定します。

図 28. 調整可能な低電圧ロックアウト(UVLO)

$$R1 = \frac{V_{START} - V_{STOP}}{I_{HYS}} \quad (2)$$

$$R2 = \frac{\frac{V_{ENA}}{V_{START} - V_{ENA}} + I_1}{R1} \quad (3)$$

## スロー・スタート/トラッキング・ピン (SS/TR)

TPS5401では、SS/TRピン電圧または内部電圧リファレンスのいずれか低い方の電圧を電源リファレンス電圧として使用し、それに従って出力のレギュレーションを行います。SS/TRピンとグランド間のコンデンサにより、スロー・スタート時間が実装されます。TPS5401には、外部のスロー・スタート・コンデンサを充電する2 $\mu$ Aのプルアップ電流源が内蔵されています。スロー・スタート時間(10%~90%)は式(4)で計算されます。電圧リファレンス( $V_{ref}$ )は0.8Vで、スロー・スタート電流( $I_{SS}$ )は2 $\mu$ Aです。スロー・スタート・コンデンサは、0.47 $\mu$ F未満、0.47nF以上とする必要があります。

$$C_{ss} (\text{nF}) = \frac{t_{ss} (\text{ms}) \times I_{ss} (\mu\text{A})}{V_{ref} (\text{V}) \times 0.8} \quad (4)$$

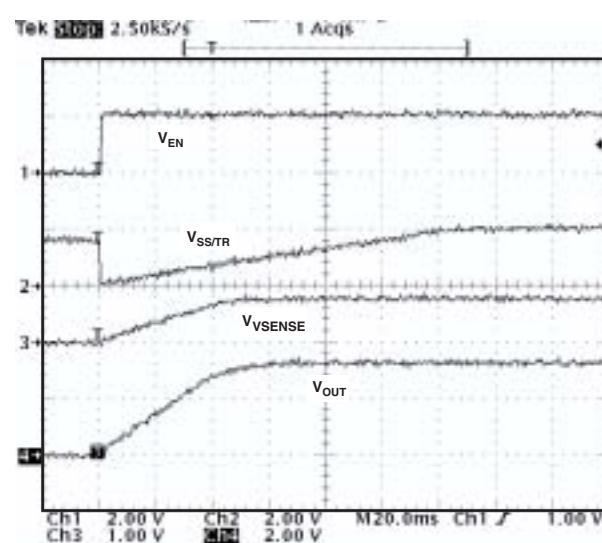

パワーアップ時、TPS5401は、適切なパワーアップを保証するために、スロー・スタート・ピンが放電されて40mVを下回るまでスイッチングを開始しません(図29を参照)。

また、通常動作中、VINがUVLOの値を超えるか、ENピンが1.25V未満にプルダウンされるか、または過熱シャットダウン事象が発生した場合、TPS5401はスイッチングを停止し、SS/TRは40mVまで放電される必要があります。

VSENSE電圧は、45mVのオフセットで内部電圧リファレンスの85%までSS/TRピン電圧に追従します。SS/TR電圧が内部リファレンス電圧の85%を上回ると、実効的なシステム・リファレンスがSS/TR電圧から内部電圧リファレンスへと遷移するため、オフセットが増加します(図23を参照)。SS/TR電圧は、1.7Vでクランプされるまで直線的に上昇します。

## 過負荷回復回路

TPS5401は、過負荷回復(OLR)回路を備えています。OLR回路は、過負荷状態が解消されると、出力を過負荷電圧から公称レギュレーション電圧へとスロー・スタートさせます。誤差増幅器が障害状態から高電圧状態へと変化すると、OLR回路は100 $\mu$ Aの内部プルダウンを使用して、SS/TRピンをVSENSEピン電圧よりわずかに高い電圧まで放電します。障害状態が解消されると、出力は障害電圧から公称出力電圧へとスロー・スタートします。

## シーケンシング

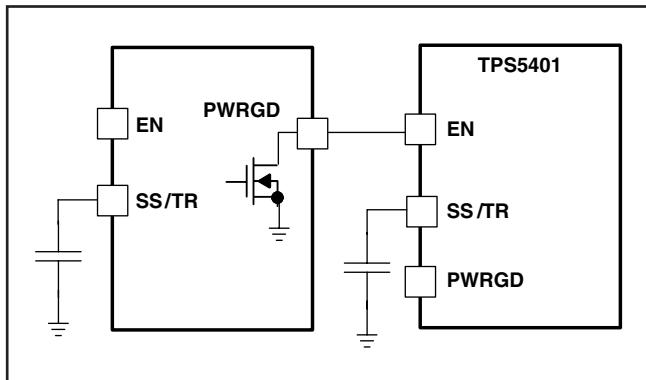

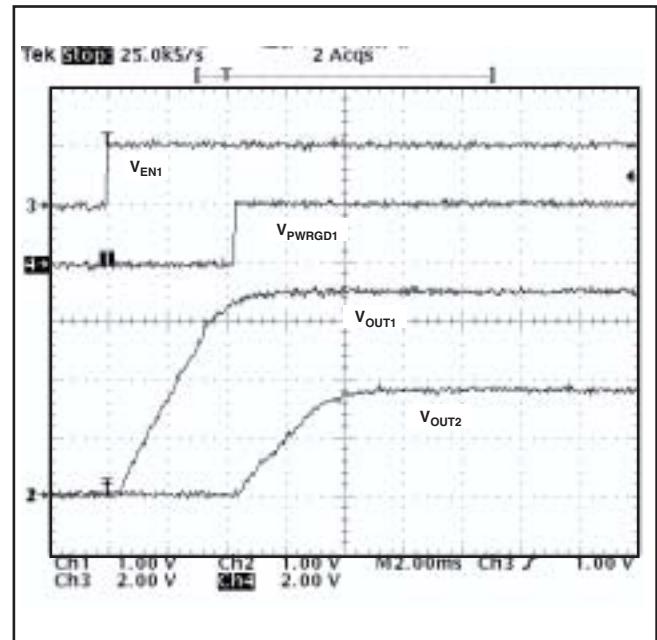

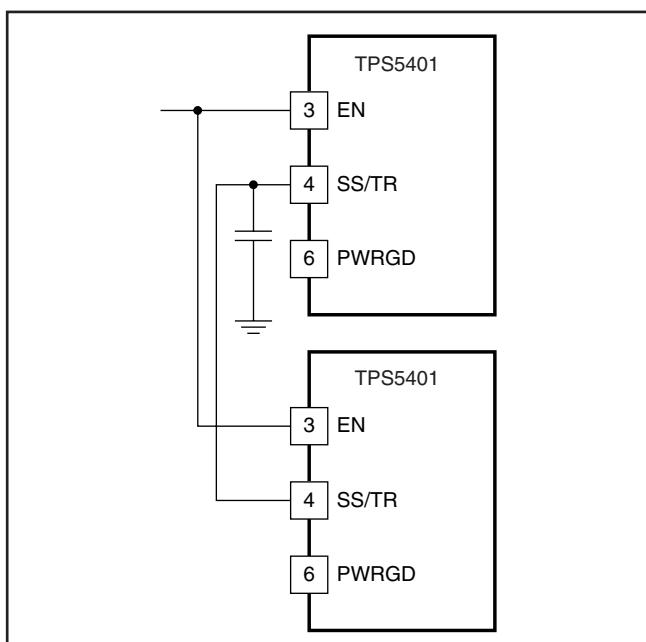

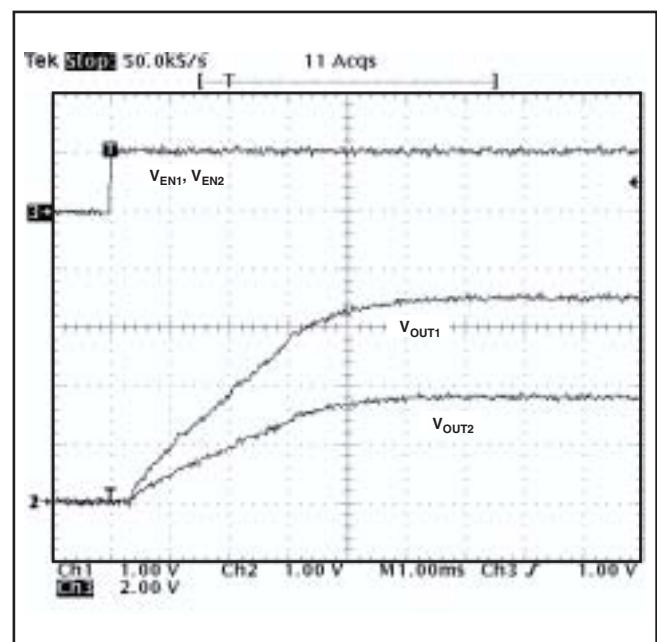

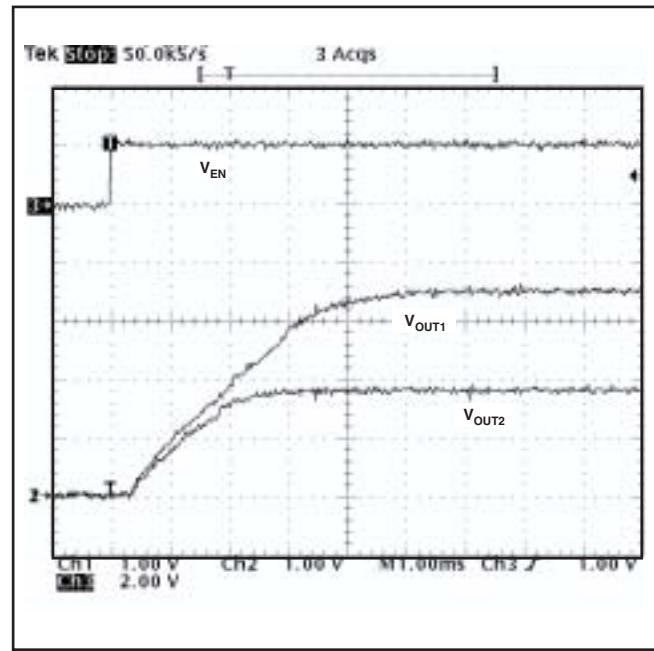

SS/TR、EN、およびPWRGDピンを使用して、多くの一般的な電源シーケンシング方法を実装できます。他のデバイスのパワーオン・リセット・ピンのオープン・ドライン出力を使用すれば、シーケンシャルな方法を実装できます。図30に、2個のTPS5401デバイスを使用したシーケンシャルな方法を示します。TPS5401のENピンにパワー・グッドを結合し、1次電源がレギュレーションに達した時点で2次電源をイネーブルにします。必要に応じて、2次電源のENピンに1nFのセラミック・コンデンサを接続することにより、1msのスタートアップ遅延を実現できます。図30の結果を図31に示します。

図 29. 起動時のSS/TRピンの動作

図 30. シーケンシャルなスタートアップ・シーケンスの回路図

図 31. ENおよびPWRGDを使用した

シーケンシャル・スタートアップ

図 32. レシオメトリックなスタートアップ・シーケンスの回路図

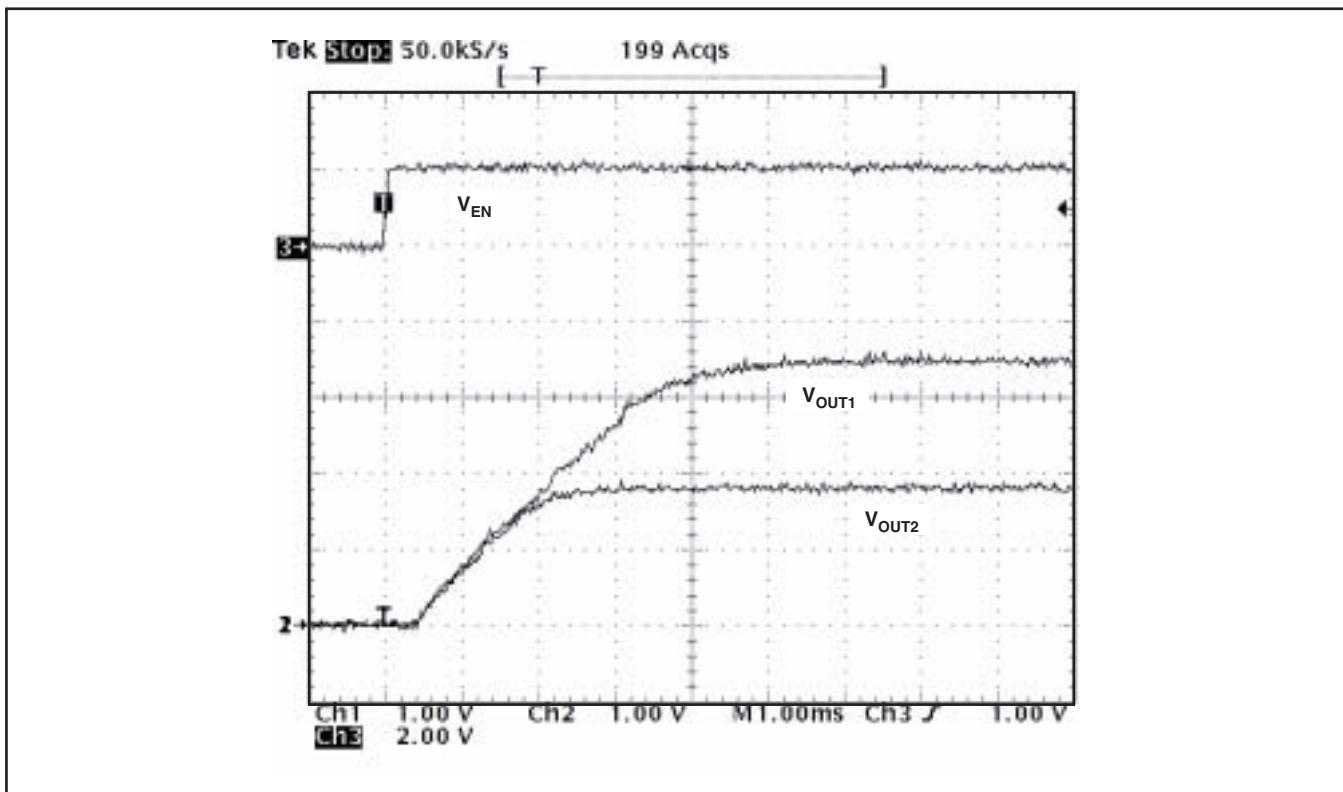

図 33. SS/TRピンの結合によるレシオメトリックな

スタートアップ

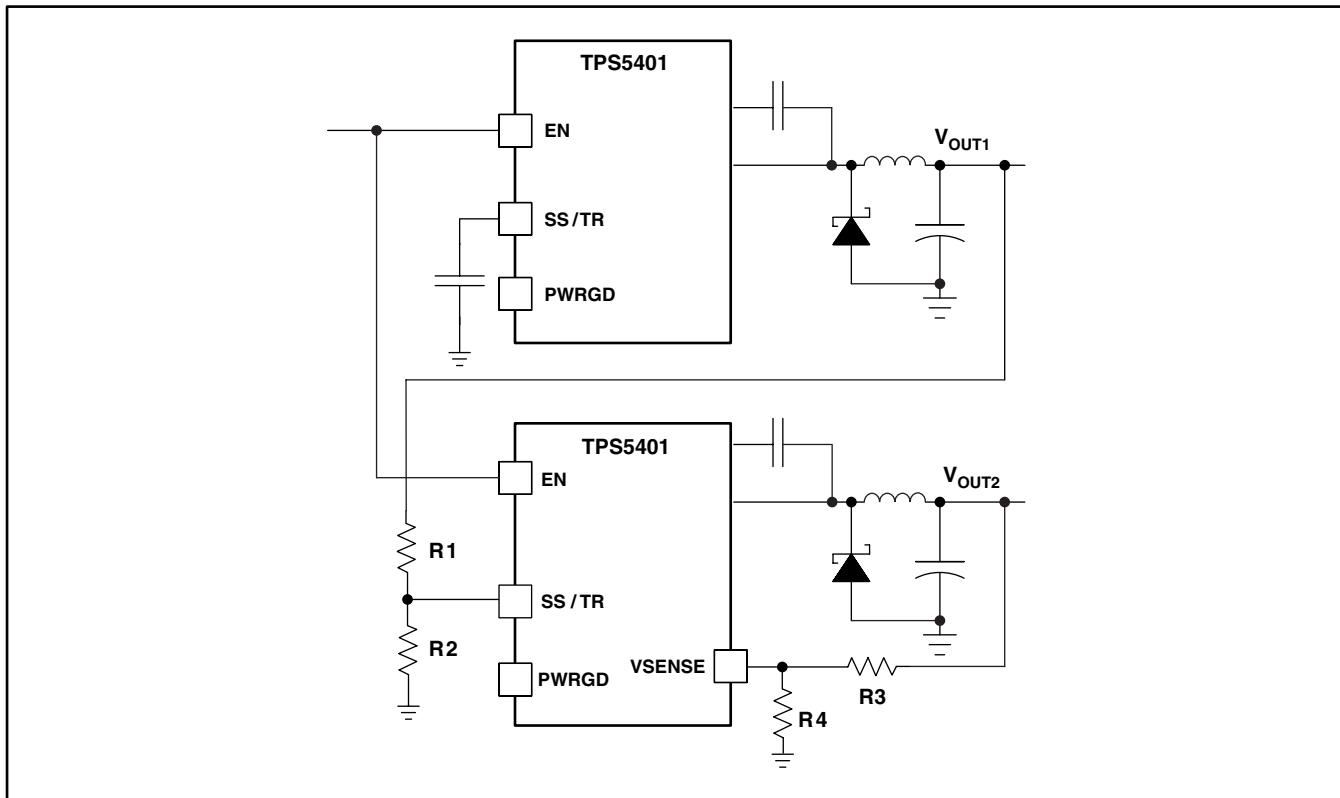

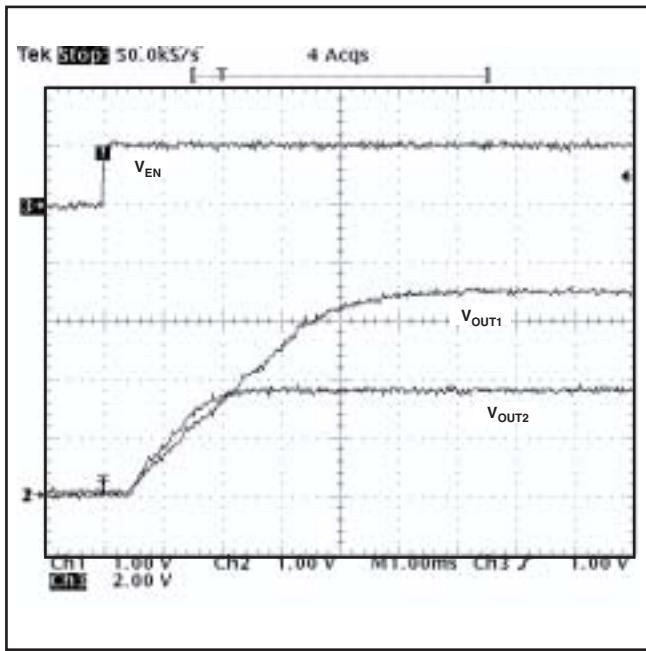

図32に、SS/TRピンを互いに接続することによるレシオメトリックなスタートアップ・シーケンスの方法を示します。各レギュレータの出力は同時に上昇してレギュレーションに達します。スロー・スタート時間を計算する際には、式(4)でプルアップ電流源を2倍にする必要があります。図32の結果を図33に示します。

図34. レシオメトリックな同時スタートアップ・シーケンスの回路図

図34に示すようなR1とR2の抵抗回路を、トラッキングが必要な電源または他の電圧リファレンス源の出力に接続することで、レシオメトリックな同時電源シーケンシングを実装できます。式(5)と式(6)を使用して、V<sub>OUT1</sub>の少し前か少し後、または同時にV<sub>OUT2</sub>を開始するようトラッキング抵抗を計算できます。式(7)は、公称出力レギュレーションの95%でのV<sub>OUT1</sub>とV<sub>OUT2</sub>の電圧差です。

変数 $\Delta V$ は、同時シーケンシングでは0Vです。スロー・スタート回路のSS/TR-VSENSE間の固有のオフセット( $V_{ssoffset}$ )、およびプルアップ電流源( $I_{ss}$ )とトラッキング抵抗によって生成されるオフセットの影響を最小限に抑えるため、 $V_{ssoffset}$ および $I_{ss}$ が変数として式に含まれています。 $\Delta V = 0V$ のときの結果を図37に示します。

$V_{OUT2}$ がレギュレーションに達したときに $V_{OUT2}$ の電圧が $V_{OUT1}$ の電圧よりわずかに大きくなるように、レシオメトリックなスタートアップを設計するには、式(5)～式(7)で $\Delta V$ に負の数を使用します。 $V_{OUT2}$ がレギュレーションに達したときに $V_{OUT2}$ が $V_{OUT1}$ よりわずかに低くなるアプリケーションでは、式(7)は正の数となります。負の $\Delta V$ と正の $\Delta V$ に対するスタートアップ波形をそれぞれ図35と図36に示します。

EN、UVLO、または過熱シャットダウン障害後には、起動前にSS/TRピンを40mV未満にプルダウンする必要があるため、

デバイスが障害後に確実に再起動できるようトラッキング抵抗を慎重に選択する必要があります。デバイスが障害から回復できるようにするには、式(5)で計算されるR1の値が式(8)の計算値よりも大きくなる必要があります。

SS/TRの電圧が公称リファレンス電圧の85%を超えると、スロー・スタート回路がレギュレーション・リファレンスを徐々に内部電圧リファレンスへと移行させ、 $V_{ssoffset}$ が大きくなります。図23に示すように、内部電圧リファレンスへと完全に移行するには、SS/TRピンの電圧が1.3Vより大きくなる必要があります。

$$R1 = \frac{V_{OUT2} + \Delta V}{V_{ref}} \times \frac{V_{ssoffset}}{I_{ss}} \quad (5)$$

$$R2 = \frac{V_{ref} \times R1}{V_{OUT2} + \Delta V - V_{ref}} \quad (6)$$

$$\Delta V = V_{OUT1} - V_{OUT2} \quad (7)$$

$$R1 > 2800 \times V_{OUT1} - 180 \times \Delta V \quad (8)$$

図 35.  $V_{out2}$ が $V_{out1}$ に先行するレシオメトリックなスタートアップ

図 36.  $V_{out1}$ が $V_{out2}$ に先行するレシオメトリックなスタートアップ

図 37. 同時スタートアップ

## 一定のスイッチング周波数、 およびタイミング抵抗 (RT/CLKピン)

TPS5401のスイッチング周波数は、RT/CLKピンに抵抗を接続することで、約100kHz~2500kHzという広い範囲にわたって調整可能です。RT/CLKピンの電圧は標準で0.5Vであり、スイッチング周波数を設定するにはグランドとの間に抵抗を接続する必要があります。特定のスイッチング周波数に対するタイミング抵抗を決定するには、式(9)を用いるか、図5または図6の曲線を使用します。ソリューション・サイズを小さくするには、一般にスイッチング周波数をできるだけ高く設定しますが、電源効率、最大入力電圧、および最小制御可能オン時間の間でトレードオフを考慮する必要があります。

最小制御可能オン時間は標準で130nsであり、これによって最大動作入力電圧が制限されます。

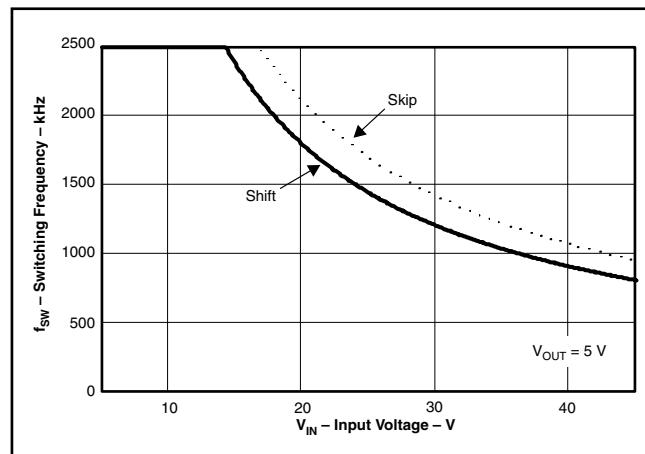

最大スイッチング周波数は、周波数シフト回路によっても制限されます。最大スイッチング周波数については、以下で詳しく説明します。

$$R_T(k\Omega) = \frac{206,003}{f_{SW}(\text{kHz})^{1.0888}} \quad (9)$$

## 過電流保護および周波数シフト

TPS5401は、電流モード制御を実装し、COMPピンの電圧を使用してハイサイドMOSFETをサイクル毎にオフにすることができます。各サイクルで、スイッチ電流とCOMPピン電圧が比較されます。ピーク・スイッチ電流がCOMP電圧と交差すると、ハイサイド・スイッチがオフになります。過電流状態で出力電圧が低下すると、スイッチ電流が増加しながら、誤差増幅器によってCOMPピンが“High”になります。誤差増幅器の出力は内部でクランプされ、スイッチ電流の制限として機能します。

高い入力電圧での最大動作スイッチング周波数を高めるために、TPS5401では周波数シフトを実装しています。VSENSEピンの電圧が0Vから0.8Vに上昇する際、スイッチング周波数は8、4、2、および1で分周されます。

デバイスではデジタル周波数シフトを実装することで、通常動作時および障害状態時に外部クロックとの同期を可能にしています。スイッチング周波数は8分周のみが可能なため、デバイスが動作しながら周波数シフト保護も得られる最大の入力電圧制限が存在します。

短絡発生時(特に、高入力電圧アプリケーションの場合)には、制御ループに有限の最小制御可能オン時間が存在し、出力は低電圧となります。スイッチのオン時間中は、高い入力電圧と最小オン時間により、インダクタ電流がピーク電流制限まで上昇します。スイッチのオフ時間中は、インダクタ電流は通常、上昇したのと同じ分だけ下降するために十分なオフ時間と出力電圧を得られません。周波数シフトを行うことで、オフ時間が実効的に増加するため、電流の下降が可能となります。

## スイッチング周波数の選択

選択されるスイッチング周波数は、式(10)と式(11)の2つの値のうち小さい方の値となる必要があります。式(10)は、最小制御可能オン時間によって設定される最大スイッチング周波数制限です。スイッチング周波数をこの値以上に設定すると、レギュレータがスイッチング・パルスをスキップします。

式(11)は、周波数シフト保護によって設定される最大スイッチング周波数制限です。高い入力電圧で十分な出力短絡保護を実現するには、スイッチング周波数を  $f_{SW}(\text{maxshift})$  より小さく設定する必要があります。式(11)で最大スイッチング周波数を計算するには、出力電圧が公称電圧から0Vまで減少する際に、周波数シフトに対応して  $f_{DIV}$  整数が1から8まで増加することを考慮に入れる必要があります。

図38では、実線が周波数シフトに関する標準の安全動作領域を示し、出力電圧は0Vと仮定し、インダクタの抵抗が0.13Ω、FETのオン抵抗が0.2Ω、ダイオードの電圧降下が0.5Vです。点線は、パルスのスキップを避けるための最大スイッチング周波数です。これらの式をスプレッドシートまたは他のソフトウェアに入力するか、またはSwitcherPro設計ソフトウェアを使用してスイッチング周波数を決定します。

$$f_{SW(\text{maxskip})} = \left( \frac{1}{t_{ON}} \right) \times \left( \frac{I_L \times R_{dc} + V_{OUT} + V_d}{V_{IN} - I_L \times r_{DS(on)} + V_d} \right) \quad (10)$$

$$f_{SW(\text{shift})} = \left( \frac{f_{DIV}}{t_{ON}} \right) \times \left( \frac{I_L \times R_{dc} + V_{OUTSC} + V_d}{V_{IN} - I_L \times r_{DS(on)} + V_d} \right) \quad (11)$$

|              |                 |

|--------------|-----------------|

| $I_L$        | インダクタ電流         |

| $R_{dc}$     | インダクタ抵抗         |

| $V_{IN}$     | 最大入力電圧          |

| $V_{OUT}$    | 出力電圧            |

| $V_{OUTSC}$  | 短絡時の出力電圧        |

| $V_d$        | ダイオードの電圧降下      |

| $r_{DS(on)}$ | スイッチのオン抵抗       |

| $t_{ON}$     | 制御可能オン時間        |

| $f_{DIV}$    | 分周数(1、2、4、または8) |

図38. 最大スイッチング周波数 vs 入力電圧

## RT/CLKピンとのインターフェイス方法

RT/CLKピンを使用して、レギュレータを外部システム・クロックに同期させることができます。同期機能を実装するには、図39に示すように、RT/CLKピンに方形波を接続します。方形波の振幅はRT/CLKピン上で0.5V未満および2.2V以上で遷移する必要があります、オン時間が40ns以上、オフ時間が40ns以上となる必要があります。同期周波数範囲は300kHz～2200kHzです。PH信号の立ち上がりエッジは、RT/CLK信号の立ち下がりエッジに同期します。

図 39. システム・クロックとの同期

## パワー・グッド (PWRGDピン)

PWRGDピンは、オープン・ドレイン出力です。VSENSEピンが内部電圧リファレンスの94%～107%になると、PWRGDピンはデアサートされてフローティングになります。5.5V以下の電圧源に対して10kΩ～100kΩの値を持つプルアップ抵抗を使用することを推奨します。VIN入力電圧が1.5Vを超えると、PWRGDは、電流シンク能力は低いですが有効となります。VIN入力電圧が3Vに近づくと、PWRGDの電流シンク能力は最大になります。

VSENSEが公称入力リファレンス電圧の92%を下回るか、または109%を上回ると、PWRGDピンは“Low”になります。また、UVLOまたは過熱シャットダウンがアサートされるか、ENピンが“Low”になった場合にも、PWRGDは“Low”になります。

## 過電圧過渡保護

TPS5401には、小さな出力容量の電源設計で、出力障害状態からの復帰や無負荷過渡応答時に発生する電圧オーバーシュートを最小限に抑える、過電圧過渡保護(OVTP)回路が備えられています。例えば、電源出力が過負荷となった場合、誤差増幅器によって実際の出力電圧が内部リファレンス電圧と比較されます。VSENSEピンの電圧が内部リファレンス電圧よりも一定時間にわたって低くなった場合、誤差増幅器の出力が高い電圧にクランプされ、最大出力電流が要求されます。この状態が解消されると、レギュレータの出力が上昇し、誤差増幅器の出力は定常状態のデューティ・サイクルに遷移します。一部のアプリケーションでは、電源出力電圧が誤差増幅器の出力よりも速く応答する場合があり、これは実際、出力のオーバーシュートにつながる可能性があります。OVTP機能では、値の小さい出力コンデンサの使用時に、VSENSEピンの電圧を内部電圧リファレンスの109%であるOVTPスレッショルドと比較する回路を実装することにより、出力のオーバーシュートを最小限に抑えます。VSENSEピンの電圧がOVTPスレッショルドより高い場合は、ハイサイドMOSFETがディスエーブルになり、出力に電流が流れるのを防いで、出力オーバーシュートを抑えます。VSENSE電圧がOVTPスレッショルドを下回ると、次のクロック・サイクルでハイサイドMOSFETがオンになります。

## 過熱シャットダウン

このデバイスは、接合部温度が182°Cを超えた場合にデバイス自身を保護する、過熱シャットダウン機能を内蔵しています。接合部温度が過熱トリップ・スレッショルドを超えると、デバイスのスイッチングが強制的に停止されます。接合部温度が182°Cを下回ると、デバイスはSS/TRピンを放電して電源投入シーケンスを再び開始します。

## 電流モード補償設計

TPS5401を使用した設計作業を単純化するために、一般的なアプリケーションに対する標準設計を表2に示します。セラミック・コンデンサを使用した設計での安定動作の解析においては、容量値の適切なディレーティングを考慮することが推奨されます。これは、セラミック・コンデンサの実際の容量値が、バイアス電圧が増すことによって標準容量値より低下していくためです。高度な設計を行う場合は、詳しいガイドラインとして「アプリケーション情報」の「ステップ毎の設計手順」を参照するか、またはSwitcherProソフトウェア・ツール(<http://focus.ti.com/docs/tools/folders/switcherpro.html>)を利用できます。

| $V_{IN}$<br>(V) | $V_{OUT}$<br>(V) | $f_{sw}$<br>(kHz) | $L_{OUT}$<br>( $\mu$ H) | $C_{OUT}$             | $R1$<br>(k $\Omega$ ) | $R2$<br>(k $\Omega$ ) | $C2$<br>(pF) | $C1$<br>(pF) | $R3$<br>(k $\Omega$ ) |

|-----------------|------------------|-------------------|-------------------------|-----------------------|-----------------------|-----------------------|--------------|--------------|-----------------------|

| 7.5 V–35 V      | 5                | 700               | 47                      | アルミ、220 $\mu$ F/260mΩ | 52.3                  | 10                    | 82           | 3300         | 698                   |

| 7.5 V–35 V      | 5                | 700               | 47                      | セラミック、47 $\mu$ F/10V  | 52.3                  | 10                    | 5.6          | 3300         | 75                    |

| 12 V–42 V       | 5                | 700               | 47                      | アルミ、100 $\mu$ F/300mΩ | 52.3                  | 10                    | 100          | 3300         | 316                   |

| 12 V–42 V       | 3.3              | 700               | 33                      | セラミック、33 $\mu$ F/10V  | 30.9                  | 10                    | 10           | 3300         | 47                    |

| 8 V–14 V        | 5                | 700               | 33                      | セラミック、47 $\mu$ F/10V  | 52.3                  | 10                    | 5.6          | 3300         | 75                    |

表 2. 標準的な設計(1ページの概略回路図を参照)

# アプリケーション情報

## 標準アプリケーション

TPS5401は、Eメーター・アプリケーションに適しています。Eメーターは、入力電力が制限された条件で、幅広い範囲の入力電圧から十分な出力電流を得る必要があるため、Eメーターの設計者にとって電源設計は難しい作業です。例えば、中国では、単相または3相のEメーターが、0.7Un～1.9Unの入力AC電圧範囲で適切に動作する必要があります。ここで、Unは220Vの相電圧です。入力の有効電力制限は1.5Wです。標準的な電源設計では、変圧器の後に整流ブリッジを配置して、低い非リギュレーションDC電圧を得ています。その後、電圧レギュレータがシステム全体用に5Vを生成します。AC変圧器は内部DC抵抗が大きく、続く整流器には電圧降下があることを考えると、整流回路の出力電圧は無負荷時と重負荷時とで異なります。それにより、AC入力電圧範囲全体で、電圧レギュレータの最大/最小入力電圧比が4といった値になる場合もあります。そのような場合、リニア・レギュレータは、高入力電圧での効率が非常に低いため、適切ではありません。

図40に、上記の要件に対するTPS5401の標準的なアプリケーション回路図を示します。入力範囲は7.5V～35Vです。このような広い入力電圧範囲では、DC抵抗の高い安価な変圧器を使用して全体のコストを低減できます。

## ステップ毎の設計手順

TPS5401の部品値を選択するには、以下の設計手順を使用できます。または、SwitcherProソフトウェアを使用して完全な設計を生成することもできます。SwitcherProソフトウェアは、反復的な設計手順を使用し、包括的な部品データベースにアクセスして設計を生成します。ここでは、設計プロセスを単純化して説明します。設計プロセスを開始するには、いくつかのパラメータを決定する必要があります。表3に、設計者が知っておく必要のあるパラメータの一覧を示します。

| 設計パラメータ                    | 例での値          |

|----------------------------|---------------|

| 入力電圧範囲                     | 7.5V～35V      |

| 出力電圧                       | 5V            |

| 入力リップル電圧                   | 300mV         |

| 出力リップル電圧                   | $V_{OUT}$ の1% |

| 0から500mAへの負荷ステップに対する出力過渡応答 | $V_{OUT}$ の4% |

| 最大出力電流                     | 500mA         |

表3.

## スイッチング周波数

最初の手順は、レギュレータのスイッチング周波数を決定することです。一般に、ユーザーは可能な限り高いスイッチング周波数を選択します。それによってソリューション・サイズを最小にできるからです。高いスイッチング周波数では、低周波数でスイッチングする電源と比較して、低い値のインダクタと小さな出力コンデンサを使用できます。または、低いスイッチング周波数を選択して効率を高めることもできます。低いスイッチング周波数では、スイッチング損失が最小限に抑えられます。選択可能なスイッチング周波数は、内部パワー・スイッチの最小オン時間、入力電圧、出力電圧、および周波数シフト制限によって制限されます。

レギュレータの最大スイッチング周波数を求めるには、式(10)と式(11)を使用し、2つの式のうち小さい方の値を選択します。これらの値よりも高いスイッチング周波数を使用すると、パルスのスキップが発生したり、短絡時に過電流保護が機能しなかったりします。

TPS5401での標準の最小オン時間  $t_{on(min)}$  は130nsです。この例では、出力電圧が5Vで最大入力電圧が35Vであるため、式(10)にインダクタ抵抗、オン抵抗、およびダイオード電圧を代入すると、最大1213kHzのスイッチング周波数を設定できます。設計で短絡発生時に過電流暴走が問題とならないようにするには、式(11)または図38の実線の曲線を使用して最大スイッチング周波数を決定します。最大入力電圧が35Vで、ダイオード電圧を0.5V、インダクタ抵抗を130mΩ、スイッチ抵抗を400mΩ、電流

図40. 標準的なアプリケーション回路図

制限値を0.94A、短絡出力電圧を0.1Vと仮定すると、最大スイッチング周波数は約1265kHzになります。高い周波数を選択すると、外部部品サイズを小さくできますが、スイッチング損失が増大します。バランスの取れた設計を実現するため、スイッチング周波数として700kHzを使用します。特定のスイッチング周波数に対するタイミング抵抗を決定するために、式(9)を用いると、最も近い標準抵抗として165kΩが求められます。スイッチング周波数は、図40に示される抵抗R3によって、698kHzに設定されます。

## 出力電圧設定点

TPS5401の出力電圧は、分圧抵抗回路を使用して外部で調整可能です。図40のアプリケーション回路では、この分圧抵抗回路はR6およびR7から構成されています。出力電圧と分圧抵抗の関係は、式(12)で与えられます。

$$R6 = \left( \frac{V_{OUT}}{V_{ref}} - 1 \right) \times R7 \quad (12)$$

R7 = 10kΩを選択すると、5Vの出力電圧に対してR6は52.3kΩと計算されます。

VSENSEピンのリーク電流があるため、出力電圧の精度を維持するには、帰還回路を流れる電流が1μAより大きい必要があります。この要件により、R7の最大値は800kΩに等しくなります。より高い抵抗値を選択すると、静止時電流が減少し、低出力電流での効率が向上しますが、ノイズ耐性の問題が生じる場合があります。

## 入力コンデンサ

TPS5401は、3μF以上の実効容量を持つ高品質のセラミック(タイプX5RまたはX7R)入力デカッピング・コンデンサを必要とし、アプリケーションによってはバルク容量も必要とします。

実効容量には、DCバイアスの影響も含まれます。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。また、コンデンサのリップル電流定格は、TPS5401の最大入力電流リップルよりも大きい必要があります。入力リップル電流は、式(13)で計算できます。

セラミック・コンデンサの値は、温度およびコンデンサに印加されるDCバイアスの大きさによって大きく変化します。温度による容量の変化は、温度に対して安定な誘電体を選択することで最小限に抑えることができます。X5RおよびX7Rセラミック誘電体は、容量/体積比が大きく、温度に対してかなり安定しているため、パワー・レギュレータのコンデンサとして一般に選択されます。また、出力コンデンサはDCバイアスも考慮して選択する必要があります。コンデンサ両端にかかるDCバイアスが増加すると、コンデンサの容量値は減少します。

この設計例では、最大入力電圧に対応するために60V以上の電圧定格を持つセラミック・コンデンサが必要です。一般的な標準セラミック・コンデンサ電圧定格は4V、6.3V、10V、16V、25V、50V、100Vであるため、ここでは100Vのコンデンサを選択します。この例では、2.2μF、100Vのコンデンサを2個並列に使用しています。高電圧コンデンサの一覧を表4に示します。入力容量の値によって、レギュレータの入力リップル電圧が決まります。入力電圧リップルは、式(14)で計算できます。

設計例の値である $I_{OUT(max)} = 0.5A$ 、 $C_{IN} = 4.4\mu F$ 、 $f_{SW} = 700kHz$ を使用すると、 $V_{IN} = 10V$ (出力電圧5Vの2倍)のときに、40.6mVの入力電圧リップルおよび0.25Aの最大RMS入力リップル電流が得られます。

$$I_{INRMS} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \frac{(V_{IN} - V_{OUT})}{V_{IN}}} \quad (13)$$

$$V_{INRIPPLE} = \frac{I_{OUT(max)} - 0.25}{C_{IN} \times f_{SW}} \quad (14)$$

| メーカー   | 値(μF)      | EIAサイズ | 電圧    | 誘電体 | 名称         |

|--------|------------|--------|-------|-----|------------|

| Murata | 1 to 2.2   | 1210   | 100 V | X7R | GRM32シリーズ  |

|        | 1 to 4.7   |        | 50 V  |     | GRM31シリーズ  |

|        | 1          | 1206   | 100 V |     | VJ X7Rシリーズ |

|        | 1 to 2.2   |        | 50 V  |     | CシリーズC4532 |

| Vishay | 1 10 1.8   | 2220   | 50 V  |     | CシリーズC3225 |

|        | 1 to 1.2   |        | 100 V |     | X7R誘電体シリーズ |

|        | 1 to 3.9   | 2225   | 50 V  |     |            |

|        | 1 to 1.8   |        | 100 V |     |            |

| TDK    | 1 to 2.2   | 1812   | 100 V |     |            |

|        | 1.5 to 6.8 |        | 50 V  |     |            |

|        | 1. to 2.2  | 1210   | 100 V |     |            |

|        | 1 to 3.3   |        | 50 V  |     |            |

| AVX    | 1 to 4.7   | 1210   | 50 V  |     |            |

|        | 1          |        | 100 V |     |            |

|        | 1 to 4.7   | 1812   | 50 V  |     |            |

|        | 1 to 2.2   |        | 100 V |     |            |

表4. コンデンサの種類

## 出力インダクタの選択

出力インダクタの最小値を計算するには、式(15)を使用します。

$$L_{OUT(min)} = \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN(max)} \times f_{SW}} \quad (15)$$

$K_{IND}$ は、最大出力電流を基準としたインダクタ・リップル電流の大きさを表す係数です。

インダクタ・リップル電流は、出力コンデンサによってフィルタリングされます。したがって、大きなインダクタ・リップル電流を選択すると、それ以上のリップル電流定格を持つ出力コンデンサが必要となるため、出力コンデンサの選択に影響が及びます。一般に、インダクタ・リップル値は設計者の裁量で決定しますが、以下のガイドラインに従うことができます。

セラミックなどの低ESR出力コンデンサを使用した設計では、最大 $K_{IND} = 0.4$ の値を使用できます。よりESRの高い出力コンデンサを使用する場合は、 $K_{IND} = 0.2$ が適切です。インダクタ・リップル電流はPWM制御システムの一部であるため、TPS5401で信頼性の高い動作を行うためには、リップル電流が常に30mAを上回っている必要があります。入力電圧範囲の広いレギュレータでは、大きい側でインダクタ・リップル電流を選択するのが最善です。これにより、最小の入力電圧でもインダクタが適度なリップル電流を持つことができます。入力インダクタンスの最大値は、式(16)で制限されます。

$$L_{OUT(max)} = \frac{V_{IN(min)} - V_{OUT}}{30mV} \times \frac{V_{OUT}}{V_{IN(min)} \times f_{SW}} \quad (16)$$

この設計例では、 $K_{IND} = 0.3$ を使用し、最小インダクタ値は42 $\mu$ Hと計算されます。最も近い標準値として47 $\mu$ Hが選択されています。出力フィルタ・インダクタについては、2乗平均平方根(RMS)電流および飽和電流の定格を超えないことが重要です。RMSおよびピーク・インダクタ電流は、式(17)～式(19)で求めることができます。

$$I_{LRIPPLE} = \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)} \times L_{OUT} \times f_{SW}} \quad (17)$$

$$I_{L(RMS)} = \sqrt{\left(I_{OUT}\right)^2 + \frac{1}{12} \times \left(\frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)} \times L_{OUT} \times f_{SW}}\right)^2} \quad (18)$$

$$I_{L(peak)} = I_{OUT} + \frac{|_{RIPPLE}}{2} \quad (19)$$

一連の式で示されるように、リップル電流が小さいとレギュレータの出力電圧リップルが減少しますが、より大きなインダクタンスが必要になります。より大きなリップル電流を選択す

るとレギュレータの出力電圧リップルが増加しますが、インダクタンスの値が小さく済みます。インダクタを流れる電流は、インダクタ・リップル電流+出力電流です。パワーアップ時、障害発生時、または負荷過渡状態では、インダクタ電流がピーク・インダクタ電流レベルを超えて増加する場合があります。過渡状態では、インダクタ電流がデバイスのスイッチ電流制限まで増加する場合があります。この理由により、最も保守的なアプローチは、ピーク・インダクタ電流ではなく、スイッチ電流制限以上の飽和電流定格を持つインダクタを指定することです。この設計では、 $I_{LRIPPLE} = 0.1303A$ 、 $I_{L(RMS)} = 0.501A$ 、 $I_{L(peak)} = 0.565A$ となります。使用しているインダクタはCoilcraftのMSS1048-473MLタイプであり、飽和電流定格は1.44A、RMS電流定格は1.83Aです。

## 出力コンデンサ

出力コンデンサ値の選択については、3つの主要な考慮事項があります。出力コンデンサは、変調器の極、出力電圧リップル、および負荷電流の大きな変化に対するレギュレータの応答を決定します。出力容量は、これら3つの条件のうち最も厳しいものに基づいて選択する必要があります。

最初の条件は、負荷電流の大きな変化に対して求められる応答です。レギュレータが電流を供給できないときには、出力コンデンサが負荷に電流を供給する必要があります。この状況は、レギュレータに対して保持時間要件があり、入力電力の停止後に指定された時間だけ、出力コンデンサが出力電圧を特定のレベルより高く保持する必要がある場合に発生します。また、無負荷から全負荷への遷移時など、負荷の電流需要に大きく高速な変化が発生した場合、レギュレータは一時的に十分な出力電流を供給できなくなります。通常、レギュレータでは、制御ループが負荷電流および出力電圧の変化を検知して、その変化に合わせてデューティ・サイクルを調整するまでに、2クロック・サイクル以上を必要とします。出力コンデンサの大きさは、制御ループが負荷の変化に応答するまでの間、負荷に追加の電流を供給できるように決定する必要があります。出力容量は、出力電圧の降下を許容範囲内に抑えながら、2クロック・サイクルにわたって電流の差分を供給するのに十分な大きさでなければなりません。そのために必要な最小の出力容量を式(20)に示します。

$$C_{OUT} > \frac{2 \times \Delta I_{OUT}}{f_{SW} \times (\Delta V_{OUT} - \Delta I_{OUT} \times R_{ESR})} \quad (20)$$

ここで

- $\Delta I_{OUT}$ は出力電流の変化です。

- $f_{SW}$ はレギュレータのスイッチング周波数です。

- $\Delta V_{OUT}$ は出力電圧で許容される変化です。

- $R_{ESR}$ は出力コンデンサの等価直列抵抗(ESR)です。

式(20)より、ESRは $\Delta V_{OUT}/\Delta I_{OUT}$ 未満とする必要があります。この例では、負荷過渡応答が、0A(無負荷)から0.5A(全負荷)までの負荷ステップに対する $V_{OUT}$ の4%の変化と指定されています。この例では、 $\Delta I_{OUT} = 0.5A$ 、および $\Delta V_{OUT} = 0.04 \times 5V = 0.2V$ です。セラミック・コンデンサの場合、ESRは通常十分に小さいため、この計算では無視できます。アルミ電解コンデンサおよびタンタル・コンデンサの場合は、ESRが比較的高いので考慮に入れる必要があります。これらの数値を使用すると、セラミック・コンデンサでは最小容量が $7.14\mu F$ 、ESRが $260m\Omega$ の電解コンデンサでは $20.4\mu F$ となります。

レギュレータのキャッチ・ダイオードは電流をシンクできないため、負荷電流が急速に減少すると、インダクタに蓄積されたエネルギーによって出力電圧にオーバーシュートが発生します。また、出力コンデンサは、高負荷電流から低負荷電流への遷移時に、インダクタに蓄積されたエネルギーを吸収できるだけの容量を持つ必要があります。出力コンデンサに蓄積された余分なエネルギーにより、コンデンサの電圧は上昇します。コンデンサの容量は、これらの過渡期間中に所定の出力電圧を保持できるような大きさでなければいけません。出力電圧オーバーシュートを所定の値に保持するための最小容量は式(21)で計算します。ここで、 $L_{OUT}$ はインダクタの値、 $I_{OH}$ は重負荷時の出力電流、 $I_{OL}$ は軽負荷時の出力電流、 $V_{FIN}$ は最終的なピーカ出力電圧、 $V_{INI}$ はコンデンサ電圧の初期値です。この例では、ワーストケースの負荷ステップは0.5Aから0Aです。この負荷遷移中は出力電圧が上昇し、仕様に規定された最大値は出力電圧の4%です。これにより、 $V_{FIN} = 1.04 \times 5V = 5.2V$ となります。 $V_{INI}$ はコンデンサ電圧の初期値であり、これは公称出力電圧の5Vです。式(21)にこれらの値を使用すると、 $5.76\mu F$ の最小容量が得られます。

$$C_{OUT} > I_{OUT} \times \frac{I_{OH}^2 - I_{OL}^2}{V_{FIN}^2 - V_{INI}^2} \quad (21)$$

式(22)は、出力電圧リップル仕様を満足するために必要な最小の出力容量を計算します。ここで、 $f_{SW}$ はスイッチング周波数、 $V_{ORIPPLE}$ は最大許容出力電圧リップル、 $I_{LRIPPLE}$ はインダクタ・リップル電流です。式(22)により、出力電圧リップル要件を満たすには、出力コンデンサのESRが $V_{ORIPPLE}/I_{LRIPPLE}$ よりも小さい必要があります。出力電圧リップルを低く保つには、低ESRのコンデンサを推奨します。高ESRの電解コンデンサを使用する場合は、出力電圧リップルを最小限に抑えるために、電解コンデンサと並列に低ESRのセラミック・コンデンサを使用することを推奨します。このアプリケーションでは、出力コンデンサとしてアルミ電解コンデンサを選択しています。このコンデンサのESRは $260m\Omega$ です。式(22)により、 $1.44\mu F$ が得られます。

$$C_{OUT} > \frac{1}{8 \times f_{SW}} \times \frac{1}{\frac{V_{ORIPPLE}}{I_{LRIPPLE}} - R_{ESR}} \quad (22)$$

この例の負荷過渡状態中に出力電圧のレギュレーションを維持するための、出力コンデンサに対する最も厳しい条件は、 $20.5\mu F$ の容量です。

エージング、温度、およびDCバイアスに対して、追加の容量ディレーティングを考慮する必要があるため、この最小値は増加します。この例では、低コスト・アプリケーション向けに、 $260m\Omega$ のESRを持つ $220\mu F$ の電解コンデンサを使用できます。

一般に、コンデンサでは、障害や過熱を発生させずに処理できるリップル電流の大きさに制限があります。インダクタ・リップル電流に対して対応可能な出力コンデンサを指定する必要があります。一部のコンデンサのデータシートでは、最大リップル電流の2乗平均平方根(RMS)値が指定されています。出力コンデンサで処理できる必要のあるRMSリップル電流値は、式(23)で計算できます。このアプリケーションでは、式(23)により $37.6mA$ が得られます。

$$I_{CO(RMS)} = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{\sqrt{12} \times V_{IN(max)} \times L_{OUT} \times f_{SW}} \quad (23)$$

## キャッチ・ダイオード

TPS5401では、PHピンとGNDの間に外付けのキャッチ・ダイオードが必要です。選択するダイオードは、 $V_{IN(MAX)}$ 以上の逆方向電圧定格を持つ必要があります。ダイオードのピーク電流定格は、最大インダクタ電流よりも大きくななければなりません。また、順方向電圧は低い必要があります。ショットキー・ダイオードは順方向電圧が低いため、一般にキャッチ・ダイオードとして優れた選択肢となります。ダイオードの順方向電圧が低いほど、レギュレータの効率は高くなります。

一般に、ダイオードの電圧および電流定格が高いと、順方向電圧は高くなります。設計例の入力電圧は最大42Vであるため、逆方向電圧が42V以上のダイオードを選択します。

この設計例では、順方向電圧の低いB160Aショットキー・ダイオードを選択します。このダイオードは、小さなデバイスよりも優れた熱特性を持つ大きなパッケージ・サイズで提供されています。B160Aの標準順方向電圧は0.5Vです。

また、このダイオードは、適切な電力定格を持つ必要があります。このダイオードは、内部パワー・スイッチのオフ時間中に出力電流を導通させます。内部スイッチのオフ時間は、最大入力電圧、出力電圧、およびスイッチング周波数の関数です。オフ時間中の出力電流とダイオードの順方向電圧の積が、ダイオードの導通損失に等しくなります。高いスイッチ周波数では、ダイオードのAC損失を考慮に入れる必要があります。ダイオードのAC損失は、接合部容量の充放電および逆方向回復によって生じます。ダイオードの合計の電力損失(導通損失 + AC損失)は、式(24)で求められます。

B160Aの接合部容量( $C_J$ )は $110pF$ です。式(24)により、選択するダイオードの損失は $0.29W$ です。この電力損失により、実装手法に応じて、入力電圧が42Vおよび負荷電流が $0.5A$ のときに $5.9^{\circ}C$ の温度上昇がダイオードに生じます。

電源が軽負荷電流やスリープ・モードで動作する時間が長い場合には、リーク電流が低く順方向電圧降下がやや大きなダイオードの使用を検討してください。

$$P_D = \frac{(V_{IN(max)} - V_{OUT}) \times I_{OUT} \times V_{FD}}{V_{IN(max)}} + \frac{C_J \times f_{SW} \times (V_{IN(max)} + V_{FD})^2}{2} \quad (24)$$

## スロー・スタート・コンデンサ

スロー・スタート・コンデンサは、パワーアップ中に出力電圧がその公称設定値に達するまでにかかる最小の時間を決定します。これは、負荷に対して制御された電圧スルーレートが必要である場合に有用です。また、出力容量が大きく、コンデンサを出力電圧レベルまでばく充電するのに大きな電流を必要とするような場合にも、利用されます。コンデンサの充電に必要な大きな電流によってTPS5401が電流制限に達したり、入力電源からの過剰な電流によって入力電圧レールが降下したりする場合があります。出力電圧のスルーレートを制限することで、その両方の問題を解決できます。

スロー・スタート時間は、レギュレータが過剰な電流を引き込むことなく出力コンデンサを出力電圧まで充電できるよう十分に長くする必要があります。式(25)を使用すると、出力コンデンサ  $C_{OUT}$  を出力電圧  $V_{OUT}$  の10%から90%まで、平均スロー・スタート電流  $I_{SSAVG}$  で充電するために必要な、最小のスロー・スタート時間  $t_{SS}$  を求めることができます。この例では、0.2Aの平均入力電流 ( $I_{SSAVG}$ ) で220μFの出力コンデンサを5Vまで充電するために、4.4msのスロー・スタート時間が必要です。

$$t_{SS} > \frac{C_{OUT} \times V_{OUT} \times 0.8}{I_{SSAVG}} \quad (25)$$

スロー・スタート時間がわかれば、式(4)を使用してスロー・スタート・コンデンサ値を計算できます。この回路ではスロー・スタート時間が3.2msに設定され、0.01μFのコンデンサが必要となります。

## ブートストラップ・コンデンサの選択

適切な動作のためには、BOOTピンとPHピンの間に0.1μFのセラミック・コンデンサを接続する必要があります。X5R以上の誘電体を持つセラミック・コンデンサの使用を推奨します。コンデンサの電圧定格は10V以上である必要があります。

## 低電圧ロックアウトの設定点

低電圧ロックアウト(UVLO)は、TPS5401のENピンに接続した外部分圧回路を使用して調整できます。UVLOには2つのスレッショルドがあり、1つは入力電圧が上昇するパワーアッ

プ中に適用され、もう1つは入力電圧が下降するパワーダウンまたはブラウンアウト中に適用されます。入力電圧がパワーアップ・スレッショルド以上に上昇(イネーブル)したときに、電源がオンになりスイッチングを開始する必要があります。レギュレータがスイッチングを開始した後は、入力電圧がパワーダウン・スレッショルドを下回る(UVLO停止)までの間、スイッチングを継続する必要があります。

プログラミング可能なUVLO電圧およびイネーブル電圧は、ENピンに接続されたVinおよびグランド間の分圧抵抗を使用して設定されます。式(2)および式(3)を使用して、必要な抵抗値を計算できます。この例のアプリケーションでは、最小入力電圧が7.5Vであるため、最大入力電圧が35Vのときには、ENピンの電圧がENピンの絶対電圧定格を上回ります。そのため、この設計ではUVLOを外部で設定しません。

## 補償

TPS5401の外部補償には、幅広い範囲の出力フィルタ構成を使用できます。さまざまなコンデンサ値および誘電体タイプがサポートされます。この設計例では、アルミ電解出力コンデンサを使用します。TPS54040データシート(SLVS918)には、セラミック出力コンデンサを使用した設計例が記載されています。より正確な設計は、SwitcherProソフトウェアで提供されます。

ピーク電流モードPWM変調回路と、出力フィルタにより、式(26)と式(27)で求められるパワー段の極とゼロのペアが生成されます。

$$f_{Pmod} = \frac{I_{OUT}}{2\pi \times V_{OUT} \times C_{OUT}} \quad (26)$$

$$f_{Zmod} = \frac{1}{2\pi \times R_{ESR} \times C_{OUT}} \quad (27)$$

TPS5401には、タイプ2Aの補償方式を推奨します。補償部品(図41の  $R_C$ 、  $C_C$ 、  $C_P$ )は、出力フィルタ部品に対して目的のループ・クロスオーバー周波数および位相マージンが得られるように選択します。タイプ2A補償は、DCゲイン、低周波数の極、および中周波数のゼロ/極ペアという特性を持っています。

図41. TPS5401の推奨補償回路

DCゲインは、式(28)で決定されます。

$$G_{DCEA} = A_{DCEA} \times \frac{V_{ref}}{V_{OUT}} \quad (28)$$

ここで

$A_{DCEA}$ は誤差増幅器の開ループDCゲインです。これは10,000V/Vです。

低周波数の極は、式(29)で決定されます。

$$f_{P0} = \frac{1}{2\pi \times R_O \times C_O} \quad (29)$$

ここで

$R_O$ は誤差増幅器の出力抵抗です。これは式(30)で計算できます。

$$R_O = \frac{A_{DCEA}}{gm_{EA}} \quad (30)$$

中周波数のゼロは、式(31)で決定されます。

$$f_{Z1} = \frac{1}{2\pi \times R_C \times C_C} \quad (31)$$

中周波数の極は、式(32)で決定されます。

$$f_{P1} = \frac{1}{2\pi \times R_C \times C_P} \quad (32)$$

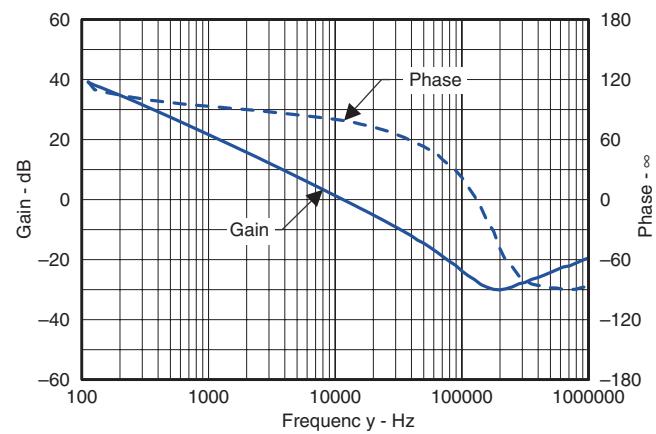

最初の手順は、閉ループ・クロスオーバー周波数 $f_{CO}$ の選択です。一般には、閉ループ・クロスオーバー周波数は最小動作周波数の1/10未満とします。ただしTPS5401では、最大閉ルー

プ・クロスオーバー周波数を40kHz以下とすることを推奨します。この例では、クロスオーバー周波数として15kHzを選択しています。次に、クロスオーバー周波数でのループ・ゲインの大きさは、定義上、0dBです。パワー段の極に補償用のゼロを配置し、パワー段のゼロに中補償極を配置することにより、 $R_C$ 、 $C_C$ 、 $C_P$ を式(33)～式(35)で近似的に計算できます。

$$R_C = \frac{2\pi \times f_{CO} \times C_{OUT}}{gm_{PS}} \times \frac{V_{OUT}}{V_{ref} \times gm_{EA}} \quad (33)$$

$$C_C = \frac{1}{2\pi \times f_{Pmod}} \quad (34)$$

$$C_P = \frac{1}{2\pi \times f_{Zmod}} \quad (35)$$

ここで

- $gm_{PS}$ はパワー段のトランスクンダクタンスです。これは1.9A/Vです。

- $gm_{EA}$ は誤差増幅器のトランスクンダクタンスです。これは97 $\mu$ A/Vです。

この設計例の場合、R4、C7、およびC8によって補償回路が構成されます。R4 = 698k $\Omega$ 、C7 = 3300pF、C8 = 82pFです。

## 不連続モードとEco-mode制御方式の境界

入力電圧が34Vの場合、出力電流が50mAを下回ると、電源が不連続モードになります。出力電流が30mAを下回ると、電源はEco-mode制御方式になります。

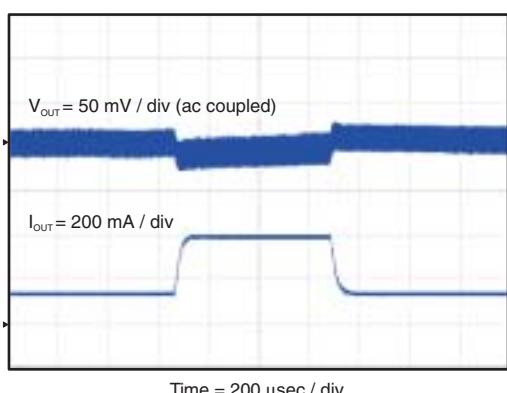

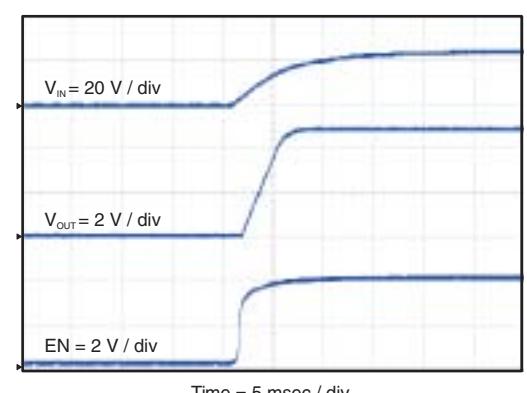

## アプリケーション曲線

図 42. 過渡応答(100mA～350mA)

図 43. 入力電圧によるスタートアップ

## アプリケーション曲線

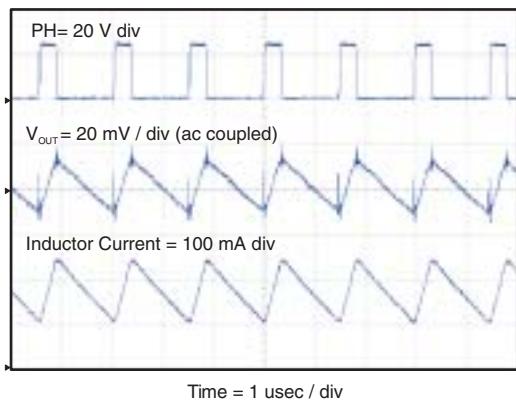

図 44. 出力リップル、CCM

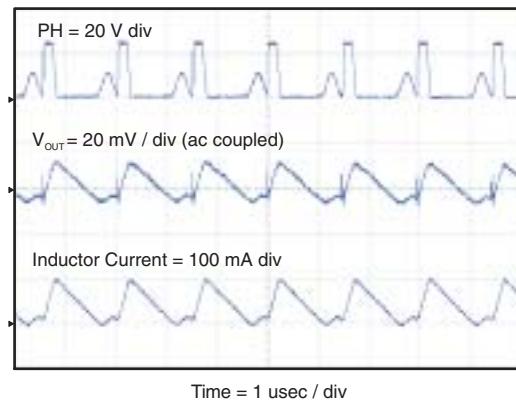

図 45. 出力リップル、DCM

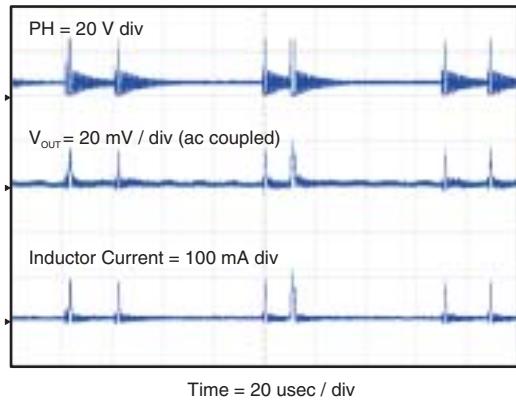

図 46. 出力リップル、PSM

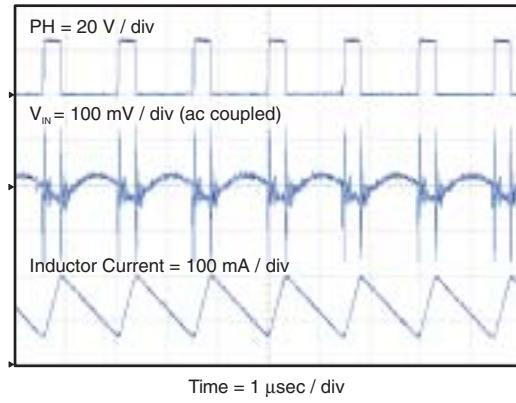

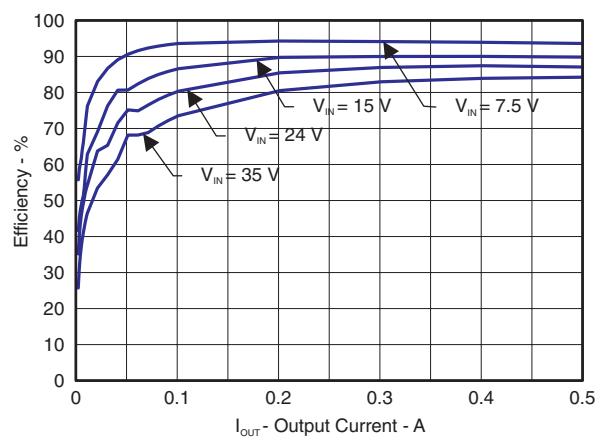

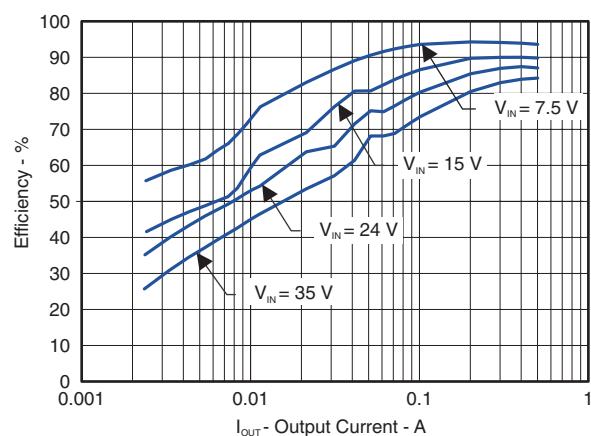

図 47. 入力リップル、CCM

図 48. 入力リップル、DCM

図 49. 効率 対 負荷電流

## アプリケーション曲線

図 50. 軽負荷効率

図 51. 全体のループ周波数応答

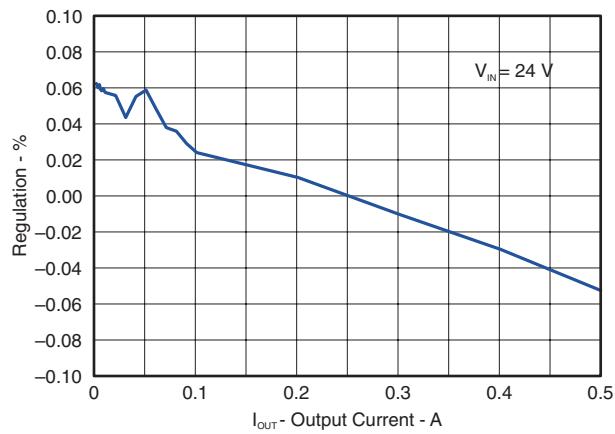

図 52. レギュレーション 対 負荷電流

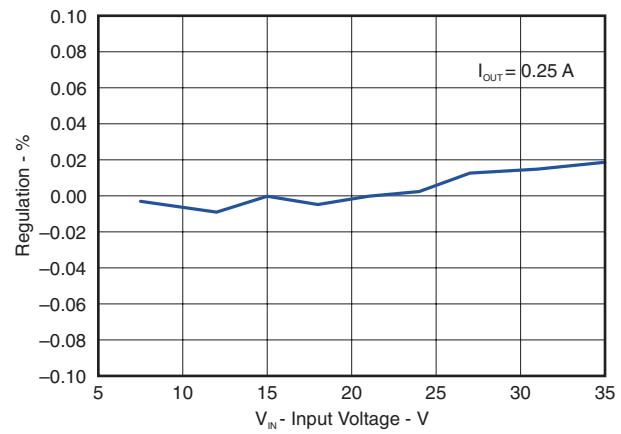

図 53. レギュレーション 対 入力電圧

## 消費電力の見積もり

以下の式は、連続導通モード (CCM) 動作でのICの消費電力を見積もる方法を示しています。デバイスが不連続導通モード (DCM) で動作している場合は、これらの式を使用しないでください。

ICの消費電力には、導通損失 ( $P_{\text{con}}$ )、スイッチング損失 ( $P_{\text{sw}}$ )、ゲート駆動損失 ( $P_{\text{GD}}$ )、および消費電流 ( $P_{\text{SUP}}$ ) が含まれます。

$$P_{\text{con}} = I_{\text{OUT}}^2 \times r_{\text{DS(on)}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \quad (36)$$

$$P_{\text{sw}} = V_{\text{IN}}^2 \times I_{\text{OUT}} \times 0.25 \times 10^{-9} \times f_{\text{sw}} \quad (37)$$

$$P_{\text{GD}} = V_{\text{IN}} \times 3 \times 10^{-9} \times f_{\text{sw}} \quad (38)$$

$$P_{\text{SUP}} = 116 \times 10^{-6} \times V_{\text{IN}} \quad (39)$$

したがって、合計消費電力は、次のようになります。

$$P_{\text{TOT}} = P_{\text{CON}} + P_{\text{sw}} + P_{\text{GD}} + P_{\text{SUP}} \quad (40)$$

特定の周囲温度  $T_A$  に対して、接合部温度  $T_J$  は式 (41) で見積もることができます。

$$T_J = T_A - \theta_{JA} \times P_{\text{TOT}} \quad (41)$$

ここで

- $\theta_{JA}$  はパッケージの熱抵抗 ( $^{\circ}\text{C}/\text{W}$ ) です。

特定の接合部温度  $T_{J(\text{max})} = 150^{\circ}\text{C}$  に対して、最大許容周囲温度は式 (42) で見積もることができます。

$$T_{A(\text{max})} = T_{J(\text{max})} - \theta_{JA} \times P_{\text{TOT}} \quad (42)$$

レギュレータ回路には、インダクタのACおよびDC損失、キャッチ・ダイオードおよびパターン抵抗による追加の電力損失があり、レギュレータ全体の効率に影響を与えます。

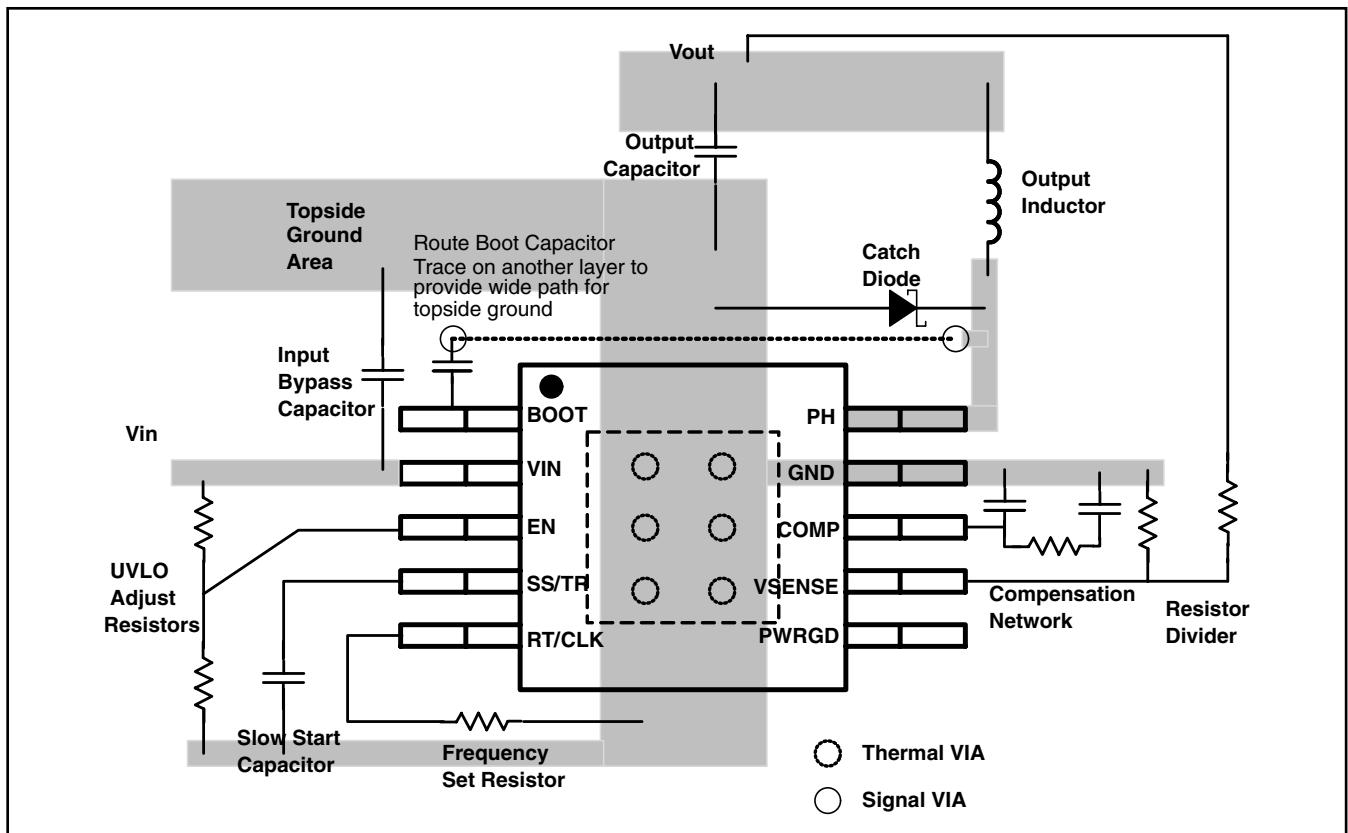

## レイアウト

レイアウトは、優れた電源設計のために重要な要素です。高速で変化する電流または電圧を通す信号バスがいくつかあるため、浮遊インダクタンスや寄生容量によってノイズが発生したり、電源の性能が低下したりする可能性があります。これらの問題をなくすために、VINピンは、X5RまたはX7R誘電体を使用した低ESRのセラミック・バイパス・コンデンサを使用してグランドにバイパスする必要があります。バイパス・コンデンサ接続、VINピン、およびキャッチ・ダイオードのアノードによって形成されるループ領域は、最小限に抑えるよう注意が必要です。PCBレイアウト例については、図54を参照してください。GNDピンは、ICの下部にあるサーマル・パッドに直接接続する必要があります。

サーマル・パッドは、ICの直下にある複数のピアを使用して内部のPCBグランド・プレーンに接続します。PHピンは、キャッチ・ダイオードのカソード、および出力インダクタに配線します。PH接続はスイッチング・ノードであるため、キャッチ・ダイオードおよび出力インダクタはPHピンに近づけて配置し、過度の容量性カップリングを避けるためにPCB導体の面積はできるだけ小さくしてください。全定格負荷で動作を行うには、上面のグランド領域が十分な熱放散面積を備えていなければなりません。RT/CLKピンはノイズの影響を受けやすいため、RTの抵抗はICにできるだけ近づけて配置し、最短のパターンで配線する必要があります。追加の外部部品は図に示されるように配置できます。別のPCBレイアウトでも許容される性能を得ることは可能ですが、このレイアウトは良好な結果が得られることが実証済みであり、ガイドラインとして示しています。

## 回路面積の見積もり

図40の設計で使用される部品に対して見積もられるプリント基板面積は、 $0.55\text{in}^2$  ( $3.55\text{cm}^2$ ) です。この面積には、テスト・ポイントおよびコネクタは含まれません。

図 54. PCBレイアウト例

# パッケージ情報

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type  | Package Drawing | Pins Qty | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL                | Peak Temp <sup>(3)</sup> | Samples (Requires Login) |

|------------------|-----------------------|---------------|-----------------|----------|-------------|-------------------------|------------------|--------------------|--------------------------|--------------------------|

| TPS5401DGQ       | ACTIVE                | MSOP-PowerPAD | DGQ             | 10       | 80          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | Purchase Samples         |                          |

| TPS5401DGQR      | ACTIVE                | MSOP-PowerPAD | DGQ             | 10       | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | Purchase Samples         |                          |

| TPS5401DGQT      | ACTIVE                | MSOP-PowerPAD | DGQ             | 10       | 250         | TBD                     | Call TI          | Call TI            |                          | Purchase Samples         |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフトайム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS) : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

Green (RoHS & no Sb/Br) : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項 : このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIバーツの購入価格の合計金額を超える責任は負いかねます。

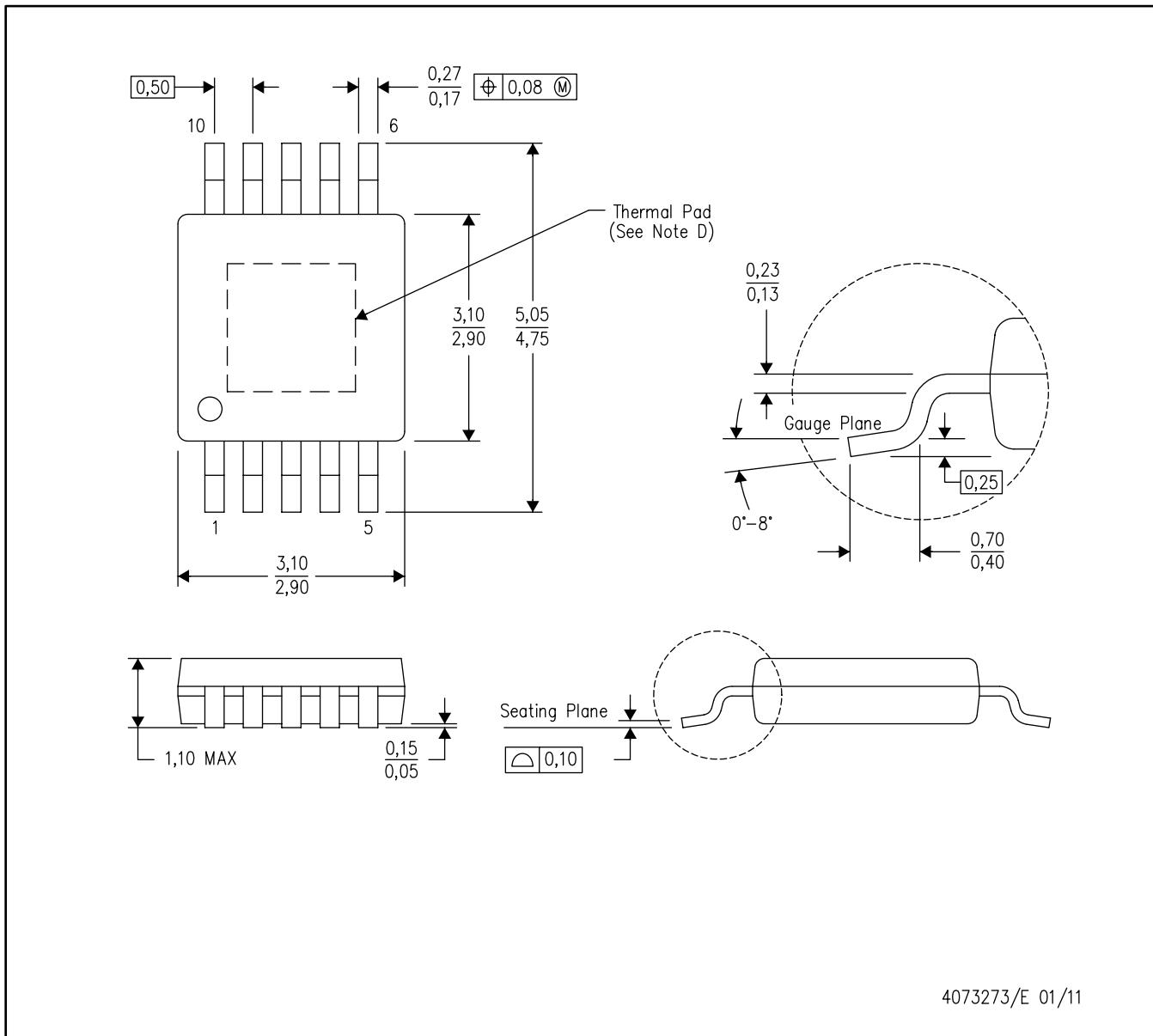

- 注：

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 本体寸法にはバリや突起を含みません。バリおよび突起は、各辺0,15を超えてはなりません。

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)を参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

- E. JEDEC MO-187 variation BA-Tに適合しています。

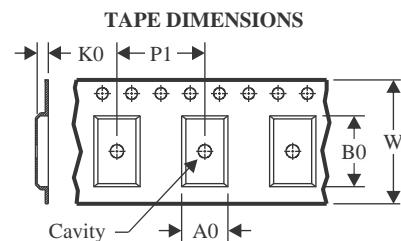

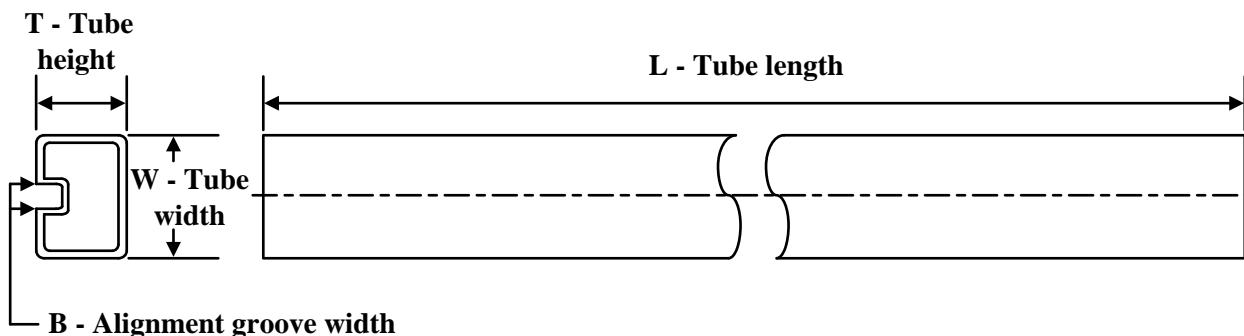

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

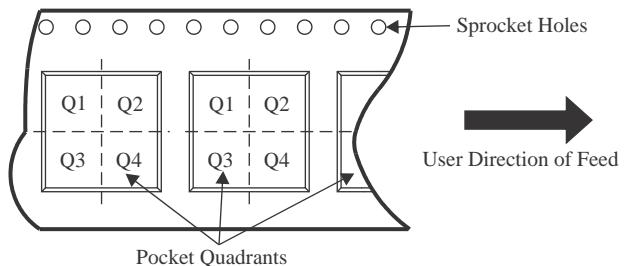

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

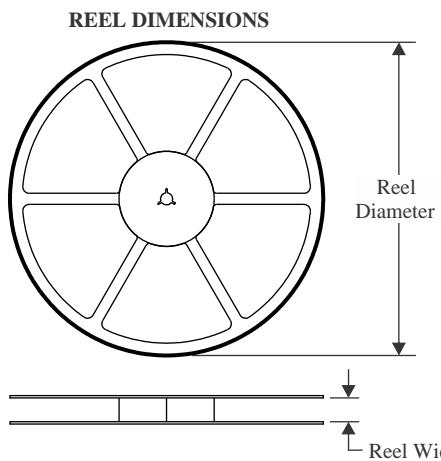

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS5401DGQR   | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.25    | 3.35    | 1.25    | 8.0     | 12.0   | Q1            |

| TPS5401DGQRG4 | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.25    | 3.35    | 1.25    | 8.0     | 12.0   | Q1            |

| TPS5401DGQT   | HVSSOP       | DGQ             | 10   | 250  | 180.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

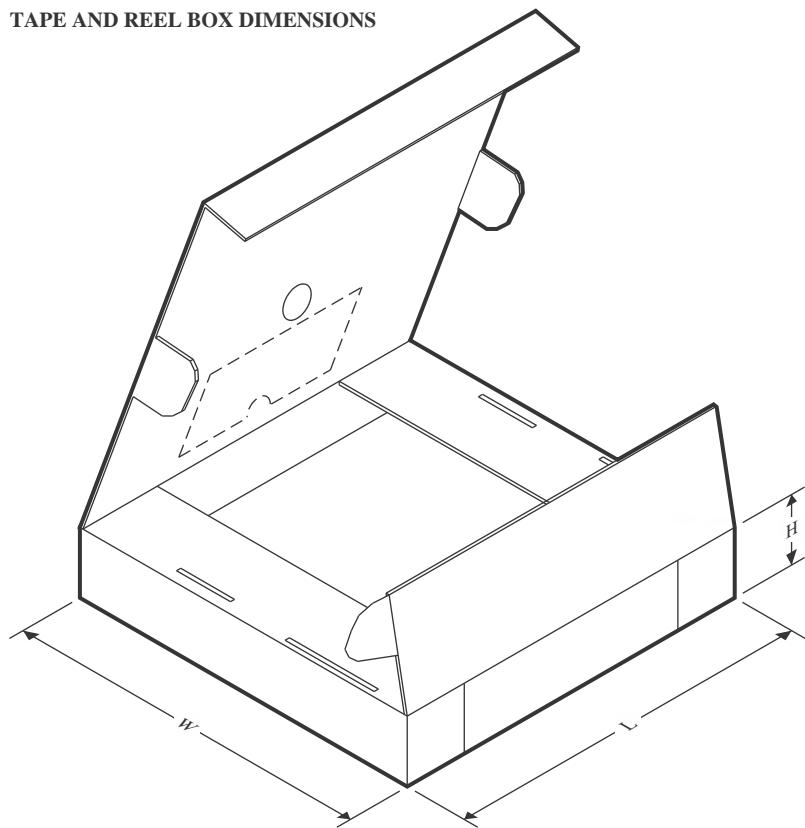

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS5401DGQR   | HVSSOP       | DGQ             | 10   | 2500 | 366.0       | 364.0      | 50.0        |

| TPS5401DGQRG4 | HVSSOP       | DGQ             | 10   | 2500 | 366.0       | 364.0      | 50.0        |

| TPS5401DGQT   | HVSSOP       | DGQ             | 10   | 250  | 200.0       | 183.0      | 25.0        |

**TUBE**

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS5401DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS5401DGQ   | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS5401DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS5401DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS5401DGQ.B | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS5401DGQ.B | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月