## TPS5331x Eco-mode 制御搭載、 高効率 8A または 14A 同期整流式降圧コンバータ

### 1 特長

- 新製品が利用可能: **TPS548A28** および **TPS548A29** リモートセンス機能搭載、16V、15A 同期整流コンバータ

- 変換入力電圧範囲: 1.5V ~ 22V

- VDD の入力電圧範囲: 4.5V ~ 25V

- 14A において 12V から 1.5V への効率: 91%

- 出力電圧範囲: 0.6V ~ 5.5V

- 5V LDO 出力

- 単一レール入力のサポート

- パワー MOSFET を内蔵: 連続出力電流 8A (TPS53318) または 14A (TPS53319)

- 自動スキップ Eco-mode により軽負荷時の効率を向上

- シャットダウン電流は 110µA 未満

- 高速過渡応答の D-CAP™ IC モード

- 外付け抵抗によりスイッチング周波数を 250kHz ~ 1MHz の範囲で選択可能

- 自動スキップまたは PWM のみの動作を選択可能

- 内蔵 1% 0.6V リファレンス

- 内部電圧サーボソフトスタートを 0.7ms、1.4ms、2.8ms、5.6ms から選択可能

- ブーストスイッチ内蔵

- プリチャージスタートアップ機能

- 調整可能な熱補償付き過電流制限

- 過電圧、低電圧、UVLO、過熱保護

- すべての出力コンデンサでセラミックコンデンサの使用をサポート

- オープンドレインのパワー グッド表示

- NexFET™ パワー MOSFET ブロックテクノロジーを内蔵

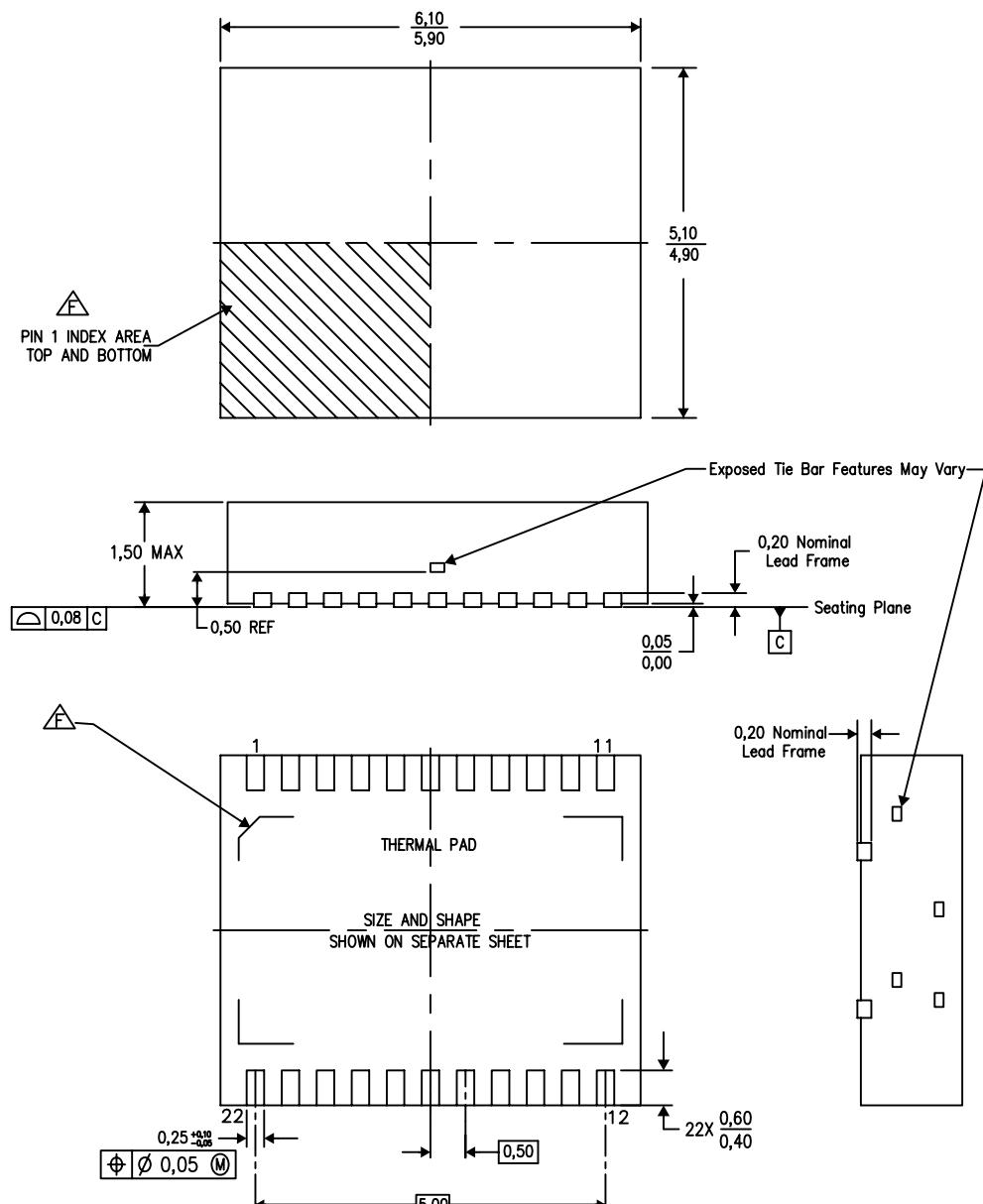

- PowerPAD™ IC パッケージを使用した 22 ピン QFN (DQP) パッケージ

### 2 アプリケーション

- サーバーおよびストレージ

- ワークステーションおよびデスクトップ

- 通信インフラストラクチャ

### 3 説明

TPS53318 および TPS53319 デバイスは、D-CAP モードに対応し、MOSFET を内蔵した、8A または 14A の同期整流スイッチャです。これらのデバイスは使いやすさに重点を置き、外部部品数の少ない省スペースの電源システム用に設計されています。

精度 1% の 0.6V リファレンスに加え、ブーストスイッチを内蔵しています。競争力のある機能の例: 1.5V ~ 22V の幅広い変換入力電圧範囲、非常に少ない外部部品数、D-CAP IC モード制御による超高速過渡応答、自動スキップモード動作、内部ソフトスタート制御、選択可能な周波数、補償が不要、などが挙げられます。

変換入力電圧範囲は 1.5V ~ 22V、電源電圧範囲は 4.5V ~ 25V、出力電圧範囲は 0.6V ~ 5.5V です。

これらのデバイスは 5mm × 6mm の 22 ピン QFN パッケージで供給され、-40°C ~ 85°C で仕様が規定されています。

TPS548A28 および TPS548A29 は、より小型の完全な鉛フリーパッケージを採用した、データセンターアプリケーション向けの新しい 15A デバイスです。

### 製品情報

| 部品番号 (3) | パッケージ (1)           | パッケージ サイズ(2)    |

|----------|---------------------|-----------------|

| TPS53318 |                     |                 |

| TPS53319 | DQP (LSON-CLIP, 22) | 6.00mm × 5.00mm |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 「[デバイス比較表](#)」を参照してください。

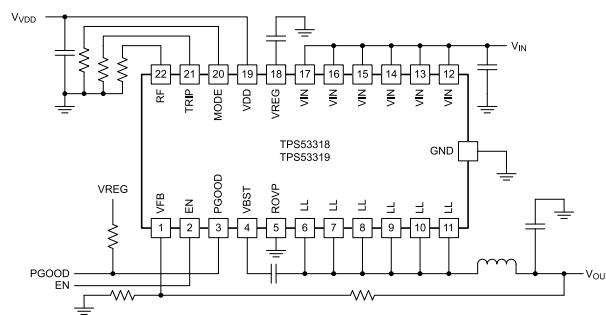

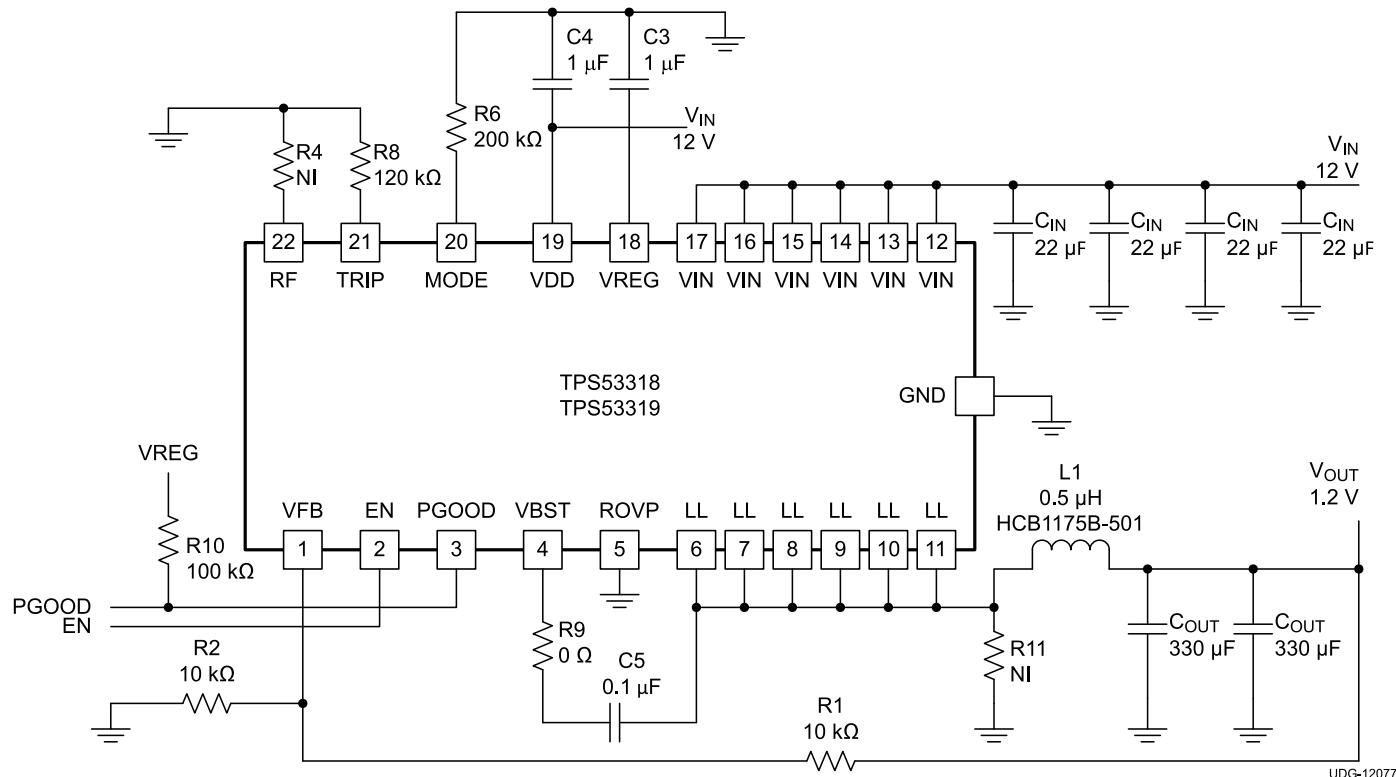

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLUSAY8](#)

## 目次

|                     |    |                        |    |

|---------------------|----|------------------------|----|

| 1 特長                | 1  | 7.3 機能説明               | 16 |

| 2 アプリケーション          | 1  | 7.4 デバイスの機能モード         | 21 |

| 3 説明                | 1  | 8 アプリケーションと実装          | 24 |

| 4 デバイス比較表           | 3  | 8.1 アプリケーション情報         | 24 |

| 5 ピン構成および機能         | 4  | 8.2 代表的なアプリケーション       | 24 |

| 6 仕様                | 6  | 8.3 電源に関する推奨事項         | 30 |

| 6.1 絶対最大定格          | 6  | 8.4 レイアウト              | 30 |

| 6.2 ESD 定格          | 6  | 9 デバイスおよびドキュメントのサポート   | 32 |

| 6.3 推奨動作条件          | 6  | 9.1 デバイス サポート          | 32 |

| 6.4 熱に関する情報         | 7  | 9.2 ドキュメントの更新通知を受け取る方法 | 32 |

| 6.5 電気的特性           | 7  | 9.3 サポート・リソース          | 32 |

| 6.6 代表的特性           | 10 | 9.4 商標                 | 32 |

| 6.7 TPS53319 の代表的特性 | 13 | 9.5 静電気放電に関する注意事項      | 32 |

| 6.8 TPS53318 の代表的特性 | 14 | 9.6 用語集                | 32 |

| 7 詳細説明              | 15 | 10 改訂履歴                | 32 |

| 7.1 概要              | 15 | 11 メカニカル、パッケージ、および注文情報 | 33 |

| 7.2 機能ブロック図         | 15 |                        |    |

## 4 デバイス比較表

| 注文番号 <sup>(1)</sup> | 出力電流 (A) |

|---------------------|----------|

| TPS53318DQP         | 8        |

| TPS53319DQP         | 14       |

(1) 注文情報の詳細については、このデータシートの末尾にある「パッケージオプション補遺」セクションを参照してください。

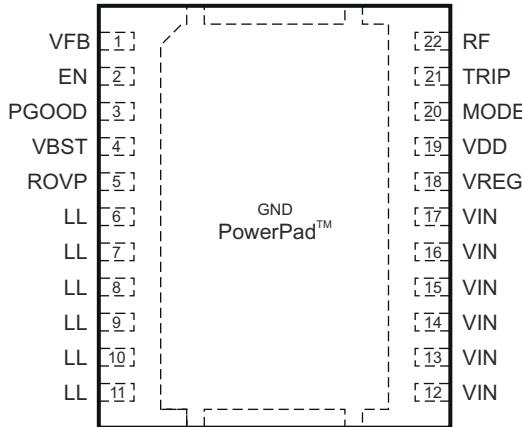

## 5 ピン構成および機能

図 5-1.22 ピン DQFN (LSON-CLIP) パッケージ (上面図)

表 5-1. ピンの機能

| ピン    |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                          |

|-------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 番号 |                    |                                                                                                                                                                             |

| EN    | 2  | I                  | イネーブル ピン。標準的なターンオンスレッショルド電圧は 1.3V です。標準的なターンオフスレッショルド電圧は 1.0V です。                                                                                                           |

| GND   |    | G                  | デバイスのグランドおよびサーマル パッド。適切な数のビアを使用して、グランド プレーンに接続します。                                                                                                                          |

| LL    | 6  | B                  | 変換された電力の出力。このピンを出力インダクタに接続します。                                                                                                                                              |

|       | 7  |                    |                                                                                                                                                                             |

|       | 8  |                    |                                                                                                                                                                             |

|       | 9  |                    |                                                                                                                                                                             |

|       | 10 |                    |                                                                                                                                                                             |

|       | 11 |                    |                                                                                                                                                                             |

| モード   | 20 | I                  | ソフトスタートおよびモード選択。表 7-3 のように抵抗を接続してソフトスタート時間を選択します。ソフトスタート時間は、スタートアップ中に検出されて内部レジスタに格納されます。                                                                                    |

| PGOOD | 3  | O                  | オーブンドレインのパワーグッドフラグ。VFB が規定の制限値に達した後、1ms のスタートアップ遅延があります。VFB 電圧が規定の制限値を外れると、2μs の遅延の後に PGOOD が Low になります。                                                                    |

| ROVP  | 5  | I                  | 冗長過電圧保護 (OVP) 入力。抵抗デバイダを使用してこのピンを V <sub>OUT</sub> に接続します。1.5MΩ 抵抗によって内部的に GND にプルダウンされます。冗長 OVP が不要な場合は、このピンを GND に接続してください。ROVP ピンはフローティングのままにしないでください (セクション 7.3.9 を参照)。 |

| RF    | 22 | I                  | スイッチング周波数の選択。抵抗を GND または VREG に接続し、表 7-1 を使ってスイッチング周波数を選択します。スイッチング周波数はスタートアップ時に検出され保存されます。                                                                                 |

| TRIP  | 21 | I                  | OCL 検出スレッショルド設定ピン。室温で I <sub>TRIP</sub> = 10μA3000ppm/°C の電流を供給し、OCL トリップ電圧を次のようにセットします。                                                                                    |

|       |    |                    | V <sub>OCL</sub> = V <sub>TRIP</sub> /32 (V <sub>TRIP</sub> ≤ 2.4V, V <sub>OCL</sub> ≤ 75mV)                                                                                |

| VBST  | 4  | P                  | ハイサイド FET ゲートドライバの電源入力 (昇圧端子)。このピンと LL ノードとの間にコンデンサを接続します。ポートストラップ MOSFET スイッチ経由で VREG に内部接続されます。                                                                           |

| VDD   | 19 | P                  | コントローラの電源入力。VDD 入力電圧範囲は 4.5V ~ 25V です。                                                                                                                                      |

| VFB   | 1  | I                  | 出力帰還入力。このピンは抵抗デバイダを介して V <sub>OUT</sub> に接続します。                                                                                                                             |

**表 5-1. ピンの機能 (続き)**

| ピン       |    | タイプ <sup>(1)</sup> | 説明                                               |

|----------|----|--------------------|--------------------------------------------------|

| 名称       | 番号 |                    |                                                  |

| VIN      | 12 | P                  | 変換電源入力。変換入力電圧の範囲は 1.5V ~ 22V です。                 |

|          | 13 |                    |                                                  |

|          | 14 |                    |                                                  |

|          | 15 |                    |                                                  |

|          | 16 |                    |                                                  |

|          | 17 |                    |                                                  |

| VREG     | 18 | P                  | 5V の低ドロップアウト (LDO) 出力。内部アナログ回路およびドライバ回路に供給します。   |

| サーマル パッド |    | G                  | デバイスのグランドおよびサーマル パッド。適切な数のビアを使用してグランドプレーンに接続します。 |

(1) I = 入力、O = 出力、B = 双方向、P = 電源、G = グランド

## 6 仕様

### 6.1 絶対最大定格

|                                           |                               | 値 <sup>(1)</sup>    |     | 単位 |

|-------------------------------------------|-------------------------------|---------------------|-----|----|

|                                           |                               | 最小値                 | 最大値 |    |

| 入力電圧範囲                                    | VIN (主電源)                     | -0.3                | 30  | V  |

|                                           | VDD                           | -0.3                | 28  |    |

|                                           | VBST                          | -0.3                | 32  |    |

|                                           | VBST (LL を基準)                 | -0.3                | 7   |    |

|                                           | EN, MODE, TRIP, RF, ROVP, VFB | -0.3                | 7   |    |

| 出力電圧範囲                                    | LL                            | DC                  | -2  | V  |

|                                           |                               | パルス < 20ns, E = 5μJ | -7  |    |

|                                           | PGOOD, VREG                   | -0.3                | 7   |    |

|                                           |                               | -0.3                | 0.3 |    |

| ソース/シンク電流                                 | VBST                          | 50                  |     | mA |

| 自由気流での動作温度 (T <sub>A</sub> )              |                               | -40                 | 85  | °C |

| 接合部温度範囲、T <sub>J</sub>                    |                               | -40                 | 150 |    |

| リード温度: ケースから 1.6mm (1/16 インチ) 離れた点で 10 秒間 |                               |                     | 300 |    |

| 保管温度、T <sub>stg</sub>                     |                               | -55                 | 150 |    |

(1) 「絶対最大定格」の記載を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみに関するものであり、絶対最大定格において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD 定格

|                         |                                                         | 値     | 単位 |

|-------------------------|---------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

|                         | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±500  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。必要な予防措置を講じれば、HBM は 500V 未満の許容差で製造できます。±2000V と記載されているピンは、実際にはそれよりも高い性能を持つ場合があります。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。必要な予防措置を講じれば、CDM の ESD 耐圧が 250V 未満でも製造可能です。±500V と記載されているピンは、実際にはそれよりも高い性能を持つ場合があります。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                        |                               | 最小値  | 最大値 | 単位 |

|------------------------|-------------------------------|------|-----|----|

| 入力電圧範囲                 | VIN (主電源)                     | 1.5  | 22  | V  |

|                        | VDD                           | 4.5  | 25  |    |

|                        | VBST                          | 4.5  | 28  |    |

|                        | VBST (LL を基準)                 | 4.5  | 6.5 |    |

|                        | EN, MODE, TRIP, RF, ROVP, VFB | -0.1 | 6.5 |    |

| 出力電圧範囲                 | LL                            | -1   | 27  | V  |

|                        | PGOOD, VREG                   | -0.1 | 6.5 |    |

| 接合部温度範囲、T <sub>J</sub> |                               | -40  | 125 | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | TPS53318<br>TPS53319 | 単位   |  |  |

|----------------------|-------------------|----------------------|------|--|--|

| DQP                  |                   |                      |      |  |  |

| 22 ピン                |                   |                      |      |  |  |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 27.2                 | °C/W |  |  |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 17.1                 |      |  |  |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 5.9                  |      |  |  |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 0.8                  |      |  |  |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 5.8                  |      |  |  |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 1.2                  |      |  |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーションレポートを参照してください。

## 6.5 電気的特性

推奨される自由気流での動作温度範囲内  $V_{VDD} = 12V$  (特に記述のない限り)

| パラメータ                | 条件                                               | 最小値                                                                                     | 標準値    | 最大値   | 単位     |    |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|--------|-------|--------|----|

| <b>電源電流</b>          |                                                  |                                                                                         |        |       |        |    |

| $V_{VIN}$            | $VIN$ ピン電力の変換入力電圧                                |                                                                                         | 1.5    | 22    | V      |    |

| $V_{VDD}$            | 電源入力電圧                                           |                                                                                         | 4.5    | 25.0  | V      |    |

| $I_{VIN(leak)}$      | $VIN$ ピンのリーク電流                                   | $V_{EN} = 0V$                                                                           |        | 1     | μA     |    |

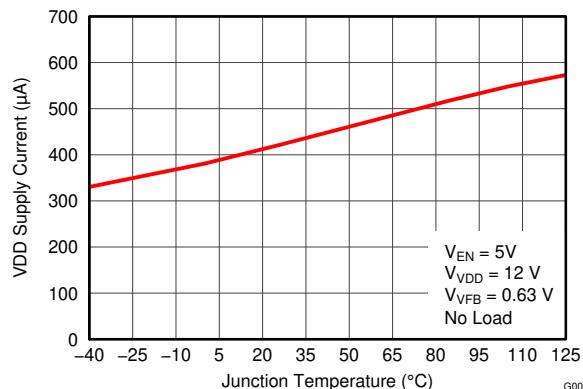

| $I_{VDD}$            | $VDD$ 電源電流                                       | $T_A = 25^\circ C$ 、無負荷、 $V_{EN} = 5V$ 、 $V_{VFB} = 0.630V$                             |        | 420   | 590    | μA |

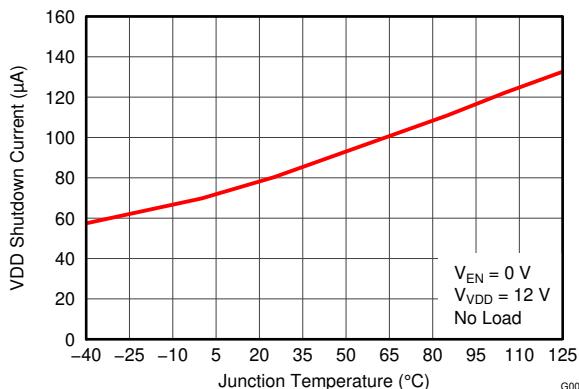

| $I_{VDDSDN}$         | $VDD$ シャットダウン電流                                  | $T_A = 25^\circ C$ 、無負荷、 $V_{EN} = 0V$                                                  |        | 122   | μA     |    |

| <b>内部リファレンス電圧</b>    |                                                  |                                                                                         |        |       |        |    |

| $V_{VFB}$            | $VFB$ のレギュレーション電圧                                | CCM 条件 <sup>(1)</sup>                                                                   | 0.600  |       | V      |    |

| $V_{VFB}$            | $VFB$ のレギュレーション電圧                                | $T_A = 25^\circ C$                                                                      | 0.597  | 0.600 | 0.603  |    |

|                      |                                                  | $0^\circ C \leq T_A \leq 85^\circ C$                                                    | 0.5952 | 0.600 | 0.6048 |    |

|                      |                                                  | $-40^\circ C \leq T_A \leq 85^\circ C$                                                  | 0.594  | 0.600 | 0.606  |    |

| $I_{VFB}$            | $VFB$ 入力電流                                       | $V_{VFB} = 0.630V$ 、 $T_A = 25^\circ C$                                                 |        | 0.01  | 0.20   | μA |

| <b>LDO 出力</b>        |                                                  |                                                                                         |        |       |        |    |

| $V_{VREG}$           | LDO 出力電圧                                         | $0mA \leq I_{VREG} \leq 30mA$                                                           | 4.77   | 5.00  | 5.36   | V  |

| $I_{VREG}$           | LDO 出力電流 <sup>(1)</sup>                          | LDO で許容される最大電流                                                                          |        | 30    | mA     |    |

| $V_{DO}$             | 低ドロップアウト電圧                                       | $V_{VDD} = 4.5V$ 、 $I_{VREG} = 30mA$                                                    |        | 250   | mV     |    |

| <b>ポートストラップスイッチ</b>  |                                                  |                                                                                         |        |       |        |    |

| $V_{FBST}$           | 順方向電圧                                            | $V_{VREG-VBST}$ 、 $I_F = 10mA$ 、 $T_A = 25^\circ C$                                     |        | 0.1   | 0.2    | V  |

| $I_{VBSTLX}$         | $VBST$ のリーク電流                                    | $V_{VBST} = 23V$ 、 $V_{SW} = 17V$ 、 $T_A = 25^\circ C$                                  |        | 0.01  | 1.50   | μA |

| <b>デューティおよび周波数制御</b> |                                                  |                                                                                         |        |       |        |    |

| $t_{OFF(min)}$       | 最小オフ時間                                           | $T_A = 25^\circ C$                                                                      | 150    | 260   | 400    | ns |

| $t_{ON(min)}$        | 最小オン時間                                           | $V_{IN} = 17V$ 、 $V_{OUT} = 0.6V$ 、 $f_{SW} = 1MHz$ 、 $T_A = 25^\circ C$ <sup>(1)</sup> |        | 35    |        | ns |

| <b>ソフトスタート時間</b>     |                                                  |                                                                                         |        |       |        |    |

| $t_{SS}$             | $V_{OUT} = 0V$ から $V_{OUT}$ の 95% までの内部ソフトスタート時間 | $R_{MODE} = 39k\Omega$                                                                  | 0.7    | ms    |        |    |

|                      |                                                  | $R_{MODE} = 100k\Omega$                                                                 | 1.4    |       |        |    |

|                      |                                                  | $R_{MODE} = 200k\Omega$                                                                 | 2.8    |       |        |    |

|                      |                                                  | $R_{MODE} = 470k\Omega$                                                                 | 5.6    |       |        |    |

推奨される自由気流での動作温度範囲内  $V_{VDD} = 12V$  (特に記述のない限り)

| パラメータ                           | 条件                           | 最小値                                                              | 標準値    | 最大値    | 単位     |

|---------------------------------|------------------------------|------------------------------------------------------------------|--------|--------|--------|

| <b>OUTPUT VOLTAGE DISCHARGE</b> |                              |                                                                  |        |        |        |

| $I_{DSCHG}$                     | $V_{EN} = 0V, V_{SW} = 0.5V$ | 5.0                                                              | 6.6    | 9.0    | mA     |

| <b>パワーグッド</b>                   |                              |                                                                  |        |        |        |

| $V_{THPG}$                      | PG スレッショルド                   | 低い方からの PG 入力                                                     | 92.5%  | 95.0%  | 98.5%  |

|                                 |                              | 高い方からの PG 入力                                                     | 107.5% | 110.0% | 112.5% |

|                                 |                              | PG ヒステリシス                                                        | 2.5%   | 5.0%   | 7.5%   |

| $R_{PG}$                        | PG トランジスタオン抵抗                |                                                                  | 15     | 30     | 60     |

| $t_{PGDEL}$                     | PG 遅延                        | PG 入力の遅延                                                         | 0.8    | 1      | 1.2    |

| <b>ロジックスレッショルドと設定条件</b>         |                              |                                                                  |        |        |        |

| $V_{EN}$                        | EN 電圧                        | イネーブル                                                            | 1.0    | 1.3    | 1.6    |

|                                 |                              | 無効                                                               | 0.8    | 1.0    | 1.2    |

| $I_{EN}$                        | EN 入力電流                      | $V_{EN} = 5V$                                                    |        | 1.0    | μA     |

| $f_{SW}$                        | スイッチング周波数                    | $R_{RF} = 0\Omega$ から GND, $T_A = 25^\circ C$ <sup>(2)</sup>     | 200    | 250    | 300    |

|                                 |                              | $R_{RF} = 187k\Omega$ から GND, $T_A = 25^\circ C$ <sup>(2)</sup>  | 250    | 300    | 350    |

|                                 |                              | $R_{RF} = 619 k\Omega$ から GND, $T_A = 25^\circ C$ <sup>(2)</sup> | 350    | 400    | 450    |

|                                 |                              | $R_{RF}$ 開放, $T_A = 25^\circ C$ <sup>(2)</sup>                   | 450    | 500    | 550    |

|                                 |                              | $R_{RF} = 866k\Omega$ から VREG, $T_A = 25^\circ C$ <sup>(2)</sup> | 540    | 600    | 660    |

|                                 |                              | $R_{RF} = 309k\Omega$ から VREG, $T_A = 25^\circ C$ <sup>(2)</sup> | 670    | 750    | 820    |

|                                 |                              | $R_{RF} = 124k\Omega$ から VREG, $T_A = 25^\circ C$ <sup>(2)</sup> | 770    | 850    | 930    |

|                                 |                              | $R_{RF} = 0\Omega$ から VREG, $T_A = 25^\circ C$ <sup>(2)</sup>    | 880    | 970    | 1070   |

| <b>保護機能: 電流検出</b>               |                              |                                                                  |        |        |        |

| $I_{TRIP}$                      | TRIP ソース電流                   | $V_{TRIP} = 1V, T_A = 25^\circ C$                                | 10     |        | μA     |

| $TC_{I_{TRIP}}$                 | TRIP 電流温度係数                  | 25°C を基準 <sup>(2)</sup>                                          | 3000   |        | ppm/°C |

| $V_{TRIP}$                      | 電流制限スレッショルドの設定範囲             | TPS53318<br>TPS53319                                             | 0.4    | 1.5    | V      |

|                                 |                              |                                                                  |        | 2.4    |        |

| $V_{OCL}$                       | Current limit threshold      | $V_{TRIP} = 1.2V$                                                | 37.5   |        | mV     |

|                                 |                              | $V_{TRIP} = 0.4$                                                 | 12.5   |        |        |

| $V_{OCLN}$                      | 負の電流制限スレッショルド                | $V_{TRIP} = 1.2V$                                                | -37.5  |        | mV     |

|                                 |                              | $V_{TRIP} = 0.4V$                                                | -12.5  |        |        |

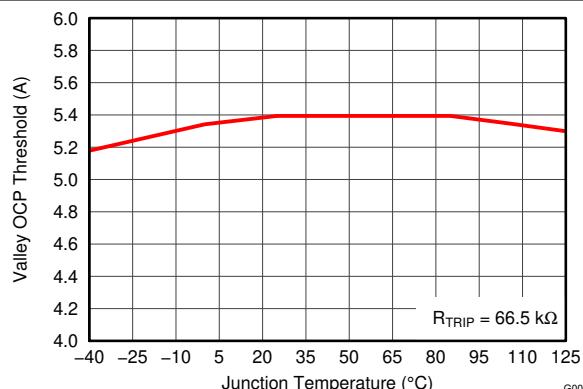

| $I_{OCP}$                       | バレー電流制限スレッショルド               | $R_{TRIP} = 66.5k\Omega, 0^\circ C \leq T_A \leq 125^\circ C$    | 4.6    | 5.4    | 6.3    |

|                                 |                              | $R_{TRIP} = 66.5k\Omega, -40^\circ C \leq T_A \leq 125^\circ C$  | 4.4    | 5.4    | 6.3    |

| $V_{AZCADJ}$                    | 自動ゼロ交差調整可能範囲                 | Positive                                                         | 3      | 15     | mV     |

|                                 |                              | 負                                                                | -15    | -3     |        |

| <b>保護機能: UVP および OVP</b>        |                              |                                                                  |        |        |        |

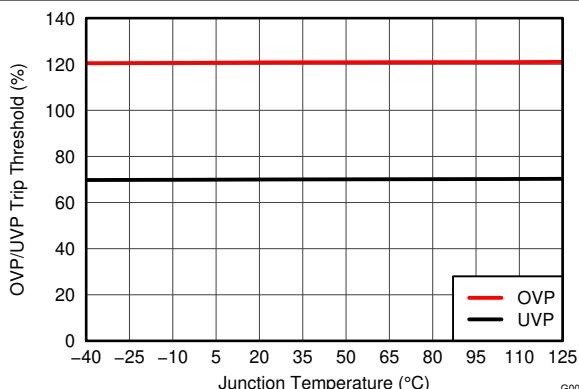

| $V_{OVP}$                       | OVP 遷移スレッショルド                | OVP 検出                                                           | 115%   | 120%   | 125%   |

| $t_{OVPDEL}$                    | OVP 伝搬遅延                     | 50mV オーバードライブでの VFB 遅延                                           | 1      |        | μs     |

| $V_{UVP}$                       | 出力 UVP トリップスレッショルド           | UVP 検出                                                           | 65%    | 70%    | 75%    |

| $t_{UVPDEL}$                    | 出力 UVP 伝搬遅延                  |                                                                  | 0.8    | 1.0    | 1.2    |

| $t_{UVPEN}$                     | 出力 UVP イネーブル遅延               | イネーブルから UVP 対応に                                                  | 1.5    | 2.3    | 3.0    |

| <b>UVLO</b>                     |                              |                                                                  |        |        |        |

推奨される自由気流での動作温度範囲内  $V_{VDD} = 12V$  (特に記述のない限り)

| パラメータ                   |                      | 条件                            | 最小値  | 標準値  | 最大値  | 単位 |

|-------------------------|----------------------|-------------------------------|------|------|------|----|

| $V_{UVVREG}$            | VREG UVLO スレッショルド    | ウェークアップ                       | 4.00 | 4.20 | 4.33 | V  |

|                         |                      | ヒステリシス                        |      | 0.25 |      |    |

| <b>保護機能:UVP および OVP</b> |                      |                               |      |      |      |    |

| $V_{OVP}$               | OVP 遷移スレッショルド        | OVP 検出                        | 115% | 120% | 125% |    |

| $t_{OVPDEL}$            | OVP 伝搬遅延             | 50mV オーバードライブでの VFB 遅延        |      | 1    |      | μs |

| $V_{UVP}$               | 出力 UVP トリップスレッショルド   | UVP 検出                        | 65%  | 70%  | 75%  |    |

| $t_{UVPDEL}$            | 出力 UVP 伝搬遅延          |                               | 0.8  | 1.0  | 1.2  | ms |

| $t_{UVPEN}$             | 出力 UVP イネーブル遅延       | イネーブルから UVP 対応に               | 1.5  | 2.3  | 3.0  | ms |

| <b>UVLO</b>             |                      |                               |      |      |      |    |

| $V_{UVVREG}$            | VREG UVLO スレッショルド    | ウェークアップ                       | 4.00 | 4.20 | 4.33 | V  |

|                         |                      | ヒステリシス                        |      | 0.25 |      |    |

| <b>サーマル シャットダウン</b>     |                      |                               |      |      |      |    |

| $T_{SDN}$               | サーマル シャットダウンのスレッショルド | シャットダウン温度 <a href="#">(2)</a> |      | 145  |      | °C |

|                         |                      | ヒステリシス <a href="#">(2)</a>    |      | 10   |      |    |

(1) 設計により規定されています。実製品の検査は行っていません。

(2) 実製品の検査は行っていません。テスト条件は、[図 8-12](#) に示すアプリケーション回路を使用した場合、 $V_{IN} = 12V$ 、 $V_{OUT} = 1.2V$ 、 $I_{OUT} = 5A$  です。

## 6.6 代表的特性

図 6-1. VDD 電源電流と接合部温度との関係

図 6-2. VDD シャットダウン電流と接合部温度との関係

図 6-3. バレー OCP スレッショルドと温度との関係

図 6-4. OVP/UVP トリップスレッショルド 対 接合部温度

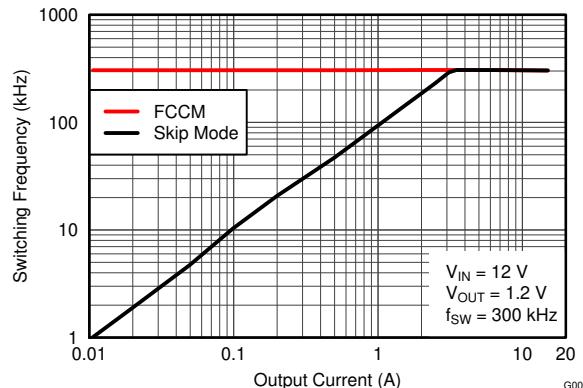

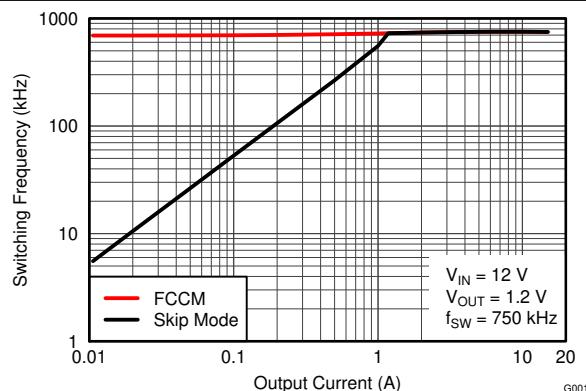

図 6-5. スイッチング周波数と出力電流との関係

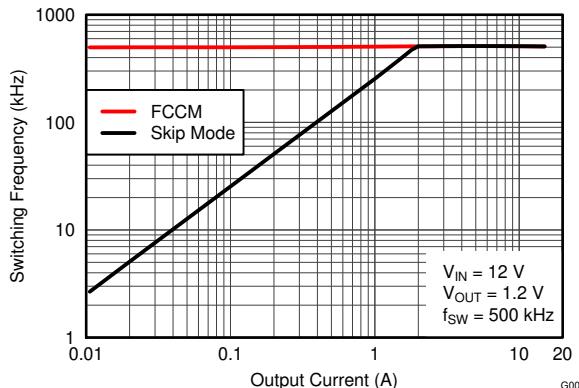

図 6-6. スイッチング周波数と出力電流との関係

## 6.6 代表的特性 (続き)

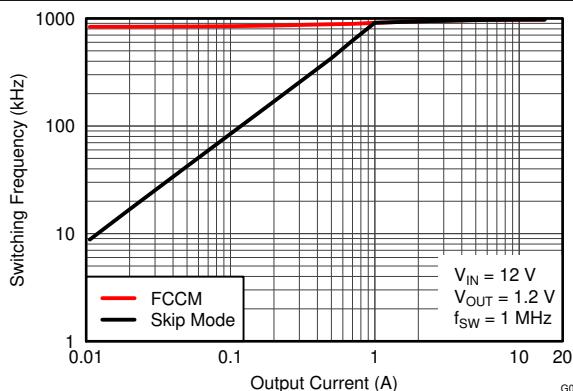

図 6-7. スイッチング周波数と出力電流との関係

図 6-8. スイッチング周波数と出力電流との関係

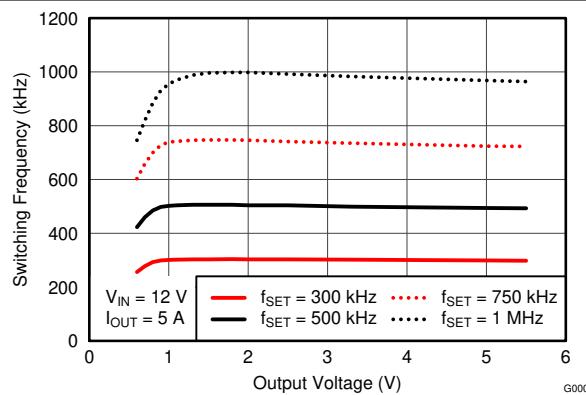

図 6-9. スイッチング周波数と出力電圧との関係

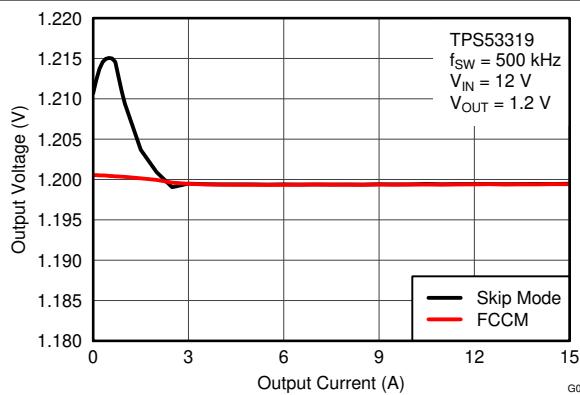

図 6-10. 出力電圧と出力電流の関係

図 6-11. 最出力電流と入力電圧との関係

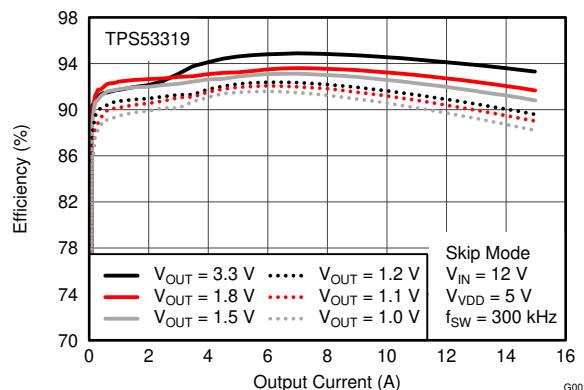

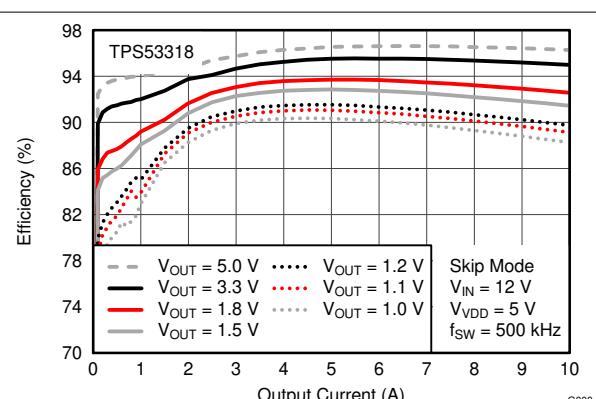

図 6-12. 効率と出力電流との関係

## 6.6 代表的特性 (続き)

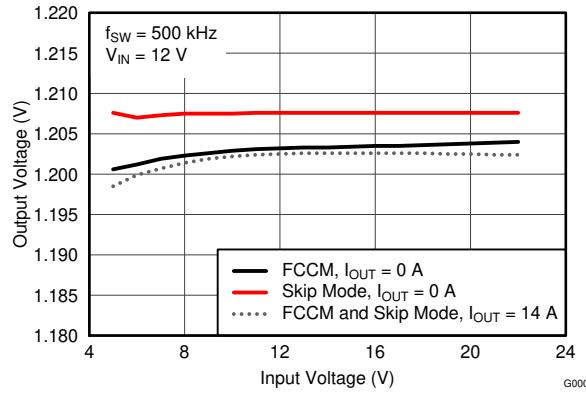

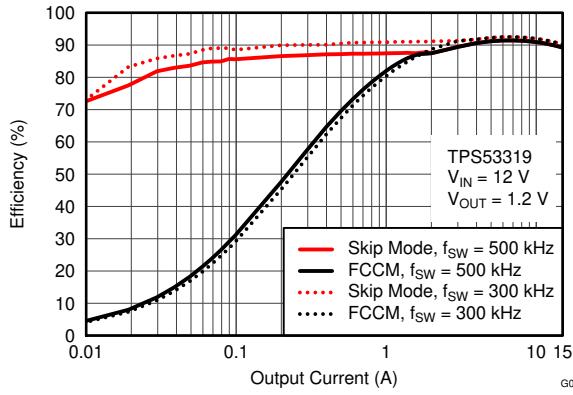

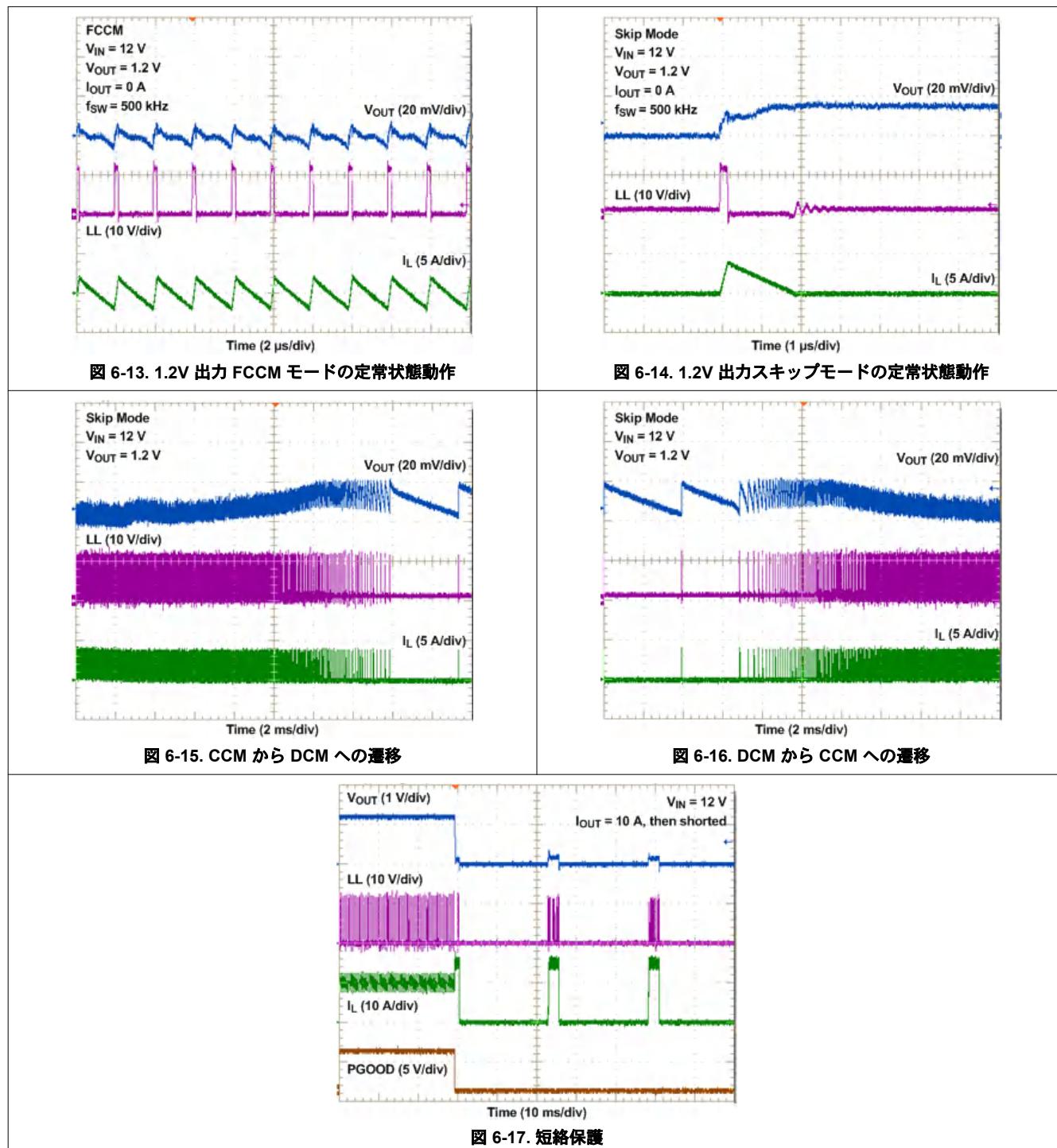

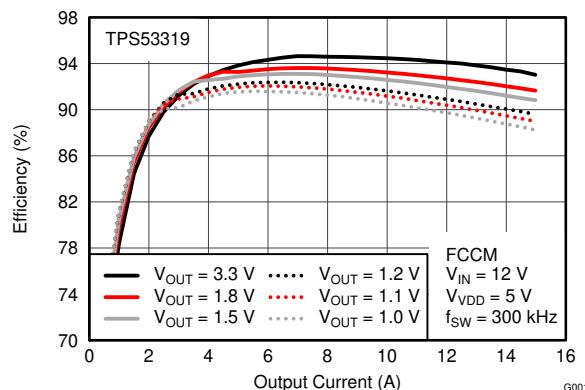

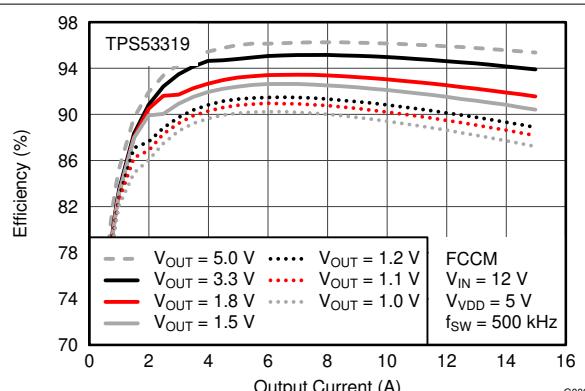

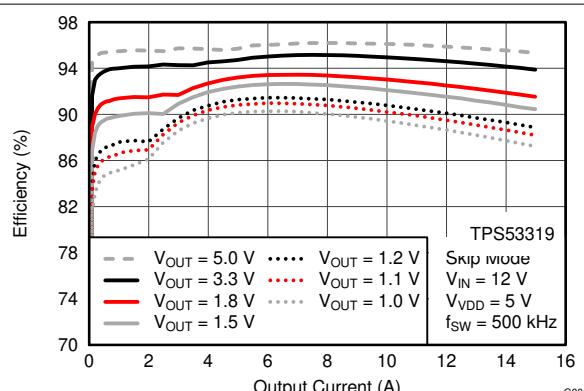

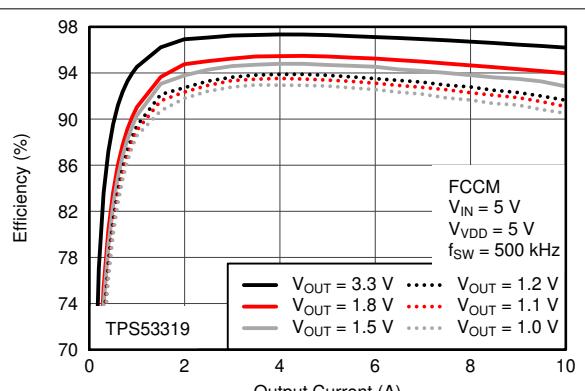

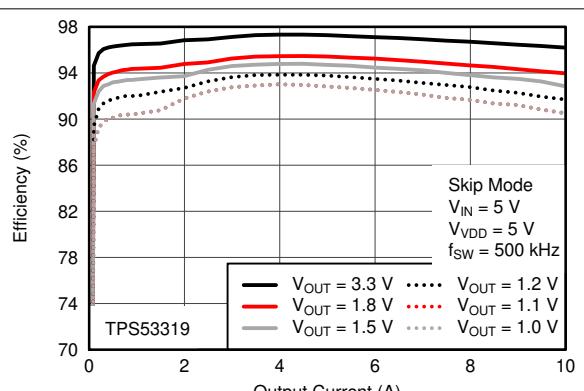

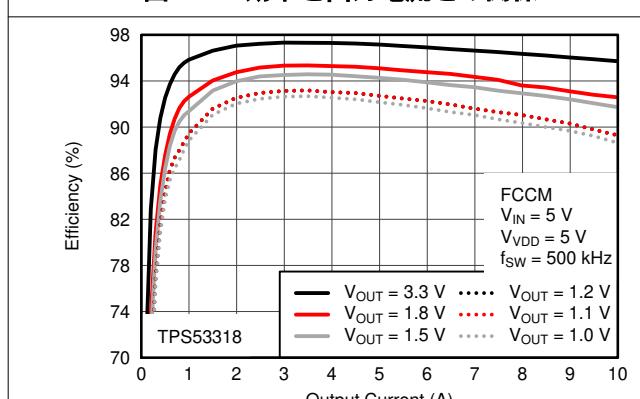

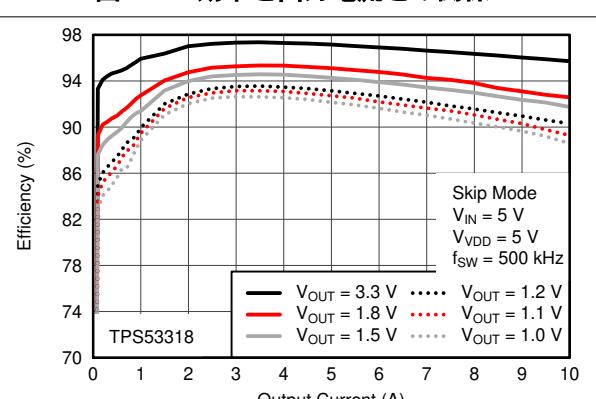

## 6.7 TPS53319 の代表的特性

図 6-18. 効率と出力電流との関係

図 6-19. 効率と出力電流との関係

図 6-20. 効率と出力電流との関係

図 6-21. 効率と出力電流との関係

図 6-22. 効率と出力電流との関係

図 6-23. 効率と出力電流との関係

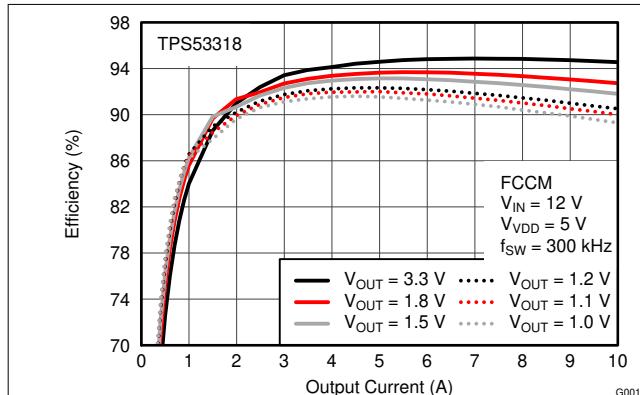

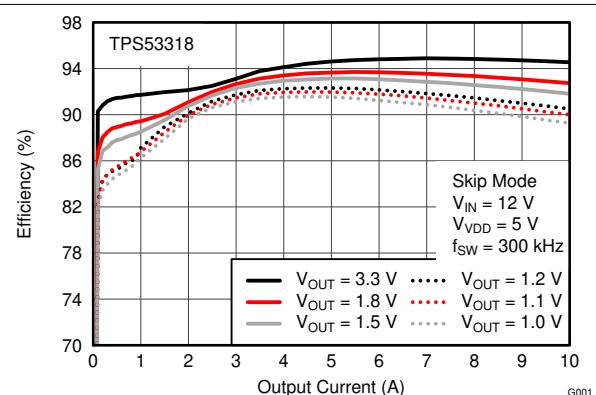

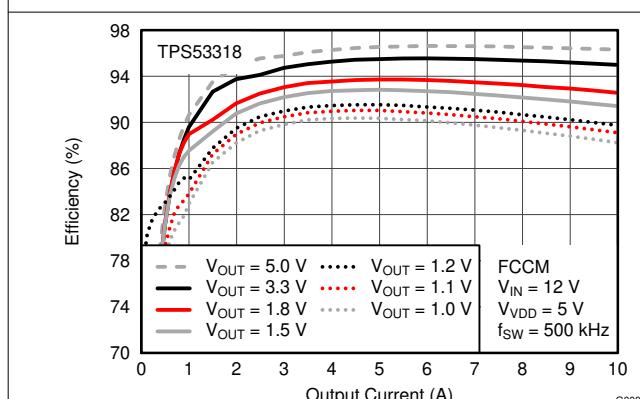

## 6.8 TPS53318 の代表的特性

図 6-24. 効率と出力電流との関係

図 6-25. 効率と出力電流との関係

図 6-26. 効率と出力電流との関係

図 6-27. 効率と出力電流との関係

図 6-28. 効率と出力電流との関係

図 6-29. 効率と出力電流との関係

## 7 詳細説明

### 7.1 概要

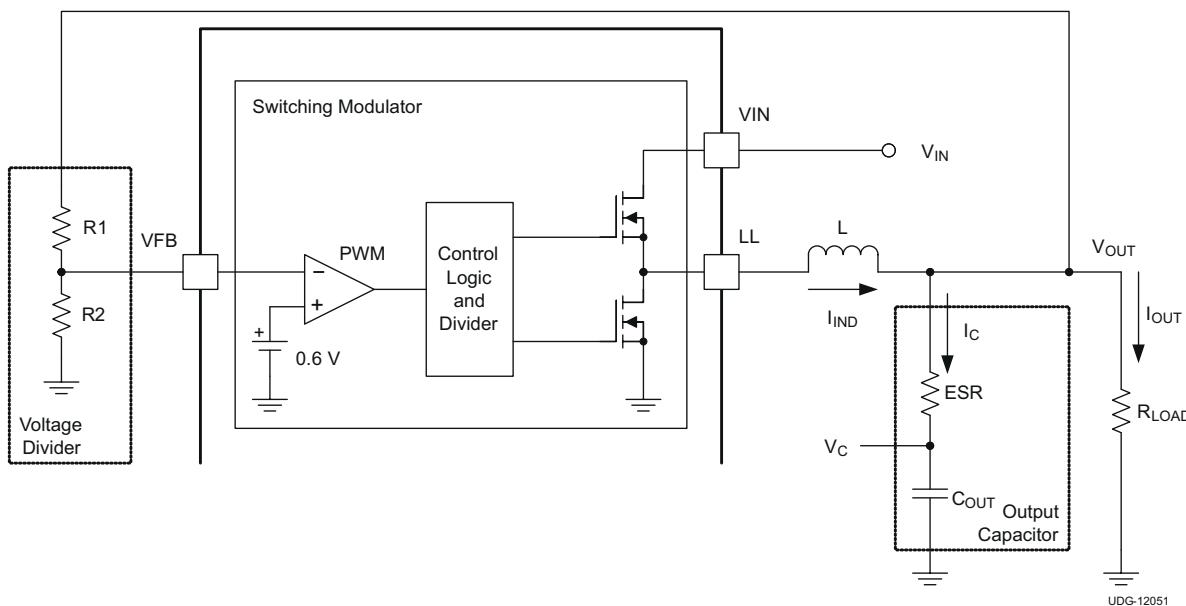

TPS53318 および TPS53319 は、高効率のシングル チャネル同期整流降圧コンバータであり、コンピュータや他の民生用デジタル機器で使用される低出力電圧のポイントオブロード アプリケーション向けに設計されています。デバイスは、独自の D-CAP IC モード制御と適応型オン時間アーキテクチャを採用しています。これらの組み合わせは、低デューティ比で超高速の負荷過渡応答が可能な最先端の DC/DC コンバータに最適な選択です。出力電圧範囲は 0.6V ~ 5.5V です。変換入力電圧範囲は 1.5V ~ 22V、VDD バイアス電圧は 4.5V ~ 25V です。D-CAP IC モードでは、出力コンデンサの等価直列抵抗 (ESR) を使用してデバイス電流を検出します。この制御方式の利点の 1 つは、外部の位相補償回路を必要としないことです。これにより、外付け部品点数の少ないシンプルな設計が可能になります。RF ピンからグランドまたは VREG に接続する抵抗を使用して、8 つのプリセットスイッチング周波数値を選択できます。適応型オン時間制御は、広い入出力電圧範囲にわたりプリセットスイッチング周波数を追跡して、負荷の昇圧時にスイッチング周波数を上昇させることができます。

これらのデバイスでは、MODE ピンを使用して、軽負荷状態時に自動スキップ モードまたは強制連続導通モード (FCCM) を選択できます。また、表 7-3 に示すように、MODE ピンを使用して、選択可能なソフトスタート時間を 0.7ms ~ 5.6ms の範囲で設定できます。

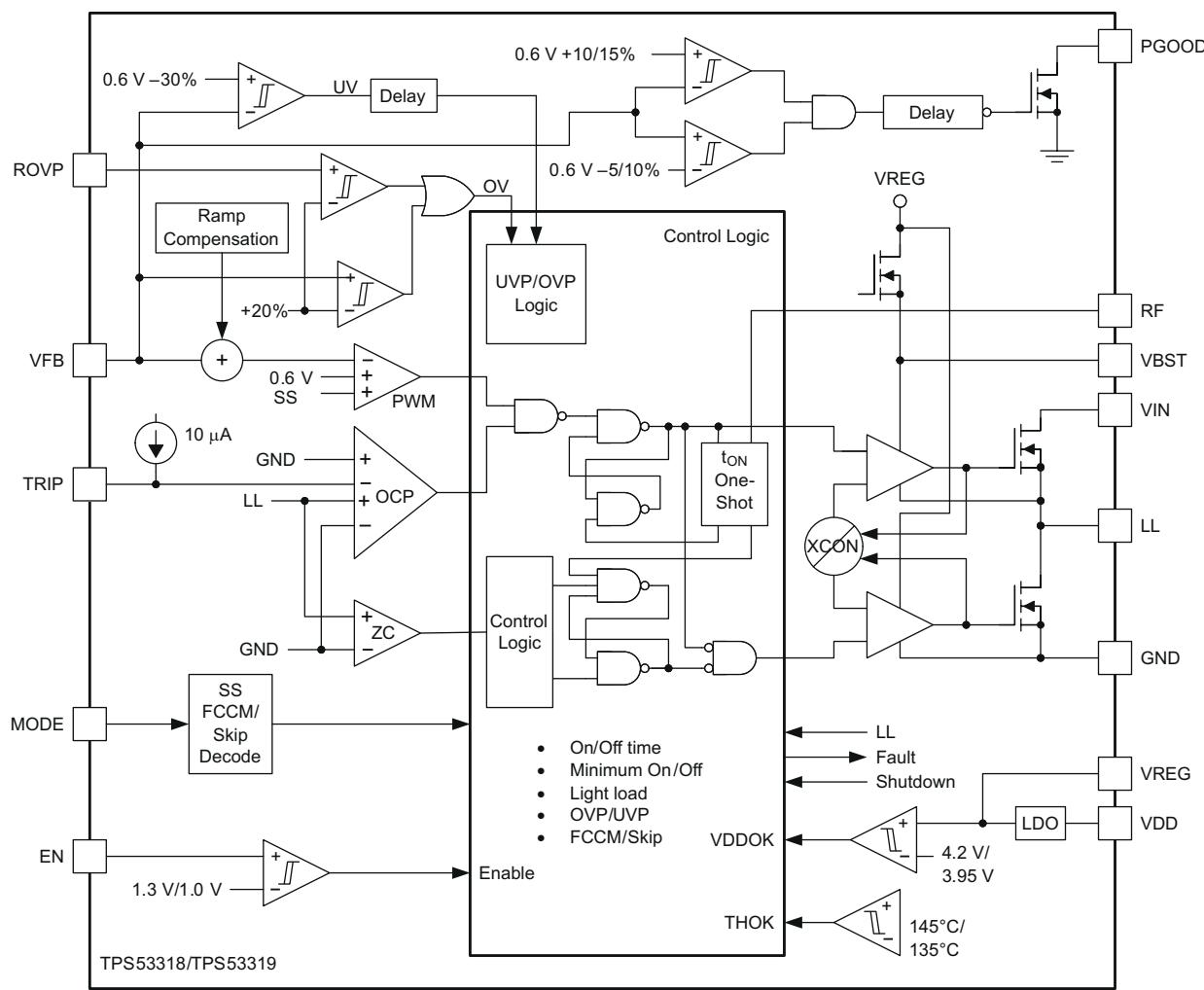

### 7.2 機能ブロック図

UDG-12041

A. セクション 7.2 に示すスレッショルドは標準値です。スレッショルドで許容される仕様については、セクション 6.5 を参照してください。

## 7.3 機能説明

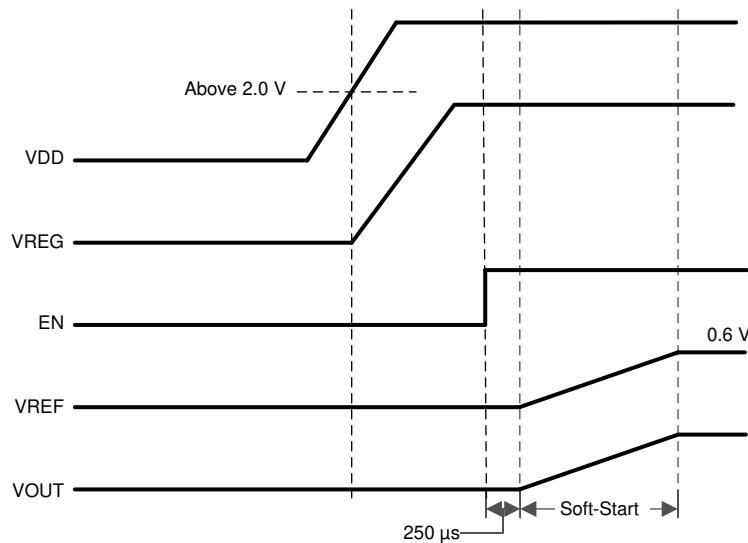

### 7.3.1 5V LDO および VREG のスタートアップ

TPS53318 と TPS53319 の両方のデバイスは、VDD からの入力と VREG への出力を利用する内部 5V LDO 機能を搭載しています。VDD 電圧が 2V を上回ると、内部 LDO が有効になり、VREG ピンに電圧が出力されます。VREG 電圧は、内部アナログ回路にバイアス電圧を提供し、ゲート駆動用電源電圧も供給します。

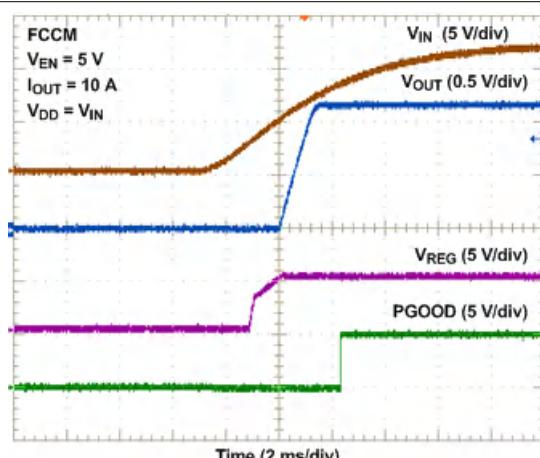

図 7-1. パワーアップシーケンス電圧波形

#### 注

5V LDO は EN ピンで制御されません。LDO は VDD が約 2V まで上昇すると常に起動します (図 7-1 を参照)。

### 7.3.2 適応型オン時間 D-CAP™ IC 制御と周波数選択

TPS53318 および TPS53319 デバイスにはスイッチング周波数を判定するための専用発振器がありません。ただし、入力電圧および出力電圧をオン時間ワンショットタイマにフィードフォワードすることにより、擬似定周波数で動作します。式 1 に示すように、適応型オン時間制御は、オン時間が入力電圧に反比例し、出力電圧に比例するよう調整します。

$$t_{ON} \propto \frac{V_{OUT}}{V_{IN}} \quad (1)$$

これにより、広い入力電圧範囲において、定常状態のスイッチング周波数がほぼ一定になります。スイッチング周波数は、表 7-1 に示すように、RF ピンと GND の間、または RF ピンと VREG ピンの間に接続された抵抗によって、8 つのプリセット値から選択できます。開放抵抗を維持すると、スイッチング周波数は 500kHz にセットされます。

表 7-1. 抵抗とスイッチング周波数

| 抵抗 ( $R_{RF}$ )<br>接続<br>値 (kΩ) | スイッチング周波数<br>( $f_{sw}$ )<br>(kHz) |     |

|---------------------------------|------------------------------------|-----|

|                                 | 接続先                                |     |

| 0                               | GND                                | 250 |

| 187                             | GND                                | 300 |

| 619                             | GND                                | 400 |

| オープン                            | n/a                                | 500 |

| 866                             | VREG                               | 600 |

| 309                             | VREG                               | 750 |

| 124                             | VREG                               | 850 |

| 0                               | VREG                               | 970 |

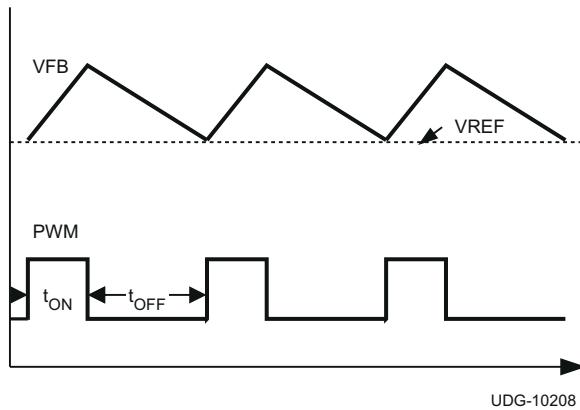

オフ時間は PWM コンパレータにより変調されます。VFB ノード電圧 (抵抗デバイダの中間点) は、ランプ信号で追加された内部 0.6V リファレンス電圧と比較されます。両方の信号が一致すると、PWM コンパレータは設定された信号をアサートしてオフ時間を終了します (ローサイド MOSFET をオフにして、ハイサイド MOSFET をオンにします)。設定された信号は、インダクタ電流レベルが OCP スレッショルドを下回ると有効になります。それ以外の場合、電流レベルがスレッショルドを下回るまでオフ時間が延長されます。

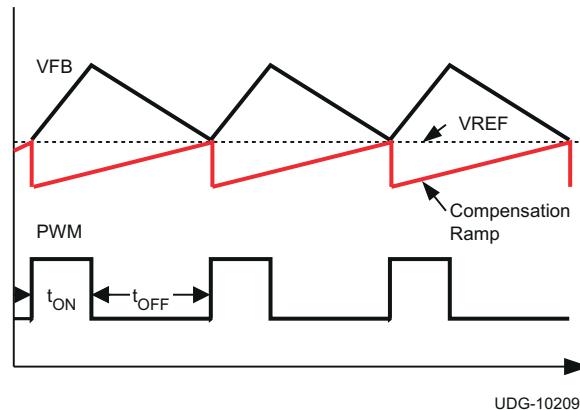

図 7-2 に示す波形はランプ補償なしのオン時間制御を示しています。図 7-3 に示す波形はランプ補償ありのオン時間制御を示しています。

図 7-2. ランプ補償なしのオン時間制御

図 7-3. ランプ補償ありのオン時間制御

### 7.3.3 ランプ信号

TPS53318 および TPS53319 デバイスでは、0.6V リファレンスにランプ信号を追加してジッタ性能を向上させています。前のセクションで説明したように、帰還電圧をリファレンス情報と比較して出力電圧をレギュレーション状態に維持します。リファレンスに小さなランプ信号を付加することで、新しいスイッチングサイクルの開始時の信号対雑音比が向上します。そのため、操作の過敏さが低減されて安定性が向上します。ランプ信号は、オンサイクルの開始時に-7mV となるよう制御され、定常状態でオフサイクルが終了すると 0mV となります。

スキップモード動作中に、不連続導通モード(DCM)になると、スイッチング周波数は公称周波数よりも低くなり、オフ時間は CCM でのオフ時間よりも長くなります。オフ時間が長いため、0mV を交差後のランプ信号が延長されます。ただし、DC オフセットを最小化するため、ランプ信号は 3mV でクランプされます。

### 7.3.4 適応型ゼロ交差

TPS53318 および TPS53319 デバイスには、適応型ゼロクロス回路が搭載され、スキップモード動作時にゼロインダクタ電流検出の最適化を行います。この機能では、ローサイド MOSFET の理想的なオフタイミングを追求し、Z-C コンパレータの固有オフセット電圧、および Z-C 検出回路の遅延時間を補償します。遅すぎる検出に起因する SW ノードのスイッチングを防止し、早すぎる検出に起因するダイオード導通期間を最小化します。その結果、軽負荷時の効率が改善されます。

### 7.3.5 出力放電制御

EN ピンが Low になると、TPS53318 および TPS53319 デバイスは、SW ピンと PGND ピンの間に接続された内部 MOSFET を使用して出力コンデンサを放電しますが、ハイサイドおよびローサイドの MOSFET はオフ状態に維持されます。標準的な放電抵抗は  $75\Omega$  です。ソフト放電は、EN が Low になったときにのみ発生します。放電回路は VDD から電力を供給されます。VDD が High の間、放電回路はアクティブのままでです。

### 7.3.6 パワーグッド

TPS53318 および TPS53319 デバイスには、スイッチャ出力がターゲット範囲内のときに High となるパワーグッド出力があります。パワーグッド機能はソフトスタートの終了後に起動されます。出力電圧が目標値の +10% および -5% 以内である場合、内部のコンパレータによりパワーグッド状態が検出され、内部で 1ms の遅延が加えられた後、パワーグッド信号が High になります。出力電圧が目標値の +15% または -10% を超えた場合、内部で 2μs の遅延が加えられた後、パワーグッド信号が Low になります。パワーグッド出力は、オープンドレイン出力であり、外部でプルアップする必要があります。

パワーグッド MOSFET には、VDD ピンを通して電源が供給されます。パワーグッドのロジックが有効であるためには、 $V_{VDD}$  が 1V より高い必要があります。TI では、PGOOD を VREG (または VREG から分圧された電圧) までプルアップすることを推奨しています。

### 7.3.7 電流センス、過電流、および短絡保護回路

TPS53318 および TPS53319 デバイスは、サイクルごとの過電流制限御を実現しています。オフ状態のとき、インダクタ電流が監視されます。インダクタ電流が過電流トリップレベルを超えている間、オフ状態が維持されます。良好な精度とコスト効率の高い設計を実現するため、TPS53319 デバイスは温度補償型 MOSFET  $R_{DS(on)}$  センシングをサポートしています。TRIP ピンはトリップ電圧設定抵抗  $R_{TRIP}$  を介して GND に接続する必要があります。TRIP 端子からは室温で標準  $10\mu\text{A}$  の電流 ( $I_{TRIP}$ ) が供給され、式 2 に示すように、トリップレベルは OCL トリップ電圧  $V_{TRIP}$  にセットされます。

$$V_{TRIP} (\text{mV}) = R_{TRIP} (\text{k}\Omega) \times I_{TRIP} (\mu\text{A}) \quad (2)$$

インダクタ電流は LL ピンで監視されます。GND ピンを正の電流センスノード、LL ピンを負の電流センスノードとして使用します。トリップ電流  $I_{TRIP}$  には、 $R_{DS(on)}$  の温度依存性を補償するための  $3000\text{ppm}/^\circ\text{C}$  の温度勾配があります。各デバイスでは、製造テストでのデバイス固有のオン抵抗測定に基づいて  $I_{TRIP}$  も調整され、デバイス間の OCP の変動が排除されます。最高精度の OCP を実現するには、デューティサイクルが 45% を超えないようにする必要があります。

オフ状態で比較されるため、 $V_{TRIP}$  によりインダクタ電流のバーレーレベルがセットされます。そのため、過電流スレッショルド  $I_{OCP}$  での負荷電流は、式 3 のように計算できます。

$$I_{OCP} = \frac{V_{TRIP}}{(32 \times R_{DS(on)})} + \frac{I_{IND(ripple)}}{2} = \frac{R_{TRIP}}{12.3 \times 10^3} + \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \quad (3)$$

ここで、

- $R_{TRIP}$  の単位は  $\Omega$  です

過電流または短絡状態では、負荷の電流が出力コンデンサの電流を上回るため、出力電圧が低下する傾向があります。最終的に、低電圧保護スレッショルドを横切ってシャットダウンされます。ヒップアップ遅延 (16ms + 0.7ms のソフトスタート)

後に、コントローラが再起動します。過電流状態が続いている場合は、同じ手順が繰り返され、デバイスはヒップ モードに入ります。

$$t_{HIC(\text{wait})} = (2^n + 257) \times 4 \mu\text{s} \quad (4)$$

ここで、

- ソフトスタート時間の選択に応じて、 $n = 8, 9, 10$ 、または  $11$  となります

$$t_{HIC(\text{dly})} = 7 \times (2^n + 257) \times 4 \mu\text{s} \quad (5)$$

**表 7-2. ヒップのタイミング**

| 選択したソフトスタート時間 ( $t_{SS}$ )<br>(ms) | ヒップ待機時間<br>( $t_{HIC(\text{wait})}$ ) (ms) | ヒップ遅延時間<br>( $t_{HIC(\text{delay})}$ ) (ms) |

|------------------------------------|--------------------------------------------|---------------------------------------------|

| 0.7                                | 2.052                                      | 14.364                                      |

| 1.4                                | 3.076                                      | 21.532                                      |

| 2.8                                | 5.124                                      | 35.868                                      |

| 5.6                                | 9.220                                      | 64.540                                      |

TPS53318 デバイスでは、OCP スレッショルドが内部的に  $10.5\text{A}$  にクランプされます。TPS53318 デバイスの推奨  $R_{TRIP}$  値は  $150\text{k}\Omega$  未満です。

### 7.3.8 過電圧および低電圧保護

TPS53318 および TPS53319 デバイスは、抵抗分割されたフィードバック電圧を監視して、過電圧および低電圧を検出します。帰還電圧がターゲット電圧の  $70\%$  を下回ると、UVP コンパレータ出力は High になり、内部 UVP 遅延カウンタがカウントを開始します。 $1\text{ms}$  後、デバイスはハイサイドとローサイド両方の MOSFET ドライバをオフにラッチします。コントローラはヒップ遅延後に再起動します (表 7-2 を参照)。この機能は、ソフトスタートの完了から  $1.5\text{ms}$  後にイネーブルになります。

帰還電圧がターゲット電圧の  $120\%$  を超えると、OVP コンパレータ出力が High になり、回路はハイサイド MOSFET ドライバをオフにラッチし、ローサイド MOSFET ドライバをオンにラッチします。出力電圧が低下します。ハイサイドドライバとローサイドドライバの両方に対するラッチオフ動作の前に、出力電圧が  $1\text{ms}$  にわたって UVP スレッショルド電圧未満にプルダウンされる必要があります。 $1\text{ms}$  が経過すると、ドライバはオフにラッチされます。

### 7.3.9 冗長過電圧保護 (OVP)

TPS53318 および TPS53319 デバイスは、OVP 保護用の冗長入力を備えています。ROVP ピンは出力電圧から分圧された電圧を検出し、OVP コンパレータに電圧を送信します。この電圧がターゲット電圧の  $120\%$  を超えると、過電圧保護が作動し、ローサイド FET がオンになります。出力電圧が UVP スレッショルドを下回ると、デバイスはオフにラッチされます。

この冗長 OVP 機能は通常、帰還ループが開いている状況や、GND に短絡した VFB ピンが存在している状況から保護します。ROVP ピンには、 $1.5\text{M}\Omega$  の内部プルアップ抵抗があります。

#### 注

冗長 OVP 機能を必要としないアプリケーションでは、ROVP ピンを GND に接続します。ROVP ピンはフローティングのままにしないでください。

### 7.3.10 UVLO 保護

TPS53318 および TPS53319 デバイスは、VREG 低電圧誤動作防止保護 (UVLO) を搭載しています。VREG 電圧が 3.95V を下回る場合、デバイスはシャットオフします。VREG の電圧が 4.2V より高くなると、デバイスは再起動します。これは非ラッチ型の保護機能です。

### 7.3.11 サーマルシャットダウン

TPS53318 および TPS53319 デバイスは、内部ダイの温度を監視します。温度がスレッショルド値 (通常 145°C) を超えると、デバイスはシャットダウンします。温度がスレッショルド値を約 10°C 下回ると、デバイスはオンに戻ります。これは非ラッチ方式の保護です。

### 7.3.12 小信号モデル

小信号ループ解析から、D-CAP IC モードを使用する降圧コンバータは、図 7-4 に示すように簡略化できます。

図 7-4. 簡略化された変調器モデル

出力電圧は内部リファレンス電圧と比較されます (単純化のため、ここではランプ信号が無視されます)。PWM コンパレータによりハイサイド MOSFET をオンにするタイミングが決定します。このコンパレータのゲインおよび速度は、各オン サイクルの開始時に電圧をほぼ一定に維持するのに十分なだけ高いと仮定できます。

$$H(s) = \frac{1}{s \times ESR \times C_{OUT}} \quad (6)$$

ループの安定性を確保するため、以下で定義される 0dB の周波数  $f_0$  をスイッチング周波数の 1/4 より低くする必要があります。

$$f_0 = \frac{1}{2\pi \times ESR \times C_{OUT}} \leq \frac{f_{SW}}{4} \quad (7)$$

式 7 によれば、D-CAP IC モード変調器のループ安定性は、主にコンデンサの化学的性質によって決定されます。たとえば、特殊ポリマー コンデンサ (SP-CAP) は数百  $\mu$ F オーダーの出力容量と 10m $\Omega$  程度の ESR を持ちます。これにより、 $f_0$  は 100kHz 以下の位数となり、安定したループが形成されます。ただし、セラミックコンデンサは  $f_0$  が 700kHz を

超えるため、この変調器で使用する場合は特別な注意が必要となります。セラミックコンデンサのアプリケーション回路については、[セクション 7.3.13](#) で説明しています。

### 7.3.13 すべてセラミック出力コンデンサを使用した外付け部品の選択

セラミック出力コンデンサを使用する場合、[式 7](#) の安定条件を満たすことはできません。図 8-1 に示すリップル注入手法は、VFB ピンのリップルを増加させて、システムを安定化するために実装します。[セクション 8.2.1.2](#) の手順 1 ~ 6 を使用して選択した部品に加え、リップル注入部品を選択する必要があります。C2 の値は 1nF に固定できます。C1 の値は 10nF ~ 200nF の範囲で選択できます。

$$\frac{L \times C_{OUT}}{R7 \times C1} > N \times \frac{t_{ON}}{2} \quad (8)$$

ここで、

- N は L および C<sub>OUT</sub> の変動を考慮するための係数です

N は安定性のために十分なマージンを確保するためにも使用されます。TI では、V<sub>OUT</sub> ≤ 1.8V には N = 2、V<sub>OUT</sub> ≥ 3.3V または L ≤ 250nH には N = 4 とすることを推奨しています。DC バイアスが大きくなると実効出力容量が大幅に小さくなるため、V<sub>OUT</sub> が高い場合は N の値を大きくする必要があります。たとえば、6.3V、22μF のセラミックコンデンサは、5V バイアス時に実効容量がわずか 8μF まで低下する場合があります。

VFB ピンの電圧はバレーでレギュレーション化されるため、VFB ピンのリップルが増加すると VFB の DC 値が上昇します。VFB ピンに結合する AC リップルには 2 つの成分があり、1 つは SW ノードから結合し、もう 1 つは VOUT ピンから結合します。その成分は、等価直列インダクタンス (ESL) に起因する出力電圧リップルを無視する場合は、[式 9](#) と [式 10](#) を使用して計算できます。

$$V_{INJ\_SW} = \frac{V_{IN} - V_{OUT}}{R7 \times C1} \times \frac{D}{f_{SW}} \quad (9)$$

$$V_{INJ\_OUT} = ESR \times I_{IND(ripple)} + \frac{I_{IND(ripple)}}{8 \times C_{OUT} \times f_{SW}} \quad (10)$$

TI では、V<sub>INJ\\_SW</sub> を 50mV 未満にすることを推奨しています。計算した V<sub>INJ\\_SW</sub> が 50mV より大きい場合は、他のパラメータを調整して V<sub>INJ\\_SW</sub> を下げる必要があります。たとえば、C<sub>OUT</sub> を増加してより高い R7 値の [式 8](#) の条件を満たして、V<sub>INJ\\_SW</sub> を低減します。

VFB ピンの DC 電圧は、[式 11](#) で計算できます：

$$V_{VFB} = 0.6 + \frac{V_{INJ\_SW} + V_{INJ\_OUT}}{2} \quad (11)$$

抵抗デバイダの値は [式 12](#) で決定できます：

$$R1 = \frac{V_{OUT} - V_{VFB}}{V_{VFB}} \times R2 \quad (12)$$

## 7.4 デバイスの機能モード

### 7.4.1 イネーブル、ソフトスタート、モード選択

EN ピンの電圧がイネーブルスレッショルド電圧 (標準 1.3V) を上回ると、コントローラはスタートアップシーケンスを開始します。内部 LDO レギュレータが直ちに起動し、VREG ピンで 5V にレギュレーション化されます。コントローラは最初の 250μs の間に RF ピンに接続されたスイッチング周波数設定抵抗をキャリブレーションします。その後、コントローラはスイ

スイッチング周波数コードを内部レジスタに保存します。この期間中に、このピンに接続された抵抗も MODE ピンでセンスされ、ソフトスタート時間が決定されます。この段階では、スイッチングは禁止されます。2 番目の段階では、内部 DAC がリファレンス電圧の 0V から 0.6V までのランプアップを開始します。MODE ピンの設定に応じて、ランプアップ時間は 0.7ms から 5.6ms まで変化します。負荷電流にかかわりなく、起動時の出力電圧は滑らかで一定のランプアップが維持されます。

注

イネーブル電圧は VREG の 0.8V を超えないようにしてください。

**表 7-3. ソフト スタートおよびモード選択**

| モード選択                 | アクション      | ソフトスタート時間<br>(t <sub>ss</sub> ) (ms) | R <sub>MODE</sub> (kΩ) |

|-----------------------|------------|--------------------------------------|------------------------|

| 自動スキップ                | GND にプルダウン | 0.7                                  | 39                     |

|                       |            | 1.4                                  | 100                    |

|                       |            | 2.8                                  | 200                    |

|                       |            | 5.6                                  | 475                    |

| 強制 CCM <sup>(1)</sup> | PGOOD に接続  | 0.7                                  | 39                     |

|                       |            | 1.4                                  | 100                    |

|                       |            | 2.8                                  | 200                    |

|                       |            | 5.6                                  | 475                    |

(1) MODE が抵抗 R<sub>MODE</sub> を介して PGOOD に接続されている場合は、PGOOD ピンが High になるとデバイスは FCCM に移行します。

ソフトスタート期間の開始後、MODE ピンは、自動スキップまたは FCCM モード動作を決定する内部コンパレータへの入力となります。MODE 電圧が 1.3V を上回ると、コンバータは FCCM モードに移行します。それ以外の場合は、コンバータは軽負荷状態で自動スキップモードで動作します。通常、FCCM モードを選択する場合、MODE ピンは R<sub>MODE</sub> 抵抗経由で PGOOD に接続されるため、PGOOD が High になるまでの間、コンバータは自動スキップモードに保持されます。

#### 7.4.2 自動スキップエコモード軽負荷動作

R<sub>MODE</sub> が MODE ピンを Low にプルする間、コントローラは高効率を維持するために軽負荷状態ではスイッチング周波数が自動的に低下します。具体的には、重負荷状態から出力電流が減少すると、インダクタ電流も減少し、最終的にはそのリップル付きバーがゼロレベルに達する点まで至ります。これは、連続導通モードと不連続導通モードの境界に当たります。このゼロインダクタ電流が検出されると、同期 MOSFET がオフになります。負荷電流がさらに減少すると、コンバータは不連続導通モード (DCM) に入ります。オン時間は連続導通モードのときとほぼ同じに保持されるため、出力コンデンサを小さな負荷電流でリファレンス電圧レベルまで放電するには、より長い時間がかかります。軽負荷動作への遷移点 I<sub>OUT(LL)</sub> (つまり、連続導通モードと不連続導通モード間のスレッショルド) は、式 13 のように計算できます。

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \quad (13)$$

ここで、

- f<sub>sw</sub> は PWM スイッチング周波数です

軽負荷状態でのスイッチング周波数と出力電流の関係は、L、V<sub>IN</sub>、V<sub>OUT</sub> の関数ですが、式 13 に示す I<sub>OUT(LL)</sub> からの出力電流にほぼ比例して減少します。たとえば、周波数設定が 300kHz の場合、I<sub>OUT(LL)</sub>/5 で 60kHz になります。

### 7.4.3 強制連続導通モード

MODE ピンが抵抗を介して PGOOD モードに接続されている場合は、軽負荷時でもコントローラが連続導通モード (CCM) で動作します。このモードでは、負荷範囲全体にわたってスイッチング周波数がほぼ一定に保たれます。これは効率低下を犠牲にしてもスイッチング周波数の厳密な制御が必要なアプリケーションに適しています。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPS53318 および TPS53319 デバイスは、高効率のシングルチャネル同期整流降圧コンバータであり、コンピュータや他の民生用デジタル機器で使用される低出力電圧のポイントオブロードアプリケーションに適しています。デバイスは、独自の D-CAP IC モード制御と適応型オン時間アーキテクチャを採用しています。これらの組み合わせにより、低デューティサイクルで超高速の負荷過渡応答が可能な最先端の DC/DC コンバータを構築できます。出力電圧範囲は 0.6V ~ 5.5V です。変換入力電圧範囲は 1.5V ~ 22V、VDD バイアス電圧は 4.5V ~ 25V です。D-CAP IC モードでは、出力コンデンサの等価直列抵抗 (ESR) を使用してデバイス電流を検出します。この制御方式の利点として、この制御方式に外部位相補償回路が必要ないことが挙げられます。これにより、外付け部品数が少なくシンプルな設計が可能になります。RF ピンからグランドまたは VREG に接続する抵抗を使用して、8 つのプリセットスイッチング周波数を選択できます。適応型オン時間制御は、広い入出力電圧範囲にわたりプリセットスイッチング周波数を追跡して、負荷の昇圧時にスイッチング周波数を上昇させることができます。

### 8.2 代表的なアプリケーション

#### 8.2.1 バルク出力コンデンサを使用するアプリケーション、冗長過電圧保護機能 (OVP) 無効化

図 8-1. 代表的なアプリケーション回路、冗長過電圧保護無効化

#### 8.2.1.1 設計要件

この設計では、表 8-1 に記載されているパラメータを使用します。

**表 8-1. 設計仕様**

| パラメータ         |              | テスト条件                                                       | 最小値   | 標準値  | 最大値 | 単位               |

|---------------|--------------|-------------------------------------------------------------|-------|------|-----|------------------|

| <b>入力特性</b>   |              |                                                             |       |      |     |                  |

| $V_{IN}$      | 電圧範囲         |                                                             | 5     | 12   | 18  | V                |

| $I_{MAX}$     | 最大入力電流       | $V_{IN} = 5V, I_{OUT} = 8A$                                 |       | 2.5  |     | A                |

|               | 無負荷時入力電流     | $V_{IN} = 12V, I_{OUT} = 0 A$ (自動スキップモード)                   |       | 1    |     | mA               |

| <b>出力特性</b>   |              |                                                             |       |      |     |                  |

| $V_{OUT}$     | 出力電圧         |                                                             | 1.2   |      |     |                  |

|               | 出力電圧レギュレーション | ラインレギュレーション、 $5V \leq V_{IN} \leq 14V$ (FCCM)               | 0.2%  |      |     | V                |

|               |              | 負荷レギュレーション、 $V_{IN} = 12V, 0 A \leq I_{OUT} \leq 8A$ (FCCM) | 0.5%  |      |     |                  |

| $V_{RIPPLE}$  | 出力電圧リップル     | $V_{IN} = 12V, I_{OUT} = 8A$ (FCCM)                         | 10    |      |     | mV <sub>PP</sub> |

| $I_{LOAD}$    | 出力負荷電流       |                                                             | 0     | 8    |     |                  |

| $I_{OVER}$    | 出力過電流        |                                                             |       | 11   |     | A                |

| $t_{SS}$      | ソフトスタート時間    |                                                             | 1     |      |     | ms               |

| <b>システム特性</b> |              |                                                             |       |      |     |                  |

| $f_{SW}$      | スイッチング周波数    |                                                             | 500   | 1000 |     | kHz              |

| $\eta$        | ピーク効率        | $V_{IN} = 12 V, V_{OUT} = 1.2 V, I_{OUT} = 4 A$             | 91%   |      |     |                  |

|               | 全負荷効率        | $V_{IN} = 12 V, V_{OUT} = 1.2 V, I_{OUT} = 8 A$             | 91.5% |      |     |                  |

| $T_A$         | 動作温度         |                                                             | 25    |      |     | °C               |

### 8.2.1.2 詳細な設計手順

有機半導体や特殊なポリマー出力コンデンサを使用する際の外付け部品の選択は簡単なプロセスです。

#### 8.2.1.2.1 ステップ1：動作モードとソフトスタート時間の選択

表 7-3 を使用して、動作モードとソフトスタート時間を選択します。

#### 8.2.1.2.2 ステップ2：スイッチング周波数の選択

表 7-1 を使用して 250kHz ~ 1MHz のスイッチング周波数を選択します。

#### 8.2.1.2.3 ステップ3：インダクタの選択

リップル電流が最大出力電流の約 1/4 ~ 1/2 になるように、インダクタンス値を決定する必要があります。リップル電流が大きくなると、出力リップル電圧が増加して信号対雑音比が向上し安定動作が保証されますが、インダクタのコア損失が増加します。1/3 リップル電流と最大出力電流比を使用する場合、インダクタンスは 式 14 で決定できます。

$$L = \frac{1}{I_{IND(ripple)} \times f_{SW}} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} = \frac{3}{I_{OUT(max)} \times f_{SW}} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} \quad (14)$$

インダクタは良好な効率を達成するために Low DCR が必要です。また、ピーク インダクタ電流から飽和までの間に十分な余裕が必要です。ピークインダクタ電流は 式 15 で推定できます。

$$I_{IND(peak)} = \frac{V_{TRIP}}{32 \times R_{DS(on)}} + \frac{1}{L \times f_{SW}} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} \quad (15)$$

#### 8.2.1.2.4 ステップ4：出力コンデンサを選択

有機半導体コンデンサまたは特殊ポリマーコンデンサを使用する際には、ループ安定性、容量、および ESR は [式 7](#) を満たす必要があります。ジッタ性能については、[式 16](#) は ESR を決定するための適切な出発点です。

$$ESR = \frac{V_{OUT} \times 10mV \times (1-D)}{0.6V \times I_{IND(ripple)}} = \frac{10mV \times L \times f_{SW}}{0.6V} = \frac{L \times f_{SW}}{60} (\Omega) \quad (16)$$

ここで、

- D はデューティサイクルです

- 必要な出力リップルスロープは、 $t_{SW}$  (スイッチング周期) ごとに (VFB 端子の電圧で) 約 10mV です。

#### 8.2.1.2.5 ステップ5：R1 と R2 の値を決定

出力電圧は、[図 7-4](#) に示す分圧抵抗 R1 および R2 によってプログラマれます。R1 を VFB ピンと出力の間に接続して、R2 を VFB ピンと GND の間に接続します。推奨の R2 値は  $10k\Omega \sim 20k\Omega$  です。[式 17](#) を使用して R1 を決定します。

$$R1 = \frac{V_{OUT} - \frac{I_{IND(ripple)} \times ESR}{2} - 0.6}{0.6} \times R2 \quad (17)$$

#### 8.2.1.2.6 ステップ6：過電流設定抵抗を選択

過電流設定抵抗  $R_{TRIP}$  は [式 18](#) で決定できます。

$$R_{TRIP} = \left( I_{OCP} - \left( \frac{1}{2 \times L \times f_{SW}} \right) \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \right) \times 12.3 \quad (18)$$

ここで、

- $R_{TRIP}$  の単位は  $k\Omega$  です。

### 8.2.1.3 アプリケーション曲線

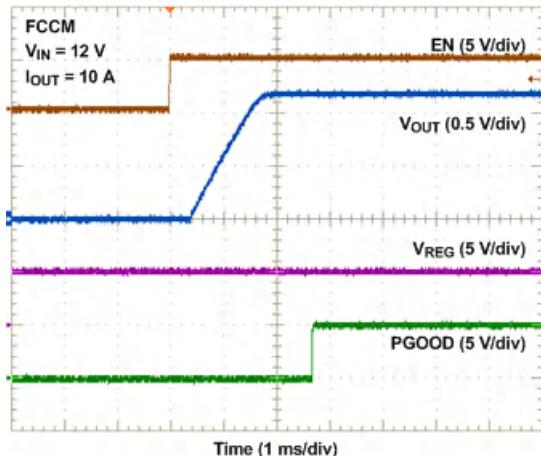

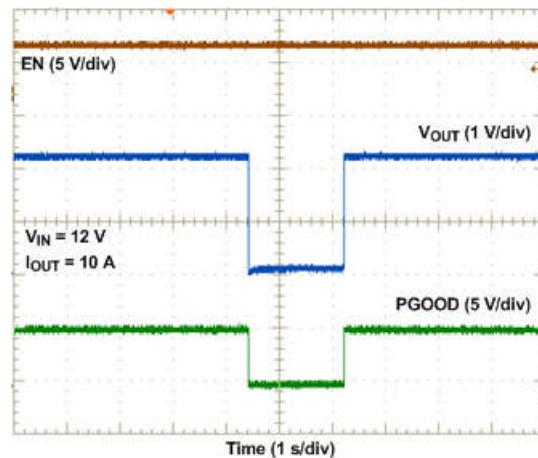

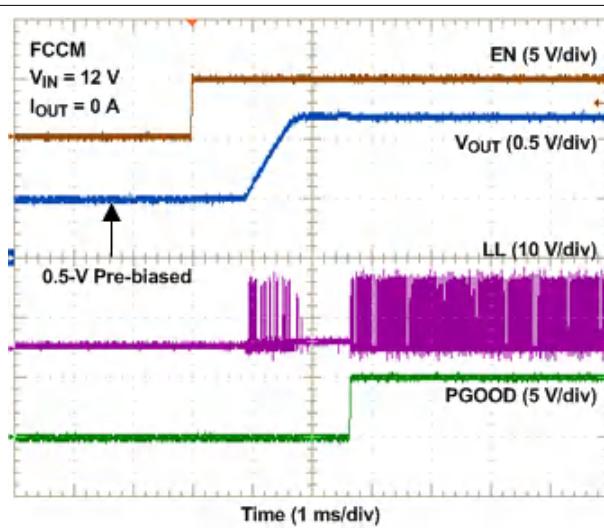

図 8-2. スタートアップ

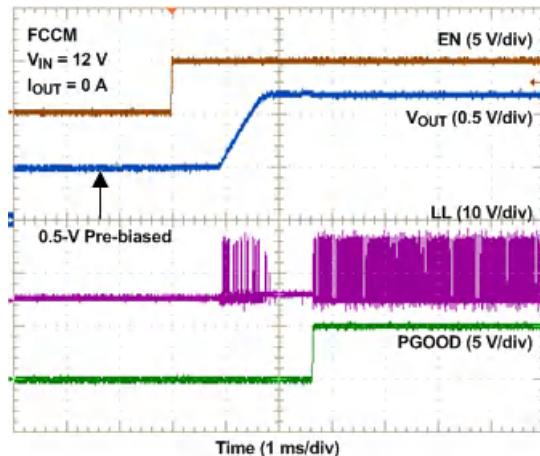

図 8-3. プリバイアス スタートアップ

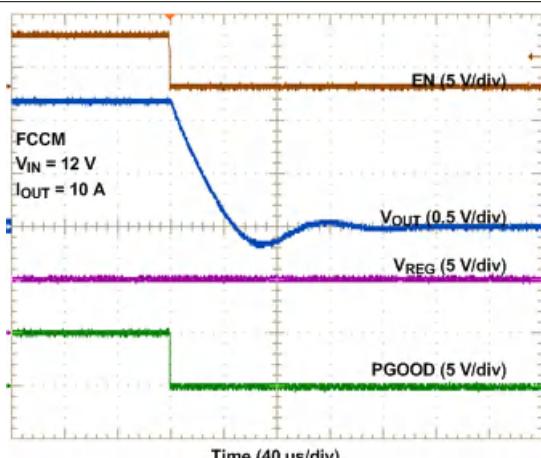

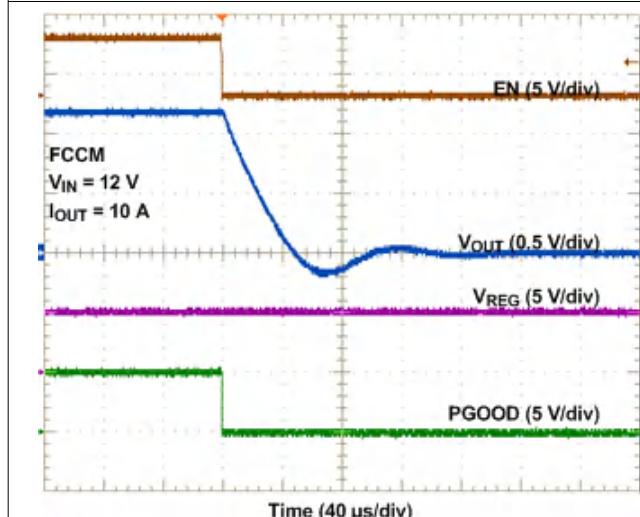

図 8-4. シャットダウン

図 8-5. UVLO のスタートアップ

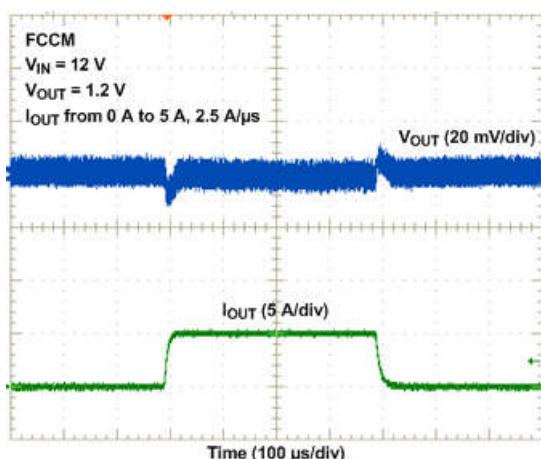

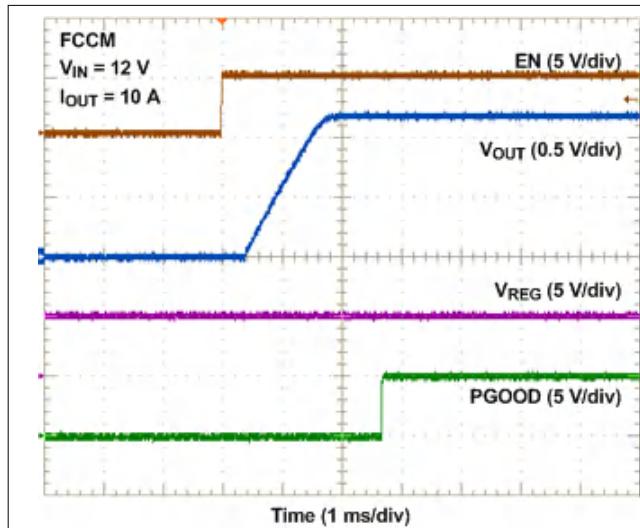

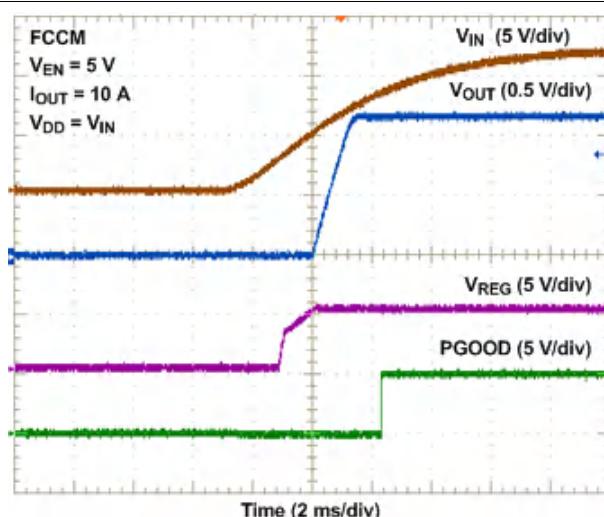

図 8-6. FCCM の負荷過渡応答

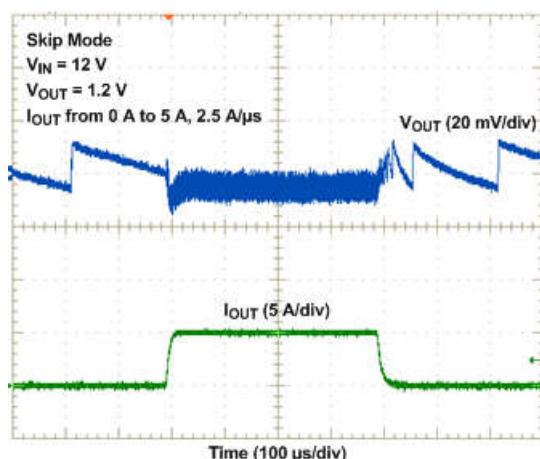

図 8-7. スキップ モード負荷過渡応答

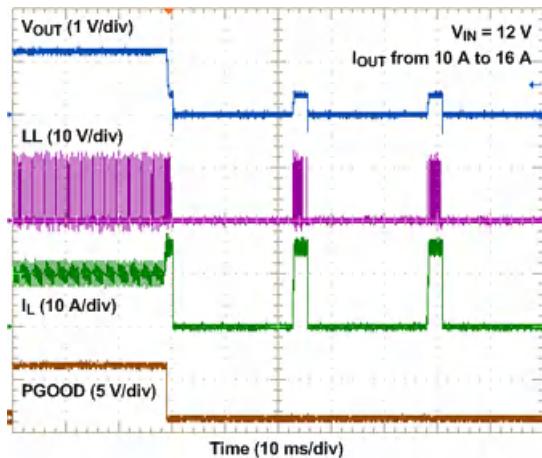

図 8-8. 過電流保護

図 8-9. 過熱保護

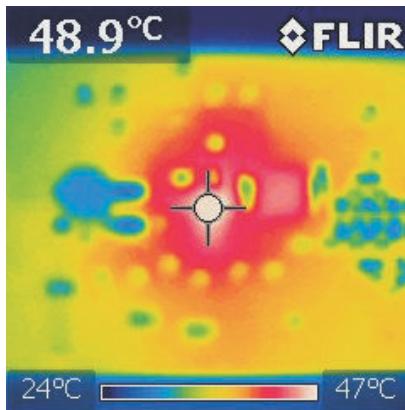

TPS53319 EVM       $V_{IN} = 12V$        $V_{OUT} = 1.2V$

$I_{OUT} = 14A$        $f_{sw} = 500kHz$        $T_A = 25^{\circ}C$

通気なし

図 8-10. サーマルシグネチャ

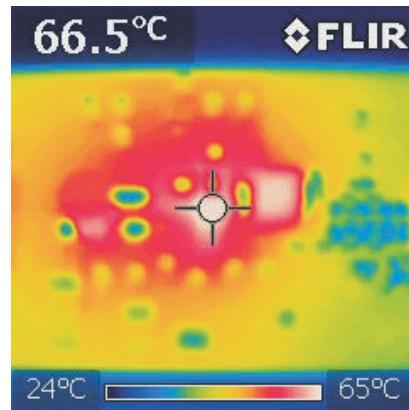

TPS53319 EVM       $V_{IN} = 12V$        $V_{OUT} = 5V$

$I_{OUT} = 14A$        $f_{SW} = 500kHz$        $T_A = 25^\circ C$

通気なし

図 8-11. サーマルシグネチャ

### 8.2.2 セラミック出力コンデンサを使用するアプリケーション、冗長過電圧保護機能(OVP) 有効化

図 8-12. 代表的なアプリケーション回路、冗長 OVP 有効化

#### 8.2.2.1 設計要件

この設計では、表 8-1 に記載されているパラメータを使用します。

#### 8.2.2.2 詳細な設計手順

この設計例の詳細な設計手順は前述の設計例の手順と似ています。違いについて次の 2 つのセクションで説明します。

##### 8.2.2.2.1 すべてセラミック出力コンデンサを使用した外付け部品の選択

すべての出力セラミックコンデンサを使用するこの設計のガイドラインについては、セクション 7.3.13 を参照してください。

##### 8.2.2.2.2 冗長過電圧保護

冗長過電圧レベルは出力電圧設定に応じてプログラムされ、図 8-12 に示すように、抵抗 R11 と R12 によって制御されます。抵抗 R11 を ROVP ピンと出力の間に接続して、抵抗 R12 を ROVP ピンと GND の間に接続します。この設計では、抵抗 R11 の値が抵抗 R1 の値 (またはわずかに大きい値) と一致し、抵抗 R2 の値が抵抗 R12 の値と一致させることを推奨します。

### 8.2.2.3 アプリケーション曲線

図 8-13. スタートアップ

図 8-14. プリバイアス スタートアップ

図 8-15. シャットダウン

図 8-16. UVLO のスタートアップ

## 8.3 電源に関する推奨事項

デバイスは、1.5V ~ 22V (4.5V ~ 25V バイアス印加) の入力電源電圧範囲で動作するように設計されています。この入力電源には適切なレギュレーションが行われる必要があります。入力電源および内部レギュレータの適切なバイパスも、PCB レイアウトや接地方式と同様に、ノイズ性能にとって重要です。セクション 8.4 の推奨事項を参照してください。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

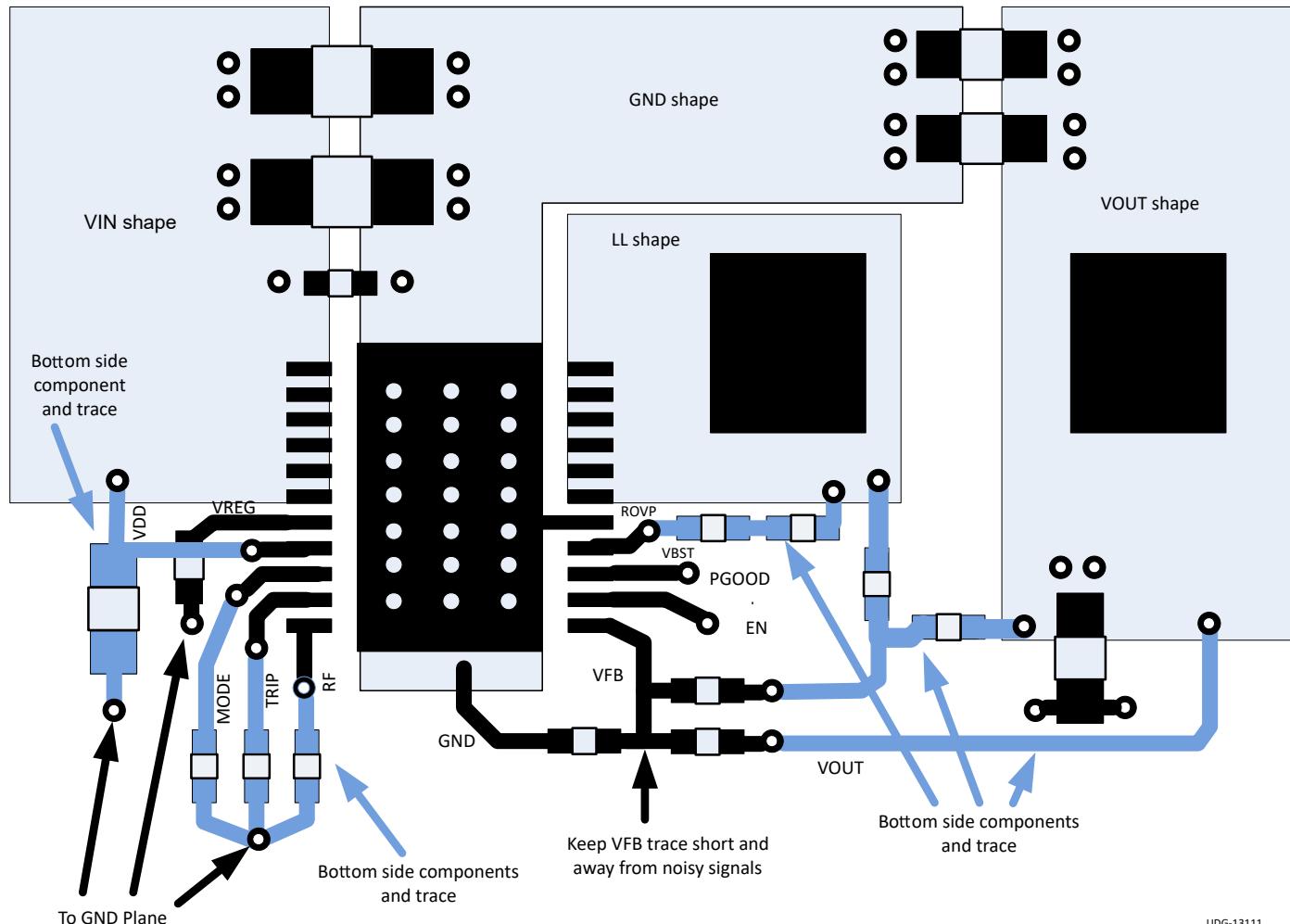

- 電源部品 (入力、出力コンデンサ、インダクタ、TPS53318 または TPS53319 デバイスを含む) は PCB の片側 (半田付けする側) に配置します。小信号パターンをノイズの多いパワーラインから遮蔽および分離するために、グランドに接続された 1 つ以上の内部プレーンを挿入する必要があります。

- カップリングを避けるために、VFB、PGOOD、TRIP、MODE、RF などの敏感なアナログパターンおよび部品はすべて、LL、VBST などの高電圧スイッチングノードから離して配置します。内部の層をグランドプレーンとして使用し、帰還パターンを電源のパターンや部品から遮蔽してください。

- 入力 AC 電流ループを最小限にするため、VIN デカップリングコンデンサは、VIN および PGND ピンにできる限り近づけて配置します。

- TPS53319 デバイスでは VOUT コンデンサの両端の電圧を基準として出力電圧を制御するため、分圧器の上側抵抗を VOUT コンデンサの正ノードに接続します。下側抵抗の GND はデバイスの GND パッドに接続する必要があります。これらの抵抗から VFB ピンへのパターンは短くかつ細くする必要があります。

- 周波数設定抵抗 ( $R_F$ )、OCP 設定抵抗 ( $R_{TRIP}$ )、モード設定抵抗 ( $R_{MODE}$ ) は、可能な限りデバイスの近くに配置します。必要に応じて、共通の GND ビアを使用して、抵抗を GND プレーンに接続します。

- VDD および VREG のデカップリングコンデンサは、できる限りデバイスの近くに配置します。各デカップリングコンデンサに対して GND ビアを設け、ループをできる限り小さくしてください。

- VDD でのノイズフィルタリングを改善するには、専用の最適化されたデカップリングを使用することを強く推奨します。

- LL ピンからインダクタの高電圧側への接続に使用する、スイッチノードとして定義された PCB パターンは、できる限り短く幅広くする必要があります。

- セラミック出力コンデンサの端子からリップル注入の  $V_{OUT}$  信号 (図 8-12 の C1 コンデンサの  $V_{OUT}$  側) を接続します。AC カップリングコンデンサ (図 8-12 の C2) はデバイスの近くに配置し、R7 および C1 は電源段の近くに配置できます。

- LL ノードをスナバ、ブートストラップコンデンサ、およびリップル注入抵抗に接続する際には、それぞれ個別のビアまたはパターンを使用します。これらの接続を組み合わせないでください。

#### 8.4.2 レイアウト例

図 8-17. レイアウトに関する推奨事項

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 開発サポート

- リファレンス デザイン: 7V ~ 12V 入力、1.2V 出力、8A 降圧コンバータ、Altera Arria V FPGA、[PMP8824](#) のレールへの電力供給用

- 評価基板: MOSFET 内蔵の同期整流スイッチャ、[TPS53319EVM-136](#)

- TPS53318 TINA-TI Transient Spice モデル、[SLUM381](#)

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.4 商標

D-CAP™, NexFET™, PowerPAD™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision F (October 2020) to Revision G (November 2025) | Page |

|----------------------------------------------------------------------|------|

| TPS548A28 および TPS548A29 へのリンクを追加.....                                | 1    |

| 商標の情報を更新.....                                                        | 1    |

| TPS548A28 および TPS548A29 に関する情報を追加.....                               | 1    |

| R <sub>VDDSDN</sub> の最大値を 110 から 122 に変更.....                        | 7    |

| Changes from Revision E (November 2016) to Revision F (October 2020) | Page |

|----------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新。.....                                  | 1    |

| ROVP ピンの説明を追加。.....                                                  | 4    |

- ROVP のピン情報を追加。 ..... 19

---

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins       | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS53318DQPR          | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPR.A        | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPR.B        | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| TPS53318DQPRG4        | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPRG4.A      | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPRG4.B      | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| TPS53318DQPT          | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPT.A        | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53318DQP            |

| TPS53318DQPT.B        | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| TPS53319DQPR          | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPR.A        | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPR.B        | Active        | Production           | LSON-CLIP (DQP)   22 | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| TPS53319DQPT          | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPT.A        | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPT.B        | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| TPS53319DQPTG4        | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPTG4.A      | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | ROHS Exempt | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 53319DQP            |

| TPS53319DQPTG4.B      | Active        | Production           | LSON-CLIP (DQP)   22 | 250   SMALL T&R       | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

---

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

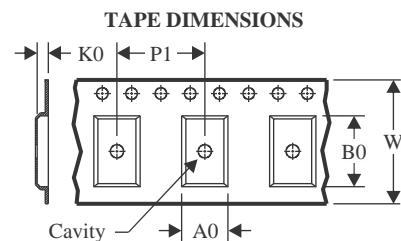

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

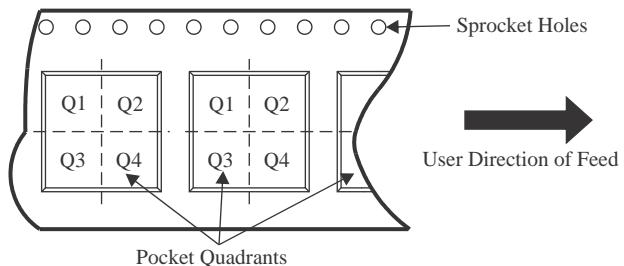

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

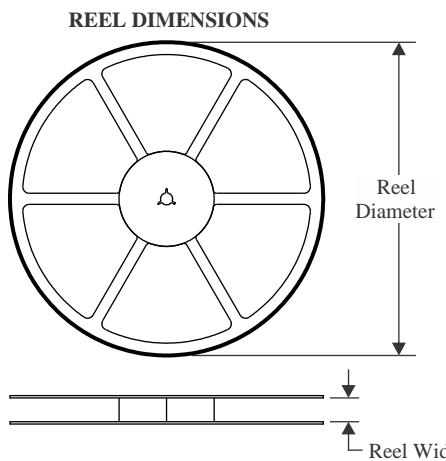

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS53318DQPR   | LSON-CLIP    | DQP             | 22   | 2500 | 330.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

| TPS53318DQPRG4 | LSON-CLIP    | DQP             | 22   | 2500 | 330.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

| TPS53318DQPT   | LSON-CLIP    | DQP             | 22   | 250  | 180.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

| TPS53319DQPR   | LSON-CLIP    | DQP             | 22   | 2500 | 330.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

| TPS53319DQPT   | LSON-CLIP    | DQP             | 22   | 250  | 180.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

| TPS53319DQPTG4 | LSON-CLIP    | DQP             | 22   | 250  | 180.0              | 12.4               | 5.3     | 6.3     | 1.8     | 8.0     | 12.0   | Q1            |

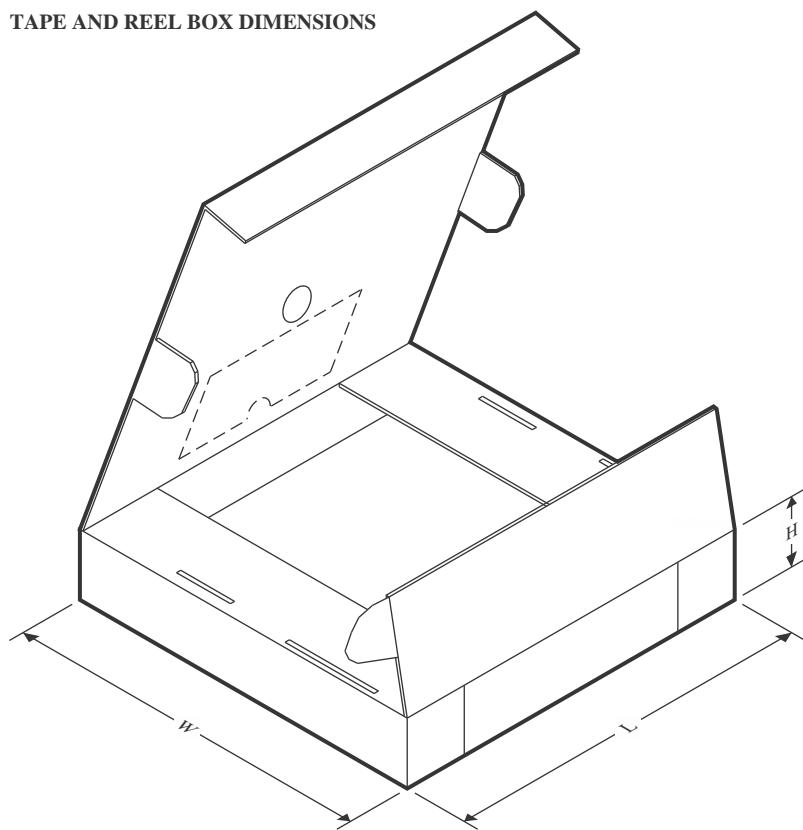

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS53318DQPR   | LSON-CLIP    | DQP             | 22   | 2500 | 346.0       | 346.0      | 33.0        |

| TPS53318DQPRG4 | LSON-CLIP    | DQP             | 22   | 2500 | 346.0       | 346.0      | 33.0        |

| TPS53318DQPT   | LSON-CLIP    | DQP             | 22   | 250  | 210.0       | 185.0      | 35.0        |

| TPS53319DQPR   | LSON-CLIP    | DQP             | 22   | 2500 | 346.0       | 346.0      | 33.0        |

| TPS53319DQPT   | LSON-CLIP    | DQP             | 22   | 250  | 210.0       | 185.0      | 35.0        |

| TPS53319DQPTG4 | LSON-CLIP    | DQP             | 22   | 250  | 210.0       | 185.0      | 35.0        |

## MECHANICAL DATA

DQP (R-PSON-N22)

PLASTIC SMALL OUTLINE NO-LEAD

Bottom View

4210472-3/E 09/11

NOTES:

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- Small Outline No-Lead (SON) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance.

- See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

Pin 1 identifiers are located on both top and bottom of the package and within the zone indicated. The Pin 1 identifiers are either a molded, marked, or metal feature.

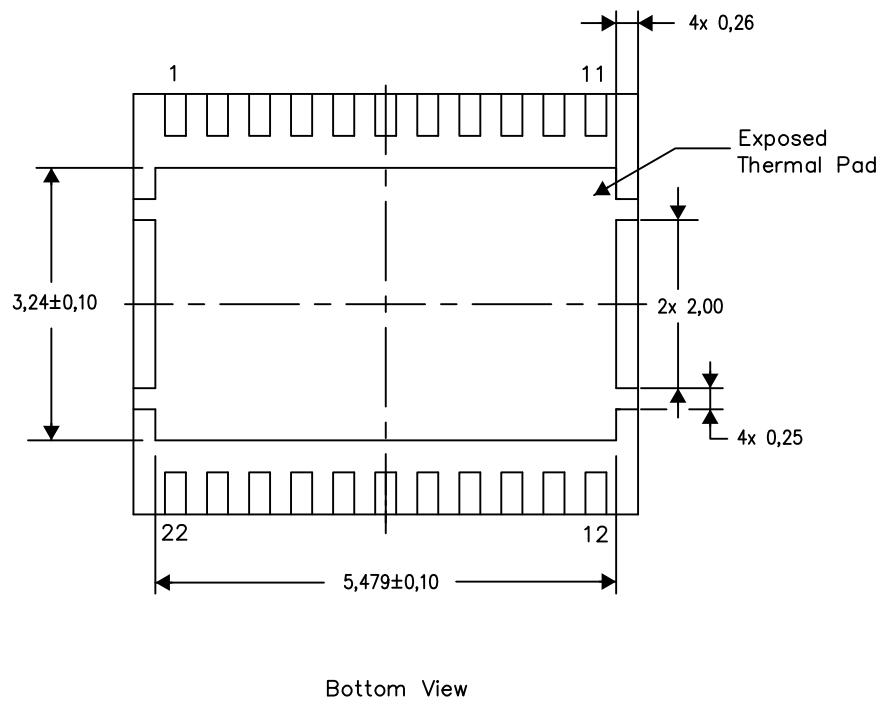

# THERMAL PAD MECHANICAL DATA

DQP (R-PSON-N22)

PLASTIC SMALL OUTLINE NO-LEAD

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

4211024-3/H 08/15

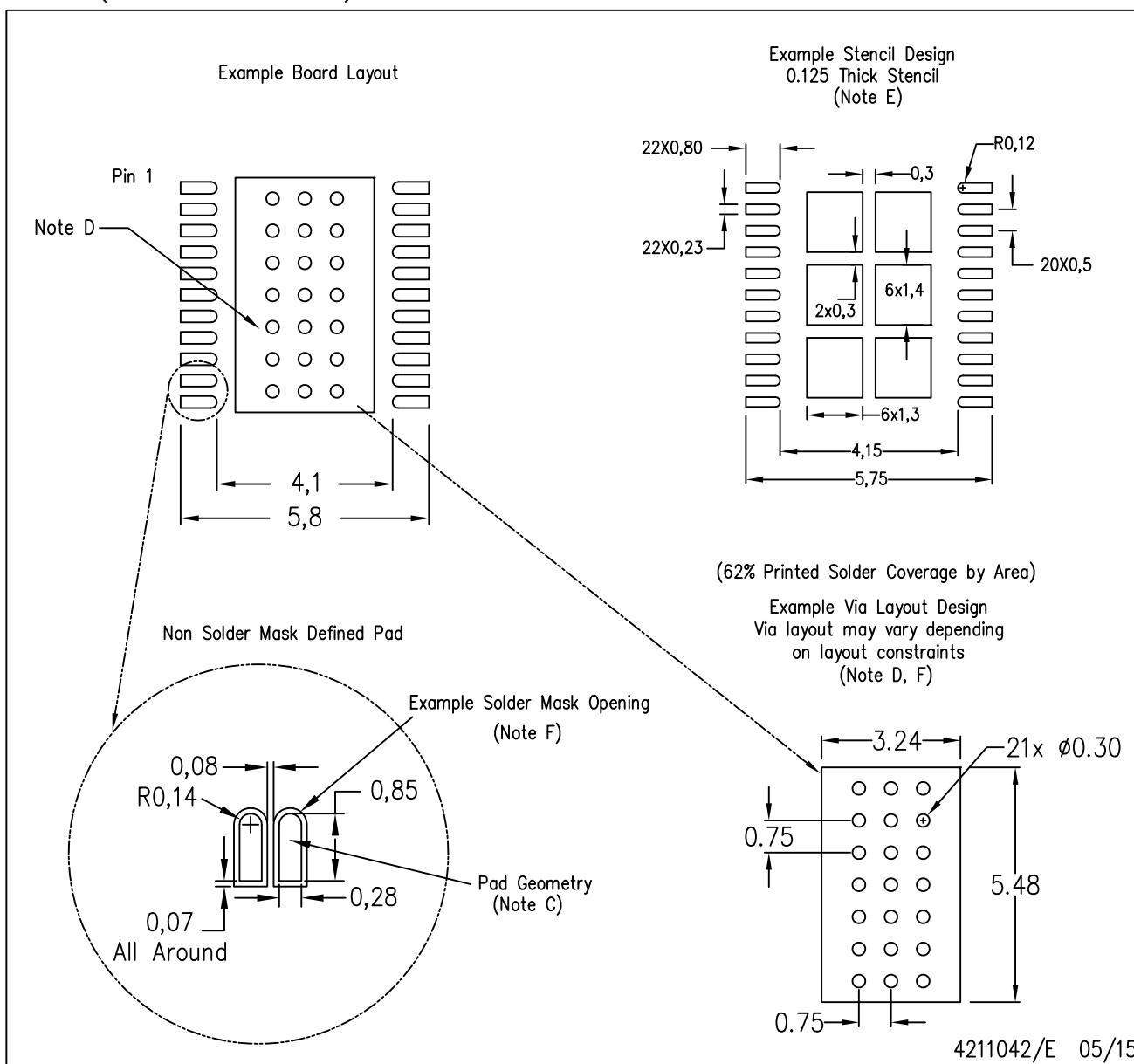

## DQP (R-PSON-N22)

## PLASTIC SMALL OUTLINE NO-LEAD

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-7351 is recommended for alternate designs.

- This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月