## ノートパソコン・システム電源用100mA スタンバイ・レギュレータ内蔵デュアル電流モード、 同期降圧型コントローラ

### 特 長

- 各独立にイネーブル可能な3.3Vおよび5Vの100mAブーストストラップ・スタンバイ・レギュレータ

- D-CAP®モードの選択により、100ns以下の高速過渡応答が可能

- 低リップル電流モードを選択可能

- 1%以内の内部リファレンス精度

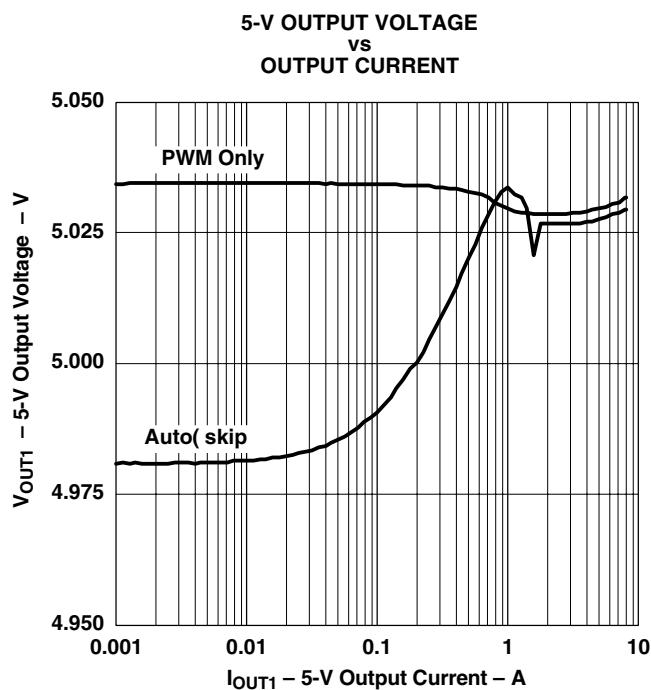

- PWMモード/オートスキップ・モードを選択可能

- ローサイド  $R_{DS(on)}$  のロスレス電流センス

- 外部抵抗  $R_{SENSE}$  による高精度電流センス・オプション

- 内部ソフトスタートおよび  $V_{OUT}$  放電トランジスタを内蔵

- 2Vリファレンスを内蔵

- ブースト・ダイオードを内蔵したアダプティブ・ゲート・ドライバ

- 各チャネルに遅延タイマ付きパワーグッド機能

- フォルト・ディスエーブル・モード

- 入力電源電圧範囲：4.5V～28V

### ア プ リ ケ シ ョ ン

- ノートパソコンのシステム・バスおよびI/O

D-CAPは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 概要

TPS51120は、高度に洗練されたデュアル電流モード同期降圧型コントローラです。3セルまたは4セルのリチウム・イオン電池から直接動作するように設計されたコントローラであり、ノートパソコン・システム内のすべてのダウンストリーム回路に高い電力と5V/3.3Vのスタンバイ・レギュレーションを提供します。高電流(100mA)の5V/3.3V内蔵リニア・レギュレータは、SMPSへのグリッヂのない切り替え機能を持ち、スタンバイ状態中に各レギュレータを独立にオンに維持することができます。擬似定周波数のアダプティブオン時間制御方式により、簡単なループ補償、セラミック出力キャパシタなどの幅広い範囲の電流モード動作をサポートし、軽負荷状態では低周波数動作へのシームレスな遷移が可能です。D-CAP<sup>TM</sup>モード動作はSP-CAPまたはPOSCAP出力キャパシタに対して最適化され、外部補償部品数をさらに減らすことができます。ダイナミックUVPにより、

5V UVPのトリップによるラッチ・オフなしでVINラインの降下をサポートしています。UVLO、UVP、OCP、OTP、またはVIN無供給の状態中、出力電圧ノードに負の電圧が生じることはありません。

TPS51120の32ピンQFNパッケージは、周囲温度-40°C～85°Cで仕様が規定されています。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 発注情報 (1)(2)

| T <sub>A</sub> | PACKAGE                      | ORDERABLE PART NUMBER | PINS | OUTPUT SUPPLY | MINIMUM ORDER QUANTITY | ECO PLAN                     |

|----------------|------------------------------|-----------------------|------|---------------|------------------------|------------------------------|

| -40°C to 85°C  | PLASTIC QUAD FLAT PACK (QFN) | TPS51120RHBT          | 32   | Tape-and-reel | 250                    | Green<br>(RoHS and no Sb/Br) |

|                |                              | TPS51120RHBR          |      | Tape-and-reel | 3000                   |                              |

(1) すべてのパッケージ・オプションがCu NiPdAuリード/ボール処理となっています。

(2) 最新のパッケージおよび発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト([www.ti.com](http://www.ti.com))をご覧ください。

## 絶対最大定格<sup>(1)</sup>

動作温度範囲内(特に記述のない限り)

|                                                              |                                                                        | TPS51120    | UNITS |

|--------------------------------------------------------------|------------------------------------------------------------------------|-------------|-------|

| Input voltage range                                          | VBST1, VBST2                                                           | -0.3 to 36  | V     |

|                                                              | VBST1, VBST2 wrt LL                                                    | -0.3 to 6   |       |

|                                                              | VIN, EN5                                                               | -0.3 to 30  |       |

|                                                              | SKIPSEL, TONSEL, EN1, EN2, CS1, CS2, V5FILT, VFB1, VFB2, EN3, VO1, VO2 | -0.3 to 6   |       |

| Output voltage range                                         | DRVH1, DRVH2                                                           | -1 to 36    | V     |

|                                                              | DRVH1, DRVH2 (wrt LL)                                                  | -0.3 to 6   |       |

|                                                              | LL1, LL2                                                               | -1 to 30    |       |

|                                                              | VREF2, VREG3, VREG5, PGOOD1, PGOOD2, DRVL1, DRVL2, COMP1, COMP2        | -0.3 to 6   |       |

|                                                              | PGND1, PGND2                                                           | -0.3 to 0.3 |       |

| Source/sink current                                          | VREF2                                                                  | 1           | mA    |

|                                                              | VBST                                                                   | 100         |       |

|                                                              | VREG5, VREG3 (source only)                                             | 200         |       |

| T <sub>A</sub>                                               | Operating ambient temperature range                                    | -40 to 85   | °C    |

| T <sub>stg</sub>                                             | Storage temperature                                                    | -55 to 150  |       |

| T <sub>J</sub>                                               | Junction temperature                                                   | -40 to 125  |       |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                                                                        | 255         |       |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。特に指定のない限り、すべての電圧値はネットワーク・グランド・ピンを基準にしています。

## 定格消費電力

| PACKAGE                   | T <sub>A</sub> < 25°C POWER RATING (W) | DERATING FACTOR ABOVE T <sub>A</sub> = 25°C (W/°C) | T <sub>A</sub> = 85°C POWER RATING (W) |

|---------------------------|----------------------------------------|----------------------------------------------------|----------------------------------------|

| 32-pin QFN <sup>(1)</sup> | 2.6                                    | 0.026                                              | 1.0                                    |

| 32-pin QFN <sup>(2)</sup> | 2.9                                    | 0.029                                              | 1.2                                    |

(1) JEDEC標準PCBです。

(2) サーマル・パッドの下の3×3個のサーマル・ビアにより熱伝導が強化されています。

## 推奨動作条件

|                                                     |                                                                           | MIN  | MAX | UNIT |

|-----------------------------------------------------|---------------------------------------------------------------------------|------|-----|------|

| Input voltage, V <sub>5FILT</sub>                   |                                                                           | 4.5  | 5.5 | V    |

| Input voltage range                                 | VBST1, VBST2                                                              | -0.1 | 34  | V    |

|                                                     | VBST1, VBST2 wrt LL                                                       | -0.1 | 5.5 |      |

|                                                     | VIN, EN5                                                                  | -0.1 | 28  |      |

|                                                     | SKIPSEL, TONSEL, EN1, EN2, CS1, CS2, V <sub>5FILT</sub> , VFB1, VFB2, EN3 | -0.1 | 5.5 |      |

|                                                     | VO1, VO2                                                                  | -0.1 | 5.5 |      |

| Output voltage range                                | DRVH1, DRVH2                                                              | -0.8 | 34  | V    |

|                                                     | DRVH1, DRVH2 (wrt LL)                                                     | -0.1 | 5.5 |      |

|                                                     | LL1, LL2                                                                  | -0.8 | 28  |      |

|                                                     | VREF2, VREG5, VREG3, PGOOD1, PGOOD2, DRVL1, DRVL2, COMP1, COMP2           | -0.1 | 5.5 |      |

|                                                     | PGND1, PGND2                                                              | -0.1 | 0.1 |      |

| Source/sink current                                 | VREF2                                                                     | 0.08 |     | mA   |

|                                                     | VBST                                                                      | 50   |     |      |

|                                                     | VREG5, VREF3 (source only)                                                | 100  |     |      |

| Operating ambient temperature range, T <sub>A</sub> |                                                                           | -40  | 85  | °C   |

## 電気的特性

動作温度範囲内、 $V_{VIN} = 12\text{ V}$ ,  $V_{VREG5} = V_{V5FILT} = 5\text{ V}$  (特に記述のない限り)

| PARAMETER                      |                                         | TEST CONDITIONS                                                                                                                                       |              | MIN   | TYP   | MAX   | UNIT          |

|--------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|-------|---------------|

| <b>SUPPLY CURRENT</b>          |                                         |                                                                                                                                                       |              |       |       |       |               |

| $I_{INCCAP}$                   | Supply current                          | VIN current, $V_{REG5} = V_{REG3} = \text{No Load}$ , $EN3 = EN5 = \text{FLOAT}$ , $EN1 = EN2 = 5\text{V}$ , $CS = 5\text{V}$ , COMP connected to Cap | Current mode | 750   | 1500  |       | $\mu\text{A}$ |

| $I_{INNOCAP}$                  | Supply current                          | VIN current, $V_{REG5} = V_{REG3} = \text{No Load}$ , $EN3 = EN5 = \text{FLOAT}$ , $EN1 = EN2 = 5\text{V}$ , $CS = 5\text{V}$ , COMP = 5V             | D-CAP mode   | 700   | 1400  |       |               |

| $I_{IN5(STBY)}$                | Stand-by current                        | VIN current, $V_{REG5} = \text{No Load}$ , $EN3 = 0\text{V}$ , $EN5 = \text{FLOAT}$ , $EN1 = EN2 = 0$                                                 | 5-V only     | 30    | 45    |       |               |

| $I_{IN3(STBY)}$                | Stand-by current                        | VIN current, $V_{REG3} = \text{No Load}$ , $EN3 = \text{FLOAT}$ , $EN5 = 0$ , $EN1 = EN2 = 0$                                                         | 3.3-V only   | 12    | 20    |       |               |

| $I_{IN532(STBY)}$              | Stand-by current                        | VIN current, $V_{REG5} = V_{REG3} = V_{REF2} = \text{No Load}$ , $EN3 = EN5 = \text{FLOAT}$ , $EN1 = EN2 = 0$                                         |              | 100   | 150   |       |               |

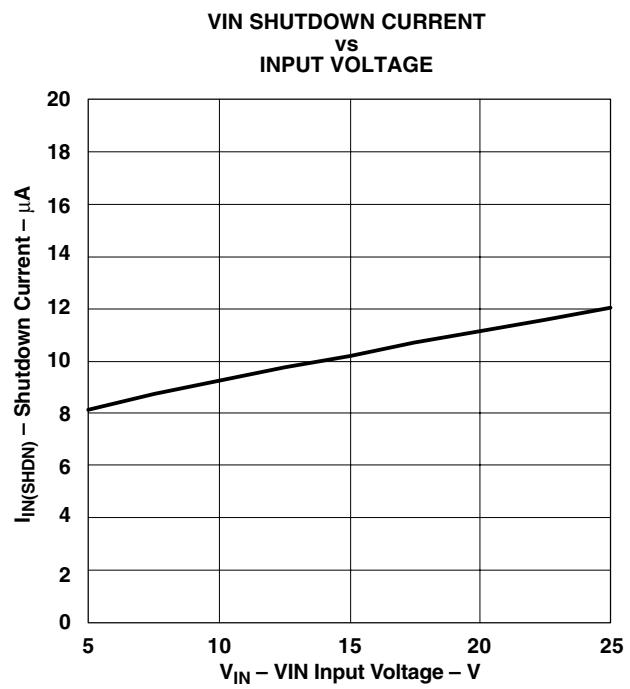

| $I_{IN(SHDN)}$                 | Shut down current                       | VIN current, $EN3 = EN5 = EN1 = EN2 = 0\text{V}$                                                                                                      |              | 10    | 20    |       |               |

| <b>VOUT and VREF2 VOLTAGES</b> |                                         |                                                                                                                                                       |              |       |       |       |               |

| $V_{OUT}$                      | Output voltage                          | $V_{FB2} = 5\text{V}$ , $T_A = 25^\circ\text{C}$ , No Load                                                                                            |              | 3.255 | 3.300 | 3.345 | $\text{V}$    |

|                                |                                         | $V_{FB2} = 5\text{V}$ , $T_A = 0$ to $85^\circ\text{C}$ , No Load                                                                                     |              | 3.241 | 3.300 | 3.359 |               |

|                                |                                         | $V_{FB2} = 5\text{V}$ , $T_A = -40$ to $85^\circ\text{C}$ , No Load                                                                                   |              | 3.234 | 3.300 | 3.366 |               |

|                                |                                         | $V_{FB1} = 5\text{V}$ , $T_A = 25^\circ\text{C}$ , No Load                                                                                            |              | 4.935 | 5.000 | 5.065 |               |

|                                |                                         | $V_{FB1} = 5\text{V}$ , $T_A = 0$ to $85^\circ\text{C}$ , No Load                                                                                     |              | 4.910 | 5.000 | 5.090 |               |

|                                |                                         | $V_{FB1} = 5\text{V}$ , $T_A = -40$ to $85^\circ\text{C}$ , No Load                                                                                   |              | 4.900 | 5.000 | 5.100 |               |

|                                |                                         | Adjustable mode output range                                                                                                                          |              | 1.0   |       | 5.5   |               |

| $V_{ADJ}$                      | Output regulation voltage               | Adjustable mode                                                                                                                                       |              | 1.00  |       |       | $\text{V}$    |

| $V_{ADJ\ T}$                   | Output regulation voltage tolerance     | Adjustable mode, $T_A = 25^\circ\text{C}$                                                                                                             |              | -0.9% | 0.9%  |       |               |

|                                |                                         | Adjustable mode, $T_A = 0$ to $85^\circ\text{C}$                                                                                                      |              | -1.3% | 1.3%  |       |               |

|                                |                                         | Adjustable mode, $T_A = -40$ to $85^\circ\text{C}$                                                                                                    |              | -1.6% | 1.6%  |       |               |

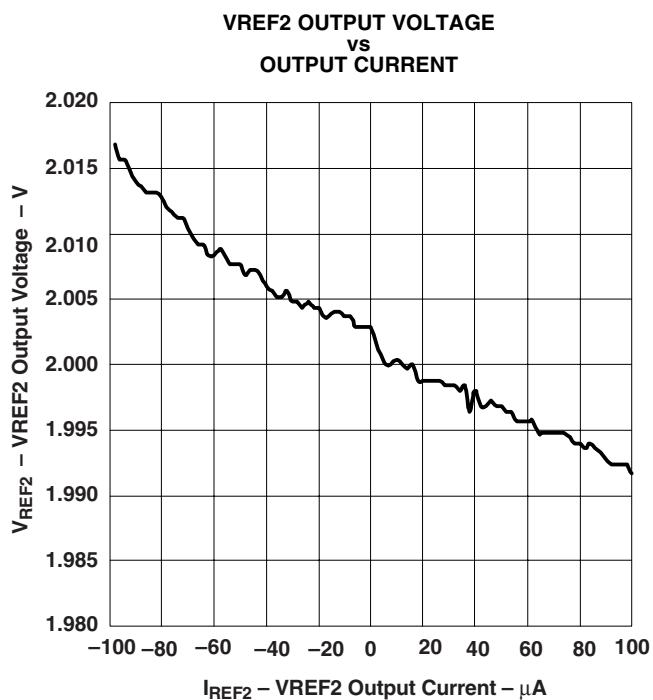

| $V_{VREF2}$                    | 2-V output regulation voltage           | $I_{VREF2} \pm 50\mu\text{A}$ , $T_A = 25^\circ\text{C}$                                                                                              |              | 1.97  | 2.00  | 2.03  | $\text{V}$    |

| $V_{VREF2T}$                   | 2-V output regulation voltage tolerance | $I_{VREF2} \pm 50\mu\text{A}$ , $T_A = 0$ to $85^\circ\text{C}$                                                                                       |              | 1.96  | 2.04  |       |               |

|                                |                                         | $I_{VREF2} \pm 50\mu\text{A}$ , $T_A = -40$ to $85^\circ\text{C}$                                                                                     |              | 1.95  | 2.05  |       |               |

| $I_{VFB}$                      | VFB input current                       | $VFBx = 1.02\text{V}$ , COMPx = open                                                                                                                  |              | 0.02  |       |       | $\mu\text{A}$ |

|                                |                                         | $VFBx = 1.02\text{V}$ , COMPx = 5V                                                                                                                    |              | 0.02  |       |       |               |

| $R_{DISCHARG}$                 | Discharge switch resistance             | $VOx = 0.5\text{V}$ , $T_A = 25^\circ\text{C}$                                                                                                        |              | 10    | 20    |       | $\Omega$      |

## 電気的特性(続き)

動作温度範囲内、 $V_{VIN} = 12\text{ V}$ ,  $V_{VREG5} = V_{V5FILT} = 5\text{ V}$  (特に記述のない限り)

| PARAMETER                         | TEST CONDITIONS                       | MIN                                                                                                    | TYP   | MAX  | UNIT          |

|-----------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|-------|------|---------------|

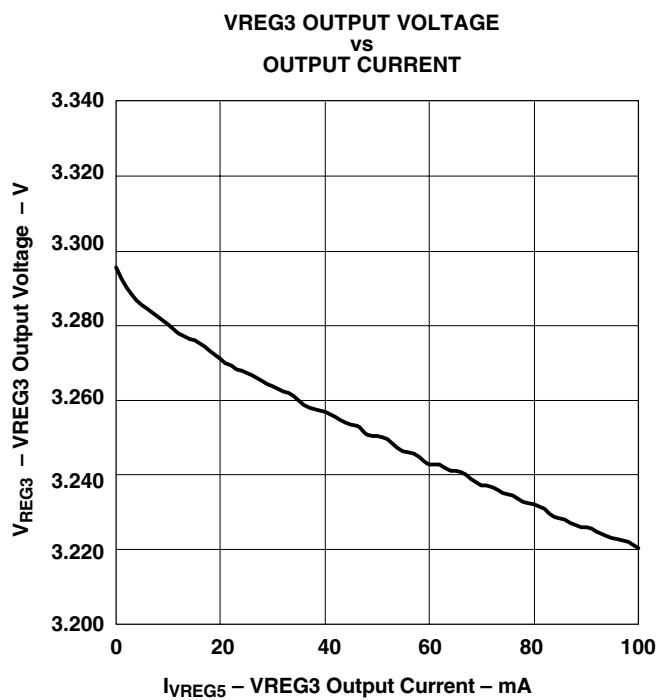

| <b>VREG3 VOLTAGE</b>              |                                       |                                                                                                        |       |      |               |

| $V_{VREG3}$                       | $V_{VREG3}$ Output Regulation Voltage | $I_{VREG3} = 20\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = 25^\circ\text{C}$               | 3.25  | 3.30 | 3.35          |

| $V_{VREG3T}$                      | $V_{VREG3}$ Output Voltage Tolerance  | $I_{VREG3} = 1 - 50\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = 0$ to $85^\circ\text{C}$    | 3.21  | 3.37 | V             |

|                                   |                                       | $I_{VREG3} = 1 - 100\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = -40$ to $85^\circ\text{C}$ | 3.16  | 3.39 |               |

|                                   |                                       | $T_A = 25^\circ\text{C}$ , $V_{REG3} = 3.14\text{ V}^{(1)}$                                            | 170   |      |               |

| $V_{LDO3SW}$                      | VREG3 Bootstrap Switch Threshold      | Rising edge of $VO_2$ , $V_{REG3}$ drops to $VO_2$ voltage                                             | 2.85  | 3.10 | V             |

|                                   |                                       | Hysteresis                                                                                             | 120   |      | mV            |

| $R_{LDO3SW}$                      | VREG3 Bootstrap Switch Resistance     |                                                                                                        | 1.3   | 3.0  | $\Omega$      |

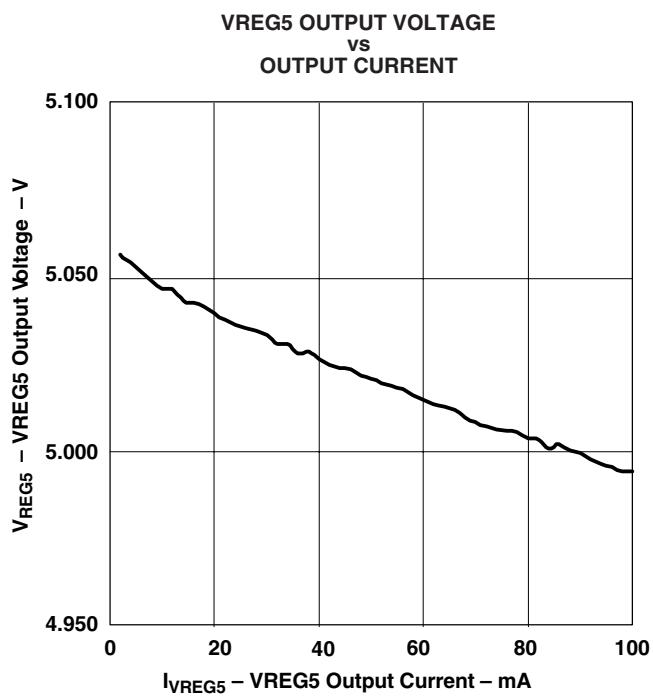

| <b>VREG5 VOLTAGE</b>              |                                       |                                                                                                        |       |      |               |

| $V_{VREG5}$                       | $V_{VREG5}$ Output Regulation Voltage | $I_{VREG5} = 20\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = 25^\circ\text{C}$               | 4.925 | 5.00 | 5.075         |

| $V_{VREG5T}$                      | $V_{VREG5}$ Output Voltage Tolerance  | $I_{VREG5} = 1 - 50\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = 0$ to $85^\circ\text{C}$    | 4.89  | 5.11 | V             |

|                                   |                                       | $I_{VREG5} = 1 - 100\text{ mA}$ , $6\text{ V} < VIN < 28\text{ V}$ , $T_A = -40$ to $85^\circ\text{C}$ | 4.80  | 5.15 |               |

|                                   |                                       | $T_A = 25^\circ\text{C}$ , $V_{REG5} = 4.75\text{ V}^{(1)}$                                            | 200   |      |               |

| $V_{LDO5SW}$                      | VREG5 Bootstrap Switch Threshold      | Rising edge of $VO_1$ , $V_{REG5}$ drops to $VO_1$ voltage                                             | 4.30  | 4.85 | V             |

|                                   |                                       | Hysteresis                                                                                             | 140   |      | mV            |

| $R_{LDO5SW}$                      | VREG5 Bootstrap Switch Resistance     |                                                                                                        | 1.3   | 3.0  | $\Omega$      |

| <b>TRANSCONDUCTANCE AMPLIFIER</b> |                                       |                                                                                                        |       |      |               |

| $G_m$                             | Gain                                  | $T_A = 25^\circ\text{C}$                                                                               | 280   |      | $\mu\text{S}$ |

| $I_{COMPSINK}$                    | COMP Maximum Sink Current             | $V_{FBx} = 1.05\text{ V}$ , $COMP_x = 1.28\text{ V}$                                                   | 8     | 12   | 16            |

| $I_{COMPSRC}$                     | COMP Maximum Source Current           | $V_{FBx} = 0.95\text{ V}$ , $COMP_x = 1.28\text{ V}$                                                   | -15   | -11  | -7            |

| $V_{COMPHI}$                      | COMP High Clamp Voltage               | $CS_x = 0\text{ V}$ , $V_{FBx} = 0.95\text{ V}$                                                        | 1.26  | 1.34 | 1.42          |

| $V_{COMPL0}$                      | COMP Low Clamp Voltage                | $CS_x = 0\text{ V}$ , $V_{FBx} = 1.05\text{ V}$                                                        | 1.08  | 1.12 | 1.20          |

| <b>OUTPUT DRIVER</b>              |                                       |                                                                                                        |       |      |               |

| $R_{DRVH}$                        | DRVH resistance                       | Source, $V_{VBST-DRVH} = 1\text{ V}$                                                                   | 3.5   | 7    | $\Omega$      |

|                                   |                                       | Sink, $V_{DRVH-LL} = 1\text{ V}$                                                                       | 1.5   | 3    |               |

| $R_{DRVL}$                        | DRVL resistance                       | Source, $V_{VREG5-DRVRL} = 1\text{ V}$                                                                 | 3.5   | 7    | $\Omega$      |

|                                   |                                       | Sink, $V_{DRVRL-PGND} = 1\text{ V}$                                                                    | 1.5   | 3    |               |

| $T_D$                             | Dead time                             | DRVH-off to DRVH-on, $T_A = 25^\circ\text{C}$                                                          | 20    |      | ns            |

|                                   |                                       | DRVL-off to DRVH-on, $T_A = 25^\circ\text{C}$                                                          | 30    | 60   |               |

| $V_{DTH}$                         | DRVH-off threshold                    | LL to GND <sup>(1)</sup>                                                                               | 2     |      | V             |

| $V_{DTL}$                         | DRVL-off threshold                    | DRVRL to GND <sup>(1)</sup>                                                                            | 1.1   |      |               |

| <b>INTERNAL BST DIODE</b>         |                                       |                                                                                                        |       |      |               |

| $V_{FBST}$                        | Forward Voltage                       | $V_{VREG5-VBST}$ , $I_F = 10\text{ mA}$ , $T_A = 25^\circ\text{C}$                                     | 0.7   | 0.8  | 0.9           |

| $I_{RBST}$                        | Reverse Current                       | $VBST = 34\text{ V}$ , $V_{REG5} = 5\text{ V}$                                                         | 0.1   | 1.0  | $\mu\text{A}$ |

| $I_{BST(LEAK)}$                   | VBST Leakage current                  | $VBST = 34\text{ V}$ , $LL = 28\text{ V}$ , $EN3 = EN5 = EN1 = EN2 = 0\text{ V}$                       | 0.1   | 1.0  |               |

(1) 設計保証。実製品のテストは行っていません。

## 電気的特性(続き)

動作温度範囲内、 $V_{VIN} = 12\text{ V}$ ,  $V_{VREG5} = V_{V5FILT} = 5\text{ V}$  (特に記述のない限り)

| PARAMETER                                                        |                                    | TEST CONDITIONS                                                                                                        | MIN  | TYP            | MAX  | UNIT                        |  |

|------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|----------------|------|-----------------------------|--|

| <b>ON-TIME TIMER, INTERNAL SOFT-START and HOUSEKEEPING CLOCK</b> |                                    |                                                                                                                        |      |                |      |                             |  |

| $T_{ON1a}$                                                       | On time, 5V, 180 kHz               | $V_{LL1} = 12\text{ V}$ , $V_{OUT1} = 5\text{ V}$ , $TONSEL = 5\text{ V}$ , $T_A = 25^\circ\text{C}$                   | 2150 | 2340           | 2530 | ns                          |  |

| $T_{ON1b}$                                                       | On time, 5V, 220 kHz               | $V_{LL1} = 12\text{ V}$ , $V_{OUT1} = 5\text{ V}$ , $TONSEL = \text{FLOAT}$ , $T_A = 25^\circ\text{C}$                 | 1790 | 1950           | 2110 |                             |  |

| $T_{ON1c}$                                                       | On time, 5V, 280 kHz               | $V_{LL1} = 12\text{ V}$ , $V_{OUT1} = 5\text{ V}$ , $TONSEL = 2\text{ V}$ , $T_A = 25^\circ\text{C}$                   | 1370 | 1490           | 1610 |                             |  |

| $T_{ON1d}$                                                       | On time, 5V, 380 kHz               | $V_{LL1} = 12\text{ V}$ , $V_{OUT1} = 5\text{ V}$ , $TONSEL = \text{GND}$ , $T_A = 25^\circ\text{C}$                   | 1020 | 1110           | 1200 |                             |  |

| $T_{ON2a}$                                                       | On time, 3.3V, 270 kHz             | $V_{LL2} = 12\text{ V}$ , $V_{OUT2} = 3.3\text{ V}$ , $TONSEL = 5\text{ V}$ , $T_A = 25^\circ\text{C}$                 | 940  | 1030           | 1120 |                             |  |

| $T_{ON2b}$                                                       | On time, 3.3V, 330 kHz             | $V_{LL2} = 12\text{ V}$ , $V_{OUT1} = 3.3\text{ V}$ , $TONSEL = \text{FLOAT}$ , $T_A = 25^\circ\text{C}$               | 780  | 850            | 920  |                             |  |

| $T_{ON2c}$                                                       | On time, 3.3V, 430 kHz             | $V_{LL2} = 12\text{ V}$ , $V_{OUT1} = 3.3\text{ V}$ , $TONSEL = 2\text{ V}$ , $T_A = 25^\circ\text{C}$                 | 580  | 650            | 720  |                             |  |

| $T_{ON2d}$                                                       | On time, 3.3V, 580 kHz             | $V_{LL2} = 12\text{ V}$ , $V_{OUT1} = 3.3\text{ V}$ , $TONSEL = \text{GND}$ , $T_A = 25^\circ\text{C}$                 | 430  | 480            | 530  |                             |  |

| $T_{ON(MIN)1}$                                                   | Minimum on time, 5V                | $T_A = 25^\circ\text{C}$ $TONSEL = \text{GND}$ , $V_{LL1} = 28\text{ V}$ , $VO1 = 1\text{ V}$                          |      | 70             |      |                             |  |

| $T_{ON(MIN)2}$                                                   | Minimum on time, 3.3V              | $T_A = 25^\circ\text{C}$ $TONSEL = \text{GND}$ , $V_{LL2} = 28\text{ V}$ , $VO2 = 1\text{ V}$                          |      | 45             |      |                             |  |

| $T_{OFF(MIN)}$                                                   | Minimum off time                   | $T_A = 25^\circ\text{C}$ $VFB = 0.9\text{ V}$ , $LL = 0.5\text{ V}$                                                    |      | 480            |      |                             |  |

| $T_{SS}$                                                         | Internal Soft Start Timer          | $T_A = 25^\circ\text{C}$ $ENx > 3\text{ V}$                                                                            |      | 772            |      | clks                        |  |

| $SL_{SS}$                                                        | Internal Soft Start Slope          | $T_A = 25^\circ\text{C}$ $ENx > 3\text{ V}$ , Slope wrt. $VFB$ <sup>(2)</sup>                                          |      | 0.3            |      | V/ms                        |  |

| $F_{CLK}$                                                        | HK clock frequency                 |                                                                                                                        | 230  | 290            | 350  | kHz                         |  |

| <b>UVLO/LOGIC THRESHOLD</b>                                      |                                    |                                                                                                                        |      |                |      |                             |  |

| $V_{ENLDOH}$                                                     | LDO enable threshold               | EN3, EN5, low to high                                                                                                  | 0.4  | 0.6            | 0.8  | V                           |  |

|                                                                  |                                    | Hysteresis                                                                                                             |      | 0.2            |      |                             |  |

| $V_{ENLDOFL3}$                                                   | EN3 pullup voltage                 | EN3 = $\text{FLOAT}$ (OPEN) <sup>(2)</sup>                                                                             |      | 1.7            |      |                             |  |

| $V_{ENLDOFL5}$                                                   | EN5 pullup voltage                 | EN5 = $\text{FLOAT}$ (OPEN) <sup>(2)</sup>                                                                             |      | 3.3            |      |                             |  |

| $I_{ENLDOFL}$                                                    | EN3, EN5 pullup current            | $VENx < 0.5\text{ V}$                                                                                                  |      | 1.5            | 4.0  | $\mu\text{A}$               |  |

| $V_{UV(VREG5)}$                                                  | VREG5 UVLO threshold               | Wake up                                                                                                                | 3.8  | 4.0            | 4.2  | V                           |  |

|                                                                  |                                    | Hysteresis                                                                                                             | 100  | 200            | 300  | mV                          |  |

| $V_{SKIPSEL}$                                                    | SKIPSEL threshold                  | Auto-SKIP Mode Enabled                                                                                                 | 0    | 0.7            |      | V                           |  |

|                                                                  |                                    | Auto-SKIP Mode Enabled, Faults Off                                                                                     | 1.3  | 2.2            |      |                             |  |

|                                                                  |                                    | PWM-Only Mode Enabled                                                                                                  | 2.7  | 5.5            |      |                             |  |

| $V_{TONSEL}$                                                     | TONSEL threshold                   | Fast Switching Frequency                                                                                               | 0    | 0.7            |      | V                           |  |

|                                                                  |                                    | Medium Switching Frequency #2                                                                                          | 1.3  | 2.2            |      |                             |  |

|                                                                  |                                    | Medium Switching Frequency #1                                                                                          | 2.7  | 3.0            |      |                             |  |

|                                                                  |                                    | Slow Switching Frequency                                                                                               | 4.5  | 5.5            |      |                             |  |

| $I_{SEL}$                                                        | SKIPSEL/TONSEL input current       | SKIPSEL, $TONSEL = 0\text{ V}$                                                                                         |      | 1              | 3    | $\mu\text{A}$               |  |

|                                                                  |                                    | SKIPSEL, $TONSEL = 5\text{ V}$                                                                                         |      | 1              | 2    |                             |  |

| $V_{ENSWSTAT}$                                                   | EN1, EN2 SS Start Voltage          | BJT Base input, Switcher begins to Track $ENx$                                                                         | 0.5  | 0.9            | 1.2  | V                           |  |

| $V_{ENSWEND}$                                                    | EN1, EN2 SS End Voltage            | 'Logic High' Level for Switcher Enable when using Internal Softstart, $0^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$ |      | 2.75           | 2.90 |                             |  |

| $I_{ENSW1,2}$                                                    | EN1, EN2 Pullup Current            | $EN1, EN2 = 0.6\text{ V}$                                                                                              | 1    | 2              | 3    | $\mu\text{A}$               |  |

| $V_{THVFB1}$                                                     | VFB1 threshold                     | 5.0V preset output                                                                                                     |      | $V5FILT - 0.3$ |      | V                           |  |

| $V_{THVFB2}$                                                     | VFB2 threshold                     | 3.3V preset output                                                                                                     |      | $V5FILT - 0.3$ |      |                             |  |

| <b>CURRENT SENSE</b>                                             |                                    |                                                                                                                        |      |                |      |                             |  |

| $V_{OCL}$                                                        | Current limit threshold            | Resistor sense scheme, $V_{PGND} - V_{CS}$ voltage, $PGOOD = \text{Hi}$                                                | 67   | 80             | 93   | mV                          |  |

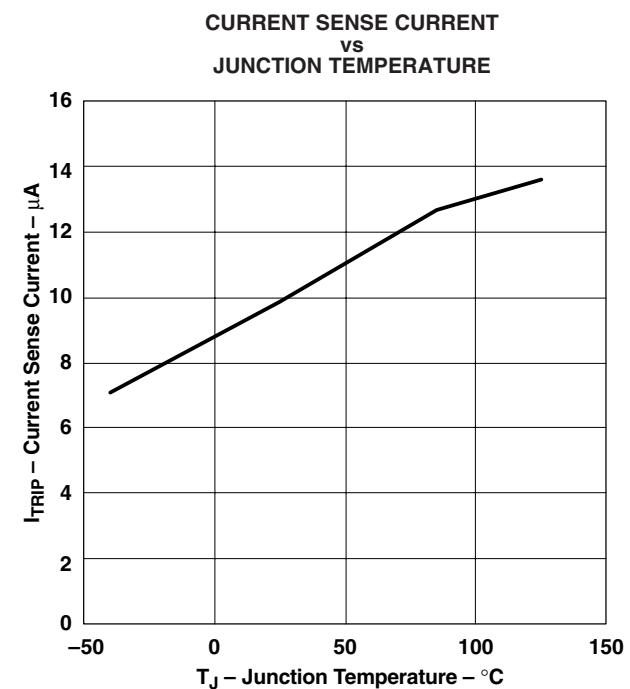

| $I_{TRIP}$                                                       | CS Sink Current                    | $R_{DS(ON)}$ sense scheme, $PGOOD = \text{Hi}$ , $T_A = 25^\circ\text{C}$                                              | 9    | 10             | 11   | $\mu\text{A}$               |  |

| $TC_{ITRIP}$                                                     | $I_{TRIP}$ temperature Coefficient | $R_{DS(ON)}$ sense scheme, On the basis of $25^\circ\text{C}$                                                          |      | 4500           |      | $\text{ppm}/^\circ\text{C}$ |  |

(2) 設計保証。実製品のテストは行っていません。

## 電気的特性(続き)

動作温度範囲内、 $V_{VIN} = 12\text{ V}$ 、 $V_{VREG5} = V_{V5FILT} = 5\text{ V}$ (特に記述のない限り)

| PARAMETER                                      |                                        | TEST CONDITIONS                                                                                | MIN       | TYP        | MAX        | UNIT |

|------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|-----------|------------|------------|------|

| $V_{OCLoff}$                                   | OCP Comparator Offset                  | ( $V_{VREG5-CS} - V_{PGND-LL}$ ) voltage, $V_{VREG5-CS} = 80\text{mV}$ ,<br>$R_{DS(ON)}$ sense | -10       | 0          | 10         | mV   |

| $V_{R(trip)}$                                  | Current limit threshold setting range  | $V_{V5FILT} - V_{CS}$ voltage                                                                  | 30        |            | 150        |      |

| $V_{ZC}$                                       | Zero cross detection Comparator offset | $V_{PGNDx} - V_{LLx}$ voltage, $SKIPSEL = 0\text{V}$                                           | -5        | 1          | 5          |      |

| <b>POWERGOOD COMPARATOR</b>                    |                                        |                                                                                                |           |            |            |      |

| $V_{TH(PG)}$                                   | PGOOD Threshold                        | Power Bad Threshold                                                                            | $\pm 7\%$ | $\pm 10\%$ | $\pm 13\%$ |      |

|                                                |                                        | Hysteresis                                                                                     |           | $\pm 5\%$  |            |      |

| $I_{PG(MAX)}$                                  | PGOOD Sink Current                     | PGOOD = 0.5V                                                                                   | 2.5       | 5.0        |            | mA   |

| $T_{PGDEL}$                                    | PGOOD Delay Timer                      | Delay for PGOOD in, 'clks' = HKClock                                                           |           | 256        |            | clks |

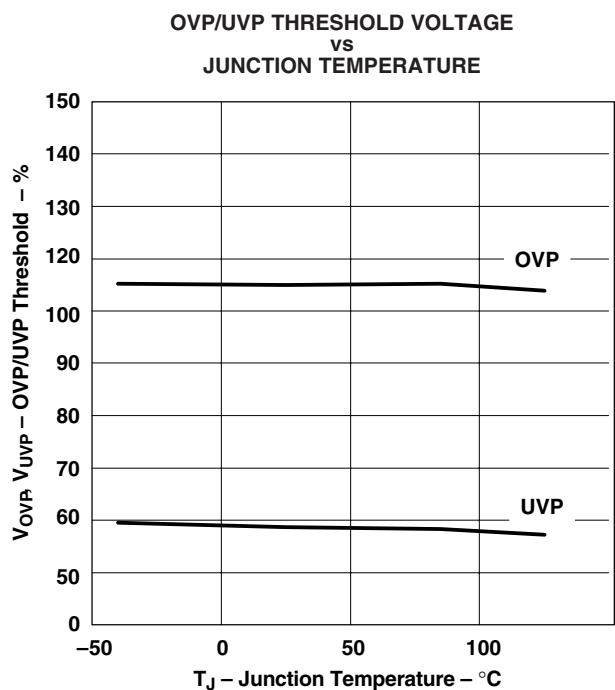

| <b>UNDERVOLTAGE and OVERVOLTAGE PROTECTION</b> |                                        |                                                                                                |           |            |            |      |

| $V_{OVP}$                                      | VFBx OVP Trip Threshold                | OVP detect                                                                                     | 110%      | 115%       | 120%       |      |

| $T_{OVPDEL}$                                   | VFBx OVP Delay Time                    |                                                                                                |           | 2          |            | ms   |

| $V_{UVP}$                                      | VFBx UVP Trip Threshold                | UVP detect                                                                                     | 65%       | 70%        | 75%        |      |

|                                                |                                        | Hysteresis                                                                                     |           | 6%         |            |      |

| $T_{UVPDEL}$                                   | VFBx UVP Delay Timer                   | 'clks' = HK Clock                                                                              |           | 128        |            | clks |

| <b>THERMAL SHUTDOWN</b>                        |                                        |                                                                                                |           |            |            |      |

| $T_{SDN1}$                                     | Thermal shutdown threshold             | Shutdown temperature                                                                           |           | 145        |            | °C   |

|                                                |                                        | Hysteresis                                                                                     |           | 10         |            |      |

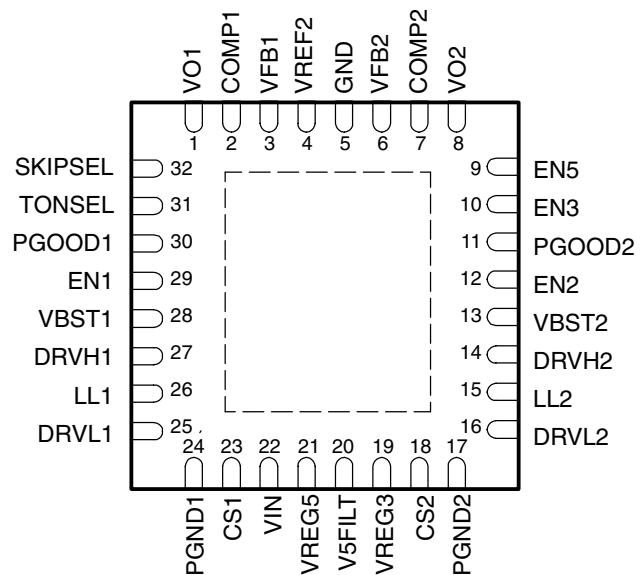

## デバイス情報

### 端子機能

| TERMINAL | I/O | DESCRIPTION                                                                                                                                                       |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. |                                                                                                                                                                   |

| COMP1    | 2   | ○ ループ補償ピン(誤差増幅器出力)。このピンとGNDの間にRCを接続することで、電流モード動作で適切なループ補償が行われます。D-CAP™モード動作の場合は、このピンをV5FILTに接続してください。                                                             |

| COMP2    | 7   | ○                                                                                                                                                                 |

| CS1      | 23  | I 抵抗センス方式用の電流センス・コンバレータ入力(-)。スレッシュホールド設定抵抗を通してV5FILTに接続した場合は、 $R_{DS(on)}$ 電流センス方式用の過電流トリップ設定入力となります                                                              |

| CS2      | 18  | I                                                                                                                                                                 |

| DRVH1    | 27  | ○ ハイサイドMOSFETゲート駆動出力。ソース3.5Ω、シンク1.5Ω、LLノード・リファレンスのフローティング・ドライバです。                                                                                                 |

| DRVH2    | 14  | ○ 駆動電圧は、VBST-LL電圧に対応します。                                                                                                                                          |

| DRVL1    | 25  | ○ 整流(ローサイド)MOSFETゲート駆動出力。ソース3.5Ω、シンク1.5Ω、PGNDリファレンスのドライバです。                                                                                                       |

| DRVL2    | 16  | ○ 駆動電圧はVREG5電圧です。                                                                                                                                                 |

| EN1      | 29  | I チャネル1およびチャネル2のSMPSイネーブル・ピン。5Vに接続することで、内部の3msソフトスタートにより起動します。                                                                                                    |

| EN2      | 12  | I これらの各ピンからグランドに外部キャバシタを接続してランプレートを調整すれば、より低速のソフトスタートも可能です。                                                                                                       |

| EN3      | 10  | I VREG3、3.3V低ドロップアウト・リニア・レギュレータのイネーブル・ピン。ディスエーブルにするには、GNDに接続します。レギュレータをオンにするには、フローティングにするか、イネーブル状態のVREG5に接続します。                                                   |

| EN5      | 9   | I VREG5、5V低ドロップアウト・リニア・レギュレータのイネーブル・ピン。ディスエーブルにするには、GNDに接続します。レギュレータをオンにするには、フローティングにするか、VBATに接続します。                                                              |

| GND      | 5   | I 信号グランド・ピン。                                                                                                                                                      |

| LL1      | 26  | I/O ハイサイドMOSFETゲート・ドライバのリターン。また、 $R_{DS(on)}$ センス用の電流センス・コンバレータ入力(-)として、およびオン時間制御回路の入力電圧モニタとしても使用されます。                                                            |

| LL2      | 15  | I/O                                                                                                                                                               |

| PGND1    | 24  | I/O 整流MOSFETゲート・ドライバのグランド・リターン。整流FETのソースまたは電流センス抵抗のGND接続の近くに、PGND2、PGND1、GNDを強くまとめて接続してください。電流センス・コンバレータ入力(+)としても使用されます。                                          |

| PGND2    | 17  | I/O                                                                                                                                                               |

| PGOOD1   | 30  | O パワーゲット・ウンドウ・コンバレータのオープン・ドレイン出力。抵抗を使用してV5FILTまたは適切な信号電圧にプルアップしてください。電流容量は5mAです。PGOODは、VFBが指定の制限内に入ってから1ms後に“ハイ”になります。パワーバッド(ピンが“ロー”)は、10μs以内です。                  |

| PGOOD2   | 11  | O                                                                                                                                                                 |

| SKIPSEL  | 32  | I スキップおよびフォルトモード選択ピン。表2を参照してください。                                                                                                                                 |

| TONSEL   | 31  | I オン時間選択ピン。表1および表2を参照してください。                                                                                                                                      |

| V5FILT   | 20  | I 制御回路全体に対する5V電源入力。RCフィルタを通してVREG5から供給してください。                                                                                                                     |

| VBST1    | 28  | I ハイサイドMOSFETドライバの電源入力。このピンと対応するLLピンとの間にキャバシタを接続します。VBST1およびVBST2の各ピンとVREG5の間には、内部でPNダイオードが接続されています。パワーMOSFETの駆動にPNダイオードの順方向電圧降下が重要となる場合は、外部にショットキー・ダイオードを接続できます。 |

| VBST2    | 13  | I                                                                                                                                                                 |

| VFB1     | 3   | I SMPS帰還入力。出力電圧の設定を行う場合には、帰還抵抗デバイダを接続します。固定出力オプションを使用する場合は、V5FILTに接続します。表2を参照してください。                                                                              |

| VFB2     | 6   | I                                                                                                                                                                 |

| VIN      | 22  | I 5Vおよび3.3Vリニア・レギュレータの電源入力。通常はVBATに接続します。                                                                                                                         |

| VO1      | 1   | I これらのピンには、4つの機能があります。オン時間調整、出力放電、VREG5/VREG3切り替え入力、および5V/3.3V固定出力オプション用帰還入力です。該当するスイッチ・モード電源の出力キャバシタの正側端子に接続してください。                                              |

| VO2      | 8   | I                                                                                                                                                                 |

| VREF2    | 4   | O 2Vリファレンス出力。0~85°Cの温度範囲で±50μA、±2%の精度を持ちます。1nFのセラミック・キャバシタを使用してGNDにバイパスしてください。このピンをGNDに接続すると、両方のSMPSがディスエーブルになります。                                                |

| VREG3    | 19  | O 3.3V、100mA低ドロップアウト・リニア・レギュレータ出力。10μFのセラミック・キャバシタを使用してPGNDにバイパスしてください。VNI電源で動作します。EN3でオフにできます。VO2が3.1V以上が印加されると、VO2に切り替わります。                                     |

| VREG5    | 21  | O 5V、100mA低ドロップアウト・リニア・レギュレータ出力。10μFのセラミック・キャバシタを使用してPGNDにバイパスしてください。VNI電源で動作します。内部でVBSTおよびDRV1に接続されています。EN5でオフにできます。VO1が4.8V以上が印加されると、VO1に切り替わります。               |

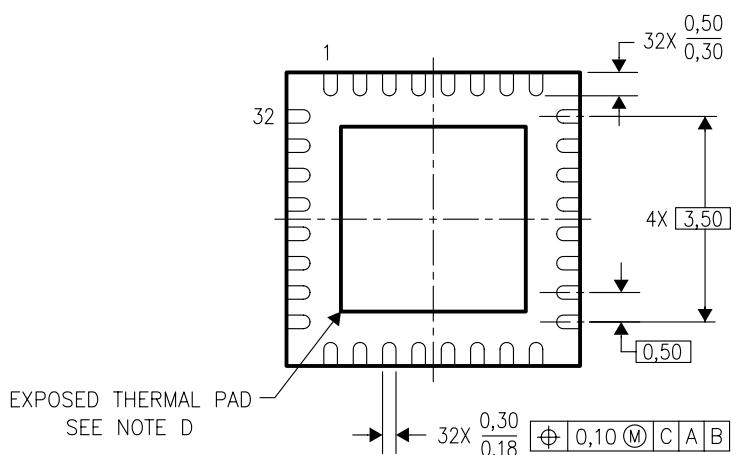

QFNパッケージ（底面図）

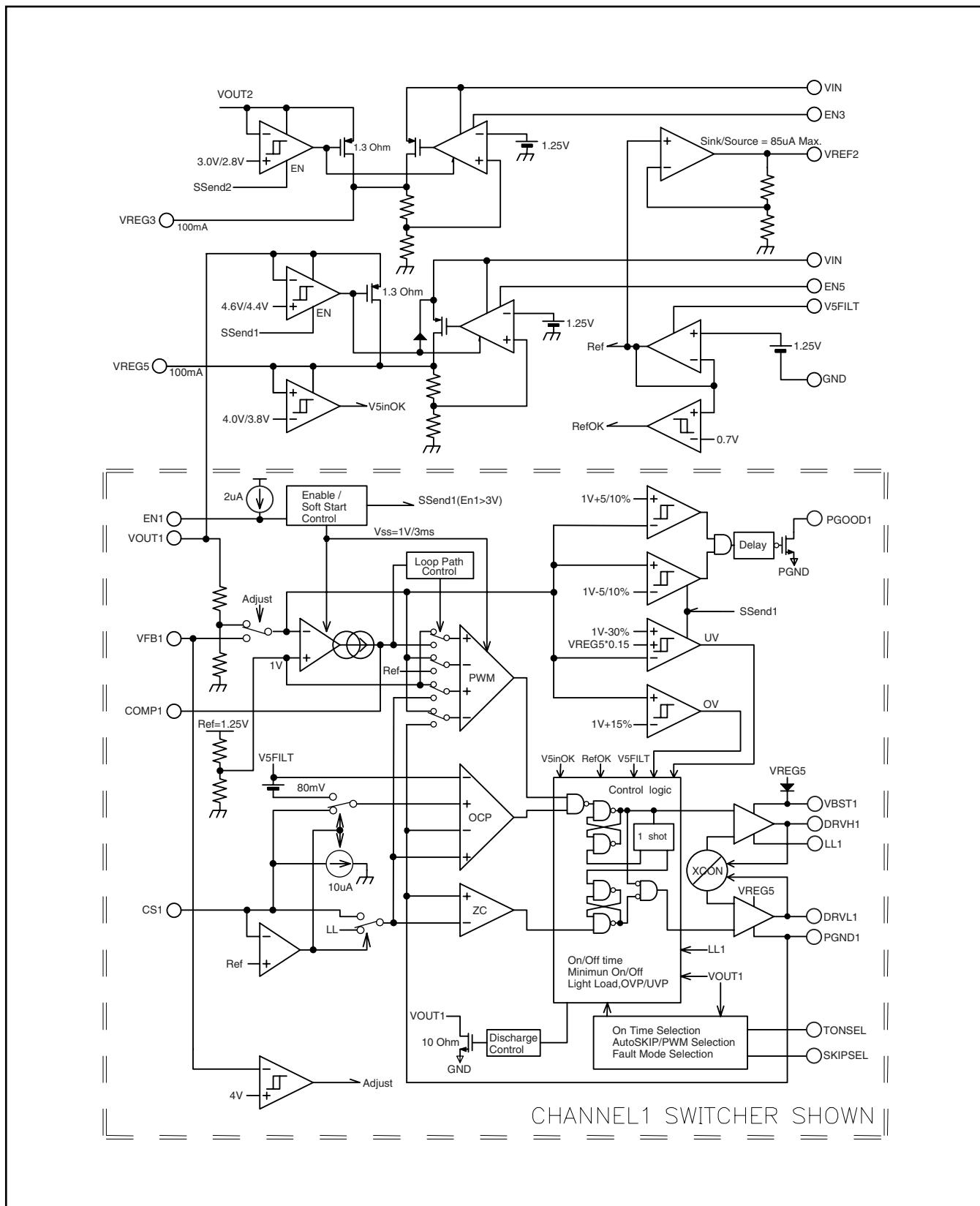

ブロック図(1チャンネルのみ示す)

## 詳細説明

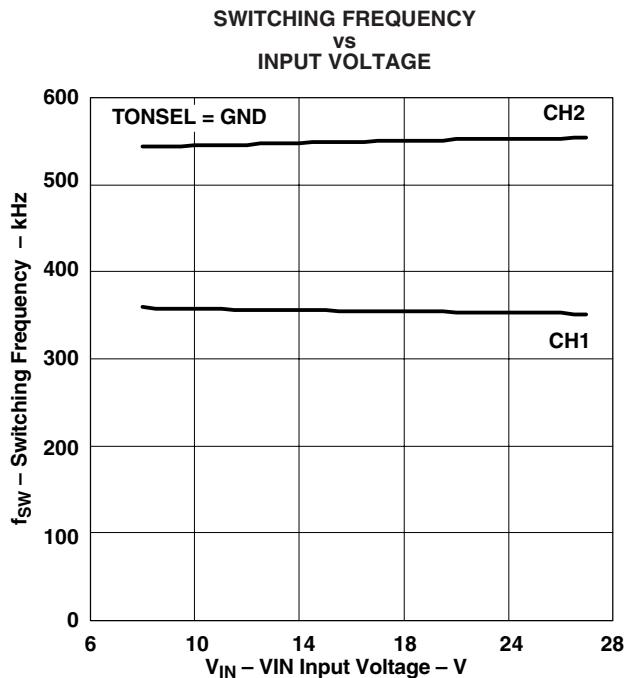

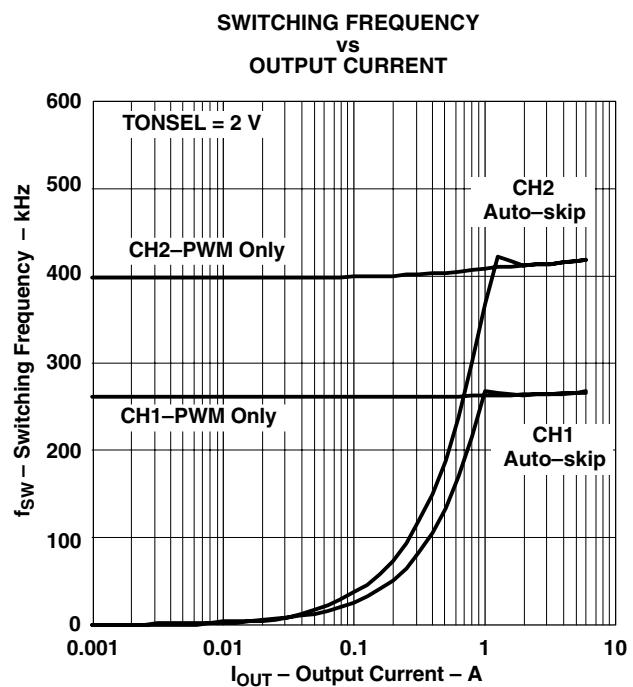

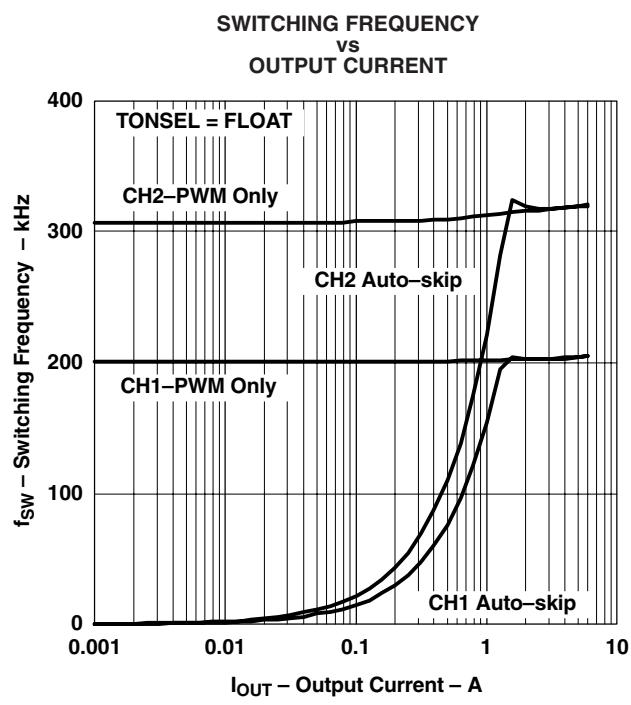

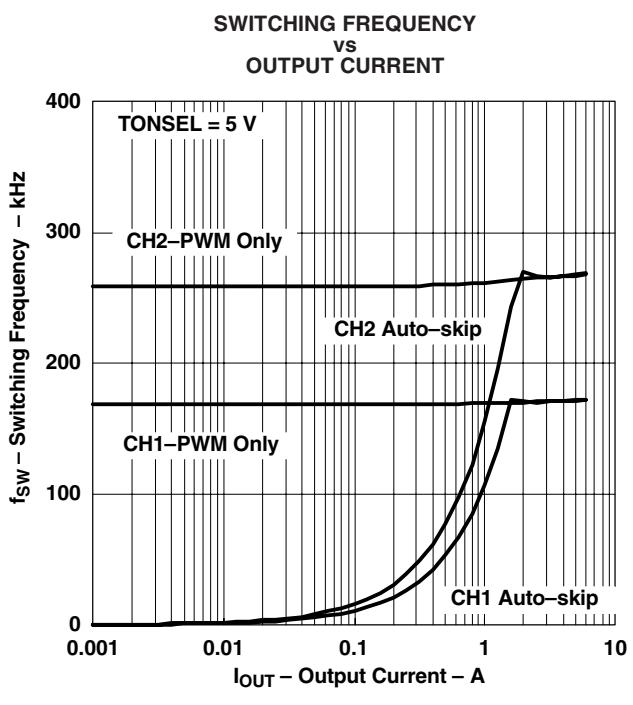

### PWM動作

TPS51120のスイッチング・モード電源(SMPS)ブロックは、アダプティブオン時間制御パルス幅変調(PWM)をサポートしています。スイッチング周波数は、効率が最大となる周波数(5V/180kHz、3.3V/270kHz)、部品サイズが最小となる周波数(5V/380kHz、3.3V/580kHz)、および2つの中間周波数の計4つから選択できます。TPS51120は、真の電流モード制御とD-CAP<sup>TM</sup>モード制御の両方をサポートし、システム設計の要件に合わせて選択することができます。外部スイッチに対しては、全NチャネルMOSFETトータムポール・アキテクチャが採用されています。上側(ハイサイド)の同期MOSFETは、各サイクルの開始時にオン(SET)になります。ユーザが選択した周波数と入力および出力電圧比によって定義される一定の“オン時間”が経過した後、このMOSFETはオフ(RESET)になります。インダクタ電流が減少して次の両方の条件を満足すると、上側MOSFETはオンになります。

1. 電流レベルが出力電圧の誤差量に対応している。

2. 過電流制限レベルを下回っている。

上記の動作を繰り返すことで、コントローラは出力電圧をレギュレーションします。下側(ローサイド)の同期MOSFET(整流MOSFET)は、上側MOSFETへの負の位相中の各サイクルでオンになり、導通損失を最小限に抑えます。整流MOSFETは、逆方向のインダクタ電流が検出されるとオフになります。これにより、スキップ・モード機能へのシームレスな遷移が可能となり、幅広い範囲の負荷電流に対して高い効率が維持されます。ソフトスタート期間の開始時には、上側MOSFETが少なくとも1回オンになるまでの間、整流MOSFETはオフ状態にとどまります。

### 電流モード

電流モード方式は、次に示すような帰還制御のシーケンスです。電圧デバイダ抵抗の中点で出力電圧がモニタされ、トランスコンダクタンス増幅器にフィードバックされます。増幅器は、帰還電圧と内部の1Vリファレンス電圧の間の誤差量に比例した、目標電流レベルを出力します。整流MOSFETがオンになっている場合、オフ・サイクルの間インダクタ電流レベルがモニ

タされます。PWMコンパレータは、インダクタ電流信号を、COMPピン電圧で示されるこの目標電流レベルと比較します。両方の信号が(電流センス信号の谷において)等しい場合、コンパレータはゲート・ドライバ・ラッチにSET信号を供給します。電流モード・オプションは、COMPピンに提供される外部補償ネットワークによって、比較的高い柔軟性を備えています。また、超低ESRの出力キャパシタにより、リップルを最低限に抑えた設計に適しています。ループ補償およびパラメータ設計に関する詳細については、「ループ補償および外部部品」を参照してください。インダクタ電流をセンスする際には、精度とコストが常にトレードオフの関係にあります。回路設計者がそのいずれかを選べるよう、TPS51120は外部抵抗センスとMOSFET R<sub>DS(on)</sub>センスの両方をサポートしています。R<sub>SENSE</sub>機能を持つ電流モードEVMについては、弊社までお問い合わせください。

### D-CAP<sup>TM</sup>モード

D-CAP<sup>TM</sup>モード動作は、COMPピンをV5FILTに接続することでイネーブルになります。このモードでは、PWMコンパレータが帰還電圧を直接モニタし、それを内部の1Vリファレンスと比較します。両方の信号が(電圧センス信号の谷において)等しい場合、コンパレータは上側MOSFETゲート・ドライバにSET信号を供給します。補償ネットワークが部品上に実装され、出力波形自体が誤差信号として使用されるため、外部回路設計はかなり単純化されます。D-CAP<sup>TM</sup>モードのもう1つの利点は、本質的に過渡応答が高速であることです。トレードオフは、出力キャパシタに十分な大きさのESRが必要であることです。SPCAPまたはPOSCAPを推奨します。インダクタ電流情報は、過電流保護と軽負荷動作のために、D-CAP<sup>TM</sup>モードでも使用されます。このモードで電流センス設計を無視しないでください。要約すると、D-CAP<sup>TM</sup>モードは、外部部品の数を最低限に減らして過渡応答を最大限高速にする設計に適していますが、リップル電圧が比較的大きくなります。適切な出力キャパシタおよびインダクタ電流リップルを選択すれば、ループの設計は簡単です。詳細については、「ループ補償と外部部品」のセクションでループ補償およびパラメータ設計の説明を参照してください。

| TONSEL CONNECTION | CH1 (LL1 = VIN = 12V) |                     | CH2 (LL2 = VIN = 12V) |                      |

|-------------------|-----------------------|---------------------|-----------------------|----------------------|

|                   | FREQUENCY (kHz)       | ON - TIME @ 5V (ns) | FREQUENCY (kHz)       | ON-TIME @ 3.3 V (ns) |

| V5FILT            | 180                   | 2340                | 270                   | 1030                 |

| FLOAT (OPEN)      | 220                   | 1950                | 330                   | 850                  |

| VREF2             | 280                   | 1490                | 430                   | 650                  |

| GND               | 380                   | 1111                | 580                   | 480                  |

表 1. 周波数選択および標準的なオン時間

## アダプティブオン時間制御

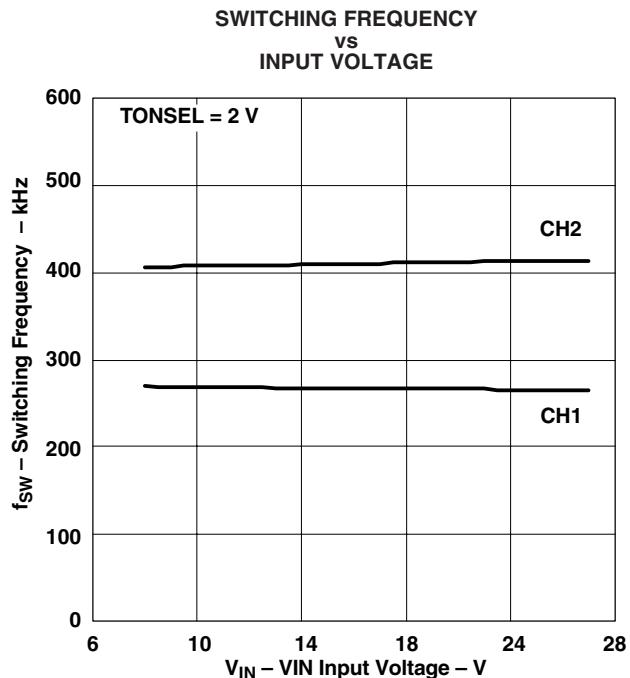

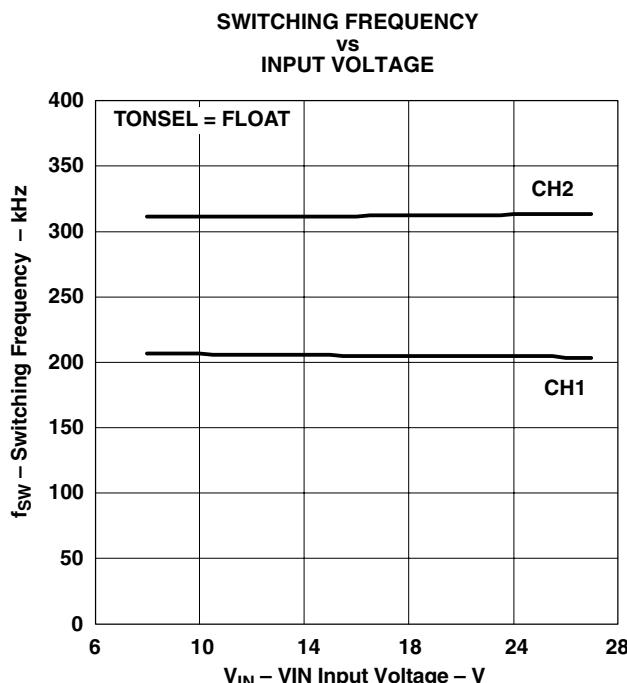

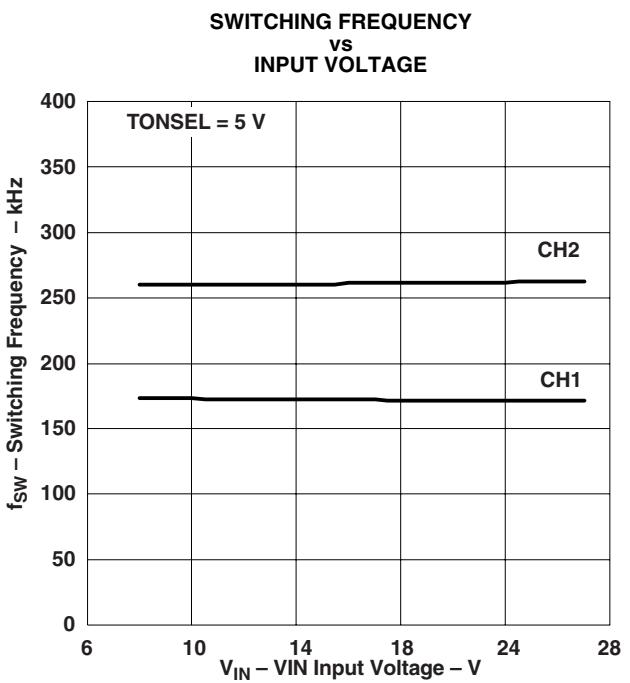

TPS51120は、適応型オン時間制御方式を採用し、専用の発振器は内蔵していません。しかし、入力および出力電圧をオン時間ワンショット・タイマにフィードフォワードすることで、入力電圧範囲全体にわたってほぼ一定の周波数で動作します(擬似定周波数)。オン時間は、入力電圧に逆比例し、出力電圧に比例して制御されるため、デューティは実用上同じサイクル時間で  $V_{OUT}/V_{IN}$  に保持されます。入力電圧のモニタは、オン状態中に LL ノード ( $V_{IN}$  ノードではなく) のセンスによって行われます。これにより、上側MOSFETでの電圧降下が特に重負荷条件下で周波数に影響を与えるのを防ぎます。 $V_{IN}$  ピンはオン時間制御には使用されず、5Vおよび3.3Vレギュレータの電源にのみ使用されます。スイッチング周波数は、TONSELピン電圧を設定することにより、上の表に示す4つの組み合わせから選択できます。これにより、システム設計で効率を最大とする(5V/180kHz、3.3V/270kHz)か、部品サイズを最小とする(5V/380kHz、

3.3V/580kHz)か、またはその中間でバランスを取るかを選択できます。また、 $V_{IN} = 12V$  のときの各周波数における5V、3.3V出力のオン時間も示しています。スタートアップを安定させるために、出力電圧フィードフォワードは、出力電圧が1.0Vを超えた後でイネーブルになります。

## プログラマブル構成

TPS51120には、さまざまな構成の選択肢があります。システム設計の要件に合わせて適切に調整することが重要です。下の表は、制御方式選択、周波数選択、出力電圧選択、およびスキップ選択用のプログラミング表です。“FAULTS OFF”では、UVP、OVP、およびUVLOがディスエーブルになります。これは主にデバッグの目的に使用します。LDOのEN3、EN5ピンおよびSMPSのEN1、EN2ピンのイネーブル状態および可能な接続についても示しています。

| PIN                    | GND                                                 | VREF2                  | FLOAT                               | V5FILT             |

|------------------------|-----------------------------------------------------|------------------------|-------------------------------------|--------------------|

| COMP                   | N/A                                                 | N/A                    | Current Mode<br>(apply R-C network) | D-CAP™ Mode        |

| TONSEL (CH1/CH2) [kHz] | 380 / 580                                           | 280 / 430              | 220 / 330                           | 180 / 270          |

| VFB1                   | Adjustable output (connect to the resistor divider) |                        |                                     | 5V fixed output    |

| VFB2                   | Adjustable output (connect to the resistor divider) |                        |                                     | 3.3 V fixed output |

| SKIPSEL                | AUTO-SKIP                                           | AUTO-SKIP (FAULTS OFF) | PWM                                 | PWM                |

| EN1, EN2               | Switcher Off                                        | Not used               | Switcher on                         | Switcher on        |

| EN3, EN5               | LDO Off                                             | Not used               | LDO on                              | LDO on (EN3 only)  |

表 2. 機能プログラミング表

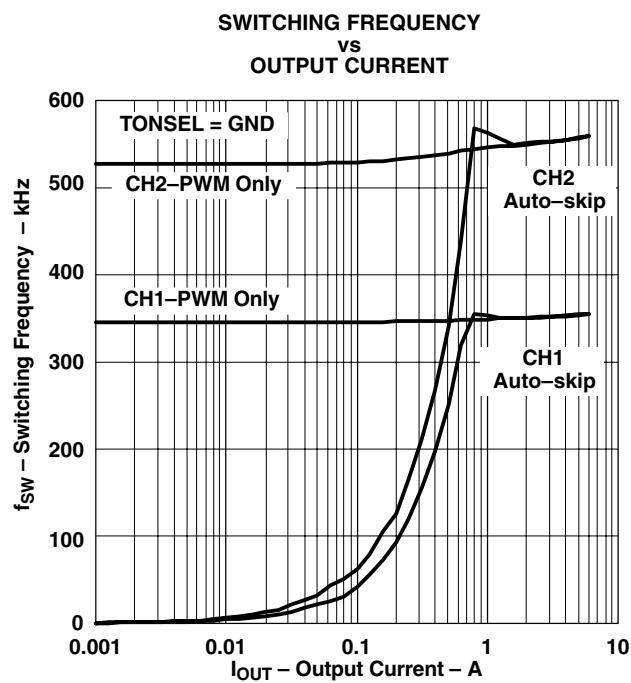

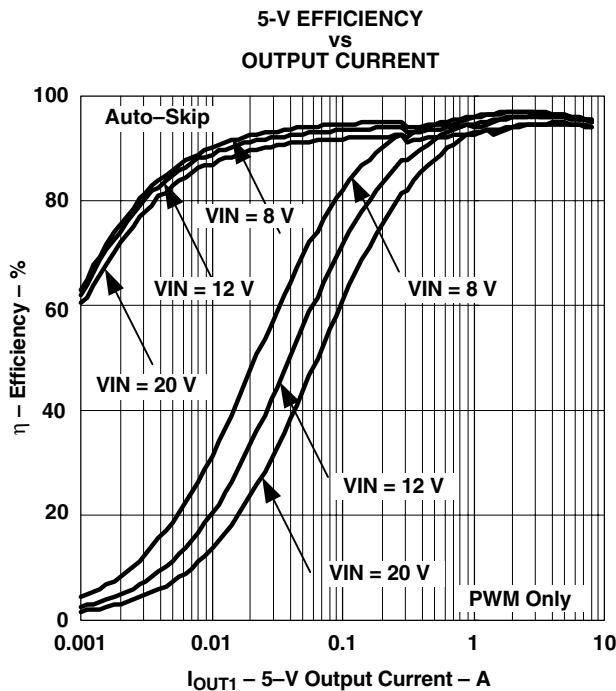

## 軽負荷動作

TPS51120は、高効率を維持するために、軽負荷状態ではスイッチング周波数を自動的に低くします。これは、ロードレギュレーションを増加させることなく、スムーズに行われます。動作の詳細を次に示します。重負荷状態から出力電流が減少すると、インダクタ電流も減少し、最終的にはその“谷”がゼロ電流に達する点まで至ります。これは、連続導通モードと不連続導通モードの境界に当たります。このゼロ・インダクタ電流が検出されると、整流MOSFETがオフになります。オン時間は、重負荷状態のときと同じままです。負荷電流がさらに減少すると、コンバータは不連続導通モードで動作し、次のオン・サイクルを必要とするレベルまで出力キャパシタを放電するのにかかる時間がどんどん長くなります。その結果、スイッチング周波数が低くなります。逆に、出力電流が軽負荷から重負荷へと増加すると、インダクタ電流が連続導通に移行するので、スイッチング周波数は設定済みの一定周波数まで増加します。軽負荷動作への遷移負荷点  $I_{OUT(LL)}$  (つまり、連続導通モードと不連続導通モードの間のスレッシュホールド) は、式1で計算できます。

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \quad (1)$$

ここで、 $f$ はTONSELピンで決定されるPWMスイッチング周波数です。軽負荷状態での出力電流に対するスイッチング周波数は、 $L$ 、 $f$ 、 $V_{IN}$ 、および $V_{OUT}$ の関数ですが、式1で得られる  $I_{OUT(LL)}$  から出力電流にほぼ比例して減少します。

## 強制PWM動作

SKIPSELをV5FILTに接続するか、またはフローティングにすると、ゼロ・インダクタ電流の検出がディスエーブルになり、負荷範囲全体にわたって連続導通モードで動作します。スイッチング周波数は、TONSEL入力で選択された周波数に維持されます。システム設計者は、このモードを使用することにより、効率をある程度犠牲にした上で、軽負荷状態において特定の周波数を回避することが可能です。ただし、このモードでは、出力が電流のシンクとソースの両方になり得ることに注意してください。出力端子がレギュレーション電圧よりも高い電圧ソースに接続されている場合、コンバータは出力から電流をシンクし、入力キャパシタへの充電量を増加させます。それにより、VINに予期しない高電圧が生じて、製品が破損する場合があります。

## 5V /100mA、LDOおよび切り替え (VREG5)

TPS51120には、5Vの100mAリニア・レギュレータが内蔵されています。この低ドロップアウト (LDO) レギュレータは、ICのメイン・アナログ電源を供給し、ゲート・ドライバ用の電流を提

供します。レギュレータはPMOSタイプでトランスクンダクタンス制御を備え、極は出力容量の値によって決定されます。一般に、このキャパシタの値は4.7μFよりも大きくする必要があります。標準的な設計には、10μFのセラミック・キャパシタを推奨します。レギュレータは、電流制限および過熱保護機能を備えています。また、VO1電圧が4.8Vを超えた場合、レギュレータはオフになります、5Vレールは5Vスイッチャ出力にブートストラップされ、コンバータの効率を向上させます。切り替えはグリッチなしで行われます。このブートストラップが実行されるときに、VREG5出力電圧には、4.8V以上で“グリッチ”は生じません。VO1からVREG5への切り替えインピーダンスは標準で1.3Ωです。スタンバイ電流は30μAに設計されており、最大限のバッテリ寿命を保ちながらレギュレータをオンに保つことができます。EN5ピンは、高電圧入力であり、VBATに接続するかまたはオープンにすると、5Vレギュレータをイネーブルになります。この5Vレギュレータは、スイッチング・レギュレータをイネーブルにする前にイネーブルにする必要があります。レギュレータをオフにするには、EN5をグランドにプルダウンします。レギュレータをディスエーブルにしても、一度ブートストラップ・パスを介して5Vが供給されるとスイッチャのシャットダウンは保証されません。切り替えが行われるため、デバイスをシャットダウンするにはLDOとともに5Vスイッチャをオフにする必要があります。EN5は、マスター ディスエーブルとしては機能しません。

## 3.3V /100mA、LDOおよび切り替え (VREG3)

TPS51120には、第2のレギュレータとして、3.3Vの100mAリニア・レギュレータが内蔵されています。このLDOは、ノートパソコン・システムで使用される3.3Vの“常時オン”電圧用にスタンバイ電源を提供します。このLDOの特性は、切り替え電圧を除いて5V LDOと同じです。VREG3とPGNDの間に、10μFのセラミック・キャパシタをデバイスに隣接させて配置してください。VO2電圧が3.1Vを超えると、このレギュレータはオフになります、3.3Vレールが3.3Vスイッチャにブートストラップされます。外部の帰還デバイダによってVO2電圧がそれより高い値 (5Vなど) に設定された場合、切り替え後にその高い電圧がVREG3に現れることに注意してください。EN3ピンは、低電圧入力であり、V5FILTに接続するかまたはオープンにすると、3.3Vレギュレータをイネーブルになります。この3.3Vレギュレータは、5Vレギュレータとは独立にオンにでき、その状態を維持できます。

## 2V、50 $\mu$ Aシンク/ソース・リファレンス(VREF2)

これは補助電圧を生成するために利用できるリファレンスです。50 $\mu$ A負荷および0°C～85°Cの周囲温度範囲で、許容差は±2%です。4ステート・ロジック(SKIPSEL、TONSEL)では、このリファレンスを利用して追加の選択モードを提供します。このリファレンスは、EN3およびEN5が“ハイ”になるとインペーブルになります。両方のスイッチャがオフになり、VREG5またはVREG3がシャットダウンされると、リファレンスはシャットダウンされます。表4を参照してください。この出力が強制的にグランドに接続されると、両方のSMPSがラッチなしでオフになります。VREF2ピンは、1nFのキャパシタを使用してGNDにバイパスしてください。

## ローサイド・ドライバ

ローサイド・ゲート・ドライバ(DRVL)は、高電流、低R<sub>DSON</sub>のNチャネルMOSFETを駆動するように設計されています。最大駆動電圧は、VREF5ピンから得られ、5.5Vです。瞬時駆動電流は、VREF5ピンの出力キャパシタから供給されます。平均駆動電流は、VGS = 5VでのFETのゲート電荷にスイッチング周波数を掛けた値になります。VREG5ピンの電圧には、ゲート・キャパシタへの配線や流れる電流に起因する寄生インダクタンスにより、高周波雑音が含まれる可能性があります。駆動能力は、その内部抵抗によって表され、VREG5～DRVL間は3.5Ω、DRVL～PGND間は1.5Ωです。アダプティブ・デッド・タイム制御により、上側MOSFETがオフになってから下側MOSFETがオンになるまで、および下側MOSFETがオフになってから上側MOSFETがオンになるまでの間に遅延時間が生成され、トーテムポール・スイッチの貫通を防ぎます。上側MOSFETのオフは、LLノード電圧が2V以下に低下することで検出されます。下側MOSFETのオフは、DRVL電圧が1.1Vになることで検出されます。

## ハイサイド・ドライバ

ハイサイド・ゲート・ドライバ(DRVH)は、高電流、低R<sub>DSON</sub>のNチャネルMOSFETを駆動するように設計されています。LLノード・リファレンスのフローティング・ドライバとして構成する場合は、対応するVBSTピンとLLピンの間に0.1 $\mu$ Fのセラミック・キャパシタを接続してください。5Vバイアス電圧は、VREG5電源から供給されます。VBSTは、内部で高電圧PNダイオードを通してVREG5に接続されています。この内部ダイオードにより、通常の4.5V駆動パワーMOSFETに対して十分なゲート電圧が供給され、外部部品数の削減に役立ちます。ただし、上側MOSFETの駆動にゲート・バイアス電圧が重要となる場合は、VREG5ピンからVBSTピンの間に外部ショットキー・ダイオードを追加することができます。ショットキー・ダイオードでは、高温時に逆方向リーケ電流がかなり大きくなることに注意してください。瞬時駆動電流は、VBSTピンとLLピンの間に接続されたフライン

グ・キャパシタによって供給されます。平均駆動電流は、VGS = 5Vでのゲート電荷にスイッチング周波数を掛けた値になります。駆動能力は、その内部抵抗によって表され、VBST～DRVH間は3.5Ω、DRVH～LLは1.5Ωです。DRVHピンとLLピンの間に印加できる最大推奨電圧は5.5V、DRVHピンとPGNDピンの間では34Vです。

## ソフトスタート

TPS51120には、各チャネルに3msの電圧サーボ・ソフトスタートが内蔵されています。EN1またはEN2ピンが0.9Vを超えると、内部DACによってリファレンス電圧が上昇し始めます。スタートアップ中には出力電圧のスムーズな制御が維持されます。ただし、より低速なソフトスタートが必要な場合は、EN1またはEN2ピンからGNDとの間に外部キャパシタを接続することができます。この場合、TPS51120は内蔵の2 $\mu$ A電流ソースによって外部キャパシタを充電します。スタートアップ時の上昇レートは主に、EN電圧のスルーレートと内部ソフトスタートのスルーレートのうち低い方に依存します。また、トランкиング放電が必要である場合は、ENピンを使用して、出力電圧放電をスムーズに制御することができます。ソフトスタート・リファレンス電圧の概算値はEN電圧の関数であり、 $V_{SSREF} = (V_{ENX} - 0.9) / 1.5 < 1$  Vとなります。ソフトスタート期間の開始時には、上側MOSFETが少なくとも1回オンになるまでの間、整流MOSFETはオフ状態にとどまります。これにより、出力キャパシタのプリチャージ済み状態において、出力キャパシタから高い負電流が流れ込むのを防ぎます。

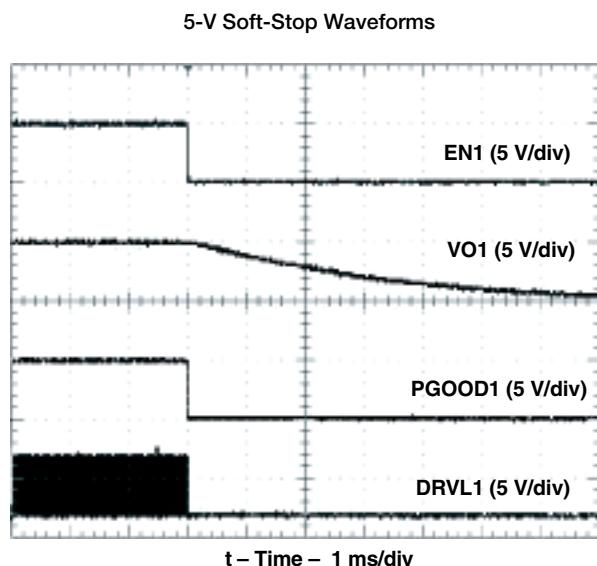

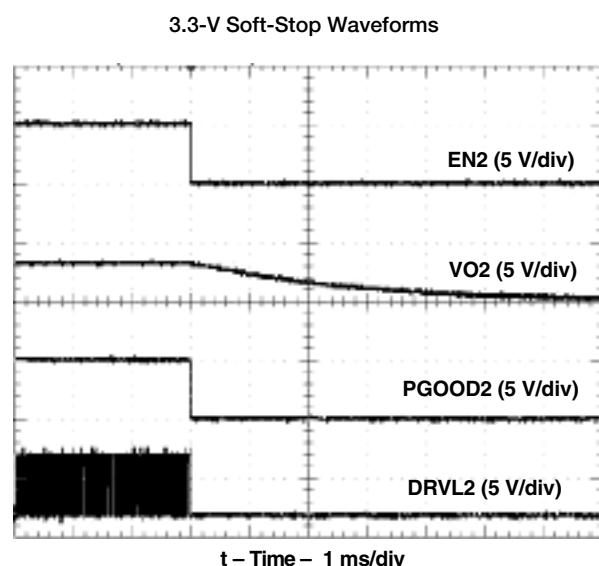

## ソフトトップ

放電モード(ソフトトップ)は、フォルトまたはディスエーブル状態時に常にオンになります。このモードでは、スイッチャがオフになるような状況(EN1またはEN2が“ロー”、OVP、UVP、UVLO)になると、VOピン内部の10Ωトランジスタを通して出力が放電されます。外部整流MOSFETはソフト・オフ動作に対してオンにならず、出力に負の電圧が生じるのを防いでいます。ソフトトップ時定数は、出力容量および放電トランジスタの抵抗値の関数です。この放電により、再起動時に、レギュレーション電圧が常に0Vから開始されるようになります。放電完了前にSMPSが再起動されると、ソフトトップは終了し、リファレンス・レベルが残りの出力電圧に戻った後で、スイッチングが再開されます。

## パワーグッド

TPS51120には、各SMPSに、それぞれに専用のパワーグッド出力(PGOOD1、PGOOD2)があります。PGOODモニタは、オープン・ドレーンの5mAプルダウン出力です。これらの出力は、スタートアップ時には“ロー”であり、スイッチャの帰還電圧が256クロック(約1ms)の間指定された範囲内にとどまるまで、“ロー”に維持されます。VFBピンが10%の許容範囲外になると、PGOODピンが数マイクロ秒以内に“ロー”になります。その後、VFBピンが目標値(1V)の5%以内に1ms以上とどまると、PGOODピンは再び“ハイ”になります。PGOODピンは、一般に100kΩ以上の抵抗を介してV5FILTピンにプルアップする必要があります。�ルト状態(過熱保護、UVLO、UVP、OVP)およびディスエーブル状態中は、両方のPGOODピンが“ロー”になります。

## 電流センスおよび過電流保護

SMPSには、サイクル毎の過電流制限があります。整流MOSFETがオンの間にインダクタ電流がモニタされ、電流レベルがトリップ・スレッシュホールドを上回っている間は、次のオン・サイクルが許可されません。高精度で費用対効果の高いソリューションを提供するために、TPS51120では外部抵抗センスとMOSFET  $R_{DS(on)}$ センスの両方がサポートされ、CSピンによっていずれかを選択できます。抵抗センス方式の場合は、下側MOSFETのソース端子とPGNDとの間に、適切な電流センス抵抗を接続する必要があります。CSピンは、下側MOSFETのソース端子ノードに接続されます。インダクタ電流は、PGNDピンとCSピンの間の電圧によってモニタされます。この方式では、トリップ・レベルは固定値の80mVです。 $R_{DS(on)}$ センス方式の場合は、トリップ電圧設定抵抗 $R_{TRIP}$ を介してCSピンがV5FILTに接続されます。この方式では、CSピンが10μAの $I_{TRIP}$ 電流をシンクし、トリップ・レベルは $R_{TRIP}$ 両端の電圧に設定されます。トリップ・レベルは、30mV～150mVの範囲内にしてください。それにより、下側にさまざまな種類のMOSFETを選択できます。インダクタ電流は、PGNDピンとLLピンの間の電圧によってモニタされるため、LLピンは下側MOSFETのド

レイン端子に接続する必要があります。 $I_{TRIP}$ は、 $R_{DS(on)}$ の温度依存性を補償するために、25°Cの値を基準とした4500ppm/°Cの温度スロープを持っています。いずれの方式においても、PGNDを正の電流センス・ノードとして使用するため、PGNDピンは適切な電流センス・デバイス(センス抵抗、または下側MOSFETのソース端子)に接続する必要があります。過電流状態では、負荷からの引き込みが増える一方で出力キャパシタへの電流が制限されるため、出力電圧は低下する傾向にあります。その結果、低電圧保護が働き、DRVHとDRVLの両方が“ロー”的な状態でラッチ・オフされます。

## 過電圧保護

過電圧保護(OVP)のために、TPS51120はVFB電圧をモニタしています。VFB電圧が目標値の115%より高くなると、OVPコンバレータ出力が“ハイ”になり、両方のスイッチャがラッチされます。原因となったチャネルはDRVHが“ロー”、DRVLが“ハイ”でラッチされ、他のチャネルはDRVHとDRVLのいずれも“ロー”でラッチされます。パワー・インダクタと出力キャパシタによって構成されるLC共振により、原因チャネルの出力端子に負の電圧が現れる可能性があることに注意してください。保護が必要な場合は、システム設計者がこの負の電圧に対処する必要があります。OVPの伝播遅延は、3μs未満です。

## 低電圧保護

低電圧保護(UVP)のために、TPS51120はVFB電圧をモニタしています。VFB電圧が目標値の70%より低くなると、UVPコンバレータ出力が“ハイ”になり、内部のUVP遅延カウントがカウントを開始します。128クロック(約0.5ms)後、TPS51120はDRVHおよびDRVLが“ロー”的な状態で両方のチャネルをラッチ・オフします。スタートアップを保証するために、この機能は、ソフトスタート・リファレンスが内部の1Vリファレンス動作を上回った後でイネーブルになります。表5を参照してください。

|                      | CS                                              | Threshold                               | Temperature Coefficient (ppm/°C) |

|----------------------|-------------------------------------------------|-----------------------------------------|----------------------------------|

| $R_{DS(on)}$ sensing | V5FILT                                          | $I_{TRIP} \times R_{TRIP} / R_{DS(on)}$ | 4500                             |

| $R_{SENSE}$ sensing  | Bottom FET source node (= $R_{SENSE}$ (-) node) | 80 mV / $R_{SENSE}$                     | none                             |

表3. 電流センス接続

## 5V電源とUVLO保護

TPS51120には2つの5V端子があります。VREG5は、5Vリニア・レギュレータの出力です。この端子は、ゲート・ドライバ回路の入力ピンとしても使用されます。このピンとVO1との間に、内部切り替えFETが接続されています。V5FILTは、チップ上の制御回路用のVCC電源入力です。高周波スパイク雑音を防ぐために、VREG5とこのV5FILTとの間にRCローパス・フィルタを接続してください。SKIPSEL、TONSEL、VFB(固定出力の場合)、COMP(D-CAPモードの場合)などの安定した5Vを必要とする状態定義ピンやCS抵抗には、V5FILTをリファレンスとする必要があります。本製品には、電力が不十分な状態での予期しない動作を防ぐために、5V低電圧ロックアウト保護(UVLO)を備えています。TPS51120は、VREG5の電圧をモニタし、VREG5電圧がUVLOスレッシュホールドを下回ると、SMPSがオフになります。出力放電(ソフトストップ)機能は、チャネル1およびチャネル2に対してイネーブルになっています。ただし、放電回路の電源は5Vラインから得ているため、シャットダウン中に放電が完了するよう十分長い時間電源が供給される必要があります。また、パワーアップ中に、TPS51120はUVLO(on)スレッシュホールドに達するまで出力キャパシタを放電しようとします。5V UVLOは、ラッチ無しの保護であり、5Vが回復すると自動的に復帰します。

## VINライン降下保護(ダイナミックUVP)

TPS51120は主にシステム電源として(つまり、3.3Vおよび5Vの生成に)使用されるため、VIN電源が6Vを下回ったときにUVP状態に入らないことが非常に重要です。UVPは、入力ラインの降下による5V出力の低下によって発生します。VINピンが5Vレギュレータ電圧を下回ると、5VレギュレータはVINを“追跡”します(LDO動作)。VREG5が4.8Vを下回ると、UVPスレッシュホールドは低く調整されます。これにより、UVPのラッチ状態になる前に5V電源UVLOがトリップするようになり、システム電源はVINの回復時に正常に回復できます。この機能は、アダプタの挿入時のような過渡的なVIN事象に対して非常に有用です。

## 過熱保護

TPS51120は、スイッチャを145°Cでシャットダウンする過熱保護機能を採用しています。これは、10°Cのヒステリシスを持つ非ラッチ保護です。両方のスイッチング・レギュレータと両方の内部レギュレータが停止します。スタートアップ前に製品が回復温度以上に加熱されている場合、VREG5およびVREG3 LDOはオフにならない可能性があります。動作を安全に再開するには、温度をT<sub>A</sub>=85°C以下に下げてください。

| EN5 <sup>(1)</sup> | EN3         | EN1         | EN2         | VREG5   | VREG3     | VREF2 <sup>(2)</sup> | SMPS1 | SMPS2 |

|--------------------|-------------|-------------|-------------|---------|-----------|----------------------|-------|-------|

| Low                | Low         | High or Low | High or Low | Off     | Off       | Off                  | Off   | Off   |

| Low-to-High        | Low         | High or Low | High or Low | LDO 5 V | Off       | Off                  | Off   | Off   |

| Low                | Low-to-High | High or Low | High or Low | Off     | LDO 3.3 V | Off                  | Off   | Off   |

| Low-to-High        | Low-to-High | Low         | Low         | LDO 5 V | LDO 3.3 V | On                   | Off   | Off   |

| High               | High        | Low         | Low-to-High | LDO 5 V | SW 3.3 V  | On                   | Off   | On    |

| High               | High        | Low-to-High | Low         | SW 5 V  | LDO 3.3 V | On                   | On    | Off   |

| High               | High        | High        | High        | SW 5 V  | SW 3.3 V  | On                   | On    | On    |

| High-to-Low        | High-to-Low | High        | High        | SW 5 V  | SW 3.3 V  | On                   | On    | On    |

| High               | High        | High-to-Low | High-to-Low | LDO 5 V | LDO 3.3 V | On                   | Off   | Off   |

| High-to-Low        | High        | High-to-Low | High        | Off     | LDO 3.3 V | Off                  | Off   | Off   |

| High               | High-to-Low | High        | High-to-Low | SW 5 V  | Off       | On                   | On    | Off   |

| High               | High-to-Low | Low         | High-to-Low | LDO 5 V | Off       | Off                  | Off   | Off   |

| High-to-Low        | High        | Low         | Low         | Off     | LDO 3.3 V | Off                  | Off   | Off   |

| High               | High-to-Low | Low         | Low         | LDO 5 V | Off       | Off                  | Off   | Off   |

表4. イネーブル・ロジック状態(VOUT1 = 5 V、VOUT2 = 3.3 V)

(1) 切り替えが行われるため、デバイスをシャットダウンするにはLDOとともに5Vスイッチャをオフにする必要があります。EN5は、マスター ディスエーブルとしては機能しません。

(2) VREF2出力を強制的にグランドに落とすと、SMPS1およびSMPS2がラッチなしでディスエーブルになります。

|                      | DRVH1           | DRV1             | DRVH2           | DRV2             | PGOOD1<br>PGOOD2 | VREG5               | VREG3     | VREF2 | FOR<br>RESTART                                    |

|----------------------|-----------------|------------------|-----------------|------------------|------------------|---------------------|-----------|-------|---------------------------------------------------|

| UVPch1               | Low             | Low              | Low             | Low              | Low/Low          | LDO 5 V             | LDO 3.3 V | On    | Toggle EN1                                        |

| UVPch2               | Low             | Low              | Low             | Low              | Low/Low          | LDO 5 V             | LDO 3.3 V | On    | Toggle EN2                                        |

| OVPch1               | Low             | High             | Low             | Low              | Low/Low          | LDO 5 V             | LDO 3.3 V | On    | Toggle EN1                                        |

| OVPch1               | Low             | Low              | Low             | High             | Low/Low          | LDO 5 V             | LDO 3.3 V | On    | Toggle EN2                                        |

| Thermal SHDN         | Low             | Low              | Low             | Low              | Low/Low          | Off                 | Off       | Off   | Lower Package Temperature                         |

| VIN < 5.0            | Normal          | Normal           | Normal          | Normal           | Low/Normal       | SW 5 V              | SW 3.3 V  | On    | Raise VIN                                         |

| VREG<br>UVLO         | Low             | Low              | Low             | Low              | Low/Low          | LDO but<br>dropping | LDO 3.3 V | On    | Raise VIN, Re-<br>duce 5V current                 |

| OCPch1               | Limited<br>Duty | Extended<br>Duty | Normal          | Normal           | Low/Normal       | LDO 5 V             | SW 3.3 V  | On    | Reduce CH1<br>Current                             |

| OCPch2               | Normal          | Normal           | Limited<br>Duty | Extended<br>Duty | Normal/Low       | SW 5 V              | LDO 3.3 V | On    | Reduce CH2<br>Current                             |

| EN1 Low              | Low             | Low              | Normal          | Normal           | Low/Normal       | LDO 5 V             | SW 3.3 V  | On    | Float or tie to<br>VREG5                          |

| EN2 Low              | Normal          | Normal           | Low             | Low              | Normal/Low       | SW 5 V              | LDO 3.3 V | On    | Float or tie to<br>VREG5                          |

| EN1, EN2, EN3<br>Low | Low             | Low              | Low             | Low              | Low/Low          | LDO 5 V             | Off       | Off   | Float EN3, then<br>float EN1, 2or<br>tie to VREG5 |

| EN5, EN1 Low         | Low             | Low              | Low             | Low              | Low/Low          | Off                 | LDO 3.3 V | Off   | Float EN5 or tie<br>to VBAT, tie<br>EN1 to VREG5  |

表 5. 保護状態 (VOUT1 = 5V、VOUT2 = 3.3V)

## ループ補償と外部部品の選択

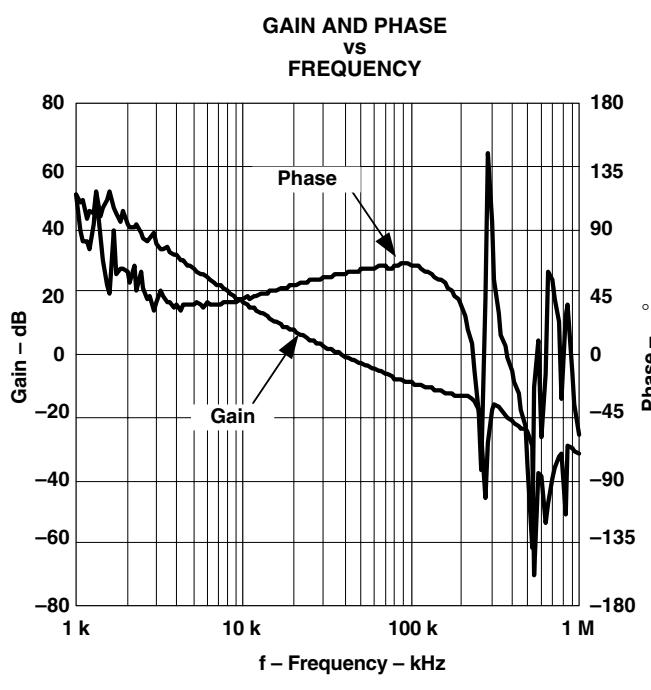

### 電流モード動作

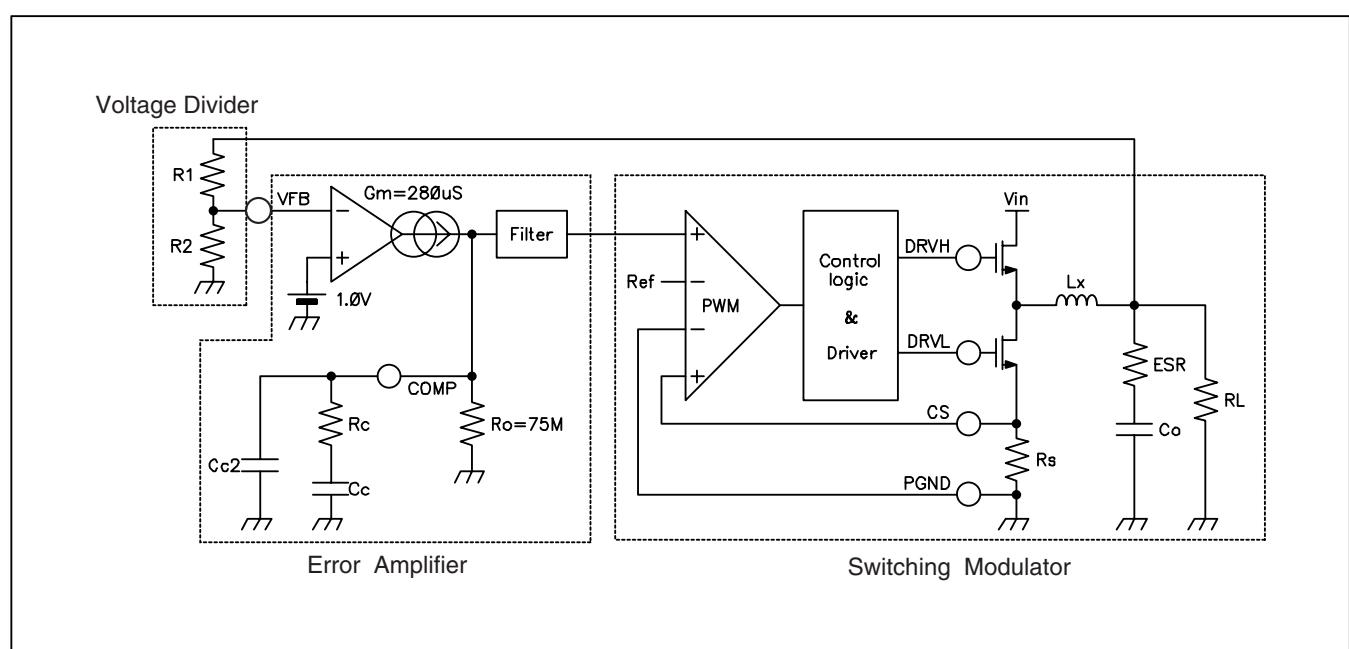

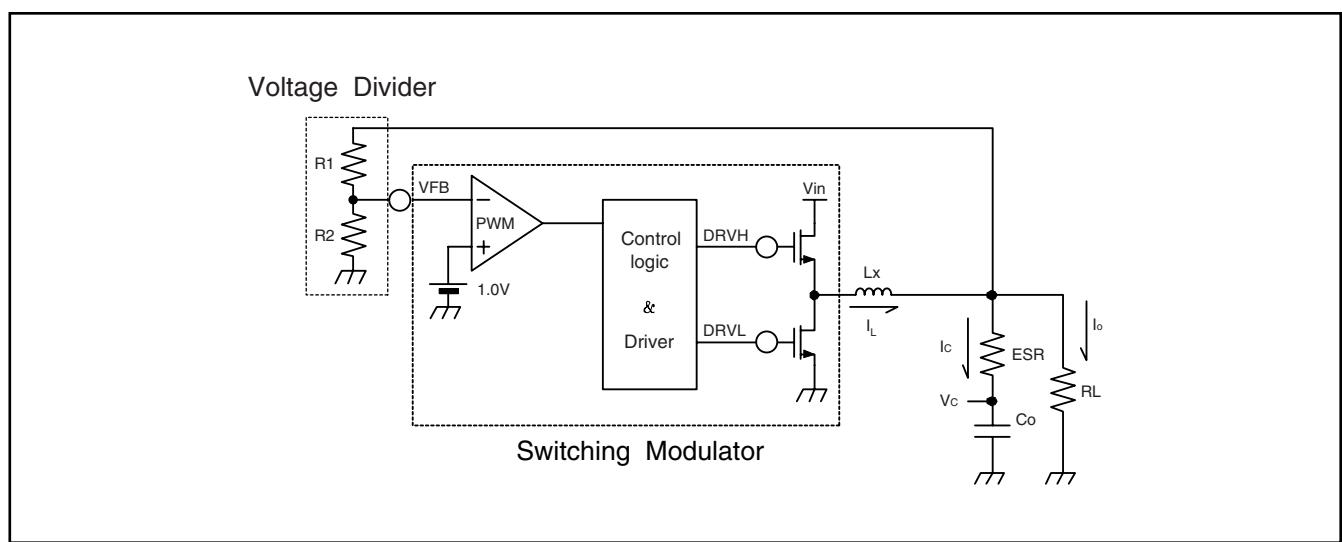

TTPS51120の電流モード動作を使用したバック・コンバータは、電圧デバイダ、誤差増幅器、スイッチング変調器の3つの部分に分けることができます。スイッチング変調器を線形化する

ことで、システム全体の伝達関数を求めることができます。電流モード方式はインダクタ電流を直接制御するため、変調器は図1に示すように線形化できます。

図 1. 変調器の線形化

ここでは、インダクタがローカル帰還ループの内部に配置され、そのインダクタンスは小信号モデルには現れません。その結果、パワー・インダクタを含む変調された電流ソースは、トランスコンダクタンスが $1/R_S$ の電流ソースとしてモデル化でき、出力キャパシタは変調器部分を表します。この単純化したモデルは、スイッチング周波数の約1/2までの周波数空間に適用できます。1つ注意すべき点として、インダクタンスは小信号モデルには影響しませんが、電流ソースのスルーレートを制限するため、大信号モデルには影響を及ぼします。したがって、ループの安定性に影響を与えないでインダクタンスを小さくすることにより、大信号動作の1つであるバック・コンバータの負荷過渡応答を向上させることができます。

システム全体の合計オープン・ループ伝達関数は、式2で得られます。

$$H(s) = H_1(s) \times H_2(s) \times H_3(s) \quad (2)$$

$RL \gg ESR$ 、 $R_O \gg R_C$ 、および $C_C \gg C_{C2}$ と仮定して、3つのブロックそれぞれの伝達関数を式3～式5に示します。

$$H_1(s) = \frac{R_2}{(R_2 + R_1)} \quad (3)$$

$$H_2(s) = -Gm \times \frac{R_O(1 + s \times C_C \times R_C)}{(1 + s \times C_C \times R_O)(1 + s \times C_{C2} \times R_C)} \quad (4)$$

$$H_3(s) = \frac{(1 + s \times C_O \times ESR)}{(1 + s \times C_O \times RL)} \times \frac{RL}{R_S} \quad (5)$$

$H(s)$ には3つの極と2つのゼロがあります。各極およびゼロは、式6～式10で求められます。

$$\omega_{P1} = \frac{1}{(C_C \times R_O)} \quad (6)$$

$$\omega_{P2} = \frac{1}{(C_O \times RL)} \quad (7)$$

$$\omega_{P3} = \frac{1}{(C_{C2} \times R_C)} \quad (8)$$

$$\omega_{Z1} = \frac{1}{(C_C \times R_C)} \quad (9)$$

$$\omega_{Z2} = \frac{1}{(C_O \times ESR)} \quad (10)$$

通常、これらの極およびゼロの各周波数は、0dB周波数 ( $f_0$ )よりも低くなります。ただし、スイッチング回路遅延の影響を避けるために、 $f_0$ はスイッチング周波数の1/3未満に維持する必要があります。 $f_0$ は、次の式11で表されます。

$$\begin{aligned} f_0 &= \frac{1}{2\pi} \times \frac{R_2}{R_1 + R_2} \times \frac{Gm}{C_O} \times \frac{R_C}{R_S} \\ &= \frac{1}{2\pi} \times \frac{1.0}{V_{OUT}} \times \frac{Gm}{C_O} \times \frac{R_C}{R_S} \end{aligned} \quad (11)$$

上記の小信号解析に基づき、外部部品は次のように選択することができます。

## 1. インダクタの選択

インダクタンス値は、リップル電流が最大出力電流の約1/4～1/2になるよう決定する必要があります。

$$\begin{aligned} L &= \frac{1}{I_{IND(ripple)} \times f} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} \\ &= \frac{2}{I_{OUT(max)} \times f} \times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} \end{aligned} \quad (12)$$

また、インダクタは良好な効率が得られるように低いDCRを持つ必要があります、ピーク・インダクタ電流から飽和するまでに十分な余裕も必要です。ピーク・インダクタ電流は式13で見積もることができます。

$$\begin{aligned} I_{IND(peak)} &= \frac{V_{TRIP}}{R_{DS(on)}} + \frac{1}{L \times f} \\ &\times \frac{(V_{IN(max)} - V_{OUT}) \times V_{OUT}}{V_{IN(max)}} \end{aligned} \quad (13)$$

## 2. 整流(下側)MOSFETの選択

$R_{DS(on)}$ センス方式を選択した場合は、整流MOSFETのオン抵抗がこの $R_S$ として使用されるため、低い $R_{DS(on)}$ が必ずしも良好な性能につながるわけではありません。インダクタ電流を明確に検出するには、インダクタ・リップル電流でリップル電圧が15mV以上になるような値を最小 $R_S$ 値として推奨します。これにより、CCMからDCM、またはDCMからCCMへの遷移がスムーズになります。もちろん、 $R_{DS(on)}$ の上限は効率要件によって制限され、通常この抵抗は高負荷条件下でより大きく効率に影響します。外部抵抗電流センスを使用する場合は、低 $R_{DS(on)}$ に対する制限はありません。ただし、電流センス抵抗 $R_S$ 自体が効率に影響してきます。

### 3. 出力キャパシタの選択

有機半導体キャパシタ (OS-CON) または特殊ポリマー・キャパシタ (SP-CAP) を使用する場合は、安定状態または負荷過渡状態で必要なリップル値を得るためにESRによって、必要なキャパシタの量が決まり、それによって安定動作を満足させるのに十分な容量が得られます。ピークツーピークのリップル値は、(ESR×安定状態のインダクタ・リップル電流) または(ESR×高速負荷過渡応答時の負荷電流ステップ) として見積もることができます。セラミック・キャパシタの場合は、通常、ESRはリップル要件を満たすのに十分小さい値です。その一方で、出力容量によって駆動される過渡的なアンダーシュートおよびオーバーシュートが、キャパシタを決定する重要な要素となります。

### 4. $f_0$ を決定し、式14から $R_C$ を計算

$R_C$ を大きくすると、安定性は低下しますが過渡応答が高速になります。 $R_C$ を大きくしても過渡応答が十分でない場合は、出力容量を大きくしてみてください。 $f_0$ の推奨値は $f/4$ です。

$$R_C \leq 2\pi \times f_0 \times V_{OUT} \times \frac{C_O}{Gm} \times R_S \quad (14)$$

### 5. $C_{C2}$ を計算

この容量の目的は、出力キャパシタのESRに起因するゼロをキャンセルすることです。セラミック・キャパシタを使用する場合は、 $C_{C2}$ は不要です。

$$\omega_{z2} = \frac{1}{(C_O \times ESR)} = \omega_{p3} = \frac{1}{(C_{C2} \times R_C)} \quad (15)$$

$$C_{C2} = \frac{C_O \times ESR}{R_C} \quad (16)$$

### 6. $C_C$ を計算

$C_C$ の目的は、DC成分をカットして高いDC帰還ゲインを得ることです。ただし、それにより位相遅延が生じるので、 $f_0$ 周波数でこの影響をキャンセルするために別のゼロが必要になります。このゼロ ( $\omega_{z1}$ ) は、 $C_C$ と $R_C$ によって決定されます。 $\omega_{z1}$ の推奨値は、 $f_0$ 周波数の1/10です。

$$f_{z1} = \frac{1}{2\pi \times C_C \times R_C} = \frac{f_0}{10} \quad (17)$$

### 7. 電圧調整可能モードの場合、 $R1$ および $R2$ を決定

$R2$ の推奨値は、 $10k\Omega \sim 20k\Omega$ です。 $R1$ は、式18で決定します。

$$R_1 = (V_{OUT} - 1.0) \times R_2 \quad (18)$$

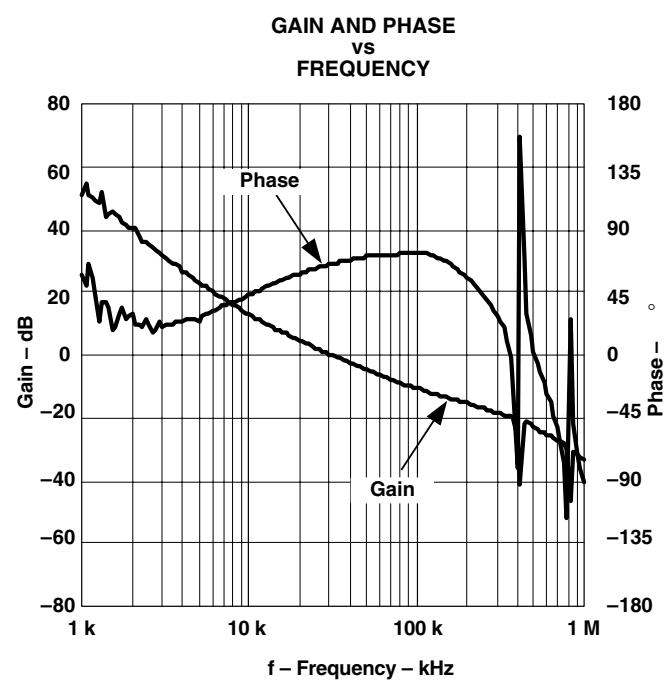

### D-CAP<sup>TM</sup>モード動作

D-CAP<sup>TM</sup>モードを使用したバック・コンバータ・システムは、図2に示すように単純化できます。

VO電圧は、デバイダ抵抗を介した内部リファレンス電圧と比較されます(内部抵抗モードの場合。電圧調整可能モードの場合はVFBと直接比較されます)。PWMコンパレータにより、上側MOSFETをオンにするタイミングが決定されます。コンパレータのゲインおよび速度は、各オン・サイクル開始時(またはオフ・サイクル終了時)の電圧を実質上一定に保持するのに十分なほど高い値です。DC出力電圧には、入力電圧の増加とともにわずかに増加するリップル振幅によって、ライン・レギュレーションをもつ場合があります。

ループの安定性のために、次に定義する0dB周波数( $f_0$ )がスイッチング周波数の1/3より低い必要があります。

$$f_0 = \frac{1}{2\pi \times ESR \times C_O} \leq \frac{f_{SW}}{3} \quad (19)$$

図 2. 変調器の線形化

$f_0$ は出力キャパシタの特性のみによって決まるため、D-CAP<sup>TM</sup>モードのループ安定性はキャパシタの化学的性質によって決定されます。たとえば、特殊ポリマー・キャパシタ(S-P-CAP)は数百 $\mu$ FのCoと10m $\Omega$ 程度のESRを持ちます。その場合、 $f_0$ は100kHzまたはそれ以下となり、ループは安定します。一方、セラミック・キャパシタの $f_0$ は700kHzを超えるため、この動作モードには不適切です。

D-CAP<sup>TM</sup>モードには使いやすさ、外部部品数が最小、非常に短い応答時間など多くの利点がありますが、ループ内に誤差増幅器を含まないため、外部回路で十分な帰還信号を提供してジッタ・レベルを抑える必要があります。必要な信号レベルは比較ポイントにおいて約15mVです(内部または外部VFB電圧)。出力キャパシタのESRはこの要件を満足する必要があります。

D-CAP<sup>TM</sup>モードでは、外部部品の選択は非常に単純です。

## 1. 周波数および許容可能なリップル電流に基づいてインダクタを選択。

## 2. 出力キャパシタを選択

有機半導体キャパシタまたは特殊ポリマー・キャパシタを推奨します。上記の必要なリップル電圧を満足するようにESRを決定します。簡単な近似式を式20に示します。

$$ESR = \frac{V_{OUT} \times 0.015}{I_{RIPPLE}} \quad (20)$$

## レイアウトについての考察

TPS51120を使用したレイアウト作業を開始する前に、いくつかの点を考察する必要があります。

- VREG5からV5FILTに対してRCローパス・フィルタを接続します。1 $\mu$ Fおよび5.1 $\Omega$ を推奨します。デバイスに近接させてフィルタ・キャパシタを配置します。可能であれば、12mm(0.5インチ)以内に配置します。

- VREG5およびVREG3には4.7 $\mu$ F以上が必要です。VREF2には、1nFのセラミック・バイパス・キャパシタが必要です。これはデバイスに近接させて配置し、トレースは10mm以下としてください。

- CSxとV5FILT(VREG5ではなく)の間に過電流設定抵抗を接続します。これはデバイスに近接させて、可能であればデバイスのすぐ隣りに配置します。CSxとV5FILTの間のトレースは、高電圧スイッチング・ノードへのカップリングを避けてください。

- 外部抵抗デバイダを用いた調整可能な出力電圧を使用する場合、放電パス(VOx)には出力キャパシタへの専用トレースを設ける必要があります。これは出力電圧センス・トレースとは別個にし、ループのない幅1.5mm以上のトレースとします。帰還電流設定抵抗(VFBxとGNDの間の抵抗)は、デバイスのGNDに近接させて接続してください。部品実装面に配置し、この抵抗とデバイスの間にビアの使用は避けます。

- ドライバからハイサイドまたはローサイドMOSFETの各ゲートまでの接続は、浮遊インダクタンスを低減するために、できるだけ短くします。幅0.65mm(25mils)以上のトレースを使用してください。

- VOx、COMPx、VFBx、VREF2、GND、ENx、PGOODx、CSx、V5FILT、TONSEL、SKIPSELなど、すべての敏感なアナログ・トレースおよび部品は、カップリングを避けるために、LLx、DRVlx、またはDRVHxノードなどの高電圧スイッチング・ノードから離して配置します。内部の層をグランド・プレーンとして使用し、帰還トレースをパワートレースやパワー部品からシールドしてください。

- VINキャパシタ、VOUTキャパシタ、およびローサイドMOSFETのソースの各グランド端子は、できる限り1つにまとめてください。GND(信号グランド)とPGNDx(パワー・グランド)は、デバイスの近くで強くまとめて接続してください。ハイサイドMOSFETのソース、ローサイドMOSFETのドレンおよびインダクタの高電圧側に接続されるLLxノードと定義されたPCBトレースは、できる限り短く幅広くします。

- パッケージから効率的に熱を除去するために、サーマル・ランドを用意してパッケージのサーマル・パッドに半田付けします。放熱を助けるために、サーマル・ランドと内部グランド・プレーンとの間に直径0.33mm(13mils)のビアを3×3個以上設けます。PGNDxは、このパッケージ下のサーマル・ランドには接続しないでください。

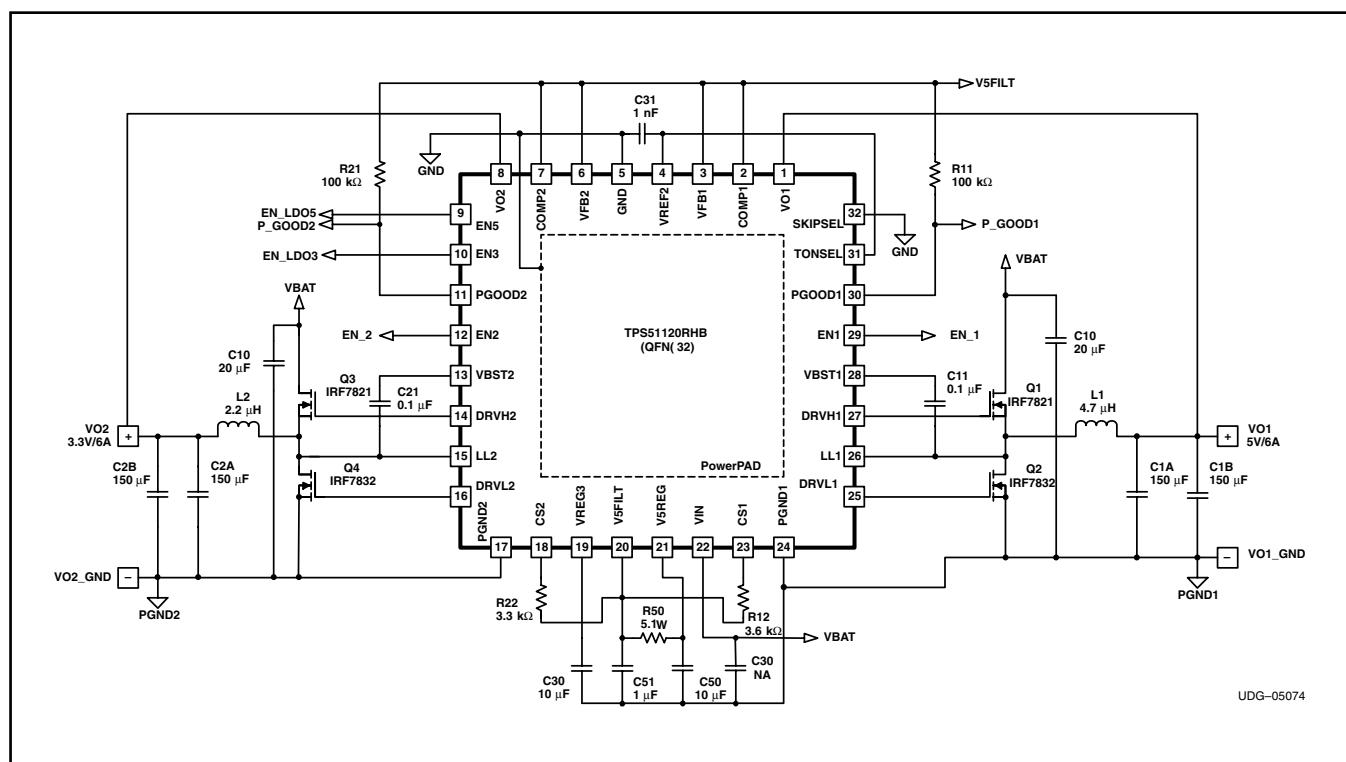

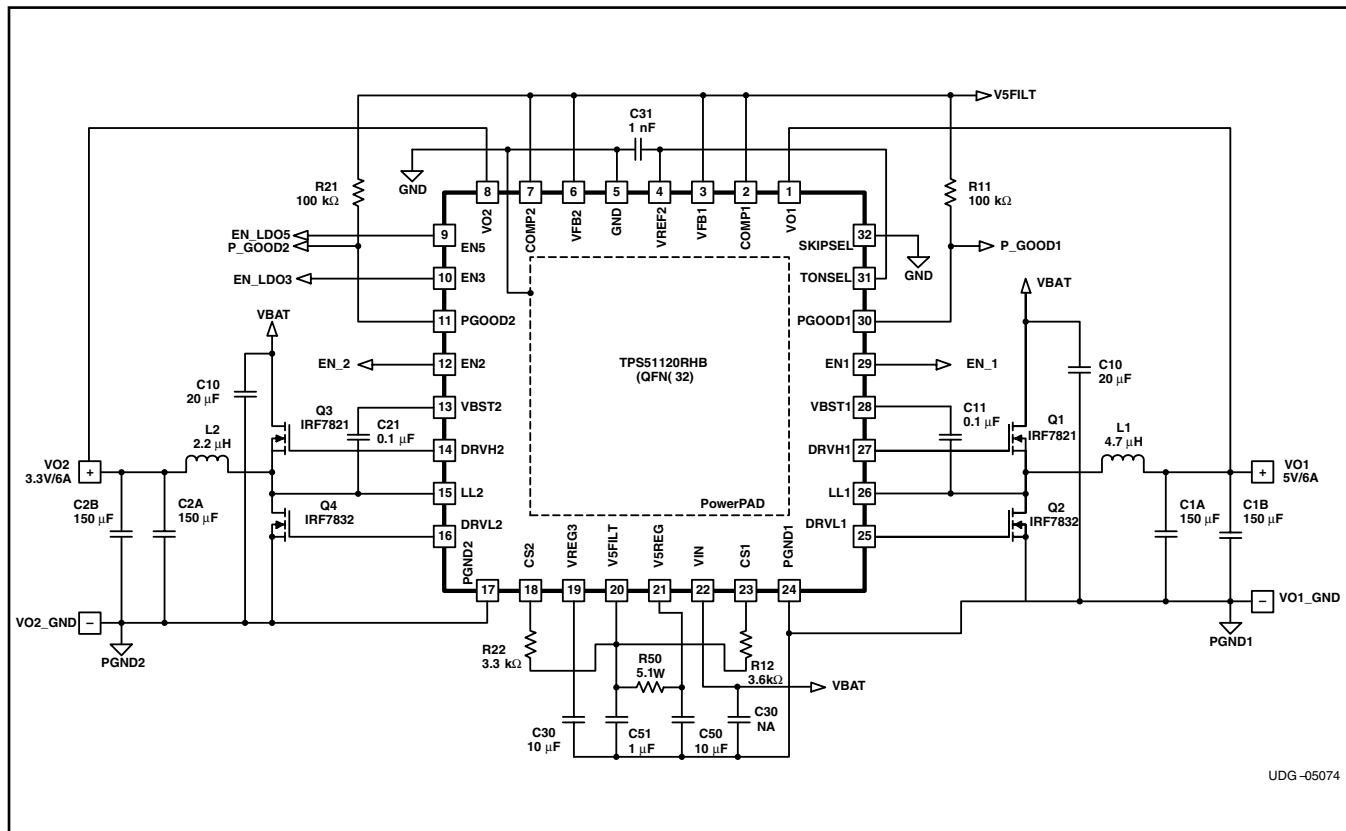

図3. D-CAP<sup>TM</sup>モード、固定5V/6A、+3.3V/6A、R<sub>DS(on)</sub>センシング

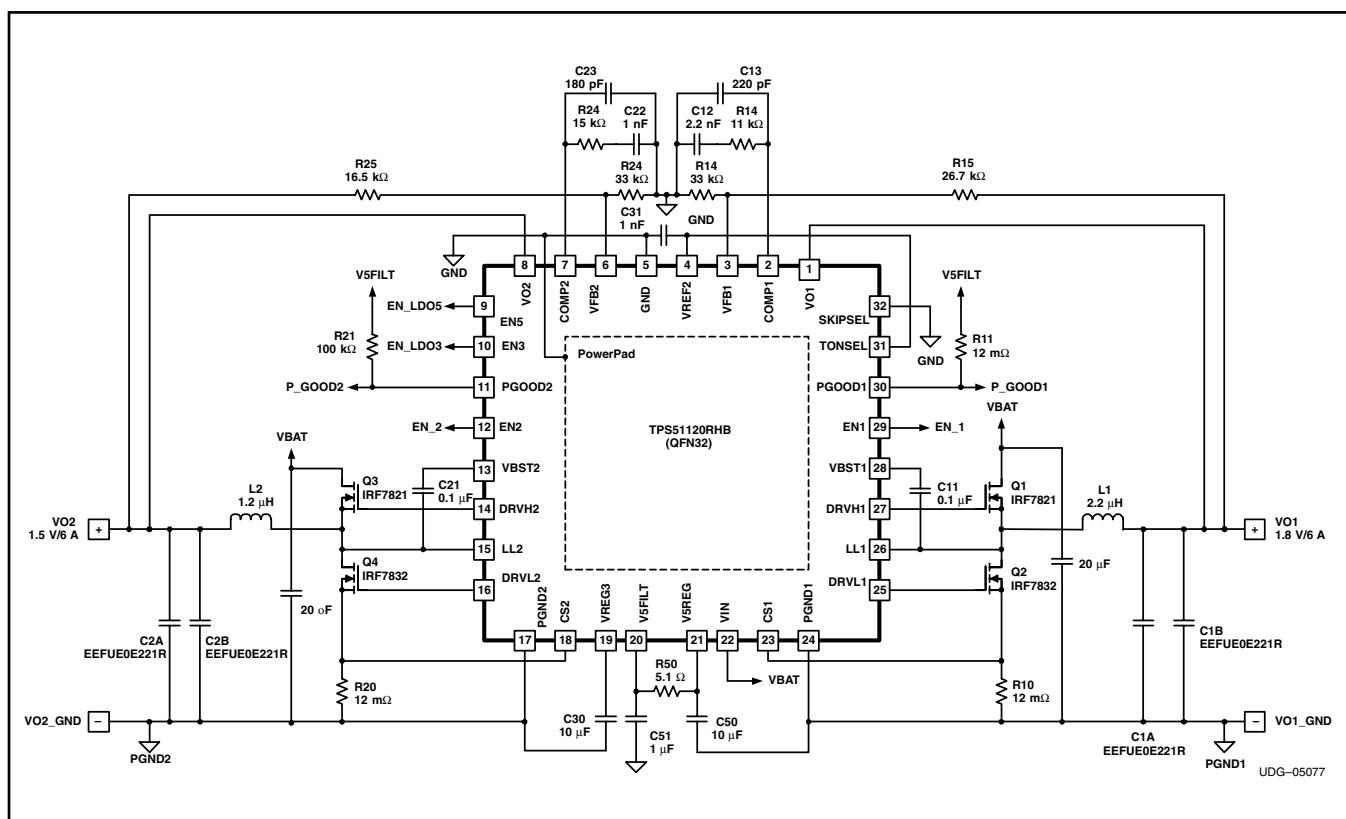

図4. 電流モード、外部1.8V/6A、+1.5V/6A、RSENSEセンシング

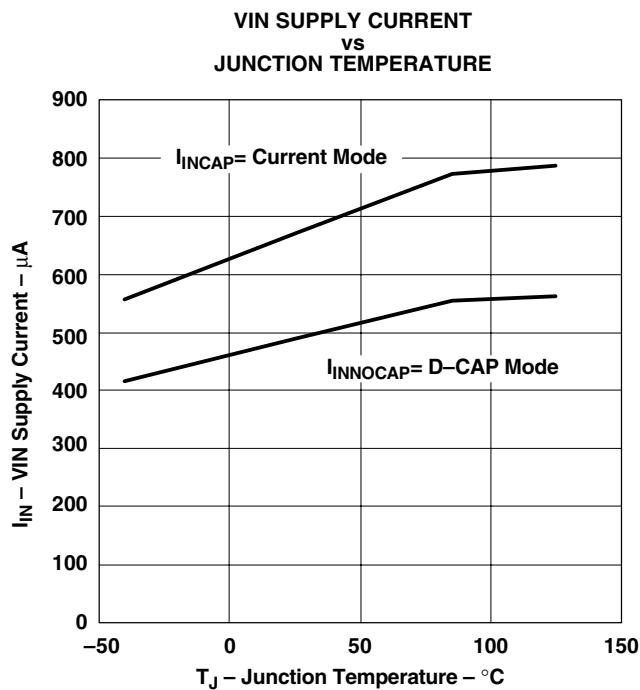

## 代表的特性

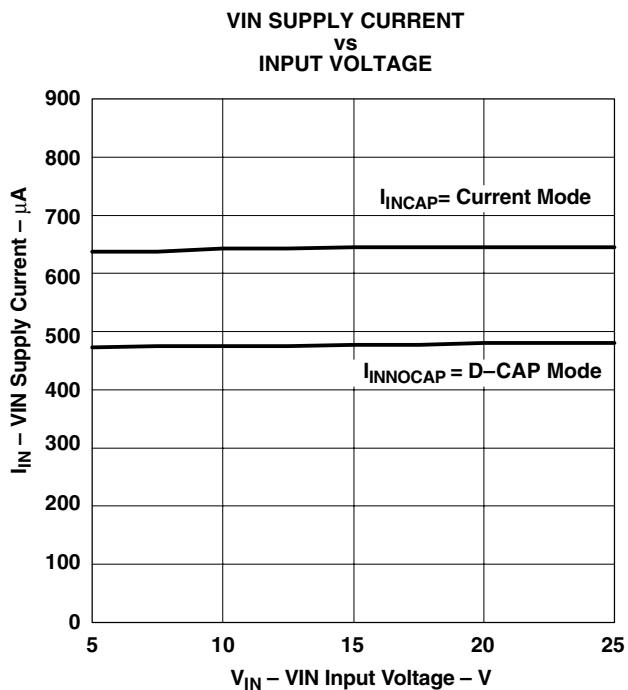

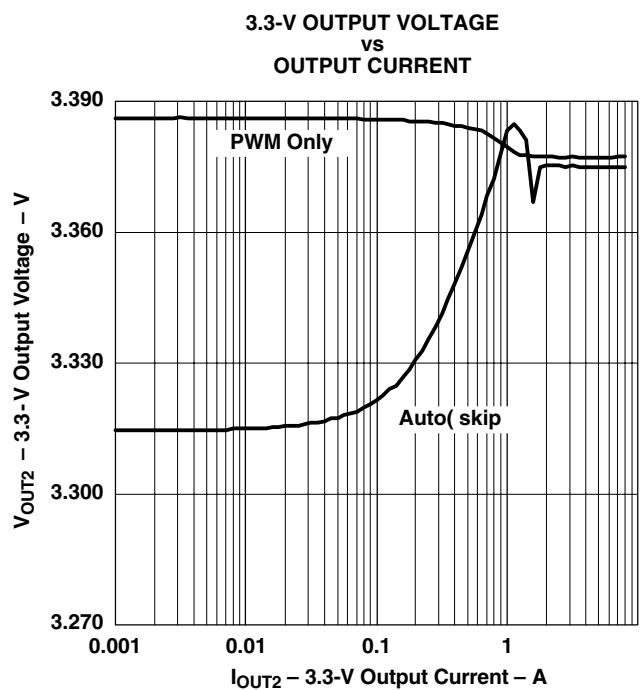

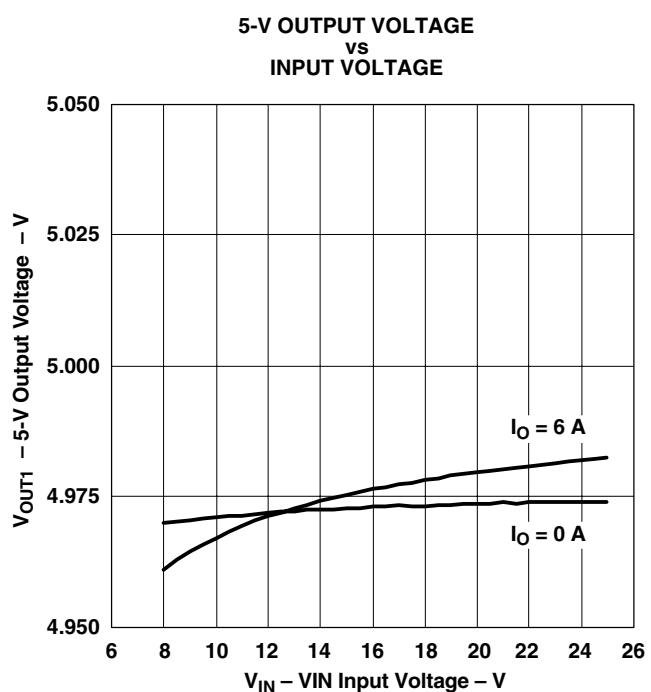

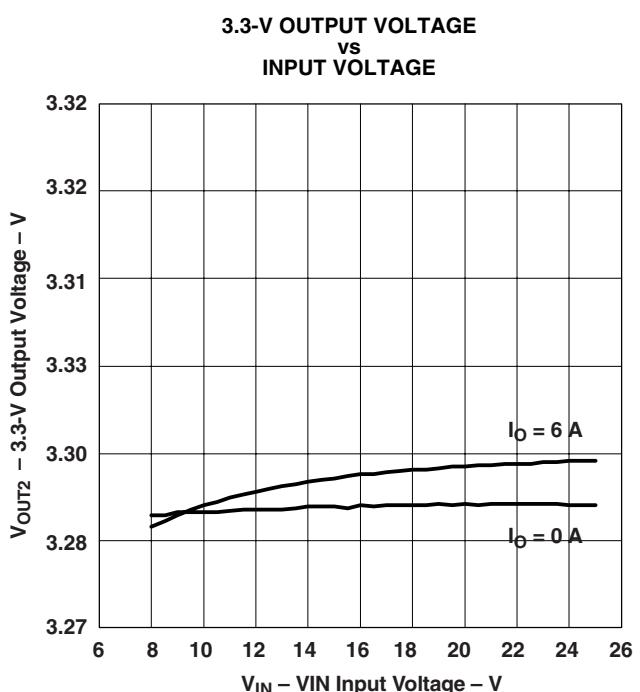

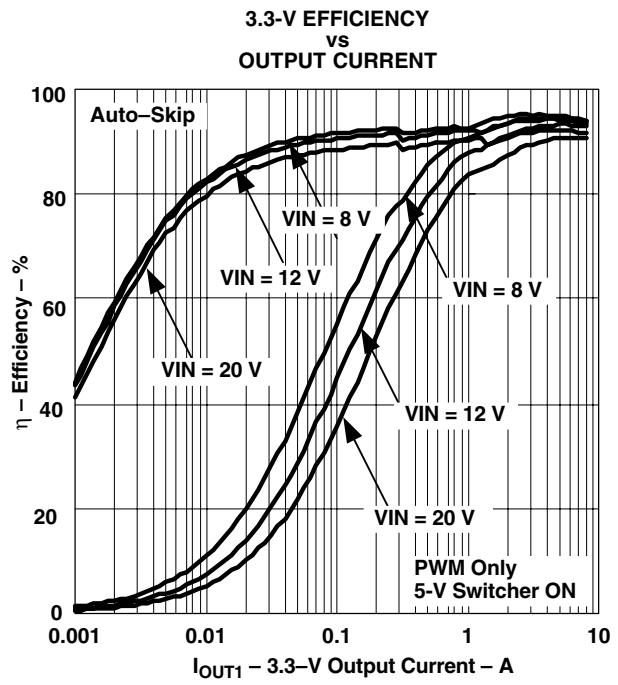

図 5

図 6

図 7

図 8

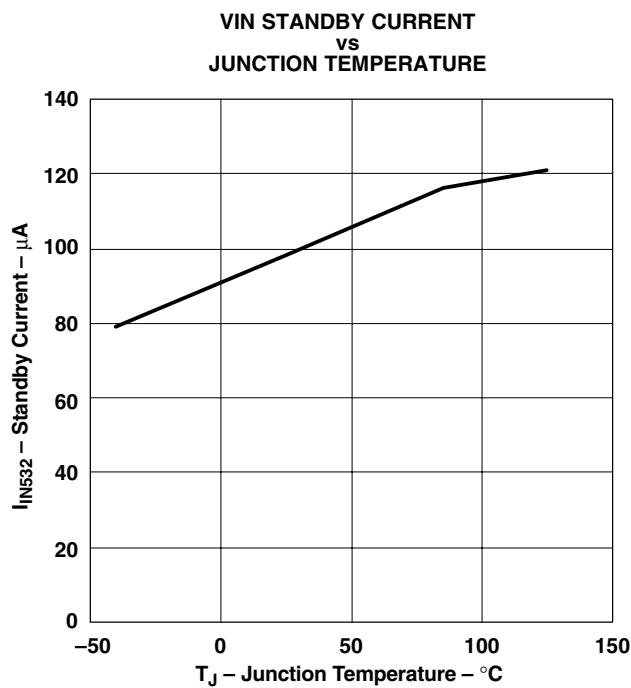

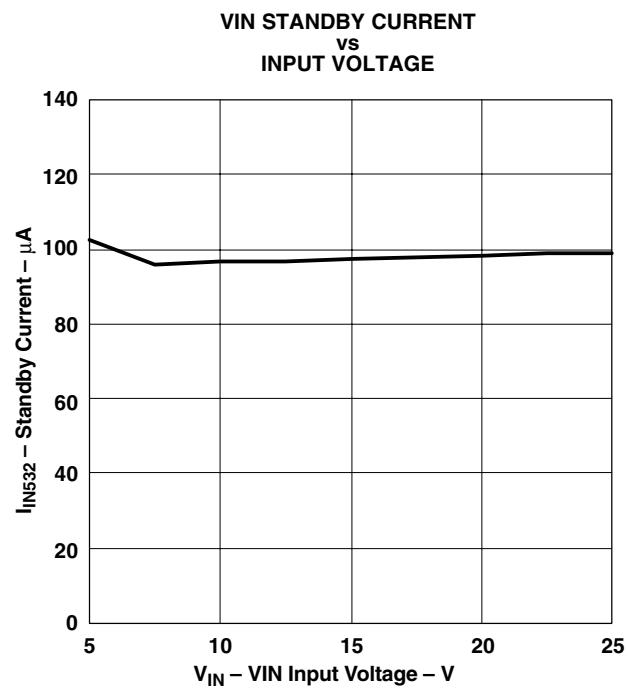

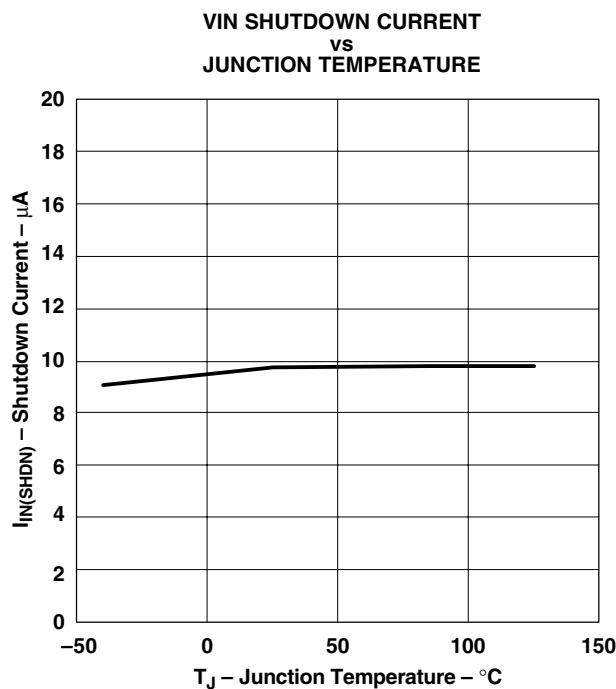

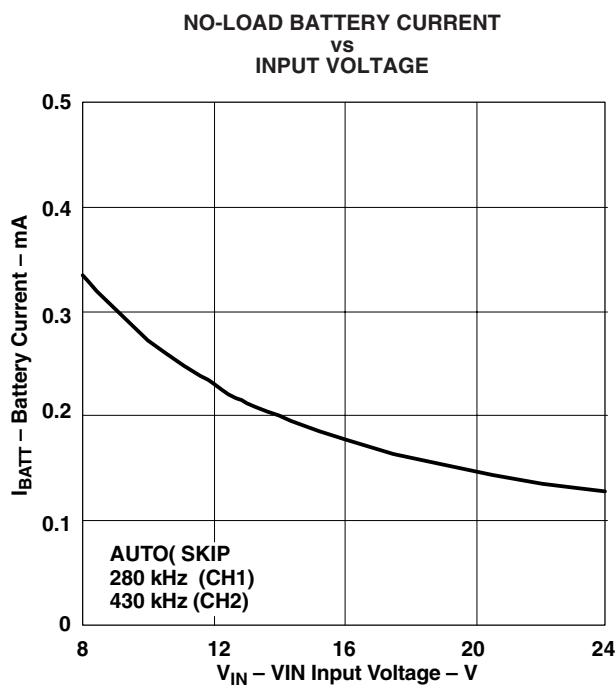

## 代表的特性

図 9

図 10

図 11

図 12

## 代表的特性

図 13

図 14

図 15

図 16

## 代表的特性

図 17

図 18

図 19

図 20

## 代表的特性

図 21

図 22

図 23

図 24

## 代表的特性

図 25

図 26

図 27

図 28

## 代表的特性

図 29

図 30

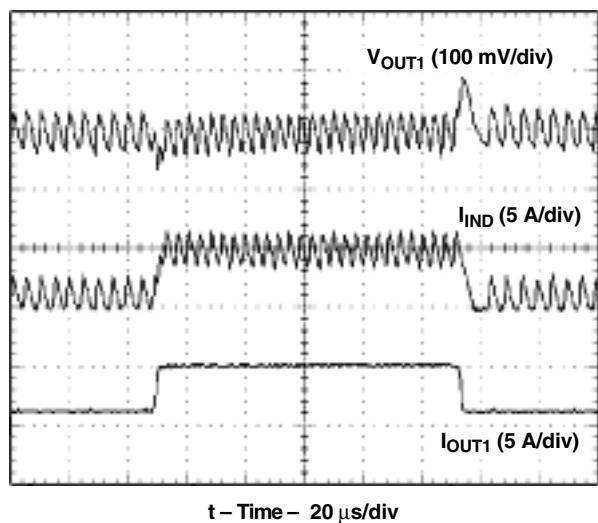

5-V Load Transient Response

図 31

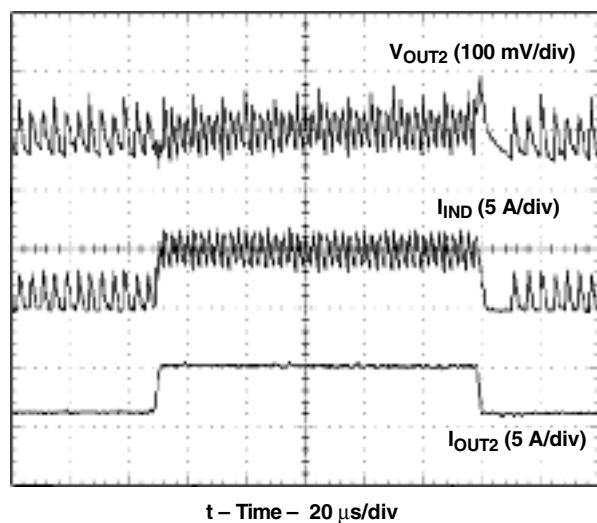

3.3-V Load Transient Response

図 32

## 代表的特性

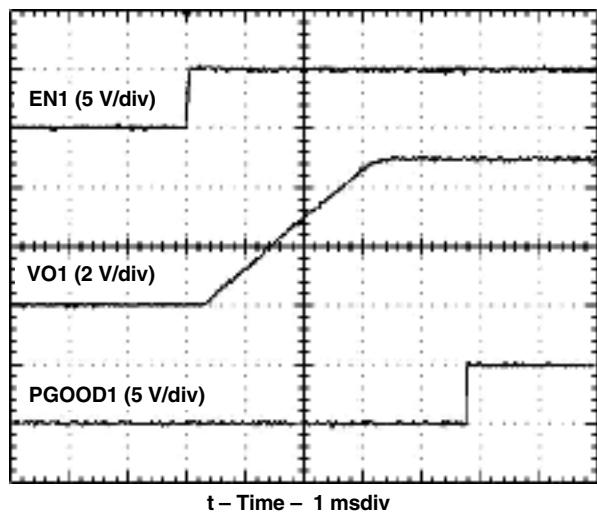

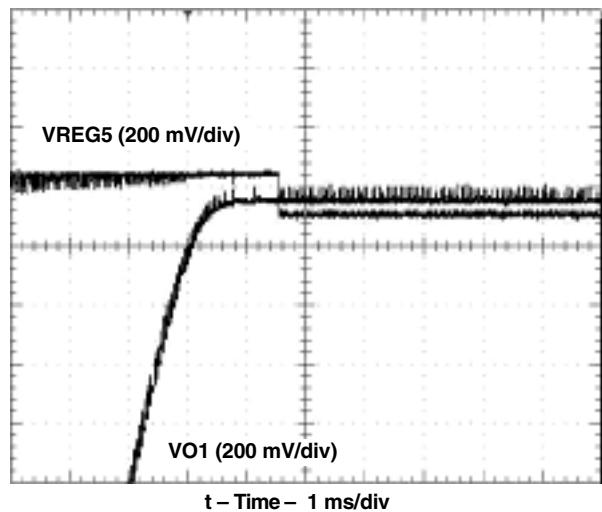

5-V Startup Waveforms

图 33

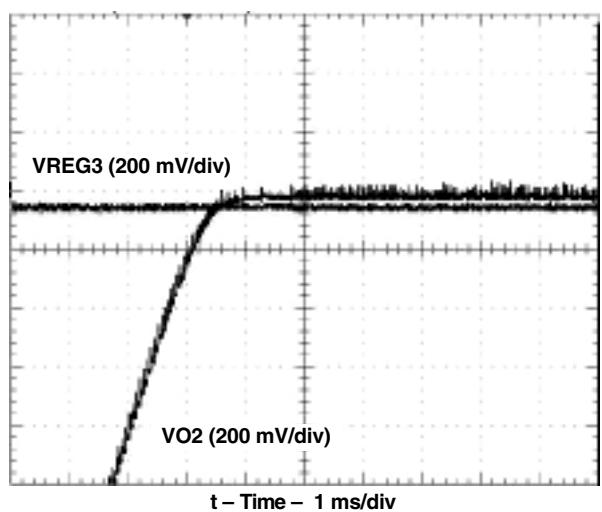

3.3-V Startup Waveforms

图 34

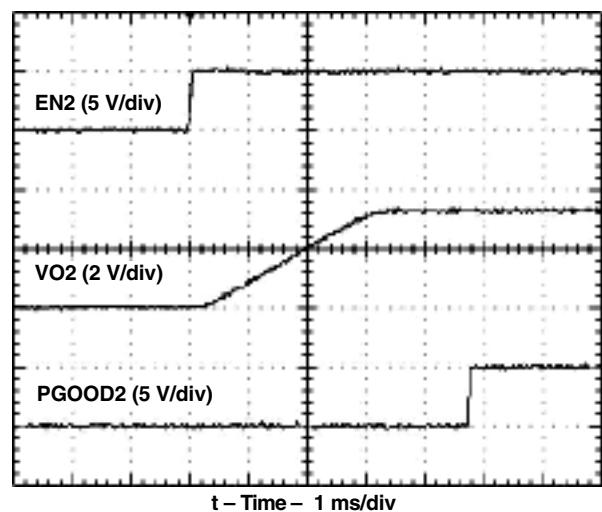

5-V Switchover Waveforms

图 35

3.3-V Switchover Waveforms

图 36

## 代表的特性

図 37

図 38

図 39

図 40

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| TPS51120RHBR     | ACTIVE                | QFN          | RHB             | 32   | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS51120RHBT     | ACTIVE                | QFN          | RHB             | 32   | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類ランであり、Pb-Free(RoHS)およびGreen(RoHS & no Sb/Br)があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS) : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Green (RoHS & no Sb/Br) : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項 : このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じるTIの責任は、TIによって年次ベースで顧客に販売される、このドキュメント発行時点でのTI製品の合計購入価格を超えることはありません。

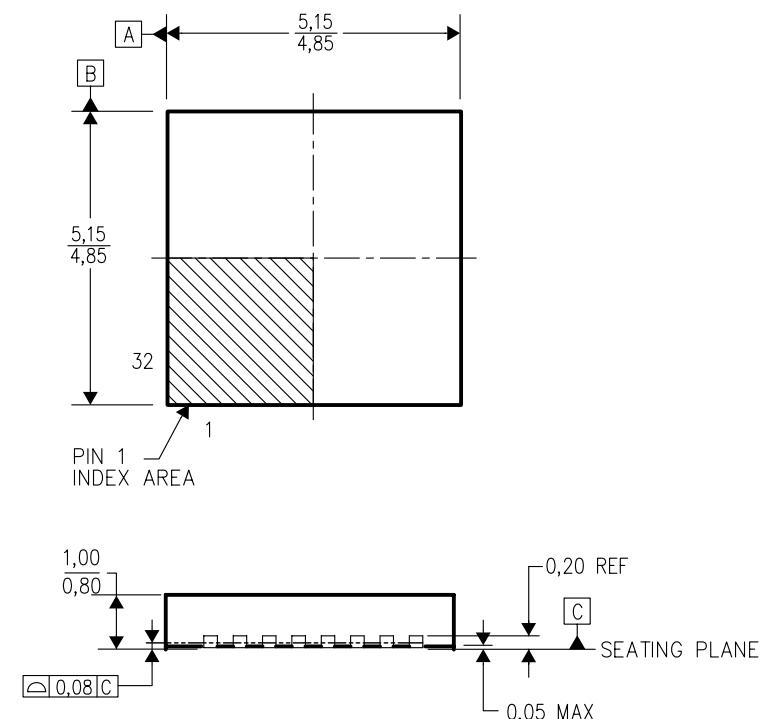

# メカニカル・データ

RHB (S-PQFP-N32)

PLASTIC QUAD FLATPACK

Bottom View

4204326/C xx/04

- 注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. QFN (Quad Flatpack No-Lead) パッケージ構成

D. 最良の熱特性および機械的特性を得るには、パッケージのサーマル・パッドを基板に半田付けする必要があります。

露出したサーマル・パッドの寸法に関する詳細は、製品データシートを参照してください。

E. JEDEC MO-220に適合しています。

SLUS370A

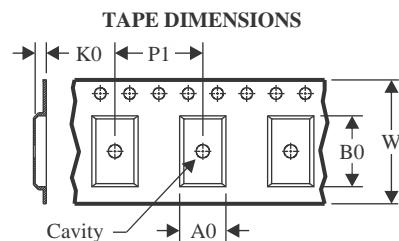

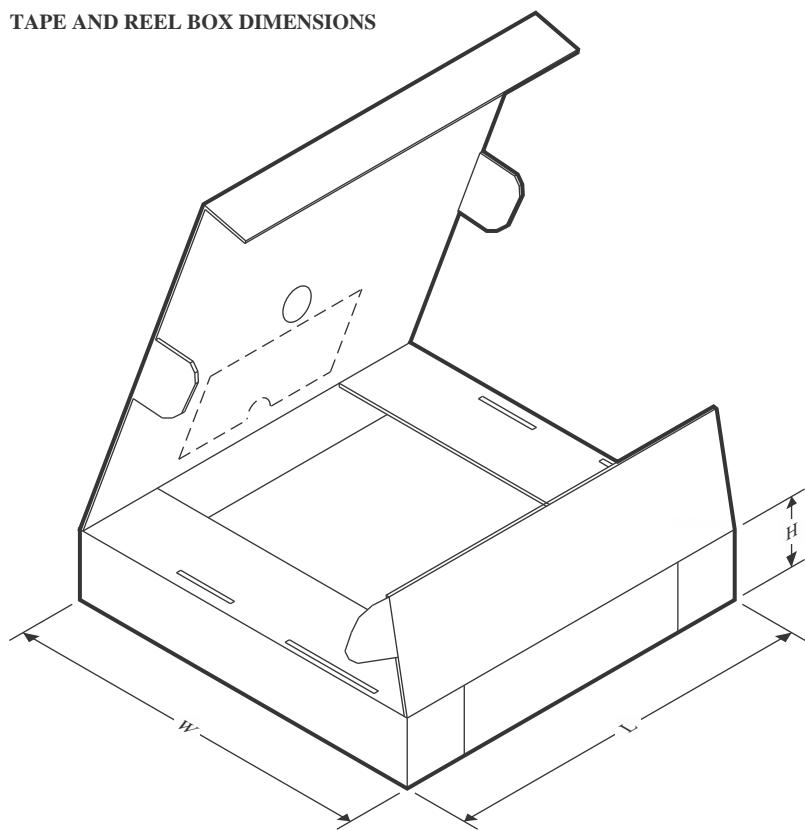

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |