## 低入力電圧(2.5V~5.5V)同期式降圧型 DC/DCコントローラ(イネーブル付き)

### 特長

- 入力電圧 : 2.25V~5.5V

- 出力電圧 : 0.6V~VIN × 90%

- NチャネルFET用ハイサイド駆動

- プリバイアス出力に対応

- アダプティブ・アンチクロス導通のゲート駆動

- 基準電圧 : 0.6V (公差1%)

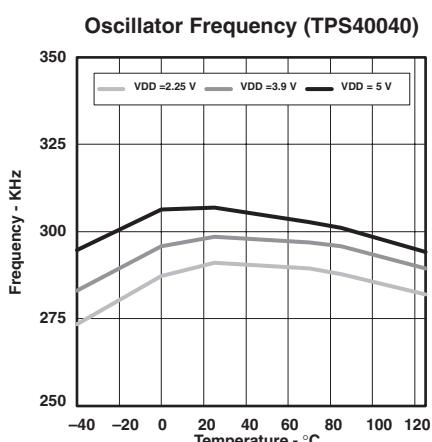

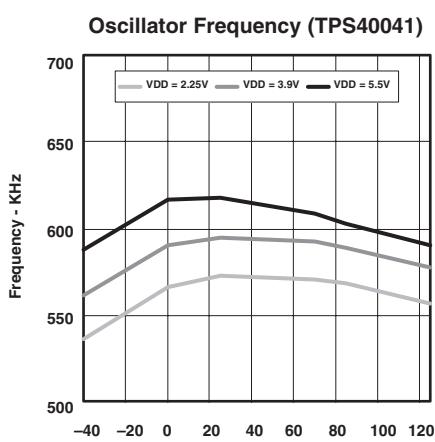

- 2種類の固定スイッチング周波数バージョン

- TPS40040 (300kHz)

- TPS40041 (600kHz)

- 選択可能な3種類の短絡保護レベル (105mV、180mV、310mV)

- 異常からのヒッカップ・リスタート

- 電圧モード・コントロール

- アクティブ “L” レベルのイネーブル入力

- サーマル・シャットダウン保護 (145°C)

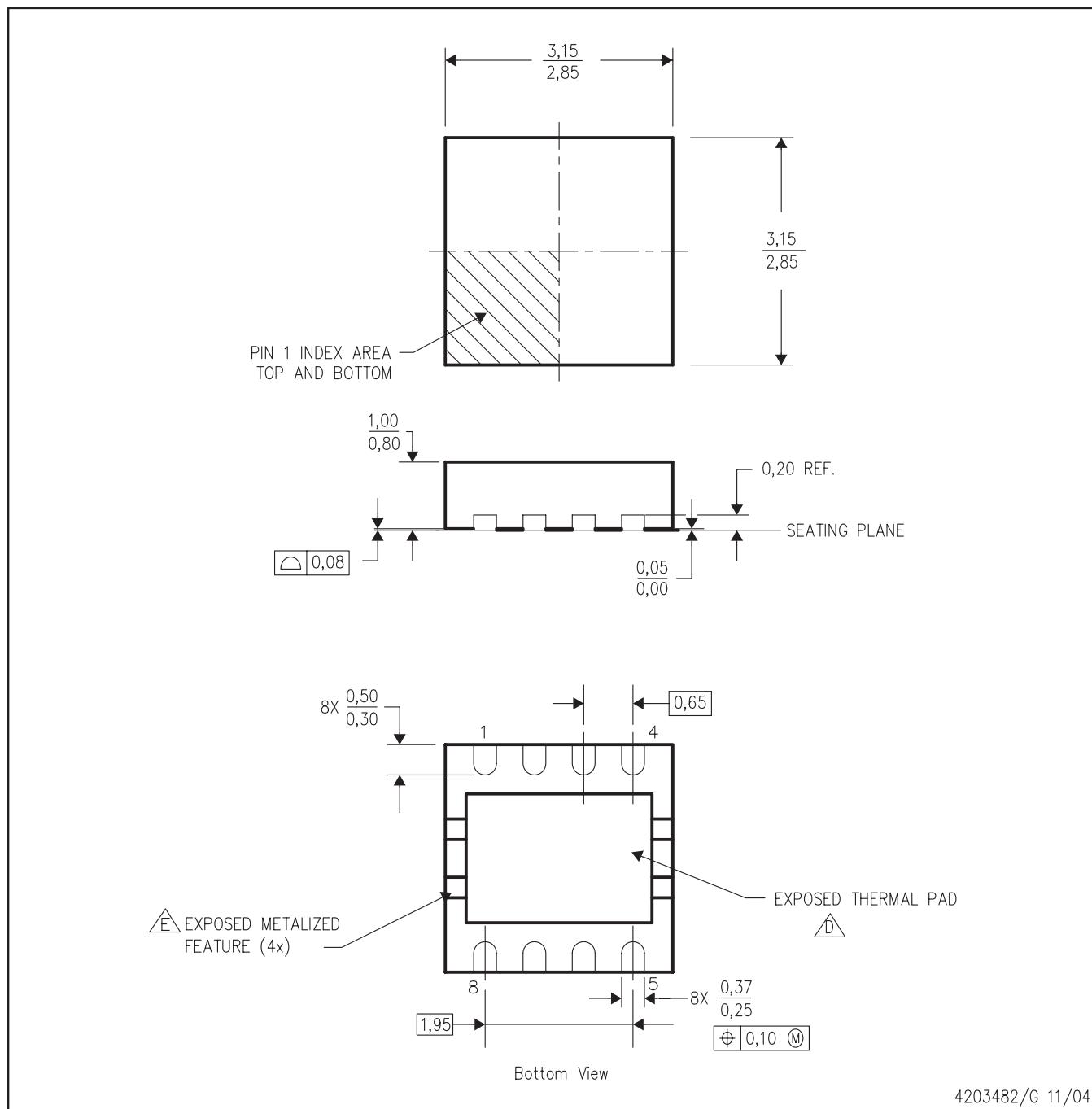

- 3×3mm 8ピンSONパッケージ (グランドがサーマル・パッドに接続)

### アプリケーション

- ポイント・オブ・ロード電源

- 通信機器

- DC/DCモジュール

- セットトップ・ボックス

### 概要

TPS40040及びTPS40041 DC/DCコントローラは2.25Vから5.5Vの入力電源で動作するよう設計されています。外付け部品点数を削減するため、いくつかの動作パラメータ、周波数、ソフトスタート時間、短絡保護(SCP)レベルが内部で固定されています。例えば、TPS40040/1の動作周波数はそれぞれ300kHz/600kHzです。

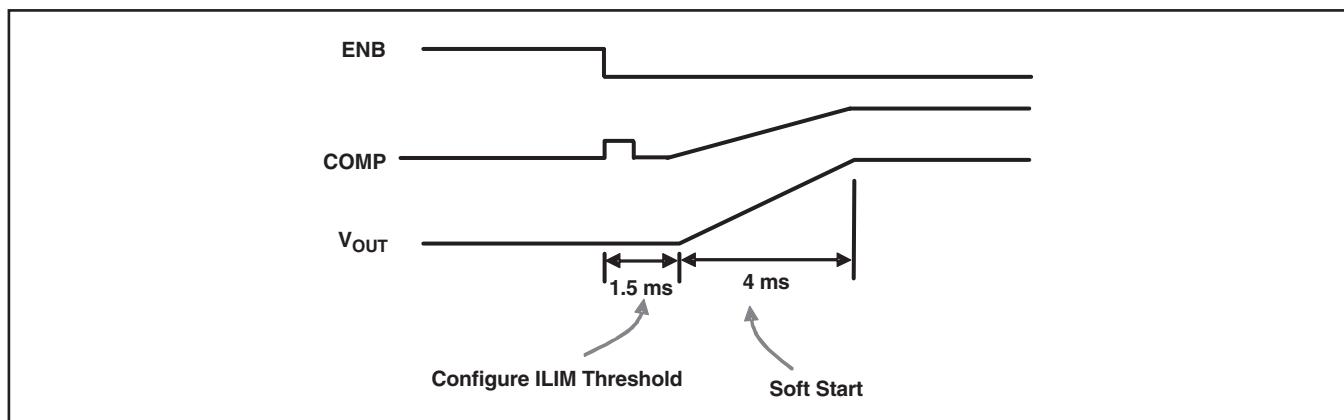

COMPピンから回路グランドへ外付け抵抗を追加することで3種類の短絡回路のスレッシュホールド・レベルの中から1つを選択することができます。電源オン時、及び内部のソフトスタートが出力電圧を上昇するよう指示する前に、TPS40040/1はキャリブレーション・サイクルになり、COMPピンから流れる電流を測定し、内部のSCPスレッシュホールド電圧を選択します。

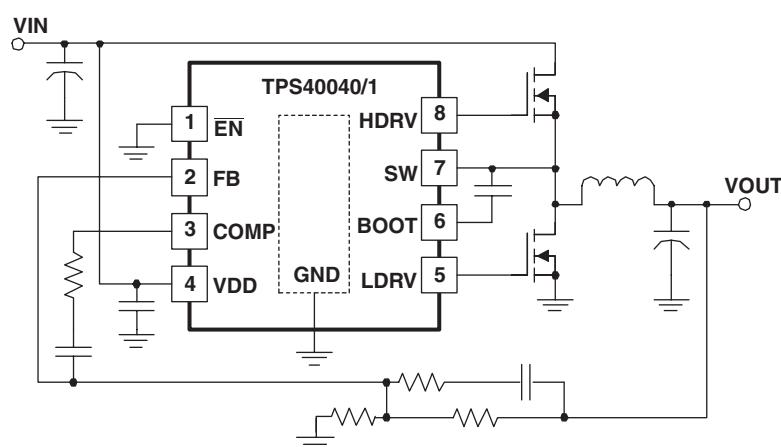

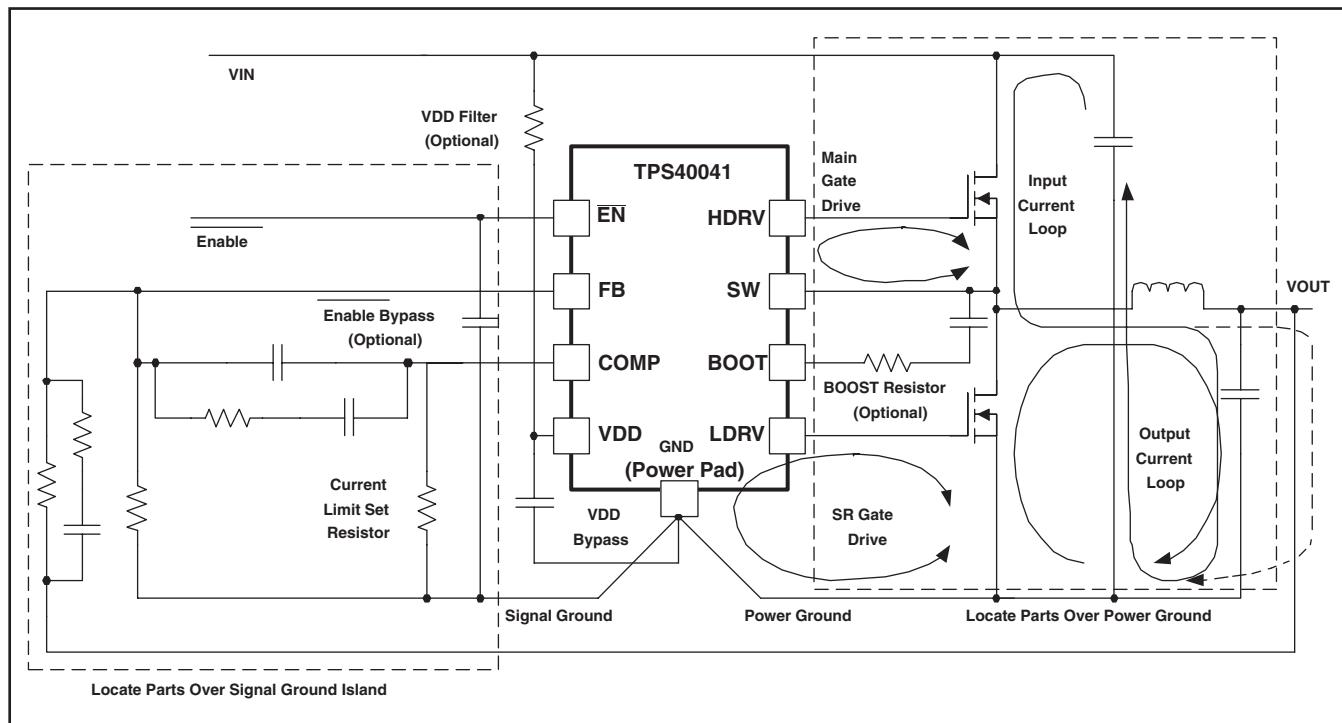

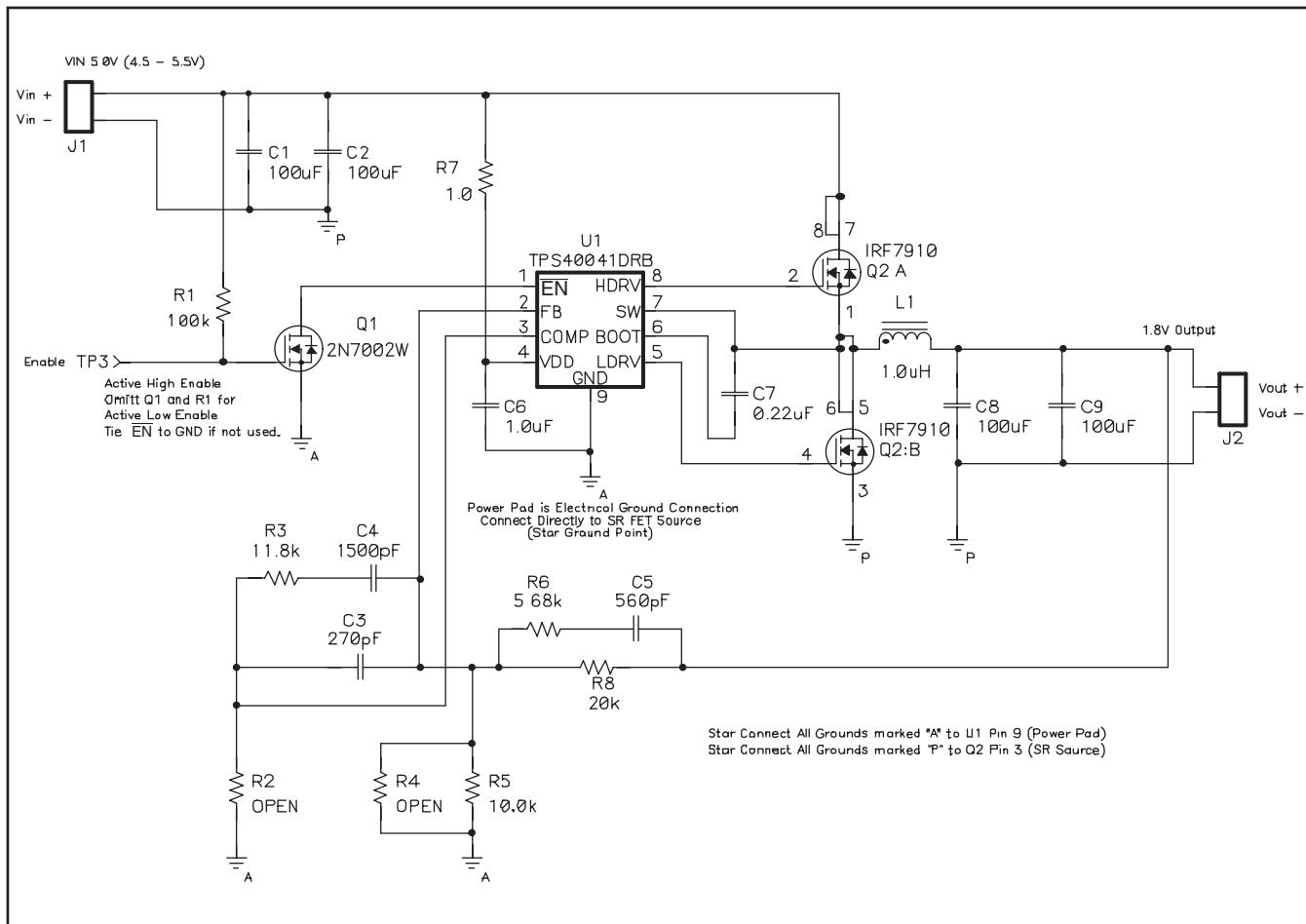

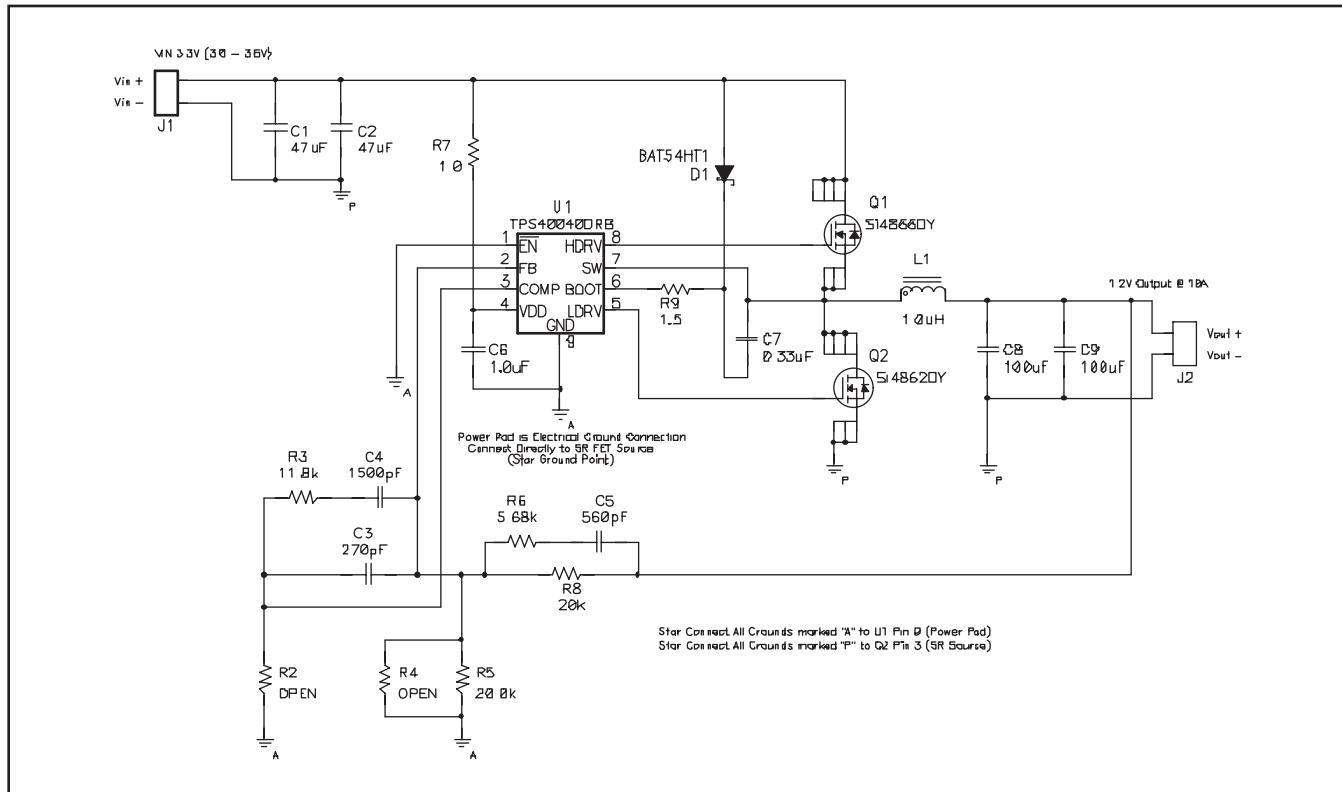

### SIMPLIFIED APPLICATION DIAGRAM

PowerPAD、Predictive Gate Driveは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

1.6msのキャリブレーション時間が終わった時に、出力電圧は4msのソフトスタート時間で上昇することができます。動作時、選択されたSCPスレッシュホールド電圧は過負荷状態が存在しているかどうかを判断するためそのオン時間で上側MOSFETの電圧降下と比較されます。

TPS40040/1のパッケージは独特な接続を持っており、PowerPAD™は熱的接続に加えて電気的なグランド接続としても使用されます。

## 静電気放電対策

これらのデバイスは、限定的なESD（静電破壊）保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## オーダー情報

| 動作周波数   | パッケージ                   | テープ・リール数量 | 注文番号         |

|---------|-------------------------|-----------|--------------|

| 300 kHz | Plastic 8-pin SON (DRB) | 250       | TPS40040DRBT |

| 300 kHz | Plastic 8-pin SON (DRB) | 3000      | TPS40040DRBR |

| 600 kHz | Plastic 8-pin SON (DRB) | 250       | TPS40041DRBT |

| 600 kHz | Plastic 8-pin SON (DRB) | 3000      | TPS40041DRBR |

## デバイス定格

### 絶対最大定格

動作温度範囲内(特に記述のない限り、全ての電圧は、GND基準)

| パラメータ                          | 規格値          | 単位 |

|--------------------------------|--------------|----|

| VDD                            | 6.5          |    |

| SW                             | -3 to 10.5   |    |

| SW transient (< 50 ns)         | -5           |    |

| BOOT                           | SW+6.5       | V  |

| HDRV                           | SW to SW+6.5 |    |

| EN, FB, LDRV                   | -0.3 to 6.5  |    |

| COMP                           | -0.3 to 3    |    |

| Operating junction temperature | -40 to 150   | °C |

| Storage junction temperature   | -55 to 150   |    |

### 推奨動作条件

動作温度範囲内(特に記述のない限り)

| パラメータ           | MIN  | TYP | MAX | 単位 |

|-----------------|------|-----|-----|----|

| V <sub>IN</sub> | 2.25 |     | 5.5 | V  |

| T <sub>J</sub>  | -40  |     | 125 | °C |

### 静電(ESD)保護

| パラメータ            | MIN  | TYP | MAX | 単位 |

|------------------|------|-----|-----|----|

| Human body model | 2500 |     |     | V  |

| CDM              | 1500 |     |     | V  |

### パッケージ損失定格<sup>(1)</sup>

| 熱インピーダンス<br>接合部 | $T_A = 25^\circ\text{C}$ POWER RATING |    | $T_A = 85^\circ\text{C}$ POWER RATING |  |

|-----------------|---------------------------------------|----|---------------------------------------|--|

|                 | 48°C/W                                | 2W | 0.8W                                  |  |

(1) DRBパッケージとテスト方法についての詳細な情報は、TIのテクニカル・ブリーフ、文献番号SZZA017を参照してください。

## 電気的特性

$T_J = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  VDD = 5 V, (特に記述がない限り)

| パラメータ                                 |                                                          | テスト条件                                                                                          | MIN   | TYP   | MAX   | 単位            |

|---------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| <b>Input Supply</b>                   |                                                          |                                                                                                |       |       |       |               |

| VDD                                   | Input voltage range                                      |                                                                                                | 2.25  |       | 5.5   | V             |

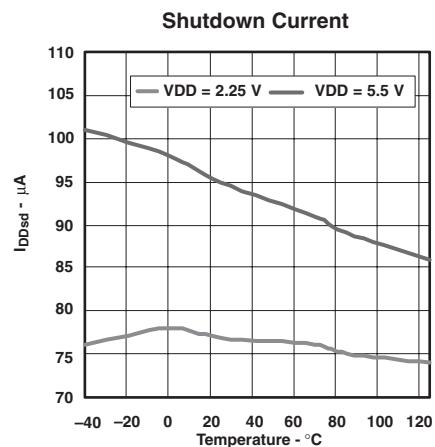

| IDD <sub>sd</sub>                     | Shutdown                                                 | $\overline{\text{EN}} = \text{VDD}$                                                            |       | 100   | 180   | $\mu\text{A}$ |

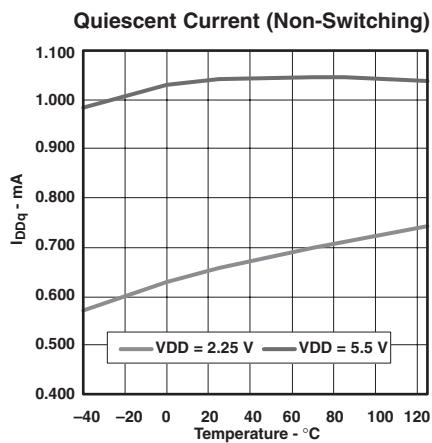

| IDDq                                  | Quiescent                                                | $\text{FB} = 0.8 \text{ V}$                                                                    |       | 1.0   | 2.0   | mA            |

| IDDs                                  | Switching current                                        | No load at HDRV/LDRV                                                                           |       | 2.0   |       |               |

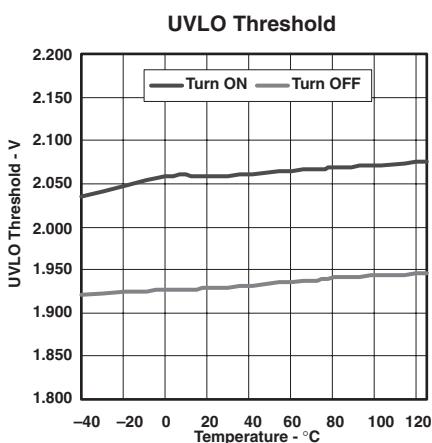

| UVLO <sub>ON</sub>                    | Minimum turn-on voltage                                  |                                                                                                | 1.95  | 2.05  | 2.15  | V             |

| UVLO <sub>HYS</sub>                   | Hysteresis                                               |                                                                                                | 80    | 130   | 200   | mV            |

| <b>Oscillator/ Ramp Generator</b>     |                                                          |                                                                                                |       |       |       |               |

| f <sub>PWM</sub>                      | TPS40040 PWM frequency                                   | $2.25 \text{ V} < \text{VDD} < 5.5 \text{ V}$                                                  | 250   | 300   | 350   | kHz           |

| f <sub>PWM</sub>                      | TPS40040 PWM frequency                                   | $\text{VDD} = 5.0 \text{ V}, 0^{\circ}\text{C} < T_J < 70^{\circ}\text{C}$                     | 270   | 300   | 330   | kHz           |

| f <sub>PWM</sub>                      | TPS40041 PWM frequency                                   | $2.25 \text{ V} < \text{VDD} < 5.5 \text{ V}$                                                  | 500   | 600   | 700   | kHz           |

| f <sub>PWM</sub>                      | TPS40041 PWM frequency                                   | $\text{VDD} = 5.0 \text{ V}, 0^{\circ}\text{C} < T_J < 70^{\circ}\text{C}$                     | 540   | 600   | 660   | kHz           |

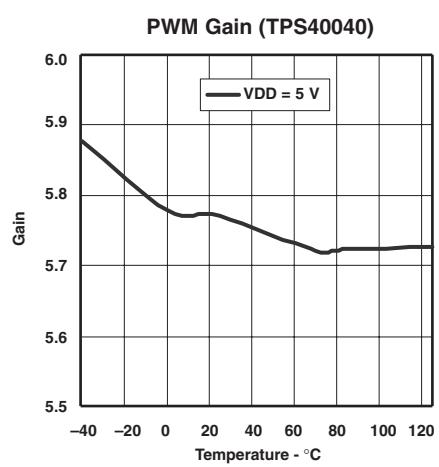

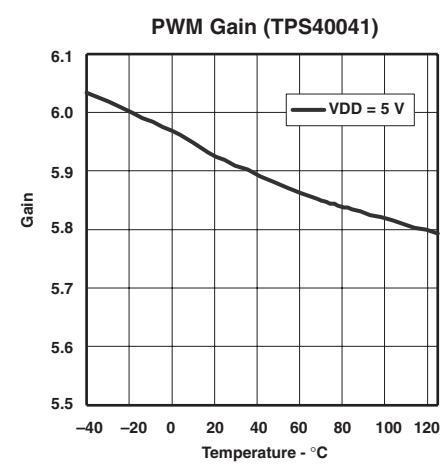

| V <sub>RAMP</sub>                     | Ramp amplitude PP                                        | $V_{\text{PEAK}} - V_{\text{VALLEY}}$                                                          | 0.75  | 0.87  | 1.0   | V             |

| V <sub>VALLEY</sub>                   | Ramp valley voltage                                      |                                                                                                |       | 0.37  |       | V             |

| <b>PWM</b>                            |                                                          |                                                                                                |       |       |       |               |

| MAXDUTY                               | Maximum duty cycle, TPS40040                             | $V_{\text{FB}} = 0 \text{ V}, 2.25 \text{ V} < \text{VDD} < 5.5 \text{ V}$                     | 90    | 95    |       | %             |

|                                       | Maximum duty cycle, TPS40041                             | $V_{\text{FB}} = 0 \text{ V}, 2.25 \text{ V} < \text{VDD} < 5.5 \text{ V}$                     | 88    | 95    |       |               |

| MINDUTY                               | Minimum duty cycle                                       |                                                                                                |       |       | 0     |               |

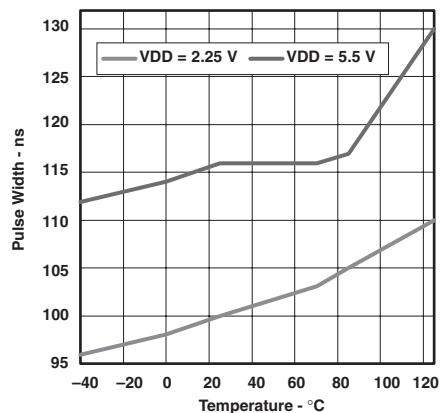

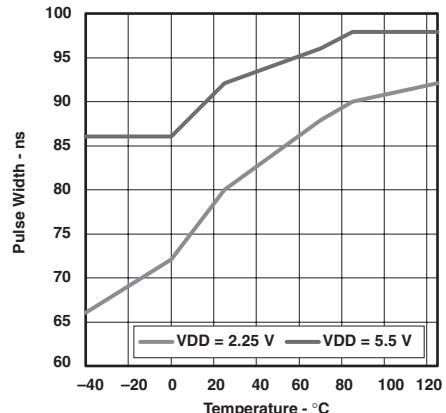

| MIN pulse width <sup>(1)</sup>        | Minimum controllable pulse width                         | Minimum width control range before jumping to zero.                                            |       | 90    | 150   | ns            |

| <b>Error Amplifier</b>                |                                                          |                                                                                                |       |       |       |               |

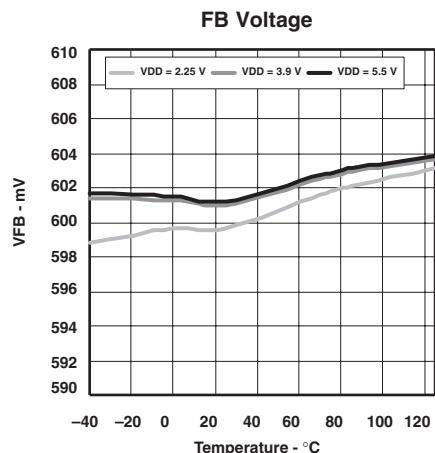

| V <sub>FB</sub>                       | FB input voltage                                         | $\text{VDD} = 5.0 \text{ V}, 0^{\circ}\text{C} < T_J < 70^{\circ}\text{C}$                     | 593.5 | 600.0 | 606.5 | mV            |

|                                       |                                                          | $2.25 \text{ V} < \text{VDD} < 5.5 \text{ V}, -40^{\circ}\text{C} < T_J < 125^{\circ}\text{C}$ | 590   |       | 610   |               |

| I <sub>FB</sub>                       | FB input bias current                                    |                                                                                                |       | 50    | 150   | nA            |

| V <sub>OH</sub>                       | High level output voltage                                | $I_{\text{OH}} = 0.5 \text{ mA}, V_{\text{FB}} = 0 \text{ V}, \text{VDD} = 5.5 \text{ V}$      | 2.0   | 2.5   |       | V             |

| V <sub>OL</sub>                       | Low level output voltage                                 | $I_{\text{OL}} = 0.5 \text{ mA}, V_{\text{FB}} = \text{VDD}$                                   |       | 80    | 150   | mV            |

| I <sub>OH</sub>                       | Output source current                                    | $V_{\text{COMP}} = 0.7 \text{ V}, V_{\text{FB}} = \text{GND}$                                  | 1     | 6     |       | mA            |

| I <sub>OL</sub>                       | Output sink current                                      | $V_{\text{COMP}} = 0.7 \text{ V}, V_{\text{FB}} = \text{VDD}$                                  | 2     | 8     |       |               |

| G <sub>BW</sub> <sup>(1)</sup>        | Gain bandwidth                                           |                                                                                                | 5     | 10    |       | MHz           |

| A <sub>OL</sub>                       | Open loop gain                                           |                                                                                                | 55    | 85    |       | dB            |

| <b>Short Circuit Protection</b>       |                                                          |                                                                                                |       |       |       |               |

| TH1                                   | Low short circuit threshold voltage                      | Resistor COMP to GND = 2.4 k $\Omega$ , $T_J = 25^{\circ}\text{C}$                             | 80    | 105   | 130   | mV            |

| V <sub>TH2</sub>                      | Medium short circuit threshold voltage                   | Default: No resistor COMP to GND, $T_J = 25^{\circ}\text{C}$                                   | 145   | 180   | 215   |               |

| V <sub>TH3</sub>                      | High short circuit threshold voltage                     | Resistor COMP to GND = 12 k $\Omega$ , $T_J = 25^{\circ}\text{C}$                              | 250   | 310   | 370   |               |

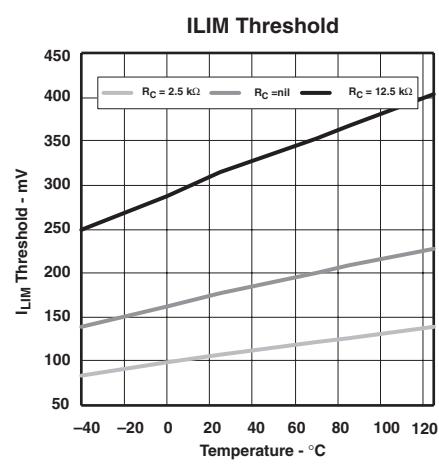

| V <sub>TH(tc)</sub> <sup>(1)</sup>    | Threshold temperature coefficient                        |                                                                                                |       | 3100  |       | ppm           |

| t <sub>ON(oc)</sub> <sup>(1)</sup>    | Minimum HDRV pulse time in over current                  |                                                                                                |       | 200   |       | ns            |

| t <sub>SWOCblank</sub> <sup>(1)</sup> | SW leading edge blanking pulse in over current detection |                                                                                                |       | 100   |       |               |

| t <sub>HICCU</sub>                    | Hiccup time between restarts                             |                                                                                                |       | 40    |       | ms            |

(1) 設計で保証されており、テストは行われていません。

## 電気的特性

$T_J = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  VDD = 5 V, (特に記述がない限り)

| パラメータ                       |                                          | テスト条件                                                                                  | MIN  | TYP  | MAX  | 単位                 |

|-----------------------------|------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|--------------------|

| <b>Soft Start/Enable</b>    |                                          |                                                                                        |      |      |      |                    |

| $t_{\text{CAL}}^{(2)}$      | Calibration time before softstart begins |                                                                                        | 1.0  | 1.6  | 2.5  | ms                 |

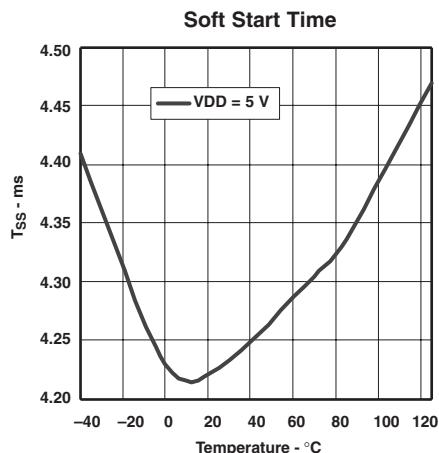

| $t_{\text{SS}}^{(2)}$       | Soft start time                          |                                                                                        | 3.0  | 4.0  | 6.0  |                    |

| $t_{\text{REG}}$            | Time to voltage regulation               |                                                                                        | 4.0  | 5.6  | 8.5  |                    |

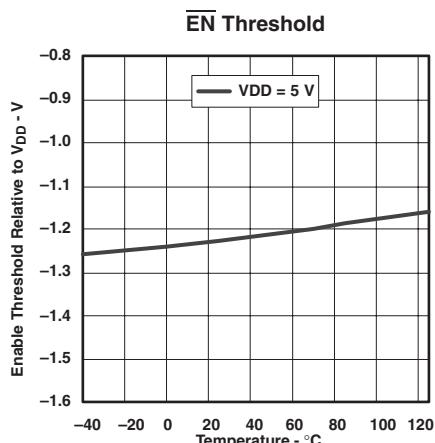

| $V_{\text{EN}}$             | Enable threshold                         |                                                                                        | -0.8 | -1.2 | -1.6 | V                  |

| $V_{\text{ENHYS}}$          | Enable hysteresis                        |                                                                                        |      | 50   |      | mV                 |

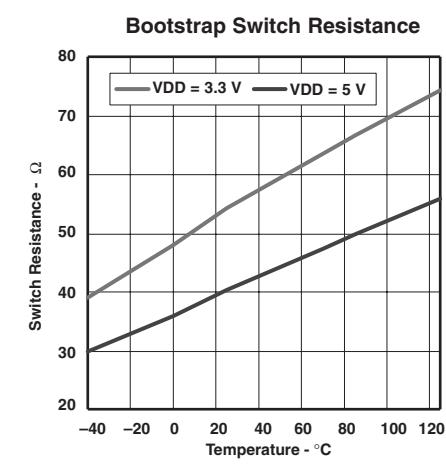

| <b>Bootstrap</b>            |                                          |                                                                                        |      |      |      |                    |

| $R_{\text{BOOT}3\text{V}3}$ | Bootstrap switch resistances             | $V_{\text{BOOT}}$ to VDD, VDD = 3.3 V                                                  |      | 50   |      | $\Omega$           |

| $R_{\text{BOOT}5\text{V}}$  |                                          | $V_{\text{BOOT}}$ to VDD, VDD = 5 V                                                    |      | 30   |      |                    |

| <b>Output Driver</b>        |                                          |                                                                                        |      |      |      |                    |

| $R_{\text{HDHI}3\text{V}3}$ | HDRV pull-up resistance                  | $V_{\text{BOOT}} - V_{\text{SW}} = 3.3 \text{ V}$ , $I_{\text{SRCE}} = 100 \text{ mA}$ |      | 3.0  | 5.5  | $\Omega$           |

| $R_{\text{HDLO}3\text{V}3}$ | HDRV pull-down resistance                | $V_{\text{BOOT}} - V_{\text{SW}} = 3.3 \text{ V}$ , $I_{\text{SINK}} = 100 \text{ mA}$ |      | 1.5  | 3    |                    |

| $R_{\text{LDHI}3\text{V}3}$ | LDRV pull-up resistance                  | $V_{\text{DD}} = 3.3 \text{ V}$ , $I_{\text{SOURCE}} = 100 \text{ mA}$                 |      | 3.0  | 5.5  |                    |

| $R_{\text{LDLO}3\text{V}3}$ | LDRV pull-down resistance                | $V_{\text{DD}} = 3.3 \text{ V}$ , $I_{\text{SINK}} = 100 \text{ mA}$                   |      | 1.0  | 2.0  |                    |

| $t_{\text{RISE}}^{(3)}$     | LDRV, HDRV rise time                     | $C_{\text{LOAD}} = 1 \text{ nF}$                                                       |      | 15   | 35   | ns                 |

| $t_{\text{FALL}}^{(3)}$     | LDRV, HDRV fall time                     | $C_{\text{LOAD}} = 1 \text{ nF}$                                                       |      | 10   | 25   |                    |

| $T_{\text{DEAD HL}}$        | Adaptive timing HDRV to LDRV             | No load                                                                                | 15   | 30   |      |                    |

| $T_{\text{DEAD LH}}$        | Adaptive timing LDRV to HDRV             | No load                                                                                | 5    | 15   |      |                    |

| <b>SW Node</b>              |                                          |                                                                                        |      |      |      |                    |

| $I_{\text{LEAK}}$           | Leakage current                          | $\overline{\text{EN}} = \text{VDD}$                                                    | -2   |      |      | $\mu\text{A}$      |

| <b>Thermal Shutdown</b>     |                                          |                                                                                        |      |      |      |                    |

| $t_{\text{SD}}^{(3)}$       | Shutdown temperature                     |                                                                                        |      | 145  |      | $^{\circ}\text{C}$ |

|                             | Hysteresis                               |                                                                                        |      | 15   |      |                    |

(2)  $t_{\text{CAL}}$ と $t_{\text{SS}}$ は温度と入力電圧により変化します。

(3) 設計で保証されており、テストは行われていません。

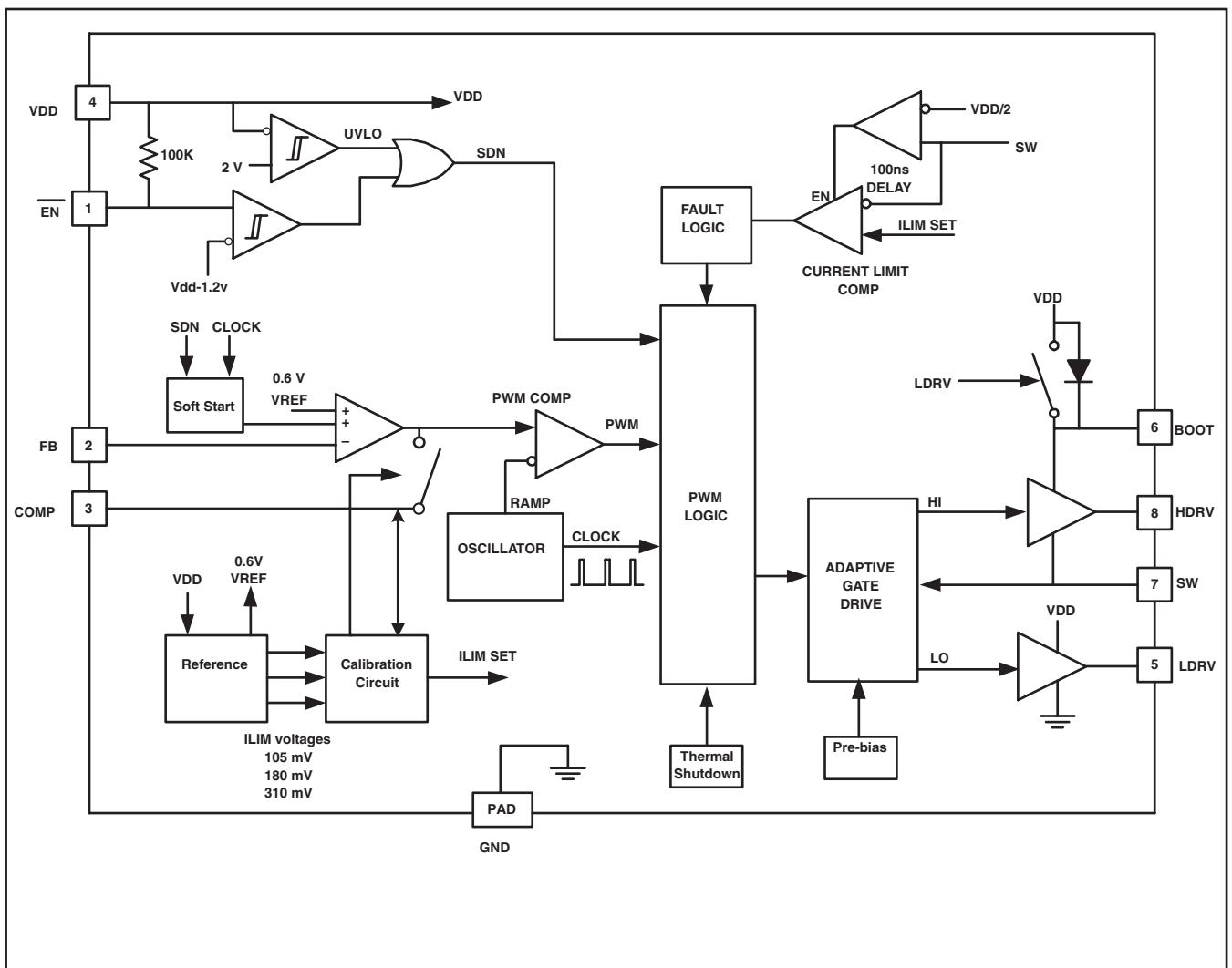

## 代表的特性

図 1

図 2

図 3

図 4

図 5

図 6

## 代表的特性

図 7

図 8

図 9

図 10

図 11

図 12

## 代表的特性

Minimum Controllable Pulse Width (TPS40040)

图 13

Minimum Controllable Pulse Width (TPS40041)

图 14

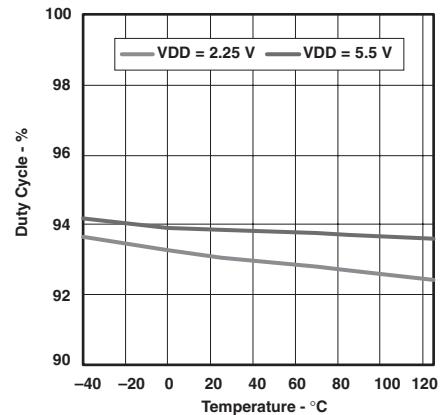

Maximum Duty Cycle

图 15

SW Node Leakage Current

图 16

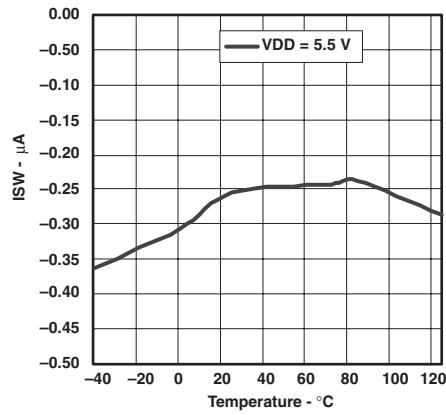

# デバイス情報

## 端子構成

パッケージは8ピンのSON(DRB)パッケージです。サーマル・パッドは電気的にグランドに接続されていることに注意してください。

図 17. DRB Package Terminal Configuration (TopView)

| 端子<br>名称 | 端子番号        | I/O | 概要                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT     | 6           | I   | ハイサイドFETのゲートが入力電源レールより高い電圧で駆動されることを可能にするPWM用のハイサイド・ゲート・ドライバへの入力(ブートストラップされた)電源です。このピンからSWにセラミック・コンデンサを接続してください。このコンデンサはVDDピンの電圧から内部スイッチを介して充電されます。このスイッチはコンバータのオフ時間でオンになります。外付けMOSFETのターンオンの速度を遅くするために、小さな抵抗( $1\Omega \sim 3\Omega$ )をブートストラップ・コンデンサに直列に挿入することができます。この適切な値を計算するにはアプリケーションの項を参照してください。                                                                   |

| COMP     | 3           | O   | 誤差増幅器の出力及びループ・フィードバック部品の接続ノードです。このピンの電圧によりPWMのデューティ・サイクルが決まります。オプションとして、短絡保護用に用いられる電圧スレッショールドを決めるためこのピンからグランドに抵抗を使用します(アプリケーションの項を参照してください)。 <ul style="list-style-type: none"> <li>下側スレッショールド <math>R = 2.4\text{ k}\Omega, +/-10\%</math></li> <li>中間スレッショールド <math>R = \text{使用しない}</math></li> <li>上側スレッショールド <math>R = 12\text{ k}\Omega, +/-10\%</math></li> </ul> |

| EN       | 1           | I   | アクティブ“L”レベルのイネーブル入力でコントローラのオン/オフ動作を可能にします。ENピンが“H”レベルの間電源がTPS40040/1に加わっても、TPS40040/1はディスエーブルのままです(両方の外付けスイッチともオフに保持されます)。ENピンがVDDより1.2V低くなった時のみ、TPS40040/1は動作を開始することができます。プルアップ用に内部に $100\text{k}\Omega$ の抵抗がVDDとEN間に接続されています。イネーブル機能を無視するにはこのピンをGNDに接続してください。                                                                                                          |

| FB       | 2           | I   | 誤差増幅器の反転入力です。閉ループの動作では、このピンの電圧は $600\text{mV}$ の内部基準電圧レベルになっています。このピンに中点を接続する、コンバータの出力からグランドへの直列の抵抗デバイスによりレギュレーションされる出力電圧の値が決まります。また、このピンはループ・フィードバック部品の接続ノードでもあります。                                                                                                                                                                                                     |

| HDRV     | 8           | O   | このピンはPWM用ハイサイドDNチャネルMOSFETスイッチのゲート駆動出力です。これはSWを基準としており、ハイサイド・スイッチのエンハンスマント用にブートストラップされます。                                                                                                                                                                                                                                                                                |

| LDRV     | 5           | O   | このピンはローサイド同期整流器(SR)NチャネルMOSFET用のゲート駆動出力です。                                                                                                                                                                                                                                                                                                                               |

| VDD      | 4           | I   | デバイスの電源入力です。このピンは $1\text{A}$ またはそれより大きな低ESRのセラミック・コンデンサで端子の近くでGNDにバイパスしなければなりません。                                                                                                                                                                                                                                                                                       |

| SW       | 7           | O   | コンバータのスイッチ・ノード及び上側ゲート・ドライバの電源リターンの接続ピンです。上側MOSFETのソースからこのピンに大電流のリターン・バスが存在しています。また、このピンは上側MOSFETと下側MOSFETの導通間のデッドタイムを最小限に抑えるためアダプティブ・ゲート・ドライブ回路により使用されます。                                                                                                                                                                                                                |

| GND      | Thermal Pad |     | デバイスのグランド接続ピンです。また、このピンはデバイスからの熱を伝導するのにも使用されるサーマル・パッドです。この接続には2つの目的があります。最初の目的是デバイスに電気的なグランド接続を供給することです。2番目はデバイスのチップからPCBに低いサーマル・インピーダンスのバスを供給することです。このパッドは外部でグランド・プレーンに接続しなければなりません。PCボードのレイアウト情報についてはアプリケーションの項を参照してください。                                                                                                                                              |

表 1. TERMINAL FUNCTIONS

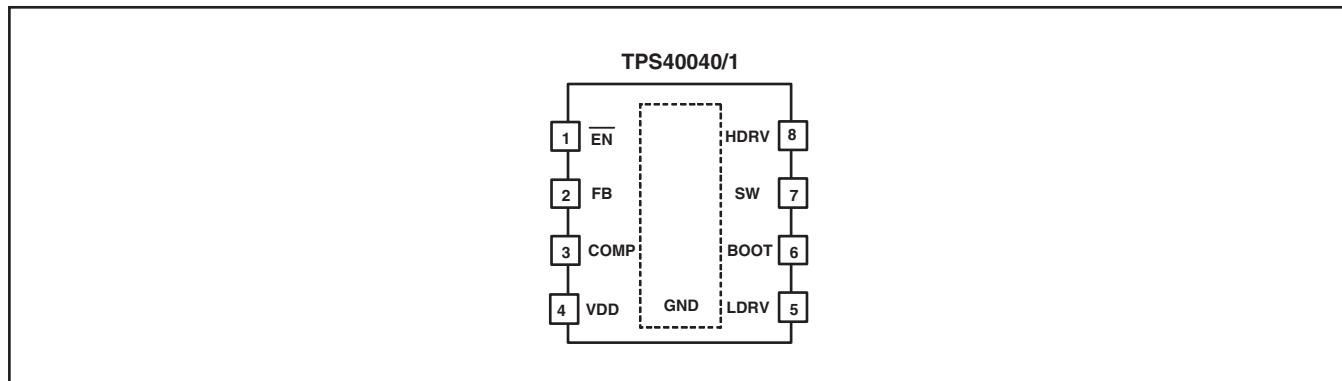

## ブロック図

図 18. Functional Block Diagram

# アプリケーション情報

## 機能説明

TPS40040 (300kHz) 及び TPS40041 (600kHz) は固定周波数で動作する電圧モードの同期式降圧型コントローラです。動作時、同期整流器 (SR) は両方向に電流を導通することができるため、無負荷状態下でもコンバータは連続モードで動作することができます。フィードバック・ループ補償の要件が簡素化されます。起動時、内部回路は出力にプリバイアス状態が存在している場合、出力の放電を防止するよう同期整流器のスイッチングを調整します。

## 基準電圧

600mVのバンドギャップ基準電圧セルが内部で誤差増幅器の非反転入力に接続されています。この基準電圧はアンプのオフセットを最終のレギュレーション電圧から除去するため誤差増幅器が単一ゲイン構成となるようにしてトリミングされています。

## 電圧誤差増幅器

誤差増幅器は5MHzより高い帯域幅と最小55dBの開ループ・ゲインをもっています。出力電圧の振幅は過渡応答を改善するため発振器のランプ・レベルのちょうど上下に制限されています。

## ループ補償

電圧モードの降圧型コンバータは一般的にタイプIIIの回路を用いて補償されます。電圧モード・コンバータ用のフィードバック・ループを設計する際の詳細な方法については設計例を参照してください。

## 発振器

発振周波数は内部で固定されています。TPS40040/1の動作周波数はそれぞれ300kHz/600kHzです。

## UVLO

入力電圧がUVLOスレッシュホールドより低い時、TPS40040/1は内部の発振器をオフにし、全てのゲート駆動出力を“L”レベル（オフ）の状態に保持します。入力がUVLOスレッシュホールドより高くなり、 $\overline{EN}$ ピンがターンオン・スレッシュホールドより低い時、起動シーケンスを開始することができます。

## イネーブルと起動シーケンス

TPS40040/1の $\overline{EN}$ ピンは内部でVDDに接続されています。電源がVDDに印加された時、 $\overline{EN}$ ピンは“H”レベルになり、TPS40040/1はオフのままです。 $\overline{EN}$ ピンが外部からVDD-1.2Vのスレッシュホールド電圧以下に引き下げられた時のみ、TPS40040/1は動作を開始することができます。イネーブルされた時、TPS40040/1は短絡電流のスレッシュホールドが決まるキャリブレーション・サイクルに入ります。TPS40040/1はCOMPピンから流れる電流を監視し、検出された電流値に基づいてスレッシュホールドを選択します。詳細については短絡電流制限スレッシュホールドの選択の項を参照してください。このキャリブレーション時間が完了した時、ソフトスタート・サイクルを開始することができます。以下の図19を参照してください。

**設計上のヒント：**イネーブル機能を使用しない場合は、 $\overline{EN}$ ピンはグランド(GND)に接続しておかなければなりません。

**設計上のヒント：**フィードバック・ループ補償を設計する際には、使用するコンデンサがCOMPピンのキャリブレーション波形を歪めるほど大きくならないようにします。

図 19. Startup

## ソフトスタート

キャリブレーション・サイクルが終わった時、TPS40040/1は誤差増幅器の非反転入力への電圧をゆっくりと増加させます。このようにして、出力電圧は誤差増幅器への非反転入力の電圧が内部基準電圧に達するまでゆっくりと上昇します。この時点で、誤差増幅器への非反転入力の電圧は基準電圧に保持されます。

ソフトスタート期間では、パルスごとの電流制限がアクティブとなっています。連続電流制限パルスが7つ検出されると、過電流が宣言され、7つのキャリブレーション/ソフトスタート・サイクルに等しいタイムアウト時間が発効します。詳細については出力短絡保護の項を参照してください。

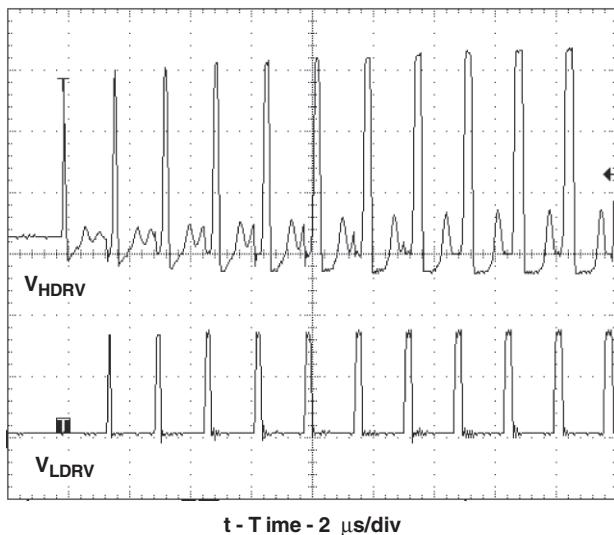

## プリバイアス起動

TPS40040/1はプリバイアスされた出力電圧のアプリケーションに対応しています。TPS40040/1がオフであるのに、出力電圧が外部からの手段により持ち上がっている場合、同期整流は出力電圧をソフトスタートさせる初期段階ではディスエーブルです。ソフトスタート動作中に最初のPWMパルスが検出された時、コントローラは狭いオン時間で同期整流器を動作開始することでゆっくりと同期整流を始めます。次に、(1-D)で決まる時間に一致するまでサイクルごとの基準でオン時間を増加させてゆきます。ここで、Dはコンバータのデューティー・サイクルです。この方法によりプリバイアスされた出力からの電流のシンクが防止され、確実に出力電圧の起動やレギュレーション電圧への上昇が円滑にコントロールされることになります。

注：出力がプリバイアスされていると、PWMパルスは内部のソフトスタート電圧が誤差増幅器の入力(FBピン)より高くなった時開始します。

図 20. MOSFET Driversat Beginning of SoftStart

以下の図20にPWMパルスの開始時でのHDRV/LDRV出力信号の波形を示します。HDRVがオフになった時、ダイオードの整流が可能になります。次のPWMサイクルが開始する前に、LDRVは短いパルスでオンになります。クロック・サイクルごとにLDRVのリーディング・エッジが調整され、同期整流器のオン時間が増加します。最終的に、同期整流を完全に達成するためLDRVのリーディング・エッジはHDRVの立下りエッジに一致するようになります。コンバータの通常動作時は、TPS40040/1は完全な2象限のソース/シンク・モードで動作します。

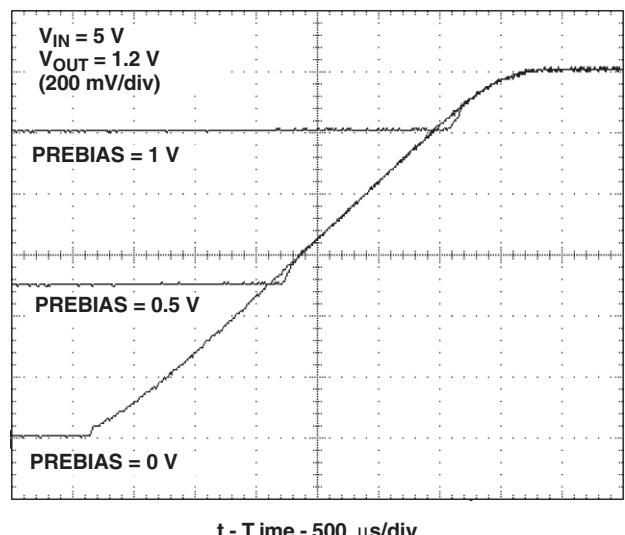

図21に、3種類のプリバイアス出力状態下での1.2V出力のコンバータの起動波形を示します。もっとも下の曲線は出力にプリバイアスがない場合です。中央と最上部の曲線はコンバータが0.5Vと1.0Vのプリバイアス状態で起動する場合を示しています。

推奨する出力電圧のプリバイアス範囲は最終レギュレーション電圧の90%以下です。最終レギュレーション電圧の90%から100%に出力電圧がプリバイアスされているとプリバイアス源から電流がシンクしてしまうことがあります。プリバイアスされる電圧がコンバータの設計出力レギュレーション電圧よりも高いと、ソフトスタート期間の終了時にTPS40040/1は出力電圧をレギュレーションするため出力から電流を引き込んでしまいます。

図 21. Startup Waveforms

## 出力短絡保護

回路の損失を最小限に抑えるため、TPS40040/1は電流を検出する素子として上側MOSFETスイッチの $R_{DS(on)}$ を使用します。各スイッチング・サイクルの最初の部分で初期的にブランкиングされた電流制限コンパレータが、フルにオンになっている時のハイサイドMOSFET端の電圧を検出します。この電圧は内部で選択されている短絡回路電流(SCC)制限のスレッシュホールド電圧と比較されます。このコンパレータはSCC制限スレッシュホールドより大きなハイサイドMOSFET端の電圧降下を検出すると、OCパルスを出力します。このことにより、さらなる電流の上昇を防止するよう現在のPWMパルスが終了し、次のクロック・サイクルで1カウントをカウントアップするようフォルト・カウンタがセットされます。同様に、OCパルスが検出されないと、フォルト・カウンタは1カウント減少します。フォルト・カウンタが7カウントに達すると、フォルト状態が宣言され、チップのPWM出力の上側スイッチが直ちにディスエーブル(オフ)になります。フォルトのタイムアウト期間が経過するまでその状態を保持します。HDRVとLDRVドライバの両方ともフォルト・タイムアウト時はオフ状態を保持しています。

フォルト・タイムアウト期間は7回内部ソフトスタートサイクルを繰り返すことにより決まります。フォルト・タイムアウト期間が終わった時、再度起動が試みられます。

この主な目的はパワー・スイッチのハード・フォルトの異常保護です。内部のSCC電圧は温度による短絡回路スレッシュホールドの公差変動を改善するよう設計された正の温度係数をもっていますが、電圧スレッシュホールドの公差とMOSFETの $R_{DS(on)}$ 範囲を考慮すると、外付けのMOSFETを熱的に損傷させる負荷が加わることもあり得ます。

## 短絡電流制限スレッシュホールドの選択

TPS40040/1はユーザーが選択可能な3種類の電圧スレッシュホールドのうちの1つを使用します。電源オンまたはイネーブル時のキャリブレーション期間で、TPS40040/1はCOMPピンから流れる電流を監視し、その検出値をもとにスレッシュホールドを選択します。電流がゼロであると、つまり、COMPとGND間に抵抗が接続されていないと、スレッシュホールド電圧レベルは180mVです。COMPとGND間に2.4kΩの抵抗が接続されていると、スレッシュホールド電圧レベルは105mVです。また、COMPとGND間に12kΩの抵抗が接続されていると、スレッシュホールド電圧は310mVです。

キャリブレーションが完了すると、選択されたSCPスレッシュホールド・レベルはそこでラッチされ、一定に維持されます。また、キャリブレーション時のCOMPピンの検出回路はCOMPピンから切断され、ソフトスタートを開始することができるようになります。

## 同期整流とゲート駆動

降圧型コンバータでは、上側のスイッチMOSFETがオフになった時、電流はインダクタから負荷に流れています。この電流は無限の電圧を使用せずにすぐには止めることはできません。この電流に流れる経路を与え、電圧レベルを安全なレベルに保つために、整流器またはキャッチ・デバイスが用いられます。このデバイスはダイオード、またはコントロールされたアクティブ・デバイスとなります。TPS40040/1は同期整流器(SR)としてのNチャネルMOSFETを駆動するための信号を供給します。このコントロール信号はSRがオフになり上側のスイッチMOSFETがオンになる時間からの最小デッドタイムと、上側のスイッチMOSFETがオフになりSRがオンになる時からの最小遅延が存在するよう慎重にメイン・スイッチ用の駆動信号と調整されます。

注：整流器の導通期間でダイオードの導通にかかる時間が長くなると、コンバータの効率が低くなります。

外付けのHDRV及びLDRVのMOSFET用のドライバは約5Vのゲート・ソース電圧に駆動する能力があります。VDD = 5Vの時、ドライバは15Aのコンバータに応じたMOSFETを駆動することができます。LDRVドライバはVDDとグランド間でスイッチし、一方、HDRVドライバはSWを基準としBOOTとSW間でスイッチします。これらのドライバには同期整流器のボディ・ダイオードの導通を最小限に抑えるアダプティブ遅延回路によってオーバーラップしないようなタイミングにコントロールされます。

## ゲート駆動抵抗

TPS40040/1のアダプティブ・ゲート遅延回路は外付けMOSFETスイッチの状態を決めるためHDRV-SW間及びLDRV-GND間の電圧をモニタしています。外付けの直列ゲート駆動抵抗端の電圧降下がターンオフ時に低下したゲート電圧として検出され、MOSFETのタイミングを妨げる可能性があります。

設計上のヒント：この抵抗は同期整流器のゲートに直列に挿入してはならず、ゲートの配線はレイアウト上で実利的な短さにしておかなければなりません。

## 総ゲート電荷

ターンオフとターンオン間のデッドタイムをコントロールするためTPS40040/1で使用される外付けMOSFETのゲート電圧の内部の電圧検出は、特に異なるゲート電荷がハイサイドMOSFETとローサイドMOSFETに用いられる時に、MOSFETのゲート電荷が大きいことに敏感です。ゲート電荷が増加するとMOSFETのスイッチング時間が増加し、MOSFETのスイッチング間のデッドタイムが減少します。

設計上のヒント：総ゲート電荷が40nC以下のMOSFETを選択しなければなりません。上側のスイッチMOSFETのゲート電荷はハイサイドMOSFETとローサイドMOSFET間のターンオン/ターンオフ遅延の不整合を最小限に抑えるため同期整流器のゲート電荷の60%以上でなければなりません。

## 同期整流器のdV/dtターンオン

上側のスイッチMOSFETがオンになると、スイッチ・ノードの電圧は非常に短い時間(標準10ns~30ns)でグランドの近くからVINに上昇し、スイッチ・ノードの電圧スパイクが極めて高くなってしまいます。MOSFETの構造によりその端子間、特にゲート/ドレイン間とゲート/ソース間に寄生容量が生じ、ゲートをその中点としてMOSFETのドレインとソース間に容量デバイダが生成されます。ゲート/ドレイン間の電荷( $Q_{GD}$ )がゲート/ソース間の電荷( $Q_{GS}$ )より大きいと、スイッチ・ノードの電圧が上昇する時、容量デバイダがそれに比例してMOSFETのゲートに電荷を与えます。極端な場合、このことにより同期整流器のゲート電圧がMOSFETのターンオン・スレッシュホールド電圧より高くなり、クロス導通が生じます。このことはdV/dtターンオンと呼ばれます。これはハイサイド及びローサイドMOSFETの両方の消費電力を増加させるため、効率が低下します。

**設計上のヒント:**  $Q_{GS}$ に対する $Q_{GD}$ の比が1より小さい同期整流MOSFETを選択し、同期整流器のゲート駆動回路は広く、低抵抗で低インダクタンスのループとなるようにしてください(レイアウトについての考察を参照してください)。

**設計上のヒント:** ブースト・コンデンサに直列に抵抗を挿入するとハイサイドMOSFETのターンオンが遅くなり、スイッチ・ノードのdV/dtが減少します。ブースト・コンデンサの直列抵抗の項を参照してください。

## NチャネルMOSFET駆動用ブーストストラップ

PWMのデューティ・サイクルは最大95%に制限されているため、ブーストストラップ・コンデンサは毎サイクル充電することができます。PWMがオフの各期間で、VDDの電圧がブーストストラップ・コンデンサを充電します。PWMスイッチが次にオンになるよう指示された時、MOSFETを駆動するのに使用される電圧がこのコンデンサの電圧から得られます。これは電荷移動回路であるため、ブーストストラップ・コンデンサの値はサイクルごとの基準でコンデンサに貯えられているエネルギーが、使用されているMOSFETのゲート電荷要件より大きくなるよう調整しなければなりません。詳細については設計例の項を参照してください。

## ブーストストラップ・コンデンサの直列抵抗

抵抗はハイサイドのゲートに直列に配置してはならないため、メイン・スイッチングMOSFETのターンオンをコントロールし、スイッチ・ノードの電圧の立上がりのdV/dtレートを低減するよう、ブーストストラップ・コンデンサに直列に1Ωから3Ωの小さな抵抗を挿入することが必要となることがあります。BOOTピンとブーストストラップ・コンデンサ間に挿入した抵抗はハイサイドMOSFETのターンオン時直列抵抗を増加させ、ハイサイドMOSFETのターンオフ期間では影響はありません。このことにより、TPS40040/1が上側のスイッチMOSFETのターンオフを過度に早く検出することや、上側のスイッチMOSFETのターンオフからSR MOSFETのターンオンまでの遅延タイミングを極端に低減することが防止されます。

**設計上のヒント:** EMIを低減するには、メイン・スイッチングFETのターンオンをコントロールするようブーストストラップ・コンデンサに直列に1Ωから3Ωの小さな抵抗を挿入してください。

## 低入力電圧用外付けショットキー・ダイオード

TPS40040/1は同期整流器の導通時にブーストストラップ・コンデンサを充電するためにVDDとBOOT間に内蔵しているPチャネルMOSFETスイッチを使用します。低入力電圧時、このMOSFETは(高いゲート電荷の)外部のハイサイドMOSFETをオンにするのに必要な電荷を急速に補充するほど十分にはオンにはなりません。こうした場合、VDDピンとBOOTピンの間にショットキー・ダイオードを外付けすることができます。ダイオードは非常に小さな平均電流( $Q_G \times F_{SW}$ )を運びますが、数百ミリアンペアのピーク・サージ電流を運ぶことが必要とされることがあります。このダイオードのサージ電流定格は最小500mAである必要があります。入力電圧が低いアプリケーションでは、抵抗がブーストストラップ・コンデンサに直列で使用された場合、コンデンサの充電パスから追加抵抗を取り除くために抵抗とコンデンサの接合部にダイオードを接続してください。

**設計上のヒント:** 入力電圧が低く、上側のスイッチMOSFETのゲート電荷が高い場合、小型のショットキー・ダイオードをVDDからBOOTに挿入しなければなりません。ブーストストラップ・コンデンサに直列に抵抗を使用しないでください。

## VDDのバイパスとフィルタ

TPS40040/1のコントロール回路に入り込むスイッチングノイズを防止するには、セラミック・コンデンサ(最小 $1\mu\text{F}$ )をできるだけVDDピンとGNDパッドに近づけて配置しなければなりません。

## VDDフィルタ抵抗

VDDのノイズをさらに制限するため、VDDへの小型フィルタを生成する $1\Omega$ から $2\Omega$ の小さな抵抗を入力電圧とVDDピンの間に挿入することができます。この抵抗は配線のIRドロップにより検出された電圧降下が増加するのを防ぐため上側のスイッチMOSFETのドレインの近くで接続しなければなりません。抵抗それ自体は4pinの近くに配置することが必要です。

抵抗を流れる電流には $2\text{mA}$ のデバイスの無負荷時スイッチング電流にゲートのスイッチング電流が加わった電流が含まれます。この抵抗端に生じた電圧降下によりデバイス内部の過電流保護回路で検出されたVDDとSW間の検出電圧が低下します。このことにより、保護回路が動作するためにはスイッチMOSFET端の電圧降下が設定値より抵抗によるドロップ分だけ大きくなる必要があります、その結果動作電流が大きくなります。この影響を最小限に抑えるには $25\text{mV}$ より小さな電圧降下となるような抵抗値を選択しなければなりません。

## サーマル・シャットダウン

デバイスの接合部温度がサーマル・シャットダウンのレベルに達すると、PWMと発振器はオフになります。HDRVとLDRVはオフに駆動されます。接合部が必要なレベルまで冷却されると、通常の起動サイクル時のようにPWMのソフトスタートが開始します。

## パッケージの消費電力

コントローラの消費電力はMOSFETのドライバ電流と入力電圧に大きく依存します。ドライバ電流は外付けMOSFETの総ゲート電荷 $Q_G$ とコンバータの動作周波数に比例します。ドライバの電力は、外付けのゲート抵抗を無視すると、以下の式で計算されます。

$$P_{D(\text{driver})} = Q_G \times V_{\text{DRIVE}} \times F_{\text{SW}} (\text{W}/\text{driver}) \quad (1)$$

総消費電力は、ハイサイド及び同期整流器の両方に同じMOSFETが選択されていると仮定すると、以下のようにになります。

$$P_T = \left( \frac{2 \times P_D}{V_{\text{DRIVE}}} + I_Q \right) \times V_{\text{DD}} (\text{W}) \quad (2)$$

または、

$$P_T = \left( 2 \times Q_G \times F_{\text{SW}} + I_Q \right) \times V_{\text{DD}} (\text{W}) \quad (3)$$

但し、 $I_Q$ は静止時の動作電流です(ドライバは無視)。

PowerPAD™パッケージの最大電力能力はエアーフローに加えてレイアウトにも依存します。2オンスの銅配線、はんだ付けされたサーマル・パッド、及びエアーフローがないと仮定した場合の接合部/大気間のサーマル・インピーダンスは参考資料[5]に詳述されています。

## PCBレイアウトのガイドライン

同期式降圧型コントローラのパワー段には、大きな交流不連続電流を運ぶ入力電流ループと大きな直流連続電流を運ぶ出力電流ループの2つの主な電流ループがあります。出力電流ループはインダクタの小さな交流リップル電流を運びます。

図 22. Synchronous BUCK Power Stage

## パワー部品の配線経路

図22に示されているように、入力電流ループには入力コンデンサ、スイッチングMOSFET、インダクタ、出力コンデンサ、入力コンデンサに戻るグランド・バスが含まれています。このループをできるだけ小さく保つのに、験的に良い方法としては、MOSFETの真下の電源グランドのプレーンを通ってメイン・スイッチングMOSFETのドレインと同期整流器(SR)のソース間に直接セラミック容量を挿入することです。

出力電流ループにはフィルタ・インダクタ、出力コンデンサ、出力コンデンサと同期整流MOSFETのソース間のグランド・リターンが含まれています。入力電流ループと同様に、出力コンデンサのグランドとSRのソース間のグランド・リターンはループ領域を最小限に抑えるためインダクタとMOSFETの下を通りなければなりません。

## デバイスとパワー段のインターフェイス

TPS40040/1は電力損失を最小限に抑えるため非常に高速のブレーク・ビフォー・メーク方式のアンチクロス導通回路を使用します。スイッチングMOSFETのゲートに直列にインピーダンスを外付けするとコンバータの動作に悪影響を与えるため避けなければなりません。ループ・インピーダンス(HDRV-ゲート間 + ソース-SW間及び、LDRV-SRゲート間 + SRのソース-GND間)はクロス導通を回避するため20nHより小さくしておかなければなりません。HDRVとLDRVの接続はできるだけデバイス・ピンから離して20ミルの配線幅で行わなければなりません。

メイン・スイッチングMOSFETのゲート駆動のリターンはTPS40040/1のSWピンです。SWピンはループ・インピーダンスを最小限に抑えるためできるだけHDRVの配線に近づけて少なくとも20ミル幅でメイン・スイッチングFETのソースに配線しなければなりません。

SR MOSFETのゲート駆動のリターンはTPS40040/1のGNDパッドです。GNDパッドはLDRVの配線の真下で少なくとも20ミル幅でSRのソースに直接接続しなければなりません。多層が用いられた場合はGNDパッドをSRのソースに接続するには最低2つの並列ビアを使用してください。

上側のスイッチMOSFETのターンオンを遅らせるため3Ω未満の小さな抵抗をBOOTピンに直列に挿入することができます。これによってスイッチ・ノードの立上がりエッジのスルーレートが低減します。同様に、このことでEMIも減少し、上側MOSFETのオフからSRのオンへのデッドタイムが増加し、上側のスイッチMOSFETがオンになった時SRの誘導dV/dtターンオンが最小になります。ボード上にこの抵抗を準備しておき、MOSFETのゲートのリード線に直列に抵抗を用いないことを推奨します。

## VDDのフィルタ

最小1μFのセラミック・コンデンサを15ミル幅(またはそれ以上)の配線でできるだけVDDピンとGNDパッドに近づけて配置しなければなりません。VDDピンへのスイッチング・ノイズの影響をさらにおさえるために、1~2Ω程の小さな抵抗を電源入力電圧とVDDピン間にTPS40040/1から100ミル以内に追加することができます。

注: この抵抗端の電圧降下は、センスされるVDD電圧にフィルタを施すことにより過電流回路が動作するレベルに影響を与えます。

## デバイスの接続

電流制限抵抗(COMPからGND)を用いる場合、PWMコンペレータにノイズが入るのを制限するためCOMPピンから100ミル以内にこの抵抗を配置する必要があります。補償部品(フィードバック・デバイダ、誤差増幅器に関連した部品)は10ミル幅の配線でGNDパッドで電源グランドに接続された信号グランドのアイランド上に配置しなければなりません。多層が用いられた場合は、同期整流器のソースへの接続の反対側で内層の1つのビアを通してGNDに接続してください。

## PowerPAD™のレイアウト

PowerPAD™パッケージはデバイスから熱を取り除くため低いサーマル・インピーダンスを提供します。PowerPAD™はその名前の由来のとおりデバイスの底面の大きな接合用パッドによりサーマル・インピーダンスが低くなります。回路ボードにはパッケージの真下にはんだ/スズめっき/銅の領域があることが必要です。この領域の大きさはPowerPAD™パッケージの寸法により決まります。詳細な情報についてはPCBレイアウトのガイドラインの項を参照してください。

放熱用ビアは、この領域を内部または外部の銅のプレーンに接続し、また、そのビア穴が銅めっきされる場合効率よく埋まるよう十分に小さな直径にしておきます。この埋め栓は、はんだリフロー時パッケージ本体とデバイスの下のはんだ/スズめっき領域との接触面からはんだが逃げるの防ぐために必要です。1オンスの銅がボード表面にめっきされ、同時にビア穴をめっきした場合、ビアの直径は0.33 mm(13ミル)が適切です。銅めっきされる場合に放熱用ビアを埋めなければ、ビア直径に最小0.1mmを加えた直径のはんだマスク材を使ってビアに蓋をしてください。この蓋により、はんだが放熱用ビアの中を通って逃げ、可能性として起こりうるパッケージの下にはんだのボイドができることが防止されます。PowerPAD™パッケージの詳細な情報についてはPowerPAD™ Thermally Enhanced Package[2]を参照してください。

## 設計例

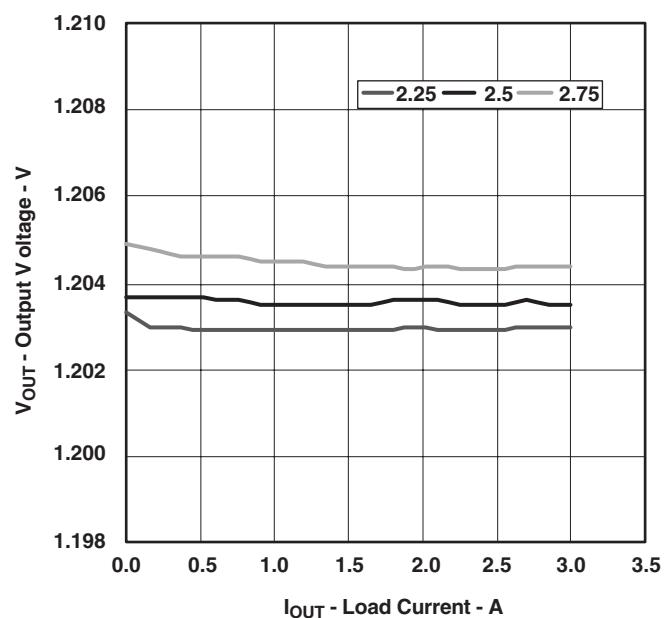

### 例1. TPS40041を使用した入力5V/出力1.8VのDC/DCコンバータ

以下の例で入力5V/出力1.8Vのポイント・オブ・ロード同期式降圧型コンバータの設計プロセスと部品選定について説明します。この設計目標のパラメータを以下の表に示します。記号の定義のリストはこの項の終わりにあります。

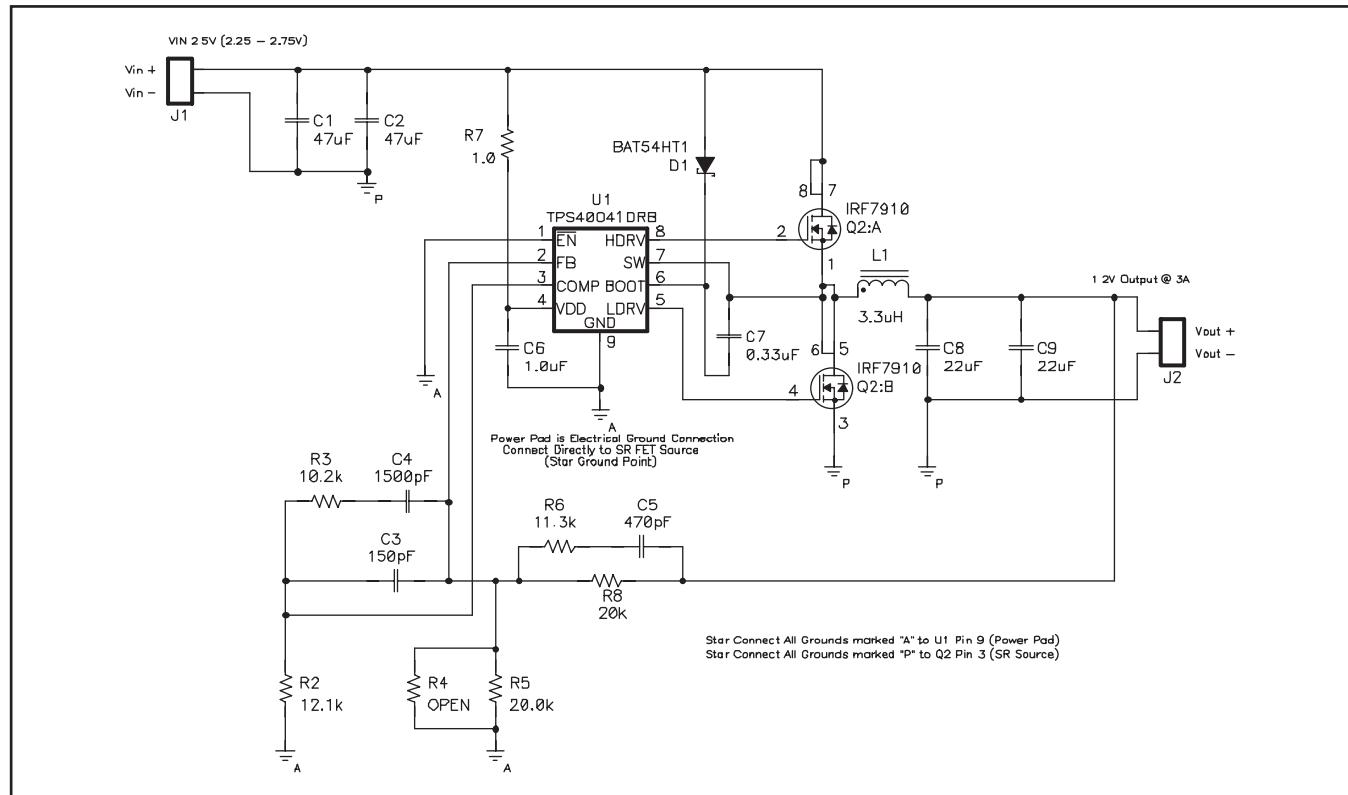

ここでの例では、図23に示されている回路図を使用します。インダクタとコンデンサの大きさを低減するため $F_{SW} = 600\text{kHz}$ のTPS40041が選択されています。

#### 設計目標のパラメータ

| 記号                    | パラメータ        | 測定条件                                                                     | MIN   | TYP  | MAX   | 単位              |

|-----------------------|--------------|--------------------------------------------------------------------------|-------|------|-------|-----------------|

| $V_{IN}$              | 入力電圧         |                                                                          | 4.5   |      | 5.5   | V               |

| $V_{IN\text{ripple}}$ | 入力リップル       | $I_{OUT} = 6\text{ A}$                                                   |       |      | 75    | mV              |

| $V_{OUT}$             | 出力電圧         | $I_{OUT} = 0\text{ A}, V_{IN} = 5\text{ V}$                              | 1.764 | 1.8  | 1.836 | V               |

|                       | ライン・レギュレーション | $V_{IN} = 4.5\text{ A to }5.5\text{ V}$                                  |       | 0.5% |       |                 |

|                       | ロード・レギュレーション | $I_{OUT} = 0\text{ A to }6\text{ A}$                                     |       | 0.5% |       |                 |

| $V_{RIPPLE}$          | 出力リップル       | $I_{OUT} = 6\text{ A}$                                                   |       |      | 36    | mV              |

| $V_{TRANS}$           | 過渡偏位         | $I_{OUT} = 1\text{ A to }5\text{ A}, I_{OUT} = 5\text{ A to }1\text{ A}$ |       | 50   |       |                 |

| $I_{OUT}$             | 出力電流         | $V_{IN} = 4.5\text{ V to }5.5\text{ V}$                                  | 0     |      | 6     | A               |

| $F_{SW}$              | スイッチング周波数    |                                                                          |       | 600  |       | kHz             |

|                       | 寸法           |                                                                          |       |      | 1     | In <sup>2</sup> |

図 23. TPS40041 Sample Schematic

## インダクタの選択

インダクタは一般的にはピーク間リップル電流 ( $I_{RIPPLE}$ ) を出力電流の30%とすることで決定します。この目標リップル電流を前提とすると、要求されるインダクタの大きさは以下の式で計算されます。

$$L = \frac{V_{IN(max)} - V_{OUT}}{0.3 \times I_{OUT}} \times \frac{V_{OUT}}{V_{IN(max)}} \times \frac{1}{F_{SW}} \quad (4)$$

$V_{IN(max)} = 5.5V$ を用いてこの式を解くと、インダクタ値は  $1.12\mu H$ となります。標準値の $1.0\mu H$ を選択すると、ピーク間リップル電流は $2A$ になります。インダクタを流れるRMS電流は以下の式で概算されます。

$$\begin{aligned} I_{L(rms)} &= \sqrt{\left(I_{L(avg)}\right)^2 + \frac{1}{12}\left(I_{RIPPLE}\right)^2} \\ &= \sqrt{\left(I_{OUT}\right)^2 + \frac{1}{12}\left(I_{RIPPLE}\right)^2} \end{aligned} \quad (5)$$

式(5)を用いると、インダクタの最大RMS電流は約 $6.03A$ になります。

## 出力コンデンサの選択 (C8 & C9)

出力コンデンサの選択は一般的に出力負荷の過渡応答の要件で行われます。式(6)と式(7)で、与えられた出力電圧の過渡変動を満たすために必要となる出力容量が見積られます。

$$C_{OUT(min)} = \frac{I_{TRAN(max)}^2 \times L}{(V_{IN(min)} - V_{OUT}) \times V_{TRAN}} \quad (6)$$

$$\text{when } V_{IN(min)} < 2 \times V_{OUT}$$

$$C_{OUT(min)} = \frac{I_{TRAN(max)}^2 \times L}{(V_{OUT}) \times V_{TRAN}} \quad (7)$$

$$\text{when } V_{IN(min)} > 2 \times V_{OUT}$$

ここでの例では、最小出力容量の計算には式(7)を用います。最大偏位が $50mV$ で負荷過渡電流が $4A$ であることにより、最小 $178\mu F$ の出力容量が必要になります。

出力リップルは2つの要素に分けられます。最初は出力コンデンサの容量を流れるインダクタのリップル電流によって生じるリップル電圧で、2番目は出力コンデンサのESRに流れるリップル電流により生じる電圧です。よって、最大許容ESRは最大リップル電圧により決まり、以下の式で概算されます。

$$\begin{aligned} ESR_{MAX} &= \frac{V_{RIPPLE(total)} - V_{RIPPLE(cap)}}{I_{RIPPLE}} \\ &= \frac{V_{RIPPLE(total)} - \left(\frac{I_{RIPPLE}}{C_{OUT} \times F_{SW}}\right)}{I_{RIPPLE}} \end{aligned} \quad (8)$$

容量が $178\mu F$ 、リップル電流が $2A$ 、スイッチング周波数が $600kHz$ 、リップル電圧の設計目標が $36mV$ であることに基づいて計算すると容量性のリップル成分が $18.7mV$ 、最大ESRが $8.6m\Omega$ となります。 $8.6m\Omega$ よりかなり小さなESRとなるよう、2つの1206、 $100\mu F/6.3V$ 、X5Rタイプのセラミック・コンデンサを選択します。

## インダクタのピーク電流定格

既知の出力容量を用いて、起動時の充電電流を計算し、インダクタの最小飽和電流定格を決めることができます。起動時の充電電流は以下の式で概算されます。

$$I_{CHARGE} = \frac{V_{OUT} \times C_{OUT}}{T_{SS}} \quad (9)$$

TPS40041の $4.5ms$ の固定ソフトスタート時間と、 $C_{OUT}=200\mu F$ 、 $V_{OUT} = 1.8V$ を用いると、 $I_{CHARGE}$ は $80mA$ になります。よって、インダクタのピーク電流定格は以下の式で求められます。

$$I_{L(peak)} = I_{OUT(max)} + \frac{1}{2}(I_{RIPPLE}) + I_{CHARGE} \quad (10)$$

インダクタの要件を以下の表にまとめます。

寸法が小さく、DCRが低く、大電流処理能力があるため $1.0\mu H$ のPG0083.102を選択します。

## インダクタの要件

| パラメータ       | 記号            | 値    | 単位      |

|-------------|---------------|------|---------|

| インダクタンス     | L             | 1.0  | $\mu H$ |

| RMS電流(熱定格)  | $I_{L(rms)}$  | 6.03 | A       |

| ピーク電流(飽和定格) | $I_{L(peak)}$ | 7.08 |         |

## 入力コンデンサの選択 (C1 & C2)

入力電圧リップルは容量とESRに分けられます。ここでの設計では、 $V_{\text{RIPPLE}(\text{CAP})} = 50\text{mV}$ 、 $V_{\text{RIPPLE}(\text{ESR})} = 25\text{mV}$ です。最小容量と最大ESRは以下の式で見積もられます。

$$C_{\text{IN}(\text{min})} = \frac{I_{\text{LOAD}} \times V_{\text{OUT}}}{V_{\text{RIPPLE}(\text{cap})} \times V_{\text{IN}} \times F_{\text{SW}}} \quad (11)$$

$$\text{ESR}_{\text{MAX}} = \frac{V_{\text{RIPPLE}(\text{ESR})}}{I_{\text{LOAD}} + \frac{1}{2}(I_{\text{RIPPLE}})} \quad (12)$$

ここで設計では、 $C_{\text{IN}} > 120\mu\text{F}$ 、 $\text{ESR} < 3.5\text{m}\Omega$ になります。入力コンデンサのRMS電流は以下の式で見積もられます。

$$\begin{aligned} I_{\text{RMS}(\text{cin})} &= I_{\text{IN}(\text{rms})} - I_{\text{IN}(\text{avg})} \\ &= \sqrt{\left(I_{\text{OUT}}^2 + \frac{1}{12}(I_{\text{RIPPLE}})^2\right)} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \\ &- \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{V_{\text{IN}}} \end{aligned} \quad (13)$$

$V_{\text{IN}} = V_{\text{IN}(\text{max})}$  とすると、入力コンデンサは $1.56\text{A}_{\text{RMS}}$ のリップル電流に対応する必要があります。ESRが約 $5\text{m}\Omega$ 、RMS電流定格が $2\text{A}$ の2つの1206、 $100\mu\text{F}$ 、X5Rタイプのセラミック・コンデンサを選択します。確実にコンデンサが動作電圧で十分な容量を供給するよう直流バイアス電圧の軽減曲線を確認することが重要です。

## MOSFETスイッチの選択 (Q1 & Q2)

上側のスイッチMOSFETのスイッチング損失は以下の式で見積もられます。

$$\begin{aligned} P_{\text{G1SW}} &= \frac{1}{2} \times V_{\text{IN}} \times I_{\text{OUT}} \times (T_{\text{RISE}} + T_{\text{FALL}}) \times F_{\text{SW}} \\ &= V_{\text{IN}} \times I_{\text{OUT}} \times \frac{Q_{\text{GS2\_Q1}} + Q_{\text{GD\_Q1}}}{V_{\text{DD}} - V_{\text{TH}}} \times F_{\text{SW}} \end{aligned} \quad (14)$$

ここで設計では、低入力電圧時ゲート駆動電流が小さいためスイッチング損失は高くなります。総損失が両方のMOSFETで $1\text{W}$ 、スイッチング損失がMOSFETの総損失の $20\%$ として設

計すると、ゲート/ドレイン間の最大電荷は以下の式で見積もられます。

$$Q_{\text{GS2\_Q1}} + Q_{\text{GD\_Q1}} < \frac{P_{\text{G1SW}}}{V_{\text{IN}} \times I_{\text{OUT}}} \times \frac{V_{\text{DD}} - V_{\text{t}}}{R_{\text{DRIVE}}} \times \frac{1}{F_{\text{SW}}} \quad (15)$$

MOSFETのゲート・スレッシュホールドが低く、TPS40041のゲート抵抗が $5\Omega$ と $3\Omega$ であるため、 $Q_{\text{GS2}} + Q_{\text{GD}}$ の最大値は $10.8\text{nC}$ と見積もられます。

上側のスイッチMOSFETの導通損失はMOSFETを流れるRMS電流にその $R_{\text{DS}(\text{on})}$ を乗じて見積もられます。

$$\begin{aligned} P_{\text{CON\_Q1}} &= D \times \left[ \left( I_{\text{OUT}} \right)^2 + \frac{1}{12} \left( I_{\text{RIPPLE}} \right)^2 \right] \times R_{\text{DS}(\text{on})} \\ &= \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times I_{\text{L}(\text{rms})}^2 \times R_{\text{DS}(\text{on\_Q1})} \end{aligned} \quad (16)$$

MOSFETの総損失の約 $30\%$ がハイサイドの導通損失であると推定すると、ハイサイドMOSFETの最大 $R_{\text{DS}(\text{on})}$ は以下の式で見積もることができます。

$$R_{\text{DS}(\text{on\_Q1})} = \frac{P_{\text{CON\_Q1}}}{I_{\text{L}(\text{rms})}^2 \times \frac{V_{\text{OUT}}}{V_{\text{IN}}}} \quad (17)$$

ここで設計では、 $I_{\text{L,RMS}} = 6\text{A}_{\text{RMS}}$ 、入力電圧 =  $4.5\text{V}$ /出力電圧 =  $1.8\text{V}$ とすると上側のスイッチMOSFETの $R_{\text{DS}(\text{on\_Q1})}$ は $19.5\text{m}\Omega$ 未満になります。

導通損失でMOSFETの総損失の $50\%$ が電流FETの分であると推定して、式(14)を再び使用します。次に、電流FETの最大 $R_{\text{DS}(\text{on})}$ を以下の式で計算します。

$$R_{\text{DS}(\text{on\_Q2})} = \frac{P_{\text{CON\_Q2}}}{I_{\text{L}(\text{rms})}^2 \times \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)} \quad (18)$$

ここで設計では、 $I_{\text{L,RMS}} = 6\text{A}_{\text{RMS}}$ 、入力電圧 =  $5.5\text{V}$ /出力電圧 =  $1.8\text{V}$ とすると $R_{\text{DS}(\text{on\_Q2})}$ は $19.6\text{m}\Omega$ 未満になります。MOSFETの要件を以下の表にまとめます。

IRF7910は $4.5\text{V}$ のゲート駆動時 $R_{\text{DS}(\text{on,max})}$ が $15\text{m}\Omega$ 、 $Q_{\text{GD}}$ が $6.2\text{nC}$ 、 $Q_{\text{GS2}}$ が $2\text{nC}$ です。

## MOSFETの要件

| パラメータ                               | 記号                                       | 値    | 単位               |

|-------------------------------------|------------------------------------------|------|------------------|

| ハイサイドFET $R_{\text{DS}(\text{on})}$ | $R_{\text{DS}(\text{on\_Q1})}$           | 19.5 | $\text{m}\Omega$ |

| ハイサイドFETのターンオン電荷                    | $Q_{\text{GS2\_Q1}} + Q_{\text{GD\_Q1}}$ | 10.8 | $\text{nC}$      |

| ローサイドFET $R_{\text{DS}(\text{on})}$ | $R_{\text{DS}(\text{on\_Q2})}$           | 19.6 | $\text{m}\Omega$ |

## ブートストラップ・コンデンサ (C7)

確実に上側のスイッチMOSFETのゲートを正しく充電するには、ブートストラップ・コンデンサのリップル電圧を3.0Vの最小ゲート駆動電圧の5%未満に制限します。

$$C_{\text{BOOST}} = \frac{20 \times Q_{\text{GS\_Q1}}}{V_{\text{IN(min)}}} \quad (19)$$

26nCの最大総ゲート電荷をもつIRF7910 MOSFETにより、計算結果は最小容量が116nFになります。これより大きな標準値の220nFを選択します。

## VDDバイパス・コンデンサ (C6)

VDDに1.0μFのセラミック・バイパス・コンデンサを選択します。

## VDDフィルタ抵抗 (R7)

オプションとしてVDDに直列に抵抗を挿入するとデバイスからスイッチング・ノイズにフィルタを施すのに役立ちます。各17nCの標準の総QGをもつ2つのIRF7910 MOSFETを駆動すると、最大I<sub>DD</sub>は22mAです。式(20)の結果により、1Ωの抵抗が選択されることになり、よってこの抵抗端の電圧降下が25mV未満に制限されます。

$$R_{\text{VDD}} < \frac{V_{\text{RVDD(max)}}}{I_{\text{DD}}} = \frac{25 \text{ mV}}{2 \text{ mA} + (Q_{\text{G\_Q1}} + Q_{\text{G\_Q2}}) F_{\text{SW}}} \quad (20)$$

## 短絡保護 (R2)

TPS40040/1はインダクタ電流を測定するのにオン時間での上側MOSFET端の電圧降下を使用します。ハイサイドMOSFET端の電圧降下は以下の式で求められます。

$$V_{\text{CS}} = I_{\text{L(peak)}} \times R_{\text{DS(on\_Q1)}} \quad (21)$$

$V_{\text{IN}} = 4.5\text{V}\sim 5.5\text{V}$ 、 $I_{\text{L PEAK}} = 7.2\text{A}$ 時で、IRF7910 MOSFETを用いると、ピークの電圧降下の計算結果は108mVになります。TPS40040/1の内部の3100ppmの温度係数はMOSFETの $R_{\text{DS(on)}}$ の温度係数を補償するのに役立ちます。ここでの設計では、R2をオープンとして選ぶことで短絡保護の電圧スレッシュホールドには180mVを選択しています。

## フィードバック・ループの設計

フィードバック回路を設計するには、小信号の平均モデル化手法が使用されます。この手法についての詳細な情報は参考資料にあります。

## パワー段のモデル化

電気的特性表に定められているピーク間ランプ電圧により変調器のゲインは以下のように計算することができます。

$$A_{\text{MOD}} = \frac{V_{\text{IN}}}{V_{\text{RAMP(p-p)}}} \quad (22)$$

ここでの設計では、変調器のゲインの計算結果は7.3(17.3dB)です。

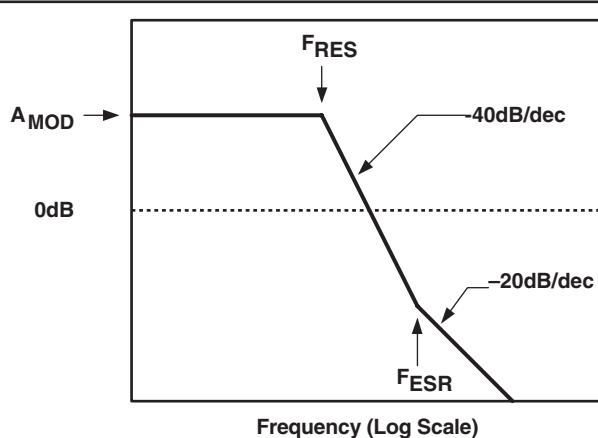

LCフィルタにより2つの極が共振周波数で加わります。

$$F_{\text{RES}} = \frac{1}{2 \times \pi \times \sqrt{L \times C}} \quad (23)$$

ここでの設計では、共振周波数は約11.3kHzです。この周波数より低い周波数では、パワー段の直流ゲインは17.3dBで、この周波数より高い周波数ではパワー段のゲインは-40dB/decadeで低下します。ESRゼロは以下の式で概算されます。

$$F_{\text{ESR}} = \frac{1}{2 \times \pi \times C_{\text{OUT}} \times R_{\text{ESR}}} \quad (24)$$

$C_{\text{OUT}} = 2 \times 100\mu\text{F}$ 、 $R_{\text{ESR}} = 2.5\text{m}\Omega$ の場合、 $F_{\text{ESR}} = 318\text{kHz}$ になります。この値はスイッチング周波数の1/5より大きく、誤差増幅器の設計の範囲外です。パワー段のゲインはFESRより高い周波数では-20dB/decadeで変化します。パワー段のゲインの直線近似を図24に示します。

図 24. Power Stage Frequency Response Straight Line Approximation

## フィードバック・デバイダ (R4, R5 & R8)

R8を10kΩ～100kΩの間で選択します。ここで設計では20kΩを選択します。次に、V<sub>FB</sub> = 0.600Vの時の目的とする出力電圧を生成するため以下の式を用いてR5を選択します。

$$R5 \text{ in parallel with } R4 = \frac{V_{FB} \times R8}{V_{OUT} - V_{FB}} \quad (25)$$

V<sub>OUT</sub> = 1.8Vの場合にV<sub>FB</sub> = 0.600V、R8 = 20 kΩにより、R5 = 10kΩになります。計算結果が標準の抵抗ではない場合、少し高い抵抗値を選択し、R4を並列に接続して目的とする出力電圧を得られるようにします。

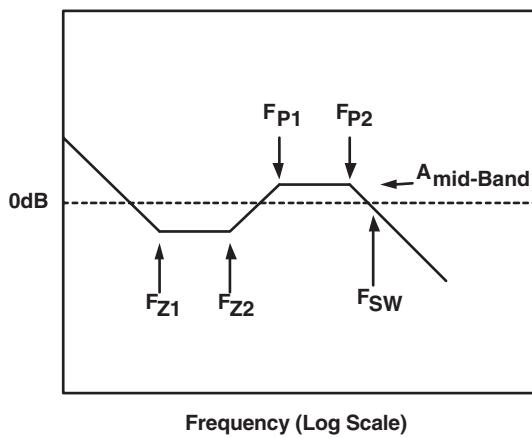

## 誤差増幅器の極/ゼロ選択

LとCの公差を考慮して実際の共振周波数を2つのゼロの間に保持するために共振周波数の80%と125%に2つのゼロを置きます。F<sub>RES</sub> = 11.3kHzの場合、F<sub>Z1</sub> = 9.0kHz、F<sub>Z2</sub> = 14kHzです。コントロール・ループのクロスオーバー周波数(F<sub>CO</sub>)をLCフィルタの共振周波数の3倍とスイッチング周波数の1/5の間に選択します。ほとんどのアプリケーションでは、スイッチング周波数の1/10にすると設計の容易さと高速過渡応答がうまく両立します。

F<sub>ESR</sub> < F<sub>CO</sub>の場合、F<sub>P1</sub> = 1/2 F<sub>CO</sub>、F<sub>P2</sub> = 2 × F<sub>CO</sub>

F<sub>ESR</sub> > 2 × F<sub>CO</sub>の場合、F<sub>P1</sub> = F<sub>CO</sub>、F<sub>P2</sub> = 4 × F<sub>CO</sub>

F<sub>SW</sub> = 600kHzのここでの設計では、F<sub>RES</sub> = 11.3kHz、F<sub>ESR</sub> = 318kHzです。

F<sub>CO</sub> = 60kHz、またF<sub>ESR</sub> > 2 × F<sub>CO</sub>であるためF<sub>P1</sub> = F<sub>CO</sub>、F<sub>P2</sub> = 4 × F<sub>CO</sub>です。

F<sub>CO</sub> < F<sub>ESR</sub>なので、目的とするクロスオーバー周波数でのパワー段のゲインは以下の式で概算できます。

$$A_{PS(fcc)} = A_{MOD} - 40 \times \log\left(\frac{F_{CO}}{F_{RES}}\right) \quad (26)$$

A<sub>PS(F<sub>CO</sub>)</sub> = -11.7dBであるため、2つの極の間の誤差増幅器のゲインは10<sup>(11.7/20)</sup> = 3.84です。

誤差増幅器のゲインがF<sub>SW</sub>で0dBより大きいと、コンバータは2つの安定したデューティ・サイクルを交互に繰り返す動作モードとなり、出力はF<sub>SW</sub>の1/2での出力リップル成分でレギュレーションされます。この現象を回避するには、以下の式でF<sub>P2</sub>を確認します。

$$F_{P2(max)} = \frac{F_{SW}}{A_{MID(band)}} \quad (27)$$

F<sub>P2</sub> > F<sub>P2(max)</sub>であるため、このループは上述の動作モードとなる可能性があります。これを回避するには、F<sub>CO</sub>を減少させ、A<sub>PS(F<sub>CO</sub>)</sub>、F<sub>P1</sub>、F<sub>P2(max)</sub>を再計算します。

F<sub>CO</sub> = 50kHz、A<sub>MID\_BAND</sub> = 2.67、F<sub>P1</sub> = 50kHz、F<sub>P2</sub> = 200kHzとなります。

以下の表に誤差増幅器の補償回路の設計基準をまとめます。

## 誤差増幅器の補償回路

| パラメータ     | 記号                    | 値    | 単位  |

|-----------|-----------------------|------|-----|

| 最初のゼロ周波数  | F <sub>Z1</sub>       | 9    | kHz |

| 2番目のゼロ周波数 | F <sub>Z2</sub>       | 14   |     |

| 最初の極周波数   | F <sub>P1</sub>       | 50   |     |

| 2番目の極周波数  | F <sub>P2</sub>       | 200  |     |

| 中間帯域ゲイン   | A <sub>MID-BAND</sub> | 2.67 | V/V |

## フィードバック部品 (R3,R6,C3,C4,C5)

以下の式を用いてC5を概算します。

$$C5 = \frac{1}{2 \times \pi \times R8 \times F_{Z2}} \quad (28)$$

$C5 = 560\text{pF}$  (計算結果の $568\text{pF}$ にもっとも近い標準コンデンサ値)となり、次に、以下の式を用いてR6を概算します。

$$R6 = \frac{1}{2 \times \pi \times C5 \times F_{P1}} \quad (29)$$

$R6 = 4.75\text{k}\Omega$  (計算結果の $4.74\text{k}\Omega$ にもっとも近い標準抵抗値)となります。次に、以下の式を用いてR3を計算します。

$$R3 = \frac{A_{\text{MID(band)}} \times (R6 \times R8)}{R6 + R8} \quad (30)$$

$A_{\text{MID\_BAND}} = 3.84$ 、 $R6 = 4.75\text{k}\Omega$ 、 $R8 = 20\text{k}\Omega$ を用いると、 $R3 = 14.7\text{k}\Omega$  (計算結果の $14.7\text{k}\Omega$ にもっとも近い標準抵抗値)となります。次に、以下の式を用いてC3とC4を計算します。

$$C4 = \frac{1}{2 \times \pi \times R3 \times F_{Z1}} \quad (31)$$

$$C3 = \frac{1}{2 \times \pi \times R3 \times F_{P2}} \quad (32)$$

$R3 = 14.7\text{k}\Omega$ の場合、 $C3 = 47\text{pF}$  (計算結果の $45\text{pF}$ にもっとも近い標準値)、 $C4 = 1200\text{pF}$  (計算結果の $1.2\text{nF}$ にもっとも近い標準値)となります。

誤差増幅器の直線近似の伝達関数は図25のようになります。

図 25. Error Amplifier Frequency Response Straight Line Approximation

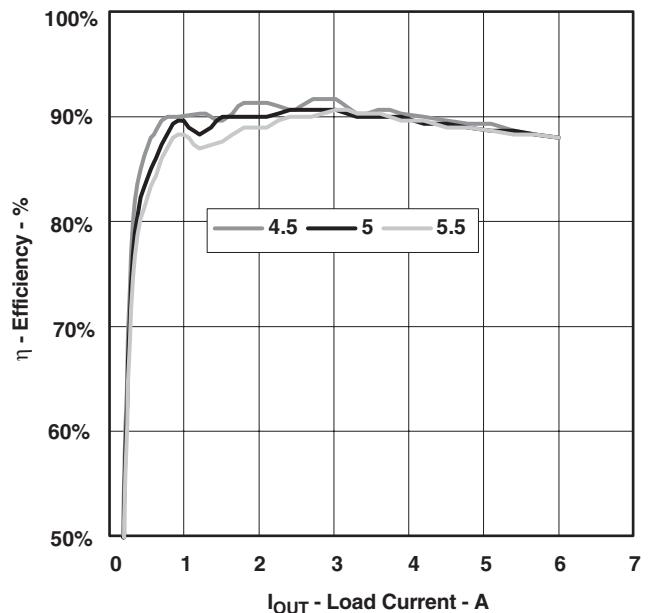

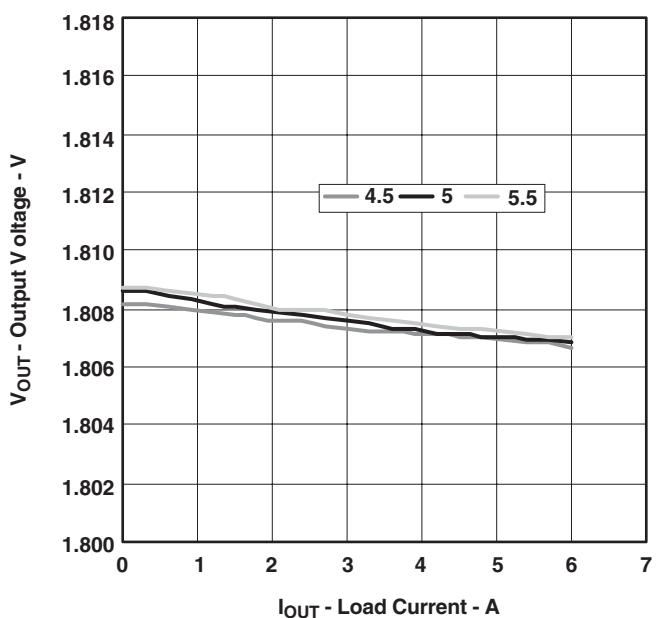

図 26. Typical Efficency for 5-V to 1.8-V at 6-A Converter Using TPS40041

図 27. Typical Line/Load Regulation for 5-V to 1.8-V at 6-A Converter Using TPS40041

部品表

| 記号                    | 数量 | 内容                                                                           | メーカー        | 型番             |

|-----------------------|----|------------------------------------------------------------------------------|-------------|----------------|

| C1                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 100 $\mu$ F, 1210                              | TDK         | C325X5R0J107M  |

| C2                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 100 $\mu$ F, 1210                              | TDK         | C3225X5R0J107M |

| C3                    | 1  | セラミック・コンデンサ, 50 V, X7R, 20%, 270pF, 0402                                     | TDK         | C1005C01H271M  |

| C4                    | 1  | セラミック・コンデンサ, 50 V, X7R, 20%, 1500pF, 0402                                    | TDK         | C1005X7R1H152M |

| C5                    | 1  | セラミック・コンデンサ, 50 V, X7R, 20%, 560pF, 0402                                     | TDK         | C1005X7R1H561M |

| C6                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 1.0 $\mu$ F, 0402                              | TDK         | C1005X7R0J105M |

| C7                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 0.22 $\mu$ F, 0402                             | TDK         | C1005X7R0J224M |

| C8                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 100 $\mu$ F, 1210                              | TDK         | C3225X5R0J107M |

| C9                    | 1  | セラミック・コンデンサ, 6.3 V, X5R, 20%, 100 $\mu$ F, 1210                              | TDK         | C3225X5R0J107M |

| L1                    | 1  | Iインダクタ, SMT, 1.0 $\mu$ H, 12 A, 6.6 m $\Omega$ , ED1514, 0.268 x 0.268       | Pulse       | PG0083.102     |

| Q2                    | 1  | MOSFET, デュアルNチャネル, 20 V, 6.6 A, 29 m $\Omega$ , 1.0 $\mu$ H, SO8             | IR          | IRF7311        |

| R2                    | 1  | 抵抗, チップ, 1/16 W, %, IRF7910, 0402                                            | Std         | Std            |

| R3                    | 1  | 抵抗, チップ, 1/16 W, 1%, オープン, 0402                                              | Std         | Std            |

| R4                    | 1  | 抵抗, チップ, 1/16 W, 1%, 11.8k $\Omega$ , 0402                                   | Std         | Std            |

| R5                    | 1  | 抵抗, チップ, 1/16 W, 1%, オープン, 0402                                              | Std         | Std            |

| R6                    | 1  | 抵抗, チップ, 1/16 W, 1%, 10.0k $\Omega$ , 0402                                   | Std         | Std            |

| R7                    | 1  | 抵抗, チップ, 1/16 W, 1%, 5.62k $\Omega$ , 0402                                   | Std         | Std            |

| R8                    | 1  | 抵抗, チップ, 1/16 W, 1%, 20k $\Omega$ , 0402                                     | Std         | Std            |

| U1                    | 1  | デバイス, 低電圧DC/DC同期式降圧型コントローラ,<br>TPS40041DRB, SON-8P                           | TPS40041DRB | TI             |

| アクティブ “H” レベル・イネーブル回路 |    |                                                                              |             |                |

| R1                    | 1  | 抵抗, チップ, 1/16 W, 1%, 100k $\Omega$ , 0402                                    | Std         | Std            |

| Q1                    | 1  | MOSFET, Nチャネル、VDS 60V, RDS 2 $\Omega$ , ID 115mA,<br>2N7002W, SOT-323(SC-70) | 2N7002W-7   | Diodes Inc     |

## 記号の定義

| 記号                | 内容                                                                                      |

|-------------------|-----------------------------------------------------------------------------------------|

| $V_{IN(max)}$     | 最大動作入力電圧                                                                                |

| $V_{IN(min)}$     | 最小動作入力電圧                                                                                |

| $V_{INRIPPLE}$    | $V_{IN}$ のピーク間acリップル電圧                                                                  |

| $V_{OUT}$         | 目標出力電圧                                                                                  |

| $V_{OUTRIPPLE}$   | $V_{OUT}$ のピーク間acリップル電圧                                                                 |

| $I_{OUT(max)}$    | 最大動作負荷電流                                                                                |

| $I_{RIPPLE}$      | 出力フィルタ・インダクタを流れるピーク間リップル電流                                                              |

| $I_{L\_PEAK}$     | 出力フィルタ・インダクタを流れるピーク・リップル電流                                                              |

| $I_{L\_RMS}$      | 出力フィルタ・インダクタを流れるRMS電流                                                                   |

| $I_{RMS\_CIN}$    | 入力コンデンサのRMS電流                                                                           |

| $F_{SW}$          | スイッチング周波数                                                                               |

| $F_{CO}$          | コントロール・ループのクロスオーバー周波数                                                                   |

| $A_{MOD}$         | パルス幅変調器の低周波ゲイン                                                                          |

| $V_{CONTROL}$     | PWMコントロール電圧 (誤差増幅器の出力電圧 - $V_{COMP}$ )                                                  |

| $F_{RES}$         | L-Cフィルタの共振周波数                                                                           |

| $F_{ESR}$         | 出力コンデンサのESRゼロ周波数                                                                        |

| $F_{P1}$          | 誤差増幅器の補償回路の最初の極周波数                                                                      |

| $F_{P2}$          | 誤差増幅器の補償回路の2番目の極周波数                                                                     |

| $F_{Z1}$          | 誤差増幅器の補償回路の最初のゼロ周波数                                                                     |

| $F_{Z2}$          | 誤差増幅器の補償回路の2番目のゼロ周波数                                                                    |

| $Q_{G1\_Q1}$      | 上側のスイッチングMOSFETの総ゲート電荷                                                                  |

| $Q_{G2\_Q2}$      | 同期整流MOSFETの総ゲート電荷                                                                       |

| $R_{DS(on\_Q1)}$  | 上側のスイッチングMOSFETのドレイン/ソース間オン抵抗                                                           |

| $R_{DS(on\_Q2)}$  | 同期整流MOSFETのドレイン/ソース間オン抵抗                                                                |

| $P_{CON\_Q1}$     | 上側のスイッチMOSFETの導通損失                                                                      |

| $P_{SW\_Q1}$      | 上側のスイッチMOSFETのスイッチング損失                                                                  |

| $P_{CON\_Q2}$     | 同期整流MOSFETの導通損失                                                                         |

| $Q_{GD\_Q1}$      | 上側のスイッチMOSFETのゲート/ドレイン間電荷                                                               |

| $Q_{GS2\_Q1}$     | 上側のスイッチMOSFETのポスト・スレッシュホールド・ゲート/ソース間電荷 (MOSFETのデータシートに記載されていない場合 $Q_G$ 対 $V_{GS}$ から推定) |

| $V_{FB}$          | FBピンで測定された内部基準電圧                                                                        |

| $V_{RAMP\_slope}$ | 内部PWMランプの勾配                                                                             |

| $A_{PS(Fco)}$     | ループのクロスオーバー周波数での $V_{OUT}$ に対する $V_{COMP}$ のゲイン (dB)                                    |

| $A_{MID-BAND}$    | ループのクロスオーバー周波数での $V_{COMP}$ に対する $V_{OUT}$ のゲイン (V/V)                                   |

## 例2. TPS40041を使用した入力2.5V/出力1.2VのDC/DCコンバータ

ここでの例ではTPS40041を使用した入力2.5V/出力1.2V、出力電流3Aの同期式降圧型のアプリケーションについて説明します。低入力電圧時ブートストラップ・コンデンサの充電電流を増

加させるためダイオードが追加されています。低入力電圧時RDS(on)が増加するため最大の電流制限スレッシュホールドが選択されています。

図 28. Schematic for 2.5-V to 1.2-V at 3-A Converter Using the TPS40041

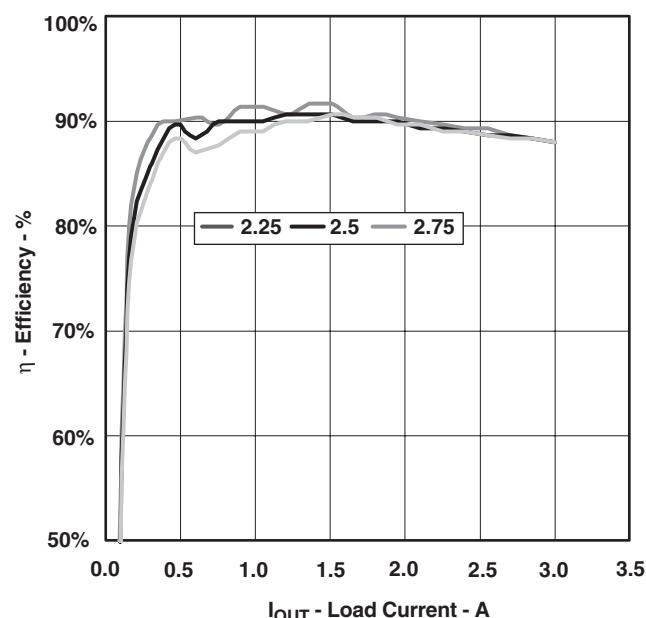

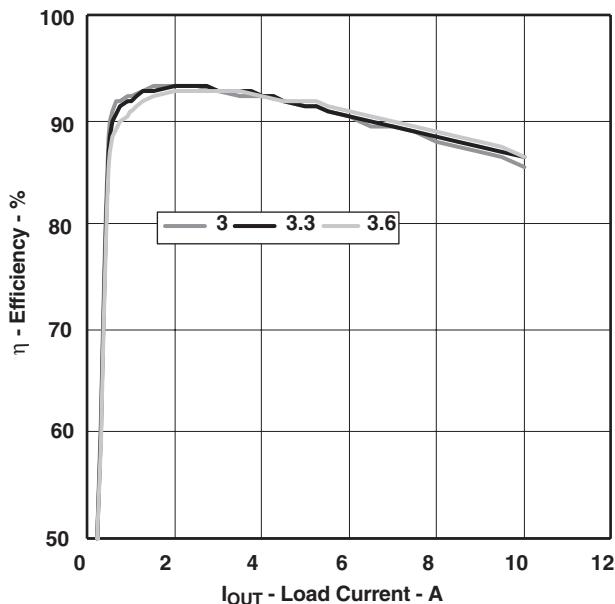

図 29. Typical Efficency for 2.5-V to 1.2-V at 3-A Converter Using TPS40041

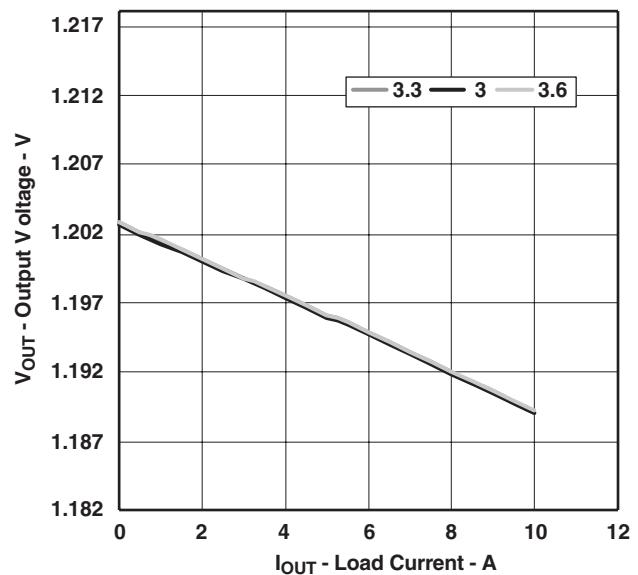

図 30. Typical Line/Load Regulation for 2.5-V to 1.2-V at 3-A Converter Using TPS40041

### 例3. TPS40040を使用した入力3.3V/出力1.2VのDC/DCコンバータ

ここで例では300kHzでスイッチングするTPS40040を使用した入力3.3V/出力1.2V、出力電流10Aの同期式降圧型のアプリケーションについて説明します。このアプリケーションでは大電流

に対応するため別々のSO-8ピンMOSFETが選択されており、また、スイッチ・ノードの立上がりエッジを遅らせコンバータの入力のEMIを低減するためBOOTピンに直列に抵抗が付加されています。

図 31. Schematic for 3.3-V to 1.2-V at 10-A Converter Using the TPS40040

図 32. Typical Efficiency for 3.3-V to 1.2-V at 10-A Converter Using TPS40040

図 33. Typically Load Regulation for 3.3-V to 1.2-V at 10-A Converter Using TPS40040

## 参考資料

### 関連製品

TPS40040/1と類似した特性を持つ製品としては以下の製品が存在します。

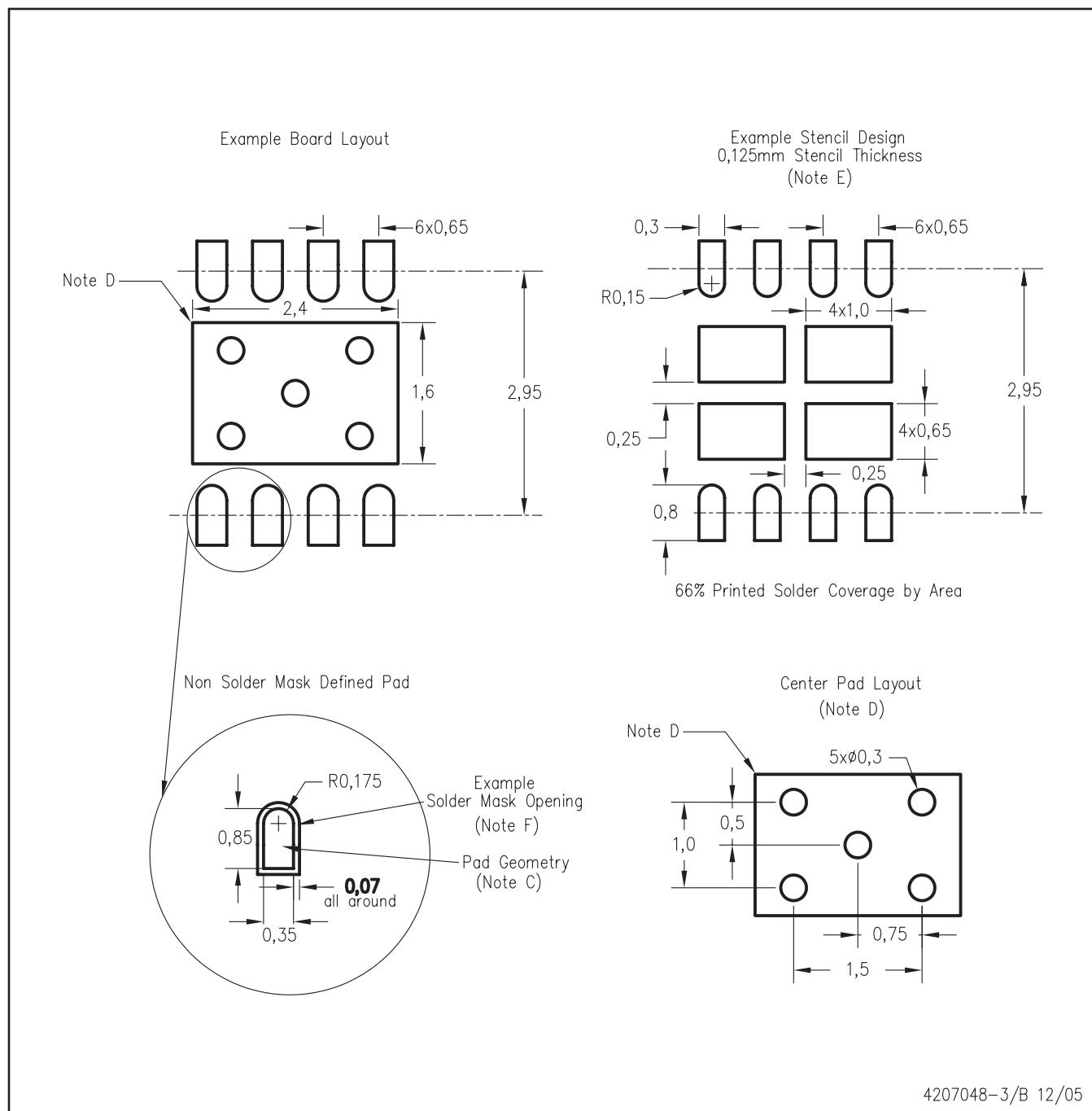

### パッケージ・アウトライン

以下にDRBパッケージの機械的寸法を示します。

### 推奨PCBフットプリント

以下に推奨するPCBレイアウトを示します。

### 関連製品

| デバイス       | 機能                         |

|------------|----------------------------|

| TPS40007/9 | 低電圧入力で動作する同期式降圧型コントローラ     |

| TPS40021   | 低電圧入力で動作可能な同期式降圧型コントローラ    |

| TPS40190   | 中間バス入力電圧で動作可能な同期式降圧型コントローラ |

## 参考資料

以下の参考資料はwww.ti.comのテクニカル・ドキュメントにあります。また、デザイン・ソフトウェアなどの設計ツールや他の参考資料へのリンクもwww.power.ti.comから入手可能です。

1. Under The Hood Of Low Voltage DC/DC Converters, SEM1500 Topic 5, 2002 Seminar Series

2. Understanding Buck Power Stages in Switchmode Power Supplies, SLVA057, March 1999

3. Design and Application Guide for High Speed MOSFET Gate Drive Circuits, SEM 1400, 2001 Seminar Series

4. Designing Stable Control Loops, SEM 1400, 2001 Seminar Series

5. Additional PowerPADTM information may be found in Applications Briefs SLMA002 and SLMA004

6. QFN/SON PCB Attachment, Texas Instruments Literature Number SLUA271, June 2002

# メカニカル・データ

DRB (S-PDSO-N8)

PLASTIC SMALL OUTLINE

4203482/G 11/04

注: A. 全ての線寸法の単位はミリメートルです。寸法/公差はASME Y14.5M-1994によります。

B. 図は予告なく変更することがあります。

C. スモール・アウトライン、ノーリード(SON)パッケージ構成です。

D. パッケージのサーマル・パッドは熱的/機械的特性のためボードにはんだ付けしなければなりません。露出しているサーマル・パッドの寸法についての詳細はデータシートを参照してください。

E. メッキ機構はメーカー・オプションで、パッケージ上にないことがあります。

# サーマルパッド・メカニカル・データ

DRB (S-PDSO-N8)

## 熱情報

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板(PCB)に直接はんだ付けされなければなりません。はんだ付けの後、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはグランドまたは電源プレーン(どちらか当てはまる方)、またはもう1つの方法としてPCBに設計された特別なヒートシンク構造に直接接続することができます。この設計により、集積回路(IC)からの熱移動が最適化されます。

クワッド・フラットパック・ノーリード(QFN)パッケージとその利点についての情報はアプリケーション・レポート“Quad Flatpack No-Lead Logic Packages” TI文献番号SCBA017を参照してください。この文献はホームページwww.ti.comで入手できます。

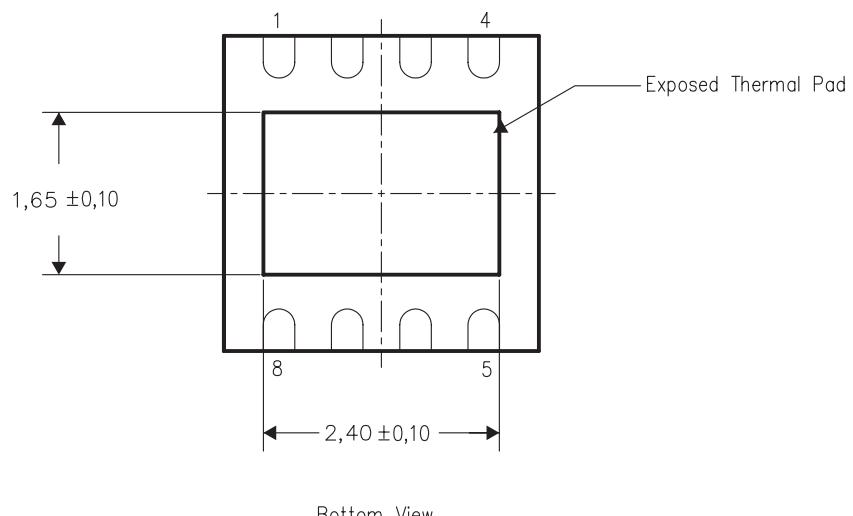

このパッケージの露出サーマル・パッドの寸法は以下の図に示されています。

Bottom View

注：全ての線寸法の単位はミリメートルです。

サーマル・パッド寸法図

# LAND PATTERN

DRB (S-PDSO-N8)

4207048-3/B 12/05

- 注： A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. スモール・アウトライン、ノーリード(SON)パッケージ構成です。

D. このパッケージはボードのサマール・パッドにはんだ付けされるよう設計されています。個別の熱情報、ビアの要件、推奨するボード・レイアウトについてはアプリケーション・ノート“QFN Packages” TI文献番号SCBA017とSLUA271、及びプロダクト・データシートを参照してください。これらの文献はホームページwww.ti.comで入手できます。

E. レーザーカットの開口部に台形の壁をつけ、角に丸みをつけるとペースト離れがよくなります。カスタマはステンシルの設計についてボード製作側に提案しなければなりません。ステンシルを設計する際の考察についてはIPC-7525を参照してください。

F. カスタマははんだマスクの推奨許容値についてボード製作側に連絡しなければなりません。

(XXXXXXXXXX)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS40040DRBR          | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 85    | 0040                |

| TPS40040DRBR.A        | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0040                |

| TPS40040DRBT          | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 85    | 0040                |

| TPS40040DRBT.A        | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0040                |

| TPS40041DRBR          | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

| TPS40041DRBR.A        | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

| TPS40041DRBRG4        | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

| TPS40041DRBT          | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

| TPS40041DRBT.A        | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

| TPS40041DRBTG4        | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 0041                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "-" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

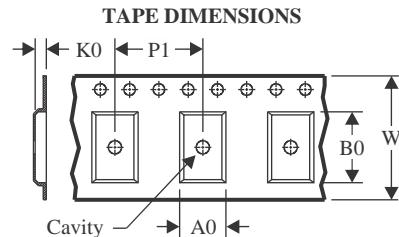

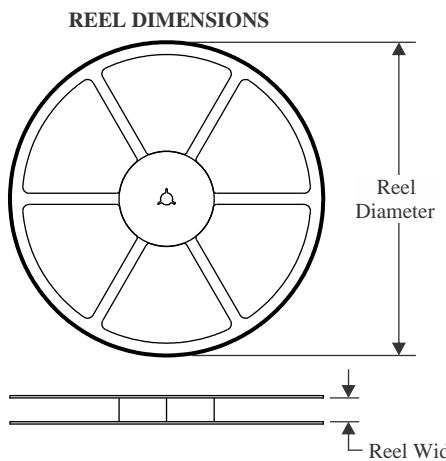

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

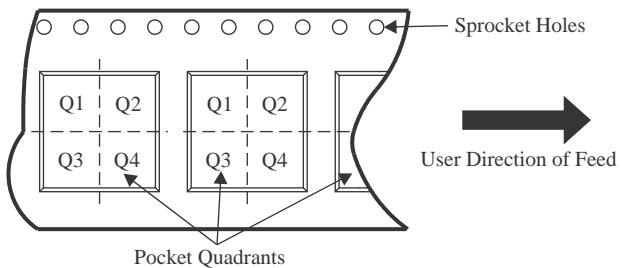

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS40040DRBR | SON          | DRB             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS40040DRBT | SON          | DRB             | 8    | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS40041DRBR | SON          | DRB             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS40041DRBT | SON          | DRB             | 8    | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

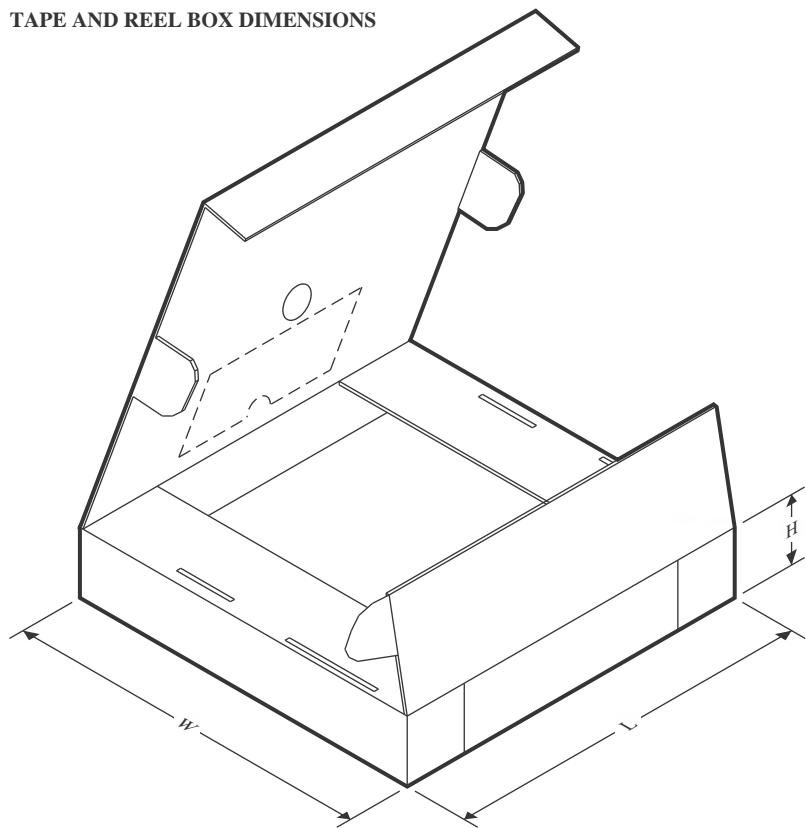

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS40040DRBR | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS40040DRBT | SON          | DRB             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TPS40041DRBR | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS40041DRBT | SON          | DRB             | 8    | 250  | 210.0       | 185.0      | 35.0        |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月