JAJSWD6 - APRIL 2025

# TPS388C0x-Q1 マルチチャネル過電圧および低電圧 I<sup>2</sup>C プログラマブル電圧 スーパーバイザおよびモニタ、ウィンドウ ウォッチドッグ付き

### 1 特長

- ASIL-B機能安全準拠の製品

- 機能安全アプリケーション用の開発向け

- ISO 26262 システムの設計に役立つ資料

- ASIL Dまでの決定論的対応能力

- ASIL B までのハードウェア機能

- 以下の結果で AEC-Q100 認定済み:

- デバイス温度グレード 1:-40℃ ~ +125℃

- 最新の SoC を監視

- 2~6の電圧モニタチャネルオプションが利用可 能です

- 入力電圧範囲:2.6V ~ 5.5V

- 低電圧誤動作防止 (UVLO) (立ち下がり):2.6V

- 高いスレッショルド精度:

- ±6mV (−40°C ~ +125°C)

- 固定ウィンドウのスレッショルドレベル

- 0.2V~1.475V、5mV ステップ

- 0.8V~5.5V、20mV ステップ

- トリガ ウィンドウ ウォッチドッグ

- I<sup>2</sup>C によりプログラム可能な OPEN/CLOSE ウォッ チドッグ タイミング  $(1ms\sim864ms)$

- SoC 起動初期化によるスタートアップ遅延 (2ms

- WDO アサート前のプログラマブル最大制限超過 数(最大7つのエラー)

- プログラマブル WDO 遅延

- ウォッチドッグ ディスエーブル ピン (WDE)

- 小さなパッケージ サイズと最小限の部品コスト

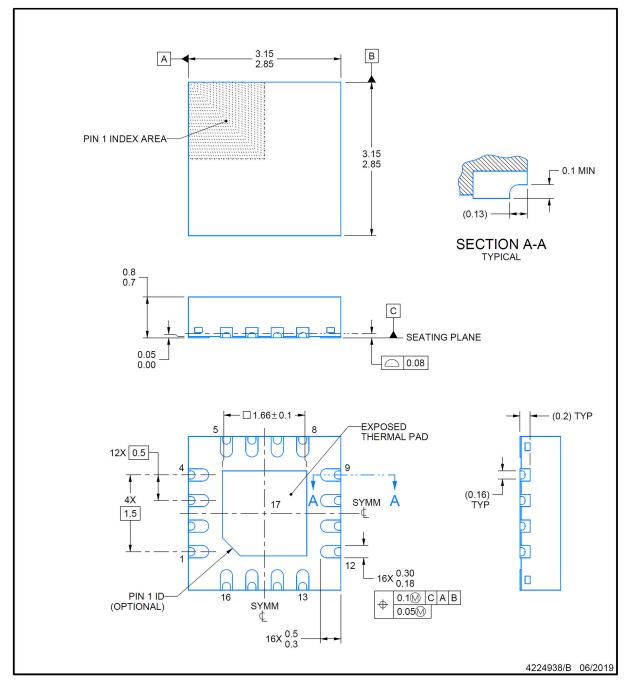

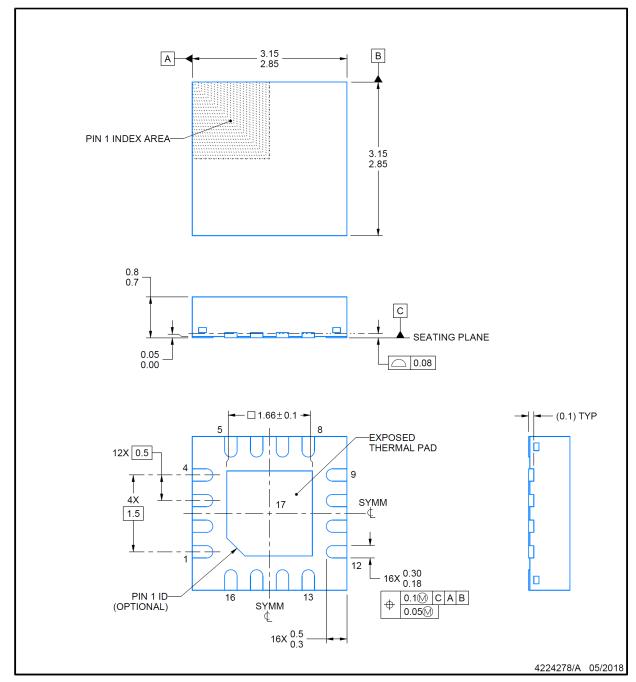

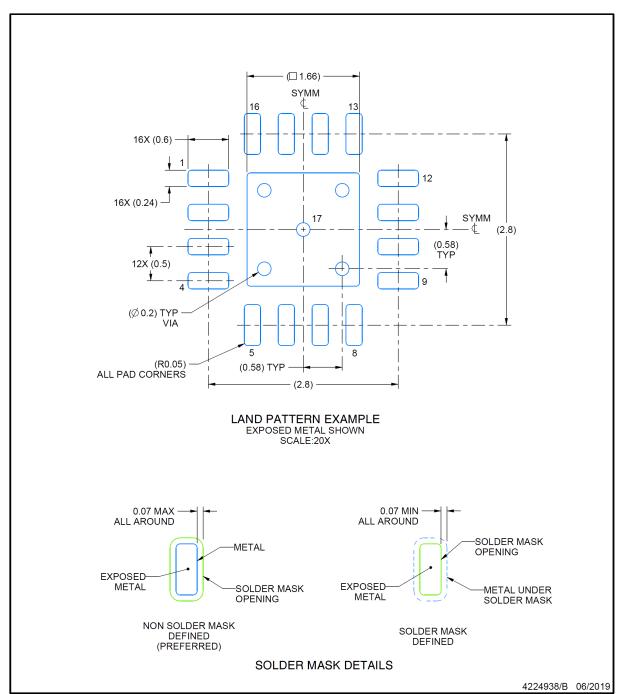

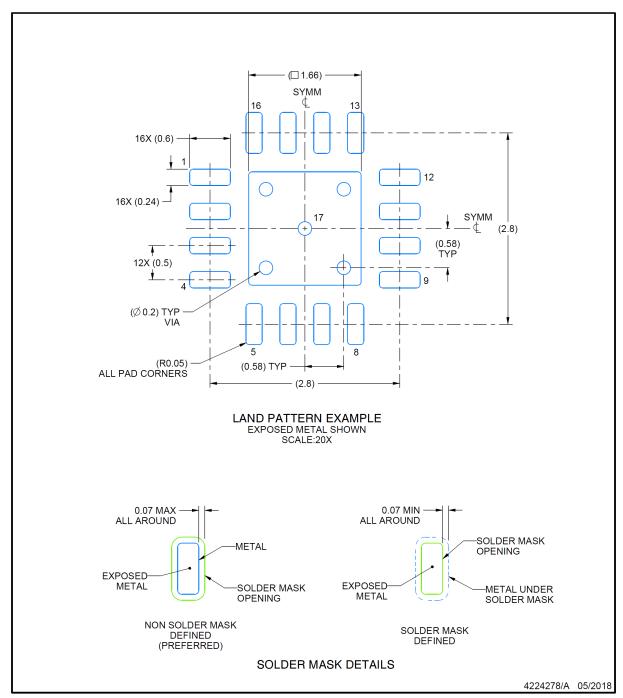

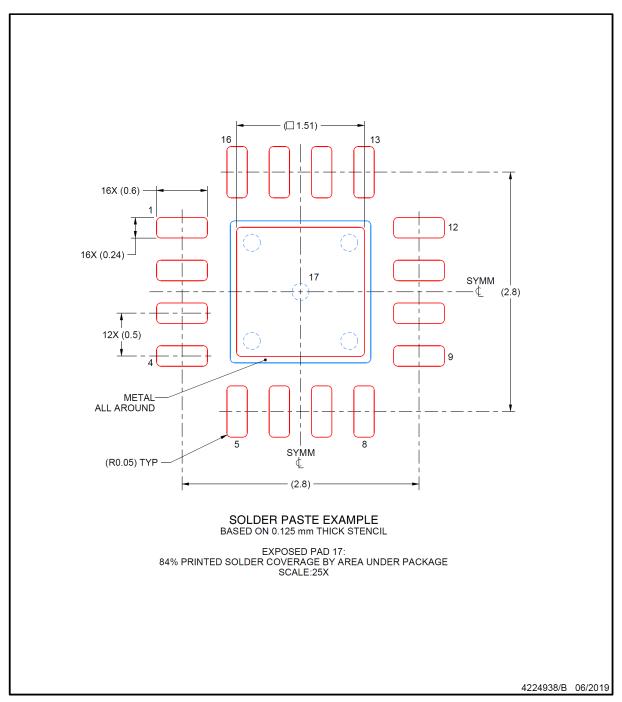

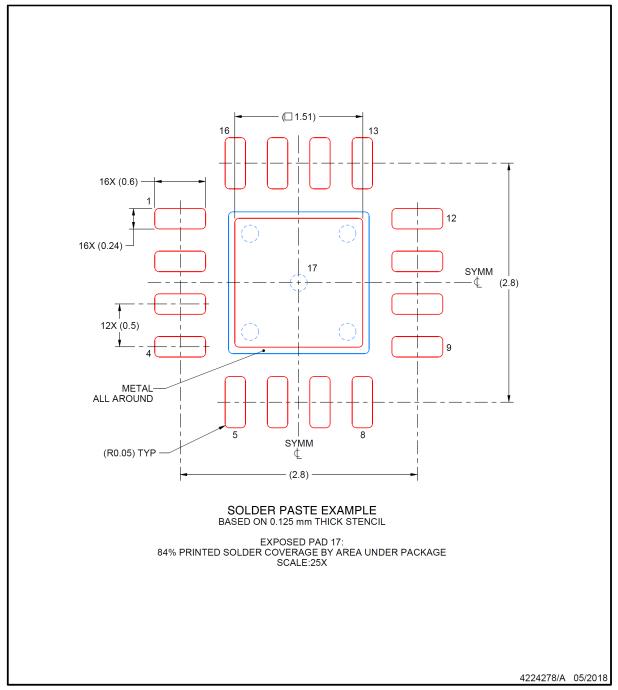

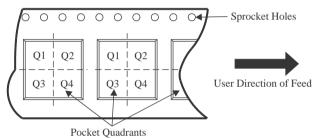

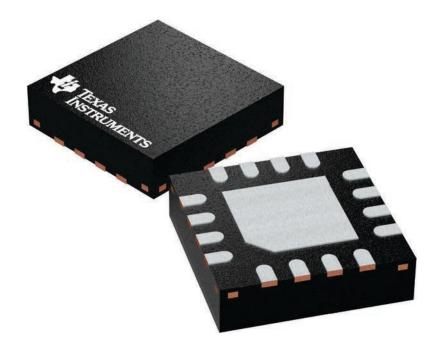

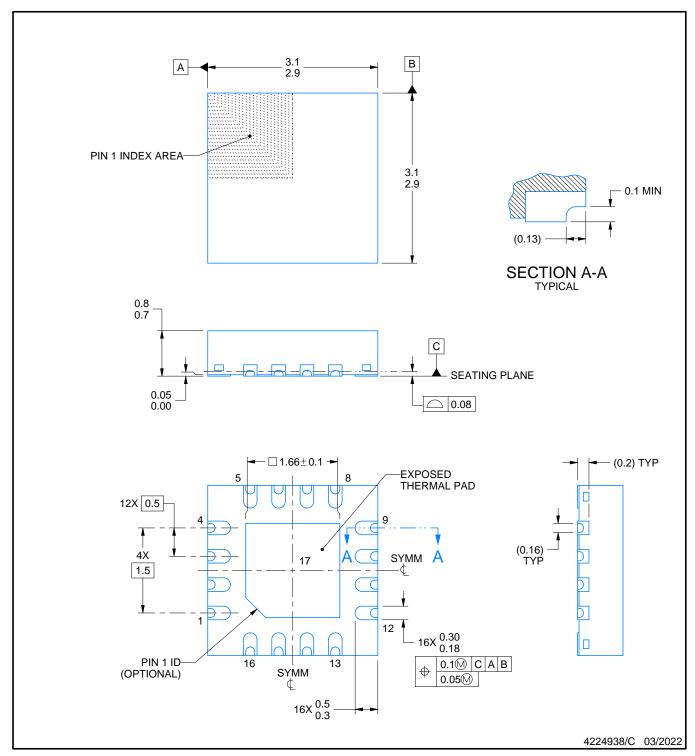

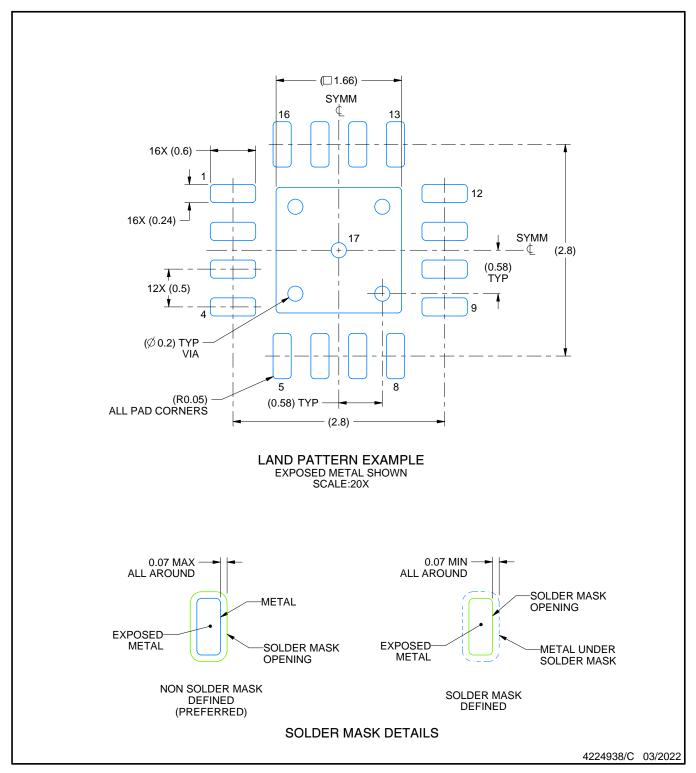

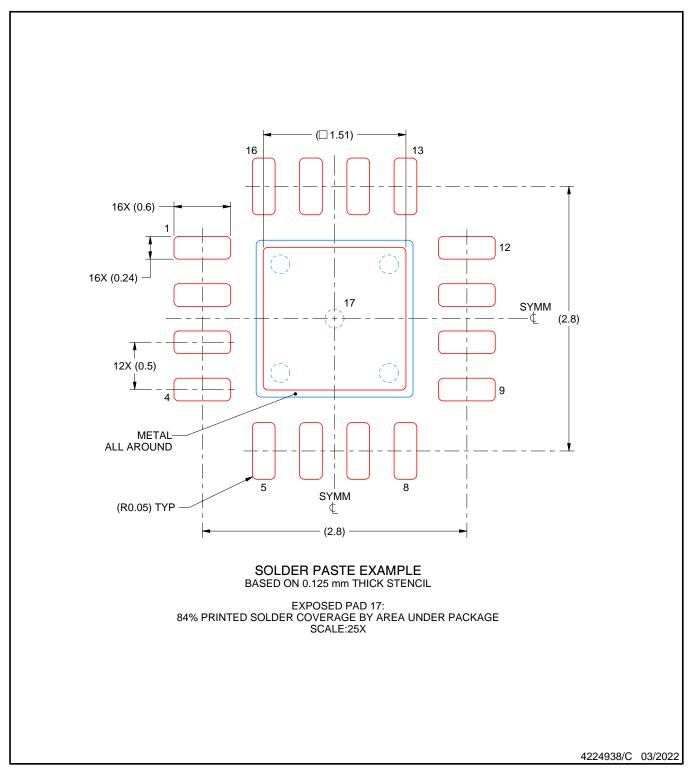

- 3mm × 3mm の QFN パッケージ

- 調整可能な電圧スレッショルドレベル (I<sup>2</sup>C 利用)

- 調整可能なグリッチ耐性とヒステリシス レベル (I<sup>2</sup>C

- 安全アプリケーション向けに設計

- CRC エラー チェック (静的および動的)

- アクティブ Low、オープンドレインの NIRQ、 NRST、WDO 出力

## 2 アプリケーション

- 先進運転支援システム (ADAS)

- センサ フュージョン

### 3 概要

TPS388C0x-Q1 デバイスは、リモート センス ピン オプシ ョンと一体型ウィンドウ ウォッチドッグを備えた一体型マル チチャネル ウィンドウ モニター リセット IC で、16 ピンの 3mm x 3mm QFN パッケージで提供されています。

この高精度のマルチチャネル電圧スーパーバイザは、低 電圧電源レールで動作する、電源誤差の余地が小さいシ ステムに理想的です。内部的なグリッチ耐性およびノイズ フィルタにより、信号エラーによる誤ったリセットも回避され ます。この TPS388C0x-Q1 デバイスは、外付け抵抗なし で過電圧および低電圧リセットのスレッショルドを設定でき るため、総合的な精度、コスト、サイズをさらに最適化で き、安全性システムの信頼性も向上します。I<sup>2</sup>C機能によ り、スレッショルド、リセット遅延、グリッチフィルタ、ピン機 能を柔軟に選択できます。このデバイスは、CRC エラー チェック機能を備えています。このデバイスは、独立したウ オッチドッグが有効化されたウィンドウ ウォッチドッグを内 蔵しています。

このデバイスは、静止電流仕様がわずか 1500µA です (標準値)。TPS388C0x-Q1 は車載用アプリケーション向 けに設計されており、AEC-Q100 グレード 1 認定済み、 ASIL-B 定格の機能安全準拠デバイスとして認定済みで す。

### 製品情報

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ (公称) (2) |

|--------------|----------------------|----------------|

| TPS388C0x-Q1 | WQFN (16)            | 3mm × 3 mm     |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ(長さ×幅)は公称値であり、該当する場合、こ れにはピンも含まれます。

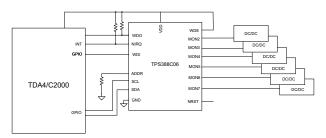

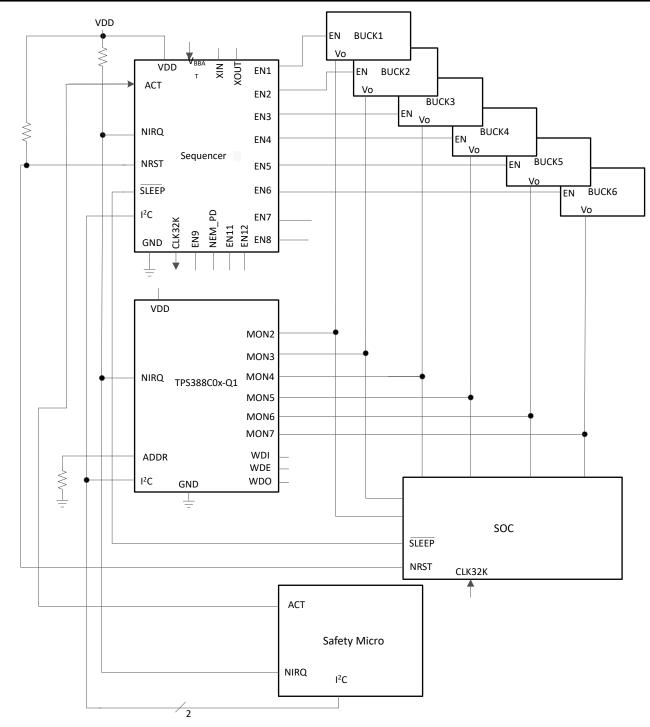

TPS388C0x-Q1 の回路例

## 目次

| 1 特長 1              | 7.4 機能説明               | 21               |

|---------------------|------------------------|------------------|

| 2 アプリケーション1         | 7.5 レジスタマップ            |                  |

| 3 概要1               | 8 アプリケーションと実装          |                  |

| 4 デバイスの比較4          | 8.1 アプリケーション情報         | 63               |

| <b>5</b> ピン構成および機能5 | 8.2 代表的なアプリケーション       | 64               |

| 6 仕様7               | 8.3 電源に関する推奨事項         | <mark>7</mark> 0 |

| 6.1 絶対最大定格7         | 8.4 レイアウト              | 71               |

| 6.2 ESD 定格7         | 9 デバイスおよびドキュメントのサポート   | 72               |

| 6.3 推奨動作条件7         | 9.1 デバイスの命名規則          | 72               |

| 6.4 熱に関する情報8        | 9.2ドキュメントのサポート         | 73               |

| 6.5 電気的特性8          | 9.3ドキュメントの更新通知を受け取る方法  | 73               |

| 6.6 タイミング要件10       | 9.4 サポート・リソース          | 73               |

| 6.7 代表的特性14         | 9.5 商標                 | 73               |

| 7 詳細説明15            | 9.6 静電気放電に関する注意事項      | 73               |

| 7.1 概要15            | 9.7 用語集                | 73               |

| 7.2 機能ブロック図15       | 10 改訂履歴                | 73               |

| 7.3 デバイスの機能モード17    | 11 メカニカル、パッケージ、および注文情報 | 73               |

|                     |                        |                  |

JAJSWD6 - APRIL 2025

## 4 デバイスの比較

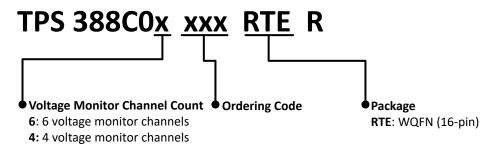

図 4-1 に、デバイスの命名規則が示されています。表 4-1 に、利用可能なデバイス機能と対応する型番の概要が示されています。詳細とその他のオプションの提供状況については、TI の販売代理店にお問い合わせください。または、オンラインで TI の E2E フォーラムにアクセスしてください。最小注文数量が適用されます。

デバイスの注文コードの詳細については、セクション 9.1 を参照してください。

図 4-1. TPS388C0x-Q1 デバイスの命名規則

表 4-1. マルチチャネル スーパーバイザの概要表

| 仕様                 | TPS38900x-Q1 | TPS389R0x-Q1 | TPS38800x-Q1 | TPS388R0x-Q1 | TPS389C0x-Q1 | TPS388C0x-Q1 |

|--------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| ハードウェア ASIL 定格     | D            | D            | В            | В            | D            | В            |

| チャネル数の監視           | 4~8          | 4~7          | 4~8          | 4~7          | 3~6          | 3~6          |

| 監視範囲               | 0.2~5.5V     | 0.2~5.5V     | 0.2~5.5V     | 0.2~5.5V     | 0.2~5.5V     | 0.2~5.5V     |

| コンパレータ監視 (HF フォルト) | ✓            | ✓            | ✓            | ✓            | ✓            | ✓            |

| ADC 監視 (LF フォルト)   | ✓            | ✓            | х            | х            | ✓            | х            |

| ウォッチドッグ            | х            | х            | x            | х            | Q&A          | ウィンドウ        |

| 電圧テレメトリ            | ✓            | ✓            | x            | х            | ✓            | х            |

| グリッチ フィルタリングの監視    | ✓            | ✓            | ✓            | ✓            | ✓            | ✓            |

| シーケンスログ            | ✓            | ✓            | ✓            | ✓            | x            | ✓            |

| NIRQ ピン            | ✓            | ✓            | ✓            | ✓            | ✓            | ✓            |

| NRST ピン            | Х            | ✓            | x            | ✓            | ✓            | ✓            |

| SYNC ピン            | ✓            | х            | х            | х            | х            | х            |

| WDO ピン             | х            | х            | x            | х            | ✓            | ✓            |

| WDIピン              | х            | x            | х            | x            | х            | ✓            |

| ESM ピン             | х            | х            | х            | х            | ✓            | х            |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

Product Folder Links: TPS388C0-Q1

## 5 ピン構成および機能

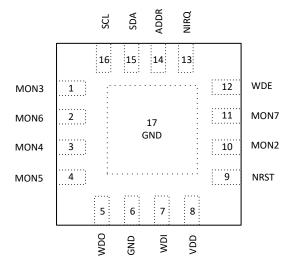

図 5-1. RTE パッケージ 16 ピン WQFN TPS388C06-Q1 上面図

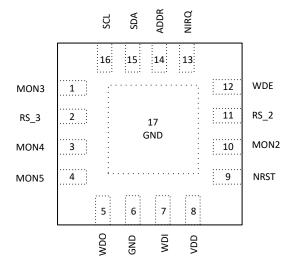

図 5-2. RTE パッケージ 16- ピン WQFN TPS388C04-Q1 上面図

## 表 5-1. ピンの機能

|       | ピン           |              |     | > VIXHE                                            |

|-------|--------------|--------------|-----|----------------------------------------------------|

| 3E 17 | TPS388C06-Q1 | TPS388C04-Q1 | I/O | 概要                                                 |

| 番号    | 名称           | 名称           |     |                                                    |

| 1     | MON3         | MON3         | I   | 電圧モニタ チャネル 3                                       |

| 2     | MON6         | RS_3         | ı   | MON6: 電圧モニタ チャネル 6<br>RS_3: 電圧モニタ チャネル 3 のリモート センス |

| 3     | MON4         | MON4         | I   | 電圧モニタ チャネル 4                                       |

| 4     | MON5         | MON5         | I   | 電圧モニタ チャネル 5                                       |

| 5     | WDO          | WDO          | 0   | オープン ドレイン ウォッチドッグ エラー出力                            |

| 6     | GND          | GND          | -   | 電源グランド                                             |

| 7     | WDI          | WDI          | I   | ウォッチドッグ入力                                          |

| 8     | VDD          | VDD          | -   | 電源レール                                              |

| 9     | NRST         | NRST         | I/O | オープンドレインリセットピン                                     |

| 10    | MON2         | MON2         | I   | 電圧モニタ チャネル 2                                       |

| 11    | MON7         | RS_2         | ı   | MON7: 電圧モニタ チャネル 7<br>RS_2: 電圧モニタ チャネル 2 のリモート センス |

| 12    | WDE          | WDE          | I   | ウォッチドッグ有効                                          |

| 13    | NIRQ         | NIRQ         | 0   | アクティブ Low オープンドレイン割り込み出力                           |

| 14    | ADDR         | ADDR         | I I | I <sup>2</sup> C アドレス選択ピン                          |

| 15    | SDA          | SDA          | I/O | I <sup>2</sup> C データピン                             |

| 16    | SCL          | SCL          | I   | I <sup>2</sup> C クロック ピン                           |

| 17    | GND          | GND          | -   | 露出した電源グランド パッド                                     |

## 6 仕様

## 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)(1)

|                                    |                              | 最小値          | 最大值 | 単位 |

|------------------------------------|------------------------------|--------------|-----|----|

| 電圧                                 | VDD                          | -0.3         | 6   | V  |

| 電圧                                 | NIRQ, NRST, WDO, WDI, WDE    | -0.3         | 6   | V  |

| 電圧                                 | SCL, SDA                     | -0.3         | 6   | V  |

| 電圧                                 | ADDR                         | -0.3         | 2   | V  |

| 電圧                                 | MONx                         | -0.3         | 6   | V  |

| 電圧                                 | RS_x                         | -0.2         | 0.2 | V  |

| 電流                                 | NIRQ, NRST, WDO              |              | ±10 | mA |

|                                    | 連続総許容損失                      | 「熱に関する情報」を参照 |     |    |

| 》<br>》<br>》<br>第一 <del>年</del> (2) | 動作時の接合部温度、TJ                 | -40          | 150 | °C |

| 温度 <sup>(2)</sup>                  | 自由気流での動作温度 (T <sub>A</sub> ) | -40          | 125 | °C |

|                                    | 保管温度、T <sub>stg</sub>        | -65          | 150 | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみに関するものであり、絶対最大定格において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

## 6.2 ESD 定格

|                    |      |                                                      |        | 値     | 単位 |

|--------------------|------|------------------------------------------------------|--------|-------|----|

|                    |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> |        | ±2000 |    |

| V <sub>(ESD)</sub> | 静電放電 | デバイス帯電モデル (CDM)、AEC                                  | すべてのピン | ±500  | V  |

|                    |      | Q100-011 準拠                                          | 角のピン   | ±750  |    |

<sup>(1)</sup> AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています

## 6.3 推奨動作条件

|                                                          |                      | 最小値  | 公称值 最大值 | 単位 |

|----------------------------------------------------------|----------------------|------|---------|----|

| VDD                                                      | 電源ピンの電圧              | 2.6  | 5.5     | V  |

| NIRQ, NRST, WDI,<br>WDO, WDE                             | ピン電圧                 | 0    | 5.5     | V  |

| I <sub>NIRQ</sub> , I <sub>NRST</sub> , I <sub>WDO</sub> | ピン電流                 | 0    | ±5      | mA |

| ADDR                                                     | アドレスピン電圧             | 0    | 1.8     | V  |

| MONx                                                     | モニタピン                | 0    | 5.5     | V  |

| SCL, SDA                                                 | ピン電圧                 | 0    | 5.5     | V  |

| RS_x                                                     | リモート センス ピン          | -0.1 | 0.1     | V  |

| R <sub>UP</sub> (1)                                      | プルアップ抵抗 (オープンドレイン構成) | 1    | 100     | kΩ |

| T <sub>J</sub>                                           | 接合部温度 (自由気流の温度)      | -40  | 125     | °C |

<sup>(2)</sup> このデバイスの消費電力は低いため、 $T_J = T_A$ と想定されます。

## 6.4 熱に関する情報

|                             |                     | TPS388C0-Q1 |      |

|-----------------------------|---------------------|-------------|------|

| <b>熱評価基準</b> <sup>(1)</sup> |                     | RTE (WQFN)  | 単位   |

|                             |                     | ピン          |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 53.4        | °C/W |

| $R_{\theta JC(top)}$        | 接合部からケース (上面) への熱抵抗 | 51.4        | °C/W |

| R <sub>0JB</sub>            | 接合部から基板への熱抵抗        | 17.2        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.3         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 20.7        | °C/W |

| R <sub>0JC(bot)</sub>       | 接合部からケース(底面)への熱抵抗   | 3.9         | °C/W |

<sup>(1)</sup> 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le V_{MONX} \le 5.5V$ 、NIRQ、NRST、WDO Rpullup =  $10k\Omega \sim V_{DD}$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲  $-40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。代表値は  $_{J} = 25^{\circ}C$ 、代表条件は VDD= 3.3V。

|                        | パラメータ                                              | テスト条件                                                                 | 最小値  | 標準値  | 最大値   | 単位   |

|------------------------|----------------------------------------------------|-----------------------------------------------------------------------|------|------|-------|------|

| 共通パラメータ                | •                                                  |                                                                       |      |      |       |      |

| VDD                    | 入力電源電圧                                             |                                                                       | 2.6  |      | 5.5   | V    |

| VDD                    | 立ち上がりスレッショルド                                       |                                                                       | 2.67 |      | 2.81  | V    |

| VDD <sub>UVLO</sub>    | 立ち下がりスレッショルド                                       |                                                                       | 2.48 |      | 2.6   | V    |

| V <sub>POR</sub>       | パワー オン リセット電圧 <sup>(2)</sup>                       |                                                                       |      |      | 1.65  | V    |

| I <sub>DD_Active</sub> | VDD ピンへの電源電流 (MON = HF アクティブ)                      | VDD≤5.5V                                                              |      | 1.55 | 2     | mA   |

| V <sub>MONX</sub>      | MON 電圧範囲                                           |                                                                       | 0.2  |      | 5.5   | V    |

| I <sub>MONX</sub>      | 入力電流 MONx ピン                                       | V <sub>MON</sub> =5V                                                  |      |      | 20    | μA   |

| VMON LIE               | スケーリングなし                                           |                                                                       | 0.2  |      | 1.475 | V    |

| VMON_HF                | 4X スケーリング                                          |                                                                       | 0.8  |      | 5.5   | V    |

| スレッショルド                | スケーリングなし                                           |                                                                       |      | 5    |       | mV   |

| の粒度                    | 4X スケーリング                                          |                                                                       | ,    | 20   |       | mV   |

|                        | VACON                                              | 0.2V≤V <sub>MONX</sub> ≤1.0V                                          | -6   |      | 6     | mV   |

| water code             |                                                    | 1.0V≤V <sub>MONX</sub> ≤1.475V                                        | -7.5 |      | 7.5   | mV   |

| 精度                     | VMON                                               | 1.475V≤V <sub>MONX</sub> ≤2.95V                                       | -0.6 |      | 0.6   | %    |

|                        |                                                    | VMONX>2.95V                                                           | -0.5 |      | 0.5   | %    |

|                        |                                                    | 0.2V <v<sub>MONX≤1.475V</v<sub>                                       |      | 5    | 11    | mV   |

| $V_{HYS}$              | UV、OV ピンのヒステリシス (ヒステリシスはトライポイント (UV)、(OV) に対して)(1) | 1.475V≤V <sub>MONX</sub> ≤2.95V                                       |      | 9    | 16    | IIIV |

|                        |                                                    | VMONX>2.95V                                                           |      | 17   | 28    | mV   |

| MON_OFF                | OFF 電圧スレッショルド                                      | 監視対象の V <sub>MON</sub> 立ち下がりエッジ                                       | 140  |      | 215   | mV   |

| I <sub>LKG</sub>       | 出力リーク電流 -NIRQ、NRST                                 | VDD=V <sub>NIRQ</sub> =V <sub>NRST</sub> =5.5V                        |      |      | 300   | nA   |

| V <sub>OL</sub>        | Low レベル出力電圧-NIRQ                                   | NIRQ 外部 10K の 3.3V へのプルアップ                                            |      |      | 100   | mV   |

| I <sub>lkg(OD)</sub>   | オープンドレイン出力リーク電流-NIRQ                               | NIRQ ピンがハイインピーダンス、<br>V <sub>NIRQ</sub> = 5.5V、V <sub>IT+</sub> < VDD |      |      | 90    | nA   |

| NIRQ                   | 内部プルダウン                                            | オープンドレイン                                                              |      | 100  |       | Ω    |

| V <sub>OL</sub>        | Low レベル出力電圧-NRST                                   | NRST 外部 10K の 3.3V へのプルアップ                                            |      |      | 100   | mV   |

## 6.5 電気的特性 (続き)

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le V_{MONX} \le 5.5V$ 、NIRQ、NRST、WDO Rpullup =  $10k\Omega \sim V_{DD}$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲  $-40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。代表値は  $_{\rm J} = 25^{\circ}C$ 、代表条件は VDD= 3.3V。

|                       | パラメータ                | テスト条件                                                                | 最小値          | 標準値  | 最大値          | 単位 |

|-----------------------|----------------------|----------------------------------------------------------------------|--------------|------|--------------|----|

| I <sub>lkg(OD)</sub>  | オープンドレイン出力リーク電流-NRST | NRST ピンがハイインピーダンス、<br>V <sub>NRST</sub> = 5.5、V <sub>IT+</sub> < VDD |              |      | 90           | nA |

| V <sub>OL</sub>       | Low レベル出力電圧-WDO      | WDO 外部 10K の 3.3V へのプルアップ                                            |              |      | 100          | mV |

| I <sub>lkg(OD)</sub>  | オープンドレイン出力リーク電流-WDO  | WDO ピンがハイ インピーダンス、 $V_{WDO}$ = 5.5、 $V_{IT+}$ < VDD                  |              |      | 500          | nA |

| WDO                   | Low にアサートするとオン抵抗     | オープンドレイン                                                             |              | 12   | 17           | Ω  |

| NRST                  | 内部プルダウン              | オープンドレイン                                                             |              | 100  |              | Ω  |

| WDI_L                 | ロジック Low 入力          |                                                                      |              |      | 0.24xVD<br>D | V  |

| WDI_H                 | ロジック High 入力         | VDD>4.5V                                                             | 0.55xVD<br>D |      |              | V  |

| WDI_H                 | ロジック High 入力         | VDD<4.5V                                                             | 0.60xVD<br>D |      |              | V  |

| WDE_L                 | ロジック Low 入力          |                                                                      |              |      | 0.36         | V  |

| WDE_H                 | ロジック High 入力         |                                                                      | 1.26         |      |              | V  |

| I <sub>ADDR</sub>     | ADDR ピン電流            |                                                                      |              | 20   |              | μΑ |

|                       |                      | R=5.36k                                                              |              | 0x30 |              |    |

|                       |                      | R=16.2k                                                              |              | 0x31 |              |    |

|                       |                      | R=26.7k                                                              |              | 0x32 |              |    |

| I <sup>2</sup> C ADDR | (16 進形式)             | R=37.4k                                                              |              | 0x33 |              |    |

| . 07.551              |                      | R=47.5k                                                              |              | 0x34 |              |    |

|                       |                      | R=59.0k                                                              |              | 0x35 |              |    |

|                       |                      | R=69.8k                                                              |              | 0x36 |              |    |

|                       |                      | R=80.6k                                                              |              | 0x37 |              |    |

| TSD                   | サーマル シャットダウン         |                                                                      |              | 155  |              | °C |

| TSD Hys               | サーマル シャットダウン ヒステリシス  |                                                                      |              | 25   |              | °C |

| I <sup>2</sup> C 電気的仕 | 様                    |                                                                      |              |      |              |    |

| C <sub>B</sub>        | SDA および SCL の容量性負荷   |                                                                      |              |      | 400          | pF |

| SDA, SCL              | Low スレッショルド          | 1.2V の I <sup>2</sup> C ロジック                                         |              |      | 0.36         | V  |

| SDA, SCL              | High スレッショルド         | <b>1.2V</b> の I <sup>2</sup> C ロジック                                  | 0.84         |      |              | V  |

| SDA, SCL              | Low スレッショルド          | 1.8V の I <sup>2</sup> C ロジック                                         |              |      | 0.54         | V  |

| SDA, SCL              | High スレッショルド         | 1.8V の I <sup>2</sup> C ロジック                                         | 1.26         |      |              | V  |

| SDA, SCL              | Low スレッショルド          | 3.3V の I <sup>2</sup> C ロジック                                         |              |      | 0.99         | V  |

| SDA, SCL              | High スレッショルド         | 3.3V の I <sup>2</sup> C ロジック                                         | 2.31         |      |              | V  |

| SDA                   | V <sub>OL</sub>      | I <sub>OL</sub> =5mA                                                 |              |      | 0.4          | V  |

<sup>(1)</sup> ヒステリシスは、トリポイント ( $V_{\text{IT-(UV)}}$ 、 $V_{\text{IT+(OV)}}$ ) と関連しています。

<sup>(2)</sup>  $V_{POR}$  は、制御された出力状態の最小  $V_{DDX}$  電圧レベルです。

## 6.6 タイミング要件

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le VMON \le 5.5V$ 、NIRQ、NRST、WDO 電圧 =  $10k\Omega \sim VDD$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲 –  $40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。 代表値は  $T_J = 25^{\circ}C$ 、代表条件は VDD = 3.3V。

|                      |                                                     |                                      | 最小値 | 公称值 | 最大値 | 単位   |

|----------------------|-----------------------------------------------------|--------------------------------------|-----|-----|-----|------|

| 共通パラメー               | P                                                   |                                      |     |     | '   |      |

| t <sub>BIST</sub>    | BIST 付きで POR を準備完了、TEST_CFG.AT_POR=1                | OTP 負荷を含む                            |     |     | 12  | ms   |

| NBIST                | BIST なしで POR を準備完了、TEST_CFG.AT_POR=0                | OTP 負荷を含む                            |     |     | 2   | ms   |

| BIST                 | BIST 時間、TEST_CFG.AT_POR=1 または<br>TEST_CFG.AT_SHDN=1 |                                      |     |     | 10  | ms   |

| t <sub>I2C_ACT</sub> | BIST 完了から I <sup>2</sup> C がアクティブ                   |                                      |     |     | 0   | μs   |

| NRST                 | フォルト検出から NRST のアサートまでのレイテンシ                         |                                      |     |     | 25  | μs   |

| WDO                  | フォルト検出から WDO のアサートまでのレイテンシ                          |                                      |     |     | 25  | μs   |

| NIRQ                 | フォルト検出から NIRQ アサートまでのレイテンシ (OV / UV フォルトを除く)        |                                      |     |     | 25  | μs   |

| PD_NIRQ_1X           | HF フォルト伝搬検出遅延 (デフォルトのグリッチ除去フィルタ) には、デジタル遅延が含まれます    | VIT_OV / UV +/-<br>100mV             |     |     | 650 | ns   |

| PD_NIRQ_4X           | HF フォルト伝搬検出遅延 (デフォルトのグリッチ除去フィルタ) には、デジタル遅延が含まれます    | VIT_OV / UV +/-<br>400mV             |     |     | 750 | ns   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 000  |     | 200 |     | μs   |

|                      | RESET 時間遅延                                          | I <sup>2</sup> C レジスタ時間遅<br>延 = 001  |     | 1   |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 010  |     | 10  |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 011  |     | 16  |     | ms   |

| D                    |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 100  |     | 20  |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ 時間遅<br>延 = 101 |     | 70  |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 110  |     | 100 |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 111  |     | 200 |     | ms   |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 000  |     | 1   |     |      |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 001  |     | 2   |     |      |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 010  |     | 5   |     |      |

| D WE                 | WDT 遅延                                              | I <sup>2</sup> C レジスタ時間遅<br>延 = 011  |     | 10  |     | ms   |

| <sup>†</sup> о_wо    | ········ · · · · · · · · · · · · · · ·              | I <sup>2</sup> C レジスタ時間遅<br>延 = 100  |     | 20  |     | 1110 |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 101  |     | 50  |     |      |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 110  |     | 100 |     |      |

|                      |                                                     | I <sup>2</sup> C レジスタ時間遅<br>延 = 111  |     | 200 |     |      |

Copyright © 2025 Texas Instruments Incorporated

## 6.6 タイミング要件 (続き)

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le VMON \le 5.5V$ 、NIRQ、NRST、WDO 電圧 =  $10k\Omega \sim VDD$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲 –  $40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。 代表値は  $T_J = 25^{\circ}C$ 、代表条件は VDD = 3.3V。

|                   |                                         |           | 最小值 | 公称值 | 最大値   | 単位 |

|-------------------|-----------------------------------------|-----------|-----|-----|-------|----|

| t <sub>GI_R</sub> | I <sup>2</sup> C を介した UV および OV デバウンス範囲 | FLT_HF(N) | 0.1 |     | 102.4 | μs |

## 6.6 タイミング要件 (続き)

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le VMON \le 5.5V$ 、NIRQ、NRST、WDO 電圧 =  $10k\Omega \sim VDD$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲 –  $40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。代表値は  $T_J = 25^{\circ}C$ 、代表条件は VDD = 3.3V。

|                      |                              |            | 最小値  | 公称值 | 最大値  | 単位  |

|----------------------|------------------------------|------------|------|-----|------|-----|

| I <sup>2</sup> C のタイ | ミング特性                        |            |      |     |      |     |

| f <sub>SCL</sub>     | シリアル クロック周波数                 | スタンダード モード |      |     | 100  | kHz |

| f <sub>SCL</sub>     | シリアル クロック周波数                 | ファスト モード   |      |     | 400  | kHz |

| f <sub>SCL</sub>     | シリアル クロック周波数                 | ファスト モード+  |      |     | 1    | MHz |

| t <sub>LOW</sub>     | SCL Low 時間                   | スタンダード モード | 4.7  |     |      | μs  |

| t <sub>LOW</sub>     | SCL Low 時間                   | ファスト モード   | 1.3  |     |      | μs  |

| t <sub>LOW</sub>     | SCL Low 時間                   | ファスト モード+  | 0.5  |     |      | μs  |

| t <sub>HIGH</sub>    | SCL High 時間                  | スタンダード モード | 4    |     |      | μs  |

| t <sub>HIGH</sub>    | SCL High 時間                  | ファスト モード+  | 0.26 |     |      | μs  |

| t <sub>SU;DAT</sub>  | データ セットアップ時間                 | スタンダード モード | 250  |     |      | ns  |

| t <sub>SU;DAT</sub>  | データ セットアップ時間                 | ファスト モード   | 100  |     |      | ns  |

| t <sub>SU;DAT</sub>  | データ セットアップ時間                 | ファスト モード+  | 50   |     |      | ns  |

| t <sub>HD;DAT</sub>  | データホールド時間                    | スタンダード モード | 10   |     | 3450 | ns  |

| t <sub>HD;DAT</sub>  | データホールド時間                    | ファスト モード   | 10   |     | 900  | ns  |

| t <sub>HD;DAT</sub>  | データホールド時間                    | ファスト モード+  | 10   |     |      | ns  |

| t <sub>SU;STA</sub>  | 開始または反復開始条件のセットアップ時間         | スタンダード モード | 4.7  |     |      | μs  |

| t <sub>SU;STA</sub>  | 開始または反復開始条件のセットアップ時間         | ファスト モード   | 0.6  |     |      | μs  |

| t <sub>SU;STA</sub>  | 開始または反復開始条件のセットアップ時間         | ファスト モード+  | 0.26 |     |      | μs  |

| t <sub>HD:STA</sub>  | 開始または反復開始条件のホールド時間           | スタンダード モード | 4    |     |      | μs  |

| t <sub>HD:STA</sub>  | 開始または反復開始条件のホールド時間           | ファスト モード   | 0.6  |     |      | μs  |

| t <sub>HD:STA</sub>  | 開始または反復開始条件のホールド時間           | ファスト モード+  | 0.26 |     |      | μs  |

| t <sub>BUF</sub>     | STOP 条件と START 条件の間のバス フリー時間 | スタンダード モード | 4.7  |     |      | μs  |

| t <sub>BUF</sub>     | STOP 条件と START 条件の間のバス フリー時間 | ファスト モード   | 1.3  |     |      | μs  |

| t <sub>BUF</sub>     | STOP 条件と START 条件の間のバス フリー時間 | ファスト モード+  | 0.5  | -   |      | μs  |

| t <sub>SU;STO</sub>  | 停止条件のセットアップ時間                | スタンダード モード | 4    |     |      | μs  |

| t <sub>SU;STO</sub>  | 停止条件のセットアップ時間                | ファスト モード   | 0.6  |     |      | μs  |

| t <sub>SU;STO</sub>  | 停止条件のセットアップ時間                | ファスト モード+  | 0.26 |     |      | μs  |

| t <sub>rDA</sub>     | SDA 信号の立ち上がり時間               | スタンダード モード |      |     | 1000 |     |

| t <sub>rDA</sub>     | SDA 信号の立ち上がり時間               | ファスト モード   | 20   |     | 300  | ns  |

| t <sub>rDA</sub>     | SDA 信号の立ち上がり時間               | ファスト モード+  |      | -   | 120  | ns  |

| t <sub>fDA</sub>     | SDA 信号の立ち下がり時間               | スタンダード モード |      |     | 300  | ns  |

| t <sub>fDA</sub>     | SDA 信号の立ち下がり時間               | ファスト モード   | 1.4  |     | 300  | ns  |

| t <sub>fDA</sub>     | SDA 信号の立ち下がり時間               | ファスト モード+  | 6.5  |     | 120  | ns  |

| t <sub>rCL</sub>     | SCL 信号の立ち上がり時間               | スタンダード モード |      |     | 1000 | ns  |

| t <sub>rCL</sub>     | SCL 信号の立ち上がり時間               | ファスト モード   | 20   |     | 300  | ns  |

| t <sub>rCL</sub>     | SCL 信号の立ち上がり時間               | ファスト モード+  |      |     | 120  | ns  |

| t <sub>fCL</sub>     | SCL 信号の立ち下がり時間               | スタンダード モード |      |     | 300  | ns  |

| t <sub>fCL</sub>     | SCL 信号の立ち下がり時間               | ファスト モード   | 6.5  |     | 300  | ns  |

| t <sub>fCL</sub>     | SCL 信号の立ち下がり時間               | ファスト モード+  | 6.5  |     | 120  | ns  |

## 6.6 タイミング要件 (続き)

At  $2.6V \le VDD \le 5.5V$ 、 $0.2V \le VMON \le 5.5V$ 、NIRQ、NRST、WDO 電圧 =  $10k\Omega \sim VDD$ 、NIRQ、NRST、WDO 負荷 = 10pF、および自由気流での動作温度範囲 –  $40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)。代表値は  $T_J = 25^{\circ}C$ 、代表条件は VDD = 3.3V。

|                 |                               |                                 | 最小値 | 公称值 | 最大値 | 単位 |

|-----------------|-------------------------------|---------------------------------|-----|-----|-----|----|

| t <sub>SP</sub> | 抑制されている SCL および SDA スパイクのパルス幅 | 標準モード、ファスト<br>モード、ファスト モー<br>ド+ |     |     | 50  | ns |

13

Product Folder Links: TPS388C0-Q1

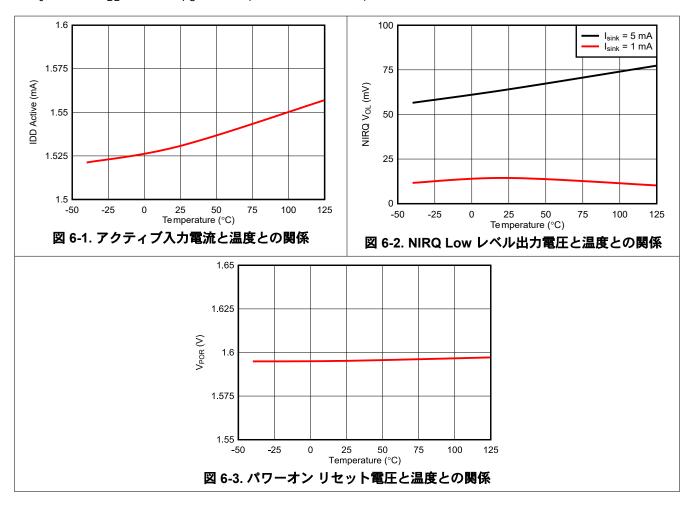

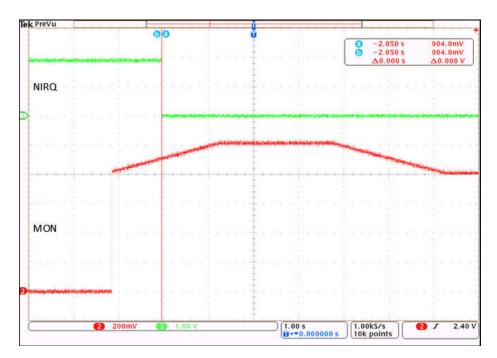

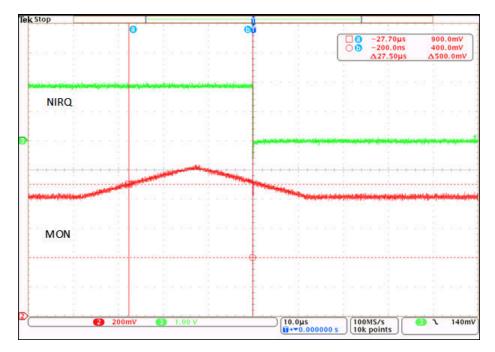

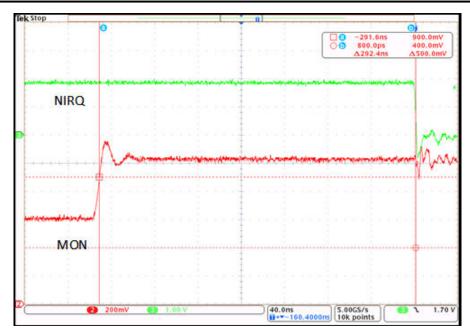

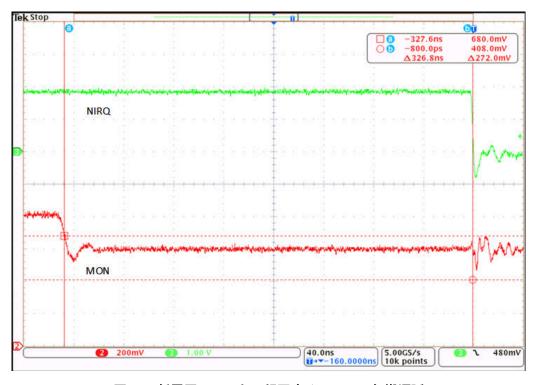

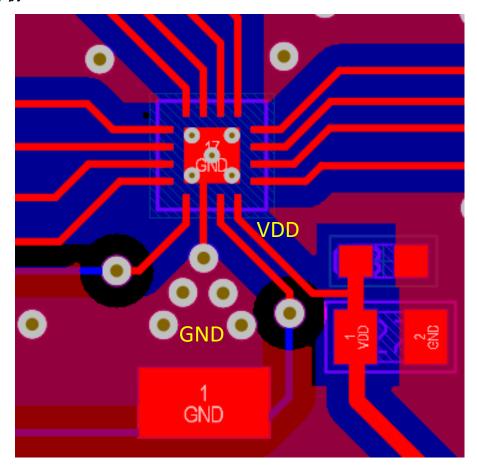

### 6.7 代表的特性

At  $T_J = 25$ °C、 $V_{DD} = 3.3V$ 、 $R_{PU} = 10k\Omega$  (特に記述のない限り)

TEXAS

### 7 詳細説明

#### 7.1 概要

TPS388C0x-Q1 ファミリのデバイスには  $2 \sim 6$  つのチャネルがあり、ウィンドウ構成で過電圧、低電圧、または両方に構成できます。 TPS388C0x-Q1 は、高精度のウィンドウ スレッショルド電圧 (最大  $\pm 6$ mV) および各種の電圧スレッショルドを備えています。 これは、工場出荷時の構成を使用するか、起動時に  $I^2C$  コマンドで構成することができます。

TPS388C0x-Q1 には、デバイス内部で過電圧スレッショルドおよび低電圧スレッショルドを設定するための抵抗が含まれています。これらの内部抵抗によって、部品点数が削減でき、外部抵抗の精度を考慮したマージンを追加する必要がないため、設計を大幅に簡略化できます。

TPS388C0x-Q1 は、監視対象の電圧が安全なウィンドウ外であるときに、アクティブ Low の出力信号 (NIRQ または NRST) をアサートするように設計されています。TPS388C0x-Q1 は、 $I^2$ C を使用して高度に構成でき、割り込み有効、シーケンス タイムアウト、BIST、電圧監視ウィンドウ、ウォッチドッグ ウィンドウ タイミング、グリッチ デバウンス タイミングの 工場出荷時プログラミング オプションも利用可能です。

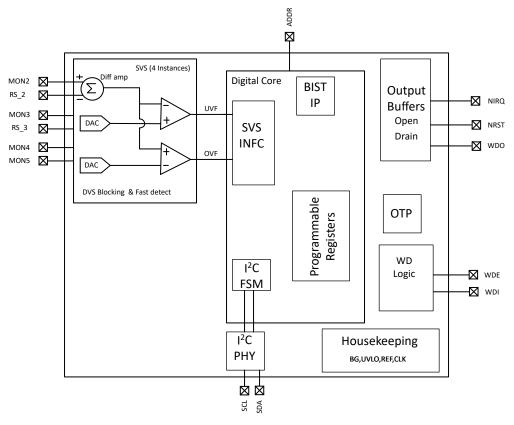

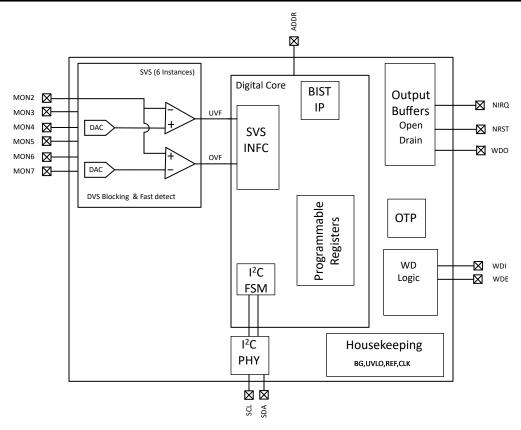

### 7.2 機能ブロック図

図 7-1. TPS388C04-Q1 のブロック図

図 7-2. TPS388C06-Q1 のブロック図

### 7.3 デバイスの機能モード

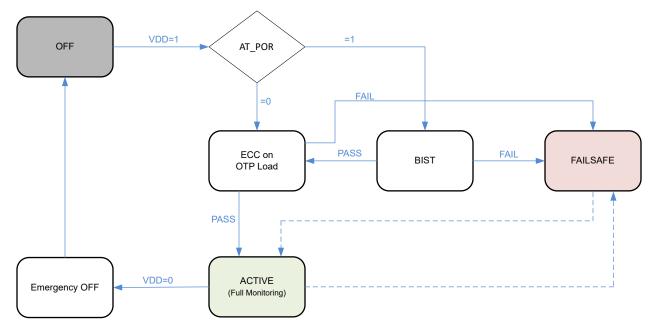

図 7-3. TPS388C0x-Q1 状態遷移図

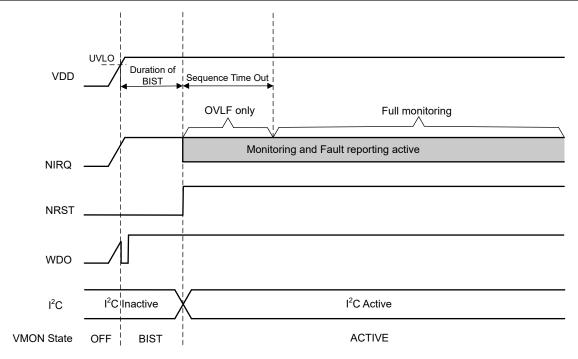

#### 7.3.1 TPS388C0x-Q1 電源オン

TPS388C0x-Q1 が電源オンになると、オプションで BIST が実行されます (TEST\_CFG.AT\_POR レジスタ ビットに応じて)。 BIST が完了すると、直ちに  $I^2$ C およびフォルト通知 (NIRQ 経由) がアクティブになり、OTP から構成がロードされます (ECC によるアシスト、SEC-DED をサポート)。

構成ロード ECC および BIST 結果の詳細が TEST INFO レジスタに通知されます。

UVLO を超えた VIN 立ち上がりエッジを検出すると、TPS388C0x-Q1 はシーケンス タイムアウト タイマおよび電源 ON シーケンスの監視を開始します。

図 7-4. TPS388C0x-Q1 電源 ON 信号処理と内部状態

BIST の完了は、割り込みまたはレジスタのポーリングによって検出できます:

- 割り込み: INT TEST I BIST C フラグがセットされ、IEN TEST C = 1 の場合は NIRQ がアサートされます

- ポーリング: VMON\_STAT レジスタは、ポーリングにより ST\_BIST\_C ビットを読み出すことができます

#### 7.3.2 組み込みセルフ テストと構成の読み込み

内蔵セルフ テスト (BIST) が実行されます:

1. TEST CFG.AT POR=1 の場合、パワーオン リセット (POR) 時

OTP からの構成ロードは、ECC によってアシストされます (SEC-DED をサポート)。これは、データの整合性の問題から保護し、システムの可用性を最大化するためです。

BIST 中、NIRQ はアサート解除され (故障時にアサートされる)、入力ピンは無視され、 $I^2C$  ブロックは非アクティブで、SDA および SCL はアサート解除されます。BIST には、技術安全要件を満たすためのデバイス テストが含まれています。障害なしで BIST が完了すると、 $I^2C$  が直ちにアクティブになり、デバイスは OTP から構成データをロードした後、IDL 状態に入ります。BIST に失敗するか、ECC がダブル エラー検出 (DED) を通知すると、NIRQ がアサートされ、デバイスはフェイルセーフ状態に入り、アクティブな  $I^2C$  に対して最善の取り組みが試みられます。TEST\_INFO レジスタでは、テスト結果の追加情報を提供できます。

BIST の成功 / 失敗時の詳細な動作は、INT\_TEST および IEN\_TEST レジスタによって制御されます。BIST 結果の通知は、以下によって実行されます。

- NIRQ ピン: テスト結果および IEN\_TEST の BIST\_C と BIST ビットに応じて Low になります

- IEN TEST 設定に応じて、INT TEST レジスタの I BIST C ビットと BIST ビット

- VMON STAT.ST BIST C レジスタ ビット

- TEST\_INFO[3:0] レジスタ ビット

#### 7.3.2.1 BIST 実行に関する注意事項

TPS388C0x-Q1 は、POR 時に、TEST\_CFG.AT\_POR レジスタ ビットの値に基づいて、BIST を実行するかどうかを決定する必要があります。BIST が ECC ロジックをチェックした後にこのレジスタの ECC が実行されたと仮定すると、BIST を実行する前にデータの整合性を証明することはできません。

Copyright © 2025 Texas Instruments Incorporated

#### 7.3.3 一般監視

#### 7.3.3.1 ACTIVE 監視

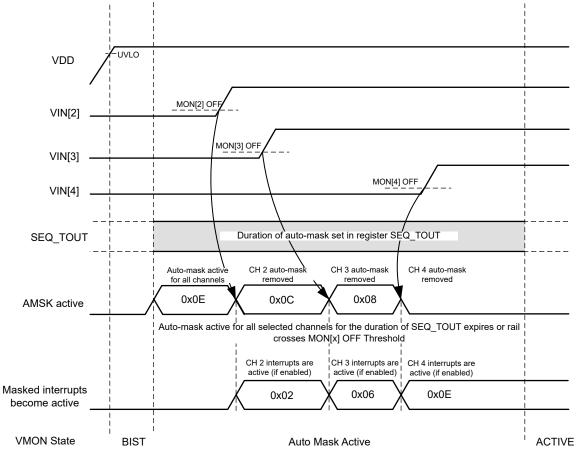

図 7-5 に示されているように、BIST および SEQ\_TOUT (自動マスク\_ タイムアウトが完了すると、TPS388C0x-Q1 は ACTIVE 状態になります。

SEQ\_TOUT 中、自動マスクレジスタ AMSK\_ON で選択されたすべての TPS388C0x-Q1 入力は、低電圧高周波数 (UVHF) および過電圧高周波数 (OVHF) 状態のマスクされた (無効) 割り込みから開始します。各レールが MON の OFF スレッショルドを超えると、自動的に (約 5  $\sim$  10 $\mu$ s 以内に発生すると予想される) 関連する UV および OV 割り込みがマスク解除され、IEN\_UVHF および IEN\_OVHF レジスタに従って、有効化 / 無効化されます。

SEQ\_TOUT が期限切れになると、アクティブ状態に移行されます。 VMON モニタは、低電圧高周波数 (UVHF) および 過電圧高周波数 (OVHF) スレッショルドに対して高周波数チャネル レベルをモニタします。 表 7-1 に、アクティブ状態の詳細が示されています。

表 7-1. ACTIVE モードの動作の概要

| モード   | 条件           | lq    | 監視対象 - Chx が有効の場合に NIRQ をトリガします |

|-------|--------------|-------|---------------------------------|

| アクティブ | 自動マスク タイムアウト | 1.5mA | OVHF, UVHF                      |

図 7-5. アクティブ状態のタイミング図

TPS388C0x-Q1 は、パワーアップ遷移時に複数のアクションを実行します。

1. VDD が UVLO に達し、BIST が完了すると、TPS388C0x-Q1 は自動マスクが以下に従って有効になるシーケンス 監視 1 の状態に入ります。

- a. 自動マスクレジスタ AMSK\_ON で選択されたすべての TPS388C0x-Q1 入力は、低電圧高周波数 (UVHF) および過電圧高周波数 (OVHF) 状態の場合、マスクされた (無効) 割り込みから開始します。

- b. 各レールが MON の OFF スレッショルドを超えると、10µs IEN\_UVHF および IEN\_OVHF レジスタに従って、 関連する UV および OV 割り込みがマスクされず、有効 / 無効になります。

- 2. SEQ\_TOUT タイムアウトの後:

- a. TPS388C0x-Q1 は、ACTIVE 状態で、通常の監視を開始します。

Copyright © 2025 Texas Instruments Incorporated

### 7.4 機能説明

#### 7.4.1 VDD

TPS388C0x-Q1 は、2.6V ~ 5.5V の入力電源電圧範囲で動作するように設計されています。このデバイスには入力電源コンデンサは必要ありませんが、入力電源にノイズが多い場合は、VDD ピンと GND ピンの間に 1μF コンデンサを配置する方法がアナログ手法として適切です。

デバイスが完全に機能するには、スタートアップ遅延 (t<sub>BIST</sub>) の V<sub>DD</sub> が少なくとも VDD<sub>LMIO</sub> 以上である必要があります。

#### 7.4.2 マスカブル割り込み (AMSK)

パワーアップの場合は、AMSK\_ON レジスタが適用されます。MON 電圧が MON の OFF スレッショルドまたはシーケンス タイムアウトのいずれか早い方に達するまで、AMSK\_ON が割り込みをマスクします。パワーダウンの場合は、AMSK\_OFF レジスタが適用されます。MON 電圧が OFF スレッショルドを下回るまで、AMSK\_OFF が割り込みをマスクします。

表 7-2 に、パワーアップ時およびパワーダウン時の自動マスク動作が示されています。

| 玖 / -2:ハラーテラスト Cハラーテラスト N フラバト |              |                     |                                                           |                                        |  |  |

|--------------------------------|--------------|---------------------|-----------------------------------------------------------|----------------------------------------|--|--|

| 遷移                             | 自動マスクが適用されます | 自動マスクが以下に適用さ<br>れます | 自動マスクは非アクティブです                                            | MON チャネルの割り込みア<br>クティブは自動マスクにあり<br>ません |  |  |

| パワーアップ                         | AMSK_ON      | IEN_UVHF、IEN_OVHF   | SEQ_TOUT が期限切れに<br>なるか、レールが MON の<br>OFF スレッショルドを超えま<br>す | パワーアップ時                                |  |  |

| パワーダウン                         | AMSK_OFF     |                     | SEQ_TOUT が期限切れに<br>なるまで、遷移で自動マスク<br>がアクティブになります           | SEQ_TOUT が期限切れる<br>まで                  |  |  |

表 7-2. パワーアップ時とパワーダウン時の自動マスク動作

#### 7.4.3 MON

TPS388C0x-Q1 には、高精度リファレンス電圧を備えた 2 つのコンパレータおよびモニタ (MON) チャネルごとに調整された抵抗デバイダが組み合わさっています。この構成によって、すべての抵抗許容誤差が精度と性能仕様において考慮されているため、デバイスの精度が最適化されます。両方のコンパレータには、ノイズ耐性と安定した動作を実現するヒステリシスも内蔵されています。

各 MON チャネルは、高周波 (HF) フォルト検出に設定できます。HF フォルト検出では、スレッショルド電圧を基準とする UV と OV の測定にコンパレータを使用します。グリッチ耐性のデバウンス フィルタは、各 MON チャネルに対応する BANK1 の FLT\_HF レジスタを使用して、HF フォルトに構成できます。HF フォルトは、BANK1 の UV\_HF および OV\_HF レジスタを使用して構成されます。各 MON チャネルには、独自の UV\_HF および OV\_HF レジスタがあります。

大半の場合必要ではありませんが、ノイズの多いアプリケーションでは、MON 入力に 1nF ~ 10nF のバイパス コンデン サを配置して、監視対象の信号の過渡電圧に対する感度を低減する方法が優れたアナログ設計手法といえます。 具体的なデバウンス時間やグリッチ除去時間は、I<sup>2</sup>C レジスタにより各 MON に対して個別に設定することもできます

VDD 電源電圧を監視する場合、MON ピンを VDD に直接接続できます。MON ピンの電圧がスレッショルドの上限と下限の間にあるときは、出力 NIRQ および NRST はハイインピーダンスになります。

#### 7.4.4 NRST

NRST ピンにはプログラマブル リセット遅延時間があり、 $TI\_CONTROL$  レジスタを使用する場合、 $0.2ms \sim 200ms$  の範囲で調整できます。NRST はオープンドレイン出力で、 $1k\Omega \sim 100k\Omega$  のプルアップ抵抗を介してプルアップする必要があります。デバイスのパワーアップ時に POR が完了すると、BIST が完了するまで NRST が Low にアサートされます。BIST の後、マッピング可能なフォルト条件によってトリガされるまで、NRST は High のままです (アサートされない)。NRST ピンが予期しない状態にプルされると、 $nRST\_MISMATCH$  フォルトがアサートされます。たとえば、NRST ピンがハイインピーダンス状態 (ロジック High) で、外部から Low に駆動されると、 $NRST\_MISMATCH$  フォルトがアサートされ

ます。NRST トグルの間、2μs の後で NRST 不一致がアクティブになります。ロジック High 状態と見なされるには、NRST が 0.6\*VDD を超えている必要があります。

NRST は、IEN\_Vendor レジスタを使用してウォッチドッグ フォルトにマッピングできます。NRST がウォッチドッグ フォルトに割り当てられている場合、ウォッチドッグ フォルト中に NRST ピンがアサートされ、リセット遅延  $(t_D)$  後にデアサートされます。

NRST は、FC\_LF[n] レジスタを使用して、OVHF および UVHF フォルトにもマッピングできます。監視対象の電圧がプログラムされた OVHF および UVHF スレッショルドを下回る、または上回ると、NRST がアサートされ、NRST ピンが Low に駆動されます。監視対象の電圧が有効なウィンドウに戻ると、リセット遅延回路が有効になり、指定されたリセット遅延期間 (t<sub>D</sub>) にわたって NRST を Low に保持します。NRST がアサートされているときに、NRST が OVHF および UVHF フォルトからマッピングされない場合、NRST はデアサートされ、電圧が有効なウィンドウ外にあると仮定して再マッピングされると、NRST が再アサートされることに注意してください。

$t_D$  期間は、TI\_CONTRO L レジスタにある RST\_DLY[2:0] の値によって決定されます。リセット遅延が経過すると、NRST ピンはハイインピーダンス状態に移行し、プルアップ抵抗を使用して NRST を High に保持します。他のデバイスを正し いインターフェイス電圧で接続できるように、プルアップ抵抗を適切な電圧レールに接続する必要があります。適切な電圧 レベルを設計するためには、プルアップ抵抗の値を選択する際にある程度の配慮が必要になります。プルアップ抵抗の値は、Low 電圧出力 (VOL)、容量性負荷、リーク電流によって決定されます。

#### 7.4.5 NIRQ

NIRQ は、ラッチ動作による割り込みエラー出力です。監視対象の電圧が、プログラムされた OVHF および UVHF スレッショルドを下回る、または上回ると、NIRQ がアサートされます。NIRQ は、フォルトの原因となっている動作が解消され、フォルトが発生したことを示すビットに「1 でビットをクリア」が書き込まれるまで Low 状態を維持します。異常検出出力レジスタからの NIRQ のマッピングが解除されても、NIRQ 信号はデアサートされません。一般的な TPS389C03-Q1 アプリケーションでは、NIRQ は NIRQ 出力がプロセッサ (デジタル信号プロセッサ [DSP]、特定用途向 IC [ASIC]、またはその他のプロセッサ タイプなど) のリセット入力またはイネーブル入力に接続されます。

TPS388C0x-Q1 にはオープンドレインのアクティブ Low 出力があり、これらのラインを必要な電圧ロジックまで High に保持するためにプルアップ抵抗が必要です。プルアップ抵抗を適切な電圧レールに接続し、出力を適切なインターフェイス電圧レベルで他のデバイスに接続できるようにします。適切な電圧レベルを設計するためには、プルアップ抵抗の値を選択する際にある程度の配慮が必要になります。プルアップ抵抗の値は、V<sub>OL</sub>、出力容量性負荷、および出力リーク電流によって決定されます。セクション 6 に、これらの値が指定されています。オープンドレイン出力は、別の TPS388C0x-Q1 NIRQ ピンなどの他のオープンドレイン信号を使って有線 OR ロジックとして接続できます。

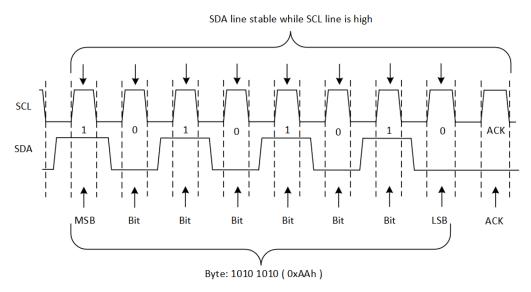

### 7.4.6 I<sup>2</sup>C

TPS388C0x-Q1 デバイスは I<sup>2</sup>C プロトコル (最大 1Mhz) に従っており、MCU またはシステム オン チップ (SoC) などの ホスト デバイスとの通信を管理できます。I<sup>2</sup>C は、クロック (SCL) とデータ (SDA) という 2 つの信号を使用して実装された 2 線式通信プロトコルです。ホスト デバイスは、通信の主なコントローラです。TPS388C0x-Q1 デバイスは、I<sup>2</sup>C プロトコルで定義されている読み取りまたは書き込み動作中に、データ ライン上で応答します。SCL 信号と SDA 信号はいずれもオープンドレイントポロジであり、他のデバイスとの有線 OR 構成で通信バスを共有するために使用できます。SCL ピンと SDA ピンの両方に、電源電圧に対する外付けプルアップ抵抗が必要です (10kΩ 推奨)。

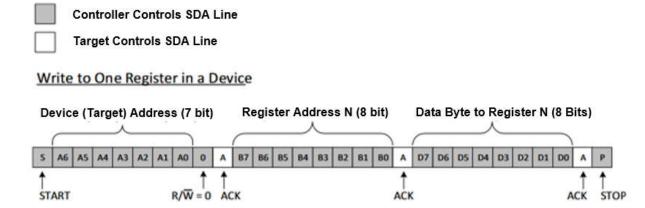

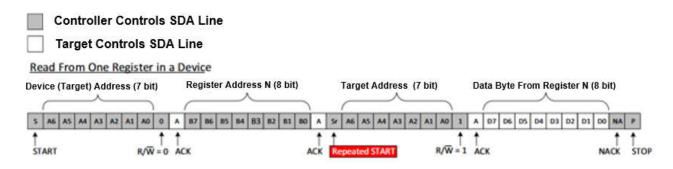

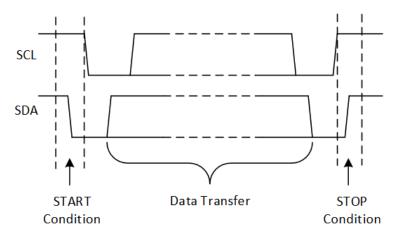

図 7-6 に、SCL ラインと SDA ライン間の 1 バイトのデータを転送するタイミング関係が示されています。 SCL ラインは常に、ホストによって制御されます。 1 バイトのデータを転送するには、ホストは SCL で 9 クロックを送信する必要があります。 データの場合は 8 クロック、ACK または NACK の場合は 1 クロックです。 SDA ラインは、読み取りまたは書き込みの動作に基づいて、ホストまたは TPS388C0x-Q1 デバイスによって制御されます。 図 7-7 および 図 7-8 に、アクティブな通信中にさまざまなインスタンスで SDA ラインを制御する通信プロトコルのフロー、およびどのデバイスが SDA ラインを制御するかが示されています。

図 7-6.1 バイトのデータ転送の SCL から SDA へのタイミング

図 7-7. I<sup>2</sup>C 書き込みプロトコル

図 7-8. I<sup>2</sup>C 読み取りプロトコル

I<sup>2</sup>C プロトコルで通信を開始する前に、ホストは I<sup>2</sup>C バスが通信で利用可能であることを確認する必要があります。SCL と SDA ラインを監視し、いずれかのラインが Low にプルされると、I<sup>2</sup>C バスが使用されます。ホストは、バスが通信に利用可能になるまで待機する必要があります。通信にバスが利用可能になると、ホストは START 条件を発行して、読み取りまた

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

は書き込み動作を開始できます。 $I^2C$  通信が完了したら、STOP コマンドを発行してバスを解放します。図 7-9 に、START 条件および STOP 条件の実装方法が示されています。

図 7-9. I<sup>2</sup>C の START 条件と STOP 条件

ホストから必要な数のクロックが供給されない場合、SDA ラインはロジック Low レベルに固着することがあります。この場合は、SDA ラインが High になるまで、ホストは SCL ライン上に複数のクロックを供給できます。このイベントの後、ホストは I<sup>2</sup>C STOP コマンドを発行できます。この結果として、I<sup>2</sup>C バスや他のデバイスは I<sup>2</sup>C バスを使用できます。

表 7-3 に、I<sup>2</sup>C でプログラムする際に利用できる各種の機能が示されています。

表 7-3. ユーザー プログラマブル I<sup>2</sup>C 機能

| 機能                              | 説明                                                          |

|---------------------------------|-------------------------------------------------------------|

| OV / UV- HF のスレッショルド            | 0.2V ~ 1.475V の範囲で 5mV ステップ、0.8V ~ 5.5V の範囲で 20mV ステップで調整可能 |

| 電圧監視スケーリング                      | 1 または 4                                                     |

| OV / UV- HF のグリッチ耐性             | 0.1us∼102.4us                                               |

| シーケンスのタイムアウトを有効化                | 1ms~4s                                                      |

| I <sup>2</sup> C のパケット エラー チェック | 有効化または無効化                                                   |

| NIRQ / NRST / WDO のアサートを強制      | I <sup>2</sup> C レジスタによる制御                                  |

| 個別チャネル MON                      | 有効または無効                                                     |

| 割り込み無効化機能                       | BIST、PEC、TSD、CRC                                            |

| リセット遅延                          | $200\mu s \sim 200ms$                                       |

| 最大制限超過数                         | 0~7                                                         |

| ウォッチドッグ スタートアップ遅延逓倍器            | 0~7                                                         |

| ウォッチドッグ オープン / クローズ ウィンドウ時間     | 1ms から 864ms に変更                                            |

| ウォッチドッグ出力遅延                     | 200μs ~ 200ms (ラッチなし WDO のみに適用)                             |

| OV / UV / WDT                   | NIRQ、NRST、WDO に個別にマッピング可能                                   |

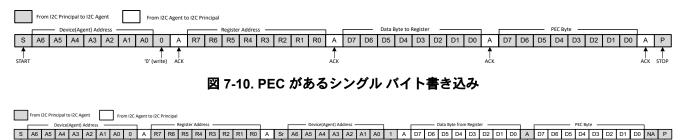

### 7.4.7 パケット エラー チェック (PEC)

TPS388C0x-Q1 は、CRC (巡回冗長性検査) 実装する方法として、パケット エラー チェック (PEC) をサポートしています。PEC とは動的 CRC で、読み取りまたは書き込みトランザクションが有効されている場合にのみ発生します。 CRC の 初期値が 0x00 に設定されている場合、PEC は次の多項式で表される CRC-8 を使用します。

$$C(x) = x^8 + x^2 + x + 1 \tag{1}$$

多項式は、I<sup>2</sup>C 通信のビット反転やノイズを捕捉することを目的としており、データと PEC バイトの不一致が生じます。 PEC の計算には、アドレス、コマンド、データを含め、送信のすべてのバイトが含まれます。 PEC の計算には、ACK ビット と NACK ビット、または START、STOP、反復 START 条件は含まれません。 PEC が有効で、TPS388C0x-Q1 がデー タを送信している場合、TPS388C0x-Q1 が PEC バイトを送信します。 PEC が有効で、TPS388C0x-Q1 が MCU からデ ータを取得している場合、MCU が PEC バイトを送信します。ウォッチドッグの処理など、通信を高速化する必要がある場 合、必要な PEC 機能を効果的に使用して、PEC 情報の消失を処理し、フォルトをトリガすることを防止できます。図 7-10 および 図 7-11 に、アクティブな通信中にさまざまなインスタンスで PEC が必要な場合に SDA ラインを制御する通信プ ロトコルのフロー、およびどのデバイスが SDA ラインを制御するかが示されています。

図 7-11. PEC があるシングル バイト読み取り

表 7-4 に、PEC 書き込みコマンドに関連するレジスタ、およびその結果のデバイス動作が示されています。 表 7-5 に、 PEC 読み取りコマンドに関連するレジスタ、およびその結果のデバイス動作が示されています。 キャル DEC 書き込むの輝西

|      |         |         | 女/サ・トロン 首と心のり気女                       |

|------|---------|---------|---------------------------------------|

| _PEC | REQ_PEC | PEC_INT | 割り込みス                                 |

| _    |         |         | **** * ** ** ** * * * * * * * * * * * |

| EN_PEC | REQ_PEC | PEC_INT | 割り込みステータス                                                                                                                                                                                                                                                          |

|--------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | x       | x       | 書き込み動作では PEC バイトは必要なく、NIRQ のアサートは不要です。                                                                                                                                                                                                                             |

| 1      | 0       | x       | PEC バイトが欠如している書き込みコマンドは OK と見なされ、書き込みコマンドが実行されて、I <sup>2</sup> C の ACK が返されます。PEC が正しくない書き込みコマンドはエラーとして扱われ、書き込みコマンドは実行されず、I <sup>2</sup> C NACK が発生します。NIRQ のアサートなし。                                                                                               |

| 1      | 1       | 0       | PEC が欠けている場合はエラーとして処理されます。正しい PEC バイトが供給された場合にのみ、書き<br>込みコマンドが実行されます。 I <sup>2</sup> C 通信は、書き込みコマンドが実行されなくても、ACK で応答します。<br>PEC が正しくない書き込みコマンドはエラーとして扱われ、書き込みコマンドは実行されず、I <sup>2</sup> C NACK が<br>発生します。 NIRQ のアサートなし。                                            |

| 1      | 1       | 1       | PEC が欠けている場合はエラーとして処理されます。正しい PEC バイトが供給された場合にのみ、書き<br>込みコマンドが実行されます。 I <sup>2</sup> C 通信は、書き込みコマンドが実行されなくても、ACK で応答します。<br>PEC が正しくない書き込みコマンドはエラーとして扱われ、書き込みコマンドは実行されず、 I <sup>2</sup> C NACK が<br>発生します。 PEC バイトが正しくない、または欠落している書き込みコマンドが試行されると、 NIRQ がアサートされます。 |

#### 表 7-5. PEC 読み取りの概要

| EN_PEC | REQ_PEC | PEC_INT | 割り込みステータス                                                                                         |

|--------|---------|---------|---------------------------------------------------------------------------------------------------|

| 0      | x       | x       | I <sup>2</sup> C 読み取り動作は、レジスタに保存されたデータによって異なり、I <sup>2</sup> C 読み取りコマンドは対応する PEC バイトのレジスタに応答しません。 |

| 1      | x       | x       | I <sup>2</sup> C 読み取り操作は、レジスタに保存されたデータおよび対応する PEC バイトで応答します。                                      |

#### 7.4.8 ウィンドウ ウォッチドッグ

TPS388C0x-Q1 には、WDE ピンによりウォッチドッグ タイマを有効化または無効化する機能があります。この機能によ り、ユーザーはウォッチドッグ タイマを無効にしてから、WDE ピンを使用してウォッチドッグ タイマを有効にできます。ウォ ッチドッグを有効化および無効化する機能は、初期化およびシャットダウン時に望ましくないウォッチドッグ フォルトを回避

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

25

するために役立ちます。WDE ピンが Low でウォッチドッグ タイマが無効になると、ピンでの変化に対して、直ちに応答が返されます。ウォッチドッグが無効から有効になると、スタートアップ遅延およびクローズ / オープン ウィンドウ シーケンスが発生します。

#### 7.4.9 ウィンドウ ウォッチドッグ タイマ

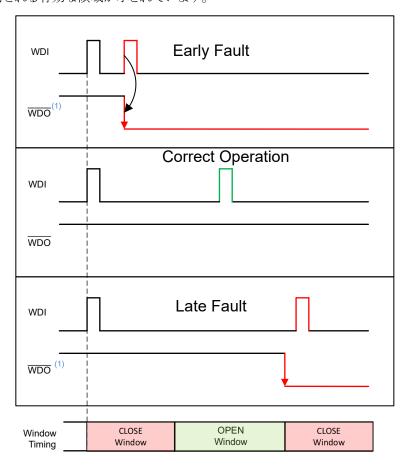

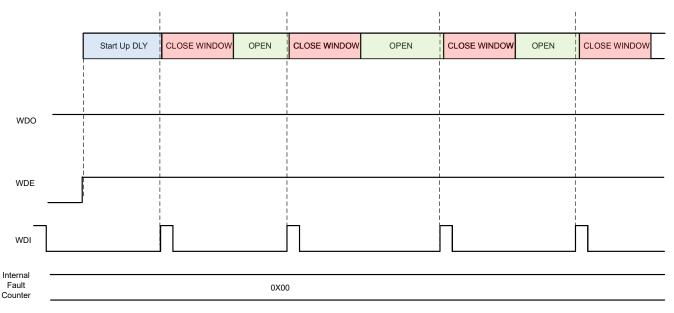

このセクションには、ウィンドウ ウォッチドッグの動作モードに関する説明が含まれています。ウィンドウ ウォッチドッグは通常、従来型のウォッチドッグ タイマが不十分な安全重視のアプリケーションで採用されます。従来のウォッチドッグでは、リセットの発生を防ぐためにパルスを発行する必要がある最大時間があります。しかし、ウィンドウ ウォッチドッグでは、オープン ウィンドウでパルスを発行する必要があります。図 7-12 に、WDO がトリガされて Low にプルされるのを防止するために WDI パルスが発行される有効な領域が示されています。

(1) WDO to WDT error mapping assumed

#### 図 7-12. ウィンドウ ウォッチドッグ有効ウィンドウ

WDE が Low から High になると、ウォッチドッグはスタートアップ ウィンドウで動作を開始します。ウィンドウが期限切れになる前に、スタートアップ ウィンドウに WDI パルスが存在している必要があります。そうでない場合は不良なイベントとなります。有効な WDI パルスは、パルス幅が少なくとも 32µs の正の立ち下がりパルスです。スタートアップ遅延は、式 2 に従って、オープン ウィンドウとクローズ ウィンドウおよび WDT\_Start\_DLY\_Multiplier[2:0] レジスタ値によって定義されます。

式 2 では、WDT\_Startup\_DLY\_MULTIPLIER [2:0]、OPEN[7:0]、CLOSE[7:0] は 10 進形式で使用されるものと仮定しています。

$WD\_StartUp\_DLY = (WDT\_Startup\_DLY\_MULTIPLIER[2:0] + 1)*(CLOSE[7:0] + OPEN[7:0])$ (2)

Copyright © 2025 Texas Instruments Incorporated

スタートアップ ウィンドウでパルスを受信すると、ウォッチドッグは直ちにクローズ ウィンドウに移動します。クローズ ウィンドウの固定時間経過後 (バンク 1 の I<sup>2</sup>C レジスタ 0xAB で設定)、ウォッチドッグはオープン ウィンドウに移行します。オープン ウィンドウ中、不良なイベントを回避するため、有効な WDI パルスが存在している必要があります。オープン ウィンドウで有効なパルスが登録されている場合は、クローズ ウィンドウが直ちに開始されます。オープン ウィンドウは動的と見なされ、WDI パルスが検知されたときに、ウィンドウ期間が決定されます。図 7-13 に示されているように、正常動作時のウォッチドッグは、オープン ウィンドウとクローズ ウィンドウ間をサイクルします。TPS388C0x-Q1 では、オープン ウィンドウとクローズ ウィンドウとクローズ ウィンドウ遅延の精度が ±5% となっています。

図 7-13 に、正常動作時の WD 動作が示されています。各オープン ウィンドウに有効なパルスが存在し、WDI パルスが検知されたときにオープン ウィンドウの期間が決定されることに注意してください。クローズ ウィンドウは WDI パルスの立ち上がりエッジの直後に続き、オープン ウィンドウに有効なパルスが登録されている間、このサイクルは継続します。

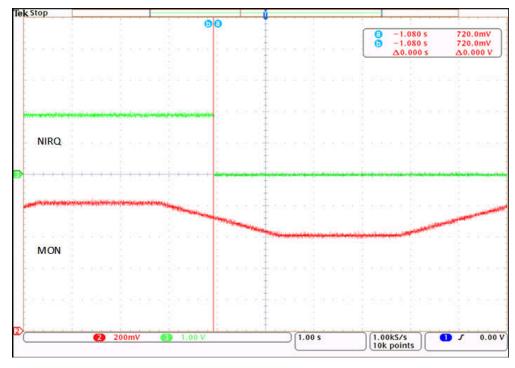

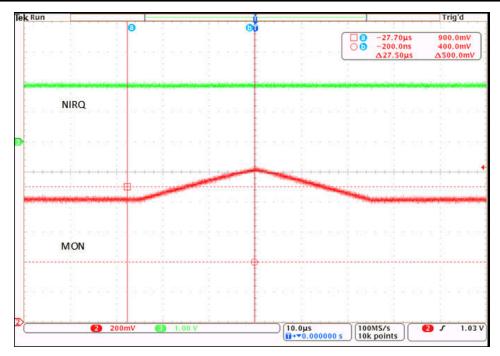

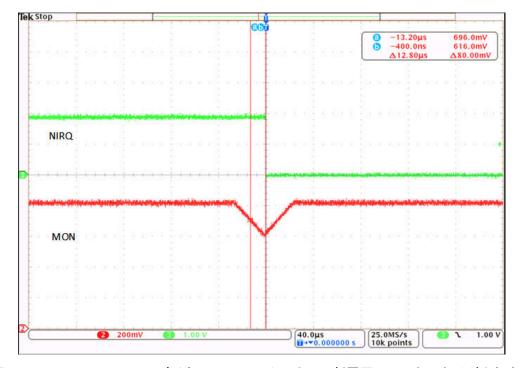

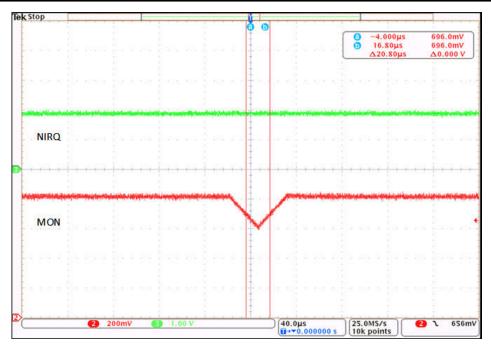

図 7-13. WD フォルトなし

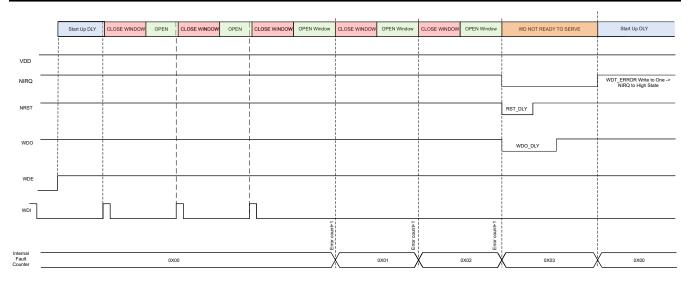

オープン ウィンドウ中に有効なパルスが登録されない場合、TPS388C0x-Q1 は不良なイベントをログに記録し (オープンウィンドウ タイムアウト後)、クローズ ウィンドウが繰り返されます。不良なイベント後、TPS388C0x-Q1 がフォルトを最大制限超過カウンタに記録すると、合計超過数がレジスタ MAX\_Violation\_COUNT[2:0] と比較されます。レジスタMAX\_Violation\_COUNT[2:0] は、WDO (および任意のマッピングされたエラー出力)がアサートされる前に伝達されるフォルトの最大数を示します。レジスタは 1~7のフォルトに設定できます。図 7-14に示されているように、1に設定すると、最初のフォルトイベントによって WDO がトリガされます。3に設定すると、3つのフォルトが発生してから、WDO (および任意のマッピングされたエラー出力)がアサートされます。NIRQとNRSTエラー出力はいずれも、IEN\_VENDORレジスタを使用してウォッチドッグフォルトを通知するようにマッピングすることができます。良好なイベントでは、制限超過数がゼロになっていない場合は、超過数がデクリメントされることに注意してください。

図 7-14 に、MAX\_Violation\_COUNT[2:0] が 3 に設定されている場合のウォッチドッグ動作が示されています。この図では、NRST と NRST の両方がウォッチドッグ フォルトを通知するようにマッピングされており、タイムアウト機能を反映するように WDO がプログラムされています。オープン ウィンドウ期間は、WDI パルスが検知されるタイミングによって決定され、WDI パルスが存在せずにウィンドウがタイムアウトした場合にのみ、オープン ウィンドウの全期間が表示されることに注意してください。同様に、スタートアップ ウィンドウの期間は、最初の WDI パルスが検知されたタイミングによって決定されます。スタートアップ ウィンドウの全期間が表示されるのは、WDI パルスが存在せずにウィンドウがタイムアウトした場合に限り、これはスタートアップ ウィンドウのタイムアウトが不良なイベントと見なされます。

図 7-14. WD フォルト WDO タイムアウトと NRST NIRQ マッピング

#### 7.5 レジスタマップ

#### 7.5.1 レジスタの概要

レジスタ マップは、以下の構成で、レジスタ バンクを使用して最大 16 個のチャネルをサポートするように設計されています。

- ・ バンク 0 ステータス レジスタ セットの概要:

- ベンダ情報および使用レジスタ (バンクに非依存)

- 割り込みレジスタ

- ステータスレジスタ

- バンク選択レジスタ (バンクに非依存)

- 保護レジスタ (バンクに非依存)

- デバイス構成レジスタ (バンクに非依存)

- バンク 1 チャネル 2-7 構成レジスタセットの概要:

- ベンダ情報および使用レジスタ (バンクに非依存)

- 制御レジスタ (デバイス グローバル レジスタ)

- モニタ構成レジスタ (チャネル固有のレジスタ)

- シーケンス構成レジスタ (デバイス グローバルおよびチャネル固有のレジスタの両方)

- バンク選択レジスタ (バンクに非依存)

- 保護レジスタ (バンクに非依存)

- デバイス構成レジスタ (バンクに非依存)

現在のバンクの選択に関係なく、バンクに非依存のレジスタは同じアドレスでアクセスできます。他のレジスタにアクセスするには、適切なバンクを選択する必要があります。

すべてのレジスタは 8 ビット幅で、ここに説明されているデフォルト値または工場出荷時にプログラムされた OTP 値が起動時にロードされます。 OTP 値は X で表されます。 これらの値は注文可能な構成によって異なります。

未使用のレジスタアドレスは、以後の使用のために予約されており、最大 16 チャネルをサポートします。

保護されたレジスタ (PROT1/2 の詳細を参照)、無効なレジスタ、または無効データが含まれている有効なレジスタへの書き込みアクセスは NACK されます。

#### 7.5.1.1 BANK0 のレジスタ

BANKO レジスタのメモリマップされたレジスタを、表 7-6 に示します。表 7-6 にないレジスタ オフセット アドレスはすべて 予約済みと見なして、レジスタの内容は変更しないでください。

表 7-6. BANK0 のレジスタ

| アドレス | 略称          | ビット7              | ビット 6                             | ビット 5             | ビット4               | ビット3          | ビット2      | ビット1                  | ビット 0             |

|------|-------------|-------------------|-----------------------------------|-------------------|--------------------|---------------|-----------|-----------------------|-------------------|

| 0x10 | INT_SRC     | F_OTHER           | OTHER RSVD                        |                   |                    |               | TEST      | 制御                    | モニタ               |

| 0x11 | INT_MONITOR |                   |                                   | OV                | HF.                |               |           | RSVD                  | UVHF              |

| 0x12 | INT_UVHF    | F_UV              | 'HF[7]                            | F_UVHF[6]         | F_UVHF[5]          | F_UVHF[4]     | F_UVHF[3] | F_UVHF[2]             | RSVD              |

| 0x16 | INT_OVHF    | F_OV              | 'HF[7]                            | F_OVHF[6]         | F_OVHF[5]          | F_OVHF[4]     | F_OVHF[3] | F_OVHF[2]             | RSVD              |

| 0x22 | INT_CONTROL |                   | F_C                               | CRC               |                    | F_NIRQ        | F_TSD     | RSVD                  | F_PEC             |

| 0x23 | INT_TEST    |                   | RSVD                              |                   |                    | ECC_SEC       | ECC_DED   | BIST_Compl<br>ete_INT | BIST_Fail_I<br>NT |

| 0x24 | INT_VENDOR  | Self-<br>Test_CRC | LDO_OV_Er<br>ror                  | NRST_MIS<br>MATCH | Freq_DEV_<br>Error | SHORT_DE<br>T | OPEN_DET  | RSVD                  | WDT_ERR<br>OR     |

| 0x30 | VMON_STAT   | FAILSAFE          | FAILSAFE ST_BIST_C ST_VDD ST_NIRQ |                   | アクティブ              |               | RS        | RSVD                  |                   |

| 0x31 | TEST_INFO   | RS                | VD                                | ECC_SEC           | ECC_DED            | BIST_VM       | BIST_NVM  | BIST_L                | BIST_A            |

| 0x32 | OFF_STAT    | MO                | N[7]                              | MON[6]            | MON[5]             | MON[4]        | MON[3]    | MON[2]                | RSVD              |

| 0xF0 | BANK_SEL    |                   | RSVD                              |                   |                    |               |           | BANK_Sele<br>ct       |                   |

| 0xF1 | PROT1       |                   | WRKC RSVI                         |                   |                    | CFG           | IEN       | MON                   | SEQ               |

| 0xF2 | PROT2       | WRKC              |                                   |                   | RSVD               | CFG           | IEN       | MON                   | SEQ               |

| 0xF3 | PROT_MON    | MON[7]            |                                   | MON[6]            | MON[5]             | MON[4]        | MON[3]    | MON[2]                | RSVD              |

| 0xF9 | I2C ADDR    | RSVD              |                                   | ADDR_N            | VM[3:0]            |               | AE        | DR_STRAP[2            | 2:0]              |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 **7-7** に、このセクションでアクセス タイプに使用しているコードを示します。

表 7-7. BANK0 のアクセス タイプ コード

| アクセス タイプ  | 表記      | 概要               |

|-----------|---------|------------------|

| 読み取りタイプ   |         |                  |

| R         | R       | 読み出し             |

| 書き込みタイプ   |         |                  |

| W         | W       | 書き込み             |

| W1C       | W<br>1C | 書き込み 1 でクリア      |

| リセットまたはデフ | オルト値    |                  |

| -n        |         | リセット後の値またはデフォルト値 |

### 7.5.1.1.1 INT\_SRC レジスタ (アドレス = 0x10) [リセット = 0x00]

表 7-8 に、INT\_SRC が示されています。

概略表に戻ります。

グローバル割り込みソースステータスレジスタ。

### 表 7-8. INT SRC レジスタのフィールドの説明

| ビット | フィールド   | タイプ | リセット  | 概要                                                                                                                             |

|-----|---------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 7   | F_OTHER | R   | Ob    | ベンダー内部定義のフォルト。詳細は、INT_Vendor に報告されています。INT_Vendor のすべてのビットの論理和の値を表します。 0 = ベンダ定義のフォルトは未検出 1 = ベンダ定義のフォルトを検出済み                  |

| 6:3 | RSVD    | R   | 0000b | RSVD                                                                                                                           |

| 2   | TEST    | R   | Ob    | 内部テストまたは構成ロード フォルト。詳細は、INT_TEST に報告されています。INT_TEST のすべてのビットの論理和の値を表します。<br>0 = テスト / 構成フォルトは未検出<br>1 = テスト / 構成フォルトを検出済み       |

| 1   | 制御      | R   | 0b    | 制御ステータスまたは通信フォルト詳細は、INT_CONTROL に報告されています。INT_CONTROL のすべてのビットの論理和の値を表します。 0 = ステータスまたは通信フォルトが検出されていない 1 = ステータスまたは通信フォルトを検出済み |

| 0   | モニタ     | R   | Ob    | 電圧モニタフォルト。詳細は、INT_MONITOR に報告されています。 INT_MONITOR のすべてのビットの論理和の値を表します。 0 = 電圧フォルトは未検出 1 = 電圧フォルトを検出済み                           |

## 7.5.1.1.2 INT\_MONITOR レジスタ (アドレス = 0x11) [リセット = 0x00]

表 7-9 に、INT\_MONITOR が示されています。

概略表に戻ります。

電圧監視割り込みステータスレジスタ。

### 表 7-9. INT\_MONITOR レジスタのフィールドの説明

| ビット | フィールド | タイプ | リセット   | 概要                                                                                                                               |

|-----|-------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | RSVD  | R   | 00000b | RSVD                                                                                                                             |

| 2   | OVHF  | R   | 0b     | コンパレータ ベースの監視によって報告された過電圧高周波フォルト。詳細は、INT_OVHF に報告されています。INT_OVHF のすべてのビットの論理和の値を表します。<br>0 = OVHF フォルトは未検出<br>1 = OVHF フォルトを検出済み |

| 1   | RSVD  | R   | 0b     | RSVD                                                                                                                             |

| 0   | UVHF  | R   | 0b     | コンパレータ ベースの監視によって報告された低電圧高周波フォルト。詳細は、INT_UVHF に報告されています。INT_UVHF のすべてのビットの論理和の値を表します。<br>0 = UVHF フォルトは未検出<br>1 = UVHF フォルトを検出済み |

## 7.5.1.1.3 INT\_UVHF レジスタ (アドレス = 0x12) [リセット = 0x00]

表 7-10 に、INT\_UVHF が示されています。

概略表に戻ります。

高周波数チャネル低電圧割り込みステータスレジスタ。

## 表 7-10. INT\_UVHF レジスタのフィールドの説明

| ビット | フィールド | タイプ | リセット | 概要   |

|-----|-------|-----|------|------|

| 7   | RSVD  | R   | 0b   | RSVD |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

31

## 表 7-10. INT\_UVHF レジスタのフィールドの説明 (続き)

| ビット | フィールド     | タイプ   | リセット | 概要                                                                                                                                                                                                                                                                                                          |

|-----|-----------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | F_UVHF[7] | R/W1C | 0b   | MON7 の低電圧高周波フォルト。MON7 高周波信号が UVHF[7] を下回                                                                                                                                                                                                                                                                    |

|     |           |       |      | るとトリップします。 0 = MON7 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON7 に UVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。 UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON7 高周波信号が UVHF[7] を上回っている場合)。                                       |

| 5   | F_UVHF[6] | R/W1C | Ob   | MON6 の低電圧高周波フォルト。MON6 高周波信号が UVHF[6]を下回るとトリップします。 0 = MON6 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON6 に UVHF フォルトを検出済みフォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON6 高周波信号がUVHF[6] を上回っている場合)。   |

| 4   | F_UVHF[5] | R/W1C | Ob   | MON5 の低電圧高周波フォルト。MON5 高周波信号が UVHF[5]を下回るとトリップします。 0 = MON5 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON5 に UVHF フォルトを検出済みフォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア)でビットがクリアされます (MON5 高周波信号がUVHF[5] を上回っている場合)。    |

| 3   | F_UVHF[4] | R/W1C | ОЬ   | MON4 の低電圧高周波フォルト。MON4 高周波信号が UVHF[4]を下回るとトリップします。 0 = MON4 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON4 に UVHF フォルトを検出済みフォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア)でビットがクリアされます (MON4 高周波信号がUVHF[4]を上回っている場合)。     |

| 2   | F_UVHF[3] | R/W1C | Ob   | MON3 の低電圧高周波フォルト。MON3 高周波信号が UVHF[3] を下回るとトリップします。 0 = MON3 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON3 に UVHF フォルトを検出済みフォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。 UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON3 高周波信号がUVHF[3] を上回っている場合)。 |

### 表 7-10. INT UVHF レジスタのフィールドの説明 (続き)

| ビット | フィールド     | タイプ   | リセット | 概要                                                                                                                                                                                                                                                                                                        |  |

|-----|-----------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | F_UVHF[2] | R/W1C | 0b   | MON2 の低電圧高周波フォルト。MON2 高周波信号が UVHF[2]を下回るとトリップします。 0 = MON2 に UVHF フォルトは未検出 (または IEN_UVHF レジスタで割り込みが無効) 1 = MON2 に UVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア)動作によってのみ、このフォルトがクリアされます。UVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア)でビットがクリアされます (MON2 高周波信号が UVHF[2] を上回っている場合)。 |  |

| 0   | RSVD      | R     | 0b   | RSVD                                                                                                                                                                                                                                                                                                      |  |

## 7.5.1.1.4 INT\_OVHF レジスタ (アドレス = 0x16) [リセット = 0x00]

表 7-11 に、INT\_OVHF が示されています。

概略表に戻ります。

高周波チャネル過電圧割り込みステータスレジスタ

## 表 7-11. INT\_OVHF レジスタのフィールドの説明

| ビット | フィールド     | タイプ   | リセット | 概要                                                                                                                                                                                                                                                                                                        |

|-----|-----------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RSVD      | R     | 0b   | RSVD                                                                                                                                                                                                                                                                                                      |

| 6   | F_OVHF[7] | R/W1C | Ob   | MON7 の過電圧高周波フォルト。MON7 高周波信号が OVHF[7]を上回るとトリップします。 0 = MON7 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON7 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア)でビットがクリアされます (MON7 高周波信号がOVHF[7]を下回っている場合)   |

| 5   | F_OVHF[6] | R/W1C | ОЬ   | MON6 の過電圧高周波フォルト。MON6 高周波信号が OVHF[6]を上回るとトリップします。 0 = MON6 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON6 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON6 高周波信号がOVHF[6]を下回っている場合)  |

| 4   | F_OVHF[5] | R/W1C | Ob   | MON5 の過電圧高周波フォルト。MON5 高周波信号が OVHF[5] を上回るとトリップします。 0 = MON5 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON5 に OVHF フォルトを検出済みフォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON5 高周波信号がOVHF[5] を下回っている場合) |

### 表 7-11. INT OVHF レジスタのフィールドの説明 (続き)

| るとトリップします。 0 = MON4 に OVHF フォルトは未検出 (または IEN_OVHF レジスター 的込みが無効) 1 = MON4 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 をき込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされ す。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むとでビットをクリア) でビットがクリアされます (MON4 高周波信号が OVHF[4] を下回っている場合)  2             |     |           |       |      | / V) / 1 / V   · V   D)L 中 1 (N)L (C)                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| るとトリップします。                                                                                                                                                                                                                                                                       | ビット | フィールド     | タイプ   | リセット | 概要                                                                                                                                                                                                                                    |

| るとトリップします。 0 = MON3 に OVHF フォルトは未検出 (または IEN_OVHF レジスターり込みが無効) 1 = MON3 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされす。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むとでビットをクリア)でビットがクリアされます (MON3 高周波信号がOVHF[3]を下回っている場合)  1 F_OVHF[2] R/W1C | 3   | F_OVHF[4] | R/W1C | Ob   | 0 = MON4 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON4 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON4 高周波信号が |

| るとトリップします。 0 = MON2 に OVHF フォルトは未検出 (または IEN_OVHF レジスターり込みが無効) 1 = MON2 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 をき込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされす。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むとでビットをクリア) でビットがクリアされます (MON2 高周波信号がOVHF[2] を下回っている場合)                   | 2   | F_OVHF[3] | R/W1C | Ob   | 0 = MON3 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON3 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON3 高周波信号が |

| 0 RSVD R 0b RSVD                                                                                                                                                                                                                                                                 | 1   | F_OVHF[2] | R/W1C | 0b   | 0 = MON2 に OVHF フォルトは未検出 (または IEN_OVHF レジスタで割り込みが無効) 1 = MON2 に OVHF フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。OVHF フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます (MON2 高周波信号が |

|                                                                                                                                                                                                                                                                                  | 0   | RSVD      | R     | 0b   | RSVD                                                                                                                                                                                                                                  |

## 7.5.1.1.5 INT\_CONTROL レジスタ (アドレス = 0x22) [リセット = 0x00]

表 7-12 に、INT\_CONTROL が示されています。

概略表に戻ります。

制御および通信割り込みステータスレジスタ。

## 表 7-12. INT\_CONTROL レジスタのフィールドの説明

| ビット | フィールド | タイプ   | リセット | 概要                                                                                                                                                                                                                                                      |

|-----|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | RSVD  | R     | 000b | RSVD                                                                                                                                                                                                                                                    |

| 4   | F_CRC | R/W1C |      | ランタイム レジスタ CRC フォルト: 0 = フォルトは未検出 (または IEN_CONTROL.RT_CRC が無効) 1 = レジスタ CRC フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。W1C (1 を書き込むことでビットをクリア)でビットがクリアされます。同じフォルトが検出された場合、次のレジスタ CRC チェック中に、このビットが再度設定されます |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

## 表 7-12. INT\_CONTROL レジスタのフィールドの説明 (続き)

| ビット | フィールド  | タイプ   | リセット | 概要                                                                                                                                                                                                                                                                                                |

|-----|--------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | F_NIRQ | R/W1C | 0b   | 割り込みピン フォルト (フォルト ビットは常に有効、イネーブル ビットなし): 0 = NIRQ ピンでフォルトは未検出 1 = NIRQ ピンで電源への低抵抗パスを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。NIRQ フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。                                                               |

| 2   | F_TSD  | R/W1C | 0b   | サーマル シャットダウン フォルト: 0 = TSD フォルトは未検出 (または IEN_CONTROL.TSD が無効) 1 = TSD フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。 TSD フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。                                                                        |

| 1   | RSVD   | R     | 0b   | RSVD                                                                                                                                                                                                                                                                                              |

| 0   | F_PEC  | R/W1C | 0b   | パケット エラー チェック フォルト: 0 = PEC 不一致は未発生 (または IEN_CONTROL.PEC が無効) 1 = PEC 不一致が発生、または VMON_MISC.REQ_PEC = 1 および PEC が書き込みトランザクションで欠落 フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。同じフォルトが検出されると、次の I2C トランザクション中にこのビットが再び設定されます。 |

## 7.5.1.1.6 INT\_TEST レジスタ (アドレス = 0x23) [リセット = 0x00]

表 7-13 に、INT\_TEST が示されています。

概略表に戻ります。

内部テストおよび構成ロード割り込みステータスレジスタ。

## 表 7-13. INT\_TEST レジスタのフィールドの説明

| ビット | フィールド             | タイプ   | リセット  | 概要                                                                                                                                                                      |

|-----|-------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | RSVD              | R     | 0000b | RSVD                                                                                                                                                                    |

| 3   | ECC_SEC           | R/W1C | 0b    | OTP 構成ロードで ECC 単一エラーを訂正: 0 = シングル エラーは未訂正 (または IEN_TEST.ECC_SEC が無効) 1 = シングル エラーを訂正済み W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。同じフォルトが検出されると、次の OTP 構成ロード時にこのビットが再度設定されます。 |

| 2   | ECC_DED           | R/W1C | 0b    | OTP 構成ロードでの ECC ダブル エラーを検出済み: 0 = OTP ロードでのダブル エラーは未検出 1 = OTP ロードでのダブル エラーを検出済み フォルトビットは常に有効です (関連付けられる割り込みイネーブル ビット はありません)。ダブル エラー検出時に、デバイスはフェイルセーフ モード に移行します。      |

| 1   | BIST_Complete_INT | R/W1C | 0b    | 内蔵セルフ テスト完了の表示: 0 = BIST は未完了 (または IEN_TEST.BIST_C が無効) 1 = BIST を完了済み W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。次の BIST 実行が完了すると、このビットが再び設定されます                             |

Product Folder Links: TPS388C0-Q1

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

35

## 表 7-13. INT\_TEST レジスタのフィールドの説明 (続き)

| ビット | フィールド         | タイプ   | リセット | 概要                                         |

|-----|---------------|-------|------|--------------------------------------------|

| 0   | BIST_Fail_INT | R/W1C | 0b   | 内蔵セルフ テスト フォルト:                            |

|     |               |       |      | 0 = BIST フォルトは未検出 (または IEN_TEST.BIST が無効)  |

|     |               |       |      | 1 = BIST フォルトを検出済み                         |

|     |               |       |      | W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。 フォルト |

|     |               |       |      | が検出されると、次の BIST 実行時にこのビットが再び設定されます         |

## 7.5.1.1.7 INT\_VENDOR レジスタ (アドレス = 0x24) [リセット = 0x00]

表 7-14 に、INT\_VENDOR が示されています。

概略表に戻ります。

ベンダ固有の内部割り込みステータスレジスタ。

## 表 7-14. INT\_VENDOR レジスタのフィールドの説明

| ビット | フィールド          | タイプ   | リセット | 概要                                                                                                                                                                                                                                                                                                   |

|-----|----------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Self-Test_CRC  | R/W1C | Ob   | スタートアップ レジスタ CRC セルフ テスト。<br>0 = セルフ テスト合格<br>1 = セルフ テスト不合格<br>W1C (1 を書き込むことでビットをクリア) でフォルトがクリアされます。                                                                                                                                                                                               |

| 6   | LDO_OV_Error   | R/W1C | Ob   | 内部 LDO 過電圧エラー。 0 = 内部 LDO 過電圧フォルトは未検出 1 = 内部 LDO 過電圧フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。LDO フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。                                                                                              |

| 5   | NRST_MISMATCH  | R/W1C | Ob   | 駆動状態と読み戻しによるエラーを指定します。NRSTトグルの間、2µs の後で NRST 不一致がアクティブになります。ロジック High 状態と見なされるには、NRST が 0.6*VDD を超えている必要があります。 0 = NRST ピンでのフォルトは未検出 1 = 駆動状態と読み戻しによるエラー。 フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。NRST フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。 |

| 4   | Freq_DEV_Error | R/W1C | Ob   | 内部周波数誤差を指定します。 0 = 内部周波数フォルトは未検出 1 = 内部周波数フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。周波数フォルト状態も解消された場合にのみ、W1C (1 を書き込むことでビットをクリア) でビットがクリアされます。                                                                                                         |

| 3   | SHORT_DET      | R/W1C | Ob   | アドレスピン短絡検出。 0 = 内部アドレスピン短絡フォルトは未検出 1 = 内部アドレスピン短絡フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 を書き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。内部アドレスピン短絡フォルト状態も解消された場合にのみ、W1C (1を書き込むことでビットをクリア) でビットがクリアされます。                                                                                            |

*資料に関するフィードバック (ご意見やお問い合わせ) を送信* Copyright © 2025 Texas Instruments Incorporated

# 表 7-14. INT\_VENDOR レジスタのフィールドの説明 (続き)

| ビット | フィールド     | タイプ   | リセット | 概要                                                                                                                                                                                                              |  |

|-----|-----------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2   | OPEN_DET  | R/W1C | Ob   | アドレス ピン開放検出。 0 = 内部アドレス ピン開放フォルトは未検出 1 = 内部アドレス ピン開放フォルトを検出済み フォルト状態が回復してもビットはクリアされません。ホストの W1C (1 き込むことでビットをクリア) 動作によってのみ、このフォルトがクリアされます。内部アドレス ピンの開放フォルト状態も解消された場合にのみ、V(1 を書き込むことでビットをクリア) でビットがクリアされます。      |  |