**TPS3850** JAJSCT6B - OCTOBER 2016 - REVISED SEPTEMBER 2021

# TPS3850 プログラマブル・ウィンドウ・ウォッチドッグ・タイマ内蔵の高精 度電圧監視 IC

# 1 特長

- 入力電圧範囲:VDD = 1.6V~6.5V

- 0.8% の電圧スレッショルド精度

- 低消費電流: $I_{DD} = 10\mu A$  (標準値)

- ウォッチドッグのタイムアウトをユーザーがプログラム可

- リセット遅延をユーザーがプログラム可能

- 工場でプログラム済みの高精度のウォッチドッグとリセ ット・タイマ

- オープン・ドレイン出力

- 高精度の過電圧および低電圧監視

- 0.9V~5.0Vの共通レールをサポート

- ±4% および ±7% のフォルト・ウィンドウを利用可能

- 0.5% のヒステリシス

- ウォッチドッグのディスエーブル機能

- 3mm × 3mm の小型 10 ピン VSON パッケージで供

- 動作時の接合部温度範囲: -40°C∼+125°C

# 2 アプリケーション

- 超音波スキャナ

- ストレージ・エリア・ネットワーク

- アクティブ・アンテナ・システム (AAS) の mMIMO

- ロボット向けサーボ・ドライブ

- 点滴用ポンプ

- HVAC コントローラ

#### 3 概要

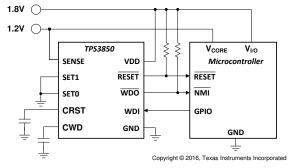

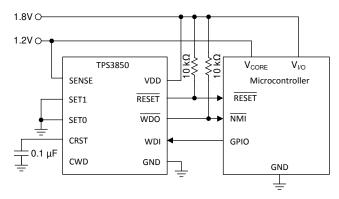

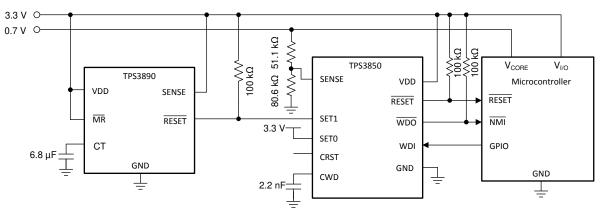

TPS3850 は、高精度の電圧スーパーバイザとプログラム 可能なウィンドウ・ウォッチドッグ・タイマを組み合わせた製 品です。TPS3850 のウィンドウ・コンパレータは、SENSE ピンの過電圧 (V<sub>IT+(OV)</sub>) および低電圧 (V<sub>IT-(UV)</sub>) スレッシ ョルドの両方について 0.8% の精度 (-40℃~+125℃) を 達成しています。また、TPS3850 には両方のスレッショル ドについて高精度のヒステリシスが含まれており、許容誤 差の厳しいシステムに理想的です。スーパーバイザの RESET 遅延は、工場でプログラムされたデフォルト遅延 設定を使用することも、外付けコンデンサによりプログラム することもできます。 工場でプログラムされる RESET 遅延 は 9.5% の精度で、高精度の遅延タイミングです。

TPS3850 にはプログラム可能なウィンドウ・ウォッチドッグ・ タイマが内蔵されており、広範なアプリケーションに使用で きます。専用ウォッチドッグ出力 (WDO) により分解能が向 上し、フォルト状況の性質を判定するために役立ちます。 ウィンドウ・ウォッチドッグのタイムアウトは、工場でプログラ ムされたデフォルト遅延設定を使用することも、外付けコン デンサによりプログラムすることもできます。ウォッチドッグ はロジック・ピンによりディスエーブルできるため、開発プロ セスにおいて望ましくないウォッチドッグのタイムアウトを回 避できます。

TPS3850 は、小型の 3.00mm × 3.00mm、10 ピンの VSON パッケージで供給されます。

#### 製品情報

|         | -4 119 194 |                 |

|---------|------------|-----------------|

| 部品番号    | パッケージ (1)  | 本体サイズ (公称)      |

| TPS3850 | VSON (10)  | 3.00mm × 3.00mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

完全に統合されたマイコン監視回路

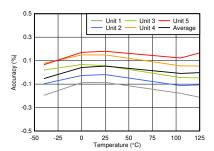

過電圧スレッショルド (V<sub>IT+(OV)</sub>) の精度と温度との関 係

# **Table of Contents**

| 1 特長                                    | 1 | 7.4 Device Functional Modes                        | 22                 |

|-----------------------------------------|---|----------------------------------------------------|--------------------|

| <b>2</b> アプリケーション                       |   | 8 Application and Implementation                   |                    |

| - / / / / · · · · · · · · · · · · · · · |   | 8.1 Application Information                        |                    |

| 4 Revision History                      |   | 8.2 Typical Applications                           |                    |

| 5 Pin Configuration and Functions       |   | 9 Power Supply Recommendations                     | 35                 |

| 6 Specifications                        |   | 10 Layout                                          |                    |

| 6.1 Absolute Maximum Ratings            |   | 10.1 Layout Guidelines                             |                    |

| 6.2 ESD Ratings                         |   | 10.2 Layout Example                                | 36                 |

| 6.3 Recommended Operating Conditions    |   | 11 Device and Documentation Support                | 37                 |

| 6.4 Thermal Information                 |   | 11.1 Device Support                                | 37                 |

| 6.5 Electrical Characteristics          |   | 11.2 Documentation Support                         |                    |

| 6.6 Timing Requirements                 |   | 11.3 Receiving Notification of Documentation Updat | es <mark>37</mark> |

| 6.7 Timing Diagrams                     |   | 11.4 サポート・リソース                                     | 37                 |

| 6.8 Typical Characteristics             |   | 11.5 Trademarks                                    | 37                 |

| 7 Detailed Description                  |   | 11.6 Electrostatic Discharge Caution               | 37                 |

| 7.1 Overview                            |   | 11.7 Glossary                                      |                    |

| 7.2 Functional Block Diagrams           |   | 12 Mechanical, Packaging, and Orderable            |                    |

| 7.3 Feature Description                 |   | Information                                        | <mark>38</mark>    |

| 1                                       |   |                                                    |                    |

**4 Revision History** 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision A (November 2016) to Revision B (September 2021)                                                                                                                                                                                 | Page           |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                                                                                                                                                                                                             | 1              |

| • | 「±15% 精度の WDT および RST 遅延」を削除                                                                                                                                                                                                                          | 1              |

| • | Web サイトへのリンクを含むようにアプリケーションを更新                                                                                                                                                                                                                         | 1              |

| • | 「SENSE ピンの」を追加                                                                                                                                                                                                                                        |                |

| • | Changed V <sub>ESD</sub> values to ±4000 V and ±1000 V                                                                                                                                                                                                | 5              |

| • | Changed I <sub>CWD</sub> min and max spec                                                                                                                                                                                                             | <mark>6</mark> |

| • | Changed V <sub>CWD</sub> min and max spec                                                                                                                                                                                                             |                |

| • | Added a footnote to for t <sub>INIT</sub>                                                                                                                                                                                                             | <mark>7</mark> |

| • | Changed minimum and maximum specifications of 2nd, 5th, 6th, and 8th rows of two parameter                                                                                                                                                            | <mark>7</mark> |

| • | Changed minimum and maximum specifications of 2nd and last rows of t <sub>WDU</sub> parameter                                                                                                                                                         |                |

| • | Added new section "Disabling the Watchdog Timer When Using the CRST Capacitor"                                                                                                                                                                        |                |

| • | Changed 0.000381 to 0.000324 and 0.000438 in Equation 4 and Equation 5, respectively                                                                                                                                                                  |                |

| • | Changed minimum and maximum specifications in 100 pF and 1 nF rows of Reset Delay Time for Cor                                                                                                                                                        |                |

|   | Ideal Capacitor Values table                                                                                                                                                                                                                          |                |

| • | Changed minimum and maximum specifications for NC SETx 01 setting for both upper and lower water boundaries, 10 k $\Omega$ to VDD SETx 00 and 01 settings for lower watchdog boundary, and 10 k $\Omega$ to VDD settings for lower watchdog boundary. |                |

|   | 11 setting for both upper and lower watchdog boundaries in <i>Factory-Programmed Watchdog Timing</i> ta                                                                                                                                               |                |

|   | Changed minimum and maximum limits on t <sub>WDU</sub> and added explanation.                                                                                                                                                                         |                |

| • | Changed 0.000381 to 0.000324 in Equation 11                                                                                                                                                                                                           |                |

| • | Changed description of factory-programmed timing options and values of two                                                                                                                                        |                |

|   | the Watchdog Window section                                                                                                                                                                                                                           | 30             |

| • | Changed 0.85 to 0.905 in Equation 14                                                                                                                                                                                                                  | 33             |

| • | Changed Equation 17 and Equation 18 so that I <sub>SENSE</sub> is no longer in the denominator                                                                                                                                                        | 34             |

| С | hanges from Revision * (October 2016) to Revision A (November 2016)                                                                                                                                                                                   | Page           |

| • | Changed units in I <sub>SENSE</sub> parameter and footnote 1 in <i>Electrical Characteristics</i> table                                                                                                                                               | 6              |

| • | Added correct operation state to Figure 2                                                                                                                                                                                                             | <mark>7</mark> |

| • | Changed Figure 3 so the SET pins do not bring the watchdog into the disabled state before going to the                                                                                                                                                | ne 1:2         |

|   | ratio                                                                                                                                                                                                                                                 | <mark>7</mark> |

# www.tij.co.jp

| • | Changed Figure 11 so it no longer has VDD and V <sub>SENSE</sub> tied together    | 1 <sup>2</sup> |

|---|-----------------------------------------------------------------------------------|----------------|

|   | Changed Figure 26 so it no longer goes through watchdog disabled                  |                |

|   | Added correct operation state to Figure 27                                        |                |

|   | Changed RESET to WDO in description of WDO assertion in WDO Functionality section |                |

|   | · · · · · · · · · · · · · · · · · · ·                                             |                |

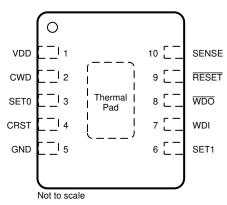

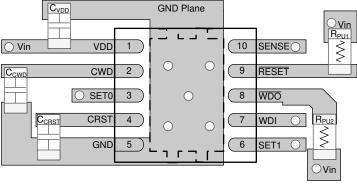

# **5 Pin Configuration and Functions**

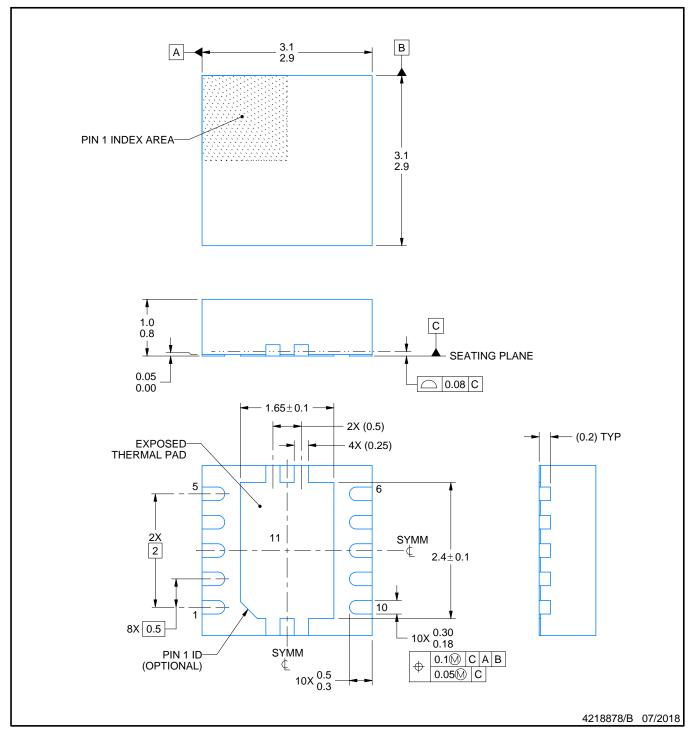

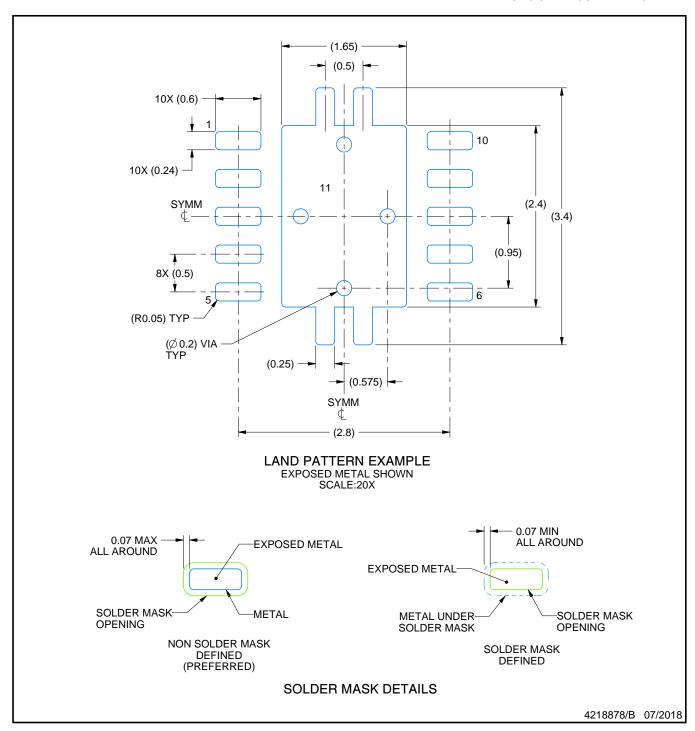

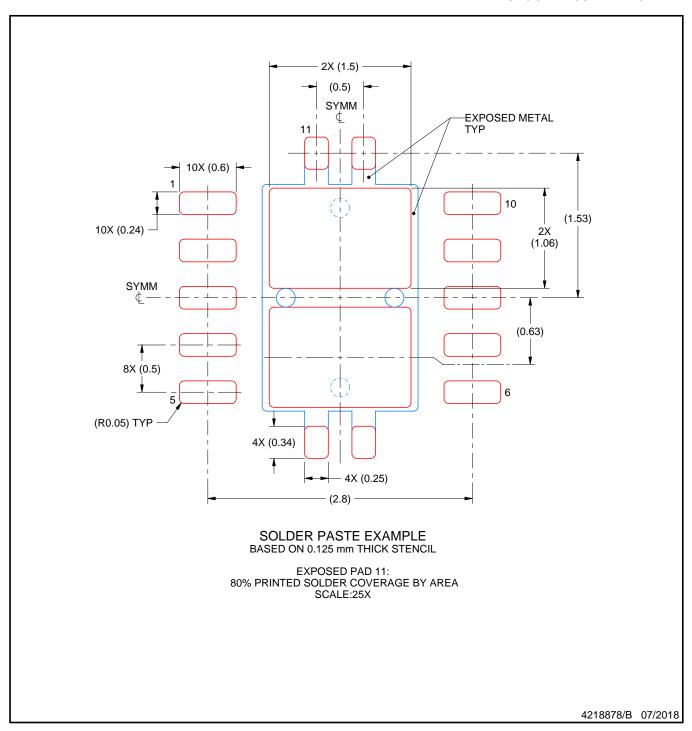

図 5-1. DRC Package: TPS3850 3-mm × 3-mm VSON-10 Top View

表 5-1. Pin Functions

|                    | PIN |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO. I/O       |     |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CRST               | 4   | ı | Programmable reset timeout pin. Connect a capacitor between this pin and GND to program the reset timeout period. This pin can also be connected by a 10-k $\Omega$ pullup resistor to VDD, or left unconnected (NC) for various factory programmed reset timeout options; see the $\cancel{\text{tOya}} \times 8.1.1$ section. When using an external capacitor, use $\cancel{\text{T}}$ 3 to determine the reset timeout.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

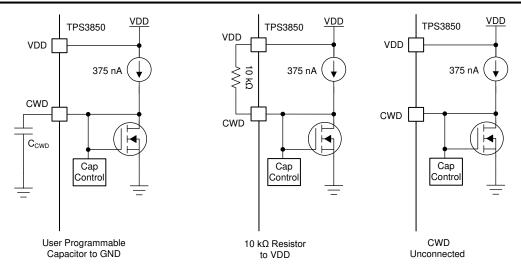

| CWD                | 2   | I | Programmable watchdog timeout input. Watchdog timeout is set by connecting a capacitor between this pin and ground. Furthermore, this pin can also be connected by a 10-k $\Omega$ resistor to VDD, or leaving unconnected (NC) further enables the selection of the preset watchdog timeouts; see the $\frac{1}{2}\frac{1}{2}\frac{1}{2}$ 6.6 table. When using a capacitor, the TPS3850 determines the window watchdog upper boundary with $\frac{1}{2}$ 6. The lower watchdog boundary is set by the SET pins, see $\frac{1}{2}$ 8.1.2 section for additional information.                                                                                                                                                                                                                                                                                                           |

| GND 5 — Ground pin |     |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET              | 9   | 0 | Reset output. Connect $\overline{\text{RESET}}$ using a 1-k $\Omega$ to 100-k $\Omega$ resistor to VDD. $\overline{\text{RESET}}$ goes low when the voltage at the SENSE pin goes below the undervoltage threshold $(V_{\text{IT-(UV)}})$ or above the overvoltage threshold $(V_{\text{IT+(OV)}})$ . When the voltage level at the SENSE pin is within the normal operating range, the $\overline{\text{RESET}}$ timeout counter starts. At timer completion, $\overline{\text{RESET}}$ goes high. During startup, the state of $\overline{\text{RESET}}$ is undefined below the specified power-on reset voltage $(V_{POR})$ . Above $V_{POR}$ , $\overline{\text{RESET}}$ goes low and remains low until the monitored voltage is within the correct operating range (between $V_{\text{IT-(UV)}}$ and $V_{\text{IT(+OV)}}$ ) and the $\overline{\text{RESET}}$ timeout is complete. |

| SENSE              | 10  | ı | SENSE input to monitor voltage rail. Connect this pin to the supply rail that must be monitored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SET0               | 3   | ı | Logic input. SET0, SET1, and CWD select the watchdog window ratios, timeouts, and disable the watchdog; see the セクション 6.6 table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SET1               | 6   | ı | Logic input. SET0, SET1, and CWD select the watchdog window ratios, timeouts, and disable the watchdog; see the セクション 6.6 table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD                | 1   | I | Supply voltage pin. For noisy systems, connecting a 0.1-µF bypass capacitor is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WDI                | 7   | I | Watchdog input. A falling transition (edge) must occur at this pin between the lower $(t_{WDL(max)})$ and upper $(t_{WDU(min)})$ window boundaries in order for $\overline{WDO}$ to not assert. When the watchdog is not in use, the SET pins can be used to disable the watchdog. The input at WDI is ignored when $\overline{RESET}$ or $\overline{WDO}$ are low (asserted) and also when the watchdog is disabled. If the watchdog is disabled, then WDI cannot be left unconnected and must be driven to either VDD or GND.                                                                                                                                                                                                                                                                                                                                                         |

| WDO                | 8   | 0 | Watchdog output. Connect $\overline{WDO}$ with a 1-k $\Omega$ to 100-k $\Omega$ resistor to VDD. $\overline{WDO}$ goes low (asserts) when a watchdog timeout occurs. $\overline{WDO}$ only asserts when $\overline{RESET}$ is high. When a watchdog timeout occurs, $\overline{WDO}$ goes low (asserts) for the set $\overline{RESET}$ timeout delay (t <sub>RST</sub> ). When $\overline{RESET}$ goes low, $\overline{WDO}$ is in a high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Thermal pa         | ad  |   | Connect the thermal pad to a large-area ground plane. The thermal pad is internally connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                    |                                                               | MIN   | MAX                      | UNIT |

|------------------------------------|---------------------------------------------------------------|-------|--------------------------|------|

| Supply voltage range               | VDD                                                           | -0.3  | 7                        | V    |

| Output voltage range               | RESET, WDO                                                    | -0.3  | 7                        | V    |

| Voltage ranges                     | SET0, SET1, WDI, SENSE                                        | -0.3  | 7                        | V    |

| Voltage ranges                     | CWD, CRST                                                     | -0.3  | VDD + 0.3 <sup>(3)</sup> | V    |

| Output pin current                 | RESET, WDO                                                    |       | ±20                      | mA   |

| Input current (all pins)           |                                                               |       | ±20                      | mA   |

| Continuous total power dissipation |                                                               | See 🕏 | クション 6.4                 |      |

|                                    | Operating junction, T <sub>J</sub> <sup>(2)</sup>             | -40   | 150                      |      |

| Temperature                        | Operating free-air temperature, T <sub>A</sub> <sup>(2)</sup> | -40   | 150                      | °C   |

|                                    | Storage, T <sub>stg</sub>                                     | -65   | 150                      |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2)  $T_J = T_A$  as a result of the low dissipated power in this device.

- (3) The absolute maximum rating is  $V_{DD}$  + 0.3 V or 7.0 V, whichever is smaller.

#### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | 1 V  |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                | MIN                | NOM | MAX                 | UNIT |

|--------------------|--------------------------------|--------------------|-----|---------------------|------|

| VDD                | Supply pin voltage             | 1.6                |     | 6.5                 | V    |

| V <sub>SENSE</sub> | Input pin voltage              | 0                  |     | 6.5                 | V    |

| V <sub>SET0</sub>  | SET0 pin voltage               | 0                  |     | 6.5                 | V    |

| V <sub>SET1</sub>  | SET1 pin voltage               | 0                  |     | 6.5                 | V    |

| C <sub>CRST</sub>  | RESET delay capacitor          | 0.1(1)             |     | 1000 <sup>(1)</sup> | nF   |

| CRST               | Pullup resistor to VDD         | 9                  | 10  | 11                  | kΩ   |

| C <sub>CWD</sub>   | Watchdog timing capacitor      | 0.1 <sup>(2)</sup> |     | 1000 <sup>(2)</sup> | nF   |

| CWD                | Pullup resistor to VDD         | 9                  | 10  | 11                  | kΩ   |

| R <sub>PU</sub>    | Pullup resistor, RESET and WDO | 1                  | 10  | 100                 | kΩ   |

| I <sub>RST</sub>   | RESET pin current              |                    |     | 10                  | mA   |

| I <sub>WDO</sub>   | Watchdog output current        |                    |     | 10                  | mA   |

| TJ                 | Junction Temperature           | -40                |     | 125                 | °C   |

<sup>(1)</sup> Using a C<sub>CRST</sub> capacitor of 0.1 nF or 1000 nF gives a reset delay of 703 μs or 3.22 seconds, respectively.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

<sup>(2)</sup> Using a C<sub>CWD</sub> capacitor of 0.1 nF or 1000 nF gives a t<sub>WDU(typ)</sub> of 62.74 ms or 77.45 seconds, respectively.

#### **6.4 Thermal Information**

|                       |                                              | TPS3850    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRC (VSON) | UNIT |

|                       |                                              | 10 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 52.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 59.7       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 26.1       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.7        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 26.0       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 9.7        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report.

### 6.5 Electrical Characteristics

at 1.6 V  $\leq$  V<sub>DD</sub>  $\leq$  6.5 V over the operating temperature range of  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  +125 $^{\circ}$ C (unless otherwise noted); the open-drain pullup resistors are 10 k $\Omega$  for each output; typical values are at T<sub>J</sub> = 25 $^{\circ}$ C

|                             | PARAMETER                                                | TEST CONDITIONS                                              | MIN                         | TYP  | MAX                         | UNIT |

|-----------------------------|----------------------------------------------------------|--------------------------------------------------------------|-----------------------------|------|-----------------------------|------|

| GENERAL C                   | HARACTERISTICS                                           |                                                              |                             | '    |                             |      |

| V <sub>DD</sub> (1) (2) (3) | Supply voltage                                           |                                                              | 1.6                         |      | 6.5                         | V    |

| I <sub>DD</sub>             | Supply current                                           |                                                              |                             | 10   | 19                          | μΑ   |

| RESET FUN                   | CTION                                                    |                                                              |                             |      |                             |      |

| V <sub>POR</sub> (2)        | Power-on reset voltage                                   | $I_{RESET} = 15 \mu A, V_{OL(MAX)} = 0.25 V$                 |                             |      | 0.8                         | V    |

| V <sub>UVLO</sub> (1)       | Undervoltage lockout voltage                             |                                                              |                             | 1.35 |                             | ٧    |

| V <sub>IT+(OV)</sub>        | Overvoltage SENSE threshold accuracy, entering RESET     |                                                              | V <sub>IT+(nom)</sub> =0.8% |      | V <sub>IT+(nom)</sub> +0.8% |      |

| V <sub>IT-(UV)</sub>        | Undervoltage SENSE threshold accuracy, entering RESET    |                                                              | V <sub>IT-(nom)</sub> -0.8% |      | V <sub>IT-(nom)</sub> +0.8% |      |

| V <sub>IT(ADJ)</sub>        | Falling SENSE threshold voltage, adjustable version only |                                                              | 0.3968                      | 0.4  | 0.4032                      | V    |

| V <sub>HYST</sub>           | Hysteresis voltage                                       |                                                              | 0.2%                        | 0.5% | 0.8%                        |      |

| I <sub>CRST</sub>           | CRST pin charge current                                  | CRST = 0.5 V                                                 | 347                         | 375  | 403                         | nA   |

| V <sub>CRST</sub>           | CRST pin threshold voltage                               |                                                              | 1.196                       | 1.21 | 1.224                       | V    |

| WINDOW WA                   | ATCHDOG FUNCTION                                         |                                                              | •                           |      |                             |      |

| I <sub>CWD</sub>            | CWD pin charge current                                   | CWD = 0.5 V                                                  | 347                         | 375  | 403                         | nA   |

| V <sub>CWD</sub>            | CWD pin threshold voltage                                |                                                              | 1.196                       | 1.21 | 1.224                       | V    |

| V <sub>OL</sub>             | RESET, WDO output low                                    | VDD = 5 V, I <sub>SINK</sub> = 3 mA                          |                             |      | 0.4                         | V    |

| I <sub>D</sub>              | RESET, WDO output leakage current                        | VDD = 1.6 V, V <sub>RESET</sub> , = V <sub>WDO</sub> = 6.5 V |                             |      | 1                           | μA   |

| V <sub>IL</sub>             | Low-level input voltage (SET0, SET1)                     |                                                              |                             |      | 0.25                        | V    |

| V <sub>IH</sub>             | High-level input voltage (SET0, SET1)                    |                                                              | 0.8                         |      |                             | V    |

| V <sub>IL(WDI)</sub>        | Low-level input voltage (WDI)                            |                                                              |                             |      | 0.3 × V <sub>DD</sub>       | V    |

| V <sub>IH(WDI)</sub>        | High-level input voltage (WDI)                           |                                                              | 0.8 × V <sub>DD</sub>       |      |                             | V    |

| 1                           | SENSE pin idle current                                   | TPS3850Xyy(y), V <sub>SENSE</sub> = 5.0 V,<br>VDD = 3.3 V    |                             | 2.1  | 2.5                         | μΑ   |

| SENSE                       | OLNOL PIII idie current                                  | TPS3850H01 only, V <sub>SENSE</sub> = 5.0 V,<br>VDD = 3.3 V  | -50                         |      | 50                          | nA   |

- (1) When V<sub>DD</sub> falls below V<sub>UVLO</sub>, RESET is driven low.

(2) When V<sub>DD</sub> falls below V<sub>POR</sub>, RESET and WDO are undefined.

(3) During power-on, V<sub>DD</sub> must be a minimum 1.6 V for at least 300 µs before the output corresponds to the SENSE voltage.

Product Folder Links: TPS3850

# **6.6 Timing Requirements**

|                       |                                     |                                                             | MIN               | TYP         | MAX    | UNIT |

|-----------------------|-------------------------------------|-------------------------------------------------------------|-------------------|-------------|--------|------|

| GENERA                | L                                   |                                                             |                   |             |        |      |

| t <sub>INIT</sub>     | CWD, CRST pin evaluation            | period <sup>(1)</sup>                                       |                   | 381         |        | μs   |

| t <sub>SET</sub>      | Time required between chan          | ging SET0 and SET1 pins                                     |                   | 500         |        | μs   |

|                       | SET0, SET1 pin setup time           |                                                             |                   | 1           |        | μs   |

|                       | Startup delay <sup>(2)</sup>        |                                                             |                   | 300         |        | μs   |

| RESET F               | UNCTION                             |                                                             |                   |             | 1      |      |

|                       | Poset timeout period                | CRST = NC                                                   | 170               | 200         | 230    | ms   |

| t <sub>RST</sub>      | Reset timeout period                | CRST = 10 kΩ to VDD                                         | 8.5               | 10          | 11.5   | ms   |

|                       | V & DECET datase                    | VDD = 5 V, V <sub>SENSE</sub> = V <sub>IT+(OV)</sub> + 2.5% |                   | 35          |        |      |

| t <sub>RST-DEL</sub>  | V <sub>SENSE</sub> to RESET delay   | VDD = 5 V, V <sub>SENSE</sub> = V <sub>IT-(UV)</sub> - 2.5% | 17                |             |        | μs   |

| WINDOW                | WATCHDOG FUNCTION                   |                                                             |                   | ,           | 1      |      |

|                       | Window watchdog ratio of            | CWD = programmable, SET0 = 0, SET1 = 0 <sup>(3)</sup>       |                   | 1/8         |        |      |

| WD ratio              | lower boundary to upper<br>boundary | CWD = programmable, SET0 = 1, SET1 = 1 <sup>(3)</sup>       |                   | 1/2         |        |      |

|                       |                                     | CWD = programmable, SET0 = 0, SET1 = 1 <sup>(3)</sup> (4)   |                   | 3/4         |        |      |

|                       | Window watchdog lower<br>boundary   | CWD = NC, SET0 = 0, SET1 = 0                                | 19.1              | 22.5        | 25.9   | ms   |

|                       |                                     | CWD = NC, SET0 = 0, SET1 = 1                                | 1.48              | 1.85        | 2.22   | ms   |

|                       |                                     | CWD = NC, SET0 = 1, SET1 = 0                                | Watchdog disabled |             | ed     |      |

|                       |                                     | CWD = NC, SET0 = 1, SET1 = 1                                | 680               | 800         | 920    | ms   |

| t <sub>WDL</sub>      |                                     | CWD = 10 k $\Omega$ to VDD, SET0 = 0, SET1 = 0              | 7.65              | 9.0         | 10.35  | ms   |

|                       |                                     | CWD = 10 k $\Omega$ to VDD, SET0 = 0, SET1 = 1              | 7.65              | 9.0         | 10.35  | ms   |

|                       |                                     | CWD = 10 k $\Omega$ to VDD, SET0 = 1, SET1 = 0              | Watchdog disabled |             | ed     |      |

|                       |                                     | CWD = 10 kΩ to VDD, SET0 = 1, SET1 = 1                      | 1.48              | 1.85        | 2.22   | ms   |

|                       |                                     | CWD = NC, SET0 = 0, SET1 = 0                                | 46.8              | 55.0        | 63.3   | ms   |

|                       |                                     | CWD = NC, SET0 = 0, SET1 = 1                                | 23.375            | 27.5        | 31.625 | ms   |

|                       |                                     | CWD = NC, SET0 = 1, SET1 = 0                                | Watch             | dog disable | ed     |      |

|                       | Window watchdog upper               | CWD = NC, SET0 = 1, SET1 = 1                                | 1360              | 1600        | 1840   | ms   |

| t <sub>WDU</sub>      | boundary                            | CWD = 10 k $\Omega$ to VDD, SET0 = 0, SET1 = 0              | 92.7              | 109.0       | 125.4  | ms   |

|                       |                                     | CWD = 10 k $\Omega$ to VDD, SET0 = 0, SET1 = 1              | 165.8             | 195.0       | 224.3  | ms   |

|                       |                                     | CWD = $10 \text{ k}\Omega$ to VDD, SET0 = 1, SET1 = 0       | Watchdog disabled |             | ed     |      |

|                       |                                     | CWD = 10 kΩ to VDD, SET0 = 1, SET1 = 1                      | 9.35              | 11.0        | 12.65  | ms   |

| t <sub>WD-setup</sub> | Setup time required for device      | ce to respond to changes on WDI after being enabled         |                   | 150         |        | μs   |

|                       | Minimum WDI pulse duration          |                                                             |                   | 50          |        | ns   |

| t <sub>WD-del</sub>   | WDI to WDO delay                    |                                                             |                   | 50          |        | ns   |

<sup>(1)</sup> Please refer to セクション 8.1.1.2

<sup>(1)</sup> Thease refer to Cypia 0.11.12

(2) During power-on, V<sub>DD</sub> must be a minimum 1.6 V for at least 300 μs before the output corresponds to the SENSE voltage.

(3) 0 refers to V<sub>SET</sub> ≤ V<sub>IL</sub>, 1 refers to V<sub>SET</sub> ≥ V<sub>IH</sub>.

(4) If this watchdog ratio is used, then t<sub>WDL(max)</sub> can overlap t<sub>WDU(min)</sub>.

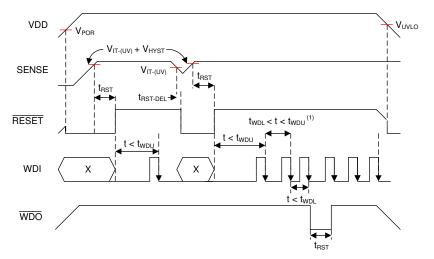

# **6.7 Timing Diagrams**

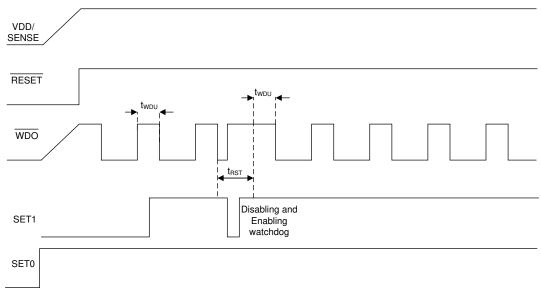

図 6-1. Timing Diagram

A. See 🗵 6-2 for WDI timing requirements.

図 6-2. TPS3850 Window Watchdog Timing

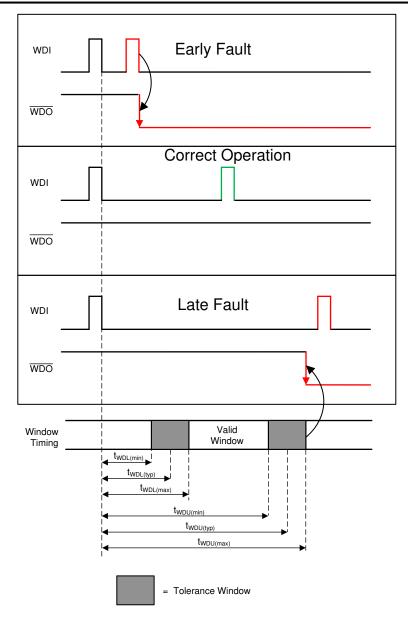

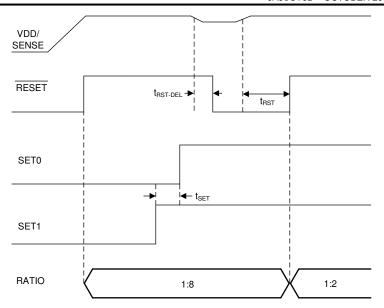

図 6-3. Changing SET0 and SET1 Pins

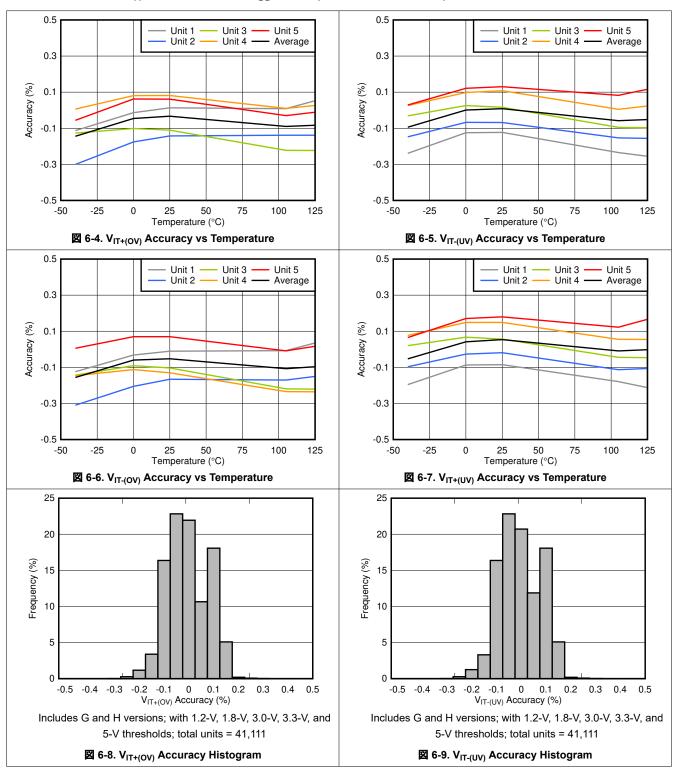

# **6.8 Typical Characteristics**

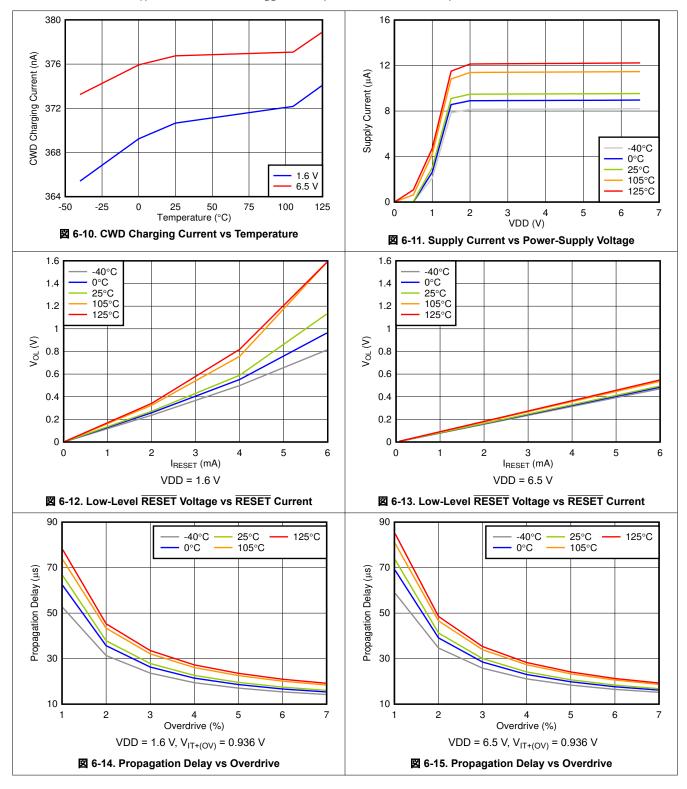

all curves are taken at  $T_A$  = 25°C with 1.6 V  $\leq$  V<sub>DD</sub>  $\leq$  6.5 V (unless otherwise noted)

# **6.8 Typical Characteristics (continued)**

all curves are taken at  $T_A = 25$ °C with 1.6 V  $\leq$  V<sub>DD</sub>  $\leq$  6.5 V (unless otherwise noted)

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

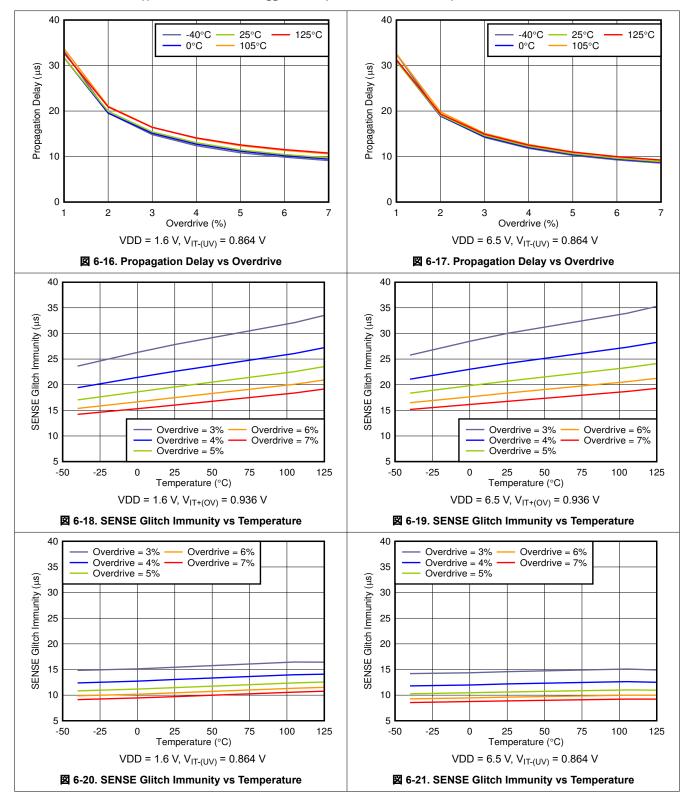

# **6.8 Typical Characteristics (continued)**

all curves are taken at  $T_A$  = 25°C with 1.6 V  $\leq$  V<sub>DD</sub>  $\leq$  6.5 V (unless otherwise noted)

# 7 Detailed Description

### 7.1 Overview

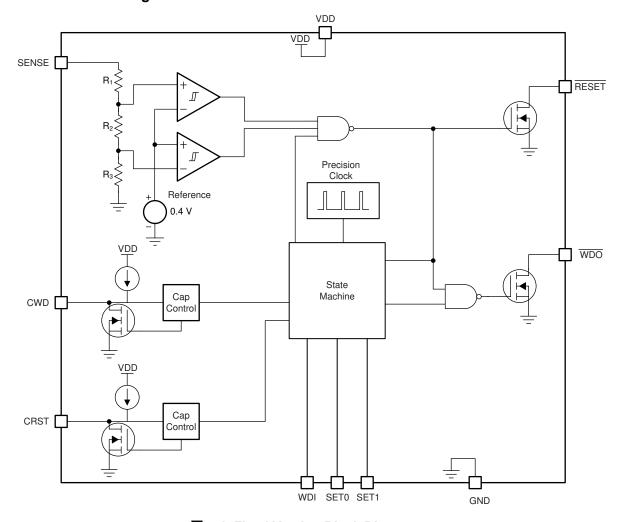

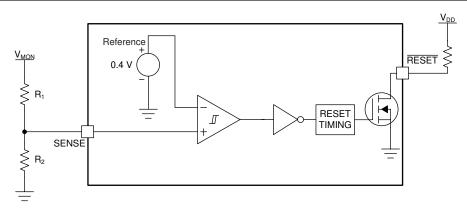

The TPS3850 is a high-accuracy voltage supervisor with an integrated watchdog timer. This device includes a precision voltage supervisor with both overvoltage ( $V_{\text{IT+(OV)}}$ ) and undervoltage ( $V_{\text{IT-(UV)}}$ ) thresholds that achieve 0.8% accuracy over the specified temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . In addition, the TPS3850 includes accurate hysteresis on both thresholds, making the device ideal for use with tight tolerance systems where voltage supervisors must ensure a RESET before the minimum and maximum supply tolerance of the microprocessor or system-on-a-chip (SoC) is reached.

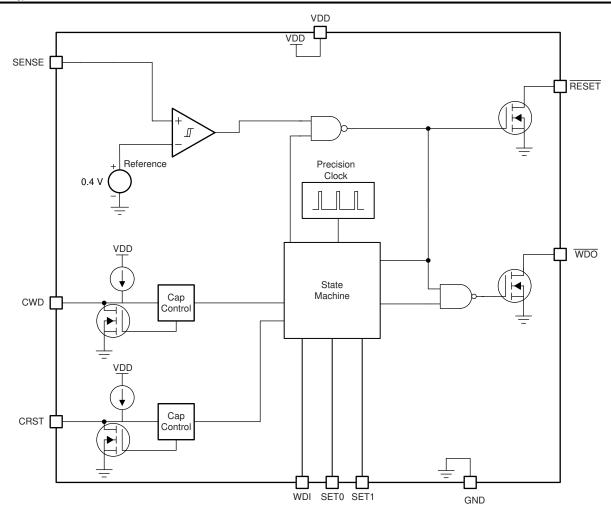

### 7.2 Functional Block Diagrams

図 7-1. Fixed Version Block Diagram

$R_{TOTAL} = R_1 + R_2 + R_3 = 4.5 \text{ M}\Omega.$

図 7-2. Adjustable Version Block Diagram

# 7.3 Feature Description

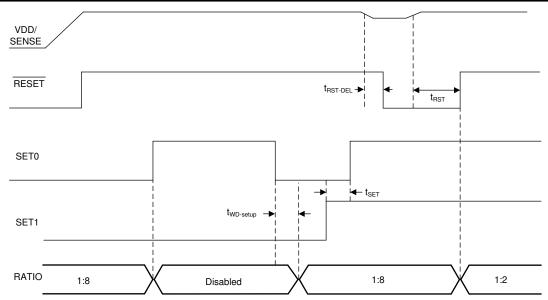

#### 7.3.1 CRST

The CRST pin provides the user the functionality of both high-precision, factory-programmed, reset delay timing options and user-programmable, reset delay timing. The CRST pin can be pulled up to VDD through a resistor, have an external capacitor to ground, or can be left unconnected. The configuration of the CRST pin is reevaluated by the device every time the voltage on the SENSE line enters the valid window ( $V_{\text{IT+(UV)}} < V_{\text{SENSE}} < V_{\text{IT-(OV)}}$ ). The pin evaluation is controlled by an internal state machine that determines which option is connected to the CRST pin. The sequence of events takes 381  $\mu$ s ( $t_{\text{INIT}}$ ) to determine if the CRST pin is left unconnected, pulled up through a resistor, or connected to a capacitor. If the CRST pin is being pulled up to VDD, then a 10-k $\Omega$  pullup resistor is required.

#### **7.3.2 RESET**

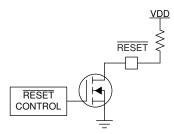

The  $\overline{\text{RESET}}$  pin features a programmable reset delay time that can be adjusted from 703 µs to 3.22 seconds when using adjustable capacitor timing.  $\overline{\text{RESET}}$  is an open-drain output that should be pulled up through a 1-k $\Omega$  to 100-k $\Omega$  pullup resistor. When  $V_{DD}$  is above  $V_{DD \text{ (min)}}$ ,  $\overline{\text{RESET}}$  remains high (not asserted) when the SENSE voltage is between the positive threshold  $(V_{\text{IT+(OV)}})$  and the negative threshold  $(V_{\text{IT-(UV)}})$ . If SENSE falls below  $V_{\text{IT-(UV)}}$  or rises above  $V_{\text{IT+(OV)}}$ , then  $\overline{\text{RESET}}$  is asserted, driving the  $\overline{\text{RESET}}$  pin to a low-impedance state. When SENSE comes back into the valid window, a  $\overline{\text{RESET}}$  delay circuit is enabled that holds  $\overline{\text{RESET}}$  low for a specified reset delay period ( $t_{RST}$ ). This  $t_{RST}$  period is determined by what is connected to the CRST pin; see  $\boxtimes$  8-1. When the reset delay has elapsed, the  $\overline{\text{RESET}}$  pin goes to a high-impedance state and uses a pullup resistor to hold  $\overline{\text{RESET}}$  high. The pullup resistor must be connected to the proper voltage rail to allow other

devices to be connected at the correct interface voltage. To ensure proper voltage levels, give some consideration when choosing the pullup resistor values. The pullup resistor value is determined by output logic low voltage ( $V_{OL}$ ), capacitive loading, and leakage current ( $I_D$ ); see the 2/222 8.1.1 section for more information.

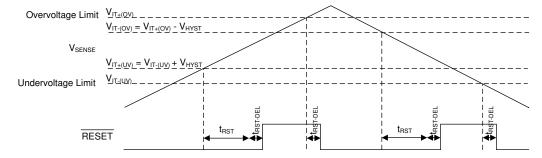

#### 7.3.3 Over- and Undervoltage Fault Detection

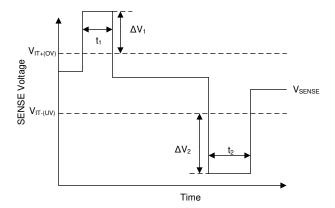

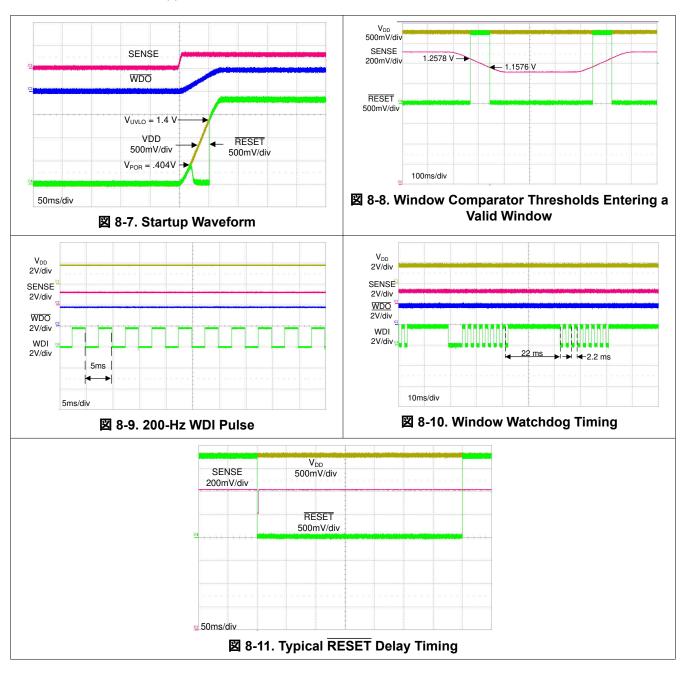

The TPS3850 features both overvoltage detection and undervoltage detection. This detection is achieved through the combination of two comparators with a precision voltage reference and a trimmed resistor divider (fixed versions only). The SENSE pin is used to monitor the critical voltage rail; this configuration optimizes device accuracy because all resistor tolerances are accounted for in the accuracy and performance specifications. Both comparators also include built-in hysteresis that provides some noise immunity and ensures stable operation. If the voltage on the SENSE pin drops below  $V_{\text{IT-(UV)}}$ , then  $\overline{\text{RESET}}$  is asserted (driven low). When the voltage on the SENSE pin is between the positive and negative threshold voltages,  $\overline{\text{RESET}}$  deasserts after the user-defined  $\overline{\text{RESET}}$  delay time, as shown in  $\boxed{2}$  7-3.

The SENSE input can vary from GND to 6.5 V, regardless of the device supply voltage used. Although not required in most cases, for noisy applications, good analog-design practice is to place a 1-nF to 10-nF bypass capacitor at the SENSE pin to reduce sensitivity to transient voltages on the monitored signal.

図 7-3. Window Comparator Timing Diagram

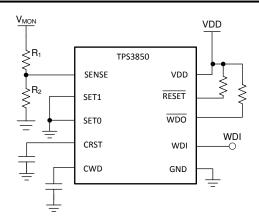

#### 7.3.4 Adjustable Operation Using the TPS3850H01

The adjustable version (TPS3850H01) can be used to monitor any voltage rail down to 0.4 V using the circuit illustrated in  $\boxtimes$  7-4. When using the TPS3850H01, the device does not function as a window comparator; instead, the device only monitors the undervoltage threshold. To monitor a user-defined voltage, the target threshold voltage for the monitored supply (V<sub>MON</sub>) and the resistor divider values can be calculated by using  $\rightrightarrows$  1 and  $\rightrightarrows$  2, respectively:

$$V_{MON} = V_{IT(ADJ)} \times \left(1 + \frac{R_1}{R_2}\right)$$

(1)

$\pm$  1 can be used to calculate either the negative threshold or the positive threshold by replacing  $V_{ITX}$  with either  $V_{ITN}$  or  $V_{ITN} + V_{HYST}$ , respectively.

$$R_{TOTAL} = R_1 + R_2 \tag{2}$$

Large resistor values minimize current consumption; however, the input bias current of the device degrades accuracy if the current through the resistors is too low. Therefore, choosing an  $R_{TOTAL}$  value so that the current through the resistor divider is at least 100 times larger than the maximum SENSE pin current ( $I_{SENSE}$ ) ensures a good degree of accuracy; see the  $I_Q$  vs Accuracy Tradeoff In Designing Resistor Divider Input To A Voltage Supervisor (SLVA450) application report for more details on sizing input resistors.

図 7-4. Adjustable Voltage Monitor

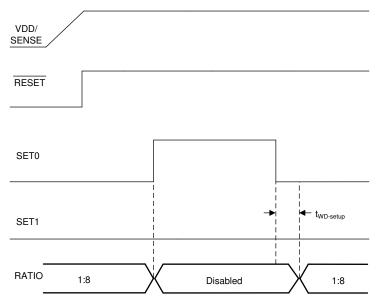

# 7.3.5 Window Watchdog 7.3.5.1 SET0 and SET1

When changing the SET0 or SET1 pins, there are two cases to consider: enabling and disabling the watchdog, and changing the SET0 or SET1 pins when the watchdog is enabled. In case 1 where the watchdog is being enabled or disabled, the changes take effect immediately. However, in case 2, a RESET event must occur in order for the changes to take place.

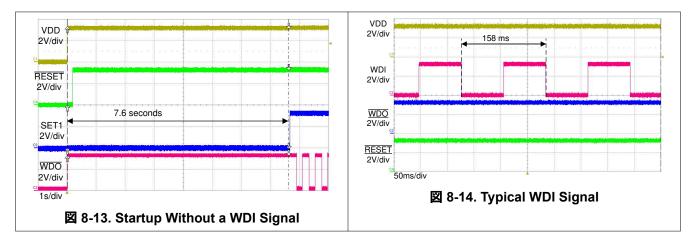

#### 7.3.5.1.1 Enabling the Window Watchdog

The TPS3850 features the ability to enable and disable the watchdog timer. This feature allows the user to start with the watchdog timer disabled and then enable the watchdog timer using the SET0 and SET1 pins. The ability to enable and disable the watchdog is useful to avoid undesired watchdog trips during initialization and shutdown. When the SETx pins are changed to disable the watchdog timer, changes on the pins are responded to immediately (as shown in  $\boxtimes$  7-5). When the watchdog goes from disabled to enabled, there is a 150  $\mu$ s ( $t_{WD-setup}$ ) transition period where the device does not respond to changes on WDI. After this 150- $\mu$ s period, the device begins to respond to changes on WDI again.

図 7-5. Enabling the Watchdog Timer

#### 7.3.5.1.2 Disabling the Watchdog Timer When Using the CRST Capacitor

When using the TPS3850-Q1 with fixed timing options, if the watchdog is disabled and reenabled while  $\overline{WDO}$  is asserted (logic low) the watchdog performs as described in the  $\overline{\overline{VDSS}}$  7.3.5.1.1 section. However, if there is a capacitor on the CRST pin, and the watchdog is disabled and reenabled when  $\overline{WDO}$  is asserted (logic low), then the watchdog behaves as shown in  $\overline{\mathbb{Z}}$  7-6. When the watchdog is disabled,  $\overline{WDO}$  goes high impedance (logic high). However, when the watchdog is enabled again, the  $t_{RST}$  period must expire before the watchdog resumes normal operation.

There is no WDI signal in this figure, WDI is always at GND.

図 7-6. Enabling and Disabling the Watchdog Timer During a WDO Reset Event

#### 7.3.5.1.3 SET0 and SET1 During Normal Watchdog Operation

The SET0 and SET1 pins can be used to control the window watchdog ratio of the lower boundary to the upper boundary. There are four possible modes for the watchdog (see 表 8-5): disabled, 1:8 ratio, 3:4 ratio, and 1:2 ratio. If SET0 = 1 and SET1 = 0, then the watchdog is disabled. When the watchdog is disabled  $\overline{WDO}$  does not assert, and the TPS3850 functions as a normal supervisor. The SET0 and SET1 pins can be changed when the device is operational, but cannot be changed at the same time. If these pins are changed when the device is operational, then there must be a 500- $\mu$ s ( $t_{SET}$ ) delay between switching the two pins. If the SET0 and SET1 are used to change the reset timing, then a reset event must occur before the new timing condition is latched. This reset can be triggered by SENSE rising above  $V_{IT+(OV)}$  or below  $V_{IT-(UV)}$ , or by bringing  $V_{DD}$  below  $V_{UVLO}$ .  $\boxtimes$  7-7 shows how the SET0 and SET1 pins do not change the watchdog timing option until a reset event has occurred.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

図 7-7. Changing SET0 and SET1 Pins

#### 7.3.6 Window Watchdog Timer

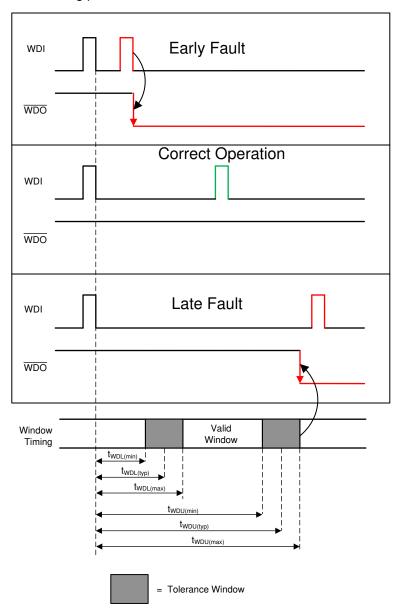

This section provides information for the window watchdog modes of operation. A window watchdog is typically employed in safety critical applications where a traditional watchdog timer is inadequate. In a traditional watchdog, there is a maximum time in which a pulse must be issued to prevent the reset from occurring. However, in a window watchdog the pulse must be issued between a maximum lower window time  $(t_{WDL(max)})$  and the minimum upper window time  $(t_{WDU(min)})$  set by the CWD pin and the SET0 and SET1 pins.  $\frac{1}{8}$  8-5 describes how  $t_{WDU}$  can be used to calculate the timing of  $t_{WDL}$ . The  $t_{WDL}$  timing can also be changed by adjusting the SET0 and SET1 pins.  $\frac{1}{8}$  7-8 shows the valid region for a WDI pulse to be issued to prevent the  $\overline{WDO}$  from being triggered and being pulled low.

図 7-8. TPS3850 Window Watchdog Timing

#### 7.3.6.1 CWD

The CWD pin provides the user the functionality of both high-precision, factory-programmed watchdog timing options and user-programmable watchdog timing. The TPS3850 features three options for setting the watchdog window: connecting a capacitor to the CWD pin, connecting a pullup resistor to VDD, and leaving the CWD pin unconnected. The configuration of the CWD pin is evaluated by the device every time  $V_{SENSE}$  enters the valid window ( $V_{IT+(UV)} < V_{SENSE} < V_{IT-(OV)}$ ). The pin evaluation is controlled by an internal state machine that determines which option is connected to the CWD pin. The sequence of events takes 381  $\mu$ s ( $t_{INIT}$ ) to determine if the CWD pin is left unconnected, pulled up through a resistor, or connected to a capacitor. If the CWD pin is being pulled up to VDD using a pullup resistor, then a 10-k $\Omega$  resistor is required.

#### 7.3.6.2 WDI Functionality

WDI is the watchdog timer input that controls the  $\overline{WDO}$  output. The WDI input is triggered by the falling edge of the input signal. For the first pulse, the watchdog acts as a traditional watchdog timer; thus, the first pulse must be issued before  $t_{WDU(min)}$ . After the first pulse, to ensure proper functionality of the watchdog timer, always issue the WDI pulse within the window of  $t_{WDL(max)}$  and  $t_{WDU(min)}$ . If the pulse is issued in this region, then  $\overline{WDO}$  remains unasserted. Otherwise, the device asserts  $\overline{WDO}$ , putting the  $\overline{WDO}$  pin into a low-impedance state.

The watchdog input (WDI) is a digital pin. To ensure there is no increase in  $I_{DD}$ , drive the WDI pin to either VDD or GND at all times. Putting the pin to an intermediate voltage can cause an increase in supply current ( $I_{DD}$ ) because of the architecture of the digital logic gates. When  $\overline{RESET}$  is asserted, the watchdog is disabled and all signals input to WDI are ignored. When  $\overline{RESET}$  is no longer asserted, the device resumes normal operation and no longer ignores the signal on WDI. If the watchdog is disabled, drive the WDI pin to either VDD or GND.

#### 7.3.6.3 WDO Functionality

The TPS3850 features a window watchdog timer with an independent watchdog output ( $\overline{WDO}$ ). The independent watchdog output provides the flexibility to flag a fault in the watchdog timing without performing an entire system reset. When  $\overline{RESET}$  is not asserted (high), the  $\overline{WDO}$  signal maintains normal operation. When asserted,  $\overline{WDO}$  remains down for  $t_{RST}$ . When the  $\overline{RESET}$  signal is asserted (low), the  $\overline{WDO}$  pin goes to a high-impedance state. When  $\overline{RESET}$  is unasserted, the window watchdog timer resumes normal operation and  $\overline{WDO}$  can be used again.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

#### 7.4 Device Functional Modes

表 7-1 summarizes the functional modes of the TPS3850.

#### 表 7-1. Device Functional Modes

| VDD                                     | WDI                                                                                | WDO  | SENSE                                         | RESET     |

|-----------------------------------------|------------------------------------------------------------------------------------|------|-----------------------------------------------|-----------|

| V <sub>DD</sub> < V <sub>POR</sub>      | _                                                                                  | _    | _                                             | Undefined |

| $V_{POR} \le V_{DD} < V_{UVLO}$         | Ignored                                                                            | High | _                                             | Low       |

|                                         | Ignored                                                                            | High | V <sub>SENSE</sub> < V <sub>IT+(UV)</sub> (1) | Low       |

|                                         | Ignored                                                                            | High | V <sub>SENSE</sub> > V <sub>IT-(OV)</sub> (1) | Low       |

| V <sub>DD</sub> ≥ V <sub>DD (min)</sub> | $t_{\text{WDL(max)}} \le t_{\text{pulse}} \stackrel{(3)}{\le} t_{\text{WDU(min)}}$ | High | $V_{IT-(UV)} < V_{SENSE} < V_{IT+(OV)}$ (2)   | High      |

|                                         | $t_{WDL(max)} > t_{pulse}$ (3)                                                     | Low  | $V_{IT-(UV)} < V_{SENSE} < V_{IT+(OV)}$ (2)   | High      |

|                                         | t <sub>WDU(min)</sub> < t <sub>pulse</sub> (3)                                     | Low  | $V_{IT-(UV)} < V_{SENSE} < V_{IT+(OV)}$ (2)   | High      |

- (1) When V<sub>SENSE</sub> has not entered the valid window.

- (2) When V<sub>SENSE</sub> is in the valid window.

- (3) Where t<sub>pulse</sub> is the time between falling edges on WDI.

# 7.4.1 $V_{DD}$ is Below $V_{POR}$ ( $V_{DD} < V_{POR}$ )

When  $V_{DD}$  is less than  $V_{POR}$ ,  $\overline{RESET}$  is undefined and can be either high or low. The state of  $\overline{RESET}$  largely depends on the load that the  $\overline{RESET}$  pin is experiencing.

# 7.4.2 Above Power-On-Reset But Less Than UVLO (V<sub>POR</sub> ≤ V<sub>DD</sub> < V<sub>UVLO</sub>)

When  $V_{DD}$  is less than  $V_{UVLO}$ , and greater than or equal to  $V_{POR}$ , the  $\overline{RESET}$  signal is asserted (logic low) regardless of the voltage on the SENSE pin. When  $\overline{RESET}$  is asserted, the watchdog output  $\overline{WDO}$  is in a high-impedance state regardless of the WDI signal that is input to the device.

# 7.4.3 Above UVLO But Less Than $V_{DD \ (min)}$ ( $V_{UVLO} \le V_{DD} < V_{DD \ (min)}$ )

When  $V_{DD}$  is less than  $V_{DD\ (min)}$  and greater than or equal to  $V_{UVLO}$ , the  $\overline{RESET}$  signal responds to changes on the SENSE pin, but the accuracy can be degraded.

#### 7.4.4 Normal Operation (V<sub>DD</sub> ≥ V<sub>DD (min)</sub>)

When  $V_{DD}$  is greater than or equal to  $V_{DD}$  (min), the  $\overline{RESET}$  signal is determined by  $V_{SENSE}$ . When  $\overline{RESET}$  is asserted,  $\overline{WDO}$  goes to a high-impedance state.  $\overline{WDO}$  is then pulled high through the pullup resistor.

Product Folder Links: TPS3850

# 8 Application and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

#### 8.1 Application Information

The following sections describe in detail proper device implementation, depending on the final application requirements.

#### 8.1.1 CRST Delay

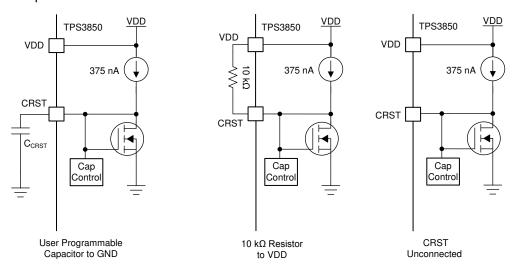

The TPS3850 features three options for setting the reset delay  $(t_{RST})$ : connecting a capacitor to the CRST pin, connecting a pullup resistor to VDD, and leaving the CRST pin unconnected.  $\boxtimes$  8-1 shows a schematic drawing of all three options. To determine which option is connected to the CRST pin, an internal state machine controls the internal pulldown device and measures the pin voltage. This sequence of events takes 381  $\mu$ s  $(t_{INIT})$  to determine which timing option is used. Every time  $\overline{RESET}$  is asserted, the state machine determines what is connected to the pin.

図 8-1. CRST Charging Circuit

### 8.1.1.1 Factory-Programmed Reset Delay Timing

To use the factory-programmed timing options, the CRST pin must either be left unconnected or pulled up to VDD through a 10-k $\Omega$  pullup resistor. Using these options enables a high-precision, 15% accurate reset delay timing, as shown in  $\frac{1}{8}$  8-1.

表 8-1. Reset Delay Time for Factory-Programmed Reset Delay Timing

| CRST         | RESI | UNIT |      |      |

|--------------|------|------|------|------|

| CR31         | MIN  | TYP  | MAX  | UNII |

| NC           | 170  | 200  | 230  | ms   |

| 10 kΩ to VDD | 8.5  | 10   | 11.5 | ms   |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

#### 8.1.1.2 Programmable Reset Delay-Timing

The TPS3850 uses a CRST pin charging current ( $I_{CRST}$ ) of 375 nA. When using an external capacitor, the rising RESET delay time can be set to any value between 700  $\mu$ s ( $C_{CRST}$  = 100 pF) and 3.2 seconds ( $C_{CRST}$  = 1  $\mu$ F). The typical ideal capacitor value needed for a given delay time can be calculated using  $\pm$  3, where  $C_{CRST}$  is in microfarads and  $t_{RST}$  is in seconds:

$$t_{RST} = 3.22 \times C_{CRST} + 0.000381$$

(3)

To calculate the minimum and maximum-reset delay time use  $\pm 4$  and  $\pm 5$ , respectively.

$$t_{RST(min)} = 2.8862 \times C_{CRST} + 0.000324$$

(4)

$$t_{RST(max)} = 3.64392 \times C_{CRST} + 0.000438$$

(5)

The slope of  $\not \equiv 3$  is determined by the time the CRST charging current ( $I_{CRST}$ ) takes to charge the external capacitor up to the CRST comparator threshold voltage ( $V_{CRST}$ ). When  $\overrightarrow{RESET}$  is asserted, the capacitor is discharged through the internal CRST pulldown resistor. When the  $\overrightarrow{RESET}$  conditions are cleared, the internal precision current source is enabled and begins to charge the external capacitor; when  $V_{CRST} = 1.21 \text{ V}$ ,  $\overrightarrow{RESET}$  is unasserted. Note that to minimize the difference between the calculated  $\overrightarrow{RESET}$  delay time and the actual  $\overrightarrow{RESET}$  delay time, use a use a high-quality ceramic dielectric COG, X5R, or X7R capacitor and minimize parasitic board capacitance around this pin.  $\not \equiv 8-2$  lists the reset delay time ideal capacitor values for  $C_{CRST}$ .

表 8-2. Reset Delay Time for Common Ideal Capacitor Values

| C                 | RESE               | UNIT |                    |      |

|-------------------|--------------------|------|--------------------|------|

| C <sub>CRST</sub> | MIN <sup>(1)</sup> | TYP  | MAX <sup>(1)</sup> | ONIT |

| 100 pF            | 0.61               | 0.70 | 0.8                | ms   |

| 1 nF              | 3.21               | 3.61 | 4.08               | ms   |

| 10 nF             | 29.2               | 32.6 | 36.8               | ms   |

| 100 nF            | 289                | 323  | 364                | ms   |

| 1 μF              | 2886               | 3227 | 3644               | ms   |

<sup>(1)</sup> Minimum and maximum values are calculated using ideal capacitors.

#### 8.1.2 CWD Functionality

The TPS3850 features three options for setting the watchdog window: connecting a capacitor to the CWD pin, connecting a pullup resistor to VDD, and leaving the CWD pin unconnected.  $\boxtimes$  8-2 shows a schematic drawing of all three options. If this pin is connected to VDD through a 10-k $\Omega$  pullup resistor or left unconnected (high impedance), then the factory-programmed watchdog timeouts are enabled; see the  $\forall \mathcal{P} \neq \mathcal{P$

Product Folder Links: TPS3850

図 8-2. CWD Charging Circuit

#### 8.1.2.1 Factory-Programmed Timing Options

If using the factory-programmed timing options (listed in  $\frac{1}{8}$  8-3), the CWD pin must either be unconnected or pulled up to VDD through a 10-kΩ pullup resistor. Using these options enables high-precision, factory-programmed watchdog timing.

| æ o-s. Factory-Programmed Watchdog mining |      |      |                   |                                             |                   |                   |                                             |        |      |

|-------------------------------------------|------|------|-------------------|---------------------------------------------|-------------------|-------------------|---------------------------------------------|--------|------|

| INPUT                                     |      |      | WATCHDOG LOV      | WATCHDOG LOWER BOUNDARY (t <sub>WDL</sub> ) |                   |                   | WATCHDOG UPPER BOUNDARY (t <sub>WDU</sub> ) |        |      |

| CWD                                       | SET0 | SET1 | MIN               | MIN TYP MAX                                 |                   | MIN               | TYP                                         | MAX    | UNIT |

|                                           | 0    | 0    | 19.1              | 22.5                                        | 25.9              | 46.8              | 55.0                                        | 63.3   | ms   |

| NC NC                                     | 0    | 1    | 1.48              | 1.85                                        | 2.22              | 23.375            | 27.5                                        | 31.625 | ms   |

| INC                                       | 1    | 0    | Watch             | Watchdog disabled                           |                   | Watchdog disabled |                                             |        |      |

|                                           | 1    | 1    | 680               | 800                                         | 920               | 1360              | 1600                                        | 1840   | ms   |

|                                           | 0    | 0    | 7.65              | 9.0                                         | 10.35             | 92.7              | 109.0                                       | 125.4  | ms   |

| 10 kΩ to VDD                              | 0    | 1    | 7.65              | 9.0                                         | 10.35             | 165.8             | 195.0                                       | 224.3  | ms   |

| 10 K22 (0 VDD                             | 1 0  |      | Watchdog disabled |                                             | Watchdog disabled |                   |                                             |        |      |

|                                           | 1    | 1    | 1.48              | 1.85                                        | 2.22              | 9.35              | 11.0                                        | 12.65  | ms   |

表 8-3. Factory-Programmed Watchdog Timing

#### 8.1.2.2 Adjustable Capacitor Timing

Adjustable capacitor timing is achievable by connecting a capacitor to the CWD pin. If a capacitor is connected to CWD, then a 375-nA constant-current source charges  $C_{CWD}$  until  $V_{CWD}$  = 1.21 V. The TPS3850 determines the window watchdog upper boundary with the formula given in  $\not \equiv 6$ , where  $C_{CWD}$  is in microfarads and  $t_{WDU}$  is in seconds.

$$t_{WDU(typ)} = 77.4 \times C_{CWD} + 0.055$$

(6)

The TPS3850 is designed and tested using  $C_{CWD}$  capacitors between 100 pF and 1  $\mu$ F. Note that  $\vec{\pm}$  6 is for ideal capacitors. Capacitor tolerances cause the actual device timing to vary such that the minimum of  $t_{WDU}$  can decrease and the maximum of  $t_{WDU}$  can increase by the capacitor tolerance. To allow for a valid watchdog window, choose a capacitor with tolerance such that  $t_{WDU(min)}$  and  $t_{WDL(max)}$  do not overlap. For the most accurate timing, use ceramic capacitors with COG dielectric material. As shown in  $\pm$  8-4, when using the minimum capacitor of 100 pF, the watchdog upper boundary is 62.74 ms; whereas with a 1- $\mu$ F capacitor, the watchdog upper boundary is 77.455 seconds. If a  $C_{CWD}$  capacitor is used,  $\pm$  6 can be used to set  $t_{WDU}$  the window watchdog upper boundary. The window watchdog lower boundary is dependent on the SET0 and SET1 pins because these pins set the window watchdog ratio of the lower boundary to upper boundary;  $\pm$  8-5 shows how  $t_{WDU}$  can be used to calculate  $t_{WDL}$  based on the SET0 and SET1 pins.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

| 表 8-4. twpu Values for Common | Ideal Capacitor Values |

|-------------------------------|------------------------|

|-------------------------------|------------------------|

| C                | WATCHDO            | WATCHDOG UPPER BOUNDARY (twdu) |                    |      |  |  |

|------------------|--------------------|--------------------------------|--------------------|------|--|--|

| C <sub>CWD</sub> | MIN <sup>(1)</sup> | TYP                            | MAX <sup>(1)</sup> | UNIT |  |  |

| 100 pF           | 56.77              | 62.74                          | 68.7               | ms   |  |  |

| 1 nF             | 119.82             | 132.4                          | 144.98             | ms   |  |  |

| 10 nF            | 750                | 829                            | 908                | ms   |  |  |

| 100 nF           | 7054               | 7795                           | 8536               | ms   |  |  |

| 1 μF             | 70096              | 77455                          | 84814              | ms   |  |  |

(1) Minimum and maximum values are calculated using ideal capacitors.

#### 表 8-5. Programmable CWD Timing

| INF              | PUT  |      | WATCHDOG LOWER BOUNDARY (t <sub>WDL</sub> ) |                          |                               | WATCHDOG UPPER BOUNDARY (t <sub>WDU</sub> ) |                       |                               | UNIT |

|------------------|------|------|---------------------------------------------|--------------------------|-------------------------------|---------------------------------------------|-----------------------|-------------------------------|------|

| CWD              | SET0 | SET1 | MIN                                         | TYP                      | MAX                           | MIN <sup>(2)</sup>                          | TYP <sup>(1)</sup>    | MAX <sup>(2)</sup>            | UNII |

|                  | 0    | 0    | t <sub>WDU(min)</sub> x 0.125               | t <sub>WDU</sub> x 0.125 | t <sub>WDU(max)</sub> x 0.125 | 0.905 x t <sub>WDU(typ)</sub>               | t <sub>WDU(typ)</sub> | 1.095 x t <sub>WDU(typ)</sub> | s    |

| C <sub>CWD</sub> | 0    | 1    | t <sub>WDU(min)</sub> x 0.75                | t <sub>WDU</sub> x 0.75  | t <sub>WDU(max)</sub> x 0.75  | 0.905 x t <sub>WDU(typ)</sub>               | t <sub>WDU(typ)</sub> | 1.095 x t <sub>WDU(typ)</sub> | s    |

| CCMD             | 1    | 0    | W                                           | atchdog disable          | d                             | Wato                                        | hdog disabled         | I                             |      |

|                  | 1    | 1    | t <sub>WDU(min)</sub> x 0.5                 | t <sub>WDU</sub> x 0.5   | t <sub>WDU(max)</sub> x 0.5   | 0.905 x t <sub>WDU(typ)</sub>               | t <sub>WDU(typ)</sub> | 1.095 x t <sub>WDU(typ)</sub> | s    |

- (1) Calculated from 式 6 using ideal capacitors.

- (2) The  $t_{WDU(min)}$  and  $t_{WDU(max)}$  include  $I_{CWD}$  and  $V_{CWD}$  minimum to maximum variation

### 8.1.3 Adjustable SENSE Configuration

The TPS3850H01 has an undervoltage supervisor that can monitor voltage rails greater than 0.4 V. 表 8-6 contains 1% resistor values for creating a voltage divider to monitor common rails from 0.5 V to 12 V with a threshold of 4% and 10%. These resistor values can be scaled to decrease the amount of current flowing through the resistor divider, but increasing the resistor values also decreases the accuracy of the resistor divider. General practice is for the current flowing through the resistor divider to be 100 times greater than the current going into the SENSE pin. This practice ensures the highest possible accuracy. 式 7 can be used to calculate the resistors required in the resistor divider. 図 8-3 shows the block diagram for adjustable operation.

$$V_{MON} = V_{IT(ADJ)} \times \left(1 + \frac{R_1}{R_2}\right) \tag{7}$$

表 8-6. SENSE Resistor Divider Values

| <b>&gt;</b> ( 0 0.0 = 1.0 = 1.0 0.0 0.0 1 0.0 0.0 0.0 0.0 0.0 0.0 0 |                     |                     |                          |                     |                     |                          |  |

|---------------------------------------------------------------------|---------------------|---------------------|--------------------------|---------------------|---------------------|--------------------------|--|

|                                                                     |                     | 4% THRESHOLD        | % THRESHOLD              |                     | 10% THRESHOLD       |                          |  |

| INPUT VOLTAGE (V)                                                   | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | THRESHOLD<br>VOLTAGE (V) | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | THRESHOLD<br>VOLTAGE (V) |  |

| 0.5                                                                 | 16.2                | 80.6                | 0.48                     | 10                  | 80.6                | 0.45                     |  |

| 0.8                                                                 | 75                  | 80.6                | 0.77                     | 64.9                | 80.6                | 0.72                     |  |

| 0.9                                                                 | 93.1                | 80.6                | 0.86                     | 82.5                | 80.6                | 0.81                     |  |

| 1.2                                                                 | 150                 | 80.6                | 1.14                     | 137                 | 80.6                | 1.08                     |  |

| 1.8                                                                 | 267                 | 80.6                | 1.73                     | 249                 | 80.6                | 1.64                     |  |