# TPS3436-Q1 車載用 Nano IQ 高精度ウィンドウ・ウォッチドッグ・タイマ付き

## 1 特長

- 下記内容で AEC-Q100 認定済み

- デバイス温度グレード 1:動作時周囲温度範囲: $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$

- 工場出荷時にプログラム済みまたはユーザーがプログラム可能なウォッチドッグ・タイムアウト

- $\pm 10\%$  精度のタイマ (最大値)

- 工場出荷時にプログラム済みのクローズ・ウィンドウ:  $1\text{msec} \sim 100\text{sec}$

- 工場出荷時にプログラム済みまたはユーザーがプログラム可能なりセット遅延

- $\pm 10\%$  精度のタイマ (最大値)

- 工場出荷時にプログラム済みのオプション:  $2\text{msec} \sim 10\text{sec}$

- 入力電圧範囲:  $V_{DD} = 1.04\text{V} \sim 6.0\text{V}$

- 超低電源電流:  $I_{DD} = 250\text{nA}$  (標準値)

- オープン・ドレイン、プッシュプル、アクティブ Low 出力

- 各種のプログラマビリティ・オプション:

- ウォッチドッグ・イネーブル / ディセーブル

- ウォッチドッグ・スタートアップ遅延: 遅延なし ~ 10 秒

- オープン・ウィンドウとクローズ・ウィンドウの比率オプション: 1 倍 ~ 511 倍

- ラッチ付き出力オプション

- MR 機能のサポート

## 2 アプリケーション

- オンボード・チャージャ (OBC) およびワイヤレス・チャージャ

- ドライバー監視

- バッテリ管理システム (BMS)

- フロント・カメラ

- サラウンド・ビュー・システムの ECU

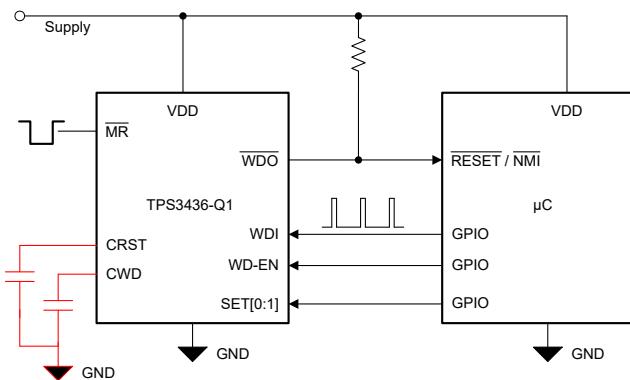

TPS3436-Q1 offers various pinout options to support different features.

Choose the suitable pinout based on application needs.

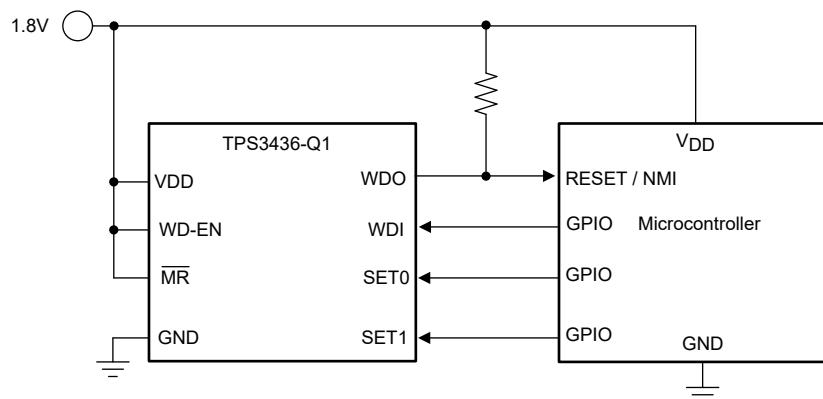

## 代表的なアプリケーション回路

## 3 概要

TPS3436-Q1 は、超低消費電力 (標準値  $250\text{nA}$ ) のデバイスであり、プログラム可能なウォッチドッグ・タイマを搭載しています。

TPS3436-Q1 は、さまざまなアプリケーションに対応する多くの機能を備えた高精度ウォッチドッグ・タイマを提供します。クローズ・ウィンドウ・タイマは、工場出荷時にプログラムするか、または、外付けコンデンサを使用してユーザーがプログラムするか、いずれかが可能です。オープン・ウィンドウとクローズ・ウィンドウの比率は、ロジック・ピンの組み合わせを使用して動作中でも変更できます。また、このウォッチドッグは、イネーブル / ディセーブル、スタートアップ遅延などの独自の機能も備えています。

**WDO** 遅延は、工場出荷時にプログラムされるデフォルトの遅延設定で設定するか、または外付けコンデンサでプログラムできます。また、このデバイスはラッチ付き出力動作も備えており、ウォッチドッグのフォルトがクリアされるまで出力がラッチされます。

TPS3436-Q1 は、TPS3430-Q1 デバイス・ファミリに代わる性能アップグレード製品です。TPS3436-Q1 は、小型の 8 ピン SOT-23 パッケージで供給されます。

## 製品情報

| 部品番号       | パッケージ (1) | 本体サイズ (公称)      |

|------------|-----------|-----------------|

| TPS3436-Q1 | DDF (8)   | 2.90mm × 1.60mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                    |    |                              |    |

|--------------------|----|------------------------------|----|

| 1 特長.....          | 1  | 8.1 概要.....                  | 14 |

| 2 アプリケーション.....    | 1  | 8.2 機能ブロック図.....             | 14 |

| 3 概要.....          | 1  | 8.3 機能説明.....                | 15 |

| 4 改訂履歴.....        | 2  | 8.4 デバイスの機能モード.....          | 23 |

| 5 デバイスの比較.....     | 3  | 9 アプリケーションと実装.....           | 24 |

| 6 ピン構成および機能.....   | 4  | 9.1 アプリケーション情報.....          | 24 |

| 7 仕様.....          | 6  | 9.2 代表的なアプリケーション.....        | 25 |

| 7.1 絶対最大定格.....    | 6  | 9.3 電源に関する推奨事項.....          | 26 |

| 7.2 ESD 定格 .....   | 6  | 9.4 レイアウト.....               | 26 |

| 7.3 推奨動作条件.....    | 6  | 10 デバイスおよびドキュメントのサポート.....   | 28 |

| 7.4 熱に関する情報.....   | 7  | 10.1 ドキュメントの更新通知を受け取る方法..... | 28 |

| 7.5 電気的特性 .....    | 8  | 10.2 サポート・リソース.....          | 28 |

| 7.6 タイミング要件 .....  | 9  | 10.3 商標.....                 | 29 |

| 7.7 スイッチング特性 ..... | 10 | 10.4 静電気放電に関する注意事項.....      | 29 |

| 7.8 タイミング図.....    | 11 | 10.5 用語集.....                | 29 |

| 7.9 代表的特性.....     | 12 | 11 メカニカル、パッケージ、および注文情報.....  | 29 |

| 8 詳細説明.....        | 14 |                              |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (October 2022) to Revision A (June 2023) | Page |

|------------------------------------------------------------------|------|

| • 事前情報から量産データのリリースに変更.....                                       | 1    |

## 5 デバイスの比較

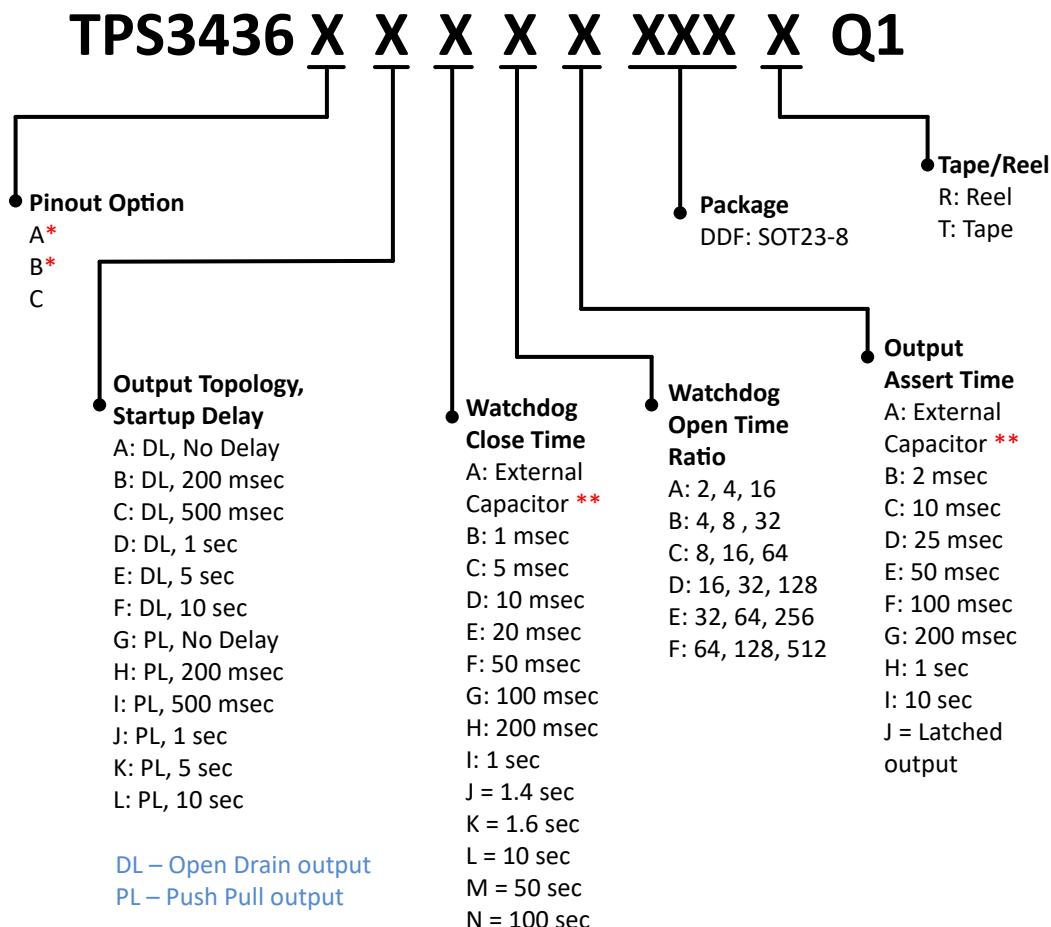

図 5-1 に、TPS3436-Q1 のデバイス命名規則を示します。可能なすべての出力タイプ、ウォッチドッグ時間オプション、および出力アサート遅延オプションの詳細については、[セクション 8](#) を参照してください。他のオプションの詳細と提供状況については、テキサス・インスツルメンツの販売代理店またはテキサス・インスツルメンツの [E2E フォーラム](#)にお問い合わせください。

\* Pinout option supports Start up Delay settings of “No Delay” and “10 sec” only.

\*\* Capacitor programmable time feature available with pinout options A & B. For fixed time and latched output features use pinout option C.

Refer ‘Mechanical, Packaging and Orderable Information’ section for list of released orderable. For any other orderable, contact local TI support.

図 5-1. デバイスの命名規則

TPS3436-Q1 表 5-1 に示すように、さまざまな機能セットを提供するピン互換デバイス・ファミリに属します。

表 5-1. ピン互換デバイス・ファミリ

| デバイス       | 電圧監視 | ウォッチドッグのタイプ |

|------------|------|-------------|

| TPS35-Q1   | あり   | タイムアウト      |

| TPS36-Q1   | あり   | ウインドウ       |

| TPS3435-Q1 | なし   | タイムアウト      |

| TPS3436-Q1 | なし   | ウインドウ       |

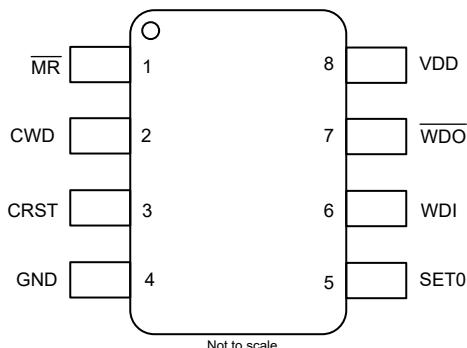

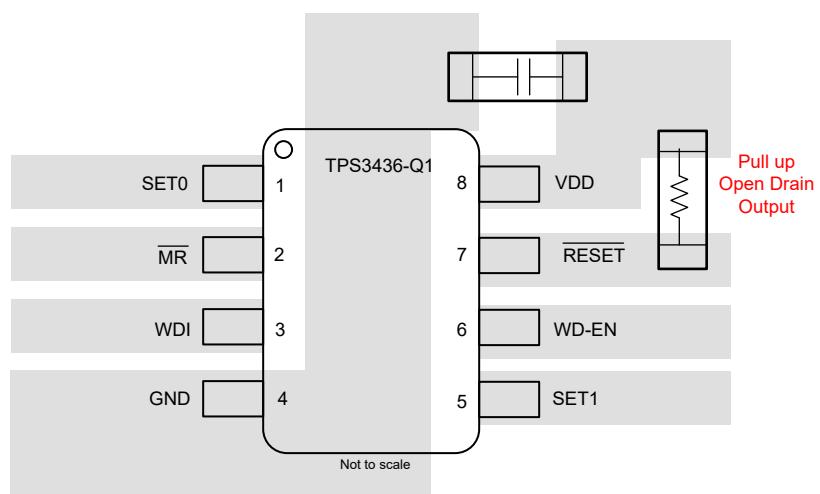

## 6 ピン構成および機能

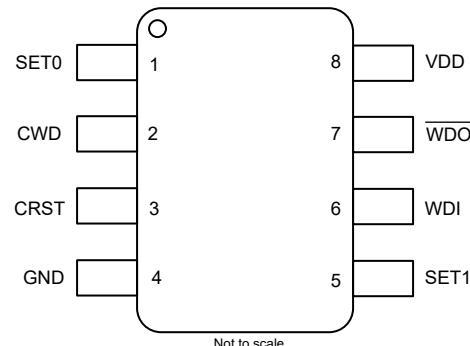

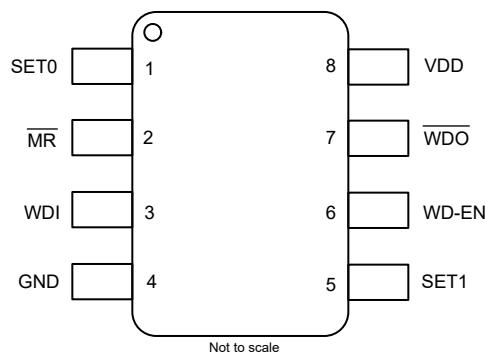

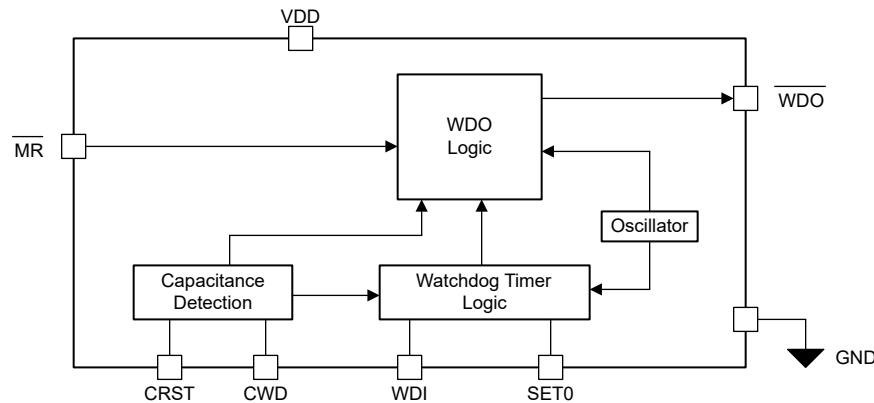

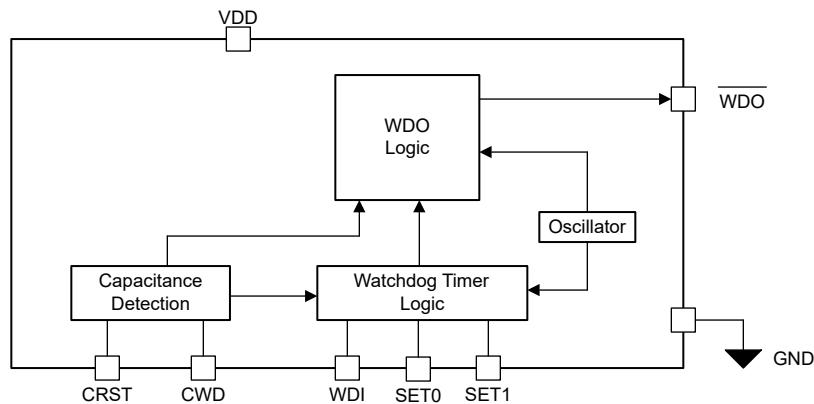

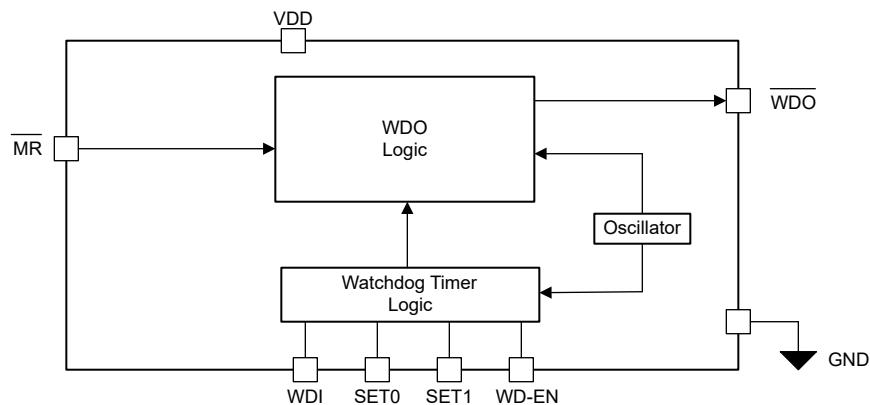

図 6-1. ピン構成オプション A

DDF パッケージ、8 ピン SOT-23、

TPS3436-Q1 上面図

図 6-2. ピン構成オプション B

DDF パッケージ、8 ピン SOT-23、

TPS3436-Q1 上面図

図 6-3. ピン構成オプション C

DDF パッケージ、8 ピン SOT-23、

TPS3436-Q1 上面図

**表 6-1. ピン機能**

| ピン名   | ピン番号      |           |           | I/O | 説明                                                                                                                                                                 |

|-------|-----------|-----------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | ピン配置<br>A | ピン配置<br>B | ピン配置<br>C |     |                                                                                                                                                                    |

| CRST  | 3         | 3         | —         | I   | プログラム可能な WDO アサート時間ピン。このピンと GND の間にコンデンサを接続して、WDO のアサート時間を設定します。詳細については、 <a href="#">セクション 8.3.3</a> を参照してください。                                                    |

| CWD   | 2         | 2         | —         | I   | プログラム可能なウォッチドッグ・タイムアウト入力。ウォッチドッグのクローズ時間は、このピンとグランドの間にコンデンサを接続することで設定します。詳細については、 <a href="#">セクション 8.3.1.1</a> を参照してください。                                          |

| GND   | 4         | 4         | 4         | —   | グランド・ピン                                                                                                                                                            |

| MR    | 1         | —         | 2         | I   | 手動のリセット・ピン。このピンがロジック Low になると、 $\overline{WDO}$ 出力がアサートされます。詳細については、 <a href="#">セクション 8.3.2</a> を参照してください。                                                        |

| WDO   | 7         | 7         | 7         | O   | ウォッチドッグ出力。オープン・ドレイン出力を使用する場合は、プルアップ抵抗を使用して WDO を VDD に接続します。ウォッチドッグ・エラーが発生するか、または MR ピンが Low に駆動されると、WDO がアサートされます。詳細については、 <a href="#">セクション 8.3.3</a> を参照してください。 |

| SET0  | 5         | 1         | 1         | I   | ロジック入力。SET0、SET1、WD-EN ピンは、ウォッチドッグ・ウンドウ比を選択し、ウォッチドッグをイネーブル / ディセーブルします。詳細については、 <a href="#">セクション 8.3.1.5</a> を参照してください。                                           |

| SET1  | —         | 5         | 5         | I   | ロジック入力。SET0、SET1、WD-EN ピンは、ウォッチドッグ・ウンドウ比を選択し、ウォッチドッグをイネーブル / ディセーブルします。詳細については、 <a href="#">セクション 8.3.1.5</a> を参照してください。                                           |

| VDD   | 8         | 8         | 8         | I   | 電源電圧ピン。ノイズの多いシステムでは、 $0.1\mu F$ のバイパス・コンデンサを接続することを推奨します。                                                                                                          |

| WD-EN | —         | —         | 6         | I   | ロジック入力。ロジック High になると、ウォッチドッグ監視機能がイネーブルになります。詳細については、 <a href="#">セクション 8.3.1.3</a> を参照してください。                                                                     |

| WDI   | 6         | 6         | 3         | I   | ウォッチドッグ入力。 $\overline{WDO}$ がアサートされないようにするには、オープン・ウンドウ中にこのピンで立ち下がり遷移 (エッジ) が発生する必要があります。詳細については、 <a href="#">セクション 8.3.1</a> を参照してください。                            |

## 7 仕様

### 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                   |                                                                                                                   | 最小値  | 最大値                           | 単位 |

|-------------------|-------------------------------------------------------------------------------------------------------------------|------|-------------------------------|----|

| 電圧                | VDD                                                                                                               | -0.3 | 6.5                           | V  |

| 電圧                | C <sub>WD</sub> , C <sub>RST</sub> , WD-EN, SETx, WDI, $\overline{MR}$ <sup>(2)</sup> , $\overline{WDO}$ (プッシュプル) | -0.3 | $V_{DD} + 0.3$ <sup>(3)</sup> | V  |

|                   | $\overline{WDO}$ (オープン・ドレイン)                                                                                      | -0.3 | 6.5                           |    |

| 電流                | $\overline{WDO}$ ピン                                                                                               | -20  | 20                            | mA |

| 温度 <sup>(4)</sup> | 動作時の周囲温度, T <sub>A</sub>                                                                                          | -40  | 125                           | °C |

| 温度                | 保存、T <sub>stg</sub>                                                                                               | -65  | 150                           |    |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2)  $\overline{MR}$  を駆動するロジック信号が V<sub>DD</sub> を下回ると、追加の電流が V<sub>DD</sub> から  $\overline{MR}$  に流れます。

- (3) 絶対最大定格は、(V<sub>DD</sub> + 0.3)V または 6.5V のどちらか小さい方です。

- (4) このデバイスの消費電力は低いため、T<sub>J</sub> = T<sub>A</sub> と想定されます。

### 7.2 ESD 定格

|                    |      | 値                                          | 単位         |

|--------------------|------|--------------------------------------------|------------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | $\pm 2000$ |

|                    |      | 荷電デバイス・モデル (CDM)、AEC Q100-011 準拠           | $\pm 750$  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 7.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                                                                                   | 最小値 | 公称値  | 最大値 | 単位 |

|------------------|-----------------------------------------------------------------------------------|-----|------|-----|----|

| 電圧               | VDD (アクティブ Low 出力)                                                                | 0.9 | 6    |     | V  |

|                  | C <sub>WD</sub> 、C <sub>RST</sub> 、WD-EN、SETx、WDI、 $\overline{MR}$ <sup>(1)</sup> | 0   | VDD  |     |    |

|                  | $\overline{WDO}$ (オープン・ドレイン)                                                      | 0   | 6    |     |    |

|                  | $\overline{WDO}$ (プッシュプル)                                                         | 0   | VDD  |     |    |

| 電流               | $\overline{WDO}$ ピン電流                                                             | -5  | 5    | mA  |    |

| C <sub>RST</sub> | C <sub>RST</sub> ピンのコンデンサ範囲                                                       | 1.5 | 1800 | nF  |    |

| C <sub>WD</sub>  | C <sub>WD</sub> ピンのコンデンサ範囲                                                        | 1.5 | 1000 | nF  |    |

| T <sub>A</sub>   | 動作時周囲温度                                                                           | -40 | 125  | °C  |    |

- (1)  $\overline{MR}$  を駆動するロジック信号が V<sub>DD</sub> を下回ると、追加の電流が V<sub>DD</sub> から  $\overline{MR}$  に流れます。V<sub>MR</sub> は V<sub>DD</sub> 以下にする必要があります。

## 7.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | TPS3436-Q1    | 単位   |

|----------------------|-------------------|---------------|------|

|                      |                   | DDF (SOT23-8) |      |

|                      |                   | 8 ピン          |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗      | 175.3         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への热抵抗 | 94.7          | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗      | 92.4          | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 8.4           | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 91.9          | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗 | 該当なし          | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびICパッケージの热評価基準』アプリケーション・レポートを参照してください。

## 7.5 電気的特性

$1.04V \leq V_{DD} \leq 6V$ 、 $\overline{MR}$  = オープン、 $\overline{WDO}$  の  $V_{DD}$  へのプルアップ抵抗 ( $R_{pull-up}$ ) =  $100k\Omega$ 、出力負荷 ( $C_{LOAD}$ ) =  $10pF$ 、自由気流での動作温度範囲内  $-40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り) $V_{DD}$  ランプ・レート  $\leq 1V/\mu s$ 。代表値は  $T_A = 25^{\circ}C$  時に測定

| パラメータ                                        |                                                            | テスト条件                                                               | 最小値  | 代表値         | 最大値 | 単位        |

|----------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|------|-------------|-----|-----------|

| <b>共通パラメータ</b>                               |                                                            |                                                                     |      |             |     |           |

| $V_{DD}$                                     | 入力電源電圧                                                     | アクティブ Low 出力                                                        | 1.04 | 6           |     | V         |

| $I_{DD}$                                     | VDD ピンへの電源電流 <sup>(1)</sup>                                | $T_A = -40^{\circ}C \sim 85^{\circ}C$                               | 0.25 | 0.8         |     | $\mu A$   |

|                                              |                                                            |                                                                     | 0.25 | 3           |     |           |

| $V_{IL}$                                     | Low レベル入力電圧 WD-EN、WDI、SETx、 $\overline{MR}$ <sup>(3)</sup> |                                                                     |      | $0.3V_{DD}$ |     | V         |

| $V_{IH}$                                     | High 入力電圧 WD-EN、WDI、SETx、 $\overline{MR}$ <sup>(3)</sup>   |                                                                     |      | $0.7V_{DD}$ |     | V         |

| $R_{MR}$                                     | 手動リセットの内部プルアップ抵抗                                           |                                                                     |      | 100         |     | $k\Omega$ |

| <b><math>WDO</math> (オープン・ドレン・アクティブ Low)</b> |                                                            |                                                                     |      |             |     |           |

| $V_{OL}$                                     | Low レベル出力電圧                                                | $V_{DD} = 1.5V$<br>$I_{OUT(Sink)} = 500\mu A$                       |      | 300         |     | mV        |

|                                              |                                                            | $V_{DD} = 3.3V$<br>$I_{OUT(Sink)} = 2mA$                            |      | 300         |     |           |

| $I_{lkg(OD)}$                                | オープン・ドレン出力リーク電流                                            | $V_{DD} = V_{PULLUP} = 6V$<br>$T_A = -40^{\circ}C \sim 85^{\circ}C$ | 10   | 30          | nA  |           |

|                                              |                                                            | $V_{DD} = V_{PULLUP} = 6V$                                          | 10   | 60          | nA  |           |

| <b><math>WDO</math> (プッシュプル・アクティブ Low)</b>   |                                                            |                                                                     |      |             |     |           |

| $V_{POR}$                                    | パワーオン $WDO$ 電圧 <sup>(5)</sup>                              | $V_{OH(min)} = 0.8V_{DD}$<br>$I_{out(source)} = 15\mu A$            |      | 900         |     | mV        |

| $V_{OL}$                                     | Low レベル出力電圧                                                | $V_{DD} = 1.5V$<br>$I_{OUT(Sink)} = 500\mu A$                       |      | 300         |     | mV        |

|                                              |                                                            | $V_{DD} = 3.3V$<br>$I_{OUT(Sink)} = 2mA$                            |      | 300         |     |           |

| $V_{OH}$                                     | High レベル出力電圧                                               | $V_{DD} = 1.8V$<br>$I_{OUT(Source)} = 500\mu A$                     |      | $0.8V_{DD}$ |     | V         |

|                                              |                                                            | $V_{DD} = 3.3V$<br>$I_{OUT(Source)} = 500\mu A$                     |      | $0.8V_{DD}$ |     |           |

|                                              |                                                            | $V_{DD} = 6V$<br>$I_{OUT(Source)} = 2mA$                            |      | $0.8V_{DD}$ |     |           |

(1)  $\overline{MR}$  を駆動するロジック信号が  $V_{DD}$  を下回ると、追加の電流が  $V_{DD}$  から  $\overline{MR}$  に流れます。

(2)  $V_{POR}$  は、制御された出力状態の最小  $V_{DD}$  電圧レベルです。

## 7.6 タイミング要件

$1.04V \leq V_{DD} \leq 6V$ 、 $\overline{MR}$  = オープン、 $\overline{WDO}$  の VDD へのプルアップ抵抗 ( $R_{pull-up}$ ) = 100kΩ、出力 RESET / WDO の負荷 ( $C_{LOAD}$ ) = 10pF、自由気流での動作温度範囲内  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に記述のない限り) VDD ランプ・レート  $\leq 1\text{V}/\mu\text{s}$ 。代表値は  $T_A = 25^{\circ}\text{C}$  時に測定

| パラメータ         |                                              | テスト条件                     | 最小値                   | 代表値 | 最大値  | 単位            |

|---------------|----------------------------------------------|---------------------------|-----------------------|-----|------|---------------|

| $t_{MR\_PW}$  | 出力をアサートするための $\overline{MR}$ ピンのパルス期間        |                           |                       | 100 |      | ns            |

| $t_{P-WD}$    | 次のフレームを開始するための WDI パルス期間 (1)                 |                           |                       | 500 |      | ns            |

| $t_{HD-WDEN}$ | WD 動作をイネーブルまたはディセーブルにするための WD-EN のホールド時間 (1) |                           |                       | 200 |      | $\mu\text{s}$ |

| $t_{HD-SETx}$ | WD タイマ設定を変更するための SETx のホールド時間 (1)            |                           |                       | 150 |      | $\mu\text{s}$ |

| $t_{WC}$      | ウォッチドッグ・クローズ・ウインドウ期間                         | 注文可能なオプション:<br>TPS3436xxB | 0.8                   | 1   | 1.2  | ms            |

|               |                                              | 注文可能なオプション:<br>TPS3436xxC | 4                     | 5   | 6    |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxD | 9                     | 10  | 11   |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxE | 18                    | 20  | 22   |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxF | 45                    | 50  | 55   |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxG | 90                    | 100 | 110  |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxH | 180                   | 200 | 220  |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxI | 0.9                   | 1   | 1.1  |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxJ | 1.26                  | 1.4 | 1.54 |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxK | 1.44                  | 1.6 | 1.76 |               |

| $t_{WO}$      | ウォッチドッグ・オープン・ウインドウ期間                         | 注文可能なオプション:<br>TPS3436xxL | 9                     | 10  | 11   | s             |

|               |                                              | 注文可能なオプション:<br>TPS3436xxM | 45                    | 50  | 55   |               |

|               |                                              | 注文可能なオプション:<br>TPS3436xxN | 90                    | 100 | 110  |               |

|               |                                              | SETx ピンが乗数 $n$ を決定        | $(n-1) \times t_{WC}$ |     |      | ms            |

(1) 量産では検査していません。

## 7.7 スイッチング特性

$1.04V \leq V_{DD} \leq 6V$ 、 $\overline{MR} = \text{オープン}$ 、 $\overline{WDO}$  の  $V_{DD}$  へのプルアップ抵抗 ( $R_{pull-up}$ ) =  $100k\Omega$ 、出力 RESET / WDO の負荷 ( $C_{LOAD}$ ) =  $10pF$ 、自由気流での動作温度範囲内  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に記述のない限り)  $V_{DD}$  ランプ・レート  $\leq 1V/\mu\text{s}$ 。代表値は  $T_A = 25^{\circ}\text{C}$  時に測定

| パラメータ         |                                                  | テスト条件                                                               | 最小値  | 代表値 | 最大値  | 単位            |

|---------------|--------------------------------------------------|---------------------------------------------------------------------|------|-----|------|---------------|

| $t_{STRT}$    | スタートアップ遅延 (1)                                    | $C_{CRST}$ ピン = オープンまたは NC                                          |      | 500 |      | $\mu\text{s}$ |

| $t_{SD}$      | ウォッチドッグのスタートアップ遅延                                | 注文可能な部品番号:<br>TPS3436xA、TPS343xG                                    |      | 0   |      | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xB、TPS3436xH                                   | 180  | 200 | 220  |               |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xC、TPS3436xI                                   | 450  | 500 | 550  |               |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xD、TPS3436xJ                                   | 0.9  | 1   | 1.1  | s             |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xE、TPS3436xK                                   | 4.5  | 5   | 5.5  |               |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xF、TPS3436xL                                   | 9    | 10  | 11   |               |

| $t_{WDO}$     | ウォッチドッグのアサート時間遅延                                 | 注文可能な部品番号:<br>TPS3436xxxxB                                          | 1.6  | 2   | 2.4  | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxC                                          | 9    | 10  | 11   | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxD                                          | 22.5 | 25  | 27.5 | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxE                                          | 45   | 50  | 55   | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxF                                          | 90   | 100 | 110  | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxG                                          | 180  | 200 | 220  | ms            |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxH                                          | 0.9  | 1   | 1.1  | s             |

|               |                                                  | 注文可能な部品番号:<br>TPS3436xxxxI                                          | 9    | 10  | 11   | s             |

| $t_{MR\_WDO}$ | $\overline{MR}$ が Low になってから WDO がアサートされるまでの伝搬遅延 | $V_{DD} \geq 1.25V$ 、<br>$\overline{MR} = V_{MR\_H}$ から $V_{MR\_L}$ |      | 100 |      | ns            |

(1) 設計パラメータにより規定されています。

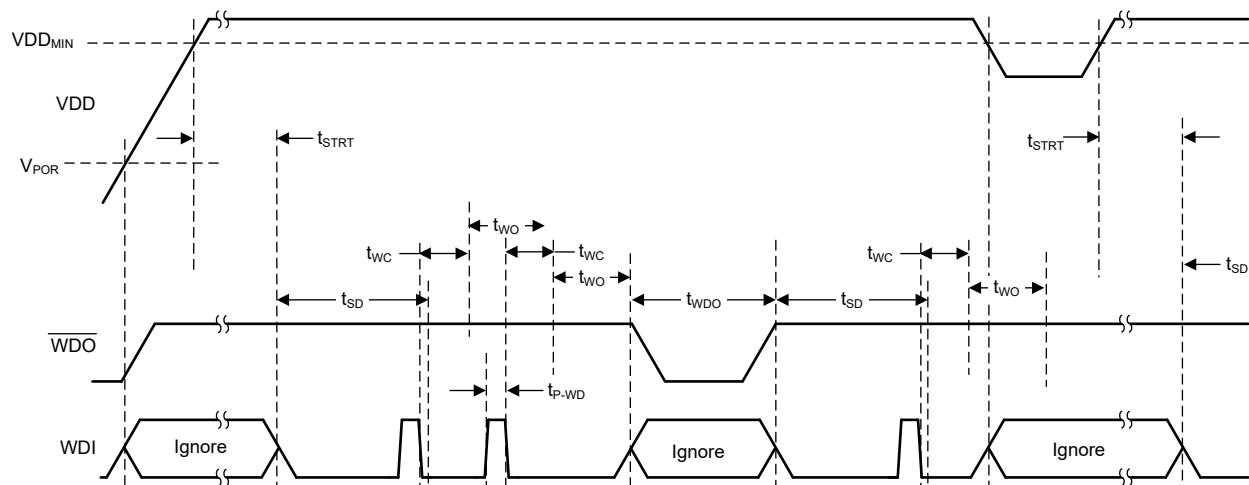

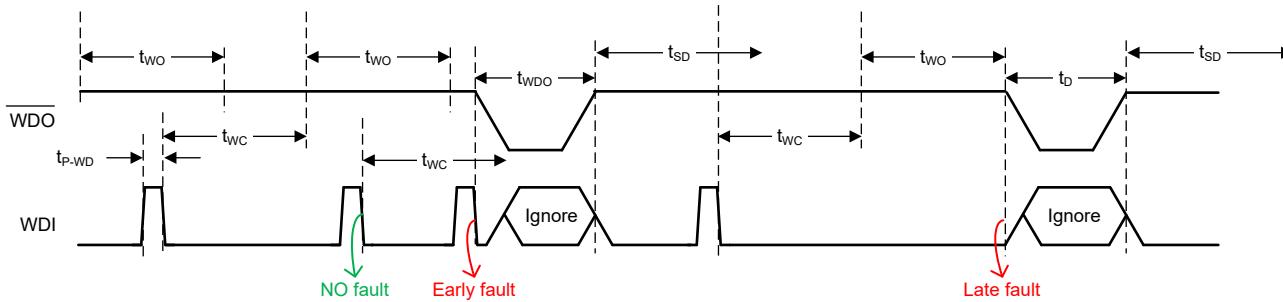

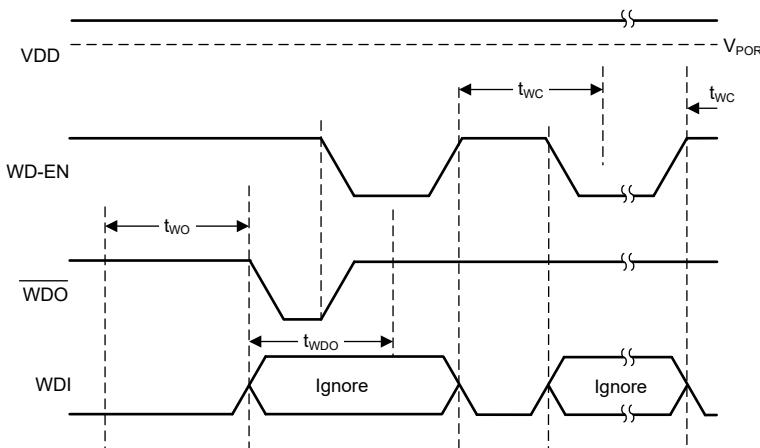

## 7.8 タイミング図

図 7-1. 動作時のタイミング図

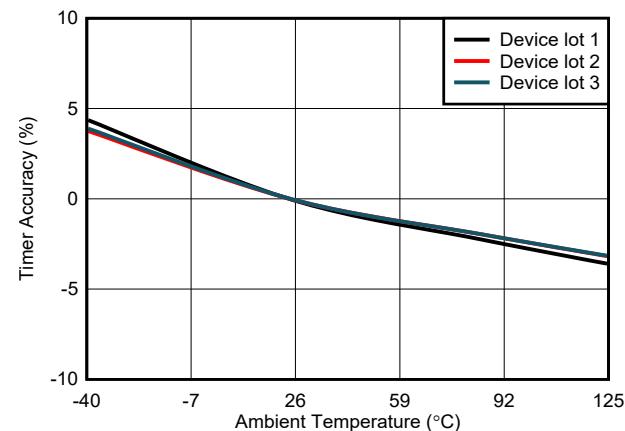

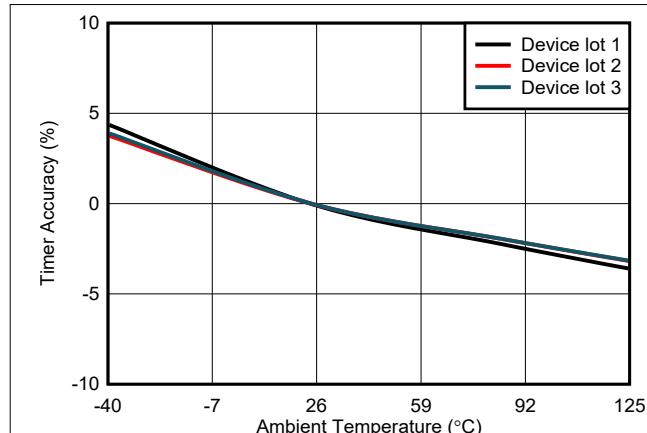

## 7.9 代表的特性

すべての曲線は  $T_A = 25^\circ\text{C}$  で測定 (特に記述のない限り)

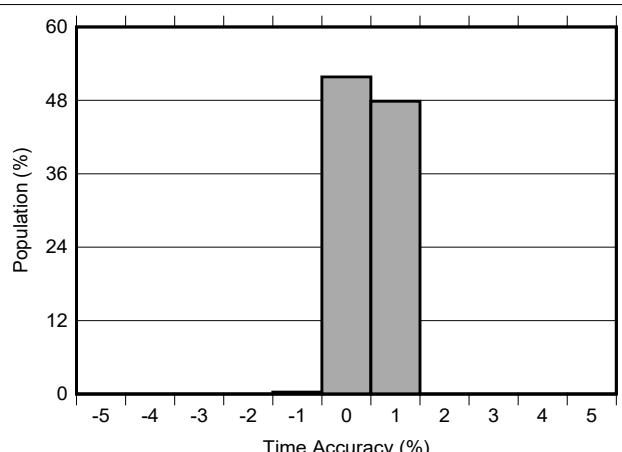

図 7-2. タイマの精度と温度との関係

図 7-3. タイマの精度ヒストグラム

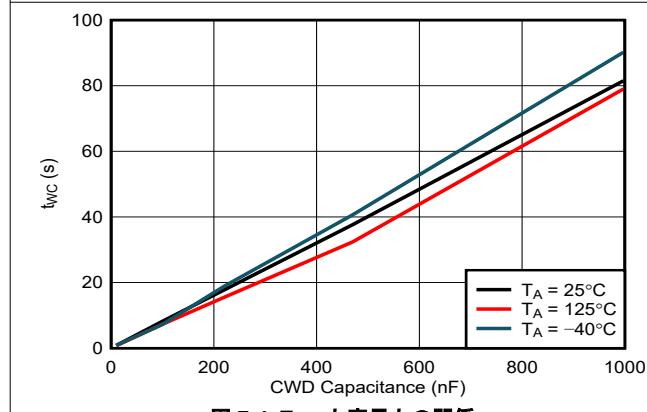

図 7-4.  $t_{WC}$  と容量との関係

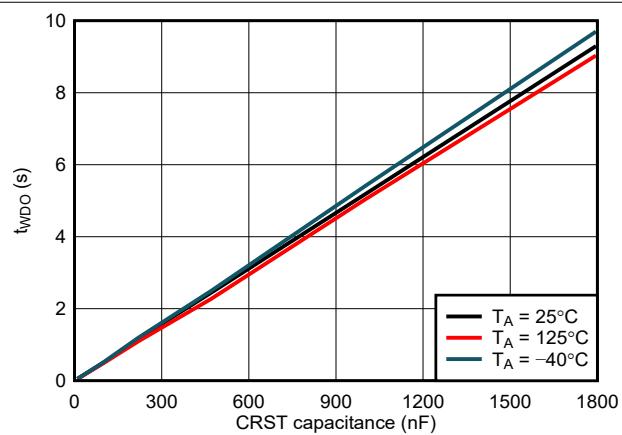

図 7-5.  $t_{WDO}$  と容量との関係

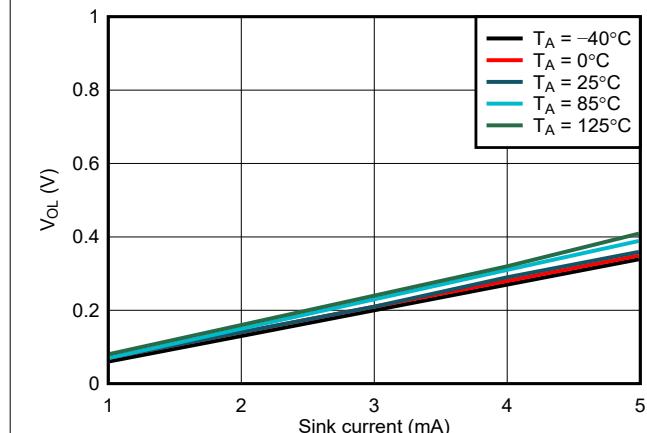

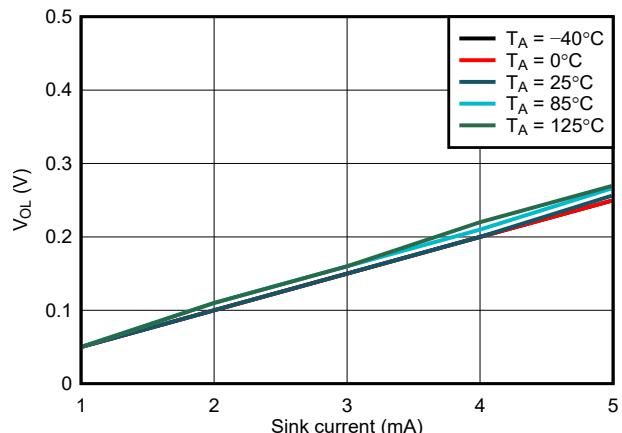

図 7-6. WDO  $V_{OL}$  と  $I_{sink}$  との関係、 $V_{DD} = 1.5\text{V}$

図 7-7. WDO  $V_{OL}$  と  $I_{sink}$  との関係、 $V_{DD} = 3.3\text{V}$

## 7.9 代表的特性 (continued)

すべての曲線は  $T_A = 25^\circ\text{C}$  で測定 (特に記述のない限り)

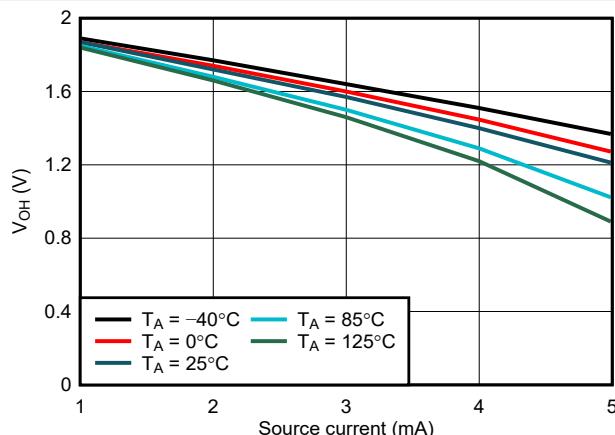

図 7-8. WDO  $V_{OH}$  と  $I_{source}$  との関係、 $V_{DD} = 2.0\text{V}$

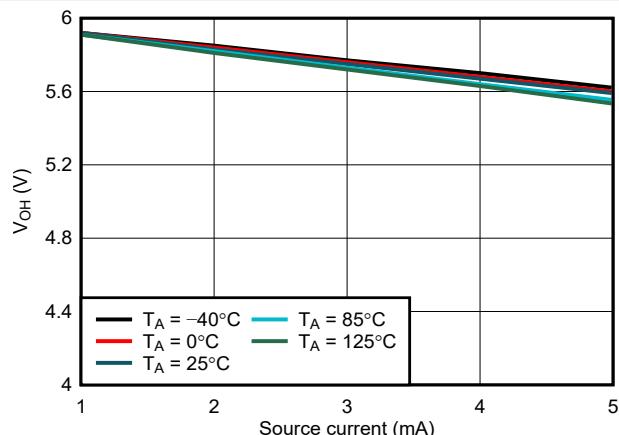

図 7-9. WDO  $V_{OH}$  と  $I_{source}$  との関係、 $V_{DD} = 6.0\text{V}$

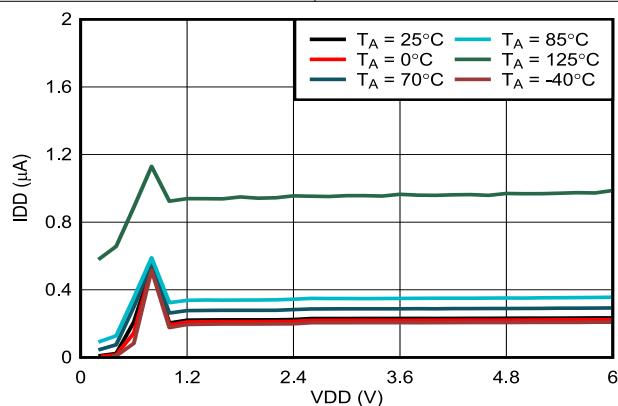

図 7-10. 電源電流と電源電圧との関係

## 8 詳細説明

### 8.1 概要

TPS3436-Q1 は、ウインドウ・ウォッチドッグ・タイマ・デバイスが内蔵された高精度のです。このデバイス・ファミリは、ウォッチドッグ動作に関する複数の機能をサポートしており、小型の 8 ピン SOT23 パッケージで提供されています。このデバイスには、3 個の異なるピン配置構成があります。ピン配置によって、さまざまなアプリケーション要件を満たす異なる機能を使用できます。このデバイス・ファミリは、-Q100 アプリケーション向けに評価されています。

### 8.2 機能ブロック図

図 8-1. ピン配置オプション A

図 8-2. ピン配置オプション B

図 8-3. ピン配置オプション C

## 8.3 機能説明

### 8.3.1 ウィンドウ・ウォッチドッグ・タイマ

TPS3436-Q1 は、高精度のウィンドウ・ウォッチドッグ・タイマ監視機能を備えています。このデバイスは、複数の機能をサポートする A~C の複数のピン配置オプションで提供されており、さまざまなアプリケーションの高まるニーズに対応しています。アプリケーションのニーズを満たす適切なピン配置が選択されていることを確認してください。

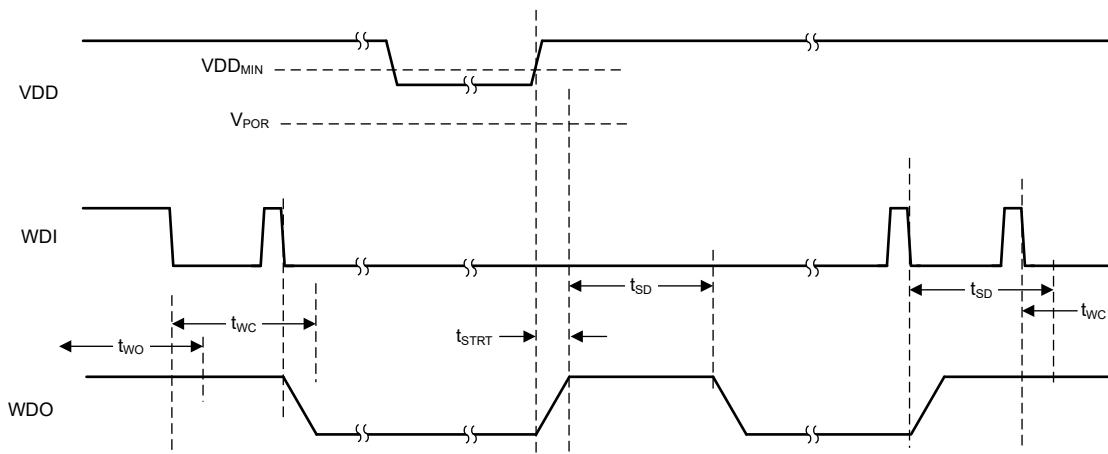

ウィンドウ・ウォッチドッグは、VDD 電圧が  $VDD_{MIN}$  を上回っており、 $\overline{MR}$  電圧が  $0.7 \times VDD$  よりも高く保持され、ウォッチドッグがイネーブルのときにアクティブになります。TPS3436-Q1 ファミリには、ホストがブート動作を完了するのに十分な時間を確保できるように、さまざまなスタートアップ時間遅延オプションが用意されています。詳細については、[セクション 8.3.1.4 セクション](#)を参照してください。

ウィンドウ・ウォッチドッグ・タイマ・フレームは、クローズ・ウィンドウ ( $t_{WC}$ ) とそれに続くオープン・ウィンドウ ( $t_{WO}$ ) の 2 つのウィンドウで構成されています。このデバイスは、WDI ピンの立ち下がりエッジを監視します。オープン・ウィンドウ時に WDI ピンに有効な立ち下がりエッジを供給する必要があります。アプリケーションに必要なクローズ・ウィンドウとオープン・ウィンドウの値については、[セクション 5](#)を参照してください。 $t_{WO}$  の期間内に WDI ピンで有効な立ち下がりエッジが検出されると、タイマ値はリセットされます。クローズ・ウィンドウ時に WDI の立ち下がりエッジが検出されると、早期フォルトが報告されます。クローズ・ウィンドウとオープン・ウィンドウの両方で WDI の立ち下がりエッジが検出されない場合、後期フォルトが報告されます。ウォッチドッグ・フォルト・イベントが発生すると、WDO 出力が  $t_{WDO}$  の時間アサートされます。アプリケーションに必要な  $t_{WDO}$  値の算出方法については、[セクション 8.3.3](#)を参照してください。

図 8-4 に、ウィンドウ・ウォッチドッグ・タイマの基本動作を示します。TPS3436-Q1 のウォッチドッグは、複数の機能をサポートしています。詳細については、以下のサブセクションを参照してください。

図 8-4. ウィンドウ・ウォッチドッグ・タイマの動作

#### 8.3.1.1 $t_{WC}$ (クローズ・ウィンドウ) タイマ

ウィンドウ・ウォッチドッグ・タイマ・フレームは、 $t_{WC}$  とそれに続く  $t_{WO}$  の 2 つのサブフレームで構成されています。ホストが  $t_{WC}$  期間中に有効な WDI 遷移を駆動することは想定されません。 $t_{WC}$  フレーム中に有効な WDI 遷移が発生すると、早期フォルト状態が発生し、WDO 出力がアサートされます。TPS3436-Q1 の  $t_{WC}$  タイマは、CWD ピンと GND ピンの間に接続された外付けコンデンサを使用して設定できます。この機能は、ピン配置オプション A, B で利用できます。スペースに制約があるアプリケーションや、提供されているタイマ・オプションを満たすタイマ値が必要なアプリケーションでは、ピン配置オプション C を使用すると便利です。TPS3436-Q1 は、1ms~100s の範囲で複数の固定タイマ・オプションを提供しています。

TPS3436-Q1 では、容量ベースのタイマを使用すると、電源オン時に容量値が検出されます。容量値を検出するため、既知の内部電流源を使用してコンデンサを 1 サイクル充電および放電します。検出された値を使用して、ウォッチドッグ動作の  $t_{WC}$  タイマを求めます。この独自の実装により、コンデンサの連続充電 / 放電電流を低減し、全体的な消費電流を低減できます。容量の連続充電と放電により、コンデンサ放電中のデッドタイムが長くなります (ウォッチドッグ・モニタ機能なし)。容量の値が大きいと、デッドタイムは長くなります。TPS3436-Q1 の独自の実装により、通常動作中は容量が連続的に充電または放電されることがないため、デッドタイムを回避できます。容量を正確にキャリブレーションするため、 $C_{CWD}$  が  $200 \times C_{CRST}$  未満であることを確認してください。クローズ時間ウィンドウは、SETx ピンの組み合わせと CWD 容量に基づいて決定されます。[表 8-1~表 8-2](#) に、 $t_{WC}$  (秒) と CWD 容量 (ファラッド) の関係を示します。 $t_{WC}$  タイマは、理想的なコンデンサに対して 20% の精度になります。容量の精度は、 $t_{WC}$  時間にさらに影響を与えます。容量が推奨動

作範囲を満たしていることを確認してください。容量が推奨範囲外の場合、デバイスの誤動作につながる可能性があります。

表 8-1.  $t_{WC}$  式 1 本の SET ピン (ピン構成 A)

| SET ピンの値 | 式                                                    |

|----------|------------------------------------------------------|

| 0        | $t_{WC}$ (秒) = $79.2 \times 10^6 \times C_{CWD}$ (F) |

| 1        | $t_{WC}$ (秒) = $39.6 \times 10^6 \times C_{CWD}$ (F) |

表 8-2.  $t_{WC}$  式 2 本の SET ピン、WD-EN なし (ピン構成 B)

| SET ピンの値 | 式                                                    |

|----------|------------------------------------------------------|

| 00       | $t_{WC}$ (秒) = $79.2 \times 10^6 \times C_{CWD}$ (F) |

| 01       | ウォッチドッグはディセーブル                                       |

| 10       | $t_{WC}$ (秒) = $39.6 \times 10^6 \times C_{CWD}$ (F) |

| 11       | $t_{WC}$ (秒) = $9.9 \times 10^6 \times C_{CWD}$ (F)  |

TPS3436-Q1 は、業界標準のさまざまな値を含め、1ms～100s の範囲で幅広い高精度の固定  $t_{WC}$  タイマ・オプションを提供しています。TPS3436-Q1 の固定時間オプションでは、 $t_{WC} \geq 10\text{ms}$  での精度は  $\pm 10\%$  です。 $t_{WC}$  が 10ms 未満の場合、精度は  $\pm 20\%$  です。アプリケーションに関連する  $t_{WC}$  の値は、注文可能な部品番号から識別できます。注文可能な部品番号と  $t_{WC}$  値のマッピングについては、[セクション 5](#) を参照してください。

### 8.3.1.2 $t_{WO}$ (オープン・ウィンドウ) タイマ

ウィンドウ・ウォッチドッグ・フレームは、 $t_{WC}$  とそれに続く  $t_{WO}$  の 2 つのサブフレームで構成されています。ホストは、 $t_{WO}$  期間中に有効な WDI 遷移を駆動する必要があります。 $t_{WO}$  フレームの開始前に有効な WDI 遷移が発生すると、早期フォルト状態が発生します。 $t_{WC}$  および  $t_{WO}$  フレーム中に有効な WDI 遷移を供給しない場合、後期フォルト状態が発生します。フォルト状態が検出されると、WDO 出力がアサートされます。

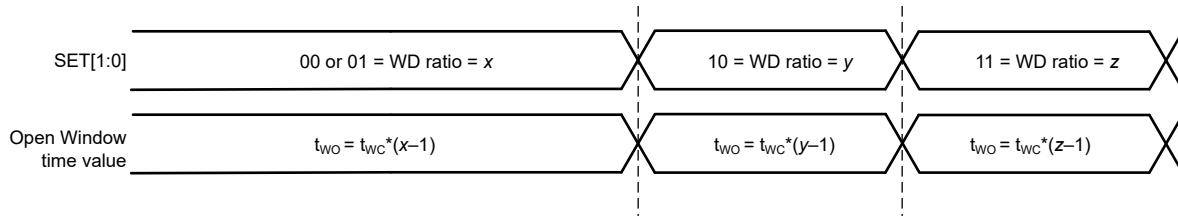

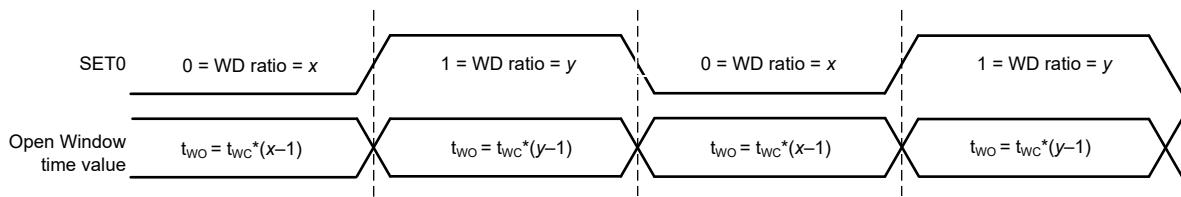

$t_{WO}$  の値は、 $t_{WC}$  の値とウィンドウ・オープン時間比  $n$  を使用して求められます。式に、 $t_{WO}$  と  $t_{WC}$  の関係を示します。使用可能な比率オプションの選択については、[セクション 5](#) を参照してください。

$$t_{WO} = (n - 1) \times t_{WC} \quad (1)$$

注文可能な各部品番号には、使用可能な SET ピンに応じて、最大 3 つの比率のオプションがあります。比率値と SET ピン制御のマッピングについては、[セクション 8.3.1.5](#) を参照してください。 $t_{WO}$  の最大値は 640 秒です。選択した  $t_{WC}$  と比率の組み合わせによって、 $t_{WO}$  値が 640 秒を超えないようにしてください。

### 8.3.1.3 ウォッチドッグのイネーブル/ディセーブル動作

TPS3436-Q1 では、ウォッチドッグをイネーブルまたはディセーブルする機能がサポートされています。この機能は、以下に示すさまざまな使用事例で重要です。

- ホストのリセットを回避するため、ファームウェアの更新中にウォッチドッグをディセーブルする。

- ソフトウェアのステップバイステップ・デバッグ動作中にウォッチドッグをディセーブルする。

- ウォッチドッグのエラー割り込みを回避するため、重要なタスクを実行するときにウォッチドッグをディセーブルする。

- ホストが起動するまで、ウォッチドッグをディセーブルに保持する。

TPS3436-Q1 では、WD-EN ピン (ピン構成 C)、SET[1:0] = 0b'01 (ピン構成 B) ロジックの組み合わせにより、ウォッチドッグのイネーブルまたはディセーブル機能がサポートされています。特定のピン配置でユーザーがウォッチドッグ動作をディセーブルにするのに使用できるのは、これらの方針のいずれか 1 つのみです。

WD-EN ピンのあるピン配置では、ウォッチドッグのイネーブル / ディセーブルは WD-EN ピンのロジック状態で制御されます。WD-EN を 1 に駆動するとウォッチドッグ動作がイネーブルになり、WD-EN を 0 に駆動するとウォッチドッグ動作がディセーブルになります。WD-EN ピンは、デバイスの動作中いつでも切り替えることができます。[図 8-5](#) の図に、WD-EN ピンの制御によるタイミング動作を示します。

図 8-5. ウオッチドッグのイネーブル：WD-EN ピンの制御

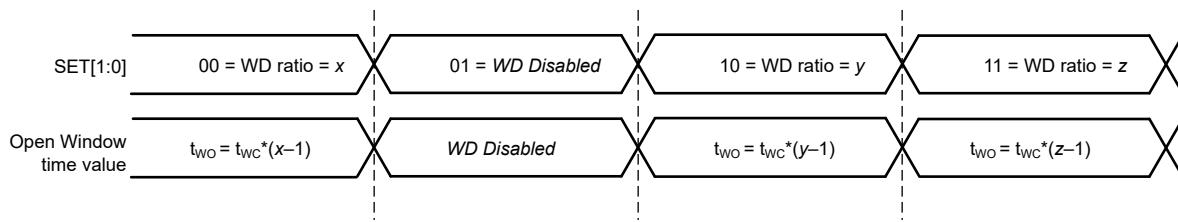

**SET[1:0] = 0b'01** の組み合わせは、SET1 ピンと SET0 ピンがあり、WD-EN ピンがないピン配置でウォッチドッグ動作をディセーブルにするのに使用できます。SET ピンのロジック状態は、ウォッチドッグ動作中いつでも変更できます。SET[1:0] ピンの動作の詳細については、[セクション 8.3.1.5](#) セクションを参照してください。

ピン配置オプション A、B では、CWD ピンと GND ピンの間に接続された容量を使用して、ウォッチドッグ・タイマを制御できます。容量値が推奨値よりも大きいか、GND に接続すると、ウォッチドッグ機能がディセーブルになります。容量ベースのディセーブル動作は、上記の他の 2 つのオプションよりも優先されます容量を動作中に変更しても、ウォッチドッグ動作はイネーブルまたはディセーブルになりません。容量の変化を検出するには、電源リサイクルが必要です。

ウォッチドッグがディセーブルになると、進行中のウォッチドッグ・フレームは終了します。ウォッチドッグ動作がディセーブルの場合、WDO はデアサートされたままになります。イネーブルになると、デバイスは直ちに  $t_{WC}$  フレームに入り、ウォッチドッグ監視動作を開始します。

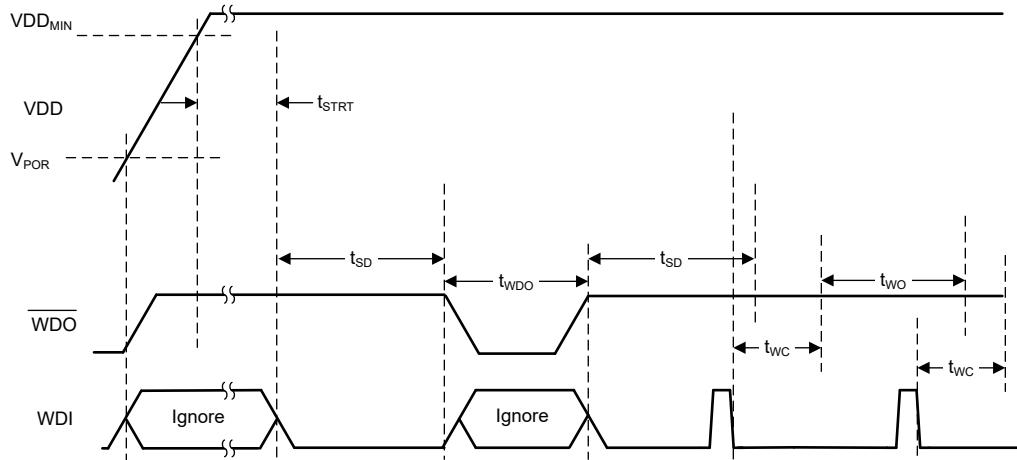

#### 8.3.1.4 $t_{SD}$ ウォッチドッグのスタートアップ遅延

TPS3436-Q1 は、ウォッチドッグのスタートアップ遅延機能をサポートしています。この機能は、電源オン後または WDO アサート・イベント後にアクティブになります。 $t_{SD}$  フレームがアクティブになると、デバイスは WDI ピンを監視しますが、WDO 出力はアサートされません。この機能により、ウォッチドッグ監視が開始する前に、ホストがブート・プロセスを完了することができます。スタートアップ遅延を使用すると、起動中に予期しない WDO アサート・イベントを回避できます。 $t_{SD}$  時間は、選択したデバイスの部品番号に基づいてあらかじめ決められています。部品番号と  $t_{SD}$  時間のマッピングの詳細については、[セクション 5](#) セクションを参照してください。ピン配置オプション A、B には、遅延なし、または 10 秒のスタートアップ遅延オプションのみがあります。

$t_{SD}$  フレームは、 $t_{SD}$  に選択された期間が経過するか、ホストが WDI ピン状に有効な遷移を供給すると完了します。ホストは、 $t_{SD}$  期間中に WDI ピンに有効な遷移を供給する必要があります。デバイスは  $t_{SD}$  フレームを終了し、有効な WDI 遷移後にウォッチドッグ監視フェーズに入ります。WDI ピンに有効な遷移が供給されないと、WDO 出力ピンがアサートされ、ウォッチドッグ・エラーがトリガされます。

[セクション 8.3.1.3](#) セクションで説明されているように、WD-EN ピン、SET[1:0] ピンの組み合わせを使用してウォッチドッグ機能がイネーブルになっている場合、 $t_{SD}$  フレームは開始しません。

図 8-6 に、 $t_{SD}$  タイム・フレームの動作を示します。

図 8-6.  $t_{SD}$  フレームの動作

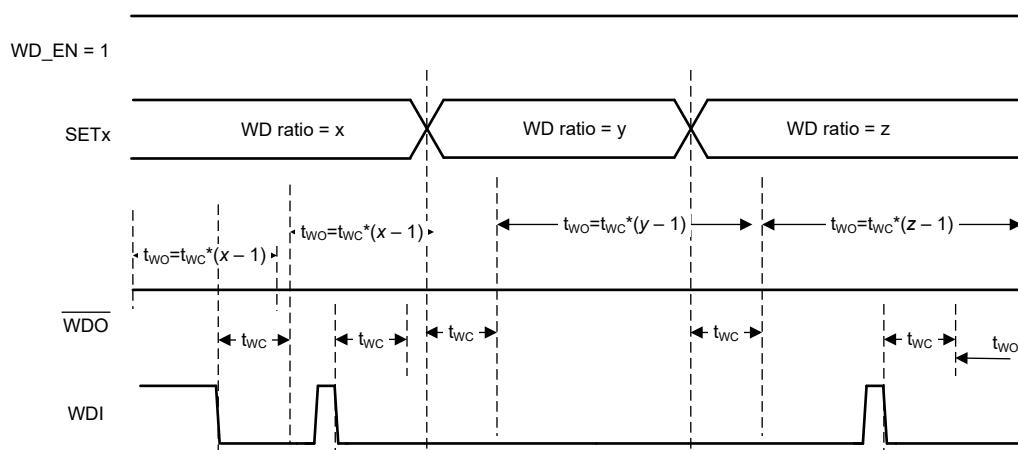

### 8.3.1.5 SET ピンの動作

TPS3436-Q1 には、選択したピン配置オプションによって、1 本または 2 本の SET ピンがあります。SET ピンを使用すると、さまざまなアプリケーション要件に合わせて、 $t_{WO}$  タイマを動作中にプログラムすることができます。SET ピンを使用できる代表的な使用事例は次のとおりです。

- ホストがスリープ・モードのときは広いオープン・ウンドウ・タイマを使用し、ホストが動作しているときはタイムアウトの短い動作に変更。ウォッチドッグを使用して、長時間経過した後にホストをウェークアップし、スリープに戻る前にアプリケーション関連のアクティビティを実行することが可能。

- ウォッチドッグにより重要なタスクが中断されないように、システム・クリティカルなタスクを実行するときに幅の広いオープン・ウンドウ・タイマに変更。重要なタスクの完了後は、タイマをアプリケーション指定の間隔に変更。

デバイスの  $t_{WO}$  タイマ値は、CWD ピンまたは固定タイマ値に基づく  $t_{WC}$  タイマの選択と、SET ピンのロジック・レベルを組み合わせて決定されます。 $t_{WC}$  タイマ値は、セクション 5 セクションのウォッチドッグ・クローズ時間セレクタに基づいて決定されます。SET ピンのロジック・レベルは、デバイスの電源投入時にデコードされます。SET ピンの値は、動作中いつでも変更できます。SETx ピンが変化すると、ウォッチドッグ・タイマ値またはイネーブル / ディセーブル状態が変化し、進行中のウォッチドッグ・フレームがただちに終了します。SETx ピンは、WDO 出力がアサートされたときにも更新されます。更新された  $t_{WO}$  タイマ値は、出力がデアサートされ、 $t_{SD}$  タイマが終了した後に適用されます。

SET0 ピンのみを持つピン配置の場合、 $t_{WO}$  比の値は、注文可能な部品番号のウォッチドッグ・オープン時間比セレクタ・フィールドに基づいて決定されます。利用可能なオプションについては、セクション 5 を参照してください。表 8-3 に、ウォッチドッグ・クローズ時間をオプション D = 10ms に設定した場合の、異なる SET0 ロジック・レベルの  $t_{WO}$  値の例を示します。

表 8-3. SET0 ピンのみの場合の  $t_{WO}$  値 (ピン構成 A)

| ウォッチドッグのオープン時間比の選択 | $t_{WO}$ |          |

|--------------------|----------|----------|

|                    | SET0 = 0 | SET0 = 1 |

| A                  | 10ms     | 30ms     |

| B                  | 30ms     | 70ms     |

| C                  | 70ms     | 150ms    |

| D                  | 150ms    | 310ms    |

| E                  | 310ms    | 630ms    |

| F                  | 630ms    | 1270ms   |

SET0 と SET1 ピンの両方を持つピン配置の場合、 $t_{WO}$  比の値は、注文可能な部品番号のウォッチドッグ・オープン時間比セレクタ・フィールドに基づいて決定されます。利用可能なオプションについては、セクション 5 を参照してください。2 つの SETx ピンにより、3 つの時間スケーリング・オプションが提供されます。SET[1:0] = 0b'01 の場合、ウォッチドッグ動

作はディセーブルになります。表 8-4 に、ウォッチドッグ・クローズ時間をオプション  $G = 100\text{ms}$  に設定した場合の、異なる SET[1:0] ロジック・レベルの  $t_{WO}$  値の例を示します。選択されたパッケージ・ピン配置には、WD-EN ピンはありません。

**表 8-4. SET0 および SET1 ピンの両方がある場合の  $t_{WO}$  値、WD-EN ピンなし (ピン構成 B)**

| ウォッチドッグのオープン時間比の選択 | $t_{WO}$         |                  |                  |                  |

|--------------------|------------------|------------------|------------------|------------------|

|                    | SET[1:0] = 0b'00 | SET[1:0] = 0b'01 | SET[1:0] = 0b'10 | SET[1:0] = 0b'11 |

| A                  | 100ms            | ウォッチドッグはディセーブル   | 300ms            | 1500ms           |

| B                  | 300ms            | ウォッチドッグはディセーブル   | 700ms            | 3100ms           |

| C                  | 700ms            | ウォッチドッグはディセーブル   | 1500ms           | 6300ms           |

| D                  | 1500ms           | ウォッチドッグはディセーブル   | 3100ms           | 12700ms          |

| E                  | 3100ms           | ウォッチドッグはディセーブル   | 6300ms           | 25500ms          |

| F                  | 6300ms           | ウォッチドッグはディセーブル   | 12700ms          | 51100ms          |

### 1. ウォッチドッグ・クローズ時間を 100ms に設定した例

選択されたパッケージ・ピン配置には、SET[1:0] に加えて WD-EN ピンがあります (ピン構成 C)。このピン配置では、WD-EN ピンでウォッチドッグのイネーブル / ディセーブル動作を制御します。SET[1:0] = 0b'01 の場合は、SET[1:0] = 0b'00 と同様に動作します。

SETx 比での  $t_{WO}$  値が 640 秒を超えないようにしてください。クローズ・ウィンドウ・タイマと比率の選択により  $t_{WO}$  が 640 秒を超える場合、タイマ値は 640 秒に制限されます。

図 8-7～図 8-9 に、SETx ステータスの変化に対するタイミング動作を示します。

**図 8-7. SETx ピンのステータスによるウォッチドッグ動作**

### SET Pin (2 Pins) Operation; WD\_EN Pin Not Available

### SET Pin (2 Pins) Operation; WD\_EN Available = 1

$t_{WC}$  = Fixed based on OPN or programmable using capacitor

$x, y, z$  = Fixed based on ratio chosen

**図 8-8. 2 本の SET ピンによるウォッチドッグ動作**

$t_{WC}$  = Fixed based on OPN or programmable using capacitor

$X, y$  = Fixed based on ratio chosen

**図 8-9. 1 本の SET ピンによるウォッチドッグ動作**

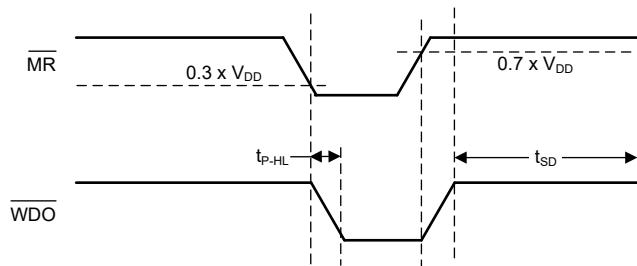

### 8.3.2 手動リセット

TPS3436-Q1 では、 $\overline{MR}$  ピンを使用した手動リセット機能がサポートされています。 $\overline{MR}$  ピンを  $0.3 \times V_{DD}$  より低い電圧で駆動すると、WDO 出力がアサートされます。 $\overline{MR}$  ピンは  $100k\Omega$  のプルアップ抵抗で  $V_{DD}$  に接続されています。 $\overline{MR}$  ピンはフローティングのままでかまいません。内部プルアップにより、 $\overline{MR}$  ピンがトリガされたときに出力がアサートされないようになっています。

$\overline{MR}$  ピンの電圧が  $0.7 \times V_{DD}$  電圧を超えると、出力がデアサートされます。詳細については、図 8-10 を参照してください。

図 8-10.  $\overline{MR}$  ピンの応答

### 8.3.3 WDO 出力

TPS3436-Q1 デバイスは、WDO 出力ピンを備えています。 $\overline{MR}$  ピンの電圧が  $0.3 \times VDD$  を下回るか、ウォッチドッグ・タイマのエラーが検出されると、WDO 出力がアサートされます。

$\overline{MR}$  イベントを除く上記の関連イベントが検出されると、出力が  $t_{WDO}$  の間アサートされます。 $t_{WDO}$  の時間は、CRST ピンと GND の間にコンデンサを接続することでプログラムできます。または、注文可能な部品番号で選択された期間  $t_{WDO}$  がアサートされます。利用可能なオプションについては、[セクション 5 セクション](#)を参照してください。

式 2 に、コンデンサ値と  $t_{WDO}$  の期間との関係を示します。容量が推奨動作範囲を満たしていることを確認してください。容量が推奨範囲外の場合、デバイスの誤動作につながる可能性があります。

$$t_{WDO} (\text{秒}) = 4.95 \times 10^6 \times C_{CRST} (\text{F}) \quad (2)$$

TPS3436-Q1 には、ラッチ付き出力のオプションも備えています。ラッチ付き出力を備えた注文可能な部品番号では、デバイスの電源を切って再投入するか、エラー状態を解消するまで、出力がアサート状態に保持されます。 $\overline{MR}$  ピンの電圧が低くなつたために出力がラッチされた場合、 $\overline{MR}$  ピンの電圧が  $0.7 \times V_{DD}$  レベルを上回ると、出力ラッチが解除されます。ウォッチドッグ・タイマのエラーが原因で出力がラッチされた場合、WDI で負のエッジが検出されたとき、またはデバイスがシャットダウンされて再度電源が投入されたときに、出力ラッチが解除されます。[図 8-11](#) に、ラッチ付き出力構成でのデバイスのタイミング動作を示します。

図 8-11. 出力ラッチのタイミング動作

## 8.4 デバイスの機能モード

表 8-5 に、TPS3436-Q1 の機能モードを示します。

**表 8-5. デバイスの機能モード**

| VDD                               | ウォッチドッグ・ステータス | WDI                                                           | WDO  |

|-----------------------------------|---------------|---------------------------------------------------------------|------|

| $V_{DD} < V_{POR}$                | 該当なし          | —                                                             | 未定義  |

| $V_{POR} \leq V_{DD} < V_{DDmin}$ | 該当なし          | 無視                                                            | High |

| $V_{DD} \geq V_{DDmin}$           | 無効化           | 無視                                                            | High |

|                                   | イネーブル         | $t_{WC(max)} \leq t_{pulse}^1 \leq t_{WC(max)} + t_{WO(min)}$ | High |

|                                   | イネーブル         | $t_{WC(max)} > t_{pulse}^1$                                   | Low  |

|                                   | イネーブル         | $t_{WC(max)} + t_{WO(max)} < t_{pulse}^1$                     | Low  |

(1)  $t_{pulse}$  は WDI の立ち下がりエッジ間の時間です。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

以下のセクションでは、最終アプリケーションの要件に応じた適切なデバイス実装について詳しく説明します。

#### 9.1.1 出力アサート遅延

TPS3436-Q1 には、出力アサート遅延 ( $t_{WDO}$ ) を設定するのに、固定タイミングを使用する方法と、外付けコンデンサを使用してタイミングをプログラミングする方法の 2 つのオプションがあります。

##### 9.1.1.1 出荷時にプログラムされた出力アサート遅延タイミング

固定出力アサート遅延タイミングは、ピン配置 C で使用できます。これらのタイミングを使用すると、高精度で 10% 精度の出力アサート遅延タイミングを実現できます。

##### 9.1.1.2 コンデンサのタイミングを調整可能

TPS3436-Q1 は、プログラマブル出力アサート遅延も利用し、高精度の電流源を使用して、デバイスのスタートアップ時に外部コンデンサを充電します。CRST ピンの外部容量により発生する遅延時間の代表値は、式 3 で計算できます。ここで、 $t_{WDO}$  は出力アサート遅延時間 (秒)、 $C_{CRST}$  は容量 (マイクロファラード) です。

$$t_{WDO} (\text{秒}) = 4.95 \times 10^6 \times C_{CRST} (\text{F}) \quad (3)$$

計算された出力アサート遅延時間と実際の出力アサート遅延時間との差を最小限に抑えるため、高品質のセラミック誘電 COG、X5R、または X7R コンデンサを使用して、このピン周辺の寄生基板容量が最小になるようにしてください。表 9-1 に、理想的なコンデンサ値に対する出力アサート遅延時間を示します。

表 9-1. 一般的な理想コンデンサ値における出力アサート遅延時間

| $C_{CRST}$ | 出力アサート<br>遅延時間 ( $t_{WDO}$ ) |      |                    | 単位 |

|------------|------------------------------|------|--------------------|----|

|            | 最小値 <sup>(1)</sup>           | 代表値  | 最大値 <sup>(1)</sup> |    |

| 10nF       | 39.6                         | 49.5 | 59.4               | ms |

| 100nF      | 396                          | 495  | 594                | ms |

| 1μF        | 3960                         | 4950 | 5940               | ms |

(1) 最小値と最大値は、理想的なコンデンサを使用して計算されています。

#### 9.1.2 ウォッチドッグ・ウィンドウの機能

TPS3436-Q1 には、クローズ・ウィンドウ・ウォッチドッグ・タイマ ( $t_{WC}$ ) を設定するのに、固定タイミングを使用する方法と、外付けコンデンサを使用してタイミングをプログラミングする方法の 2 つのオプションがあります。

##### 9.1.2.1 出荷時にプログラムされたタイミング・オプション

固定ウォッチドッグ・タイムアウト・オプションは、ピン配置 C で使用できます。これらのタイミングを使用すると、高精度で 10% 精度のウォッチドッグ・タイマ  $t_{WC}$  を実現できます。

### 9.1.2.2 コンデンサのタイミングを調整可能

コンデンサを CWD ピンに接続すると、 $t_{WC}$  のタイミングを調整できます。この方法を使用する場合は、 $C_{CWD}$  の効果は SETx ピンの値に依存するため、理想的なコンデンサを使用した  $t_{WC}$  の代表値を計算する式について、表 8-1～表 8-2 を参照してください。コンデンサの許容誤差により、デバイスの実際のタイミングにおいて  $t_{WC}$  の最小値が減少し、 $t_{WC}$  の最大値が増加することがあります。タイミングを正確なものにするため、COG 誘電体で製造されたセラミック・コンデンサを使用してください。

## 9.2 代表的なアプリケーション

### 9.2.1 設計 1：動作モードおよびスリープ・モード時のマイクロコントローラ・ウォッチドッグの監視

TPS3436-Q1 では、動作モードとスリープ・モードのあるマイクロコントローラを監視するため、高精度の電圧監視と動作中の SETx 割り当てを使用できます。

Copyright © 2023, Texas Instruments Incorporated

図 9-1. スリープ・ウォッチドッグ・モードを使用したマイクロコントローラ・ウィンドウ・ウォッチドッグ監視

#### 9.2.1.1 設計要件

| パラメータ              | 設計要件                      | 設計結果                 |

|--------------------|---------------------------|----------------------|

| 動作中のウィンドウ・クローズ時間   | 動作中の $t_{WC}$ の代表値 50ms   | $t_{WC}$ の代表値 50ms   |

| 動作中のウィンドウ・オープン時間   | 動作中の $t_{WO}$ の代表値 1.4s   | $t_{WO}$ の代表値 1.55s  |

| スリープ中のウィンドウ・クローズ時間 | スリープ中の $t_{WC}$ の代表値 50ms | $t_{WC}$ の代表値 50ms   |

| スリープ中のウィンドウ・オープン時間 | スリープ中の $t_{WO}$ の代表値 12s  | $t_{WO}$ の代表値 12.75s |

| 出力アサート遅延           | $t_{WDO}$ の代表値 200ms      | $t_{WDO}$ の代表値 200ms |

| 出力ロジック電圧           | オープン・ドレイン                 | オープン・ドレイン            |

| 最大デバイス消費電流         | 20µA                      | 代表的な消費電流 250nA       |

#### 9.2.1.2 詳細な設計手順

##### 9.2.1.2.1 動作モードおよびスリープ・モード時のウィンドウのタイミングの決定

TPS3436-Q1 では、精密な 10% 精度のウォッチドッグ・タイミングを実現できます。このアプリケーションで電力効率を最大にするには、マイクロコントローラの動作状態とスリープ状態に 2 つの異なるウィンドウ・タイミングが必要です。これを実現するため、ホストは状態間を遷移するときに SETx ピンを再割り当てします。アプリケーションの代表的な  $t_{WC}$  要件は 50ms であるため、ウィンドウ・クローズ時間  $t_{WC}$  には代表値 50ms が選択されます。このアプリケーションでは、動作中のウォッチドッグ・オープン時間 ( $t_{WO}$ ) の代表値は 1.4s、スリープ中のウォッチドッグ・オープン時間 ( $t_{WO}$ ) の代表値は 12s である必要があります。そのため、使用可能なバリエント・オプションは TPS3436xxFExDDFRQ1 に絞り込むことができます。

### 9.2.1.2.2 出力アサート遅延を満たす

TPS3436-Q1 でリセット遅延を選択するには、固定遅延とコンデンサでプログラム可能な遅延の 2 つのオプションがあります。TPS3436-Q1 では、固定ウォッチドッグ・タイミングと固定出力アサート遅延、またはプログラム可能なウォッチドッグ・タイミングとプログラム可能な出力アサート遅延のみがサポートされます。このアプリケーションでは 200ms の最小出力アサート遅延が必要なため、出力アサート遅延オプション G を使用します。これらの要件があり、スタートアップ遅延は不要なため、TPS3436CAFEGDDFRQ1 を使用します。

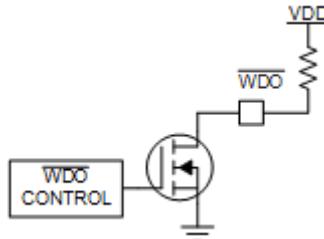

### 9.2.1.2.3 WDO ブルアップ抵抗の計算

図 9-2 に示すように、TPS3436-Q1 は  $\overline{WDO}$  回路にオープン・ドレイン構成を使用します。FET がオフになると、抵抗によってトランジスタのドレインが VDD にブルアップされ、FET がオンになると、FET のドレインがグランドにブルダウンされて、実質的に分圧抵抗を形成します。この分圧器の抵抗は、 $V_{OL}$  が最大値未満になるよう選択する必要があります。適切なブルアップ抵抗を選択するには、ブルアップ電圧 ( $V_{PU}$ )、 $\overline{WDO}$  ピンに推奨される最大電流 ( $I_{RST}$ )、 $V_{OL}$  の 3 つの仕様を考慮する必要があります。 $V_{OL}$  の最大値は 0.3V です。これは、作成される実質的な分圧抵抗が RESET ピンの電圧を 0.3V 未満にでき、 $V_{DD} \geq 3V$  の場合は  $I_{RST}$  を 2mA 未満に、 $V_{DD} = 1.5V$  の場合は 500μA 未満に維持できる必要があることを意味します。この例では、 $V_{PU} = V_{DD} = 1.5V$  なので、 $I_{RST}$  を 500μA 未満に維持する抵抗を選択する必要があります。この値が許容される最大消費電流です。この仕様を確実に満たすため、 $\overline{WDO}$  がアサートされたときに最大 180μA をシンクする 10kΩ のブルアップ抵抗値が選択されています。

図 9-2. オープン・ドレイン  $\overline{RESET}$  の構成

## 9.3 電源に関する推奨事項

このデバイスは、1.04V~6V の電圧範囲の入力電源で動作するように設計されています。このデバイスには、入力電源コンデンサは必要ありません。ただし、入力電源にノイズが多い場合は、VDD ピンと GND ピンの間に 0.1μF のコンデンサを配置するのが適切なアナログ手法です。

## 9.4 レイアウト

### 9.4.1 レイアウトのガイドライン

VDD ピンへの接続が低インピーダンスであることを確認します。適切なアナログ設計手法では、0.1μF のセラミック・コンデンサを VDD ピンのできるだけ近くに配置することが推奨されます。CRST ピンにコンデンサが接続されていない場合、このピンの寄生容量を最小限に抑え、 $\overline{WDO}$  遅延時間に悪影響を与えないようにします。

- VDD ピンへの接続が低インピーダンスであることを確認します。適切なアナログ設計手法では、0.1μF のセラミック・コンデンサを VDD ピンのできるだけ近くに配置することが推奨されます。

- $C_{CRST}$  コンデンサを CRST ピンのできるだけ近くに配置します。

- $C_{CWD}$  コンデンサを CWD ピンのできるだけ近くに配置します。

- ブルアップ抵抗は、 $\overline{WDO}$  ピンのできるだけ近くに配置します。

#### 9.4.2 レイアウト例

Copyright © 2023, Texas Instruments Incorporated

図 9-3. 以下のデバイスのピン配置 C の代表的なレイアウト : TPS3436-Q1

## 10 デバイスおよびドキュメントのサポート

### 10.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.2 サポート・リソース

[TI E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。[TI の使用条件](#)を参照してください。

### 10.3 商標

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 10.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.5 用語集

テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS3436BDADADDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | NLHOQ               |

| TPS3436BDADADDFRQ1.A  | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | NLHOQ               |

| TPS3436BFACADDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -45 to 125   | NLHOI               |

| TPS3436BFACADDFRQ1.A  | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -45 to 125   | NLHOI               |

| TPS3436CABFDDDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -45 to 125   | NLHOU               |

| TPS3436CCCACDDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -45 to 125   | NLHO3               |

| TPS3436CCCBGDDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | NLHOF               |

| TPS3436CCCBGDDFRQ1.A  | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | NLHOF               |

| TPS3436CFDBEDDFRQ1    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -45 to 125   | NLHO2               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

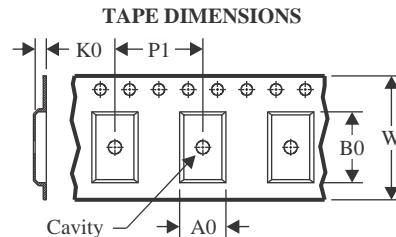

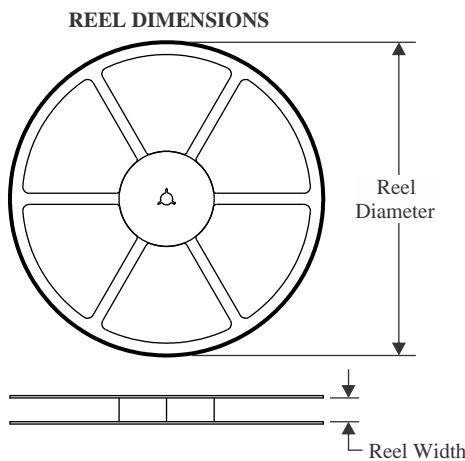

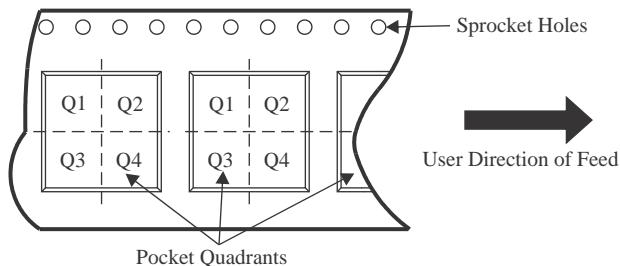

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS3436BDADADDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS3436BFACADDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS3436CABFDDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS3436CCCACDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS3436CCCBGDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS3436CFDBEDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

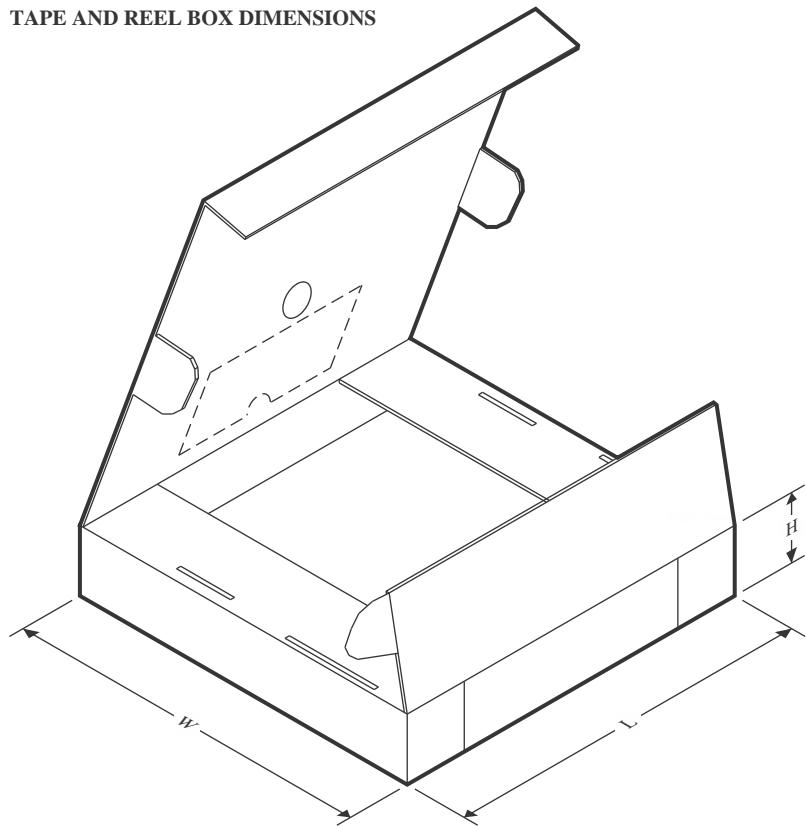

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS3436BDADADDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS3436BFACADDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS3436CABFDDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS3436CCCACDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS3436CCCBGDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS3436CFDBEDDFRQ1 | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

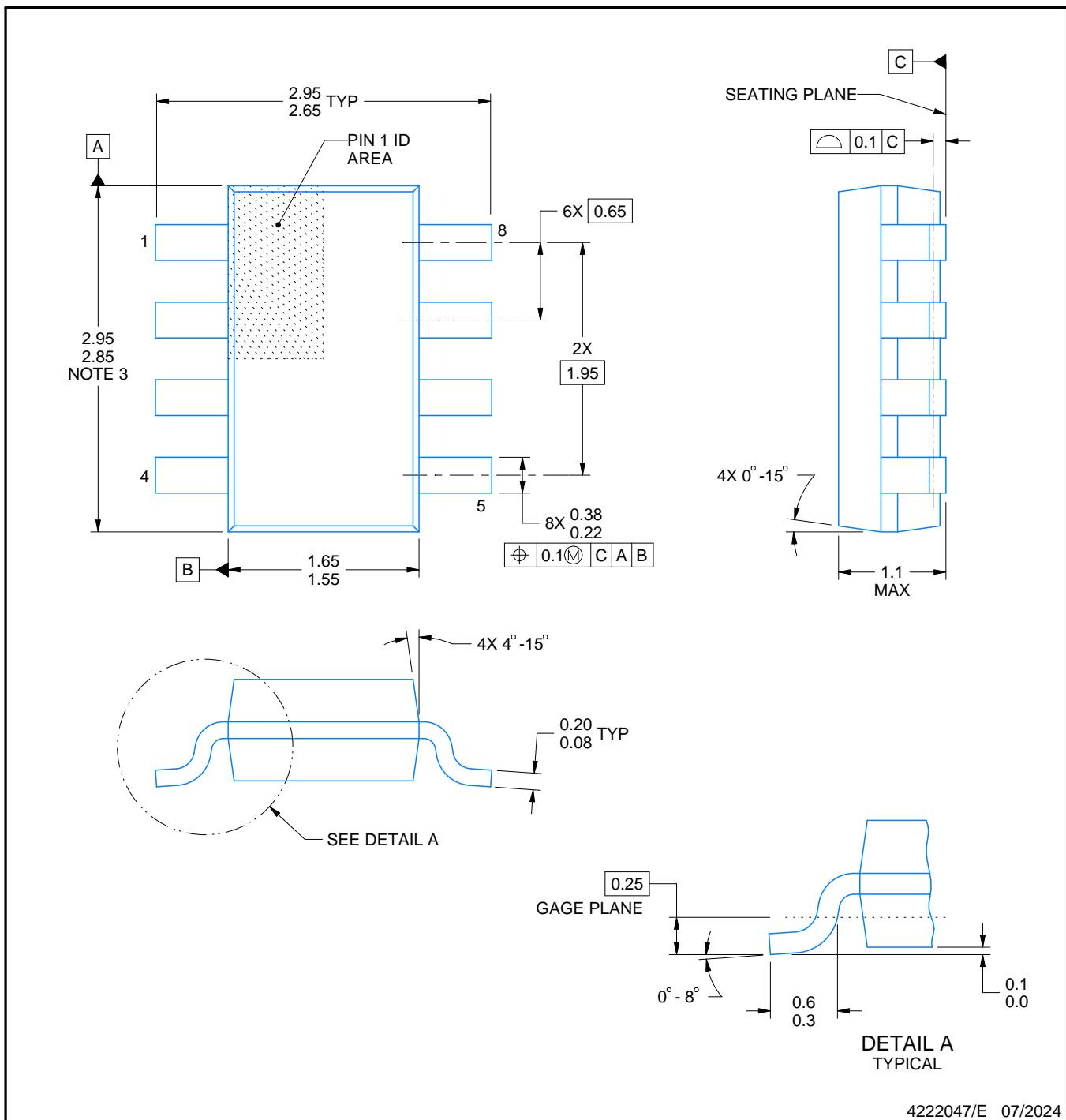

# PACKAGE OUTLINE

DDF0008A

## **SOT-23-THIN - 1.1 mm max height**

## PLASTIC SMALL OUTLINE

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

# DDF0008A

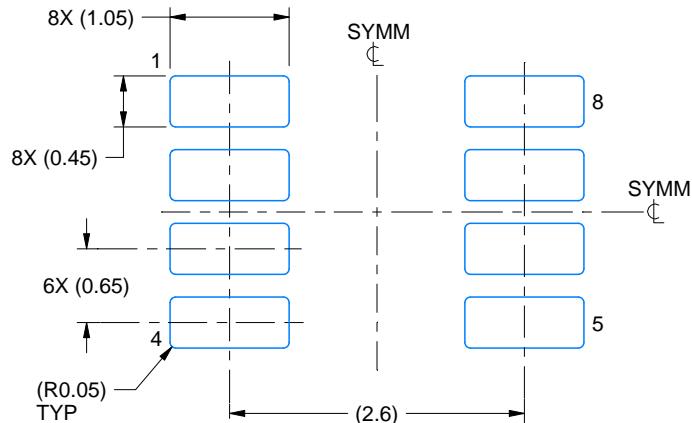

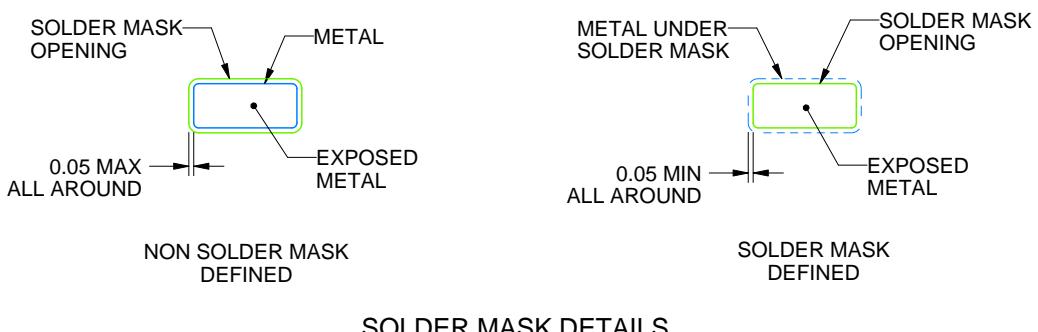

## EXAMPLE BOARD LAYOUT

### SOT-23-THIN - 1.1 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

SOLDER MASK DETAILS

4222047/E 07/2024

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

**DDF0008A**

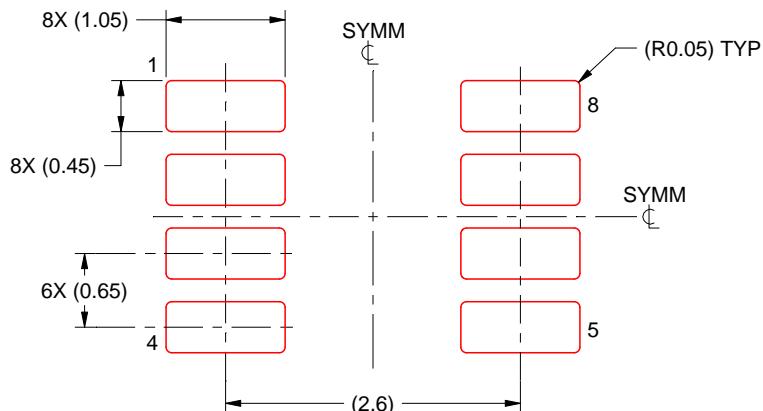

# EXAMPLE STENCIL DESIGN

**SOT-23-THIN - 1.1 mm max height**

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:15X

4222047/E 07/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月