**TPS25981**

JAJSMF7B - APRIL 2022 - REVISED JUNE 2023

# TPS25981x 過渡過電流ブランキング・タイマ搭載、2.7V~16V、10A、6mΩ eFuse

# 1 特長

- 広い動作時入力電圧範囲:2.7V~16V

- 絶対最大定格:20V

- 低オン抵抗の FET を内蔵: R<sub>ON</sub> = 6mΩ (標準値)

- 高速過電圧保護

- 調整可能な過電圧誤動作防止 (OVLO)、1.2μs (標準値)の応答時間

- 負荷電流監視出力 (ILM) を備えた過電流保護

- サーキットブレーカ応答

- 調整可能なスレッショルド (I<sub>LIM</sub>) 1.5A~11A

- 精度:±10% (I<sub>LIM</sub> > 5A)

- 可変の過渡ブランキング・タイマ (ITIMER)、最大2 × I<sub>IIM</sub> のピーク電流を許容

- 出力負荷電流監視精度:±10% (I<sub>OUT</sub>≥3A)

- 高速トリップ応答による短絡保護

- 応答時間 640ns (標準値)

- 可変 (2 × I<sub>LIM</sub>) および固定のスレッショルド

- アクティブ High のイネーブル入力、低電圧誤動作防 止 (UVLO) スレッショルドを設定可能

- アクティブ Low のイネーブル入力、低電圧誤動作防 止 (OVLO) スレッショルドを設定可能

- 可変の出力スルーレート (dVdt) 制御

- ディスエーブル/オフ状態で逆電流ブロックするため に外部 FET を駆動するオプション

- 過熱保護

- クイック出力放電

- デジタル出力

- パワー・グッド (PG) およびフォルト表示 (FLT)

- UL 2367 認定 (申請中)

- IEC 62368 CB 認証 (申請中)

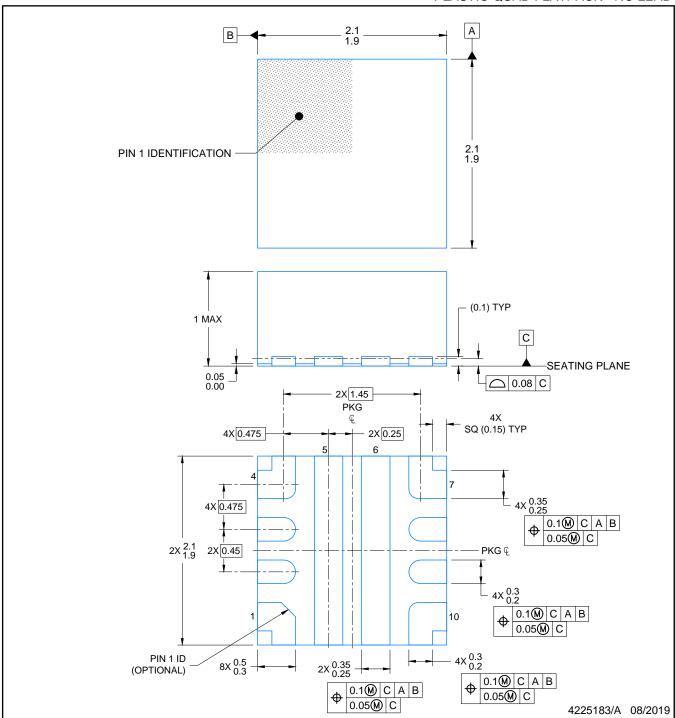

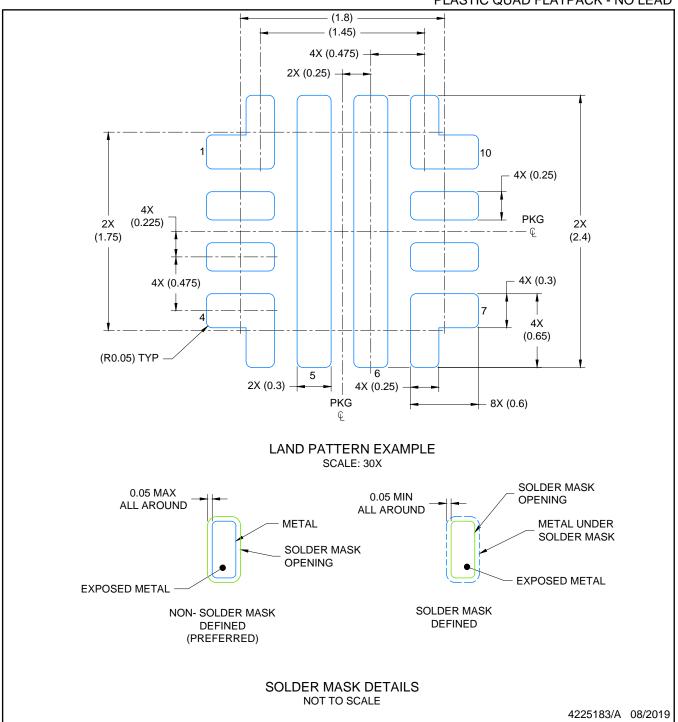

- 小型サイズ:QFN 2mm × 2mm、0.45mm ピッチ

# 2 アプリケーション

- 光モジュール

- サーバー、PC マザーボード、アドオン・カード

- エンタープライズ・ルータ、データ・センター・スイッチ

- 産業用 PC

- UHDTV

# 3 概要

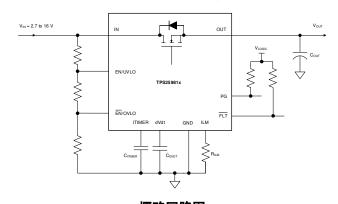

TPS25981xx ファミリの eFuse は、高集積の回路保護お よび電源管理ソリューションです。このデバイスは、非常に 少ない数の外付け部品で複数の保護モードを提供し、過 負荷、短絡、電圧サージ、および過剰な突入電流に対し て堅牢な保護を行います。

出力のスルー・レートと突入電流は、単一の外付けコンデ ンサを使用して調整できます。入力が過電圧スレッショル ド (調整可能)を上回った場合は、出力を遮断することによ り負荷を入力過電圧状態から保護します。このデバイス は、電流をアクティブに制限する(起動中の場合)、または 回路を遮断する(定常状態の場合)ことにより、出力過負 荷に対応します。過電流保護スレッショルドおよび過渡過 電流ブランキング・タイマは、ユーザーが調整可能です。 電流制限制御ピンは、アナログ負荷電流モニタとしても機 能します。

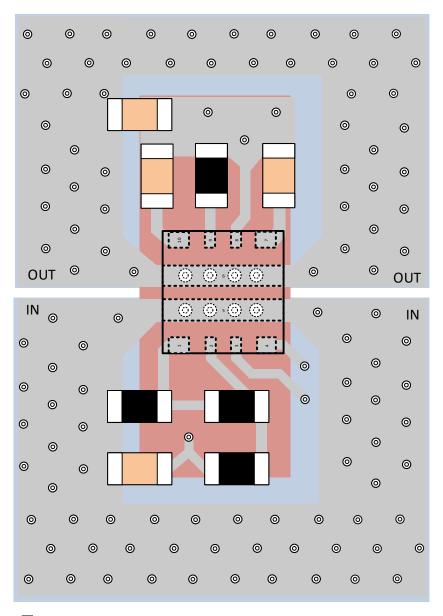

これらのデバイスは、2mm × 2mm、10 ピンの HotRod™ QFN パッケージで供給され、放熱性能の向上とシステム のフットプリントの削減に役立ちます。

これらのデバイスは、-40℃~+125℃の接合部温度範囲 で動作が規定されています。

#### 製品情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|----------|----------------------|-----------------|

| TPS25981 | RPW (VQFN-HR、10)     | 2.00mm × 2.00mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

概略回路図

# **Table of Contents**

| 1 特長                                 | 1 | 8.4 Device Functional Modes             | 30              |

|--------------------------------------|---|-----------------------------------------|-----------------|

| 2アプリケーション                            |   | 9 Application and Implementation        | <mark>31</mark> |

| 3 概要                                 |   | 9.1 Application Information             | 31              |

| 4 Revision History                   |   | 9.2 Typical Application                 | 34              |

| 5 Device Comparison Table            |   | 10 Power Supply Recommendations         | 39              |

| 6 Pin Configuration and Functions    |   | 10.1 Transient Protection               | <mark>39</mark> |

| 7 Specifications                     |   | 10.2 Output Short-Circuit Measurements  | 40              |

| 7.1 Absolute Maximum Ratings         |   | 11 Layout                               | 41              |

| 7.2 ESD Ratings                      |   | 11.1 Layout Guidelines                  | 41              |

| 7.3 Recommended Operating Conditions |   | 11.2 Layout Example                     |                 |

| 7.4 Thermal Information              |   | 12 Device and Documentation Support     | 43              |

| 7.5 Electrical Characteristics       |   | 12.1 Documentation Support              | 43              |

| 7.6 Timing Requirements              |   | 12.2ドキュメントの更新通知を受け取る方法                  | 43              |

| 7.7 Switching Characteristics        |   | 12.3 サポート・リソース                          | 43              |

| 7.8 Typical Characteristics          |   | 12.4 Trademarks                         |                 |

| 8 Detailed Description               |   | 12.5 静電気放電に関する注意事項                      | 43              |

| 8.1 Overview                         |   | 12.6 用語集                                | 43              |

| 8.2 Functional Block Diagram         |   | 13 Mechanical, Packaging, and Orderable |                 |

| 8.3 Feature Description              |   | Information                             | 44              |

| ·                                    |   |                                         |                 |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes fr                  | om Revision A (July 2022) to Revision B (June 2023)   | Page |

|-----------------------------|-------------------------------------------------------|------|

| <ul><li>「逆電流」</li></ul>     | 用に外部 FET を駆動するオプション」を追加                               | 1    |

| <ul> <li>Added v</li> </ul> | ariants TPS259813ARPW and TPS259813LRPW               | 3    |

| <ul> <li>Updated</li> </ul> | the description of the DVDT pin                       | 4    |

|                             | image formatting                                      |      |

|                             | image                                                 |      |

| <ul> <li>Updated</li> </ul> | ⊠ 8-7                                                 | 27   |

|                             | マクション 8.3.9                                           |      |

| Changes fr                  | rom Revision * (April 2022) to Revision A (July 2022) | Page |

| <ul><li>ステータン</li></ul>     | スを「事前情報」から「量産データ」に変更                                  | 1    |

# **5 Device Comparison Table**

| Part Number   | Overvoltage Response | Overcurrent Response | Reverse Current<br>Blocking FET driver | Response to Fault |

|---------------|----------------------|----------------------|----------------------------------------|-------------------|

| TPS259814ARPW |                      |                      | No                                     | Auto-Retry        |

| TPS259814LRPW | Adjustable OVLO      | Circuit-Breaker      | No                                     | Latch-Off         |

| TPS259813ARPW | Adjustable OVEO      |                      | Auto-Retry                             |                   |

| TPS259813LRPW |                      |                      | Yes                                    | Latch-Off         |

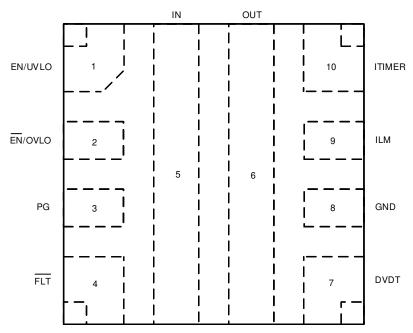

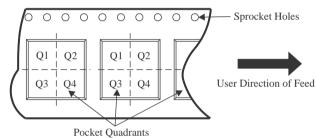

# **6 Pin Configuration and Functions**

図 6-1. TPS25981xx RPW Package 10-Pin QFN Top View

表 6-1. Pin Functions

| PI      | IN  | TYPE                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | ITPE                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

| EN/UVLO | 1   | Analog<br>Input                                                                          | Active high enable for the device. A resistor divider on this pin from input supply to GND can be used to adjust the undervoltage lockout threshold. <i>Do not leave floating.</i> Refer to <i>Undervoltage Lockout (UVLO and UVP)</i> for details.                                                                                                                                                                        |

| EN/OVLO | 2   | Analog<br>Input                                                                          | A resistor divider on this pin from supply to GND can be used to adjust the overvoltage lockout threshold. This pin can also be used as an Active low enable for the device. <i>Do not leave floating</i> . Refer to <i>Overvoltage Lockout (OVLO)</i> for details.                                                                                                                                                        |

| PG      | 3   | Digital<br>Output                                                                        | Power Good indication.  This pin is an open-drain signal which is asserted high when the power FET has fully turned ON and is ready to deliver power. Refer to <i>Power Good (PG)</i> for more details.                                                                                                                                                                                                                    |

| FLT     | 4   | Output fault is detected. Refer to Fault Response and Indication (FLI) for more details. |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IN      | 5   | Power                                                                                    | Power input                                                                                                                                                                                                                                                                                                                                                                                                                |

| OUT     | 6   | Power                                                                                    | Power output                                                                                                                                                                                                                                                                                                                                                                                                               |

| DVDT    | 7   | Analog<br>Output                                                                         | A capacitor from this pin to GND sets the output turn on slew rate. Leave this pin floating for the fastest turn-on slew rate. Refer to <i>Slew Rate (dVdt) and Inrush Current Control</i> for details. Only for TPS259813x variants, this pin can also be used to drive an external FET to implement reverse current blocking. Please refer to <i>Reverse Current Blocking FET Driver</i> for more details.               |

| GND     | 8   | Ground                                                                                   | This pin is the ground reference for all internal circuits and must be connected to system GND.                                                                                                                                                                                                                                                                                                                            |

| ILM     | 9   | Analog<br>Output                                                                         | This pin is a dual function pin used to limit and monitor the output current. An external resistor from this pin to GND sets the overcurrent protection threshold during start-up as well as steady-state. The pin voltage can also be used as analog output load current monitor signal. Do not leave floating. Refer to Circuit-Breaker During Steady-state or Active Current Limiting During Start-up for more details. |

# 表 6-1. Pin Functions (continued)

| PIN |          | PIN |                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|----------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | NAME NO. |     | 1172             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | ITIMER   | 10  | Analog<br>Output | A capacitor from this pin to GND sets the overcurrent blanking interval during which the output current can temporarily exceed set current limit (but lower than fast-trip threshold) during steady-state before the device overcurrent response takes action. Leave this pin open for fastest response to overcurrent events. Refer to Circuit-Breaker During Steady-state for more details. |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| -                    | Parameter                                                    | Pin       | MIN                  | MAX   | UNIT |

|----------------------|--------------------------------------------------------------|-----------|----------------------|-------|------|

| V <sub>IN</sub>      | Maximum input voltage range, –40°C ≤ T <sub>J</sub> ≤ 125°C  | IN        | -0.3                 | 20    | V    |

| V <sub>OUT</sub>     | Maximum output voltage range, –40°C ≤ T <sub>J</sub> ≤ 125°C | OUT       | -0.3 V <sub>IN</sub> | + 0.3 |      |

| V <sub>OUT,PLS</sub> | Minimum output voltage pulse (< 1 μs)                        | OUT       | -0.8                 |       |      |

| V <sub>EN/UVLO</sub> | Maximum Enable pin voltage range                             | EN/UVLO   | -0.3                 | 6.5   | V    |

| V <sub>OV</sub>      | Maximum EN/OVLO pin voltage range                            | EN/OVLO   | -0.3                 | 6.5   | V    |

| $V_{dVdT}$           | Maximum dVdT pin voltage range                               | dVdt      | Internally limited   |       | V    |

| V <sub>ITIMER</sub>  | Maximum ITIMER pin voltage range                             | ITIMER    | Internally limited   |       | V    |

| $V_{PG}$             | Maximum PG pin voltage range                                 | PG        | -0.3                 | 6.5   | V    |

| V <sub>FLTB</sub>    | Maximum FLT pin voltage range                                | FLT       | -0.3                 | 6.5   | V    |

| V <sub>ILM</sub>     | Maximum ILM pin voltage range                                | ILM       | Internally limited   |       | V    |

| I <sub>MAX</sub>     | Maximum continuous switch current                            | IN to OUT | Internally limited   |       | Α    |

| TJ                   | Junction temperature                                         |           | Internally limited   |       | °C   |

| T <sub>LEAD</sub>    | Maximum lead temperature                                     |           |                      | 300   | °C   |

| T <sub>stg</sub>     | Storage temperature                                          |           | -65                  | 150   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 7.2 ESD Ratings

|        |                         |                                                                       | VALUE | UNIT |

|--------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V      | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V(ESD) | Liectiostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| Parameter                                         | Pin                                                                                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                      | MAX                 | UNIT                |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|

| Input voltage range                               | IN                                                                                                                                                                                                                                      | 2.7                                                                                                                                                                                                                                                                      | 16                  | V                   |

| Output voltage range                              | OUT                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          | V <sub>IN</sub>     | V                   |

| EN/UVLO pin voltage range                         | EN/UVLO                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                          | 5 <sup>(1)</sup>    | V                   |

| EN/OVLO pin voltage range                         | EN/OVLO                                                                                                                                                                                                                                 | 0.5                                                                                                                                                                                                                                                                      | 1.5                 | V                   |

| dVdT pin capacitor voltage rating                 | dVdt                                                                                                                                                                                                                                    | V <sub>IN</sub> + 5 V                                                                                                                                                                                                                                                    |                     | V                   |

| FLT pin voltage range                             | FLT                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          | 5                   | V                   |

| PG pin voltage range                              | PG                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                          | 5                   | V                   |

| ITIMER pin capacitor voltage rating               | ITIMER                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                        |                     | V                   |

| ILM pin resistance to GND                         | ILM                                                                                                                                                                                                                                     | 600                                                                                                                                                                                                                                                                      | 4400                | Ω                   |

| Continuous switch current, T <sub>J</sub> ≤ 125°C | IN to OUT                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                          | 10                  | Α                   |

|                                                   | Input voltage range Output voltage range EN/UVLO pin voltage range EN/OVLO pin voltage range dVdT pin capacitor voltage rating FLT pin voltage range PG pin voltage range ITIMER pin capacitor voltage rating ILM pin resistance to GND | Input voltage range Output voltage range EN/UVLO pin voltage range EN/UVLO pin voltage range EN/OVLO pin voltage range dVdT pin capacitor voltage rating FLT pin voltage range FLT PG pin voltage range PG ITIMER pin capacitor voltage rating ILM pin resistance to GND | Input voltage range | Input voltage range |

Product Folder Links: TPS25981

Submit Document Feedback

# 7.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                | Parameter            | Pin | MIN | MAX | UNIT |

|----------------|----------------------|-----|-----|-----|------|

| T <sub>J</sub> | Junction temperature |     | -40 | 125 | °C   |

<sup>(1)</sup> For supply voltages below 5V, it is okay to pull up the EN pin to IN directly. For supply voltages greater than 5V , it is recommended to use a resistor divider with minimum pull-up resistor value of 350  $k\Omega$ .

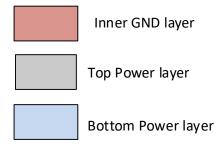

### 7.4 Thermal Information

|                  |                                              | TPS25981xx          |      |

|------------------|----------------------------------------------|---------------------|------|

|                  | THERMAL METRIC (1)                           | RPW (QFN)           | UNIT |

|                  |                                              | 10 PINS             |      |

| В                | Junction-to-ambient thermal resistance       | 49.7 <sup>(2)</sup> | °C/W |

| $R_{\theta JA}$  | Junction-to-ambient thermal resistance       | 71.8 <sup>(3)</sup> | °C/W |

| R <sub>0JB</sub> | Junction-to-board thermal resistance         | 15.7                | °C/W |

| ш                | Junction-to-top characterization parameter   | 2.1 <sup>(2)</sup>  | °C/W |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 1.3 <sup>(3)</sup>  | °C/W |

| w                | Junction-to-board characterization parameter | 23 (2)              | °C/W |

| $\Psi_{JB}$      | dunction-to-board characterization parameter | 14.5 <sup>(3)</sup> | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Based on simulations conducted with the device mounted on a custom 4-layer PCB (2s2p) with 8 thermal vias under device

<sup>(3)</sup> Based on simulations conducted with the device mounted on a JEDEC 4-layer PCB (2s2p) with no thermal vias under device

# 7.5 Electrical Characteristics

(Test conditions unless otherwise noted)  $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 125^{\circ}\text{C}$ ,  $\text{V}_\text{IN} = 12 \text{ V}$ , OUT = Open,  $\text{V}_\text{EN/UVLO} = 2 \text{ V}$ ,  $\text{V}_\text{OVLO} = 0 \text{ V}$ ,  $\text{R}_\text{ILM} = 611~\Omega$ , dVdT = Open, ITIMER = Open,  $\overline{\text{FLT}} = \text{Open}$ ,  $\overline{\text{PLT}} = \text{Open}$ , All voltages referenced to GND.

| Test<br>Parametei                              | Description                                                                                                                            | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUP                                      | PLY (IN)                                                                                                                               |       | -     |       |       |

| Q(ON)                                          | IN supply quiescent current                                                                                                            |       | 417   | 610   | μΑ    |

| Q(OFF)                                         | IN supply OFF state current (V <sub>SD(F)</sub> < V <sub>EN</sub> < V <sub>UVLO(F)</sub> )                                             |       | 68    | 90    | μΑ    |

| I <sub>SD</sub>                                | IN supply shutdown current (V <sub>EN</sub> < V <sub>SD(F)</sub> )                                                                     |       | 3     | 25    | μΑ    |

| V <sub>UVP(R)</sub>                            | IN supply UVP rising threshold                                                                                                         | 2.44  | 2.53  | 2.64  | V     |

| V <sub>UVP(F)</sub>                            | IN supply UVP falling threshold                                                                                                        | 2.35  | 2.42  | 2.55  | V     |

|                                                | DAD CURRENT MONITOR (ILM)                                                                                                              |       |       |       |       |

|                                                | Analog load current monitor gain (I <sub>MON</sub> : I <sub>OUT</sub> ), I <sub>OUT</sub> = 1.5 A, I <sub>OUT</sub> < I <sub>LIM</sub> | 82.9  | 95.3  | 107.6 | μA/A  |

|                                                | Analog load current monitor gain (I <sub>MON</sub> : I <sub>OUT</sub> ), I <sub>OUT</sub> = 3 A, I <sub>OUT</sub> < I <sub>LIM</sub>   | 87    | 95.3  | 104.5 | μΑ/Α  |

| G <sub>IMON</sub>                              | Analog load current monitor gain ( $I_{MON}$ : $I_{OUT}$ ), $I_{OUT}$ = 4.5 A, $I_{OUT}$ < $I_{LIM}$                                   | 87.6  | 95.3  | 103.1 | μA/A  |

|                                                | Analog load current monitor gain (I <sub>MON</sub> : I <sub>OUT</sub> ), I <sub>OUT</sub> = 8 A, I <sub>OUT</sub> < I <sub>LIM</sub>   | 87.7  | 95.3  | 102.6 | μA/A  |

|                                                | Analog load current monitor gain (I <sub>MON</sub> : I <sub>OUT</sub> ), I <sub>OUT</sub> = 10 A, I <sub>OUT</sub> < I <sub>LIM</sub>  | 87.8  | 95.3  | 102.4 | μA/A  |

| OVERCURE                                       | RENT PROTECTION (OUT)                                                                                                                  |       |       |       |       |

|                                                | Overcurrent threshold, $R_{ILM}$ = 3320 $\Omega$                                                                                       | 1.72  | 1.99  | 2.26  | Α     |

| OVERCURRE  I <sub>LIM</sub> I <sub>SPFLT</sub> | Overcurrent threshold, $R_{ILM}$ = 2212 $\Omega$                                                                                       | 2.64  | 2.98  | 3.32  | Α     |

|                                                | Overcurrent threshold, R <sub>ILM</sub> = 1102 kΩ                                                                                      | 5.43  | 5.98  | 6.52  | Α     |

|                                                | Overcurrent threshold, $R_{ILM}$ = 750 $\Omega$                                                                                        | 7.95  | 8.73  | 9.52  | Α     |

|                                                | Overcurrent threshold, $R_{ILM}$ = 611 $\Omega$                                                                                        | 9.8   | 10.76 | 11.73 | Α     |

| I <sub>SPFLT</sub>                             | Circuit-Breaker threshold, ILM pin open (Single point failure)                                                                         |       |       | 0.1   | Α     |

| I <sub>SPFLT</sub>                             | Circuit-Breaker threshold, ILM pin shorted to GND (Single point failure)                                                               |       | 2.24  | 3.3   | Α     |

| I <sub>FT</sub>                                | Fixed fast-trip current threshold                                                                                                      |       | 39.5  |       | Α     |

| I <sub>SCGain</sub>                            | Scalable fast-trip threshold (I <sub>SC</sub> ) : I <sub>LIM</sub> ratio                                                               | 170   | 193   | 242   | %     |

| V <sub>FB</sub>                                | V <sub>OUT</sub> threshold to exit current limit foldback                                                                              | 1.55  | 1.91  | 2.23  | V     |

| ON RESIST                                      | ANCE (IN - OUT)                                                                                                                        |       |       | 1     |       |

|                                                | $2.7 \le V_{IN} \le 4 \text{ V}, I_{OUT} = 3 \text{ A}, T_{J} = 25^{\circ}\text{C}$                                                    |       | 6.07  |       | mΩ    |

| R <sub>ON</sub>                                | 4 < V <sub>IN</sub> ≤ 16 V, I <sub>OUT</sub> = 3 A, T <sub>J</sub> = 25°C                                                              |       | 5.81  |       | mΩ    |

|                                                | $2.7 \le V_{IN} \le 16 \text{ V}, I_{OUT} = 3 \text{ A}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                        |       |       | 8.4   | mΩ    |

| ENABLE/UN                                      | NDERVOLTAGE LOCKOUT (EN/UVLO)                                                                                                          |       |       | 1     |       |

| V <sub>UVLO(R)</sub>                           | EN/UVLO rising threshold                                                                                                               | 1.176 | 1.20  | 1.224 | V     |

| V <sub>UVLO(F)</sub>                           | EN/UVLO falling threshold                                                                                                              | 1.073 | 1.09  | 1.116 | V     |

| V <sub>SD(F)</sub>                             | EN/UVLO falling threshold for lowest shutdown current                                                                                  | 0.45  | 0.75  |       | V     |

| ENLKG                                          | EN/UVLO pin leakage current                                                                                                            | -0.1  |       | 0.1   | μA    |

| OVERVOLT                                       | AGE LOCKOUT (EN/OVLO)                                                                                                                  |       |       | I     |       |

| V <sub>OV(R)</sub>                             | OVLO rising threshold                                                                                                                  | 1.176 | 1.20  | 1.224 | V     |

| $V_{OV(F)}$                                    | OVLO falling threshold                                                                                                                 | 1.074 | 1.09  | 1.116 | V     |

| I <sub>OVLKG</sub>                             | OVLO pin leakage current (0.5 V < V <sub>OVLO</sub> < 1.5 V)                                                                           | -0.1  |       | 0.1   | μA    |

|                                                | RENT FAULT TIMER (ITIMER)                                                                                                              |       |       | I     |       |

|                                                | ITIMER pin internal discharge current, I <sub>OUT</sub> > I <sub>LIM</sub>                                                             | 1.25  | 2     | 2.72  |       |

English Data Sheet: SLVSGG6

# 7.5 Electrical Characteristics (continued)

(Test conditions unless otherwise noted)  $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 125^{\circ}\text{C}$ ,  $\text{V}_\text{IN} = 12 \text{ V}$ , OUT = Open,  $\text{V}_\text{EN/UVLO} = 2 \text{ V}$ ,  $\text{V}_\text{OVLO} = 0 \text{ V}$ ,  $\text{R}_\text{ILM} = 611~\Omega$ , dVdT = Open, ITIMER = Open,  $\overline{\text{FLT}} = \text{Open}$ , PG = Open. All voltages referenced to GND.

| Test<br>Parameter      | Description                                                                                                                  | MIN  | TYP   | MAX  | UNITS |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| R <sub>ITIMER</sub>    | ITIMER pin internal pullup resistance                                                                                        |      | 15.4  |      | kΩ    |

| V <sub>INT</sub>       | ITIMER pin internal pullup voltage                                                                                           | 2.1  | 2.57  | 2.74 | V     |

| V <sub>ITIMER(F)</sub> | ITIMER comparator threshold, I <sub>OUT</sub> > I <sub>LIM</sub>                                                             | 0.6  | 1.06  | 1.37 | V     |

| $\Delta V_{ITIMER}$    | ITIMER discharge differential voltage threshold, I <sub>OUT</sub> > I <sub>LIM</sub>                                         | 1.28 | 1.51  | 1.74 | V     |

| POWER GOO              | D INDICATION (PG)                                                                                                            |      |       | •    |       |

|                        | PG pin voltage while de-asserted. $V_{IN} < V_{UVP(F)}$ , $V_{EN} < V_{SD(F)}$ , Weak pullup ( $I_{PG} = 26 \ \mu A$ )       |      | 0.66  | 0.80 | V     |

| $V_{PGD}$              | PG pin voltage while de-asserted. $V_{IN}$ < $V_{UVP(F)}$ , $V_{EN}$ < $V_{SD(F)}$ , Strong pullup ( $I_{PG}$ = 242 $\mu$ A) |      | 0.78  | 0.90 | V     |

|                        | PG pin voltage while de-asserted, V <sub>IN</sub> > V <sub>UVP(R)</sub>                                                      |      | 0     | 0.60 | V     |

| I <sub>PGLKG</sub>     | PG pin leakage current, PG asserted                                                                                          |      |       | 3    | μA    |

| R <sub>FLTB</sub>      | FLT pin internal pulldown resistance                                                                                         |      | 12.57 |      | Ω     |

| FAULT INDIC            | ATION (FLT)                                                                                                                  |      |       | ,    |       |

| I <sub>FLTLKG</sub>    | FLT pin leakage current                                                                                                      | -1   |       | 1    | μΑ    |

| OVERTEMPE              | RATURE PROTECTION (OTP)                                                                                                      |      |       | •    |       |

| TSD                    | Thermal Shutdown rising threshold, T <sub>J</sub> ↑                                                                          | 154  |       | °C   |       |

| TSD <sub>HYS</sub>     | Thermal Shutdown hysteresis, $T_J \downarrow$ 10                                                                             |      |       | °C   |       |

| DVDT                   |                                                                                                                              |      |       |      |       |

| I <sub>dVdt</sub>      | dVdt pin internal charging current                                                                                           | 1.4  | 3.45  | 5.7  | μA    |

| QUICK OUTP             | UT DISCHARGE (OUT)                                                                                                           |      |       | '    |       |

| R <sub>QOD</sub>       | Quick Output Discharge Resistance, V <sub>EN</sub> < V <sub>UVLO(F)</sub>                                                    | 455  | 488   | 530  | Ω     |

# 7.6 Timing Requirements

|                      | PARAMETER                            | TEST CONDITIONS                                                   | MIN TYP | MAX | UNIT |

|----------------------|--------------------------------------|-------------------------------------------------------------------|---------|-----|------|

| t <sub>OVLO</sub>    | Overvoltage lock-out response time   | $V_{OVLO} > V_{OV(R)}$ to $V_{OUT} \downarrow$                    | 1.2     |     | μs   |

| t <sub>CB</sub>      | Circuit-Breaker response time        | ITIMER = Open, $I_{OUT} > I_{LIM} + 30\%$ to $V_{OUT} \downarrow$ | 1.8     |     | μs   |

| t <sub>SC</sub>      | Short-circuit response time          | I <sub>OUT</sub> > 3 × I <sub>LIM</sub> to output current cut off | 640     |     | ns   |

| t <sub>FT</sub>      | Fixed fast-trip response time        | I <sub>OUT</sub> > I <sub>FT</sub> to I <sub>OUT</sub> ↓          | 640     |     | ns   |

| t <sub>TSD,RST</sub> | Thermal Shutdown auto-retry Interval | Device enabled and T <sub>J</sub> < TSD – TSD <sub>HYS</sub>      | 105     |     | ms   |

| t <sub>PGA</sub>     | PG assertion de-glitch time          |                                                                   | 14      |     | μs   |

| t <sub>PGD</sub>     | PG de-assertion de-glitch time       |                                                                   | 14      |     | μs   |

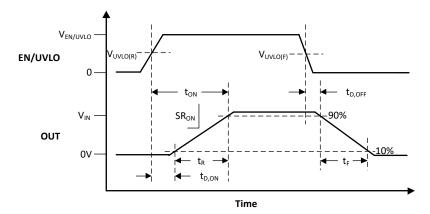

# 7.7 Switching Characteristics

The output rising slew rate is internally controlled and constant across the entire operating voltage range to ensure the turn on timing is not affected by the load conditions. The rising slew rate can be adjusted by adding capacitance from the dVdt pin to ground. As  $C_{dVdt}$  is increased it slows the rising slew rate (SR). See Slew Rate and Inrush Current Control (dVdt) section for more details. The Turn-Off Delay and Fall Time, however, are dependent on the RC time constant of the load capacitance ( $C_{OUT}$ ) and Load Resistance ( $R_L$ ). The Switching Characteristics are only valid for the power-up sequence where the supply is available in steady-state condition and the load voltage is completely discharged before the device is enabled. Typical values are taken at  $T_J = 25^{\circ}$ C unless specifically noted otherwise.  $R_L = 100 \ \Omega$ ,  $C_{OUT} = 1 \ \mu F$ .

|                    | PARAMETER               | V <sub>IN</sub> | C <sub>dVdt</sub> = Open | C <sub>dVdt</sub> = 1800 pF | C <sub>dVdt</sub> = 3300 pF | UNITS |

|--------------------|-------------------------|-----------------|--------------------------|-----------------------------|-----------------------------|-------|

|                    |                         | 2.7 V           | 8.19                     | 1.30                        | 0.78                        |       |

| SR <sub>ON</sub>   | Output rising slew rate | 5 V             | 11.28                    | 1.42                        | 0.84                        | V/ms  |

|                    |                         | 12 V            | 19.71                    | 1.68                        | 0.98                        |       |

|                    |                         | 2.7 V           | 0.14                     | 0.46                        | 0.70                        |       |

| $t_{D,ON}$         | Turn-on delay           | 5 V             | 0.14                     | 0.60                        | 0.96                        | ms    |

|                    |                         | 12 V            | 0.14                     | 0.93                        | 1.57                        |       |

|                    |                         | 2.7 V           | 0.26                     | 1.66                        | 2.77                        |       |

| t <sub>R</sub>     | Rise time               | 5 V             | 0.36                     | 2.82                        | 4.78                        | ms    |

|                    |                         | 12 V            | 0.49                     | 5.74                        | 9.84                        |       |

|                    |                         | 2.7 V           | 0.40                     | 2.11                        | 3.47                        |       |

| t <sub>ON</sub>    | Turn-on time            | 5 V             | 0.50                     | 3.42                        | 5.74                        | ms    |

|                    |                         | 12 V            | 0.63                     | 6.67                        | 11.41                       |       |

|                    |                         | 2.7 V           | 24.90                    | 24.90                       | 24.90                       |       |

| t <sub>D,OFF</sub> | Turn-off delay          | 5 V             | 21.10                    | 21.10                       | 21.10                       | μs    |

|                    |                         | 12 V            | 18.80                    | 18.80                       | 18.80                       |       |

図 7-1. TPS25981xx Switching Times

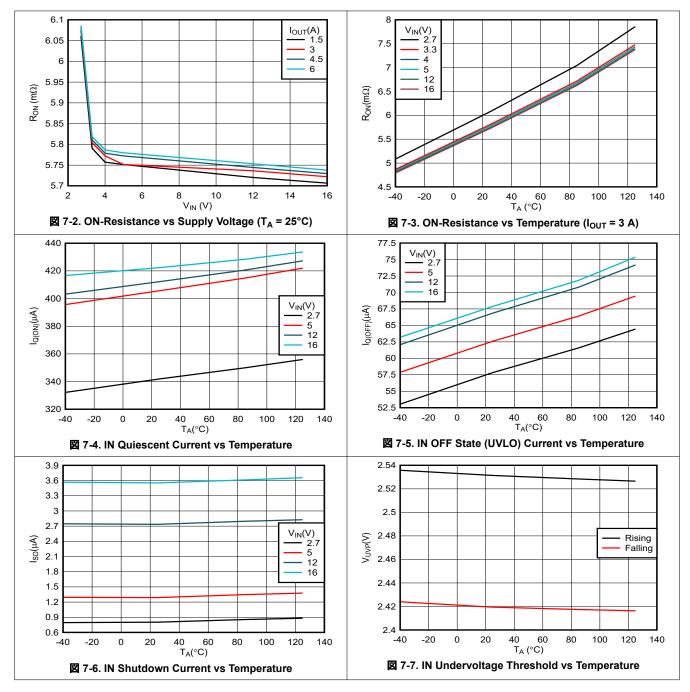

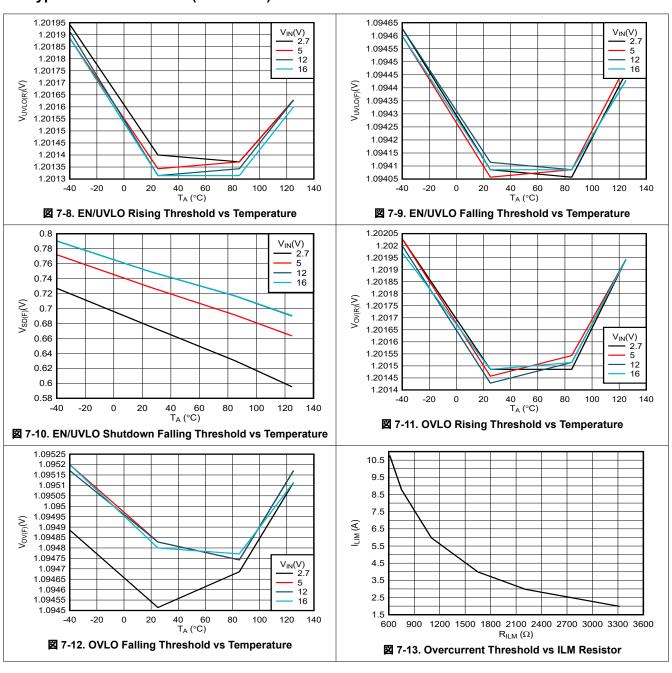

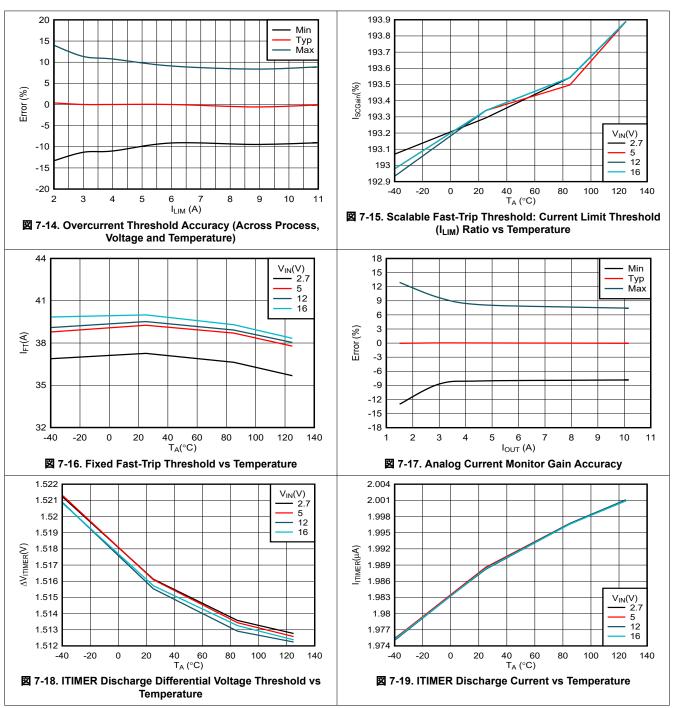

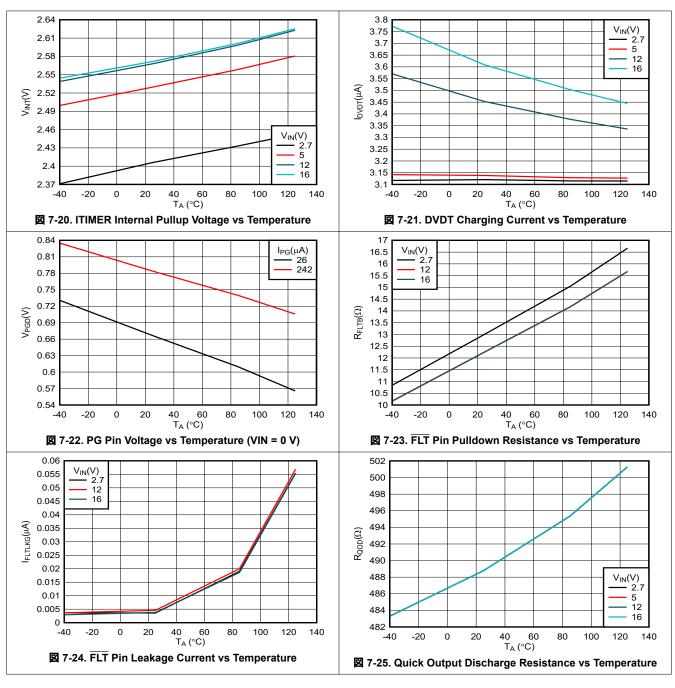

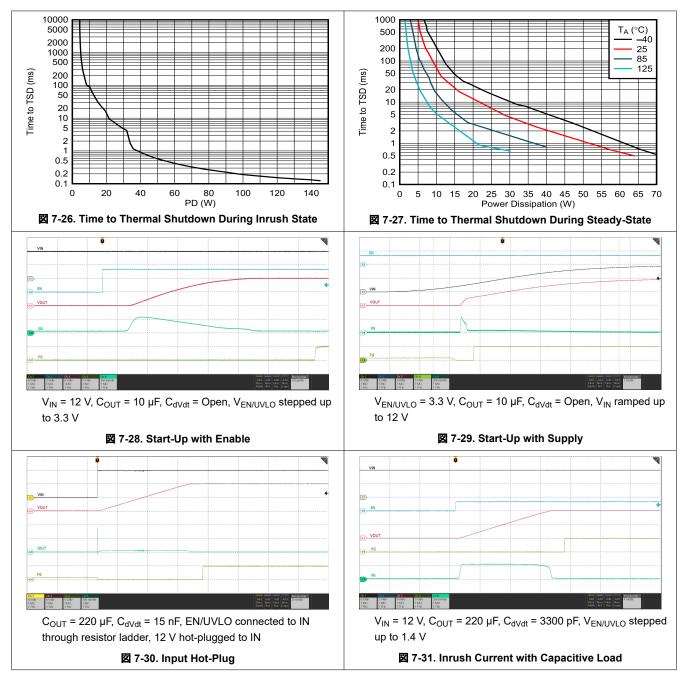

# 7.8 Typical Characteristics

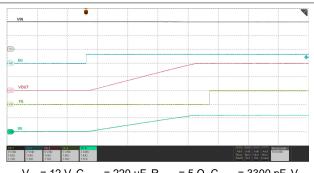

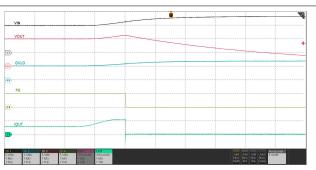

$V_{IN}$  = 12 V,  $C_{OUT}$  = 220  $\mu\text{F},\,R_{OUT}$  = 5  $\Omega,\,C_{dVdt}$  = 3300 pF,  $V_{EN/}$   $_{UVLO}$  stepped up to 1.4 V

### 図 7-32. Inrush Current with Resistive and Capacitive Load

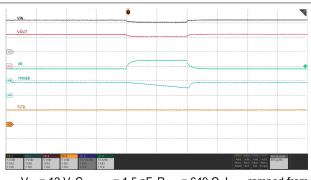

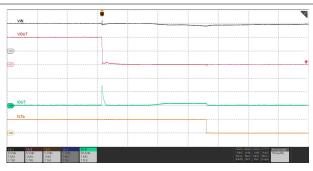

$V_{IN}$  = 12 V,  $C_{ITIMER}$  = 1.5 nF,  $R_{ILM}$  = 649  $\Omega,$   $I_{OUT}$  ramped from 8 A  $\rightarrow$  14 A  $\rightarrow$  8 A within 1 ms

#### 図 7-34. Transient Overcurrent Blanking Timer Response

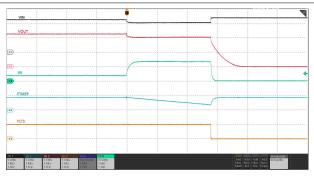

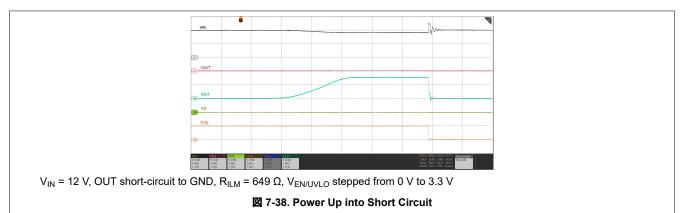

$V_{IN}$  = 12 V,  $R_{ILM}$  = 649  $\Omega,$  OUT stepped from Open  $\rightarrow$  Short-circuit to GND

Product Folder Links: TPS25981

### 図 7-36. Output Short-Circuit During Steady-State

$V_{\text{IN}}$  Overvoltage threshold set to 13.6 V using resistor ladder connected to OVLO pin,  $V_{\text{IN}}$  ramped up from 12 V to 16 V

### 図 7-33. Overvoltage Lockout Response

$V_{IN}$  = 12 V,  $C_{ITIMER}$  = 1.5 nF,  $R_{ILM}$  = 649  $\Omega,$   $I_{OUT}$  ramped from 4 A  $\rightarrow$  13 A

#### ☑ 7-35. Circuit-Breaker Response

$V_{IN}$  = 12 V,  $R_{ILM}$  = 649  $\Omega,$  OUT stepped from Open  $\rightarrow$  Short-circuit to GND

図 7-37. Output Short-Circuit During Steady-State (Zoomed In)

# 8 Detailed Description

### 8.1 Overview

The TPS25981xx is an eFuse with integrated power path that is used to ensure safe power delivery in a system. The device starts its operation by monitoring the IN bus. When the input supply voltage ( $V_{IN}$ ) exceeds the Undervoltage Protection threshold ( $V_{UVP}$ ), the device samples the EN/UVLO pin. A high level (>  $V_{UVLO}$ ) on this pin enables the internal power path to start conducting and allow current to flow from IN to OUT. When EN/UVLO is held low (<  $V_{UVLO}$ ), the internal power path is turned off.

After a successful start-up sequence, the device now actively monitors its load current and input voltage, and controls the internal FET to ensure that the user adjustable overcurrent protection threshold ( $I_{LIM}$ ) is not exceeded and overvoltage spikes are cut-off after they cross the user adjustable overvoltage lockout threshold ( $V_{OVLO}$ ). The device also provides fast protection against severe overcurrent during short-circuit events. This feature keeps the system safe from harmful levels of voltage and current. At the same time, a user adjustable overcurrent blanking timer allows the system to pass moderate transient peaks in the load current profile without tripping the eFuse. This feature ensures a robust protection solution against real faults which is also immune to transients, thereby ensuring maximum system uptime.

The device also has a built-in thermal sensor based shutdown mechanism to protect itself in case the device temperature  $(T_J)$  exceeds the recommended operating conditions.

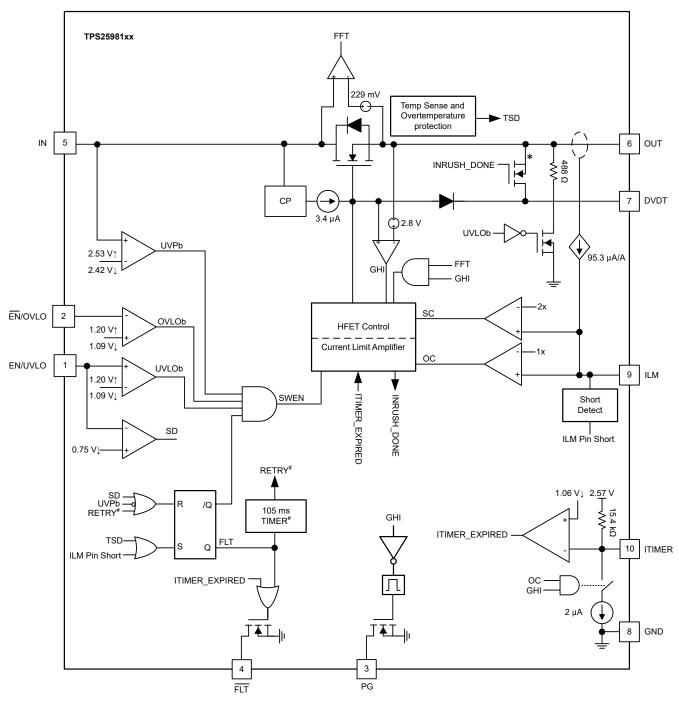

# 8.2 Functional Block Diagram

<sup>#</sup> Not applicable to TPS25981xL (Latch-off) variants \* Not applicable for TPS259813x variants

### 8.3 Feature Description

The TPS25981xx eFuse is a compact, feature rich power management device that provides detection, protection and indication in the event of system faults.

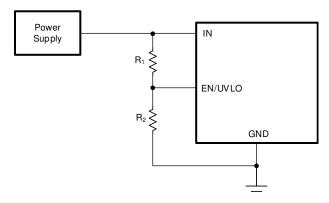

### 8.3.1 Undervoltage Lockout (UVLO and UVP)

The TPS25981xx implements undervoltage protection on IN in case the applied voltage becomes too low for the system or device to properly operate. The undervoltage protection has a default lockout threshold of  $V_{UVP}$  which is fixed internally. Also, the UVLO comparator on the EN/UVLO pin allows the undervoltage protection threshold to be externally adjusted to a user defined value.  $\boxtimes$  8-1 and  $\rightrightarrows$  1 show how a resistor divider can be used to set the UVLO set point for a given voltage supply.

図 8-1. Adjustable Undervoltage Protection

$$V_{IN(UV)} = \frac{V_{UVLO} \times (R_1 + R_2)}{R_2} \tag{1}$$

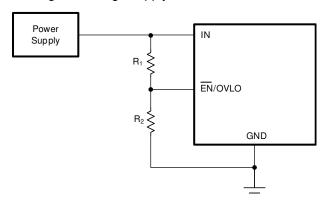

#### 8.3.2 Overvoltage Lockout (OVLO)

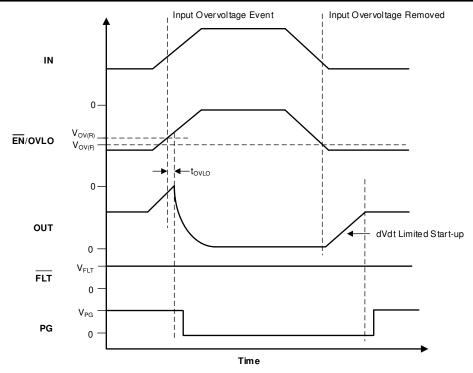

The TPS259814x devices allow the user to implement overvoltage lockout to protect the load from input overvoltage conditions. The OVLO comparator on the  $\overline{\text{EN}}/\text{OVLO}$  pin allows the overvoltage protection threshold to be adjusted to a user defined value. After the voltage at the  $\overline{\text{EN}}/\text{OVLO}$  pin crosses the OVLO rising threshold  $V_{\text{OV}(R)}$ , the device turns off the power to the output. Thereafter, the devices wait for the voltage at the  $\overline{\text{EN}}/\text{OVLO}$  pin to fall below the OVLO falling threshold  $V_{\text{OV}(F)}$  before the output power is turned ON again. The rising and falling thresholds are slightly different to provide hysteresis.  $\boxtimes$  8-2 and  $\rightrightarrows$  2 show how a resistor divider can be used to set the OVLO set point for a given voltage supply.

図 8-2. Adjustable Overvoltage Protection

$$V_{IN(OV)} = \frac{V_{OV} \times (R_1 + R_2)}{R_2} \tag{2}$$

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

図 8-3. TPS259814x Overvoltage Lockout and Recovery

While recovering from a OVLO event, the TPS259814x variants start up with inrush control (dVdt).

### 8.3.3 Inrush Current, Overcurrent, and Short-Circuit Protection

TPS25981xx incorporates four levels of protection against overcurrent:

- 1. Adjustable slew rate (dVdt) for inrush current control

- 2. Adjustable threshold (I<sub>I IM</sub>) for overcurrent protection during start-up or steady-state

- 3. Adjustable threshold (I<sub>SC</sub>) for fast-trip response to severe overcurrent during start-up or steady-state

- 4. Fixed threshold (I<sub>FT</sub>) for fast-trip response to quickly protect against hard output short circuits during steadystate

### 8.3.3.1 Slew Rate (dVdt) and Inrush Current Control

During hot-plug events or while trying to charge a large output capacitance at start-up, there can be a large inrush current. If the inrush current is not managed properly, it can damage the input connectors and cause the system power supply to droop leading to unexpected restarts elsewhere in the system. The inrush current during turn-on is directly proportional to the load capacitance and rising slew rate.  $\implies$  3 can be used to find the slew rate (SR) required to limit the inrush current ( $I_{INRUSH}$ ) for a given load capacitance ( $C_{OUT}$ ):

$$SR\left(\frac{V}{ms}\right) = \frac{I_{INRUSH}(mA)}{C_{OUT}(\mu F)} \tag{3}$$

A capacitor can be connected to the dVdt pin to control the rising slew rate and lower the inrush current during turn on. Use  $\pm 4$  to calculate the required  $C_{dVdt}$  capacitance to produce a given slew rate.

$$C_{dVdt}(pF) = \frac{3300}{SR\left(\frac{V}{ms}\right)} \tag{4}$$

The fastest output slew rate is achieved by leaving the dVdt pin open.

注

For  $C_{dVdt} > 10$  nF, TI recommends to add a 100- $\Omega$  resistor in series with the capacitor on the dVdt pin.

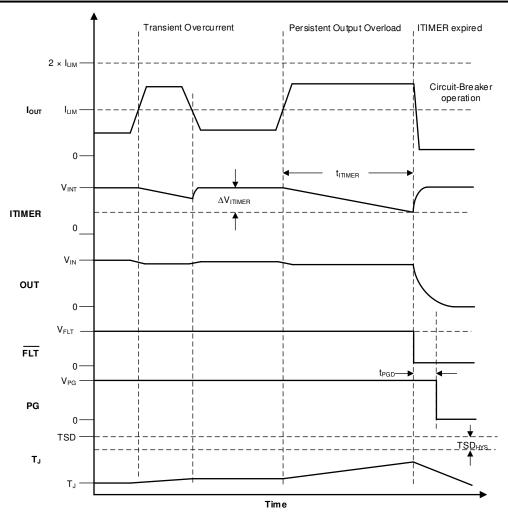

### 8.3.3.2 Circuit-Breaker During Steady-State

The TPS259814x (circuit-breaker) variants respond to output overcurrent conditions by turning off the output after a user adjustable transient fault blanking interval. When the load current exceeds the set overcurrent threshold ( $I_{LIM}$ ) set by the ILM pin resistor ( $R_{ILM}$ ), but stays lower than the fast-trip threshold ( $2 \times I_{LIM}$ ), the device starts discharging the ITIMER pin capacitor using an internal 2- $\mu$ A pulldown current. If the load current drops below  $I_{LIM}$  before the ITIMER pin capacitor ( $C_{ITIMER}$ ) discharges by  $\Delta V_{ITIMER}$ , the ITIMER is reset by pulling it up to  $V_{INT}$  internally and the circuit-breaker action is not engaged. This action allows short load transient pulses to pass through the device without tripping the circuit. If the overcurrent condition persists, the  $C_{ITIMER}$  continues to discharge and after it discharges by  $\Delta V_{ITIMER}$ , the circuit-breaker action turns off the FET immediately. At the same time, the  $C_{ITIMER}$  is charged up to  $V_{INT}$  again so that it is at its default state before the next overcurrent event. This action ensures the full blanking timer interval is provided for every overcurrent event.  $\vec{x}$  5 can be used to calculate the  $R_{IIM}$  value for a overcurrent threshold.

$$R_{ILM}\left(\Omega\right) = \frac{6585}{I_{LIM}\left(A\right)}\tag{5}$$

注

- 1. Leaving the ILM pin open sets the current limit to nearly zero and results in the part breaking the circuit with the slightest amount of loading at the output.

- 2. Shorting the ILM pin to ground at any point during normal operation is detected as a fault and the part shuts down. There is a minimum current (I<sub>FLT</sub>) which the part allows in this condition before the pin short condition is detected.

The duration for which transients are allowed can be adjusted using an appropriate capacitor value from ITIMER pin to ground. Use  $\not \equiv 6$  to calculate the C<sub>ITIMER</sub> value needed to set the desired transient overcurrent blanking interval.

Product Folder Links: TPS25981

$$C_{ITIMER}(nF) = \frac{t_{ITIMER}(ms) \times I_{ITIMER}(\mu A)}{\Delta V_{ITIMER}(V)}$$

(6)

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

図 8-4. TPS259814x Overcurrent Response

注

- 1. Leave the ITIMER pin open to allow the part to break the circuit with the minimum possible delay.

- 2. Shorting the ITIMER pin to ground results in minimum overcurrent response delay (similar to ITIMER pin open condition), but increases the device current consumption. This action is not a recommended mode of operation.

- 3. Increasing the ITIMER cap value extends the overcurrent blanking interval, but it also extends the time needed for the C<sub>ITIMER</sub> to recharge up to V<sub>INT</sub>. If the next overcurrent event occurs before the C<sub>ITIMER</sub> is recharged fully, it takes lesser time to discharge to the ITIMER expiry threshold, thereby providing a shorter blanking interval than intended.

- 4. In low voltage applications, TI recommends adding a 30 k $\Omega$  resistor between the ITIMER pin and C<sub>ITIMER</sub> for improved immunity to supply noise or fluctuations.

After the part shuts down due to a circuit-breaker fault, it either stays latched off (TPS259814L variant) or restarts automatically after a fixed delay (TPS259814A variant).

### 8.3.3.3 Active Current Limiting During Start-Up

The TPS259814x devices respond to output overcurrent conditions during start-up by actively limiting the current. If the load current exceeds the set overcurrent threshold ( $I_{LIM}$ ) set by the ILM pin resistor ( $R_{ILM}$ ), but stays lower than the short-circuit threshold ( $2 \times I_{LIM}$ ), the current limit loop starts regulating the FET to actively

limit the current to the set overcurrent threshold ( $I_{LIM}$ ).  $\gtrsim 7$  can be used to calculate the  $R_{ILM}$  value for a desired overcurrent threshold.

$$R_{ILM}\left(\Omega\right) = \frac{6585}{I_{LIM}\left(A\right)}\tag{7}$$

注

- 1. Leaving the ILM pin open sets the current limit to nearly zero and results in the part entering current limit with the slightest amount of loading at the output.

- 2. The current limit circuit employs a foldback mechanism. The current limit threshold in the foldback region (0 V <  $V_{OUT}$  <  $V_{FB}$ ) is lower than the target steady-state overcurrent threshold ( $I_{LIM}$ ).

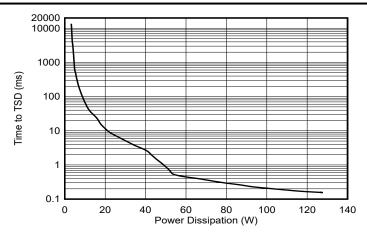

During active current limit, the output voltage drops, resulting in increased device power dissipation across the FET. If the device internal temperature  $(T_J)$  exceeds the thermal shutdown threshold (TSD), the FET is turned off. After the part shuts down due to TSD fault, it either stays latched off (TPS25981xL variants) or restarts automatically after a fixed delay (TPS25981xA variants). For more details on device response to overtemperature, see *Overtemperature Protection (OTP)*.

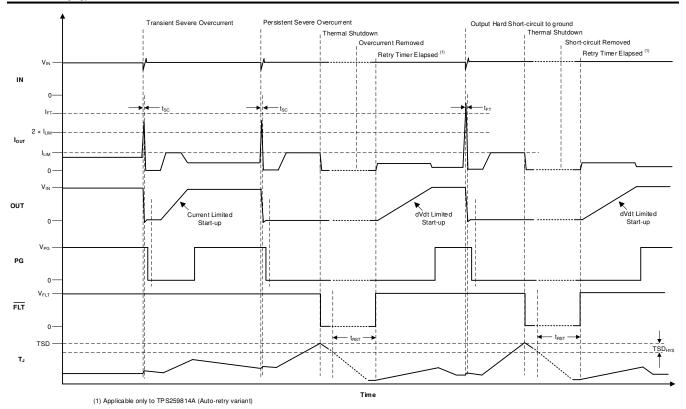

#### 8.3.3.4 Short-Circuit Protection

During an output short-circuit event, the current through the device increases very rapidly. When a severe overcurrent condition is detected, the device triggers a fast-trip response to limit the current to a safe level. The internal fast-trip comparator employs a scalable threshold ( $I_{SC}$ ) which is equal to  $2 \times I_{LIM}$ . This action enables the user to adjust the fast-trip threshold rather than using a fixed threshold which can be too high for some low current systems. The device also employs a fixed fast-trip threshold ( $I_{FT}$ ) to protect fast protection against hard short circuits during steady-state. The fixed fast-trip threshold is higher than the maximum recommended user adjustable scalable fast-trip threshold. After the current exceeds  $I_{SC}$  or  $I_{FT}$ , the FET is turned off completely within  $I_{FT}$ . Thereafter, the devices tries to turn the FET back on after a short de-glitch interval ( $I_{SC}$ ) in a current limited manner instead of a dVdt limited manner. This action ensures that the FET has a faster recovery after a transient overcurrent event and minimizes the output voltage droop. However, if the fault is persistent, the device stays in current limit causing the junction temperature to rise and eventually enter thermal shutdown. For details on the device response to overtemperature, see *Overtemperature Protection (OTP)*.

Product Folder Links: TPS25981

Copyright © 2023 Texas Instruments Incorporated

図 8-5. TPS25981xx Short-Circuit Response

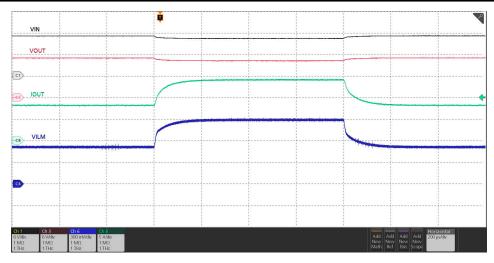

# 8.3.4 Analog Load Current Monitor

The device allows the system to accurately monitor the output load current by providing an analog current sense output on the ILM pin which is proportional to the current through the FET. The user can sense the voltage ( $V_{ILM}$ ) across the  $R_{ILM}$  to get a measure of the output load current.

$$I_{LOAD}(A) = \frac{V_{ILM}(\mu V)}{G_{IMON}(\mu A/A) \times R_{ILM}(\Omega)}$$

(8)

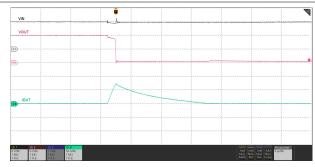

The waveform below shows the ILM signal response to a load step at the output.

$V_{IN}$  = 12 V,  $R_{ILM}$  = 649  $\Omega$ ,  $I_{OUT}$  varied dynamically between 8 A and 14 A

### **図 8-6. Analog Load Current Monitor Response**

注

The ILM pin is sensitive to capacitive loading. Careful design and layout is needed to ensure the parasitic capacitive loading on the ILM pin is < 50 pF for stable operation.

# 8.3.5 Overtemperature Protection (OTP)

The device monitors the internal die temperature  $(T_J)$  at all times and shuts down the part as soon as the temperature exceeds a safe operating level (TSD) thereby protecting the device from damage. The device does turn back on until the junction cools down sufficiently, that is the die temperature falls below (TSD – TSD<sub>HYS</sub>).

When the TPS25981xL (latch-off variant) detects thermal overload, it is shut down and remains latched-off until the device is power cycled or re-enabled. When the TPS25981xA (auto-retry variant) detects thermal overload, it remains off until it has cooled down by  $TSD_{HYS}$ . Thereafter, the device remains off for an additional delay of  $t_{RST}$  after which it automatically retries to turn on if it is still enabled.

表 8-1. Thermal Shutdown

| Device                  | Enter TSD | Exit TSD                                                                                                                                                                                                        |

|-------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS25981xL (latch-off)  | •         | $\begin{split} &T_{J} < TSD - TSD_{HYS} \\ &V_{IN} \text{ cycled to } 0 \text{ V and then above } V_{UVP(R)}  or \\ &EN/UVLO \text{ toggled below } V_{SD(F)} \end{split}$                                      |

| TPS25981xA (auto-retry) | T. > TSD  | $\begin{split} &T_{J} < TSD - TSD_{HYS} \\ &V_{IN} \text{ cycled to 0 V and then above } V_{UVP(R)}  or \\ &EN/UVLO \text{ toggled below } V_{SD(F)}  or  t_{RST} \text{ timer} \\ &\text{expired} \end{split}$ |

# 8.3.6 Fault Response and Indication (FLT)

The following table summarizes the device response to various fault conditions. Additionally, an active low external fault indication (FLT) pin is available.

表 8-2. Fault Summary

| Event                                                                               | Protection Response                       | Fault Latched Internally | FLT Pin Status | FLT Assertion Delay |  |

|-------------------------------------------------------------------------------------|-------------------------------------------|--------------------------|----------------|---------------------|--|

| Overtemperature                                                                     | Shutdown                                  | Υ                        | L              |                     |  |

| Undervoltage (UVP or UVLO)                                                          | Shutdown                                  | N                        | Н              |                     |  |

| Input overvoltage                                                                   | Shutdown                                  | N                        | Н              |                     |  |

| Transient overcurrent (I <sub>LIM</sub> < I <sub>OUT</sub> < 2 × I <sub>LIM</sub> ) | None                                      | N                        | N              |                     |  |

| Persistent overcurrent                                                              | Circuit-breaker                           | Υ                        | N/A            |                     |  |

| Output short circuit to GND                                                         | Circuit-breaker followed by current limit | N                        | Н              |                     |  |

| ILM pin open (during steady-state)                                                  | Shutdown                                  | N                        | L              | t <sub>ITIMER</sub> |  |

| ILM pin shorted to GND                                                              | Shutdown                                  | Υ                        | L              | t <sub>ITIMER</sub> |  |

Faults which are latched internally can be cleared either by power cycling the part (pulling  $V_{IN}$  to 0 V) or by pulling the EN/UVLO pin voltage below  $V_{SD}$ . This action also releases the  $\overline{FLT}$  pin and resets the  $t_{RST}$  timer for the TPS25981xA (auto-retry) variants.

During a latched fault, pulling the EN/UVLO just below the UVLO threshold has no impact on the device. This fact is true for both TPS25981xL (latch-off) and TPS25981xA (auto-retry) variants.

For TPS25981xA (auto-retry) variants, on expiry of the  $t_{RST}$ timer after a fault, the device restarts automatically and the  $\overline{FLT}$  pin is de-asserted.

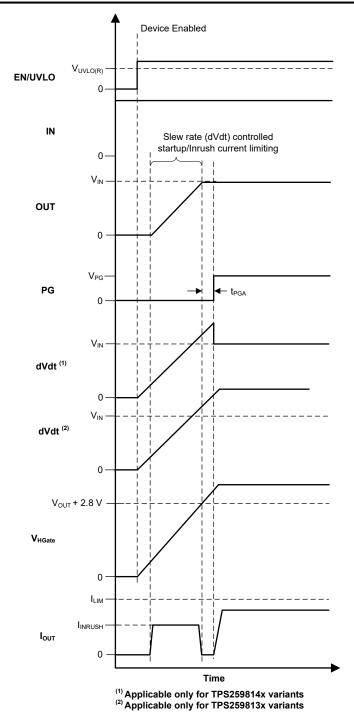

### 8.3.7 Power Good Indication (PG)

The TPS259814x provides an active high digital output (PG) which serves as a power good indication signal and is asserted high when the device is in steady-state and ready to deliver power. The PG is an open-drain pin and must be pulled up to an external supply.

After power up, PG is pulled low initially. The device initiates a inrush sequence in which the FET is turned on in a controlled manner. When the FET gate voltage reaches the full overdrive indicating that the inrush sequence is complete, the PG is asserted after a de-glitch time (t<sub>PGA</sub>).

PG is de-asserted if at any time the FET is turned off. The PG de-assertion de-glitch time is t<sub>PGD</sub>.

English Data Sheet: SLVSGG6

図 8-7. TPS25981xx PG Timing Diagram

# 表 8-3. TPS25981xx PG Indication Summary

| 2,00.1.0=0001               |                                     |        |                                        |  |  |

|-----------------------------|-------------------------------------|--------|----------------------------------------|--|--|

| Event                       | Protection Response                 | PG Pin | PG Delay                               |  |  |

| Undervoltage (UVP or UVLO)  | Shutdown                            | L      |                                        |  |  |

| Overvoltage (OVLO)          | Shutdown                            | L      | t <sub>PGD</sub>                       |  |  |

| Steady-state                | NA                                  | Н      | t <sub>PGA</sub>                       |  |  |

| Transient overcurrent       | NA                                  | Н      |                                        |  |  |

| Persistent overload         | Circuit-breaker                     | L      | t <sub>ITIMER</sub> + t <sub>PGD</sub> |  |  |

| Output short-circuit to GND | Fast-trip followed by current limit | L      | t <sub>PGD</sub>                       |  |  |

| ILM pin open                | Shutdown                            | L      | t <sub>ITIMER</sub> + t <sub>PGD</sub> |  |  |

| ILM pin shorted to GND      | Shutdown                            | L      | t <sub>PGD</sub>                       |  |  |

| Overtemperature             | Shutdown                            | L      | t <sub>PGD</sub>                       |  |  |

When there is no supply to the device, the PG pin is expected to stay low. However, there is no active pulldown in this condition to drive this pin all the way down to 0 V. If the PG pin is pulled up to an independent supply which is present even if the device is unpowered, there can be a small voltage seen on this pin depending on the pin sink current, which is a function of the pullup supply voltage and resistor. Minimize the sink current to keep this pin voltage low enough not to be detected as a logic HIGH by associated external circuits in this condition.

### 8.3.8 Quick Output Discharge (QOD)

The TPS25981xx has an integrated output discharge function which can be helpful in quickly removing residual charge left on the large output capacitors and avoids bus floating at some undefined voltage. The internal QOD pulldown FET on the OUT pin is activated when the EN/UVLO is held low ( $V_{EN} < V_{UVLO(F)}$ ). The output discharge function can result in excess power dissipation inside the device leading to increase in junction temperature. The output discharge is disabled if the junction temperature ( $T_{J}$ ) crosses the thermal shutdown threshold (TSD) to avoid long term degradation of the part.

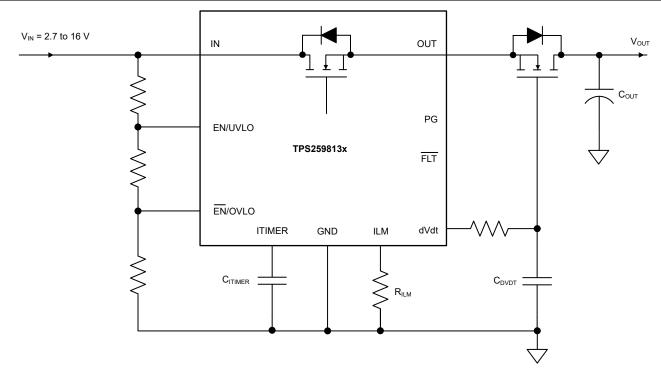

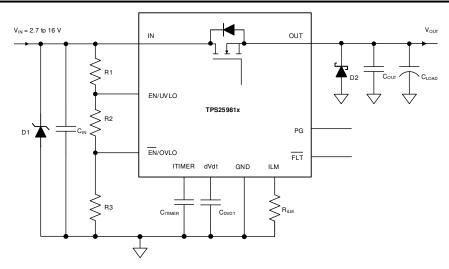

#### 8.3.9 Reverse Current Blocking FET Driver

The TPS259813x variants provide an option to drive an external N-FET for implementing reverse current blocking function. The N-FET is connected in series with the eFuse in a common source configuration as shown in 🗵 8-8. The gate of the blocking FET is controlled by the DVDT pin of the eFuse. When the eFuse is turned ON and operating in steady-state, the DVDT pin is driven high which turns the external FET fully ON to provide a low impedance power path from input to output. When the eFuse turns OFF under any condition, the DVDT pin is pulled low and the blocking FET is turned OFF. This ensures there's no current path from the output to input in the OFF state.

図 8-8. Reverse Current Blocking Using External FET

# **8.4 Device Functional Modes**

The device has one mode of operation that applies when operated within the *Recommended Operating Conditions*.

Product Folder Links: TPS25981

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 9.1 Application Information

The TPS25981xx is a 2.7-V to 16-V, 10-A eFuse that is typically used for power rail protection applications. The device operates from 2.7 V to 16 V with adjustable overvoltage and undervoltage protection. The device provides ability to control inrush current. The device can be used in a variety of systems such as server motherboard/add-on cards/NIC, optical modules, enterprise switches/routers, Industrial PC, UHDTV. The design procedure explained in the subsequent sections can be used to select the supporting component values based on the application requirement. Additionally, a spreadsheet design tool, *TPS25981xx Design Calculator*, is available in the web product folder.

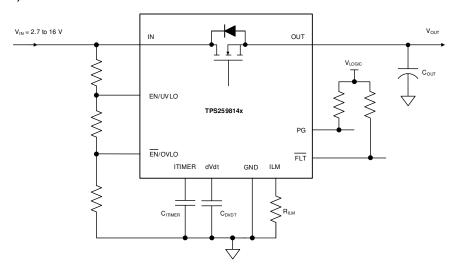

### 9.1.1 Single Device, Self-Controlled

2 9-1. Single Device, Self-Controlled

#### Other variations:

In a Host MCU controlled system, EN/UVLO or OVLO can also be driven from the host GPIO to control the device.

ILM pin can be connected to the MCU ADC input for current monitoring purpose.

注

TI recommends to keep parasitic capacitance on the ILM pin below 50 pF to ensure stable operation.

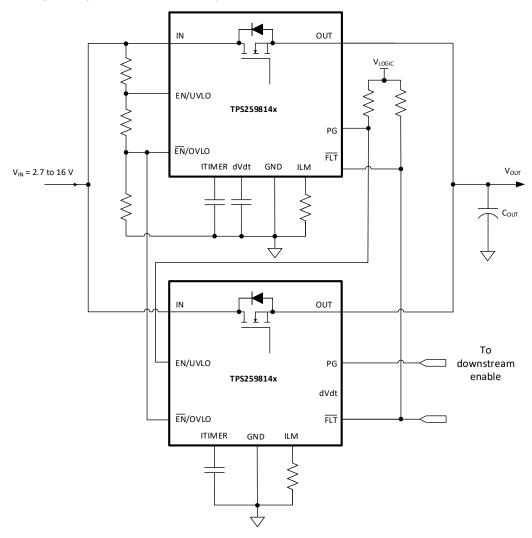

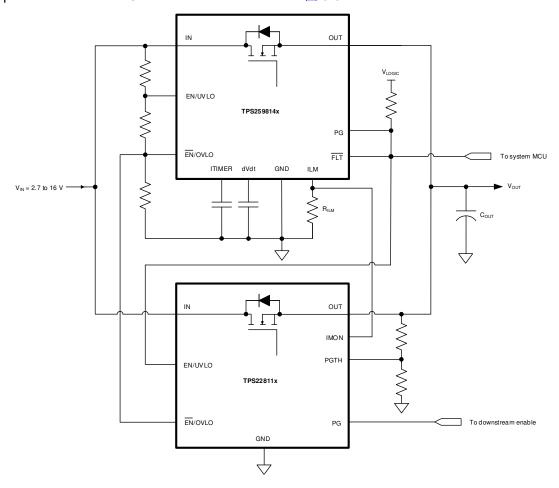

#### 9.1.2 Parallel Operation

Applications which need higher steady current can use two TPS25981xx devices connected in parallel as shown in  $\boxtimes$  9-2 below. In this configuration, the first device turns on initially to provide the inrush current limiting. The second device is held in an OFF state by driving its EN/UVLO pin low using the PG signal of the first device. After the inrush sequence is complete, the first device asserts its PG pin high and turns on the second device.

English Data Sheet: SLVSGG6

The second device asserts its PG signal to indicate when it has turned on fully, thereby indicating to the system that the parallel combination is ready to deliver the full steady-state current.

Once in steady-state, both devices share current nearly equally. There can be a slight skew in the currents depending on the part-to-part variation in the  $R_{ON}$  as well as the PCB trace resistance mismatch.

図 9-2. Two TPS259814x Devices Connected in Parallel for Higher Steady-State Current Capability

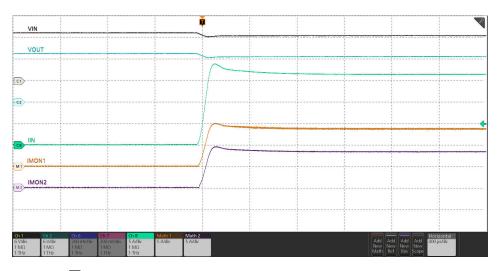

The waveforms below illustrate the behavior of the parallel configuration during start-up as well as during steady-state.

図 9-3. Parallel Devices Sequencing During Start-Up

図 9-4. Parallel Devices Load Current During Steady-State

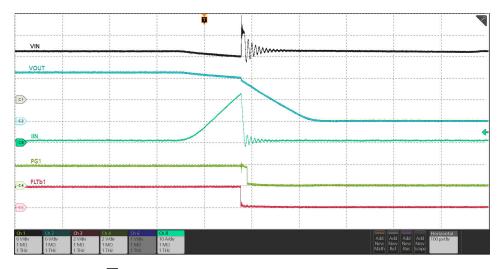

☑ 9-5. Parallel Devices Overcurrent Response

Another way to increase current handling capability of the eFuse in steady-state is by connecting a TPS25981xx eFuse in parallel with a TPS22811x load switch as shown in  $\boxtimes$  9-6.

図 9-6. TPS259814x and TPS22811x Connected in Parallel for Higher Steady-State Current Capability

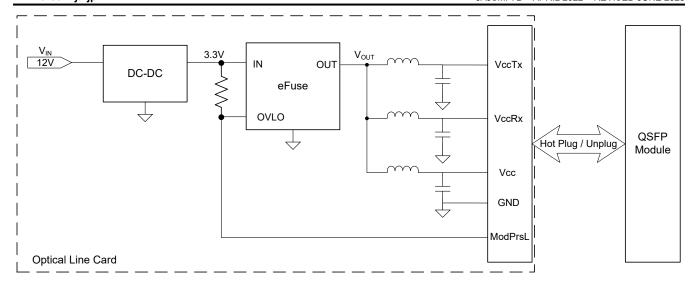

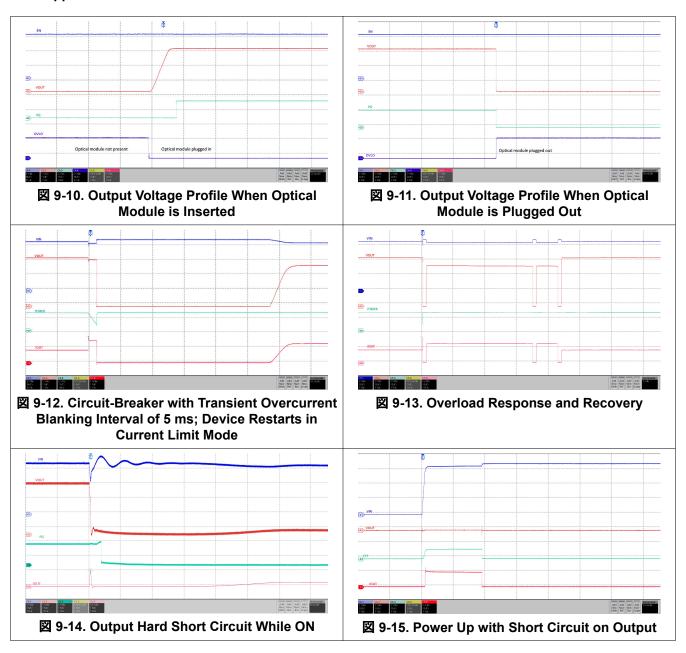

### 9.2 Typical Application

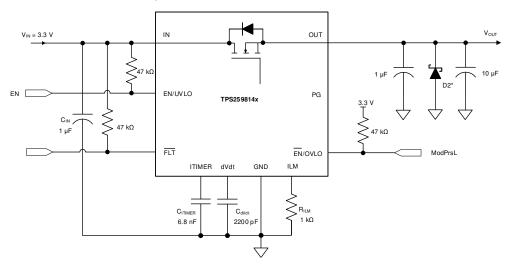

TPS259814x can be used for optical module power rail protection. Optical modules are commonly used in high-bandwidth data communication systems such as optical networking equipment, enterprise/data-center switches and routers. Several variants of optical modules are available in the market, which differ in the form-factor and the data speed support (Gbit/s). Of these, the popular variant double dense quad small form-factor pluggable (QSFP-DD) module supports speeds up to 400 Gbit/s. In addition to the system protection during hot-plug events, the other key requirement for optical module is the tight voltage regulation. The optical module uses 3.3-V supply and requires voltage regulation within ±5% for proper operation.

A typical power tree of such system is shown in  $\boxtimes$  9-7. The optical line card consists of DC-DC converter, protection device (eFuse) and power supply filters. The DC-DC converter steps-down the 12 V to 3.3 V and maintains the 3.3-V rail within ±2 %. The power supply filtering network uses 'LC' components to reduce high frequency noise injection into the optical module. The DC resistance of the inductor 'L' causes voltage drop of around 1.5% which leaves us with a voltage drop budget of just 1.5% (3.3 V × 1.5% = 50 mV) across the protection device. Considering a maximum load current of 5.5 A per module, the maximum ON-resistance of the protection device must be less than 9 m $\Omega$ . TPS259814x eFuse offers a very low ON-resistance of 6 m $\Omega$  (typical), thereby meeting the target specification with additional margin to spare and simplifying the overall system design.

Submit Document Feedback Copyright © 2023 Texas

English Data Sheet: SLVSGG6

図 9-7. Power Tree Block Diagram of a Typical Optical Line Card

As shown in 🗷 9-7, ModPrsL signal acts as a handshake signal between the line card and the optical module. ModPrsL is always pulled to ground inside the module. When the module is hot-plugged into the host "Optical Line Card" connector, the ModPrsL signal pulls down the OVLO pin and enables the TPS259814x eFuse to power the module. This action ensures that power is applied on the port only when a module is plugged in and disconnected when there is no module present.

<sup>\*</sup> Optional circuit components needed for transient protection depending on input and output inductance. Please refer to *Transient Protection* section for details.

### 図 9-8. Optical Module Port Protection

### 9.2.1 Design Requirements

表 9-1. Design Parameters

| PARAMETER                                               | VALUE |

|---------------------------------------------------------|-------|

| Input supply voltage (V <sub>IN</sub> )                 | 3.3 V |

| Maximum voltage drop in the path                        | ± 5%  |

| Maximum continuous current                              | 5.5 A |

| Load transient blanking interval (t <sub>ITIMER</sub> ) | 5 ms  |

| Output capacitance (C <sub>OUT</sub> )                  | 10 μF |

Product Folder Links: TPS25981

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

表 9-1. Design Parameters (continued)

| PARAMETER                                 | VALUE      |

|-------------------------------------------|------------|

| Output rise time (t <sub>R</sub> )        | 2.2 ms     |

| Overcurrent threshold (I <sub>LIM</sub> ) | 6.5 A      |

| Fault response                            | Auto-retry |

### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Device Selection

Because the application requires retry response after a fault, the TPS259814A variant is selected after referring to the *Device Comparison Table*.

### 9.2.2.2 Setting Output Voltage Rise Time $(t_R)$

For a successful design, the junction temperature of device must be kept below the absolute maximum rating during both dynamic (start-up) and steady-state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and inrush current limit required with system capacitance to avoid thermal shutdown during start-up.

The slew rate (SR) needed to achieve the desired output rise time can be calculated as:

$$SR\left(\frac{V}{ms}\right) = \frac{V_{IN}(V)}{t_R(ms)} = \frac{3.3 V}{2.2 ms} = 1.5 \frac{V}{ms}$$

(9)

The C<sub>dVdt</sub> needed to achieve this slew rate can be calculated as:

$$C_{dVdt}(pF) = \frac{3300}{SR(\frac{V}{ms})} = \frac{3300}{1.5 \frac{V}{ms}} = 2200 \, pF \tag{10}$$

Choose the nearest standard capacitor value as 2200 pF.

For this slew rate, the inrush current can be calculated as: