TPS25940-Q1

JAJSC83E - MAY 2016 - REVISED JANUARY 2021

# TPS25940xx-Q1 2.7V~18V eFuse、バッテリ短絡保護機能内蔵

# 1 特長

- 車載アプリケーション認定済み

- 下記内容で AEC-Q100 認定済み:

- デバイス温度グレード 1:-40°C~+125°Cの動作時 周用温度範囲

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C5

- 動作電圧 2.7V~18V、20V (最大値)

- 全 R<sub>ON</sub>:40mΩ (標準値)

- 調整可能な電流制限:0.6A~5.3A (±8%)

- IMON 電流インジケータ出力

- TPS25940-Q1/TPS25940L-Q1 で ±8% の精度

- 調整可能な低電圧/過電圧スレッショルド(±2%)

- 逆電流ブロッキング

- 1us の逆電圧シャットオフ

- プログラム可能な dV<sub>o</sub>/dt 制御

- パワーグッドおよびフォルト出力

- バッテリ短絡保護

- グランド短絡保護

- TPS25940-Q1/TPS259401A-Q1:自動再試行

- TPS25940L-Q1:ラッチオフ

# 2 アプリケーション

- 車載インフォテインメント

- ADAS カメラおよびレーダーのセンサ

- USB ハブ

- パワー・マルチプレクシング

- ホールドアップ電力管理

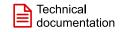

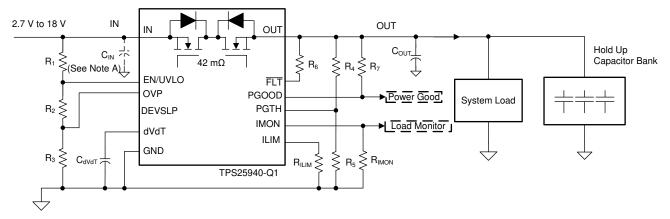

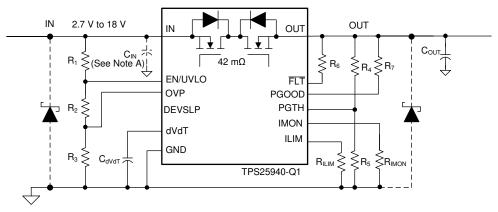

#### 概略回路図

## 3 概要

TPS25940xx-Q1 eFuse 電力スイッチは、小型で豊富な 機能を持つ電力管理デバイスで、完全な保護機能のセッ トが内蔵されています。動作電圧範囲が広いため、多くの 一般的な DC バス電圧の制御が可能です。バック・ツー・ バックの FET が内蔵され、双方向の電流制御を行いま す。それにより、障害が発生した電源バスに対して負荷側 のホールドアップ・エネルギーの逆流が許容されないよう なシステムに最適です。

負荷、ソース、およびデバイス保護が提供され、過電流、 dV<sub>o</sub>/dt ランプ、過電圧と低電圧のスレッショルドなど、多く の機能がプログラム可能です。システム・ステータスの監視 や下流負荷の制御のため、PGOOD、FLT、および高精度 の電流監視出力を備えています。高精度でプログラム可 能な低電圧および過電圧のスレッショルドとモードにより、 電力管理の設計が容易になります。

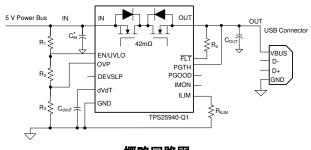

TPS25940xx-Q1 は、 $V_{(IN)}$  および  $V_{(OUT)}$  を監視し、 $V_{(IN)}$ < (V<sub>(OUT)</sub> - 66mV) のときに真の逆電流保護を提供しま す。この機能によって、出力とバッテリとの短絡障害が発 生したとき、電源バスが過電圧から保護されます。

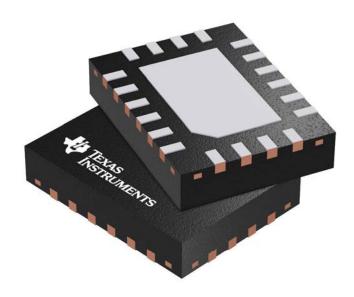

### 制品情報(1)

|               | WENN IN TIA |               |

|---------------|-------------|---------------|

| 部品番号          | パッケージ       | 本体サイズ (公称)    |

| TPS25940-Q1   |             |               |

| TPS25940L-Q1  | WQFN (20)   | 3.00mm×4.00mm |

| TPS259401A-Q1 |             |               |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

出力とバッテリ間の短絡検出と保護

## **Table of Contents**

| 1 特長                                 | 1 | 9.4 Device Functional Modes             | 23 |

|--------------------------------------|---|-----------------------------------------|----|

| 2 アプリケーション                           |   | 10 Application and Implementation       | 25 |

| 3 概要                                 |   | 10.1 Application Information            |    |

| 4 Revision History                   |   | 10.2 Typical Application                |    |

| 5 Device Comparison Table            |   | 11 Power Supply Recommendations         | 38 |

| 6 Pin Configuration and Functions    |   | 11.1 Transient Protection               | 38 |

| 7 Specifications                     |   | 11.2 Output Short-Circuit Measurements  | 39 |

| 7.1 Absolute Maximum Ratings         |   | 12 Layout                               | 40 |

| 7.2 ESD Ratings                      |   | 12.1 Layout Guidelines                  | 40 |

| 7.3 Recommended Operating Conditions |   | 12.2 Layout Example                     |    |

| 7.4 Thermal Information              |   | 13 Device and Documentation Support     | 42 |

| 7.5 Electrical Characteristics       |   | 13.1 Documentation Support              | 42 |

| 7.6 Timing Requirements              |   | 13.2 サポート・リソース                          |    |

| 7.7 Typical Characteristics          |   | 13.3 Trademarks                         |    |

| 8 Parametric Measurement Information |   | 13.4 静電気放電に関する注意事項                      | 42 |

| 9 Detailed Description               |   | 13.5 用語集                                |    |

| 9.1 Overview                         |   | 14 Mechanical, Packaging, and Orderable |    |

| 9.2 Functional Block Diagram         |   | Information                             | 42 |

| 9.3 Feature Description              |   |                                         |    |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision D (September 2018) to Revision E (January 2021)      | Page         |

|----------------------------------------------------------------------------|--------------|

| - 文書全体にわたって表、図、相互参照の採番方法を更新                                                | 1            |

| • データシートに TPS259401A-Q1 バリエーションを追加                                         |              |

| Added Device Comparison table                                              |              |

| Changes from Revision C (July 2018) to Revision D (September 2018)         | Page         |

| Changed internal ramp rate of 12 V/ms for output to 30 V/ms                | 19           |

| Changes from Revision B (November 2017) to Revision C (July 2018)          | Page         |

| -<br>・ 「量産データ」から「量産混合」に変更                                                  | 1            |

| • ラッチオフ・バリエーション (TPS25940L-Q1) を追加                                         |              |

| Changes from Revision A (June 2016) to Revision B (November 2017)          | Page         |

| <ul><li>「アプリケーション情報」セクションに、サブセクション 9.2.4.3 「TPS25940-Q1 による過負荷の検</li></ul> | 。<br>  出」を追加 |

| Changes from Revision * (May 2016) to Revision A (June 2016)               | Page         |

| <ul><li>デバイスのステータスを「製品プレビュー」から「量産データ」へ変更</li></ul>                         | 1            |

# **5 Device Comparison Table**

| Part Number   | Fault Response | R <sub>DSON</sub> (max) | Minimum Current<br>Limit | IMON Accuracy (max) |

|---------------|----------------|-------------------------|--------------------------|---------------------|

| TPS25940-Q1   | Auto-Retry     | 64 mΩ                   | 0.5 A                    | 8 %                 |

| TPS25940L-Q1  | Latch-off      | 64 mΩ                   | 0.5 A                    | 8 %                 |

| TPS259401A-Q1 | Auto-Retry     | 85 mΩ                   | 1 A                      | Not specified       |

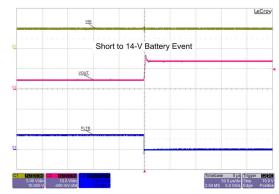

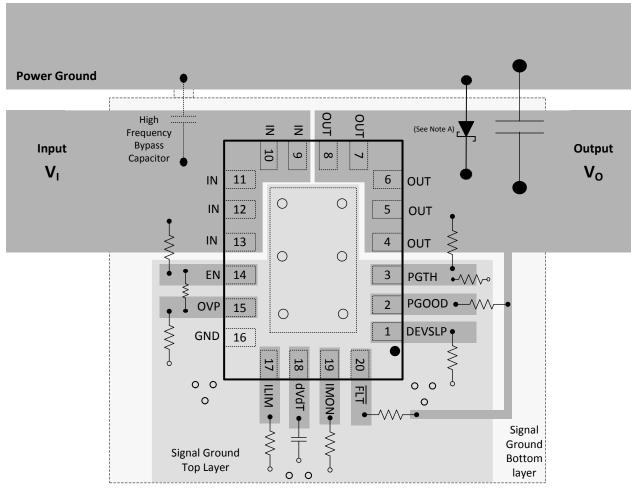

# **6 Pin Configuration and Functions**

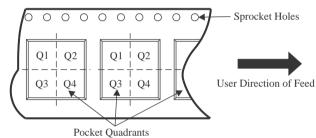

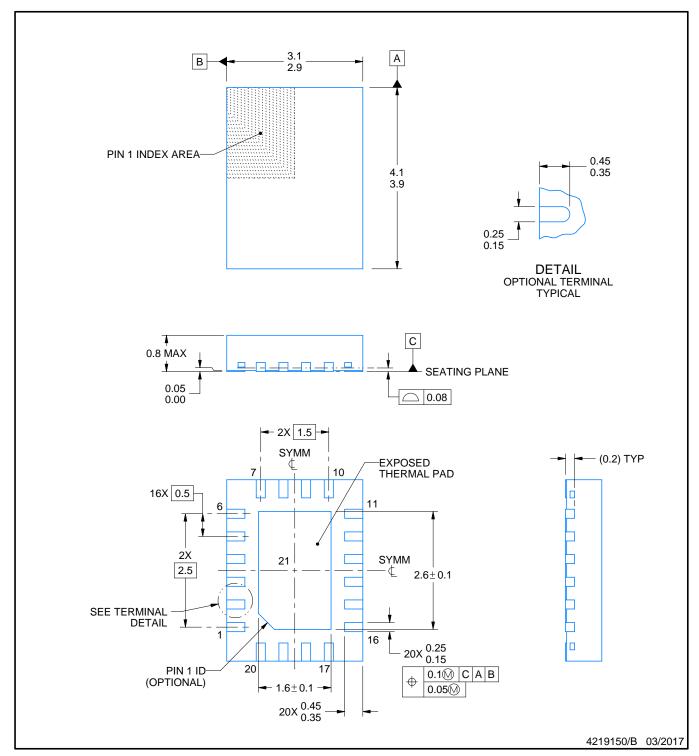

図 6-1. RVC Package 20-Pin WQFN Top View

表 6-1. Pin Functions

|     | PIN     | TYPE                                          | DESCRIPTION                                                                                                                                                                                                    |  |  |  |  |  |

|-----|---------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO. | NAME    | ITPE                                          | DESCRIPTION                                                                                                                                                                                                    |  |  |  |  |  |

| 1   | DEVSLP  | ı                                             | Active high. DevSleep mode control. A high at this pin activates the DevSleep mode (low power mode). If unused, leave floating or connect it to GND.                                                           |  |  |  |  |  |

| 2   | PGOOD   | 0                                             | Active high. A high indicates PGTH has crossed the threshold value. It is an open drain output. If unused, leave floating.                                                                                     |  |  |  |  |  |

| 3   | PGTH    | 1                                             | Positive input of PGOOD comparator. If unused connect to OUT or GND.                                                                                                                                           |  |  |  |  |  |

| 4   |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 5   |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 6   | OUT     | 0                                             | O Power output of the device.                                                                                                                                                                                  |  |  |  |  |  |

| 7   |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 8   |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 9   |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 10  |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 11  | IN      | Power input and supply voltage of the device. |                                                                                                                                                                                                                |  |  |  |  |  |

| 12  |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 13  |         |                                               |                                                                                                                                                                                                                |  |  |  |  |  |

| 14  | EN/UVLO | ı                                             | Input for setting programmable undervoltage lockout threshold. An undervoltage event opens internal FET and assert FLT to indicate power-failure.                                                              |  |  |  |  |  |

| 15  | OVP     | ı                                             | Input for setting programmable overvoltage protection threshold. An overvoltage event opens the internal FET and assert FLT to indicate overvoltage.                                                           |  |  |  |  |  |

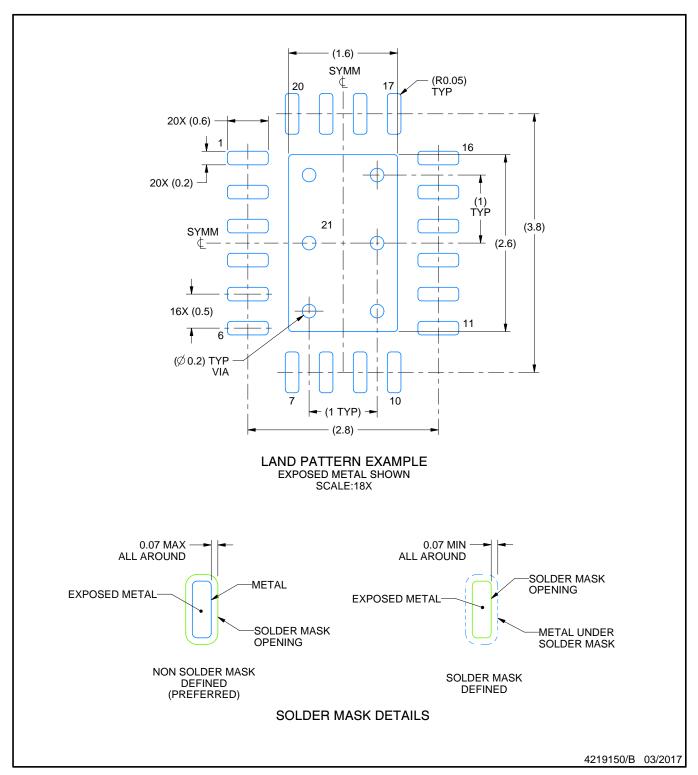

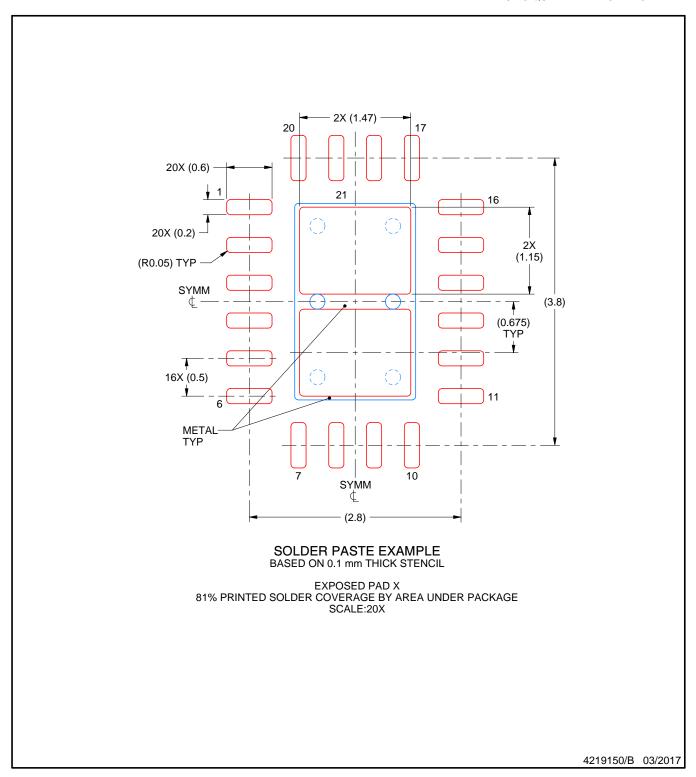

| 16  | GND     | _                                             | Ground. The GND terminal must be connected to the exposed PowerPAD. This PowerPAD must be connected to a PCB ground plane using multiple vias for good thermal performance.                                    |  |  |  |  |  |

| 17  | ILIM    | I/O                                           | A resistor from this pin to GND sets the overload and short-circuit current limit.                                                                                                                             |  |  |  |  |  |

| 18  | dVdT    | I/O                                           | A capacitor from this pin to GND sets the ramp rate of output voltage.                                                                                                                                         |  |  |  |  |  |

| 19  | IMON    | 0                                             | This pin sources a scaled down ratio of current through the internal FET. A resistor from this pin to GND converts current to proportional voltage, used as analog current monitor. If unused, leave floating. |  |  |  |  |  |

| 20  | FLT     | 0                                             | Fault event indicator, goes low to indicate fault condition because of undervoltage, overvoltage, reverse voltage and thermal shutdown event. It is an open drain output. If unused, leave floating.           |  |  |  |  |  |

Submit Document Feedback

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                 |                                                 | MIN       | MAX              | UNIT        |

|-----------------------------------------------------------------|-------------------------------------------------|-----------|------------------|-------------|

|                                                                 | IN, OUT, PGTH, PGOOD, EN/UVLO, OVP, DEVSLP, FLT | -0.3      | 20               |             |

| In positive literary                                            | IN, OUT (10 ms transient)                       |           | 22               | .,          |

| Input voltage                                                   | dVdT, ILIM                                      | -0.3      | 3.6              | V           |

|                                                                 | IMON                                            | -0.3      | 7                |             |

| Sink current                                                    | PGOOD, FLT, dVdT                                |           | 10               | mA          |

| Maximum continuous switch current,<br>$T_A = 85^{\circ}C^{(2)}$ | I <sub>MAX</sub>                                |           | 4.78             | А           |

| Source current                                                  | dVdT, ILIM, IMON                                | lı        | nternally Limite | d           |

| Continuous power dissipation                                    |                                                 | See the 7 | hermal Informa   | ation table |

| Maximum junction temperature                                    | T <sub>J</sub>                                  | -40       | 150              | °C          |

| Storage temperature                                             | T <sub>stg</sub>                                | -65       | 150              | °C          |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±3000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                             |                                | MIN  | NOM | MAX | UNIT |

|---------------------------------------------|--------------------------------|------|-----|-----|------|

| IN                                          |                                | 2.7  |     | 18  |      |

| EN/UVLO, OVP, DEVSLP, OUT, PGTH, PGOOD, FLT | Input voltage                  | 0    |     | 18  | V    |

| dVdT, ILIM                                  |                                | 0    |     | 3   |      |

| IMON                                        |                                | 0    |     | 6   |      |

| ILIM                                        | Resistance                     | 16.9 |     | 150 | kΩ   |

| IMON                                        | Resistance                     | 1    |     |     | KL2  |

| OUT                                         | External capacitance           | 0.1  |     |     | μF   |

| dVdT                                        | External capacitance           |      |     | 470 | nF   |

| TJ                                          | Operating junction temperature | -40  | 25  | 125 | °C   |

<sup>(2)</sup> Assumes 15 K power-on-hours at 100% duty cycle. This information is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI's semiconductor products.

## 7.4 Thermal Information

|                     |                                              | TPS25940xx-Q1 |      |

|---------------------|----------------------------------------------|---------------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                | RVC (WQFN)    | UNIT |

|                     |                                              | 20 PINS       |      |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 38.1          | °C/W |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 40.5          | °C/W |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 13.6          | °C/W |

| ΨЈТ                 | Junction-to-top characterization parameter   | 0.6           | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter | 13.7          | °C/W |

| R <sub>0JCbot</sub> | Junction-to-case (bottom) thermal resistance | 3.4           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} = \text{T}_{\text{A}} \le 125^{\circ}\text{C}$ ,  $2.7 \text{ V} \le \text{V}_{\text{(IN)}} = 18 \text{ V}$ ,  $\text{V}_{\text{(EN /UVLO)}} = 2 \text{ V}$ ,  $\text{V}_{\text{(OVP)}} = \text{V}_{\text{(DEVSLP)}} = \text{V}_{\text{(PGTH)}} = 0 \text{ V}$ ,  $\text{R}_{\text{(ILIM)}} = 150 \text{ k}\Omega$ ,  $\text{C}_{\text{(OUT)}} = 100 \text{ L}$ ,  $\text{R}_{\text{(ICM)}} = 100 \text{ L}$ ,  $\text{R}_{\text{(ILIM)}} = 100 \text{ L}$ ,  $\text{R}_{\text{(ICM)}} = 100 \text{ L}$ ,  $\text{R}_{\text{(IC$

|                          | PARAMETER                                                                | TEST CONDITIONS                                                | MIN   | TYP  | MAX   | UNIT |

|--------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|-------|------|-------|------|

| SUPPLY VOL               | TAGE AND INTERNAL UNDERVOLTAGE                                           | LOCKOUT                                                        |       |      | '     |      |

| V <sub>(IN)</sub>        | Operating input voltage                                                  |                                                                | 2.7   |      | 18    | V    |

| V <sub>(UVR)</sub>       | Internal UVLO threshold, rising                                          |                                                                | 2.2   | 2.3  | 2.4   | V    |

| V <sub>(UVRhys)</sub>    | Internal UVLO hysteresis                                                 |                                                                | 105   | 116  | 125   | mV   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 3 V          | 140   | 210  | 300   |      |

| I <sub>Q (ON)</sub>      | Supply current, enabled                                                  | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 12 V         | 140   | 199  | 260   | μΑ   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(IN)</sub> = 18 V         | 140   | 202  | 270   |      |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 3 V          | 4     | 8.6  | 15    |      |

| I <sub>Q (OFF)</sub>     | Supply current, disabled                                                 | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 12 V         | 6     | 15   | 20    | μΑ   |

|                          |                                                                          | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(IN)</sub> = 18 V         | 8     | 18.5 | 25    |      |

| I <sub>Q (DEVSLP)</sub>  | Supply current, devSleep mode                                            | V <sub>(DEVSLP)</sub> = 0 V, V <sub>(IN)</sub> = 2.7 V to 18 V | 70    | 95   | 130   | μΑ   |

| ENABLE ANI               | D UNDERVOLTAGE LOCKOUT (EN/UVL                                           | D) INPUT                                                       |       |      | '     |      |

| V <sub>(ENR)</sub>       | EN/UVLO threshold voltage, rising                                        |                                                                | 0.97  | 0.99 | 1.01  | V    |

| V <sub>(ENF)</sub>       | EN/UVLO threshold voltage, falling                                       |                                                                | 0.9   | 0.92 | 0.94  | V    |

| V <sub>(SHUTF)</sub>     | EN threshold voltage for Low I <sub>Q</sub> shutdown, falling            |                                                                | 0.3   | 0.47 | 0.63  | V    |

| V <sub>(SHUTF hys)</sub> | EN hysteresis for low I <sub>Q</sub> shutdown, hysteresis <sup>(1)</sup> |                                                                |       | 66   |       | mV   |

| I <sub>EN</sub>          | EN Input leakage current                                                 | 0 V ≤ V <sub>(EN/UVLO)</sub> ≤ 18 V                            | -100  | 0    | 100   | nA   |

| OVER VOLTA               | AGE PROTECTION (OVP) INPUT                                               |                                                                |       |      | ,     |      |

| V <sub>(OVPR)</sub>      | Overvoltage threshold voltage, rising                                    |                                                                | 0.97  | 0.99 | 1.01  | V    |

| V <sub>(OVPF)</sub>      | Overvoltage threshold voltage, falling                                   |                                                                | 0.9   | 0.92 | 0.94  | V    |

| I <sub>(OVP)</sub>       | OVP input leakage current                                                | 0 V ≤ V <sub>(OVP)</sub> ≤ 5 V                                 | -100  | 0    | 100   | nA   |

| DEVSLP MOI               | DE INPUT (DEVSLP): ACTIVE HIGH                                           |                                                                |       |      | ,     |      |

| V <sub>(DEVSLPR)</sub>   | DEVSLP threshold voltage, rising                                         |                                                                | 1.6   | 1.85 | 2     | V    |

| V <sub>(DEVSLPF)</sub>   | DEVSLP threshold voltage, falling                                        |                                                                | 0.8   | 0.96 | 1.1   | V    |

| I <sub>(DEVSLP)</sub>    | DEVSLP input leakage current                                             | 0.2 V ≤ V <sub>(DEVSLP)</sub> ≤ 18 V                           | 0.6   | 1    | 1.25  | μΑ   |

| OUTPUT RAI               | MP CONTROL (dVdT)                                                        |                                                                |       |      |       |      |

| I <sub>(dVdT)</sub>      | dVdT charging current                                                    | $V_{(dVdT)} = 0 V$                                             | 0.85  | 1    | 1.15  | μΑ   |

| R <sub>(dVdT)</sub>      | dVdT discharging resistance                                              | EN/UVLO = 0 V, I <sub>(dVdT)</sub> = 10 mA sinking             |       | 16   | 24    | Ω    |

| V <sub>(dVdTmax)</sub>   | dVdT maximum capacitor voltage                                           |                                                                | 2.6   | 2.88 | 3.1   | V    |

| GAIN <sub>(dVdT)</sub>   | dVdT to OUT gain                                                         | $\Delta V_{(OUT)}/\Delta V_{(dVdT)}$                           | 11.65 | 11.9 | 12.05 | V/V  |

Product Folder Links: TPS25940-Q1

## 7.5 Electrical Characteristics (continued)

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} = \text{T}_{\text{A}} \le 125^{\circ}\text{C}$ ,  $2.7 \text{ V} \le \text{V}_{(\text{IN})} = 18 \text{ V}$ ,  $\text{V}_{(\text{EN }/\text{UVLO})} = 2 \text{ V}$ ,  $\text{V}_{(\text{OVP})} = \text{V}_{(\text{DEVSLP})} = \text{V}_{(\text{PGTH})} = 0 \text{ V}$ ,  $\text{R}_{(\text{ILIM})} = 150 \text{ k}\Omega$ ,  $\text{C}_{(\text{OUT})} = 100 \text{ L}$ ,  $\text{R}_{(\text{COUT})} = 100 \text{ L}$ ,  $\text{R}_{(\text{COUT})}$

|                                    | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                  | MIN   | TYP                           | MAX   | UNIT |  |

|------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|-------|------|--|

| V <sub>(ILIM)</sub>                | ILIM bias voltage                                                                           |                                                                                                                                  |       | 0.87                          |       | V    |  |

|                                    |                                                                                             | $R_{(ILIM)}$ = 150 k $\Omega$ , $(V_{(IN)} - V_{(OUT)})$ = 1 V, Only for TPS25940-Q1/TPS25940L-Q1                                | 0.53  | 0.58                          | 0.63  |      |  |

|                                    |                                                                                             | $R_{(ILIM)} = 88.7 \text{ k}\Omega, (V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                                        | 0.9   | 0.99                          | 1.07  |      |  |

|                                    |                                                                                             | $R_{(ILIM)} = 42.2 \text{ k}\Omega, (V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                                        | 1.92  | 2.08                          | 2.25  |      |  |

| I                                  | Current limit <sup>(2)</sup>                                                                | $R_{(ILIM)} = 20 \text{ k}\Omega, (V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                                          | 4.09  | 4.45                          | 4.81  | Α    |  |

| I <sub>(LIM)</sub>                 | Surent minto                                                                                | $R_{(ILIM)} = 16.9 \text{ k}\Omega, (V_{(IN)} - V_{(OUT)}) = 1 \text{ V}$                                                        | 4.78  | 5.2                           | 5.62  | ^    |  |

|                                    |                                                                                             | R <sub>(ILIM)</sub> = OPEN, Open resistor current limit (single point failure test: UL60950)                                     | 0.35  | 0.45                          | 0.55  |      |  |

|                                    |                                                                                             | R <sub>(ILIM)</sub> = SHORT, Shorted resistor current limit (single point failure test: UL60950)                                 | 0.55  | 0.67                          | 0.8   |      |  |

| I <sub>(DEVSLP(LIM))</sub>         | DevSleep mode current limit                                                                 |                                                                                                                                  | 0.55  | 0.67                          | 0.8   | Α    |  |

|                                    |                                                                                             | $R_{(ILIM)} = 42.2 \text{ k}\Omega, V_{(VIN)} = 12 \text{ V}, (V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                              | 1.91  | 2.07                          | 2.24  |      |  |

| Ios                                | Short-circuit current limit (2)                                                             | $R_{(ILIM)} = 20 \text{ k}\Omega, V_{(VIN)} = 12 \text{ V}, (V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                                | 4     | 4.4                           | 4.7   | Α    |  |

| -                                  |                                                                                             | $R_{(ILIM)} = 16.9 \text{ k}\Omega, V_{(VIN)} = 12 \text{ V}, (V_{(IN)} - V_{(OUT)}) = 5 \text{ V}$                              | 4.7   | 5.11                          | 5.52  |      |  |

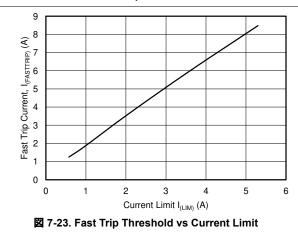

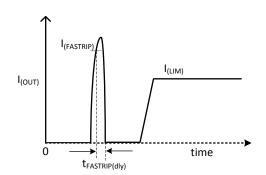

| I <sub>(FASTRIP)</sub>             | Fast-trip comparator threshold <sup>(1)</sup> (2)                                           | (ILIN)                                                                                                                           |       | 1.5 x<br>I <sub>(LIM)</sub> + |       | Α    |  |

| CLIPPENT MC                        | (many (cory                                                                                 |                                                                                                                                  |       |                               |       |      |  |

|                                    | · ,                                                                                         | 1 A <  corp. < 5 A                                                                                                               | Т     | 52.3                          |       | μA/A |  |

| GAIN <sub>(IMON)</sub>             | Gain factor I(IMON).I(OUT)                                                                  |                                                                                                                                  | 47.70 |                               | 57.00 |      |  |

| MOOFFT BC                          |                                                                                             | 1 A ≤ I <sub>(OUT)</sub> ≤ 5 A, Only for 1 PS25940-Q1/1 PS25940L-Q1                                                              | 47.78 | 52.3                          | 57.23 | μA/A |  |

| MOSFET - PO                        | OWER SWITCH                                                                                 | 1. A T. 0500                                                                                                                     | 24    | 10                            | 40    |      |  |

| R <sub>ON</sub>                    | INV. OUT. ON                                                                                | $1 \text{ A} \le I_{\text{(OUT)}} \le 5 \text{ A}, T_J = 25^{\circ}\text{C}$                                                     | 34    | 42                            | 49    | _    |  |

|                                    | IN to OUT - ON resistance                                                                   | $1 \text{ A} \le I_{(OUT)} \le 5 \text{ A}, -40^{\circ}\text{C} \le T_{J} \le +85^{\circ}\text{C}$                               | 26    | 42                            | 58    | mΩ   |  |

|                                    |                                                                                             | $1 \text{ A} \le I_{(OUT)} \le 5 \text{ A}, -40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$                              | 26    | 42                            | 64    |      |  |

|                                    |                                                                                             | 1 A $\leq$ I <sub>(OUT)</sub> $\leq$ 5 A, $-40^{\circ}$ C $\leq$ T <sub>J</sub> $\leq$ +125 $^{\circ}$ C, Only for TPS259401A-Q1 |       | 55                            | 85    | mΩ   |  |

| PASS FET OU                        | TPUT (OUT)                                                                                  |                                                                                                                                  |       |                               |       |      |  |

| l                                  | OUT leakage current in off state                                                            | $V_{(IN)}$ = 18 V, $V_{(EN/UVLO)}$ = 0 V, $V_{(OUT)}$ = 0 V (sourcing)                                                           | -2    | 0                             | 2     | μA   |  |

| I <sub>lkg(OUT)</sub>              | OUT leakage current in oil state                                                            | $V_{(IN)} = 2.7 \text{ V}, V_{(EN/UVLO)} = 0 \text{ V}, V_{(OUT)} = 18 \text{ V (sinking)}$                                      | 6     | 13                            | 20    | μΛ   |  |

| V <sub>(REVTH)</sub>               | V <sub>(IN)</sub> – V <sub>(OUT)</sub> threshold for reverse protection comparator, falling |                                                                                                                                  | -77   | -66                           | -55   | mV   |  |

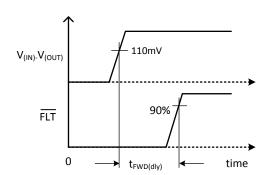

| V <sub>(FWDTH)</sub>               | V <sub>(IN)</sub> – V <sub>(OUT)</sub> threshold for reverse protection comparator, rising  |                                                                                                                                  | 86    | 100                           | 114   | mV   |  |

| FAULT FLAG                         | ( FLT): ACTIVE LOW                                                                          |                                                                                                                                  |       |                               |       |      |  |

| R <sub>(FLT)</sub>                 | FLT internal pull-down resistance                                                           | V <sub>(OVP)</sub> = 2 V, I <sub>(FLT)</sub> = 5 mA sinking                                                                      | 10    | 18                            | 30    | Ω    |  |

| I <sub>(FLT)</sub>                 | FLT input leakage current                                                                   | 0 V ≤ V <sub>(FLT)</sub> ≤ 18 V                                                                                                  | -1    | 0                             | 1     | μΑ   |  |

|                                    | UT for POWER-GOOD COMPARATOR                                                                | (PGTH)                                                                                                                           |       |                               |       |      |  |

| V <sub>(PGTHR)</sub>               | PGTH threshold voltage, rising                                                              |                                                                                                                                  | 0.97  | 0.99                          | 1.01  | V    |  |

| V <sub>(PGTHF)</sub>               | PGTH threshold voltage, falling                                                             |                                                                                                                                  | 0.9   | 0.92                          | 0.94  | V    |  |

| I <sub>(PGTH)</sub>                | PGTH input leakage current                                                                  | 0 V ≤ V <sub>(PGTH)</sub> ≤ 18 V                                                                                                 | -100  | 0                             | 100   | nA   |  |

|                                    | D COMPARATOR OUTPUT (PGOOD):                                                                |                                                                                                                                  |       |                               |       |      |  |

| R <sub>(PGOOD)</sub>               | PGOOD internal pull-down resistance                                                         | V <sub>(PGTH)</sub> = 0V, I <sub>(PGOOD)</sub> = 5 mA sinking                                                                    | 10    | 20                            | 35    | Ω    |  |

|                                    |                                                                                             | 0 V ≤ V <sub>(PGOOD)</sub> ≤ 18 V                                                                                                | -1    | 0                             | 1     | μA   |  |

|                                    | PGOOD input leakage current                                                                 | • • = • (PGOOD) = • • •                                                                                                          |       |                               |       |      |  |

| I <sub>(PGOOD)</sub>               | PGOOD input leakage current                                                                 | о т = т(ресоор) = то т                                                                                                           |       |                               |       |      |  |

| I <sub>(PGOOD)</sub><br>THERMAL SH | , ,                                                                                         | T = T(PGOOD) = TO T                                                                                                              |       | 160                           |       | °C   |  |

| I <sub>(PGOOD)</sub>               | IUT DOWN (TSD)                                                                              | - (PGOOD) = 10 1                                                                                                                 |       | 160                           |       | °C   |  |

## 7.5 Electrical Characteristics (continued)

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} = \text{T}_{\text{A}} \le 125^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{(\text{IN})} = 18 \text{ V}, \text{V}_{(\text{EN /UVLO})} = 2 \text{ V}, \text{V}_{(\text{OVP})} = \text{V}_{(\text{DEVSLP})} = \text{V}_{(\text{PGTH})} = 0 \text{ V}, \text{R}_{(\text{ILIM})} = 150 \text{ k}\Omega, \text{C}_{(\text{OUT})} = 1 \text{ MON} = 150 \text{ k}\Omega$  (OUT) = 1 \(\text{IV} \text{V}\_{\text{(dVdT)}} = \text{OPEN}, \text{PGOOD} = \(\text{FLT} = \text{IMON} = \text{OPEN}. \text{Positive current into terminals.} \text{All voltages referenced to GND} \) (unless otherwise noted)

| PARAMETER |           | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|-----------|-----------|-----------------|-----|------|-----|------|

|           | TPS25940L | -Q1             |     | Late |     |      |

- (1) These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

- (2) Pulse-testing techniques maintain junction temperature close to ambient temperature. Thermal effects must be taken into account separately.

## 7.6 Timing Requirements

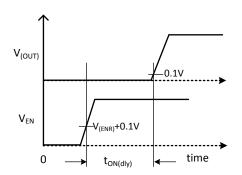

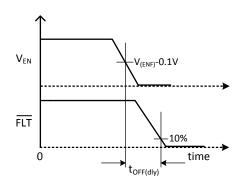

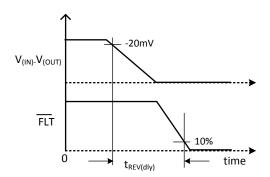

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} = \text{T}_{\text{A}} \le 125^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{(\text{IN})} = 18 \text{ V}, \text{V}_{(\text{EN}/\text{UVLO})} = 2 \text{ V}, \text{V}_{(\text{OVP})} = \text{V}_{(\text{DEVSLP})} = \text{V}_{(\text{PGTH})} = 0 \text{ V}, \text{R}_{(\text{ILIM})} = 150 \text{ k}\Omega, \text{C}_{(\text{OUT})} = 1 \text{ p}, \text{C}_{(\text{dVdT})} = \text{OPEN}, \text{PGOOD} = \overline{\text{FLT}} = \text{IMON} = \text{OPEN}. \text{Positive current into terminals. All voltages referenced to GND} (unless otherwise noted). See <math>\boxtimes$  8-1 for the timing diagrams.

|                           | PARAMETER                           | TEST CONDITIONS                                                                                                                                      | MIN  | TYP                                | MAX  | UNIT |  |

|---------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------|------|------|--|

| ENABLE and                | UVLO INPUT                          |                                                                                                                                                      |      |                                    |      |      |  |

| t <sub>ON(dly)</sub>      | EN turnon delay                     | EN/UVLO $\uparrow$ (100 mV above V <sub>(ENR)</sub> ) to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> < 0.8 nF                                   | 220  |                                    |      | μs   |  |

|                           |                                     | EN/UVLO $\uparrow$ (100 mV above V <sub>(ENR)</sub> ) to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> $\geq$ 0.8 nF, [C <sub>(dVdT)</sub> in nF] |      | 100 + 150 ×<br>C <sub>(dVdT)</sub> |      | μs   |  |

| t <sub>OFF(dly)</sub>     | EN turnoff delay                    | EN/UVLO ↓ (100 mV below $V_{(ENF)}$ ) to $\overline{FLT}$ ↓                                                                                          |      | 2                                  |      | μs   |  |

| OVERVOLTA                 | GE PROTECTION INPUT (OVP)           |                                                                                                                                                      |      |                                    | '    |      |  |

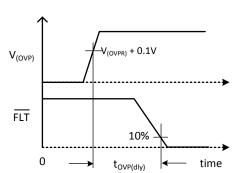

| t <sub>OVP(dly)</sub>     | OVP disable delay                   | OVP $\uparrow$ (100 mV above V <sub>(OVPR)</sub> ) to $\overline{\text{FLT}} \downarrow$                                                             | 2    |                                    |      | μs   |  |

| OUTPUT RAI                | IP CONTROL (dV/dT )                 |                                                                                                                                                      |      |                                    |      |      |  |

| t <sub>dVdT</sub>         | Output ramp time                    | EN/UVLO $\uparrow$ to V <sub>(OUT)</sub> = 4.5 V, with C <sub>(dVdT)</sub> = open                                                                    |      | 0.12                               |      |      |  |

|                           |                                     | EN/UVLO $\uparrow$ to $V_{(OUT)}$ = 11 V, with $C_{(dVdT)}$ = open                                                                                   | 0.25 | 0.37                               | 0.5  | ms   |  |

|                           |                                     | EN/UVLO $\uparrow$ to $V_{(OUT)} = 11 \text{ V, with } C_{(dVdT)} = 1 \text{ nF}$                                                                    |      | 0.97                               |      |      |  |

| CURRENT LI                | МІТ                                 |                                                                                                                                                      |      |                                    |      |      |  |

| t <sub>FASTRIP(dly)</sub> | Fast-trip comparator delay          | I <sub>(OUT)</sub> > I <sub>(FASTRIP)</sub>                                                                                                          |      | 200                                |      | ns   |  |

| REVERSE PR                | OTECTION COMPARATOR                 |                                                                                                                                                      |      |                                    | ,    |      |  |

|                           |                                     | $(V_{(IN)} - V_{(OUT)}) \downarrow (1 \text{ mV overdrive below } V_{(REVTH)}) \text{ to } \overline{FLT} \downarrow$                                |      | 10                                 |      | μs   |  |

| t <sub>REV(dly)</sub>     | Reverse protection comparator delay | $(V_{(IN)} - V_{(OUT)}) \downarrow (10 \text{ mV overdrive below } V_{(REVTH)}) \text{ to } \overline{FLT}$                                          |      | 1                                  |      |      |  |

| t <sub>FWD(dly)</sub>     |                                     | $(V_{(IN)} - V_{(OUT)}) \uparrow (10 \text{ mV overdrive above } V_{(FWDTH)}) \text{ to } \overline{FLT}$                                            |      | 3.1                                |      |      |  |

| POWER-GOO                 | D COMPARATOR OUTPUT (PGOOD): A      | CTIVE HIGH                                                                                                                                           |      |                                    |      |      |  |

| t <sub>PGOODR</sub>       | PCOOD dolay (do glitab) time        | Rising edge                                                                                                                                          | 0.42 | 0.54                               | 0.66 | ms   |  |

| t <sub>PGOODF</sub>       | PGOOD delay (de-glitch) time        | Falling edge                                                                                                                                         | 0.42 | 0.54                               | 0.66 | ms   |  |

| THERMAL SH                | IUT DOWN (TSD)                      |                                                                                                                                                      |      |                                    |      |      |  |

|                           | Retry delay in TSD                  | TPS25940-Q1/TPS259401A-Q1 Only                                                                                                                       |      | 128                                |      | ms   |  |

Product Folder Links: TPS25940-Q1

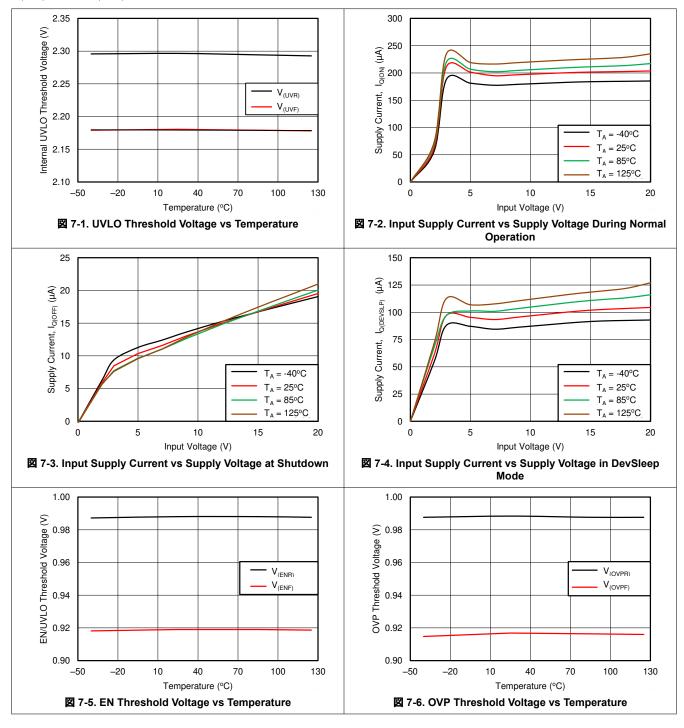

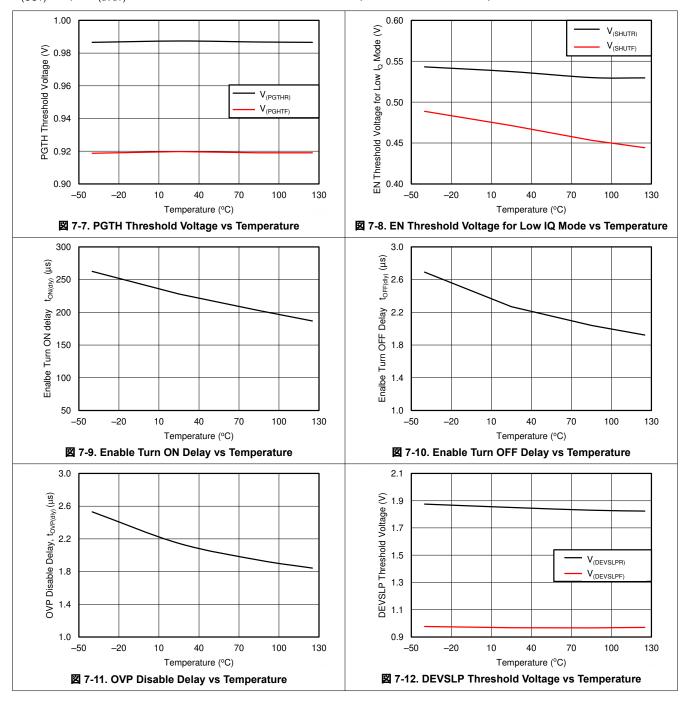

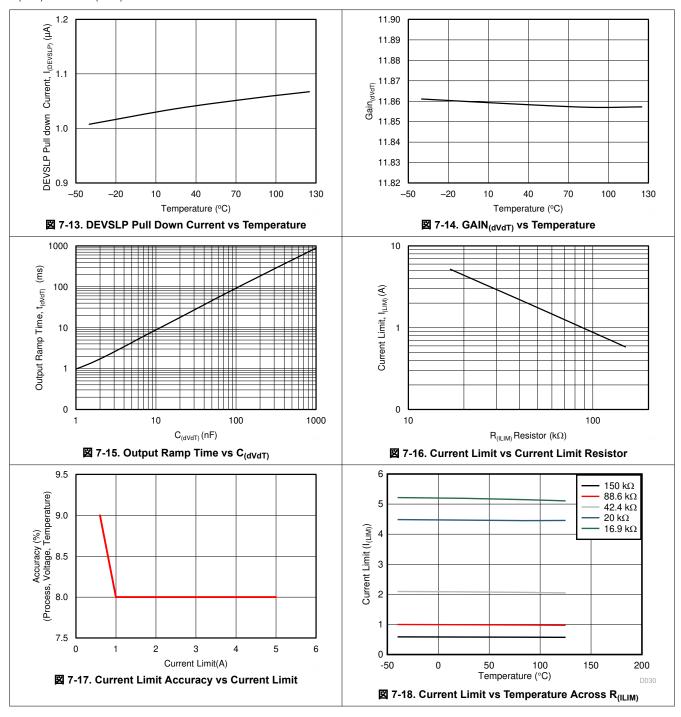

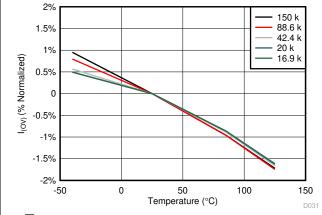

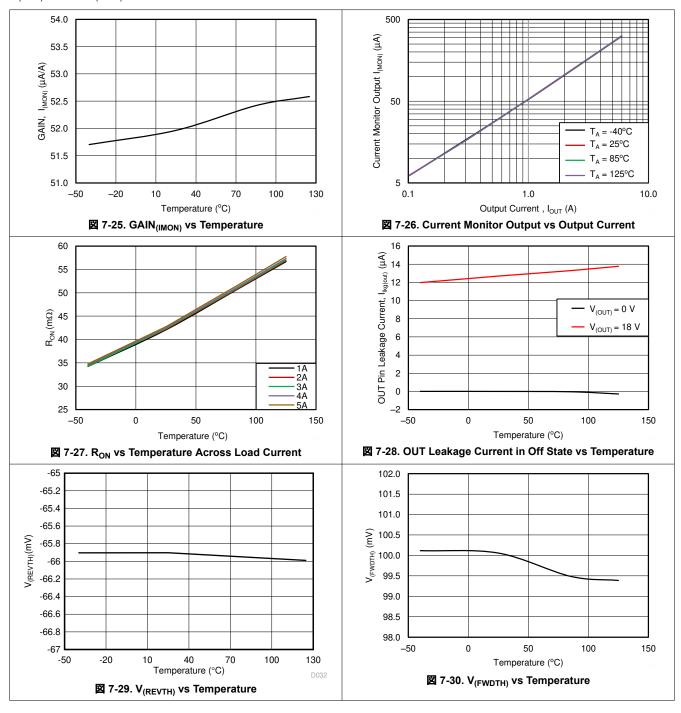

## 7.7 Typical Characteristics

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 10 \text{ k}\Omega$ ,  $R_{(OU$

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 10 \text{ k}\Omega$ ,  $R_{(OU$

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 10 \text{ k}\Omega$ ,  $R_{(OU$

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 10 \text{ k}\Omega$ ,  $R_{(OU$

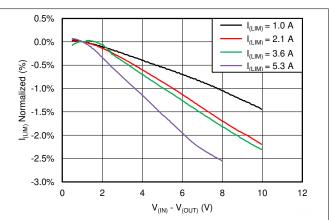

図 7-19. Current Limit (% Normalized) vs R<sub>(LIMIT)</sub> Resistor

Thermal shutdown occurs when  $I_{(LIM)}$  =  $[V_{(IN)} - V_{(OUT)}] > 8 V$

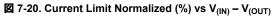

図 7-21. Current Limit for R(ILIM) = Open and Short vs Temperature

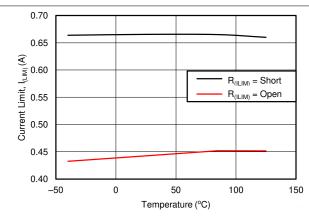

図 7-22. Current Limit in DevSleep Mode vs Temperature

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 10 \text{ k}\Omega$ ,  $R_{(OU$

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 1 \text{ } \mu\text{F}$ ,  $R_{(dVdT)} = 10 \text{ } \text{C}$ ,  $R_{(IUM)} = 10 \text{ } \text{C}$ ,  $R_{(IUM$

Submit Document Feedback

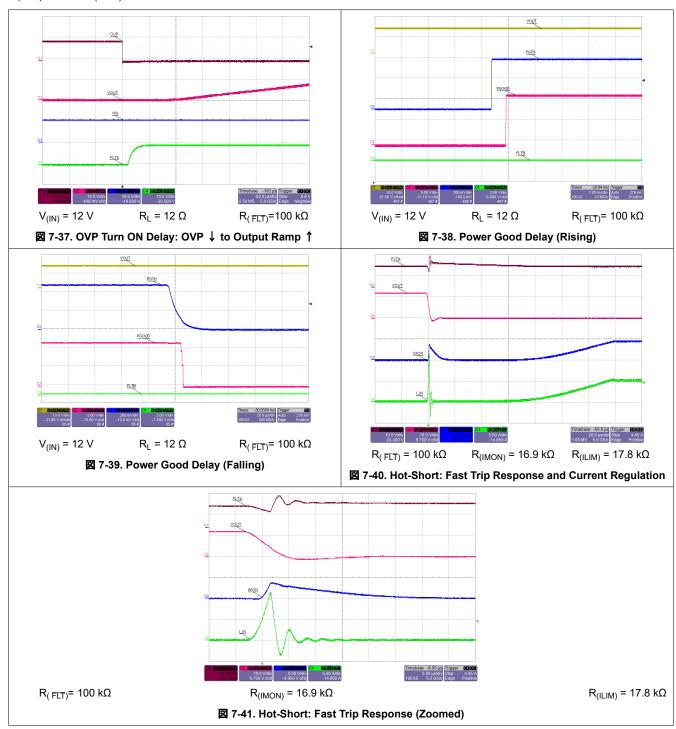

図 7-35. EN Turn OFF Delay : EN ↓ to Fault ↓

Copyright © 2022 Texas Instruments Incorporated

図 7-36. OVP Turn OFF Delay: OVP ↑ to Fault ↓

Conditions are  $-40^{\circ}\text{C} \leq T_{A} = T_{J} \leq 125^{\circ}\text{C}$ ,  $V_{(IN)} = 12 \text{ V}$ ,  $V_{(EN/UVLO)} = 2 \text{ V}$ ,  $V_{(OVP)} = V_{(DEVSLP)} = V_{(PGTH)} = 0 \text{ V}$ ,  $R_{(ILIM)} = 150 \text{ k}\Omega$ ,  $R_{(OUT)} = 1 \text{ } \mu\text{F}$ ,  $R_{(dVdT)} = 10 \text{ } \text{C}$ ,  $R_{(IUM)} = 10 \text{ } \text{C}$ ,  $R_{(IUM$

## **8 Parametric Measurement Information**

図 8-1. Timing Diagrams

# 9 Detailed Description

### 9.1 Overview

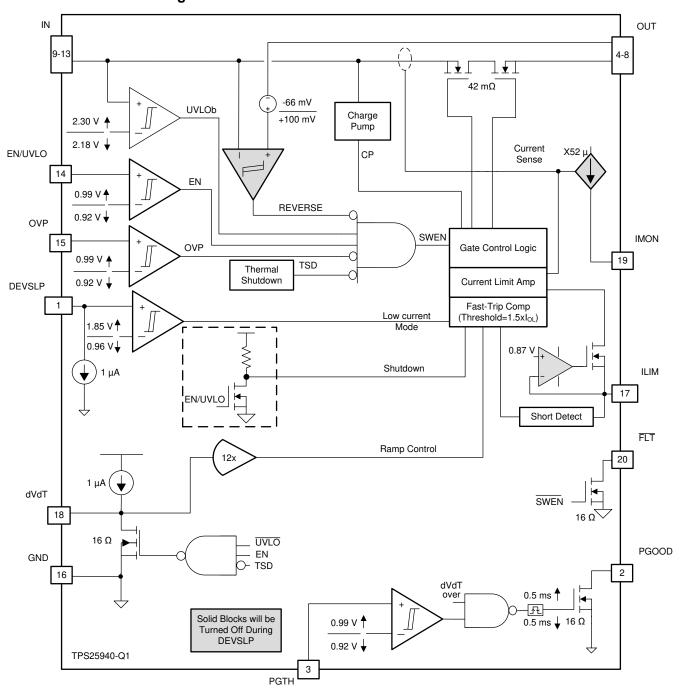

The TPS25940xx-Q1 device is a smart eFuse with integrated back-to-back FETs and enhanced built-in protection circuitry. It provides robust protection for all systems and applications powered from 2.7 V to 18 V.

For hot-plug-in boards, the device provides hot-swap power management with in-rush current control and programmable output ramp-rate. The device integrates overcurrent and short circuit protection. The precision overcurrent limit helps to minimize over design of the input power supply, while the fast response short circuit protection immediately isolates the load from input when a short circuit is detected. The device allows the user to program the overcurrent limit threshold between 0.6 A and 5.3 A via an external resistor.

The device provides precise monitoring of voltage bus for brown-out and overvoltage conditions and asserts fault for downstream system. Its overall threshold accuracy of 2% ensures tight supervision of bus, eliminating the need for a separate supply voltage supervisor chip.

The device is designed to protect systems such as USB hubs against sudden output short to battery events. The device monitors  $V_{(IN)}$  and  $V_{(OUT)}$  to provide true reverse blocking from output when output short to battery fault condition or input power fail condition is detected.

#### The additional features include:

- Precise current monitor output for health monitoring of the system

- Additional power good comparator with precision internal reference for output or any other rail voltage monitoring

- Over temperature protection to safely shutdown in the event of an overcurrent event

- · De-glitched fault reporting for brown-out and overvoltage faults

- · A choice of latched or automatic restart mode

## 9.2 Functional Block Diagram

## 9.3 Feature Description

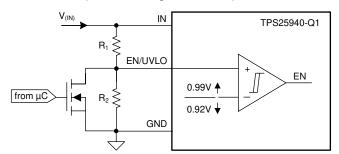

### 9.3.1 Enable and Adjusting Undervoltage Lockout

The EN/UVLO pin controls the ON and OFF state of the internal FET. A voltage  $V_{(EN/UVLO)} < V_{(ENF)}$  on this pin turns off the internal FET, thus disconnecting IN from OUT, while voltage below  $V_{(SHUTF)}$  takes the device into shutdown mode, with  $I_Q$  less than 15  $\mu$ A to ensure minimal power loss. Cycling EN/UVLO low and then back high resets the TPS25940L-Q1 that has latched off due to a fault condition.

The internal de-glitch delay on EN/UVLO falling edge is kept low for quick detection of power failure. For applications where a higher de-glitch delay on EN/UVLO is desired, or when the supply is particularly noisy, it is recommended to use an external bypass capacitor from EN/UVLO terminal to GND.

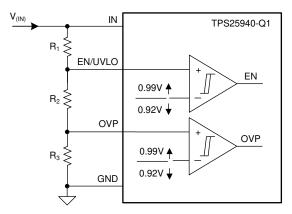

The undervoltage lock out can be programmed by using an external resistor divider from supply IN terminal to EN/UVLO terminal to GND as shown in  $\boxtimes$  9-1. When an undervoltage or input power fail event is detected, the internal FET is quickly turned off, and FLT is asserted. If the Under-Voltage Lock-Out function is not needed, the EN/UVLO terminal must be connected to the IN terminal. EN/UVLO terminal must not be left floating.

The device also implements internal undervoltage-lockout (UVLO) circuitry on the IN terminal. The device disables when the IN terminal voltage falls below internal UVLO Threshold  $V_{(UVF)}$ . The internal UVLO threshold has a hysteresis of 115 mV.

図 9-1. UVLO and OVP Thresholds Set By  $R_1$ ,  $R_2$  and  $R_3$

## 9.3.2 Overvoltage Protection (OVP)

The device incorporates circuit to protect system during overvoltage conditions. A resistor divider connected from the supply to OVP terminal to GND (as shown in  $\boxtimes$  9-1) programs the overvoltage threshold. A voltage more than  $V_{(OVPR)}$  on OVP pin turns off the internal FET and protects the downstream load. This pin must be tied to GND when not used.

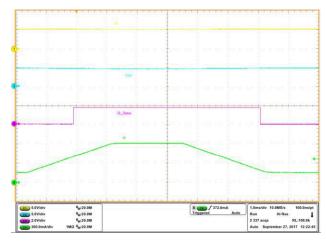

### 9.3.3 Hot Plug-In and In-Rush Current Control

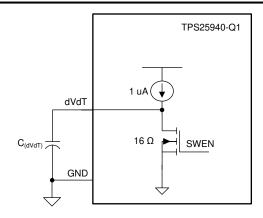

The device is designed to control the in-rush current upon insertion of a card into a live backplane or other "hot" power source. This limits the voltage sag on the backplane's supply voltage and prevents unintended resets of the system power. A slew rate controlled startup (dVdT) also helps to eliminate conductive and radiative interferences. An external capacitor connected from the dVdT pin to GND defines the slew rate of the output voltage at power-on (as shown in  $\boxtimes$  9-2). Equation governing slew rate at start-up is shown in  $\preceq$  1.

図 9-2. Output Ramp Up Time  $t_{dVdT}$  is Set by  $C_{(dVdT)}$

$$I_{(dVdT)} = \left(\frac{C_{(dVdT)}}{GAIN_{(dVdT)}}\right) \times \left(\frac{dV_{(OUT)}}{dt}\right)$$

(1)

#### where

- I<sub>(dVdT)</sub> = 1 μA (typical)

dV<sub>(OUT)</sub>

- dt = Desired output slew rate

- GAIN<sub>(dVdT)</sub> = dVdT to OUT gain = 12

The total ramp time  $(t_{dVdT})$  of  $V_{(OUT)}$  for 0 to  $V_{(IN)}$  can be calculated using  $\vec{x}$  2.

$$t_{dVdT} = 8.3 \times 10^4 \times V_{(IN)} \times C_{(dVdT)}$$

(2)

The inrush current,  $I_{(INRUSH)}$  can be calculated as shown in  $\pm$  3.

$$I_{(INRUSH)} = C_{(OUT)} \times V_{(IN)} / t_{dVdT}. \tag{3}$$

The dVdT pin can be left floating to obtain a predetermined slew rate ( $t_{dVdT}$ ) on the output. When terminal is left floating, the device sets an internal ramp rate of 30 V/ms for output ( $V_{(OUT)}$ ) ramp.

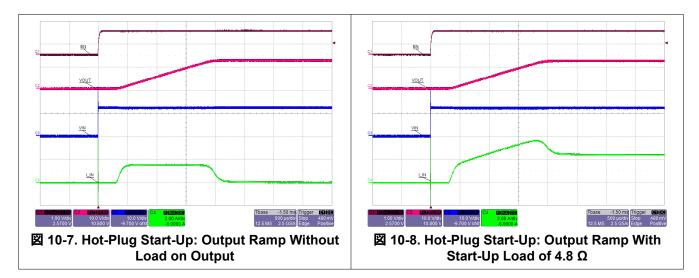

$\boxtimes$  10-7 and  $\boxtimes$  10-8 illustrate the inrush current control behavior of the device. For systems where load is present during start-up, the current never exceeds the overcurrent limit set by  $R_{(ILIM)}$  resistor for the application. For defining appropriate charging time-rate under different load conditions, see the *Setting Output Voltage Ramp Time* ( $T_{dVdT}$ ) section.

### 9.3.4 Overload and Short Circuit Protection

At all times load current is monitored by sensing voltage across an internal sense resistor. During overload events, current is limited to the current limit ( $I_{(LIM)}$ ) programmed by  $R_{(ILIM)}$  resistor as shown in  $\not \equiv 4$ .

$$I_{(LIM)} = \frac{89}{R_{(ILIM)}} \tag{4}$$

### where

- I<sub>(LIM)</sub> is overload current limit in Ampere

- R<sub>(ILIM)</sub> is the current limit resistor in kΩ

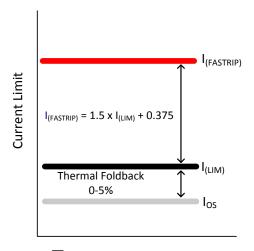

The device incorporates two distinct levels: a current limit  $(I_{(LIM)})$  and a fast-trip threshold  $(I_{(FASTRIP)})$ . Fast trip and current limit operation are shown in  $\boxtimes$  9-3.

Bias current on ILIM pin directly controls current-limiting behavior of the device, and PCB routing of this node must be kept away from any noisy (switching) signals.

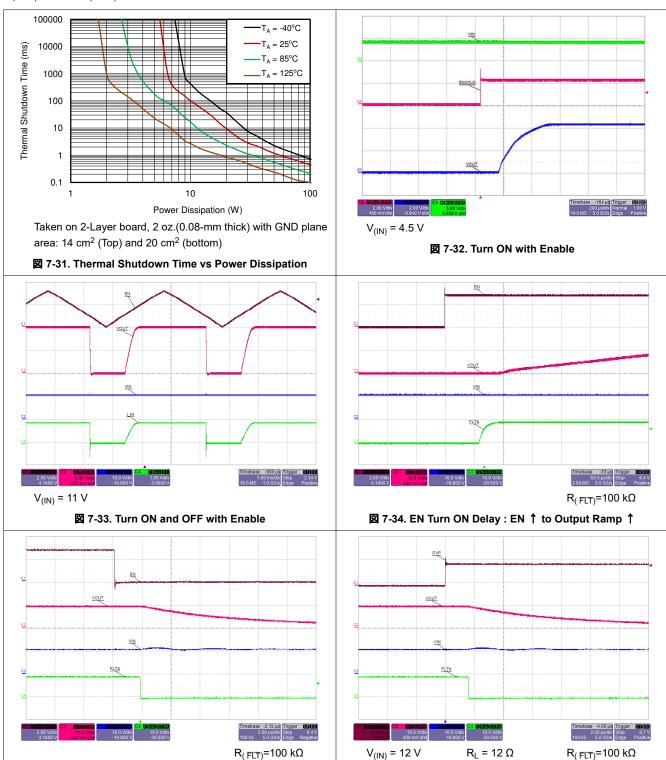

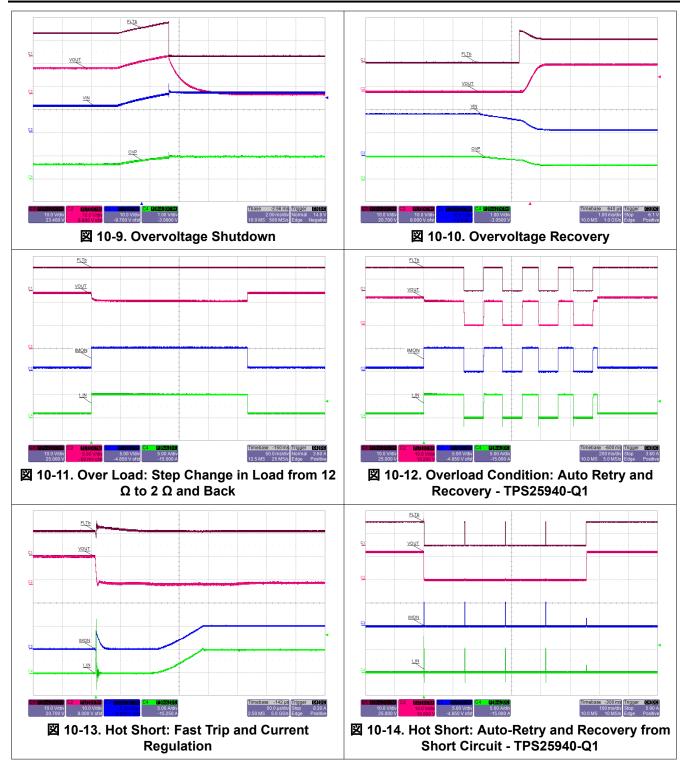

#### 9.3.4.1 Overload Protection

For overload conditions, the internal current-limit amplifier regulates the output current to  $I_{(LIM)}$ . The output voltage droops during the current regulation, resulting in increased power dissipation in the device. If the device junction temperature reaches the thermal shutdown threshold  $(T_{(TSD)})$ , the internal FET is turned off. When in thermal shutdown, the TPS25940L-Q1 version stays latched off, whereas the TPS25940-Q1/TPS259401A-Q1 versions commence an auto-retry cycle 128 ms after  $T_J < [T_{(TSD)} - 12^{\circ}C]$ . During thermal shutdown, the fault pin FLT pulls low to signal a fault condition.  $\boxtimes$  10-11 and  $\boxtimes$  10-12 illustrate overload behavior.

#### 9.3.4.2 Short Circuit Protection

During a transient short circuit event, the current through the device increases very rapidly. As current-limit amplifier cannot respond quickly to this event because of its limited bandwidth, the device incorporates a fast-trip comparator, with a threshold  $I_{(FASTRIP)}$ . This comparator shuts down the pass device within 1µs, when the current through internal FET exceeds  $I_{(FASTRIP)}$  ( $I_{(OUT)} > I_{(FASTRIP)}$ ), and terminates the rapid short-circuit peak current. The trip threshold is set to more than 50% of the programmed overload current limit ( $I_{(FASTRIP)} = 1.5 \times I_{(LIM)} + 0.375$ ). The fast-trip circuit holds the internal FET off for only a few microseconds, after which the device turns back on slowly, allowing the current-limit loop to regulate the output current to  $I_{(LIM)}$ . Then, device behaves similar to overload condition.  $\boxtimes$  10-13 through  $\boxtimes$  10-14 illustrate the behavior of the system when the current exceeds the fast-trip threshold.

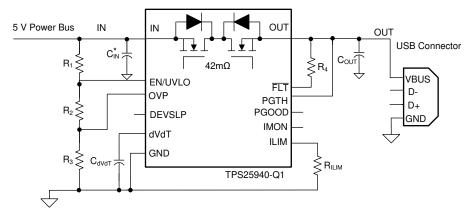

### 9.3.4.3 Start-Up with Short on Output

During start-up into a short circuit current is limited to  $I_{(LIM)}$ .  $\boxtimes$  9-3 and  $\boxtimes$  10-15 illustrate start-up with a short on the output. This feature helps in quick fault isolation and hence ensures stability of the DC bus.

### 9.3.4.4 Constant Current Limit Behavior During Overcurrent Faults

When power dissipation in the internal FET [ $P_D = (V_{(IN)} - V_{(OUT)}) \times I_{(OUT)}$ ] > 10 W, there is approximately 0% to 5% thermal fold back in the current limit value so that  $I_{(LIM)}$  drops to  $I_{OS}$ . Eventually, the device shuts down because of over temperature.

図 9-3. Fast-Trip Current

#### 9.3.5 FAULT Response

The FLT open-drain output is asserted (active low) during undervoltage, overvoltage, reverse voltage-current and thermal shutdown conditions. The FLT signal remains asserted until the fault condition is removed and the device resumes normal operation. The device is designed to eliminate false fault reporting by using an internal "de-glitch" circuit for undervoltage and overvoltage (2.2-µs typical) conditions without the need for external circuitry. This ensures that fault is not accidentally asserted during transients on input bus.

Connect  $\overline{FLT}$  with a pull up resistor to Input or Output voltage rail.  $\overline{FLT}$  may be left open or tied to ground when not used.  $V_{(IN)}$  falling below  $V_{(UVF)} = 2.1 \text{ V}$  resets  $\overline{FLT}$ .

## 9.3.6 Current Monitoring

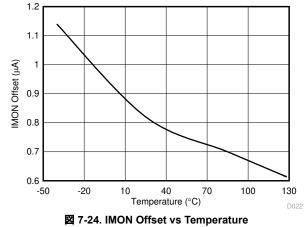

The current source at IMON terminal is configured to be proportional to the current flowing from IN to OUT. This current can be converted to a voltage using a resistor  $R_{(IMON)}$  from IMON terminal to GND terminal. This voltage, computed using  $\not \gtrsim 6$ , can be used as a means of monitoring current flow through the system.

The maximum voltage range for monitoring the current  $(V_{(IMONmax)})$  is limited to minimum( $[V_{(IN)} - 2.2 V]$ , 6 V) to ensure linear output. This puts limitation on maximum value of  $R_{(IMON)}$  resistor and is determined by  $\not\equiv$  5.

$$R_{(IMONmax)} = \frac{\text{minimum } (V_{(IN)} - 2.2, 6)}{1.6 \times I_{(LIM)} \times GAIN_{(IMON)}}$$

(5)

The output voltage at IMON terminal is calculated from 式 6.

$$V_{(IMON)} = \left[I_{(OUT)} \times GAIN_{(IMON)} + I_{(IMON\_OS)}\right] \times R_{(IMON)}$$

(6)

where

- GAIN<sub>(IMON)</sub> = Gain factor  $I_{(IMON)}:I_{(OUT)} = 52 \mu A/A$

- I<sub>(OUT)</sub> = Load current

- $I_{(IMON OS)} = 0.8 \mu A$  (typical)

This pin must not have a bypass capacitor to avoid delay in the current monitoring information.

The voltage at IMON pin can be digitized using an ADC (such as ADS1100, SBAS239) to read the current monitor information over an I<sup>2</sup>C bus.

### 9.3.7 Power Good Comparator

The device incorporates a Power Good comparator for co-ordination of status to downstream DC-DC converters or system monitoring circuits. The comparator has an internal reference of  $V_{(PGTHR)} = 0.99 \text{ V}$  at negative terminal and positive terminal PGTH can be utilized for monitoring of either input or output of the device. The comparator output PGOOD is an open-drain active high signal, which can be used to indicate the status to downstream units. PGOOD is asserted high when internal FET is fully enhanced and PGTH pin voltage is higher than internal reference  $V_{(PGTHR)}$ .

The PGOOD signal has deglitch time incorporated to ensure that internal FET is fully enhanced before heavy load is applied by downstream converters. Rising de-glitch delay is determined by  $\pm 7$ .

$$t_{PGOOD(deql)} = Maximum\{(3.5 \times 10^6 \times C_{(dVdT)}), t_{PGOODR}\}$$

(7)

Connect the PGOOD pin with a pull up resistor to Input or Output voltage rail. PGOOD may be left open or tied to ground when not used.

### 9.3.8 IN, OUT and GND Pins

The device has multiple pins for input (IN) and output (OUT).

All IN pins must be connected together and to the power source. A ceramic bypass capacitor close to the device from IN to GND is recommended to alleviate bus transients. The recommended operating voltage range is 2.7 V - 18 V.

Similarly all OUT pins must be connected together and to the load.  $V_{(OUT)}$  in the ON condition, is calculated using  $\pm 8$ .

$$V_{(OUT)} = V_{(IN)} - (R_{ON} \times I_{(OUT)})$$

(8)

where, R<sub>ON</sub> is the total ON resistance of the internal FET.

GND terminal is the most negative voltage in the circuit and is used as a reference for all voltage reference unless otherwise specified.

#### 9.3.9 Thermal Shutdown

Internal over temperature shutdown disables turns off the FET when  $T_J > 160^{\circ}\text{C}$  (typical). The TPS25940L-Q1 version stays latched off, whereas TPS25940-Q1/TPS259401A-Q1 versions commence an auto-retry cycle 128 ms after  $T_J$  drops below  $[T_{(TSD)} - 12^{\circ}\text{C}]$ . During the thermal shutdown, the fault pin  $\overline{\text{FLT}}$  pulls low to signal a fault condition.

#### 9.4 Device Functional Modes

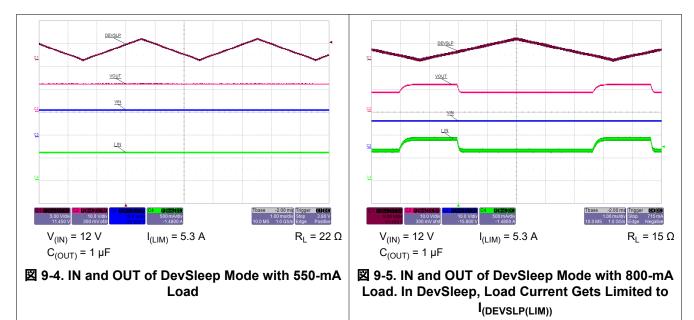

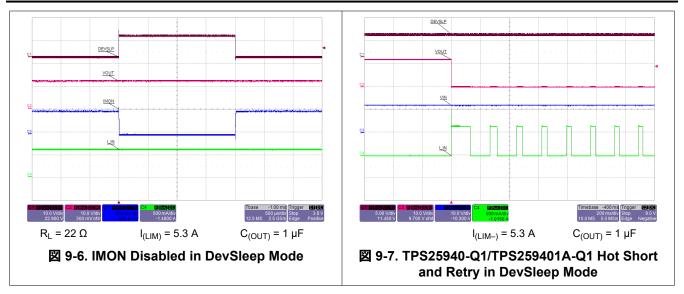

### 9.4.1 DevSleep Mode

The TPS25940xx-Q1 device provides a dedicated DevSleep interface terminal (DEVSLP) to drive the device in low power mode. When pulled high, it puts the device in low power DevSleep mode. In this mode, the quiescent current consumption of the device is limited to less than 130  $\mu$ A (95- $\mu$ A typical). During this mode, the output voltage remains active, the overload current limit is set to  $I_{(DEVSLP(LIM))}$  and functionality of reverse comparator and current monitoring is disabled. All other protections are kept active ensuring the safety of the system even in DevSleep mode.

User must ensure that load currents on the bus are limited to less than  $I_{(DEVSLP(LIM))}$ , when the device is driven to DevSleep mode. Also, while coming out of DevSleep, it is important to sequence the TPS25940xx-Q1 earlier than the load. Otherwise, the load can exceed  $I_{(DEVSLP(LIM))}$  and cause the TPS25940xx-Q1 to enter the overload mode.

#### 9.4.2 Shutdown Control

The internal FET and hence the load current can be remotely switched off by taking the UVLO pin below its 0.6-V threshold with an open collector or open drain device as shown in  $\boxtimes$  9-8. The device quiescent current is reduced to less than 20  $\mu$ A in this state. Upon releasing the UVLO pin the device turns on with soft-start cycle.

図 9-8. Shutdown Control

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

## 10 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 10.1 Application Information

The TPS25940xx-Q1 device is a smart eFuse. It is typically used for Hot-Swap and Power rail protection applications. It operates from 2.7 V to 18 V with programmable current limit, overvoltage and undervoltage protection. The device aids in controlling the in-rush current and provides fast turn-off during reverse voltage conditions for systems such as USB ports prone to Short-to-Battery faults, Servers, Power Back-up Storage units and RAID cards. The device also provides robust protection for multiple faults on the sub-system rail.

The Detailed Design Procedure section can be used to select component values for the device.

Alternatively, the WEBENCH® software may be used to generate a complete design. The WEBENCH® software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. Additionally, a spreadsheet design tool *TPS25940 Design Calculator* is available on web folder.

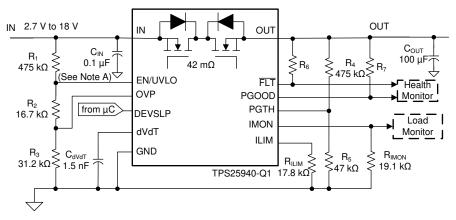

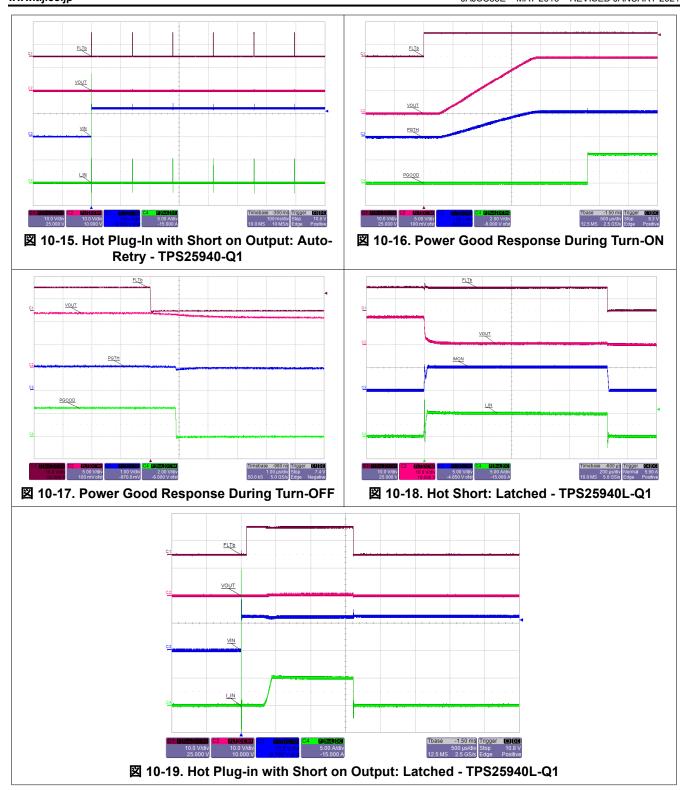

## 10.2 Typical Application

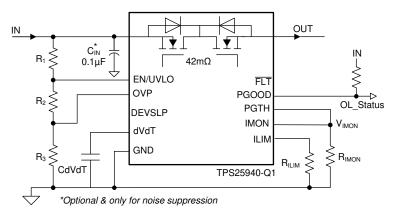

C<sub>IN</sub>: Optional and only for noise suppression.

図 10-1. Typical Application Schematic

### 10.2.1 Design Requirements

表 10-1 lists the Design Parameters.

表 10-1. Design Parameters

| DESIGN PARAMETER                                     | EXAMPLE VALUE |

|------------------------------------------------------|---------------|

| Input voltage, V <sub>(IN)</sub>                     | 12 V          |

| Undervoltage lockout set point, V <sub>(UV)</sub>    | 10.8 V        |

| Overvoltage protection set point, V <sub>(LIM)</sub> | 16.5 V        |

| Load at Start-Up, R <sub>L(SU)</sub>                 | 4.8 Ω         |

| Current limit, I <sub>(LIM)</sub>                    | 5 A           |

| Load capacitance, C <sub>(OUT)</sub>                 | 100 µF        |

| Maximum ambient temperatures, T <sub>A</sub>         | 85°C          |

### 10.2.2 Detailed Design Procedure

The following design procedure can be used to select component values for the TPS25940xx-Q1.

## 10.2.2.1 Step by Step Design Procedure

To begin the design process a few parameters must be decided upon. The designer must know the following:

- Normal input operation voltage

- · Maximum output capacitance

- · Maximum current Limit

- Load during start-up

- Maximum ambient temperature of operation

This design procedure below seeks to control the junction temperature of device under both static and transient conditions by proper selection of output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria.

### 10.2.2.2 Programming the Current-Limit Threshold: R<sub>(ILIM)</sub> Selection

The  $R_{(ILIM)}$  resistor at the ILIM pin sets the over load current limit, this can be set using  $\pm 9$ .

$$R_{\text{(ILIM)}} = \frac{89}{5} = 17.8 \text{k}\Omega \tag{9}$$

Choose closest standard value: 17.8-k, 1% standard value resistor.

## 10.2.2.3 Undervoltage Lockout and Overvoltage Set Point

The undervoltage lockout (UVLO) and overvoltage trip point are adjusted using the external voltage divider network of  $R_1$ ,  $R_2$  and  $R_3$  as connected between IN, EN, OVP and GND pins of the device. The values required for setting the undervoltage and overvoltage are calculated solving  $\pm$  10 and  $\pm$  11.

$$V_{(OVPR)} = \frac{R_3}{R_1 + R_2 + R_3} \times V_{(OV)}$$

(10)

$$V_{(ENR)} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \times V_{(UV)}$$

(11)

For minimizing the input current drawn from the power supply  $\{I_{(R123)} = V_{(IN)}/(R_1 + R_2 + R_3)\}$ , it is recommended to use higher values of resistance for  $R_1$ ,  $R_2$  and  $R_3$ .

However, leakage currents because of the external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I_{(R123)}$  must be chosen to be 20 times greater than the leakage current expected.

From the device electrical specifications,  $V_{(OVPR)} = 0.99 \text{ V}$  and  $V_{(ENR)} = 0.99 \text{ V}$ . For design requirements,  $V_{(OV)}$  is 16.5 V and  $V_{(UV)}$  is 10.8 V. To solve the equation, first choose the value of  $R_3 = 31.2 \text{ k}\Omega$  and use  $\stackrel{\prec}{\prec}$  10 to solve for  $(R_1 + R_2) = 488.8 \text{ k}\Omega$ . Use  $\stackrel{\prec}{\prec}$  11 and value of  $(R_1 + R_2)$  to solve for  $R_2 = 16.47 \text{ k}\Omega$  and finally  $R_1 = 472.33 \text{ k}\Omega$ .

Using the closest standard 1% resistor values gives  $R_1$  = 475 k $\Omega$ ,  $R_2$  = 16.7 k $\Omega$ , and  $R_3$  = 31.2 k $\Omega$ .

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 7% lower than the rising threshold,  $V_{(UV)}$ . This is calculated using  $\pm$  12.

$$V_{(PFAIL)} = 0.93 \times V_{(UV)} \tag{12}$$

## 10.2.2.4 Programming Current Monitoring Resistor—R<sub>IMON</sub>

Voltage at IMON pin  $V_{(IMON)}$  represents the voltage proportional to load current. This can be connected to an ADC of the downstream system for health monitoring of the system. The  $R_{(IMON)}$  need to be configured based on the maximum input voltage range of the ADC used.  $R_{(IMON)}$  is set using  $\pm$  13.

$$R_{\text{(IMON)}} = \frac{V_{\text{(IMONmax)}}}{I_{\text{(LIM)}} \times 52 \times 10^{-6}} \text{ k}\Omega$$

(13)

For  $I_{(LIM)} = 5$  A, and considering the operating range of ADC from 0 V to 5 V,  $V_{(IMONmax)}$  is 5 V and  $R_{(IMON)}$  is determined by:

$$R_{\text{(IMON)}} = \frac{5}{5 \times 52 \times 10^{-6}} = 19.23 \text{ k}\Omega \tag{14}$$

Selecting  $R_{(IMON)}$  value less than determined by  $\not \equiv 14$  ensures that ADC limits are not exceeded for maximum value of load current.

If the IMON pin voltage is not being digitized with an ADC,  $R_{(IMON)}$  can be selected to produce a 1V/1A voltage at the IMON pin, using  $\pm$  13.

Choose closest 1 % standard value: 19.1 kΩ.

If current monitoring up to  $I_{(FASTRIP)}$  is desired,  $R_{(IMON)}$  can be reduced by a factor of 1.6, as in  $\pm$  5.

#### 10.2.2.5 Setting Output Voltage Ramp Time ( $t_{dVdT}$ )

For a successful design, the junction temperature of device must be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The ramp-up capacitor  $C_{(dVdT)}$  needed is calculated considering the two possible cases Case 1: Start-up Without Load: Only Output Capacitance C(OUT) Draws Current During Start-up and Case 2: Start-Up With Load: Output Capacitance C(OUT) and Load Draws Current During Start-Up.

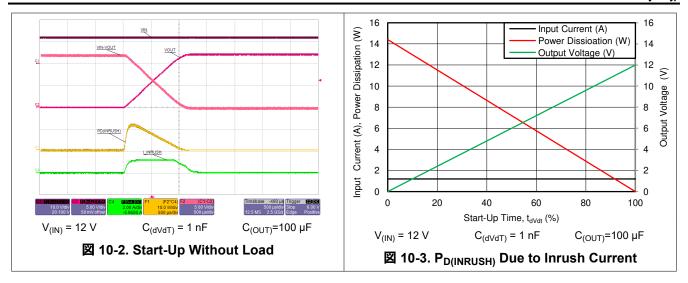

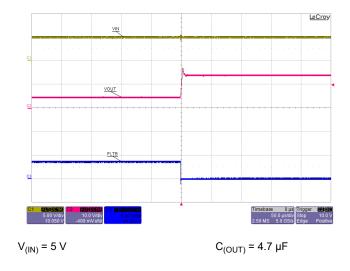

### 10.2.2.5.1 Case1: Start-Up Without Load: Only Output Capacitance C<sub>(OUT)</sub> Draws Current During Start-Up

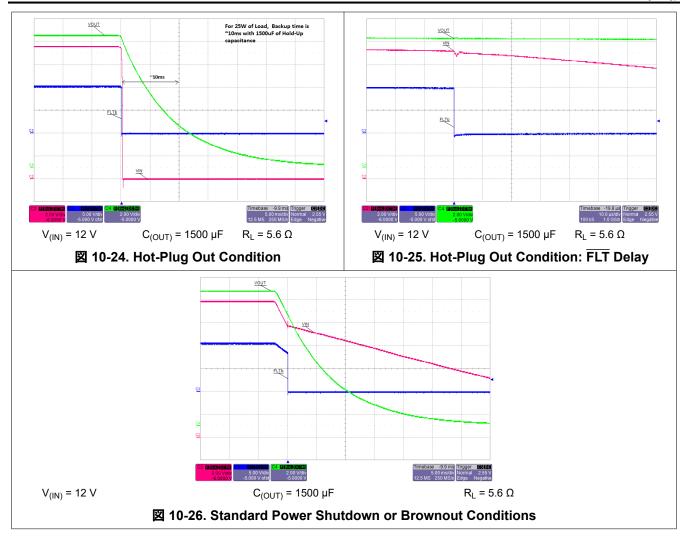

During start-up, as the output capacitor charges, the voltage difference across the internal FET decreases, and the power dissipated decreases as well. Typical ramp-up of output voltage  $V_{(OUT)}$  with inrush current limit of 1.2 A and power dissipated in the device during start-up is shown in  $\boxtimes$  10-2. The average power dissipated in the device during start-up is equal to area of triangular plot (red curve in  $\boxtimes$  10-2) averaged over  $t_{dVdT}$ .

Copyright © 2022 Texas Instruments Incorporated

For the TPS25940-Q1 device, the inrush current is determined as shown in 式 15.

$$I = C \times \frac{dV}{dT} = > I_{(INRUSH)} = C_{(OUT)} \times \frac{V_{(IN)}}{t_{dVdT}}$$

(15)

Power dissipation during start-up is given by  $\pm$  16.

$$P_{D(INRUSH)} = 0.5 \times V_{(IN)} \times I_{(INRUSH)}$$

(16)

式 16 assumes that load does not draw any current until the output voltage has reached its final value.

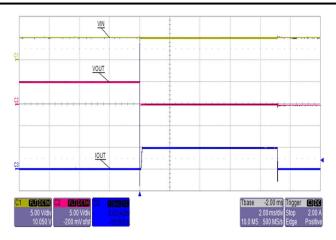

## 10.2.2.5.2 Case 2: Start-Up With Load: Output Capacitance C(OUT) and Load Draws Current During Start-Up

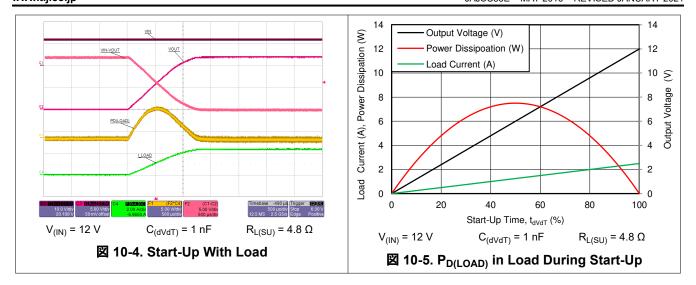

When load draws current during the turn-on sequence, there is additional power dissipated. Considering a resistive load  $R_{L(SU)}$  during start-up, load current ramps up proportionally with increase in output voltage during  $t_{dVdT}$  time. Typical ramp-up of output voltage, Load current and power dissipation in the device is shown in  $\boxtimes$  10-4 and power dissipation with respect to time is plotted in  $\boxtimes$  10-5. The additional power dissipation during start-up phase is calculated as shown in  $\overrightarrow{\times}$  17 and  $\overrightarrow{\times}$  18.

$$(V_{I} - V_{O})(t) = V_{(IN)} \times \left(1 - \frac{t}{t_{dVdT}}\right)$$

(17)

$$I_{L}(t) = \left(\frac{V_{(IN)}}{R_{L}(SU)}\right) \times \frac{t}{t_{dVdT}}$$

(18)

Where  $R_{L(SU)}$  is the load resistance present during start-up. Average energy loss in the internal FET during charging time due to resistive load is given by  $\pm$  19.

$$W_{t} = \int_{0}^{tdVdT} V_{(IN)} x \left(1 - \frac{t}{t_{dVdT}}\right) x \left(\frac{V_{(IN)}}{R_{L(SU)}} x \frac{t}{t_{dVdT}}\right) dt$$

(19)

On solving 式 19 the average power loss in the internal FET due to load is shown in 式 20.

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{V^2(IN)}{R_{L(SU)}}$$

(20)

Total power dissipated in the device during startup is shown is 式 21.

$$P_{D(STARTUP)} = P_{D(INRUSH)} + P_{D(LOAD)}$$

(21)

Total current during startup is given by 式 22.

$$I_{(STARTUP)} = I_{(INRUSH)} + I_{L}(t)$$

(22)

If  $I_{(STARTUP)} > I_{(LIM)}$ , the device limits the current to  $I_{(LIM)}$  and the current limited charging time is determined by  $\pm$  23.

$$t_{dVdT(current\ limited)} = C_{(OUT)} \times \frac{V_{(IN)}}{I_{(LIM)}}$$

(23)

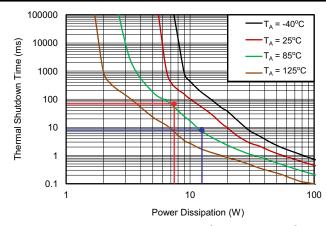

The power dissipation, with and without load, for selected start-up time must not exceed the shutdown limits as shown in  $\boxtimes$  10-6.

Taken on 2-Layer board, 2oz.(0.08-mm thick) with GND plane area: 14 cm<sup>2</sup> (Top) and 20 cm<sup>2</sup> (bottom)

#### 図 10-6. Thermal Shutdown Limit Plot

For the design example under discussion,

Select ramp-up capacitor  $C_{(dVdT)} = 1nF$ , using  $\pm 24$ .

$$t_{dvdt} = 8.3 \times 10^4 \times 12 \times 1 \times 10^{-9} = 0.996 \text{ms} = \sim 1 \text{ms}$$

(24)

The inrush current drawn by the load capacitance  $(C_{(OUT)})$  during ramp-up using  $\pm 25$ .

$$I_{\text{(INRUSH)}} = \left(100 \times 10^{-6}\right) \times \left(\frac{12}{1 \times 10^{-3}}\right) = 1.2 \text{ A}$$

(25)

The inrush Power dissipation is calculated, using  $\pm 26$ .

$$P_{D(INRUSH)} = 0.5 \times 12 \times 1.2 = 7.2 \text{ W}$$

(26)

For 7.2 W of power loss, the thermal shut down time of the device must not be less than the ramp-up time  $t_{dVdT}$  to avoid the false trip at maximum operating temperature. From thermal shutdown limit graph  $\boxtimes$  10-6 at  $T_A$  = 85°C, for 7.2 W of power the shutdown time is approximately 60 ms. So it is safe to use 1 ms as start-up time without any load on output.

Considering the start-up with load 4.8  $\Omega$ , the additional power dissipation, when load is present during start up is calculated, using  $\pm$  27.

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{12 \times 12}{4.8} = 5 \text{ W}$$

(27)

The total device power dissipation during start up is given by 式 28.

$$P_{D(STARTUP)} = (7.2+5) = 12.2 \text{ W}$$

(28)

From thermal shutdown limit graph at  $T_A$  = 85°C, the thermal shutdown time for 12.2 W is close to 7.5 ms. It is safe to have 30% margin to allow for variation of system parameters such as load, component tolerance, and input voltage. So it is well within acceptable limits to use the 1 nF capacitor with start-up load of 4.8  $\Omega$ .

If there is a need to decrease the power loss during start-up, it can be done with increase of  $C_{(dVdT)}$  capacitor.

To illustrate, choose  $C_{(dVdT)}$  = 1.5 nF as an option and recalculate: