TPS25820, TPS25821

JAJSE35C - NOVEMBER 2017 - REVISED AUGUST 2019

# TPS25820、TPS25821 USB Type-C<sup>™</sup> 1.5Aソース・コントローラおよび 電源スイッチ

## 1 特長

- USB Type-C<sup>™</sup>リリース1.3準拠のソース・コント ローラ

- CCライン上のSTD/1.5A電流能力のアドバタイズ メント

- コネクタの取り付け/取り外し検出

- スーパー・スピードの極性判定

- V<sub>BUS</sub>とV<sub>CONN</sub> (TPS25820)の印加および放電、内 部で固定された電流制限付き

- Type-Cコネクタに何も接続されていないとき、動作電流1.0μA (標準値)

- 64mΩ (標準値)のハイサイドOUT MOSFET

- USBの電流制限要件に適合

- 1.7A、±7%精度のOUT電流制限

- 高速な過電流応答: 1.5µs (標準値)

- CC1およびCC2の、±8kV接触放電および±15kV 空中放電ESD定格(IEC 61000-4-2)

- IEC/UL 認定

- US-33101-UL: IEC 60950-1:2005, AMD1:2009, AMD2:2013

- US-33102-UL: IEC 62368-1:2014

## 2 アプリケーション

- USB 2.0または3.x Type-Cのホストおよびハブ・ ポート

- ノート/デスクトップPCおよびタブレット

- LCDモニタ/ドッキング・ステーションおよび充電 クレードル

- Type-C USB壁面充電器、パワーバンク、CLA

- セットトップ・ボックスおよびオーディオ/ビデオ・システム

# 3 概要

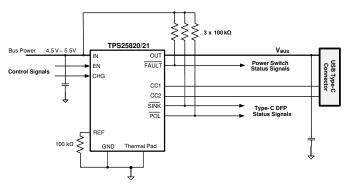

TPS25820/21はUSB Type-Cソース・コントローラで、 1.5A定格のUSB電源スイッチが内蔵されています。 TPS25820/21は、Type-C構成チャネル(CC)ラインをモニタして、USBシンクの取り付けを検出します。シンクが取り付けられた場合、TPS25820/21は $V_{BUS}$ に電力を印加し、パススルーのCCラインを経由して、選択可能な $V_{BUS}$ 電流ソーシング能力をシンクに通知します。シンクにE-Markedケーブルが接続されると、TPS25820は $V_{CONN}$ 電力もケーブルの $V_{CONN}$ ピンに印加します。TPS25821は $V_{CONN}$ 電力を印加せず、USB 2.0やデータなしの充電用実装など、 $V_{CONN}$ が必要ない機能向けです。

TPS25820/21は、何も接続されていないとき1.0μA (標準値)を消費します。FAULT出力は、スイッチが過電流または過熱状態のときに信号を発します。SINK出力は、シンクが接続されているときに信号を出力し、POL出力はケーブルのスーパー・スピード・ラインの極性を示します。

### 製品情報<sup>(1)</sup>

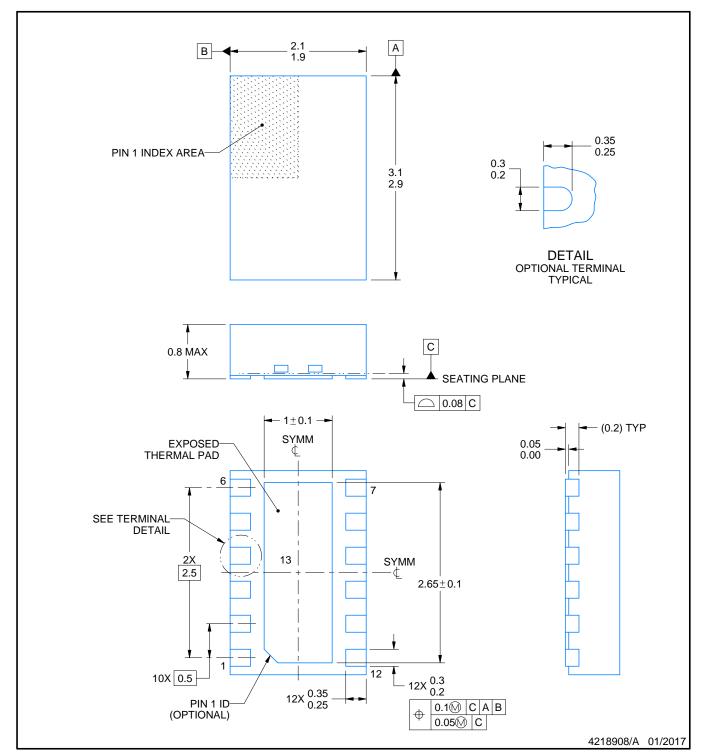

| 型番       | パッケージ     | 本体サイズ(公称)     |

|----------|-----------|---------------|

| TPS25820 | WSON (12) | 3.00mm×2.00mm |

| TPS25821 | WSON (12) | 3.00mm×2.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

### デバイスの比較

| 型番       | VCONN |

|----------|-------|

| TPS25820 | あり    |

| TPS25821 | なし    |

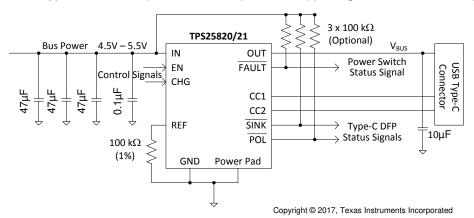

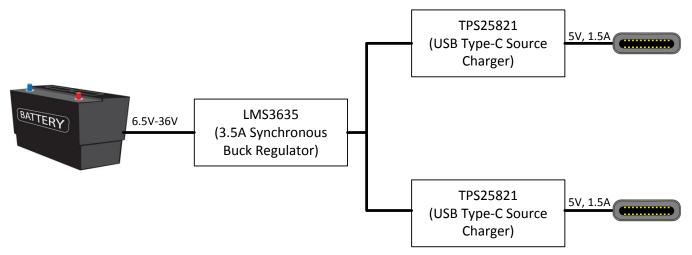

### 概略回路図

Copyright © 2017, Texas Instruments Incorporated

|                            |                                                                                                                                                                                                                                                                                                                                                                                           | 目次                                    |                    |                                                            |      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------|

| 1<br>2<br>3<br>4<br>5<br>6 | 特長 アプリケーション 概要 改訂履歴 Pin Configuration and Functions Specifications 6.1 Absolute Maximum Ratings 6.2 ESD Ratings 6.3 Recommended Operating Conditions 6.4 Thermal Information 6.5 Electrical Characteristics 6.6 Switching Characteristics 6.7 Typical Characteristics Detailed Description 7.1 Overview 7.2 Functional Block Diagrams 7.3 Feature Description 7.4 Device Functional Modes | 1 2 3 4 4 4 5 5 7 9 10 . 10 . 12 . 13 | 8<br>9<br>10<br>11 | Application and Implementation 8.1 Application Information |      |

|                            | <b>攻訂履歴</b><br>sion B (February 2019) から Revision C に変更                                                                                                                                                                                                                                                                                                                                   |                                       |                    |                                                            | Page |

| • L                        | JS-33102-UL: IEC 62368-1:2014 を「特長」セクションに                                                                                                                                                                                                                                                                                                                                                 | こ 追加                                  |                    |                                                            | 1    |

| Revi                       | sion A (December 2017) から Revision B に変更                                                                                                                                                                                                                                                                                                                                                  |                                       |                    |                                                            | Page |

| •  [                       | EC/UL 認定番号を「特長」セクションに 追加                                                                                                                                                                                                                                                                                                                                                                  |                                       |                    |                                                            | 1    |

| 2017                       | 年 <b>11</b> 月発行のものから更新                                                                                                                                                                                                                                                                                                                                                                    |                                       |                    |                                                            | Page |

TPS25821を製品プレビューから量産データに変更......1

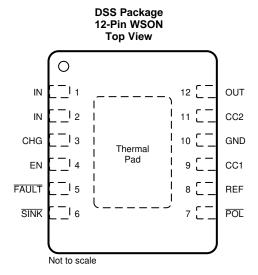

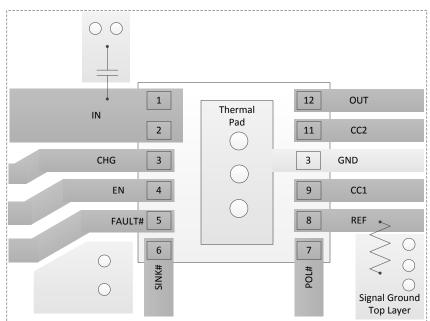

# **5 Pin Configuration and Functions**

## **Pin Functions**

| P           | IN     | 1/0 | DESCRIPTION                                                                                                                                                                                                              |

|-------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NUMBER | 1/0 | DESCRIPTION                                                                                                                                                                                                              |

| IN          | 1, 2   | 1   | Device input supply. V <sub>BUS</sub> internal power switch input supply. V <sub>CONN</sub> internal power switch input supply for the TPS25820.                                                                         |

| CHG         | 3      | ı   | Charge logic input to select between standard USB or 1.5-A Type-C current sourcing ability.                                                                                                                              |

| EN          | 4      | I   | Logic input to turn the device on and off.                                                                                                                                                                               |

| FAULT       | 5      | 0   | Open-drain logic output that asserts when the device is in overtemperature and/or V <sub>BUS</sub> is in current limit condition.                                                                                        |

| SINK        | 6      | 0   | Open-drain logic output that asserts when a Type-C Sink is identified on the CC lines.                                                                                                                                   |

| POL         | 7      | 0   | Open-drain logic output that signals which Type-C CC pin is connected to the cable CC line. This gives the information needed to mux the super speed lines. Asserted when the CC2 pin is connected to the cable CC line. |

| REF         | 8      | 1   | Analog input used to make a current reference. Connect a 0.5%, 100-ppm, 100-k $\Omega$ resistor between this pin and GND.                                                                                                |

| CC1         | 9      | I/O | Analog input/output that connects to the Type-C receptacle CC1 pin.                                                                                                                                                      |

| GND         | 10     | -   | Ground                                                                                                                                                                                                                   |

| CC2         | 11     | I/O | Analog input/output that connects to the Type-C receptacle CC2 pin.                                                                                                                                                      |

| OUT         | 12     | 0   | V <sub>BUS</sub> power switch output.                                                                                                                                                                                    |

| Thermal Pad | -      | -   | Thermal pad on bottom of package.                                                                                                                                                                                        |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range, voltages are respect to GND (unless otherwise noted) (1)

|                                                                                                                                          |                                                       | MIN  | MAX                   | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-----------------------|------|

| Pin voltage, V                                                                                                                           | IN, EN, CHG, REF, OUT, FAULT, CC1, CC2, SINK, POL     | -0.3 | 6                     | V    |

| Pin positive source current, I <sub>SRC</sub>                                                                                            | OUT, REF, CC1, CC2                                    |      | Internally<br>limited | Α    |

| CC1 CC2 (while                                                                                                                           | OUT (while applying V <sub>BUS</sub> )                |      | 2.5                   | Α    |

| Pin positive sink current long                                                                                                           | CC1, CC2 (while TPS25820 applying V <sub>CONN</sub> ) |      | 1                     | Α    |

| Pin positive source current, I <sub>SRC</sub> Pin positive sink current, I <sub>SNK</sub> Departing junction temperature, T <sub>J</sub> | FAULT, SINK, POL                                      |      | Internally<br>limited | mA   |

| Operating junction temperature, T <sub>J</sub>                                                                                           | -40 180 °                                             |      | °C                    |      |

| Storage temperature range, T <sub>stg</sub>                                                                                              |                                                       | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                        |                                                                     |                                                            | VALUE  | UNIT |

|------------------------|---------------------------------------------------------------------|------------------------------------------------------------|--------|------|

|                        |                                                                     | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)     | ±2000  |      |

| , (1) Electrostatic    | Charged-device model (CDM), per JEDEC specification JESD22-C101 (3) | ±500                                                       | \/     |      |

| V <sub>(ESD)</sub> (1) | discharge                                                           | IEC61000-4-2 contact discharge, CC1 and CC2 <sup>(4)</sup> | ±8000  | V    |

|                        |                                                                     | IEC61000-4-2 air-gap discharge, CC1 and CC2 <sup>(4)</sup> | ±15000 |      |

Electrostatic discharge (ESD) to measure device sensitivity/immunity to damage caused by assembly line electrostatic discharges into the device.

- (2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (4) Surges per IEC61000-4-2, 1999 applied between CC1/CC2 and output ground of the TPS25820EVM-835.

### 6.3 Recommended Operating Conditions

Voltages are with respect to GND (unless otherwise noted)

|                        |                                        |                                             | MIN | NOM MAX                  | UNIT |

|------------------------|----------------------------------------|---------------------------------------------|-----|--------------------------|------|

| VI                     | Supply voltage                         | IN                                          | 4.5 | 5.5                      | V    |

| $V_{I}$                | Input voltage                          | EN, CHG                                     | 0   | 5.5                      | V    |

| $V_{IH}$               | High-level input voltage               | EN, CHG                                     | 2   |                          | V    |

| $V_{IL}$               | Low-level voltage                      | EN, CHG                                     |     | 0.8                      | V    |

| $V_{PU}$               | Pull-up voltage                        | Used on FAULT, SINK, POL                    | 0   | 5.5                      | V    |

|                        | Positive source current                | OUT                                         |     | 1.5                      | Α    |

| I <sub>SRC</sub>       | Positive source current                | CC1 or CC2 when supplying V <sub>CONN</sub> |     | 5.5<br>5.5<br>0.8<br>5.5 | mA   |

|                        | Positive sink current (100 ms          | SINK, POL                                   |     | 5                        | A    |

| I <sub>SNK</sub>       | moving average)                        | FAULT                                       |     | 10                       | mA   |

| I <sub>SNK_PULSE</sub> | Positive repetitive pulse sink current | FAULT, SINK, POL                            |     | ,                        | mA   |

| TJ                     | Operating junction temperature         |                                             | -40 | 125                      | °C   |

### 6.4 Thermal Information

|                      | W                                            | TPS25820,<br>TPS25821 |      |

|----------------------|----------------------------------------------|-----------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DSS (WSON)            | UNIT |

|                      |                                              | 12 PINS               |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 57.7                  | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 53.7                  | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 24.1                  | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.6                   | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 24.1                  | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 7.4                   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ ,  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{IN}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                     | PARAMETER                                  | TEST CONDITIONS                                                                                                                                | MIN  | TYP  | MAX  | UNIT      |

|---------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| OUT - POV           | VER SWITCH                                 |                                                                                                                                                |      |      |      |           |

|                     |                                            | T <sub>J</sub> = 25°C, I <sub>OUT</sub> = 1.5 A                                                                                                |      | 64   | 70   |           |

| R <sub>DS(on)</sub> | On resistance <sup>(1)</sup>               | -40°C ≤ T <sub>J</sub> ≤ 85°C, I <sub>OUT</sub> = 1.5 A                                                                                        |      | 64   | 85   | $m\Omega$ |

|                     |                                            | -40°C ≤ T <sub>J</sub> ≤ 125°C, I <sub>OUT</sub> = 1.5 A                                                                                       |      | 64   | 98   |           |

| I <sub>REV</sub>    | OUT to IN reverse leakage current          | $V_{OUT} = 5.5 \text{ V}, 0 \le V_{IN} \le 5.5 \text{ V}, V_{EN} = 0 \text{ V},$<br>-40°C \le T <sub>J</sub> \le 85°C, measure I <sub>IN</sub> |      | 0    | 3    | μΑ        |

| OUT - CUF           | RRENT LIMIT                                |                                                                                                                                                |      |      |      |           |

|                     | Short circuit current limit (1)            |                                                                                                                                                | 1.6  | 1.72 | 1.84 | ۸         |

| los                 | Short circuit current limit \"             | $R_{REF} = 10 \Omega$                                                                                                                          |      |      | 4.0  | 4.0 A     |

| OUT - DIS           | CHARGE                                     |                                                                                                                                                |      |      |      |           |

|                     | Discharge resistance                       | V <sub>OUT</sub> = 4 V                                                                                                                         | 400  | 500  | 600  | Ω         |

|                     | Bleed discharge resistance                 | V <sub>OUT</sub> = 4 V, No Sink termination on CC lines, time > t <sub>w_OUT_DCHG</sub>                                                        | 90   | 150  | 250  | kΩ        |

| V <sub>TH</sub>     | Rising threshold for not discharged        |                                                                                                                                                |      |      | 800  | mV        |

| REF                 |                                            |                                                                                                                                                |      |      |      |           |

| los                 | Short circuit current                      | $R_{REF} = 10 \Omega$                                                                                                                          | 9.5  |      | 17.5 | μΑ        |

| Vo                  | Output voltage                             |                                                                                                                                                | 0.78 | 0.8  | 0.82 | V         |

| FAULT               |                                            |                                                                                                                                                |      |      |      |           |

| V <sub>OL</sub>     | Output low voltage                         | I FAULT = 1 mA                                                                                                                                 |      |      | 250  | mV        |

| l <sub>OFF</sub>    | Off-state leakage                          | $V_{\overline{FAULT}} = 5.5 V$                                                                                                                 |      |      | 1    | μA        |

| CC1/CC2 -           | V <sub>CONN</sub> POWER SWITCH (TPS25820)  |                                                                                                                                                |      |      |      |           |

|                     |                                            | T <sub>J</sub> = 25°C, I <sub>CCx</sub> = 250 mA                                                                                               |      | 480  | 530  |           |

| R <sub>DS(on)</sub> | On resistance                              | -40°C ≤ T <sub>J</sub> ≤ 85°C, I <sub>CCx</sub> = 250 mA                                                                                       |      | 480  | 645  | $m\Omega$ |

|                     |                                            | -40°C ≤ T <sub>J</sub> ≤ 125°C, I <sub>CCx</sub> = 250 mA                                                                                      |      | 480  | 755  |           |

| CC1/CC2 -           | V <sub>CONN</sub> POWER SWITCH - CURRENT   | LIMIT (TPS25820)                                                                                                                               |      |      |      |           |

|                     | Short circuit current limit <sup>(1)</sup> |                                                                                                                                                | 315  | 370  | 425  | mA        |

| los                 | Short circuit current limit.               | $R_{REF} = 10 \Omega$                                                                                                                          |      |      | 1000 | IIIA      |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

## **Electrical Characteristics (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ ,  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{IN}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                       |                                                                                          | TEST CONDITIONS                                                                                                                                                                                                                                                                 | ·    | TVD  | MAY | LINUT |

|-----------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

|                       | PARAMETER                                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                 | MIN  | TYP  | MAX | UNIT  |

| CC1/CC2 - (           | CONNECT MANAGEMENT                                                                       |                                                                                                                                                                                                                                                                                 |      |      |     |       |

|                       |                                                                                          | $V_{CHG} = 0 \text{ V}, 0 \text{ V} \le V_{CCx} \le 1.5 \text{ V}, \text{ after V } \frac{1}{\text{SINK}}$                                                                                                                                                                      | 73   | 80   | 85  |       |

| I <sub>SRC</sub>      | Sourcing current                                                                         | 0 V ≤ V <sub>CCx</sub> ≤ 1.5 V, after V <del>SINK</del> = 0 V                                                                                                                                                                                                                   | 168  | 180  | 190 | μΑ    |

|                       |                                                                                          | $V_{CHG} = 0 \text{ V or } V_{IN}, 0 \text{ V} \le V_{CCx} \le 1.5$<br>V, before $V_{SINK} = 0 \text{ V}$                                                                                                                                                                       | 64   | 80   | 96  |       |

| 1                     | Poverse legicage current                                                                 | CCx is the CC pin under test, CCy is the other CC pin. $V_{CCx} = 5.5 \text{ V}$ , CCy floating, $V_{EN} = 0 \text{ V}$ or $0 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ , $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 85^{\circ}\text{C}$ , $I_{REV}$ is current into CCx pin. |      | 0    | 5   | μΑ    |

| I <sub>REV</sub>      | Reverse leakage current                                                                  | CCx is the CC pin under test, CCy is the other CC pin. $V_{CCx} = 5.5 \text{ V}$ , CCy = 0 V, $-40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$ , $I_{REV}$ is current into CCx pin.                                                                                       |      | 5    | 10  |       |

| CC1/CC2 - 0           | CONNECT MANAGEMENT – V <sub>CONN</sub> I                                                 | DISCHARGE MODE                                                                                                                                                                                                                                                                  |      |      | ·   |       |

|                       | Discharge resistance (TPS25820)                                                          | CC pin that was providing V <sub>CONN</sub> before detach: V <sub>CCX</sub> = 4 V                                                                                                                                                                                               | 400  | 500  | 600 | Ω     |

| $V_{TH}$              | Falling threshold for discharged (TPS25820)                                              | CC pin that was providing V <sub>CONN</sub> before detach                                                                                                                                                                                                                       | 570  | 600  | 630 | mV    |

|                       | Discharged threshold hysteresis (TPS25820)                                               |                                                                                                                                                                                                                                                                                 |      | 100  |     | mV    |

| SINK, POL             |                                                                                          |                                                                                                                                                                                                                                                                                 |      |      | ·   |       |

| V <sub>OL</sub>       | Output low voltage                                                                       | I <sub>SNK_PIN</sub> = 1 mA                                                                                                                                                                                                                                                     |      |      | 250 | mV    |

| I <sub>OFF</sub>      | Off-state leakage                                                                        | V <sub>PIN</sub> = 5.5 V                                                                                                                                                                                                                                                        |      |      | 1   | μA    |

| EN, CHG - L           | OGIC INPUTS                                                                              |                                                                                                                                                                                                                                                                                 |      |      | •   |       |

| $V_{TH}$              | Rising threshold voltage for output logic change                                         |                                                                                                                                                                                                                                                                                 |      | 1.45 | 1.8 | V     |

| $V_{TH}$              | Falling threshold voltage for output logic change                                        |                                                                                                                                                                                                                                                                                 | 1.00 | 1.35 |     | V     |

|                       | Hysteresis (2)                                                                           |                                                                                                                                                                                                                                                                                 |      | 100  |     | mV    |

| I <sub>IN</sub>       | Input current                                                                            | V <sub>PIN</sub> = 0 V or 5.5 V                                                                                                                                                                                                                                                 | -0.5 |      | 0.5 | μA    |

| OVER TEMP             | PERATURE SHUT DOWN                                                                       |                                                                                                                                                                                                                                                                                 |      |      |     |       |

| T <sub>TH_OTSD2</sub> | Rising threshold temperature for device shutdown                                         |                                                                                                                                                                                                                                                                                 | 155  |      |     | °C    |

|                       | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                                                                                                                                                                                 |      | 20   |     | °C    |

| T <sub>TH_OTSD1</sub> | Rising threshold temperature for OUT/ V <sub>CONN</sub> switch shutdown in current limit |                                                                                                                                                                                                                                                                                 | 135  |      |     | °C    |

|                       | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                                                                                                                                                                                 |      | 20   |     | °C    |

| IN                    |                                                                                          |                                                                                                                                                                                                                                                                                 |      |      |     |       |

| $V_{TH}$              | Rising threshold voltage for not UVLO                                                    |                                                                                                                                                                                                                                                                                 | 3.9  | 4.1  | 4.3 | V     |

|                       | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                                                                                                                                                                                 |      | 100  |     | mV    |

|                       | <del>-</del>                                                                             | 1                                                                                                                                                                                                                                                                               |      |      |     |       |

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published specifications for purposes of TI's product warranty.

## **Electrical Characteristics (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ ,  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{IN}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                | PARAMETER                                                                                                                                      | TEST CONDITIONS                                                              | MIN | TYP | MAX | UNIT |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

|                | Enabled supply current with CC                                                                                                                 | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$ |     |     | 1   |      |

|                | Enabled supply current with CC lines open                                                                                                      | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                |     | 1   | 4   |      |

| I <sub>I</sub> | Enabled supply current with dangling Ra cable attached                                                                                         |                                                                              |     | 150 | 195 |      |

|                | Enabled supply current with Sink                                                                                                               | V <sub>CHG</sub> = 0 V                                                       |     | 232 | 275 |      |

|                | attached via cable that is<br>electronically marked (includes IN<br>current that provides the CC<br>output current to the sink Rd<br>resistor) |                                                                              |     | 332 | 380 | μΑ   |

|                | Enabled supply current with Sink                                                                                                               | V <sub>CHG</sub> = 0 V                                                       |     | 210 | 250 |      |

|                | attached via cable that is not electronically marked (includes IN current that provides the CC output current to the sink Rd resistor)         |                                                                              |     | 310 | 355 |      |

# 6.6 Switching Characteristics

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ ,  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{IN}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                         | PARAMETER                                                      | TEST CONDITIONS                                                                                             | MIN  | TYP  | MAX      | UNIT |

|-------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|----------|------|

| OUT - POWE              | R SWITCH                                                       |                                                                                                             |      |      | *        |      |

| t <sub>r</sub>          | Output voltage rise time                                       | $V_{IN} = 5 \text{ V}, C_L = 1 \mu\text{F}, R_L = 100 \Omega$                                               | 0.5  | 0.8  | 1.2      | ms   |

| t <sub>f</sub>          | Output voltage fall time                                       | (measure between 10% and 90% of final value)                                                                | 0.2  | 0.3  | 0.4      | ms   |

| t <sub>on</sub>         | Output voltage turn-on time                                    | $V_{IN} = 5 \text{ V, } C_{I} = 1  \mu\text{F, } R_{I} = 100  \Omega$                                       | 2.1  | 3.2  | 4.5      | ms   |

| $t_{\text{off}}$        | Output voltage turn-off time                                   | $V_{IN} = 5 \text{ V}, C_{L} = 1  \mu\text{F}, R_{L} = 100  \Omega$                                         | 0.8  | 1.3  | 1.9      | ms   |

| t <sub>w_OUT_DCHG</sub> | $R_{\mbox{\scriptsize DCHG}}$ application time at OUT turn off | V <sub>OUT</sub> = 1 V, time I <sub>SNK_OUT</sub> > 1 mA after Sink termination removed from CC lines       | 169  | 262  | 361      | ms   |

| OUT - CURRI             | ENT LIMIT                                                      |                                                                                                             |      |      | *        |      |

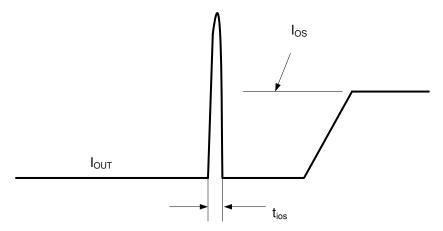

| t <sub>iOS</sub>        | Current limit response time to short circuit                   | $V_{IN}$ - $V_{OUT}$ = 1 V, $R_L$ = 10 m $\Omega$ (see $\square$                                            |      | 1.5  | 4        | μs   |

| FAULT                   |                                                                |                                                                                                             |      |      | <u> </u> |      |

| t <sub>DEGA</sub>       | Asserting deglitch due to overcurrent                          |                                                                                                             | 5.6  | 8.2  | 10.6     | ms   |

| t <sub>DEGA</sub>       | Asserting deglitch due to overtemperature in current limit     |                                                                                                             |      | 0    |          | ms   |

| t <sub>DEGD</sub>       | De-asserting deglitch                                          |                                                                                                             | 5.6  | 8.2  | 10.6     | ms   |

| CC1/CC2 - Vo            | CONN POWER SWITCH (TPS25820)                                   |                                                                                                             |      |      |          |      |

| t <sub>r</sub>          | Output voltage rise time                                       | $V_{IN2} = 5 \text{ V}, C_L = 1 \mu\text{F}, R_L = 100 \Omega$                                              | 0.13 | 0.22 | 0.3      | ms   |

| t <sub>f</sub>          | Output voltage fall time                                       | $V_{\text{IN2}} = 5 \text{ V}, C_{\text{L}} = 1  \mu\text{F},  \text{K}_{\text{L}} = 100  \text{S}\text{2}$ | 0.18 | 0.22 | 0.26     | ms   |

| t <sub>on</sub>         | Output voltage turn-on time                                    | $V_{INI2} = 5 \text{ V, } C_1 = 1  \mu\text{F, } R_1 = 100  \Omega$                                         | 1.4  | 2.2  | 3.2      | ms   |

| $t_{\text{off}}$        | Output voltage turn-off time                                   | $V_{\text{IN2}} = 3 \text{ V},  C_{\text{L}} = 1  \mu\text{F},  K_{\text{L}} = 100  22$                     | 0.25 | 0.33 | 0.4      | ms   |

|                         | Minimum VCONN discharge time                                   | TPS25820                                                                                                    | 42   | 65   | 90       | ms   |

| CC1/CC2 - Vo            | CONN POWER SWITCH - CURRENT LIN                                | IIT (TPS25820)                                                                                              |      |      |          |      |

| t <sub>res</sub>        | Current limit response time to short circuit                   | $V_{IN} - V_{CCx} = 1 \text{ V, R} = 10 \text{ m}\Omega \text{ (see } \boxed{2}$                            |      | 1    | 4        | μs   |

| SINK, POL               |                                                                |                                                                                                             | -    |      |          |      |

| t <sub>DEGA</sub>       | Asserting deglitch                                             |                                                                                                             | 100  | 150  | 200      | ms   |

| t <sub>DEGD</sub>       | De-asserting deglitch                                          |                                                                                                             | 7.9  | 12.5 | 17.7     | ms   |

図 1. Output Short Circuit Parameter Diagram

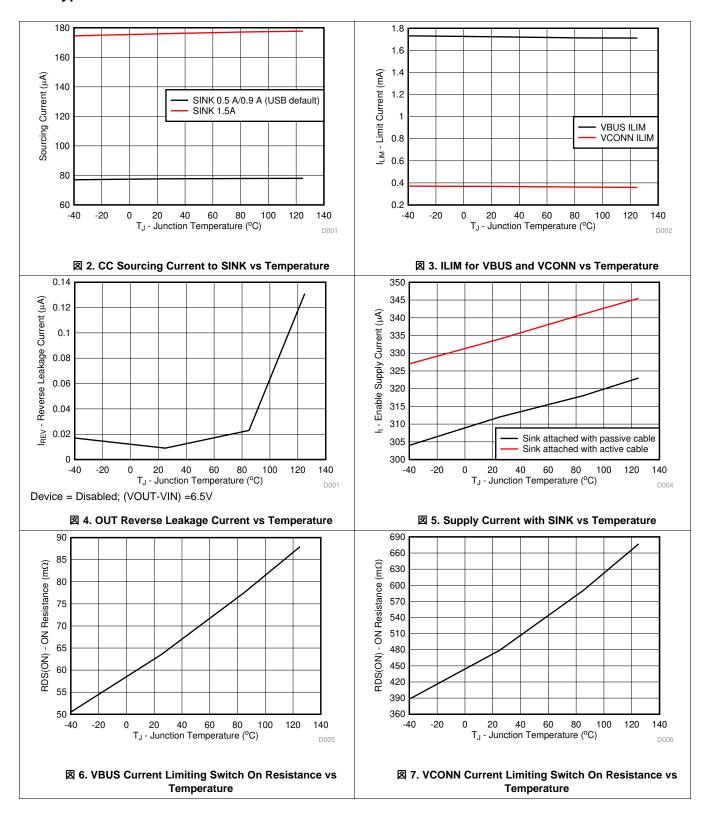

## 6.7 Typical Characteristics

## 7 Detailed Description

### 7.1 Overview

The TPS25820 and TPS25821 devices are highly integrated USB Type-C source controllers with built-in power switches developed for the USB Type-C connector and cable. The TPS25820 supports VCONN, while the TPS25821 does not. The devices provide all of the functionality needed to support a USB Type-C DFP in a system where USB power delivery (PD) source capabilities (for example,  $V_{BUS} > 5$  V) are not implemented. The devices are designed to be compliant to the USB Type-C specification, release 1.3 which added new requirements to discharge VCONN.

### 7.1.1 USB Type C Basic

For a detailed description of the Type-C spec refer to the USB-IF website to download the latest released version. Some of the basic concepts of the Type-C spec that pertains to understanding the operation of the TPS25820/21 (a Downward Facing Port, DFP device) are described as follows.

USB Type-C removes the need for different plug and receptacle types for host and device functionality. The Type-C receptacle replaces both Type-A and Type-B receptacles since the Type-C cable is plug-able in either direction between host and device. A host-to-device logical relationship is maintained via the configuration channel (CC). Optionally hosts and devices can be either providers or consumers of power when USB PD communication is used to swap roles.

All USB Type-C ports operate in one of below three data modes:

- Host mode: the port can only be host (also provider of power)

- Device mode: the port can only be device (also consumer of power)

- Dual-Role mode: the port can be either host or device

### Port types:

- DFP (Downstream Facing Port): Host, specifically associated with flow of data (Host or Hub) in a USB link

- Source: Port that asserts Rp (pull-up resistor) on CC pin and provides power on VBUS when attached to a Sink (device). At power-up a DFP is a source.

- UFP (Upstream Facing Port): Device, specifically associated with flow of data (device) in a USB link

- Sink: Port that asserts Rd (pull-down) on CC pin and consumes power from VBUS when attached. At power-up a UFP is a sink

- DRP (Dual-Role Port): Host or Device

Valid Source-to-Sink connections:

- 表 1 describes valid Source-to-Sink connections

- Source to Source or Sink to Sink have no function

### 表 1. Valid Source-to-Sink Connections

| POWER ROLES              | SOURCE ONLY | SINK ONLY   | DUAL ROLE POWER (DRP) |  |  |  |  |

|--------------------------|-------------|-------------|-----------------------|--|--|--|--|

| Source Only              | Not allowed | Allowed     | Allowed               |  |  |  |  |

| Sink Only                | Allowed     | Not allowed | Allowed               |  |  |  |  |

| Dual Role Power<br>(DRP) | Allowed     | Allowed     | Allowed               |  |  |  |  |

### 7.1.2 Configuration Channel

The function of the configuration channel is to detect connections and configure the interface across the USB Type-C cables and connectors.

Functionally the Configuration Channel (CC) is used to serve the following purposes:

- Detect connect to the USB ports

- Resolve cable orientation and twist connections to establish USB data bus routing

- Establish Source and Sink roles between two connected ports

- Discover and configure power: USB Type-C current modes or USB Power Delivery

- Discovery and configure optional Alternate and Accessory modes

· Enhances flexibility and ease of use

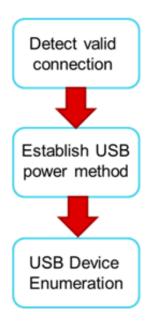

Typical flow of DFP to UFP configuration is shown in **図 8**:

図 8. DFP to UFP Connect Flow

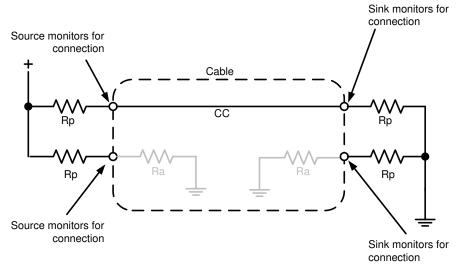

### 7.1.3 Detecting a Connection

- In the Source-Sink connection the Source monitors both CC pins for a voltage lower than the unterminated voltage.

- A Sink advertises Rd on both its CC pins (CC1 and CC2).

- A powered cable advertises Ra on its V<sub>CONN</sub> pin.

図 9. Source-Sink Connection Mechanism

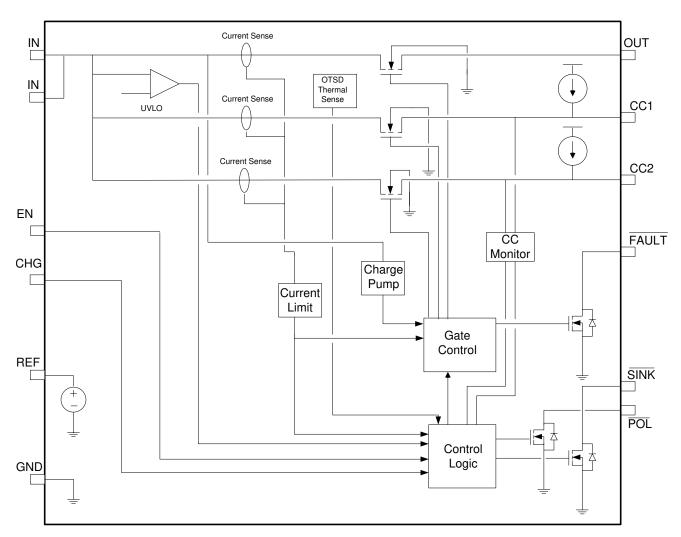

# 7.2 Functional Block Diagrams

Copyright © 2017, Texas Instruments Incorporated

図 10. TPS25820 Functional Block Diagram

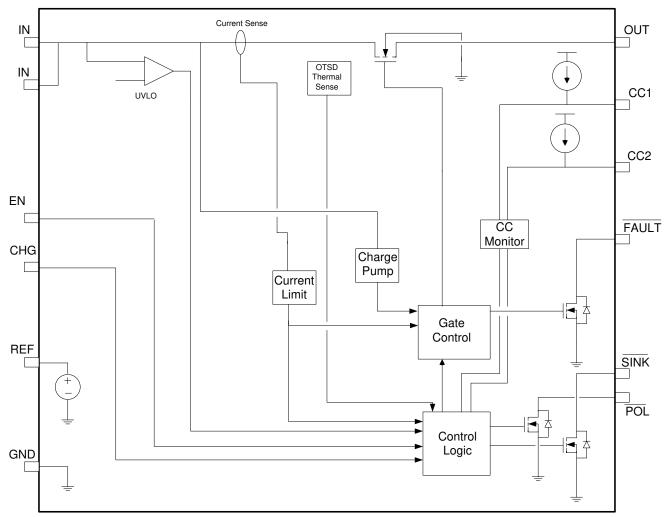

## Functional Block Diagrams (continued)

Copyright © 2017, Texas Instruments Incorporated

図 11. TPS25821 Functional Block Diagram

## 7.3 Feature Description

Both the TPS25820 and TPS25821 are source (i.e. DFP) Type-C port controllers with integrated power switches for  $V_{BUS}$ . The TPS25820 also has integrated power switches for  $V_{CONN}$ . Refer to the functional block diagrams ( $\boxtimes$  10 and  $\boxtimes$  11). The TPS25820/21 devices do not support BC1.2 charging modes, because it does not interact with USB D+ and D- data lines. However supporting DCP mode of BC1.2 can be easily accomplished in dataless ports like wall chargers and CLAs by simply tying a  $100-\Omega$  resistor between the D+ and D- pins of the Type-C connector.

The TPS25820 has a built-in  $V_{CONN}$  current limiting switch and can be used to implement USB 3.1 DFP, whereas the TPS25821 does not implement a  $V_{CONN}$  current limiting switch hence is used in the implementation in USB 2.0 DFP ports or as a USB source only port. Other than the  $V_{CONN}$  current limiting switch there are no other functional differences between the TPS25820 and TPS25821.

## 7.3.1 Configuration Channel Pins CC1 and CC2

The TPS25820/21 devices have two pins, CC1 and CC2 that serve to detect an attachment to the port and resolve cable orientation. These pins are also used to establish the current broadcast to a valid sink and configure  $V_{CONN}$  (TPS25820 only).

### **Feature Description (continued)**

表 2 lists the TPS25820/21 response to various attachments to its port.

### 表 2. Response to Attachments

|                                   |      |      | TPS25820/21 RESPONSE <sup>(1)</sup> |                                                   |      |      |  |  |  |

|-----------------------------------|------|------|-------------------------------------|---------------------------------------------------|------|------|--|--|--|

| TPS25820/21 TYPE-C PORT           | CC1  | CC2  | OUT                                 | V <sub>CONN</sub> <sup>(2)</sup><br>On CC1 or CC2 | POL  | SINK |  |  |  |

| Nothing Attached                  | OPEN | OPEN | OPEN                                | NO                                                | Hi-Z | Hi-Z |  |  |  |

| Sink Connected                    | Rd   | OPEN | IN                                  | NO                                                | Hi-Z | LOW  |  |  |  |

| Sink Connected                    | OPEN | Rd   | IN                                  | NO                                                | LOW  | LOW  |  |  |  |

| Powered Cable/No Sink Connected   | OPEN | Ra   | OPEN                                | NO                                                | Hi-Z | Hi-Z |  |  |  |

| Powered Cable/No Sink Connected   | Ra   | OPEN | OPEN                                | NO                                                | Hi-Z | Hi-Z |  |  |  |

| Powered Cable/Sink Connected      | Rd   | Ra   | IN                                  | CC2                                               | Hi-Z | LOW  |  |  |  |

| Powered Cable/Sink Connected      | Ra   | Rd   | IN                                  | CC1                                               | LOW  | LOW  |  |  |  |

| Debug Accessory Connected         | Rd   | Rd   | OPEN                                | NO                                                | Hi-Z | Hi-Z |  |  |  |

| Audio Adapter Accessory Connected | Ra   | Ra   | OPEN                                | NO                                                | Hi-Z | Hi-Z |  |  |  |

<sup>(1)</sup> POL and SINK are open drain outputs; pull high with 100 kΩ to IN when used. Tie to GND or leave open when not used.

## 7.3.2 Current Capability Advertisement and VBUS Overload Protection

The TPS25820/21 supports two Type-C current advertisements as defined by the USB Type-C standard. Current broadcast to a connected Sink is controlled by the CHG pin. For each broadcast level the device protects itself from a Sink that draws current in excess of the port's USB Type-C Current advertisement by setting the current limit as shown in 表 3.

表 3. USB Type-C Current Advertisement

| CHG | CC CAPABILITY BROADCAST       | CURRENT LIMIT |

|-----|-------------------------------|---------------|

| 0   | STD (500 mA for USB 2.0 port) | 1.67 A        |

| 0   | STD (900 mA for USB 3.1 port) | 1.67 A        |

| 1   | 1.5 A                         | 1.67 A        |

Under overload conditions, the internal current-limit regulator limits the output current on the OUT pin as shown in the Electrical Characteristics table. When an overload condition is present, the device maintains a constant output current, with the output voltage determined by ( $I_{OS} \times R_{LOAD}$ ). Two possible overload conditions can occur. The first overload condition occurs when either: 1) input voltage is first applied, enable is true, and a short circuit is present (load which draws  $I_{OUT} > I_{OS}$ ), or 2) input voltage is present and the TPS25820/21 is enabled into a short circuit. The output voltage is held near zero potential with respect to ground and the TPS25820/21 ramps the output current to  $I_{OS}$ .

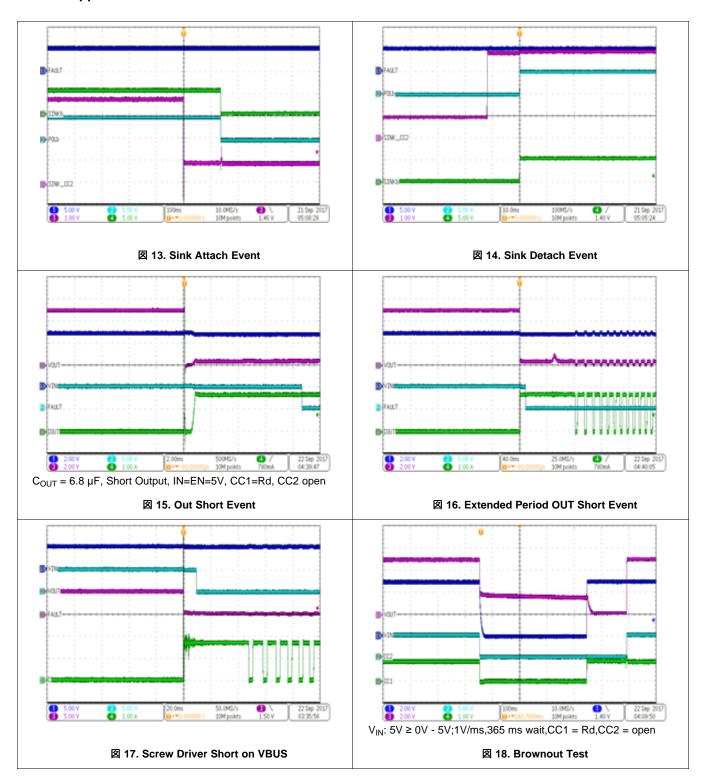

In either case the TPS25820/21 will limit the load current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle. This is demonstrated in  $\boxtimes$  16 where the device was enabled into a short, and subsequently cycles current off and on as the thermal protection engages.

### 7.3.3 FAULT Response

The  $\overline{\text{FAULT}}$  pin is an open drain output that asserts (active low) after a deglitch time ( $t_{DEGA}$ ) when device OUT current exceeds its programmed value and/or overtemperature threshold is crossed. The FAULT signal remains asserted until the fault condition is removed for  $t_{DEGD}$ . The TPS25820/21 are designed to eliminate false overcurrent fault reporting by using an internal deglitch circuit.

Connect  $\overline{\mathsf{FAULT}}$  with a 100-k $\Omega$  pull-up resistor to IN.  $\overline{\mathsf{FAULT}}$  can be left open or tied to GND when not used.

<sup>(2)</sup> TPS25820 Only

### 7.3.4 Thermal Shutdown

The device has two internal overtemperature shutdown thresholds,  $T_{TH\_OTSD1}$  and  $T_{TH\_OTSD2}$ , to protect the internal FET from damage and overall safety of the system. When the device temperature exceeds  $T_{TH\_OTSD1}$ , any switch in current limit (OUT switch or VCONN switch) is disabled. The device does auto-retry recovery by reenabling the switch when die temperature decreases by 20°C. When  $T_{TH\_OTSD2}$  is exceeded all open drain outputs are left open and the device is disabled such that minimum power/heat is dissipated. The device does auto-retry recovery by attempting to power-up when die temperature decreases by 20°C.

#### 7.3.5 REF

A 100-k $\Omega$  resistor is connected from this pin to GND. This pin sets the reference current required to bias the internal circuitry of the device. The overload current limit tolerance and CC currents depend upon the accuracy of this resistor. A  $\pm 0.5\%$  low temp CO resistor, or better, yields the best current limit accuracy and overall device performance. If the CC capability broadcast will only be set to STD (CHG pulled low) then up to a  $\pm 10\%$  resistor may be used as long as the additional error in the current limit is acceptable.

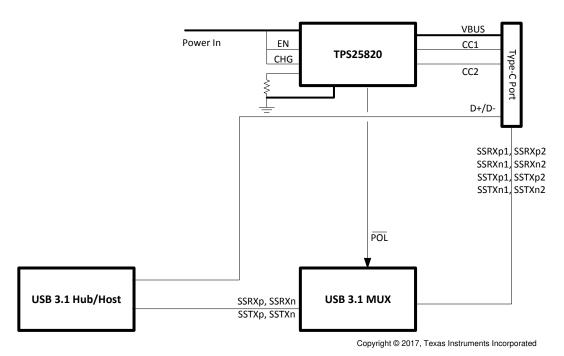

### 7.3.6 Plug Polarity Detection

Reversible Type-C plug orientation is reported by the POL pin when a Sink is connected, however when no Sink is attached, POL remains de-asserted irrespective of cable plug orientation. 表 2 describes the POL state based on which device CC pin detects  $V_{Rd}$  from an attached Sink pull-down. In a typical USB 3.x DFP port, this pin controls a superspeed data MUX for proper data connectivity irrespective of plug orientation. See  $\boxtimes$  20.

#### 7.3.7 Sink Attachment Indicator

The attachment of a Type-C sink is reported by SINK. See 表 2.

### 7.3.8 Device Enable Control

The logic enable pin controls the power switch and device supply current. The supply current is reduced to less than 1  $\mu$ A when a logic low is present on EN. The EN pin provides a convenient way to turn on or turn off the device while it is powered. When this pin is pulled high, the device is turned on or enabled. When the device is disabled (EN pulled low), the internal FETs tied to IN are disconnected, all open drain outputs are left open (Hi-Z), and the CC1/CC2 monitor block is turned off. The EN pin should not be left floating.

### 7.3.9 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage droop during turn on.

### 7.4 Device Functional Modes

The TPS25820/21 is a Type-C controller with integrated power switch that supports all Type-C functions in a downstream facing port (DFP). It is also used to manage current advertisement and protection to a connected sink and active cable. The device starts its operation by monitoring the IN bus. When IN exceeds the undervoltage lockout threshold, the device samples the EN pin. A high level on this pin enables the device and normal operation begins. Having successfully completed its start-up sequence, the device now actively monitors its CC1 and CC2 pins for attachment to a sink. When a sink is detected on either the CC1 or CC2 pin the internal MOSFET starts to turn-on after the required de-bounce time is met. The internal MOSFET starts conducting and allows current to flow from IN to OUT. For the TPS25820 if Ra is detected on the other CC pin (not connected to sink), VCONN is applied to allow current to flow from IN to the CC pin connected to Ra. For a complete listing of various device operational modes refer to ₹ 2.

## 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The TPS25820/21 are Type-C source controllers. The TPS25820 supports all Type-C DFP required functions to support a USB 3.x port and the TPS25821 supports all required functions for a USB 2.0 DFP. The TPS25820/21 only applies power to  $V_{BUS}$  when it detects a sink is attached and removes power when it detects the sink is detached. The device exposes its identity via its CC pin advertising its current capability based on the CHG pin setting. The TPS25820/21 also limits its advertised current internally and provides robust protection against faults on the system  $V_{BUS}$  power rail.

After a connection is established by the TPS25820/21, the TPS25820/21 device is capable of providing  $V_{CONN}$  to power circuits in the cable plug on the CC pin that is not connected to the CC wire in the cable.  $V_{CONN}$  is internally current limited. The TPS25820/21 do not support Type-C optional accessory modes (Ra/Ra and Rd/Rd in 表 2).

The following design procedure can be used to implement a full featured Type-C source.

### 8.2 Typical Applications

### 8.2.1 Type-C Source Port Implementation without BC 1.2 Support

☑ 12 shows a minimal Type-C source implementation capable of supporting 5-V and 1.5-A charging.

図 12. Type-C Source Port Implementation without BC 1.2 Support

### 8.2.1.1 Design Requirements

## 8.2.1.1.1 Input and Output Capacitance Considerations

Input and output capacitance improves the performance of the device. The actual capacitance should be optimized for the particular application. For all applications, a 0.1- $\mu F$  or greater ceramic bypass capacitor between IN and GND is recommended as close to the device as possible for local noise decoupling.

All protection circuits, including those of the TPS25820/21 device, have the potential for input voltage overshoots and output voltage undershoots. Input voltage overshoots can be caused by either of two effects. The first cause is an abrupt application of input voltage in conjunction with input power-bus inductance and input capacitance when the IN pin is high-impedance (before OUT turn-on, i.e. not connected to a Type-C sink device). Theoretically, the peak voltage is 2 times the applied voltage. The second cause is due to the abrupt reduction of

output short-circuit current when the device turns off and energy stored in the input inductance drives the input voltage high. Input voltage droops may also occur with large load steps and as the output is shorted. Applications with large input inductance (for instance, connecting the evaluation board to the bench power supply through long cables) may require large input capacitance to prevent the voltage overshoot from exceeding the absolute maximum voltage of the device.

The fast current-limit speed of the TPS25820/21 device to hard output short circuits isolates the input bus from faults. However, ceramic input capacitance in the range of 1  $\mu$ F to 22  $\mu$ F adjacent to the input aids in both response time and limiting the transient seen on the input power bus. Output voltage undershoot is caused by the inductance of the output power bus just after a short has occurred and the device has abruptly reduced the OUT current. Energy stored in the inductance drives the OUT voltage down, and potentially negative, as it discharges. An application with large output inductance (such as from a cable) benefits from the use of a high-value output capacitor to control voltage undershoot.

Since the source is considered cold socketed when not attached to a sink, the output capacitance should be placed at the IN pin rather than the OUT pin, which has been commonly used in USB Type-A ports. A 120- $\mu$ F capacitance is recommended in this situation. It is also recommended to a ceramic capacitor less than 10  $\mu$ F on the OUT pin for better voltage bypass and compliance to Type-C spec.

### 8.2.1.1.2 System Level ESD Protection

System-level ESD (per EN61000-4-2) may occur as the result of a cable being plugged in, or a user touching the USB receptacle or cable plug exposed pins. The recommended capacitor on the OUT pin helps reduce the severity of ESD hit on the VBUS path thereby protecting the OUT pin of device. The device has ESD protection built into the CC1 and CC2 pins so that no external protection is necessary as long as proper trace layout guidelines are practiced. Refer to the Layout Guidelines section for external component placement and routing recommendations.

### 8.2.1.2 Detailed Design Procedure

Design considerations are listed below:

- Place at least 120  $\mu F$  of bypass capacitance close to the IN pins versus OUT as Type C is a cold socket connector.

- A <10-μF bypass capacitor is recommended placed near Type-C receptacle V<sub>BUS</sub> pin to handle load transients.

- Depending on the max current level advertisement supported by the Type-C port in the system, set CHG levels accordingly.

- EN and CHG pins can be tied directly to GND or IN without a pull-up resistor.

- CHG can also be dynamically controlled by a μC to change the current advertisement level to the sink.

- When an open drain output of the TPS25820 is not used, it can be left as NC or tied to GND or when used, pulled up to IN supply via a 100-kΩ resistor.

- Connect a 0.5% 100- $k\Omega$  resistor between the REF and GND pins placing it close to the device pin and isolated from switching noise on the board.

# 8.2.1.3 Application Curves

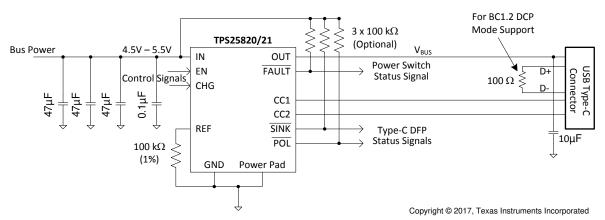

### 8.2.2 Type -C Source Port Implementation with BC 1.2 (DCP Mode) Support

BC1.2 charging is not supported in the TPS25820/21, however adding BC1.2 DCP (Dedicated Charging Port) support with the TPS25820/21 can be done by having the D+ and D- shorted together with a maximum impedance of 200  $\Omega$  between them and left floating with respect to ground. This is shown in  $\square$  19. However with DCP implementation the port will not support any data transfer, but is capable of advertising charge currents up to 1.5 A to a legacy device that is connected using a Type-C to Type-A or Micro-B cable. This type of port allows for wall chargers and car chargers with high-charge capability without the need for enumeration.  $\square$  19 shows a Type-C source implementation capable of supporting 5-V and 1.5-A charging in a Type-C port that is also able to support charging of legacy devices when used with a Type-C -  $\mu$ B cable assembly.

図 19. Type-C Source Port Implementation with BC 1.2 (DCP Mode) Support

### 8.2.2.1 Design Requirements

Refer to Design Requirements for the Design Requirements.

### 8.2.2.2 Detailed Design Procedure

Refer to *Detailed Design Procedure* for the Detailed Design Procedure.

### 8.2.2.3 Application Curves

Refer to *Application Curves* for the Application Curves.

## 8.2.3 Implementing a USB 3.1 Type-C Charging Port with the TPS25820

№ 20 shows a conceptual implementation of USB 3.1 capable Type-C DFP, used in notebook, desktop, LCD monitor or dock application where both USB data and charging is supported. USB 2.0 data lines are connected directly to Type-C receptacle while USB 3.1 data is connected through a USB 3.1 MUX. The TPS25820 controls the USB 3.1 MUX via its POL pin. In this implementation if the USB host/hub is capable of supporting BC1.2 charging then it is possible to support both BC1.2 and Type-C charging from the same Type-C port.

図 20. USB 3.1 Type-C Charging Port

### 8.2.3.1 Design Requirements

Refer to *Design Requirements* for the Design Requirements.

### 8.2.3.2 Detailed Design Procedure

Refer to *Detailed Design Procedure* for the Detailed Design Procedure.

### 8.2.3.3 Application Curves

Refer to *Application Curves* for the Application Curves.

### 8.2.4 Implementing TPS25821 in USB Car Chargers

Given its small footprint, highly integrated design and ultralow standby current, the TPS25821 is ideal for use in cigarette lighter adapter (CLA) USB car chargers capable of supporting Type-C 1.5-A and BC1.2 DCP charging from same Type-C port. This makes it suitable for fast charging phones with either μB or Type-C connector. 21 shows such an implementation for a two port CLA design. The LMS3635 was chosen for its wide VIN and high efficiency to allow for the compact design needed in a CLA body.

Copyright © 2017, Texas Instruments Incorporated

図 21. USB Car Charger

## 8.2.4.1 Design Requirements

Refer to *Design Requirements* for the Design Requirements.

## 8.2.4.2 Detailed Design Procedure

Refer to *Detailed Design Procedure* for the Detailed Design Procedure.

### 8.2.4.3 Application Curves

Refer to Application Curves for the Application Curves.

## 9 Power Supply Recommendations

The device has one power supply input, IN, which is the chip supply. It is connected to the OUT pin via a power integrated MOSFET and in the case of the TPS25820 it also is MUXed either to CC1 or CC2 pin in the Type-C receptacle depending on cable plug polarity.

USB Specification Revision 2.0 and 3.1 requires VBUS voltage at the connector be between 4.75 V to 5.5 V. Depending on layout and routing from supply to the connector, the voltage droop on VBUS has to be tightly controlled especially when providing 1.5 A. Locate the input supply close to the device. For all applications, a ceramic bypass capacitor between OUT and GND less than 10  $\mu$ F is recommended and should be placed as close to the Type-C connector and device as possible for local noise decoupling. The power supply should be rated higher than the current limit set to avoid voltage droops during overcurrent and short-circuit conditions. Also see *Input and Output Capacitance Considerations* on chip by-passing considerations.

# 10 Layout

### 10.1 Layout Guidelines

Layout best practices as it applies to the TPS25820/21 are listed below.

- For all applications a ceramic capacitor less than 10 μF is recommended near the Type-C receptacle and another 120-μF ceramic capacitor placed close to the IN pin.

- The optimum placement of the 120-μF capacitor is closest to the IN and GND pins of the device.

- High current carrying power path connections to the device should be as short as possible and should be sized to carry at least twice the full-load current.

- Have the input and output traces as short as possible. The most common cause of voltage drop failure in USB power delivery is the resistance associated with the VBUS trace. Trace length, maximum current being supplied for normal operation, and total resistance associated with the VBUS trace must be taken into account while budgeting for voltage drop.

- For example, a power carrying trace that supplies 1.5 A, at a distance of 20 inches, 0.100-in. wide, with 2-oz. copper on the outer layer will have a total resistance of approximately 0.046  $\Omega$  and voltage drop of 0.07 V. The same trace at 0.050-in.-wide will have a total resistance of approximately 0.09  $\Omega$  and voltage drop of 0.14 V.

- Make power traces as wide as possible.

- The resistor attached to the REF pin of the device has several requirements:

- It is recommended to use a 0.5% 100-k $\Omega$  resistor.

- It should be connected to pins REF and GND.

- The trace routing between the REF and GND pins of the device should be as short as possible to reduce parasitic effects on the current limit and current advertisement accuracy. These traces should not have any coupling to switching signals on the board.

- Locate all TPS25820/21 pull-up resistors for open-drain outputs close to their connection pin. Pull-up resistors should be 100 k $\Omega$ .

- When a particular open drain output is not used/needed in the system leave the associated pin open or tied to GND.

- Keep the CC lines close to the same length.

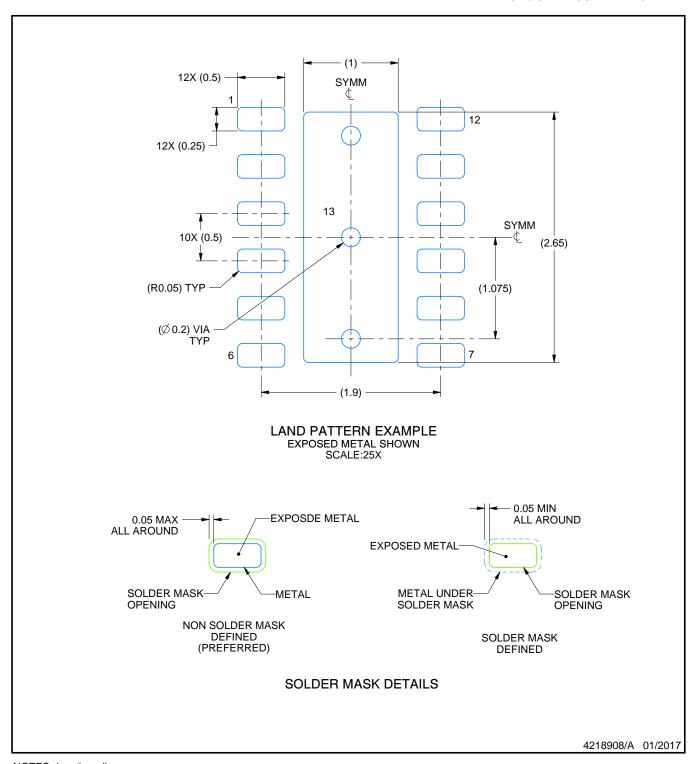

- Thermal Considerations:

- When properly mounted, the thermal pad package provides significantly greater cooling ability than an ordinary package. To operate at rated power, the thermal pad must be soldered to the board GND plane directly under the device. The thermal pad is at GND potential and can be connected using multiple vias to inner layer GND. Other planes, such as the bottom side of the circuit board can be used to increase heat sinking in higher current applications. Refer to Technical Briefs: PowerPad<sup>TM</sup> Thermally Enhanced Package (TI literature Number SLMA002) and PowerPAD<sup>TM</sup> Made Easy (TI Literature Number SLMA004) or more information on using this thermal pad package.

- The thermal via land pattern specific to the TPS25820/21 can be downloaded from the device web page at www.ti.com.

- Obtaining acceptable performance with alternate layout schemes is possible; however the layout example

in the following section has been shown to produce good results and is intended as a guideline.

# 10.2 Layout Example

□ Top Layer Signal Trace

□ Top Layer Signal Ground Plane

□ Bottom Layer Signal Ground Plane

○ Via to Bottom Layer Ground Plane

図 22. Layout Example

## 11 デバイスおよびドキュメントのサポート

## 11.1 デバイス・サポート

### 11.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供される場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワークの製品またはサービスの是認の表明を意味するものではありません。

## 11.2 ドキュメントのサポート

### 11.2.1 関連資料

関連資料については、以下を参照してください。

- 『放熱特性の優れたPowerPad™パッケージ』(TI文書番号SLMA002)

- 『PowerPAD™の簡単な使用法』(TI文書番号SLMA004)

- 『TPS25810EVM-745ユーザー・ガイド』(SLVUAIO)

- 『高電圧DFPからのTPS25810の保護』(SLVA751)

### 11.3 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック・アクセスが含まれます。

### 表 4. 関連リンク

| 製品       | プロダクト・フォルダ | ご注文はこちら | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |

|----------|------------|---------|---------|------------|-------------|

| TPS25820 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

| TPS25821 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

### 11.4 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.5 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.6 商標

E2E is a trademark of Texas Instruments.

## 11.7 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 11.8 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 10-Nov-2025

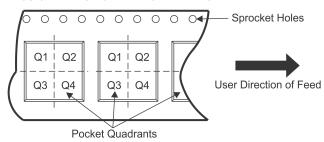

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | (4)                           | (5)                        |              | (6)          |

| TPS25820DSSR          | Active | Production    | WSON (DSS)   12 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 25820        |